Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

102 results about "Subthreshold swing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The subthreshold swing of a device is defined as the change in gate voltage which must be applied in order to create a one decade increase in the output current ". The other one is that the amount of gate voltage that is needed to bring down the sub threshold current by one decade . which of them is correct and in which context.

Ferroelectric tunnel fet switch and memory

ActiveUS20100140589A1Reduce power consumptionLimited successMaterial nanotechnologySemiconductor/solid-state device detailsCapacitanceSubthreshold swing

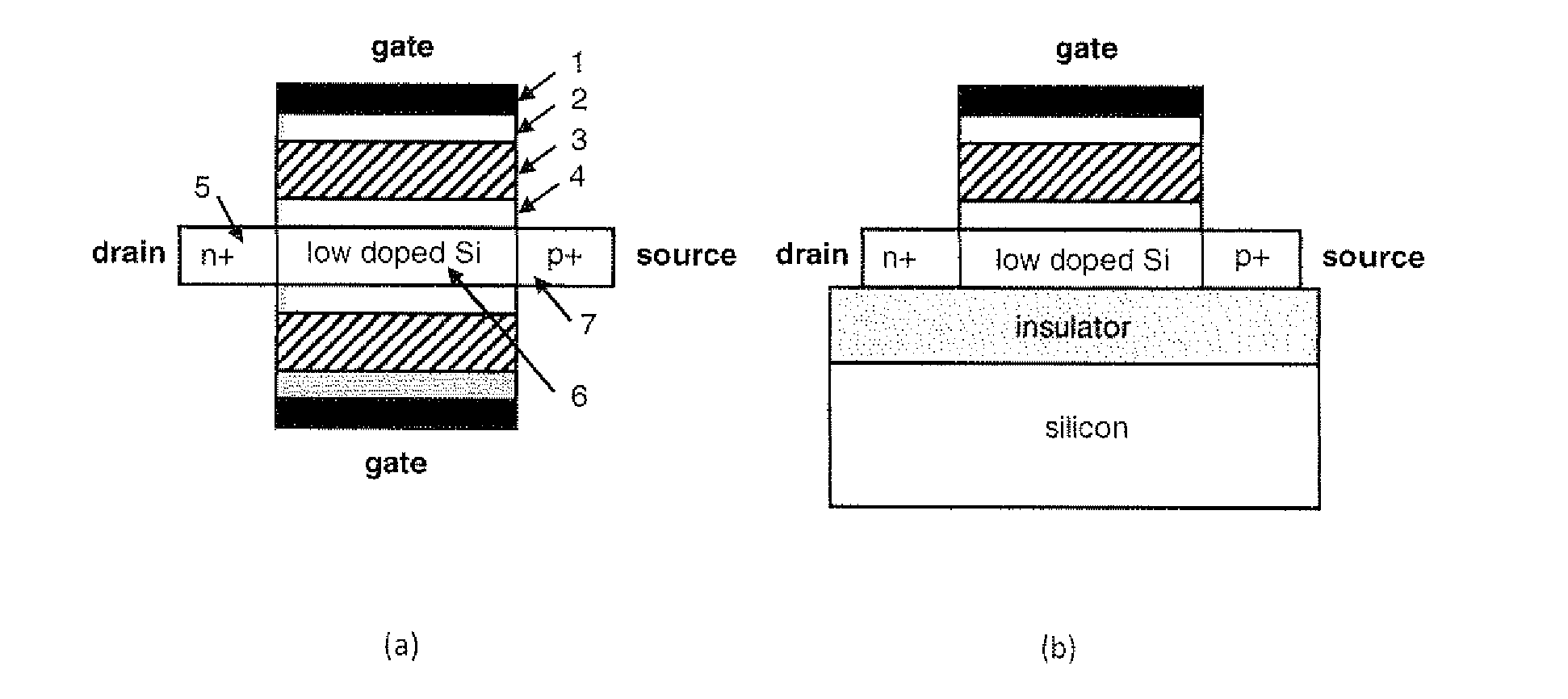

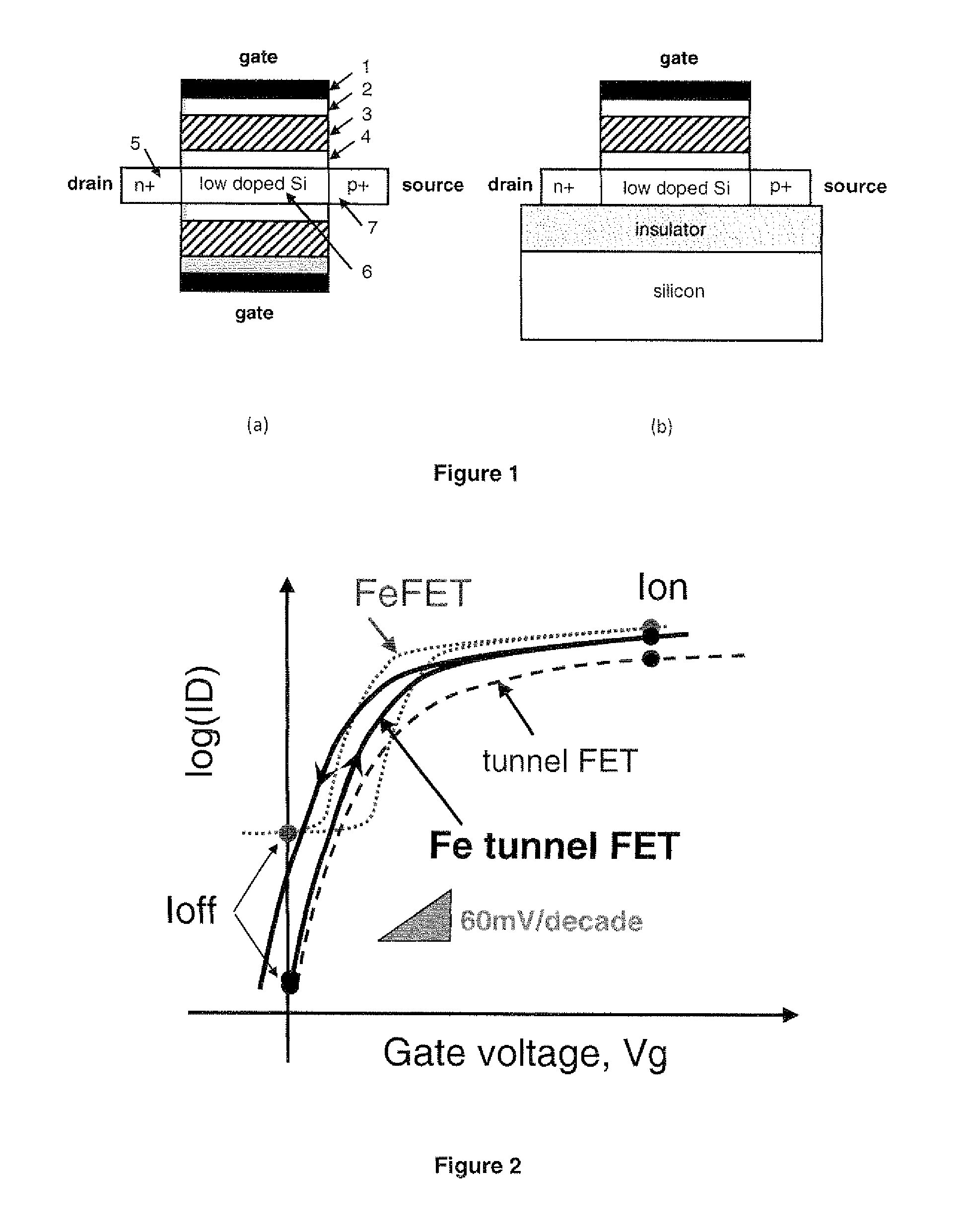

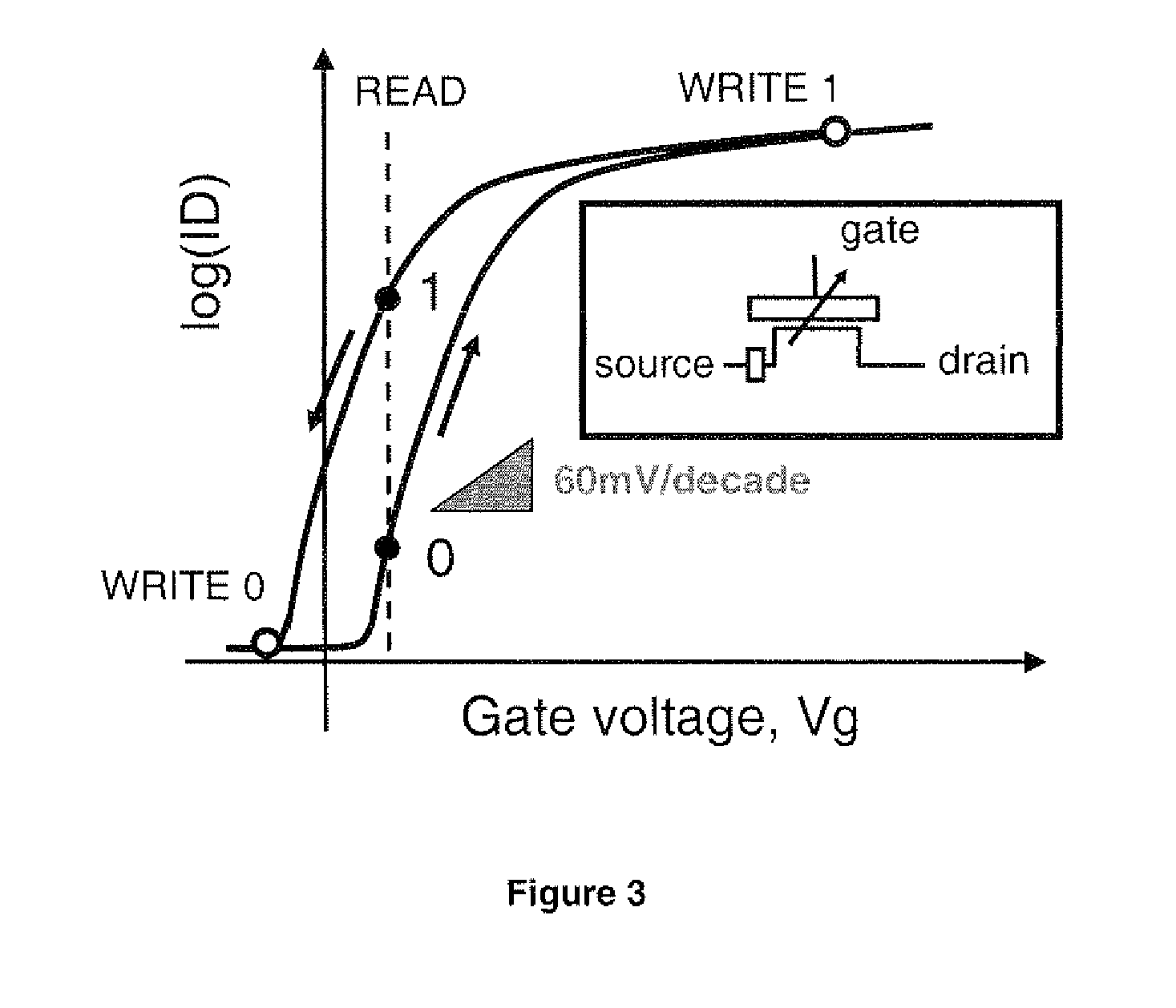

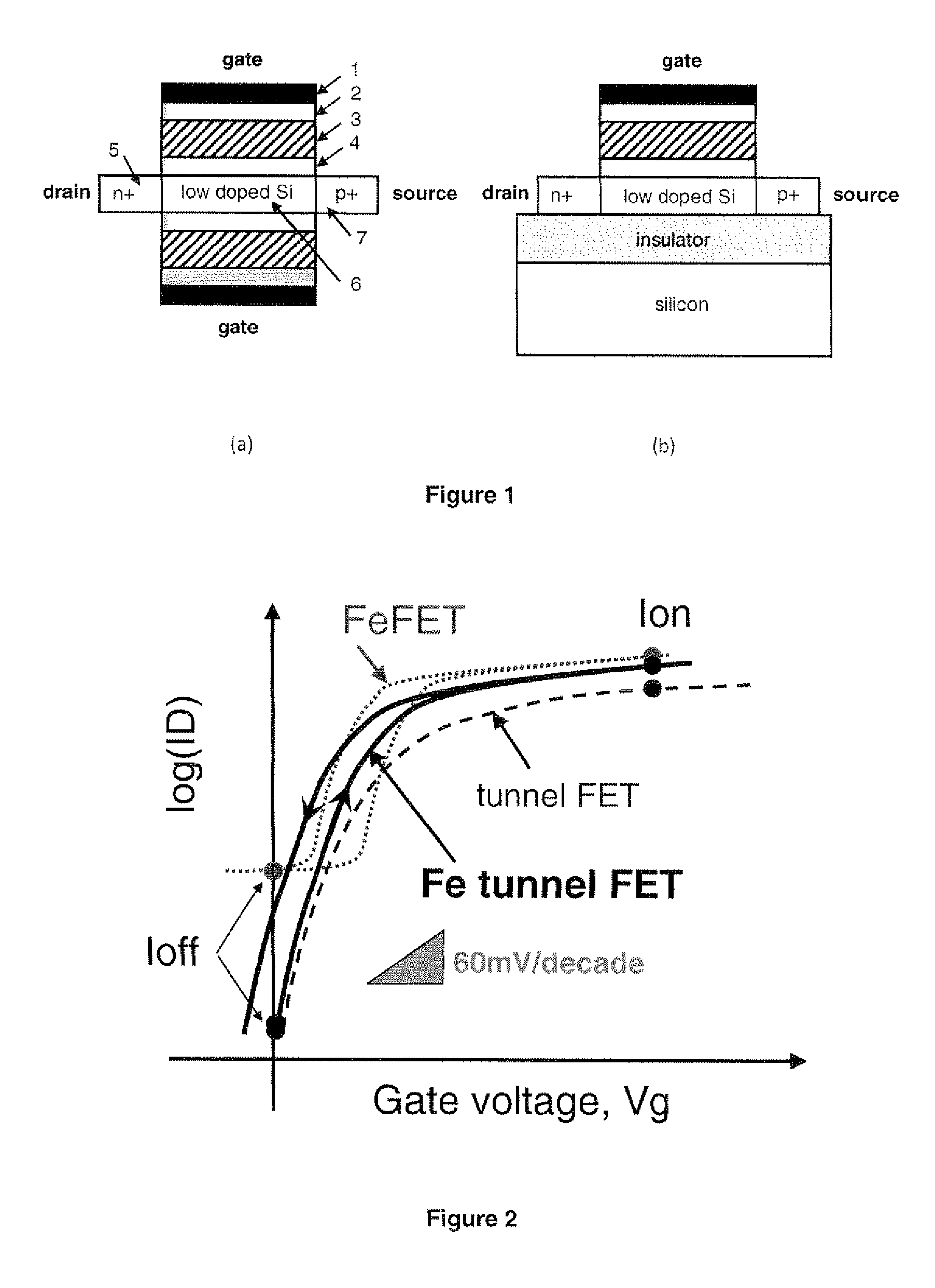

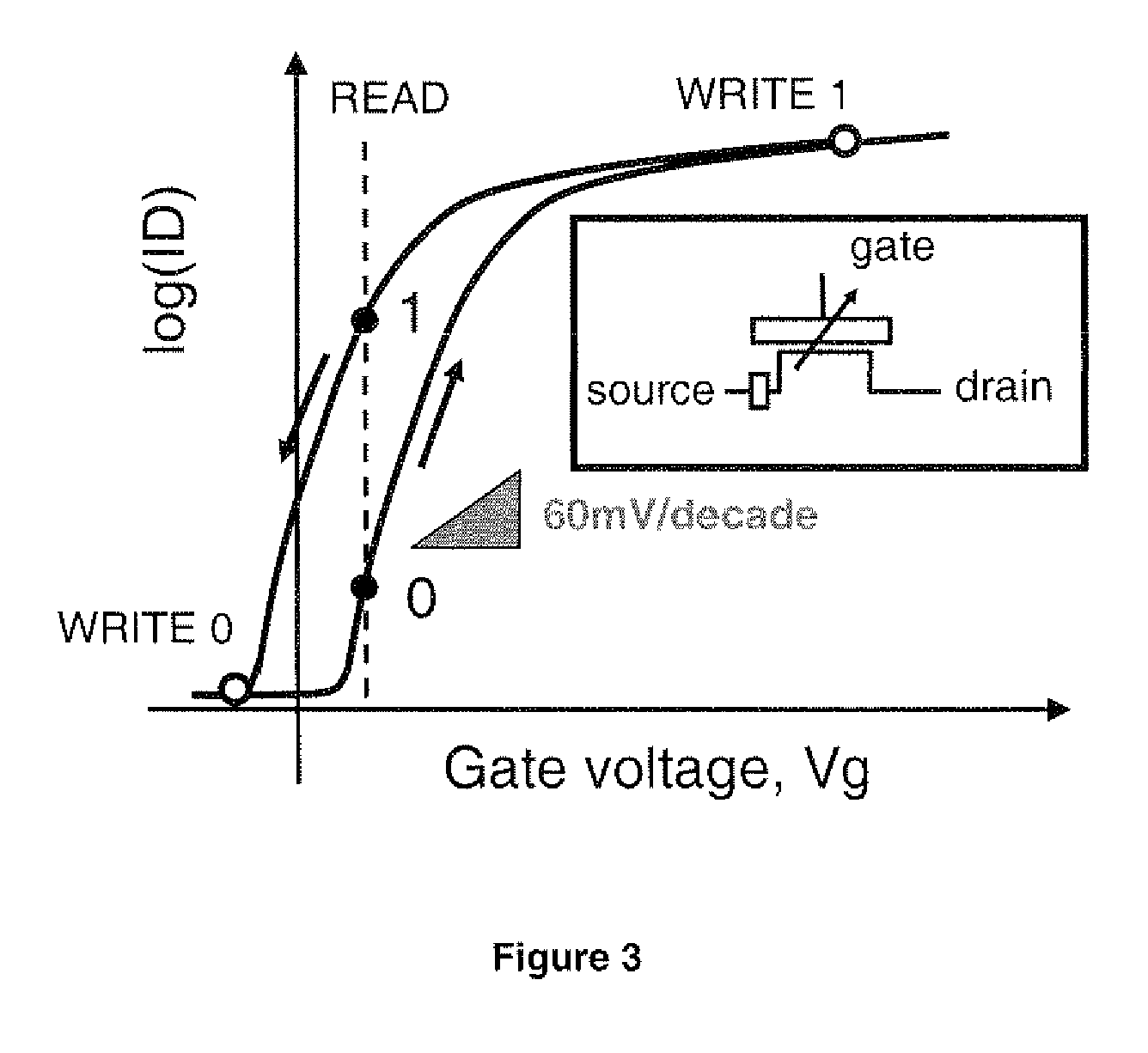

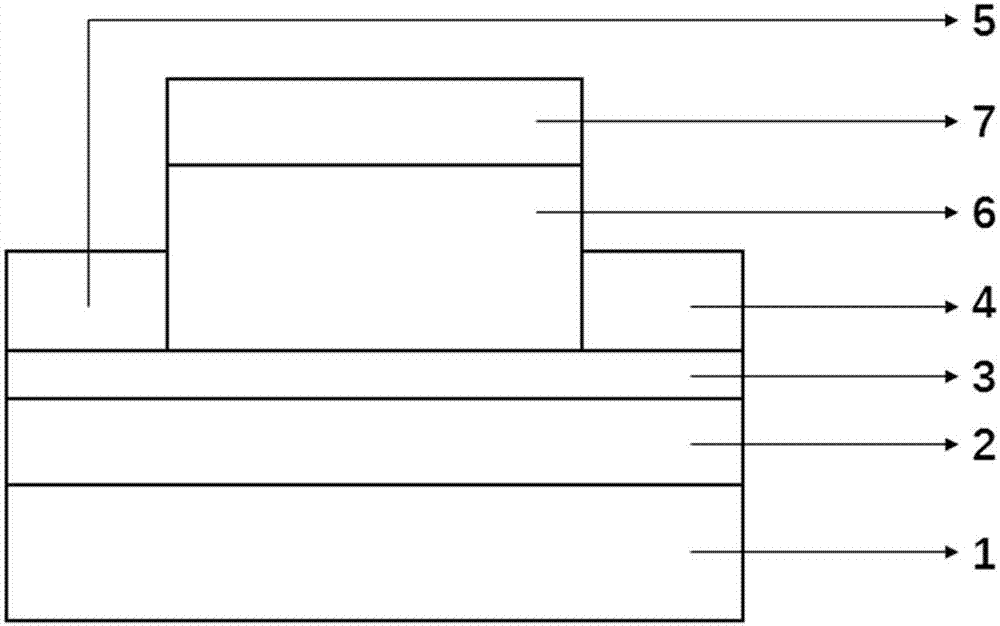

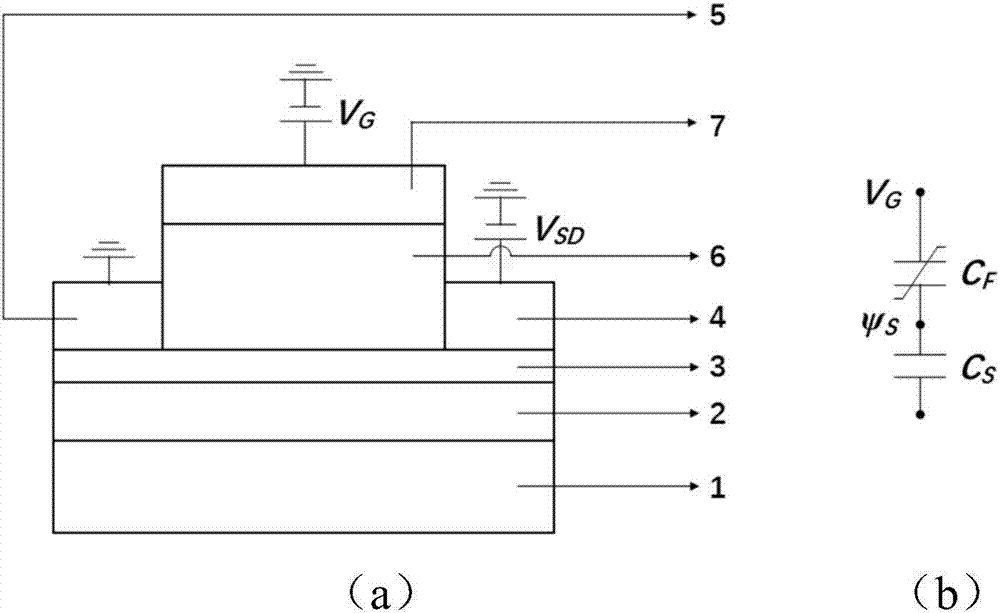

A Ferroelectric tunnel FET switch as ultra-steep (abrupt) switch with subthreshold swing better than the MOSFET limit of 60 mV / decade at room temperature combining two key principles: ferroelectric gate stack and band-to-band tunneling in gated p-i-n junction, wherein the ferroelectric material included in the gate stack creates, due to dipole polarization with increasing gate voltage, a positive feedback in the capacitive coupling that controls the band-to-band (BTB) tunneling at the source junction of a silicon p-i-n reversed bias structure, wherein the combined effect of BTB tunneling and ferroelectric negative capacitance offers more abrupt off-on and on-off transitions in the present proposed Ferroelectric tunnel FET than for any reported tunnel FET or any reported ferroelectric FET.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

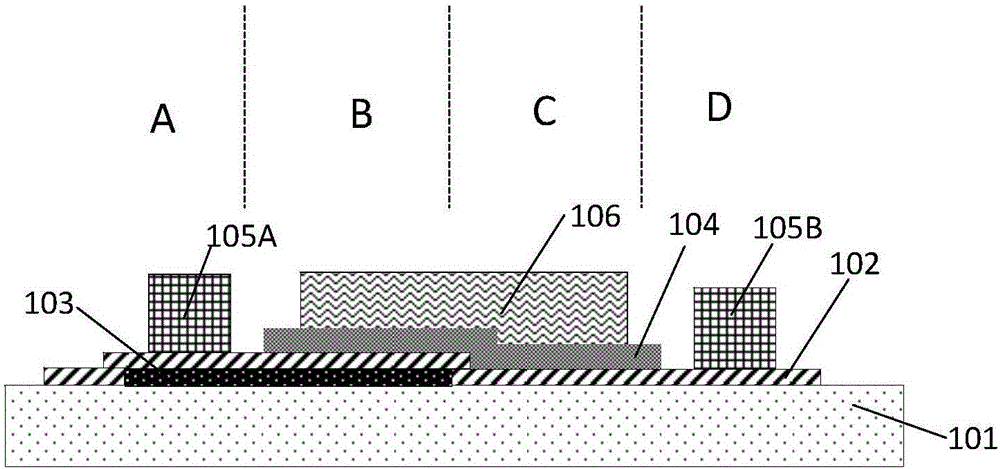

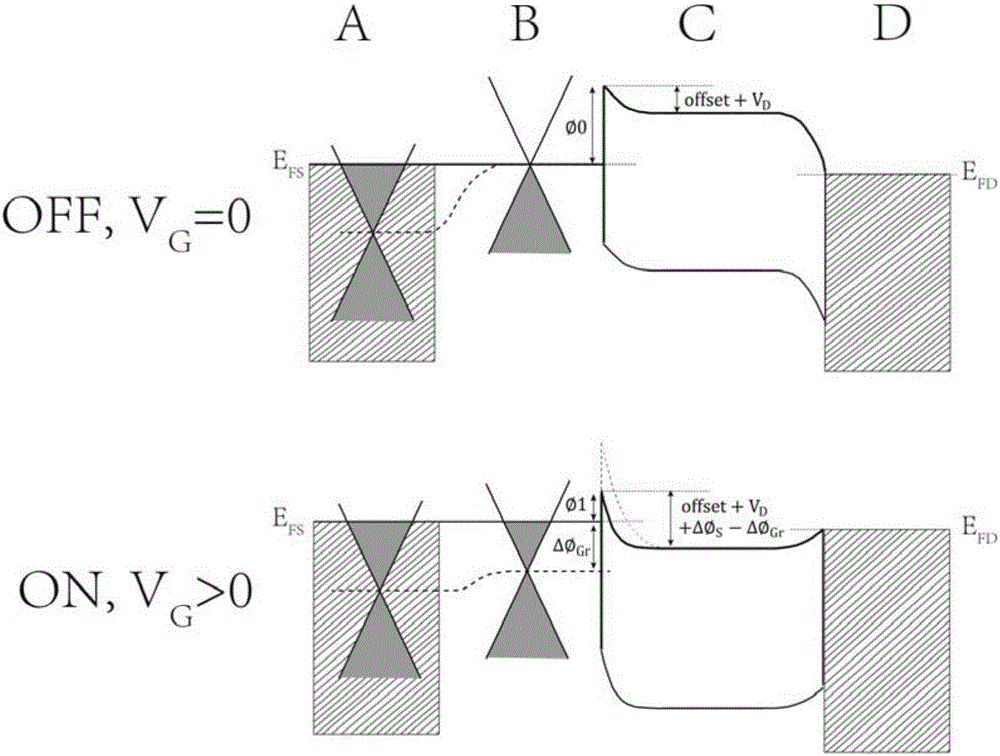

Heterojunction carbon nano-tube field effect transistor and preparation method thereof

ActiveCN106356405AGuaranteed driving abilityGuaranteed speedSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionCarbon nano tube field effect transistor

The invention provides a heterojunction carbon nano-tube field effect transistor of which a subthreshold swing is smaller than 60 millivolt / magnitude in the room temperature and a preparation method thereof. The device uses the semiconductor carbon nano-tube as the active layer, the heterojunction formed by the graphene layer and the semiconductor carbon nano-tube is used as the source end of the device, the gate medium and the gate electrode modulate the carbon nano-tube channel and the graphene / carbon nano-tube junction at the same time, so that the turn-off of the transistor is accelerated by using the character that the graphene / carbon nano-tube junction barrier is modulated by the gate voltage. The transistor can control the polarity through the selection of the source-drain metal, namely the metal of high power function is used as the source-drain electrode for realizing the p-type field effect transistor, and the metal of low power function is used as the source-drain electrode for realizing the n-type field effect transistor.

Owner:BEIJING HUA TAN YUAN XIN ELECTRONICS TECH CO LTD

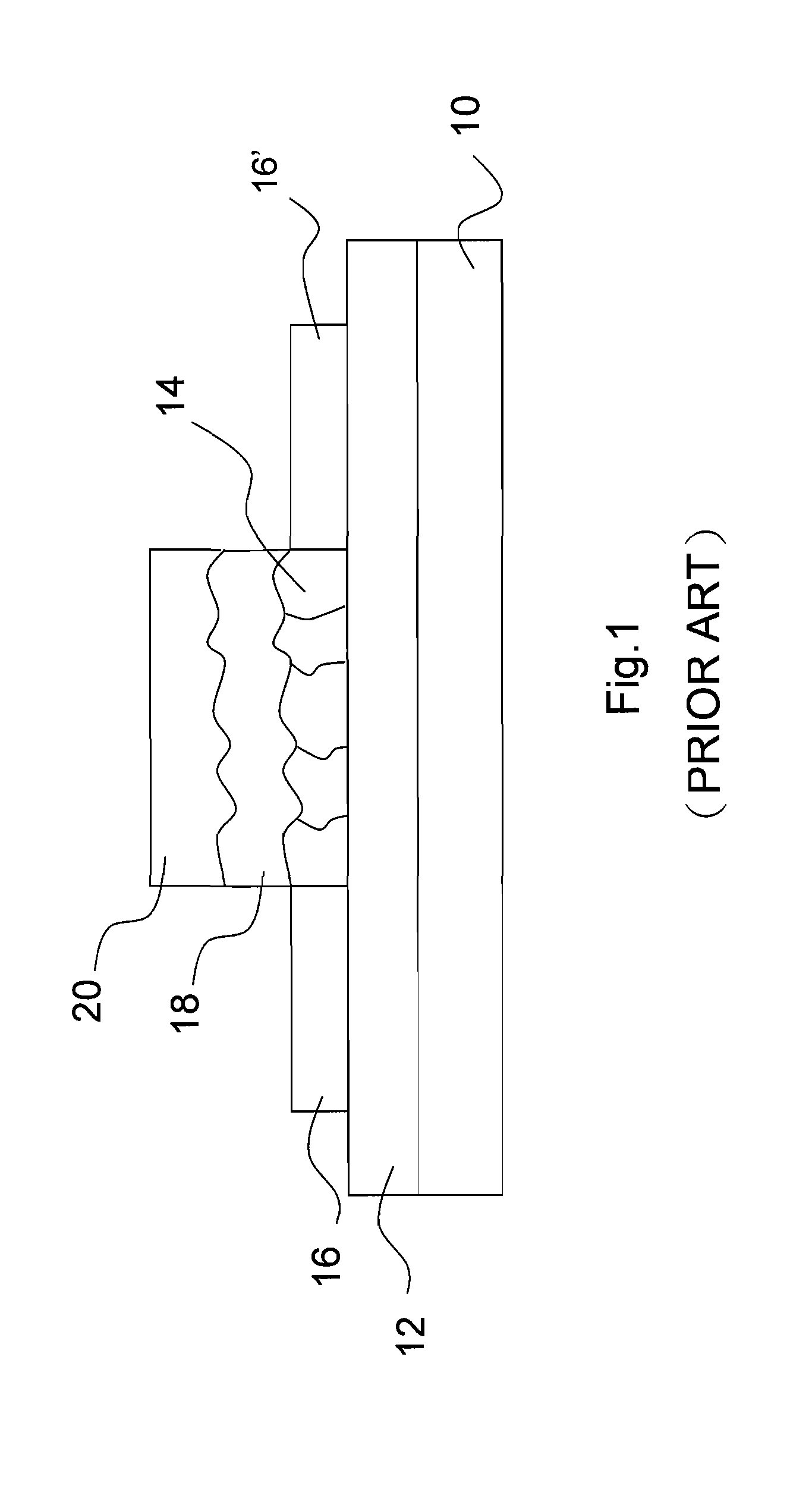

TFT backboard manufacturing method and structure suitable for AMOLED

InactiveCN104659285AThe production process is simpleIncreased subthreshold swingSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerSubthreshold swing

The invention provides a TFT backboard manufacturing method and structure suitable for AMOLED. The method comprises the following steps: 1, providing a baseboard (10) and depositing a buffer layer (20); 2, forming a source layer (30) and a gate insulation layer (40) on the buffer layer (20) in sequence; 3, carrying out patterning processing on the gate insulation layer (40) to form a recession part (401); 4, forming a gate (50) for switching a thin film transistor and a gate (60) for driving the thin film transistor, wherein the gate (50) for switching the thin film transistor is positioned at the recession part (401); 5, depositing an interlayer insulation layer (70). According to the method, a single-layer gate insulation layer with height different is manufactured, so that the manufacturing process of the TFT backboards is simplified, the subthreshold swing of the gate (60) for driving the thin film transistor and the grey scale switching and control properties of the AMOLED panes are improved.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD +1

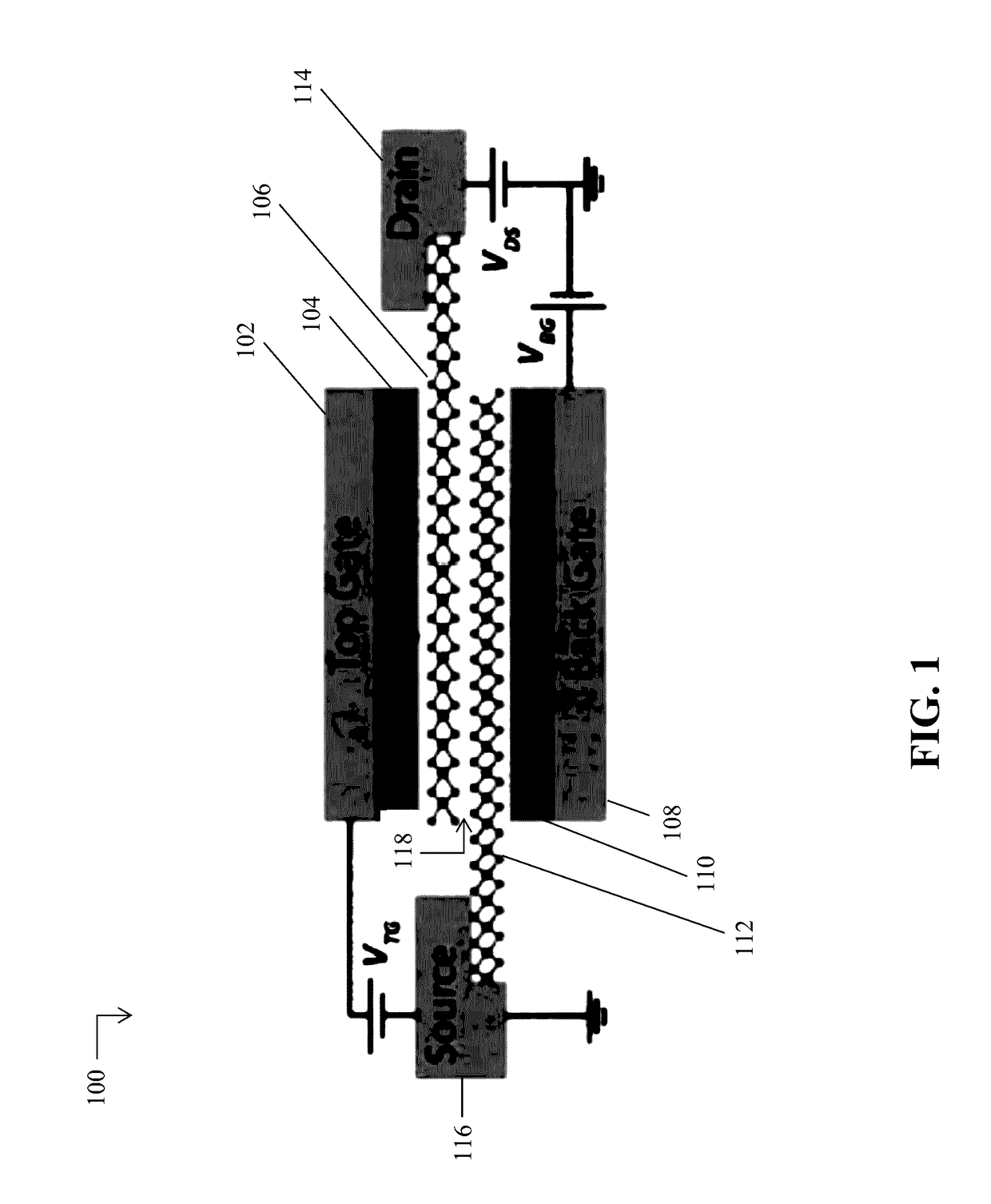

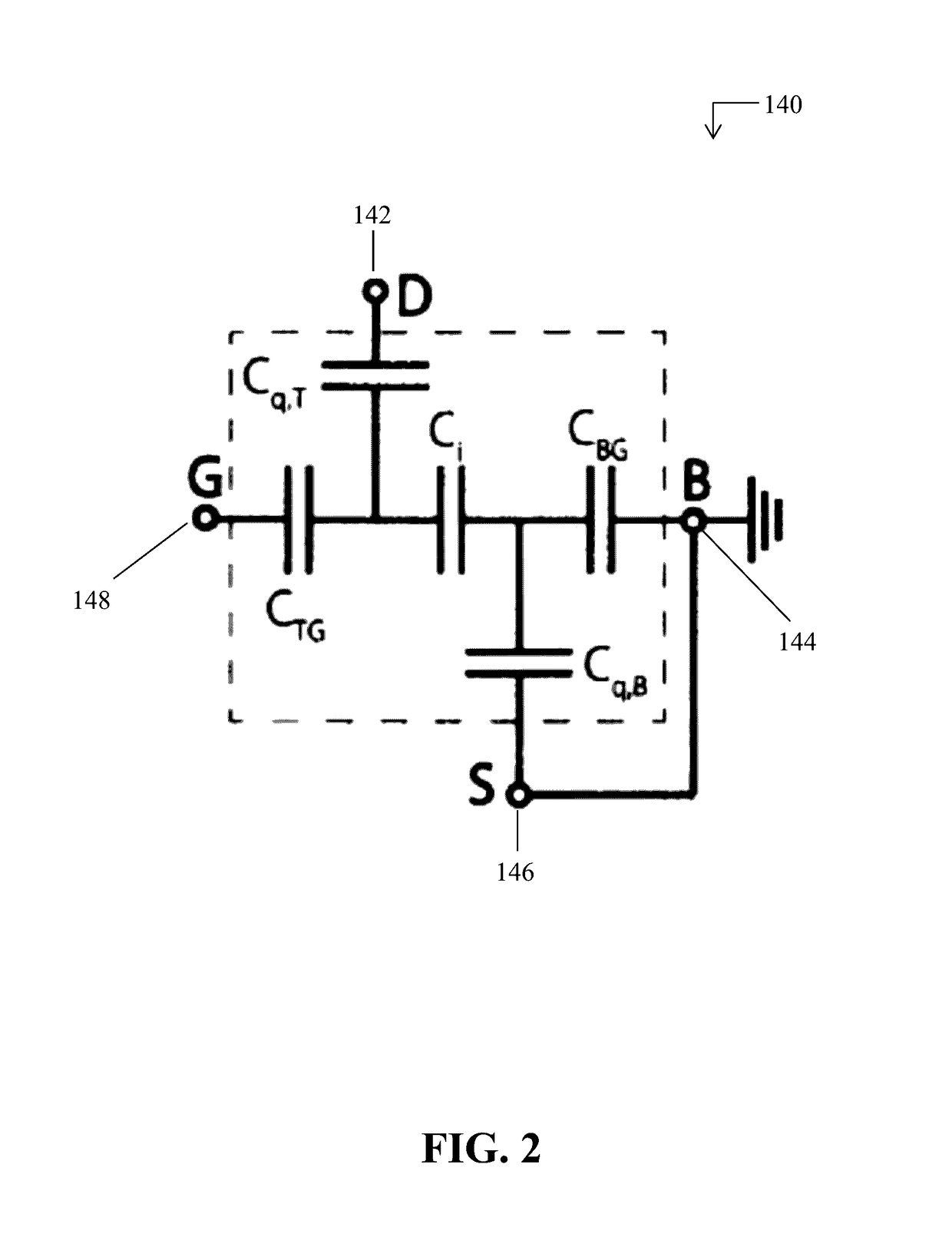

Two-dimensional heterojunction interlayer tunneling field effect transistors

A two-dimensional (2D) heterojunction interlayer tunneling field effect transistor (Thin-TFET) allows for particle tunneling in a vertical stack comprising monolayers of two-dimensional semiconductors separated by an interlayer. In some examples, the two 2D materials may be misaligned so as to influence the magnitude of the tunneling current, but have a modest impact on gate voltage dependence. The Thin-TFET can achieve very steep subthreshold swing, whose lower limit is ultimately set by the band tails in the energy gaps of the 2D materials produced by energy broadening. These qualities in turn make the Thin-TFET an ideal low voltage, low energy solid state electronic switch.

Owner:UNIV OF NOTRE DAME DU LAC

Ferroelectric tunnel FET switch and memory

ActiveUS8362604B2Reduce additionalMaterial nanotechnologySemiconductor/solid-state device detailsCapacitanceSubthreshold swing

A Ferroelectric tunnel FET switch as ultra-steep (abrupt) switch with subthreshold swing better than the MOSFET limit of 60 mV / decade at room temperature combining two key principles: ferroelectric gate stack and band-to-band tunneling in gated p-i-n junction, wherein the ferroelectric material included in the gate stack creates, due to dipole polarization with increasing gate voltage, a positive feedback in the capacitive coupling that controls the band-to-band (BTB) tunneling at the source junction of a silicon p-i-n reversed bias structure, wherein the combined effect of BTB tunneling and ferroelectric negative capacitance offers more abrupt off-on and on-off transitions in the present proposed Ferroelectric tunnel FET than for any reported tunnel FET or any reported ferroelectric FET.

Owner:ECOLE POLYTECHNIQUE FEDERALE DE LAUSANNE (EPFL)

Two-dimensional semiconductor negative capacitance field-effect transistor and preparation method thereof

PendingCN107195681ASimple structureEasy to manufactureSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceCapacitive effect

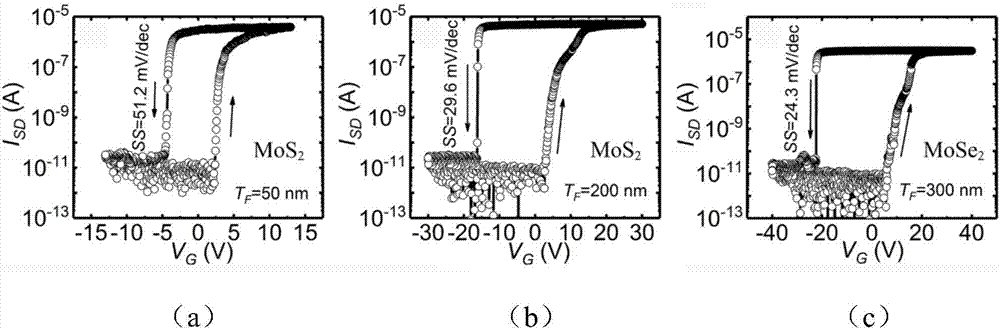

The invention discloses a two-dimensional semiconductor negative capacitance field-effect transistor and a preparation method thereof. The device structure sequentially comprises a substrate, a two-dimensional semiconductor, a metal source-drain electrode, a ferroelectric gate medium with a negative capacitance effect and a metal gate electrode from bottom to top. The preparation method comprises the steps of firstly, preparing the transition metal chalcogenide two-dimensional conductor on a substrate; secondly, preparing the metal source-drain electrode by employing an electron beam lithography technology and combining a stripping process; thirdly, preparing a ferroelectric thin film with the negative capacitance effect on the structure; and finally, preparing the metal gate electrode on the thin film to form ferroelectric-controlled two-dimensional semiconductor negative capacitance field-effect transistor. Different from other two-dimensional semiconductor negative capacitance field-effect device structures, the metal-ferroelectric-semiconductor structure has the advantages that a high-performance negative capacitance field-effect device can be achieved; and an electrical test result shows that the subthreshold swing of the device is far smaller than 60mV / dec, the Boltzmann limit is broken through, and the two-dimensional semiconductor negative capacitance field-effect device simultaneously has the characteristics of extremely low power consumption, high-speed turnover and the like.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

Method for fabricating bottom-gate low-temperature polysilicon thin film transistor

InactiveUS20080171409A1Improve mobilitySmooth interfaceSolid-state devicesSemiconductor/solid-state device manufacturingBottom gateCharge carrier mobility

The present invention discloses a method for fabricating a bottom-gate low-temperature polysilicon thin film transistor, wherein the bottom gate structure is used to form an amorphous silicon layer with varied thicknesses; the amorphous silicon layer in the step region on the border of the bottom gate structure is partially melted by an appropriate amount of laser energy; the partially-melted amorphous silicon layer in the step region functions as crystal seeds and makes crystal grains grow toward the channel region where the amorphous silicon layer is fully melted, and the crystal grains are thus controlled to grow along the lateral direction to form a lateral-grain growth low-temperature polysilicon thin film. The lateral grain growth can reduce the number of the grain boundaries carriers have to pass through. Thus, the present invention can promote the carrier mobility in the active region and the electric performance. Further, the present invention can achieve a superior element motive force and a steeper subthreshold swing.

Owner:CHENG HUANG CHUNG +2

Indium-doped N-type organic thin-film transistor and preparation method thereof

ActiveCN110265548AHigh switching ratioHigh carrier mobilitySolid-state devicesSemiconductor/solid-state device manufacturingIndiumSubthreshold swing

The invention discloses an indium-doped N-type organic thin-film transistor and a preparation method thereof. The N-type organic thin-film transistor has a top gate bottom contact structure. The preparation method comprises the following steps: firstly, preparing a layer of gold on a glass substrate through a mask plate to serve as a source electrode and a drain electrode; secondly preparing a layer of indium on a gold electrode to serve as a doped layer; thirdly forming an N-type organic semiconductor active layer on the surface of a sample subjected to electrode preparation by using a sol-gel method; fourthly spin-coating an active layer with a layer of dielectric material to serve as an insulating layer; and finally, preparing aluminum on the surface of the insulating layer through the mask plate to form a gate electrode. Compared with a traditional organic thin-film transistor, the organic thin-film transistor prepared by the method has the advantages that the switching ratio and the carrier mobility are obviously improved, and the subthreshold swing amplitude and the threshold voltage of a device are greatly reduced. The method improves the electrical property of the N-type organic thin-film transistor with the top gate bottom contact structure, and has the characteristics of low cost, simple process steps and wide applicability to the N-type organic thin-film transistor.

Owner:EAST CHINA NORMAL UNIV

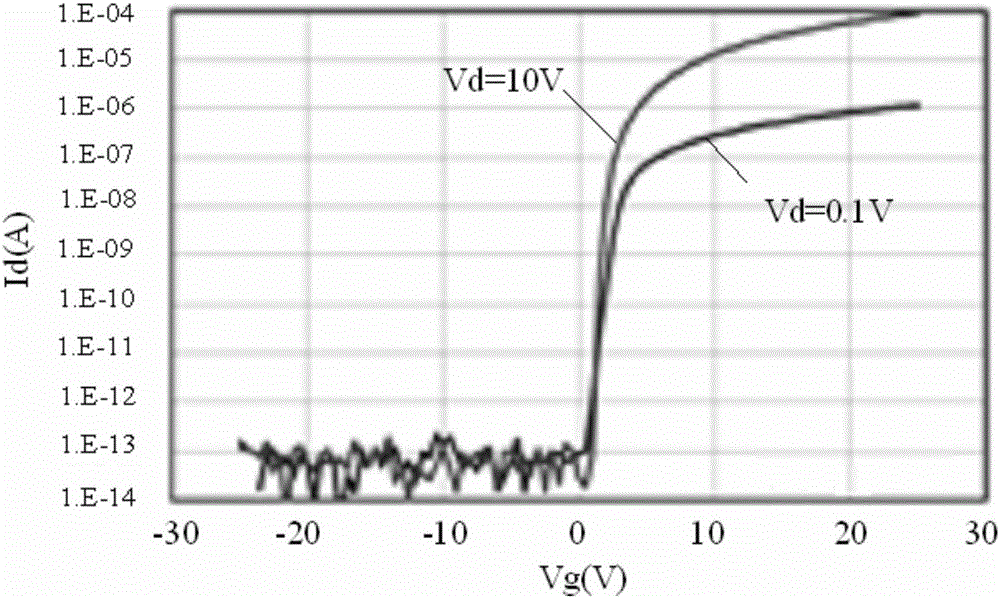

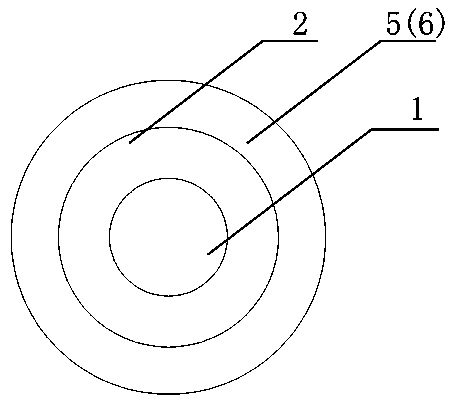

Ultra steep average subthreshold swing nano wire tunneling field effect transistor and method for preparing same

ActiveCN104835840ASteep Minimum Subthreshold SwingIncrease chance of tunnelingSemiconductor/solid-state device manufacturingDiodeCMOSSubthreshold swing

The present invention provides an ultra steep average subthreshold swing nano wire tunneling field effect transistor and a method for preparing the same which belong to the field effect transistor logic device field of the CMOS ultra large scale integration (ULSI). The tunneling field effect transistor adopts a nano wire structure of core-multilayered shell, and the material band gap of a multilayered shell part is increased continuously along the radius direction of the nano wire. According to the present invention, a subthreshold slope degradation phenomenon in a device transfer characteristic can be restrained effectively, at the same time, an average subthreshold slope of the tunneling field effect transistor is reduced remarkably, and a more steep minimum subthreshold slope is kept.

Owner:PEKING UNIV

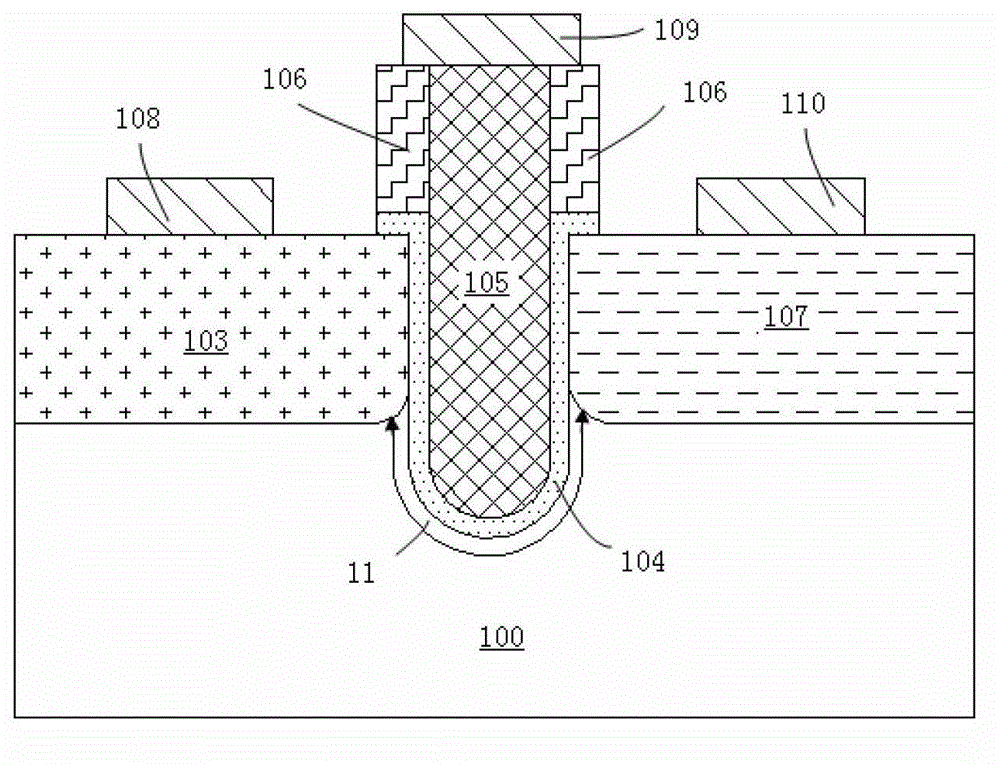

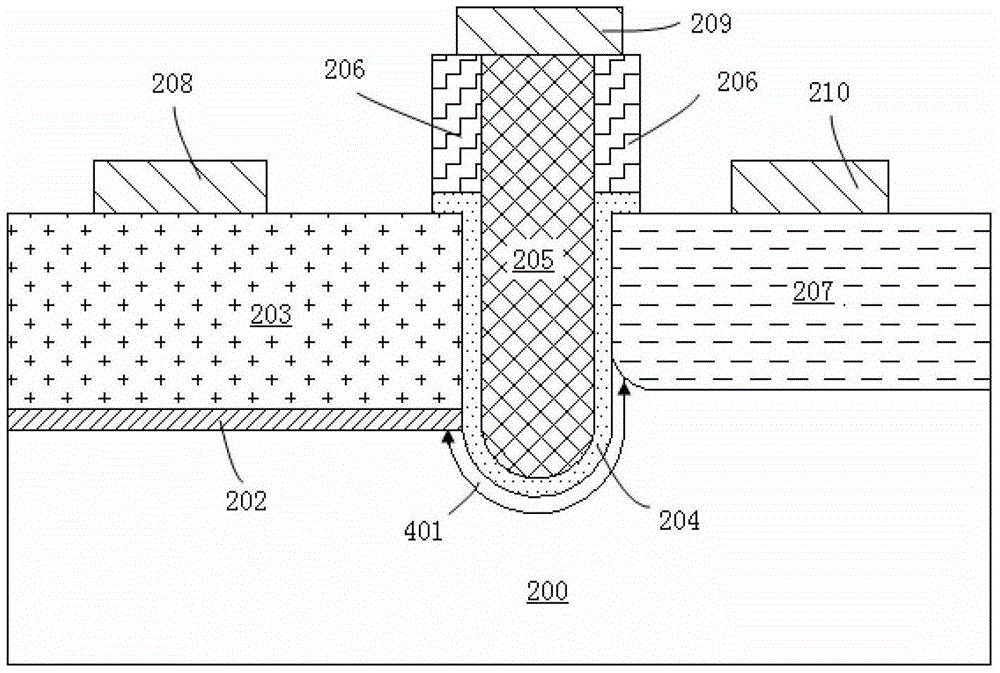

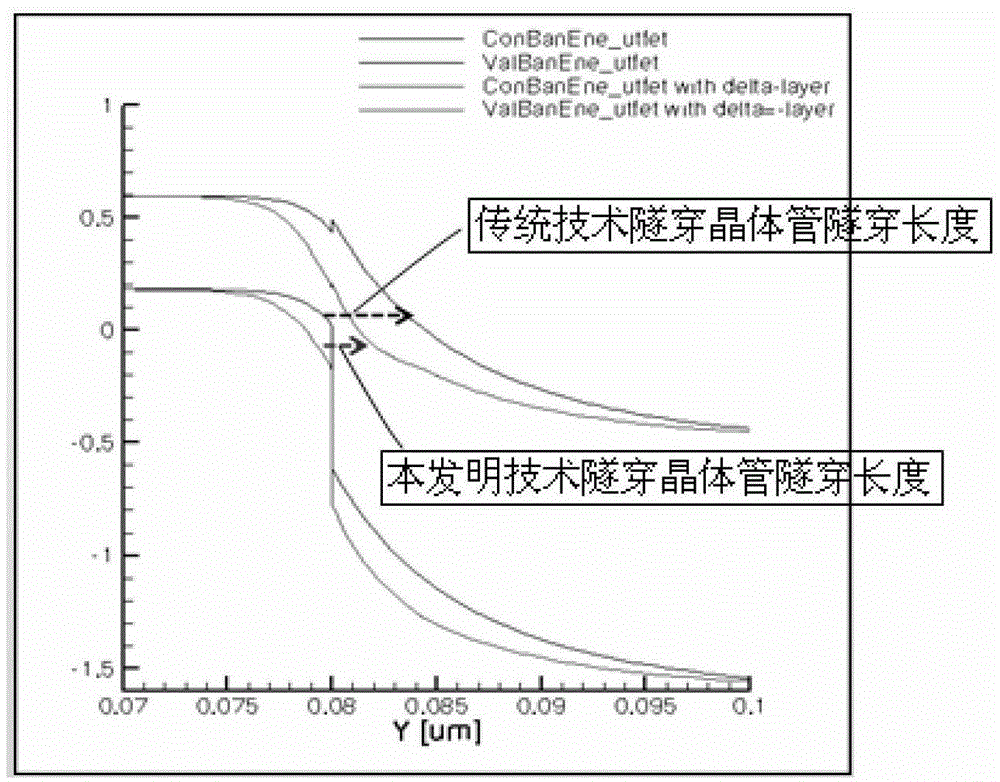

U-shaped channel tunneling transistor with laminated structure and preparation method thereof

InactiveCN103151383ANarrow band gapIncreased band bendingSemiconductor/solid-state device manufacturingSemiconductor devicesBand bendingPower flow

The invention belongs to the technical field of semiconductor devices, and particularly relates to a U-shaped channel tunneling transistor with a laminated structure and a preparation method thereof. According to the invention, a highly doped silicon layer of which the doping type is opposite to that of a SiGe source area is formed under the SiGe source area of the tunneling transistor by an epitaxial growth method; and the forbidden bandwidth of the SiGe is narrower than that of silicon, so that the band bending degree between the source area and a channel region can be improved, then the length of tunneling can be reduced and the tunneling efficiency is improved. The U-shaped channel tunneling transistor with the laminated structure which is provided by the invention can substantially improve firing current and reduces subthreshold swing under the circumstance that shutdown current is not influenced.

Owner:FUDAN UNIV

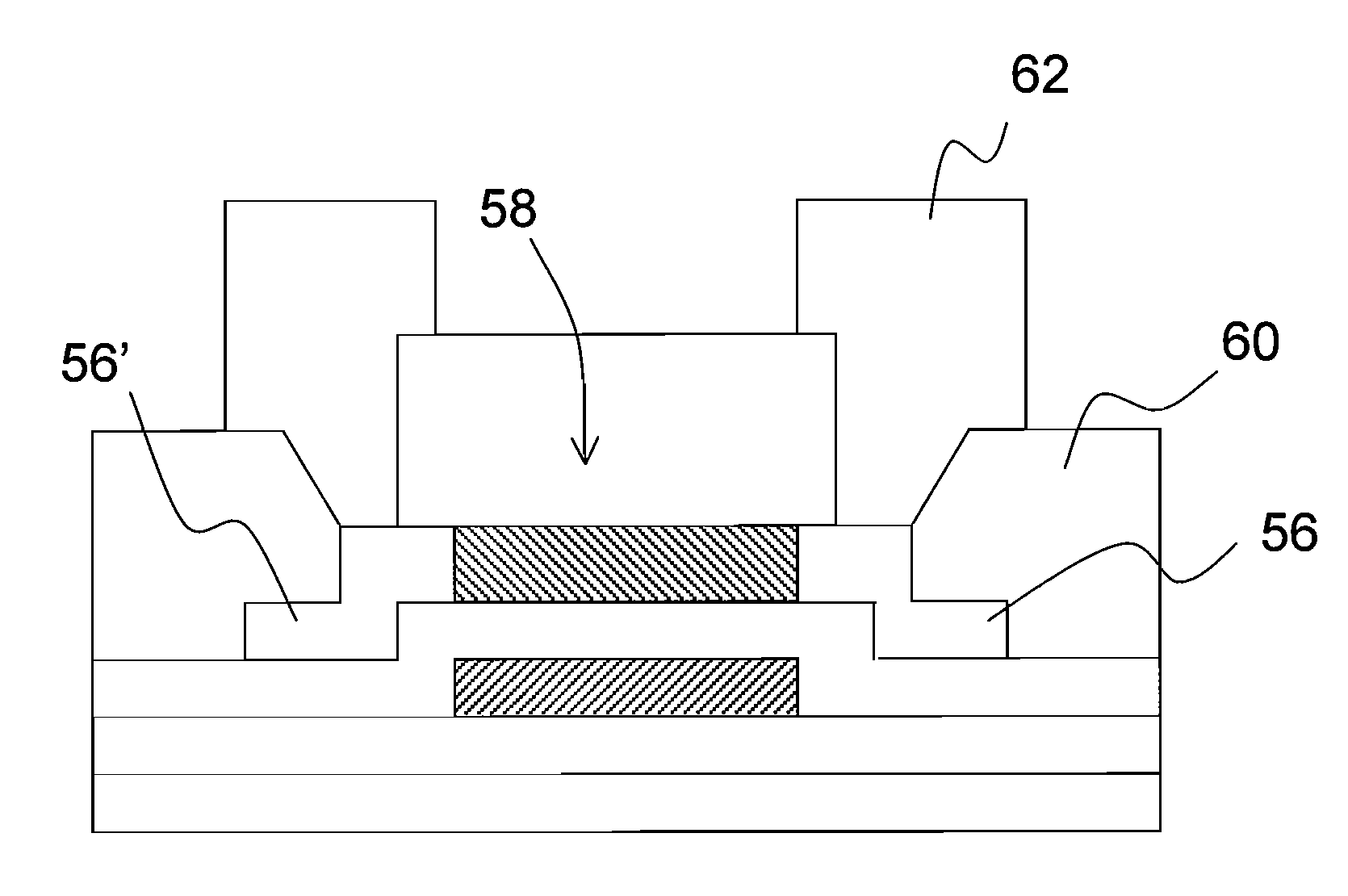

Method for manufacturing semiconductor device

InactiveUS20080311709A1Restore crystallinityIncrease in of region regionSolid-state devicesSemiconductor/solid-state device manufacturingResistElectrical conductor

A highly responsive semiconductor device in which the subthreshold swing (S value) is small and reduction in on-current is suppressed is manufactured. A semiconductor layer in which a thickness of a source region or a drain region is larger than that of a channel formation region is formed. A semiconductor layer having a concavo-convex shape which is included in the semiconductor device is formed by the steps of forming a first semiconductor layer over a substrate; forming a first insulating layer and a conductive layer over the first semiconductor layer; forming a second insulating layer over a side surface of the conductive layer; forming a second semiconductor layer over the first insulating layer, the conductive layer and the second insulating layer; etching the second semiconductor layer using a resist formed partially as a mask; and performing heat treatment to the first semiconductor layer and the second semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device

ActiveUS9705004B2Reduce leakage currentExcellent electrical propertiesTransistorSolid-state devicesElectrical conductorDevice material

Owner:SEMICON ENERGY LAB CO LTD

Low off-state current tunneling field effect transistor

InactiveCN105405875AReduce performanceImprove performanceSemiconductor devicesGate dielectricSubthreshold swing

The invention discloses a low off-state current tunneling field effect transistor, comprises a source region, a channel region, a drain region and a first gate dielectric layer, wherein the channel region is provided with the first gate dielectric layer, the first gate dielectric layer is provided with a first grid, the source region is arranged under the channel region and close to the lower part of the channel region, the source region is provided with a source electrode, the drain region is arranged at one side of the channel region, a drain electrode is arranged at the right end of the drain region, an adjusting region is arranged between the channel region and the drain region, a transition region is arranged between the channel region and the adjusting region, a second gate dielectric layer is arranged on the adjusting region and is provided with a second grid, the first grid and the second grid are connected together through a lead to function as the grid of the whole field effect transistor, and an isolation region is arranged on the transition region. Since the adjusting region is introduced between the channel region and the drain region, the equivalent resistance of the adjusting region functions so that the low off-state current tunneling field effect transistor can obtain lower subthreshold swing and quiescent dissipation, thus improving the performance of the low off-state current tunneling field effect transistor.

Owner:XIANGTAN UNIV

Method for manufacturing semiconductor device

InactiveUS20160079430A1Low densityExcellent electrical propertiesTransistorSolid-state devicesSubthreshold swingLow leakage

Provided is a transistor containing a semiconductor with low density of defect states, a transistor having a small subthreshold swing value, a transistor having a small short-channel effect, a transistor having normally-off electrical characteristics, a transistor having a low leakage current in an off state, a transistor having excellent electrical characteristics, a transistor having high reliability, or a transistor having excellent frequency characteristics. An insulator is formed, a layer is formed over the insulator, oxygen is added to the insulator through the layer, the layer is removed, an oxide semiconductor is formed over the insulator to which the oxygen is added, and a semiconductor element is formed using the oxide semiconductor.

Owner:SEMICON ENERGY LAB CO LTD

Semiconductor device and manufacturing method thereof

InactiveUS20080220570A1Decrease in on-state current is suppressedEasy to manufactureLight-sensitive devicesSolid-state devicesSubthreshold swingSemiconductor package

A semiconductor device having a highly responsive thin film transistor (TFT) with low subthreshold swing and suppressed decrease in the on-state current and a manufacturing method thereof are demonstrated. The THF of the present invention is characterized by its semiconductor layer where the thickness of the source region or the drain region is larger than that of the channel formation region. Manufacture of the TFT is readily achieved by the formation of an amorphous semiconductor layer on a projection portion and a depression portion, which is followed by subjecting the melting process of the semiconductor layer, resulting in the formation of a crystalline semiconductor layer having different thicknesses. Selective addition of impurity to the thick portion of the semiconductor layer provides a semiconductor layer in which the channel formation region is thinner than the source or drain region.

Owner:SEMICON ENERGY LAB CO LTD

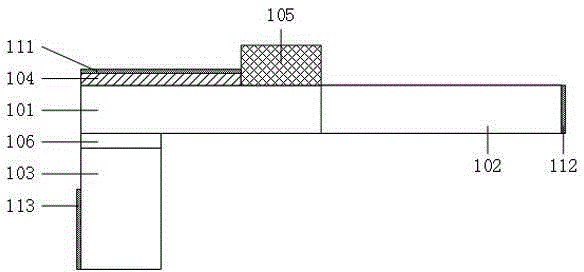

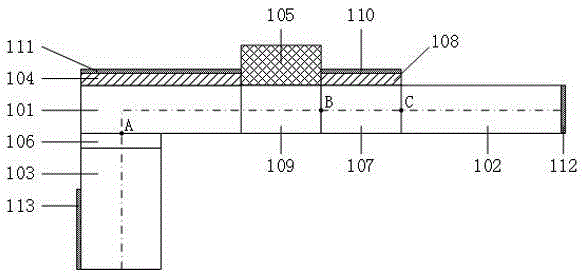

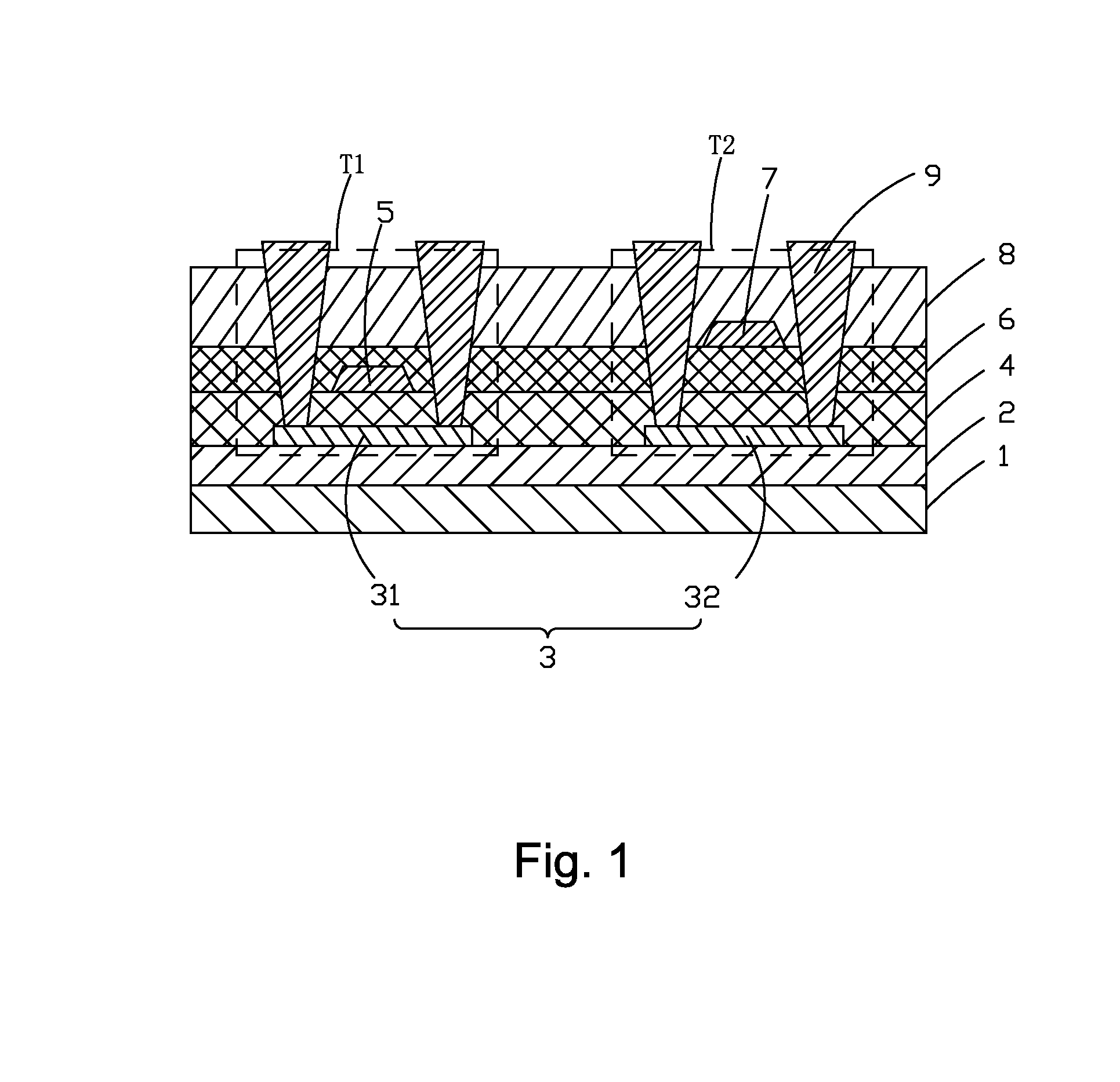

Manufacture method and structure of TFT backplate applicable to amoled

InactiveUS20160307929A1Simple manufacturing processReduce in quantityTransistorSolid-state devicesInsulation layerSubthreshold swing

The present invention provides a manufacture method and a structure of a TFT backplate applicable to an AMOLED. The method comprises: step 1, providing a substrate (10) and deposing a buffer layer (20); step 2, sequentially forming an active layer (30) and a gate isolation layer (40) on the buffer layer (20); step 3, patterning the gate isolation layer (40) to form a concave part (401); step 4, forming a gate (50) of the switch thin film transistor and a gate (60) of the drive thin film transistor on the gate isolation layer, and the gate (50) of the switch thin film transistor is in the concave part (401); step 5, deposing an interlayer insulation layer (70). The method simplifies the manufacture process of the TFT backplate and increases the subthreshold swing of the drive thin film transistor by manufacturing a single layer gate isolation layer with height difference to raise the gray scale switch and control performance of the AMOLED panel.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD +1

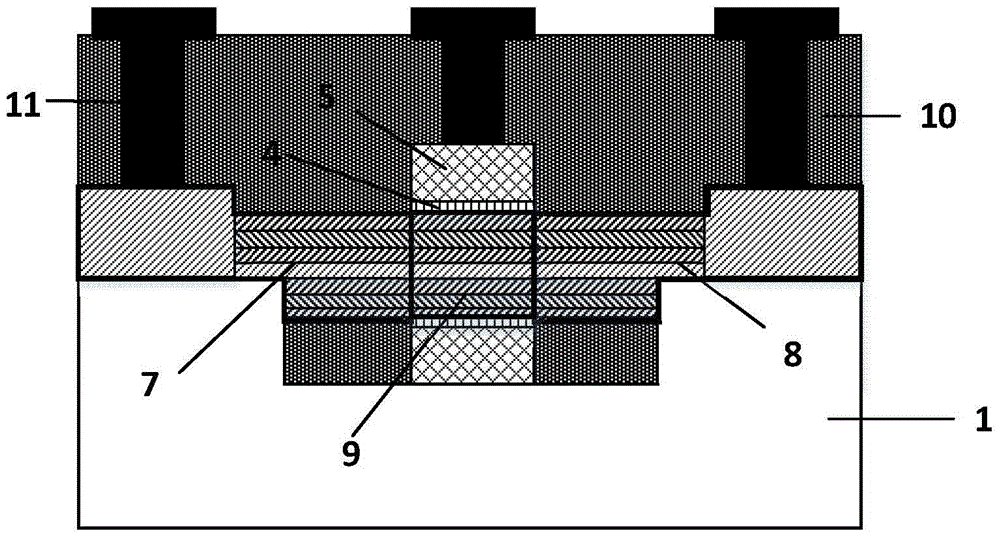

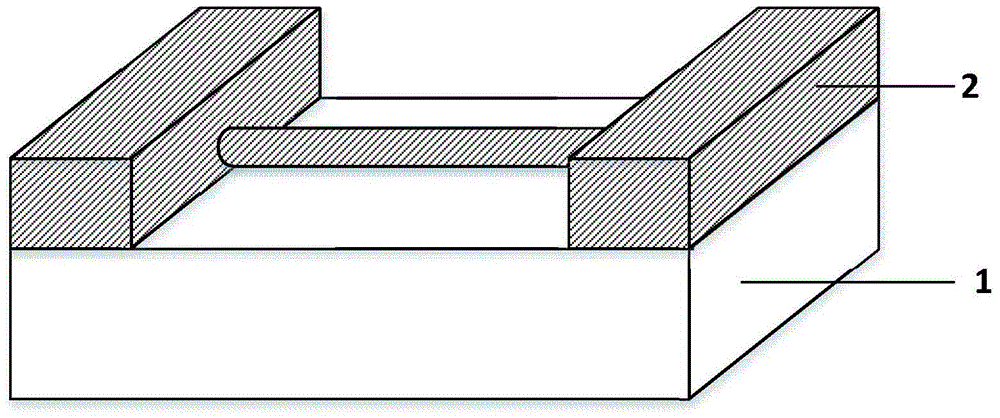

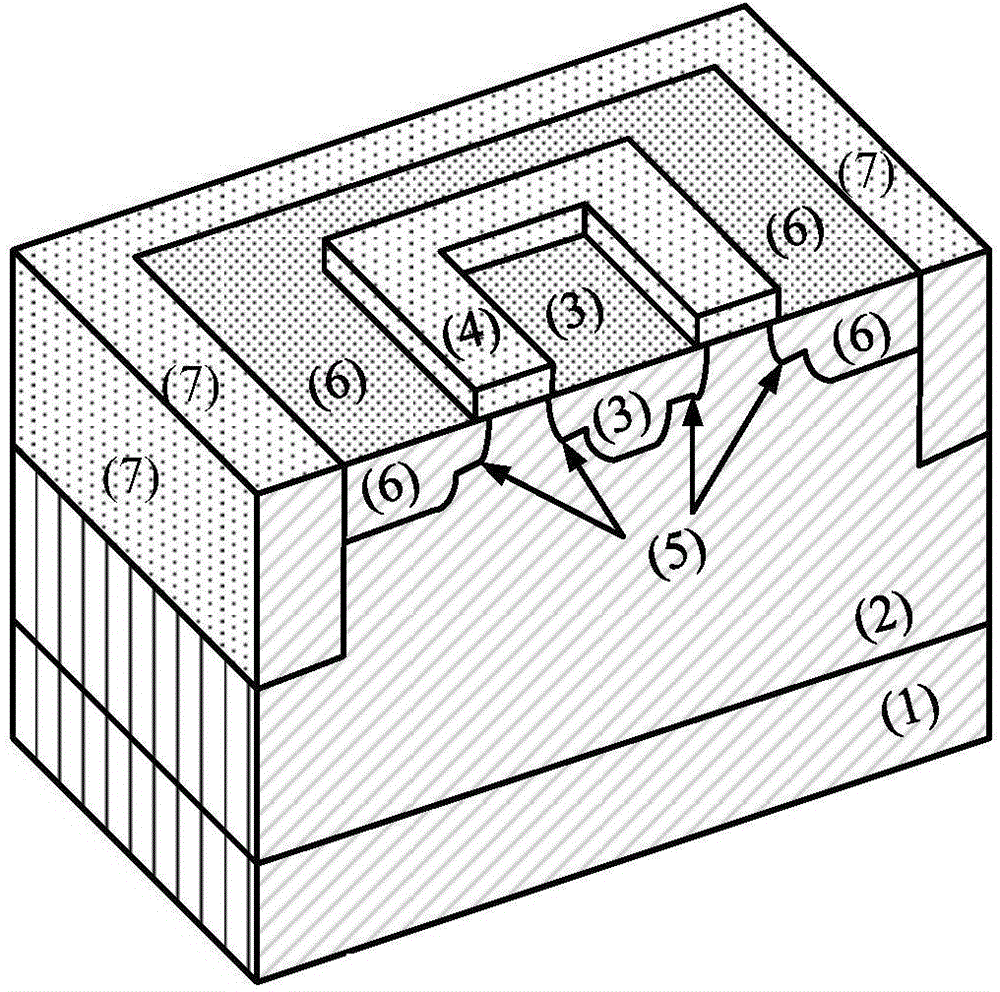

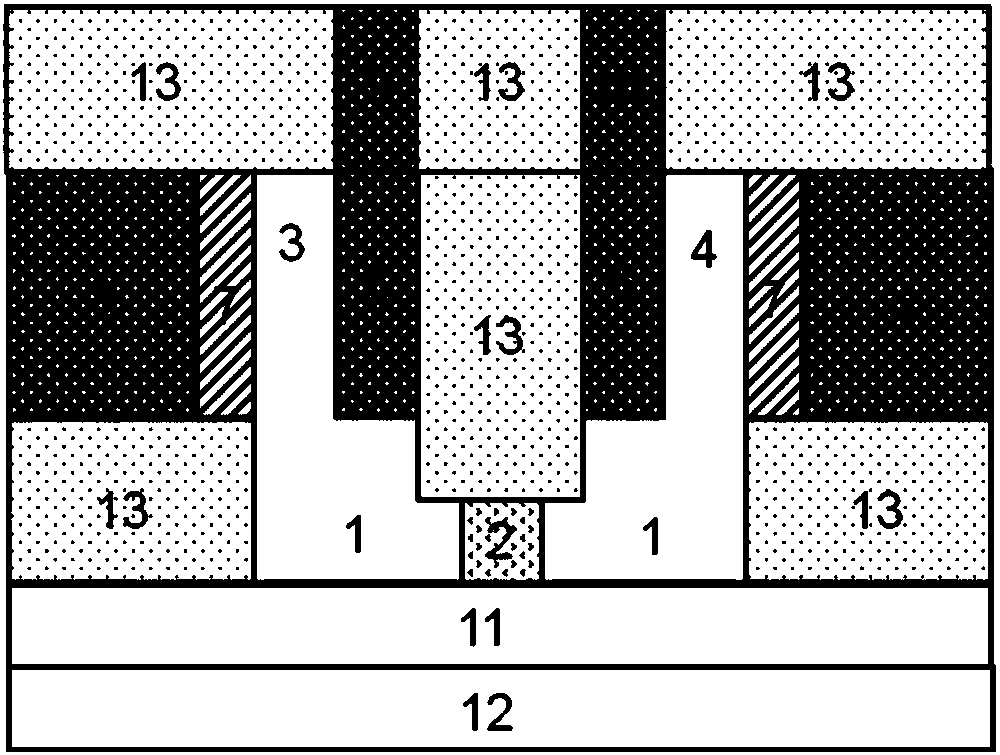

Gate-all-around anti-irradiation MOS field effect transistor based on 65 nm technology

InactiveCN104934475AReduce leakage currentHigh working reliabilityTransistorSemiconductor/solid-state device manufacturingGratingSubthreshold swing

The present invention discloses a gate-all-around anti-irradiation MOS field effect transistor based on a 65 nm technology for mainly solving the problems of threshold voltage drift, subthreshold swing degeneration and off-state leakage current degeneration of a conventional 65 nm MOS field effect transistor under a total dose radiation environment. The gate-all-around anti-irradiation MOS field effect transistor based on the 65 nm technology comprises a P-type substrate (1) and an epitaxial layer (2) located on the substrate, a drain region (3) is arranged in the middle of the epitaxial layer, and a grid (4) is arranged above the epitaxial layer adjacent to the periphery of the drain region (3). Light doping source drain regions (5) are arranged in the epitaxial layer below the boundaries at the inner and outer sides of the grid, an area between the light doping source drain regions forms a channel, and a source region (6) is arranged in the epitaxial layer adjacent to the periphery of the grid. An isolating groove (7) is arranged in the epitaxial layer adjacent to the periphery of source region, and a grating ring, a source ring and an isolating groove ring sleeve structure surrounding the exterior of an active region orderly are formed. The gate-all-around anti-irradiation MOS field effect transistor based on the 65 nm technology of the present invention enables the device anti-total dose radiation capability to be improved, and can be used to manufacture a large-scale integrated circuit.

Owner:XIDIAN UNIV

Organic light-emitting display device and manufacturing method thereof

ActiveCN106298857AOpen and close quicklyReduced subthreshold swingSolid-state devicesSemiconductor/solid-state device manufacturingSubthreshold swingDisplay device

The present invention discloses an organic light-emitting display device and a manufacturing method thereof. The organic light-emitting display device includes a switching thin film field effect transistor, a driving thin film field effect transistor, and a storage capacitor connected with the switching thin film field effect transistor and the driving thin film field effect transistor; the switching thin film field effect transistor is provided with a first active layer for reducing the subthreshold swing of the transfer characteristic curve of the switching film field effect transistor; and the driving thin film field effect transistor is provided with a second active layer for increasing the subthreshold swing of the transfer characteristic curve of the driving thin film field effect transistor. According to the organic light-emitting display device of the invention, fast switching on and switching off of the switching thin film field effect transistor and slow debugging of the grayscale of an OLED (Organic Light Emitting Diode) by the driving thin film field effect transistor can be simultaneously realized.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

Amorphous phase yttrium-doped indium zinc oxide thin film transistors and method for making same

InactiveUS20140014943A1Accurate doping ratioLow costTransistorSemiconductor/solid-state device manufacturingSubthreshold swingAmorphous phase

Sol-gel-processed thin-film transistors (TFTs) with amorphours Y—In—Zn—O (YIZO) as an active layer are fabricated with various mole ratios of Y, which indicates that Y3+ could play the role of carrier suppressor in InZnO (IZO) systems and reduce off current of YIZO-TFT and its channel mobility, threshold voltage, subthreshold swing voltage, and on / off ratio.

Owner:NATIONAL CHUNG CHENG UNIV

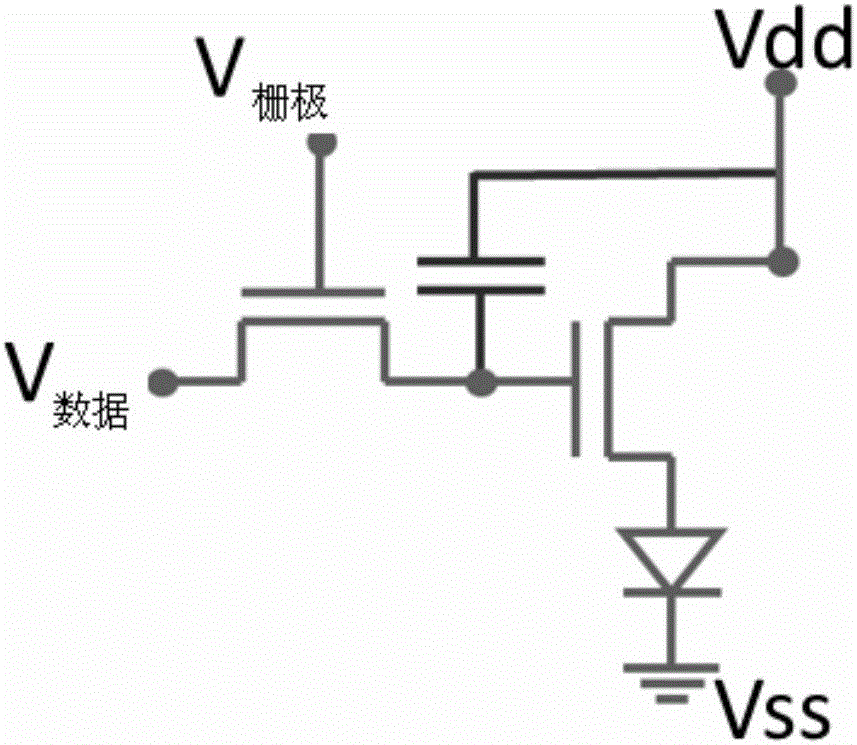

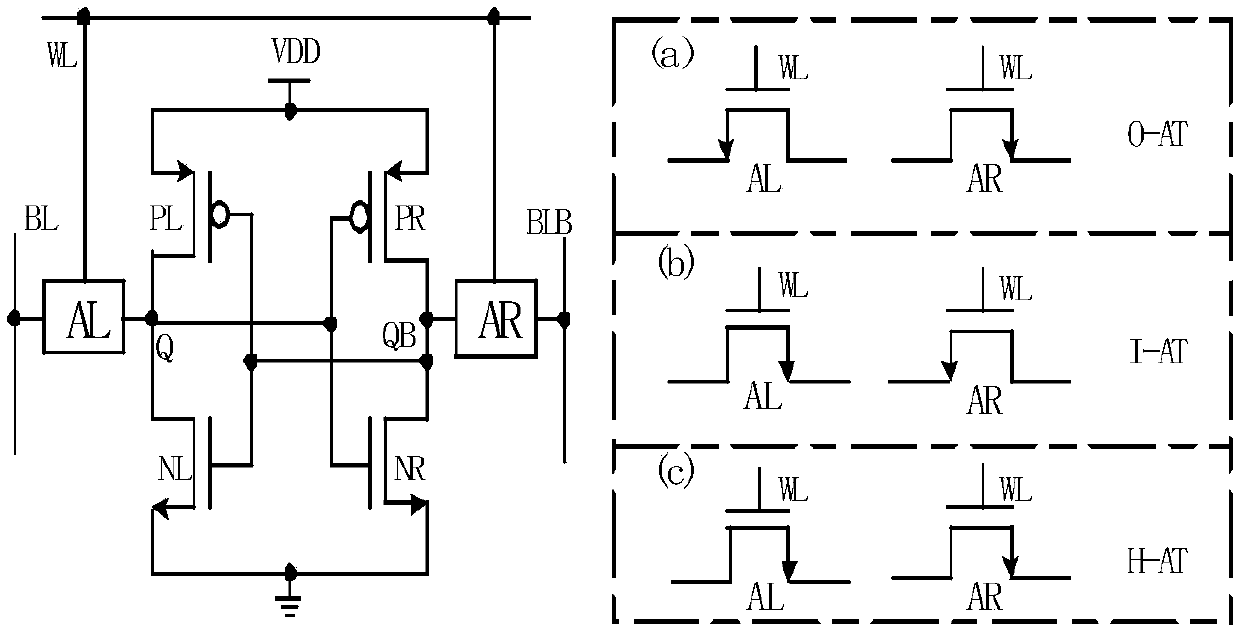

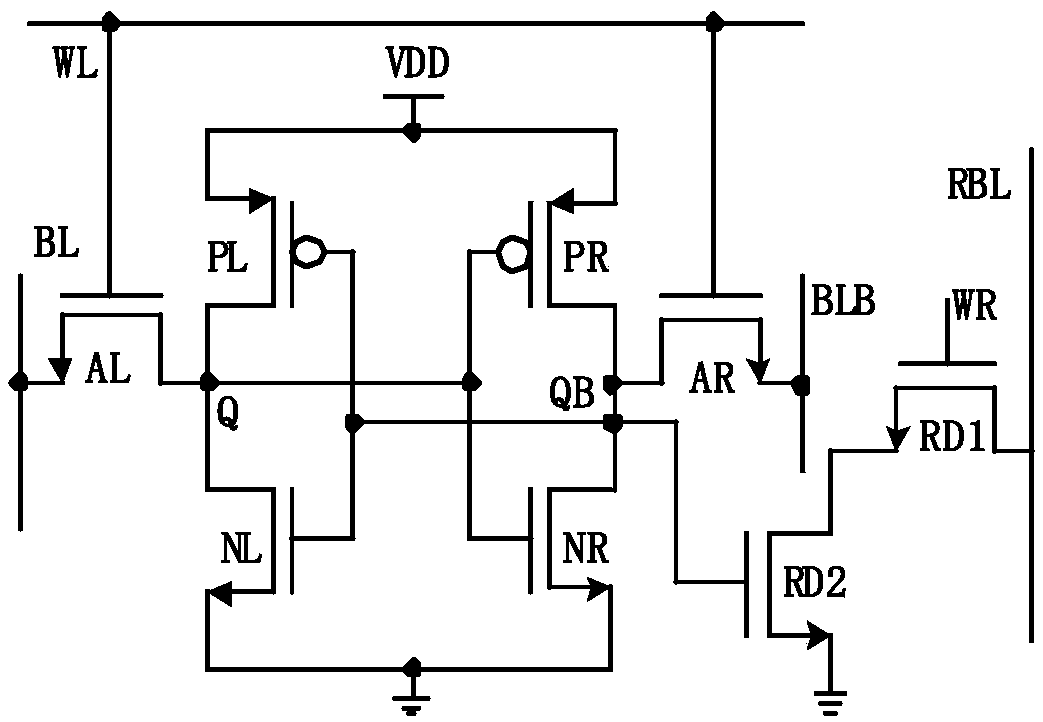

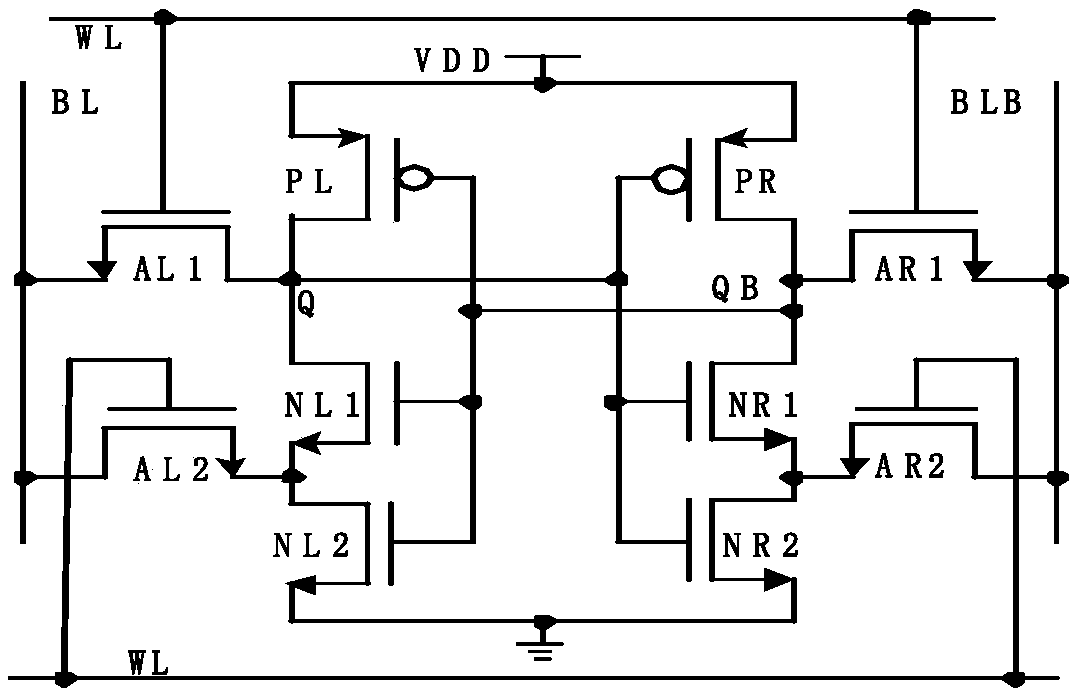

A 12T TFET SRAM cell circuit having ultra-low power consumption and high write margin

PendingCN109658960ASolve the problem of high static power consumptionReduce static power consumptionDigital storageWrite marginSubthreshold swing

The invention discloses a 12T TFET SRAM unit circuit with ultra-low power consumption and high write margin. Compared with a metal oxide semiconductor field effect transistor (MOSFET), the characteristics of smaller subthreshold swing, higher switching ratio and the like of the TFET are utilized; the problem of high static power consumption of a traditional MOSFET SRAM unit structure is solved; Under the same working voltage, such as 0.3 V to 0.6 V, compared with other TFET SRAM unit structures, the static power consumption of the TFET SRAM unit structure is at least reduced by four orders ofmagnitudes, and the write margin and the stability of the TFET SRAM unit structure are improved; Therefore, the problem of positive bias leakage current occurring when the TFET is used as the SRAM transmission tube is eliminated, the static power consumption of the cell is reduced, and the stability and the writing capability of the cell are improved.

Owner:ANHUI UNIVERSITY

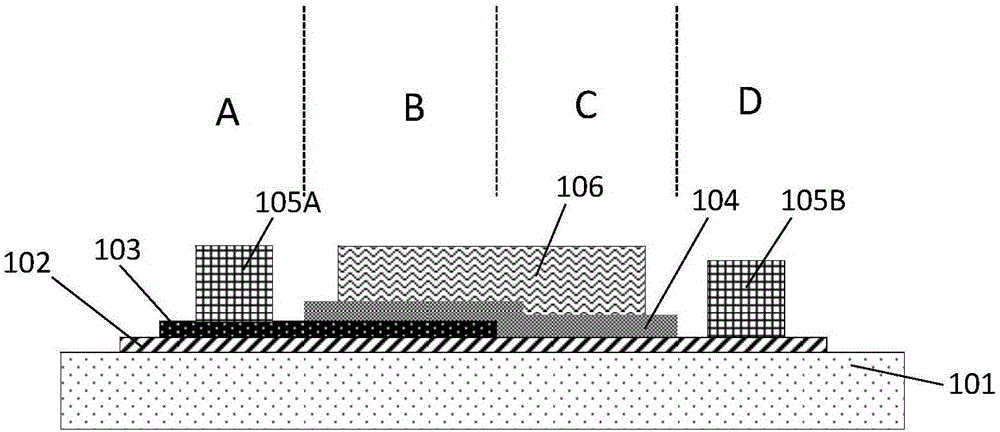

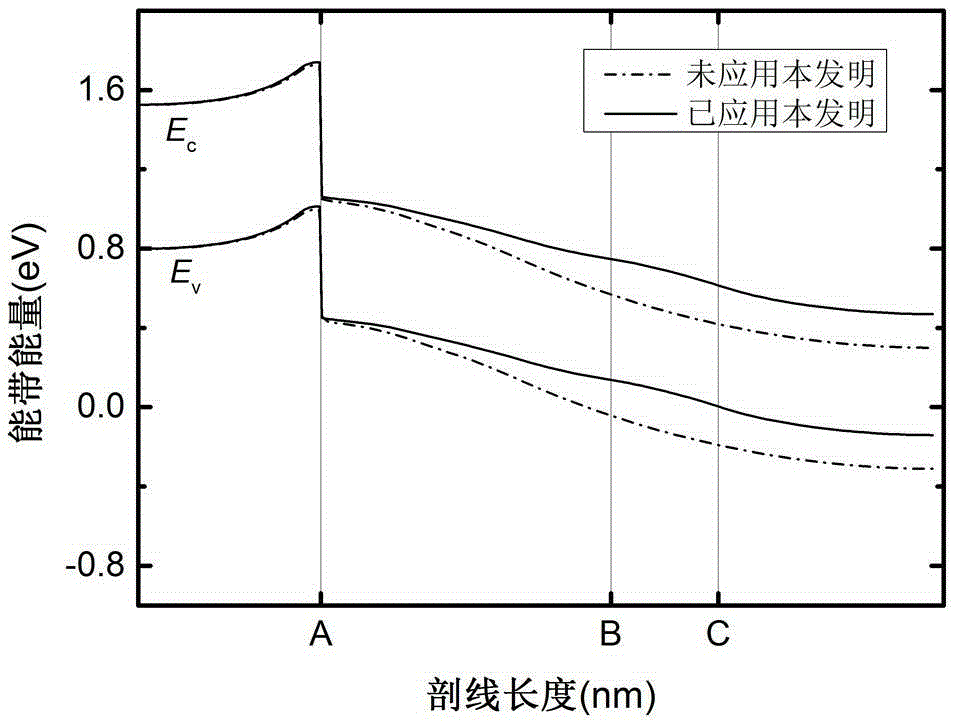

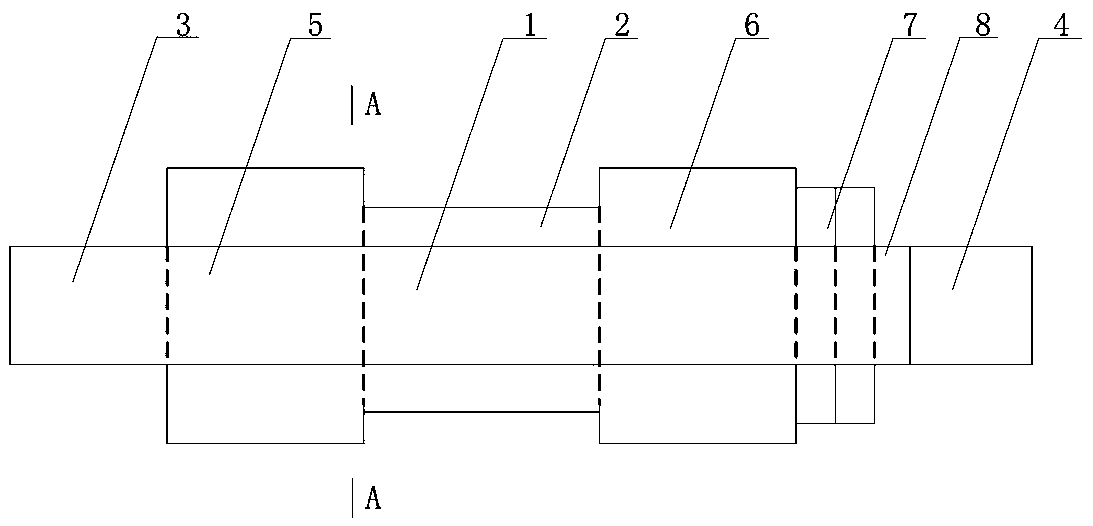

Ferroelectric field effect transistor based on GeSn material, and preparation method for ferroelectric field effect transistor

InactiveCN105762178AIncrease the on-currentOvercome the disadvantage of small conduction currentSemiconductor/solid-state device manufacturingSemiconductor devicesSubthreshold swingDielectric layer

The invention discloses a ferroelectric field effect transistor based on a GeSn material, and a preparation method for the ferroelectric field effect transistor, and solves problems that a conventional ferroelectric field effect transistor is small in conduction current and is larger in subthreshold swing. The ferroelectric field effect transistor comprises a substrate 1, a source electrode 2, a trench 3, a drain electrode 4, an insulating dielectric film 5, an internal grid electrode 6, a ferroelectric grid dielectric layer 7, and a grid electrode 8. The trench 3 is located at the center above the substrate 1, and the source electrode 2 and the drain electrode 4 are located at two sides of the trench 3. The insulating dielectric film 5, the internal grid electrode 6, the ferroelectric grid dielectric layer 7 and the grid electrode 8 are sequentially distributed above the trench 3 from the bottom to the top in a vertical manner. According to the invention, the GeSn material is introduced as the trench material of the transistor, thereby enabling the transistor to be able to obtain a smaller subthreshold swing and a higher switching speed at a low working voltage.

Owner:XIDIAN UNIV

Method for manufacturing semiconductor device

InactiveUS7772054B2Simple stepsImprove responseSolid-state devicesSemiconductor/solid-state device manufacturingResistElectrical conductor

A highly responsive semiconductor device in which the subthreshold swing (S value) is small and reduction in on-current is suppressed is manufactured. A semiconductor layer in which a thickness of a source region or a drain region is larger than that of a channel formation region is formed. A semiconductor layer having a concavo-convex shape which is included in the semiconductor device is formed by the steps of forming a first semiconductor layer over a substrate; forming a first insulating layer and a conductive layer over the first semiconductor layer; forming a second insulating layer over a side surface of the conductive layer; forming a second semiconductor layer over the first insulating layer, the conductive layer and the second insulating layer; etching the second semiconductor layer using a resist formed partially as a mask; and performing heat treatment to the first semiconductor layer and the second semiconductor layer.

Owner:SEMICON ENERGY LAB CO LTD

Array substrate, preparation method of array substrate, display panel, and display device

InactiveCN109872998ADoes not affect resolutionEasy to controlSolid-state devicesSemiconductor devicesPower flowSubthreshold swing

The invention discloses an array substrate, a preparation method of the array substrate, a display panel, and a display device. The array substrate is characterized in that the thickness of a gate oxidation layer of a driving transistor is larger than the thickness of a gate oxidation layer of a switching transistor. According to I=K(Vgs-Vth)<2> and (the formula is as shown in the description), the fact that the thickness of the gate oxidation layer of the driving transistor is larger than the thickness of the gate oxidation layer of the switching transistor indicates that K of the driving transistor is smaller than K of the switching transistor, so that current changes of the driving transistor with voltages are smaller, i.e., subthreshold swing requirements are higher, which facilitatesbetter grayscale control, and current changes of the switching transistor with the voltages are larger, i.e., subthreshold swing requirements are lower, which ensures good switching performance; and therefore, effective grayscale and switching control in the display panel can be simultaneously achieved.

Owner:BOE TECH GRP CO LTD +1

Thin-film transistor, manufacturing method of thin-film transistor, array substrate and display device

ActiveCN104167448AReduced subthreshold swingImprovement of semiconductor characteristicsTransistorSemiconductor/solid-state device detailsSubthreshold swingNitrogen

The invention provides a thin-film transistor, a manufacturing method of the thin-film transistor, an array substrate and a display device. The manufacturing method of the thin-film transistor comprises the steps that a grid, a gate insulator, an active area, a source and a drain are formed on the substrate, the active area is made of a ZnON material, and nitrogen ions are implanted in the active area while the active area is formed, so that the subthreshold swing of the thin-film transistor is smaller than or equal to 0.5 mV / dec. According to the manufacturing method, as the nitrogen ions are implanted in the active area while the active area is formed, the concentration of the nitrogen ions, at the effective electricity conducting position, in the active area can be greatly improved, when the thin-film transistor works, nitrogen, lost due to the diffusion effect, in the active area can be supplemented sufficiently, the migration rate of nitrogen vacancy in the active area can be greatly increased, namely, the migration rate of current carriers in the active area is greatly increased, the subthreshold swing of the thin-film transistor is further reduced, and the semi-conductor property of the thin-film transistor is improved.

Owner:BOE TECH GRP CO LTD

SOI (silicon on insulator) substrate based ring-gate radiation-proof MOS (metal oxide semiconductor) field-effect transistor

InactiveCN106449760AReduce leakage currentHigh working reliabilitySemiconductor/solid-state device manufacturingSemiconductor devicesSubthreshold swingSoi substrate

Owner:XIDIAN UNIV

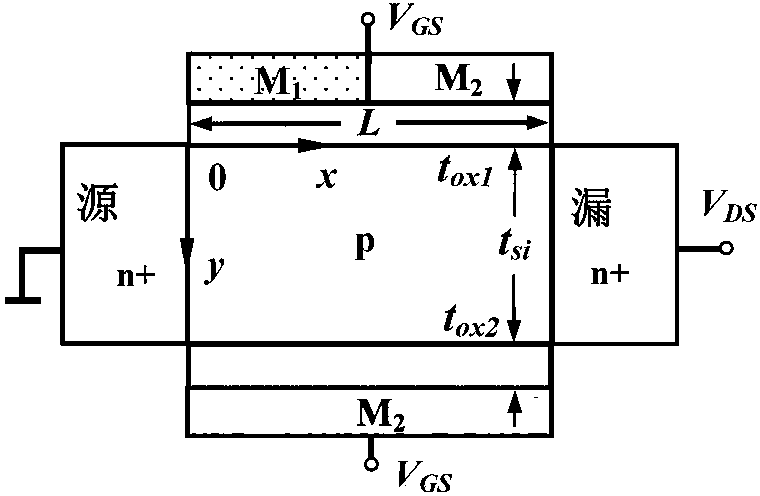

Method for extracting subthreshold swing of MOSFET of double-material double-gate structure

InactiveCN104076266ASpecial data processing applicationsIndividual semiconductor device testingSubthreshold swingEngineering

The invention belongs to the technical field of semiconductors, and particularly discloses a method for extracting the subthreshold swing of an MOSFET of a double-material double-gate structure. Potential distribution of the MOSFET of the double-material double-gate structure is acquired, and then an analysis model of the subthershold swing is acquired through acquired potentials according to the definition of the subthreshold swing. The analysis model of the subthreshold swing is simple in form and clear in physical concept, and a rapid tool is provided for circuit stimulation software on research on a novel device of the double-material double-gate structure.

Owner:FUDAN UNIV

TFT preparation method, TFT, array substrate and display device

ActiveCN109659235AImprove performanceWill not be affected by other electrical characteristic parametersTransistorSemiconductor/solid-state device manufacturingSubthreshold swingDisplay device

An embodiment of the invention discloses a TFT preparation method, a TFT, an array substrate and a display device. The TFT preparation method comprises the steps of: forming a buffer layer, a polysilicon layer, a gate insulating layer, a source layer, a drain layer and a gate layer on a substrate, wherein the polysilicon layer is formed on the buffer layer, the source layer and the drain layer areformed on both sides of the polysilicon layer, and the gate insulating layer is formed on the polysilicon layer, the source layer and the drain layer; and performing primary ion implantation on the polysilicon layer after the buffer layer and the polysilicon layer are formed on the substrate and before the gate insulating layer is formed on the substrate, so as to adjust a subthreshold swing to be not lower than a preset threshold value and enable a peak value of the implanted ion concentration falls in the buffer layer under the polysilicon layer. According to the TFT preparation method, adverse effect on other electrical characteristic parameters of the TFT cannot be caused under the condition of adjusting the subthreshold swing of the TFT, and the overall product performance of the TFTis improved.

Owner:WUHAN CHINA STAR OPTOELECTRONICS SEMICON DISPLAY TECH CO LTD

Source drain variable-resistance rectangular grid controlled U-shaped channel bidirectional transistor and production method thereof

InactiveCN107785436ACan change the direction of tunneling currentAchieving bi-directional switching characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesSubthreshold swingReverse leakage current

The invention relates to a source drain variable-resistance rectangular grid controlled U-shaped channel bidirectional transistor and a production method thereof. The element is provided with a rectangular grid electrode, has a transversely symmetrical structural feature, has high grid control capacity and can control a metal source drain interchangeable region as a source region or a drain regionthrough adjustment of source drain interchangeable electrode voltage, and the direction of a tunneling current is changed. The element has the advantages of low static power consumption, small reverse leakage current, high grid control capacity, low subthreshold swing and realization of a bidirectional switch function. Compared with a common MOSFETs-type element, a better switch characteristic isachieved by means of a tunneling effect; compared with a common tunneling field effect transistor, the bidirectional transistor has a source drain interchangeable bidirectional symmetrical switch characteristic; compared with a Schottky barrier transistor, the bidirectional transistor has a better switch characteristic; it is unnecessary to conduct blending in the source and drain regions, a Schottky barrier is easy to form, the rectangular grid electrode can better control the source and drain regions, and thus the bidirectional transistor is suitable for application and popularization.

Owner:山东光岳九州半导体科技有限公司

Ferroelectric/piezoelectric field effect transistor and preparation method thereof

InactiveCN110034181ALow working voltageIncrease opening/closing speedSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceSubthreshold swing

The invention provides a ferroelectric / piezoelectric field effect transistor and a preparation method thereof. The iron / piezoelectric field effect transistor comprises a substrate, a source electrode, a drain electrode and a gate electrode. The gate electrode comprises silicon dioxide, a high dielectric layer, a piezoelectric material layer, a titanium nitride layer, a ferroelectric material layer and a tantalum nitride layer, which are sequentially stacked from bottom to top. The preparation method comprises the following steps: providing a silicon substrate, and doping P-type ions into thesilicon substrate to form a substrate; forming a source electrode and a drain electrode at two sides of the substrate; sequentially forming the silicon dioxide layer and the high dielectric layer between the source electrode and the drain electrode above the substrate; and sequentially forming the piezoelectric material layer, the titanium nitride layer, the ferroelectric material layer and the tantalum nitride layer on the high dielectric layer. Based on the field effect transistor, the ferroelectric material and the piezoelectric material are introduced into the gate electrode, and the negative capacitance effect of the ferroelectric material and the electrostrictive effect of the piezoelectric material are used for jointly achieving the voltage amplification function. The working voltage of the device is reduced, the subthreshold swing is reduced, the on / off speed of the device is improved, and the working power consumption is further reduced.

Owner:SHANGHAI HUALI INTEGRATED CIRCUTE MFG CO LTD

A reconfigurable field effect transistor with asymmetric structure

ActiveCN109037339AIdeal off-state currentIncrease the current switch ratioSemiconductor/solid-state device manufacturingSemiconductor devicesSubthreshold swingElectrical polarity

The invention discloses a reconfigurable field effect transistor with an asymmetric structure, comprises a source electrode and a drain electrode arranged on both ends of the channel, and a field effect transistor composed of a control gate electrode and a polar gate electrode respectively arranged on one side of the source electrode and the drain electrode. The polar gate electrode is provided with an underoverlapped region of a deposition side wall on the side close to the drain electrode to form a reconfigurable field effect transistor with an asymmetric structure. Compared with the prior art, the device of the invention has ideal on-state, off-state current, larger current switching ratio, steep subthreshold swing and the like. The current switching ratio is improved significantly whenthe device is of an n-FET structure compared with a p-FET structure, and the off-state current is almost the same compared with a symmetric reconfigurable transistor, so the leakage current is controlled effectively.

Owner:EAST CHINA NORMAL UNIV +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com