Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

170results about How to "Reduced subthreshold swing" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

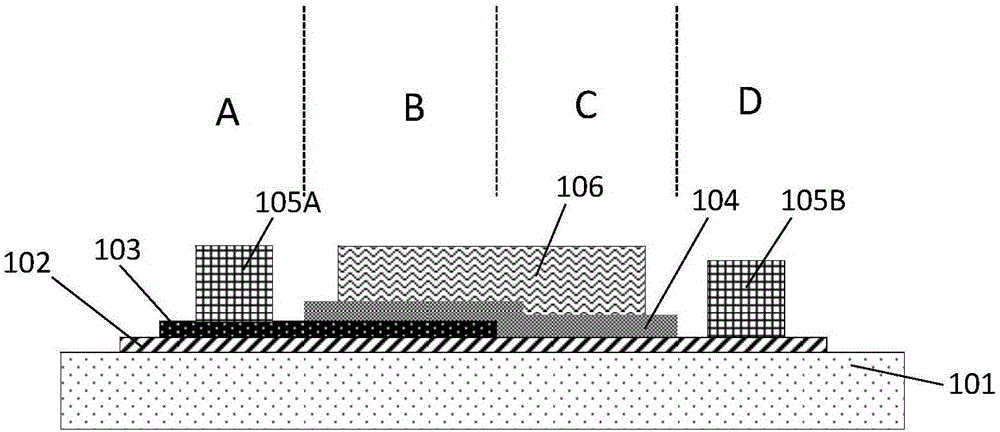

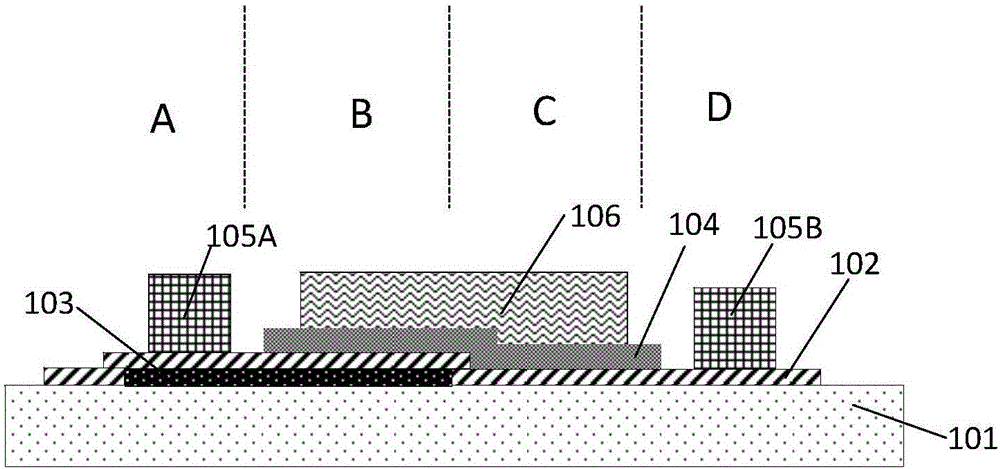

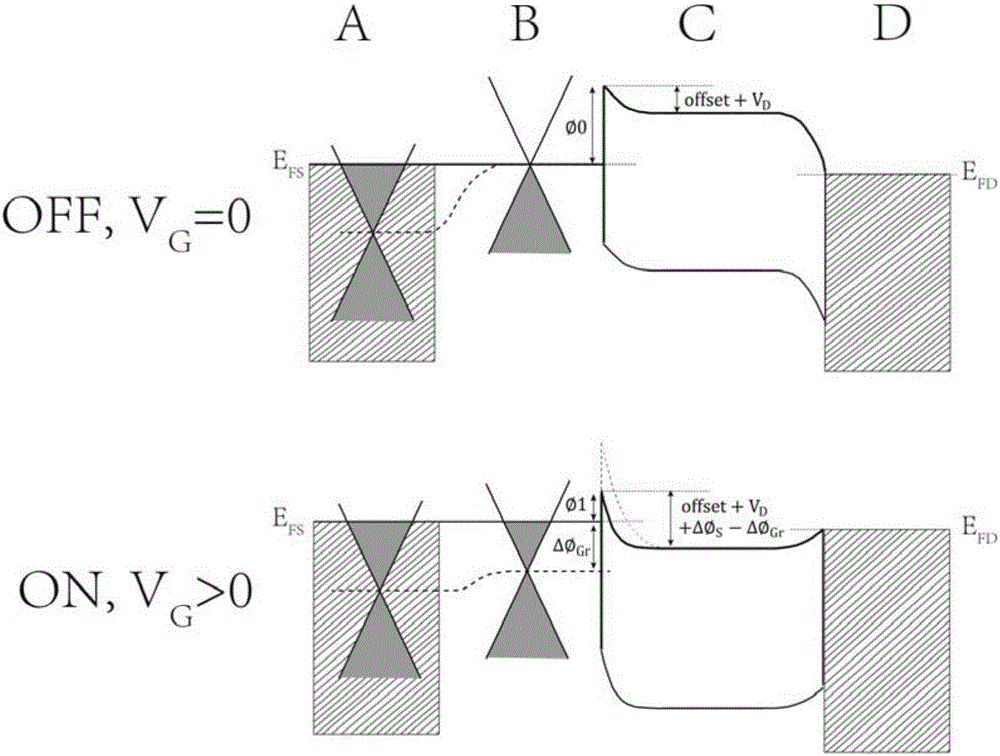

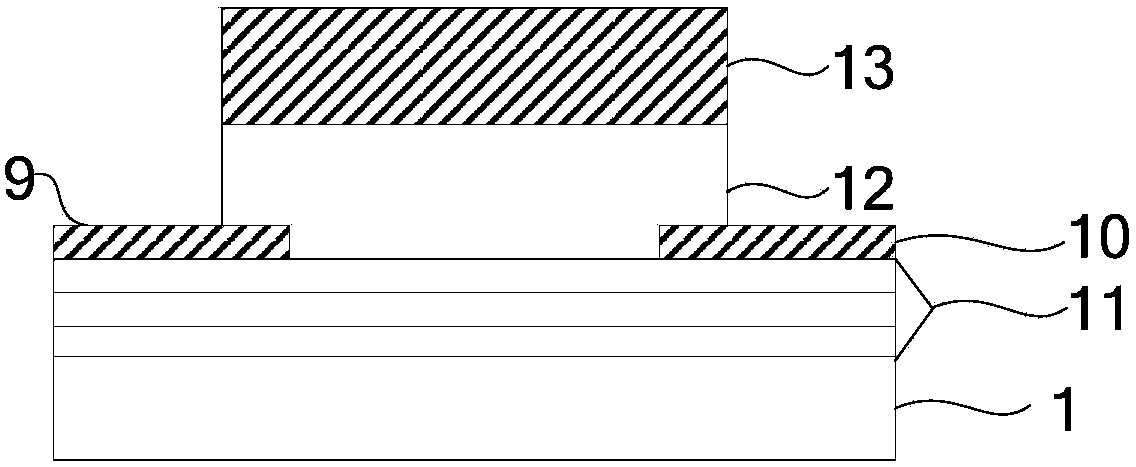

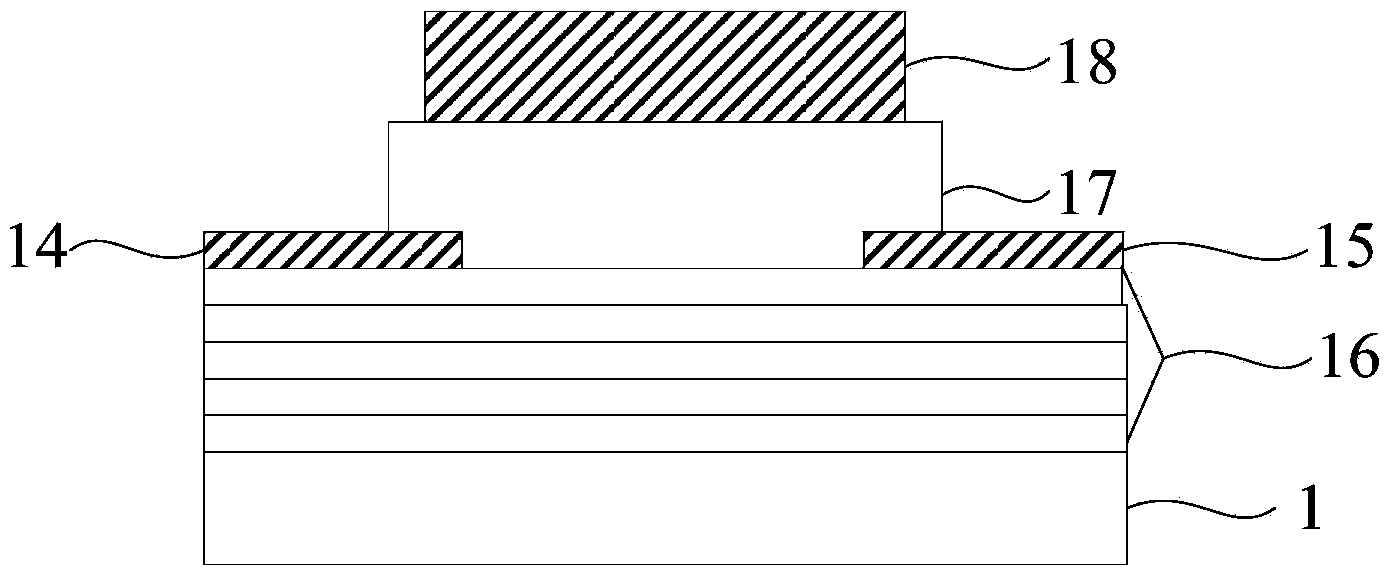

Heterojunction carbon nano-tube field effect transistor and preparation method thereof

ActiveCN106356405AGuaranteed driving abilityGuaranteed speedSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionCarbon nano tube field effect transistor

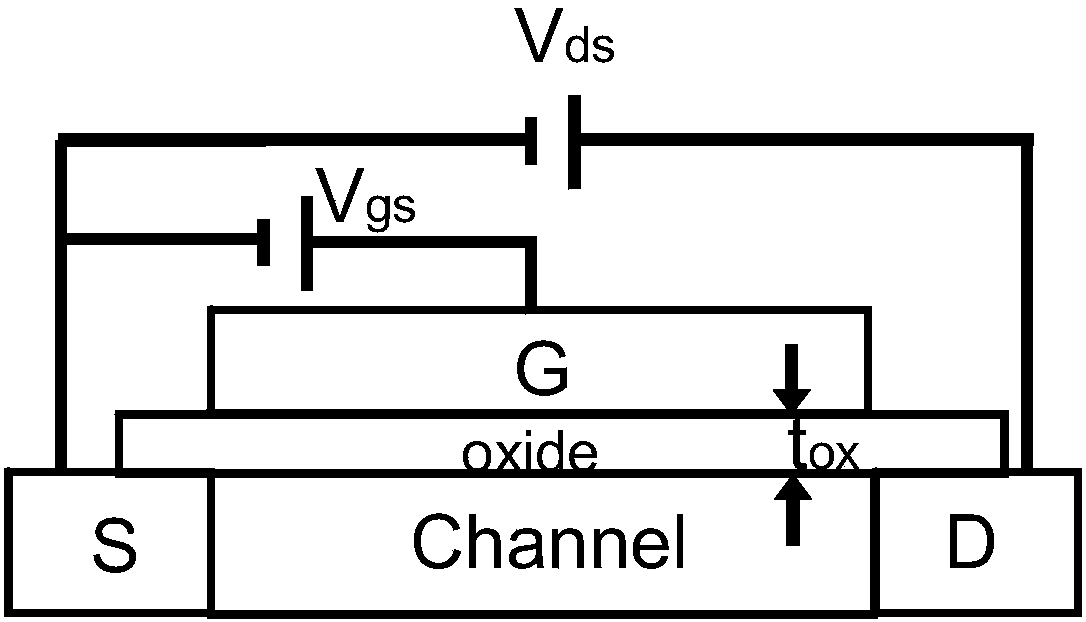

The invention provides a heterojunction carbon nano-tube field effect transistor of which a subthreshold swing is smaller than 60 millivolt / magnitude in the room temperature and a preparation method thereof. The device uses the semiconductor carbon nano-tube as the active layer, the heterojunction formed by the graphene layer and the semiconductor carbon nano-tube is used as the source end of the device, the gate medium and the gate electrode modulate the carbon nano-tube channel and the graphene / carbon nano-tube junction at the same time, so that the turn-off of the transistor is accelerated by using the character that the graphene / carbon nano-tube junction barrier is modulated by the gate voltage. The transistor can control the polarity through the selection of the source-drain metal, namely the metal of high power function is used as the source-drain electrode for realizing the p-type field effect transistor, and the metal of low power function is used as the source-drain electrode for realizing the n-type field effect transistor.

Owner:BEIJING HUA TAN YUAN XIN ELECTRONICS TECH CO LTD

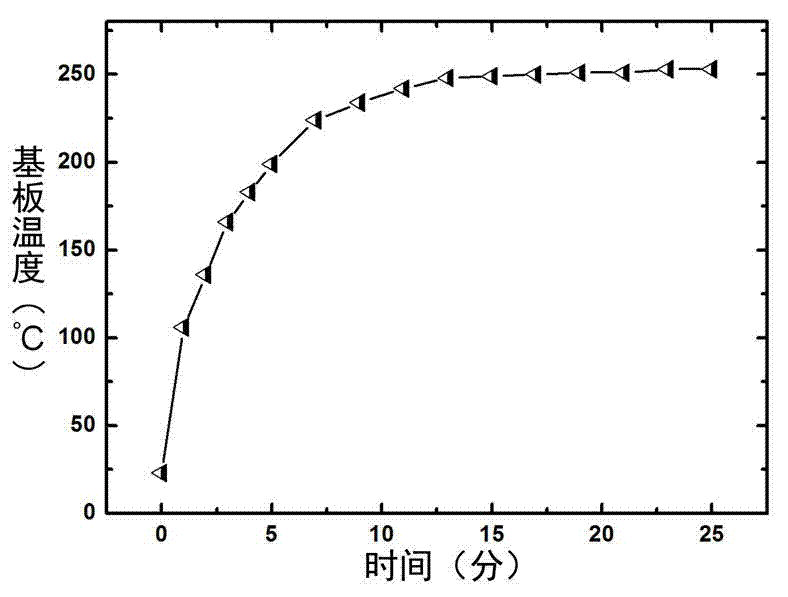

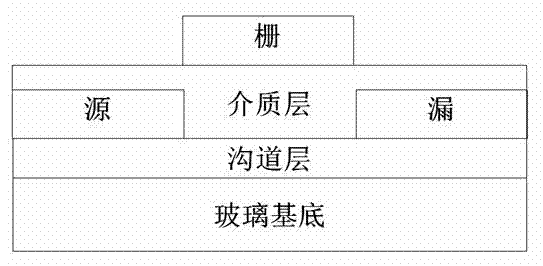

Method for producing indium gallium zinc oxide semiconductor thin film by using sol-gel method

InactiveCN102768945ASimple processReduce the temperatureSemiconductor/solid-state device manufacturingOptical propertySwitched current

The invention belongs to the technical field of preparation of semiconductor thin films, and particularly relates to a low-temperature treatment method for producing an indium gallium zinc oxide (IGZO) semiconductor thin film by using a sol-gel method. The method comprises the following steps of: dissolving In(NO3)3.4*5H2O, Ga(NO3)3.4*5H2O and Zn(C2H3O2)2*5H2O into ethylene glycol monomethyl ether serving as a solvent and monoethanolamine serving as a stabilization agent to form a clear stable precursor solution; and coating the precursor solution on a glass substrate in a rotatable manner, and irradiating by using an infrared heating lamp to obtain the flat and transparent IGZO semiconductor thin film. Compared with the conventional method for preparing the IGZO thin film through annealing of a heat plate by using the sol-gel method, the method has the advantages that the IGZO thin film irradiated by the infrared heating lamp is relatively high in semiconductor and optical properties, and the process temperature is relatively low and lower than 250 DEG C; the IGZO thin film is used as a thin film transistor with a trench layer material; the switch current ratio is more than 5*10<6>; the saturated migration rate is more than 1.8 cm<2> / Vs; and the subthreshold amplitude is less than 2.2 V / dec.

Owner:FUDAN UNIV

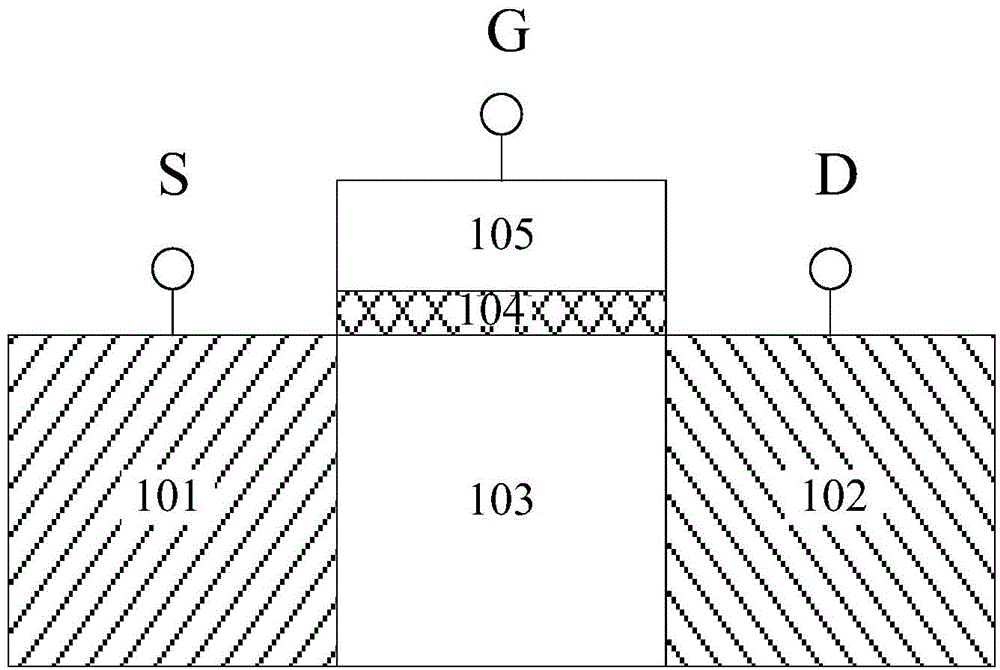

Field effect device and preparation method thereof

ActiveCN104617137AImprove engineering flexibilityImprove voltage control capabilitySemiconductor/solid-state device manufacturingSemiconductor devicesGate dielectricDielectric layer

The invention discloses a field effect device and a preparation method thereof. The field effect device and the preparation method thereof are used for solving the disadvantages of an existing tunneling transistor. The field effect device comprises a semiconductor substrate with a first doping type, a drain region formed at the surface of the semiconductor substrate and having the first doping type, a convex body formed at the surface of the drain region, a grid formed at the surface of the drain region outside the convex body and higher than the convex body, and gate dielectric layers located between the grid and the drain region and between the grid and the convex body; a semiconductor film formed at the surface of the structure composed of the gate dielectric layers and convex body serves as a pocket layer; a source region is formed at the surface of the pocket layer, and the source region is a semiconductor substrate with a second doping type; the convex body serves as a channel between the drain region and source region.

Owner:HUAWEI TECH CO LTD

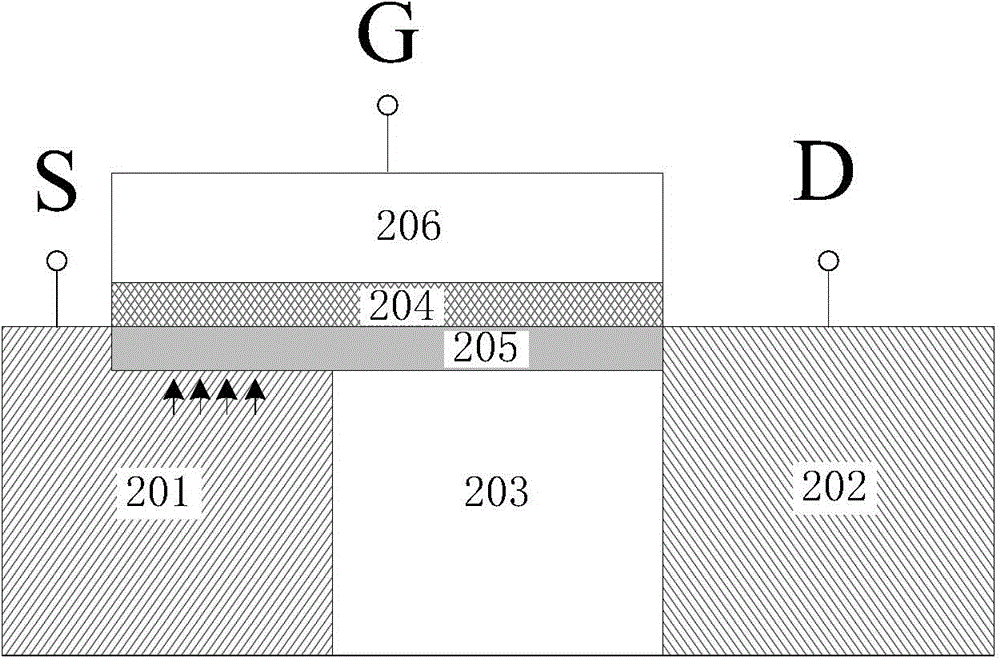

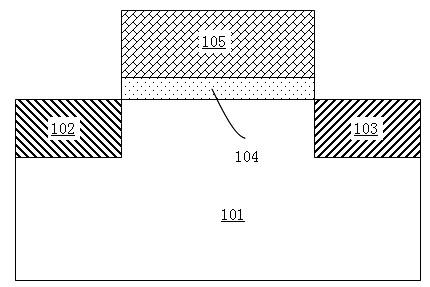

Field effect transistor based on negative capacitance and preparation method thereof, and biosensor and preparation method thereof

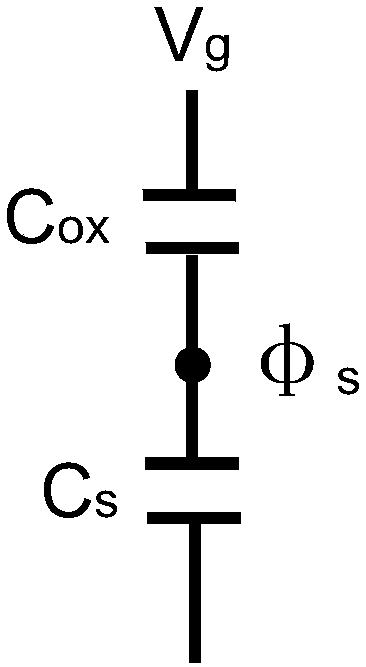

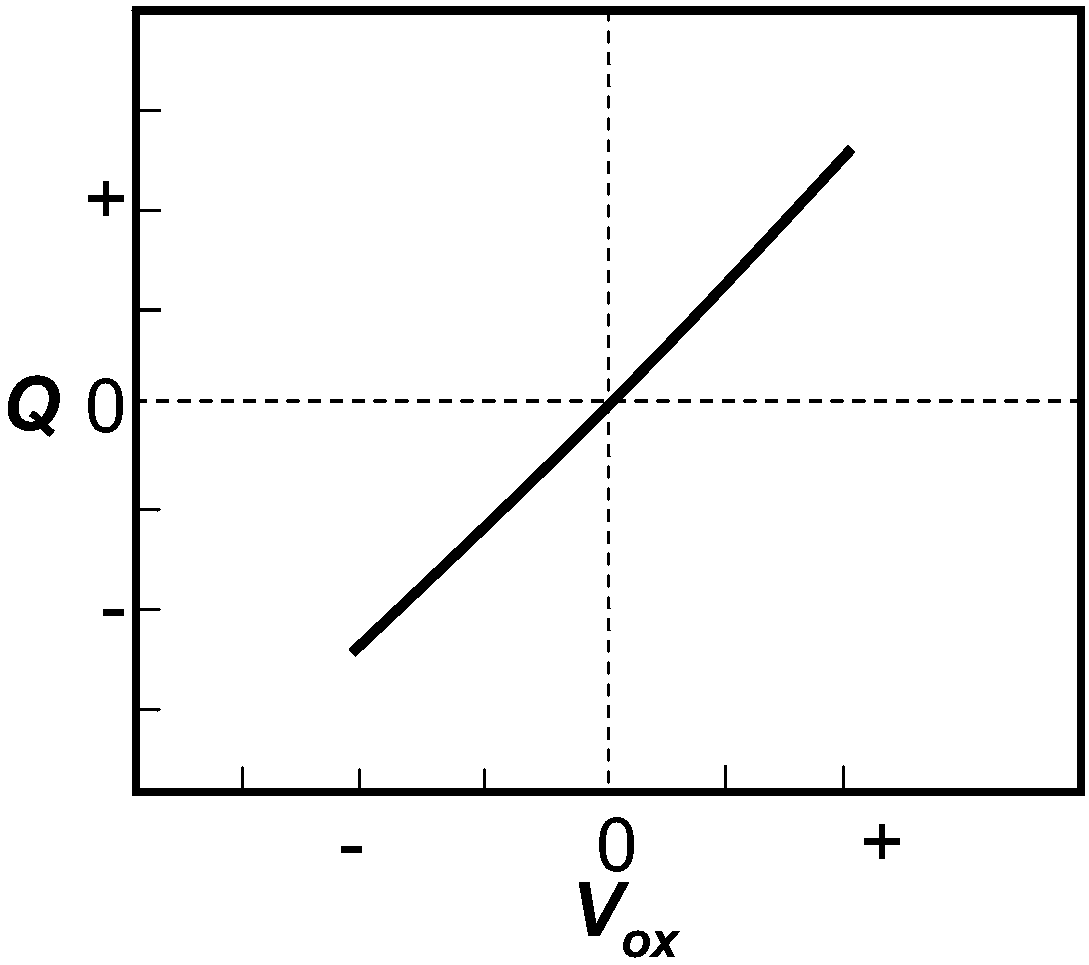

InactiveCN108231901AReduced subthreshold swingLow powerTransistorMaterial analysis by electric/magnetic meansCapacitanceCMOS

The present invention provides a field effect transistor based on negative capacitance and a preparation method thereof, and a biosensor and a preparation method thereof. The preparation method of thefield effect transistor comprises the steps of: providing a semiconductor substrate comprising underlying silicon, buried oxide and top silicon; defining a channel figure, and a source figure and a drain figure which are connected with two ends; performing ion implantation to positions corresponding to the source figure and the drain figure to form a channel region, a source region and a drain region; forming a dielectric layer at the surface of the channel region; forming a conductive layer at the surface of the dielectric layer, and forming a ferroelectricity material layer at the surface of the conductive layer; and making a source electrode, a drain electrode and a gate electrode. According to the scheme, a traditional field effect transistor is integrated with the ferroelectricity negative capacitance to reduce the subthreshold amplitude of a device, improve the sensing sensitivity and the response speed and facilitate reduction of the device power; and moreover, the ferroelectric-doping hafnium oxide is taken as a ferroelectric negative capacitance medium so as to solve the problem that inorganic ferroelectric materials are difficult to a CMOS technology.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

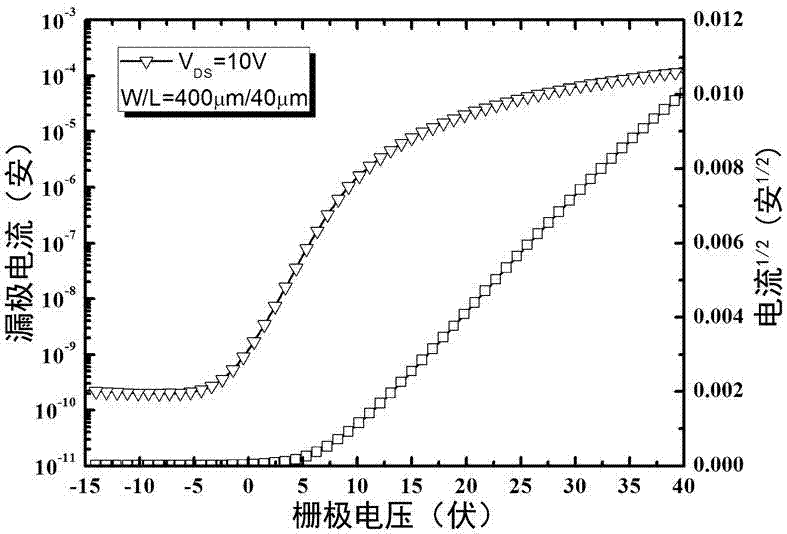

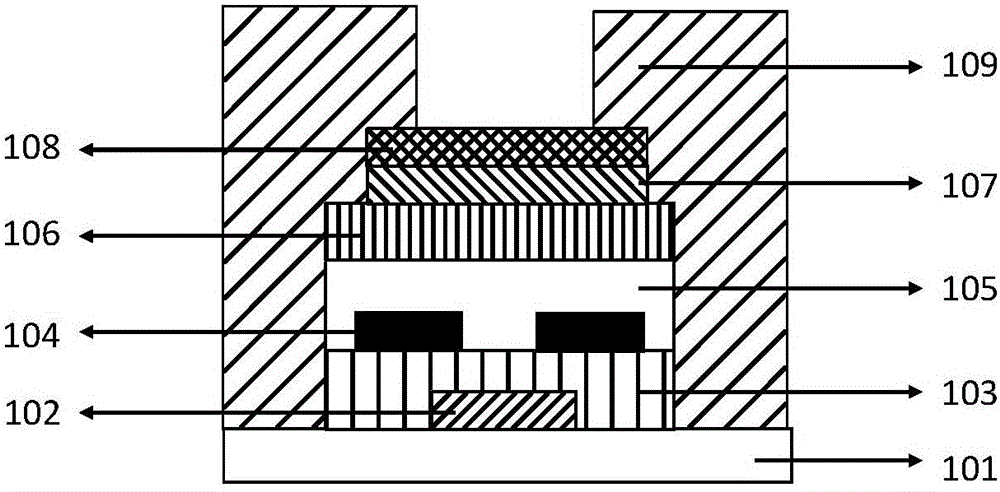

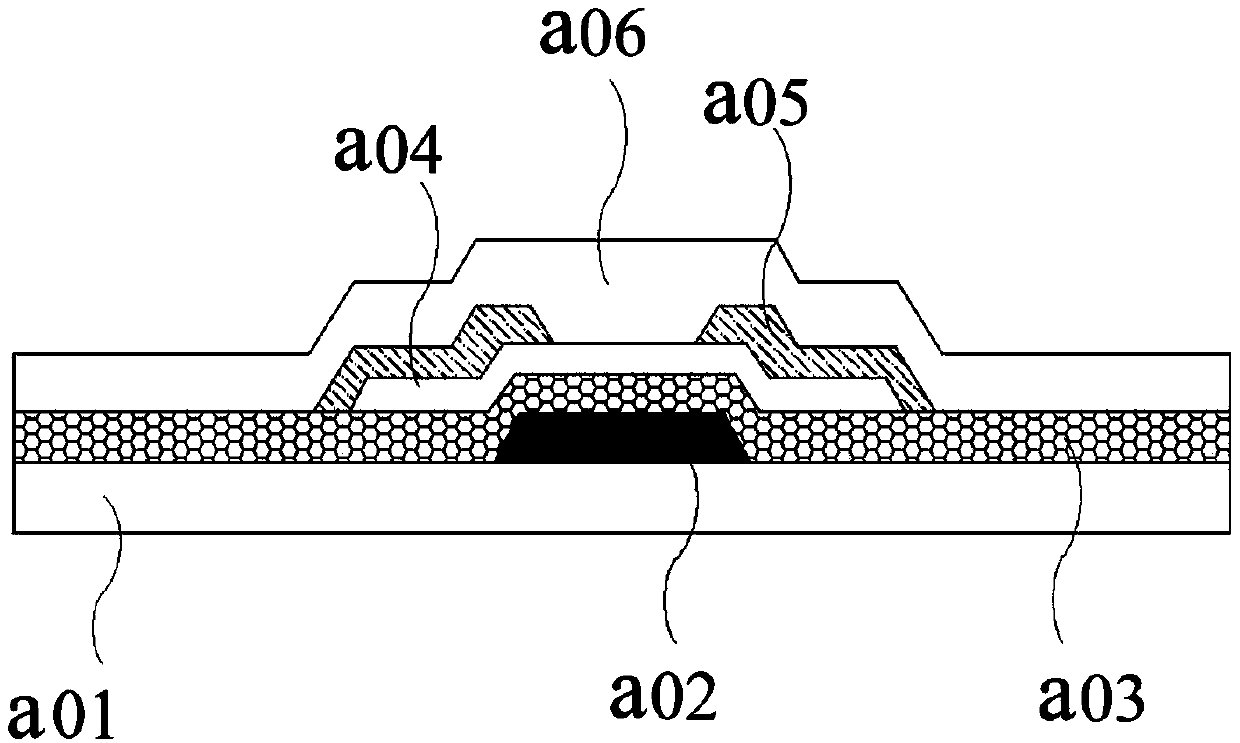

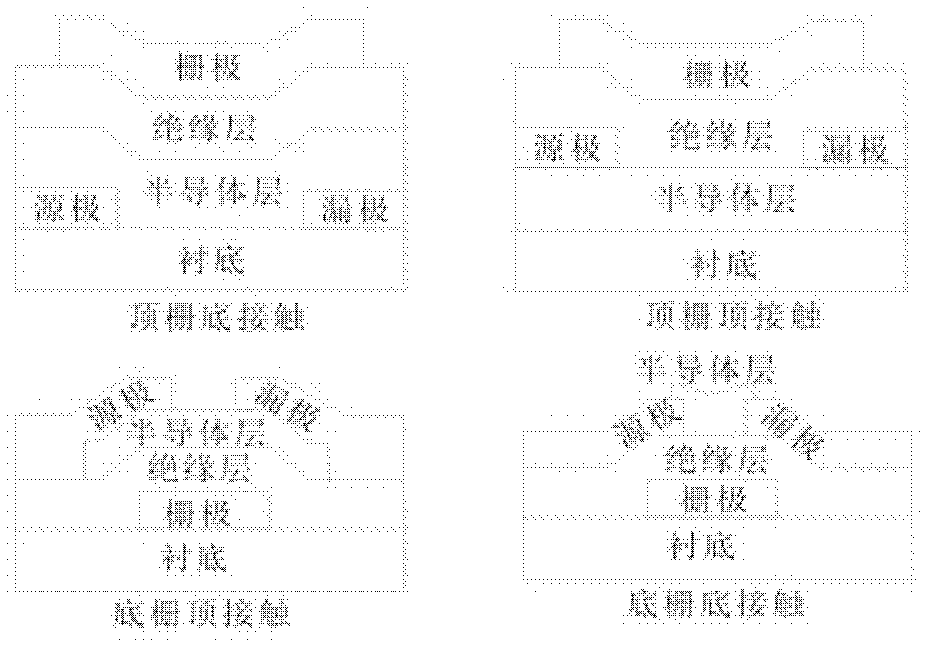

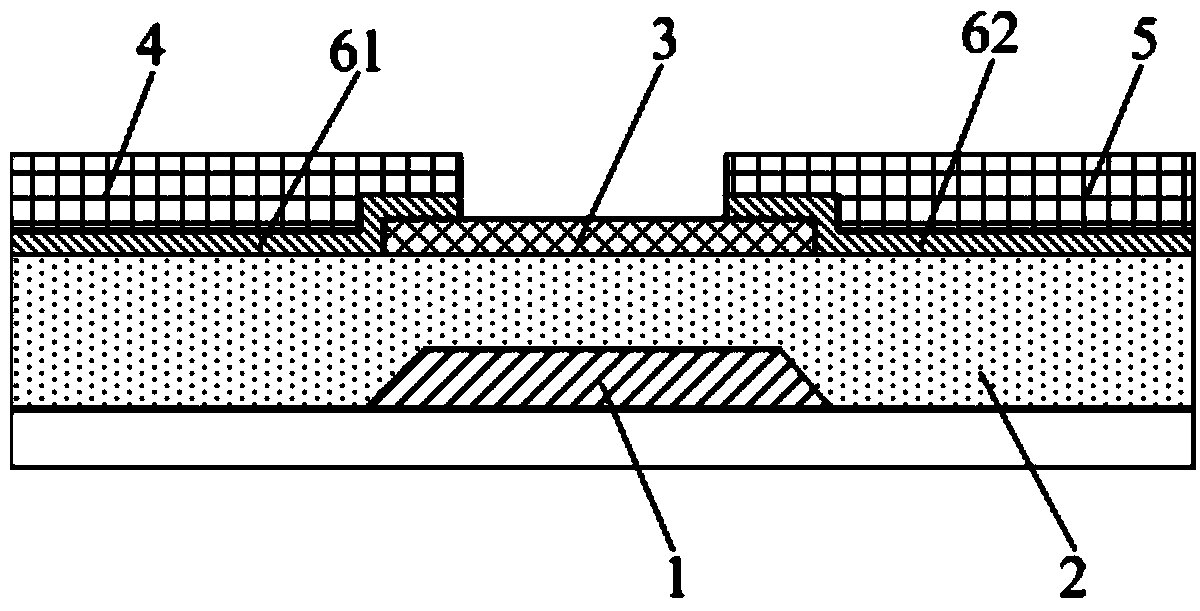

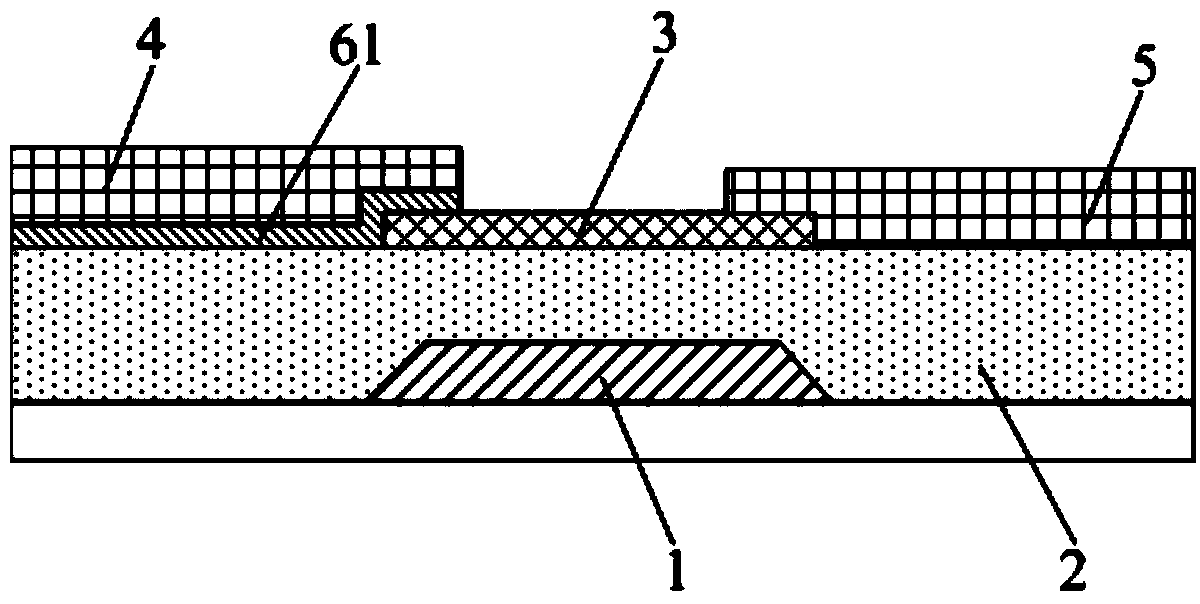

Biological/chemical sensor on basis of organic thin-film transistors

ActiveCN105954322AHigh sensitivityReduced subthreshold swingTransistorSolid-state devicesLow voltageBottom gate

The invention discloses a biological / chemical sensor on the basis of organic thin-film transistors. The biological / chemical sensor comprises a substrate, a first gate electrode, a first gate insulating layer, source / drain electrodes, an organic semiconductor layer, a second gate insulating layer, a second gate electrode, a sensitive film and encapsulation layers which are sequentially laminated on one another from bottom to top. A bottom gate transistor which is arranged at the bottom of the biological / chemical sensor is formed by the first gate electrode, the first gate insulating layer, the source / drain electrodes and the organic semiconductor layer and is used as a reference device, a top gate transistor which is arranged on the top of the biological / chemical sensor is formed by the source / drain electrodes, the organic semiconductor layer, the second gate insulating layer and the second gate electrode and is used as a sensitive device, the organic thin-film transistors which are of low-voltage double-gate structures are formed by the top gate transistor and the bottom gate transistor, the top gate transistor and the bottom gate transistor have gate capacitance values which are greatly different from one another, and the organic semiconductor layer has low sub-gap density of states. The biological / chemical sensor has the advantages of low working voltage and cost, high sensitivity, detection target diversity and the like. Besides, the biological / chemical sensor is compatible to large-area high-speed printing / coating preparation processes, can be used for manufacturing wearable or mobile sensors and has a broad application prospect in the field of health monitoring and healthcare medical treatment.

Owner:杭州领挚科技有限公司

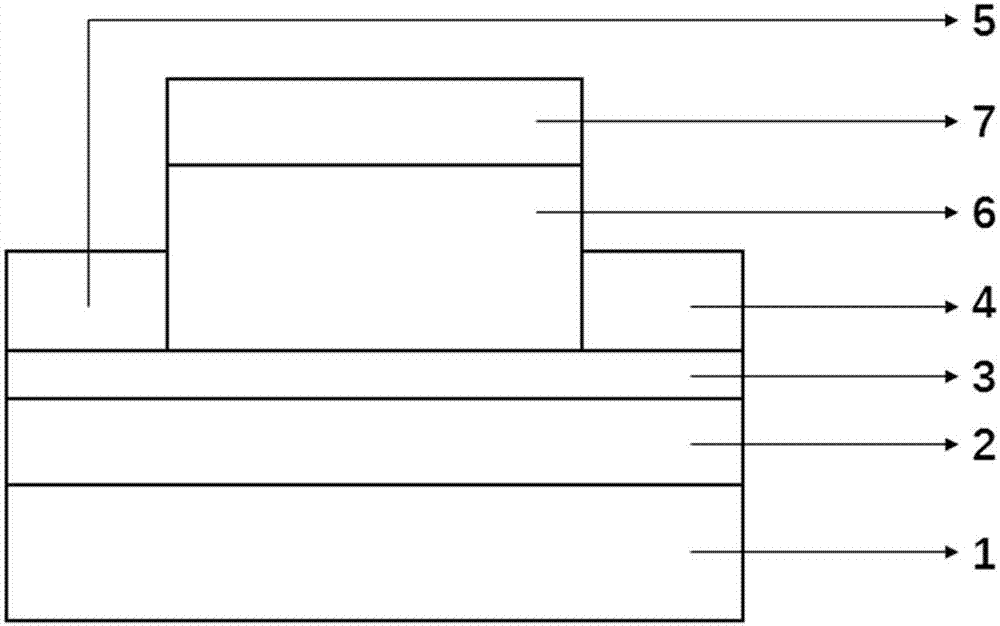

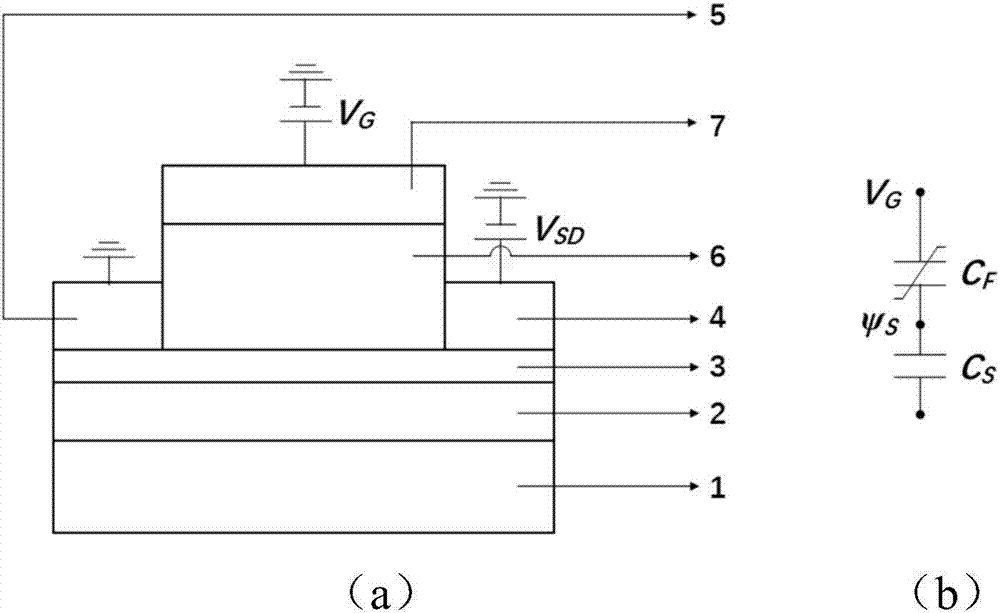

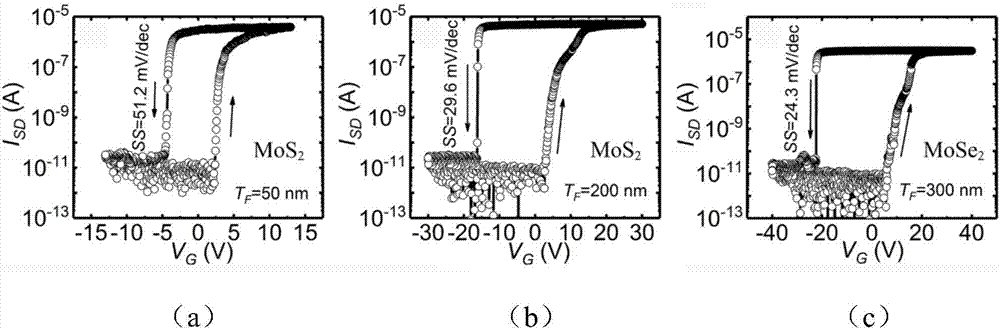

Two-dimensional semiconductor negative capacitance field-effect transistor and preparation method thereof

PendingCN107195681ASimple structureEasy to manufactureSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceCapacitive effect

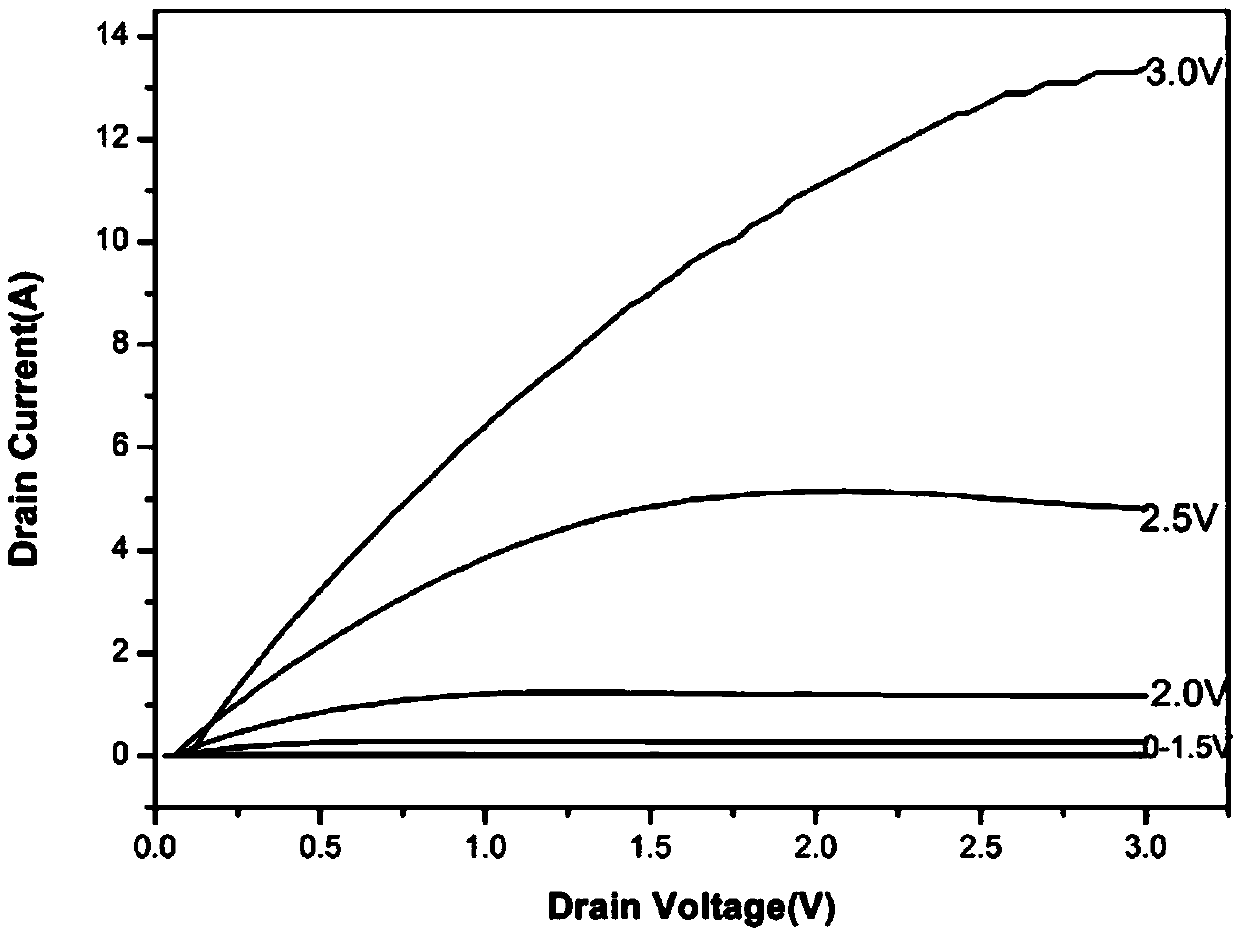

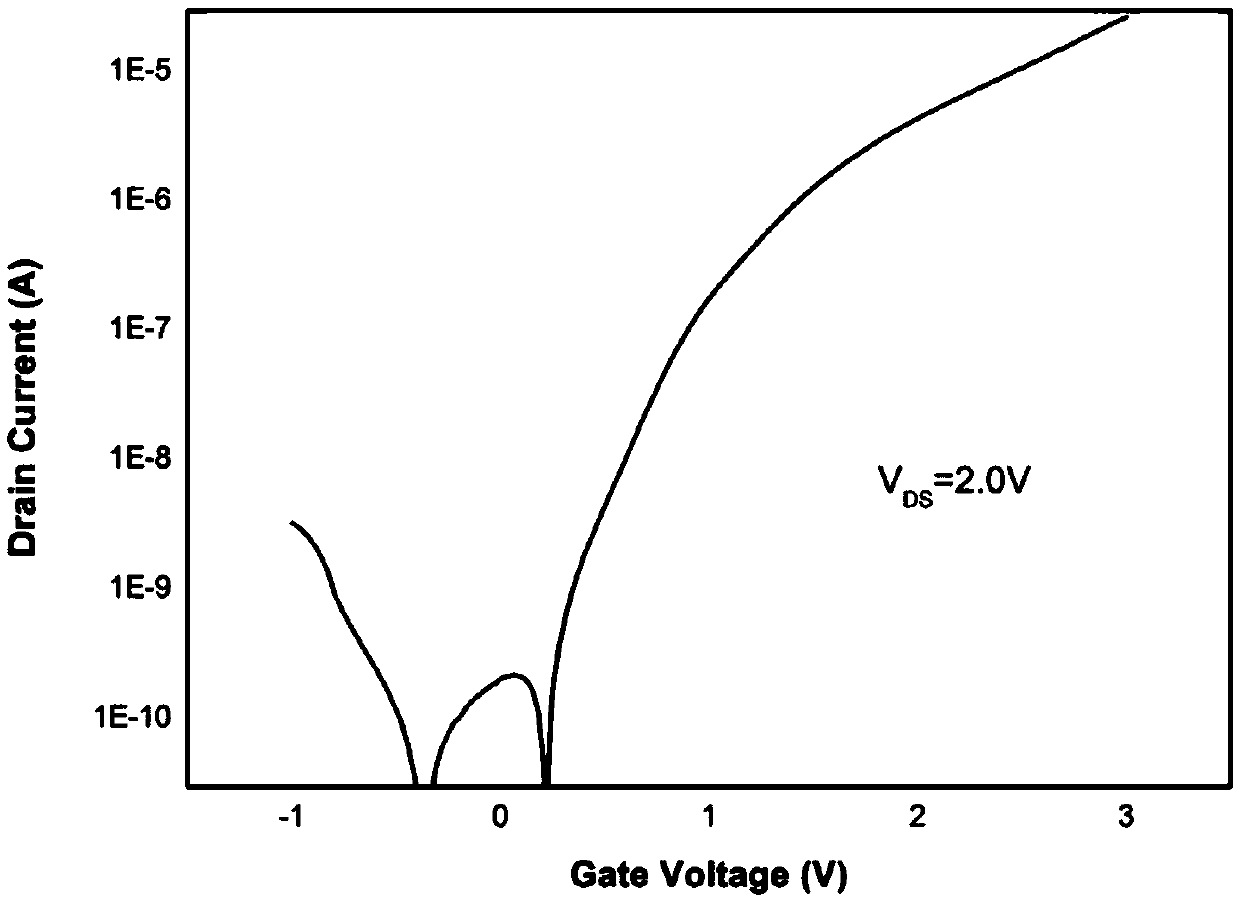

The invention discloses a two-dimensional semiconductor negative capacitance field-effect transistor and a preparation method thereof. The device structure sequentially comprises a substrate, a two-dimensional semiconductor, a metal source-drain electrode, a ferroelectric gate medium with a negative capacitance effect and a metal gate electrode from bottom to top. The preparation method comprises the steps of firstly, preparing the transition metal chalcogenide two-dimensional conductor on a substrate; secondly, preparing the metal source-drain electrode by employing an electron beam lithography technology and combining a stripping process; thirdly, preparing a ferroelectric thin film with the negative capacitance effect on the structure; and finally, preparing the metal gate electrode on the thin film to form ferroelectric-controlled two-dimensional semiconductor negative capacitance field-effect transistor. Different from other two-dimensional semiconductor negative capacitance field-effect device structures, the metal-ferroelectric-semiconductor structure has the advantages that a high-performance negative capacitance field-effect device can be achieved; and an electrical test result shows that the subthreshold swing of the device is far smaller than 60mV / dec, the Boltzmann limit is broken through, and the two-dimensional semiconductor negative capacitance field-effect device simultaneously has the characteristics of extremely low power consumption, high-speed turnover and the like.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

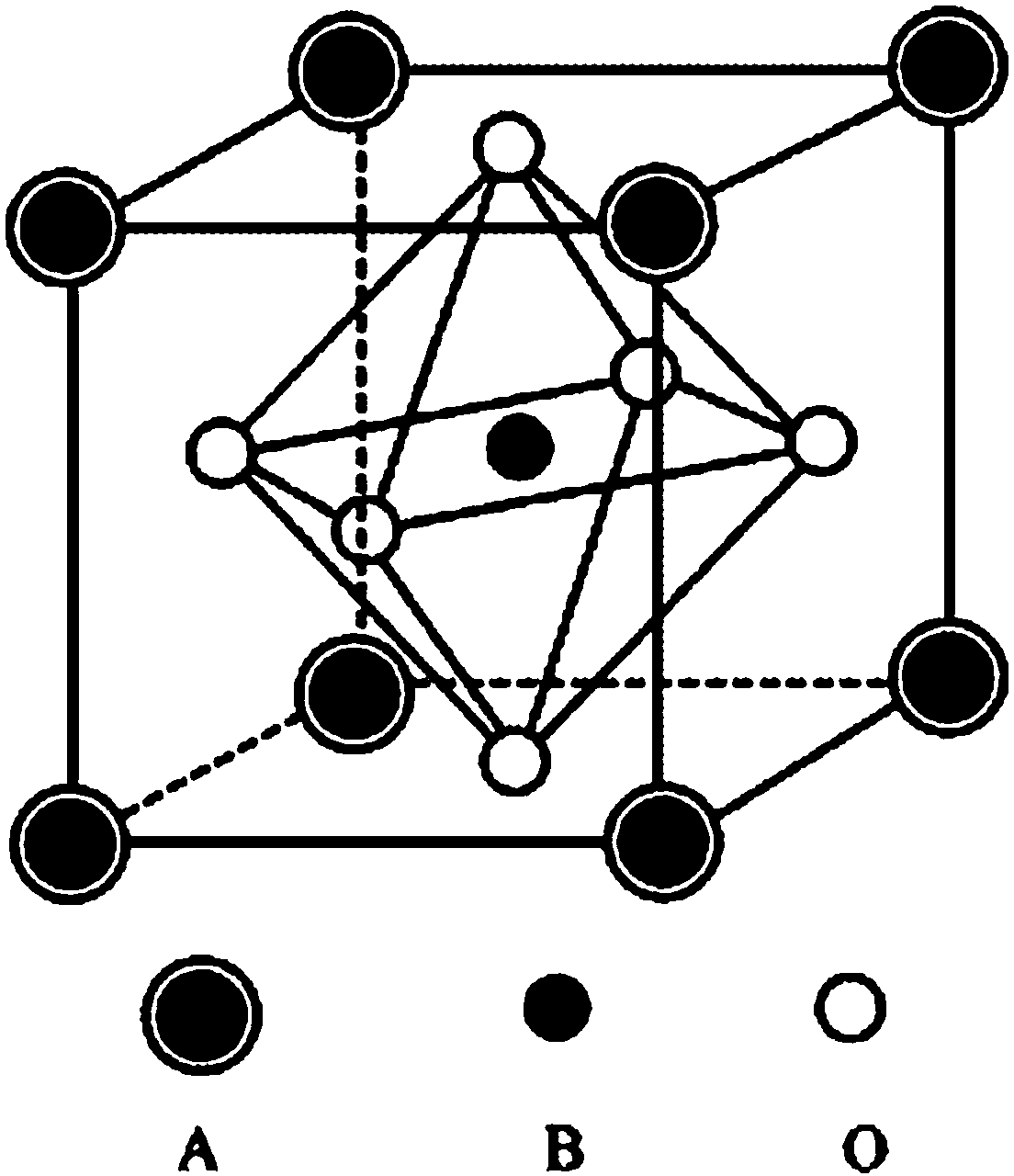

Inorganic metal oxide semiconductor film of perovskite structure and metallic oxide thin film transistor

ActiveCN104218096AStrong acid resistanceSimple preparation processTransistorRare-earth elementOxide thin-film transistor

The invention provides an inorganic metal oxide semiconductor film of a perovskite structure and a metallic oxide thin film transistor. The inorganic metal oxide semiconductor film of the perovskite structure is used as an active layer. The inorganic metal oxide semiconductor film of the perovskite structure is expressed as the chemical expression: MxA1-xBo3, wherein 0.01<=x<=0.5, A is at least one chemical element of Ca, Sr and Ba, B is a chemical element of Ti and Sn, and M is at least one chemical element of Sc, Y, rare earth elements, Al and In. The inorganic metal oxide semiconductor film of the perovskite structure is composed of crystal particles of the perovskite structure, and sizes of the crystal particles vary from 2mm to 900mm. The thickness of the inorganic metal oxide semiconductor film of the perovskite structure varies from 10nm to 500nm. When the inorganic metal oxide semiconductor film of the perovskite structure is used as the active layer, electronic mobility is high, and the metallic oxide thin film transistor prepared by using the inorganic metal oxide semiconductor film of the perovskite structure is good in light stability, low in sub-threshold swing amplitude, simple in preparation technology and low in cost.

Owner:SOUTH CHINA UNIV OF TECH

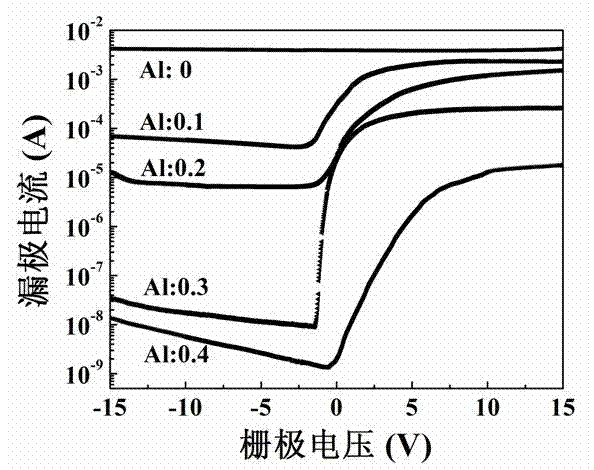

Amorphous semiconductor film and preparation method and application thereof

InactiveCN104218074AImprove driving abilityMinus interface defect statesTransistorSemiconductor/solid-state device manufacturingRare-earth elementMetallurgy

The invention discloses an aluminum zinc oxide amorphous semiconductor film material and a preparation method and application thereof and belongs to the technical field of semiconductor integrated circuits and manufacture thereof. The amorphous semiconductor film comprises, by mole percent content, 85-98% of zinc element, 1-10% of aluminum element and 1-14% of rare earth element, wherein the rare earth element is at least one of Gd, Lu, Y and Sc. A radio frequency magnetron sputtering method is adopted to prepare the aluminum zinc oxide film material doped with the rare earth element, the voltage division ratio of oxygen atmosphere is adjusted in the sputtering process to form a channel material which has amorphous characteristics and is high in migration rate. The preparation method is compatible with a traditional complementary metal oxide semiconductor (CMOS) process, and a rare earth doped oxide semiconductor film transistor can be prepared, is high in practical value and can be applied to future thin film transistor (TFT) integrated circuits.

Owner:PEKING UNIV

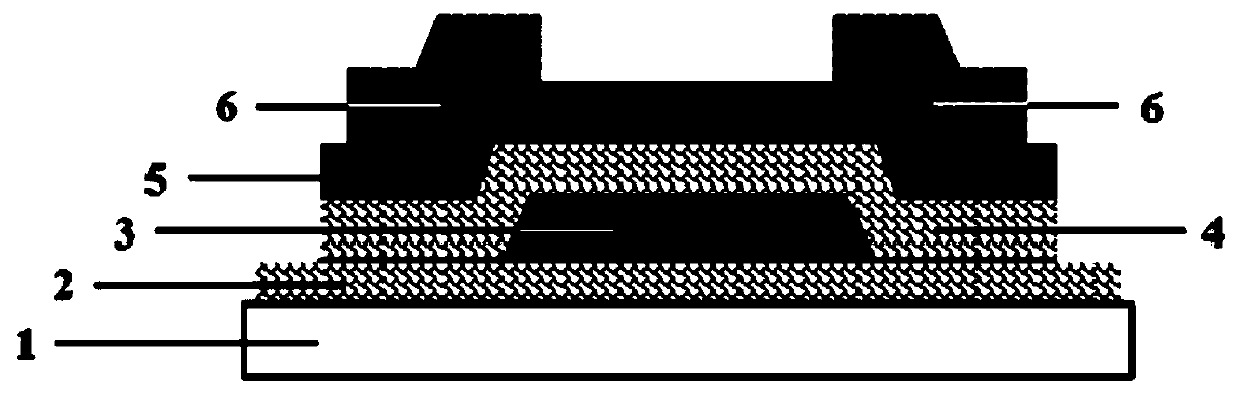

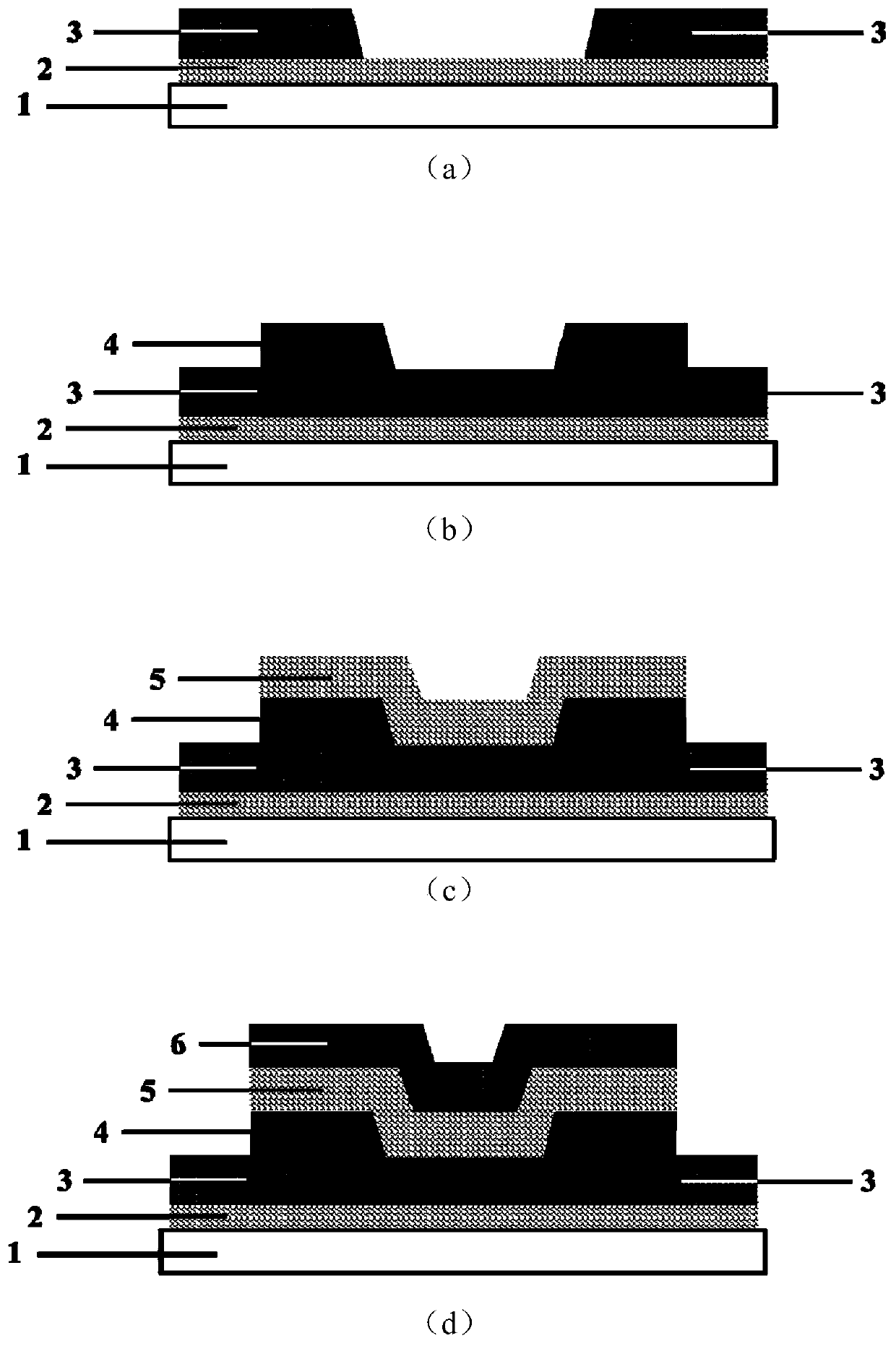

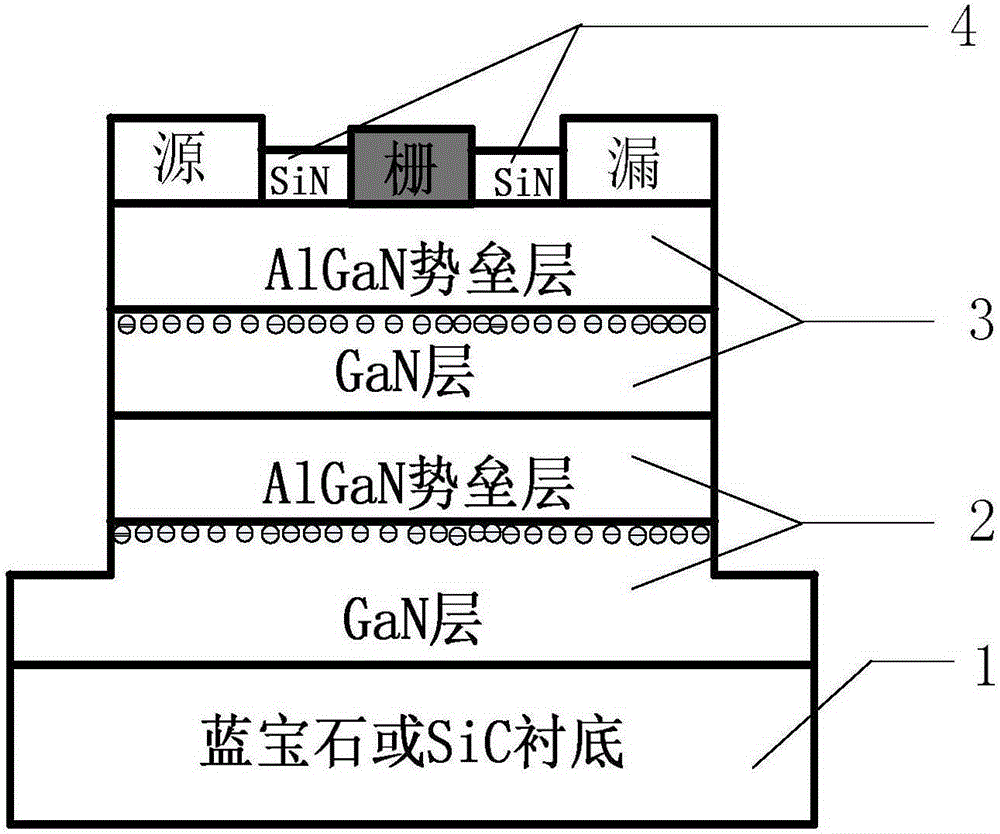

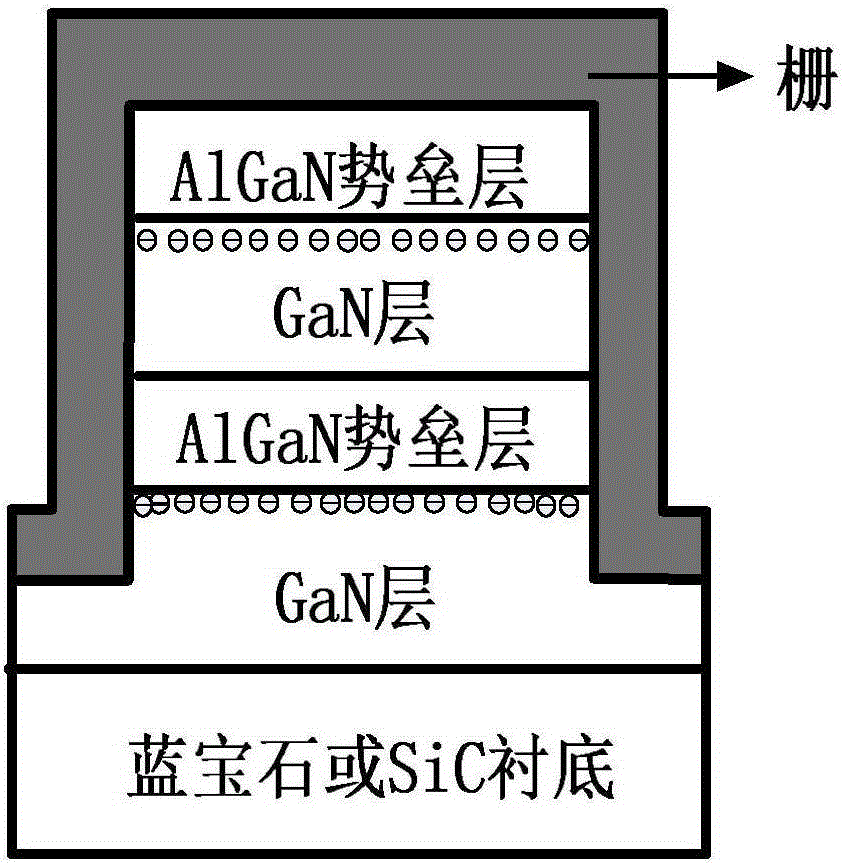

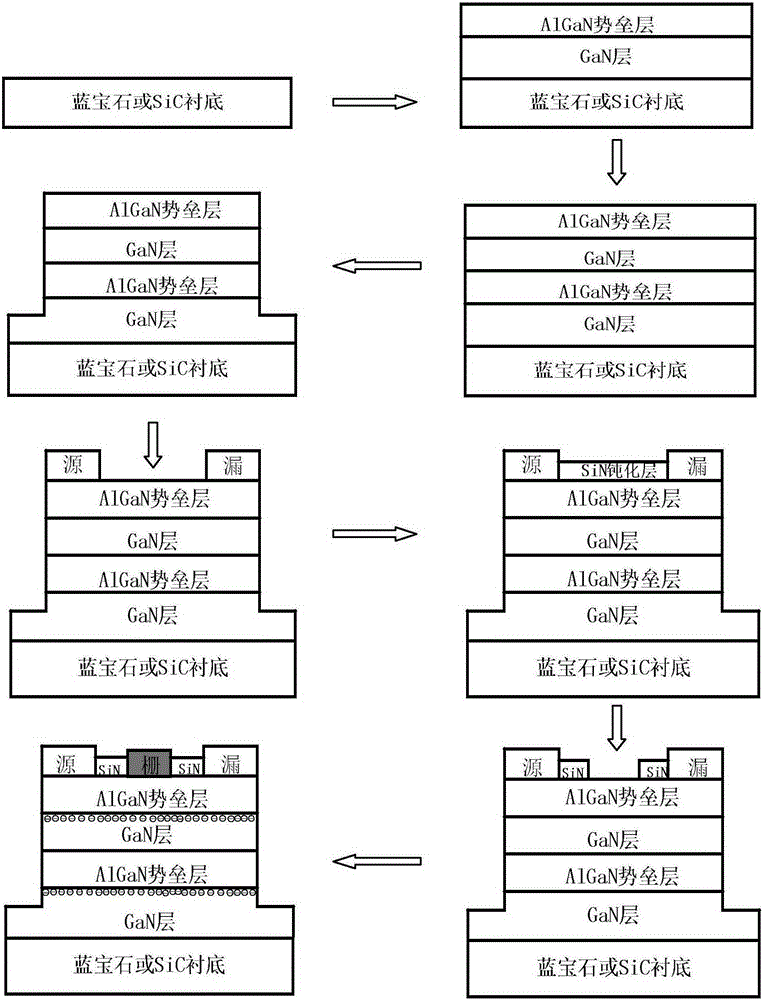

AlGaN/GaN high electron mobility transistor with multi-channel fin-type structure

InactiveCN105280696AReduce widthLower resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHeterojunctionLow noise

The invention discloses a AlGaN / GaN high electron mobility transistor structure with a multi-channel fin-type structure and a manufacturing method, wherein the AlGaN / GaN high electron mobility transistor is designed mainly to solve the problems of the poor gate control ability of a multi-channel apparatus and low electric current of a FinFET apparatus; the AlGaN / GaN high electron mobility transistor comprises a substrate (1), a first layer AlGaN / GaN heterojunction (2), a SiN passivation layer (4) and a source electrode, a drain electroce, and a gate electrode successively from bottom to top; the source electrode and the drain electrode are located on AlGaN potential barrier layers on top layers at two sides of the SiN passivation layer respectively; the AlGaN / GaN high electron mobility transistor is characterized in that a GaN layer and the AlGaN potential barrier layer are set between the first layer AlGaN / GaN heterojunction and the SiN passivation layer so as to form a second layer AlGaN / GaN heterojuntion (3); and the gate electrode covers the top portion of a second layer heterojuntion and the two side walls of the first and the second heterojunctions. According to the invention, the gate control ability is strong; the saturation current is large; the subthreshold property is good; and the AlGaN / GaN high electron mobility transistor can be used for microwave power apparatus with a shrot gate length, low power consumption and low noise.

Owner:XIDIAN UNIV

Display panel and display device

ActiveCN107768385AReduced subthreshold swingOptimization definitionSolid-state devicesSemiconductor devicesDisplay deviceEngineering

The invention provides a display panel and a display device, and relates to the technical field of display. The display substrate comprises a switch transistor and a drive transistor. The switch transistor and the drive transistor comprise active layers which comprise a first active layer in the switch transistor and a second active layer in the drive transistor gate insulating layers which are disposed on the active layers and comprise a first gate insulating layer in the switch transistor and a second gate insulating layer in the drive transistor. The first gate insulating layer comprises afirst silicon nitride layer and a first silicon oxide layer. The second gate insulating layer just comprises a second silicon oxide layer, and the thickness of the second silicon oxide layer is greater than the thickness of the first silicon oxide layer; or the second gate insulating layer comprises a second silicon nitride layer and a second silicon oxide layer, wherein the thickness of the second silicon oxide layer is greater than the thickness of the first silicon oxide layer, and the thickness of the second silicon nitride layer is less than the thickness of the first silicon nitride layer. The display panel can meet the quick start demands of the switch transistor while achieving the better definition of gray scale.

Owner:SHANGHAI TIANMA MICRO ELECTRONICS CO LTD

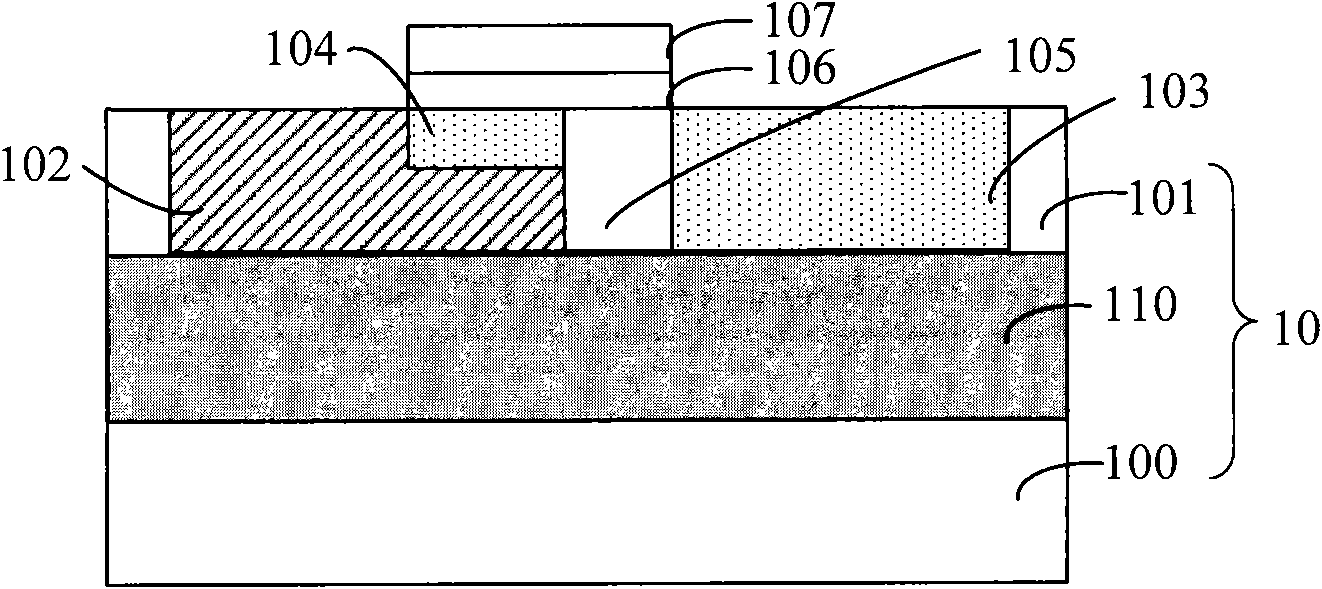

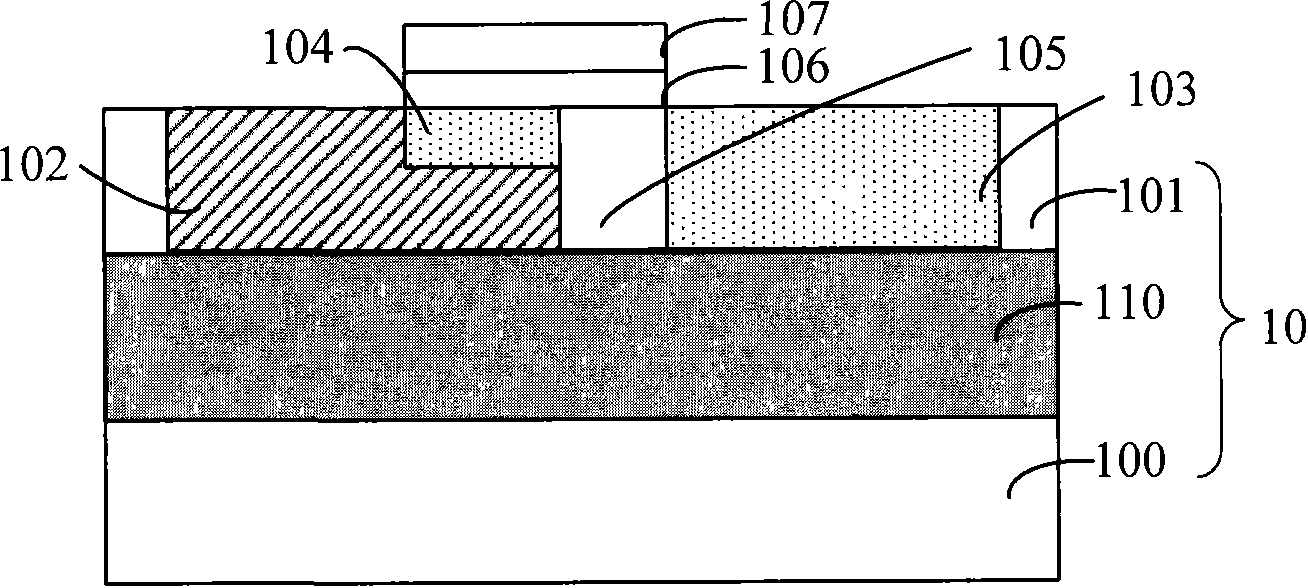

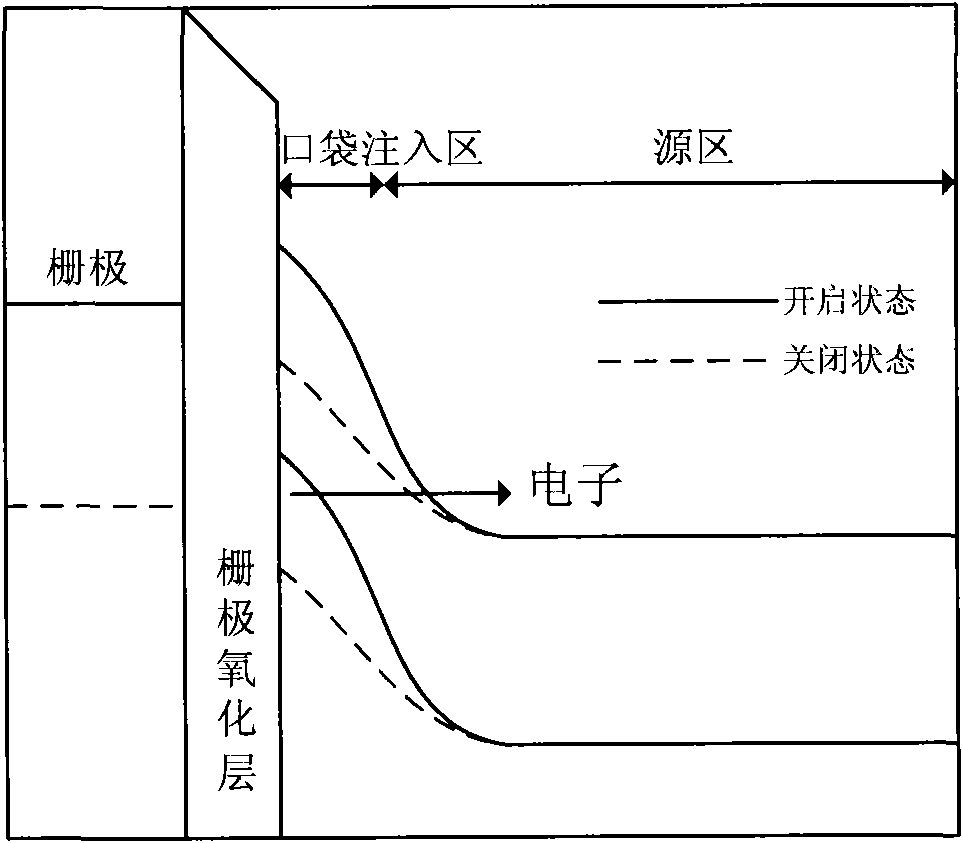

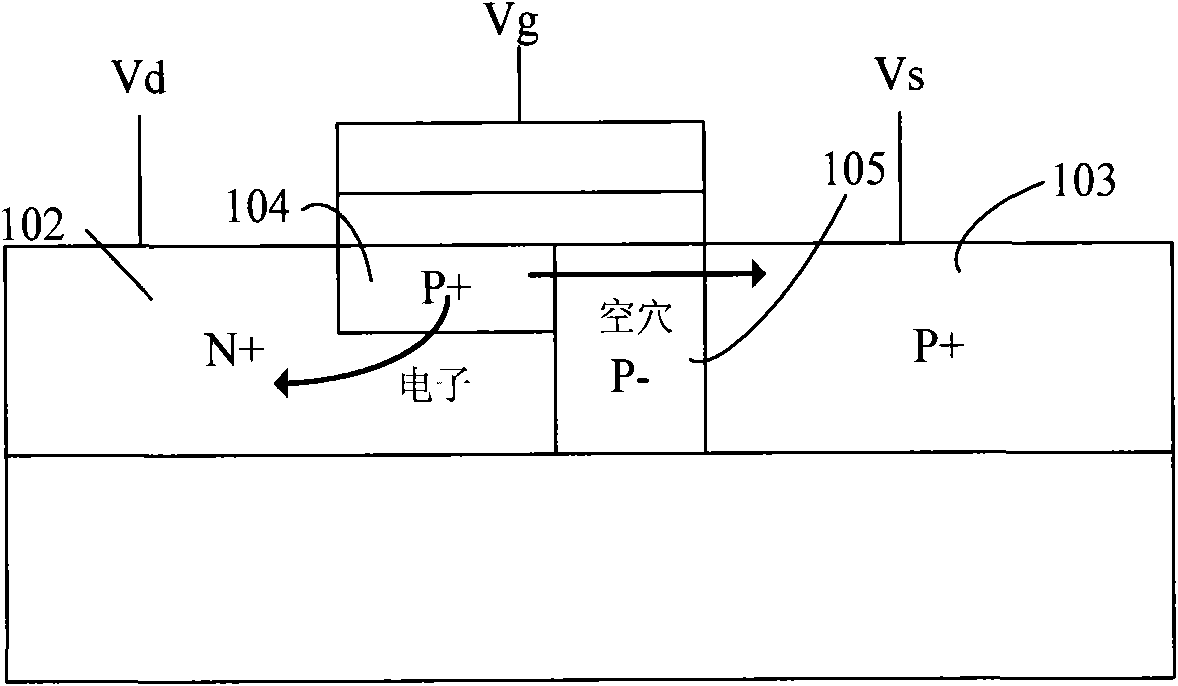

Dual-gate field-effect transistor

ActiveCN101894864AReduced subthreshold swingSmall threshold swingSemiconductor devicesScale downField-effect transistor

The invention provides a dual-gate field-effect transistor which comprises a device layer, a source, a drain, a channel region positioned between the source and the drain, a first gate structure and a second gate structure, wherein the device layer comprises a first surface and a second surface which are opposite to each other; the source and the drain are positioned in the device layer, isolated mutually and have different conduction types; the channel region sequentially comprises a first pocket injection region, a source connection region and a second pocket injection region from the first surface to the second surface of the device layer, the first and the second pocket injection regions are electrically connected with the drain, and the source connection region is electrically connected with the source; the first gate structure is positioned on the first surface of the device layer and corresponds to the position of the first pocket injection region; and the second gate structure is positioned on the second surface of the device layer and corresponds to the position of the second pocket injection region. The dual-gate field-effect transistor has high response speed and sensitive switching property, and can meet the demand of reducing the energy consumption after scaling down a device under small size and avoid the production of a series of secondary effects.

Owner:SEMICON MFG INT (SHANGHAI) CORP

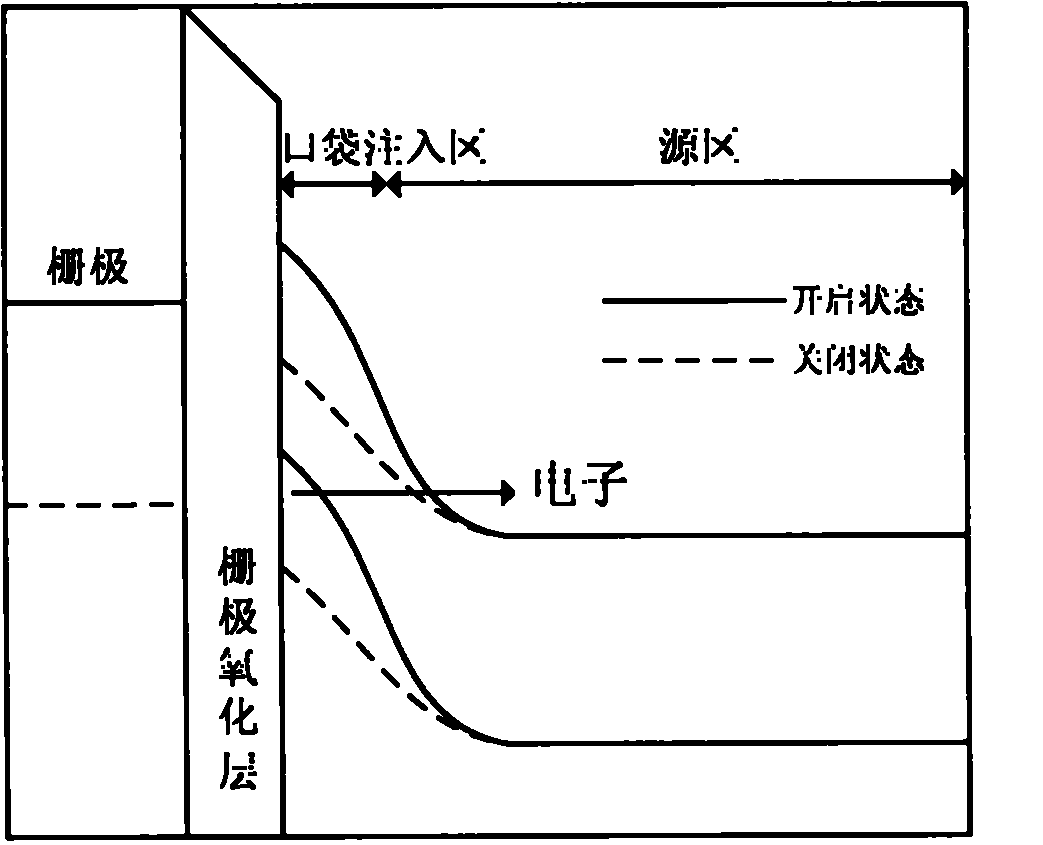

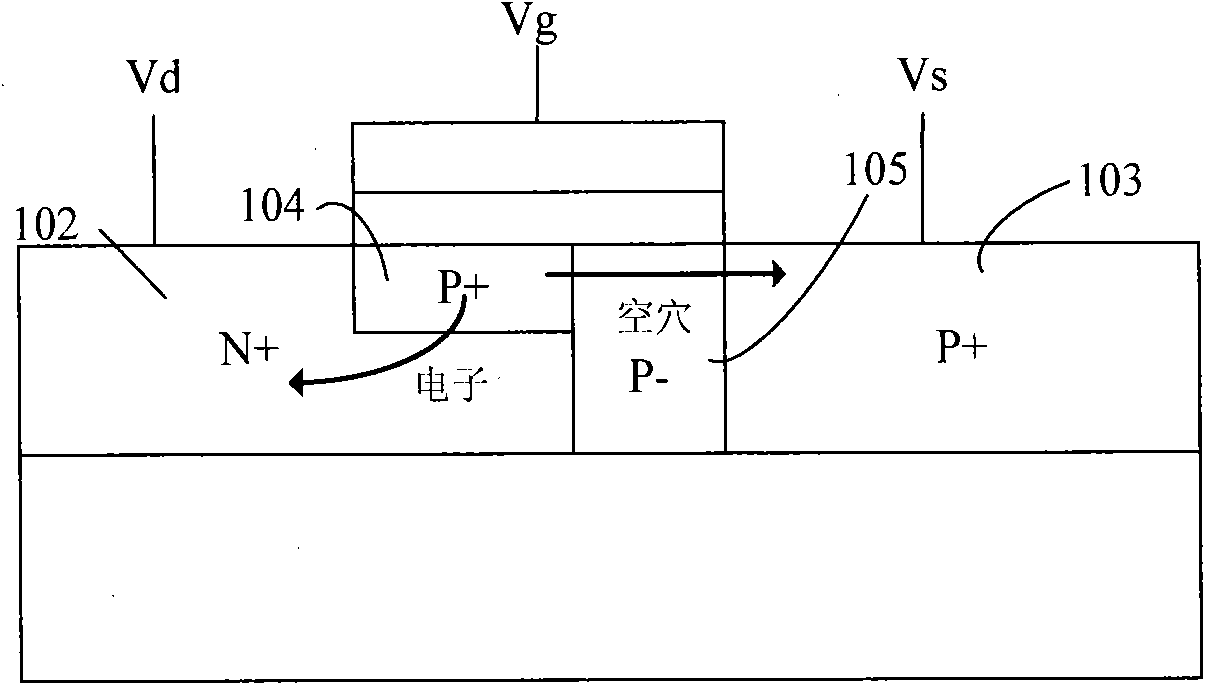

Green field effect transistor and manufacturing method thereof

ActiveCN101958344ALower energy requirementsReduced subthreshold swingSemiconductor/solid-state device manufacturingSemiconductor devicesCylindrical channelScale down

The invention relates to a green field effect transistor and a manufacturing method thereof, wherein the green field effect transistor comprises a silicon on insulator, a source electrode, a drain electrode and a channel body, wherein the silicon on insulator comprises a silicon substrate as well as a buried oxide layer and top layer silicon which are sequentially located on the silicon substrate; the source electrode and the drain electrode are located in the top layer silicon and isolated from each other and have different doping types; the cylindrical channel body is located between the source electrode and the drain electrode and sequentially comprises a source connector and a pocket injection layer from a cylindrical core to outside, one end of the channel body is connected to the source electrode, and the other end of the channel body is connected to the drain electrode; the source connector is electrically connected with the source electrode, and the pocket injection layer is electrically connected with the drain electrode; and a grid electrode structure located on the surface of the pocket injection layer of the channel body comprises a grid dielectric layer and a grid electrode on the surface of the grid dielectric layer. The green field effect transistor has the advantages of high response speed and sensitive switching characteristic, satisfies the requirements of a small size scaled-down device on reducing energy consumption and avoids generating a series of second-order effects.

Owner:SEMICON MFG INT (SHANGHAI) CORP

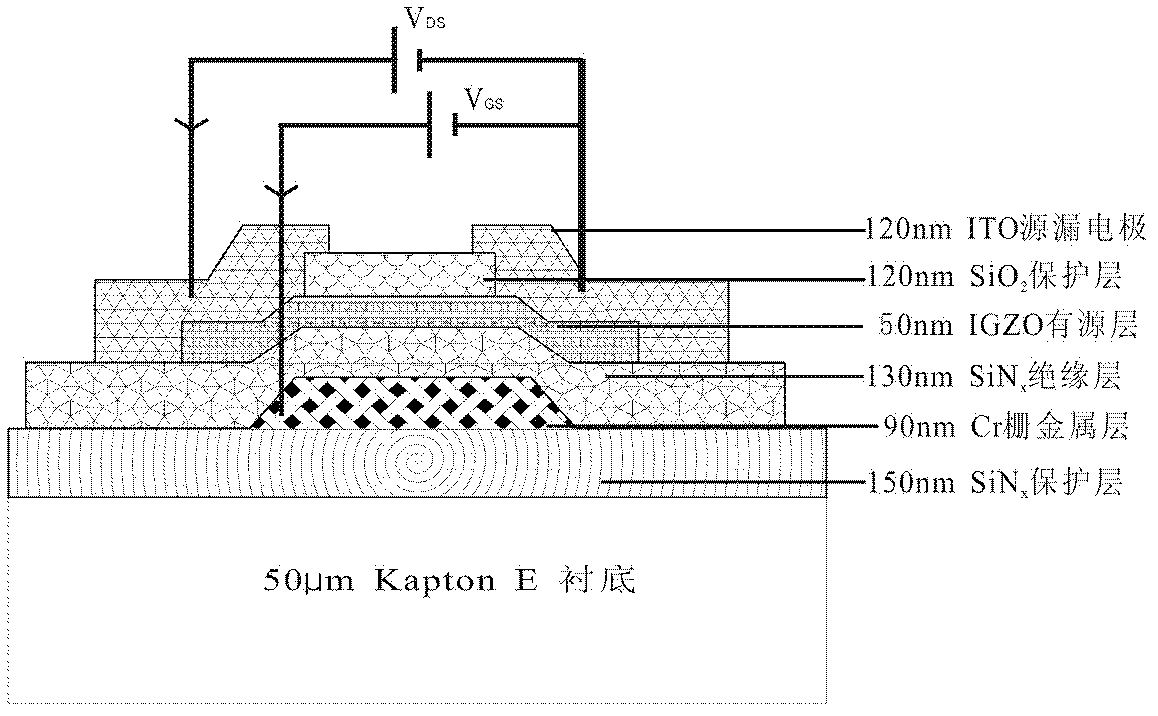

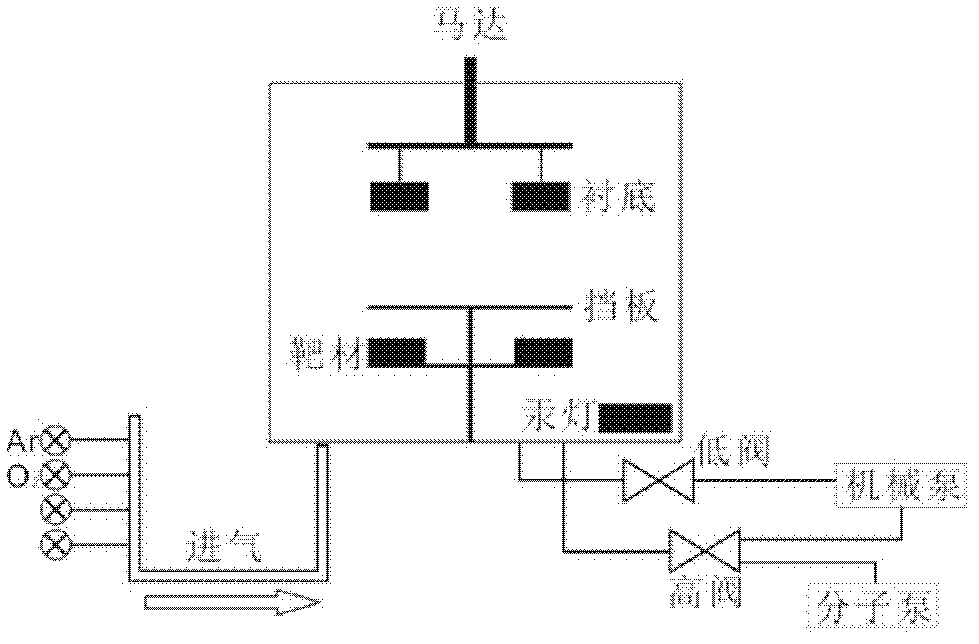

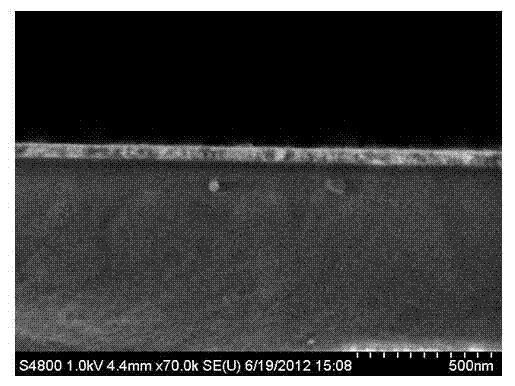

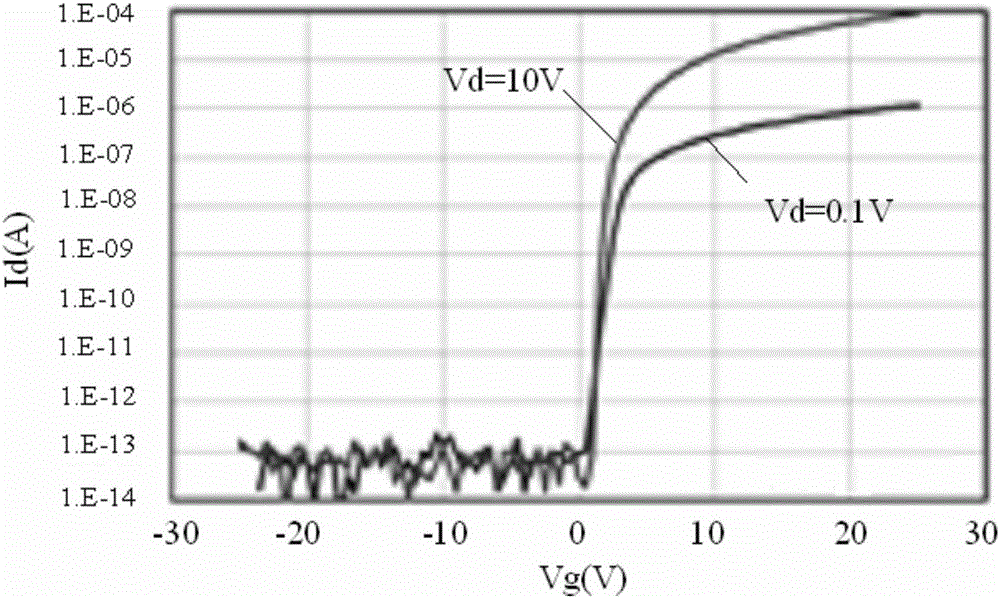

Method for manufacturing flexible IGZO (In-Ga-Zn-O) thin film transistor

InactiveCN102832131AOptimize deposition powerIncreasing the thicknessSemiconductor/solid-state device manufacturingIndividual semiconductor device testingDeposition temperatureEngineering

The invention provides a method for manufacturing a flexible IGZO (In-Ga-Zn-O) thin film transistor. The method comprises the following steps: step one, cleaning a flexible substrate; step two, depositing SiNx isolating layer by using PECVD (Plasma Enhanced Chemical Vapor Deposition); step three, preparing a gate electrode pattern; step four, preparing a gate insulating layer; step five, preparing an IGZO semiconductor layer; step six, preparing a source drain electrode; and step seven, preparing a protection layer. As the deposition temperature is reduced, and the deposition power of the protection layer and the thickness of a silicon nitride insulating layer are optimized, a flexible IGZO-TFT (Thin Film Transistor) device is manufactured successfully, the performances of the flexible IGZO-TFT are as follows: the threshold voltage is 8V, the switching ratio is 5*107, the saturated migration rate is 7.8cm2 / V.s, and the subthreshold slope factor is 0.9V / dec; the device is arranged on a cylinder with the curvature radius being 10mm is bent for 3 minutes, and the performances can not be changed basically; and the protection layer plays an important role in the stability of the device.

Owner:GUANGDONG SINODISPLAY TECH

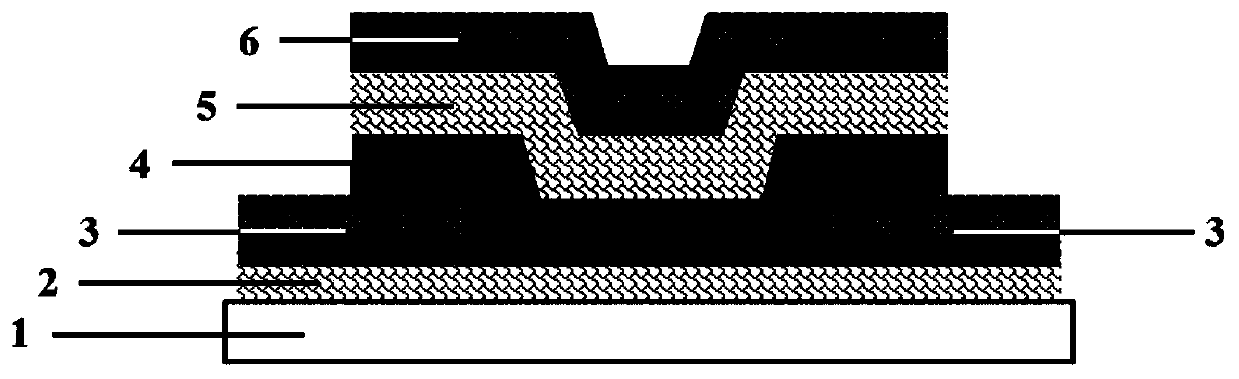

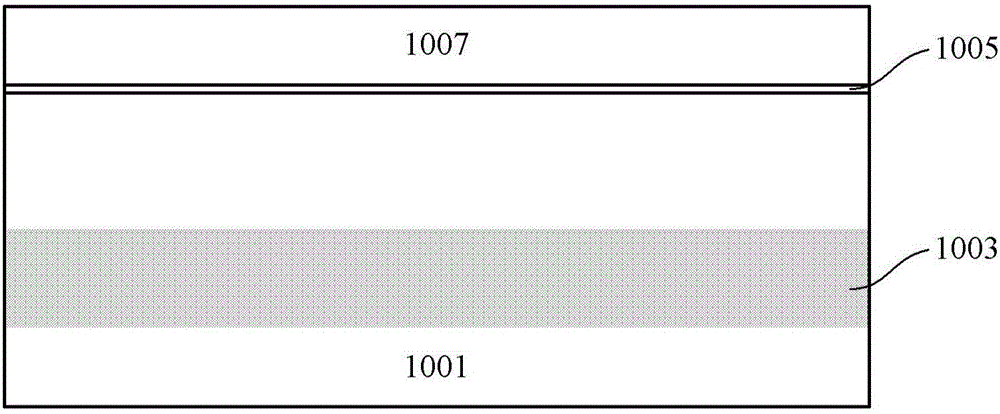

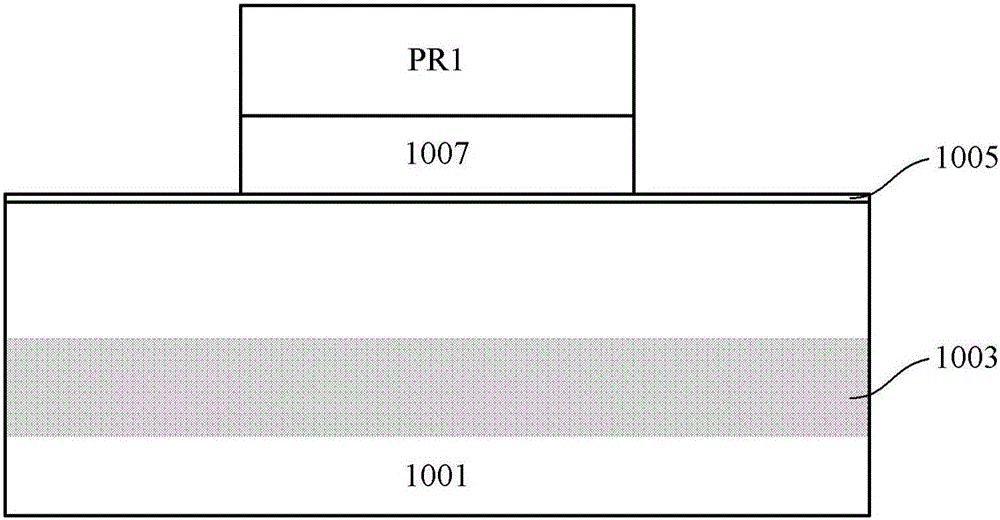

Low temperature poly silicon thin film transistor and fabrication method thereof

InactiveCN105140294AReduce leakage currentReduced subthreshold swingTransistorSemiconductor/solid-state device manufacturingInsulation layerSilicon thin film

The invention discloses a low temperature poly silicon thin film transistor and a fabrication method thereof. The low temperature poly silicon thin film comprises a substrate, a shading layer, a buffer layer, a poly silicon layer, a gate insulation layer, a gate and at least gate surrounding channel. With the design of the gate surrounding channel, the leakage current generated by the thin film transistor can be effectively reduced.

Owner:WUHAN CHINA STAR OPTOELECTRONICS TECH CO LTD

Manufacturing method of gate controlled diode semiconductor device

InactiveCN102592997AReduce manufacturing costSimple processSemiconductor/solid-state device manufacturingDiodeDriving currentPower semiconductor device

The invention belongs to the technical field of the manufacture of semiconductor devices, and specifically relates to a manufacturing method of a gate controlled diode semiconductor device. The manufacturing method is characterized in that a low temperature technology is adopted to prepare the gate controlled diode semiconductor device, the technical process is simple, the manufacturing cost is low, and the manufactured gate control diode device has the advantages of large drive current and small sub-threshold amplitude. The manufacturing method of the gate controlled diode semiconductor device provided by the invention is particularly suitable for panel display and a read-write device of a phase change memorizer and manufacture based on the semiconductor device of a flexible substrate.

Owner:FUDAN UNIV

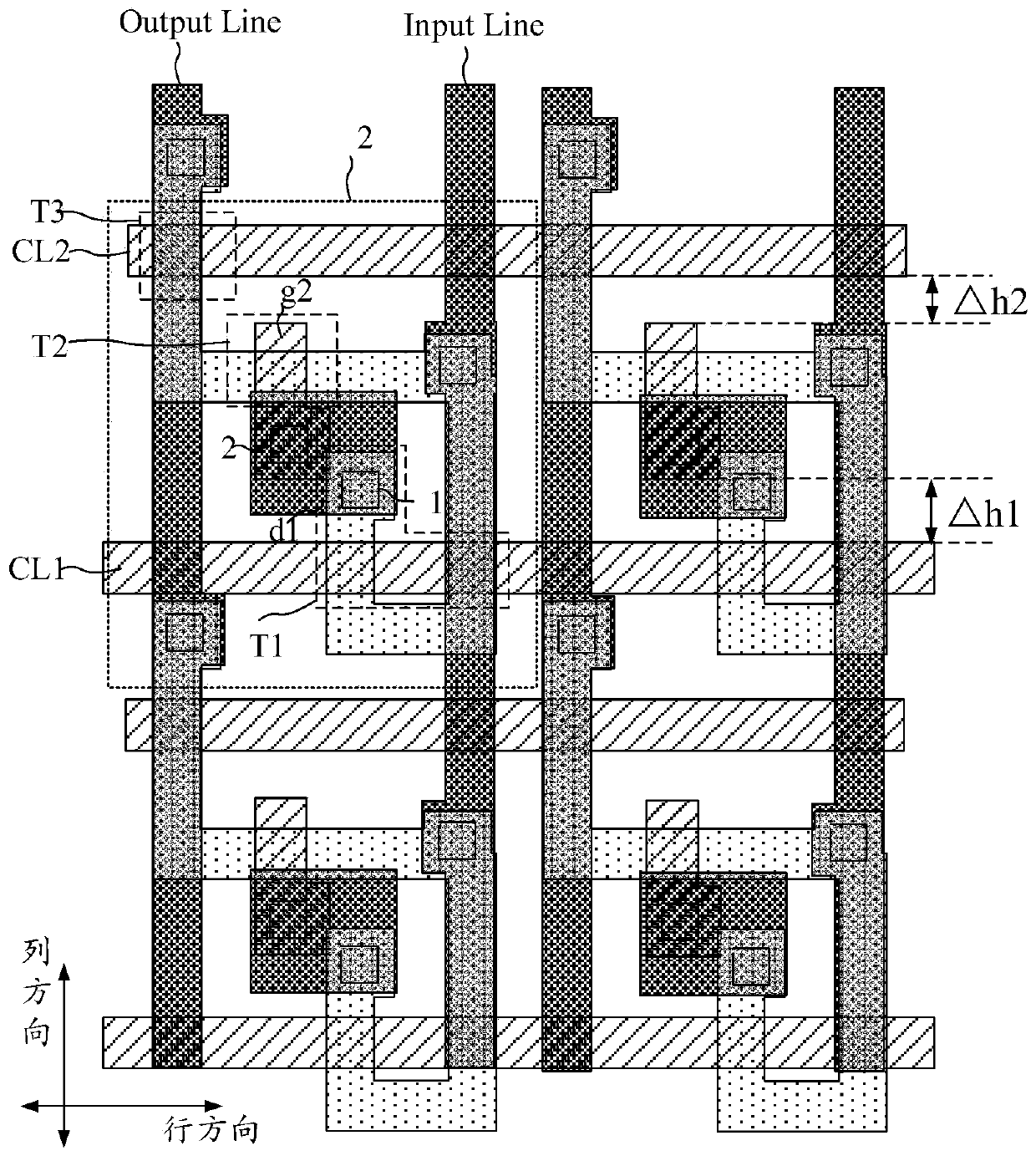

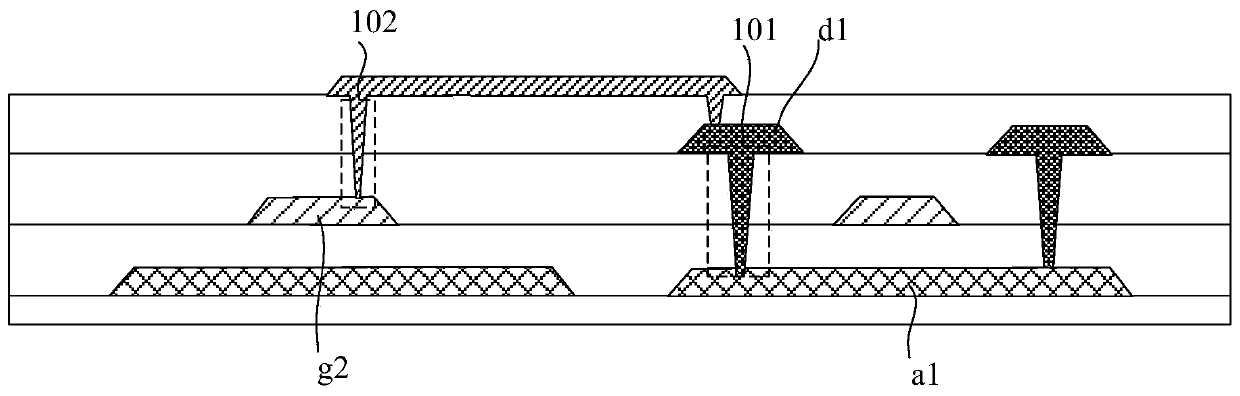

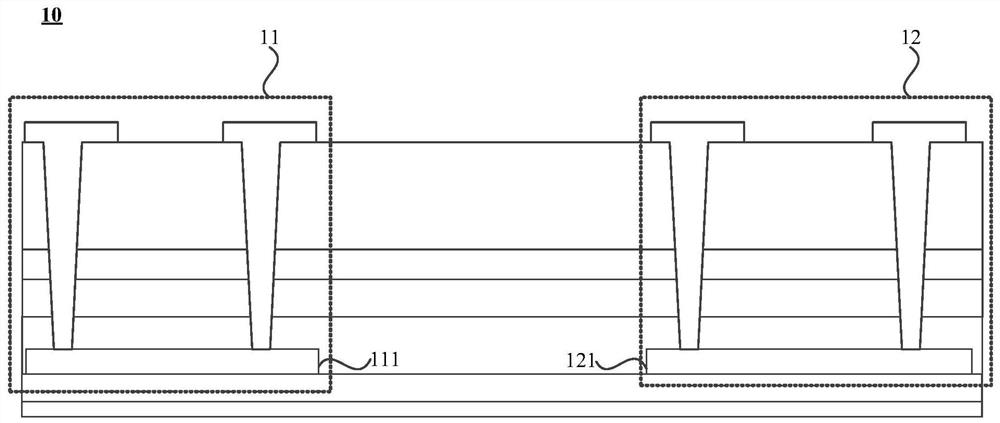

Array substrate, manufacturing method thereof and display device

ActiveCN110516637AReduce widthReduce spacingSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringDisplay device

The embodiment of the invention provides an array substrate, a manufacturing method of the array substrate and a display device, relates to the technical field of display. The number of sensor drivingcircuits per unit area is increased. The array substrate comprises a sensor driving circuit, and the sensor driving circuit comprises a first transistor which comprises a first active layer, a firstgrid electrode connected with a first control signal line, a first source electrode and a first drain electrode; a second transistor which comprises a second active layer, a second grid electrode connected with the first drain electrode, a second source electrode and a second drain electrode; a third transistor which comprises a third active layer, and a third grid electrode, a third source electrode and a third drain electrode which are connected with the second control signal line; wherein the first control signal line, the second control signal line, the first gate and the third gate are positioned on the first film layer; the first source electrode, the second source electrode, the second drain electrode, the third source electrode and the third drain electrode are located on the second film layer, the first drain electrode and the second grid electrode are located on the third film layer, the first film layer, the second film layer and the third film layer are located on differentlayers, and the first drain electrode is connected with the first active layer through a via hole.

Owner:SHANGHAI AVIC OPTOELECTRONICS

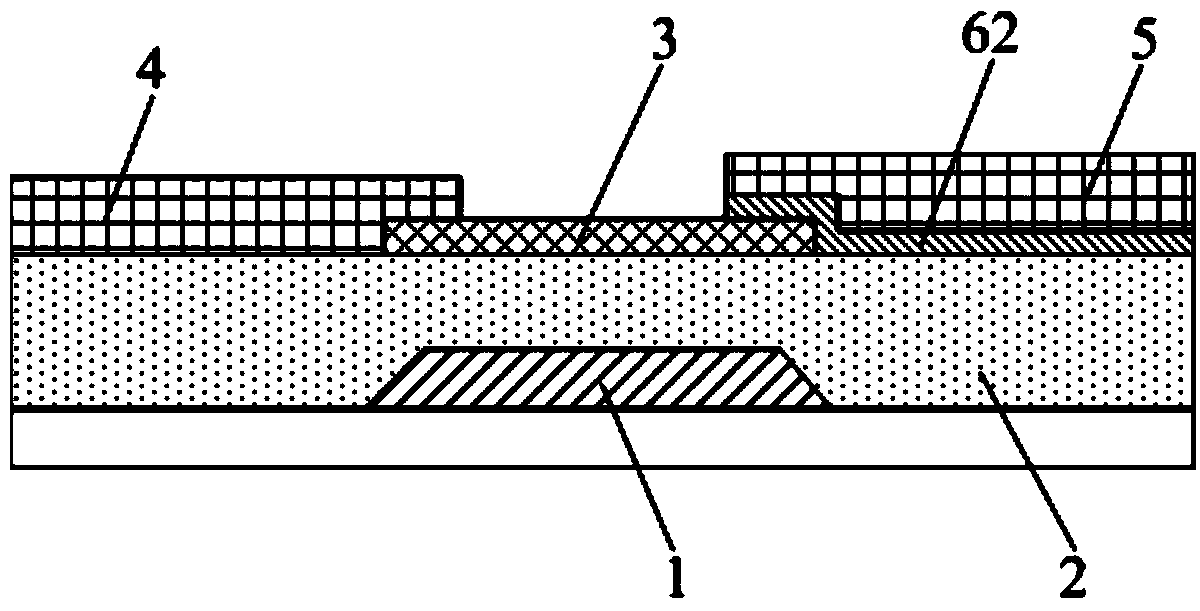

Oxide semiconductor thin-film transistor and preparation method thereof

InactiveCN102637742AImprove driving abilityMinus interface defect statesSemiconductor/solid-state device manufacturingSemiconductor devicesCMOSRadio frequency magnetron sputtering

The invention discloses an oxide semiconductor thin-film transistor and a preparation method for the oxide semiconductor thin-film transistor, belonging to the technical fields of semiconductor integrated circuits and manufacturing of the semiconductor integrated circuits. Two layers of AlZnO thin-film materials are formed as active areas by adoption of a radio frequency magnetron sputtering method, and the two layers of the AlZnO thin-film materials contain different oxygen ion contents. The oxide semiconductor thin-film transistor disclosed by the invention has the advantages of high migration rate. The preparation method disclosed by the invention and the existing CMOS (complementary metal-oxide-semiconductor transistor) technology are compatible, so that the preparation method has higher practical value, and can be applied in future TFT (thin-film transistor) integrated circuits.

Owner:PEKING UNIV

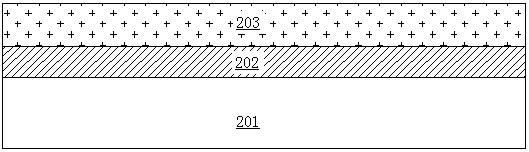

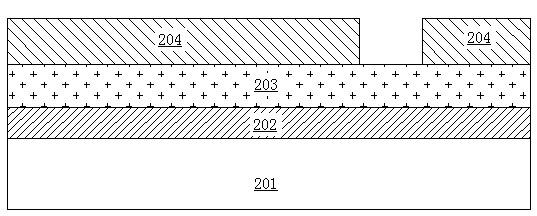

Negative capacitance-based surrounding gate field effect transistor and manufacturing method thereof

InactiveCN107845679ASimple preparation processReduced subthreshold swingNanoinformaticsSemiconductor/solid-state device manufacturingCapacitanceNanowire

The invention provides a negative capacitance-based surrounding gate field effect transistor and a manufacturing method thereof. A ferroelectric material layer is formed between a high-K dielectric layer and a metal gate layer of a gate region structure of the negative capacitance-based surrounding gate field effect transistor; and the ferroelectric material layer has negative capacitance. The ferroelectric material layer with negative capacitance is used as a built-in voltage amplifier, so that the subthreshold range of oscillation of the device can be lowered to be 60mV / decade or below. Thetransistor adopts Si nanowires as a channel material, and the high-K metal gate fully surrounds the Si nanowires, so that higher gate control capability can be obtained and a short channel effect canbe avoided. The manufacturing method of the negative capacitance-based surrounding gate field effect transistor is simple in manufacturing process, and lowering of production cost can be facilitated.

Owner:ZING SEMICON CORP

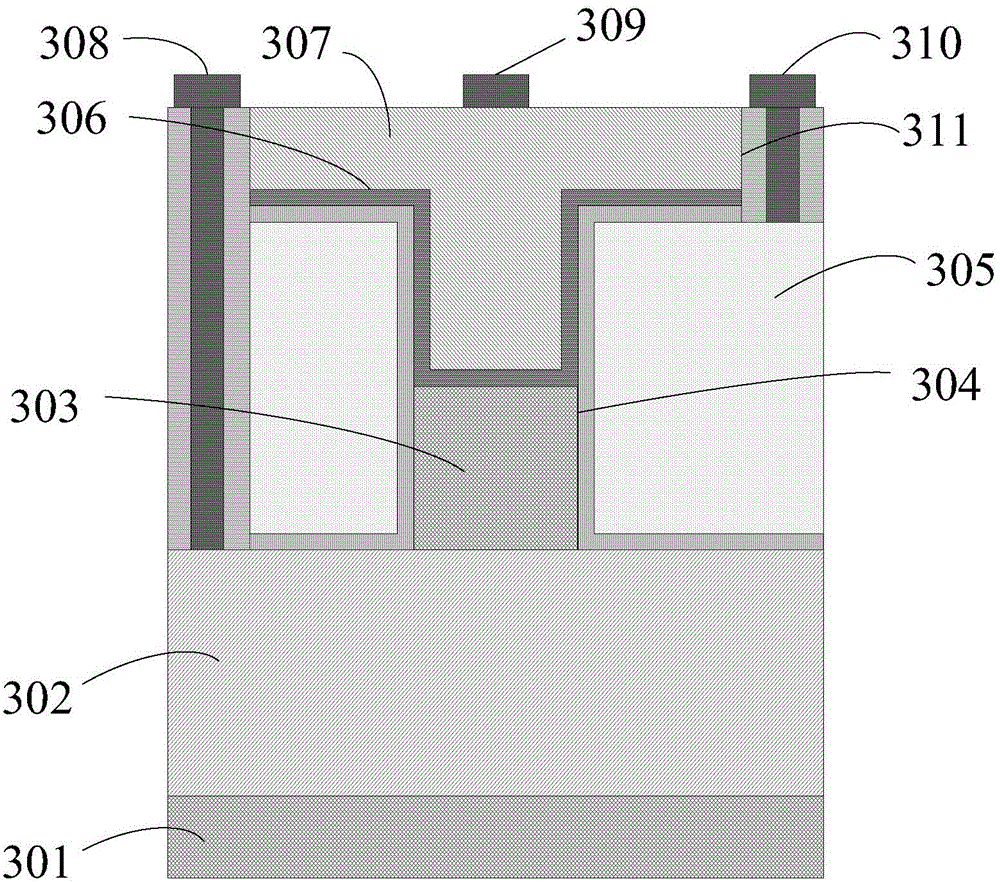

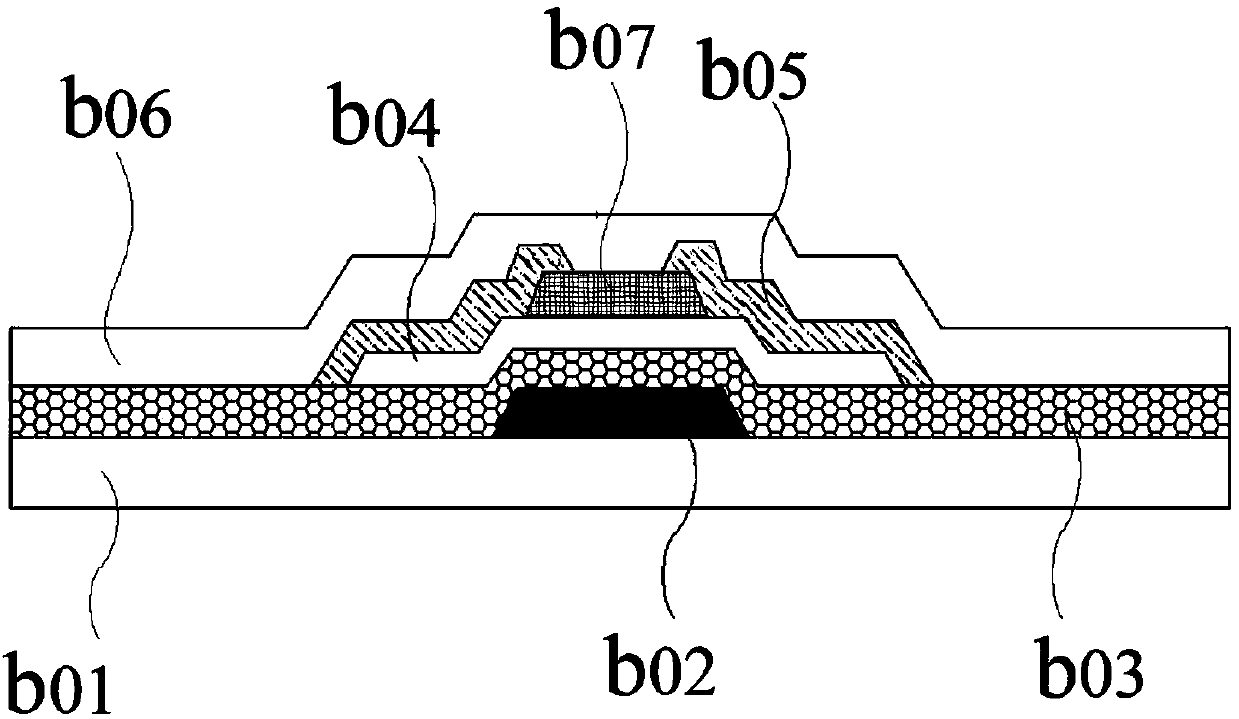

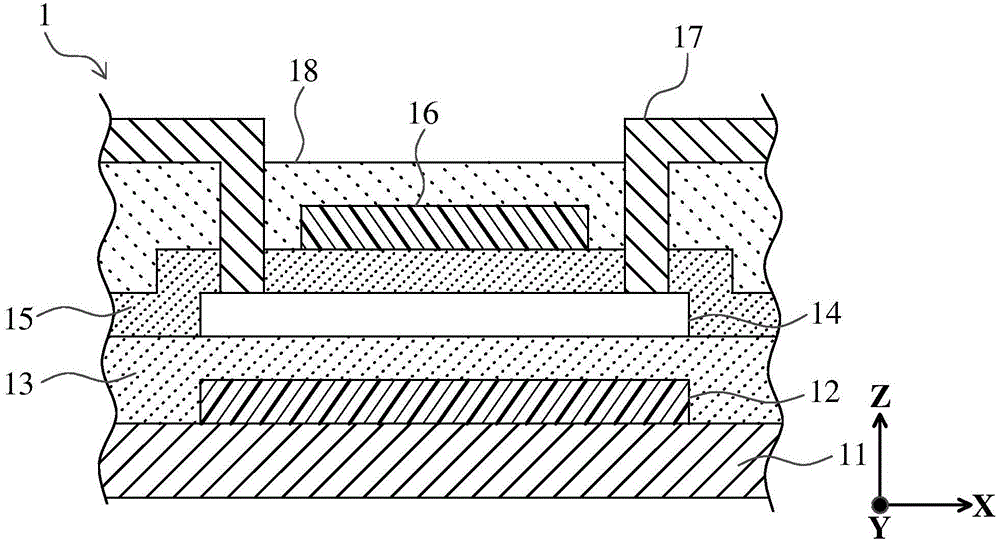

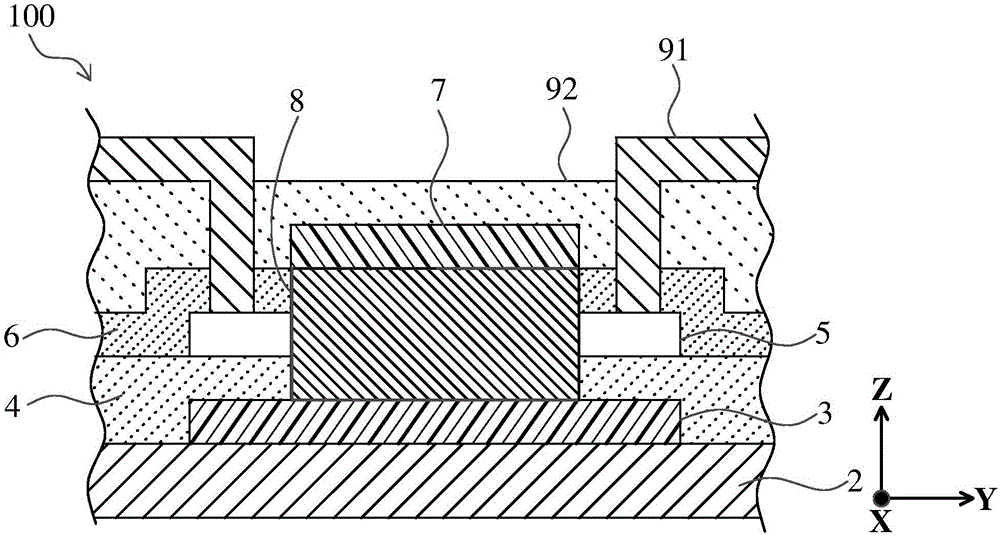

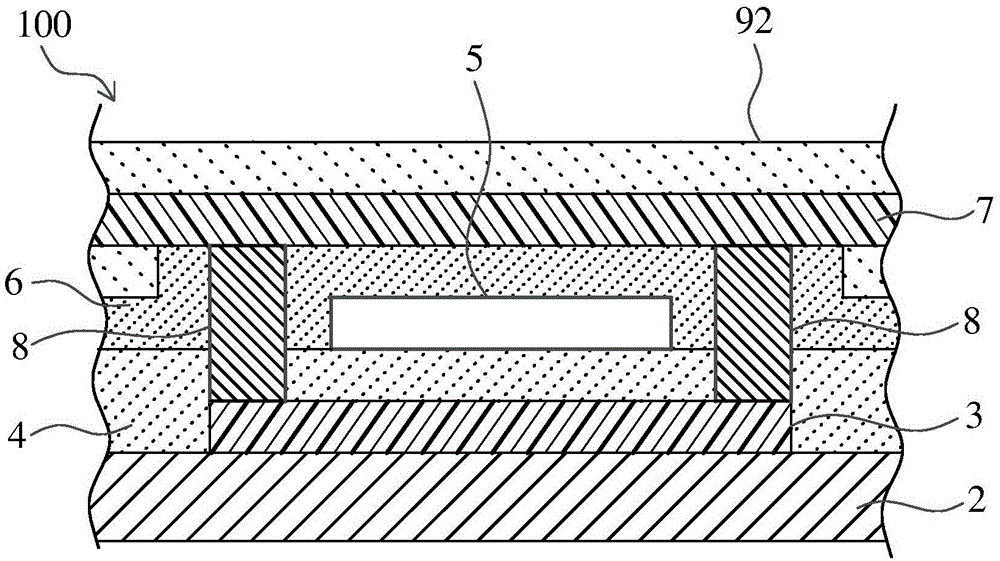

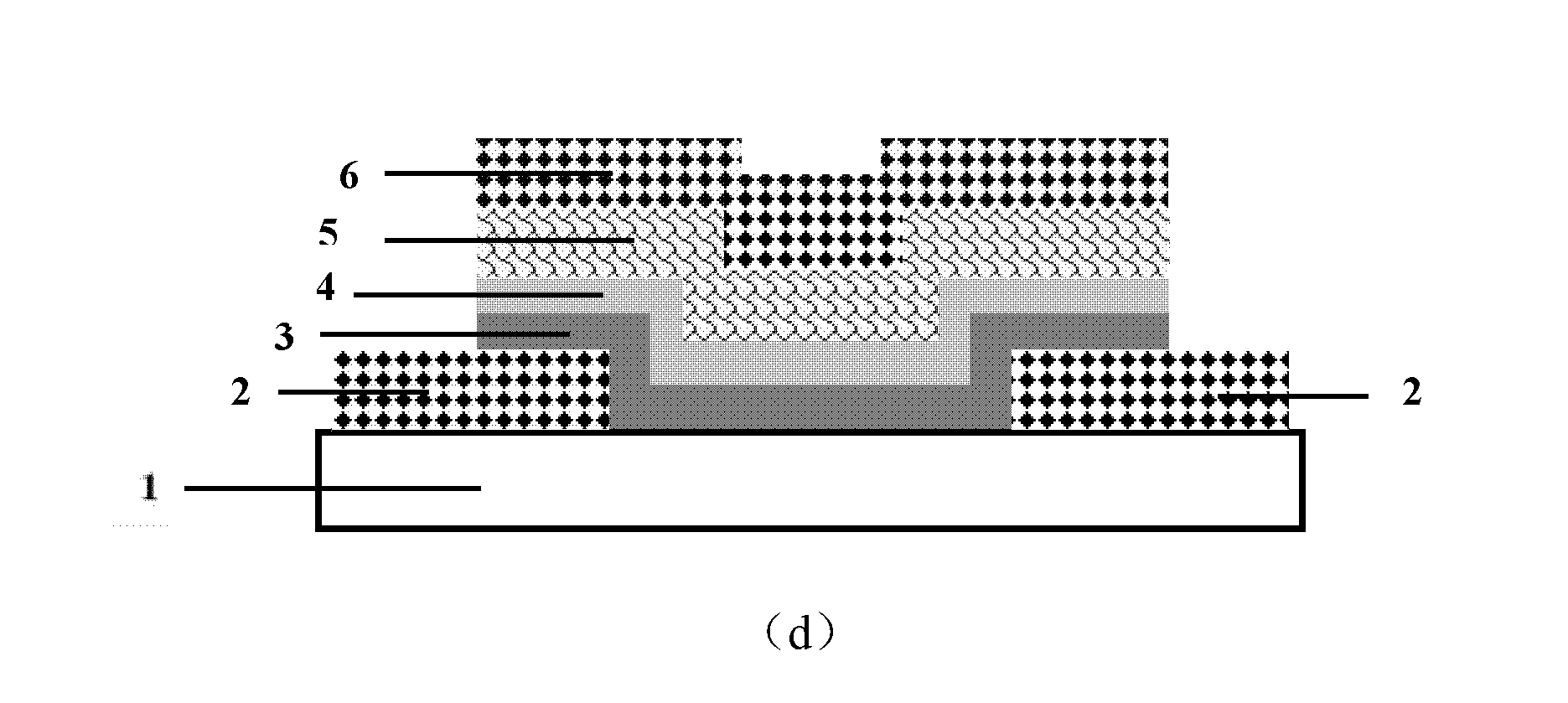

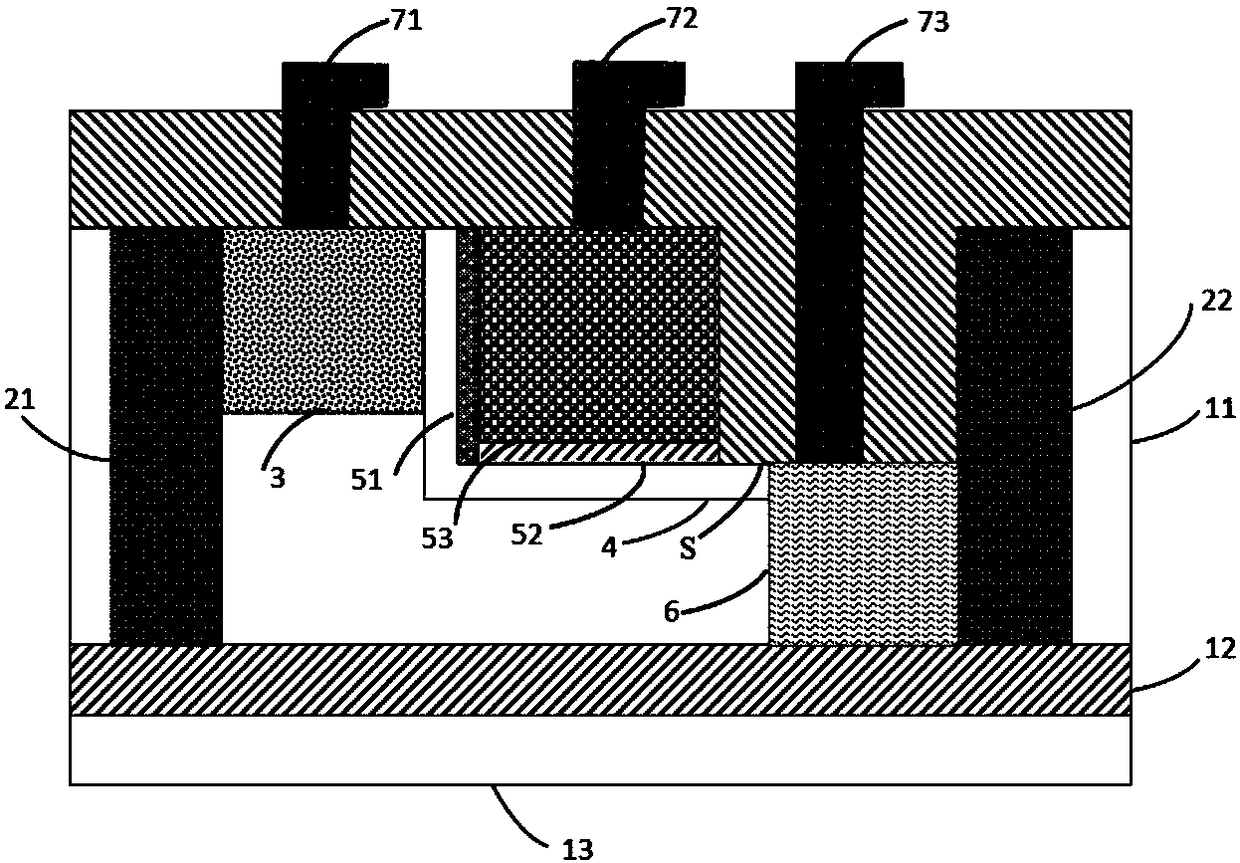

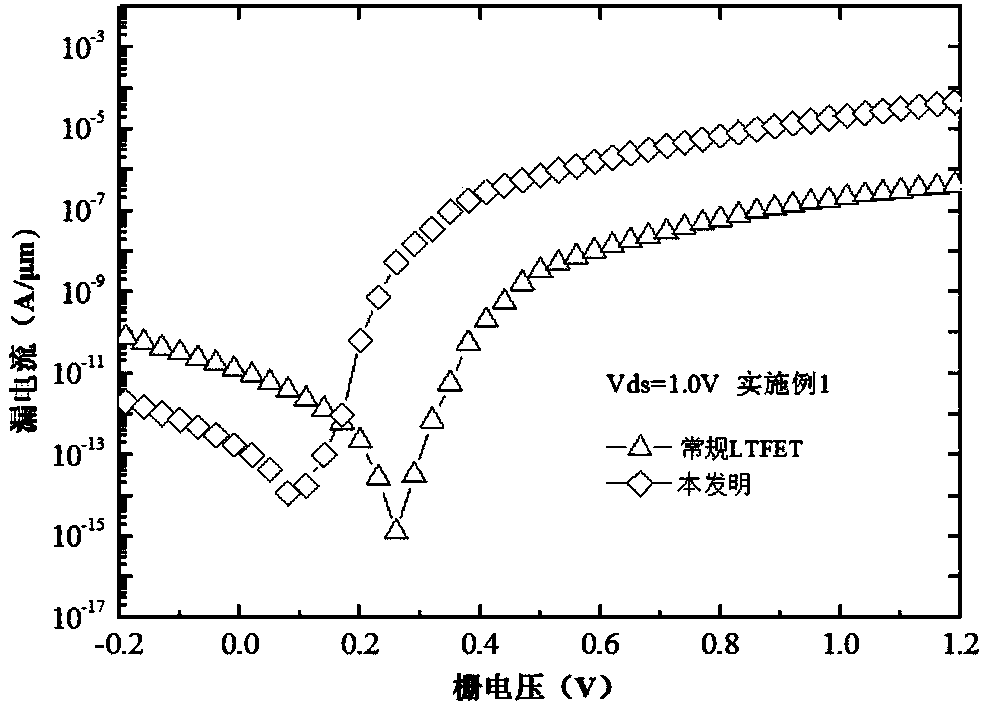

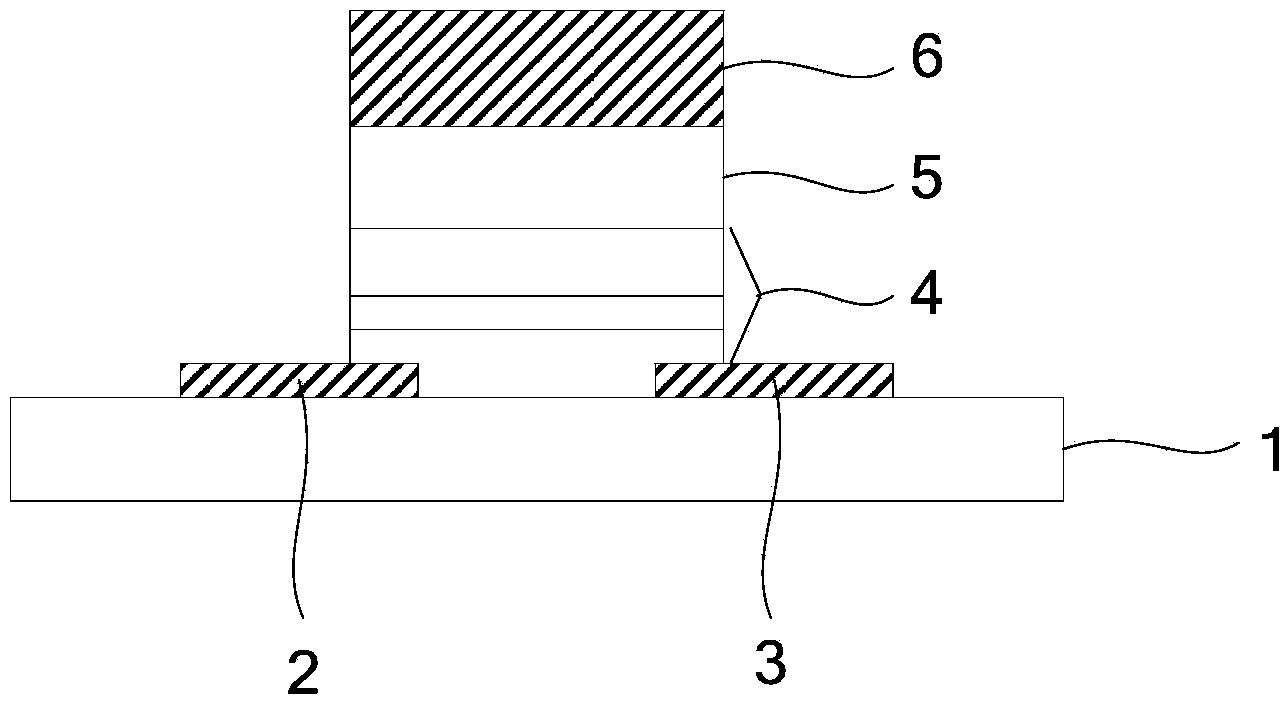

Optimized L-type tunneling field effect transistor and preparation method thereof

ActiveCN108538911AShorten tunneling distanceIncrease drive currentSemiconductor/solid-state device manufacturingDiodeDriving currentSemiconductor materials

The invention discloses an optimized L-type tunneling field effect transistor and a preparation method thereof and mainly solves the problems of low on state current and severe bipolar effect of an existing device. The optimized L-type tunneling field effect transistor comprises an SOI (silicon on insulator) substrate (1), isolation grooves (2), a source region (3), a channel region (4), a drain region (6), a gate region (5) and a conducting layer (7), wherein the isolation grooves (2) are located on two sides of the SOI substrate (1), and the source region (3), the channel region (4) and thedrain region (6) are located on the upper surface of the SOI substrate; the gate region (5) is located on the upper side of the channel region (4); the source region (3) is made of a germanium semiconductor material, the gate region (5) is of a hetero-gate dielectric structure, a high-k dielectric material is adopted on one side close to the source region, and a low-k dielectric material is adopted on one side close to the drain region; a space S is formed between the drain region (6) and the right margin of the gate region (5). The optimized L-type tunneling field effect transistor can effectively inhibit the bipolar effect, increases drive current and can be applied to manufacture of large-scale integrated circuits.

Owner:西安电子科技大学重庆集成电路创新研究院

Oxide thin film transistor and manufacturing method thereof

ActiveCN103545377AImprove electrical stabilityImprove bindingTransistorSemiconductor/solid-state device manufacturingOxide thin-film transistorAlloy thin film

The invention discloses an oxide thin film transistor and a manufacturing method of the oxide thin film transistor. The transistor comprises a source electrode, a drain electrode and an IGZO thin film layer and further comprises a hafnium neodymium alloy thin film layer, wherein a first surface of the IGZO thin film layer makes contact with the source electrode and the drain electrode, and the other surface back on to the first surface of the IGZO thin film layer makes contact with the hafnium neodymium alloy thin film layer. The oxide thin film transistor has stable electrical properties.

Owner:SHENZHEN DANBANG INVESTMENT GROUP

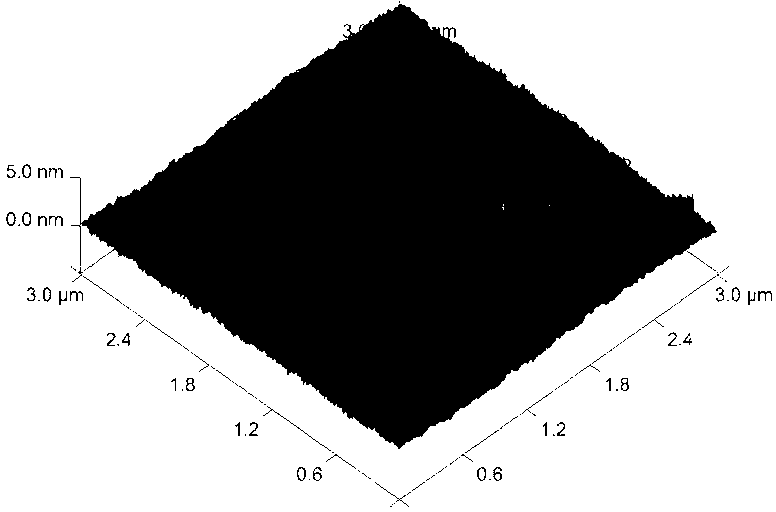

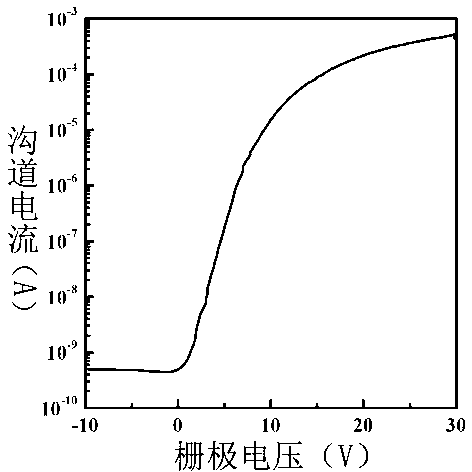

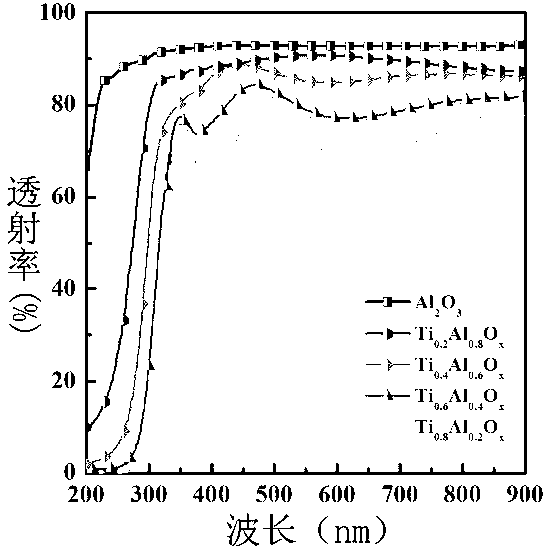

Titanium aluminum oxide thin film and preparation method and application thereof

InactiveCN103274435AImprove performanceAvoid hydrolysisAluminium oxides/hydroxidesGate dielectricSwitched current

The invention belongs to the technical field of preparation of transistors, and in particular relates to a titanium aluminum oxide thin film and a preparation method and application thereof. The aluminum oxide titanium thin film is prepared by a sol-gel method. The method comprises the following steps of: with ethylene glycol monomethyl ether as a solvent and concentrated hydrochloric acid as an additive, dissolving Al(C4H9O)3 and Ti(C4H9O)4 in the solvent to form a clear and stable precursor solution; and spirally coating the precursor solution on a glass substrate, and obtaining the aluminum oxide titanium thin film after thermal pretreatment and subsequent high-temperature heat treatment. The invention further relates to a preparation method of a thin film transistor by using titanium aluminum oxide as a gate dielectric layer. According to the IZO thin film transistor with the titanium aluminum oxide as the gate dielectric layer, the switching current ratio is greater than 1*10<6>, the saturation migration rate is greater than 1.1cm<2> / Vs, and the subthreshold amplitude is less than 1.5V / dec.

Owner:FUDAN UNIV

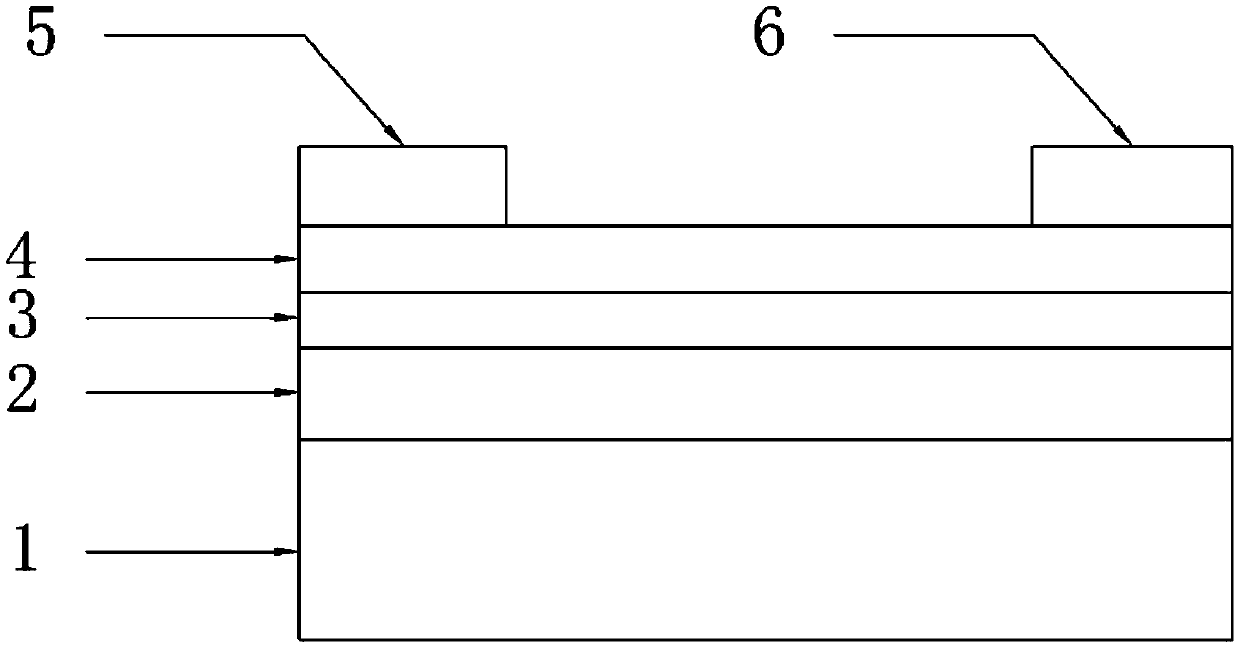

Low-voltage transparent oxide thin film transistor and preparation method thereof

ActiveCN105514172ALow preparation temperatureMild conditionsTransistorSemiconductor/solid-state device manufacturingDielectricLow voltage

The invention discloses a low-voltage transparent oxide thin film transistor and a preparation method thereof. The thin film transistor comprises a substrate, a gate electrode insulating layer, an active layer, a source electrode and a drain electrode, wherein the substrate is a piece of ITO conductive glass, an upper ITO conductive film on the ITO conductive glass is an ITO gate electrode, the gate electrode insulating layer is a transparent ZrO2 film and is disposed on the ITO gate electrode, the active layer is a transparent oxide film and is disposed on the gate electrode insulating layer, and the source electrode and the drain electrode are transparent ITO films and are disposed on the active layer. According to the transparent oxide thin film transistor, as the gate electrode insulating layer is a ZrO2 film with high dielectric constant, full transparency and low-voltage switching-on characteristics of the thin film transistor are achieved, the thin film transistor is of high switching ratio and carrier mobility, and the thin film transistor has a broad application prospect in flat display, transparent electronic devices, flexible display and other fields. By using the thin film transistor as a pixel switch, the opening ratio of an active matrix is improved greatly, the brightness is improved, and the power consumption is reduced.

Owner:HENAN UNIVERSITY

Thin film transistor, array substrate, and display device

ActiveCN104167446AReduced subthreshold swingImprove conduction performanceTransistorSolid-state devicesSub thresholdOxygen vacancy

The invention provides a thin film transistor, an array substrate, and a display device. The thin film transistor consists of a gate electrode, a gate insulating layer, an active layer, a source electrode and a drain electrode; the gate insulating layer is arranged between the gate electrode and the active layer; the source electrode and the drain electrode are respectively and correspondingly arranged at the two ends of the active layer; and the active layer is made of a metallic nitrogen-oxide material. Besides, the thin film transistor also includes a conductive oxygen vacancy reduction layer that is arranged between the active layer and the source electrode and / or is arranged between the active layer and the drain electrode; and the conductive oxygen vacancy reduction layer is used for carrying out oxygen vacancy reduction in the active layer. According to the thin film transistor, because the oxygen vacancy reduction layer is arranged, the number of oxygen vacancy units in the active layer is substantially reduced, thereby improving the transmission rate of the carrier; and the sub threshold swinging of the thin film transistor is also reduced and thus the conduction performance of the thin film transistor is substantially improved.

Owner:BOE TECH GRP CO LTD

Manufacture method of thin film transistor and with indium zinc aluminum oxide as channel layer

InactiveCN102779758AImprove performanceLow costSemiconductor/solid-state device manufacturingIndiumOxide thin-film transistor

The invention belongs to the technical field of thin film transistors and particularly relates to a manufacture method of a thin film transistor and with indium zinc aluminum oxide as a channel layer. The method utilizes aluminum to be mingled with indium zinc aluminum oxide to obtain an indium zinc aluminum oxide semiconductor film and improve performance of the channel layer of an indium zinc aluminum oxide semiconductor. The manufacture method utilizes the impregnation pulling method process which is low in cost, simple in process, easy to prepare in large area to prepare an indium zinc aluminum oxide thin film which is smooth in surface and even and compact in thickness, and the indium zinc aluminum oxide thin film is applied to manufacture of oxide thin film transistors. A manufactured thin film transistor device is good in comprehensive performance and has high saturation migration rate which is 26.8cm<2> / Vs and low subthreshold amplitude which is 0.24V / decade. The switch ratio is larger than 104.

Owner:FUDAN UNIV

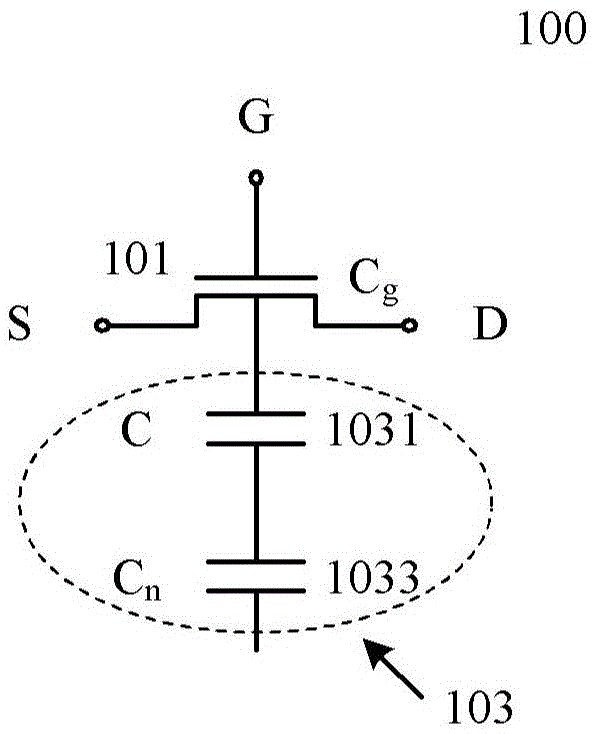

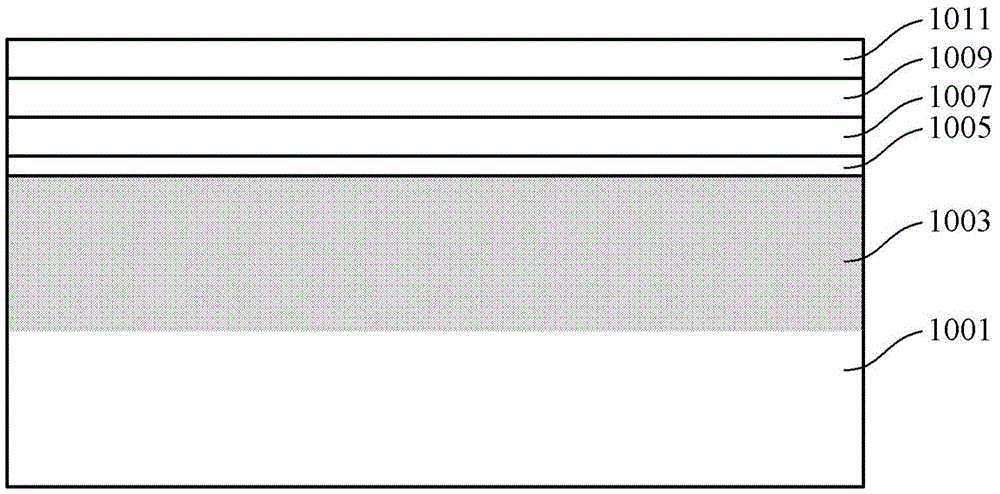

Semiconductor device having back gate connected with negative capacitor, manufacturing method for semiconductor device, and electronic equipment

ActiveCN105609562AReduced subthreshold swingReduced shutdown currentTransistorSolid-state devicesCapacitanceCapacitor

The invention discloses a semiconductor device having a back gate connected with a negative capacitor, a manufacturing method for the semiconductor device, and electronic equipment including the semiconductor device. According to embodiments, the semiconductor device can comprise a transistor and the negative capacitor, wherein the transistor can comprise a control gate and the back gate, and the negative capacitor is connected with the back gate in series.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

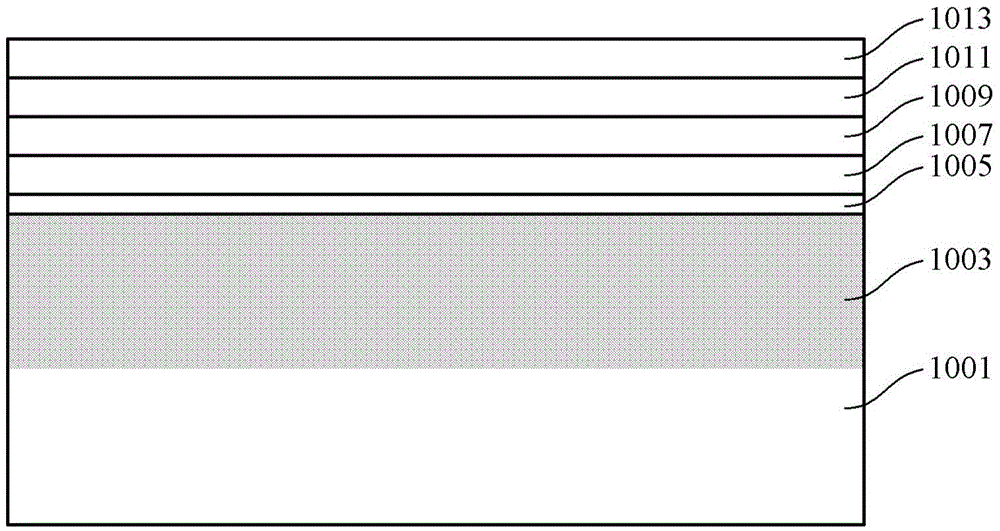

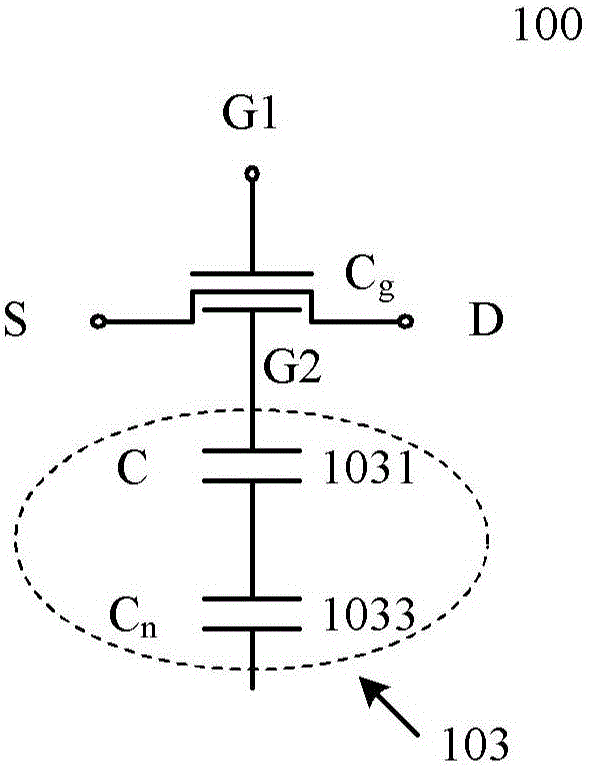

Semiconductor device with multi-gate FinFETs and manufacturing method of semiconductor device and electronic equipment

ActiveCN105742362AReduced subthreshold swingReduced shutdown currentSolid-state devicesSemiconductor/solid-state device manufacturingCapacitorSemiconductor

The invention discloses a semiconductor device and a manufacturing method thereof and electronic equipment comprising the semiconductor device. The semiconductor device comprises multi-gate FinFETs, wherein one of gates of the multi-gate FinFETs is connected to a negative capacitor. According to the embodiment, the semiconductor device can comprise the first FinFET, the second FinFET and the negative capacitor; the first FinFET can comprise first fins and gates; the first fins are formed on a substrate; the gates are formed on the substrate and are intersected with the first fins; the second FinFET can comprise second fins, first gates and second gates; the second fins are formed on the substrate; each first gate is formed at the first side of the corresponding second fin on the substrate and is intersected with the corresponding second fin; each second gate is formed at the second side, opposite to the first side, of the corresponding second fin on the substrate, is intersected with the corresponding second fin and is opposite to the corresponding first gate; and the negative capacitor is connected to the second gates of the second FinFET.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

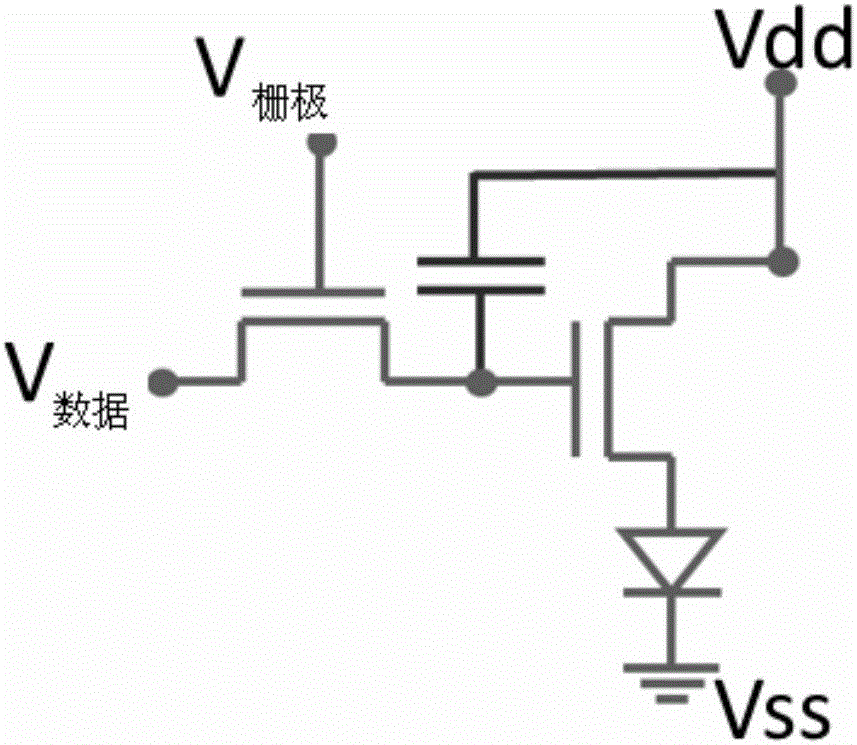

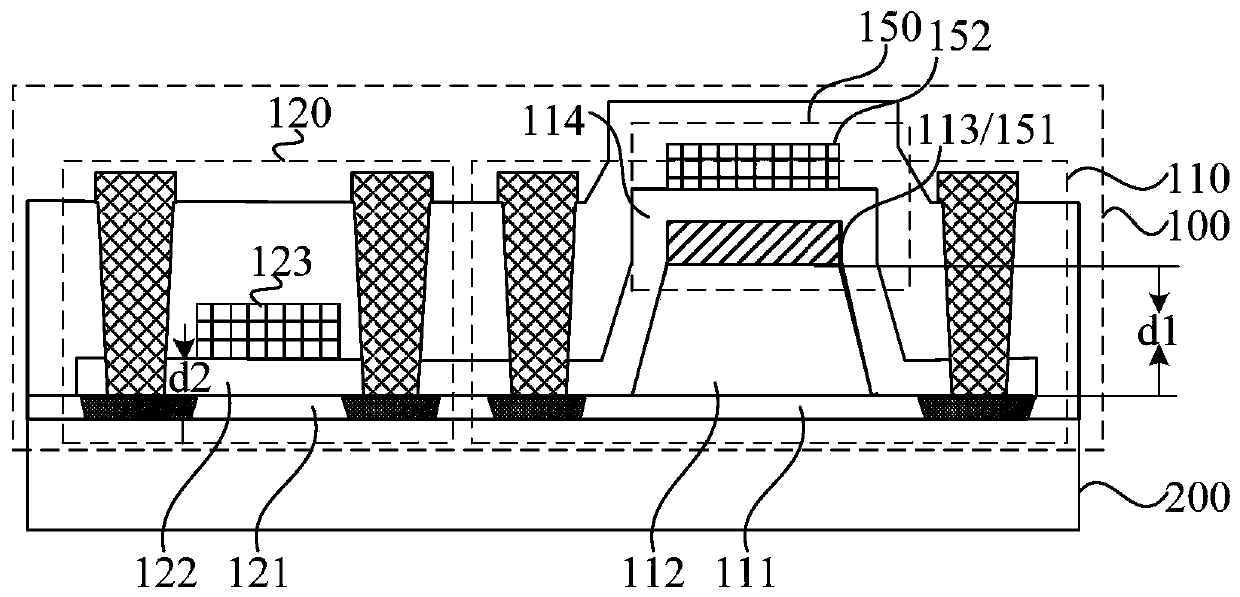

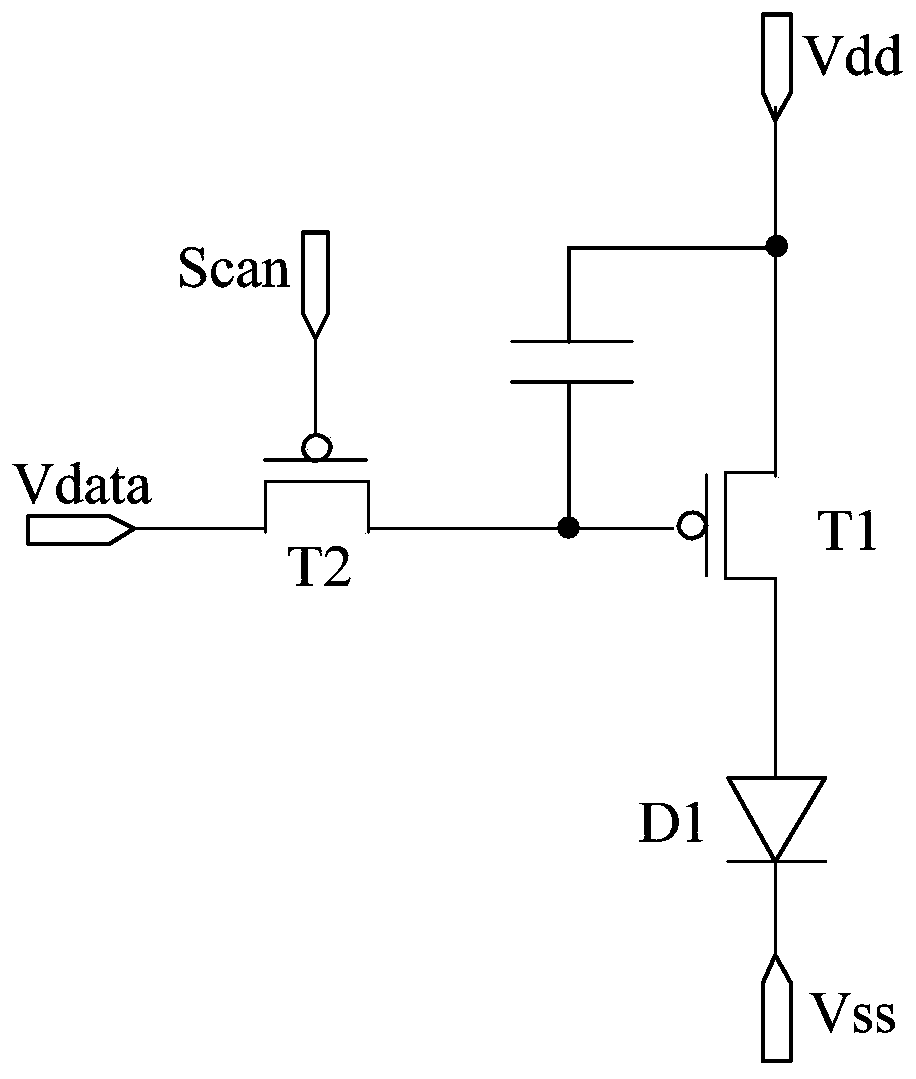

Organic light-emitting display device and manufacturing method thereof

ActiveCN106298857AOpen and close quicklyReduced subthreshold swingSolid-state devicesSemiconductor/solid-state device manufacturingSubthreshold swingDisplay device

The present invention discloses an organic light-emitting display device and a manufacturing method thereof. The organic light-emitting display device includes a switching thin film field effect transistor, a driving thin film field effect transistor, and a storage capacitor connected with the switching thin film field effect transistor and the driving thin film field effect transistor; the switching thin film field effect transistor is provided with a first active layer for reducing the subthreshold swing of the transfer characteristic curve of the switching film field effect transistor; and the driving thin film field effect transistor is provided with a second active layer for increasing the subthreshold swing of the transfer characteristic curve of the driving thin film field effect transistor. According to the organic light-emitting display device of the invention, fast switching on and switching off of the switching thin film field effect transistor and slow debugging of the grayscale of an OLED (Organic Light Emitting Diode) by the driving thin film field effect transistor can be simultaneously realized.

Owner:TCL CHINA STAR OPTOELECTRONICS TECH CO LTD

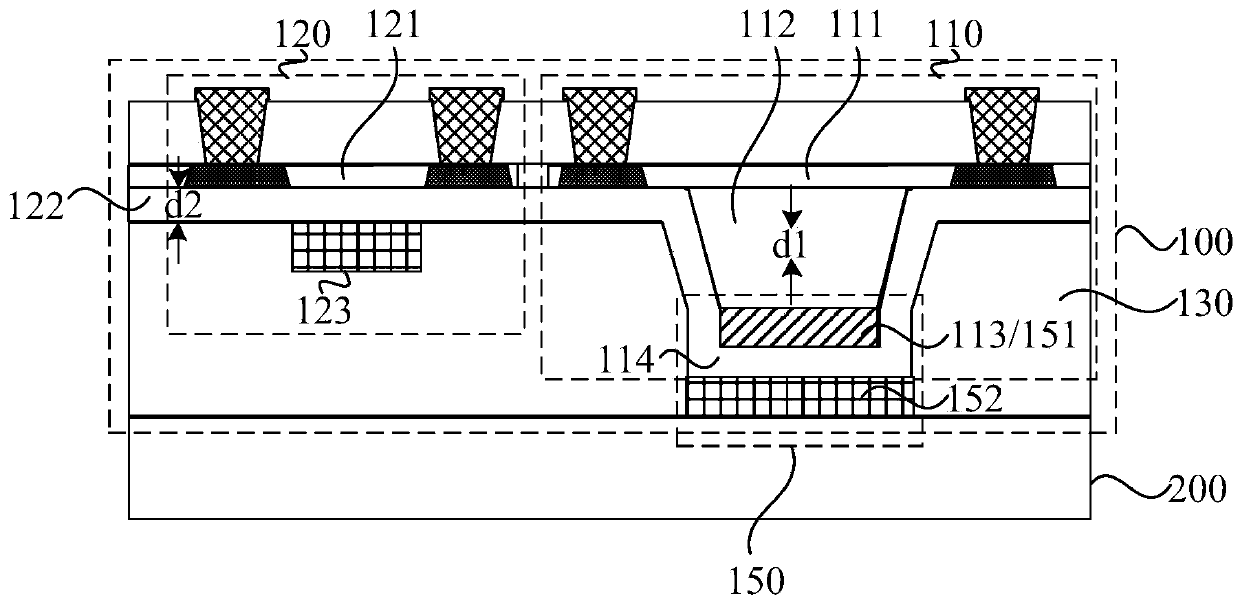

Array substrate, preparation method thereof and display panel

ActiveCN110880518AReduced subthreshold swingGuaranteed driving abilitySolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceThin membrane

The embodiment of the invention discloses an array substrate, a preparation method thereof and a display panel, the array substrate comprises a thin film transistor array layer, and the thin film transistor array layer comprises a driving transistor, a switching transistor and a capacitor; wherein the driving transistor comprises a first active layer, a first gate insulating layer, a first gate and an insulating dielectric layer which are stacked in sequence; the switching transistor comprises a second active layer, a second gate insulating layer and a second gate which are sequentially stacked; wherein the insulating dielectric layer and the second gate insulating layer are the same layer; the thickness of the first gate insulating layer is larger than that of the second gate insulating layer, so that the sub-threshold swing of the driving transistor is large, meanwhile, the sub-threshold swing of the switching transistor is small, and the driving capacity of the driving transistor and the switching control capacity of the switching transistor can be guaranteed at the same time.

Owner:YUNGU GUAN TECH CO LTD

Array substrate, preparation method thereof, display panel and device

PendingCN112366210AImprove featuresImprove work performanceSolid-state devicesSemiconductor/solid-state device manufacturingHemt circuitsEngineering

The invention discloses an array substrate, a preparation method thereof, a display panel and a device. The array substrate comprises a pixel circuit, the pixel circuit comprises a first transistor and a second transistor, the first transistor comprises a first active layer, the second transistor comprises a second active layer, and both the first active layer and the second active layer comprisesilicon; the array substrate further comprises a first type inorganic layer, a second type inorganic layer and a first via hole, the first via hole is located above the first active layer and at leastpenetrates through the second type inorganic layer, and the hydrogen ion concentration in the first active layer is smaller than that in the second active layer. The first active layer is subjected to high-temperature processing through the first via hole, so that the hydrogen ion concentration in the first active layer is smaller than that in the second active layer, the high-temperature processing frequency of the second transistor is reduced while good performance of the first transistor is guaranteed, and it is guaranteed that the second transistor is small in sub-threshold swing, good inturn-off characteristic and small in leakage current; and good overall characteristics of the pixel circuit are ensured.

Owner:XIAMEN TIANMA MICRO ELECTRONICS

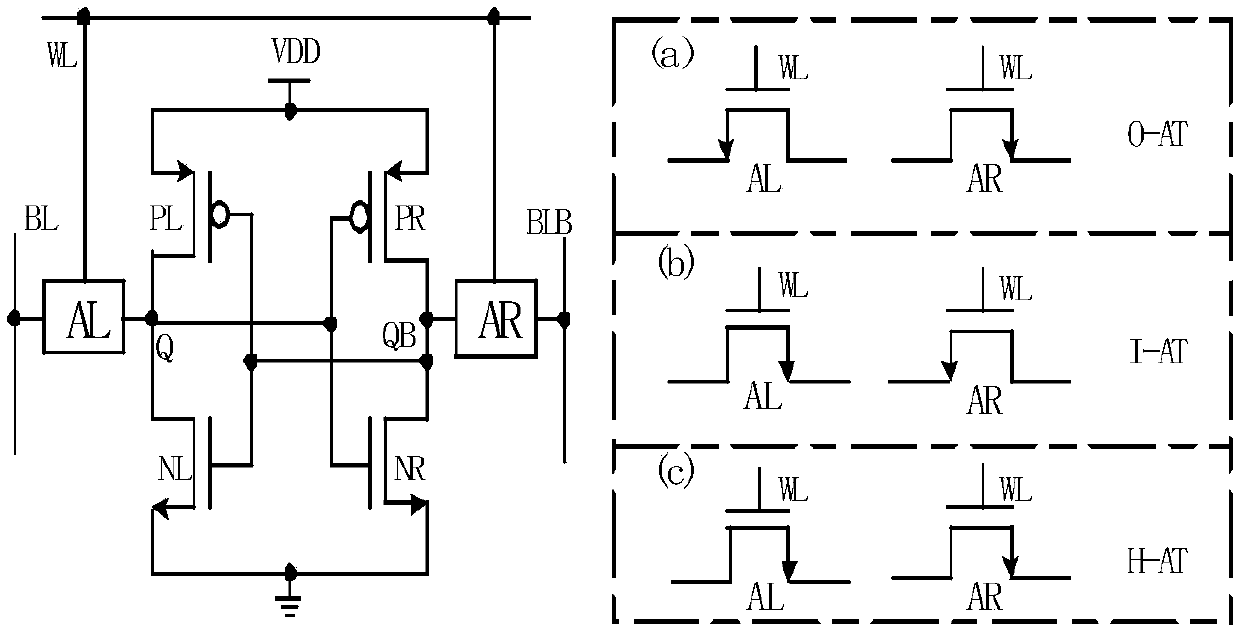

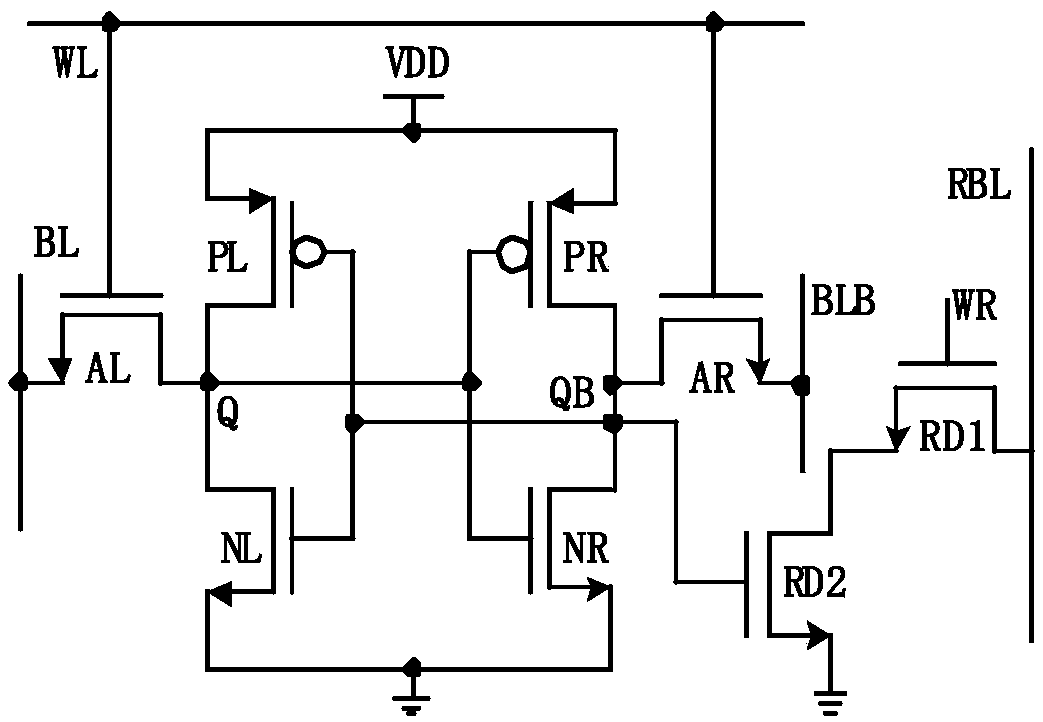

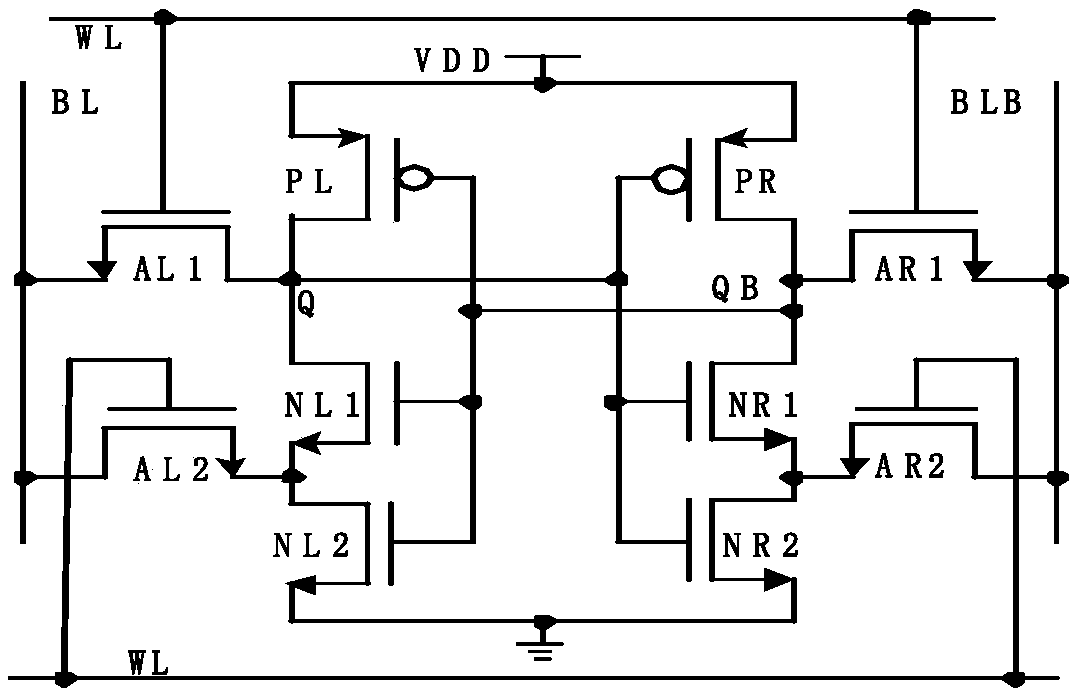

A 12T TFET SRAM cell circuit having ultra-low power consumption and high write margin

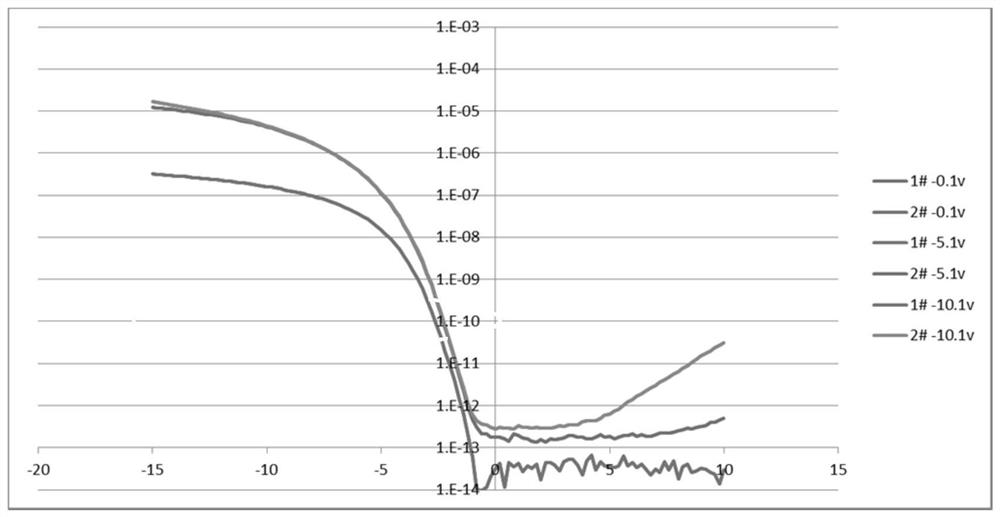

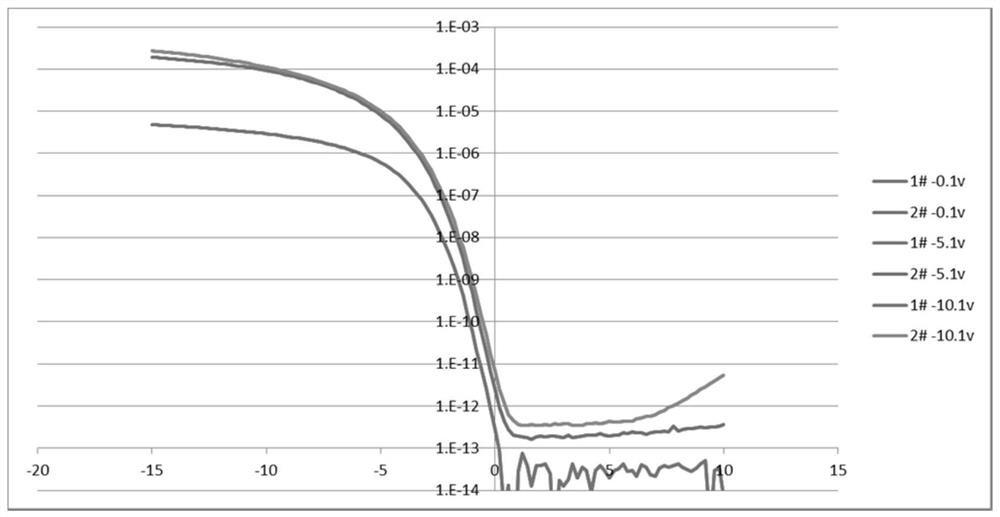

PendingCN109658960ASolve the problem of high static power consumptionReduce static power consumptionDigital storageWrite marginSubthreshold swing

The invention discloses a 12T TFET SRAM unit circuit with ultra-low power consumption and high write margin. Compared with a metal oxide semiconductor field effect transistor (MOSFET), the characteristics of smaller subthreshold swing, higher switching ratio and the like of the TFET are utilized; the problem of high static power consumption of a traditional MOSFET SRAM unit structure is solved; Under the same working voltage, such as 0.3 V to 0.6 V, compared with other TFET SRAM unit structures, the static power consumption of the TFET SRAM unit structure is at least reduced by four orders ofmagnitudes, and the write margin and the stability of the TFET SRAM unit structure are improved; Therefore, the problem of positive bias leakage current occurring when the TFET is used as the SRAM transmission tube is eliminated, the static power consumption of the cell is reduced, and the stability and the writing capability of the cell are improved.

Owner:ANHUI UNIVERSITY

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com