Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

359results about How to "Shorten the switching time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

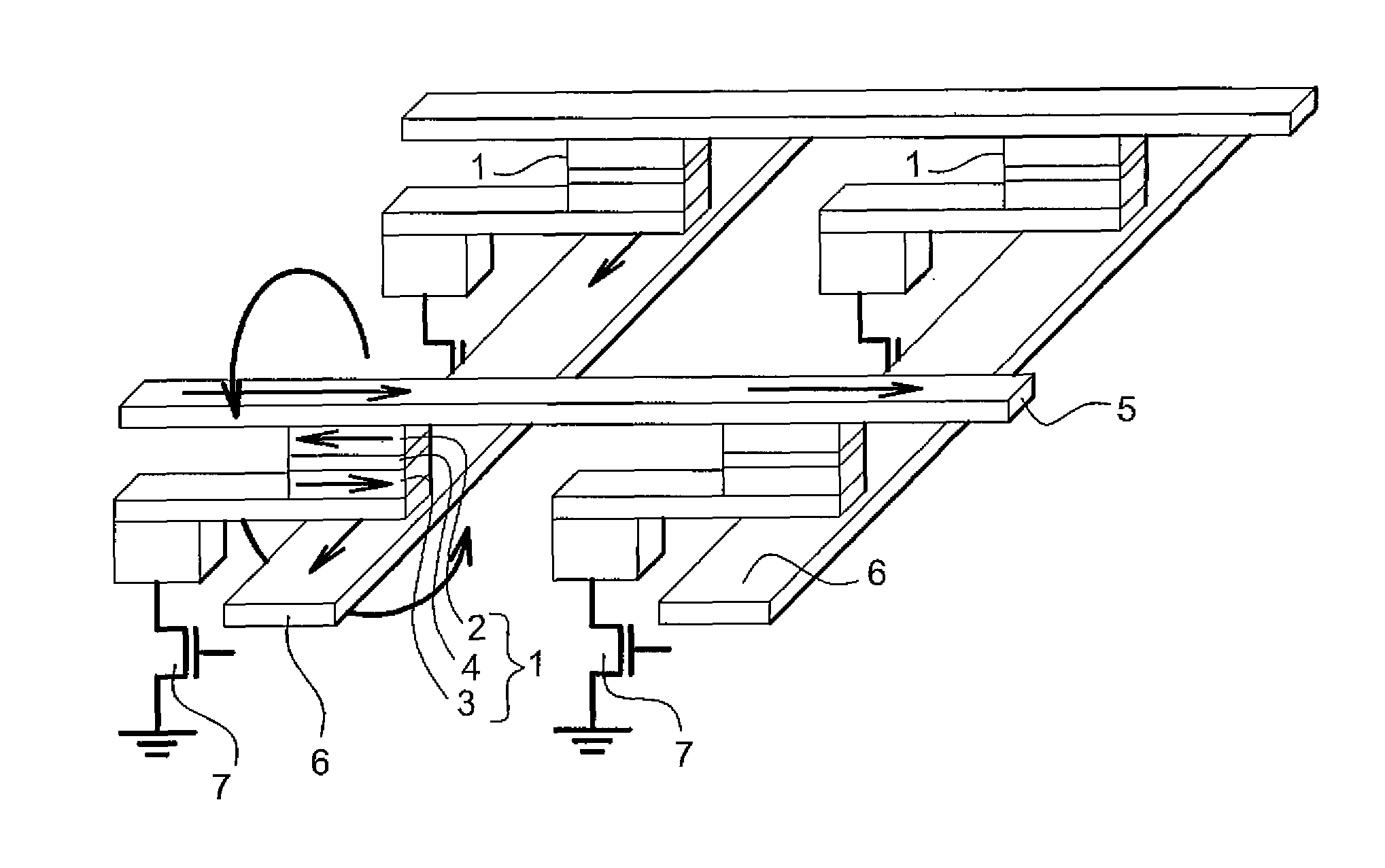

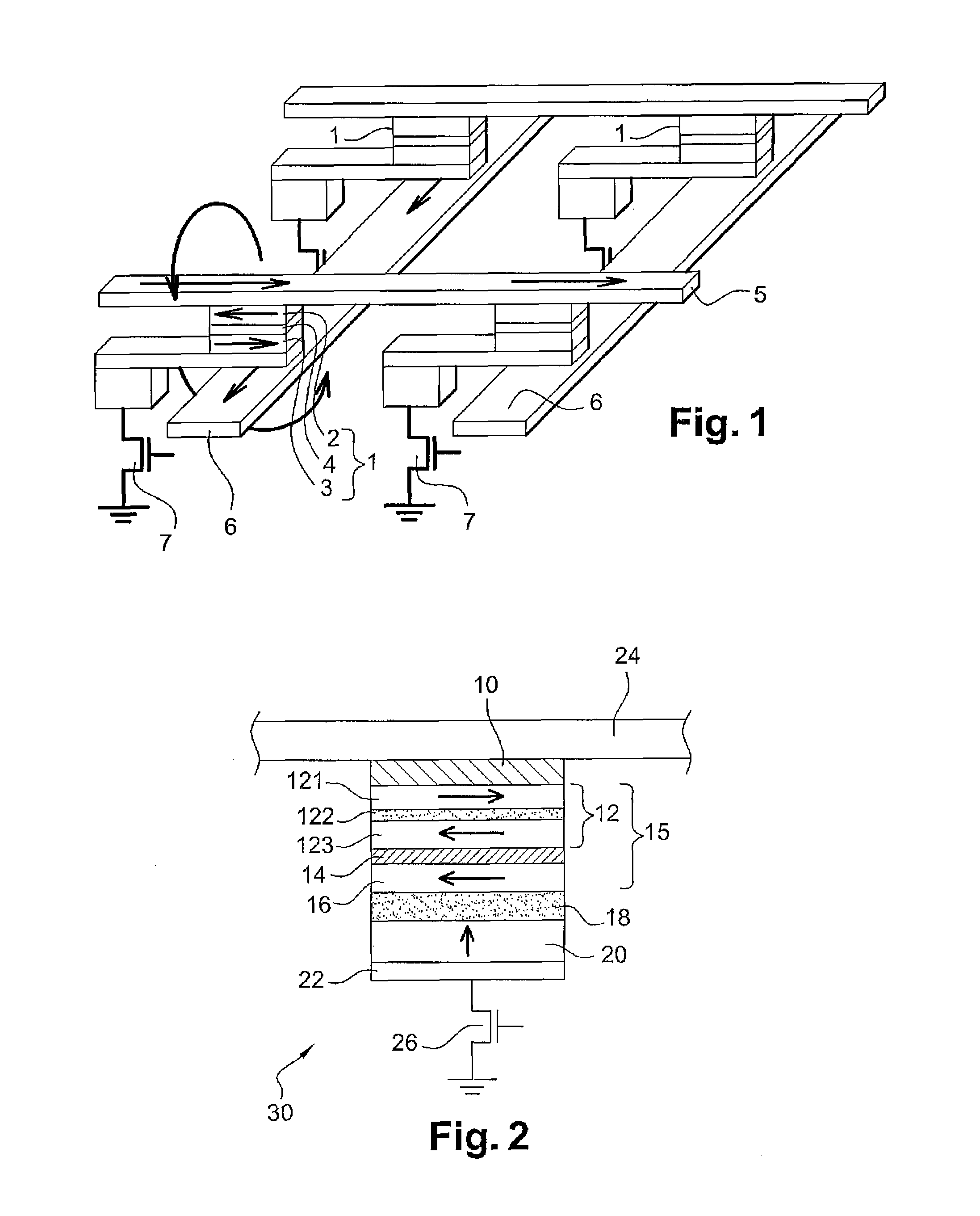

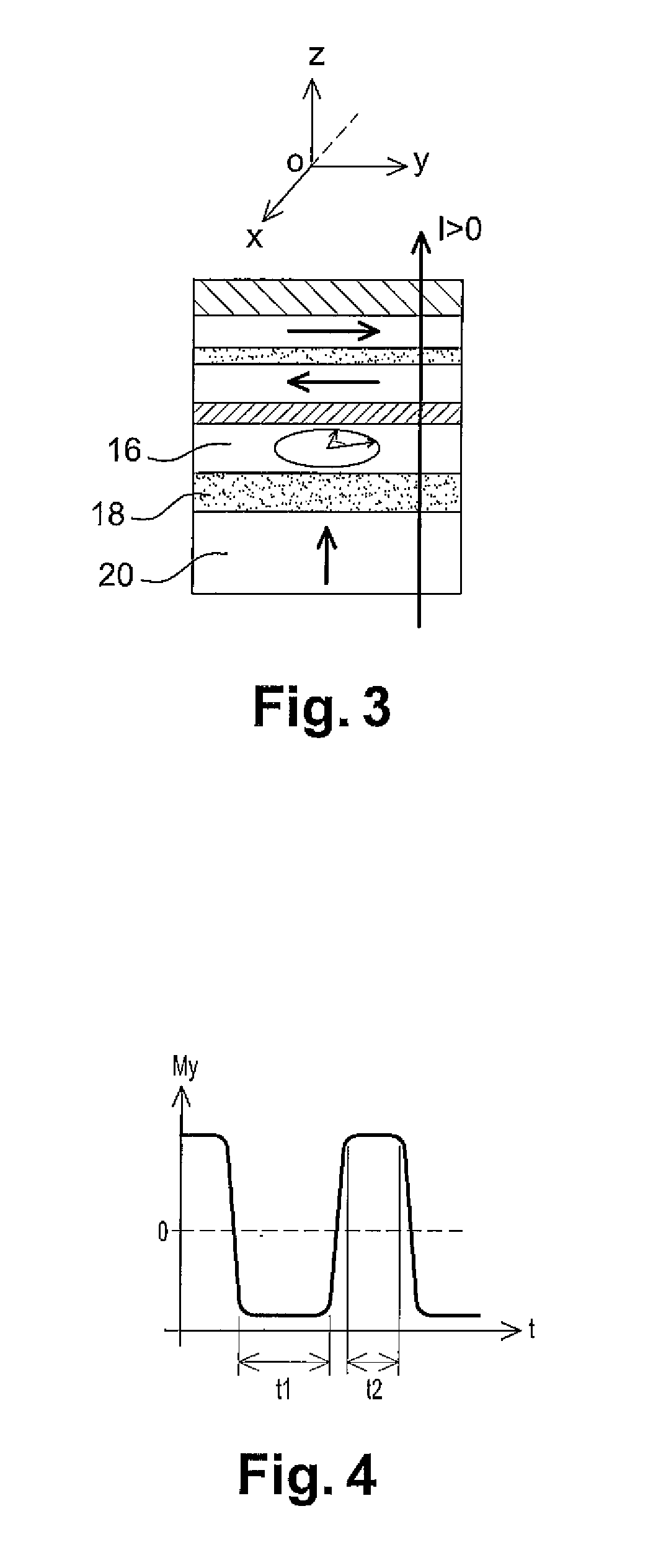

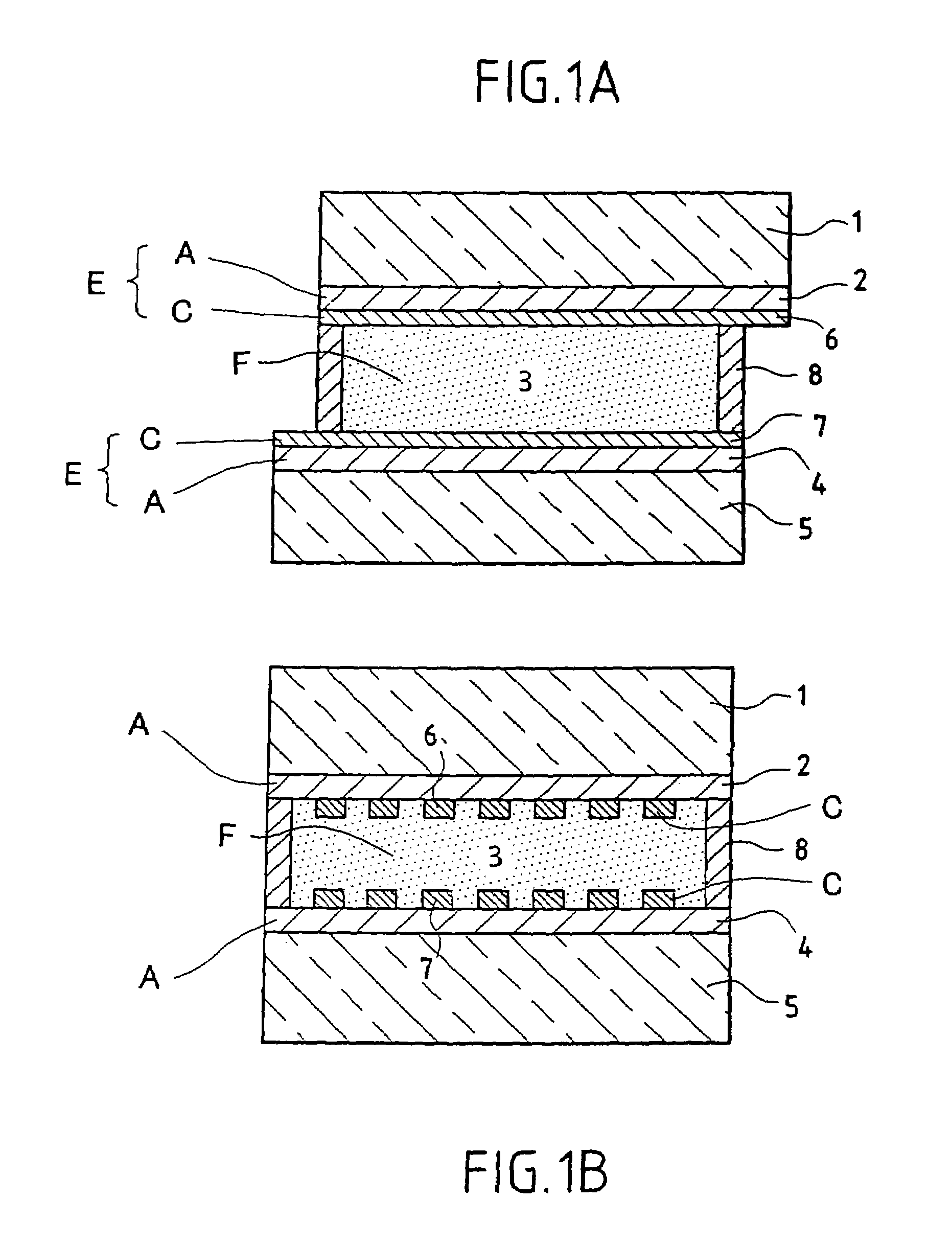

Spin polarised magnetic device

ActiveUS8279666B2Reducing the stochastic fluctuations in the magnetisation reversal timeTotal current dropNanomagnetismMagnetic measurementsMagnetic storageSpins

A magnetic device includes a magnetic reference layer with a fixed magnetization direction located either in the plane of the layer or perpendicular to the plane of the layer, a magnetic storage layer with a variable magnetization direction, a non-magnetic spacer separating the reference layer and the storage layer and a magnetic spin polarizing layer with a magnetization perpendicular to that of the reference layer, and located out of the plane of the spin polarizing layer if the magnetization of the reference layer is directed in the plane of the reference layer or in the plane of the spin polarizing layer if the magnetization of the reference layer is directed perpendicular to the plane of the reference layer. The spin transfer coefficient between the reference layer and the storage layer is higher than the spin transfer coefficient between the spin polarizing layer and the storage layer.

Owner:INSTITUT NAT POLYTECHN DE GRENOBLE +2

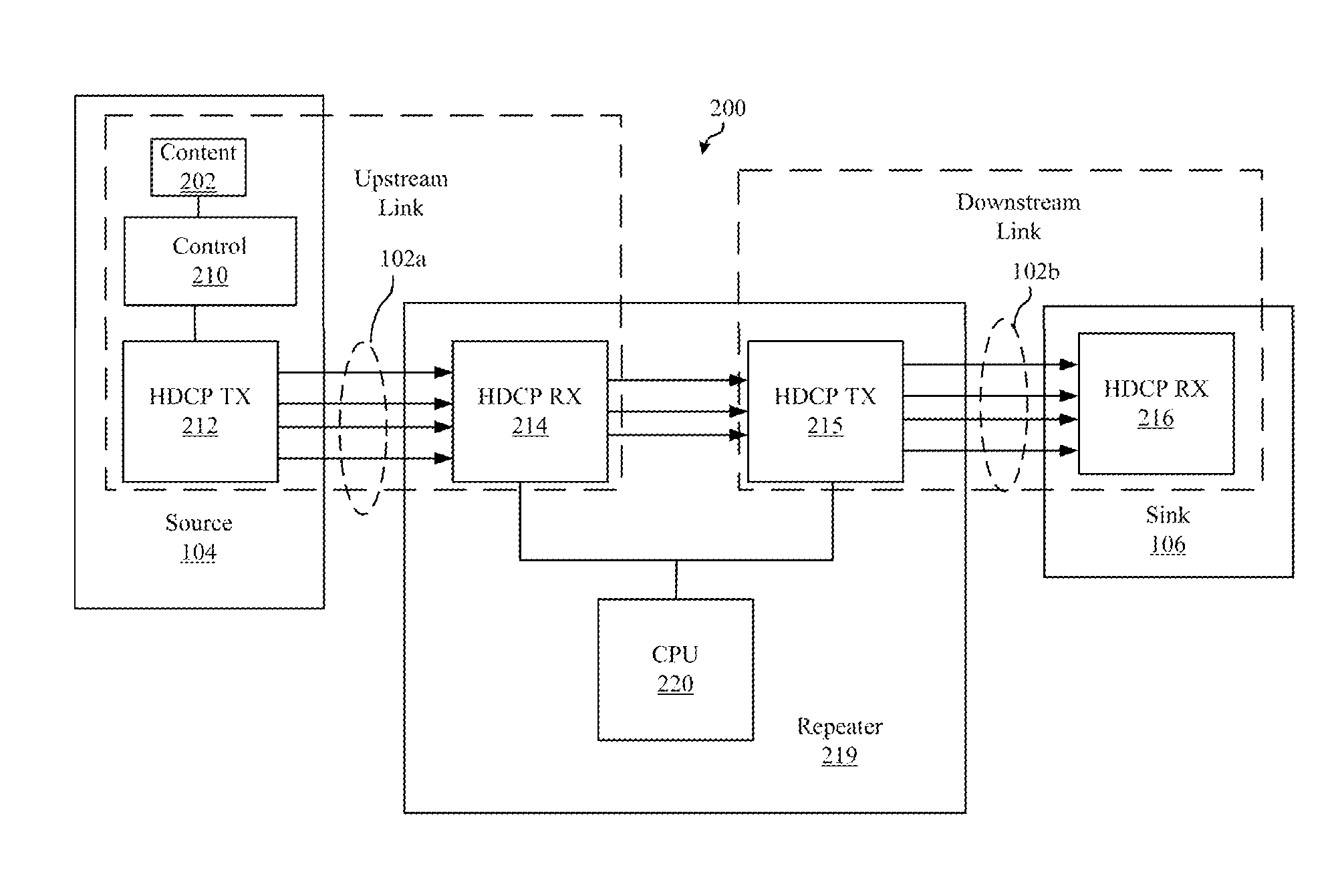

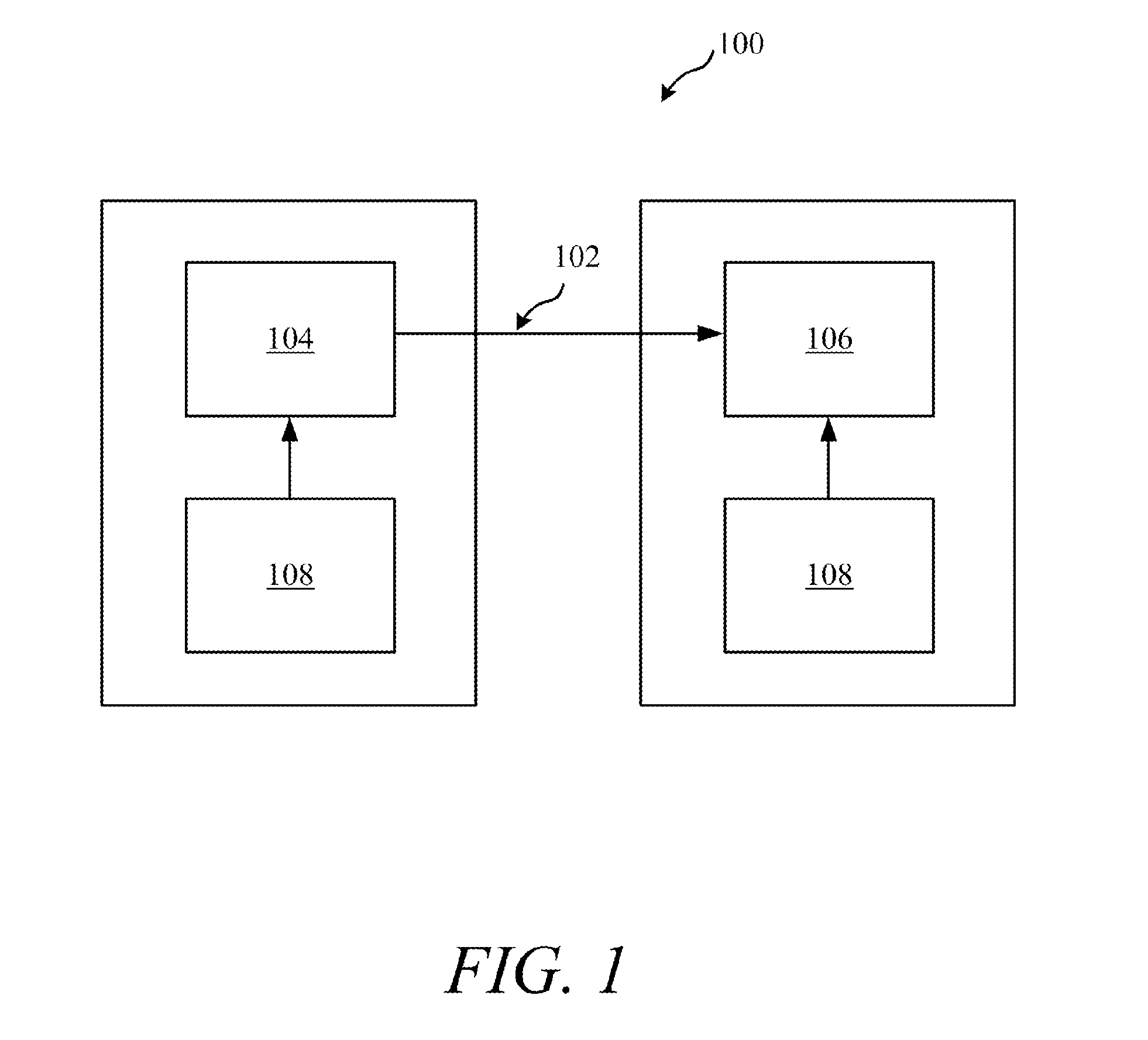

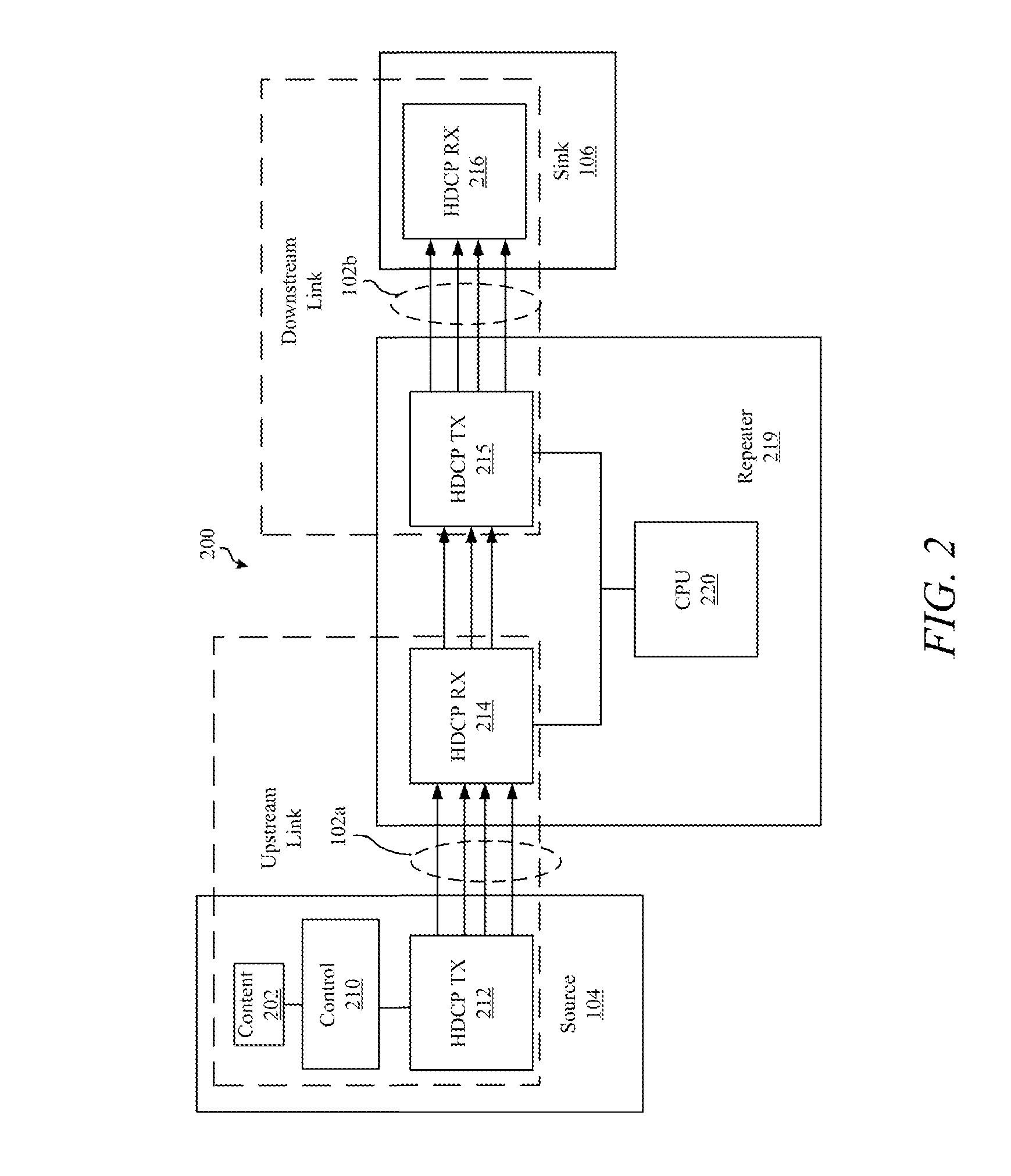

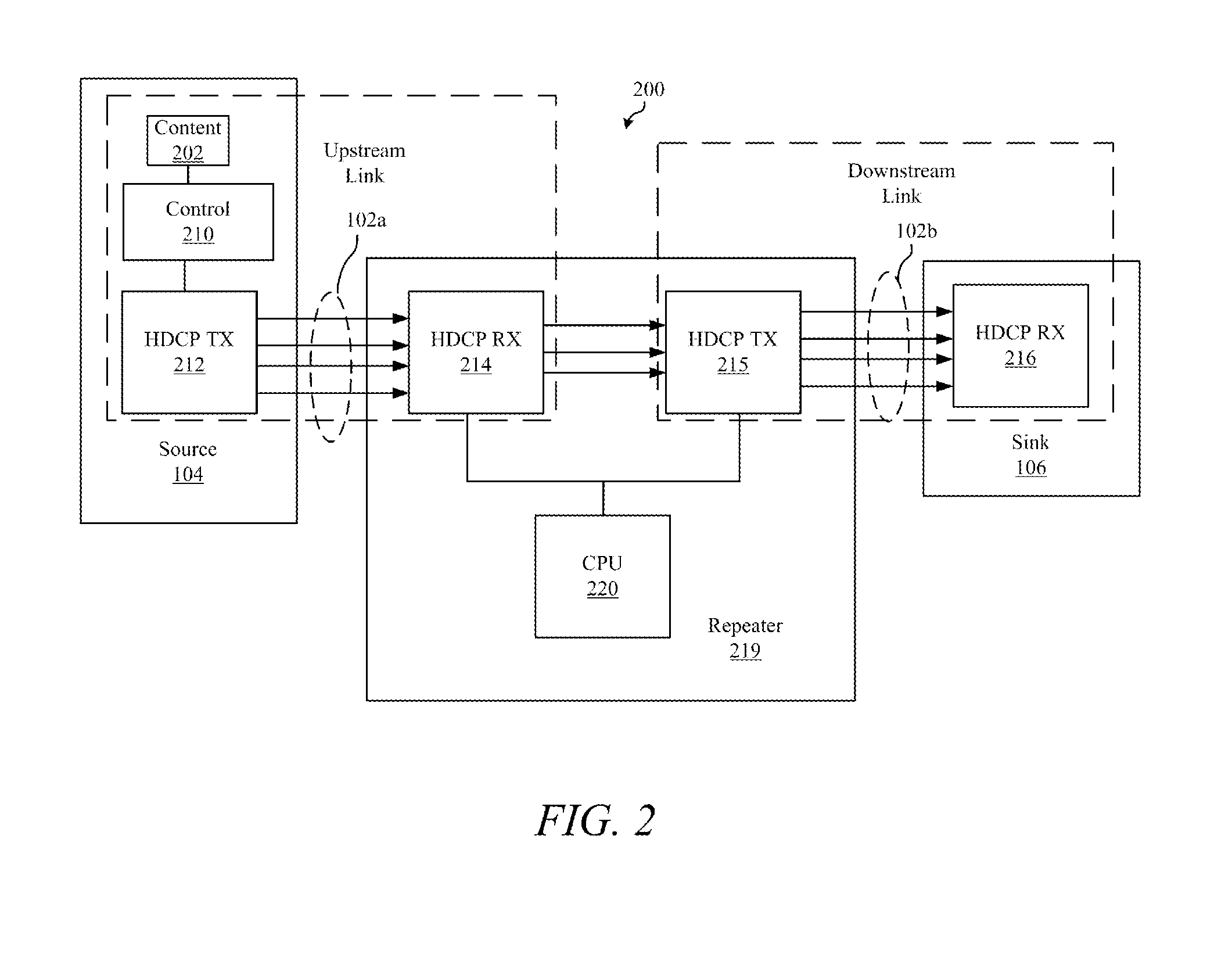

Systems, Devices and Methods for Reducing Switching Time in a Video Distribution Network

ActiveUS20150020088A1Reduce switching delayReducing actual and perceived switching timeAnalogue secracy/subscription systemsTwo-way working systemsSecurity authenticationSwitching time

When switching sources, resolutions or refresh rates in a video distribution network, switching times are reduced by maintaining video lock and security authentication between a video switcher and a video sink. The scaler maintains video lock and security authentication by continuing to generate video timing data during switching events. The scaler also facilitates an aesthetically pleasing transition by generating image content data prior to and after the switching event.

Owner:CRESTRON ELECTRONICS

Devices, Systems and Methods for Reducing Switching Time in a Video Distribution Network

ActiveUS20130212613A1Reduce switching delayShorten the switching timeAnalogue secracy/subscription systemsSelective content distributionSecurity authenticationSwitching time

When switching sources, resolutions or refresh rates in a video distribution network, switching times are reduced by maintaining video lock and security authentication between a video switcher and a video sink. The scaler maintains video lock and security authentication by continuing to generate video timing data during switching events. The scaler also facilitates an aesthetically pleasing transition by generating image content data prior to and after the switching event.

Owner:CRESTRON ELECTRONICS

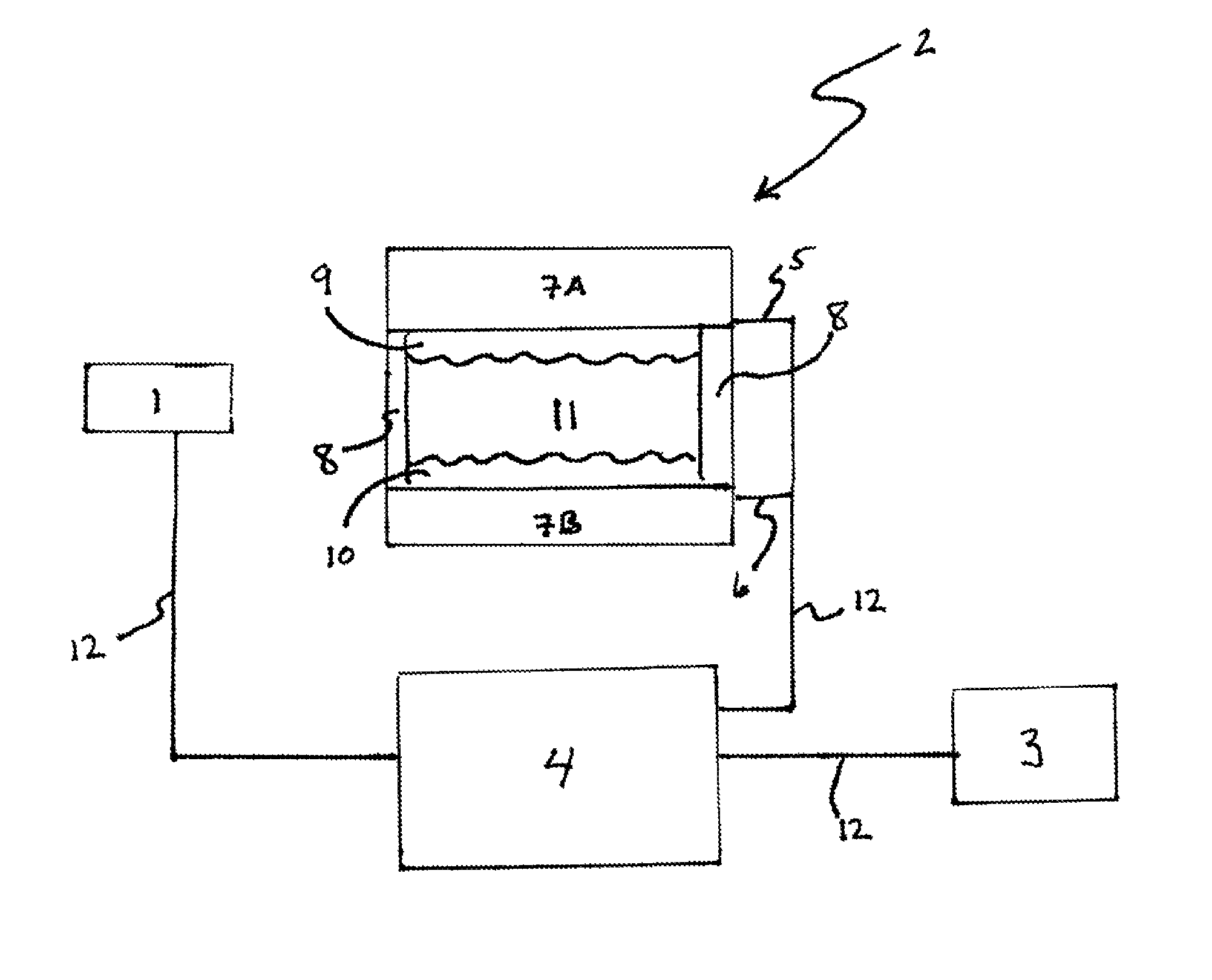

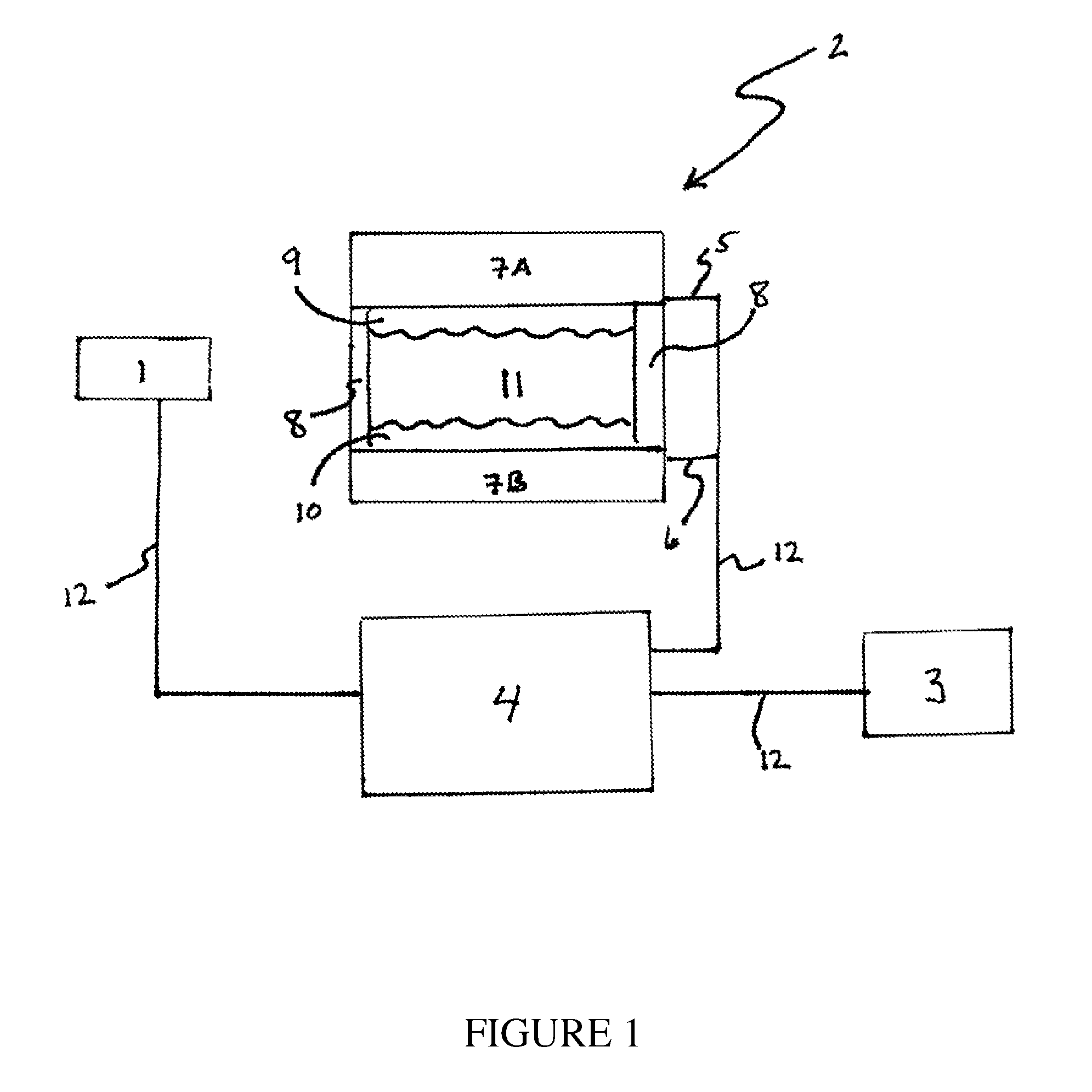

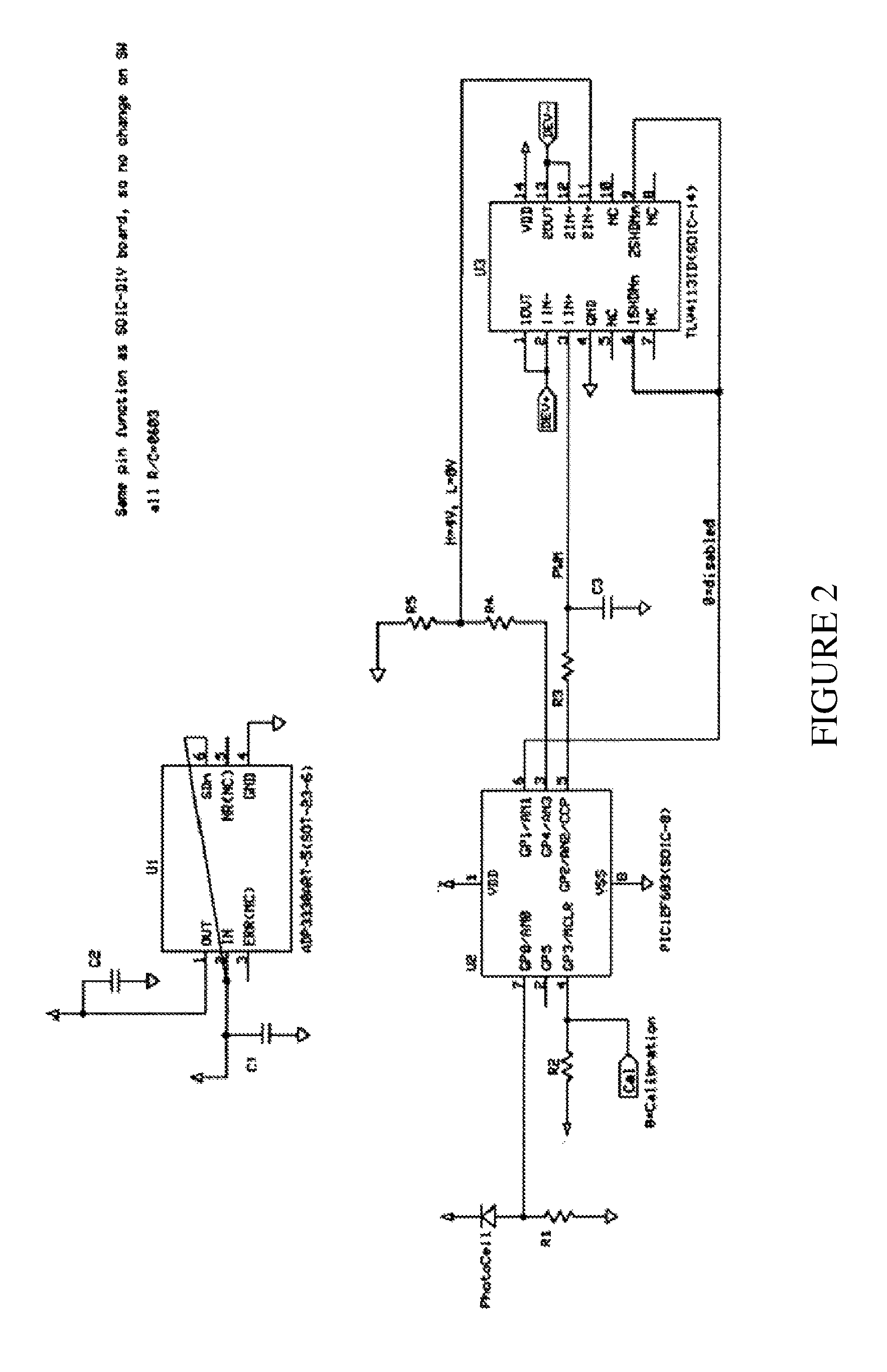

Method and apparatus for control of electrochromic devices

ActiveUS8902486B1Fast switching speedShorten the switching timeNon-linear opticsOptical partsEngineeringElectrochromic devices

The present invention provides apparatuses and methods for modulating the transmissivity of electrochromic devices utilizing a controller that provides a continuous potential that may be pulsed to the electrochromic device.

Owner:ASHWIN USHAS

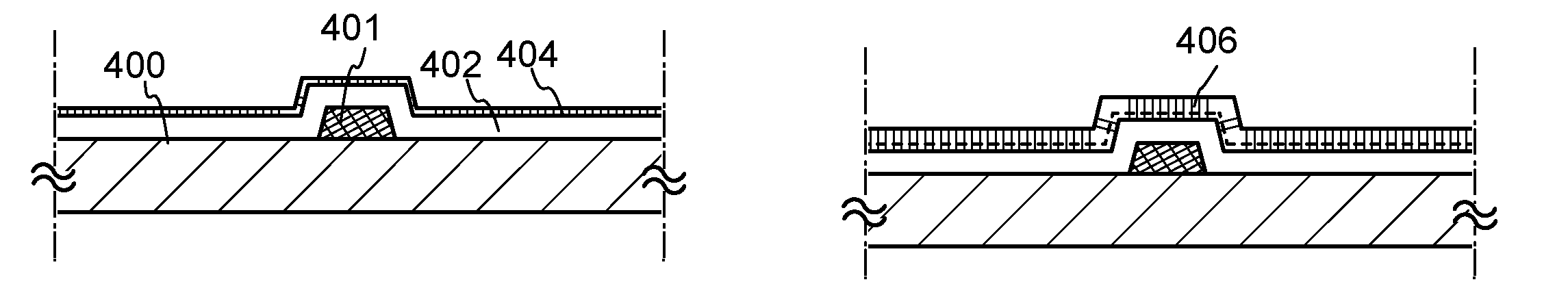

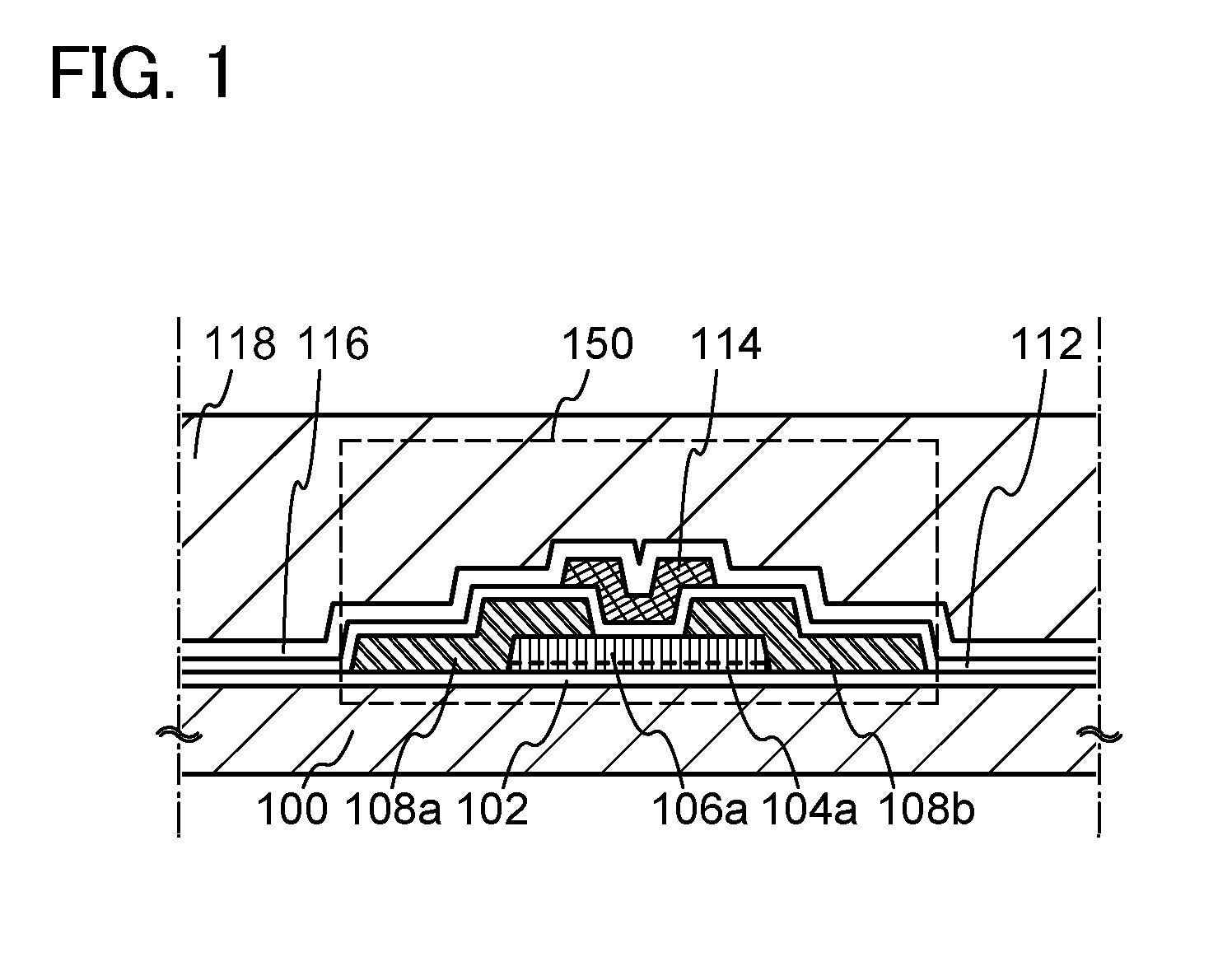

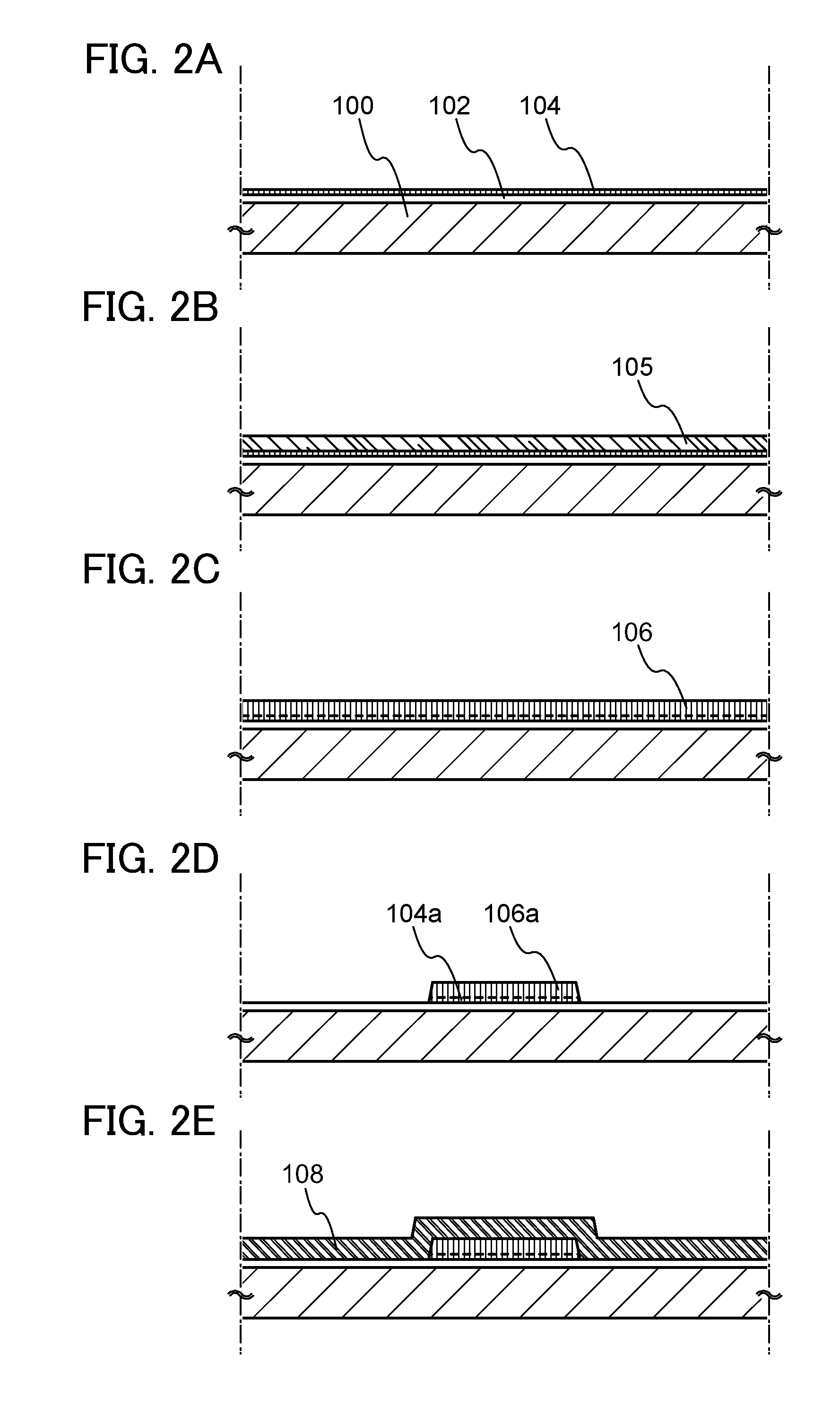

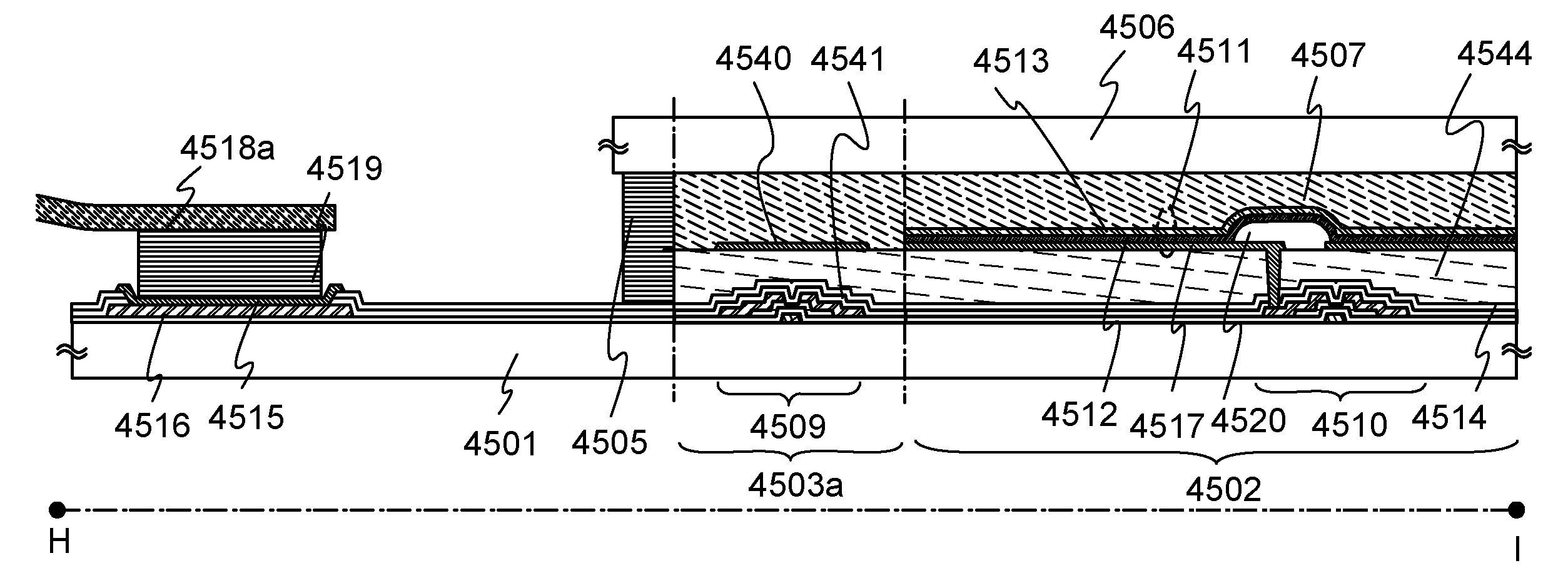

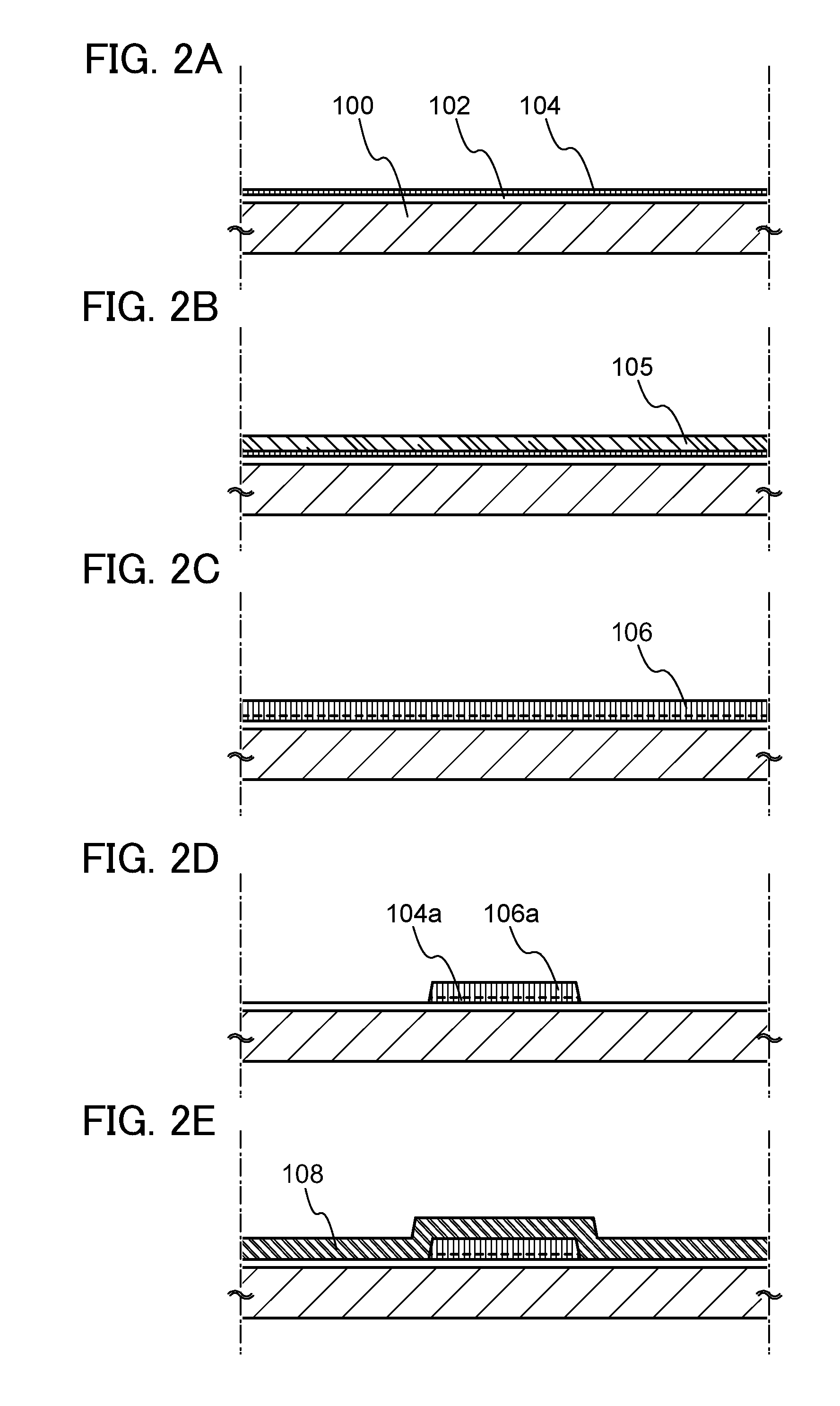

Semiconductor device and manufacturing method thereof

ActiveUS8293661B2Improve mobilityHigh crystallinitySolid-state devicesSemiconductor/solid-state device manufacturingHydrogenDisplay device

One embodiment of the present invention is to achieve high mobility in a device using an oxide semiconductor and provide a highly reliable display device. An oxide semiconductor layer including a crystal region in which c-axis is aligned in a direction substantially perpendicular to a surface is formed and an oxide insulating layer is formed over and in contact with the oxide semiconductor layer. Oxygen is supplied to the oxide semiconductor layer by third heat treatment. A nitride insulating layer containing hydrogen is formed over the oxide insulating layer and fourth heat treatment is performed, so that hydrogen is supplied at least to an interface between the oxide semiconductor layer and the oxide insulating layer.

Owner:SEMICON ENERGY LAB CO LTD

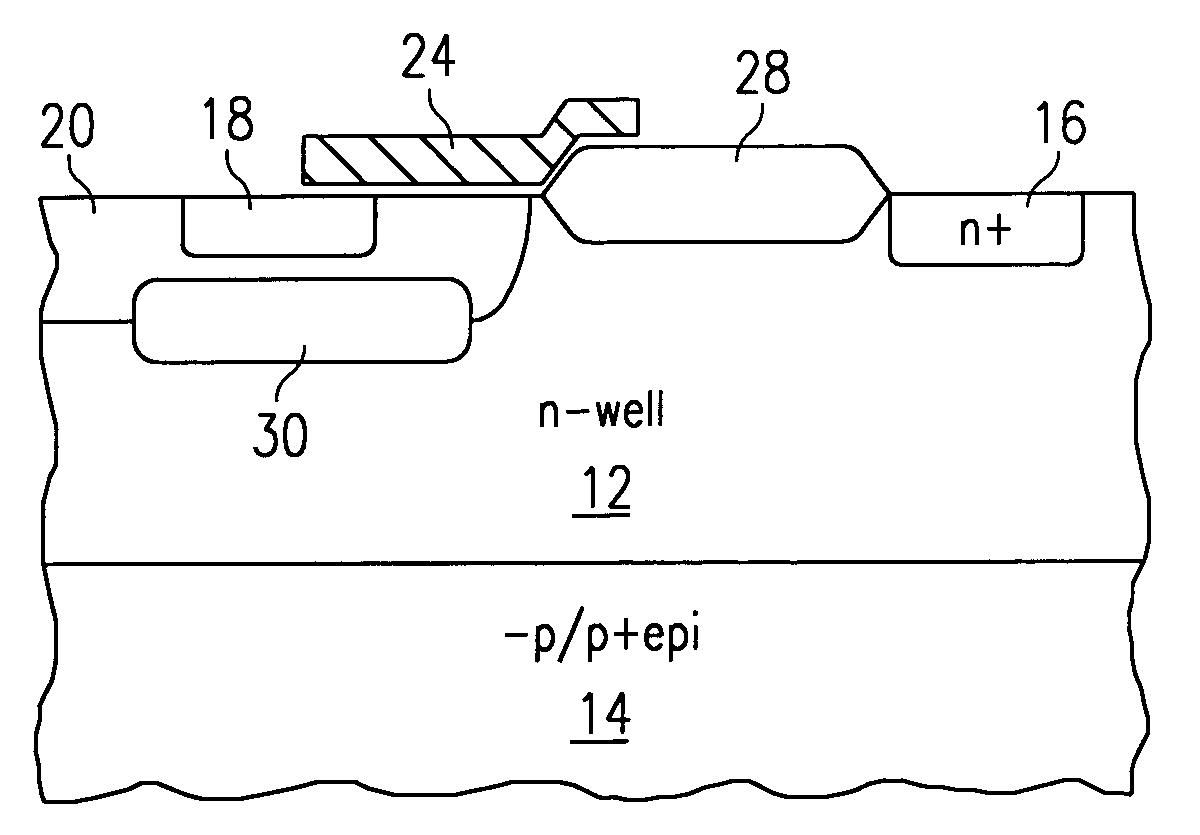

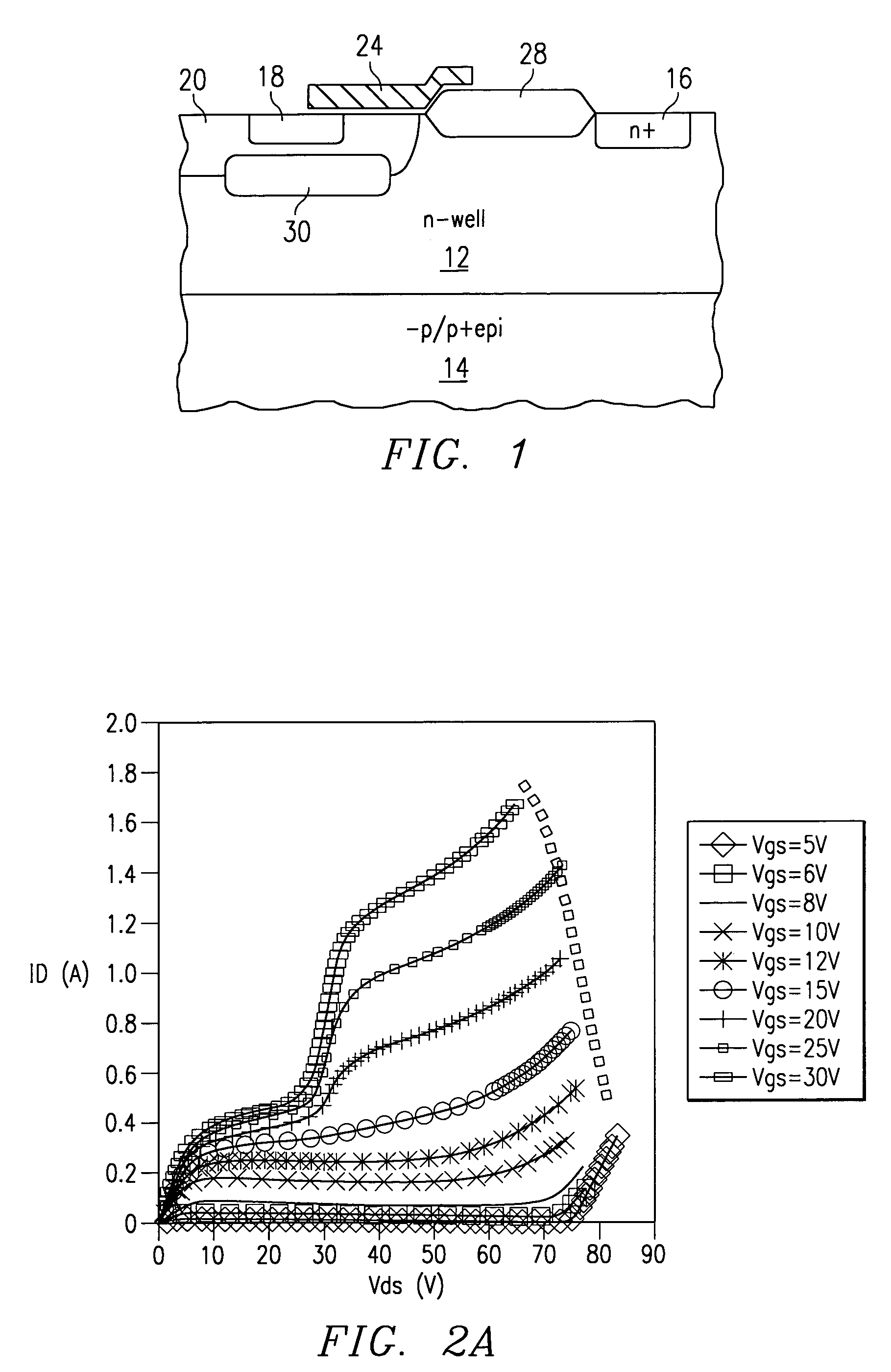

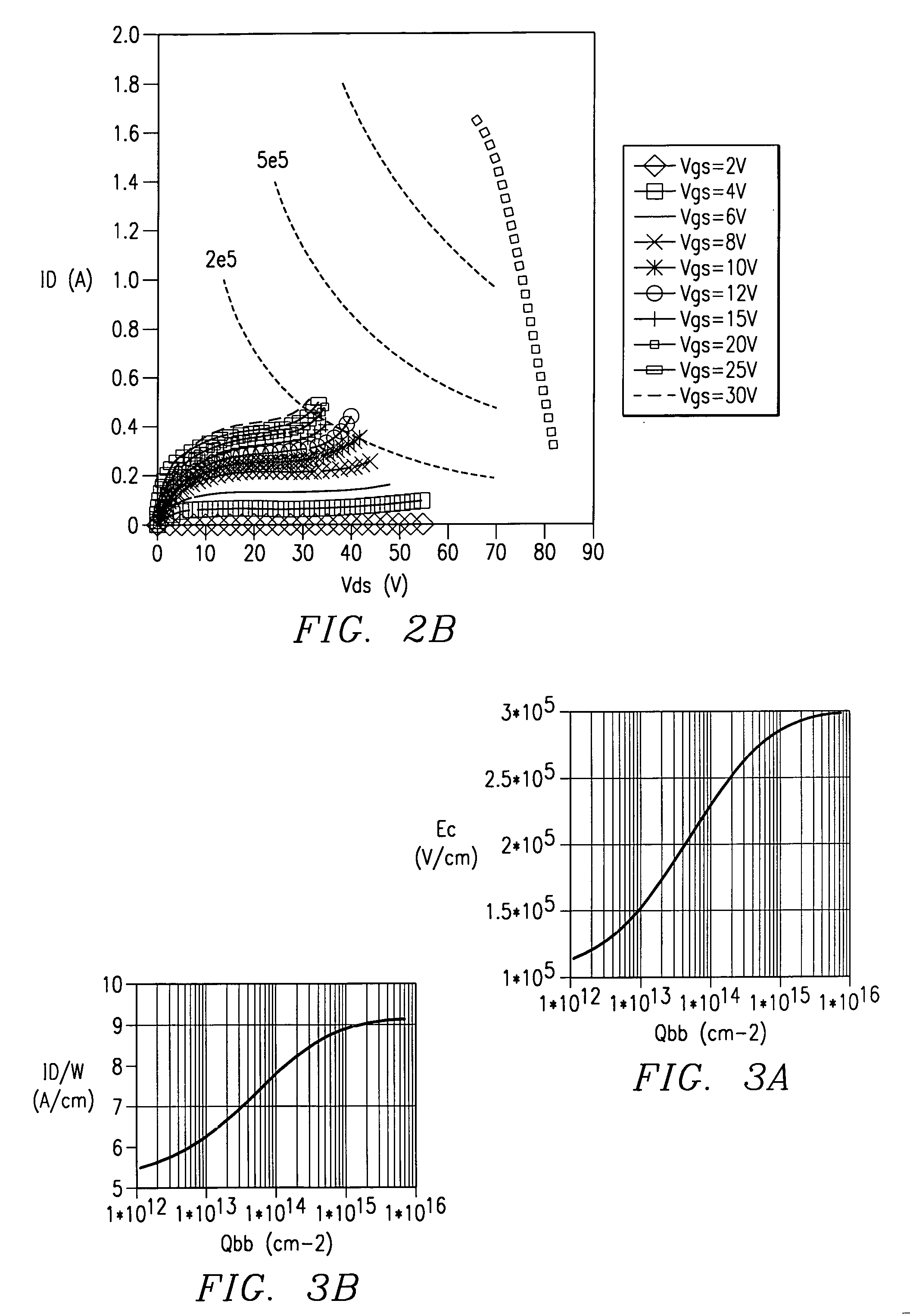

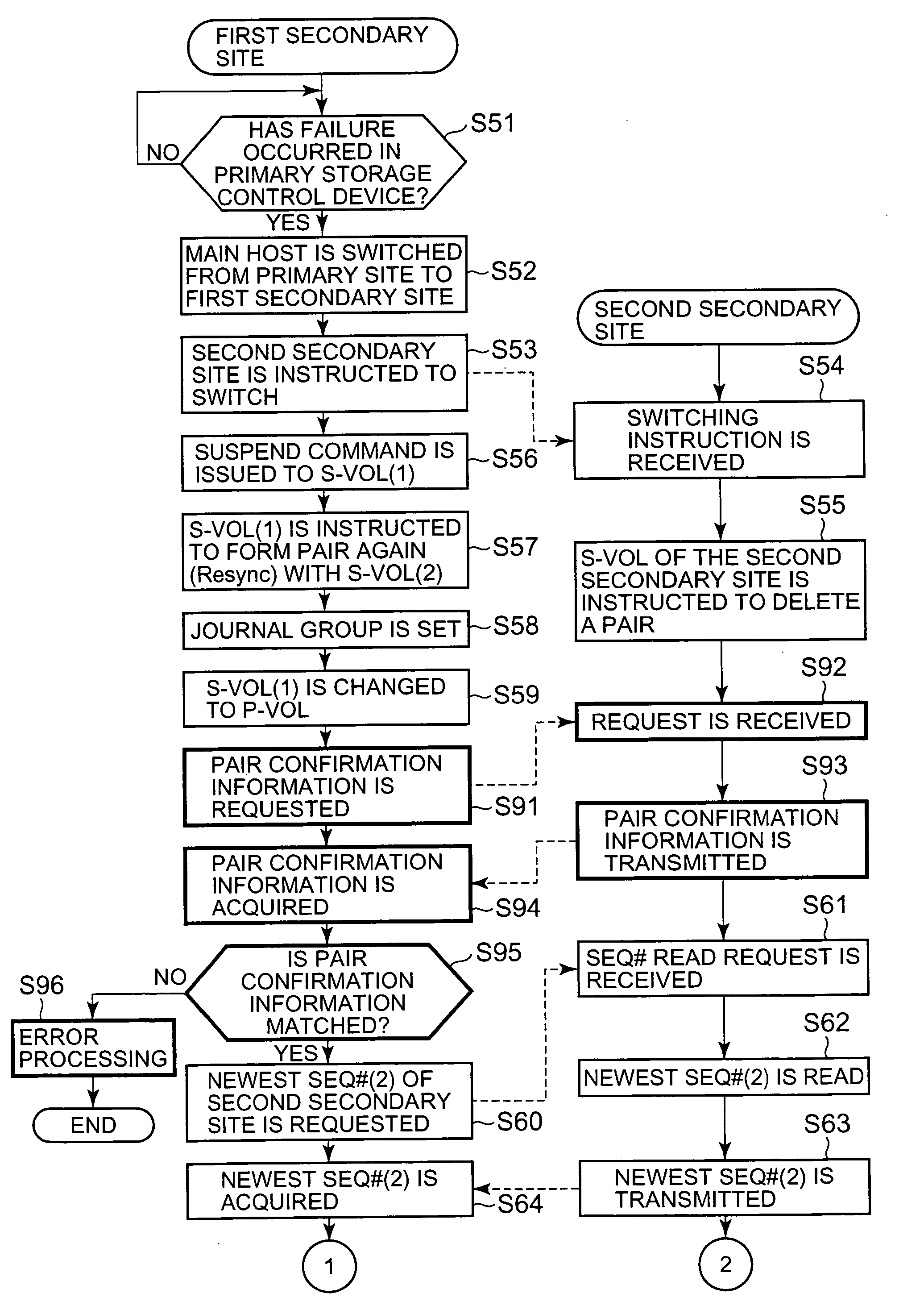

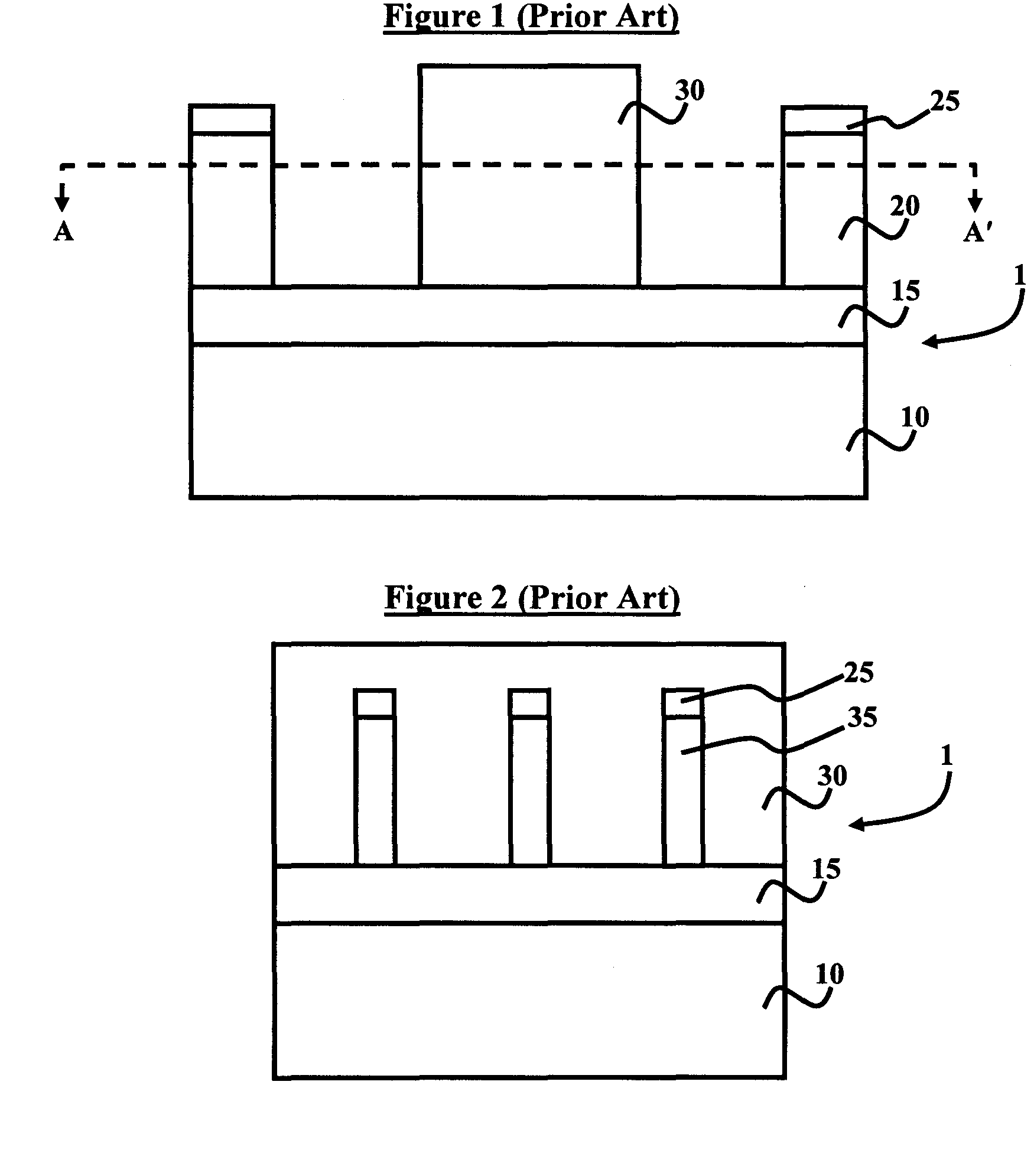

N-channel LDMOS with buried p-type region to prevent parasitic bipolar effects

InactiveUS6958515B2Reduces base resistance and hence base-emitter voltage dropEfficient collectionSemiconductor/solid-state device detailsSolid-state devicesSafe operating areaBody region

An improved n-channel integrated lateral DMOS (10) in which a buried body region (30), beneath and self-aligned to the source (18) and normal body diffusions, provides a low impedance path for holes emitted at the drain region (16). This greatly reduces secondary electron generation, and accordingly reduces the gain of the parasitic PNP bipolar device. The reduced regeneration in turn raises the critical field value, and hence the safe operating area.

Owner:TEXAS INSTR INC

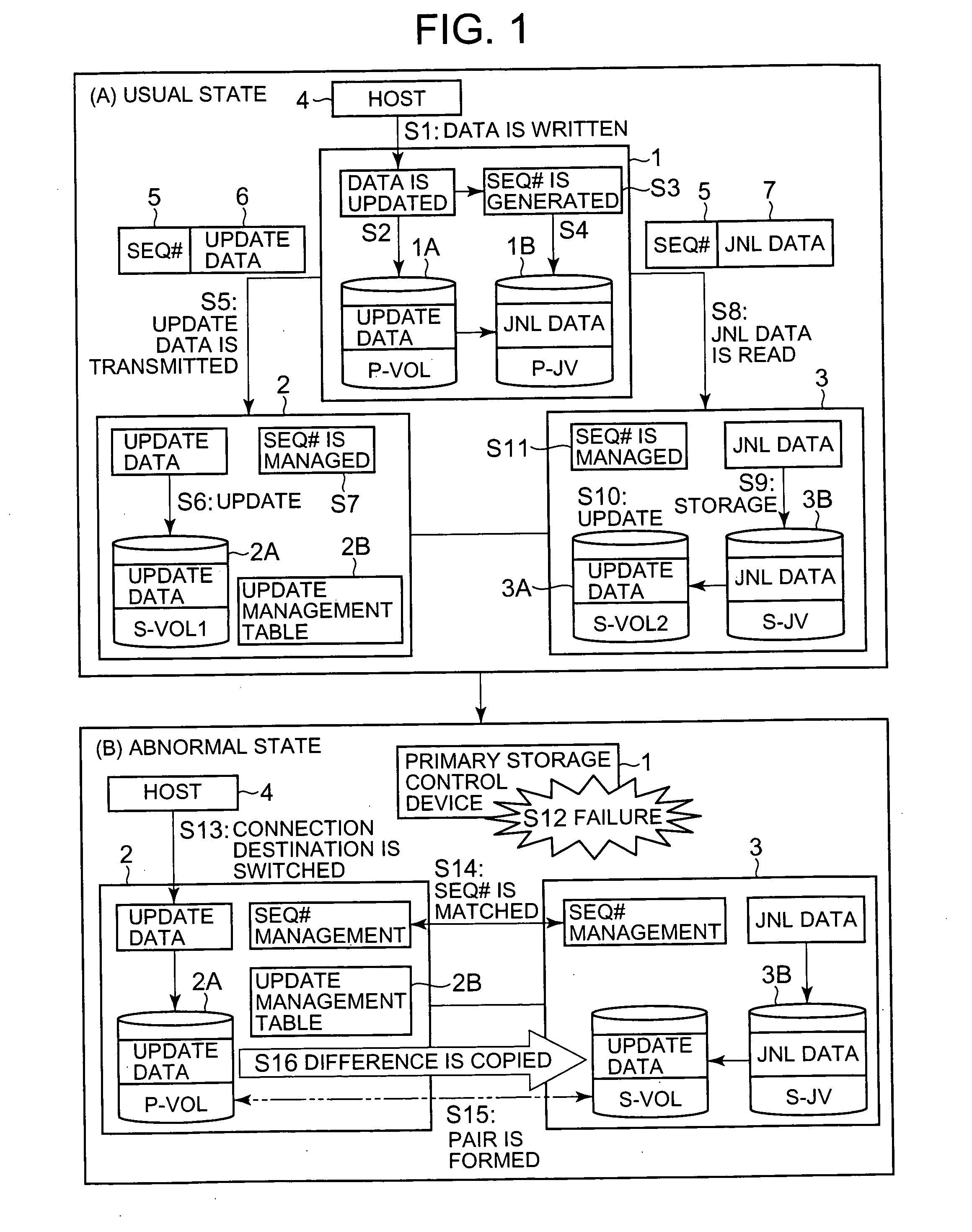

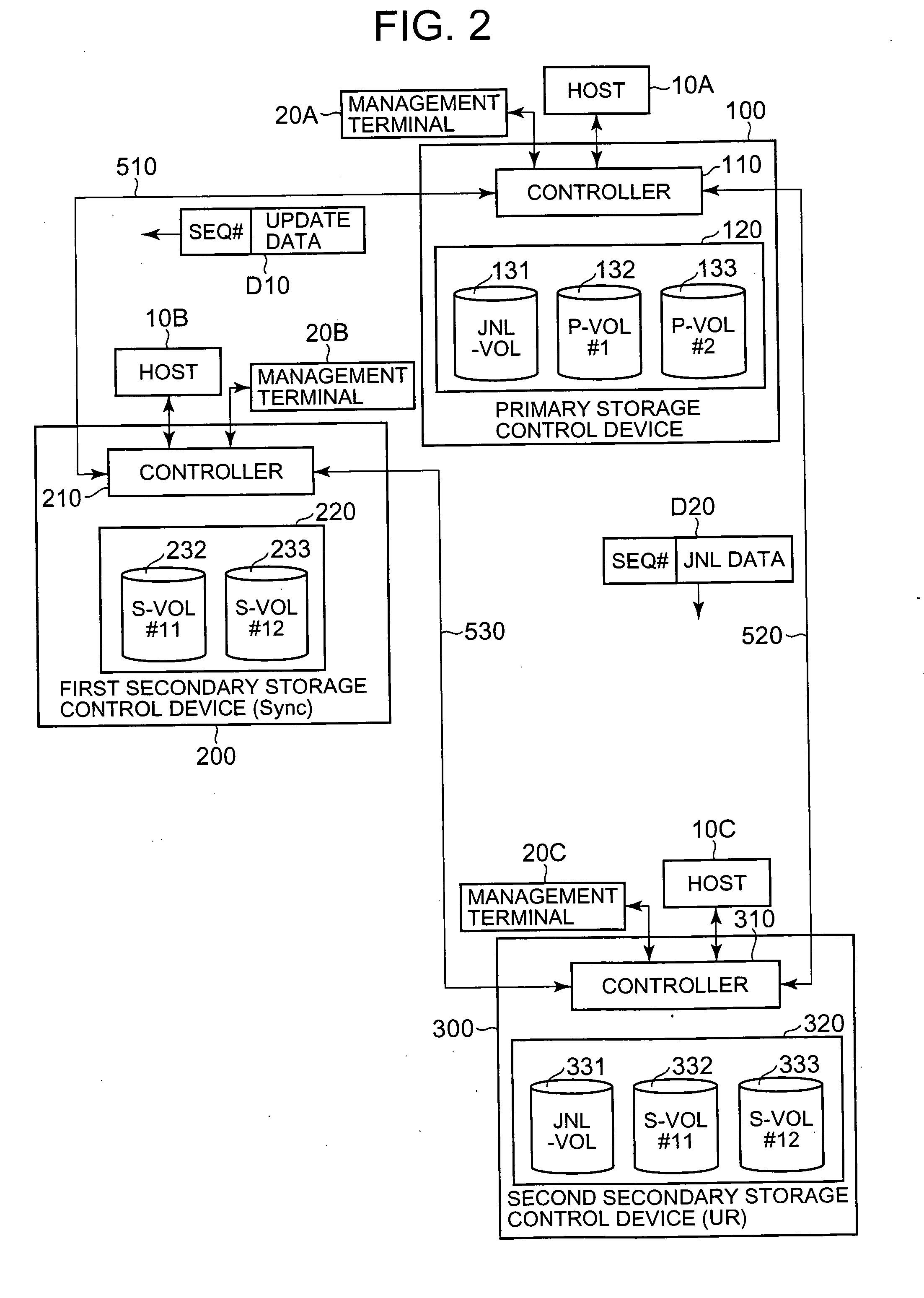

Storage system and storage system management method

InactiveUS20070050547A1Shorten the switching timeImprove usabilityMemory loss protectionError detection/correctionSystems managementSystem structure

The storage system of the present invention has a simple configuration and ensures redundancy of the system. The primary storage control device and the first secondary storage control device are connected by a synchronous read method, and the primary storage control device and the second secondary storage control device are connected by an asynchronous read method. The primary storage control device sets a management number in the update data and saves a journal data. The primary storage control device associates the management number with the update data and transmits them to the first secondary storage control device. The first secondary storage control device writes the update data to the first secondary volume, associates the management number with the storage destination address of the update data and stores them in the maintenance table. If the primary storage control device stops, the first secondary storage control device becomes anew a primary storage control device. The first secondary storage control device is connected to the second secondary storage control device by an asynchronous read method.

Owner:HITACHI LTD

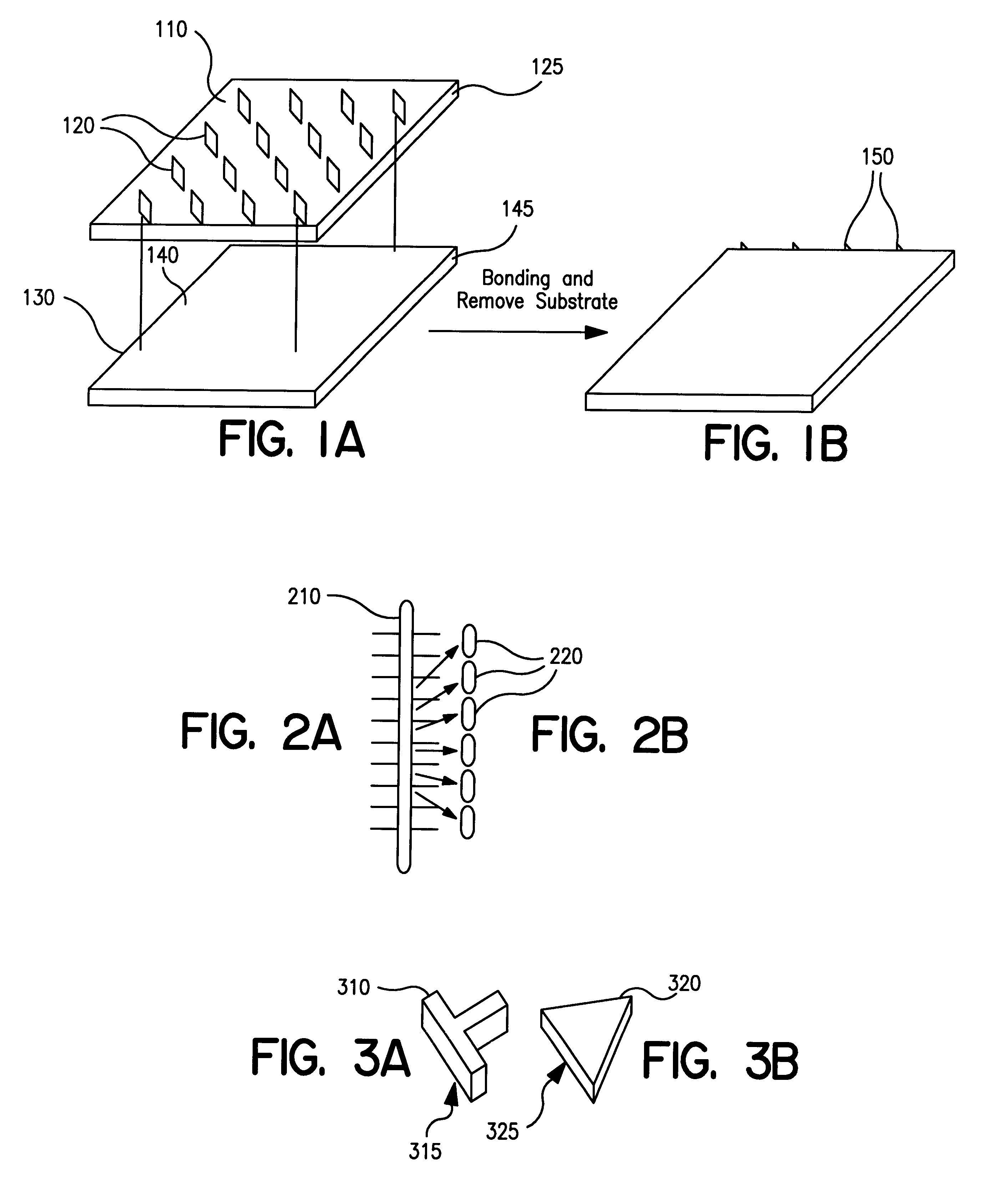

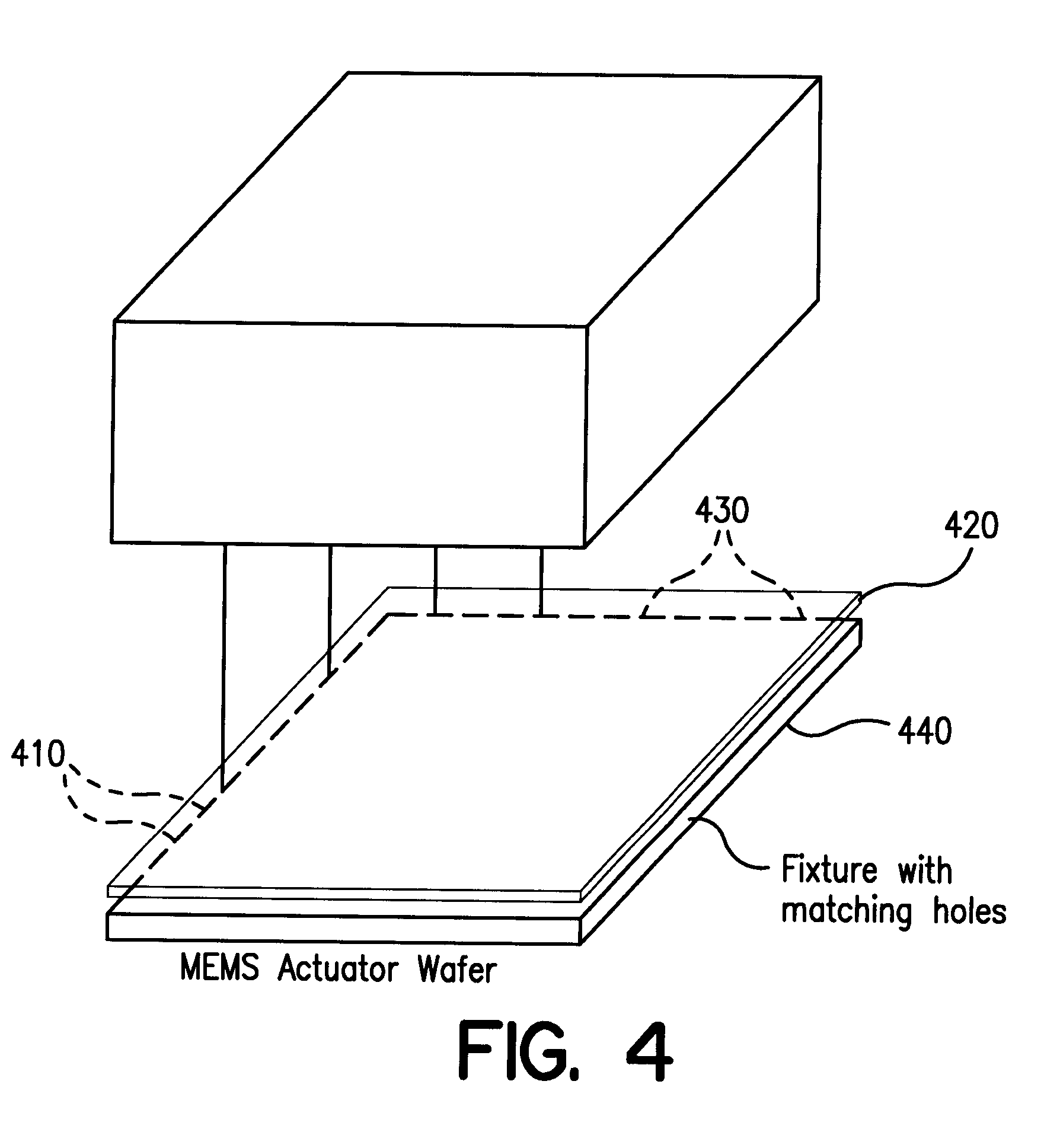

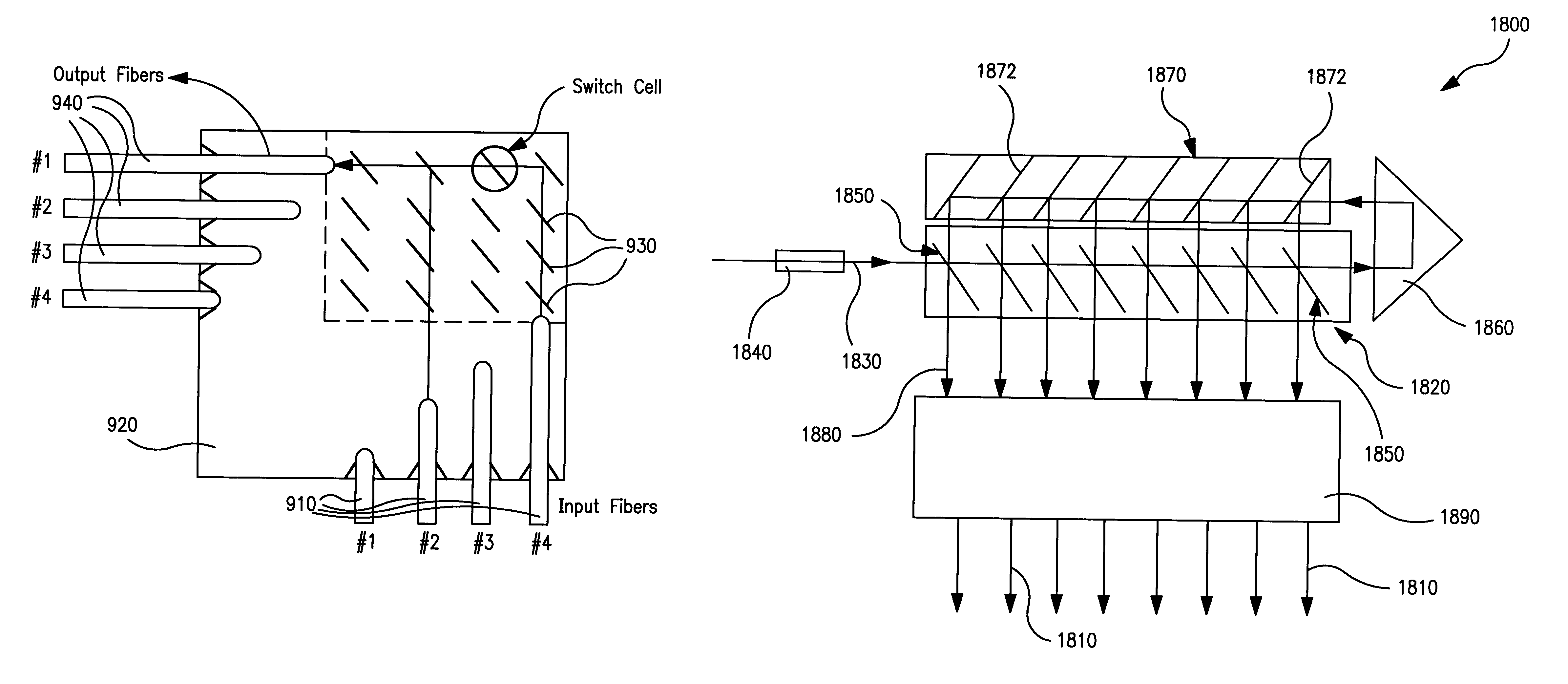

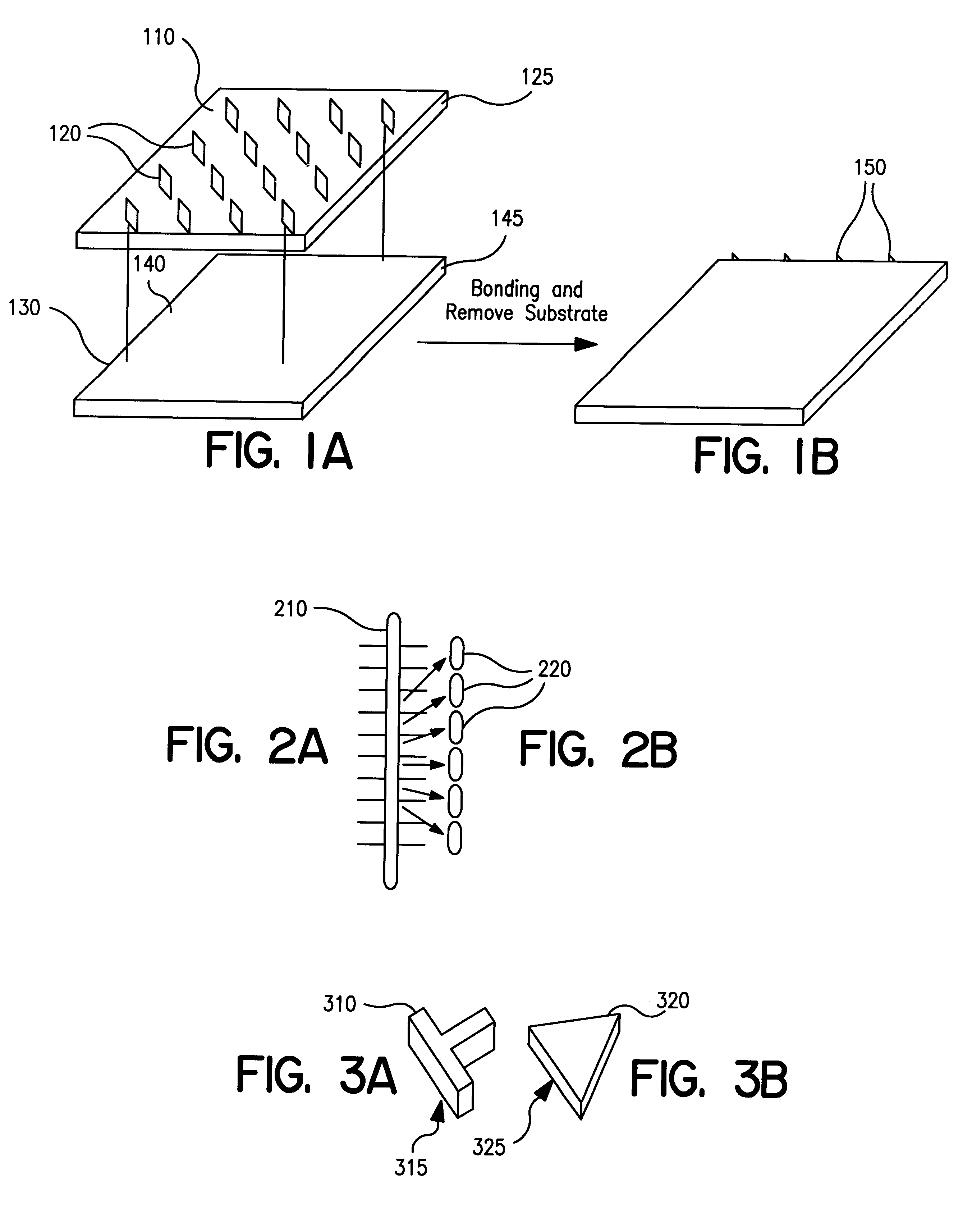

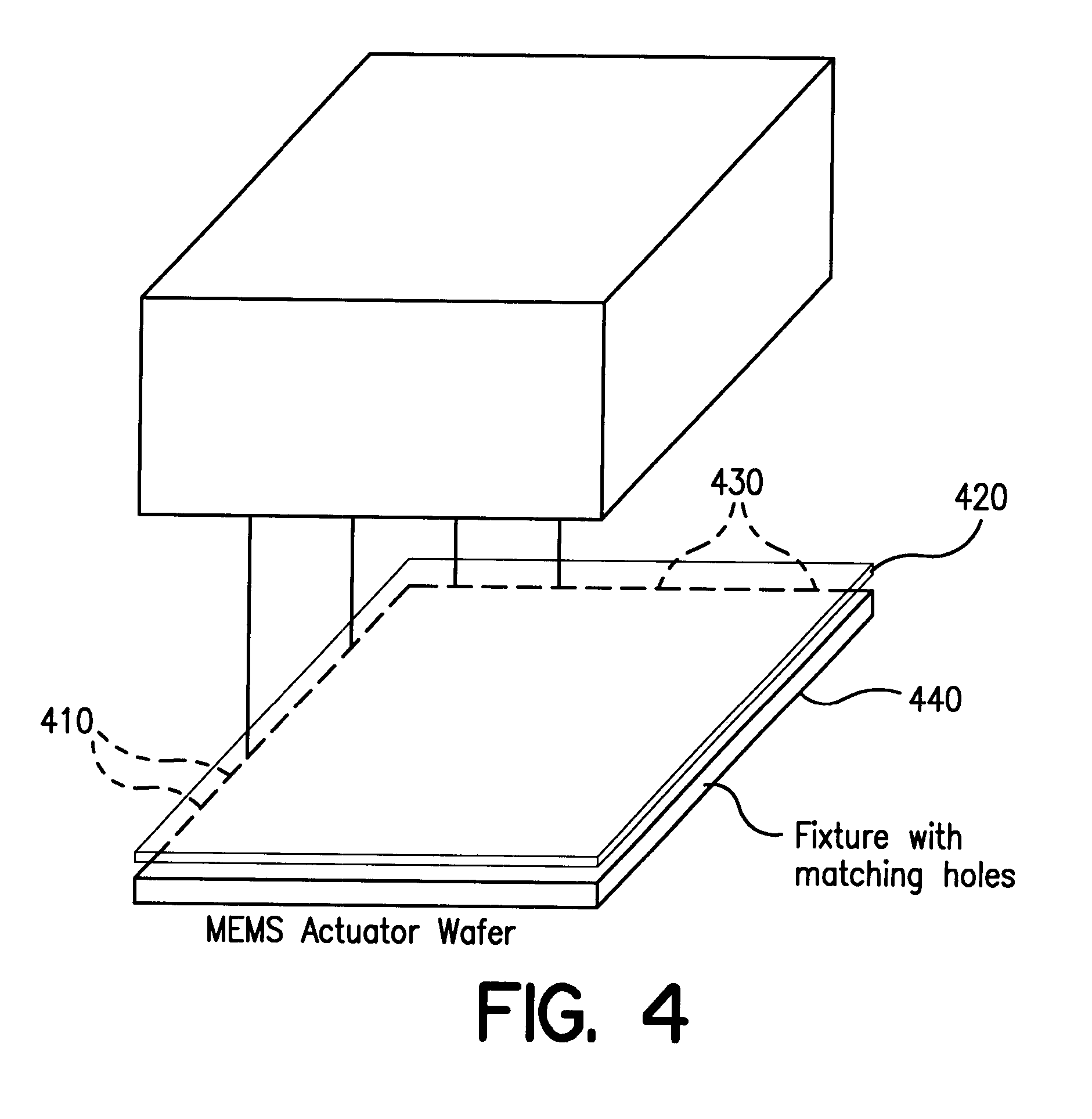

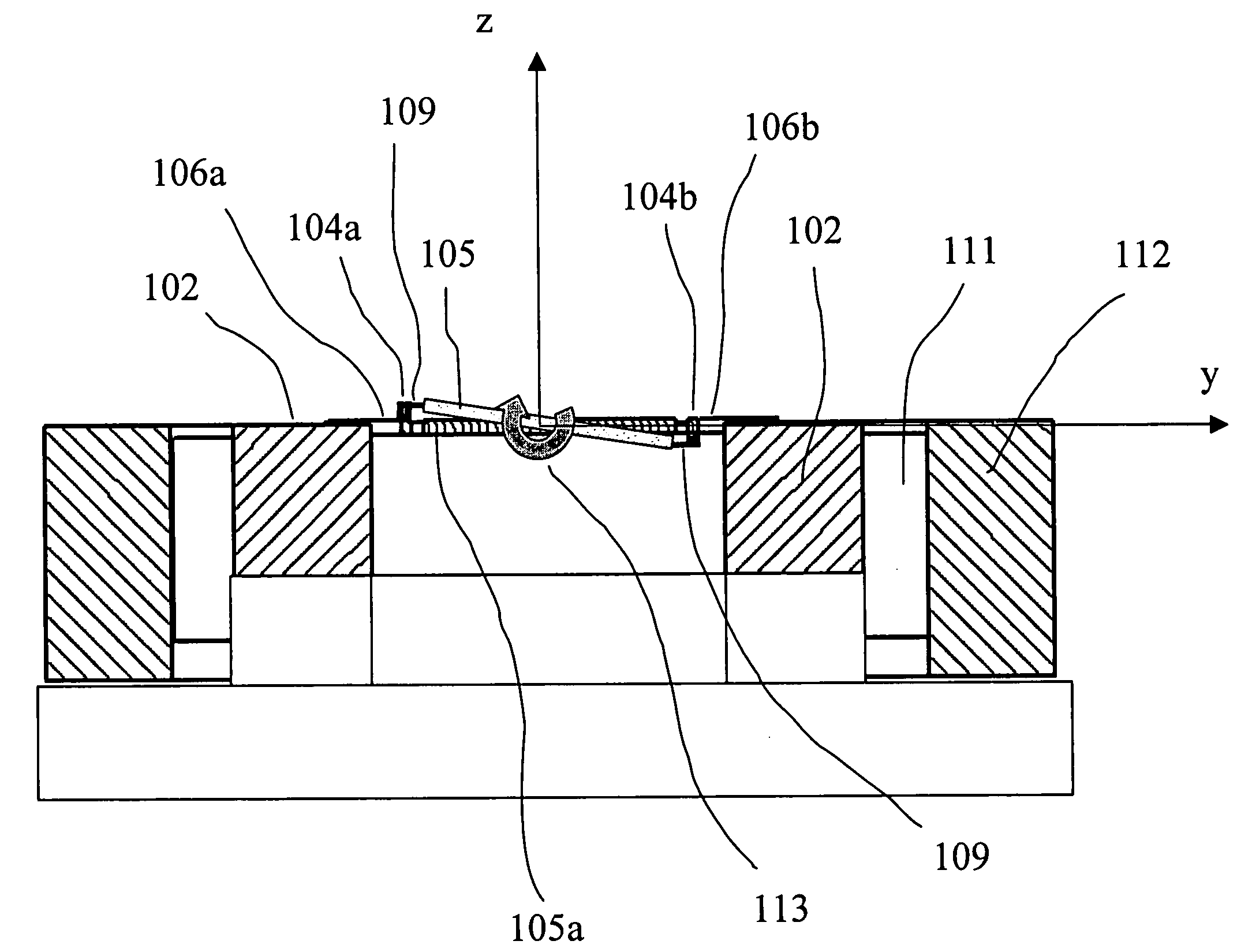

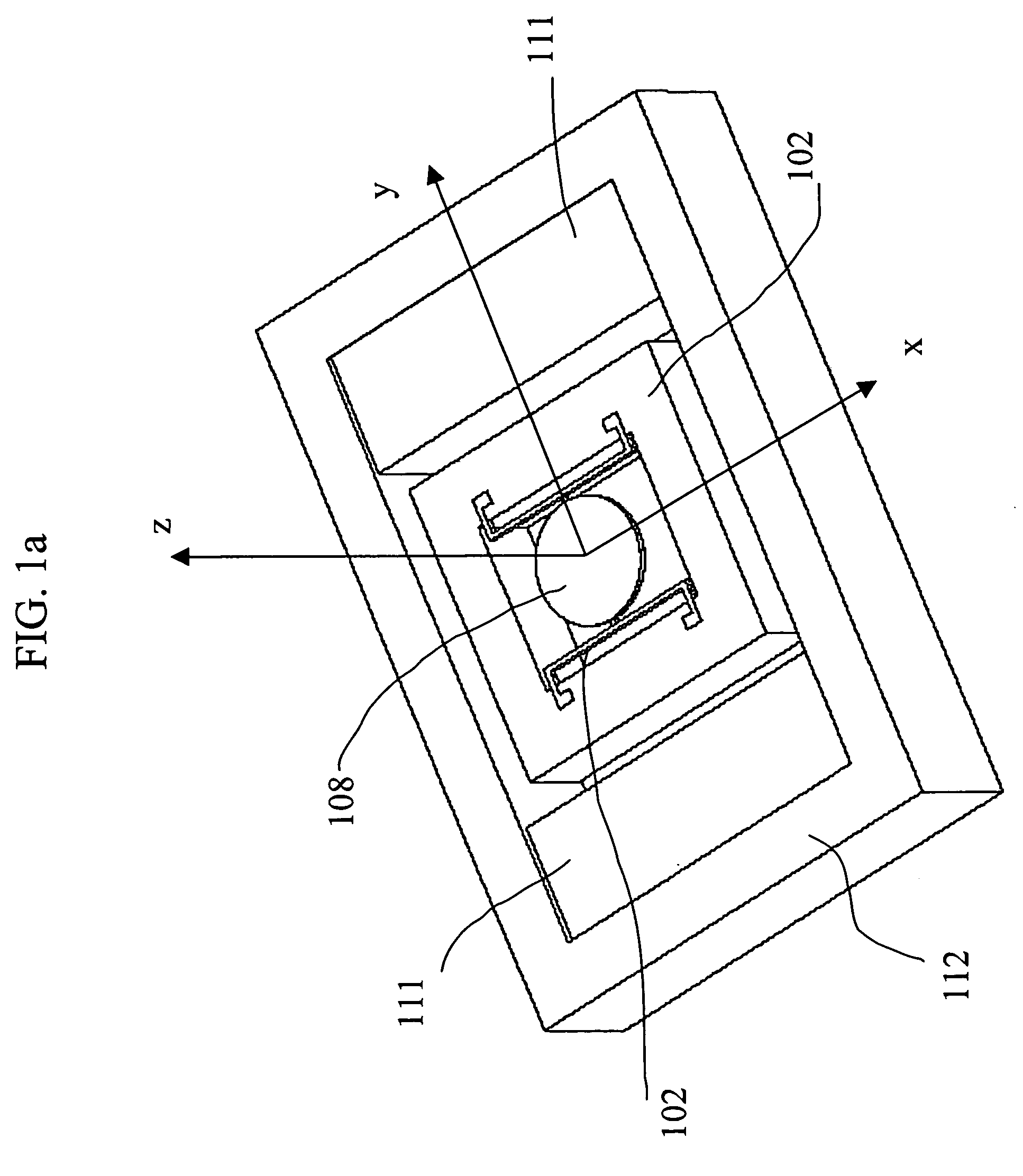

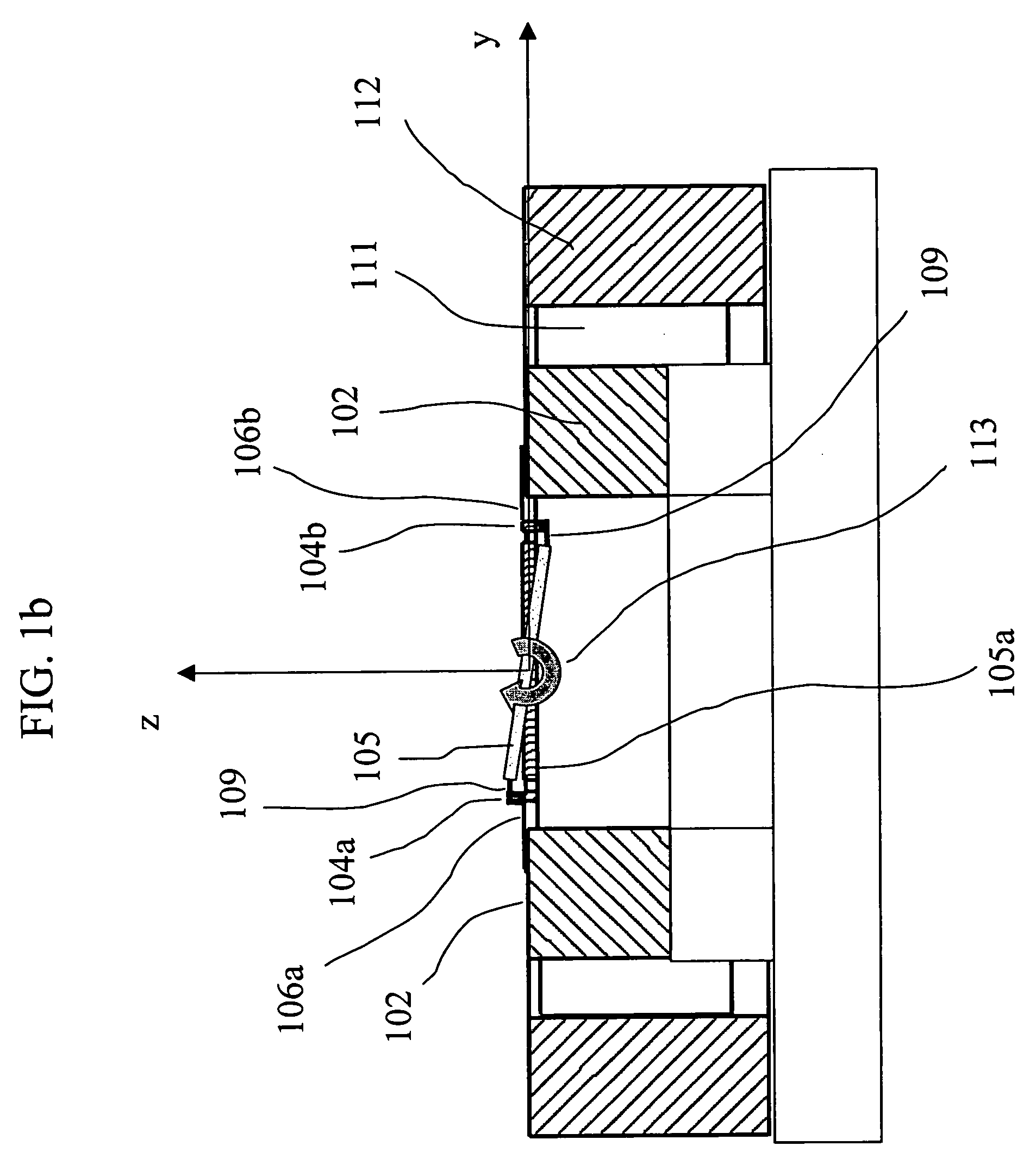

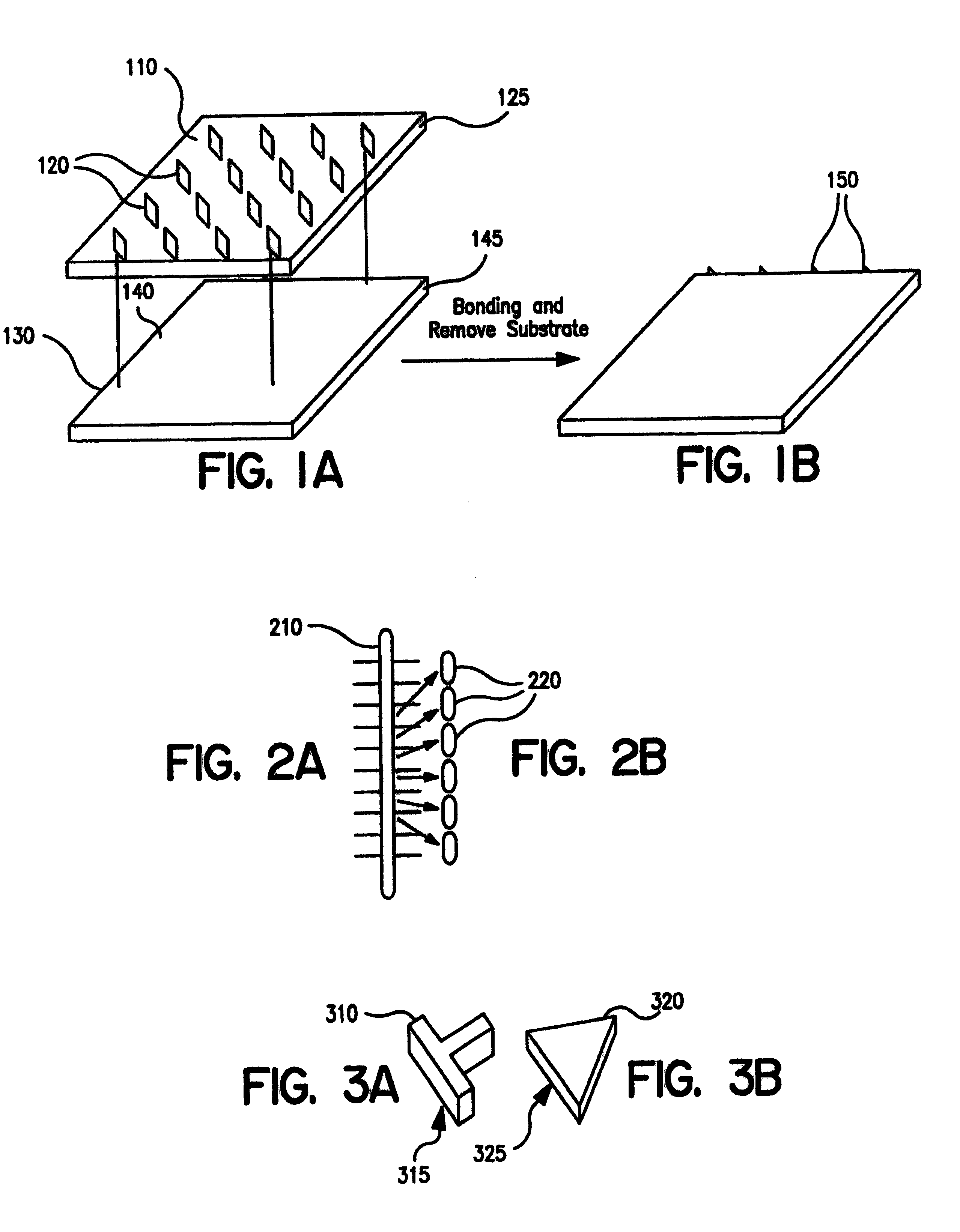

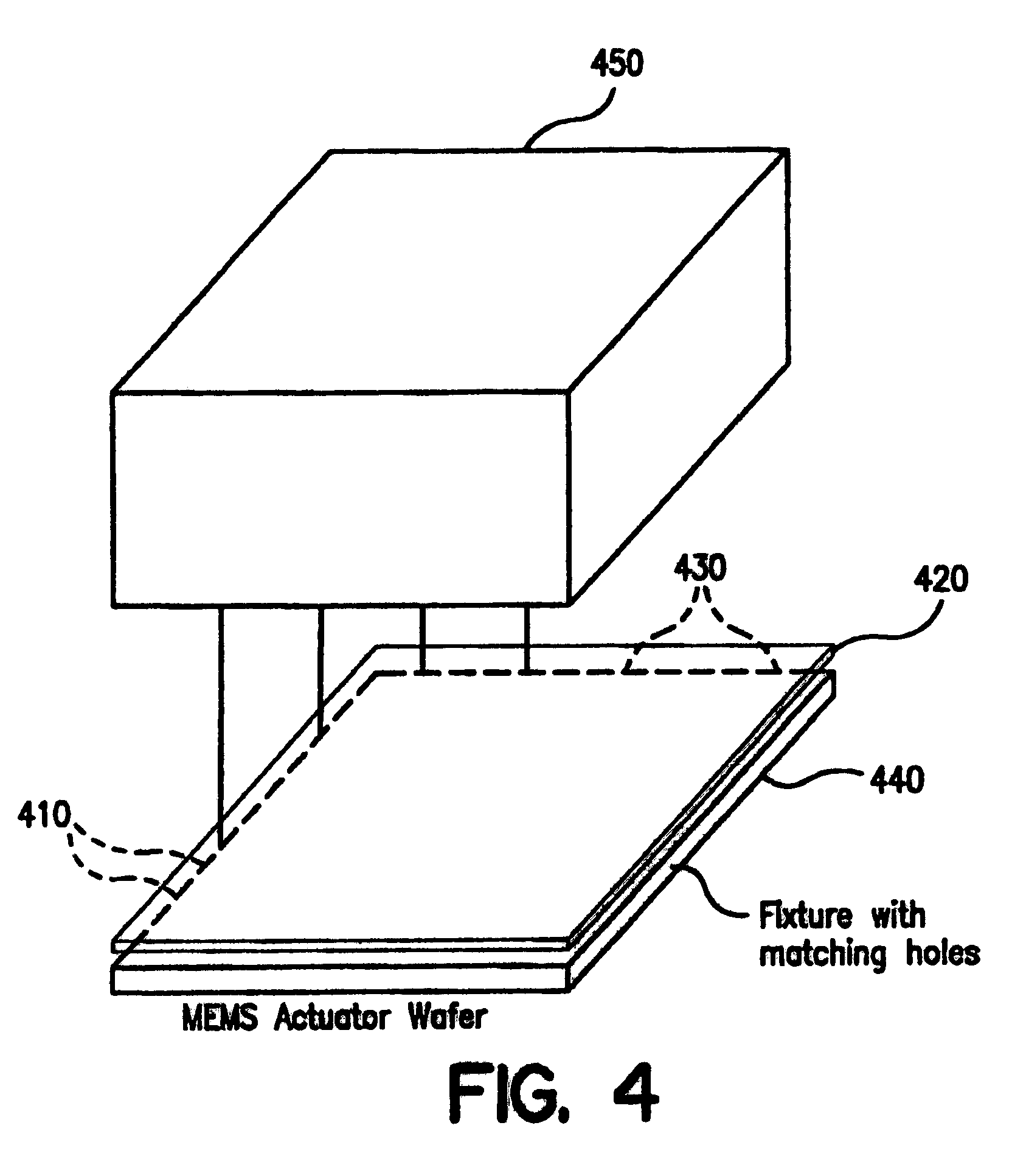

Micromachined optomechanical switching devices

InactiveUS6449406B1Reduce packaging costsSmall massMultiplex system selection arrangementsCoupling light guidesEngineeringActuator

Various configurations of micromachined optomechanical switching cells are disclosed herein. In accordance with the invention, an optomechanical switching cell is provided which includes an actuator positioned on a substrate and a mirror coupled to the actuator. The switching cell also includes an electrode disposed upon the substrate under the actuator. An insulator may also be interposed between the substrate and the electrode. In another aspect of the present invention the switching cell includes a latch having a first end region connected to the substrate and a second end region engaged by the mirror.

Owner:OMM +1

Semiconductor device and manufacturing method thereof

ActiveUS20110133180A1High field-effect mobilityHigh crystallinitySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceSemiconductor device

One embodiment of the present invention is to achieve high mobility in a device using an oxide semiconductor and provide a highly reliable display device. An oxide semiconductor layer including a crystal region in which c-axis is aligned in a direction substantially perpendicular to a surface is formed and an oxide insulating layer is formed over and in contact with the oxide semiconductor layer. Oxygen is supplied to the oxide semiconductor layer by third heat treatment. A nitride insulating layer containing hydrogen is formed over the oxide insulating layer and fourth heat treatment is performed, so that hydrogen is supplied at least to an interface between the oxide semiconductor layer and the oxide insulating layer.

Owner:SEMICON ENERGY LAB CO LTD

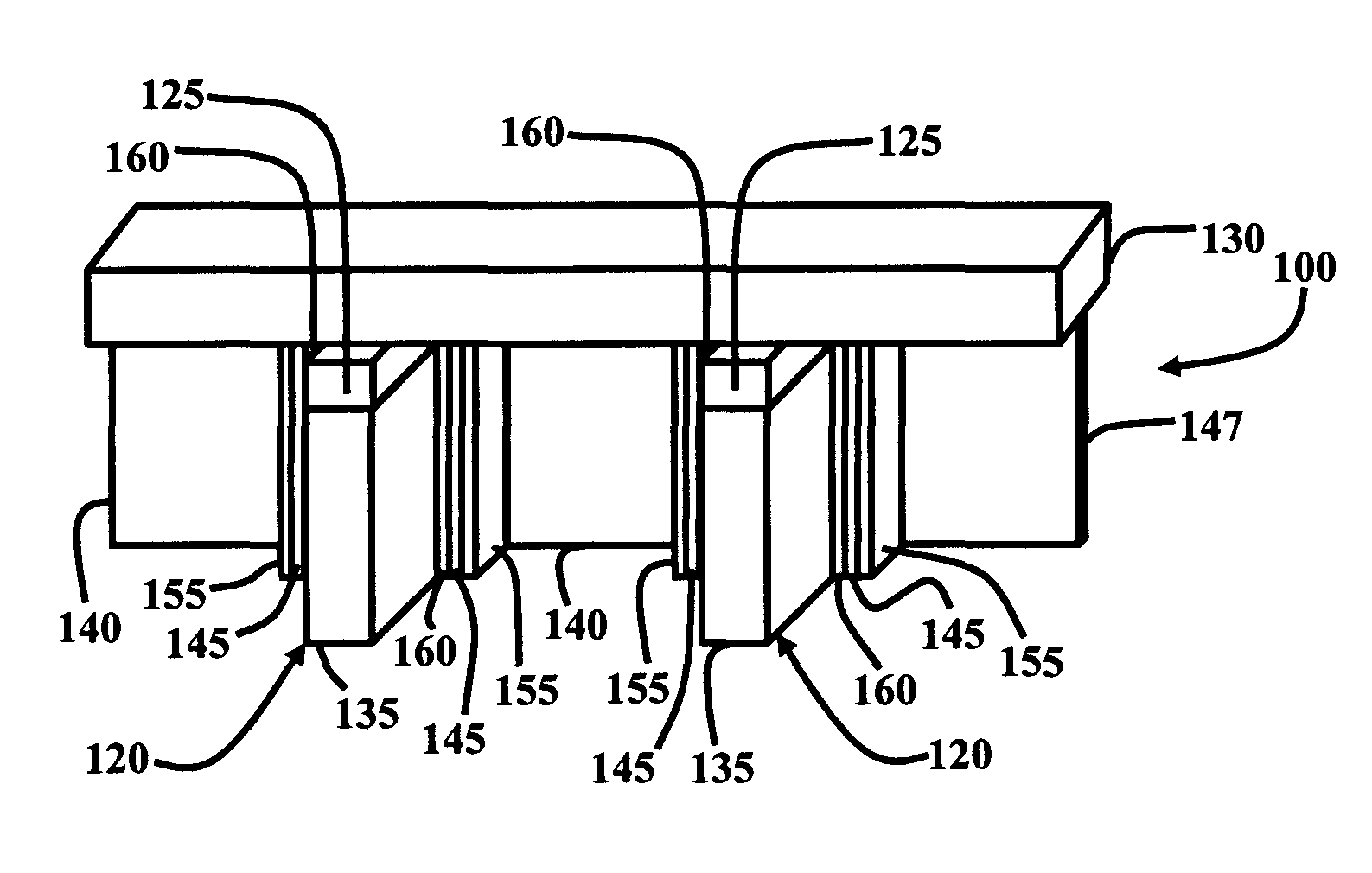

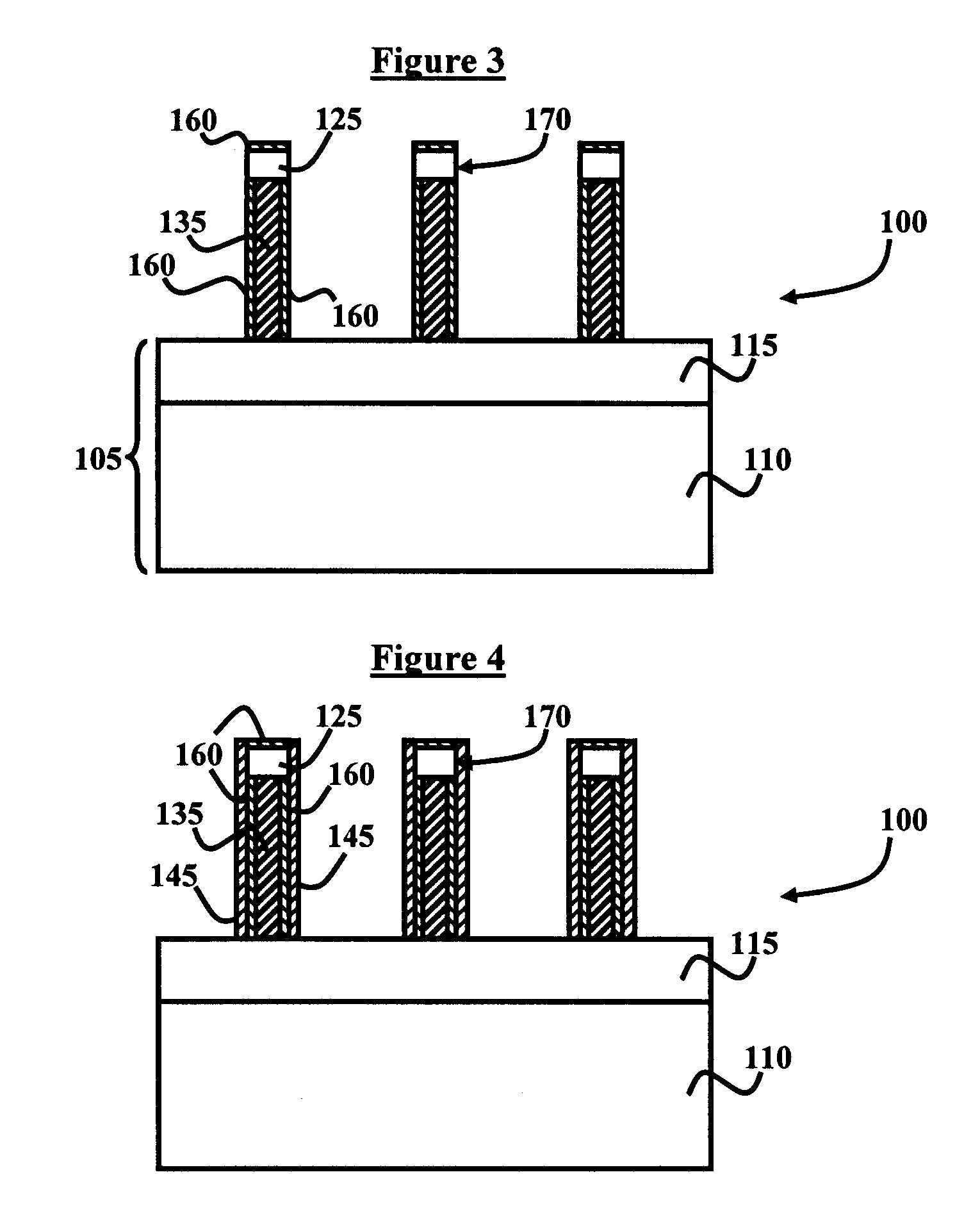

FinFET with low gate capacitance and low extrinsic resistance

ActiveUS7105934B2Reduce gate capacitanceReduce capacitanceSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceGate insulator

A FinFET device and a method of lowering a gate capacitance and extrinsic resistance in a field effect transistor, wherein the method comprises forming an isolation layer comprising a BOX layer over a substrate, configuring source / drain regions above the isolation layer, forming a fin structure over the isolation layer, configuring a first gate electrode adjacent to the fin structure, disposing a gate insulator between the first gate electrode and the fin structure, positioning a second gate electrode transverse to the first gate electrode, and depositing a third gate electrode on the fin structure, the first gate electrode, and the second gate electrode, wherein the isolation layer is formed beneath the insulator, the first gate electrode, and the fin structure. The method further comprises sandwiching the second gate electrode with a dielectric material. The fin structure is formed by depositing an oxide layer over a silicon layer.

Owner:MICROSOFT TECH LICENSING LLC

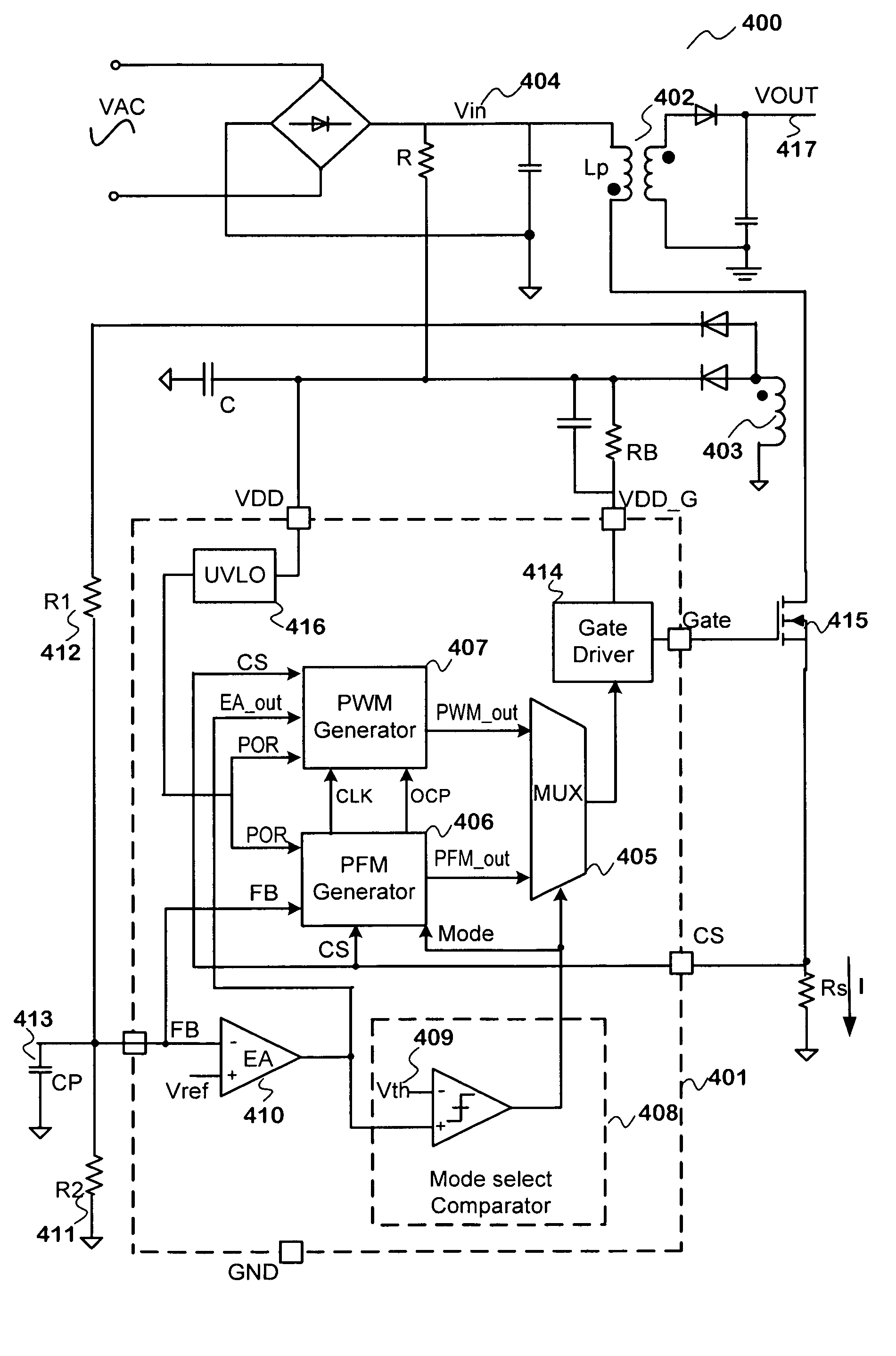

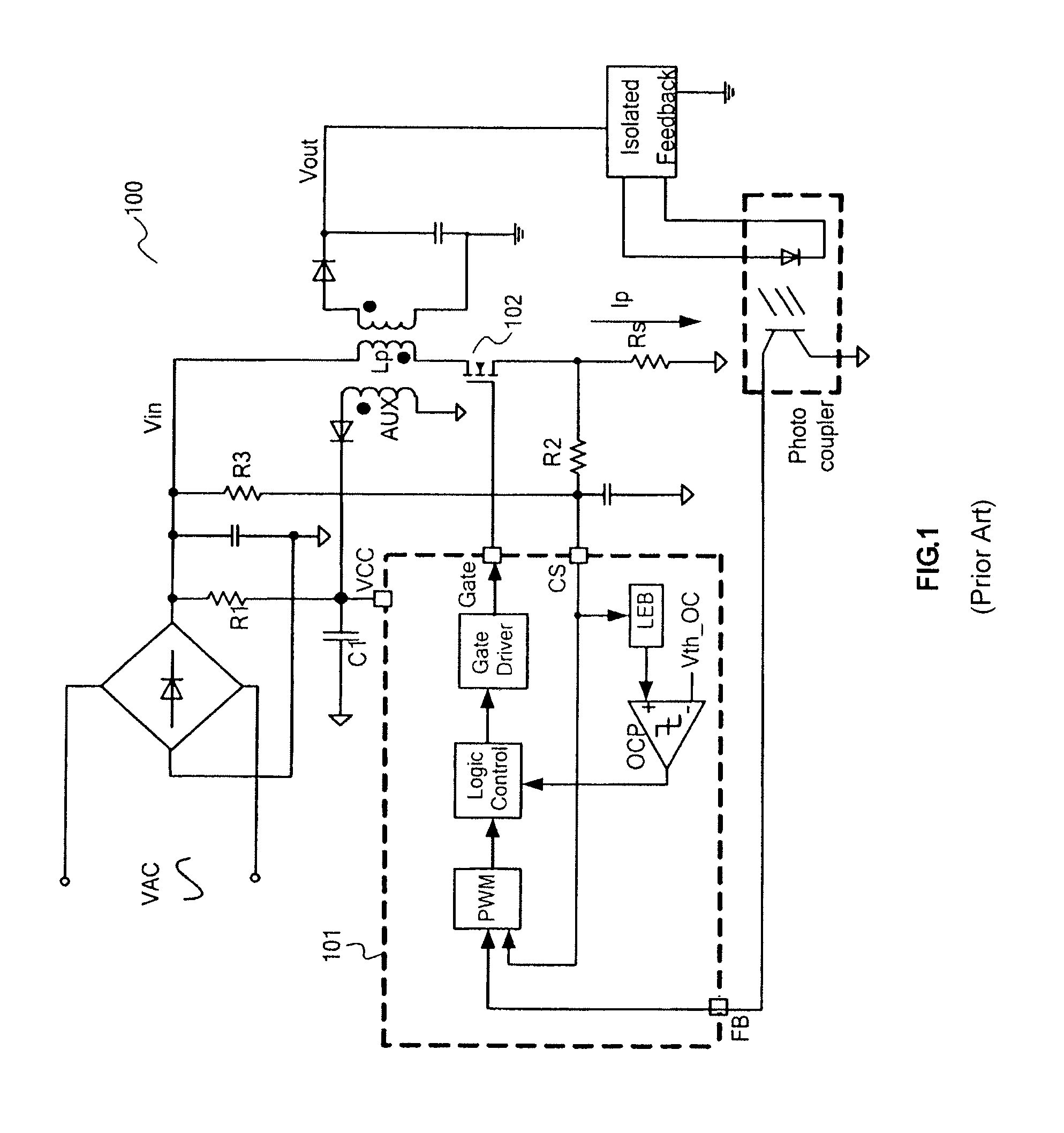

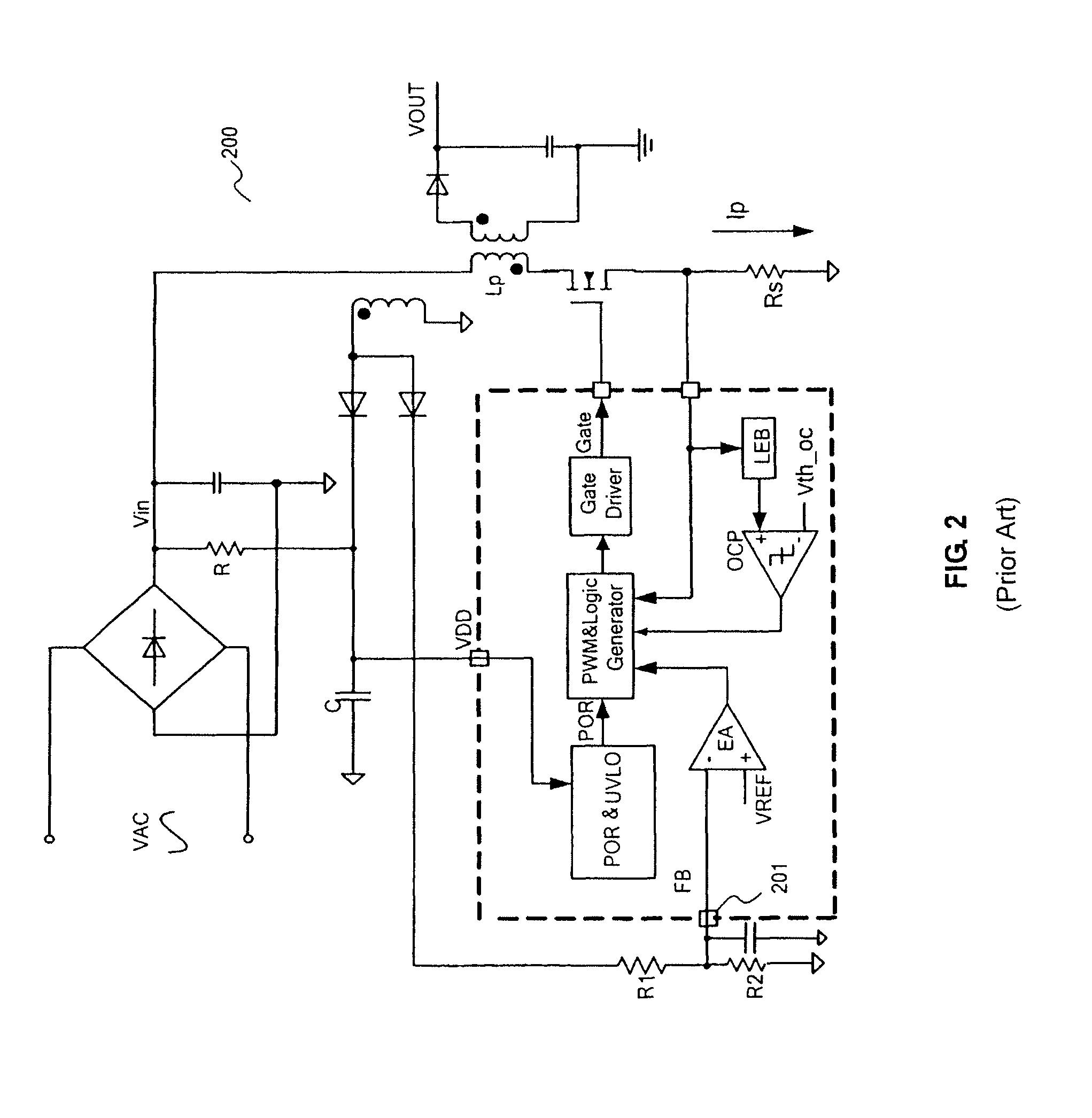

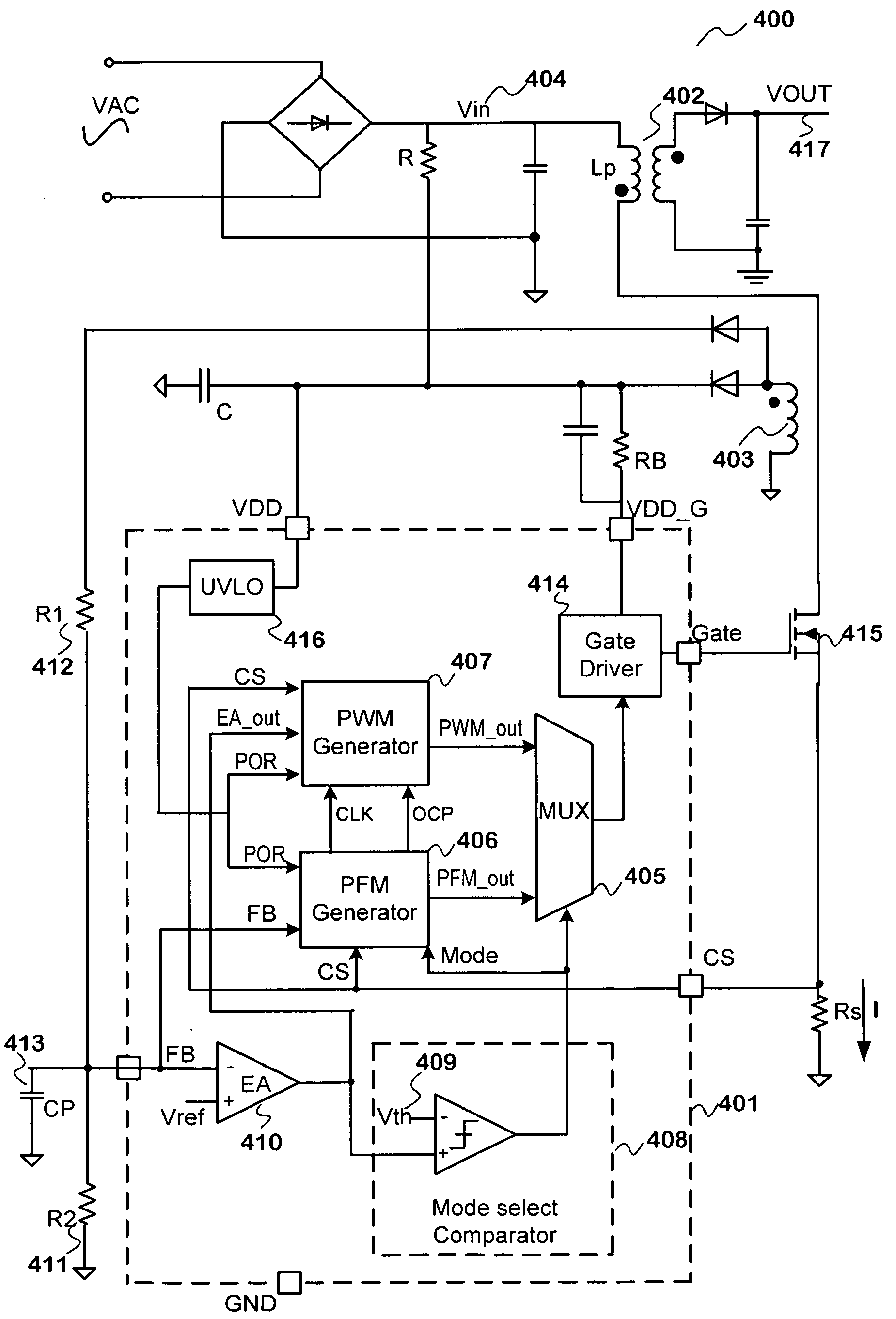

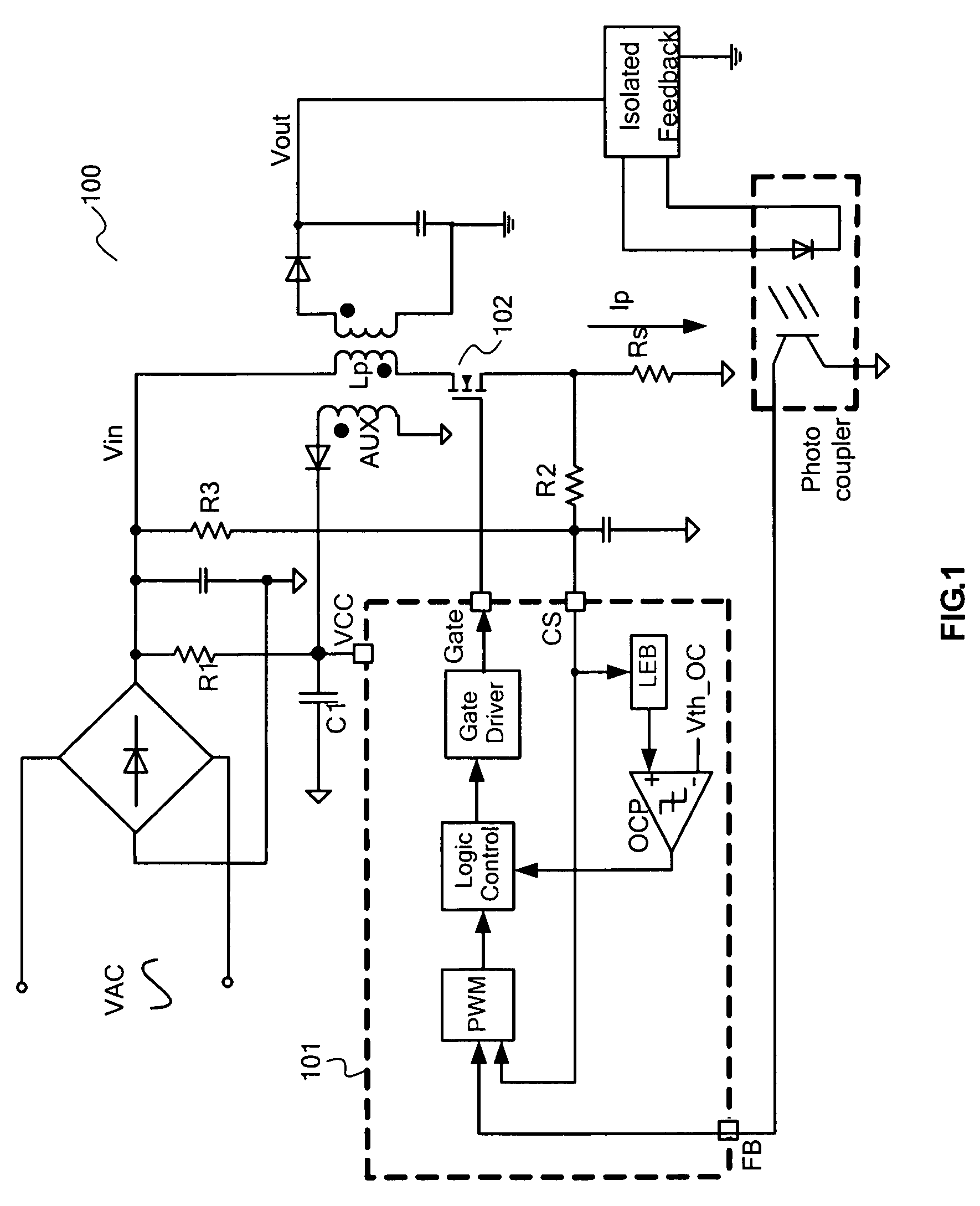

Method and system for efficient power control with multiple modes

InactiveUS7826237B2Improve performanceImprove stabilityEfficient power electronics conversionDc-dc conversionElectricityPower mode

Method and system for efficient power control with multiple modes. According to an embodiment, the present invention provides a power system with selectable power modes. The power system includes a first terminal for outputting energy, and the first terminal is electrically coupled to a load. The system also includes a pulse-frequency modulation (PFM) component that is configured to adjust a pulse frequency based on the load. The system additionally includes a pulse-width modulation (PWM) component that is configured to adjust a pulse width based on the load. The system further includes a switch that is electrically coupled to the first terminal. Also, the system includes a control component, the control component being configured to provide a control signal that is capable of causing the switch to be turned on or off. The control signal is associated with an output of the PWM component and the pulse width if an output is greater than a predetermined value. The control signal is associated with an output of the PFM component and the pulse frequency if an output is lower than a predetermined value.

Owner:ON BRIGHT ELECTRONICS SHANGHAI

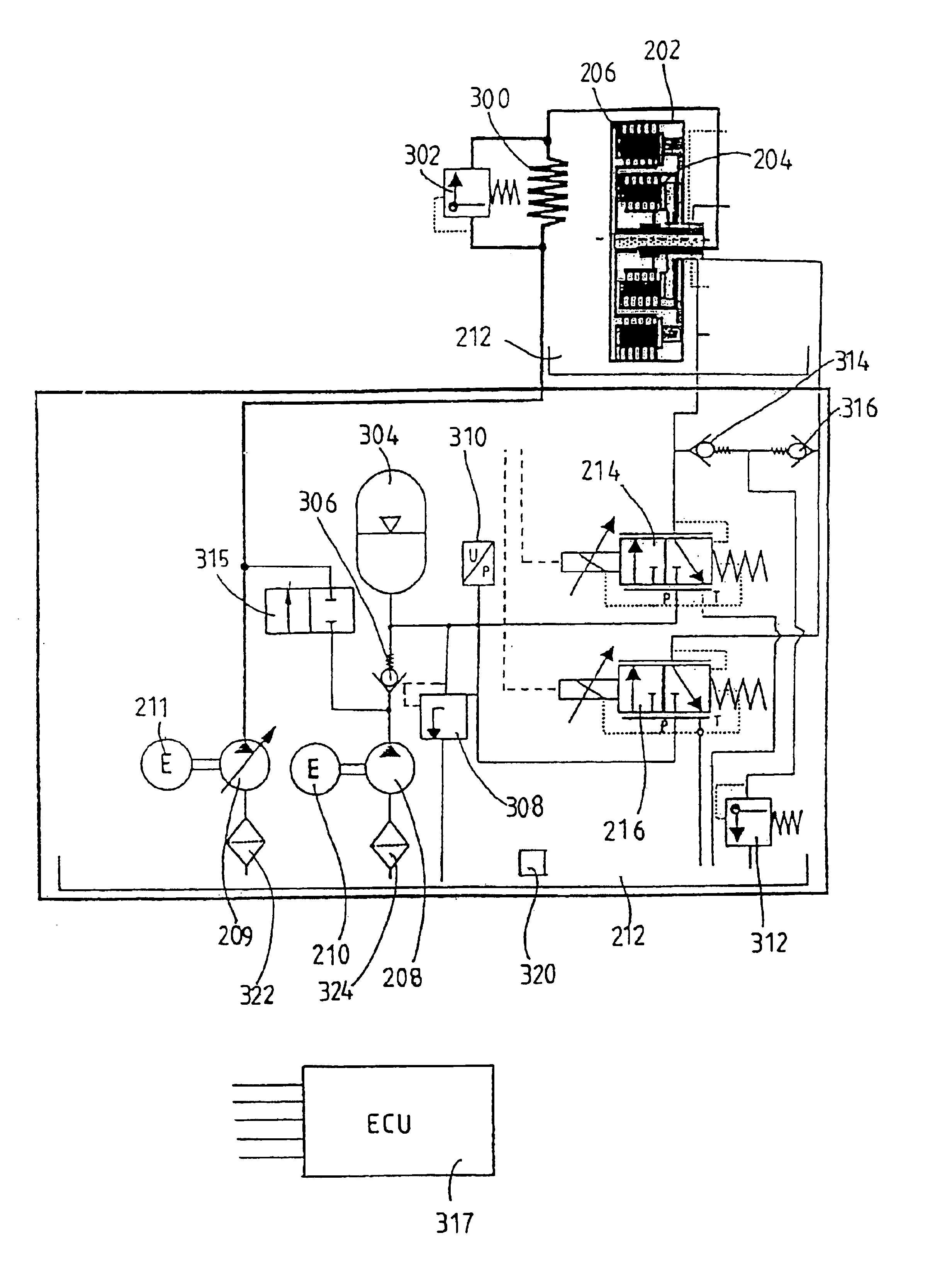

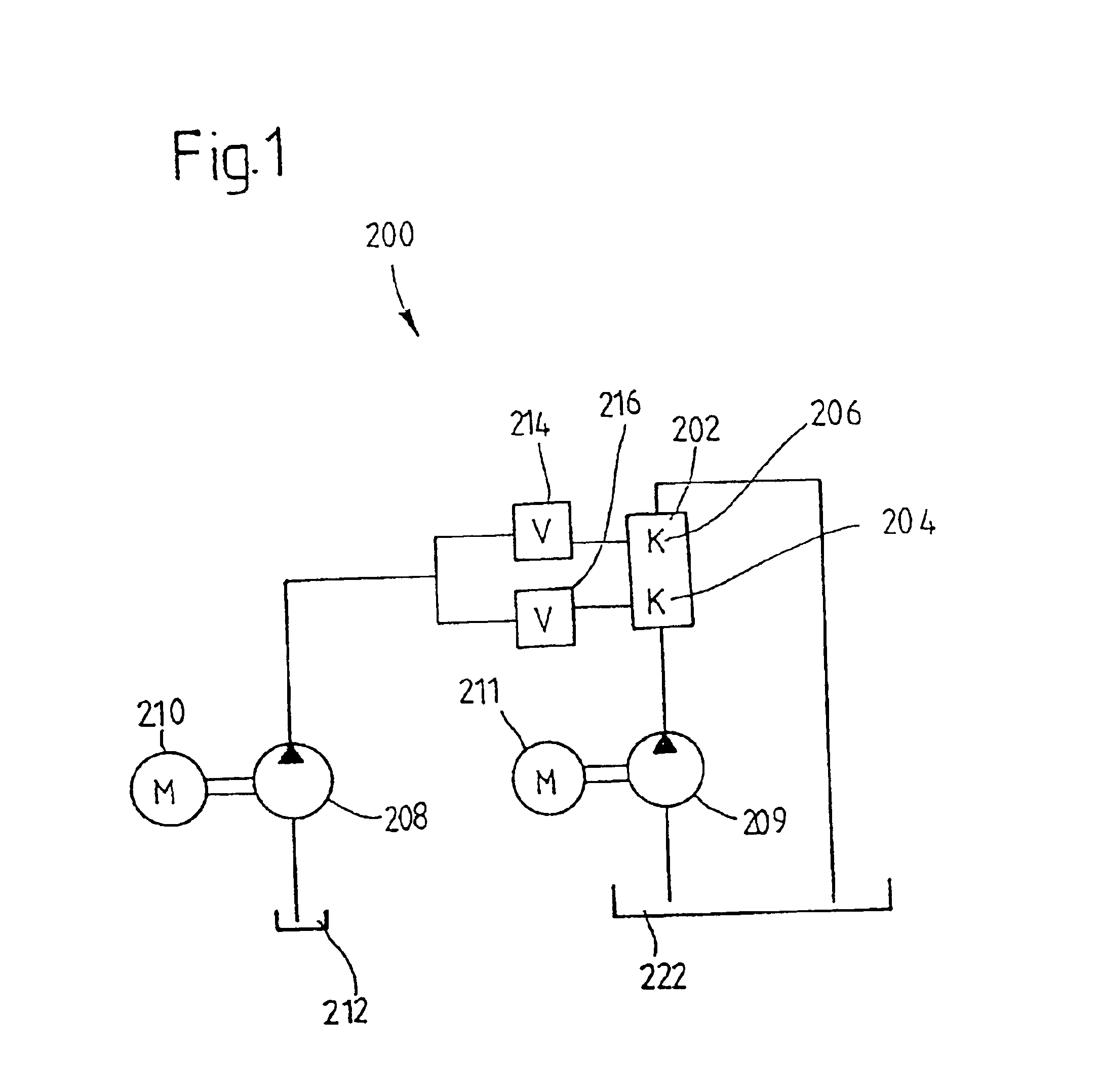

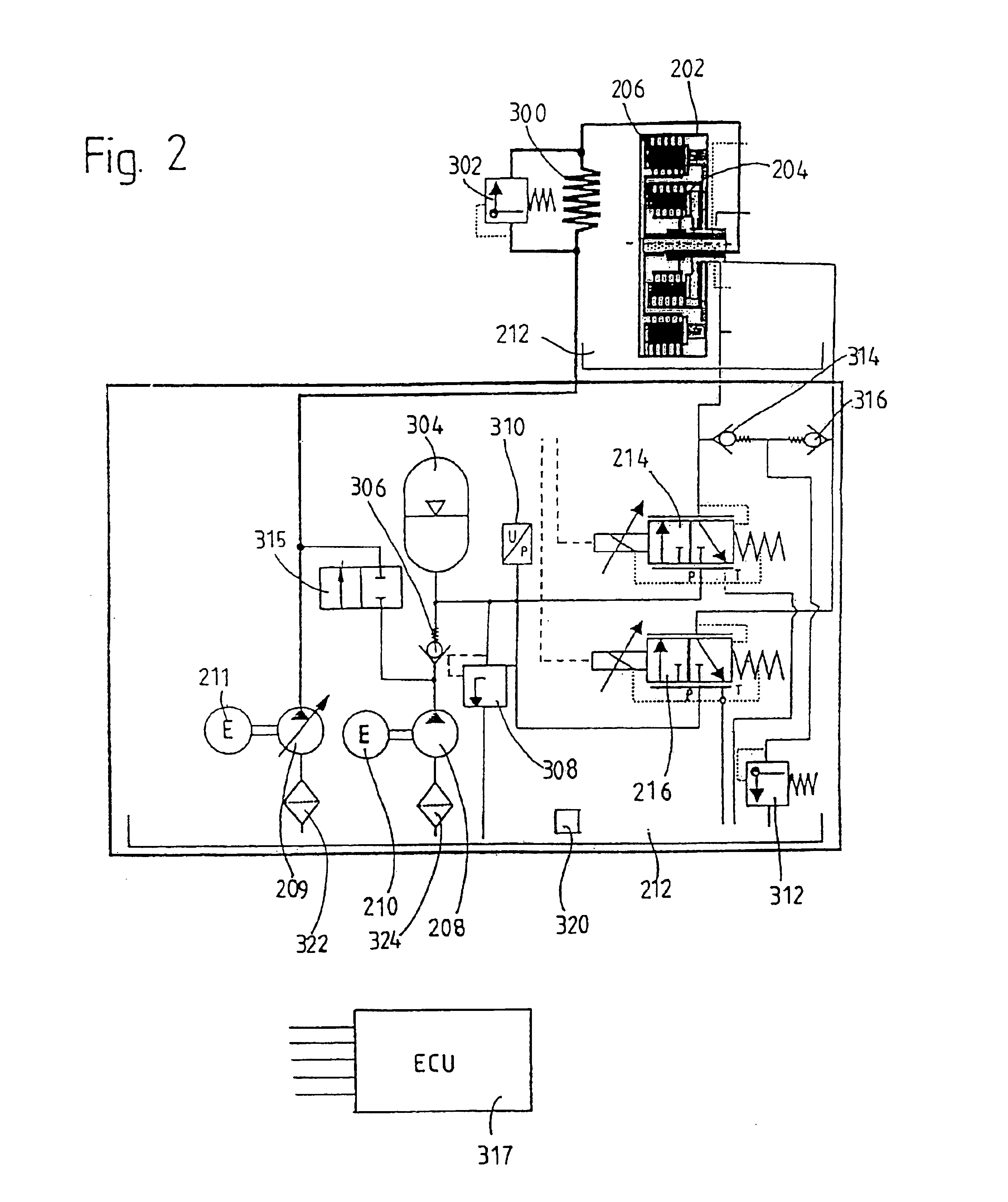

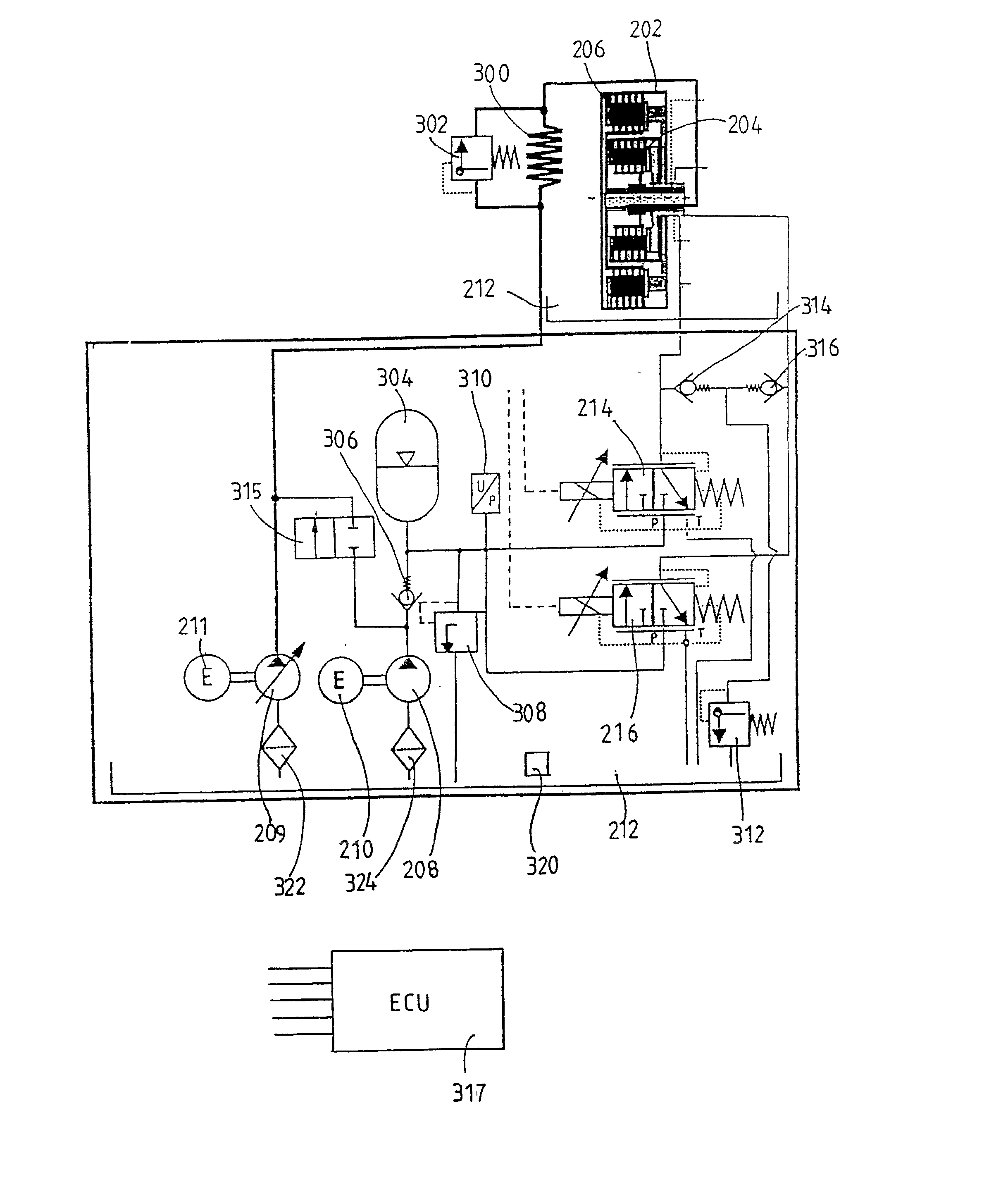

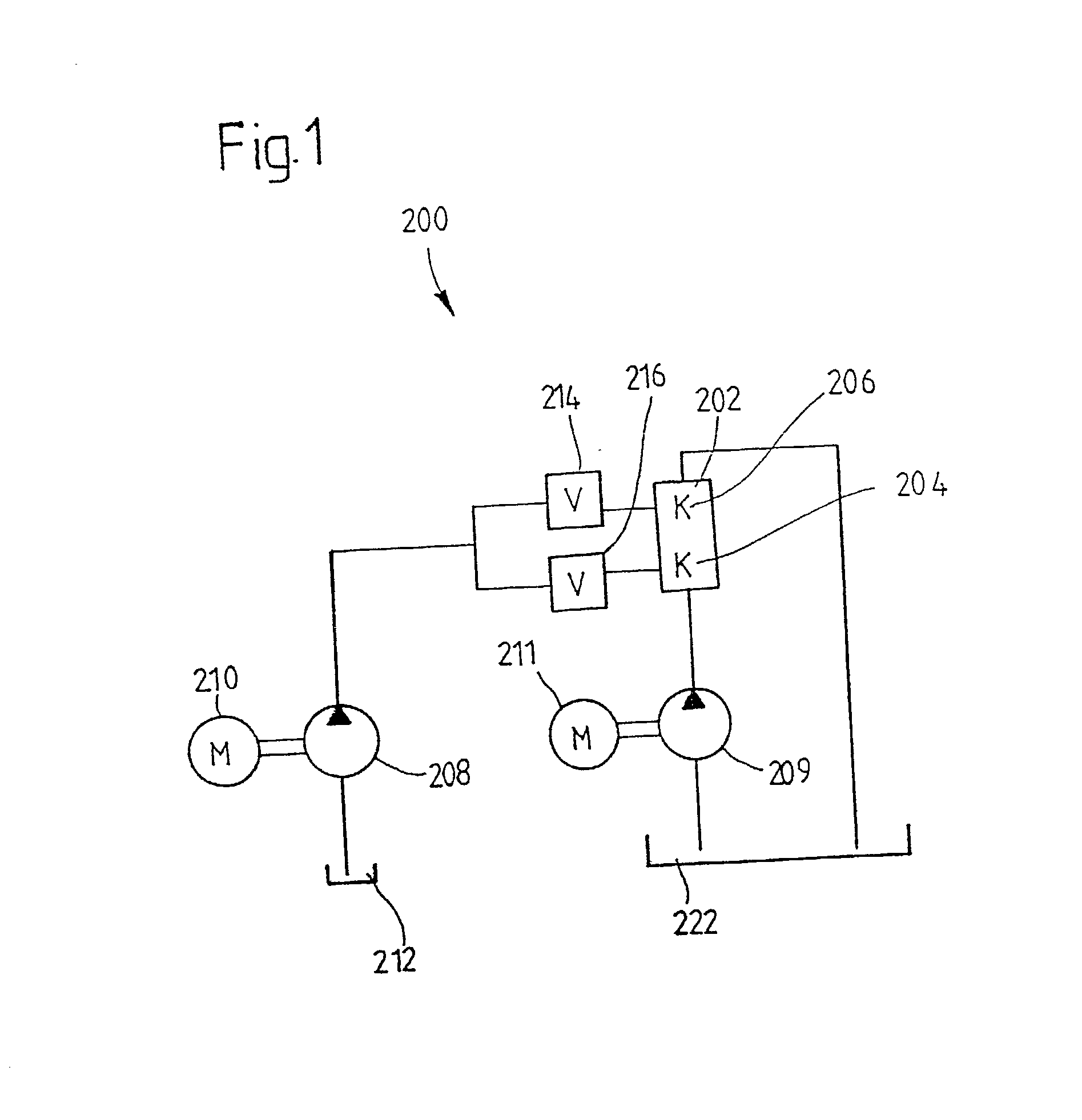

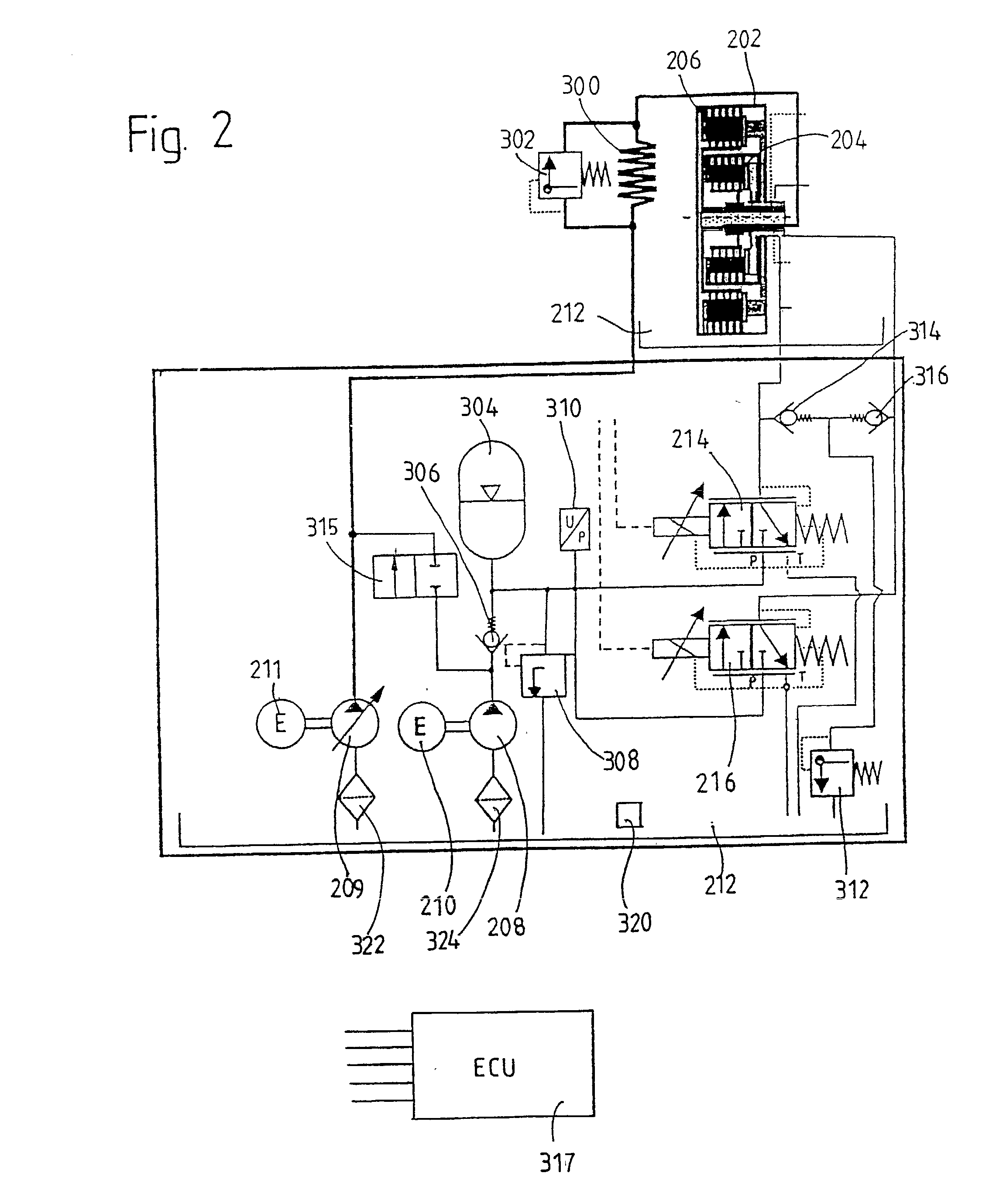

Clutch system

InactiveUS6789658B2Lower the volumeShort switching timeMechanical actuated clutchesFluid actuated clutchesMobile vehicleMotorized vehicle

Owner:ZF FRIEDRICHSHAFEN AG

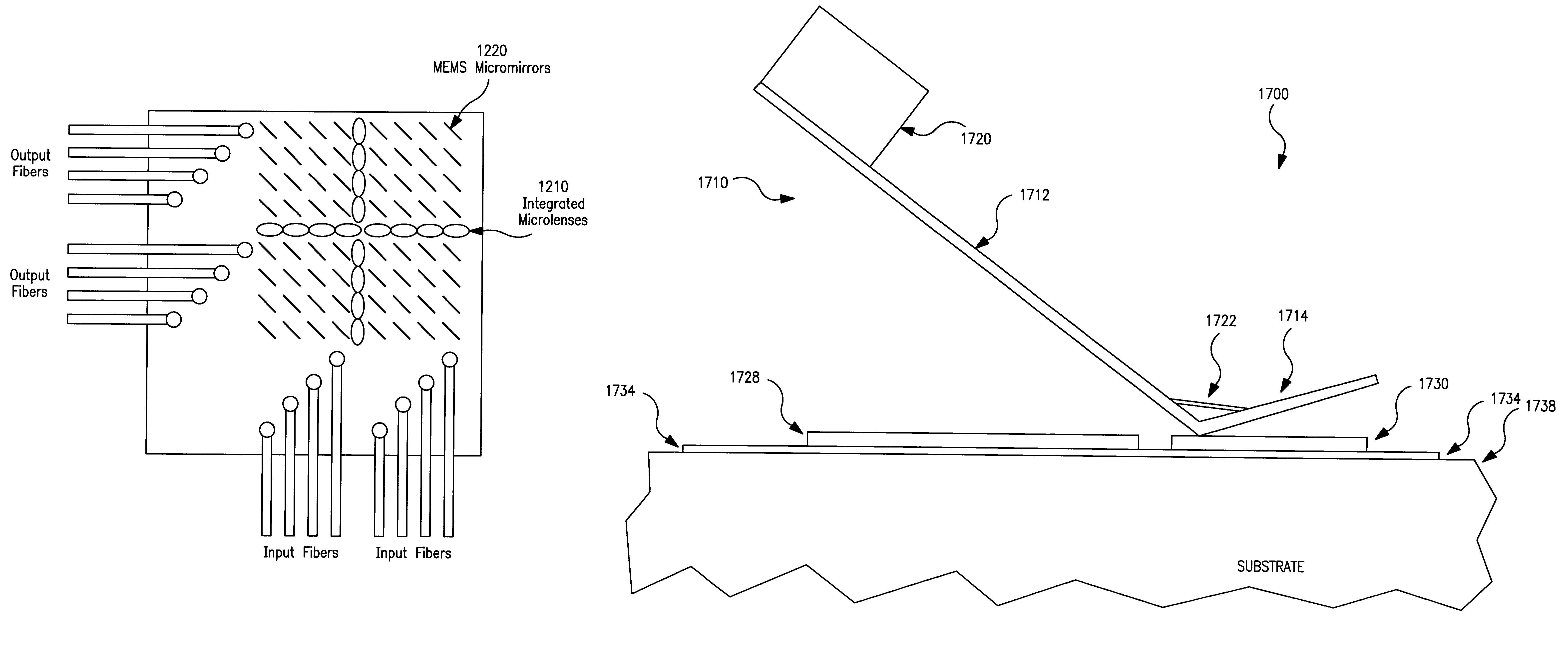

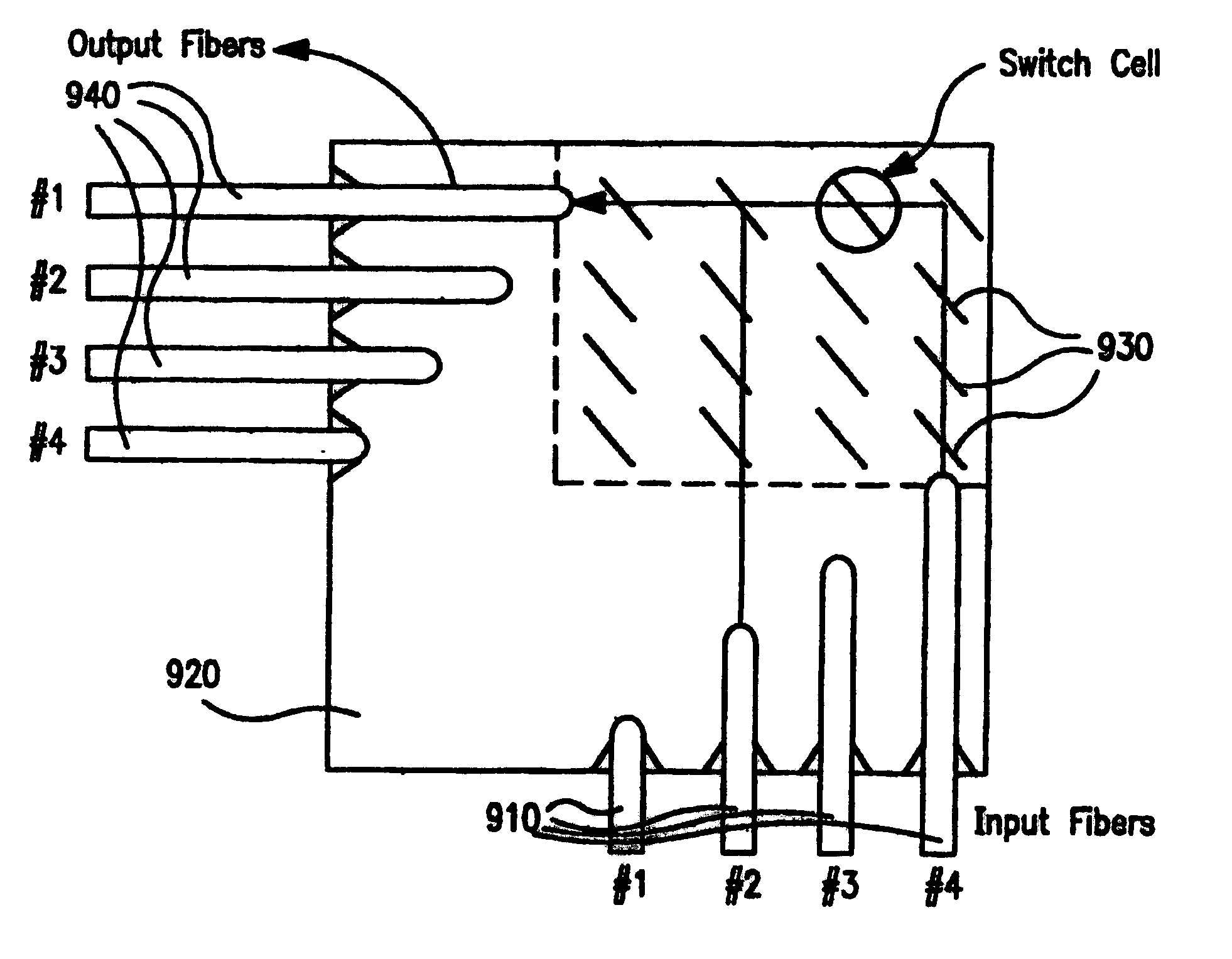

Optomechanical matrix switches including collimator arrays

InactiveUS6445841B1Reduce packaging costsSmall massMultiplex system selection arrangementsCoupling light guidesActuatorOptical alignment

Various configurations of optomechanical matrix and broadcast switches are disclosed herein. One such optomechanical matrix switch includes a substrate and a plurality of optomechanical switching cells coupled thereto. Each of the optomechanical switching cells includes a mirror and an actuator. The matrix switch further includes an array of collimator elements, each of the collimator elements being in optical alignment with one of the optomechanical switching cells. Also disclosed herein is a distributed matrix switch including first and second optomechanical matrix switches. The first and second optomechanical matrix switches respectively include first and second pluralities of optomechanical switching cells mounted upon first and second substrates. A collimator array is interposed between the first and second matrix switches in optical alignment with the first and second pluralities of optomechanical switching cells.

Owner:CROSSFIBER +1

Method and system for efficient power control with multiple modes

InactiveUS20090206814A1Improve performanceImprove stabilityEfficient power electronics conversionDc-dc conversionEffective powerPower mode

Method and system for efficient power control with multiple modes. According to an embodiment, the present invention provides a power system with selectable power modes. The power system includes a first terminal for outputting energy, and the first terminal is electrically coupled to a load. The system also includes a pulse-frequency modulation (PFM) component that is configured to adjust a pulse frequency based on the load. The system additionally includes a pulse-width modulation (PWM) component that is configured to adjust a pulse width based on the load. The system further includes a switch that is electrically coupled to the first terminal. Also, the system includes a control component, the control component being configured to provide a control signal that is capable of causing the switch to be turned on or off. The control signal is associated with an output of the PWM component and the pulse width if an output is greater than a predetermined value. The control signal is associated with an output of the PFM component and the pulse frequency if an output is lower than a predetermined value.

Owner:ON BRIGHT ELECTRONICS SHANGHAI

Semiconductor memory

InactiveUS20060076549A1Short switching timeLow programming voltageDigital storageBulk negative resistance effect devicesSilicon matrixRetention time

The object of providing a non-volatile semiconductor memory that stands out by good scalability and a high retention time as well as ensures low switching voltages at low switching times and achieves a great number of switching cycles at good temperature stability is solved by the present invention with a semiconductor memory whose memory cells comprise at least one silicon matrix material layer with open or disturbed nanocrystalline or amorphous network structures and structural voids which has a resistively switching property between two stable states, utilizing the ion drift in the silicon matrix material layer. The memory concept suggested in the present invention thus offers an alternative to the flash and DRAM memory concepts since it is not based on the storing of charges, but on the difference of the electric resistance between two stable states that are caused by the mobility of ions in the amorphous silicon matrix material with an externally applied electric field.

Owner:POLARIS INNOVATIONS LTD

Magnetically actuated fast MEMS mirrors and microscanners

InactiveUS20050018322A1Quick scanImprove accuracyMirrorsDiffusing elementsMagnetic actuationEngineering

Magnetically and electromagnetically driven MEMS devices for reflecting light signals and for switching radio frequency (RF) signals are provided. In a preferred embodiment, a light reflecting device such as a mirror or micro-scanner comprises a plate operative to reflect light and at least two conductive flexural actuators connected to the plate and to a substrate and operative to impart a rotation or tilt motion to the plate under a force arising from the interaction of a current passing through the conductive flexural actuators and a magnetic field parallel to the substrate. An RF switch comprises a substrate and a membrane having a longitudinal dimension and a lateral dimension, the membrane positioned substantially parallel to and attached to the substrate and operative to provide at least two switching positions in response to actuation by a Lorenz force acting on it.

Owner:TERRAOP

Micromachined optomechanical switching cell with parallel plate actuator and on-chip power monitoring

InactiveUS6453083B1Reduce packaging costsSmall massMultiplex system selection arrangementsCoupling light guidesParallel plateOptical power

A number of micromachined optomechanical switching cells and matrix switches including such switching cells are disclosed herein. One optomechanical switching cell of the present invention includes a parallel plate actuator positioned on a substrate. A mirror coupled to the actuator is disposed to selectively redirect an incident optical beam. The present invention also contemplates an optomechanical matrix switch including a substrate and a plurality of optomechanical switching cells coupled thereto. The matrix switch further includes an arrangement for monitoring the optical power incident upon, and output by, the matrix switch.

Owner:OMM

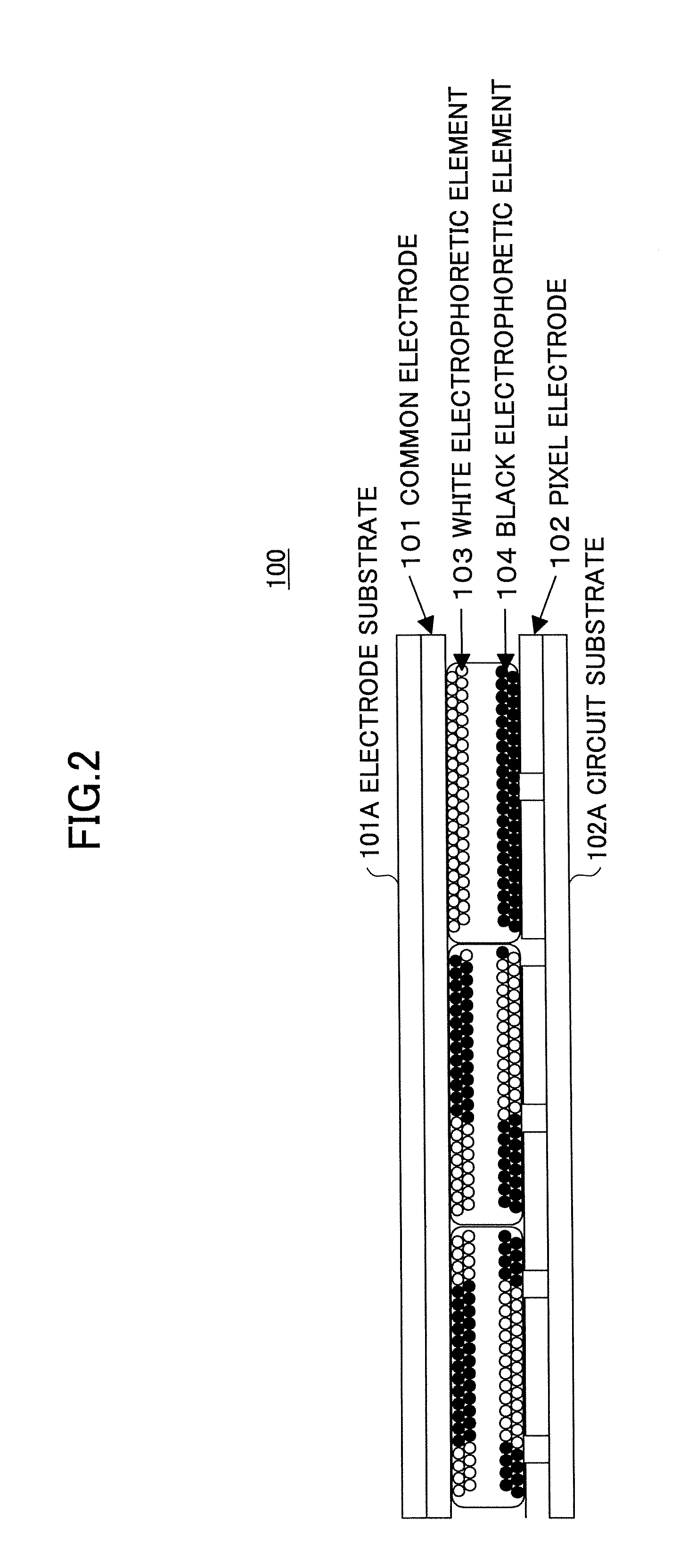

Display apparatus using electrophoretic element

InactiveUS20080048968A1Shorten the switching timeEasy to displayStatic indicating devicesMechanical vibrations separationElectrophoresisControl unit

A display apparatus is disclosed that includes two opposing substrates, an electrophoretic element arranged between the substrates; pixel electrodes that are arranged on one of the substrates and are divided into pixel groups including at least a first pixel group and a second pixel group, a common electrode that is arranged on the other substrate, and a control unit that controls frame display operations of the pixel groups. The control unit controls the first pixel group to start frame display operations for displaying a frame and then controls the second pixel group to start frame display operations for displaying another frame before the frame display operations of the first pixel group are completed.

Owner:RICOH KK

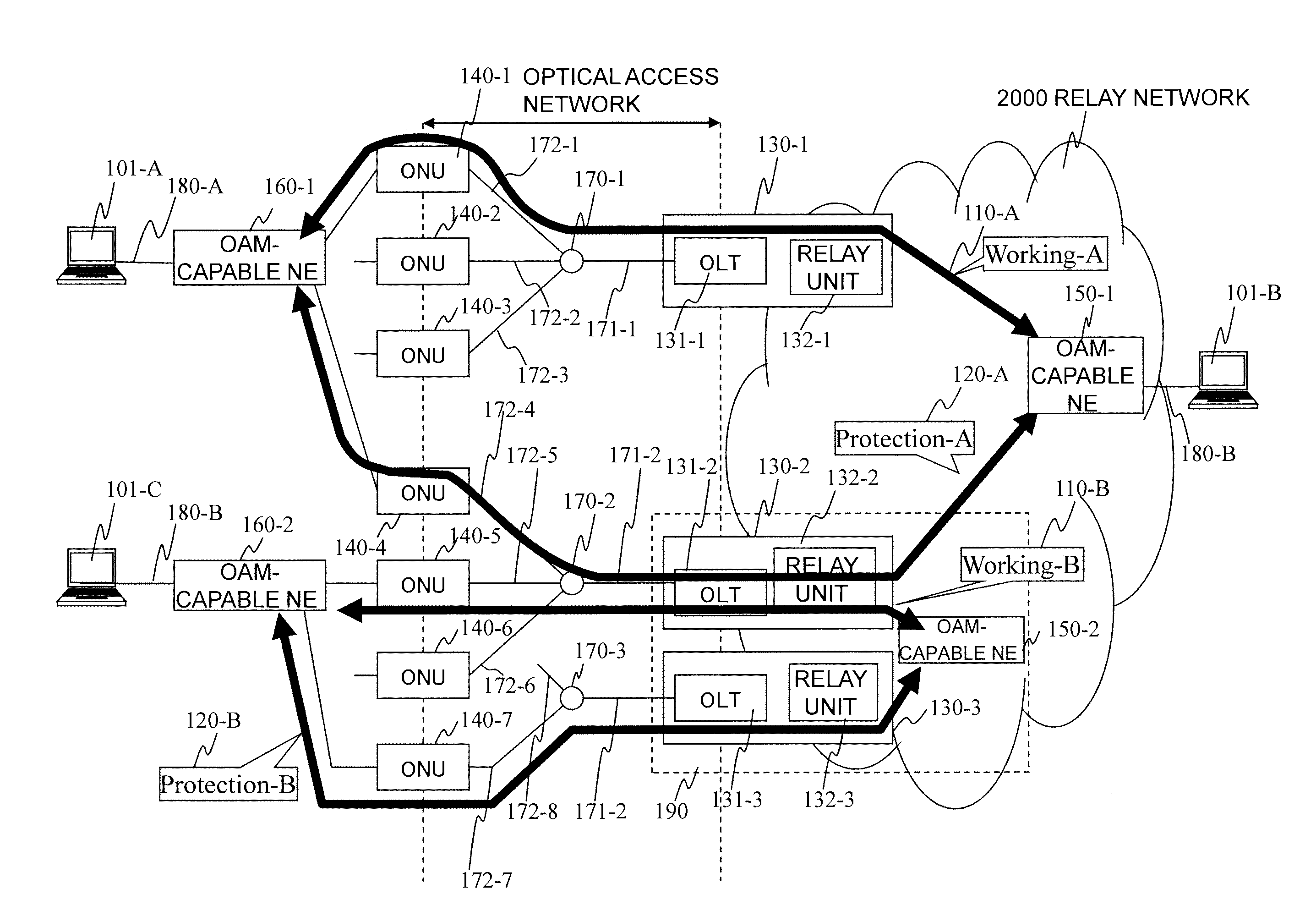

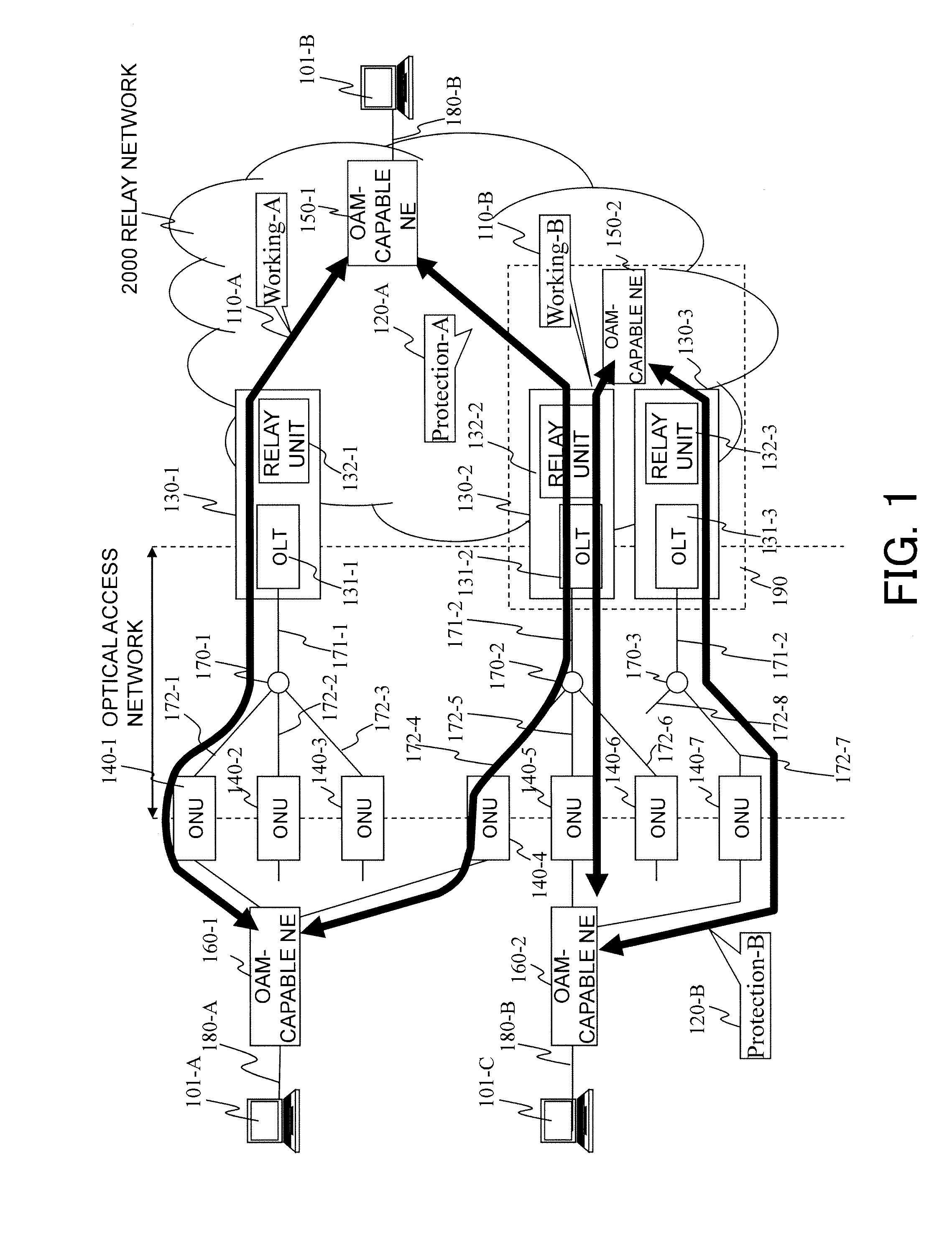

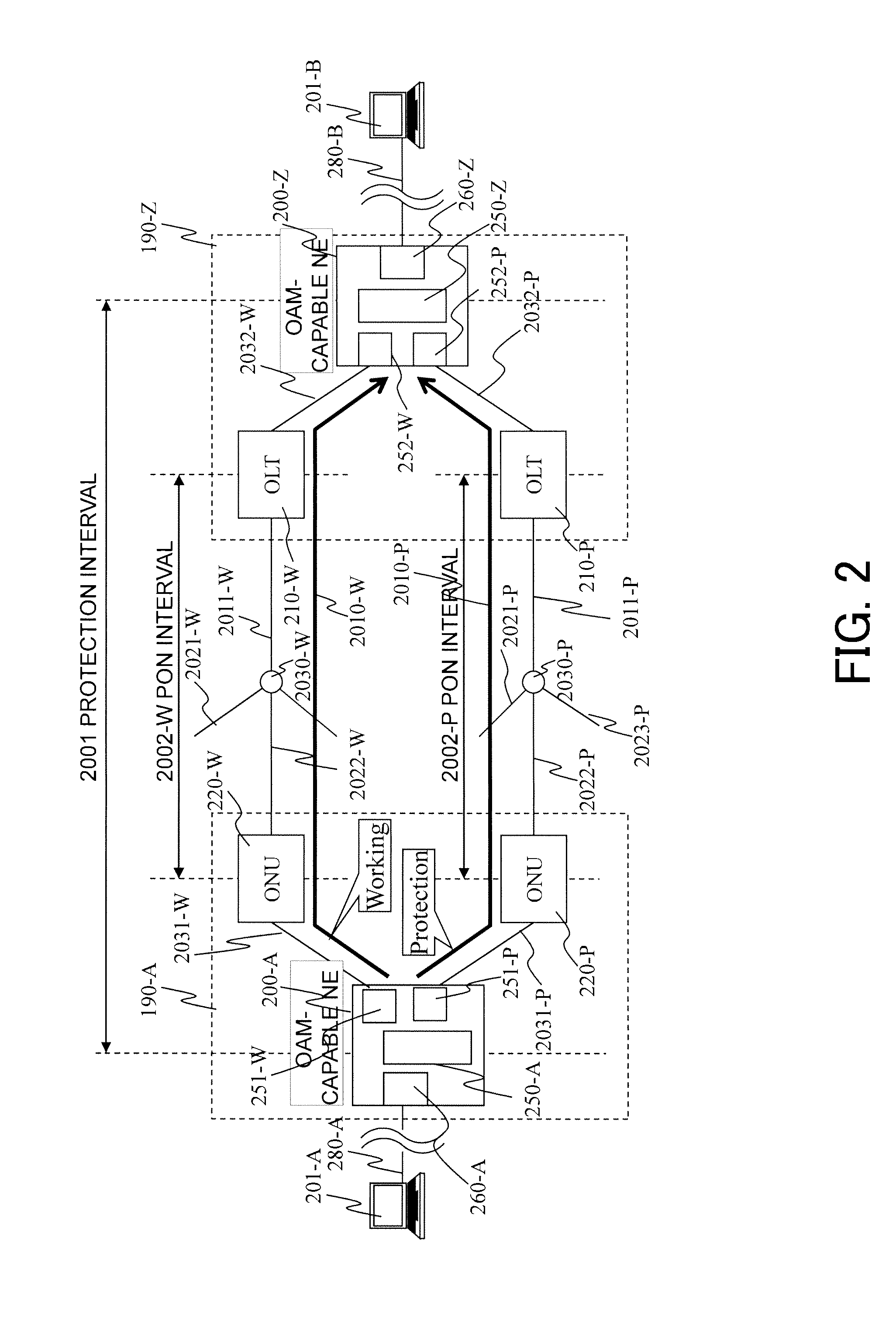

Communication system, subscriber accommodating apparatus and communication method

InactiveUS20110268435A1Packet lossReduce the packet lossMultiplex system selection arrangementsLaser detailsCommunications systemReal-time computing

Switching process at the occurrence of a path trouble is performed more quickly to reduce the number of packet discards during a traffic transition from a currently used system path to a standby system path within a section to be protected. An OLT (210-W) refers to the DBA information of a PON section and, if receiving no CCM frame at a timing at which the same should be received, then determines that some trouble has occurred on the path (S801) and transmits, to an OAM-compliant NE (200-Z), an application-for-switching frame (1501) to notify the OAM-compliant NE (200-Z) of the abnormal condition. The OAM-compliant NE (200-Z) monitors the occurrence of the trouble within the PON section nearly in real time, starts a switching process (S802) and generates and transmits a standby-system delivery request (321) (S302, S803). An OAM-compliant NE (200-A) switches the communication path to the standby-system passing through an OLT (210-P).

Owner:HITACHI LTD

Method and apparatus for partial duplex protection switching by using single splitter in PON

InactiveUS20080131124A1Quick switchEasy to switchMultiplex system selection arrangementsTime-division multiplexOptical network terminalEngineering

A method and apparatus for duplex protection switching by using a single splitter in a passive optical network (PON) are provided. The apparatus for duplex protection switching in a PON, in which a single optical line termination (OLT) and many optical network terminations (ONTs) are connected together in a multiple-access manner, includes: a 2:2 splitter connected to two PON line terminations (LTs) in the OLT; and two N:1 splitters which are connected to the 2:2 splitter, and each of which is connected to two PON LTs in the ONT. According to the method and apparatus, an economical effect can be provided in which two links, an operational link and a protection link, in the PON can provide a partial duplex function at a lower cost. Also, a protection switching time can be reduced by simplifying a restoration process so that when an error is detected, an operational state is returned by protection switching.

Owner:ELECTRONICS & TELECOMM RES INST

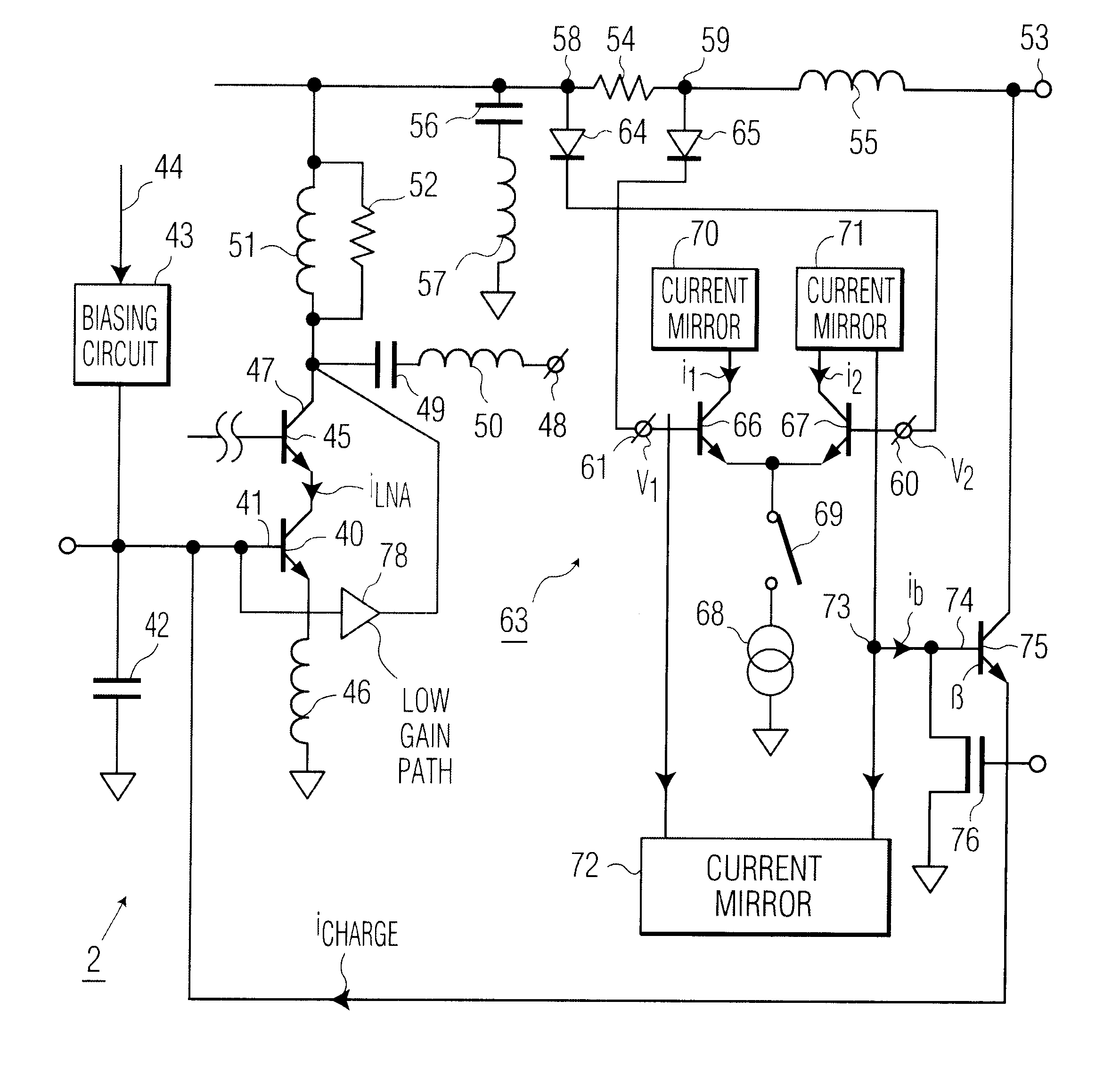

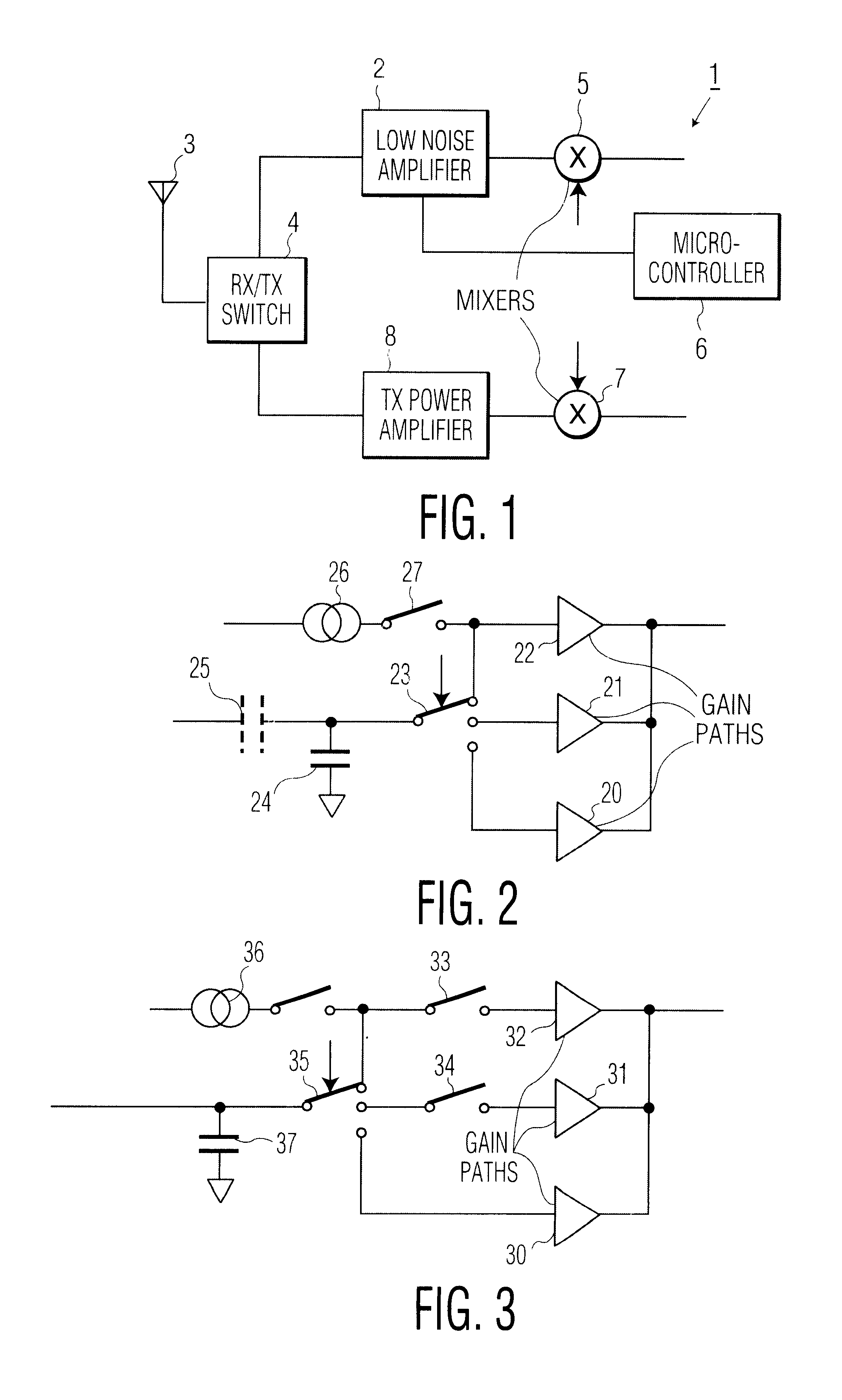

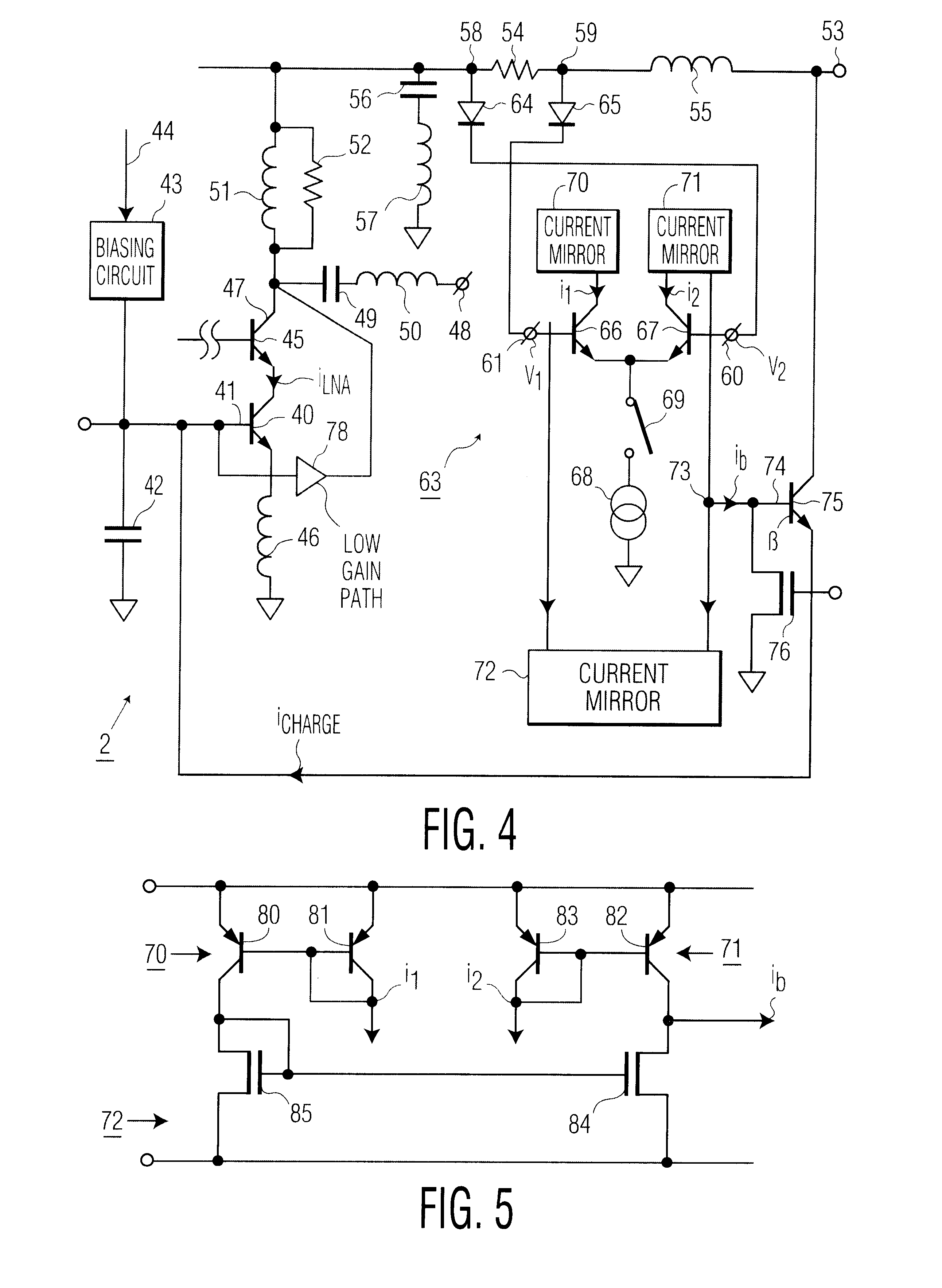

Radio frequency device with fast charging of an input capacitance

InactiveUS6438364B1Highly linear gain-modeShort switching timeAmplifier modifications to reduce non-linear distortionGated amplifiersCapacitanceFast charging

A radio frequency device has an input transistor from which a capacitance is seen, and a fast charging circuit for charging the capacitance. The input transistor receives a radio frequency signal. The capacitance is quickly charged when the device is switched from off to on and / or from low gain to high gain, thereby reducing the switching-on time of the device.

Owner:CALLAHAN CELLULAR L L C

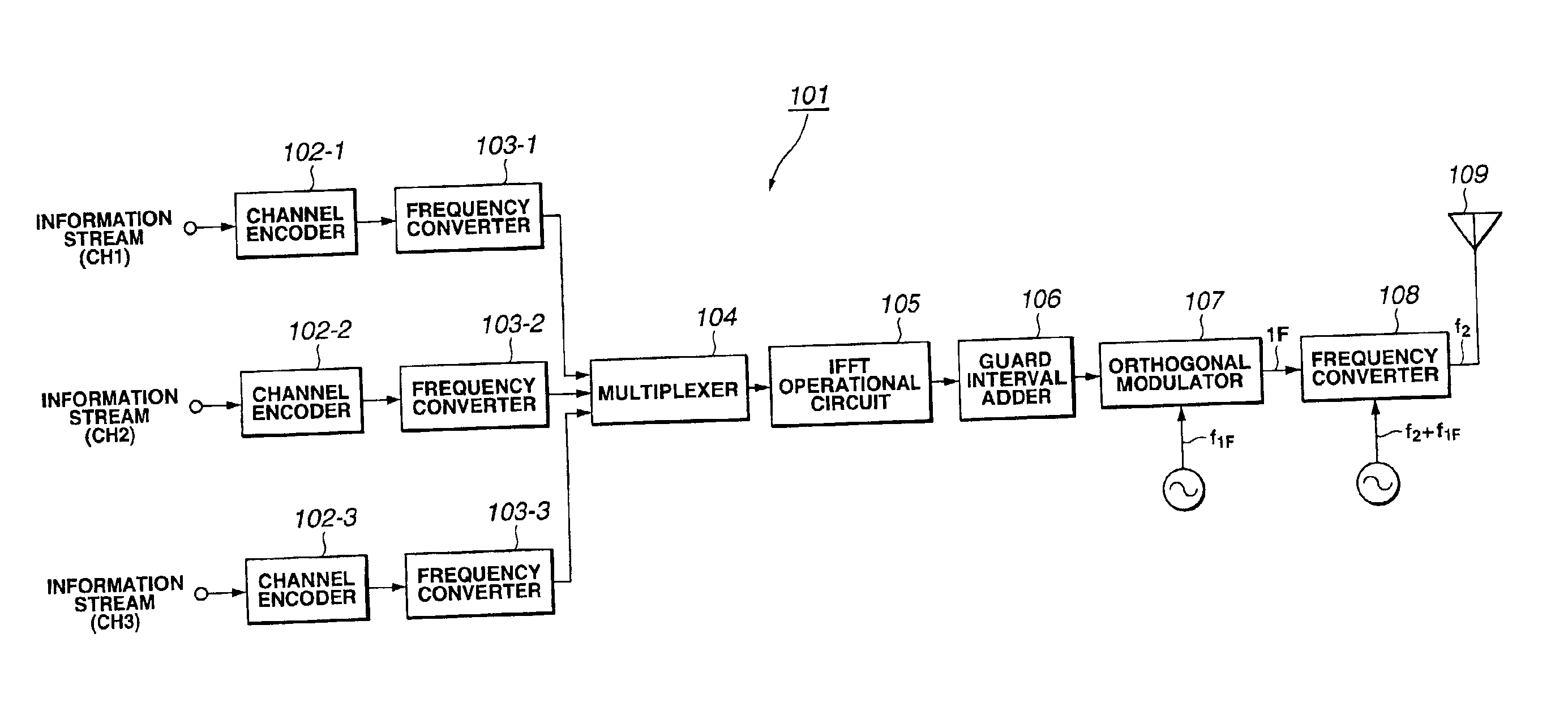

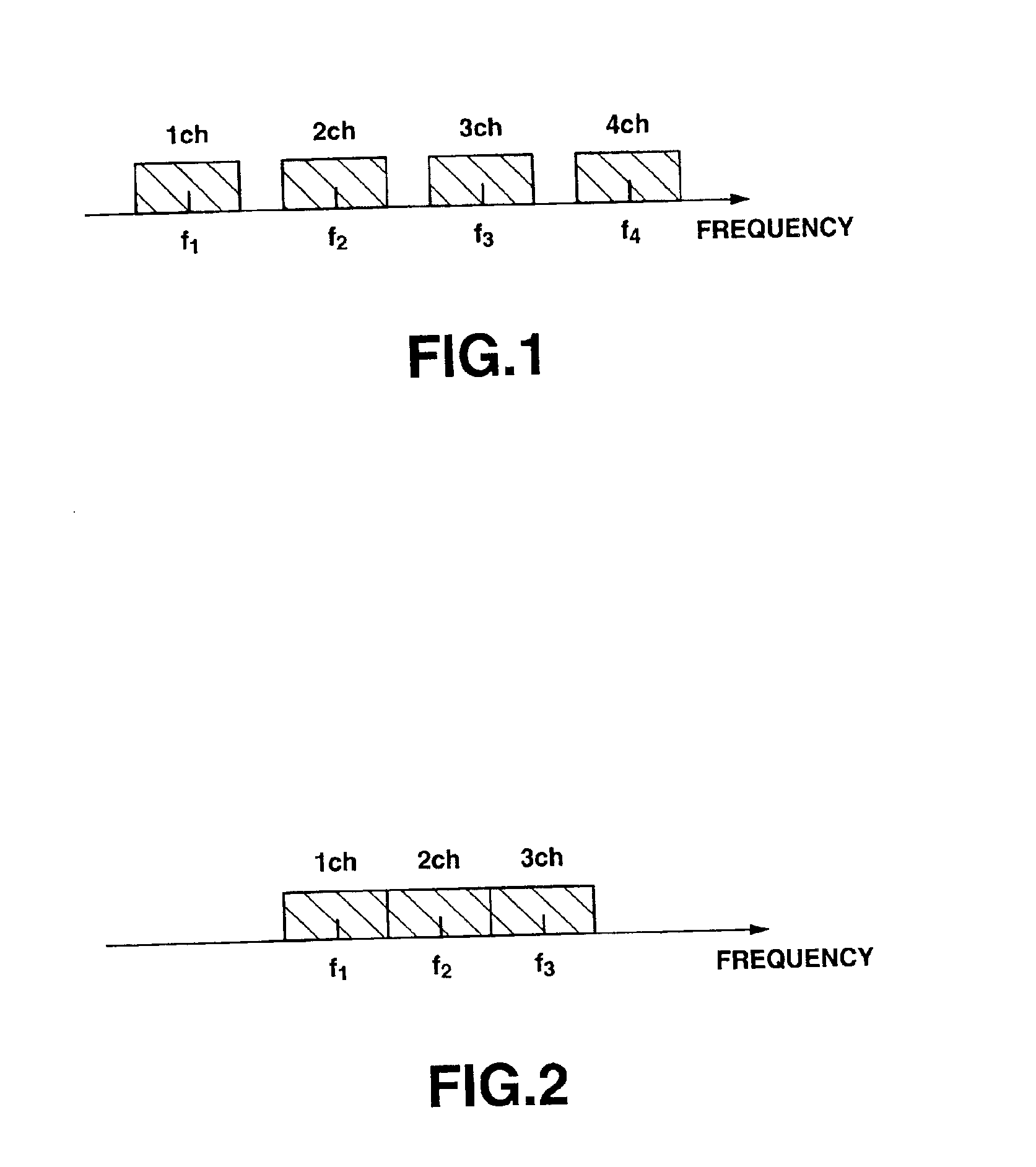

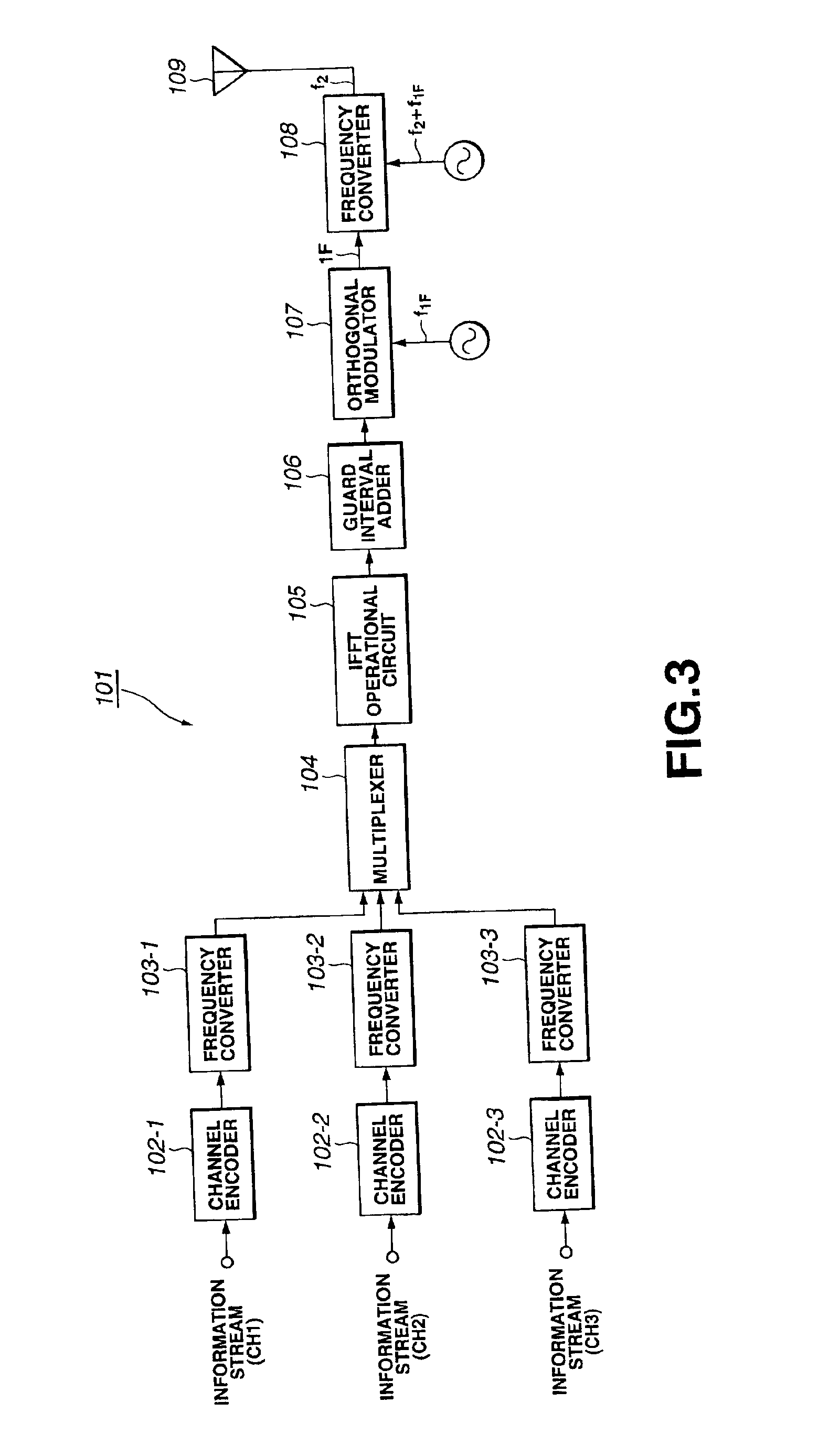

OFDM transmission device and OFDM transmission method

InactiveUS6856590B2Shorten the timeShorten the switching timeSynchronisation signal speed/phase controlOrthogonal multiplexElectrical and Electronics engineeringOfdm transmission

The time required for switch the channel can be remarkably curtailed. When broadcasting signals through a plurality of information channels with an OFDM system, the plurality of information channels are multiplexed in the sense of frequency and collectively subjected to IFFT modulation for connected transmission instead of subjecting the plurality of information channels independently to OFDM modulation for transmission. With this arrangement, the efficiency of exploitation of frequencies is improved. According to the invention, the OFDM frames are synchronized for each information channel for the purpose of connected transmission. Then, the OFDM receiver can switch the information channel for signal reception, maintaining the frame synchronizing signals.

Owner:SONY CORP

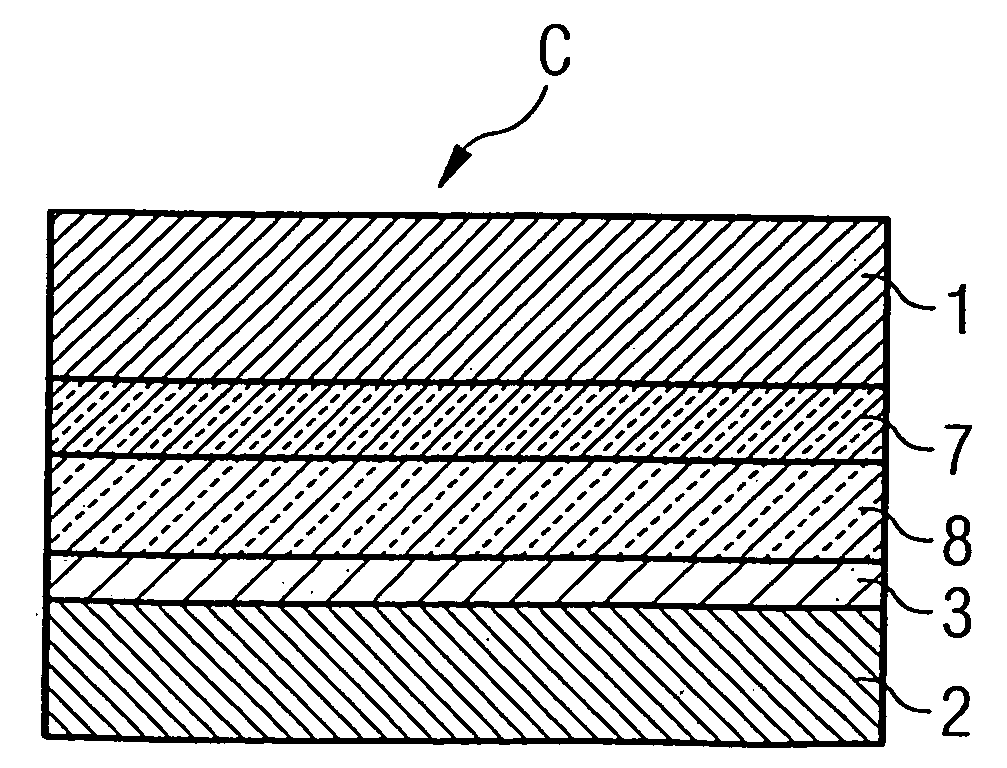

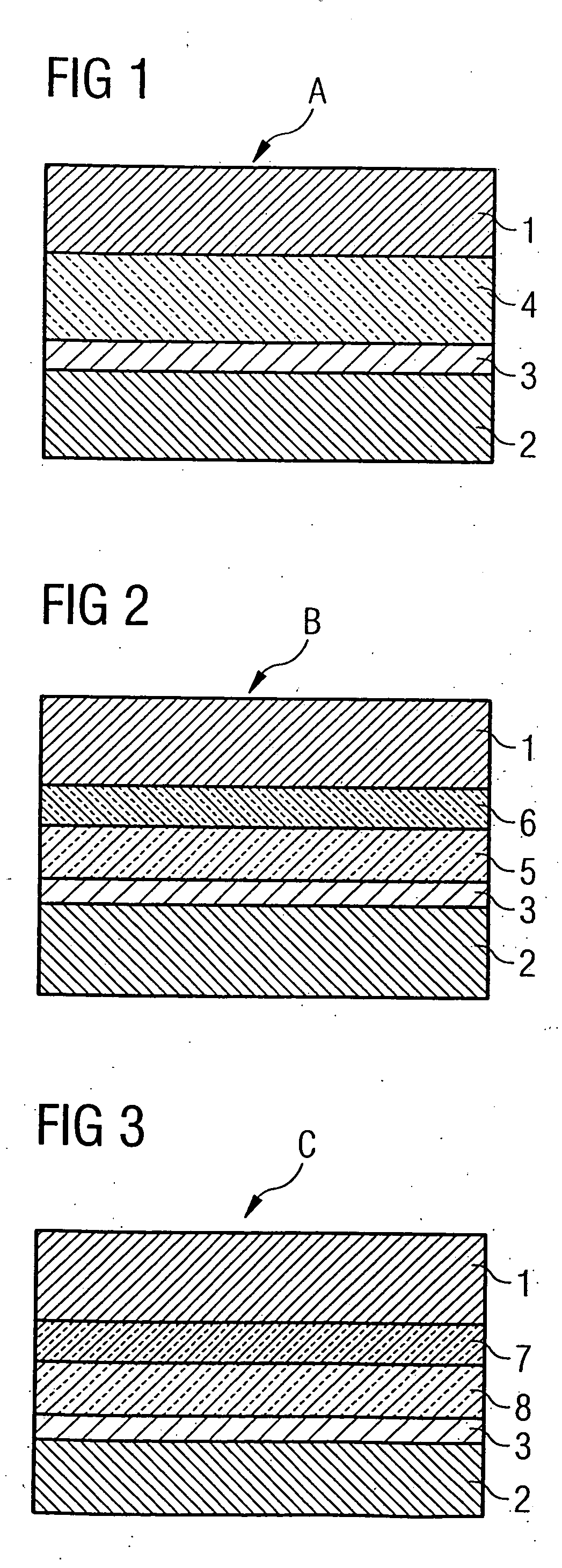

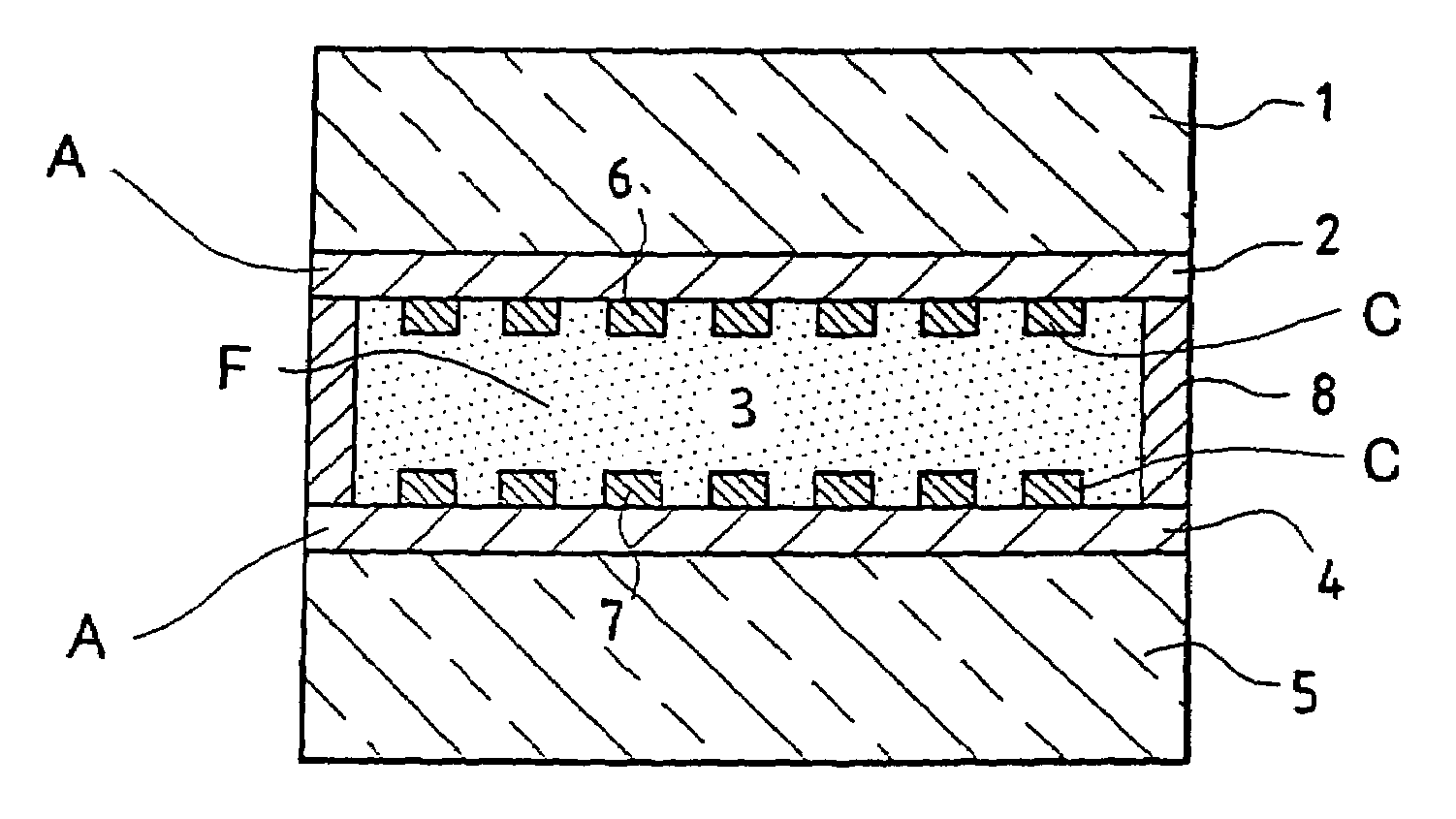

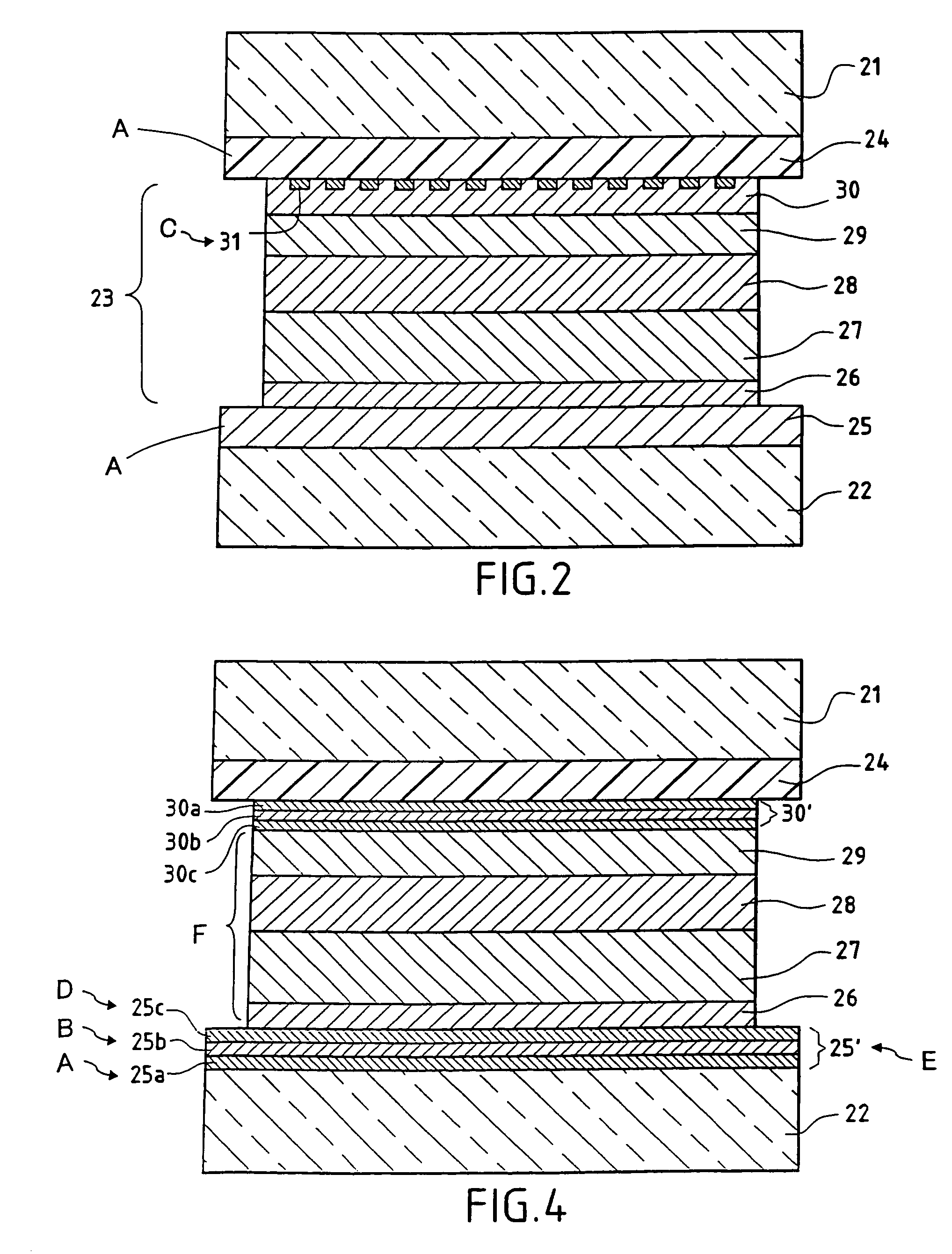

Electrochemical device, such as an electrically controlled system with variable optical and/or energy properties

InactiveUS7012728B2Improve conductivityNot possible to discernElectric lighting sourcesElectrode carriers/collectorsElectrical resistance and conductanceGlasses type

An electrochemical device includes at least one carrier substrate, and a stack of functional layers including at least one electrically conducting layer that includes metal oxide(s), and a multicomponent electrode including at least one electrochemically active layer, at least one higher-conductivity material and at least one network of one of conducting wires and conducting strips. The higher-conductivity material has a surface resistance that is lower than a surface resistance of the electrically conducting layer. The stack of functional layers is arranged between two substrates, and each may be rigid, of glass type or rigid polymer or semi-rigid or flexible of PET type.

Owner:SAINT GOBAIN VITRAGE SA

Clutch system

InactiveUS20030047410A1Lower the volumeShort switching timeMechanical actuated clutchesFluid actuated clutchesMobile vehicleEngineering

A clutch system includes a clutch device with at least one clutch arrangement for installation in a motor vehicle drive train between a drive unit and a transmission. The at least one clutch arrangement is actuated by a slave cylinder using a pressure medium which is supplied to the clutch device by a first pump. A further medium is also supplied to the clutch device by a second pump arrangement as an operating medium used during operation of the clutch device. The further medium is selectively supplied as a pressure medium to the slave cylinder.

Owner:ZF FRIEDRICHSHAFEN AG

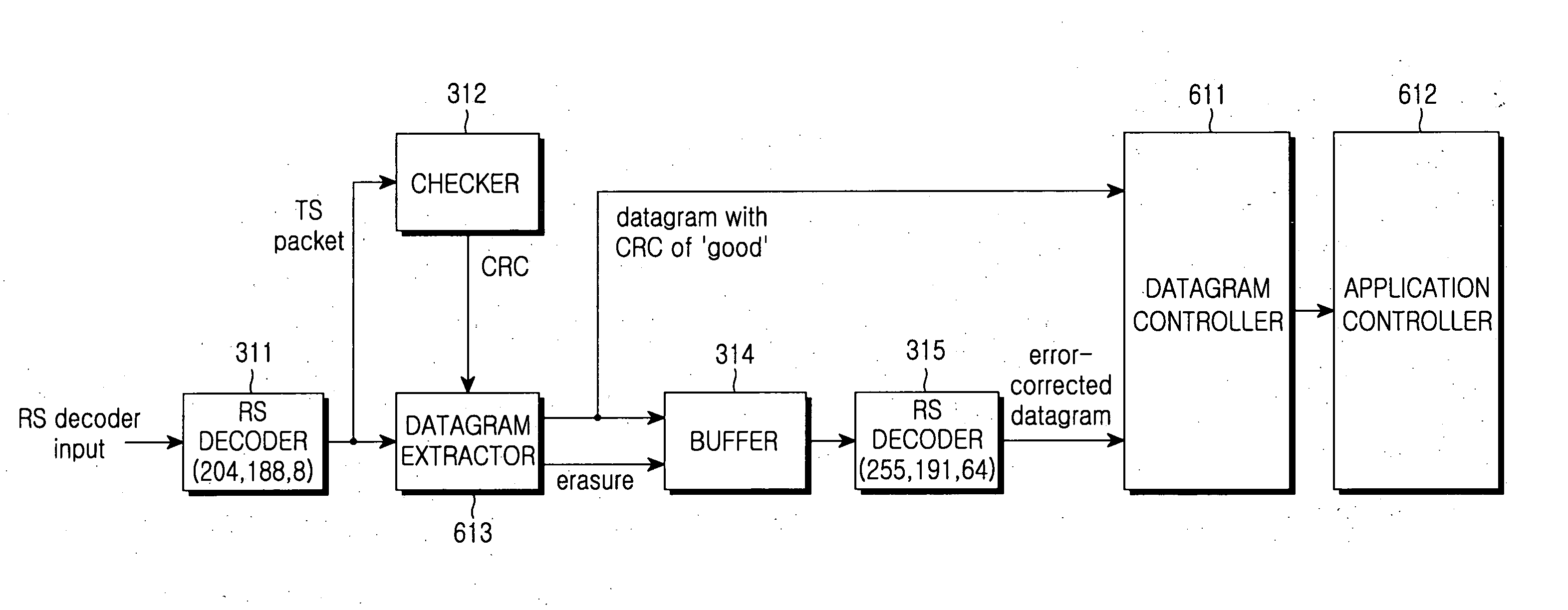

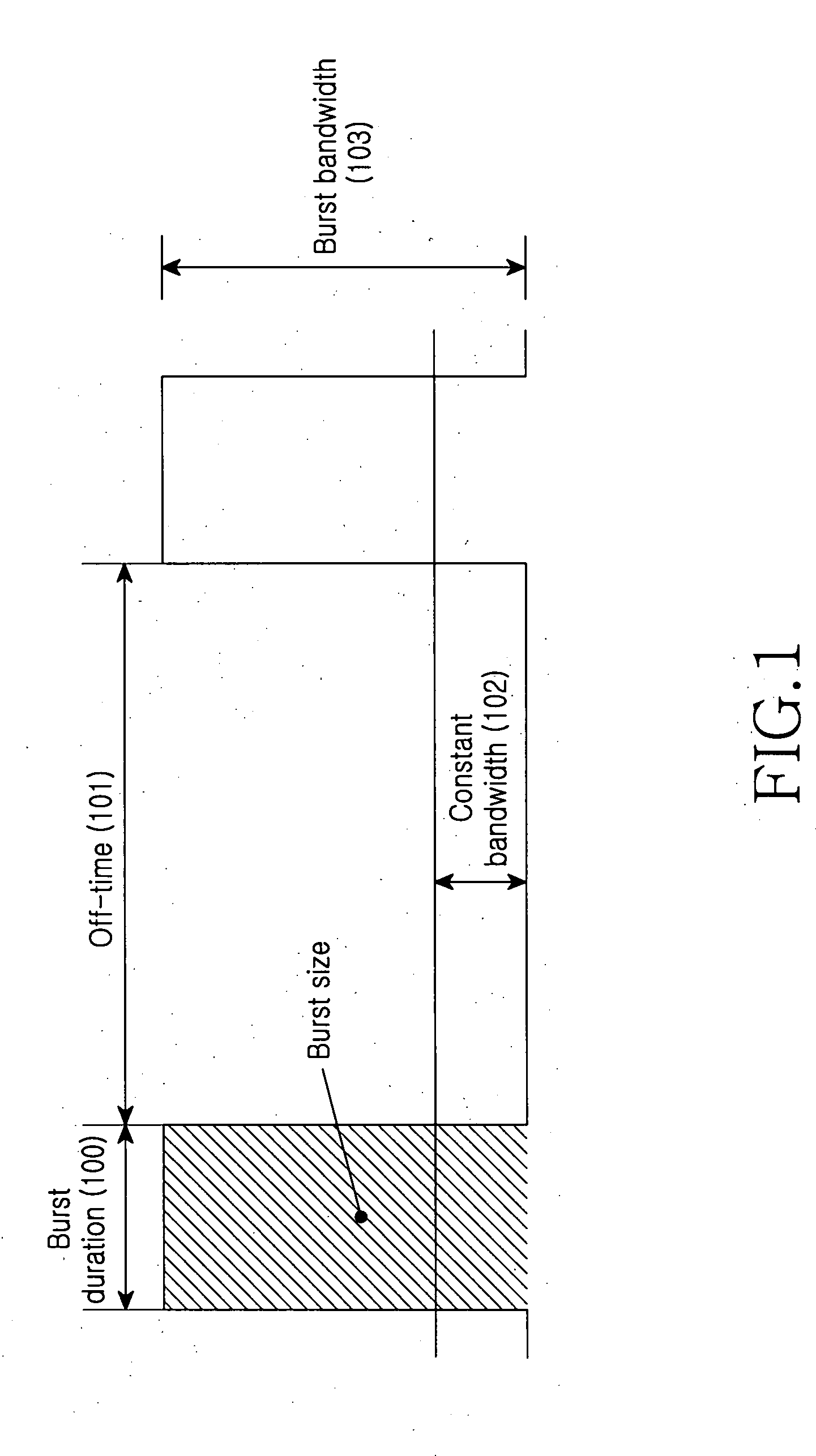

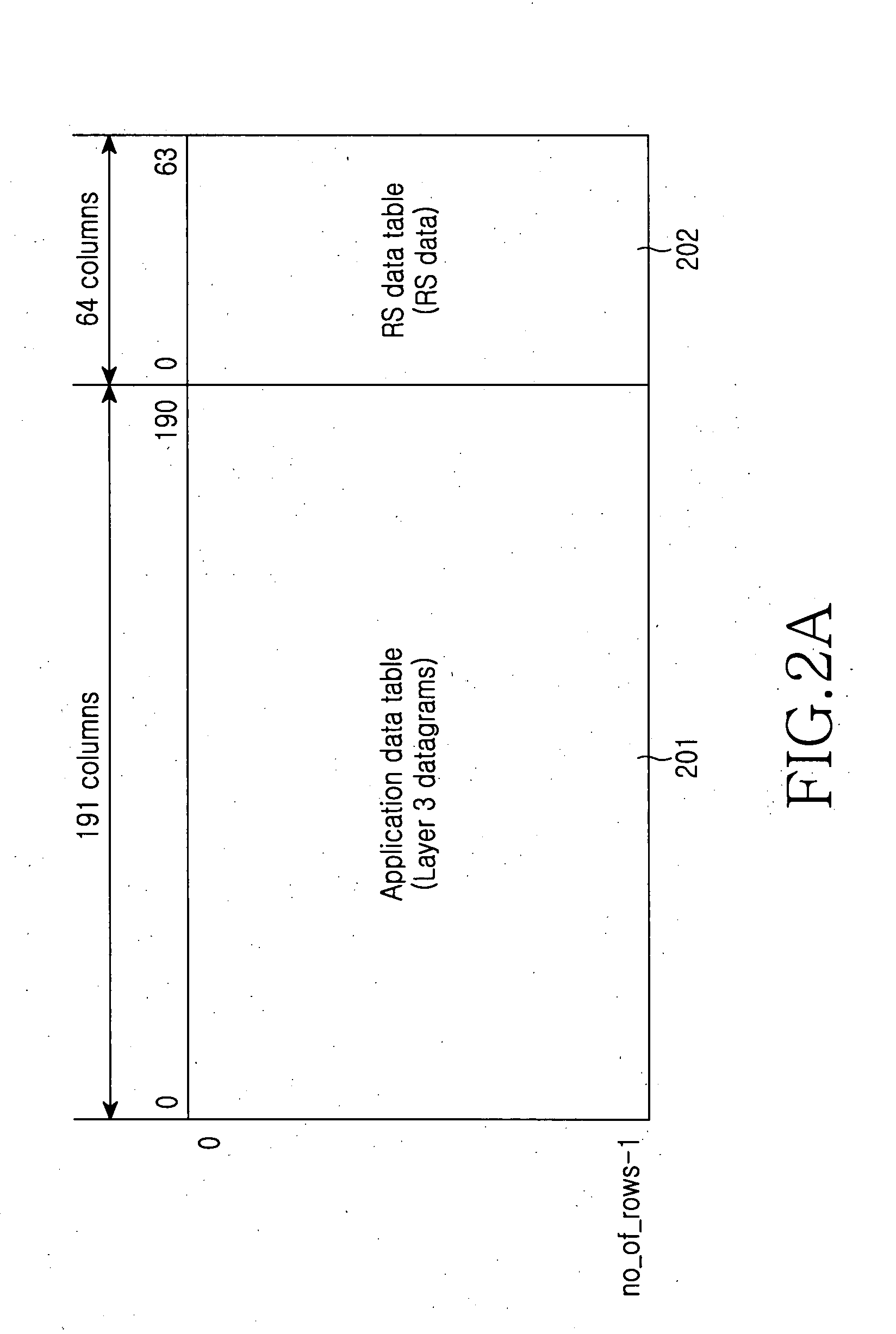

Apparatus and method for receiving data in a mobile broadcasting terminal

InactiveUS20070230387A1Shorten receiving timeReduce power consumptionTransmission systemsBroadcast specific applicationsData packBroadcast data

An apparatus for receiving and processing a broadcast signal in a mobile broadcasting terminal is provided. A preprocessor receives a broadcast signal, converts the broadcast signal into a baseband signal, and then performs OFDM demodulation, Viterbi decoding, and convolutional deinterleaving thereon. A first Reed-Solomon (RS) decoder RS-decodes the signal output from the preprocessor, and outputs a Transport Stream (TS) packet. A checker checks Cyclic Redundancy Check (CRC) of the TS packet. A datagram extractor extracts a datagram having a good CRC result. A datagram controller receives the datagram having a good CRC result and outputs the received datagram to an application controller. The application controller decodes the broadcast data using the datagram received from the datagram controller and provides the decoded broadcast data to a user.

Owner:SAMSUNG ELECTRONICS CO LTD

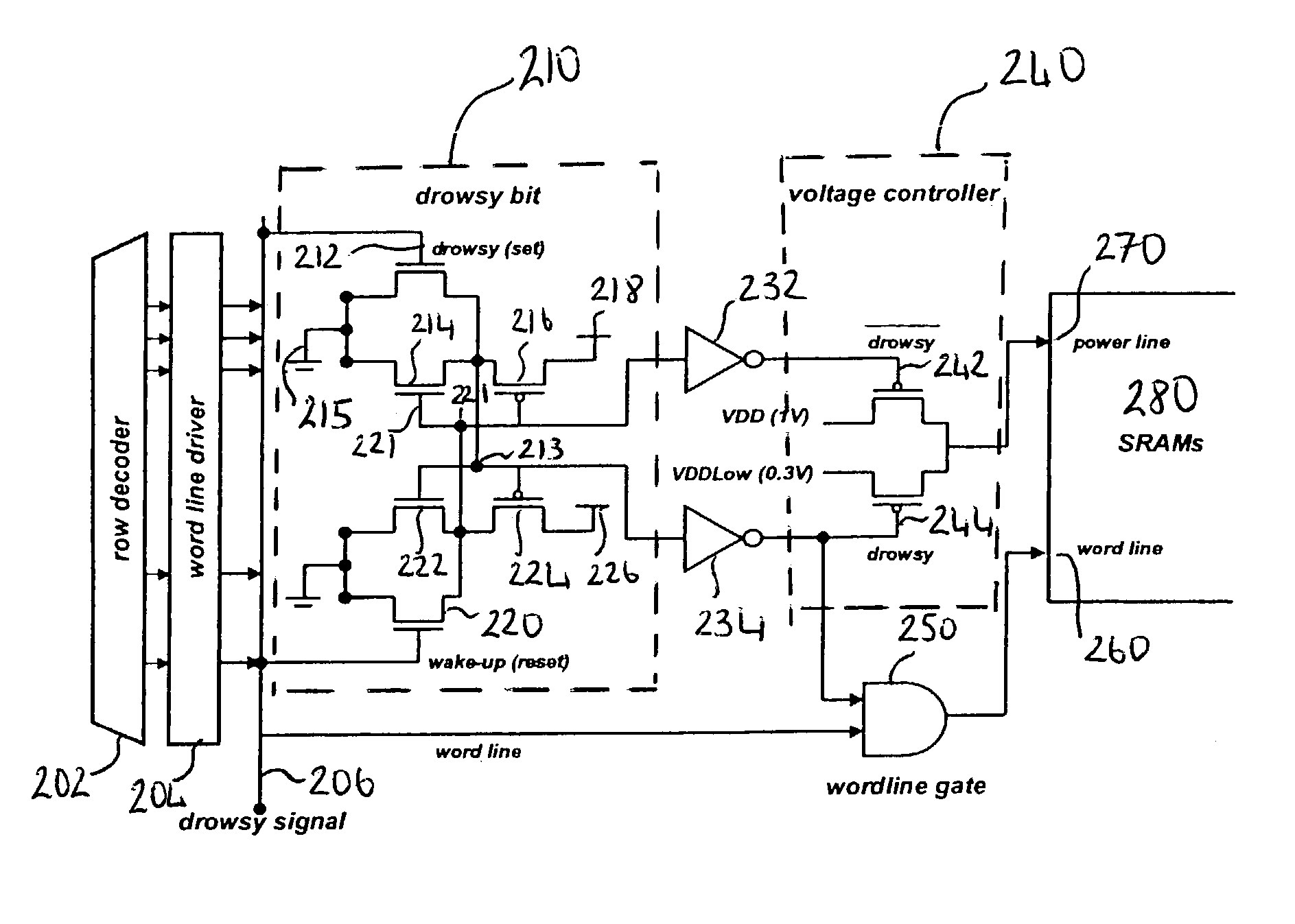

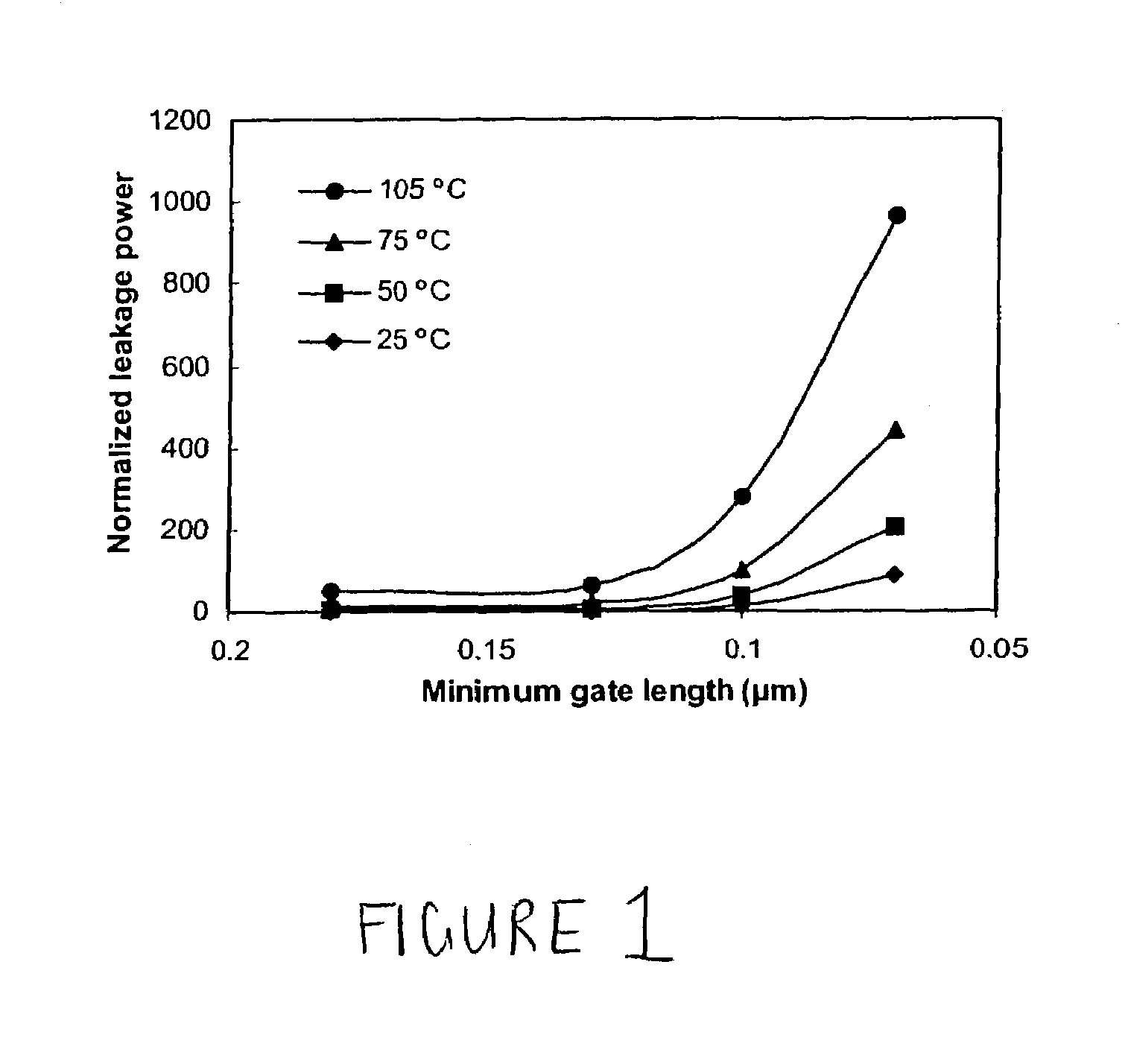

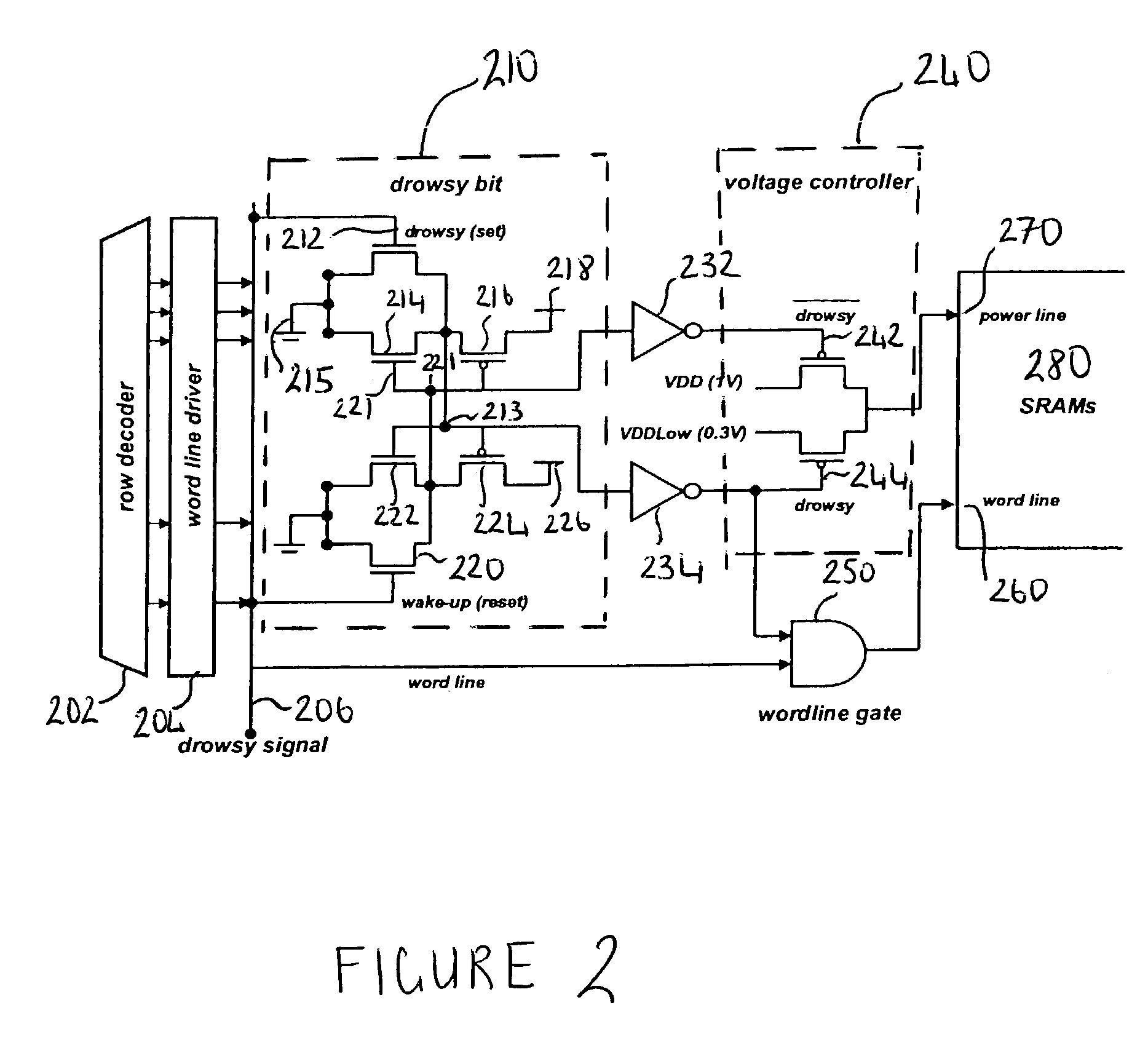

Data processor memory circuit

ActiveUS7055007B2Reduce leakageRaise the threshold voltageMemory architecture accessing/allocationEnergy efficient ICTMemory circuitsComputer science

A memory circuit for use in a data processing circuit is described, in which memory cells have at least two states, each state being determined by both a first voltage level corresponding to a first supply line and a second voltage level corresponding to a second supply line. The memory circuit comprises a readable state in which information stored in a memory cell is readable and an unreadable state in which information stored in said memory cell is reliably retained but unreadable. Changing the first voltage level but keeping the second voltage level substantially constant effects a transition between the readable state and the unreadable state. In use, the static power consumption of the memory cell in the unreadable state is less than static power consumption of the memory cell in the readable state.

Owner:ARM LTD +1

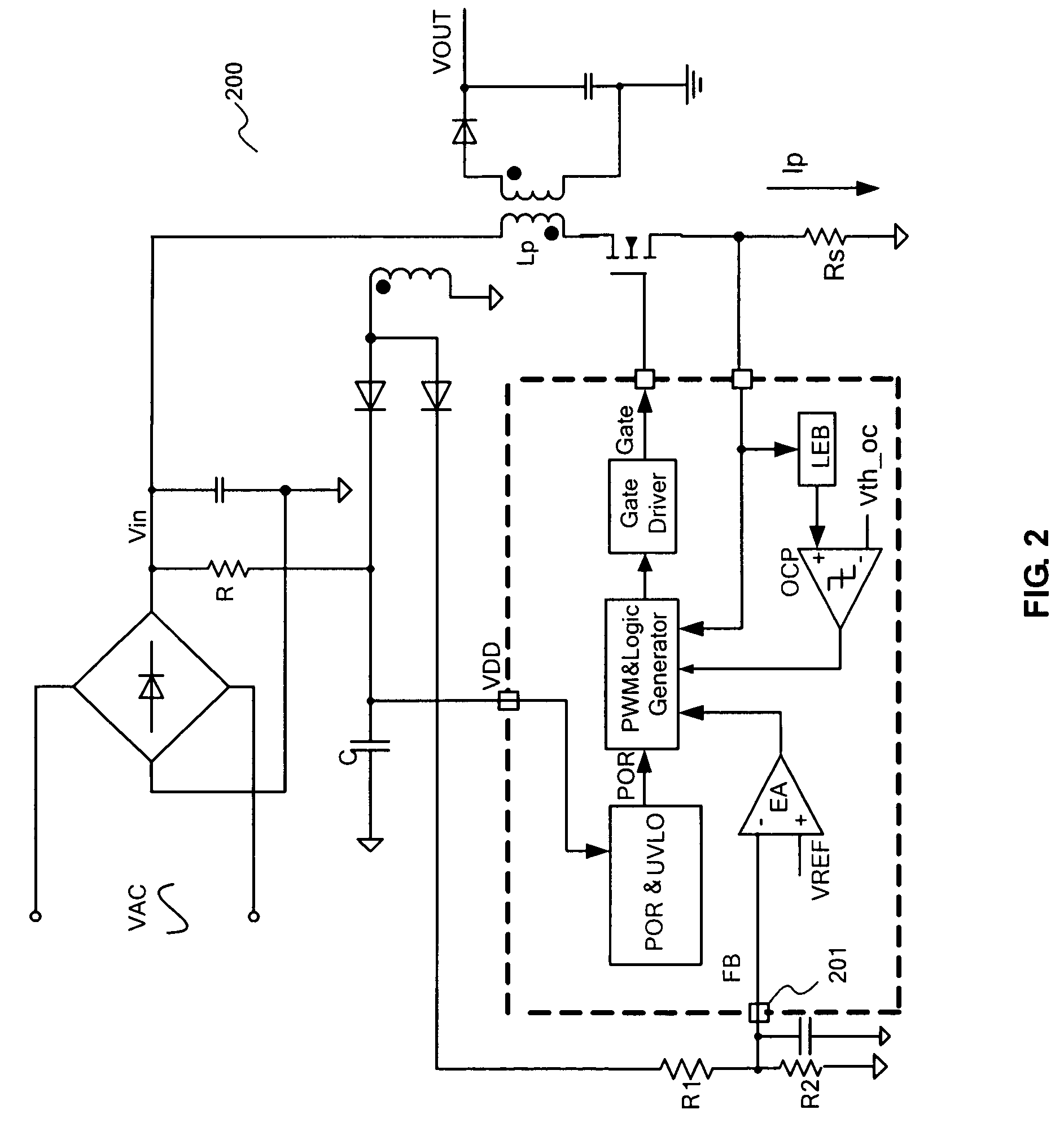

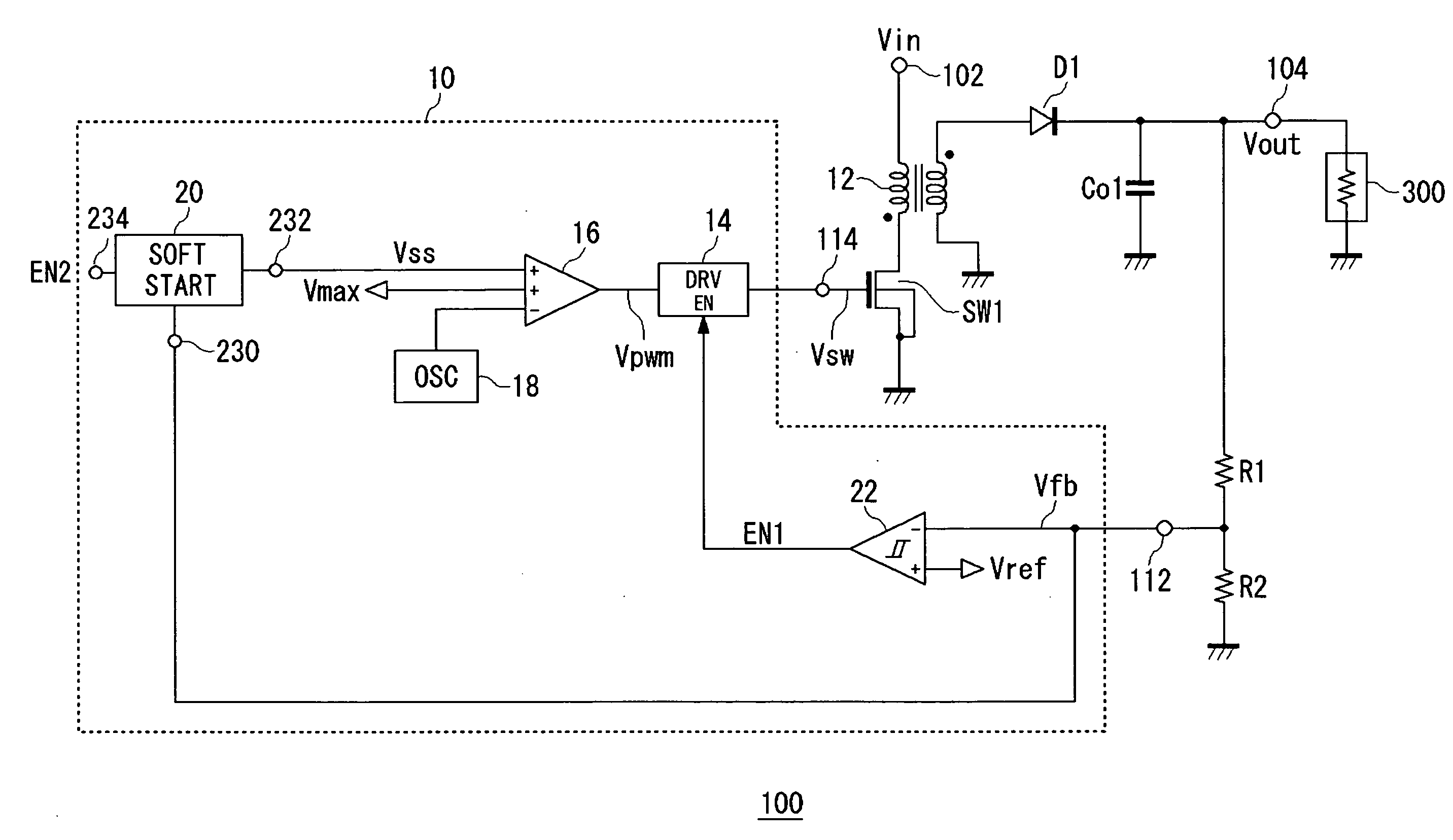

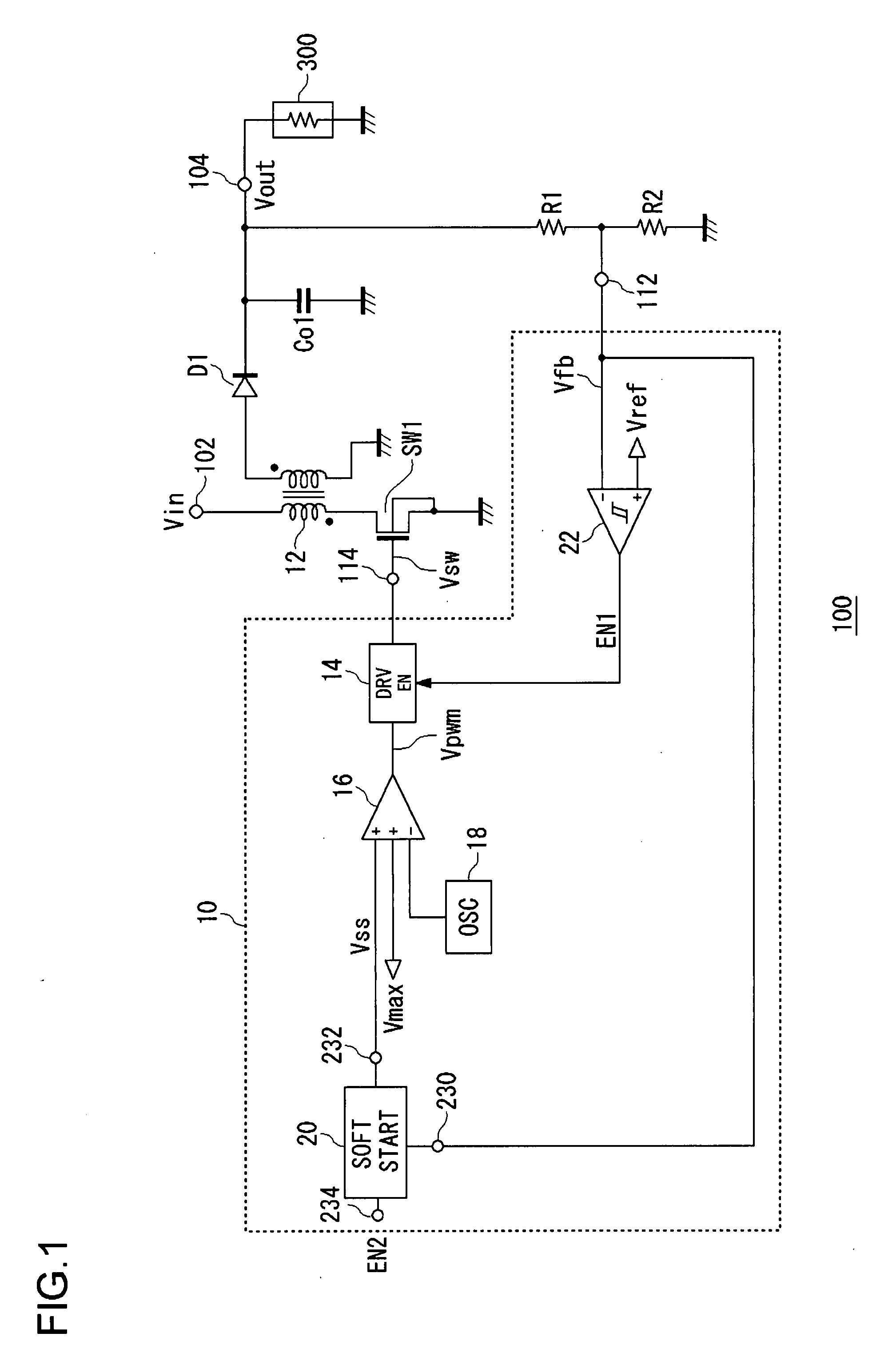

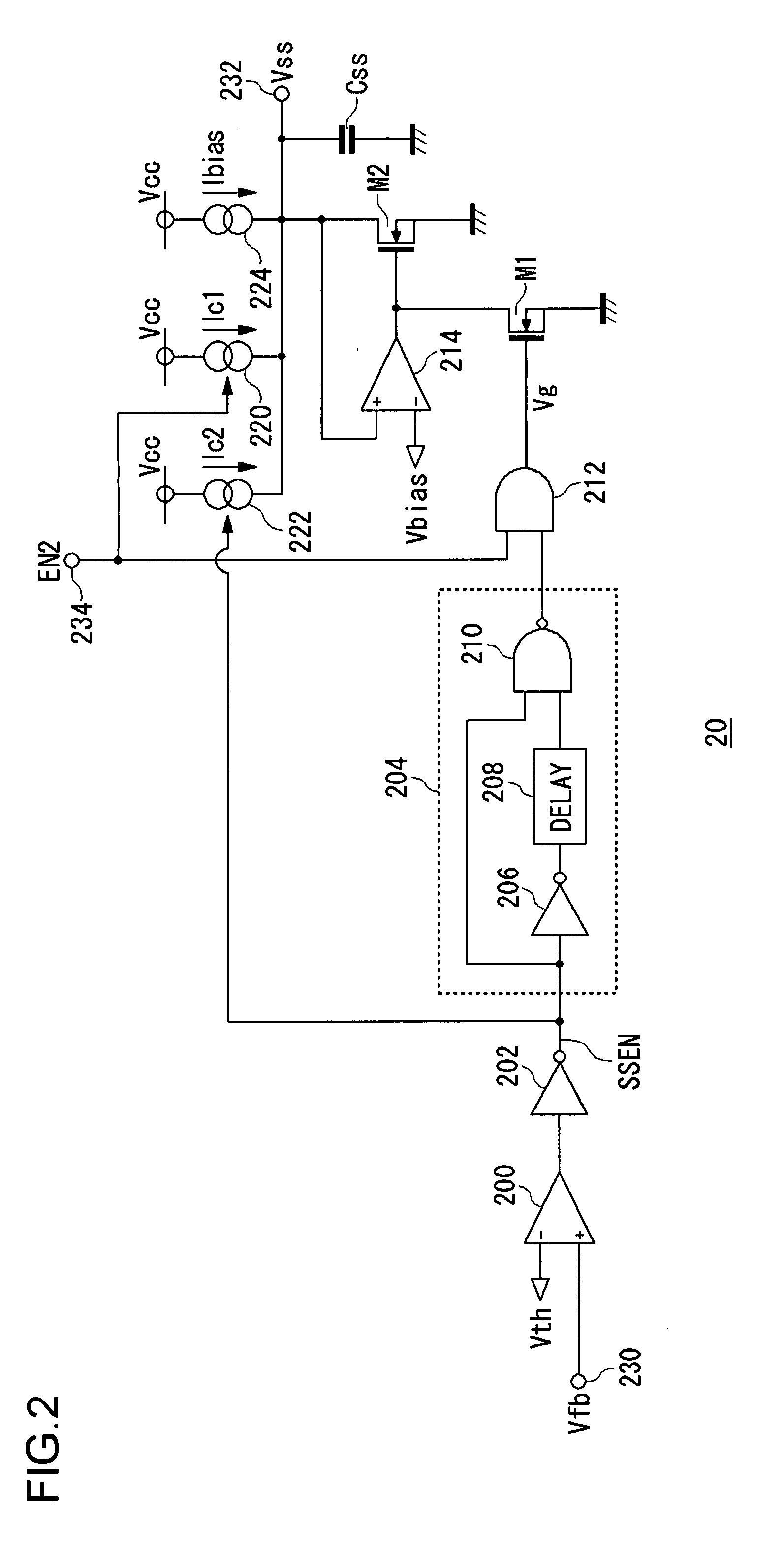

Switching Power Supply and its Control Circuit, and Electronic Apparatus Employing Such Switching Power Supply

ActiveUS20080136341A1Enough timeShorten the timeElectric light circuit arrangementApparatus with intermediate ac conversionSwitching signalVoltage reference

A control circuit for controlling a switching element in a switching power supply by generating a switching signal is disclosed. The control circuit may include a short start circuit that generates a switching signal so that an output voltage of the switching power supply gradually increases for a period until the output voltage reaches a predetermined reference voltage. The soft start circuit may increase the output voltage at a first limiting speed when the output voltage is lower than a predetermined threshold voltage, and may increase the output voltage at a second limiting speed which is set higher than the first limiting speed when the output voltage is higher than the threshold voltage.

Owner:ROHM CO LTD

Switching gate driver

ActiveUS20110273206A1Reduce switching lossesShorten the switching timeElectronic switchingElectric pulse generatorControl signalEngineering

Disclosed is a switching gate driver of an IGBT device, including a resistor unit to control a gate current of the IGBT device; and a voltage reader that outputs a control signal to control a variable resistor unit of the resistor unit to the resistor unit, according to a collector-emitter voltage of the IGBT device.

Owner:LSIS CO LTD

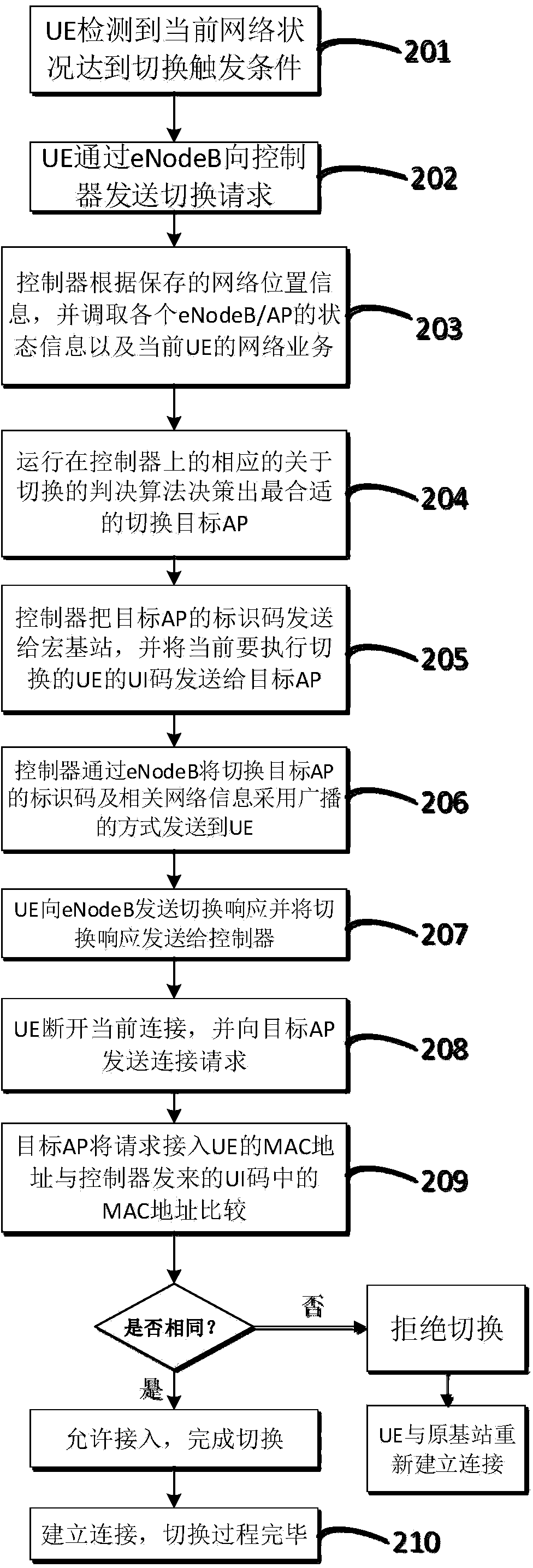

SDN (Software Defined Network)-based heterogeneous network convergence framework

InactiveCN104023335AEasy to manageEasy to apply innovationNetwork topologiesSecurity arrangementEngineeringHeterogeneous network

The invention provides a SDN (Software Defined Network)-based heterogeneous network convergence framework. According to the framework, the core idea of control and data separation in the software defined network is referred, a controller is added in an EPC core network, user identity information is packaged to be a unique user identifier to serve as the identity certificate during the network access and switching process. The concept of the user identifier is used, a method of realizing virtual switching under the control of the controller is brought forward, the switching access process can be theoretically simplified, and network access time delay can then be reduced. After switching, the IP remains unchanged, the time spent on IP layer switching in the case of heterogeneous network switching is saved, the target of reducing the entire switching time delay is achieved, IP address management and user safety management in a mobile environment are facilitated as the IP is maintained, and a feasible solution is provided for solving the problem of seamless switching between the LTE network and the WLAN network.

Owner:BEIJING UNIV OF POSTS & TELECOMM

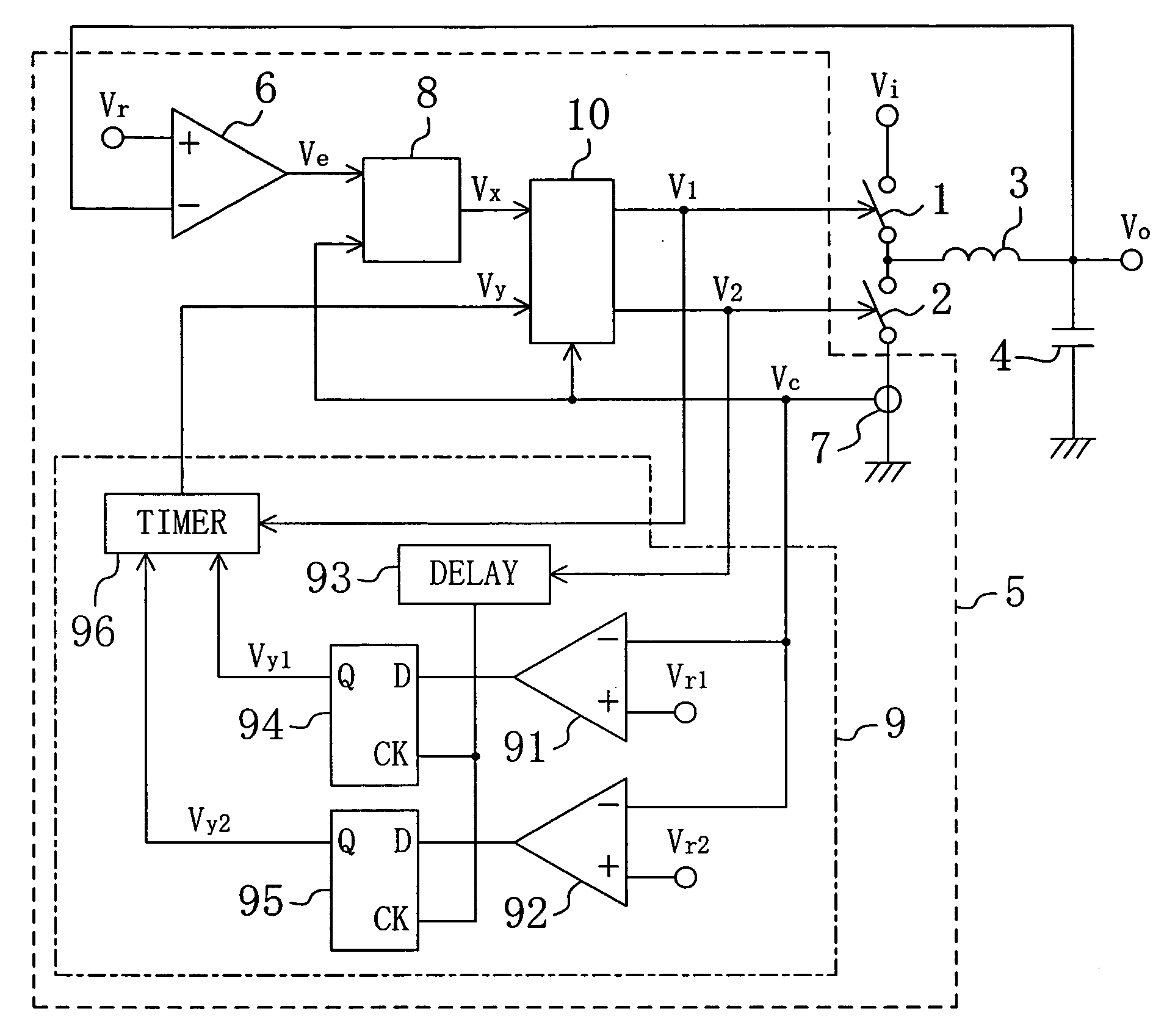

DC-DC converter

InactiveUS20060220629A1Wide load rangeReduce output ripple voltageEfficient power electronics conversionDc-dc conversionDc dc converterControl signal

A DC-DC converter includes a switch, a rectifier, a smoothing circuit, and a control circuit. The control circuit includes an output detection circuit for outputting an error signal, a current detection circuit for outputting a current detection signal in a period in which at least the switch is OFF, a first circuit for outputting a first signal for setting a timing of turning ON of the switch according to a comparison result between the error signal and the current detection signal, and a second circuit for outputting a second signal for setting an ON time of the switch, according to a reduction in output power from the smoothing circuit, so that the ON time of the switch is reduced, and generates the control signal, based on the first and second signals.

Owner:PANASONIC CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com