Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

2320results about How to "Reduce packaging costs" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

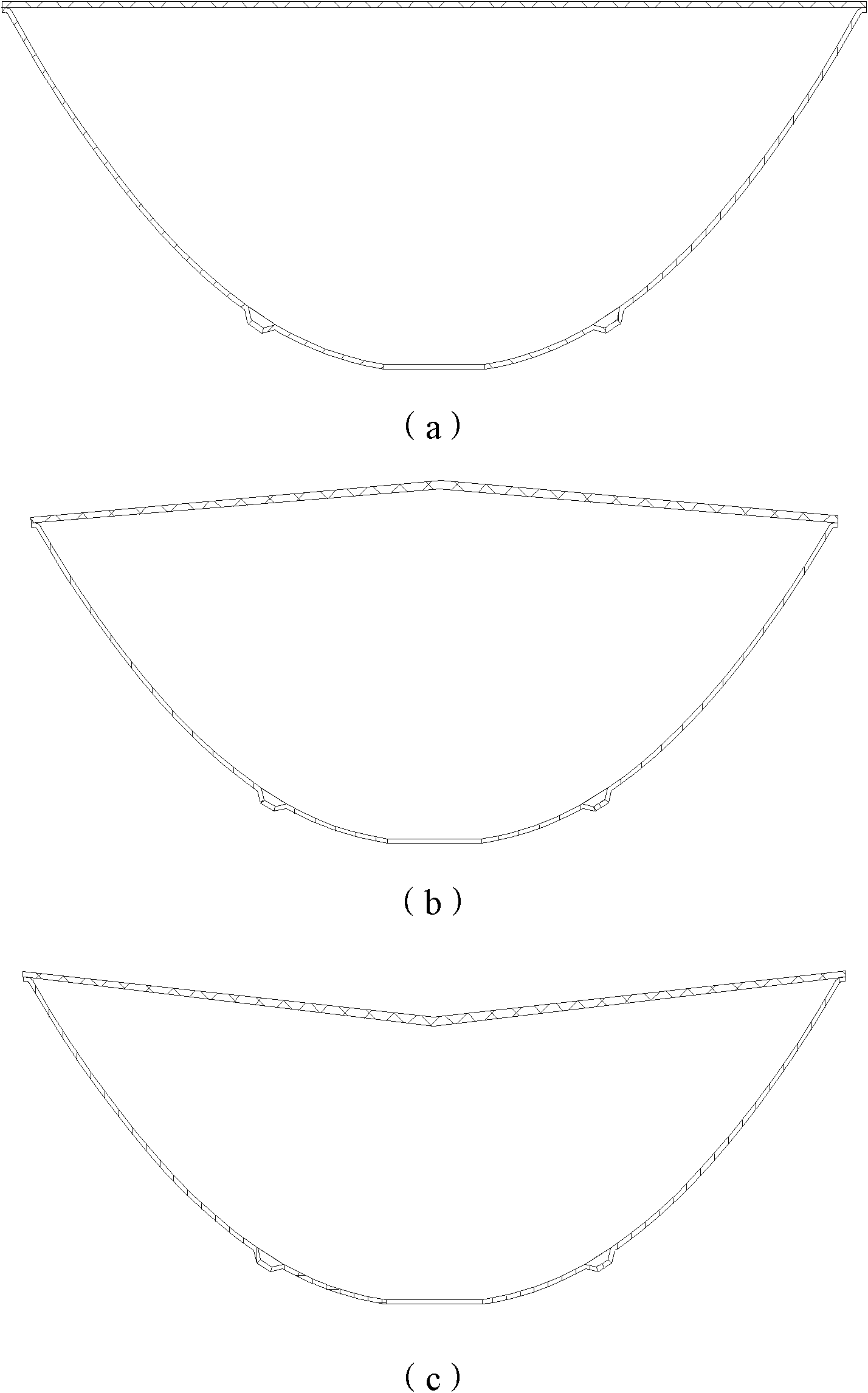

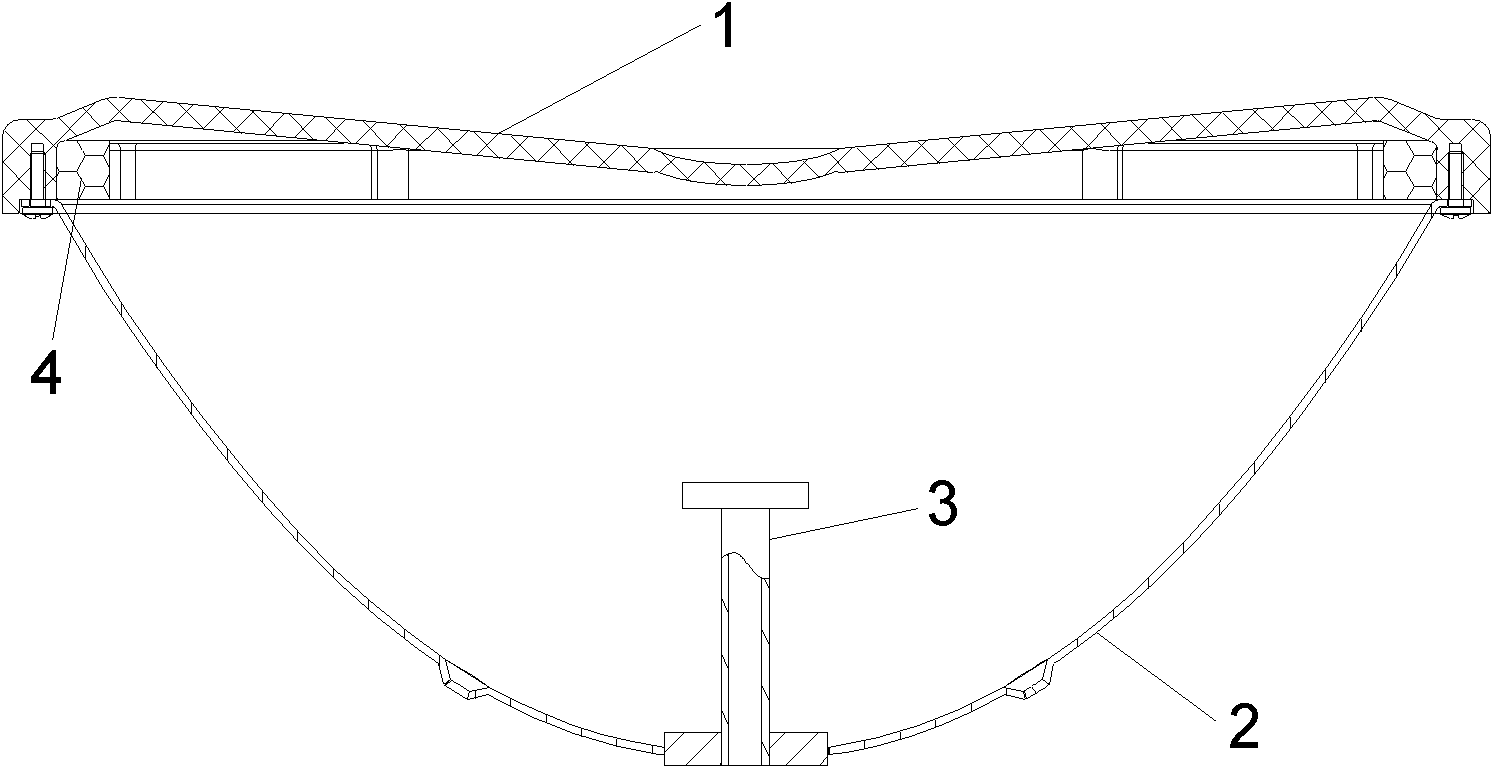

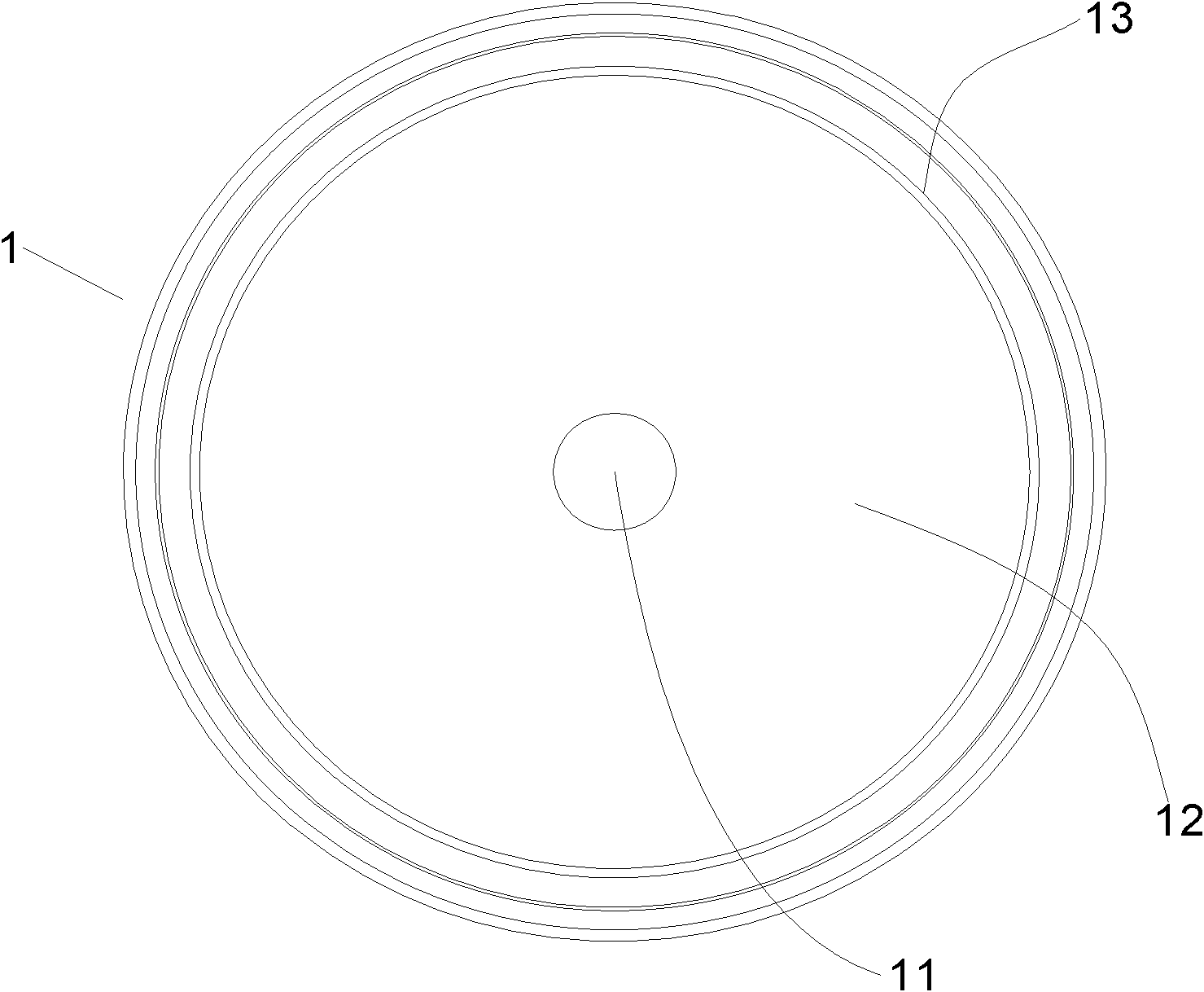

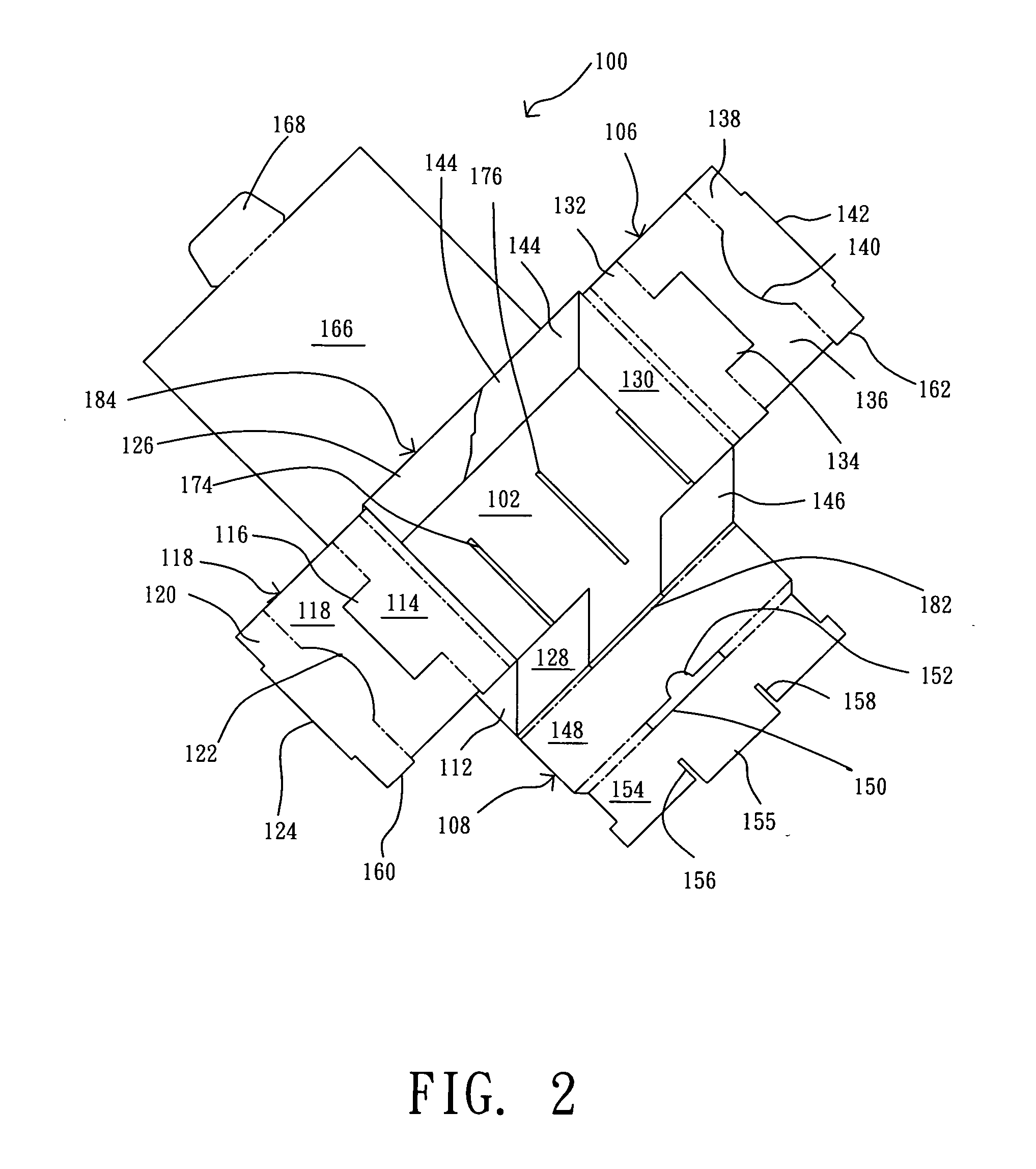

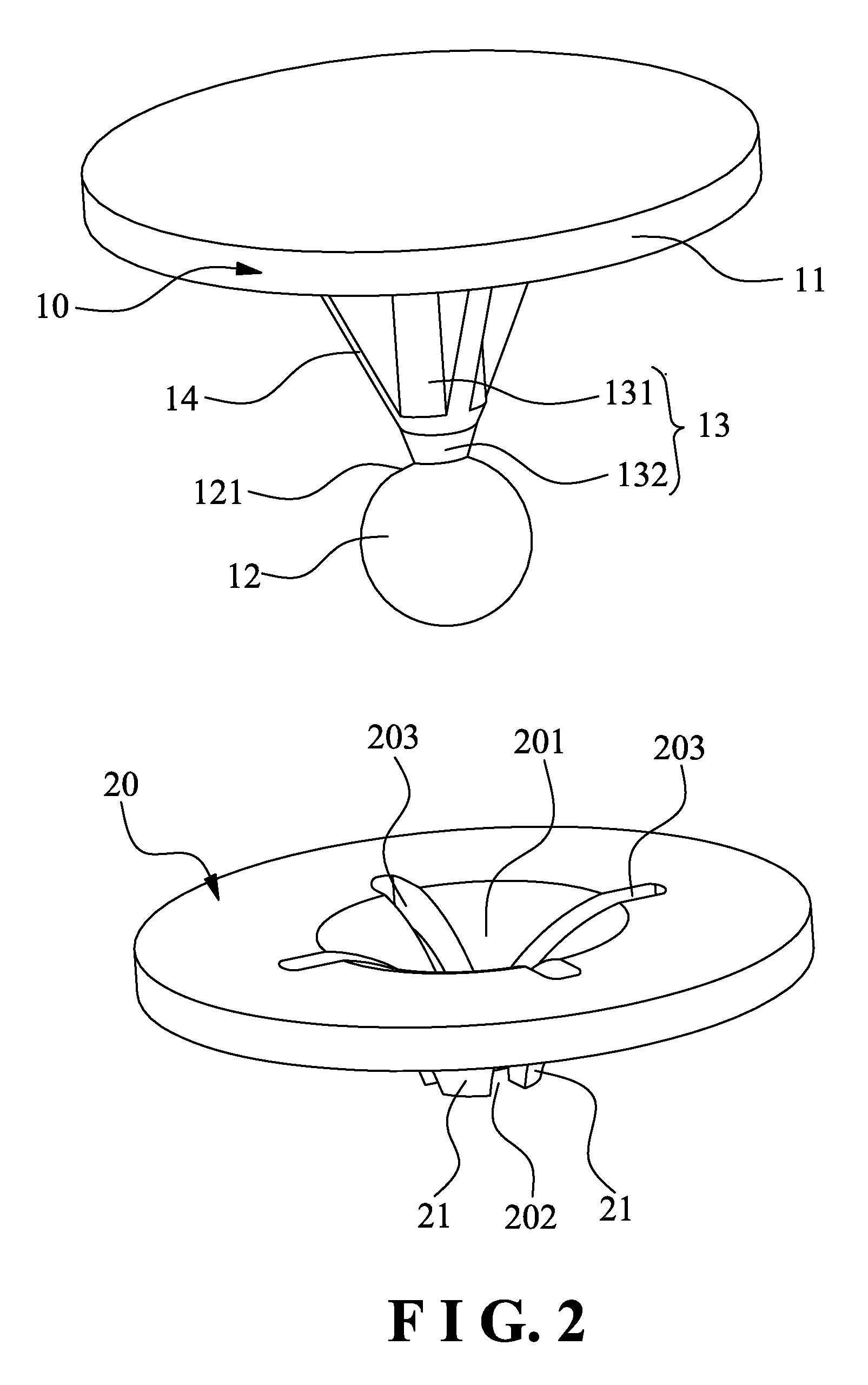

Microwave antenna and outer cover thereof

ActiveCN101958461BImproved radiation F/B performanceHigh gainRadiating element housingsMicrowavePhase retardation

A microwave antenna radome used for covering a microwave antenna and of rotatablely symmetrical includes the following components all of which are arranged concentrically; a compensation portion located at a central portion of the radome and used for compensating phase delay of electrical field at the central portion of an antenna aperture plane caused by blocking of a feed; a main reflective portion located on a periphery of the compensation portion and used for reflecting electromagnetic wave originating from the feed of the microwave antenna at a specific direction biased from the feed; and an auxiliary reflective portion located on a periphery of the main reflective portion and used for bunching and reflecting diffraction electromagnetic wave at edge of the microwave antenna. All components of the radome are specifically shaped. The microwave antenna thus formed has good electrical performance, stable structure and low cost.

Owner:COMBA TELECOM SYST (GUANGZHOU) LTD

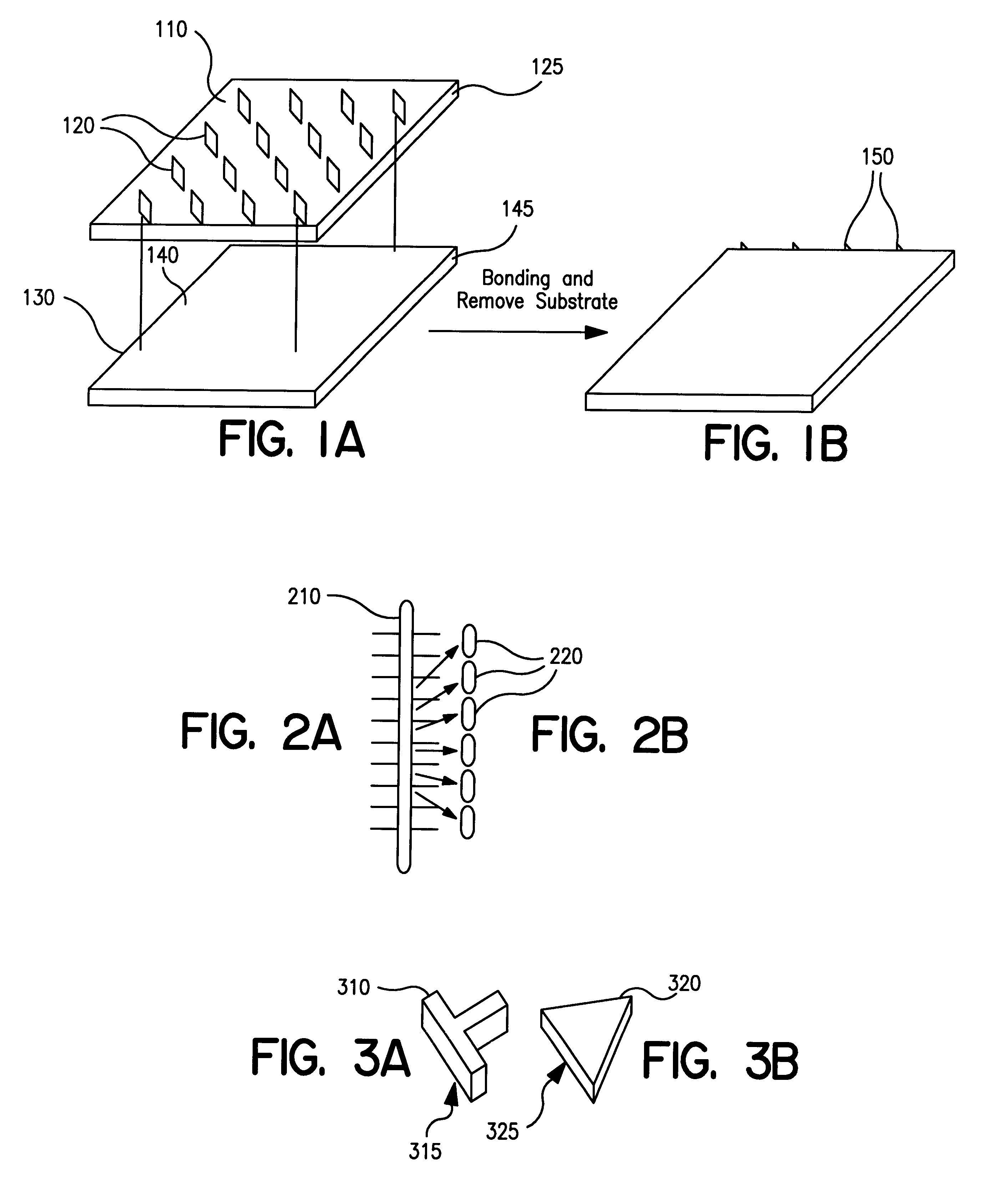

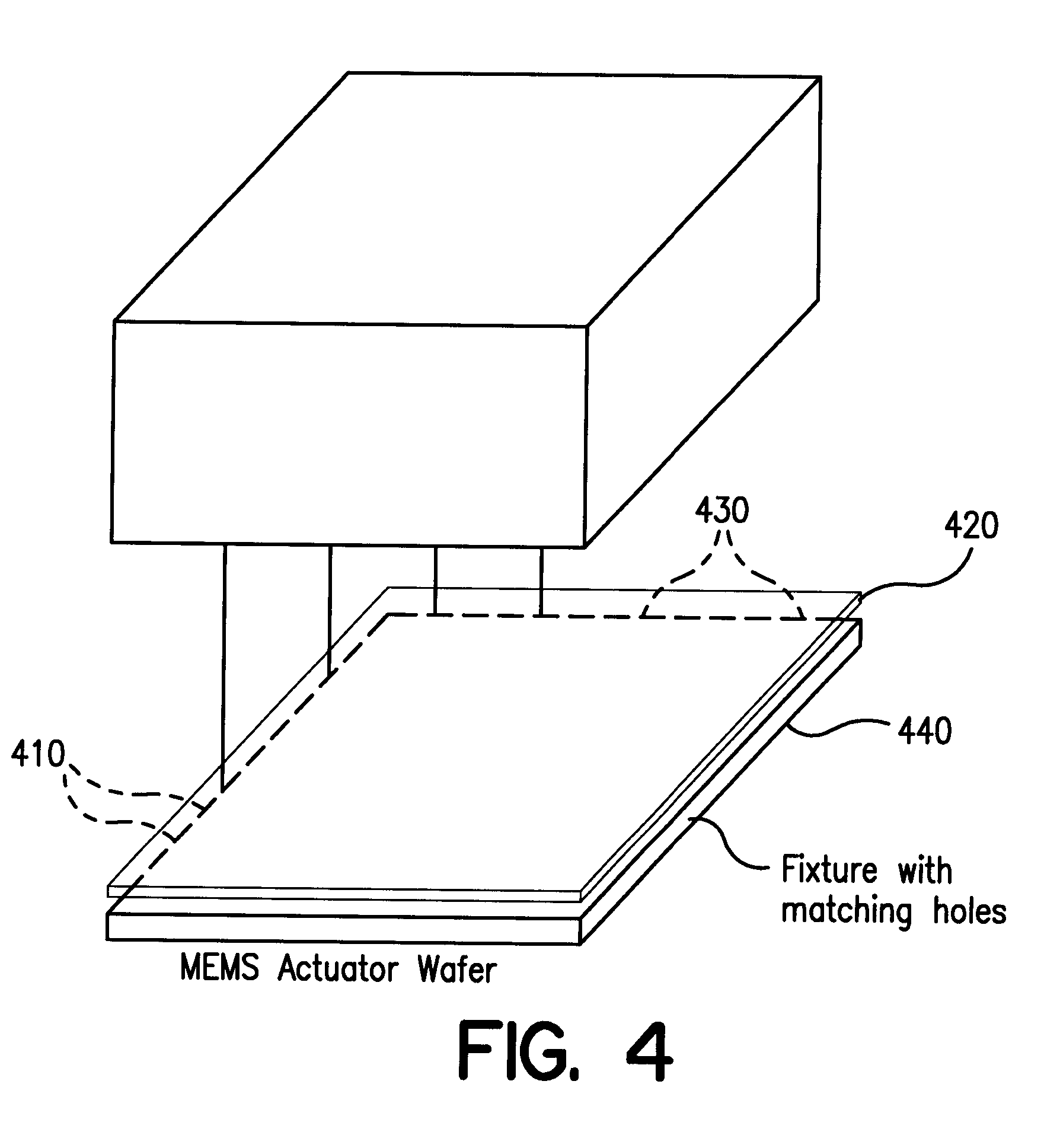

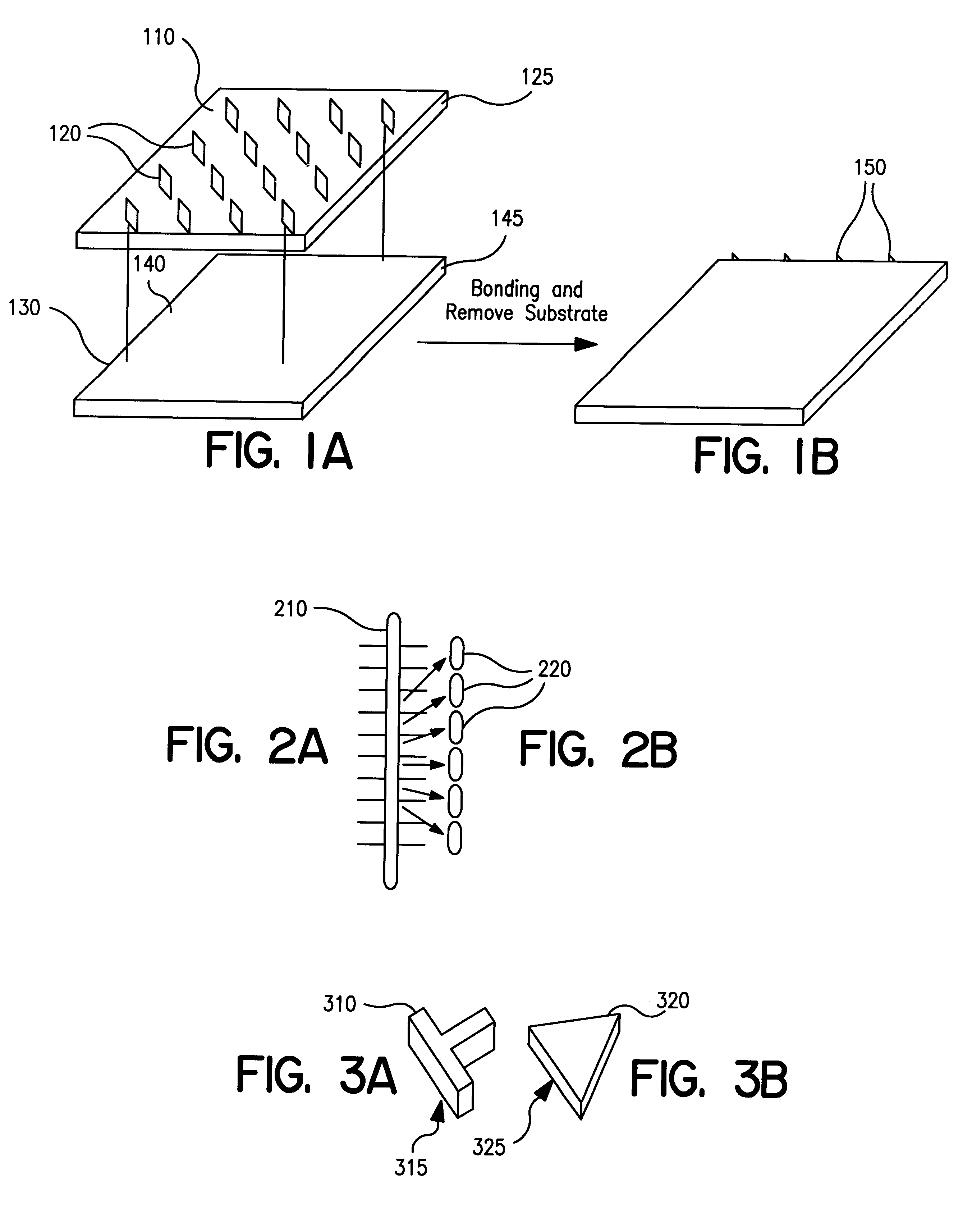

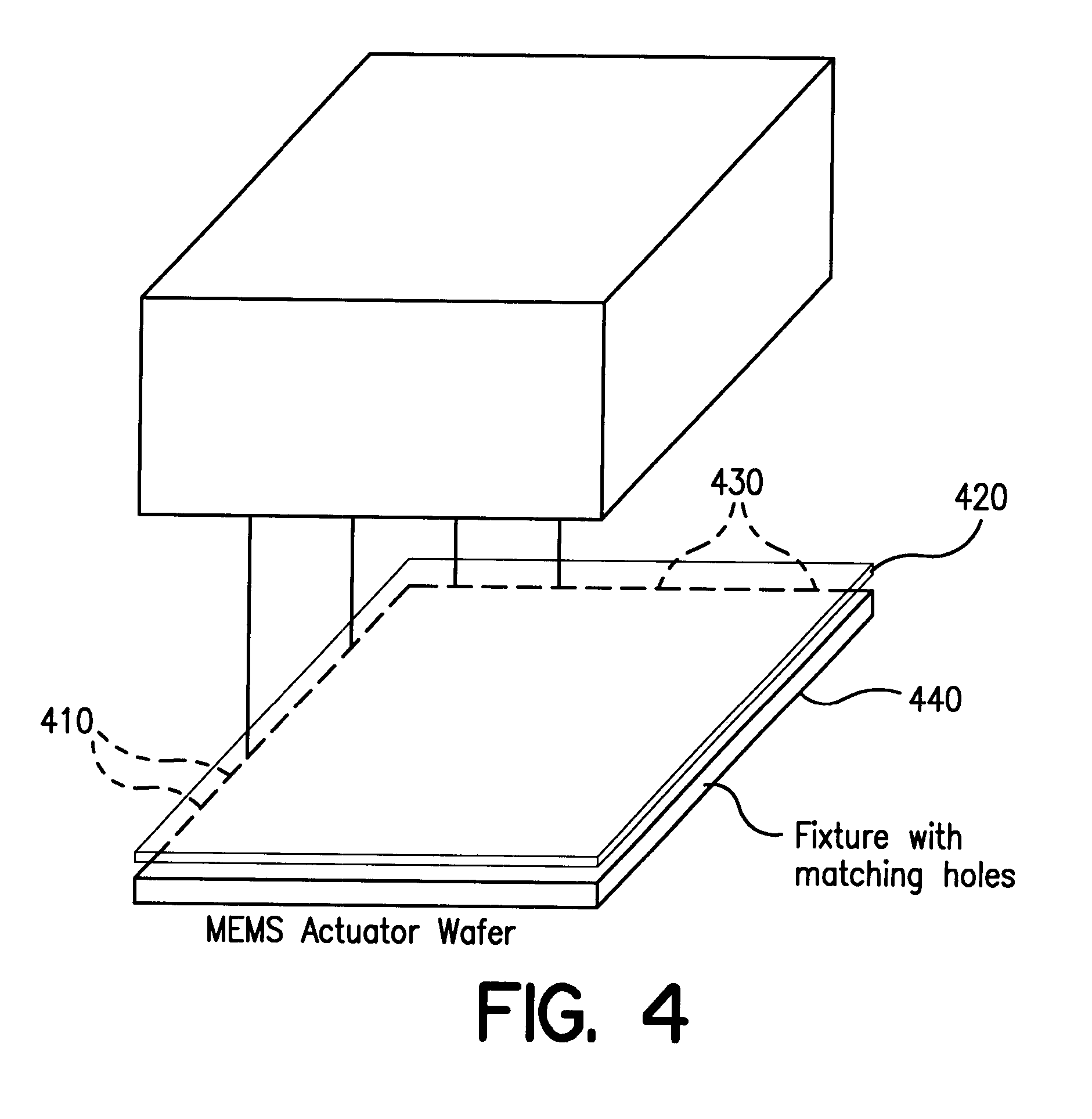

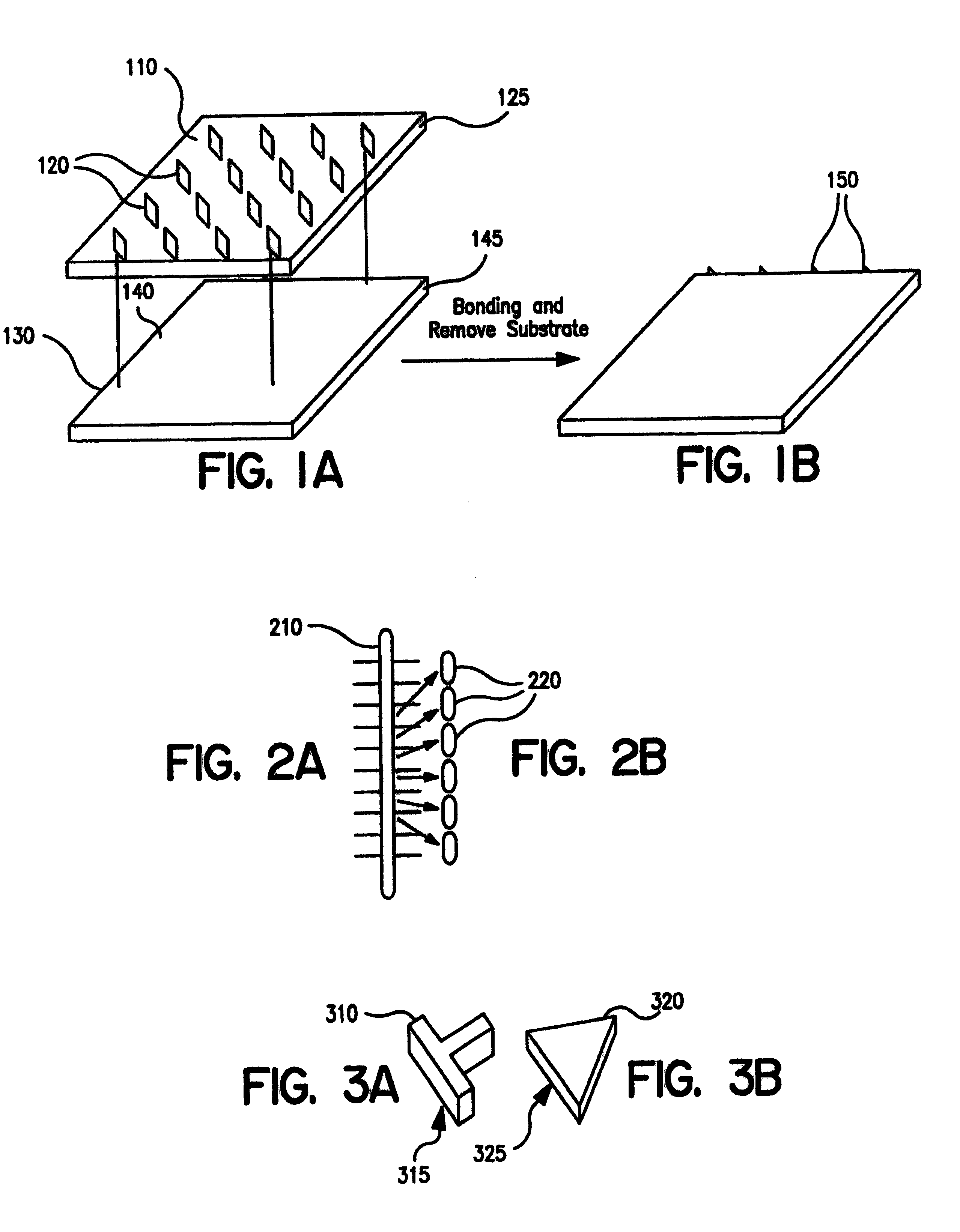

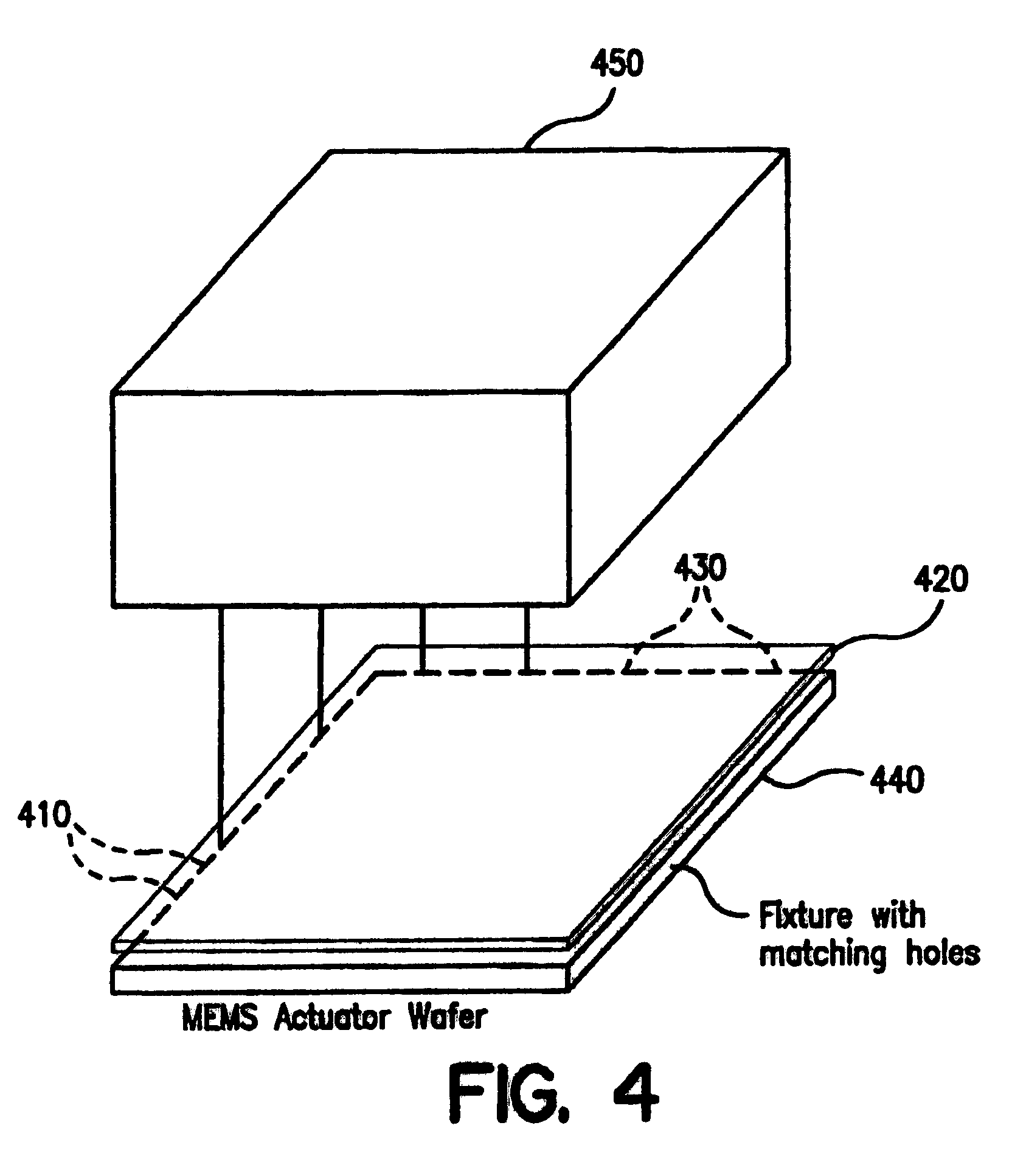

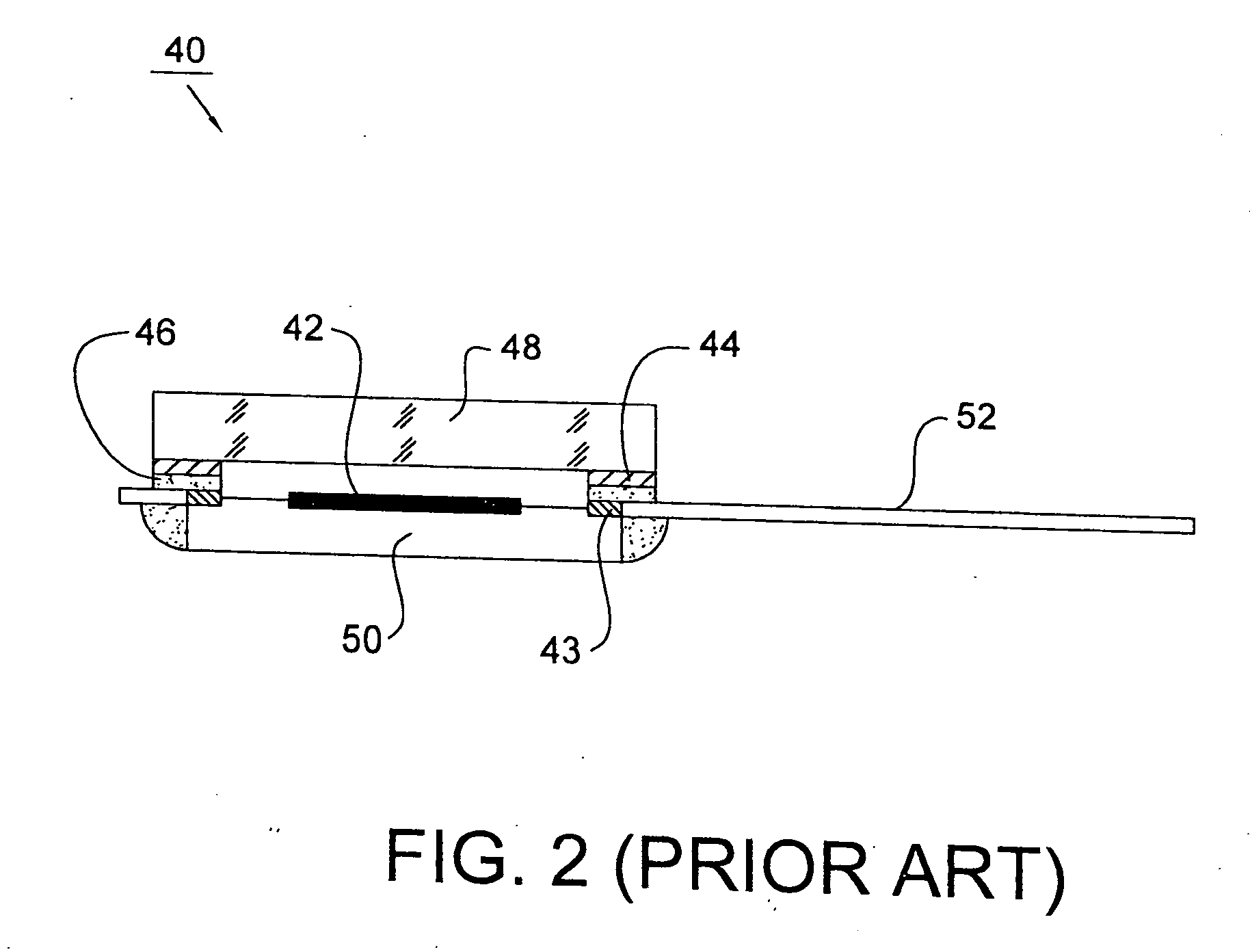

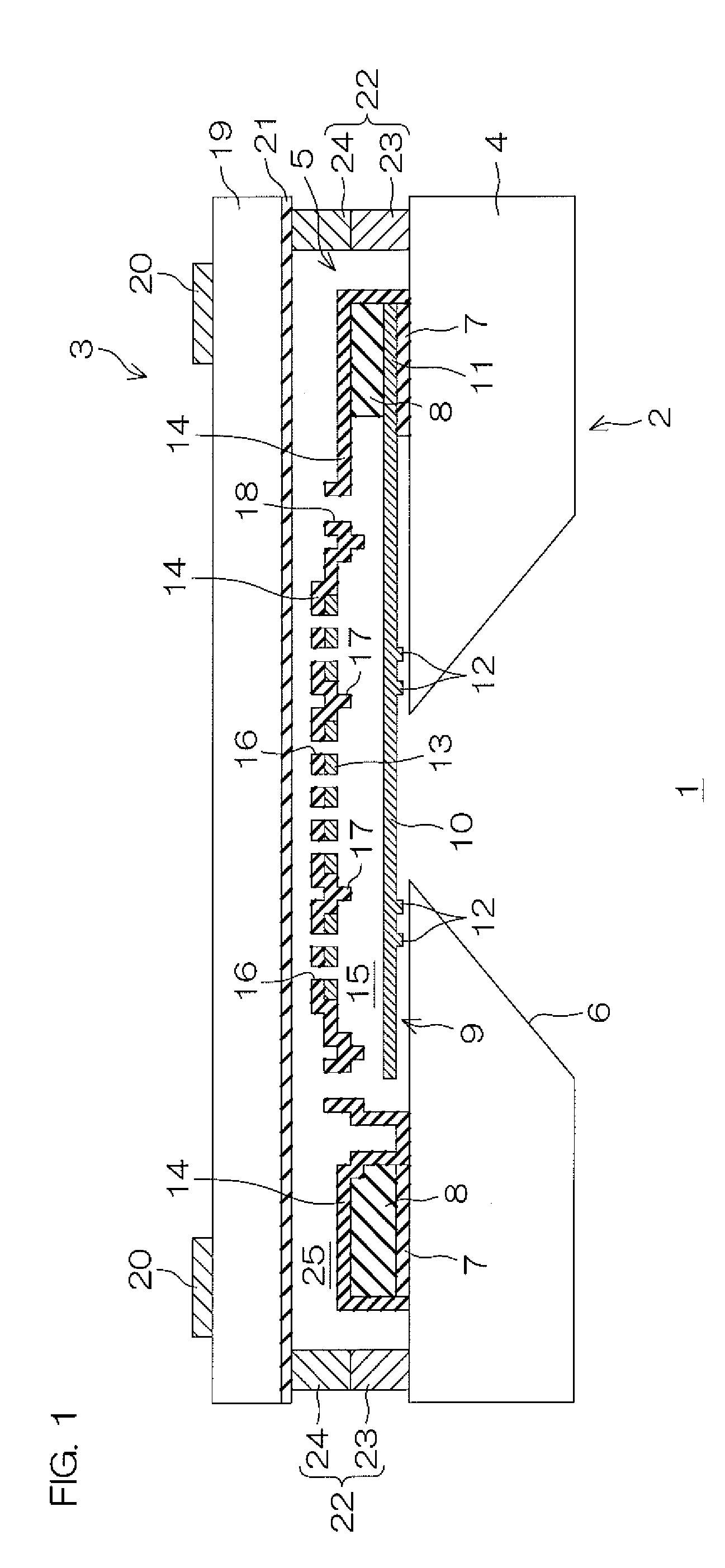

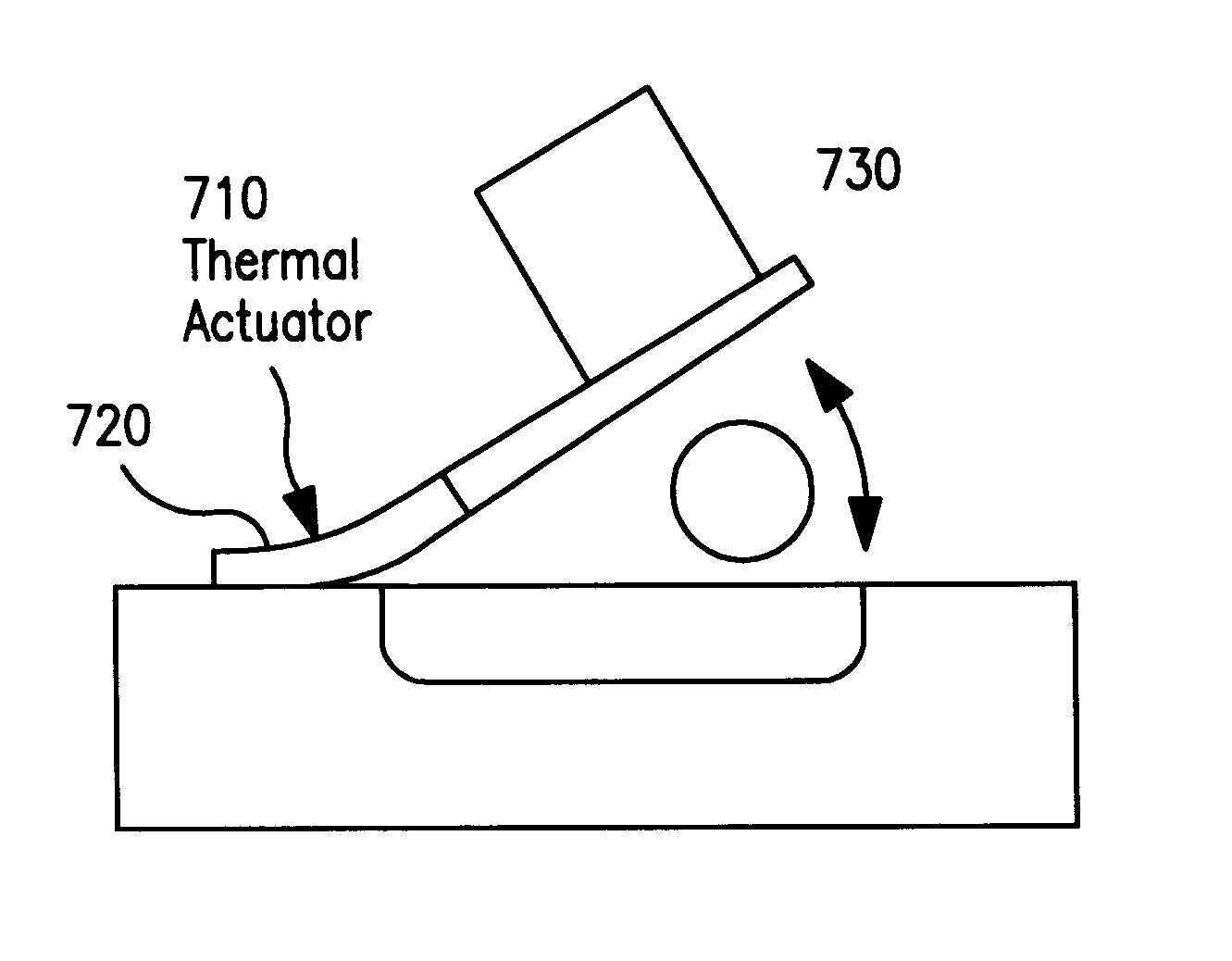

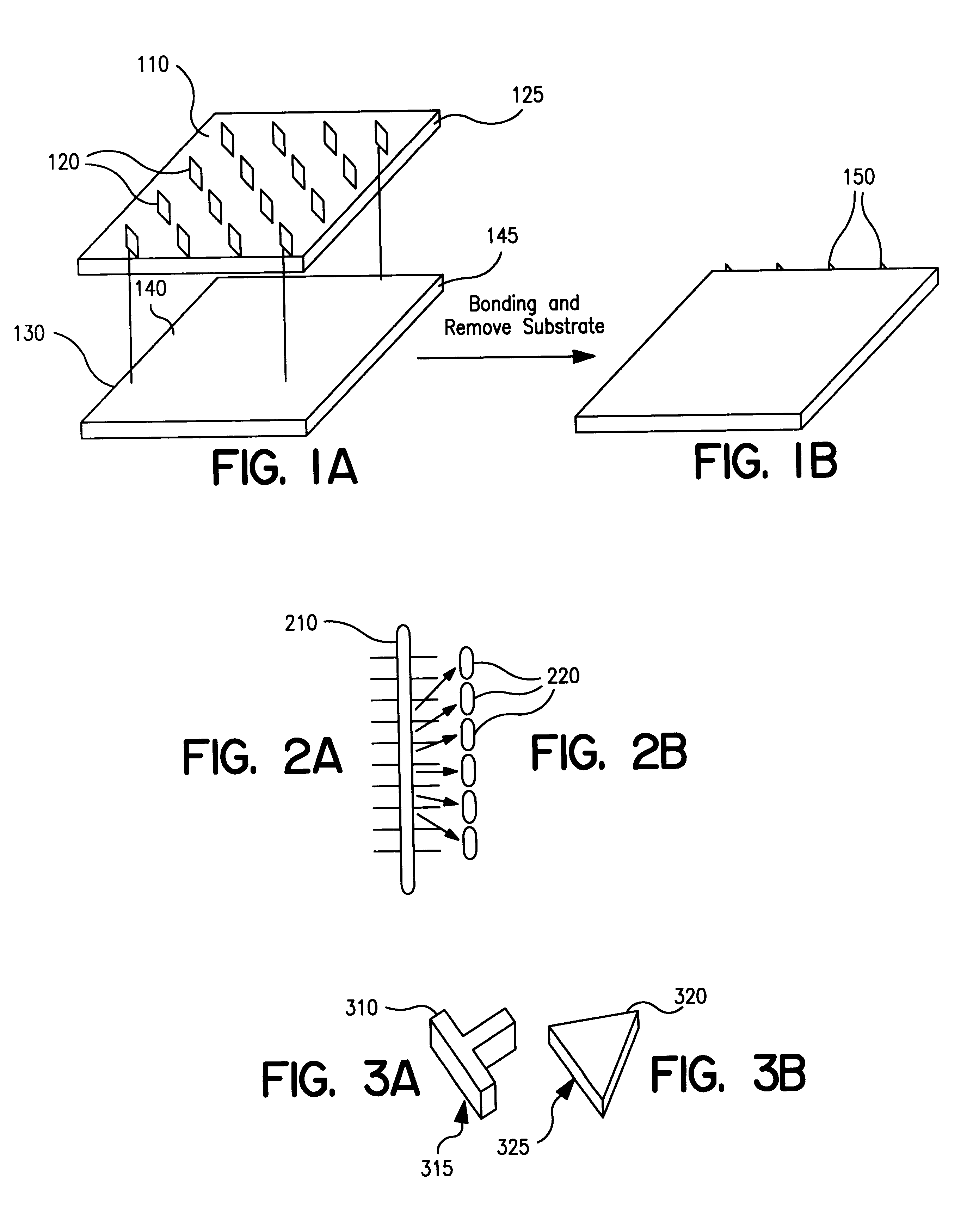

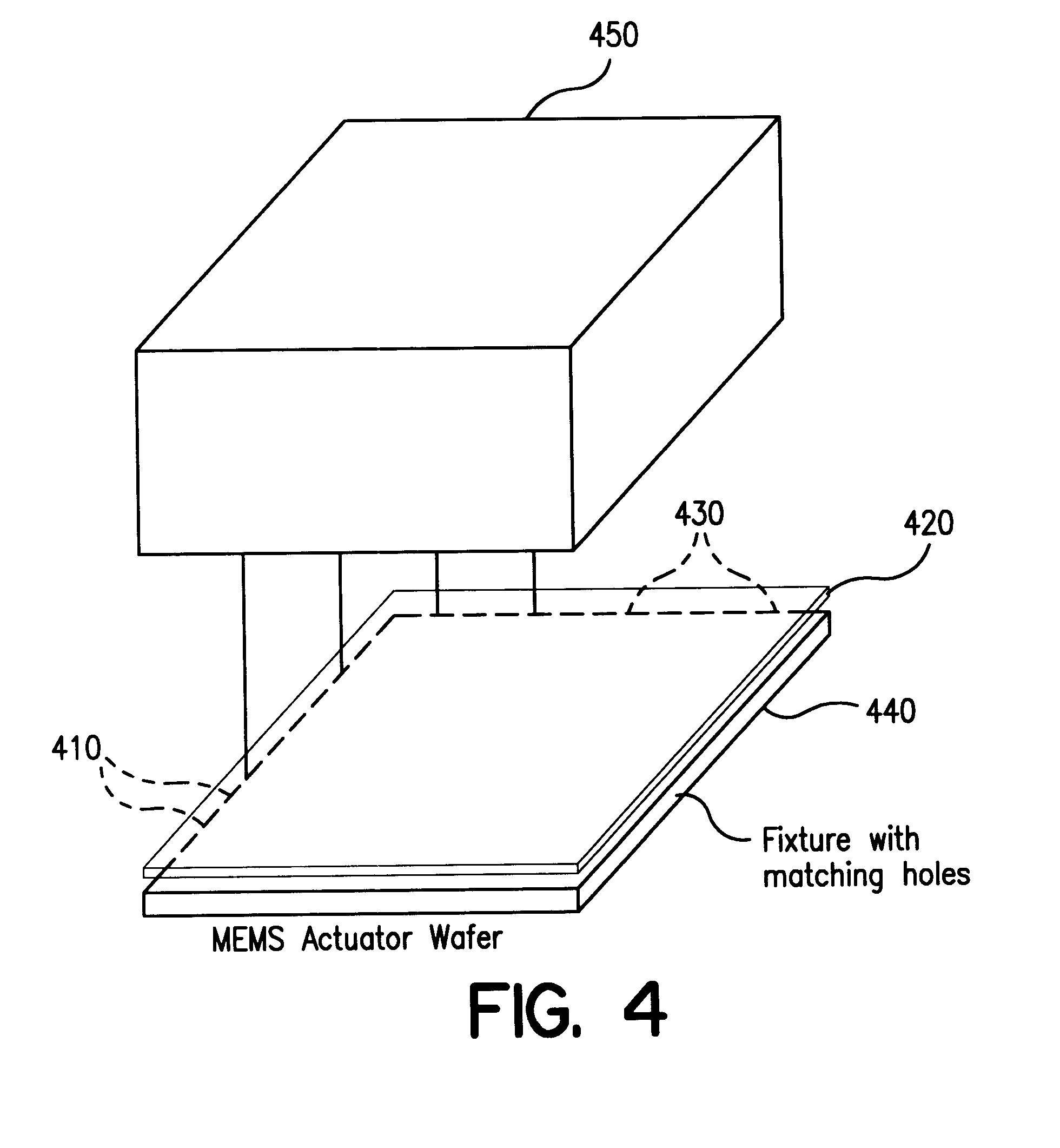

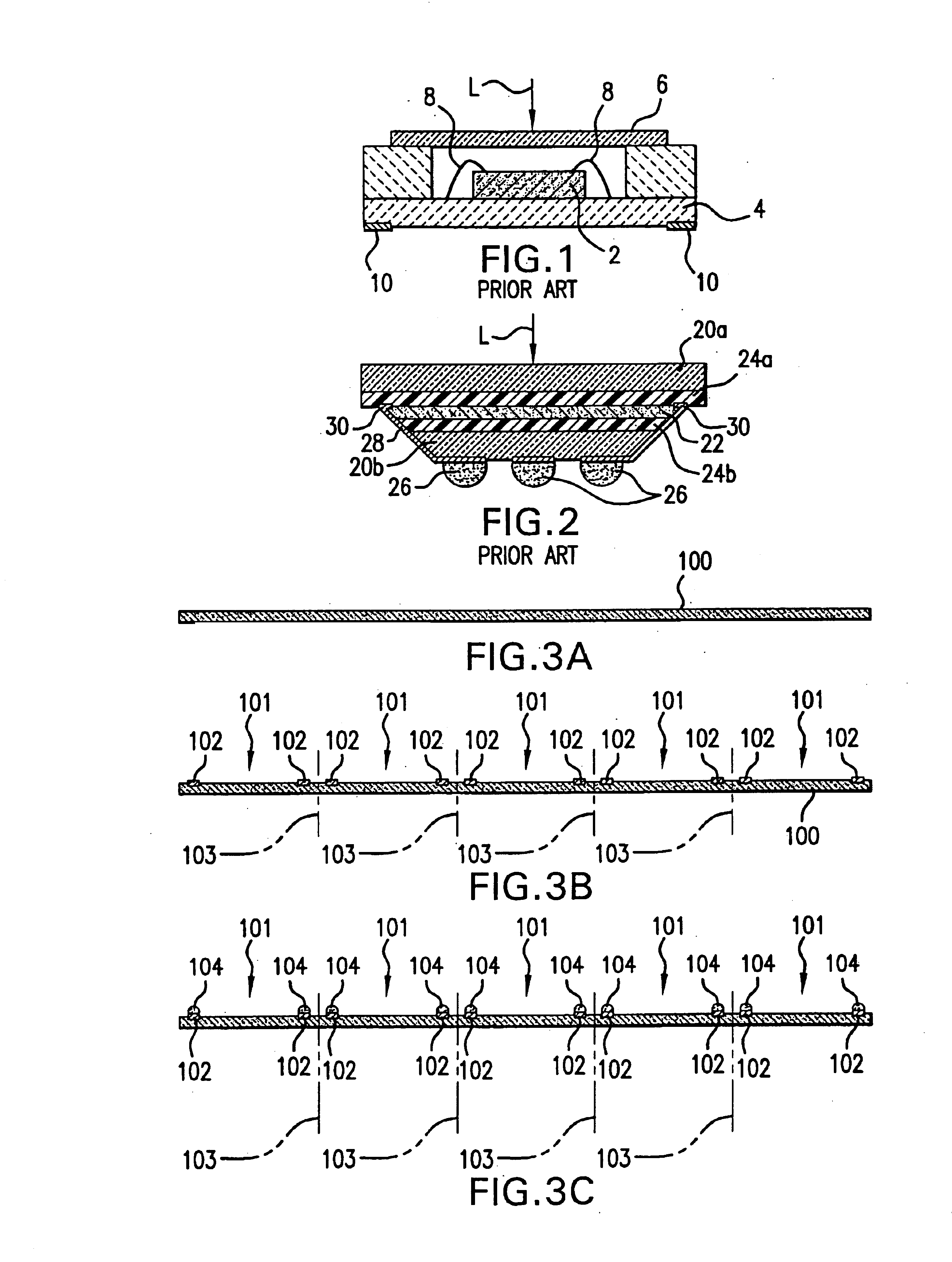

Micromachined optomechanical switching devices

InactiveUS6449406B1Reduce packaging costsSmall massMultiplex system selection arrangementsCoupling light guidesEngineeringActuator

Various configurations of micromachined optomechanical switching cells are disclosed herein. In accordance with the invention, an optomechanical switching cell is provided which includes an actuator positioned on a substrate and a mirror coupled to the actuator. The switching cell also includes an electrode disposed upon the substrate under the actuator. An insulator may also be interposed between the substrate and the electrode. In another aspect of the present invention the switching cell includes a latch having a first end region connected to the substrate and a second end region engaged by the mirror.

Owner:OMM +1

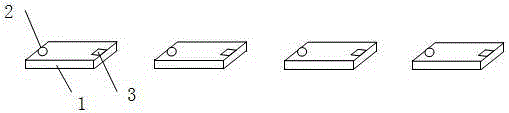

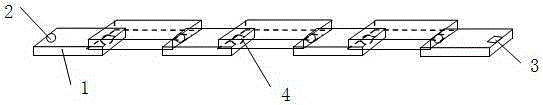

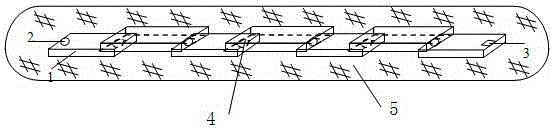

LED lamp filament illuminating strip and preparation method therefor

ActiveCN105161608AImprove yieldImprove uniformitySolid-state devicesSemiconductor devicesFluorescenceLap joint

The invention discloses an LED lamp filament illuminating strip and a preparation method therefor. The illuminating strip comprises LED chips in upper and lower rows, wherein all LED chips in the lower row are distributed at intervals, and all LED chips in the upper row are respectively connected between two adjacent LED chips in the lower row in a lap joint manner. The illuminating surfaces of the LED chips in the upper and lower rows are opposite to each other. The positive and negative electrodes of all LED chips in the upper row are respectively welded with the negative and positive electrodes of two adjacent LED chips, in lap joint connection with the LED chips in the upper row, in the lower row. The preparation method comprises the steps: coating solder paste on the positive and negative electrodes of all LED chips in the lower row; heating the solder paste and enabling the solder paste to be melted, welding the corresponding electrodes, coating the front and back surfaces of chip strips in series connection with fluorescent glue, and solidifying the fluorescent glue. The illuminating strip employs the chips which are not overlapped with each other, and the illuminating surfaces of the chips are arranged oppositely, thereby improving the light-emitting uniformity and facilitating heat dissipation. The wire crossing and tandem among chips is avoided, the packaging cost is reduced, and the yield of finished products is improved.

Owner:SHANDONG INSPUR HUAGUANG OPTOELECTRONICS

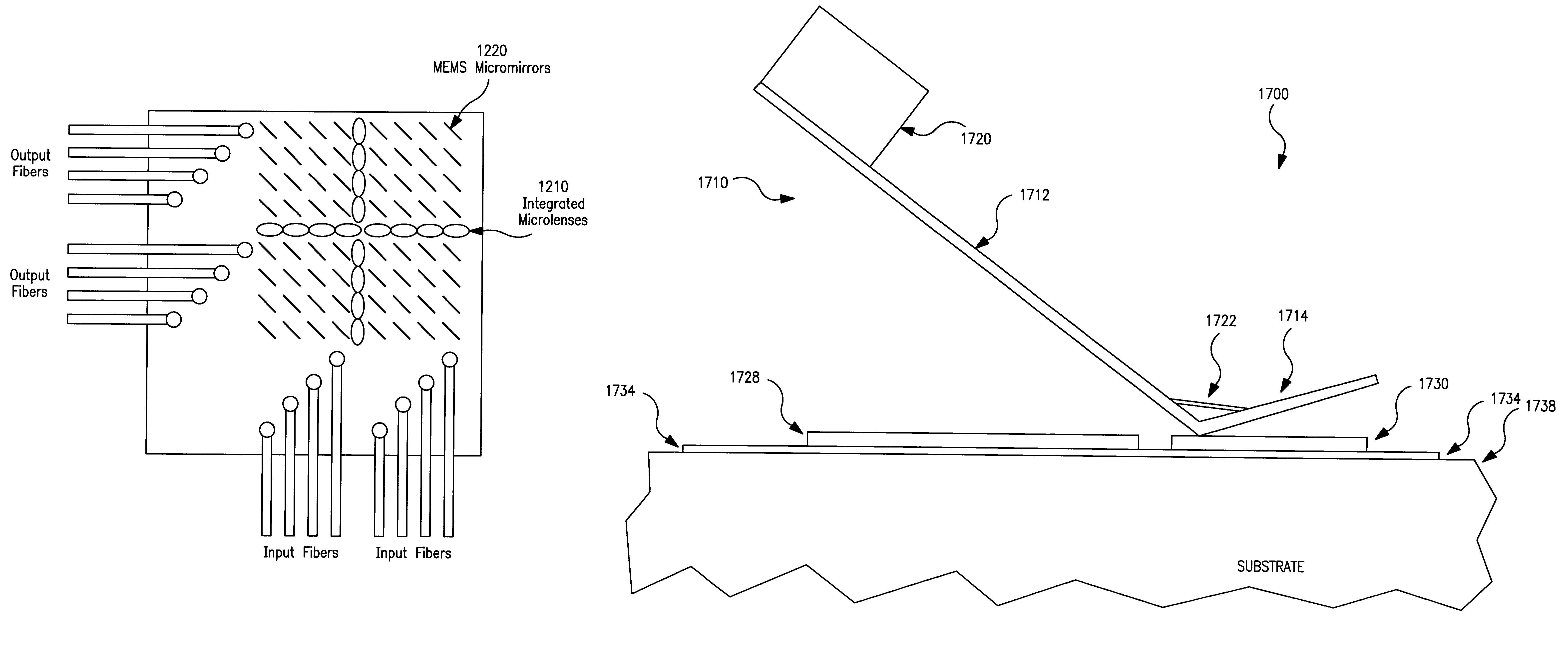

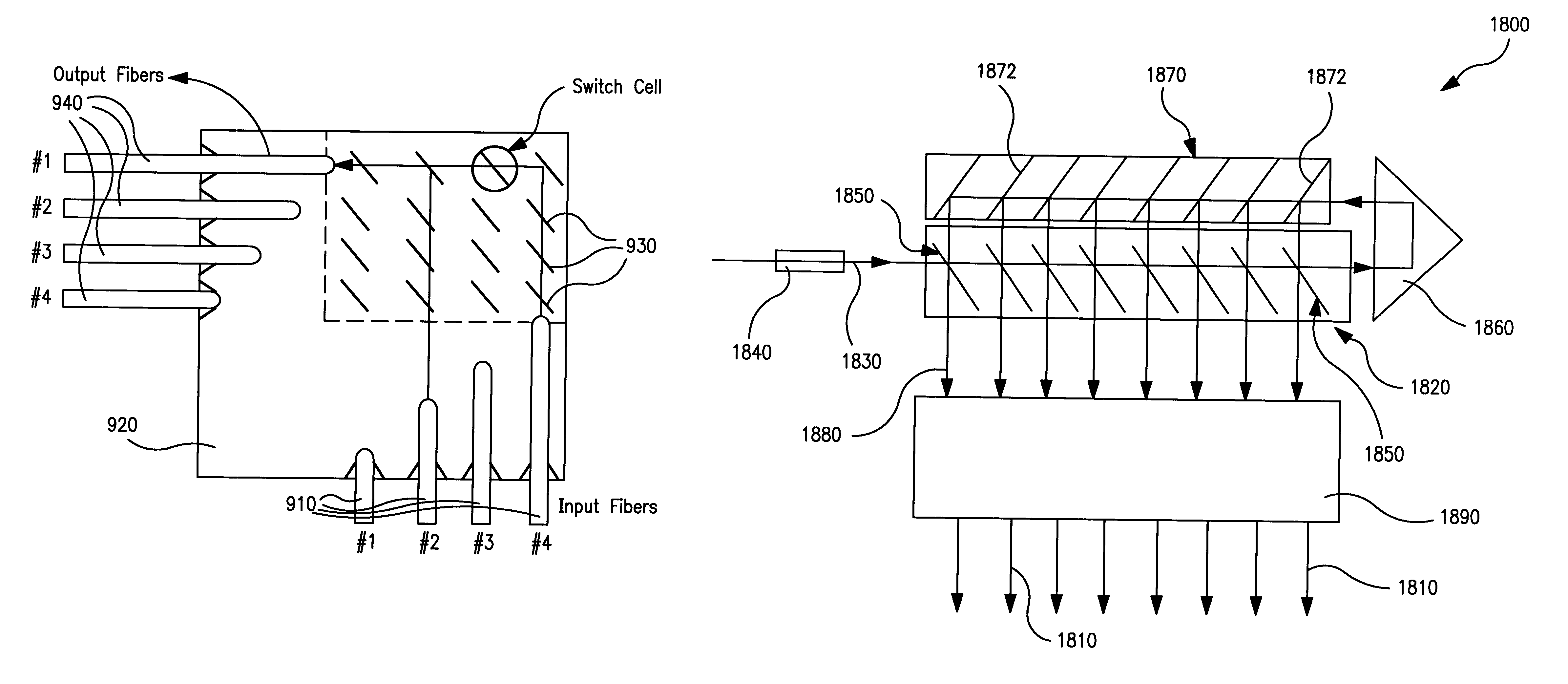

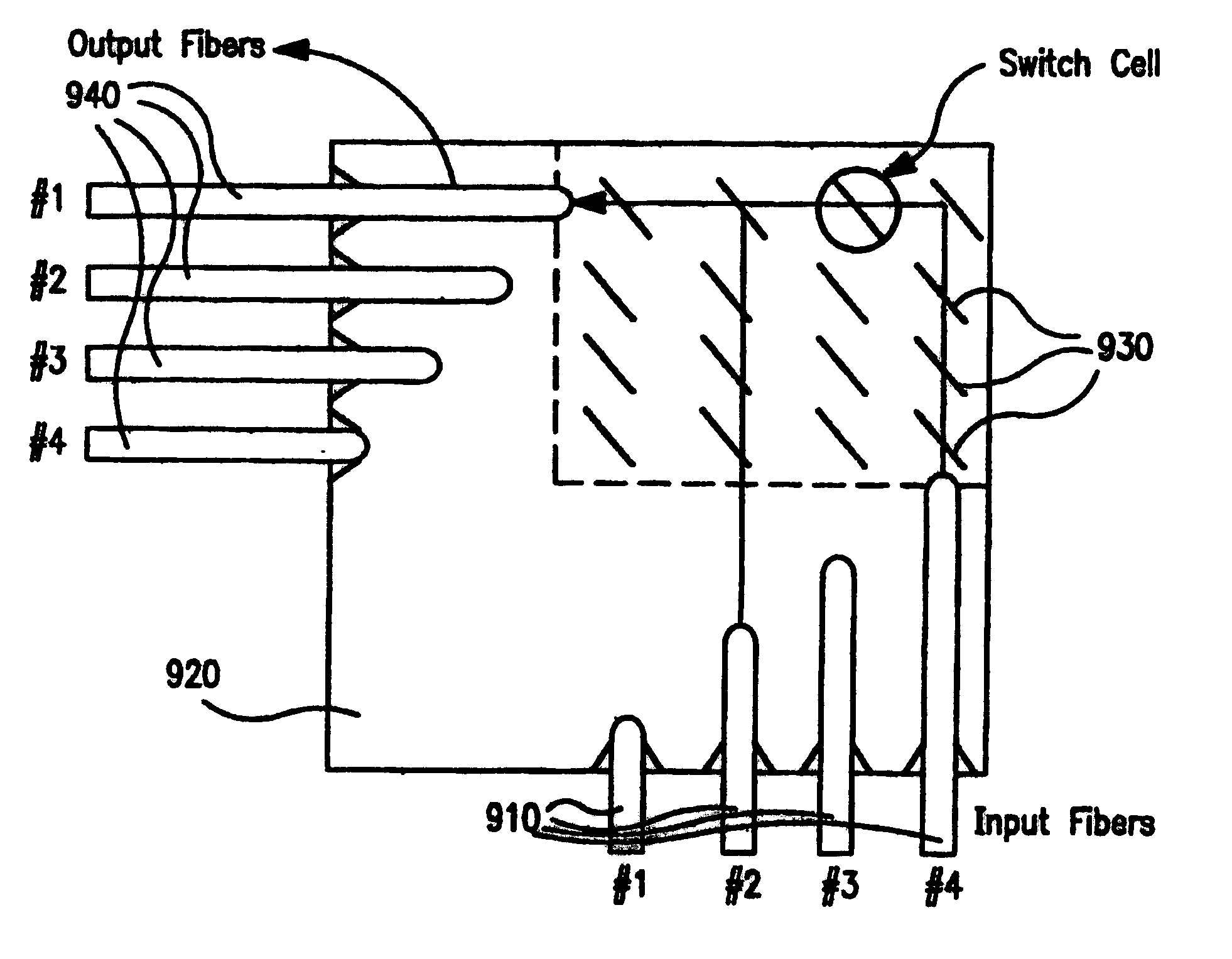

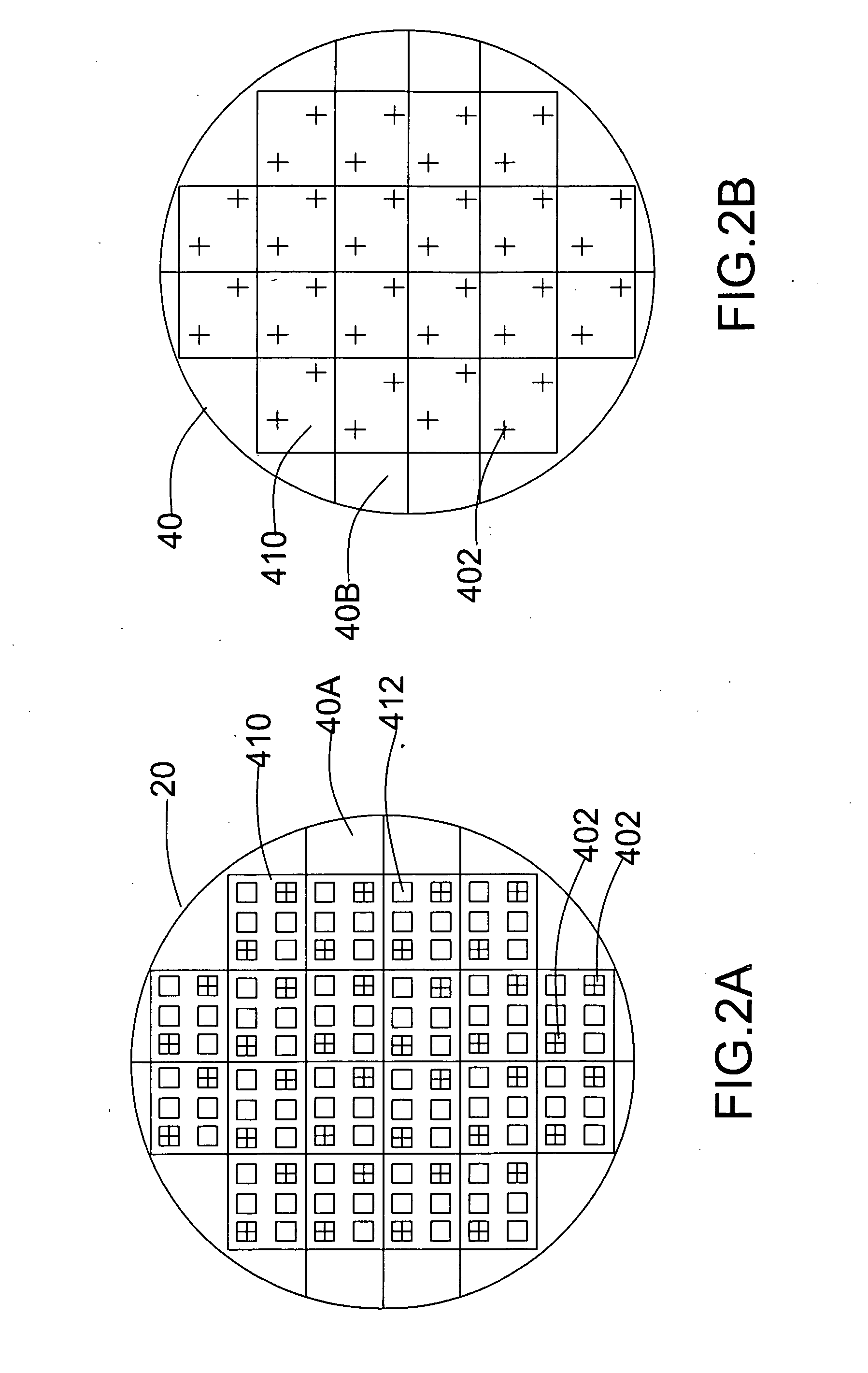

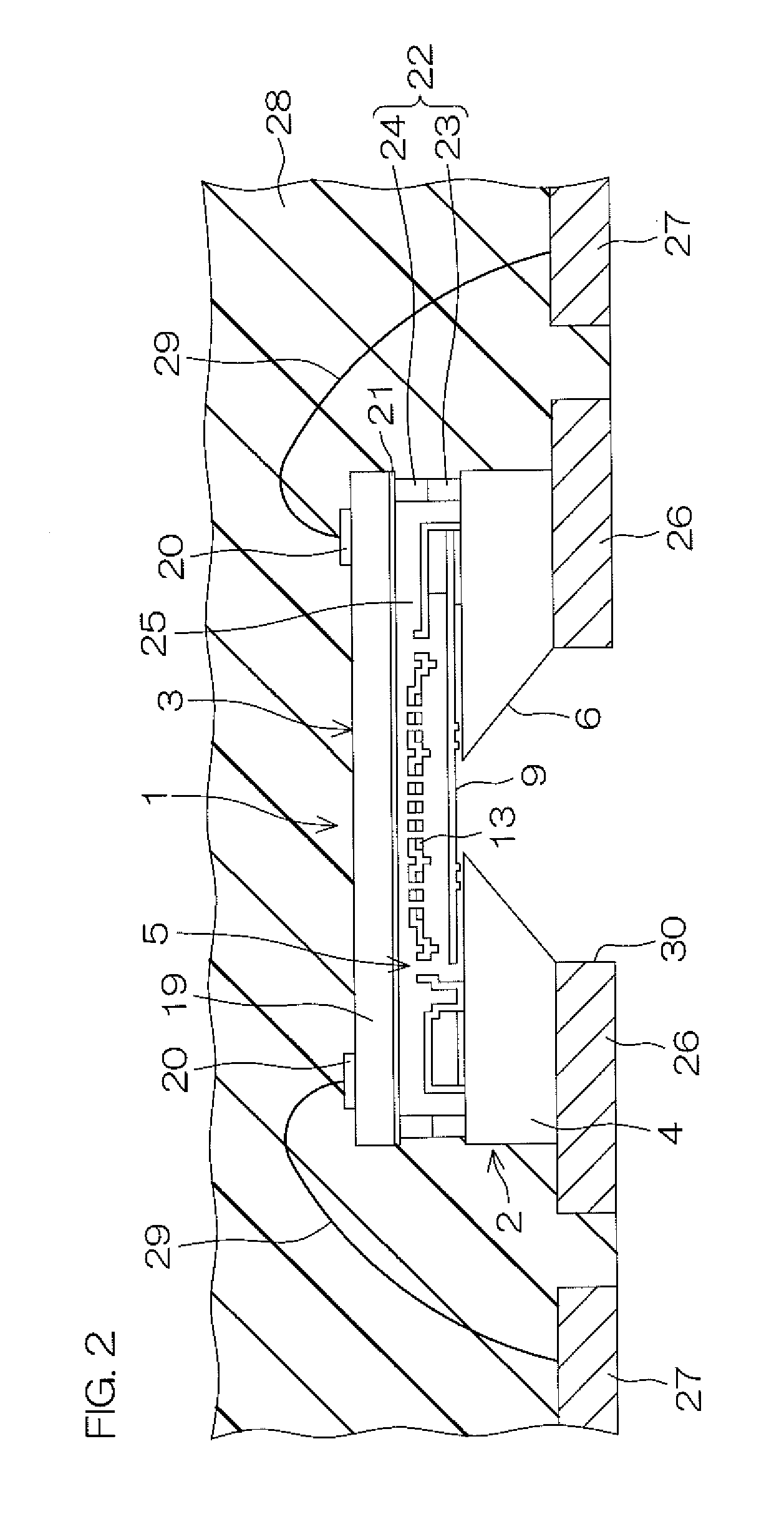

Optomechanical matrix switches including collimator arrays

InactiveUS6445841B1Reduce packaging costsSmall massMultiplex system selection arrangementsCoupling light guidesActuatorOptical alignment

Various configurations of optomechanical matrix and broadcast switches are disclosed herein. One such optomechanical matrix switch includes a substrate and a plurality of optomechanical switching cells coupled thereto. Each of the optomechanical switching cells includes a mirror and an actuator. The matrix switch further includes an array of collimator elements, each of the collimator elements being in optical alignment with one of the optomechanical switching cells. Also disclosed herein is a distributed matrix switch including first and second optomechanical matrix switches. The first and second optomechanical matrix switches respectively include first and second pluralities of optomechanical switching cells mounted upon first and second substrates. A collimator array is interposed between the first and second matrix switches in optical alignment with the first and second pluralities of optomechanical switching cells.

Owner:CROSSFIBER +1

Water soluble humic acid multi-element solid fertilizer and production method thereof

InactiveCN101570456ADissolve fastNot easy to agglomerateAlkali orthophosphate fertiliserAmmonium orthophosphate fertilisersSoil scienceWater soluble

The invention discloses a water soluble fertilizer and a production method thereof, in particular to a water soluble humic acid multi-element solid fertilizer and a production method thereof. The water soluble humic acid multi-element solid fertilizer is made by mixing water soluble humic acid, water soluble nitrogenous fertilizer, water soluble phosphorous fertilizer, water soluble potassic fertilizer and water soluble complex trace elements. Compared with the prior art, the water soluble humic acid multi-element solid fertilizer can reduce the transporting and packing cost, can be rapidly dissolved without agglomeration when in use, is applied along with water, and has the advantages of strong points, high nutrient content, complete nutrition, good water-solubility, combination of organic and inorganic matters as well as high effect of fertilizer and utilization rate. The utilization rate of product nitrogen reaches 60%, the utilization rate of phosphorus is 30-35%, and the utilization rate of potassium is 60-70%, so that the fertilizer application utilization rate is increased by more than 10% compared with the conventional fertilizer.

Owner:新疆三赢农业科技发展有限公司

Trilaminar co-extrusion thermal contraction resin film, manufacturing method and application method thereof

InactiveCN101318392AReduce pollutionReduce packaging costsWrappers shrinkageSynthetic resin layered productsThermal contractionPuncturing

The invention discloses a three-layer coextrusion heat shrinkage resin film, a production method and an application method. The-three layer coextrusion heat shrinkage resin film is produced by taking PE(LDPE, HPPE, LLDPE, mPE), EVA, PP, PA and EVOH resins as the main materials which are matched with a functional master batch and adopting a production method of one-step huffing. The largest transverse and longitudinal shrinking rates of the product can reach 60 percent and 85 percent; the largest shrinking force of the product can reach 2.0N / cm. The shrinking rate and the shrinking force of the product can be controlled and adjusted by controlling various technical parameters to lead a package to be firm and endurable. The packaged objects are pertinently led to reach the anti-rust, anti static, illumination-resistance, anti-aging, anti-puncturing, anti-low-temperature, anti-isolation, anti-bacteria and anti-degradation effects and the like by adjusting the material composition and mixture ratio of each layer. The three-layer coextrusion heat shrinkage resin film is used for replacing the traditional paper box wrappage to reduce the packaging cost. The mechanical properties are good, the pertinence is strong, the materials are saved; when the three-layer coextrusion heat shrinkage resin film is used, the shrinking temperature is low, the power is saved and the packaging cost is saved, thus effectively reducing the production cost and having extremely high application value.

Owner:大连华诺塑胶科技有限公司

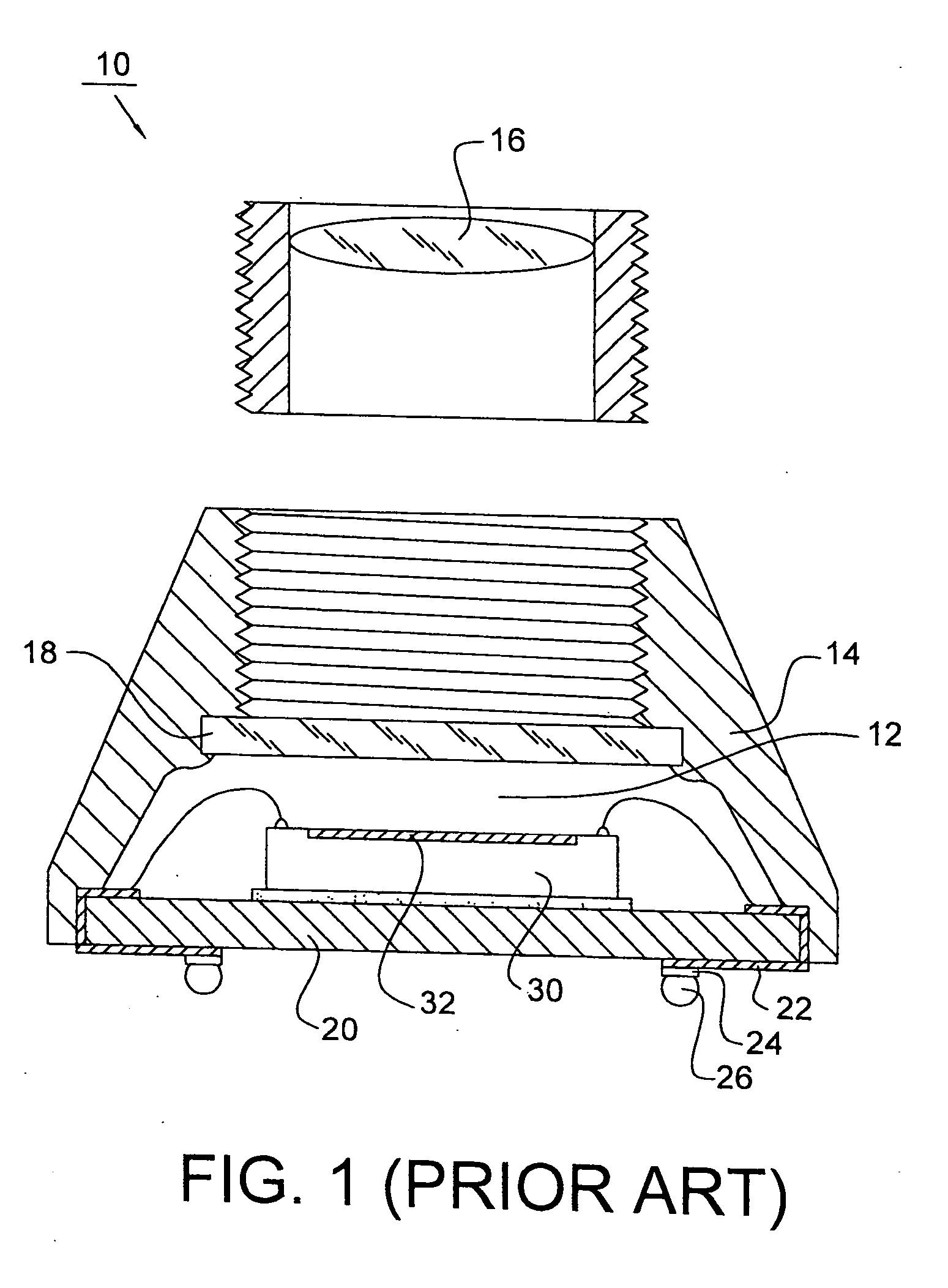

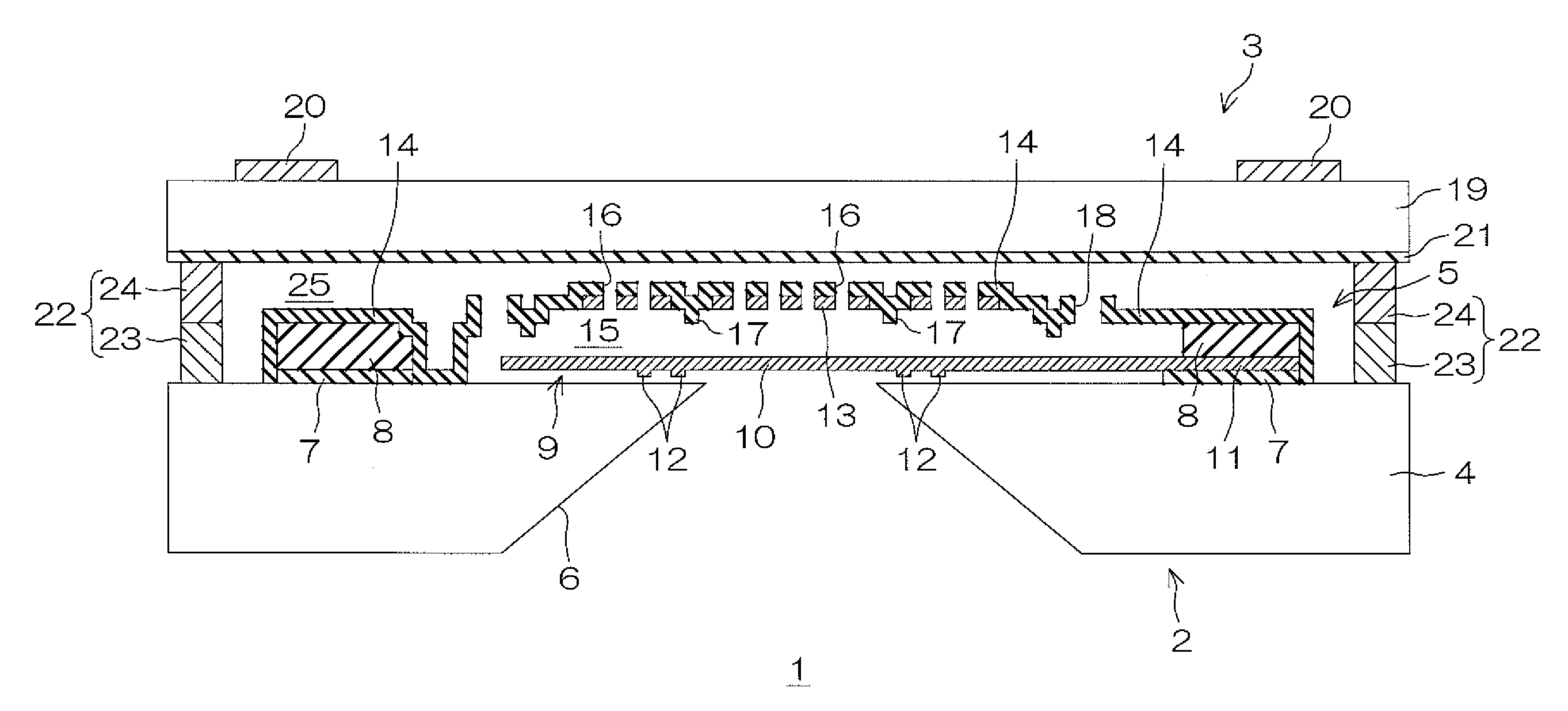

Micromachined optomechanical switching cell with parallel plate actuator and on-chip power monitoring

InactiveUS6453083B1Reduce packaging costsSmall massMultiplex system selection arrangementsCoupling light guidesParallel plateOptical power

A number of micromachined optomechanical switching cells and matrix switches including such switching cells are disclosed herein. One optomechanical switching cell of the present invention includes a parallel plate actuator positioned on a substrate. A mirror coupled to the actuator is disposed to selectively redirect an incident optical beam. The present invention also contemplates an optomechanical matrix switch including a substrate and a plurality of optomechanical switching cells coupled thereto. The matrix switch further includes an arrangement for monitoring the optical power incident upon, and output by, the matrix switch.

Owner:OMM

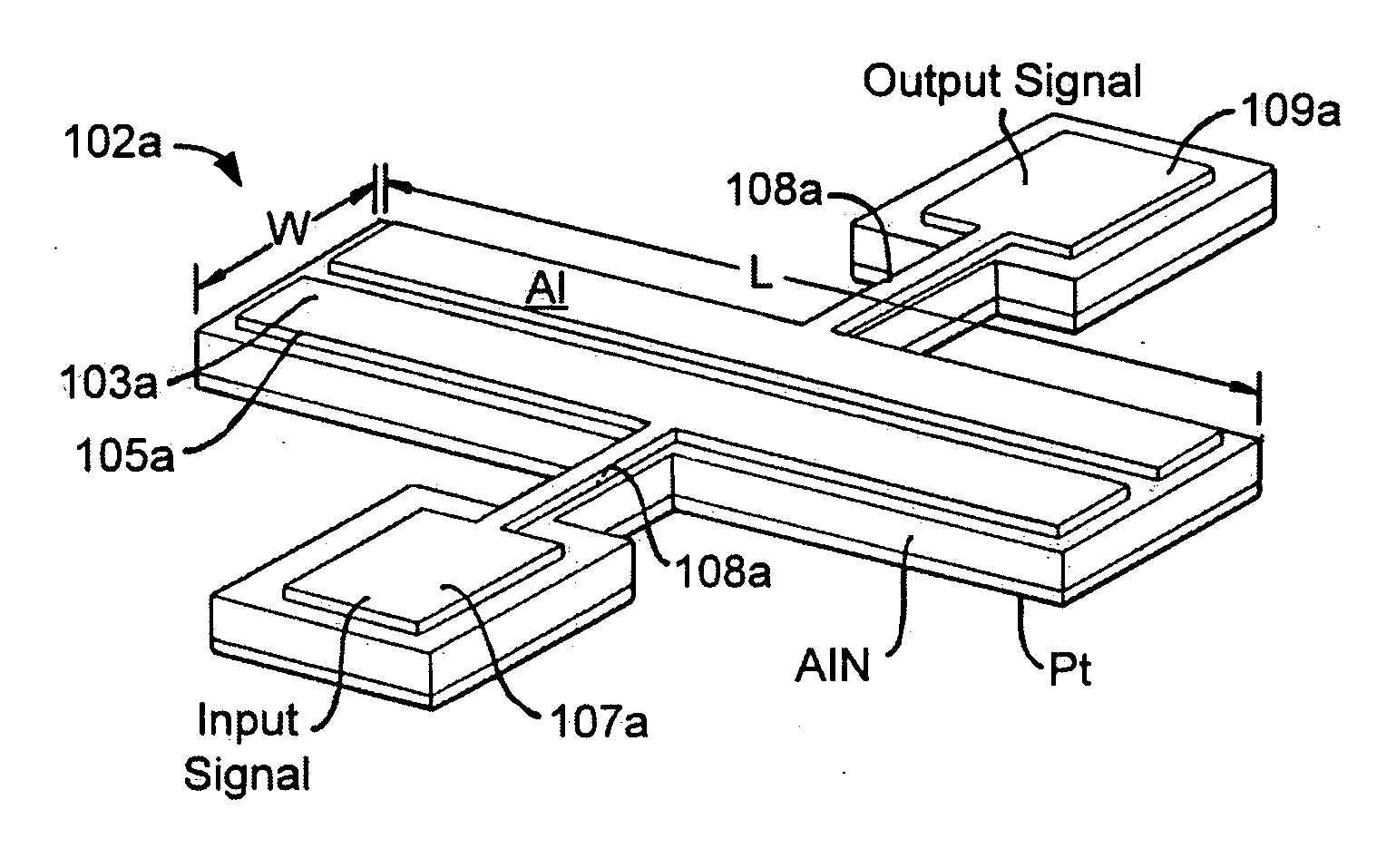

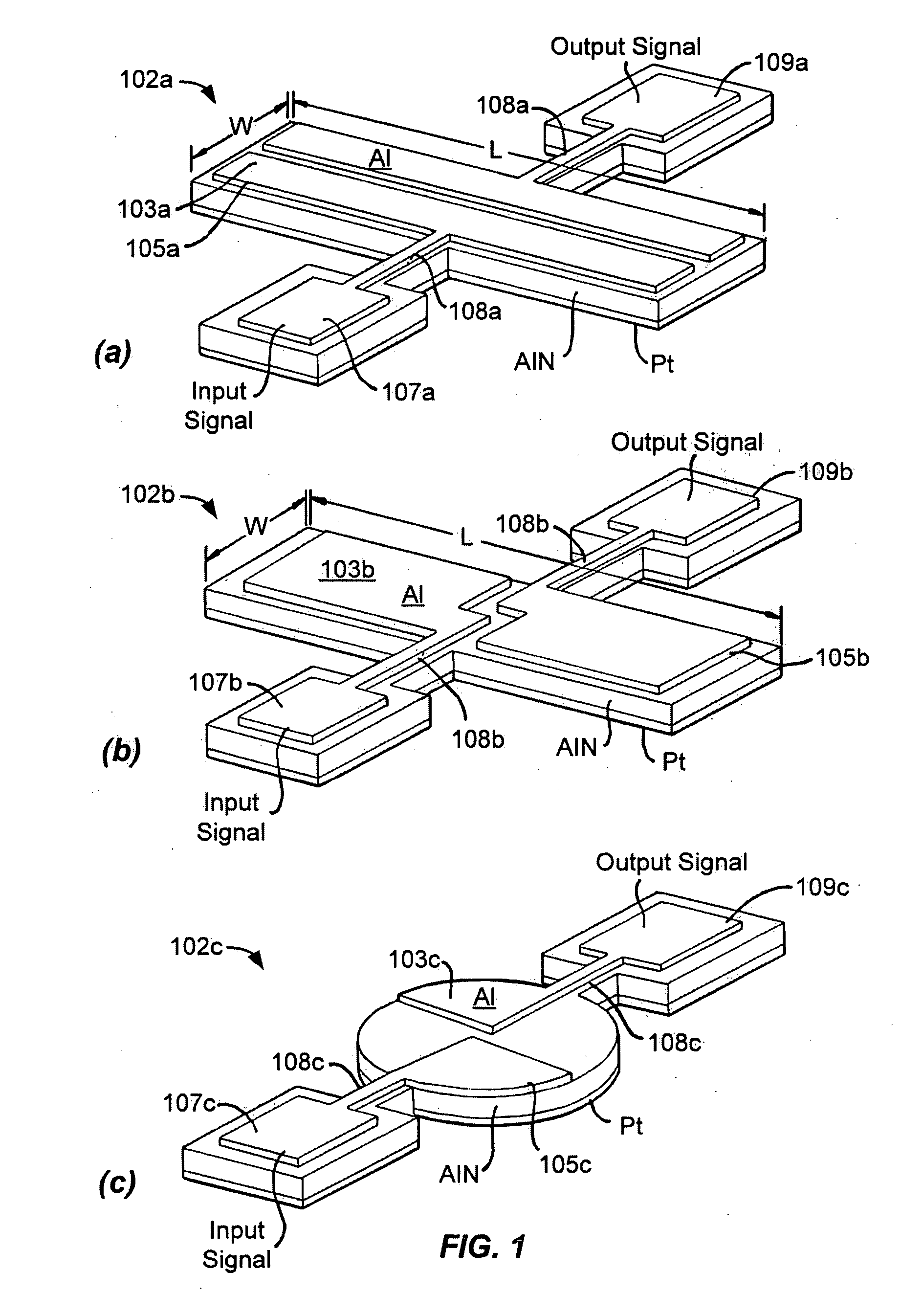

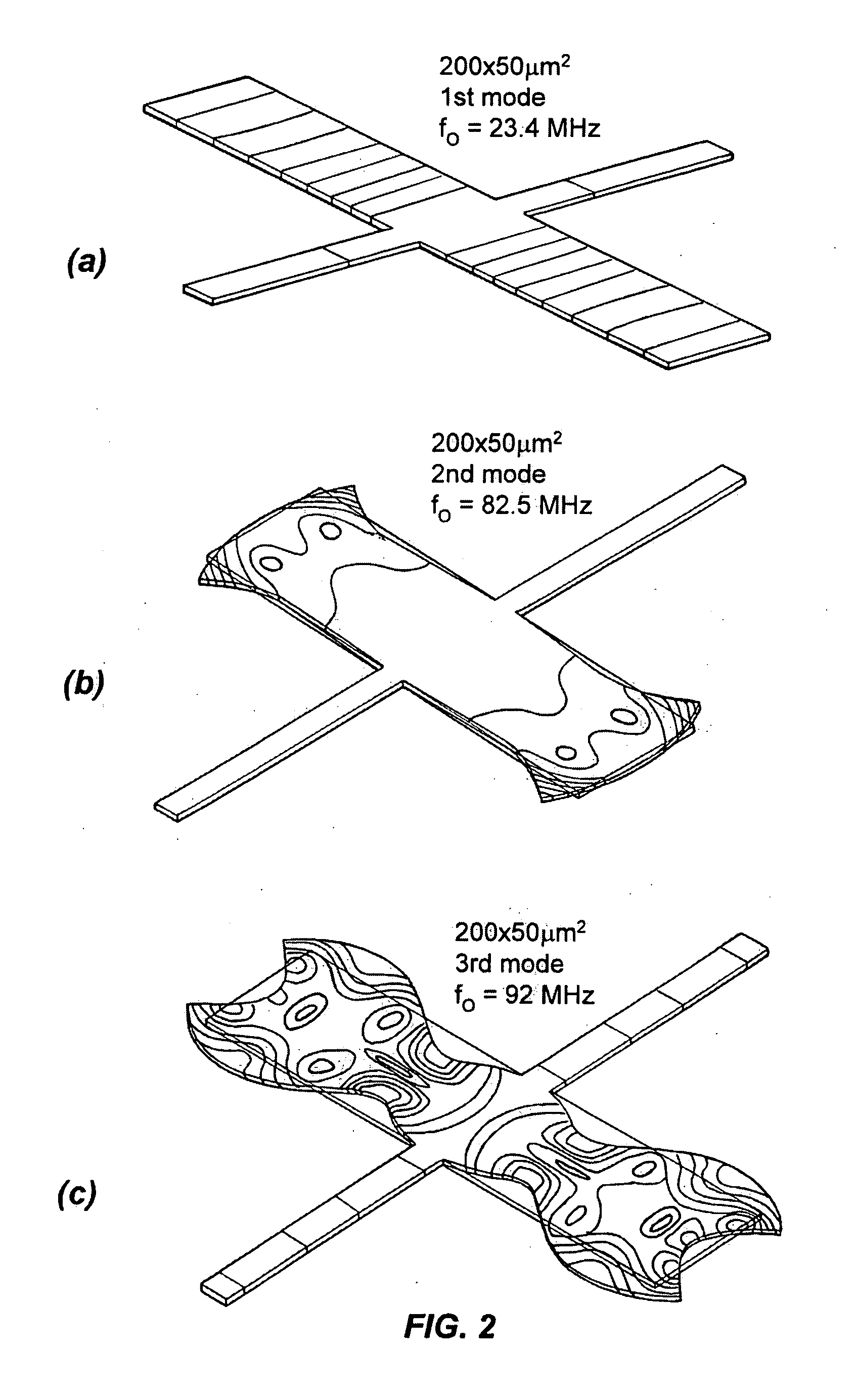

Contour-mode piezoelectric micromechanical resonators

ActiveUS20060290449A1Reduce packaging costsLower resistanceImpedence networksEngineeringMicromachinery

A contour mode micromechanical piezoelectric resonator. The resonator has a bottom electrode; a top electrode; and a piezoelectric layer disposed between the bottom electrode and the top electrode. The piezoelectric resonator has a planar surface with a cantilevered periphery, dimensioned to undergo in-plane lateral displacement at the periphery. The resonator also includes means for applying an alternating electric field across the thickness of the piezoelectric resonator. The electric field is configured to cause the resonator to have a contour mode in-plane lateral displacement that is substantially in the plane of the planar surface of the resonator, wherein the fundamental frequency for the displacement of the piezoelectric resonator is set in part lithographically by the planar dimension of the bottom electrode, the top electrode or the piezoelectric layer.

Owner:RGT UNIV OF CALIFORNIA +1

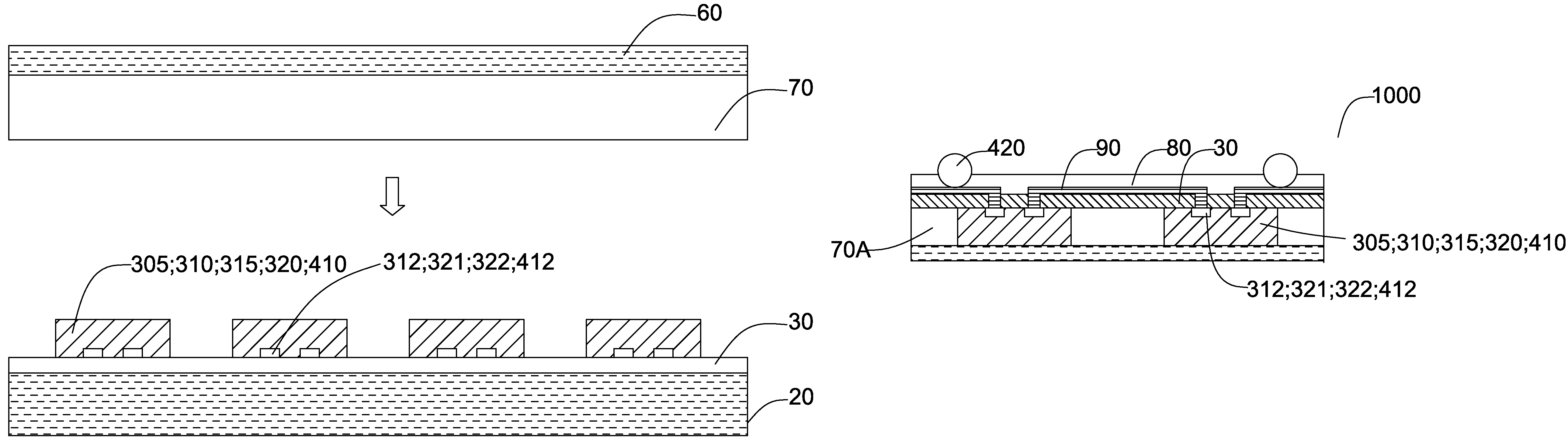

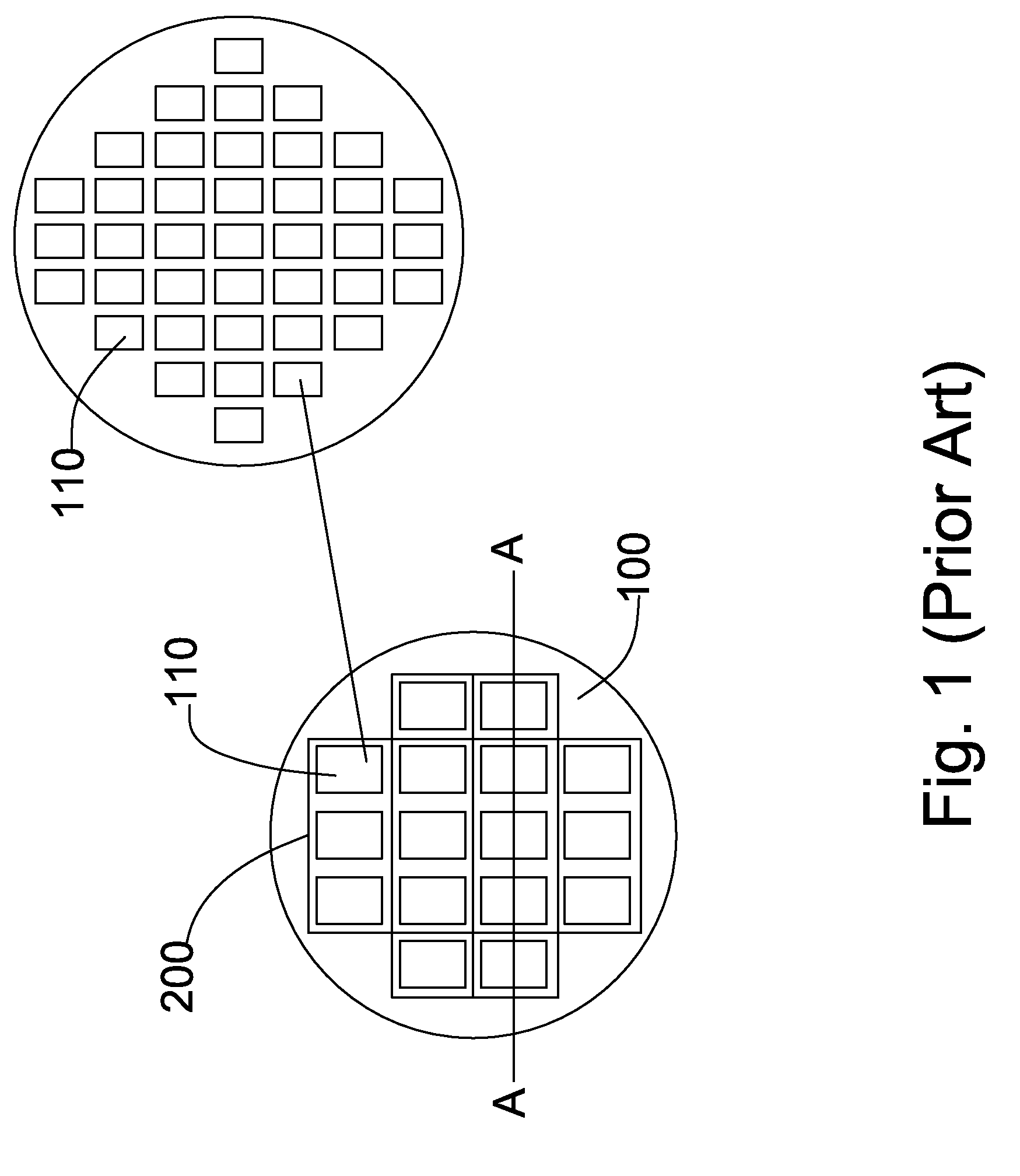

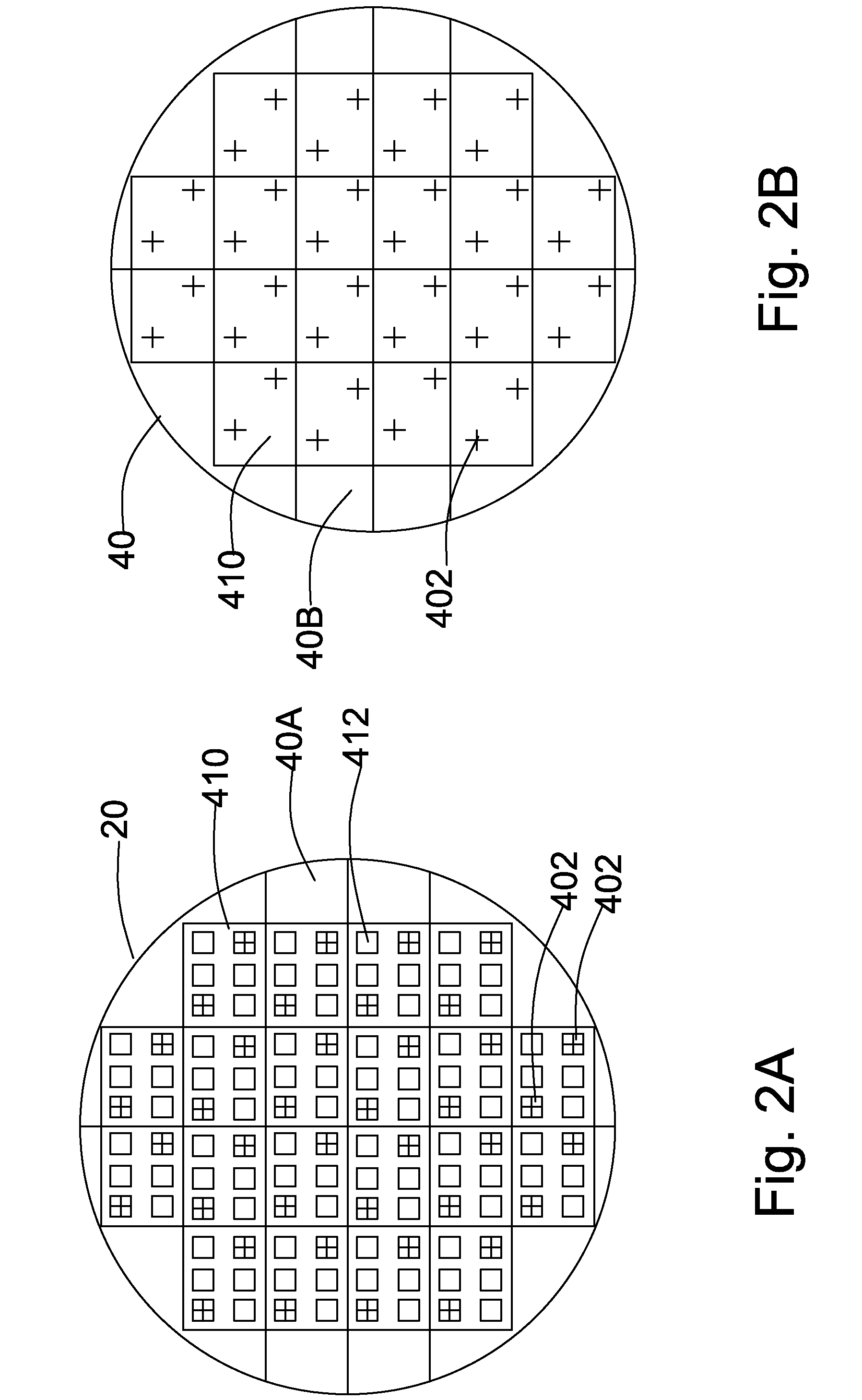

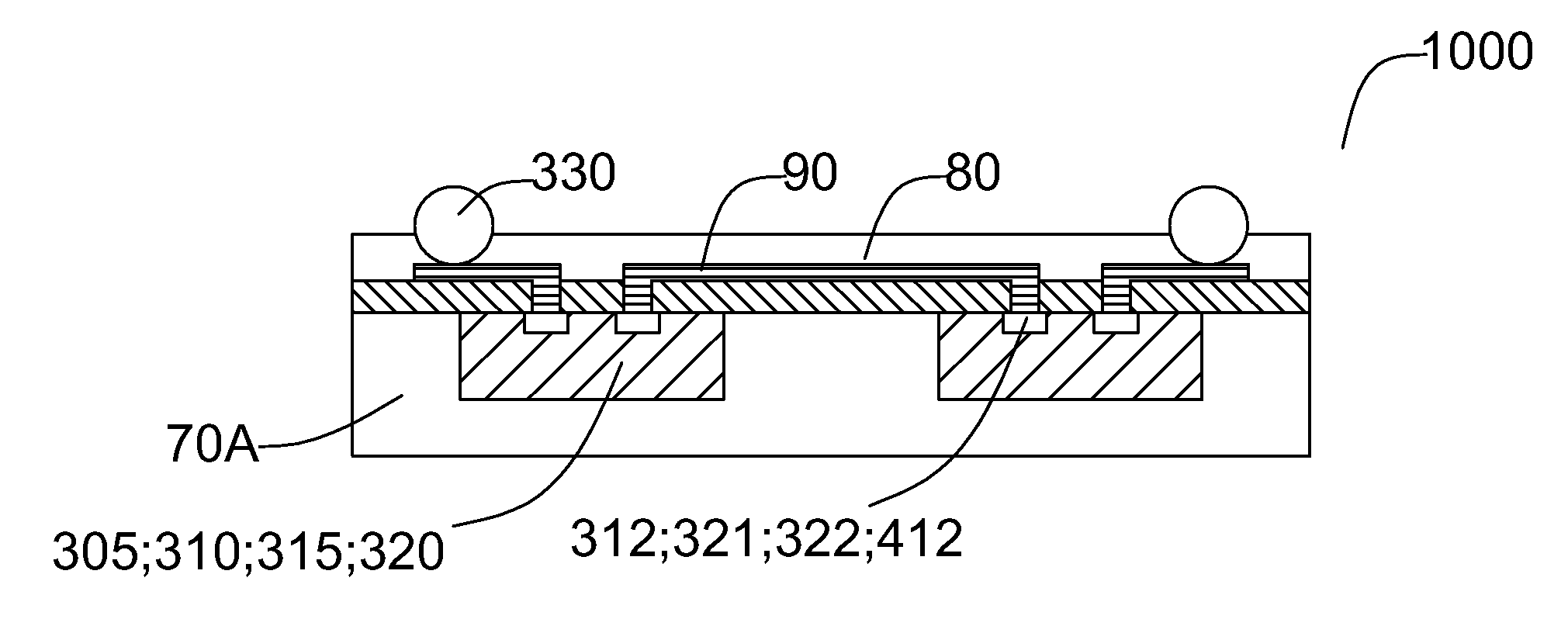

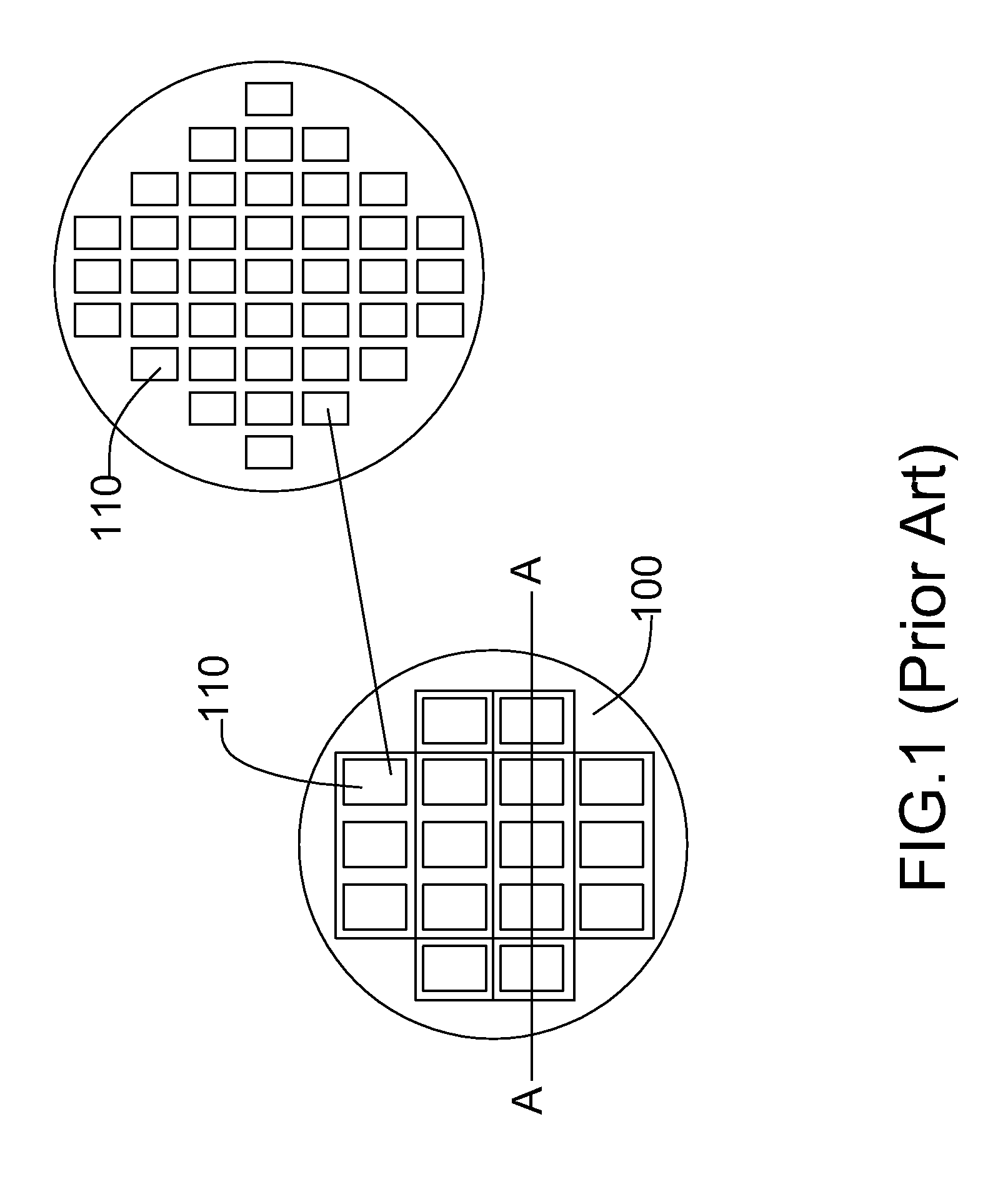

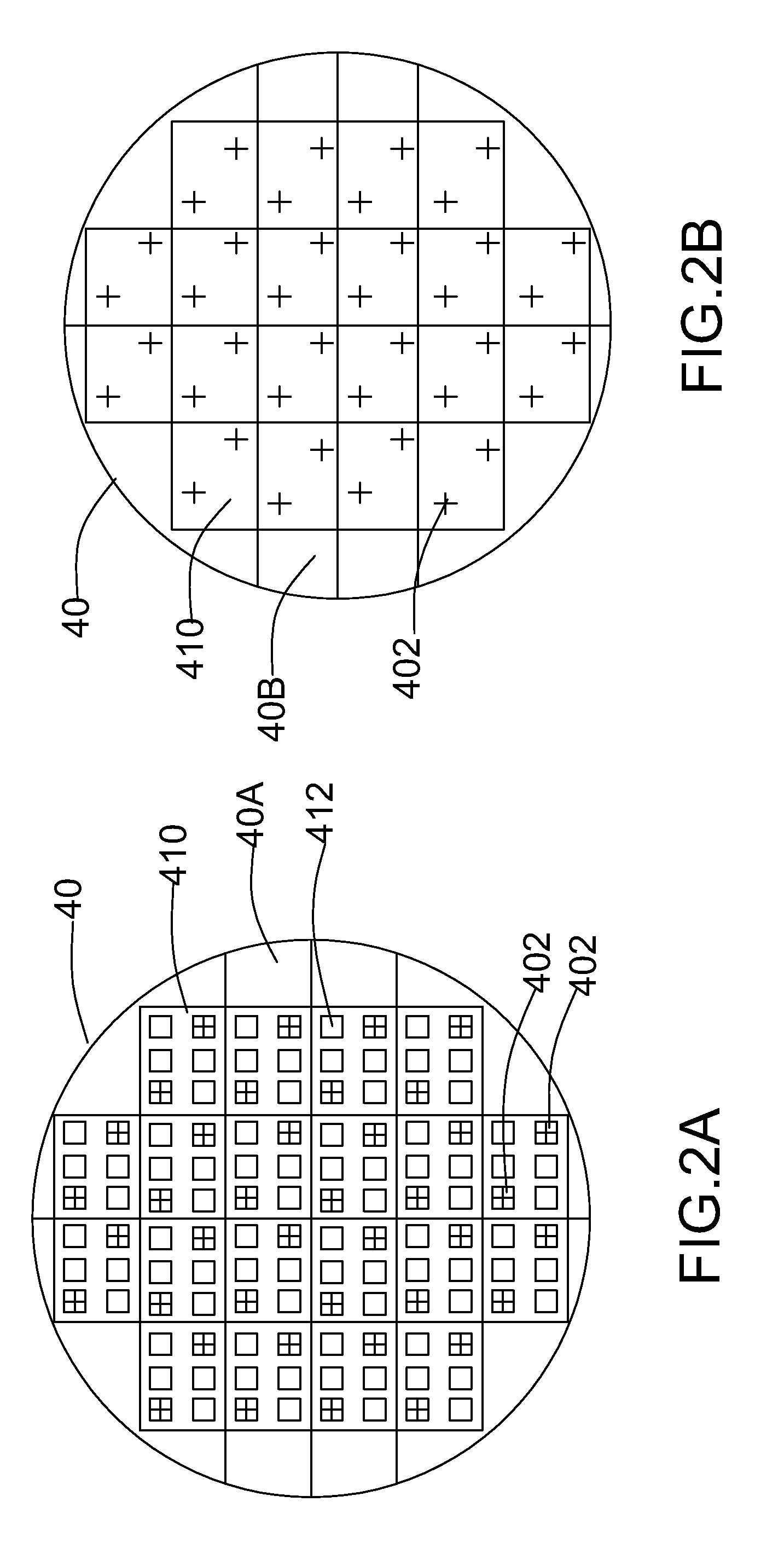

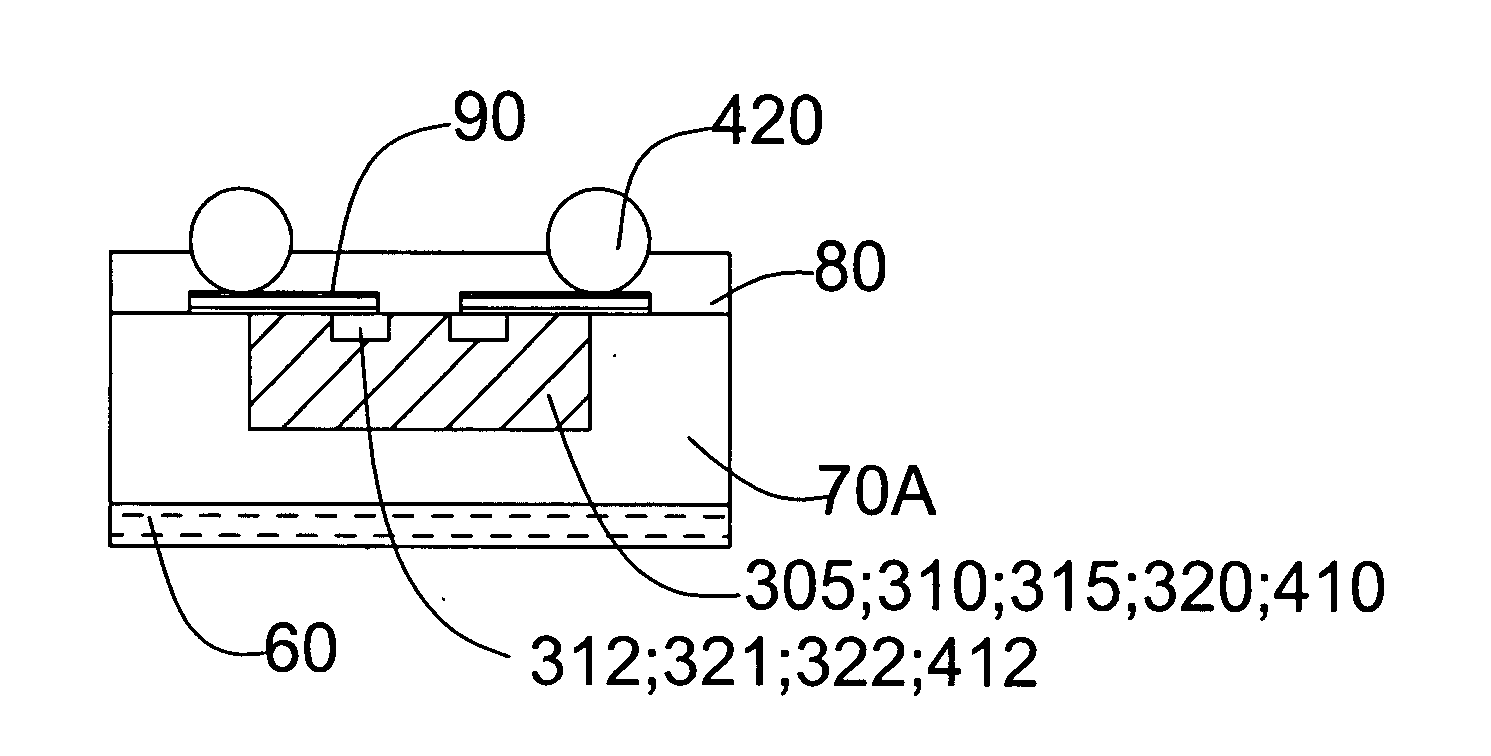

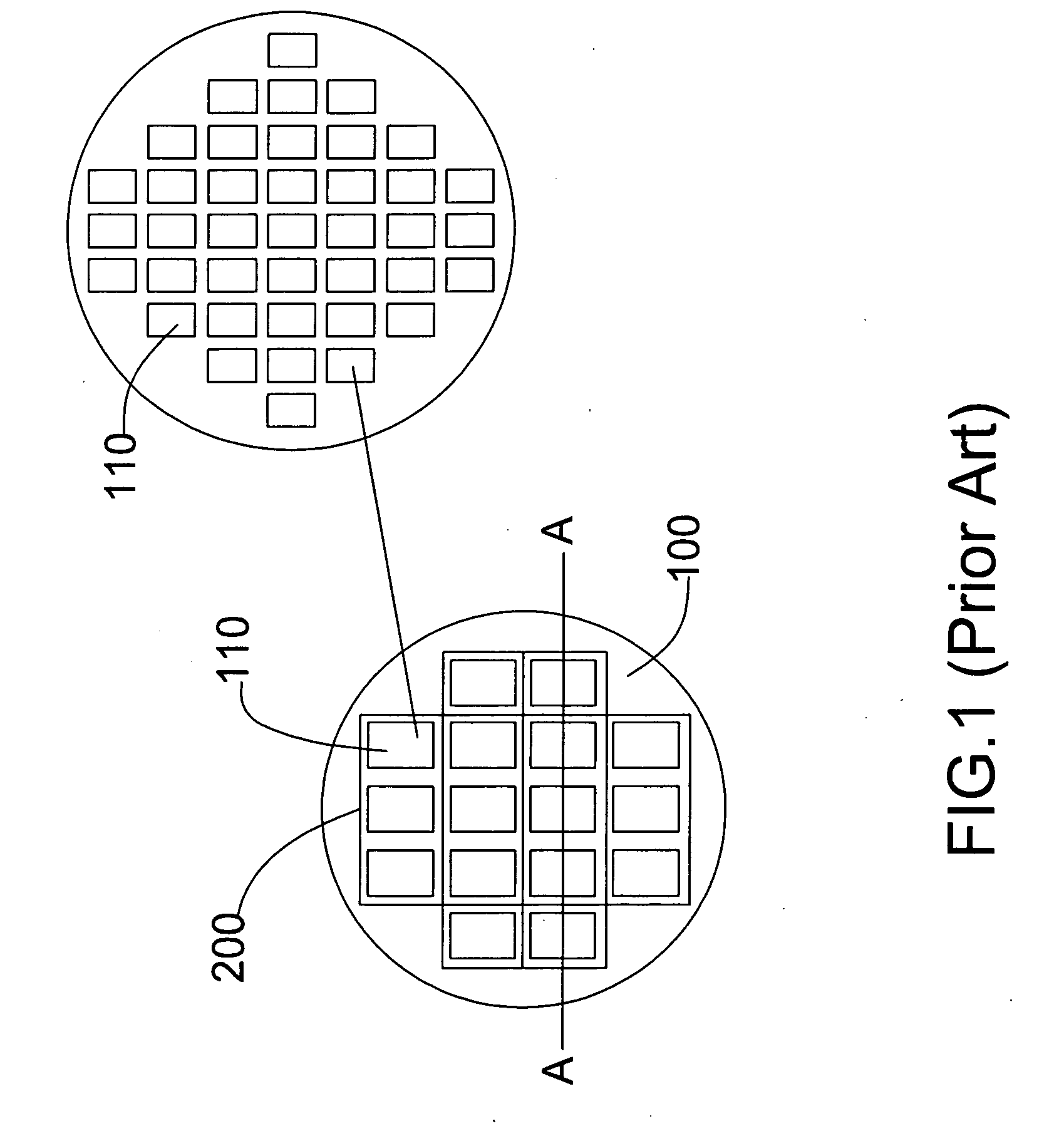

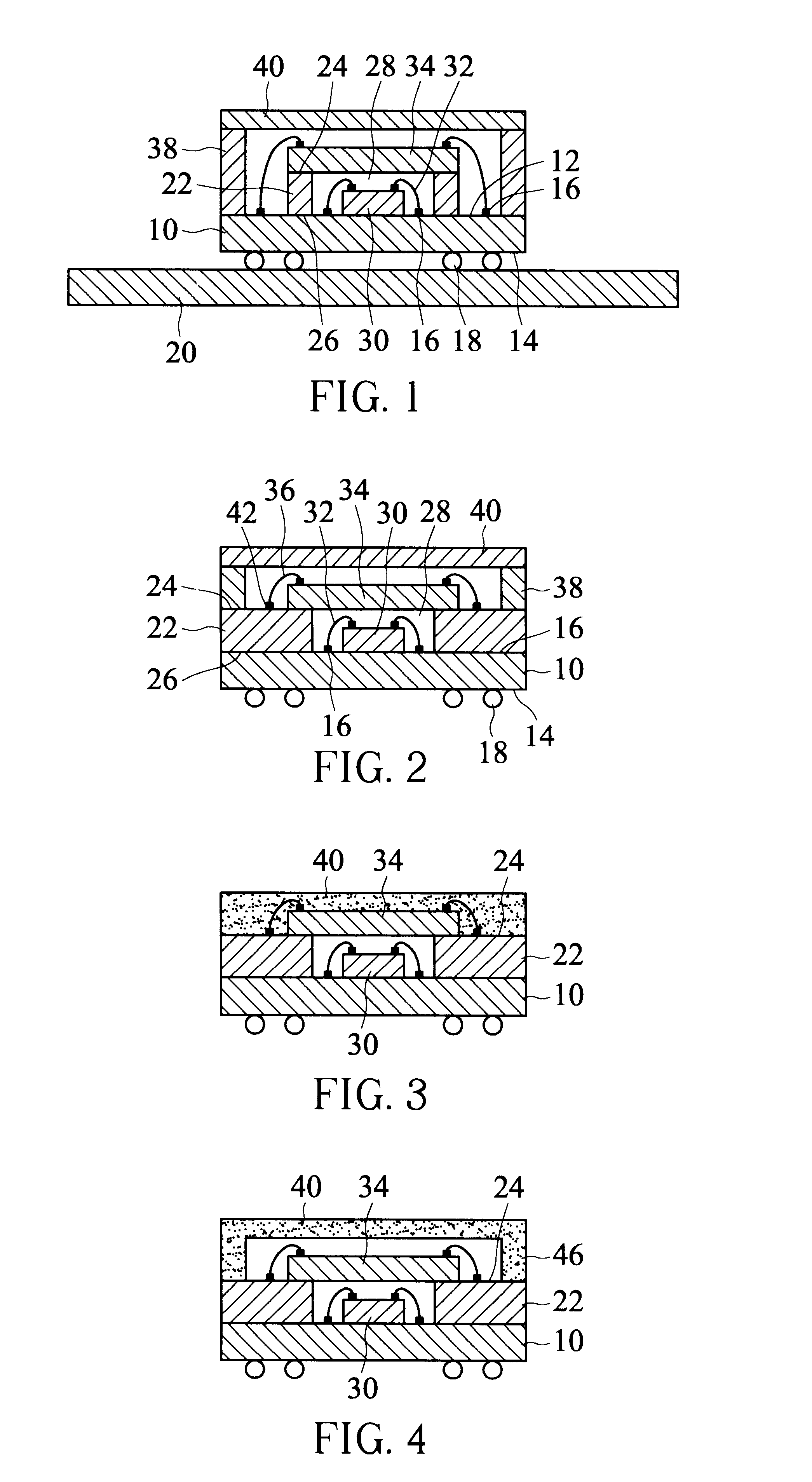

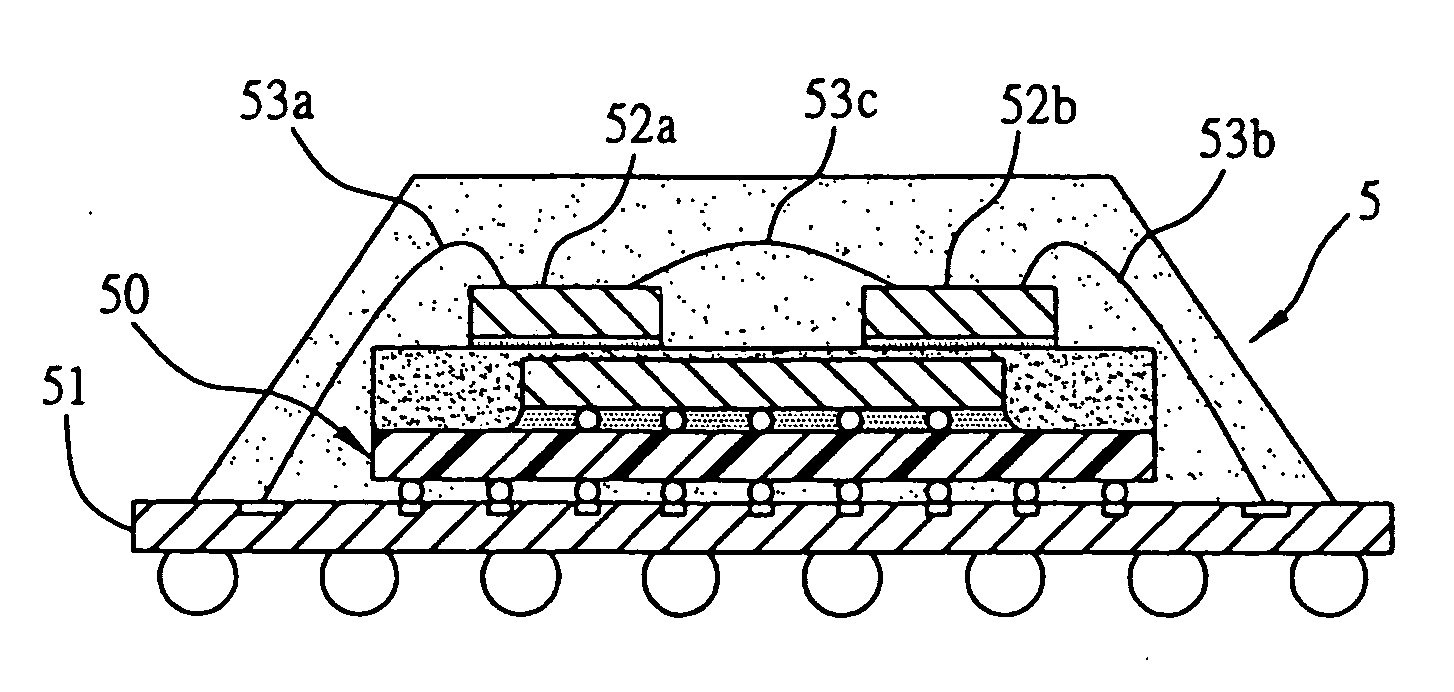

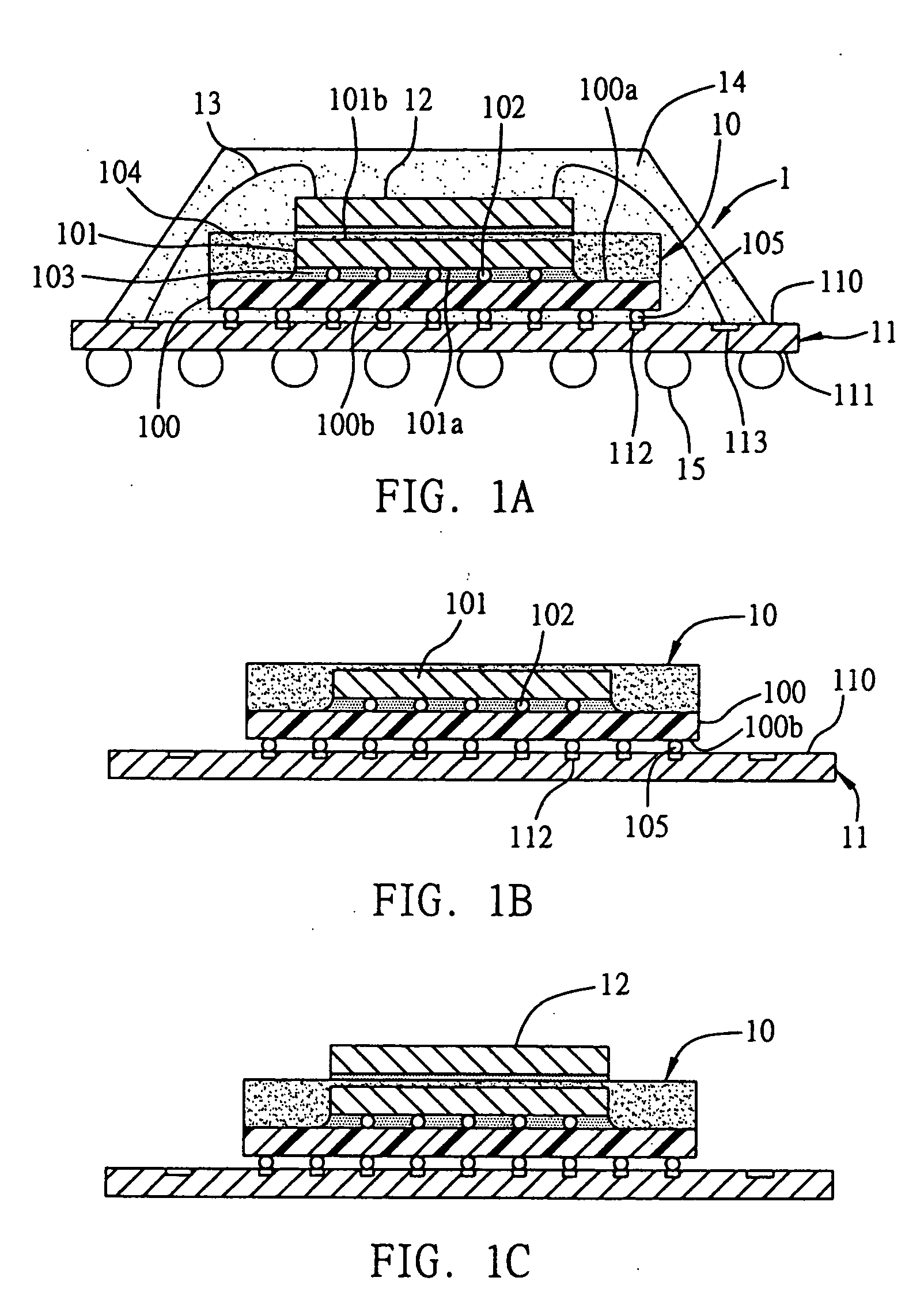

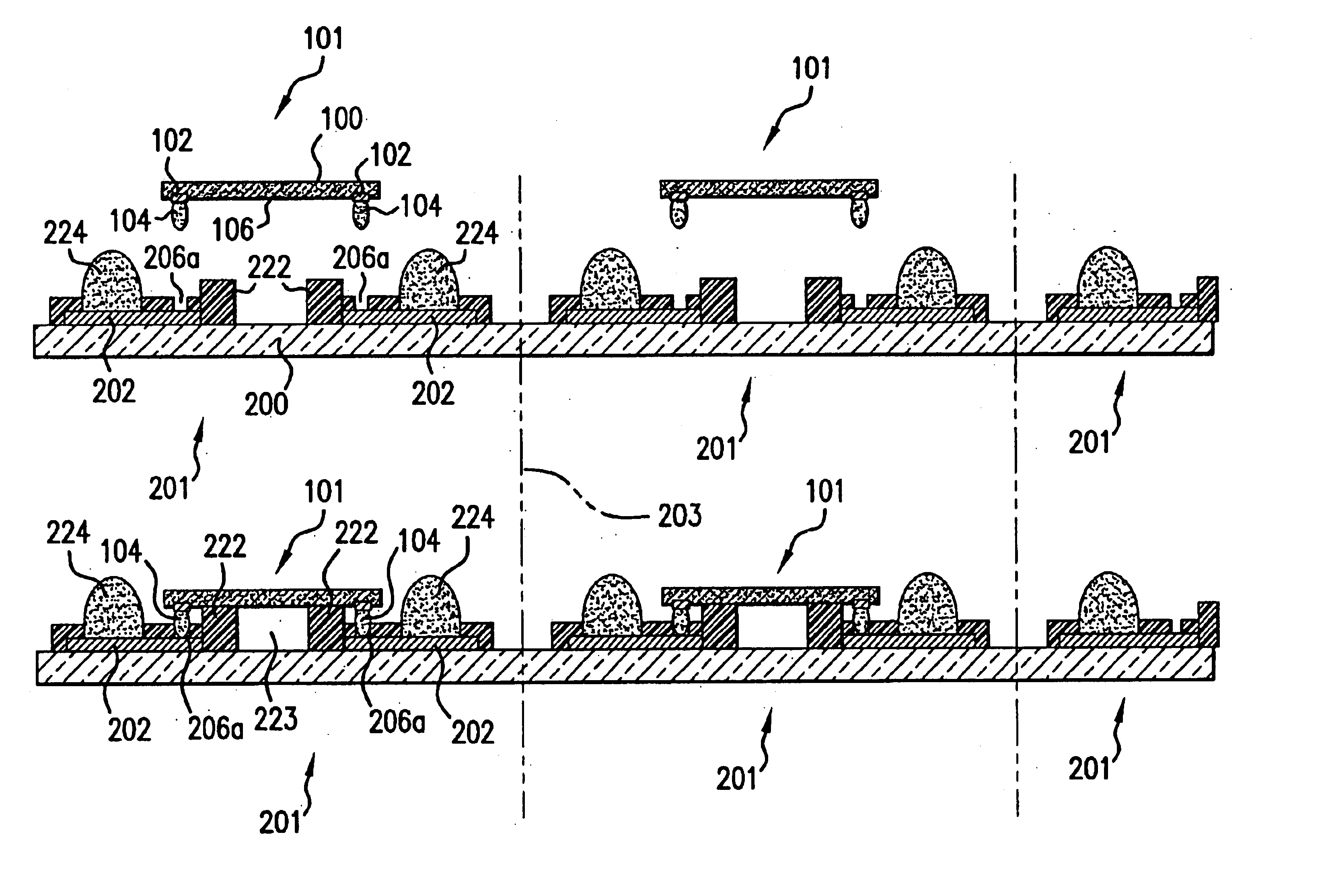

Die rearrangement package structure using layout process to form a compliant configuration

ActiveUS7662667B2Improve reliabilityHigh yieldSemiconductor/solid-state device detailsSolid-state devicesPolymerMetal

A die rearrangement package structure is provided, which includes a die that having an active surface and a bottom surface, and a plurality of pads is disposed on the active surface; a package body is provided to cover a die and the active surface being exposed; a polymer material with at least one slit is provided to cover the active surface and the pads is exposed from said slits; one ends of a plurality of metal traces is electrically connected to each pads; a protective layer is provided to cover the active surface of the dies and each metal traces, and the other ends of the metal traces being exposed; a plurality of connecting elements is electrically connected other ends of the metal traces, the characterized in that: the package body is a B-stage material.

Owner:CHIPMOS TECH INC

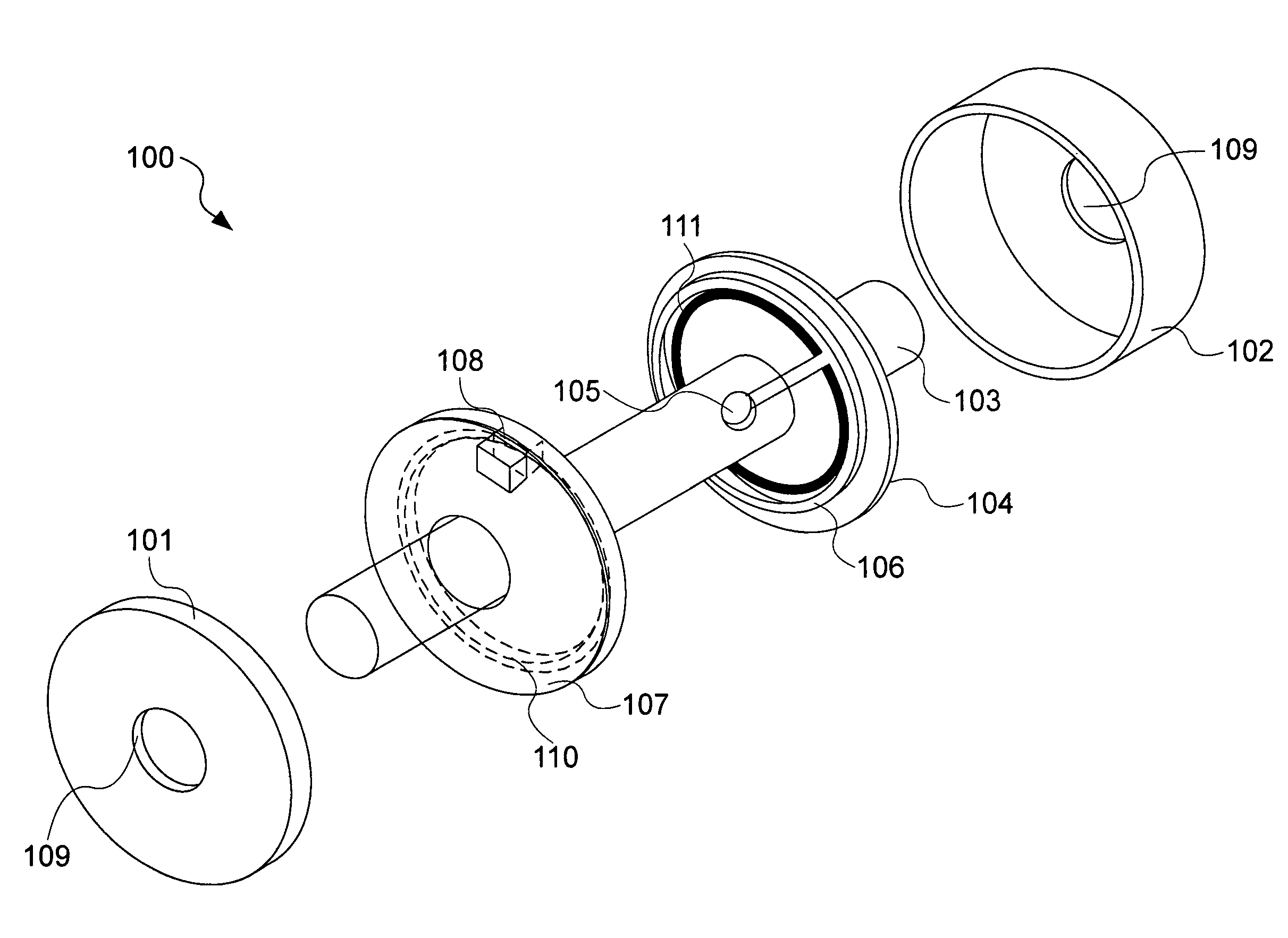

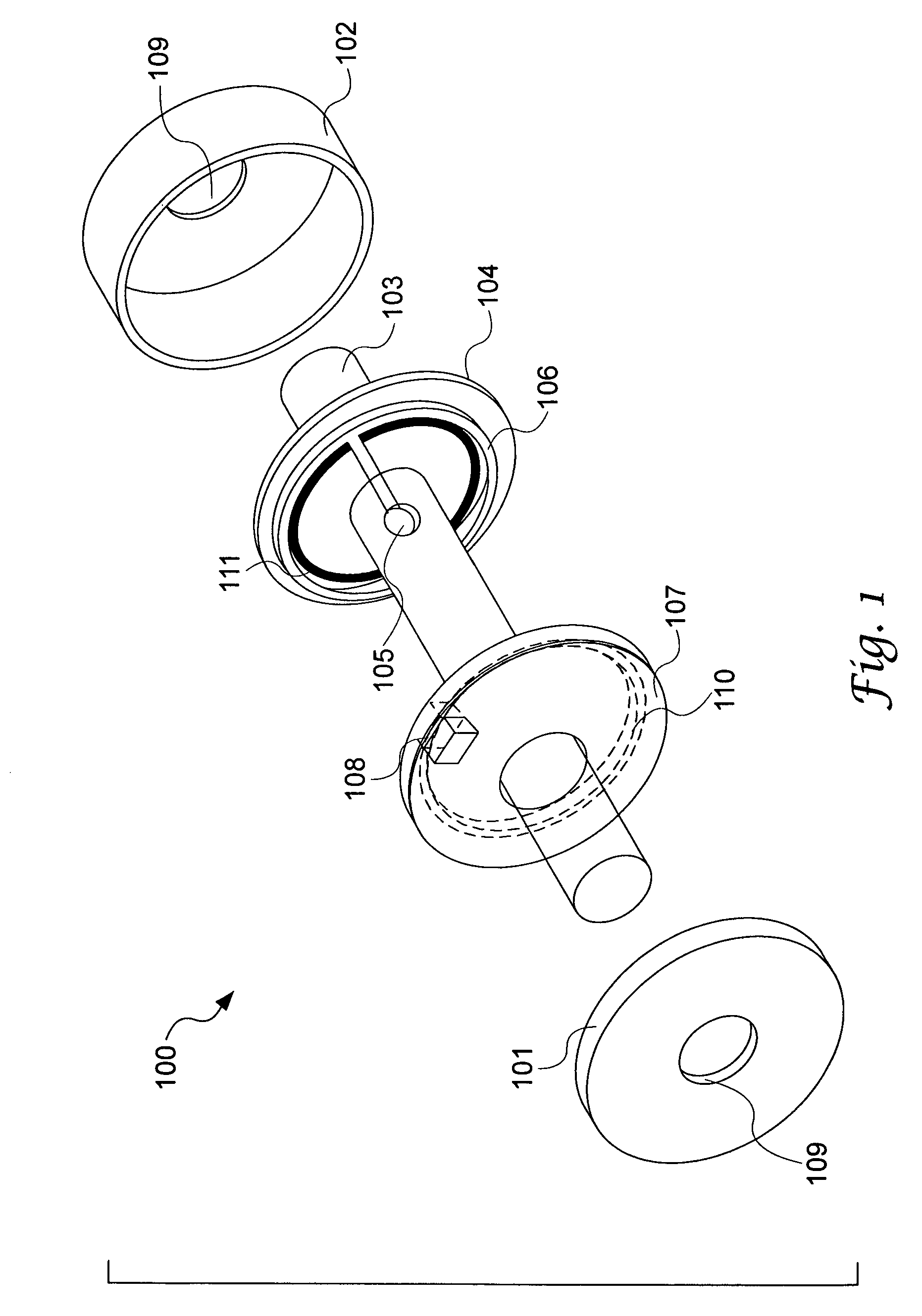

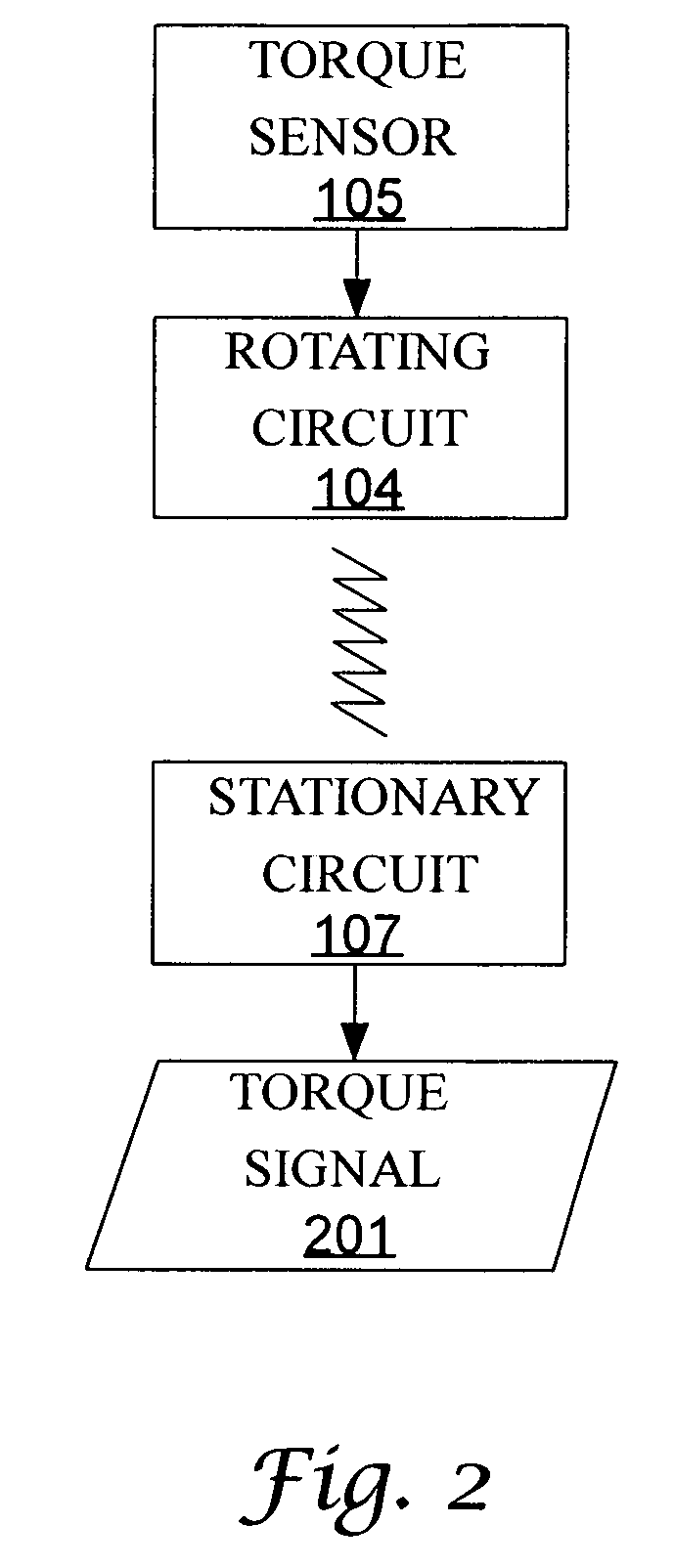

Speed sensor for a power sensor module

ActiveUS7095198B1Low costReduce assemblyDC motor speed/torque controlMeasurement of torque/twisting force while tighteningPower sensorComputer module

A power sensor module suitable for automotive and other high volume applications combines speed sensing and torque sensing operations into a single unit. A magnetic speed sensor is utilized for speed sensing. A power measurement can be derived from torque and speed. Combining torque sensing and speed sensing within a single module instead of using separate modules for each allows for reducing redundancies and lowering cost.

Owner:HONEYWELL INT INC

Dice rearrangement package structure using layout process to form a compliant configuration

ActiveUS7927922B2Improve reliabilityHigh yieldSemiconductor/solid-state device detailsSolid-state devicesProtection layerMetal

Owner:CHIPMOS TECH INC

Water-based cleaner

ActiveCN101538512ACause wasteAvoid cleaning costsInorganic/elemental detergent compounding agentsNon-ionic surface-active compoundsWater basedSodium metasilicate

A water-based cleaner is prepared by surfactant primary washing part, alkaline auxiliary washing part, solvent part, preservative and water; wherein the surfactant primary washing part is compounded by anion and nonionic surfactant; the alkaline auxiliary agent part selects trolamine, sodium metasilicate pentahydrate which has dispersive action on dirt and EDTA disodium which has chelation on metallic ions, and excludes phosphate accessory aid which pollutes water quality. The solvent part selectes alcohol, glycol ether or natural orange oil extract D-limonene which have good safety performance, strong solvency and little environmental pollution. The preservative selects food grade preservative propylparaben which is safe and nontoxic. The invention adopts concentrate formula, the preparation method is simple, users can dilute the product according to object to be washed and the degree of dirt, and operate with reasonable using concentration, thus avoiding the waste of washing cost due to excessive concentration and the waste of energy. The inventive water-based cleaner reduces package cost and transportation cost, and has no adverse effect on the environment.

Owner:SHANGHAI JIUSHENG IND

Dice Rearrangement Package Structure Using Layout Process to Form a Compliant Configuration

ActiveUS20090160043A1Improve reliabilityHigh yieldSemiconductor/solid-state device detailsSolid-state devicesEngineeringProtection layer

A dice rearrangement package structure is provided, which a dice having an active surface and a bottom surface, and a plurality of pads is disposed on the active surface; a package body is provided to cover the dices and the plurality of pads being exposed; one ends of plurality of metal traces is electrically connected to the each pads; a protection layer is provided to cover the active surface and the other ends of the exposed metal traces is electrically connected to the plurality of conductive elements, the characteristic in that the package body is a B-stage material.

Owner:CHIPMOS TECH INC

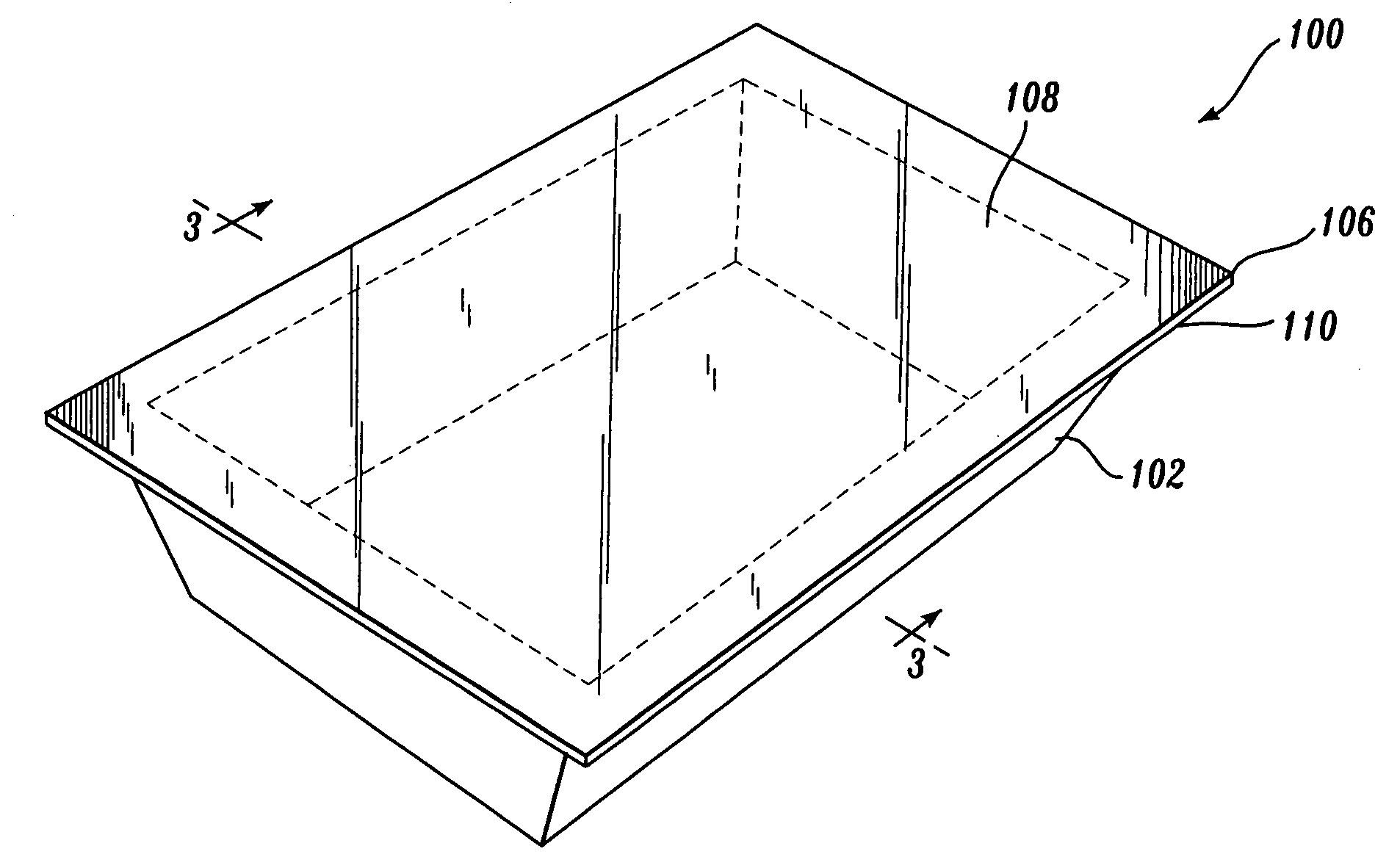

Products, methods and apparatus for fresh meat processing and packaging

InactiveUS20060147588A1Lower display costsReduce packaging costsPackaging meatMeat/fish preservation using chemicalsAtmospheric oxygenRed meat

Improved processing and packaging for perishable goods such as red meats providing a processing system wherein ambient air is excluded and suitable gases such as carbon dioxide are provided at a suitable pressure and in such a manner as to increase the quantity of the gases dissolved in the perishable goods. Then providing a base and placing the perishable goods over the base. A flexible web of plastic wrapping material (second web) is then applied over the base and the goods and air or gas evacuated therefrom and replaced with a suitable gas. The base includes a cup-shaped tray with a recess (first web), of plastics or other suitable material, with side walls extending upwardly to connect to a narrow horizontally disposed flange. The first web, goods and second web are located inside a depression in a third web of gas barrier material and there together placed into an enclosed evacuation chamber. A suitable gas is provided in the chamber in such a manner as to displace substantially all other gas and particularly atmospheric oxygen that may be present with the enclosed goods and web materials. The third web is then sealed so as to enclose the goods with first and second webs. that the pressure of the gas may be increased to a level above atmospheric pressure. Most preferably the quantity of gas dissolved into the goods will be increased. Most preferably the gas introduced into the chamber and the space will enhance preservation of the packaging goods when contacting the goods. The first web, second web and third web are sealed together thereby producing a hermetically sealed package with the goods and a gas filled space contained therein to provide a sealed package. The sealed package can be stored for any convenient period of time after which the third web is can be removed so as to allow ambient air to contact the goods. The invention further includes the method and apparatus for producing the processed goods and packaging.

Owner:STONE MICHAEL

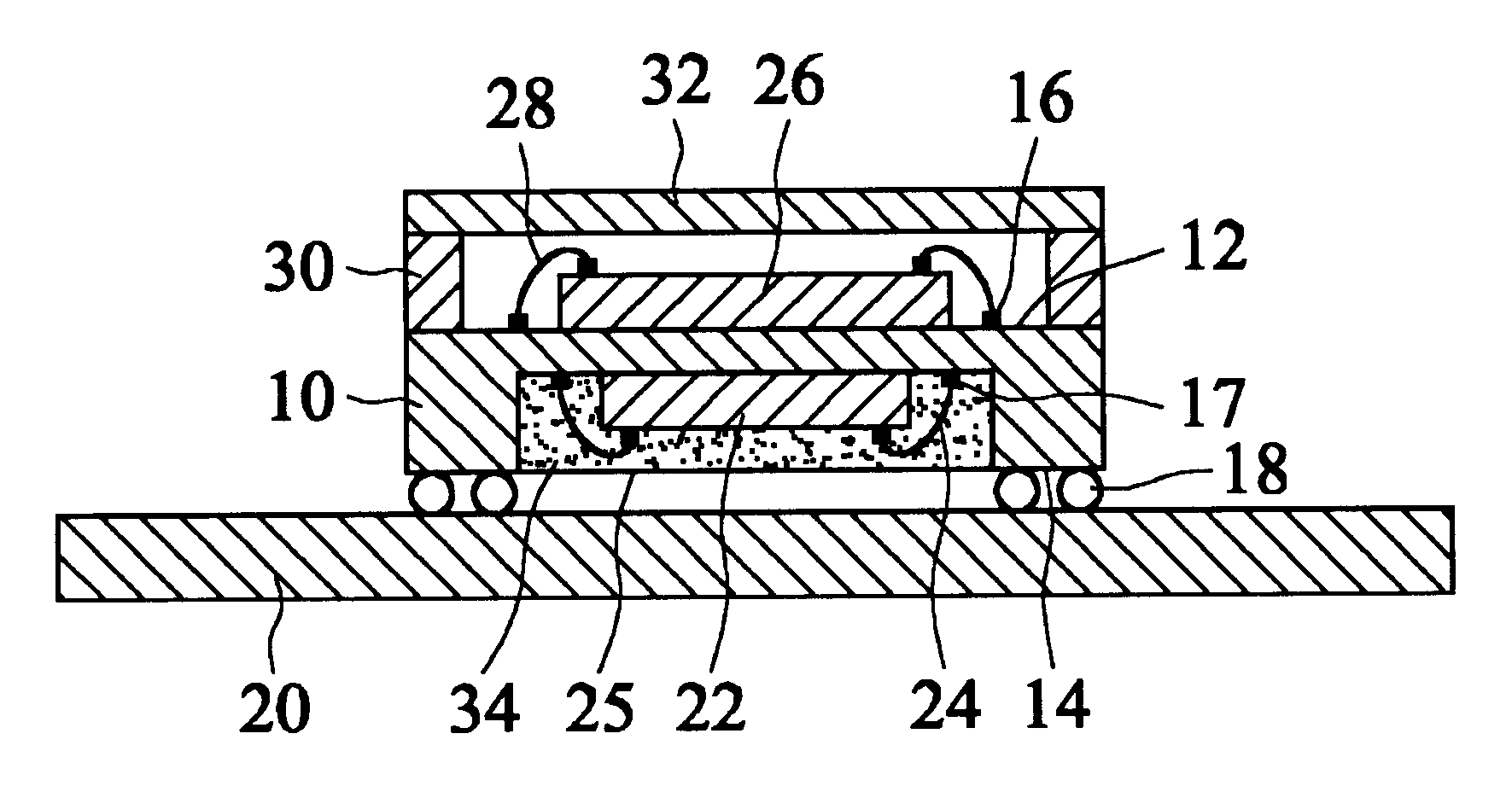

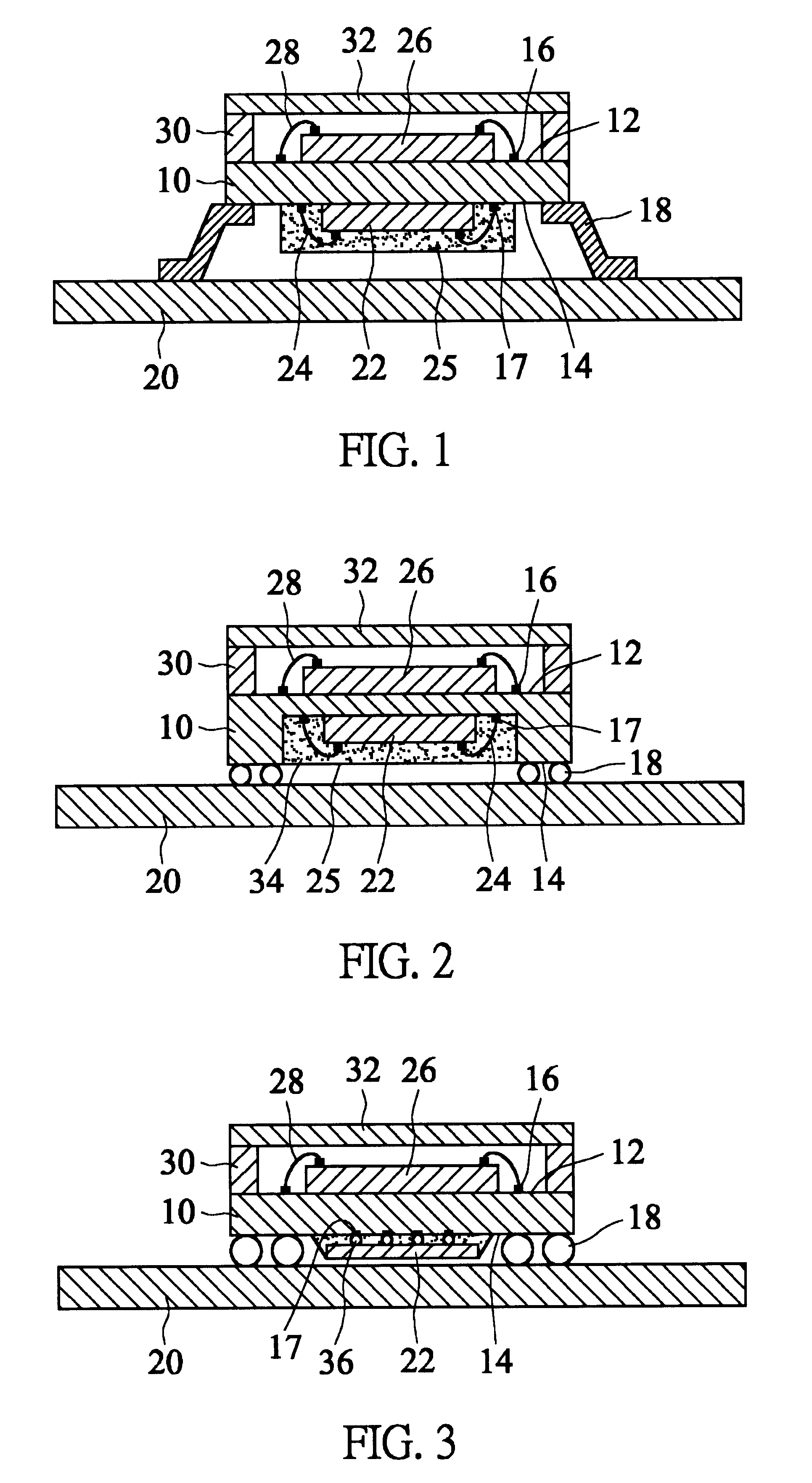

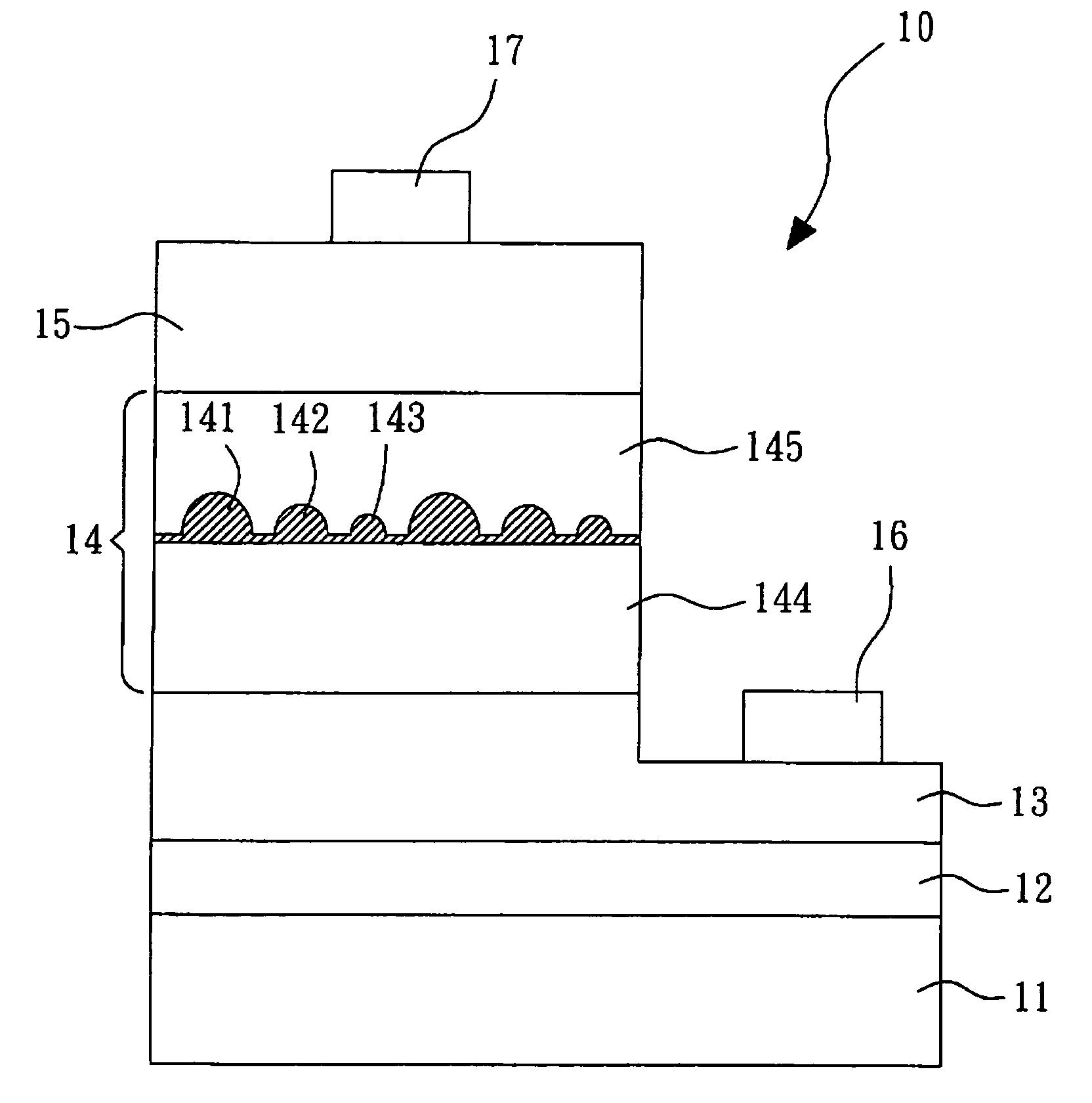

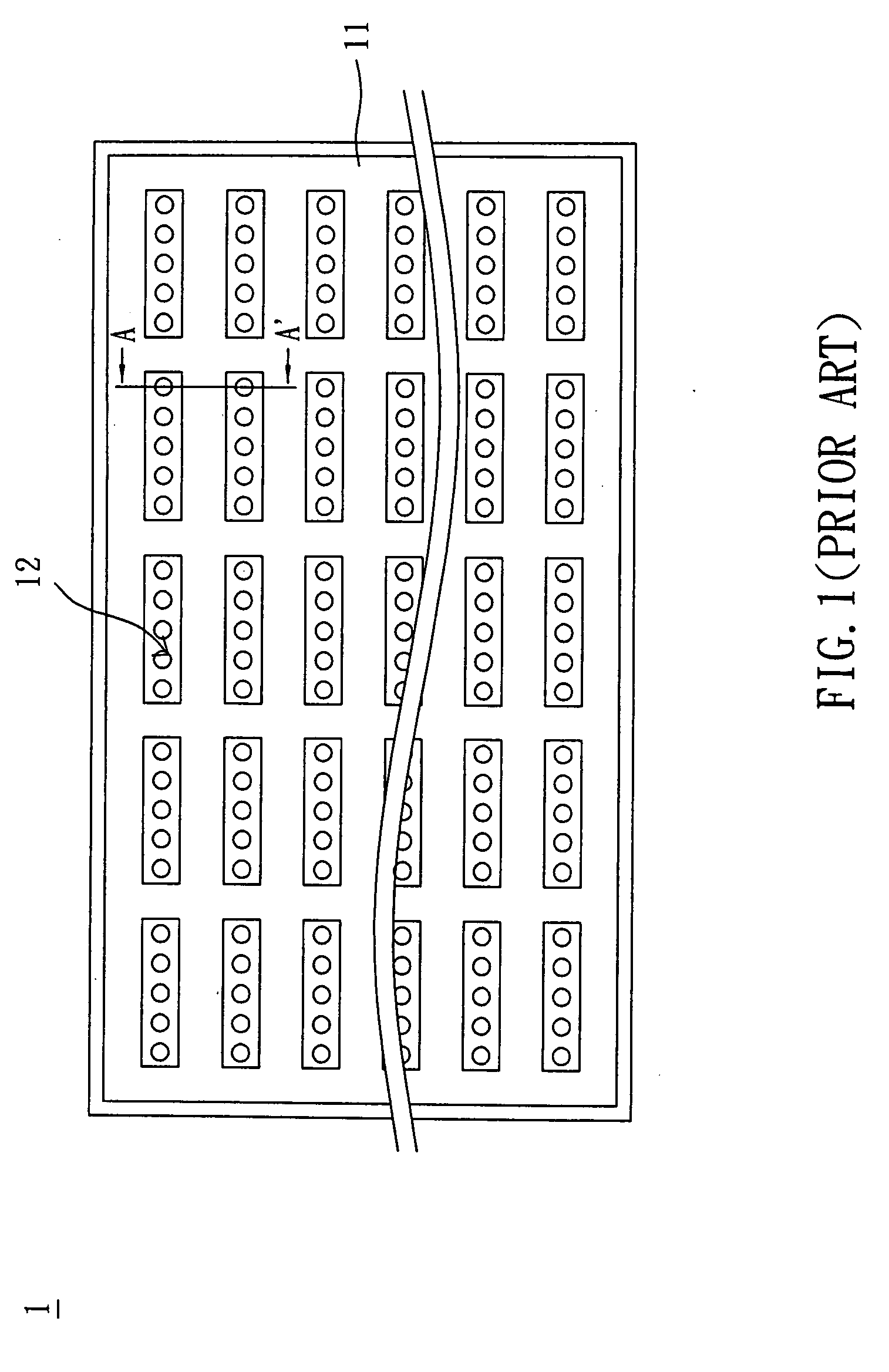

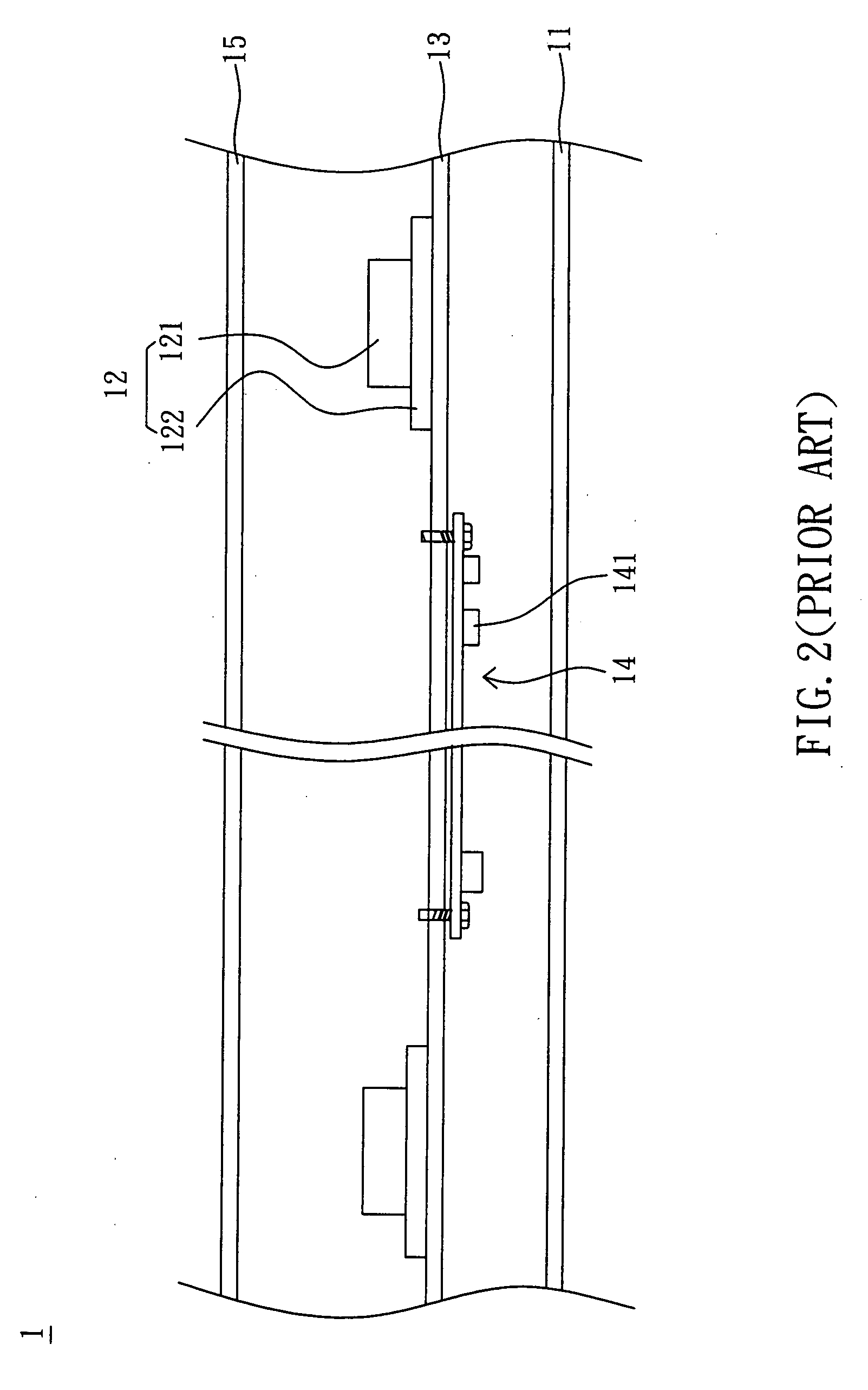

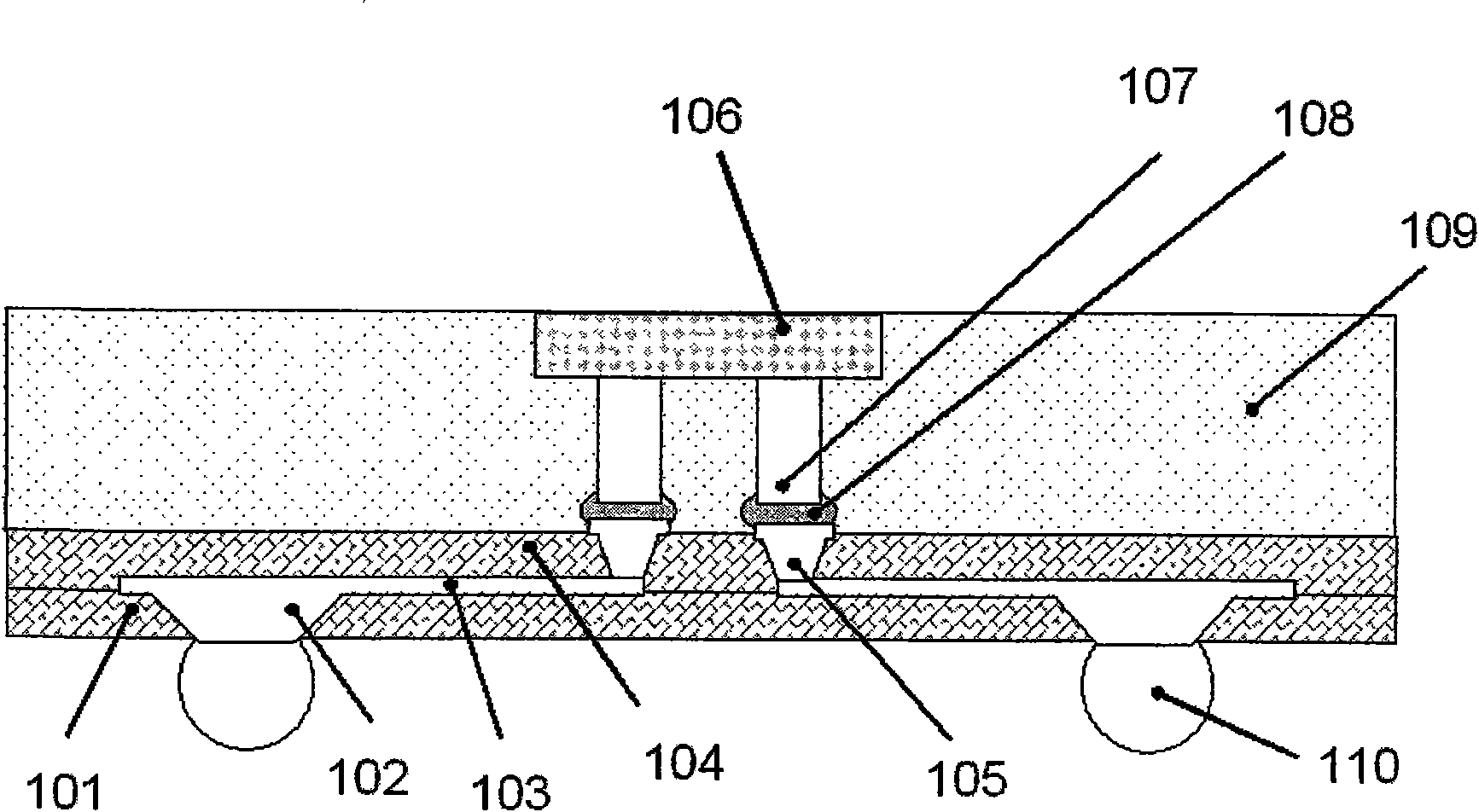

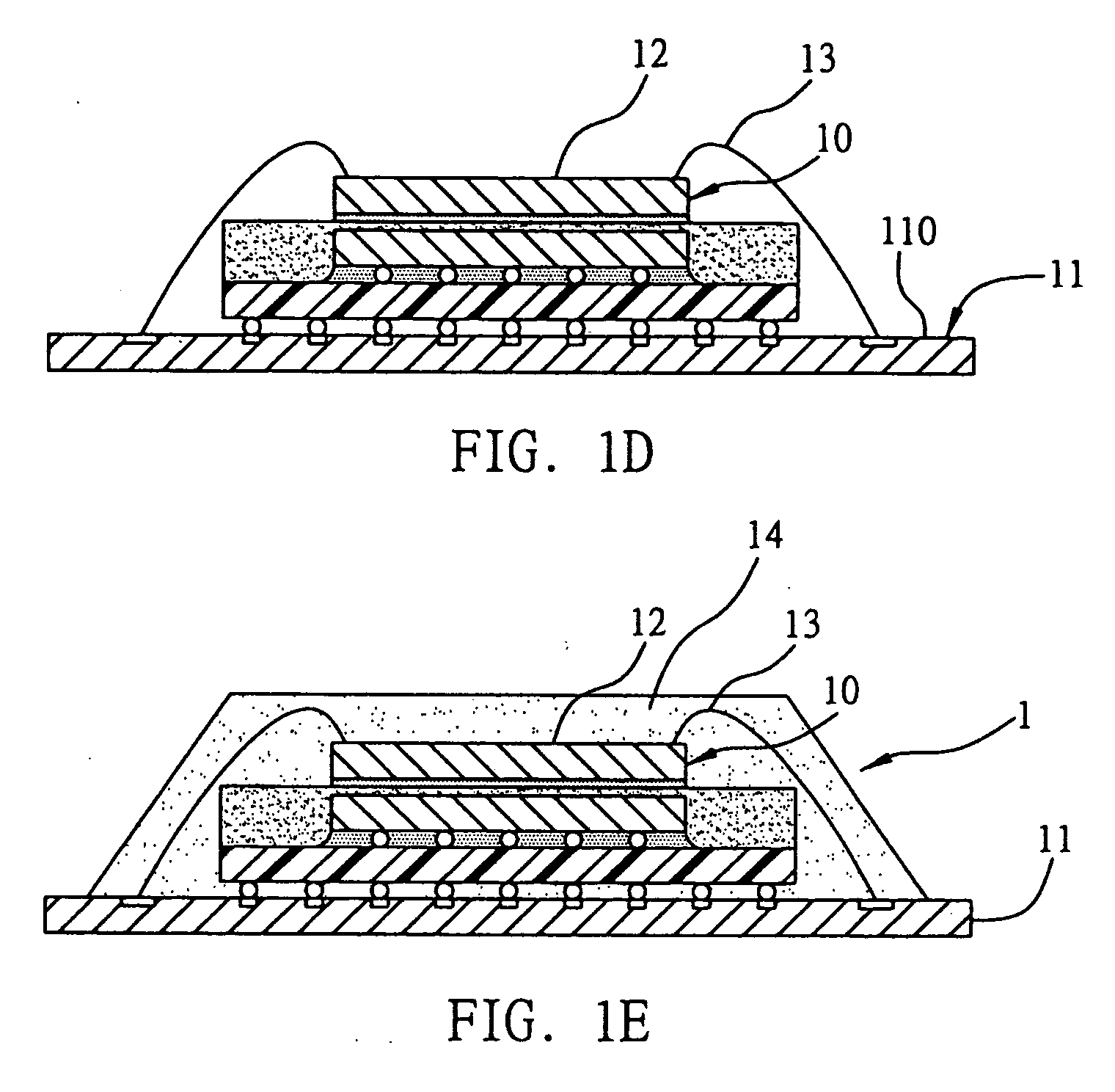

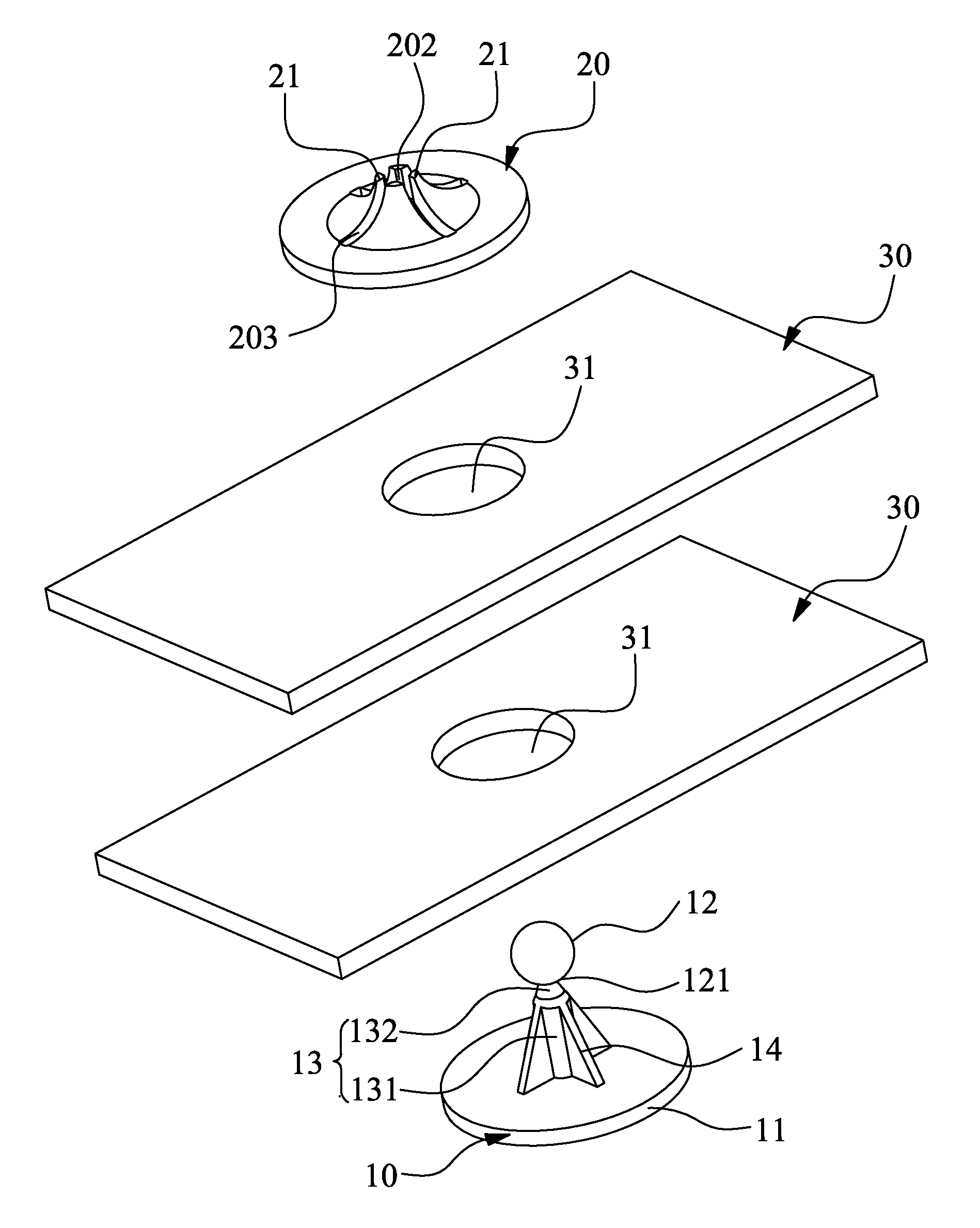

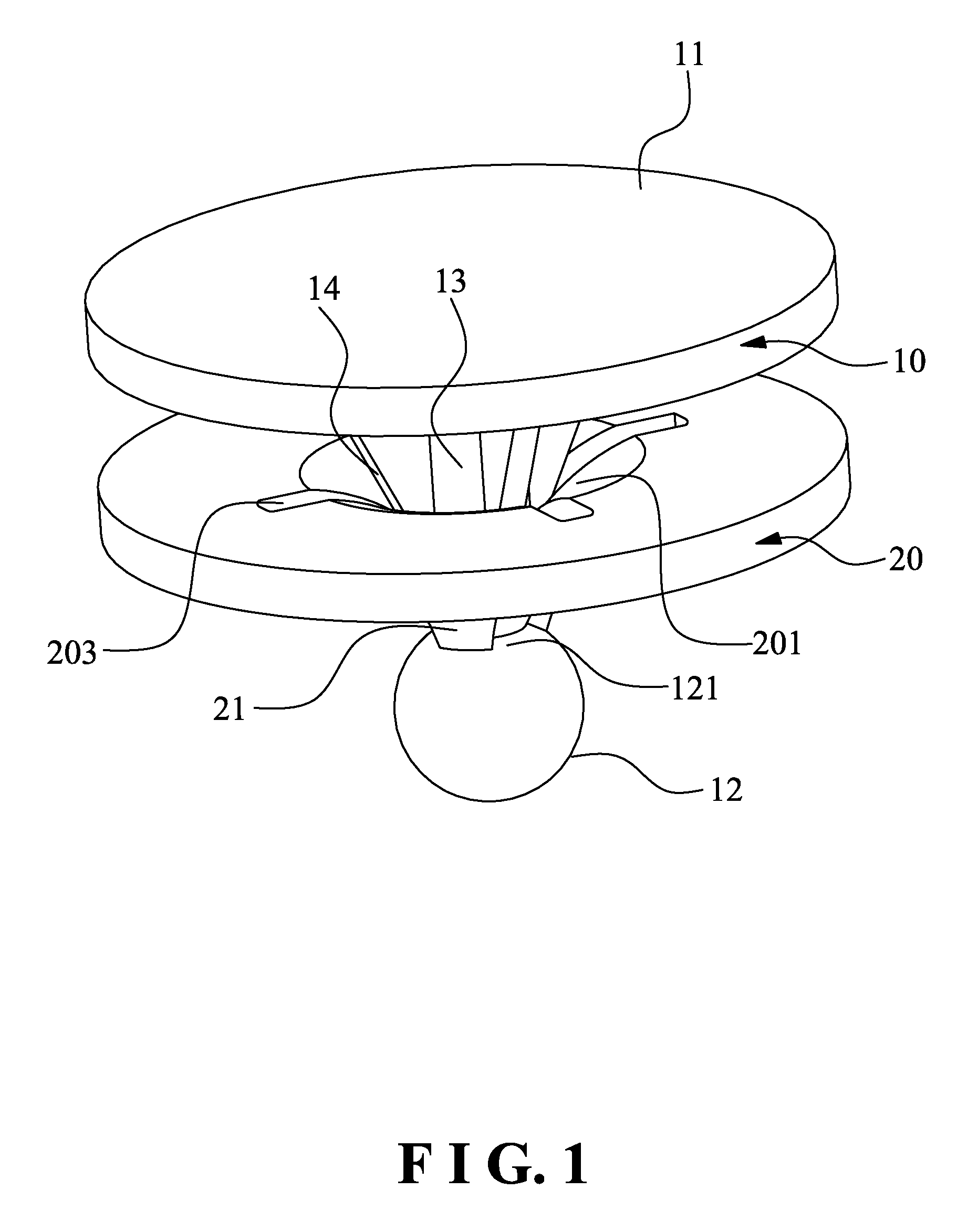

Stacked package structure of image sensor

InactiveUS6559539B2Reduce in quantityReduce packaging costsSemiconductor/solid-state device detailsSolid-state devicesEngineeringPrinted circuit board

A stacked package structure of an image sensor used for electrically connecting to a printed circuit board includes a substrate, an image sensing chip, an integrated circuit, and a transparent layer. The substrate has a first surface and a second surface. The first surface is formed with signal input terminals. The second surface is formed with signal input terminals and signal output terminals for electrically connecting to the printed circuit board. The image sensing chip is mounted on the first surface of the substrate and is electrically to the signal input terminals of the substrate. The integrated circuit is arranged on the second surface of the substrate and is electrically connected to the signal input terminals of the substrate. The transparent layer covers over the image sensing chip, which can receive the image signals via the transparent layer and convert the image signals into electrical signals that are to be transmitted to the substrate. Thus, the image sensing chip of the image sensing product and integrated circuit can be integrally packaged.

Owner:KINGPAK TECH INC

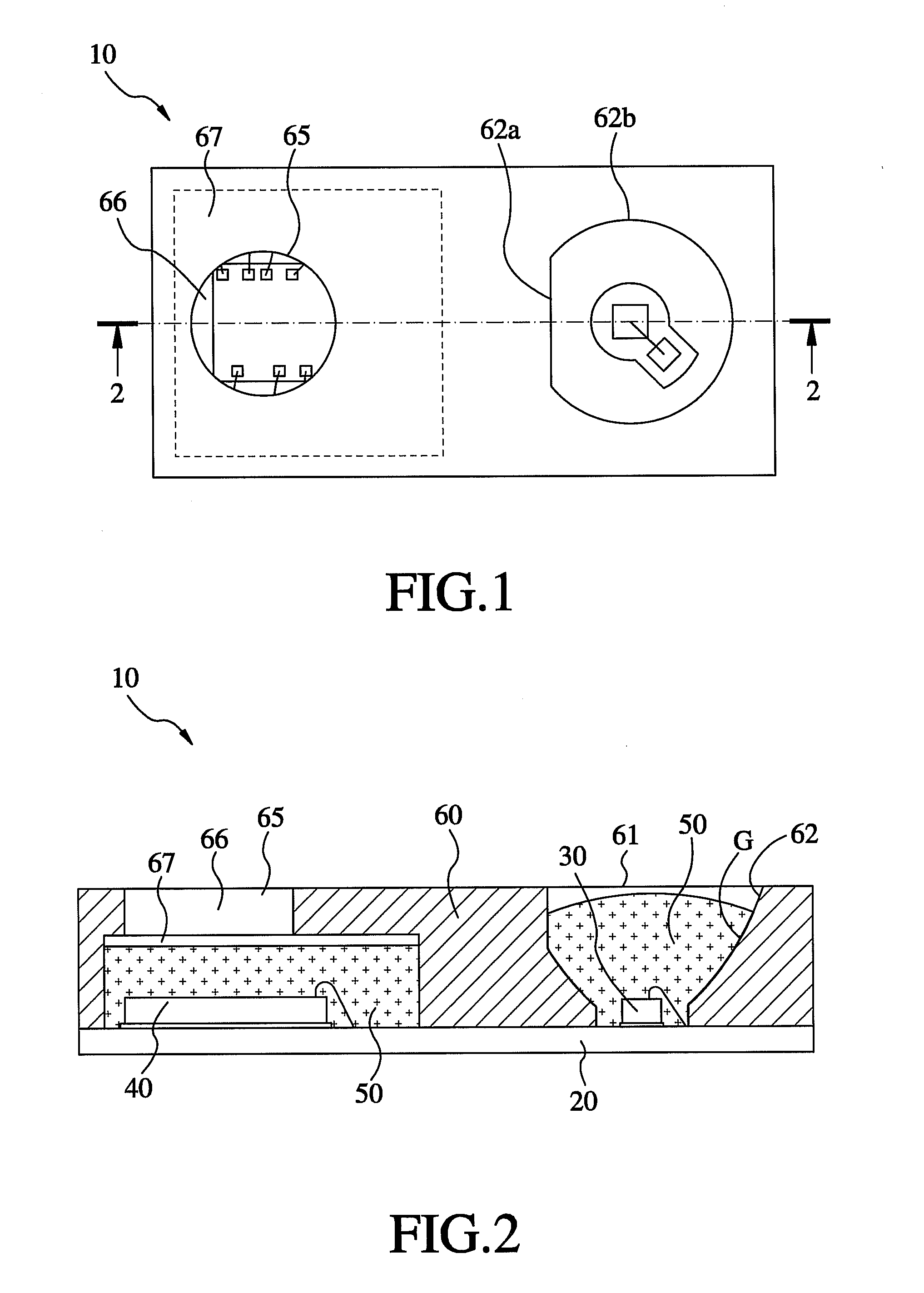

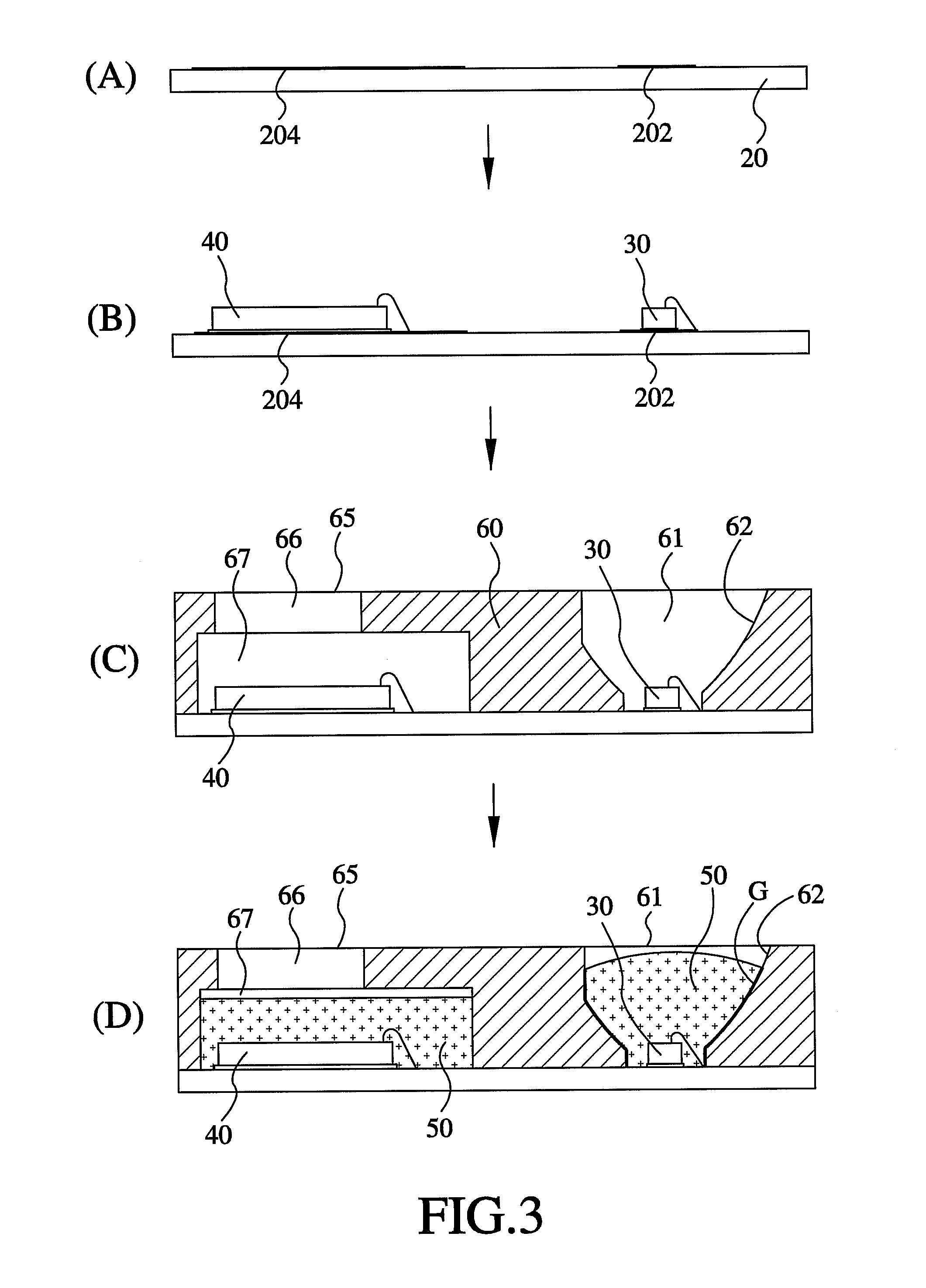

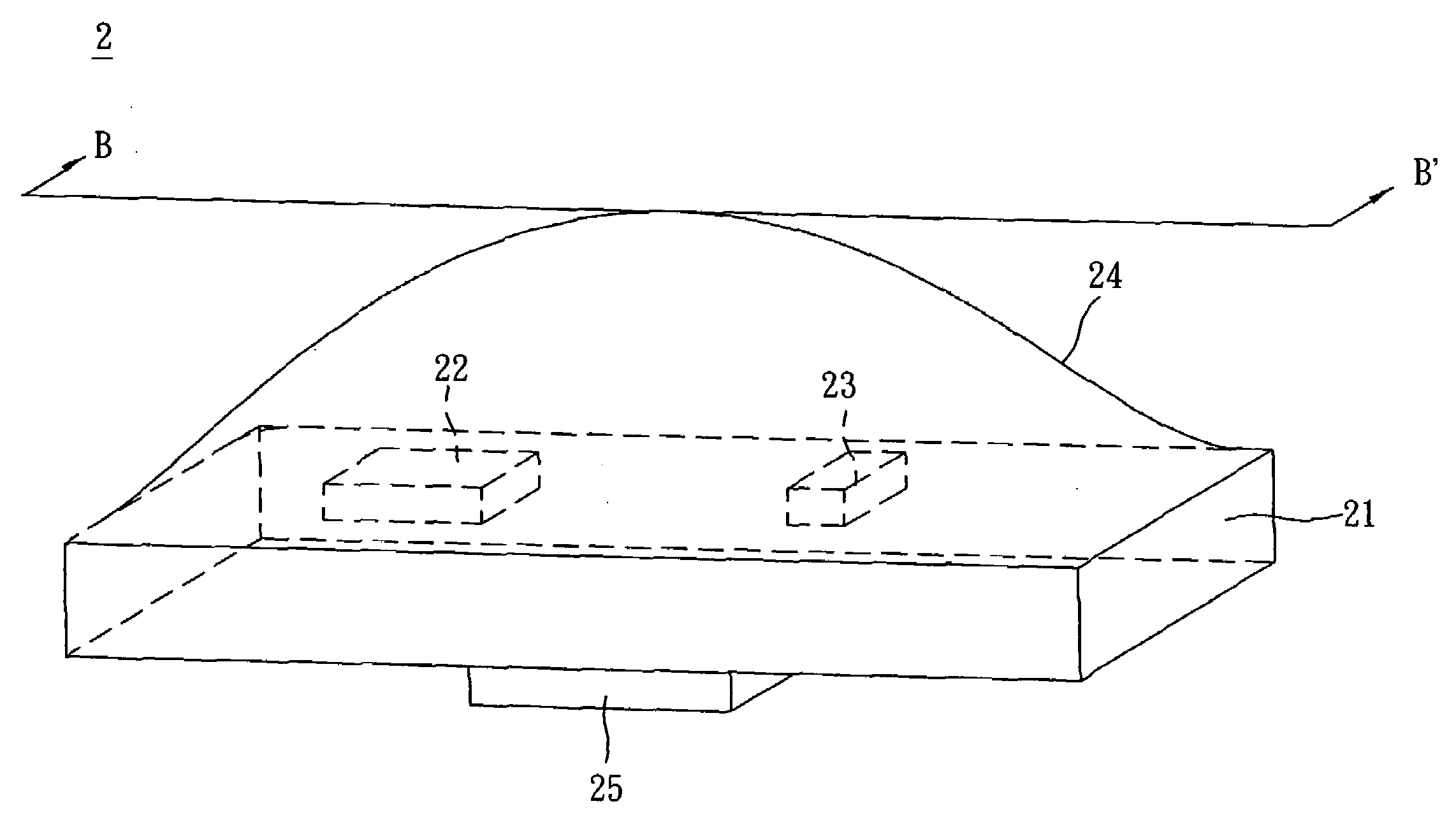

Optical module package unit

ActiveUS8362496B1Reduce packaging costsImprove product competitivenessSemiconductor/solid-state device detailsSolid-state devicesOptical ModuleLight sensing

An optical module package unit includes a light-emitting chip and a light sensor chip respectively installed in a light-emitting zone and a light-sensing zone on a substrate, a lid of plastic shell integrally formed on the substrate and defining therein a first cavity and a second cavity around the light-emitting chip and the light sensor chip respectively, and two packaging adhesive structures respectively molded in the first cavity and the second cavity to encapsulate the light-emitting chip and the light sensor chip respectively. As the light-emitting chip and the light sensor chip are integrally packaged on the substrate, the packaging cost of the optical module is significantly lowered.

Owner:LINGSEN PRECISION INDS

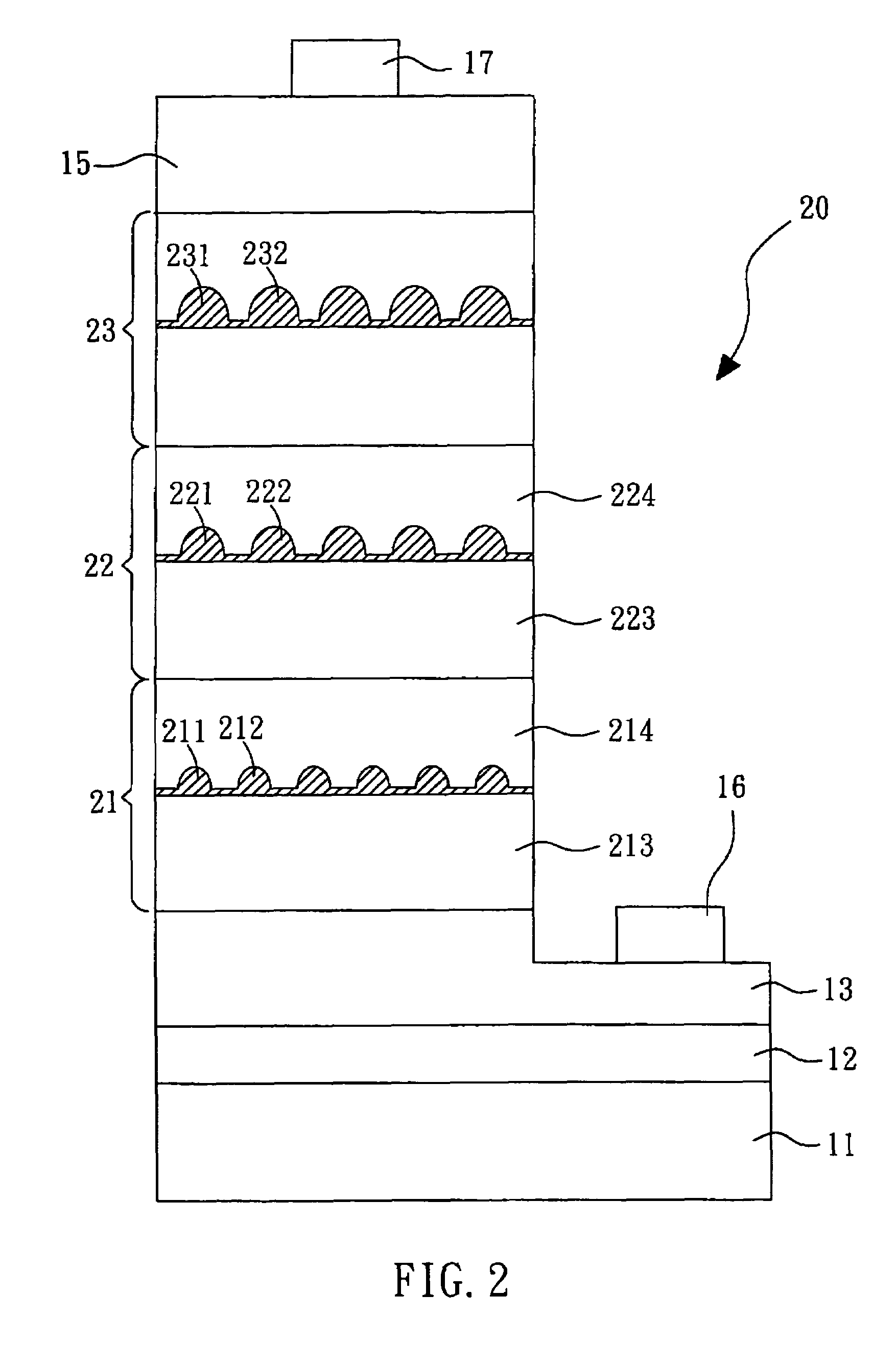

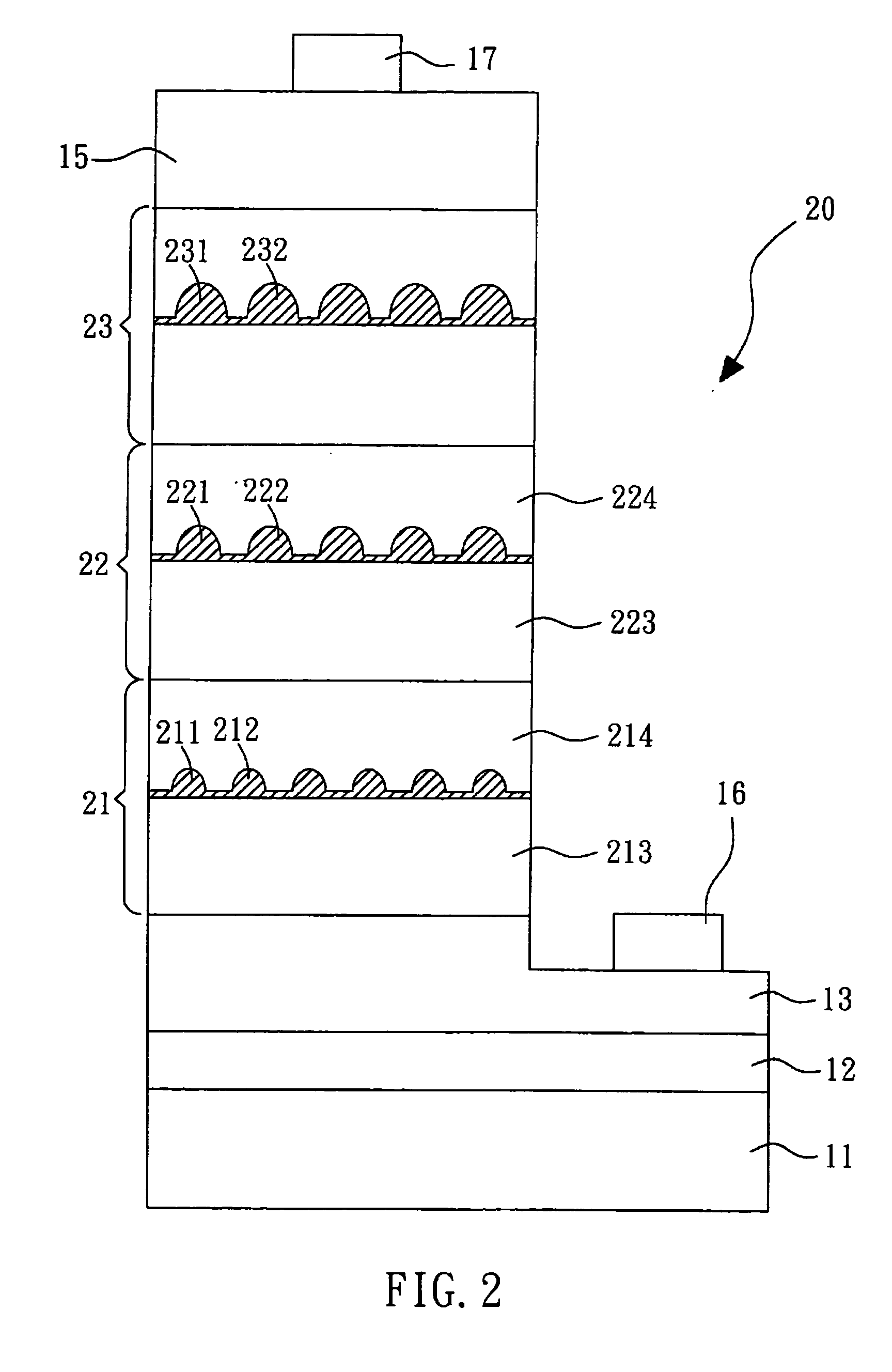

Broad-spectrum A1(1-x-y)InyGaxN light emitting diodes and solid state white light emitting devices

ActiveUS7005667B2High luminous intensityHigh indexSolid-state devicesNanoopticsIndiumLuminous intensity

A broad-spectrum Al(1-x-y)InyGaxN light emitting diode (LED), including: a substrate, a buffer layer, an N-type cladding layer, at least one quantum dot emitting layer, and a P-type cladding layer. The buffer layer is disposed over the substrate. The N-type cladding layer is disposed over the buffer layer to supply electrons. The quantum dot emitting layer is disposed over the N-type cladding layer and includes plural quantum dots. The dimensions and indium content of the quantum dots are manipulated to result in uneven distribution of character distribution of the quantum dots so as to increase the FWHM of the emission wavelength of the quantum dot emitting layer. The P-type cladding layer is disposed over the quantum dot emitting layer to supply holes. A broad-spectrum Al(1-x-y)InyGaxN yellow LED may thus be made from the LED structure of this invention, with an emission wavelength at maximum luminous intensity falling within a range of 530˜600 nm, and FWHM within a range of 20˜150 nm. After packaging an Al(1-x-y)InyGaxN blue LED to form a solid state white light emitting device, the mixing of blue light and yellow light would generate white light with a high CRI index, high luminous intensity and capable of various color temperature modulation.

Owner:GENESIS PHOTONICS

Sensor package

InactiveUS20060043555A1Maintaining gapInhibit swellingSemiconductor/solid-state device detailsSolid-state devicesAdhesiveEngineering

An image sensor package includes a bottom substrate, a transparent substrate, a plurality of spacers and adhesive. The bottom substrate includes a plurality of chips, which each includes an active surface and an image sensor disposed on the active surface. The transparent substrate includes a plurality of transparent substrate units which are respectively corresponding to the chips, wherein each transparent substrate unit is disposed above the active surface of the chip and covers the image sensor. The spacers are disposed between the transparent substrate unit and the chip for maintaining a predetermined gap between the transparent substrate unit and the image sensor. Each transparent substrate unit and chip are connected to each other by the adhesive.

Owner:HIMAX TECH LTD

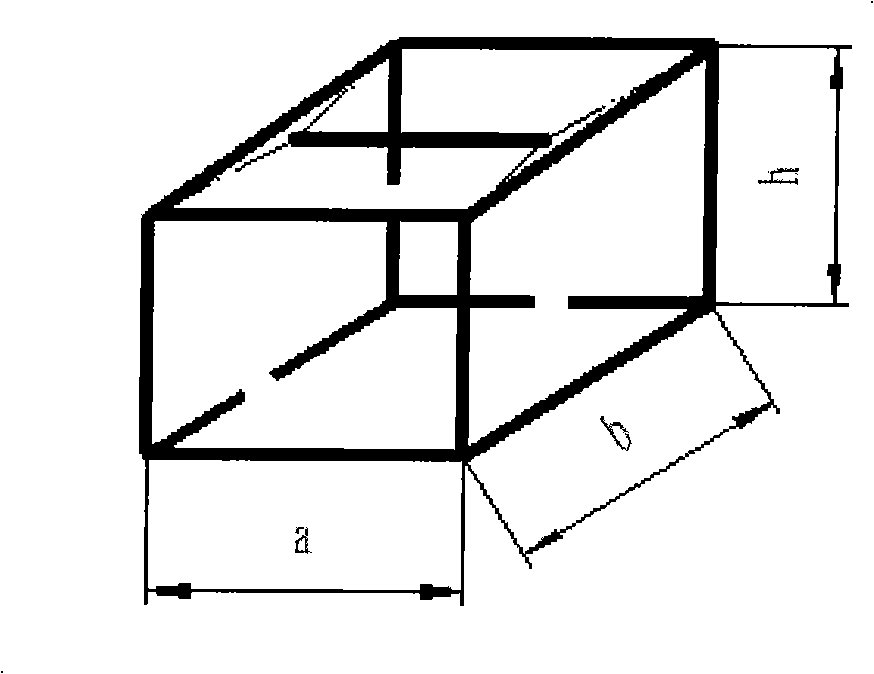

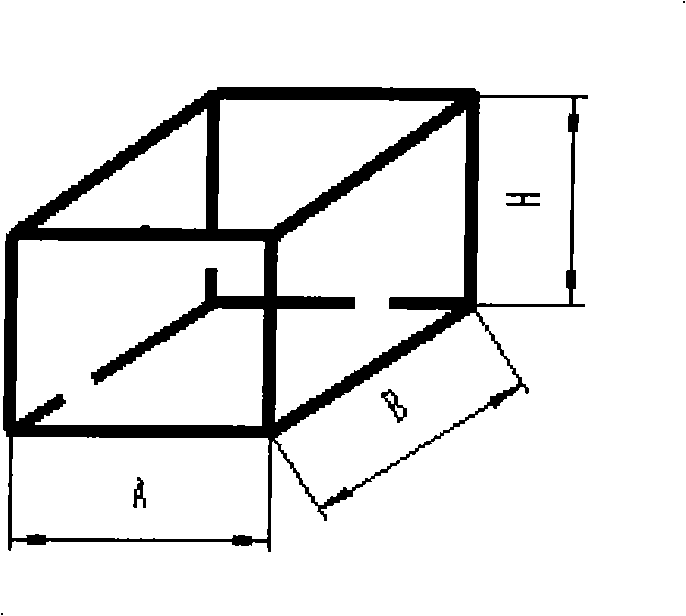

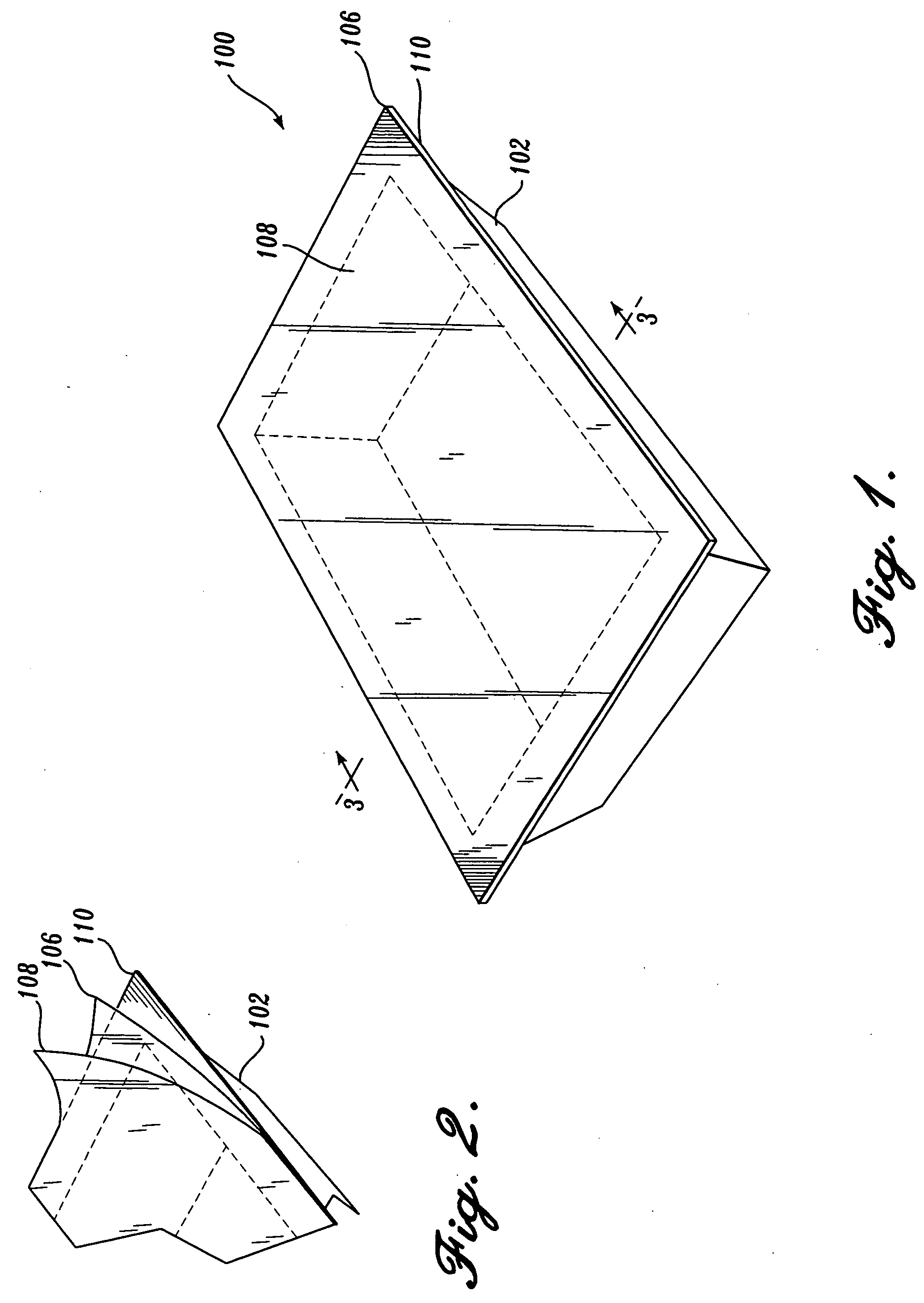

Packaging carton

InactiveUS20050023162A1Simple processReduce packaging costsOther accessoriesContainers to prevent mechanical damageCartonEngineering

A packaging carton is disclosed, suitable for packaging an electronic product, such as a peripheral product, a mobile phone, or a spare part. The packing carton is formed by folding a paper material and is one piece, and is fabricated by linking two clip slots. Furthermore, the packaging carton comprises two hollow buffer structures beside two sides of a storage chamber and two upper holding pieces adjacent to both sides of the storage chamber to protect an object packaged in the packaging carton.

Owner:QUANTA COMPUTER INC

MEMS device

InactiveUS20110108933A1Low costReduce packaging costsAcceleration measurement using interia forcesSemiconductor electrostatic transducersEngineering

Owner:ROHM CO LTD

Package module of light emitting diode

InactiveUS20070278500A1Reduce packaging costsLow costSolid-state devicesSemiconductor devicesLight-emitting diodeTransistor

A package module of a light emitting diode includes a substrate, a first light emitting diode and a transistor. The first light emitting diode is disposed on the substrate, and the transistor is electrically connected with the first light emitting diode. The transistor is disposed on the substrate and turns on or off the first light emitting diode. The first light emitting diode and the transistor are disposed in a same package.

Owner:GIGNO TECH CO LTD

Wafer level fan-out chip packaging method

ActiveCN101604638AAchieve connectionAvoid displacementSolid-state devicesSemiconductor/solid-state device manufacturingPlastic packagingMetal electrodes

The invention relates to a wafer level fan-out chip packaging method, comprising the following technological processes: a stripping foil and a film dielectric layer I are sequentially covered on the surface of the wafer of a carrier, a photoetching pattern opening I is formed on the film dielectric layer I; a metal electrode and a re-wiring metal routing wire which are connected with a base plate end are arranged on the photoetching pattern opening and the surface thereof, a film dielectric layer II is covered on the surface of the metal electrode, the surface of the re-wiring metal routing wire, and the surface of the film dielectric layer I which are connected with the base plate end, and a photoetching pattern opening II is formed on the film dielectric layer II; a metal electrode connected with a chip end is arranged on the photoetching pattern opening II, after a chip is arranged on the metal electrode connected with the chip end in an inverting way, the injection molding of packaging material and solidification are carried out, so as to form a packaging body with plastic-packaging material; the wafer of the carrier and the stripping foil are separated from the packaging body with plastic-packaging material, so as to form a plastic-packaging wafer; a welding sphere back returns to form a welding ball salient point; cutting is carried out by uniwafers for forming the final structure of the fan-out chip. The method has low cost and a carrying function, and can well solve the problem that the chip is shifted in the technological process.

Owner:JIANGYIN CHANGDIAN ADVANCED PACKAGING CO LTD

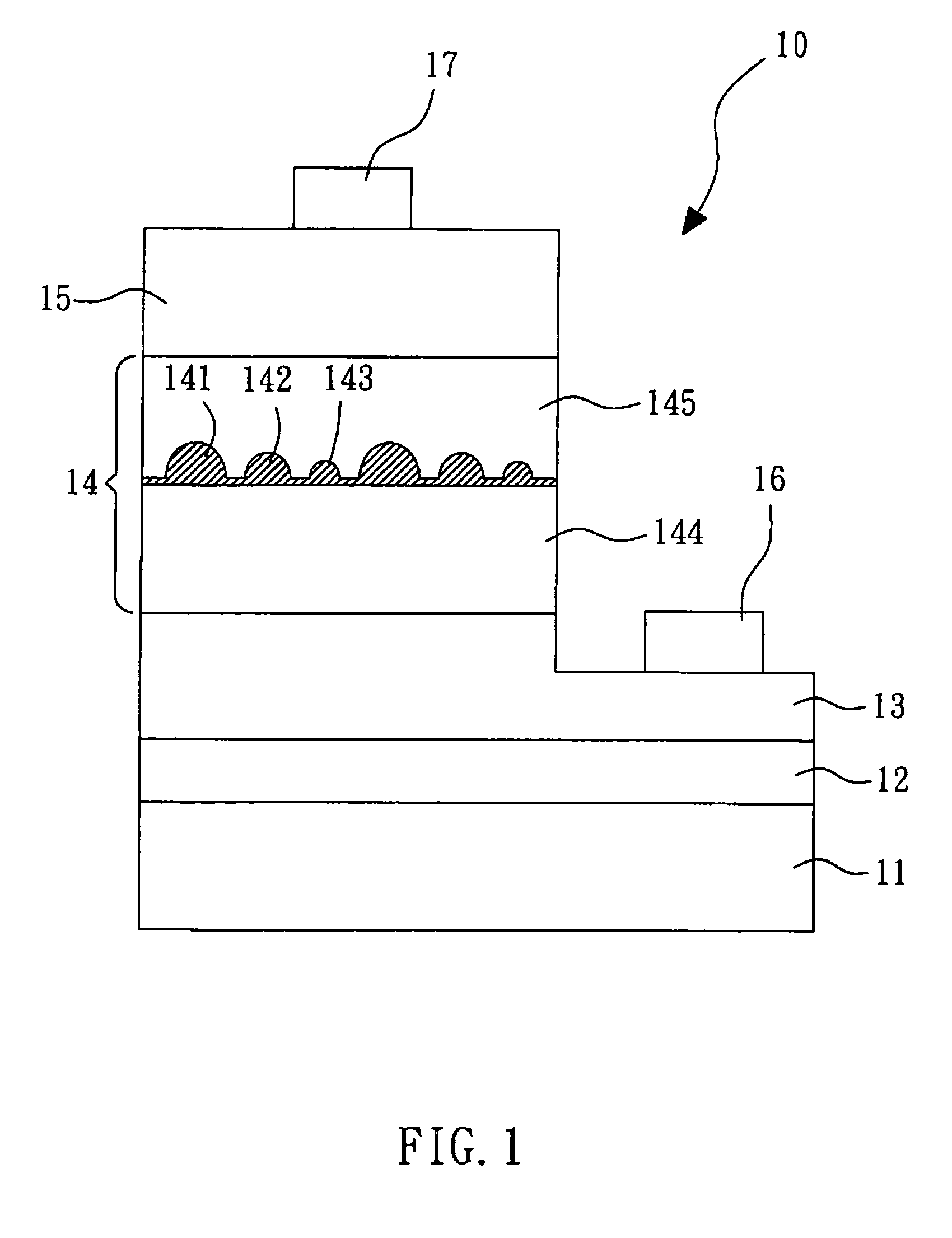

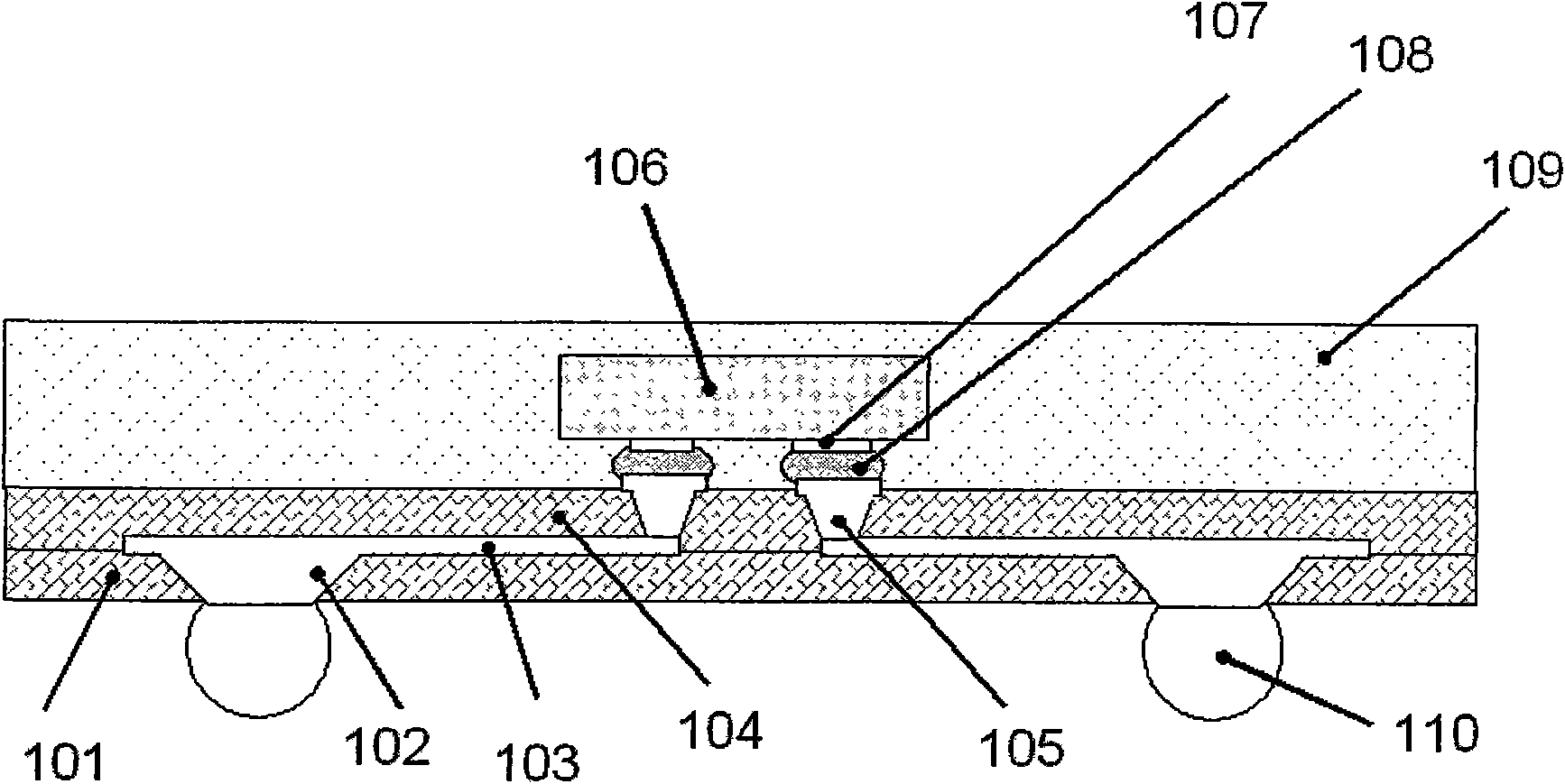

Stacked package structure of image sensor

InactiveUS6627983B2Reduce in quantityReduce packaging costsSemiconductor/solid-state device detailsSolid-state devicesEngineeringImage signal

A stacked package structure of an image sensor for electrically connecting to a printed circuit board includes a first substrate, a second substrate, an integrated circuit, an image sensing chip, and a transparent layer. The second substrate is mounted on the first substrate so as to a cavity formed between the first substrate and second substrate. The integrated circuit is located within the cavity and electrically connected the first substrate. The image-sensing chip is arranged on the second substrate. The transparent layer covers over the image sensing chip, wherein the image sensing chip receives image signals via the transparent layer and transforms the image signals into electrical signals transmitted to the first substrate. Thus, the image sensing chip of the image sensing product and the integrated circuit can be integrally package.

Owner:KINGPAK TECH INC

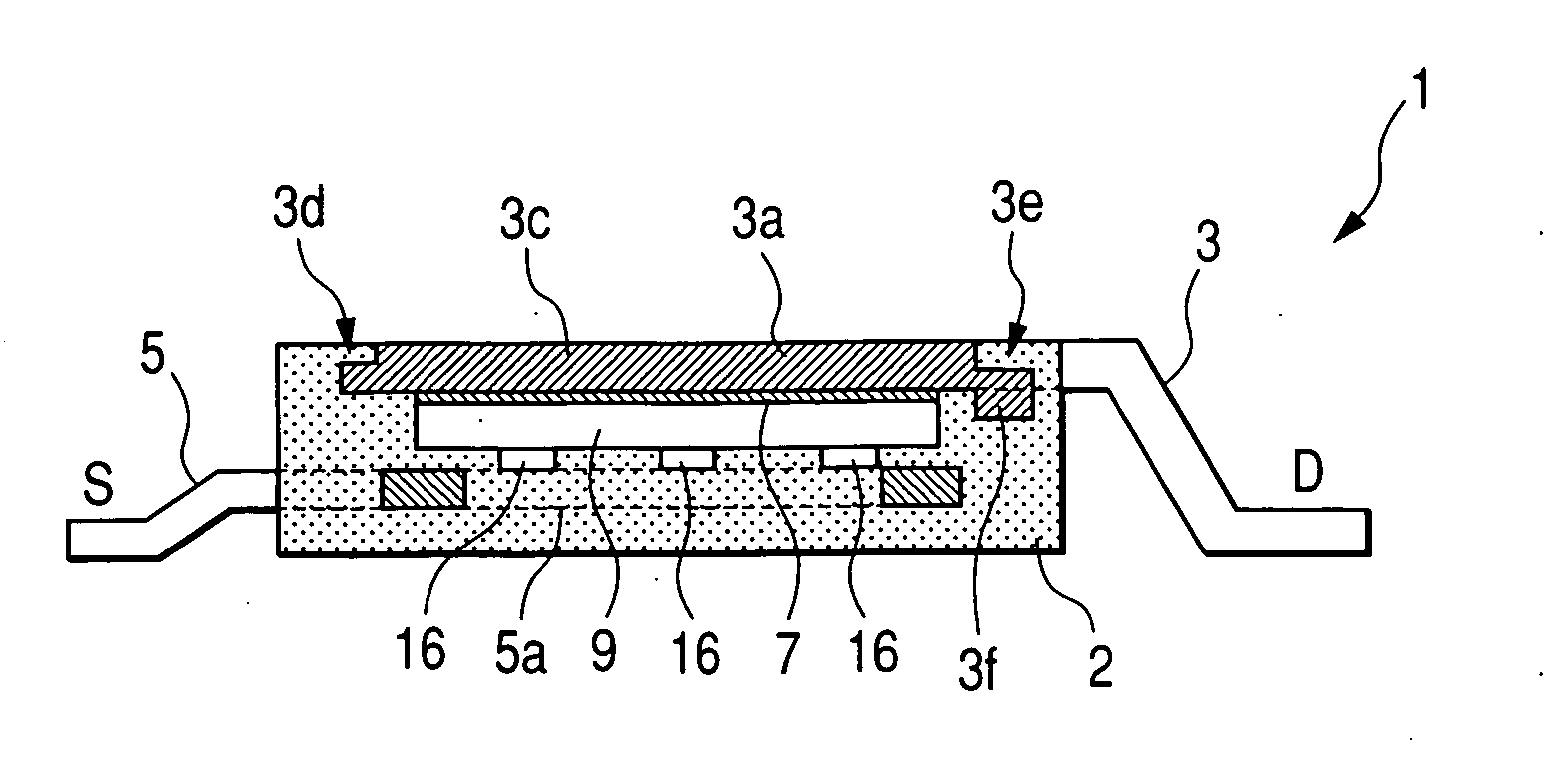

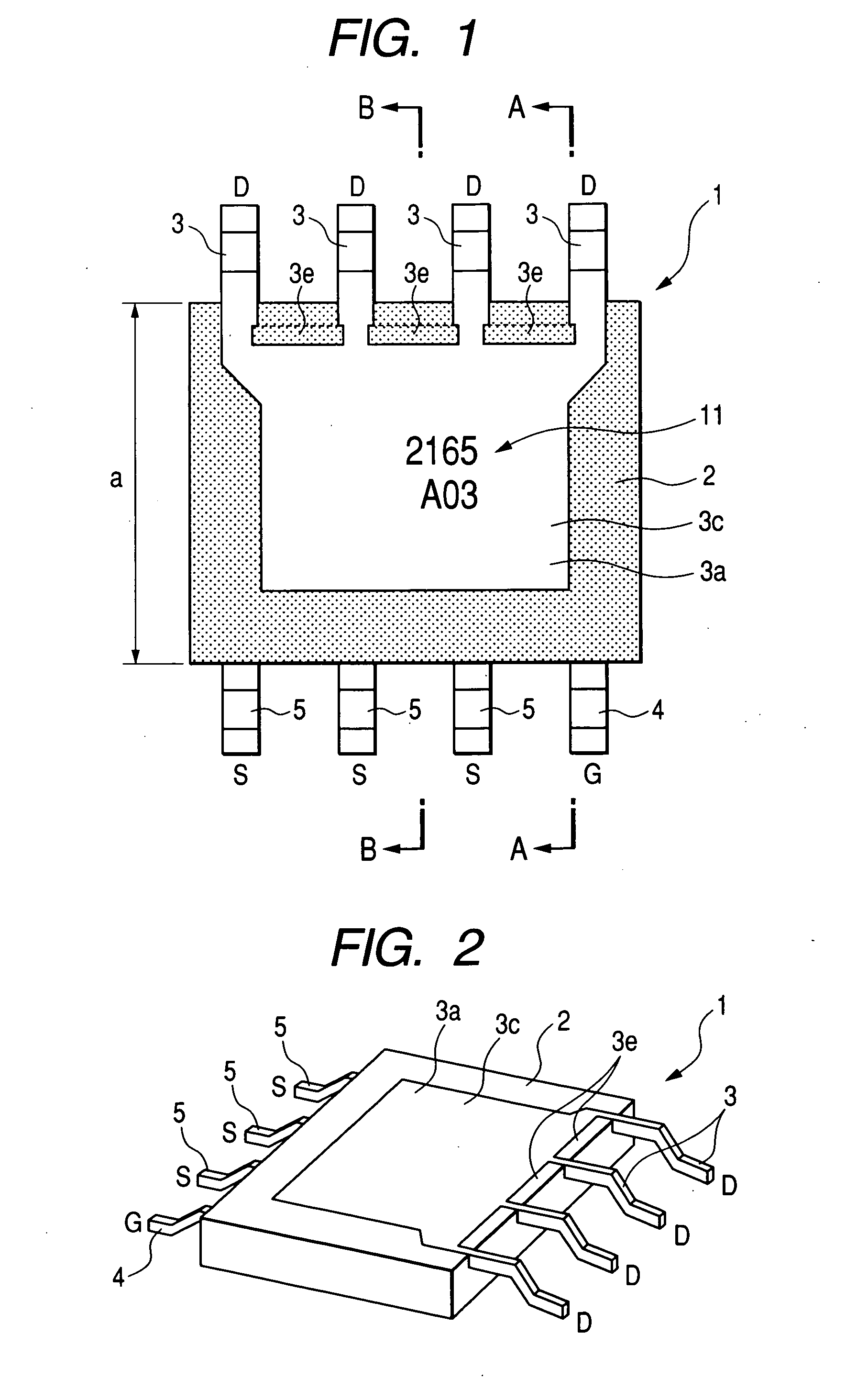

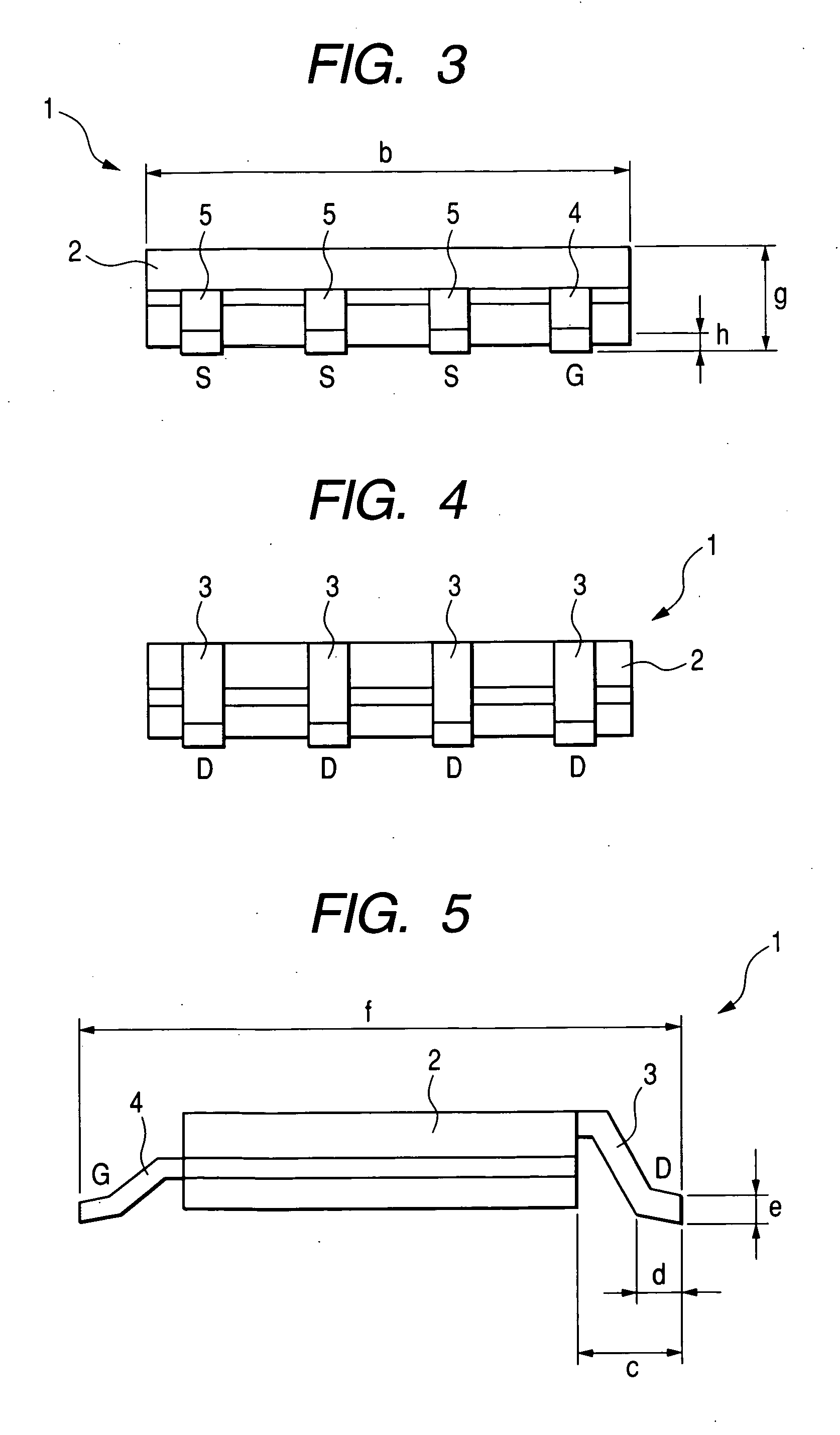

Semiconductor device

InactiveUS20050218498A1Improve cooling effectReduce packaging costsSemiconductor/solid-state device detailsSolid-state devicesAdhesiveSurface mounting

A semiconductor device superior in heat dissipating performance and permitting reduction of the packaging cost is provided. The semiconductor device comprises a sealing body formed of an insulating resin, a semiconductor chip positioned within the sealing body, the semiconductor chip having a gate electrode and a source electrode on a first main surface thereof and having a back electrode (drain electrode) on a second main surface thereof, a drain electrode plate projecting in a gull wing shape on one end side of the sealing body, an upper surface of a portion of the drain electrode plate which portion is positioned in the sealing body being exposed from the sealing body and a lower surface thereof being connected to the back electrode through an adhesive, a gate electrode plate projecting in a gull wing shape on an opposite end side of the sealing body and being connected to the gate electrode within the sealing body, a source electrode plate projecting in a gull wing shape on the opposite end side of the sealing body and being connected to the source electrode within the sealing body, a depression formed in the surface of the drain electrode plate within the sealing body and filled with the resin which forms the sealing body, and a projecting portion formed on the surface of the drain electrode plate within the sealing body and engaged with the sealing body. The drain electrode plate and the source electrode plate branch into plural branch pieces (leads) serving as gull wing-shaped surface mounting terminals.

Owner:RENESAS ELECTRONICS CORP

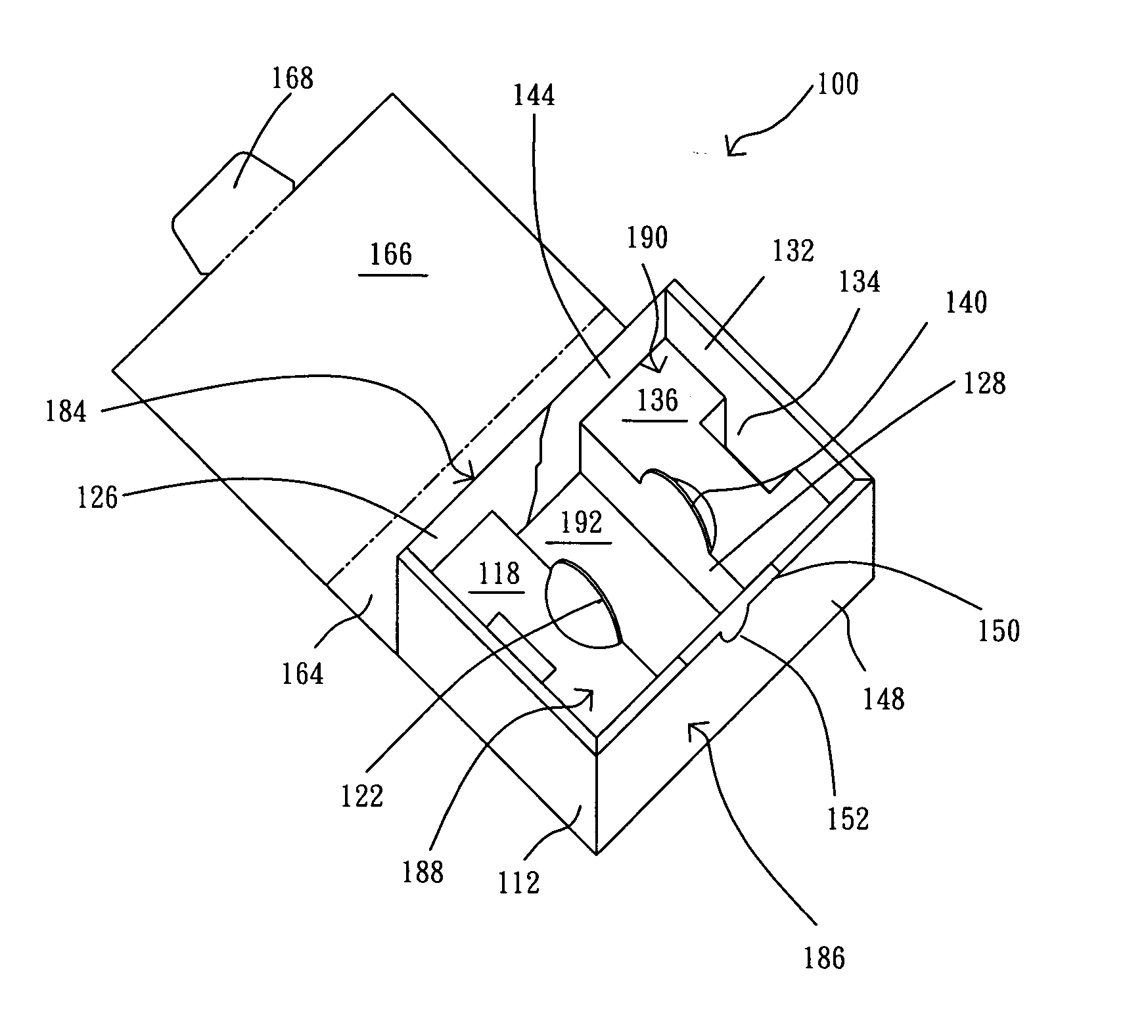

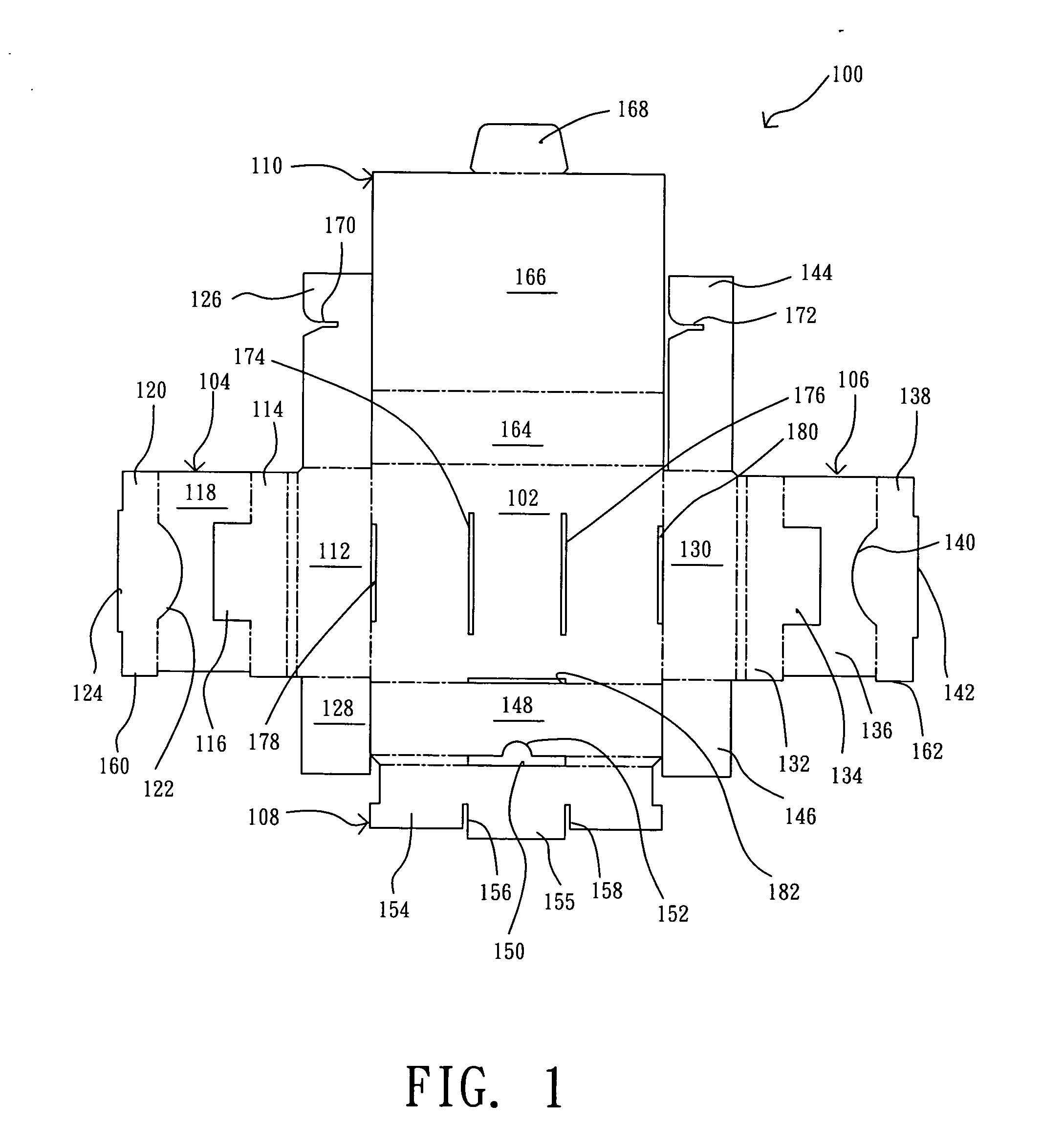

Micromachined optical switching devices

InactiveUS6445840B1Reduce packaging costsSmall massMultiplex system selection arrangementsCoupling light guidesOptical alignmentOptical switch

Various 3-port and 4-port micromachined optomechanical matrix switches are disclosed herein. In accordance with one aspect of the invention there is provided an optomechanical matrix switch including a substrate and a first plurality of optomechanical switching cells coupled thereto. Each of the first plurality of optomechanical switching cells is arranged to be in optical alignment with a first input port. A second plurality of optomechanical switching cells is also coupled to the substrate, each of the second plurality of optomechanical switching cells being in optical alignment with a second input port. In another aspect of the present invention an optomechanical matrix switch is provided which includes a substrate and a first plurality of optomechanical switching cells coupled thereto. Each of the first plurality of optomechanical switching cells is placed in optical alignment with one of a corresponding first plurality of input ports and with one of a corresponding first plurality of output ports. The matrix switch further includes a second plurality of optomechanical switching cells coupled to the substrate. Each of the second plurality of optomechanical switching cells is placed in optical alignment with one of a corresponding second plurality input ports and with one of a corresponding second plurality of output ports.

Owner:CROSSFIBER +1

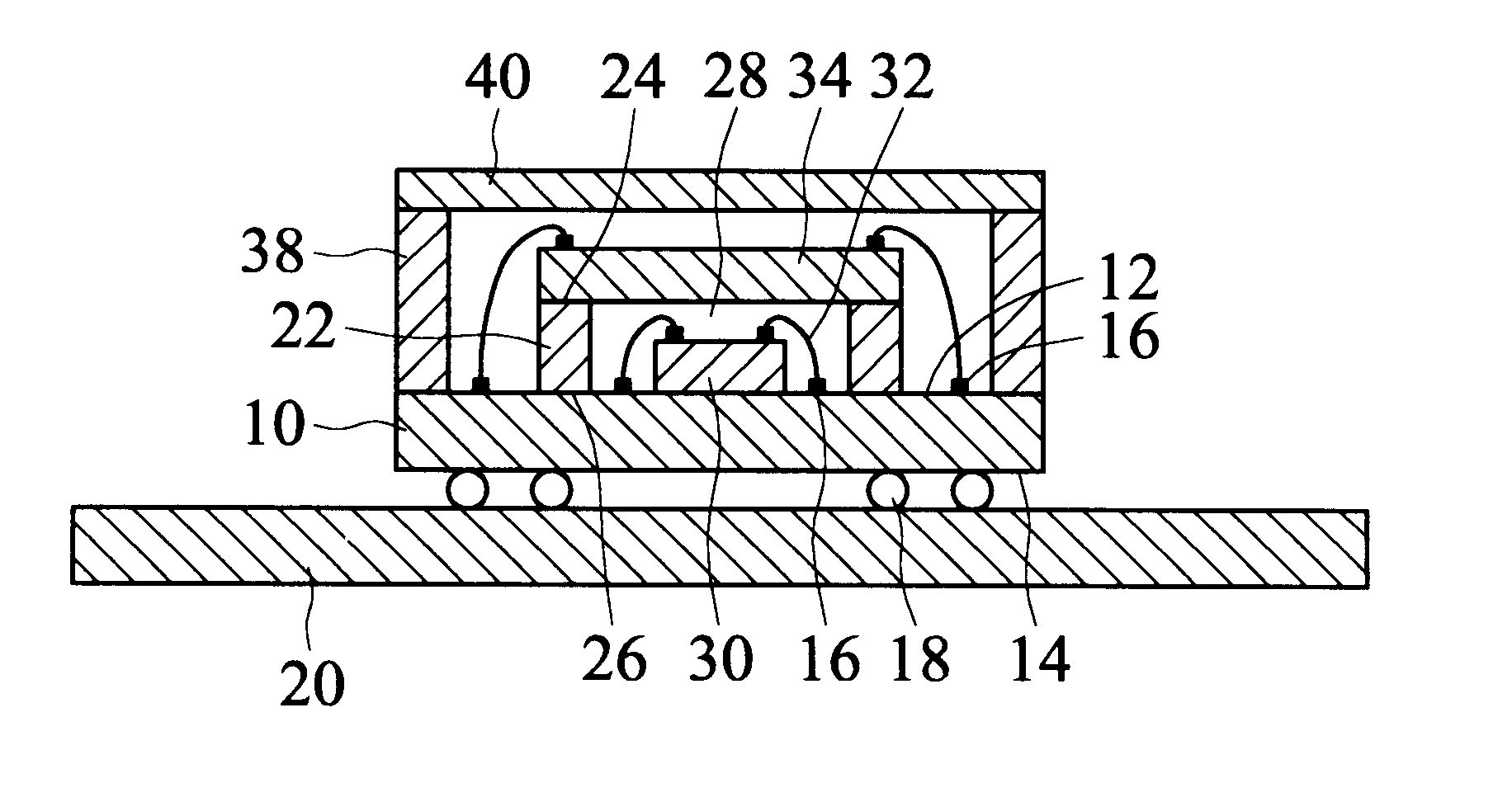

Semiconductor device having flip-chip package and method for fabricating the same

InactiveUS20060097402A1Reduce thicknessIncrease productionSemiconductor/solid-state device detailsSolid-state devicesDevice materialSolder ball

A semiconductor device having a flip-chip package and a method for fabricating the same are provided. A flip-chip package after being tested to be functionally workable is mounted on a carrier and is electrically connected to the carrier by a plurality of first conductive elements, the flip-chip package having a first chip mounted on a substrate in a flip-chip manner. At least a second chip is mounted on the flip-chip package and is electrically connected to the carrier by a plurality of second conductive elements. An encapsulant is formed on the carrier for encapsulating the flip-chip package and the second chip. A plurality of solder balls are implanted on a bottom surface of the carrier, such that the first and second chips can be electrically connected to an external device via the solder balls. The above arrangement can effectively improve the yield of a fabricated product and reduce packaging costs.

Owner:SILICONWARE PRECISION IND CO LTD

Broad-spectrum A1(1-x-y)InyGaxN light emitting diodes and solid state white light emitting devices

ActiveUS20050092980A1High luminous intensityHigh indexSolid-state devicesNanoopticsIndiumLuminous intensity

A broad-spectrum Al(1-x-y)InyGaxN light emitting diode (LED), including: a substrate, a buffer layer, an N-type cladding layer, at least one quantum dot emitting layer, and a P-type cladding layer. The buffer layer is disposed over the substrate. The N-type cladding layer is disposed over the buffer layer to supply electrons. The quantum dot emitting layer is disposed over the N-type cladding layer and includes plural quantum dots. The dimensions and indium content of the quantum dots are manipulated to result in uneven distribution of character distribution of the quantum dots so as to increase the FWHM of the emission wavelength of the quantum dot emitting layer. The P-type cladding layer is disposed over the quantum dot emitting layer to supply holes. A broad-spectrum Al(1-x-y)InyGaxN yellow LED may thus be made from the LED structure of this invention, with an emission wavelength at maximum luminous intensity falling within a range of 530˜600 nm, and FWHM within a range of 20˜150 nm. After packaging an Al(1-x-y)InyGaxN blue LED to form a solid state white light emitting device, the mixing of blue light and yellow light would generate white light with a high CRI index, high luminous intensity and capable of various color temperature modulation.

Owner:GENESIS PHOTONICS

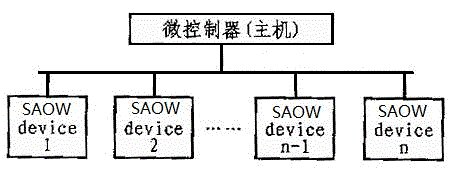

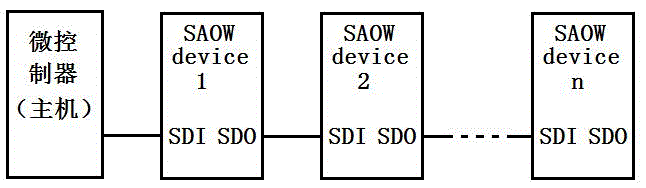

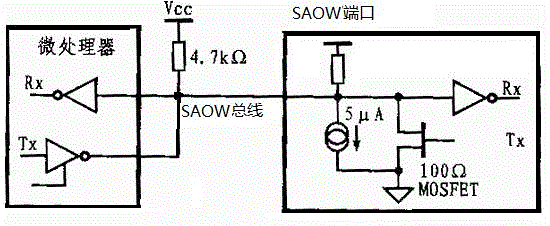

Implement method for high speed single bus communication

ActiveCN104811273ALarge tolerance rangeSimple interfaceBus networksTransmission format adaptationBaudData information

The invention relates to an implement method for high speed single bus communication. Data double-way transmission is performed on basis of an SDI signal line, the SDI signal line is connected with a host and a slave, the host sends signals through the SDI signal line, the slave is automatically adapted to receiving rate and starting and stopping of communication according to the received signals so that a self adaption one wire (SAOW) host-slave structure is formed, data information is transmitted by means of a command frame structure in terms of the data double-way transmission, and a command frame comprises a frame header, a slave address, a register address, data length, data and a frame tail. By means of the implement method for high speed single bus communication, one-bus double-way communication can be achieved, two communication parties are not required to use fixed baud rate, the baud rate can be changed whenever possible, and the method can be applied to occasions with unstable working frequency.

Owner:FUZHOU UNIVERSITY

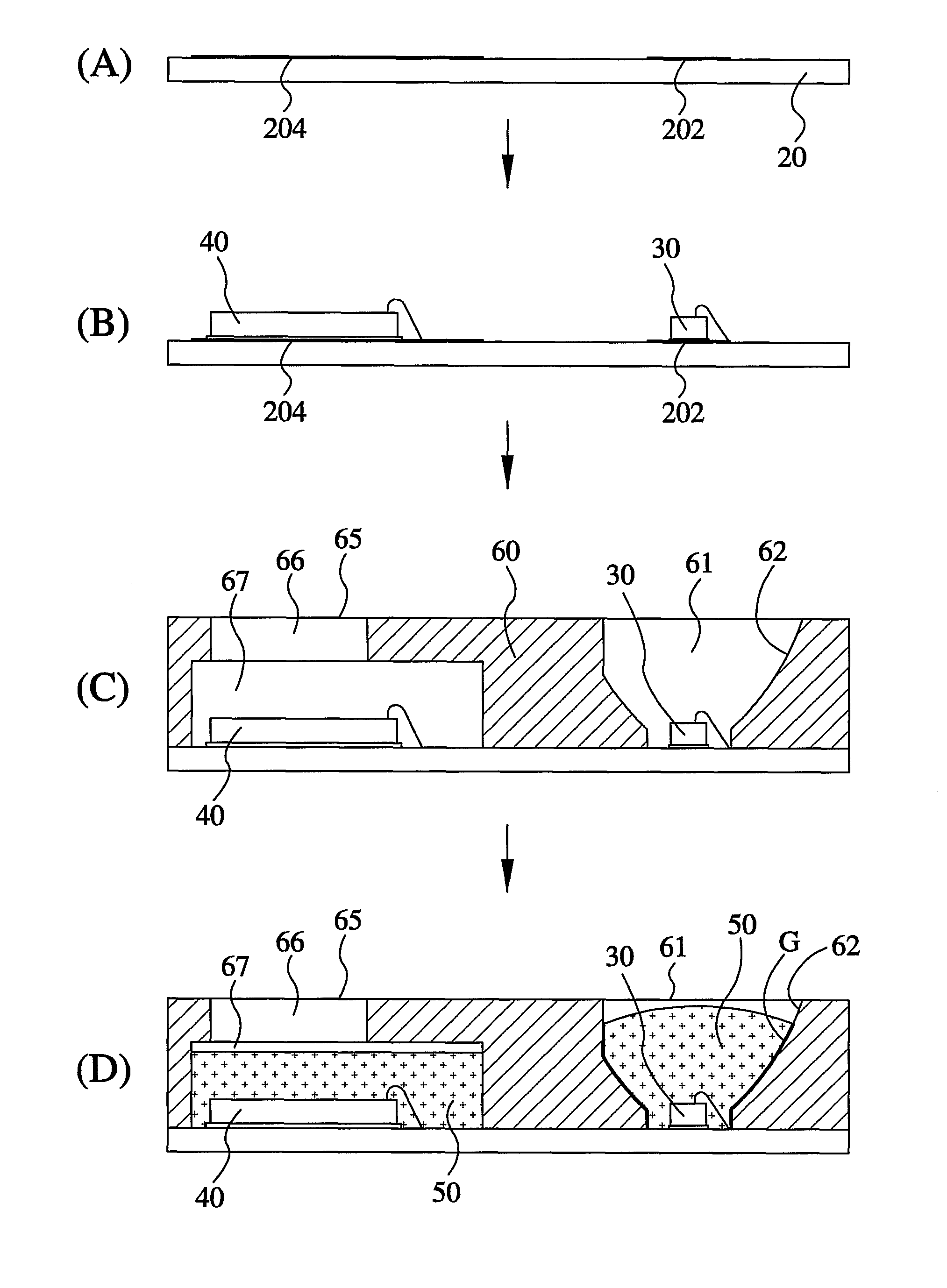

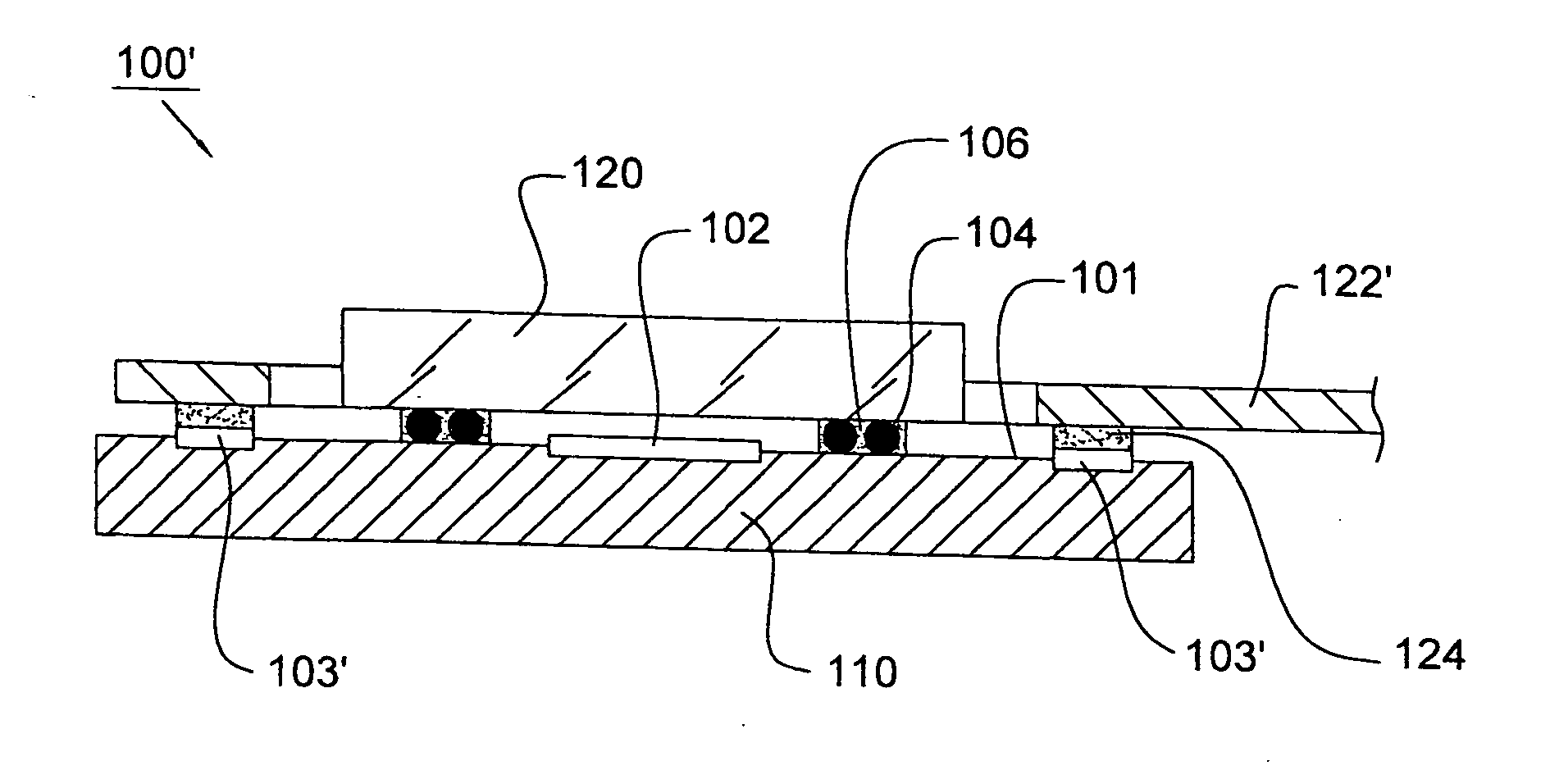

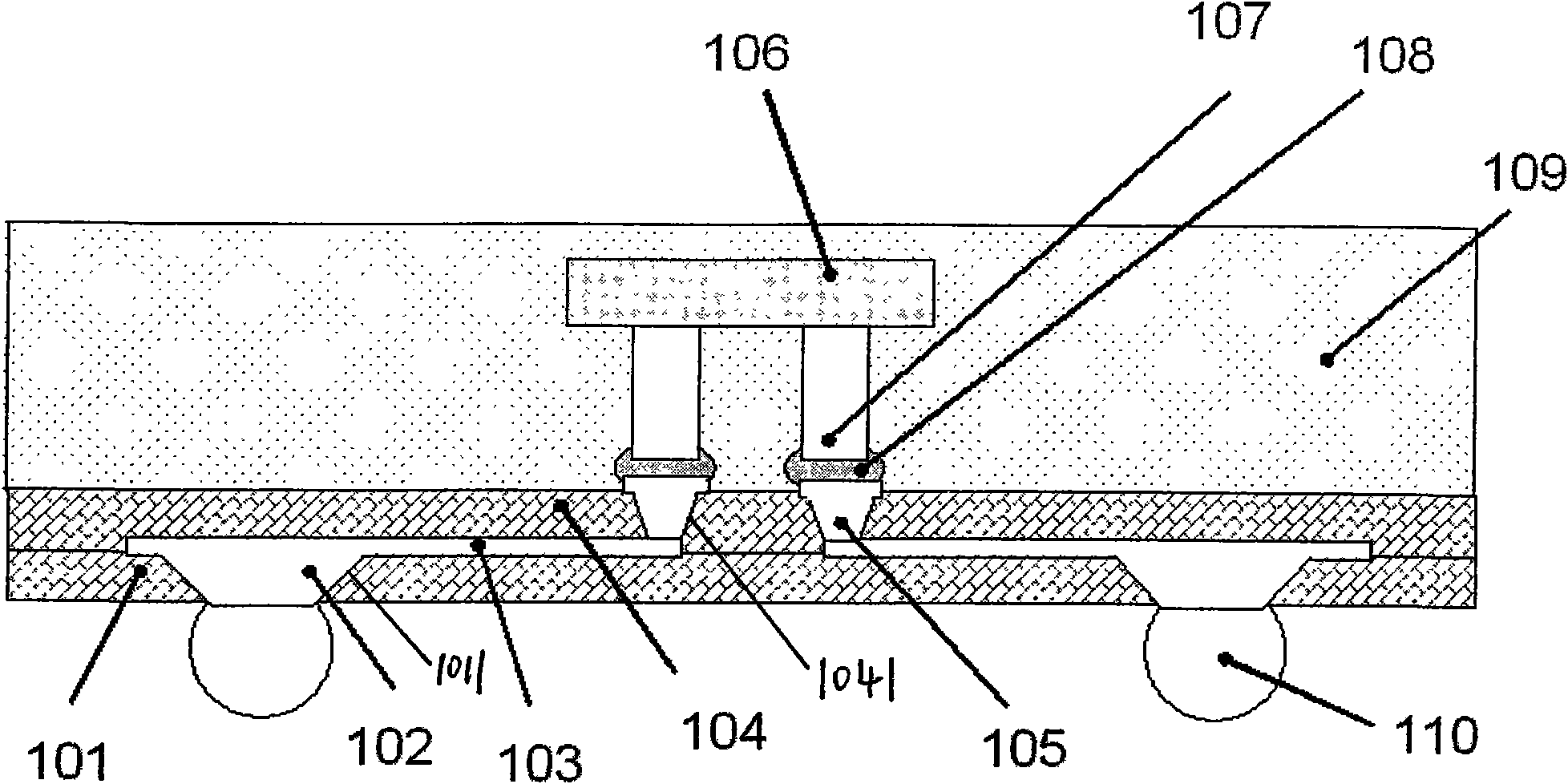

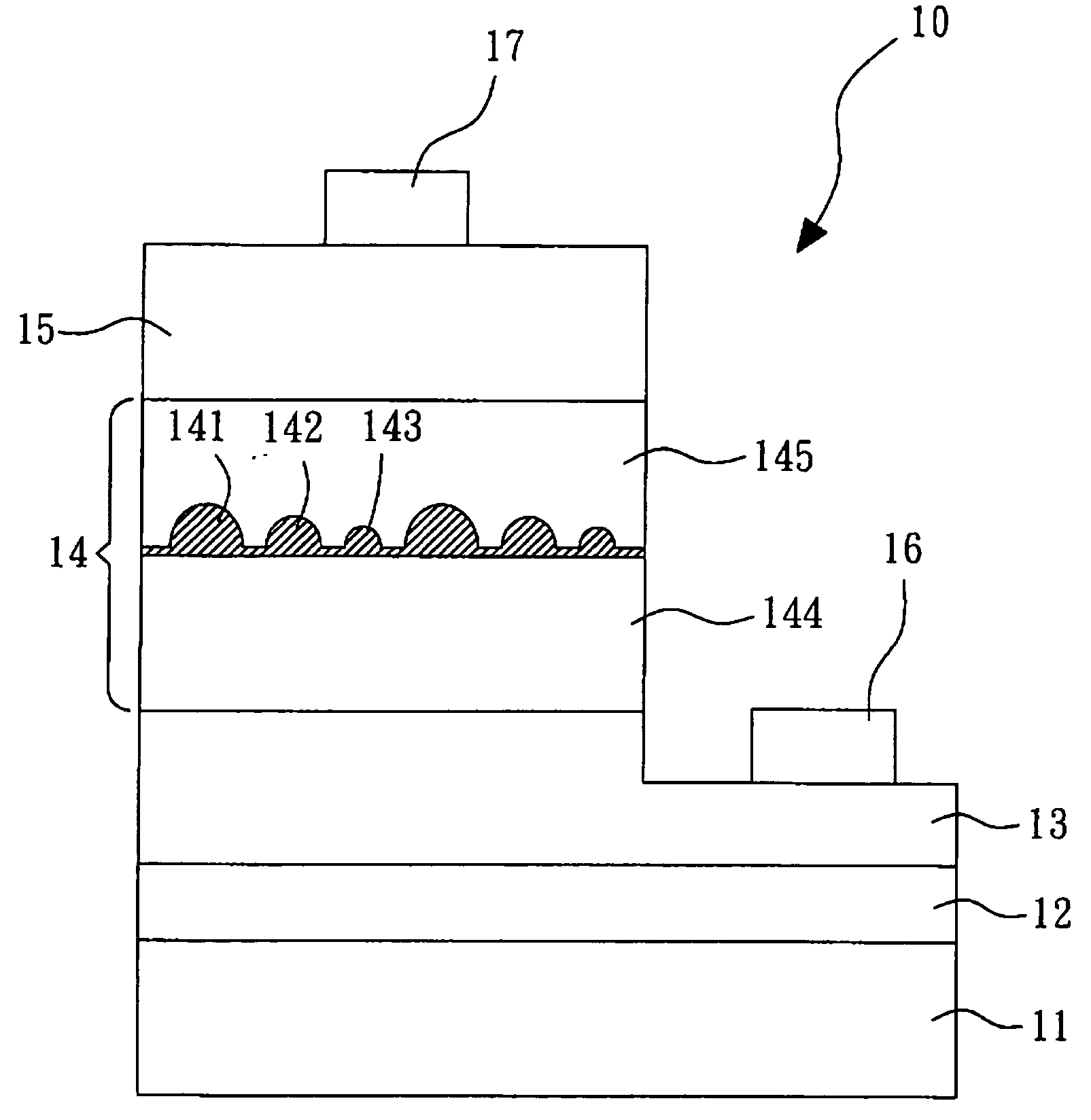

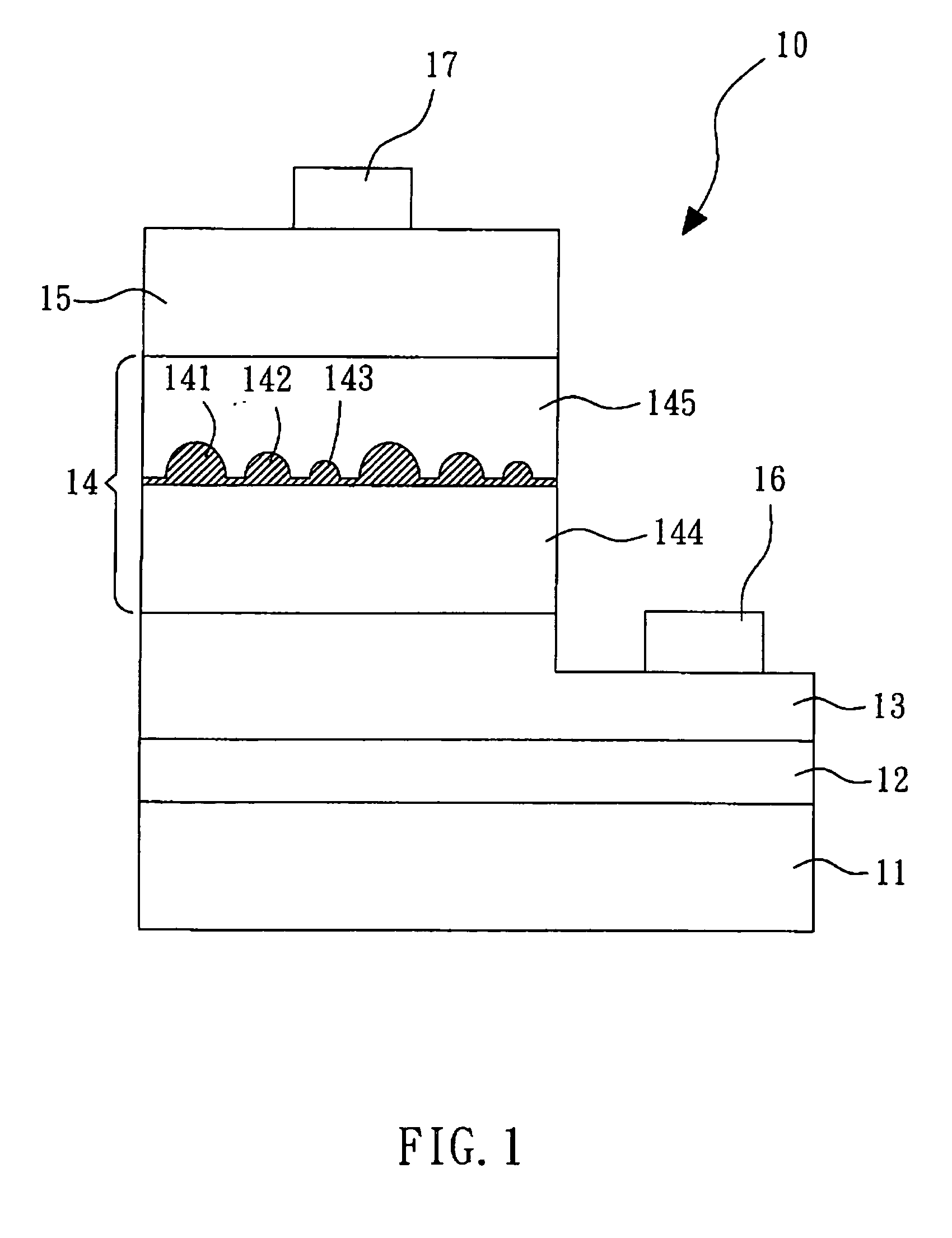

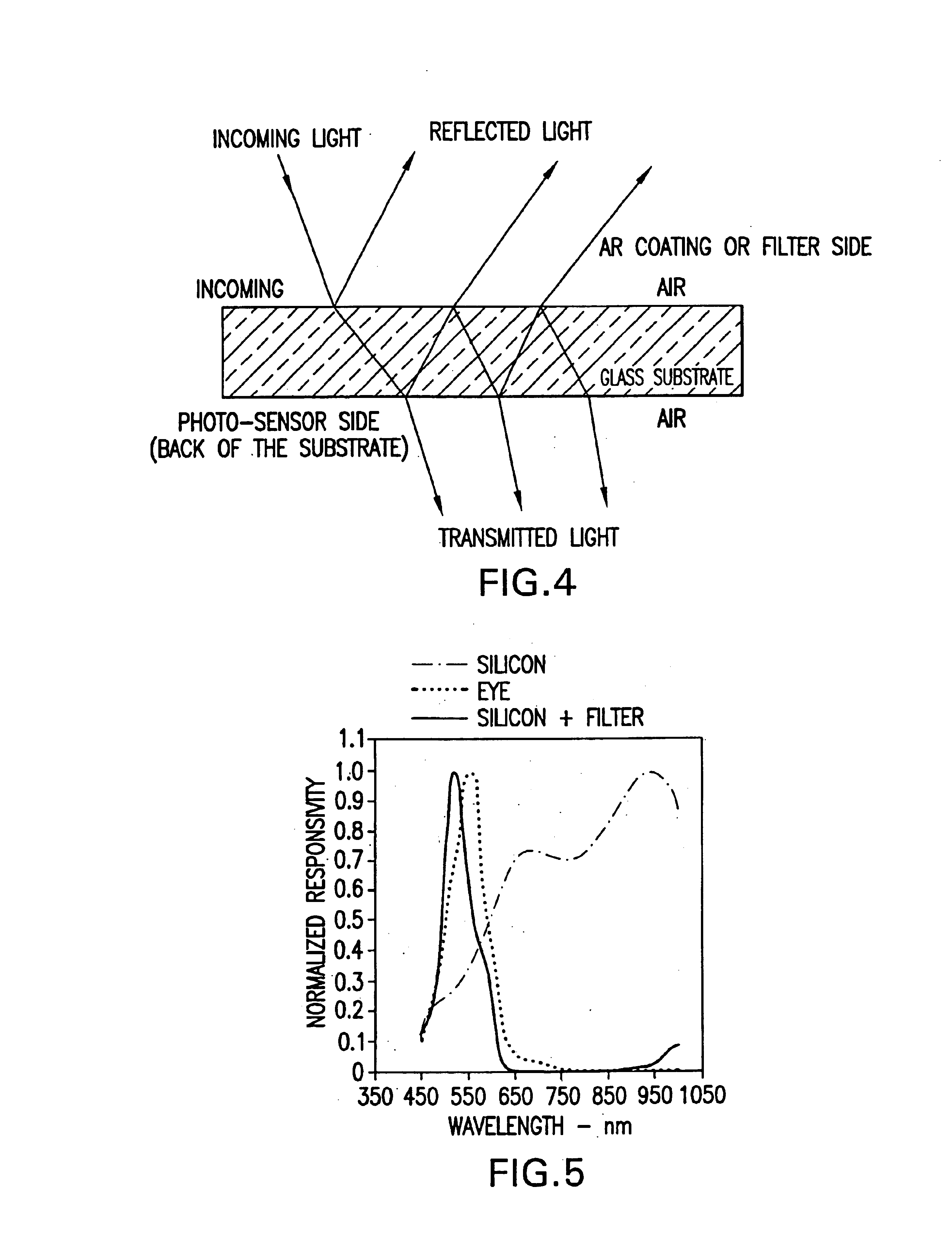

Electronic package of photo-sensing semiconductor devices, and the fabrication and assembly thereof

ActiveUS6864116B1Sufficient transparencyReduce packaging costsSemiconductor/solid-state device detailsSolid-state devicesEngineeringLength wave

A photo-sensing device package and the method of packaging such device is provided. The package includes an assembly portion having a substrate formed of a material substantially transparent to light within a predetermined range of wavelengths; a sensing portion including at least one photo-sensing die photo-electronically transducing light within the predetermined range of wavelengths; and, a plurality of first solder joints joining the sensing and assembly portions. The assembly portion is formed with at least a first metal layer disposed on the substrate about a front surface region thereof; and, at least one passivation layer formed to extend over the first metal layer. The passivation layer is patterned to define a plurality of first and second access openings which respectively describe on the first metal layer a plurality of first and second solder bump pads, each of which is interconnected to at least one of the second solder bump pads. The sensing portion's photo-sensing die is positioned with its photo-sensing area opposing the front surface region of the assembly portion's substrate, and has formed thereon a plurality of solder bump pads electrically coupled to the photo-sensing area. Each of the first solder joints extends between one of the sensing portion's solder bump pads and one of the assembly portion's first solder bump pads.

Owner:OPTOPAC

Self-Locking Fastener

InactiveUS20130031756A1Easy and convenient to useEasy and convenient to and operateSnap fastenersFlexible elementsEngineeringSelf locking

Owner:DONGGUAN MASTER INK CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com