Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

51results about How to "Minimize capacitance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

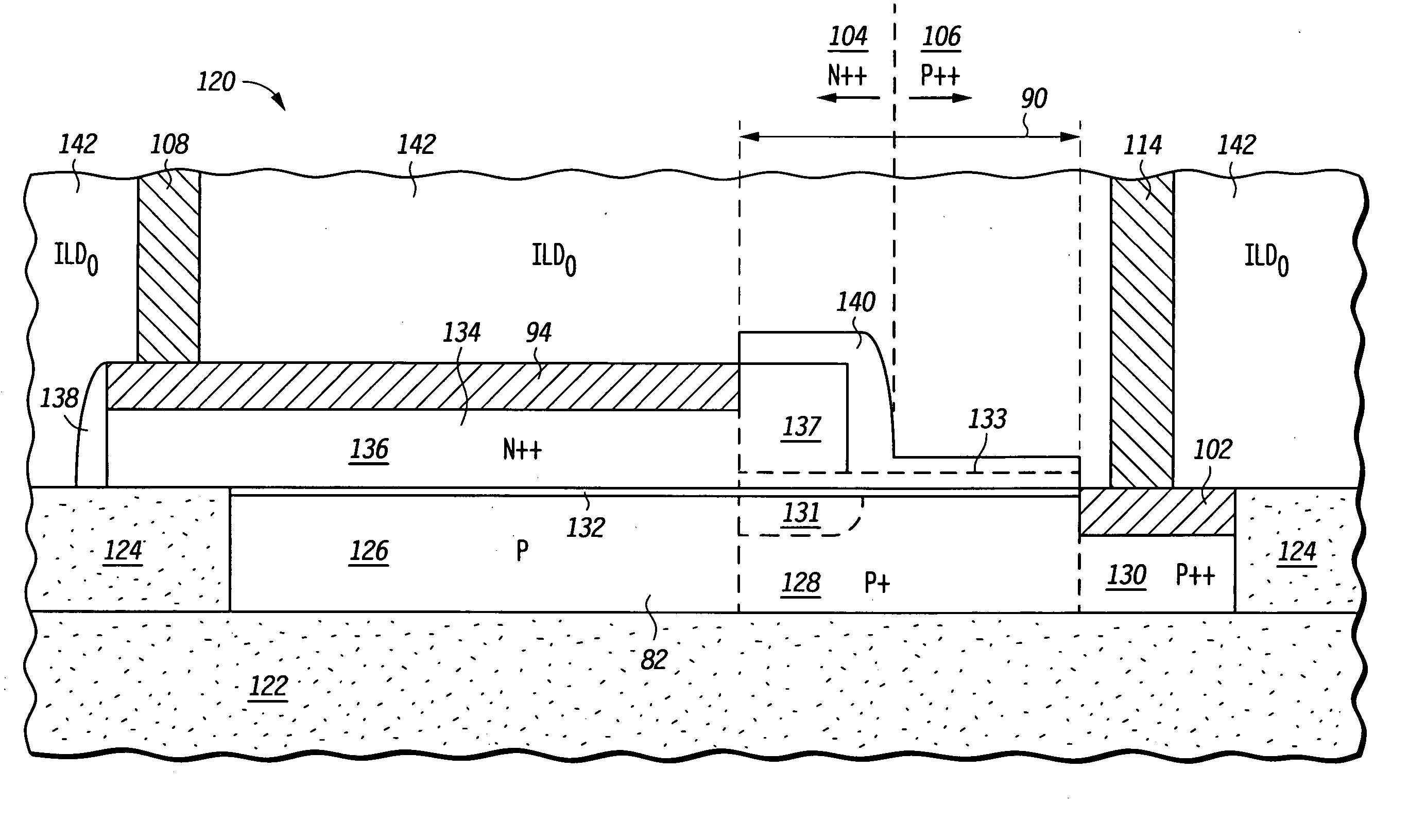

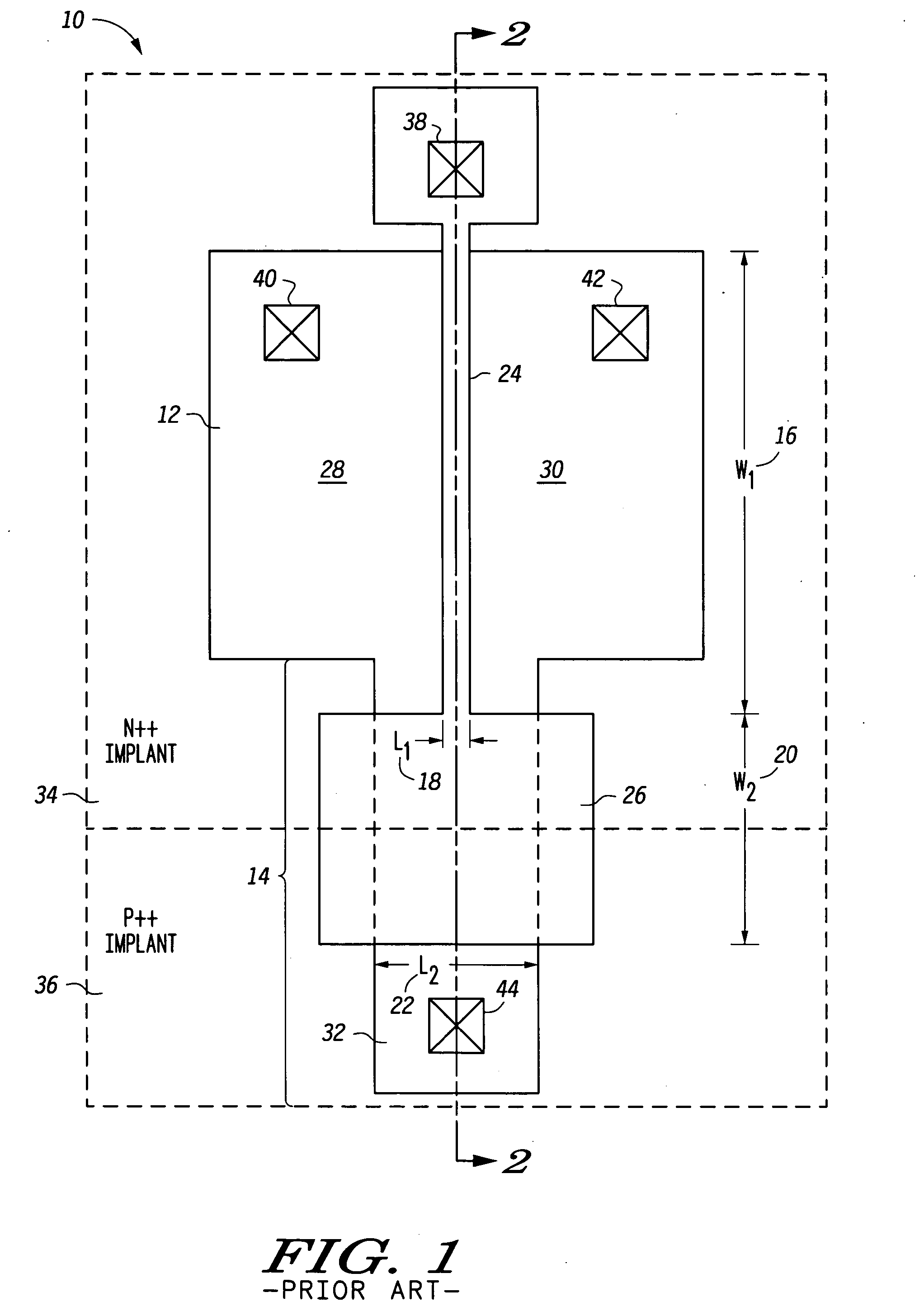

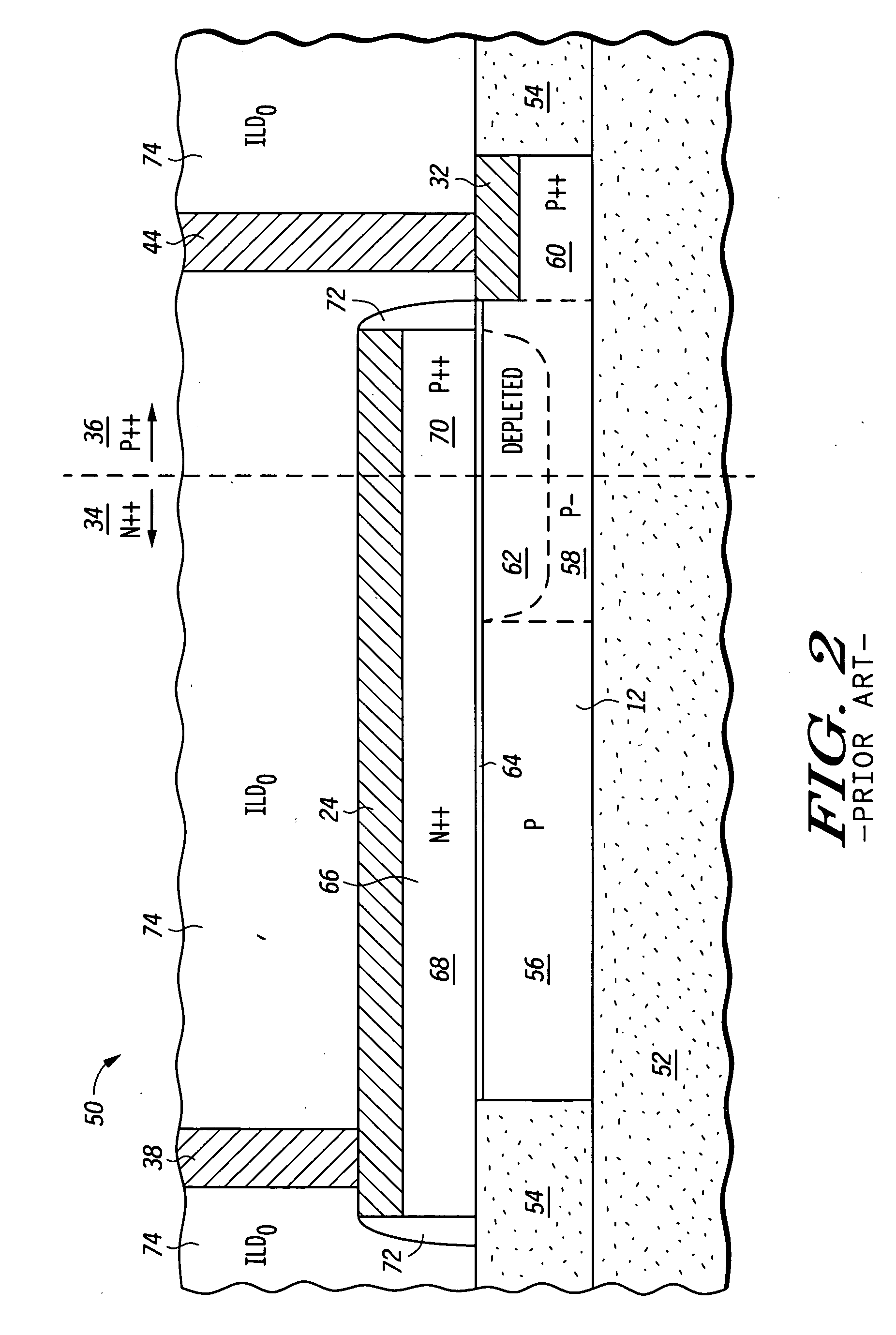

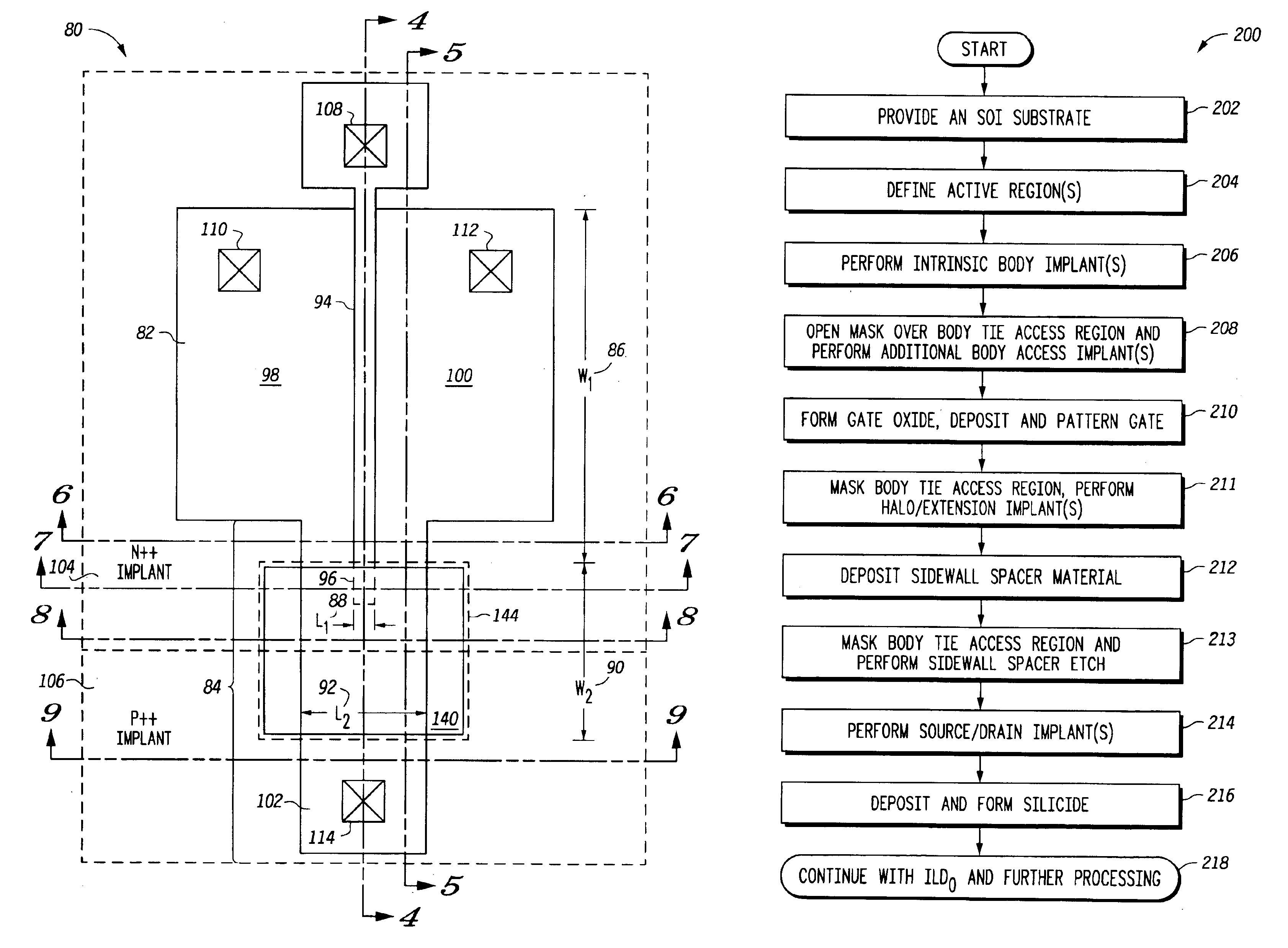

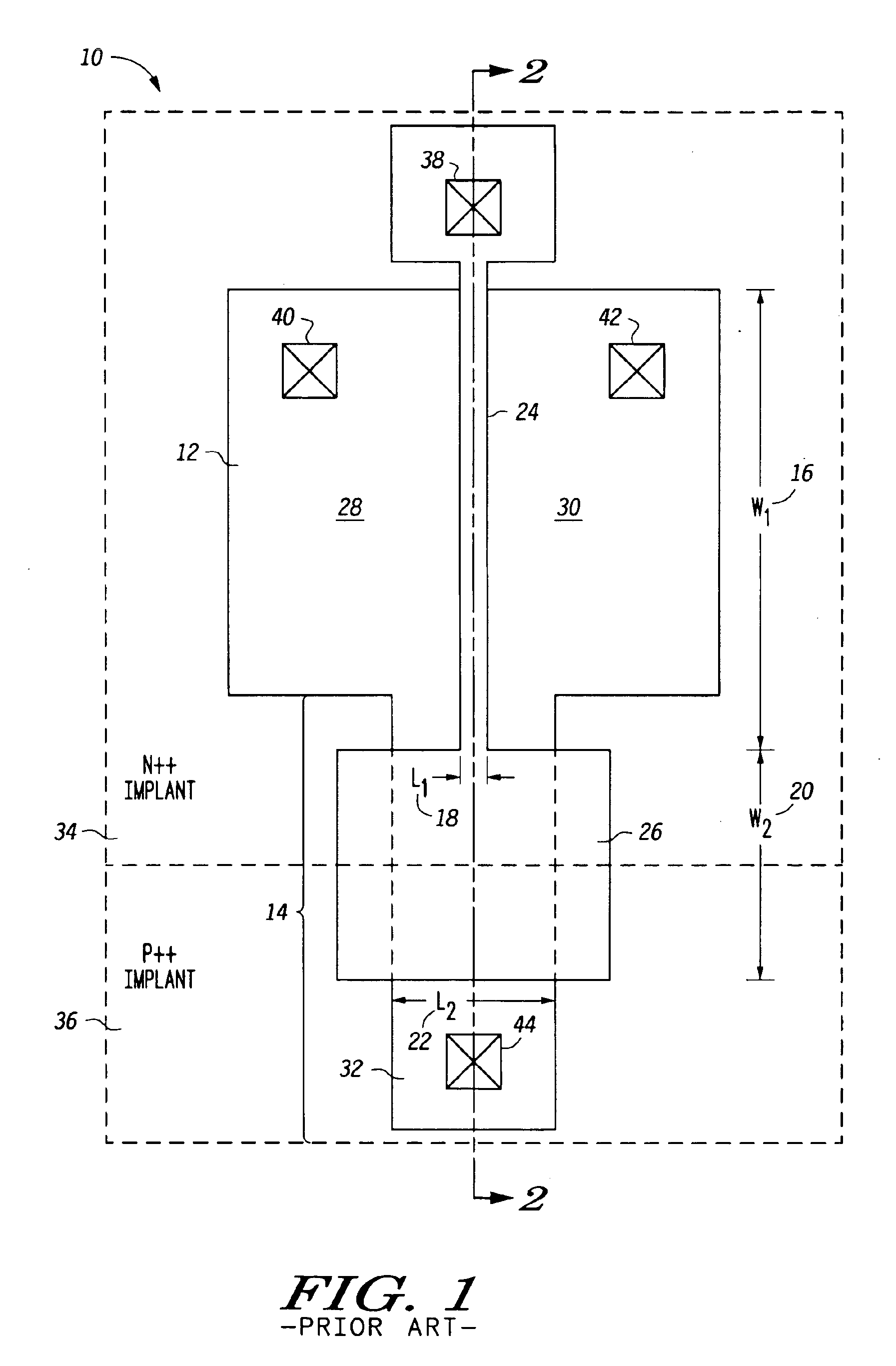

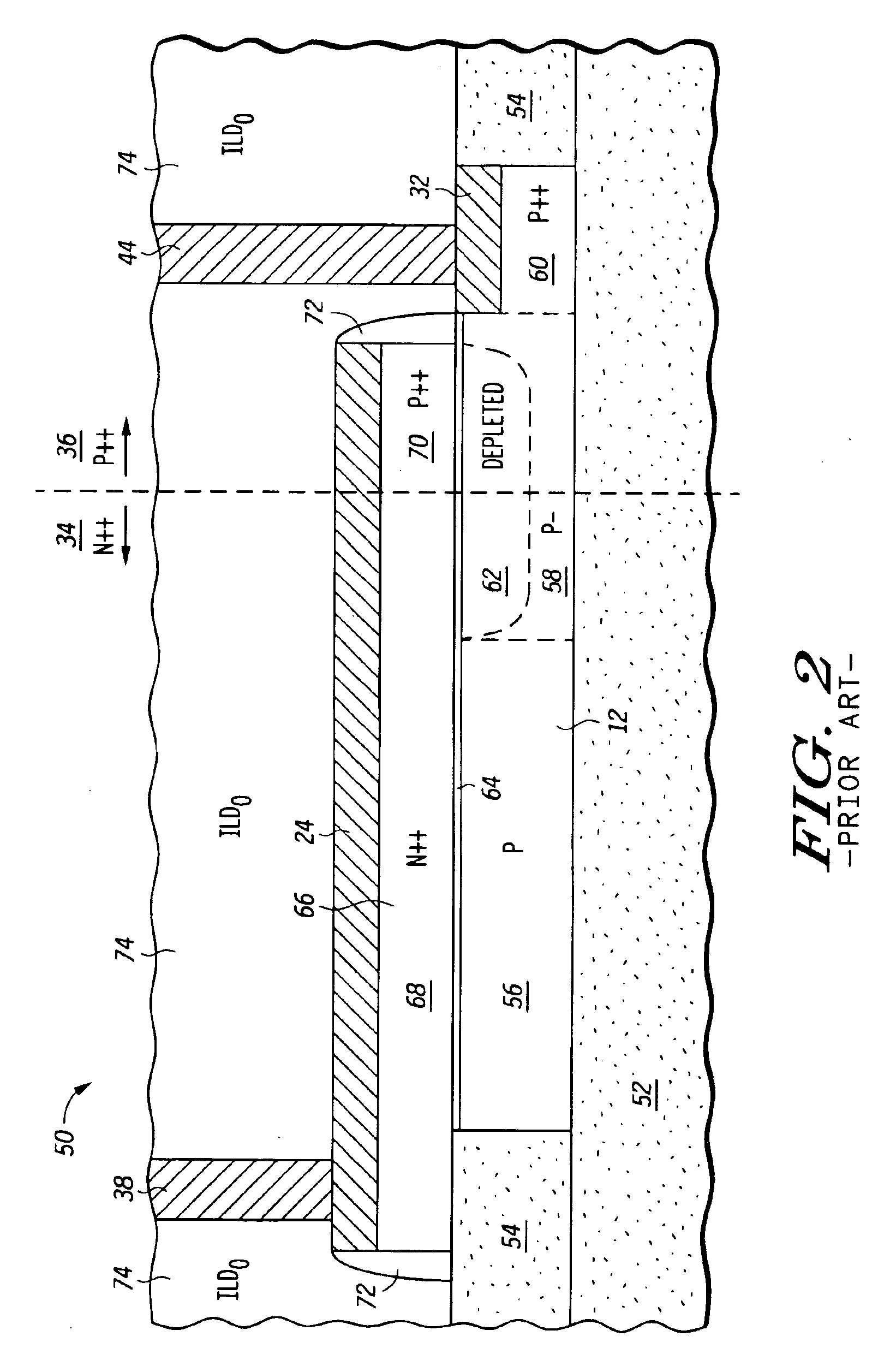

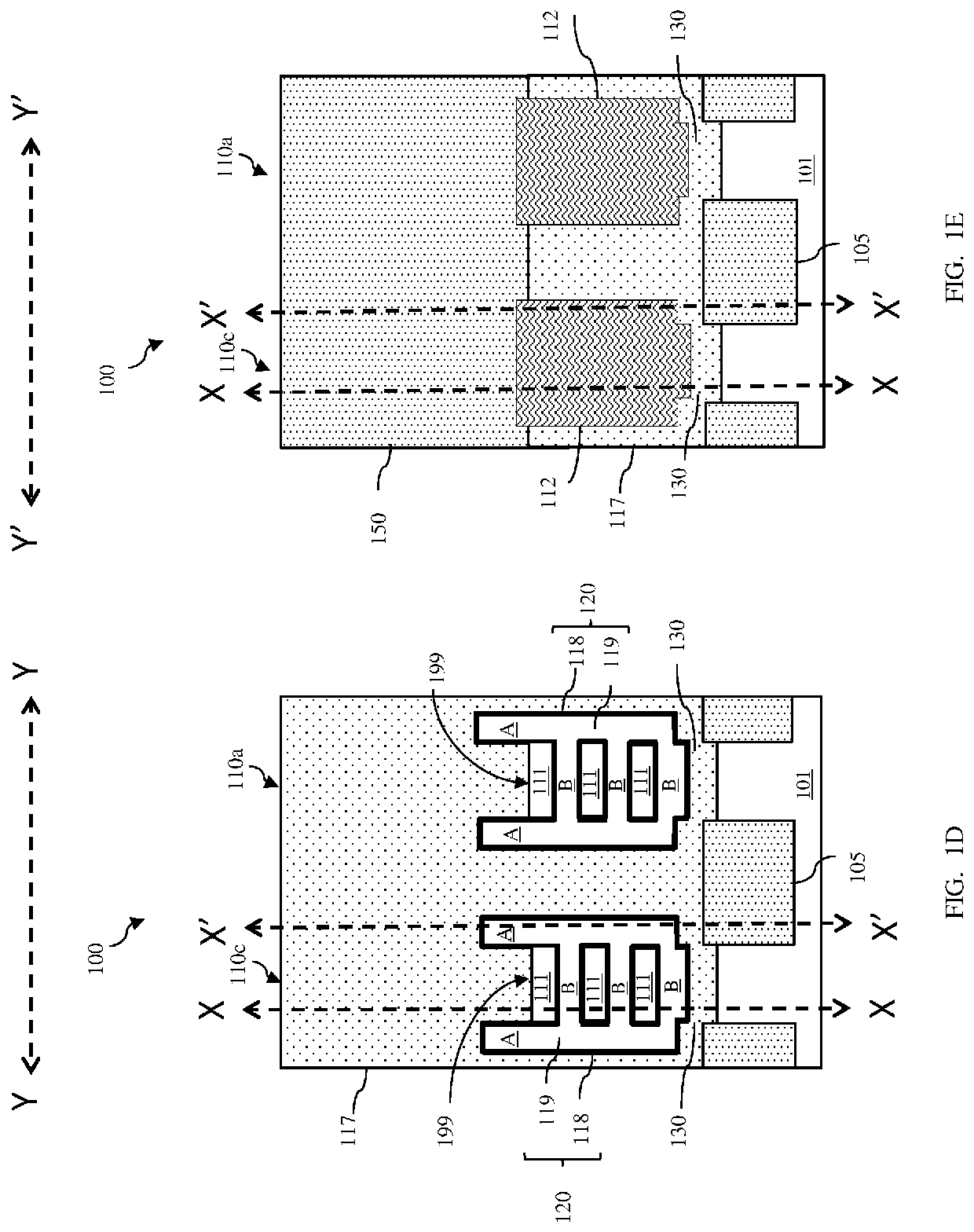

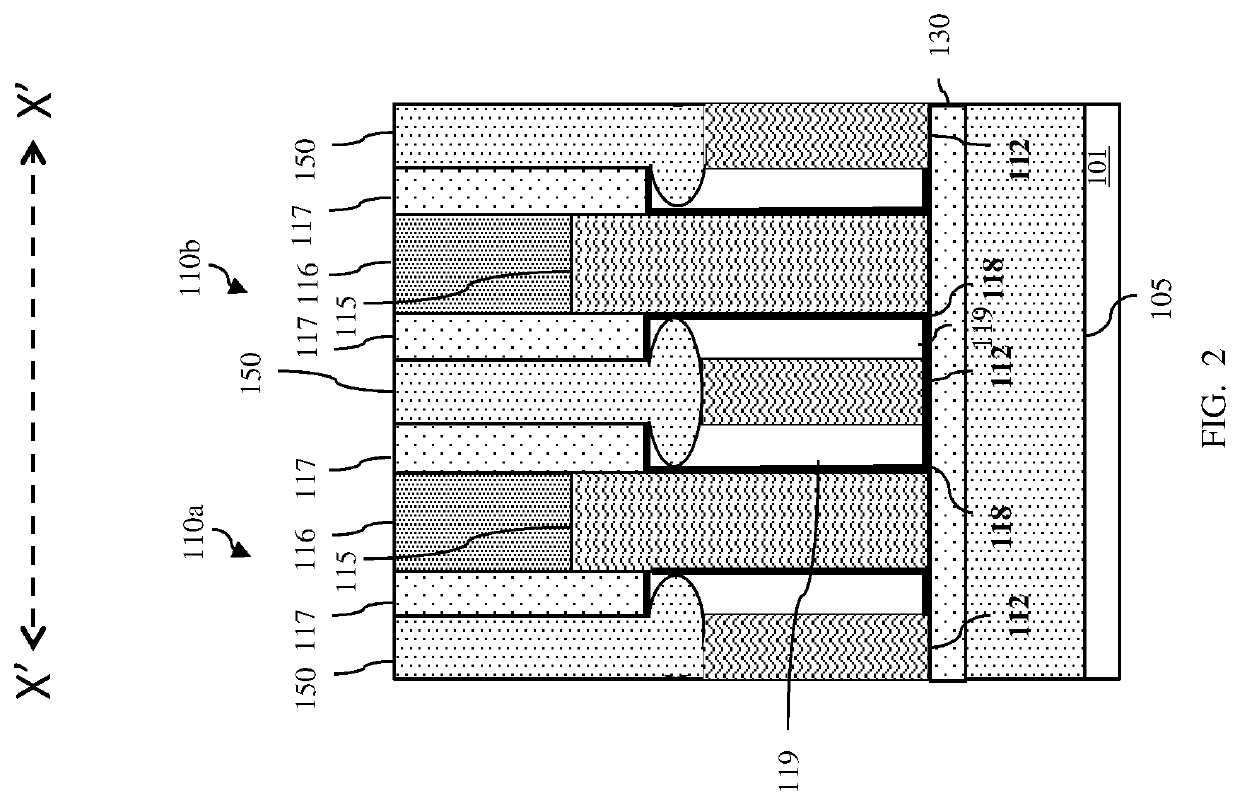

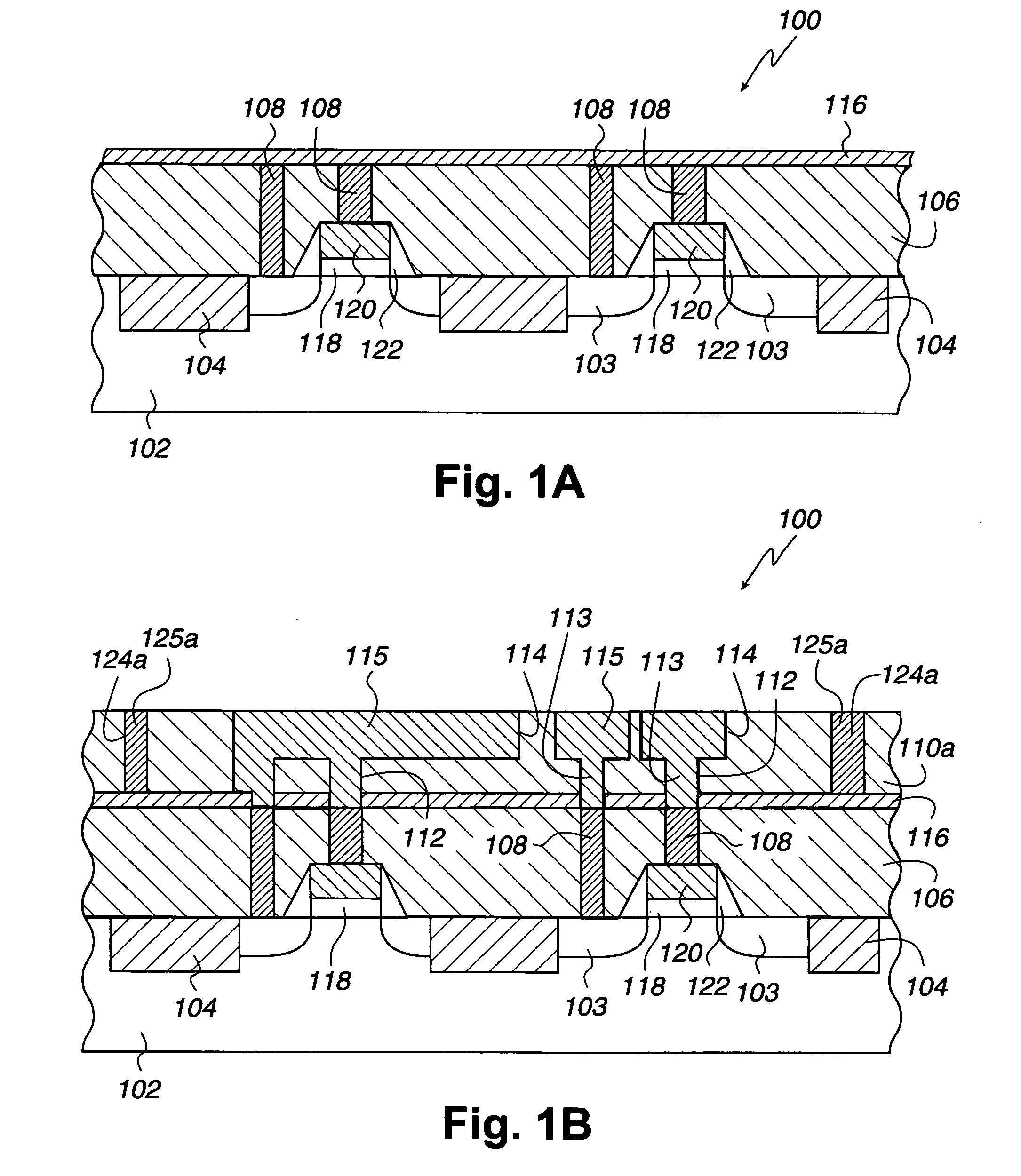

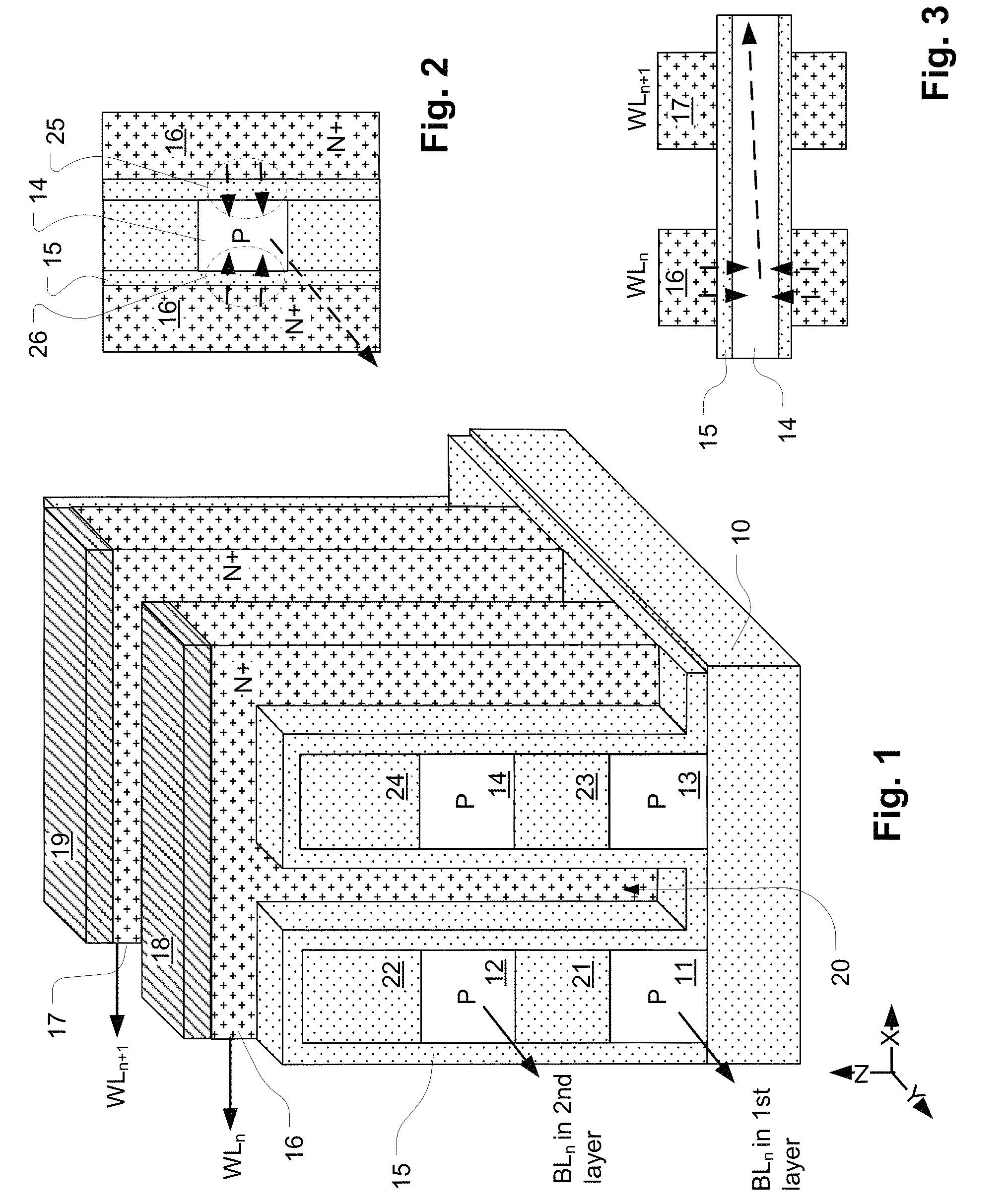

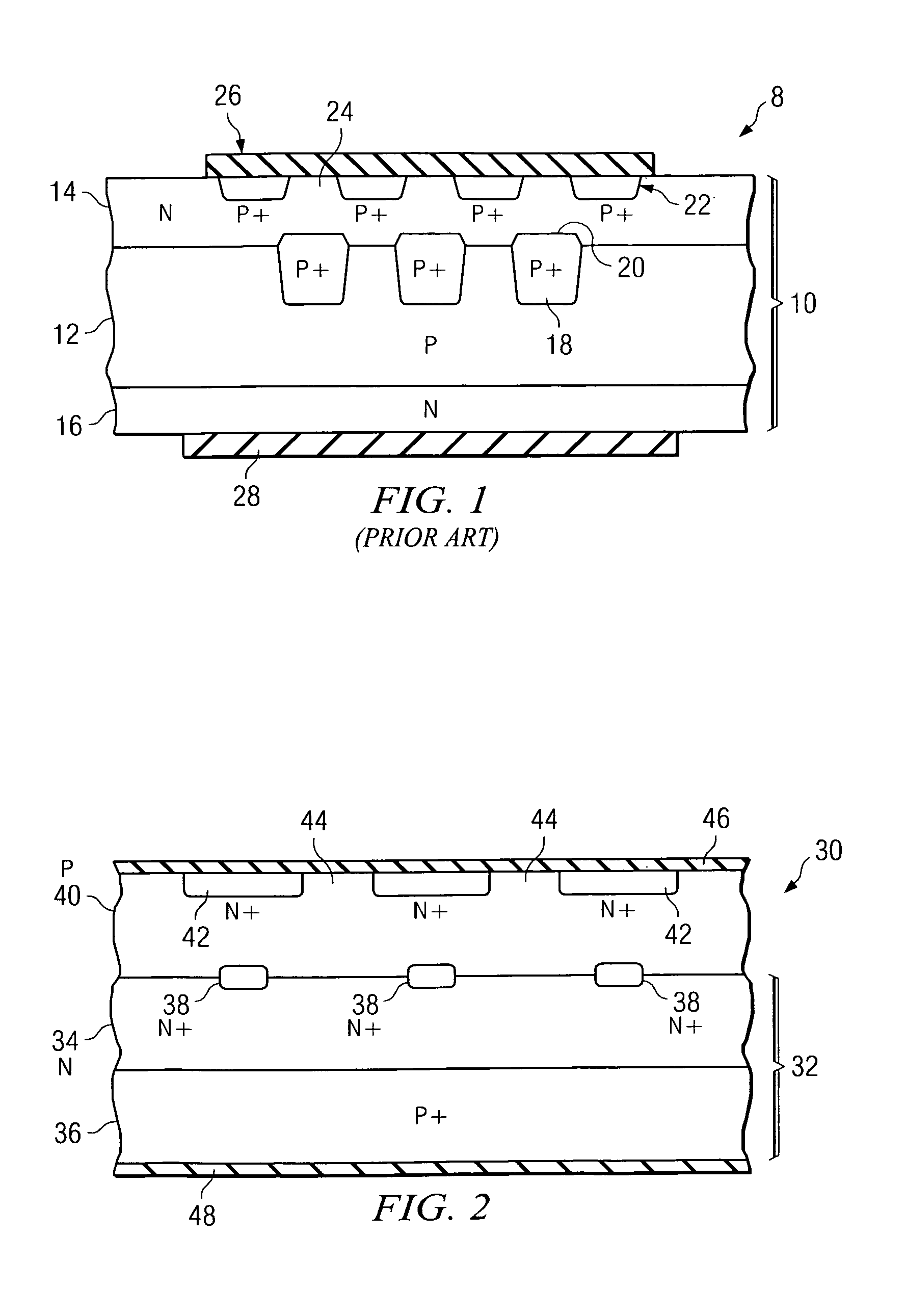

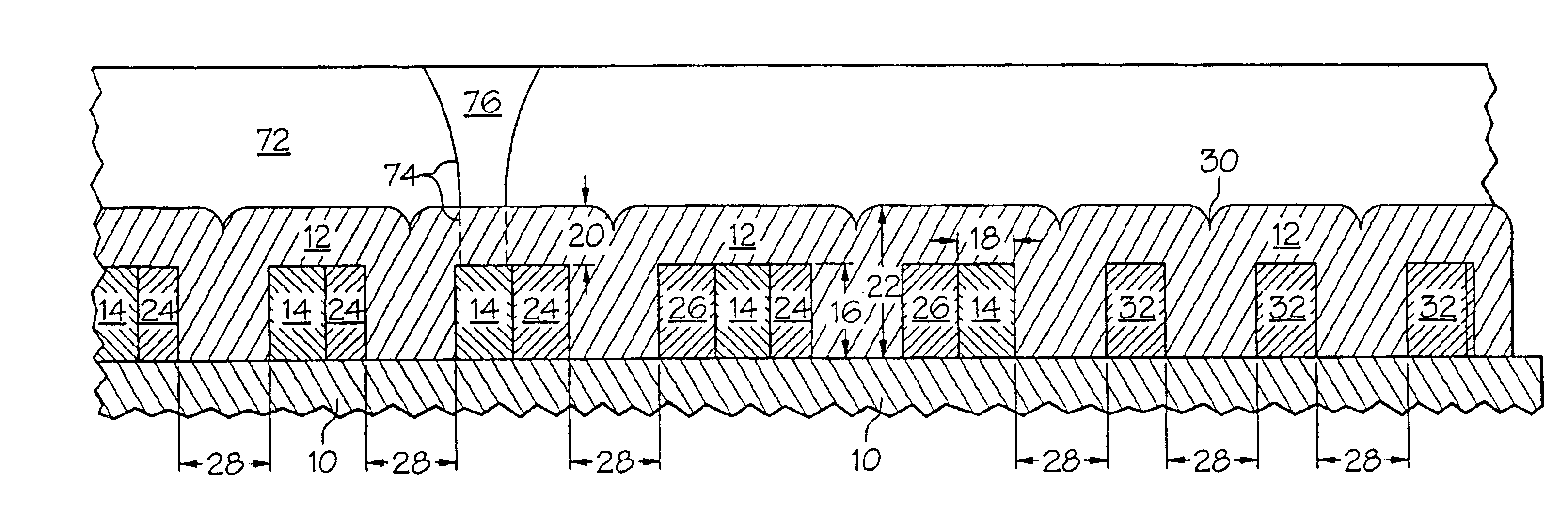

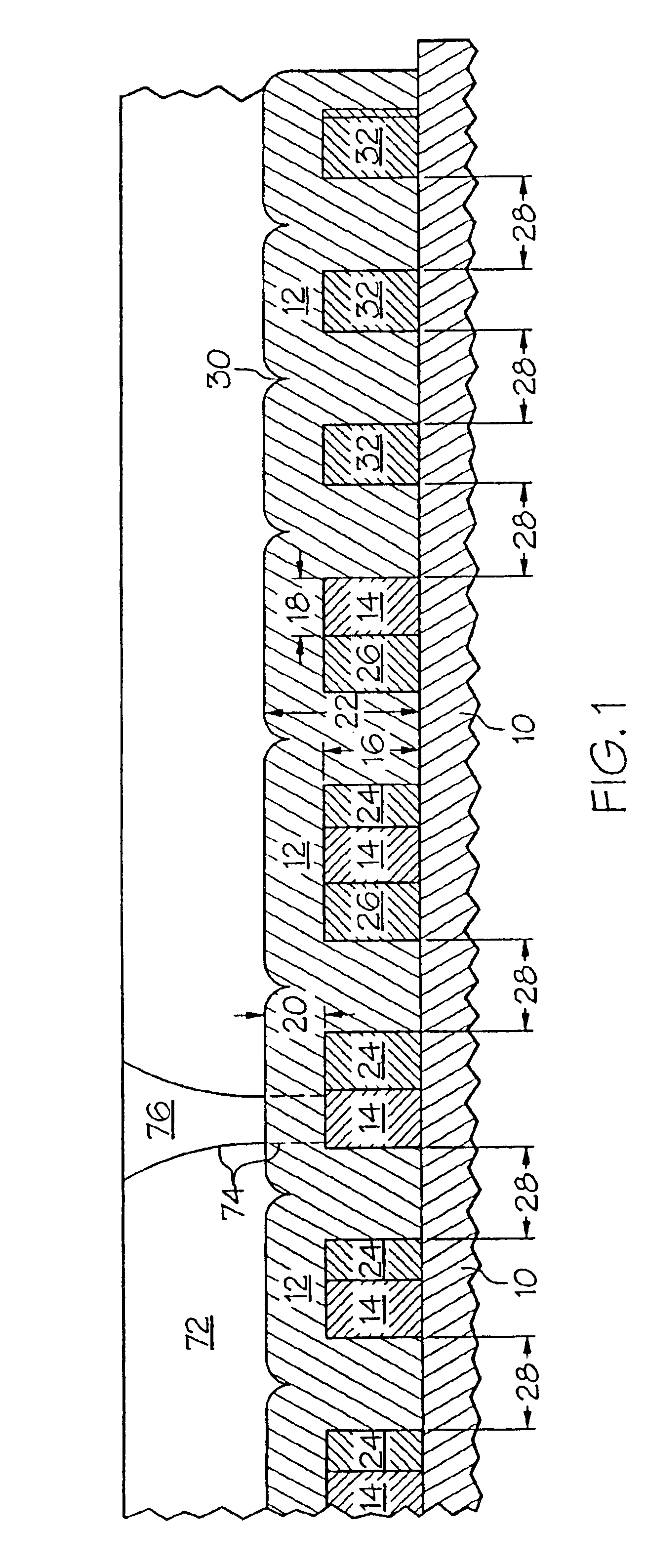

Method and apparatus for forming an SOI body-contacted transistor

ActiveUS20050127442A1Minimize parasitic capacitanceMinimize gate electrode leakageTransistorSolid-state devicesBody contactParasitic capacitance

A method for forming a silicon-on-insulator transistor (80) includes forming an active region (82) overlying an insulating layer (122), wherein a portion of the active region provides an intrinsic body region (126). A body tie access region (128) is also formed within the active region, overlying the insulating layer and laterally disposed adjacent the intrinsic body region, making electrical contact to the intrinsic body region. A gate electrode (134) is formed overlying the intrinsic body region for providing electrical control of the intrinsic body region, the gate electrode extending over a portion (137) of the body tie access region. The gate electrode is formed having a substantially constant gate length (88) along its entire width overlying the intrinsic body region and the body tie access region to minimize parasitic capacitance and gate electrode leakage. First and second current electrodes (98,100) are formed adjacent opposite sides of the intrinsic body region. In addition, a body tie diffusion (130) is formed within the active region and laterally offset from the body tie access region and electrically coupled to the body tie access region.

Owner:NORTH STAR INNOVATIONS

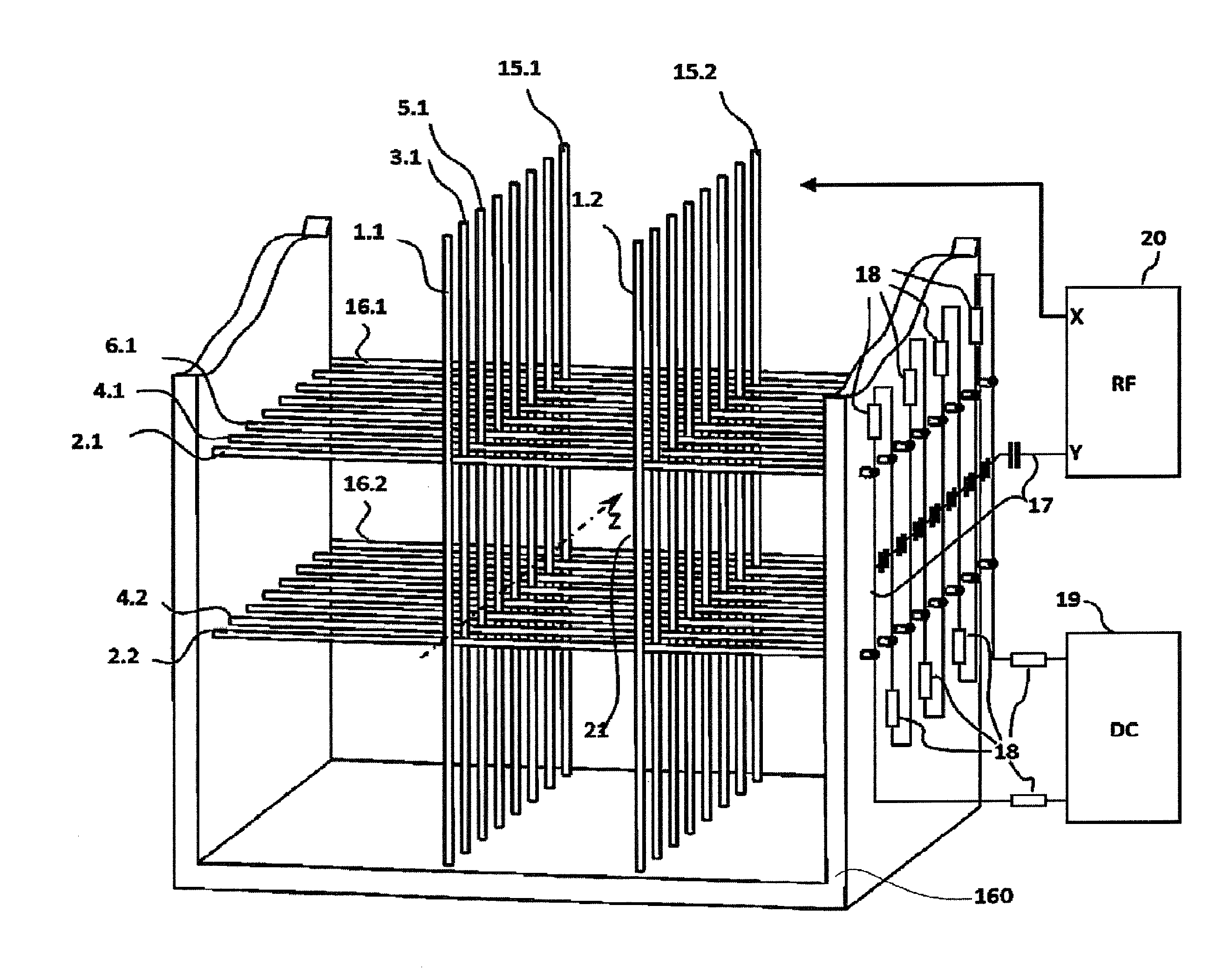

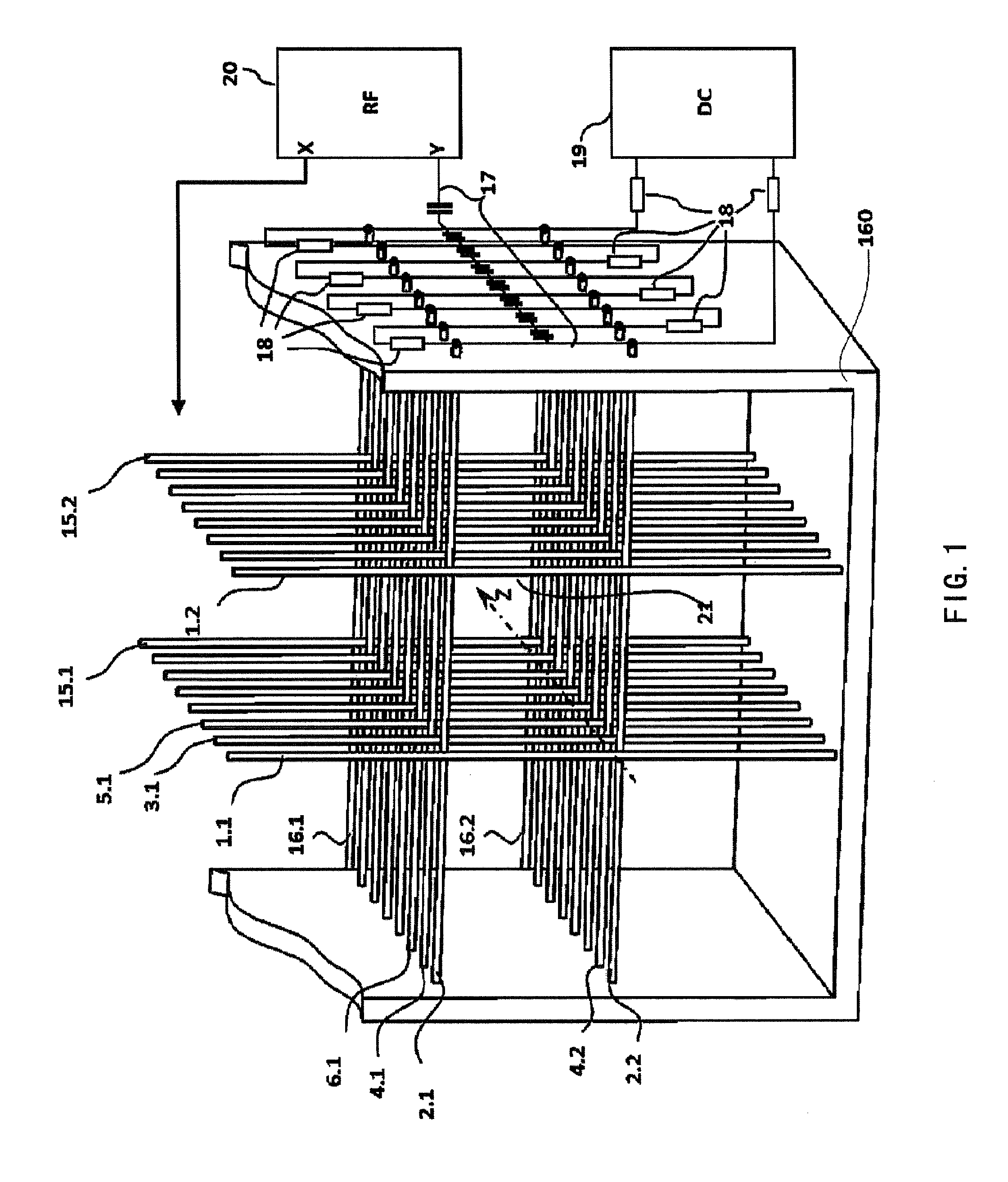

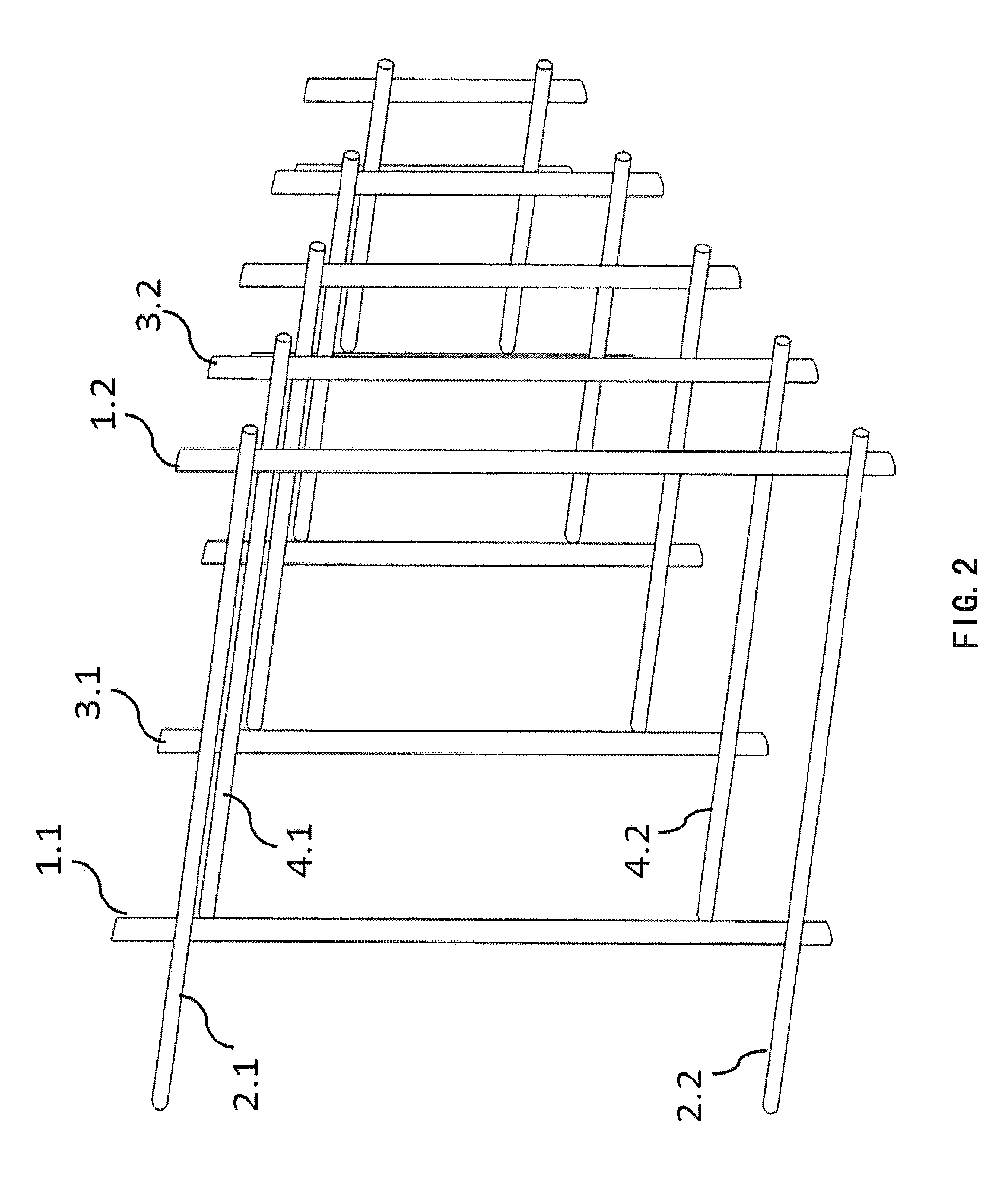

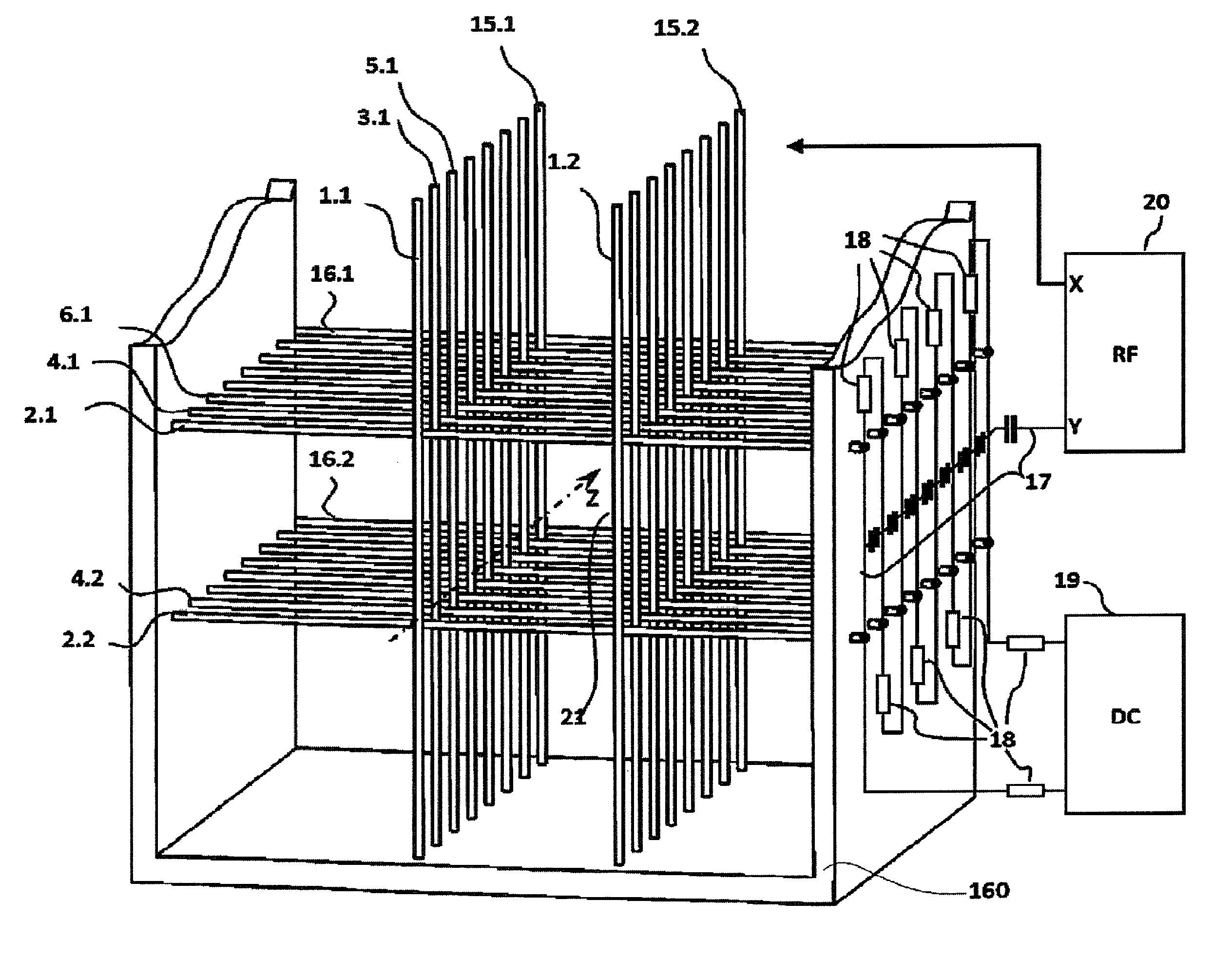

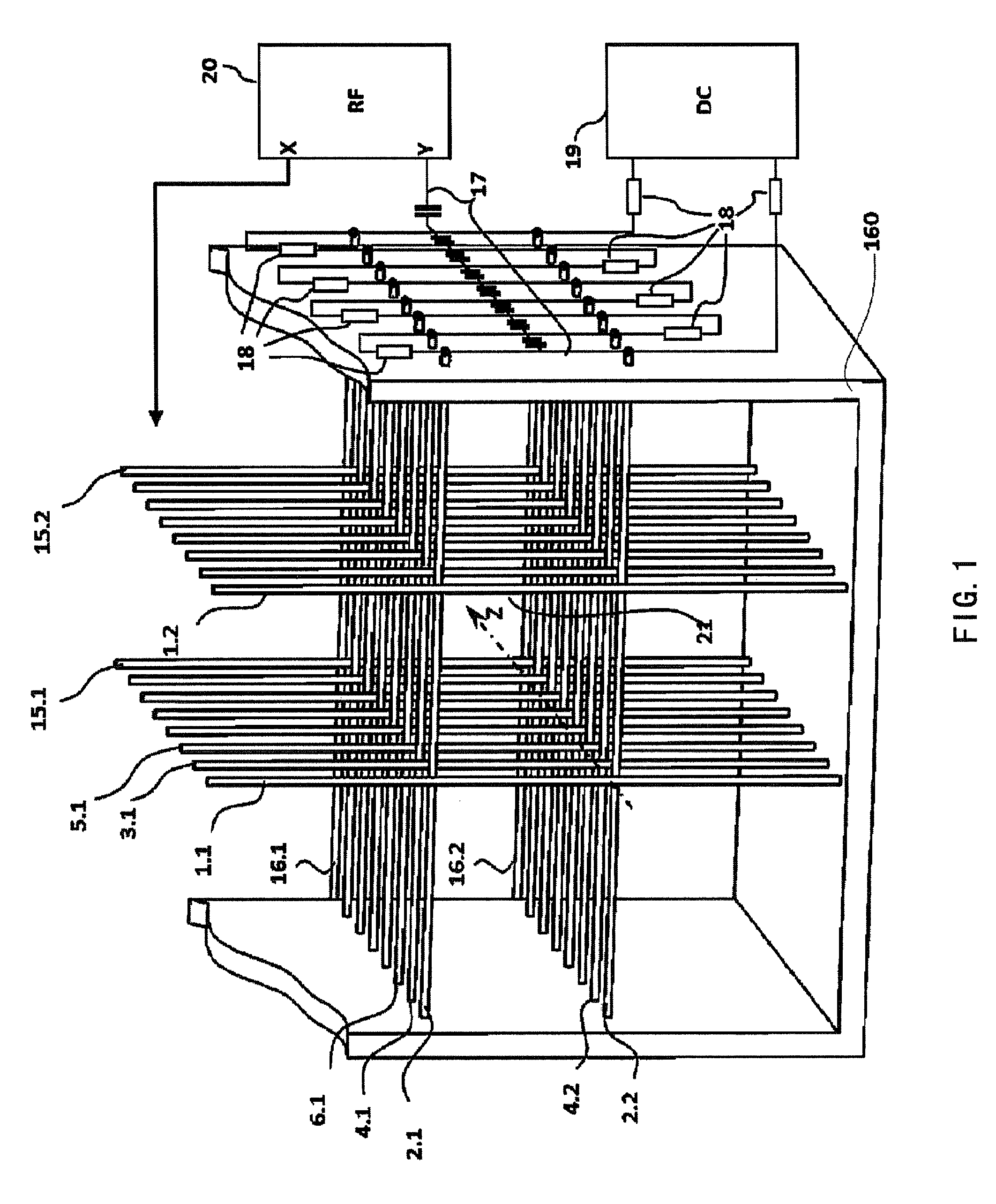

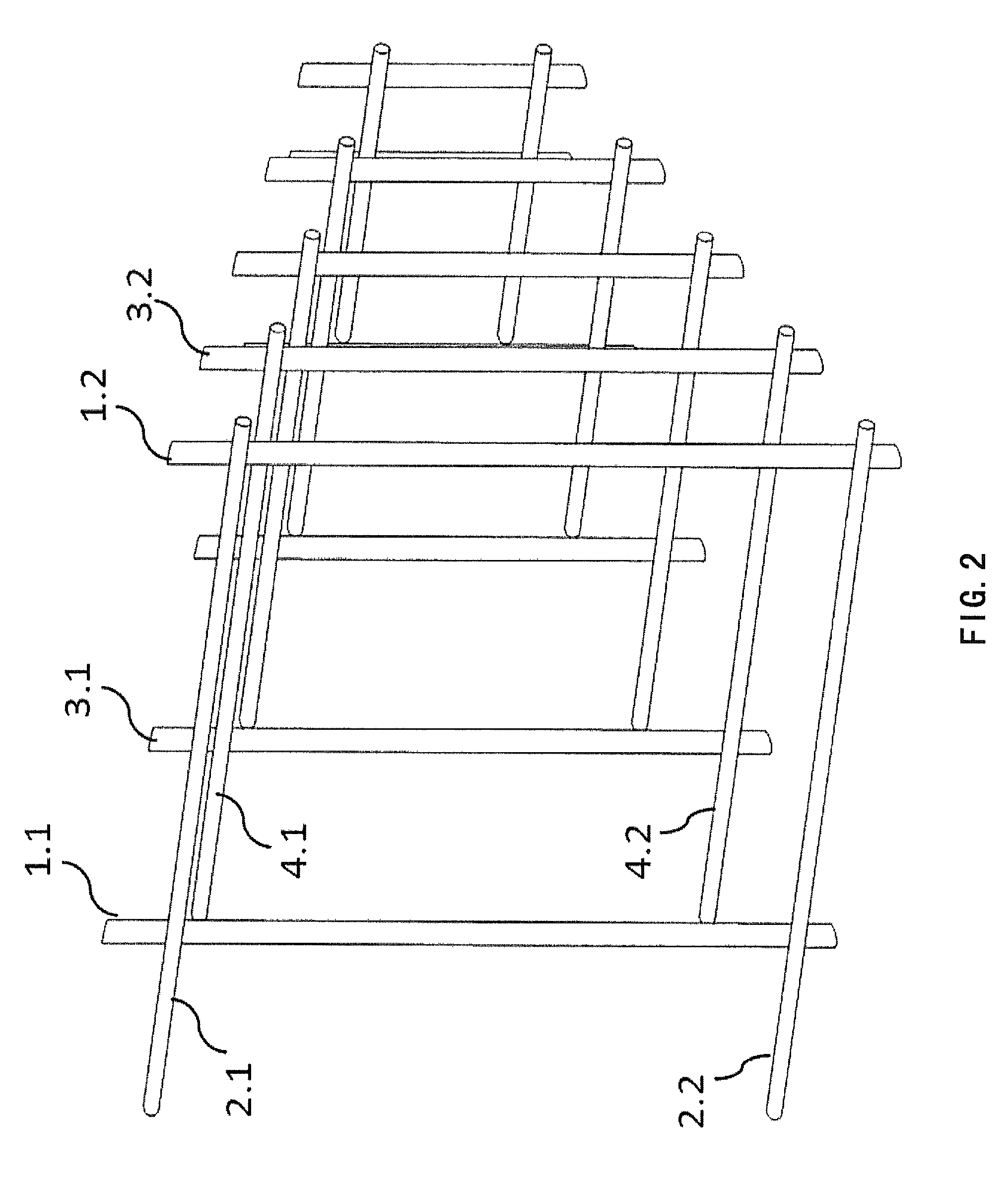

A wire electrode based ion guide device

InactiveUS20130187044A1Efficiently focusMinimize impactTime-of-flight spectrometersIsotope separationElectric fieldMultiple layer

This invention presents a kind of ion guide device comprising multiple layers of stretched wire electrodes crossing in space. These wire electrodes are distributed along a defined ion guiding axis in the ion guide device. Each layer of wire electrodes contains at least two wire electrodes with some distance away from the guiding axis, and rotates with an angle relative to wire electrodes on neighboring layer. The ion guide contains multiple layers of wire electrodes to form a cage-like ion guide tunnel and keeps the mounting framework of those wire electrodes outside of the ion guide tunnel, thus reducing the interference of the gas flows from the ion guide device. A power supply provides voltage to each layer of wire electrodes, creates an electric field which focuses the ions towards the guiding axis.

Owner:SHIMADZU RES LAB SHANGHAI +1

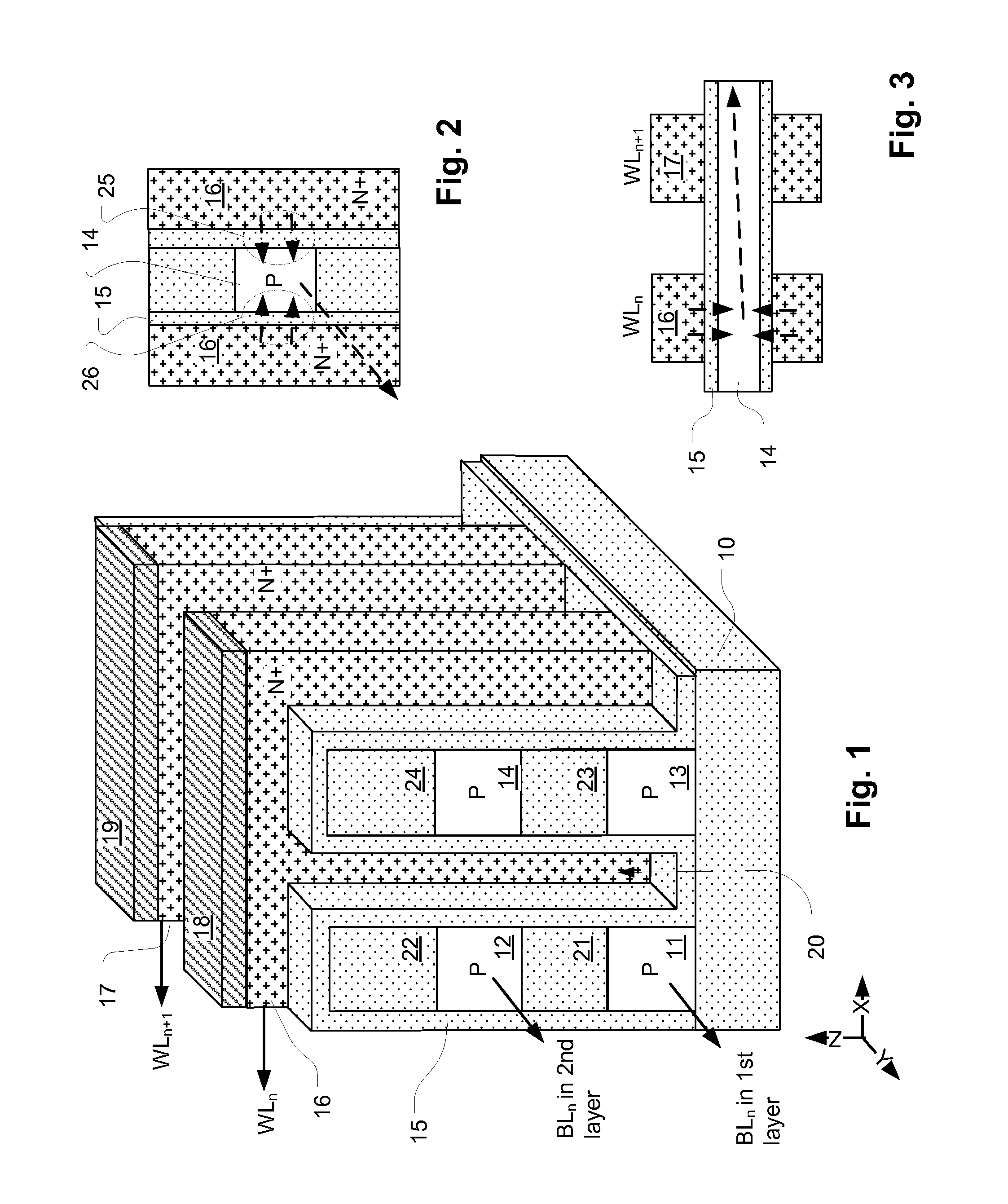

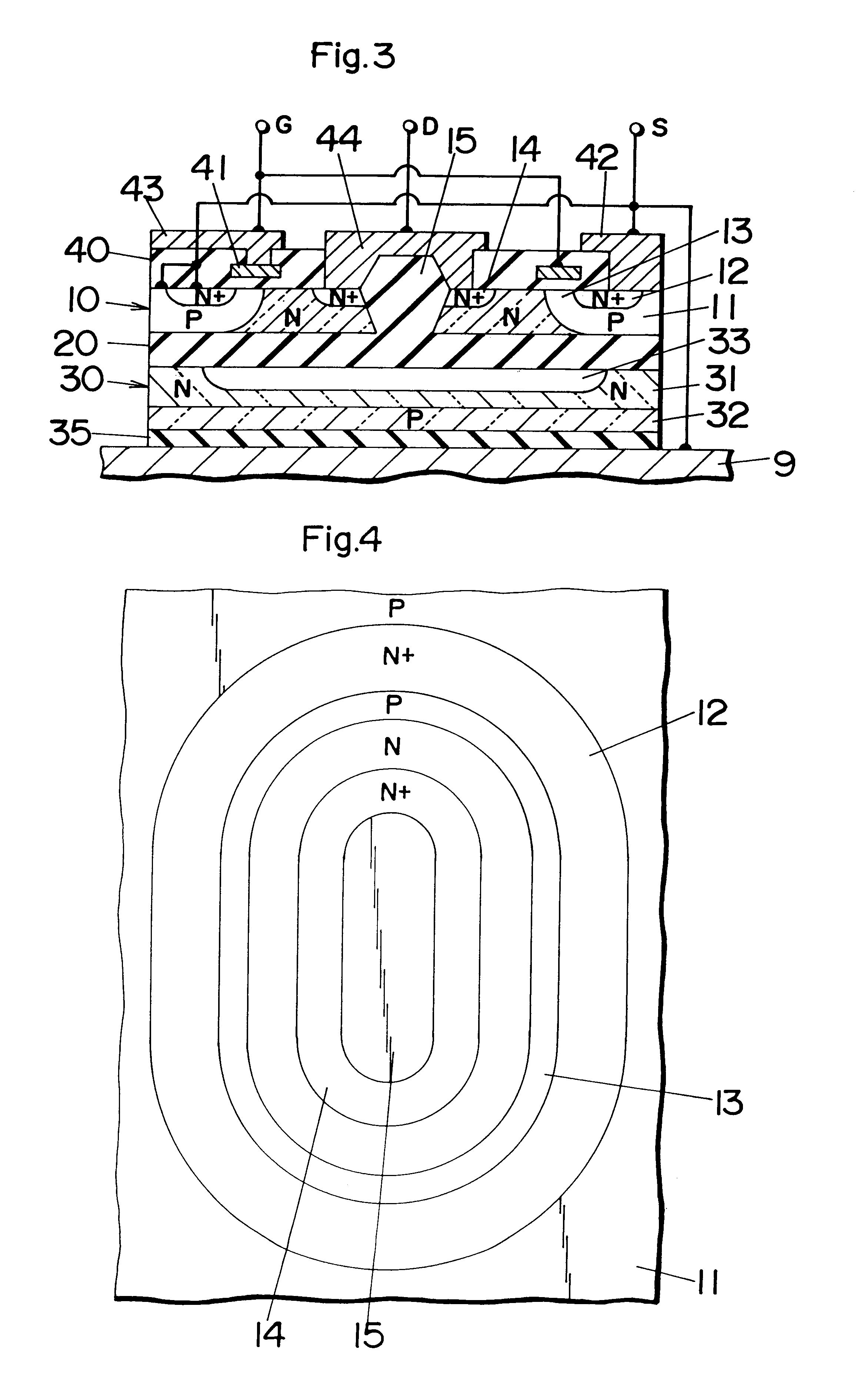

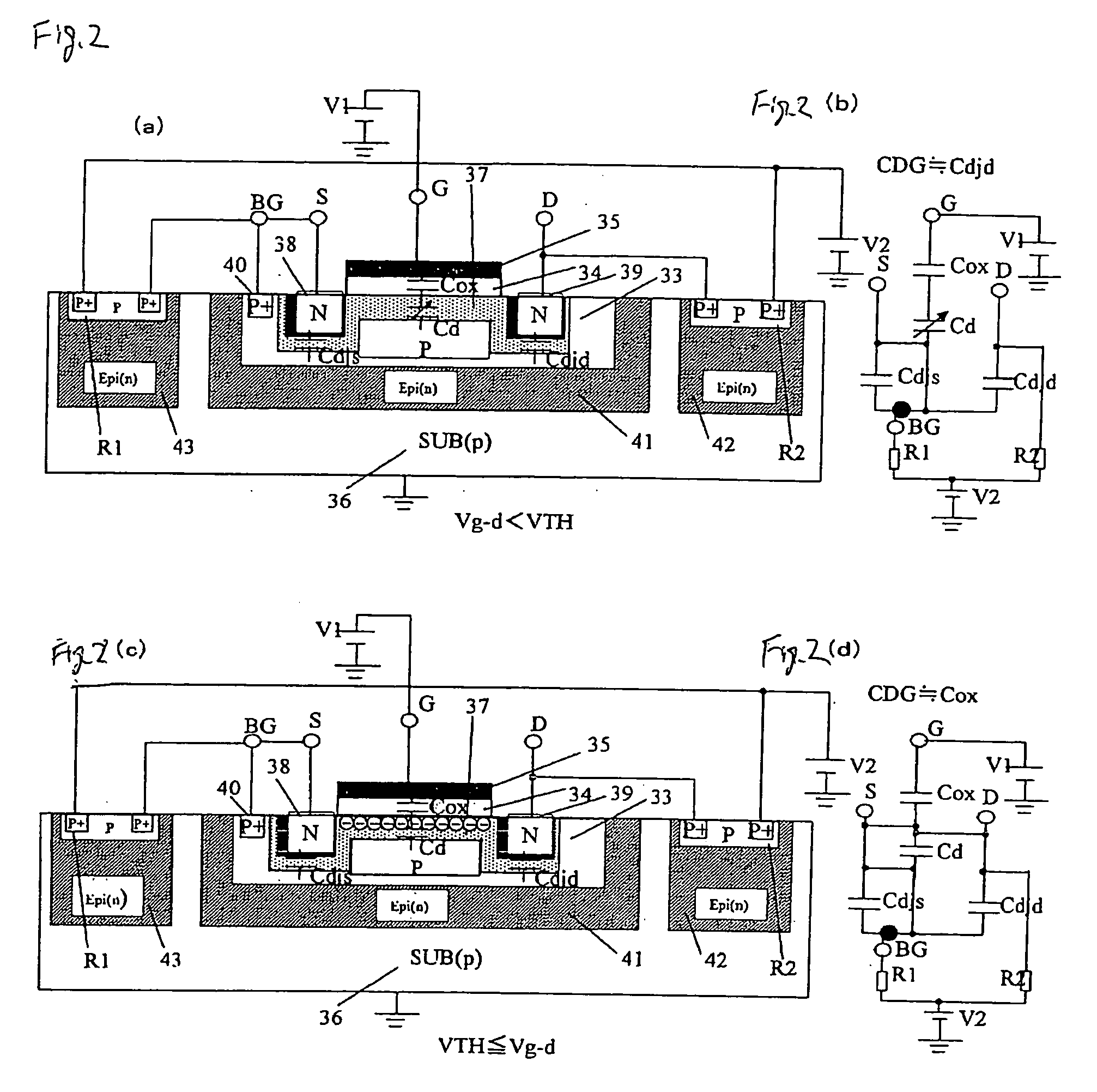

Method of making a device threshold control of front-gate silicon-on-insulator MOSFET using a self-aligned back-gate

InactiveUS7018873B2Minimize capacitanceImprove performanceTransistorSemiconductor/solid-state device manufacturingCapacitanceMOSFET

Owner:GLOBALFOUNDRIES INC

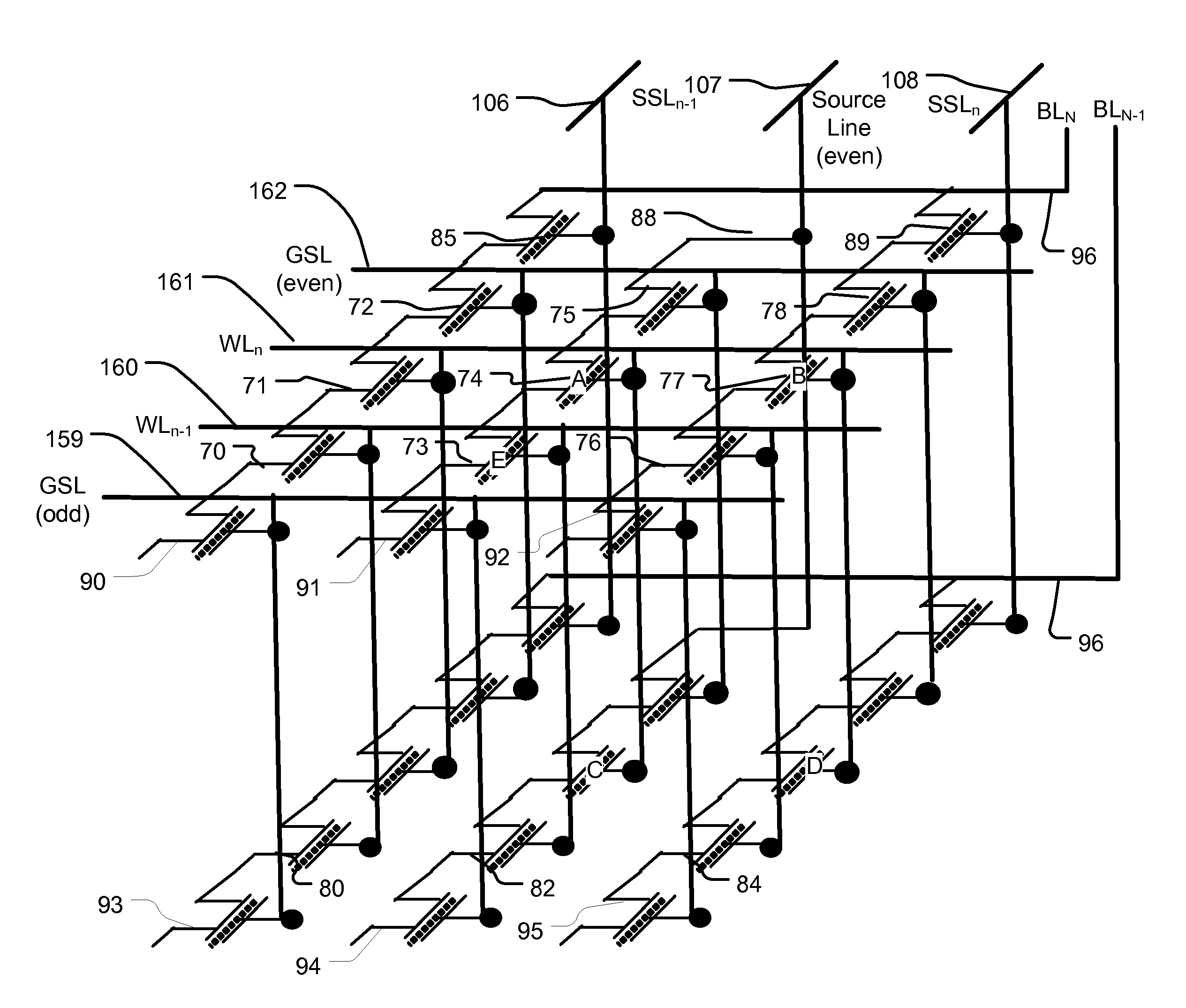

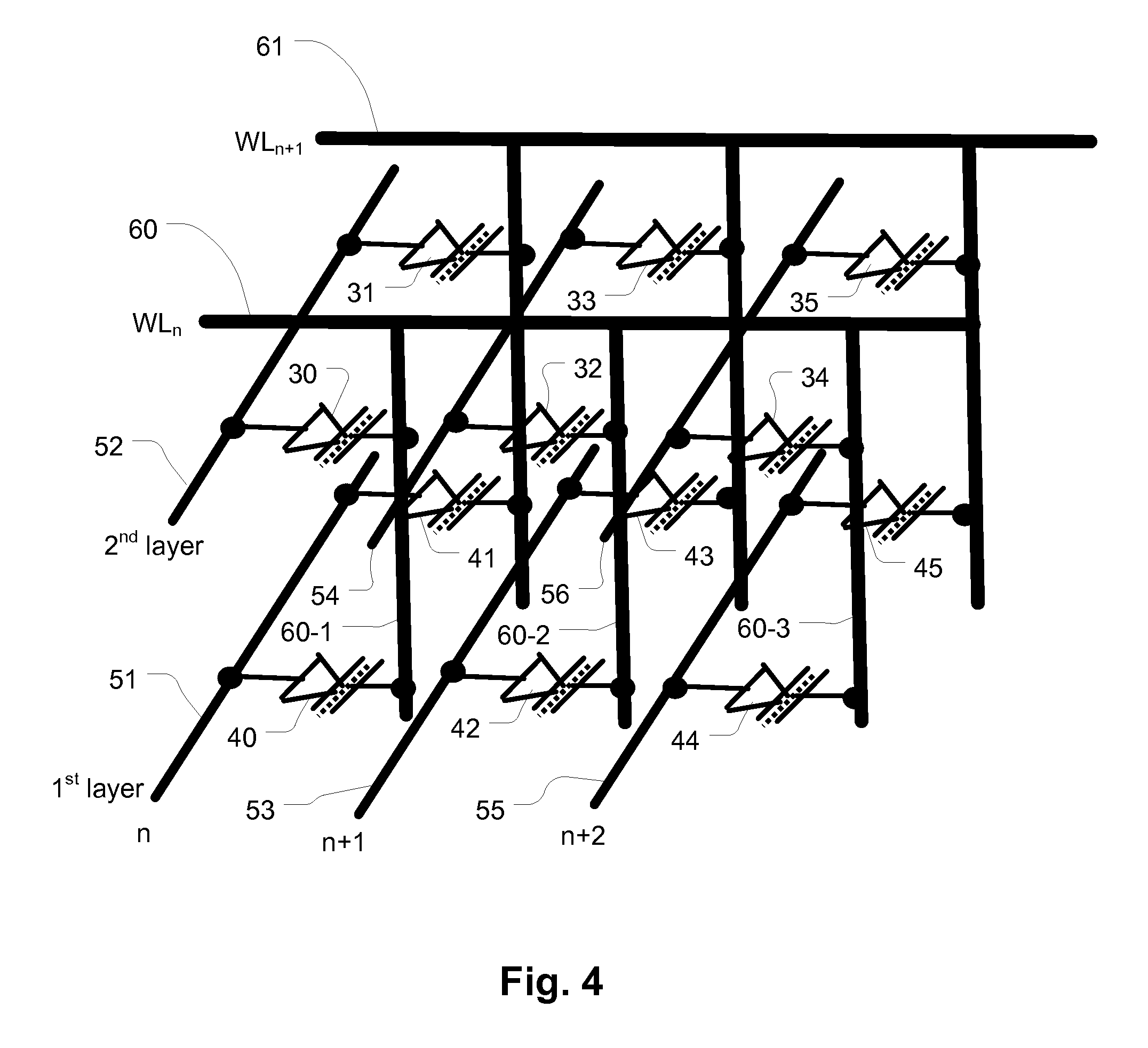

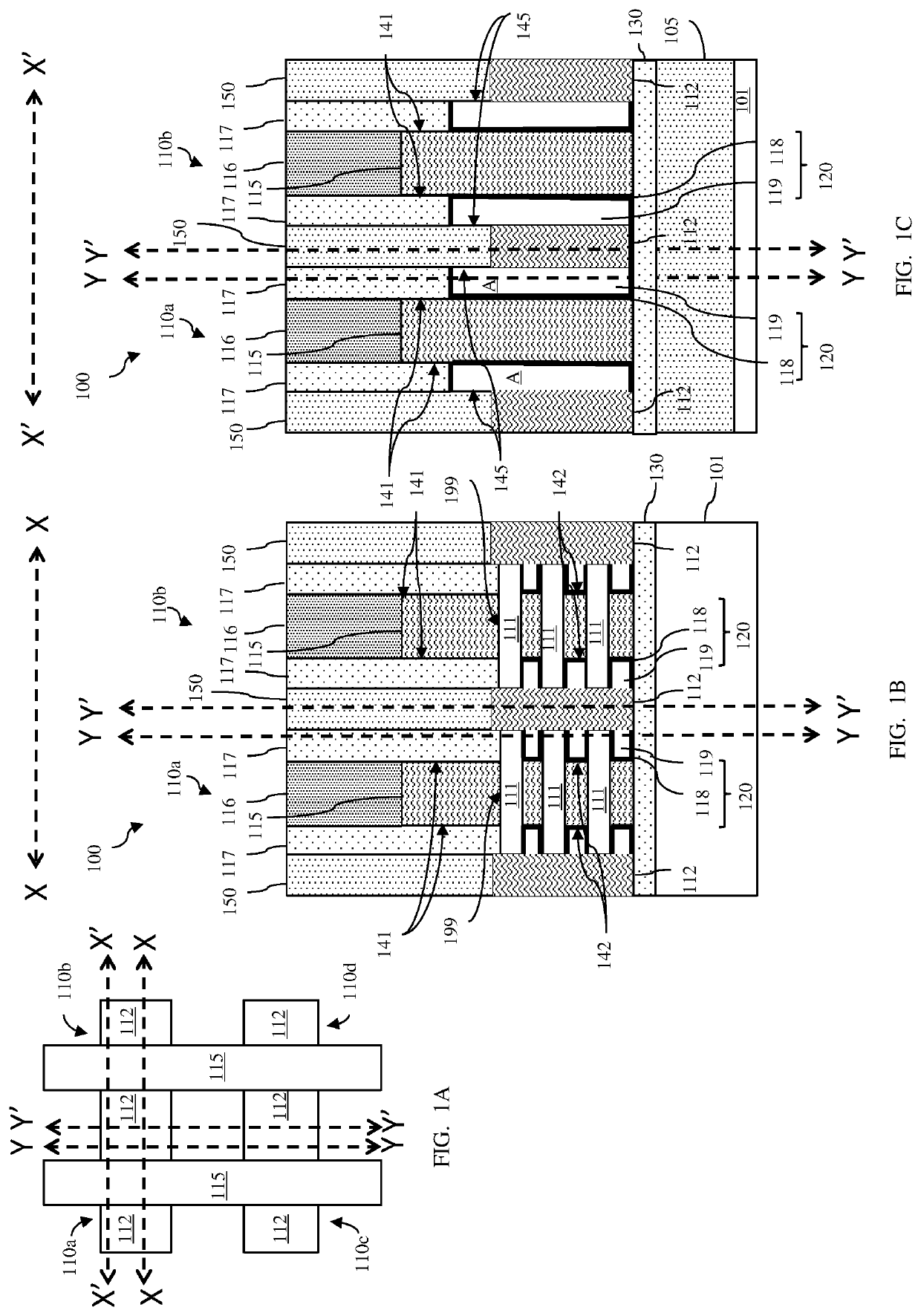

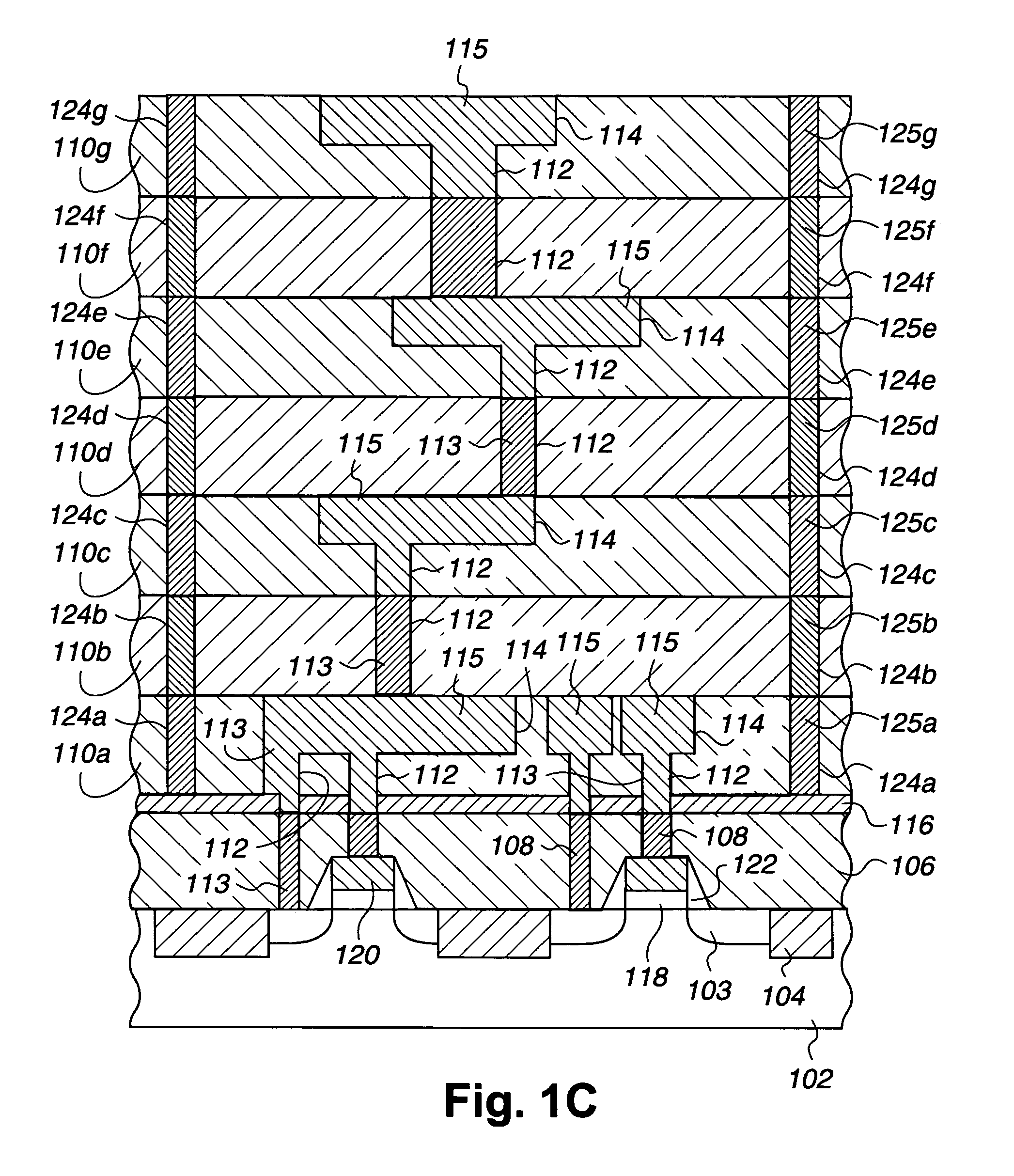

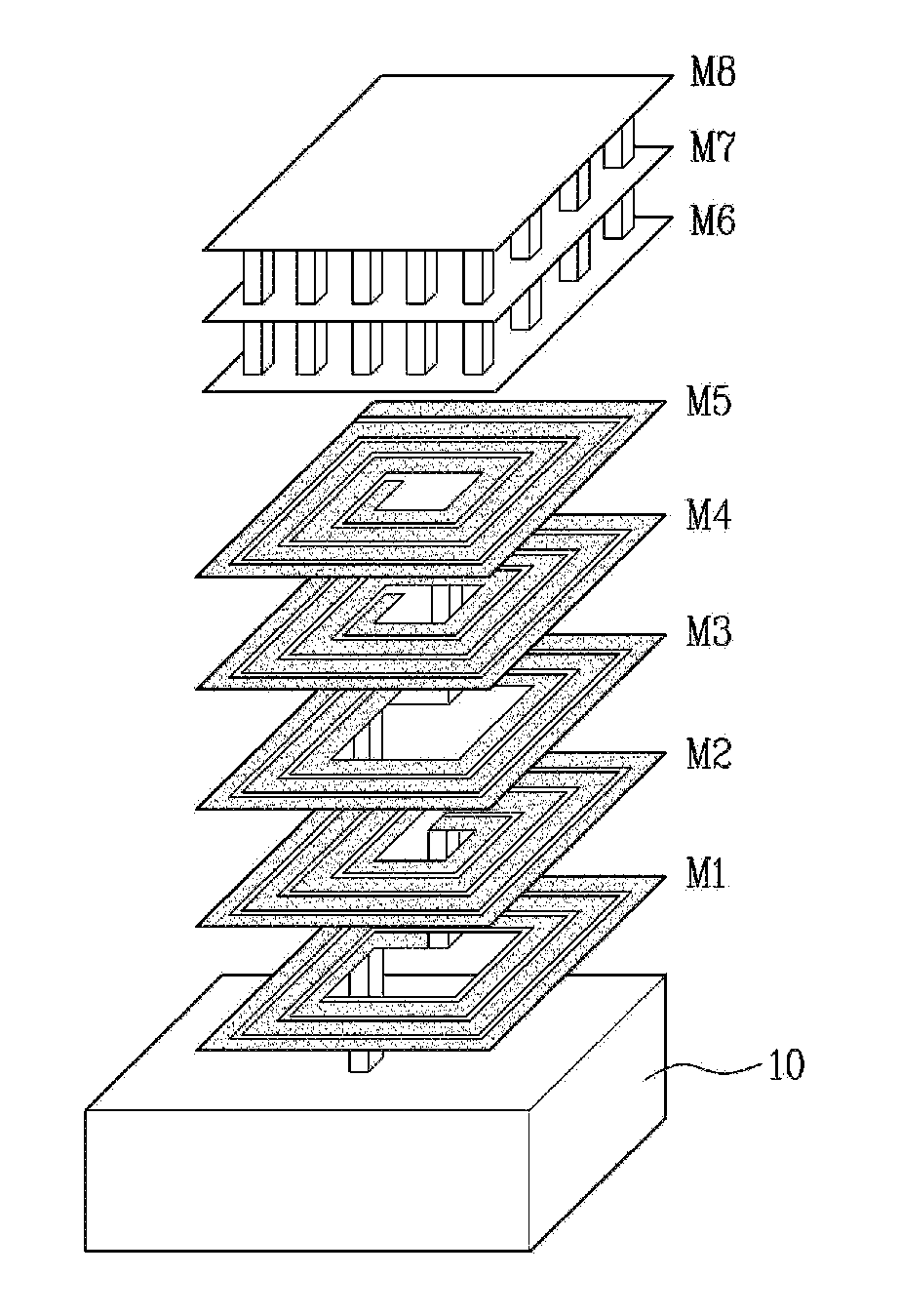

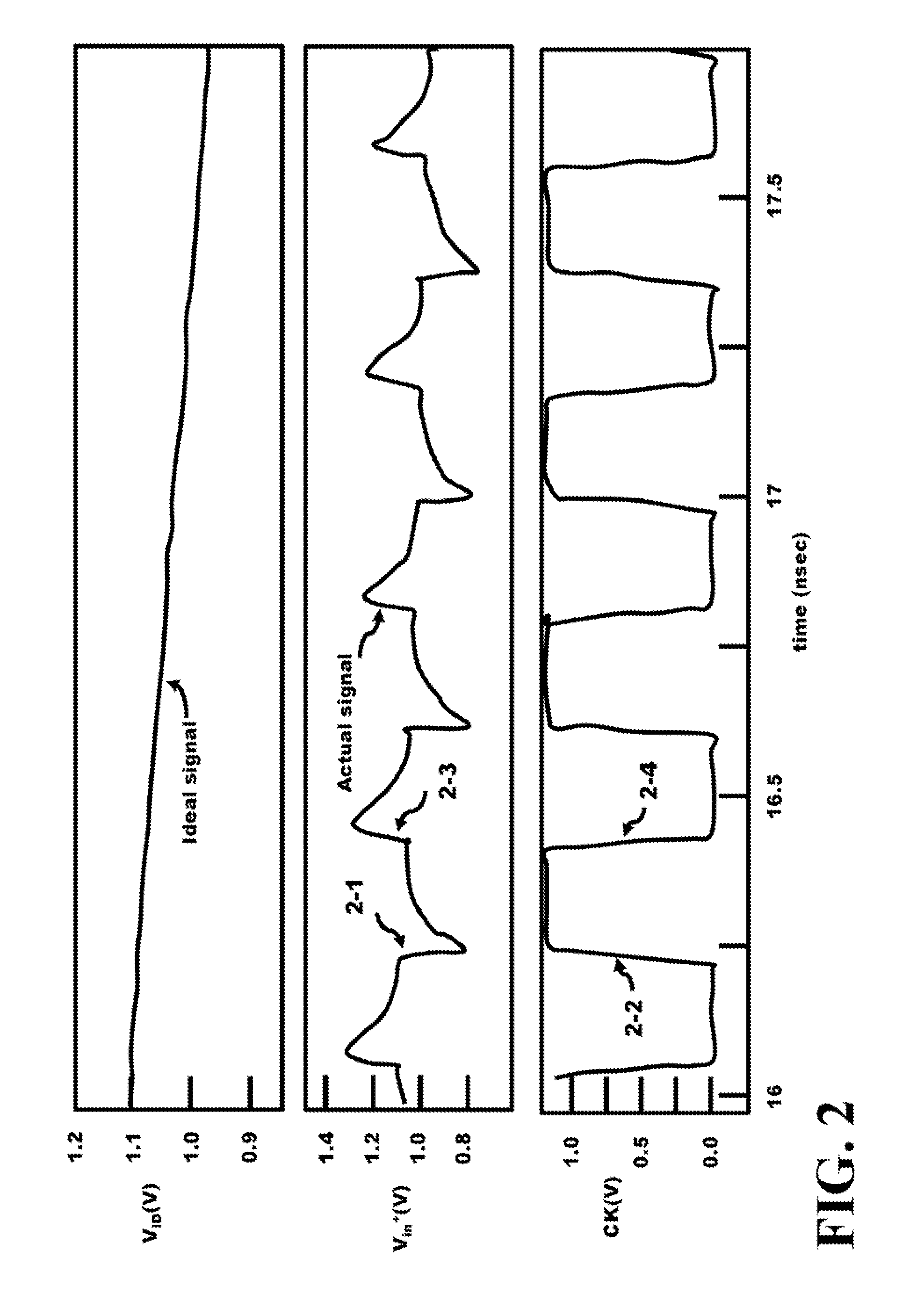

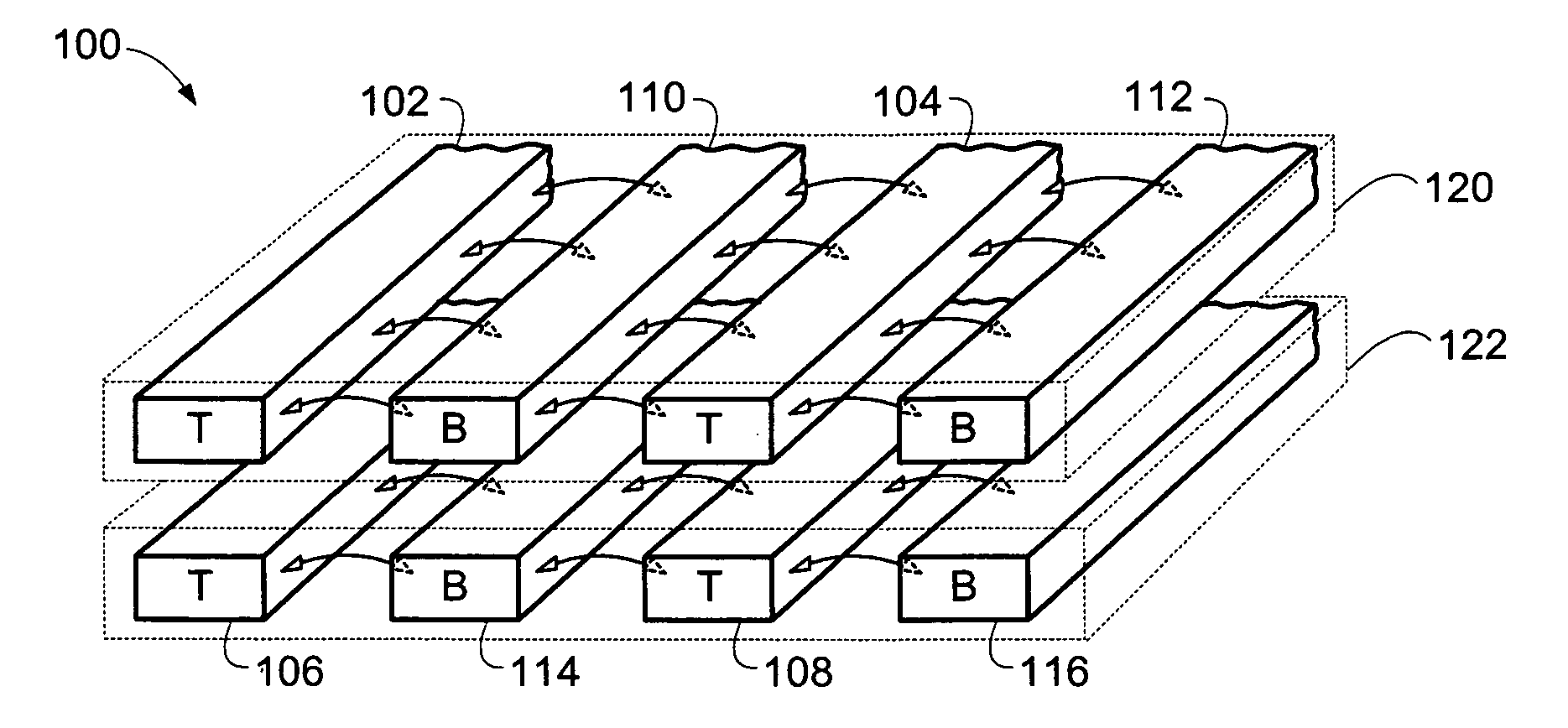

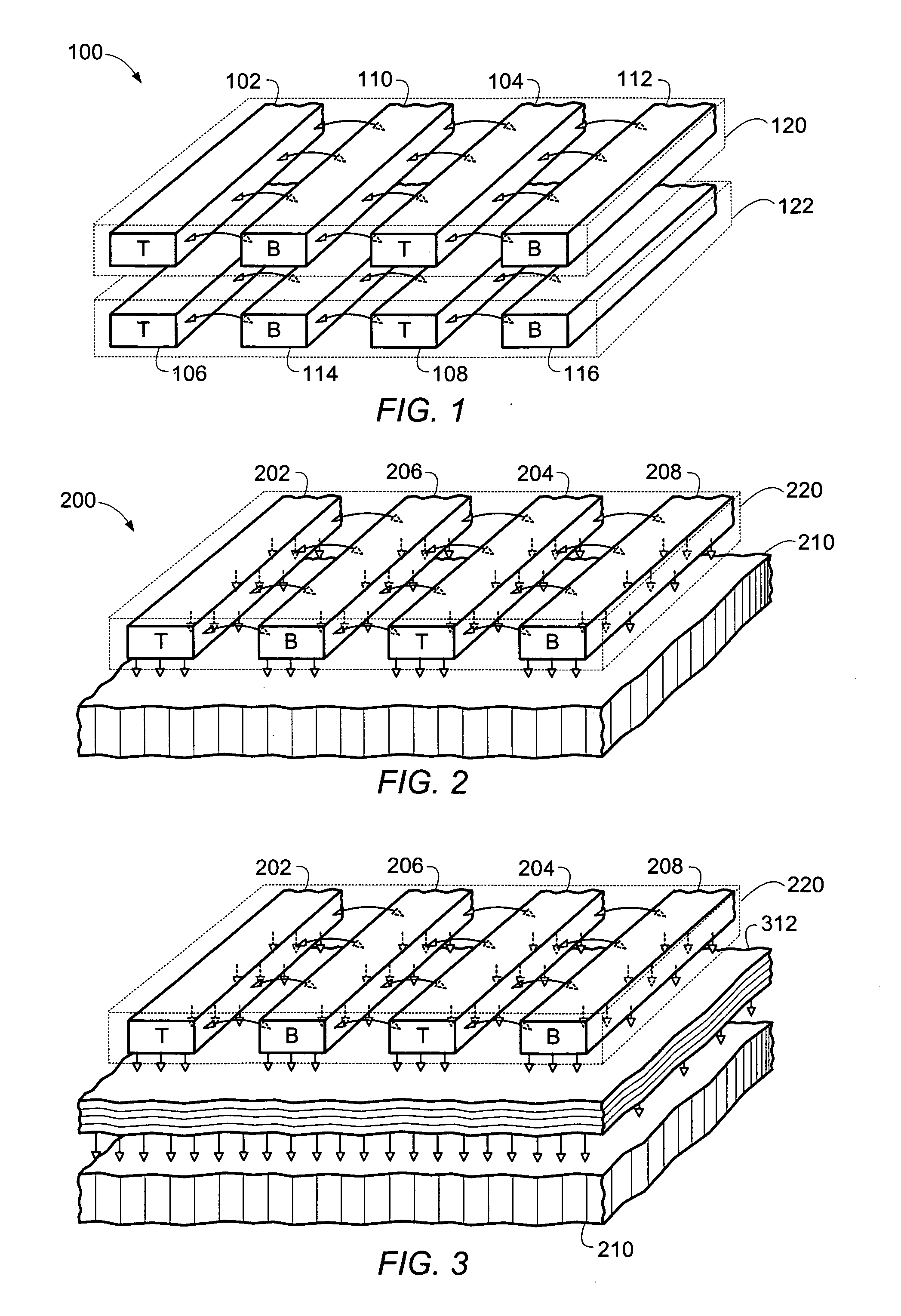

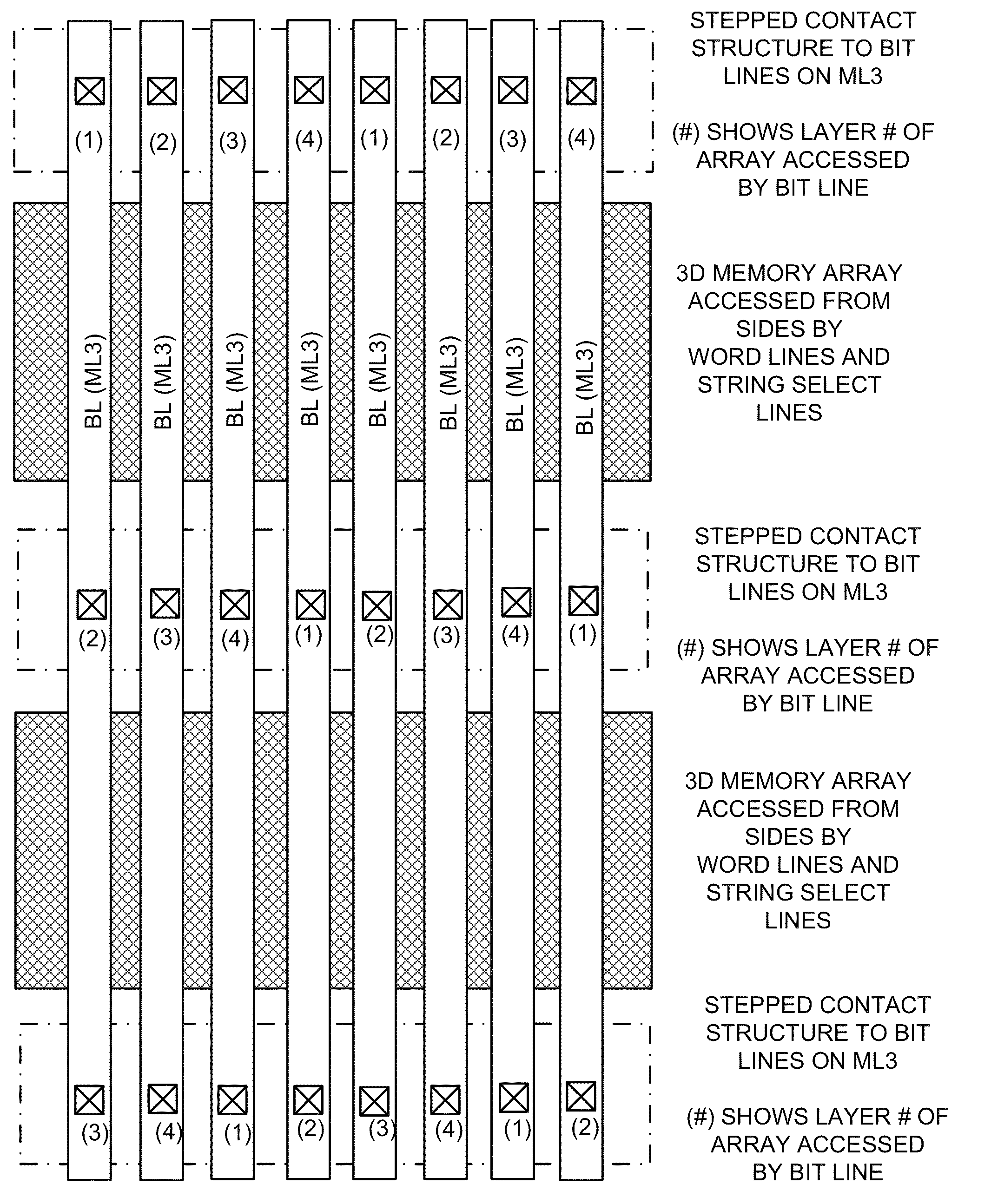

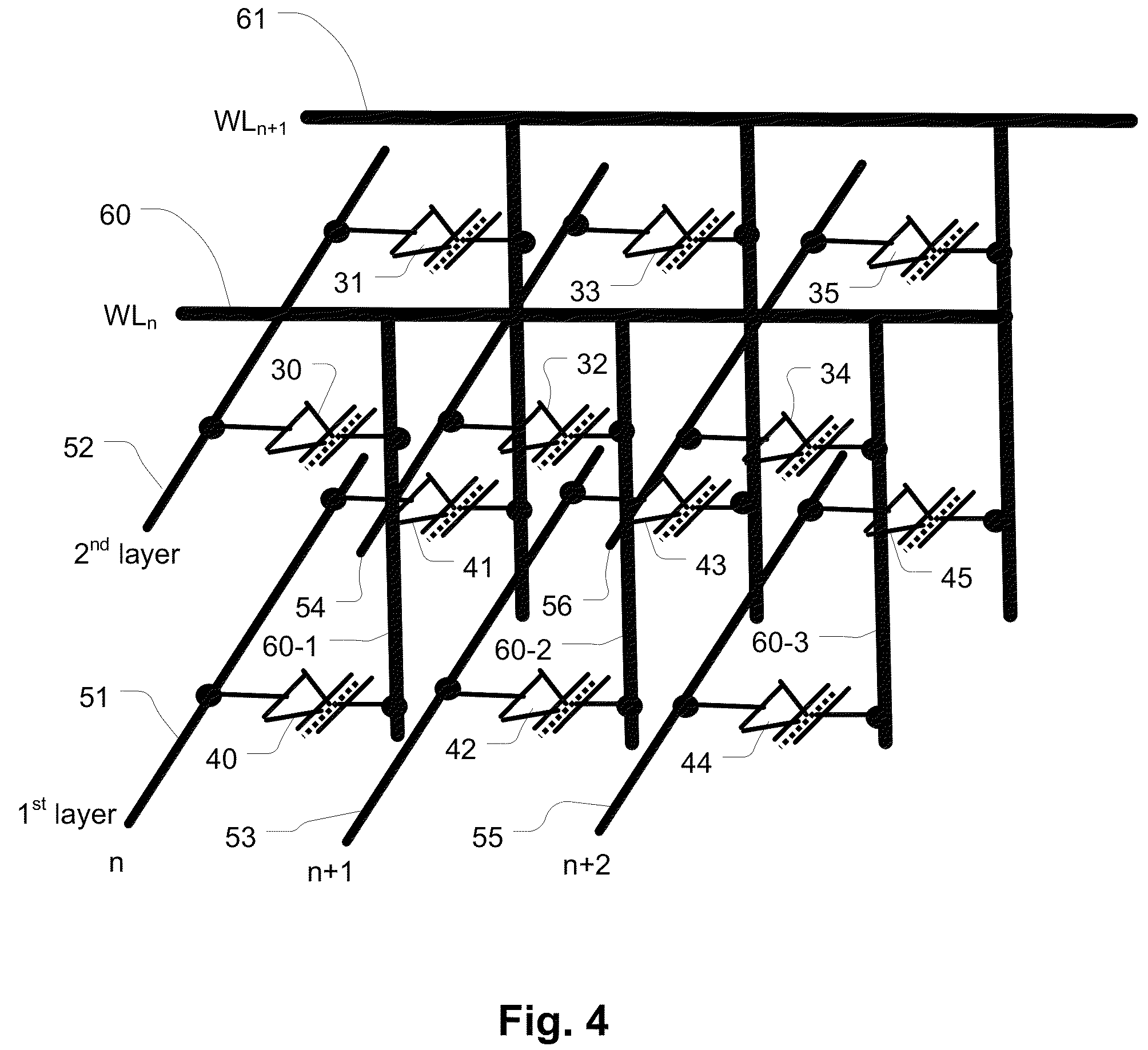

Memory Architecture of 3D Array With Improved Uniformity of Bit Line Capacitances

ActiveUS20120182802A1Good senseMinimize capacitanceTransistorSolid-state devicesCapacitance3d integrated circuit

A 3D integrated circuit memory array has a plurality of plane positions. Multiple bit line structures have a multiple sequences of multiple plane positions. Each sequence characterizes an order in which a bit line structure couples the plane positions to bit lines. Each bit line is coupled to at least two different plane positions to access memory cells at two or more different plane positions.

Owner:MACRONIX INT CO LTD

Method and apparatus for forming an SOI body-contacted transistor

ActiveUS6953738B2Minimize capacitanceMinimize leakageTransistorSolid-state devicesBody contactElectrical control

A method for forming a silicon-on-insulator transistor (80) includes forming an active region (82) overlying an insulating layer (122), wherein a portion of the active region provides an intrinsic body region (126). A body tie access region (128) is also formed within the active region, overlying the insulating layer and laterally disposed adjacent the intrinsic body region, making electrical contact to the intrinsic body region. A gate electrode (134) is formed overlying the intrinsic body region for providing electrical control of the intrinsic body region, the gate electrode extending over a portion (137) of the body tie access region. The gate electrode is formed having a substantially constant gate length (88) along its entire width overlying the intrinsic body region and the body tie access region to minimize parasitic capacitance and gate electrode leakage. First and second current electrodes (98,100) are formed adjacent opposite sides of the intrinsic body region. In addition, a body tie diffusion (130) is formed within the active region and laterally offset from the body tie access region and electrically coupled to the body tie access region.

Owner:NORTH STAR INNOVATIONS

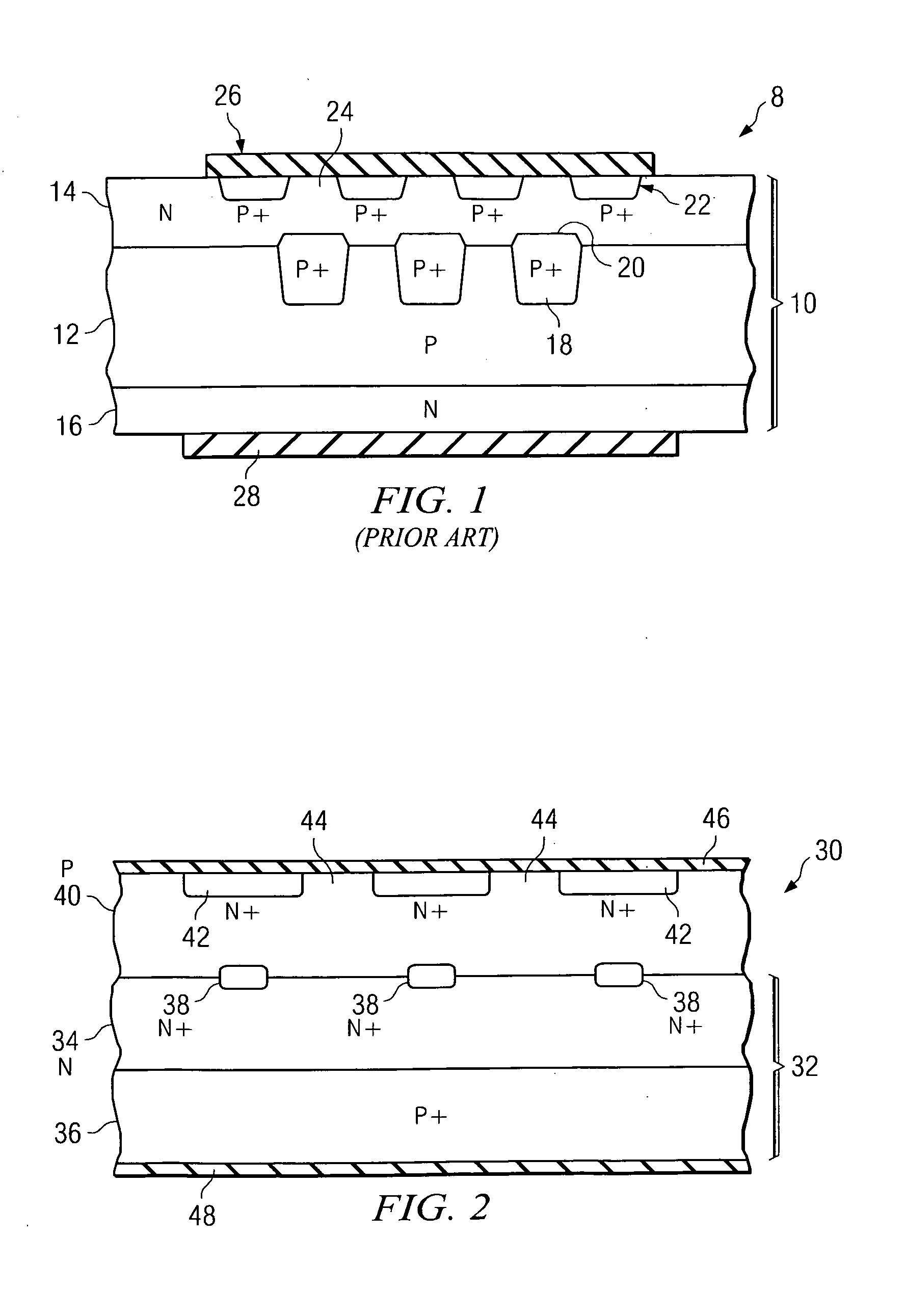

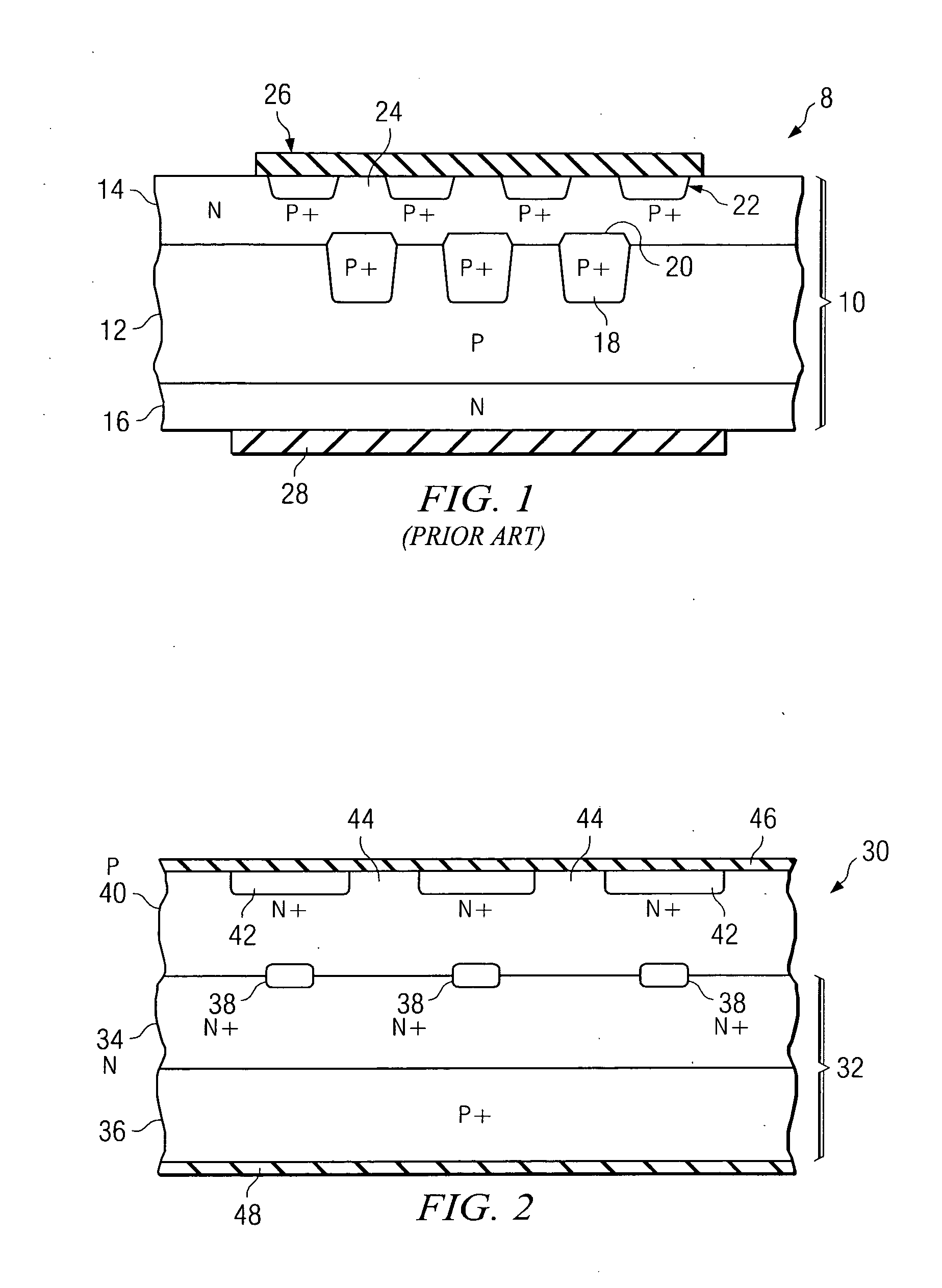

Solid-state relay

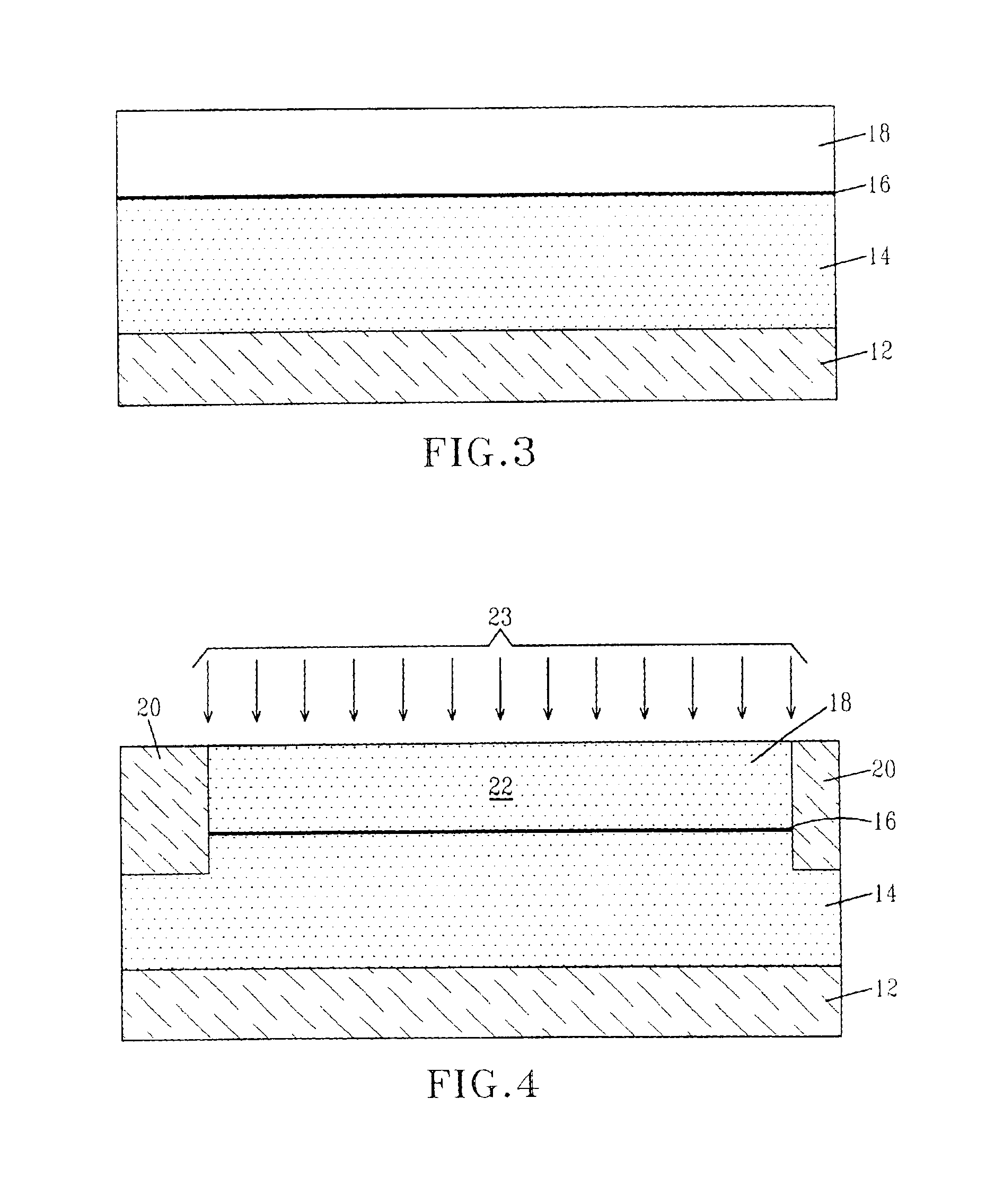

InactiveUS6211551B1Sufficient flexibilityReduce interfaceTransistorSemiconductor/solid-state device detailsCapacitanceInductance

A solid state relay composed of a series connected pair of LDMOSFETs has a minimized output capacitance. Each LDMOSFET is configured to have a silicon layer of a first conductive type, a drain region of the first conductive type diffused in the top surface of the silicon layer, a well region of a second conductive type diffused in the silicon layer in a laterally spaced relation from the drain region, and a source region of the first conductive type diffused within the well region to define a channel extending between the source region and a confronting edge of the well region along the top surface of the silicon layer. Each LDMOSFET is of an SOI (Silicon-On-Insulator) structure composed of a silicon substrate placed on a supporting plate, a buried oxide layer on the silicon substrate, and the silicon layer on the buried oxide layer. The well region is diffused over the full depth of the silicon layer to have its bottom in contact with the buried oxide layer, so that the well region forms with the silicon layer a P-N interface only at a small area adjacent the channel. Because of this reduced P-N interface and also because of the buried oxide layer exhibiting a much lower inductive capacitance than the silicon layer, it is possible to greatly reduce a drain-source capacitance for minimizing the output capacitance of the relay in the non-conductive condition.

Owner:CORNELL RES FOUNDATION INC

Gate-all-around field effect transistors with air-gap inner spacers and methods

ActiveUS20200083352A1Minimize capacitanceSmall sizeNanoinformaticsSemiconductor/solid-state device manufacturingEngineeringField effect

Disclosed are structures including a gate-all-around field effect transistor (GAAFET) with air-gap inner spacers. The GAAFET includes a stack of nanoshapes that extend laterally between source / drain regions, a gate that wraps around a center portion of each nanoshape, and a gate sidewall spacer on external sidewalls of the gate. The GAAFET also includes air-gap inner spacers between the gate and the source / drain regions. Each air-gap inner spacer includes: two vertical sections within the gate sidewall spacer on opposing sides of the stack and adjacent to a source / drain region; and horizontal sections below the nanoshapes and extending laterally between the vertical sections. Also discloses are methods of forming the structures and the method include forming preliminary inner spacers in inner spacer cavities prior to source / drain region formation. After source / drain regions are formed, the preliminary inner spacers are removed and the cavities are sealed off, thereby forming the air-gap inner spacers.

Owner:GLOBALFOUNDRIES US INC

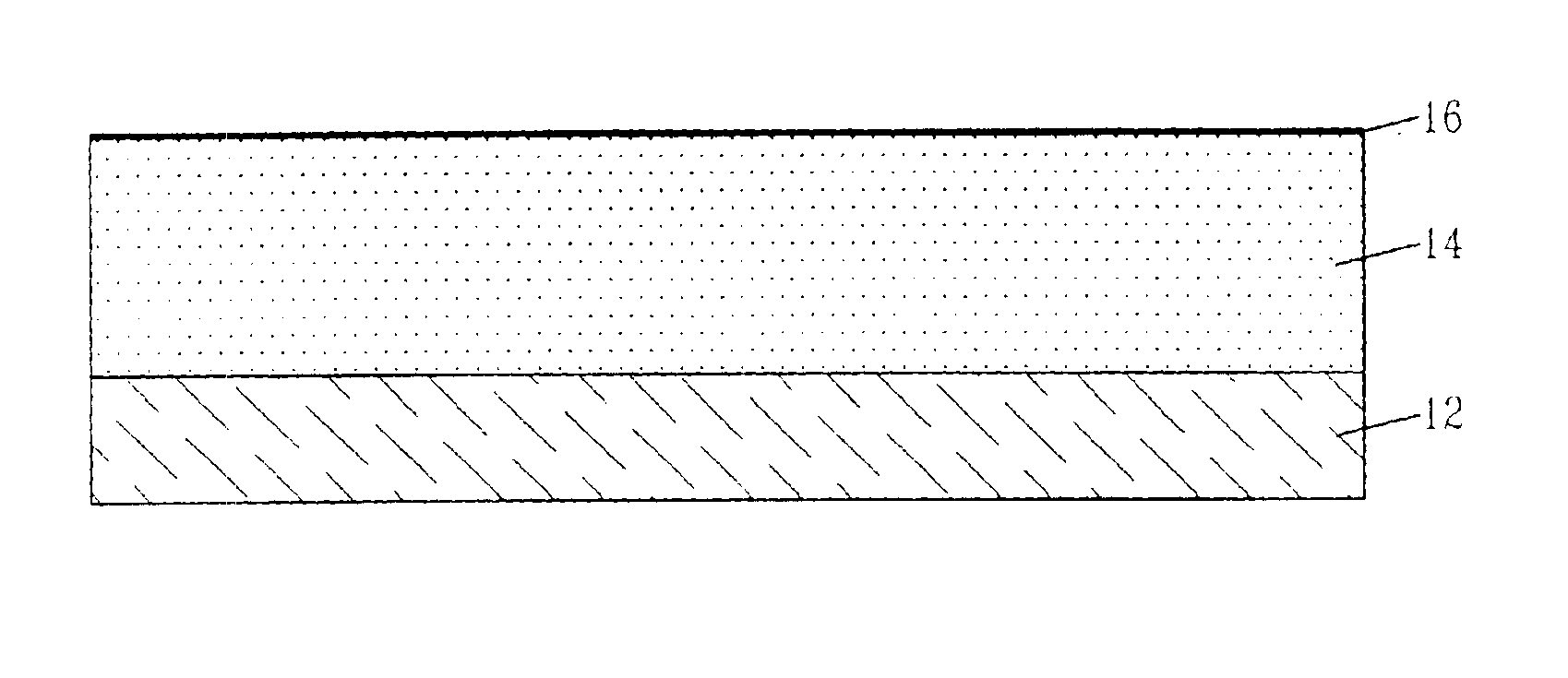

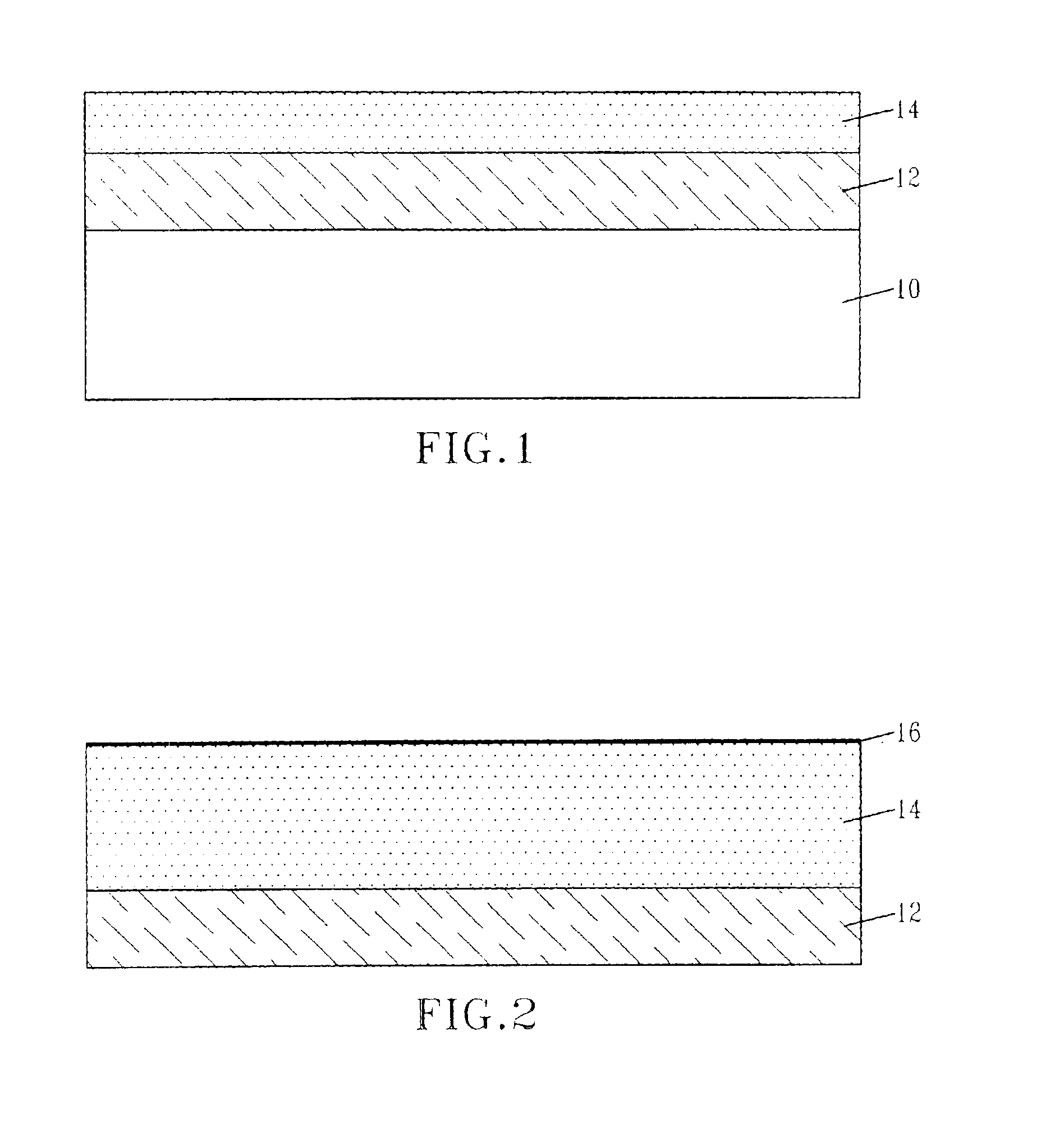

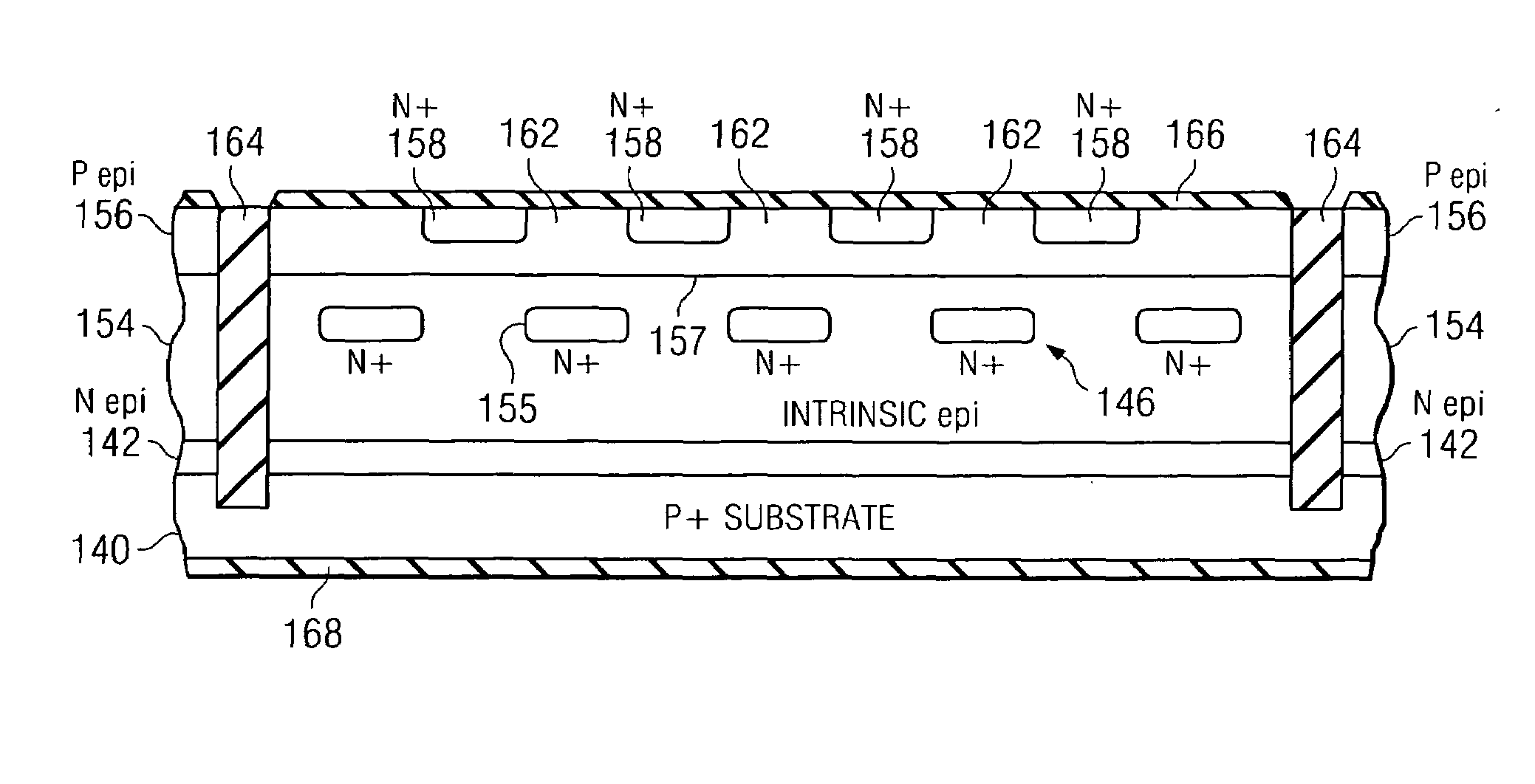

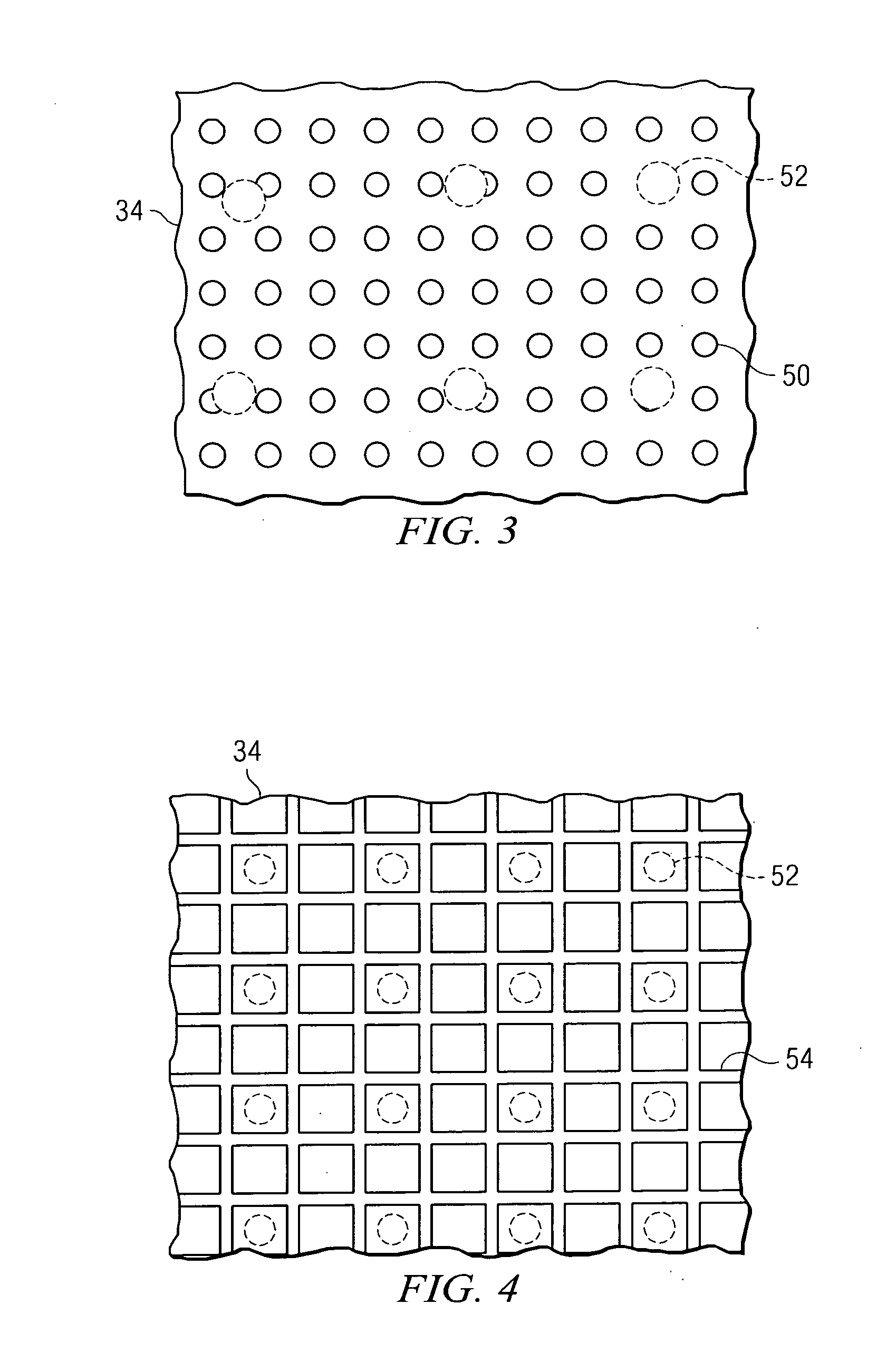

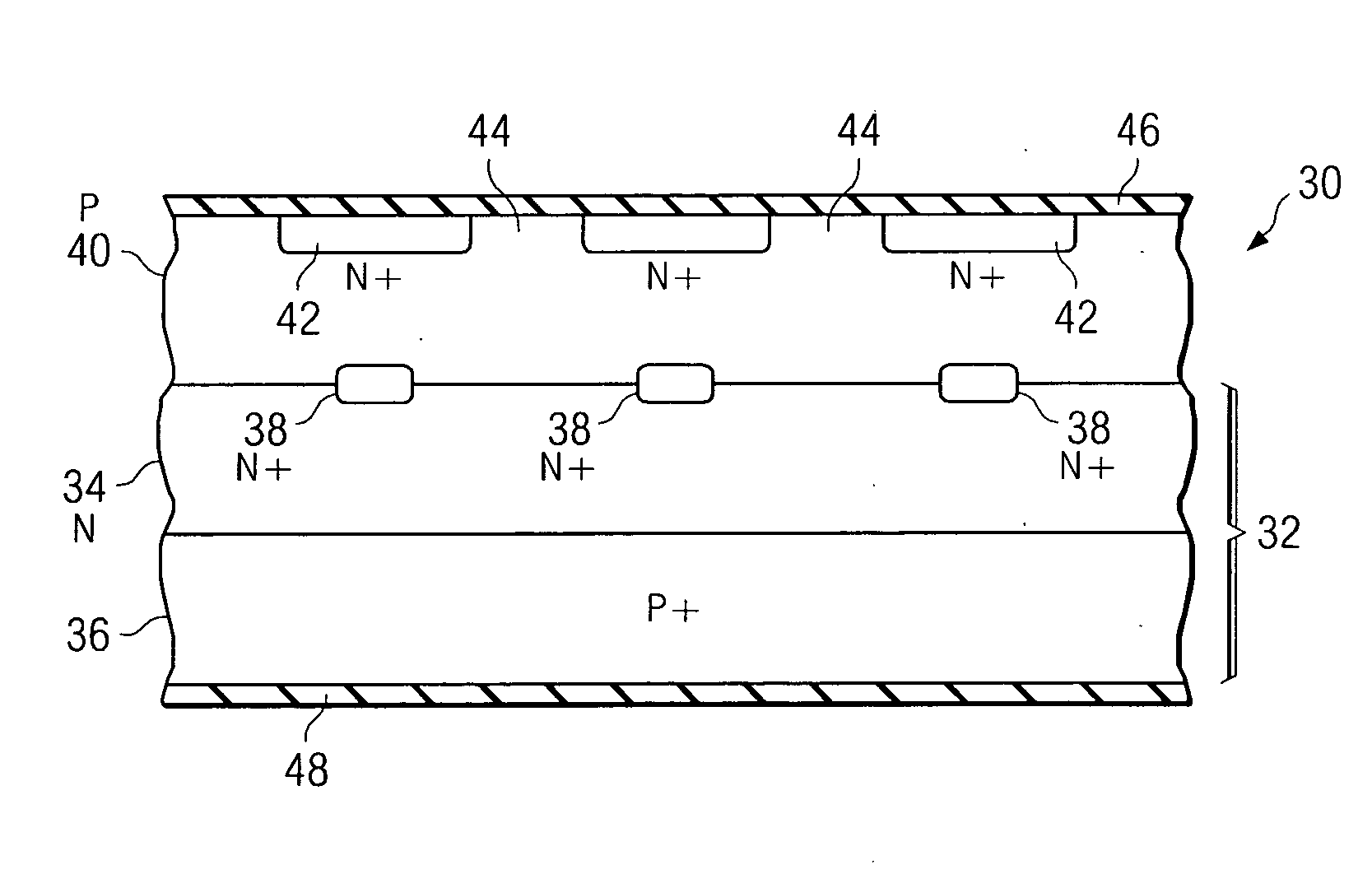

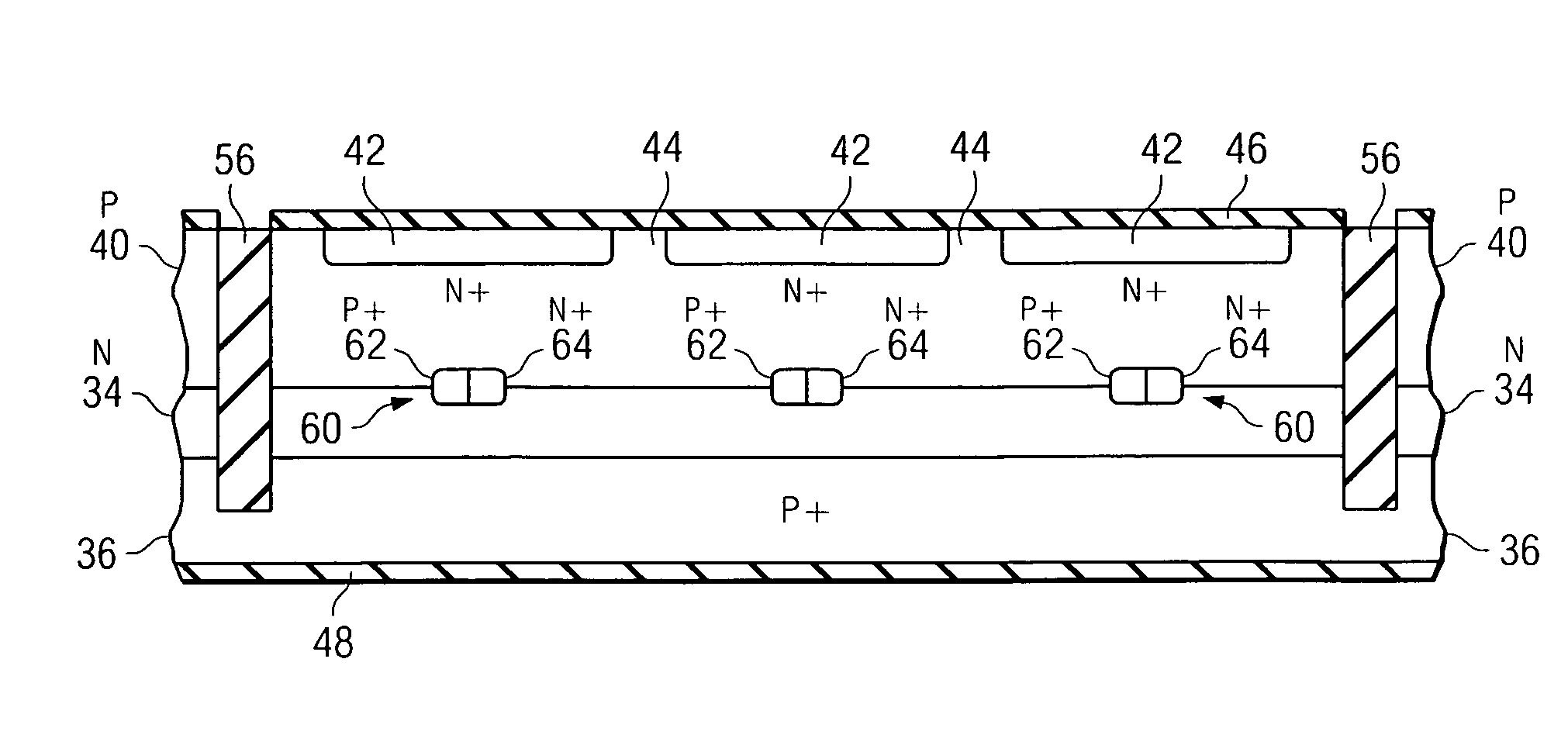

Low capacitance semiconductor device

A surge protection device with small-area buried regions (38, 60) to minimize the device capacitance. The doped regions (38, 60) are formed either in a semiconductor substrate (34), or in an epitaxial layer (82), and then an epitaxial layer (40, 84) is formed thereover to bury the doped regions (38, 60). The small features of the buried regions (38, 60) are maintained as such by minimizing high temperature and long duration processing of the chip. An emitter (42, 86) is formed in the epitaxial layer (40, 84).

Owner:LITTELFUSE INC

Semiconductor structure implementing low-K dielectric materials and supporting stubs

InactiveUS6984892B2Minimize capacitanceFaster integrated circuit devicesSemiconductor/solid-state device detailsSolid-state devicesCopper interconnectSemiconductor structure

Owner:LAM RES CORP

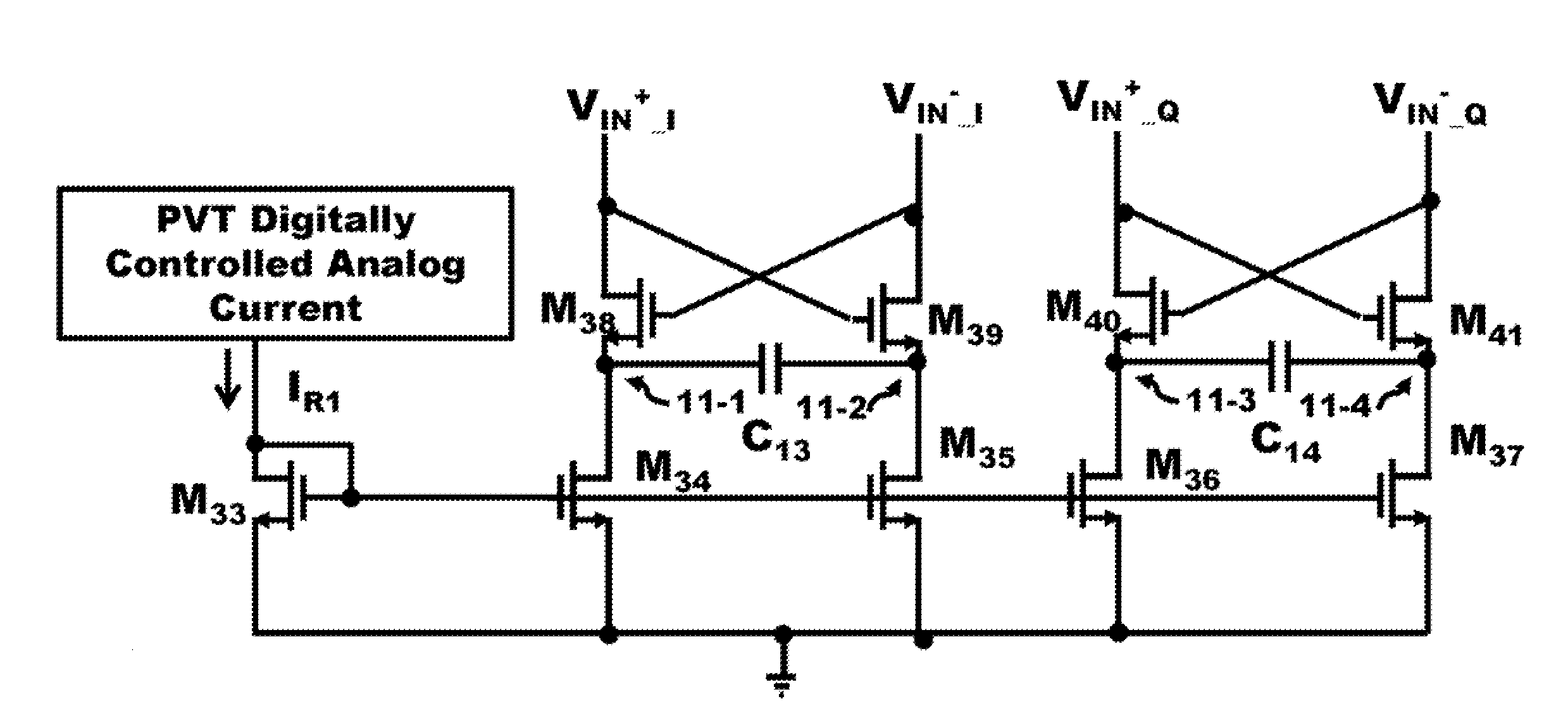

Method and apparatus for an active negative-capacitor circuit to cancel the input capacitance of comparators

ActiveUS9124279B2Reduce voltageLower performance requirementsPower saving provisionsMultiple input and output pulse circuitsCapacitanceEngineering

The differential output of a Programmable Gain Amplifier (PGA) is loaded by the input differential gate capacitance of a plurality of Analog to Digital converters (ADC) comparators and the differential metal layer traces to interconnect these comparators to the PGA. The differential capacitive load presented to the PGA is quite large and reduces the bandwidth of this interconnect between the PGA and ADC. To overcome the performance degradation due to the differential capacitive load, an active negative-capacitor circuit cancels the effect of the large input capacitance of the ADC comparators. This cancellation extends the gain characteristics of the interconnect between the PGA's output and the inputs of the first stage of the comparators. The active negative-capacitance is comprised of a cross pair NMOS with a capacitor connecting their sources where each NMOS is biased by a current source.

Owner:TENSORCOM

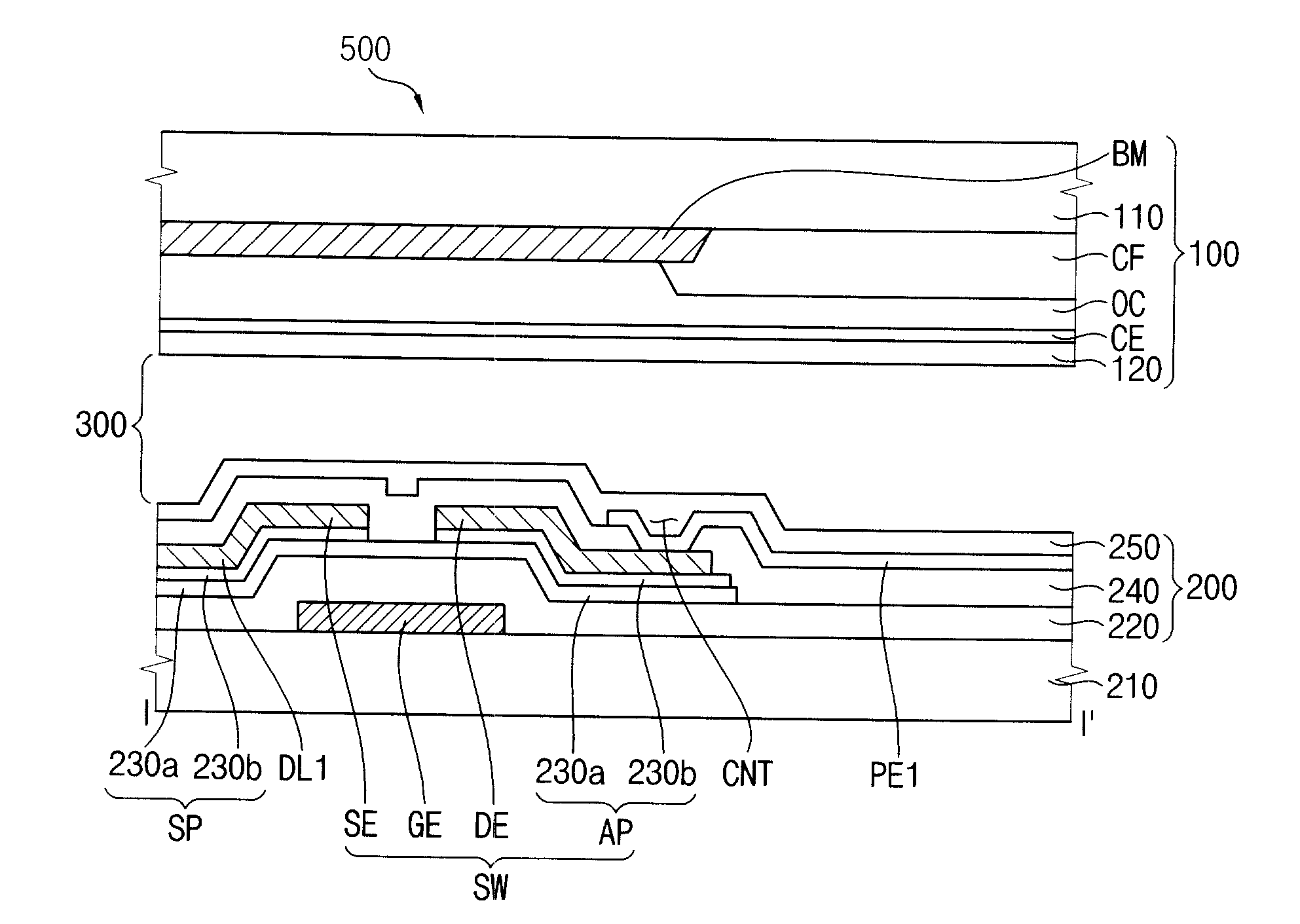

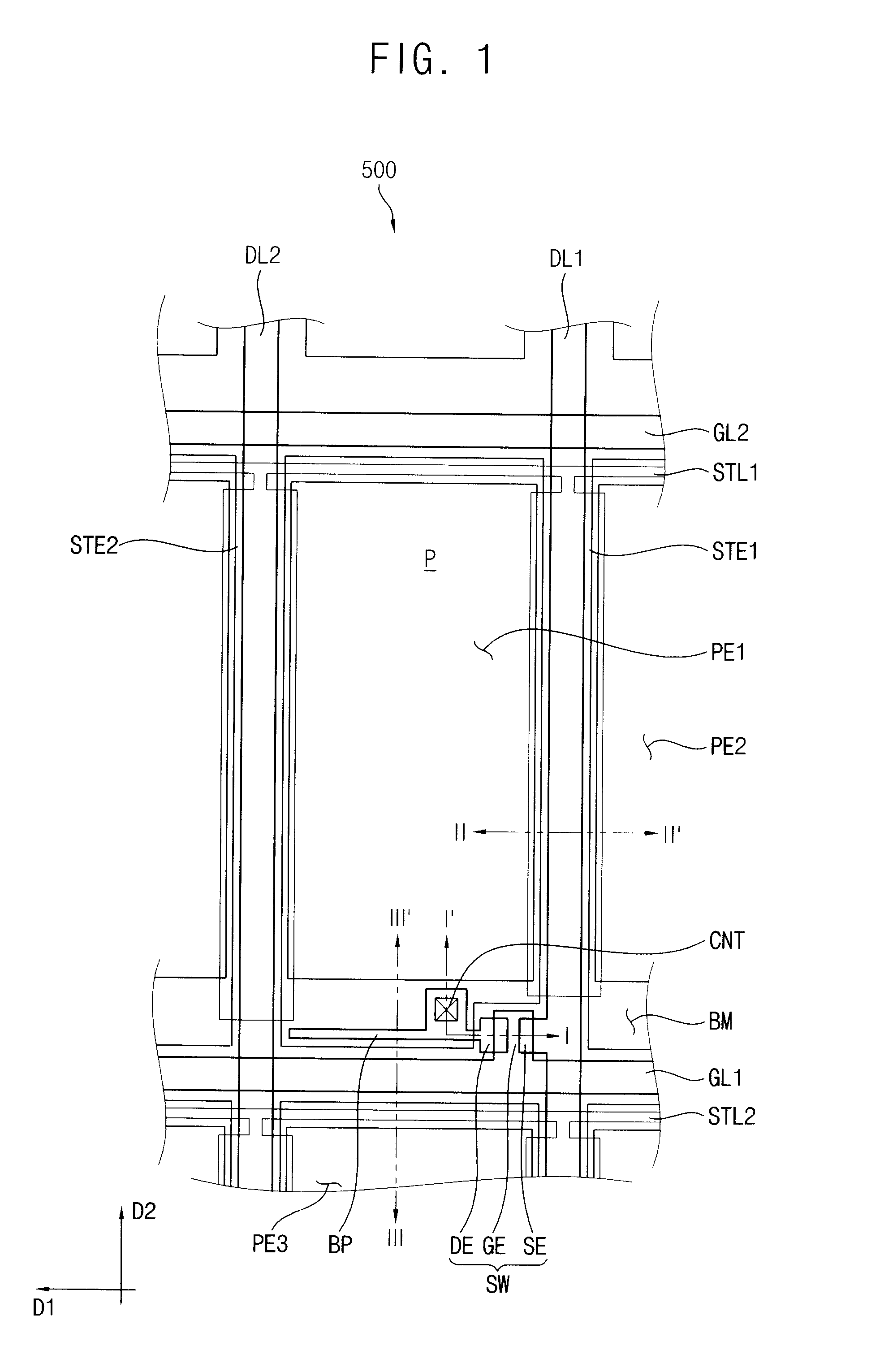

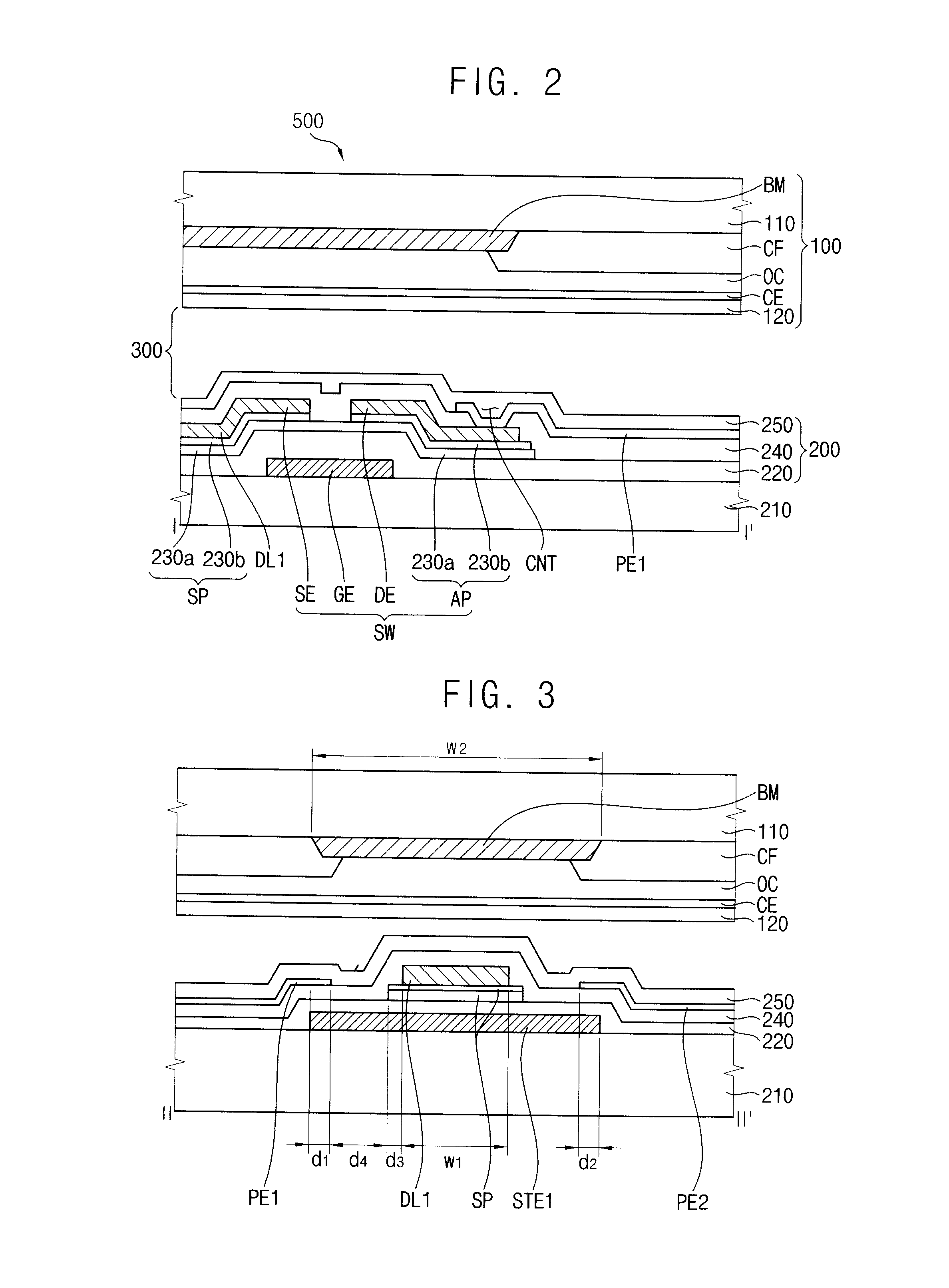

Display substrate, method of manufacturing the same and display panel having the same

ActiveUS20110187949A1Increase the aperture ratioReduce power consumptionStatic indicating devicesSolid-state devicesOptoelectronicsData lines

A display substrate includes a data line disposed on a base substrate, a first pixel electrode disposed at a first side of the data line, a second pixel electrode disposed at a second side of the data line and a storage electrode overlapping with the data line. The storage electrode overlaps with the first pixel electrode by a first overlapping width, and overlaps with the second pixel electrode by a second overlapping width larger than the first overlapping width.

Owner:SAMSUNG DISPLAY CO LTD

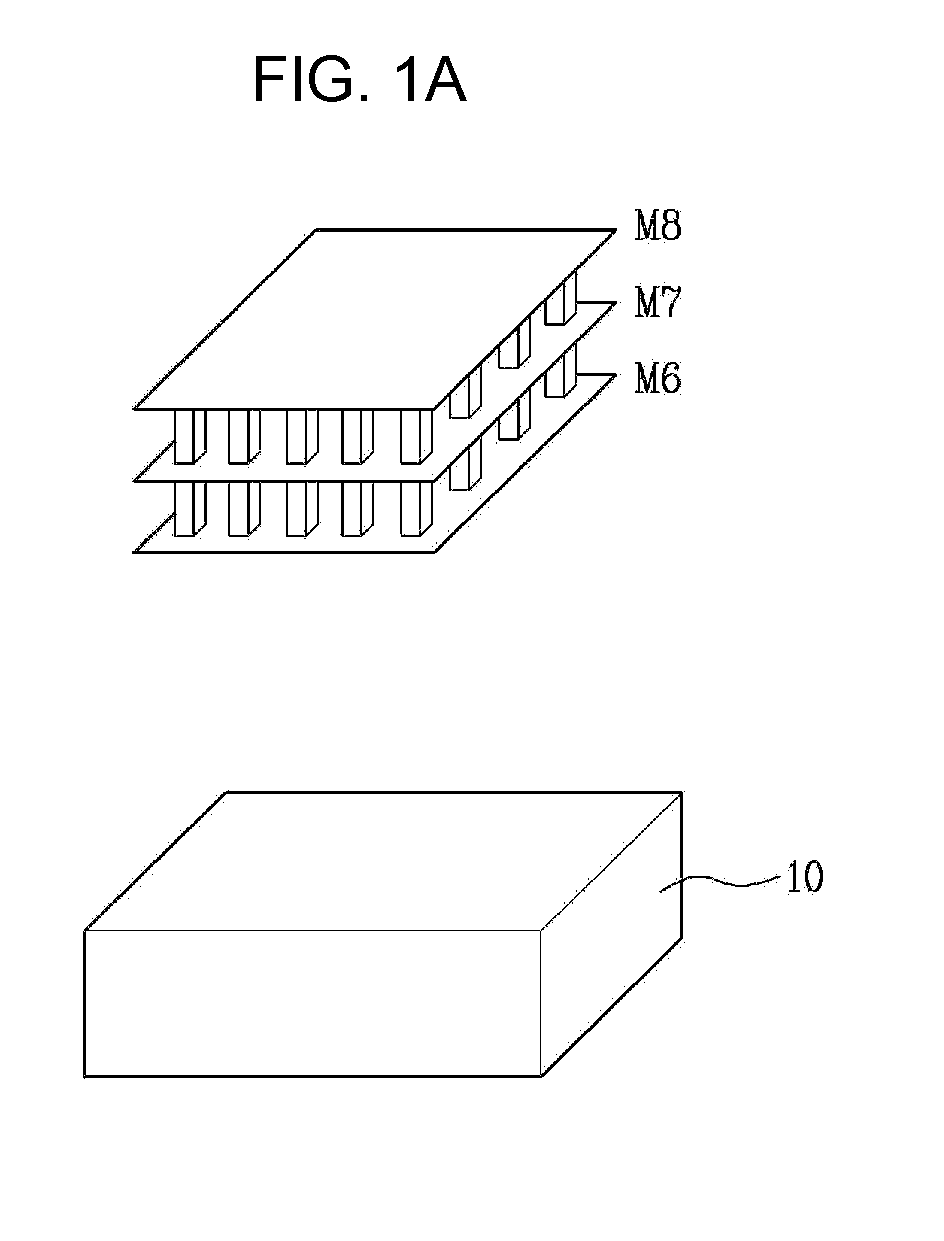

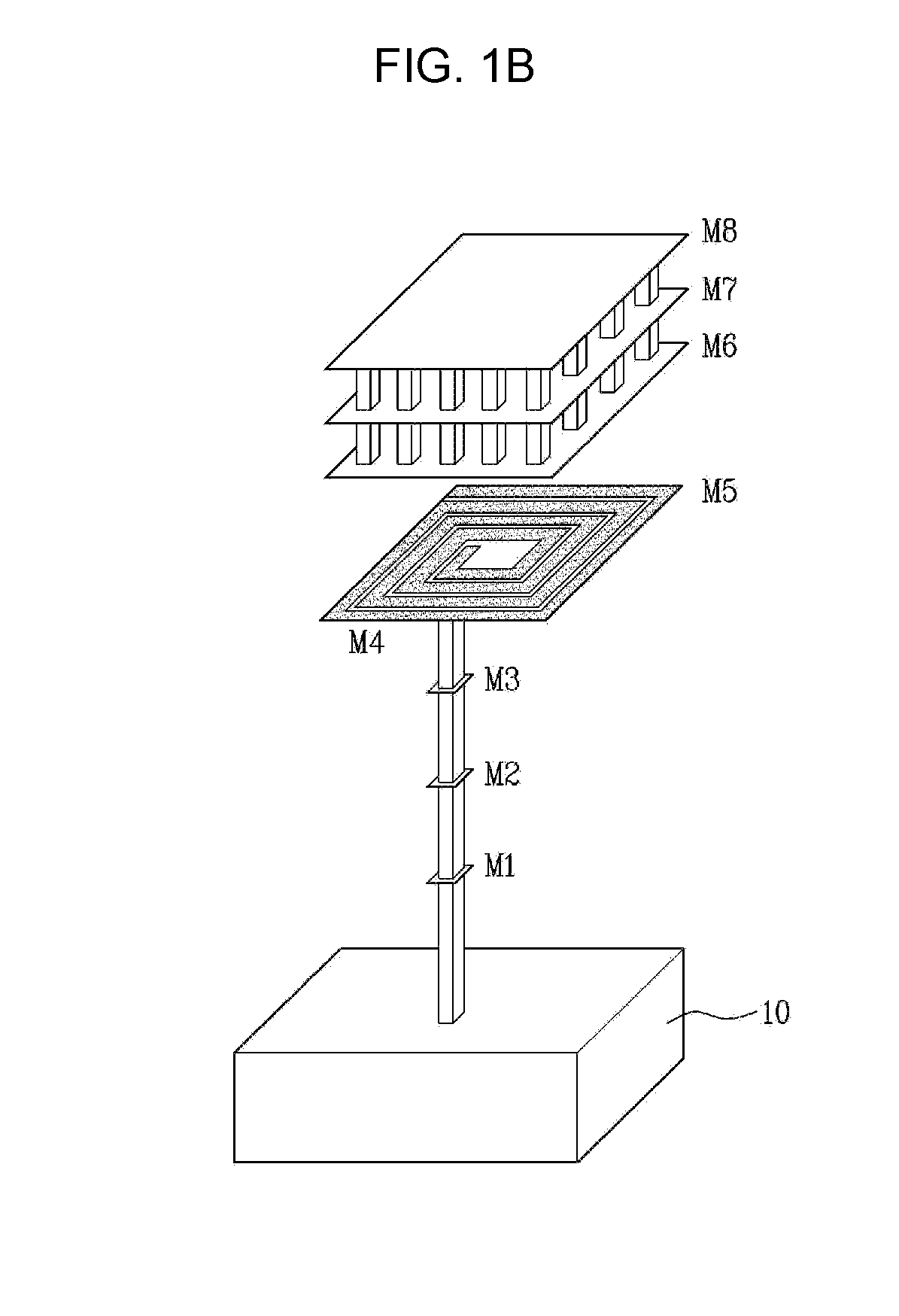

Pad in Semicondcutor Device and Fabricating Method Thereof

InactiveUS20090168293A1Reduces total parasitic capacitance componentMinimizing design error(s)Multiple fixed capacitorsSemiconductor/solid-state device detailsResonanceParasitic capacitance

A pad in a semiconductor device and fabricating method thereof are disclosed. The pad includes an uppermost metal layer first to Nth intermediate metal layers, wherein capacitors configured or formed by the uppermost metal layer and the first to Nth intermediate metal layers are serially connected. Accordingly, the pad reduces total parasitic capacitance components by connecting MIM type capacitors in series, and not necessarily overlapping with each other, thereby minimizing design errors attributed to the pad by reducing parasitic factors generated from the integrated circuit design. The pad may also minimize capacitance attributed to resonance at a specific frequency. Moreover, the pad avoids affecting an adjacent pad or circuit without additional processing, despite maintaining the above-mentioned effects, thereby reducing cost.

Owner:DSS TECH MANAGEMENT

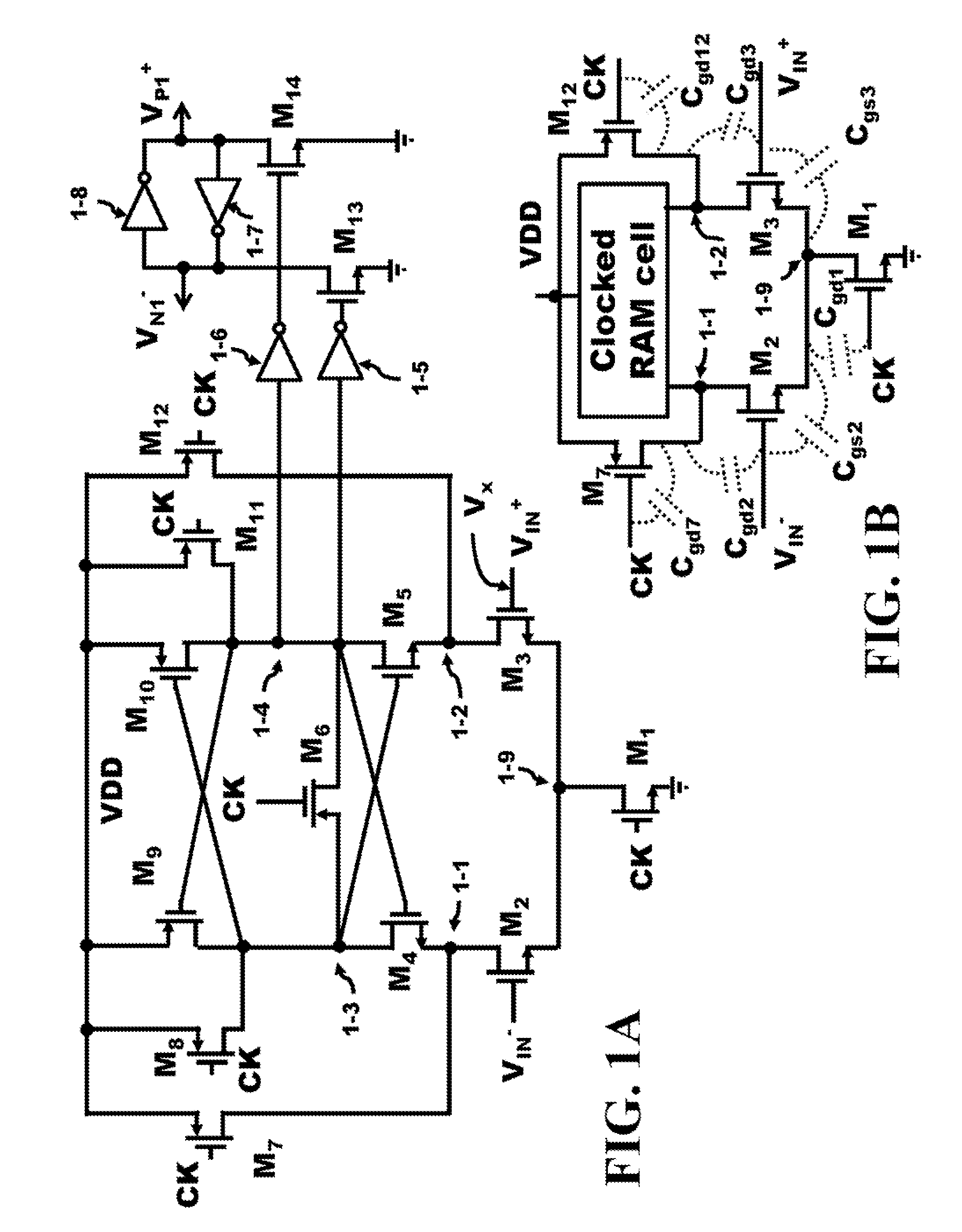

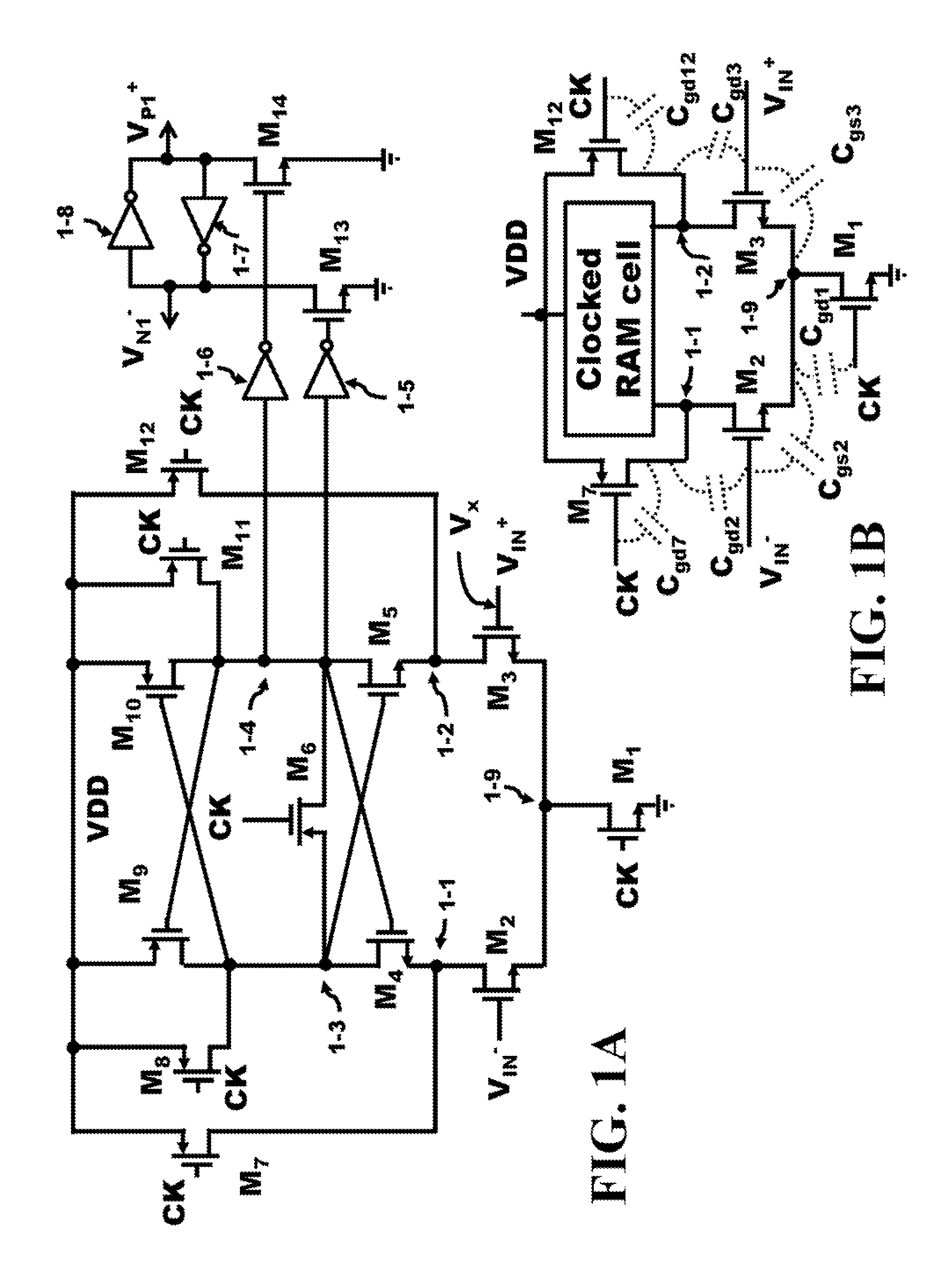

Method and Apparatus for an Active Negative-Capacitor Circuit to Cancel the Input Capacitance of Comparators

ActiveUS20140062621A1Reduce voltageLower performance requirementsPower saving provisionsImpedence convertorsCapacitanceAnalog-to-digital converter

The differential output of a Programmable Gain Amplifier (PGA) is loaded by the input differential gate capacitance of a plurality of Analog to Digital converters (ADC) comparators and the differential metal layer traces to interconnect these comparators to the PGA. The differential capacitive load presented to the PGA is quite large and reduces the bandwidth of this interconnect between the PGA and ADC. To overcome the performance degradation due to the differential capacitive load, an active negative-capacitor circuit cancels the effect of the large input capacitance of the ADC comparators. This cancellation extends the gain characteristics of the interconnect between the PGA's output and the inputs of the first stage of the comparators. The active negative-capacitance is comprised of a cross pair NMOS with a capacitor connecting their sources where each NMOS is biased by a current source.

Owner:TENSORCOM

Epitaxial surge protection device

ActiveUS20090057716A1Reduce capacitanceReduce diffuseTransistorSemiconductor/solid-state device manufacturingCapacitanceSemiconductor

A surge protection device with small-area buried regions (38, 60) to minimize the device capacitance. The doped regions (38, 60) are formed either in a semiconductor substrate (34), or in an epitaxial layer (82), and then an epitaxial layer (40, 84) is formed thereover to bury the doped regions (38, 60). The small features of the buried regions (38, 60) are maintained as such by minimizing high temperature and long duration processing of the chip. An emitter (42, 86) is formed in the epitaxial layer (40, 84).

Owner:LITTELFUSE INC

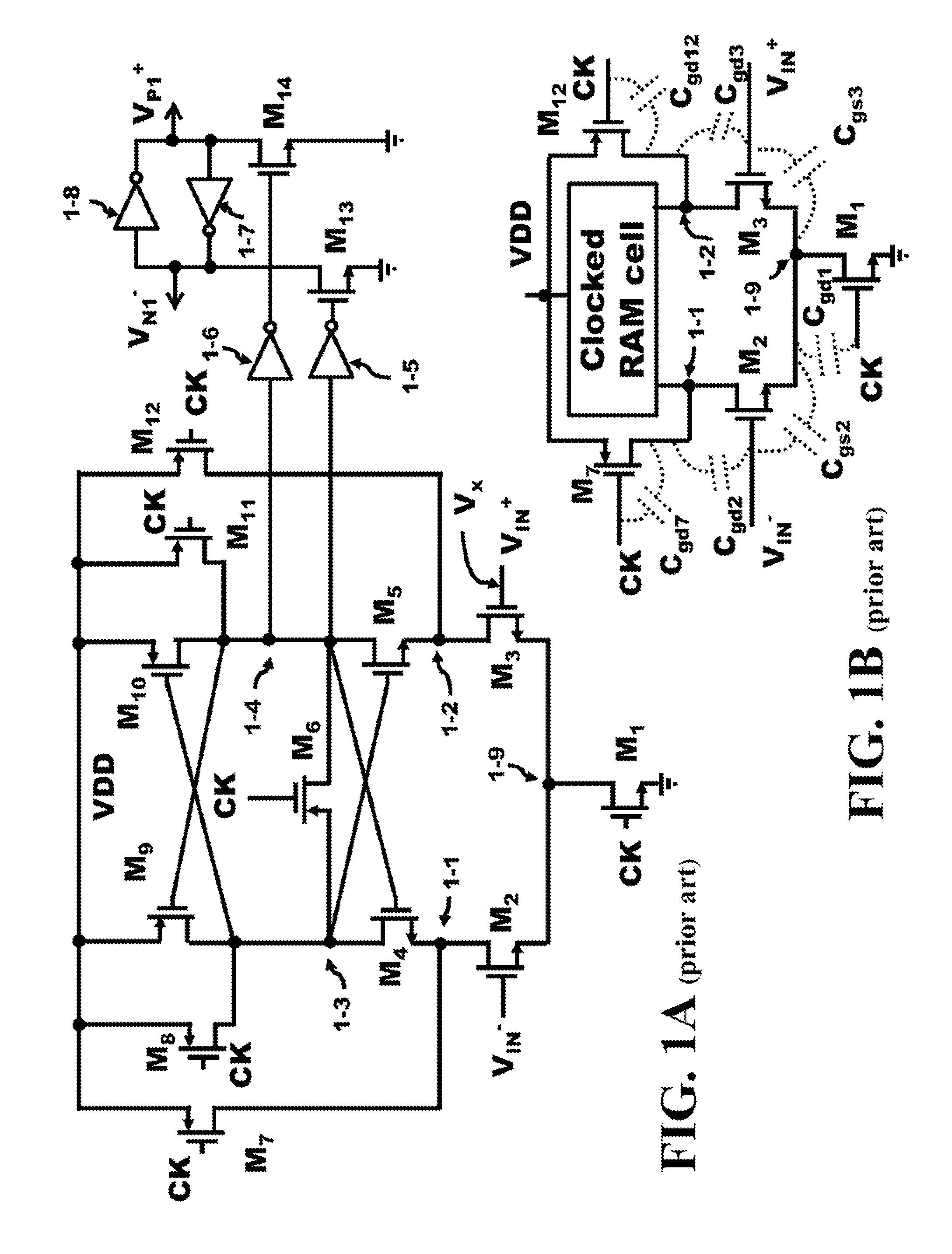

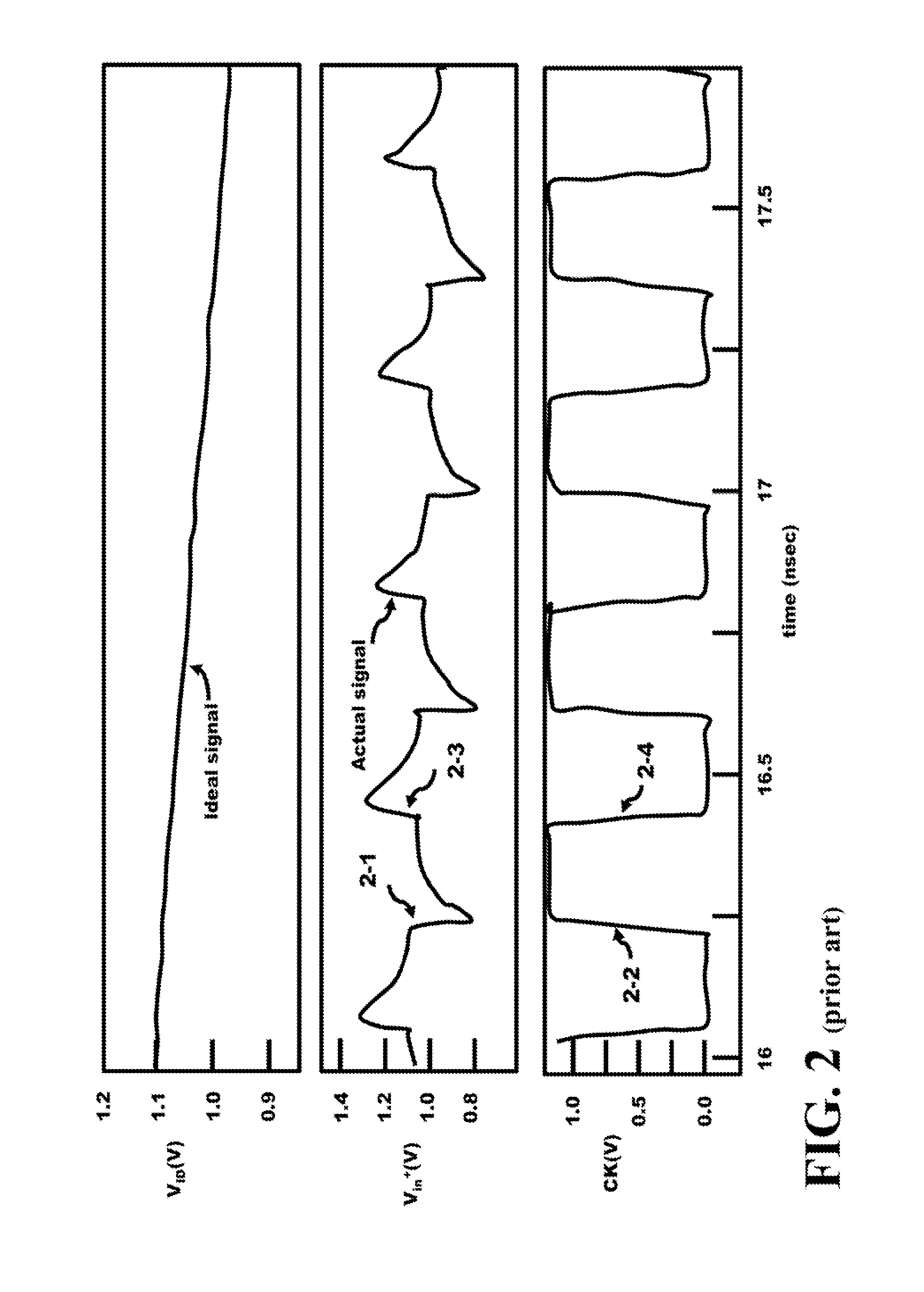

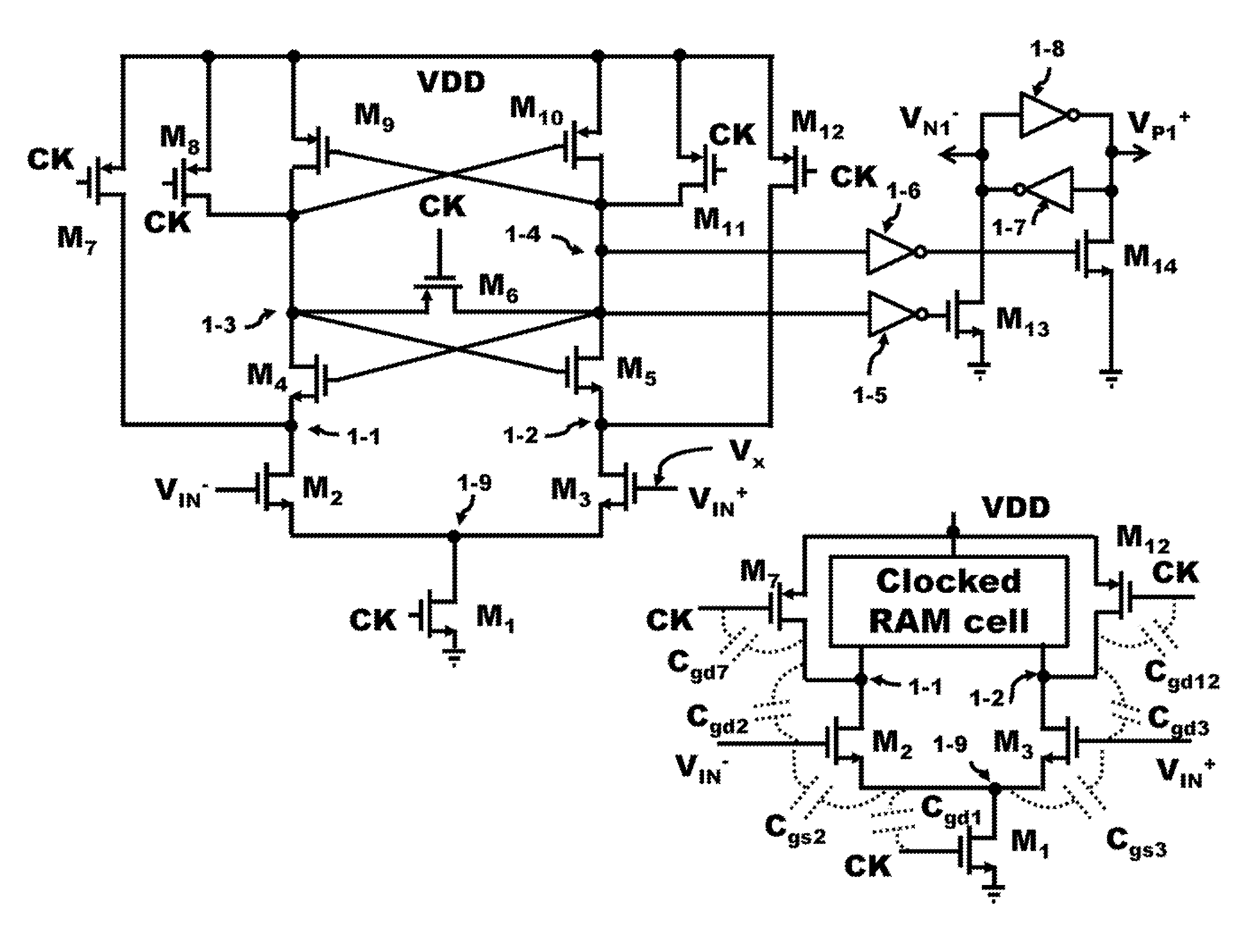

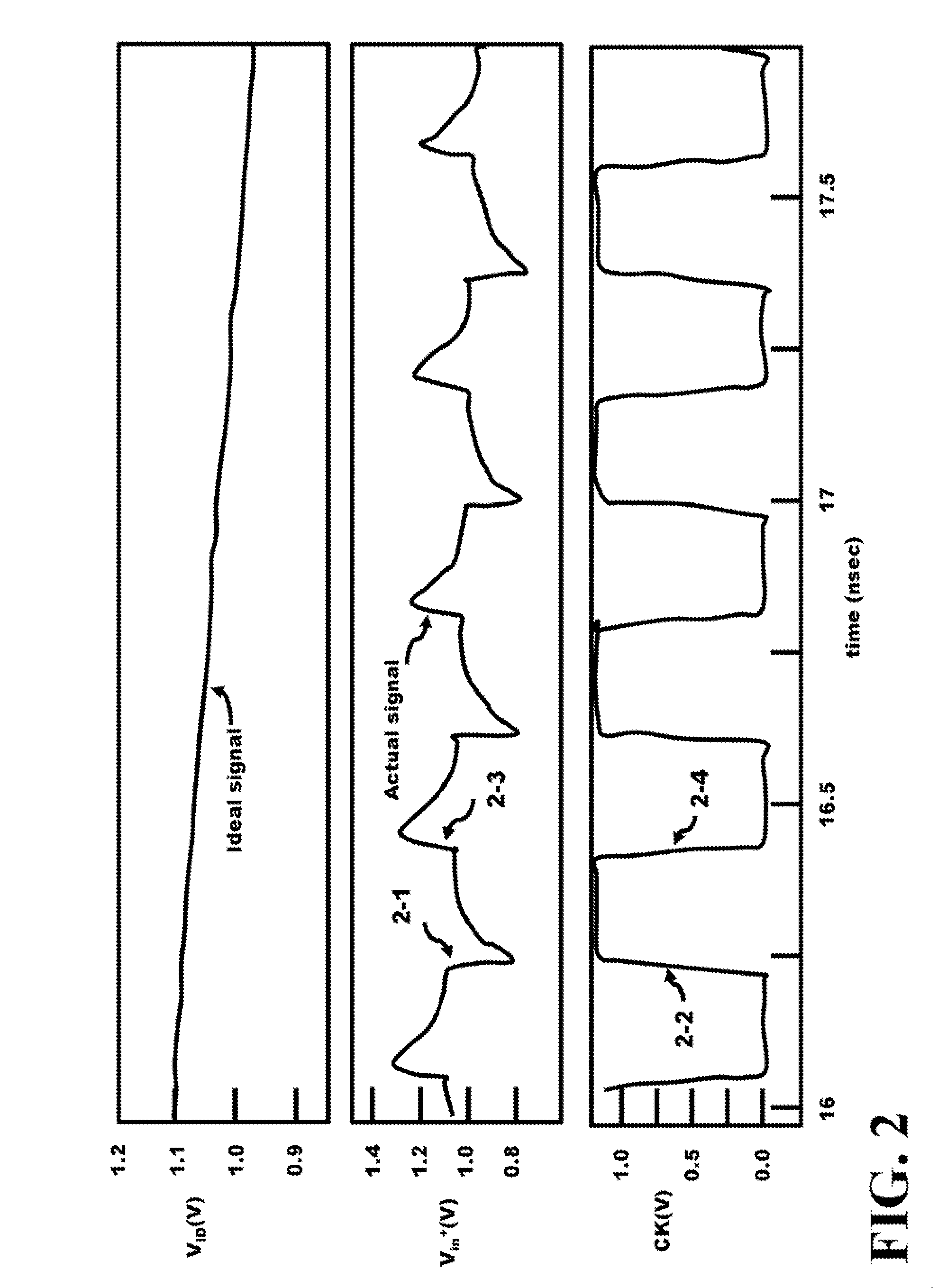

Method and Apparatus for Reducing the Clock Kick-Back of ADC Comparators While Maintaining Transistor Matching Behavior

InactiveUS20140062545A1Reduced voltage headroomLower performance requirementsAnalogue/digital conversionPulse automatic controlTransceiverClock signal

The core concept of this ADC is the high-speed fully-differential comparators which are clocked at 2.64 GHz and used in a 60 GHz transceiver. The comparator consists of a pre-amplifier stage, a capture stage, a regeneration cell and an output latch. The pre-amplifier stage is not clocked; therefore, the pre-amplifier stage does not suffer initialization and transient behavior effects when the clock signal switches state. The transient response of being enabled and disabled is eliminated. Instead, a capture stage transfers the contents of the pre-amplifier stage into a memory regeneration stage. The capture stage is clocked by pulses that are timed to minimize the clock kick-back generated by the memory regeneration stage. The clock kick-back is reduced even when many comparators are coupled to the PGA. The comparators, instead of having extra dummy fingers, are also aligned right next to each other to minimize the mismatching layout effect.

Owner:TENSORCOM

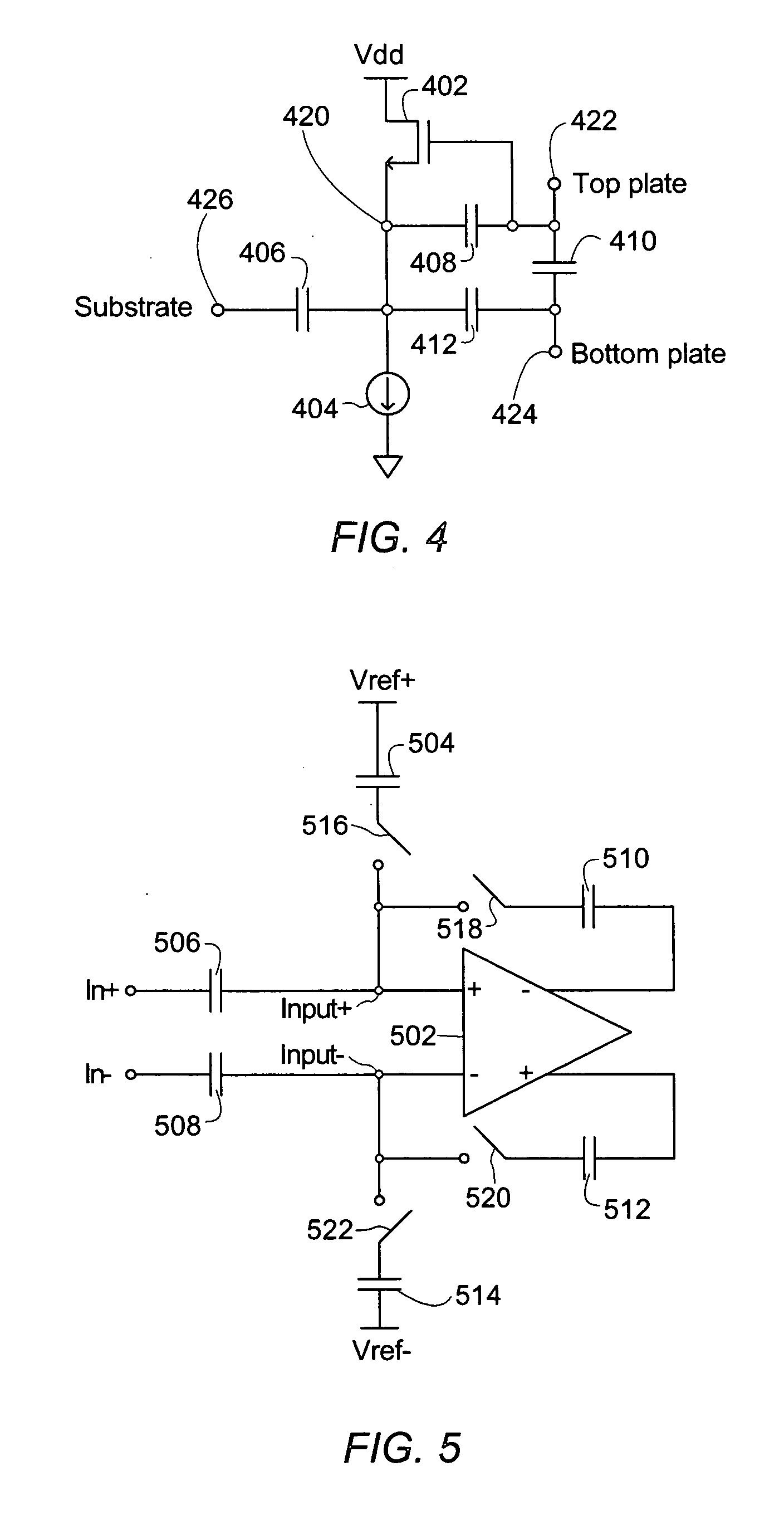

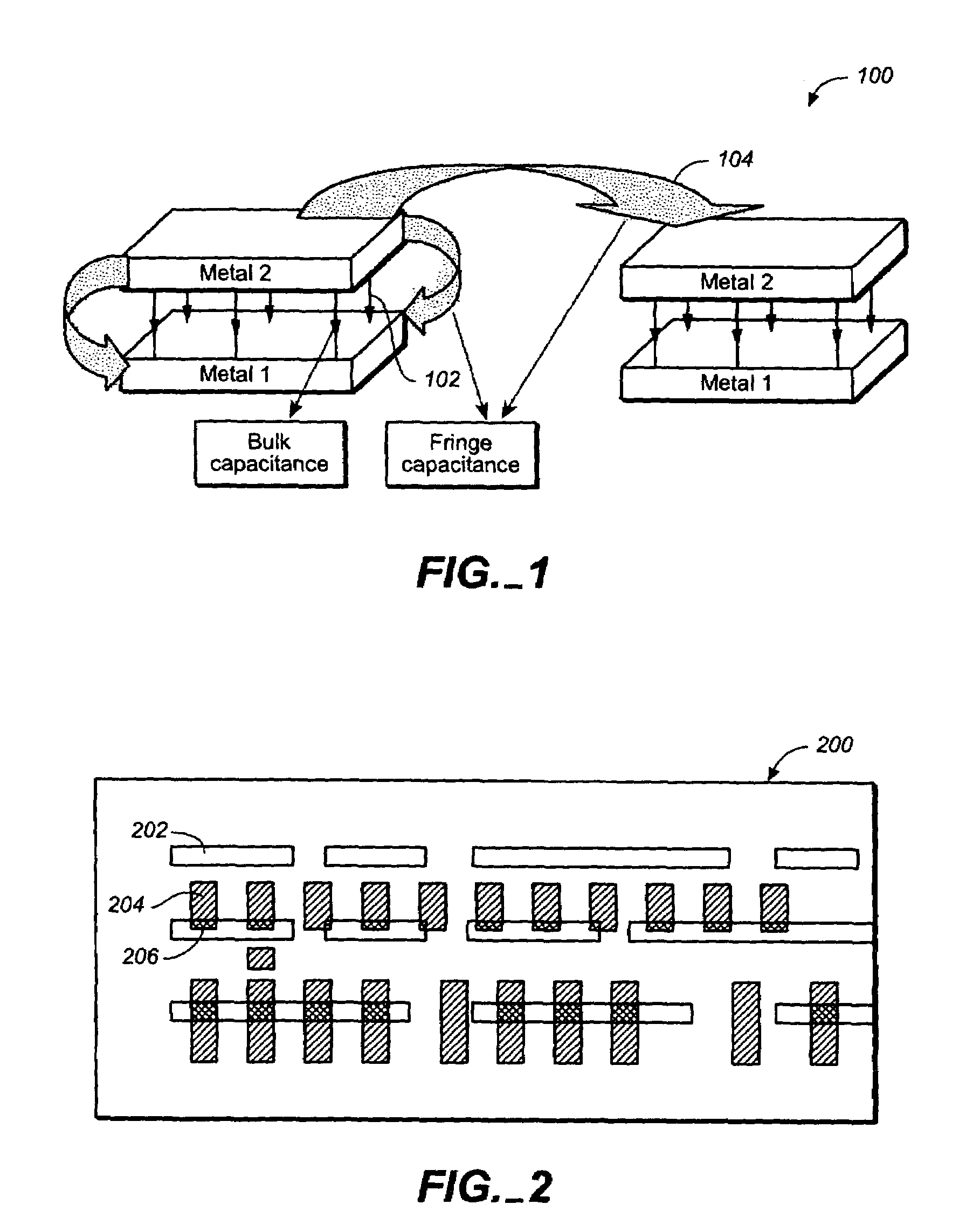

Fringe capacitor using bootstrapped non-metal layer

InactiveUS20070215928A1Maximize fringe-capacitanceMinimize and eliminate any charge transferTransistorSemiconductor/solid-state device detailsAudio power amplifierParallel plate

Capacitors configured in a switched-capacitor circuit on a semiconductor device may comprise very accurately matched, high capacitance density metal-to-metal capacitors, using top-plate-to-bottom-plate fringe-capacitance for obtaining the desired capacitance values. A polysilicon plate may be inserted below the bottom metal layer as a shield, and bootstrapped to the top plate of each capacitor in order to minimize and / or eliminate the parasitic top-plate-to-substrate capacitance. This may free up the bottom metal layer to be used in forming additional fringe-capacitance, thereby increasing capacitance density. By forming each capacitance solely based on fringe-capacitance from the top plate to the bottom plate, no parallel-plate-capacitance is used, which may reduce capacitor mismatch. Parasitic bottom plate capacitance to the substrate may also be eliminated, with only a small capacitance to the bootstrapped polysilicon plate remaining. The capacitors may be bootstrapped by coupling the top plate of each capacitor to a respective one of the differential inputs of an amplifier comprised in the switched-capacitor circuit.

Owner:MICROCHIP TECH INC

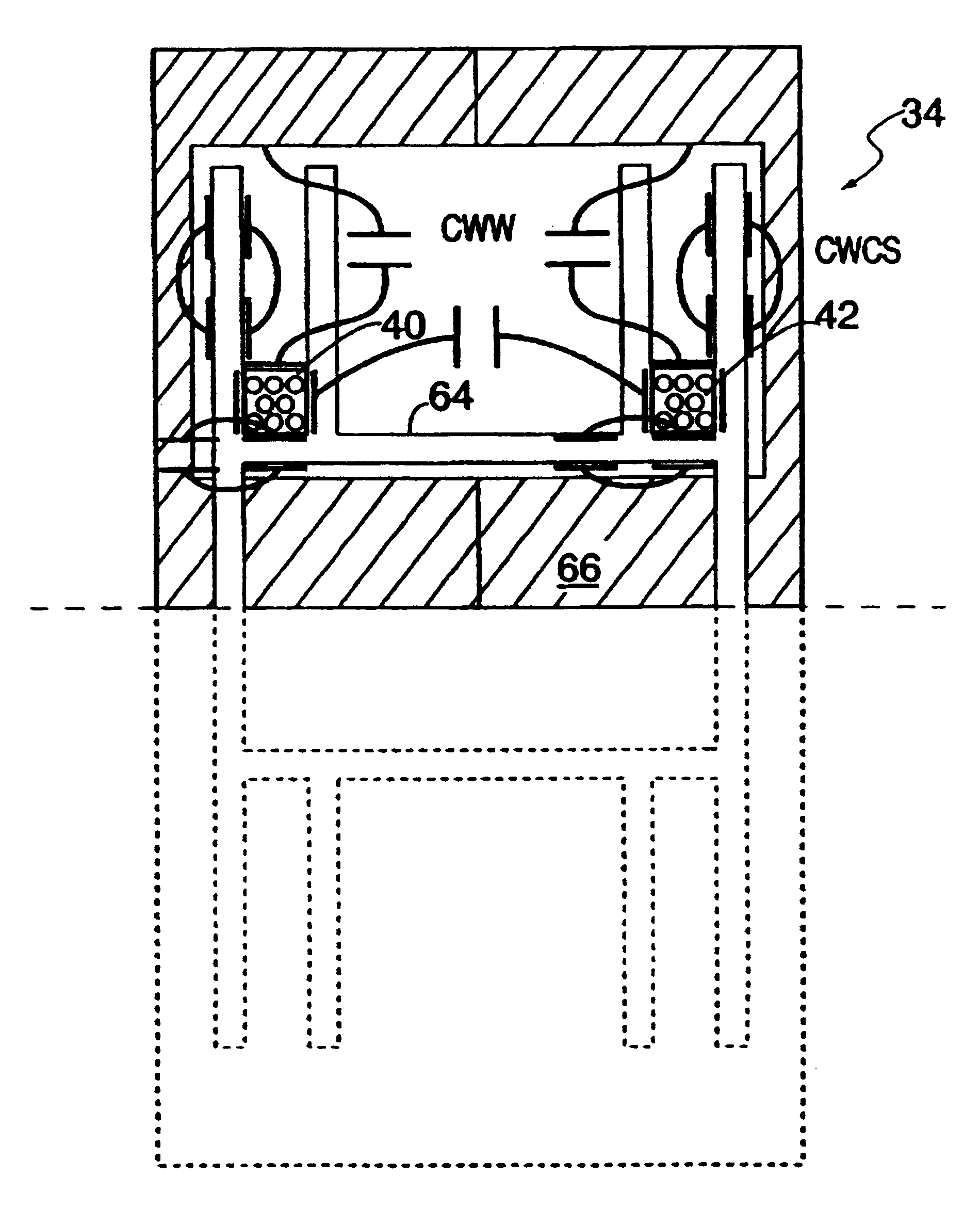

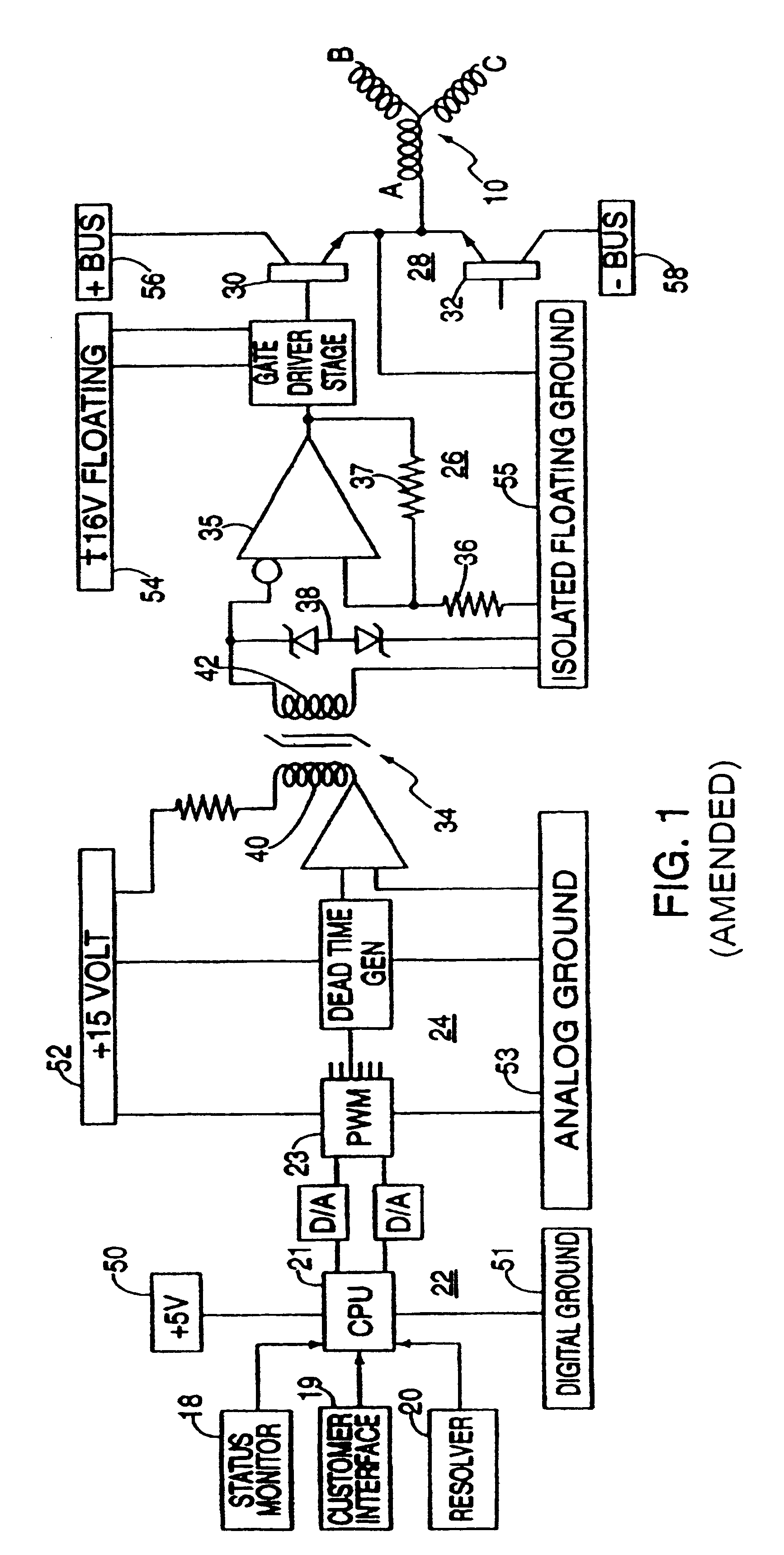

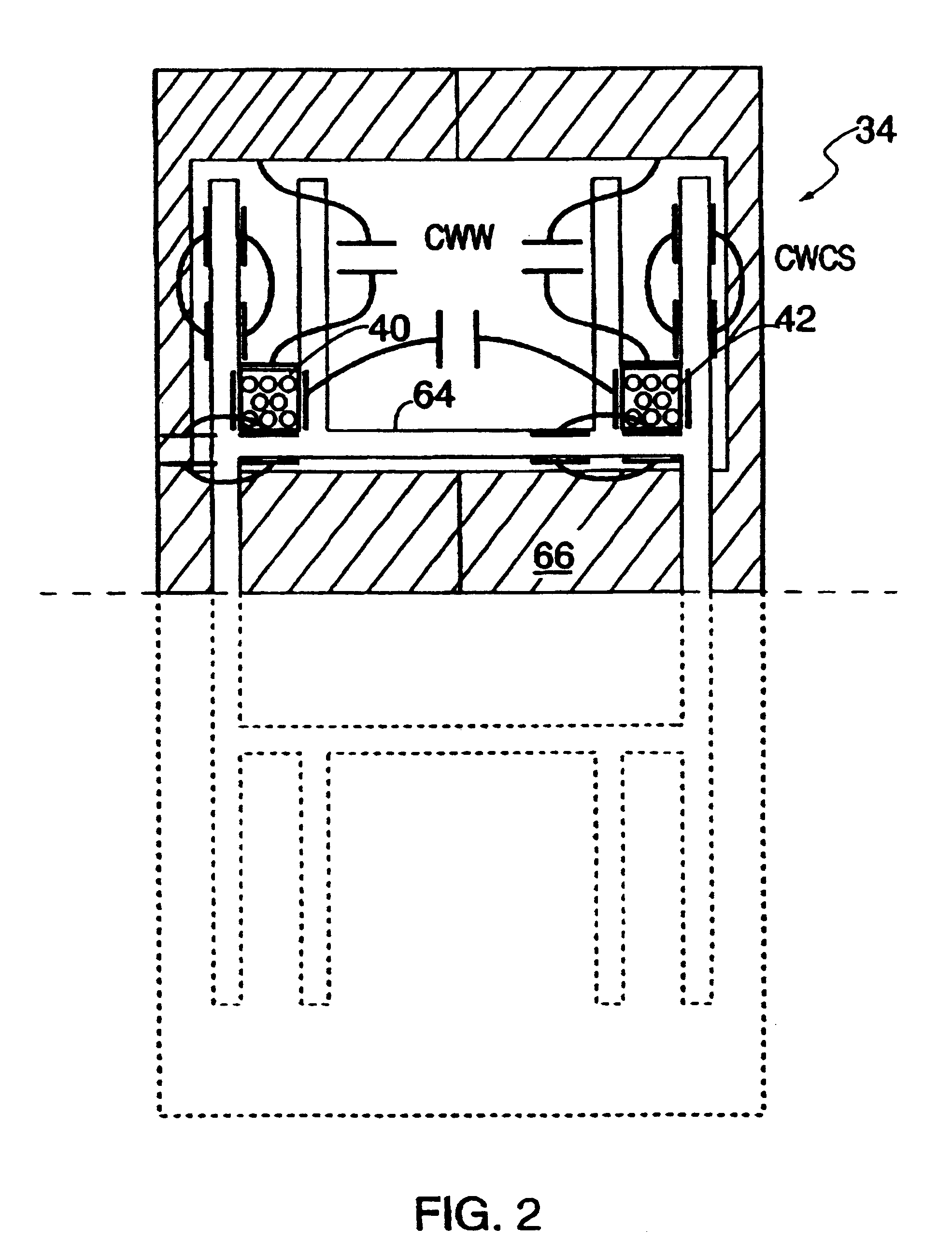

High frequency pulse transformer for an IGBT gate drive

InactiveUSRE38082E1Improve isolationLittle high-frequency power lossAC motor controlSingle motor speed/torque controlCapacitanceEngineering

A pulse transformer for use in a high frequency motor controller to isolate the electronic control stages from the power stages in a motor controller. The primary and secondary windings are wound on a common ferrite core and spaced apart from one another. The wire size used for the windings is relatively small (gauge 37 or less). Each of the windings has between 10 and 13 turns. The interwinding capacitance must be below 5 picofarads, preferably below 1 picofarad, and most preferably below 0.2 picofarads.

Owner:KOLLMORGEN CORP

Wire electrode based ion guide device

InactiveUS8507848B1Efficiently focusMinimize impactStability-of-path spectrometersTime-of-flight spectrometersElectric fieldMultiple layer

This invention presents a kind of ion guide device comprising multiple layers of stretched wire electrodes crossing in space. These wire electrodes are distributed along a defined ion guiding axis in the ion guide device. Each layer of wire electrodes contains at least two wire electrodes with some distance away from the guiding axis, and rotates with an angle relative to wire electrodes on neighboring layer. The ion guide contains multiple layers of wire electrodes to form a cage-like ion guide tunnel and keeps the mounting framework of those wire electrodes outside of the ion guide tunnel, thus reducing the interference of the gas flows from the ion guide device. A power supply provides voltage to each layer of wire electrodes, creates an electric field which focuses the ions towards the guiding axis.

Owner:SHIMADZU RES LAB SHANGHAI +1

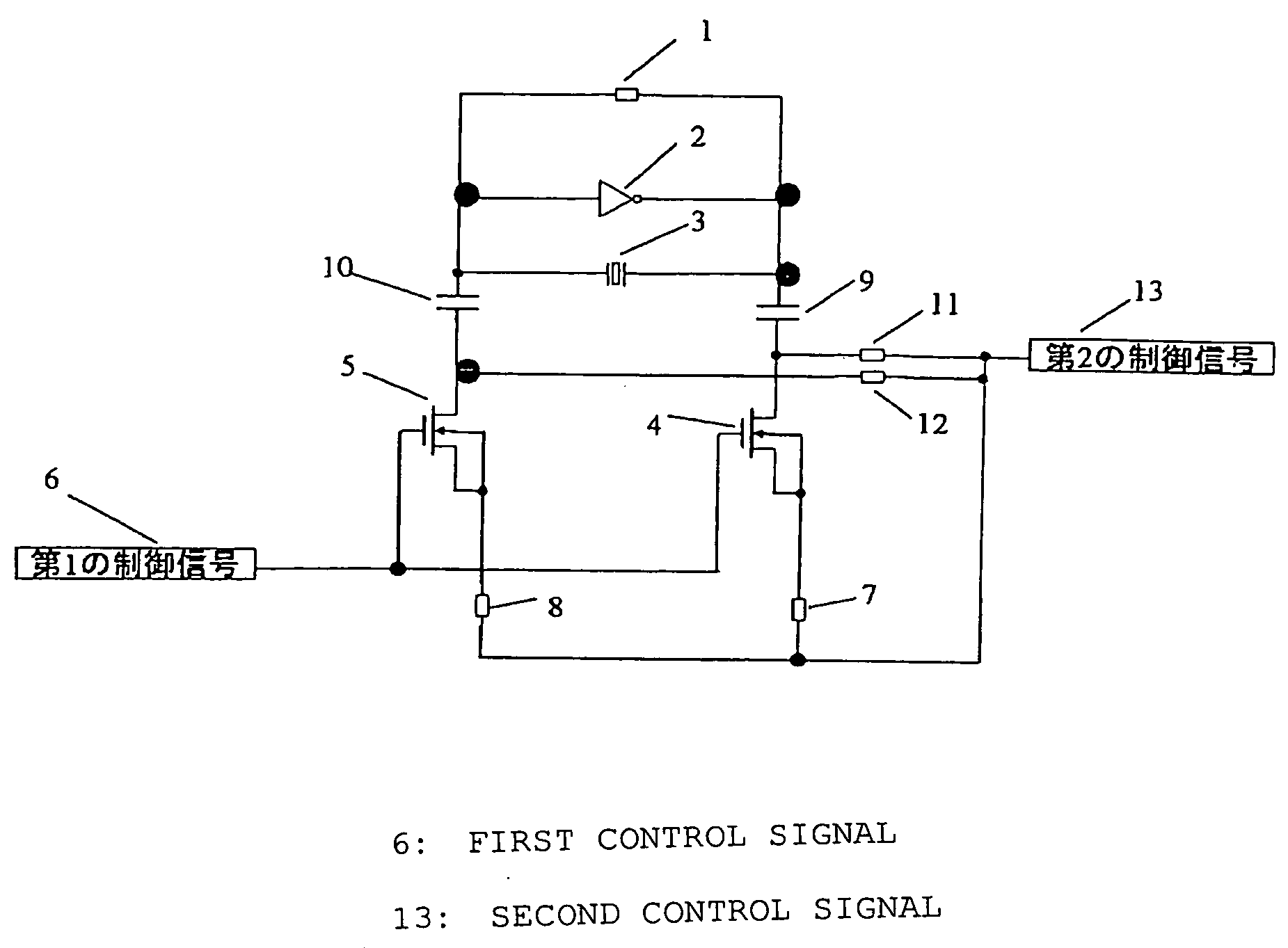

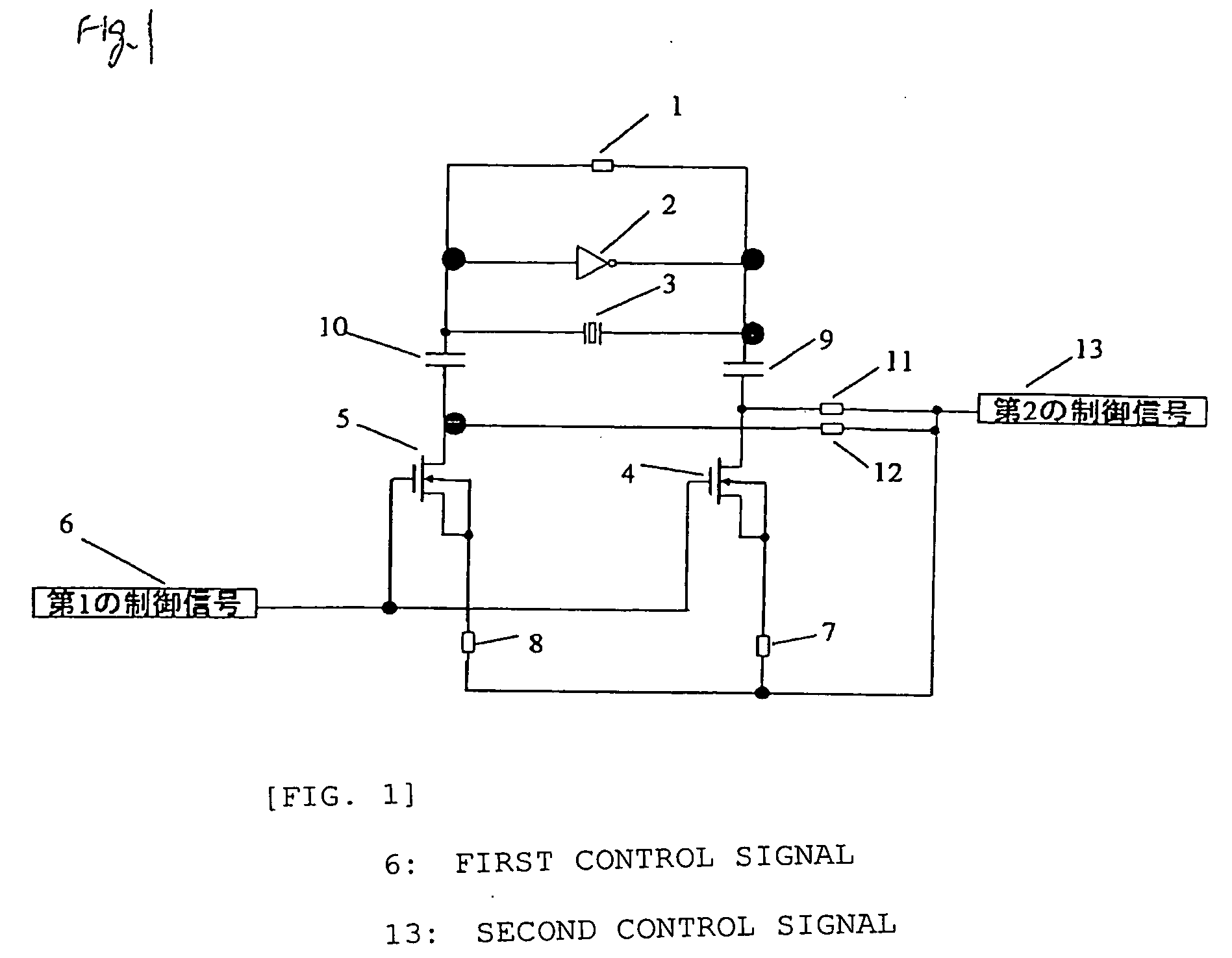

Voltage-controlled oscillator

InactiveUS20060164178A1Reduce deviationMinimize capacitancePulse automatic controlGenerator stabilizationVariable capacitorCapacitance

With a variable capacitor including a load capacitor of an oscillation circuit having a feedback resistor 1, an inverter 2, and a crystal oscillator 3, and a static capacitance generated between a drain terminal and a gate terminal of MOS transistors 4 and 5, in which source and backgate terminals are shorted to each other, a serial connection of a DC cut capacitor 9, 10 and a variable capacitors (MOS transistor) 4 and 5 is formed between one end and the other end of the crystal oscillator 3. For example, a threshold voltage control signal of the MOS transistors 4 and 5 is input to the drain terminal through a high-frequency elimination resistor 11, 12, and is input to the source-backgate terminal through a high-frequency elimination resistor 7, 8. In addition, a signal obtained by overlapping a temperature characteristic compensation signal and a threshold voltage control signal of the MOS transistor 4, 5 is input to the gate terminal. Accordingly, it is possible to indiscriminately determine an output bias of a temperature compensation control circuit or an external voltage frequency control circuit.

Owner:COLLABO INNOVATIONS INC

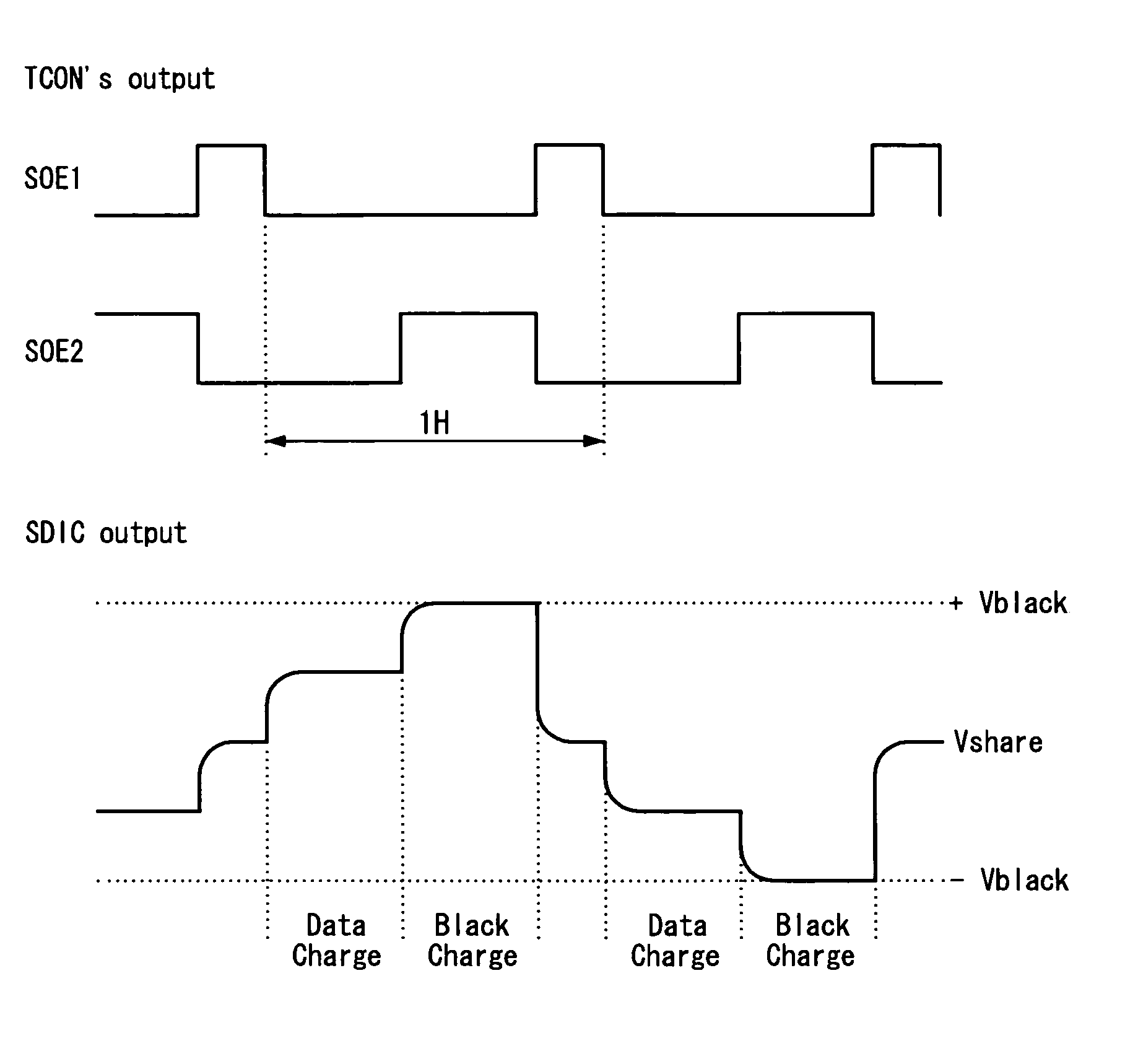

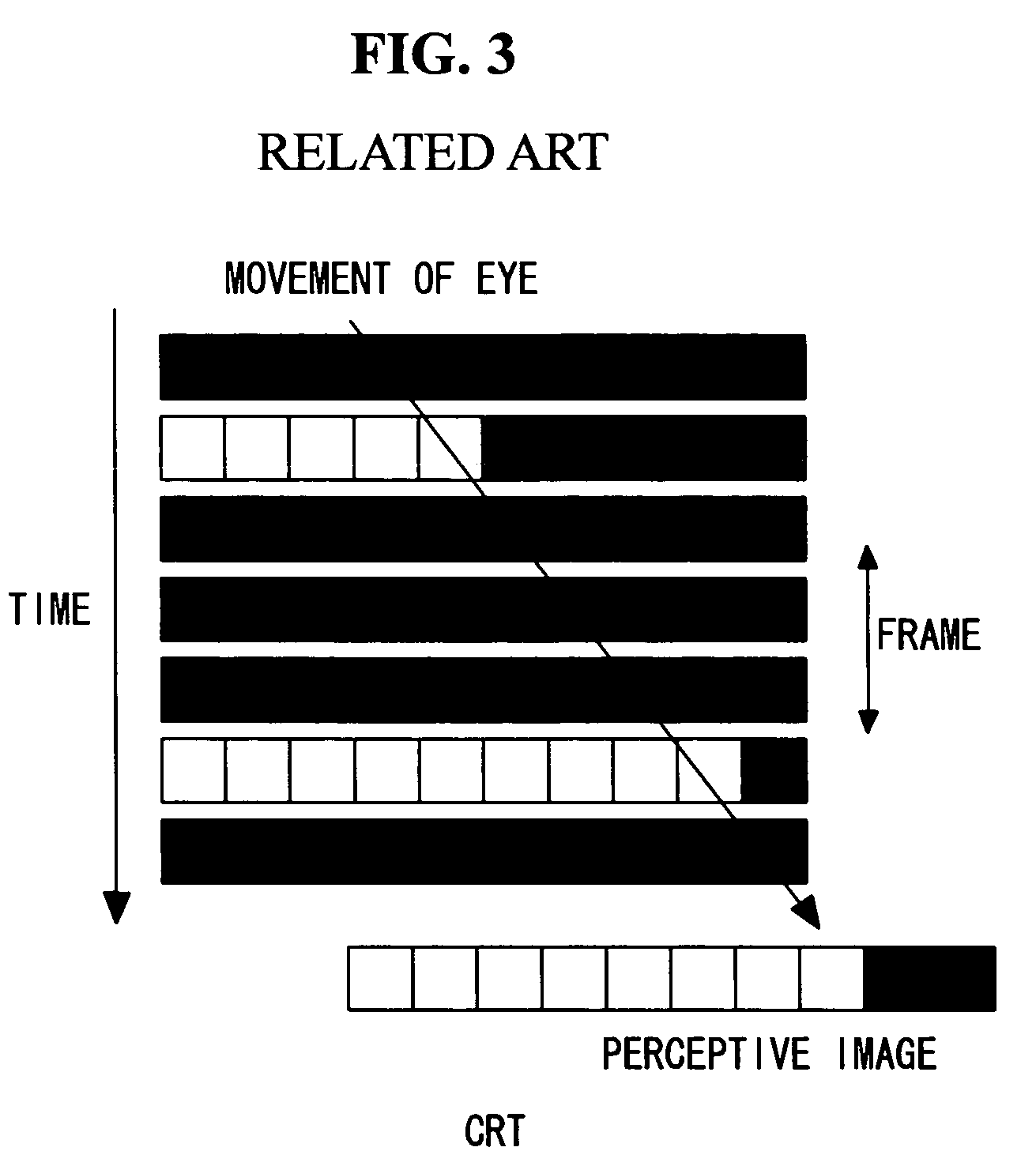

Liquid crystal display device and driving method thereof

ActiveUS8872748B2Simple hardware structureMinimize capacitanceCathode-ray tube indicatorsNon-linear opticsCapacitanceLiquid-crystal display

Owner:LG DISPLAY CO LTD

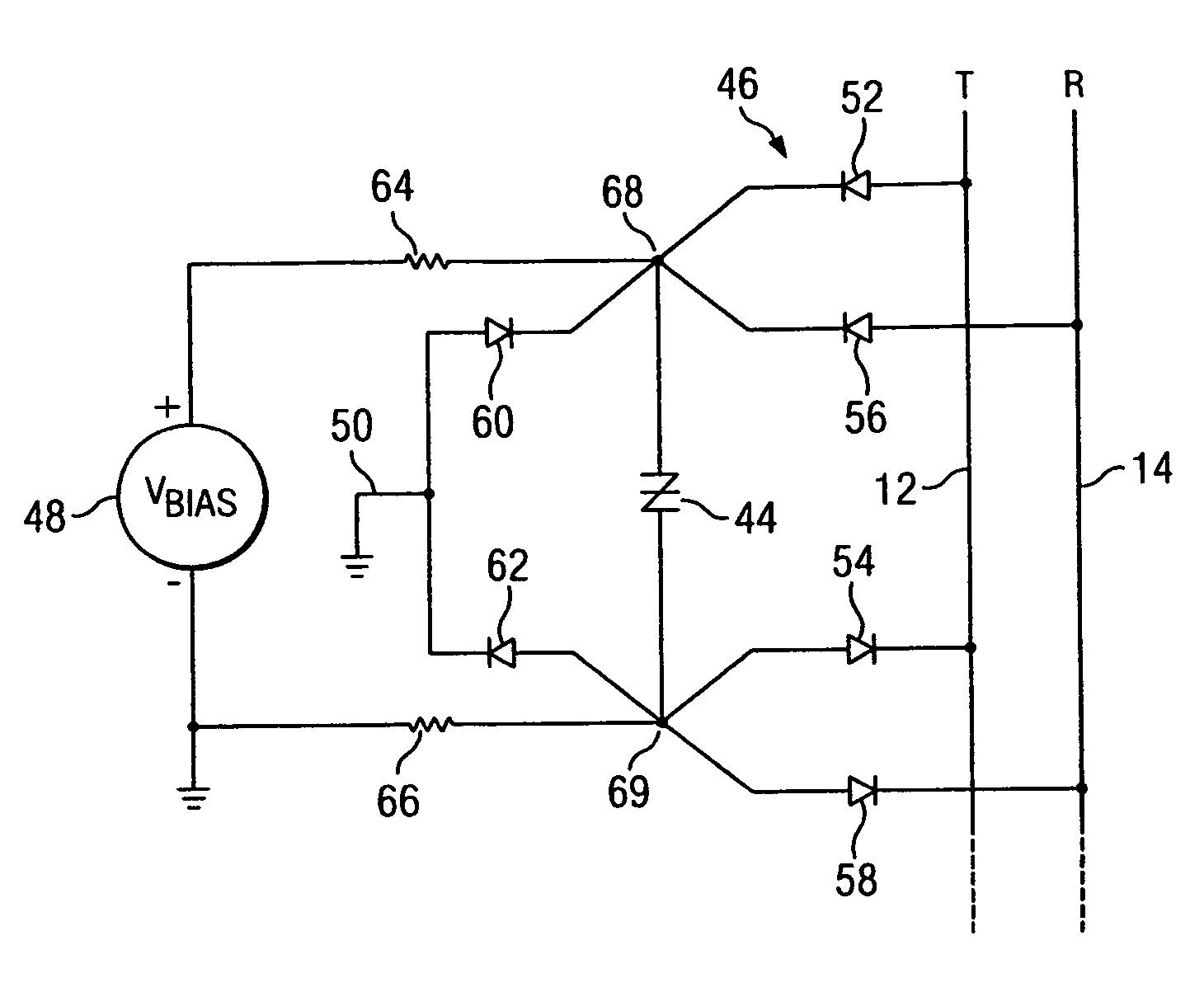

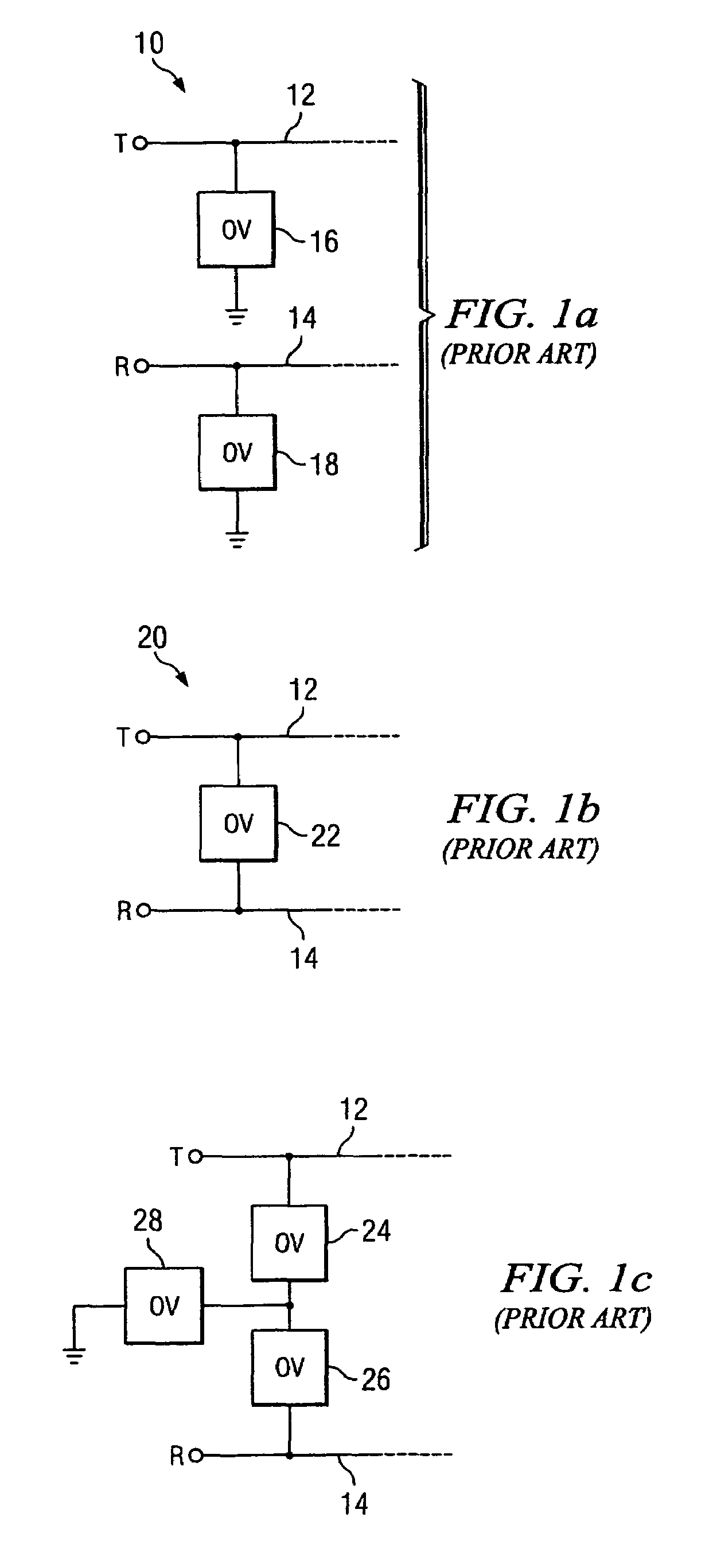

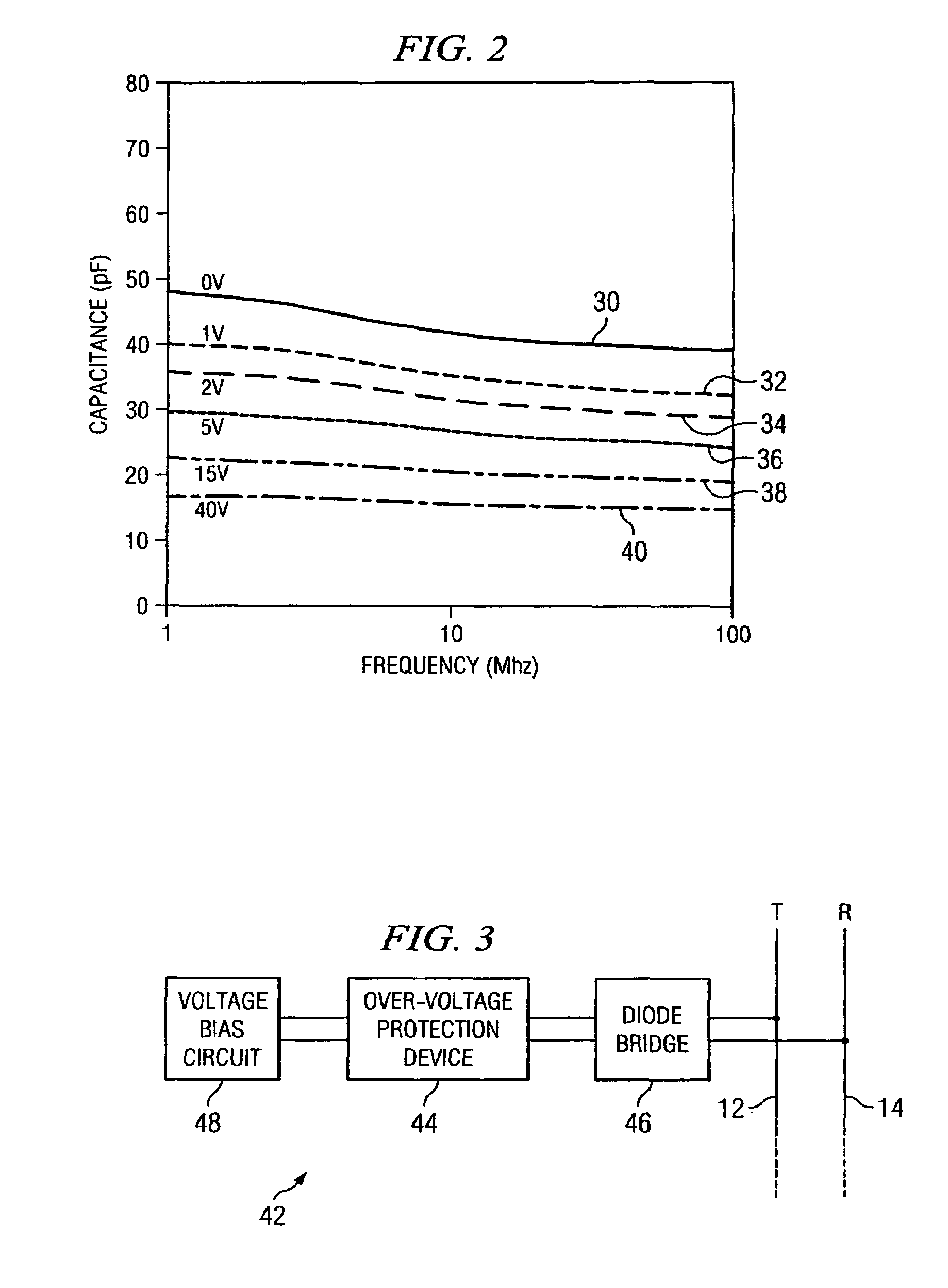

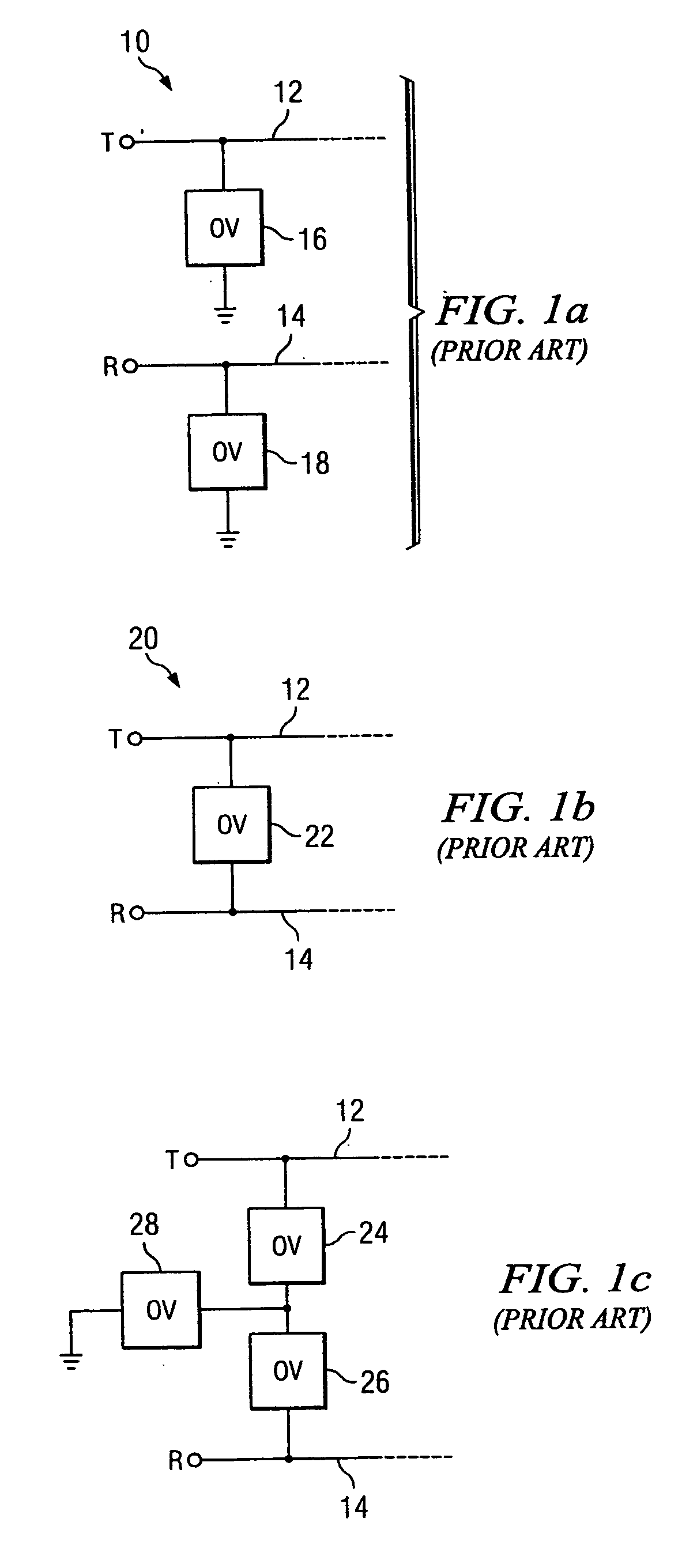

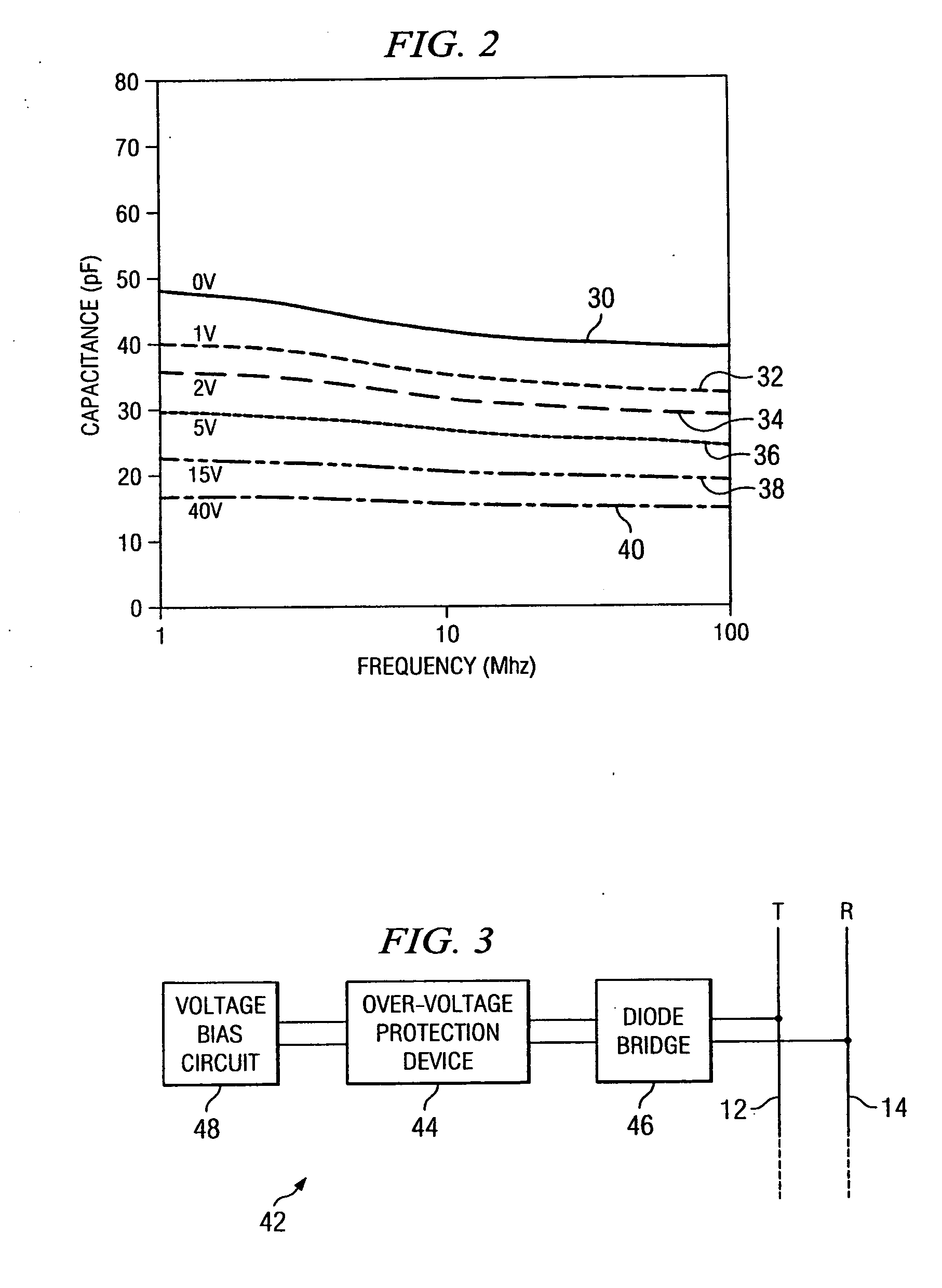

Linear low capacitance overvoltage protection circuit

ActiveUS7515391B2Minimize capacitanceLower impedanceInterconnection arrangementsEmergency protective arrangement detailsOvervoltageCapacitance

Owner:LITTELFUSE INC

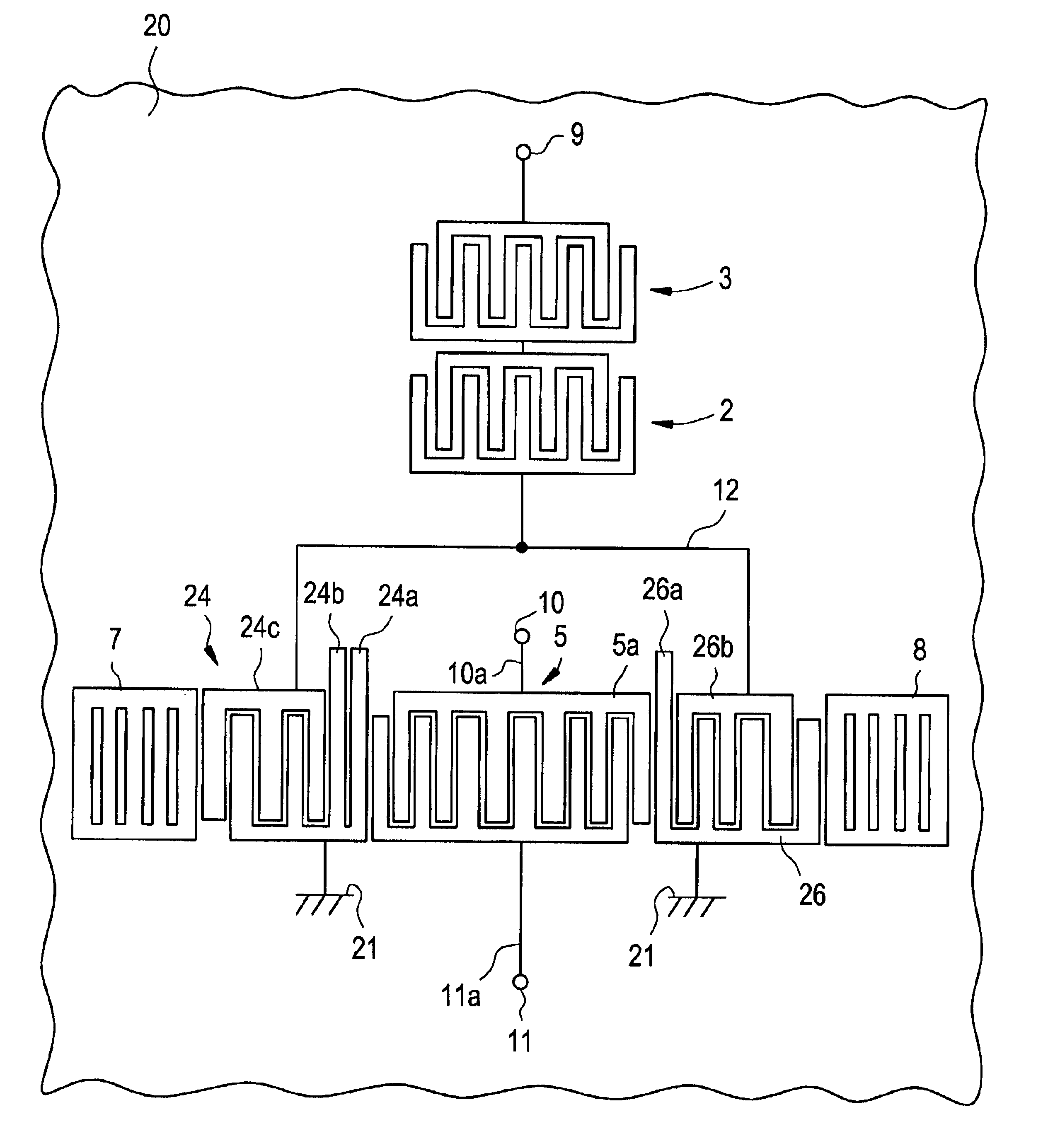

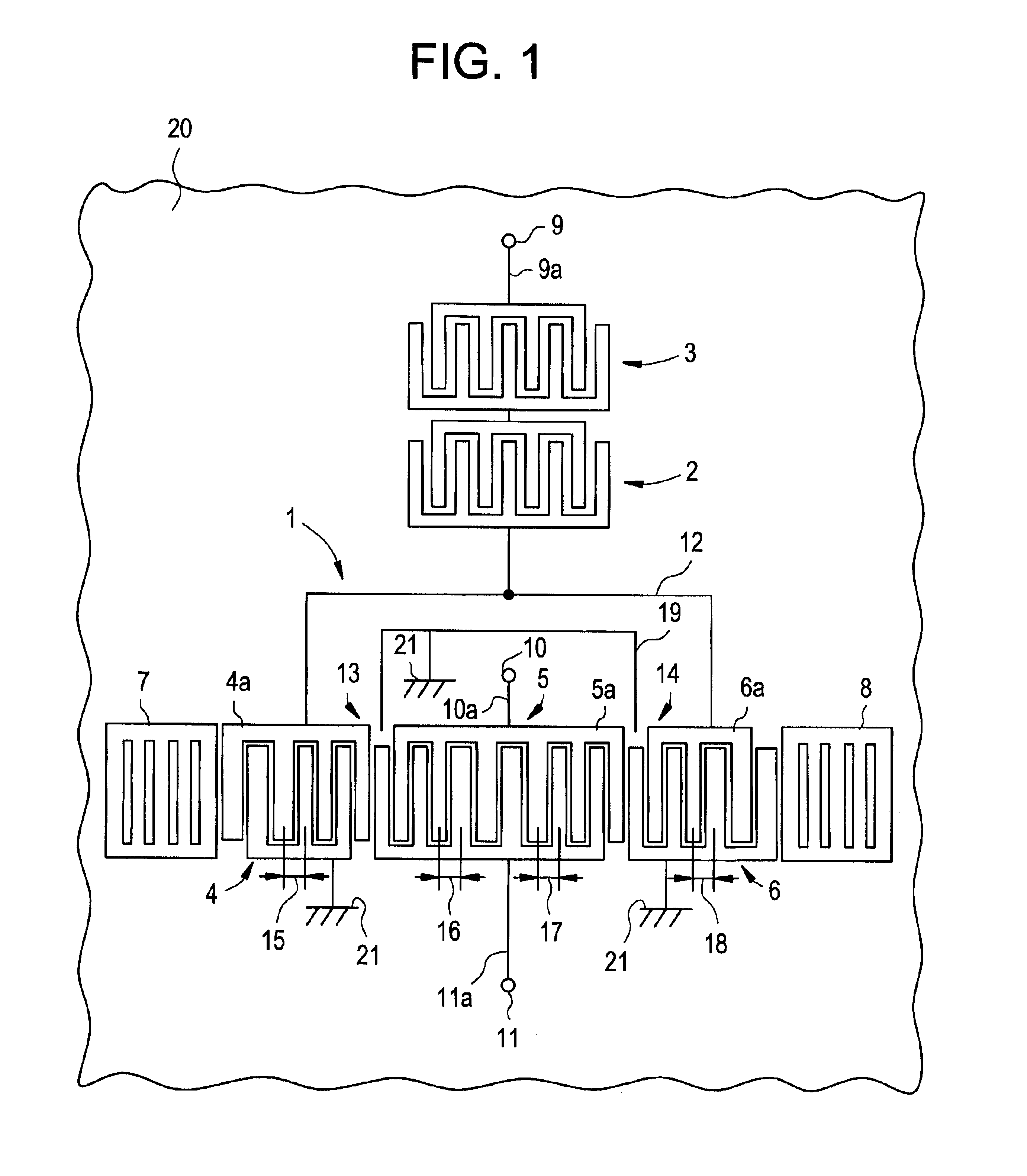

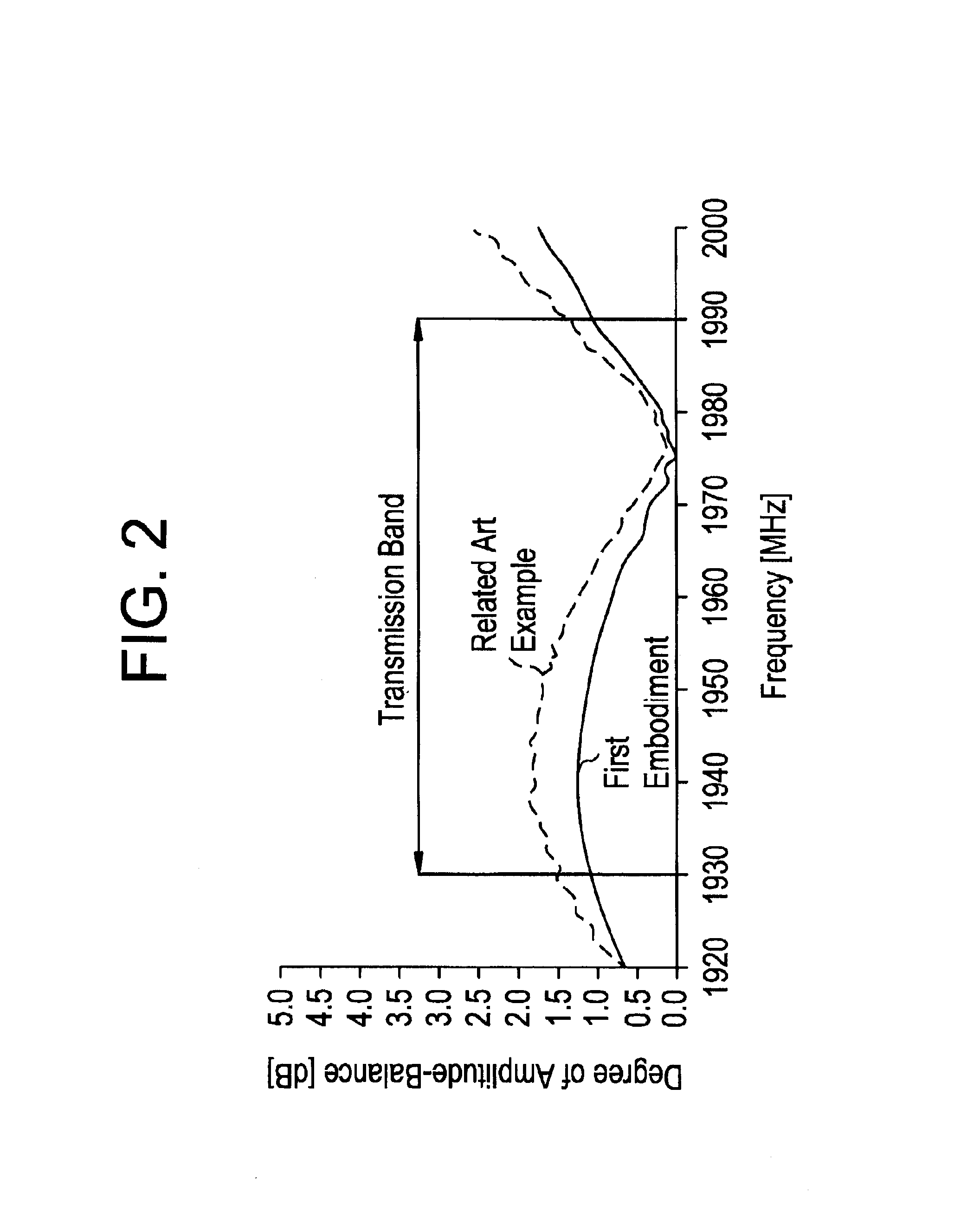

Surface acoustic wave device and communication device

InactiveUS6753641B2Balance degreeHigh frequencyPiezoelectric/electrostriction/magnetostriction machinesImpedence networksCapacitanceElectricity

A surface acoustic wave device includes interdigital electrodes for generating a surface acoustic wave and detecting the wave, which are provided on a piezoelectric substrate having piezoelectric properties. A signal line is arranged so as to be connected to the interdigital electrodes which are unbalanced-side electrodes. Balanced-signal terminals are arranged so as to be connected to the interdigital electrode which is a balanced-side electrode. A ground line is provided between a balanced-signal terminal and the adjacent signal line. A capacitance generated between the signal line and the balanced-signal terminal is minimized by the ground line. Thus, the balance degrees between the balanced-signal terminals are greatly improved.

Owner:MURATA MFG CO LTD

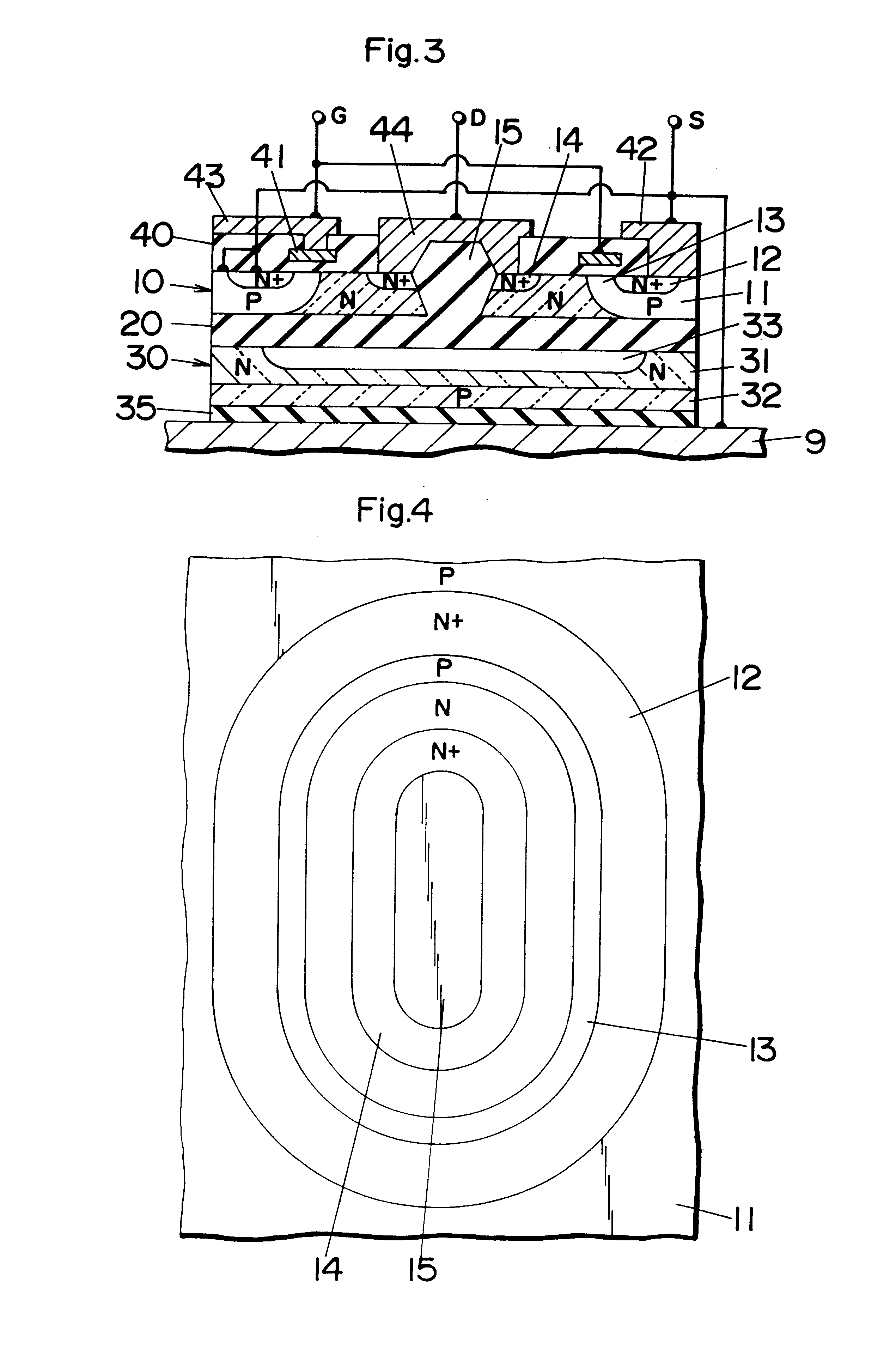

Solid-state relay

InactiveUS6373101B1Sufficient flexibilityReduce interfaceTransistorSemiconductor/solid-state device detailsCapacitanceInductance

A solid state relay composed of a series connected pair of LDMOSFETs has a minimized output capacitance. Each LDMOSFET is configured to have a silicon layer of a first conductive type, a drain region of the first conductive type diffused in the top surface of the silicon layer, a well region of a second conductive type diffused in the silicon layer in a laterally spaced relation from the drain region, and a source region of the first conductive type diffused within the well region to define a channel extending between the source region and a confronting edge of the well region along the top surface of the silicon layer. Each LDMOSFET is of an SOI (Silicon-On-Insulator) structure composed of a silicon substrate placed on a supporting plate, a buried oxide layer on the silicon substrate, and the silicon layer on the buried oxide layer. The well region is diffused over the full depth of the silicon layer to have its bottom in contact with the buried oxide layer, so that the well region forms with the silicon layer a P-N interface only at a small area adjacent the channel. Because of this reduced P-N interface and also because of the buried oxide layer exhibiting a much lower inductive capacitance than the silicon layer, it is possible to greatly reduce a drain-source capacitance for minimizing the output capacitance of the relay in the non-conductive condition.

Owner:MATSUSHITA ELECTRIC WORKS LTD

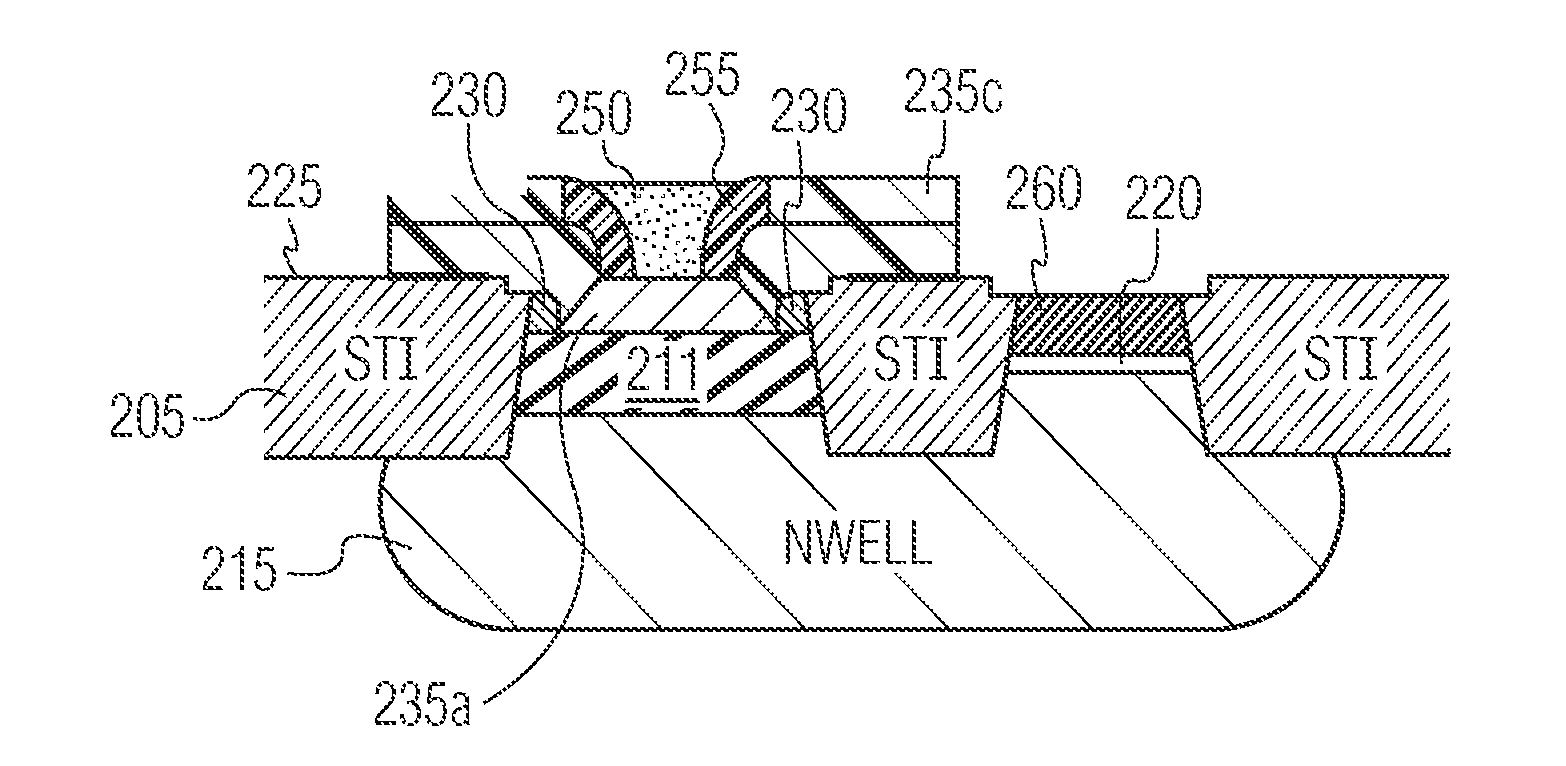

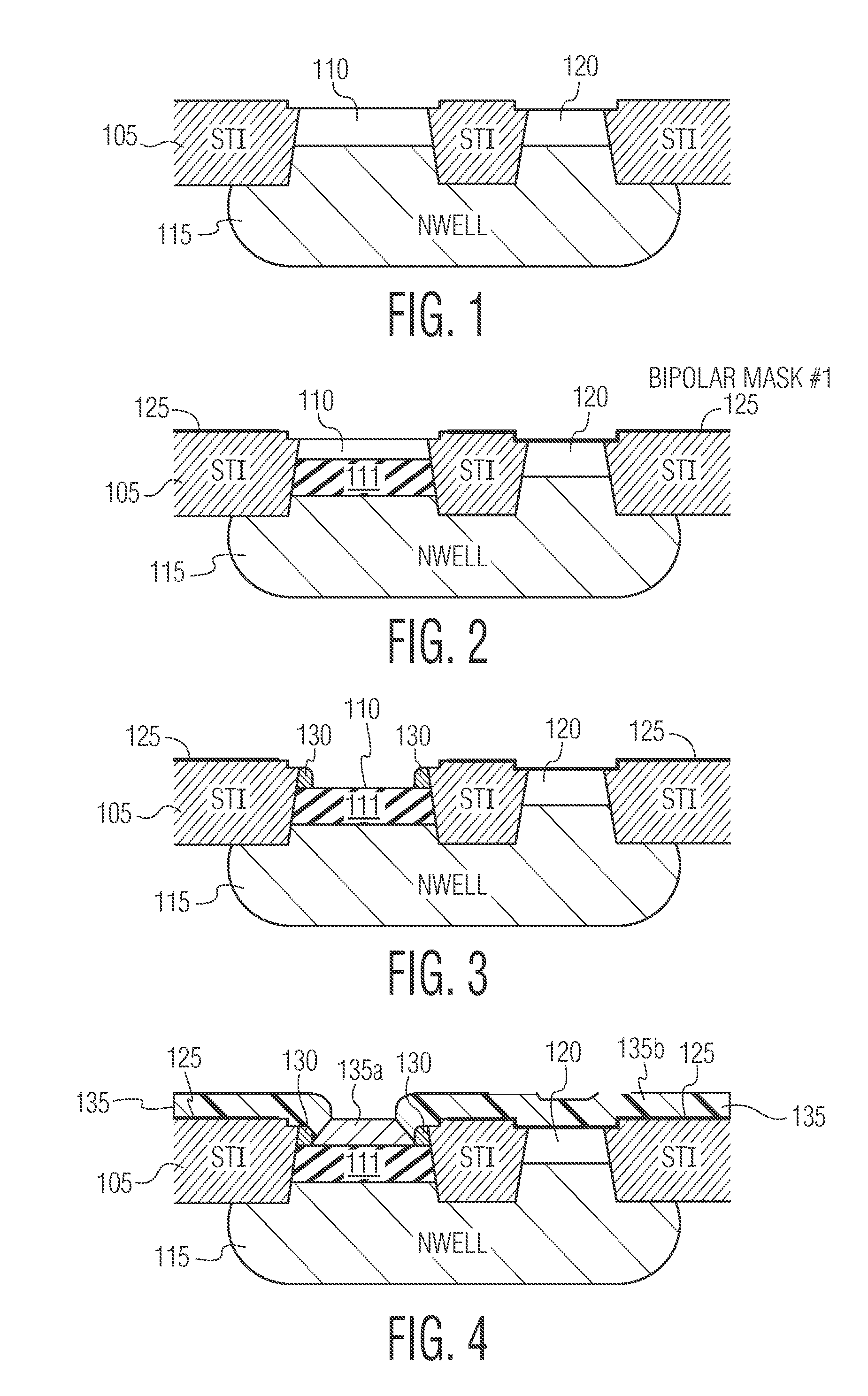

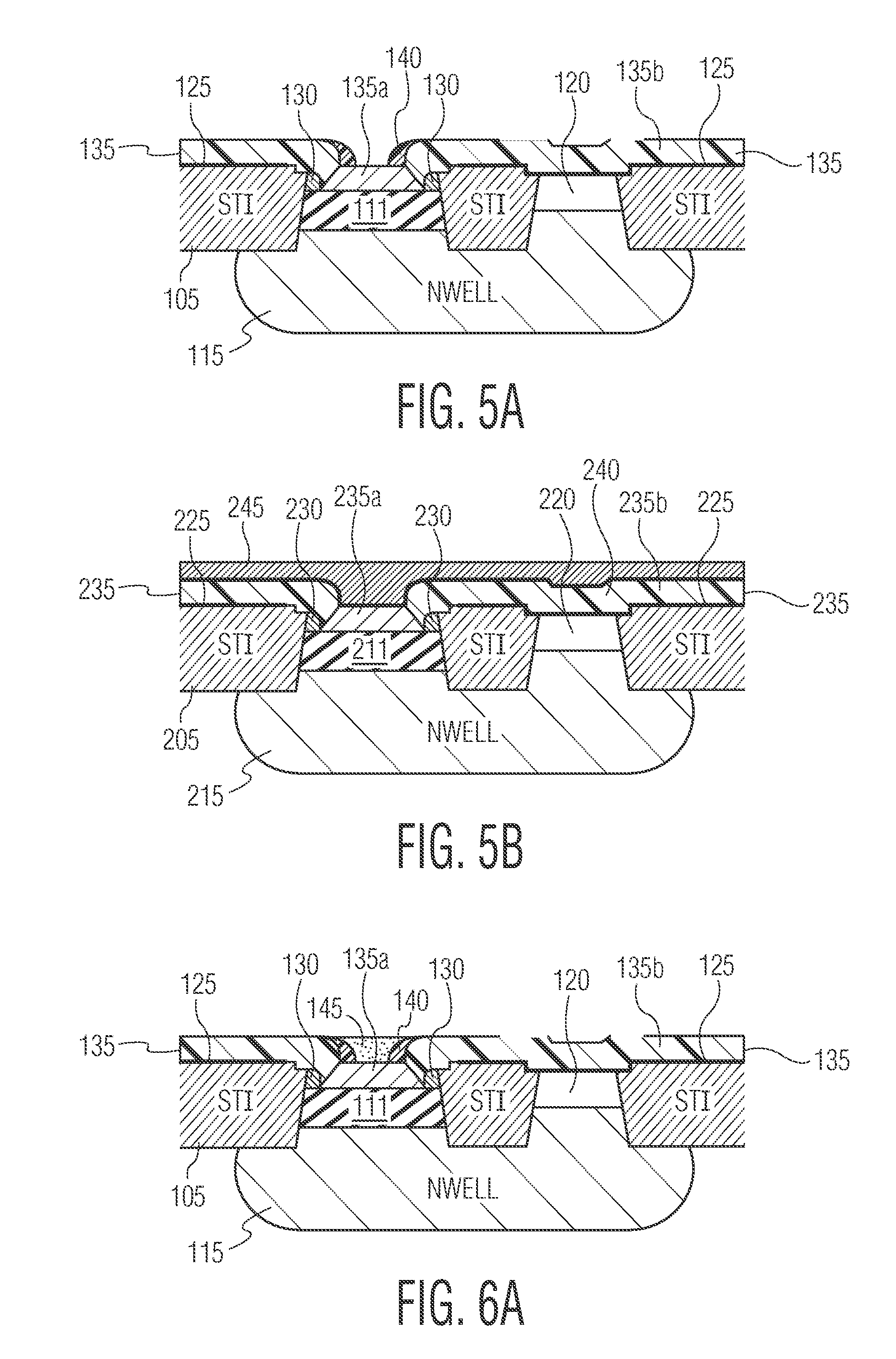

Self-aligned epitaxially grown bipolar transistor

ActiveUS7883954B2Minimize capacitanceMinimizes base resistanceTransistorSemiconductor/solid-state device manufacturingTotal internal reflectionLighting system

The illumination system has a light source (1) with a plurality of light emitters (R, G, B). The light emitters comprise at least a first light-emitting diode of a first primary color and at least a second light-emitting diode of a second primary color, the first and the second primary colors being distinct from each other. The illumination system has a facetted light-collimator (2) for collimating light emitted by the light emitters. The facetted lightcollimator is arranged along a longitudinal axis (25) of the illumination system. Light propagation in the facetted light-collimator is based on total internal reflection or on reflection at a reflective coating provided on the facets of the facetted light-collimator. The facetted light-collimator merges into a facetted light-reflector (3) at a side facing away from the light source. The illumination system further comprises a light-shaping diffuser (17). The illumination system emits light with a uniform spatial and spatio-angular color distribution.

Owner:NXP BV

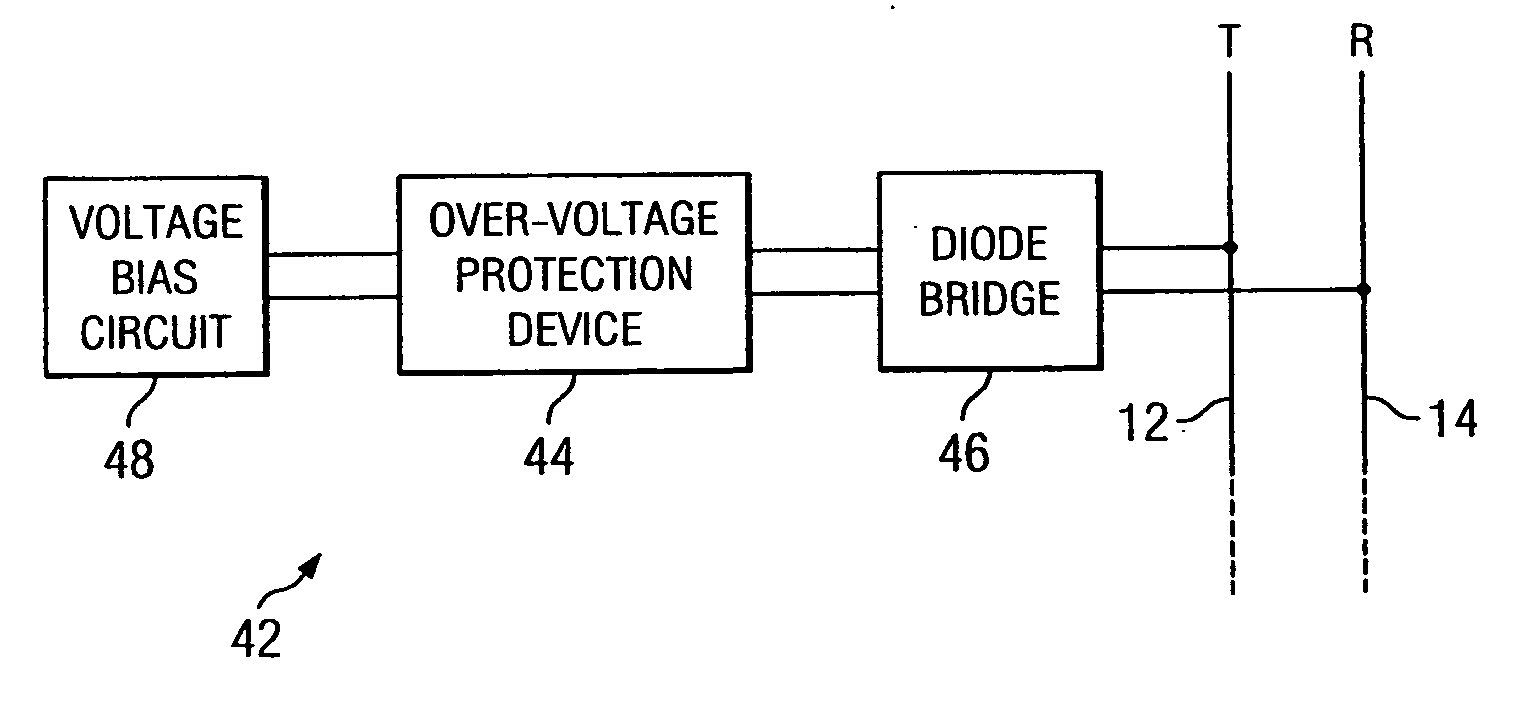

Linear low capacitance overvoltage protection circuit

ActiveUS20070086137A1Minimize capacitanceLower impedanceInterconnection arrangementsEmergency protective arrangement detailsError ratioCapacitance

A bipolar semiconductor overvoltage protection circuit presents less capacitance to a communication line. The overvoltage protection circuit includes an overvoltage protection device that is biased with a voltage to not only reduce the capacitance thereof, but also to reduce the change in capacitance as a function of frequency. Changes in communication line voltages thus change the capacitance of the overvoltage protection device less, resulting in the ability to allow the transmission of high capacity data protocols with reduced error rates.

Owner:LITTELFUSE INC

Memory architecture of 3D array with improved uniformity of bit line capacitances

ActiveUS8811077B2Good senseMinimize capacitanceTransistorSolid-state devices3d integrated circuitBit line

Owner:MACRONIX INT CO LTD

Low capacitance semiconductor device

ActiveUS7943959B2Reduce areaMinimizing junction capacitanceTransistorSemiconductor/solid-state device detailsCapacitanceSemiconductor

Owner:LITTELFUSE INC

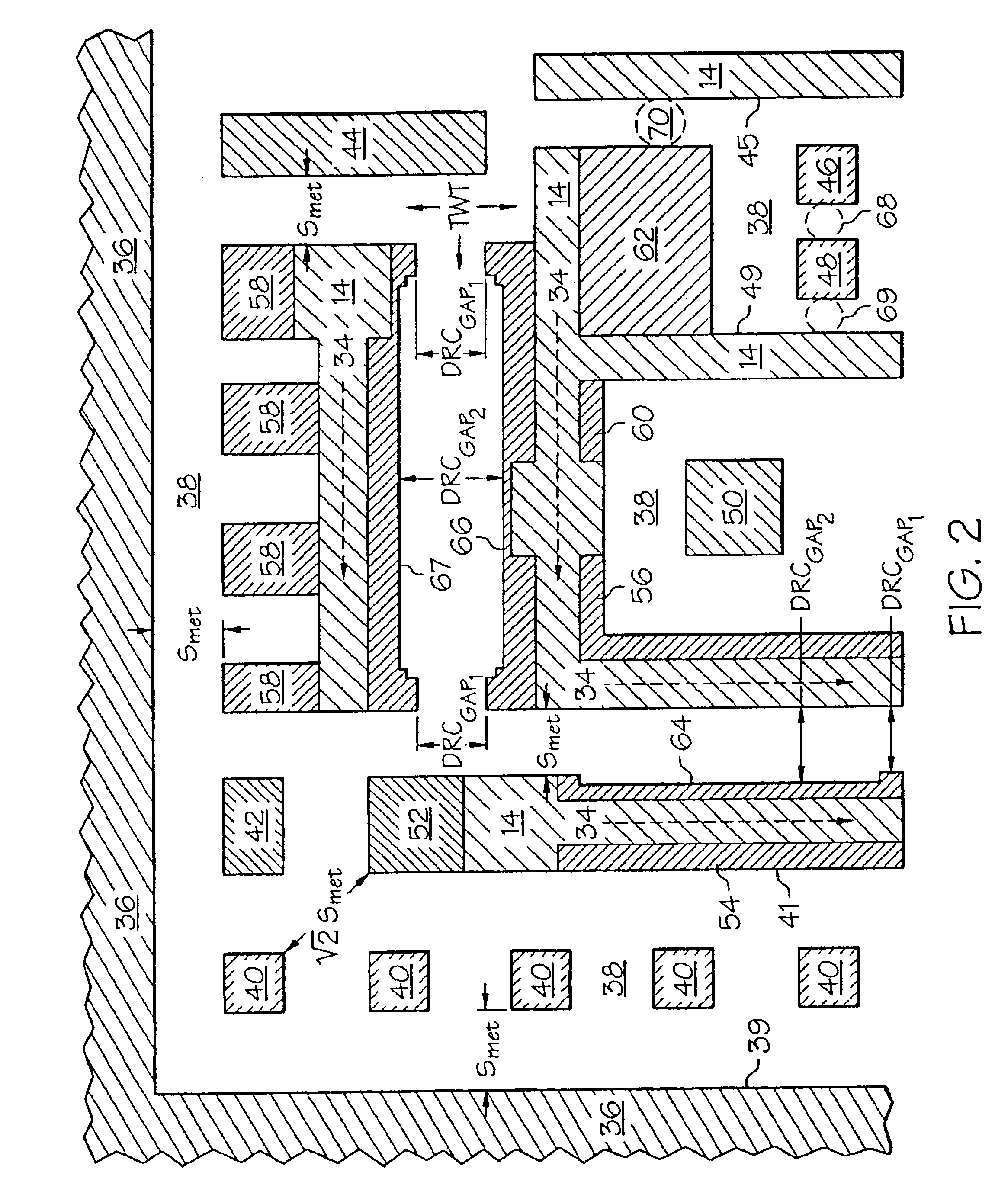

Metal line layout of an integrated circuit

InactiveUS6867498B2Decrease spacingMinimize capacitanceSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuitCapacitance

A metal line layout which includes two separate control spaces to address capacitive issues along speed sensitive pathways in an integrated circuit structure without negatively impacting Werner Fill processing. One control space (i.e., DRCgap1) is for decreasing the spacing between various metal features to standardize such spacing, and a second control space (i.e., DRCgap2) is for addressing capacitance issues along speed sensitive pathways. Between speed sensitive pathways, spacing of added metal features provided to long parallel metal lines are maintained at the second control spacing DRCgap2. Spaces at the ends of such long parallel metal lines are reduced to the first control spacing DRCgap1 in order to best fill three-way-intersections (TWIs) with subsequent depositions.

Owner:MICRON TECH INC

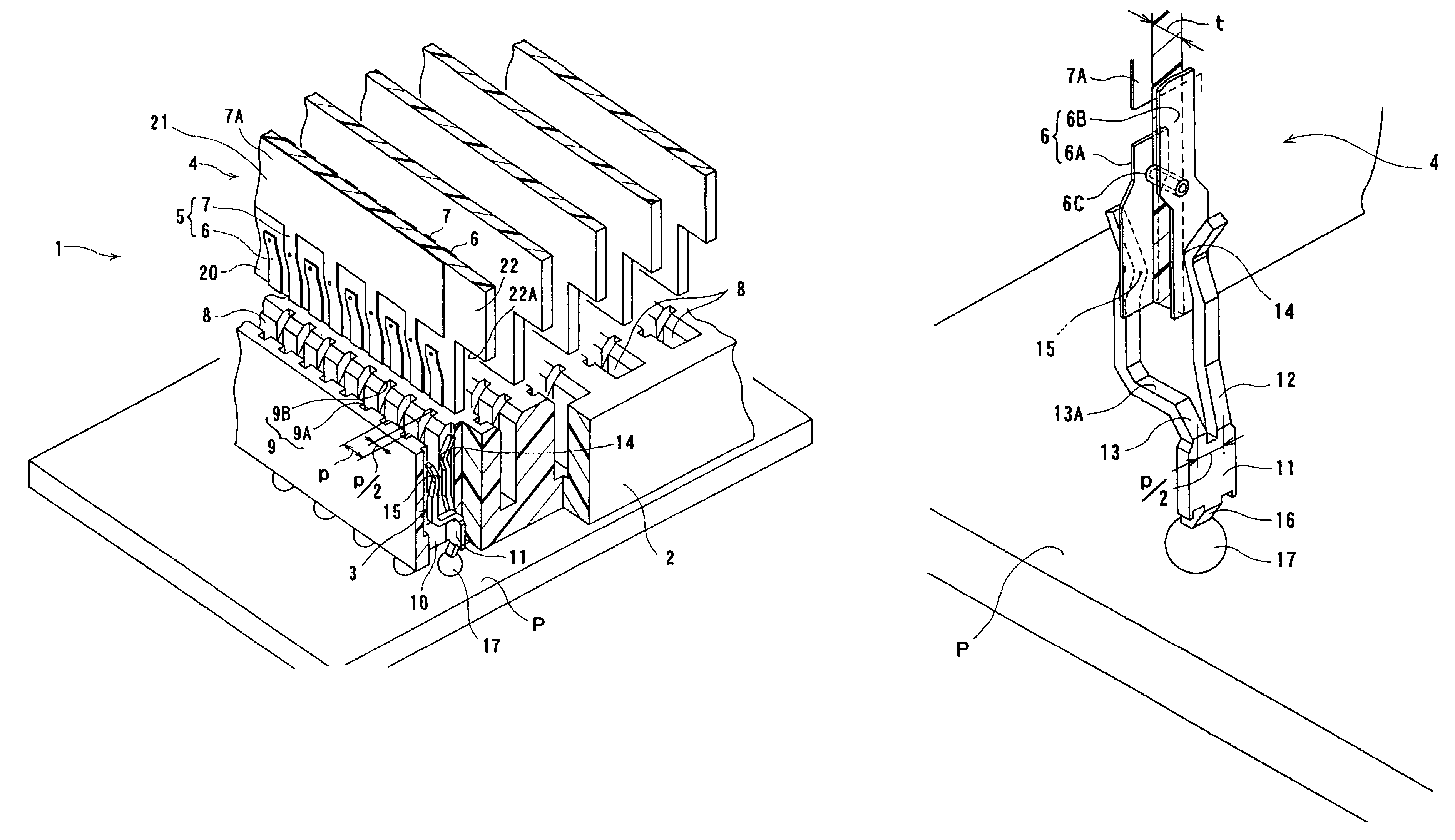

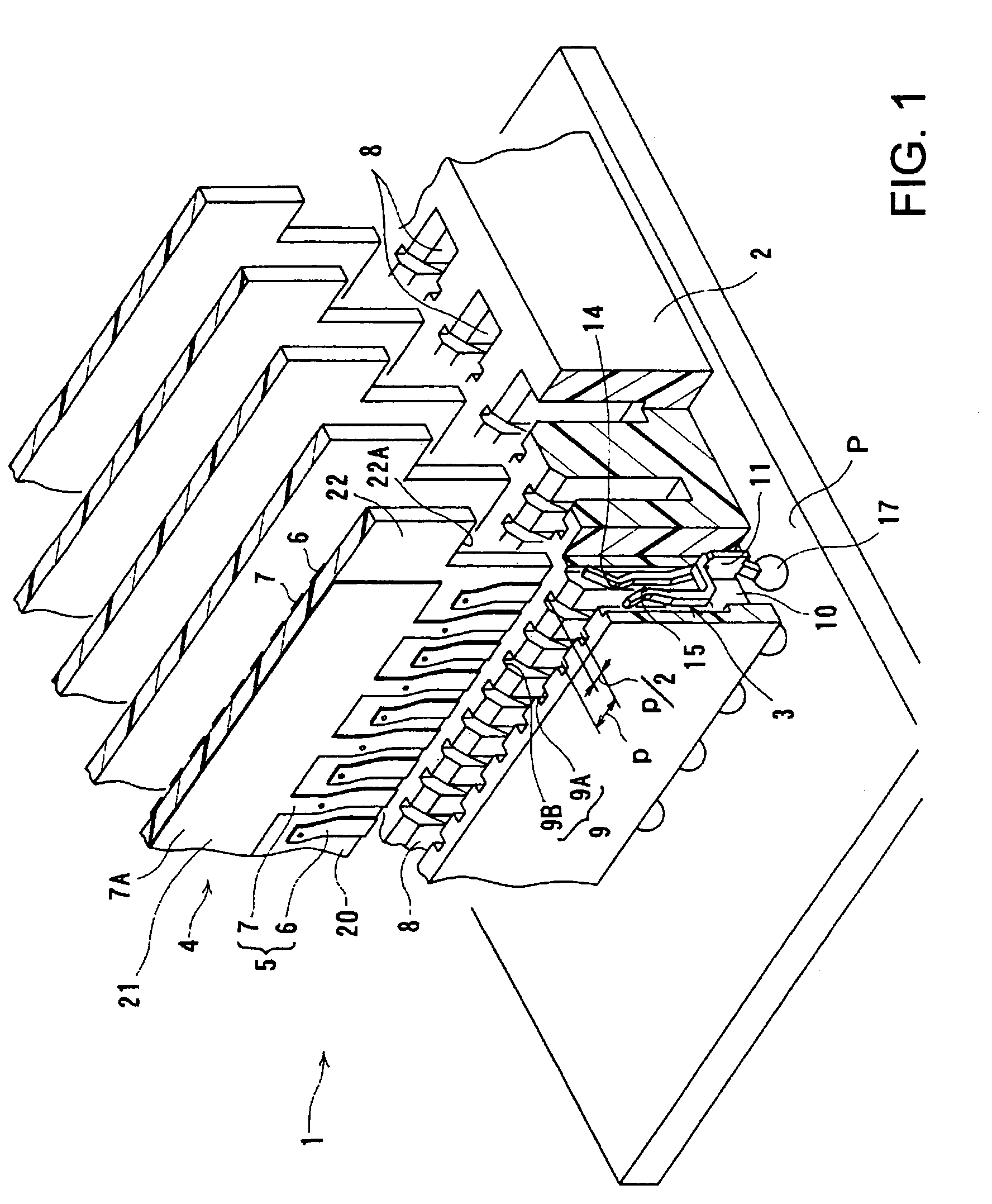

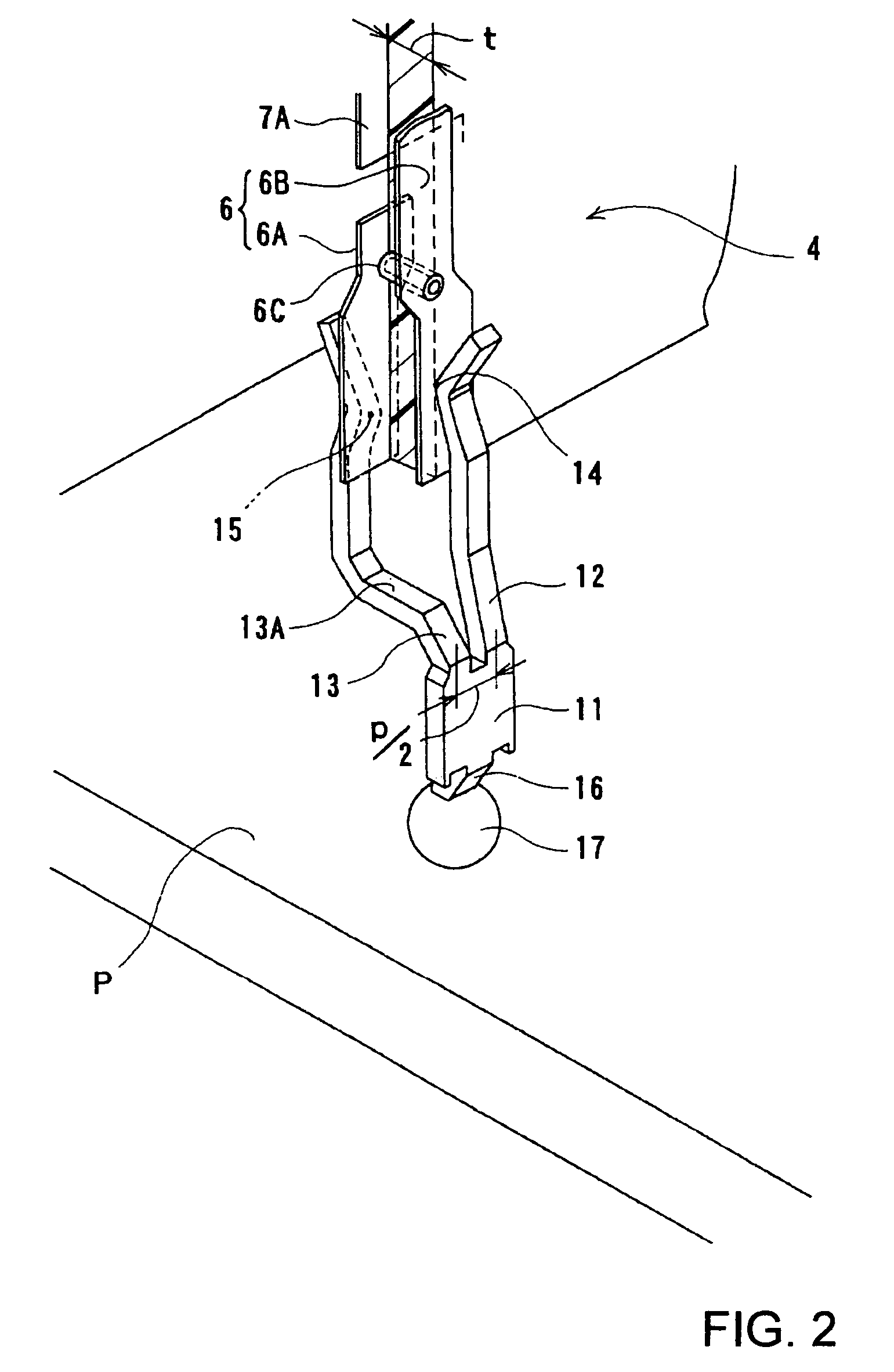

Electrical connector

InactiveUS7086903B2Minimize capacitanceReduce overlap areaCoupling device detailsSoldered/welded conductive connectionsOn boardEngineering

An electrical connector includes an insulative housing (2) attachable to a first board and having a receiving recess (8) for receiving a second board in a first direction; and a plurality of terminals (3) arranged in the receiving recess in a second direction perpendicular to the first direction. Each terminal (3) has a pair of contact sections (14, 15) to be brought into spring contact with a pair of connection lands (5) provided on front and back edge sections (20) on front and back surfaces of a second board. The pair of connection lands (5) on the front and back edge sections are short-circuited and offset in the second direction. The pair of contact sections are offset in the second direction.

Owner:HIROSE ELECTRIC GROUP

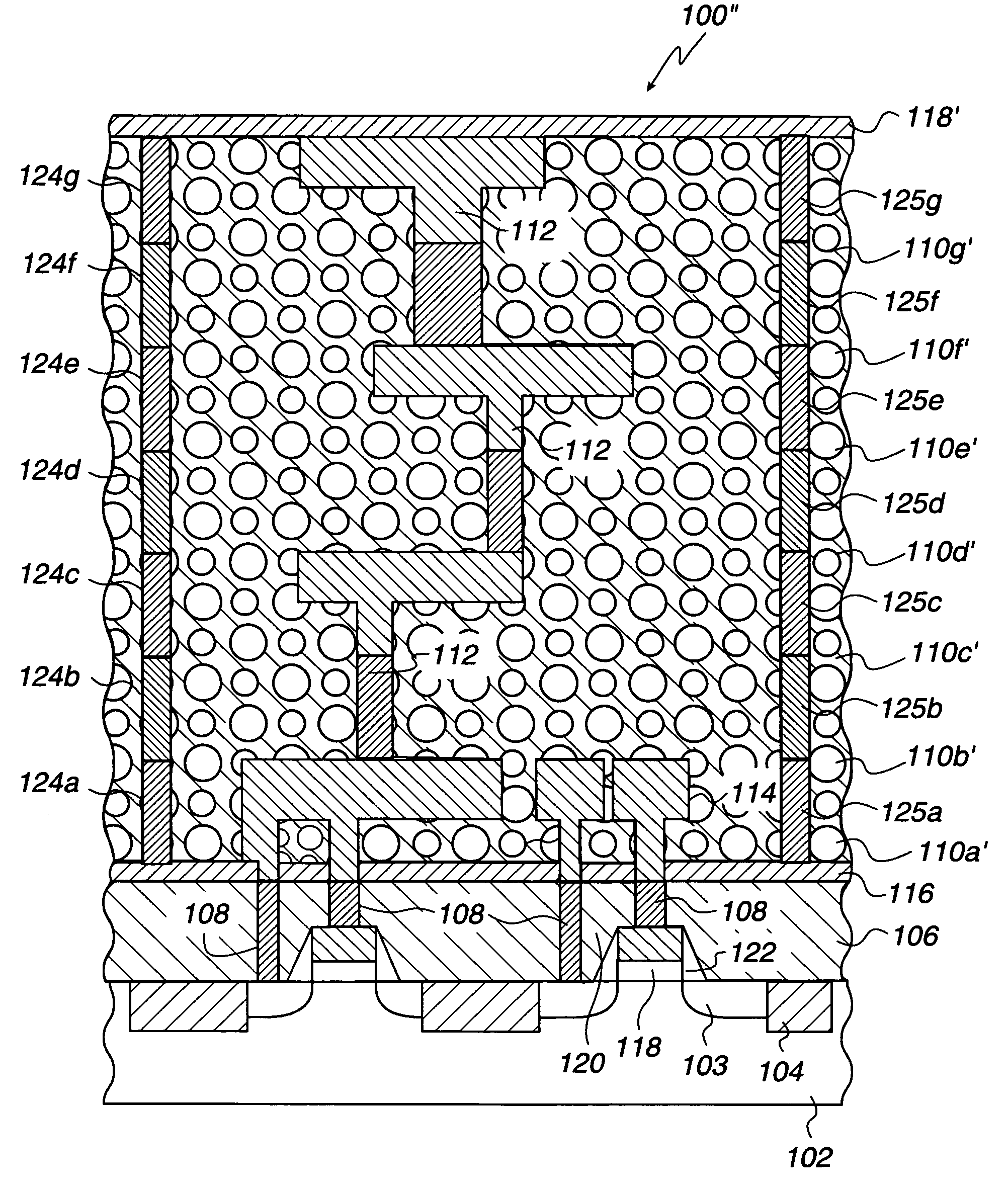

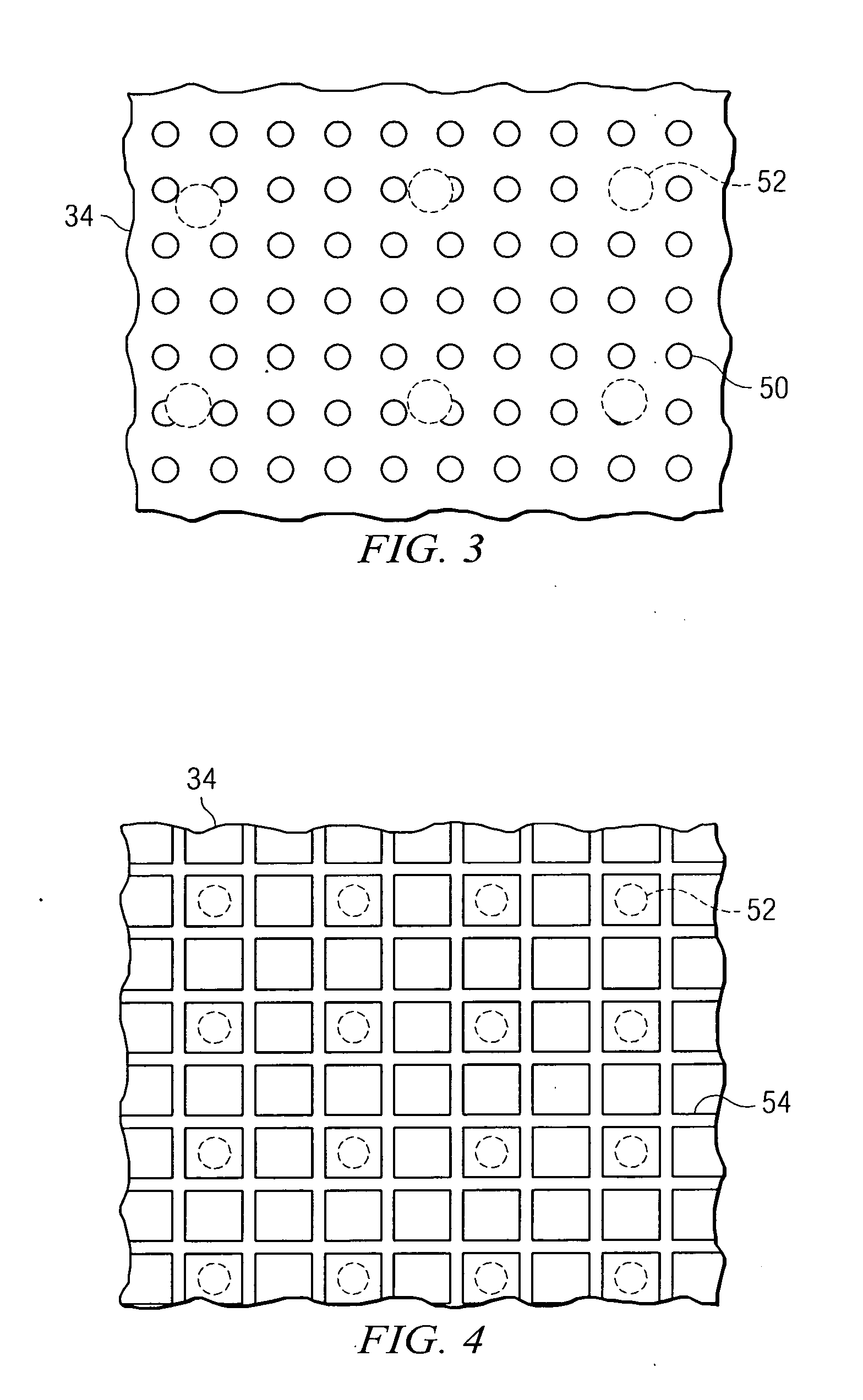

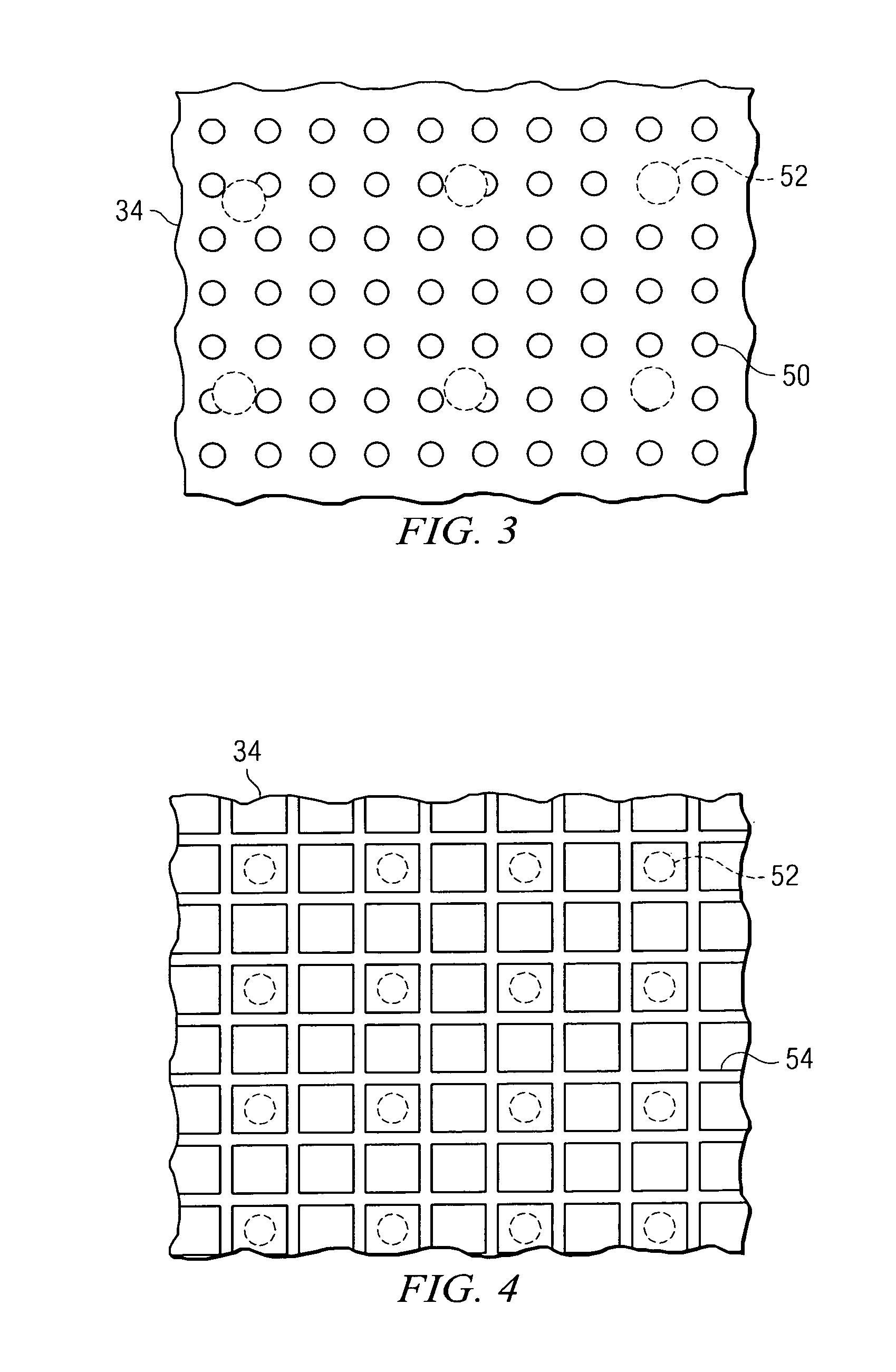

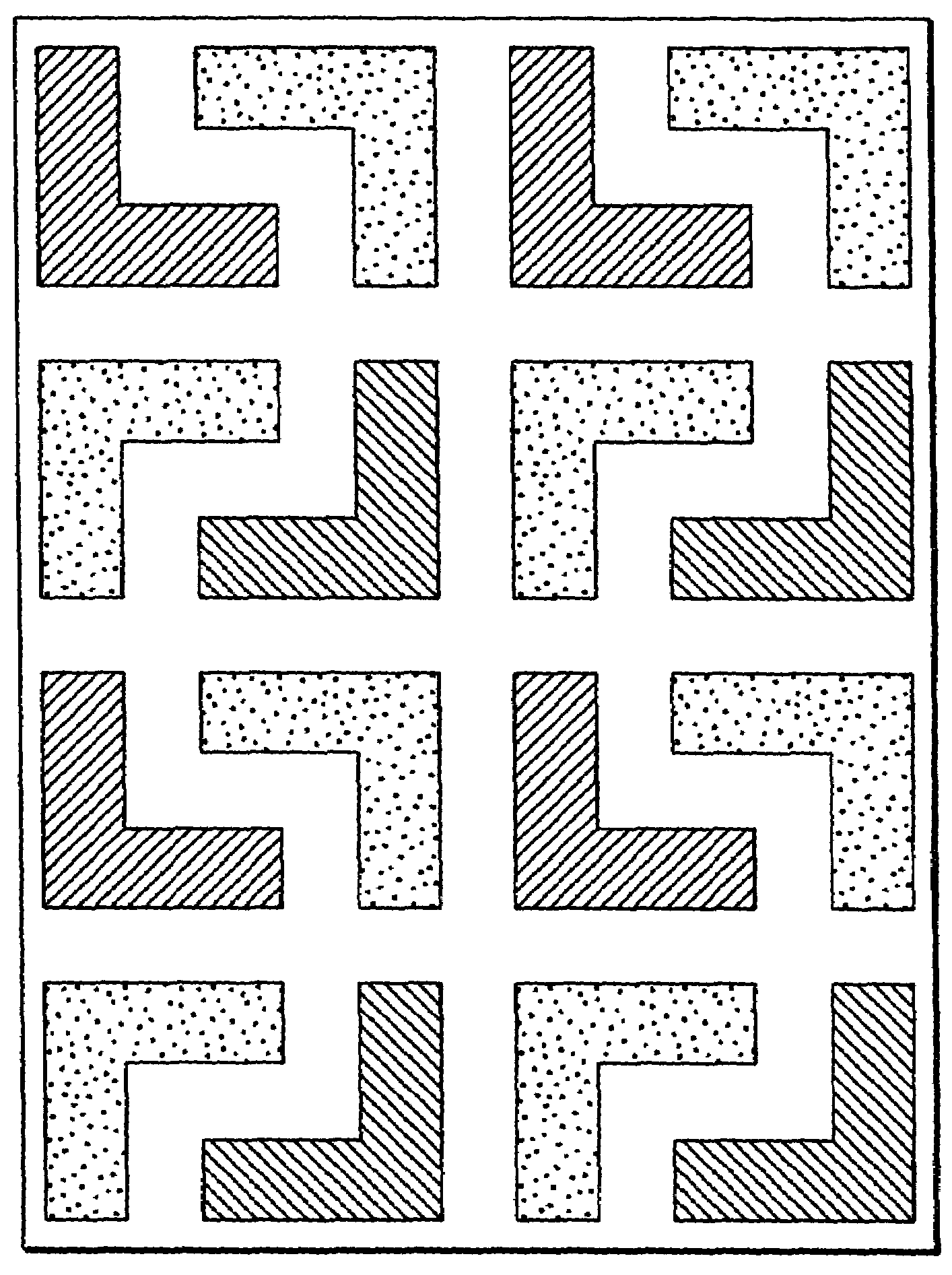

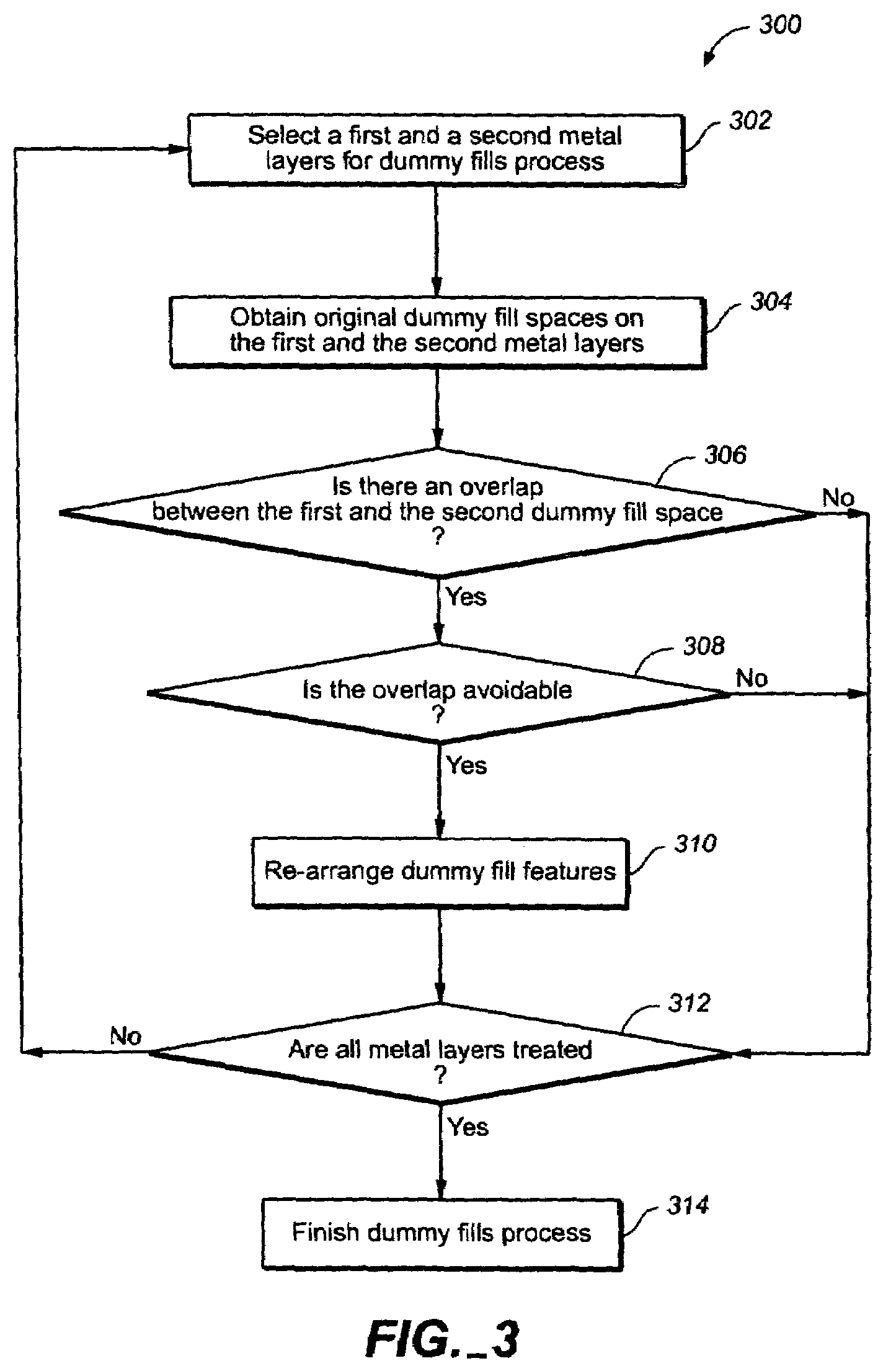

Method and system for reducing inter-layer capacitance in integrated circuits

ActiveUS7396760B2Minimize capacitanceSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsCapacitanceInter layer

The present invention is directed to a method and system of intelligent dummy filling placement to reduce inter-layer capacitance caused by overlaps of dummy filling area on successive layers. The method and system treats each consecutive pair of layers together so as to minimize dummy filling overlaps between each layer. In particular, dummy fill features on each layer may be placed in a checkerboard pattern to avoid overlaps. As such, the present invention may eliminate large overlap area of the dummy patterns on consecutive layers by utilizing intelligent dummy filling placement.

Owner:BELL SEMICON LLC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com