Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

47results about How to "Shorten interconnect length" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

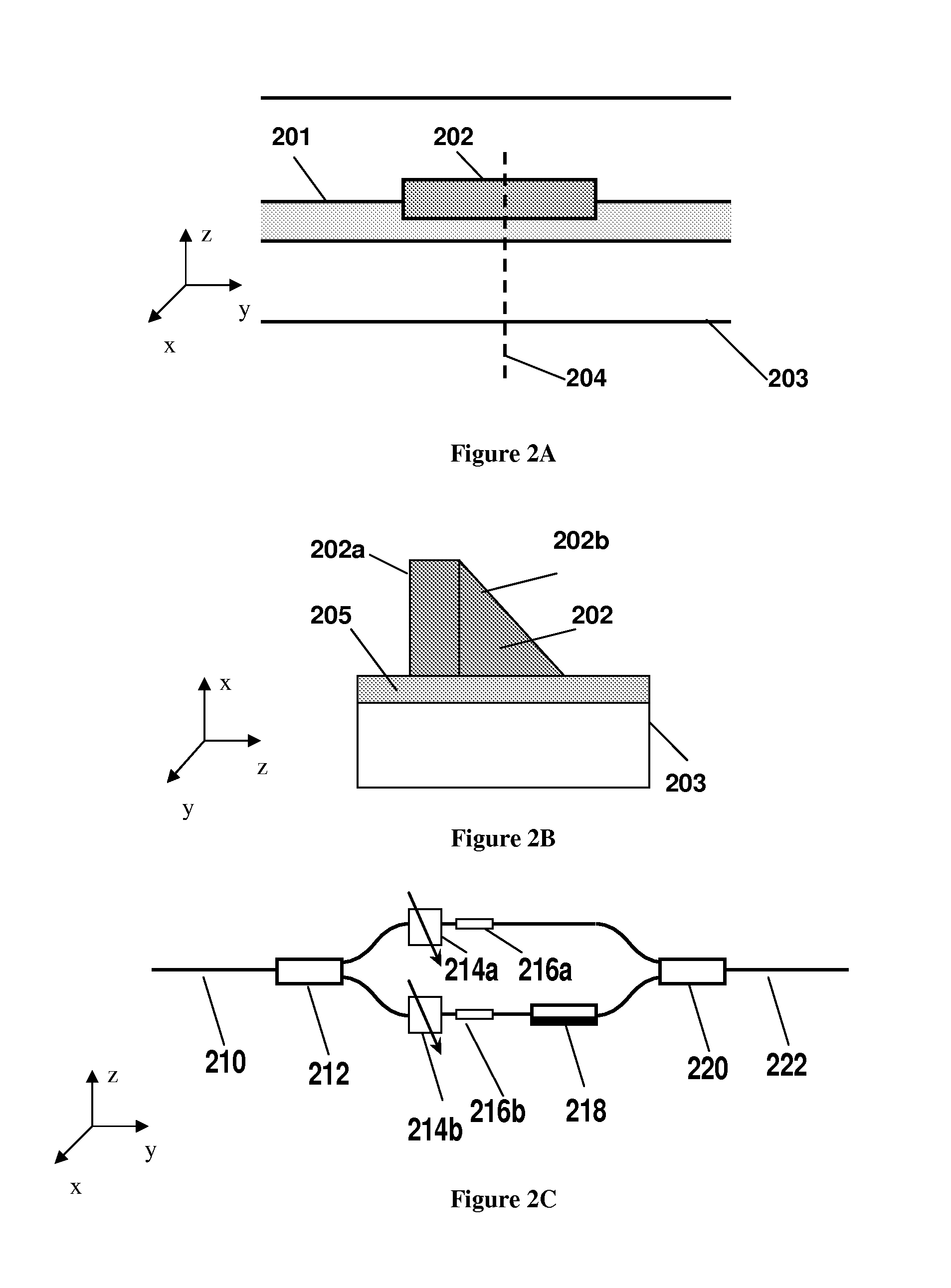

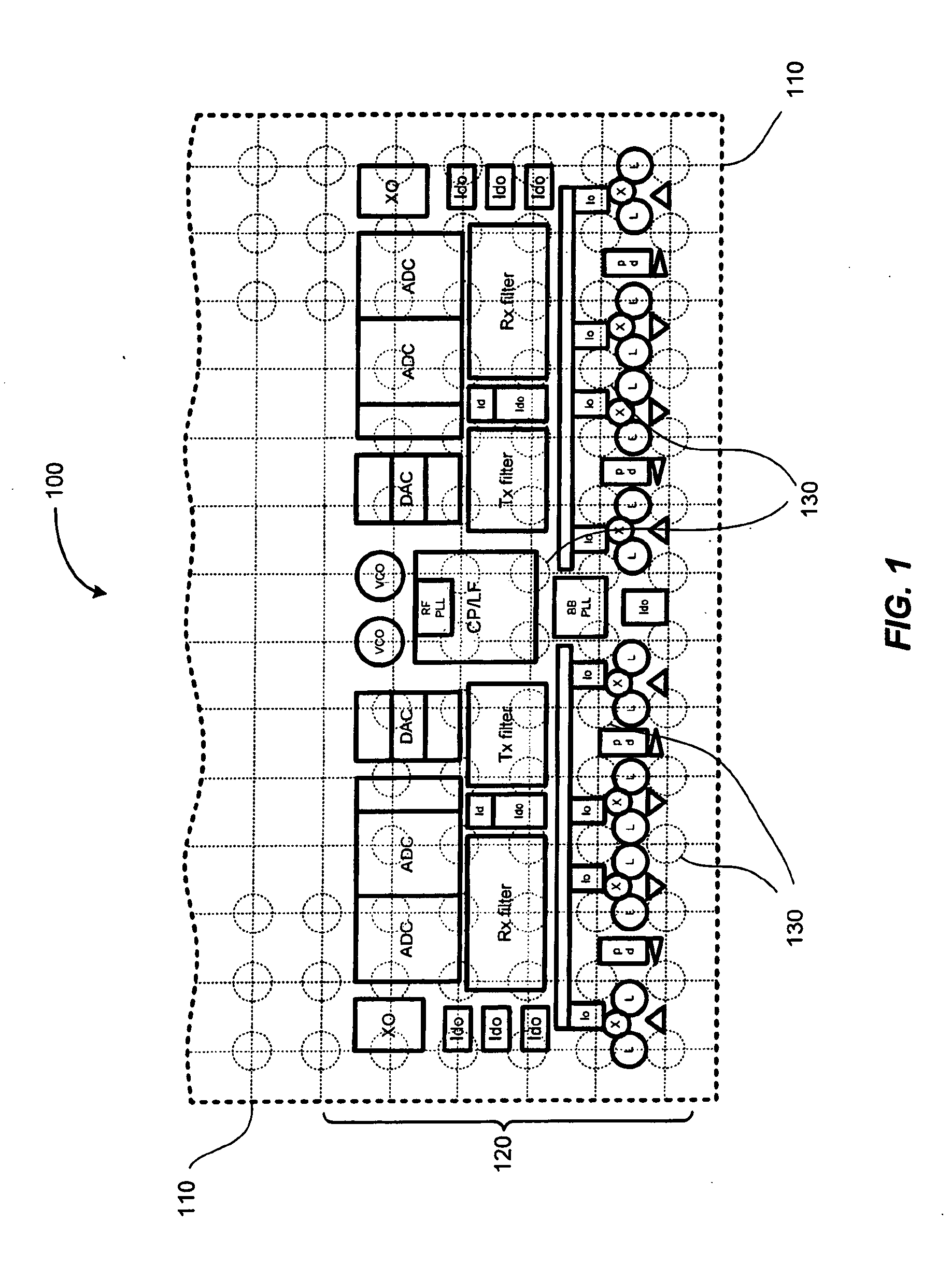

Monolithic widely-tunable coherent receiver

ActiveUS20100303476A1Reduce mold sizeIncrease productionWavelength-division multiplex systemsPolarising elementsLocal oscillatorLength wave

Various embodiments of a coherent receiver including a widely tunable local oscillator laser are described herein. In some embodiments, the coherent receiver can be integrated with waveguides, optical splitters and detectors to form a monolithic optical hetero / homodyne receiver. In some embodiments, the coherent receiver can demodulate the full phase information in two polarizations of a received optical signal over a range of optical wavelengths.

Owner:FREEDOM PHOTONICS LLC

Hybrid circuit substrate with optical and electrical interconnects, hybrid circuit module with optical and electrical interconnects and manufacturing methods thereof

InactiveUS20060110099A1Low costImprove accuracyCircuit optical detailsPrinted circuit aspectsComputer moduleEngineering

Transmission of electric and optical signal, realization of high-speed and high capacity of transmission of information signals. A base substrate section having an interconnect layer formed on an insulating substrate by a printed circuit process; a micro interconnect circuit section having a micro electrical interconnect layer which is finer than the interconnect layer of the base substrate section, formed on an insulating resin layer by a semiconductor process; and an optical interconnect circuit section adapted to transfer and / or receive an optical signal and provided with an optical wave-guide having an input section and an output section of a optical signal at opposite ends thereof; and at least a pair of optical elements composed of a light emitting device with a light emitting section thereof facing the input section and a photo detecting device with a photo detecting section thereof facing the output section are provided and the micro interconnect circuit section and the optical interconnect circuit section are mounted on the base substrate section.

Owner:SONY CORP

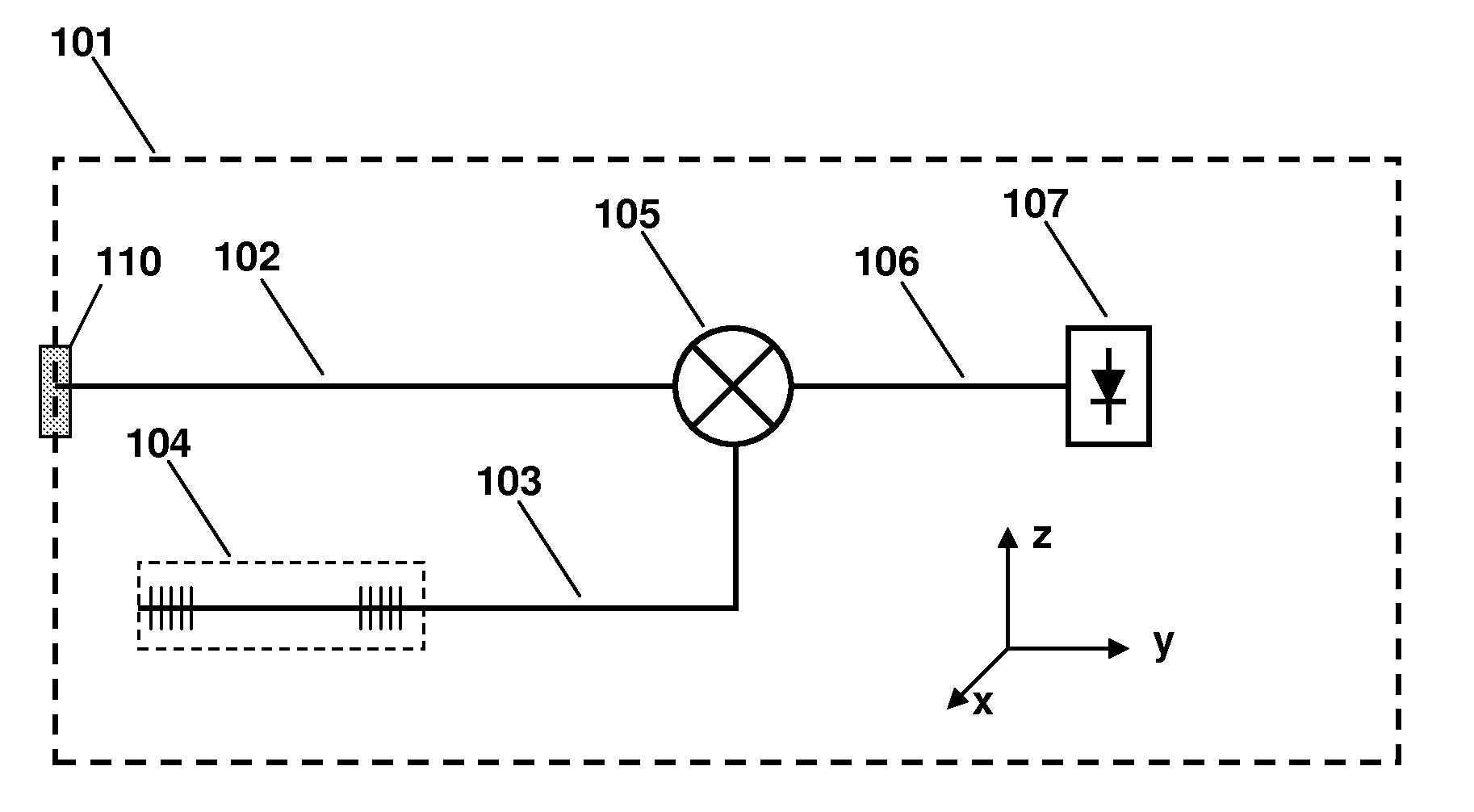

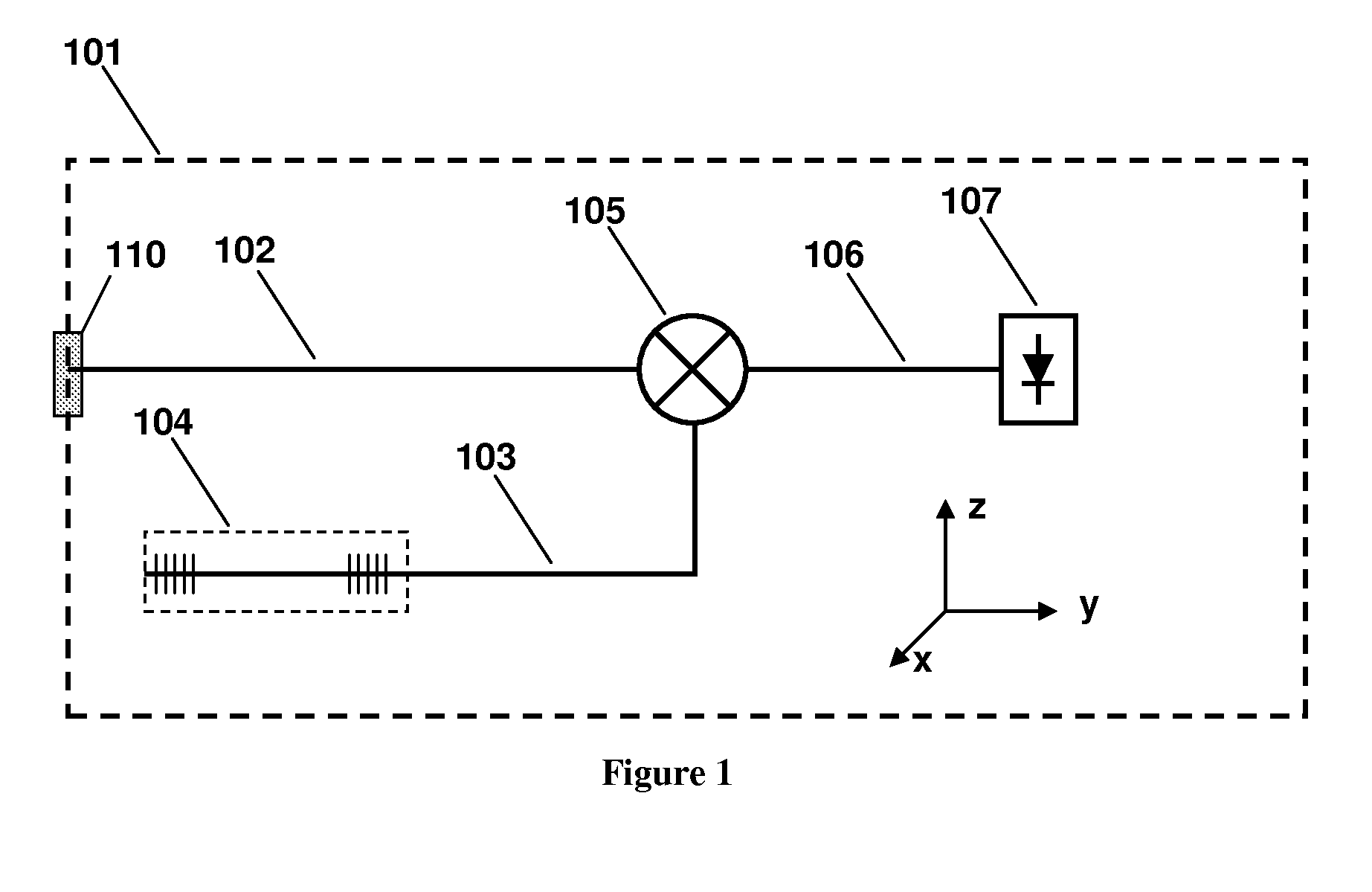

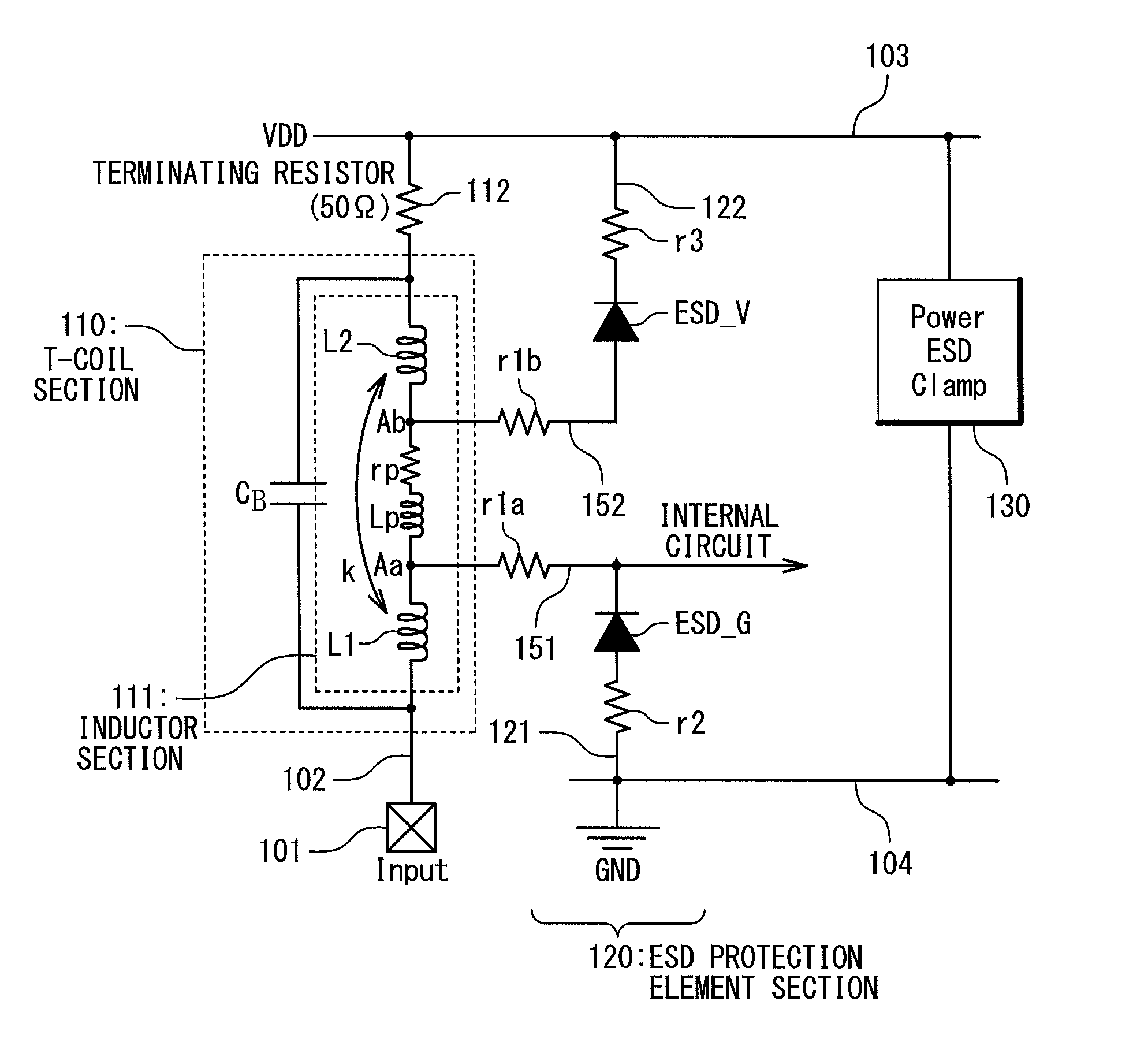

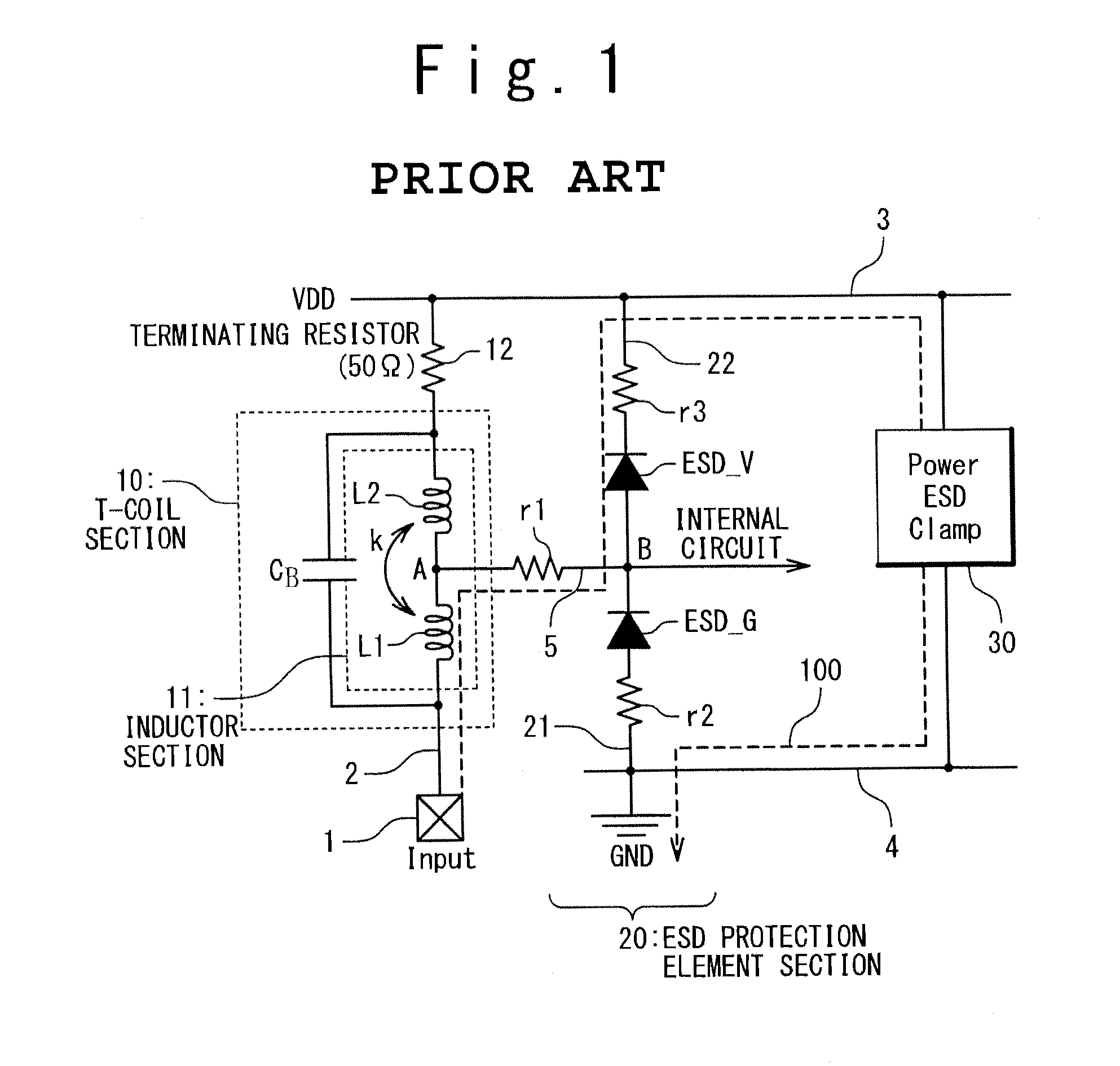

Semiconductor device

InactiveUS8395234B2Shorten interconnect lengthReduce resistanceSemiconductor/solid-state device detailsSolid-state devicesInductorEngineering

A semiconductor device has: a signal pad; a power supply line; a ground line; an inductor section whose one end is connected to the signal pad; a terminating resistor connected between the other end of the inductor section and the power supply line or the ground line. The semiconductor device further has: a first ESD protection element connected to a first node in the inductor section; and a second ESD protection element connected to a second node whose position is different from that of the first node in the inductor section.

Owner:RENESAS ELECTRONICS CORP

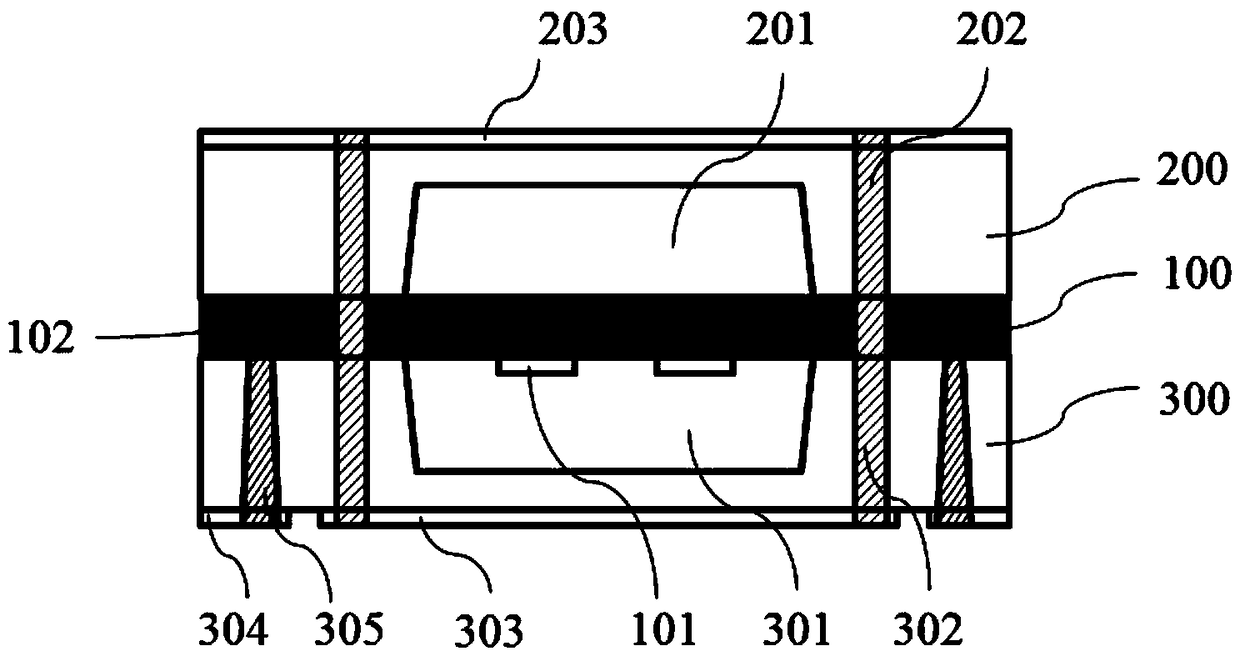

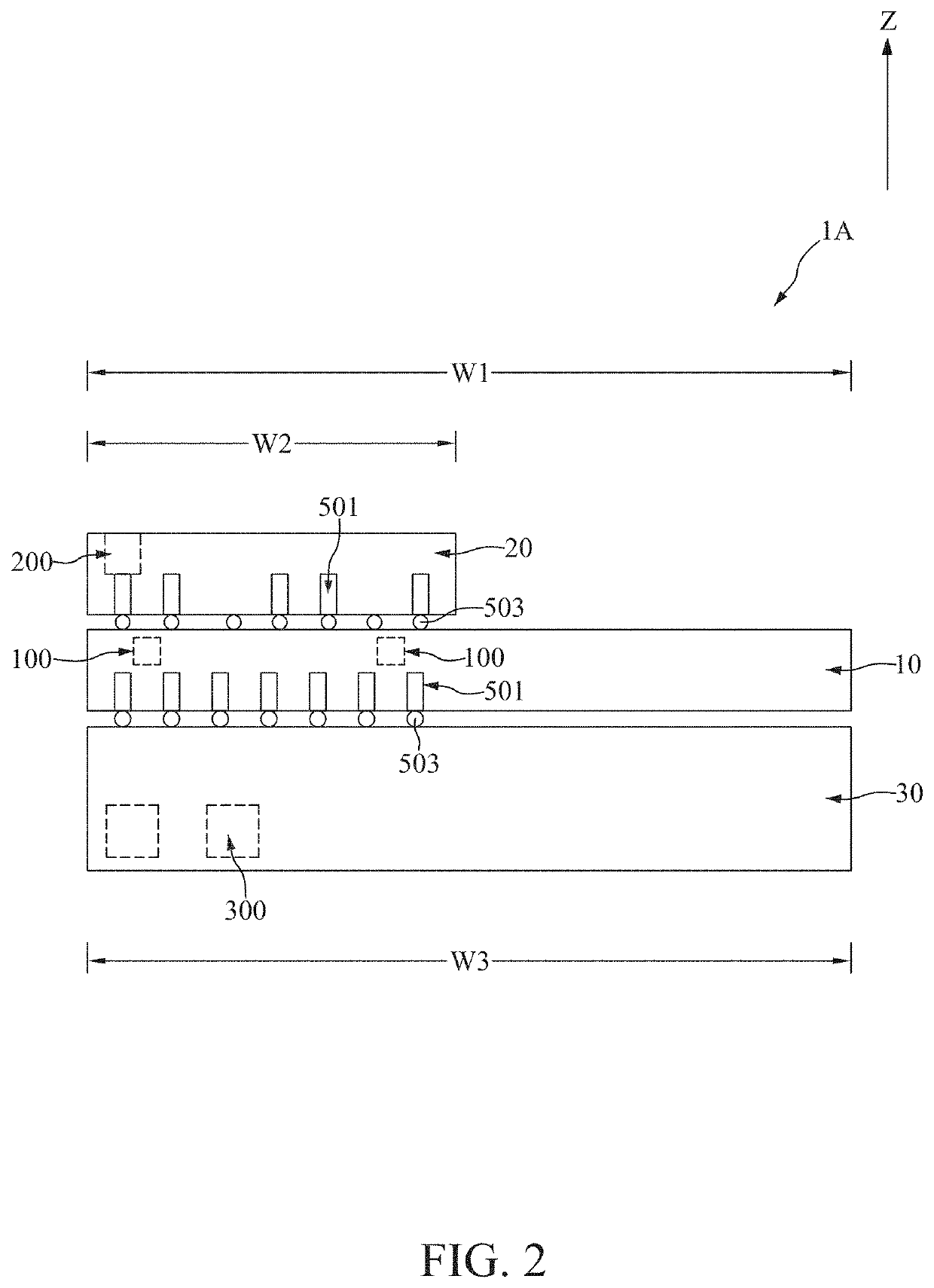

Thermally enhanced face-to-face semiconductor assembly with built-in heat spreader and method of making the same

InactiveUS20160351549A1Serious warping problemShorten interconnect lengthSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorEngineering

A face-to-face semiconductor assembly is characterized in that first and second semiconductor devices are face-to-face mounted on two opposite sides of a first routing circuitry and is further electrically connected to an interconnect board through the first routing circuitry. The interconnect board has a heat spreader to provide thermal dissipation for the second semiconductor device, and a second routing circuitry formed on the heat spreader and electrically coupled to the first routing circuitry. The first routing circuitry provides primary fan-out routing for the first and second semiconductor devices, whereas the second routing circuitry provides further fan-out wiring structure for the first routing circuitry.

Owner:BRIDGE SEMICON

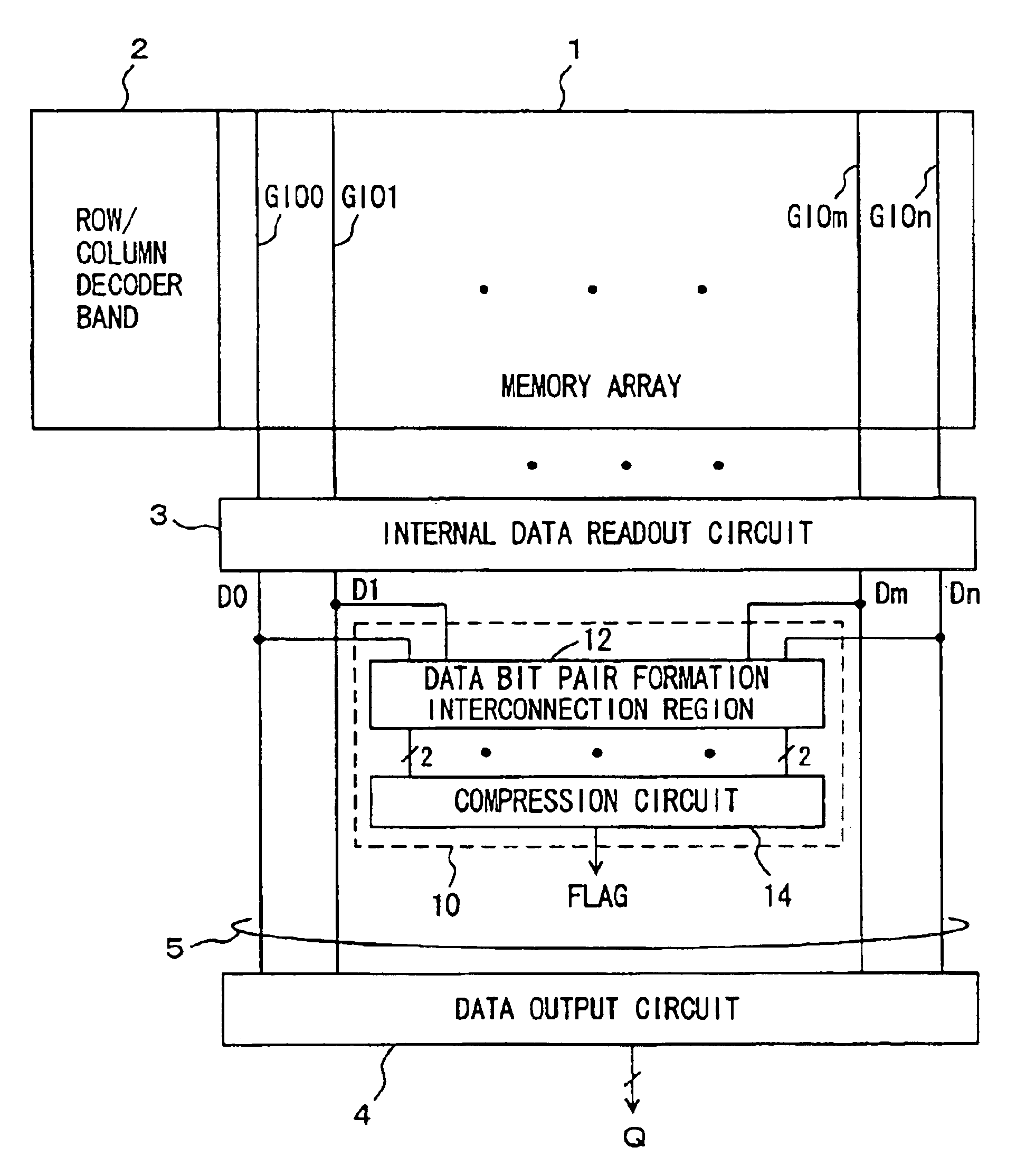

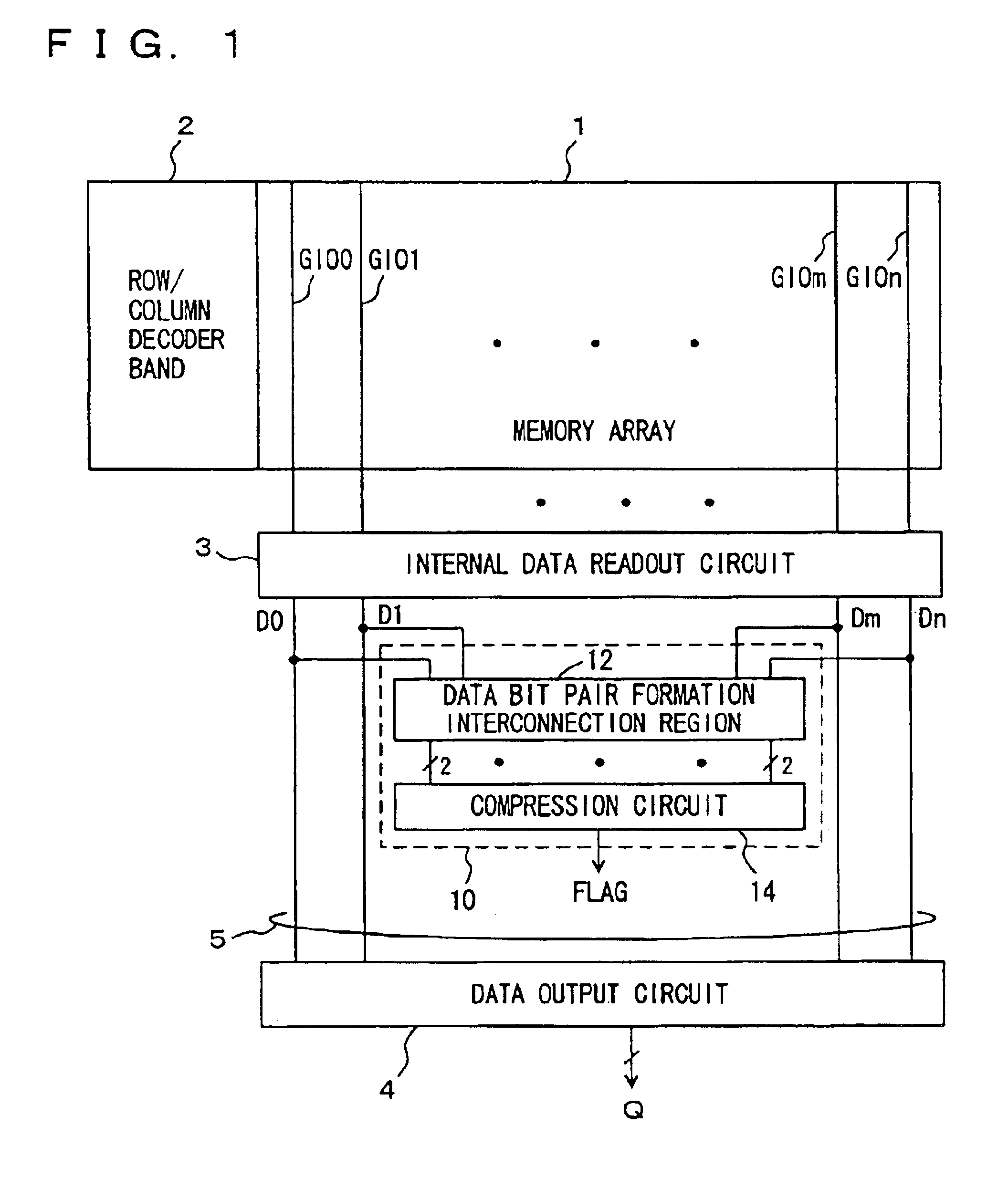

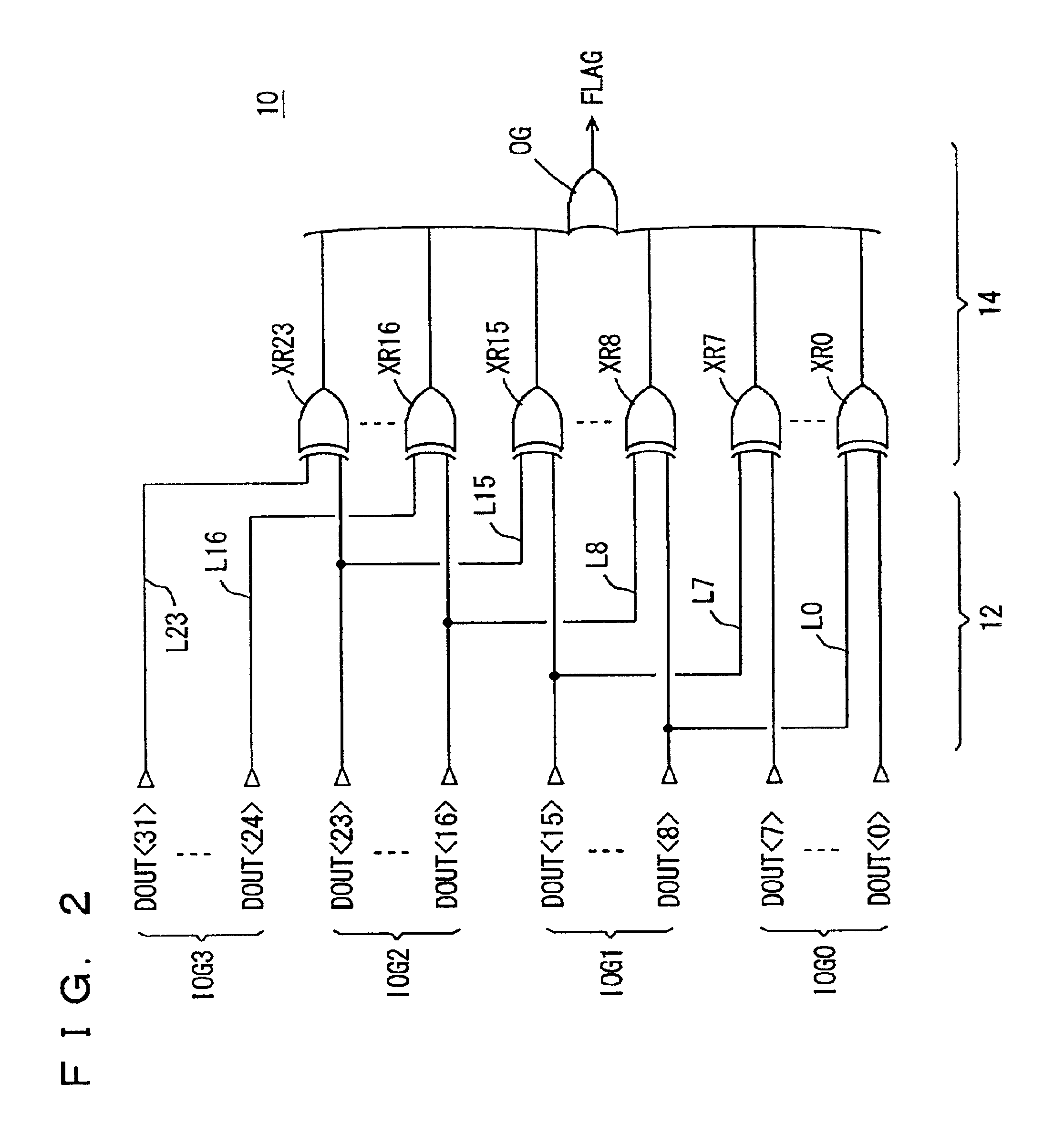

Multi-bit test circuit

InactiveUS6854078B2Fast timeShorten interconnect lengthElectronic circuit testingDigital storageBit TestMatch/mismatch

Internal read out data bits are divided into a plurality of data groups, and data bits in corresponding positions in different data groups are paired off. A determination gate is provided to each pair of data bits, and determining operation is performed in each pair to compress the result of determination to finally generate a 1-bit flag indicating a match / mismatch in logic level among the internal read out data. Consequently, a multi-bit test circuit that has a reduced layout area and can perform high-speed multi-bit determination is provided.

Owner:RENESAS ELECTRONICS CORP

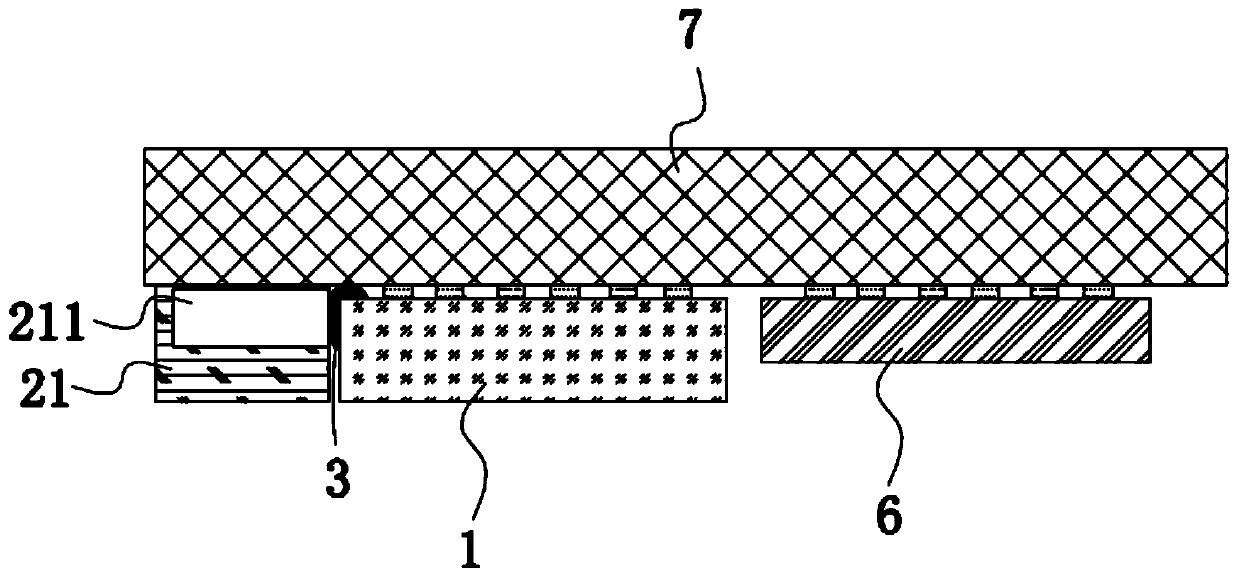

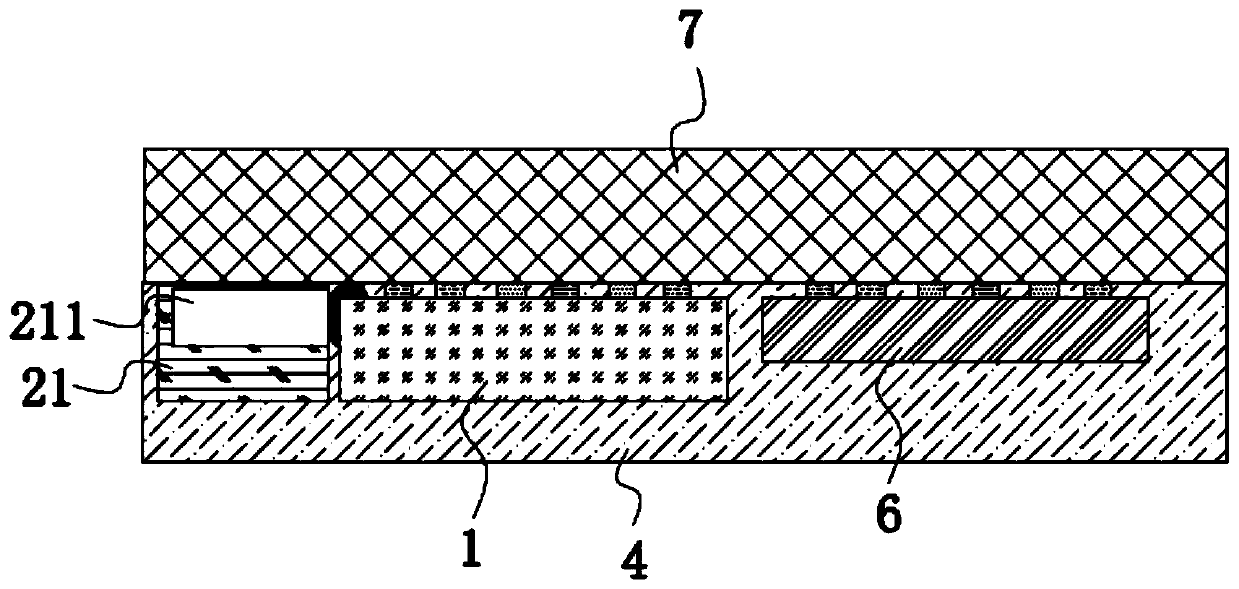

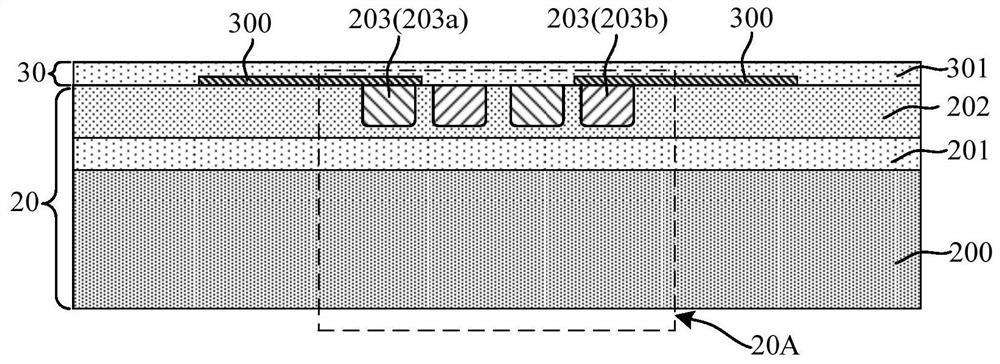

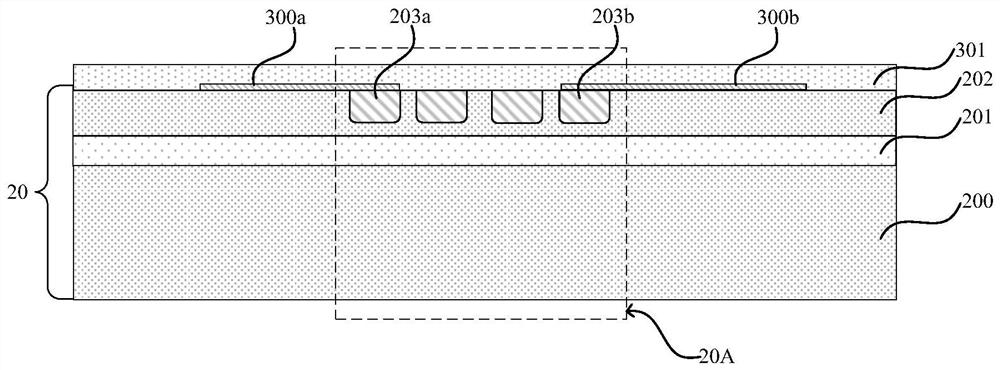

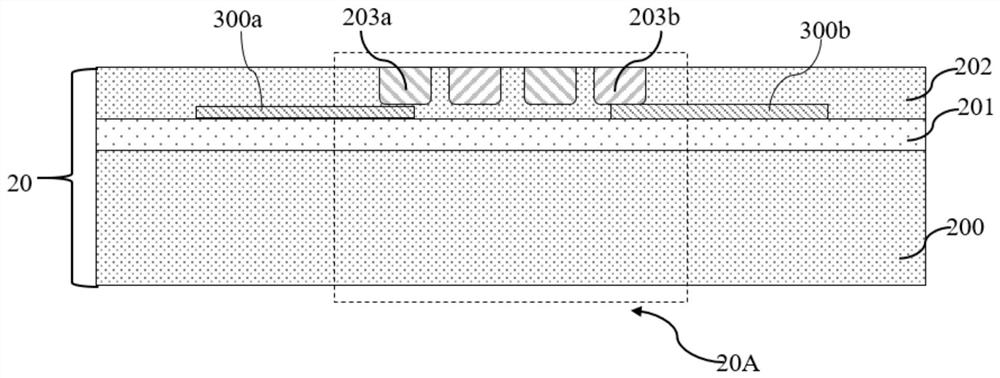

Edge coupling photoelectric device packaging structure and preparation method thereof

PendingCN110673279AHigh precisionSimple structureCoupling light guidesOptical couplingMaterials science

The invention belongs to the field of photoelectric devices and relates to an edge coupling photoelectric device packaging structure. The edge coupling photoelectric device packaging structure comprises an optical chip, an optical coupling structure block and a transparent resin protection structure block; the edge coupling structure is arranged on the optical chip; the optical coupling structureblock abuts against the side coupling structure; a through hole used for fixing an optical fiber is formed in the optical coupling structure block; the transparent resin protection structure block isarranged between the optical chip and the optical coupling structure block and is used for covering the coupling surface of the optical chip so as to ensure normal light transmission; and the opticalchip, the coupling structure block and the transparent protection resin are all located in a packaging layer. In the use process of the edge coupling photoelectric device packaging structure, it justneeds to directly insert the optical fiber into the through hole so as to be fixed, so that high-precision alignment between the optical fiber and the optical chip can be achieved. The edge couplingphotoelectric device packaging structure has the advantages of passive alignment, simple structure, high precision and easiness in assembling process and mass production.

Owner:NAT CENT FOR ADVANCED PACKAGING

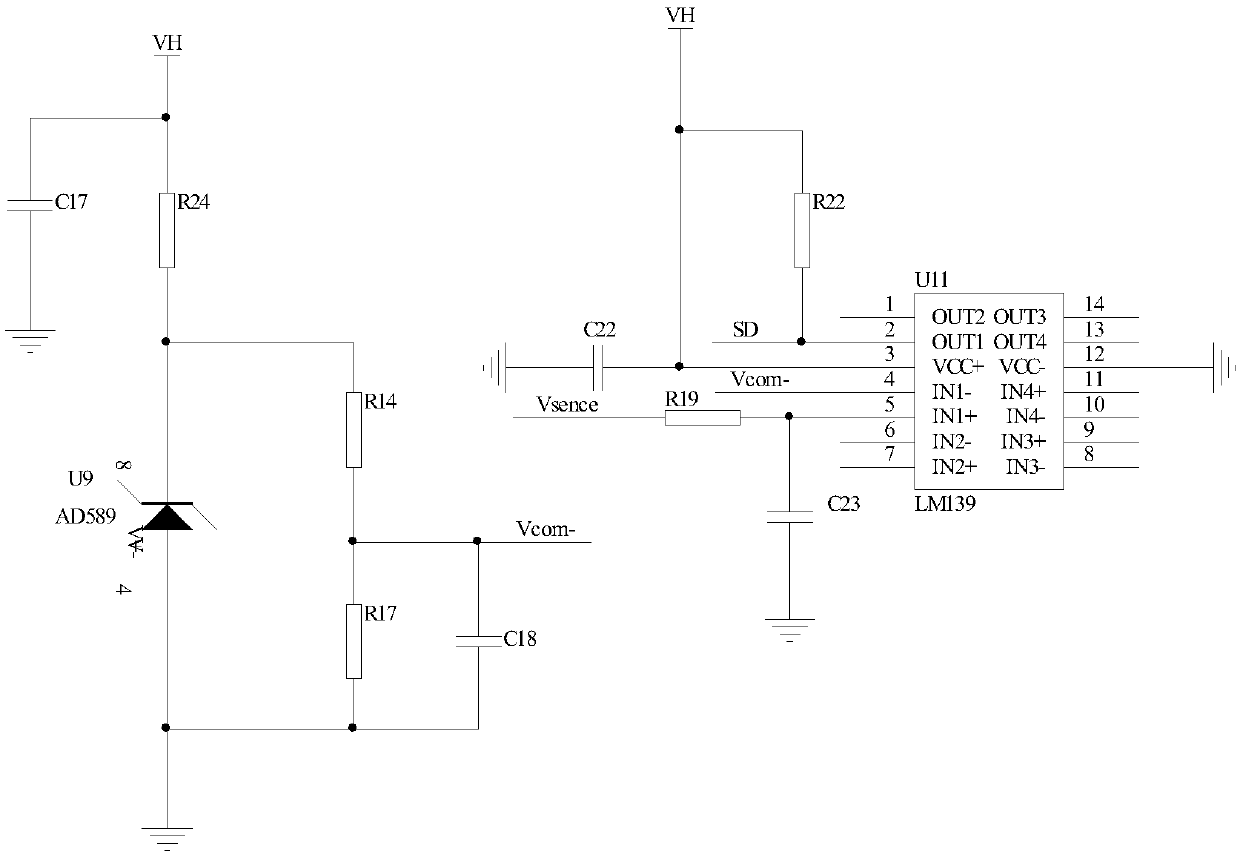

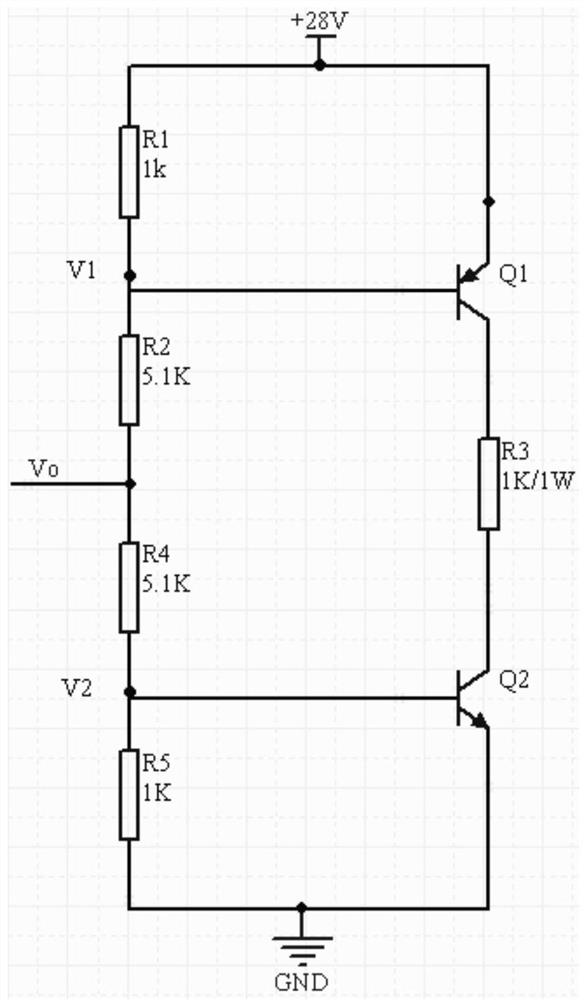

Digital isolation type high-power three-phase brushless motor driving module

InactiveCN107863911AImprove assembly densityShorten interconnect lengthAssociation with control/drive circuitsSingle motor speed/torque controlEngineeringThree-phase

The invention belongs to the field of electromechanical servo driving, and specifically discloses a digital isolation type high-power three-phase brushless motor driving module. The signal output endof an optical coupling isolation unit and the signal output end of an overcurrent protection unit are both connected with the signal input end of a logic unit; the signal output end of the logic unitand the signal output end of the overcurrent protection unit are both connected with the signal input end of an H bridge driving control unit; the signal output end of the H bridge driving control unit is connected with the signal input end of a field effect transistor output unit; the signal output end of the field effect transistor output unit is connected with the signal input end of the overcurrent protection unit and external motor windings U, V and W separately; the optical coupling isolation unit, the logic unit and the H bridge driving control unit are all connected with a working power supply V<cc>; and the overcurrent protection unit and the field effect transistor output unit are both connected with a power power-supply V<s>. The driving module disclosed in the invention is highin reliability, integration, working current and power density, and short in production period.

Owner:BEIJING RES INST OF PRECISE MECHATRONICS CONTROLS +1

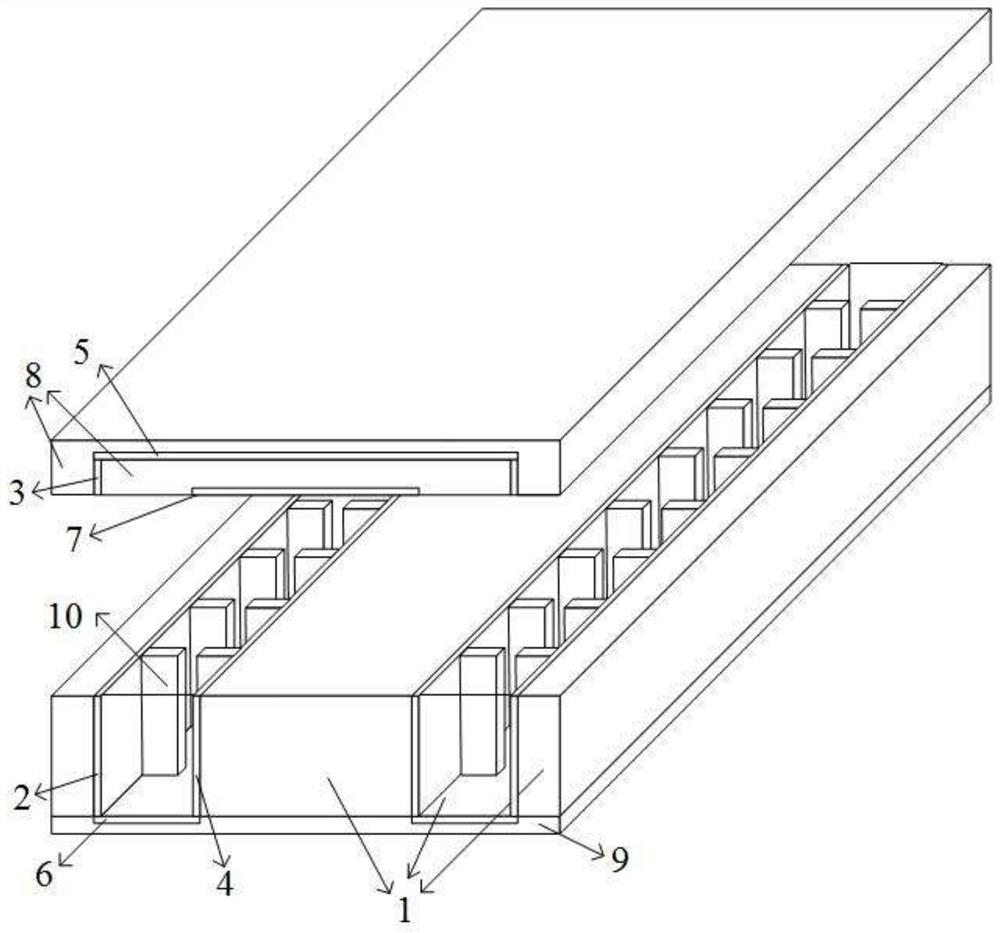

Silicon-based cavity shielding filter

ActiveCN109378560AReduce volumeHigh quality factorWaveguide type devicesCavity shieldHigh resistance

The invention relates to a silicon-based cavity shielding filter, which is fabricated by a MEMS process. The silicon-based cavity shielding filter comprises a first substrate, a second substrate, an intermediate layer and a metal suspension circuit; the first substrate and the second substrate adopt a high resistance silicon substrate; the first substrate, the intermediate layer and the second substrate are sequentially stacked and combined into a silicon cavity structure; a microwave ground electrode is arranged on the intermediate layer; a metal shielding layer connected with the microwave grounding electrode is arranged on the outer surface of the silicon cavity structure; a first air cavity is formed between the first substrate and the intermediate layer, and / or a second air cavity isformed between the second substrate and the intermediate layer; the metal suspension circuit is disposed on a surface of the intermediate layer and suspended in the first air chamber or / and the secondair chamber. The silicon-based cavity shielding filter of the invention is fabricated by the silicon-based MEMS process, so that the final filter has the advantages of small size, high quality factors, excellent performance, good integration, batchization, etc., and can achieve higher integration and an integrated system with a smaller size.

Owner:北京航天微电科技有限公司

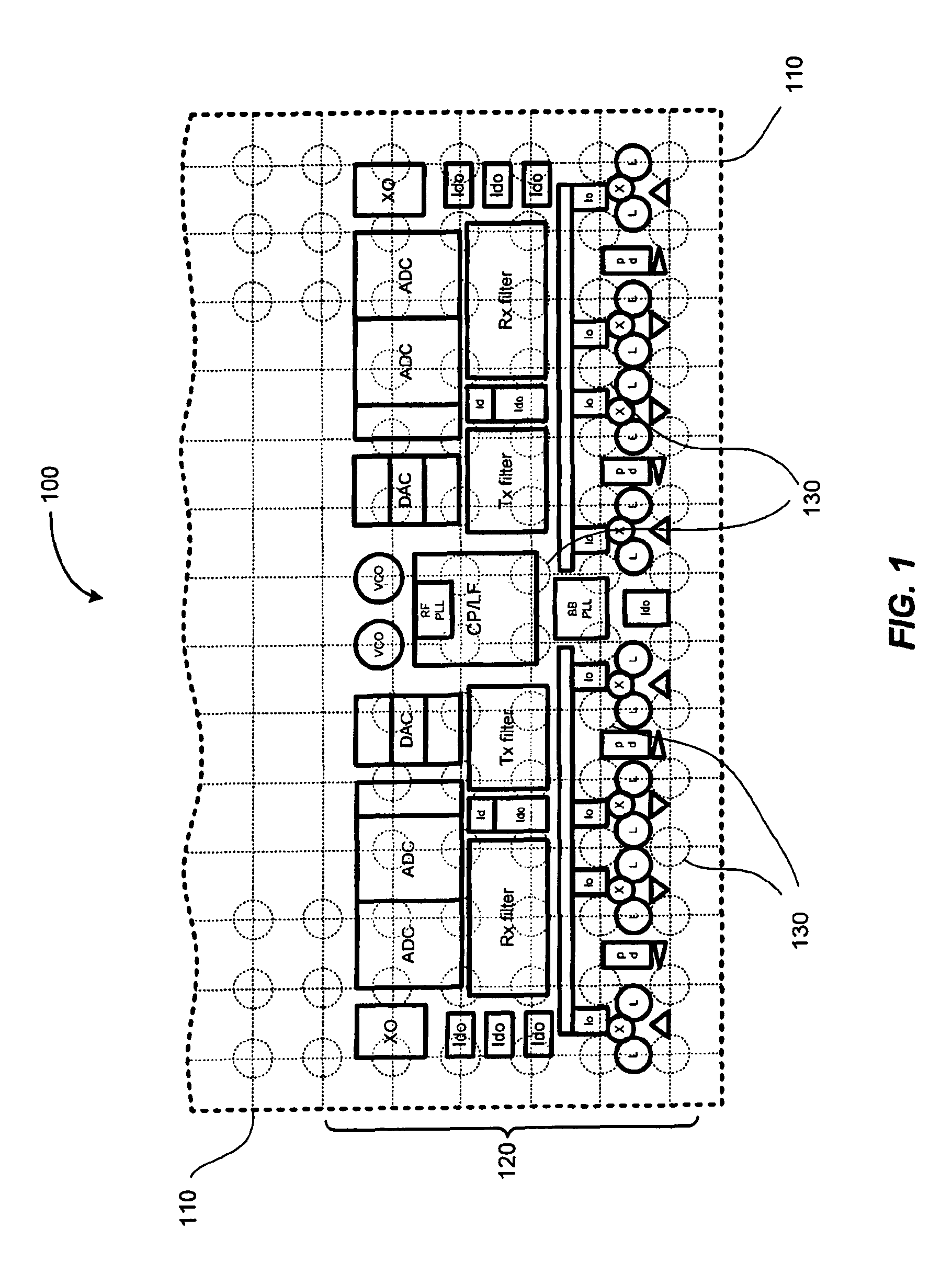

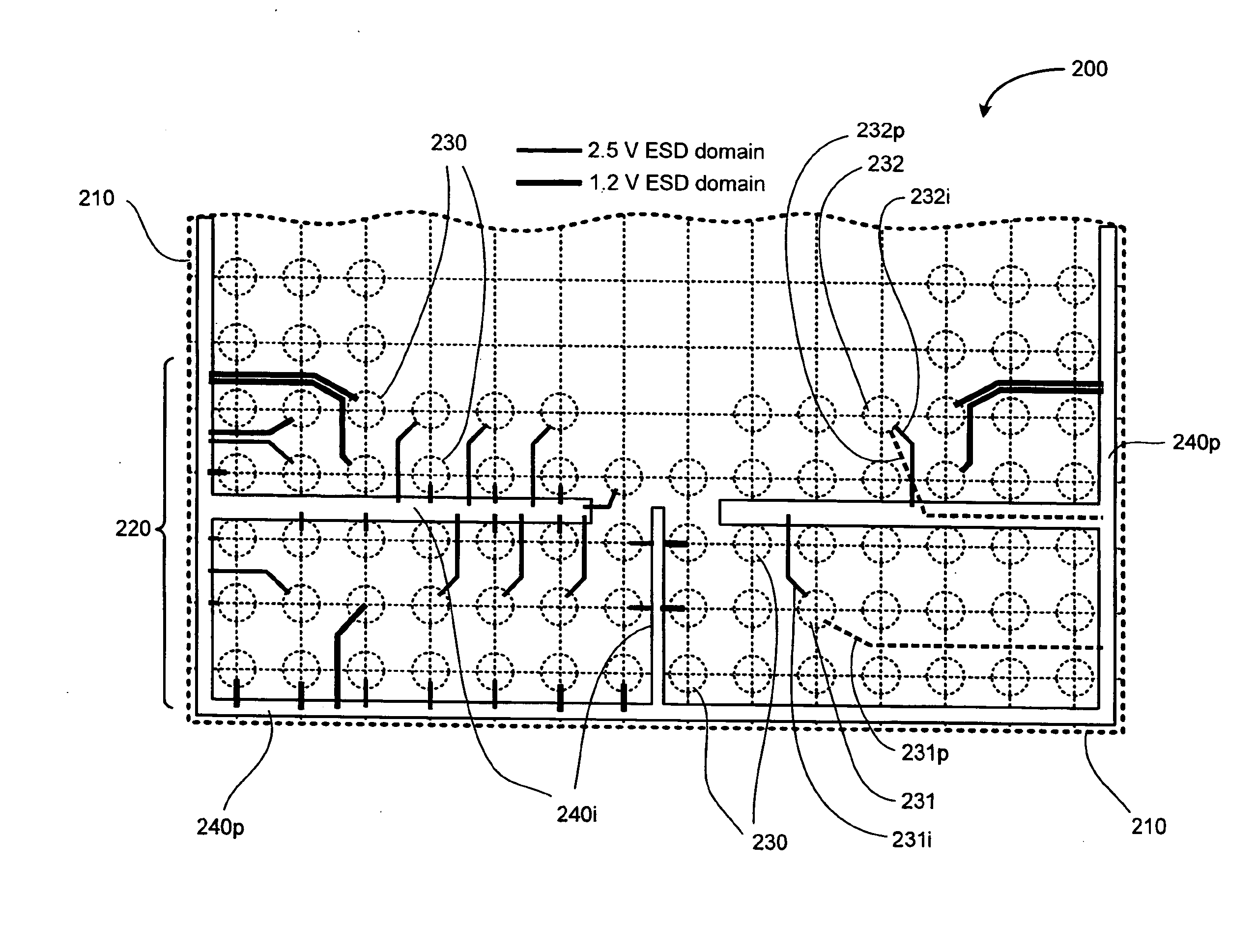

ESD networks for solder bump integrated circuits

ActiveUS8427797B2Shorten interconnect lengthSemiconductor/solid-state device detailsSolid-state devicesEngineeringAverage path length

Semiconductor dice (100, 200) of integrated circuit chips are provided with solder bump pads (130, 230) distributed over active areas of the dice to supply the I / O interconnects without including peripheral wire bond pads. The dice are further provided with protective ESD structures (140p / 140i, 240p / 240i) arranged in a network that includes ESD structures that extend into the interior areas of the dice. This allows the ESD structures to be placed proximate to respective power and ground connections, and positioned to reduce an average interconnect length between interior bump pads and the ESD structures relative to an average path length between the interior bump pads and the die peripheral area.

Owner:NXP BV

Three-dimensional power VDMOS device and integration method thereof

ActiveCN106098687AIncrease transfer speedImprove transmission characteristicsTransistorSemiconductor/solid-state device detailsComputer terminalInterconnection

The invention discloses a three-dimensional power VDMOS device and an integration method thereof. The three-dimensional power VDMOS device comprises power units and two or more chip layers, wherein two or more power units are uniformly distributed on each chip layer, an independent terminal is arranged on the periphery of each power unit, interlayer conductive interconnecting TSV through holes are arranged in the periphery of each power unit, and chip layers stack together to form the three-dimensional power VDMOS device. The technical problems that since a VDMOS device employs a plane integration technology, the area of the device increases with the increasing of the current capacity, the integration level of a power system is severely affected, and signal delay time and interconnection line power consumption proportion are greater can be solved.

Owner:GUIZHOU UNIV

Reduced inductance interconnect for enhanced microwave and millimeter-wave systems

ActiveUS20090085823A1Eliminates and greatly reduces disadvantageEliminates and greatly reduces and problemAntenna arraysSemiconductor/solid-state device detailsMicrowaveDielectric layer

According to one embodiment of the present invention, a microwave or millimeter wave module includes a dielectric layer having a pocket formed substantially through the dielectric layer. The dielectric is attached to a metal substrate. The pocket has substantially vertical sidewalls. An integrated circuit is disposed in the pocket. Opposing sides of the integrated circuit are substantially parallel to the sidewalls of the pocket. An interconnect electrically couples the integrated circuit to a bond pad disposed on the outer surface of the dielectric layer. The interconnect has a length that is minimized to result in reduced inductance of the semiconductor device.

Owner:RAYTHEON CO

Manufacturing method of thermopile sensor

ActiveCN112117369ASimple processReduce process costThermoelectric device manufacture/treatmentFinal product manufacturePhysicsElectrically conductive

A manufacturing method of a thermopile sensor comprises the steps of: providing a thermopile structure plate and a substrate, and forming a thermopile structure on the thermopile structure plate; forming a first interconnection layer on the thermopile structure plate, wherein at least a first conductive interconnection structure electrically connected with the thermopile structure is formed in thefirst interconnection layer; forming a support structure on the substrate, forming a sacrificial structure in the support structure, and exposing the sacrificial structure from the top surface of thesupport structure; bonding the thermopile structure plate on the support structure, so that the first interconnection layer is positioned below the thermopile structure, and after bonding, the thermopile structure is arranged above the sacrificial structure; and after bonding, removing the sacrificial structure to form a first cavity. According to the invention, the process flow is simplified, the process cost is reduced, and the measurement precision of the thermopile sensor is improved.

Owner:NINGBO SEMICON INT CORP

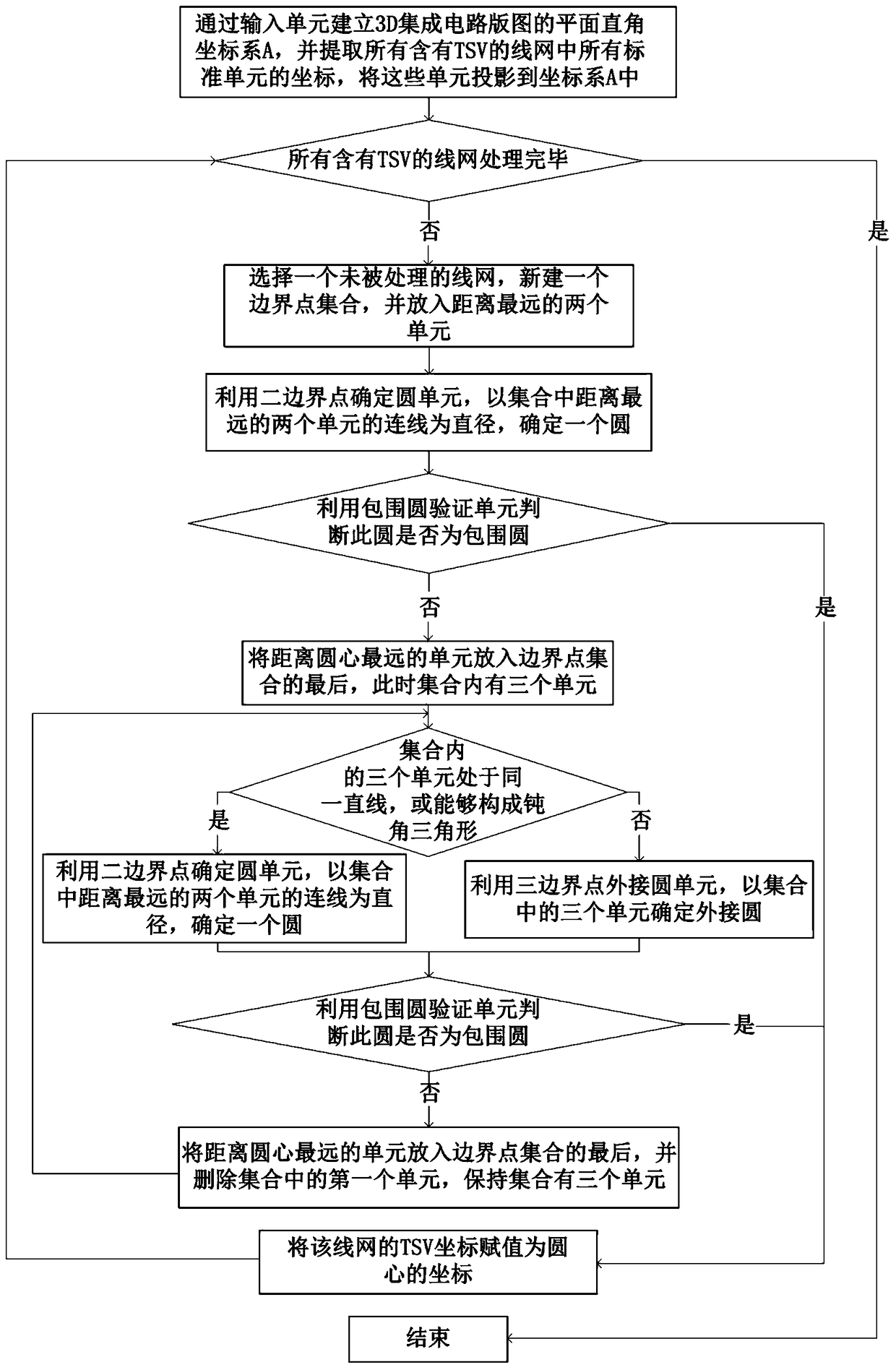

Method for automatic positioning of TSV (Through Silicon Vias) through utilizing smallest enclosing circle

InactiveCN105468821ARealize OKShorten interconnect lengthCAD circuit designSpecial data processing applications3d integrated circuitInterconnection

The invention discloses a method for automatic positioning of TSVs (Through Silicon Vias) through utilizing a smallest enclosing circle, belonging to the field of circuit design. The method comprises the following steps of firstly, establishing a rectangular plane coordinate system for layout of a 3D integrated circuit and projecting coordinates of all standard units in all nets containing the TSVs into the coordinate system; secondly, respectively processing each net containing the TSV; thirdly, forming a discrete point set through all standard units in the nets and utilizing a smallest enclosing circle algorithm to solve the smallest enclosing circle of discrete points, wherein the center coordinates are coordinates of all TSVs of the nets; and lastly, processing the all nets to obtain the coordinates of all TSVs in the 3D integrated circuit. The method has the following beneficial effects that the positions of the TSVs of all nets can be determined; and the positions of the TSVs are determined by utilizing the smallest enclosing circle, so that the method is beneficial to shortening of an interconnection length of the 3D integrated circuit.

Owner:BEIJING UNIV OF TECH

Multi-chip three-dimensional packaging structure and packaging method

PendingCN114121680AShorten lead lengthShorter interconnect lengthSemiconductor/solid-state device detailsSolid-state devicesElectrically conductiveHeat sink

The invention belongs to the technical field of chip packaging, and particularly relates to a multi-chip three-dimensional packaging structure and packaging method.The packaging method comprises the following steps that a carrier plate is provided, a preset circuit is manufactured on one side face in the thickness direction of the carrier plate, and the preset circuit is electrically led out towards the edge of the carrier plate; a plurality of elements are provided, the elements are one or more of chips, wafers, cooling fins or functional areas, and ports of the chips, the wafers and the functional areas are arranged on respective edges of the chips, the wafers and the functional areas; the method comprises the following steps: spatially overturning a plurality of elements in a vacuum environment to form a cubic structure, and hermetically connecting the edges of the cubic structure through an adhesive; connecting the port of the preset circuit of the carrier plate with the ports of the plurality of elements through a flexible conductive wire rod in a bonding manner; and wrapping the outer surface of the cubic structure with a plastic package material to form a plastic package layer. According to the invention, the interconnection among a plurality of chips is realized through the flexible conductive wire rod, the length of the interconnection wire can be obviously shortened, the influence on signal transmission is reduced, and the performance of the chip is improved.

Owner:广东佛智芯微电子技术研究有限公司 +1

ESD networks for solder bump integrated circuits

ActiveUS20110019320A1Shorten interconnect lengthSemiconductor/solid-state device detailsSolid-state devicesAverage path lengthSemiconductor

Semiconductor dice (100, 200) of integrated circuit chips are provided with solder bump pads (130, 230) distributed over active areas of the dice to supply the I / O interconnects without including peripheral wire bond pads. The dice are further provided with protective ESD structures (140p / 140i, 240p / 240i) arranged in a network that includes ESD structures that extend into the interior areas of the dice. This allows the ESD structures to be placed proximate to respective power and ground connections, and positioned to reduce an average interconnect length between interior bump pads and the ESD structures relative to an average path length between the interior bump pads and the die peripheral area.

Owner:NXP BV

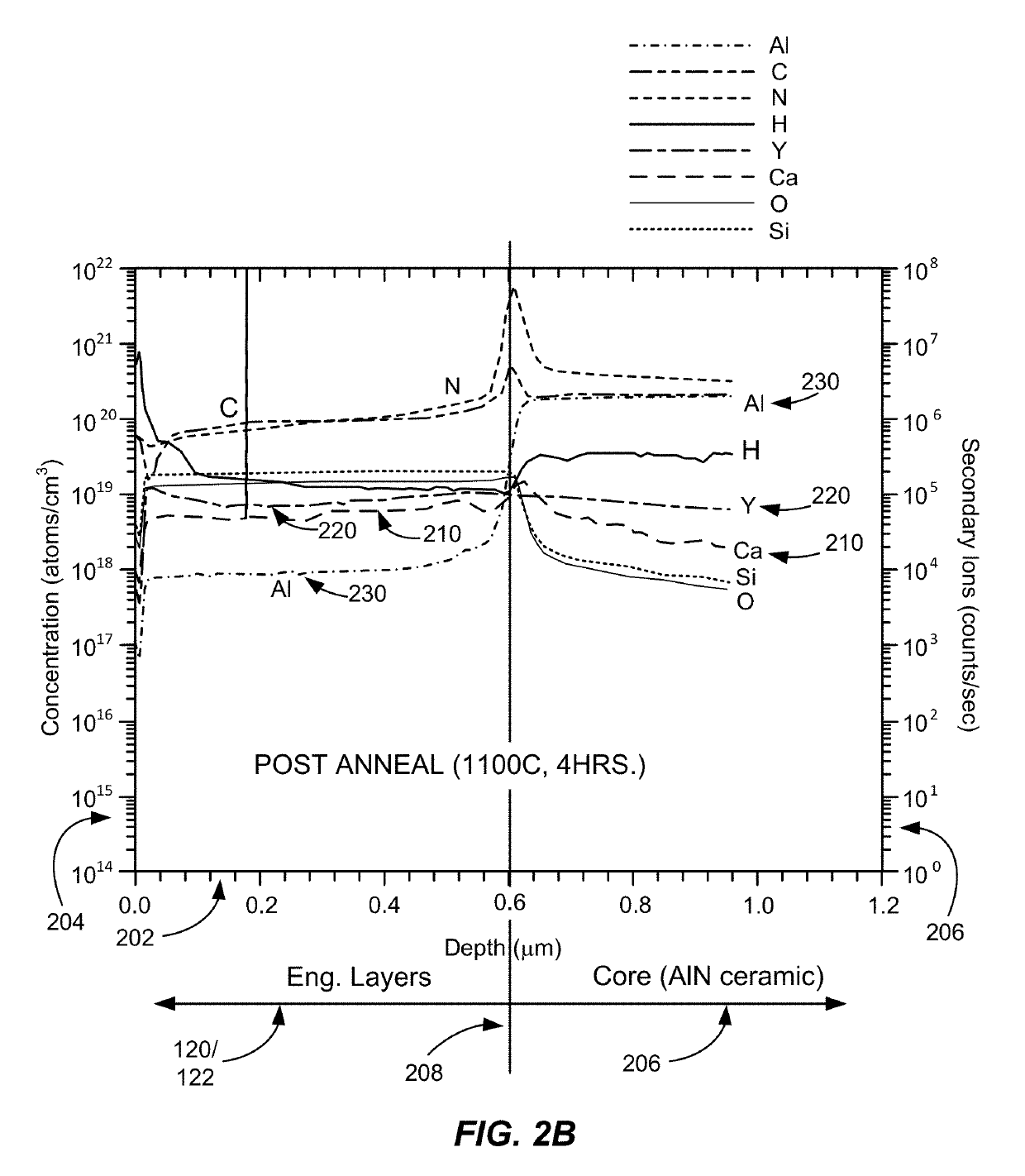

Method and system for electronic devices with polycrystalline substrate structure interposer

ActiveUS20190181121A1Reduce power consumptionIncrease bandwidth of interconnectionSemiconductor/solid-state device detailsSolid-state devicesMetallurgyInterposer

An interposer includes a polycrystalline ceramic core disposed between a first surface and a second surface of the interposer, an adhesion layer encapsulating the polycrystalline ceramic core, a barrier layer encapsulating the adhesion layer, and one or more electrically conductive vias extending from the first surface to the second surface through the polycrystalline ceramic core, the adhesion layer, and the barrier layer.

Owner:QROMIS INC

Reduced inductance interconnect for enhanced microwave and millimeter-wave systems

ActiveUS7528792B2Eliminates and greatly reduces disadvantageEliminates and greatly reduces and problemAntenna arraysSemiconductor/solid-state device detailsMicrowaveEngineering

According to one embodiment of the present invention, a microwave or millimeter wave module includes a dielectric layer having a pocket formed substantially through the dielectric layer. The dielectric is attached to a metal substrate. The pocket has substantially vertical sidewalls. An integrated circuit is disposed in the pocket. Opposing sides of the integrated circuit are substantially parallel to the sidewalls of the pocket. An interconnect electrically couples the integrated circuit to a bond pad disposed on the outer surface of the dielectric layer. The interconnect has a length that is minimized to result in reduced inductance of the semiconductor device.

Owner:RAYTHEON CO

Three-dimensional integrated circuit stack

ActiveUS9337146B1Limited benefitShorten connection lengthSemiconductor/solid-state device detailsSolid-state devicesEngineeringThree-dimensional integrated circuit

A particular three-dimensional integrated circuit stack includes a first die including a first bonding interface and a first plurality of interconnect layers arranged according to a first Manhattan wiring scheme. The three-dimensional integrated circuit stack also includes a second die including a second bonding interface and a second plurality of interconnect layers arranged according to a second Manhattan wiring scheme. The first die and the second die stacked with the first bonding interface coupled to the second bonding interface such that the first Manhattan wiring scheme and the second Manhattan wiring scheme are non-Manhattan with respect to each other.

Owner:QUALCOMM INC

tsv automatic positioning method using minimum enclosing circle

InactiveCN105468821BRealize OKShorten interconnect lengthCAD circuit designSpecial data processing applications3d integrated circuitInterconnection

The invention discloses a method for automatic positioning of TSVs (Through Silicon Vias) through utilizing a smallest enclosing circle, belonging to the field of circuit design. The method comprises the following steps of firstly, establishing a rectangular plane coordinate system for layout of a 3D integrated circuit and projecting coordinates of all standard units in all nets containing the TSVs into the coordinate system; secondly, respectively processing each net containing the TSV; thirdly, forming a discrete point set through all standard units in the nets and utilizing a smallest enclosing circle algorithm to solve the smallest enclosing circle of discrete points, wherein the center coordinates are coordinates of all TSVs of the nets; and lastly, processing the all nets to obtain the coordinates of all TSVs in the 3D integrated circuit. The method has the following beneficial effects that the positions of the TSVs of all nets can be determined; and the positions of the TSVs are determined by utilizing the smallest enclosing circle, so that the method is beneficial to shortening of an interconnection length of the 3D integrated circuit.

Owner:BEIJING UNIV OF TECH

Manufacturing method of thermopile sensor

PendingCN112117365AHigh measurement accuracyShorten interconnect lengthThermoelectric device manufacture/treatmentDecorative surface effectsPhysicsThermal radiation

The embodiment of the invention provides a manufacturing method of a thermopile sensor, which comprises the following steps: providing a thermopile structure plate and a circuit substrate, wherein thethermopile structure plate comprises a thermal radiation induction area, a thermopile structure is formed in the thermal radiation induction area, and the circuit substrate comprises a thermal radiation isolation area; forming a supporting structure on the circuit substrate, forming a thermal radiation isolation plate and a sacrificial structure which are longitudinally stacked from bottom to topin the supporting structure, wherein the thermal radiation isolation plate and the sacrificial structure at least cover the thermal radiation isolation area; bonding the thermopile structure plate onthe surface of one side of the circuit substrate, which is provided with the support structure, so that the thermal radiation induction region vertically corresponds to the thermal radiation isolation area; and removing the sacrificial structure, and forming a first cavity between the thermopile structure plate and the circuit substrate. The manufacturing method of the thermopile sensor can improve the measurement precision of the thermopile sensor.

Owner:NINGBO SEMICON INT CORP

Semiconductor packaging structure and preparation method

PendingCN114361153ASmall sizeShorten interconnect lengthSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingSemiconductor package

The invention provides a semiconductor packaging structure and a preparation method. The semiconductor package structure includes: a second redistribution structure; the voltage supply chip is inversely arranged on the second rewiring structure, and the first functional chip is positively arranged on one side, deviating from the second rewiring structure, of the voltage supply chip; the first plastic packaging layer is positioned on one side of the second rewiring structure and covers the first functional chip and the voltage supply chip; the first conductive connecting piece is positioned at the side parts of the first functional chip and the voltage supply chip; the first rewiring structure is located on the side, away from the second rewiring structure, of the first plastic packaging layer, the first rewiring structure is electrically connected with the front face of the first functional chip, and the first conductive connecting piece is electrically connected with the first rewiring structure and the second rewiring structure; and the second functional chip is inversely arranged on one side, deviating from the second rewiring structure, of the first rewiring structure and is electrically connected with the first rewiring structure. The semiconductor packaging structure is high in integration density and large in transmission bandwidth.

Owner:NAT CENT FOR ADVANCED PACKAGING +1

Ridge-shaped substrate integrated waveguide band-pass filter based on TSV

ActiveCN111934071AReduce volumeRealize stacked chip interconnectionWaveguide type devicesRadio frequencyCmos process

The invention discloses a ridge-shaped substrate integrated waveguide band-pass filter based on a TSV. The filter comprises a high-resistance silicon substrate, two rectangular metal grooves A are formed in the high-resistance silicon substrate; a plurality of pairs of diaphragms are arranged on the two sides in the metal groove A; the side walls of the diaphragm and the metal groove A are formedby arranging silicon through holes; the top surface insulating layer is arranged at the top of the high-resistance silicon substrate, the rectangular metal groove B is embedded into the top surface insulating layer, the ridge surface metal layer is arranged in the middle of the bottom of the top surface insulating layer, the adjacent side walls of the two rectangular metal grooves A are connectedthrough the ridge surface metal layer, and the other two side walls of the two rectangular metal grooves A are connected through the rectangular metal groove B. The manufacturing process of the ridge-shaped substrate integrated waveguide band-pass filter based on the TSV is compatible with the CMOS process, and the manufacturing cost is low; the size is small, the filter can be conveniently integrated in a miniaturized chip, stacked chip interconnection is realized, the length of an interconnection line is shortened, and the chip performance is greatly improved; and the filter is large in bandwidth and can be applied to the microwave / radio frequency field.

Owner:河北鹏博通信设备有限公司

Semiconductor device with active interposer and method for fabricating the same

ActiveUS20210375837A1Shorten interconnect lengthImprove semiconductor device performanceSemiconductor/solid-state device detailsSolid-state devicesDevice materialInterposer

The present application discloses a semiconductor device and a method for fabricating the semiconductor device. The semiconductor device includes an active interposer including a programmable unit, a first memory die positioned above the active interposer and including a storage unit, and a first logic die positioned below the active interposer. The active interposer, the first memory die, and the first logic die are electrically coupled.

Owner:NAN YA TECH

Manufacturing method of thermopile sensor

ActiveCN112117372AHigh measurement accuracyAvoid conductionThermoelectric device manufacture/treatmentDecorative surface effectsThermopileHemt circuits

The embodiment of the invention provides a manufacturing method of a thermopile sensor, and the method comprises the steps: providing a thermopile structure plate which comprises a thermal radiation induction region, and forming a thermopile structure in the thermal radiation induction region; providing a circuit substrate, forming a heat radiation reflecting plate on the circuit substrate, forming a first groove in the supporting layer covering the circuit substrate, and enabling the heat radiation reflecting plate to be located below the first groove; and bonding the supporting layer with the thermopile structure plate, so that the first groove is clamped between the thermopile structure plate and the circuit substrate to form a first cavity, and locating the thermal radiation reflectingplate below the thermopile structure. The thermopile sensor obtained by adopting the manufacturing method of the thermopile sensor provided by the embodiment of the invention can avoid the loss of infrared radiation and improve the measurement precision.

Owner:NINGBO SEMICON INT CORP

Thermopile sensor and manufacturing method thereof and electronic device

ActiveCN112117361AHigh measurement accuracyMiniaturizationThermoelectric device with peltier/seeback effectThermal insulationThermopileHemt circuits

The invention provides a thermopile sensor and a manufacturing method thereof, and an electronic device, the thermopile sensor comprises in order in the incident radiation direction: a thermopile structure plate, wherein the thermopile structure plate is provided with a heat radiation induction area, and a thermopile structure is formed in the heat radiation induction area; a support layer; and acircuit substrate, wherein a first cavity is defined by the circuit substrate, the thermopile structure plate and the support layer, the thermopile structure is arranged above the first cavity, a heatradiation reflection plate and a heat radiation isolation plate are arranged at the bottom of the first cavity, the heat radiation reflection plate is located above the heat radiation isolation plate, and the heat radiation isolation plate is located above the thermopile structure plate. Therefore, the measurement precision of the thermopile sensor can be improved.

Owner:NINGBO SEMICON INT CORP

Multilayer interconnection structure of wafer level package, manufacturing method and application

InactiveCN101656249BControl thicknessHighly integratedSemiconductor/solid-state device detailsSolid-state devicesInterconnectionTransmission loss

The invention provides a multilayer interconnection structure of wafer level package, a manufacturing method and application thereof. The multilayer interconnection structure is used for microwave multi chip modules. The invention is characterized by using benzocyclobutene (BCB) as a dielectric layer, realizing the multilayer connection structure of a metal / organic polymer by combining wafer level processing technics such as photoetching, electroplating, mechanical polishing and the like and embedding integrated varied passive devices and transmission lines for interconnection. The whole process is matched with IC process, is completed on the basis of wafer level and has higher integration of packaging and lower high-frequency transmission loss. The structure can effectively integrate varied function device units, reduce the interconnection loss among the devices and improve the properties of the whole module while improving the density and integration of packaging and reducing the cost of packaging.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Single power supply integrated h-bridge DC motor drive module with complementary dead zone and isolation

ActiveCN107800337BReduce volumeAvoid thruField or armature current controlControl signalElectric machine

The invention belongs to the field of electromechanical servo drive, and specifically discloses a single power supply integrated H-bridge DC motor drive module with complementary dead zone and isolation. The input terminal of the isolation unit is connected to the external pins of the module, and receives the TTL control signal or uses the DSP control signal to directly control the motor. The output terminal of the optocoupler isolation unit is connected to the input terminal of the complementary dead zone circuit, and the output terminal of the complementary dead zone circuit is connected to the The input terminals of the FET output unit are connected. The module has the advantages of high integration, small size, light weight, large working current, high power density, single power supply, and dead zone protection function.

Owner:BEIJING RES INST OF PRECISE MECHATRONICS CONTROLS +1

Flexible installation of a hydrocarbon liquefaction unit

PendingUS20210310731A1Limit thermal lossReduce mechanical effectSolidificationLiquefactionHydrocotyle bowlesioidesNitrogen gas

Natural gas liquefaction unit including at least one cryogenic cold box having at least one heat exchanger; a fixed assembly zone on its outer wall; at least one closed loop nitrogen refrigeration cycle; at least one device for equipment required for implementing the liquefaction of a natural gas stream from a hydrocarbon supply stream; at least one interconnection module comprising a pipe holder means and a set of pipes and valves, designed to connect said at least one cold box to at least one equipment device for the cycle for refrigerating and / or separating C6+ type hydrocarbon elements contained in the natural gas, wherein the interconnection module rests on a frame allowing it to be handled and is connected to the cold box and to the other method or equipment sub-assemblies located around said fixed assembly zone.

Owner:LAIR LIQUIDE SA POUR LETUDE & LEXPLOITATION DES PROCEDES GEORGES CLAUDE

Three dimensional CMOS integrated circuits having device layers built on different crystal oriented wafers

InactiveCN100342523CIncrease packing densityPacking Density ImprovementsTransistorSemiconductor/solid-state device details3d integrated circuitCMOS

Three-dimensional (3D) integration schemes of fabricating a 3D integrated circuit in which the pFETs are located on an optimal crystallographic surface for that device and the nFETs are located on a optimal crystallographic surface for that type of device are provided. In accordance with a first 3D integration scheme of the present invention, first semiconductor devices are pre-built on a semiconductor surface of a first silicon-on-insulator (SOI) substrate and second semiconductor devices are pre-built on a semiconductor surface of a second SOI substrate. After pre-building those two structures, the structure are bonded together and interconnect through wafer-via through vias. In a second 3D integration scheme, a blanket silicon-on-insulator (SOI) substrate having a first SOI layer of a first crystallographic orientation is bonded to a surface of a pre-fabricating wafer having second semiconductor devices on a second SOI layer that has a different crystallographic orientation than the first SOI layer; and forming first semiconductor device on the first SOI layer.

Owner:GLOBALFOUNDRIES INC

Nano-capacitor three-dimensional integrated structure and manufacturing method thereof

ActiveCN112201655ATo achieve parallel connectionReduce process stepsSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceEngineering

The invention discloses a nano-capacitor three-dimensional integrated structure and a manufacturing method thereof. The nano-capacitor three-dimensional integrated structure comprises a first nano-capacitor structure and a second nano-capacitor structure which are formed on the front surface and the back surface of an aluminum foil, the first top metal electrode layer of the first nano capacitor structure is electrically communicated with the second top metal electrode layer of the second nano capacitor structure through the first groove structure, the second groove structure, the aluminum through hole structure, the fourth groove structure and the fifth groove structure; and the first bottom metal electrode layer of the first nano capacitor structure is electrically communicated with thesecond bottom metal electrode layer of the second nano capacitor structure through the third groove structure, the aluminum foil and the sixth groove structure. According to the invention, the capacitance density can be obviously increased, the length of the interconnection line can be shortened, the interconnection resistance and energy loss can be reduced, the process steps can be reduced, the process complexity can be reduced, and the production cost can be effectively reduced.

Owner:FUDAN UNIV +1

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com