Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1240 results about "P type doping" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

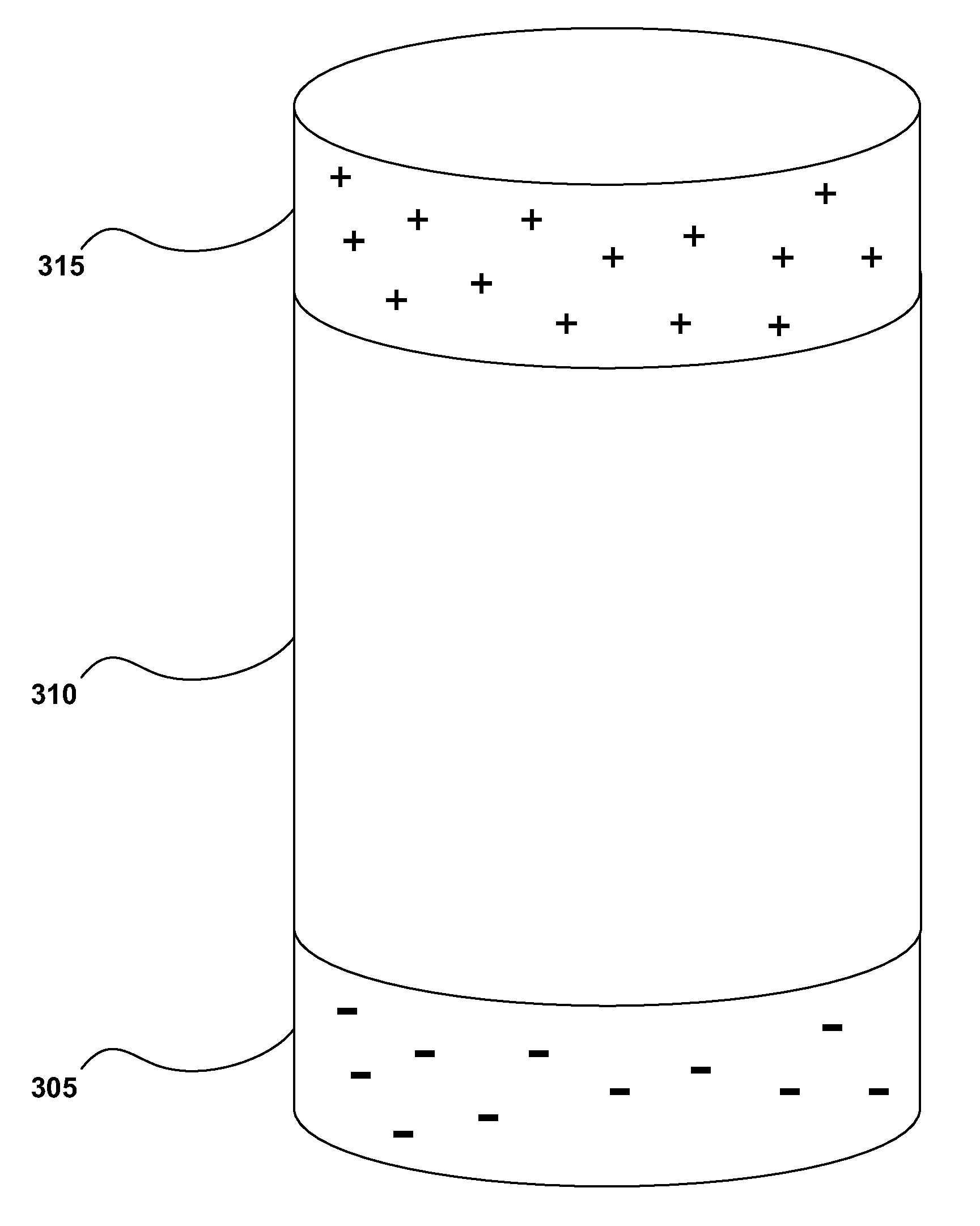

In p type doping a donor with less valence electrons as needed in the semiconductor lattice is introduced . As a result they "accept" electrons from the semiconductor's valence band. This provides excess holes to the intrinsic semiconductor creating a p-type semiconductor .

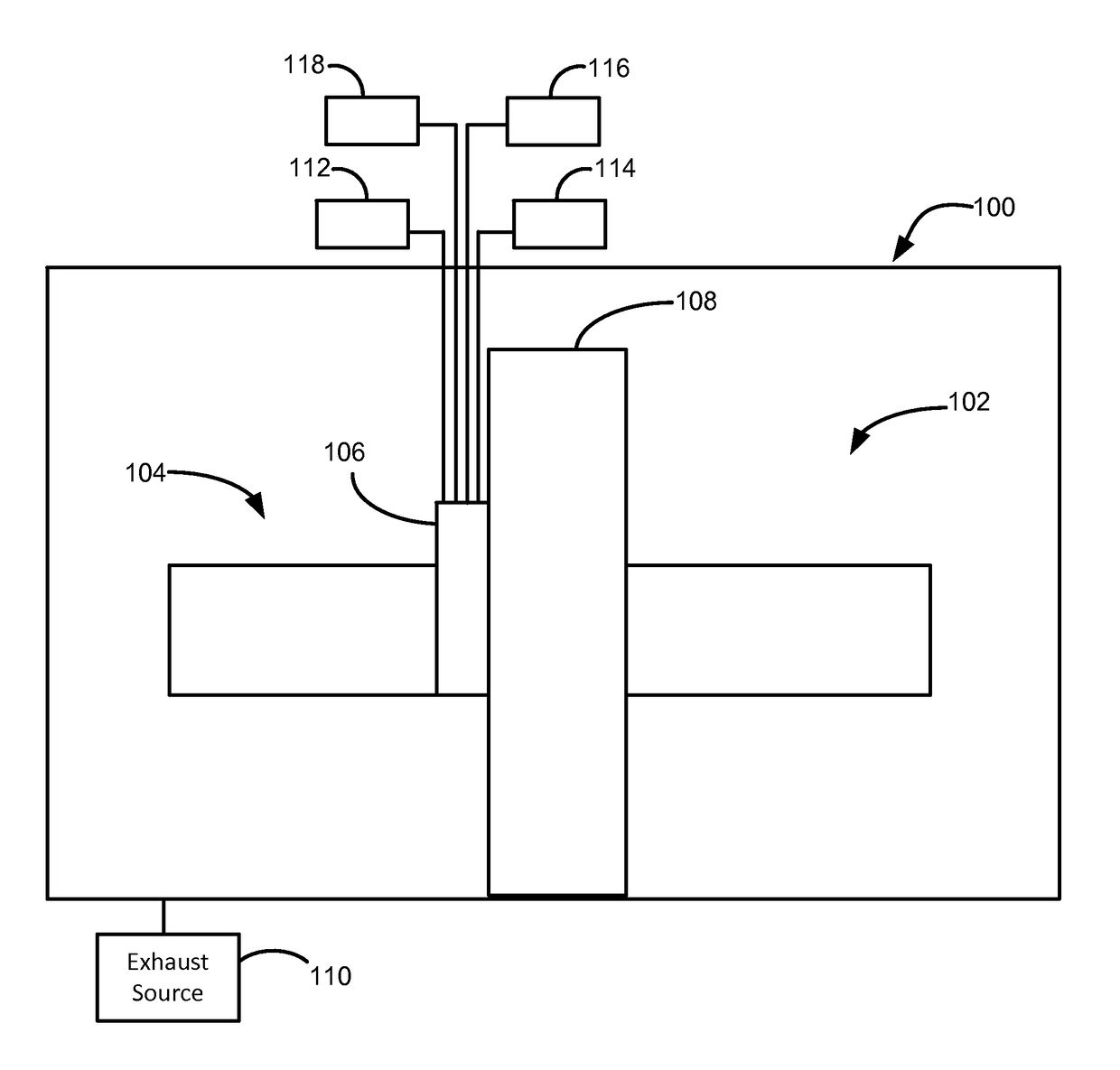

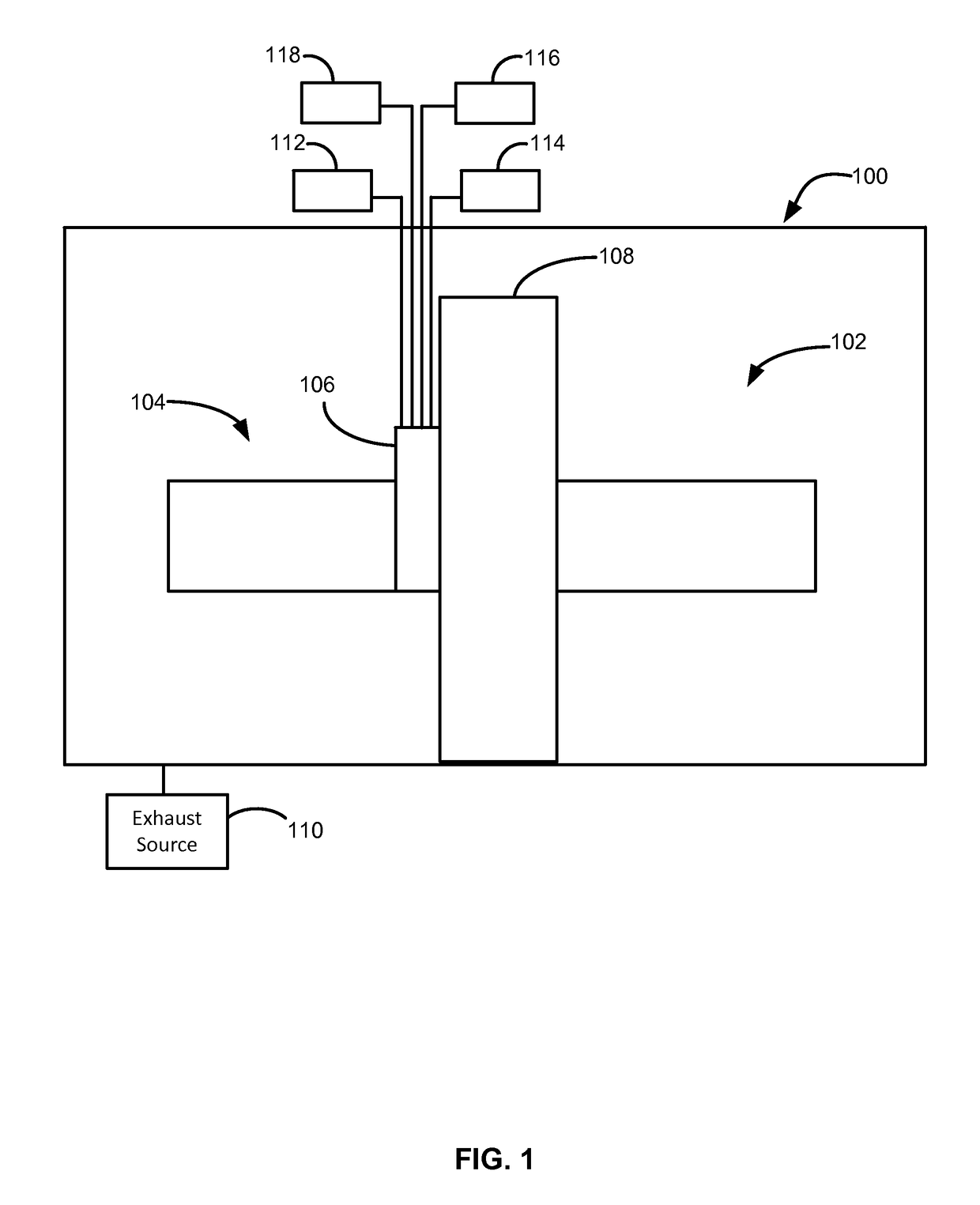

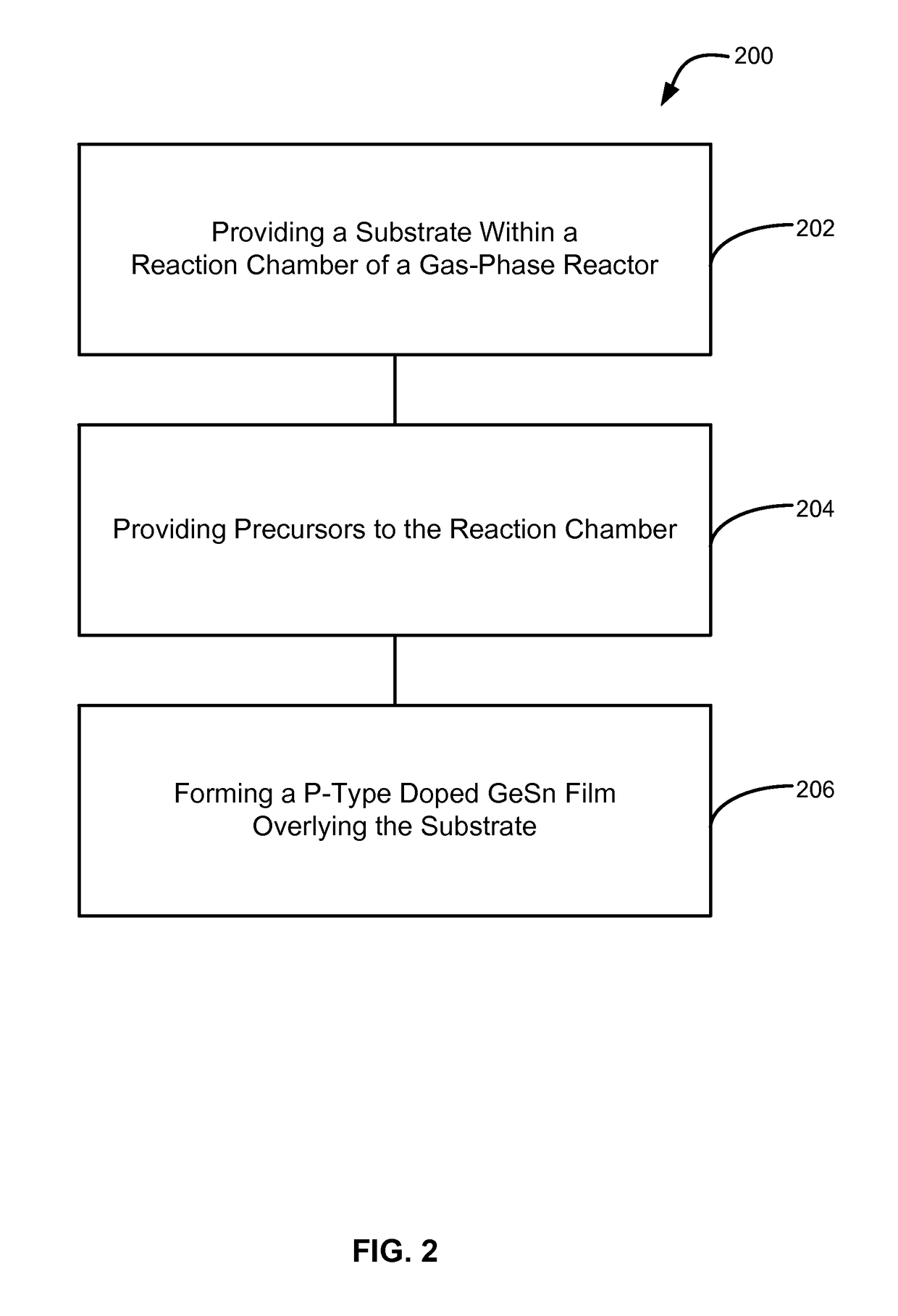

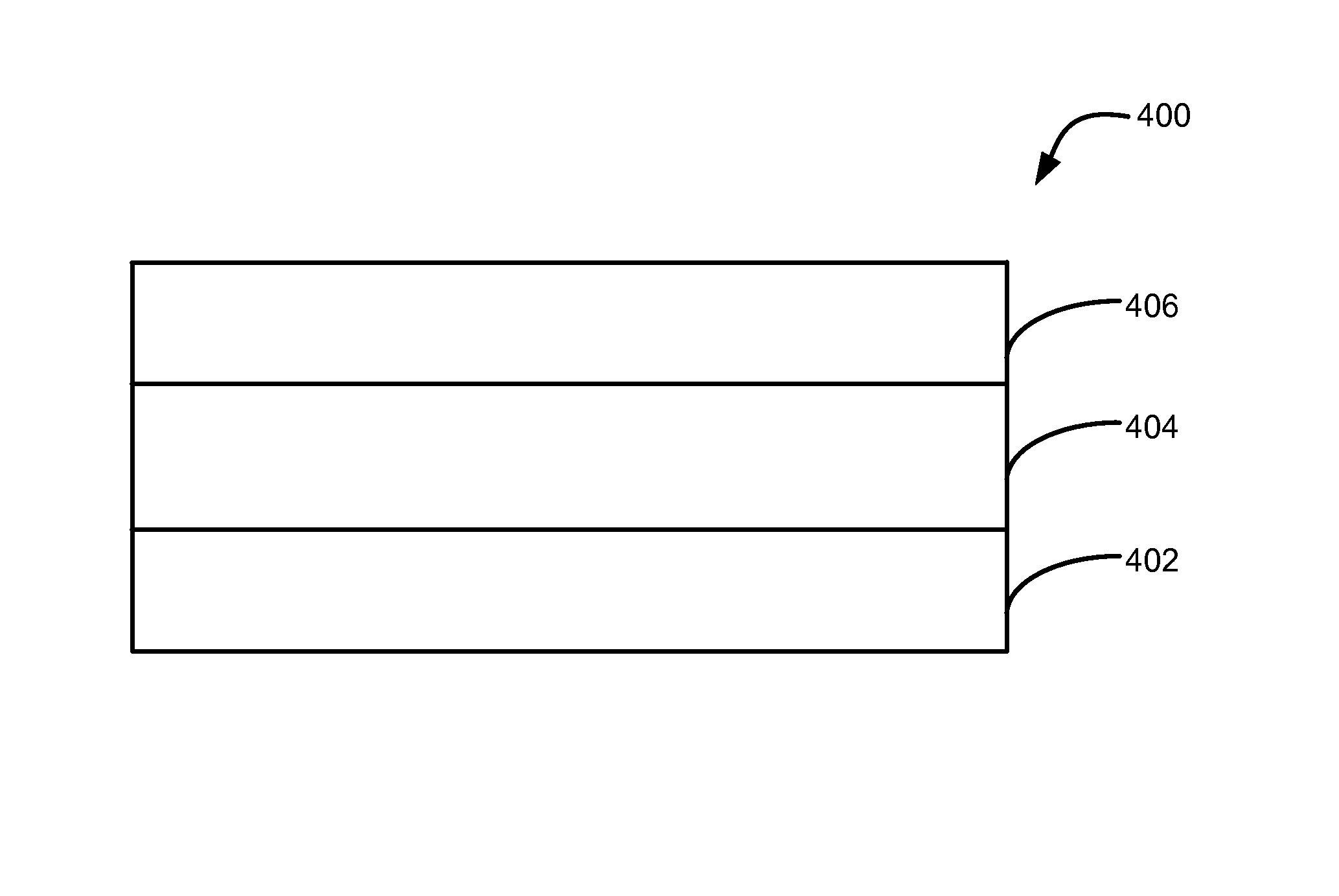

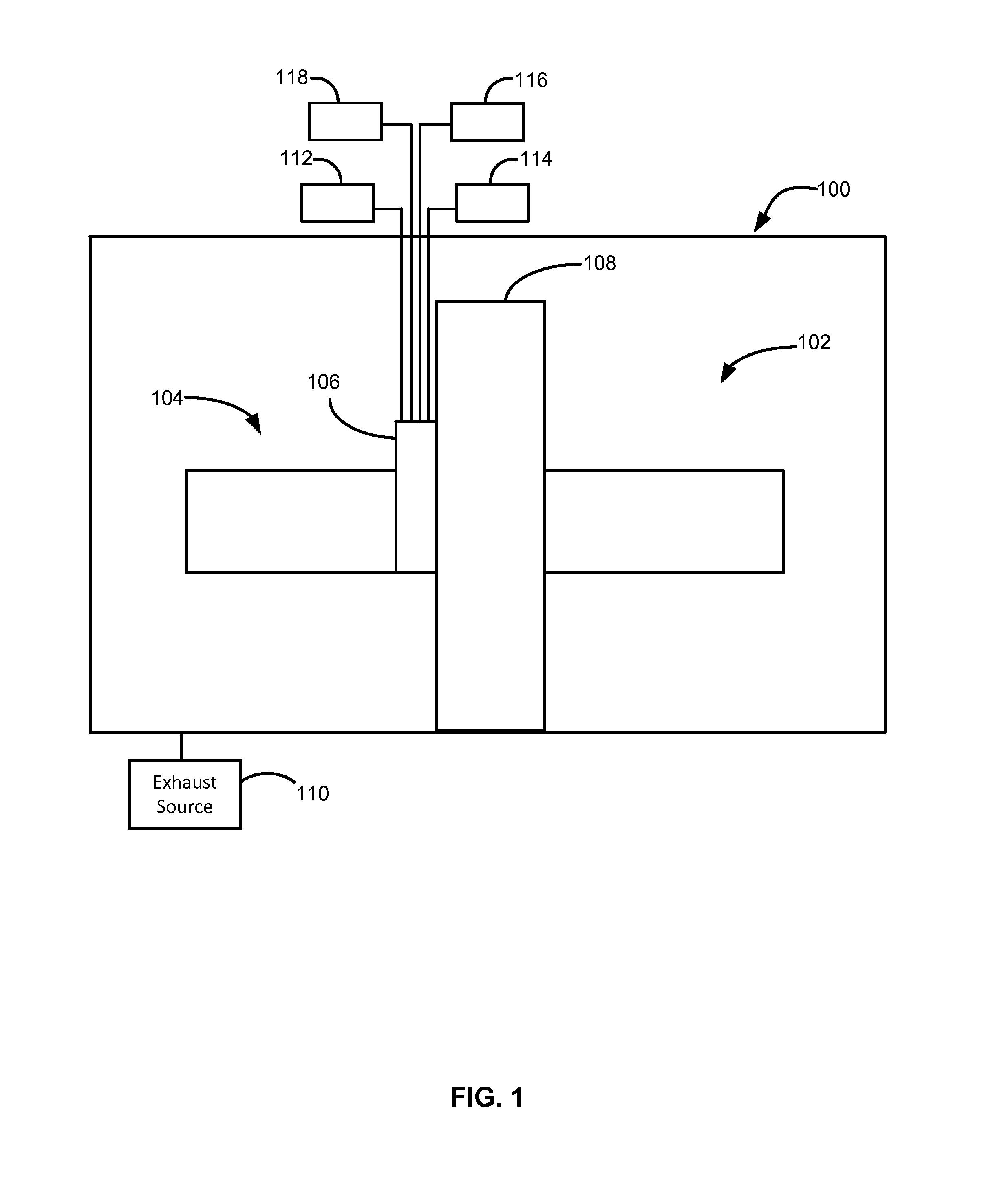

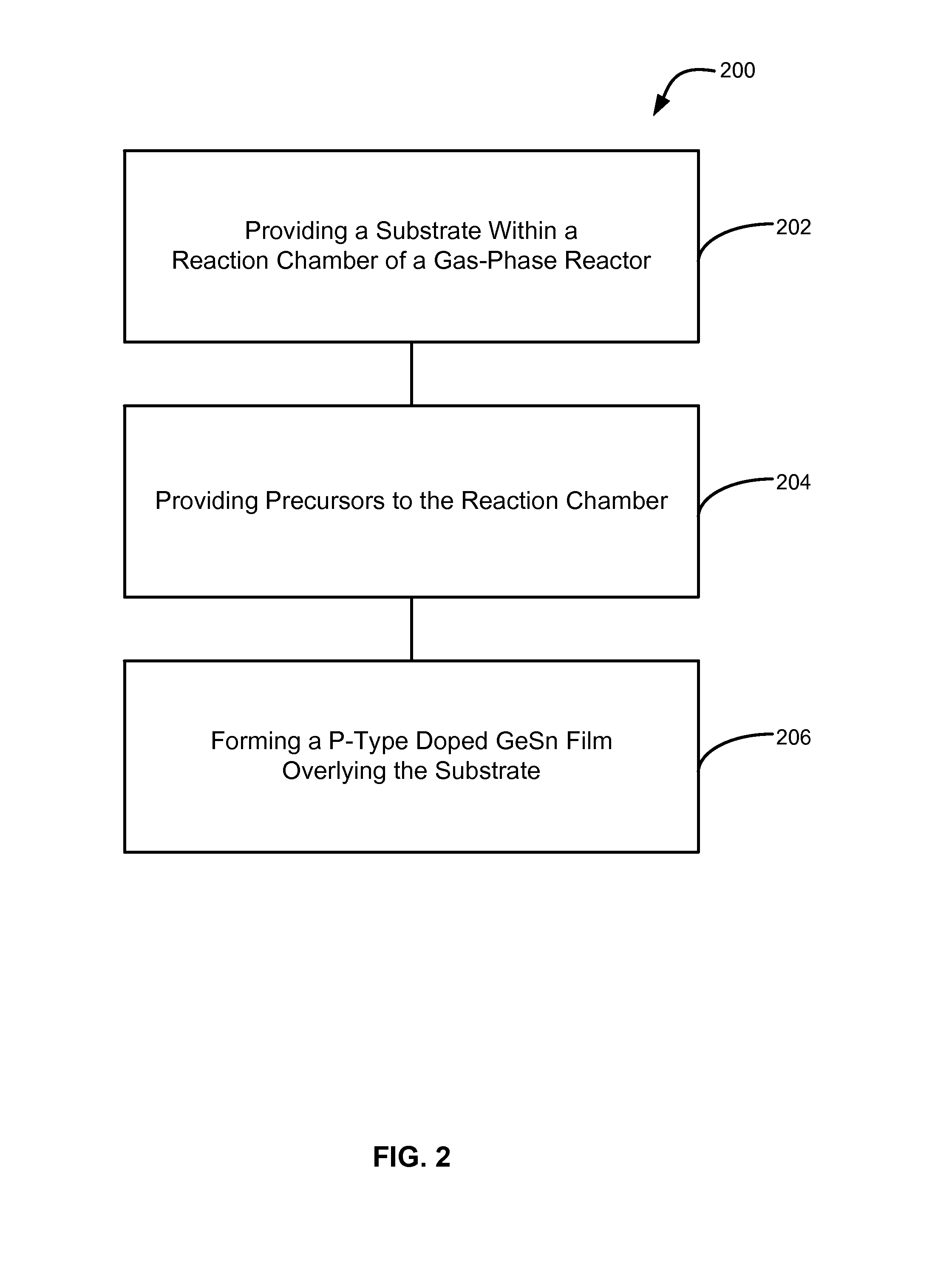

Methods of forming highly p-type doped germanium tin films and structures and devices including the films

ActiveUS9647114B2Polycrystalline material growthSemiconductor/solid-state device manufacturingDopantP type doping

Methods of forming p-type doped germanium-tin layers, systems for forming the p-type doped germanium-tin layers, and structures including the p-type doped germanium-tin layers are disclosed. The p-type doped germanium-tin layers include an n-type dopant, which allows relatively high levels of tin and / or p-type dopant to be included into the p-type doped germanium-tin layers.

Owner:ASM IP HLDG BV

Methods of forming highly p-type doped germanium tin films and structures and devices including the films

ActiveUS20170047446A1High tin contentSuitable for applicationPolycrystalline material growthSemiconductor/solid-state device manufacturingDopantP type doping

Methods of forming p-type doped germanium-tin layers, systems for forming the p-type doped germanium-tin layers, and structures including the p-type doped germanium-tin layers are disclosed. The p-type doped germanium-tin layers include an n-type dopant, which allows relatively high levels of tin and / or p-type dopant to be included into the p-type doped germanium-tin layers.

Owner:ASM IP HLDG BV

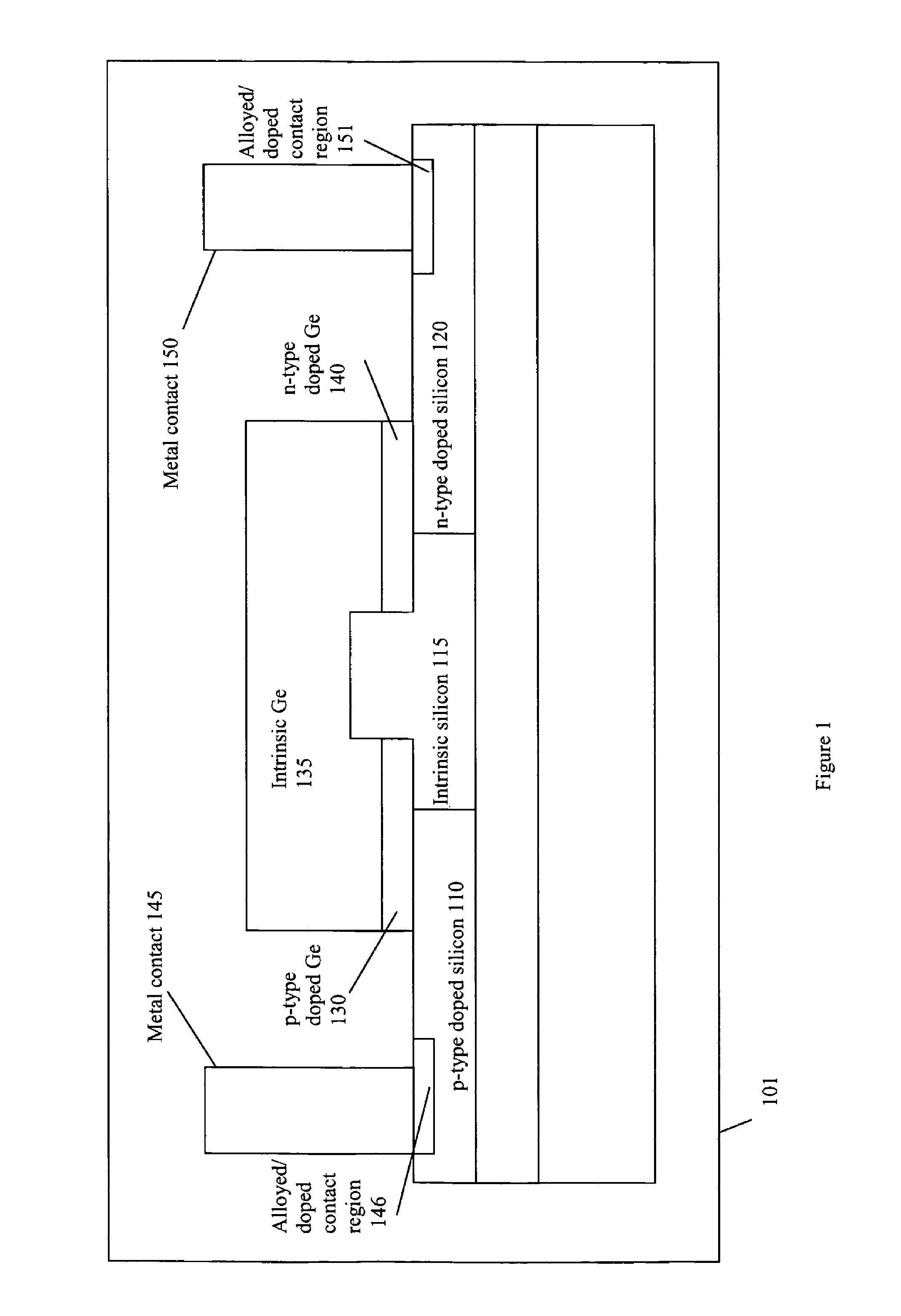

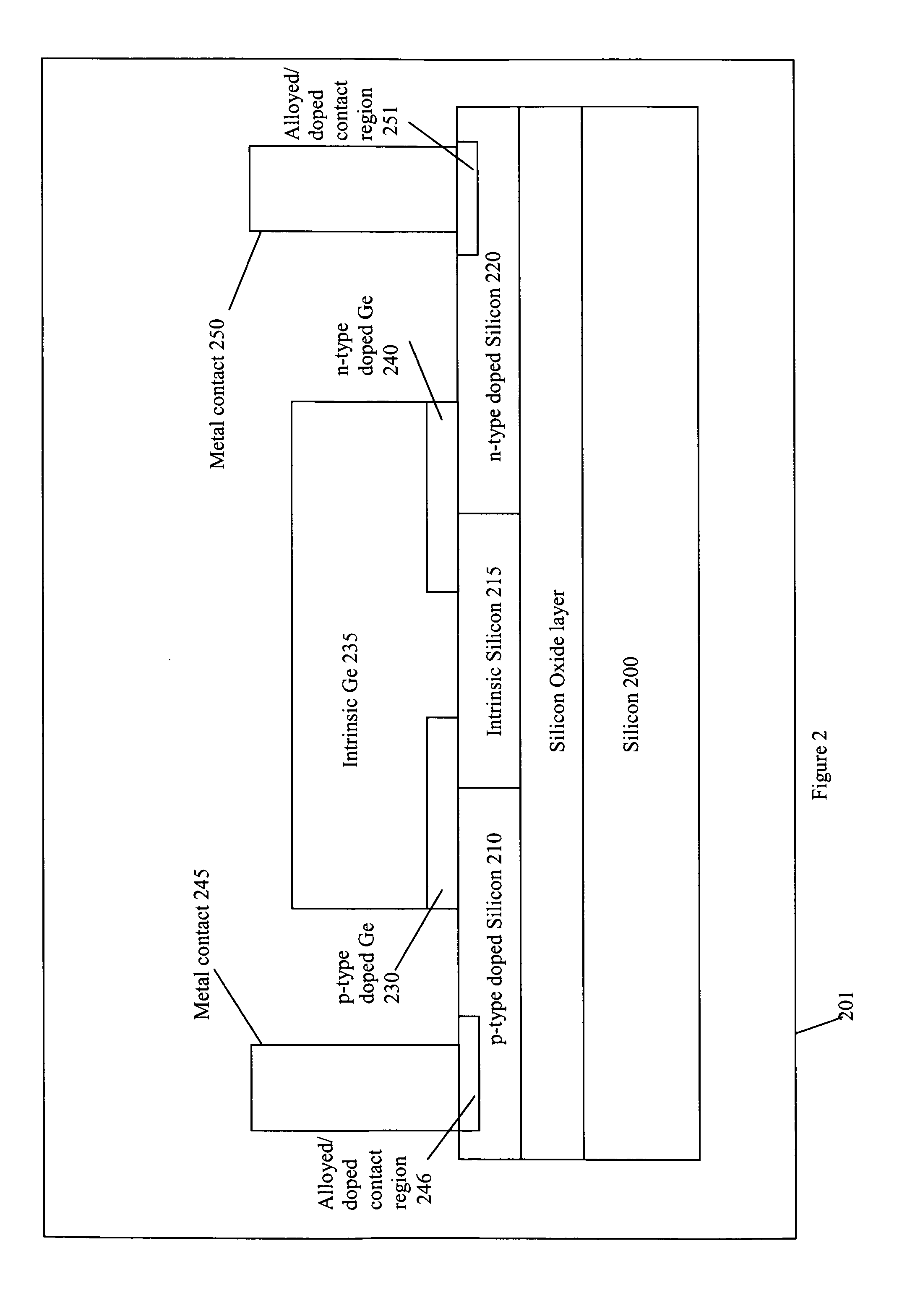

Germanium silicon heterostructure photodetectors

ActiveUS7397101B1Good electrical contactSemiconductor/solid-state device manufacturingPhotovoltaic energy generationPhotovoltaic detectorsPhotodetector

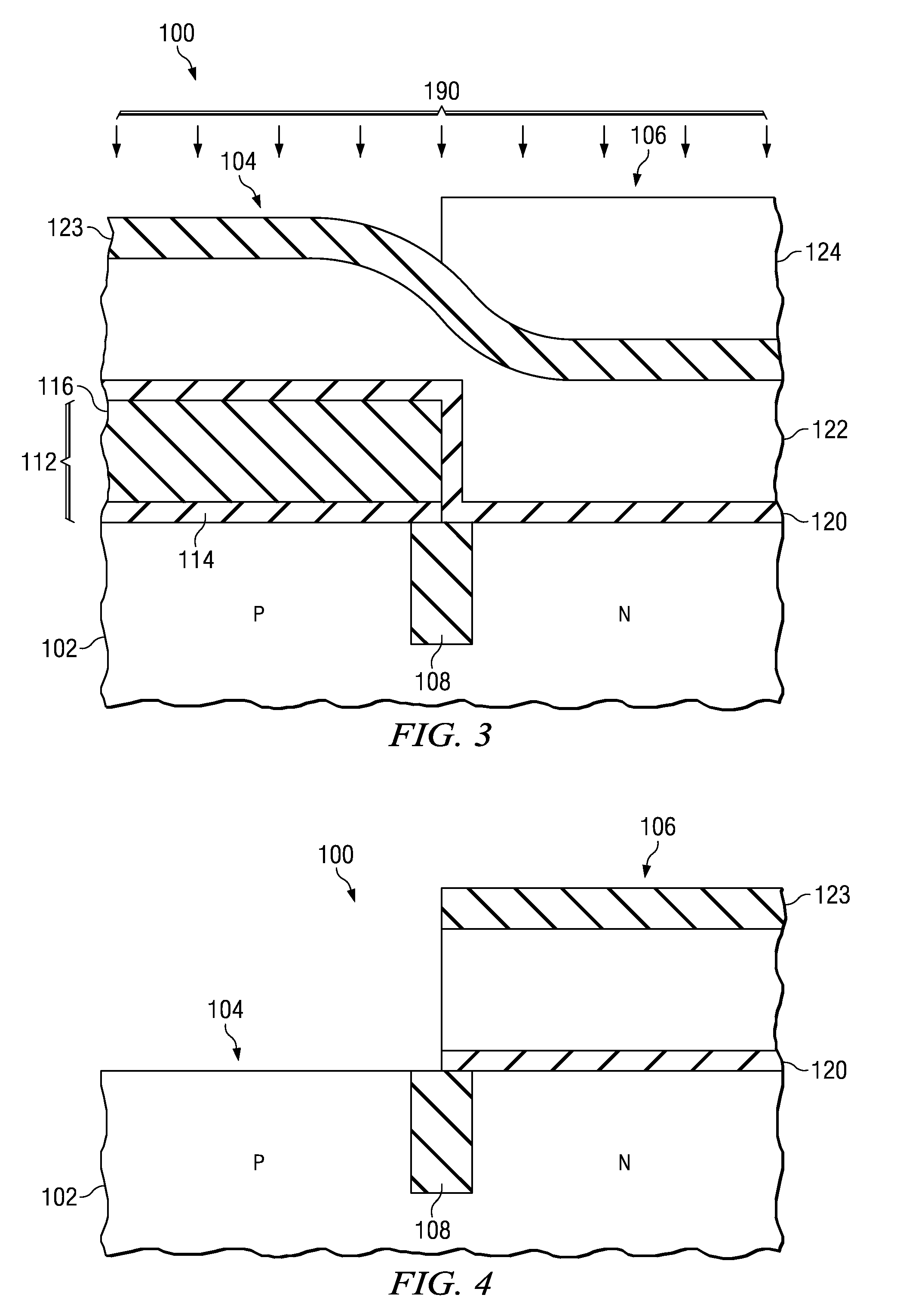

A horizontal germanium silicon heterostructure photodetector comprising a horizontal germanium p-i-n diode disposed over a horizontal parasitic silicon p-i-n diode uses silicon contacts for electrically coupling to the germanium p-i-n through the p-type doped and n-type doped regions in the silicon p-i-n without requiring direct physical contact to germanium material. The current invention may be optically coupled to on-chip and / or off-chip optical waveguide through end-fire or evanescent coupling. In some cases, the doping of the germanium p-type doped and / or n-type doped region may be accomplished based on out-diffusion of dopants in the doped silicon material of the underlying parasitic silicon p-i-n during high temperature steps in the fabrication process such as, the germanium deposition step(s), cyclic annealing, contact annealing and / or dopant activation.

Owner:CISCO TECH INC

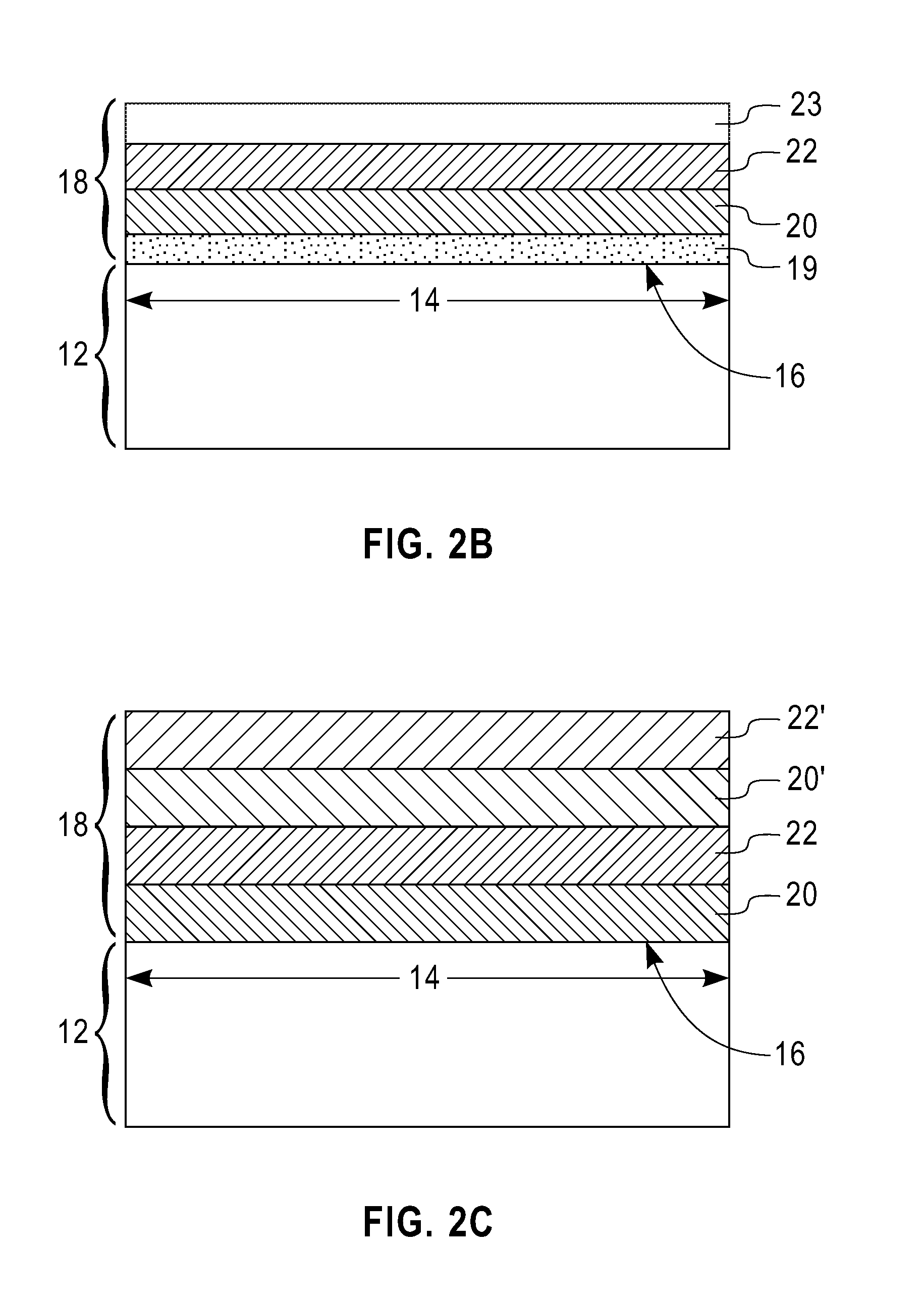

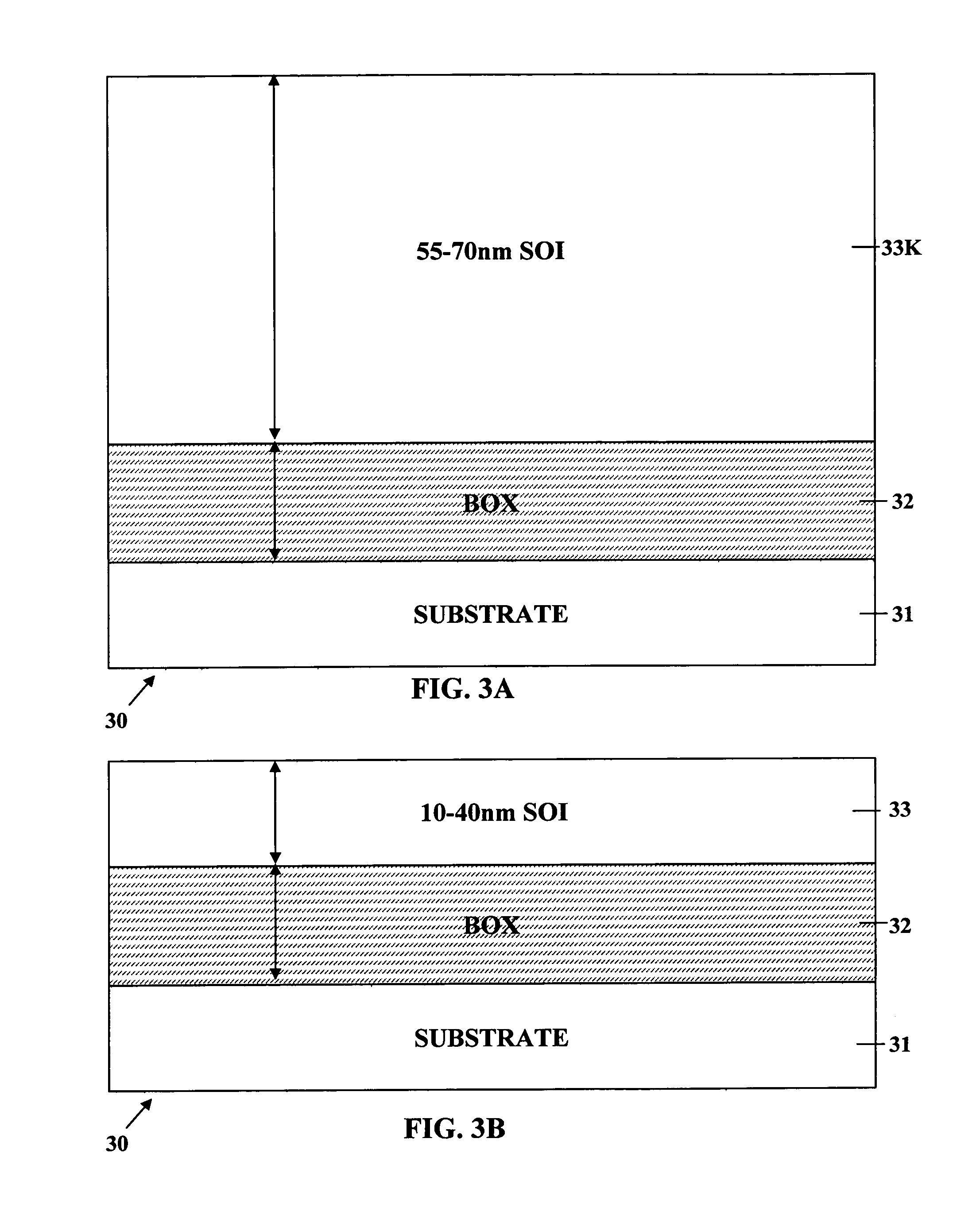

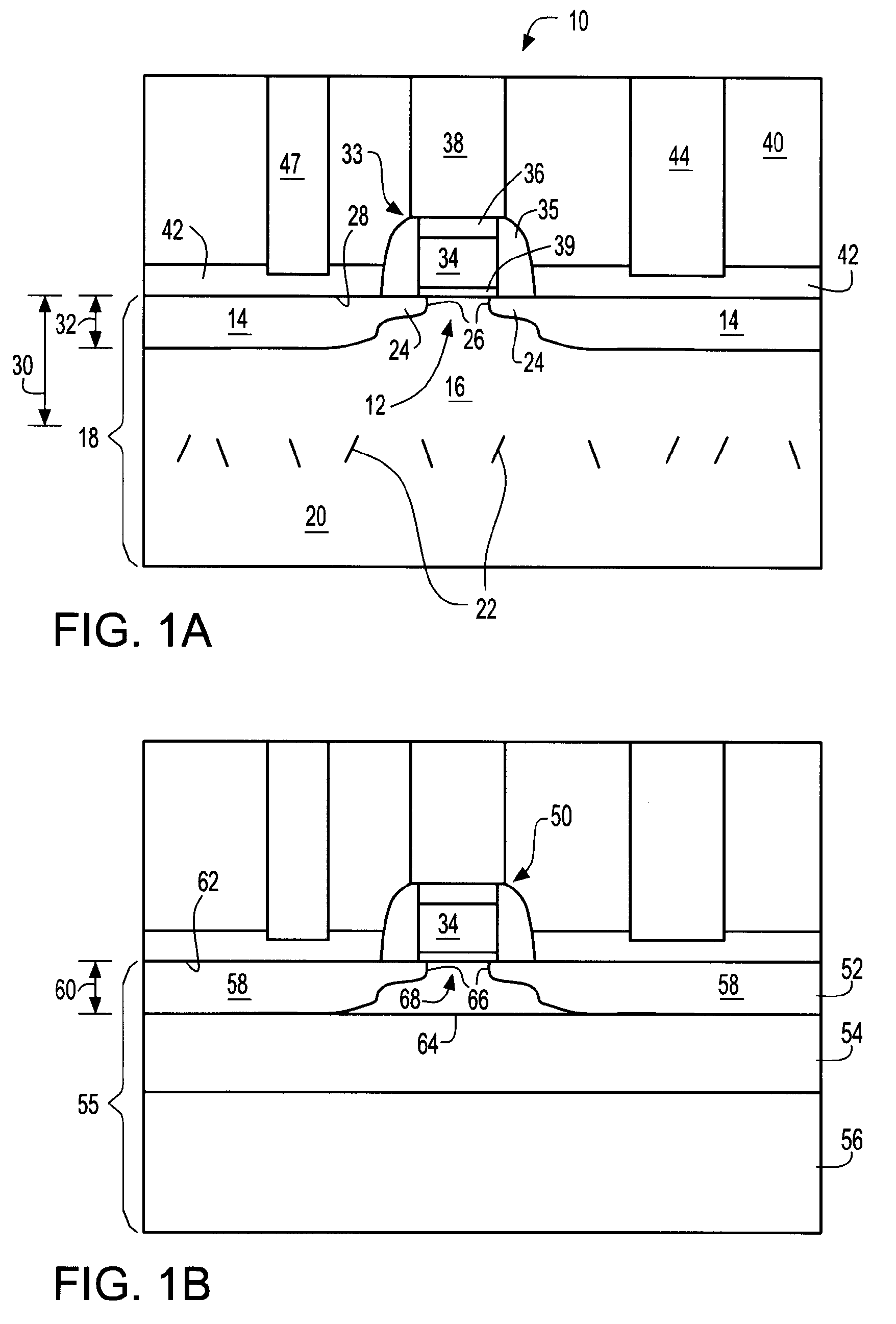

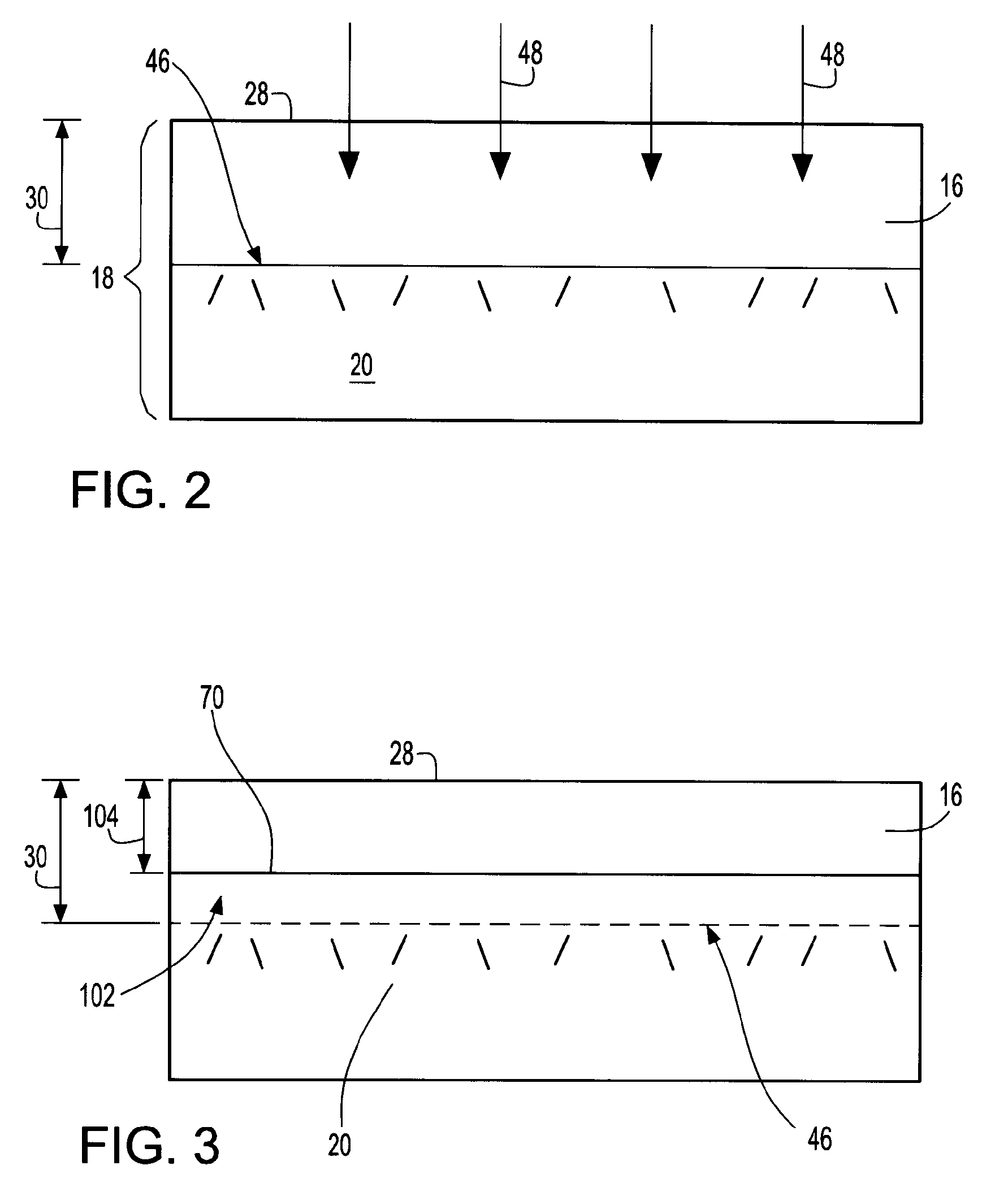

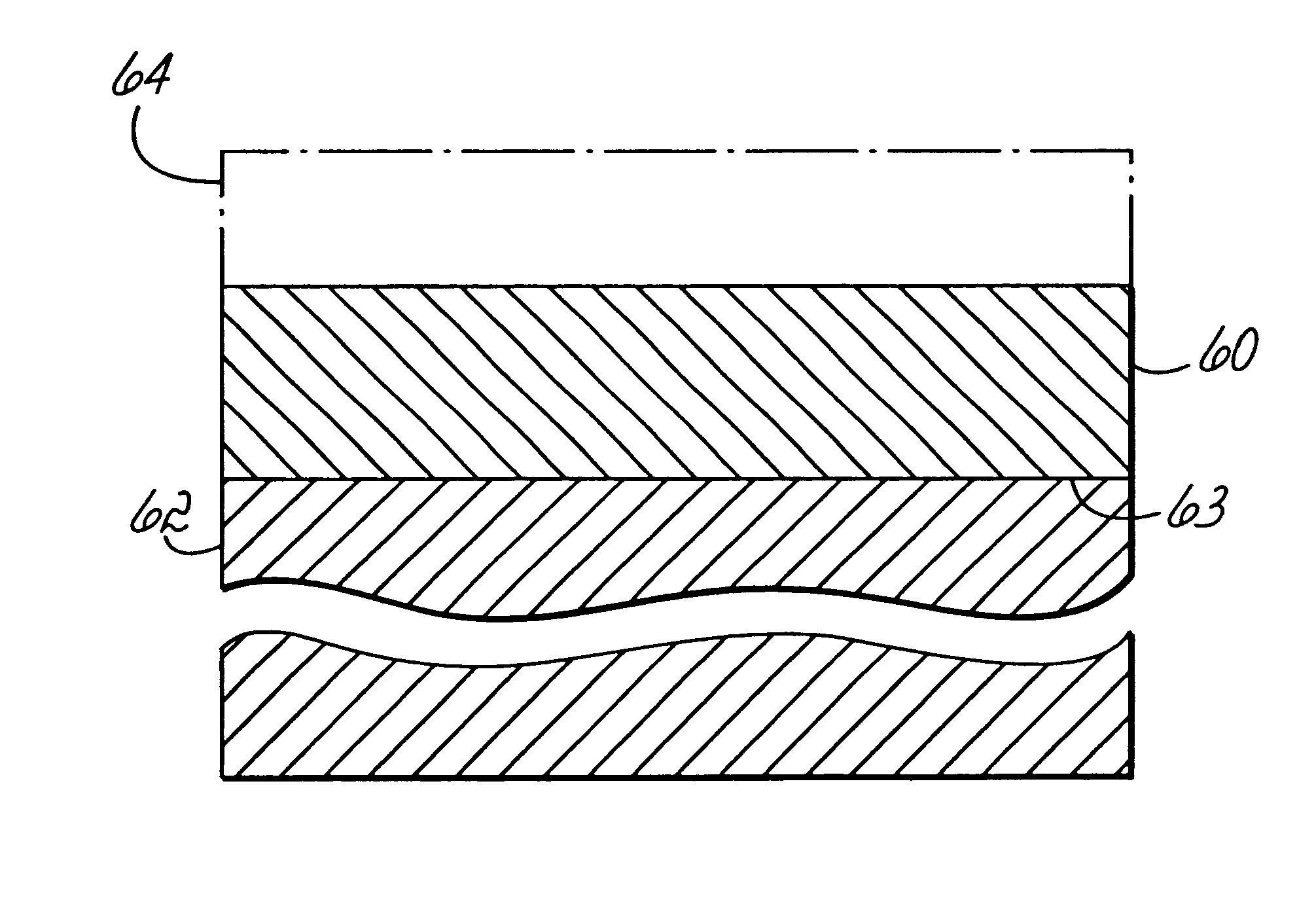

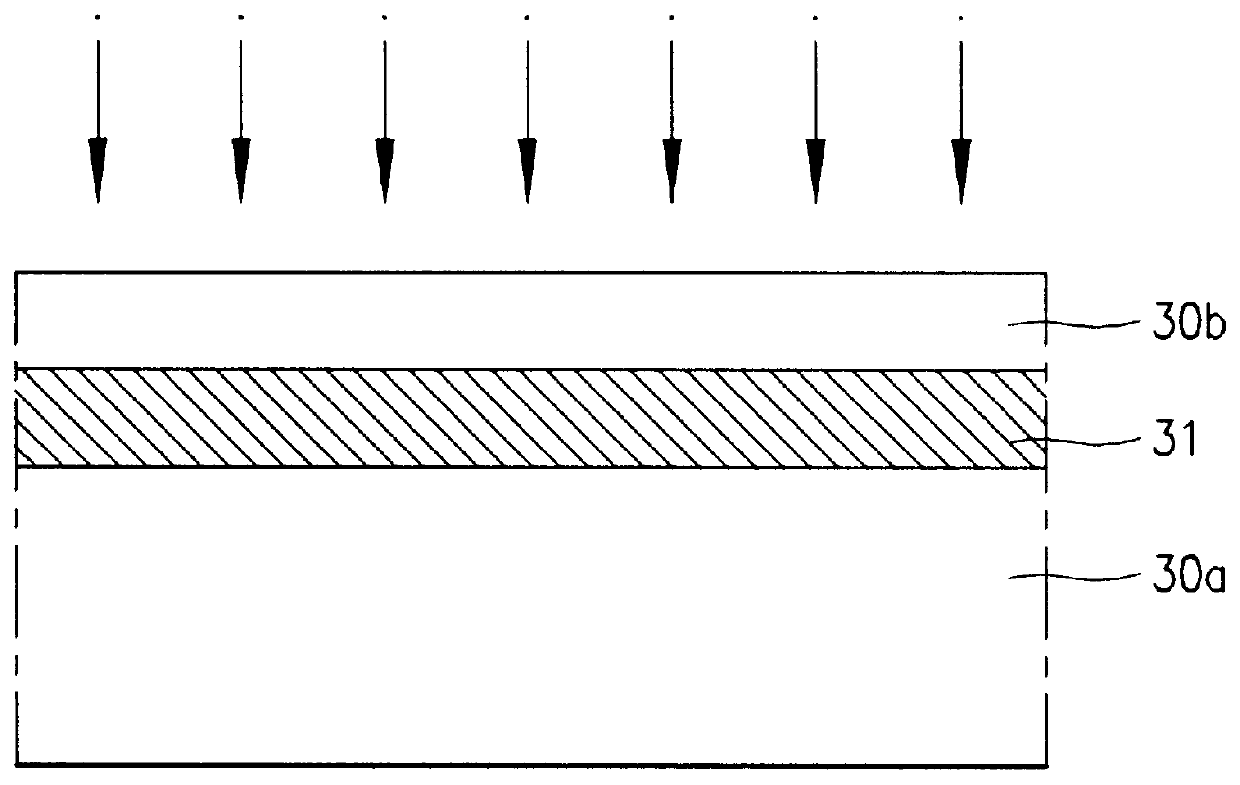

Low cost soi substrates for monolithic solar cells

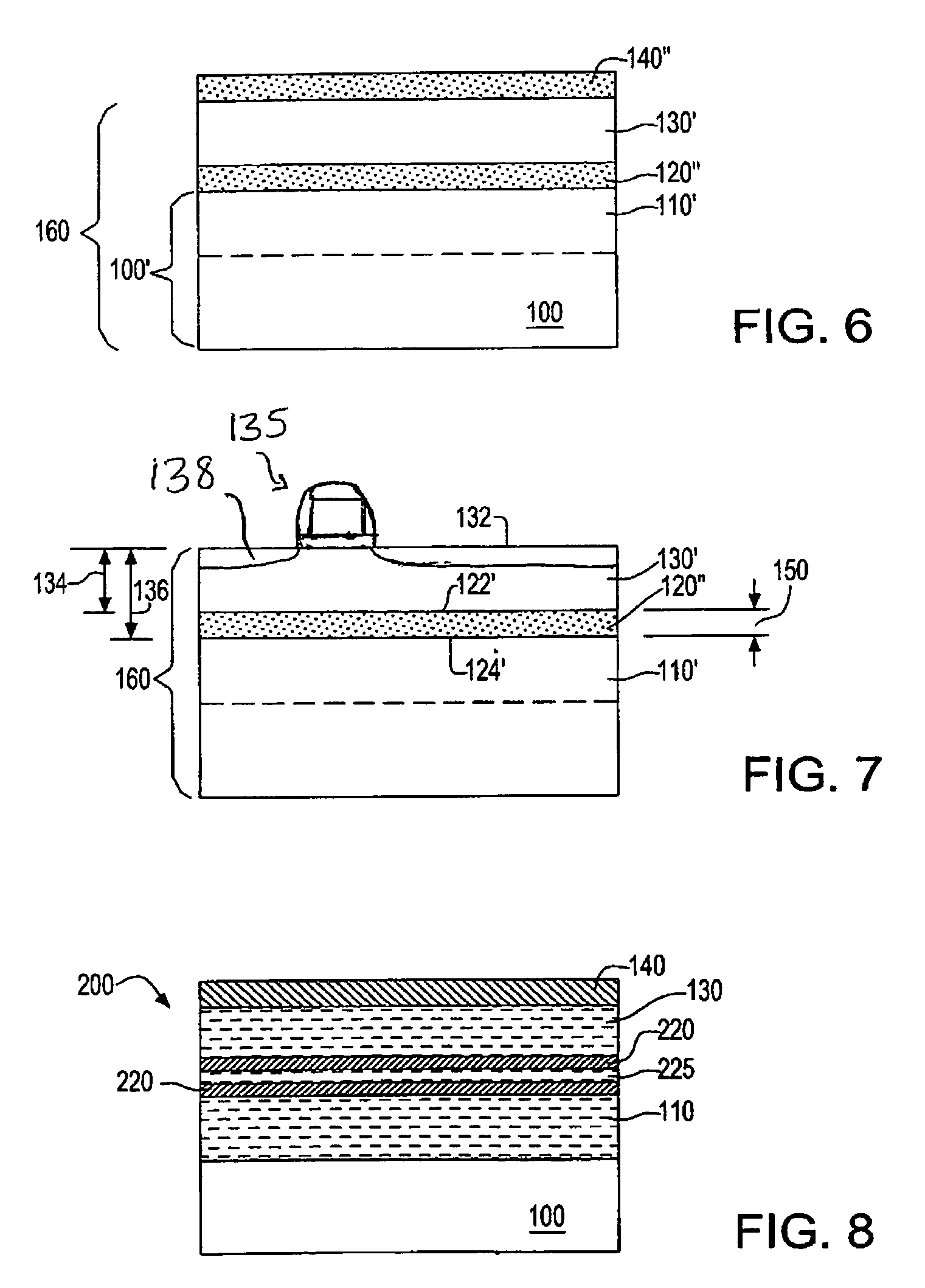

InactiveUS20100221867A1Reduce defect densityFinal product manufactureSemiconductor/solid-state device manufacturingSoi substrateSingle crystal

A lost cost method for fabricating SOI substrates is provided. The method includes forming a stack of p-type doped amorphous Si-containing layers on a semiconductor region of a substrate by utilizing an evaporation deposition process. A solid phase recrystallization step is then performed to convert the amorphous Si-containing layers within the stack into a stack of p-type doped single crystalline Si-containing layers. After recrystallization, the single crystalline Si-containing layers are subjected to anodization and at least an oxidation step to form an SOI substrate. Solar cells and / or other semiconductor devices can be formed on the upper surface of the inventive SOI substrate.

Owner:GLOBALFOUNDRIES INC

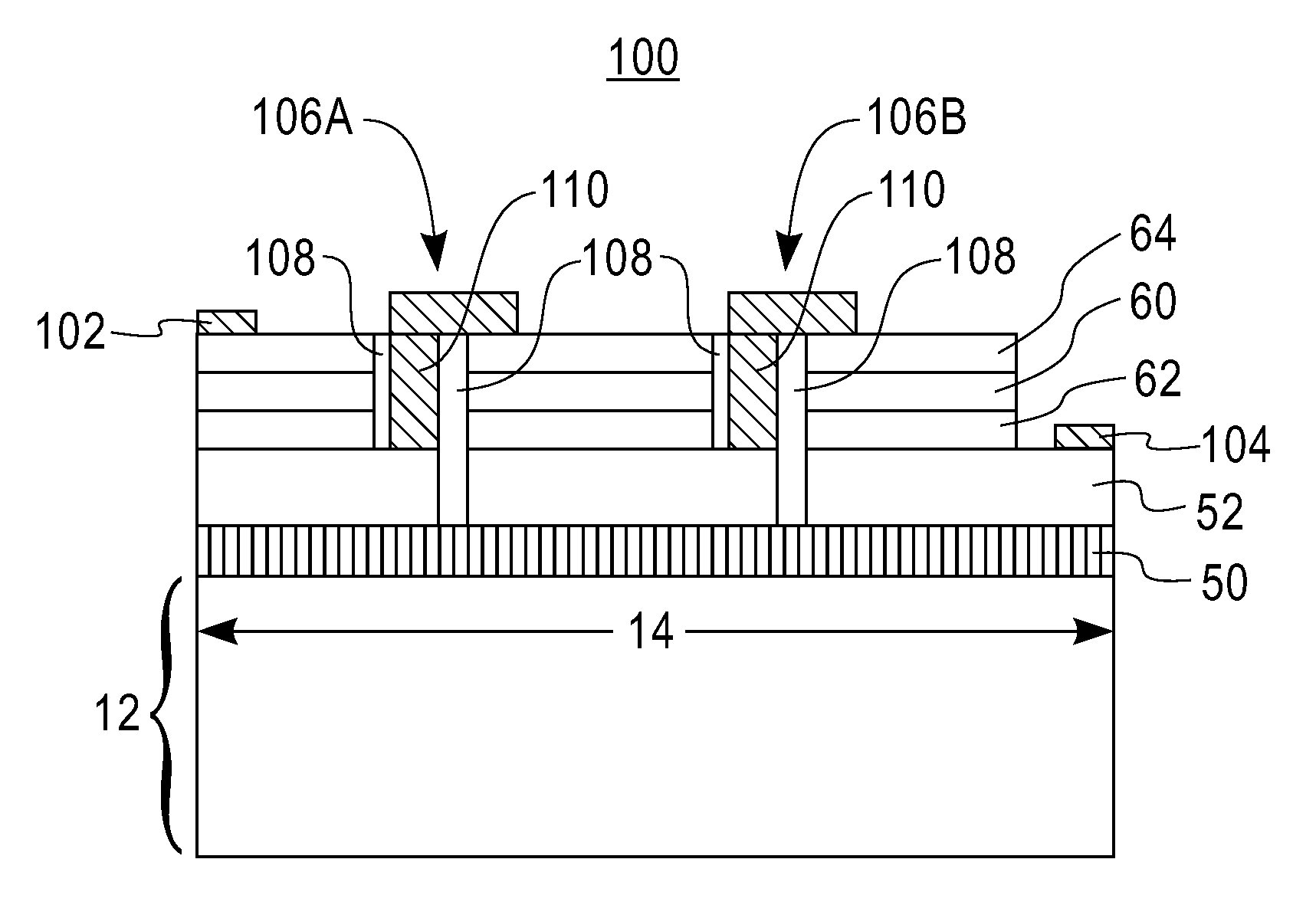

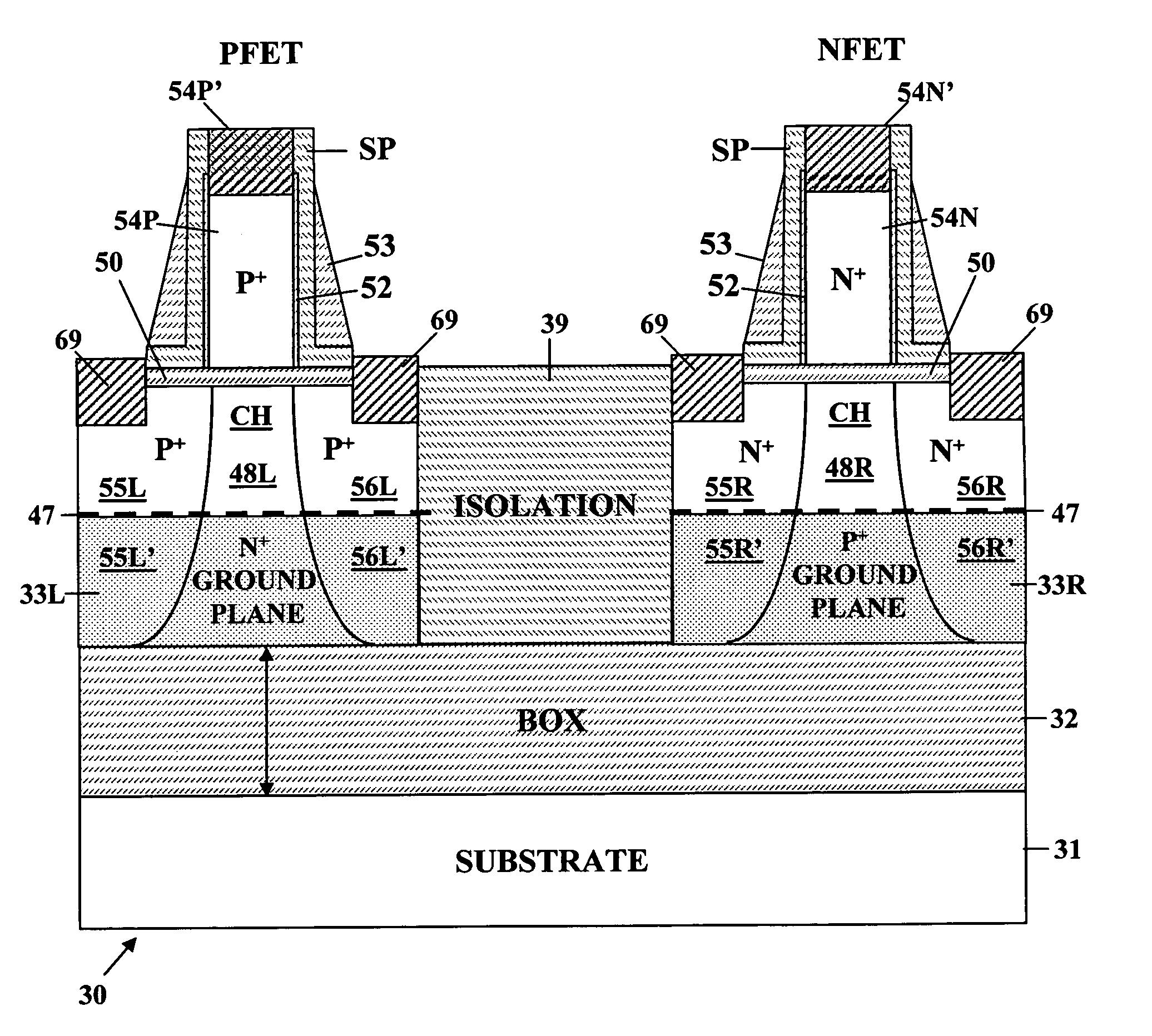

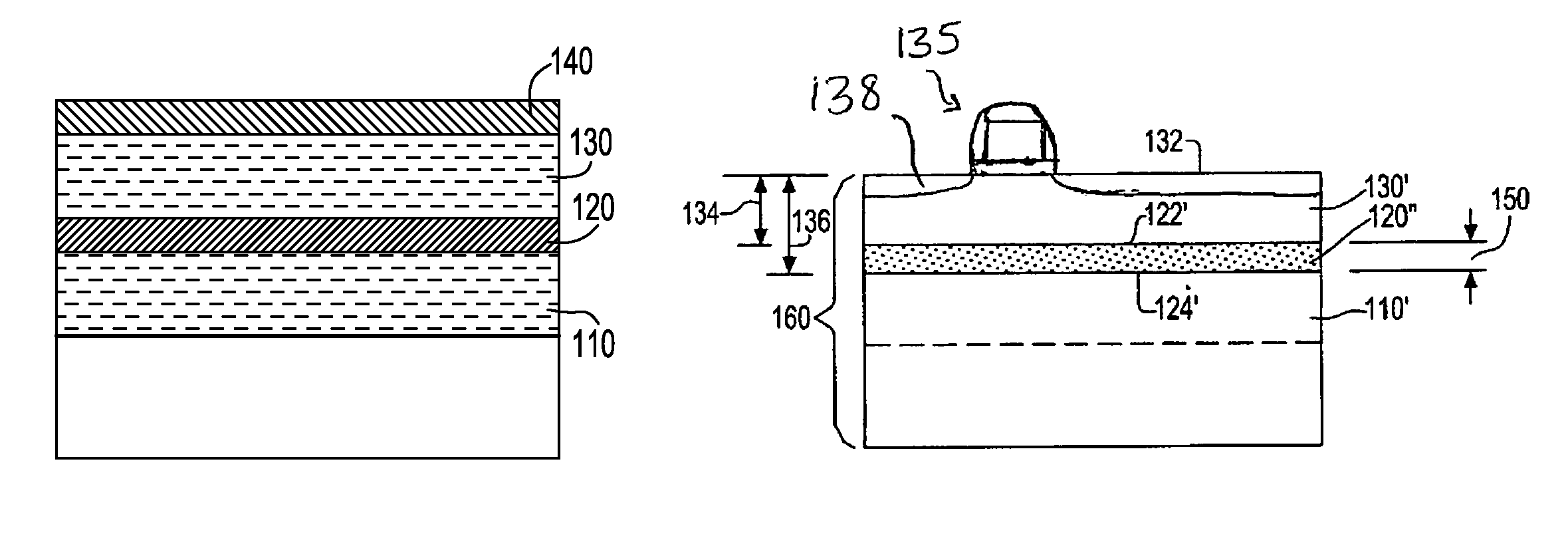

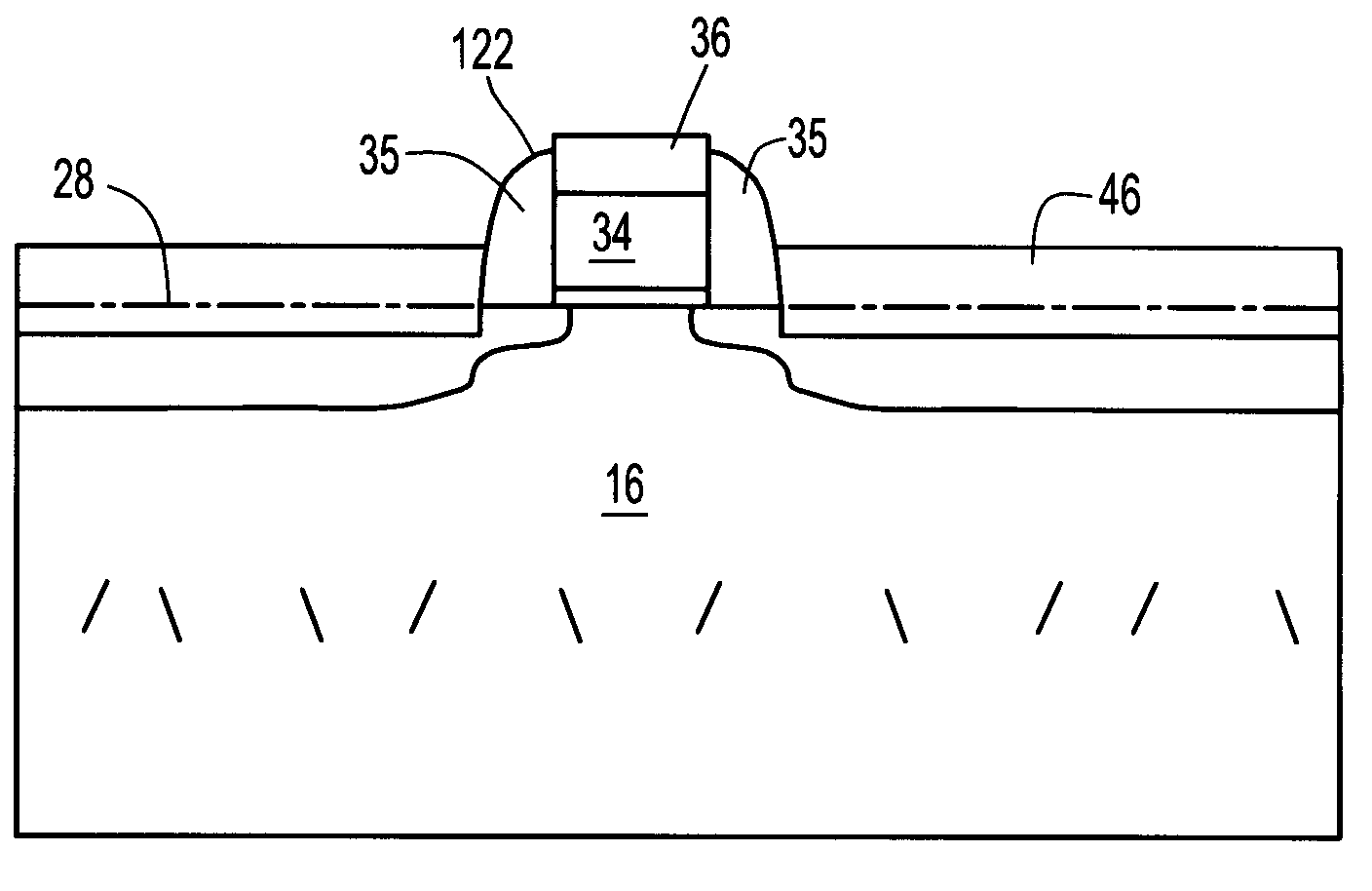

Ultra-thin body super-steep retrograde well (SSRW) FET devices

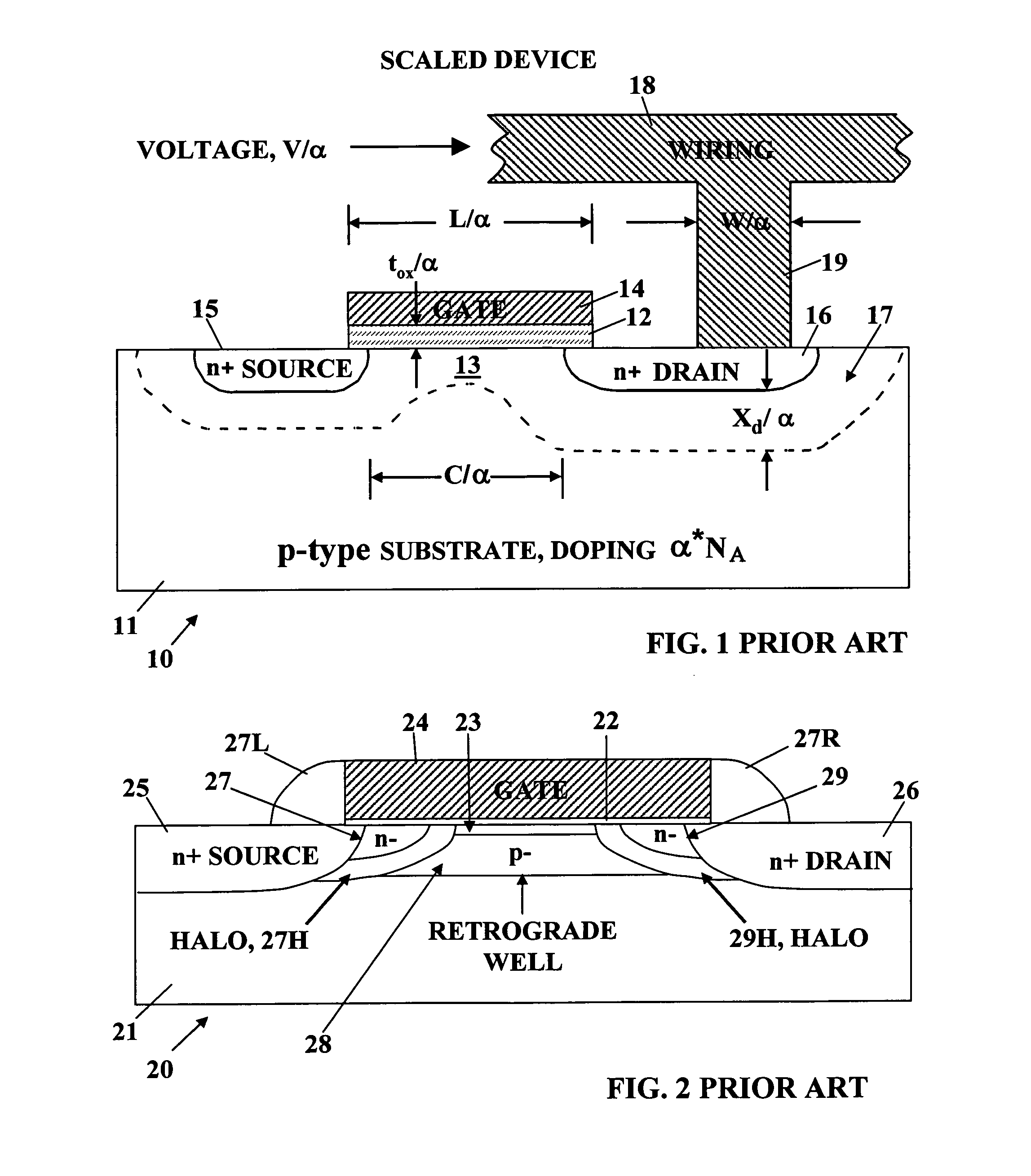

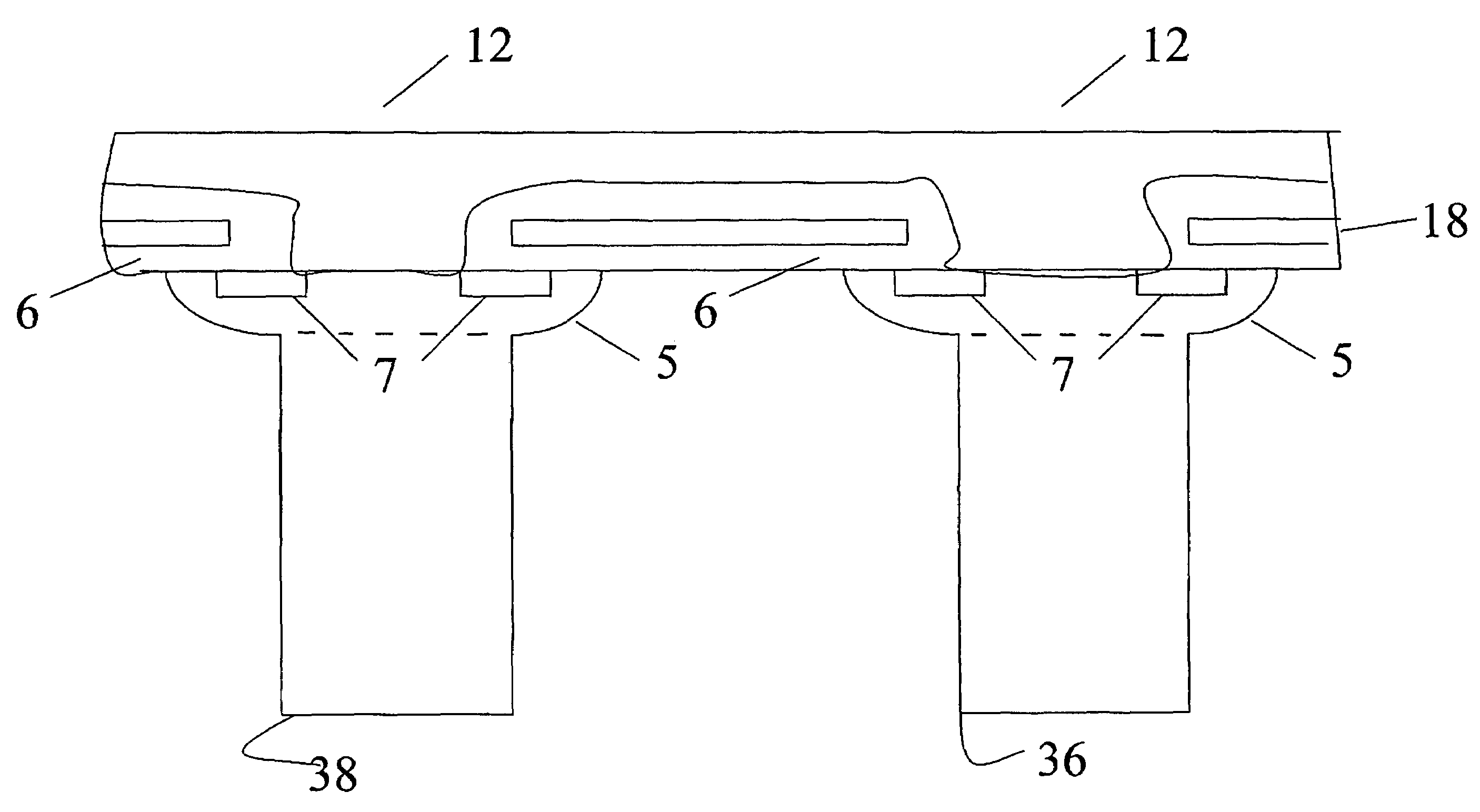

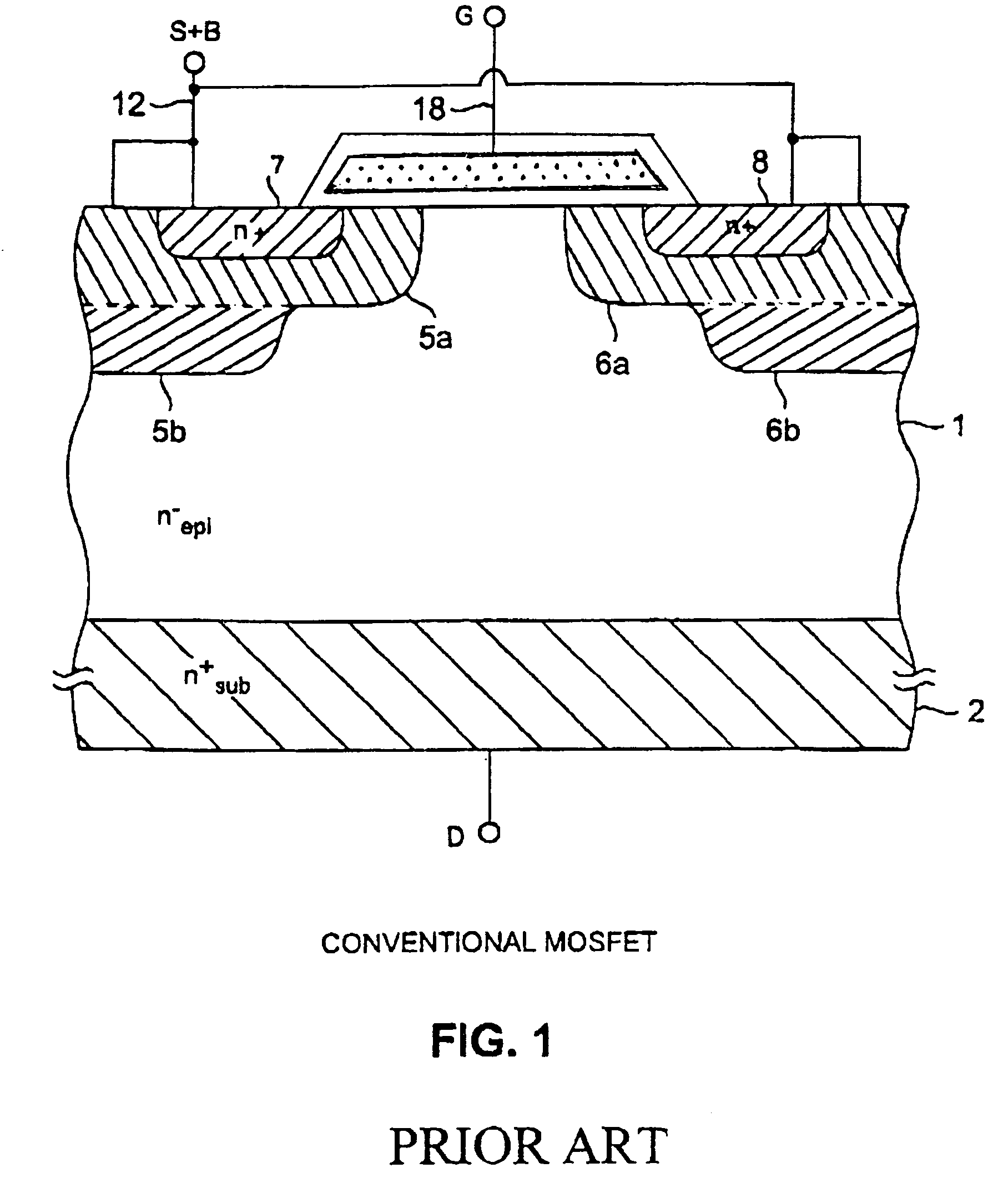

ActiveUS7002214B1Reduce capacitanceReduce junctionSolid-state devicesSemiconductor/solid-state device manufacturingDopantGround plane

A method of manufacture of a Super Steep Retrograde Well Field Effect Transistor device starts with an SOI layer formed on a substrate, e.g. a buried oxide layer. Thin the SOI layer to form an ultra-thin SOI layer. Form an isolation trench separating the SOI layer into N and P ground plane regions. Dope the N and P ground plane regions formed from the SOI layer with high levels of N-type and P-type dopant. Form semiconductor channel regions above the N and P ground plane regions. Form FET source and drain regions and gate electrode stacks above the channel regions. Optionally form a diffusion retarding layer between the SOI ground plane regions and the channel regions.

Owner:GLOBALFOUNDRIES US INC

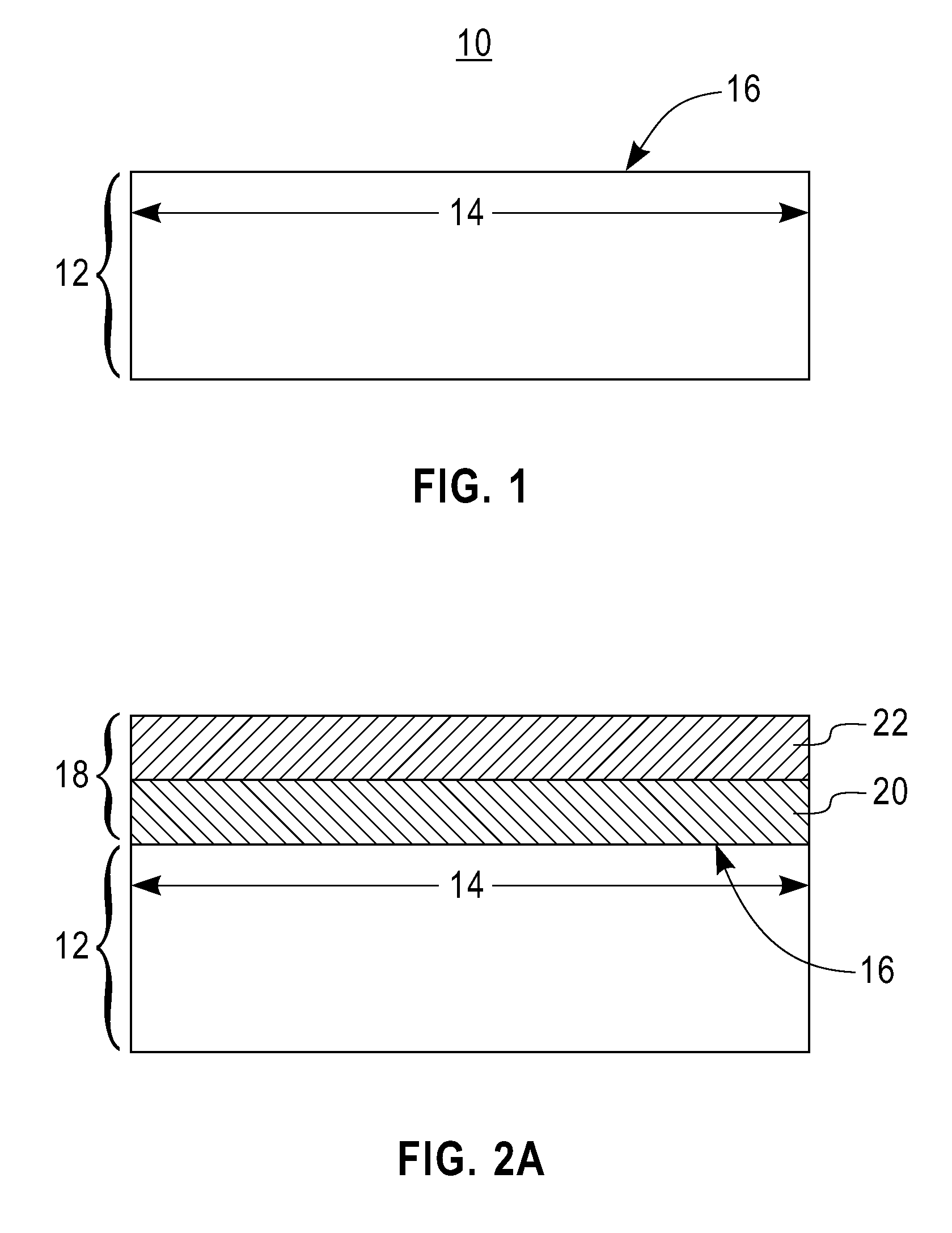

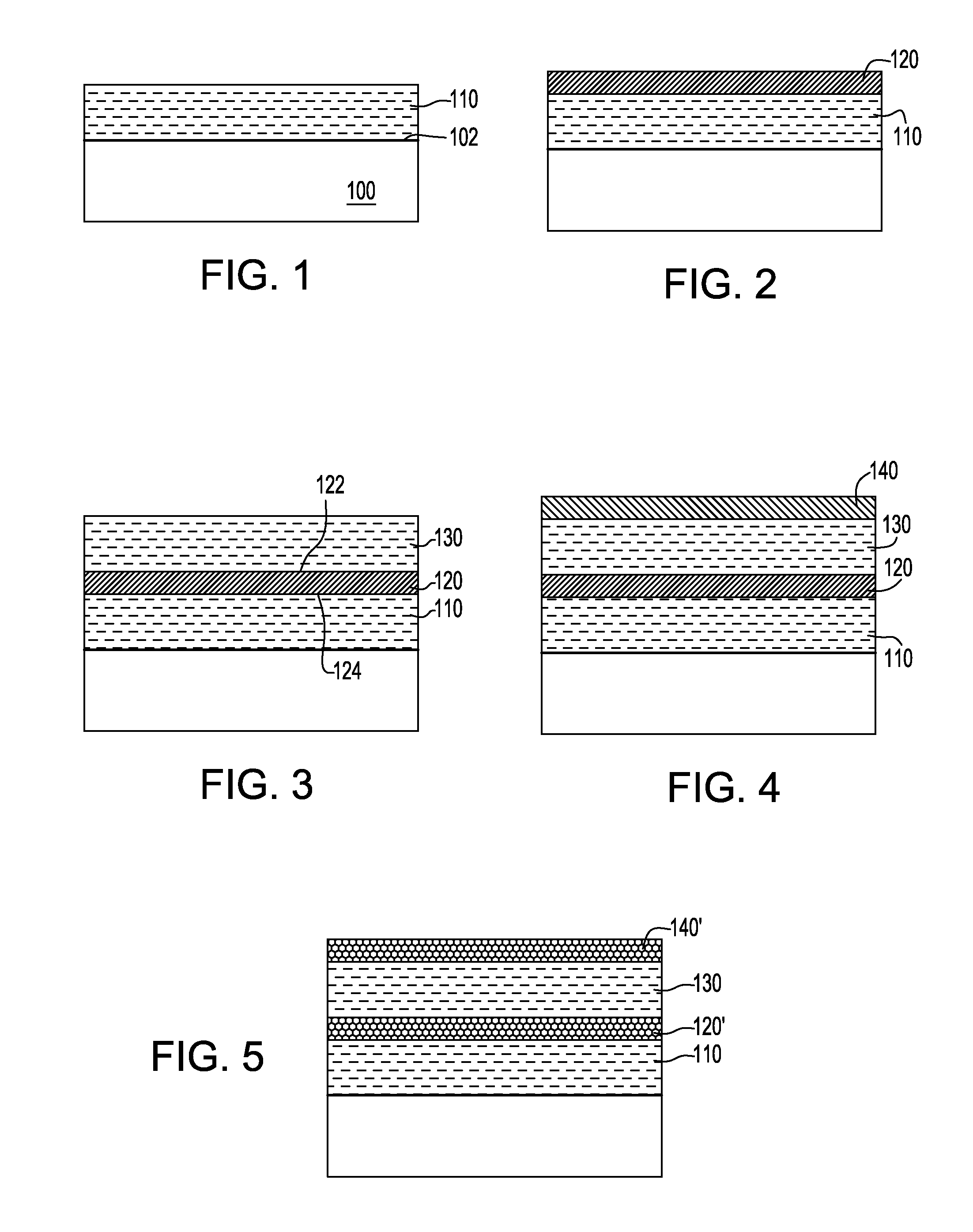

Formation of SOI by oxidation of silicon with engineered porosity gradient

InactiveUS7772096B2Semiconductor/solid-state device detailsSolid-state devicesPorositySingle crystal

A method is provided for making a silicon-on-insulator substrate. Such method can include epitaxially growing a highly p-type doped silicon-containing layer onto a major surface of an underlying semiconductor region of a substrate. Subsequently, a non-highly p-type doped silicon-containing layer may be epitaxially grown onto a major surface of the p-type highly-doped epitaxial layer to cover the highly p-type doped epitaxial layer. The overlying non-highly p-type doped epitaxial layer can have a dopant concentration substantially lower than the dopant concentration of the highly p-type doped epitaxial layer. The substrate can then be processed to form a buried oxide layer selectively by oxidizing at least portions of the highly p-type doped epitaxial layer covered by the non-highly p-type doped epitaxial layer, the buried oxide layer separating the overlying monocrystalline semiconductor layer from the underlying semiconductor region. Such processing can be performed while simultaneously annealing the non-highly p-type doped epitaxial layer.

Owner:GLOBALFOUNDRIES INC

Method for fabricating a type of trench mask ROM cell

A method for fabricating a type of Trench Mask ROM cell comprises steps including: providing a substrate doped lightly with p-type dopant, sequentially forming a pad oxide layer and a nitride layer on the substrate; etching back the pad oxide layer, the nitride layer and the substrate to form plural trenches; a gate oxide layer being formed on surfaces of each trench; then, implanting n+-type ions into the substrate beneath the pad oxide layer and between each two adjacent trenches; and, forming a polysilicon layer on the gate oxide and pad oxide; finally, implanting n+-type ions into the substrate beneath the gate oxide layer on bottoms of selected trenches. And, it is appreciated that the sequence of the formation of plural trenches and implanting n+-type ions into substrate between each trench can be reversed in the embodiment without affecting subsequent steps.

Owner:PROMOS TECH INC

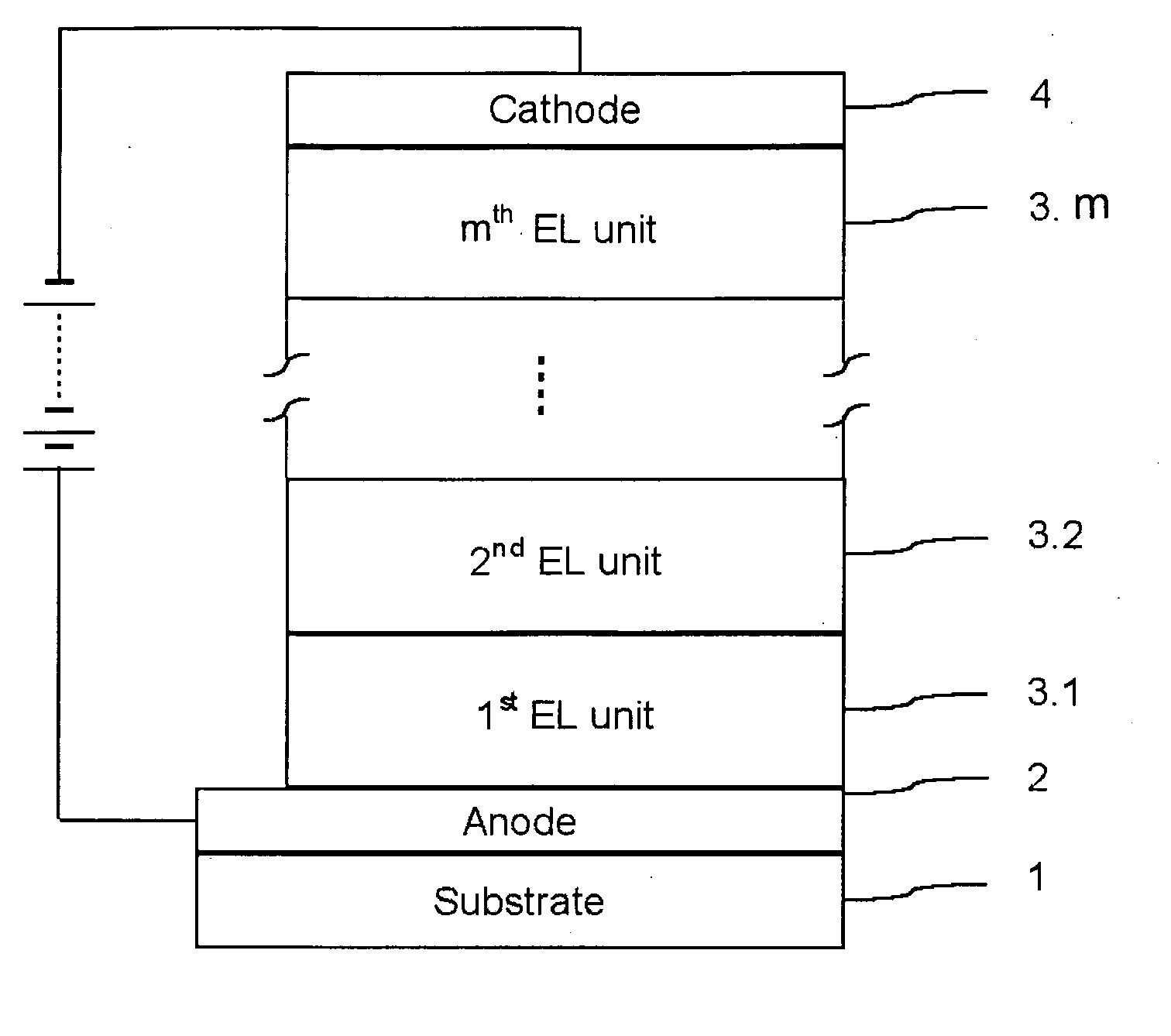

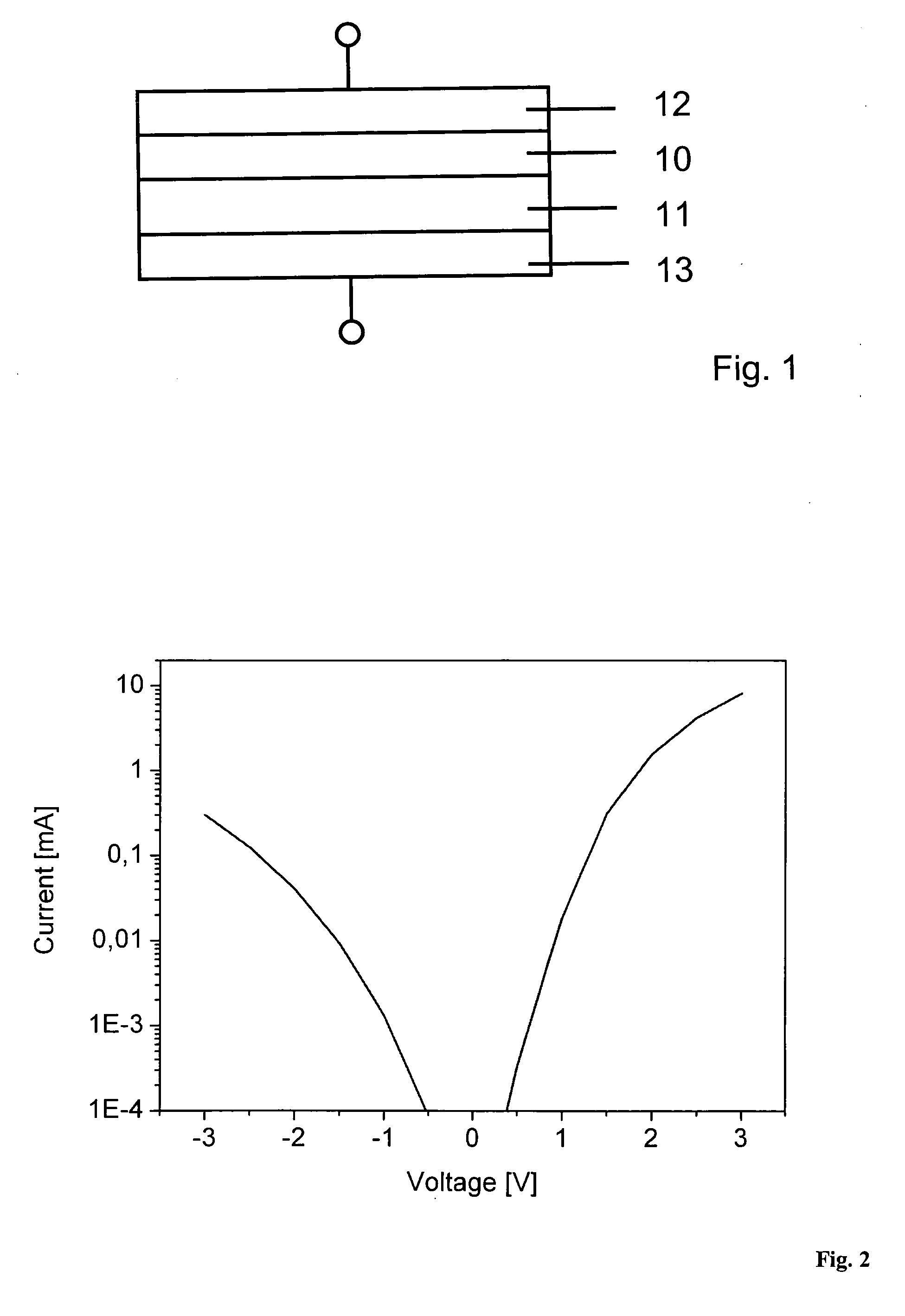

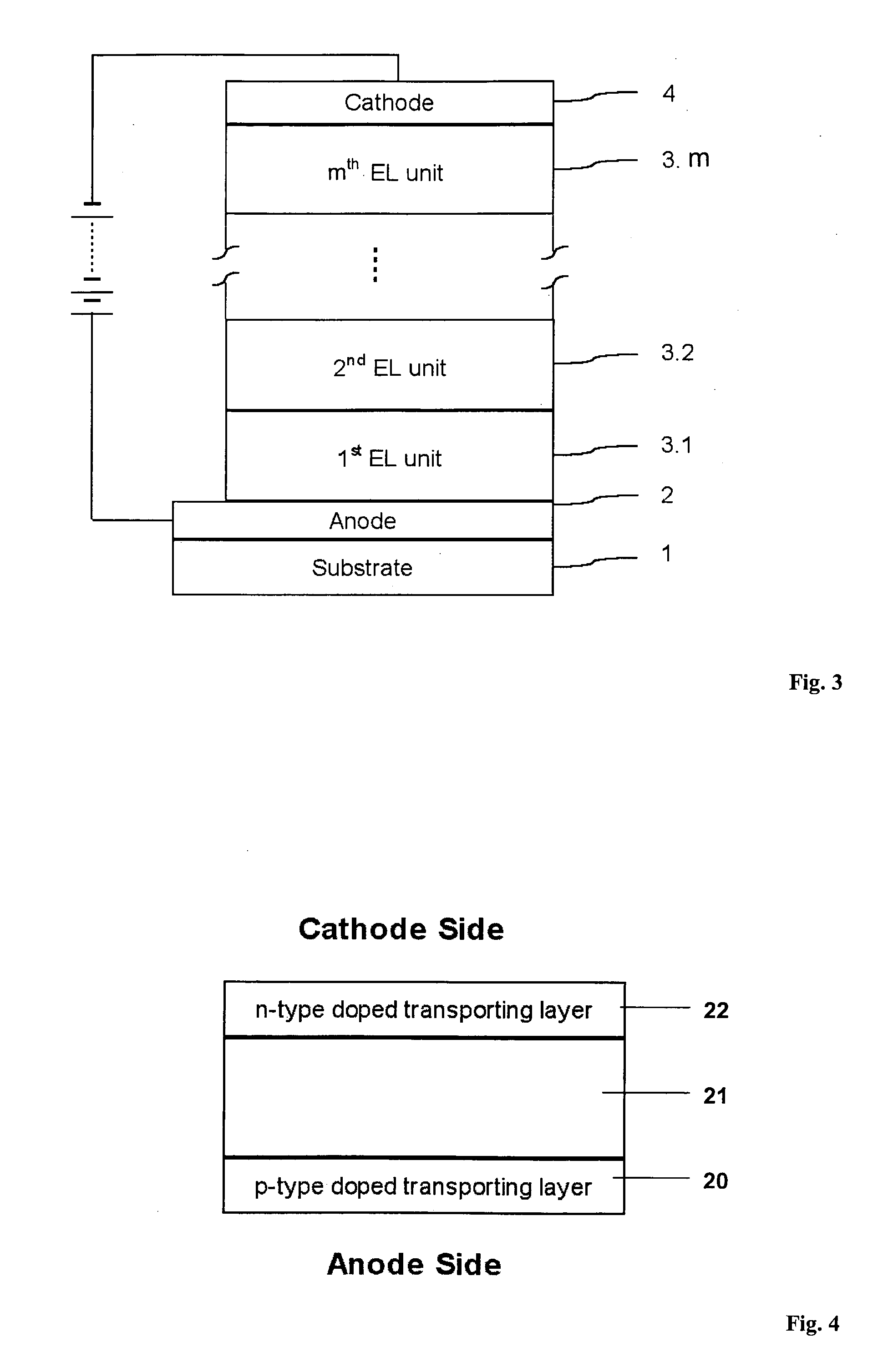

Electronic device with a layer structure of organic layers

ActiveUS20090045728A1Need long operating lifetimesTailoring of interface stabilityDischarge tube luminescnet screensLamp detailsDopantOrganic layer

The invention relates to an electronic device comprising a layer structure of organic layers, wherein said layer structure comprises a p-n-junction between an n-type doped organic layer provided as an organic matrix material doped with an n-type dopant and a p-type doped organic layer provided as a further organic matrix material doped with a p-type dopant, and wherein the n-type dopant and the p-type dopant both are molecular dopants, a reduction potential of the p-type dopant is equal or larger than about 0 V vs. Fc / Fc+, and an oxidation potential of the n-type dopant is equal or smaller than about −1.5 V vs. Fc / Fc+.

Owner:NOVALED AG

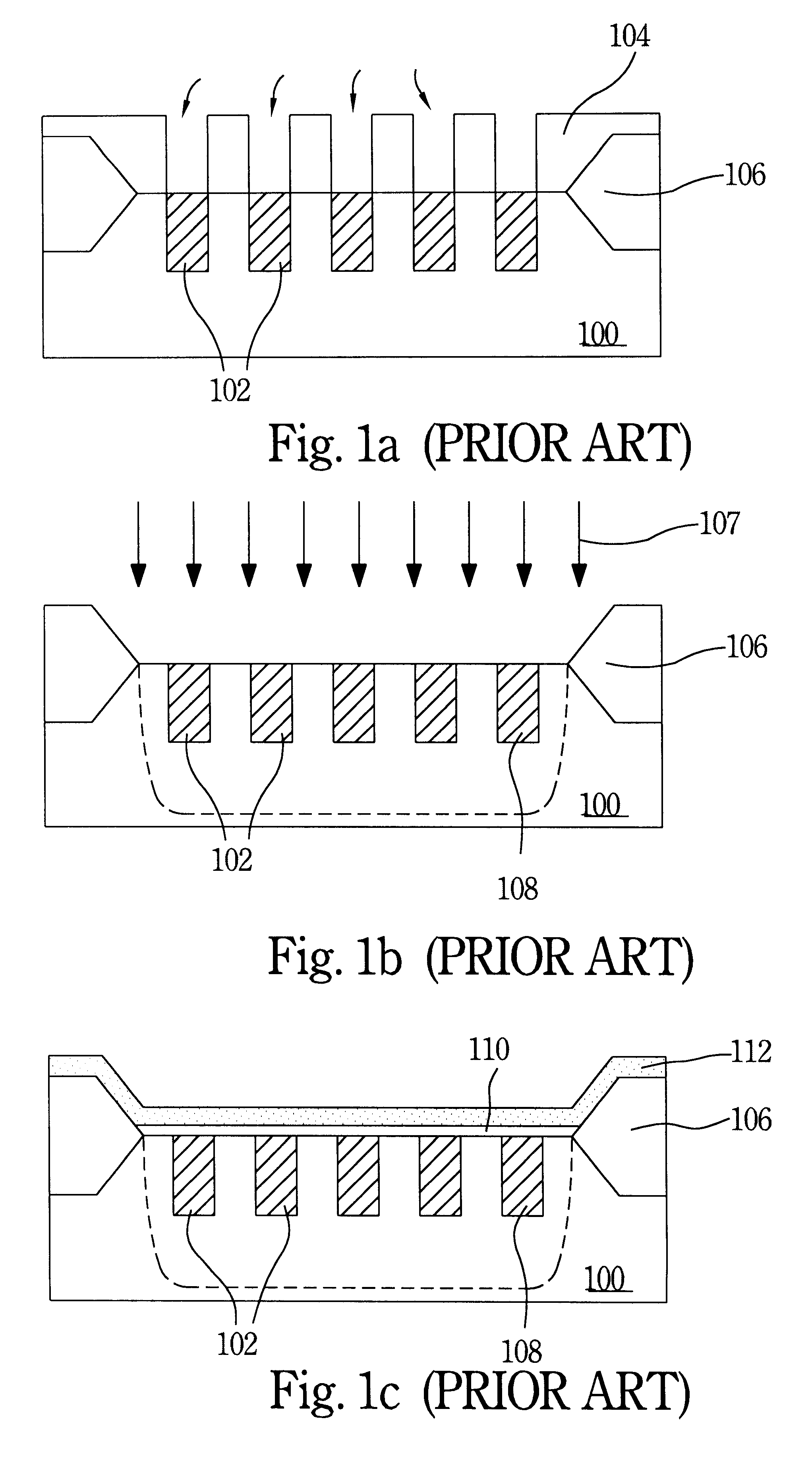

Ion implantation device and a method of semiconductor manufacturing by the implantation of boron hydride cluster ions

InactiveUS20060097193A1Improve productivityLow costTransistorSemiconductor/solid-state device manufacturingMolecular clusterDevice material

An ion implantation device and a method of manufacturing a semiconductor device is described, wherein ionized boron hydride molecular clusters are implanted to form P-type transistor structures. For example, in the fabrication of Complementary Metal-Oxide Semiconductor (CMOS) devices, the clusters are implanted to provide P-type doping for Source and Drain structures and for Polygates; these doping steps are critical to the formation of PMOS transistors. The molecular cluster ions have the chemical form BnHx+ and BnHx− where 10

Owner:SEMEQUIP

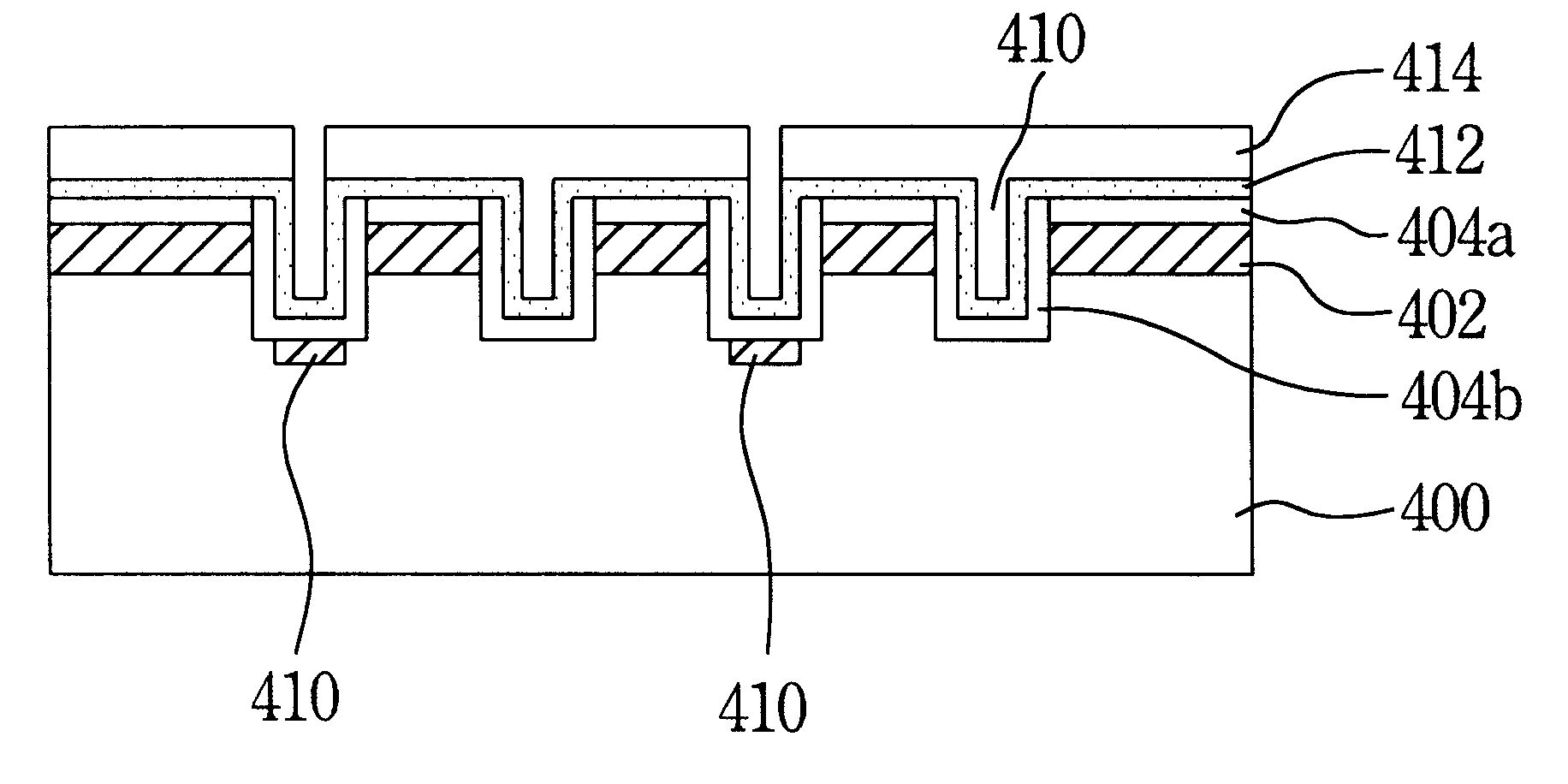

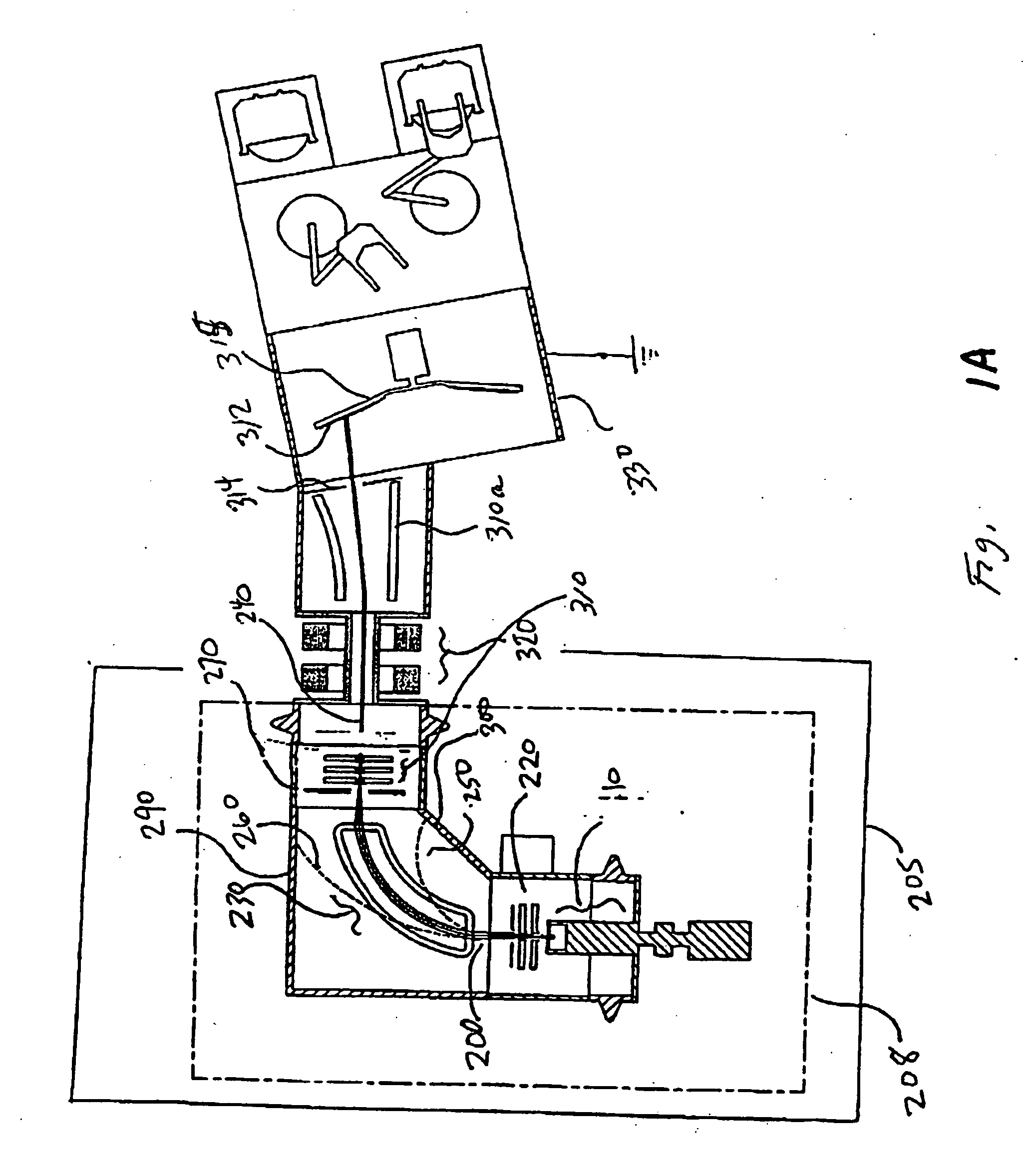

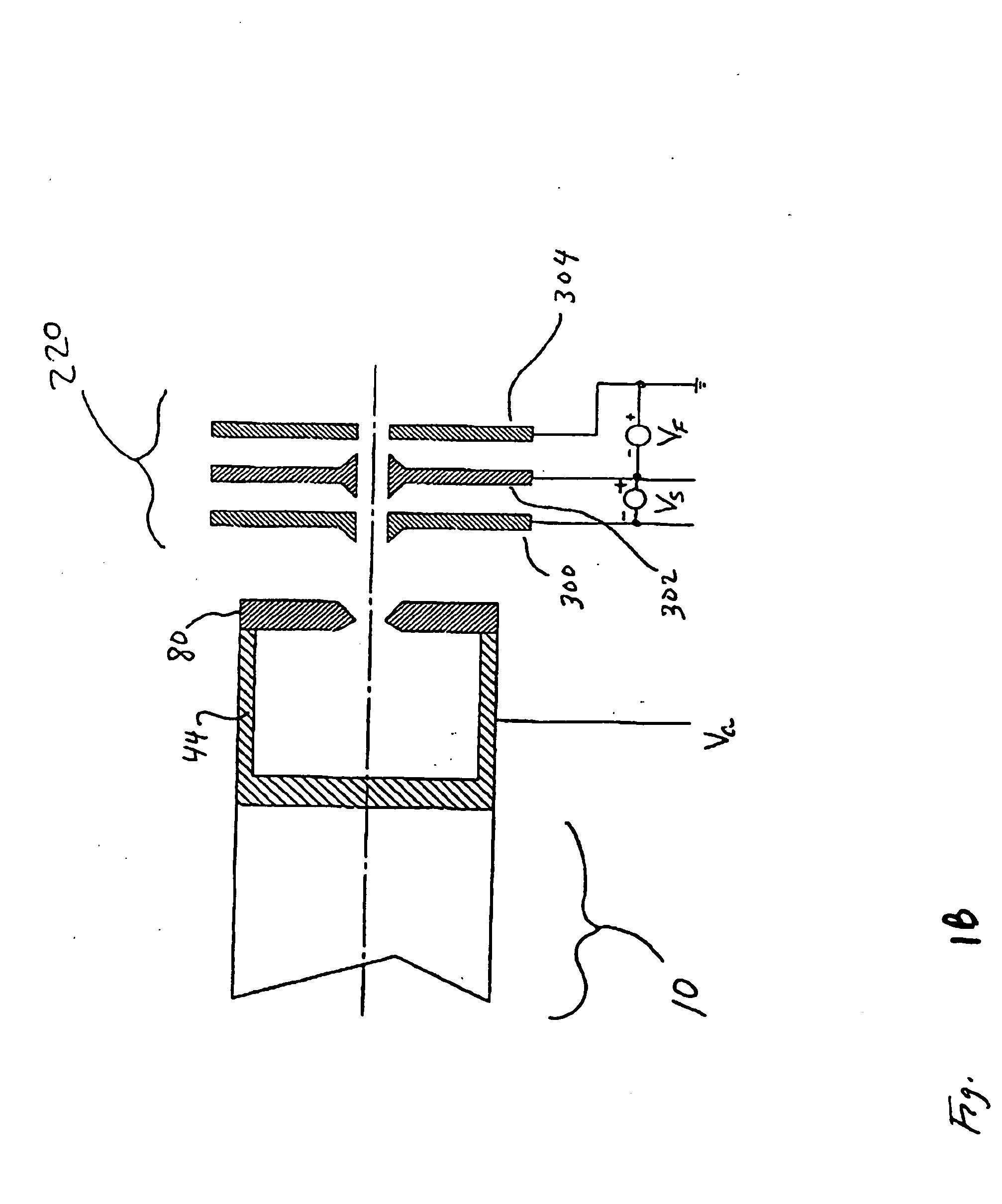

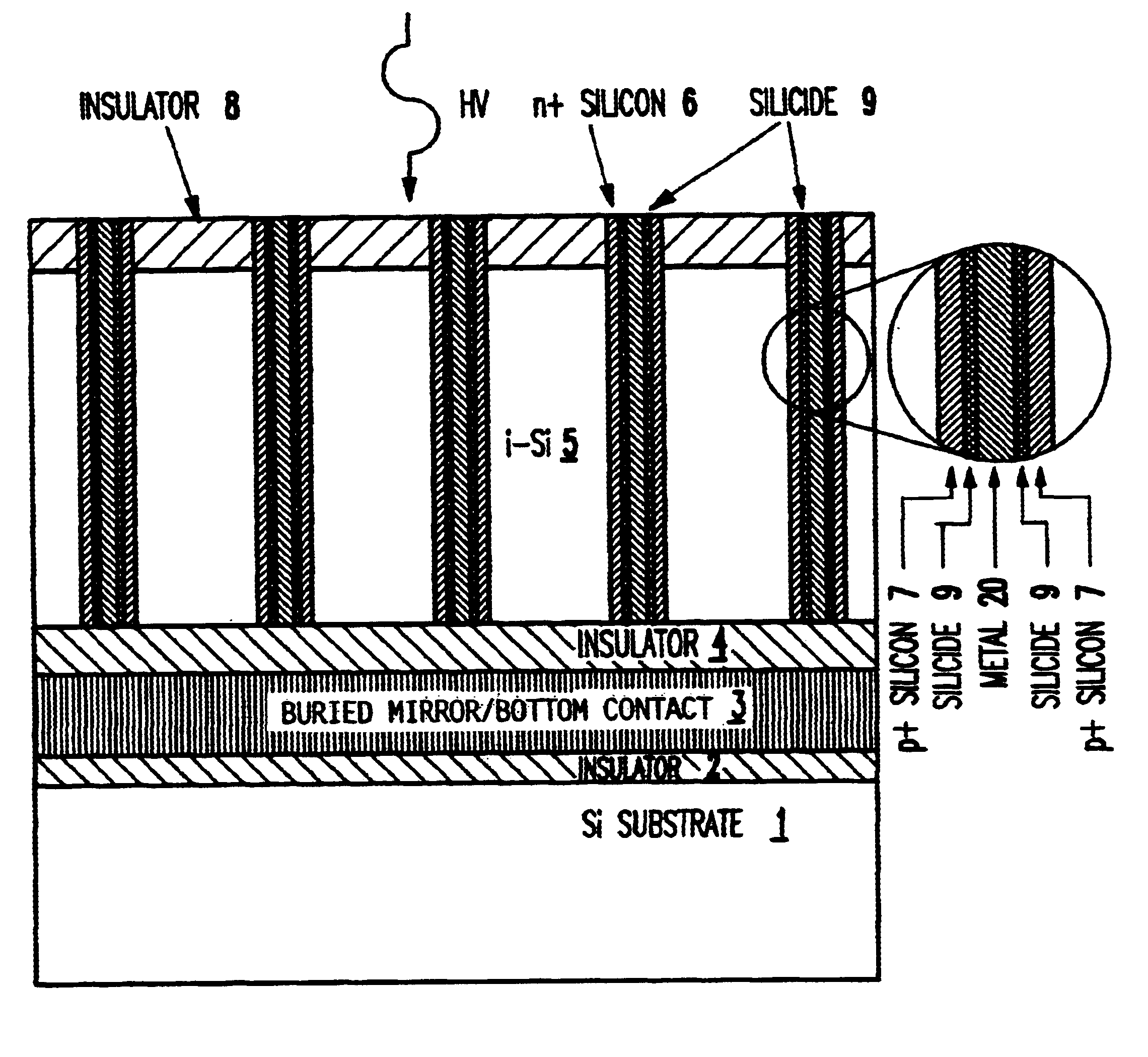

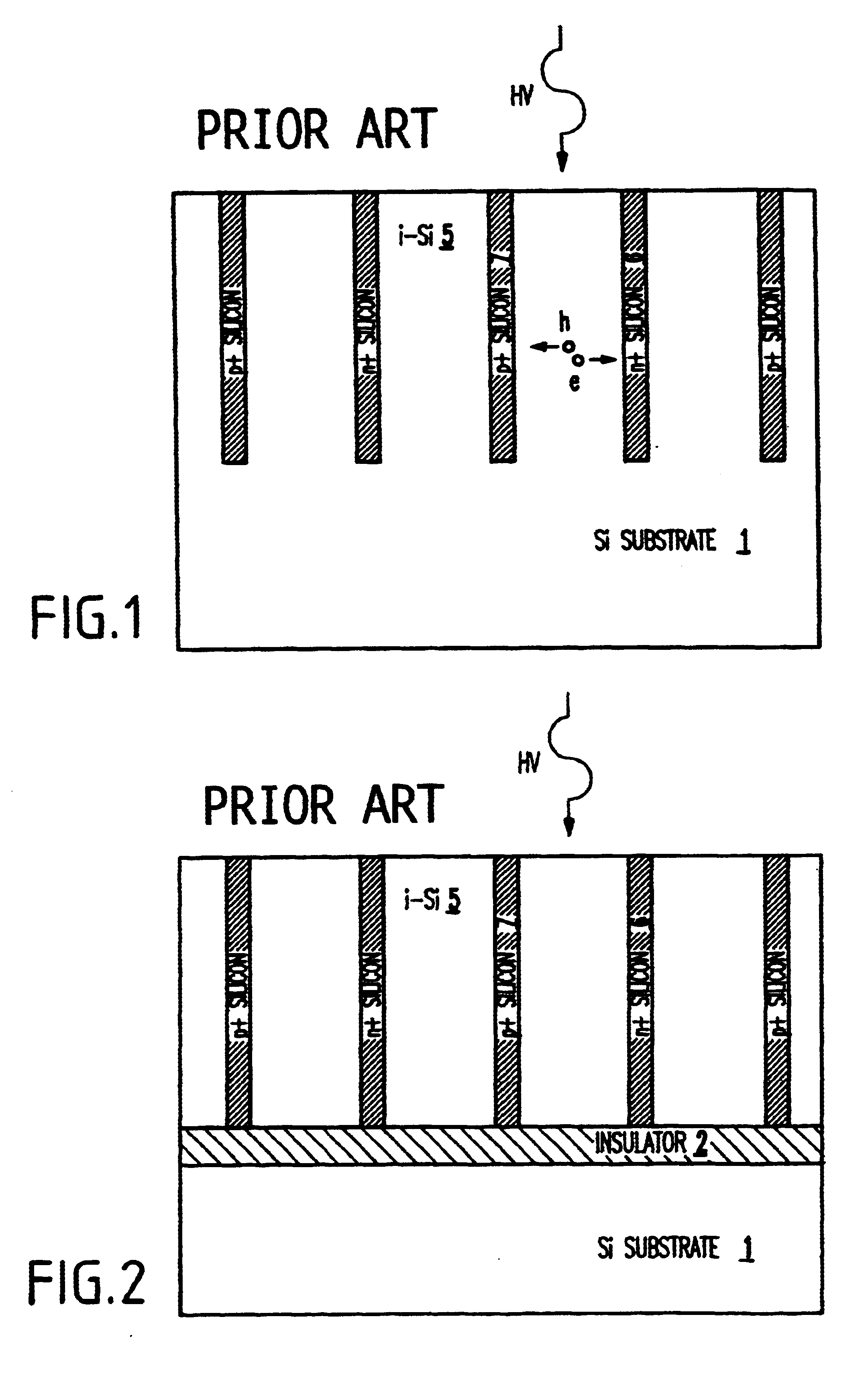

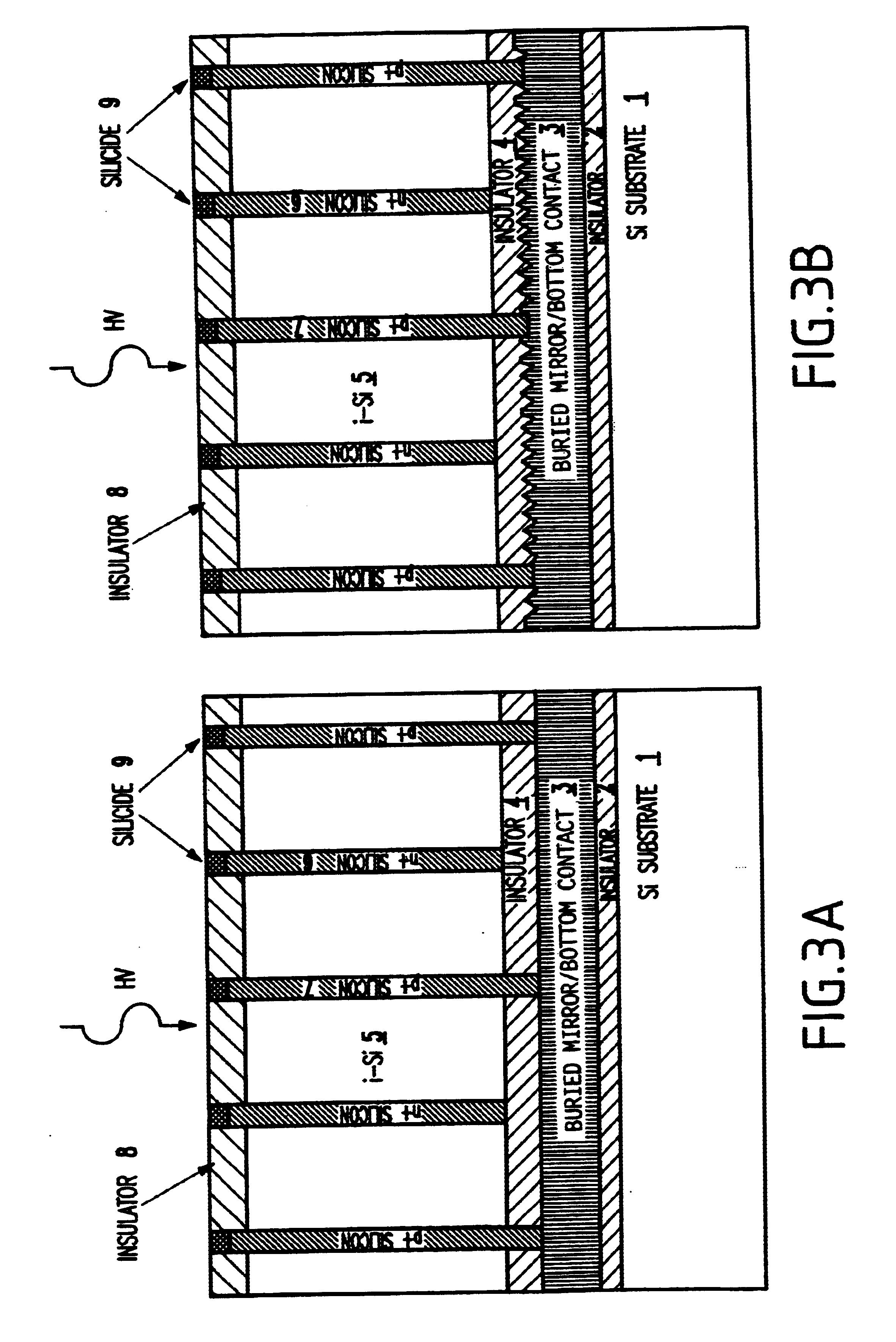

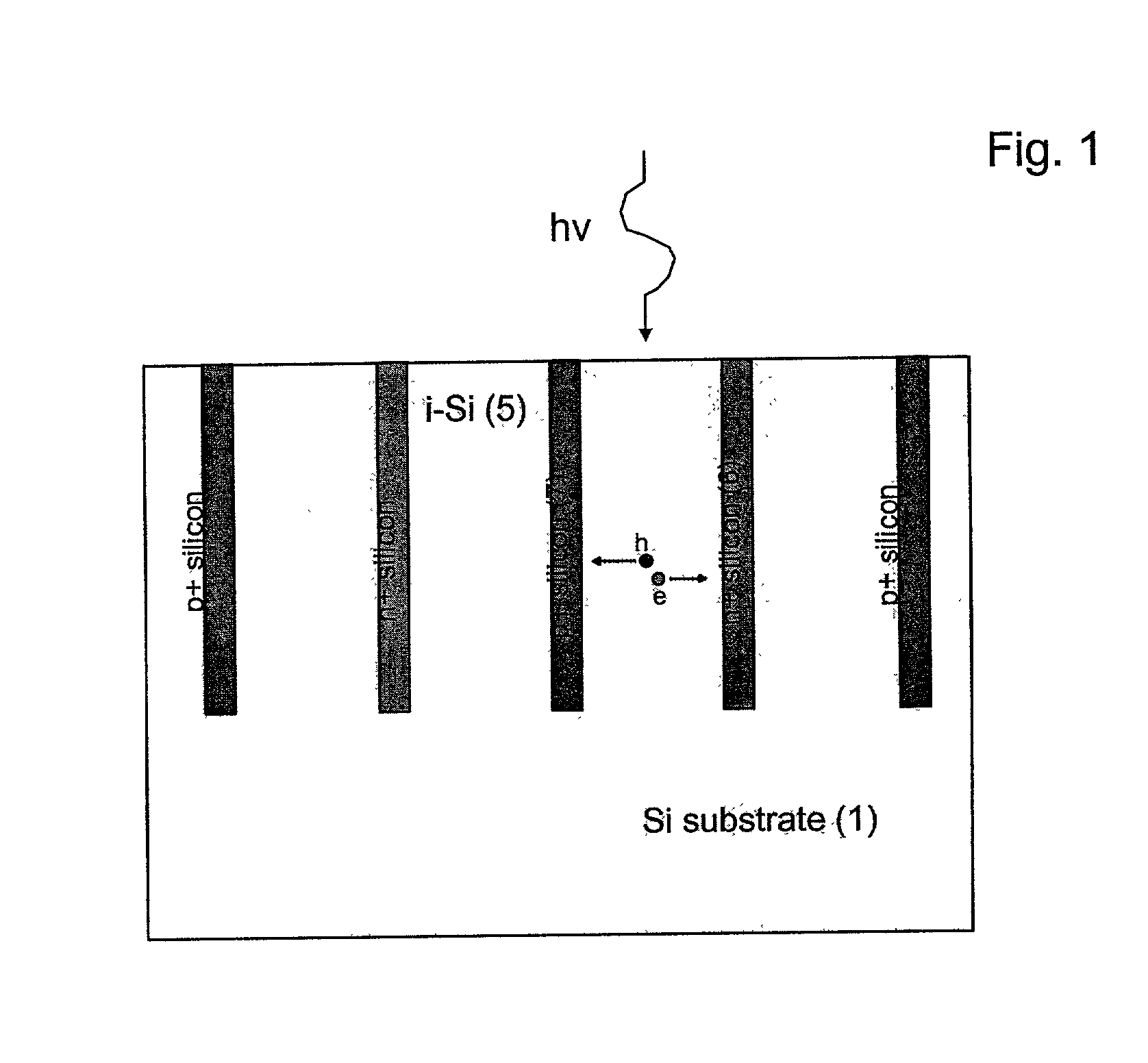

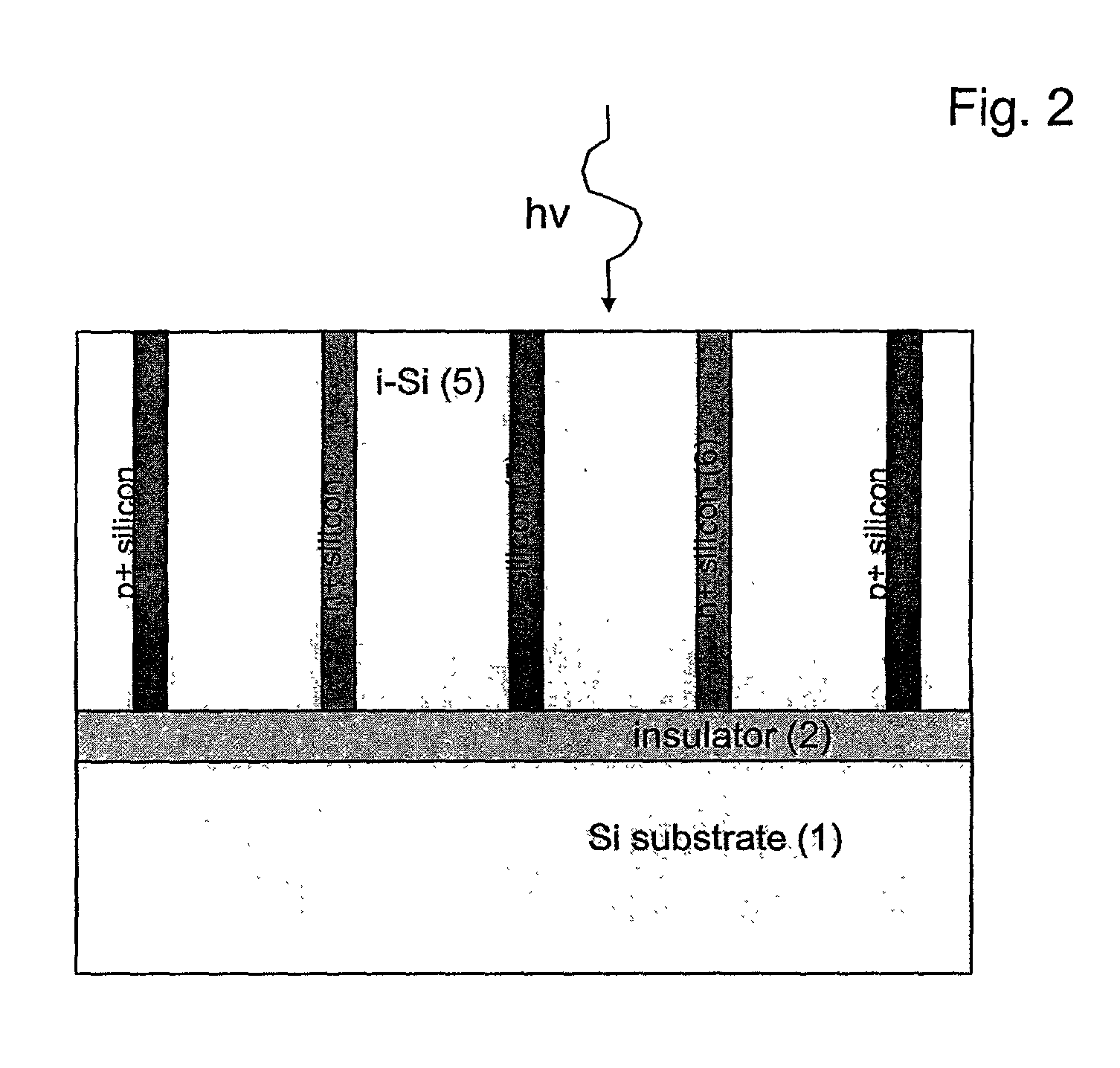

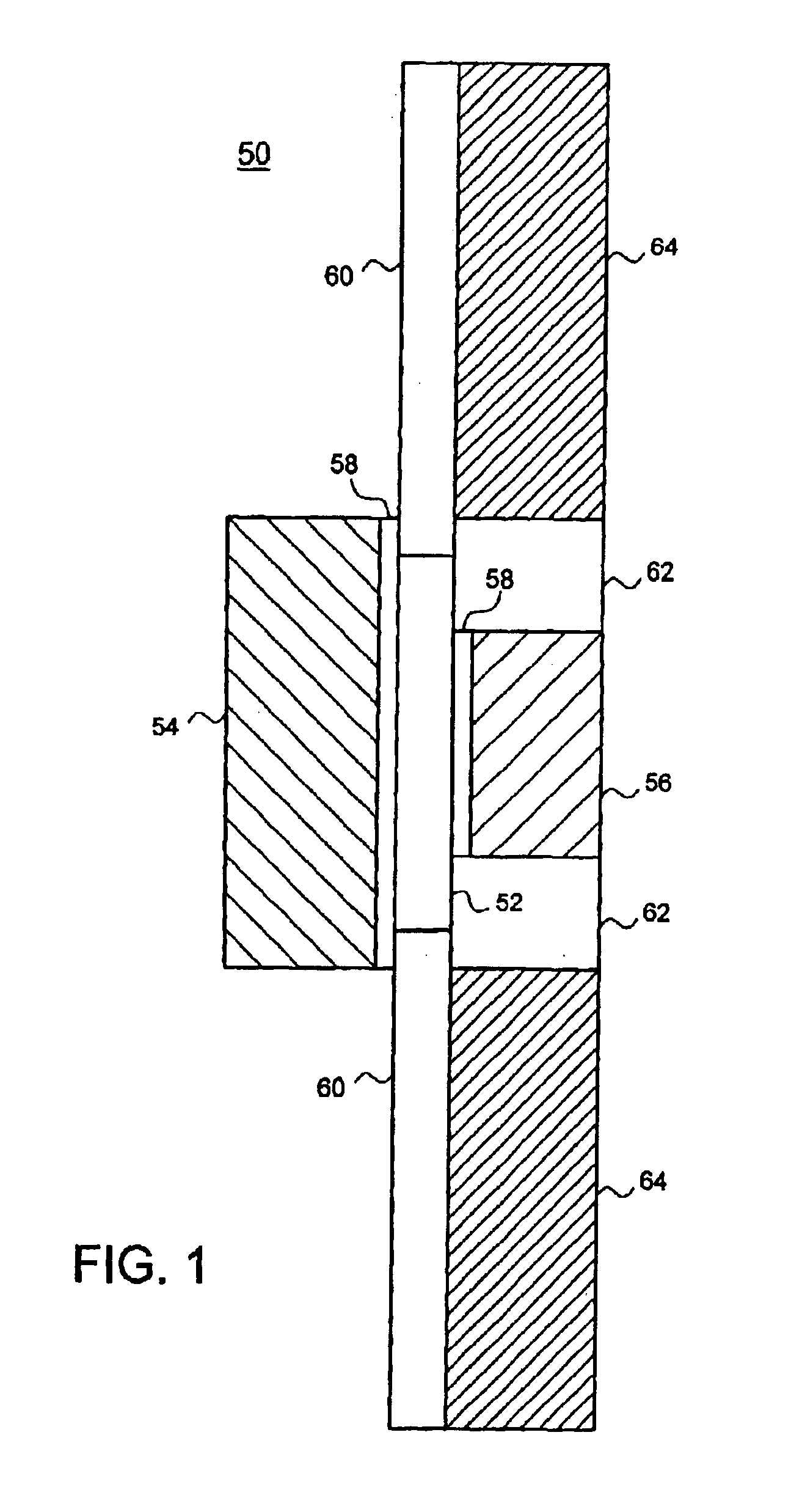

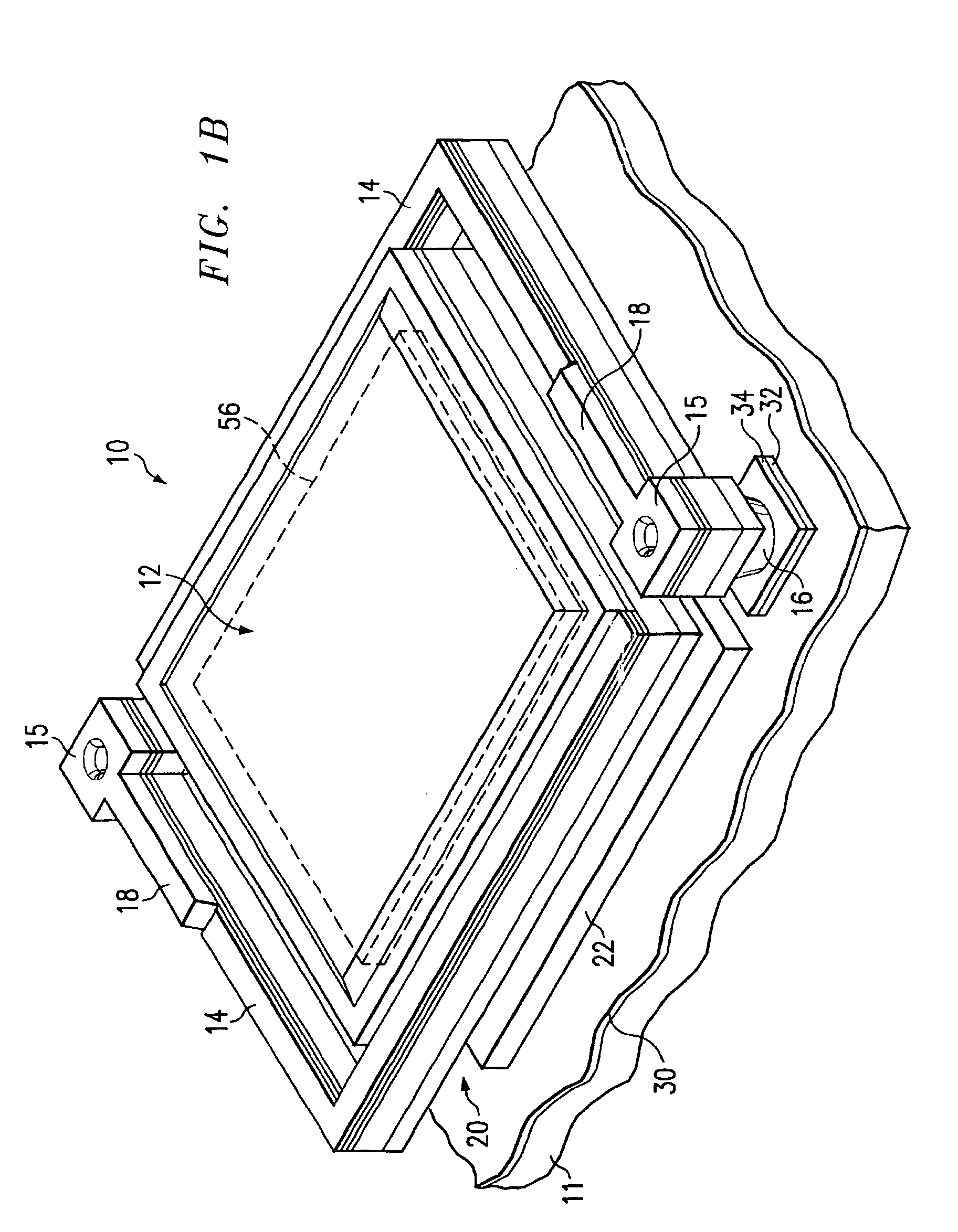

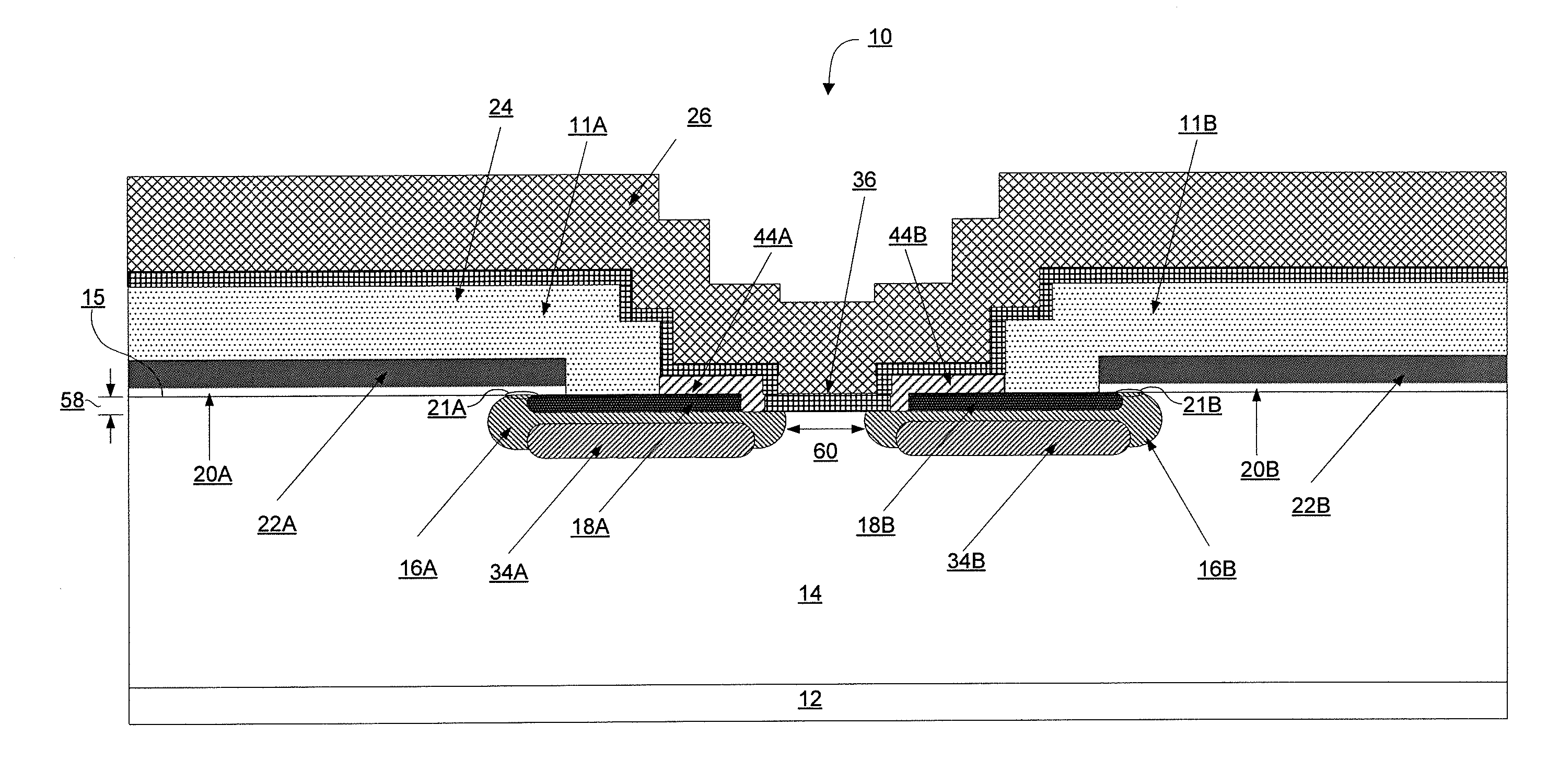

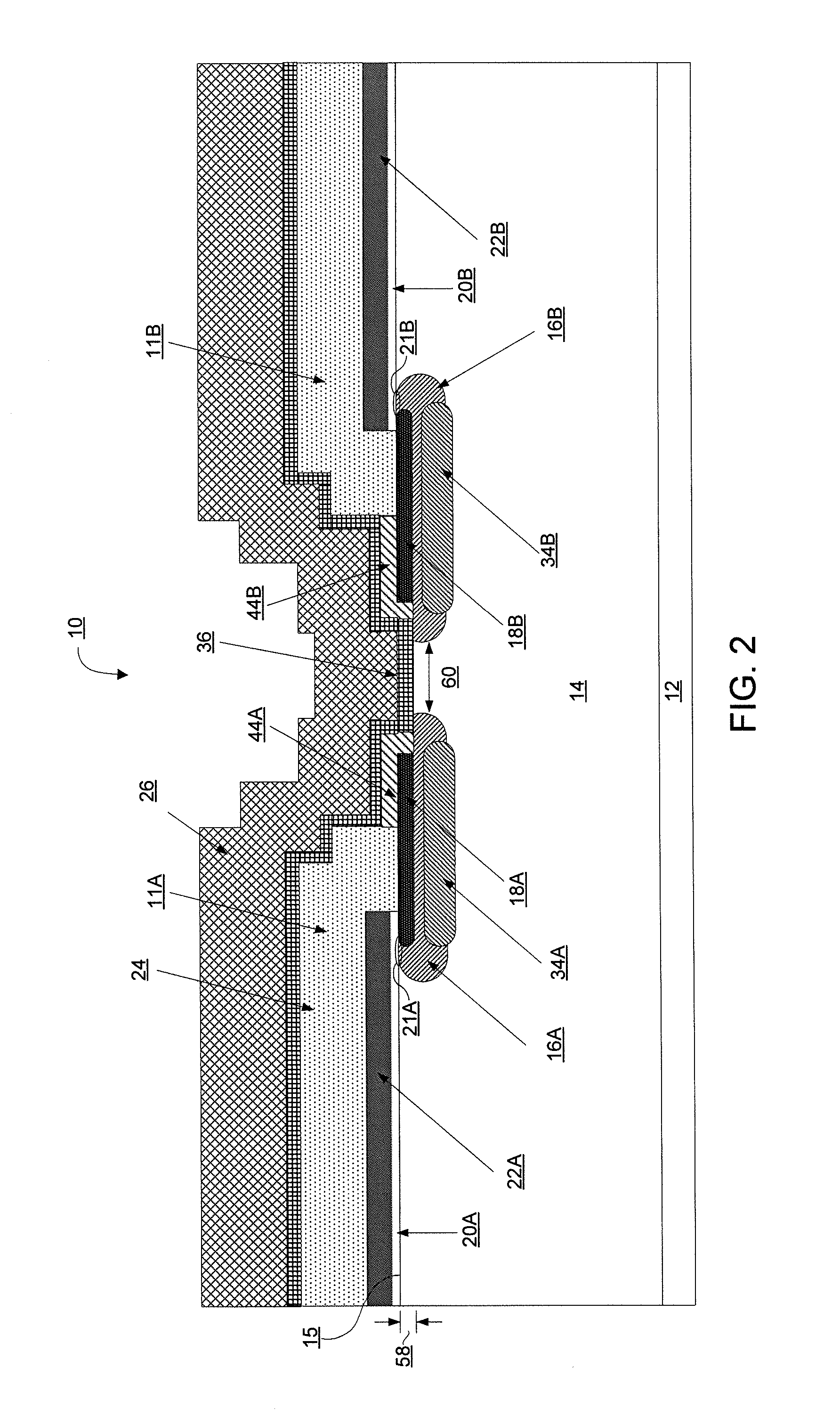

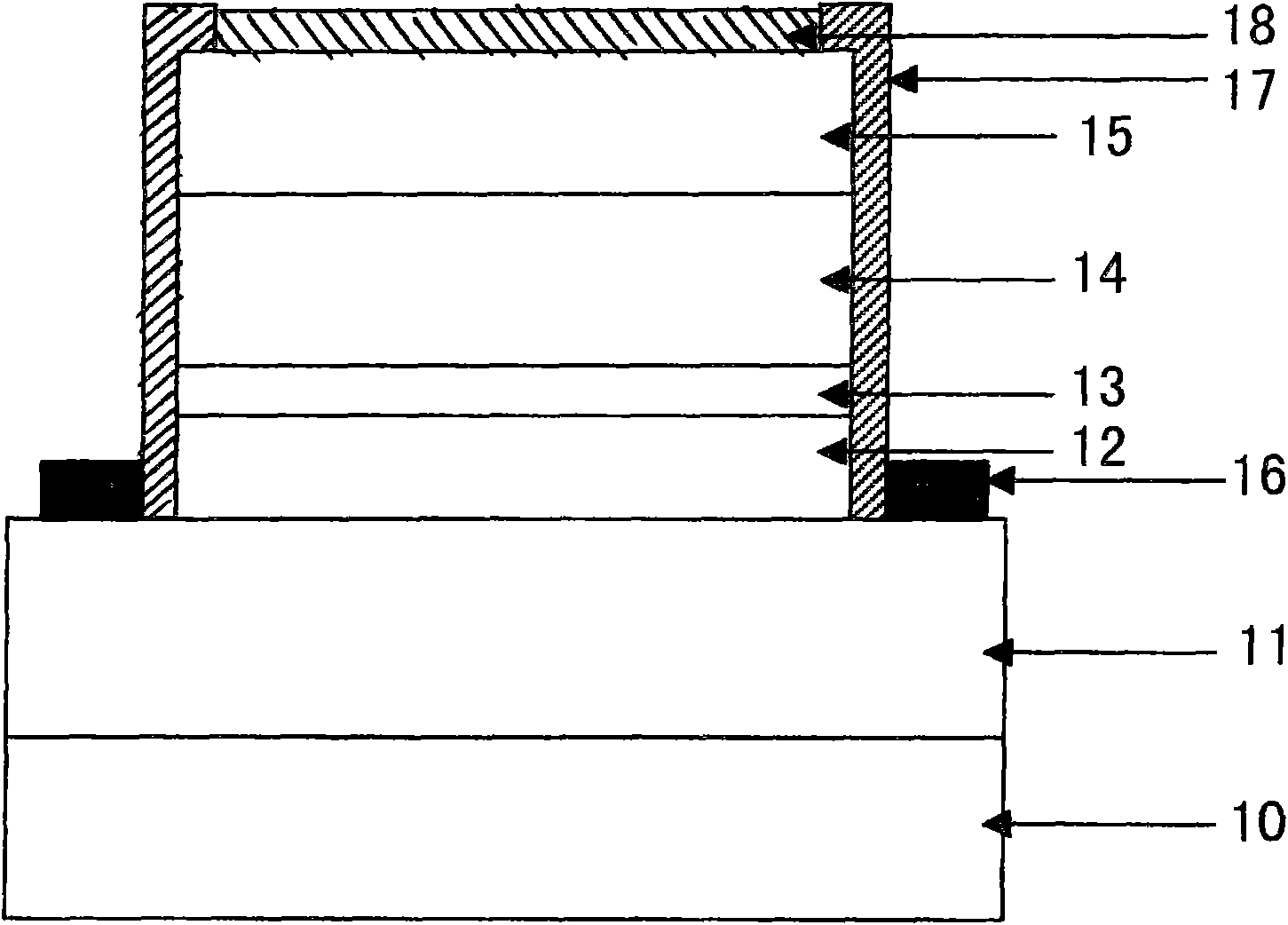

Semiconductor-on-insulator lateral p-i-n photodetector with a reflecting mirror and backside contact and method for forming the same

InactiveUS6667528B2Final product manufactureSolid-state devicesPhotovoltaic detectorsElectrical conductor

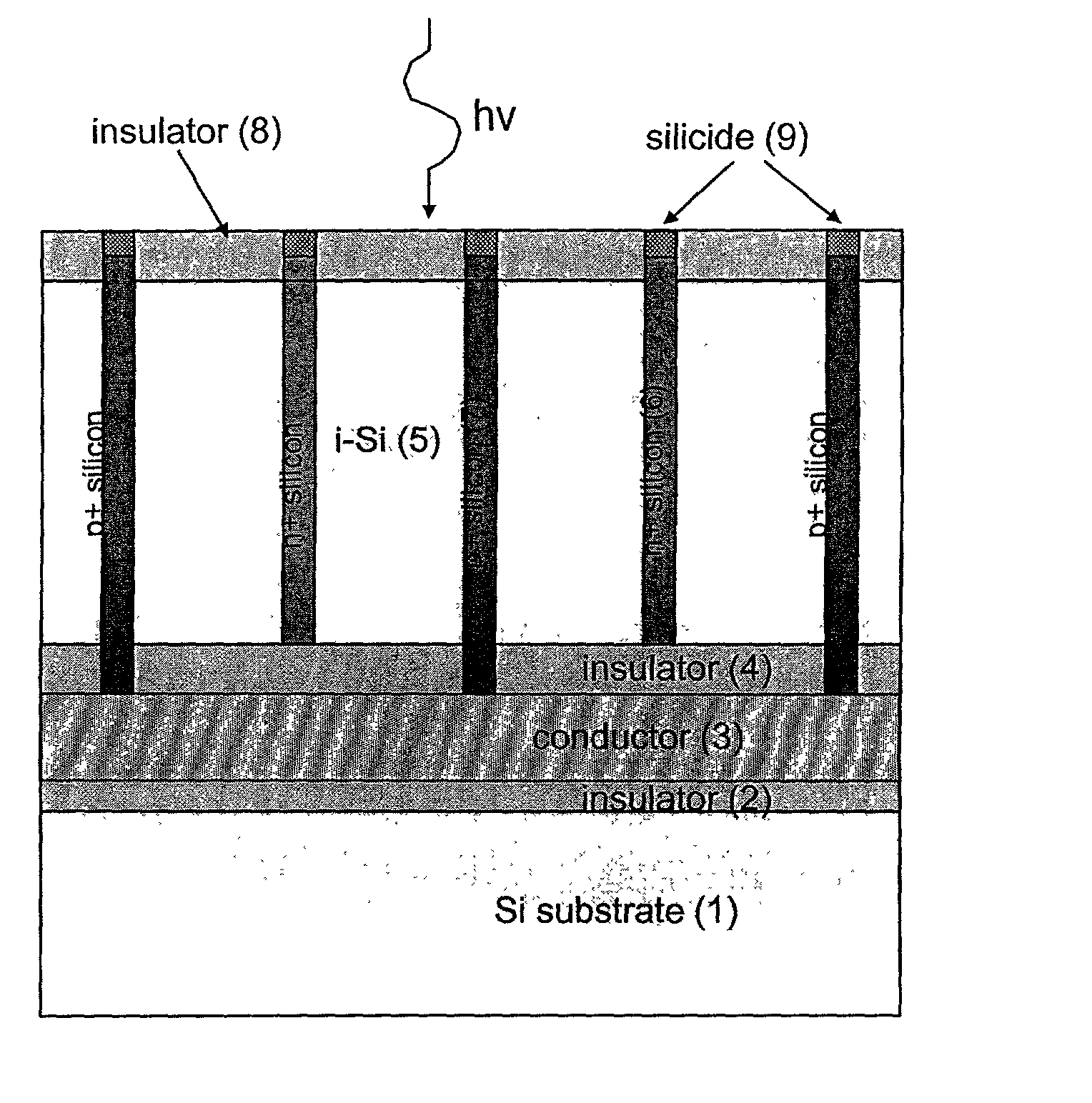

A photodetector (and method for producing the same) includes a semiconductor substrate, a buried insulator formed on the substrate, a buried mirror formed on the buried insulator, a semiconductor-on-insulator (SOI) layer formed on the conductor, alternating n-type and p-type doped fingers formed in the semiconductor-on-insulator layer, and a backside contact to one of the p-type doped fingers and the n-type doped fingers.

Owner:GLOBALFOUNDRIES US INC

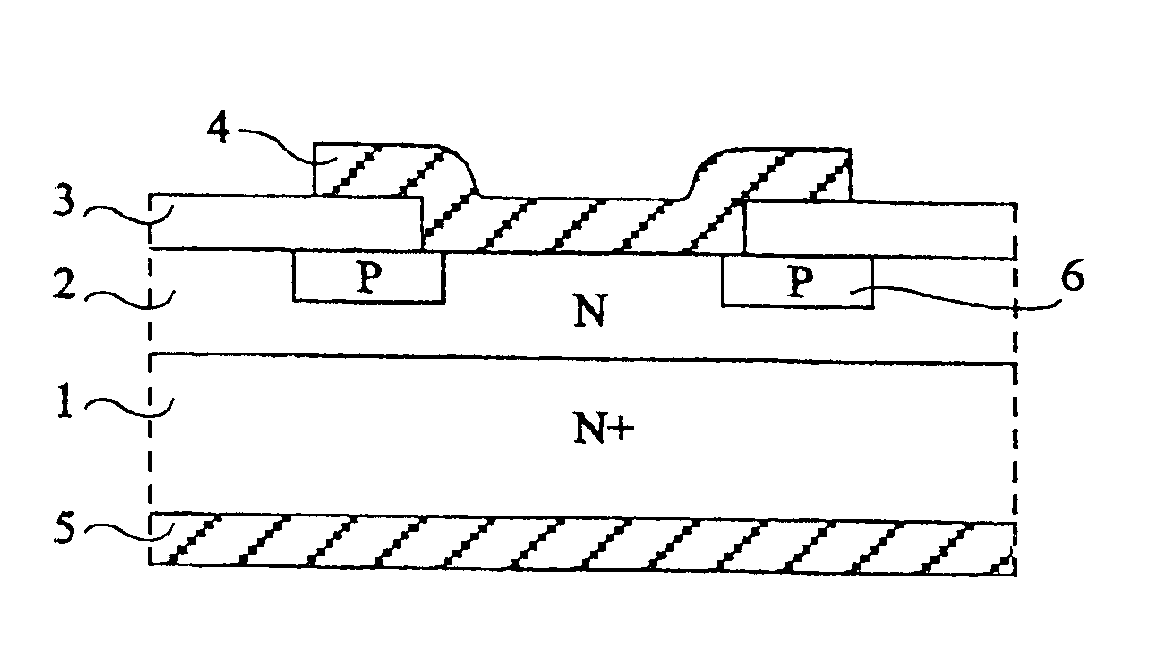

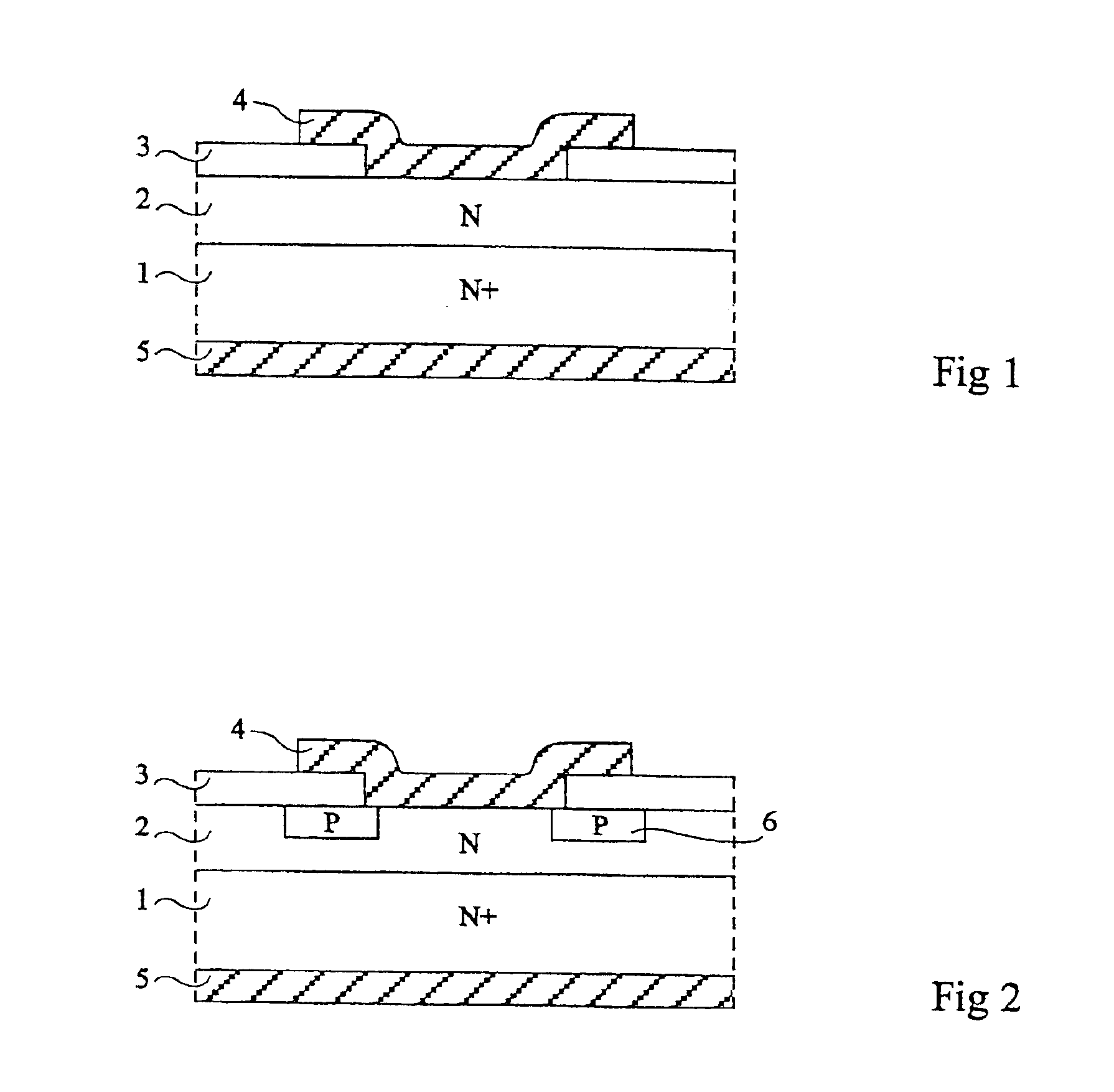

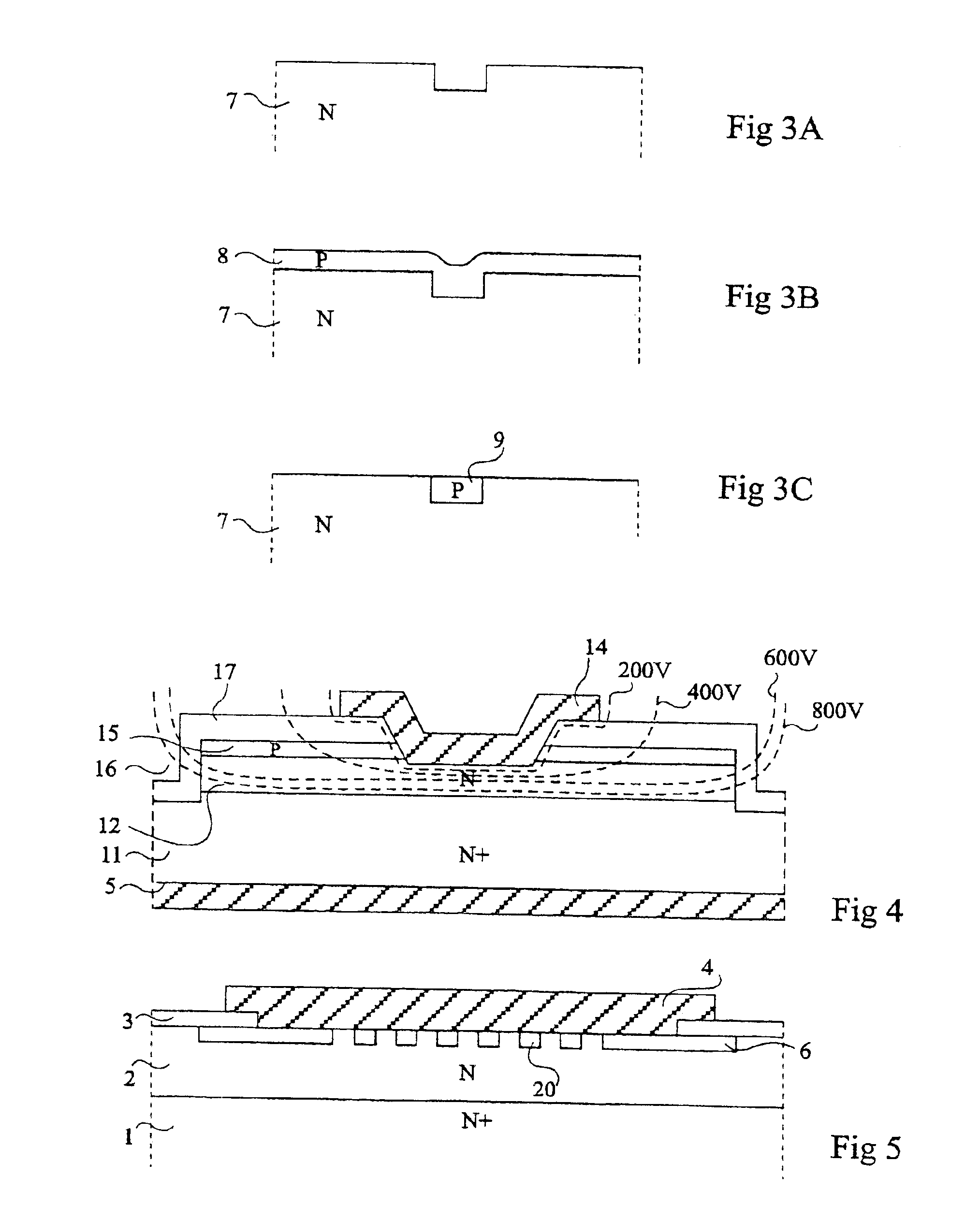

Method for producing a schottky diode in silicon carbide

InactiveUS6897133B2Semiconductor/solid-state device manufacturingSemiconductor devicesSchottky barrierCarbide

The invention concerns a method for making a vertical Schottky diode on a highly doped N-type silicon carbide substrate (1), comprising steps which consist in forming an N-type lightly doped epitaxial layer (2); etching out a peripheral trench at the active zone of the diode; forming a type P doped epitaxial layer; carrying out a planarization process so that a ring (6) of the P type epitaxial layer remains in the trench; forming an insulating layer (3) on the outer periphery of the component, said insulating layer partly covering said ring; and depositing a metal (4) capable of forming a Schottky barrier with the N type epitaxial layer.

Owner:STMICROELECTRONICS SRL

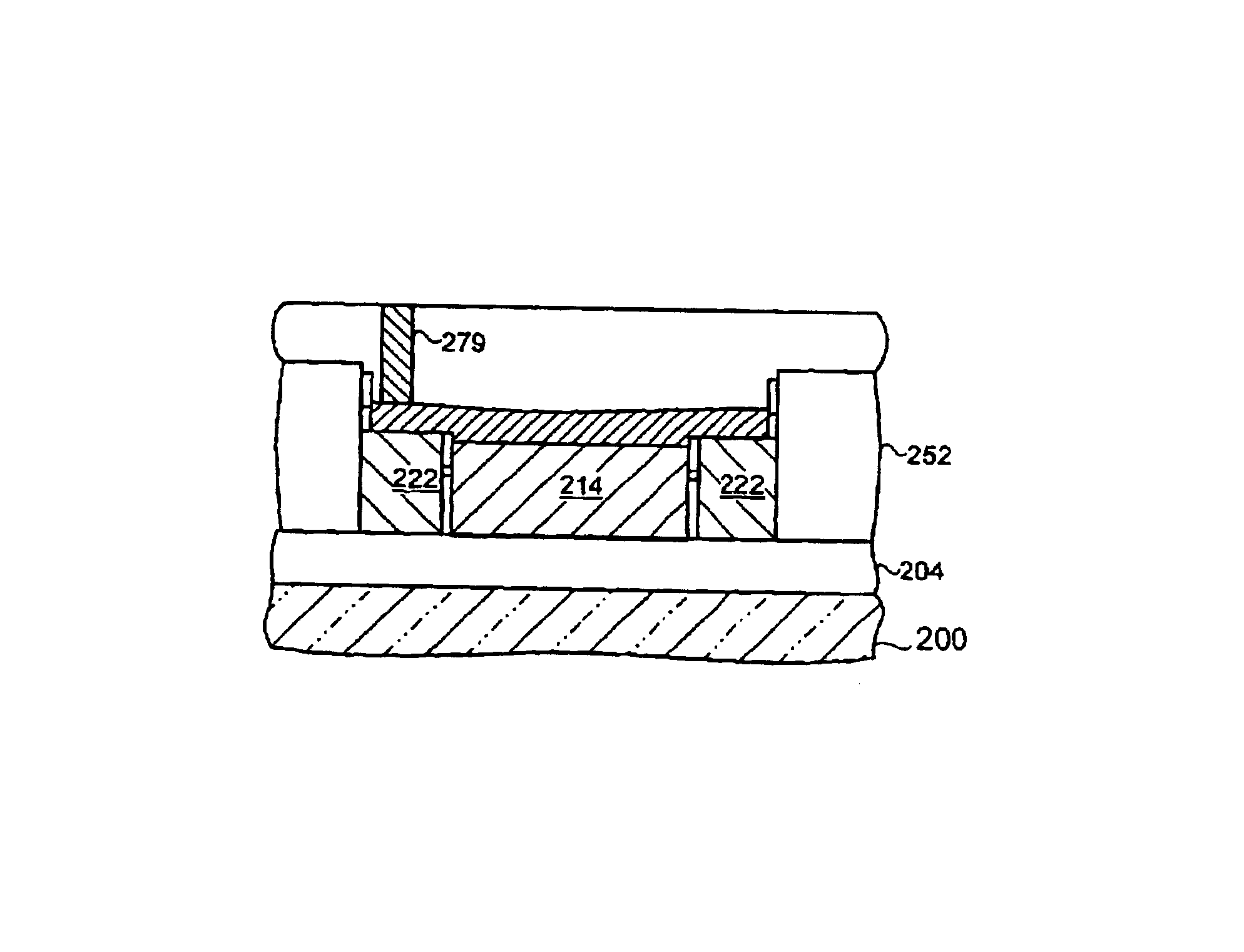

High mobility monolithic p-i-n diodes

InactiveUS20110136327A1Reduce interfaceHigh electron mobilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingHigh current densityDopant

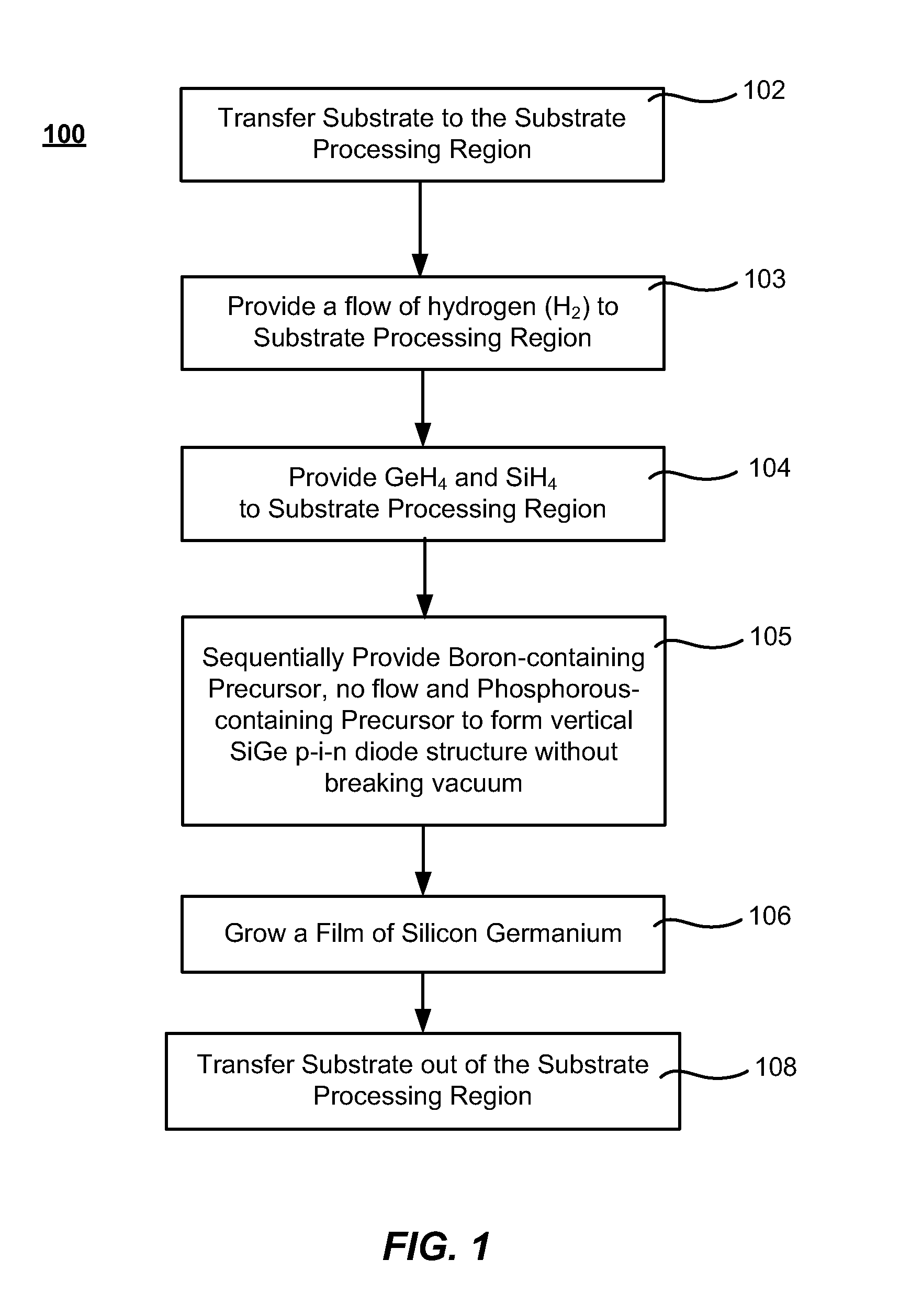

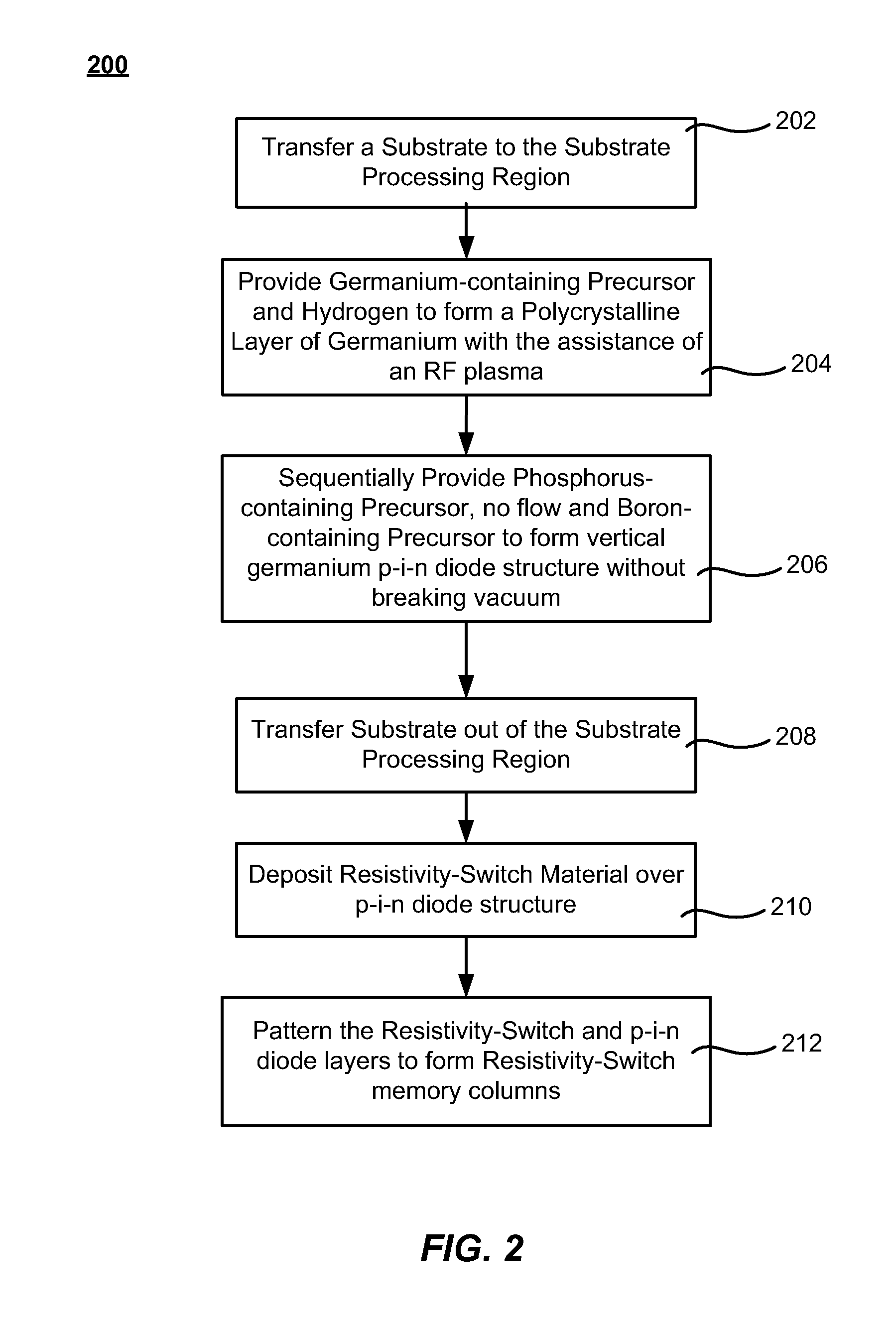

Methods of forming high-current density vertical p-i-n diodes on a substrate are described. The methods include the steps of concurrently combining a group-IV-element-containing precursor with a sequential exposure to an n-type dopant precursor and a p-type dopant precursor in either order. An intrinsic layer is deposited between the n-type and p-type layers by reducing or eliminating the flow of the dopant precursors while flowing the group-IV-element-containing precursor. The substrate may reside in the same processing chamber during the deposition of each of the n-type layer, intrinsic layer and p-type layer and the substrate is not exposed to atmosphere between the depositions of adjacent layers.

Owner:APPLIED MATERIALS INC

Semiconductor-on-insulator lateral p-i-n photodetector with a reflecting mirror and backside contact and method for forming the same

InactiveUS20030122210A1Final product manufactureSolid-state devicesPhotovoltaic detectorsElectrical conductor

A photodetector (and method for producing the same) includes a semiconductor substrate, a buried insulator formed on the substrate, a buried mirror formed on the buried insulator, a semiconductor-on-insulator (SOI) layer formed on the conductor, alternating n-type and p-type doped fingers formed in the semiconductor-on-insulator layer, and a backside contact to one of the p-type doped fingers and the n-type doped fingers.

Owner:GLOBALFOUNDRIES US INC

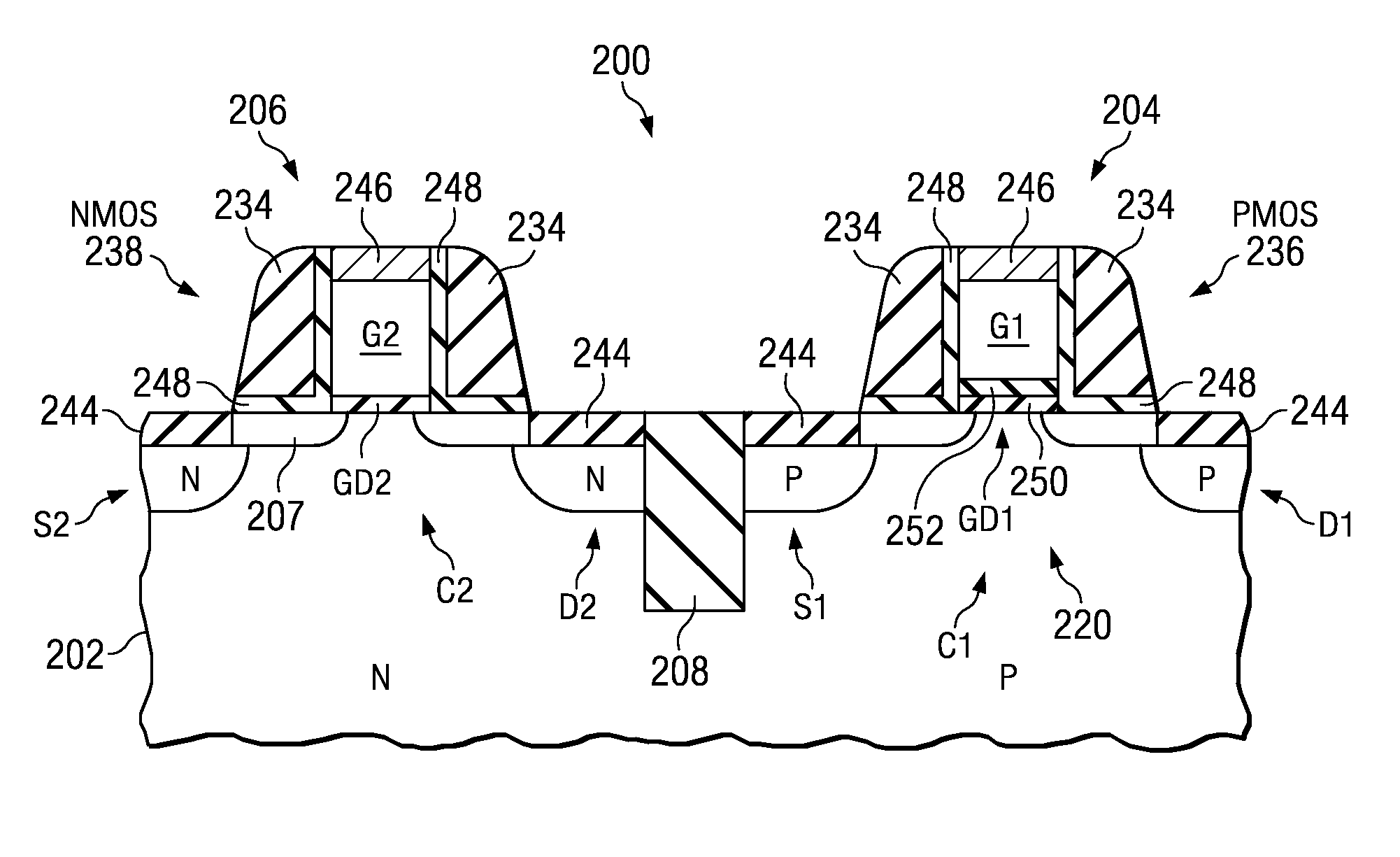

Transistor Device and Method of Manufacture Thereof

InactiveUS20080233694A1Depletion effect is reduced and avoidedEasy to adjustTransistorSolid-state devicesDopantCMOS

A CMOS device includes high k gate dielectric materials. A PMOS device includes a gate that is implanted with an n-type dopant. The NMOS device may be doped with either an n-type or a p-type dopant. The work function of the CMOS device is set by the material selection of the gate dielectric materials. A polysilicon depletion effect is reduced or avoided.

Owner:INFINEON TECH AG

Photodiode structure and image pixel structure

InactiveUS7009227B2Increase capacitanceSmall sizeSolid-state devicesSemiconductor/solid-state device manufacturingCMOSCapacitance

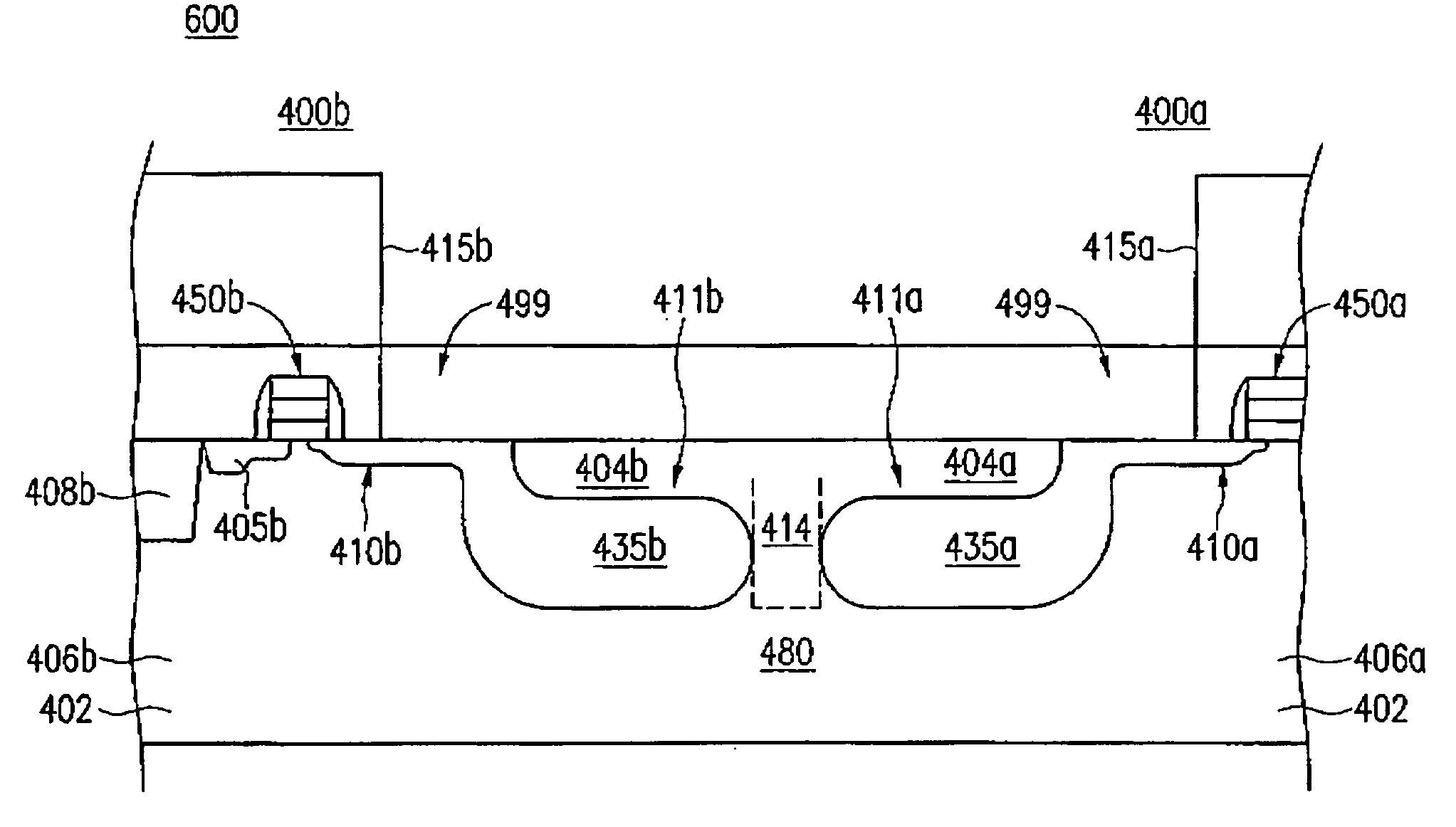

A CMOS imager with two adjacent pixel active area regions without the presence of an intervening trench isolation region that typically separates two adjacent pixels and their associated photodiodes is provided. The shared active area region isolates the two adjacent photodiodes and provides good substrate to surface pinned layer contact without the presence of n− type dopant ions and due to the presence of p-type dopant ions. As a result, the size of the imager can be reduced and the photodiodes of the two adjacent pixels have increased capacitance.

Owner:APTINA IMAGING CORP

Method of fabricating a field effect transistor having improved junctions

InactiveUS7247547B2TransistorSemiconductor/solid-state device manufacturingDopantElectrical conductor

A method of forming a field effect transistor is provided which includes forming an amorphized semiconductor region having a first depth from a single-crystal semiconductor region and subsequently forming a first gate conductor above a channel portion of the amorphized semiconductor region. A first dopant including at least one of an n-type dopant and a p-type dopant is then implanted to a second depth into portions of the amorphized semiconductor region not masked by the first gate conductor to form source / drain portions adjacent to the channel portion. The substrate is then heated to recrystallize the channel portion and the source / drain portions of the amorphized semiconductor region. After the heating step, at least a part of the recrystallized semiconductor region is locally heated to activate a dopant in at least one of the channel portion and the source / drain portion.

Owner:GOOGLE LLC

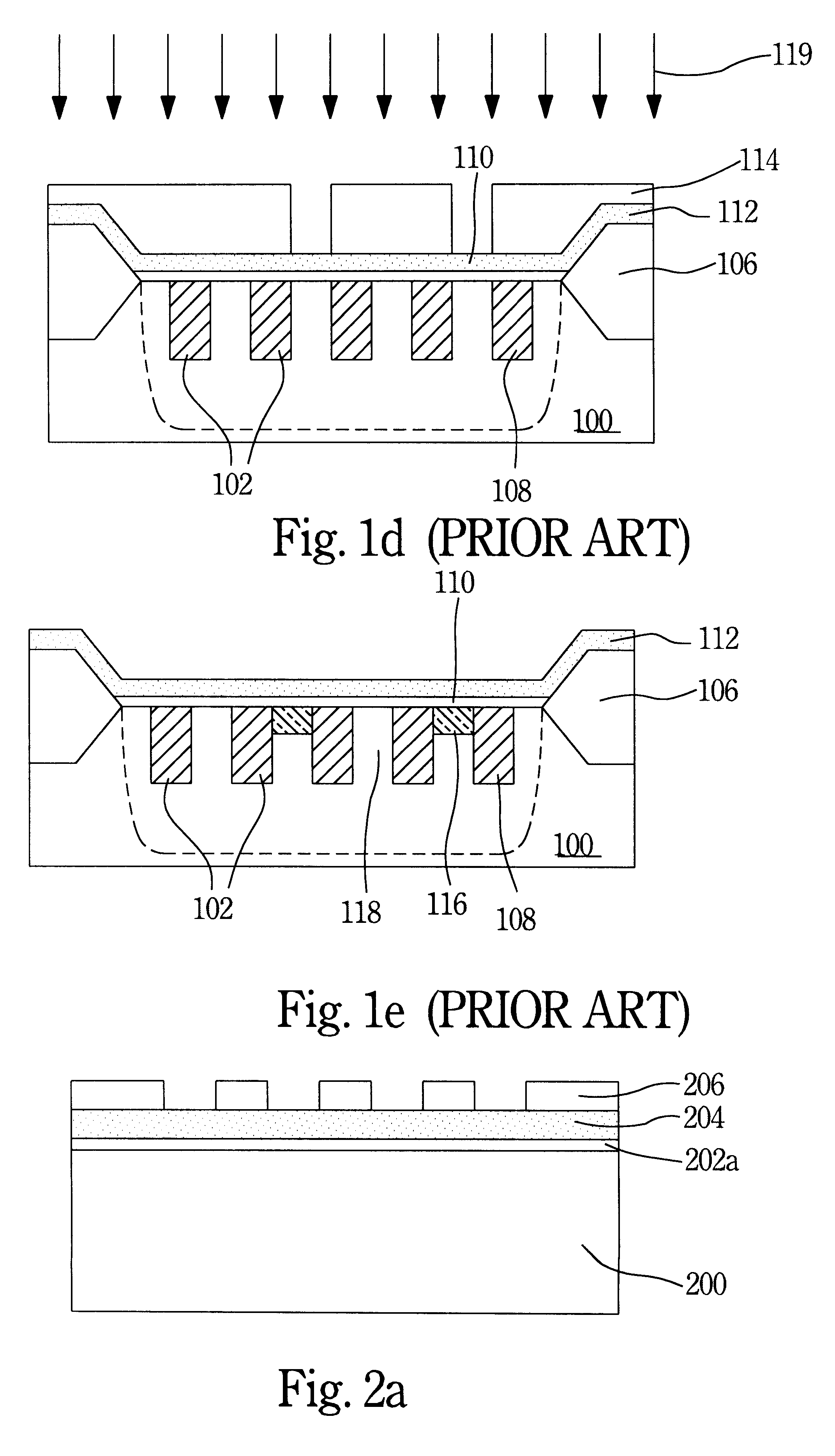

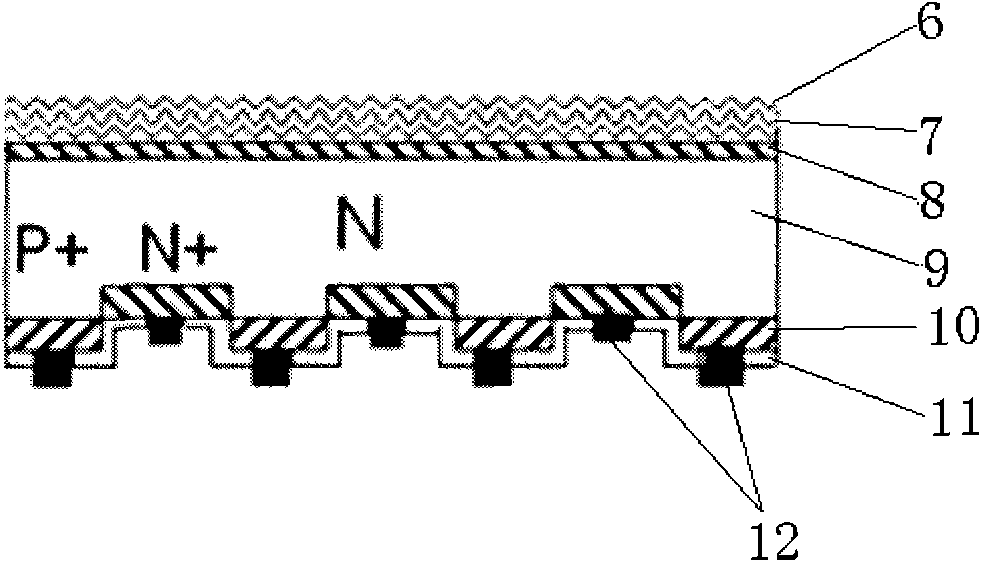

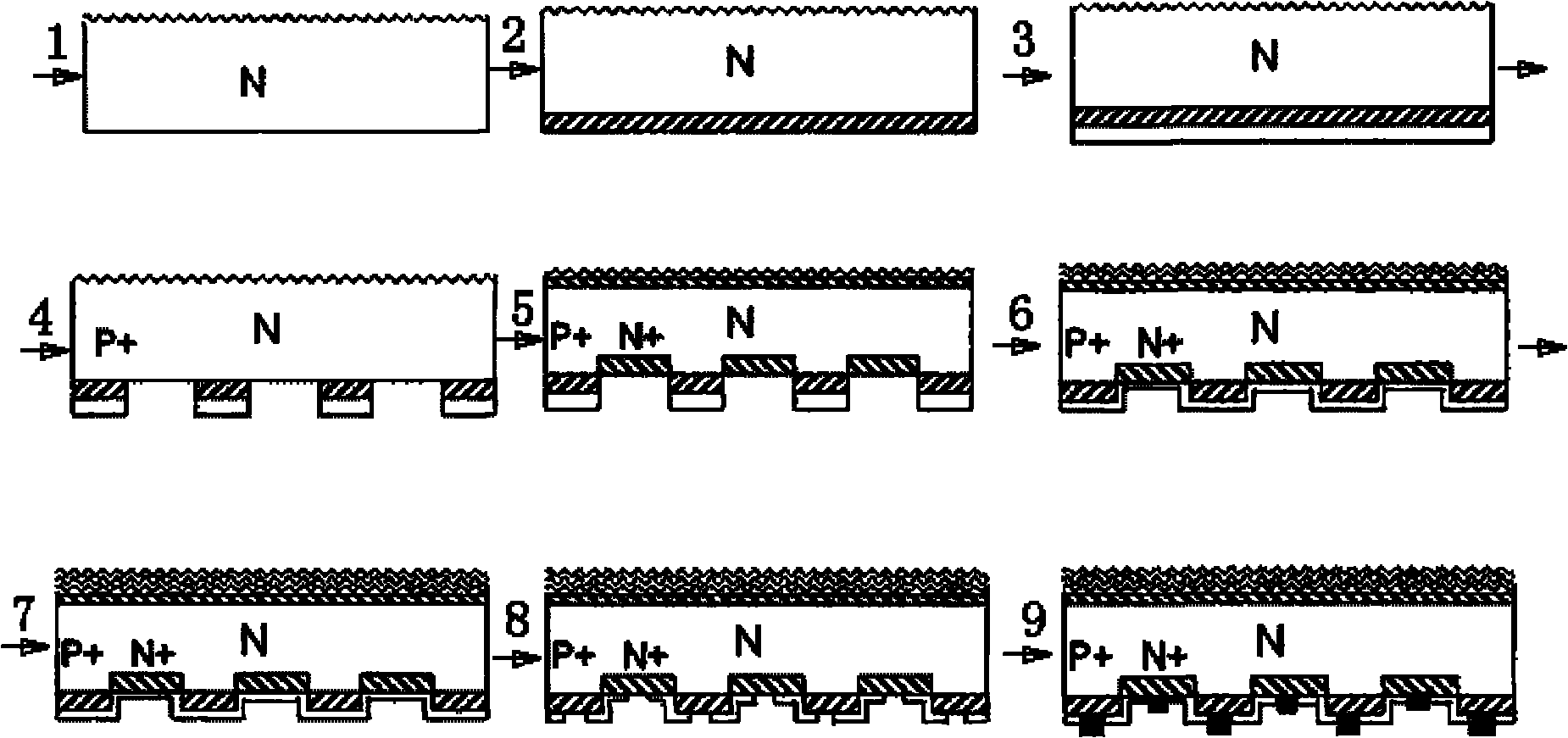

Method for manufacturing back contact solar energy batteries

ActiveCN101777603ASimple processEasy to implementFinal product manufactureSemiconductor devicesNon dopedSolar cell

The invention discloses a method for manufacturing back contact solar energy batteries, comprises the following steps of: firstly growing a P type doped silicon dioxide layer on an N type silicon chip; then growing a non-doped silicon dioxide layer on a P type doped layer; after that, printing a corrosive agent or an anti corrosive agent on the non-doped silicon dioxide layer to corrode the P type doped silicon dioxide layer and the non-doped silicon dioxide layer so as to form required patterns; and finally carrying out N type adulteration on the back face and the front face of the silicon chip to form an N type doped layer. The P type doped layer is protected by the non-doped silicon dioxide layer, and an N front surface field on the front face of the battery and a PN alternating doped layer on the back face of the battery are realized in the N type doped step at the same time, thereby reducing the diffusion step, reducing the cost and simplifying the process.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

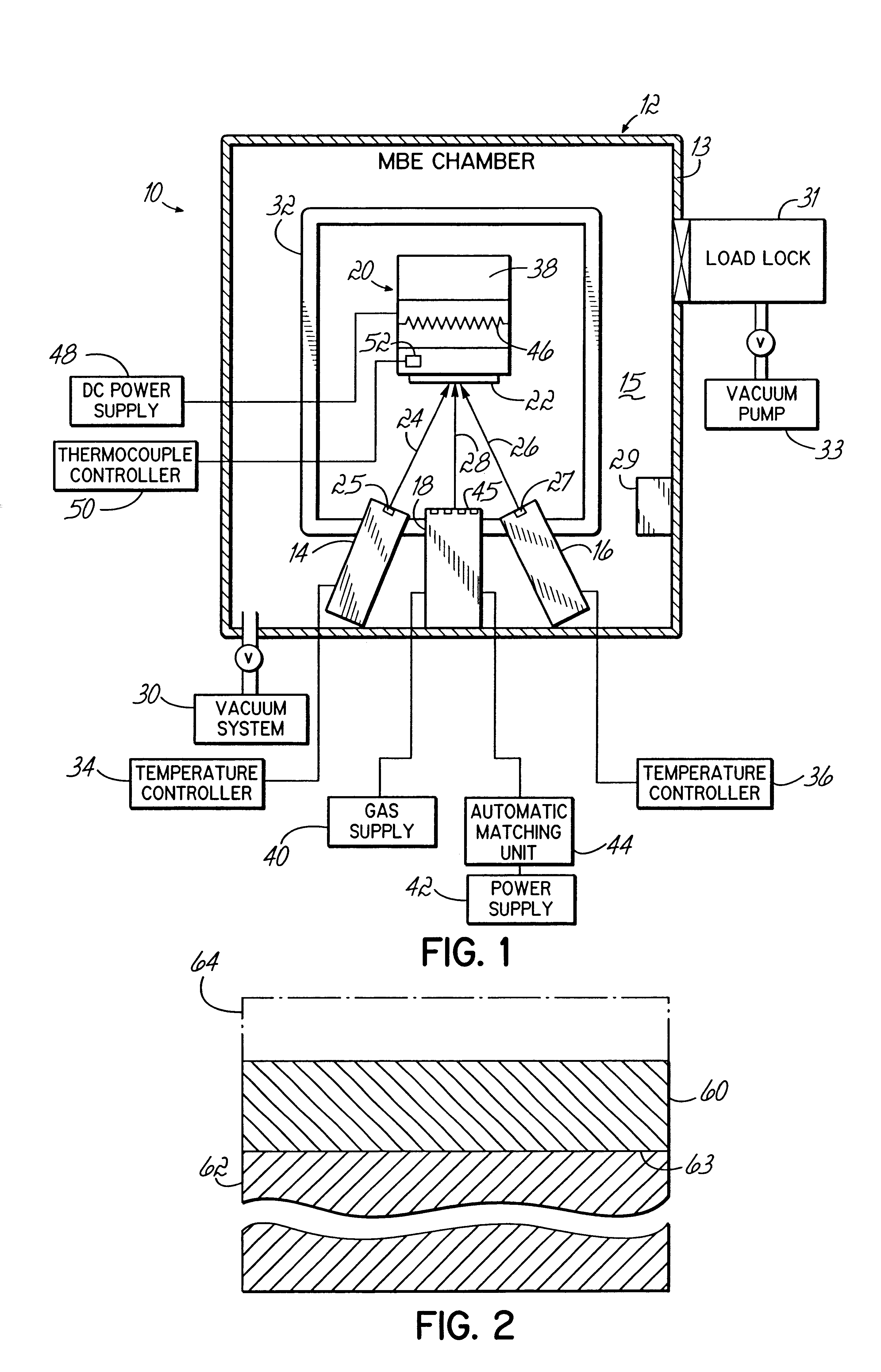

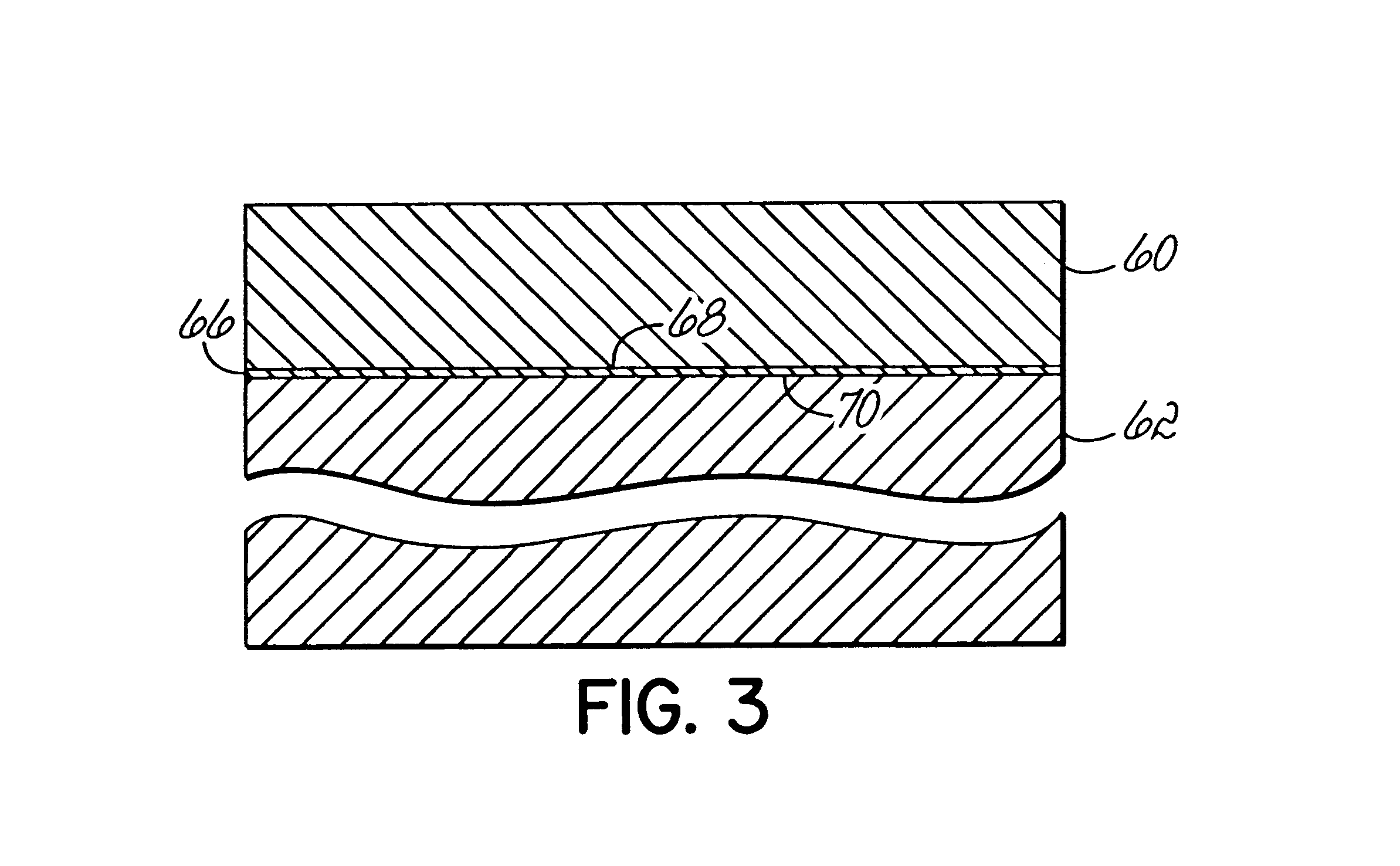

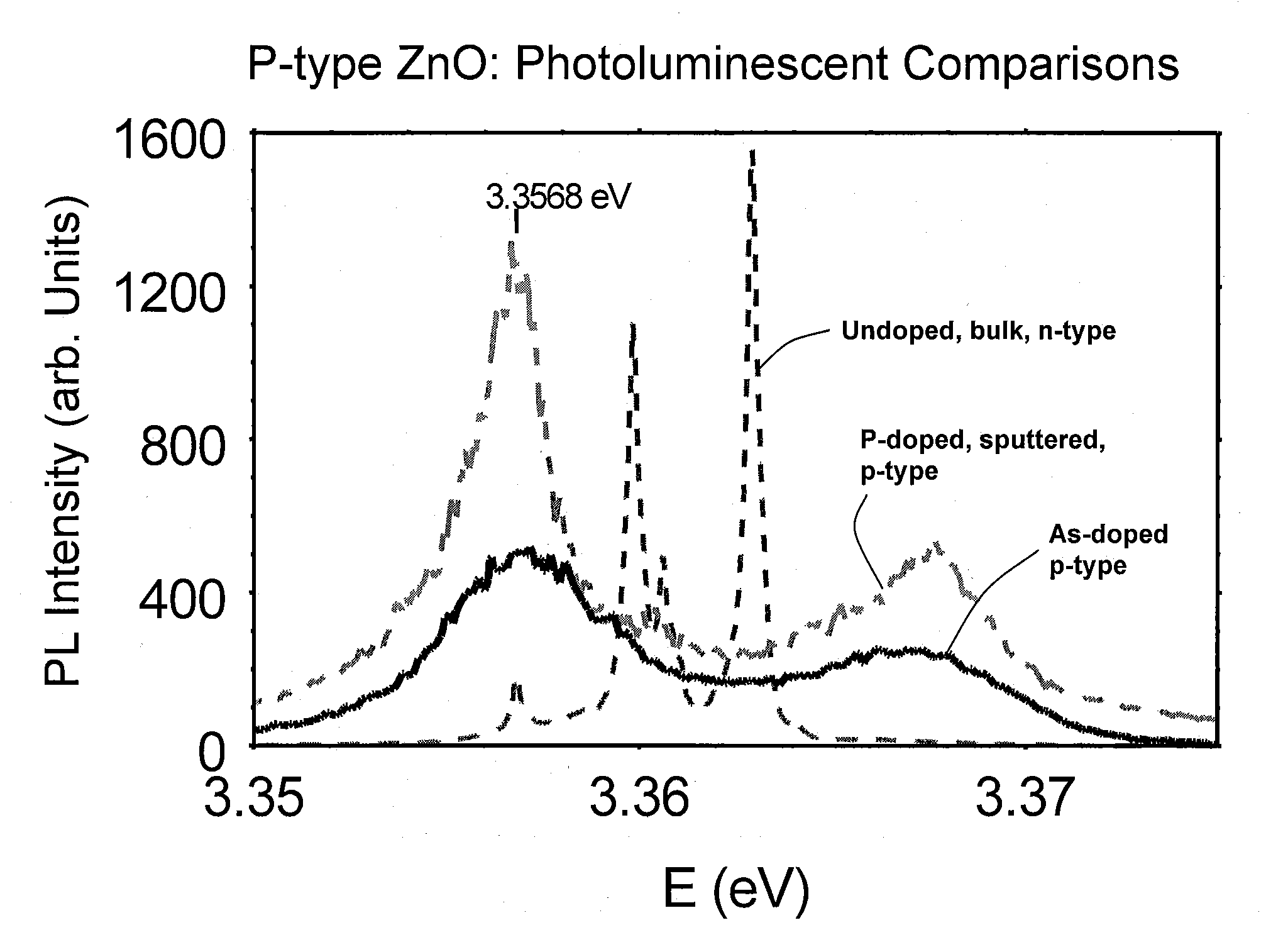

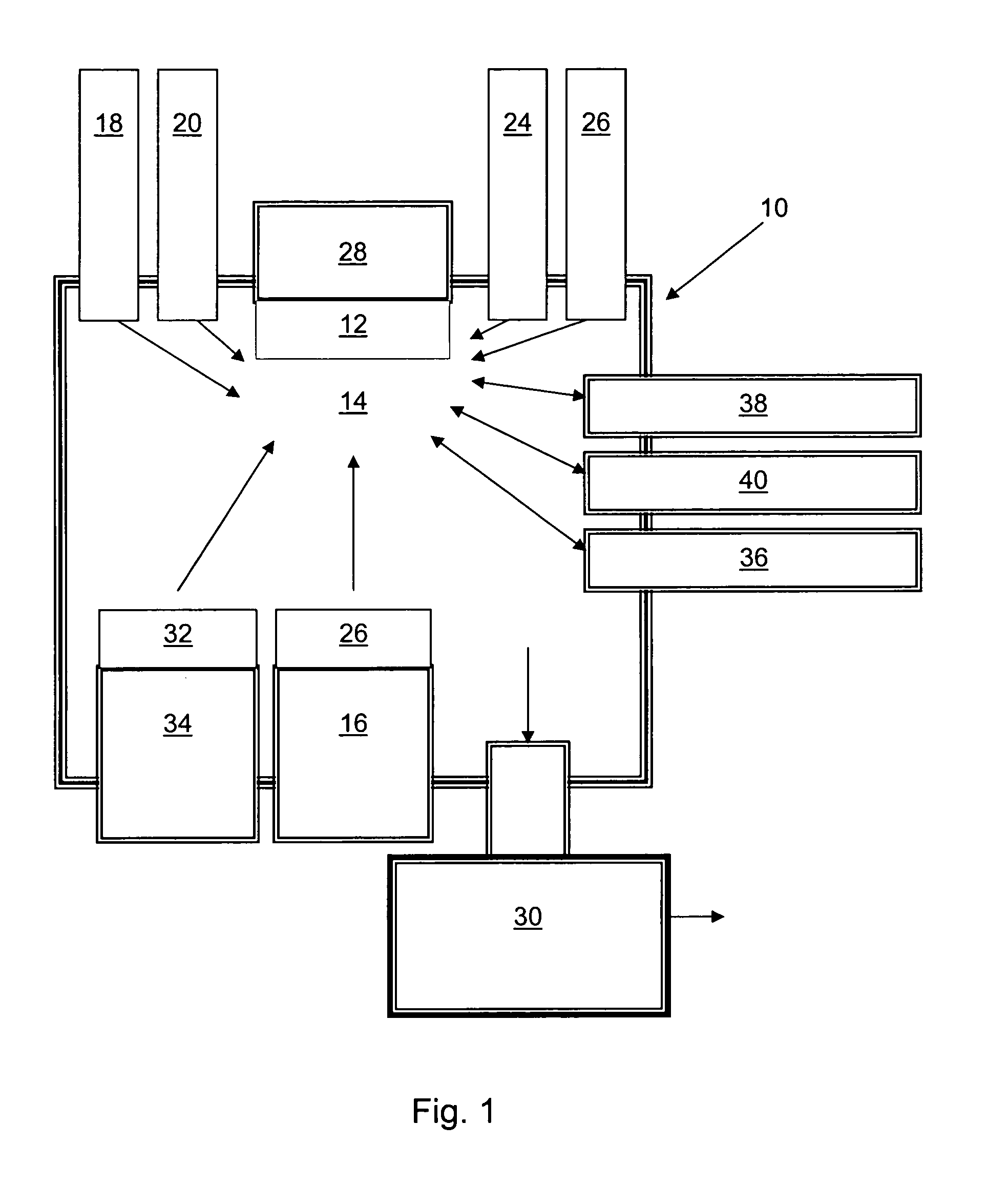

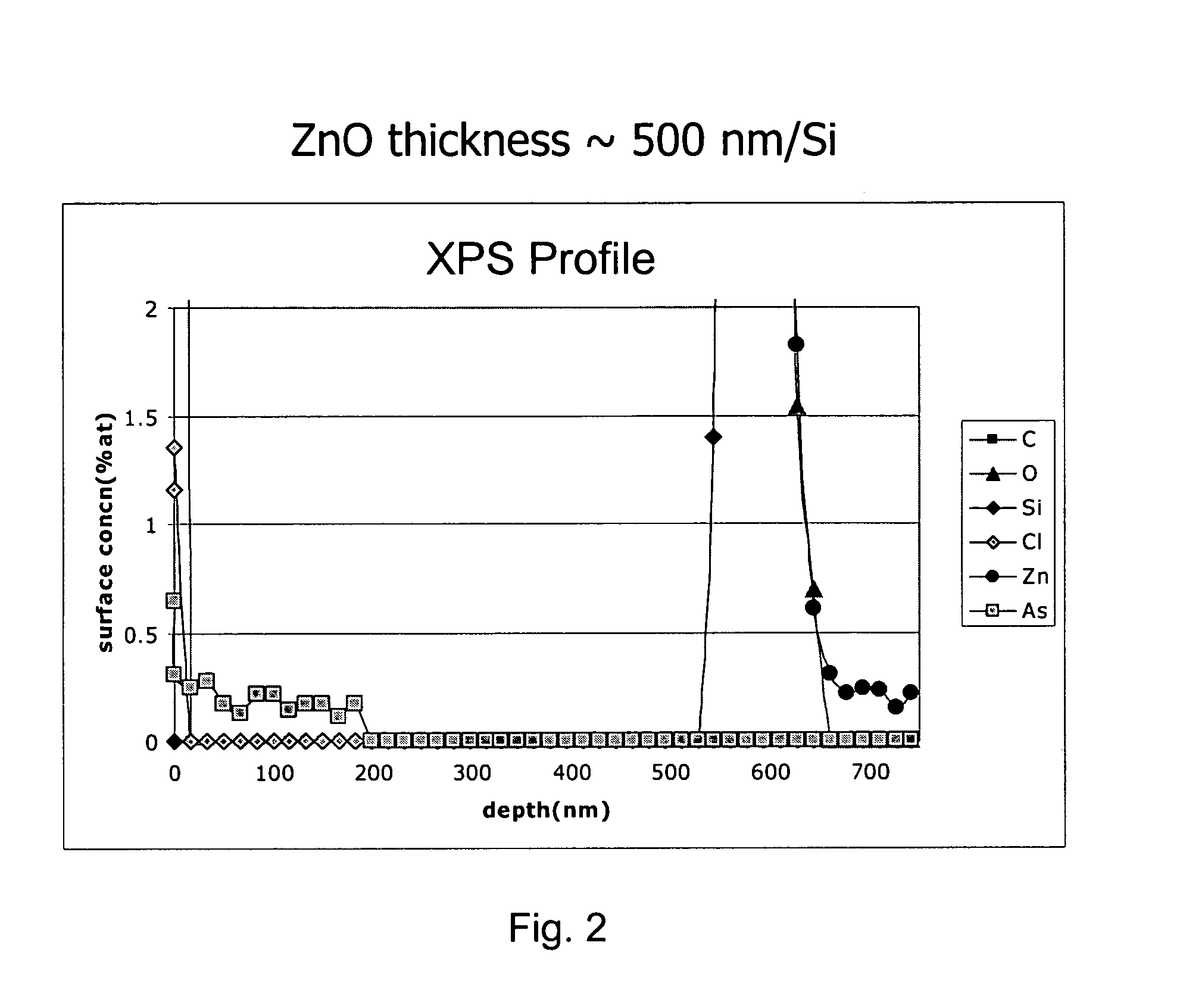

Homoepitaxial layers of p-type zinc oxide and the fabrication thereof

InactiveUS6624441B2Reduces and limits diffusionImprove crystal qualityPolycrystalline material growthSolid-state devicesLithiumDopant

A semiconductor structure for providing an epitaxial zinc oxide layer having p-type conduction for semiconductor device manufacture and methods of depositing the p-type zinc oxide layer. A zinc oxide layer is deposited epitaxially by molecular beam epitaxy on a crystalline zinc oxide substrate. The zinc oxide layer incorporates a p-type dopant, such as nitrogen, in an atomic concentration adequate to provide p-type conduction. The p-type zinc oxide layer may further incorporate an atomic concentration of a compensating species, such as lithium, sufficient to electronically occupy excess donors therein so that the efficiency of the p-type dopant may be increased.

Owner:NEW EAGLEPICHER TECH

Group II-VI semiconductor devices

Semiconductor devices containing group II-VI semiconductor materials are disclosed. The devices may include a p-n junction containing a p-type group II-VI semiconductor material and an n-type semiconductor material. The p-type group II-VI semiconductor includes a single crystal group II-VI semiconductor containing atoms of group II elements, atoms of group VI elements, and one or more p-type dopants. The p-type dopant concentration is greater than about 1016 atoms·cm−3, the semiconductor resistivity is less than about 0.5 ohm·cm, and the carrier mobility is greater than about 0.1 cm2 / V·s. The semiconductor devices may include light emitting diodes, laser diodes, field effect transistors, and photodetectors.

Owner:ZENO MATERIALS LLC

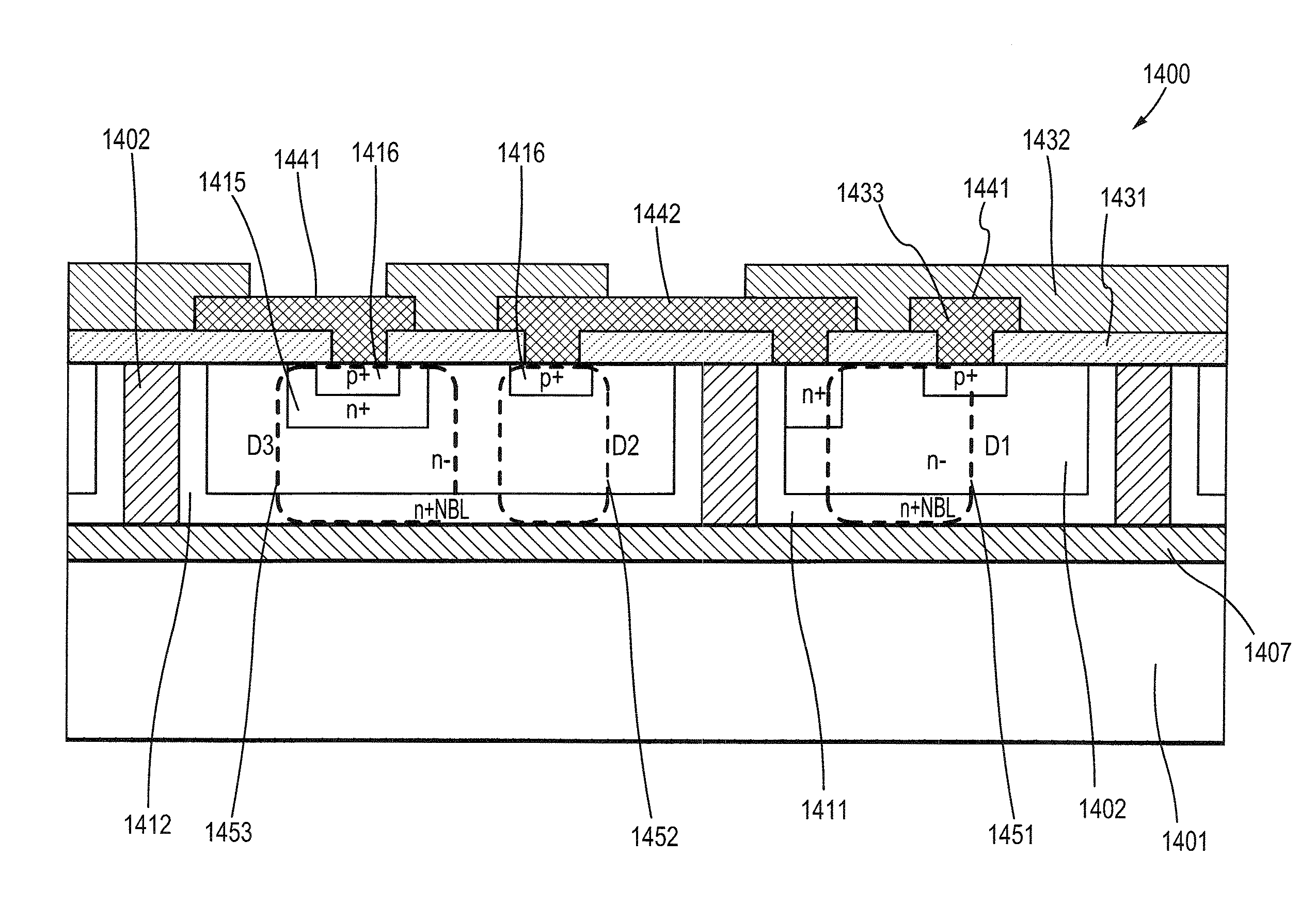

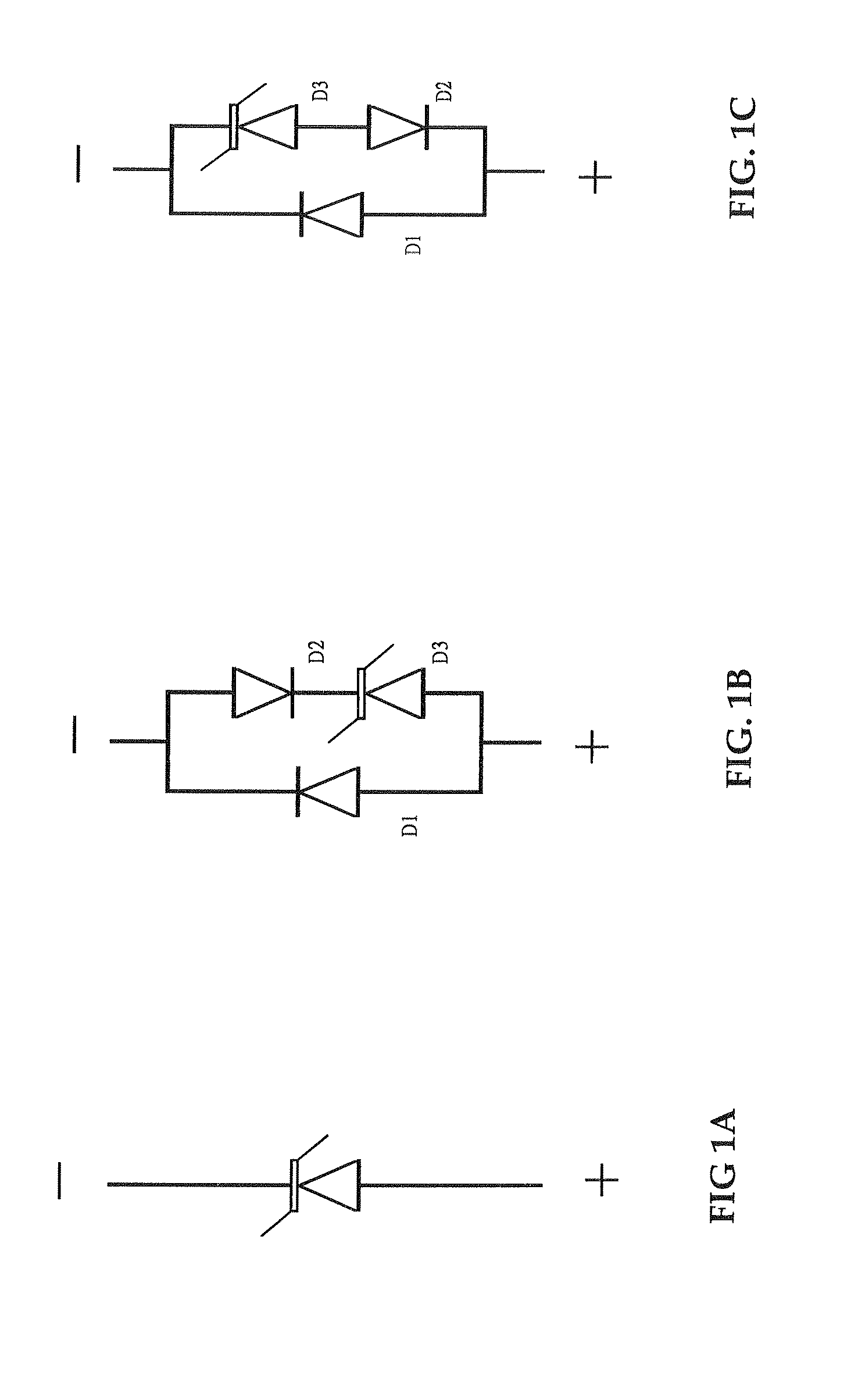

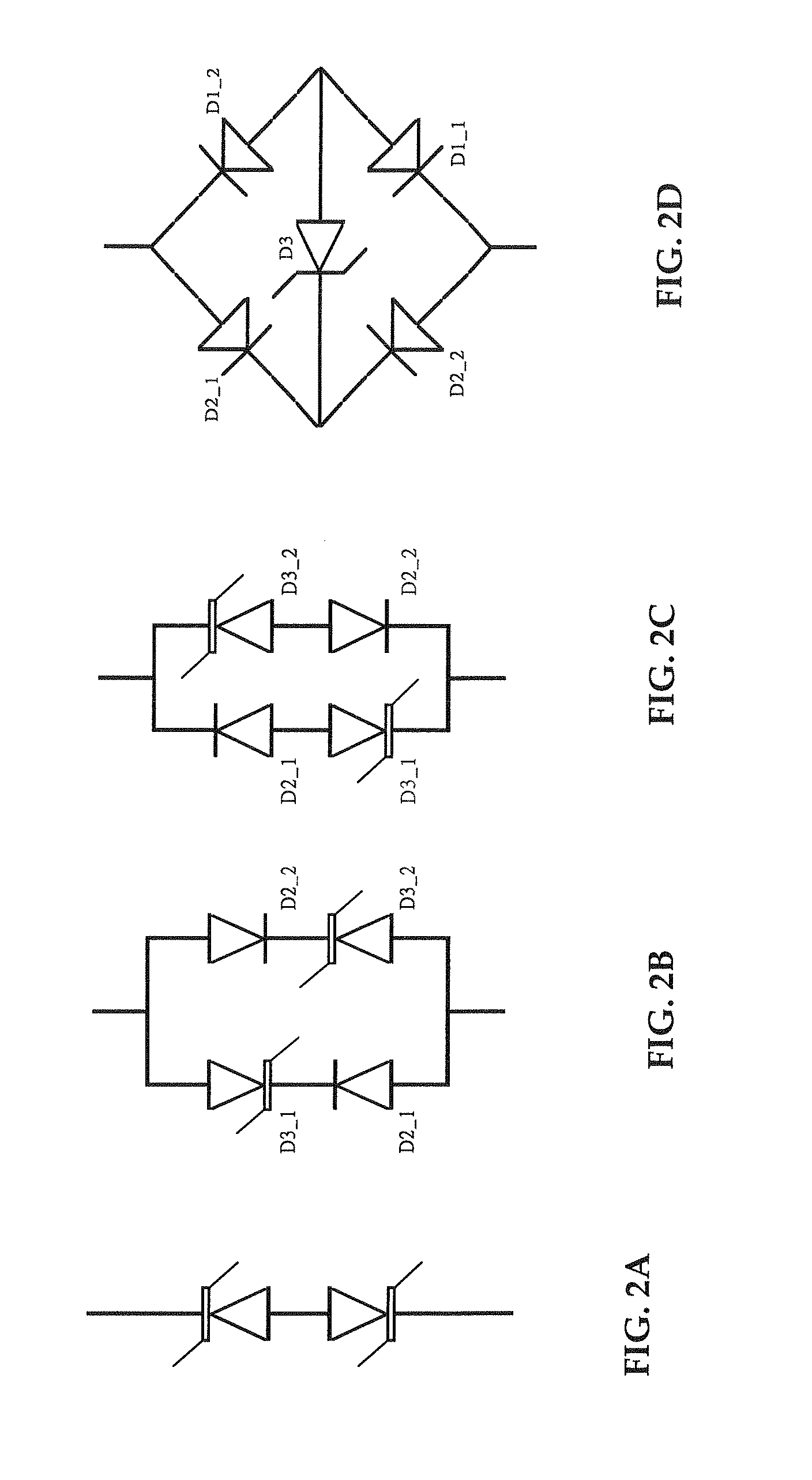

Semiconductor device structure and methods of making

InactiveUS20110212595A1Reduce doping concentrationReduce thermal cyclesThyristorSemiconductor/solid-state device manufacturingCapacitanceGas phase

A process for fabricating a semiconductor device having reduced capacitance for high frequency circuit protection is disclosed that comprises first forming an n+ buried layer in a p-type substrate by depositing n-type dopant on the top surface of the substrate and then drive in or by implanting n-type material into the substrate, and then growing an n-type epitaxial layer atop the n+ buried layer as the device layer. Trenches that surrounds the device region with depth extending from the top surface, going through the n+ buried layer and reaching down to the substrate are then formed and then an n+ layer on the sidewalls of the trenches is formed by diffusion or ion implantation. The trenches are then filled by growing a layer of thermal oxide on the sidewalls of the trenches and followed by deposition of plasma enhanced oxide, nitride, TEOS oxide CVD oxide, or polysilicon into the trenches and then planarizing the top surface by plasma etch back or polishing. Then n+ region of the device is formed by forming an oxide layer on the top surface of the device layer and then etching the oxide by photolithography, then depositing n-type dopant material and then driving in by high temperature diffusion. Finally p+ region of the device is formed by etching the oxide using photolithography, then depositing p-type dopant material by solid or gas phase deposition or ion implantation and then driving in by high temperature diffusion so that the breakdown voltage between cathode and anode of the device is set to a targeted voltage for high frequency circuit protection.

Owner:HU JERRY +2

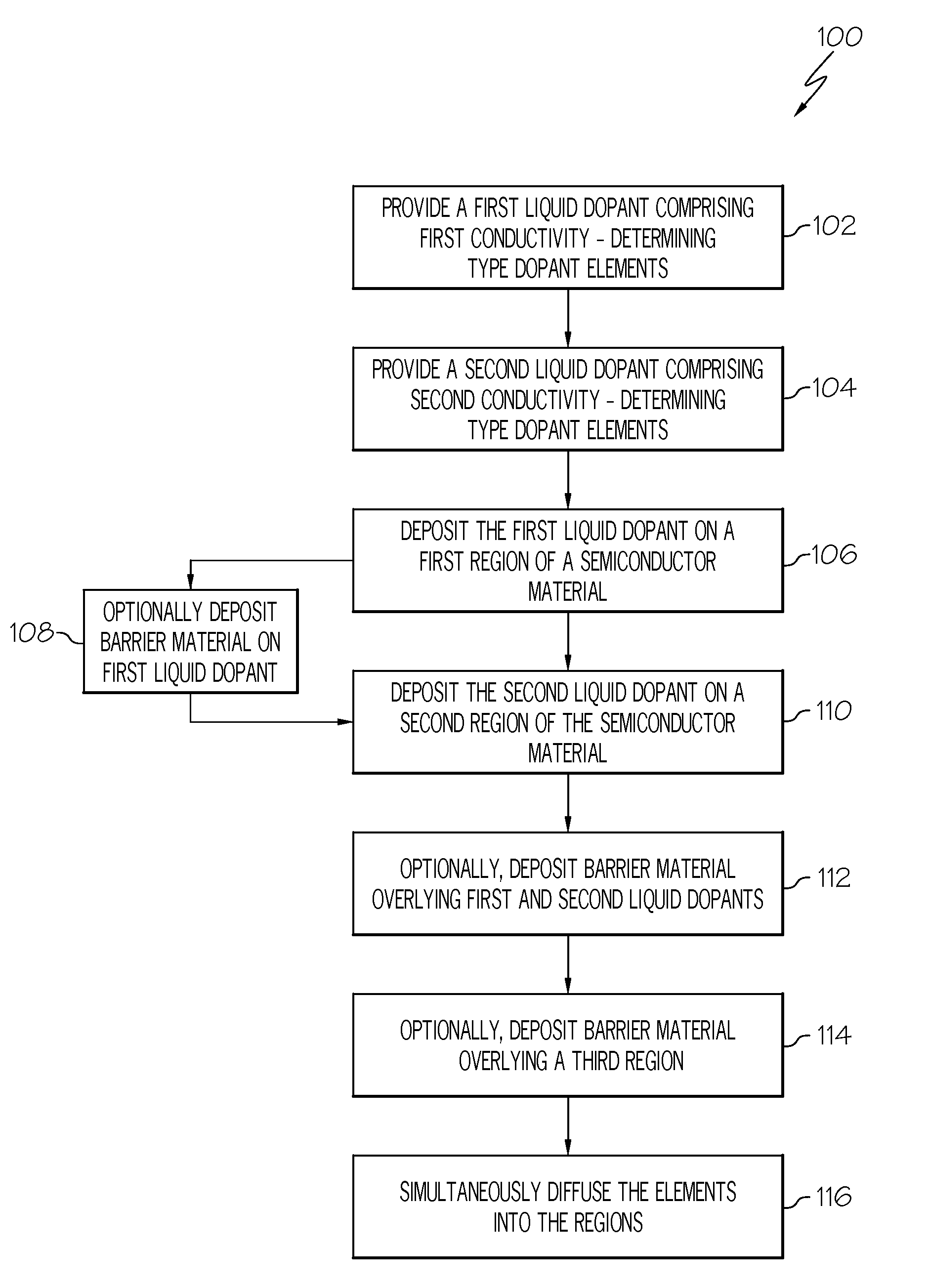

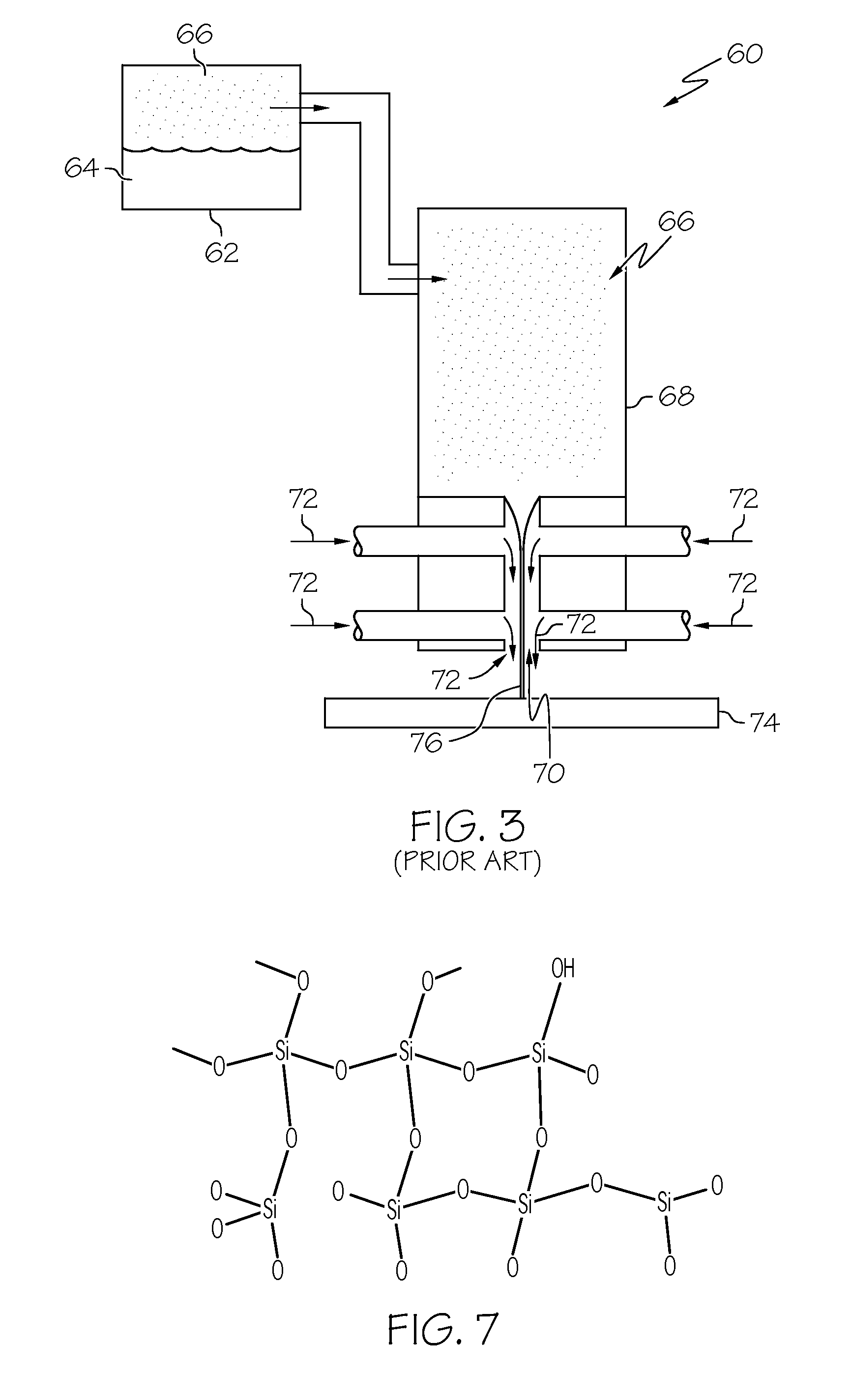

Methods for simultaneously forming n-type and p-type doped regions using non-contact printing processes

InactiveUS20100081264A1Final product manufactureSemiconductor/solid-state device manufacturingDopantSemiconductor materials

Methods for simultaneously forming doped regions of opposite conductivity using non-contact printing processes are provided. In one exemplary embodiment, a method comprises the steps of depositing a first liquid dopant comprising first conductivity-determining type dopant elements overlying a first region of a semiconductor material and depositing a second liquid dopant comprising second conductivity-determining type dopant elements overlying a second region of the semiconductor material. The first conductivity-determining type dopant elements and the second conductivity-determining type dopant elements are of opposite conductivity. At least a portion of the first conductivity-determining type dopant elements and at least a portion of the second conductivity-determining type dopant elements are simultaneously diffused into the first region and into the second region, respectively.

Owner:HONEYWELL INT INC

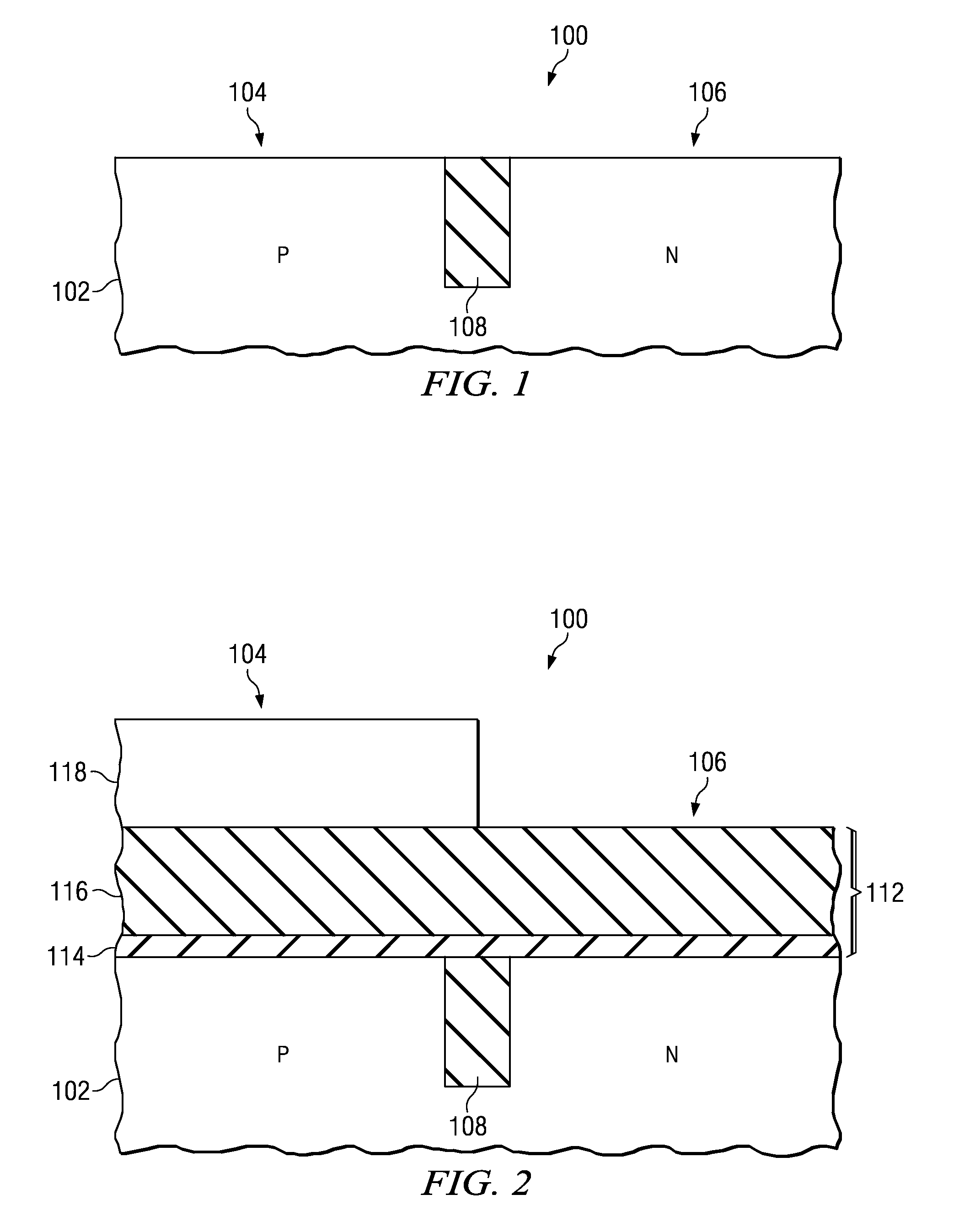

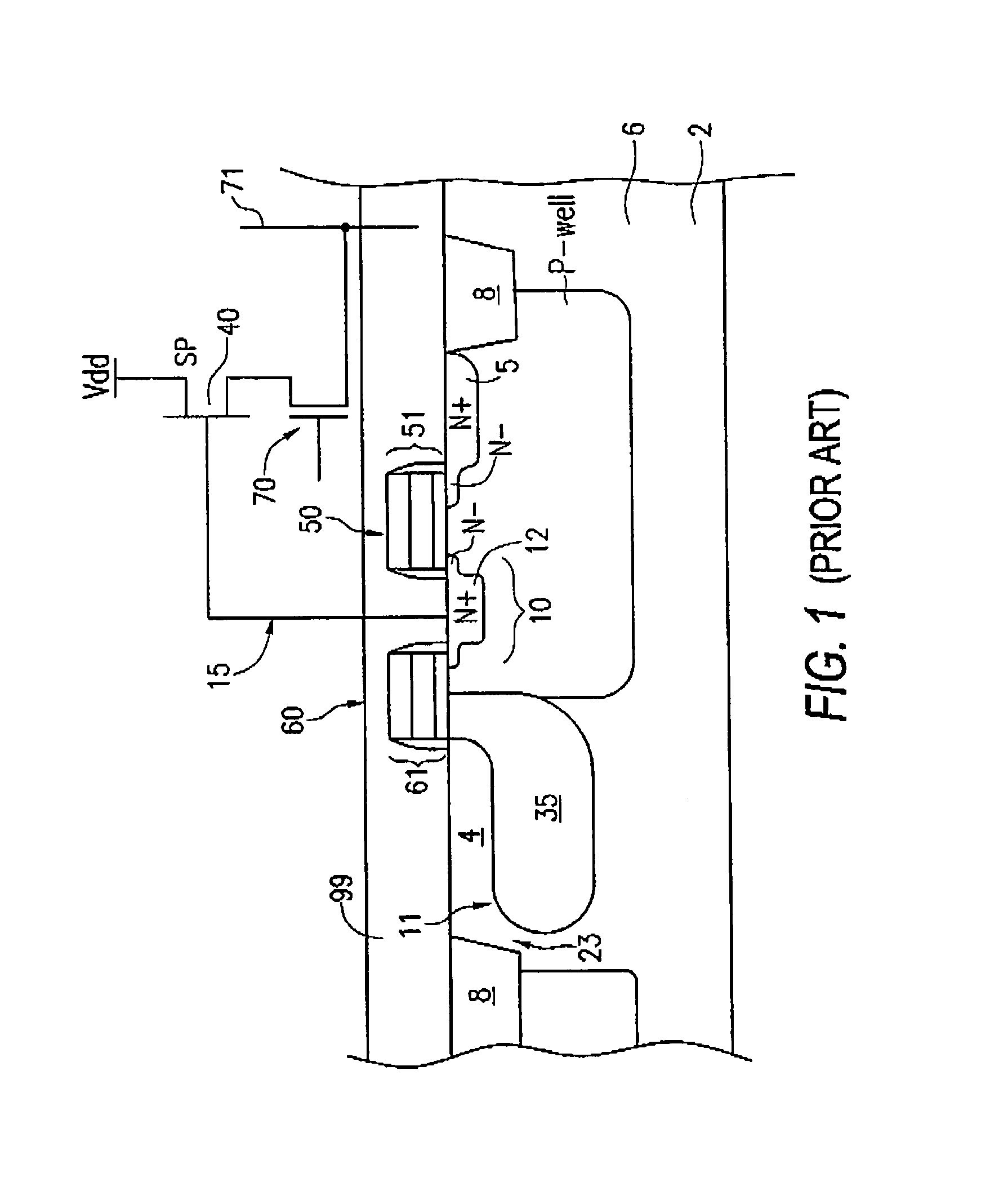

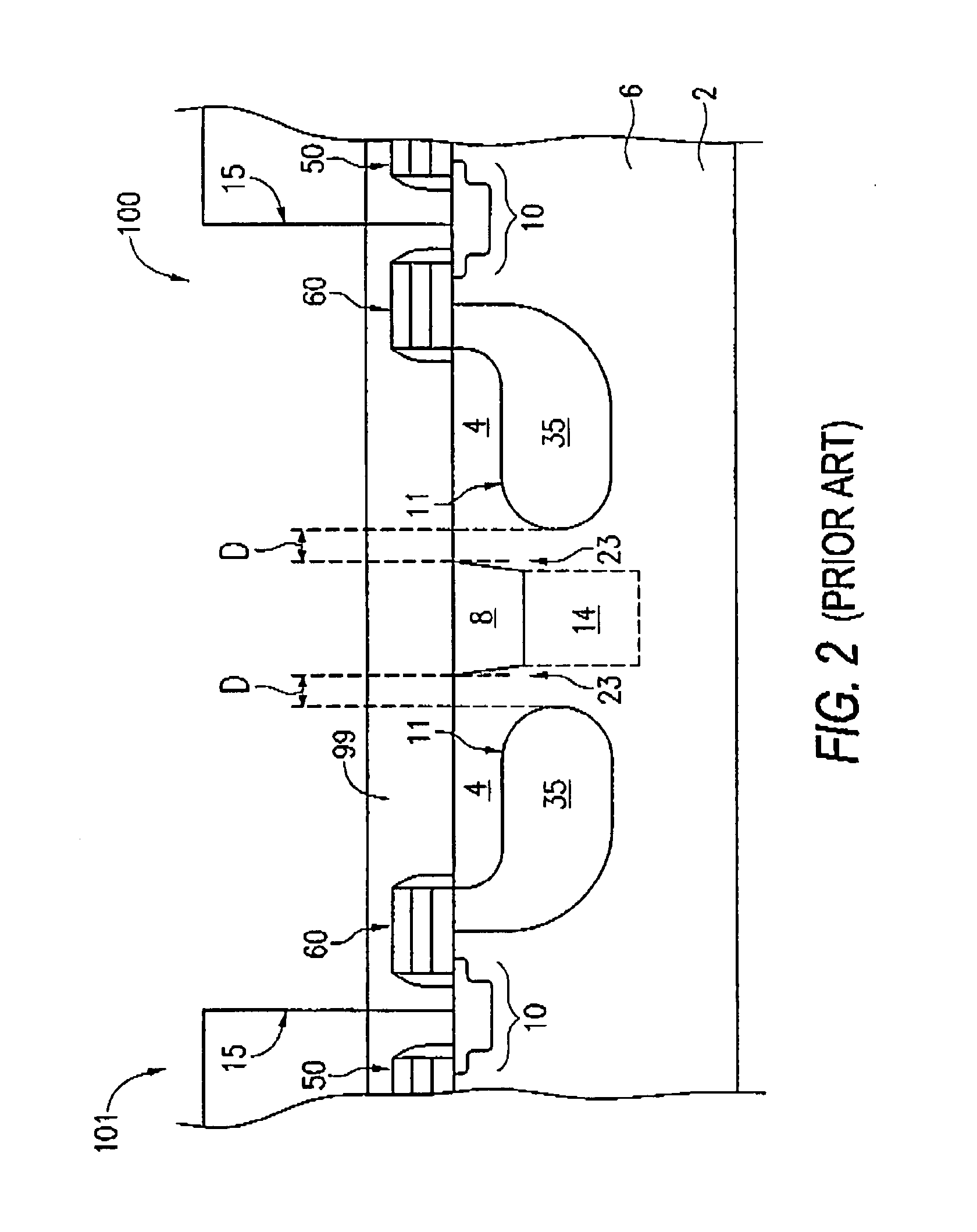

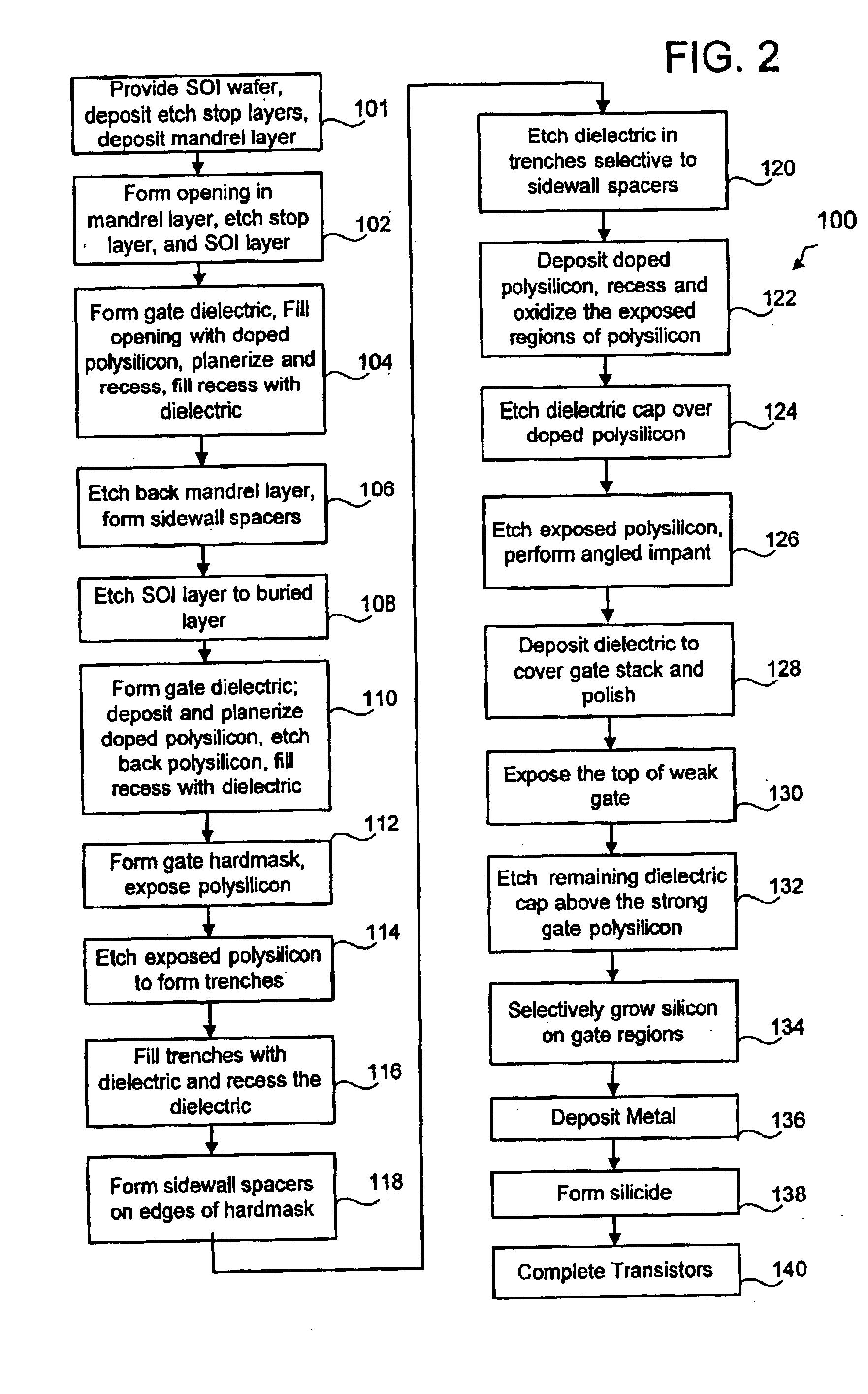

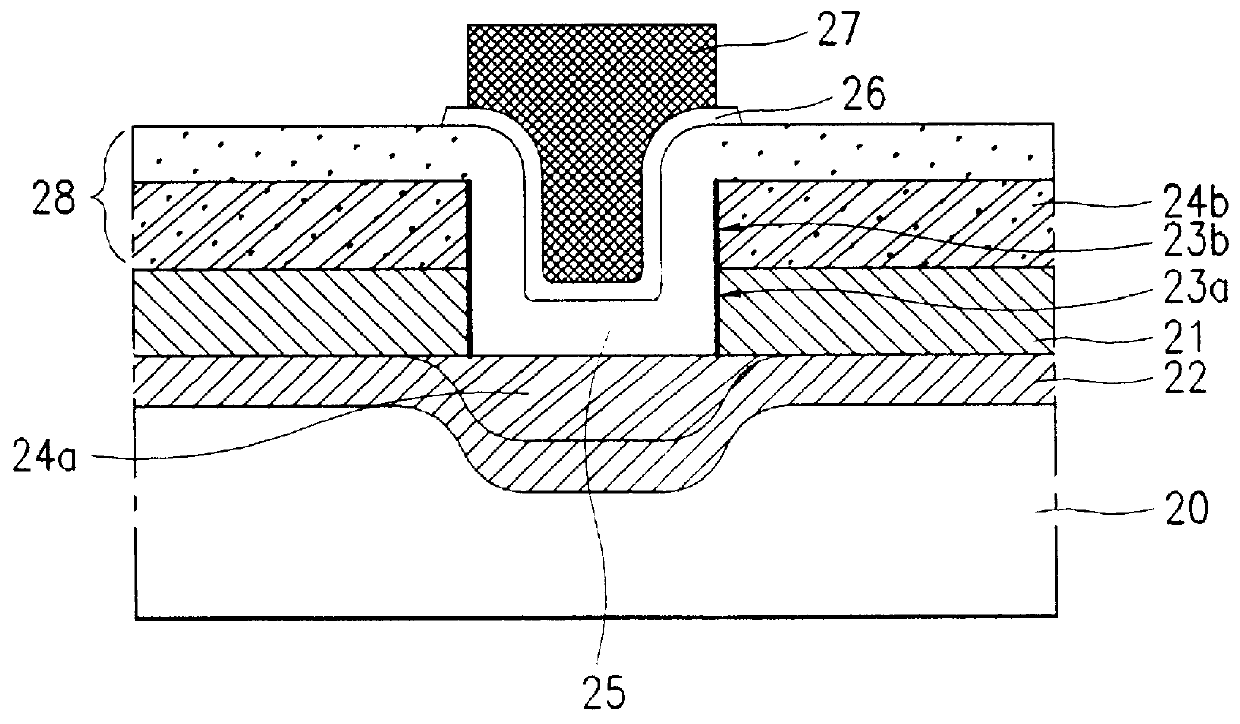

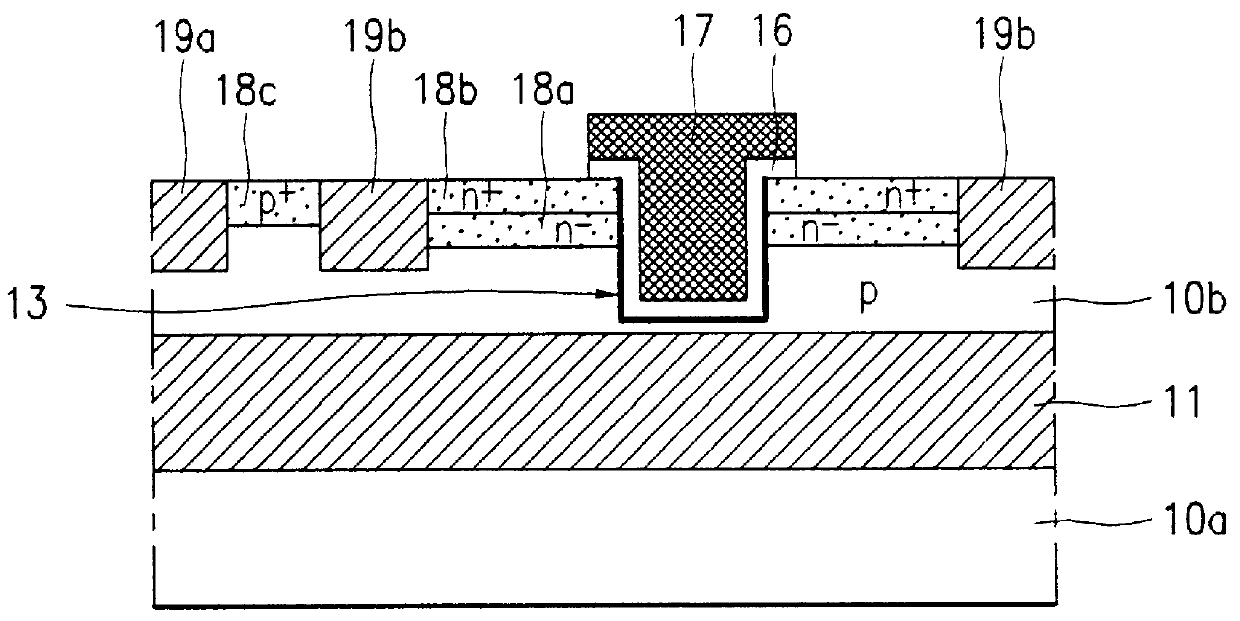

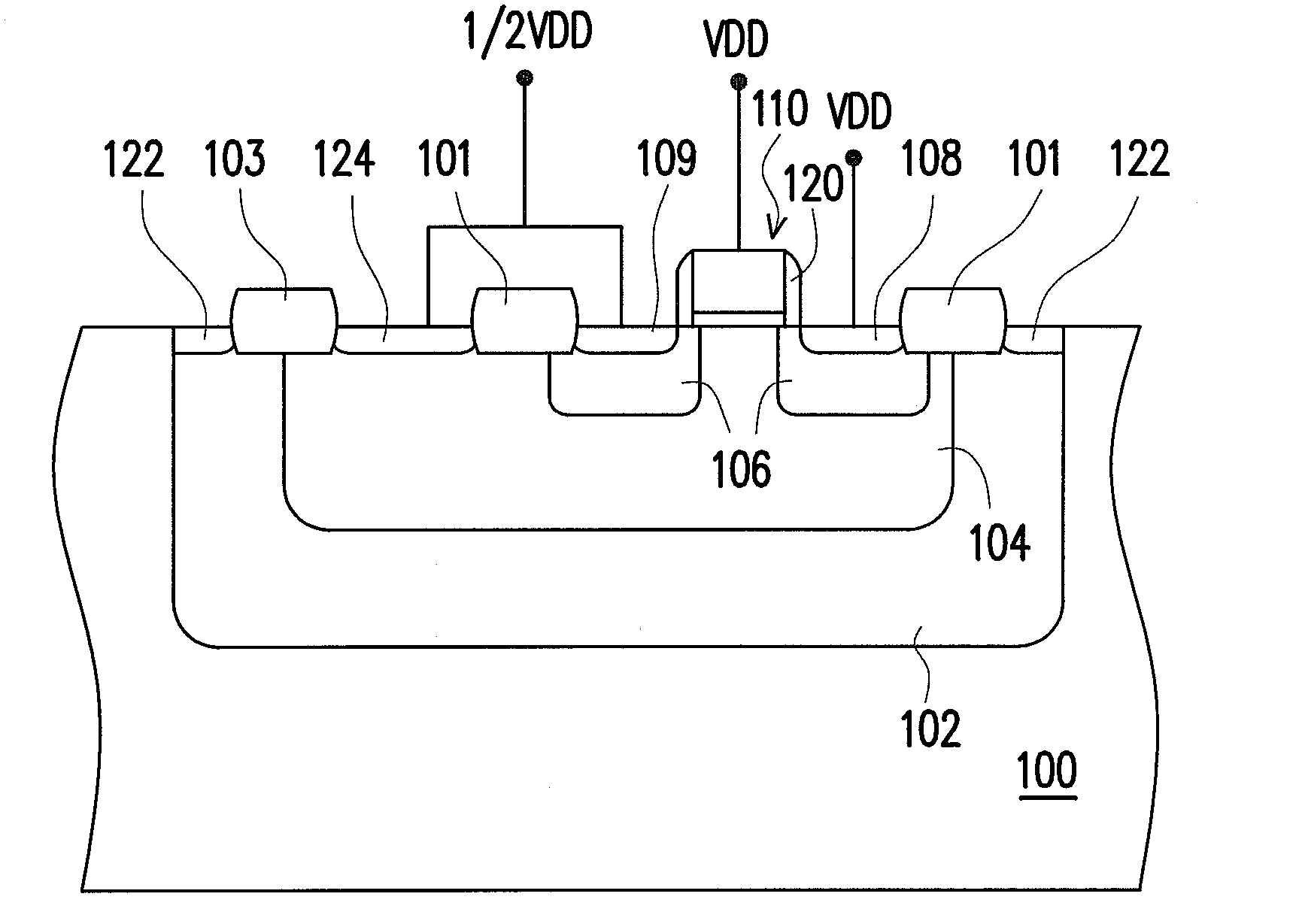

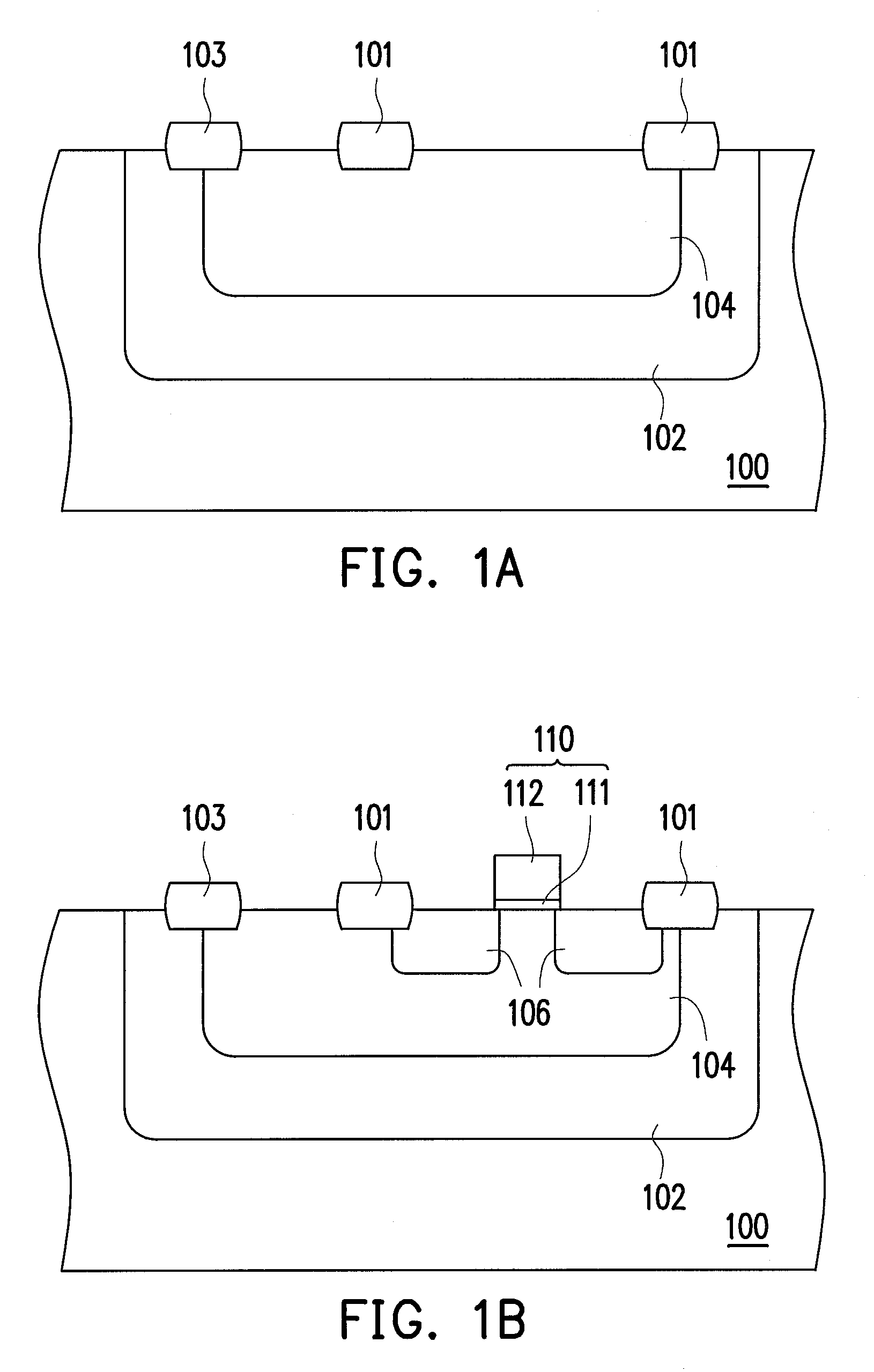

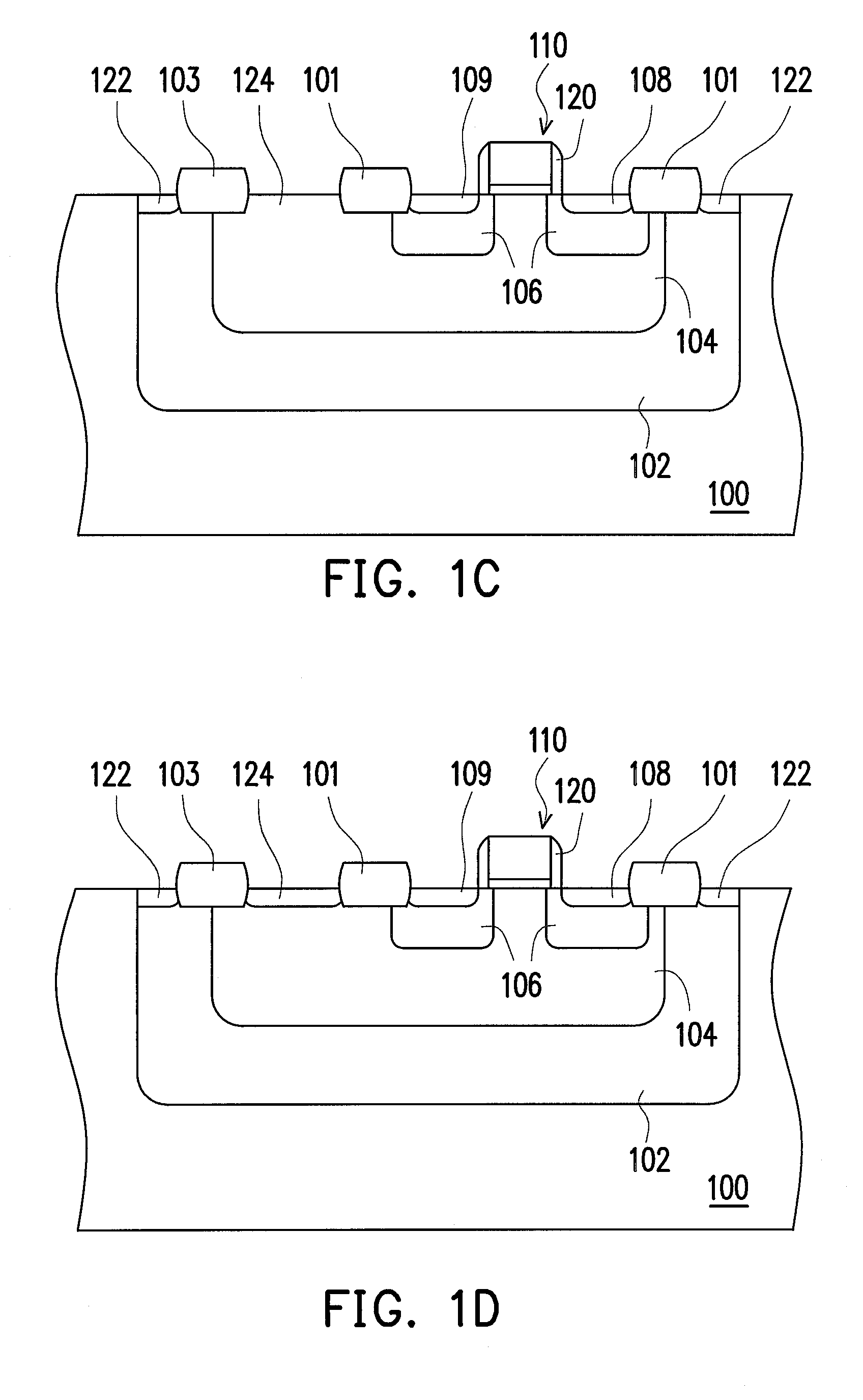

Doubly asymmetric double gate transistor structure

The present invention provides a double gated transistor and a method for forming the same that results in improved device performance and density. The preferred embodiment of the present invention provides a double gated transistor with asymmetric gate doping, where one of the double gates is doped degenerately n-type and the other degenerately p-type. By doping one of the gates n-type, and the other p-type, the threshold voltage of the resulting device is improved. Additionally, the preferred transistor design uses an asymmetric structure that results in reduced gate-to-drain and gate-to-source capacitance. In particular, dimensions of the weak gate, the gate that has a workfunction less attractive to the channel carriers, are reduced such that the weak gate does not overlap the source / drain regions of the transistor. In contrast the strong gate, the gate having a workfunction that causes the inversion layer to form adjacent to it, is formed to slightly overlap the source / drain regions. This asymmetric structure allows for the performance benefits of a double gate design without the increased capacitance that would normally result.

Owner:IBM CORP

Silicon-on-insulator-device and fabrication method thereof

A two-layer buried oxide enables fabrication of a silicon-on-insulator MOSFET with thick-film source / drain regions and a thin-film channel region. After a hole has been etched in the substrate above a first buried oxide layer (i.e., in the upper substrate), oxygen is implanted to form a second buried layer within the substrate below the first buried layer (i.e., within the lower substrate). After a hole (aligned with the hole through the upper substrate) has been etched in the first buried layer, p-type dopants are implanted to form upper doped regions within the upper substrate to either side of the holes and a lower doped region within the lower substrate below the holes but above the second buried layer. An epitaxial layer roughly as thick as first buried layer is grown on the upper and lower substrates, a conformal insulating film is deposited onto the epitaxial layer, and a gate electrode is formed on the on the insulating film. Implantation of n-type dopants into both the epitaxial layer and the upper substrate to either side of the holes completes fabrication of the silicon-on-insulator device.

Owner:LG SEMICON CO LTD

Metal oxide semiconductor device

ActiveUS20100148250A1Reduce electricity consumptionLow working voltageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringP type doping

A metal oxide semiconductor device comprising a substrate, at least an isolation structure, a deep N-type well, a P-type well, a gate, a plurality of N-type extension regions, an N-type drain region, an N-type source region and a P-type doped region is provided. The N-type extension regions are disposed in the substrate between the isolation structures and either side of the gate, while the N-type drain region and the N-type source region are respectively disposed in the N-type extension regions at both sides of the gate. The P-type well surrounds the N-type extension regions, and the P-type doped region is disposed in the P-type well of the substrate and is isolated from the N-type source region by the isolation structure.

Owner:UNITED MICROELECTRONICS CORP

Microbolometer infrared detector elements and methods for forming same

ActiveUS20100133536A1Improved stability and performance characteristicImprove performanceSemiconductor/solid-state device manufacturingMaterial analysis by optical meansDopantMicrobolometer

Microbolometer infrared detector elements that may be formed and implemented by varying type / s of precursors used to form amorphous silicon-based microbolometer membrane material / s and / or by varying composition of the final amorphous silicon-based microbolometer membrane material / s (e.g., by adjusting alloy composition) to vary the material properties such as activation energy and carrier mobility. The amorphous silicon-based microbolometer membrane material / s materials may include varying amounts of one or more additional and optional materials, including hydrogen, fluorine, germanium, n-type dopants and p-type dopants.

Owner:DRS NETWORK & IMAGING SYST

Monolithically integrated sic mosfet and schottky barrier diode

InactiveUS20130313570A1Improve system reliabilityReduce connectionsTransistorSemiconductor/solid-state device manufacturingMOSFETSchottky barrier

A SIC VDMOS transistor is integrated with a SiC SBD, in a seamless way, without any increase of the device area. The SiC SBD is integrated in the active area of the VDMOS by splitting the P-Wells, such that the lightly doped drift region extents all the way to the surface of semiconductor, and by trenching through the source of the VDMOS and partially through the P-Wells to reach the peak of the P-type doping in the P-Well regions. The source of the VDMOS is contacted from the top surface and from the vertical sidewalls of the trenched source and the forward voltage of the Schottky Barrier diode is tailored by using two different metals for the ohmic contact on the source and for the SBD.

Owner:MICROSEMI CORP ANALOG MIXED SIGNAL GRP LTD

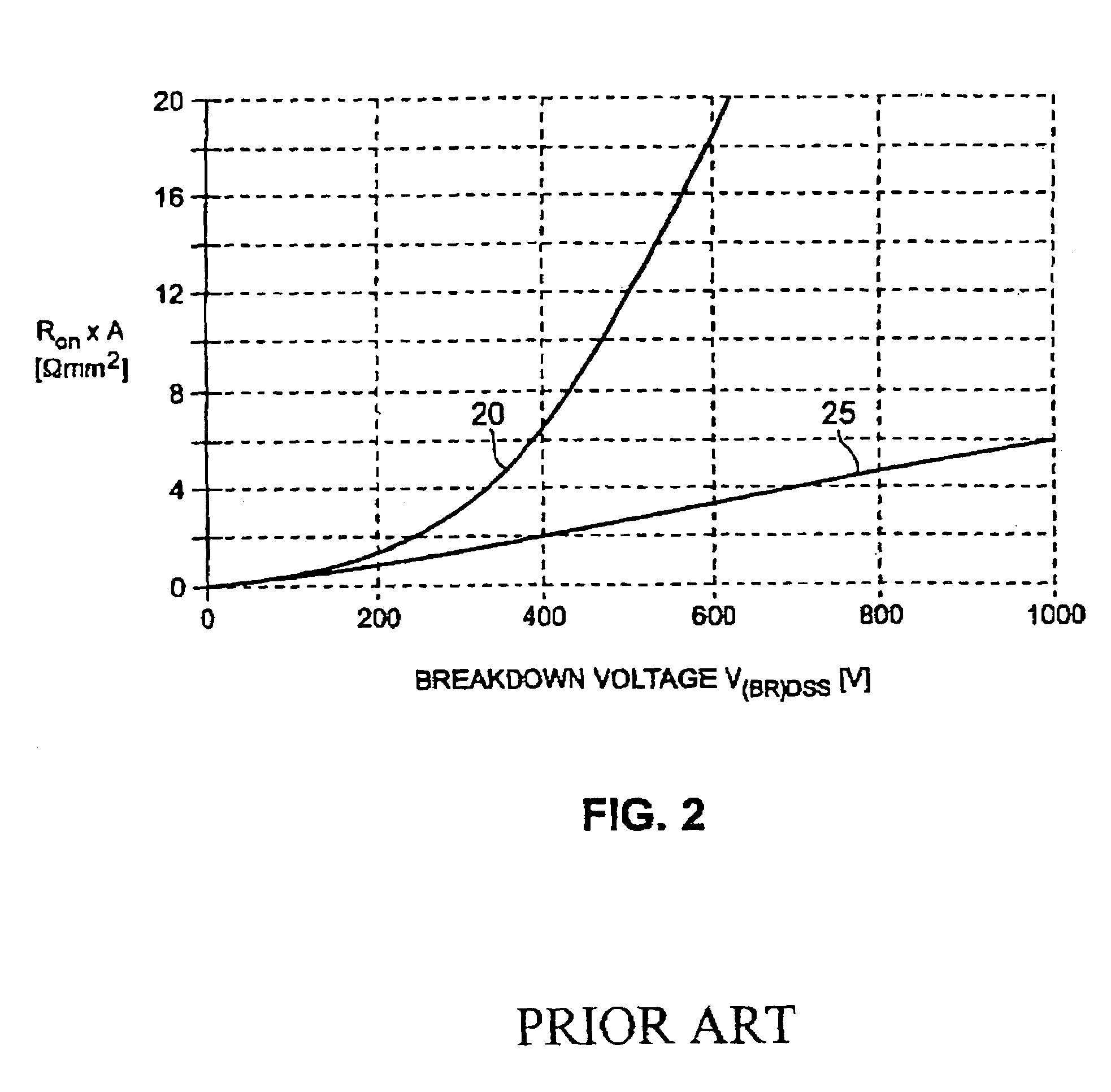

Technique for forming the deep doped columns in superjunction

A method of manufacturing a semiconductor device is disclosed and starts with a semiconductor substrate having a heavily doped N region of at the bottom main surface and having a lightly doped N region at the top main surface. There are a plurality of trenches in the substrate, with each trench having a first extending portion extending from said top main surface towards the heavily doped region. Each trench has two sidewall surfaces in parallel alignment with each other. A blocking layer is formed on the sidewalls and the bottom of each trench. Then a P type dopant is obliquely implanting into the sidewall surfaces to form P type doped regions. The blocking layer is then removed. The bottom of the trenches is then etched to remove any implanted P type dopants. The implants are diffused and the trenches are filled.

Owner:THIRD DIMENSION 3D SEMICON

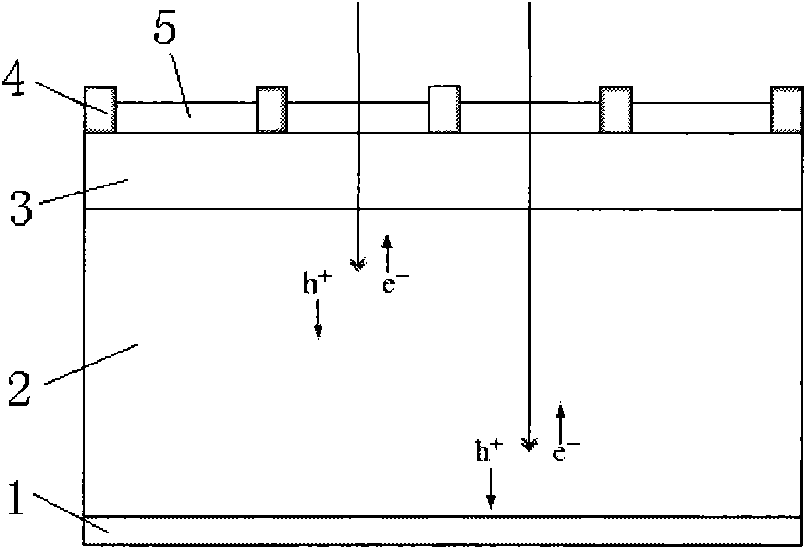

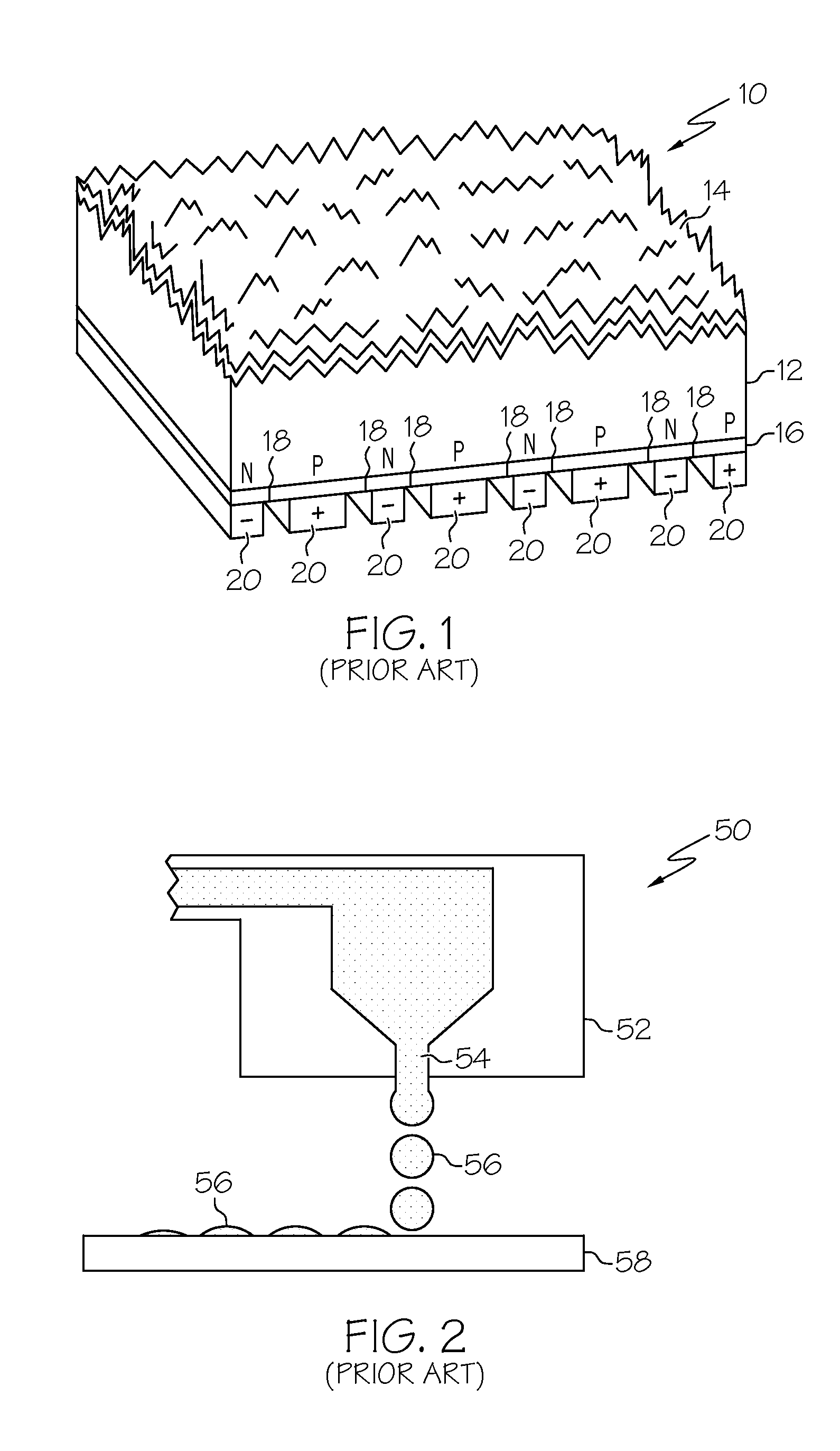

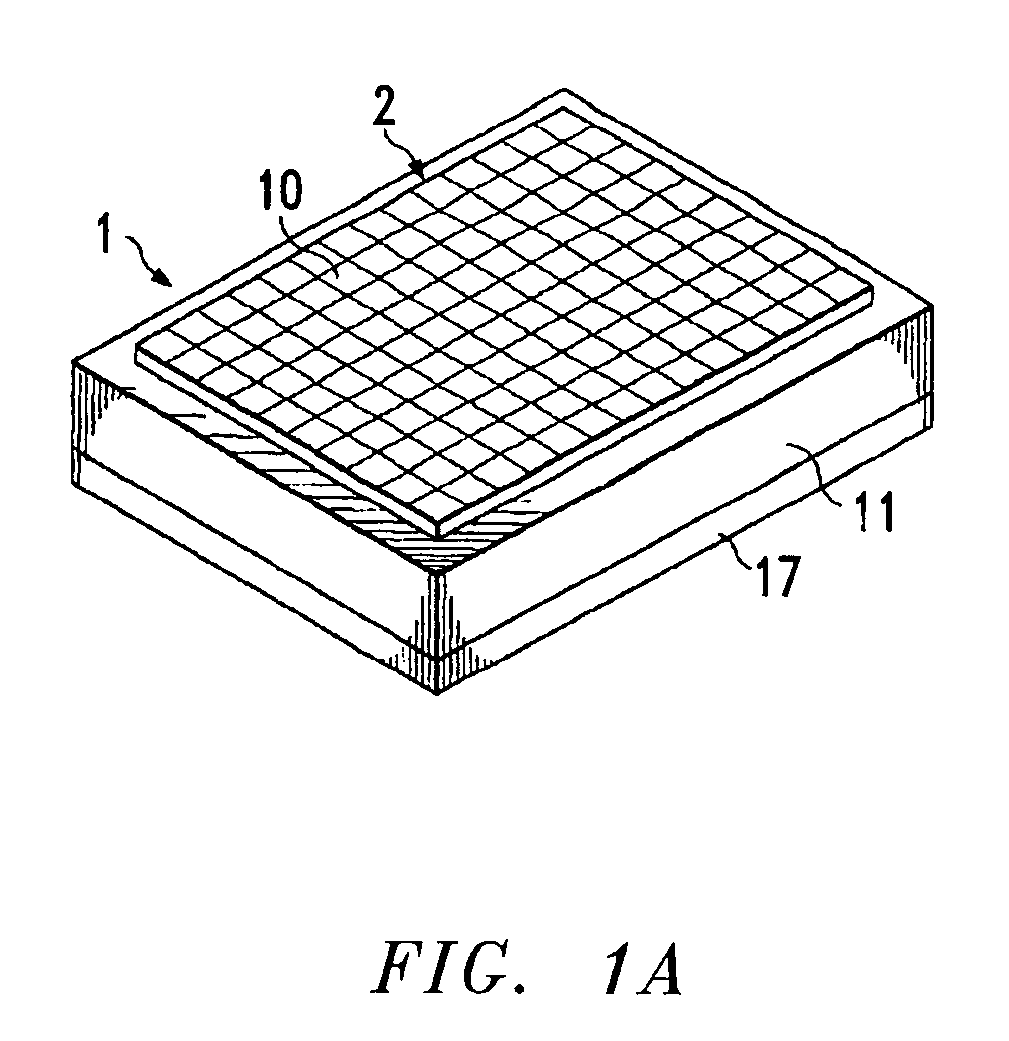

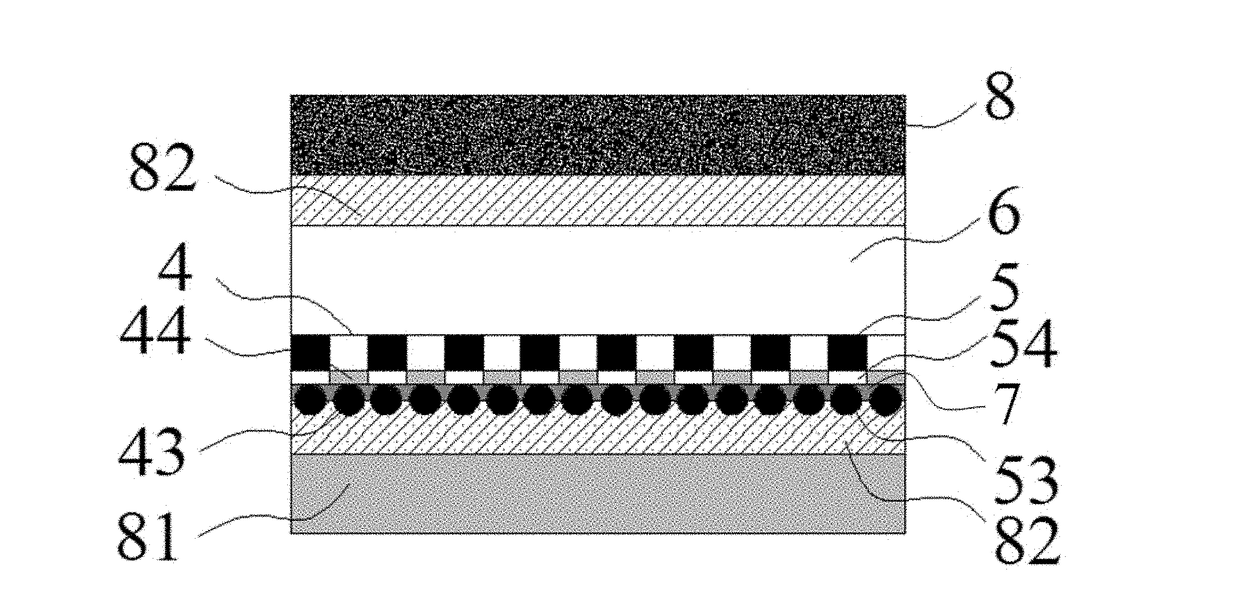

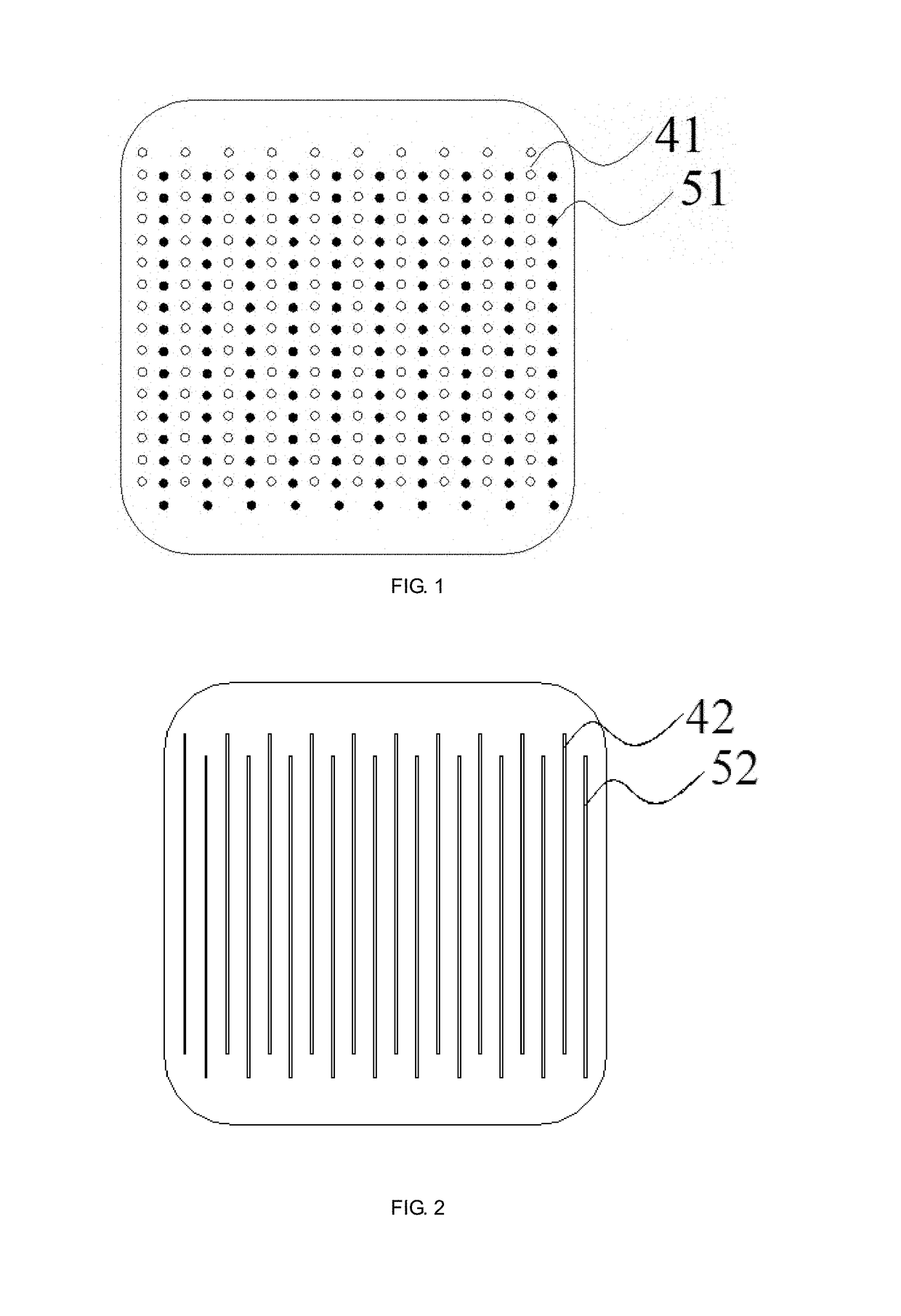

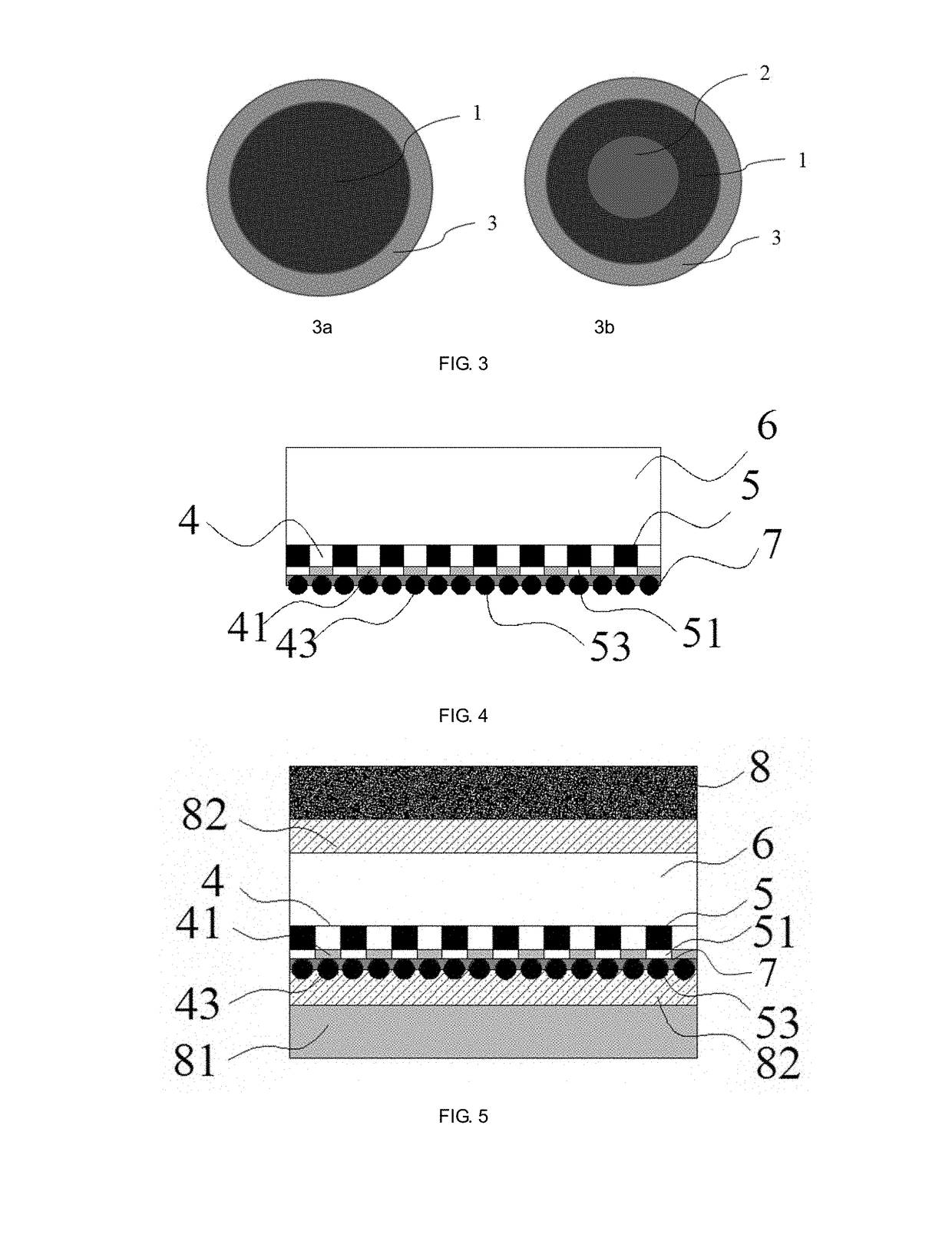

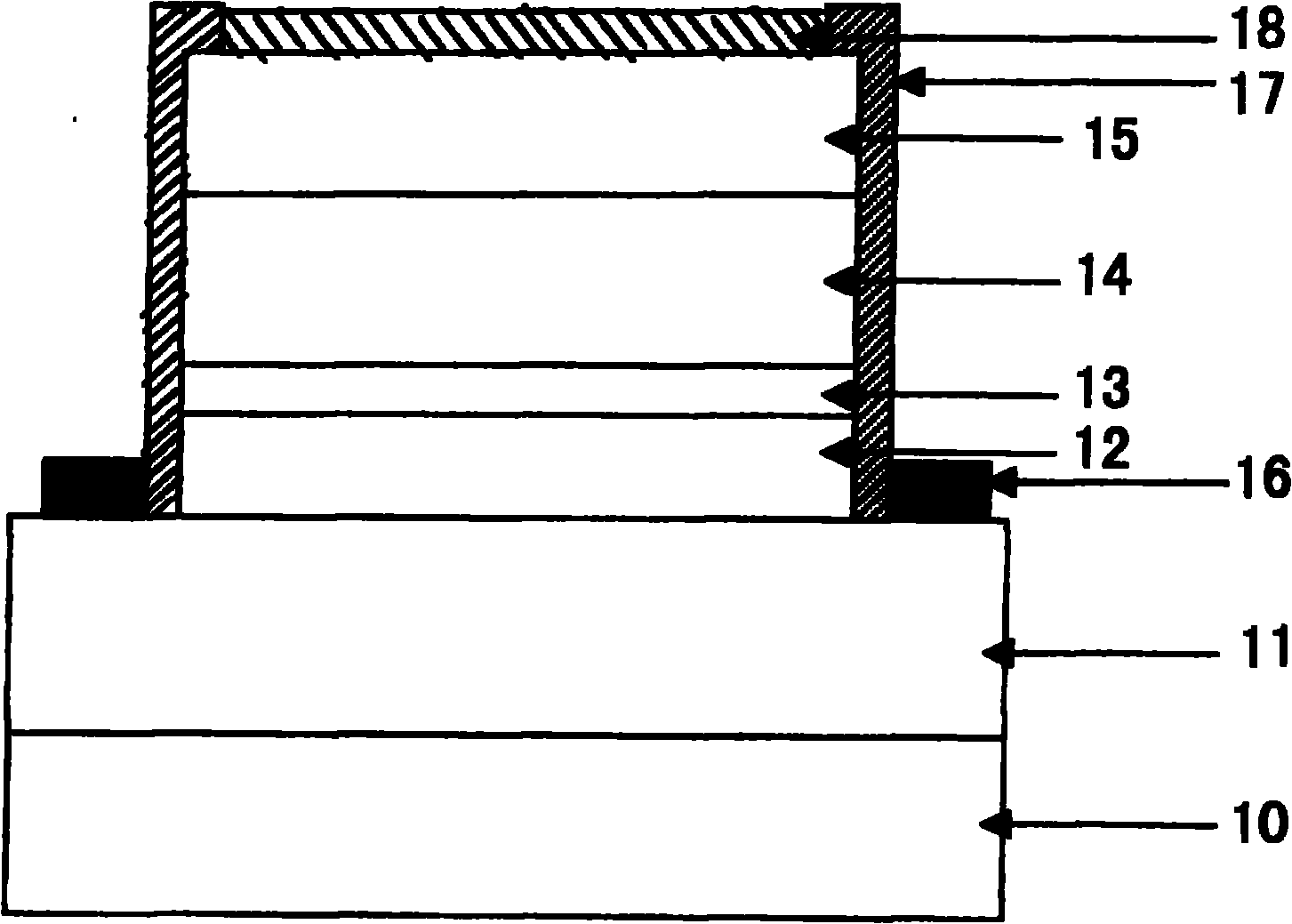

Main-gate-free and high-efficiency back-contact solar cell module, main-gate-free and high-efficiency back-contact solar cell assembly, and preparation process thereof

ActiveUS20170222082A1Reduces electron collection distanceReduced series resistanceFinal product manufacturePV power plantsElectricityCrack resistance

The present invention relates to the field of solar cells, and in particular to a main-gate-free and high-efficiency back-contact solar cell module, a main-gate-free and high-efficiency back-contact solar cell assembly, and a preparation process thereof. The solar cell module, comprising cells and an electrical connection layer, a backlight side of the cells having P-electrodes connected to a P-type doping layer and N-electrodes connected to a N-type doping layer, is characterized in that the electrical connection layer comprises a number of parallel leads each electrically connected to the P-electrodes or the N-electrodes. The present invention has the beneficial effect that a main-gate-free and high-efficiency back-contact solar cell module, a main-gate-free and high-efficiency back-contact solar cell assembly, and a preparation process thereof are provided, which can effectively the short-circuiting of the P-electrodes and the N-electrodes and has the advantages of low cost, high hidden-cracking resistance, high efficiency and high stability.

Owner:JOLYWOOD SUZHOU SUNWATT

Gallium nitride based avalanche detector and preparation method thereof

InactiveCN101814537APromote growthHigh sensitivityFinal product manufactureSemiconductor devicesOhmic contactGallium nitride

The invention relates to a gallium nitride based avalanche detector and a preparation method thereof. The gallium nitride based avalanche detector comprises a substrate, an N-type doped GaN ohmic contact layer, an unintentional doped GaN absorbing layer, an N-type doped Al component gradual changed AlGaN layer, an unintentional doped AlGaN avalanche multiplying layer, a P-type doped AlGaN ohmic contact layer, an N-type ohmic contact electrode and a P-type ohmic contact electrode, wherein the N-type doped GaN ohmic contact layer is prepared on the substrate; the unintentional doped GaN absorbing layer is prepared on the N-type doped GaN ohmic contact layer, and the area of the unintentional doped GaN absorbing layer is smaller than that of the N-type doped GaN ohmic contact layer; the N-type doped Al component gradual changed AlGaN layer is prepared on the unintentional doped GaN absorbing layer; the unintentional doped AlGaN avalanche multiplying layer is prepared on the N-type doped Al component gradual changed AlGaN layer; the P-type doped AlGaN ohmic contact layer is prepared on the unintentional doped AlGaN avalanche multiplying layer; the N-type ohmic contact electrode is prepared on the N-type doped GaN ohmic contact layer; and the P-type ohmic contact electrode is prepared on the P-type doped AlGaN ohmic contact layer.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

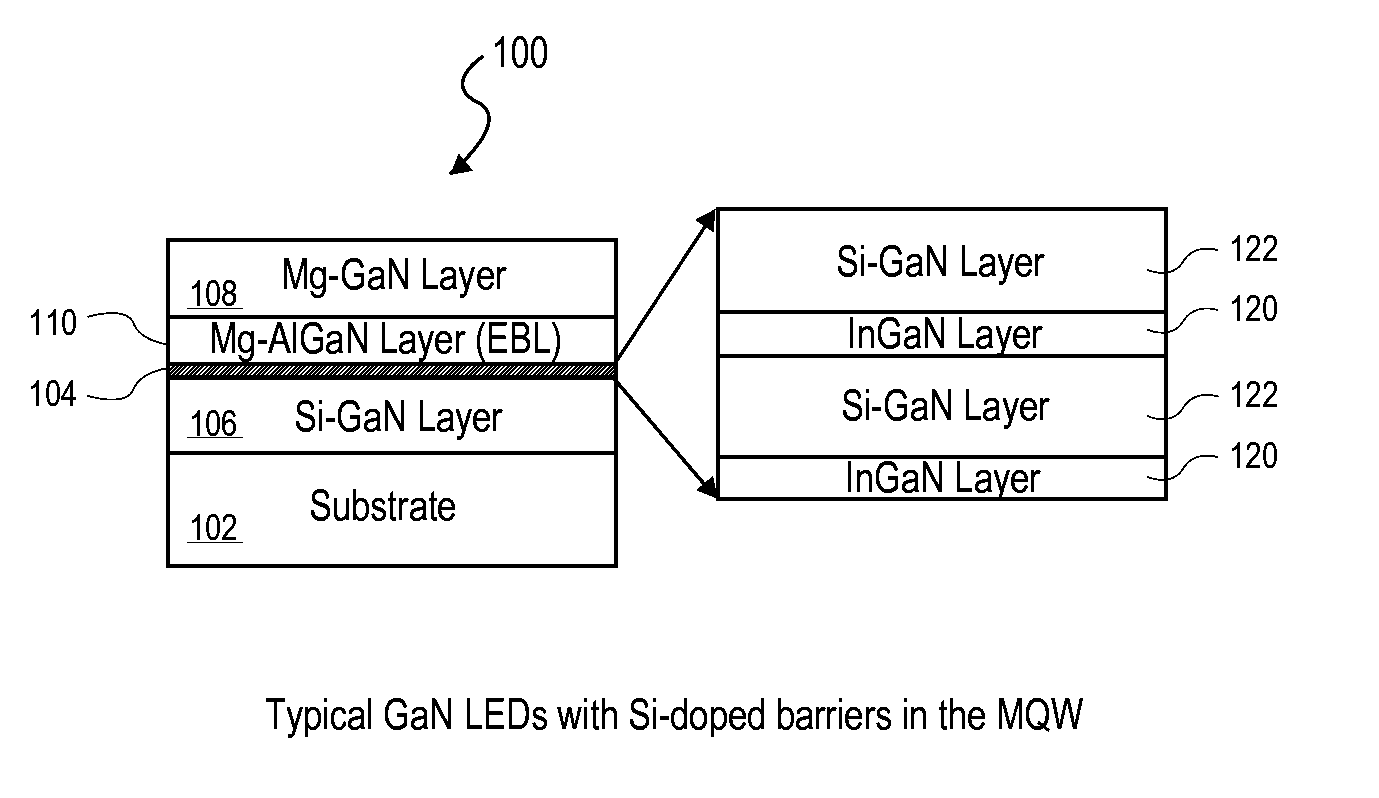

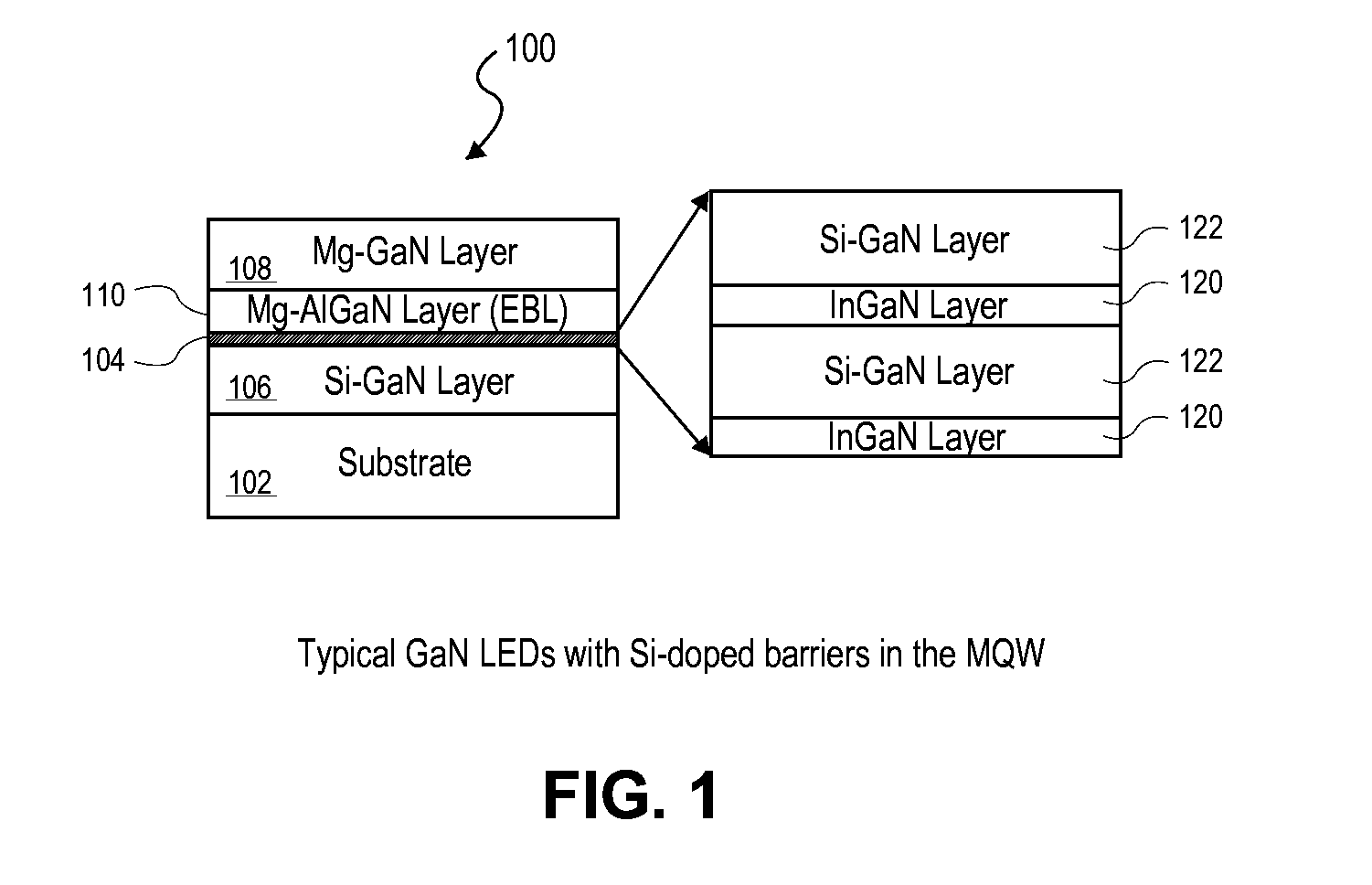

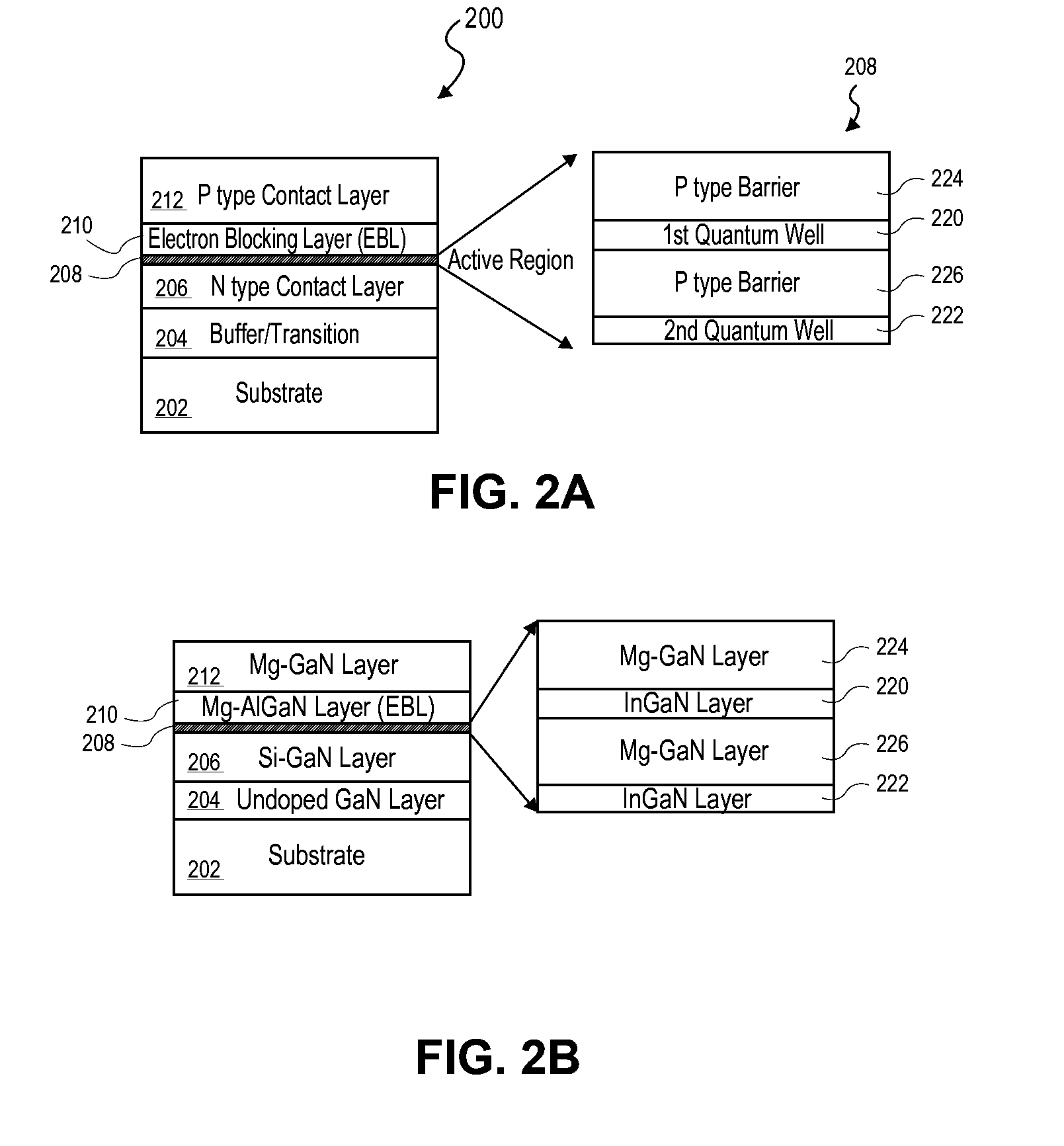

Light emitting diode with enhanced quantum efficiency and method of fabrication

InactiveUS20120235116A1Low costIncrease varietyPolycrystalline material growthConductive materialIndiumAlloy

One embodiment of a quantum well structure comprises an active region including active layers that comprise quantum wells and barrier layers wherein some or all of the active layers are p type doped. P type doping some or all of the active layers improves the quantum efficiency of III-V compound semiconductor light emitting diodes by locating the position of the P-N junction in the active region of the device thereby enabling the dominant radiative recombination to occur within the active region. In one embodiment, the quantum well structure is fabricated in a cluster tool having a hydride vapor phase epitaxial (HVPE) deposition chamber with a eutectic source alloy. In one embodiment, the indium gallium nitride (InGaN) layer and the magnesium doped gallium nitride (Mg—GaN) or magnesium doped aluminum gallium nitride (Mg—AlGaN) layer are grown in separate chambers by a cluster tool to avoid indium and magnesium cross contamination. Doping of group III-nitrides by hydride vapor phase epitaxy using group III-metal eutectics is also described. In one embodiment, a source is provided for HVPE deposition of a p-type or an n-type group III-nitride epitaxial film, the source including a liquid phase mechanical (eutectic) mixture with a group III species. In one embodiment, a method is provided for performing HVPE deposition of a p-type or an n-type group III-nitride epitaxial film, the method including using a liquid phase mechanical (eutectic) mixture with a group III species.

Owner:APPLIED MATERIALS INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com