Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

64 results about "P i n diode" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A p-i-n diode is a p-n junction with a doping profile tailored so that an intrinsic layer, the 'i region,' is sandwiched between a p layer and an n layer.

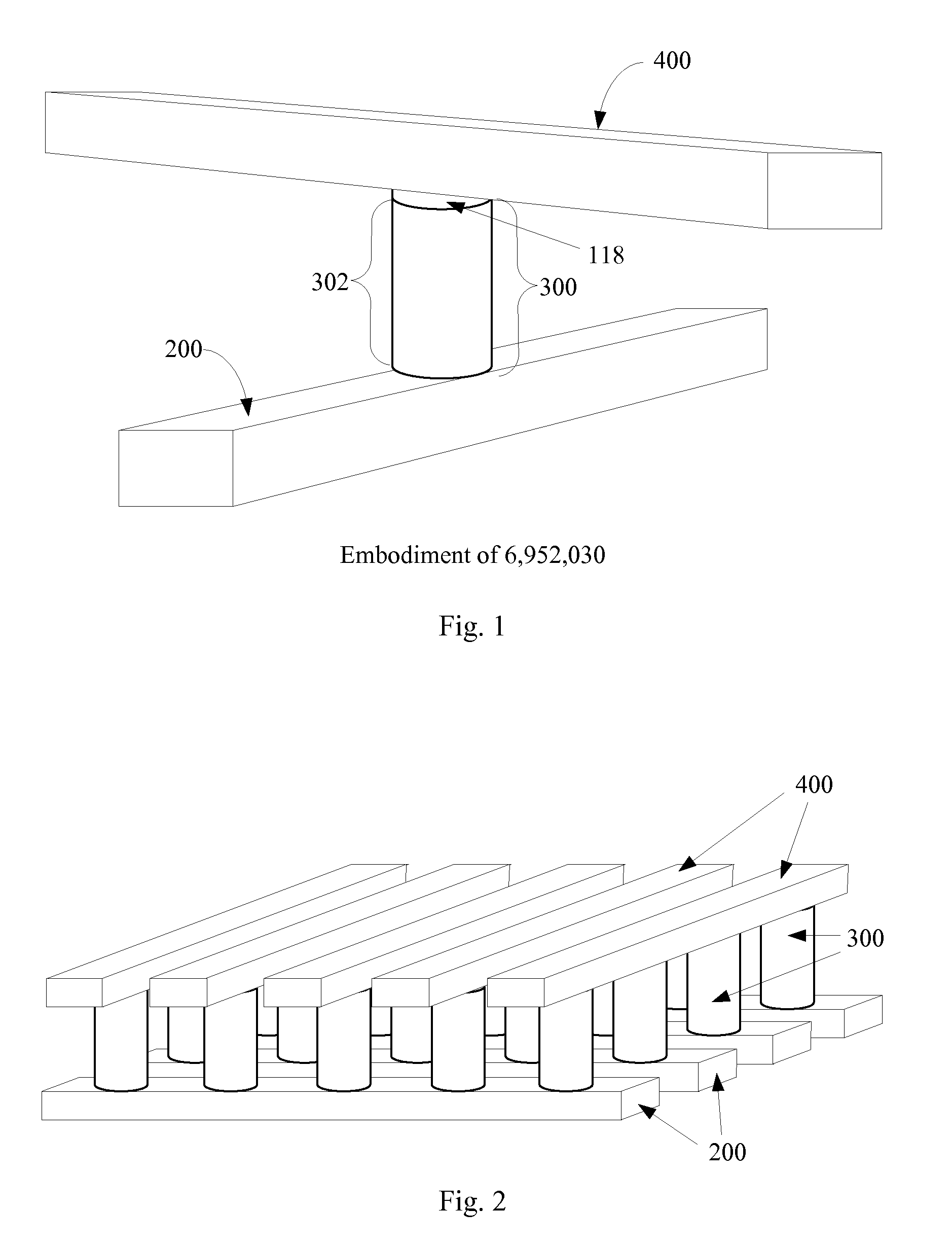

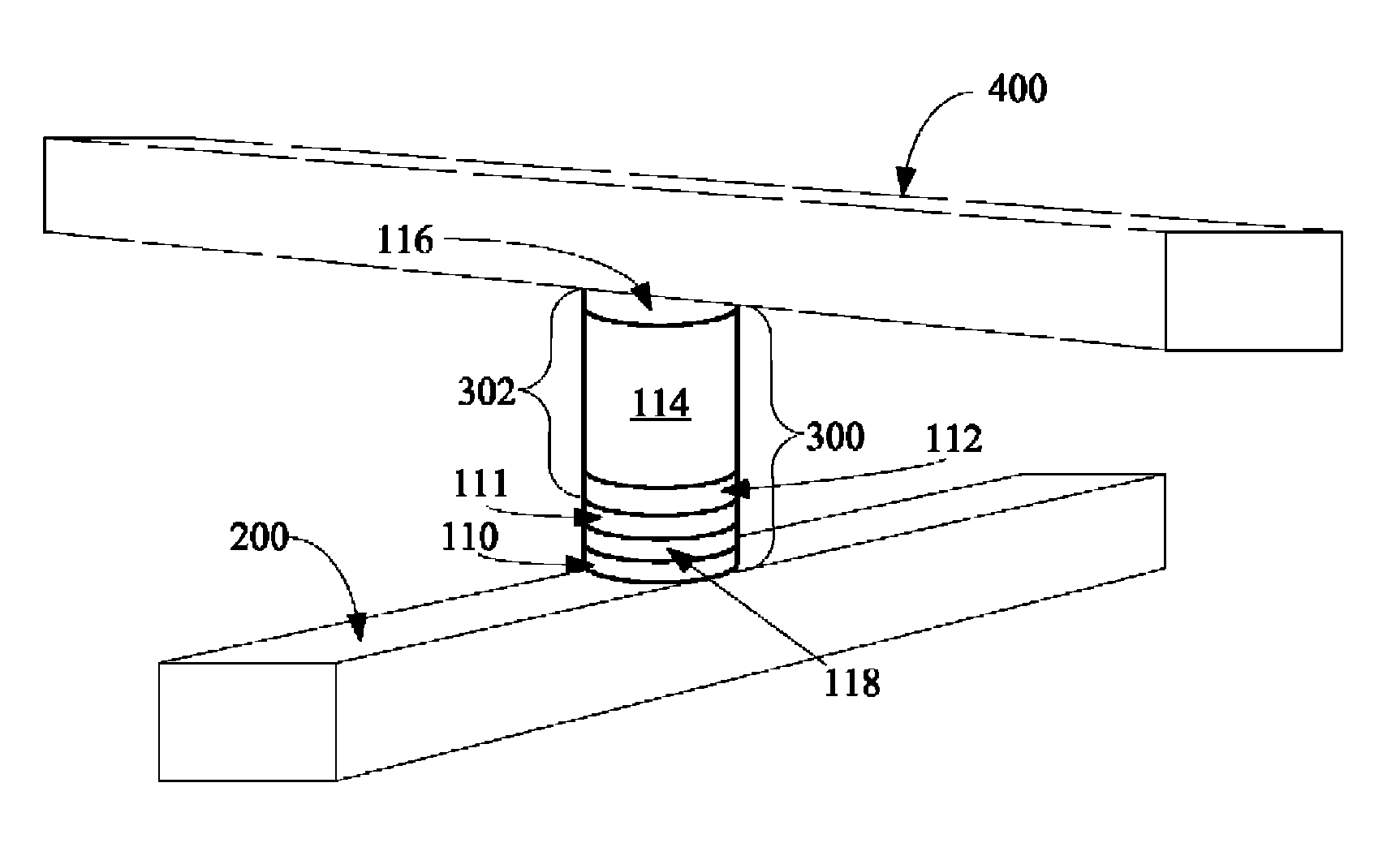

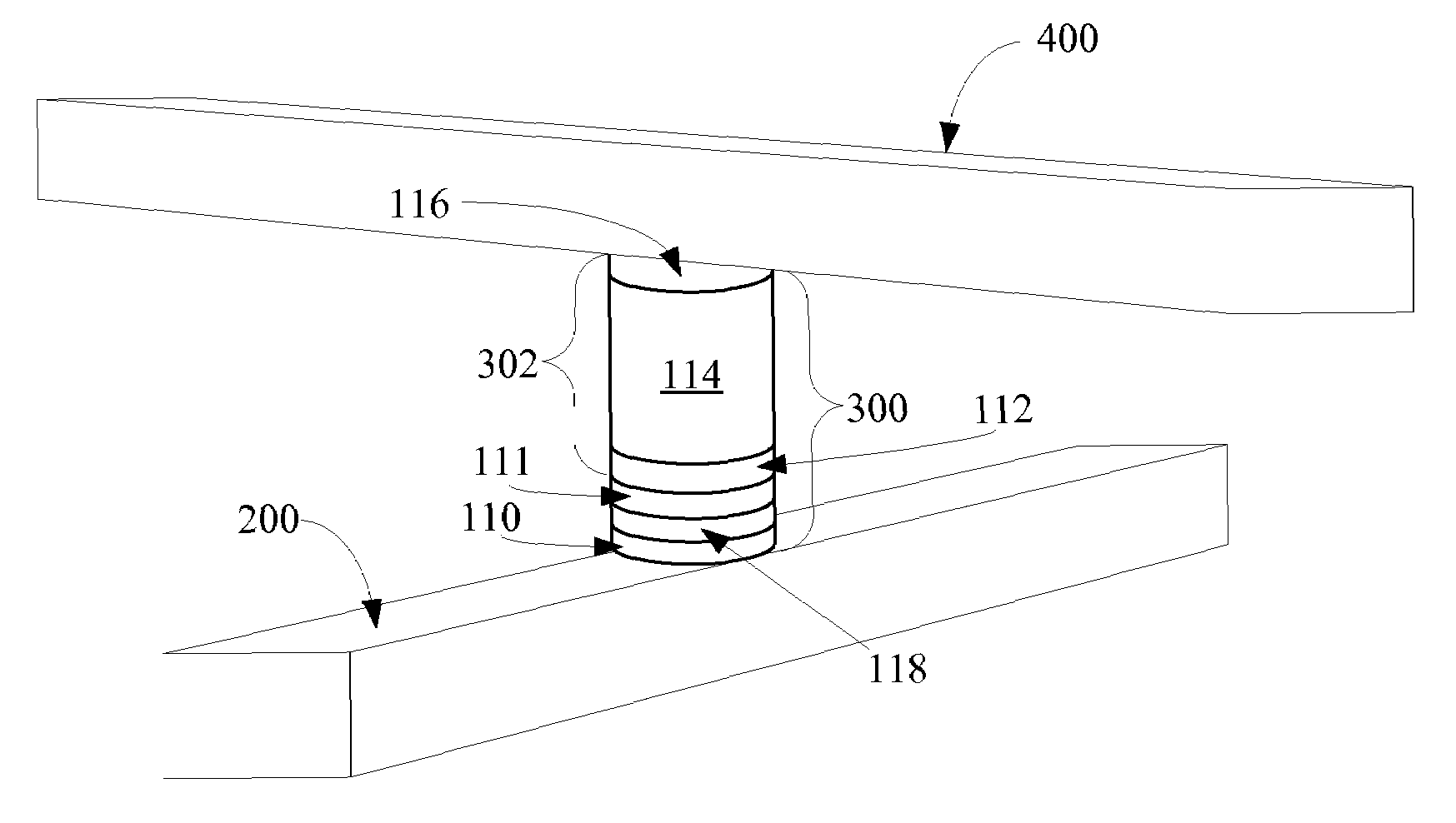

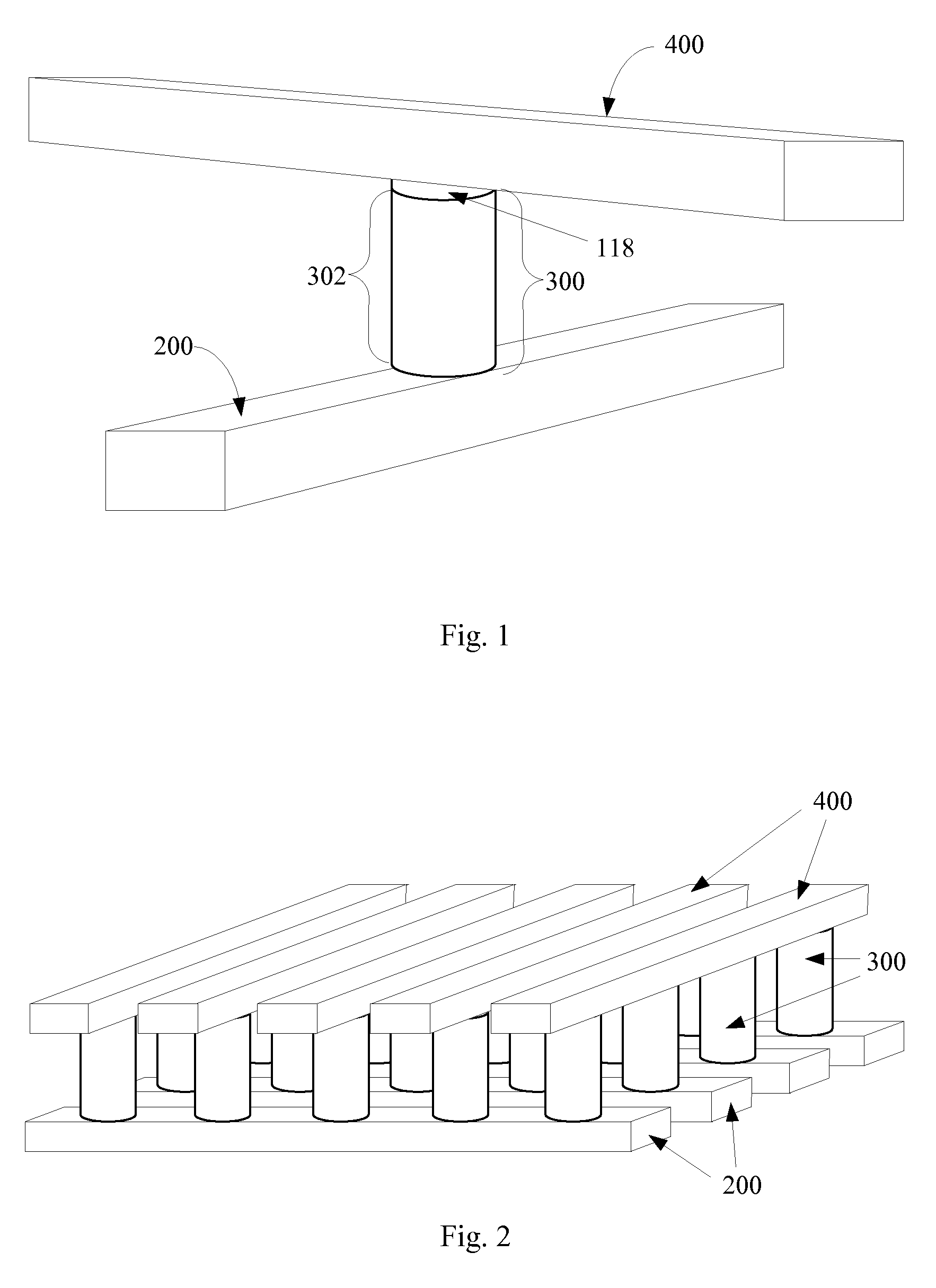

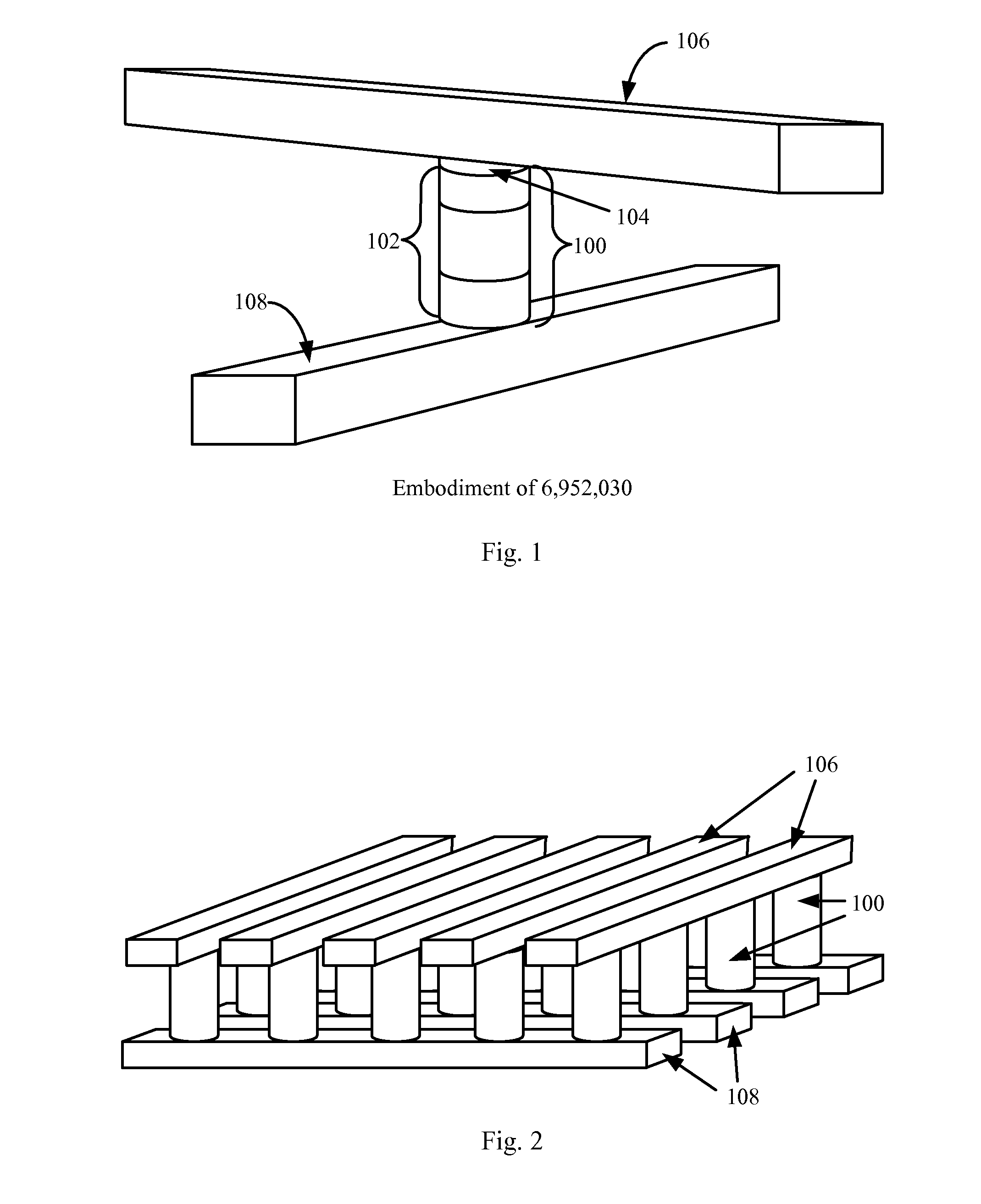

Method to form upward pointing p-i-n diodes having large and uniform current

A method is disclosed to form an upward-pointing p-i-n diode formed of deposited silicon, germanium, or silicon-germanium. The diode has a bottom heavily doped p-type region, a middle intrinsic or lightly doped region, and a top heavily doped n-type region. The top heavily doped p-type region is doped with arsenic, and the semiconductor material of the diode is crystallized in contact with an appropriate silicide, germanide, or silicide-germanide. A large array of such upward-pointing diodes can be formed with excellent uniformity of current across the array when a voltage above the turn-on voltage of the diodes is applied. This diode is advantageously used in a monolithic three dimensional memory array.

Owner:SANDISK TECH LLC

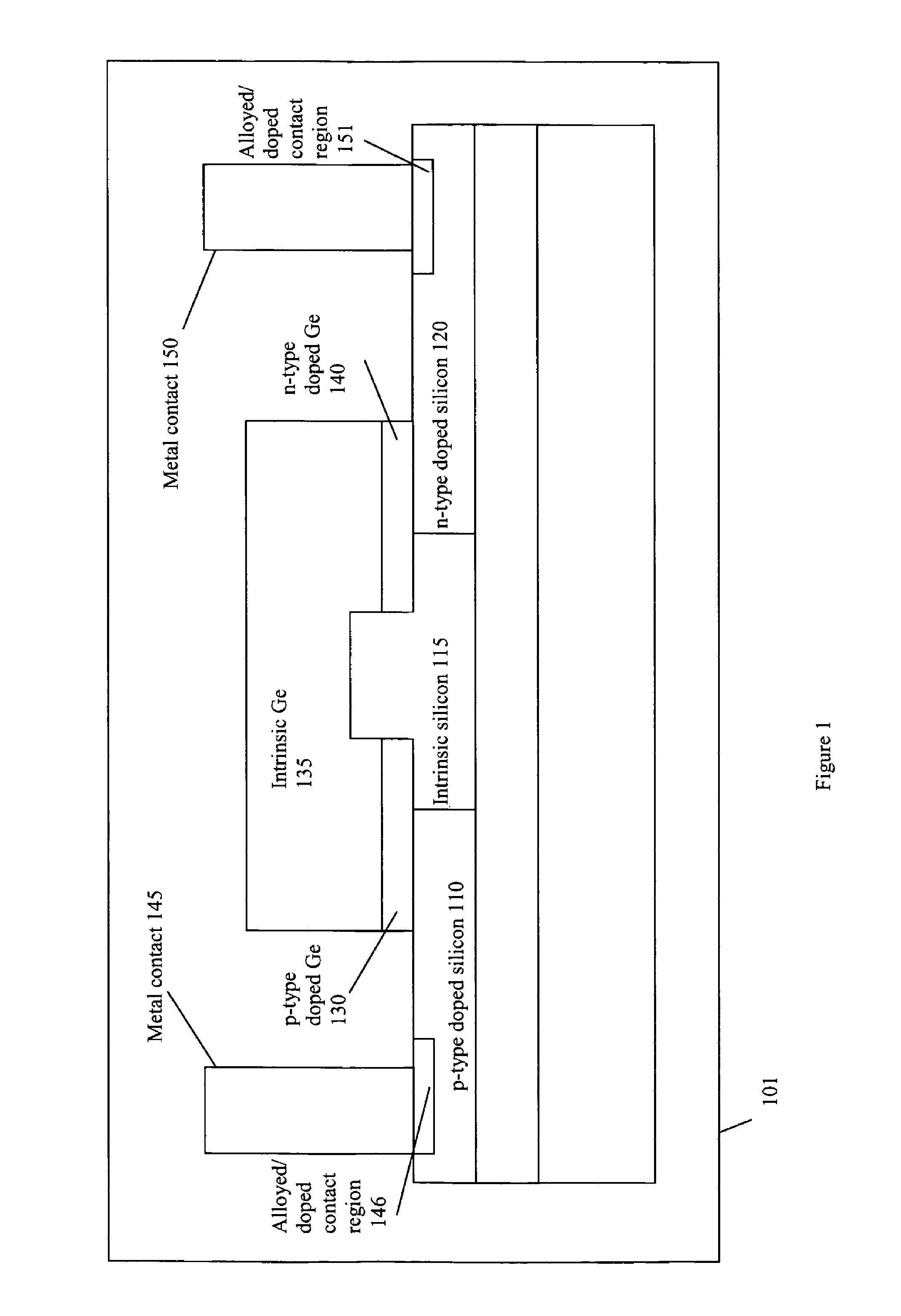

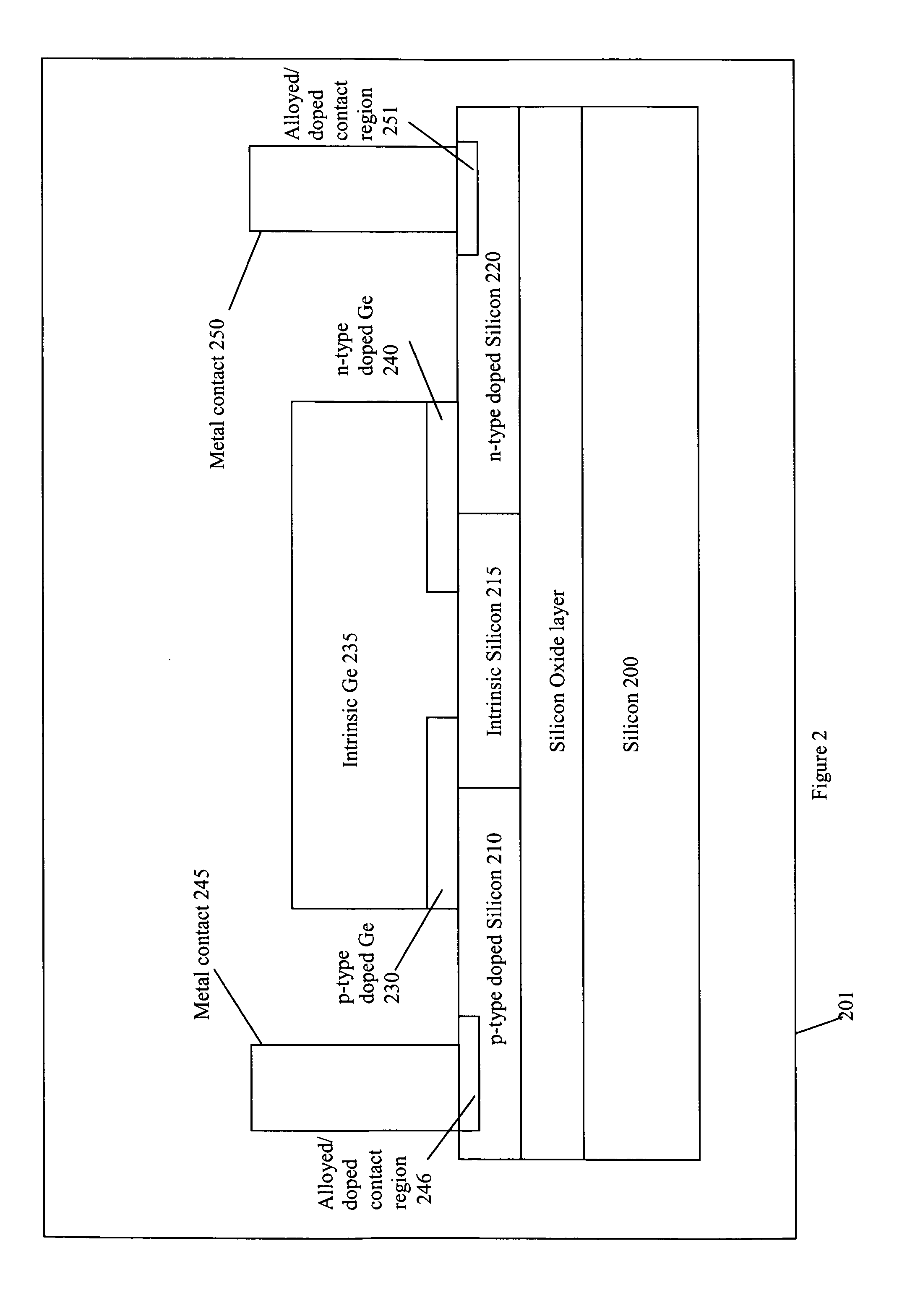

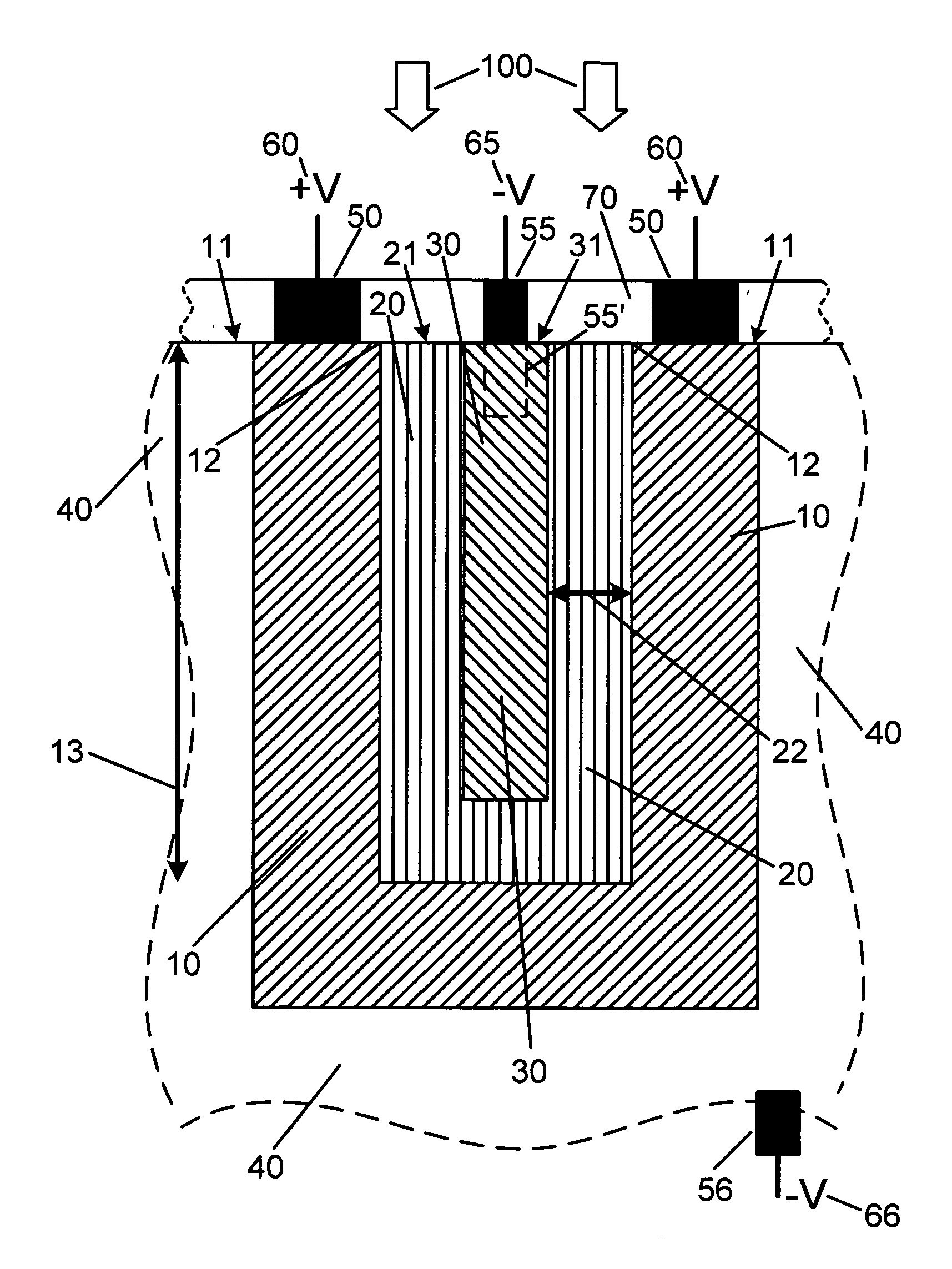

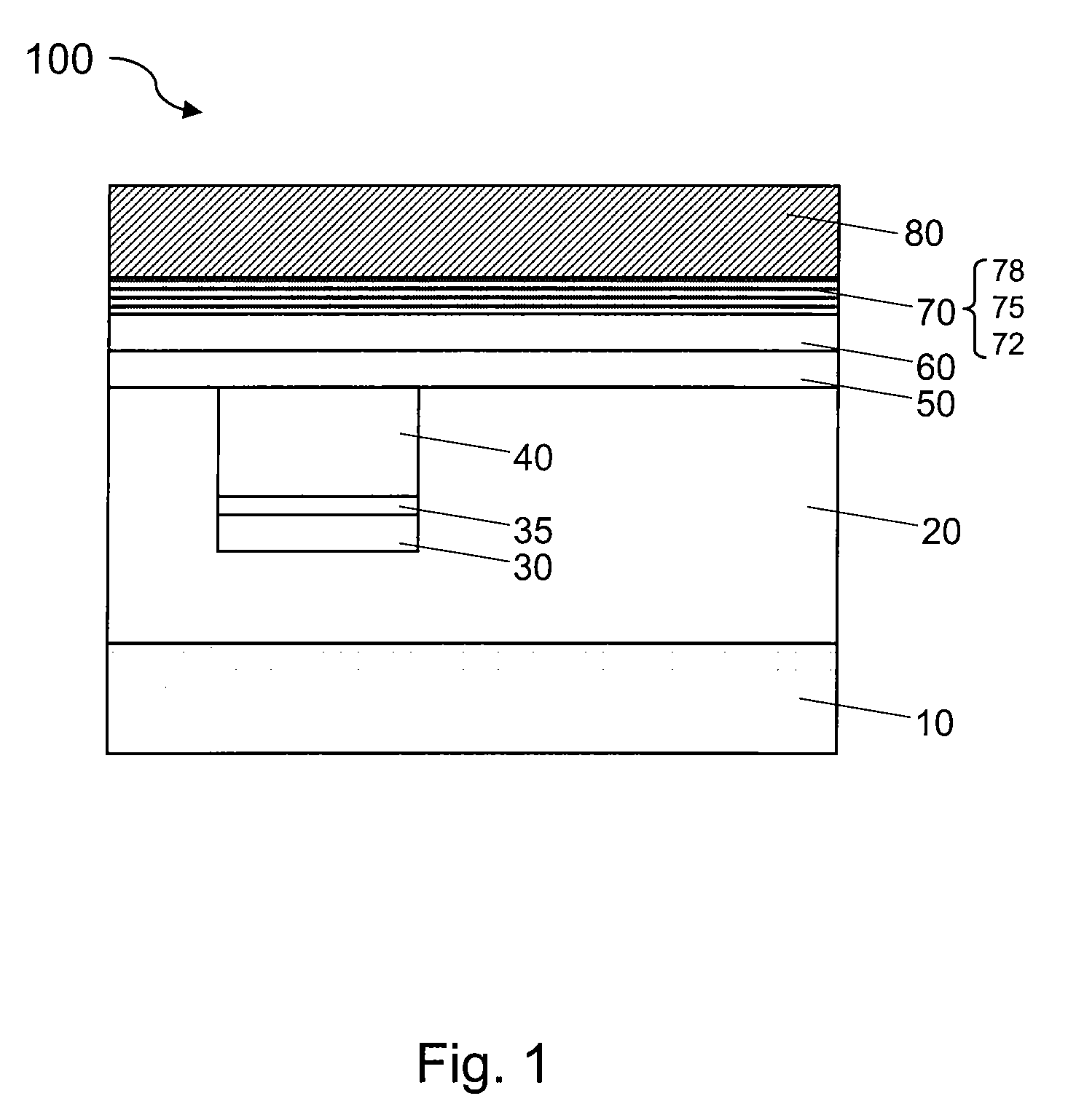

Germanium silicon heterostructure photodetectors

ActiveUS7397101B1Good electrical contactSemiconductor/solid-state device manufacturingPhotovoltaic energy generationPhotovoltaic detectorsPhotodetector

A horizontal germanium silicon heterostructure photodetector comprising a horizontal germanium p-i-n diode disposed over a horizontal parasitic silicon p-i-n diode uses silicon contacts for electrically coupling to the germanium p-i-n through the p-type doped and n-type doped regions in the silicon p-i-n without requiring direct physical contact to germanium material. The current invention may be optically coupled to on-chip and / or off-chip optical waveguide through end-fire or evanescent coupling. In some cases, the doping of the germanium p-type doped and / or n-type doped region may be accomplished based on out-diffusion of dopants in the doped silicon material of the underlying parasitic silicon p-i-n during high temperature steps in the fabrication process such as, the germanium deposition step(s), cyclic annealing, contact annealing and / or dopant activation.

Owner:CISCO TECH INC

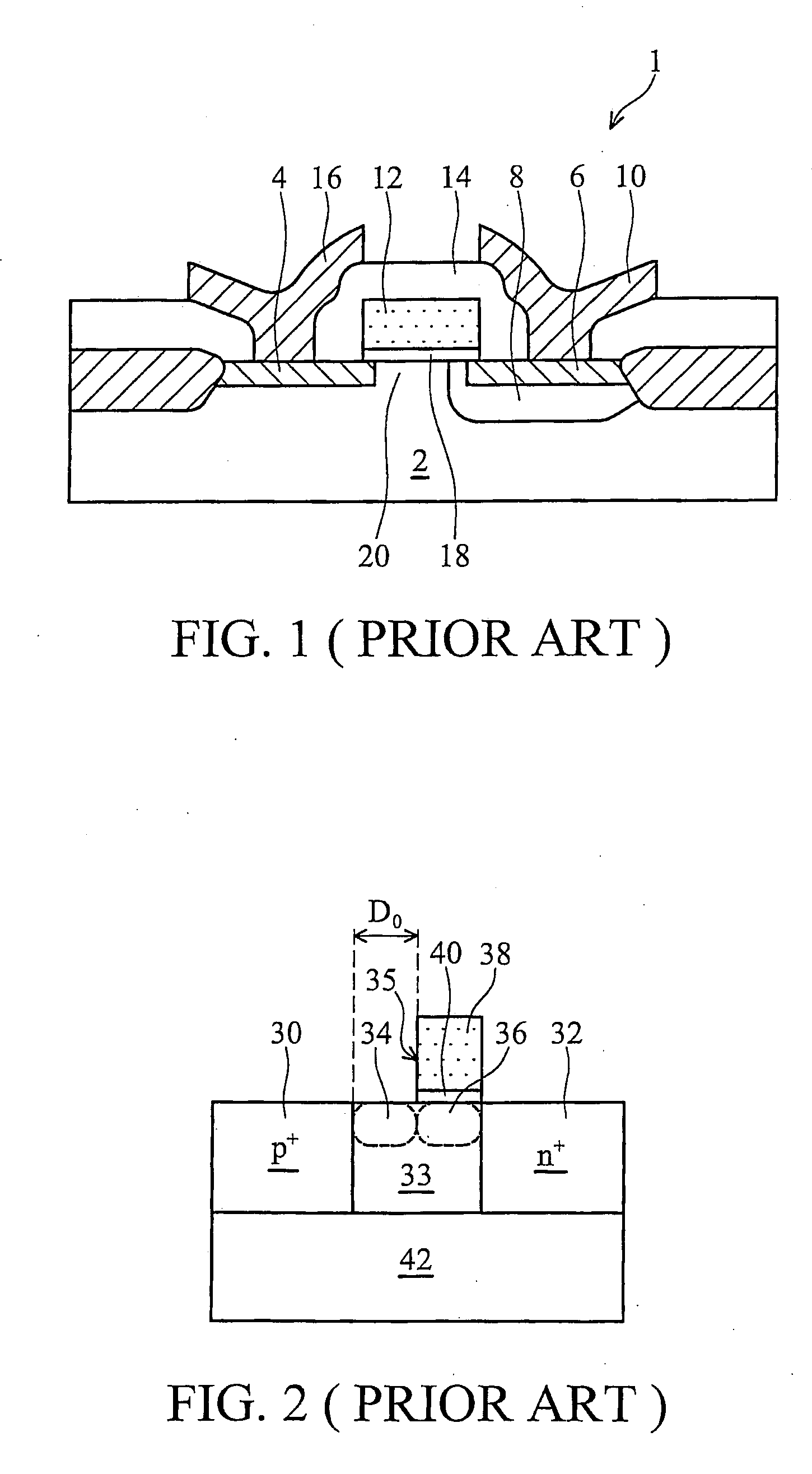

Self-aligned gated p-i-n diode for ultra-fast switching

A gated p-i-n diode and a method for forming the same. The gated p-i-n diode comprises: a semiconductor substrate; a gate dielectric over the semiconductor substrate; a gate electrode on the gate dielectric; a source gate spacer and a drain gate spacer along respective edges of the gate dielectric and the gate electrode; a source doped with a first type of dopant substantially under the source gate spacer wherein the source has a horizontal distance from a first edge of the gate electrode; a drain doped with the opposite type of the source substantially under the drain spacer and substantially aligned horizontally with a second edge of the gate electrode; a source silicide adjacent the source; and a drain silicide adjacent the drain.

Owner:TAIWAN SEMICON MFG CO LTD

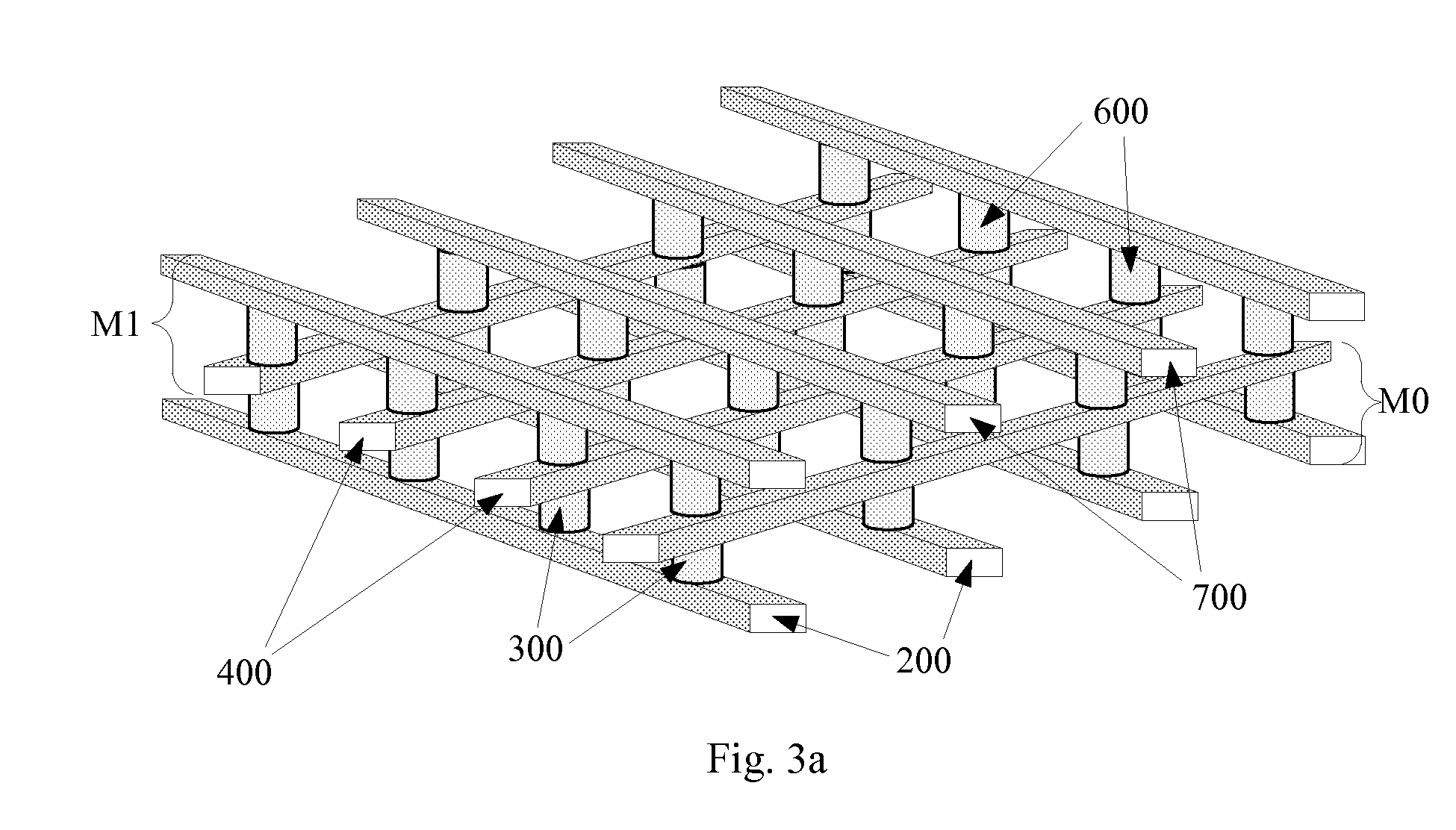

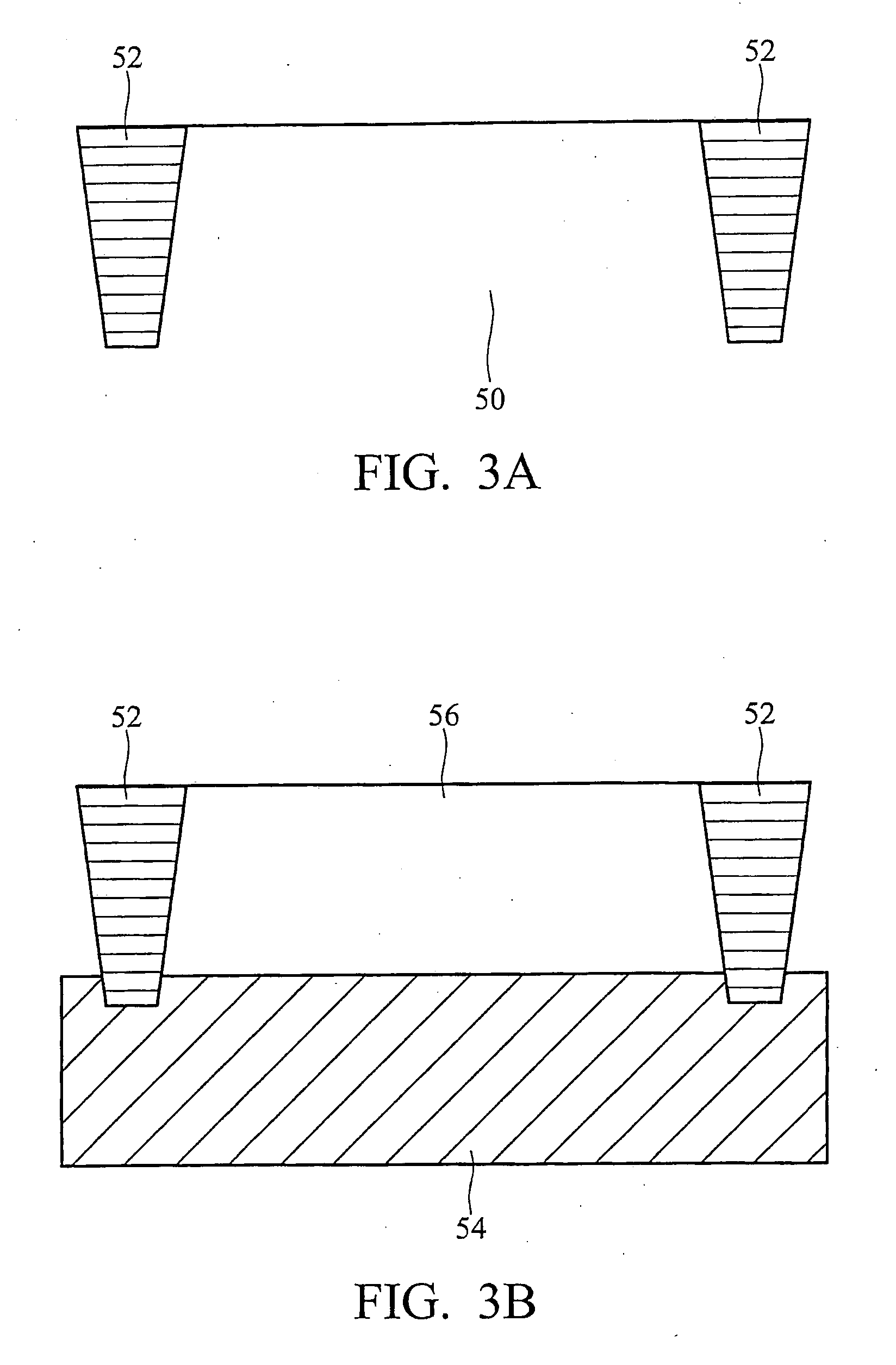

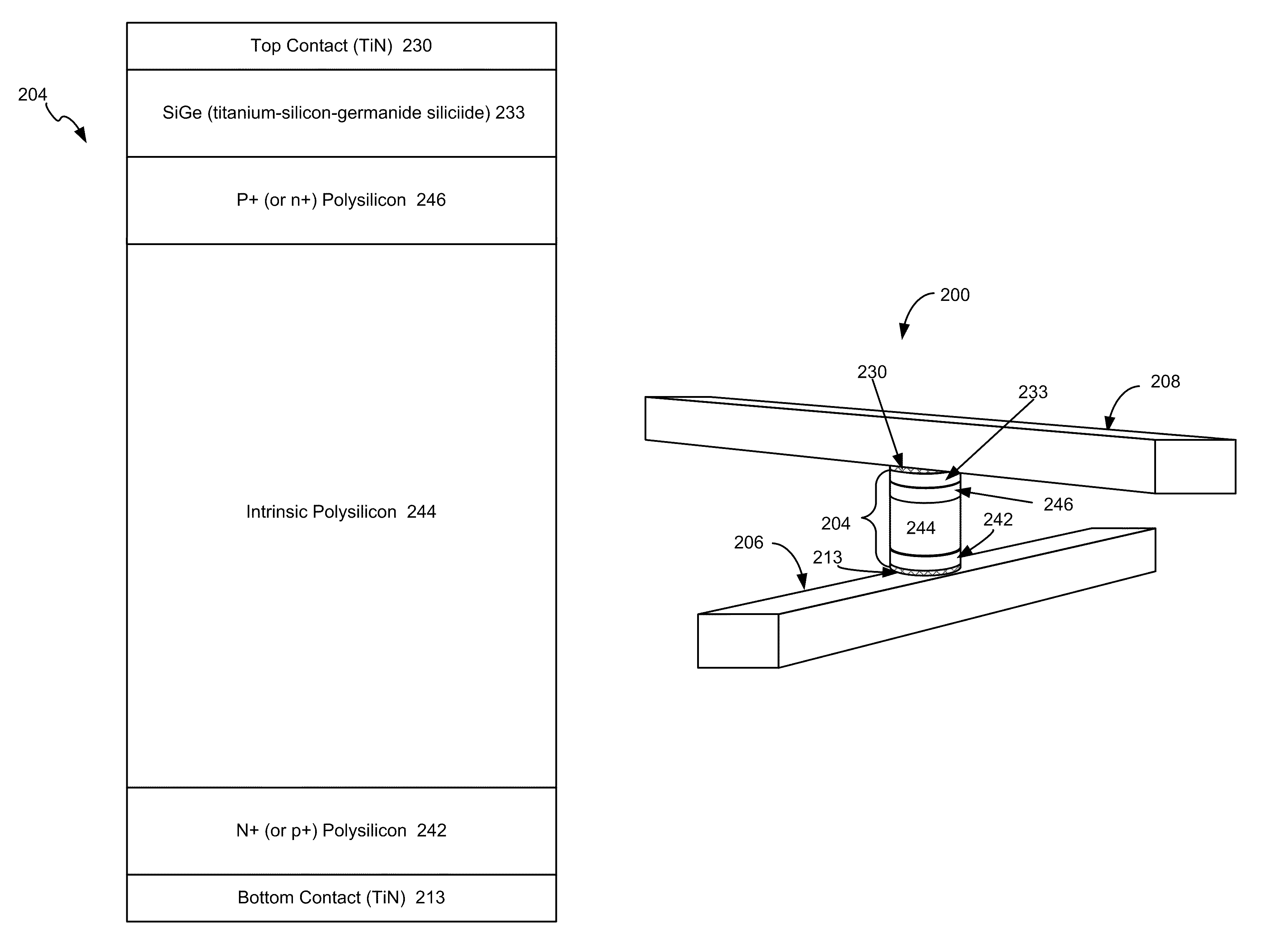

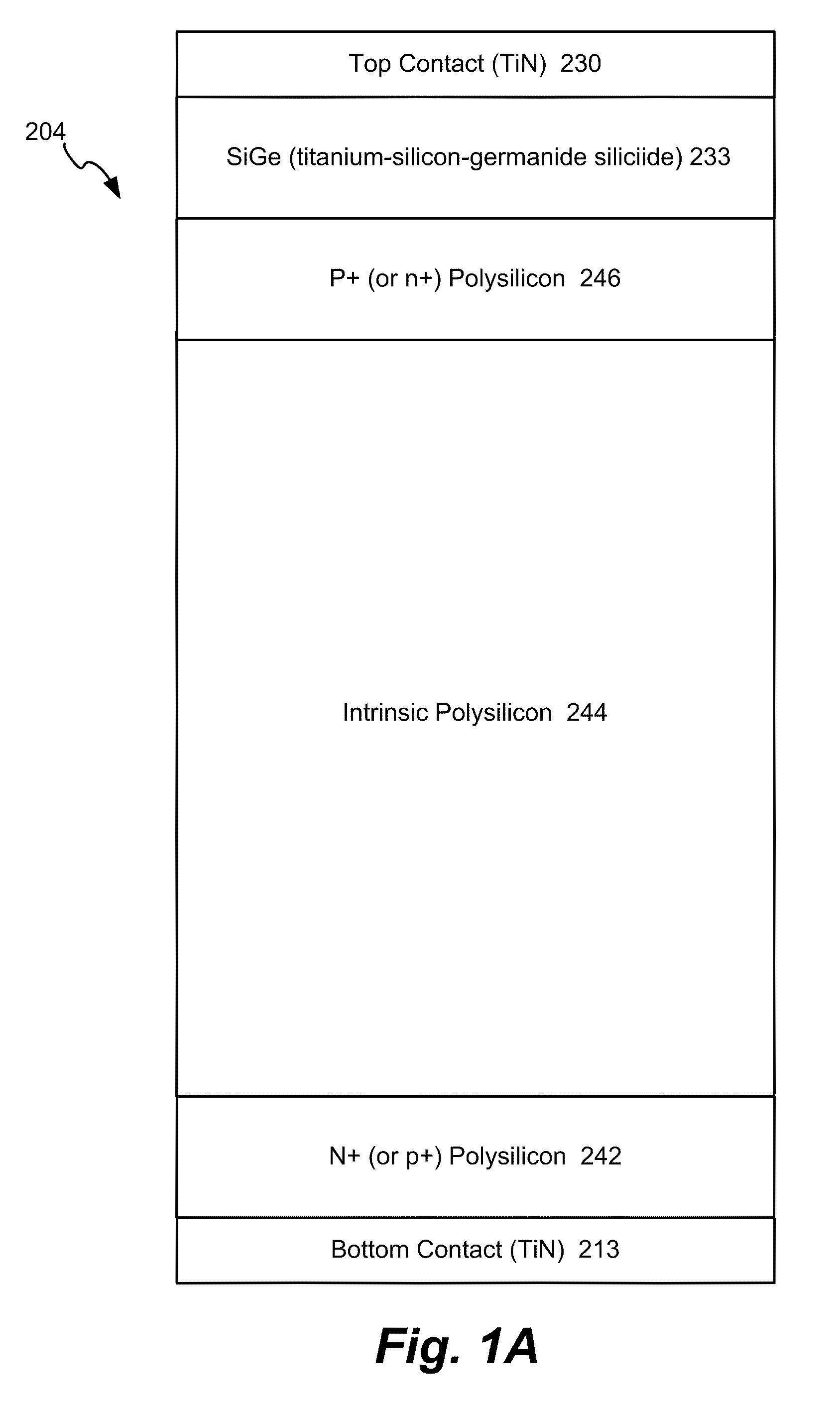

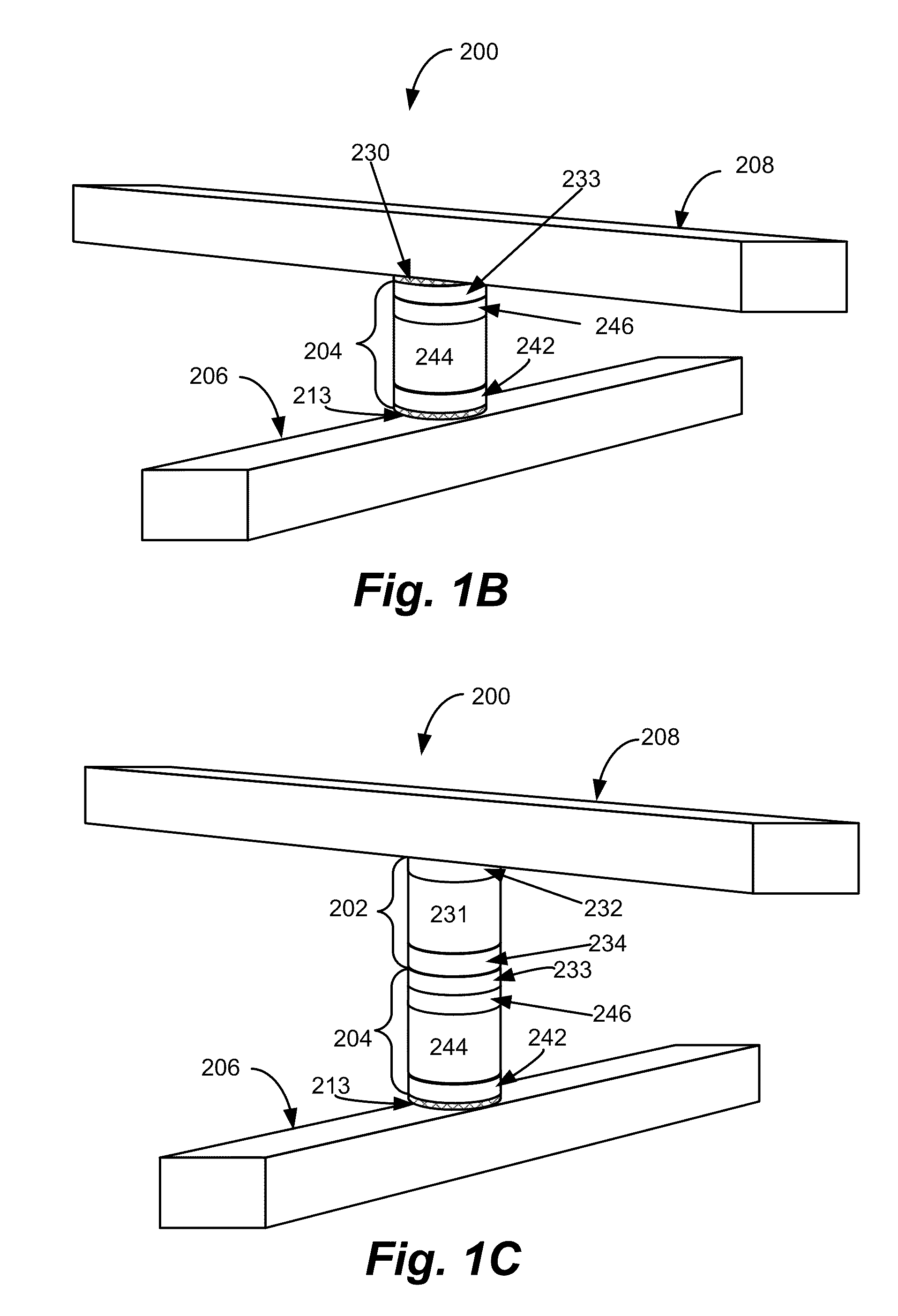

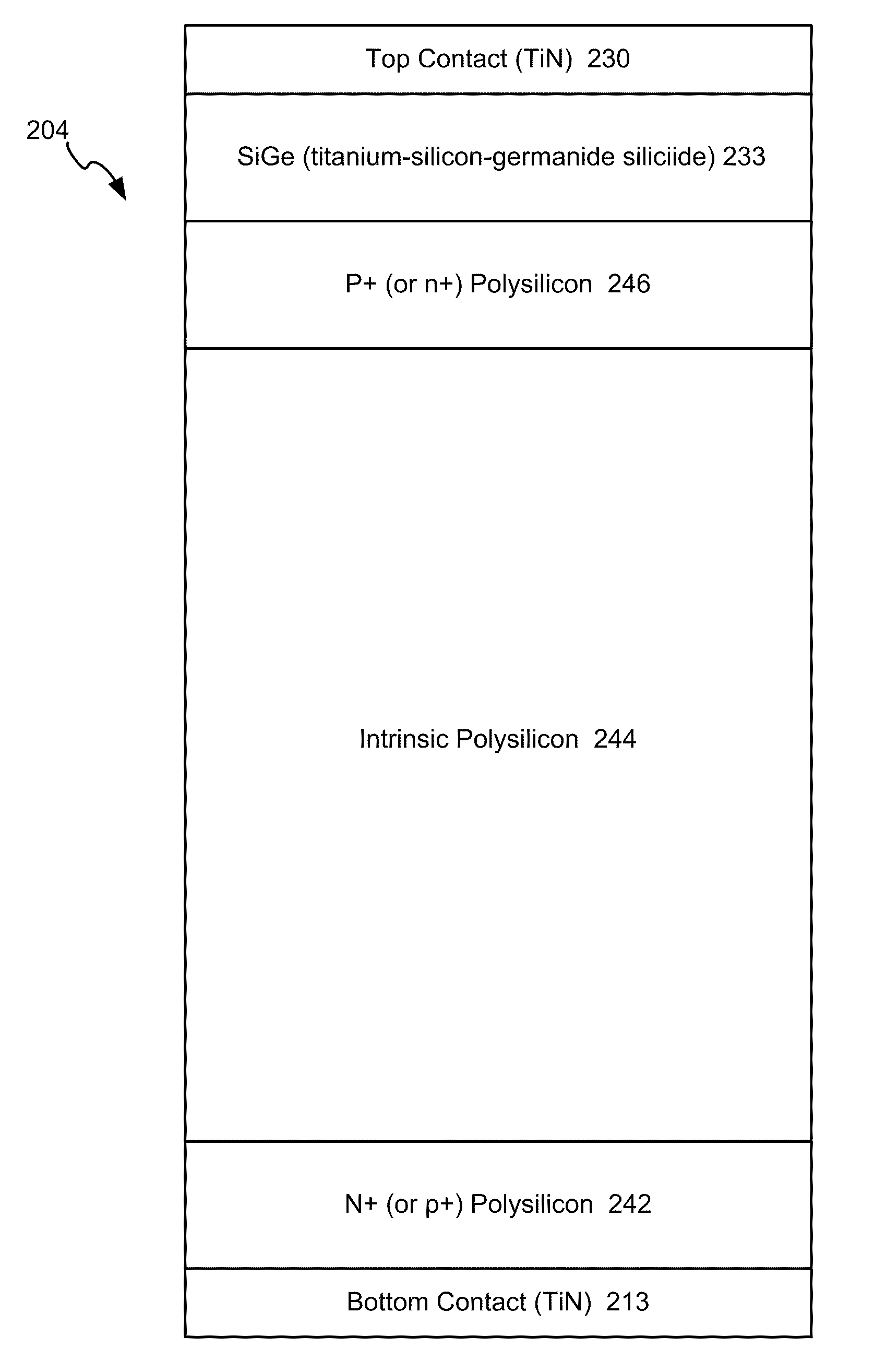

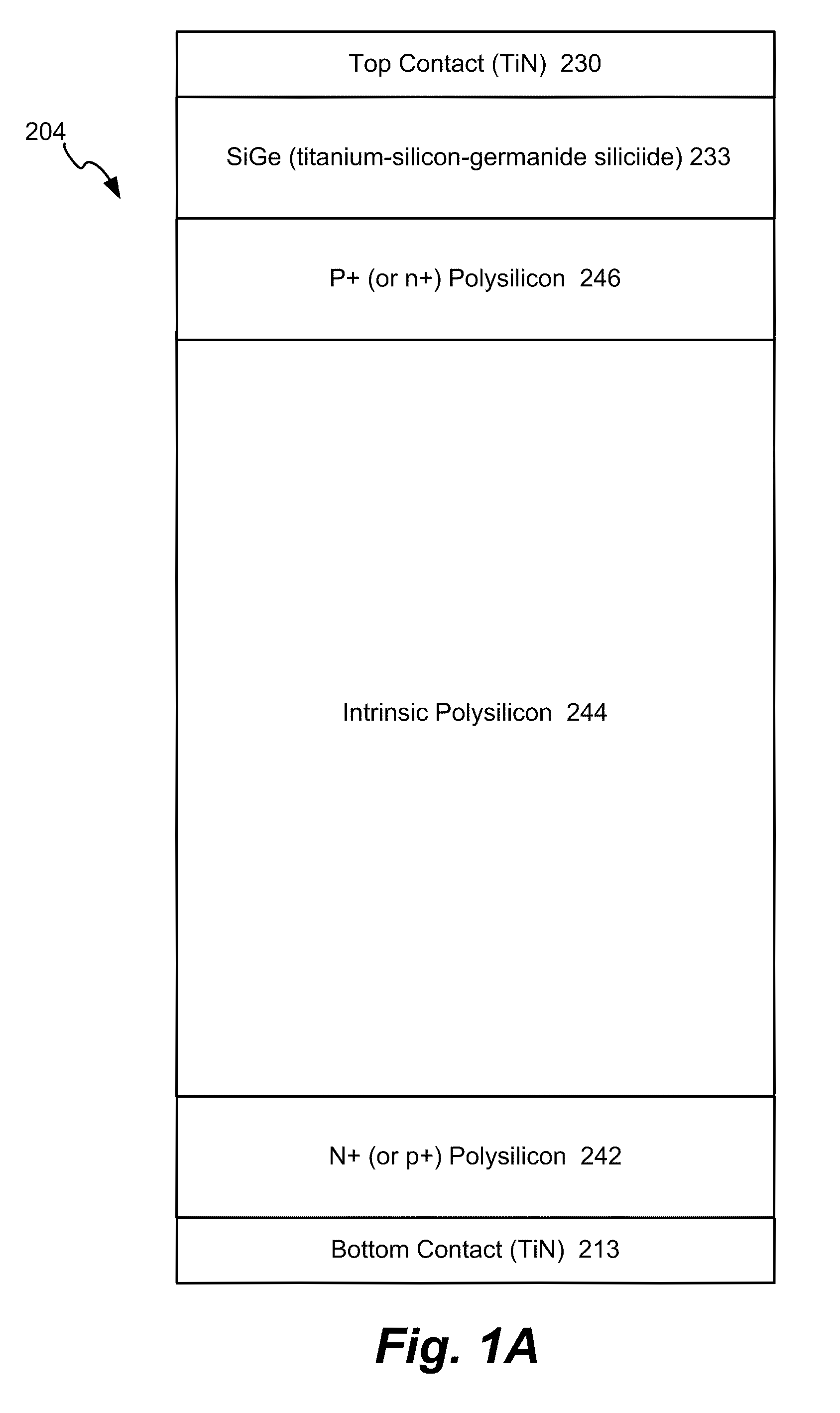

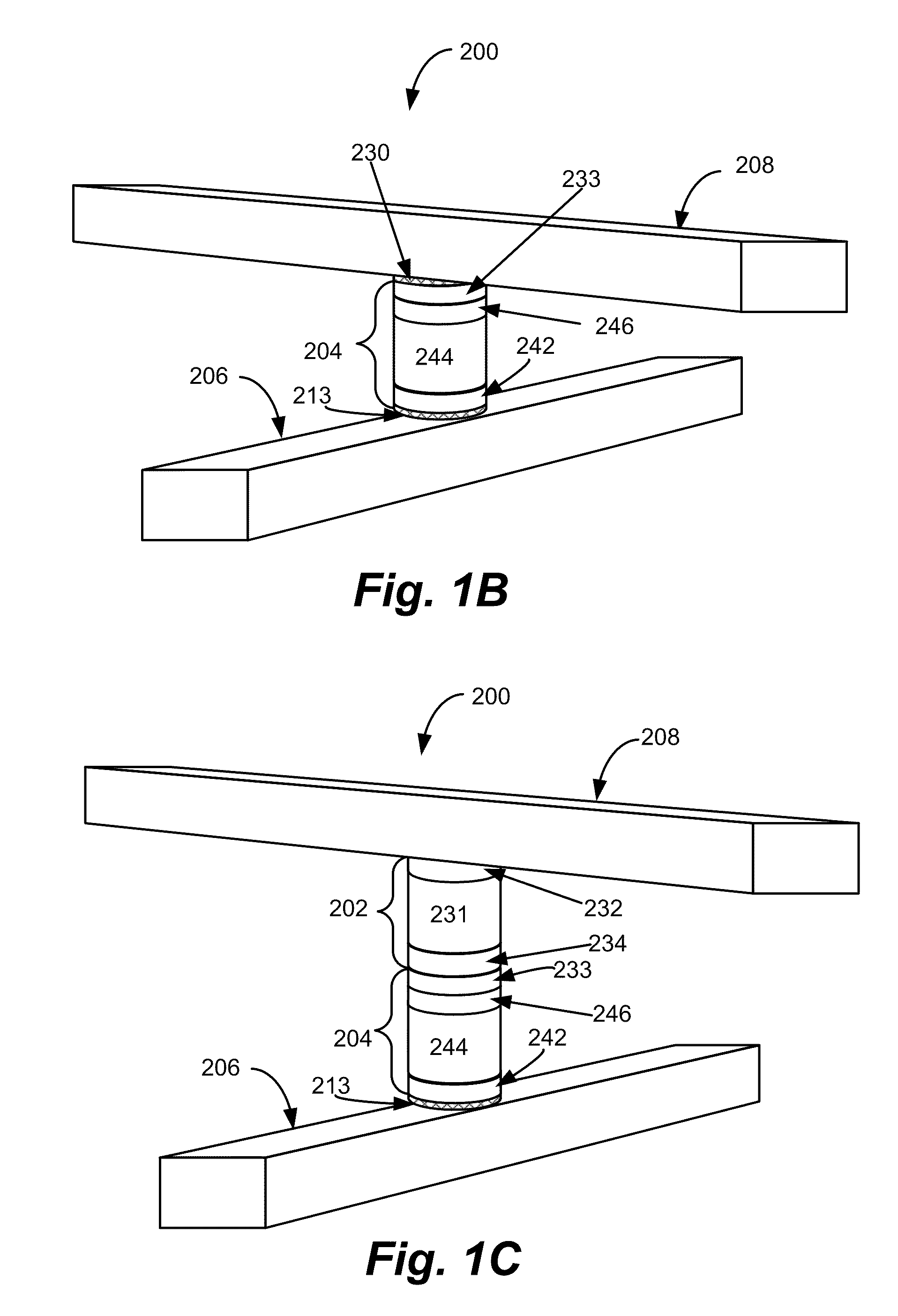

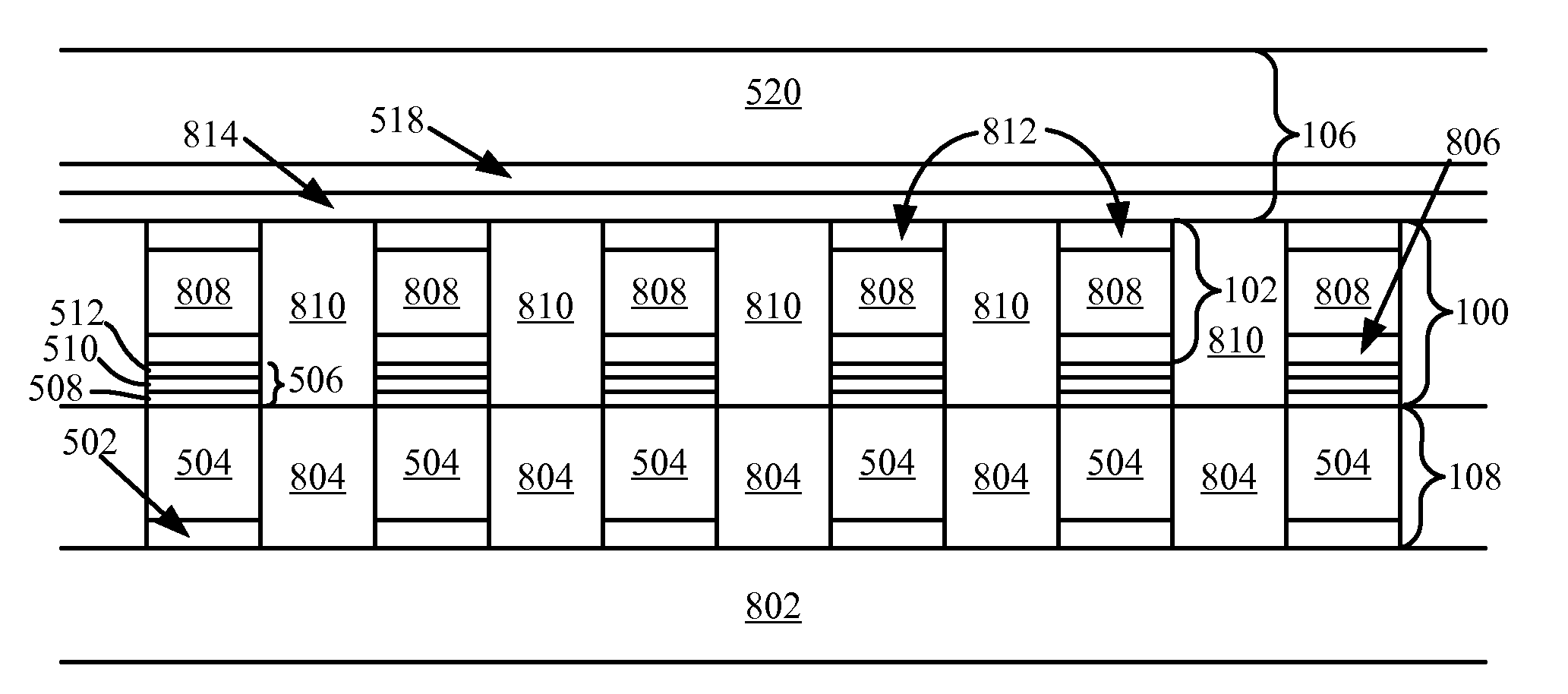

3D polysilicon diode with low contact resistance and method for forming same

ActiveUS8207064B2Solid-state devicesSemiconductor/solid-state device manufacturingPower flowReverse bias

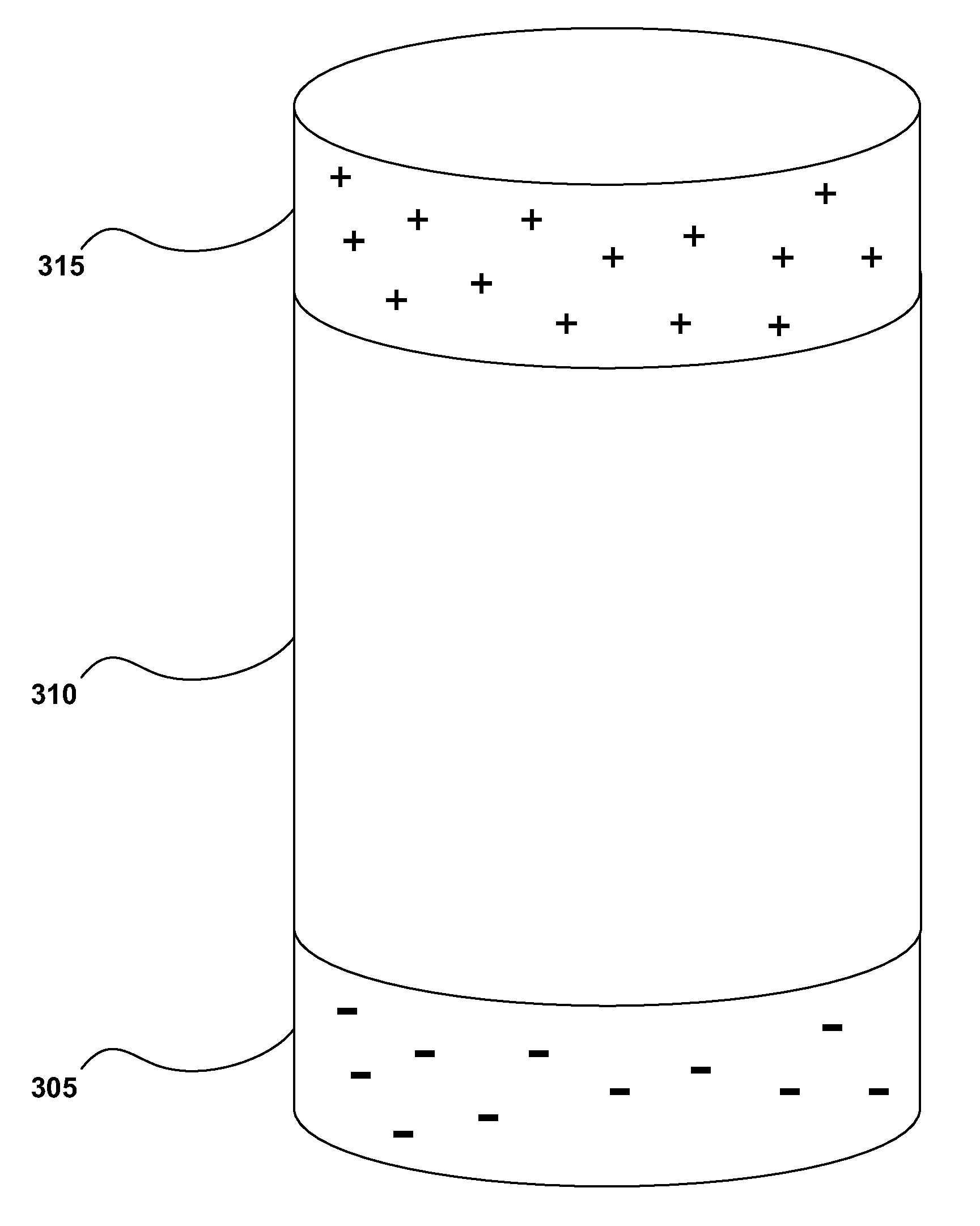

A semiconductor p-i-n diode and method for forming the same are described herein. In one aspect, a SiGe region is formed between a region doped to have one conductivity (either p+ or n+) and an electrical contact to the p-i-n diode. The SiGe region may serve to lower the contact resistance, which may increase the forward bias current. The doped region extends below the SiGe region such that it is between the SiGe region and an intrinsic region of the diode. The p-i-n diode may be formed from silicon. The doped region below the SiGe region may serve to keep the reverse bias current from increasing as result of the added SiGe region. In one embodiment, the SiGe is formed such that the forward bias current of an up-pointing p-i-n diode in a memory array substantially matches the forward bias current of a down-pointing p-i-n diode which may achieve better switching results when these diodes are used with the R / W material in a 3D memory array.

Owner:SANDISK TECH LLC

High mobility monolithic p-i-n diodes

InactiveUS20110136327A1Reduce interfaceHigh electron mobilitySemiconductor/solid-state device manufacturingChemical vapor deposition coatingHigh current densityDopant

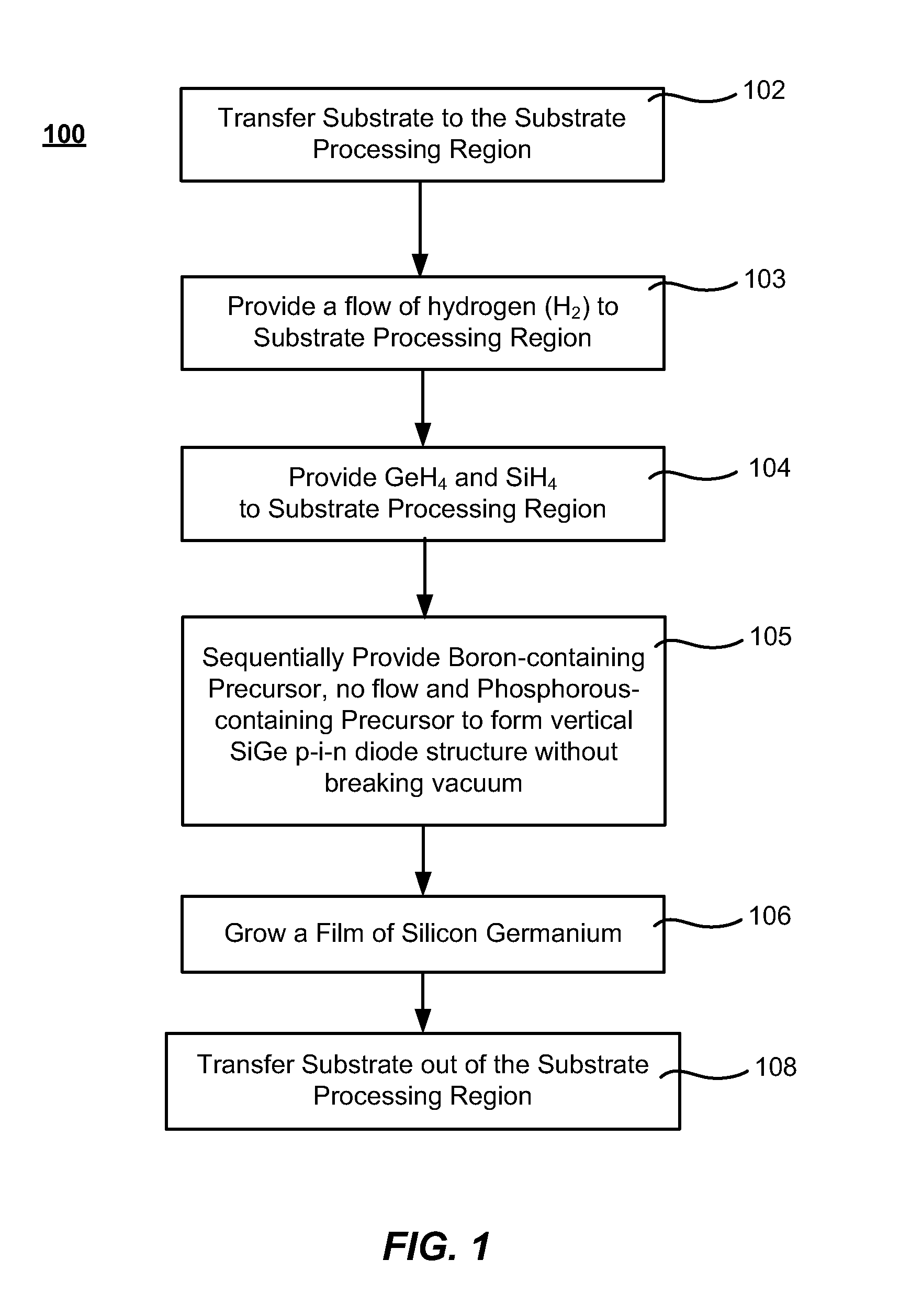

Methods of forming high-current density vertical p-i-n diodes on a substrate are described. The methods include the steps of concurrently combining a group-IV-element-containing precursor with a sequential exposure to an n-type dopant precursor and a p-type dopant precursor in either order. An intrinsic layer is deposited between the n-type and p-type layers by reducing or eliminating the flow of the dopant precursors while flowing the group-IV-element-containing precursor. The substrate may reside in the same processing chamber during the deposition of each of the n-type layer, intrinsic layer and p-type layer and the substrate is not exposed to atmosphere between the depositions of adjacent layers.

Owner:APPLIED MATERIALS INC

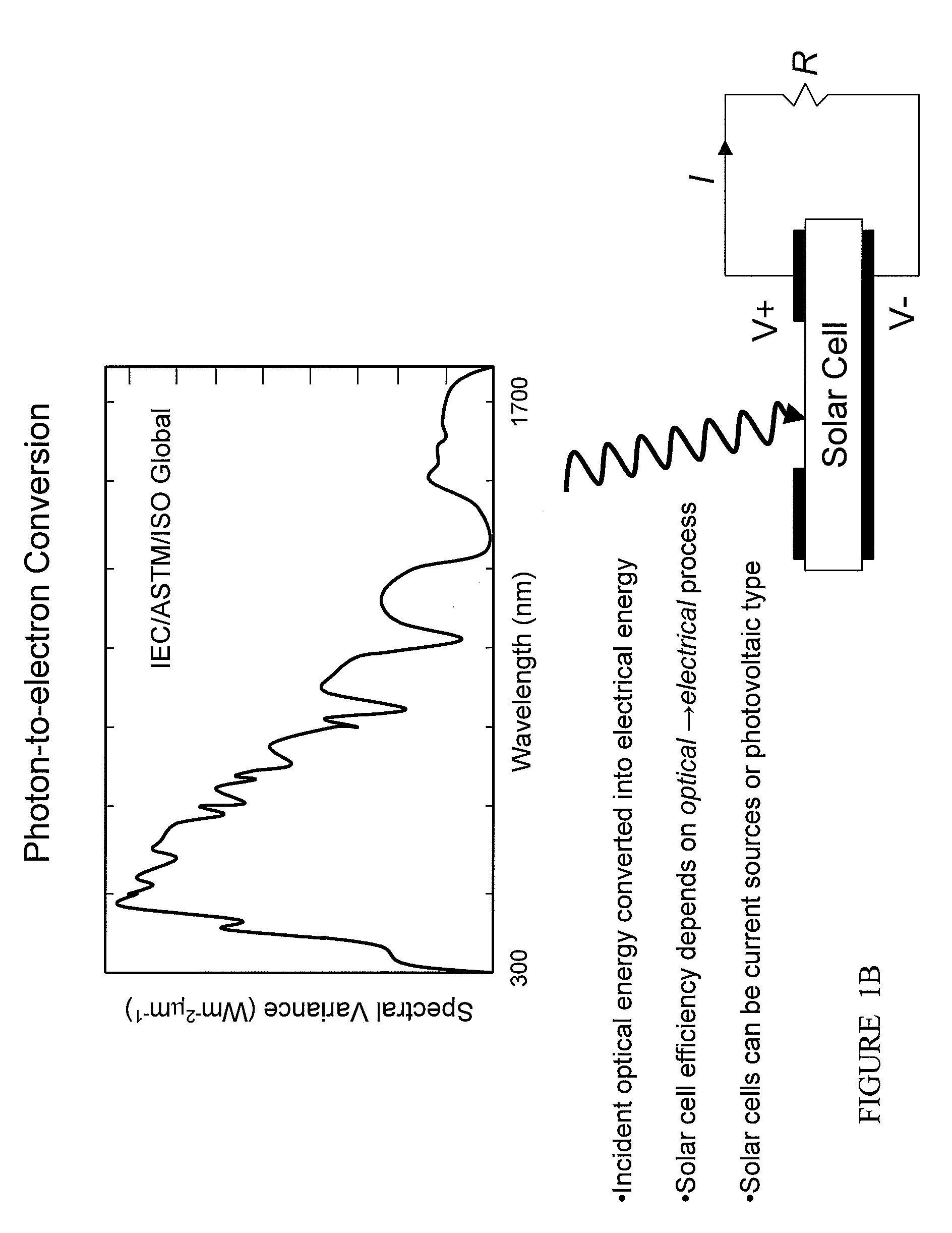

Photovoltaic device

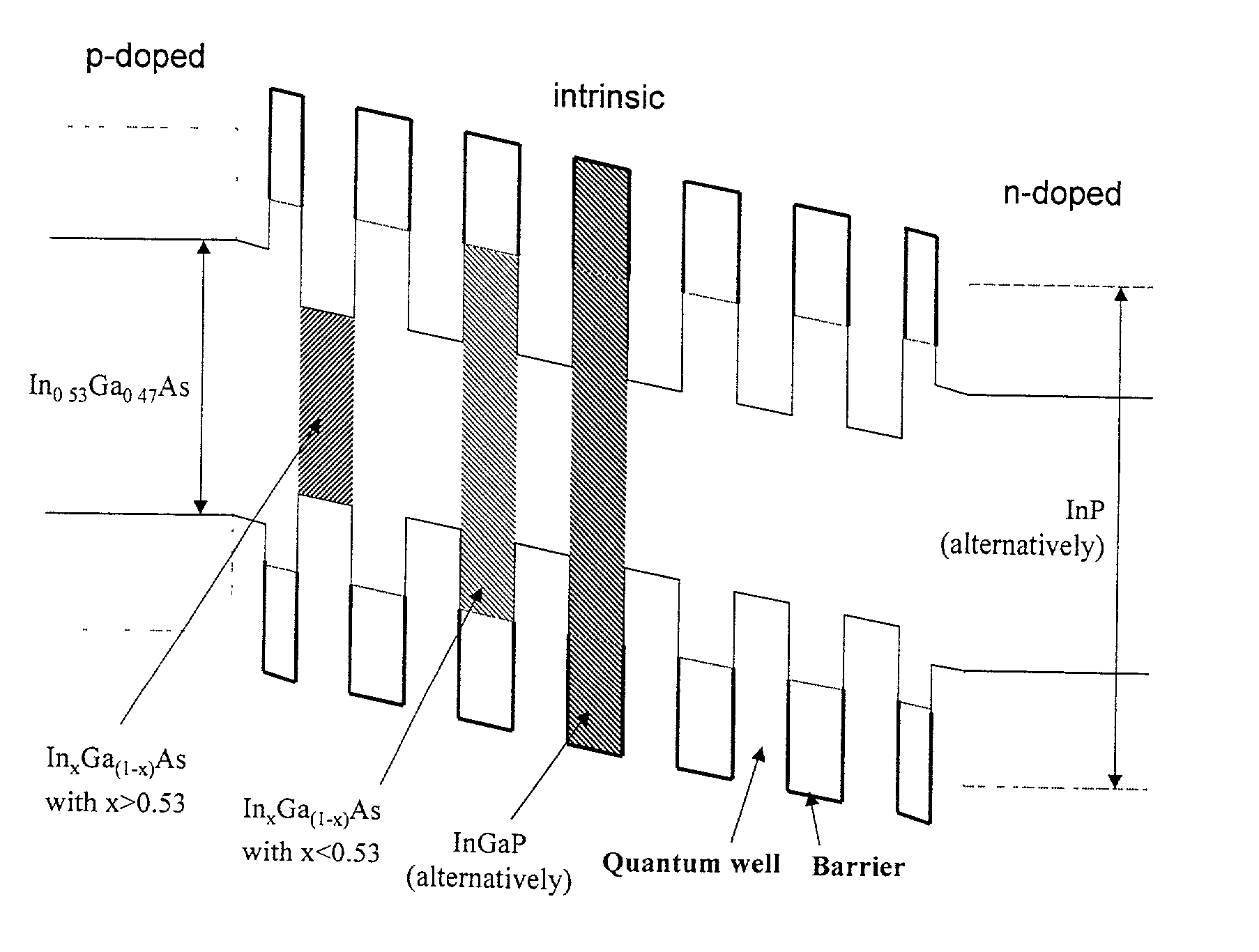

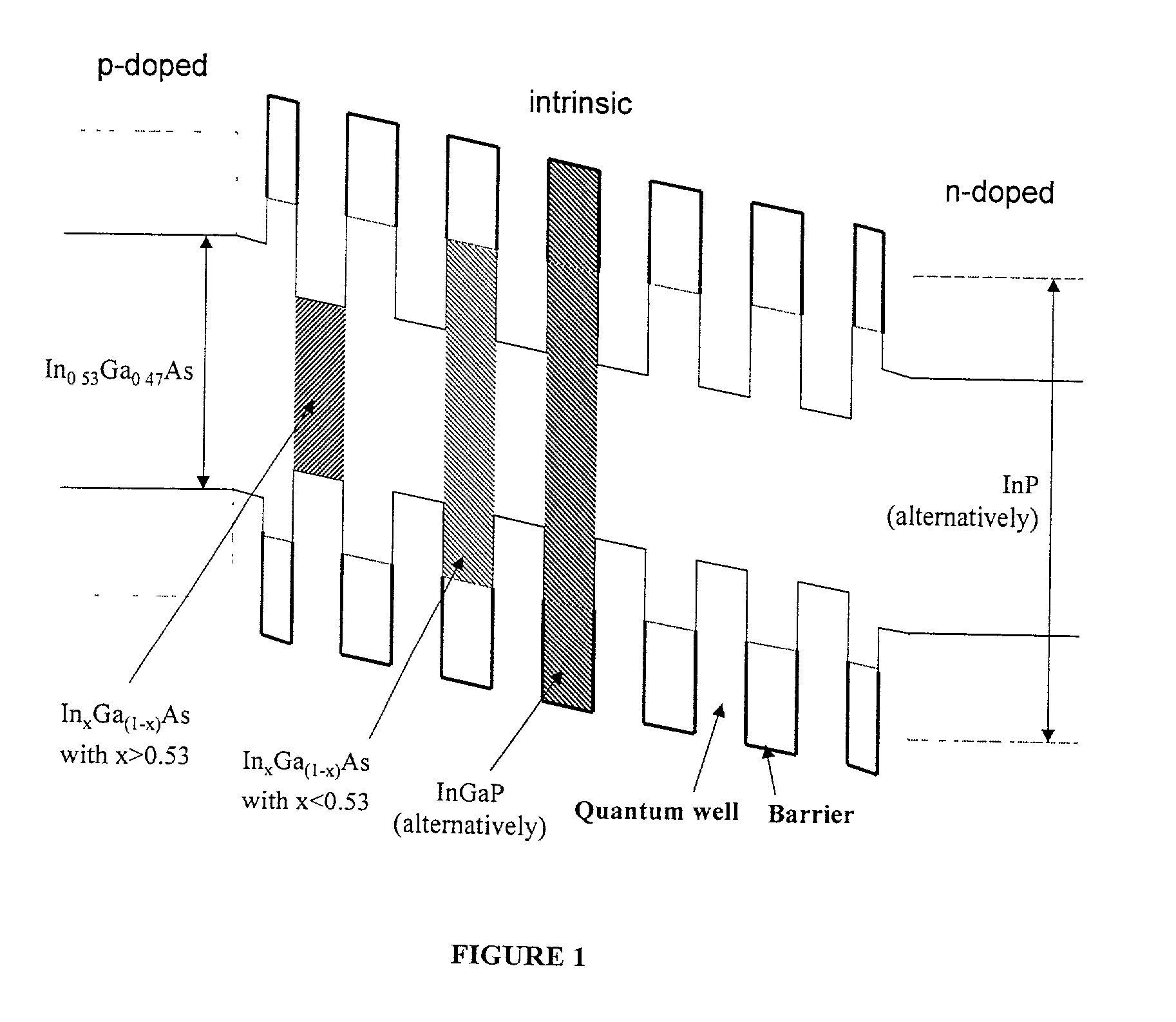

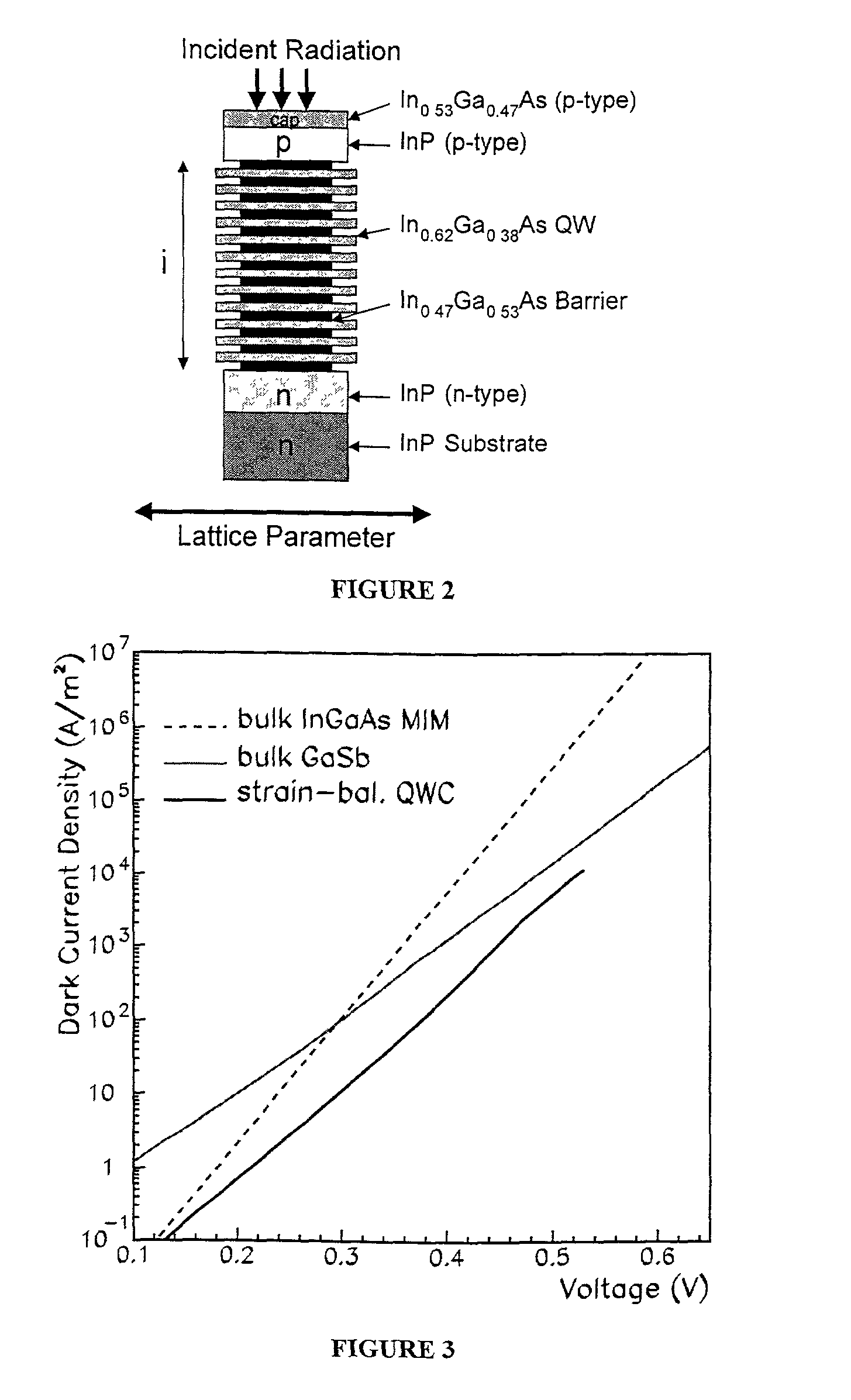

InactiveUS20030089392A1Promote absorptionHigh bandgap barriersPV power plantsNanoopticsQuantum wellActive cell

A photovoltaic cell to convert low energy photons is described, consisting of a p-i-n diode with a strain-balanced multi-quantum-well system incorporated in the intrinsic region. The bandgap of the quantum wells is lower than that of the lattice-matched material, while the barriers have a much higher bandgap. Hence the absorption can be extended to longer wavelengths, while maintaining a low dark current as a result of the higher barriers. This leads to greatly improved conversion efficiencies, particularly for low energy photons from low temperature sources. This can be achieved by strain-balancing the quantum wells and barriers, where each individual layer is below the critical thickness and the strain is compensated by quantum wells and barriers being strained in opposite directions minimizing the stress. The absorption can be further extended to longer wavelengths by introducing a strain-relaxed layer (virtual substrate) between the substrate and the active cell.

Owner:IMPERIAL INNOVATIONS LTD

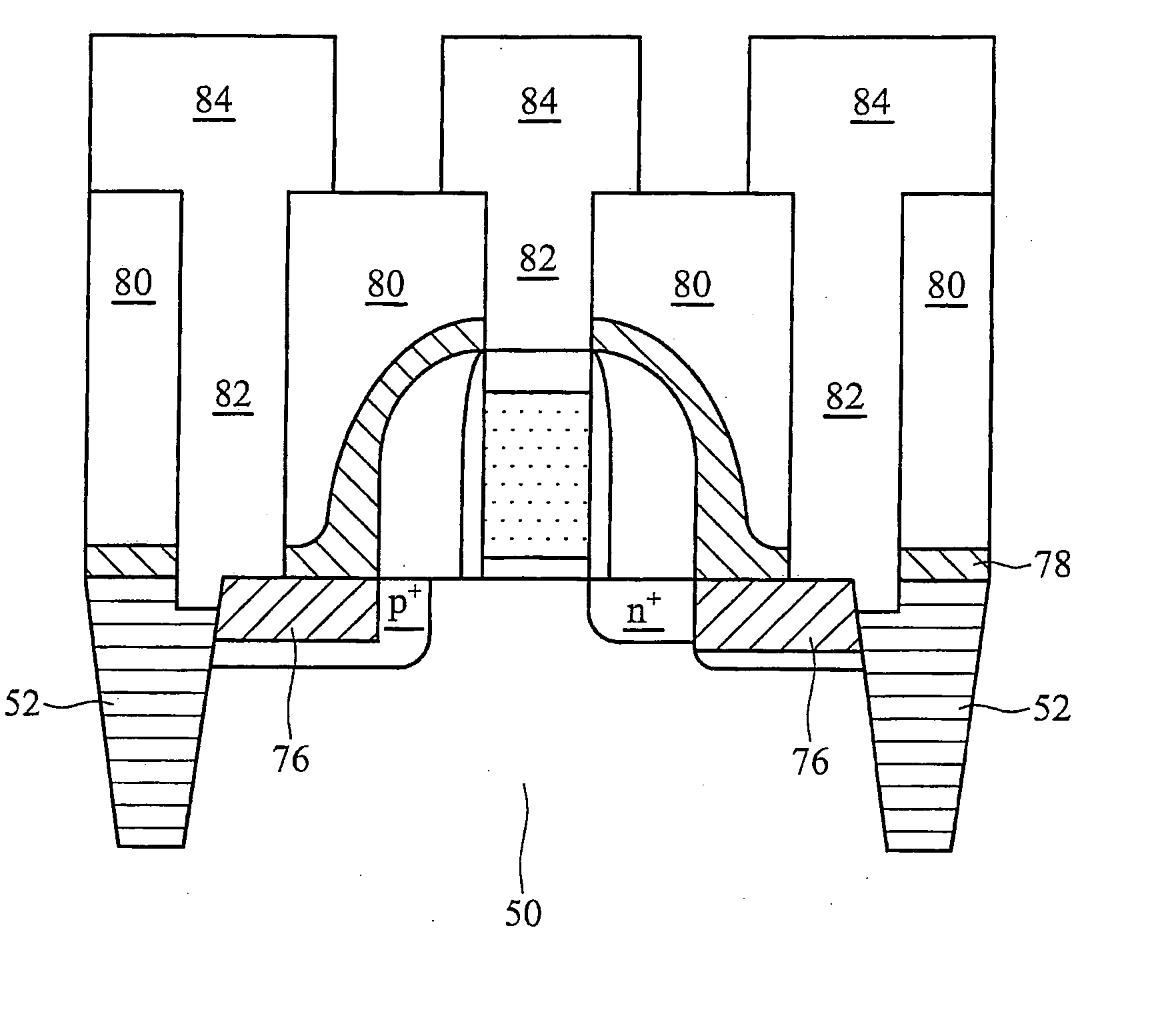

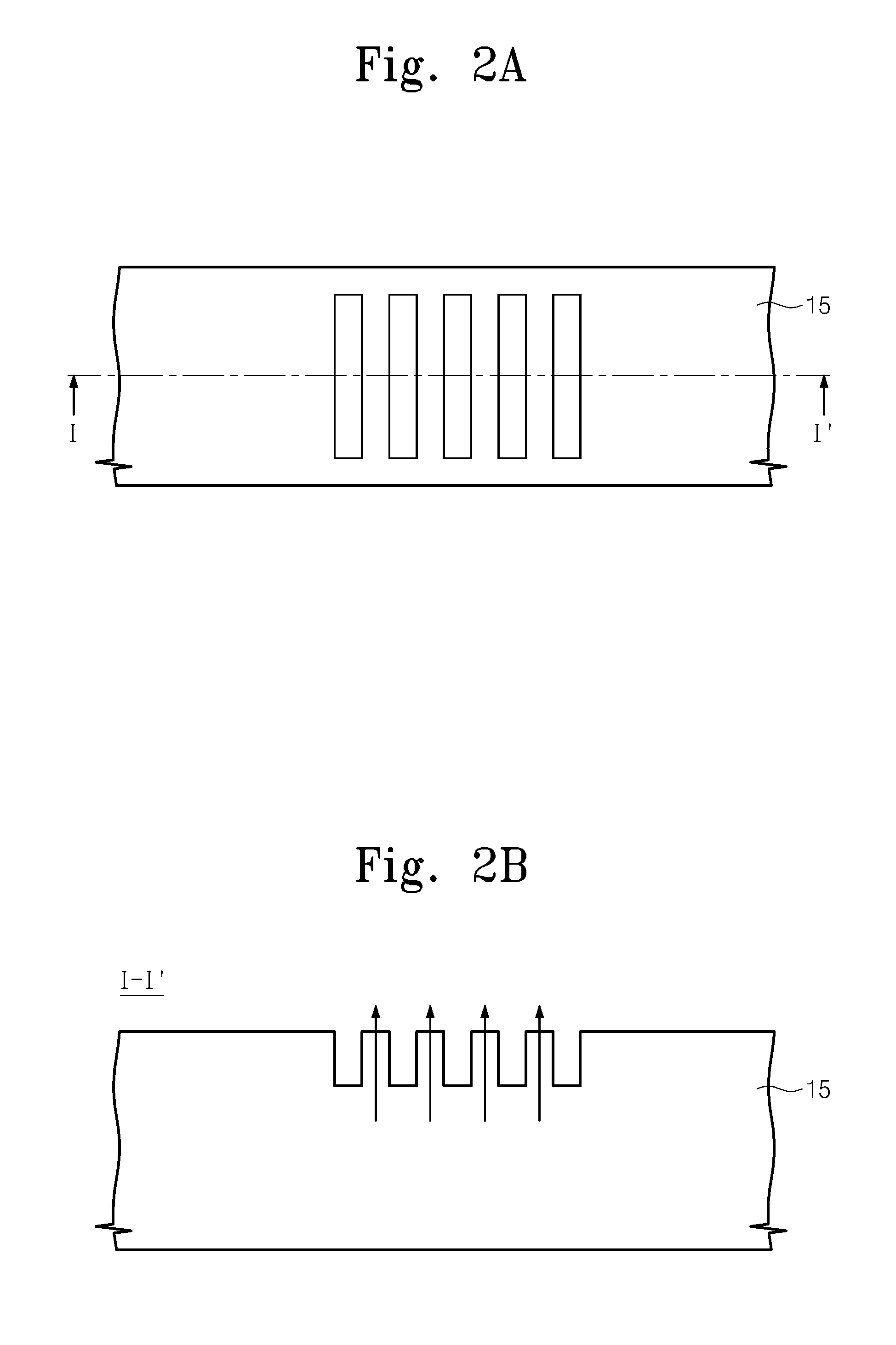

P-i-n semiconductor diodes and methods of forming the same

InactiveUS20080083963A1Improve performanceHigh structural reliabilityFinal product manufactureSolid-state devicesLight energySemiconductor

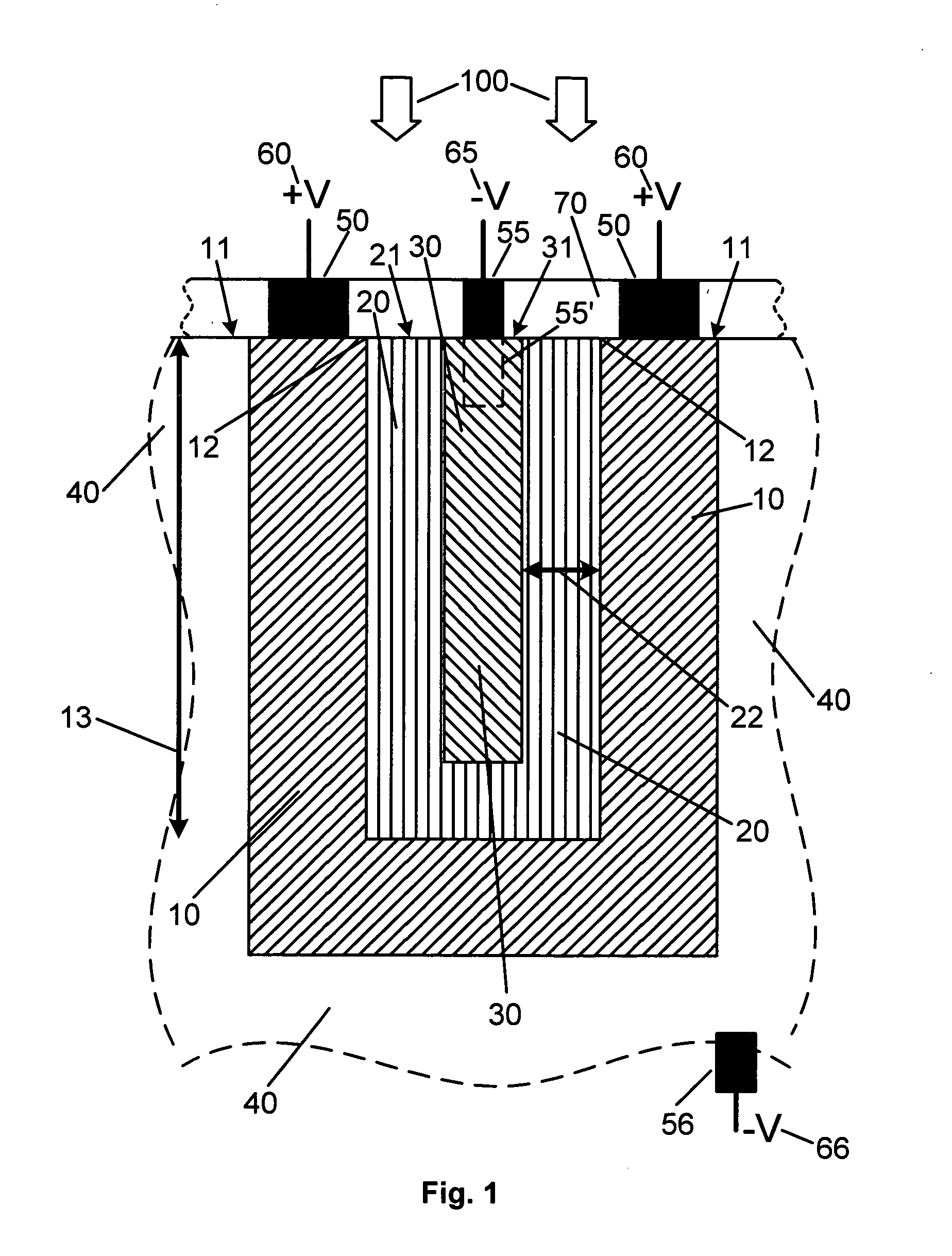

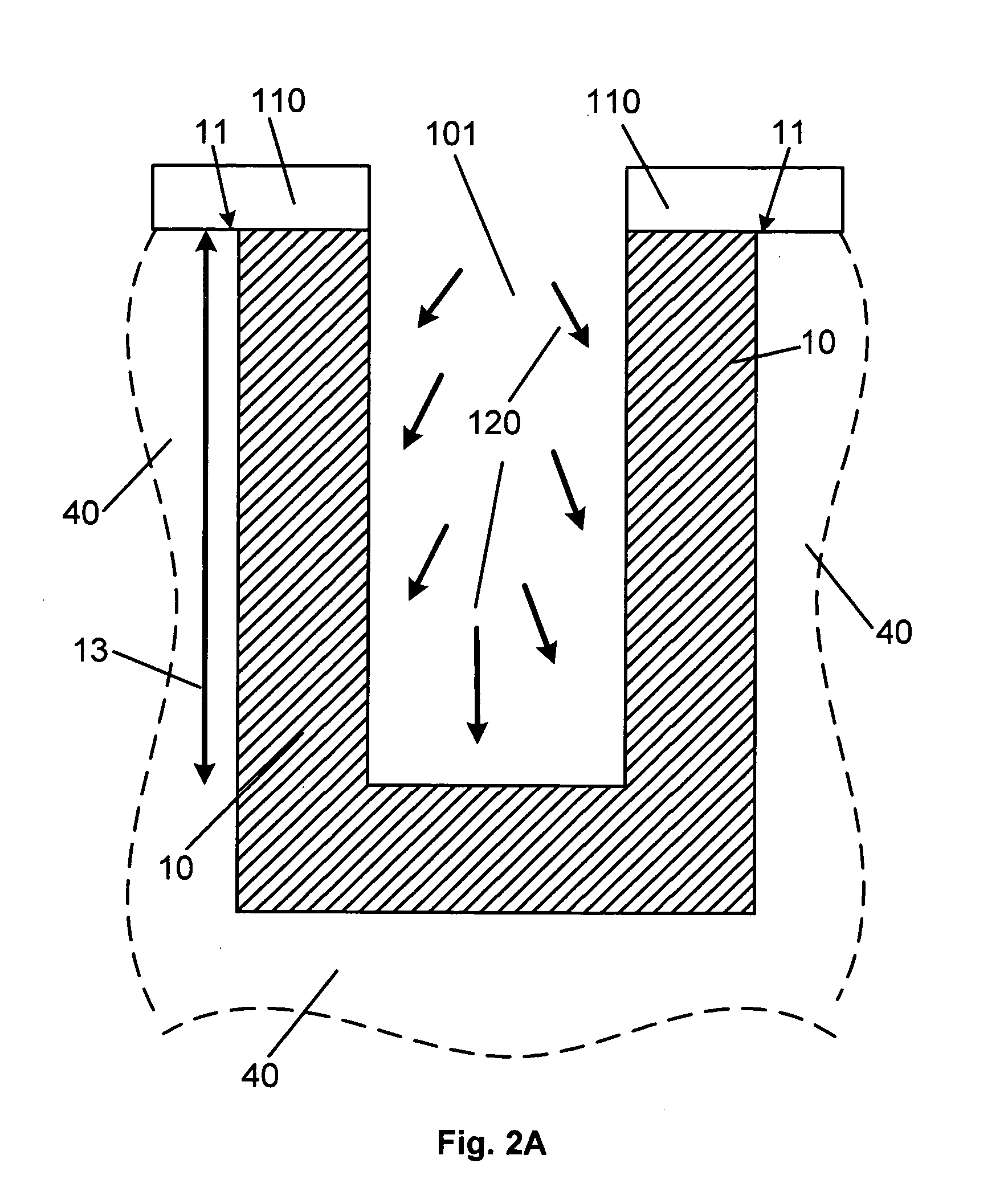

An arrangement of pillar shaped p-i-n diodes having a high aspect ration are formed on a semiconductor substrate. Each device is formed by an intrinsic or lightly doped region (i-region) positioned between a P+ region and an N+ region at each end of the pillar. The arrangement of p-i-n diodes is embedded in an optical transparent medium. For a given surface area, more light energy is absorbed by the pillar arrangement of p-i-n diodes than by conventional planar p-i-n diodes. The p-i-n diodes are configured in an array formation to enable photons reflected from one p-i-n diode to be captured and absorbed by another p-i-n diode adjacent to the first one, thereby optimizing the efficiency of the energy conversion.

Owner:IBM CORP

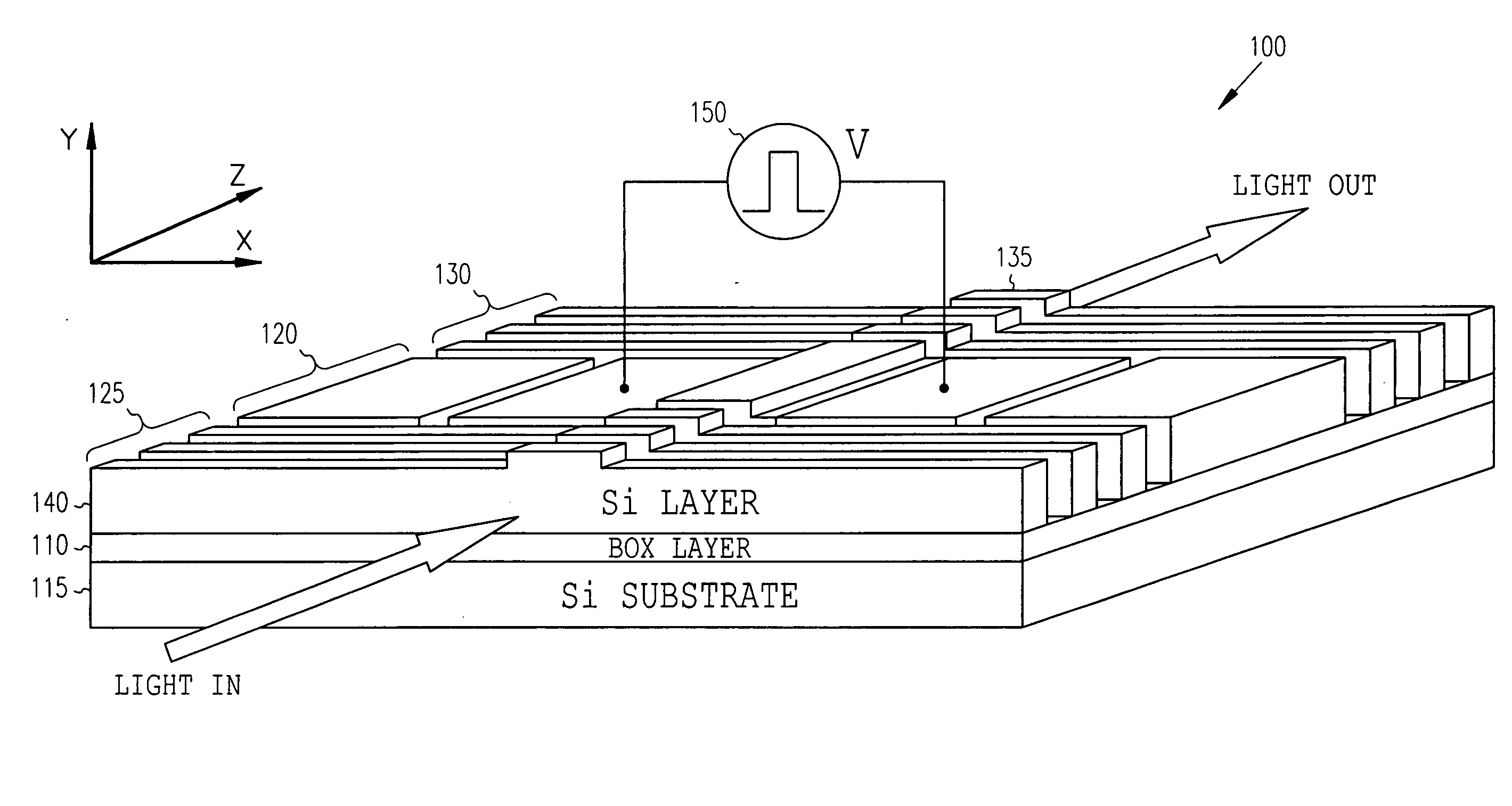

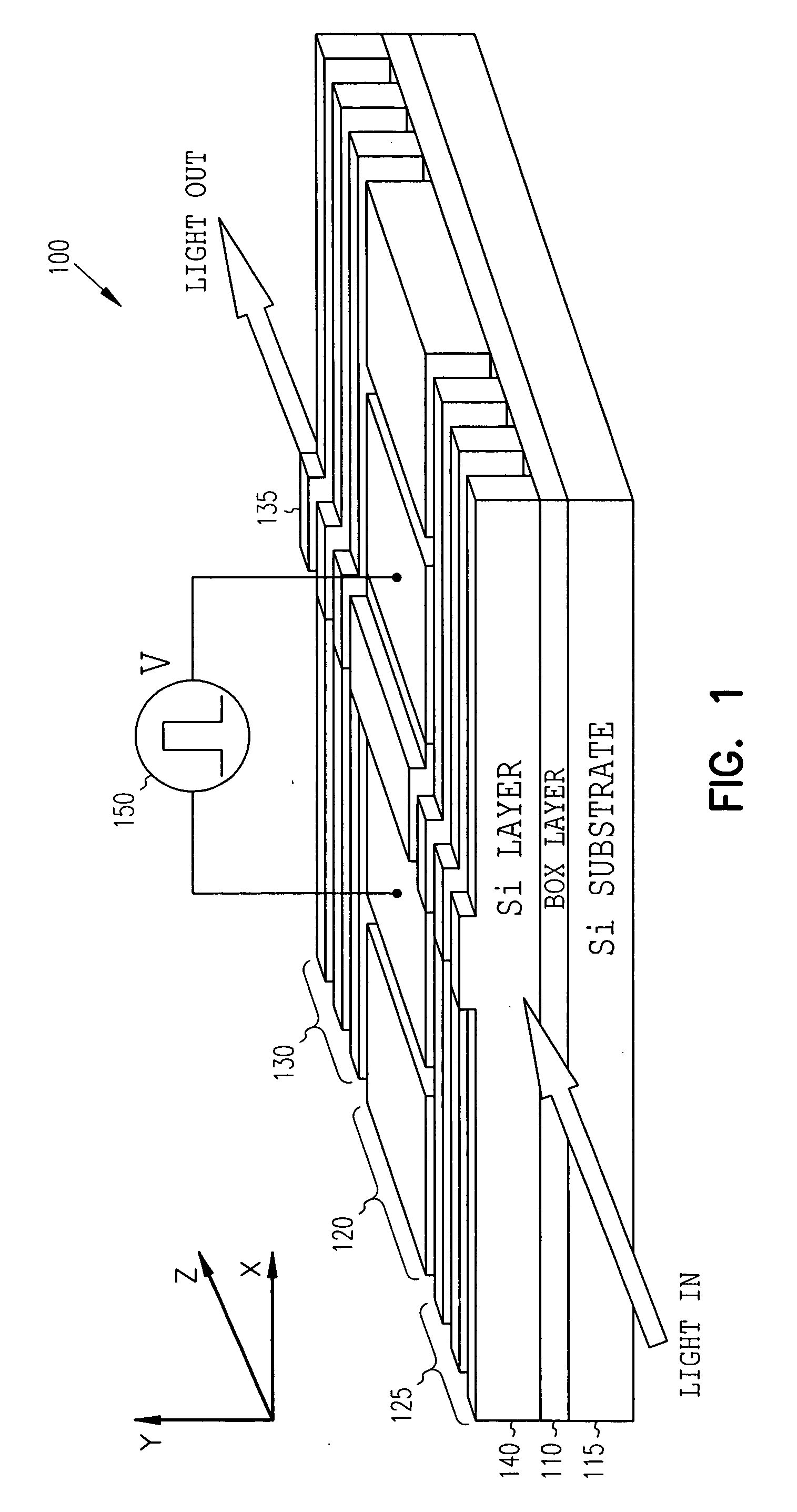

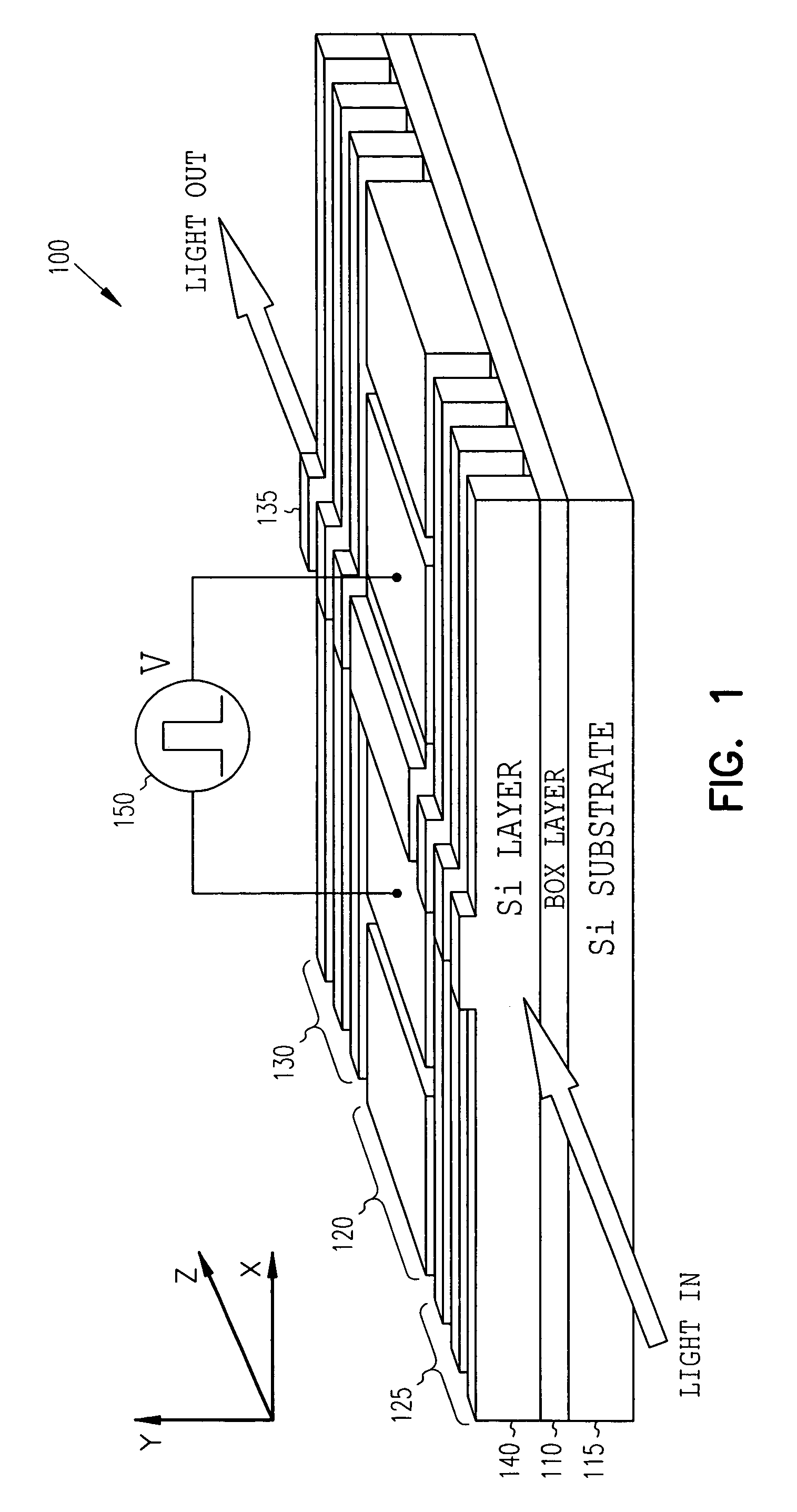

Electro-optic modulator on rib waveguide

InactiveUS20050089257A1Refractive index variesOptical waveguide light guideNon-linear opticsCharge carrierRefractive index

An electro-optic modulator is formed on a silicon-on-insulator (SOI) rib waveguide. An optical field in the modulator is confined by using an electrically modulated microcavity. The microcavity has reflectors on each side. In one embodiment, a planar Fabry-Perot microcavity is used with deep Si / SiO2 Bragg reflectors. Carriers may be laterally confined in the microcavity region by employing deep etched lateral trenches. The refractive index of the microcavity is varied by using the free-carrier dispersion effect produced by a p-i-n diode formed about the microcavity. In one embodiment, the modulator confines both optical field and charge carriers in a micron-size region.

Owner:CORNELL RES FOUNDATION INC

3D polysilicon diode with low contact resistance and method for forming same

ActiveUS20110062557A1Solid-state devicesSemiconductor/solid-state device manufacturingReverse biasContact resistance

A semiconductor p-i-n diode and method for forming the same are described herein. In one aspect, a SiGe region is formed between a region doped to have one conductivity (either p+ or n+) and an electrical contact to the p-i-n diode. The SiGe region may serve to lower the contact resistance, which may increase the forward bias current. The doped region extends below the SiGe region such that it is between the SiGe region and an intrinsic region of the diode. The p-i-n diode may be formed from silicon. The doped region below the SiGe region may serve to keep the reverse bias current from increasing as result of the added SiGe region. In one embodiment, the SiGe is formed such that the forward bias current of an up-pointing p-i-n diode in a memory array substantially matches the forward bias current of a down-pointing p-i-n diode which may achieve better switching results when these diodes are used with the R / W material in a 3D memory array.

Owner:SANDISK TECH LLC

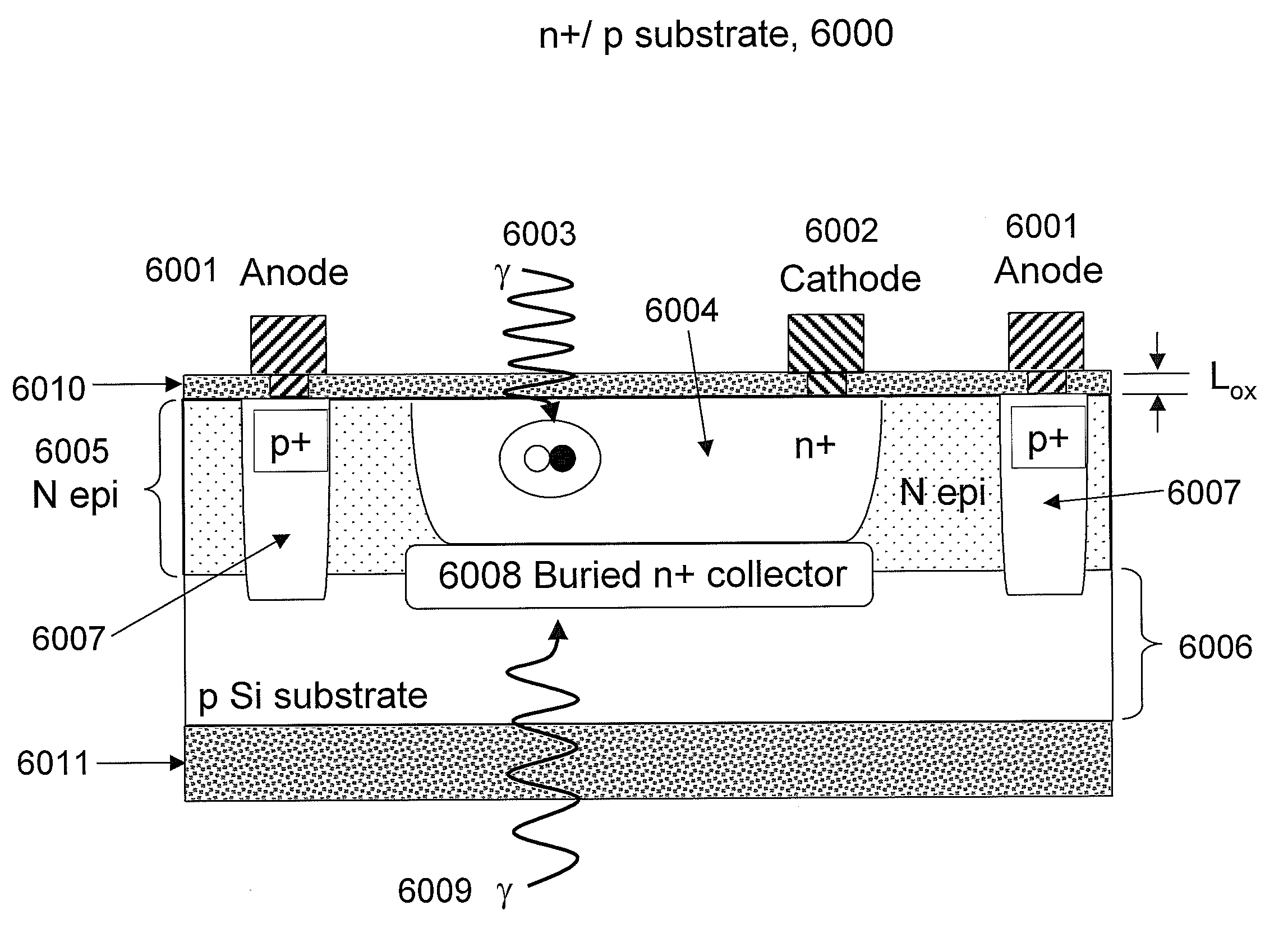

Thin Film Solar Cell III

InactiveUS20090038669A1Low costImprove throughputPV power plantsFinal product manufactureSemiconductor materialsSingle crystal

The present invention teaches a device for converting solar radiation to electrical energy comprising a thin film, single crystal device chosen from a variety of semiconductor materials, optionally, employing an alternative substrate, and various combinations of p-n, p-i-n and avalanche p-i-n diodes to enable high conversion efficiency photo-voltaic devices.

Owner:TRANSLUCENT

Method to form upward pointing p-i-n diodes having large and uniform current

A method is disclosed to form an upward-pointing p-i-n diode formed of deposited silicon, germanium, or silicon-germanium. The diode has a bottom heavily doped p-type region, a middle intrinsic or lightly doped region, and a top heavily doped n-type region. The top heavily doped p-type region is doped with arsenic, and the semiconductor material of the diode is crystallized in contact with an appropriate silicide, germanide, or silicide-germanide. A large array of such upward-pointing diodes can be formed with excellent uniformity of current across the array when a voltage above the turn-on voltage of the diodes is applied. This diode is advantageously used in a monolithic three dimensional memory array.

Owner:SANDISK TECH LLC

Quantum confinement solar cell fabricated by atomic layer deposition

InactiveUS20100240167A1Semiconductor/solid-state device manufacturingNanoopticsQuantum wellQuantum dot

The current invention provides a method of fabricating quantum confinement (QC) in a solar cell that includes using atomic layer deposition (ALD) for providing at least one QC structure embedded into an intrinsic region of a p-i-n diode in the solar cell, where optical and electrical properties of the confinement structure are adjusted according to at least one dimension of the confinement structure. The QC structures can include quantum wells, quantum wires, quantum tubes, and quantum dots.

Owner:THE BOARD OF TRUSTEES OF THE LELAND STANFORD JUNIOR UNIV

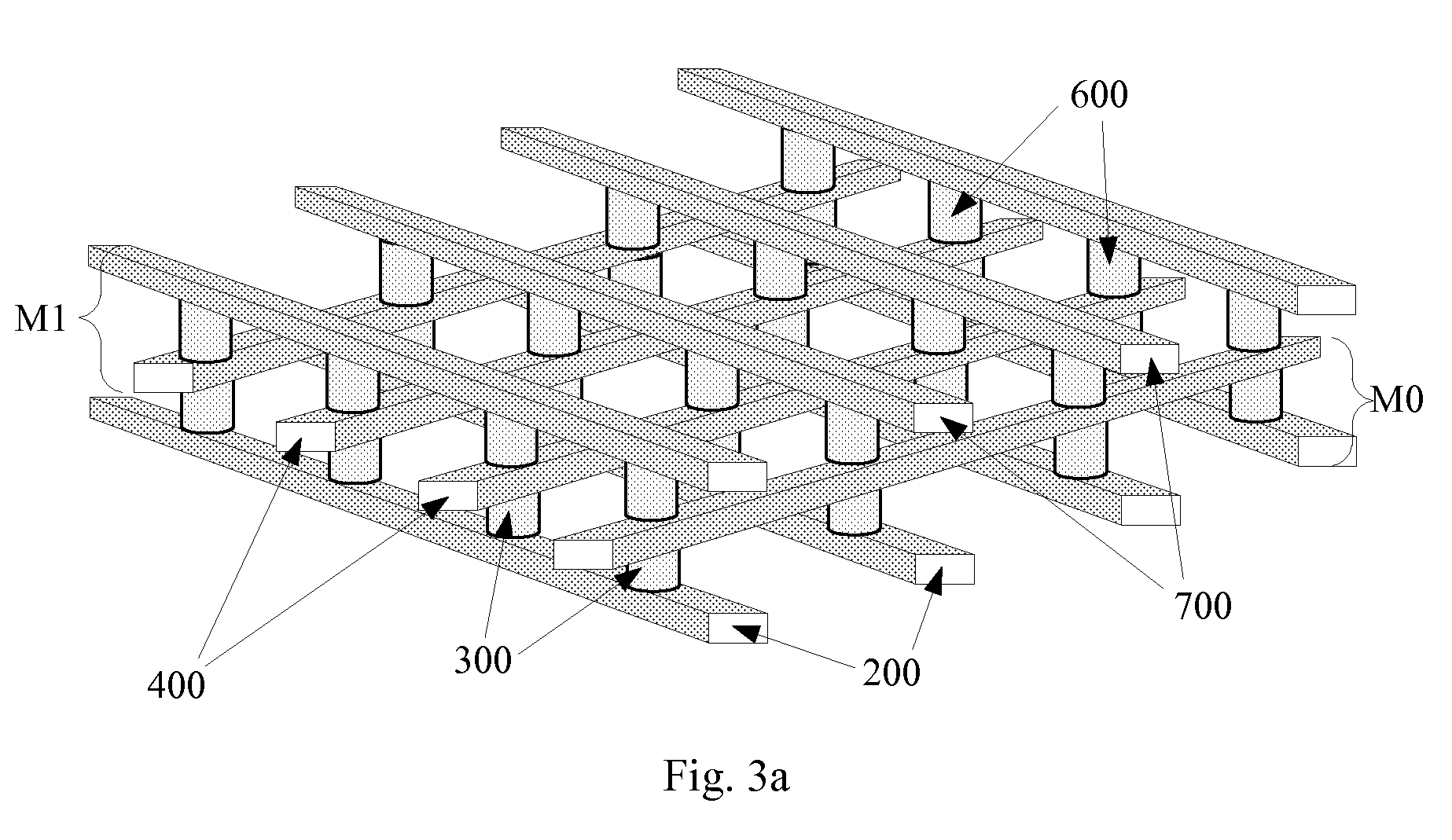

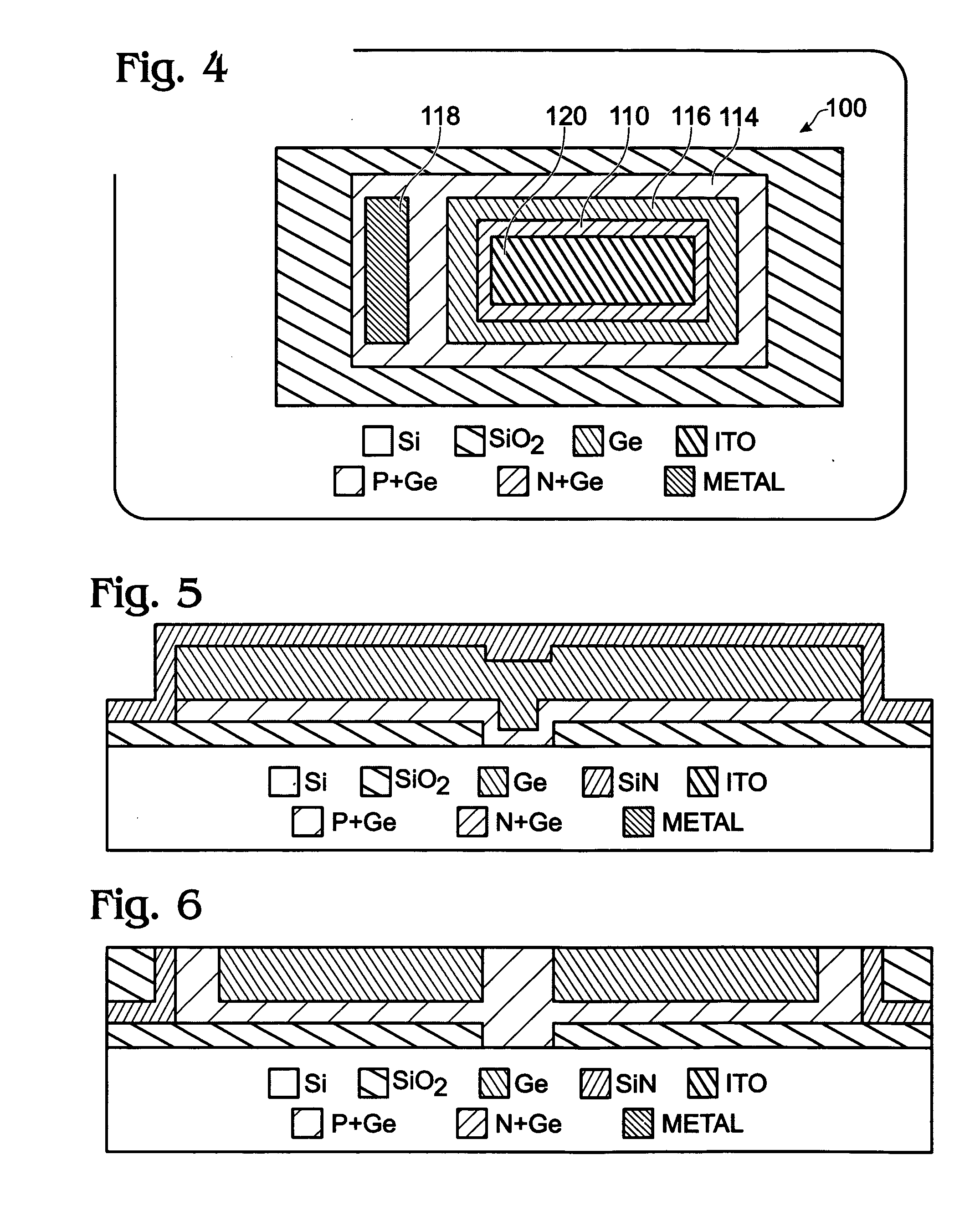

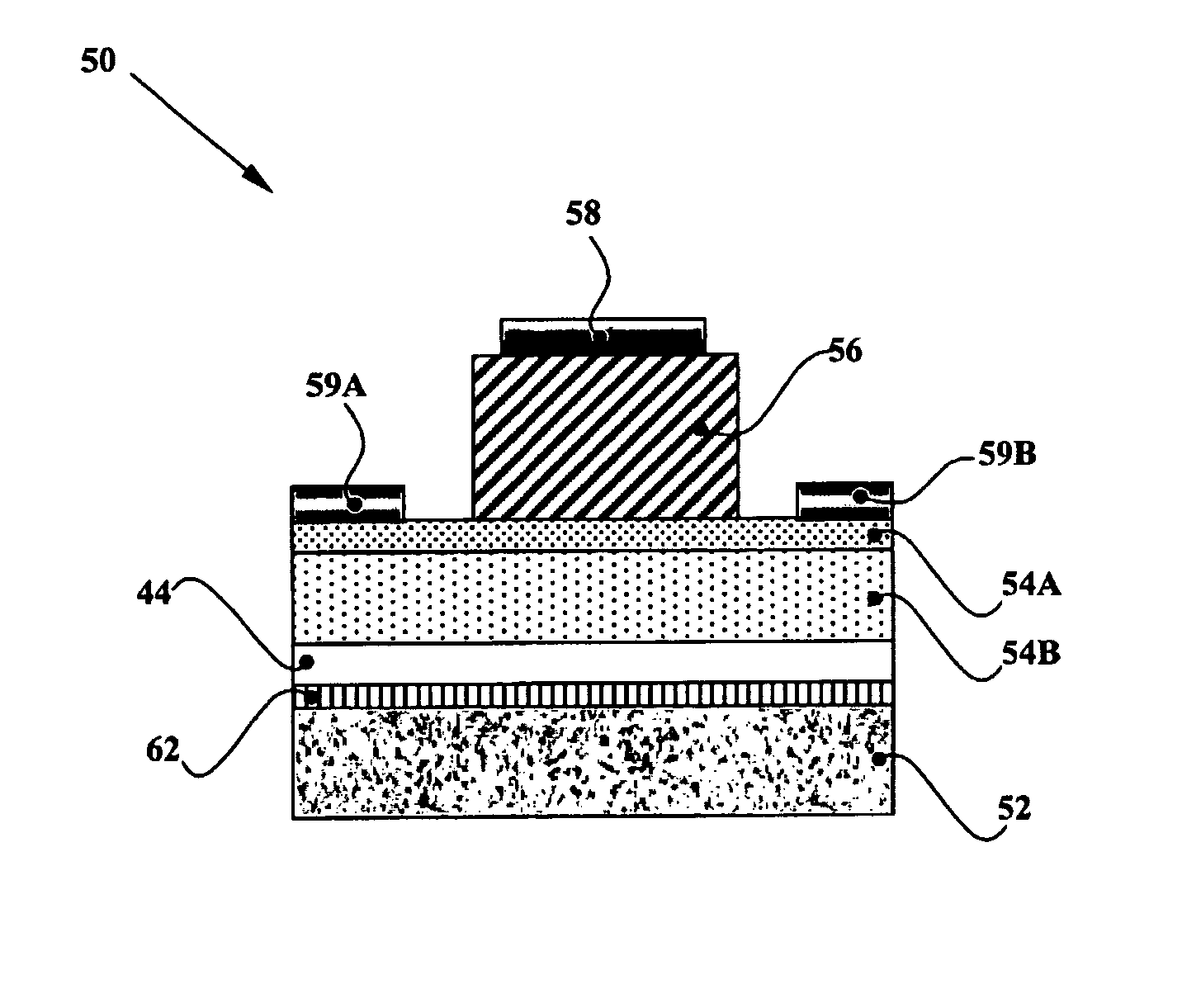

Liquid phase epitaxial GOI photodiode with buried high resistivity germanium layer

InactiveUS20070170536A1Significant problemEliminate leakage currentPhotovoltaic energy generationSemiconductor devicesHigh resistivityAdemetionine

A device and associated method are provided for fabricating a liquid phase epitaxial (LPE) Germanium-on-Insulator (GOI) photodiode with buried high resistivity Germanium (Ge) layer. The method provides a silicon (Si) substrate, and forms a bottom insulator overlying the Si substrate with a Si seed access area. Then, a Ge P-I-N diode is formed with an n +-doped (n+) mesa, a p+-doped (p+) Ge bottom insulator interface and mesa lateral interface, and a high resistivity Ge layer interposed between the p+ Ge and n+ Ge. A metal electrode is formed overlying a region of the p+ Ge lateral interface, and a transparent electrode is formed overlying the n+ Ge mesa. In one aspect, the method deposits a silicon nitride layer temporary cap overlying the high resistivity Ge layer, and an annealing is performed to epitaxially crystallize the Ge bottom interface and high resistivity Ge layer.

Owner:SHARP LAB OF AMERICA INC

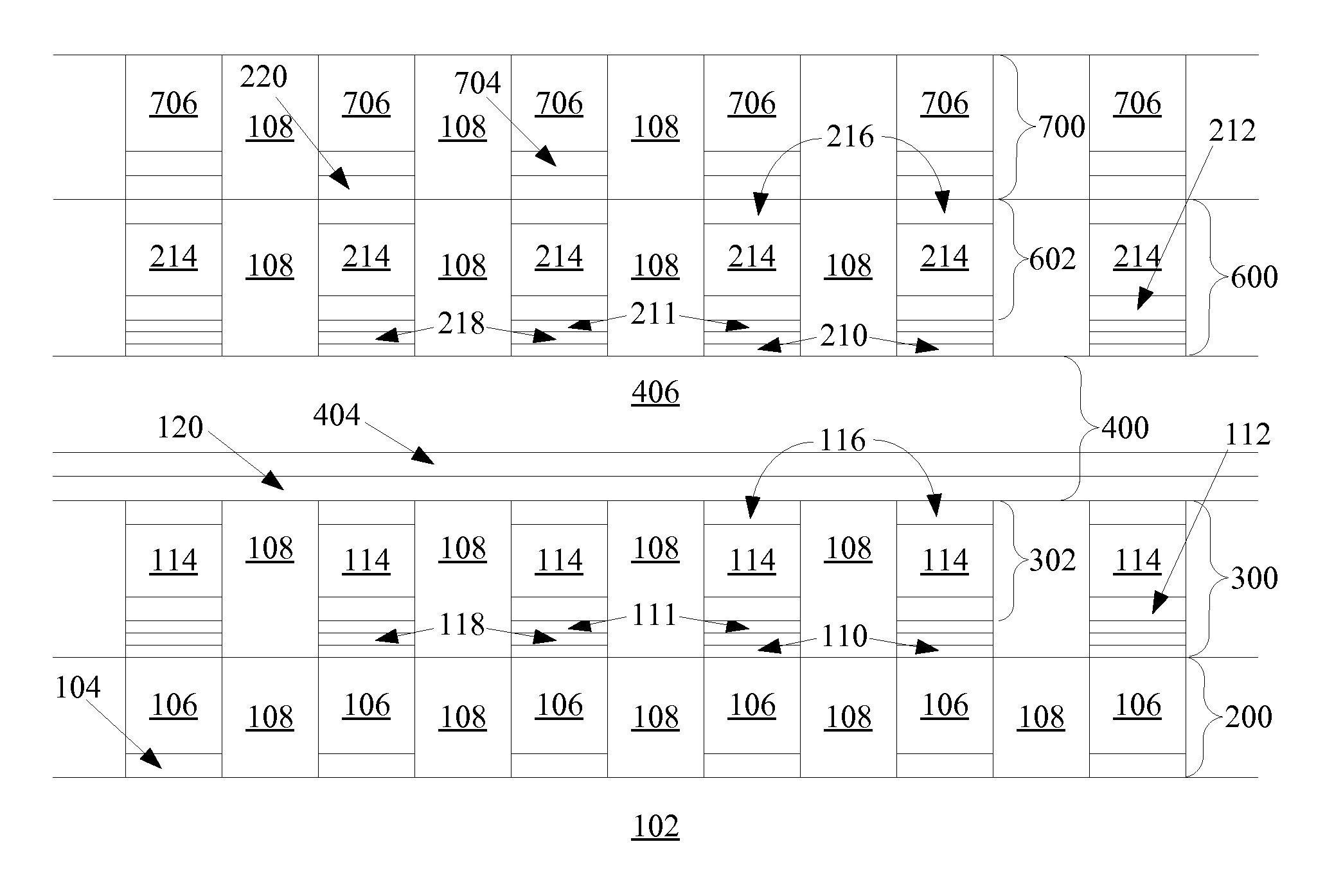

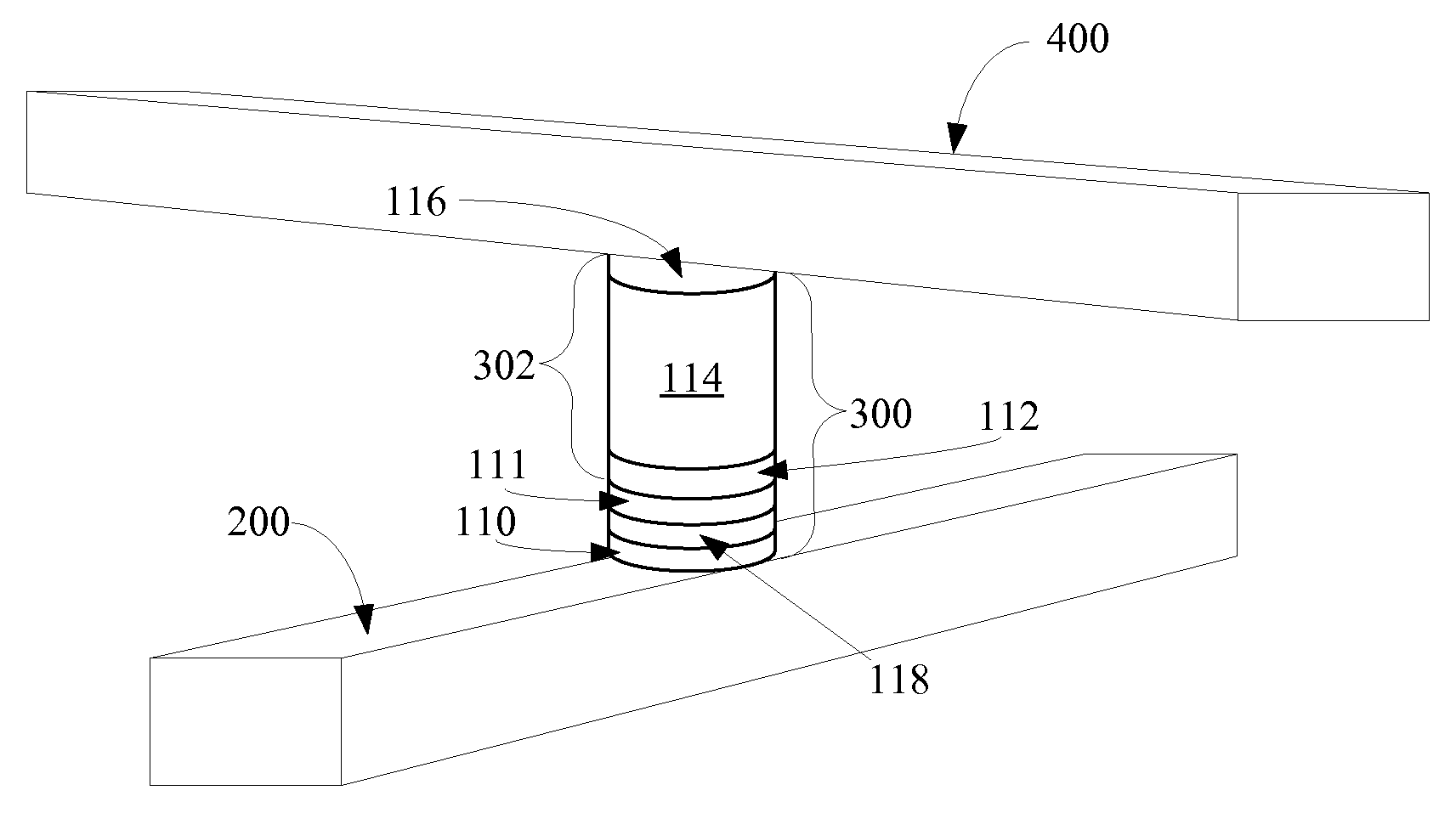

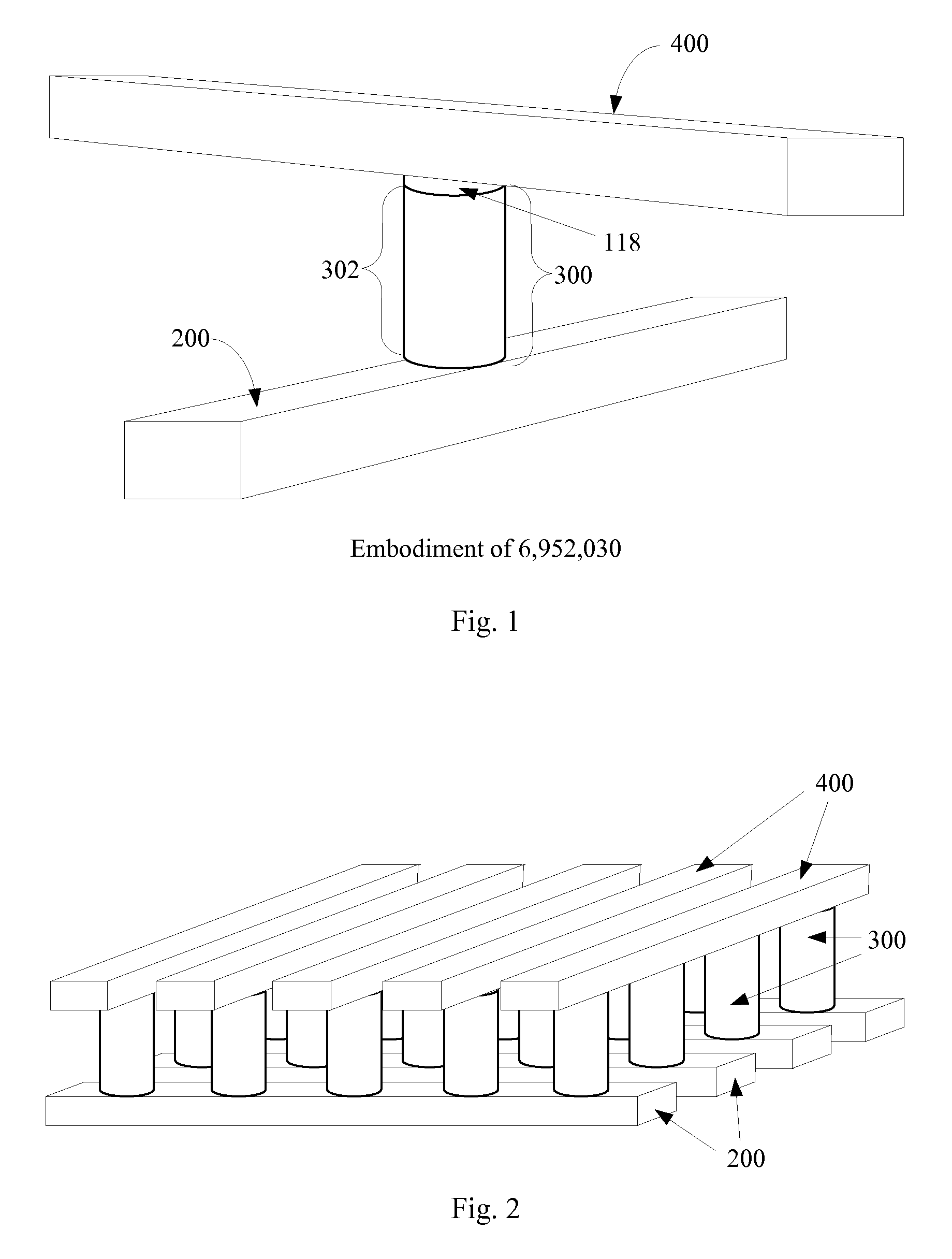

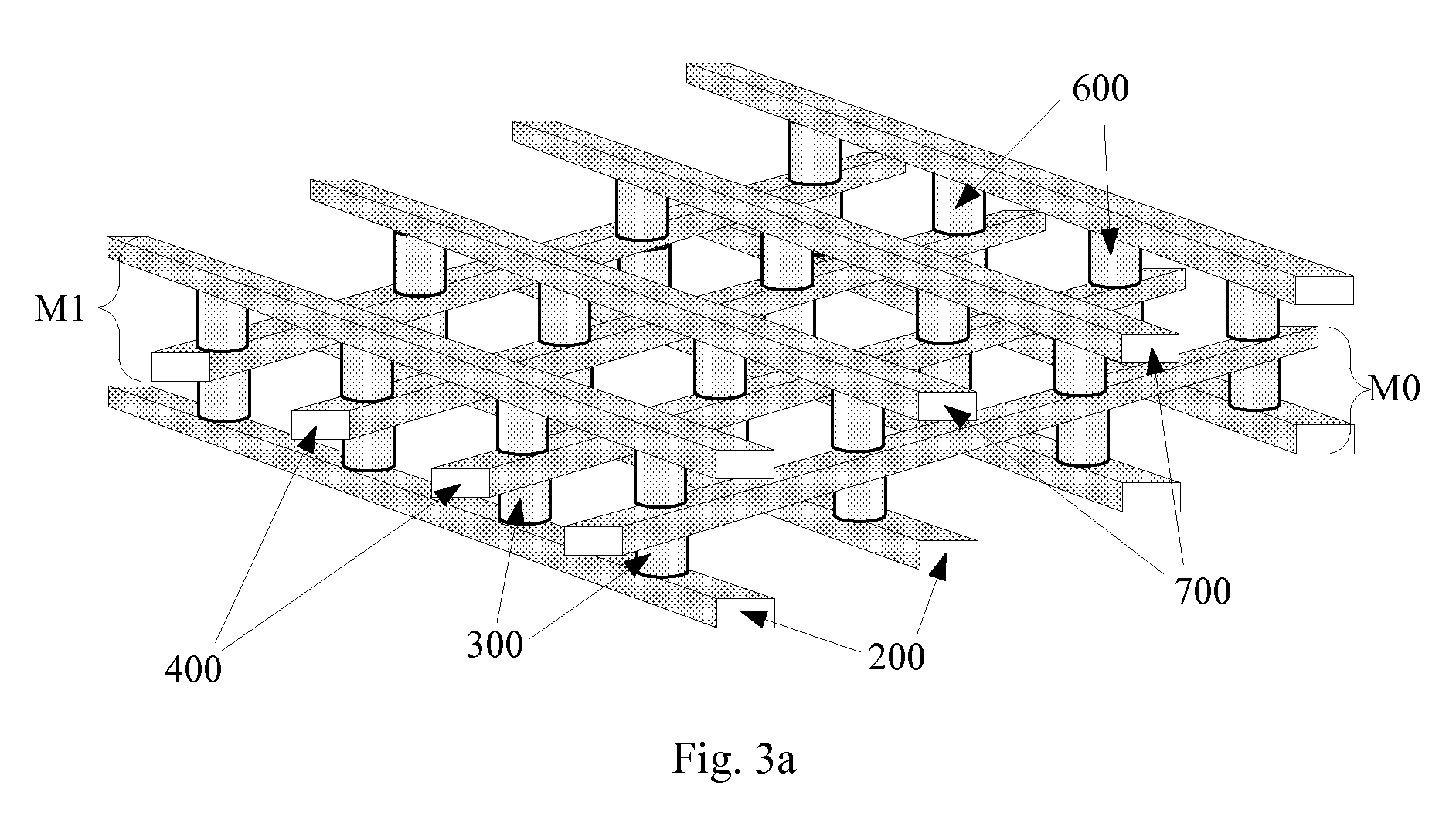

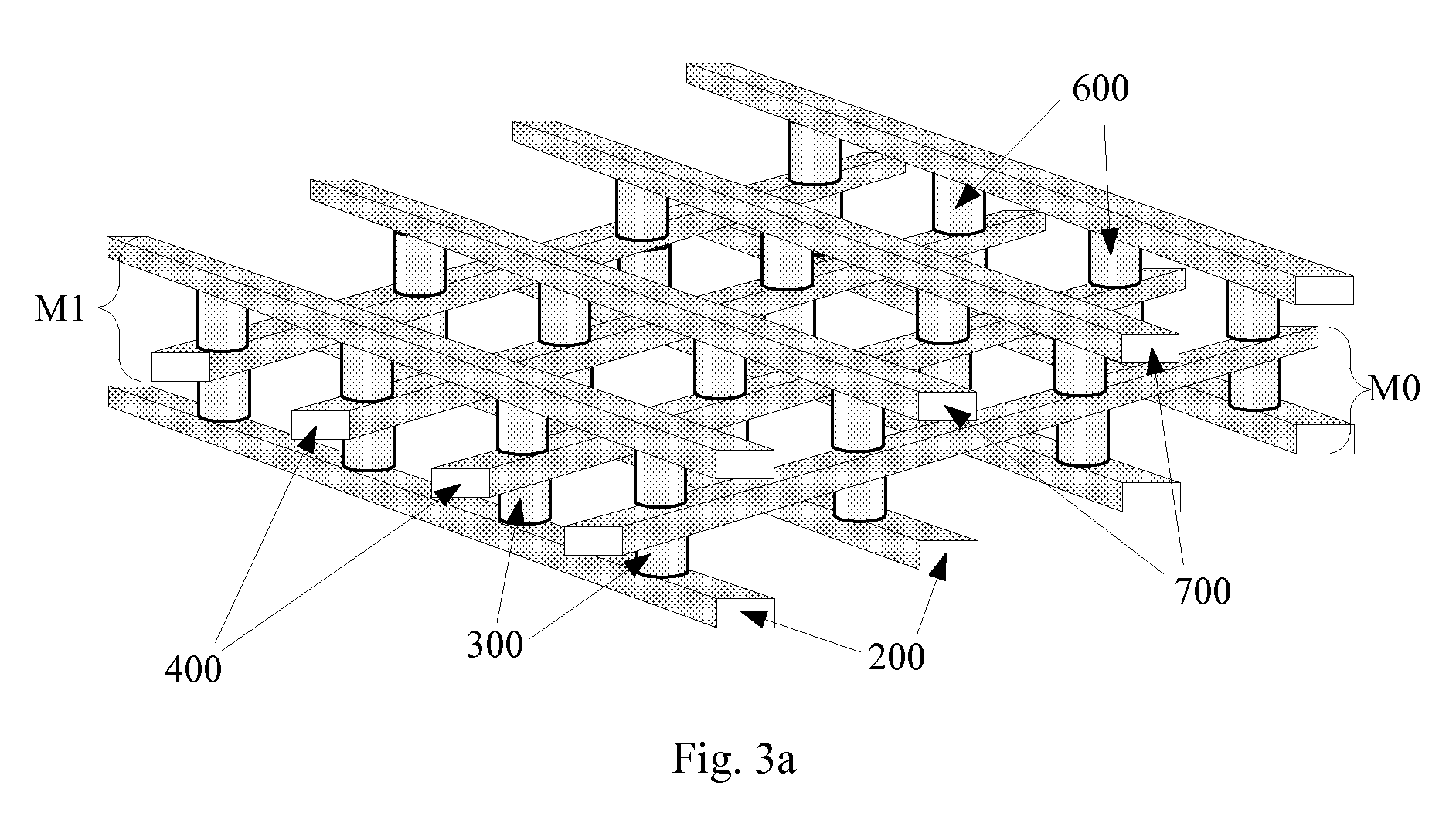

Large array of upward pointing p-i-n diodes having large and uniform current

An upward-pointing p-i-n diode formed of deposited silicon, germanium, or silicon-germanium is disclosed. The diode has a bottom heavily doped p-type region, a middle intrinsic or lightly doped region, and a top heavily doped n-type region. The top heavily doped p-type region is doped with arsenic, and the semiconductor material of the diode is crystallized in contact with an appropriate silicide, germanide, or silicide-germanide. A large array of such upward-pointing diodes can be formed with excellent uniformity of current across the array when a voltage above the turn-on voltage of the diodes is applied. This diode is advantageously used in a monolithic three dimensional memory array.

Owner:SANDISK TECH LLC

Large array of upward pointing p-i-n diodes having large and uniform current

An upward-pointing p-i-n diode formed of deposited silicon, germanium, or silicon-germanium is disclosed. The diode has a bottom heavily doped p-type region, a middle intrinsic or lightly doped region, and a top heavily doped n-type region. The top heavily doped p-type region is doped with arsenic, and the semiconductor material of the diode is crystallized in contact with an appropriate silicide, germanide, or silicide-germanide. A large array of such upward-pointing diodes can be formed with excellent uniformity of current across the array when a voltage above the turn-on voltage of the diodes is applied. This diode is advantageously used in a monolithic three dimensional memory array.

Owner:SANDISK TECH LLC

Photodetector with hetero-structure using lateral growth

InactiveUS20050127275A1Increase speedRapid responseFinal product manufactureMaterial analysis by optical meansPhotovoltaic detectorsPhotodetector

A structure and method of fabrication for a Si based material p-i-n photodetector is disclosed. The light is absorbed in an undoped layer containing SiGe or Ge in such a manner that the absorption length is not limited by a critical thickness of the SiGe or Ge layer. The result is achieved by growing the SiGe or Ge layer from the walls of a trench in monocrystalline Si using lateral epitaxial. A second, doped material is disposed over the undoped layer for biasing and photocarrier collection in the p-i-n diode.

Owner:IBM CORP

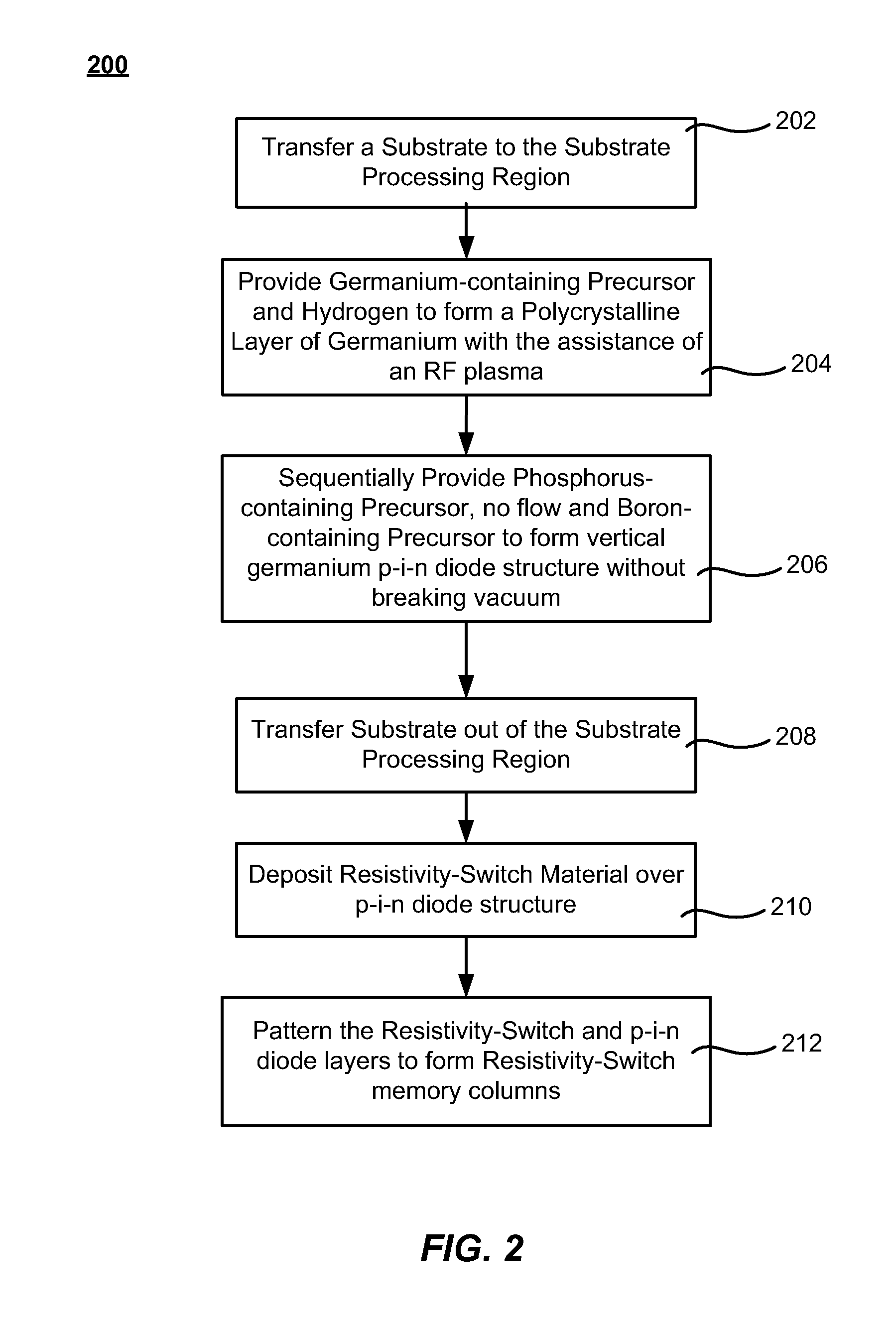

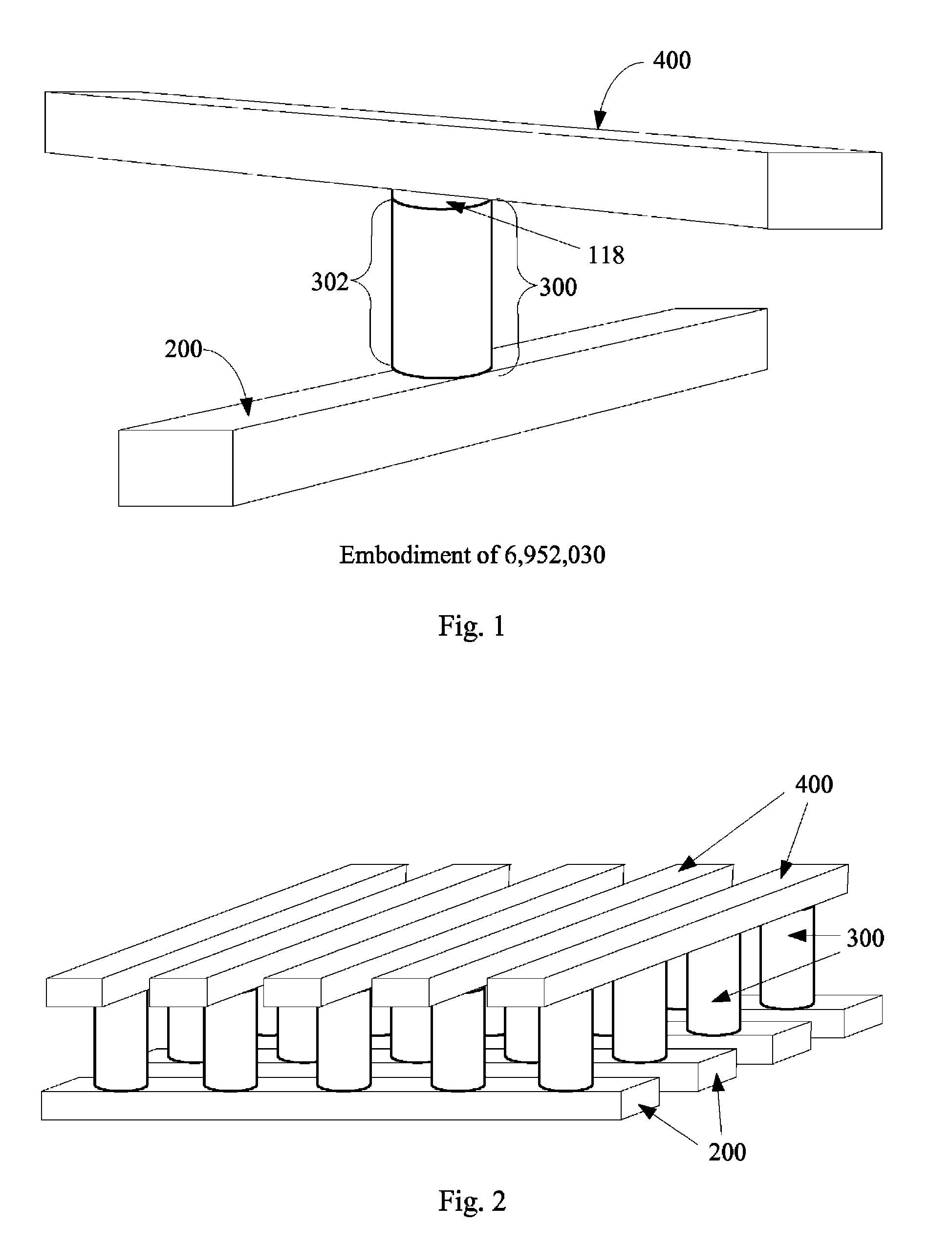

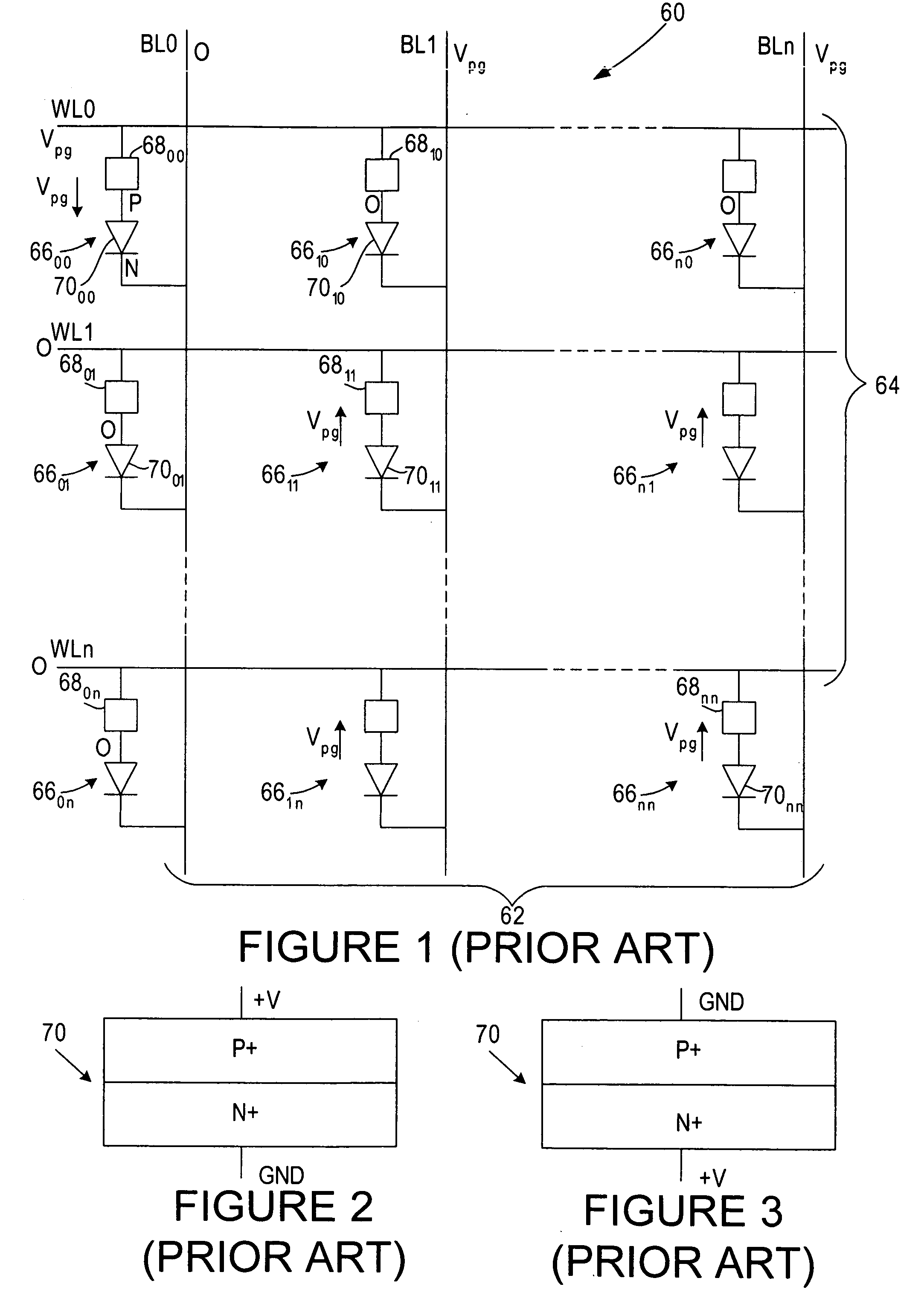

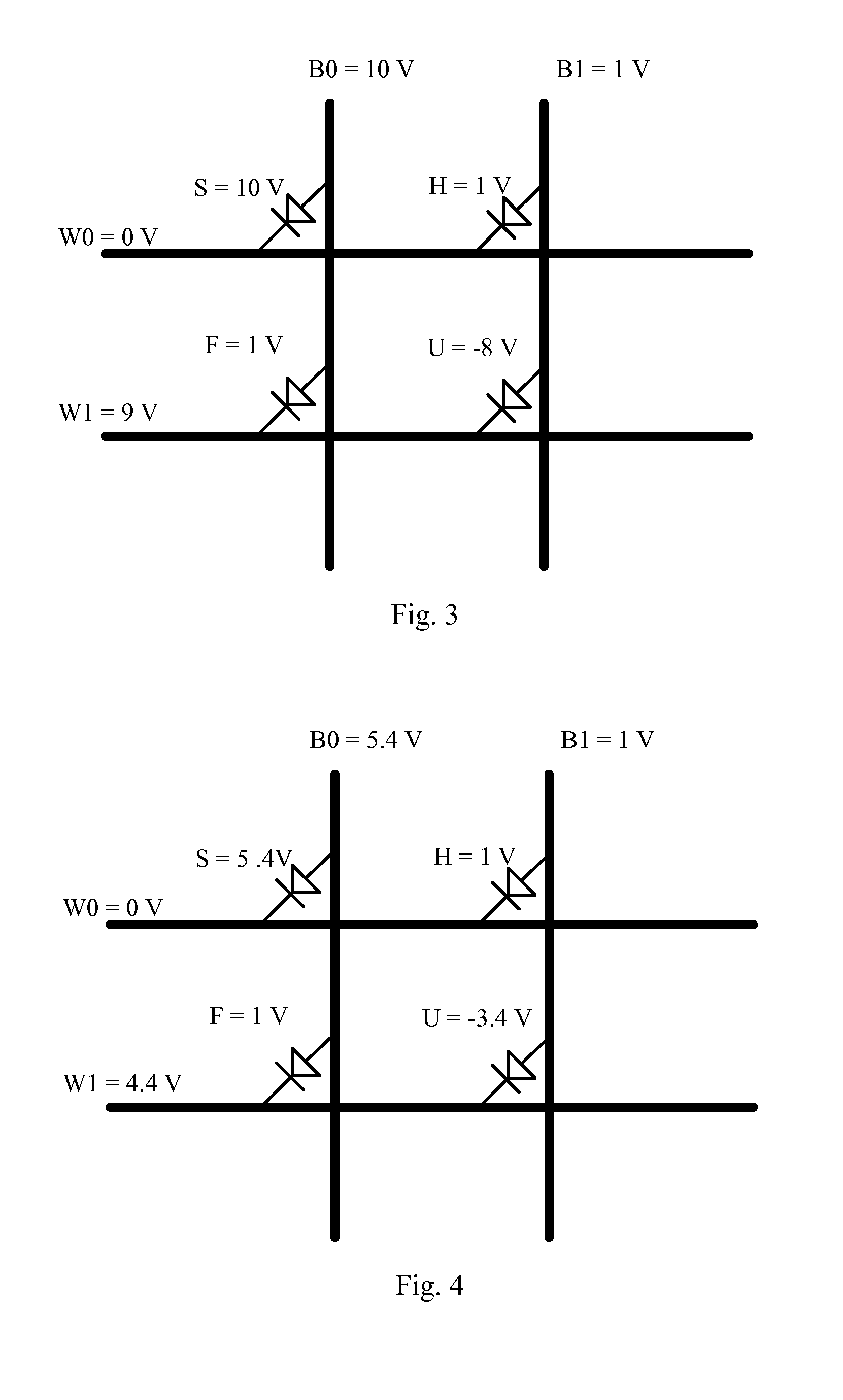

Resistive memory array using P-I-N diode select device and methods of fabrication thereof

An electronic structure includes a resistive memory device, and a P-I-N diode in operative association with the resistive memory device. A plurality of such electronic structures are used in a resistive memory array, with the P-I-N diodes functioning as select devices in the array. Methods are provided for fabricating such resistive memory device-P-I-N diode structures.

Owner:CYPRESS SEMICON CORP

Vertical diode based memory cells having a lowered programming voltage and methods of forming the same

ActiveUS20090085154A1TransistorSemiconductor/solid-state device detailsMetal-insulator-metalSemiconductor materials

In a first aspect, a method for forming a non-volatile memory cell is provided. The method includes (1) forming a metal-insulator-metal (MIM) antifuse stack including (a) a first metal layer; (b) a silicon dioxide, oxynitride or silicon nitride antifuse layer formed above the first metal layer; and (c) a second metal layer formed above the antifuse layer. The method also includes (2) forming a contiguous p-i-n diode above the MIM stack, the contiguous p-i-n diode comprising deposited semiconductor material; (3) forming a layer of a silicide, silicide-germanide, or germanide in contact with the deposited semiconductor material; and (4) crystallizing the deposited semiconductor material in contact with the layer of silicide, silicide-germanide, or germanide. The memory cell comprises the contiguous p-i-n diode and the MIM stack. Other aspects are provided.

Owner:SANDISK TECH LLC

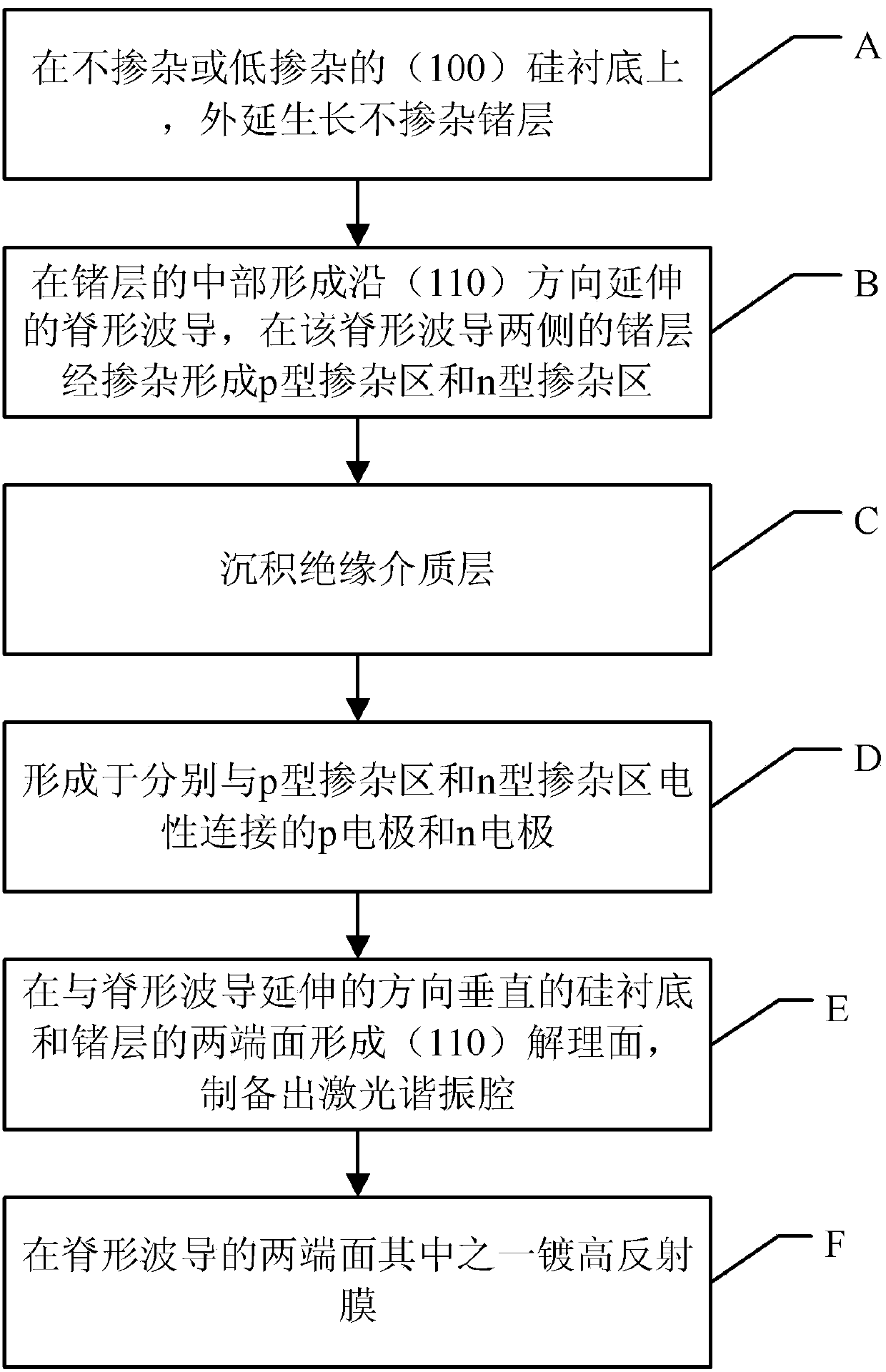

Silicon-based germanium laser device and method for manufacturing same

InactiveCN103427332AImprove crystal qualityImprove performanceOptical wave guidanceResonant cavityCrystal orientation

The invention provides a silicon-based germanium laser device and a method for manufacturing the same. The silicon-based germanium laser device comprises a silicon material, a germanium layer, a p-type doped region, an n-type doped region, an insulating dielectric layer, a p electrode and an n electrode; the silicon material is provide with corresponding crystal orientation; the germanium layer epitaxially grows on the silicon material and comprises a germanium ridge waveguide, the germanium layer is etched to form the germanium ridge waveguide, and the germanium ridge waveguide forms all or partial laser resonant cavities; the p-type doped region and the n-type doped region are positioned on two sides of the germanium ridge waveguide; the p-type doped region, the germanium ridge waveguide and the n-type doped region form a transverse p-i-n diode structure; the insulating dielectric layer is formed above the germanium ridge waveguide, the p-type doped region, the n-type doped region; the p electrode and the n electrode are formed above the insulating dielectric layer and are respectively electrically connected with the p-type doped region and the n-type doped region. The silicon-based germanium laser device and the method have the advantages that the silicon-based germanium laser device is of a horizontal transverse p-i-n germanium ridge waveguide structure, a silicon substrate does not need to be doped, the crystal quality of the germanium layer which epitaxially grows on the silicon substrate can be high, and accordingly the integral performance of the silicon-base germanium laser device can be improved advantageously.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

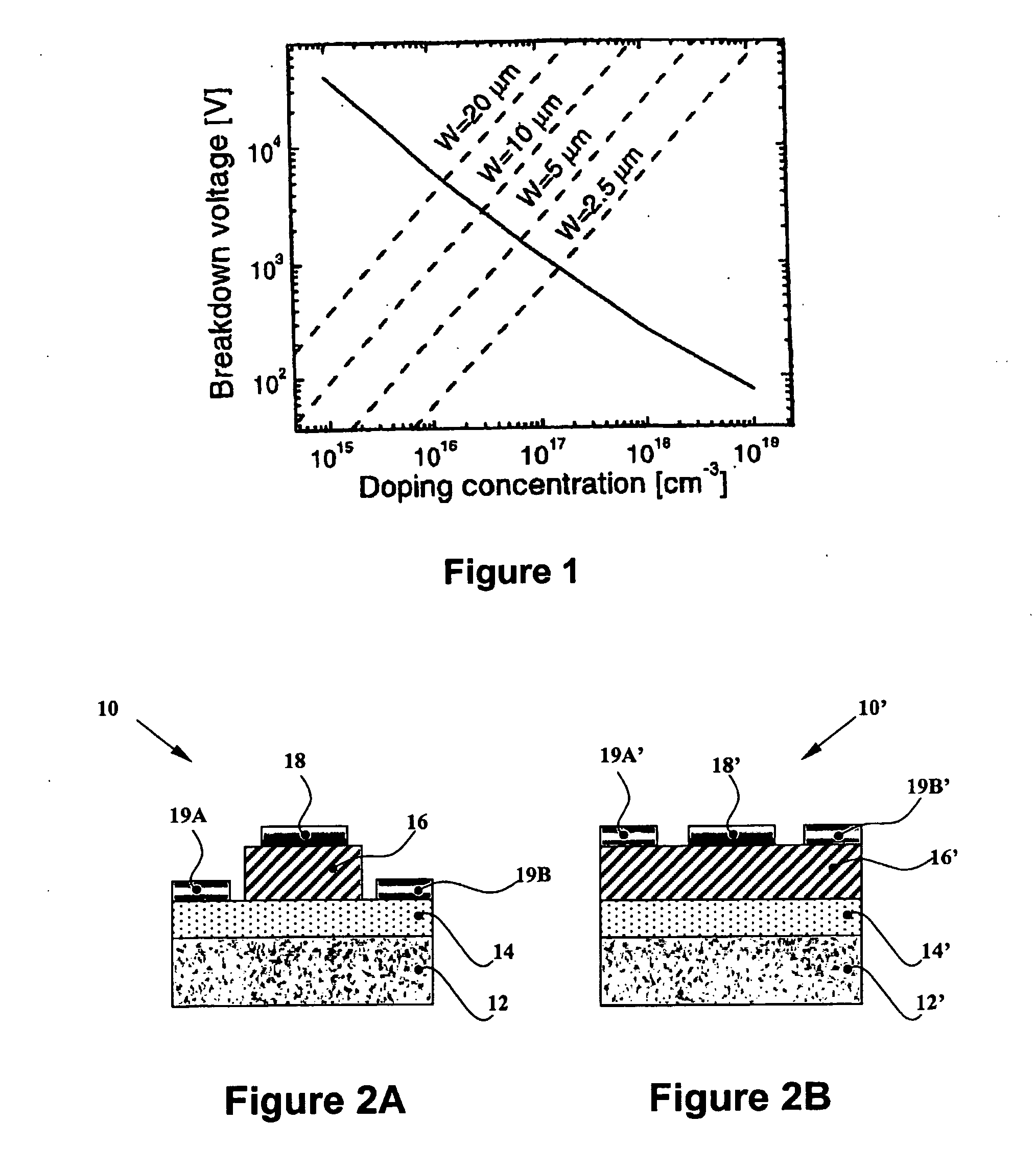

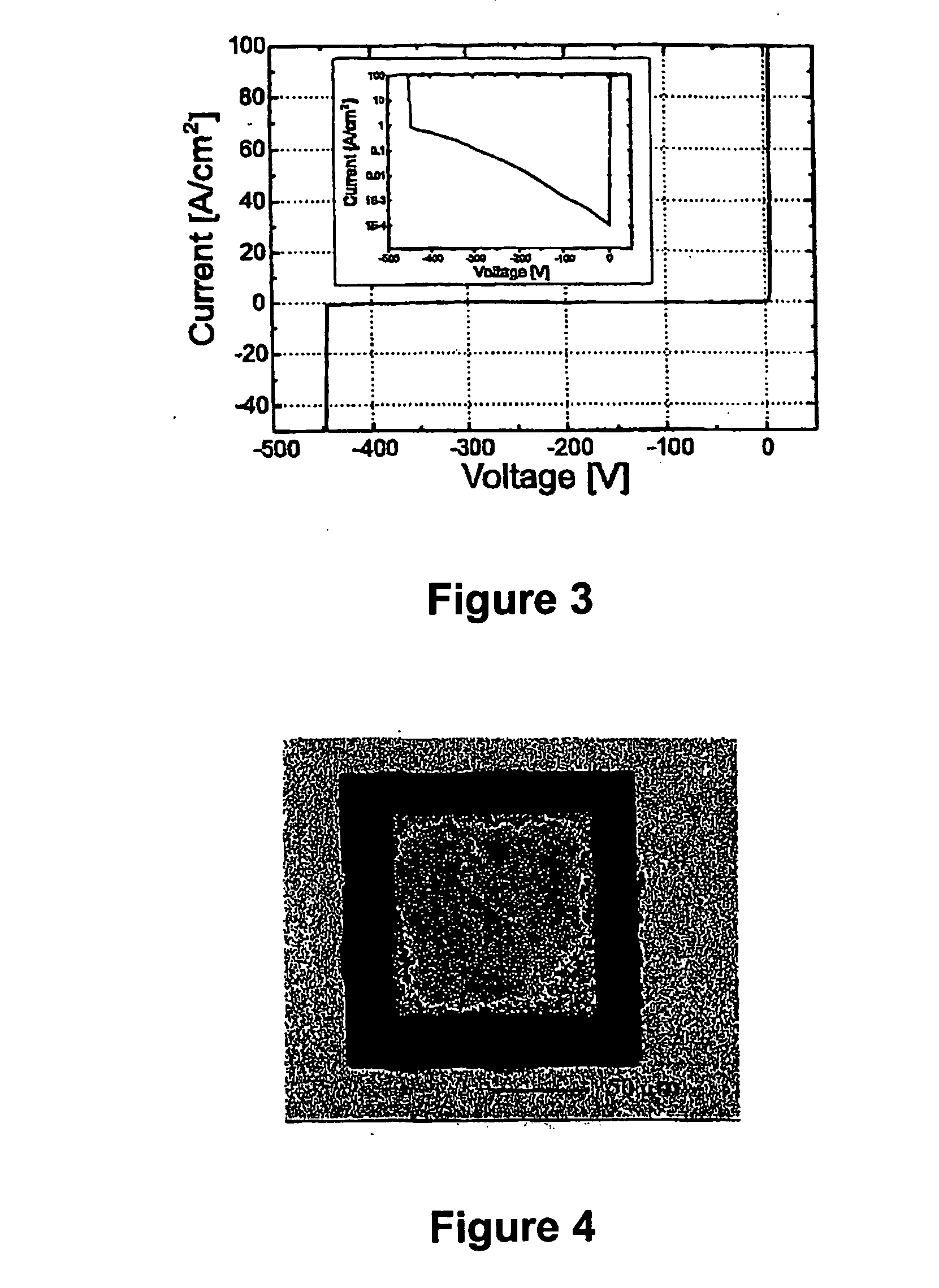

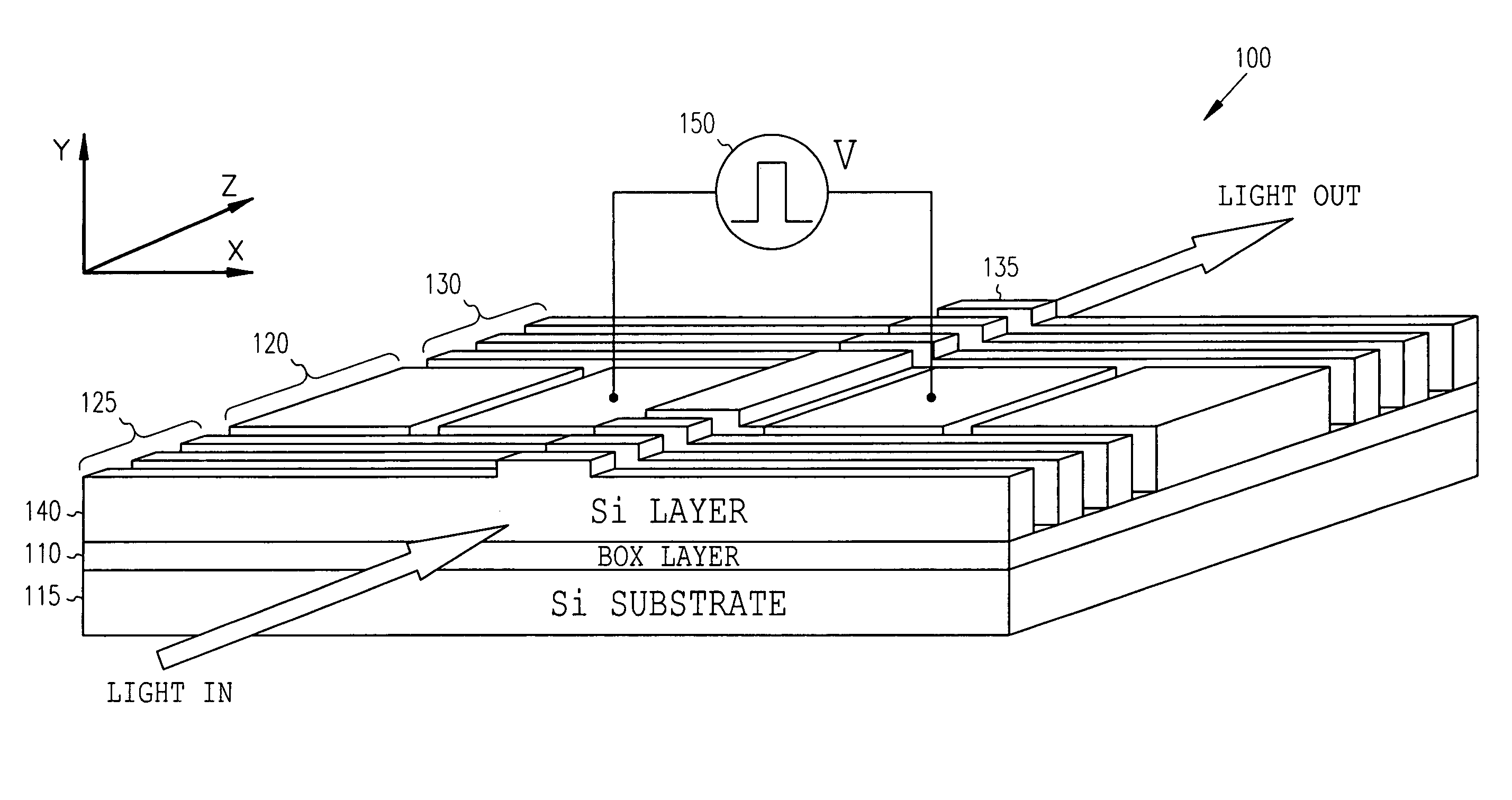

High voltage switching devices and process for forming same

ActiveUS20050167697A1Increase concentrationReduce concentrationPolycrystalline material growthSemiconductor/solid-state device manufacturingHigh pressureP–n diode

The present invention relates to various switching device structures including Schottky diode (10), P-N diode, and P-I-N diode, which are characterized by low defect density, low crack density, low pit density and sufficient thickness (>2.5 um) GaN layers (16) of low dopant concentration (<1E16 cm−3) grown on a conductive GaN layer (14). The devices enable substantially higher breakdown voltage on hetero-epitaxial substrates (<2 KV) and extremely high breakdown voltage on homo-epitaxial substrates (>2 KV).

Owner:WOLFSPEED INC

Photodetector with hetero-structure using lateral growth

InactiveUS7095006B2Increase capacityFinal product manufactureMaterial analysis by optical meansPhotovoltaic detectorsPhotodetector

A structure and method of fabrication for a Si based material p-i-n photodetector is disclosed. The light is absorbed in an undoped layer containing SiGe or Ge in such a manner that the absorption length is not limited by a critical thickness of the SiGe or Ge layer. The result is achieved by growing the SiGe or Ge layer from the walls of a trench in monocrystalline Si using lateral epitaxial. A second, doped material is disposed over the undoped layer for biasing and photocarrier collection in the p-i-n diode.

Owner:IBM CORP

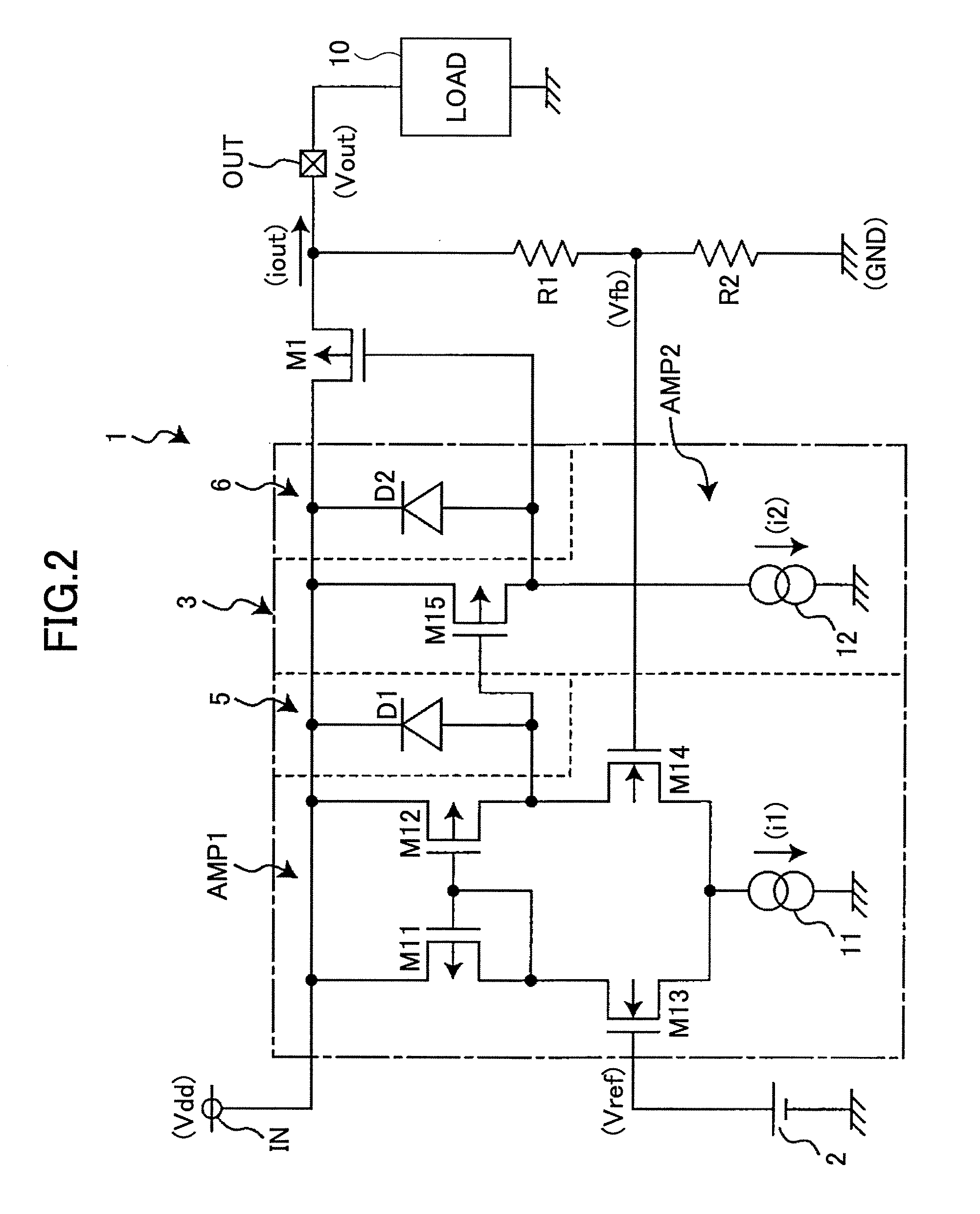

Bandgap reference circuit

InactiveUS6853164B1Moderate accuracyReduce power consumptionBatteries circuit arrangementsSecondary cellsAudio power amplifierEngineering

A bandgap reference circuit and method of using the same are provided. The bandgap reference circuit may provide start-up requirements at substantially any voltage and at substantially any temperature. The circuit comprises an op amp (two stages of transistors) and a network of resistors and bipolar diodes. When an artificial offset of about −5 mV is introduced to the op amp, the op amp output will be high as soon as the power supply exceeds the transistors' threshold voltages. The op amp output supplies the resistor and diode network and brings the op amp inputs within desired regulation voltages.

Owner:SEMICON COMPONENTS IND LLC

Electro-optic modulator on rib waveguide

Owner:CORNELL RES FOUNDATION INC

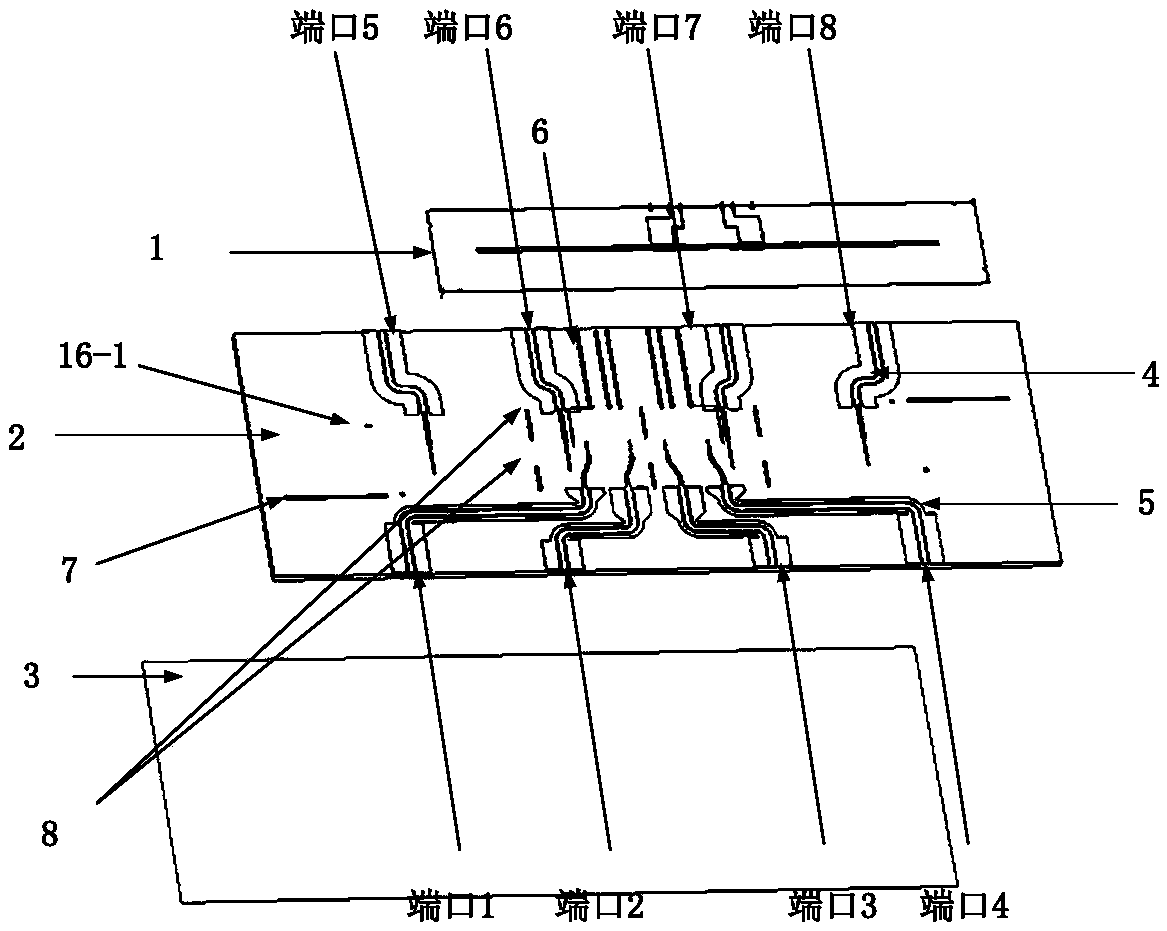

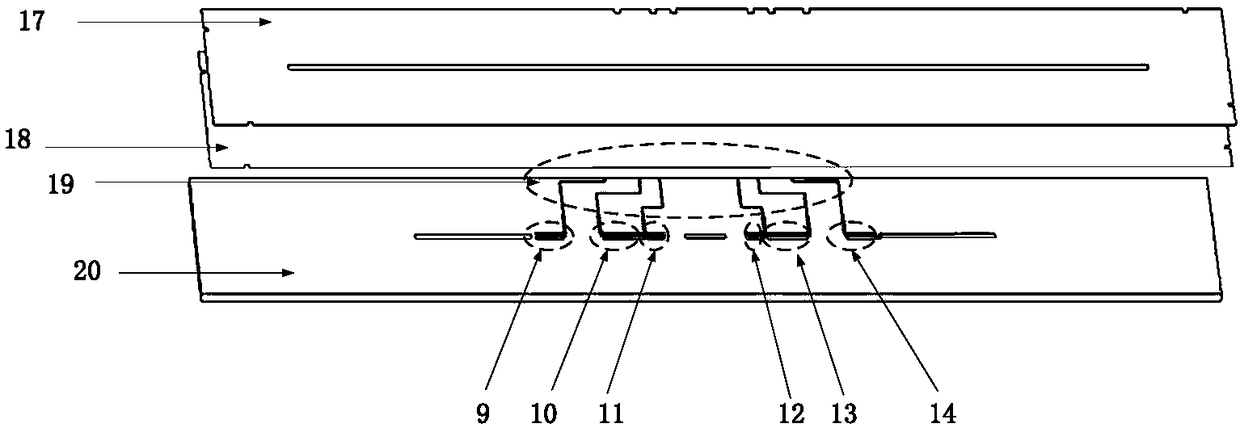

Common-caliber frequency reconfigurable on-chip slit array antenna and use method

ActiveCN108711671AIncrease freedomAchieving frequency reconfigurabilityParticular array feeding systemsSimultaneous aerial operationsReconfigurable antennaMicrowave

The invention provides a common-caliber frequency reconfigurable on-chip slit array antenna and a use method. The antenna comprises a silicon-based reconfigurable radiator layer, a PCB feeder line layer, a jumper line connection structure of a PCB and a silicon-base radiator, and a metal reflection cavity. The silicon-based reconfigurable radiator layer comprises a metal layer, multiple surface P-I-N diode (S-PIN) units, an insulation isolation layer, an S-PIN direct current bias layer and an intrinsic silicon medium layer, wherein slits are etched in the metal layers and the surface P-I-N diode (S-PIN) units are connected into the slits of the metal layer in a crossing manner. The PCB feeder line layer comprises a direct current lead connected with the silicon-based reconfigurable radiator layer, a microwave feeding device and a structure aligned to the silicon-based reconfigurable radiator layer. The reflection face layer is achieved by use of a metal box body. According to the invention, by controlling on and off of the S-PIN units connected into the metal slits of the silicon-based reconfigurable radiator layer in a crossing manner, working frequency and unit intervals of the array antenna are controlled, and frequency reconfiguration of the slit array antenna is finally achieved. Meanwhile, by use of the novel silicon-based S-PIN bias technology, radiation characteristicsof reconfigurable antenna are improved.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Semiconductor device with amorphous silicon mas memory cell structure and manufacturing method thereof

ActiveUS20100001271A1Improve signal-to-noise ratioReduce scaleSolid-state devicesSemiconductor/solid-state device manufacturingTrappingAmorphous silicon

A semiconductor device with an amorphous silicon (a-Si) metal-aluminum oxide-semiconductor (MAS) memory cell structure. The device includes a substrate, a dielectric layer overlying the substrate, and one or more source or drain regions embedded in the dielectric layer with a co-planar surface of n-type a-Si and the dielectric layer. Additionally, the device includes a p-i-n a-Si diode junction. The device further includes an aluminum oxide charge trapping layer on the a-Si p-i-n diode junction and a metal control gate overlying the aluminum oxide layer. A method is provided for making the a-Si MAS memory cell structure and can be repeated to integrate the structure three-dimensionally.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Absorption modulator and manufacturing method thereof

InactiveUS20100142878A1Improve featuresIncrease speedSemiconductor/solid-state device manufacturingOptical waveguide light guideElectro-absorption modulatorInsulation layer

An absorption modulator is provided. The absorption modulator includes a substrate, an insulation layer disposed on the substrate, and a waveguide having a P-I-N diode structure on the insulation layer. Absorptance of an intrinsic region in the P-I-N diode structure is varied when modulating light inputted to the waveguide. The absorption modulator obtains the improved characteristics, such as high speed, low power consumption, and small size, because it greatly reduces the cross-sectional area of the P-I-N diode structure.

Owner:ELECTRONICS & TELECOMM RES INST

Pillar P-i-n semiconductor diodes

InactiveUS7525170B2Improve efficiencyPromote absorptionFinal product manufactureSolid-state devicesLight energySemiconductor

Owner:INT BUSINESS MASCH CORP

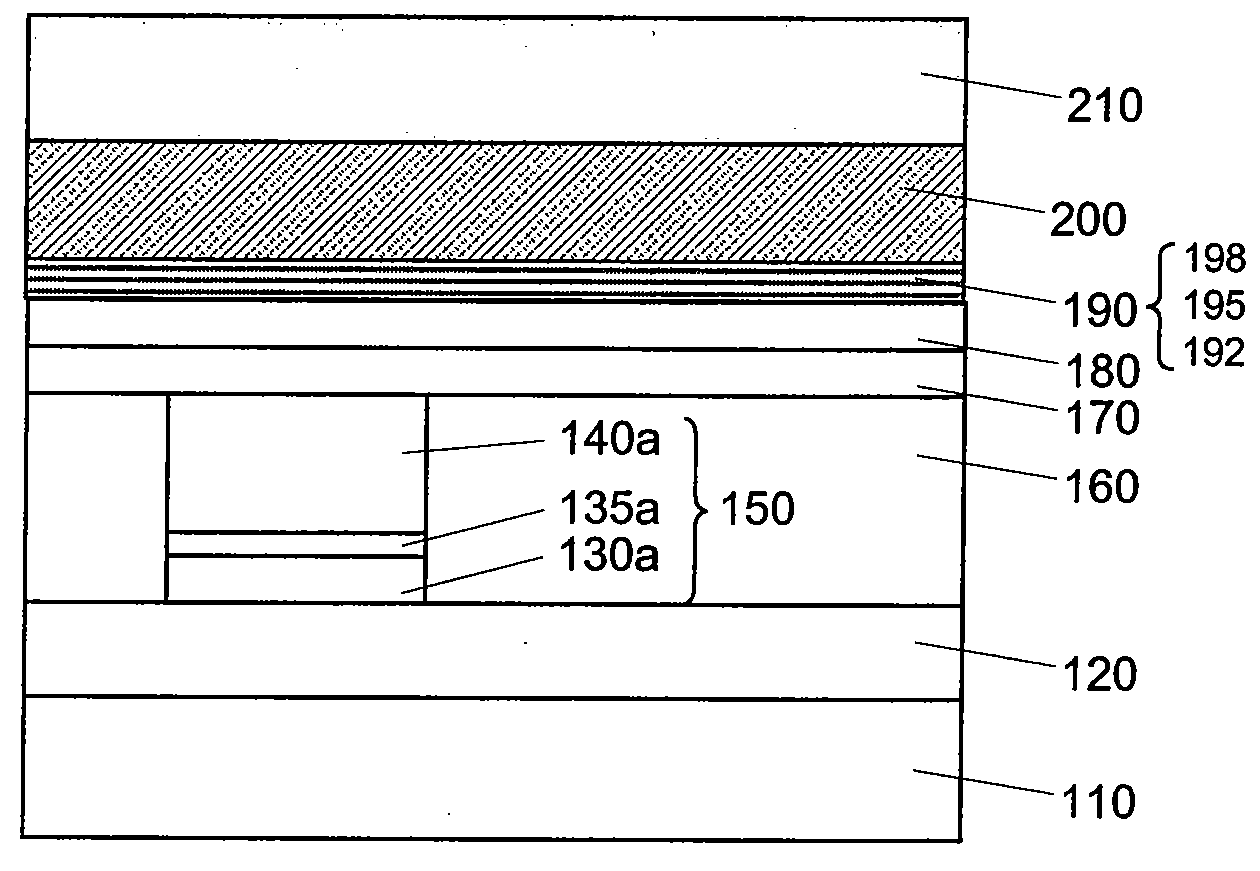

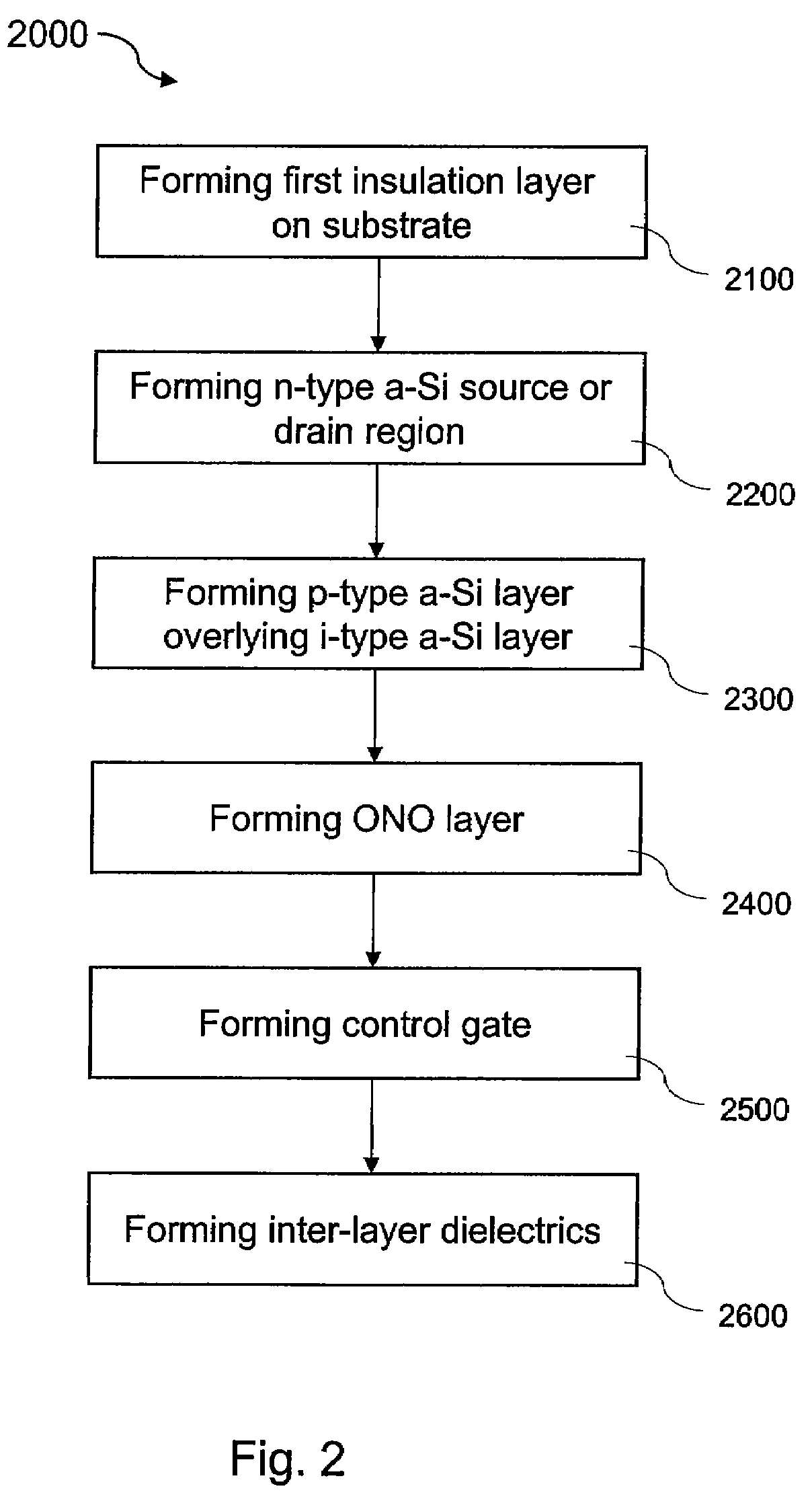

Semiconductor device with amorphous silicon monos memory cell structure and method for manufacturing thereof

ActiveUS20080138949A1Improve signal-to-noise ratioReduce scaleSolid-state devicesSemiconductor/solid-state device manufacturingOxide semiconductorP i n diode

A semiconductor device with an amorphous silicon (a-Si) metal-oxide-nitride-oxide-semiconductor (MONOS) memory cell structure. The device includes a substrate, a dielectric layer overlying the substrate, and one or more source or drain regions embedded in the dielectric layer with a co-planar surface of n-type a-Si and the dielectric layer. Additionally, the device includes a p-i-n a-Si diode junction. The device further includes an oxide-nitride-oxide (ONO) charge trapping layer overlying the a-Si p-i-n diode junction and a metal control gate overlying the ONO layer. A method for making the a-Si MONOS memory cell structure is provided and can be repeated to expand the structure three-dimensionally.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Semiconductor device with amorphous silicon MONOS memory cell structure and method for manufacturing thereof

ActiveUS7625796B2Improve signal-to-noise ratioReduce scaleSolid-state devicesSemiconductor/solid-state device manufacturingTrappingAmorphous silicon

A semiconductor device with an amorphous silicon (a-Si) metal-oxide-nitride-oxide-semiconductor (MONOS) memory cell structure. The device includes a substrate, a dielectric layer overlying the substrate, and one or more source or drain regions embedded in the dielectric layer with a co-planar surface of n-type a-Si and the dielectric layer. Additionally, the device includes a p-i-n a-Si diode junction. The device further includes an oxide-nitride-oxide (ONO) charge trapping layer overlying the a-Si p-i-n diode junction and a metal control gate overlying the ONO layer. A method for making the a-Si MONOS memory cell structure is provided and can be repeated to expand the structure three-dimensionally.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Operational amplifier circuit, constant voltage circuit using the same, and apparatus using the constant voltage circuit

ActiveUS20090033420A1Improved fast responseImprove featuresAmplifier combinationsDifferential amplifiersAudio power amplifierEngineering

A disclosed operational amplifier circuit with a multi-stage amplifier configuration provides fast-response and high withstand-voltage characteristics without using high withstand-voltage transistors as output transistors in its amplifying stages. The output voltage range of a differential amplifier circuit in a first stage is limited by voltage clamping based on a reverse withstand voltage of a bipolar diode. The output voltage range of an amplifier circuit in a second stage is limited by voltage clamping based on a reverse withstand voltage of another bipolar diode. A constant voltage circuit and an apparatus including such an operational amplifier circuit are also disclosed.

Owner:NISSHINBO MICRO DEVICES INC

Popular searches

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com