Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

574 results about "Reconfigurable antenna" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A reconfigurable antenna is an antenna capable of modifying its frequency and radiation properties dynamically, in a controlled and reversible manner. In order to provide a dynamic response, reconfigurable antennas integrate an inner mechanism (such as RF switches, varactors, mechanical actuators or tunable materials) that enable the intentional redistribution of the RF currents over the antenna surface and produce reversible modifications of its properties. Reconfigurable antennas differ from smart antennas because the reconfiguration mechanism lies inside the antenna, rather than in an external beamforming network. The reconfiguration capability of reconfigurable antennas is used to maximize the antenna performance in a changing scenario or to satisfy changing operating requirements.

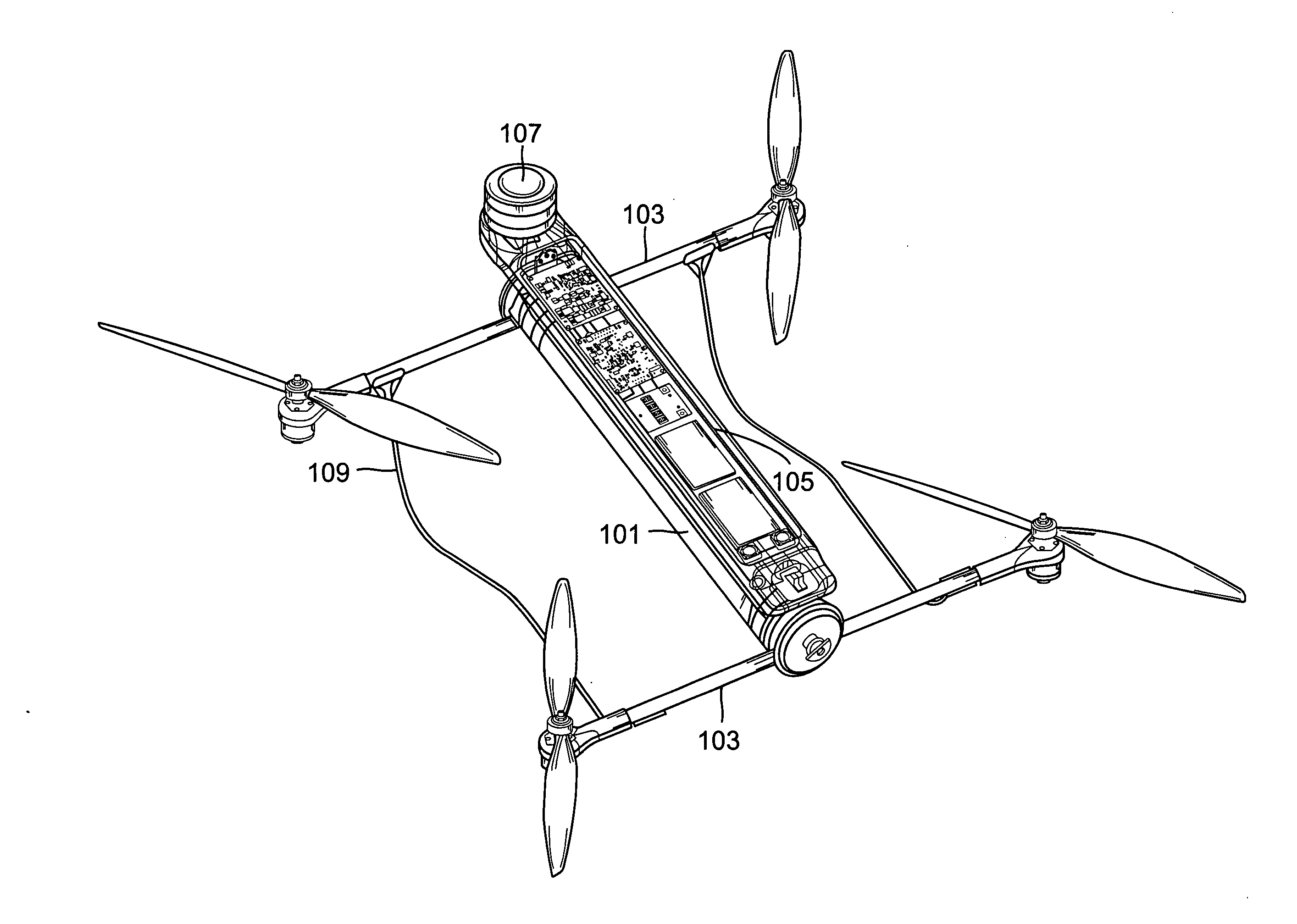

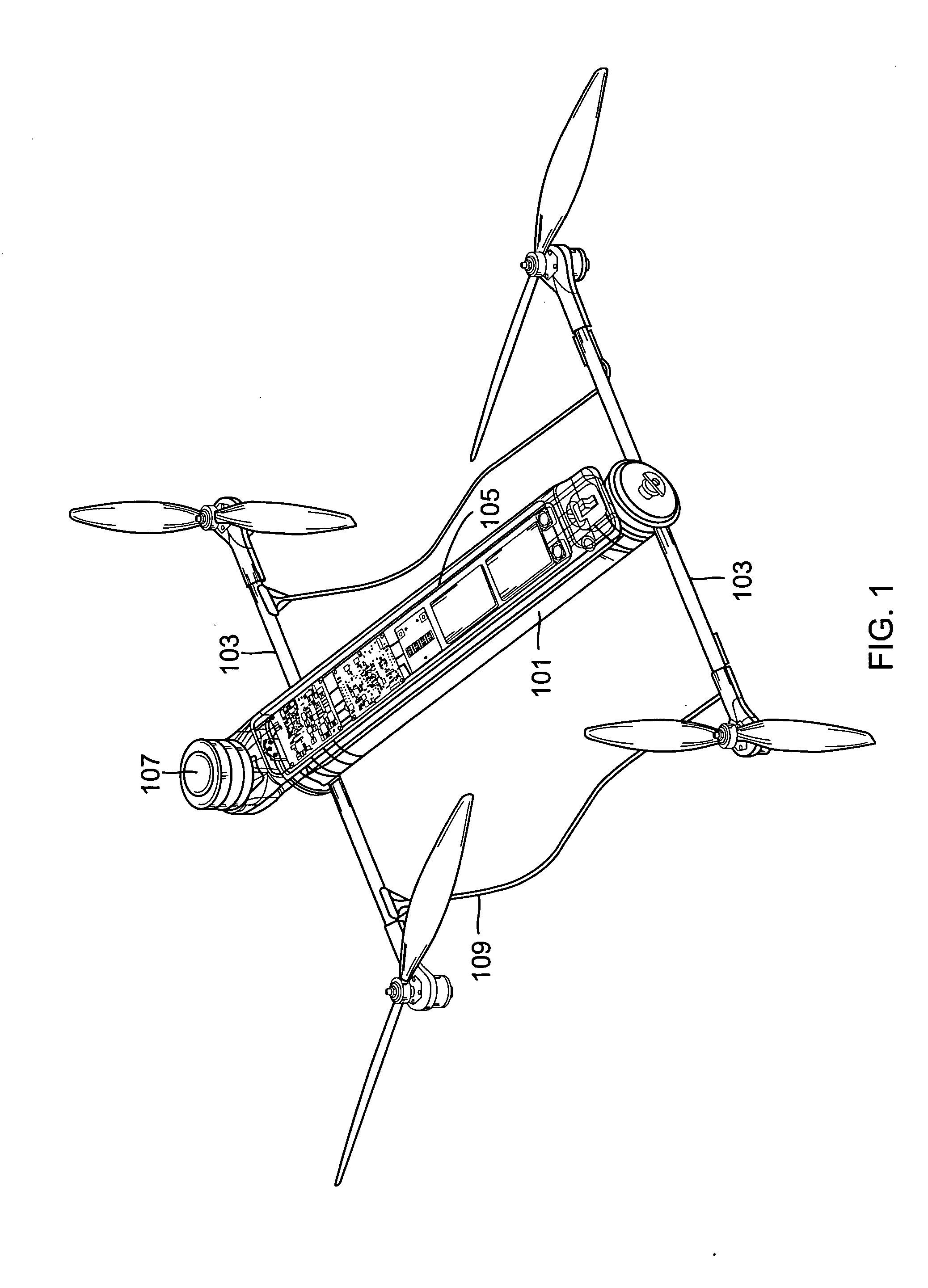

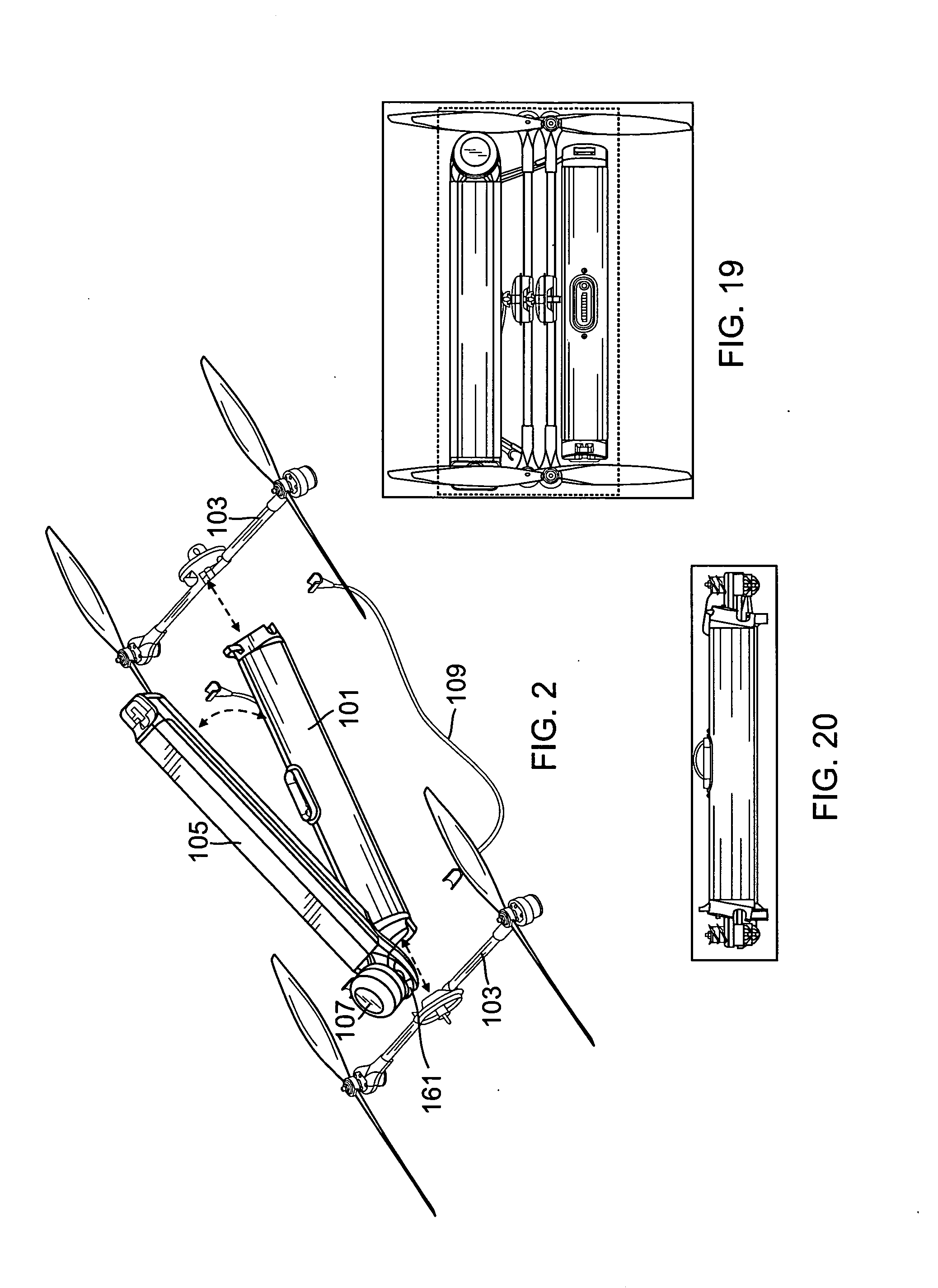

Reconfigurable battery-operated vehicle system

InactiveUS20140061376A1Reduce weightStable structureUnmanned surface vesselsRemote controlled aircraftReconfigurable antennaComputer module

A quadrotor UAV including ruggedized, integral-battery, load-bearing body, two arms on the load-bearing body, each arm having two rotors, a control module mounted on the load-bearing body, a payload module mounted on the control module, and skids configured as landing gear. The two arms are replaceable with arms having wheels for ground vehicle use, with arms having floats and props for water-surface use, and with arms having pitch-controlled props for underwater use. The control module is configured to operate as an unmanned aerial vehicle, an unmanned ground vehicle, an unmanned (water) surface vehicle, and an unmanned underwater vehicle, depending on the type of arms that are attached.

Owner:AEROVIRONMENT INC

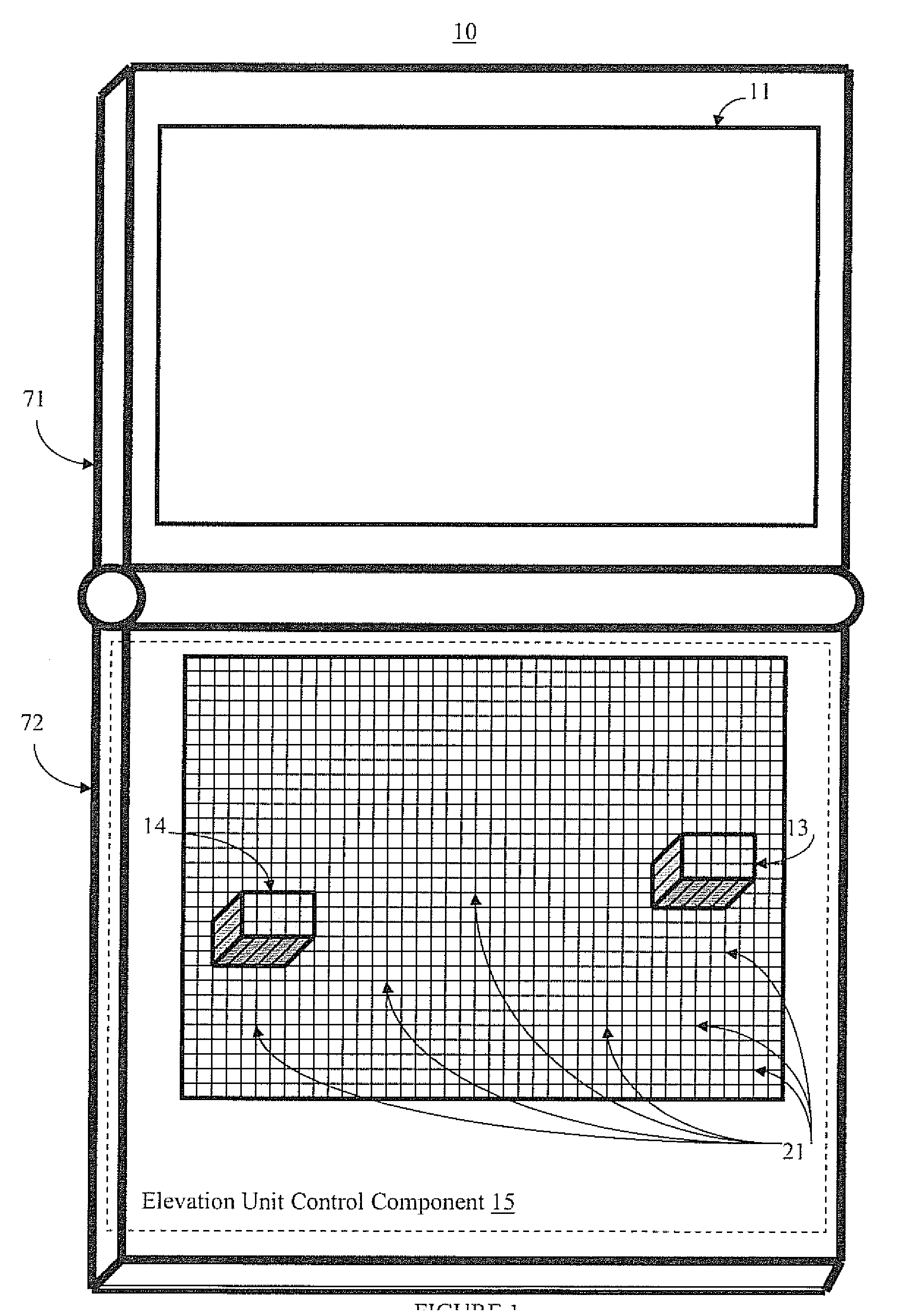

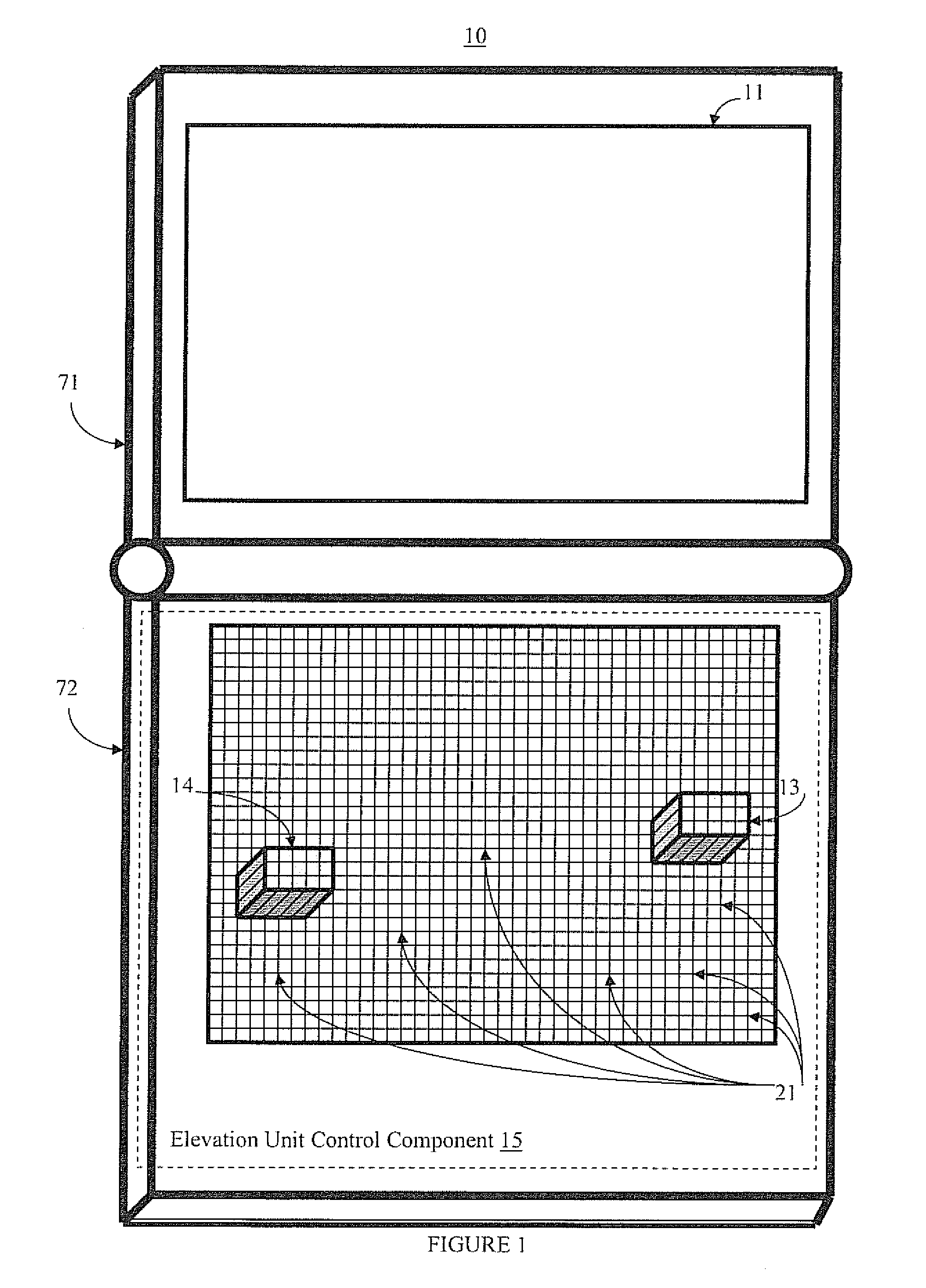

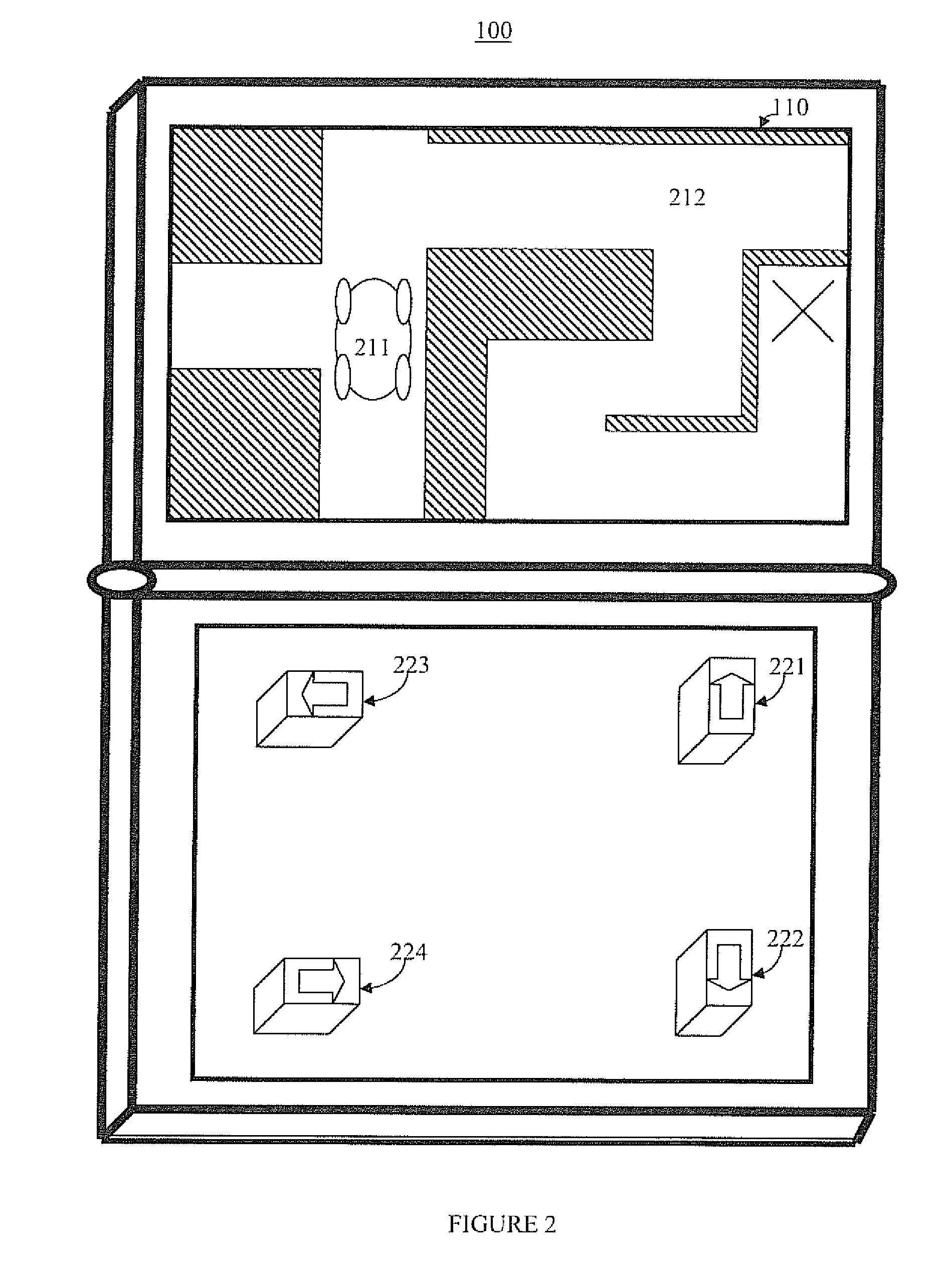

Physically reconfigurable input and output systems and methods

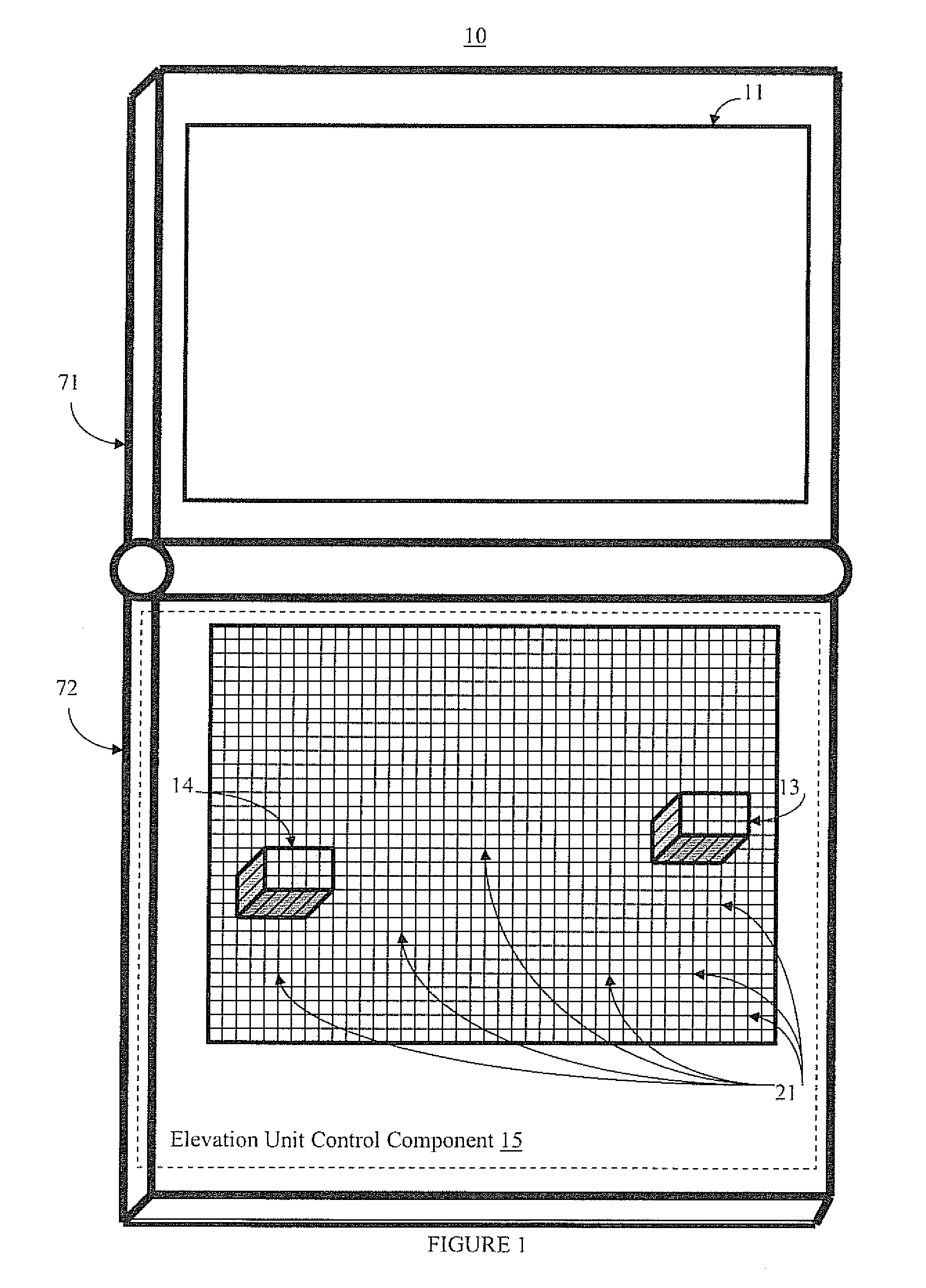

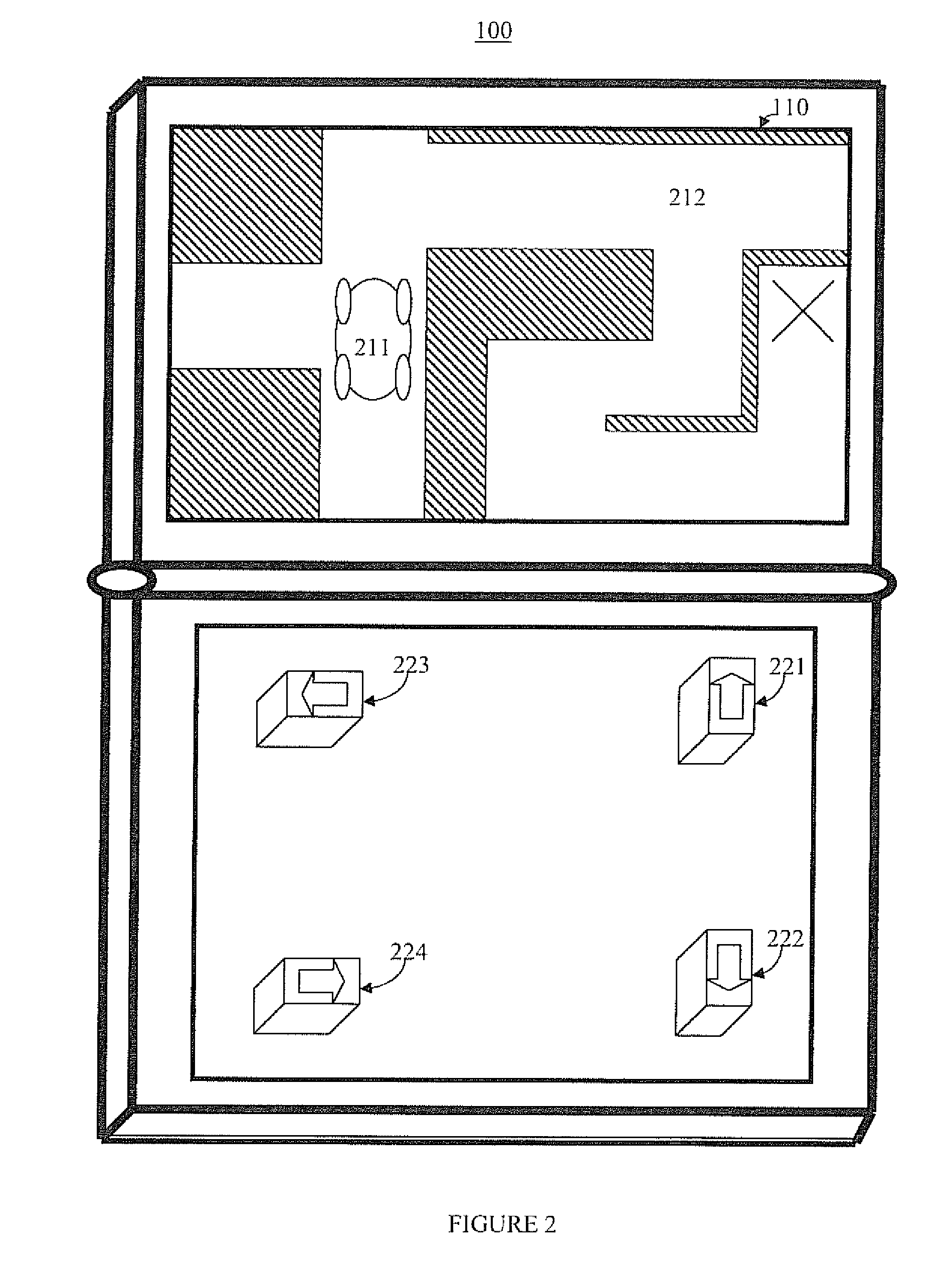

InactiveUS20110234502A1Effective interactionInput/output for user-computer interactionCathode-ray tube indicatorsUser needsReconfigurable antenna

Systems and methods for altering the shape of a reconfigurable surface area are presented. The present systems and methods facilitate efficient and effective interaction with a device or system. In one embodiment, a surface reconfiguration system includes a flexible surface; an elevation unit that creates alterations in the contours of the surface; and an elevation control component that controls adjustments to the elevation unit. Thus, the surface of the device is reconfigurable based on system, application, mode, and / or user needs. Accordingly, the surface can be used to provide input and output functionality. The surface can include touch detection functionality for added input functionality.

Owner:PANASONIC OF NORTH AMERICA

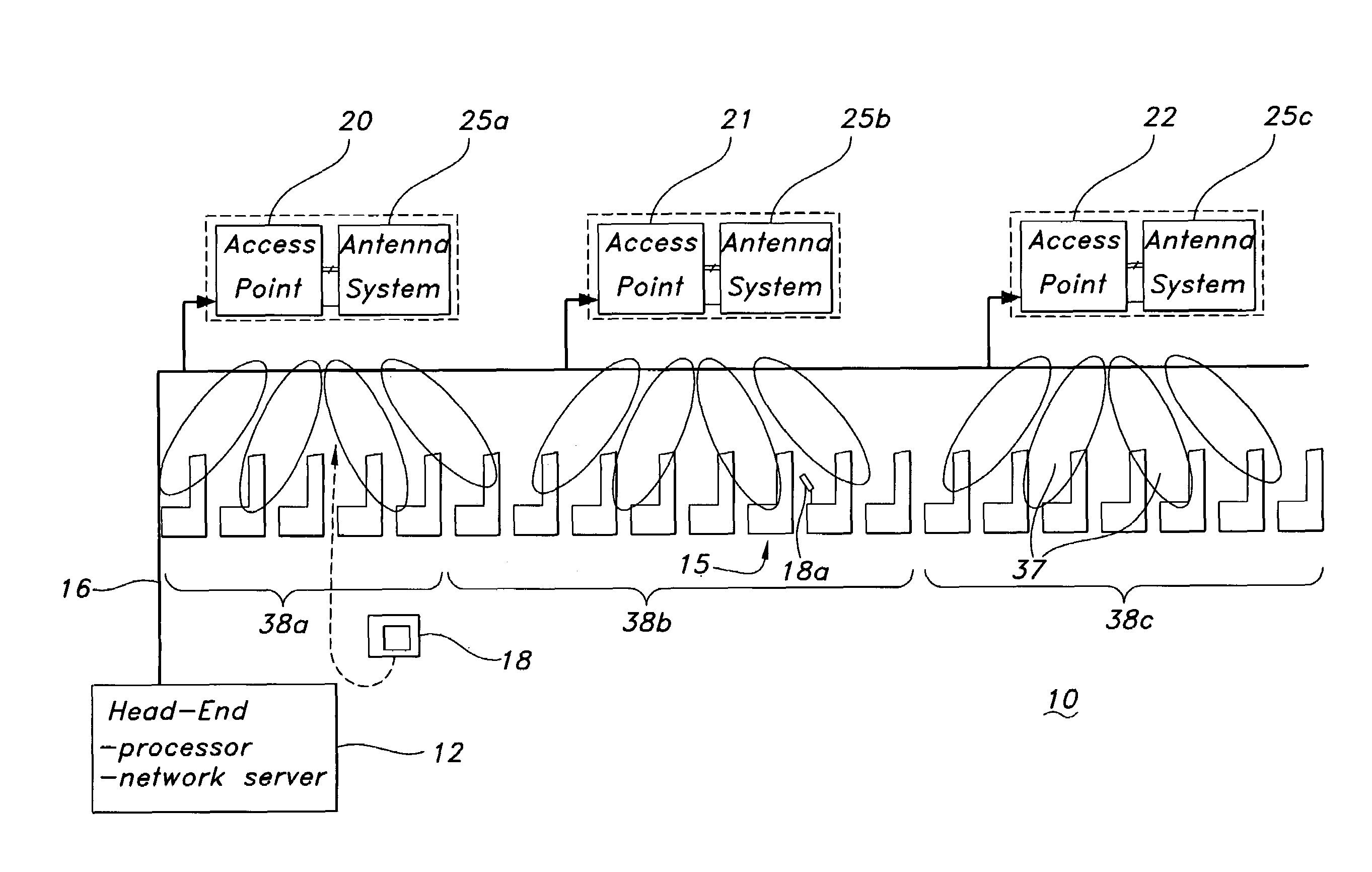

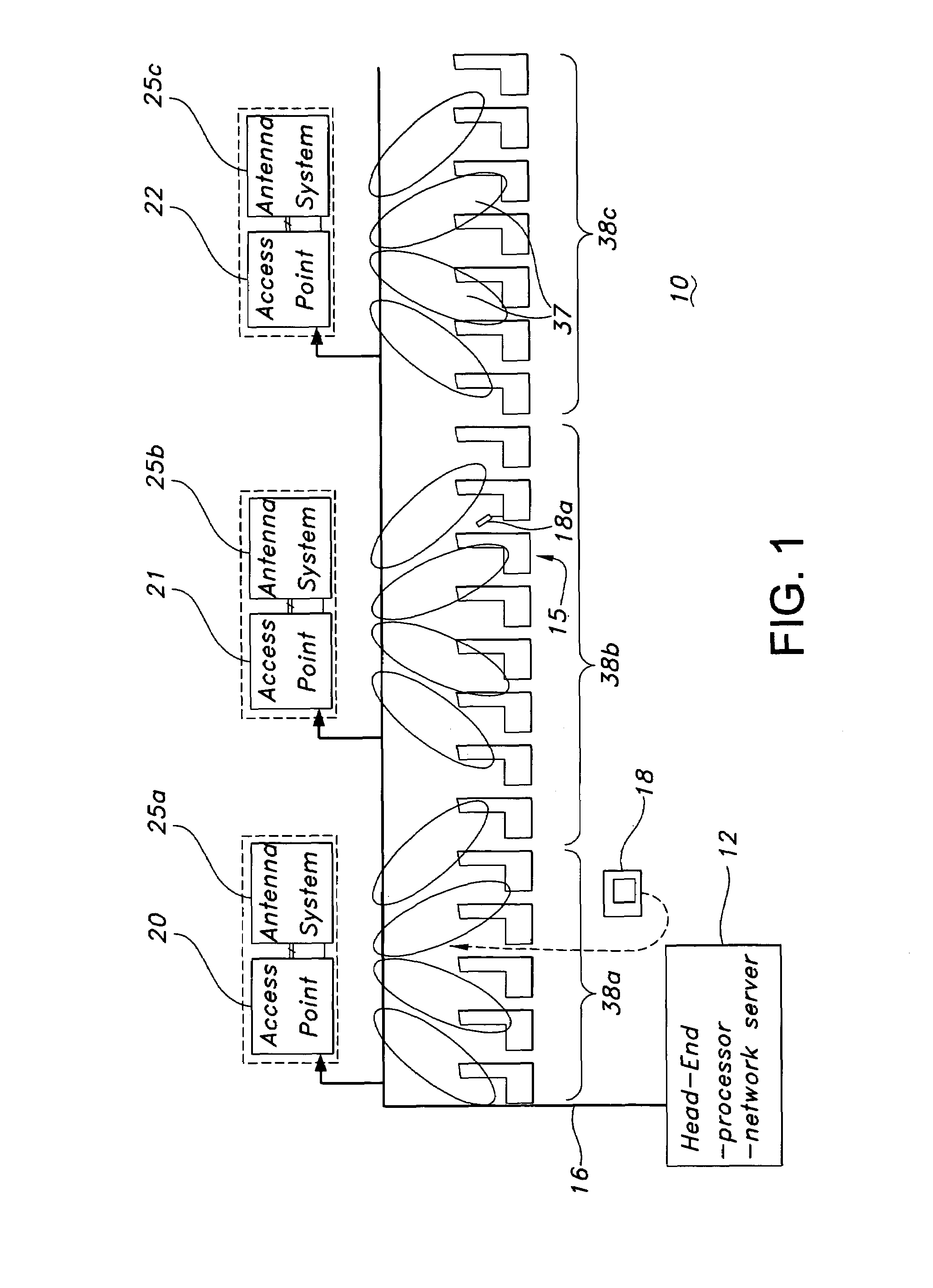

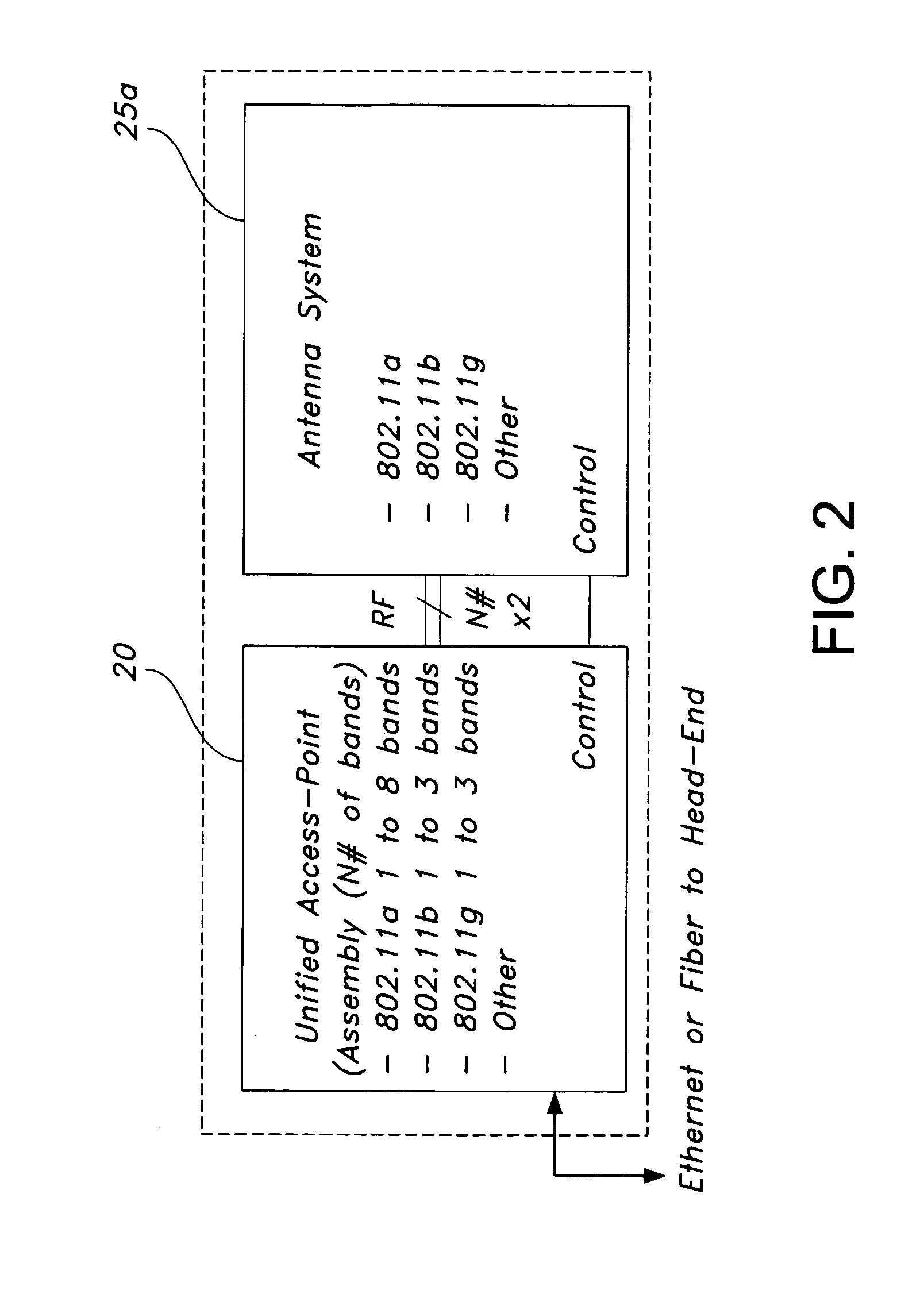

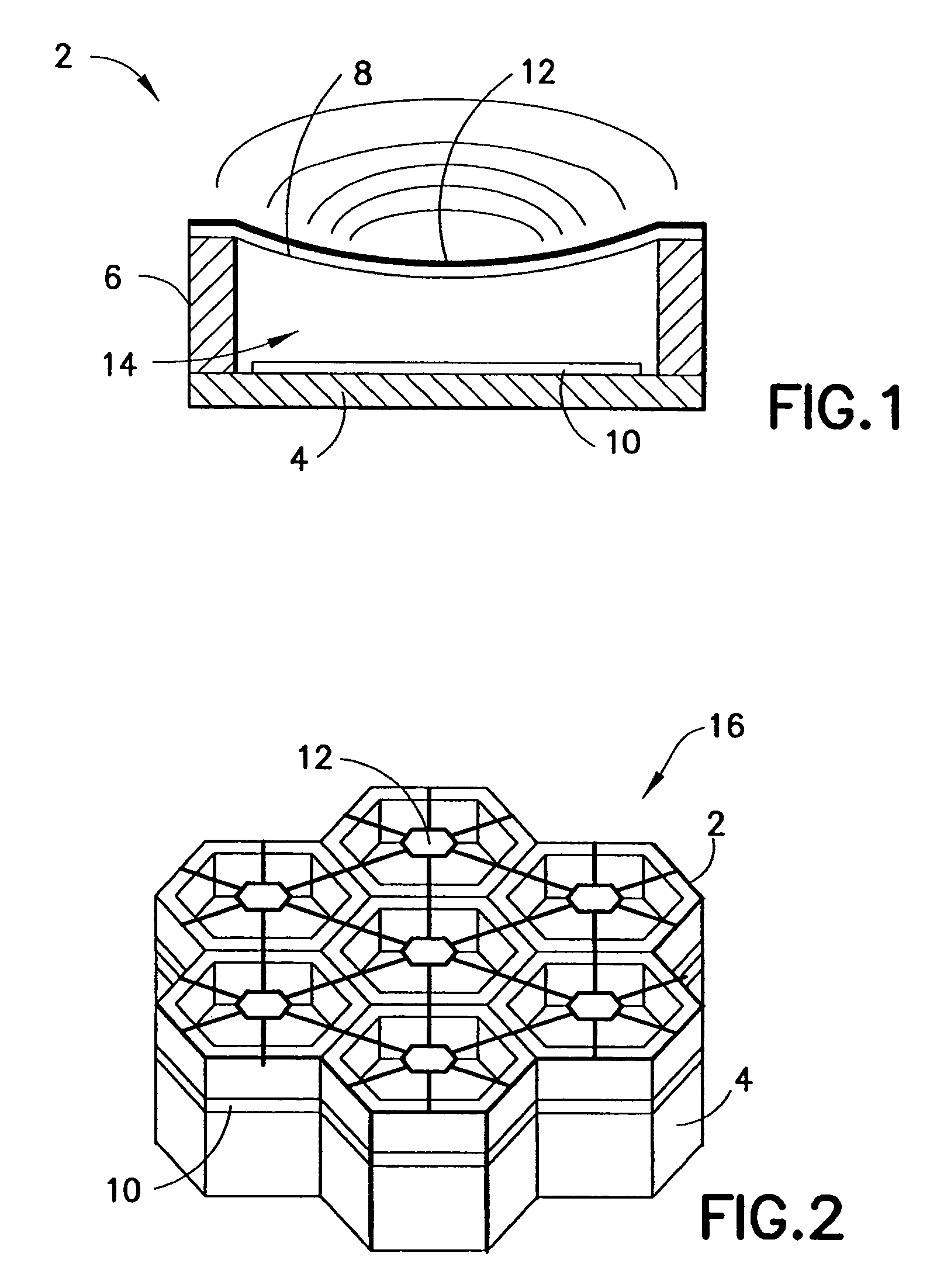

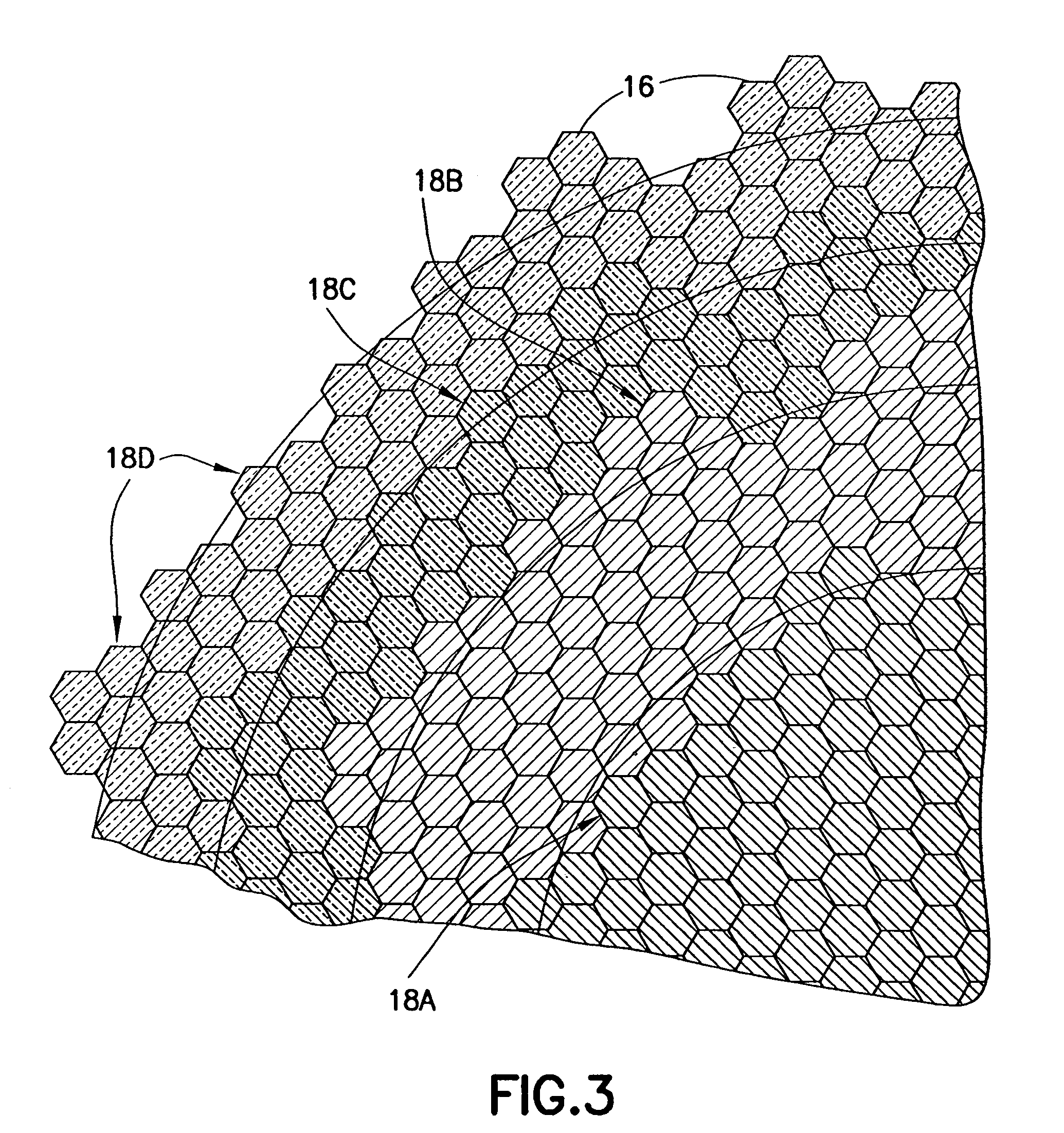

Cellular wireless network for passengers cabins

ActiveUS7483696B1Maximize connectivityAvoid OverloadingRadio transmissionWireless commuication servicesReconfigurable antennaFrequency reuse

A cellular wireless in-flight entertainment (IFE) system is used in an aircraft for delivering programming to passengers. A head end server provides data and programming to cells. Each cell comprises a wireless access point / configurable antenna to receive the data and the programming. The wireless access point / configurable antenna is disposed at an optimum location in a passenger cabin and operates with a predetermined frequency, radiation pattern, and polarization to provide the programming at optimum coverage. Wireless seat displays receive the programming from the wireless access point / configurable antenna and have a seat display antenna with selectable polarization. The cellular wireless IFE system provides for frequency reuse within the cells, registration of passengers upon log in to identify placement of the wireless seat displays, load balancing to prevent exceeding a capacity of a wireless access point / configurable antenna, and a scalable architecture where data and video each utilize a different band and wireless access point / configurable antenna.

Owner:ROCKWELL COLLINS INC

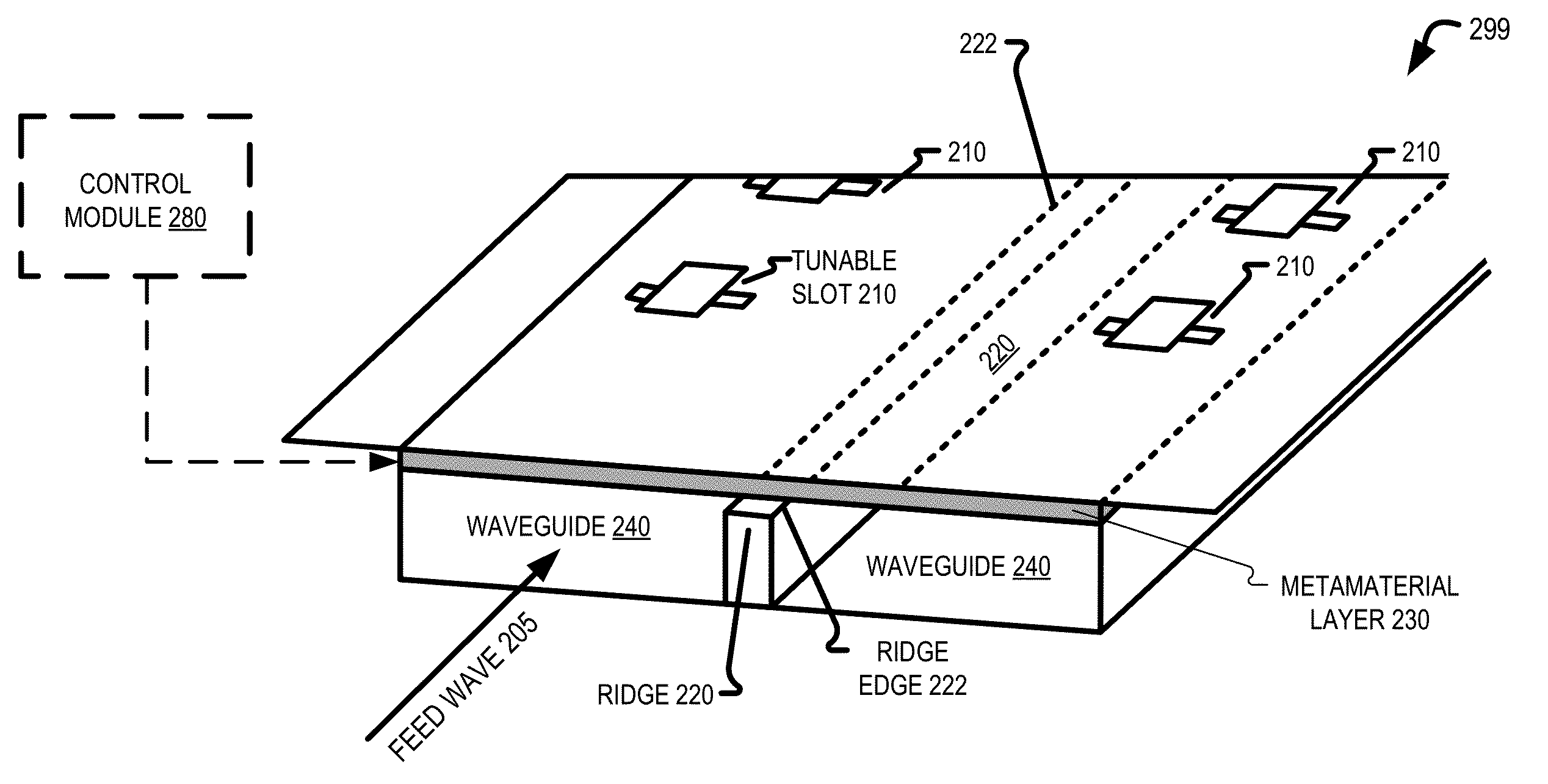

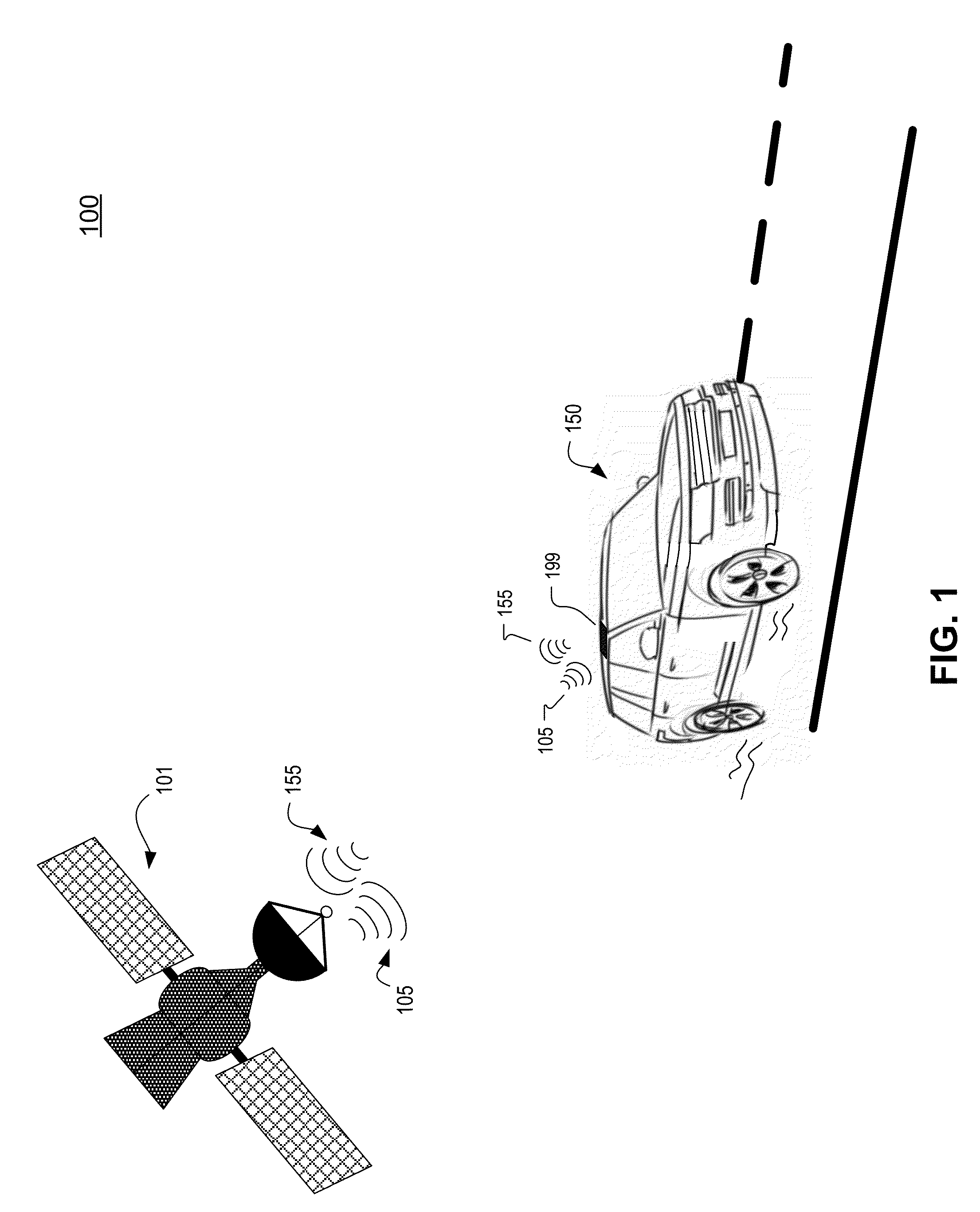

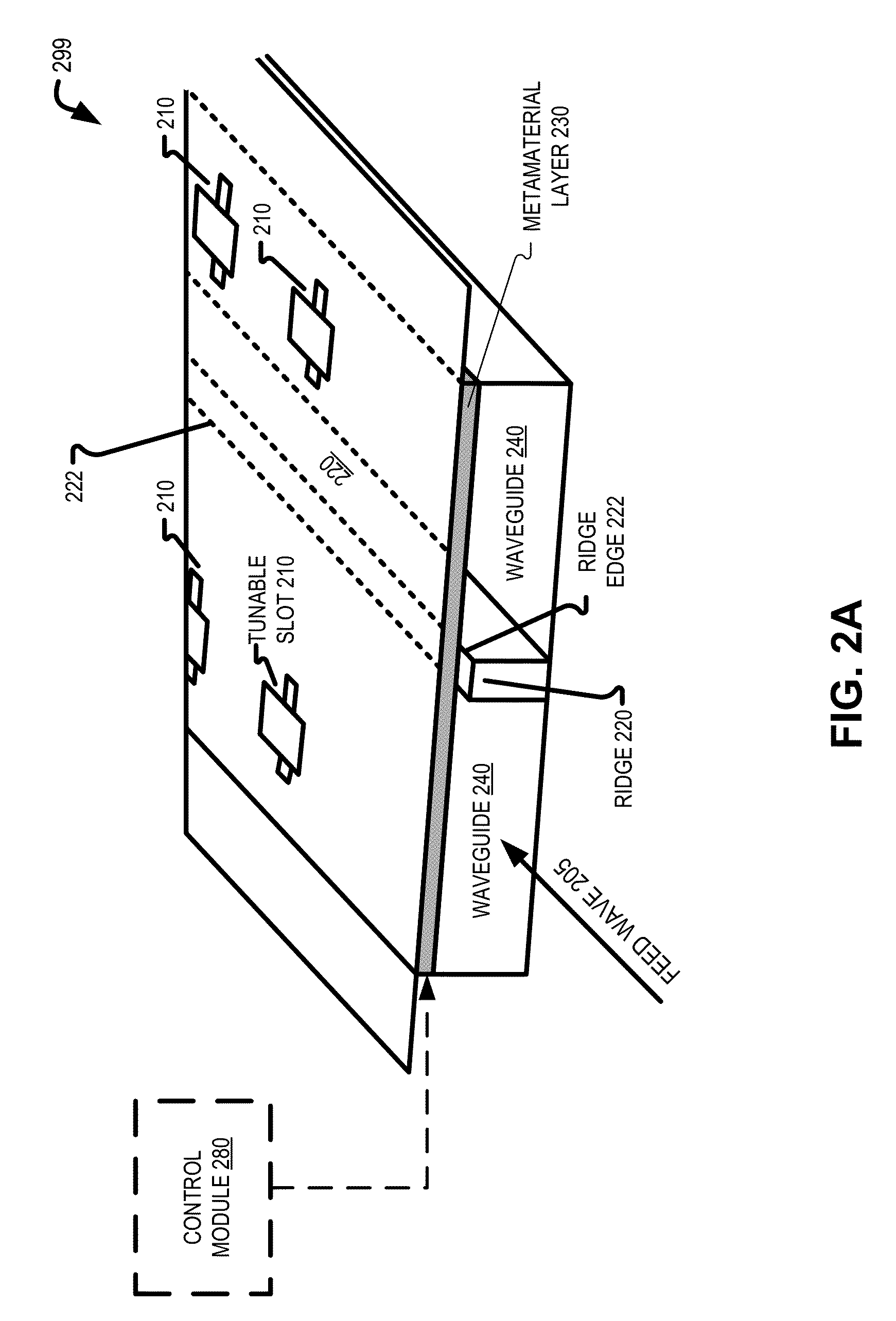

Ridged waveguide feed structures for reconfigurable antenna

A reconfigurable holographic antenna includes a metamaterial layer and a waveguide with at least one ridge. The metamaterial layer includes an array of tunable slots configurable to form holographic diffraction patterns. A reactance of each tunable slot in the array of tunable slots is individually tunable. The at least one ridge influences coupling between tunable slots in the array of tunable slots. The holographic diffraction patterns formed by the array of tunable slots generate a desired antenna wave in response to a received feed wave.

Owner:KYMETA

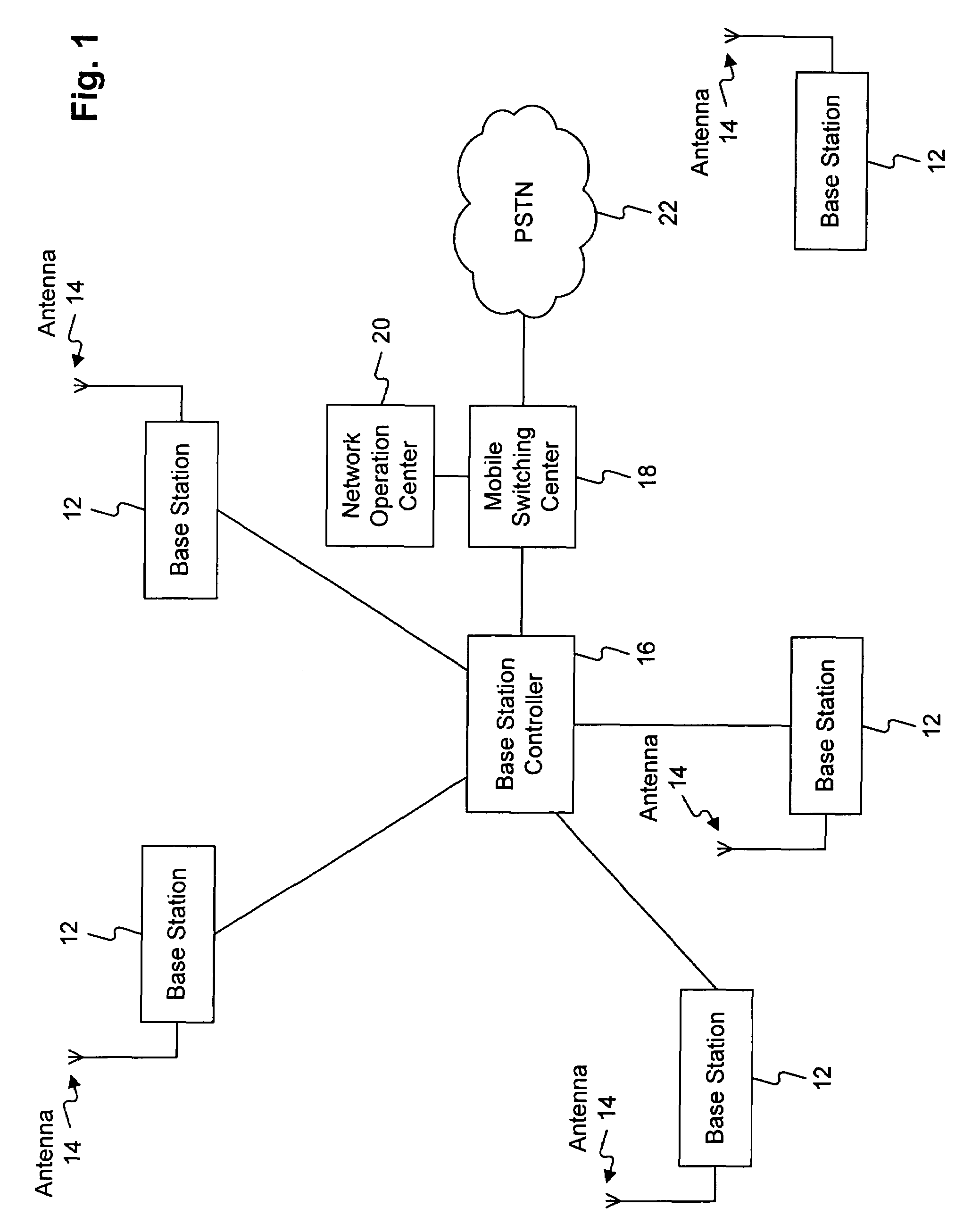

Method for configuring a communication network, related network architecture and computer program product therefor

InactiveUS7286854B2Quality improvementIncrease the number ofPower managementTransmission control/equalisingReconfigurable antennaUltrasound attenuation

Owner:PIRELLI & C +1

Physically reconfigurable input and output systems and methods

InactiveUS8232976B2Effective interactionInput/output for user-computer interactionCathode-ray tube indicatorsUser needsReconfigurable antenna

Systems and methods for altering the shape of a reconfigurable surface area are presented. The present systems and methods facilitate efficient and effective interaction with a device or system. In one embodiment, a surface reconfiguration system includes a flexible surface; an elevation unit that creates alterations in the contours of the surface; and an elevation control component that controls adjustments to the elevation unit. Thus, the surface of the device is reconfigurable based on system, application, mode, and / or user needs. Accordingly, the surface can be used to provide input and output functionality. The surface can include touch detection functionality for added input functionality.

Owner:PANASONIC OF NORTH AMERICA

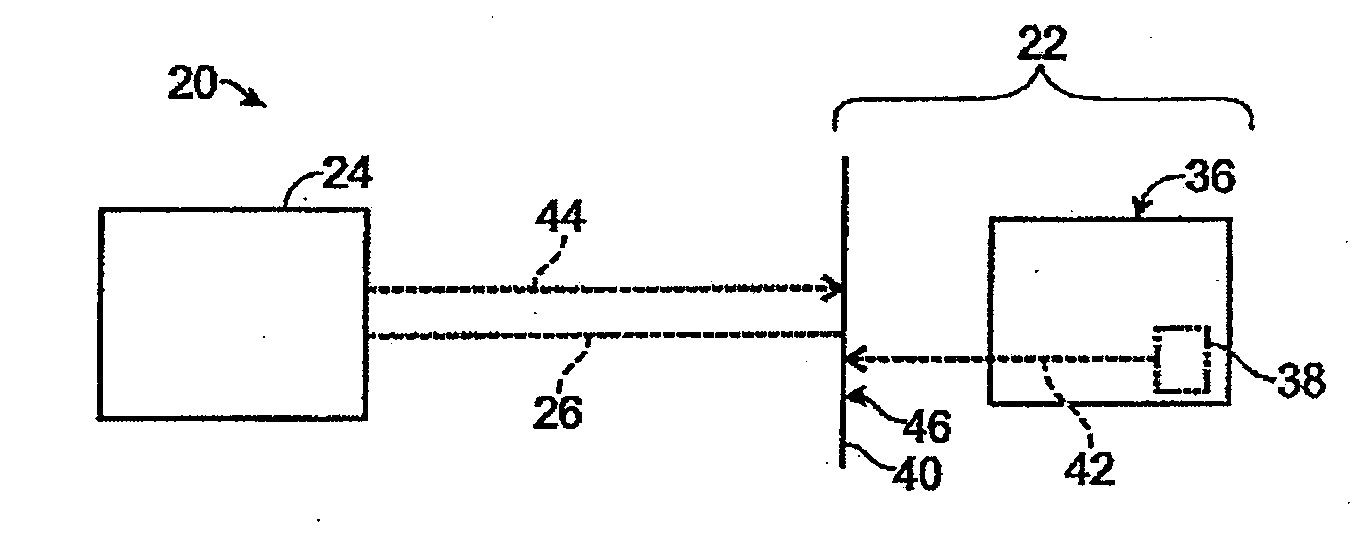

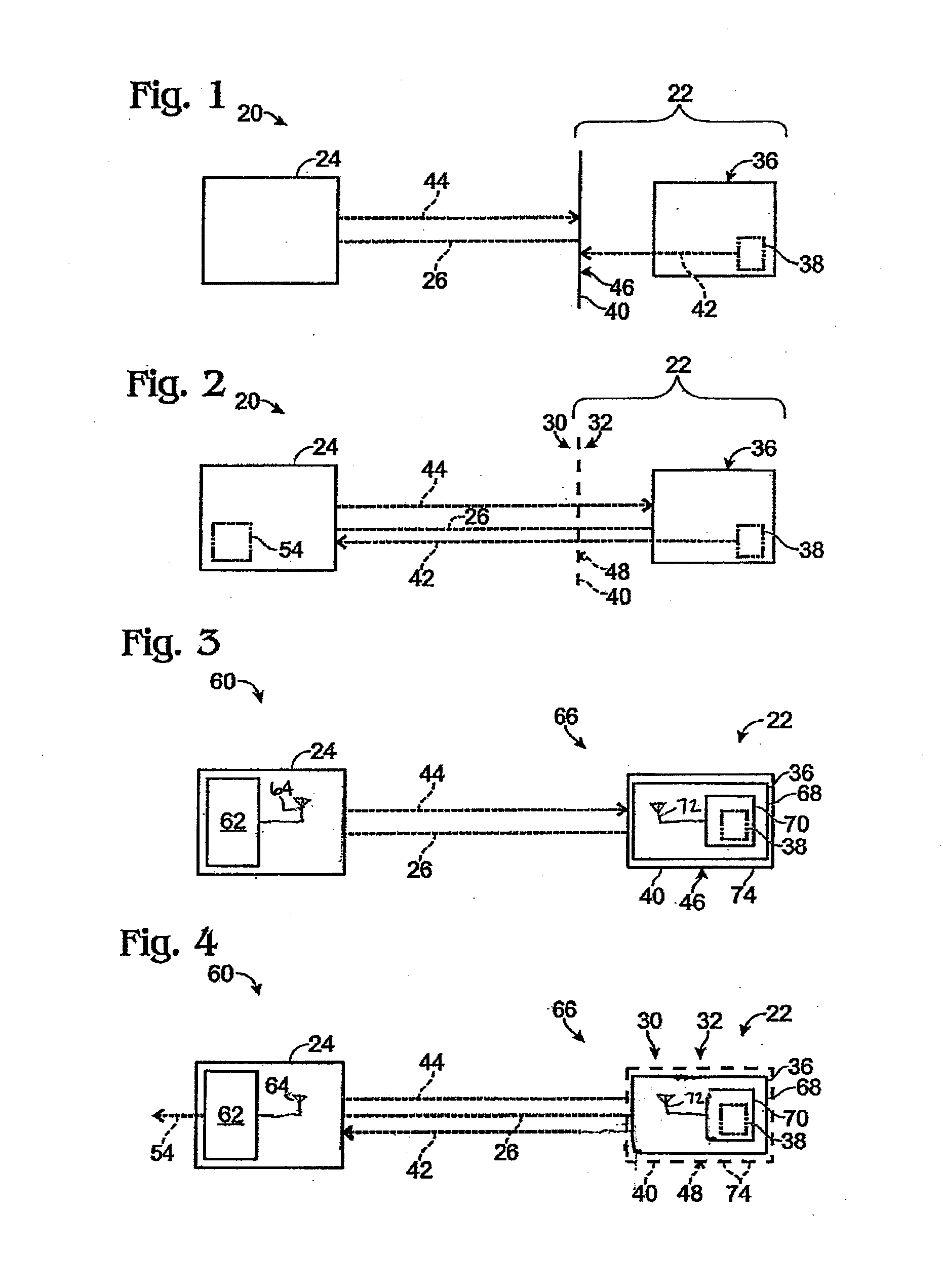

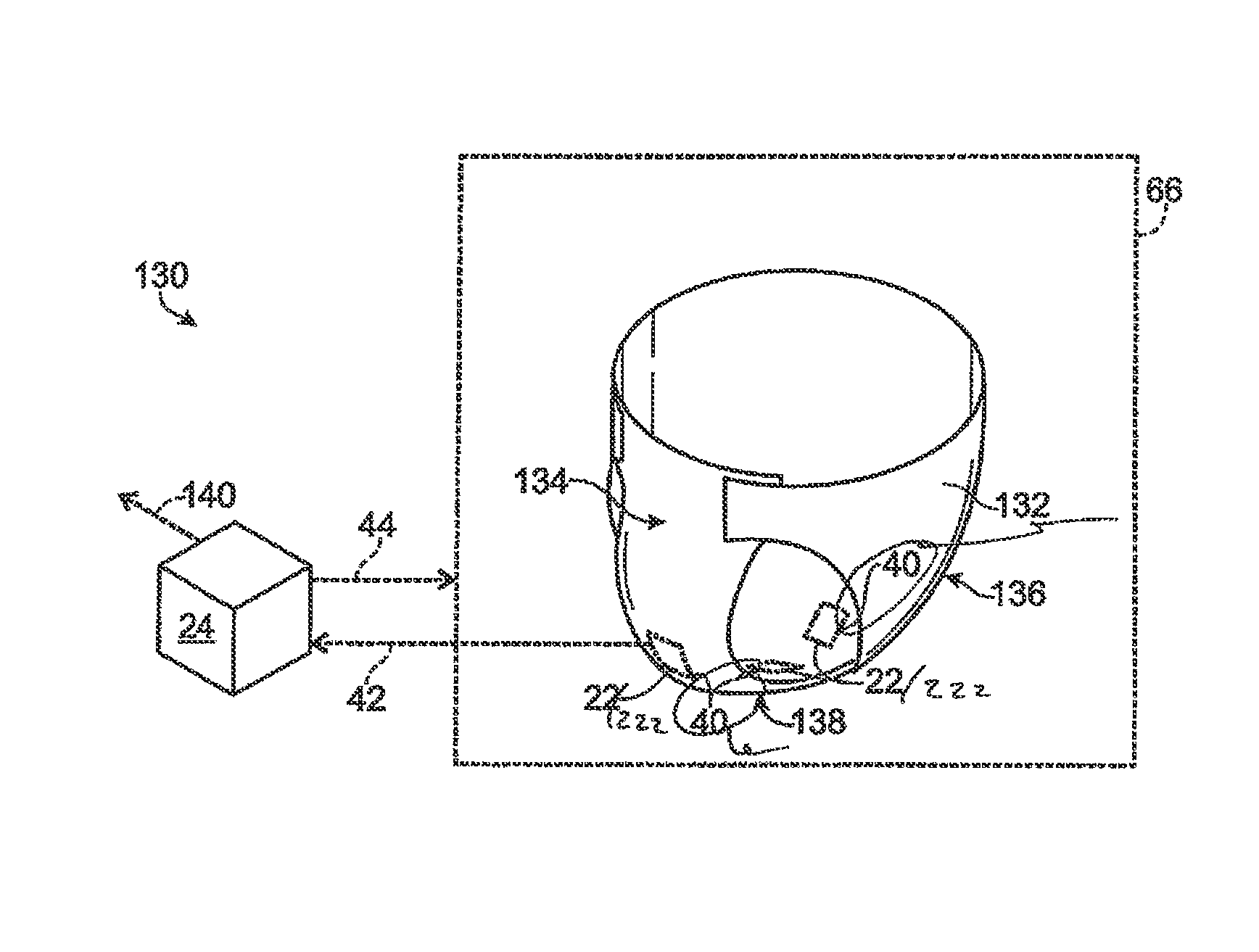

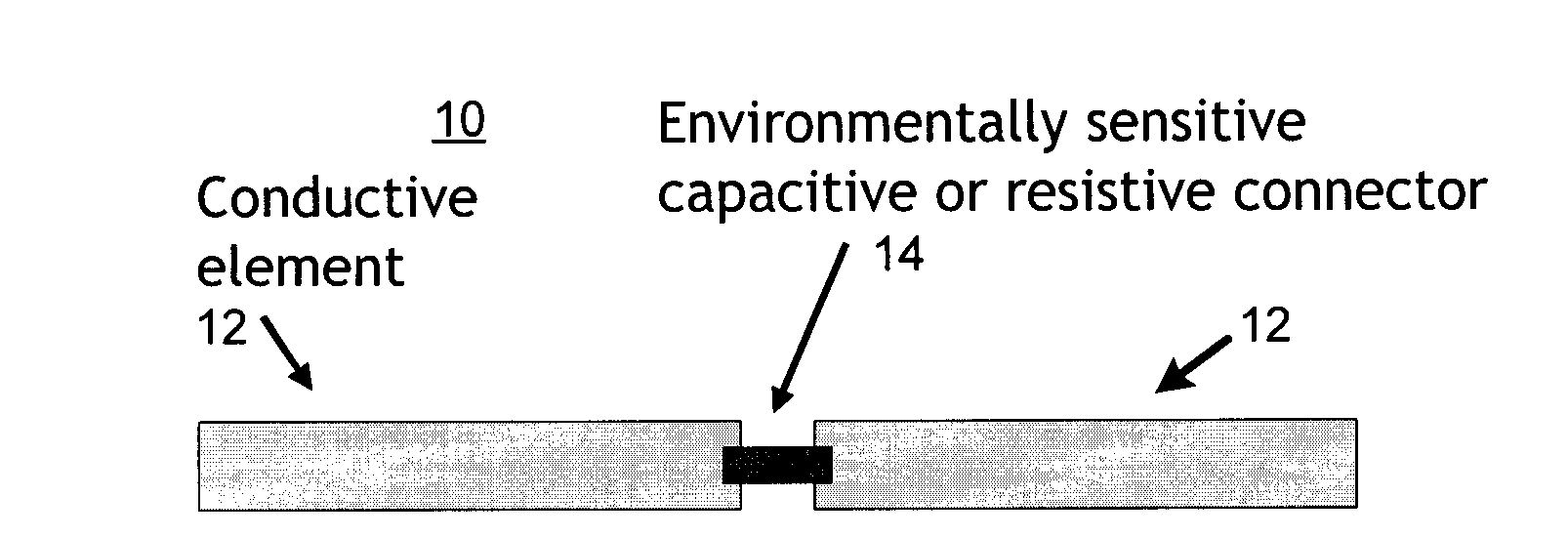

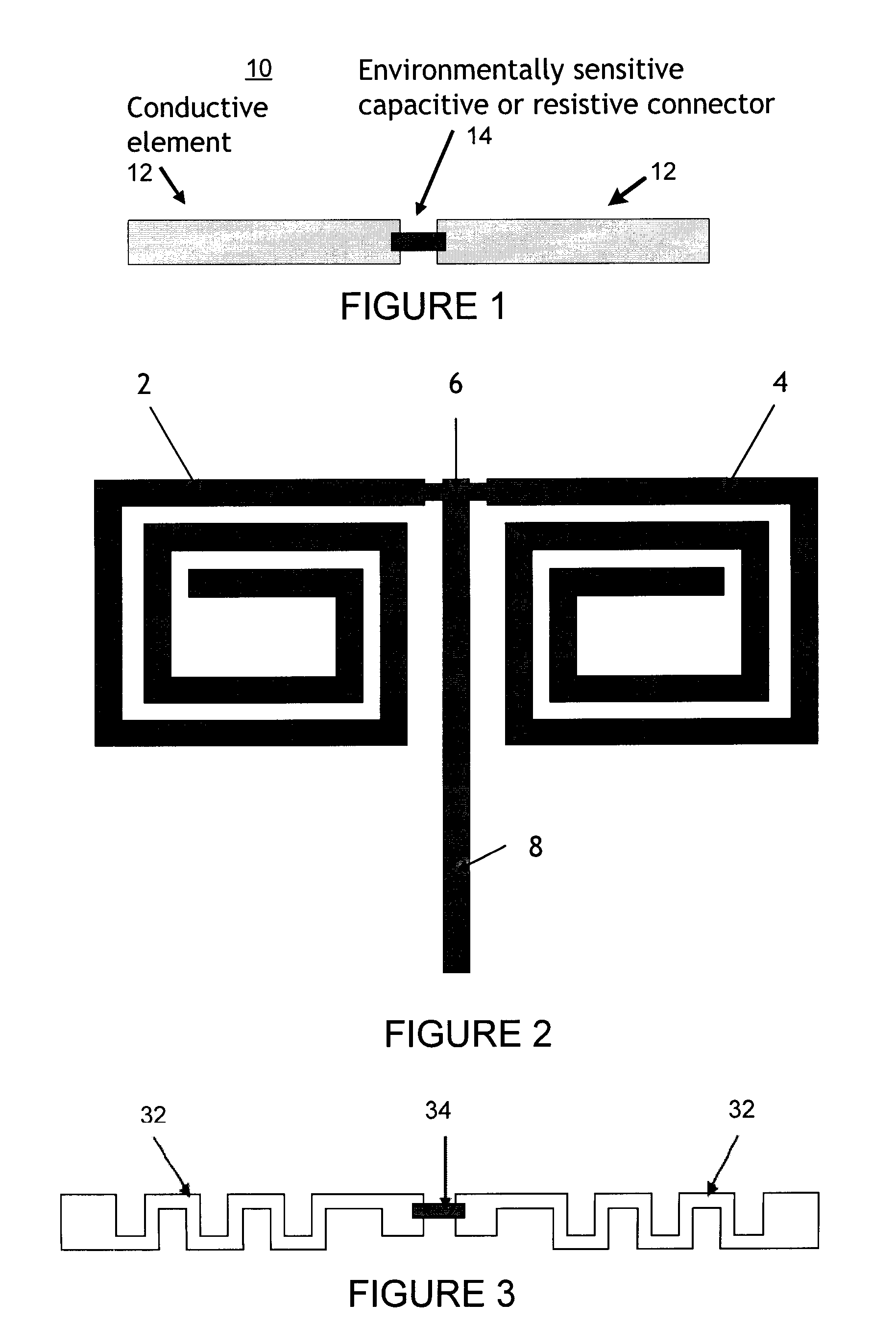

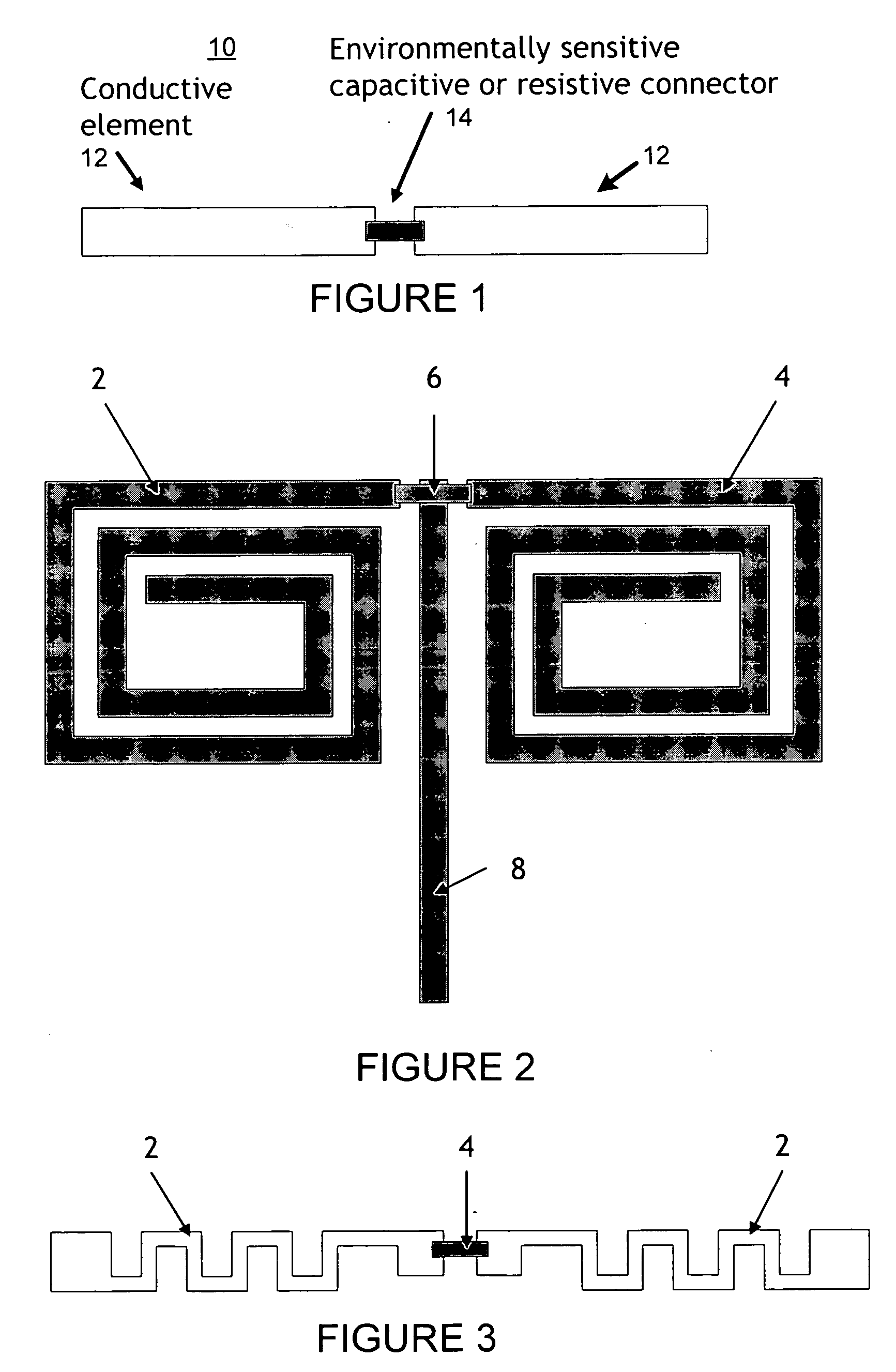

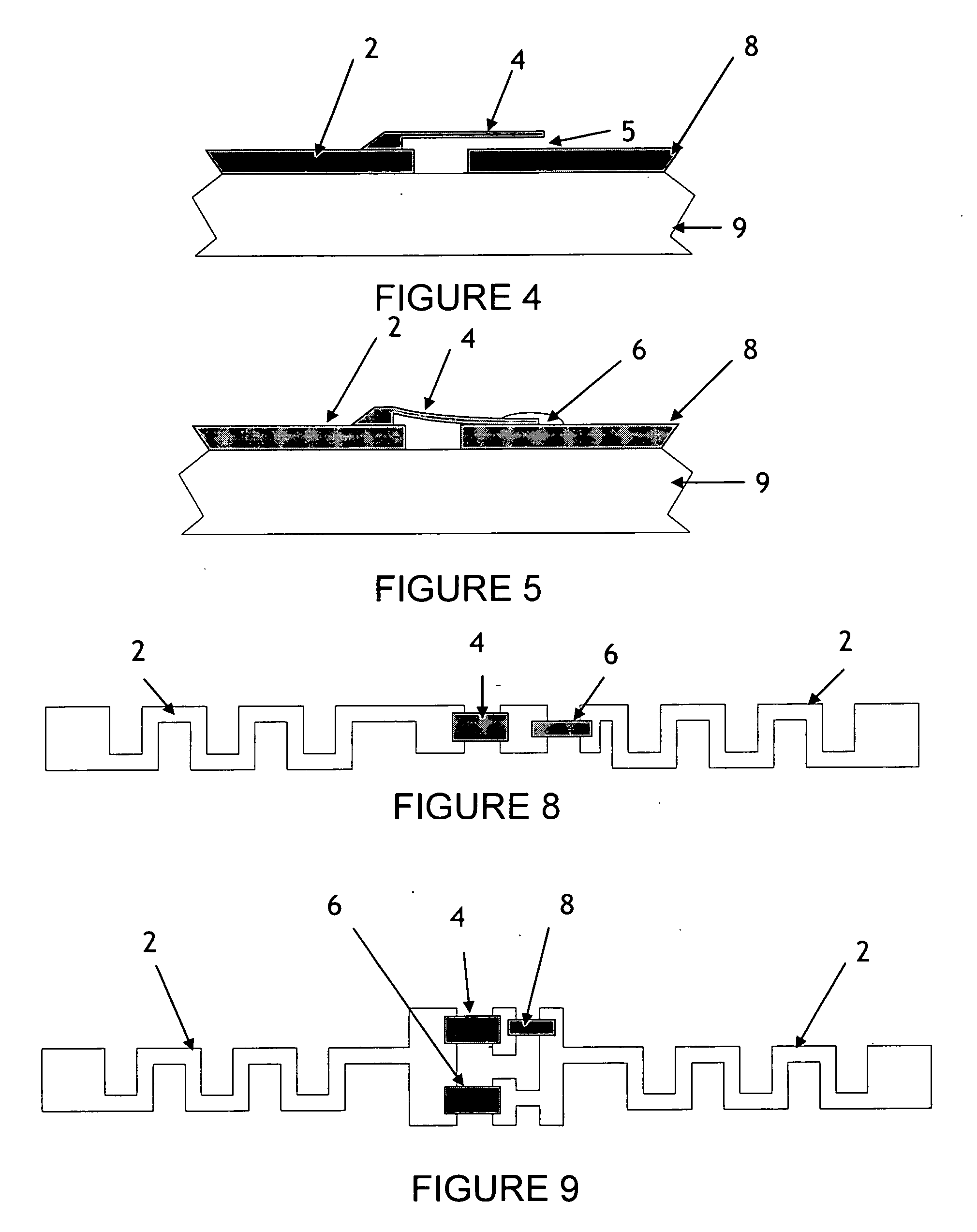

Sensors and systems for detecting environmental conditions or changes

Sensors and systems for detecting predetermined environmental conditions or changes may include a device capable of providing information. The device may include either a shield or reconfigurable antenna. For example, in a first condition, a shield is configured to prevent communications with the device and, in a second condition, the shield is configured to enable communications with the device. Alternately, in a first condition, a reconfigurable antenna is configured to enable communications with the device and in a second condition the reconfigurable antenna is configured to prevent communications with the device. The shield or reconfigurable antenna may be configured to transition from first conditions to second conditions upon exposure to a predetermined environmental condition or change.

Owner:BUNZA GEOFFREY J +1

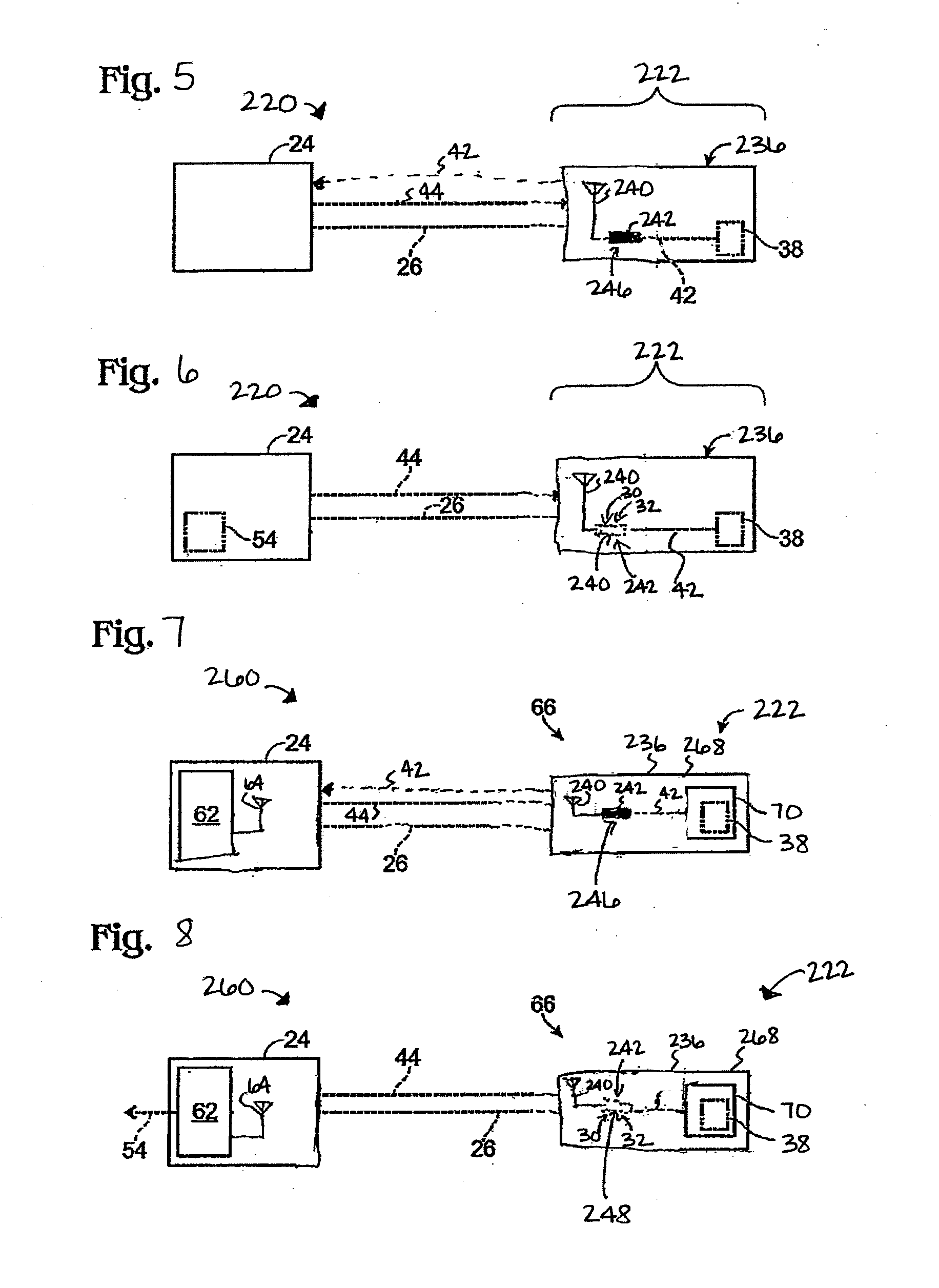

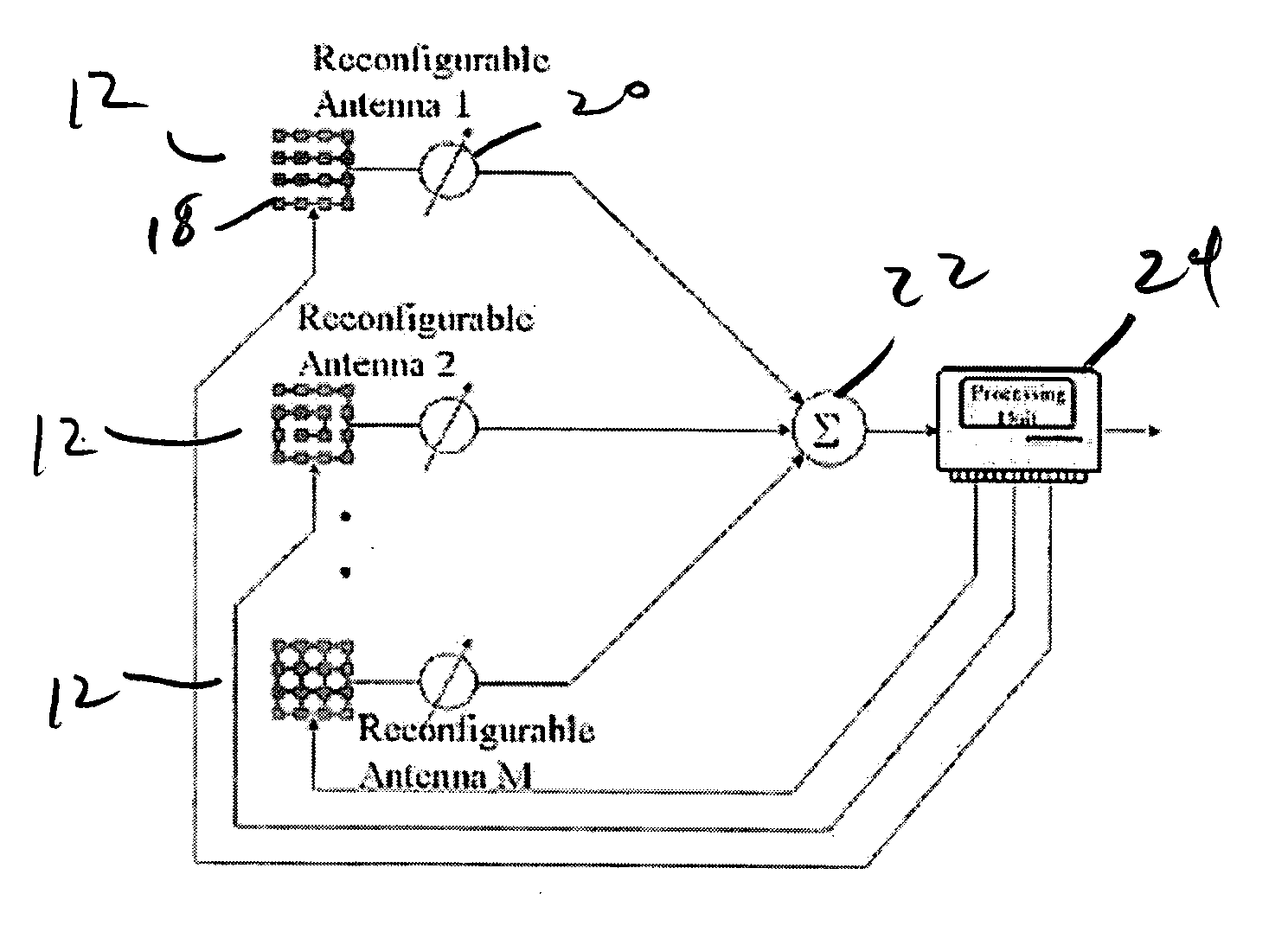

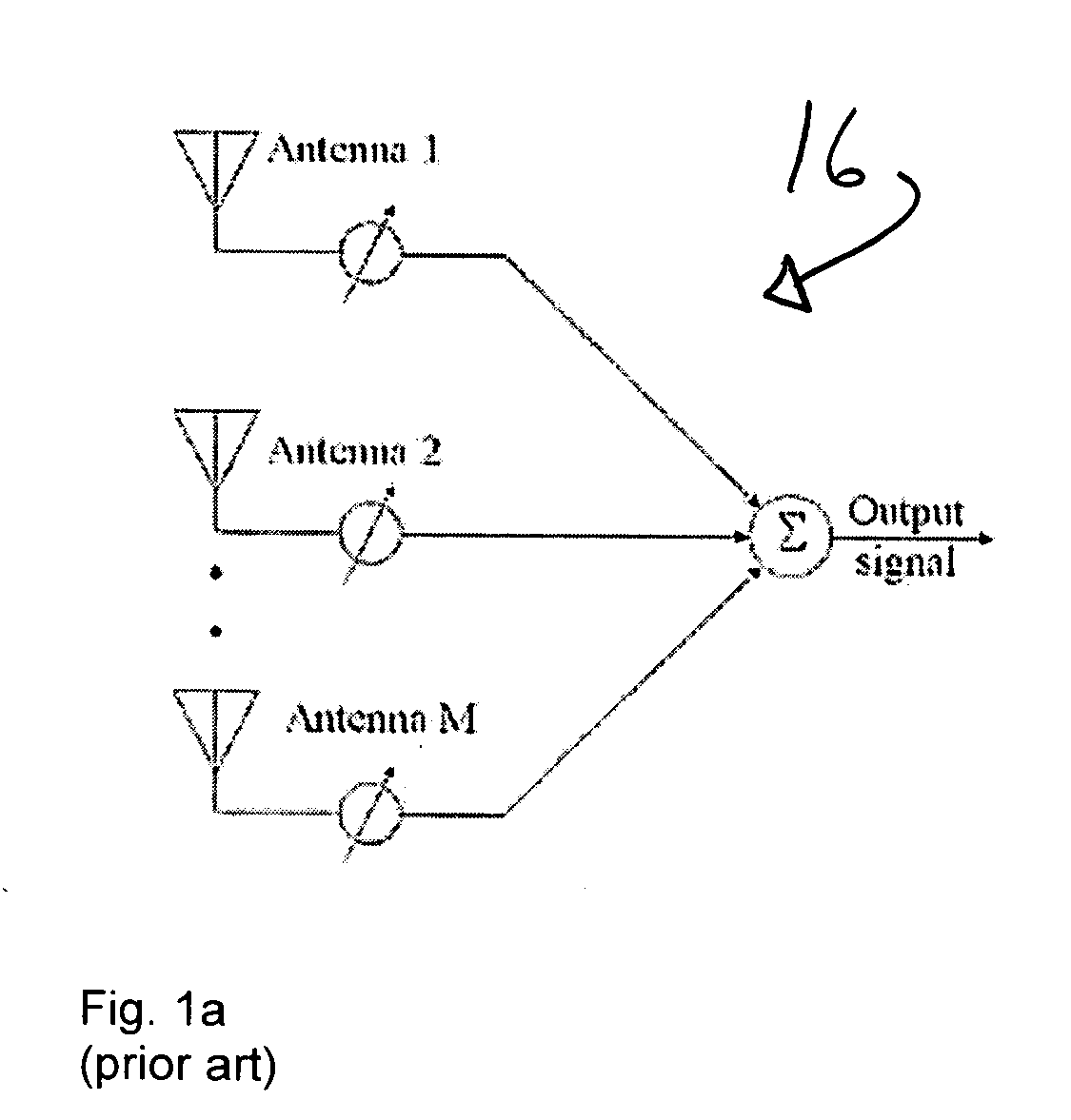

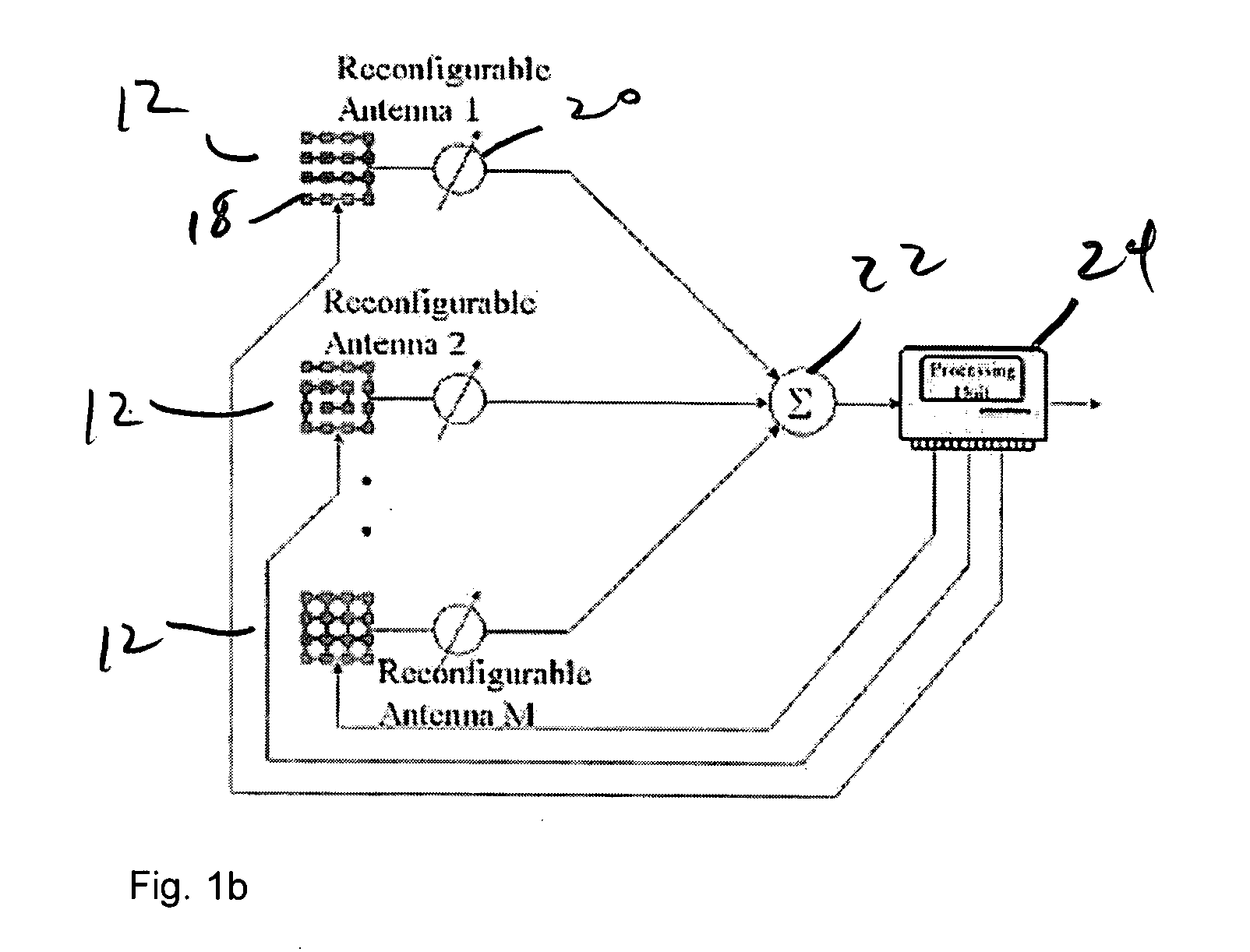

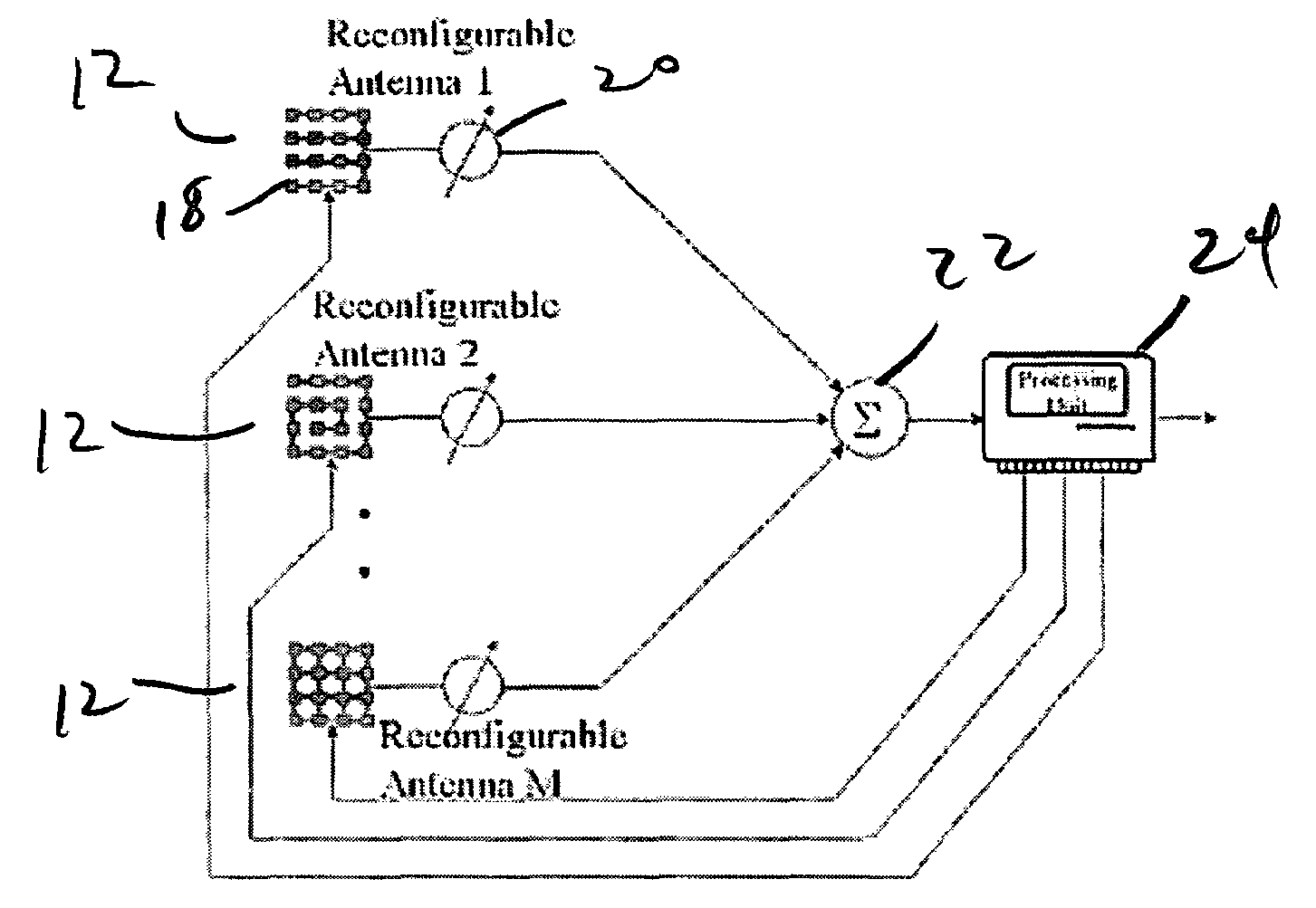

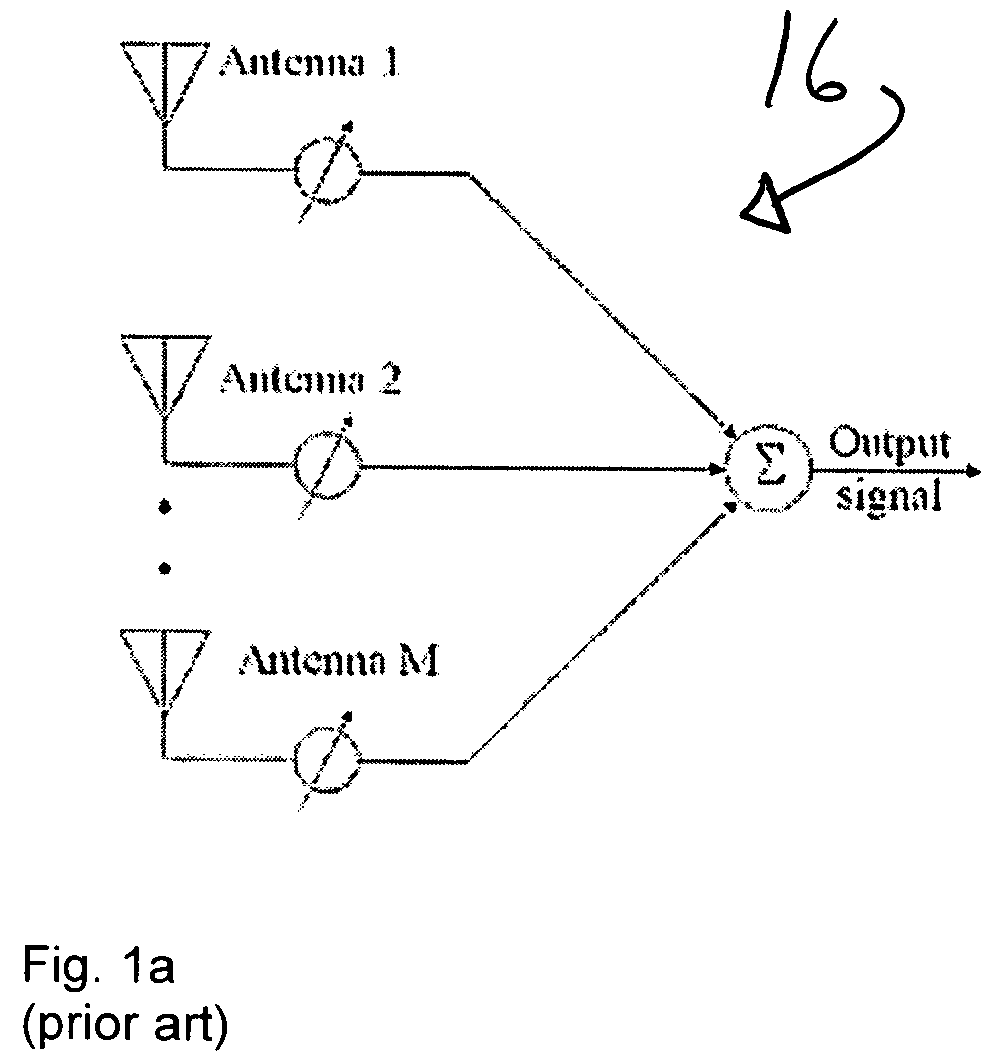

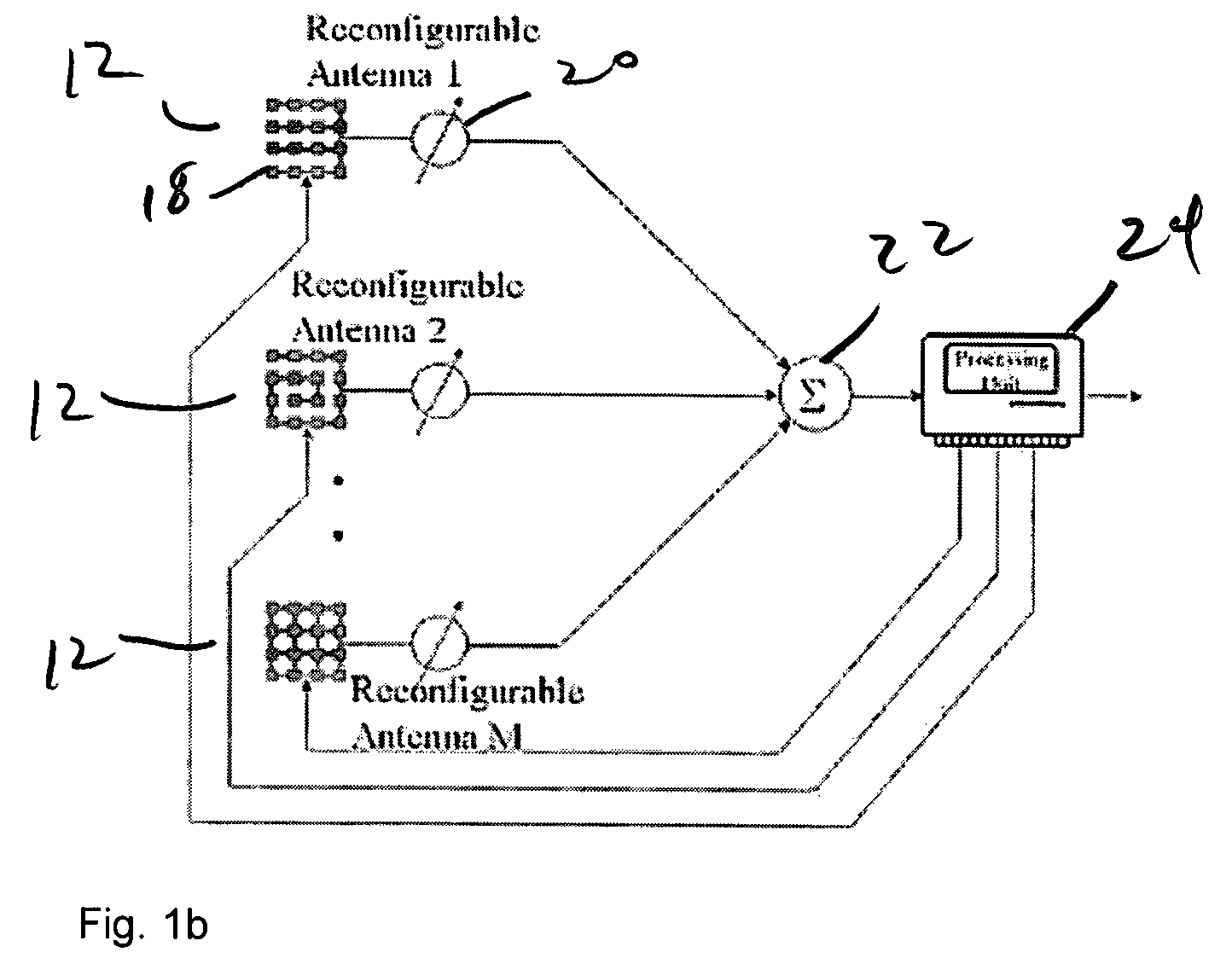

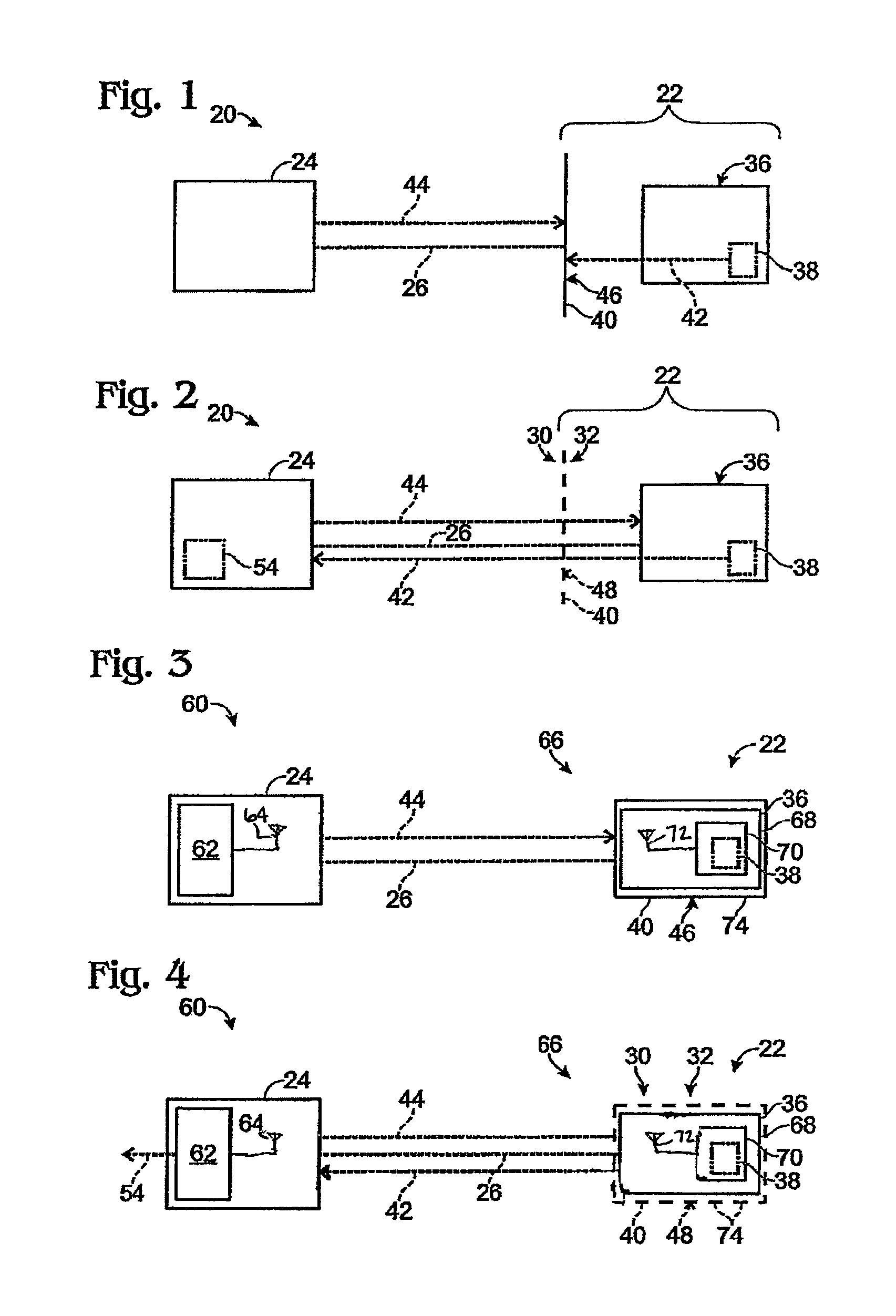

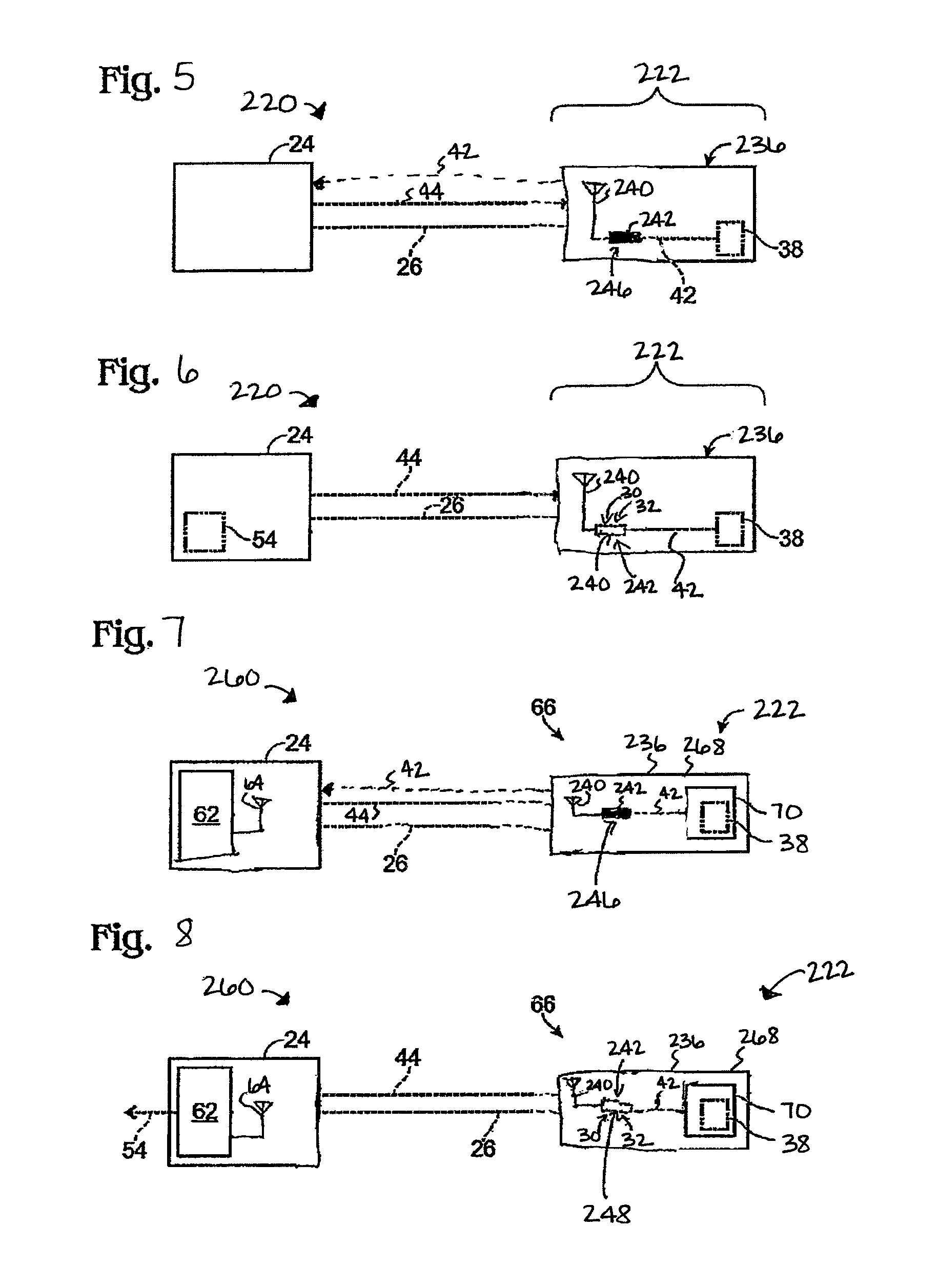

Method and apparatus for an adaptive multiple-input multiple-output (MIMO) wireless communications systems

ActiveUS20060222101A1Improves system performance characteristicPossible to selectSpatial transmit diversityAntenna arraysEngineeringMultiple input

An adaptive MIMO communications system includes a multifunctional reconfigurable antenna with a selectively alterable effective physical antenna array configuration and radiation / polarization properties, which configuration and properties is a component in the optimization of the adaptive system parameters. The multifunctional reconfigurable antenna comprises a plurality of antenna components and a plurality of selectively controllable switches coupling selected ones of the plurality of antenna components together into a multifunctional reconfigurable subarray of antenna components. A processing unit coupled to the multifunctional reconfigurable antenna determines communication channel conditions for generating adaptive control signals to the plurality of selectively controllable switches to selectively apply a selected space-time coding protocol or a selected beam forming protocol together on the plurality of antenna components depending on channel conditions.

Owner:RGT UNIV OF CALIFORNIA

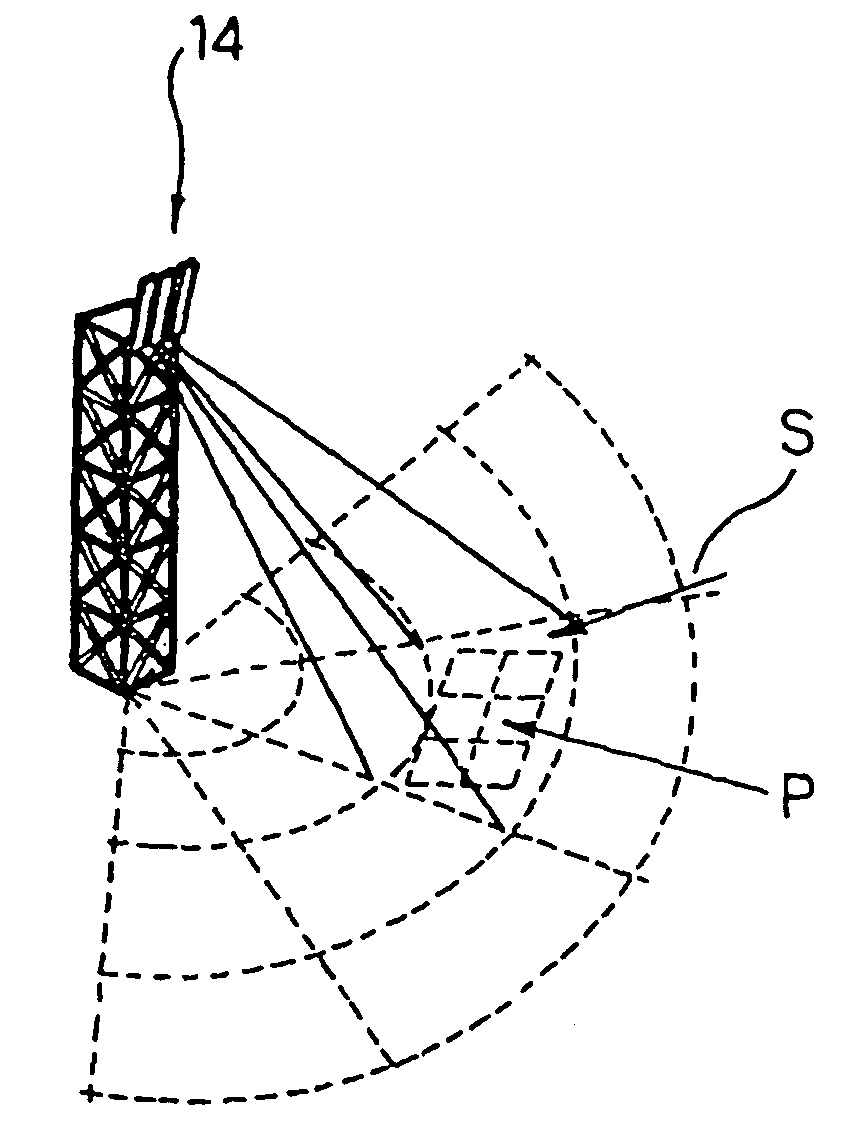

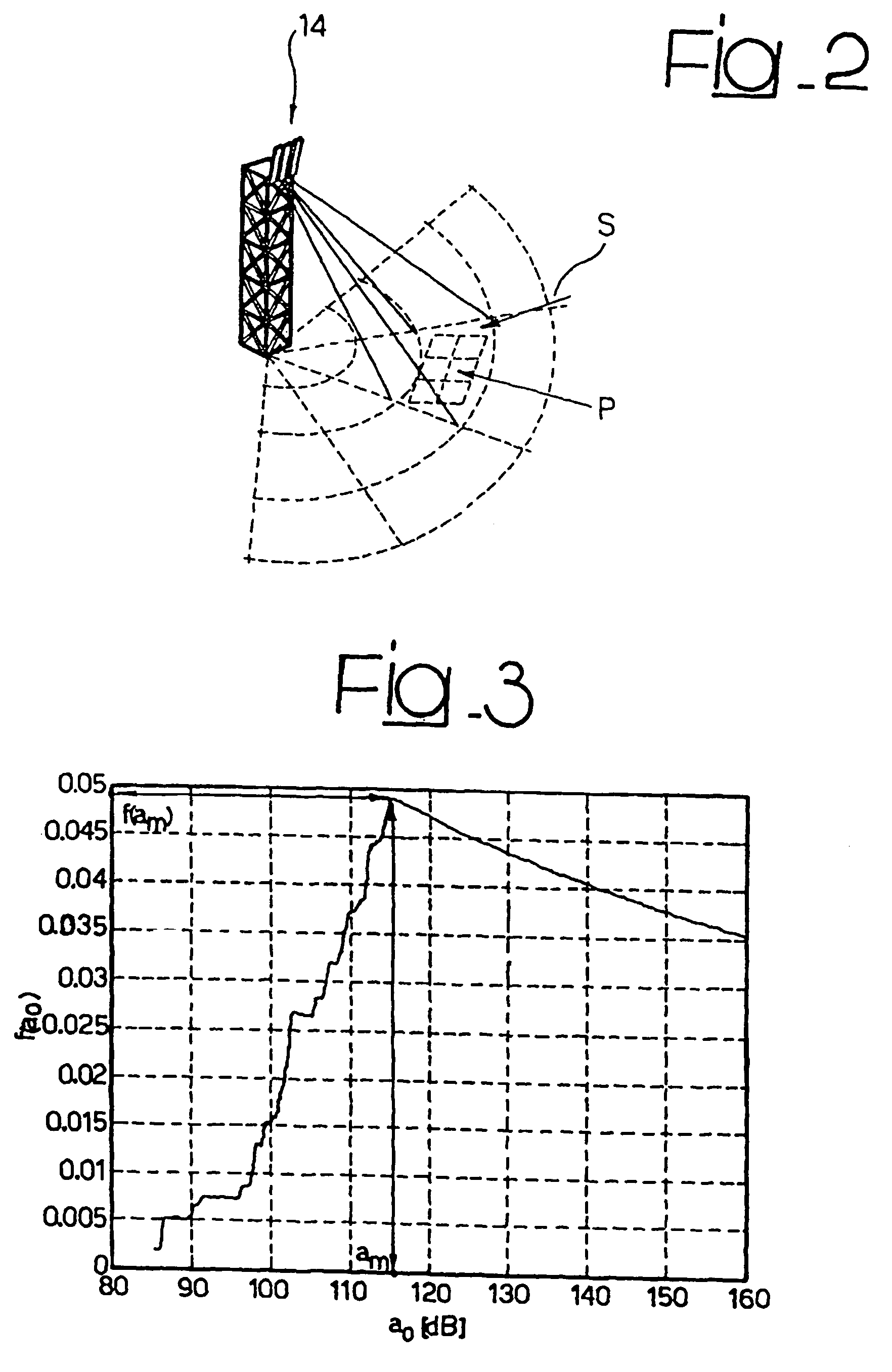

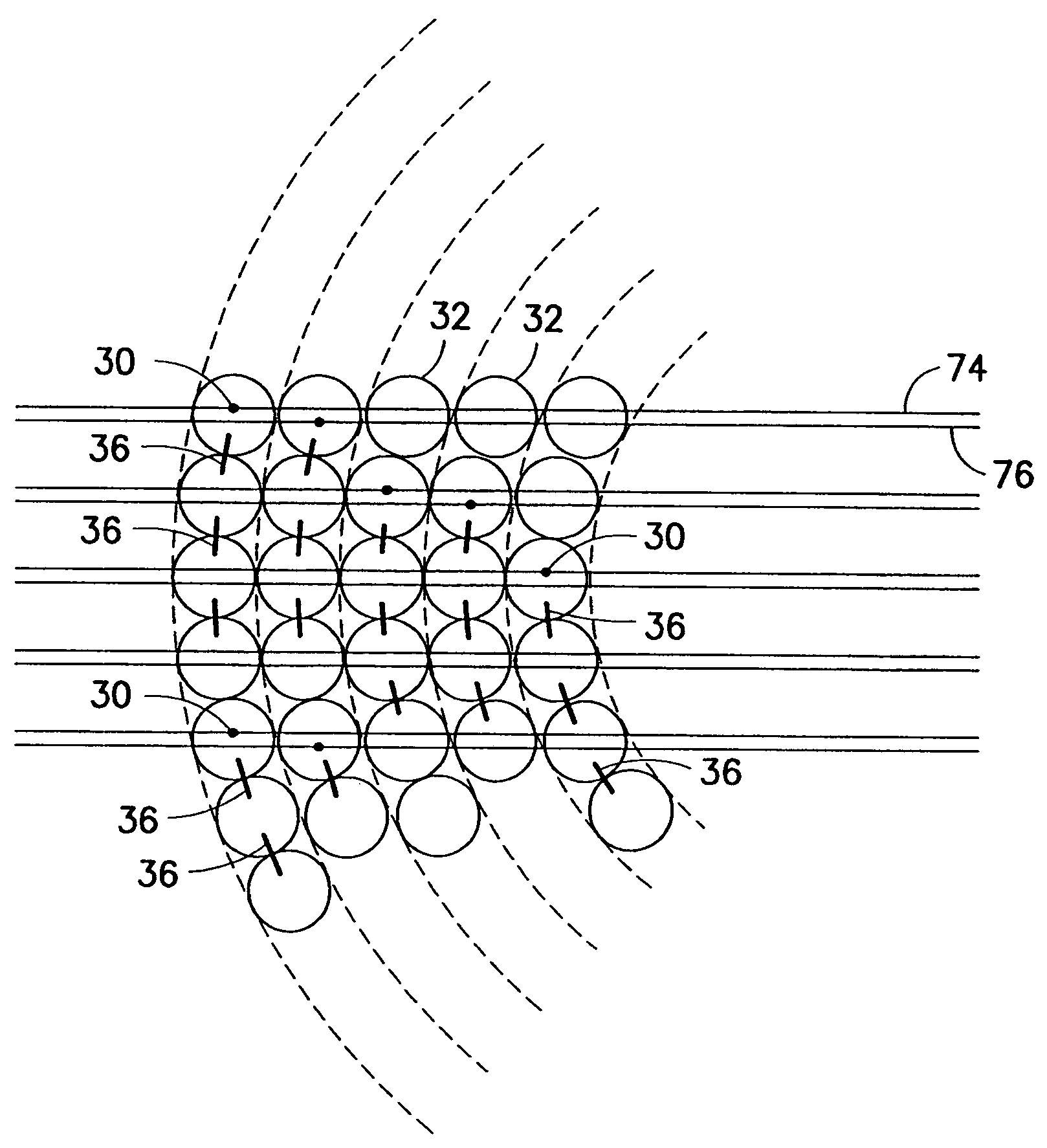

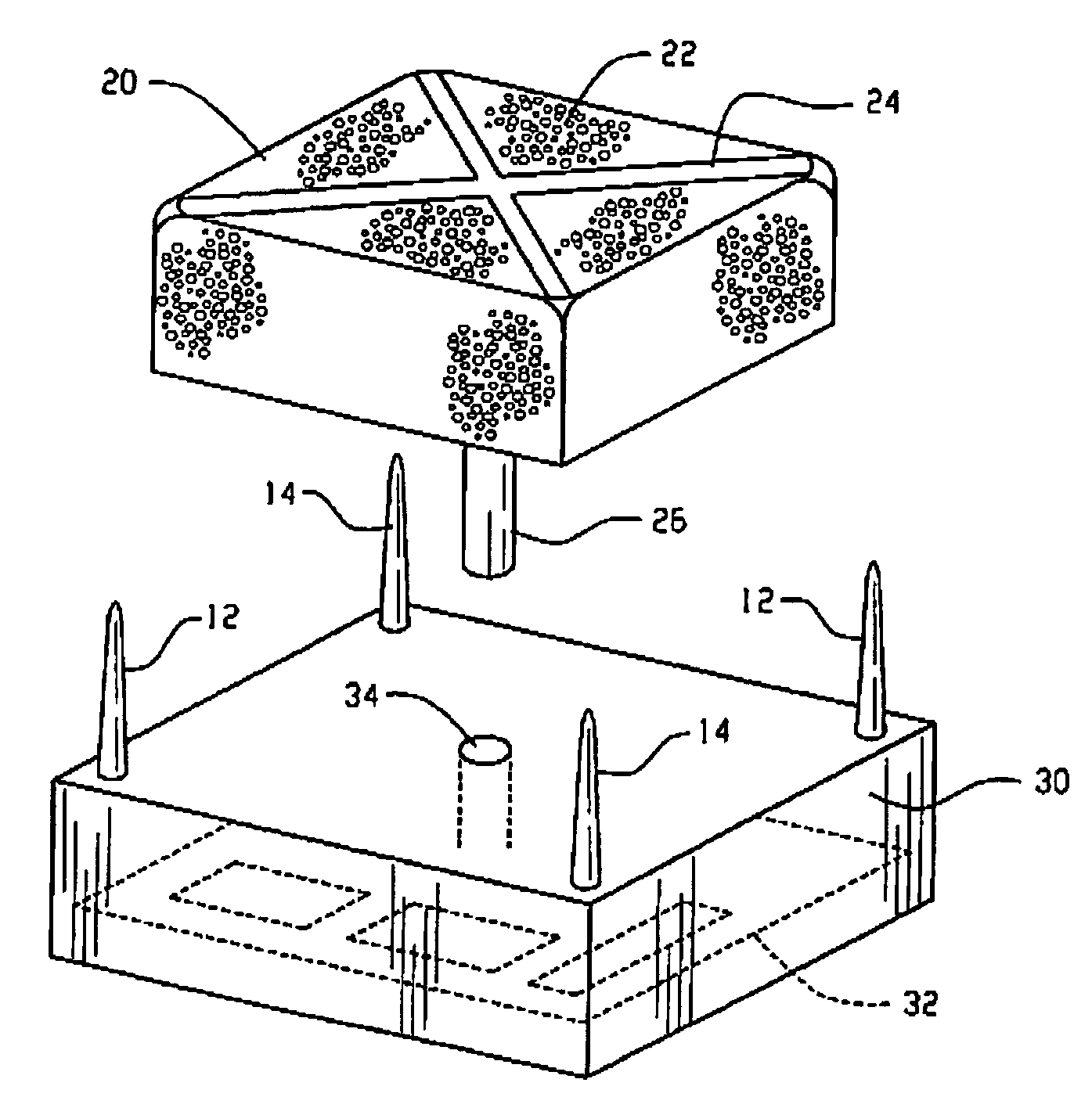

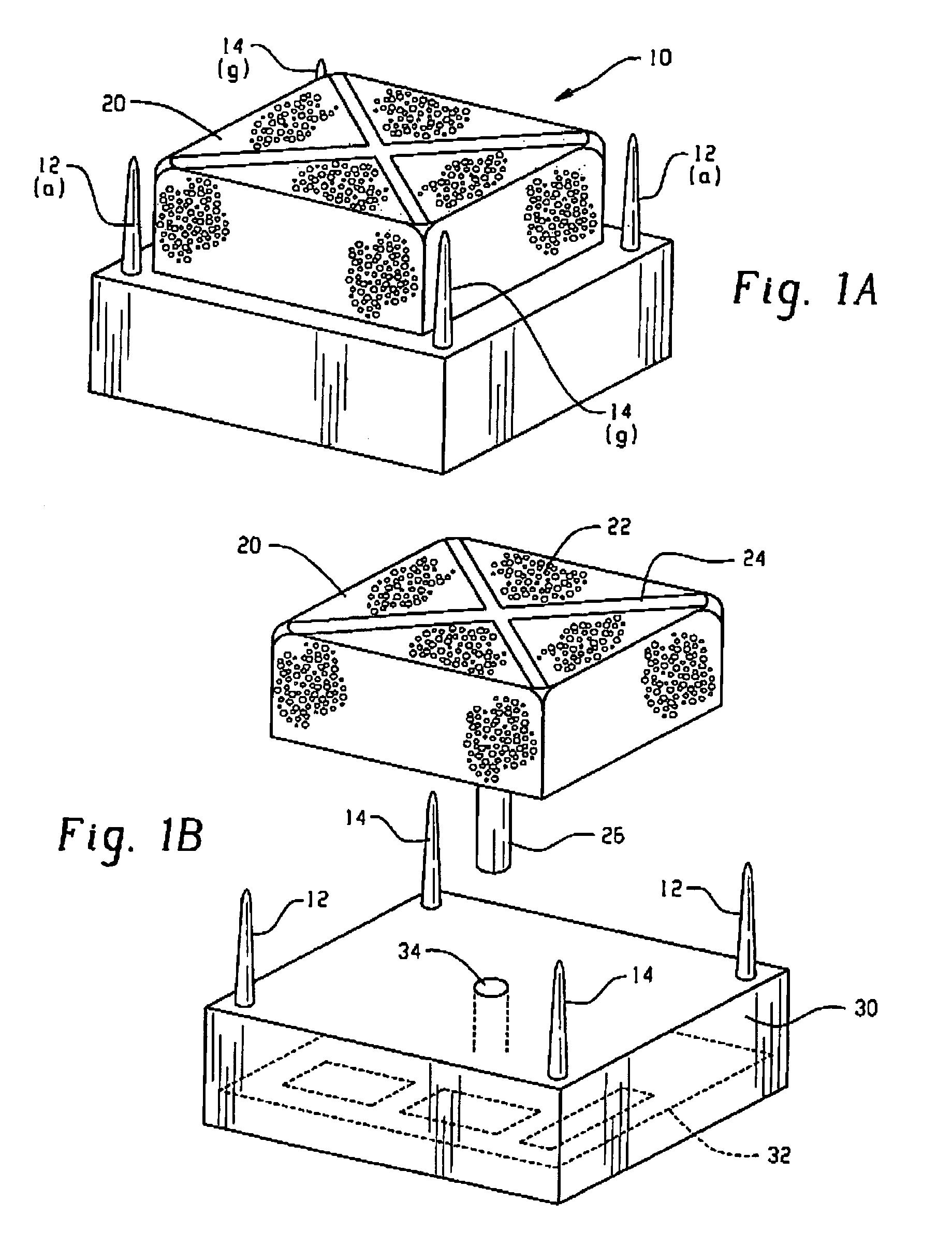

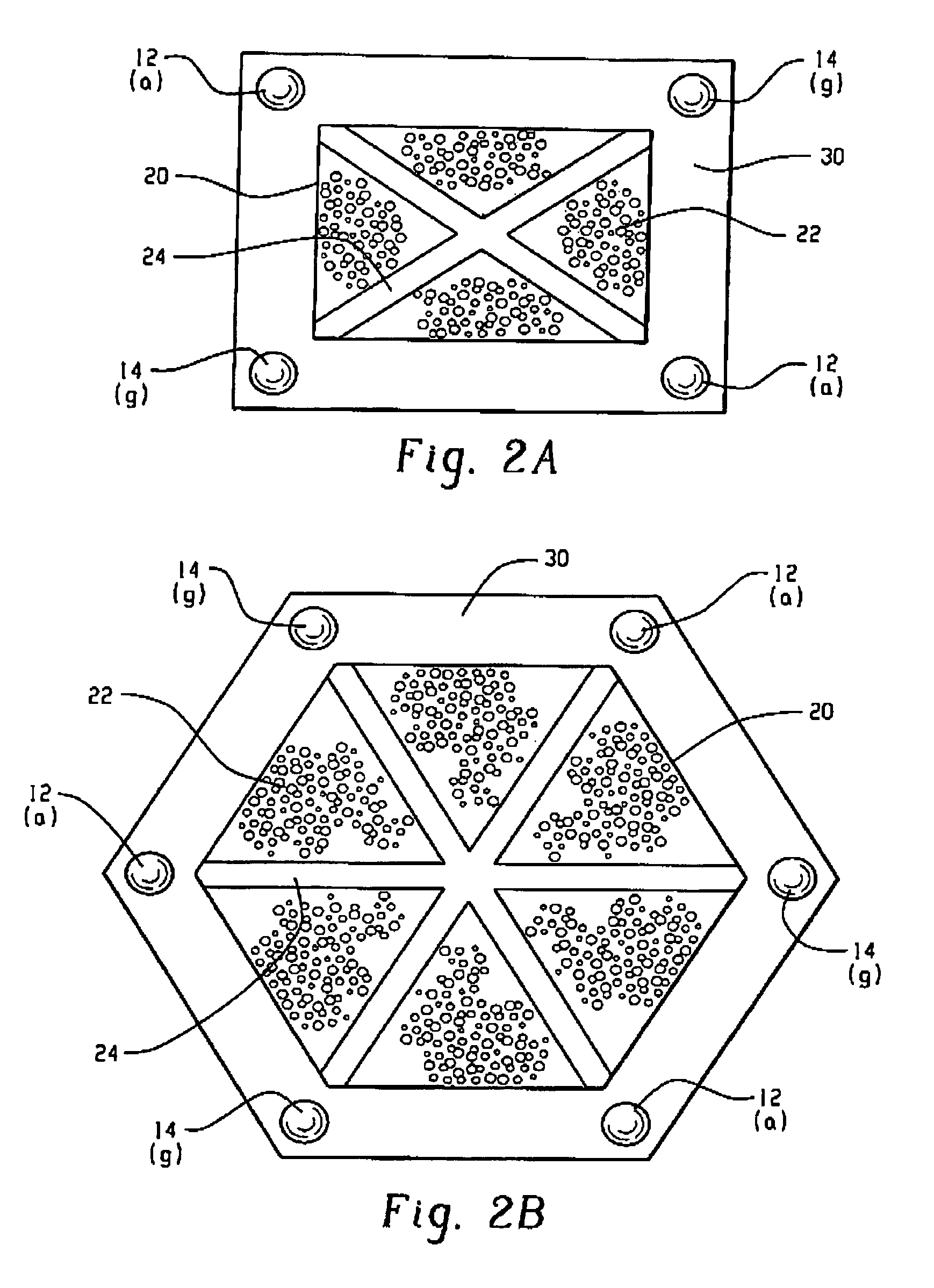

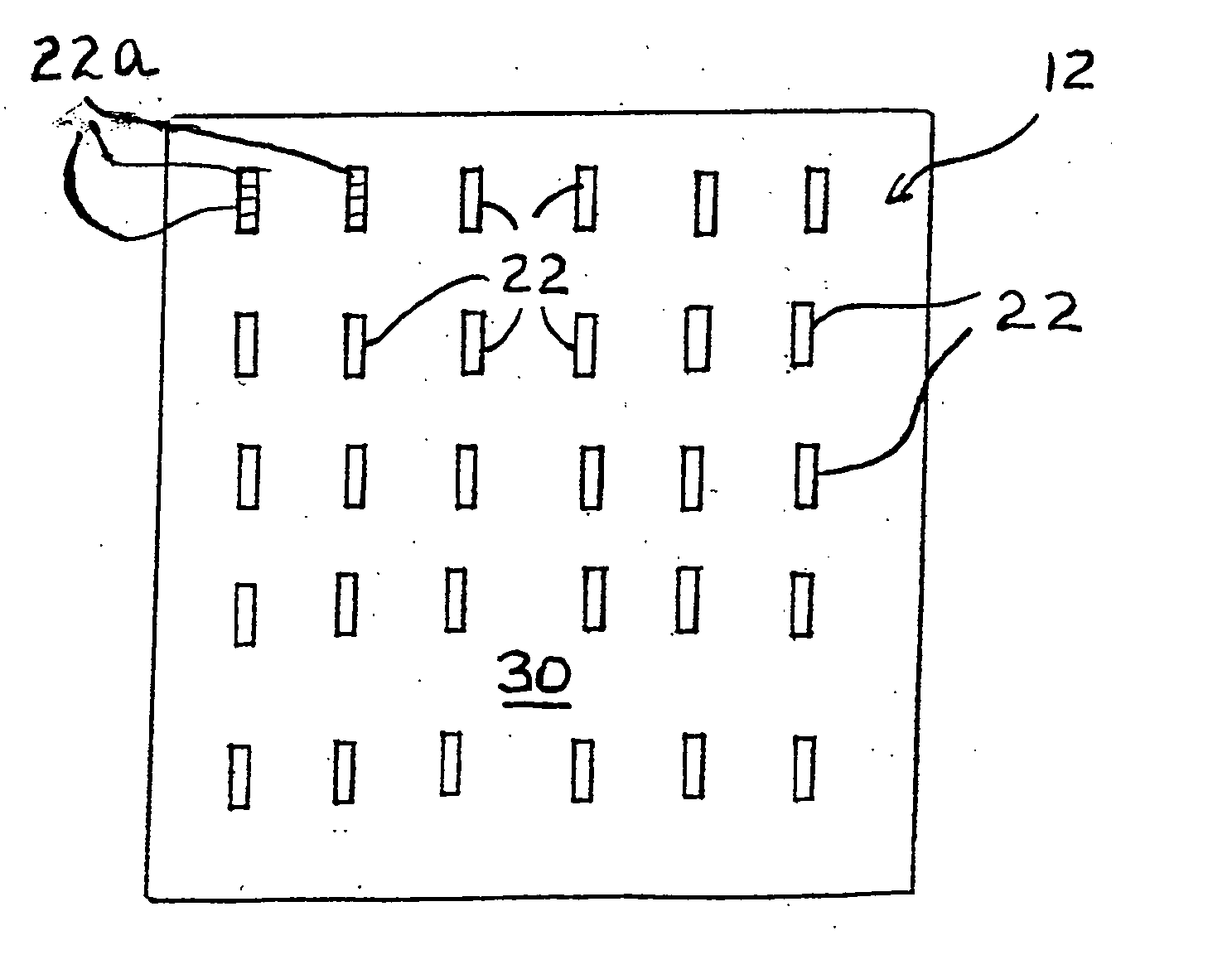

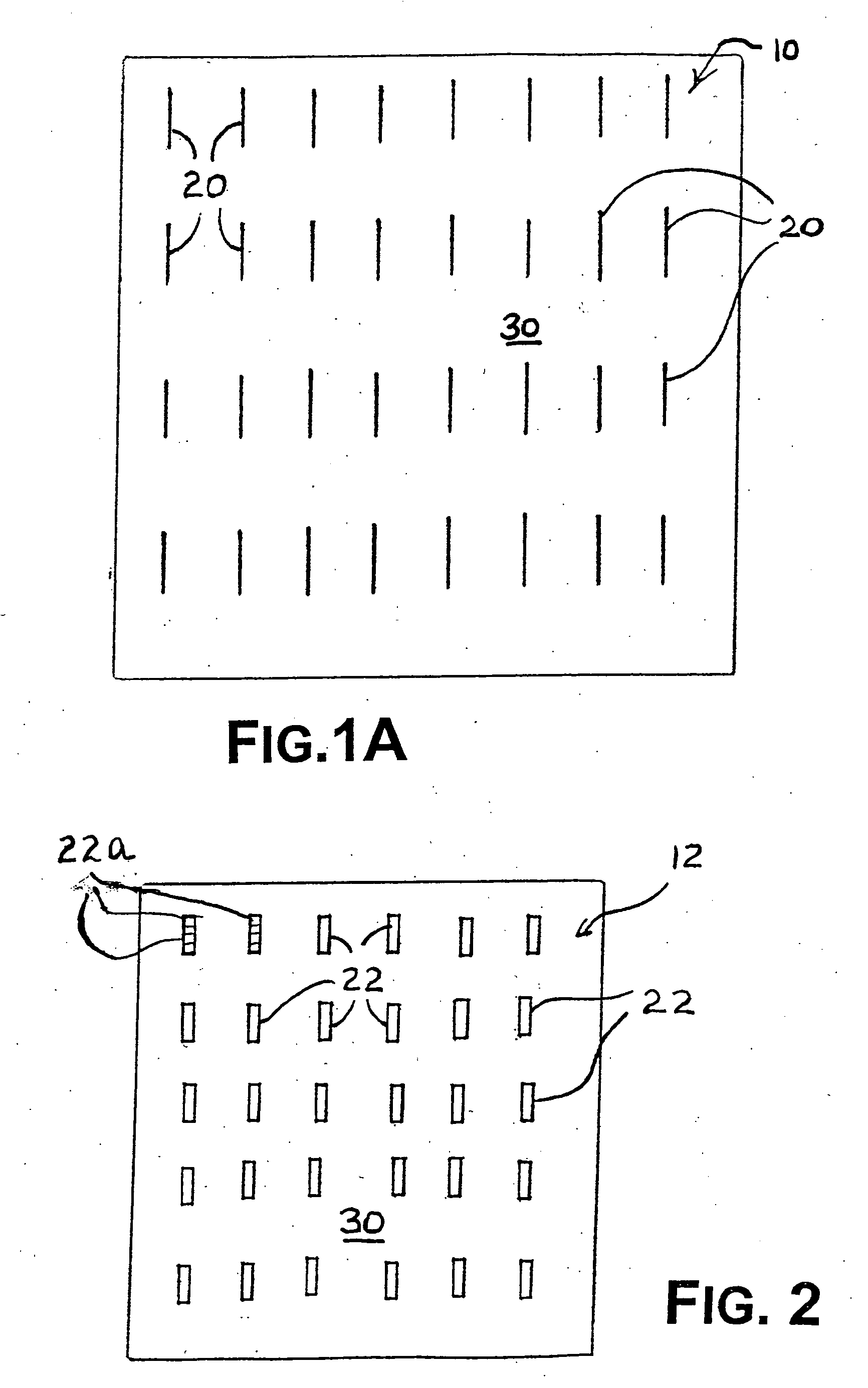

Configurable arrays for steerable antennas and wireless network incorporating the steerable antennas

InactiveUS6870517B1Improve data transfer performanceControl moreAntenna supports/mountingsRadiating elements structural formsReconfigurable antennaEngineering

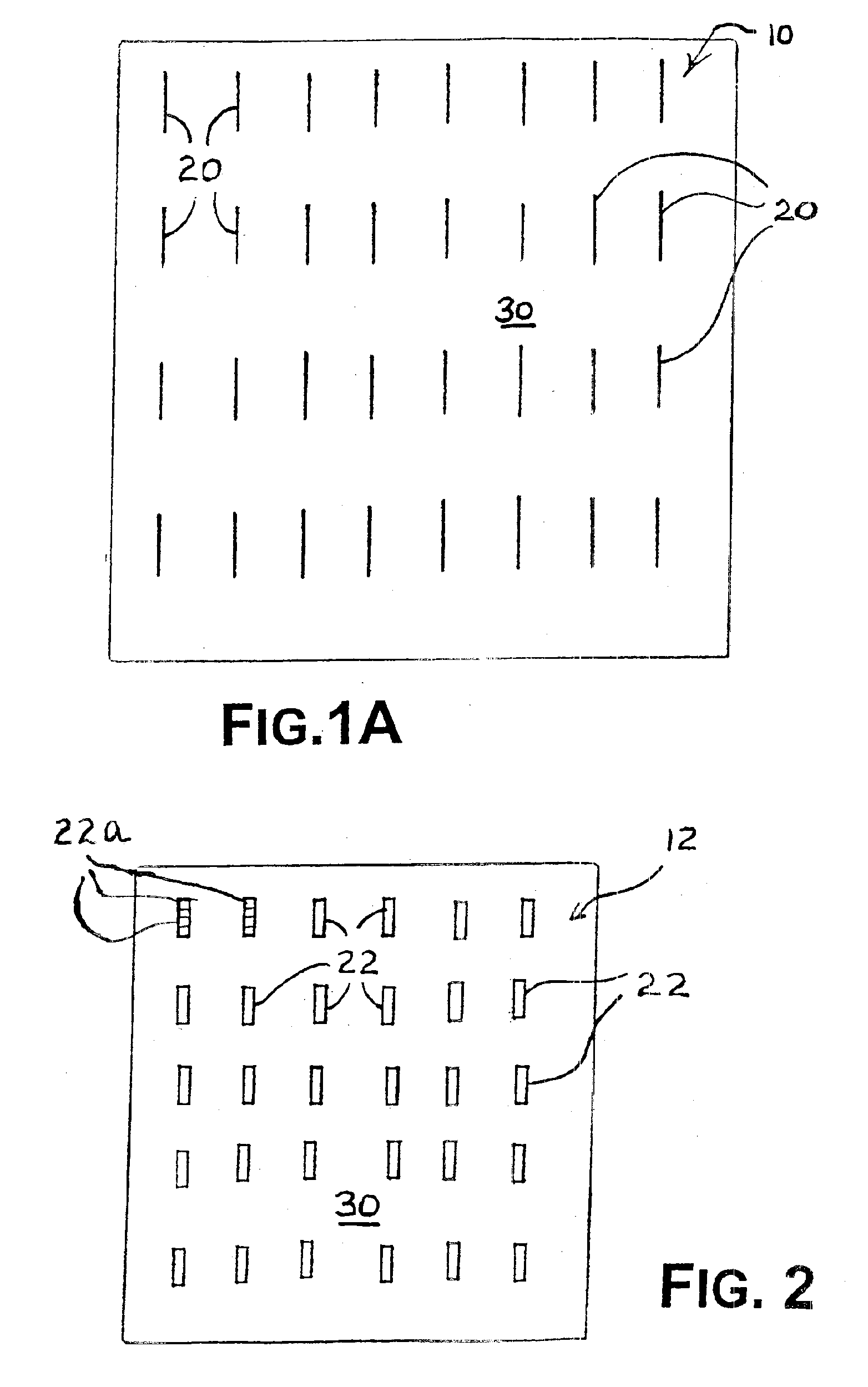

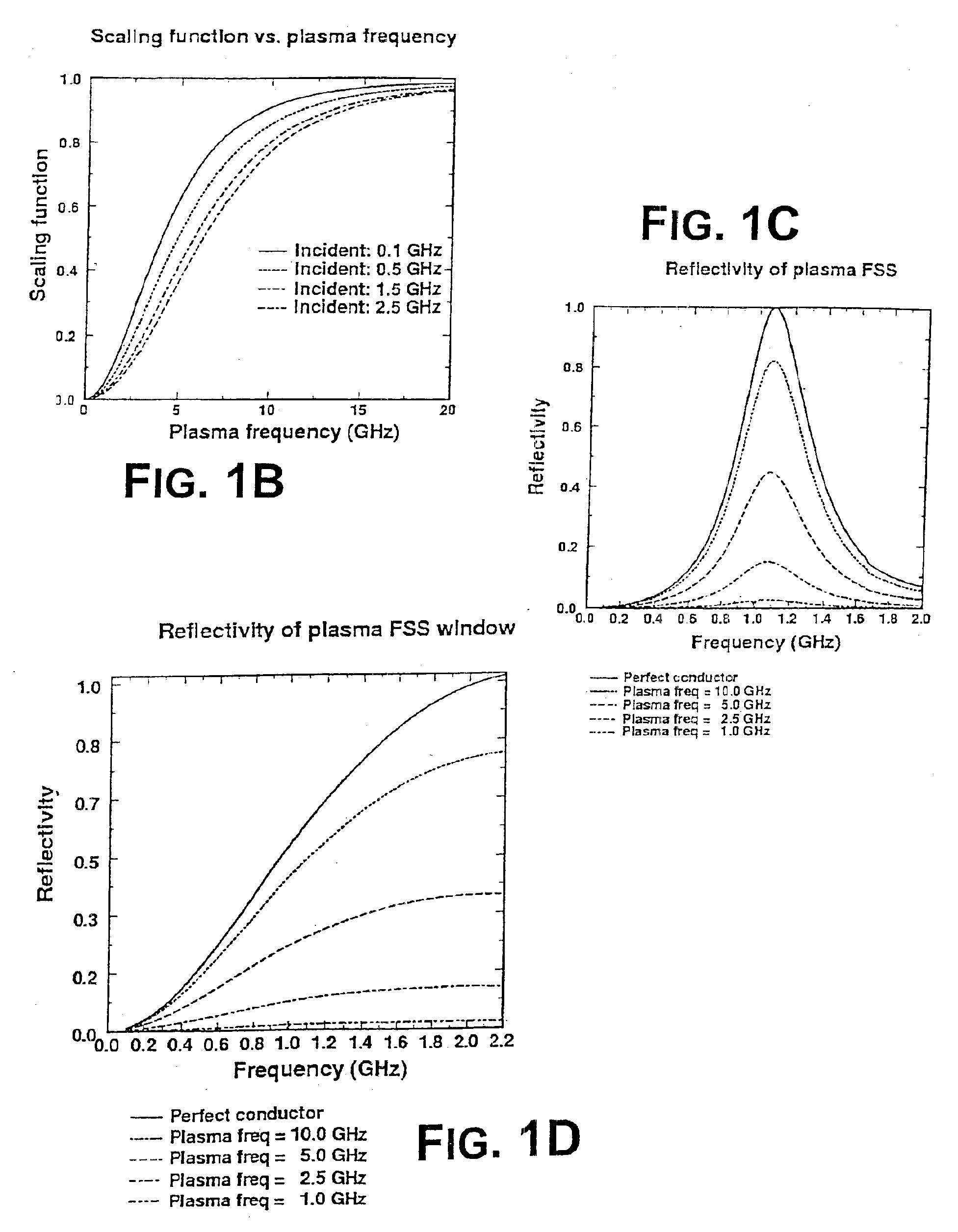

An reconfigurable array of variable conductive elements is provided for reflecting, filtering and steering electromagnetic radiation across a wide range of frequencies. The reconfigurable array is combined with a transmitting antenna to make a steerable antenna. The reconfigurable array surrounds the transmitting antenna and reflects all transmissions except on selected radials where apertures in the reconfigurable array are formed for permitting transmission lobes. The reconfigurable arrays can be arranged in stacked layers to make transceiving multiband antennas. Communications networks using the steerable antennas nas and arrays are also disclosed.

Owner:ANDERSON THEODORE R

Compact antenna system for polarization sensitive null steering and direction-finding

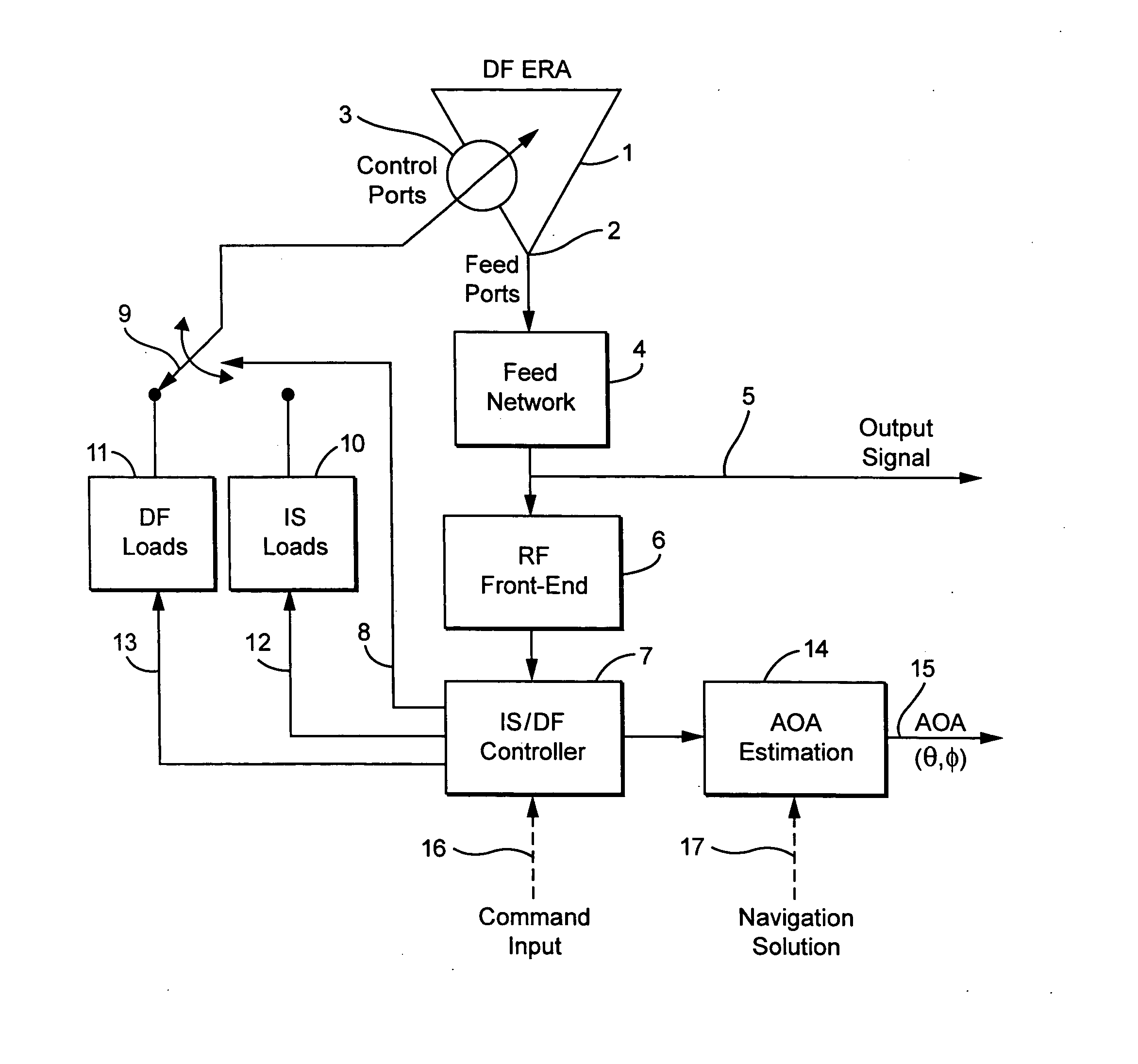

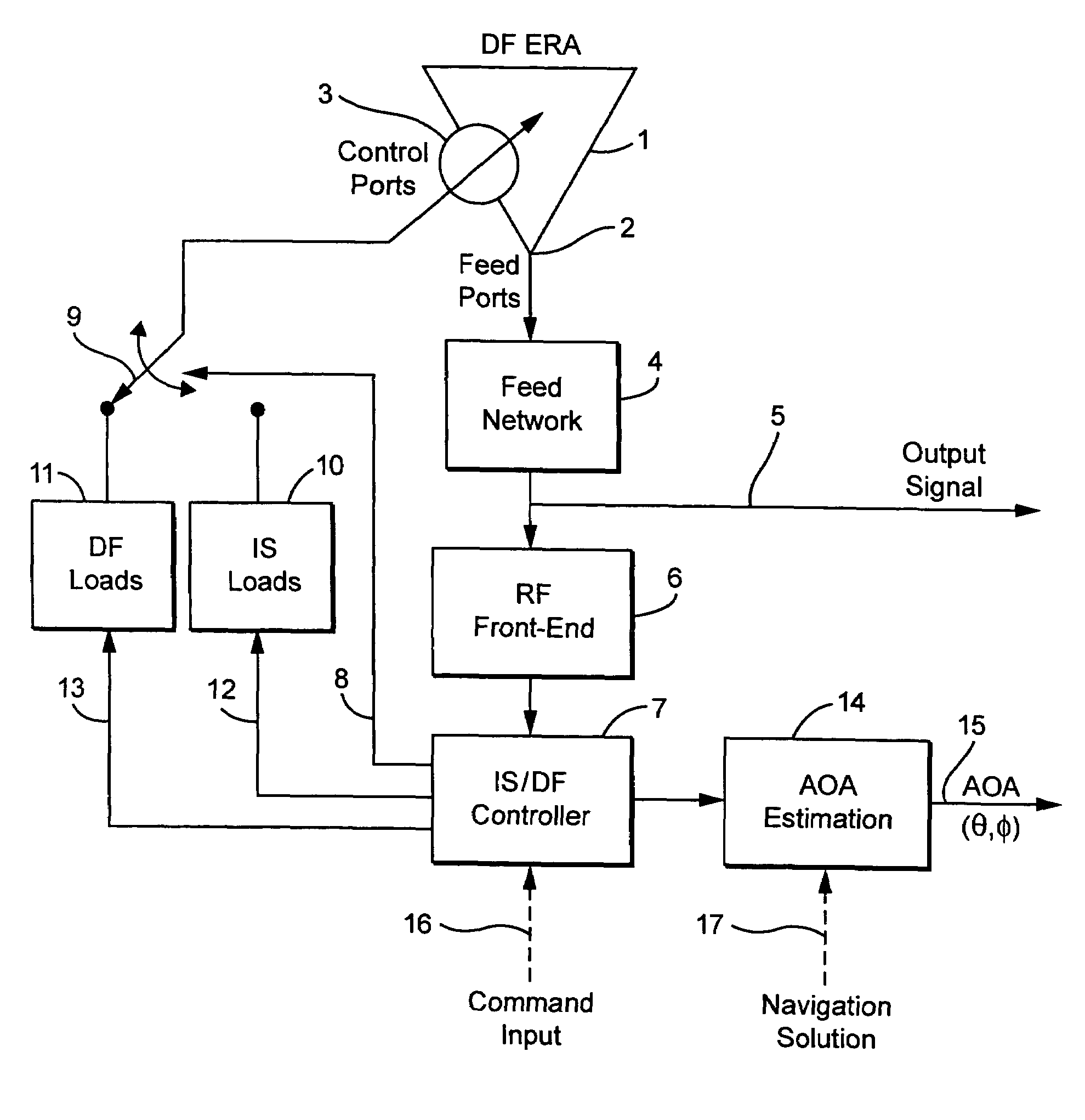

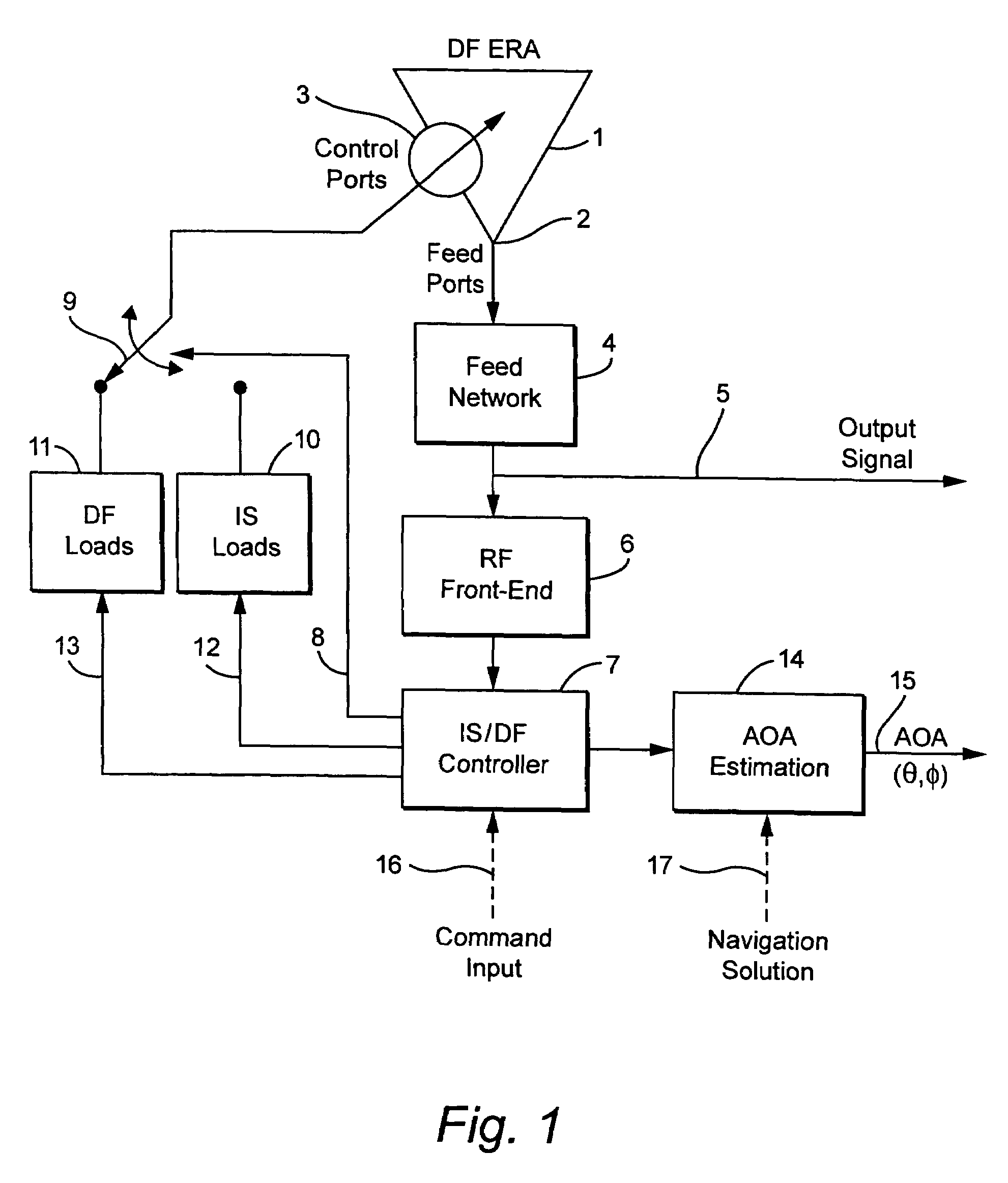

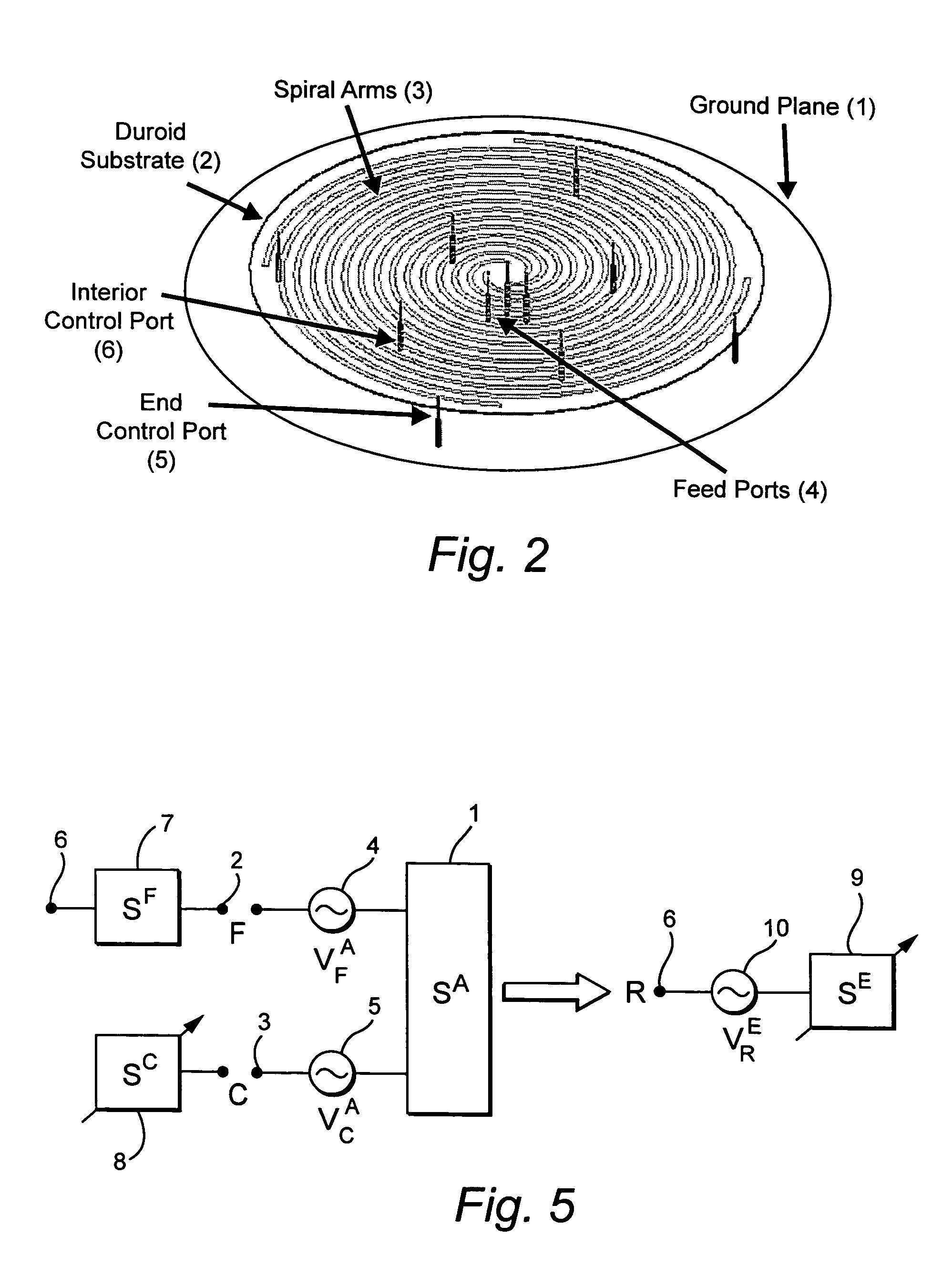

ActiveUS20070293150A1Reduce adverse effectsEnhance jammer-to-signal (J/S) toleranceSubstation equipmentAntenna feed intermediatesRadio frequencyFeedback control

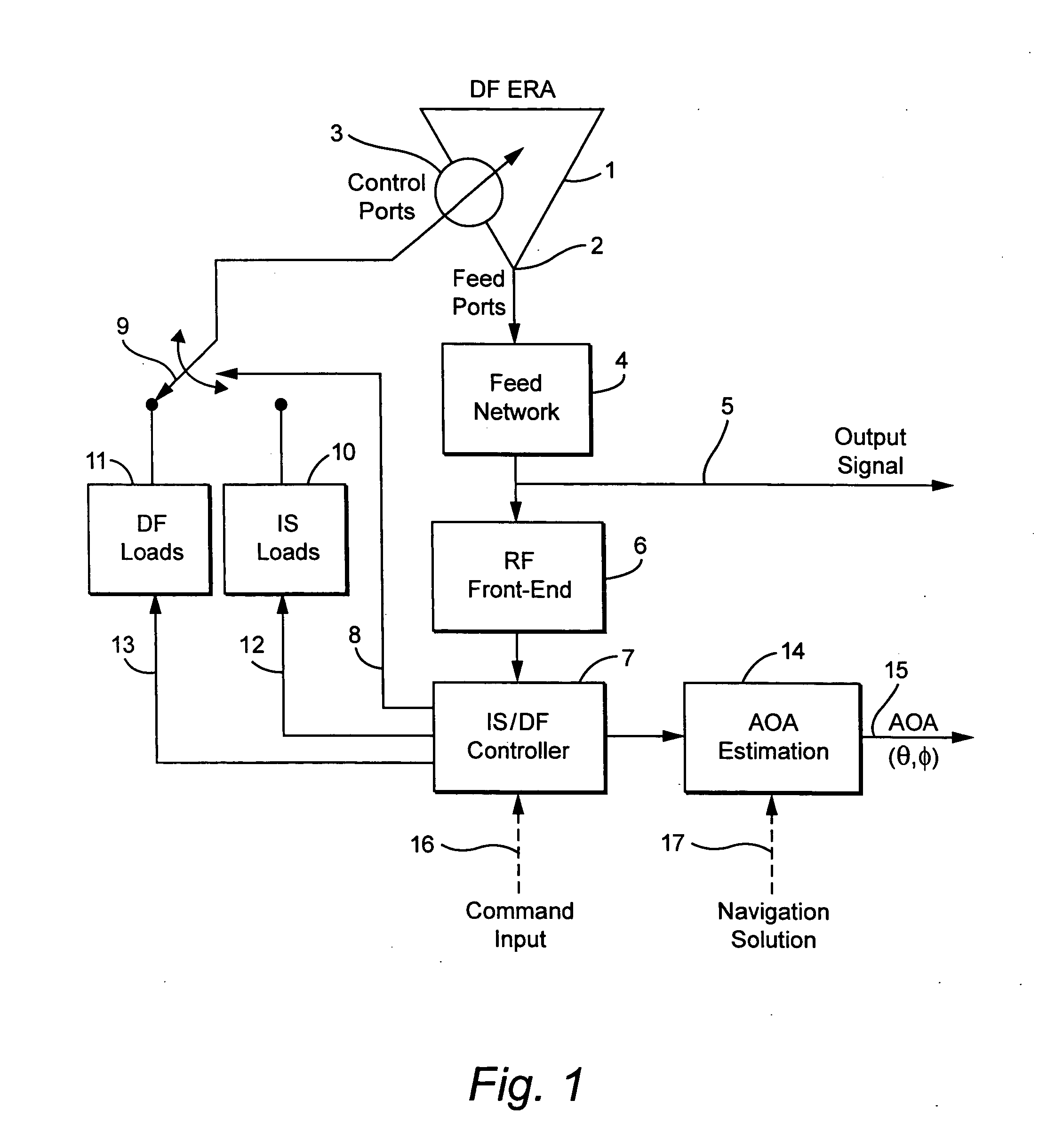

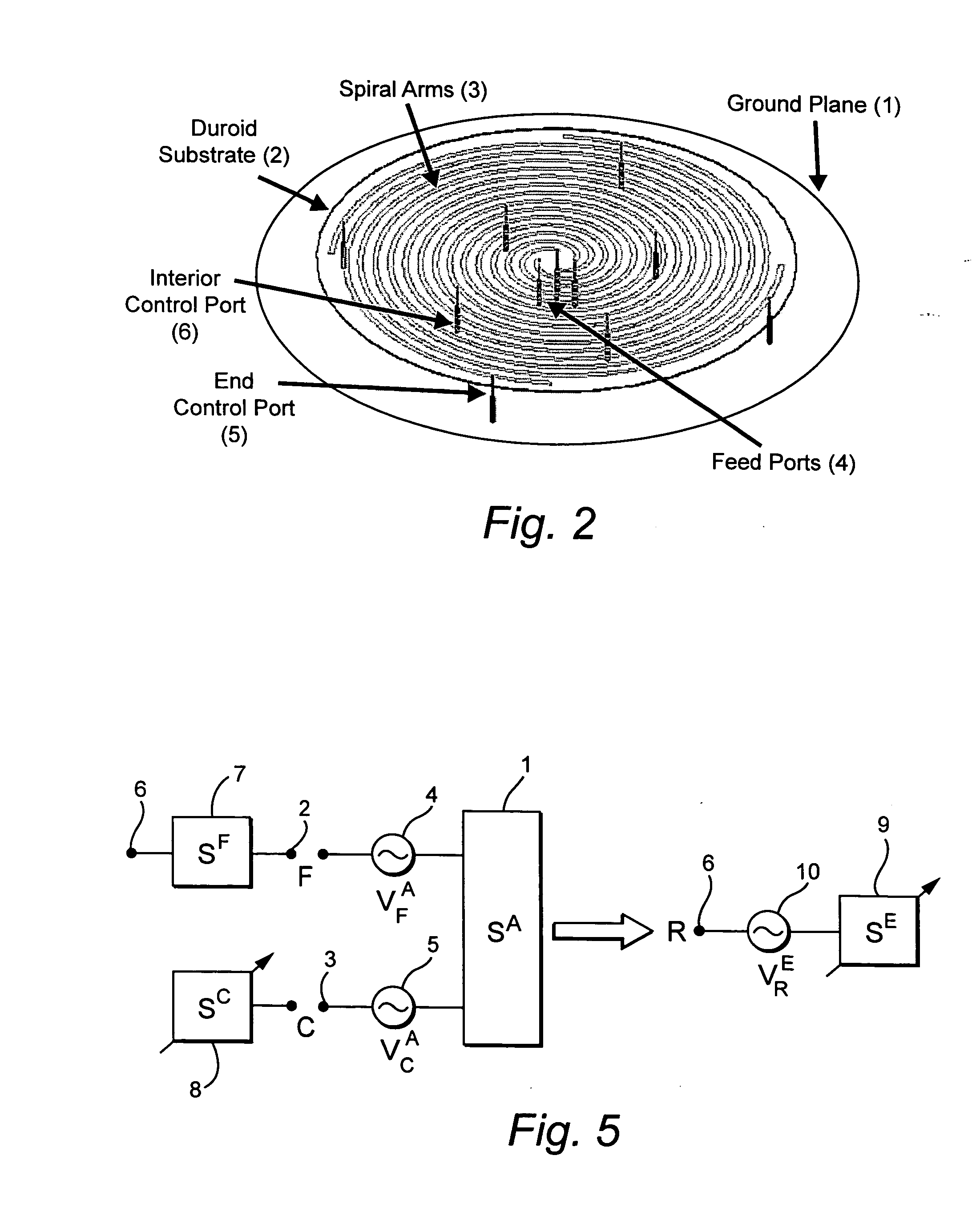

A compact, non-phased-array, electronically reconfigurable antenna (ERA) system with at least two operational modes has a first operational objective that is polarization-sensitive null steering (PSNS) and a second operational objective that is direction-finding (DF). The system can rapidly switch between two operational states. In the first state, the system behaves like a polarization filter (PF) and operates as a controlled reception pattern antenna (CRPA), while in the second state the system behaves as an angle-of-arrival (AOA) sensor and operates as a fixed reception pattern antenna (FRPA). The system may include a spiral-mode antenna with both feed and load ports; a mode-forming network; an electronics package; and feedback control electronics. Radio frequency (RF) interference rejection and RF direction-finding may be performed as well as reduction and / or elimination of multiple jamming signals that are intentionally or unintentionally directed at a Global Positioning System (GPS). The determination of direction and location of the source of jamming signals may also be achieved.

Owner:TOYON RES CORP

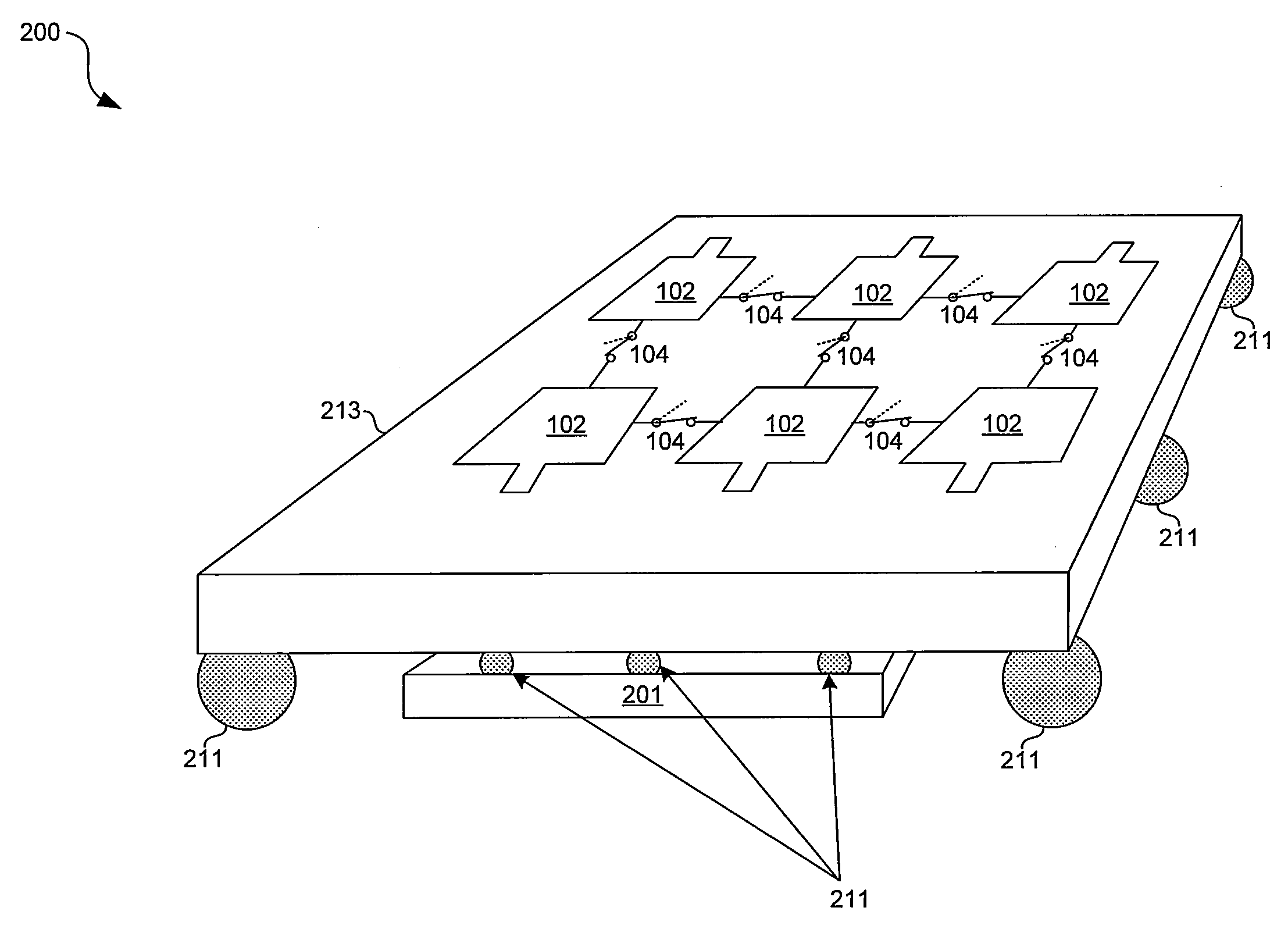

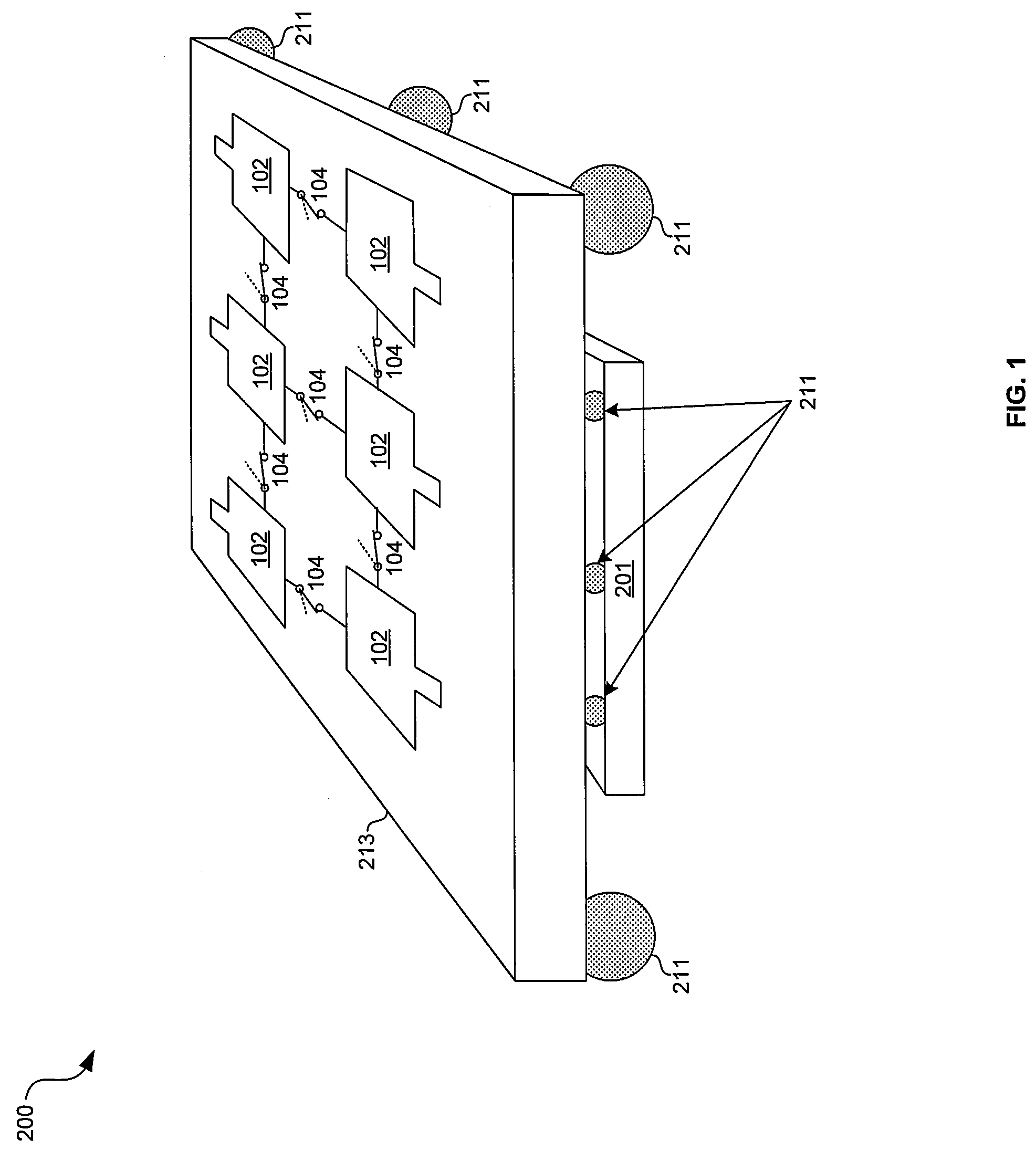

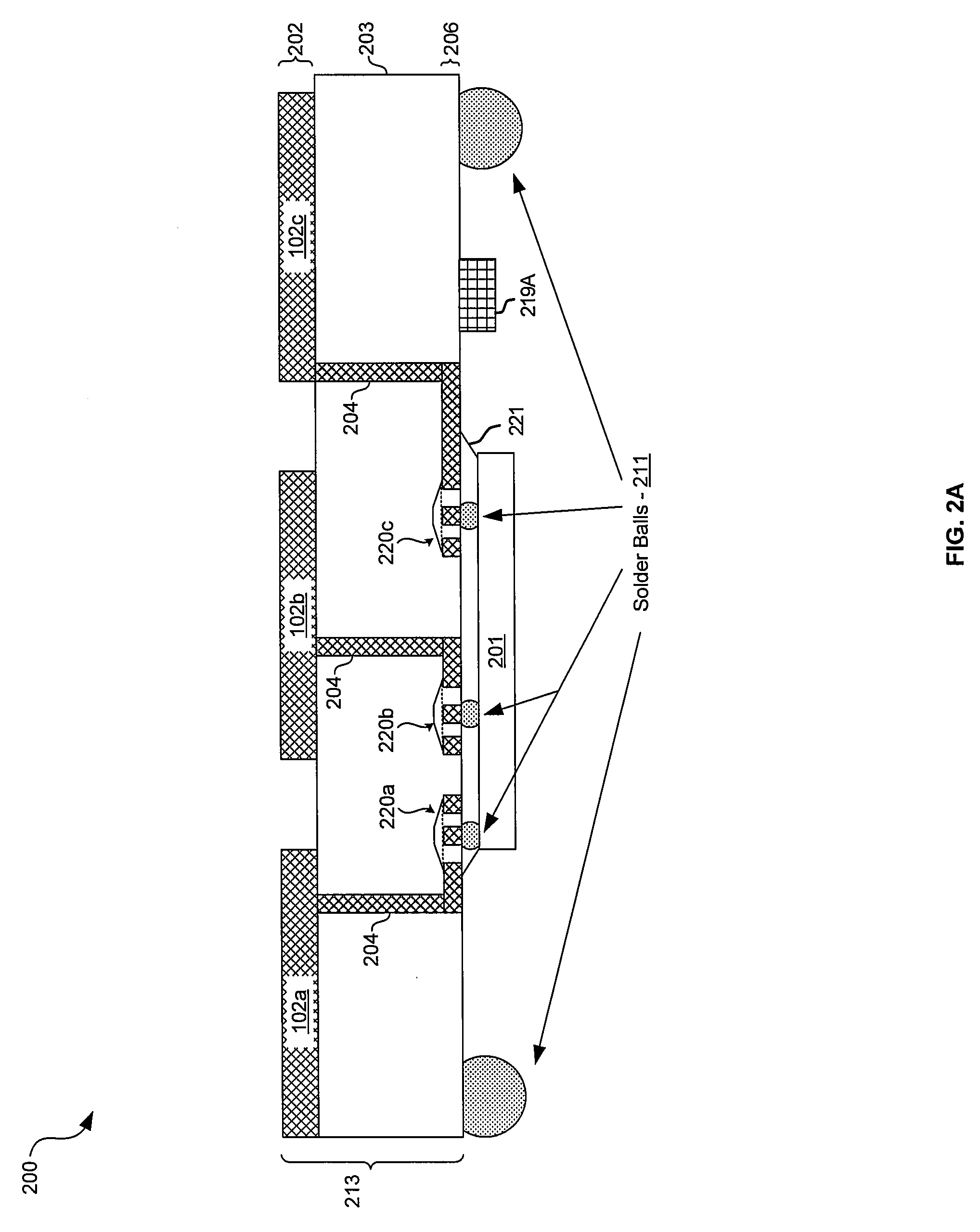

Method and system for configurable antenna in an integrated circuit package

Aspects of a method and system for a configurable antenna in an integrated circuit package are provided. In a hybrid circuit comprising an integrated circuit bonded to a multi-layer package, one or more antenna parameters may be adjusted by configuring a plurality of antenna elements via one or more switching elements. In this regard, the antenna elements and / or the switching elements may be within and / or on the multi-layer package and / or within the integrated circuit. The switching elements may be MEMS switches on and / or within the IC and / or the multi-layer package. The IC may be bonded or mounted to the underside of the package and signals may be communicated between the IC and the package via one or more solder balls. The IC may comprise suitable logic, circuitry, and / or code for configuring the antenna elements. The antenna elements may be configured based on desired polarization, antenna gain, and / or frequency.

Owner:AVAGO TECH INT SALES PTE LTD

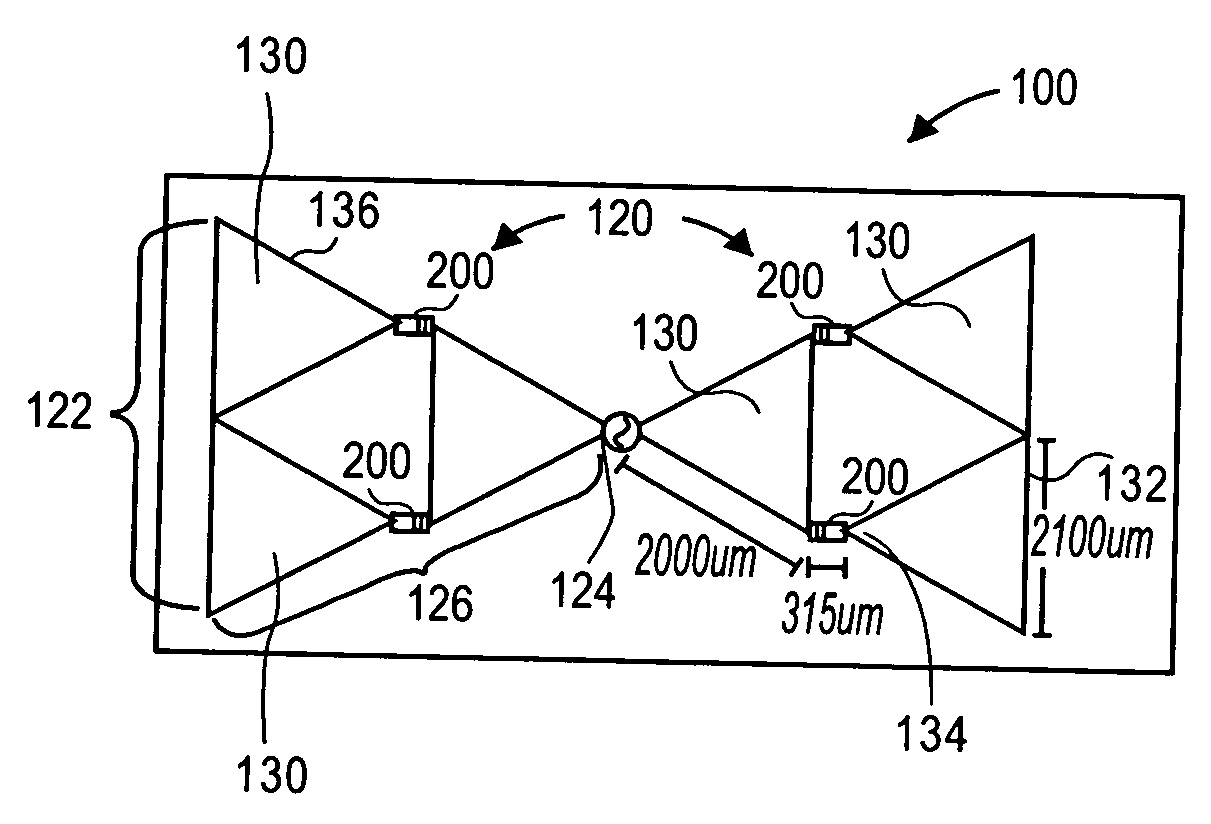

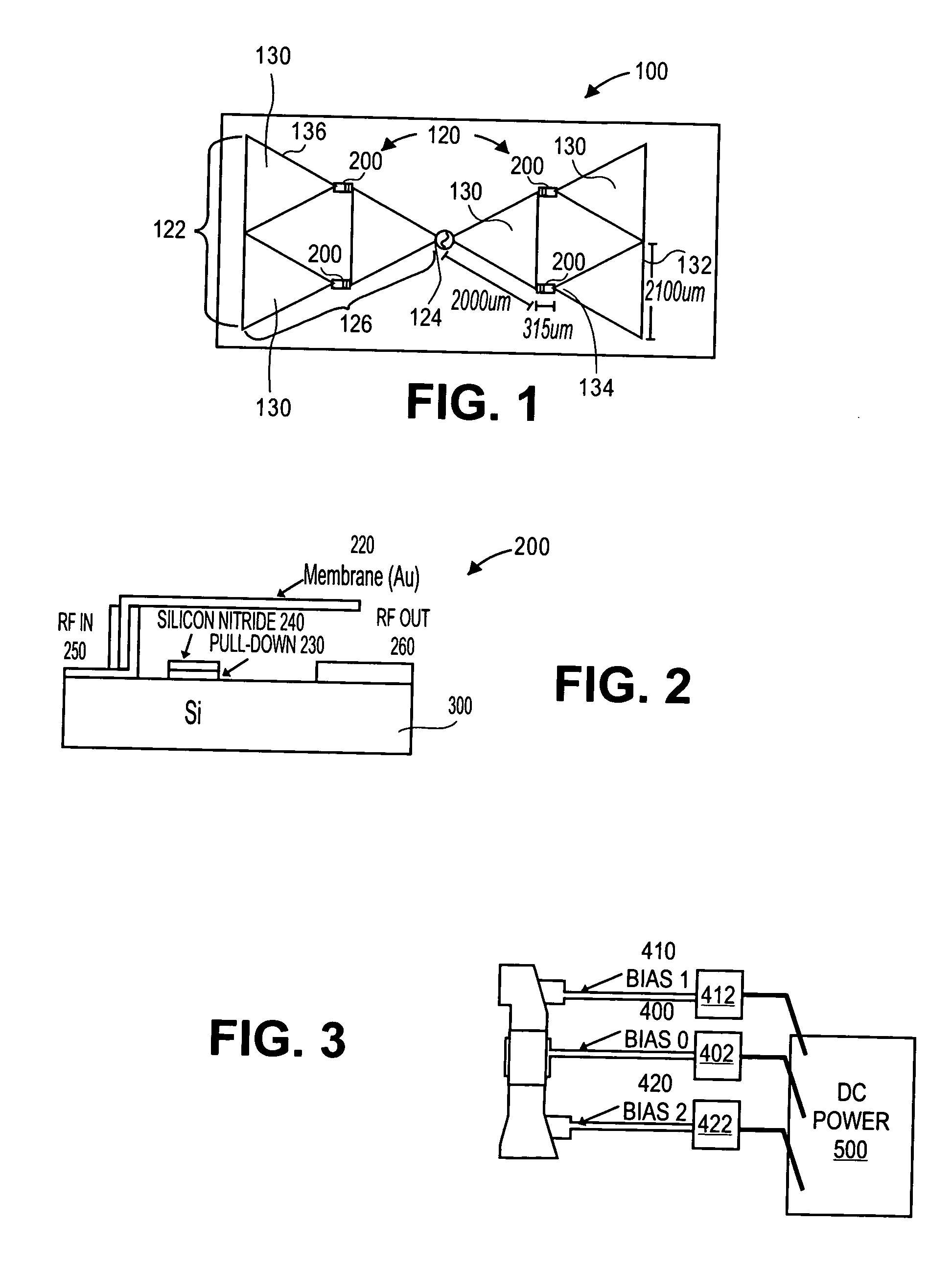

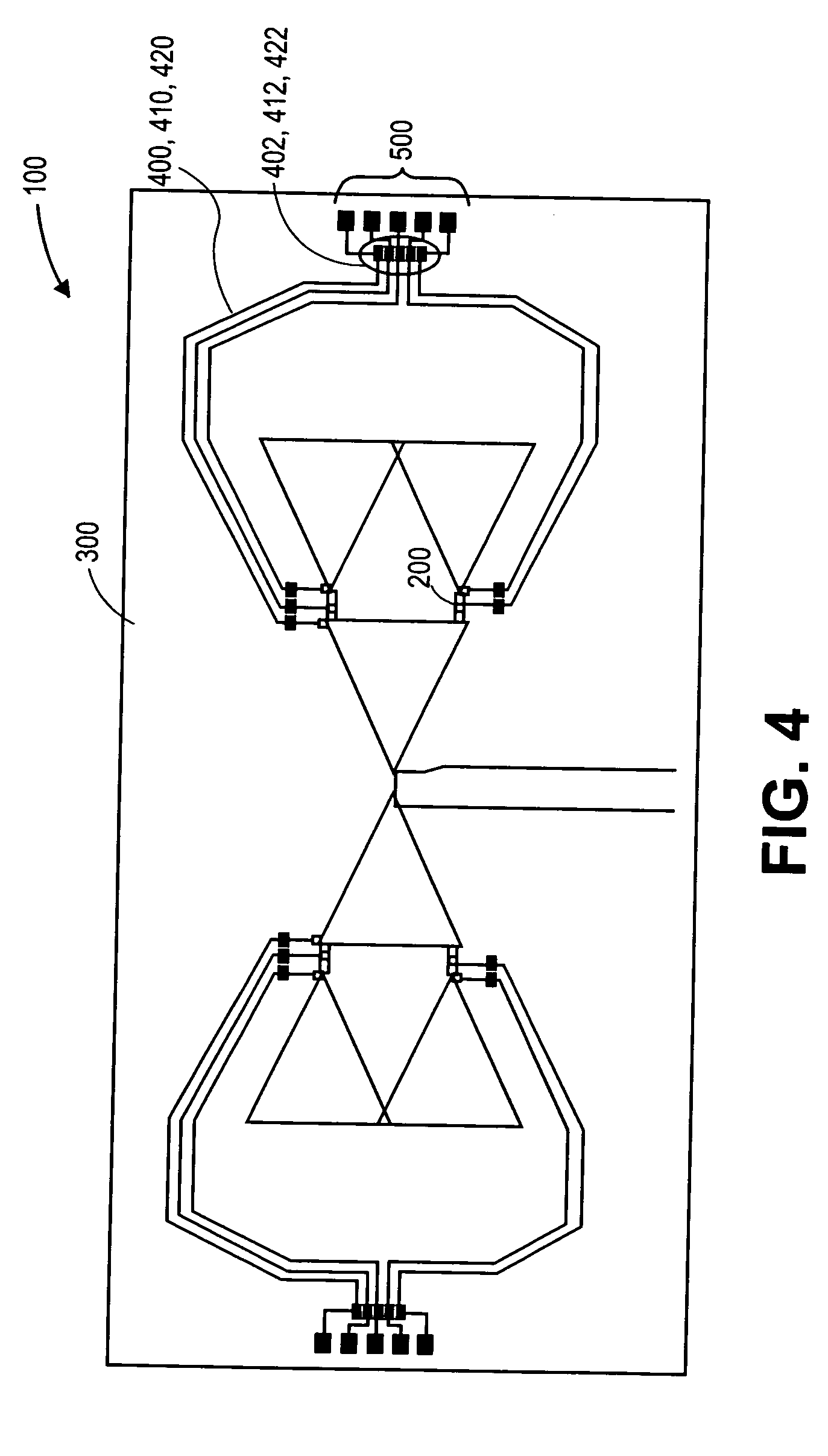

Reconfigurable multifrequency antenna with rf-mems switches

ActiveUS20090207091A1Antenna feed intermediatesSeparate antenna unit combinationsReconfigurable antennaVoltage source

A self-similar multiband reconfigurable antenna includes a planar antenna structure formed on a surface of a substrate, the antenna structure including symmetrically opposed self-similar geometry antenna arms defining a self-similar or Sierpinski gasket configuration for each arm of the antenna. MEMS type switches are provided for operatively connecting adjacent antenna patches on each arm of the antenna configuration, and a voltage source is provided for selectively actuating the switches. Selective actuation of the switches enables up to four different antenna configurations each having a different resonant frequency, and wherein each resonant frequency demonstrates a similar radiation pattern.

Owner:STC UNM +1

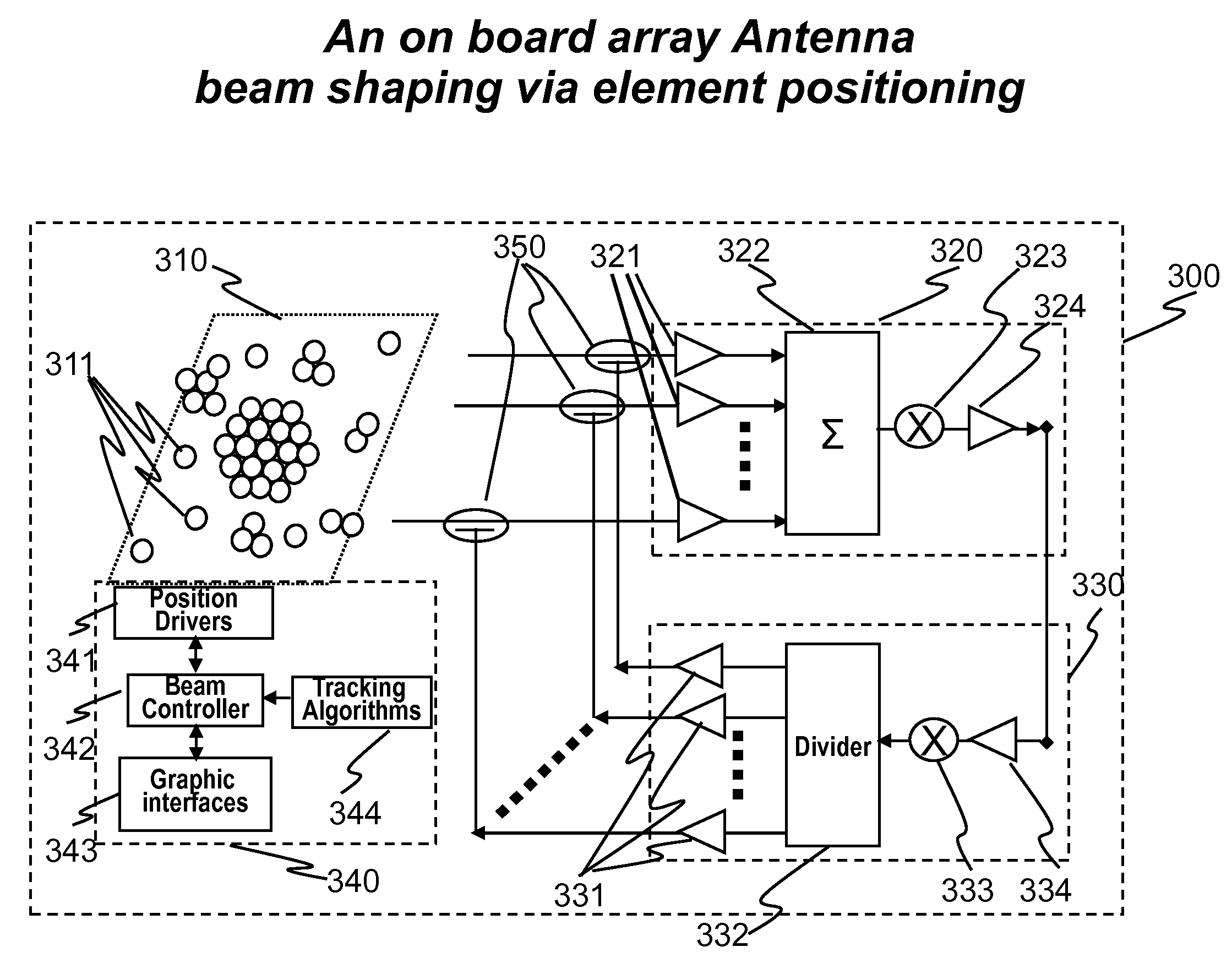

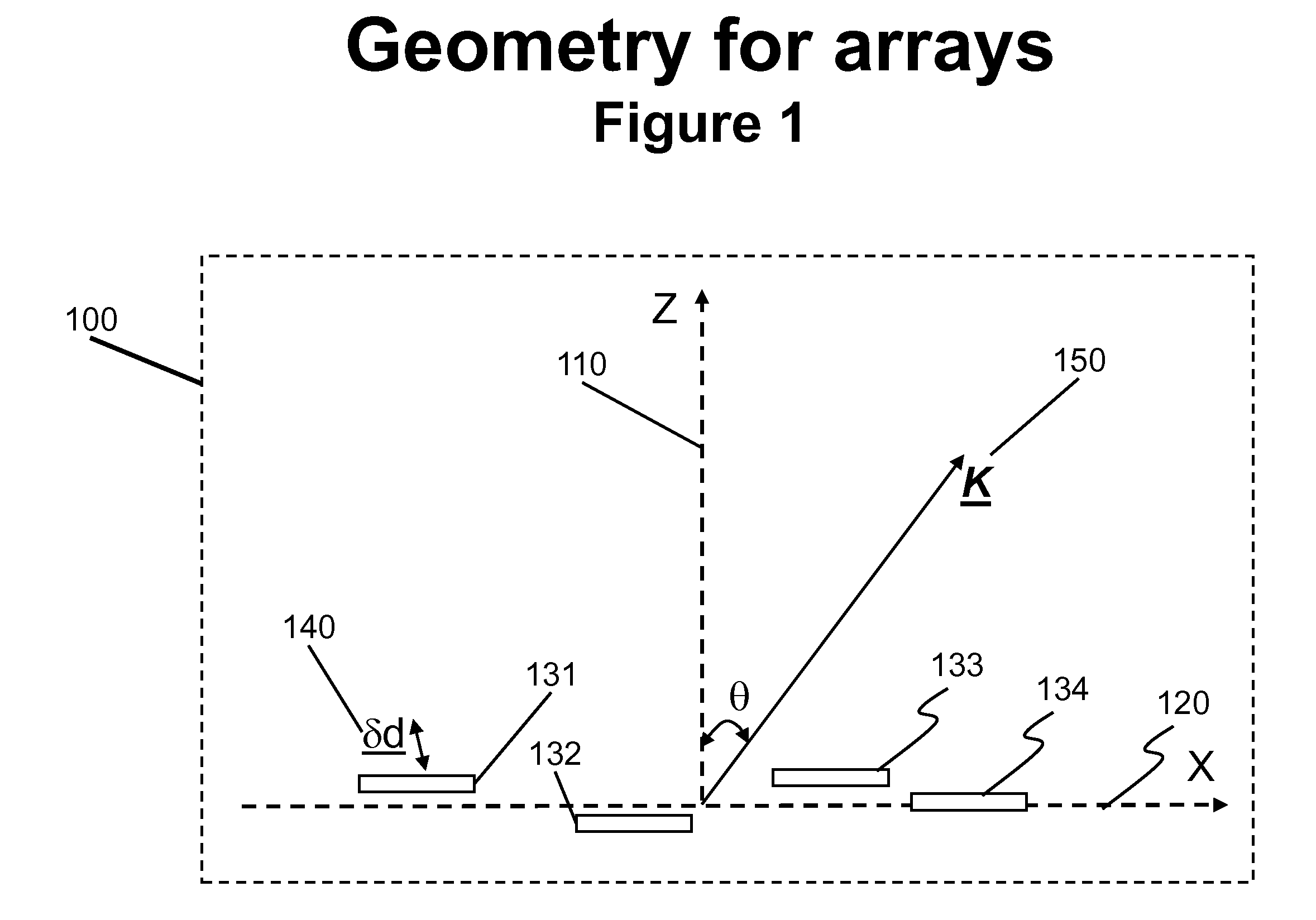

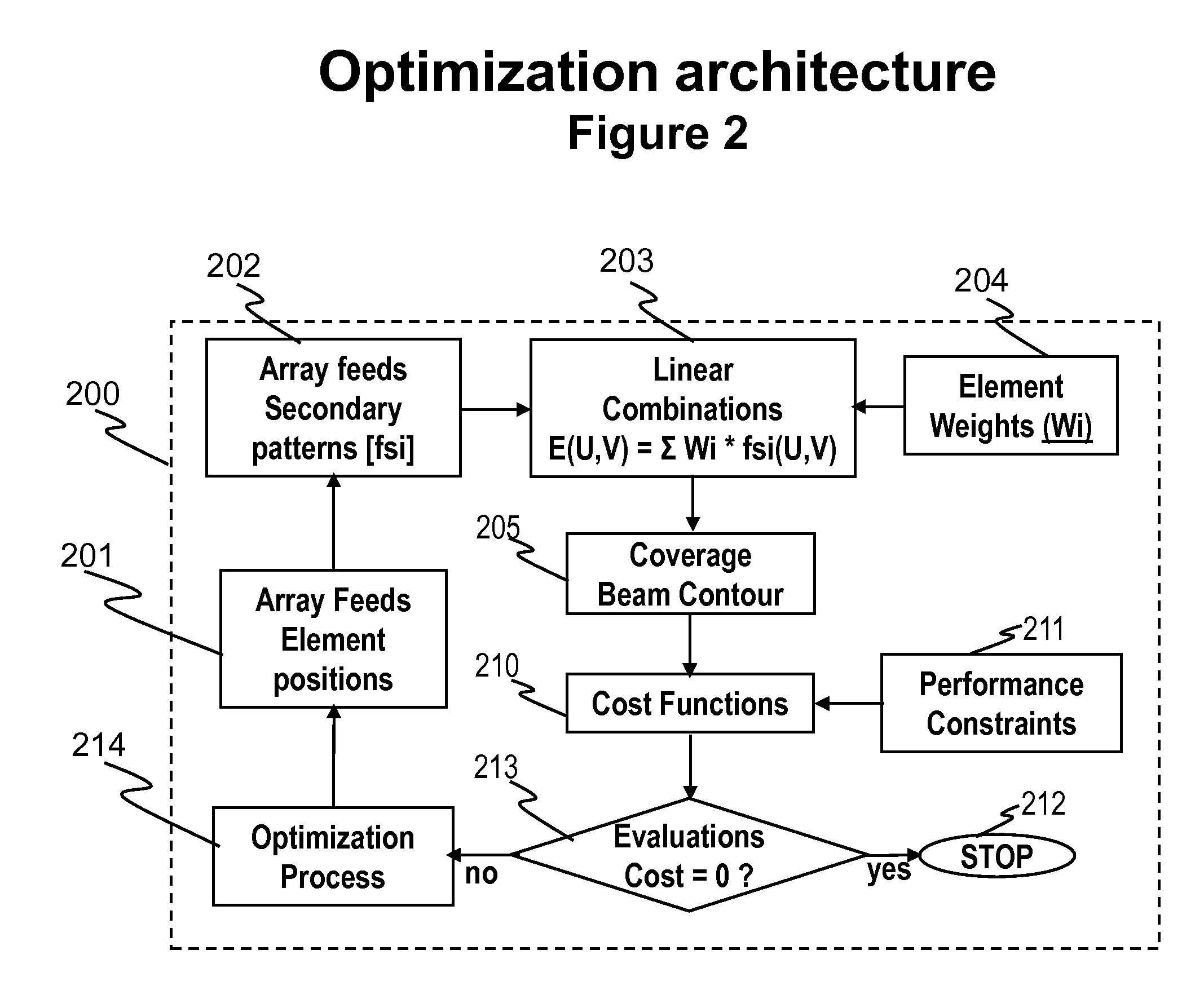

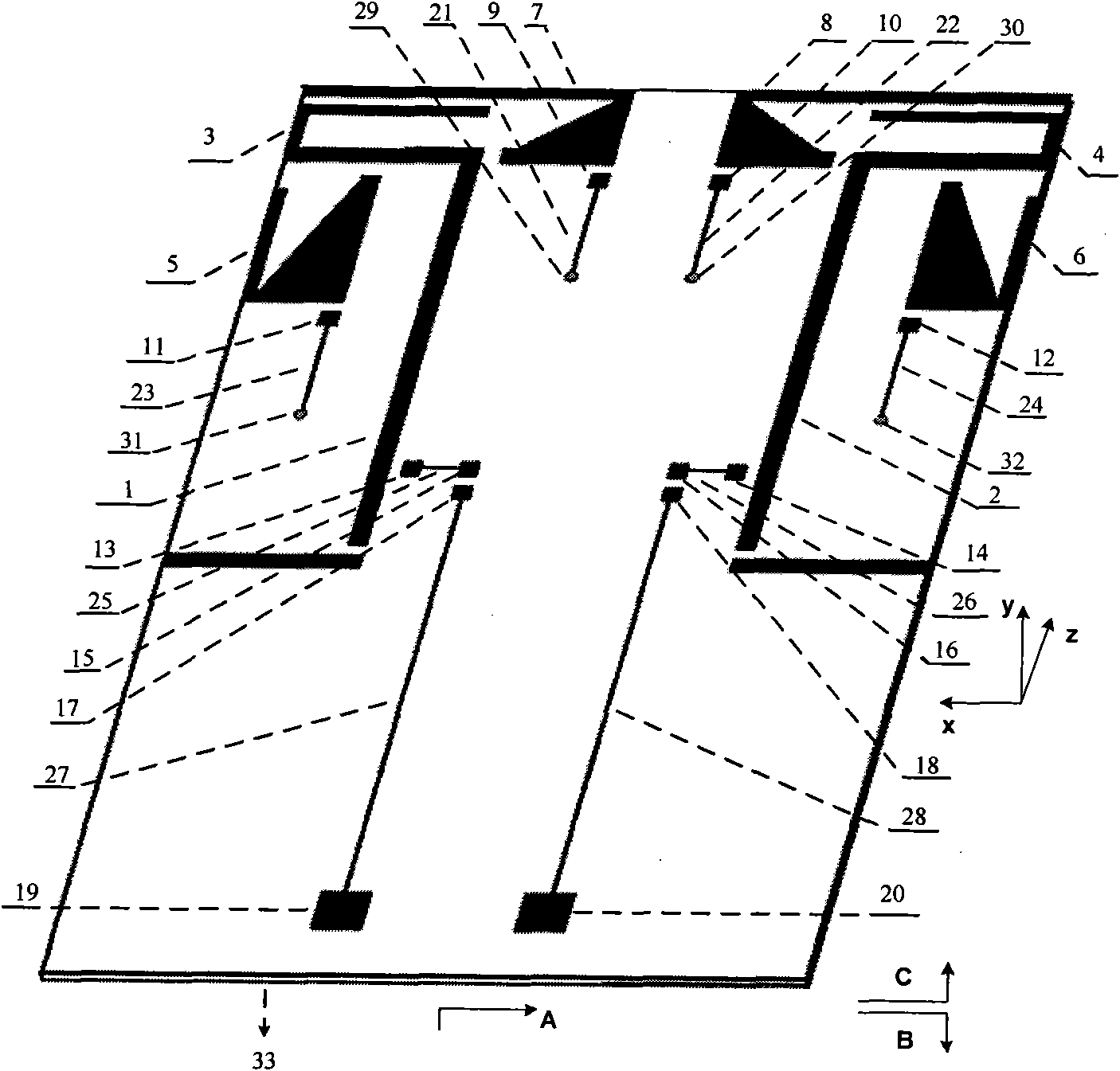

Architectures and Methods for Novel Antenna Radiation Optimization via Feed Repositioning

ActiveUS20110032173A1Complex antenna designCost-effective methodCollapsable antennas meansAntenna designSatellite antennas

The present invention relates to antenna architectures and methods on re-configurable multi-element antennas via feed re-positioning for various optimized radiation contours, including beam forming (or shaping) and / or null steering on contoured beams, spot beams, and orthogonal beams. The feed re-positioning techniques can also be used in radiation pattern optimization processing during antennas designing phases for fixed beams. The techniques are applicable for satellite communications. For satellite antennas, the beam shaping capability via element repositioning can be utilized for (1) optimized geometries on satellite antennas for given desired coverage areas, (2) re-optimizing radiation contours for reconfigurable antenna on board satellites in operation, (3) additional flexibility for satellite antennas using ground based beam forming (GBBF). As to satellite ground terminals, the same techniques are applicable for both fixed and mobile satellite terminals featuring either single beam or multiple beams. For fixed terminals, are applicable for terrestrial based communications; such as retrofitting existing antennas eliminating interference radiations coming from fixed or slow varying directions.

Owner:SPATIAL DIGITAL SYST

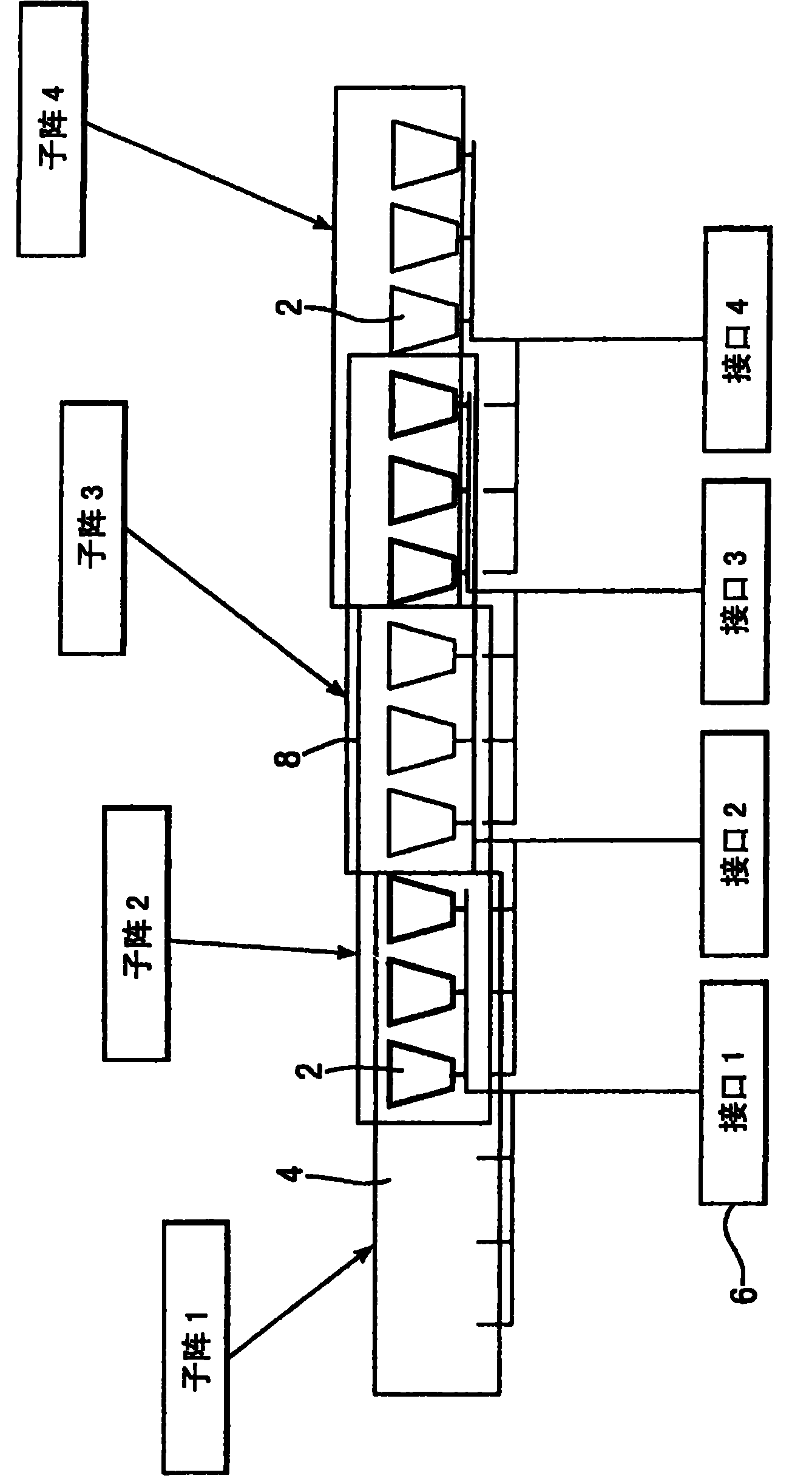

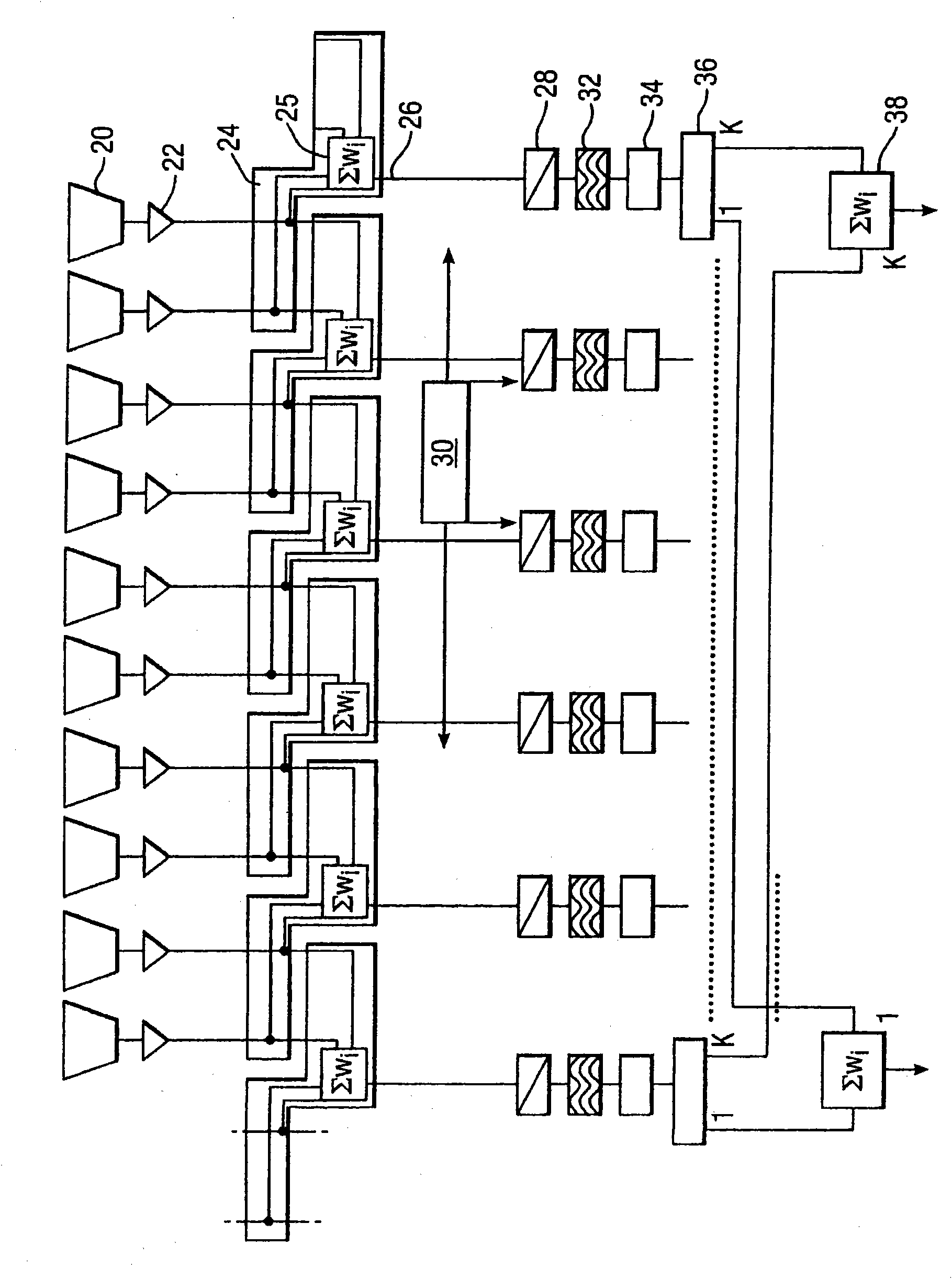

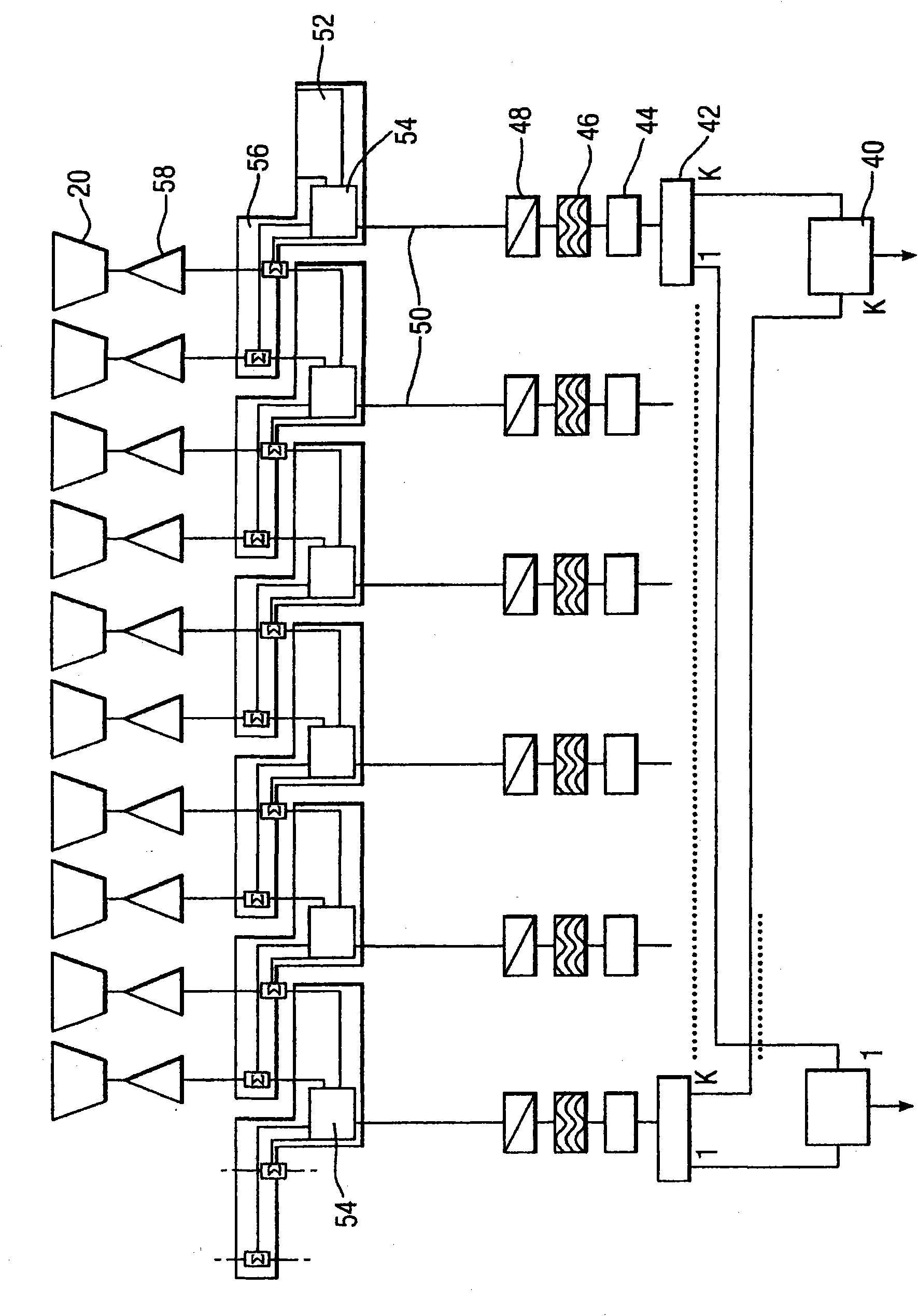

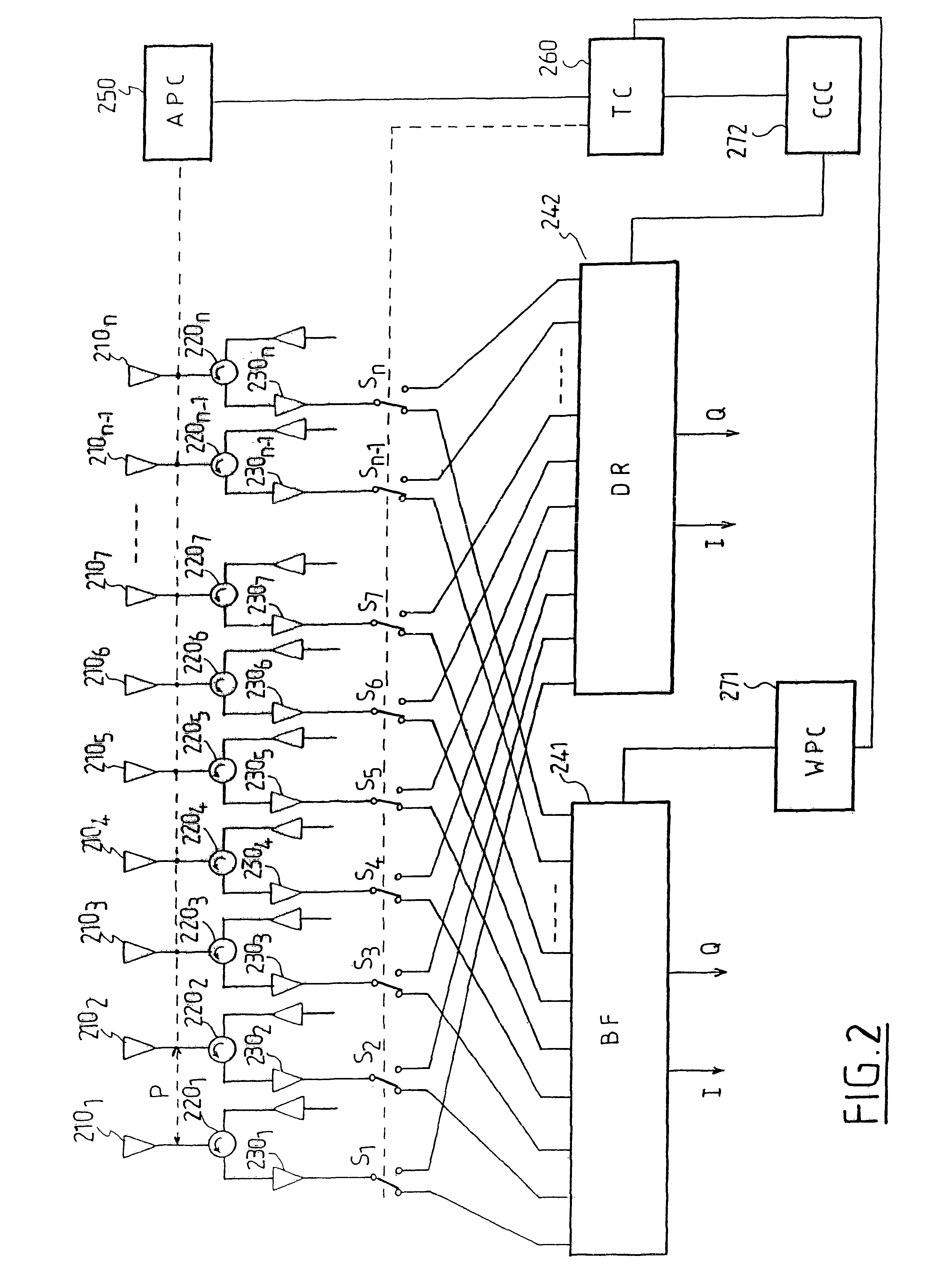

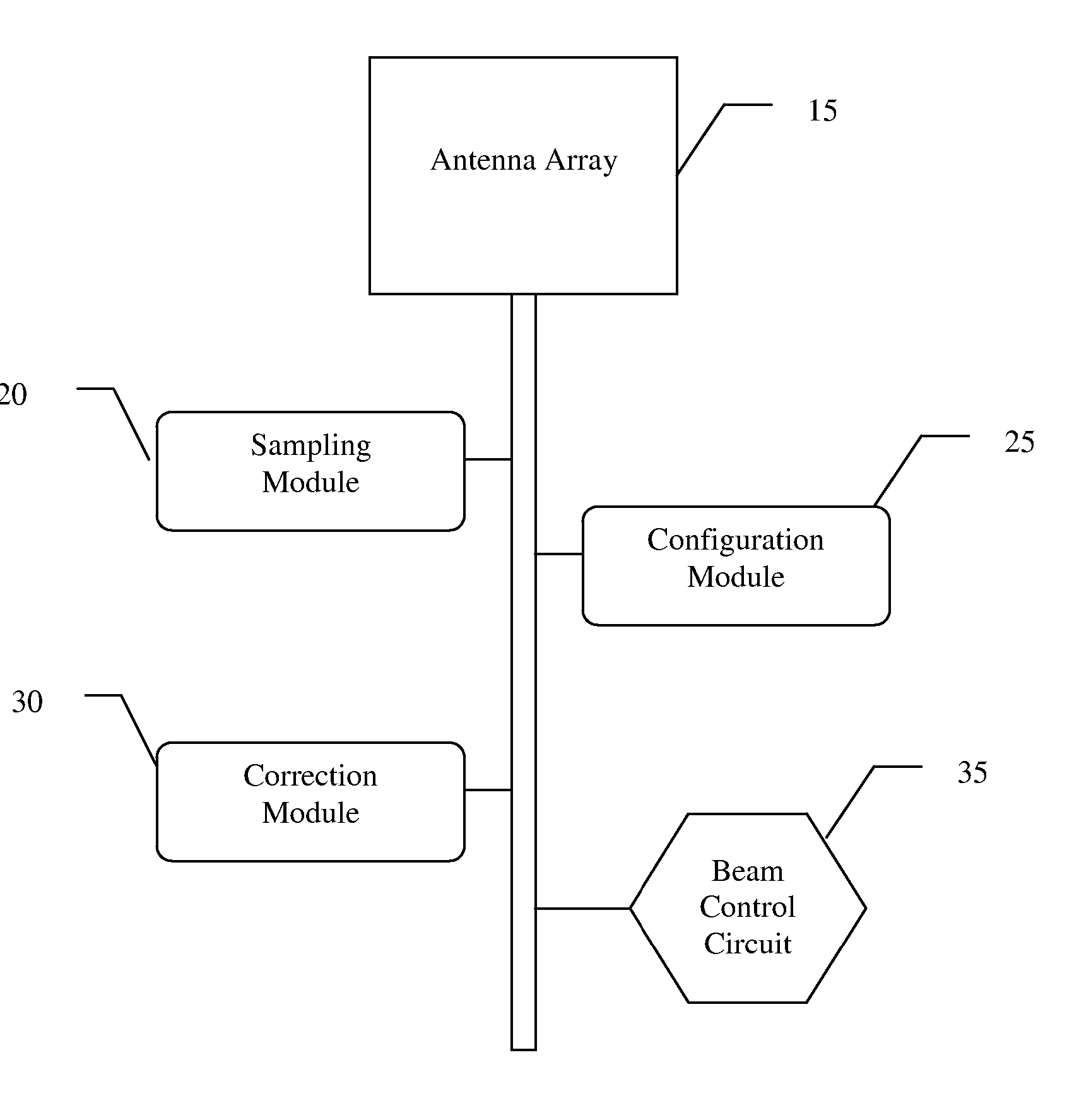

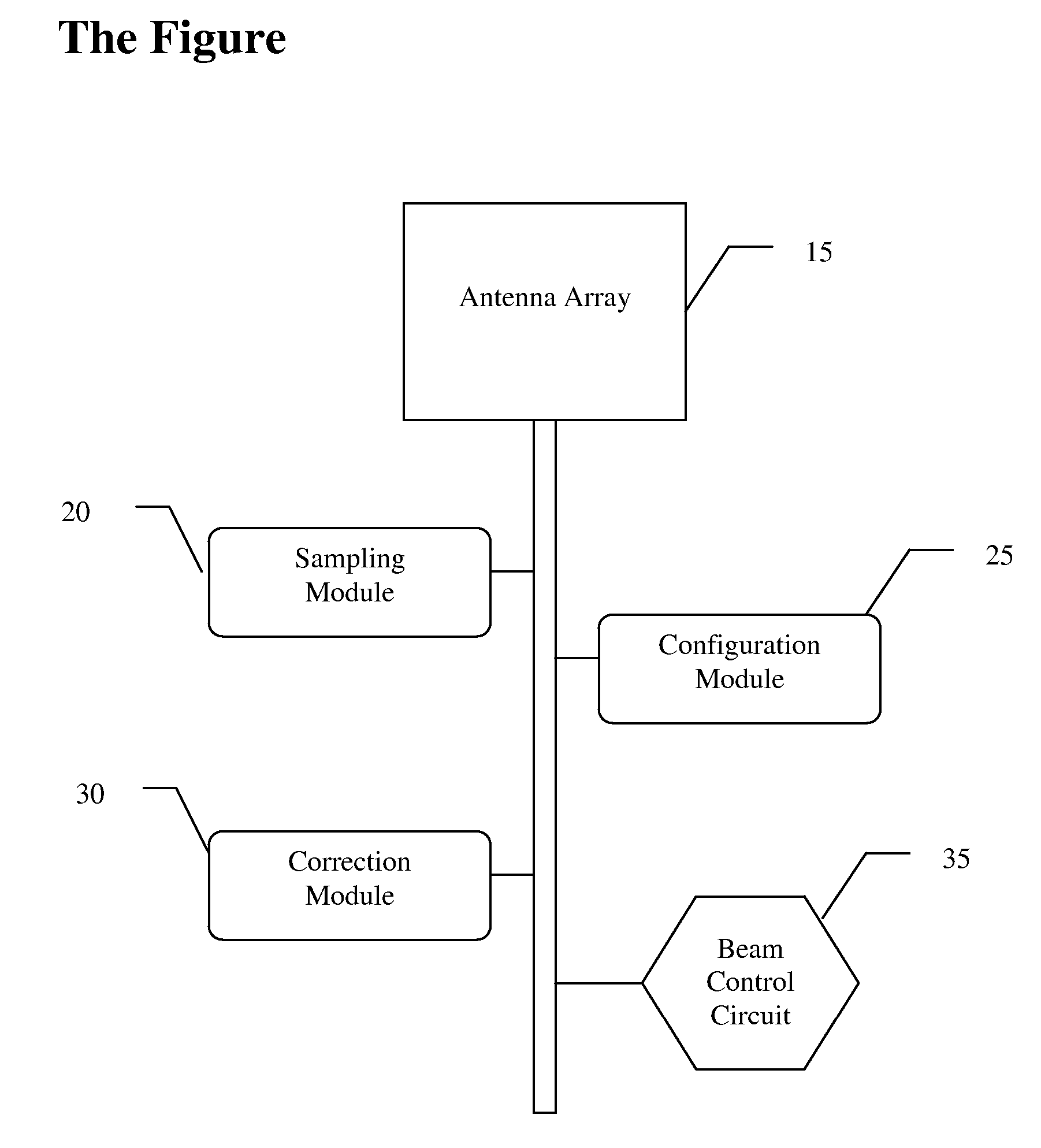

System for simplification of reconfigurable beam-forming network processing within a phased array antenna for a telecommunications satellite

ActiveCN101803113AParticular array feeding systemsAntenna adaptation in movable bodiesReconfigurable antennaMultiplexing

A telecommunications satellite having a phased array antenna, wherein the beam-forming function within the phased array is simplified by partitioning it into two stages, in which the sub-array stage relates to a fixed, or infrequently changed,set of overlapping sub-arrays and the main stage provides the main pattern reconfiguration, typically in the form of multiple reconfigurable spot beams within a defined coverage region. The key advantage lies in the significant reduction in number of second stage beam-forming control points (at which independent amplitude and phase is applied) when compared with a conventional phased array (where amplitude and phase control is applied for each element of the array). The sub-array stage beam-forming may be implemented in analogue technology. The main beam-former may be implemented in digital technology, where the key processing functions of A / D or D / A conversion, frequency (de)multiplexing and digital beam-forming all scale with the number of control points.

Owner:ASTRIUM GMBH

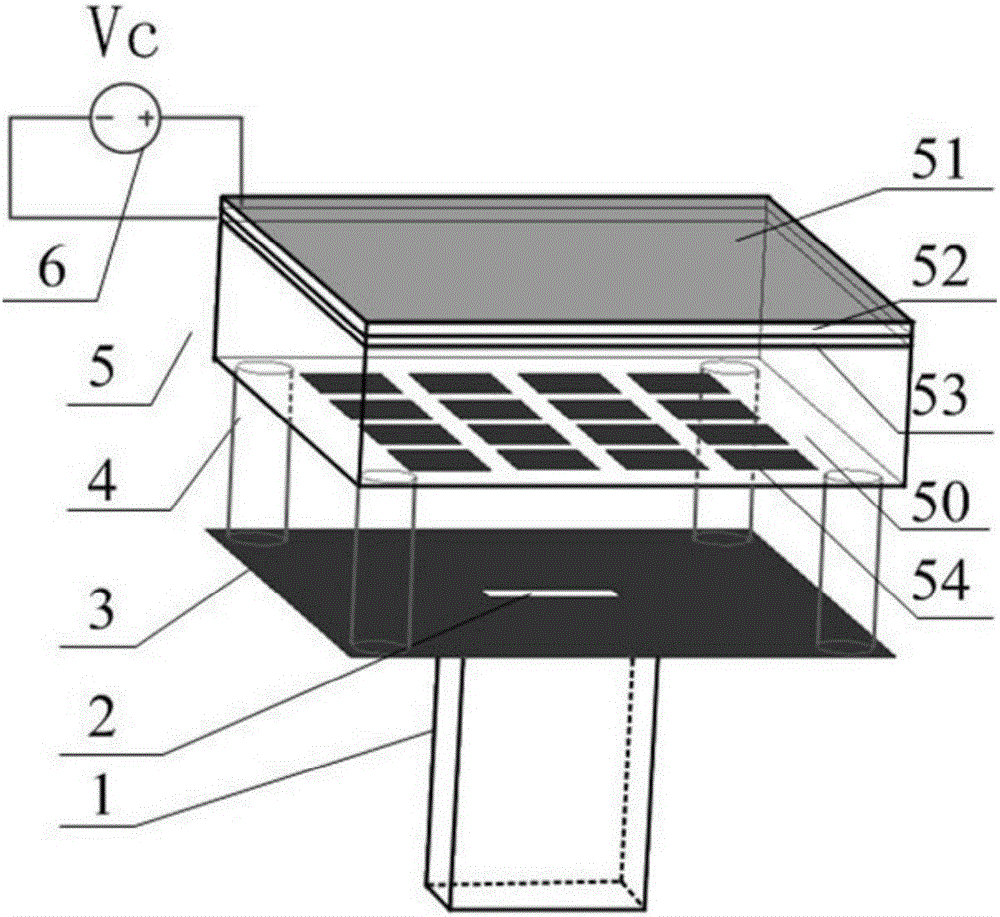

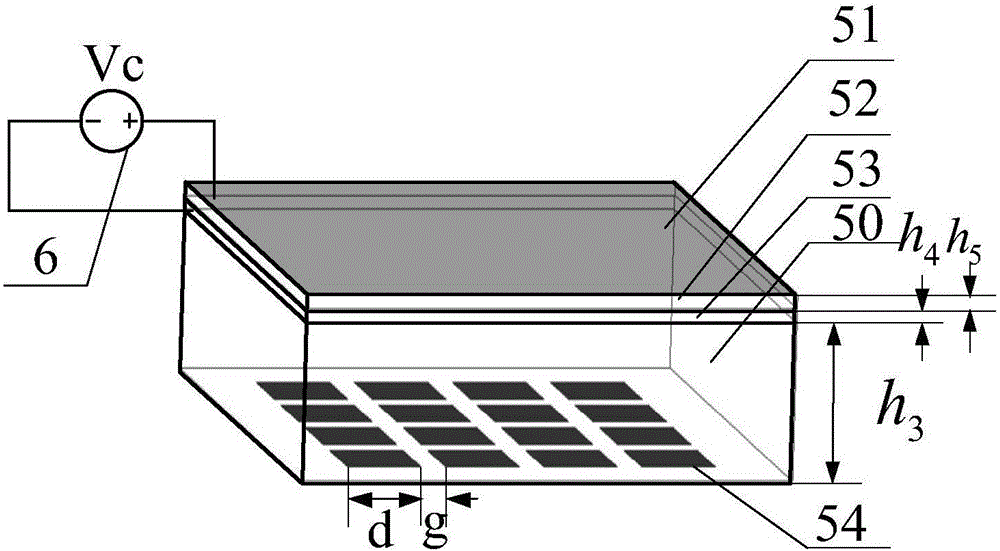

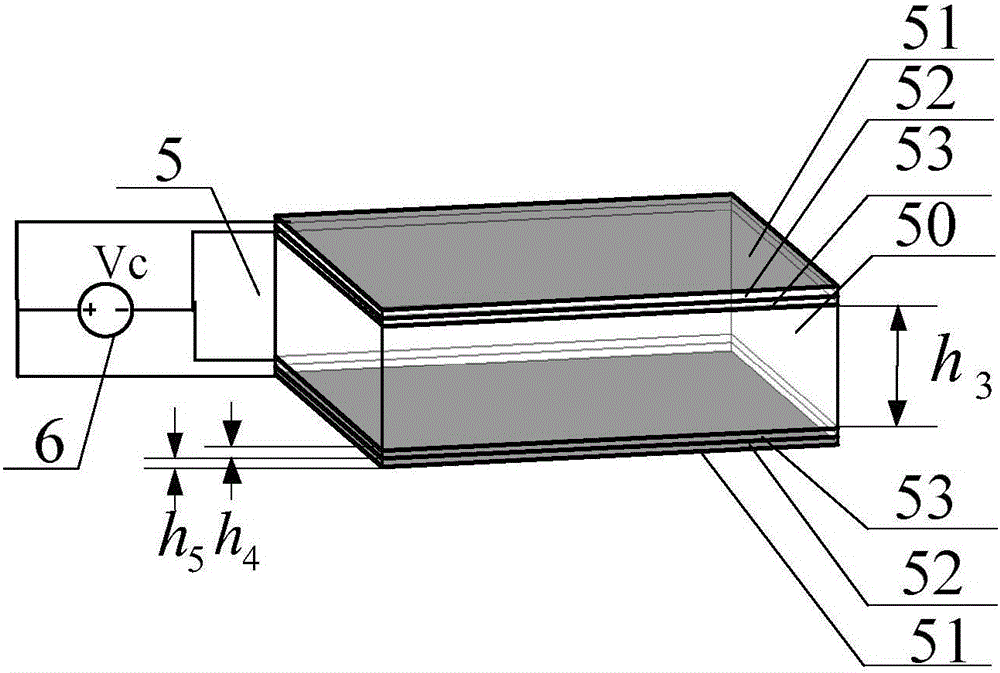

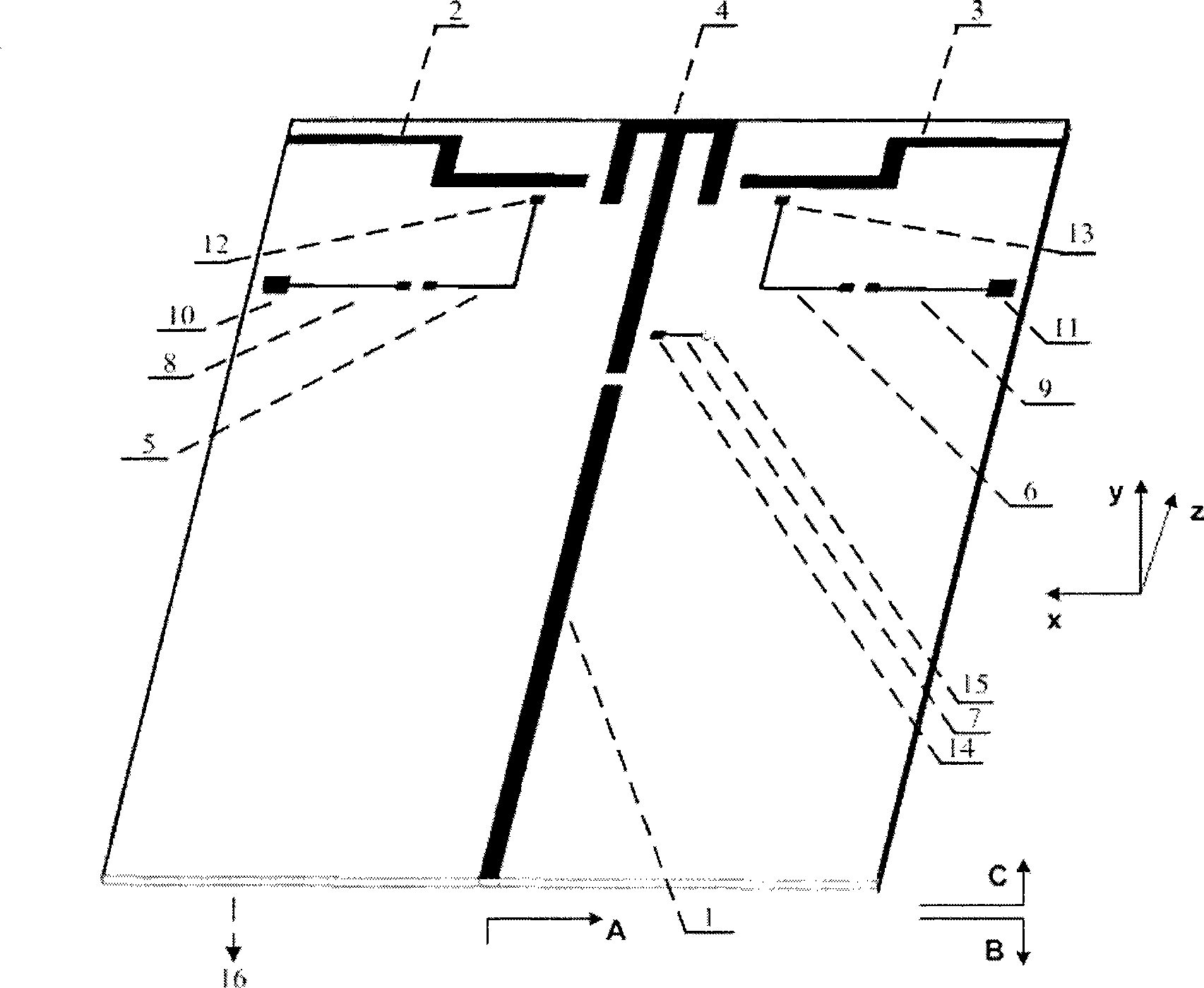

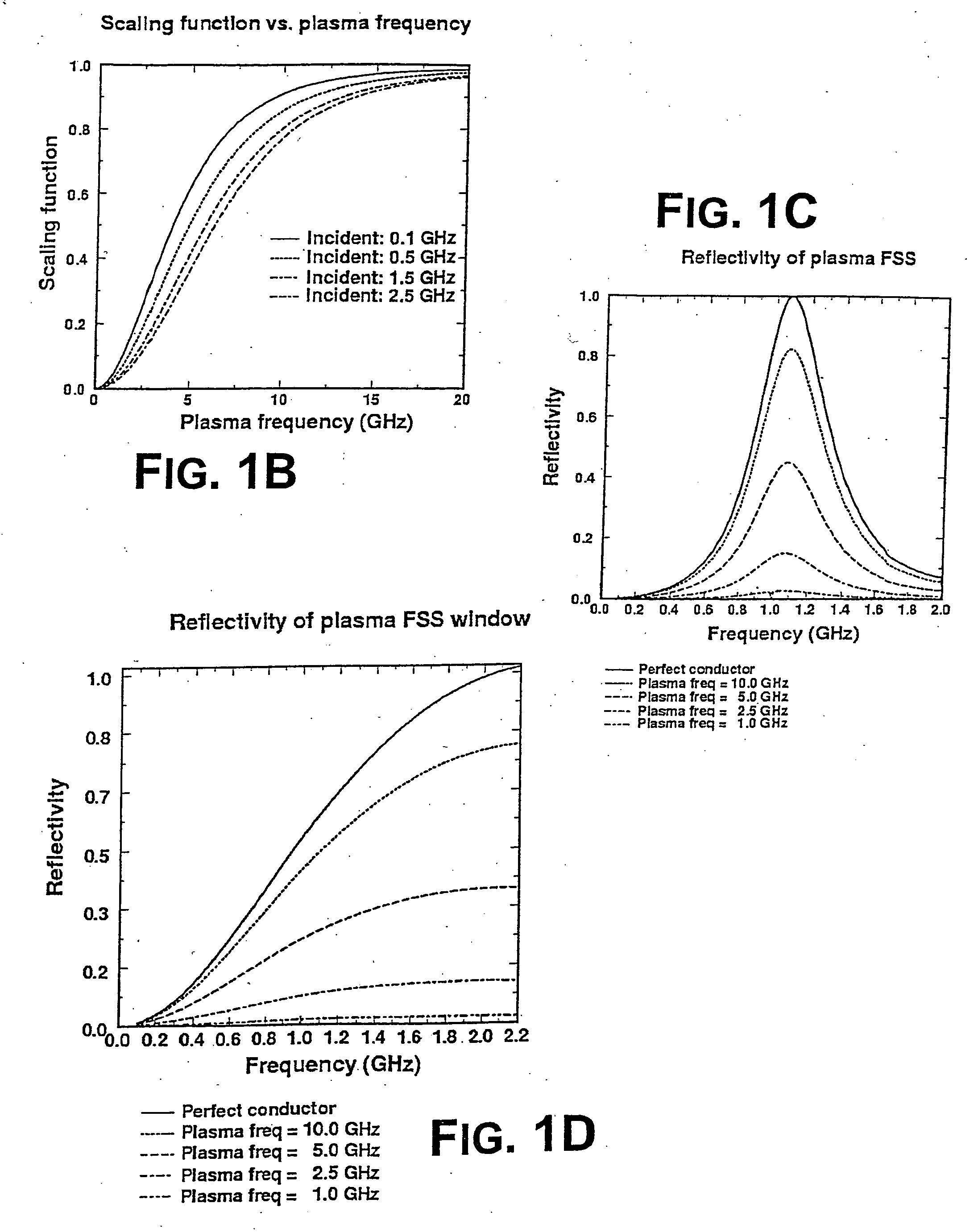

Pattern-reconfigurable antenna based on graphene composite structure frequency selective surface

The invention provides a pattern-reconfigurable antenna based on a graphene composite structure frequency selective surface to solve the problem that the gain and beam bandwidth of an antenna cannot be changed flexibly in the prior art. The pattern-reconfigurable antenna comprises a rectangular waveguide feeder, a rectangular radiation element, a baffle board, a frequency selective surface, and a direct-current bias voltage Vc. The frequency selective surface includes a graphene composite structure, a dielectric substrate, and a square patch array or graphene composite structure, which are stacked from top to bottom. The graphene composite structure is composed of a graphene layer, an alumina layer and a polycrystalline silicon layer which are stacked sequentially. The direct-current bias voltage Vc is applied between the graphene layer and the polycrystalline silicon layer. The rectangular radiation element is arranged on the baffle board, the frequency selective surface is fixed above the baffle board through four support columns, and the rectangular waveguide feeder is fixed below the baffle board. The radiation gain and beam bandwidth of the antenna can be changed flexibly, and reconfigurable pattern of a millimeter wave antenna is realized.

Owner:XIDIAN UNIV

Method and apparatus for an adaptive multiple-input multiple-output (MIMO) wireless communications systems

ActiveUS7469152B2Enhancing adaptability featureImproving dramatically the performance characteristics of the systemSpatial transmit diversityAntenna arraysEngineeringMultiple input

An adaptive MIMO communications system includes a multifunctional reconfigurable antenna with a selectively alterable effective physical antenna array configuration and radiation / polarization properties, which configuration and properties is a component in the optimization of the adaptive system parameters. The multifunctional reconfigurable antenna comprises a plurality of antenna components and a plurality of selectively controllable switches coupling selected ones of the plurality of antenna components together into a multifunctional reconfigurable subarray of antenna components. A processing unit coupled to the multifunctional reconfigurable antenna determines communication channel conditions for generating adaptive control signals to the plurality of selectively controllable switches to selectively apply a selected space-time coding protocol or a selected beam forming protocol together on the plurality of antenna components depending on channel conditions.

Owner:RGT UNIV OF CALIFORNIA

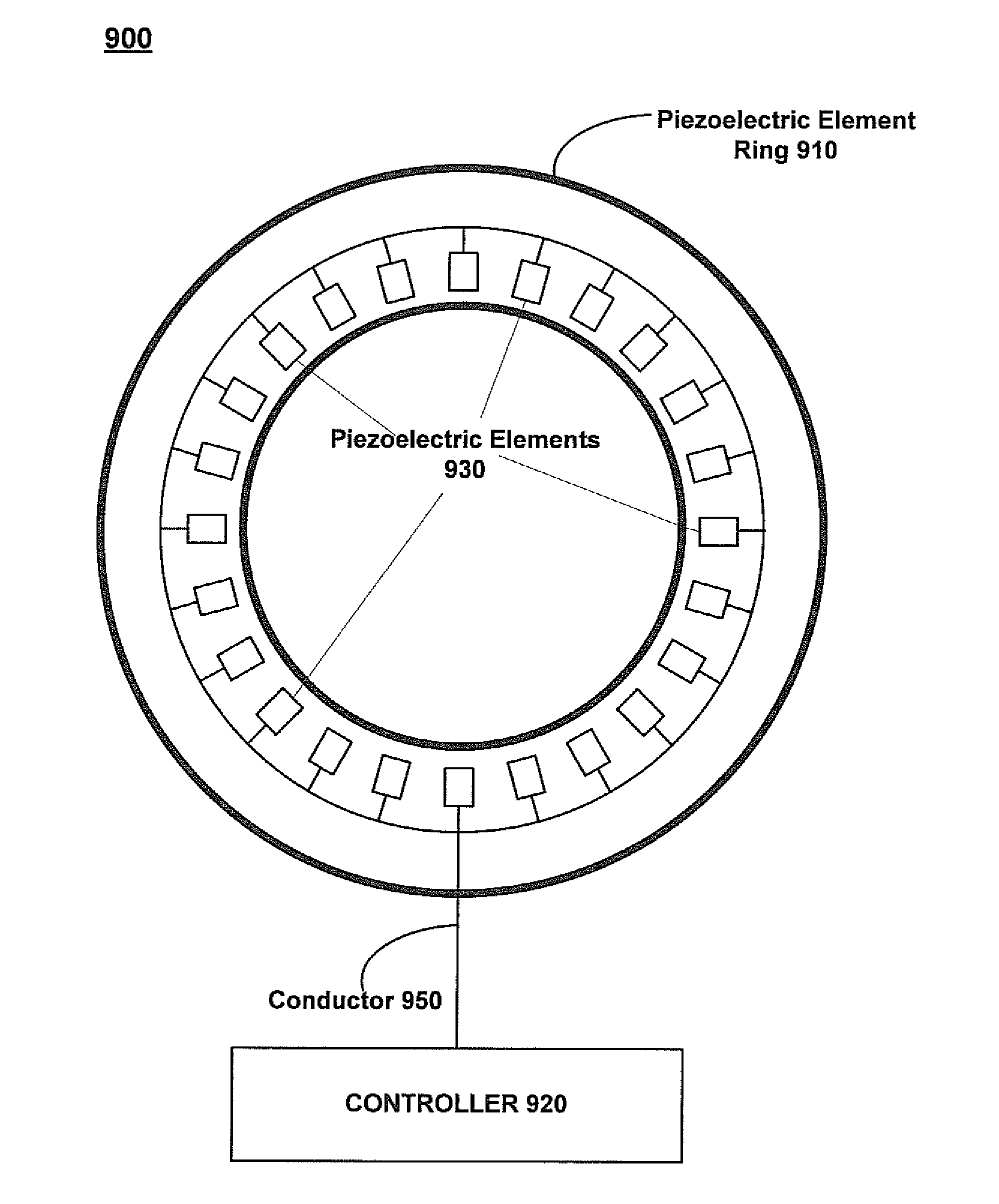

Optimized switching configurations for reconfigurable arrays of sensor elements

InactiveUS7353056B2Minimize cost functionUltrasonic/sonic/infrasonic diagnosticsImage analysisReconfigurable antennaReconfigurability

Owner:GENERAL ELECTRIC CO

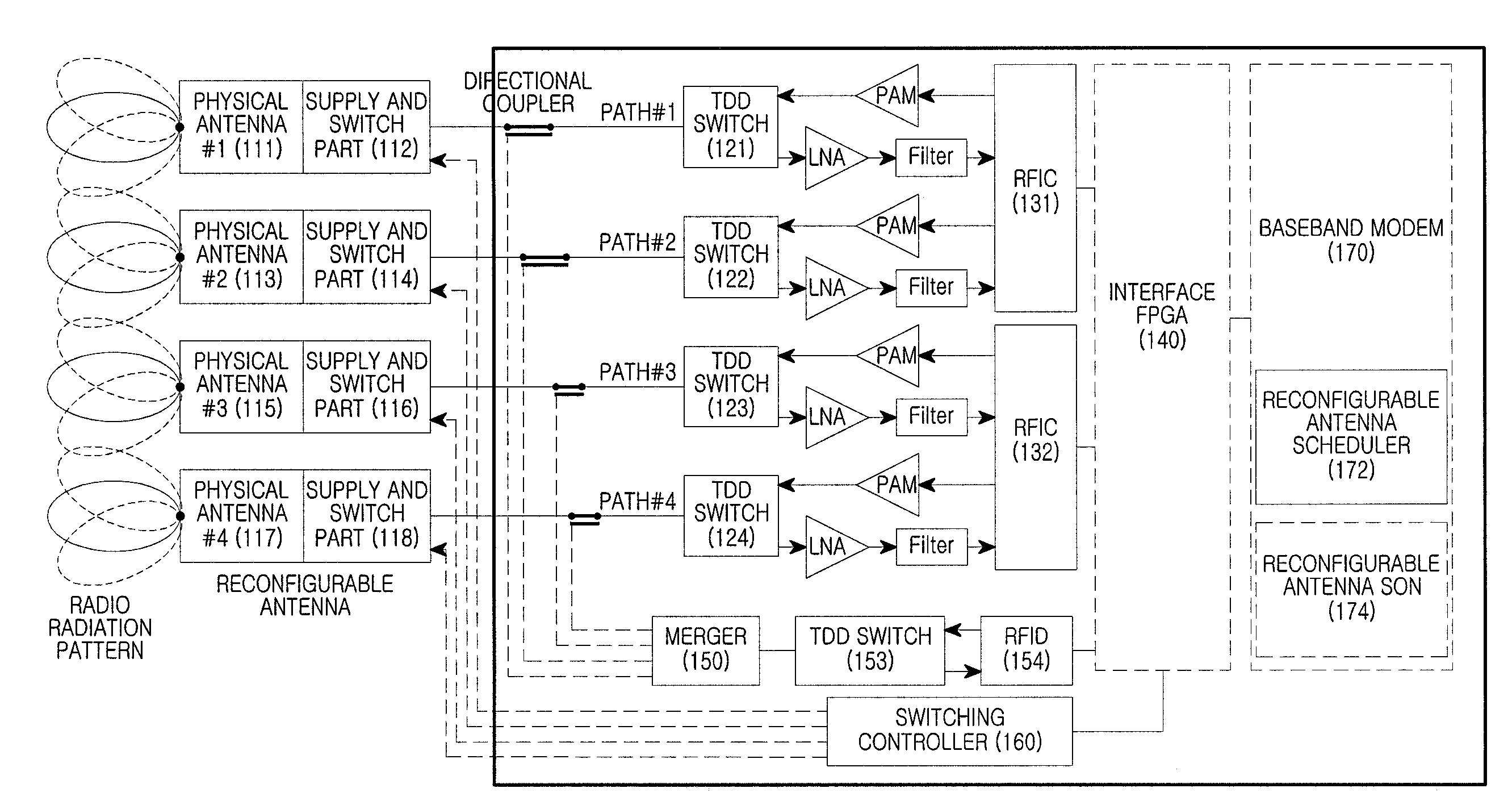

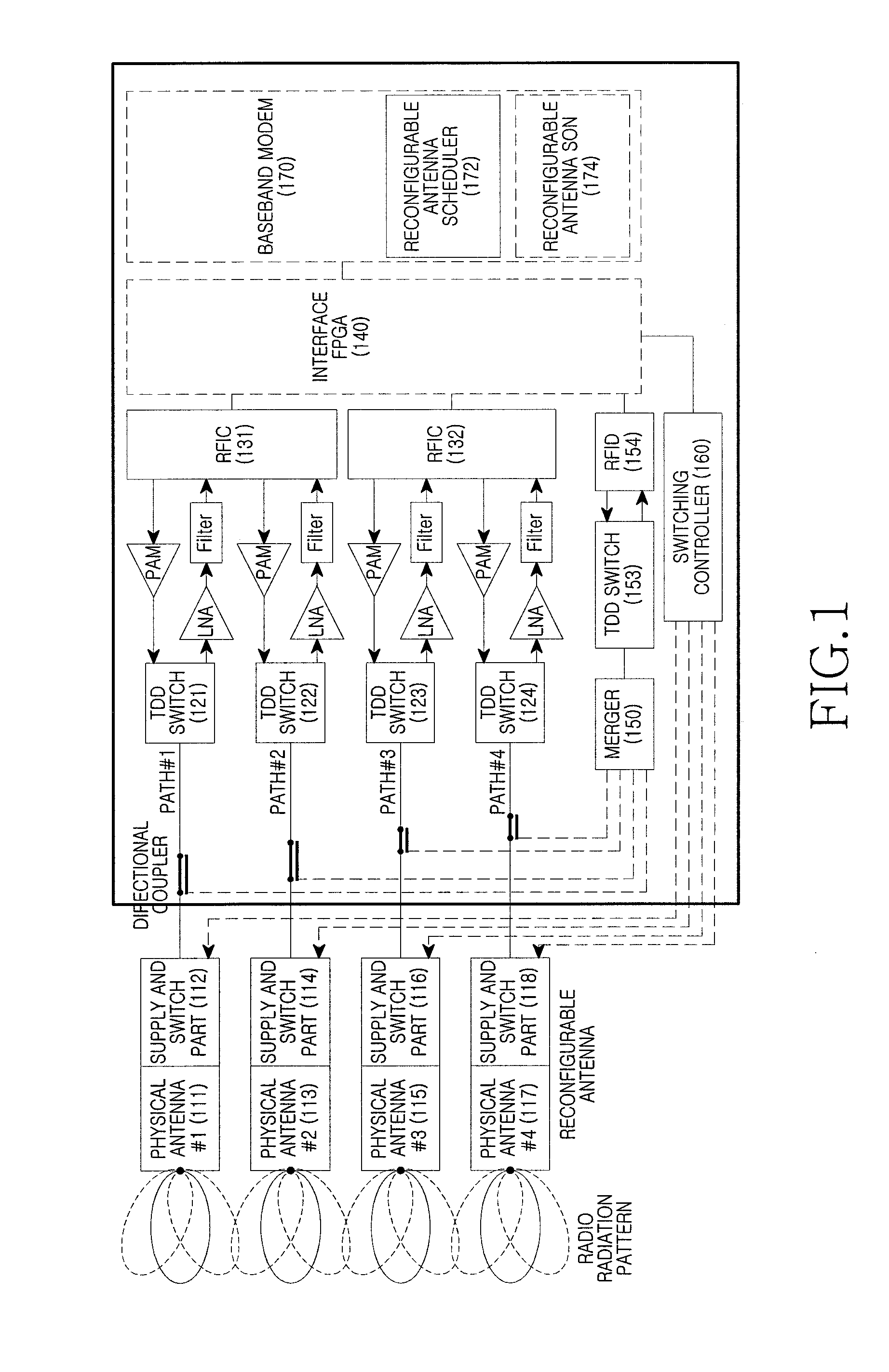

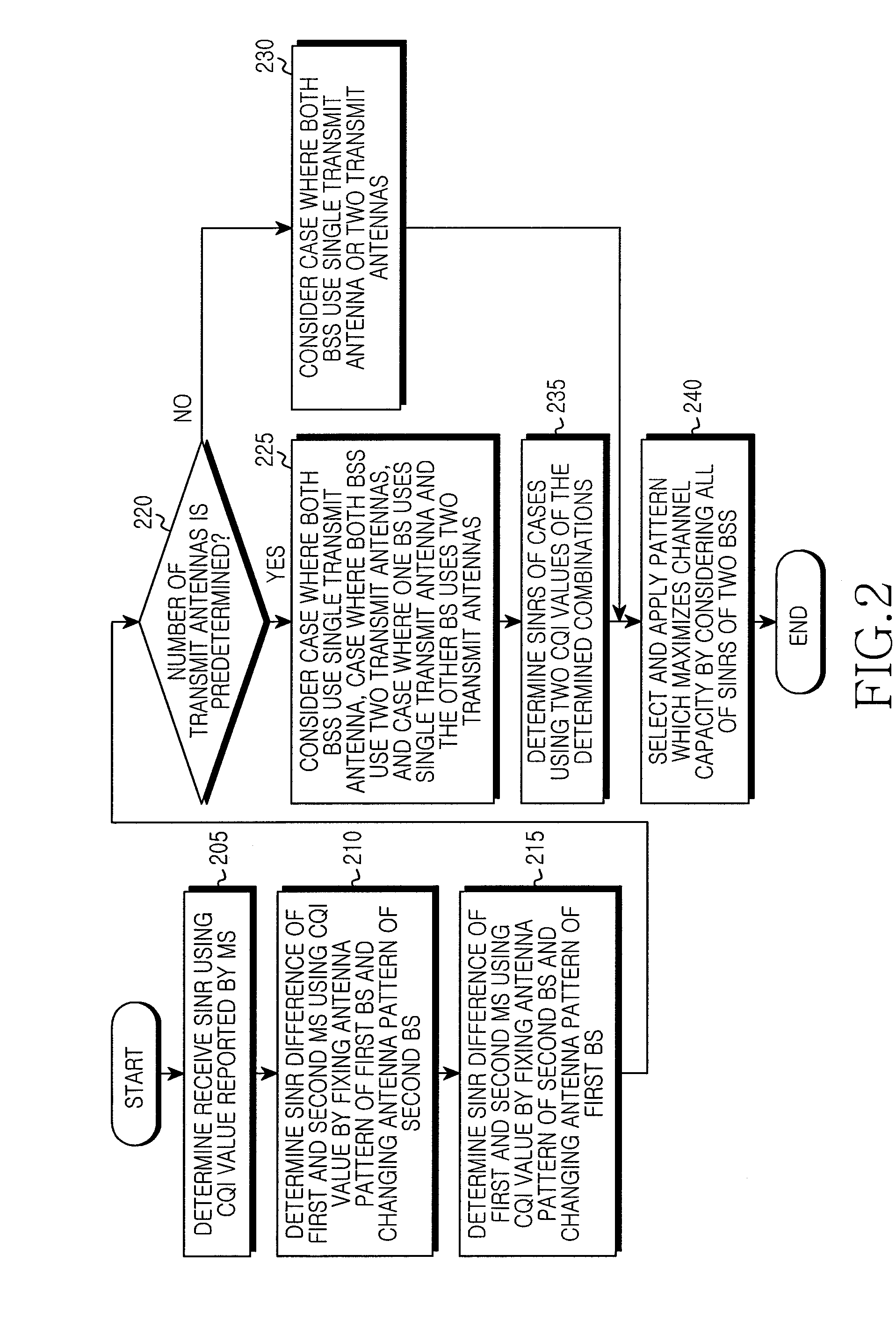

Method and apparatus for down link interference cancelation between adjacent base stations in base station with reconfigurable antenna

ActiveUS20120207048A1Canceling downlink interferenceError preventionFrequency-division multiplex detailsReconfigurable antennaInterference cancelation

A transmit antenna pattern is provided. A method for determining the transmit antenna pattern includes determining first Signal to Interference and Noise Power Ratios (SINRs) of a first mobile station and a second mobile station based on first Channel Quality Indicator (CQI) values received from a first base station and a second base station in the first operation when a transmit antenna pattern of the first base station is fixed and a transmit antenna pattern of the second base station is changed, determining second SINRs of the first mobile station and the second mobile station based on second CQI values received from the first base station and the second base station when the transmit antenna pattern of the first base station is changed and the transmit antenna pattern of the second base station is changed, and determining a transmit antenna pattern exhibiting the best performance based on the determined SINRs.

Owner:SAMSUNG ELECTRONICS CO LTD

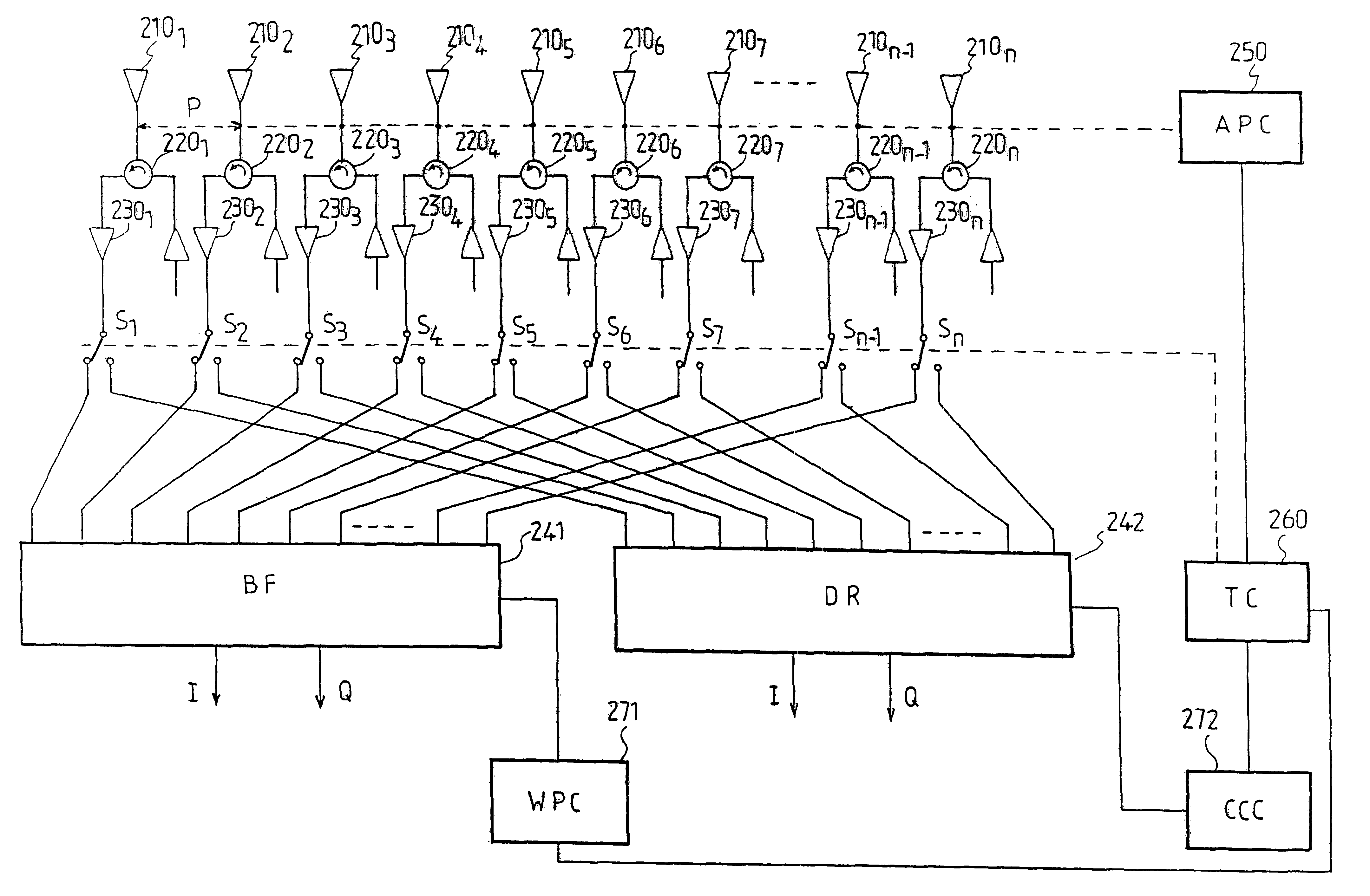

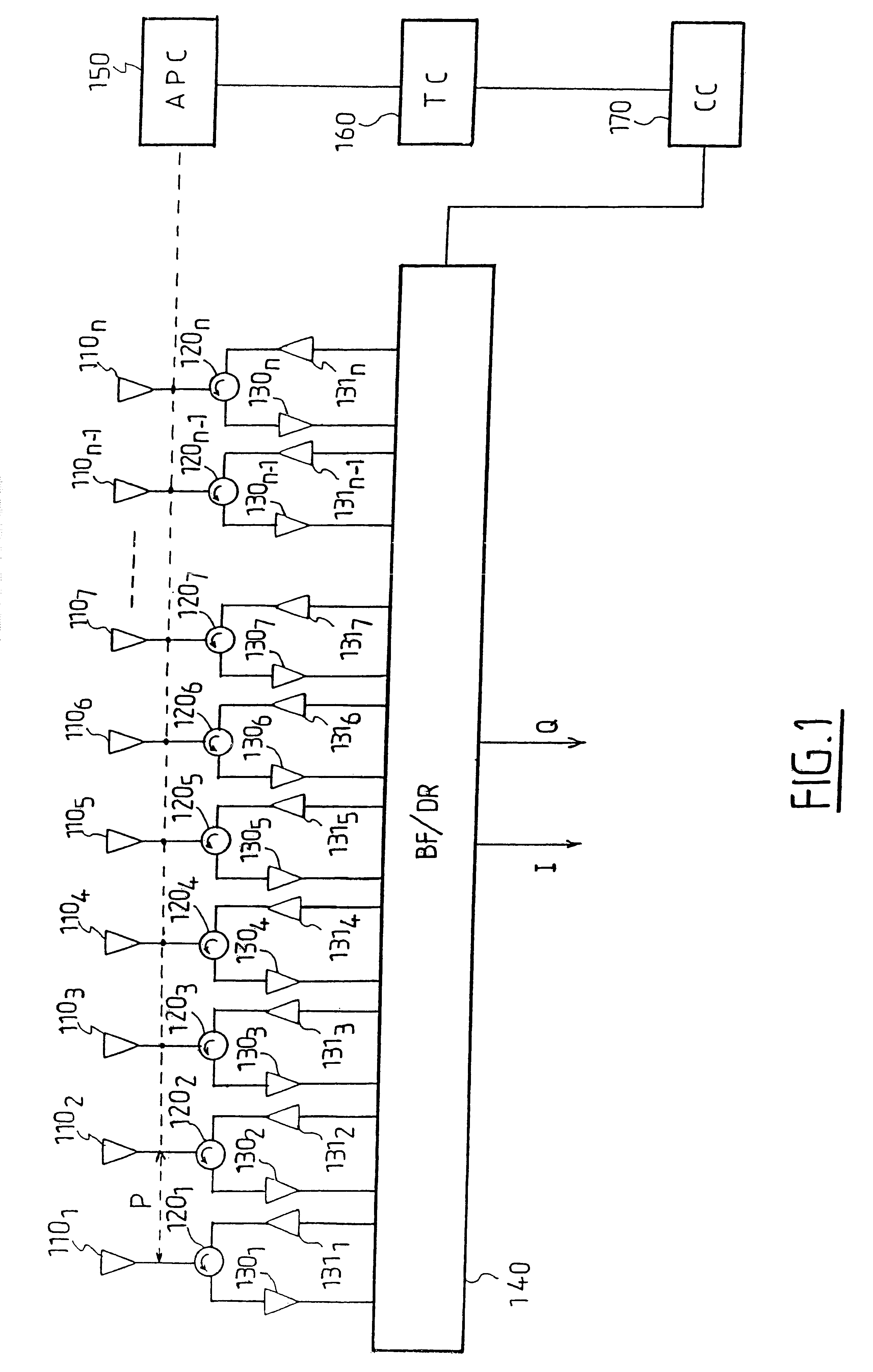

Reconfigurable antenna device for a telecommunication station

InactiveUS6496157B1Remove changeSpatial transmit diversityPolarisation/directional diversityReconfigurable antennaEngineering

The invention in general terms relates to an antenna device for a telecommunication station, able to transmit or receive a signal and comprising a plurality of radiating elements disposed in a periodic arrangement having at least one spatial periodicity. The device has antenna configuration means adapted to cause the value of the said spatial periodicity to vary according to the transmission conditions. The antenna device can in particular be configured so as to operate according to a beam shaping mode or according to a spatial diversity mode.

Owner:MITSUBISHI ELECTRIC CORP

Compact antenna system for polarization sensitive null steering and direction-finding

ActiveUS7577464B2Reduce adverse effectsEnhance jammer-to-signal (J/S) toleranceSubstation equipmentAntenna feed intermediatesEngineeringOperation mode

A compact, non-phased-array, electronically reconfigurable antenna (ERA) system with at least two operational modes has a first operational objective that is polarization-sensitive null steering (PSNS) and a second operational objective that is direction-finding (DF). The system can rapidly switch between two operational states. In the first state, the system behaves like a polarization filter (PF) and operates as a controlled reception pattern antenna (CRPA), while in the second state the system behaves as an angle-of-arrival (AOA) sensor and operates as a fixed reception pattern antenna (FRPA). The system may include a spiral-mode antenna with both feed and load ports; a mode-forming network; an electronics package; and feedback control electronics. Radio frequency (RF) interference rejection and RF direction-finding may be performed as well as reduction and / or elimination of multiple jamming signals that are intentionally or unintentionally directed at a Global Positioning System (GPS). The determination of direction and location of the source of jamming signals may also be achieved.

Owner:TOYON RES CORP

Configurable antenna for a wireless access point

InactiveUS7119744B2Simultaneous aerial operationsAntenna supports/mountingsReconfigurable antennaAntenna element

The difficulties and drawbacks of the previous-type systems are overcome by the present antenna system, alone and in combination with a wireless access point. The present antenna system includes a plurality of antenna elements for providing a respective plurality of communications signals over a wireless channel. An isolating structure is provided, selectively positioned with respect to the antenna elements, for selective varying signal isolation between the respective antenna elements. In this way, the present system is selectable between a high-throughput / short-range configuration and a low-throughput / long-range configuration.

Owner:CISCO TECH INC

Sensors and systems for detecting environmental conditions or changes

InactiveUS8502684B2Bed wetting preventionDiagnostic recording/measuringReconfigurable antennaEngineering

Sensors and systems for detecting predetermined environmental conditions or changes may include a device capable of providing information. The device may include either a shield or reconfigurable antenna. For example, in a first condition, a shield is configured to prevent communications with the device and, in a second condition, the shield is configured to enable communications with the device. Alternately, in a first condition, a reconfigurable antenna is configured to enable communications with the device and in a second condition the reconfigurable antenna is configured to prevent communications with the device. The shield or reconfigurable antenna may be configured to transition from first conditions to second conditions upon exposure to a predetermined environmental condition or change.

Owner:BUNZA GEOFFREY J +1

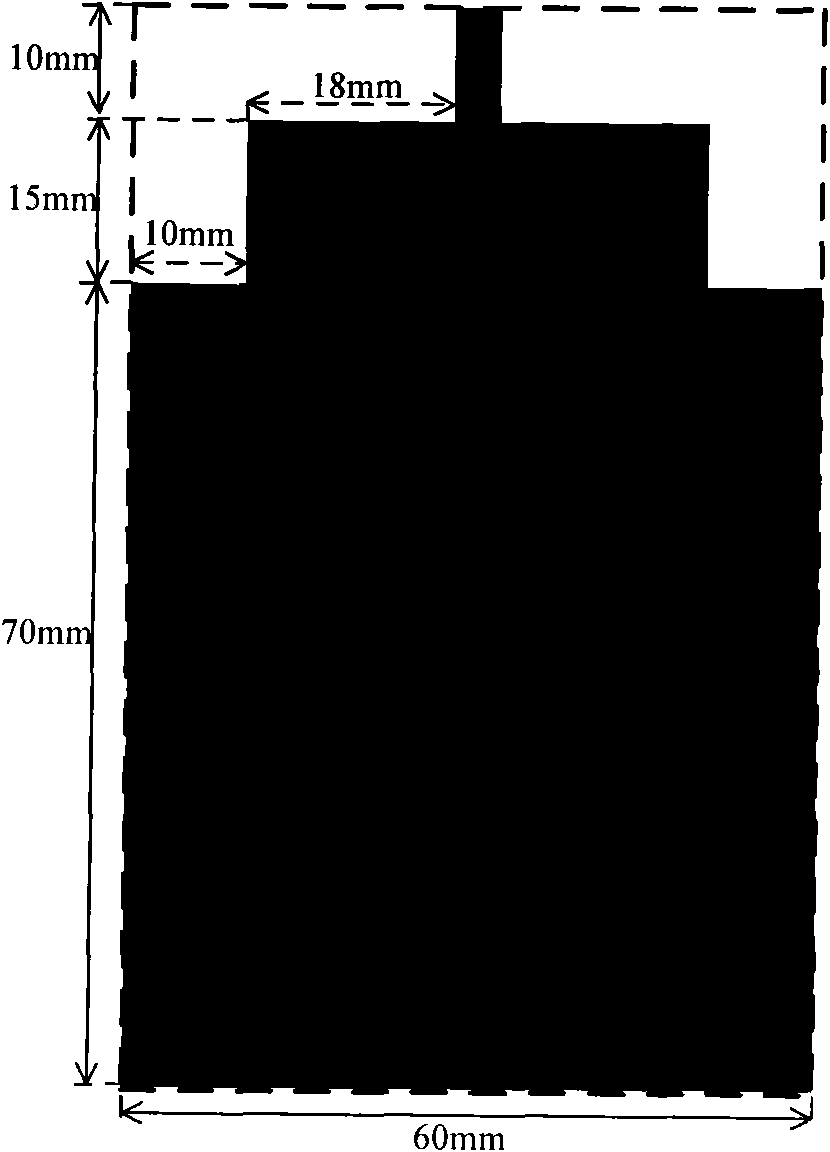

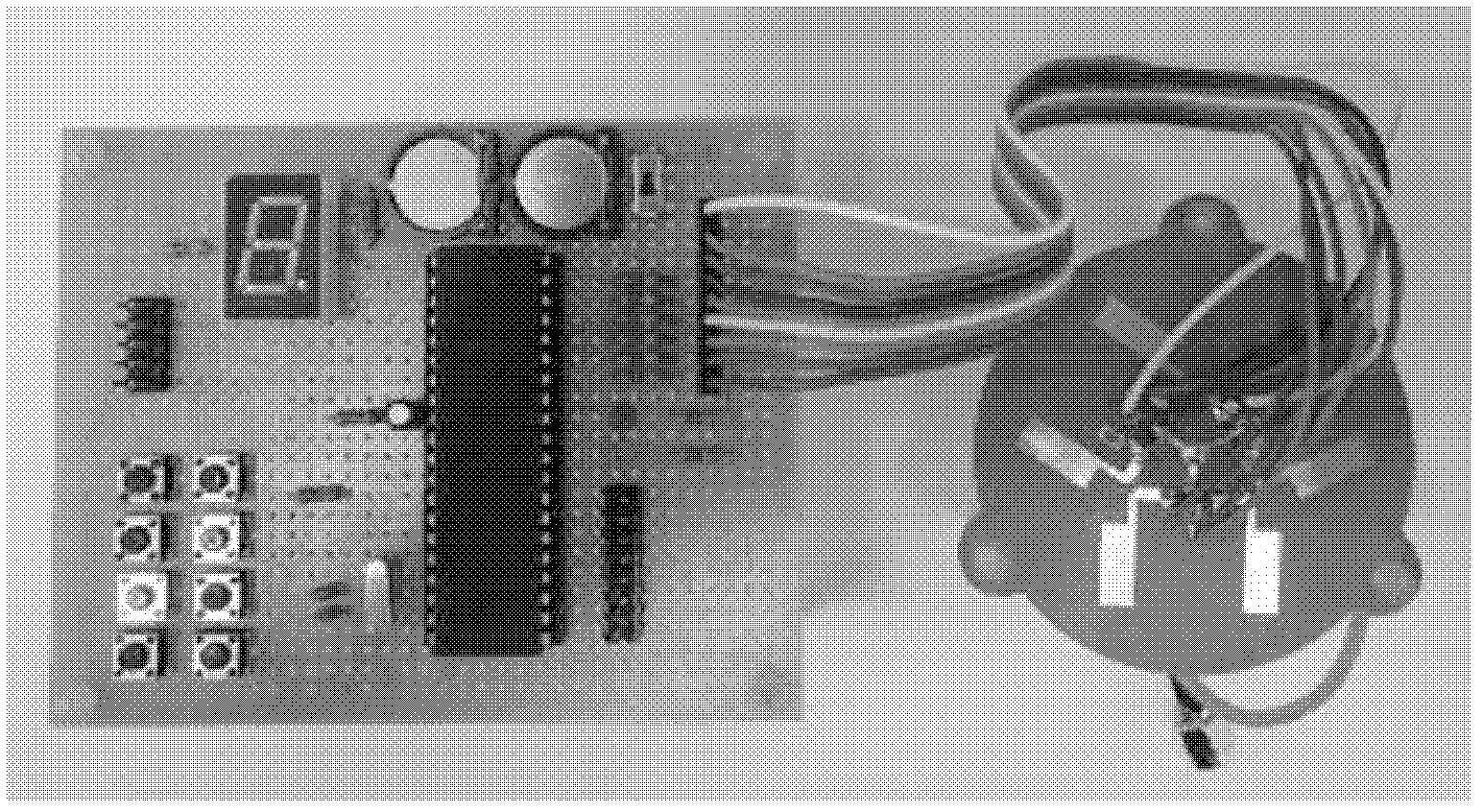

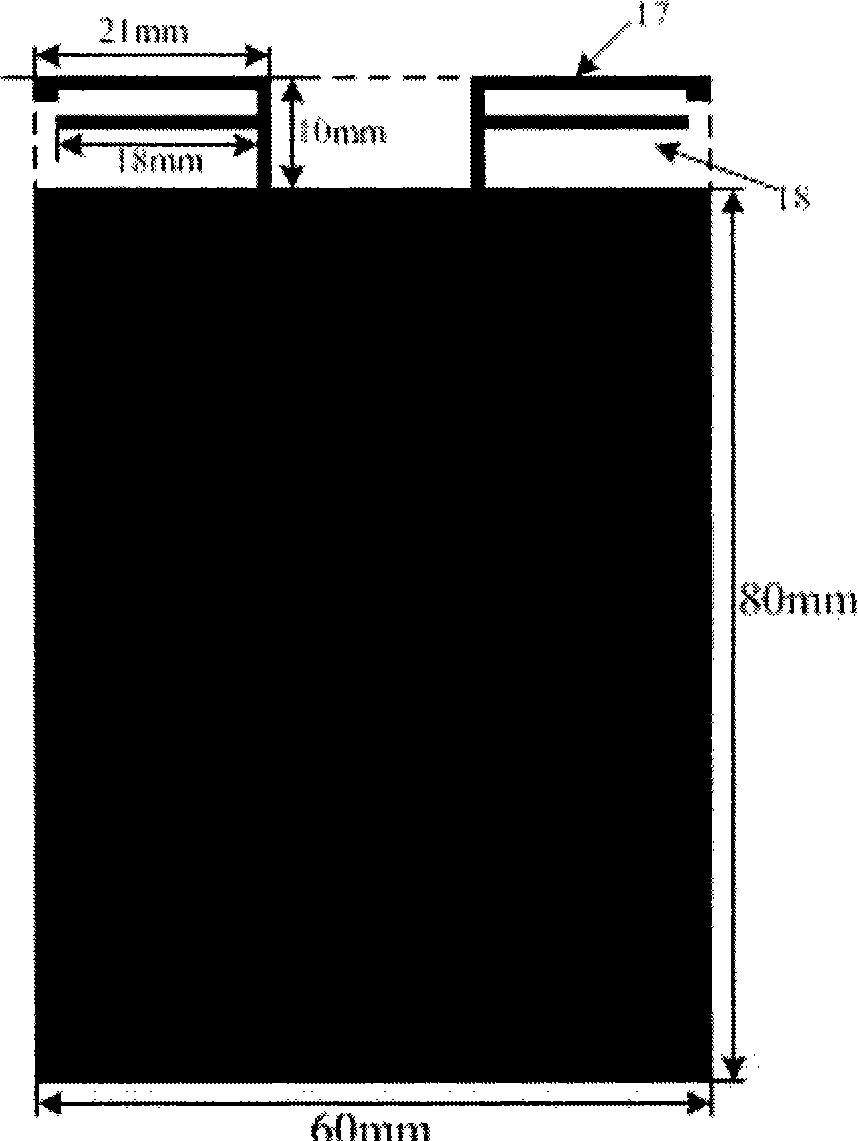

Reconfigurable double-antenna system for mobile terminal

InactiveCN101577366ACompact structureEasy to integrateSimultaneous aerial operationsAntenna supports/mountingsAlternating currentAntenna feed

A reconfigurable double-antenna system used for a mobile terminal belongs to the field of mobile terminal multi-antenna and is characterized in that the reconfigurable antenna system is printed on a printed circuit board and comprises a radiation unit, a feeder wire, a direct current power supply circuit and a metal floor. The radiation unit comprises a spurious radiation structure and a monopolestructure which are connected by a PIN diode switch. The antenna specification is 25 X 10 X 0.8 mm<3> + 18 X 10 X 0.8 mm<3>, and antenna feed is conducted by a 50-Ohm microstrip line. A direct current biasing circuit below the radiation unit controls the connection and disconnection of a PIN diode. An isolated alternate current inductor is used in a direct current path to prevent the alternating current on the radiation unit from passing through. The metal floor is one of the two surfaces of the circuit board, which does not consist of the antenna radiation unit, and is used for simulating rectangular metal patches on parts other than antennas in the mobile terminal of a wireless communication system. The reconfigurable double-antenna system has the advantages of compact structure and easy integration and a function of supporting the reconfiguration of a directional diagram and is applicable to a mobile communication terminal, in particular to a reconfigurable double-antenna structure of a small mobile terminal.

Owner:TSINGHUA UNIV

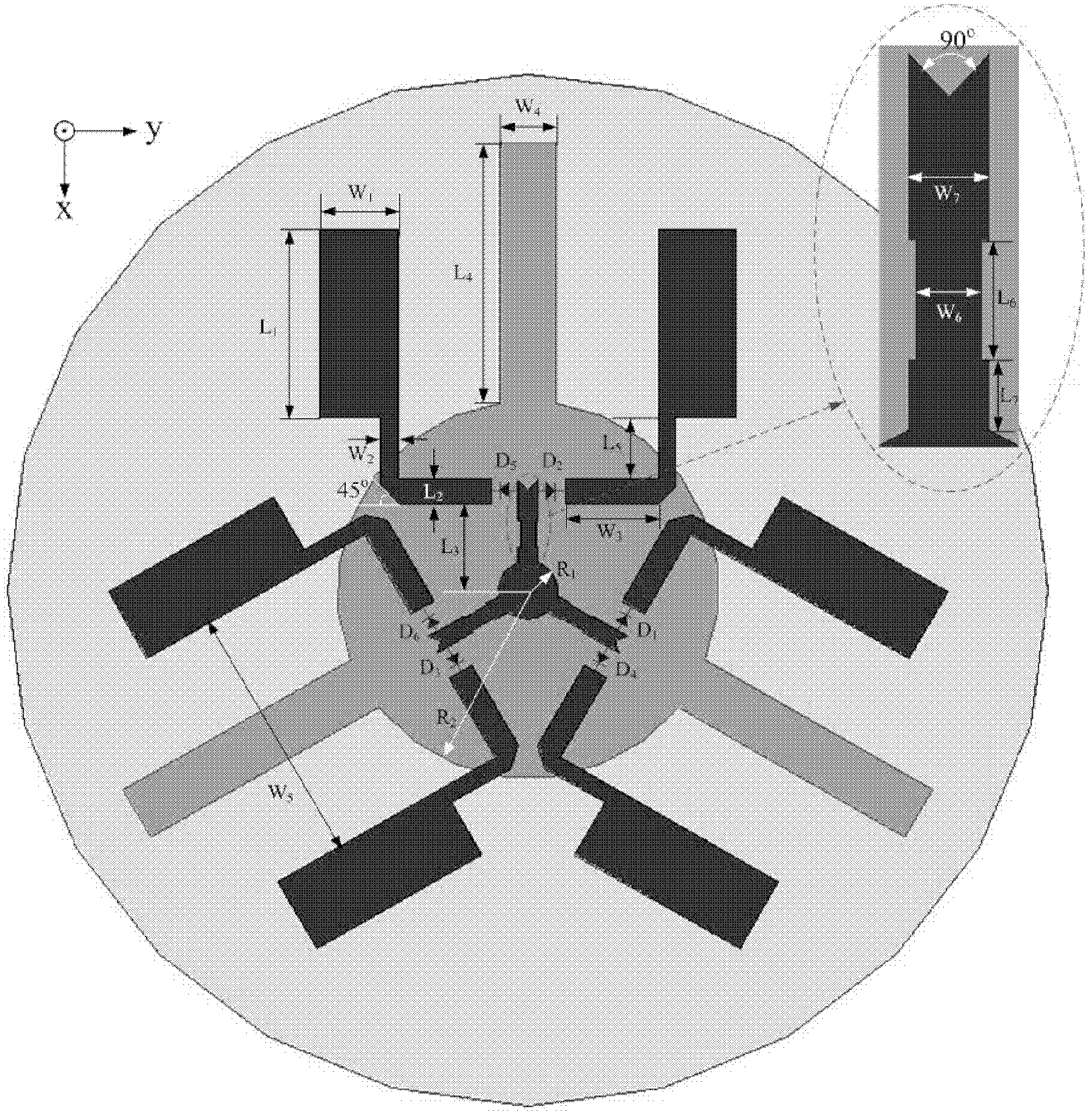

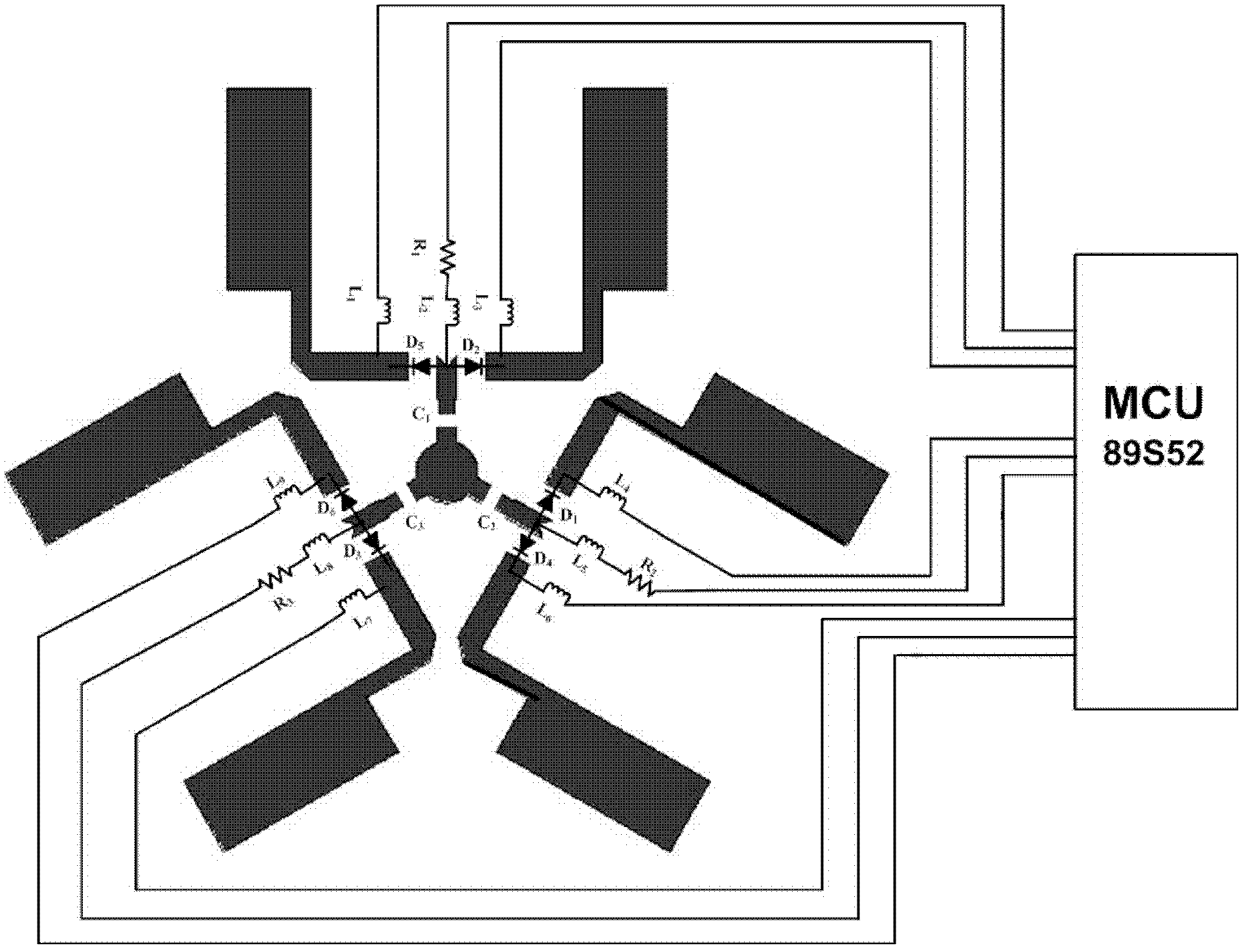

Planar directional pattern reconfigurable method and antenna with six-wave-beam selectivity

InactiveCN102437423AImplement refactoringSimple structureRadiating elements structural formsAntenna earthingsReconfigurabilityAntenna design

The invention relates to antennas in wireless communication, and provides an antenna which can carry out pattern reconfigurability for more directions and has stronger practicability. The technical scheme in the invention is as follows: the planar directional pattern reconfigurable antenna with six-wave-beam selectivity consists of an antenna substrate, a radiation unit layer and a grounding plate layer, wherein the radiation unit layer consists of a circular active patch positioned at the center of the radiation unit layer and rectangular parasitic patches arranged around the radiation unit layer, and the rectangular parasitic patches are connected with a circular unit at the center of the antenna through strip lines and micro-strip lines; a radio frequency PIN diode is inserted into each micro-strip line; the circumferential rectangular parasitic patches selectively radiate outwards by controlling the on-off status of the diode; the grounding plate layer of the antenna adopts a partial grounding mode and is formed by connecting the center circular patch with the rectangular patches at equal angle-intervals; and the antenna substrate is in a circular disk shape and is made from apolytetrafluoroethylene (PTFE) material. The technical scheme is mainly applied to design and manufacture of the antenna.

Owner:TIANJIN UNIV

Zero-Order Energy Smart Antenna and Repeater

ActiveUS20070132653A1Improve signal receptionFacilitate transmissionAntenna supports/mountingsActive radio relay systemsReconfigurable antennaSmart antenna

The invention is a new device that will improve the radio link quality for low power wireless devices. An example application is for low power, miniaturized wireless sensor nodes that are statically deployed in a slowly varying environment or that have limited mobility. The device is a reconfigurable antenna that is novel in that it operates with very low (zero-order) energy in contrast to existing system that required both significant computational and DC power.

Owner:UNIV OF SOUTH FLORIDA +1

Reconfigurable antenna used for mobile terminal

InactiveCN101431182ACompact structureEasy to integrateSimultaneous aerial operationsRadiating elements structural formsMulti bandEngineering

A reconfigurable antenna system for a mobile terminal belongs to the field of mobile terminal antennae and is characterized in that the reconfigurable antenna system is printed on a printed circuit board and comprises a variable radiation unit, a feeder line, a direct current power supply circuit and a metal ground. The radiation unit comprises a variable radiation structure and a public unit structure which are connected by using a PIN diode switch. The height of the antenna is 10mm, and the antenna feeds by a 50-ohm microstrip line. A direct current bias circuit which is arranged below the radiation unit controls the switching-on and off of a PIN diode; and a direct current pathway adopts an alternating current isolation inductor to prevent the alternating current on the radiation unit from passing. The metal ground is the metal surface that does not contain the antenna radiation unit of the two surfaces of the circuit board, and the metal ground comprises a rectangular metal patch and two F-shaped metal patches of the other parts except the antenna in the mobile terminal of an analog wireless communication system. The reconfigurable antenna system has the advantages of multi-band, compact structure and easy integration and is characterized in that the reconfigurable antenna system can support the reconfigurable function of a directional pattern and be applicable to the mobile communication terminal, in particular to the reconfigurable antenna structure of the small-sized mobile terminal.

Owner:TSINGHUA UNIV

Configurable arrays for steerable antennas and wireless network incorporating the steerable antennas

ActiveUS20050057432A1More selective controlGuaranteed effective sizeAntenna supports/mountingsRadiating elements structural formsReconfigurable antennaEngineering

An reconfigurable array of variable conductive elements is provided for reflecting, filtering and steering electromagnetic radiation across a wide range of frequencies. The reconfigurable array is combined with a transmitting antenna to make a steerable antenna. The reconfigurable array surrounds the transmitting antenna and reflects all transmissions except on selected radials where apertures in the reconfigurable array are formed for permitting transmission lobes. The reconfigurable arrays can be arranged in stacked layers to make transceiving multiband antennas. Communications networks using the steerable antennas and arrays are also disclosed.

Owner:ANDERSON THEODORE R

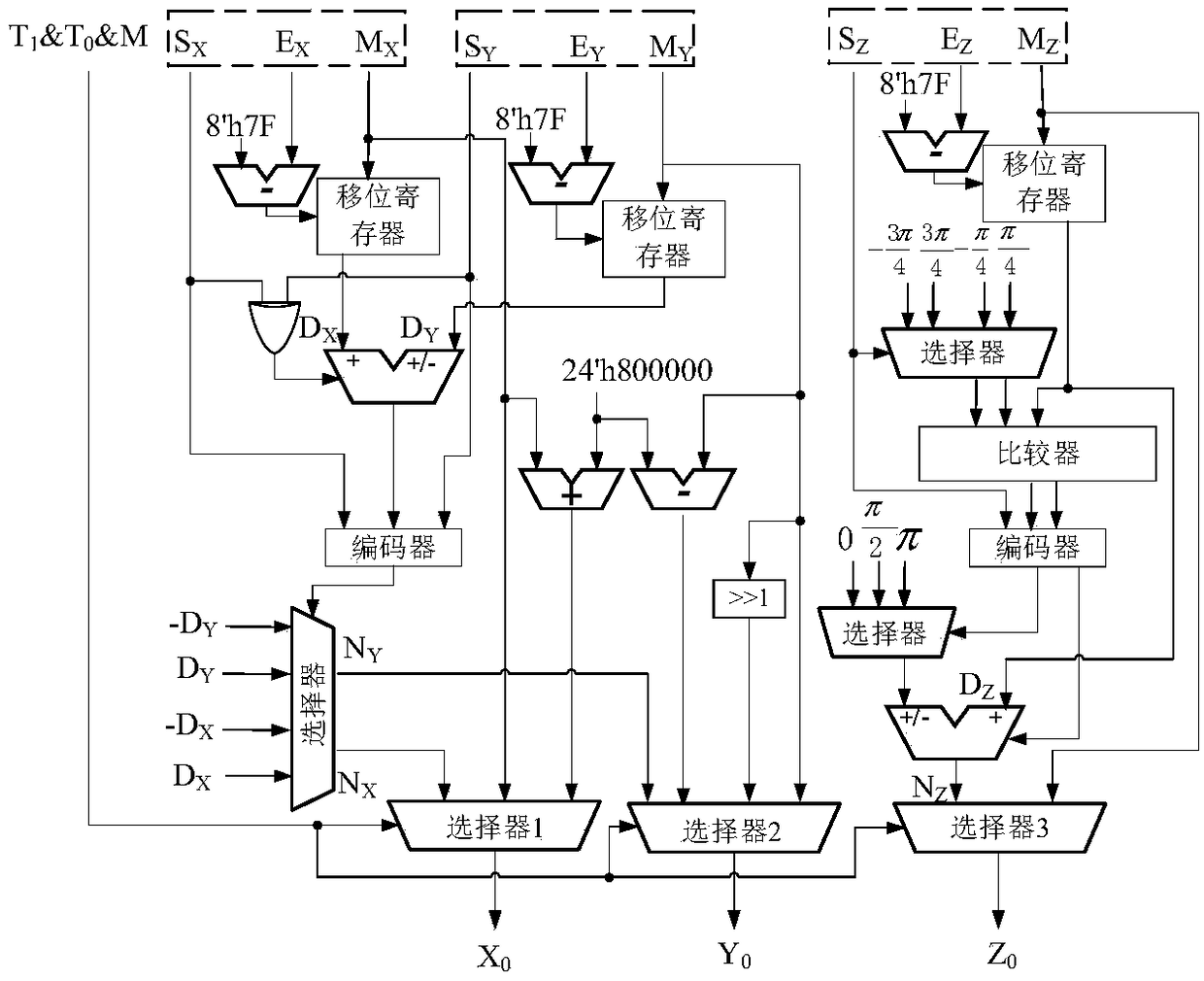

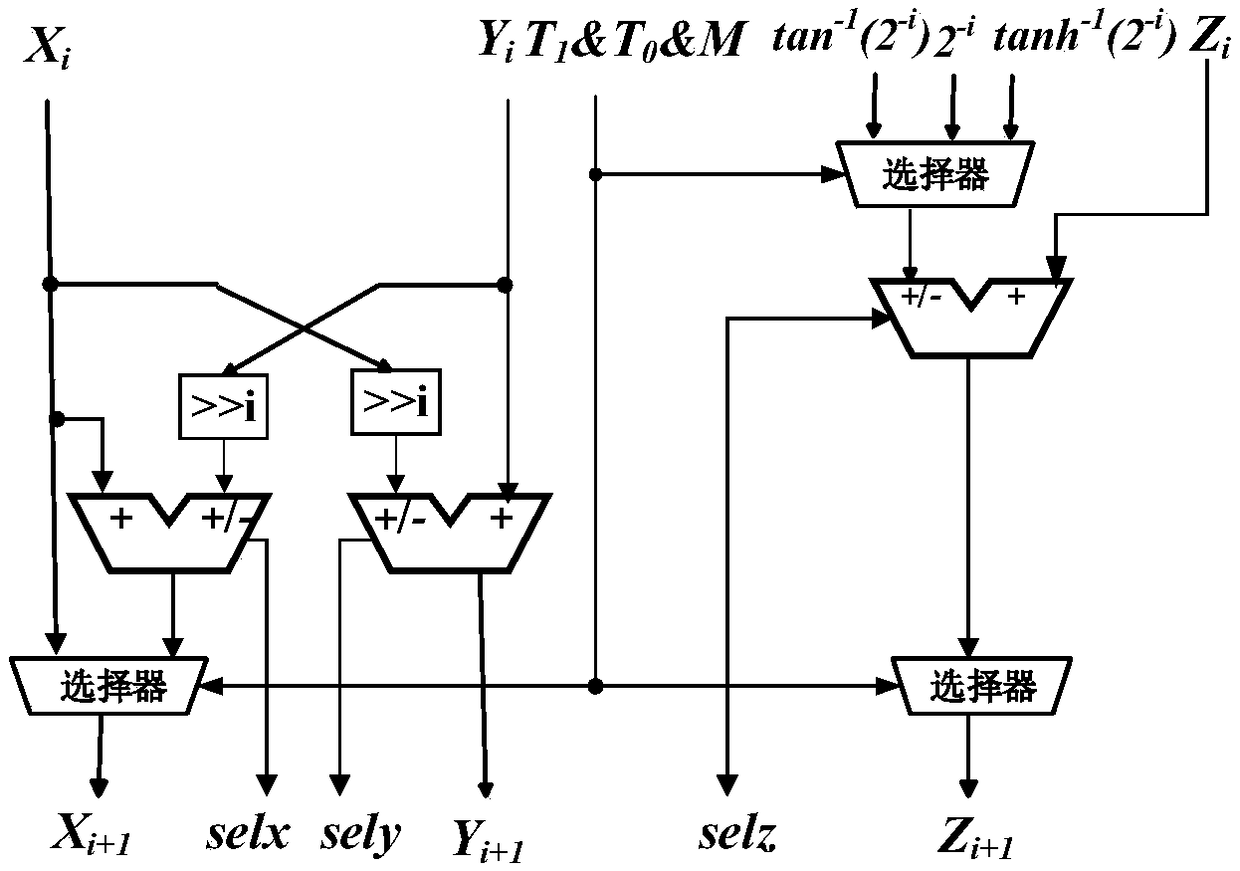

Reconfigurable floating-point operation device based on CORDIC algorithm

ActiveCN109062540AExtended region of convergenceReduce clock cyclesDigital data processing detailsReconfigurable antennaComputer module

A reconfigurable floating-point arithmetic device based on CORDIC algorithm comprises a preprocessing module for completing input data from IEEE-754 standard, and maps it into the convergence region;a series-parallel hybrid reconfigurable CORDIC iterative unit module. The iterative operation part of CORDIC algorithm is composed of two parts: rotation modules A and B, wherein, the rotation moduleA is used to realize serial pipeline structure to maximize module reuse, the rotation module B is based on parallel prediction method of rotation direction and adopts tree adder structure to realize parallel structure in rotation mode; in the post-processing module, the corresponding result output is selected according to the encoded signal of the pre-processing module, and the mantissa normalization processing is completed to output the single-precision floating-point data format calculation result. The invention has the characteristics of simple principle, low delay, high precision and low hardware cost.

Owner:BEIJING INSTITUTE OF TECHNOLOGYGY

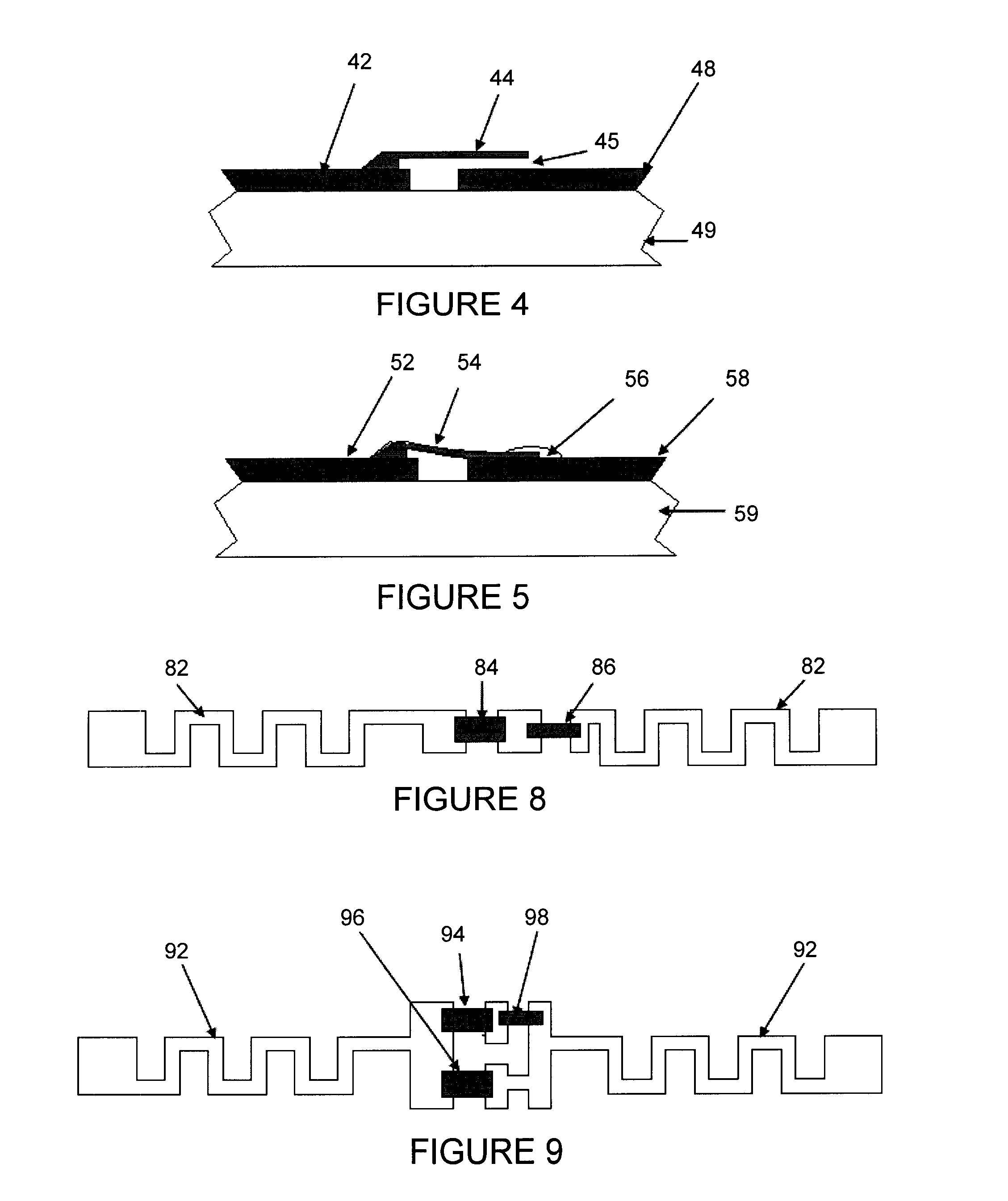

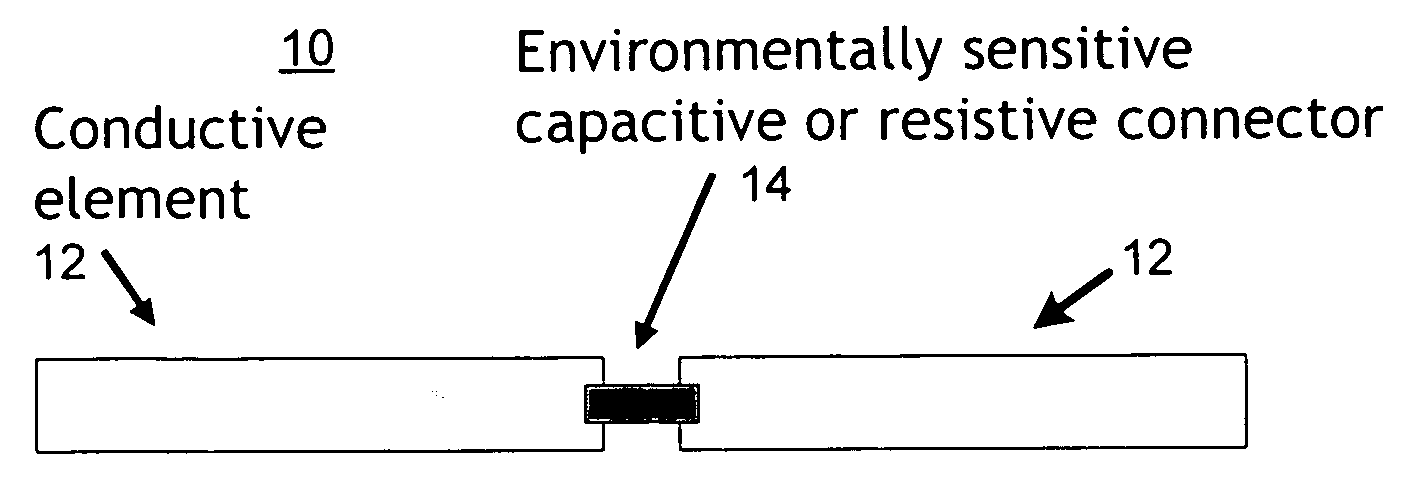

Environmentally sensitive reconfigurable antenna

ActiveUS7570169B2Improve localizationAntennas earthing switches associationSubscribers indirect connectionReconfigurable antennaWireless transmission

Owner:RGT UNIV OF CALIFORNIA

Environmentally sensitive reconfigurable antenna

ActiveUS20060244606A1Improve localizationAntennas earthing switches associationSubscribers indirect connectionReconfigurable antennaWireless transmission

An antenna whose resonance and electromagnetic radiation properties can be modified by environmental conditions, acoustic conditions, and the like. The reconfiguring antenna acts to facilitate wireless transmission of information about the local environment without the need for local power.

Owner:RGT UNIV OF CALIFORNIA

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com