Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

182 results about "Active memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

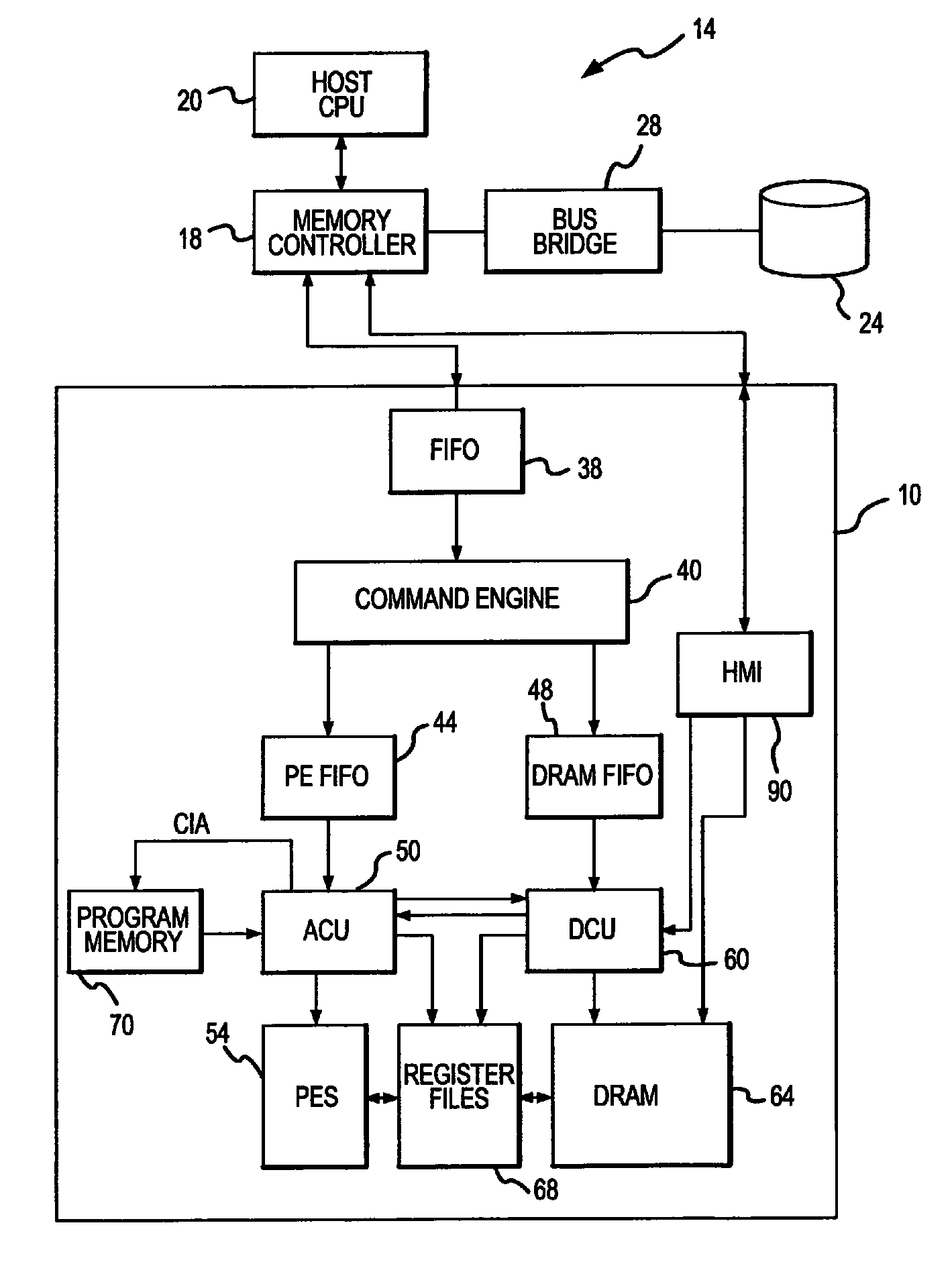

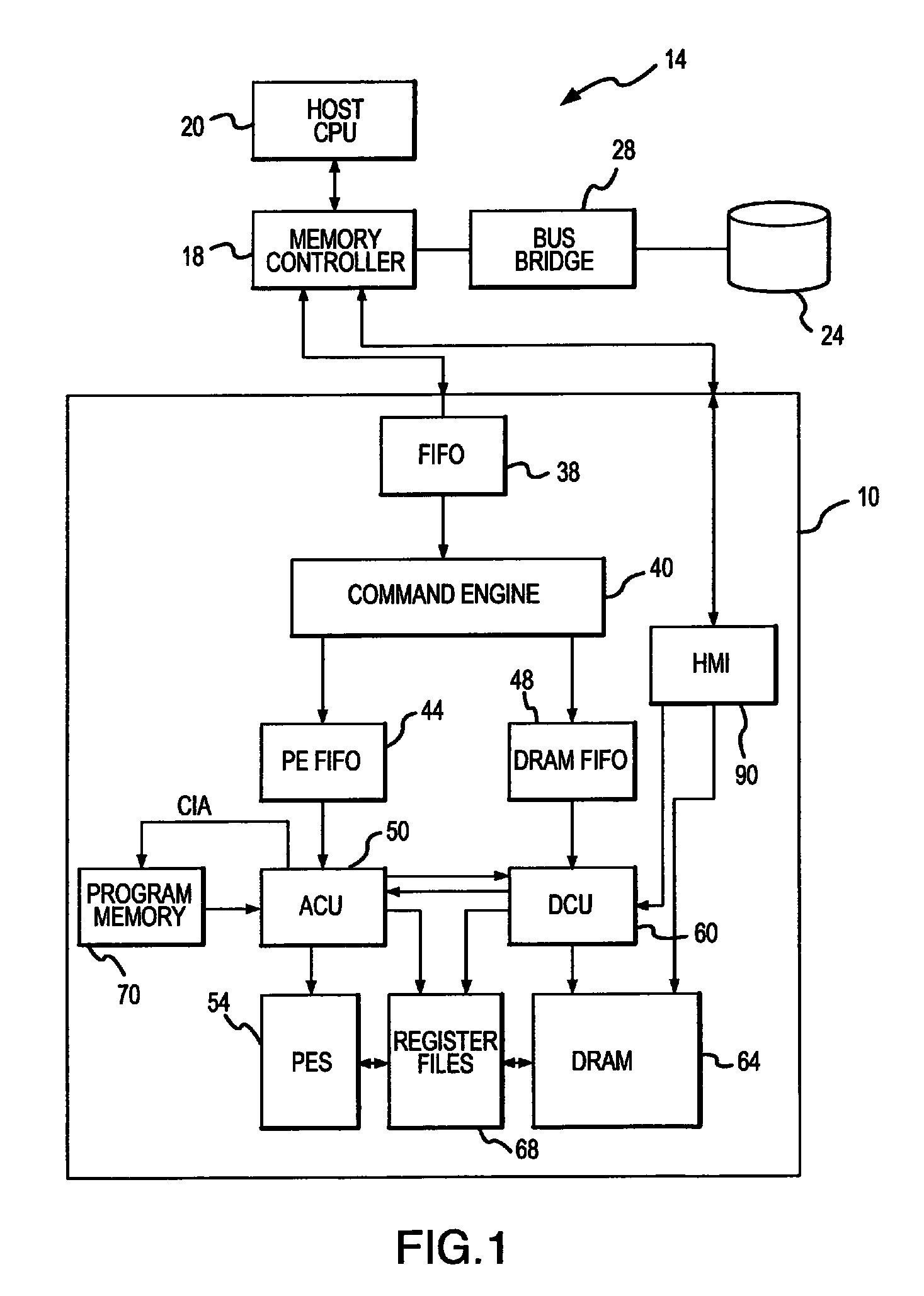

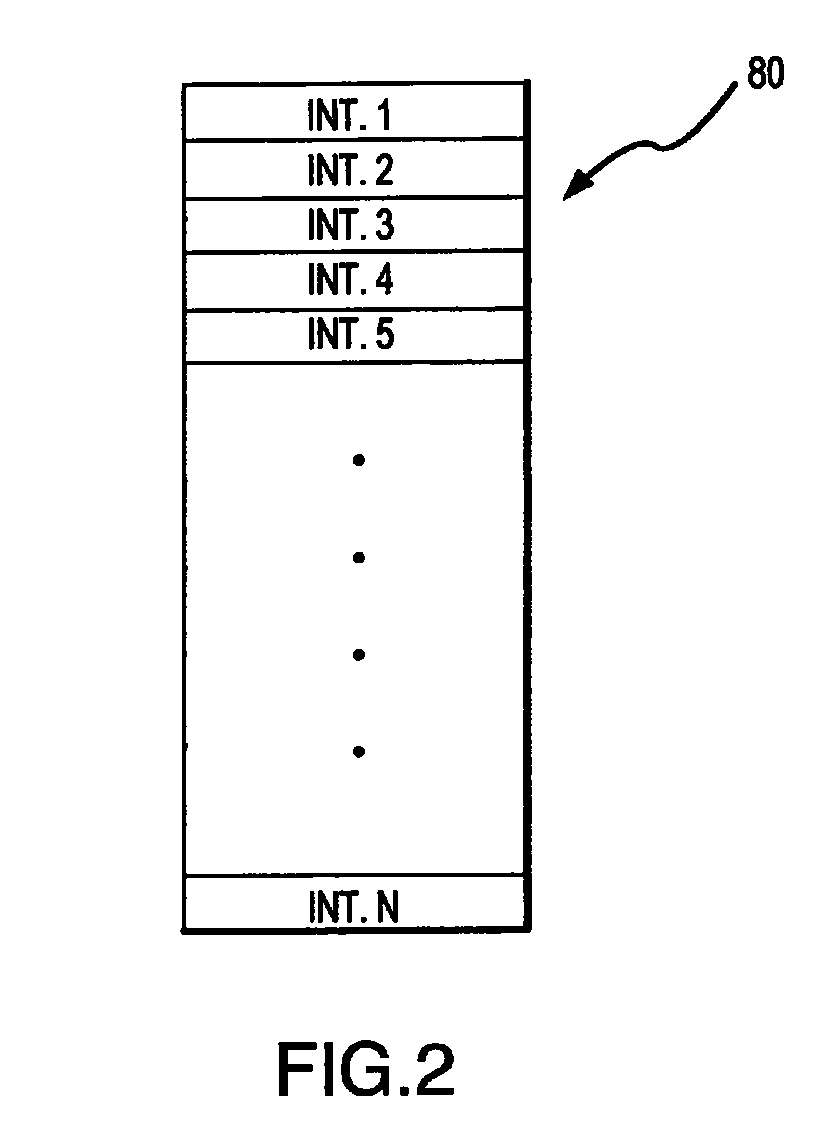

Active memory data compression system and method

ActiveUS9015390B2Concurrent instruction executionArchitecture with single central processing unitMass storageData compression

An integrated circuit active memory device receives task commands from a component in a host computer system that may include the active memory device. The host system includes a memory controller coupling the active memory device to a host CPU and a mass storage device. The active memory device includes a command engine issuing instructions responsive to the task commands to either an array control unit or a DRAM control unit. The instructions provided to the DRAM control unit cause data to be written to or read from a DRAM and coupled to or from either the processing elements or a host / memory interface. The processing elements execute instructions provided by the array control unit to decompress data written to the DRAM through the host / memory interface and compress data read from the DRAM through the host / memory interface.

Owner:MICRON TECH INC

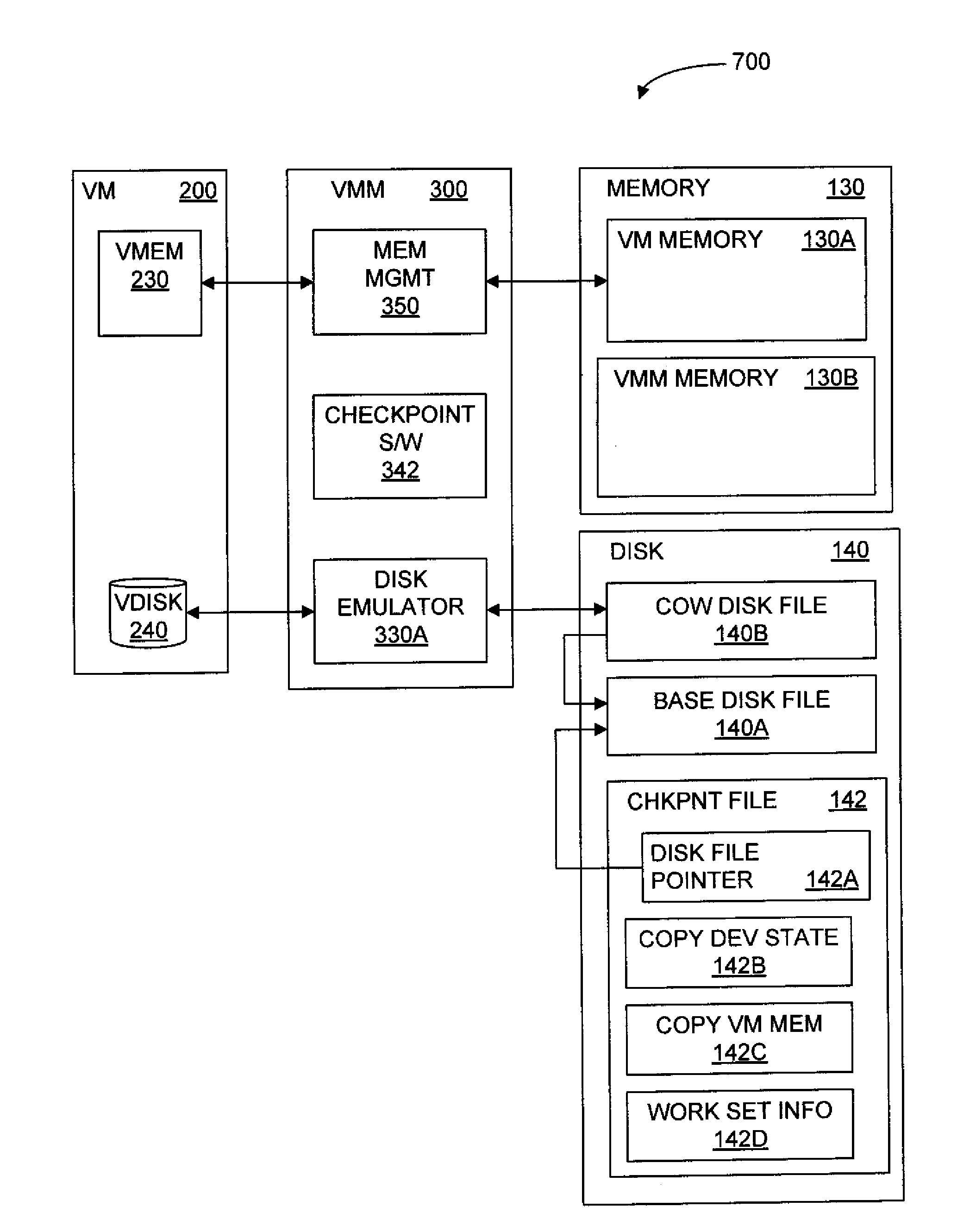

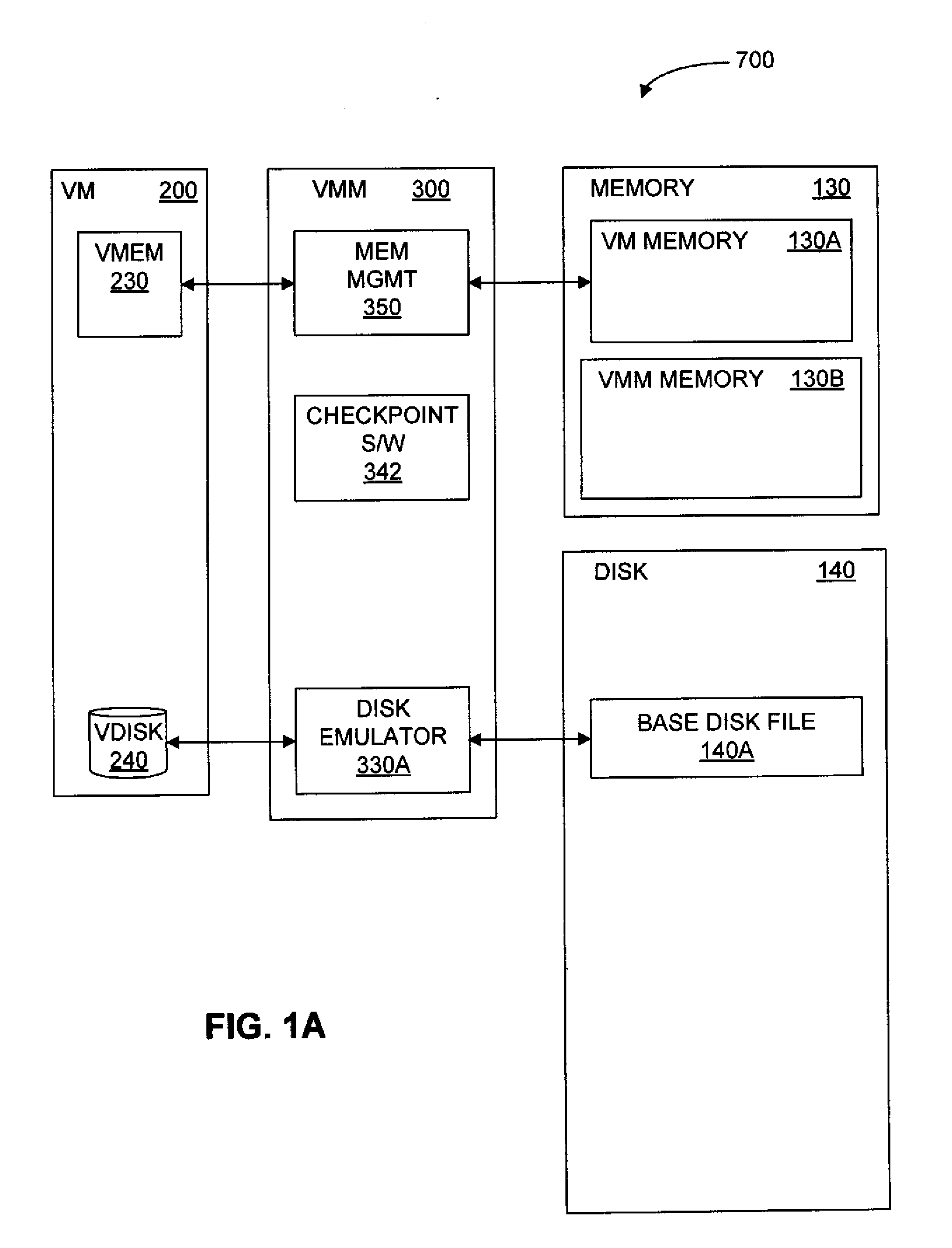

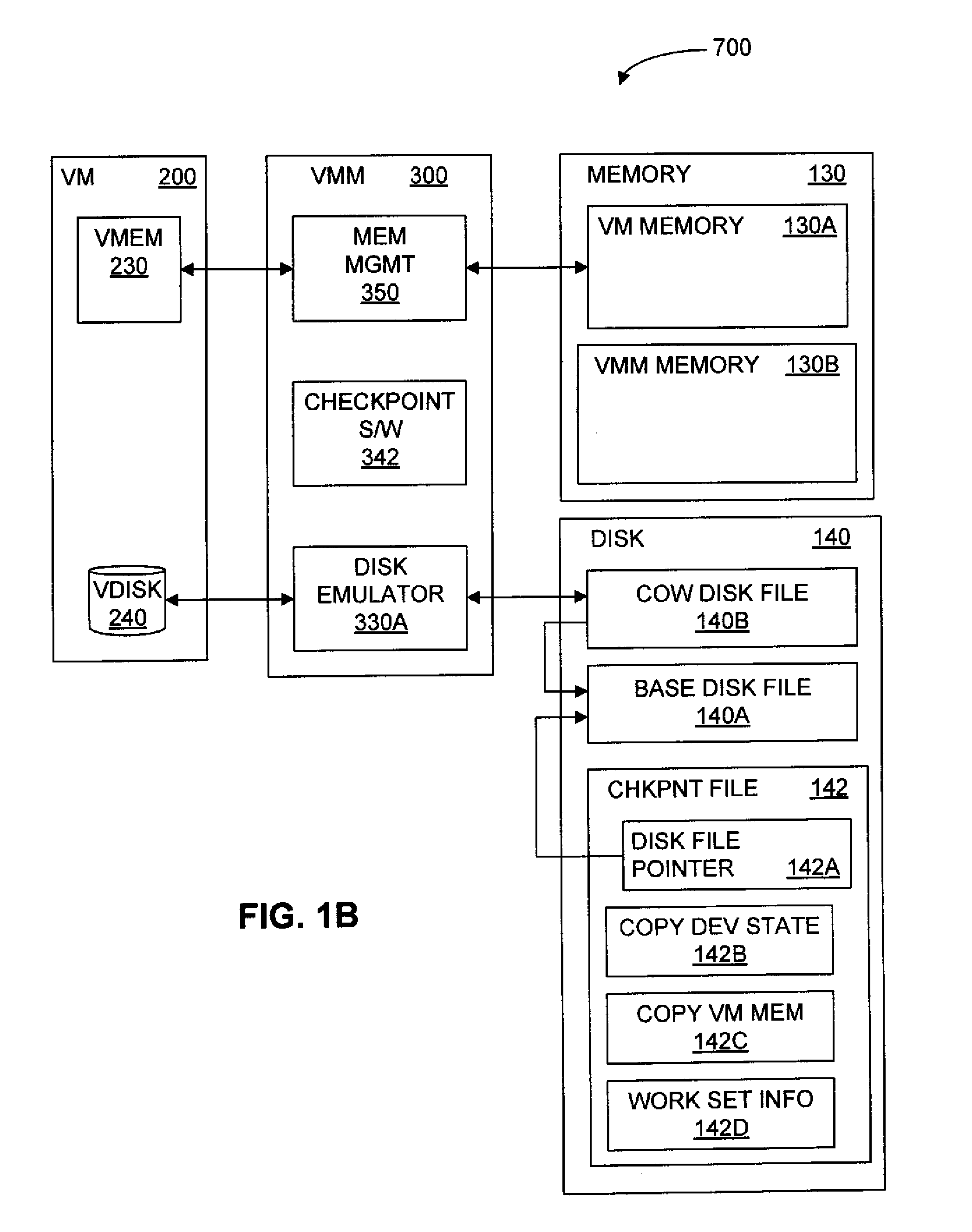

Saving and Restoring State Information for Virtualized Computer Systems

InactiveUS20100070678A1Error detection/correctionMemory adressing/allocation/relocationComputerized systemActive memory

Prior to or while the state of a virtual machine (“VM”) is being saved, such as in connection with the suspension or checkpointing of a VM, a set of one or more “active” memory pages is identified, this set of active memory pages comprising memory pages that are in use within the VM before operation of the VM is suspended. This set of active memory pages may constitute a “working set” of memory pages. To restore the state of the VM and resume operation, in some embodiments, (a) access to persistent storage is restored to the VM, device state for the VM is restored, and one or more of the set of active memory pages are loaded into physical memory; (b) operation of the VM is resumed; and (c) additional memory pages from the saved state of the VM are loaded into memory after operation of the VM has resumed.

Owner:VMWARE INC

System and method for thermal throttling of memory modules

InactiveUS20050289292A1Digital data processing detailsDigital storageParallel computingActive memory

Some embodiments of the invention accurately account for power dissipation in memory systems that include individual memory modules by keeping track of the number of read requests, the number of write requests, and the number of activate requests that are applied to the individual memory modules during selected time periods. If the sum of these totals exceeds a threshold level, the embodiments throttle the memory system, either by throttling the entire memory system based in response to the most active memory module, or by throttling individual memory modules as needed. Other embodiments of the invention may assign the same or different weights to activate requests, read requests, and write requests. Other embodiments are described and claimed.

Owner:INTEL CORP

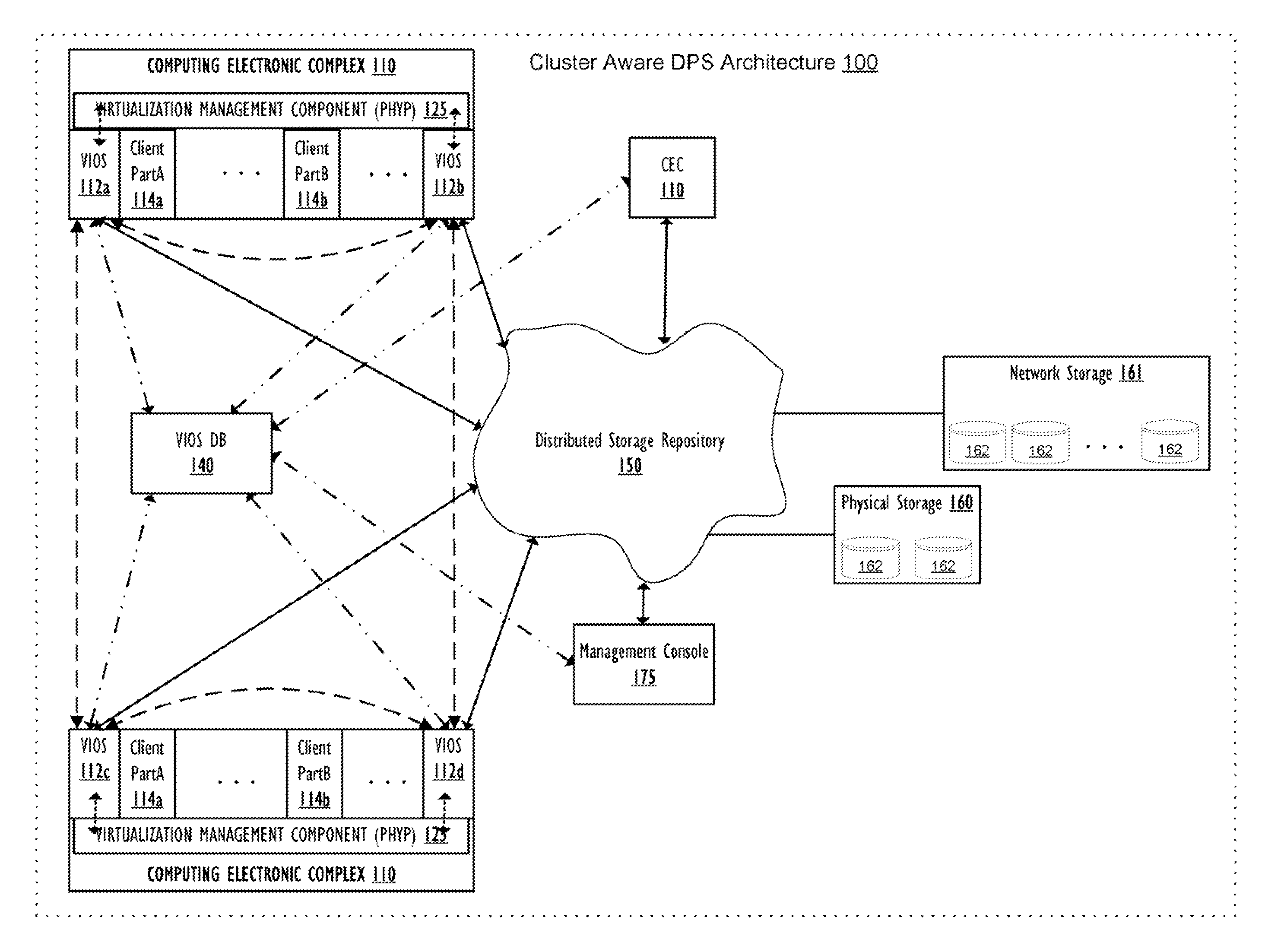

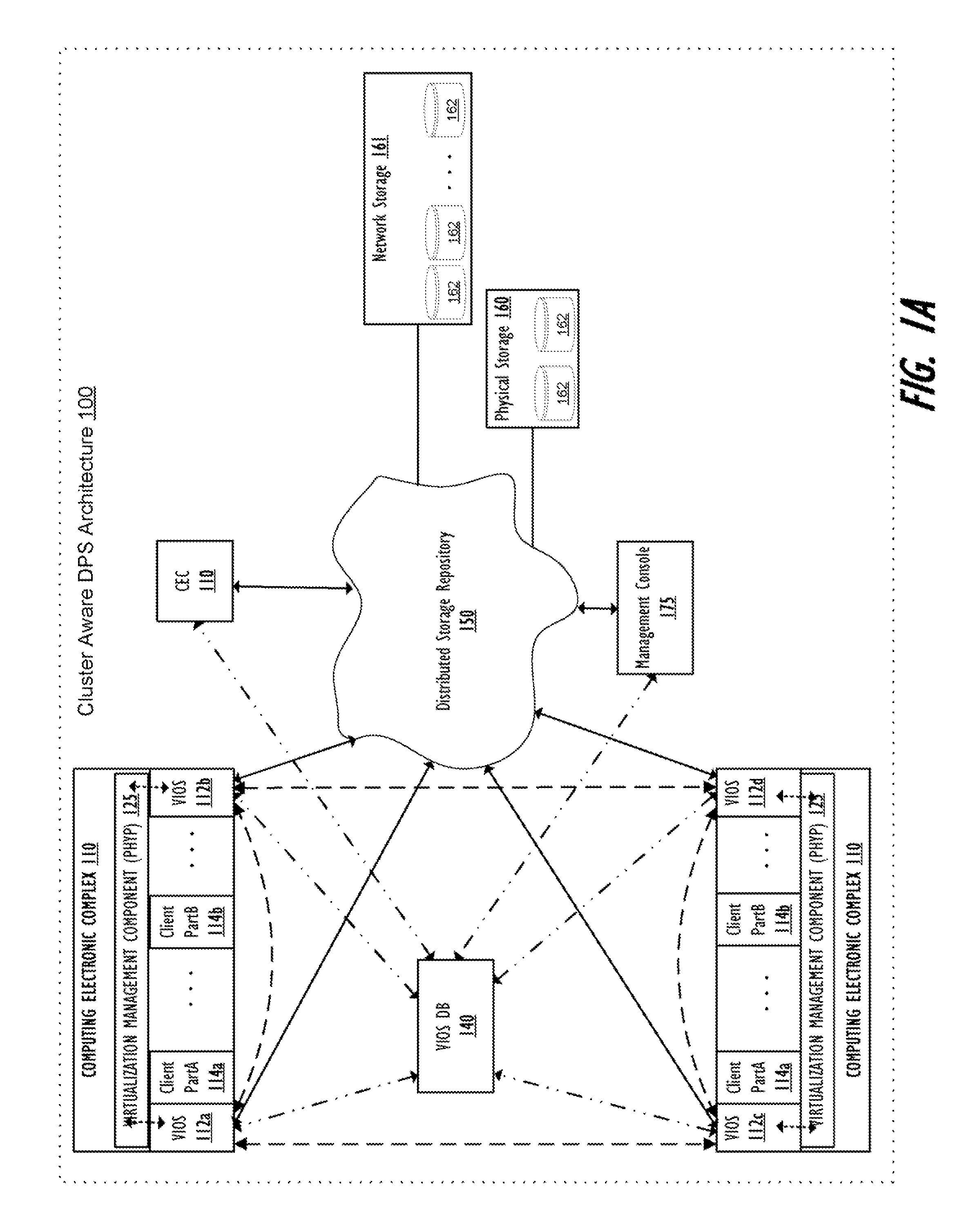

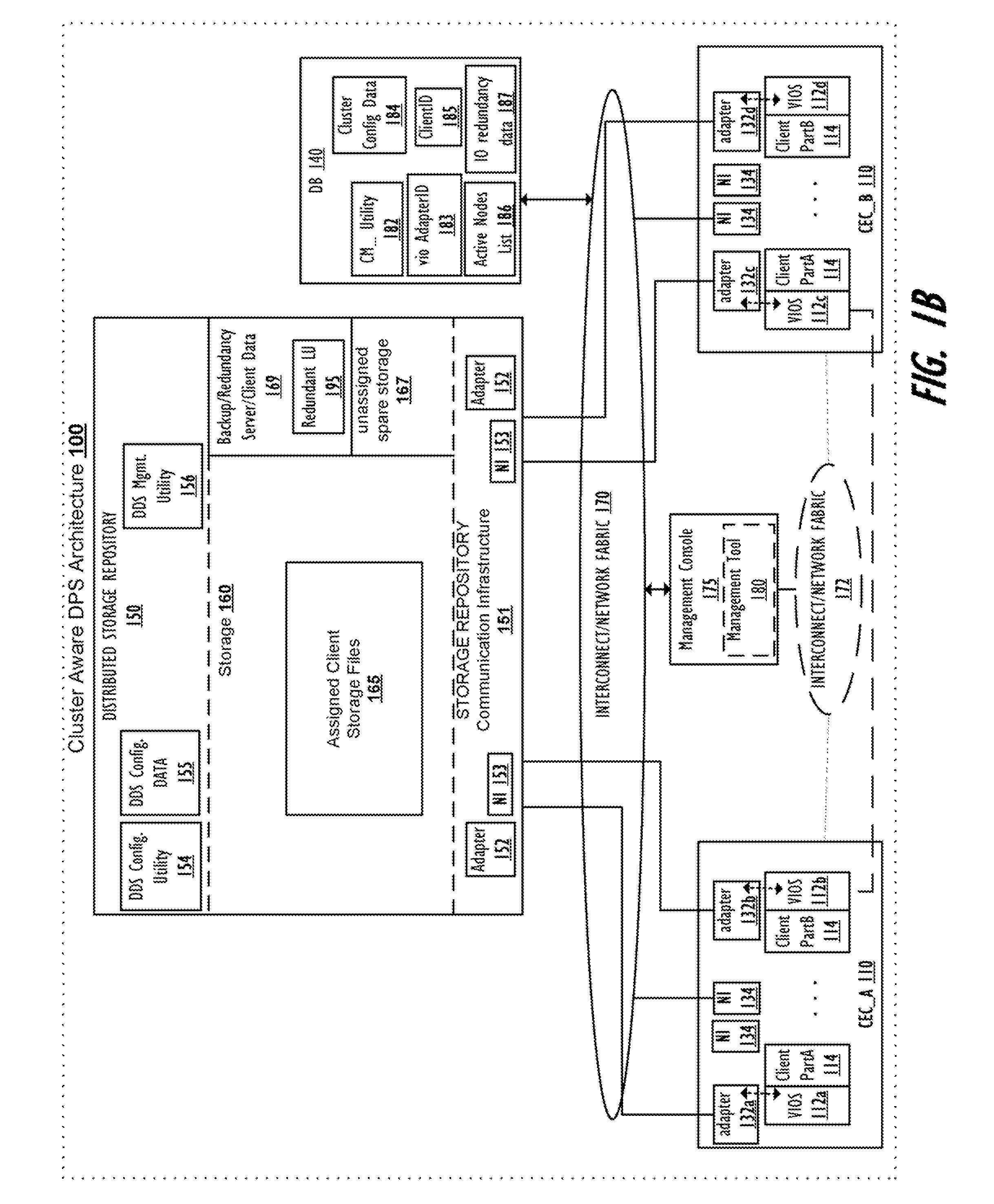

Supporting Virtual Input/Output (I/O) Server (VIOS) Active Memory Sharing in a Cluster Environment

InactiveUS20120110275A1Promote migrationMemory architecture accessing/allocationMemory adressing/allocation/relocationVirtual memoryActive memory

A method, system, and computer program product provide a shared virtual memory space via a cluster-aware virtual input / output (I / O) server (VIOS). The VIOS receives a paging file request from a first LPAR and thin-provisions a logical unit (LU) within the virtual memory space as a shared paging file of the same storage amount as the minimum required capacity. The VIOS also autonomously maintains a logical redundancy LU (redundant LU) as a real-time copy of the provisioned / allocated LU, where the redundant LU is a dynamic copy of the allocated LU that is autonomously updated responsive to any changes within the allocated LU. Responsive to a second VIOS attempting to read a LU currently utilized by a first VIOS, the read request is autonomously redirected to the logical redundancy LU. The redundant LU can be utilized to facilitate migration of a client LPAR to a different computing electronic complex (CEC).

Owner:IBM CORP

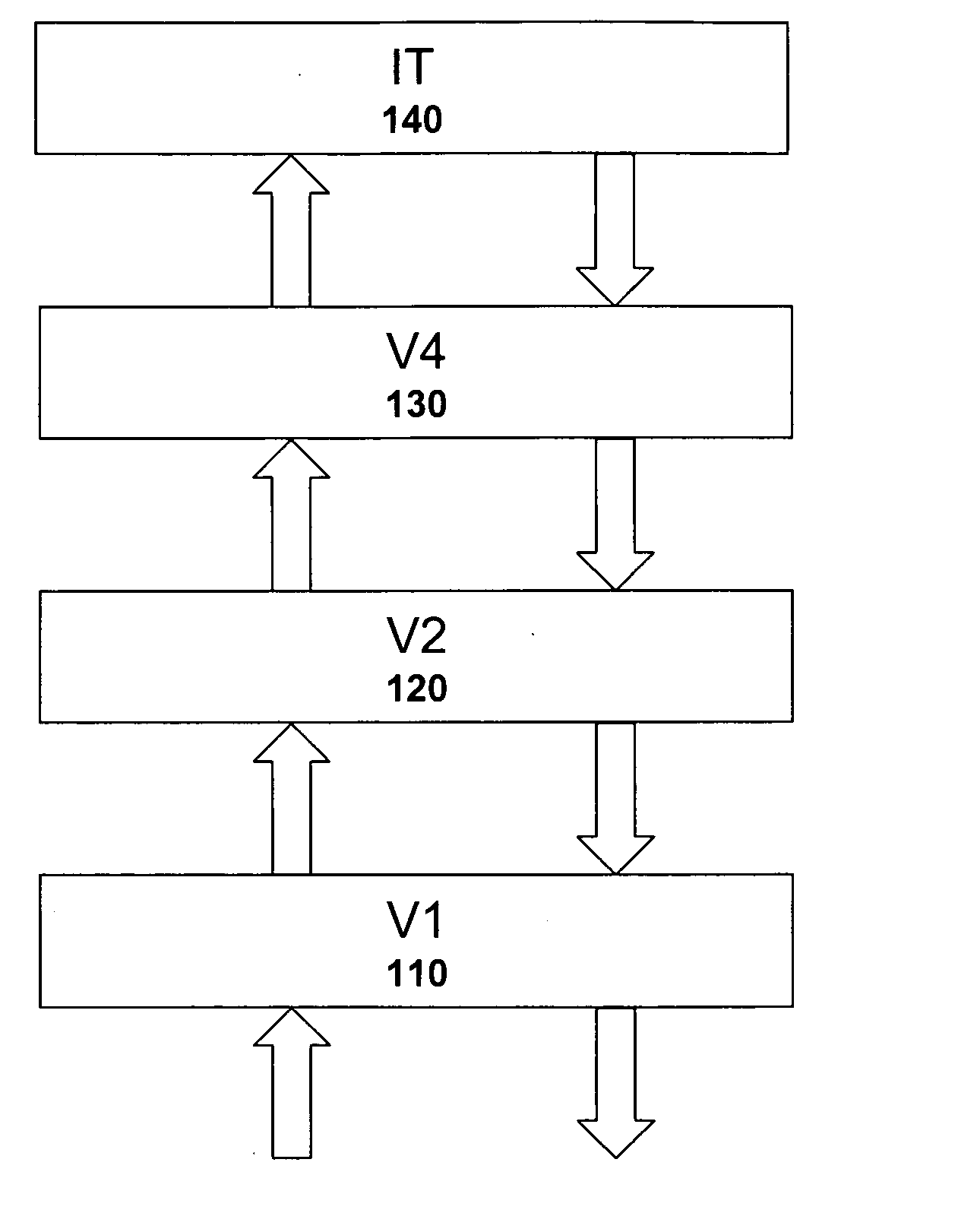

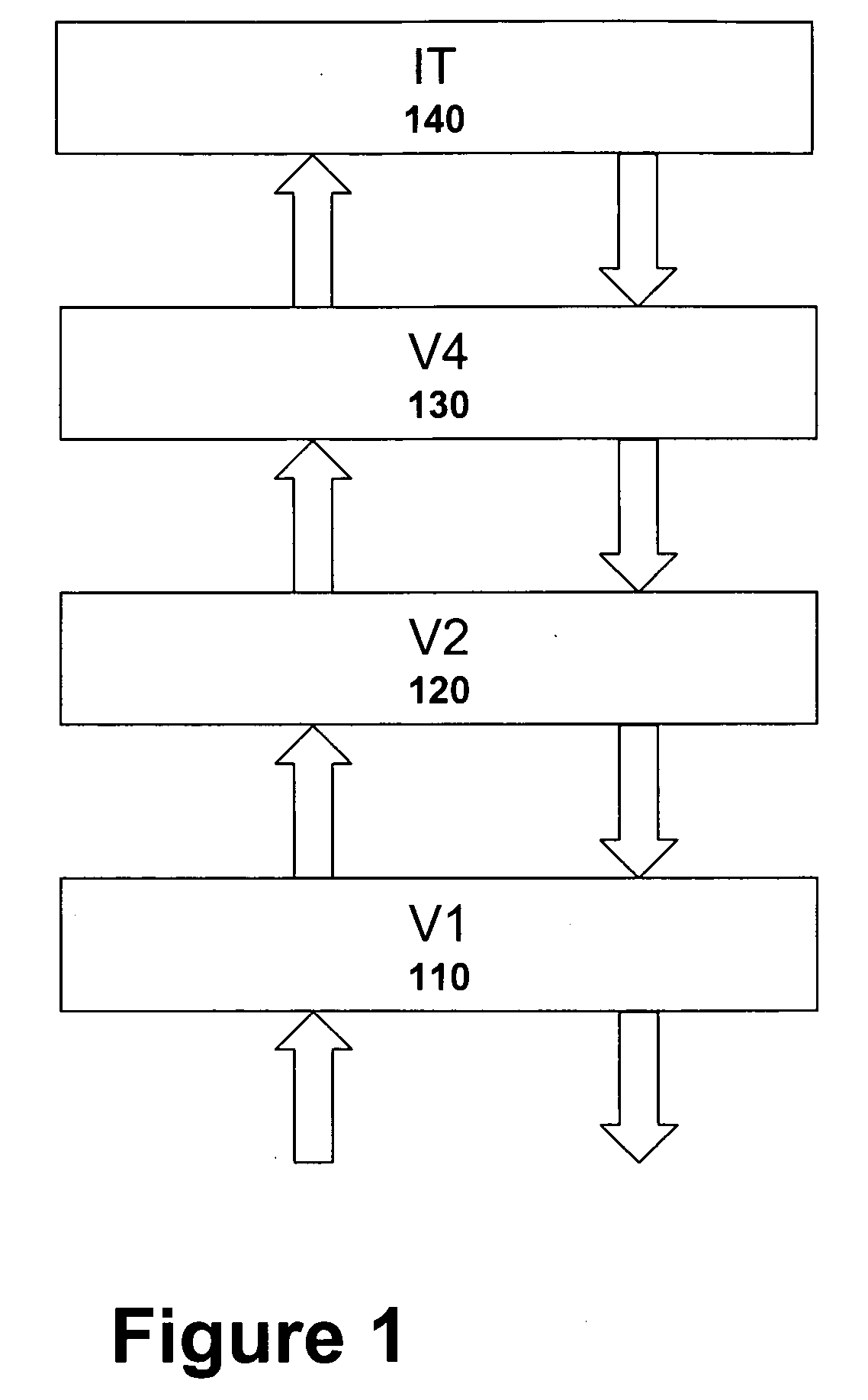

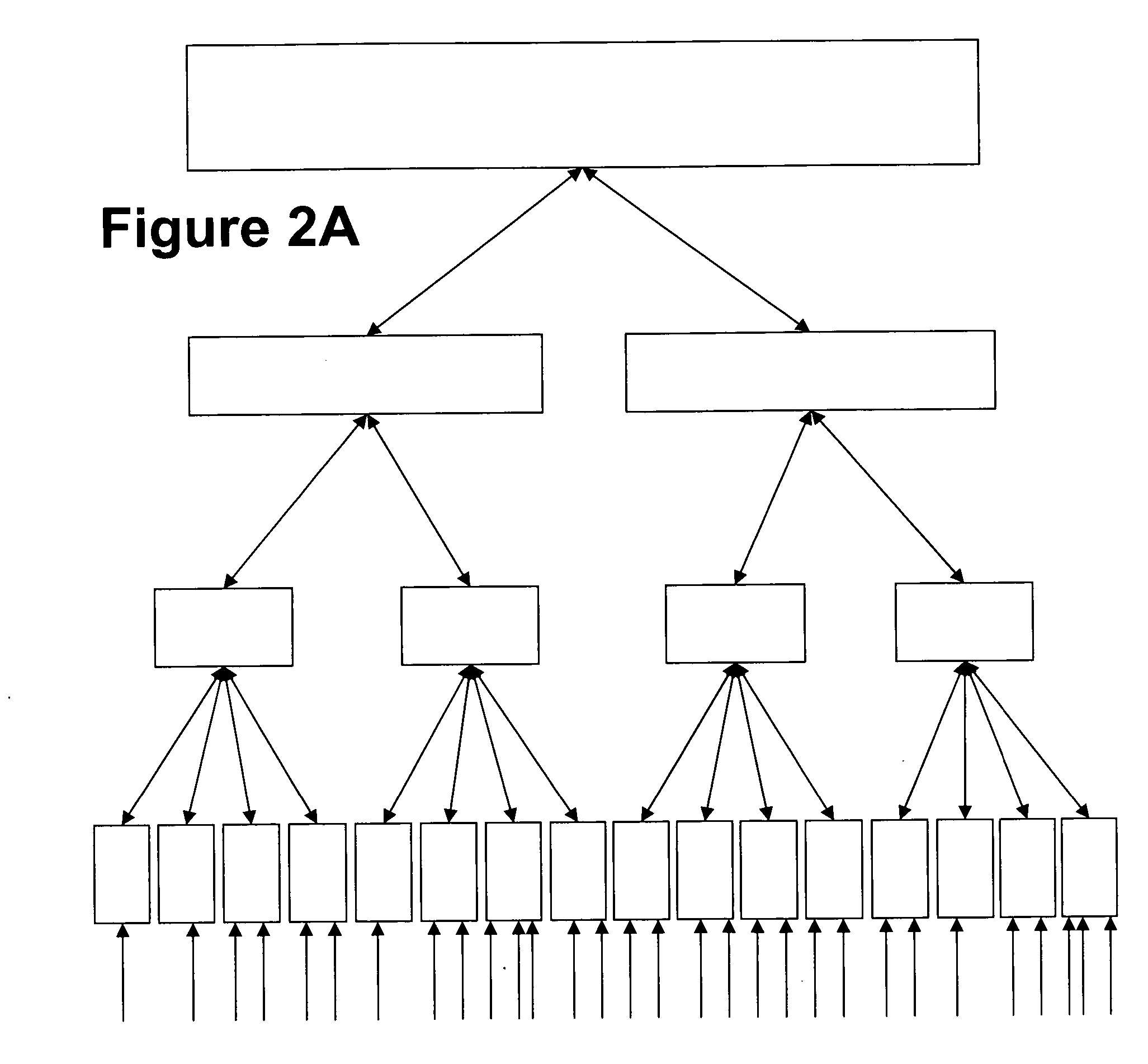

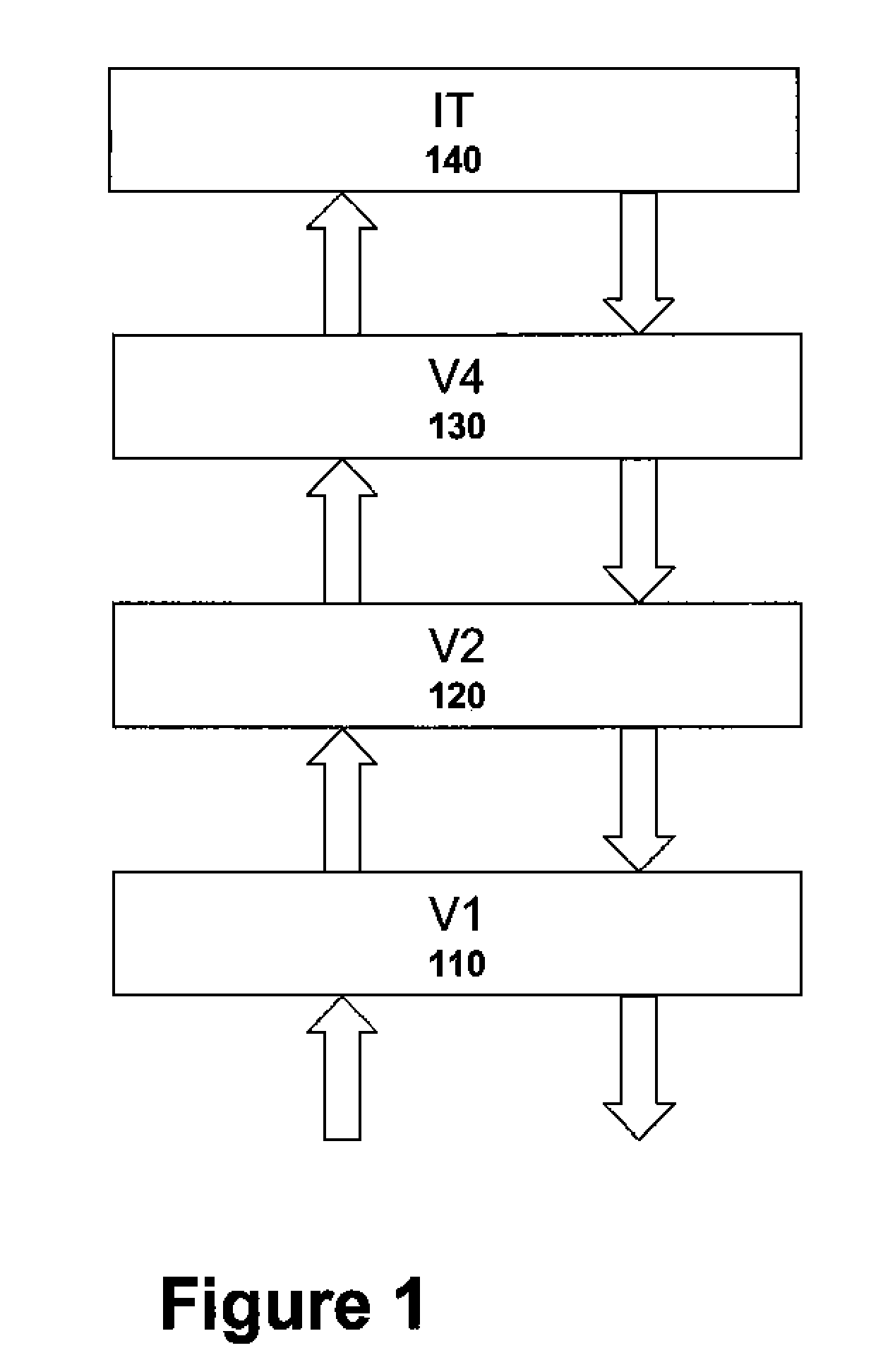

Methods, architecture, and apparatus for implementing machine intelligence and hierarchical memory systems

InactiveUS20060184462A1Accurate identificationMathematical modelsDigital computer detailsPattern sequenceActive memory

Sophisticated memory systems and intelligent machines may be constructed by creating an active memory system with a hierarchical architecture. Specifically, a system may comprise a plurality of individual cortical processing units arranged into a hierarchical structure. Each individual cortical processing unit receives a sequence of patterns as input. Each cortical processing unit processes the received input sequence of patterns using a memory containing previously encountered sequences with structure and outputs another pattern. As several input sequences are processed by a cortical processing unit, it will therefore generate a sequence of patterns on its output. The sequence of patterns on its output may be passed as an input to one or more cortical processing units in next higher layer of the hierarchy. A lowest layer of cortical processing units may receive sensory input from the outside world. The sensory input also comprises a sequence of patterns.

Owner:NUMENTA INC

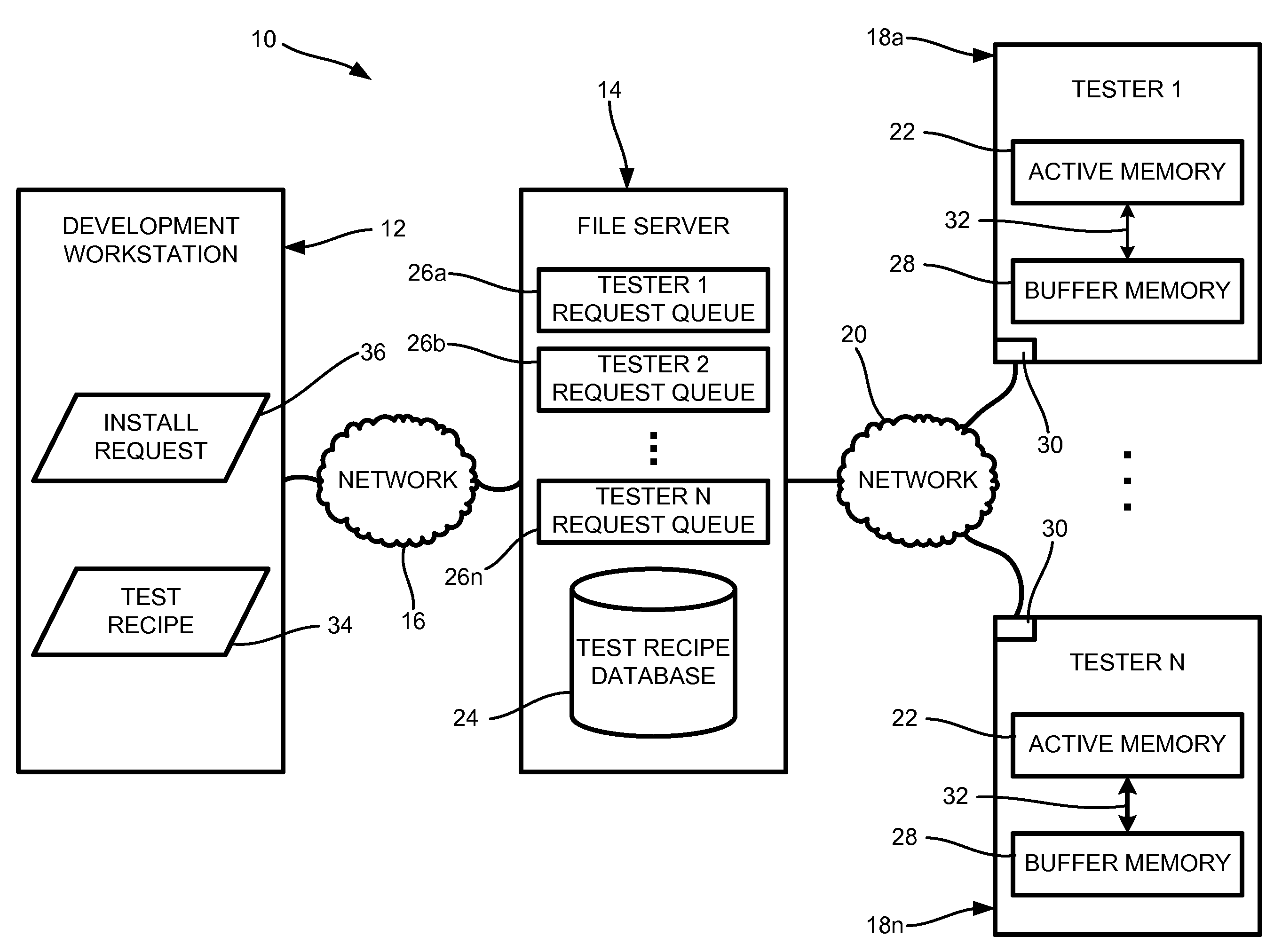

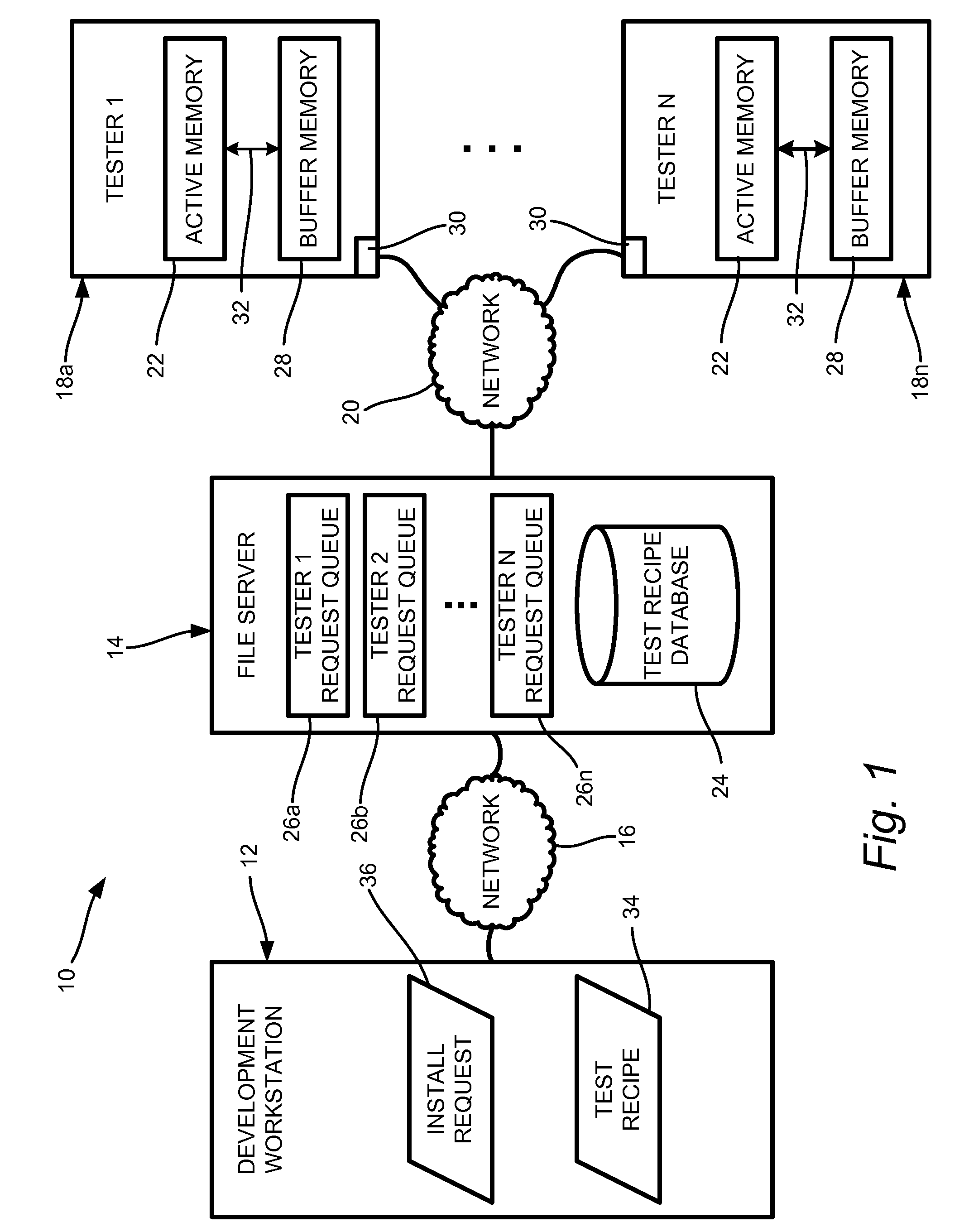

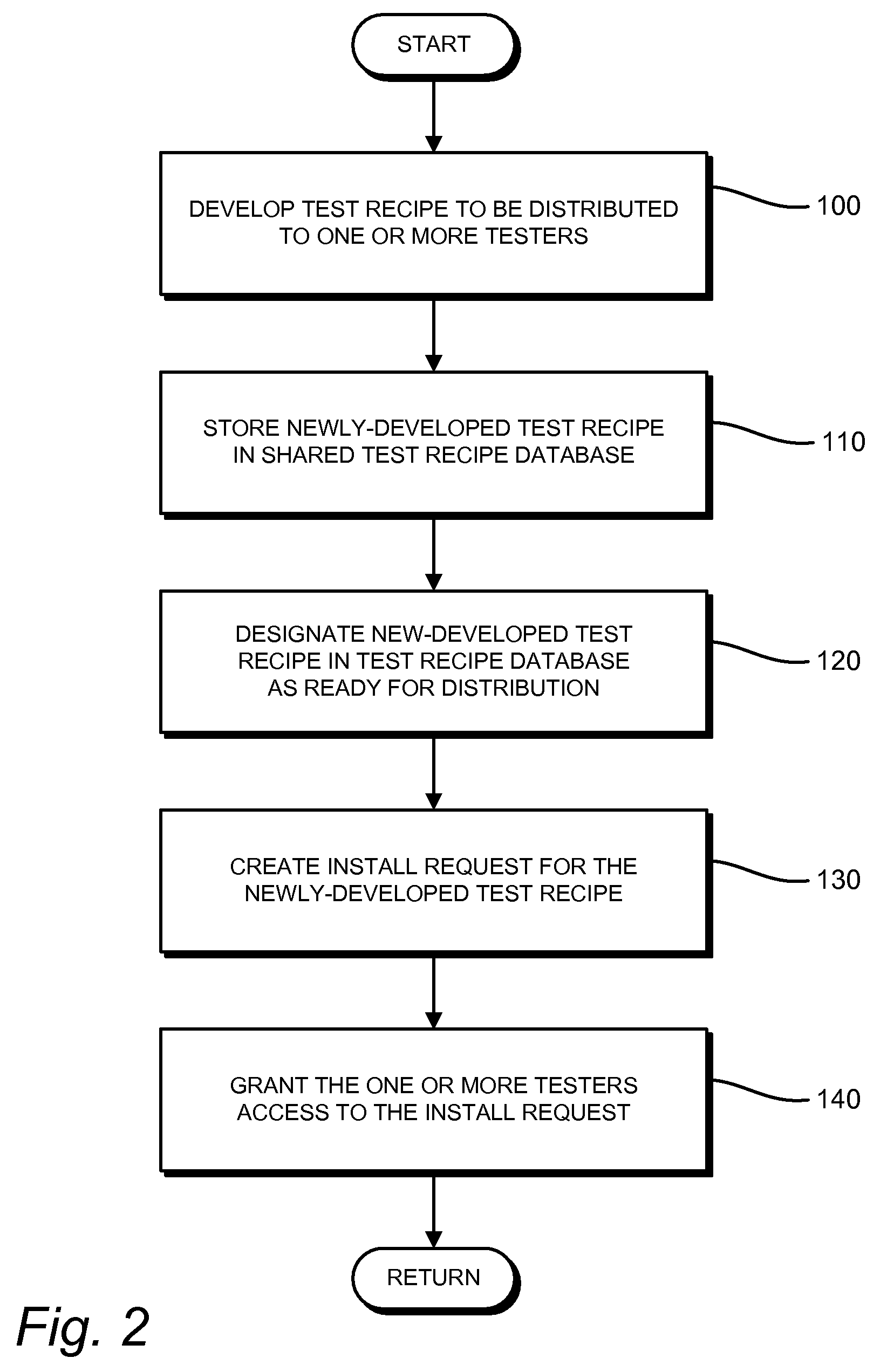

Test recipe distribution method and system

InactiveUS8452567B1Error detection/correctionSpecial data processing applicationsDistribution methodActive memory

Provided is a method and system for distributing a test recipe to a tester for conducting a test to determine if a device under test operates as designed. The method includes storing an active test recipe in an active memory in local communication with the tester, and initiating the test of the device under test to be performed by the tester according to a parameter included in the active test recipe stored in the active memory. A second parameter included in a second test recipe is received by the tester while conducting the test of the device under test according to the parameter included in the active test recipe. The method further includes storing the second parameter in a buffer memory in local communication with the active memory, and initiating a transfer of the second parameter from the buffer memory to the active memory. After initiation of the transfer of the second parameter to the active memory, a subsequent test to be performed by the tester according to the second parameter included in the second test recipe is initiated.

Owner:KEITHLEY INSTRUMENTS INC

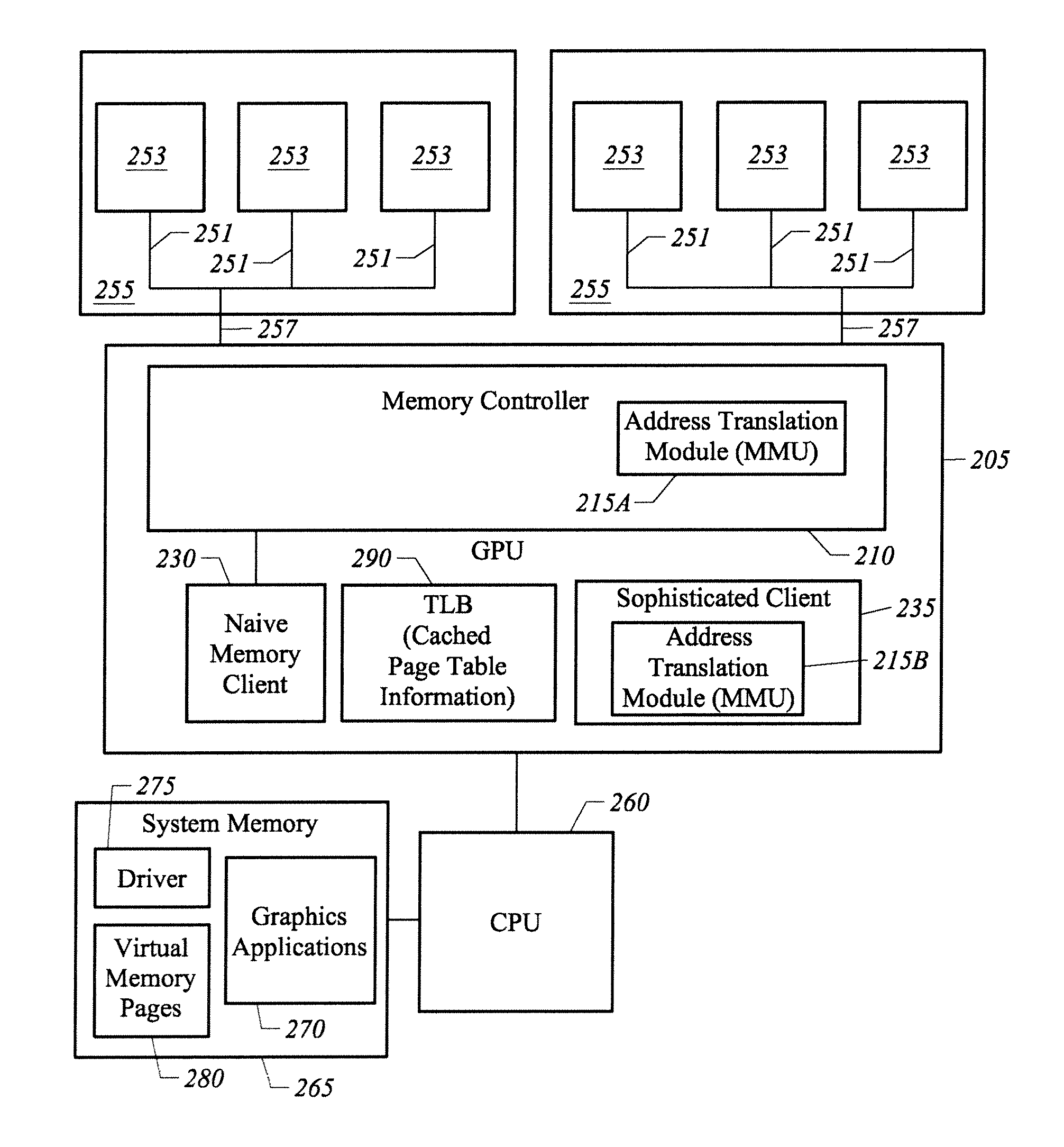

Graphics system with virtual memory pages and non-power of two number of memory elements

ActiveUS8072463B1Memory adressing/allocation/relocationCathode-ray tube indicatorsGraphicsVirtual memory

A graphics system utilizes virtual memory pages and has a partitioned graphics memory that includes memory elements. The system supports having an non-power of two number of active memory elements. Additionally, a partition swizzling operation is used to adjust the partition numbers associated with individual units of virtual memory allocation on particular virtual memory pages to achieve a selected partition interleaving pattern.

Owner:NVIDIA CORP

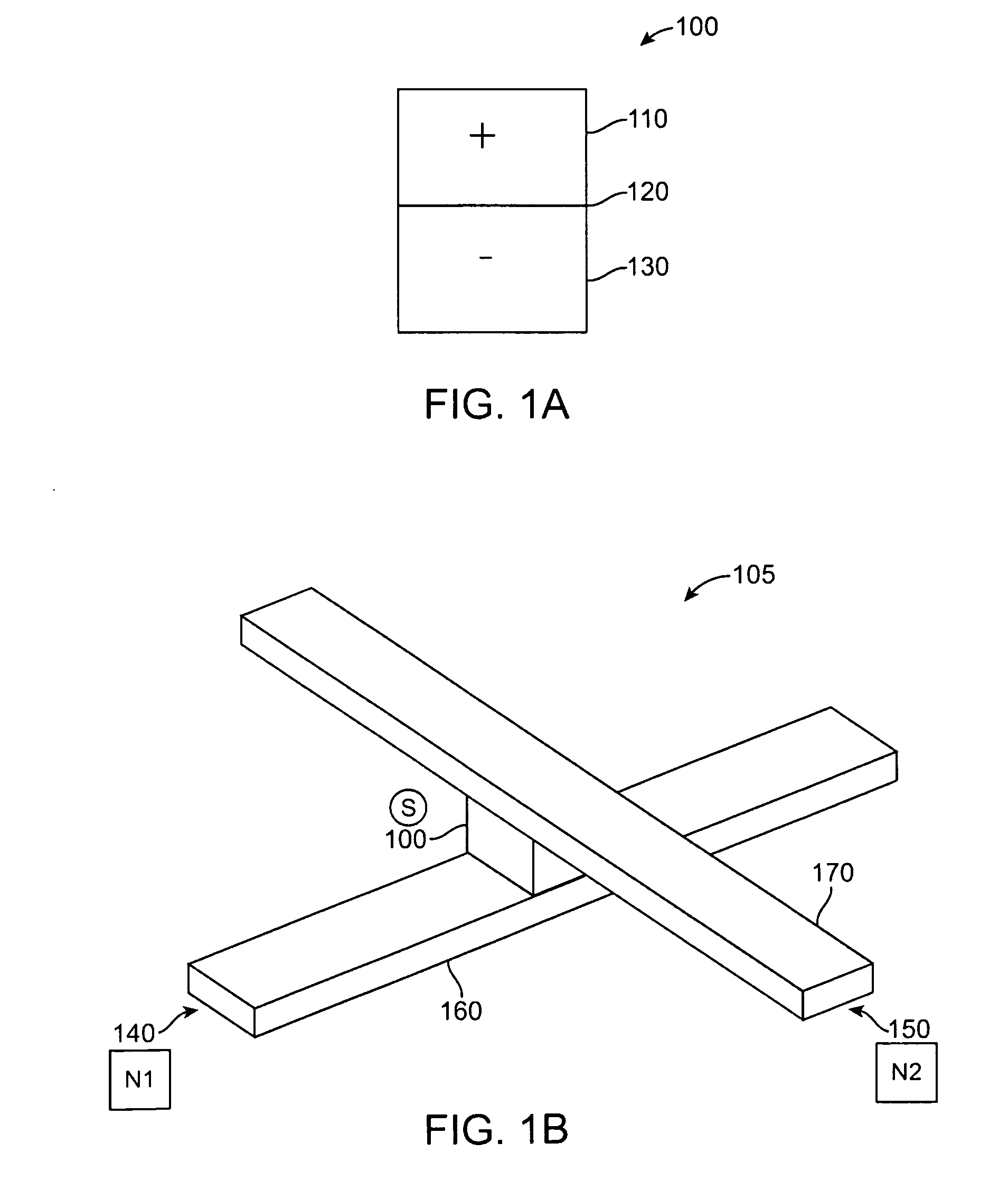

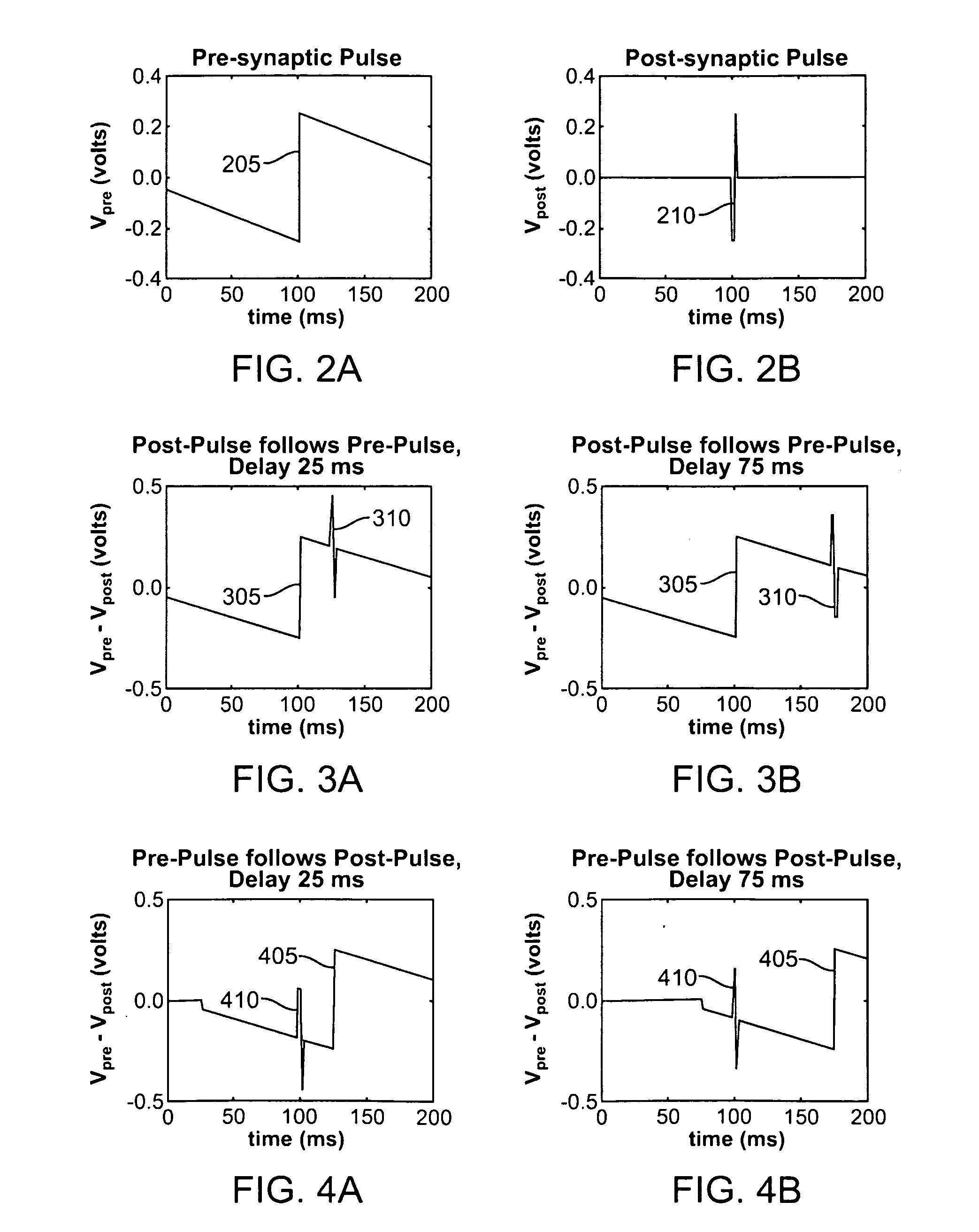

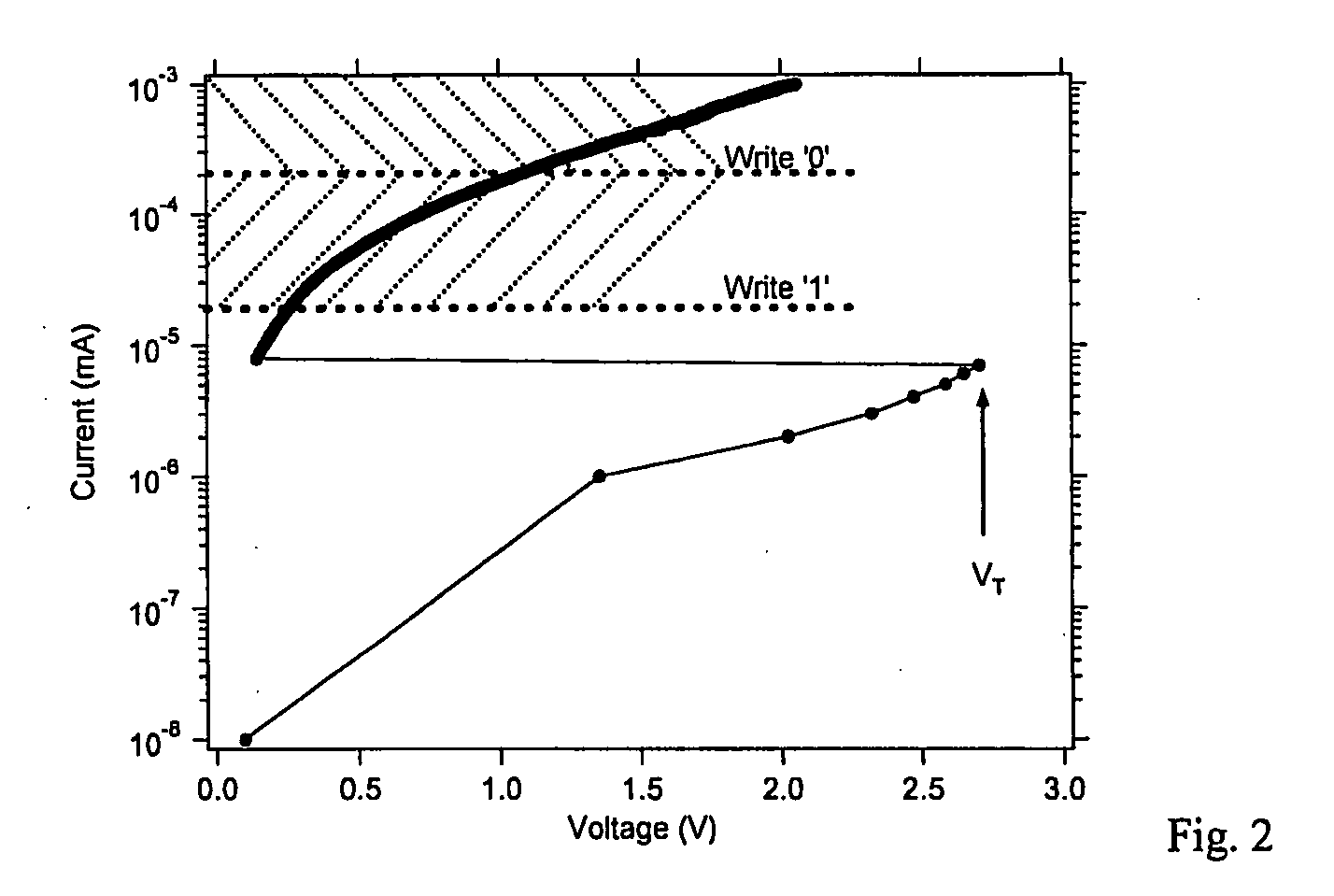

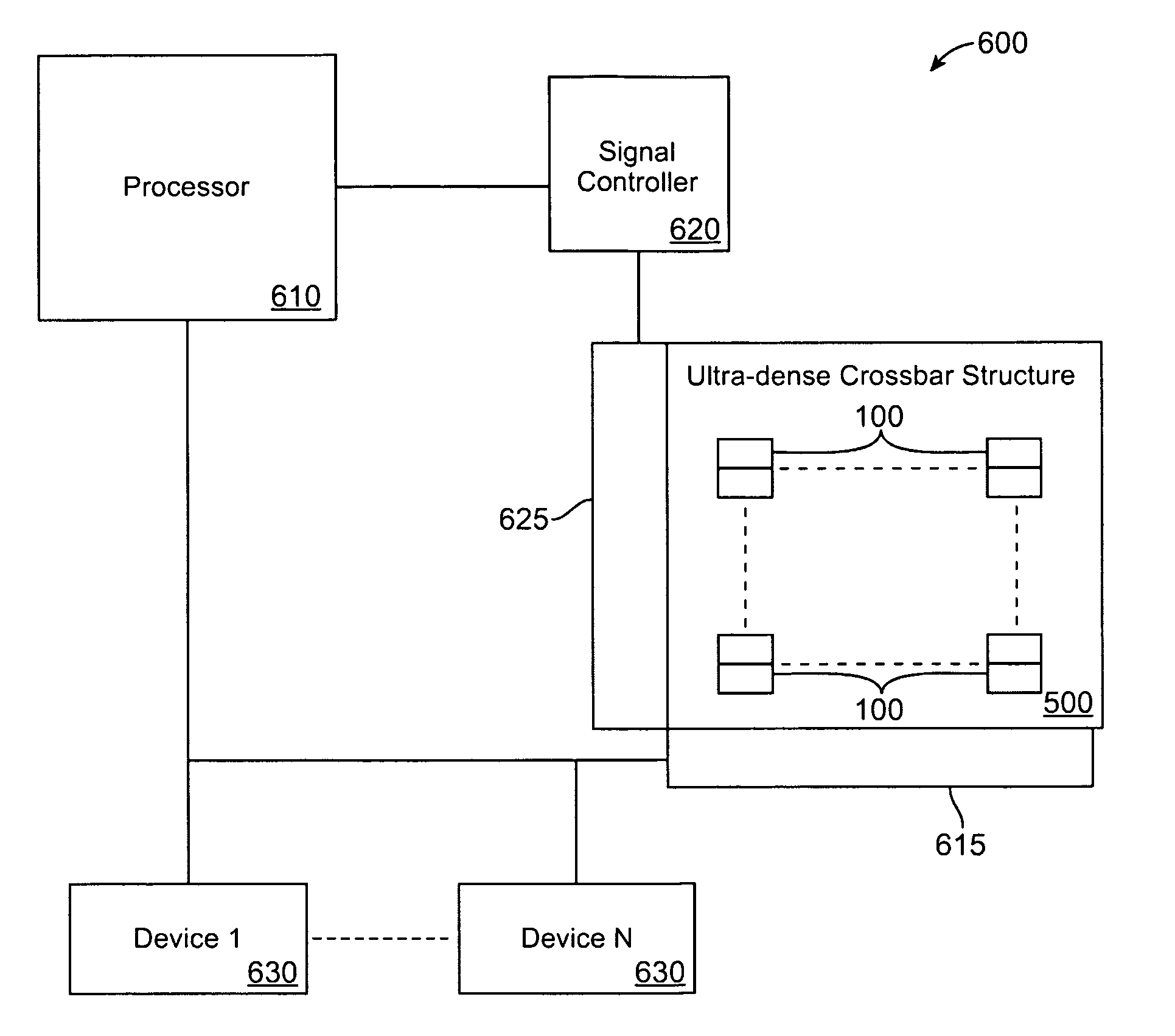

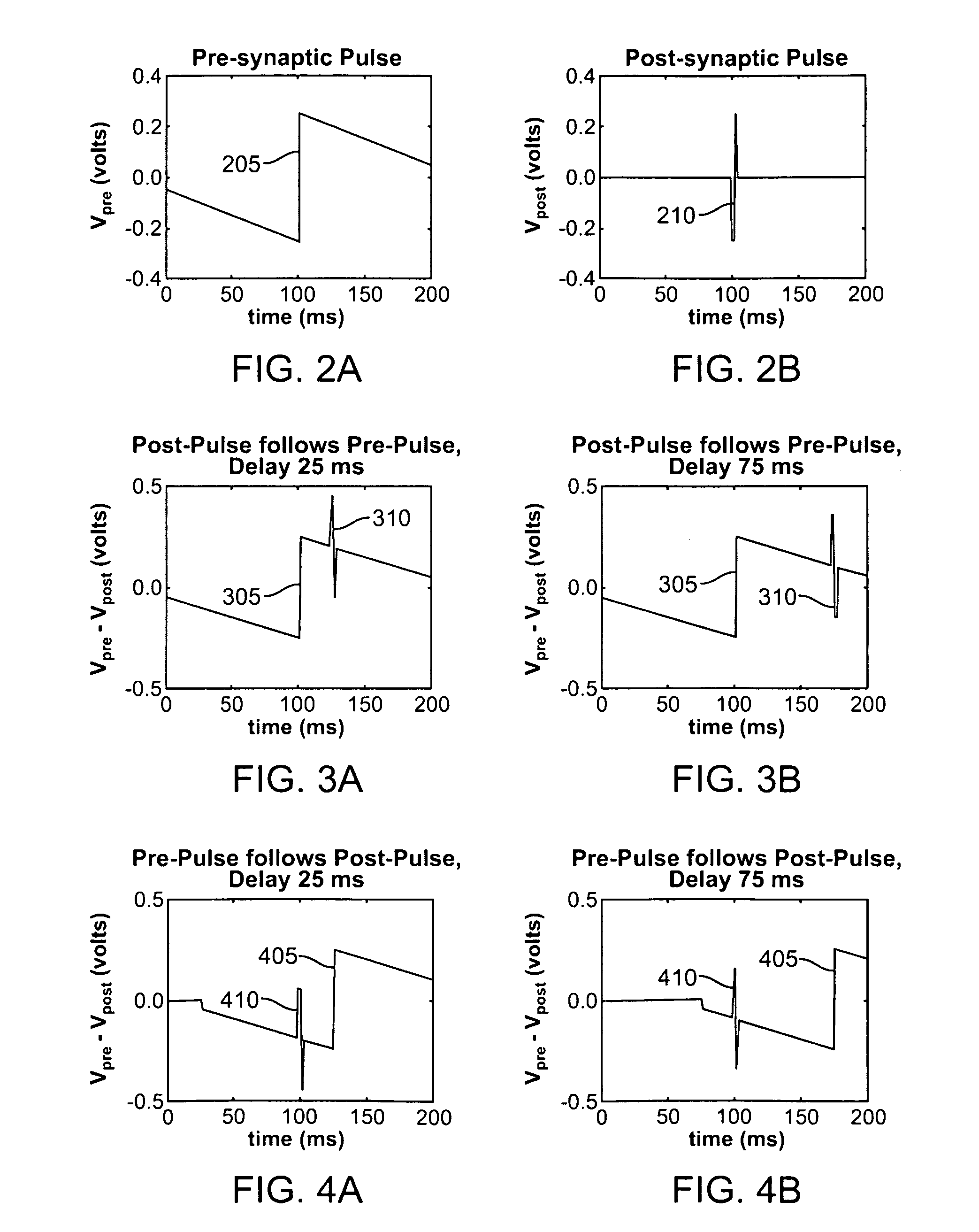

Stochastic synapse memory element with spike-timing dependent plasticity (STDP)

An active memory element is provided. One embodiment of the invention includes a bi-polar memory two-terminal element having polarity-dependent switching. A probability of switching of the bi-polar memory element between a first state and a second state decays exponentially based on time delay and a difference between received signals at the two terminals and a switching threshold magnitude.

Owner:IBM CORP

System and method for thermal throttling of memory modules

Some embodiments of the invention accurately account for power dissipation in memory systems that include individual memory modules by keeping track of the number of read requests, the number of write requests, and the number of activate requests that are applied to the individual memory modules during selected time periods. If the sum of these totals exceeds a threshold level, the embodiments throttle the memory system, either by throttling the entire memory system based in response to the most active memory module, or by throttling individual memory modules as needed. Other embodiments of the invention may assign the same or different weights to activate requests, read requests, and write requests. Other embodiments are described and claimed.

Owner:INTEL CORP

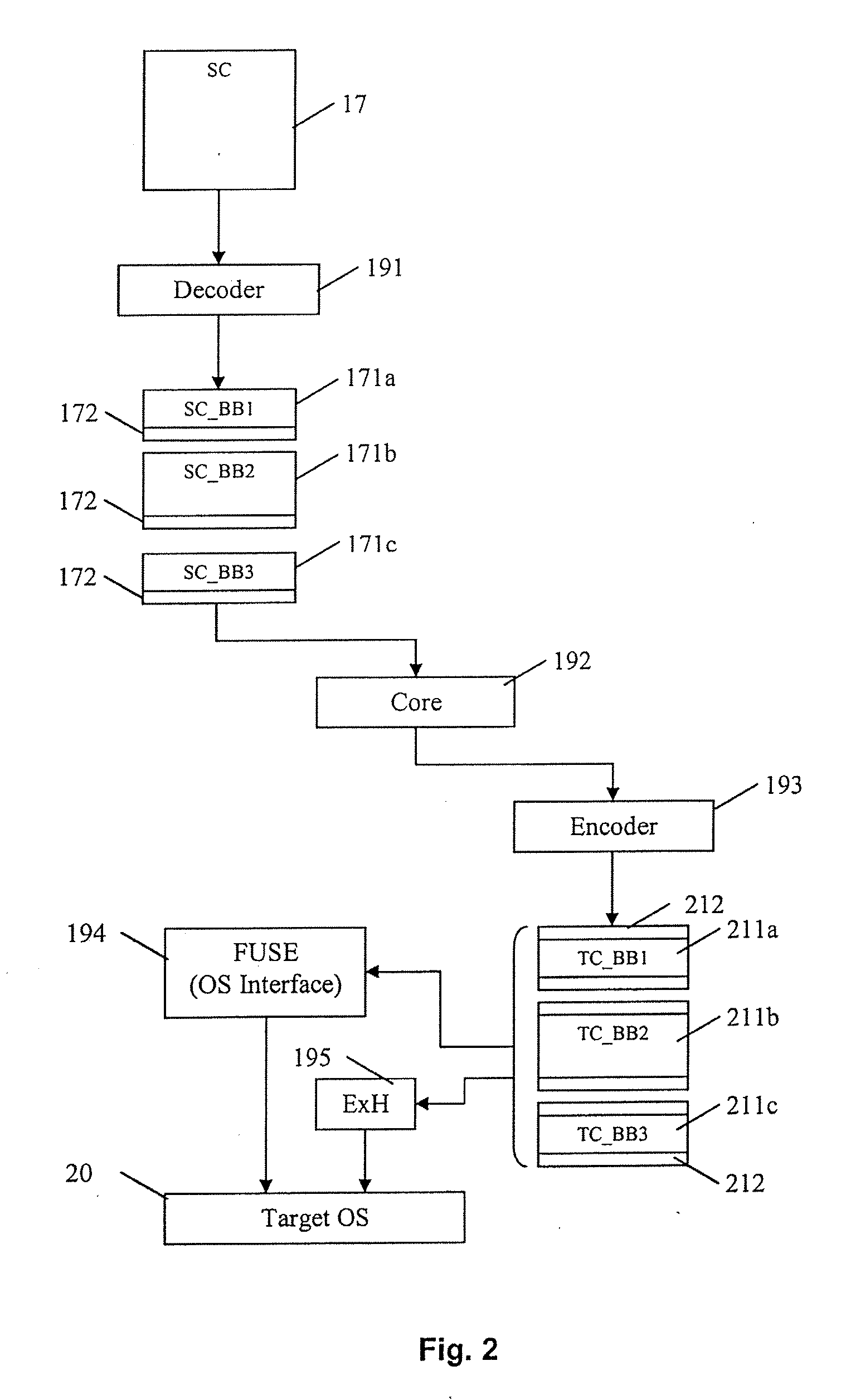

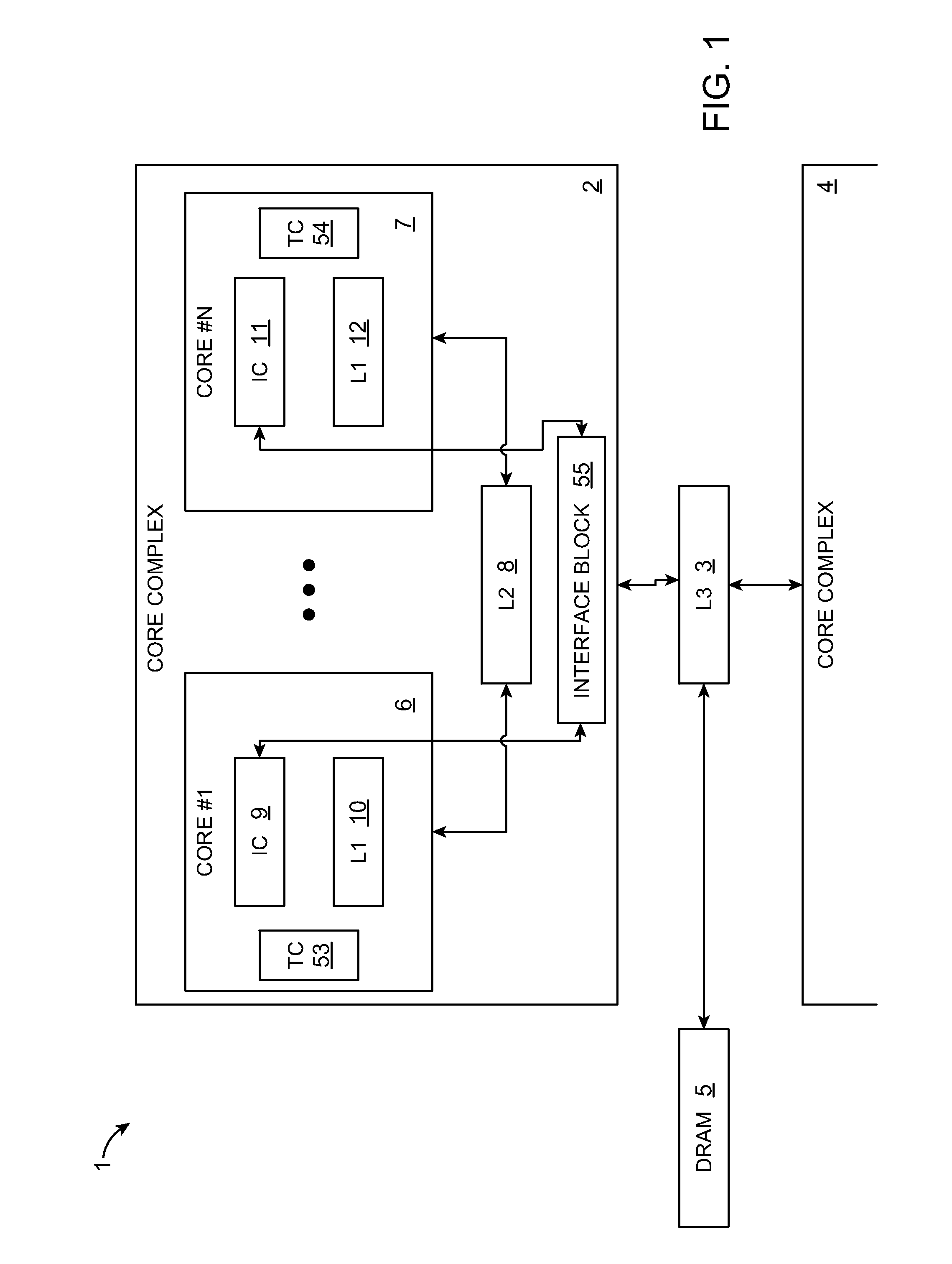

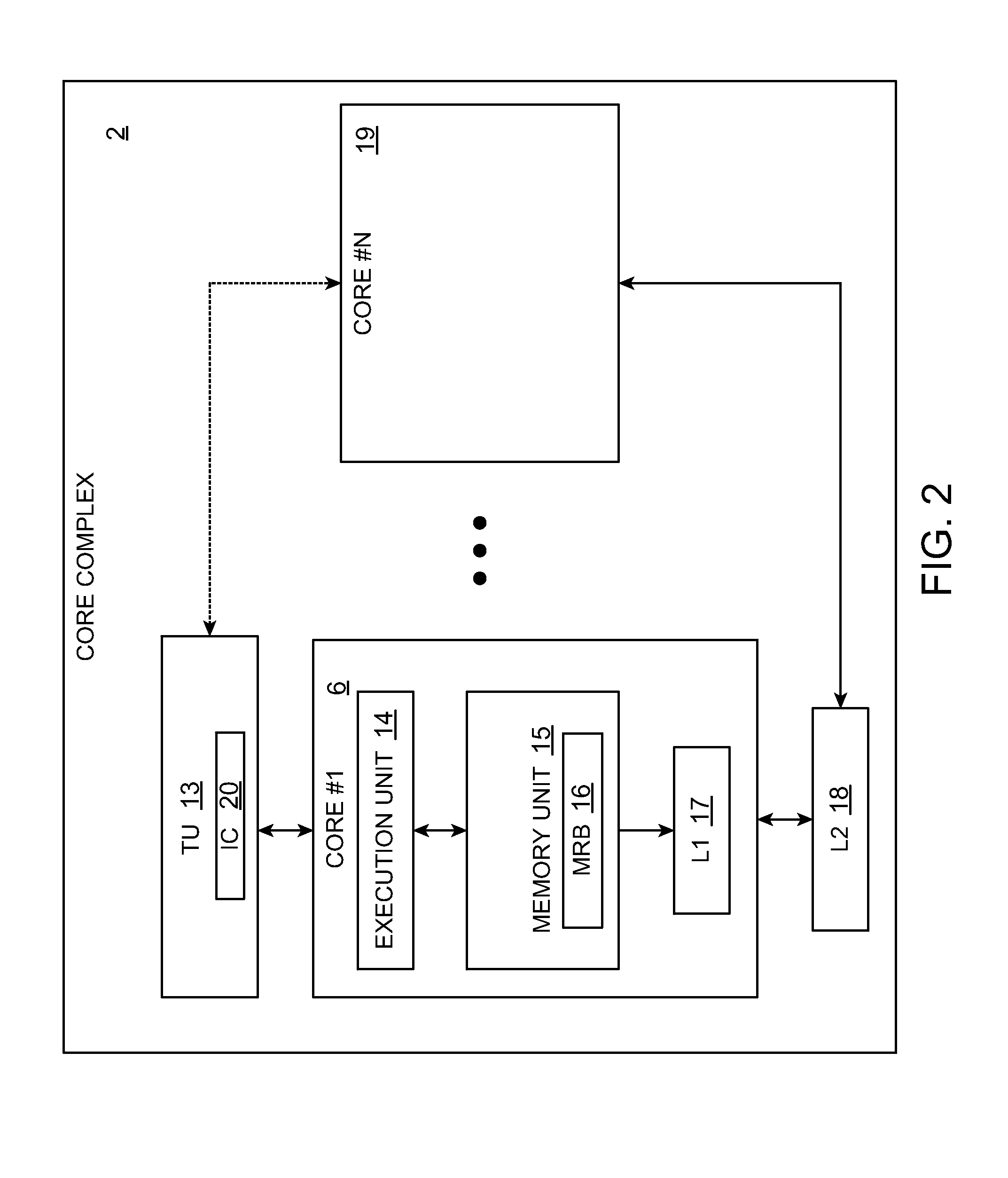

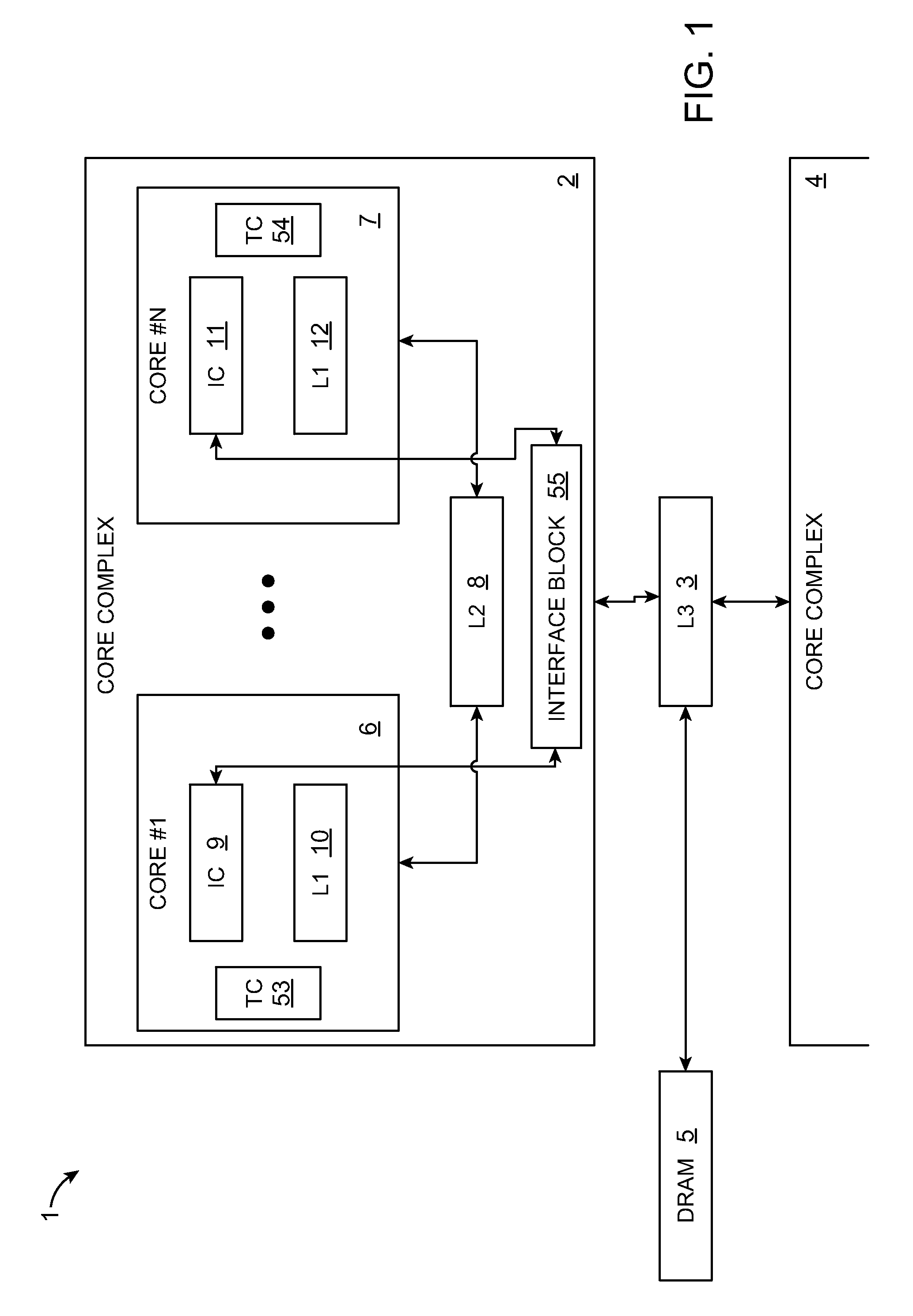

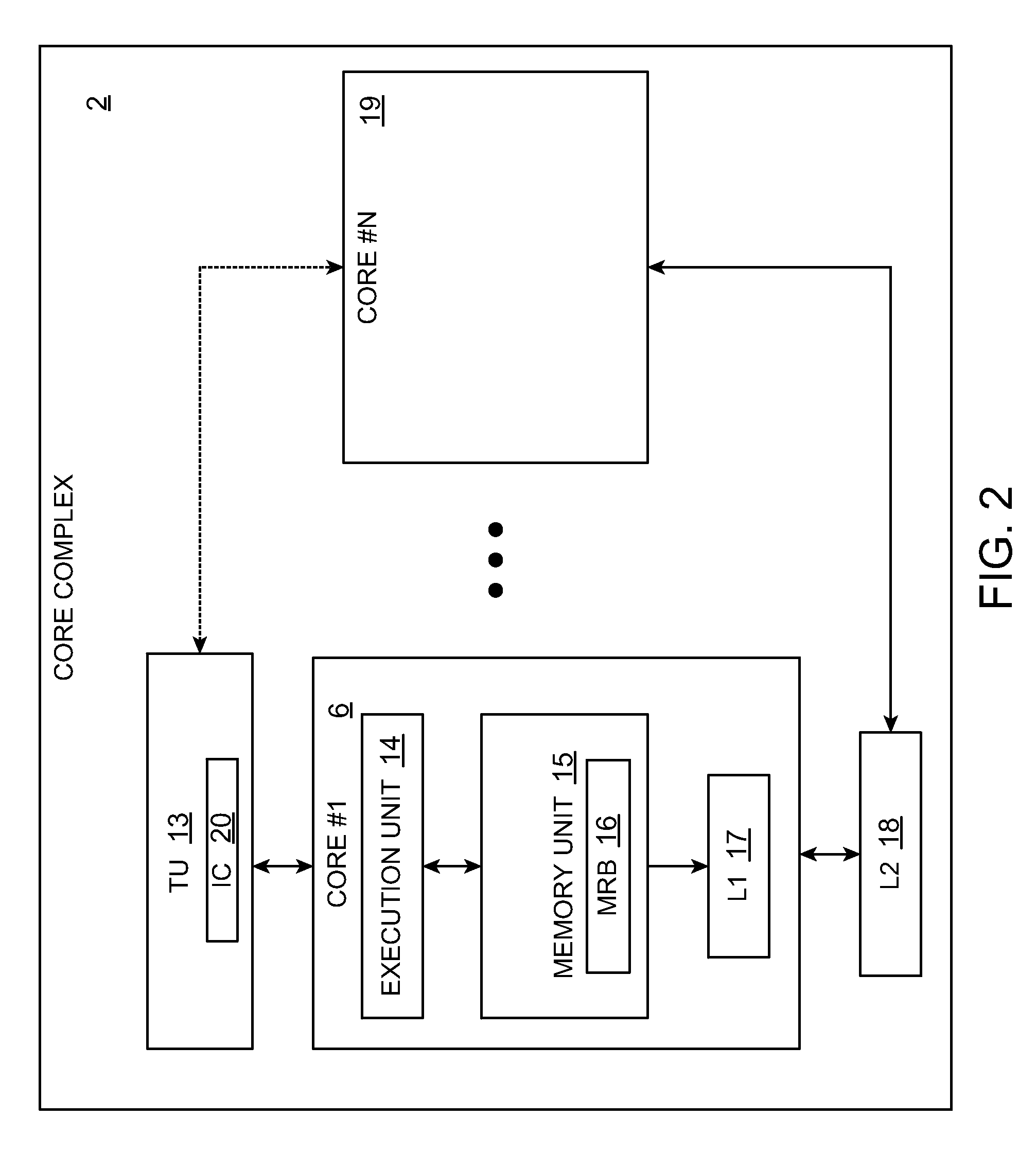

Multiprocessor computing system with multi-mode memory consistency protection

ActiveUS20090210649A1Memory architecture accessing/allocationMemory adressing/allocation/relocationMulti processorActive memory

Disclosed are a method and apparatus for protecting memory consistency in a multiprocessor computing system, relating to program code conversion such as dynamic binary translation. The exemplary multiprocessor computing system provides memory and multiple processors, and a set of controller / translator units TX1, TX2, TX3 arranged to convert respective application programs into program threads T1, T2, etc., which are executed by the processors. Each controller / translator unit sets a first mode where a single thread T1 executes on a single processor P1, orders a second mode for two or more threads T1, T2 that are forced to execute one at a time on a single processor P2 such as by setting affinity with that processor, and orders a third mode to selectively apply active memory consistency protection in relation to accesses to explicit or implicit shared memory while allowing the multiple threads T1, T2, T3, T4 to execute on the multiple processors.

Owner:IBM CORP

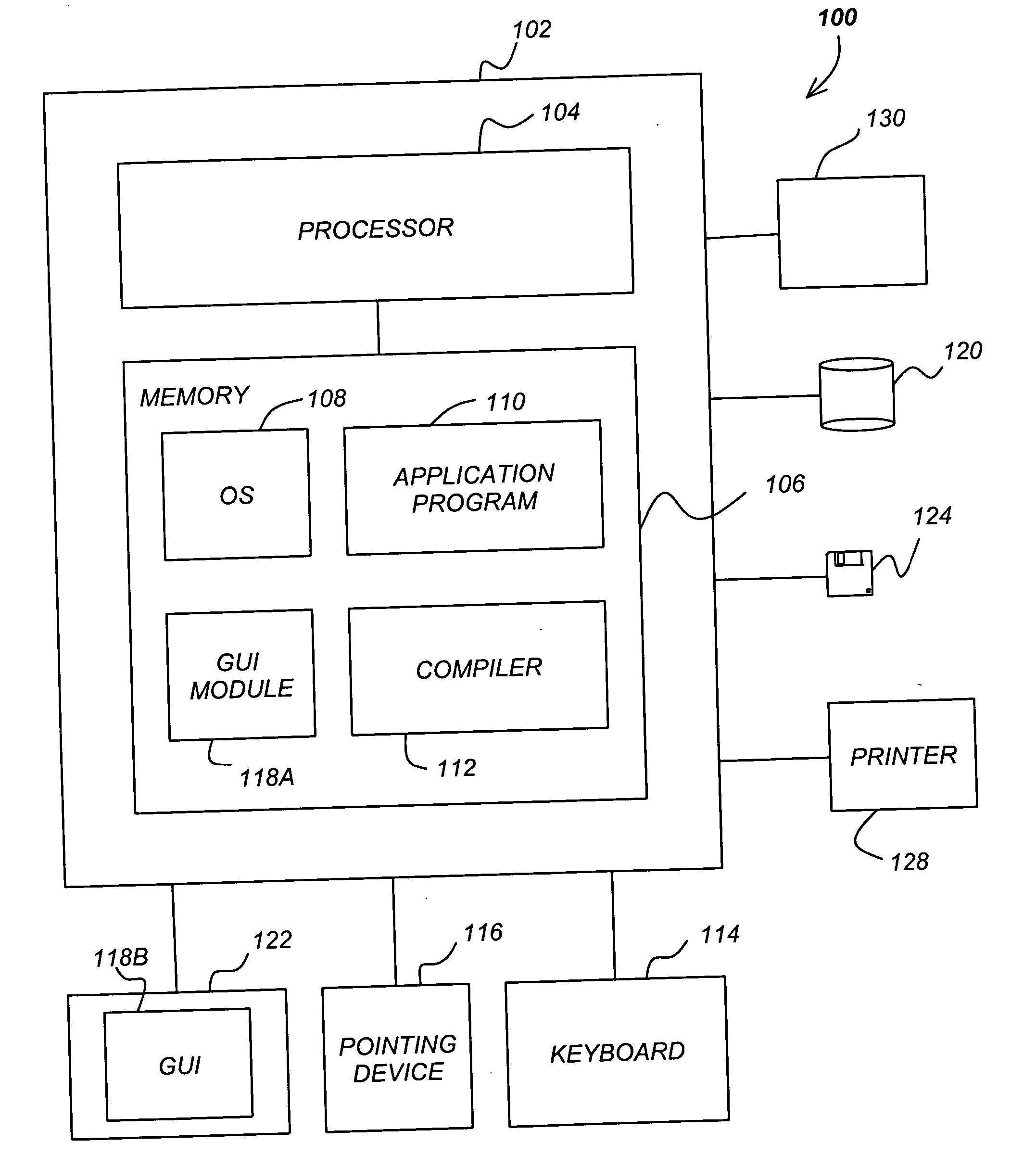

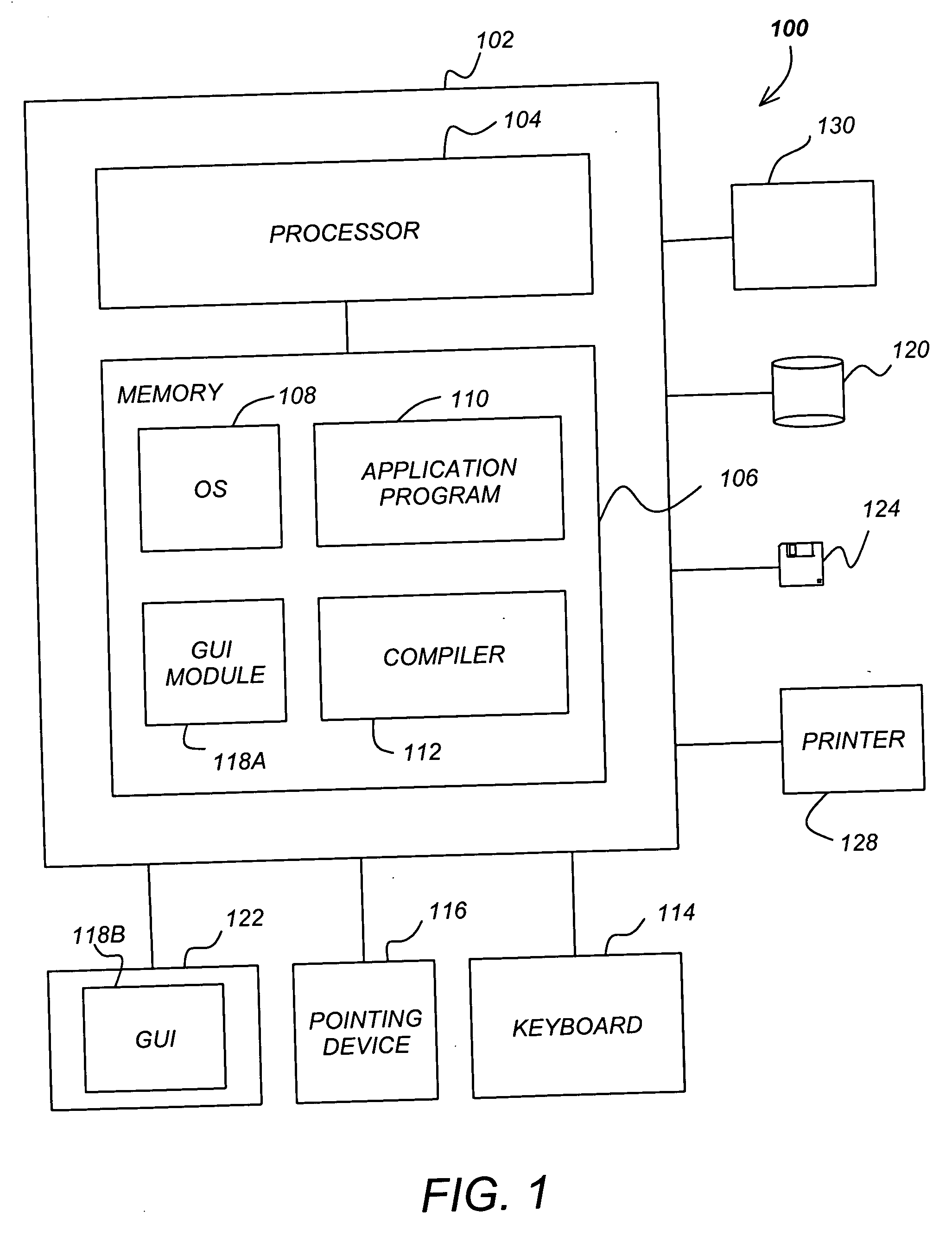

Low memory rendering of graphical objects

InactiveUS20090064045A1Low memory usageImprove performanceInput/output processes for data processingArray data structureData store

A method for displaying graphical objects is provided. In one embodiment, the method includes accessing a data structure including a plurality of sequential data objects and the location of associated graphical data stored in a non-volatile storage device. Further, the method may include rendering a first graphical object associated with a first data object of the data structure in a viewport of a device, including loading the graphical data for the first data object from the non-volatile storage into an active memory. The method may also include rendering a second graphical object in the viewport based on the location of the second data object with respect to the first data object within the data structure. In one embodiment, graphical data for data objects is loaded into the active memory on an as-needed basis. Various devices, machine-readable media, and other methods for displaying graphical objects are also provided.

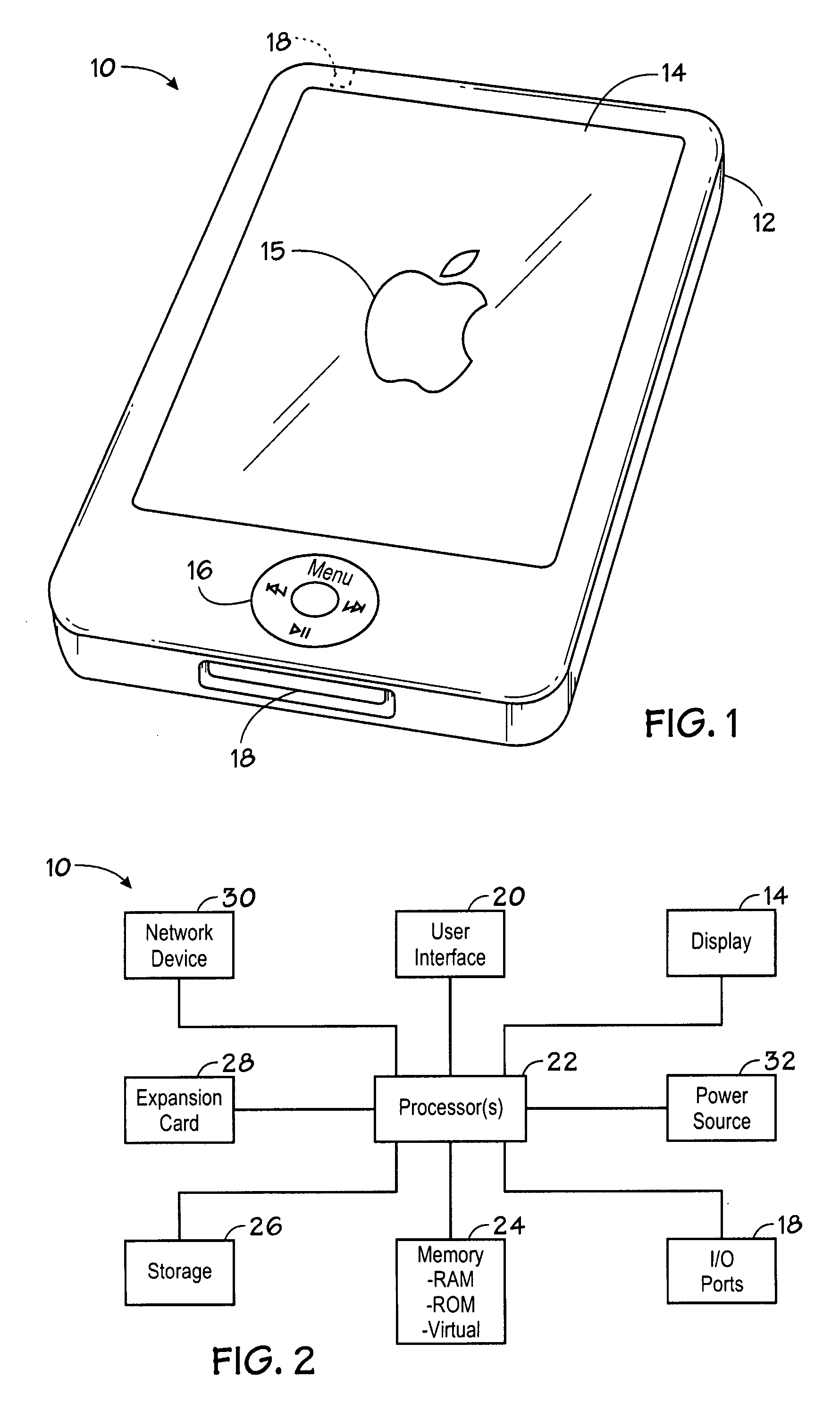

Owner:APPLE INC

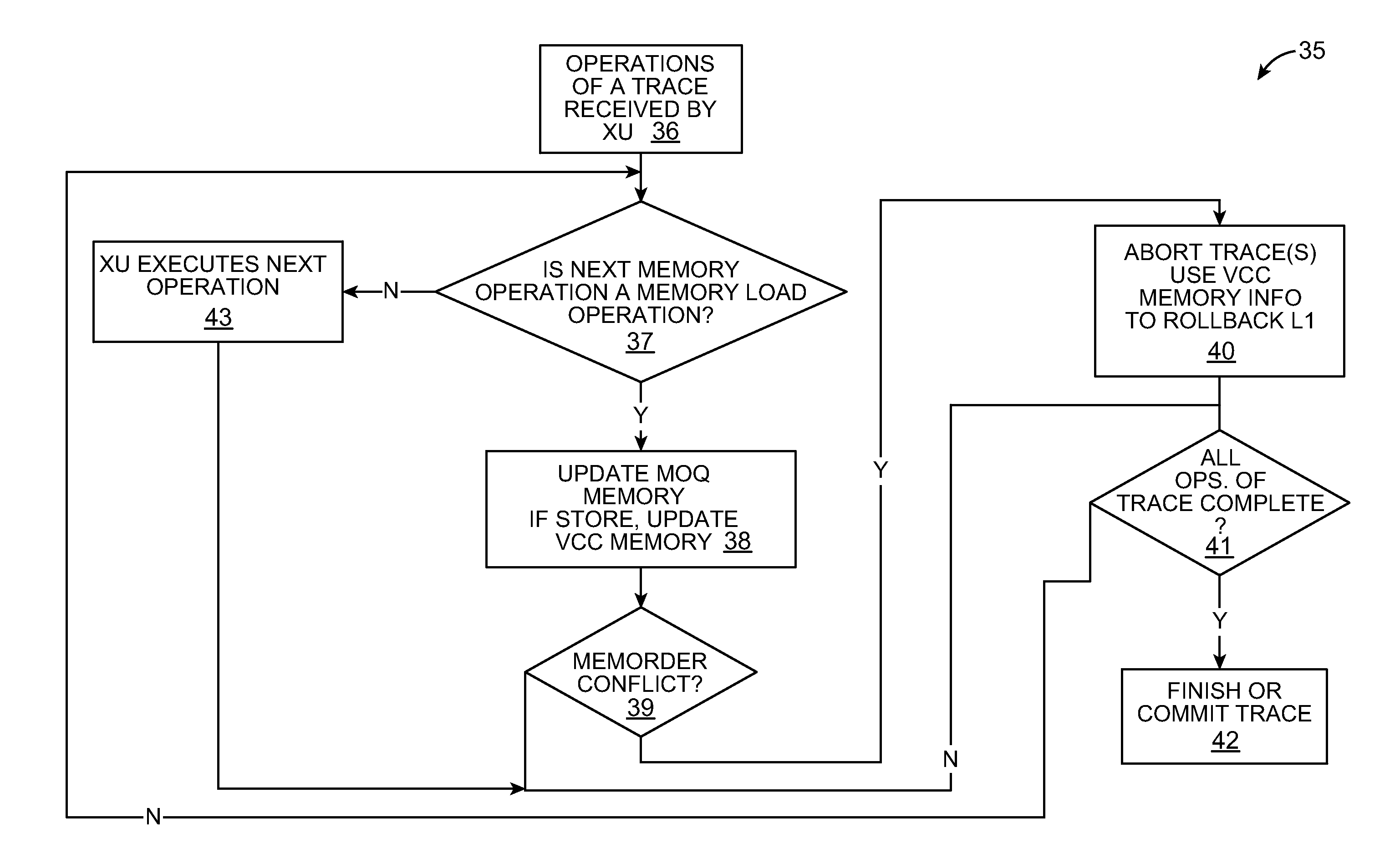

Data cache rollbacks for failed speculative traces with memory operations

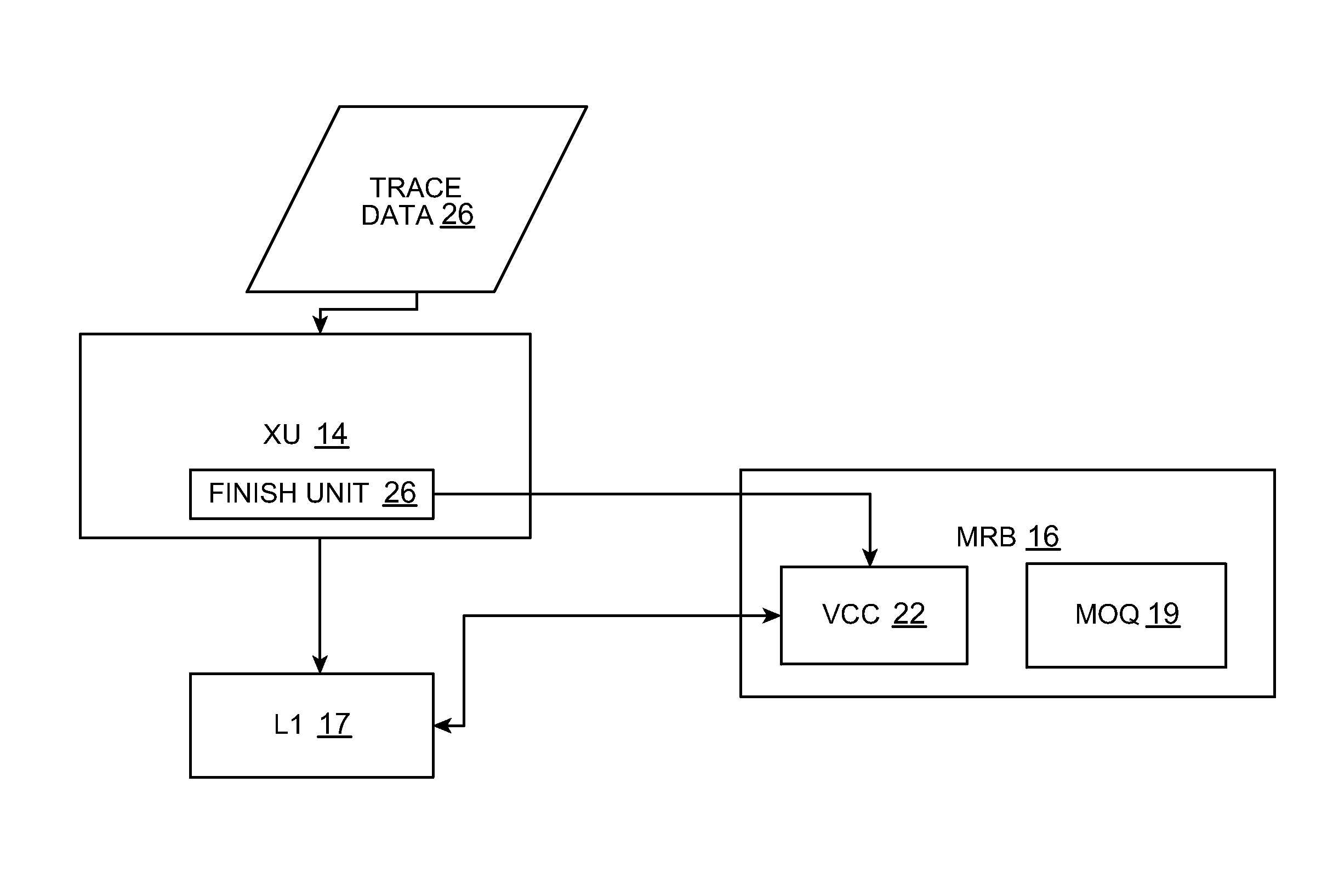

This invention includes a circuit for tracking memory operations with trace-based execution. Each trace includes a sequence of operations that includes zero or more of the memory operations. The memory operations being executed form a set of active memory operations that have a predefined program order among them and corresponding ordering constraints. At least some of the active memory operations access the memory in an execution order that is different from the program order. Checkpoint entries are associated with each trace. Each entry refers to a checkpoint location. Memory operation ordering entries correspond to each one of the active memory operations. Violations of the ordering constraints result in overwriting the checkpoint locations associated with the selected trace as well as the checkpoint locations associated with traces that are younger than the selected trace.

Owner:SUN MICROSYSTEMS INC

Managing and querying moving point data

InactiveUS7010308B2Simple methodRadio/inductive link selection arrangementsWireless commuication servicesTelecommunications linkLocation data

An improved client locating and user discovery system is disclosed. Methods and systems are described that provide the ability for a telecommunications network to frequently update the location data for telecommunications units within the network, while preventing the performance degradation that is inherent in the prior art. In the patented invention, the most frequently updated data is stored outside the main database in active memory in a tree structure, and is accessed through an API that converts the tree data into a database query language readable format.

Owner:UBER TECH INC

Memory ordering queue/versioning cache circuit

A processor includes a circuit for tracking memory operations with trace-based execution. Each trace includes a sequence of operations that includes zero or more of the memory operations. The memory operations being executed form a set of active memory operations that have a predefined program order among them. At least some of the active memory operations access the memory in an execution order that is different from the program order. During the operation of the circuit, none of the operations of a given trace has any effect on the execution unit's architectural state prior to committing that trace. Each trace becomes eligible for commitment after all operations in the trace complete executing. The circuit also includes a sub-circuit that holds memory operation ordering information corresponding to the active memory operations. The sub-circuit detects violations of ordering constraints. After each trace is committed, the sub-circuit invalidates all of the memory operation ordering information associated with the trace.

Owner:SUN MICROSYSTEMS INC

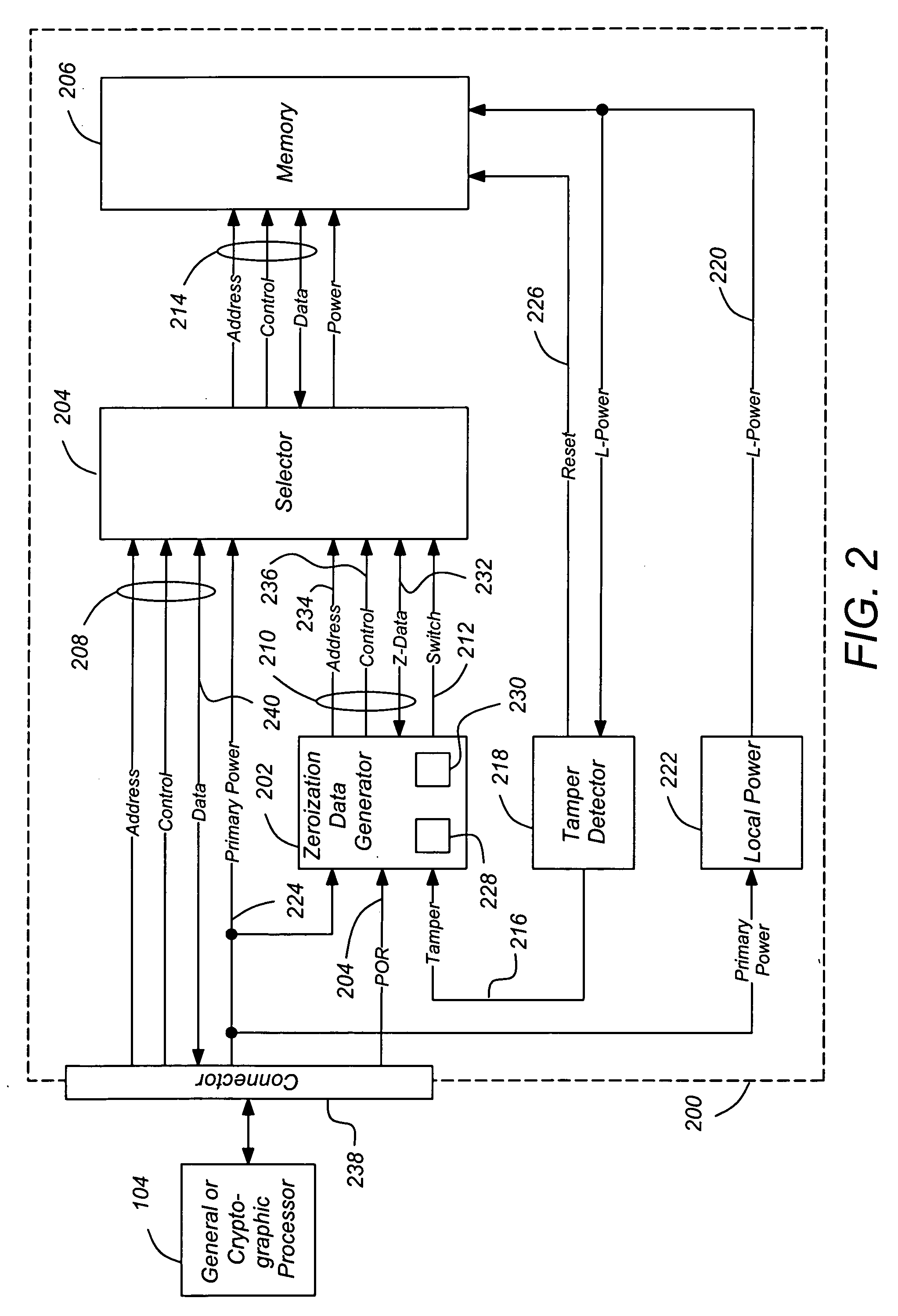

High-assurance processor active memory content protection

ActiveUS20060023486A1High assurance data zeroizationData recoveryDigital storageInternal/peripheral component protectionActive memoryTerm memory

A method and apparatus for preventing compromise of data stored in a memory by assuring the deletion of data and minimizing data remanence affects is disclosed. The method comprises the steps of monitoring the memory to detect tampering, and if tampering is detected, generating second signals having second data differing from the first data autonomously from the first processor; providing the generated second signals to the input of the memory; and storing the second data in the memory. Several embodiments are disclosed, including self-powered embodiments and those which use separate, dedicated processors to generate, apply, and verify the zeroization data.

Owner:SAFENET

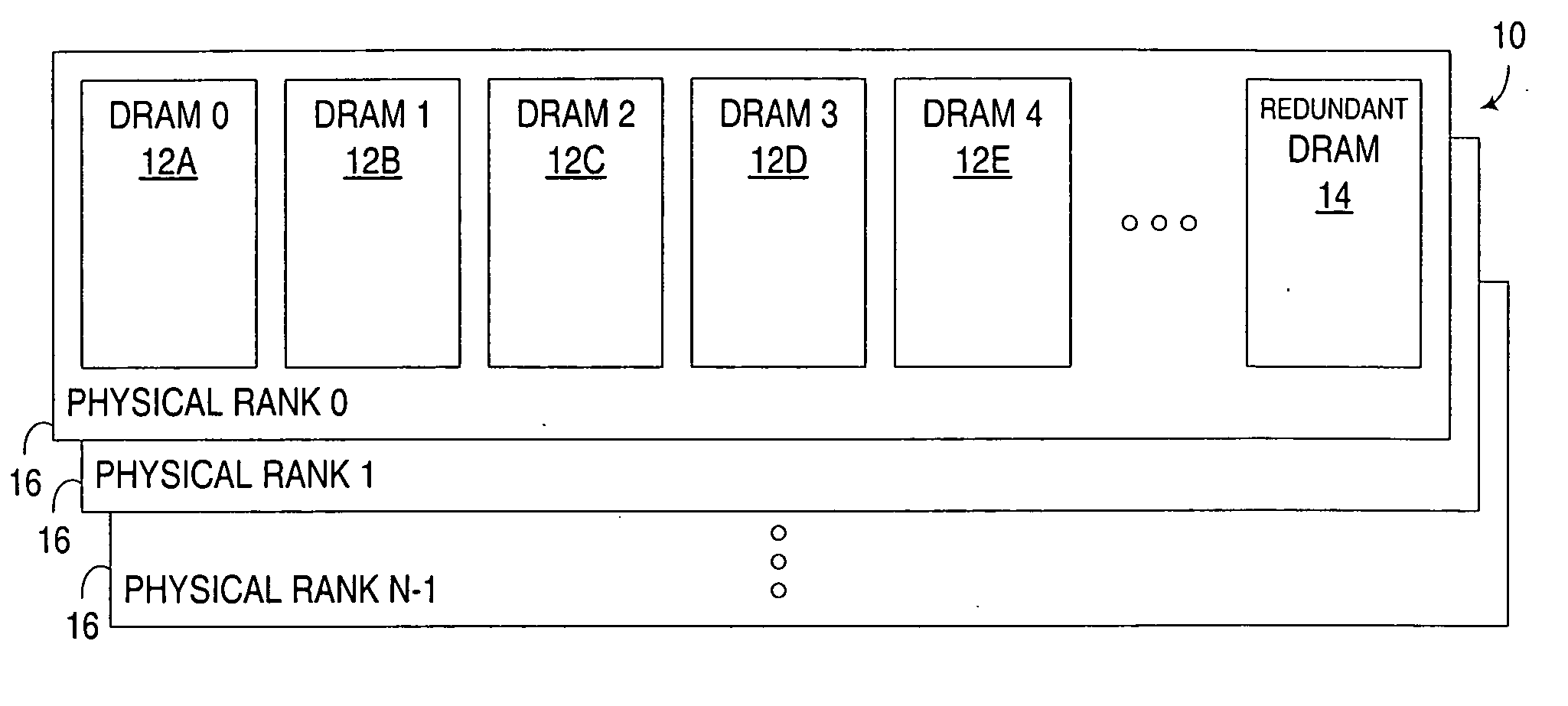

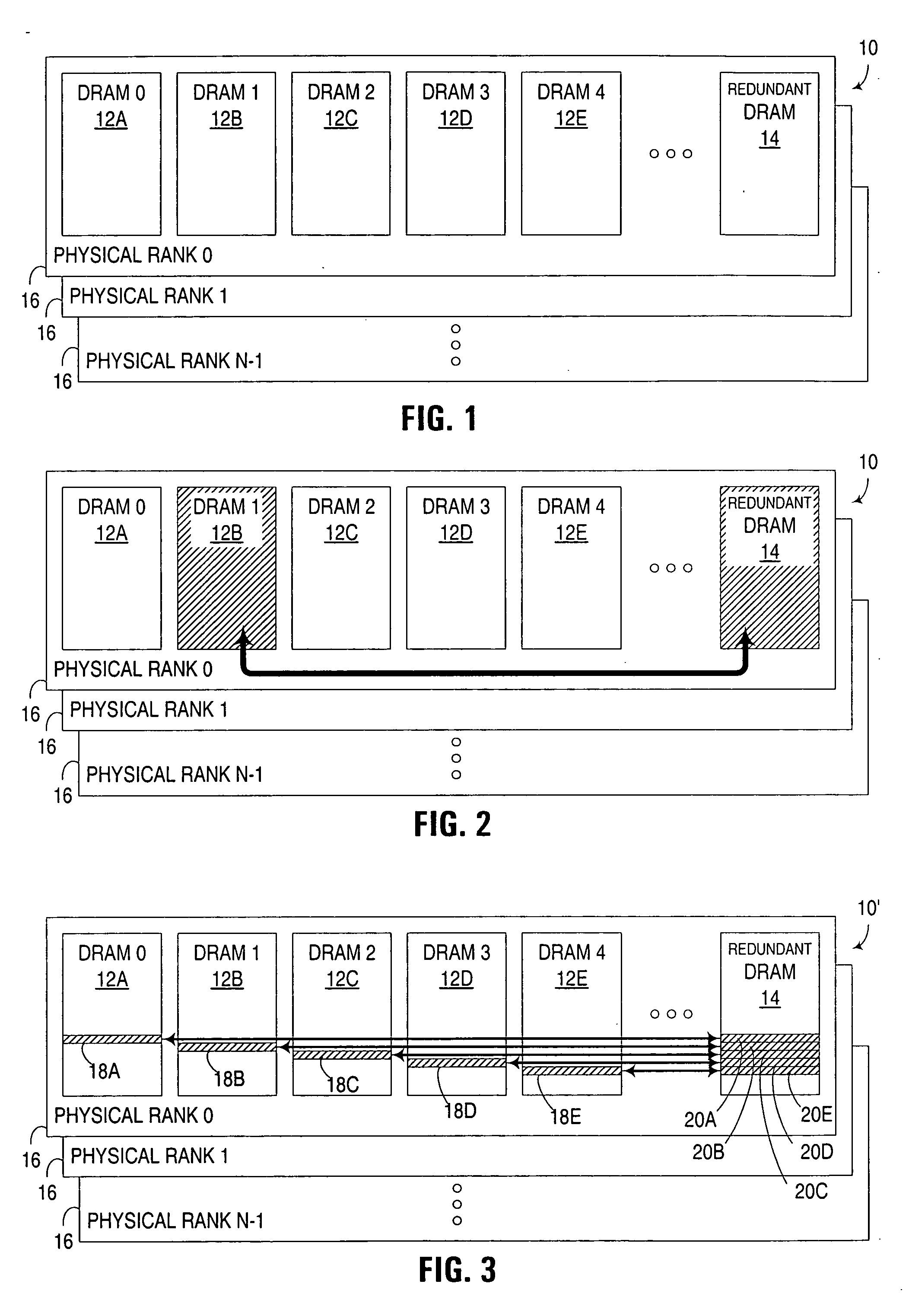

Monitoring of solid state memory devices in active memory system utilizing redundant devices

ActiveUS20060129899A1Facilitate active monitoringError detection/correctionStatic storageMemory addressActive monitoring

Redundant capacity in a memory system is utilized to facilitate active monitoring of solid state memory devices in the memory system. All or part of the data stored in an active solid state memory device, and used in an active data processing system, may be copied to at least one redundant memory device, e.g., by transitioning a memory address range that was allocated to the active memory device to the redundant memory device. By doing so, memory access requests for the memory address range, which would normally be directed to the active memory device, may instead be directed to the redundant memory device, thus enabling the active memory device to be tested (e.g., via writing and reading test data patterns to the active memory device) without interrupting system access to that memory address range.

Owner:IBM CORP

Massive data storage method

ActiveCN102737127AIndex orderedSolve immediacy issuesSpecial data processing applicationsArray data structureIp address

The invention relates to the technical field of computer data storage, and discloses a massive data storage method, which comprises the following steps of: 1, obtaining a currently active memory database server list; 2, organizing data to be stored into a format storable for a database, and mapping the data to be stored into an annular Hash space, wherein the data also comprises a host Internet protocol (IP) address of a data source and an IP address of a destination memory database server; 3, mapping the IP address of the memory database server to the annular Hash space; and 4, establishing a mapping array for the Hash positions of two databases, namely a Hash position storage array for each virtual server of a database server, to obtain mapping relationships between the data, a virtual database and an actual database, and storing the data to be stored by pieces. The method is applied to the instant storage of massive data.

Owner:XIAMEN UNIV

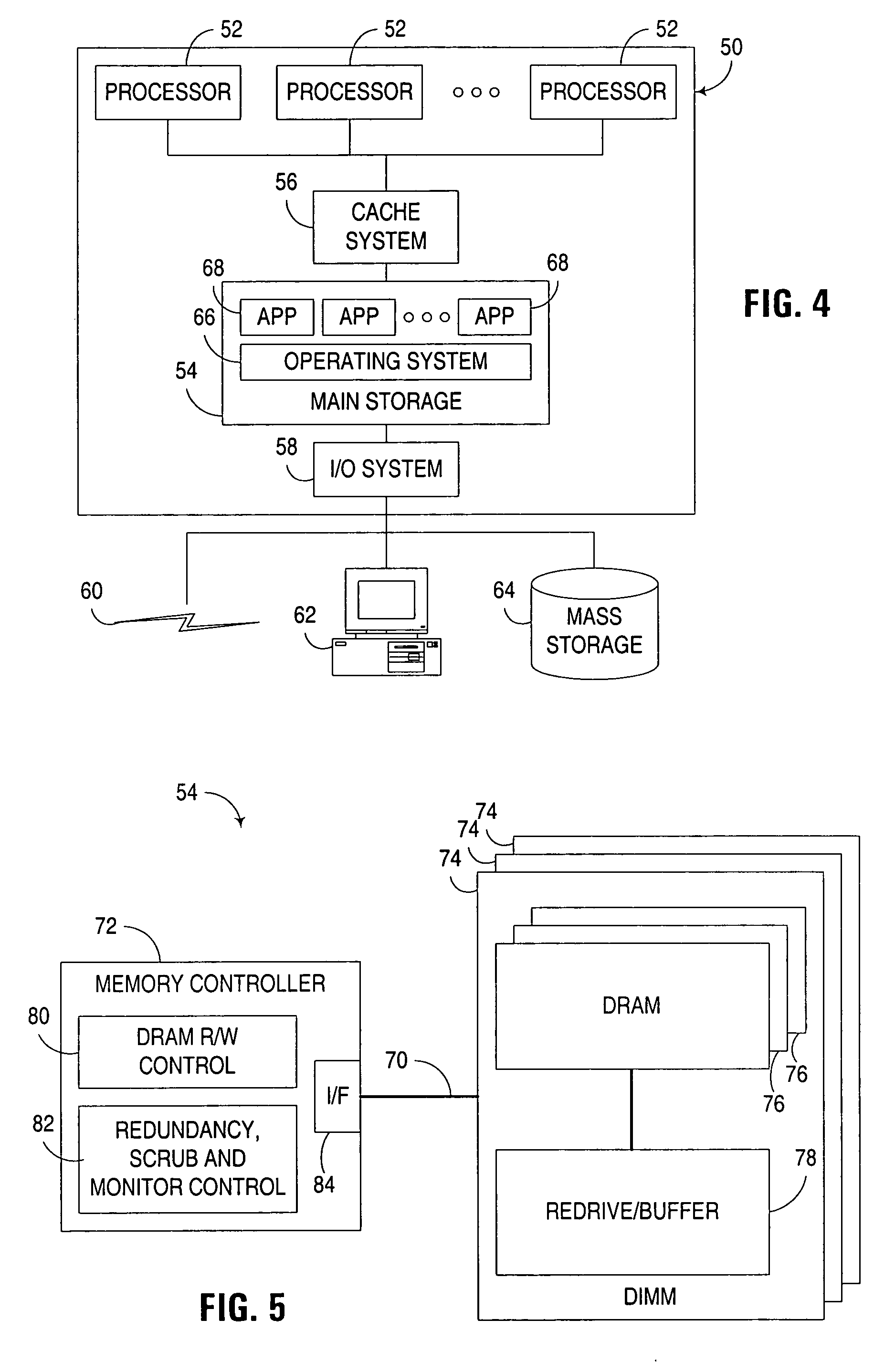

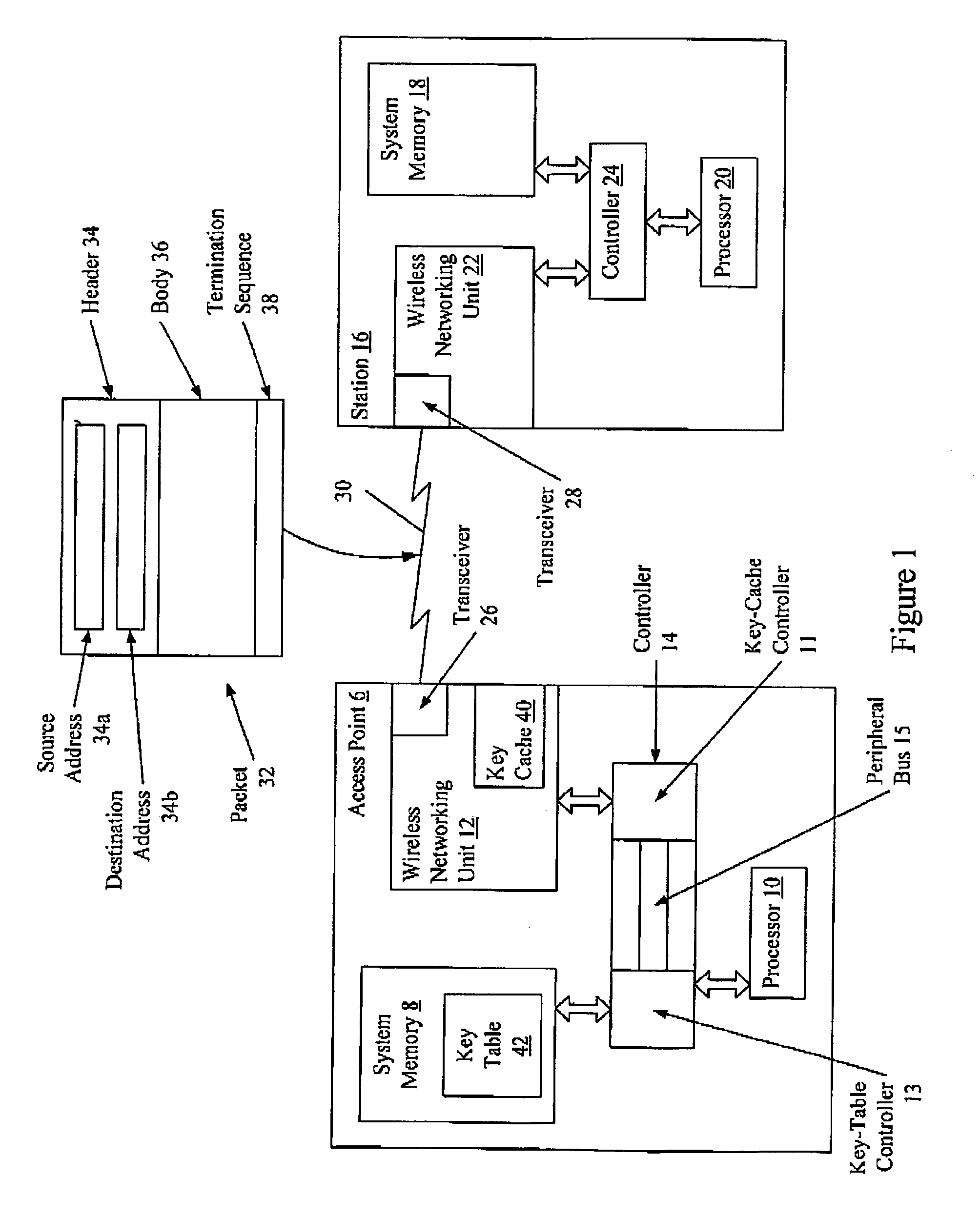

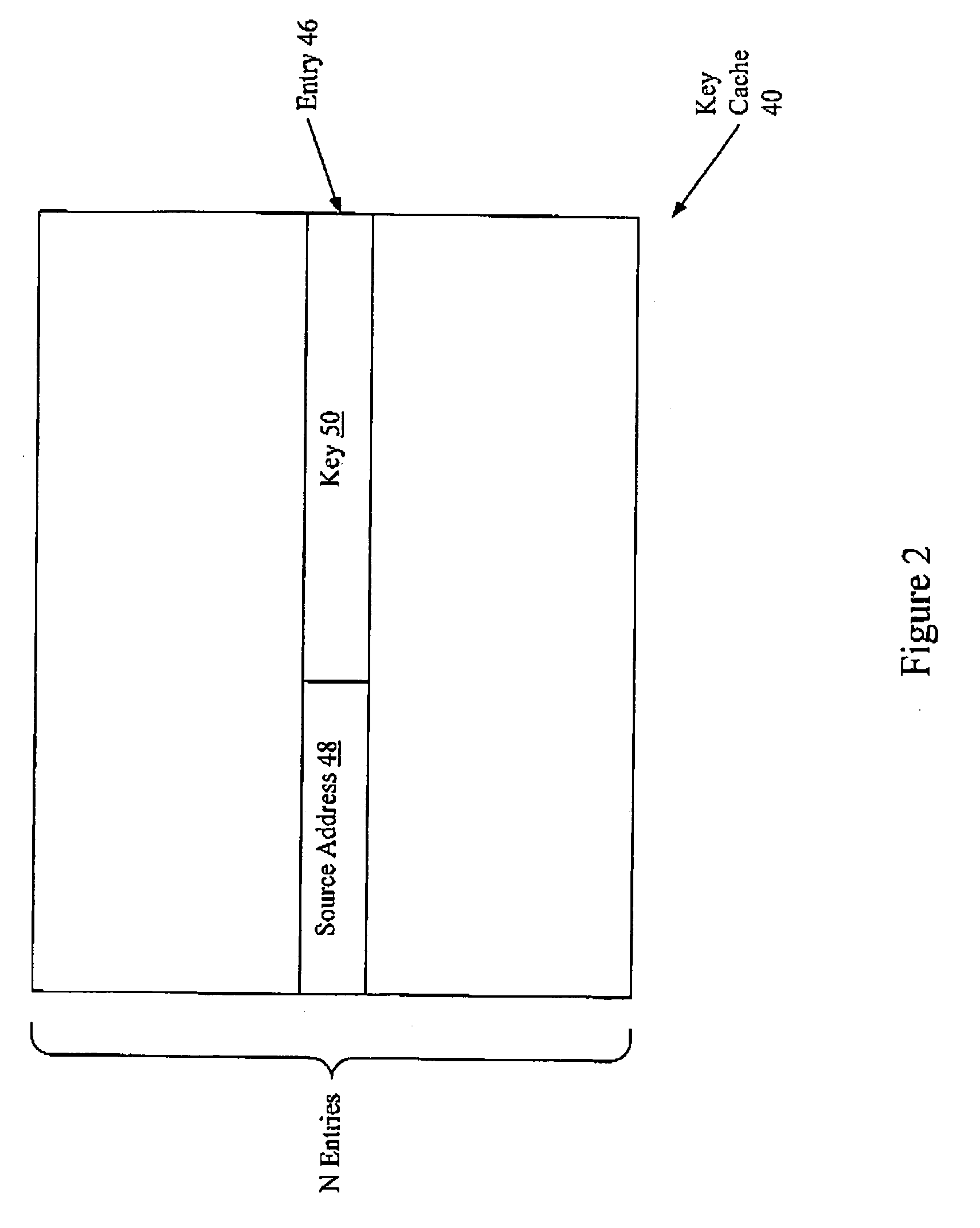

Key caching system

InactiveUS7185196B1Improve system performanceIncrease system bandwidthError preventionNetwork topologiesParallel computingActive memory

A key-caching system retrieves actively used keys from a relatively fast cache memory for fast processing of wireless communications. Additional keys are stored in relatively slow system memory that has high storage capacity. As keys become needed for active use, the keys are retrieved from the system memory and stored in the cache memory. By using active memory for keys actively being used, system performance is enhanced. By using system memory for keys not being used, a greater number of keys are available for transfer to the cache and subsequent active use.

Owner:QUALCOMM INC

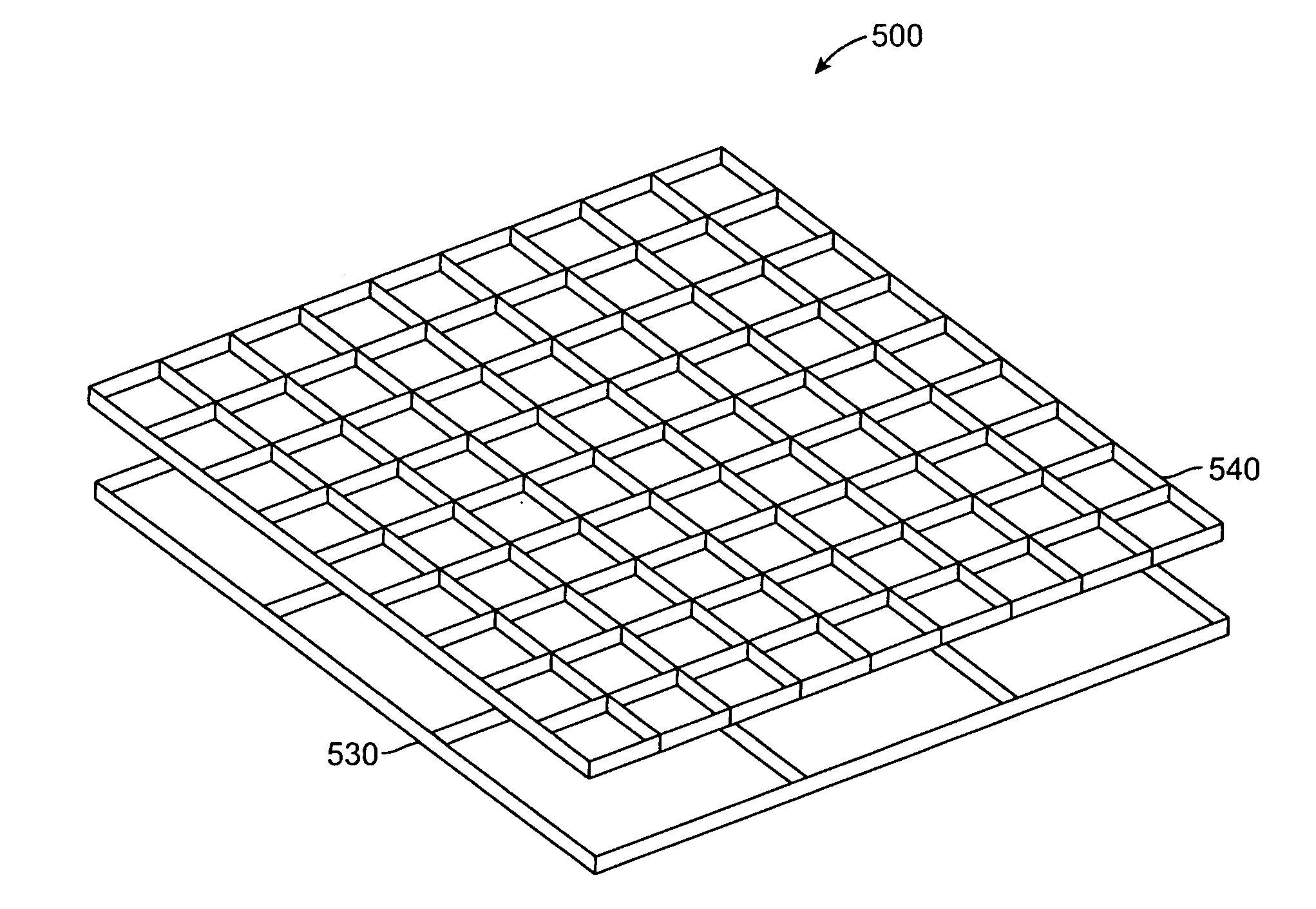

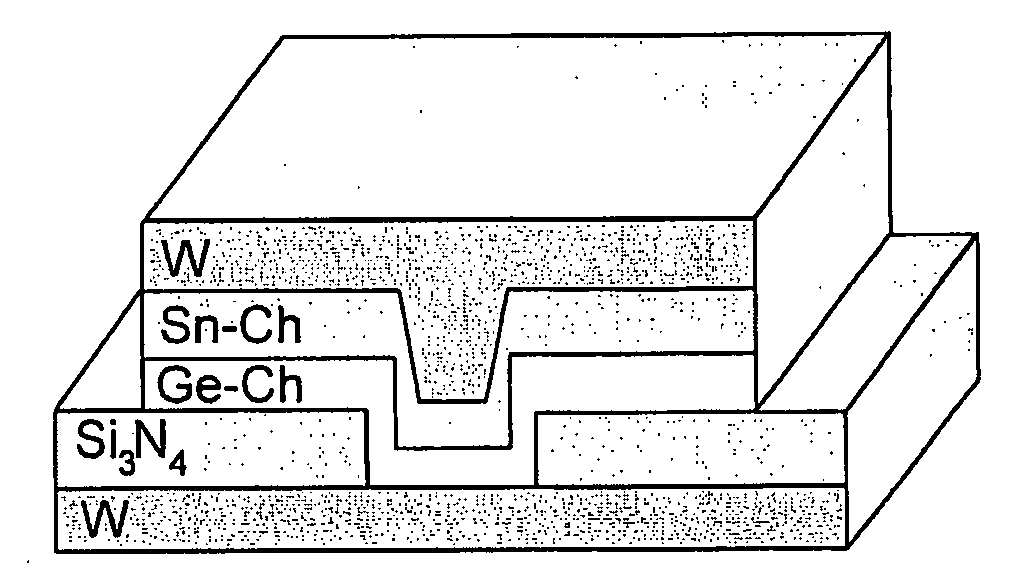

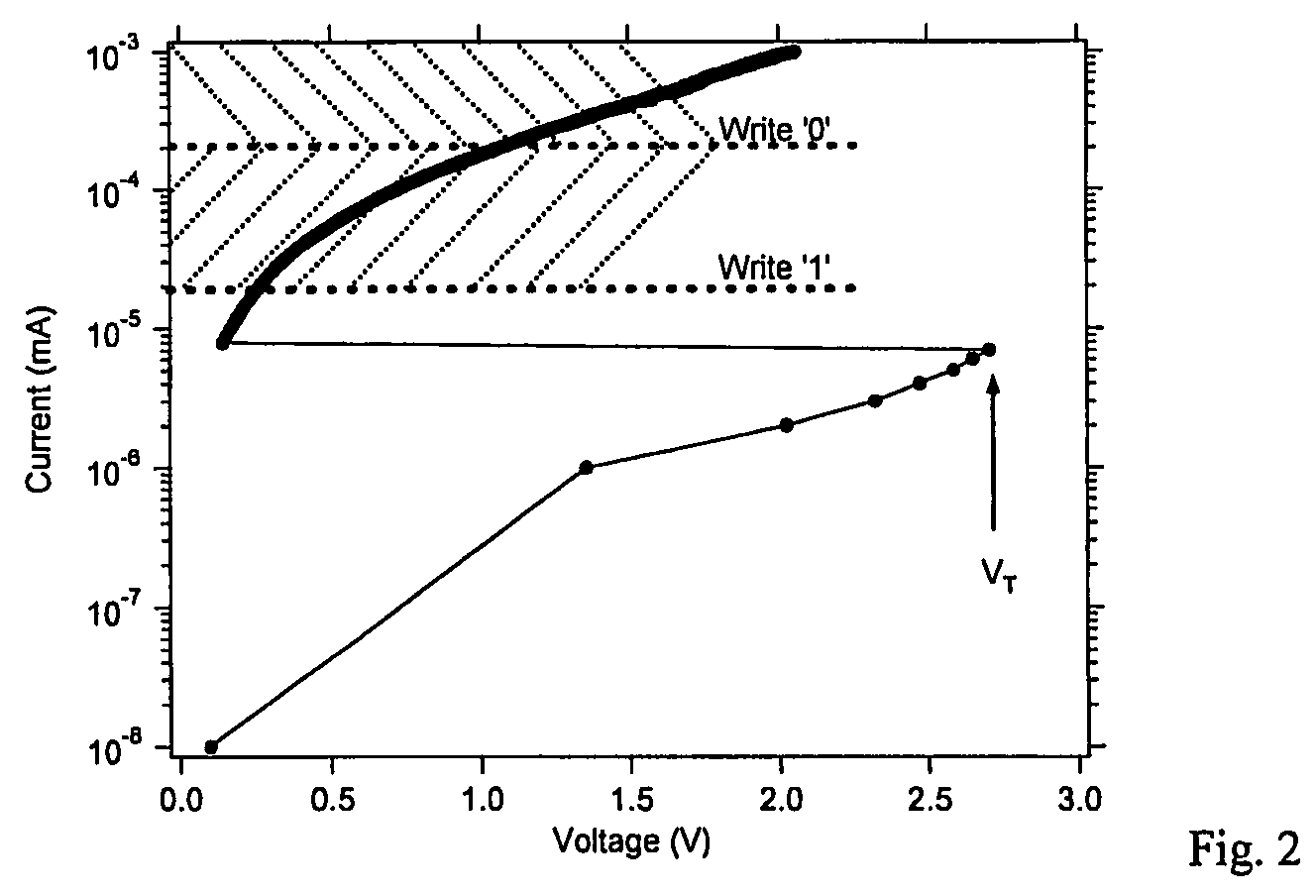

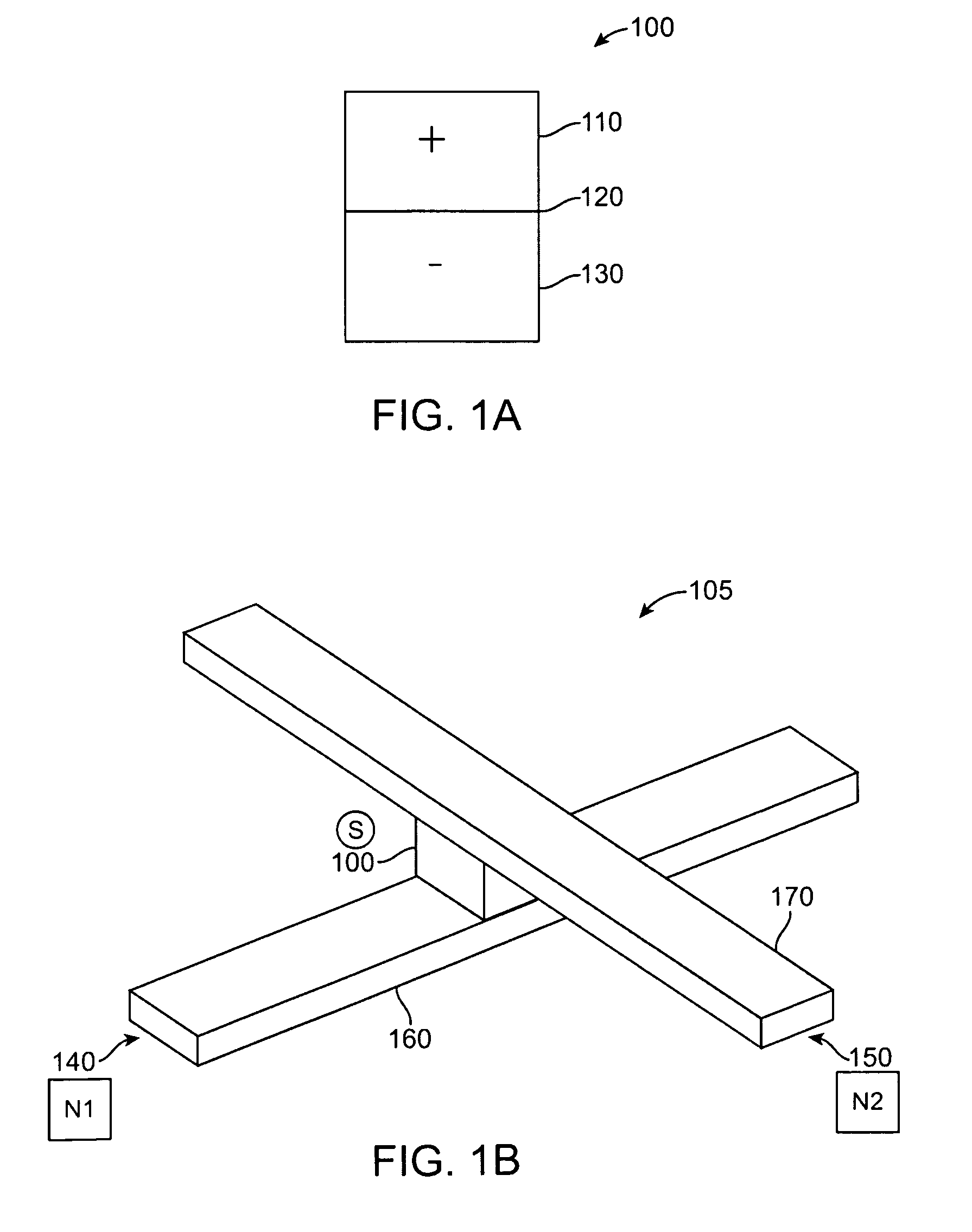

Forced ion migration for chalcogenide phase change memory device

ActiveUS20080121859A1Improve adhesionAvoid layeringNanotechSemiconductor/solid-state device manufacturingPhase-change memoryElectron

Non-volatile memory devices with two stacked layers of chalcogenide materials comprising the active memory device have been investigated for their potential as phase change memories. The devices tested included GeTe / SnTe, Ge2Se3 / SnTe, and Ge2Se3 / SnSe stacks. All devices exhibited resistance switching behavior. The polarity of the applied voltage with respect to the SnTe or SnSe layer was critical to the memory switching properties, due to the electric field induced movement of either Sn or Te into the Ge-chalcogenide layer. One embodiment of the invention is a device comprising a stack of chalcogenide-containing layers which exhibit phase change switching only after a reverse polarity voltage potential is applied across the stack causing ion movement into an adjacent layer and thus “activating” the device to act as a phase change random access memory device or a reconfigurable electronics device when the applied voltage potential is returned to the normal polarity. Another embodiment of the invention is a device that is capable of exhibiting more that two data states.

Owner:BOISE STATE UNIVERSITY

Controlled Shut-Down of Partitions Within a Shared Memory Partition Data Processing System

ActiveUS20090307441A1Volume/mass flow measurementComputer security arrangementsData processing systemActive memory

Controlled partition shut-down is provided within a shared memory partition data processing system including a shared memory partition, a paging service partition, a hypervisor and a shared memory pool within physical memory. The hypervisor manages access to logical pages within the pool and page-out of pages from the pool to external paging storage via the paging service partition. A respective paging service stream exists between the paging service partition and hypervisor for each shared memory partition, with each stream including a stream state. The control method includes: responsive to a shut-down initiating event, notifying the paging service partition to shut down, and determining whether a shared memory partition is currently active, and if so, signaling the hypervisor to complete paging activity for the active memory partition and waiting for its stream state to enter a suspended or a completed state before automatically shutting down the paging service partition.

Owner:IBM CORP

Forced ion migration for chalcogenide phase change memory device

ActiveUS7924608B2Improve adhesionAvoid layeringNanotechSemiconductor/solid-state device manufacturingPhase-change memoryElectron

Non-volatile memory devices with two stacked layers of chalcogenide materials comprising the active memory device have been investigated for their potential as phase change memories. The devices tested included GeTe / SnTe, Ge2Se3 / SnTe, and Ge2Se3 / SnSe stacks. All devices exhibited resistance switching behavior. The polarity of the applied voltage with respect to the SnTe or SnSe layer was critical to the memory switching properties, due to the electric field induced movement of either Sn or Te into the Ge-chalcogenide layer. One embodiment of the invention is a device comprising a stack of chalcogenide-containing layers which exhibit phase change switching only after a reverse polarity voltage potential is applied across the stack causing ion movement into an adjacent layer and thus “activating” the device to act as a phase change random access memory device or a reconfigurable electronics device when the applied voltage potential is returned to the normal polarity. Another embodiment of the invention is a device that is capable of exhibiting more that two data states.

Owner:BOISE STATE UNIVERSITY

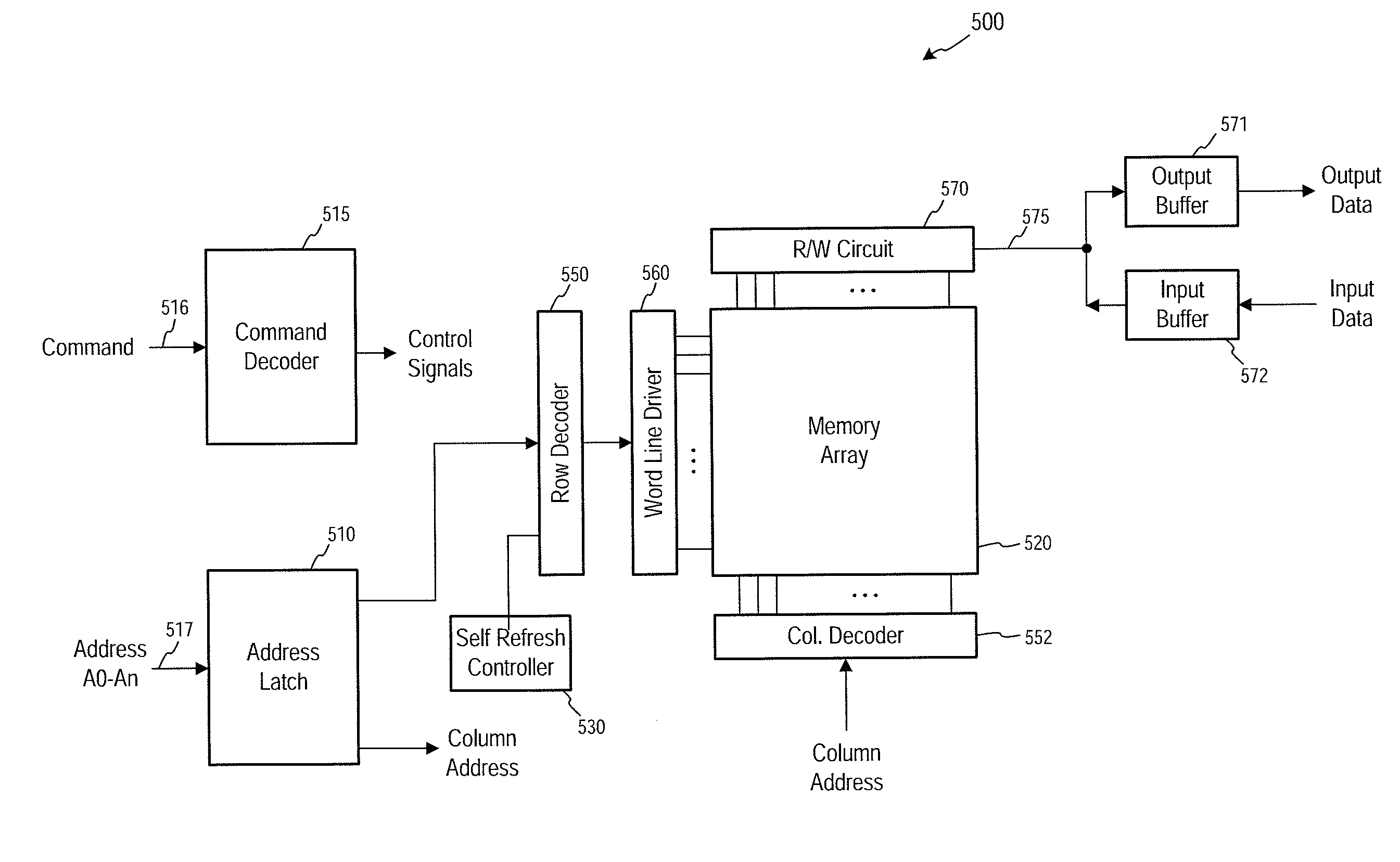

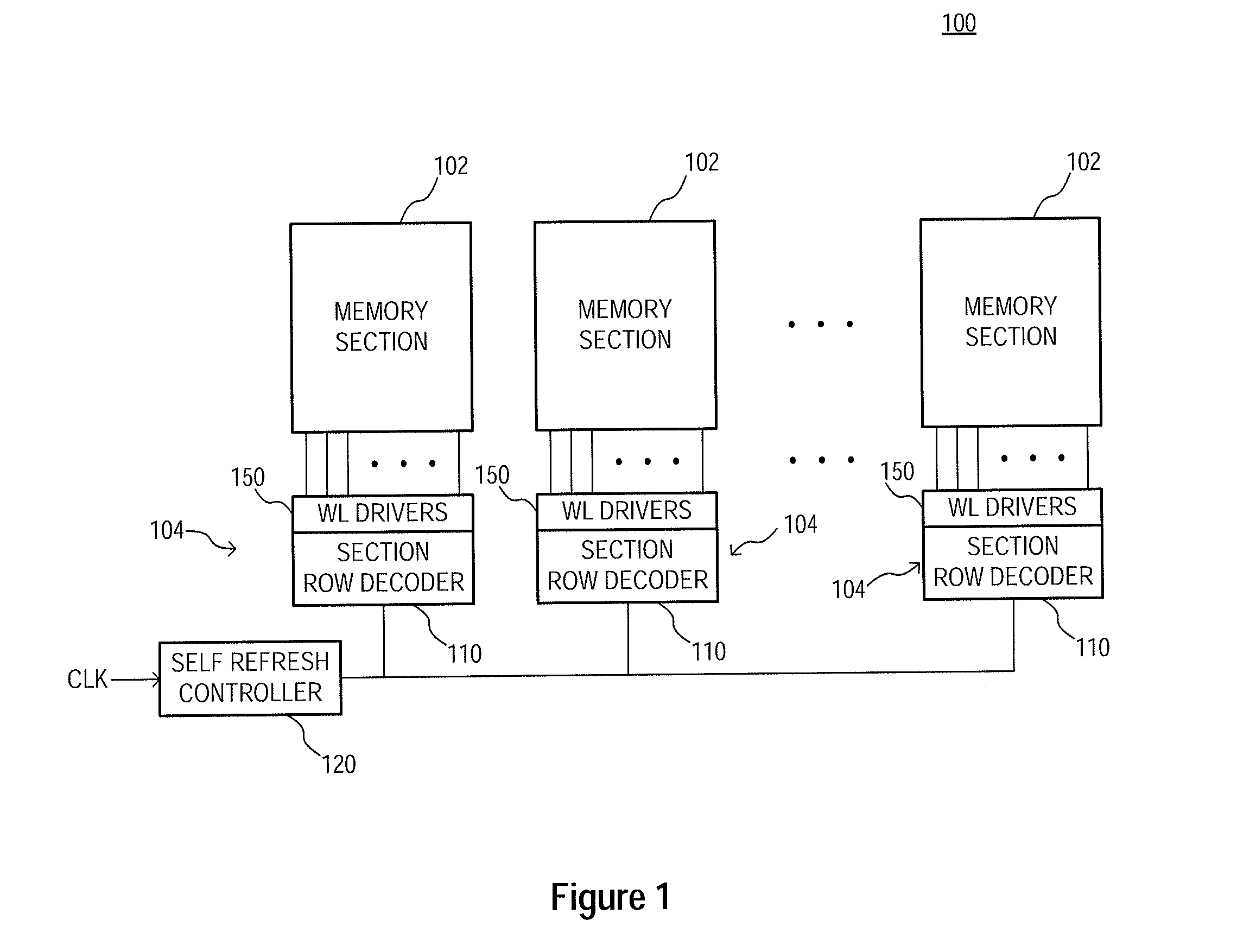

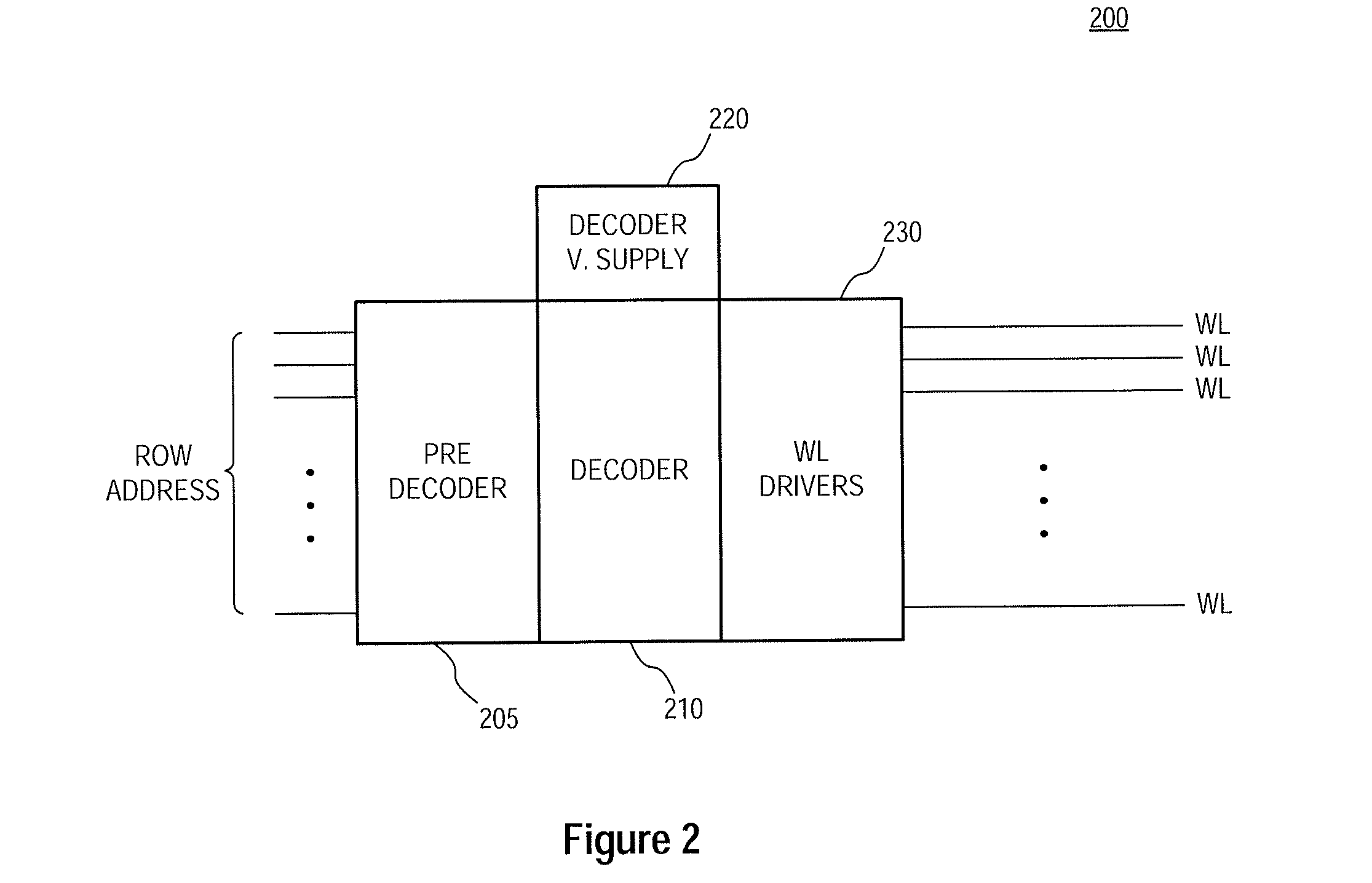

Memory refresh methods, memory section control circuits, and apparatuses

Apparatuses, memory section control circuits, and methods of refreshing memory are disclosed. An example apparatus includes a plurality of memory sections and a plurality of memory section control circuits. Each memory section control circuit is coupled to a respective one of the plurality of memory sections and includes a plurality of access line drivers, each of which includes a plurality of transistors having common coupled gates. During an operation of the apparatus a first voltage is provided to the commonly coupled gates of the transistors of at least some of the access line drivers of the memory section control circuit coupled to an active memory section and a second voltage is provided to the commonly coupled gates of the transistors of the access line drivers of the memory section control circuit coupled to an inactive memory section control circuit, wherein the first voltage is greater than the second voltage.

Owner:MICRON TECH INC

Methods, Architecture, and Apparatus for Implementing Machine Intelligence and Hierarchical Memory Systems

ActiveUS20080201286A1Accurate identificationMathematical modelsDigital computer detailsPattern sequenceAlgorithm

Sophisticated memory systems and intelligent machines may be constructed by creating an active memory system with a hierarchical architecture. Specifically, a system may comprise a plurality of individual cortical processing units arranged into a hierarchical structure. Each individual cortical processing unit receives a sequence of patterns as input. Each cortical processing unit processes the received input sequence of patterns using a memory containing previously encountered sequences with structure and outputs another pattern. As several input sequences are processed by a cortical processing unit, it will therefore generate a sequence of patterns on its output. The sequence of patterns on its output may be passed as an input to one or more cortical processing units in next higher layer of the hierarchy. A lowest layer of cortical processing units may receive sensory input from the outside world. The sensory input also comprises a sequence of patterns.

Owner:NUMENTA INC

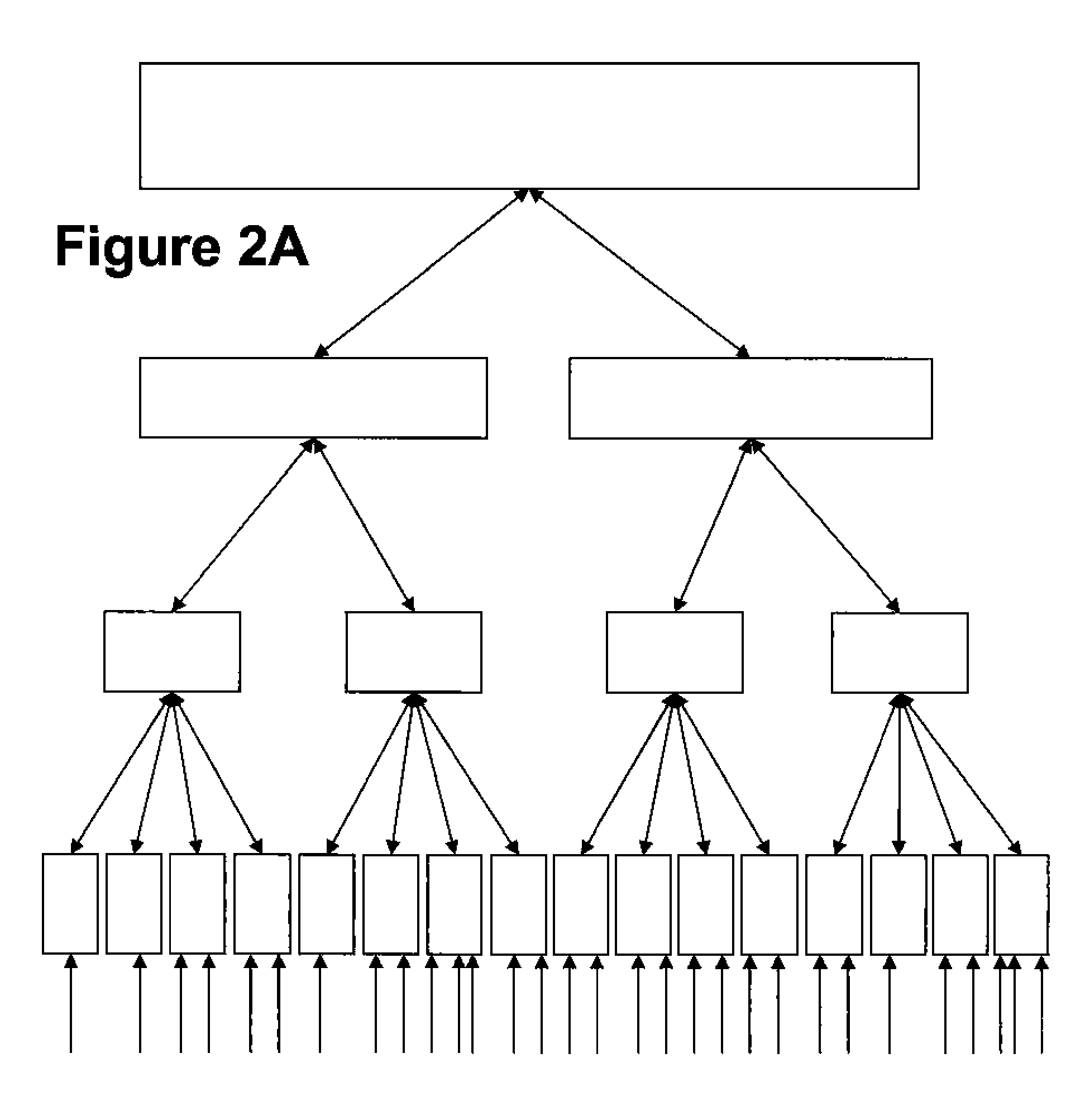

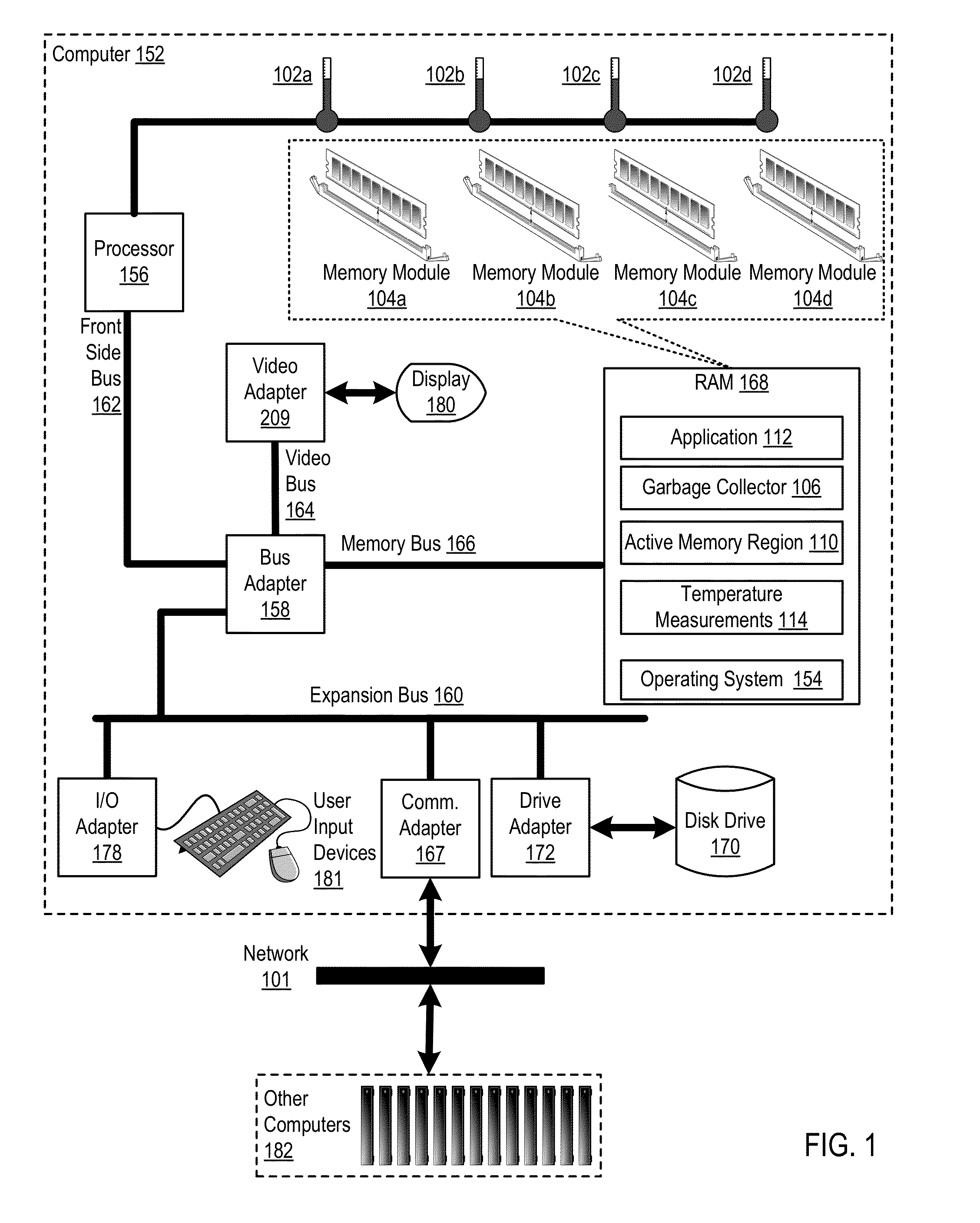

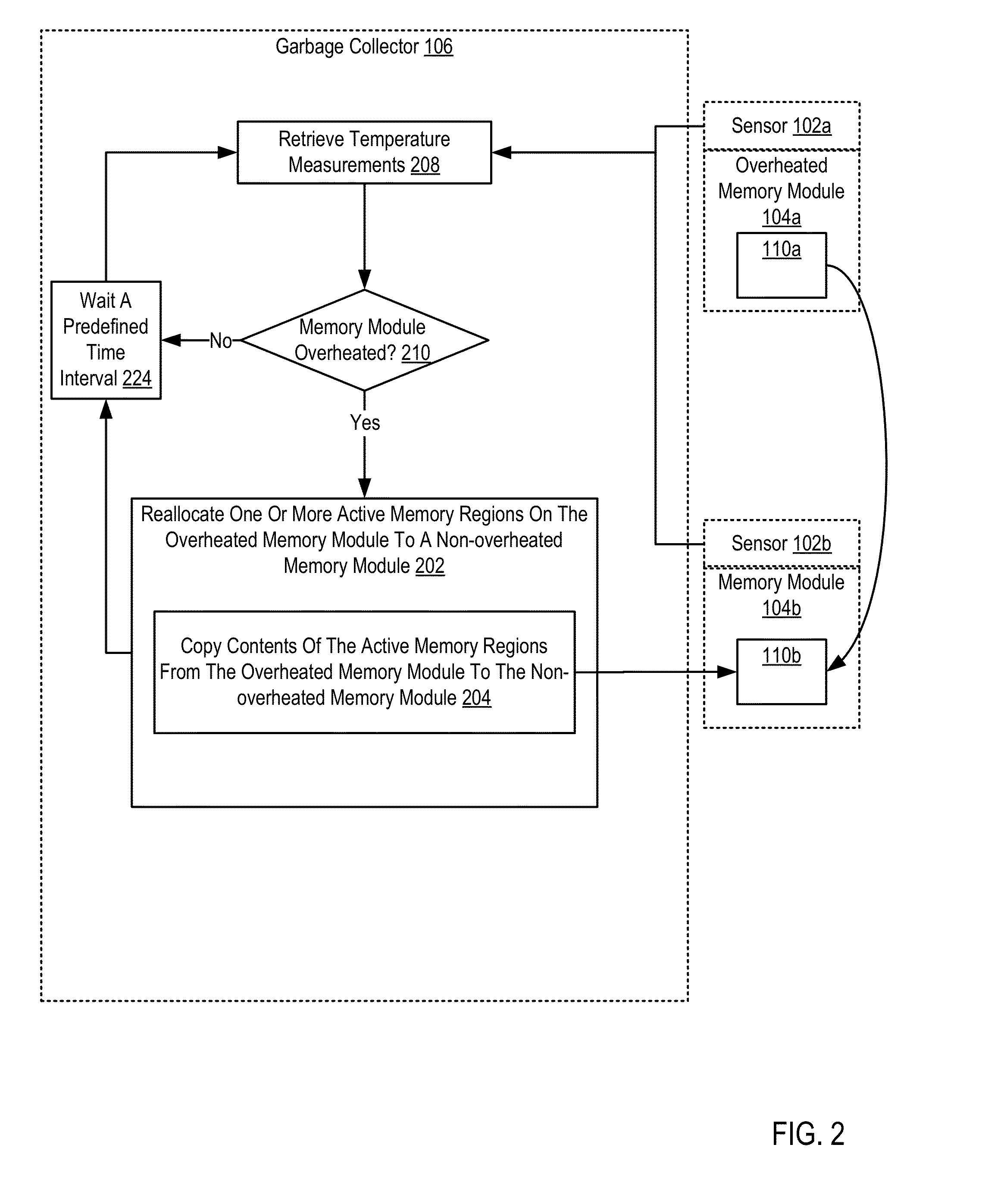

Administering Thermal Distribution Among Memory Modules Of A Computing System

InactiveUS20130067136A1Energy efficient ICTMemory adressing/allocation/relocationWaste collectionParallel computing

A computing system includes a number of memory modules and temperature sensors. Each temperature sensor measures a temperature of a memory module. In such a computing system a garbage collector during garbage collection, determines whether a temperature measurement of a temperature sensor indicates that a memory module is overheated and, if a temperature measurement of a temperature sensor indicates a memory module is overheated, the garbage collector reallocates one or more active memory regions on the overheated memory module to a non-overheated memory module. Reallocating the active memory regions includes copying contents of the active memory regions from the overheated memory module to the non-overheated memory module.

Owner:IBM CORP

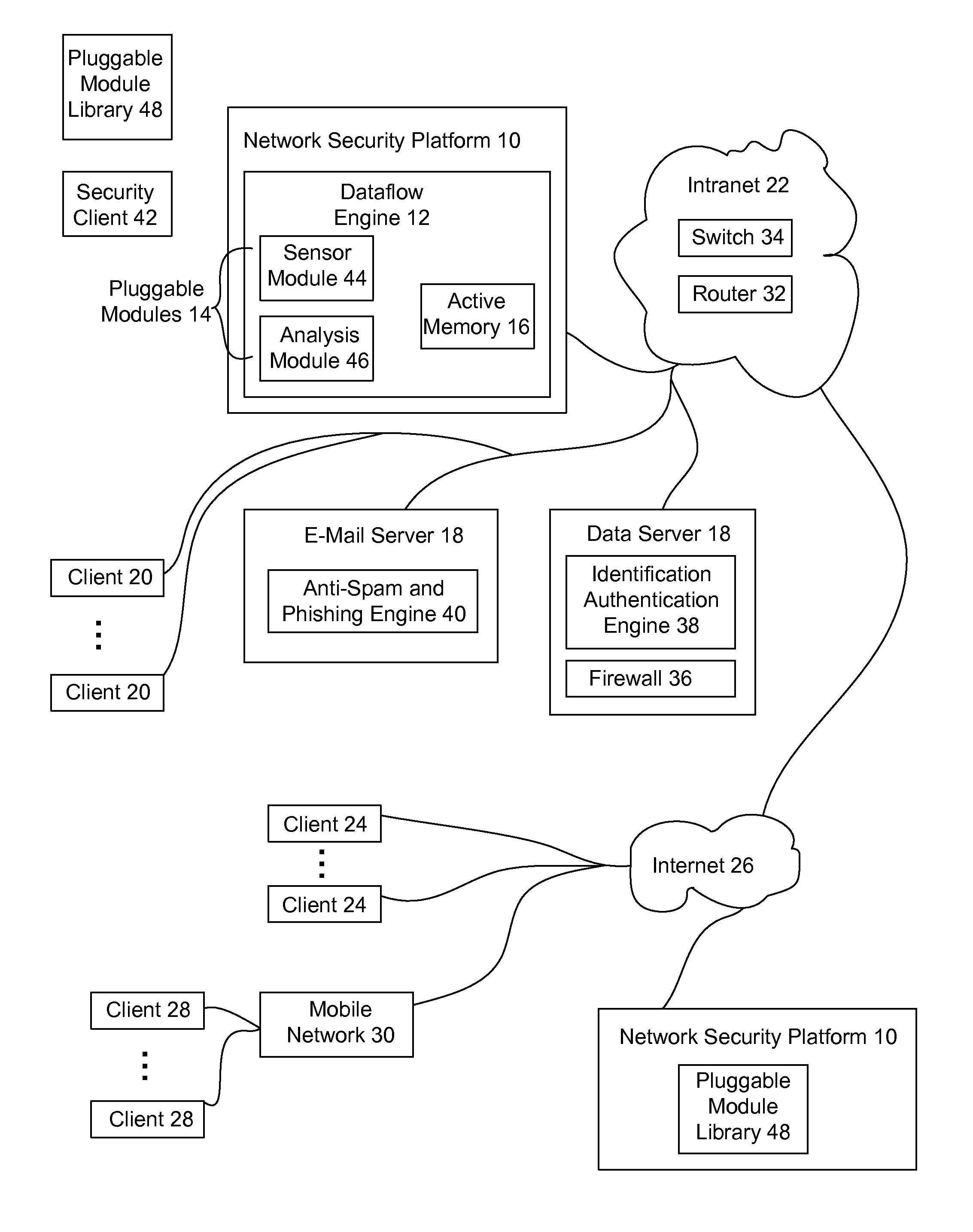

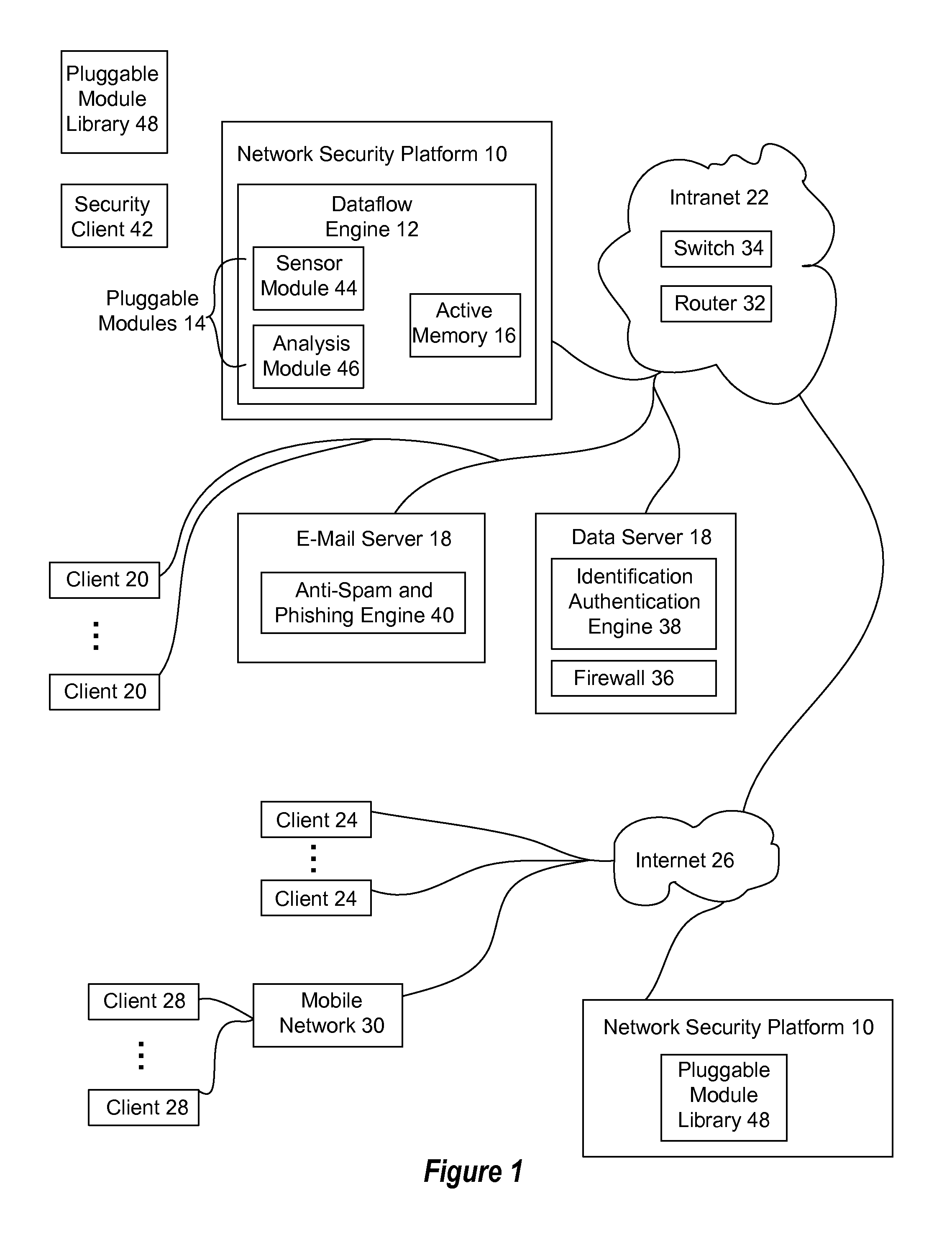

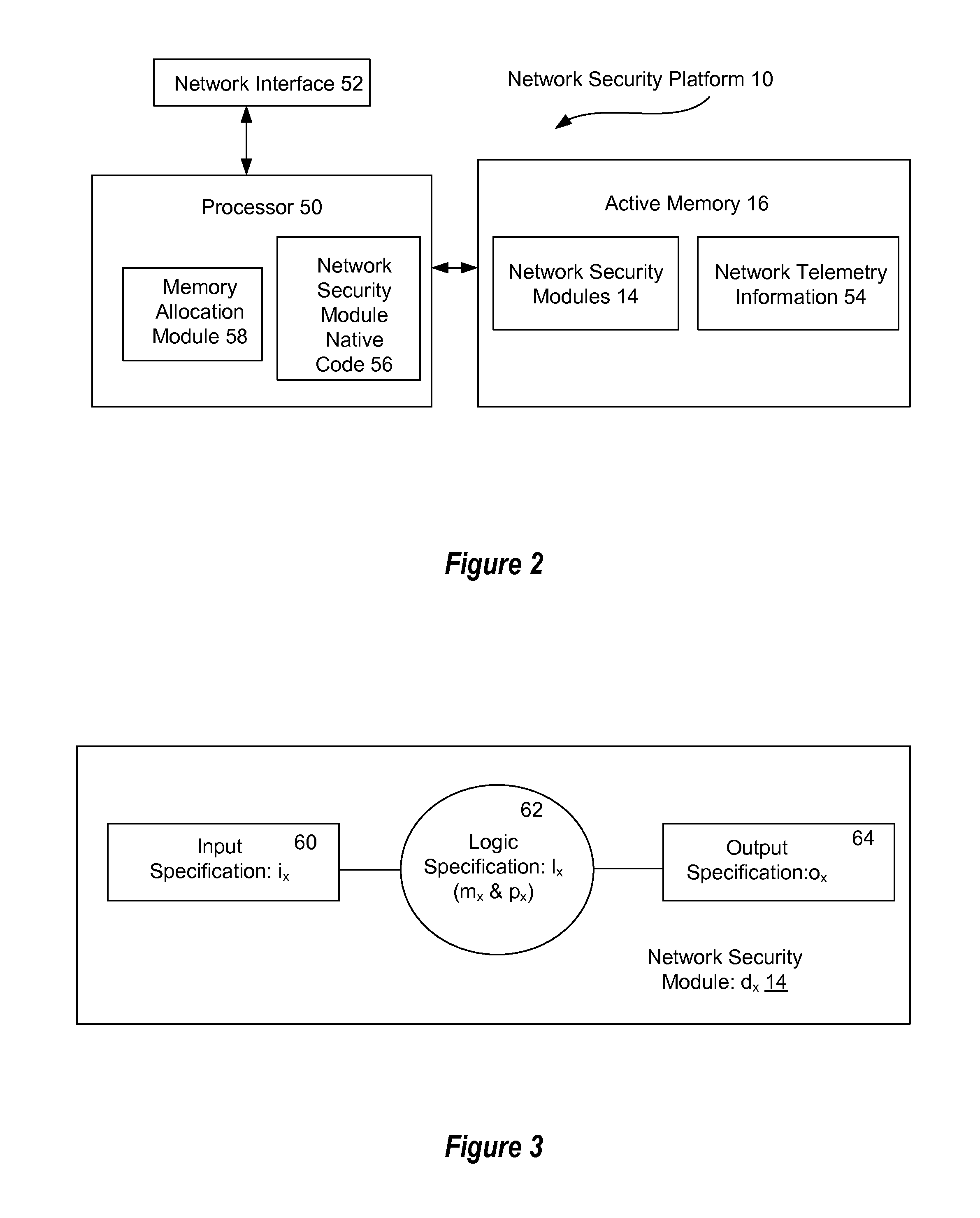

Automated security analytics platform

ActiveUS20140137240A1Reduce the amount requiredIncreased retrieval timeMemory loss protectionError detection/correctionReal-time dataActive memory

A network security platform stores network telemetry information in an active memory, such as DRAM, and analyzes the network telemetry information to detect and respond to network security threats. Using a common active memory to store sensed network telemetry information and analyze that information provides a real-time dataflow engine for detecting security threats and neutralizing detected threats.

Owner:ALERT LOGIC

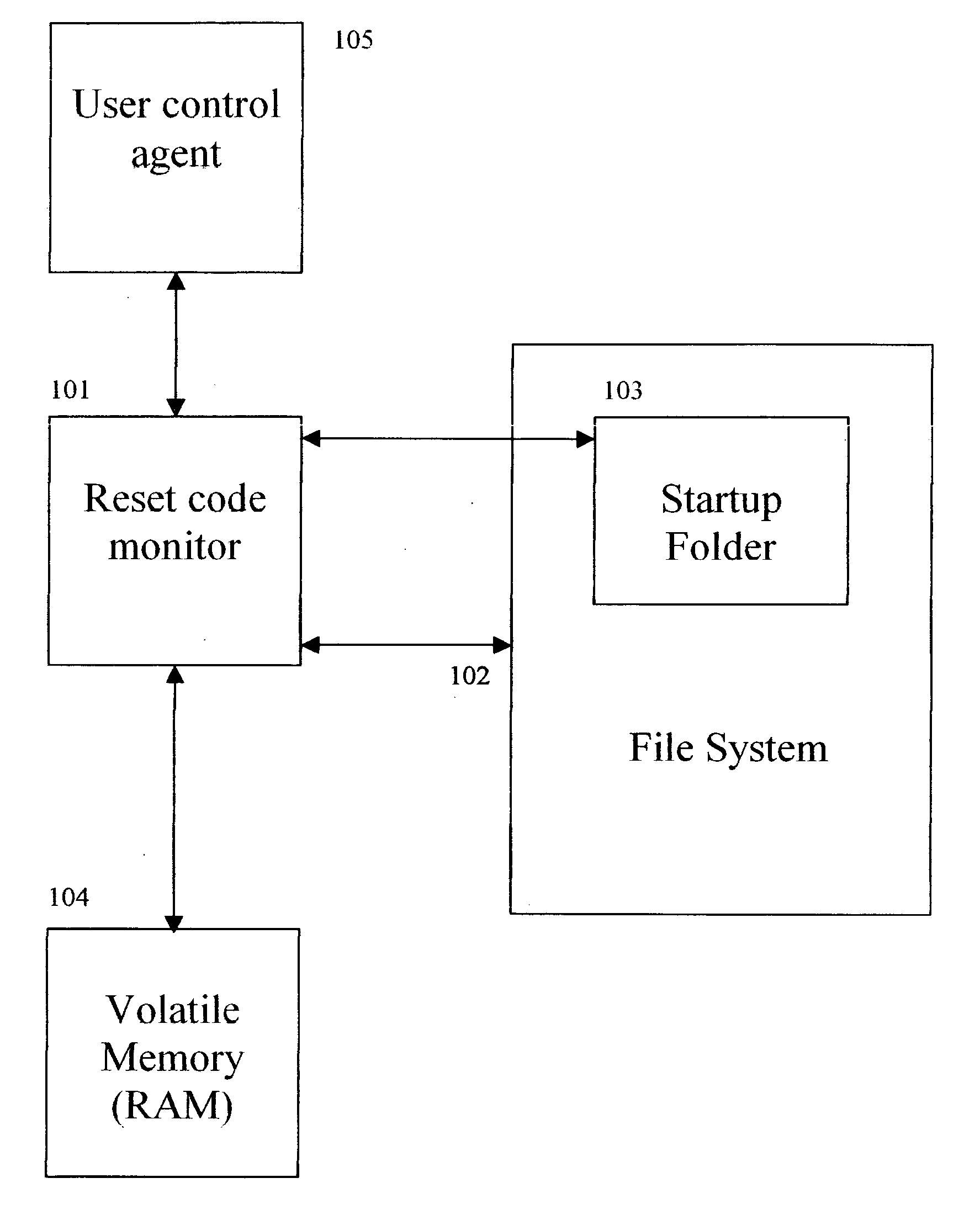

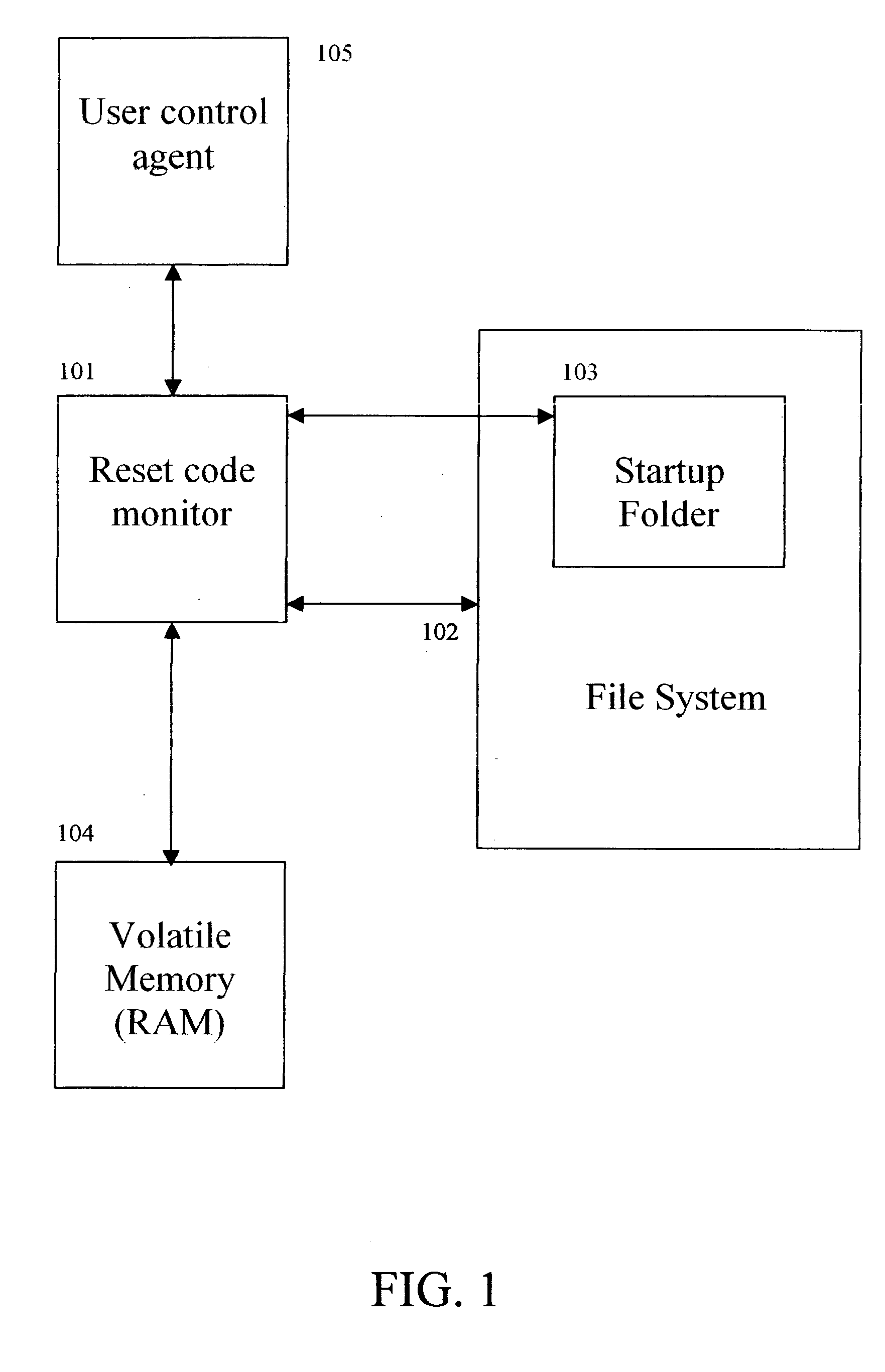

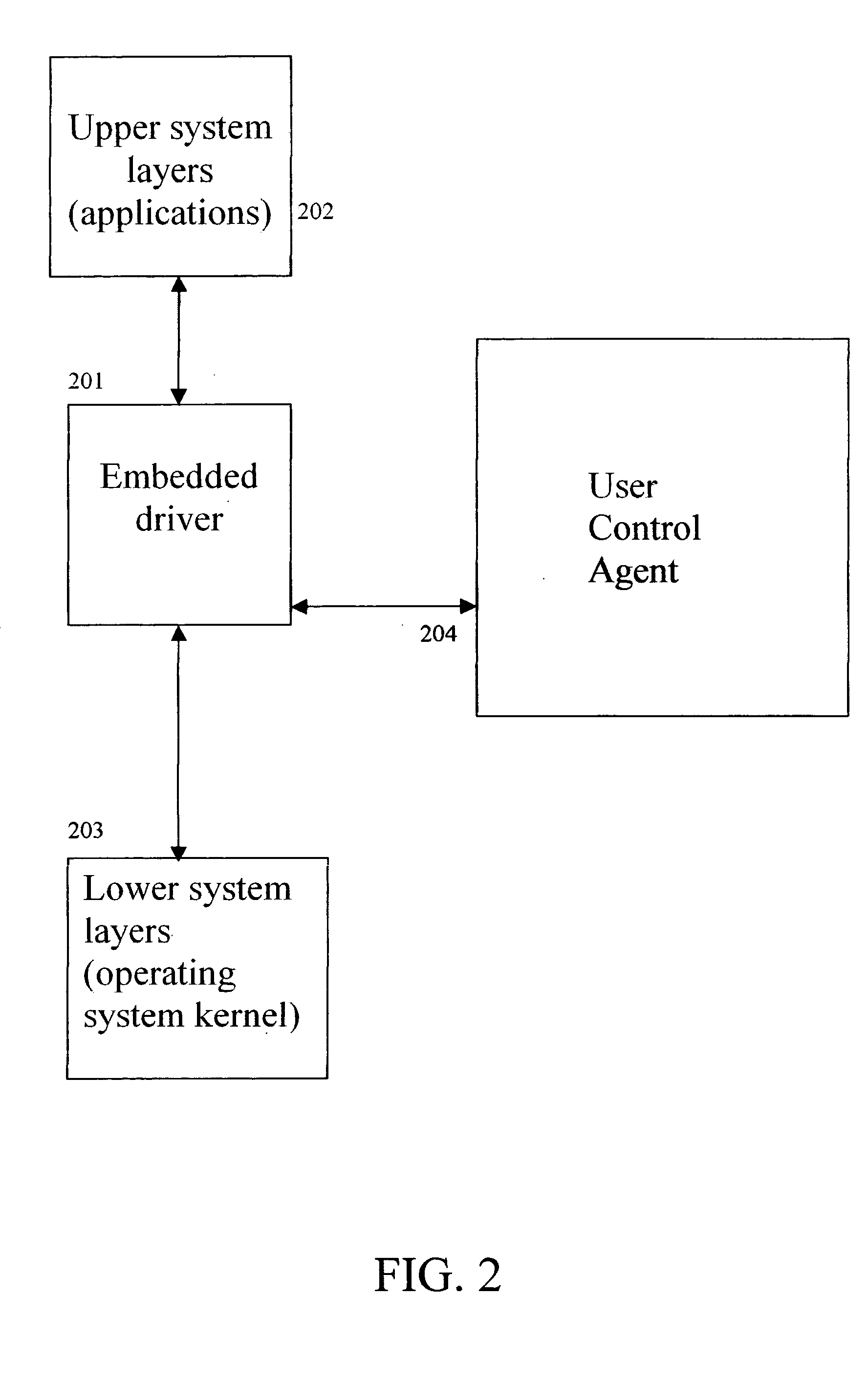

Protecting embedded devices with integrated reset detection

A system for optimizing the security of embedded, mobile devices such as personal data assistants and Smartphones by protecting against soft and hard reset code attacks. In a preferred embodiment, this is achieved by 1. Scanning the active memory for evidence of “hard reset attack” code. 2. Scanning the filesystem for evidence of “hard reset attack” code. 3. Scanning the active memory for evidence of “soft reset attack” code. 4. Scanning the filesystem for evidence of “soft reset attack” code. 5. Automatically blocking and cleaning the reset code, based on user preference. 6. Providing optional user control over which programs are allowed to write to the startup folder.

Owner:PEIKARI CYRUS

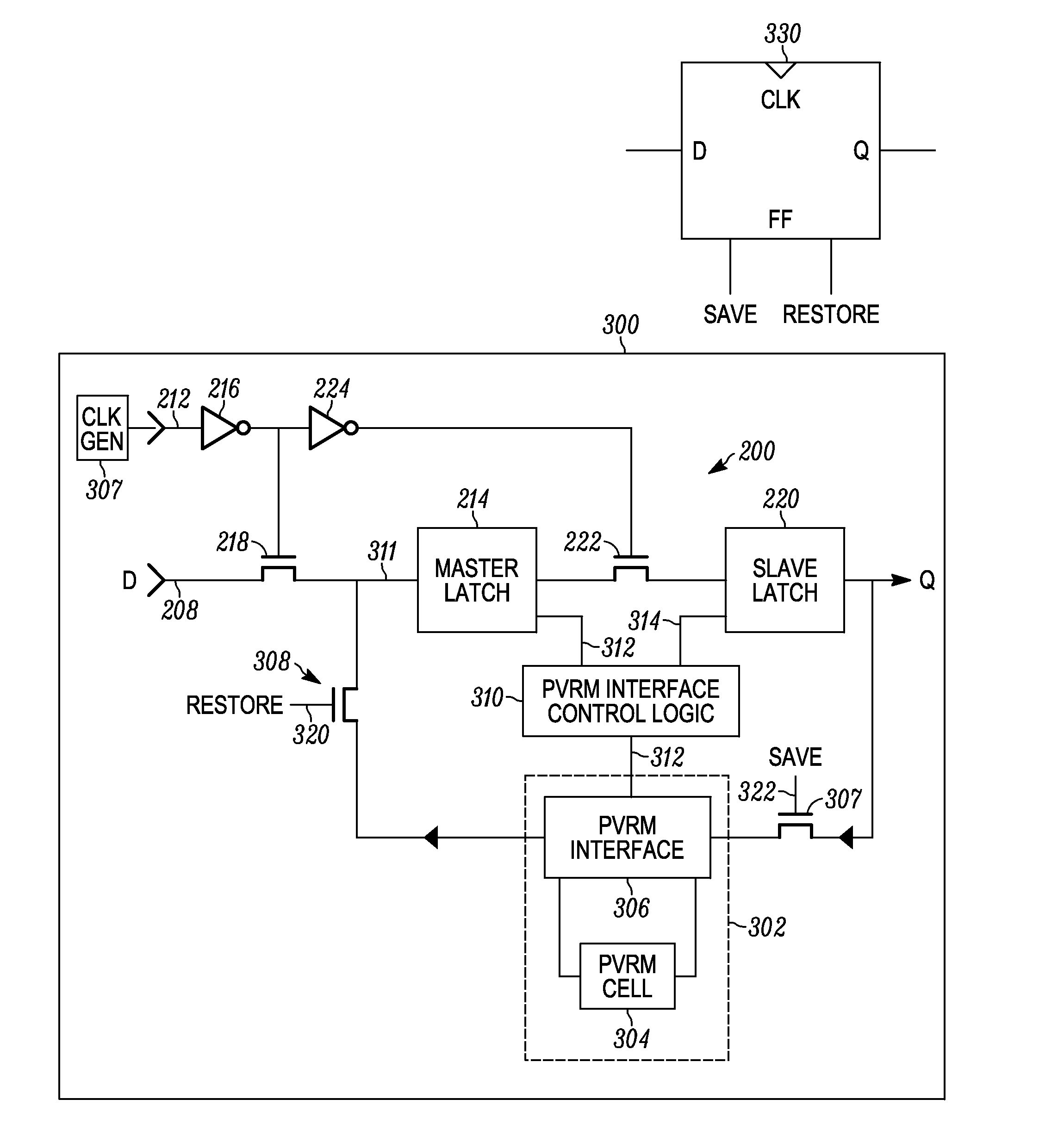

Method and apparatus for providing complimentary state retention

ActiveUS20130069964A1Semiconductor/solid-state device manufacturingImage memory managementActive memoryMemory circuits

A method, integrated circuit and apparatus are operative to control a plurality of passive variable resistance memory cells to store complimentary state information from at least one active memory circuit, such as a flop, latch, or any other suitable state generation circuit. The method, apparatus and integrated circuit may be operative to control the plurality of passive variable resistance memory cells to also restore the stored complimentary state information for the at least one active memory.

Owner:ADVANCED MICRO DEVICES INC

Trace based rollback of a speculatively updated cache

This invention includes a circuit for tracking memory operations with trace-based execution. Each trace includes a sequence of operations that includes zero or more of the memory operations. Traces execute atomically and become eligible for commitment after all the operations in the trace have executed. The memory operations being executed form a set of active memory operations that have a predefined program order among them and corresponding ordering constraints. At least some of the active memory operations access the memory in an execution order that is different from the program order. Checkpoint entries are associated with each trace. Each entry refers to a checkpoint location. Memory operation ordering entries correspond to each one of the active memory operations. Rollback requests result in overwriting the checkpoint locations associated with the selected trace as well as the checkpoint locations associated with traces that are younger than the selected trace.

Owner:SUN MICROSYSTEMS INC

Stochastic synapse memory element with spike-timing dependent plasticity (STDP)

Owner:INT BUSINESS MASCH CORP

Active memory expansion in a database environment to query needed/uneeded results

ActiveUS20120124016A1Digital data information retrievalDigital data processing detailsActive memoryDatabase

Techniques are described for estimating and managing memory compression for request processing. Embodiments of the invention may generally include receiving a request for data, determining if the requested data contains any compressed data, and sending the requesting entity only the uncompressed data. A separate embodiment generally includes receiving a request for data, determining if the requested data contains any compressed data, gathering uncompression criteria about the requested data, and using the uncompression criteria to selectively determine what portion of the compressed data to uncompress.

Owner:IBM CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com