Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

431 results about "Dataflow" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Dataflow is a term used in computing which has various meanings depending on application and the context in which the term is used. In the context of software architecture, data flow relates to stream processing or reactive programming.

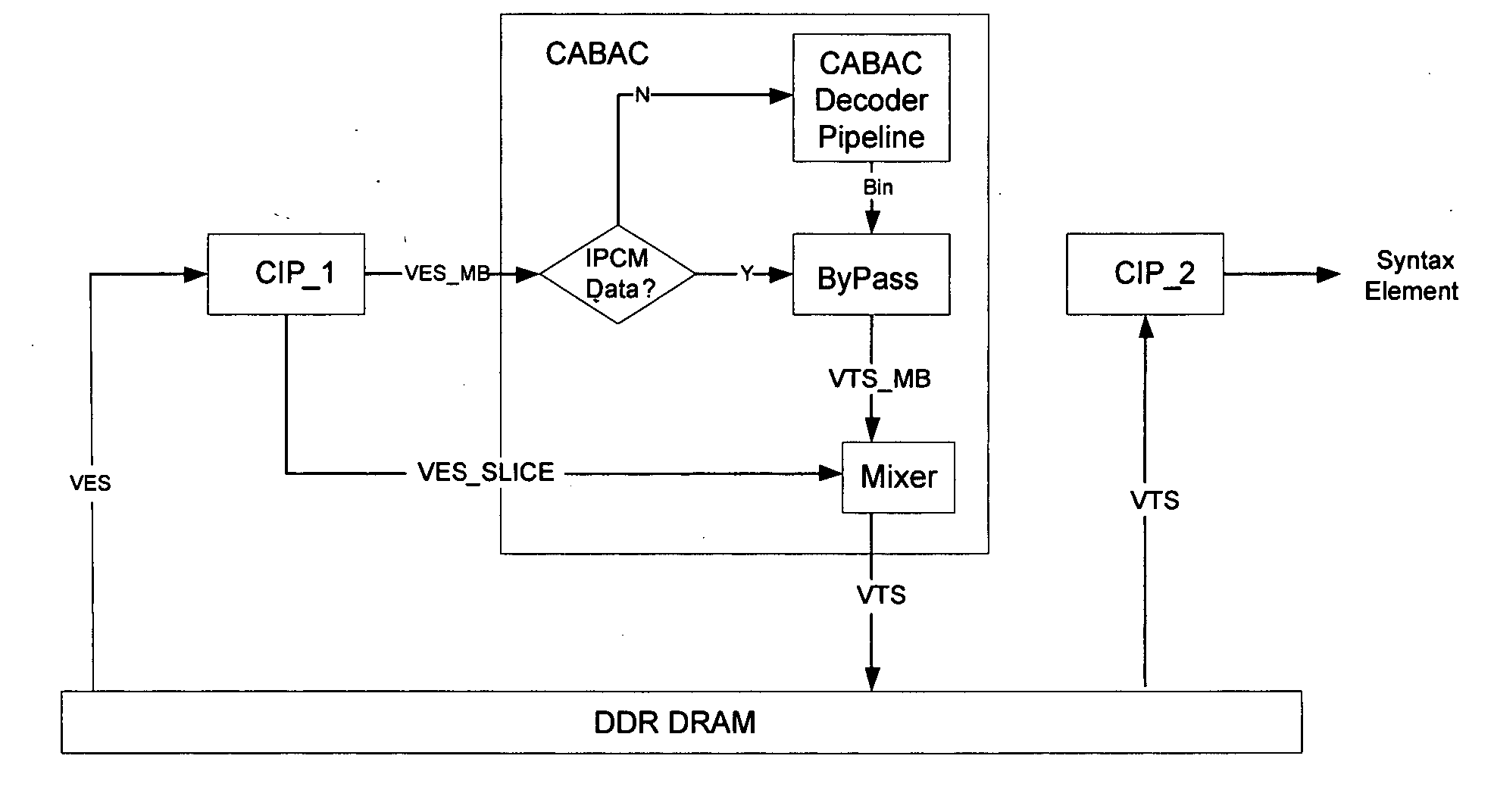

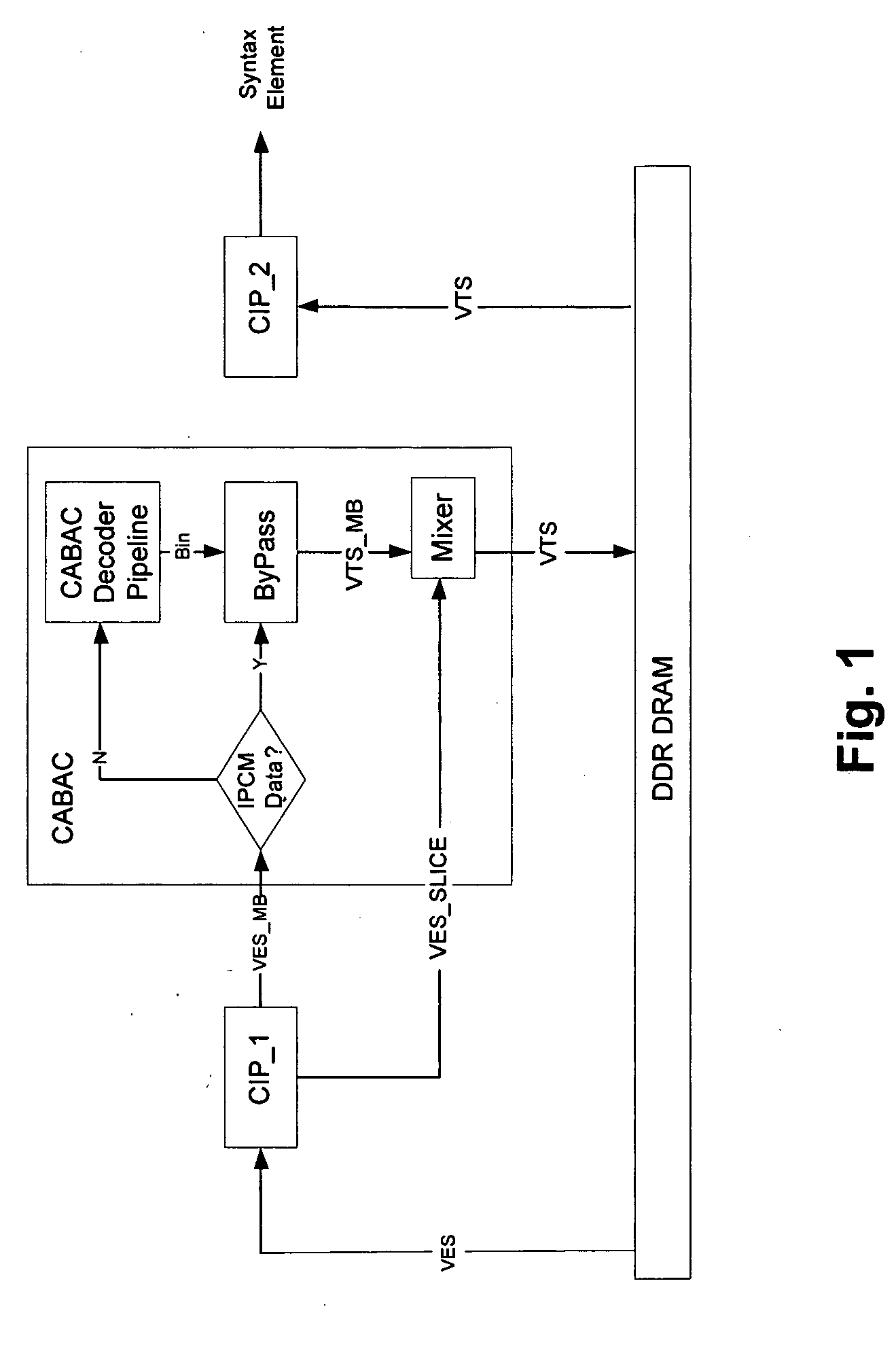

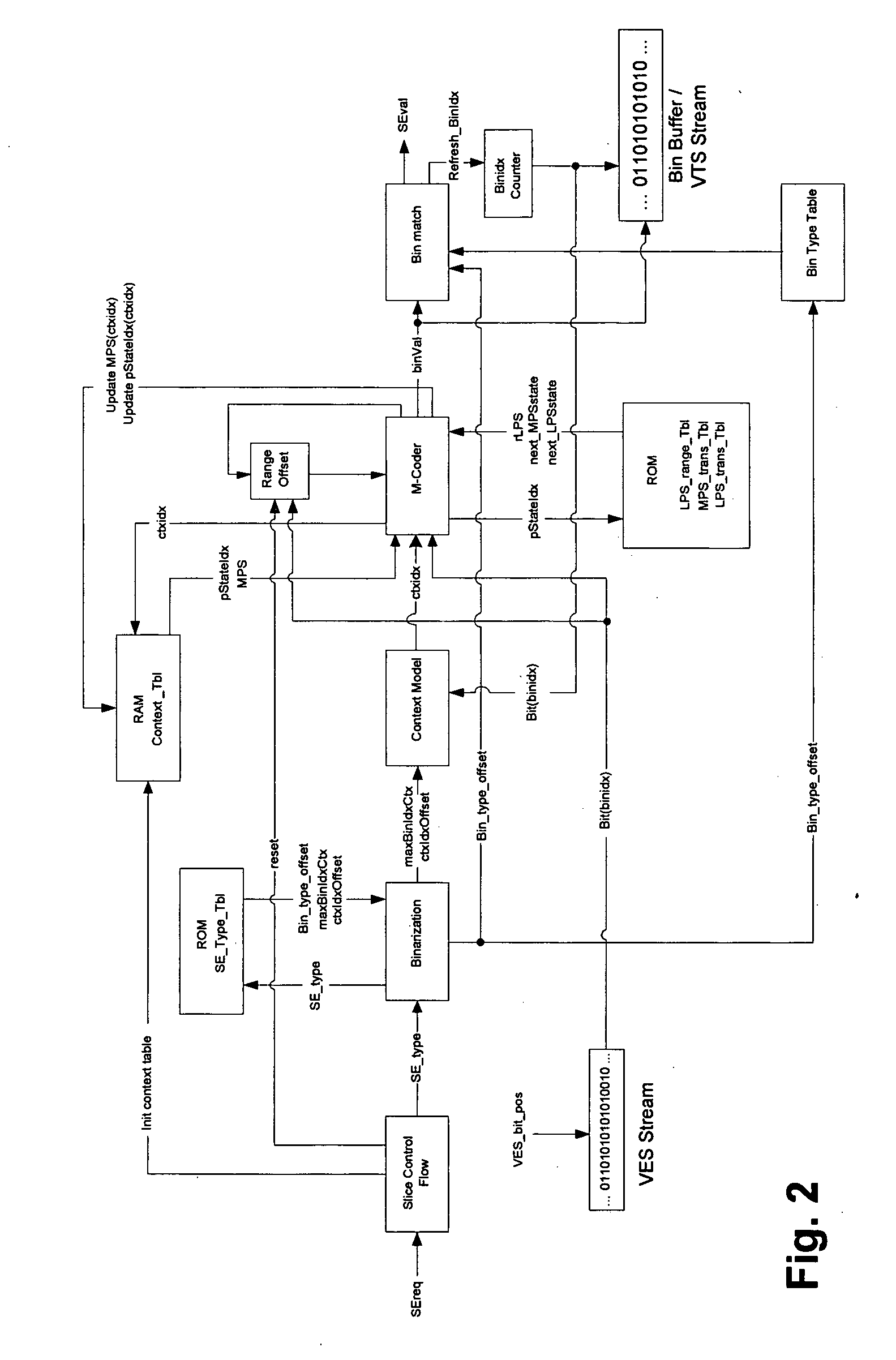

Two pass architecture for H.264 CABAC decoding process

InactiveUS20060126744A1Eliminate dependenciesHigh performance throughputColor television with pulse code modulationColor television with bandwidth reductionHigh-definition televisionComputer architecture

An architecture capable of stream parsing of the H.264 Content Based Adaptive Binary Arithmetic Coding (CABAC) format is disclosed. The architecture employs a two pass dataflow approach to implement the functions of CABAC bit parsing and decoding processes (based on the H.264 CABAC algorithm). The architecture can be implemented, for example, as a system-on-chip (SOC) for a video / audio decoder for use high definition television broadcasting (HDTV) applications. Other such video / audio decoder applications are enabled as well.

Owner:MICRONAS

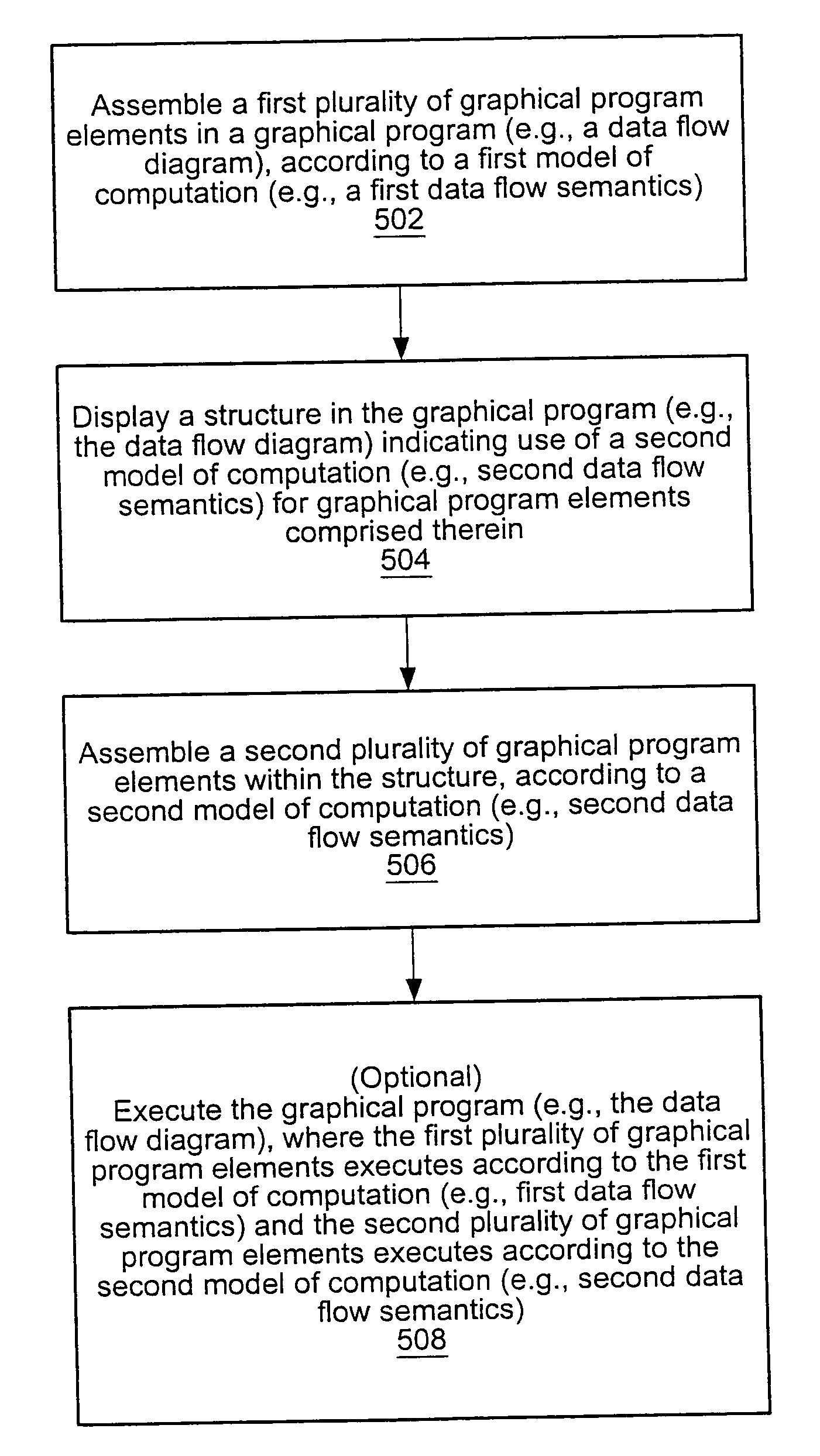

Creating and executing a graphical program with first model of computation that includes a structure supporting second model of computation

ActiveUS20050257195A1Suitable for deploymentVisual/graphical programmingSpecific program execution arrangementsMockupDataflow

System and method for creating and executing a graphical program. A first plurality of graphical program elements (GPEs) having a first model of computation (MoC), e.g., homogenous dataflow, are assembled in a graphical program in response to first input. A structure, including an interior portion, is displayed in the graphical program, indicating use of a second MoC, e.g., multi-rate dataflow, for GPEs within the interior portion. A second plurality of GPEs having the second MoC are assembled within the interior portion of the structure in response to second input. The second plurality of GPEs are converted into a new third plurality of GPEs having the first MoC, e.g., by parsing the second plurality of GPEs to determine multiple primitives according to the second MoC, determining the third plurality of GPEs based on the primitives, and assembling the third plurality of GPEs in the graphical program.

Owner:NATIONAL INSTRUMENTS

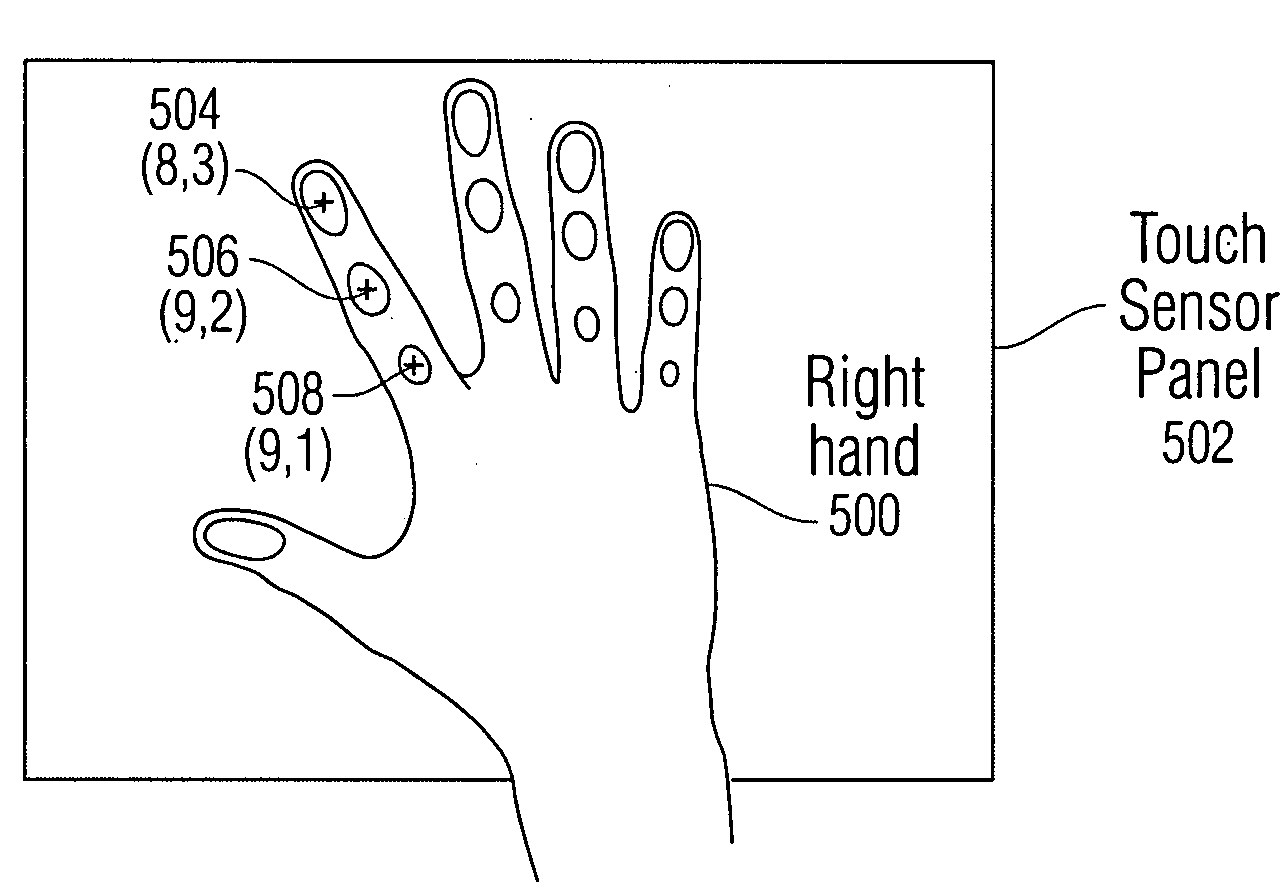

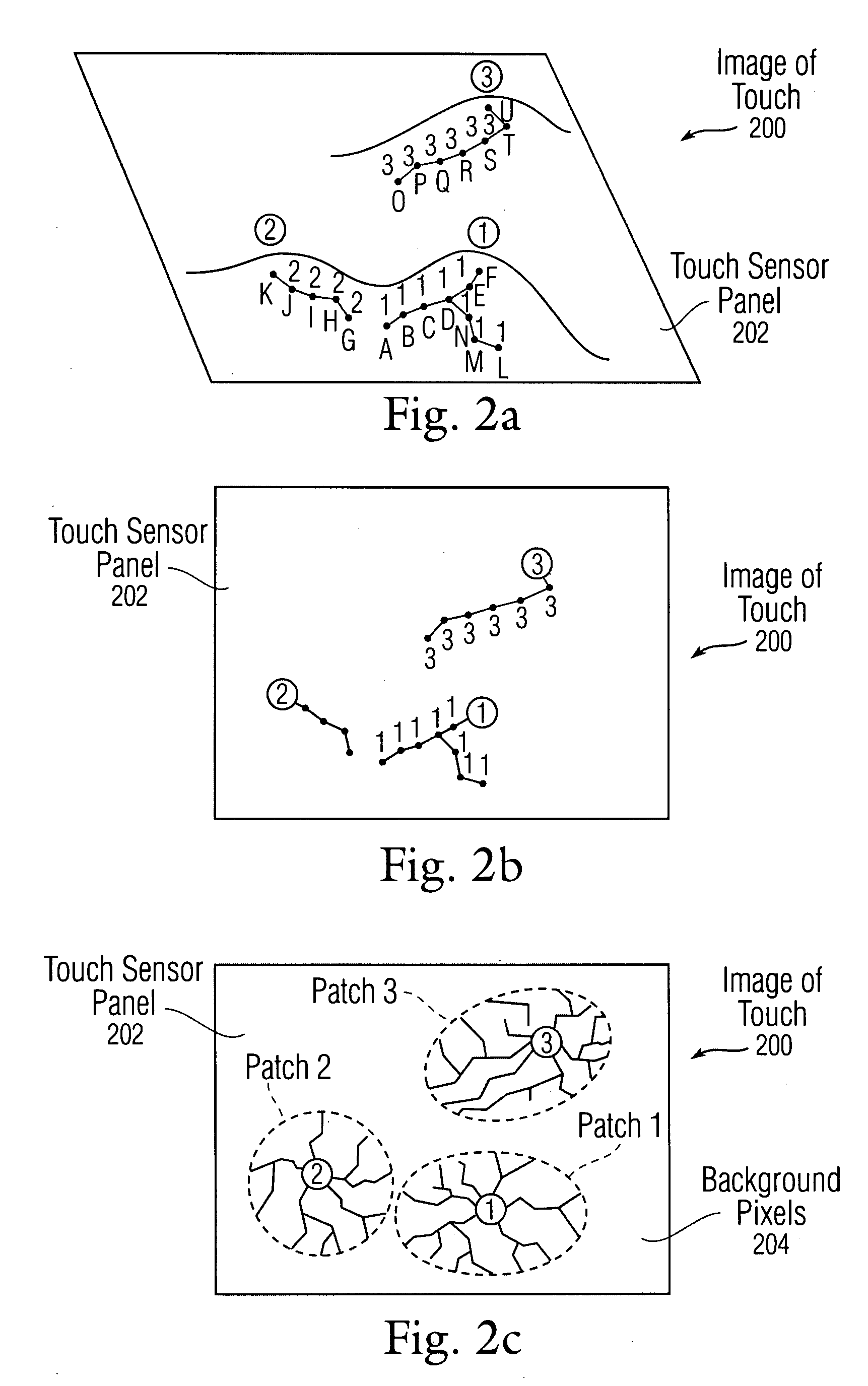

Bottom up watershed dataflow method and region-specific segmentation based on historic data

InactiveUS20080309629A1Reduce in quantityInaccurate centroid calculationImage analysisCharacter and pattern recognitionPattern recognitionMerge algorithm

The application of a watershed algorithm to pixels and their touch values obtained from a scan of a touch sensor panel to determine patches corresponding to images of touch is disclosed. Prior to applying the watershed algorithm, background pixels having little or no touch values can be eliminated. A primary merge algorithm can then merge adjacent patches together when the saddle point between them is shallow as compared to the peak represented by the patches. However, if two candidate patches for merging have a total number of pixels below a certain threshold, these two patches may not be merged under the assumption that the patches might have been caused by different fingertips. Conversely, if two candidate patches for merging have a total number of pixels above a certain threshold, these two patches can be merged under the assumption that the patches were caused by a single thumb or palm.

Owner:APPLE INC

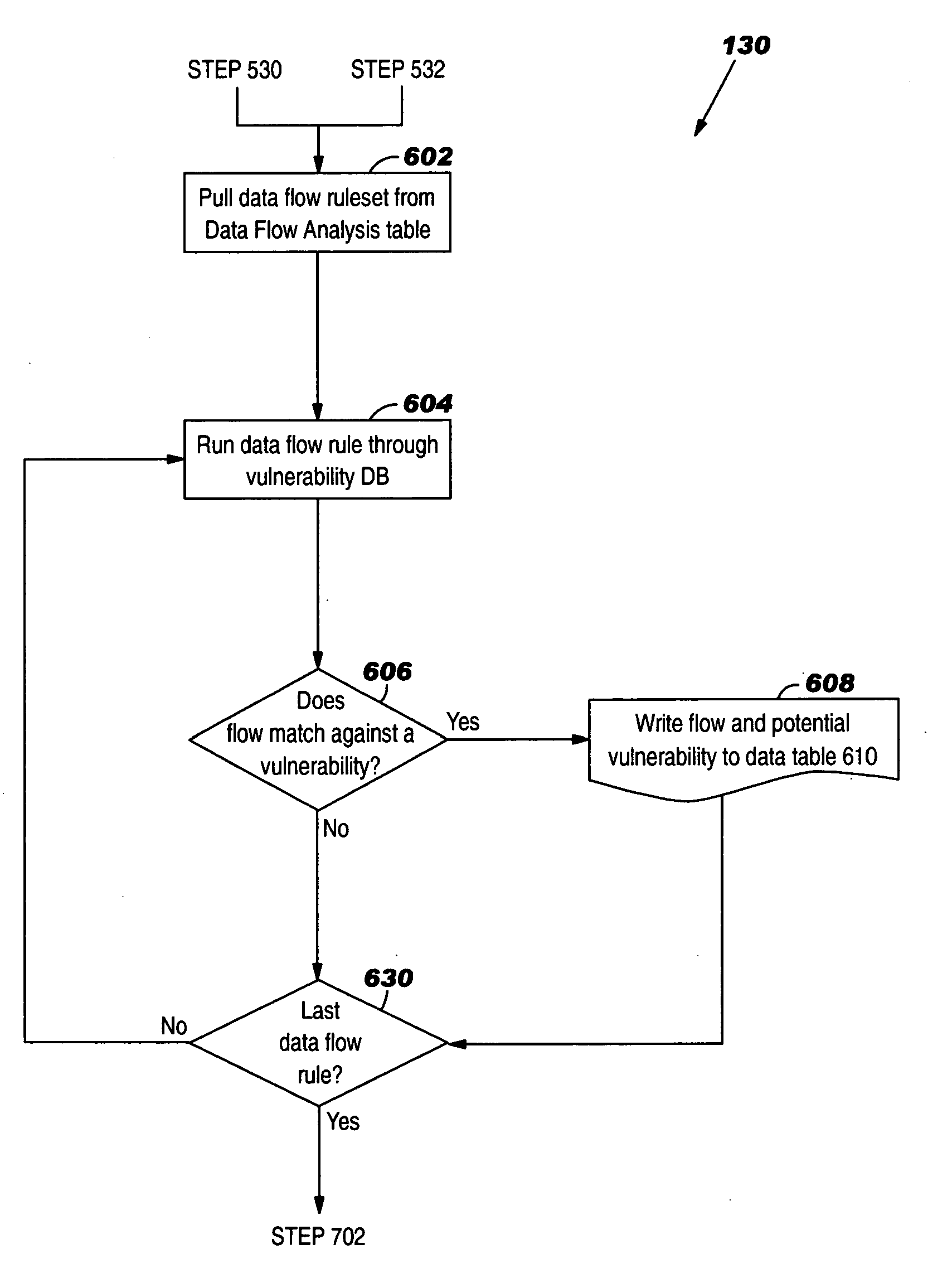

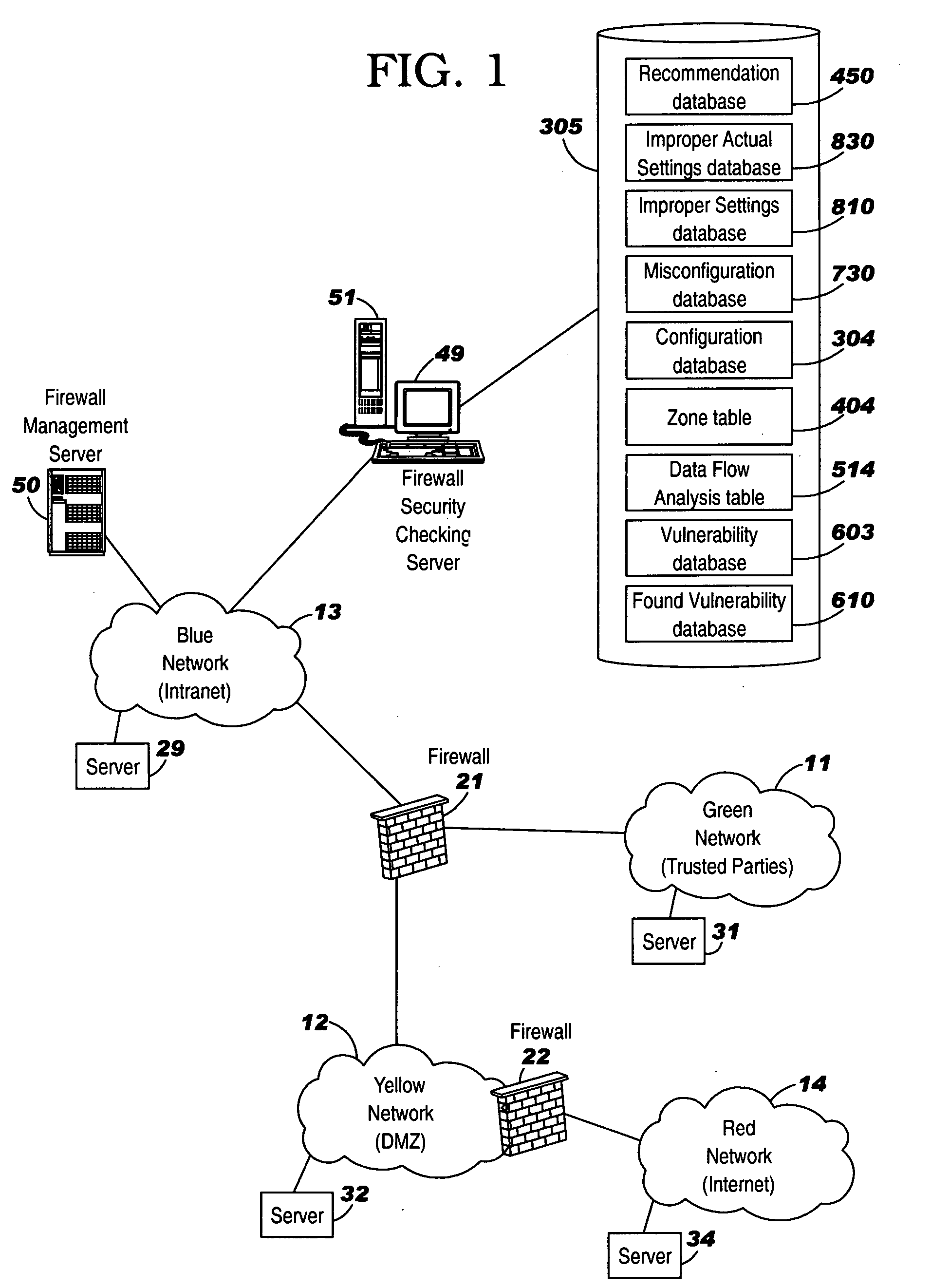

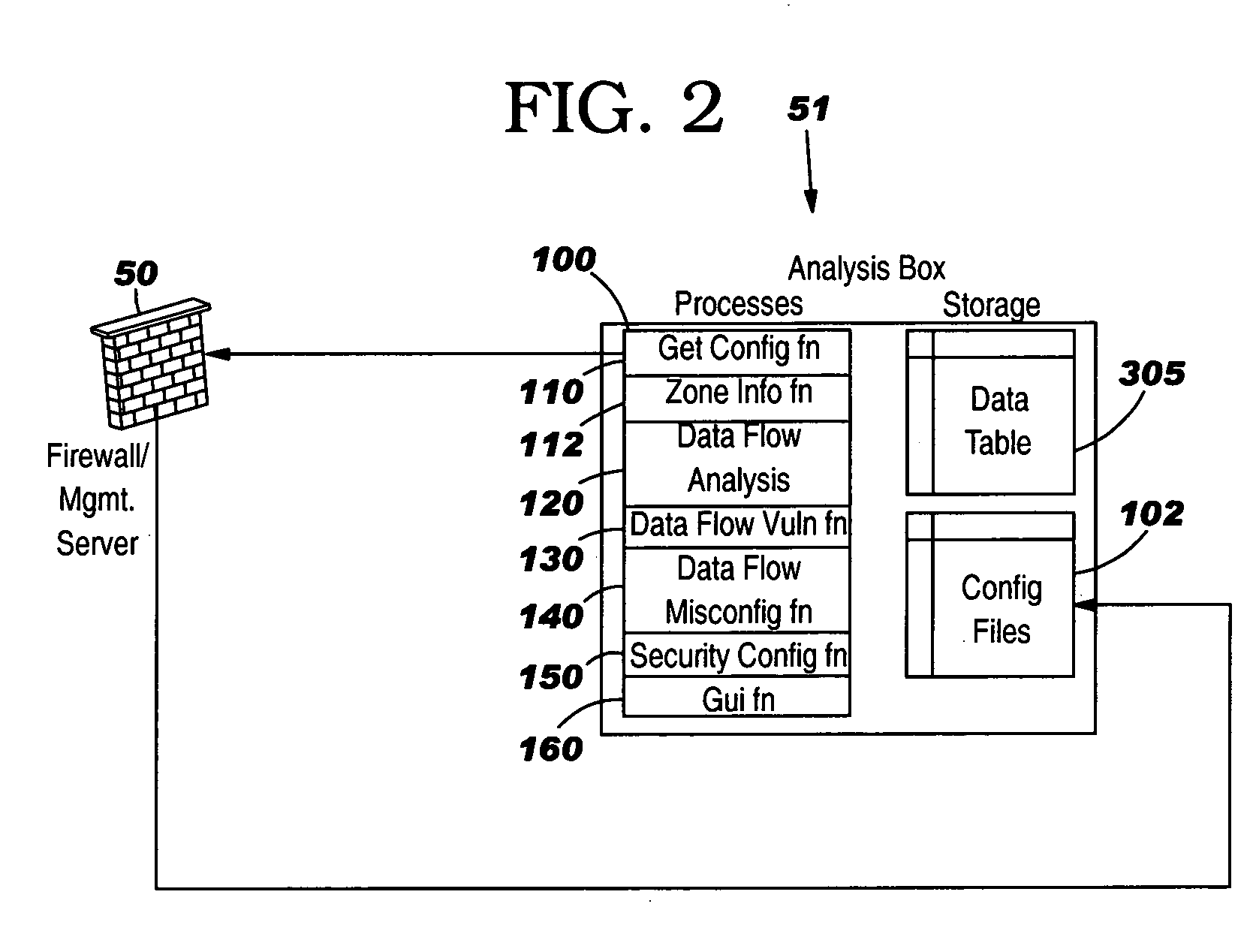

Method and apparatus for graphical presentation of firewall security policy

A graphical representation of the firewall and a network coupled to the firewall is generated and displayed. A number of an inbound port of the network is displayed. An arrow adjacent to the port number pointing toward the network is displayed to indicate that a communication is permitted to the port. The port number and the arrow are located between an icon for the network and an icon for the firewall. A port number of a destination of a communication originating from the network is displayed. Also, another arrow adjacent to the destination port number pointing toward the firewall is displayed to indicate that a communication is permitted to the destination port number. The destination port number and the other arrow are located between an icon for the network and an icon for the firewall. A table including definitions of a plurality of rules is generated and displayed. Each of the definitions includes entries for a source IP address and destination IP address of a permitted but vulnerable data flow. The source IP address and destination IP address entries are color coded to indicate security levels of respective source and destination networks. Another table includes definitions of a misconfigured data flow, and entries for a source IP address and destination IP address of the misconfigured data flow. The source IP address and destination IP address are color coded to indicate security levels of respective source network and destination network.

Owner:KYNDRYL INC

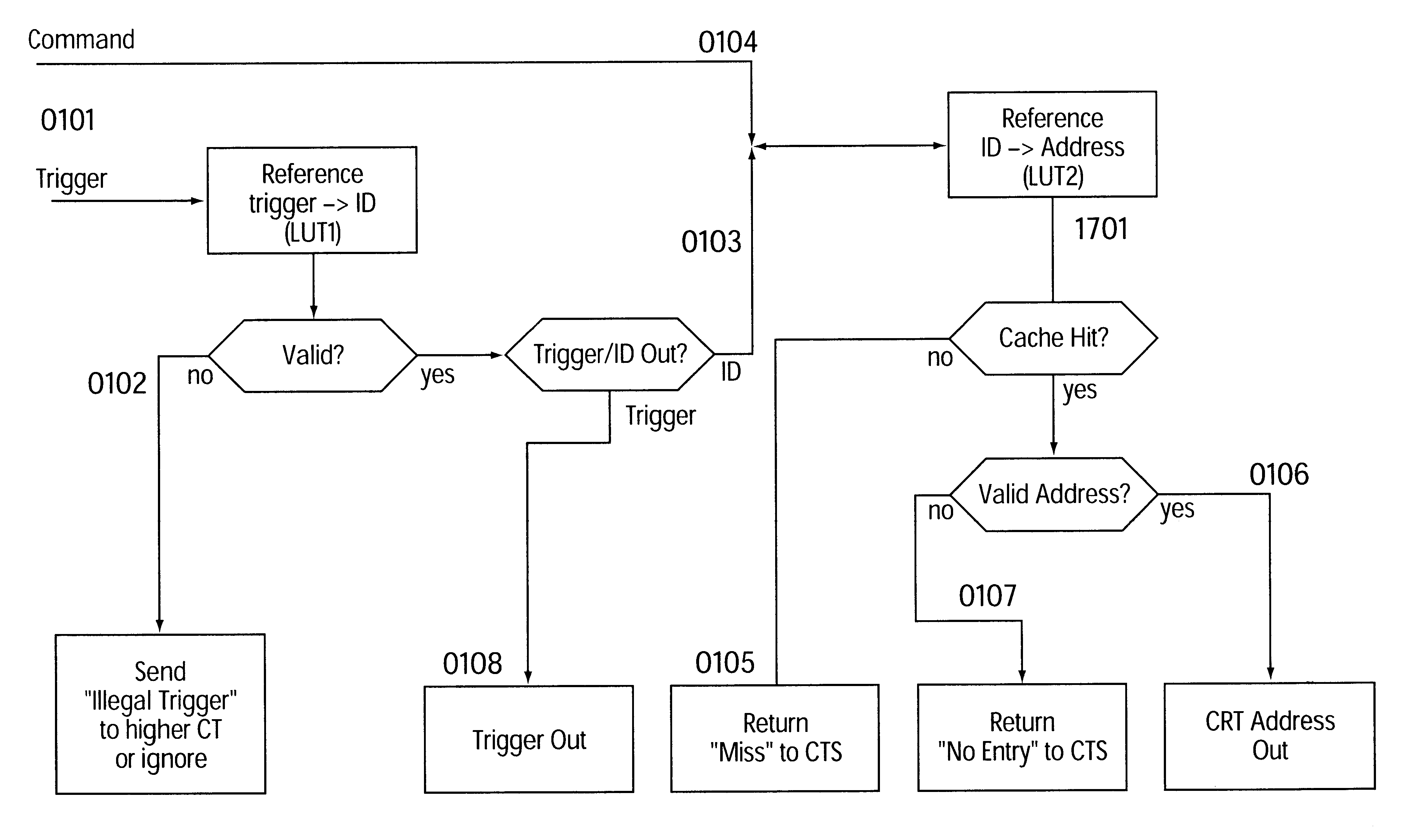

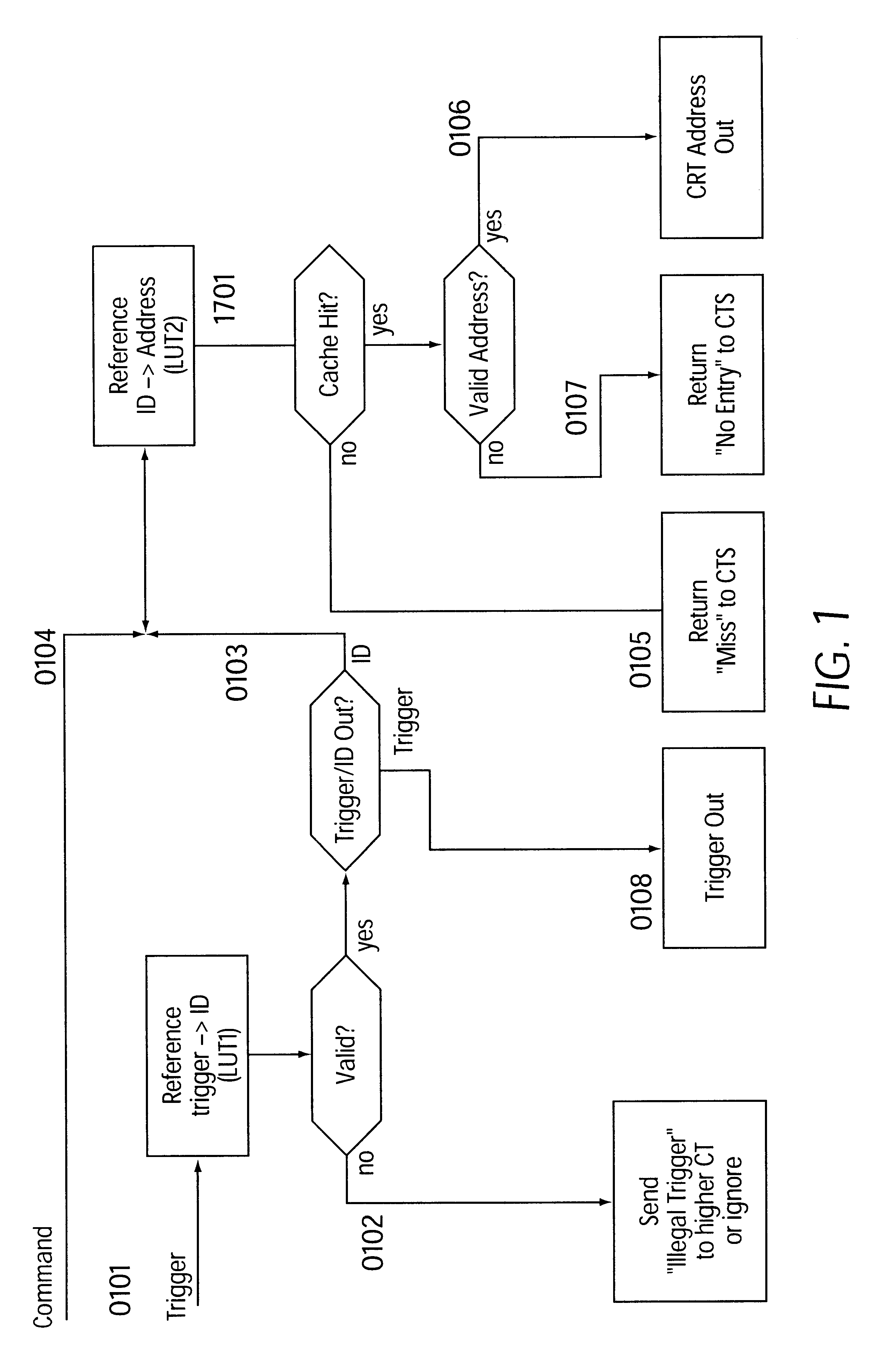

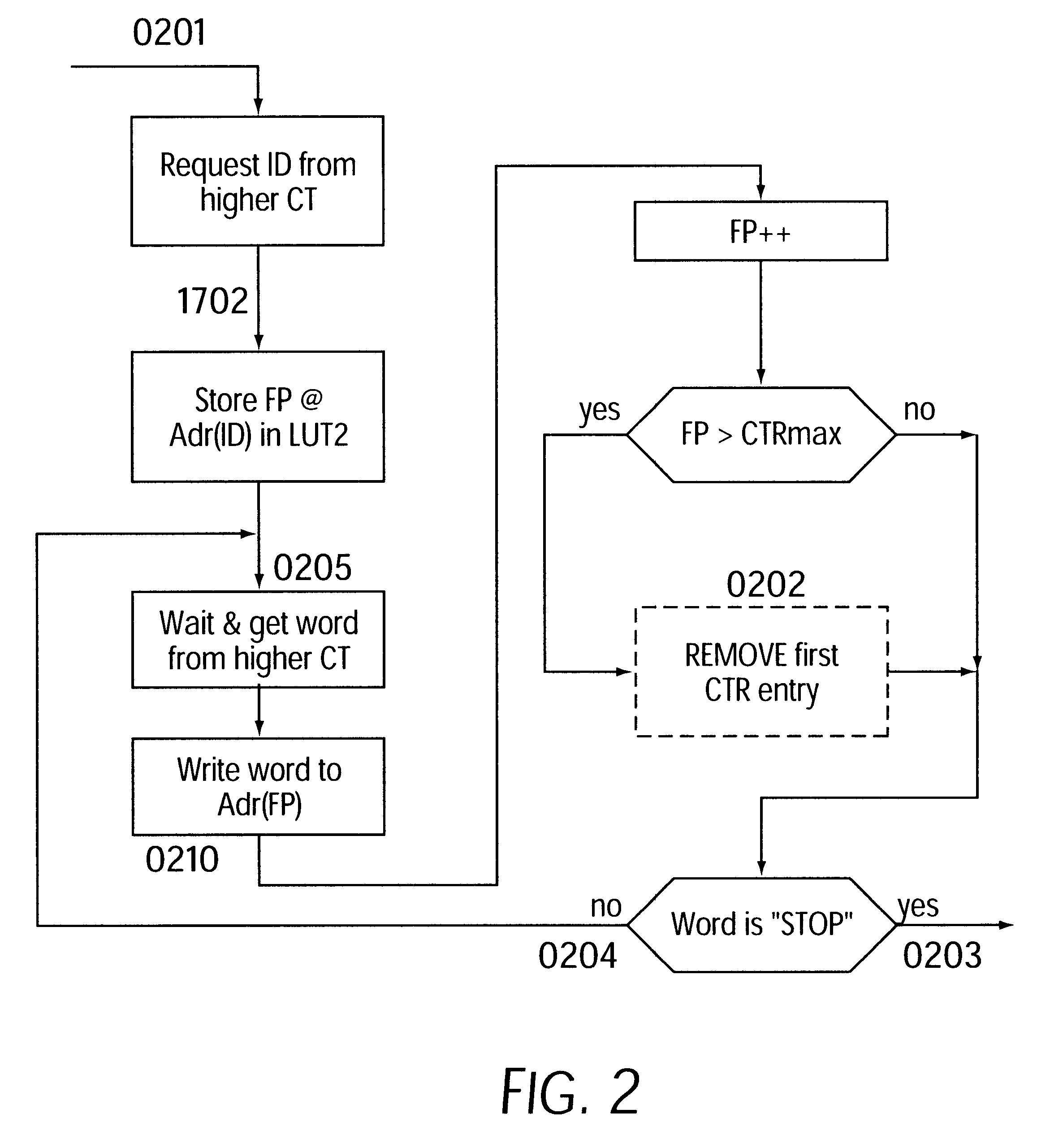

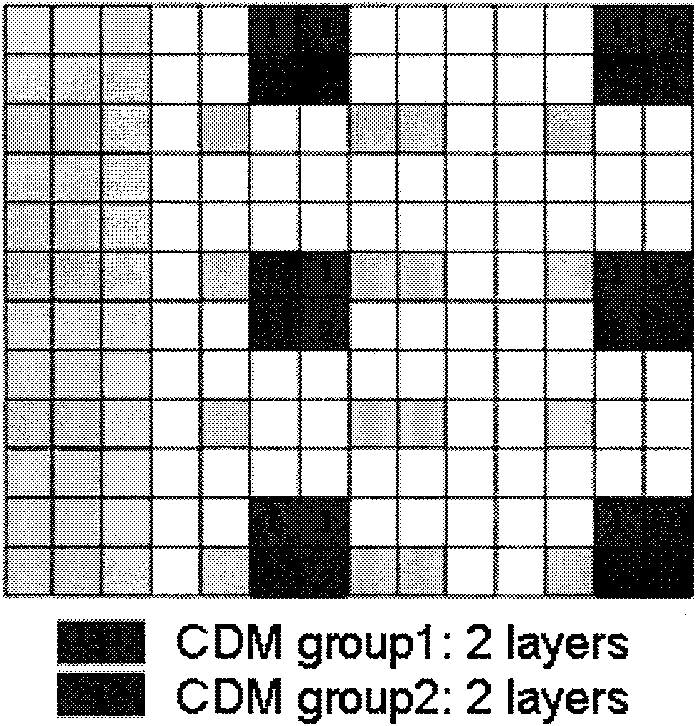

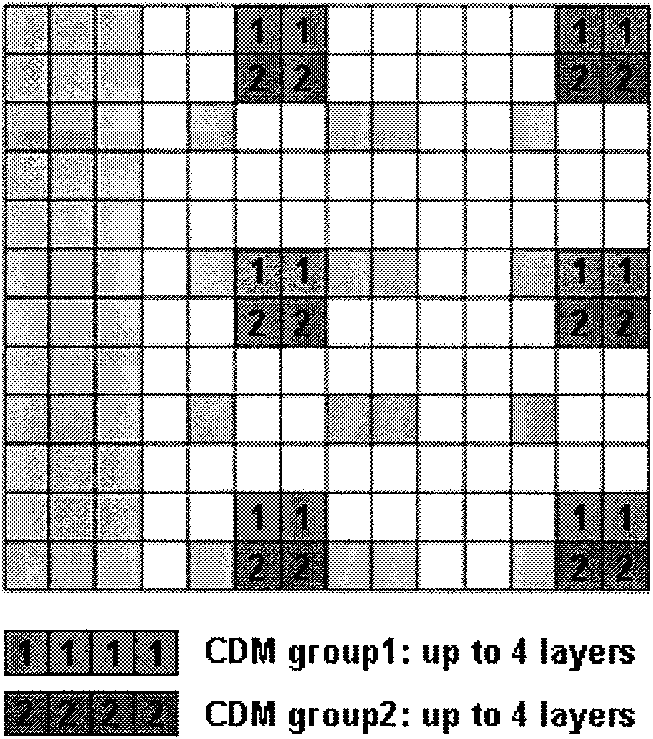

Method for hierarchical caching of configuration data having dataflow processors and modules having two-or multidimensional programmable cell structure (FPGAs, DPGAs, etc.)--

InactiveUS6480937B1Improve performanceEasy transferMemory adressing/allocation/relocationProgram controlData stream processingComputer module

A method of caching commands in microprocessors having a plurality of arithmetic units and in modules having a two- or multidimensional cell arrangement is provided. The method includes combining a plurality of cells and arithmetic units to form a plurality of groups, assigning a cache unit to a group, and connecting the cache unit to a higher level unit via a tree structure. The cache unit may send requests for required commands to the higher level cache unit, which may return a command sequence including the required command, if the higher level cache unit holds the first command sequence including the required command in the higher level cache unit's local memory.

Owner:SCIENTIA SOL MENTIS AG +1

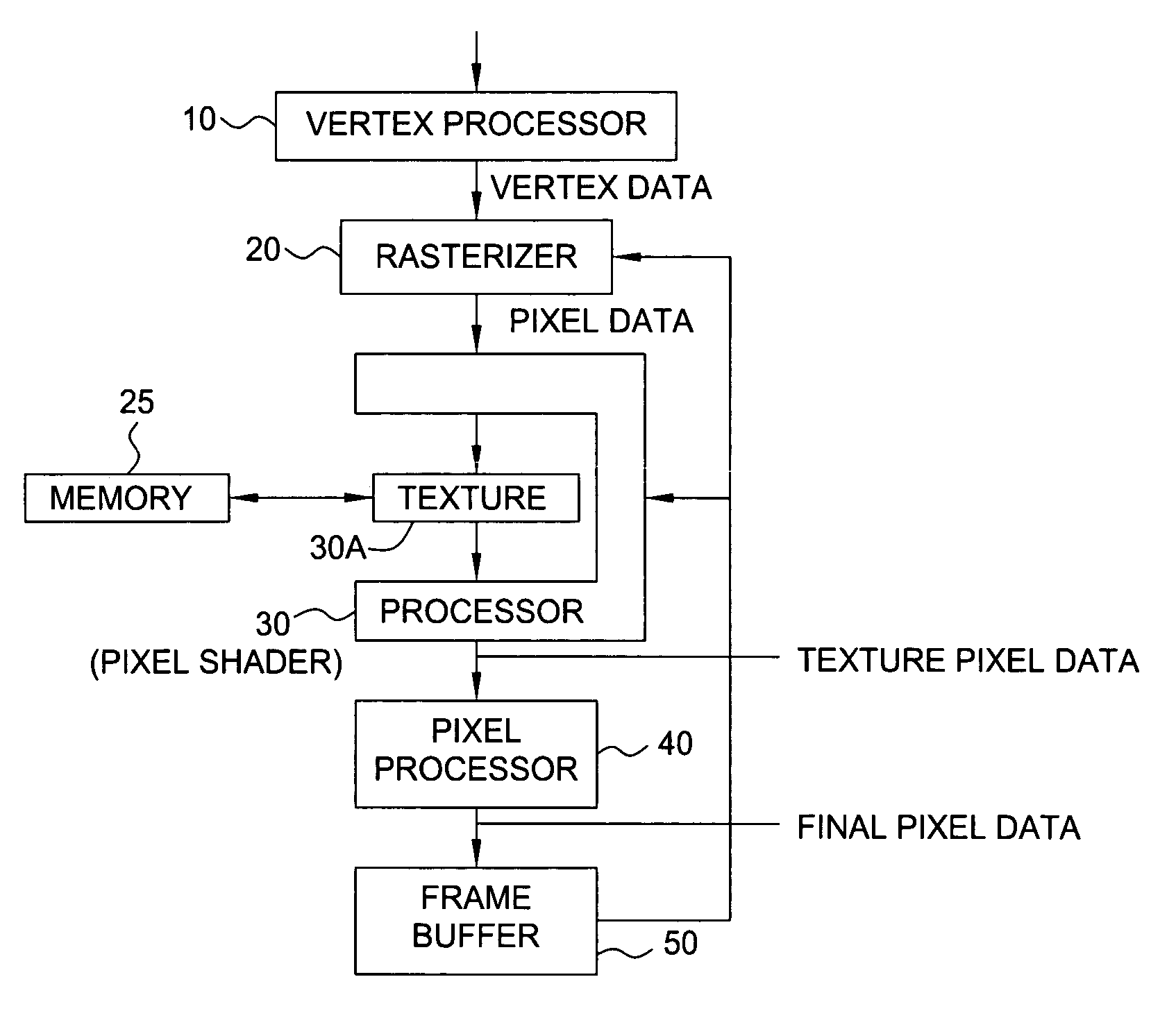

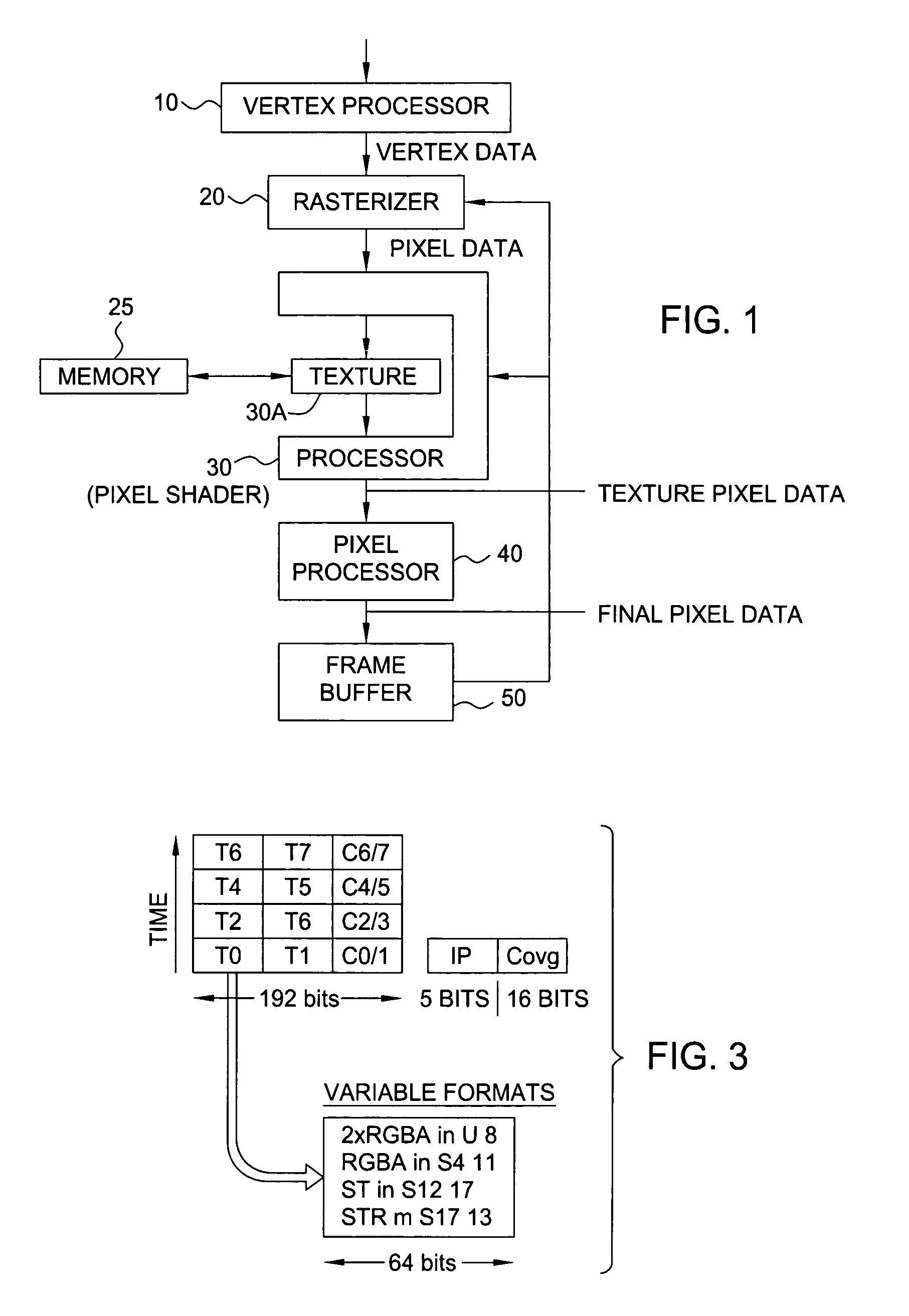

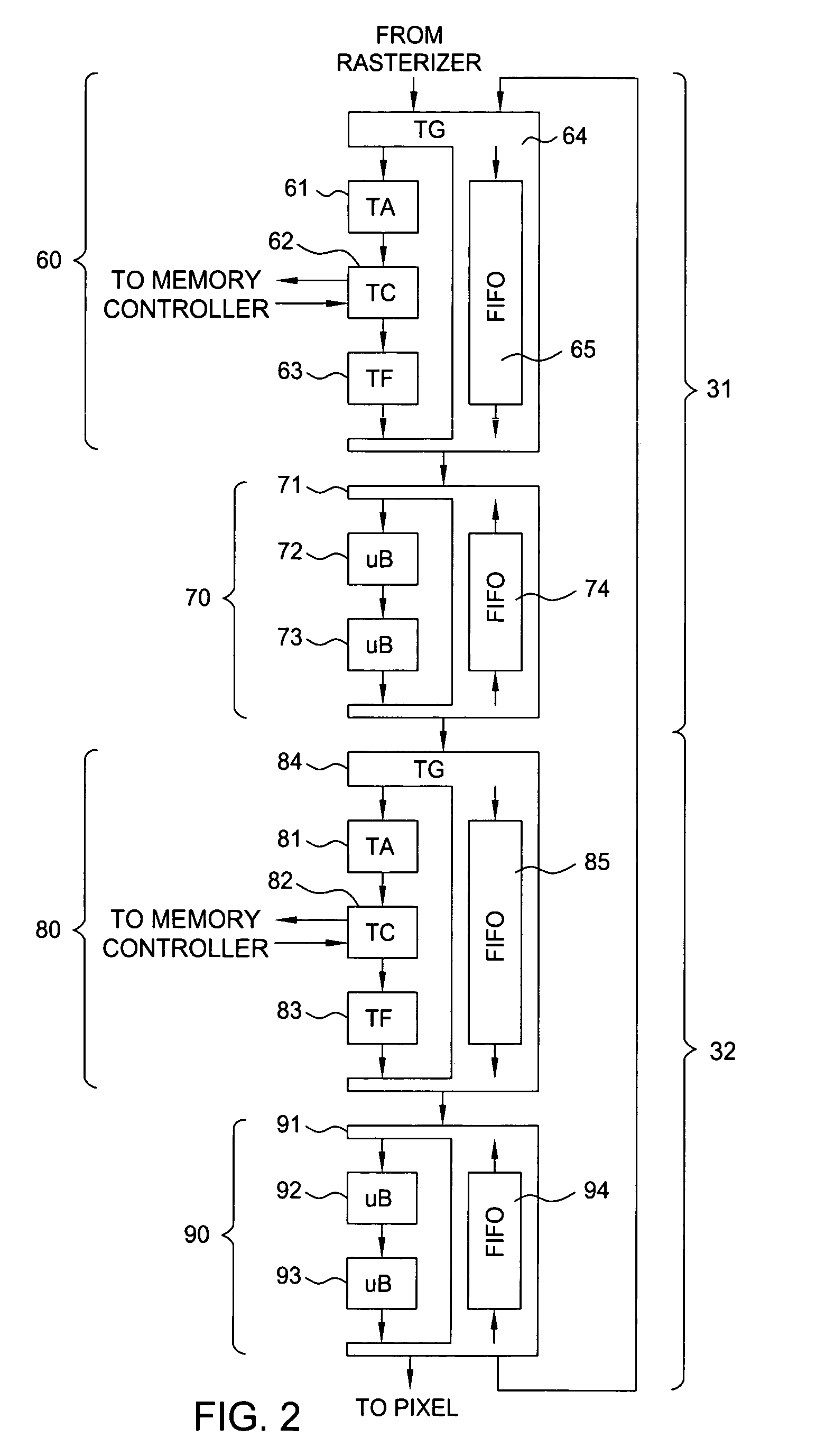

Method and system for scalable, dataflow-based, programmable processing of graphics data

ActiveUS6980209B1Improve system performanceLess system performanceCathode-ray tube indicatorsProcessor architectures/configurationArray data structureNetwork packet

A scalable pipelined pixel shader that processes packets of data and preserves the format of each packet at each processing stage. Each packet is an ordered array of data values, at least one of which is an instruction pointer. Each member of the ordered array can be indicative of any type of data. As a packet progresses through the pixel shader during processing, each member of the ordered array can be replaced by a sequence of data values indicative of different types of data (e.g., an address of a texel, a texel, or a partially or fully processed color value). Information required for the pixel shader to process each packet is contained in the packet, and thus the pixel shader is scalable in the sense that it can be implemented in modular fashion to include any number of identical pipelined processing stages and can execute the same program regardless of the number of stages. Preferably, each processing stage is itself scalable, can be implemented to include an arbitrary number of identical pipelined instruction execution stages known as microblenders, and can execute the same program regardless of the number of microblenders. The current value of the instruction pointer (IP) in a packet determines the next instruction to be executed on the data contained in the packet. Any processing unit can change the instruction that will be executed by a subsequent processing unit by modifying the IP (and / or condition codes) of a packet that it asserts to the subsequent processing unit. Other aspects of the invention include graphics processors (each including a pixel shader configured in accordance with the invention), methods and systems for generating packets of data for processing in accordance with the invention, and methods for pipelined processing of packets of data.

Owner:PVC CONTAINER CORP +1

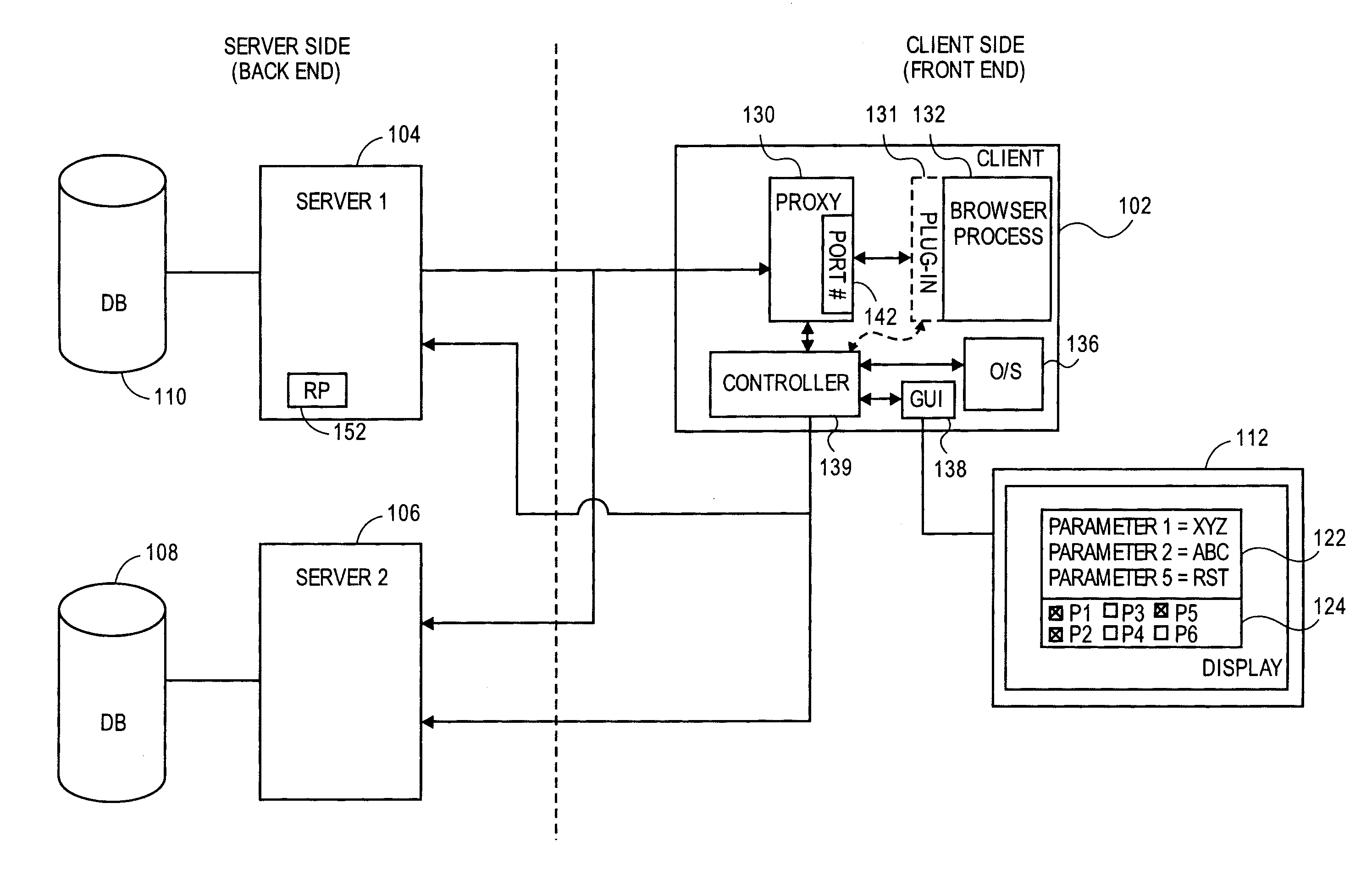

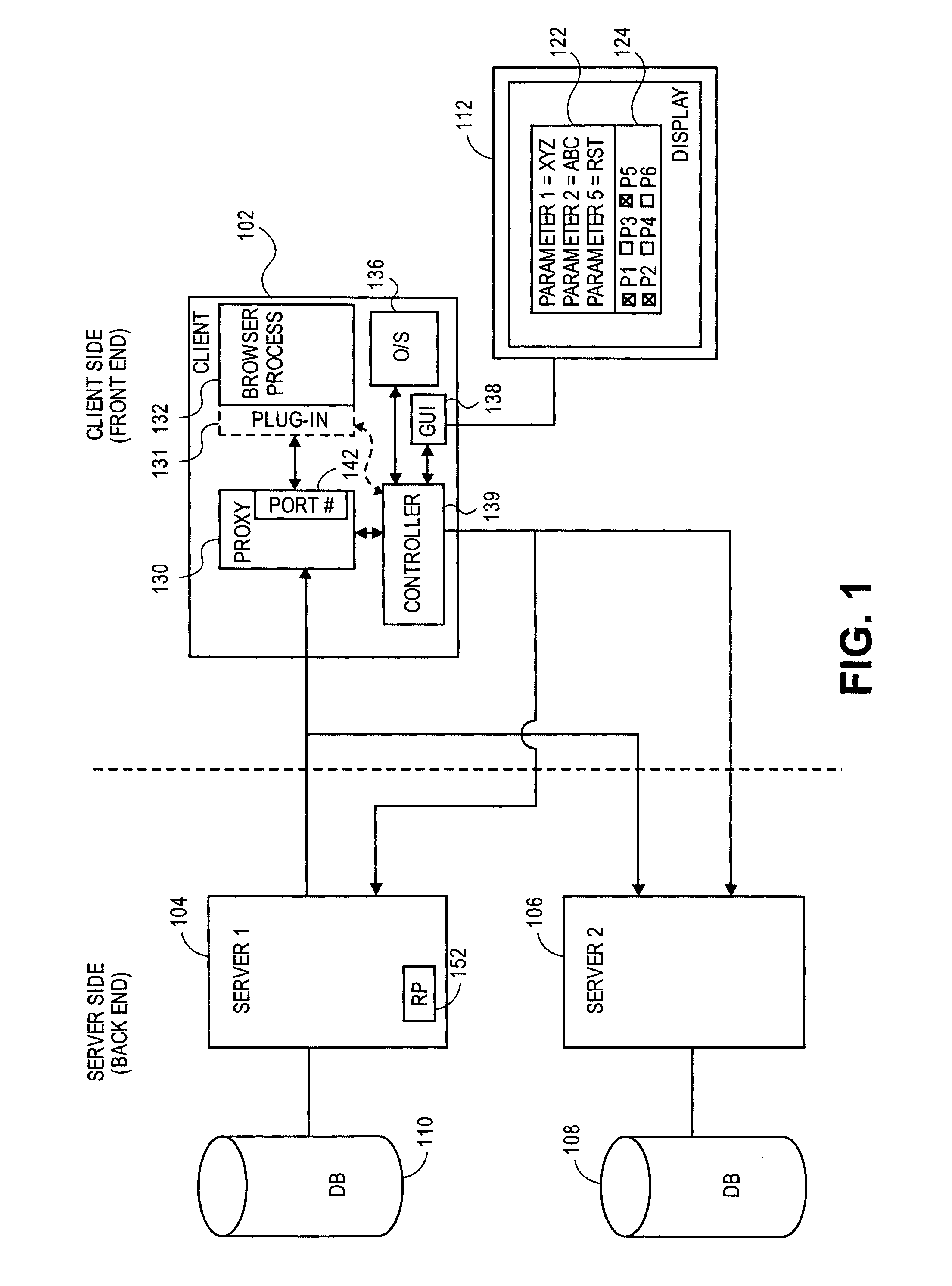

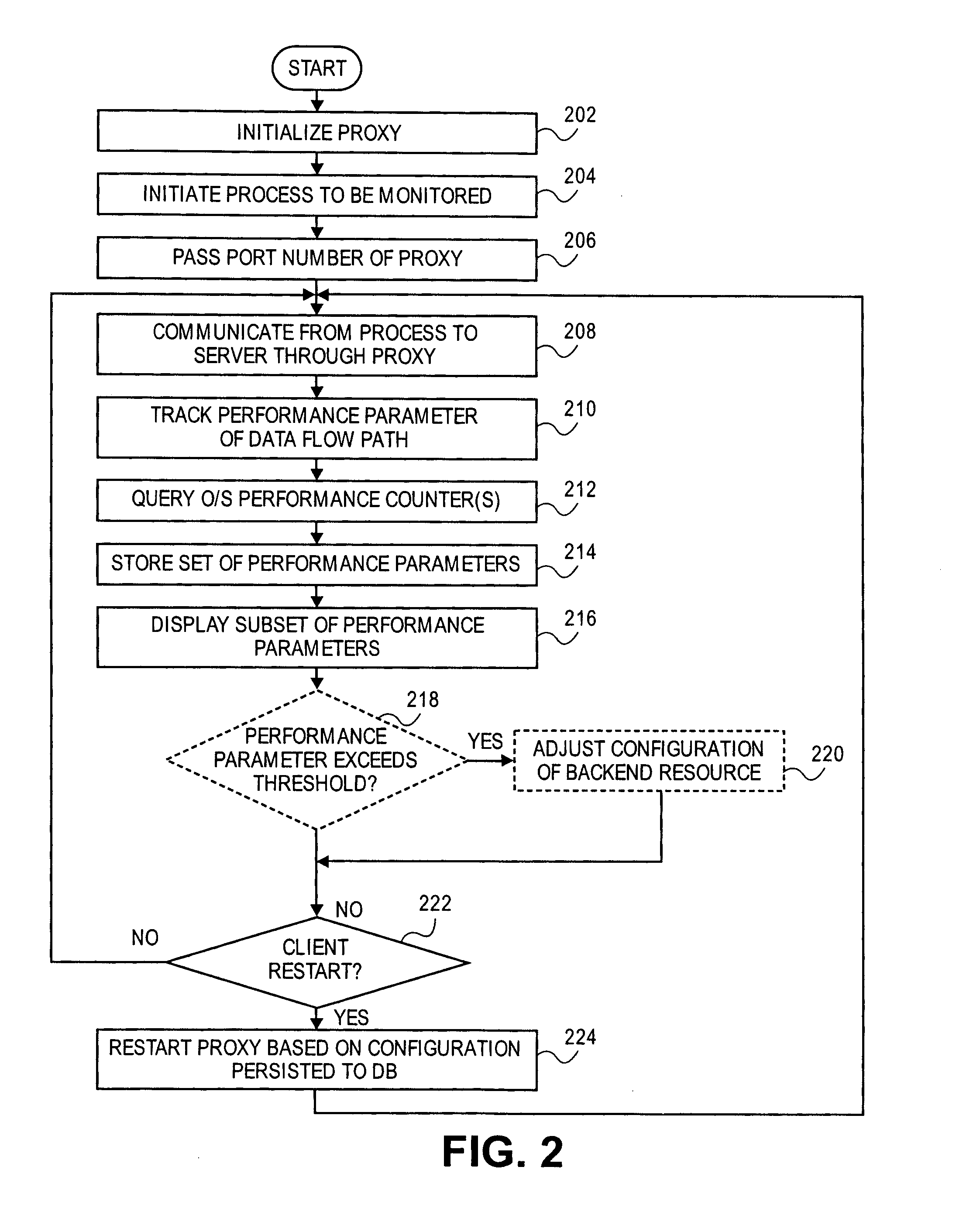

Method and system to monitor parameters of a data flow path in a communication system

ActiveUS20080126534A1Error detection/correctionMultiple digital computer combinationsCommunications systemDatapath

A system and method of monitoring a dataflow path in a multilevel client server environment. A proxy is introduced into the dataflow path between a communication process on the client and the server. The proxy acts as a conduit in the data path and monitors the performance parameters of the dataflow. These parameters may then be visualized or used to adjust backend resources.

Owner:SAP AG

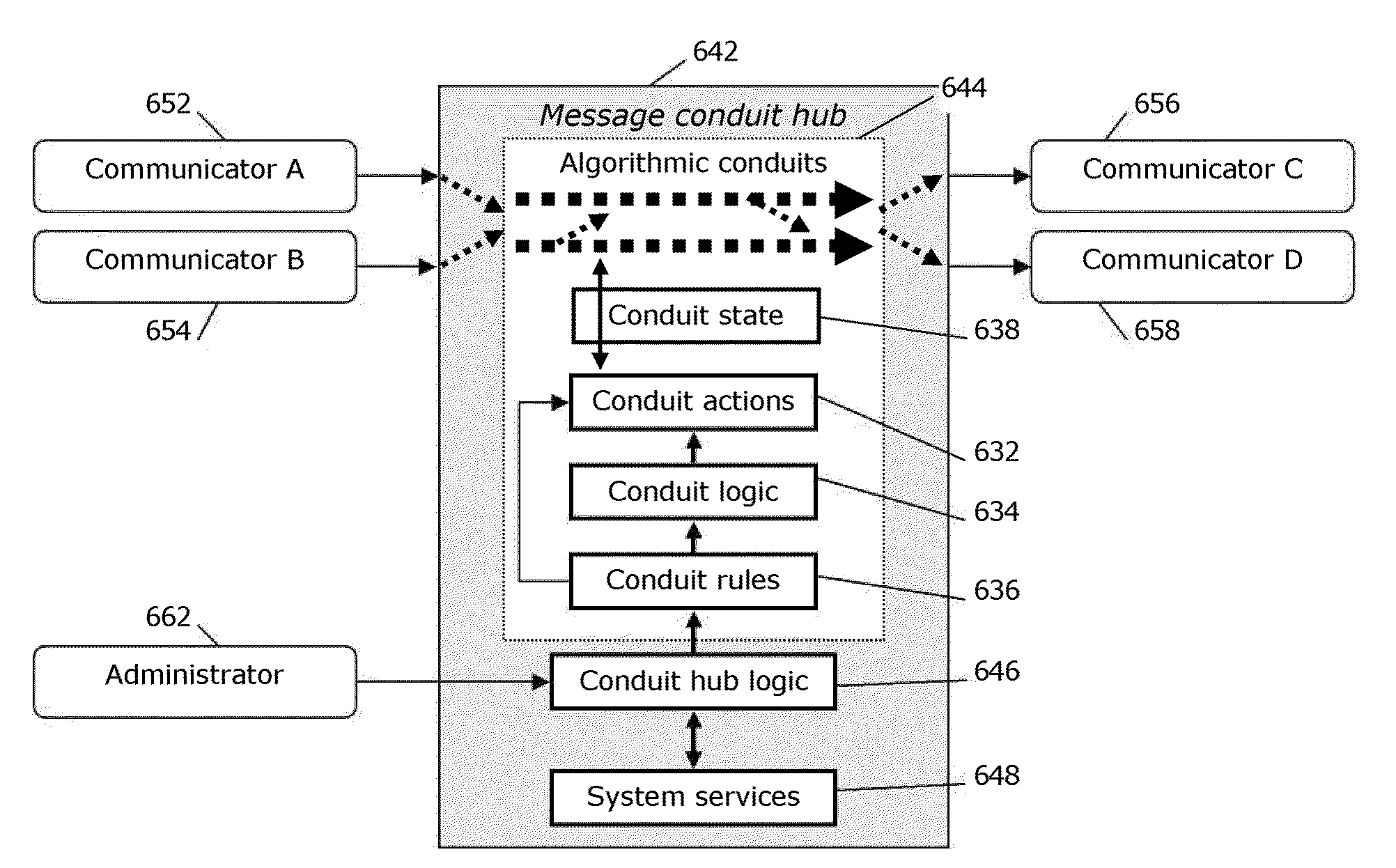

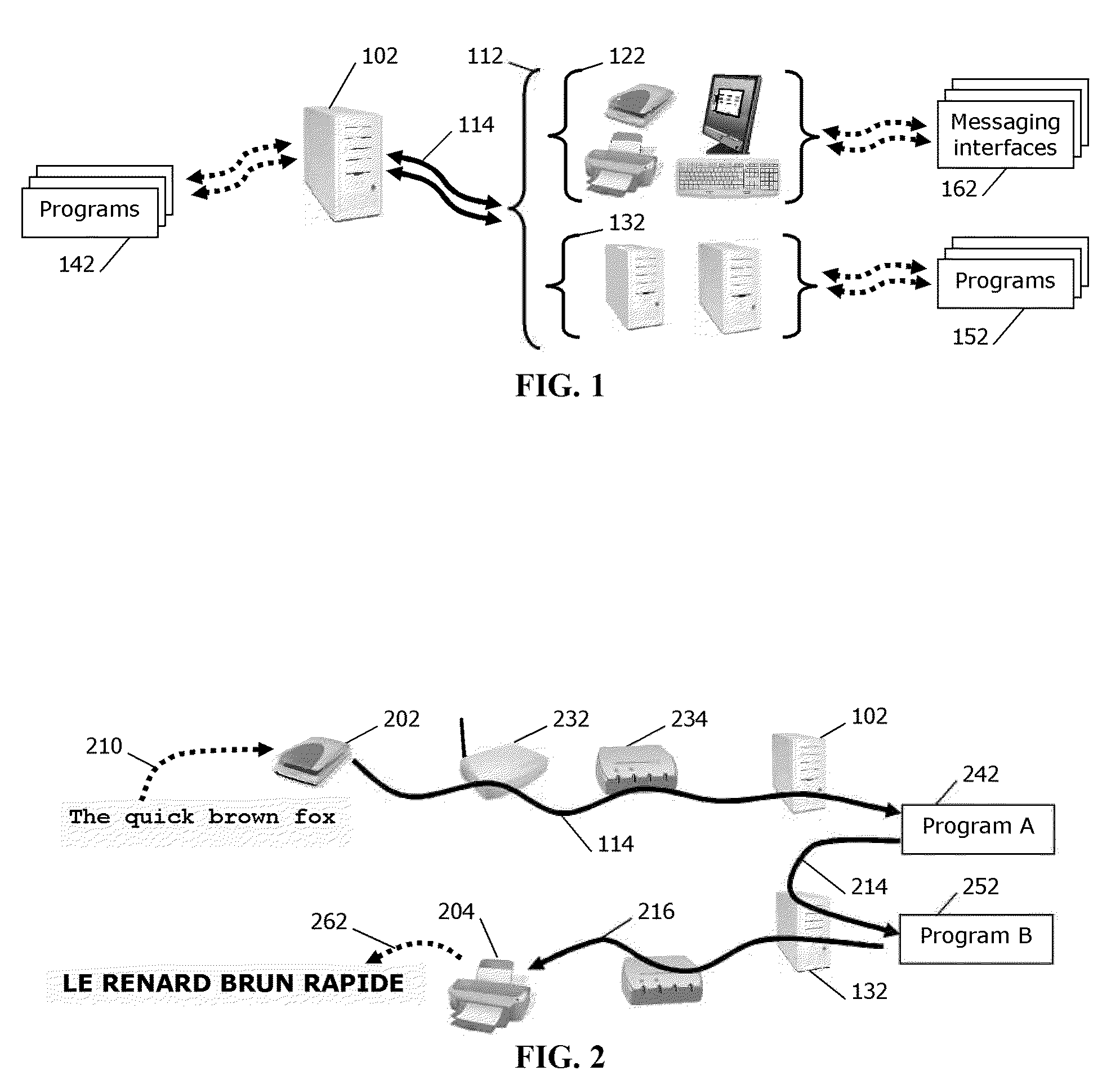

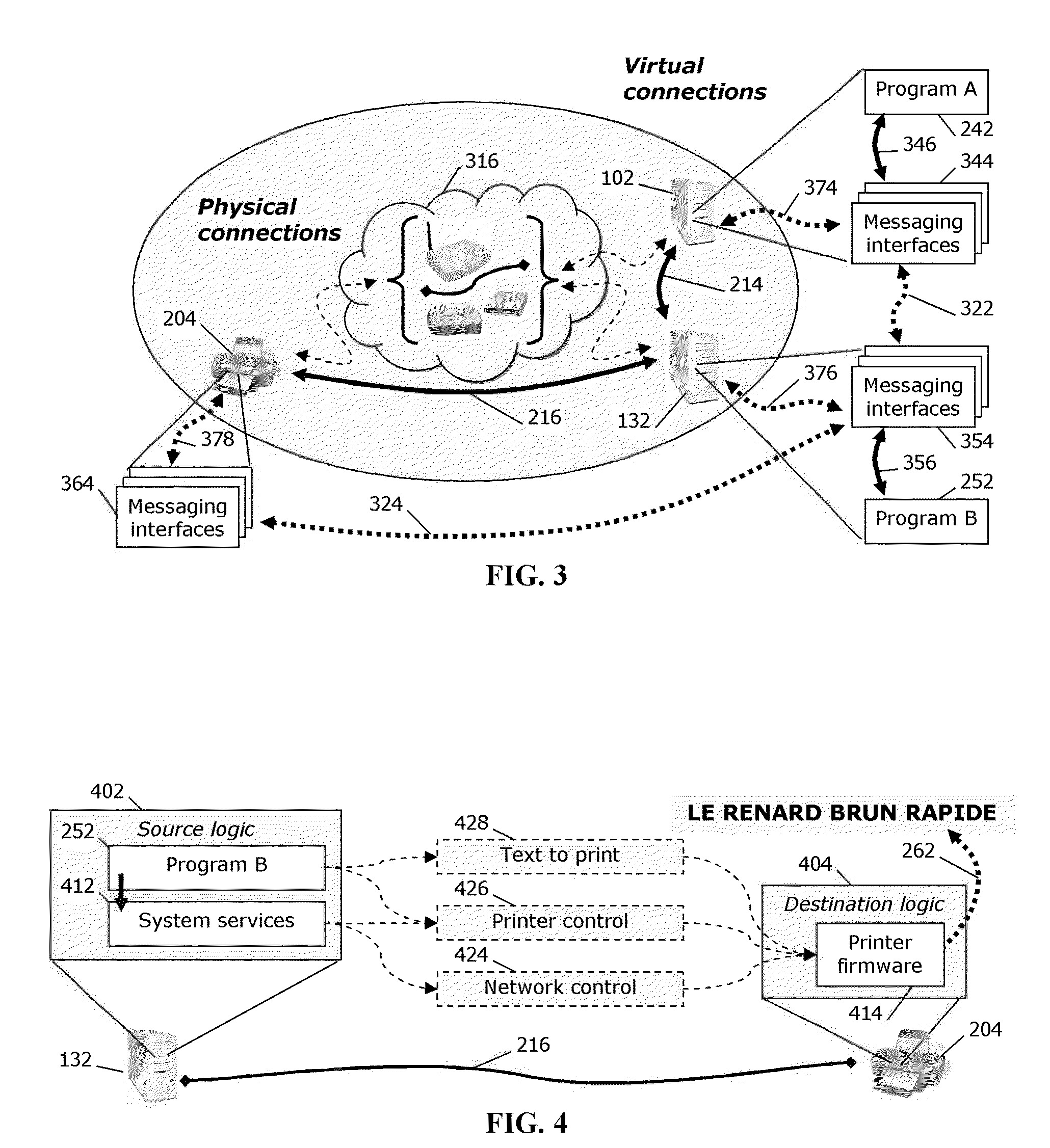

Message conduit systems with algorithmic data stream control and methods for processing thereof

InactiveUS20090259612A1Simple designEasy to build programKnowledge representationTransmissionVirtualizationManagement algorithm

A method for processing messages is provided where at least one algorithmic conduit is defined, and at least one conduit rule for controlling at least one algorithmic conduit is defined. An algorithmic conduit is a persistent connection, controlled by explicit, independent, dynamic rules, and capable of processing messages among data communicators such as devices, systems, or programs. Messages can be monitored, filtered, transformed, correlated, or processed in other ways without modifying the data communicators. A message conduit hub system allows creation and management of algorithmic conduits to serve as active, virtualized links carrying rules-based data streams among configurable endpoints. These “smart” connections are managed using parameters, logic, and other control interfaces for tailoring behavior to a particular application, site, or user. A message conduit hub system may be implemented as a stand-alone device, as part of a larger system, or as an “encapsulation layer” for an existing application.

Owner:HANSON TREVOR

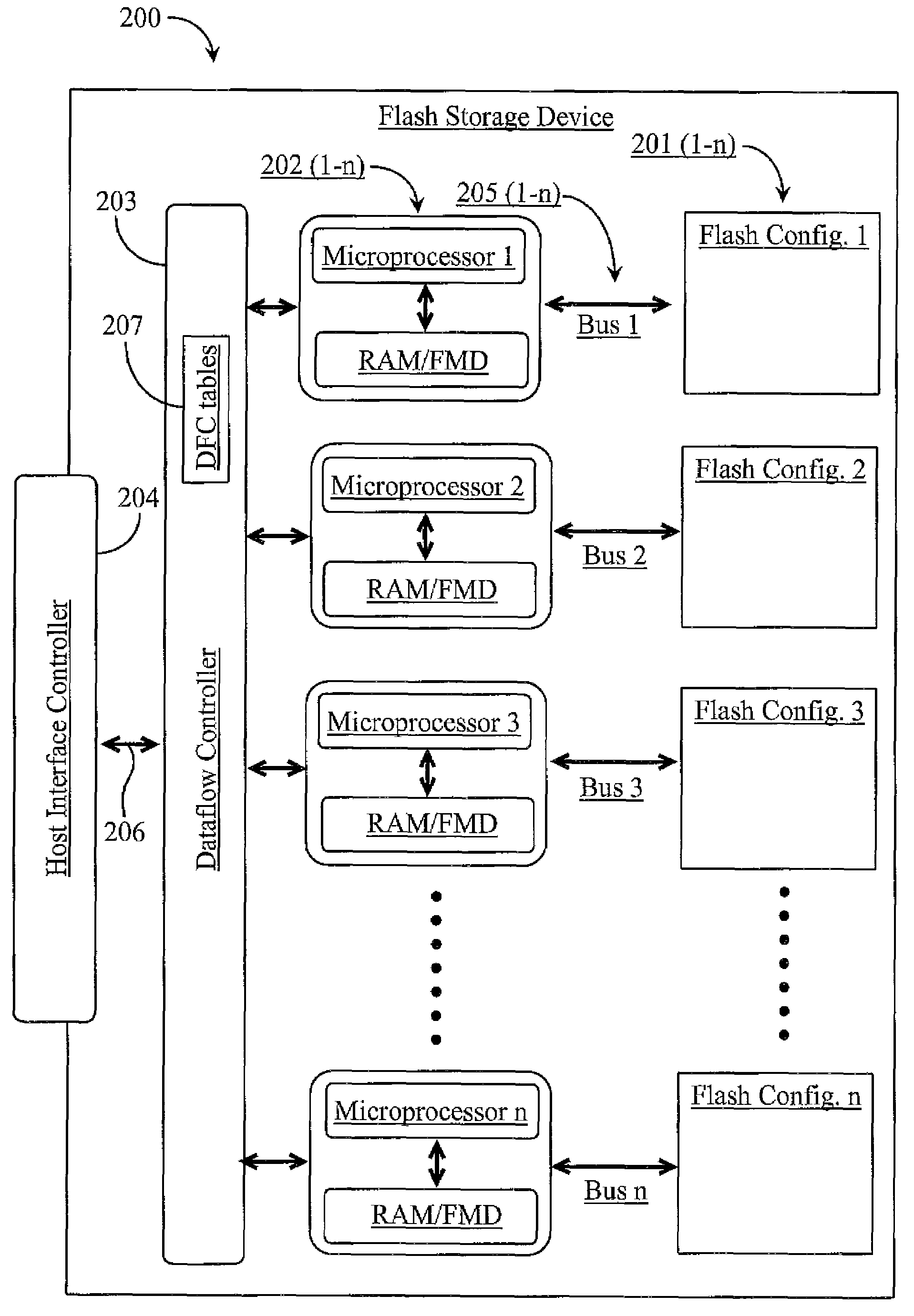

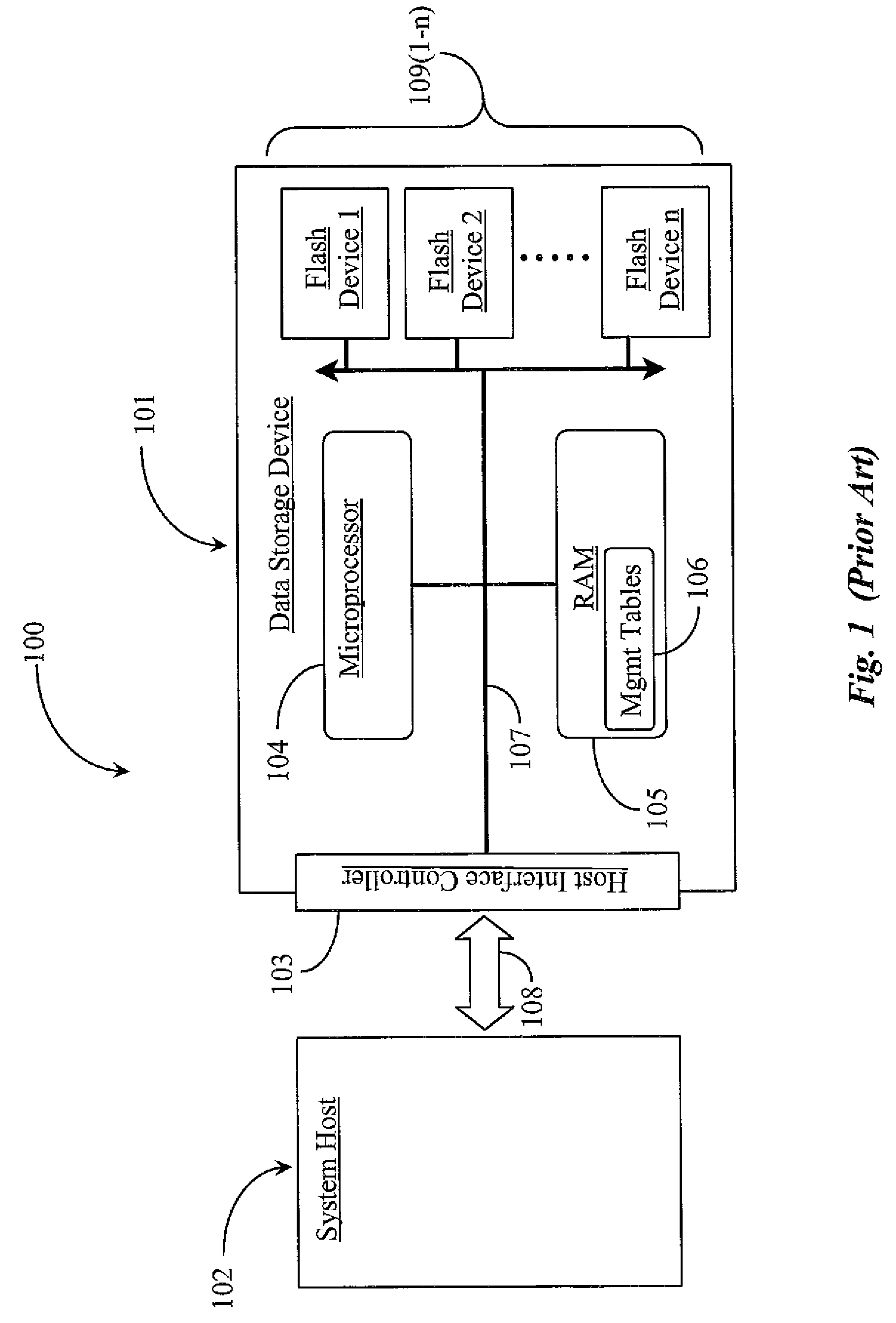

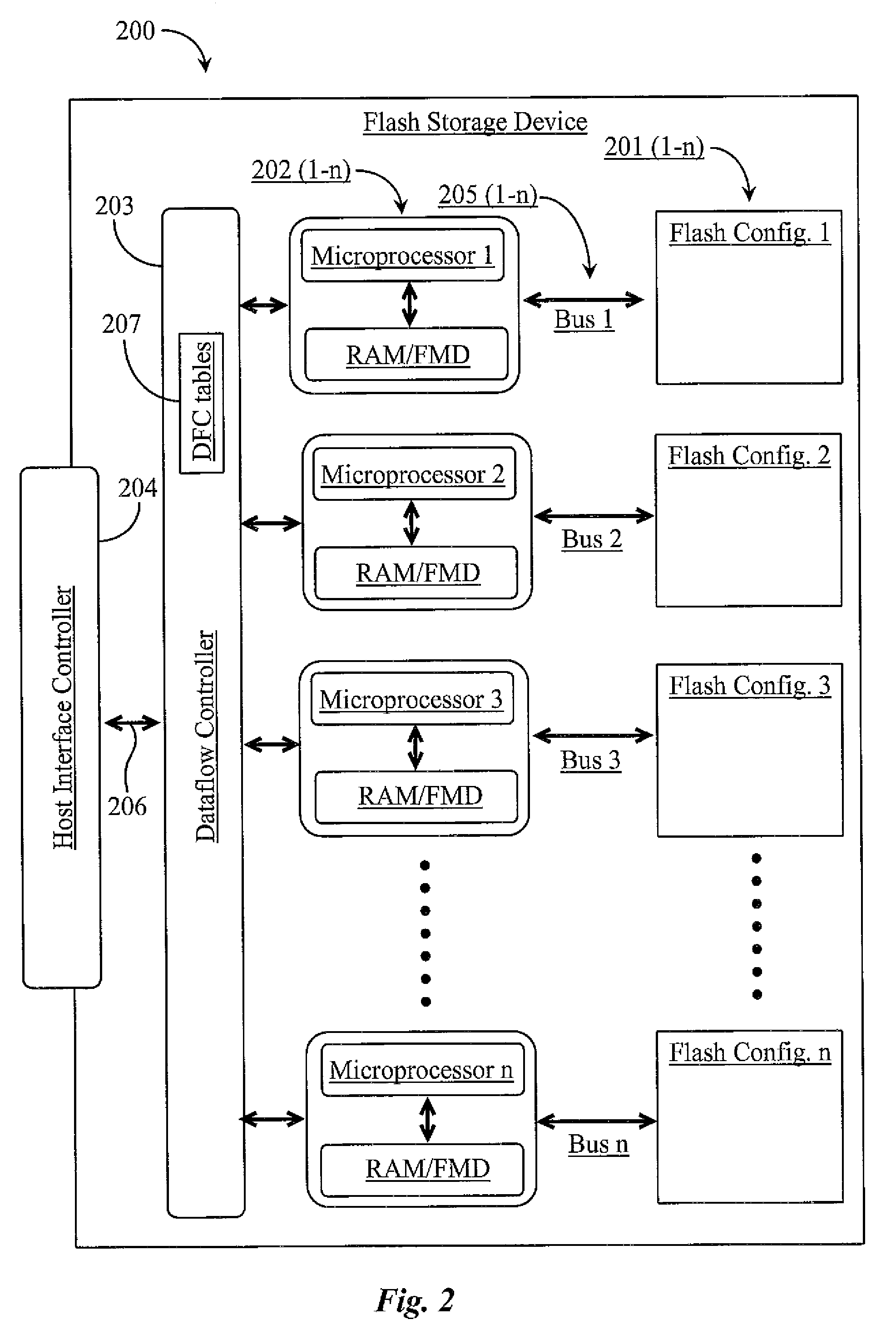

Multi-Processor Flash Memory Storage Device and Management System

ActiveUS20080209116A1Less-expensive to implementFew RAM and bus contention issueInput/output to record carriersMemory adressing/allocation/relocationMulti processorRandom access memory

A data storage device has a host controller interface, a plurality of microprocessor units each having a portion of random access memory (RAM) dedicated thereto, a plurality of Flash device configurations each having dedicated bus connections to individual ones or multiples of the microprocessor units, and a dataflow controller accessible to the host controller interface for managing access to the Flash device configurations.

Owner:INTELLECTUAL VENTURES II

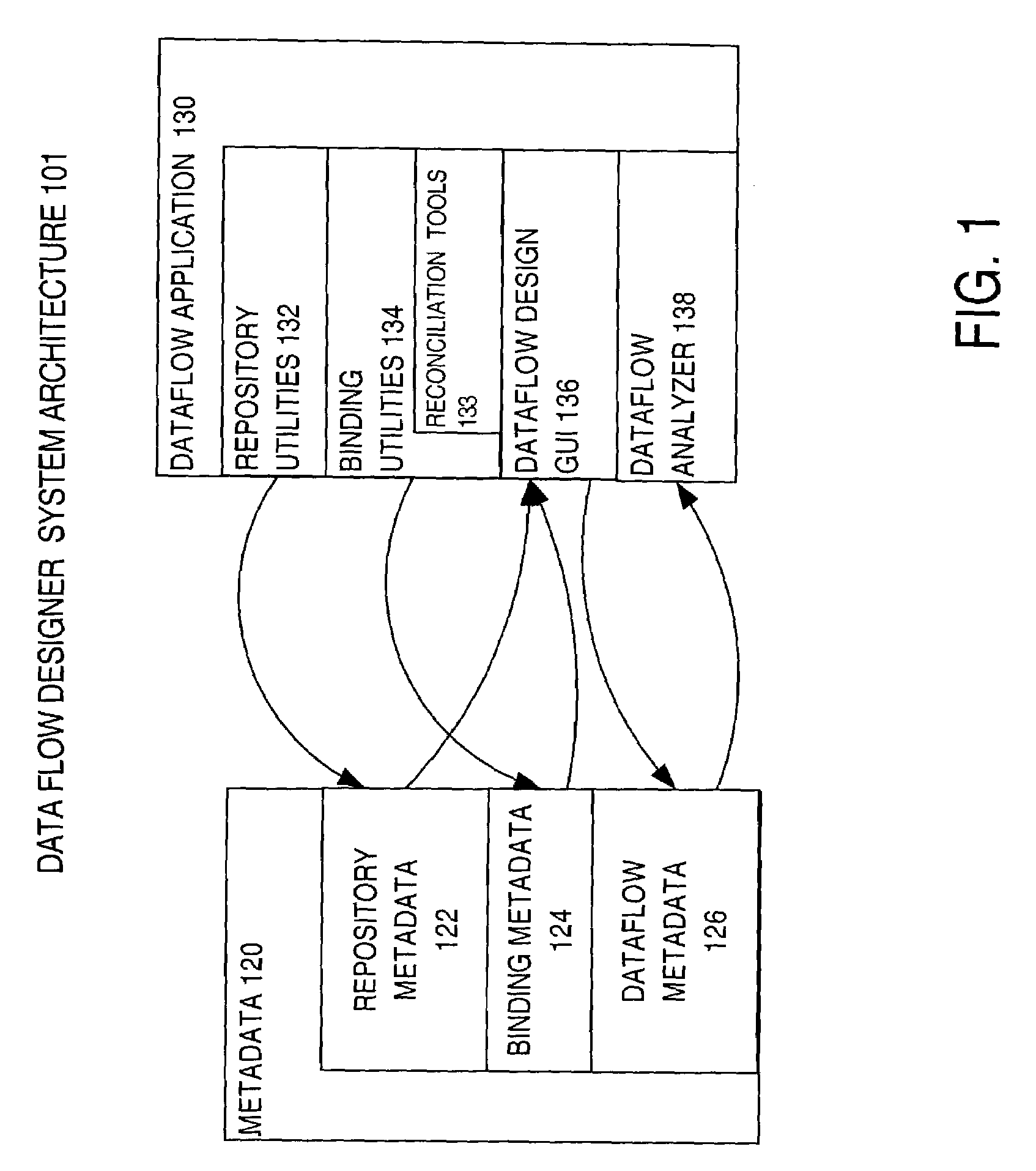

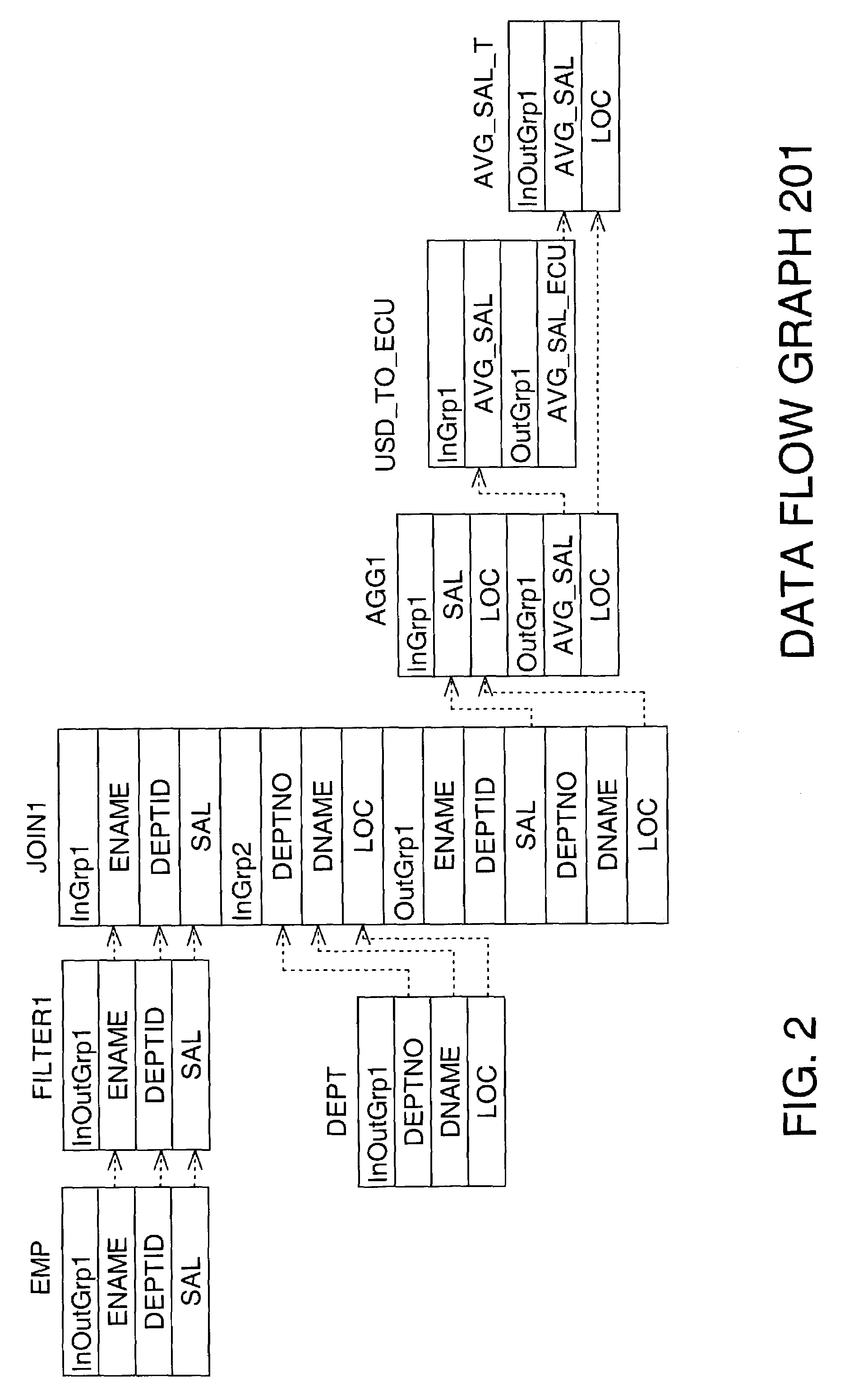

Operator approach for generic dataflow designs

ActiveUS7343585B1Digital data information retrievalSpecial data processing applicationsData warehousePrimitive operation

Described herein is an operator-based approach to representing dataflows. A dataflow is a set of one or more operations and one or more flows of data that are processed successively by the set of operations. A dataflow is described by a generic description in which operations in a dataflow are represented by operators. An operator defines a primitive operation (e.g. join, filter), specifying not only the type of operation, but the inputs and outputs, rules, and criteria that govern the operation. From the generic description, a code implementation is generated that may be completely executed on a source database system and target data warehouse, without need for an intermediate system to participate in the execution of the code implementation, such as a data movement engine.

Owner:ORACLE INT CORP

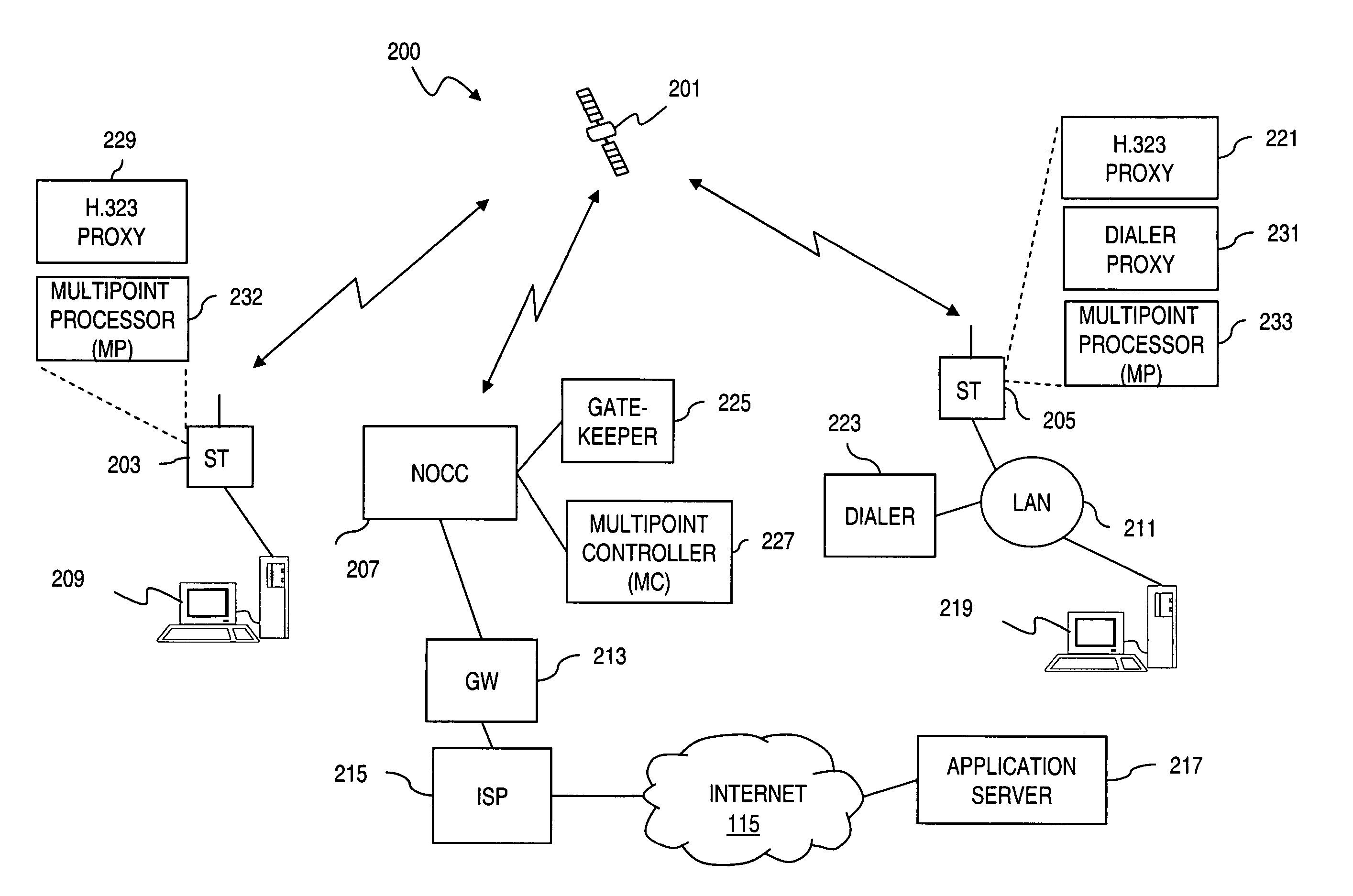

Proxy architecture for providing quality of service(QoS) reservations

ActiveUS20050198261A1Minimizing software upgradeDigital computer detailsData switching networksQuality of serviceClassification rule

An approach is provided for providing quality of service reservations in a packet-based radio communication network is disclosed. Connection information including connection rate is extracted from a dataflow from an application requesting connection-oriented service. A request message is sent to a proxy for establishing a connection based on the connection information over the network, wherein the proxy configures a classification rule based on flow criteria from the request message and accordingly initiates establishment of the connection over the network to a destination terminal. A confirmation that the connection can be established is selectively received according to the connection information, wherein the dataflow satisfying the flow criteria from the application is transported over the established connection to the destination terminal. This approach as particular applicability to shared capacity systems, such as a satellite communication system.

Owner:HUGHES NETWORK SYST

Proxy architecture for providing quality of service(QoS) reservations

ActiveUS7353279B2Minimizing software upgradeMultiple digital computer combinationsGenerating/distributing signalsQuality of serviceClassification rule

An approach is provided for providing quality of service reservations in a packet-based radio communication network is disclosed. Connection information including connection rate is extracted from a dataflow from an application requesting connection-oriented service. A request message is sent to a proxy for establishing a connection based on the connection information over the network, wherein the proxy configures a classification rule based on flow criteria from the request message and accordingly initiates establishment of the connection over the network to a destination terminal. A confirmation that the connection can be established is selectively received according to the connection information, wherein the dataflow satisfying the flow criteria from the application is transported over the established connection to the destination terminal. This approach as particular applicability to shared capacity systems, such as a satellite communication system.

Owner:HUGHES NETWORK SYST

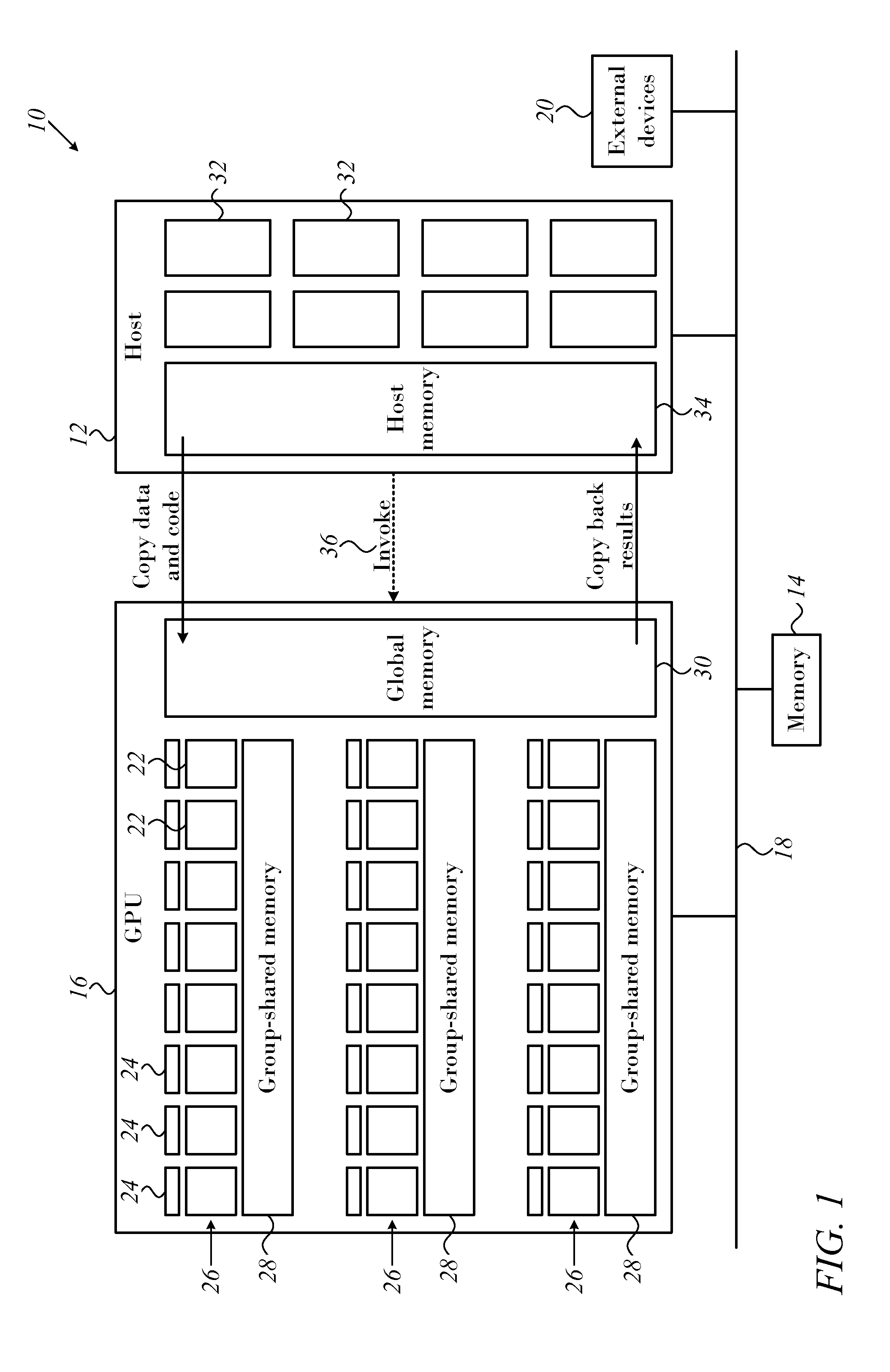

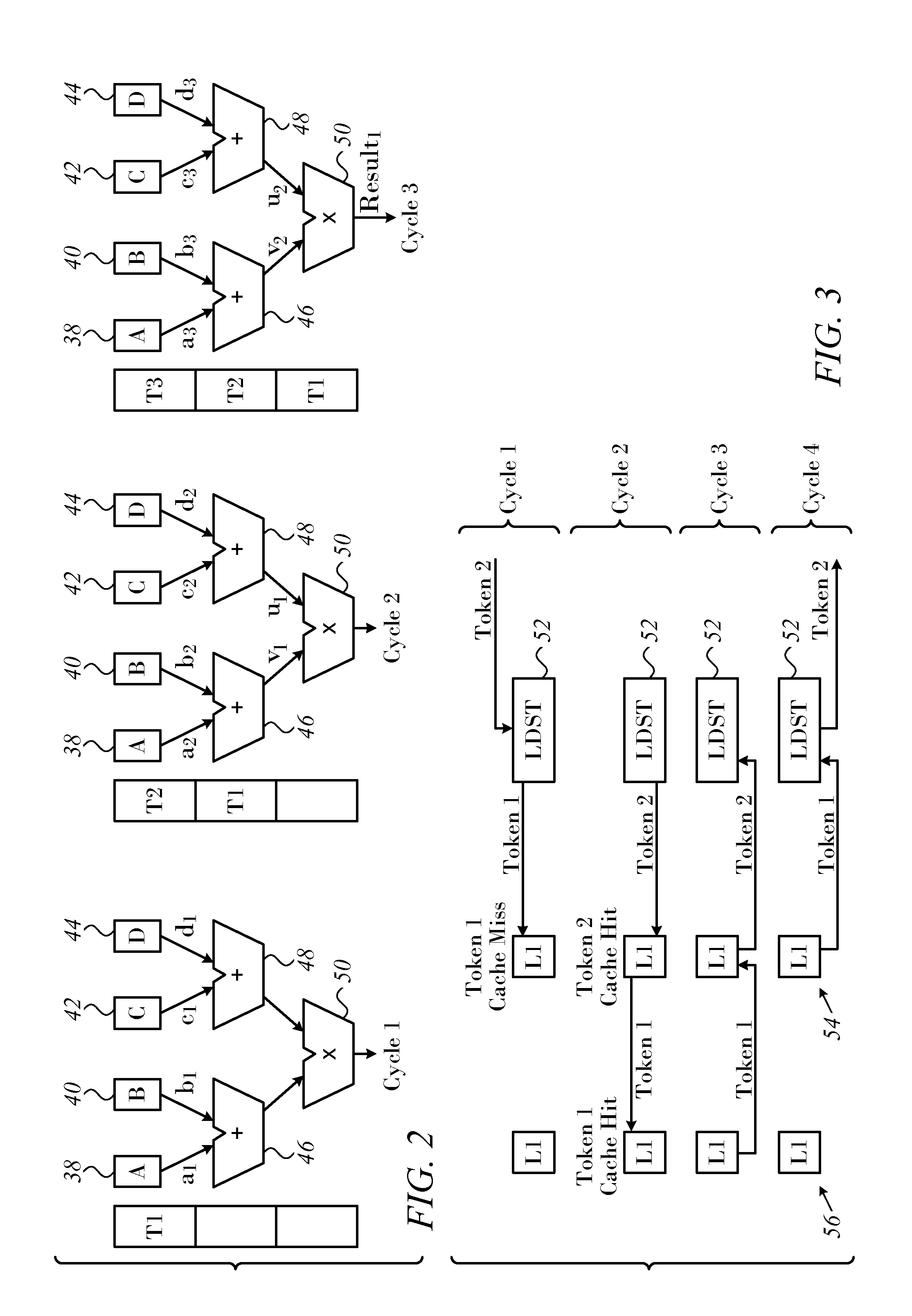

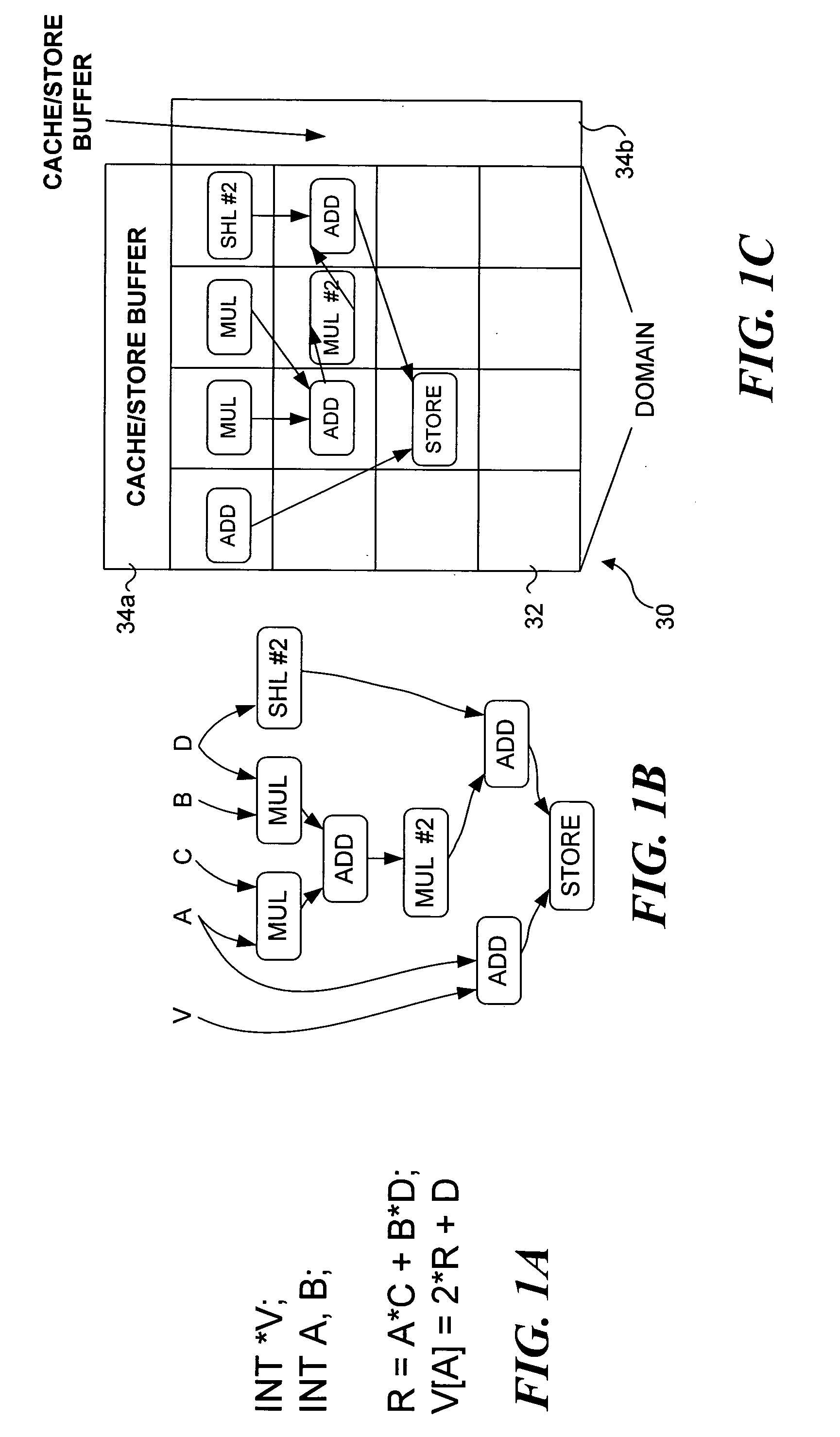

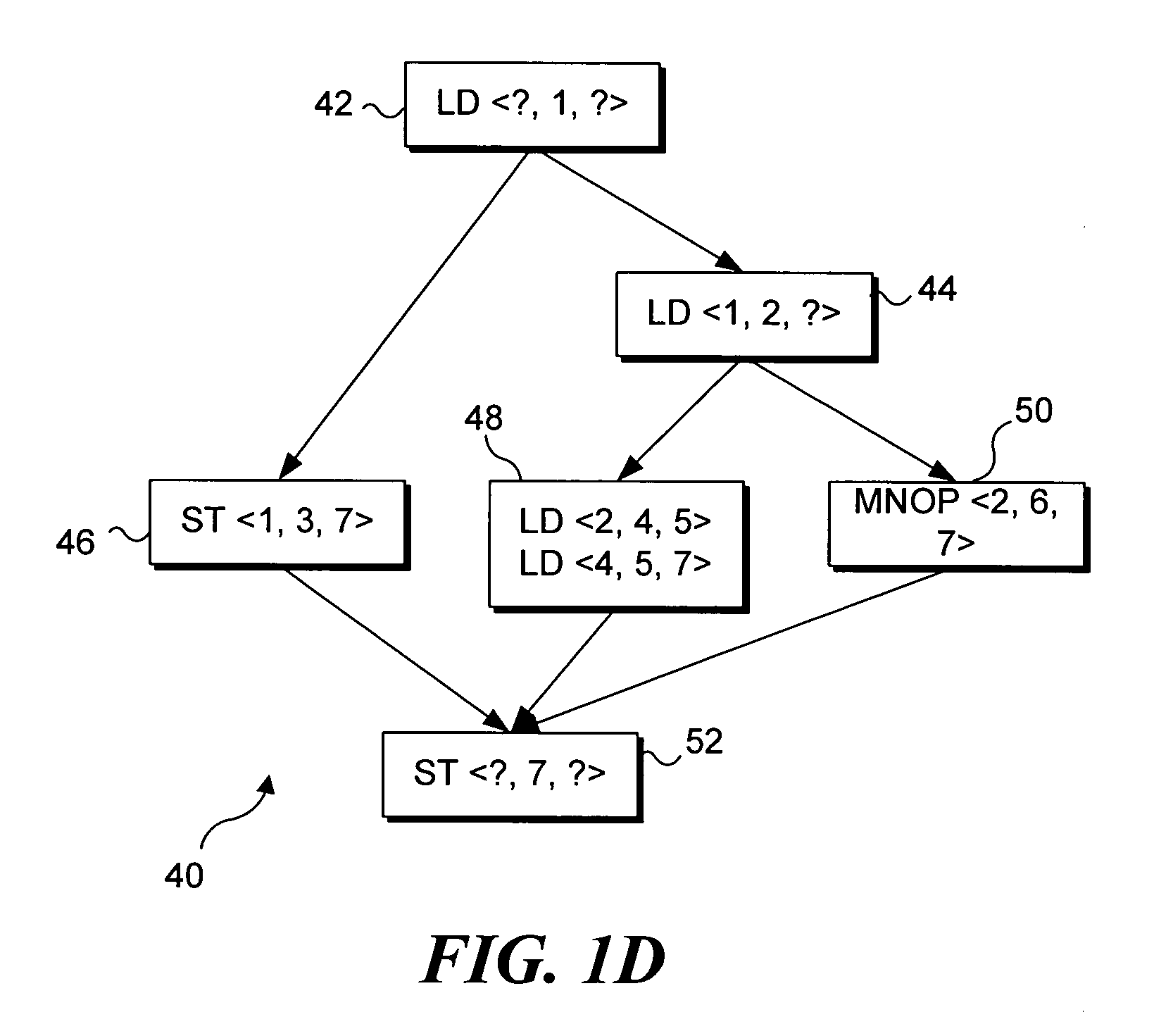

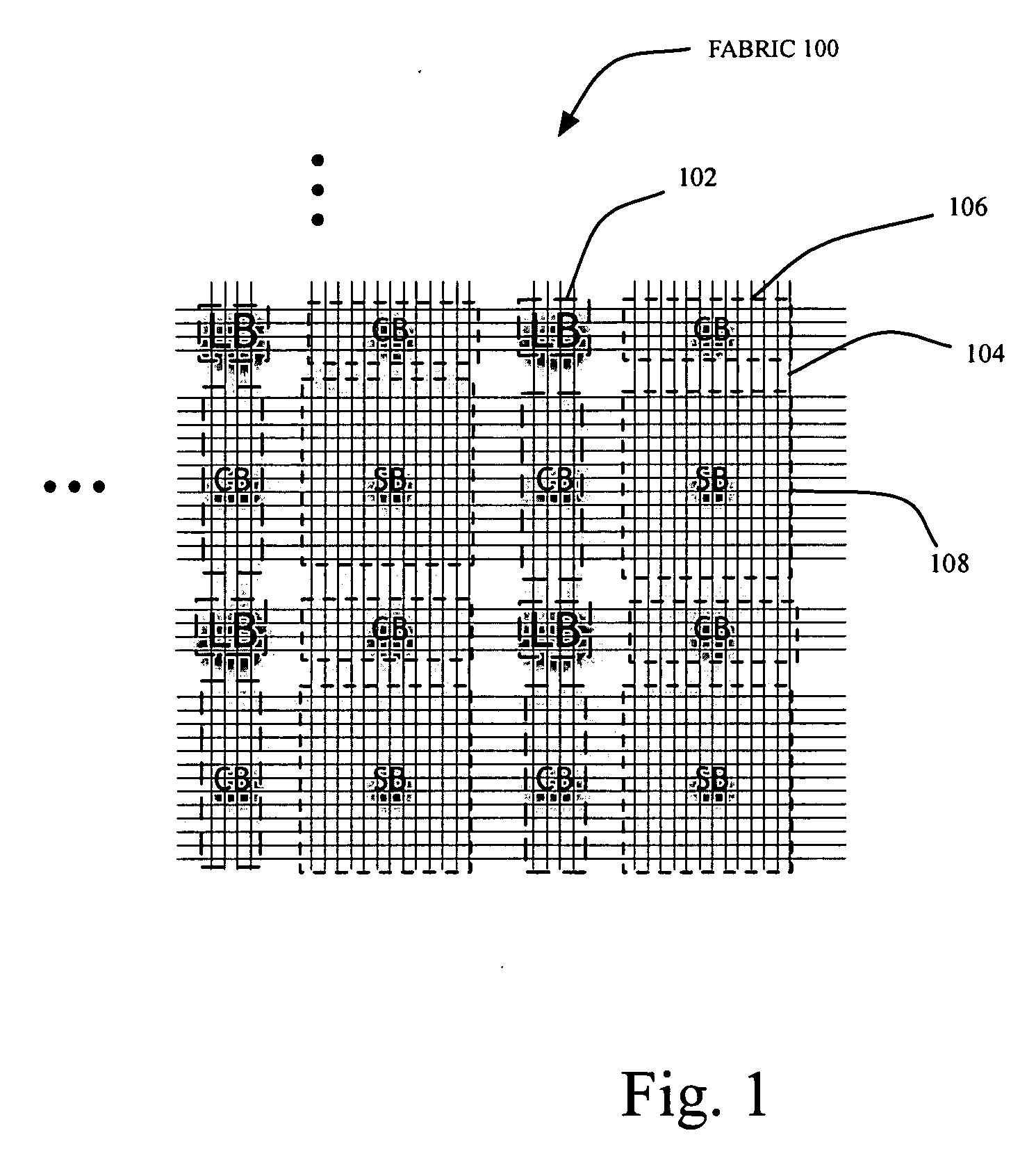

Execution of data-parallel programs on coarse-grained reconfigurable architecture hardware

InactiveUS20150268963A1Accelerate execution throughputImprove performanceProgram initiation/switchingDigital computer detailsStatic mappingDynamic data

A GPGPU-compatible architecture combines a coarse-grain reconfigurable fabric (CGRF) with a dynamic dataflow execution model to accelerate execution throughput of massively thread-parallel code. The CGRF distributes computation across a fabric of functional units. The compute operations are statically mapped to functional units, and an interconnect is configured to transfer values between functional units.

Owner:TECHNION RES & DEV FOUND LTD

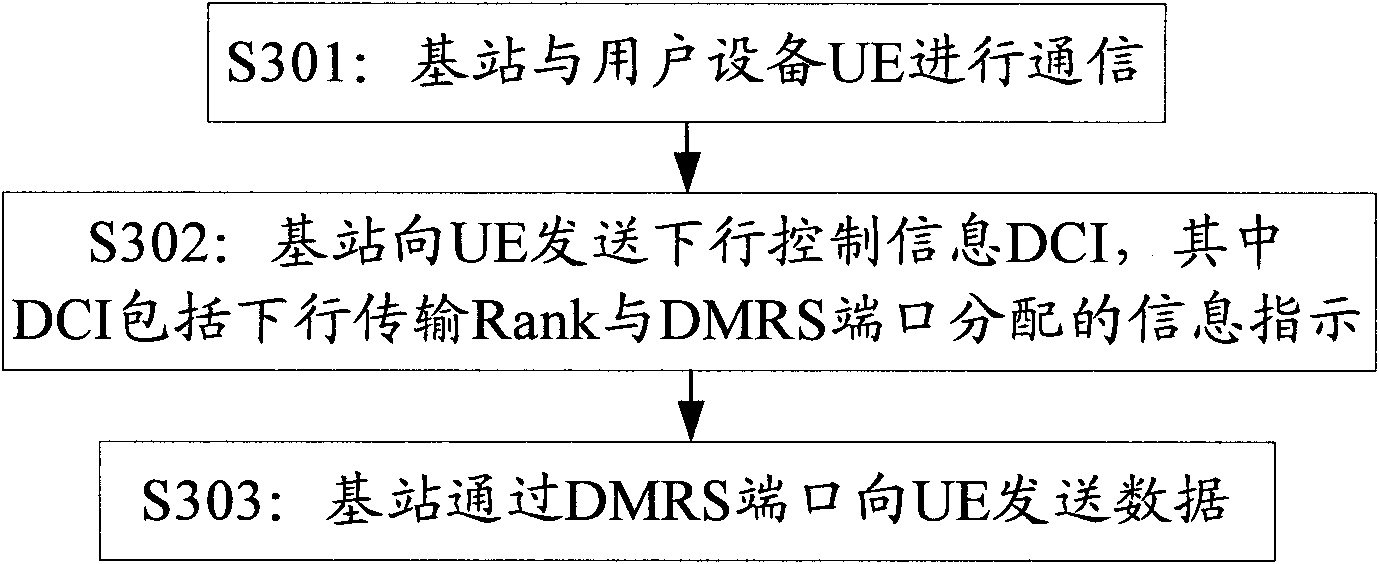

Method and device for indicating information

ActiveCN102158302AReduce overheadMinor changesError preventionHigh level techniquesUser equipmentDemodulation

The embodiment of the invention provides a method for indicating information, and the method comprises the following steps: a base station communicates with user equipment (UE) and allocates a corresponding dataflow to the UE according to the attribute of the UE; the base station sends downlink control information (DCI) to the UE, wherein the DCI contains information indications allocated to a downlink transmission Rank and a demodulation reference sign (DMRS) port; and the base station sends the corresponding dataflow to the UE through the DMRS port. By using the technical scheme provided bythe invention, the signaling overhead is reduced by using a transmission block switch and through the combined coding of NDI (non-damage inspection) bits in the mono-code transmission, thereby supporting the combined indication of the DMRS port and bus Rank with a lower overhead.

Owner:DATANG MOBILE COMM EQUIP CO LTD

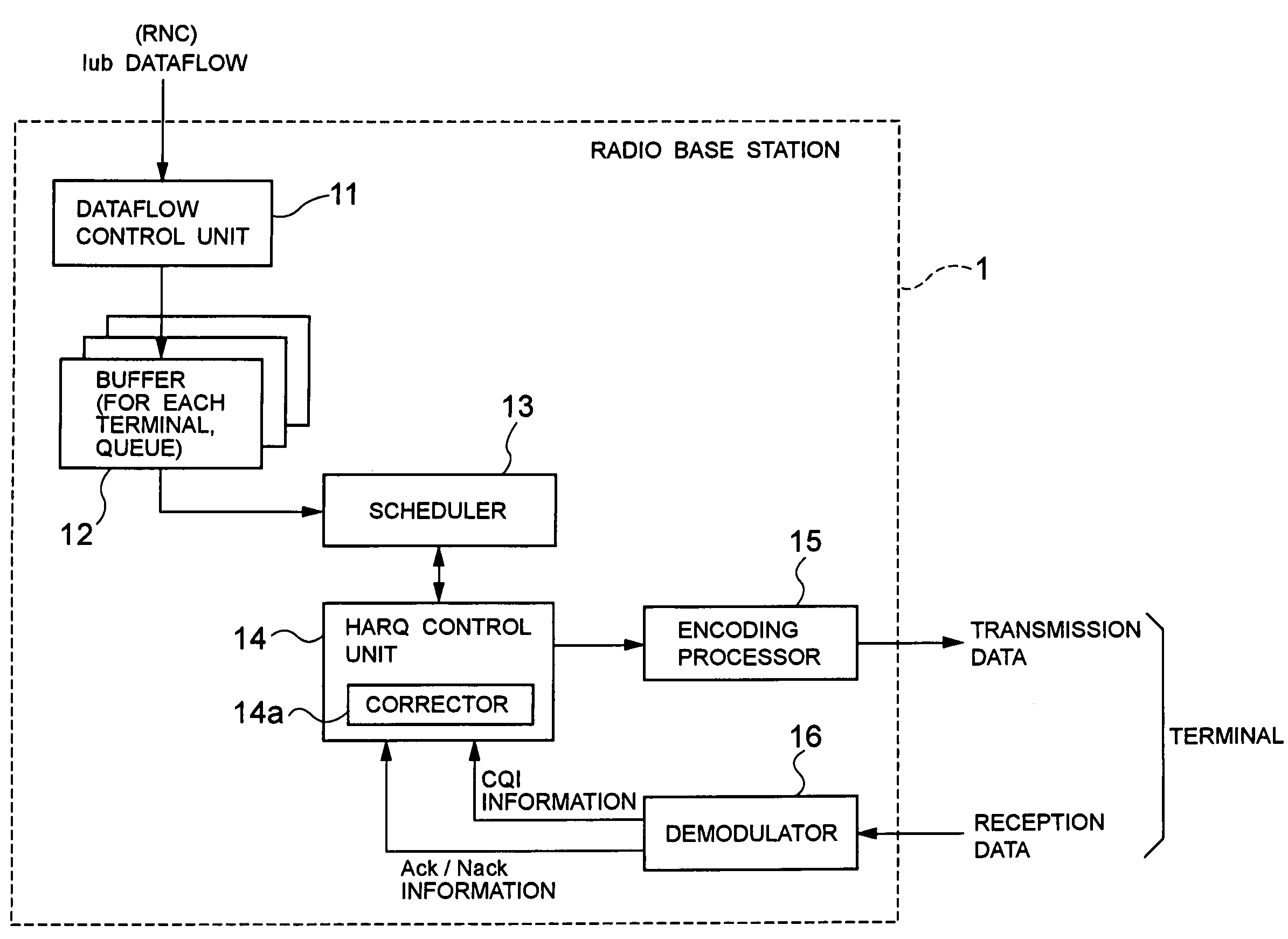

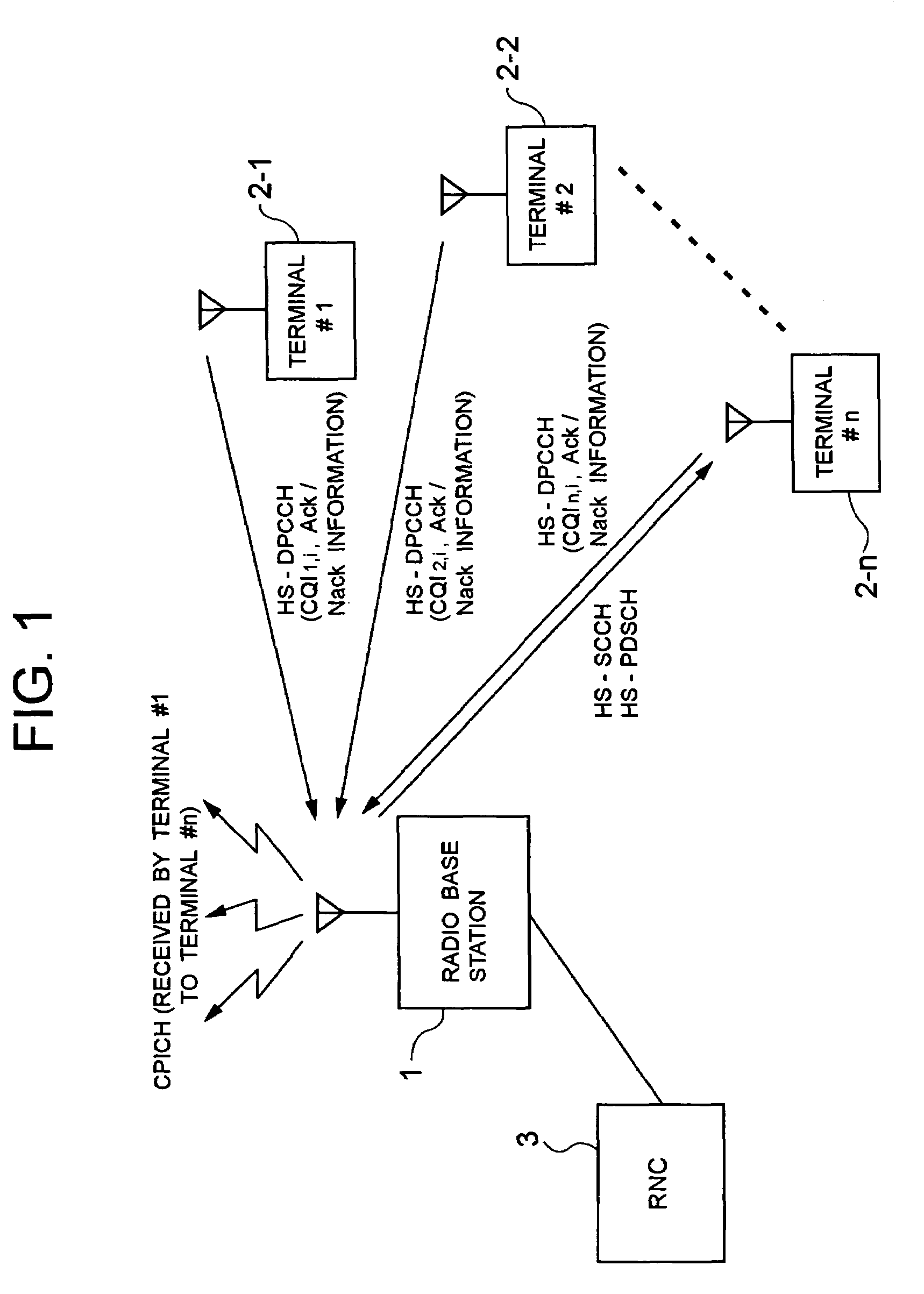

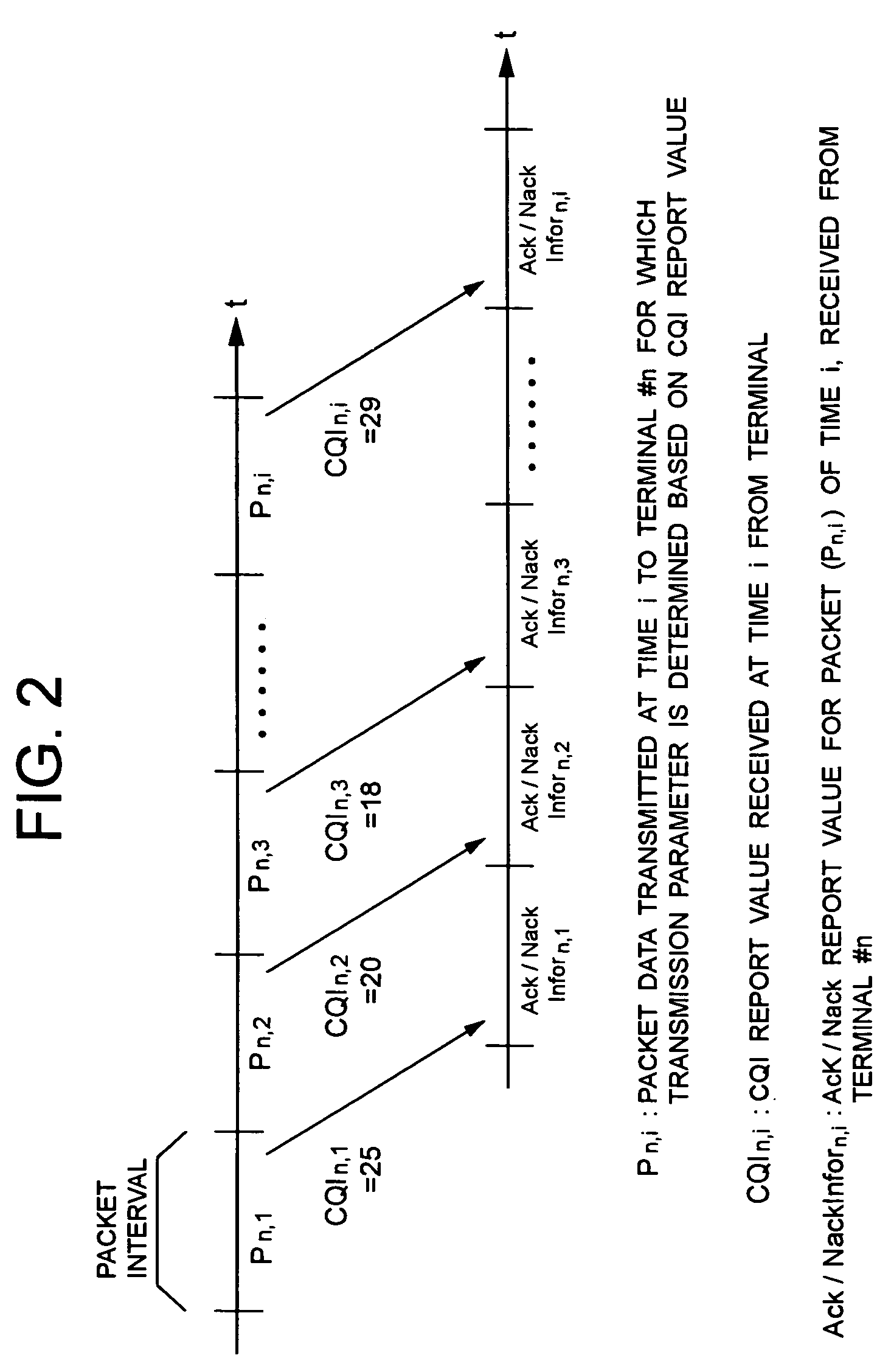

Radio communication system, base station, method of correcting radio link quality information employed therefor, and its program

InactiveUS7359327B2Reduces throughput of systemReduce throughputError prevention/detection by using return channelError detection/prevention using signal quality detectorCommunications systemMobile communication systems

A mobile communication system is provided which is capable of preventing a reduction in user throughput and system throughput. In a radio base station, a dataflow control unit controls an Iub dataflow from an RNC, a buffer stores the dataflow for each terminal in each corresponding queue, and a scheduler schedules the dataflow. An HARQ control unit controls retransmission of the dataflow and corrects CQI report values received from a terminal at a corrector. An encoding processor encodes the dataflow, and a demodulator demodulates data received from the terminal. After the demodulation of the data received from the terminal, the demodulator sends CQI information and Ack / Nack information to the HARQ control unit. The corrector in the HARQ control unit then corrects the CQI report value in accordance with these received CQI information and Ack / Nack information.

Owner:NEC CORP

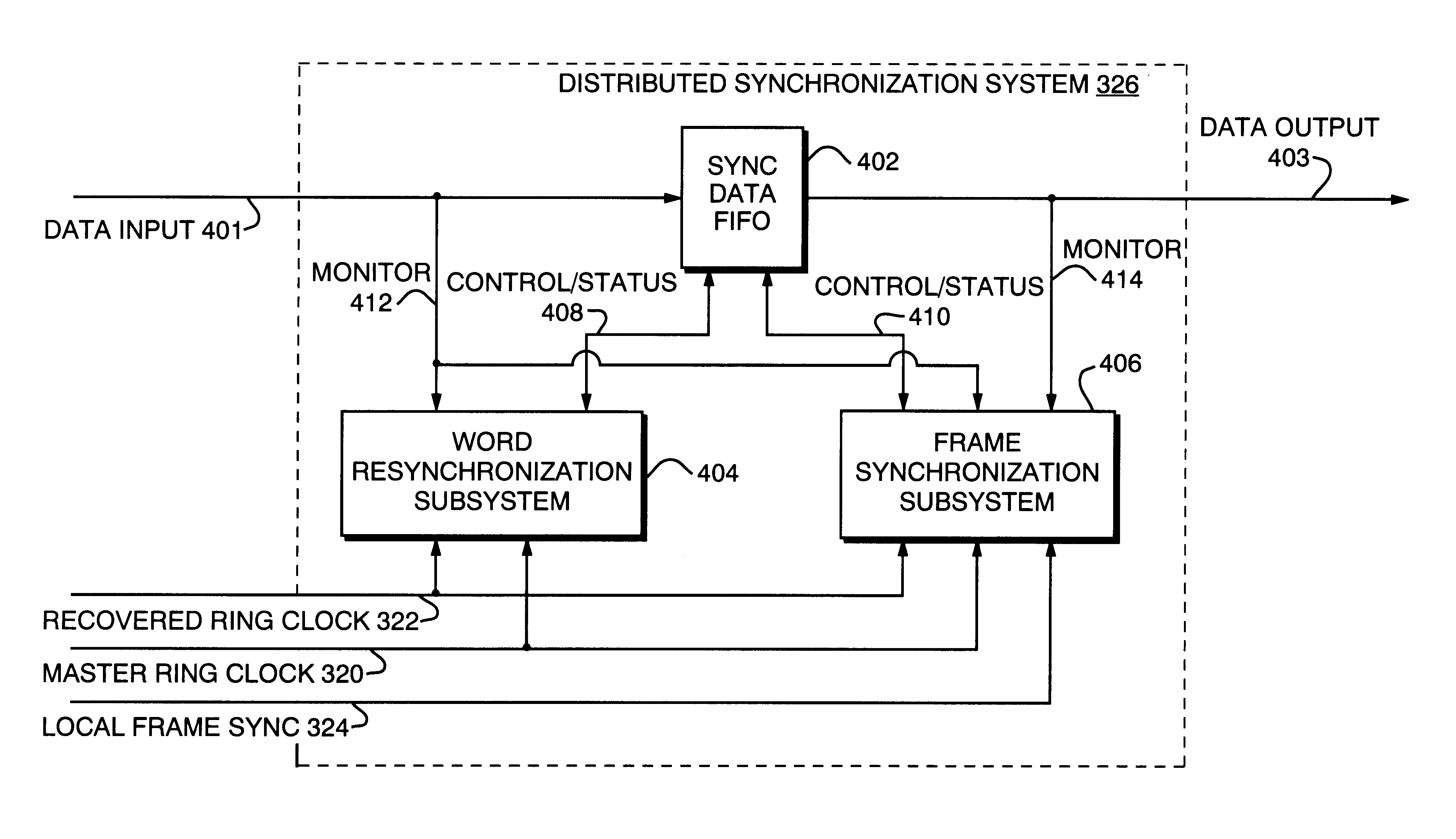

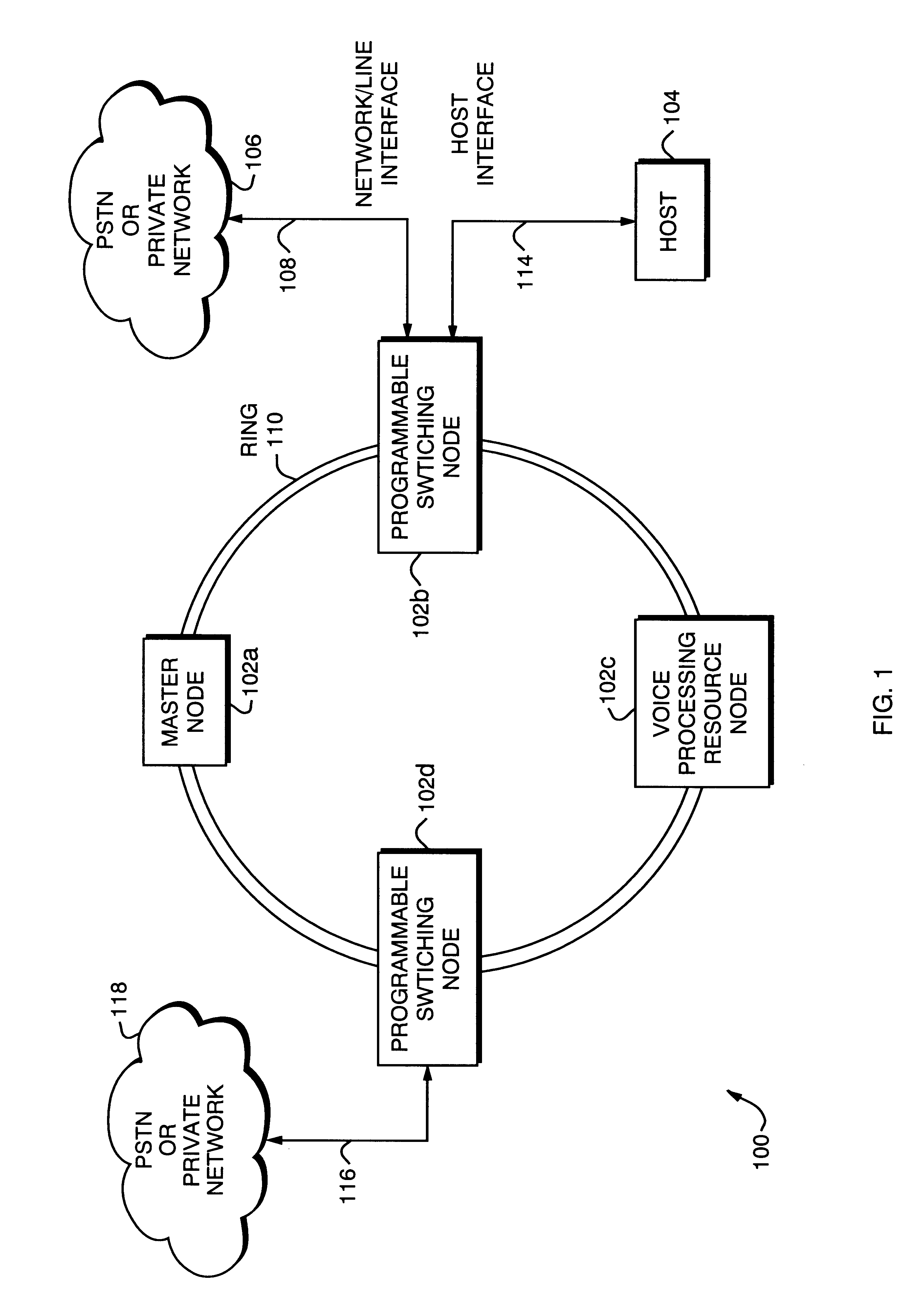

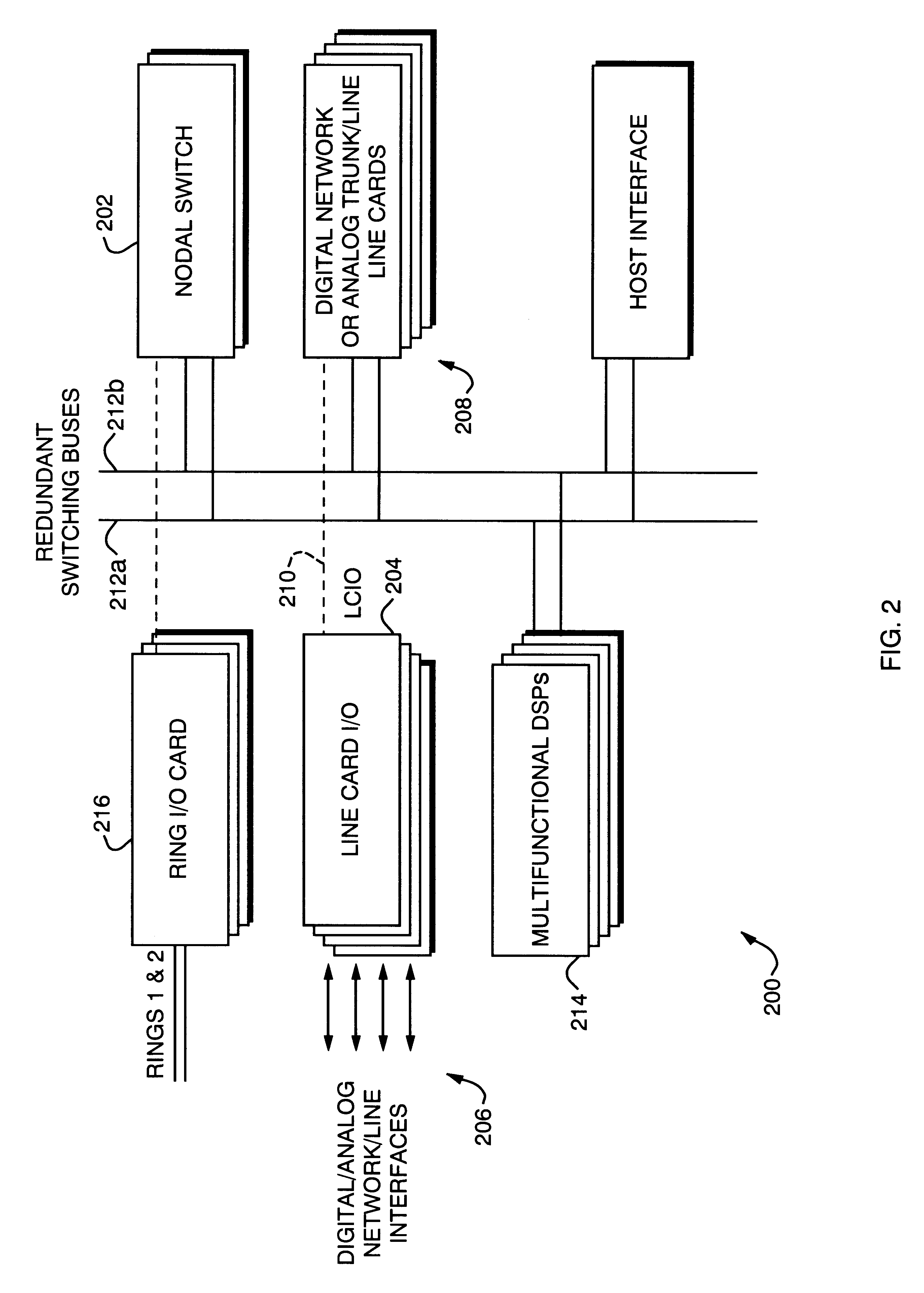

Distributed network synchronization system

InactiveUS6278718B1Effective absorptionOptimization rangeTime-division multiplexLoop networksAsynchronous communicationTelecommunications network

A distributed synchronization system for use in each node of a distributed asynchronous telecommunications network system that continually monitors and controls the flow of data through an implementing node to prevent dataflow errors due to phase and frequency differences in source and destination nodal clocks, and to control inter-nodal network latency so as to support the transmission of synchronous data. A synchronization data FIFO buffers predetermined fields or portions of fields of a unique frame packet received from a source node before retransmission to a destination node on the network. The frame packet includes a frame synchronization field indicating the beginning of a new frame packet; a payload field containing valid data; and a dead zone field providing bandwidth during which the present invention performs synchronization functions. A frame synchronization subsystem, implemented in a designated master node, guarantees that a frame is released at the beginning of an independently-determined frame regardless of network latency. A word resynchronization subsystem manages the flow of data through the data FIFO of each non-master node, receiving and storing data at the source node's clock rate and transmitting the data according to its own clock, thereby guaranteeing the efficient receipt and transmission of data between asynchronously-communicating nodes.

Owner:EXCEL SWITCHING

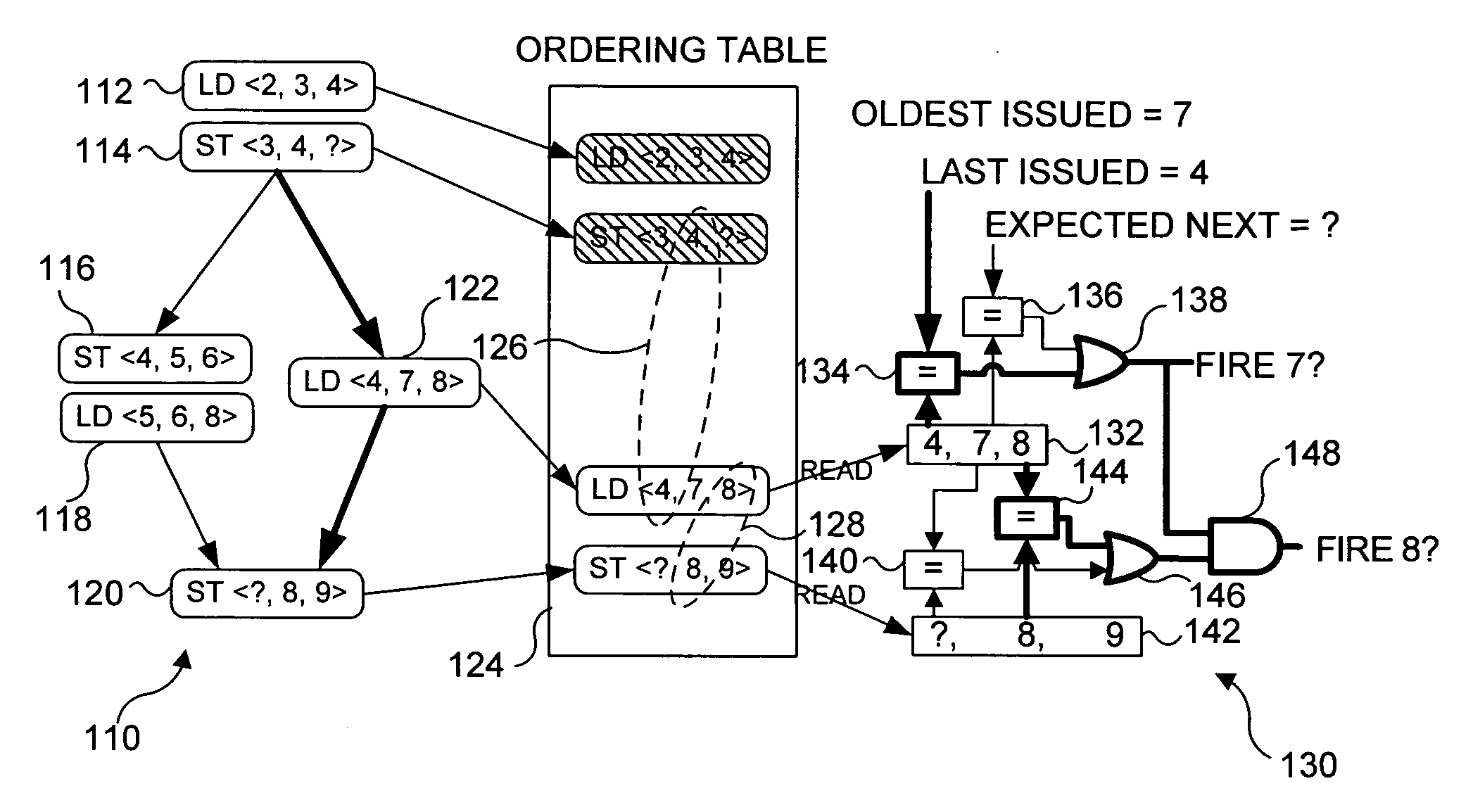

Wavescalar architecture having a wave order memory

InactiveUS20050166205A1Reduce communication costsMaximizing processor utilizationSingle instruction multiple data multiprocessorsProgram synchronisationTerm memoryLow complexity

A dataflow instruction set architecture and execution model, referred to as WaveScalar, which is designed for scalable, low-complexity / high-performance processors, while efficiently providing traditional memory semantics through a mechanism called wave-ordered memory. Wave-ordered memory enables “real-world” programs, written in any language, to be run on the WaveScalar architecture, as well as any out-of-order execution unit. Because it is software-controlled, wave-ordered memory can be disabled to obtain greater parallelism. Wavescalar also includes a software-controlled tag management system.

Owner:UNIV OF WASHINGTON

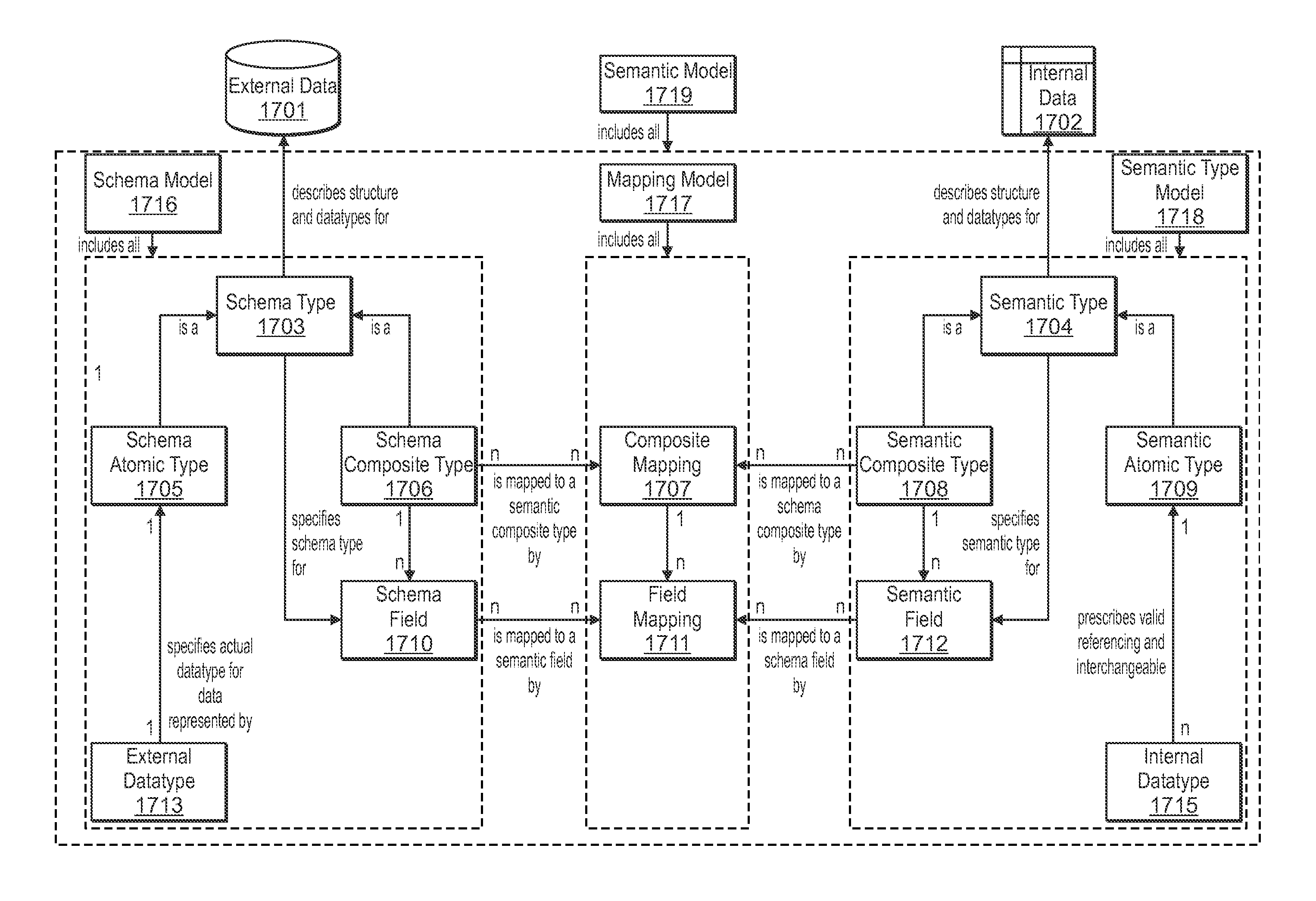

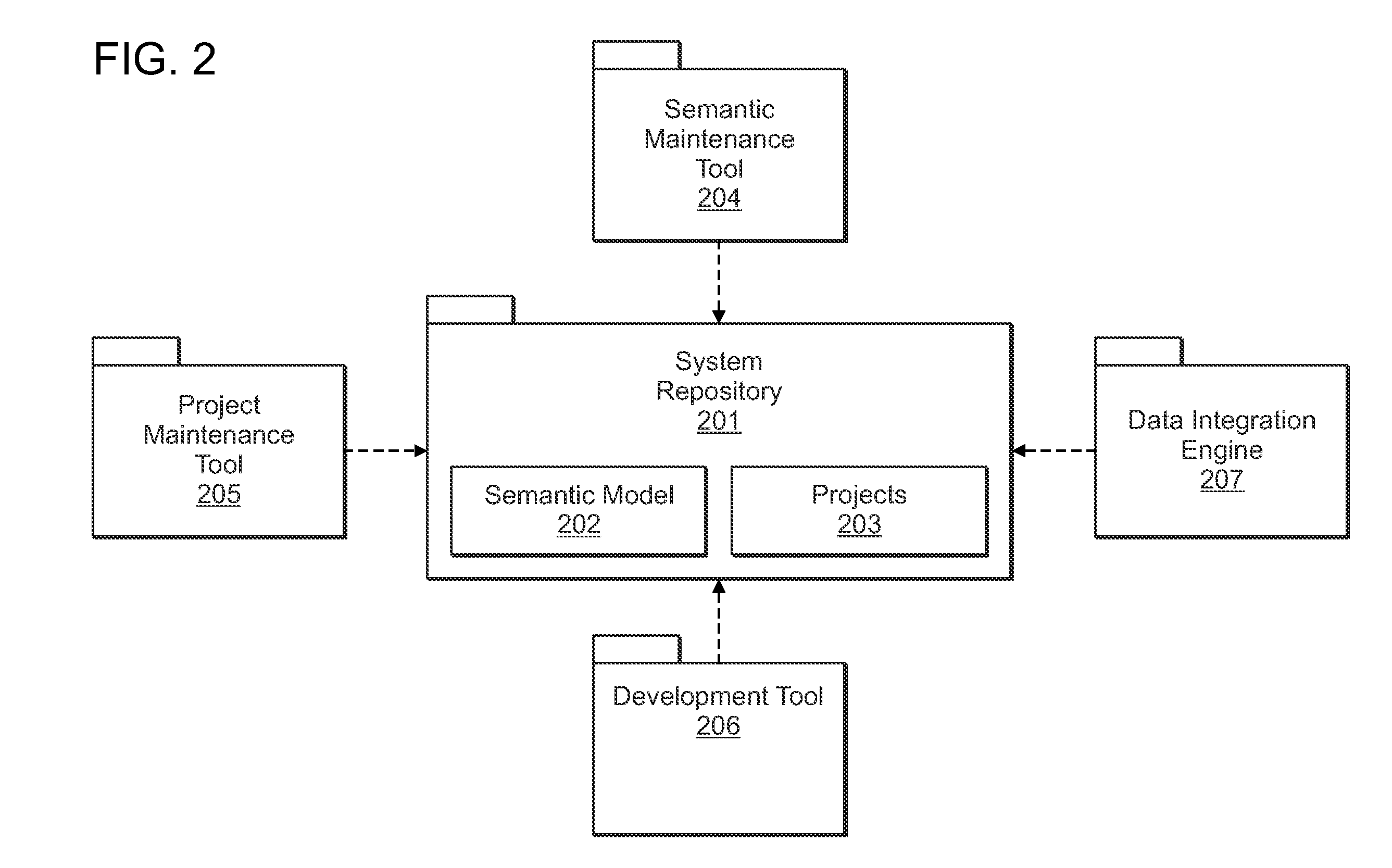

Method and system for developing data integration applications with reusable semantic types to represent and process application data

ActiveUS20120095973A1Low costMinimizes riskDigital data processing detailsSoftware maintainance/managementExternal dataApplication software

A method and system for developing data integration applications with reusable semantic types to represent and process application data. Methods include creating schemas to describe external data, creating semantic types to describe internal data, mapping schemas to semantic types, developing dataflows that configure input and output operations using schemas, mappings, and semantic types and all other transformation operations and functions based solely on semantic types, and executing dataflows defined in this manner.

Owner:QLIKTECH INT

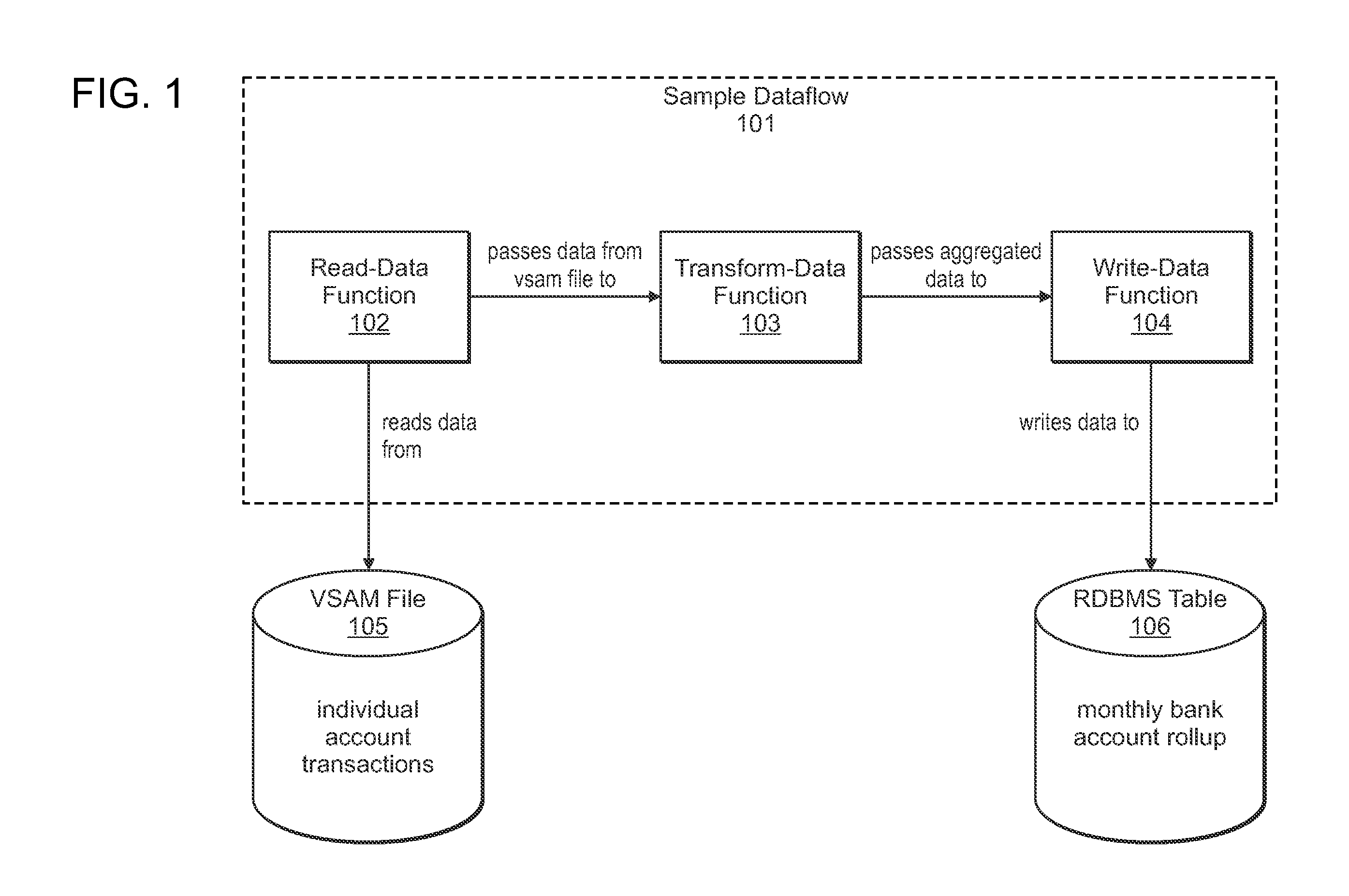

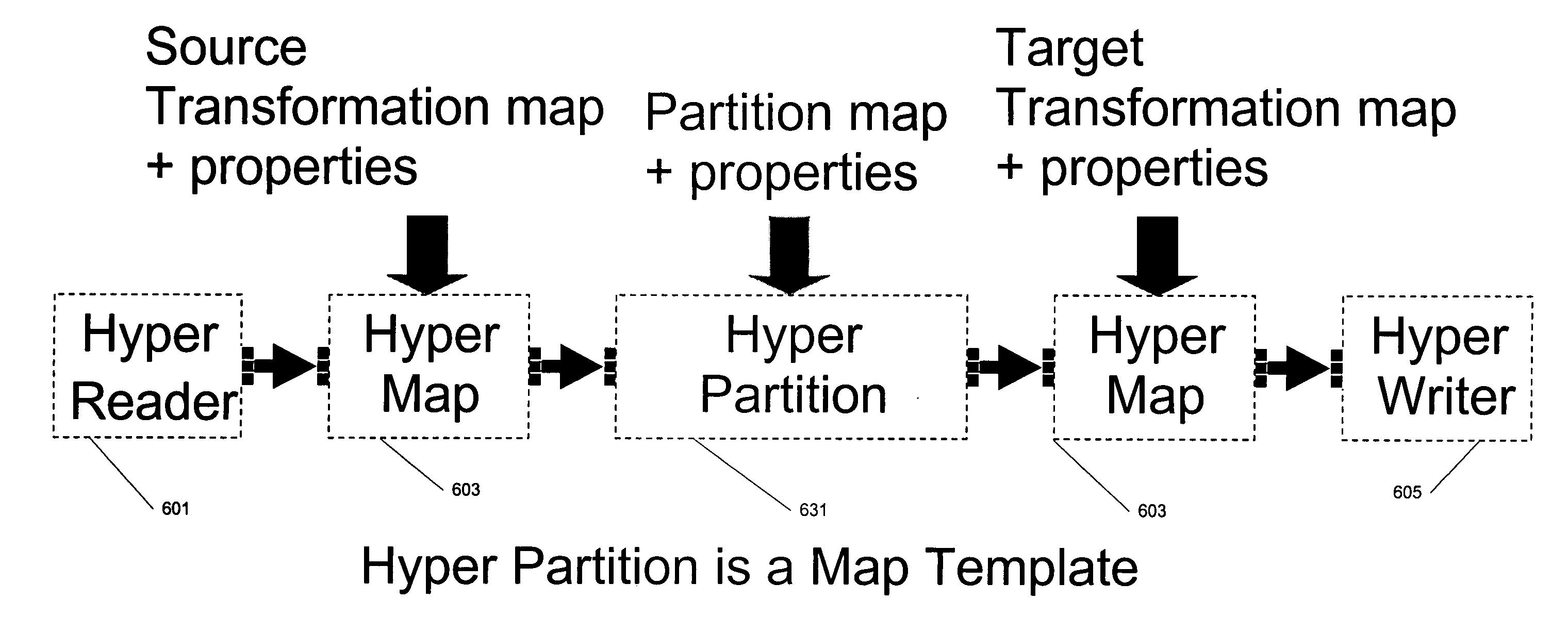

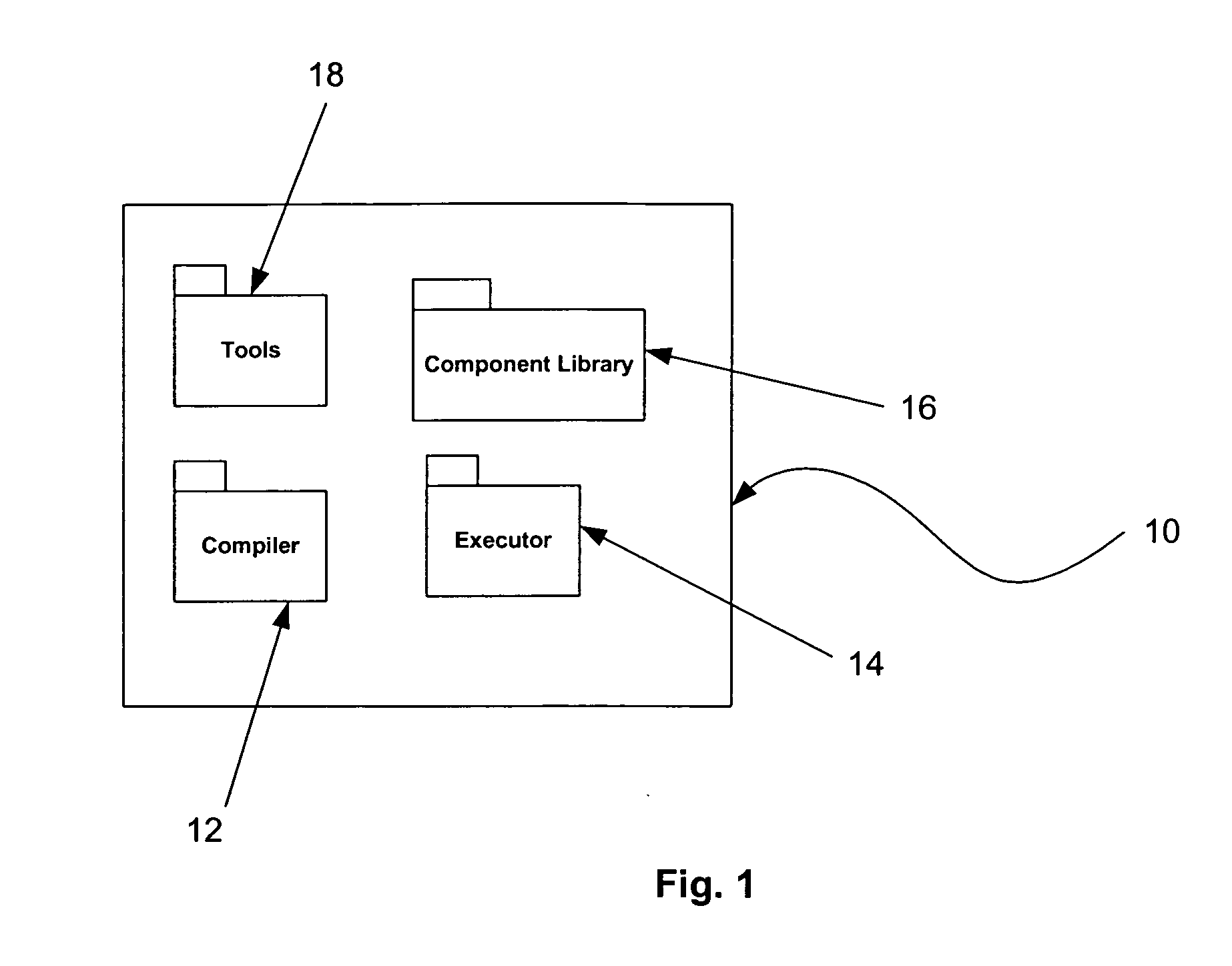

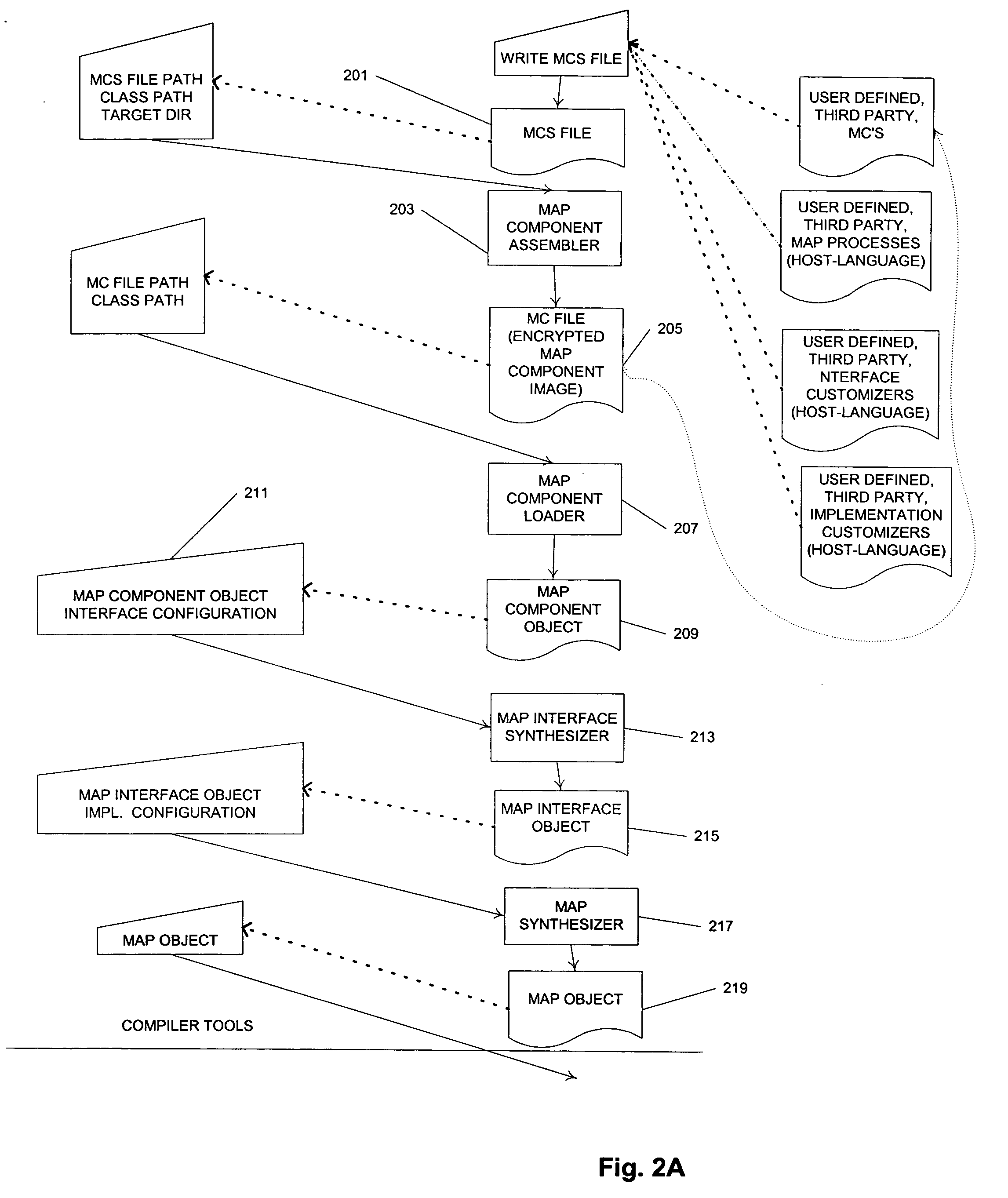

Execution environment for data transformation applications

ActiveUS20070271562A1Error preventionFrequency-division multiplex detailsExtensibilityData transformation

The execution environment provides for scalability where components will execute in parallel and exploit various patterns of parallelism. Dataflow applications are represented by reusable dataflow graphs called map components, while the executable version is called a prepared map. Using runtime properties the prepared map is executed in parallel with a thread allocated to each map process. The execution environment not only monitors threads, detects and corrects deadlocks, logs and controls program exceptions, but also data input and output ports of the map components are processed in parallel to take advantage of data partitioning schemes. Port implementation supports multi-state null value tokens to more accurately report exceptions. Data tokens are batched to minimize synchronization and transportation overhead and thread contention.

Owner:ACTIAN CORP

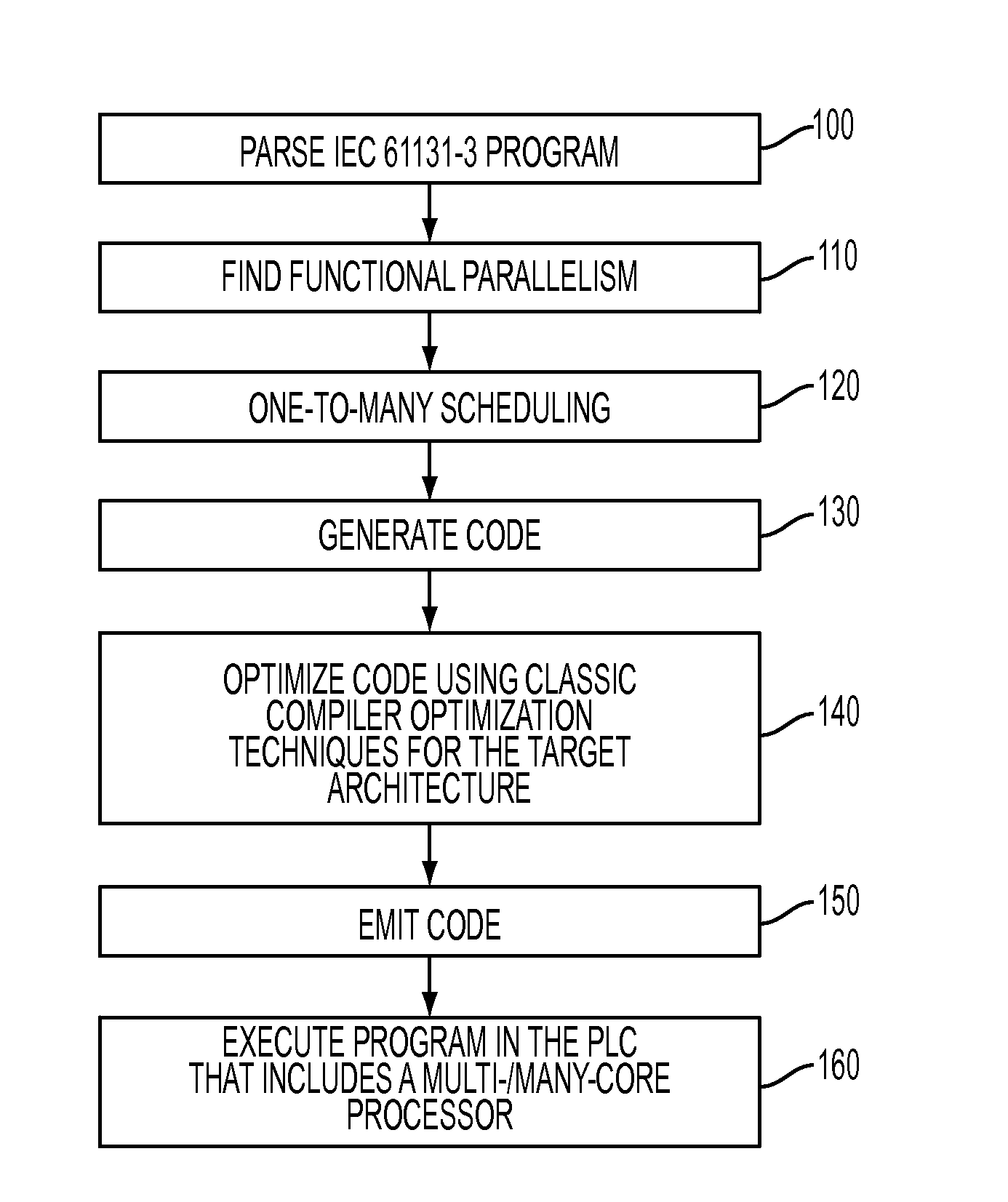

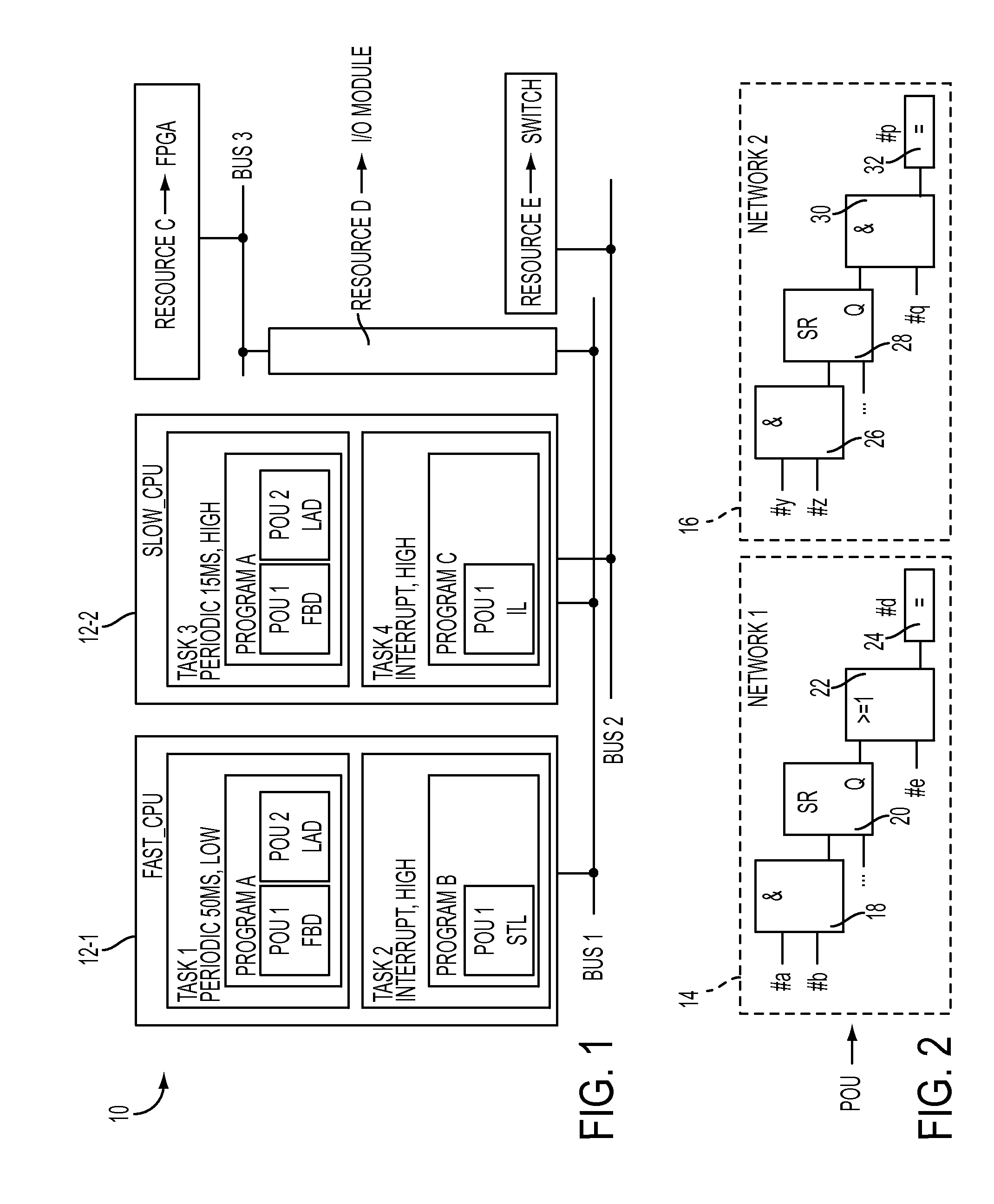

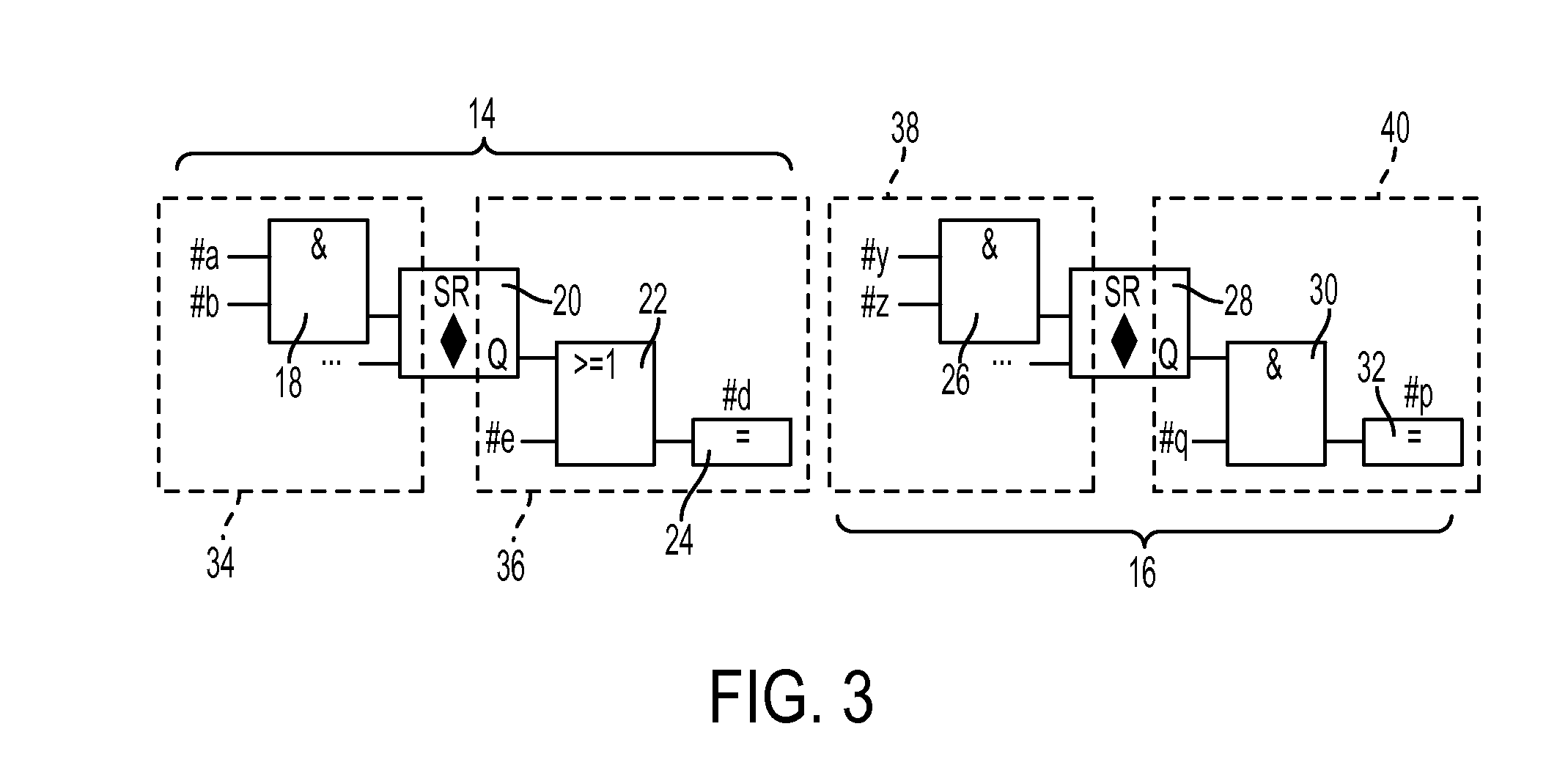

Parallelization of PLC programs for operation in multi-processor environments

ActiveUS20120260239A1Break dependenciesEfficient use ofSoftware engineeringProgram controlProgram fragmentMulti processor

A method of identifying and extracting functional parallelism from a PLC program has been developed that results in the ability of the extracted program fragments to be executed in parallel across a plurality of separate resources, and a compiler configured to perform the functional parallelism (i.e., identification and extraction processes) and perform the scheduling of the separate fragments within a given set of resources. The inventive functional parallelism creates a larger number of separable elements than was possible with prior dataflow analysis methodologies.

Owner:SIEMENS AG

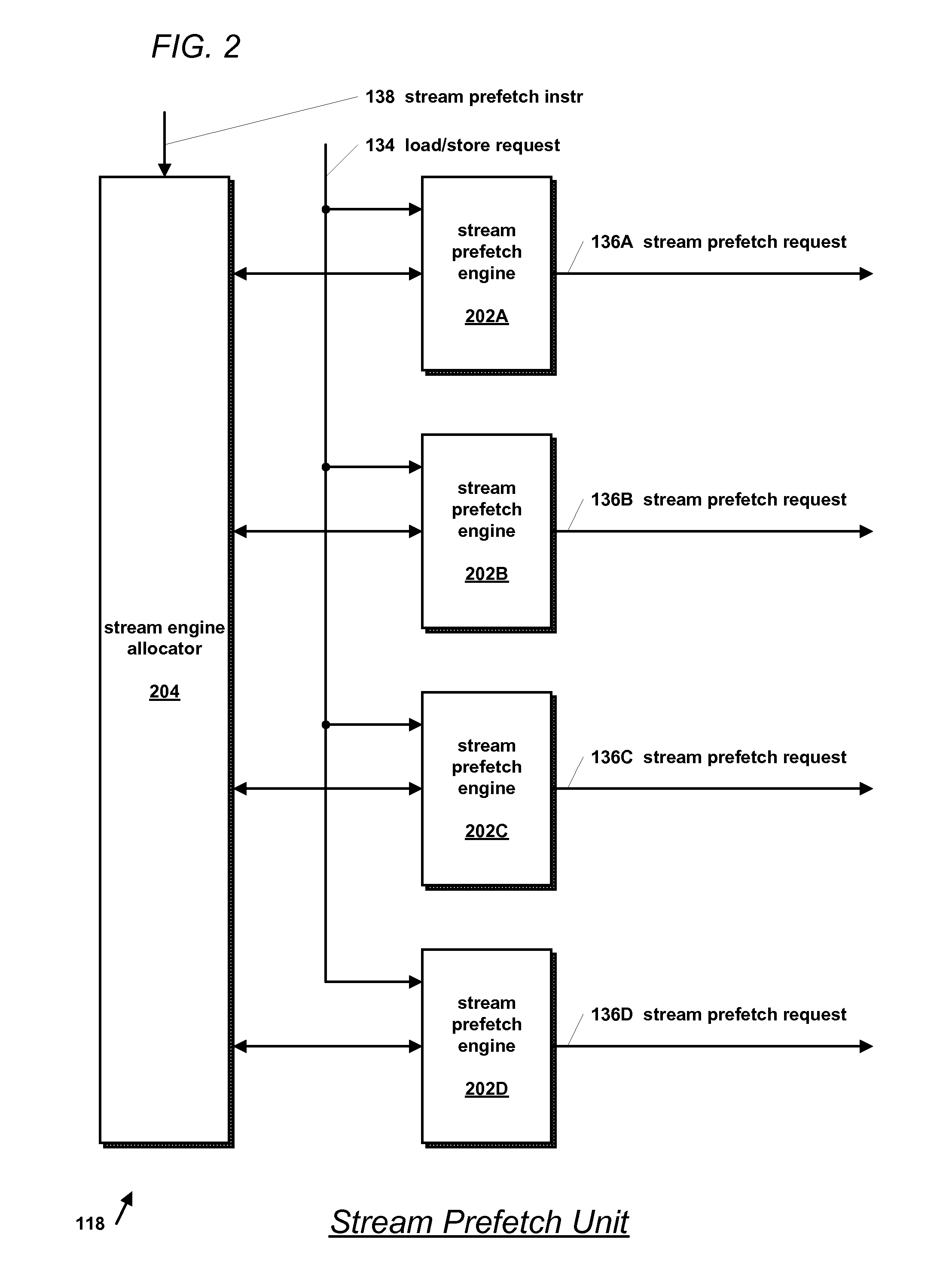

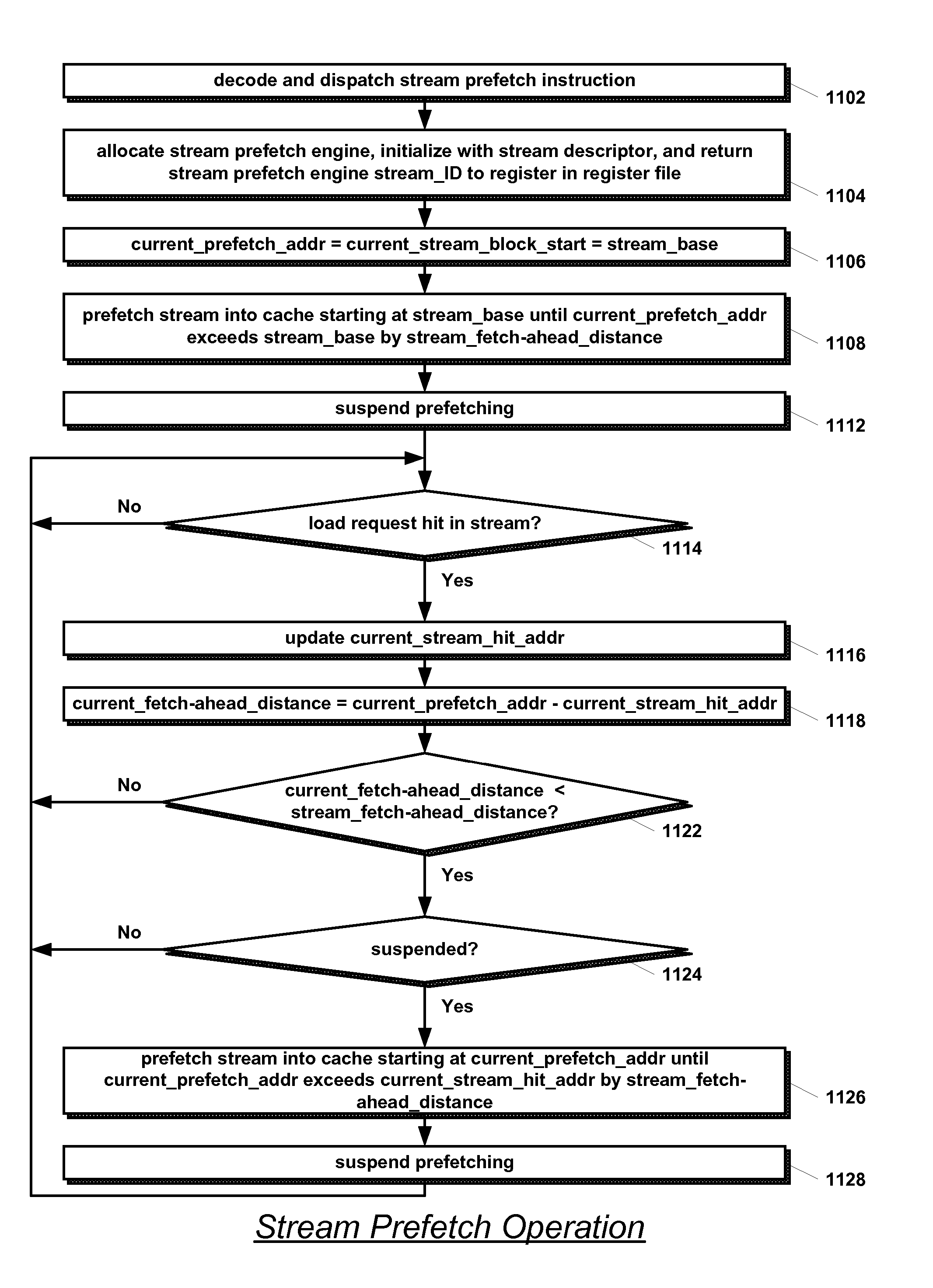

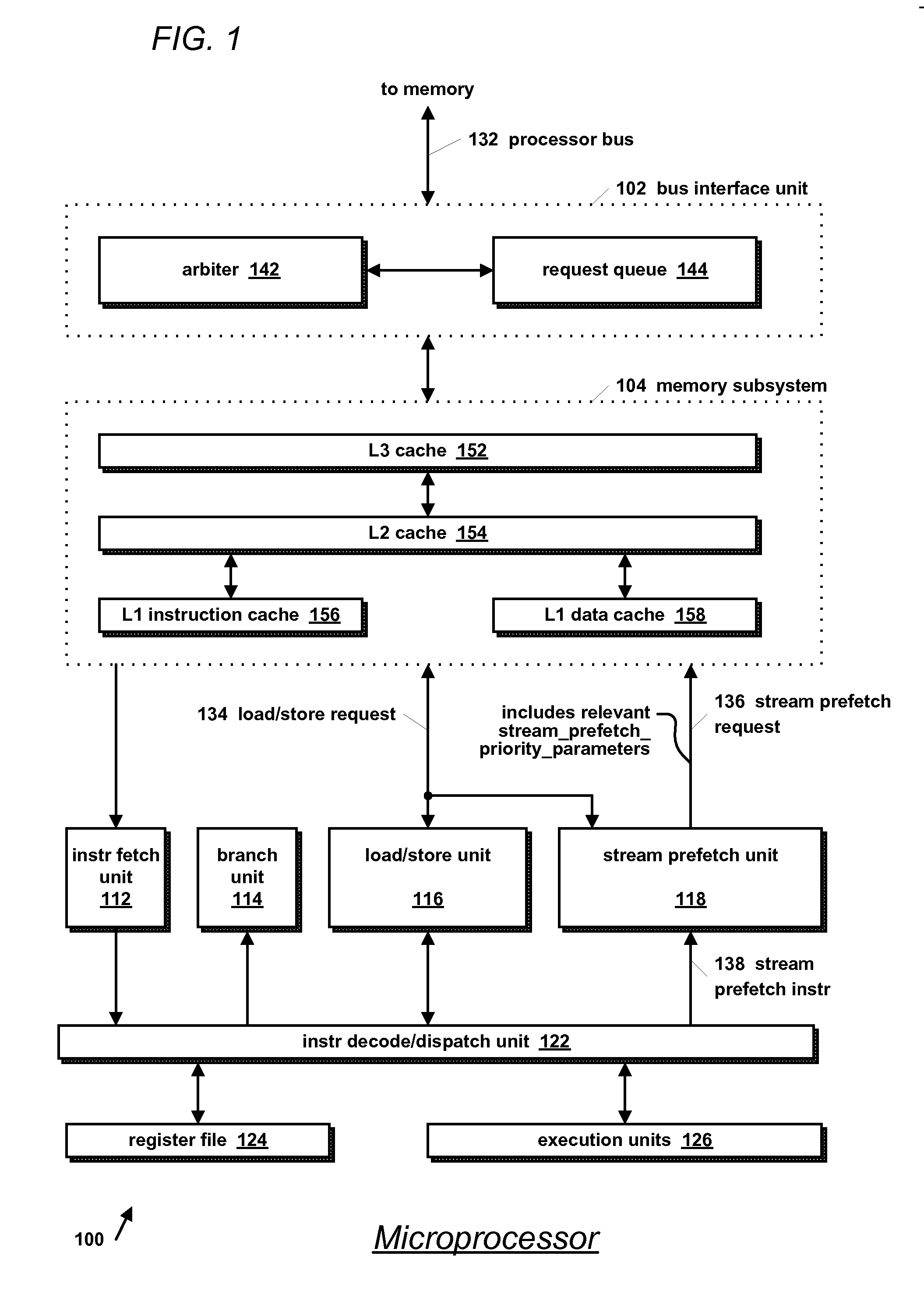

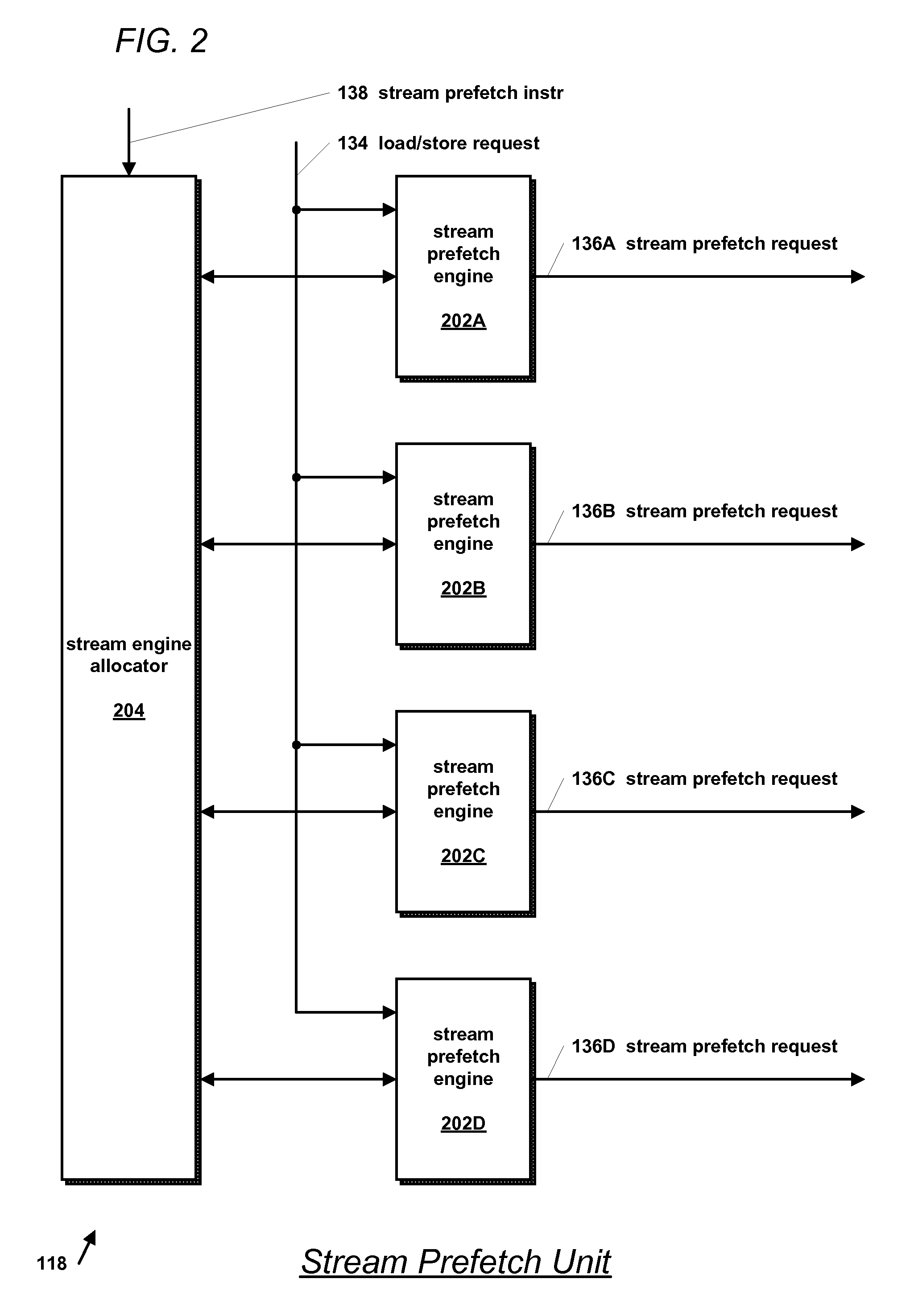

Microprocessor with improved data stream prefetching

InactiveUS20070043908A1Memory architecture accessing/allocationDigital computer detailsMicroprocessorDataflow

A microprocessor includes a hierarchical memory subsystem, an instruction decoder, and a stream prefetch unit. The decoder decodes an instruction that specifies a locality characteristic parameter. In one embodiment, the parameter specifies a relative urgency with which a data stream specified by the instruction is needed rather than specifying exactly which of the cache memories in the hierarchy to prefetch the data stream into. The prefetch unit selects one of the cache memory levels in the hierarchy for prefetching the data stream into based on the memory subsystem configuration and on the relative urgency. In another embodiment, the prefetch unit instructs the memory subsystem to mark the prefetched cache line for early, late, or normal eviction according to its cache line replacement policy based on the parameter value.

Owner:ARM FINANCE OVERSEAS LTD

Creating and executing a graphical program with first model of computation that includes a structure supporting second model of computation

ActiveUS7530052B2Visual/graphical programmingSpecific program execution arrangementsGraphicsMulti rate

System and method for creating and executing a graphical program. A first plurality of graphical program elements (GPEs) having a first model of computation (MoC), e.g., homogenous dataflow, are assembled in a graphical program in response to first input. A structure, including an interior portion, is displayed in the graphical program, indicating use of a second MoC, e.g., multi-rate dataflow, for GPEs within the interior portion. A second plurality of GPEs having the second MoC are assembled within the interior portion of the structure in response to second input. The second plurality of GPEs are converted into a new third plurality of GPEs having the first MoC, e.g., by parsing the second plurality of GPEs to determine multiple primitives according to the second MoC, determining the third plurality of GPEs based on the primitives, and assembling the third plurality of GPEs in the graphical program.

Owner:NATIONAL INSTRUMENTS

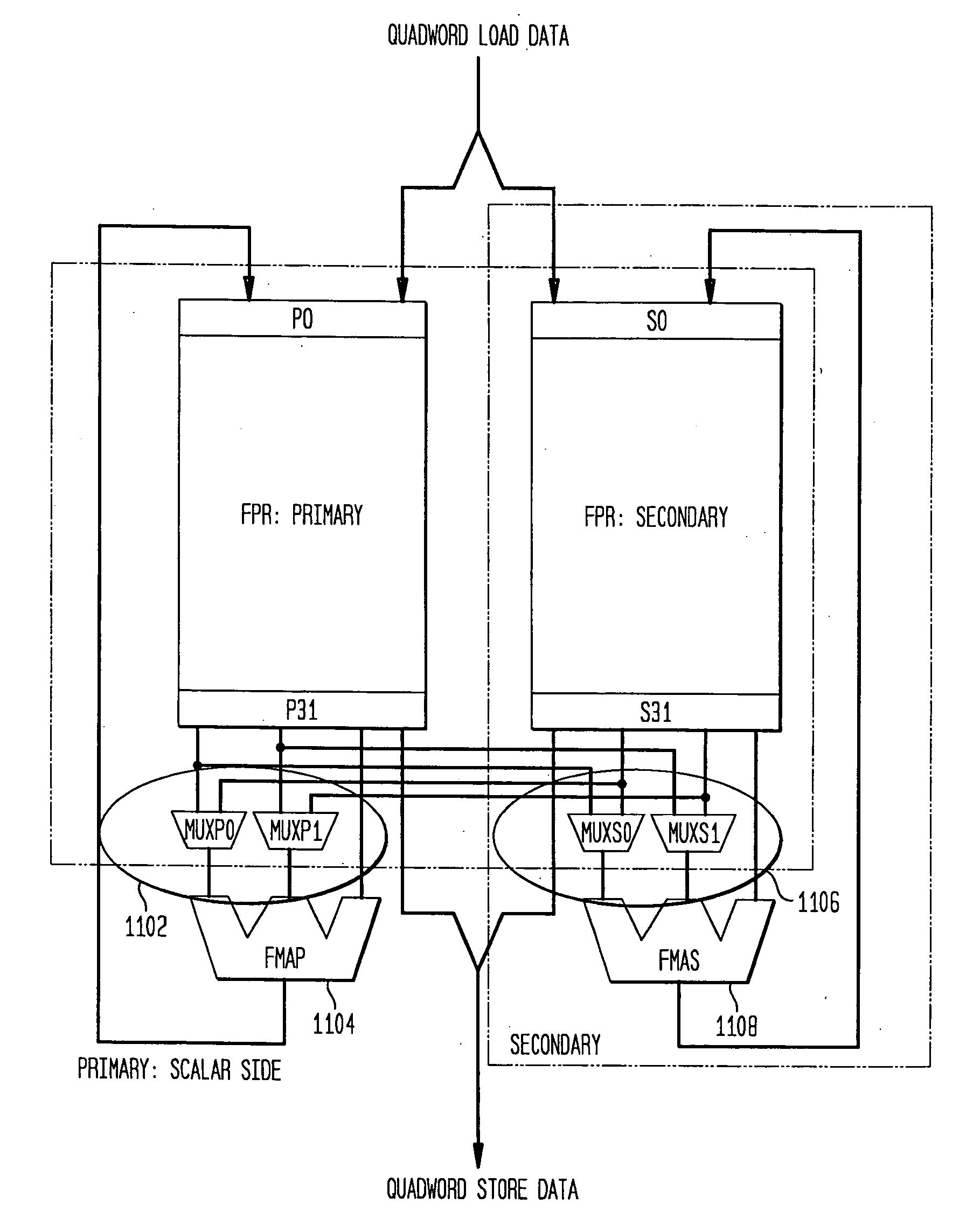

Method and system for data-driven runtime alignment operation

A method for processing instructions and data in a processor includes steps of: preparing an input stream of data for processing in a data path in response to a first set of instructions specifying a dynamic parameter; and processing the input stream of data in the same data path in response to a second set of instructions. A common portion of a dataflow is used for preparing the input stream of data for processing in response to a first set of instructions under the control of a dynamic parameter specified by an instruction of the first set of instructions, and for operand data routing based on the instruction specification of a second set of instructions during the processing of the input stream in response to the second set of instructions.

Owner:IBM CORP

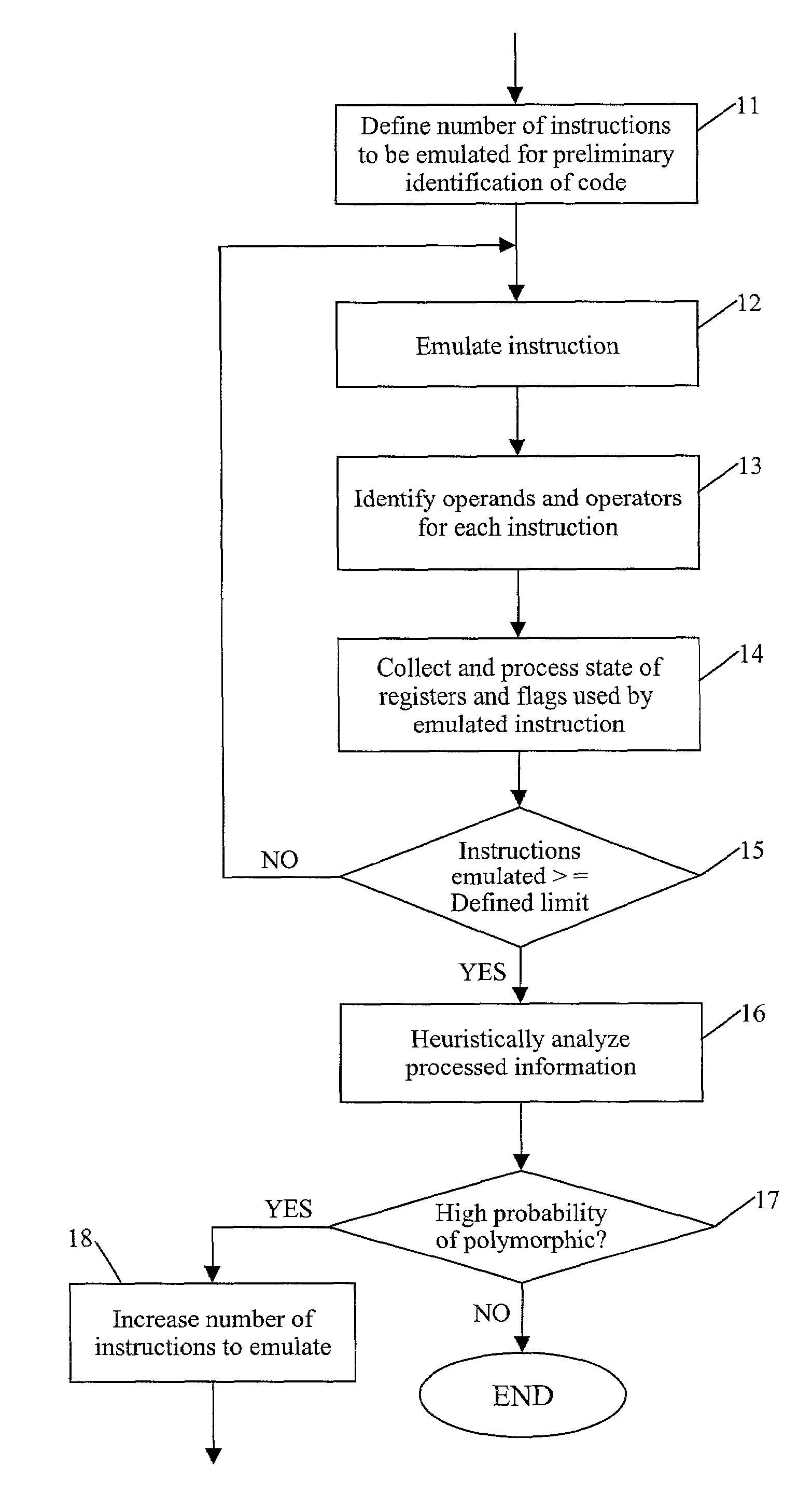

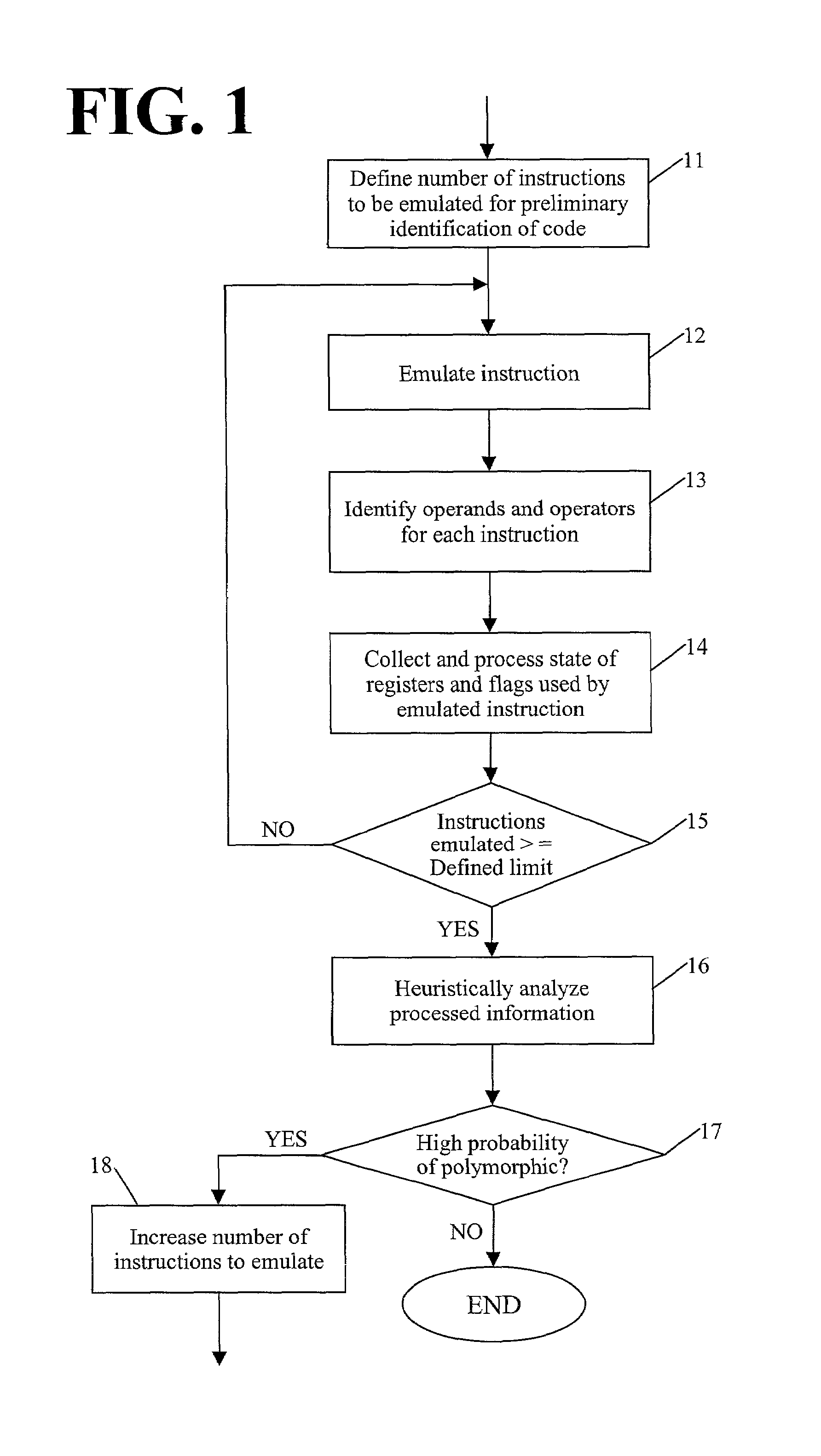

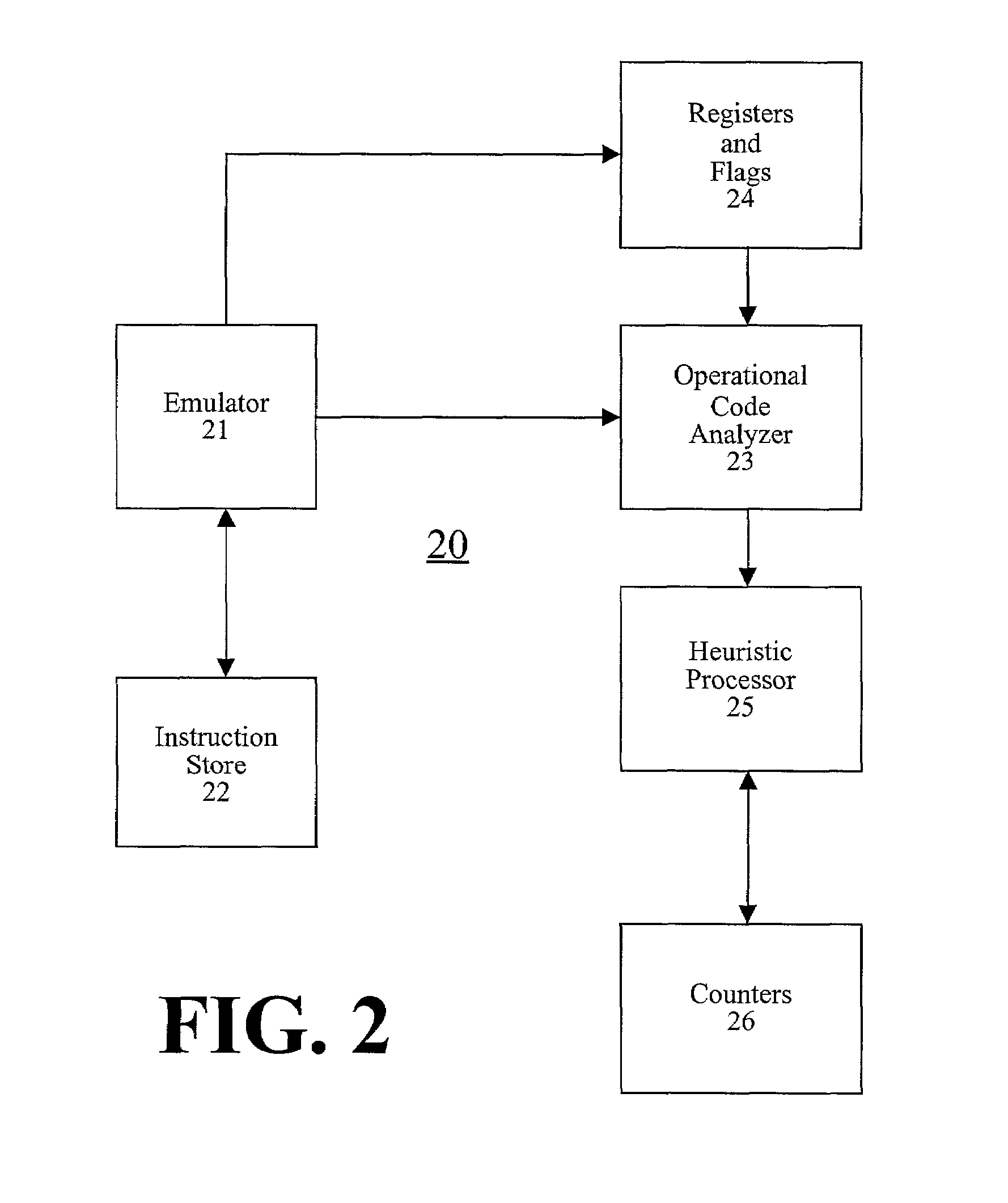

Detection of polymorphic virus code using dataflow analysis

A method and apparatus for detecting polymorphic viral code in a computer program is provided. The apparatus comprises an emulator, an operational code analyzer and an heuristic analyzer. The emulator emulates a selected number of instructions of the computer program. The operational code analyzer collects and stores information corresponding to operands and operators used in the instructions and the state of registers / flags after each emulated instruction execution. The heuristic analyzer determines a probability that the computer program contains viral code based on an heuristic analysis of register / flag state information supplied by the operational code analyzer.

Owner:COMP ASSOC THINK INC

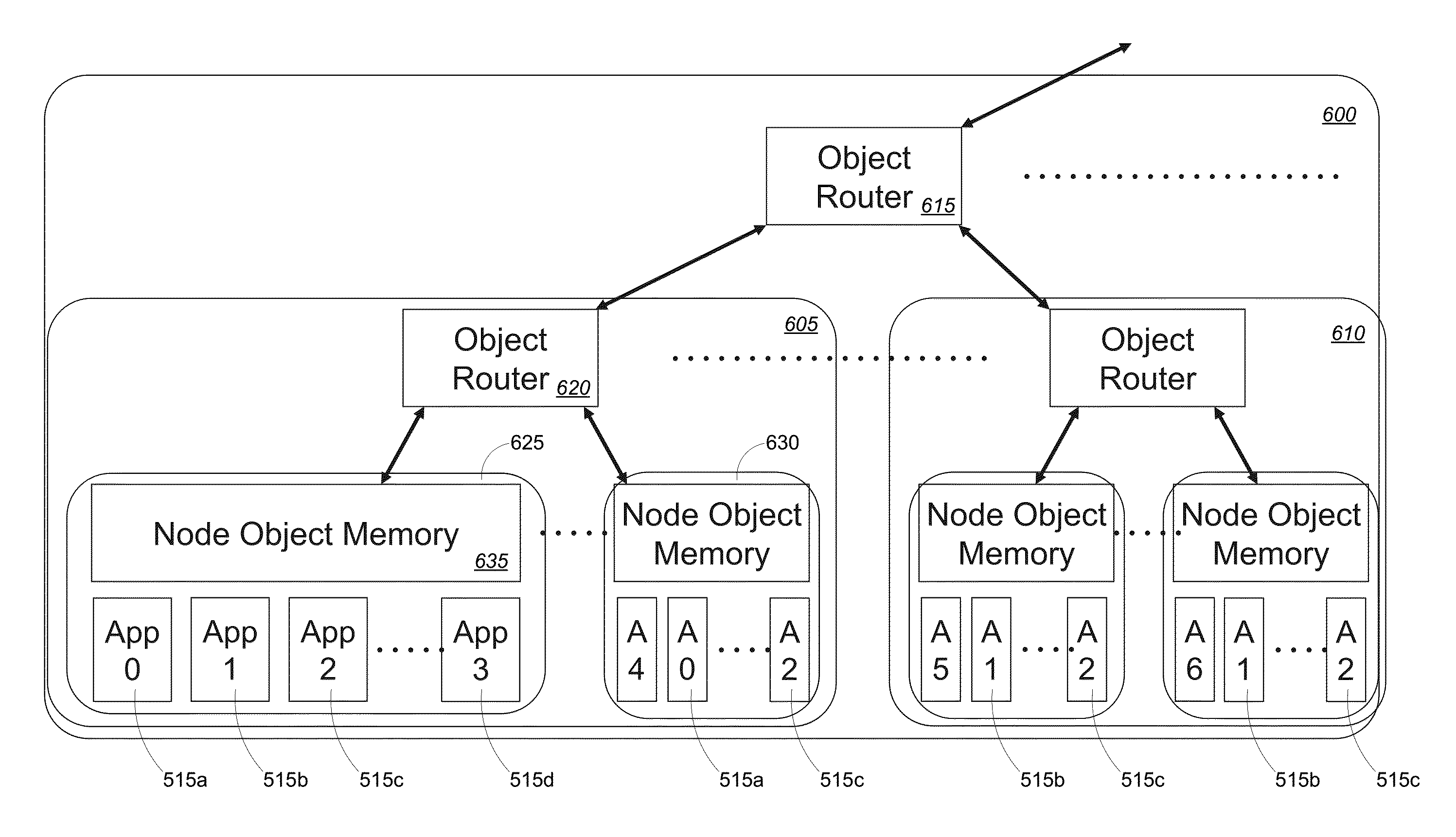

Object memory data flow instruction execution

ActiveUS20160210080A1Improve efficiencyImprove performanceMemory architecture accessing/allocationInput/output to record carriersMemory objectData access

Embodiments of the invention provide systems and methods for managing processing, memory, storage, network, and cloud computing to significantly improve the efficiency and performance of processing nodes. More specifically, embodiments of the present invention are directed to an instruction set of an object memory fabric. This object memory fabric instruction set can be used to provide a unique instruction model based on triggers defined in metadata of the memory objects. This model represents a dynamic dataflow method of execution in which processes are performed based on actual dependencies of the memory objects. This provides a high degree of memory and execution parallelism which in turn provides tolerance of variations in access delays between memory objects. In this model, sequences of instructions are executed and managed based on data access. These sequences can be of arbitrary length but short sequences are more efficient and provide greater parallelism.

Owner:ULTRATA LLC

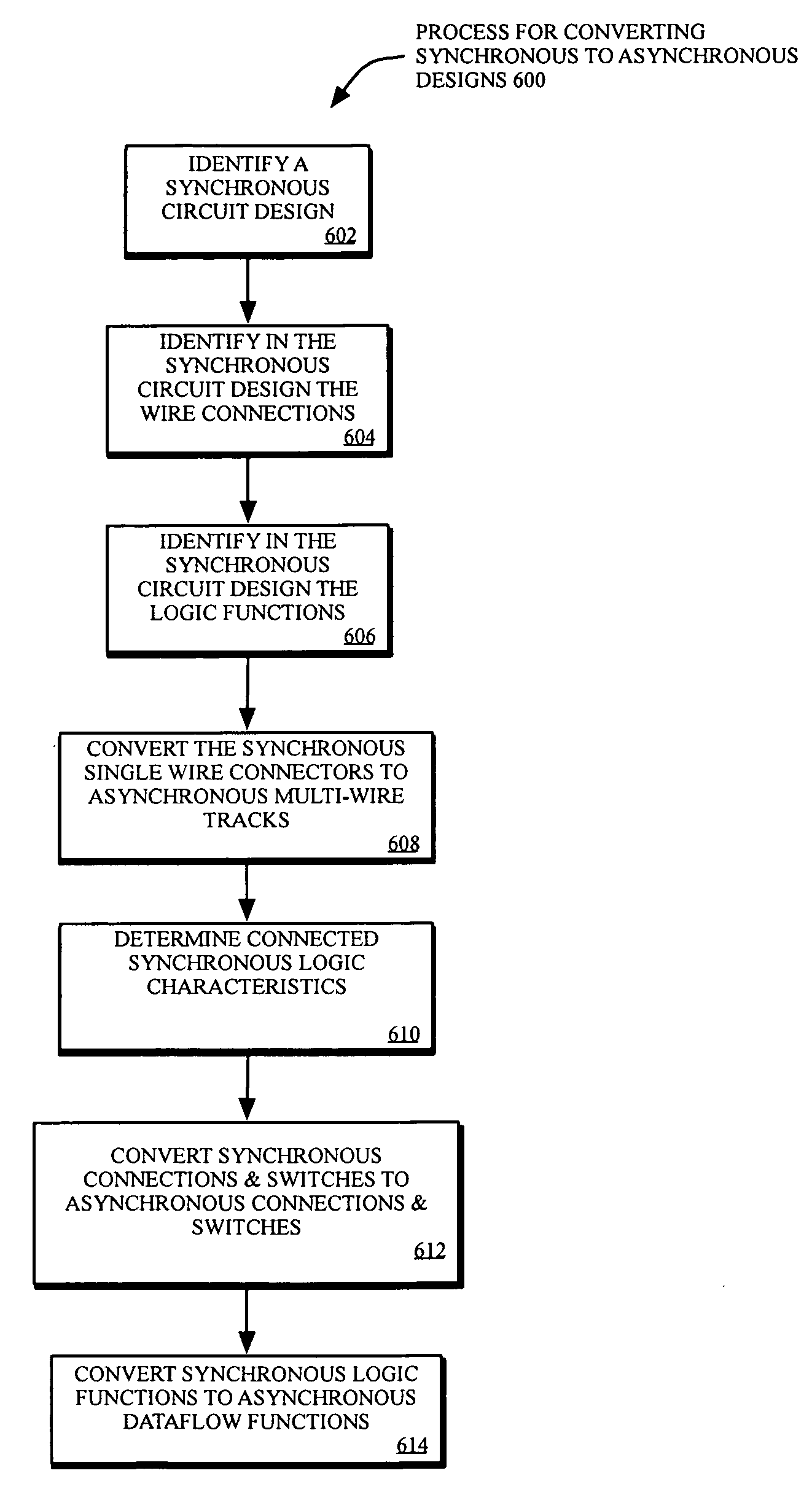

Methods and systems for converting a synchronous circuit fabric into an asynchronous dataflow circuit fabric

Methods and systems for converting synchronous circuit designs to asynchronous circuit designs, and particularly programmable asynchronous circuit designs. Provide is a systematic, workable and repeatable process for evaluating synchronous circuit designs, converting the wires, switches / connections and logic functions to equivalent-function asynchronous circuit designs and hence implementing a functionally equivalent asynchronous circuit with all the benefits thereof. Further provided are a process for systematically doing the conversion and hardware equivalents (in form or functional description) for the asynchronous components. Using the present invention, any synchronous circuit design can be converted to an asynchronous equivalent, typically with no change to the original design implementation.

Owner:ACHRONIX SEMICON CORP

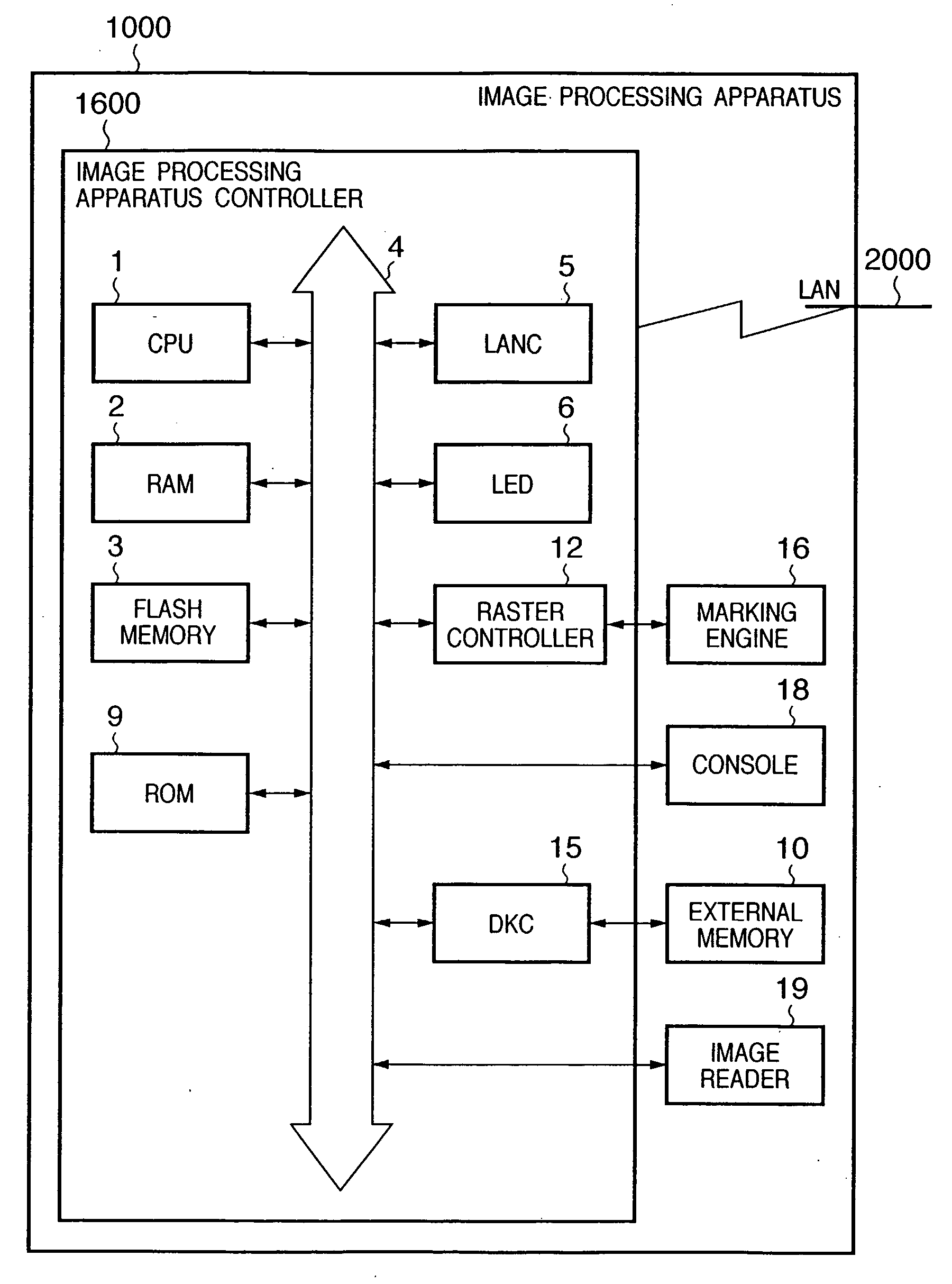

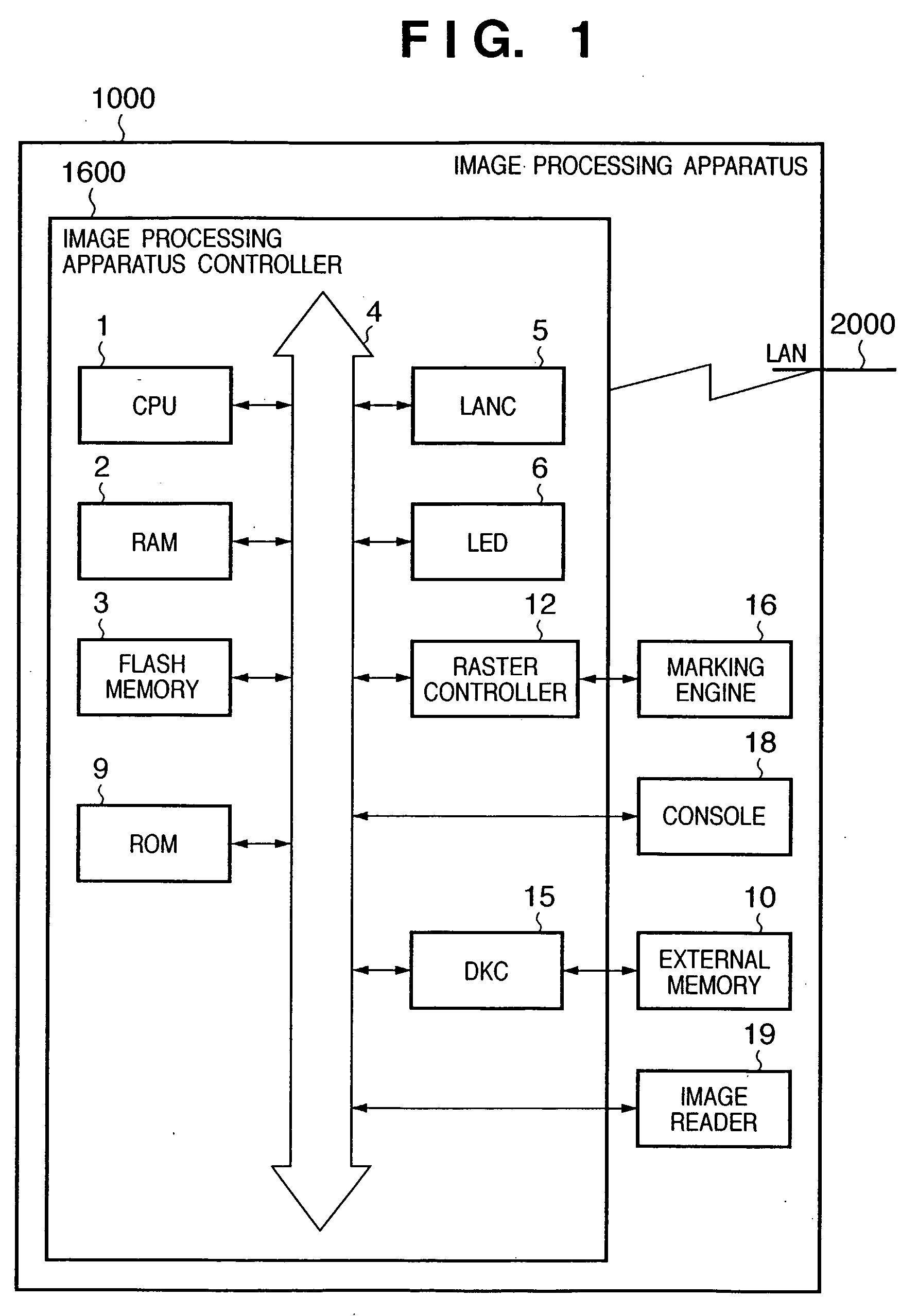

Image Processing Apparatus and Control Method Thereof

InactiveUS20070240124A1Reduce defectsEasy to implementDigitally marking record carriersMultiple digital computer combinationsImaging processingDataflow

A data processing apparatus has an interpreter environment for dynamically implementing a program constructed based on a command set defined independently of a native command group, in a native environment constructed based on the native command group processed by a processor configuring hardware. The apparatus generates an intermediate data stream in each of a plurality of stages into which an input data stream is divided in interpretation in the native environment and filters the intermediate data stream to generate a filtered data stream in the interpreter environment.

Owner:CANON KK

Microprocessor with improved data stream prefetching

InactiveUS20070055824A1Improving data stream prefetchingMemory architecture accessing/allocationDigital computer detailsLoad instructionDataflow

Owner:ARM FINANCE OVERSEAS LTD

Method of evaluating an architecture for an integrated circuit device

ActiveUS8146040B1CAD circuit designSoftware simulation/interpretation/emulationComputer architectureArchitecture of Integrated Information Systems

A method of evaluating an architecture for an integrated circuit device is disclosed. The method comprises generating a library of primitives for a predetermined architecture; transforming an original dataflow program into an intermediate format; transforming the intermediate format to a dataflow program defined in terms of the predefined library of primitives; and generating an implementation profile comprising information related to an implementation of the original dataflow program in an integrated circuit having the predetermined architecture. A method of evaluating an architecture for an integrated circuit device is also disclosed.

Owner:XILINX INC

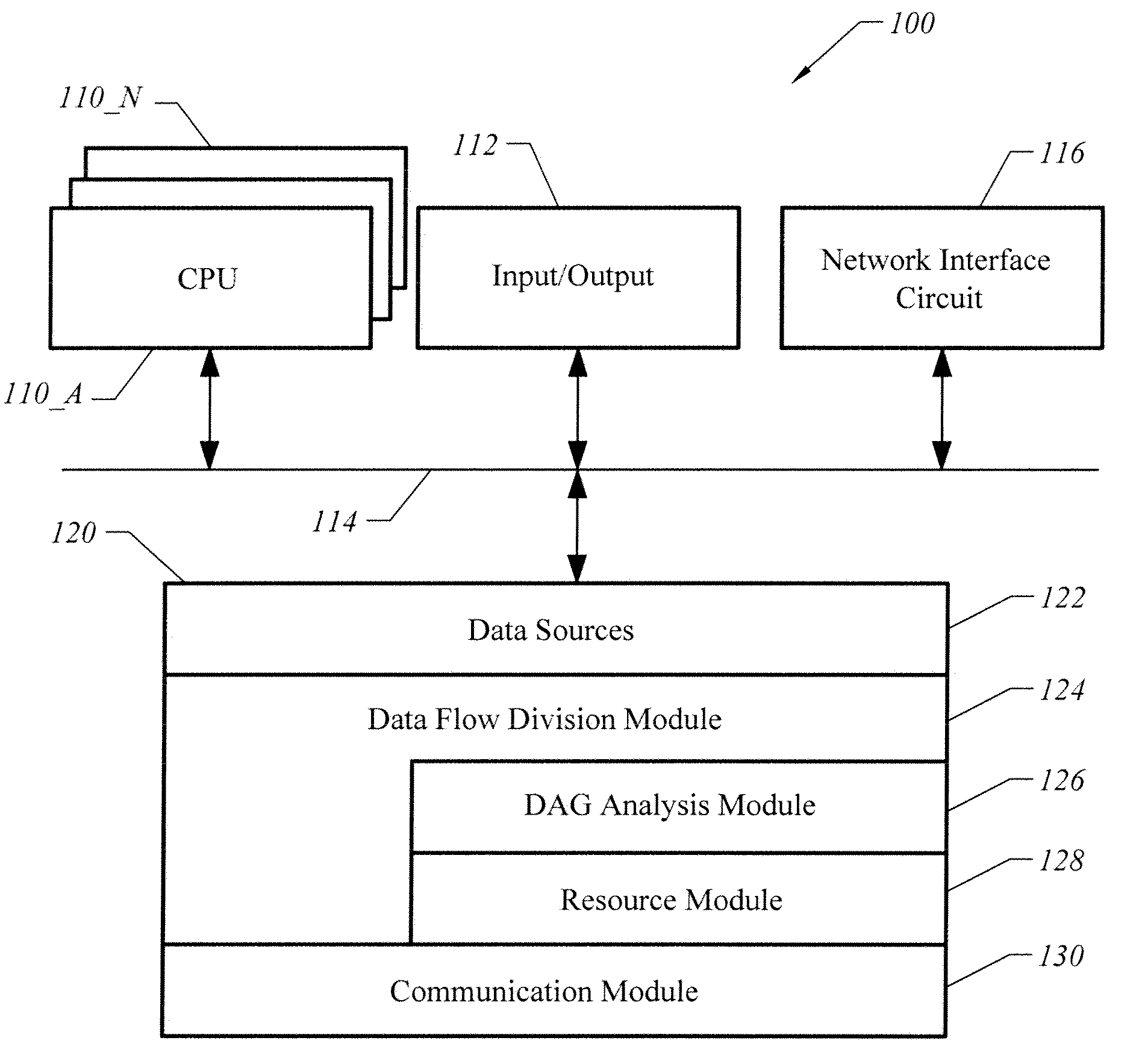

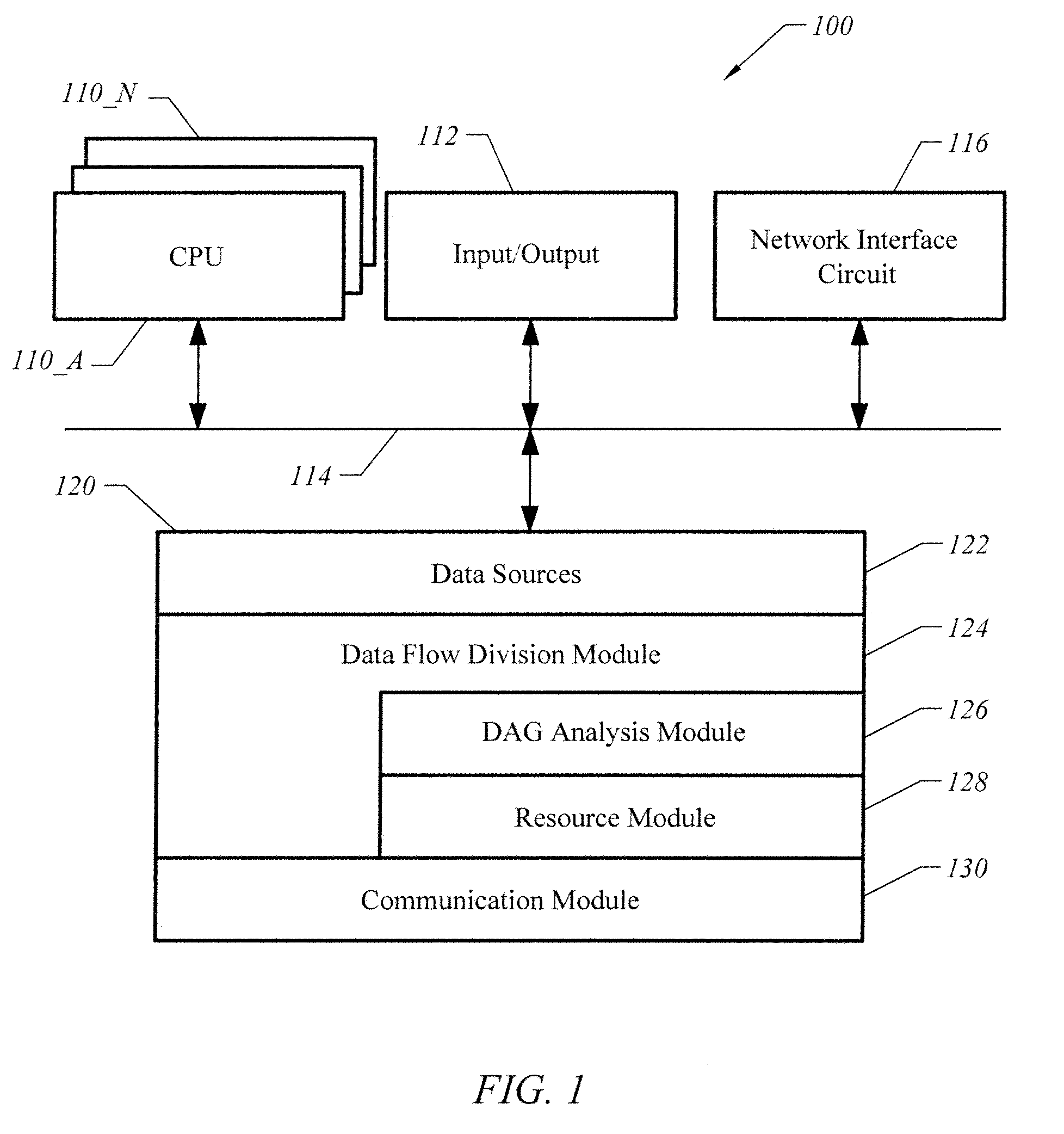

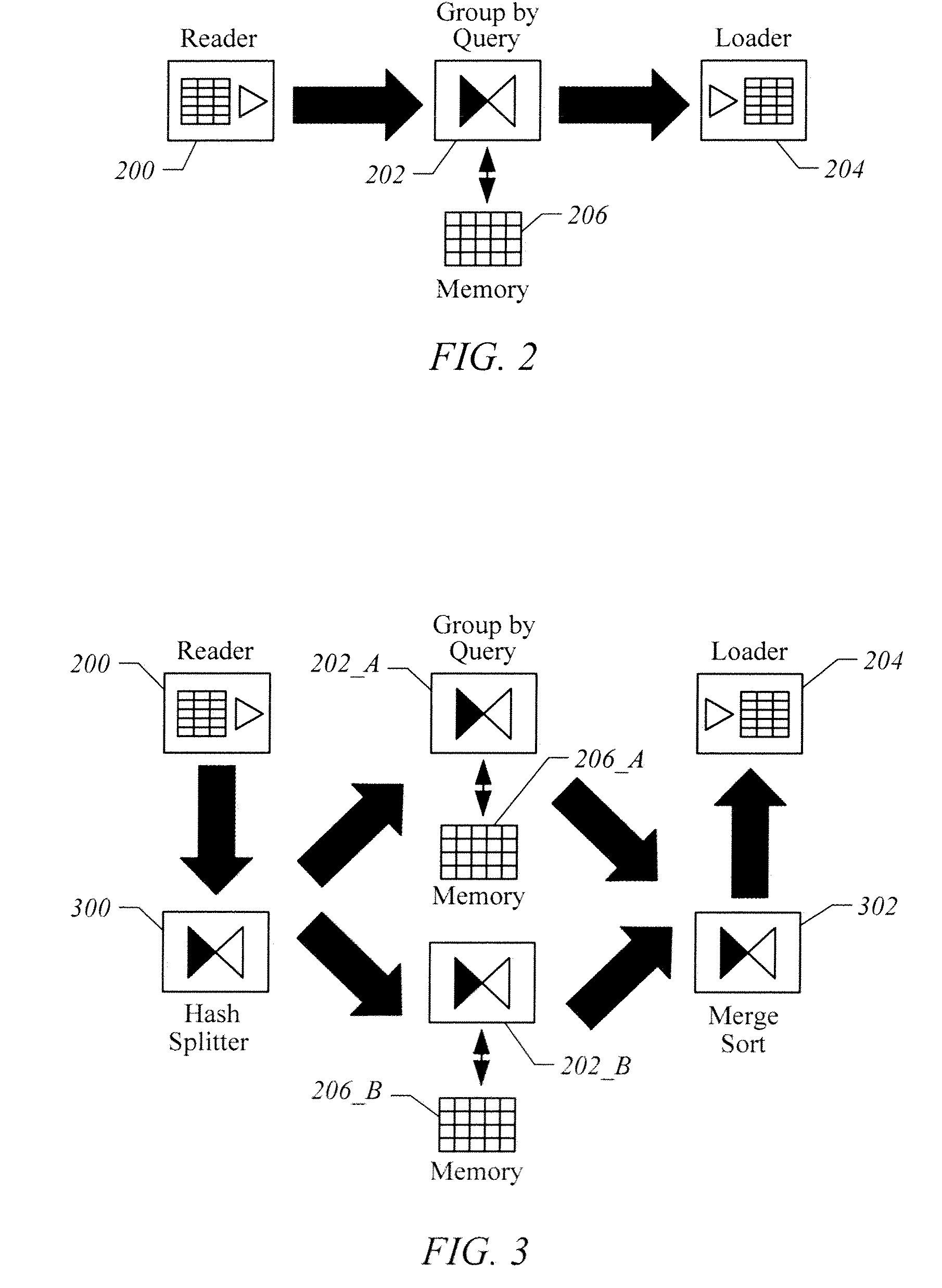

Apparatus and method for distributed dataflow execution in a distributed environment

ActiveUS20080172674A1Digital data information retrievalMultiprogramming arrangementsInter-process communicationEvaluation system

A computer readable storage medium includes executable instructions to assess system cache resources, inter-process communication requirements and staging requirements to divide an extract, transform, load (ETL) dataflow task into a plurality of sub-tasks. The sub-tasks are then executed in parallel on distributed resources.

Owner:SAP FRANCE

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com