Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

104 results about "Texture memory" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

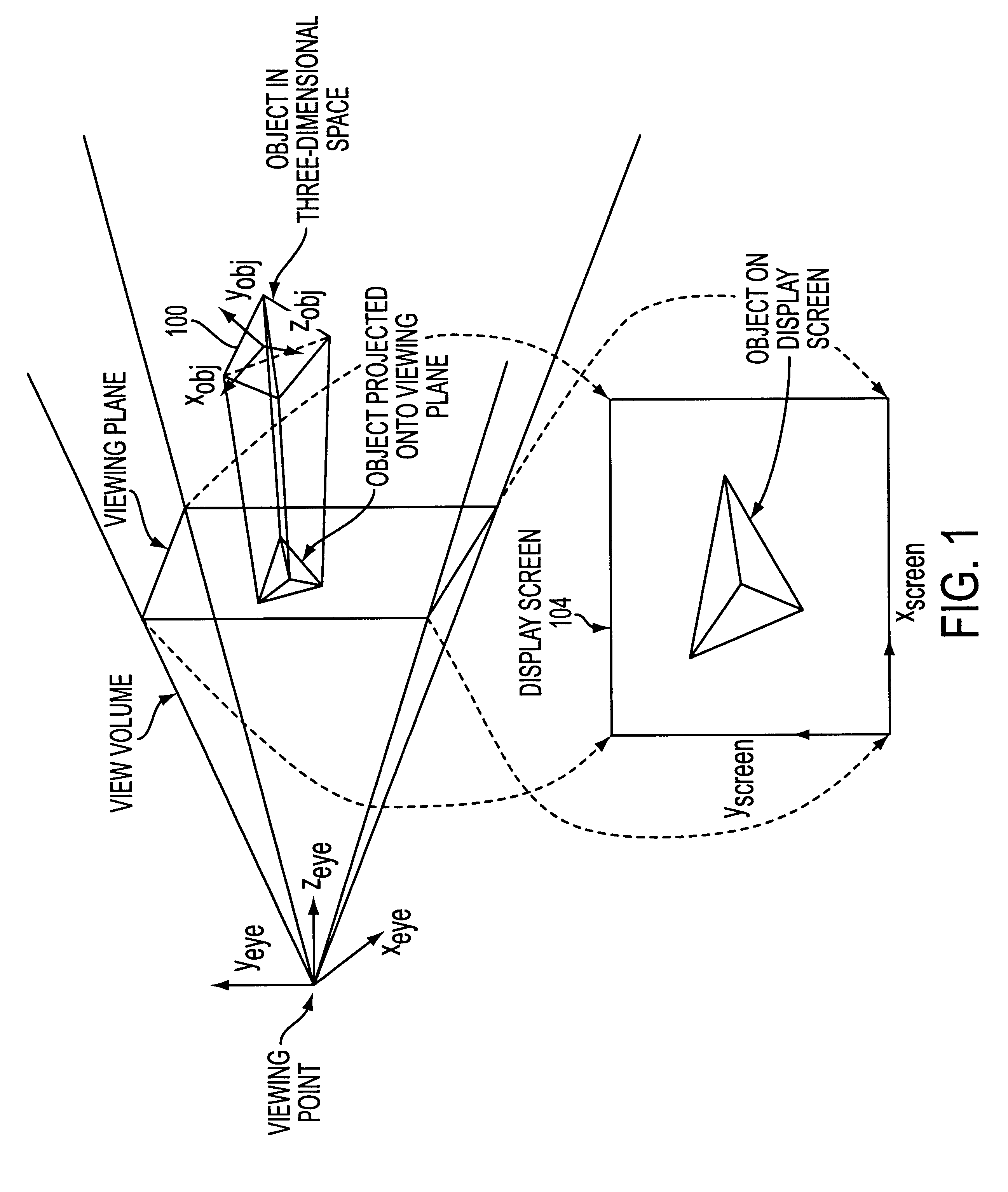

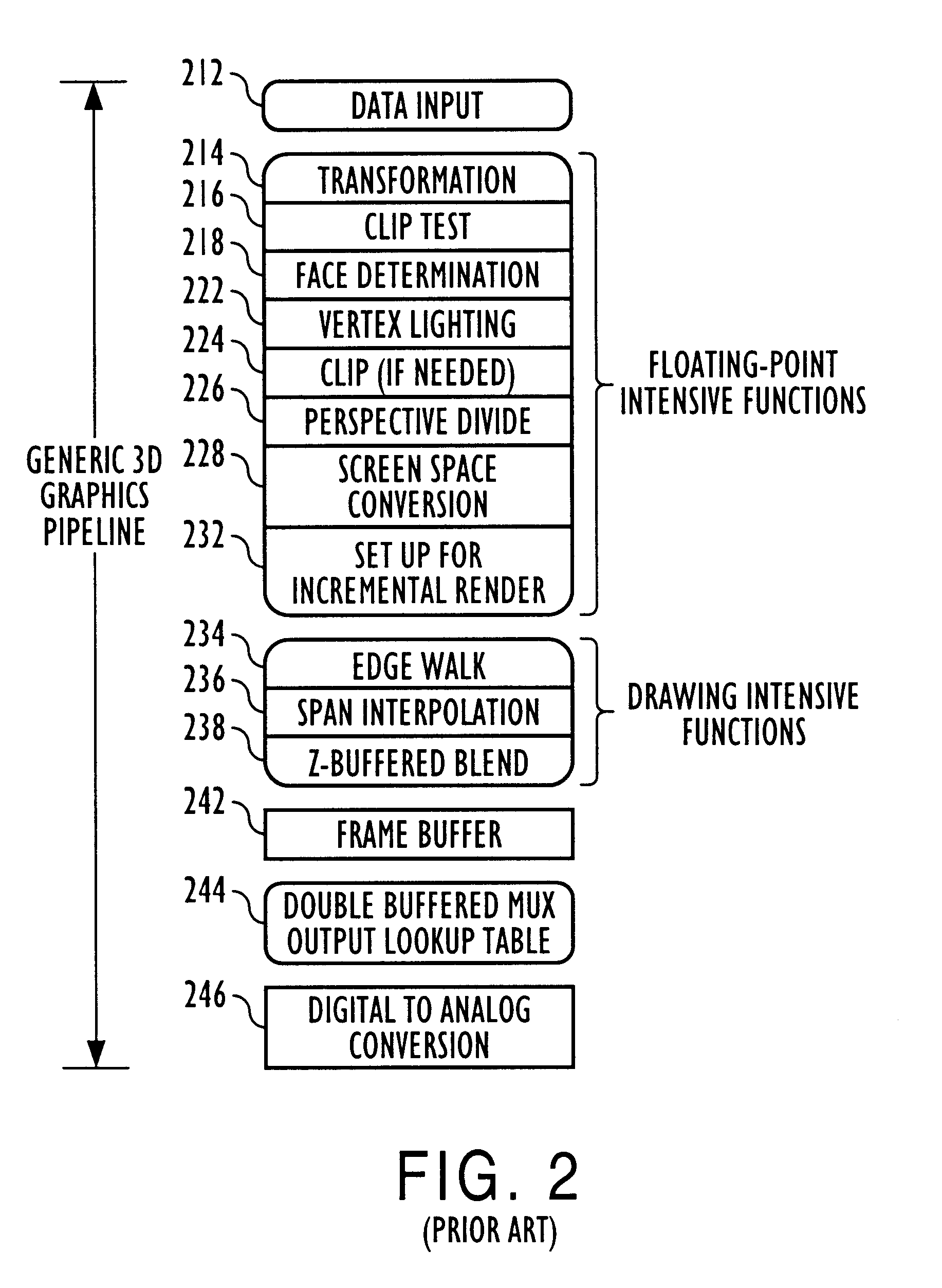

Texture memory is a type of digital storage that makes texture data readily available to video rendering processors (also known as GPUs), typically 3D graphics hardware. It is most often (but not always) implemented as specialized RAM (TRAM) that is designed for rapid reading and writing, enabling the graphics hardware increased performance in rendering 3D imagery.

Deferred shading graphics pipeline processor

InactiveUS6229553B1Lower communication bandwidthAttenuation bandwidthTexturing/coloringImage memory managementPhong shadingDeferred shading

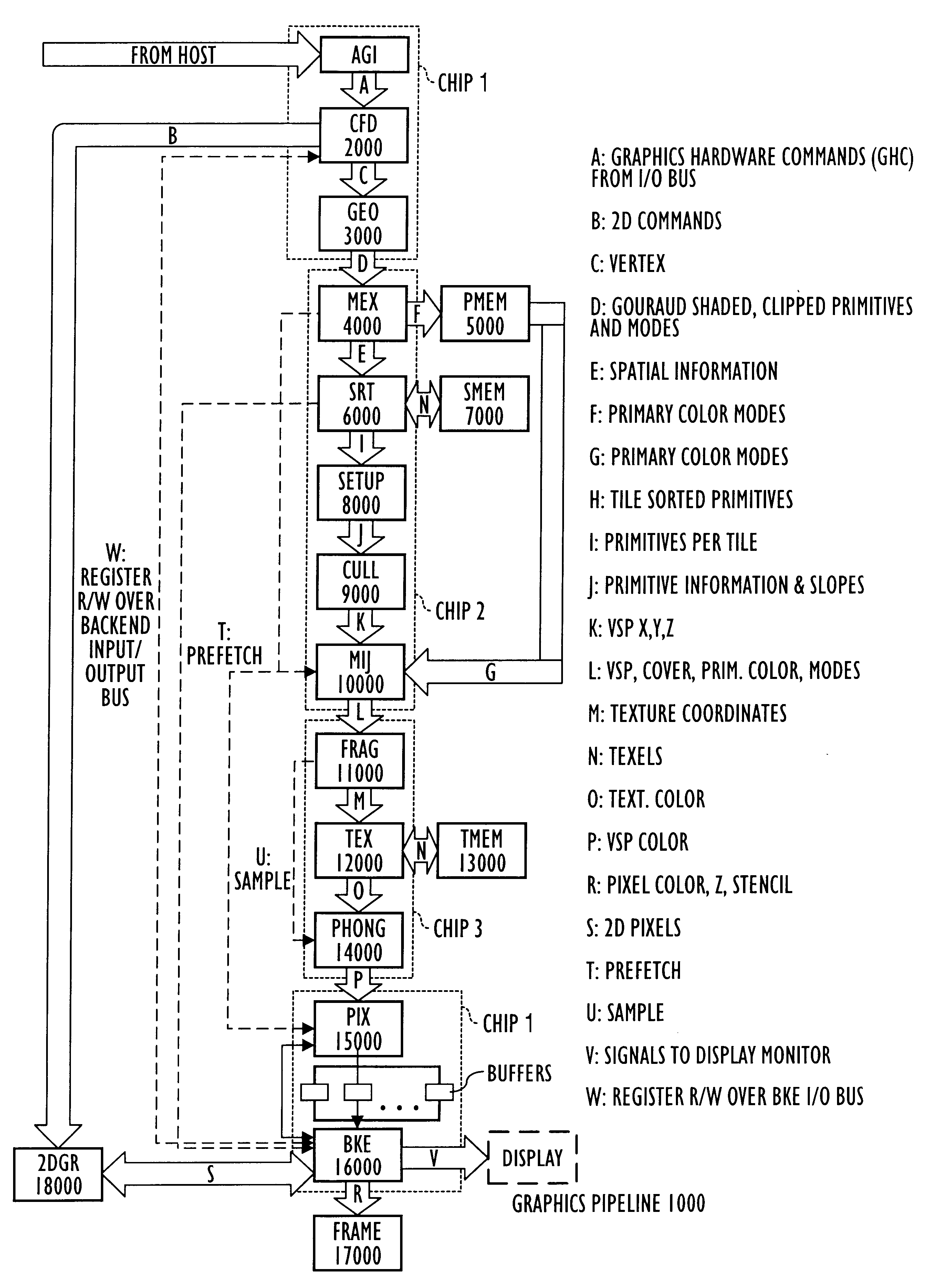

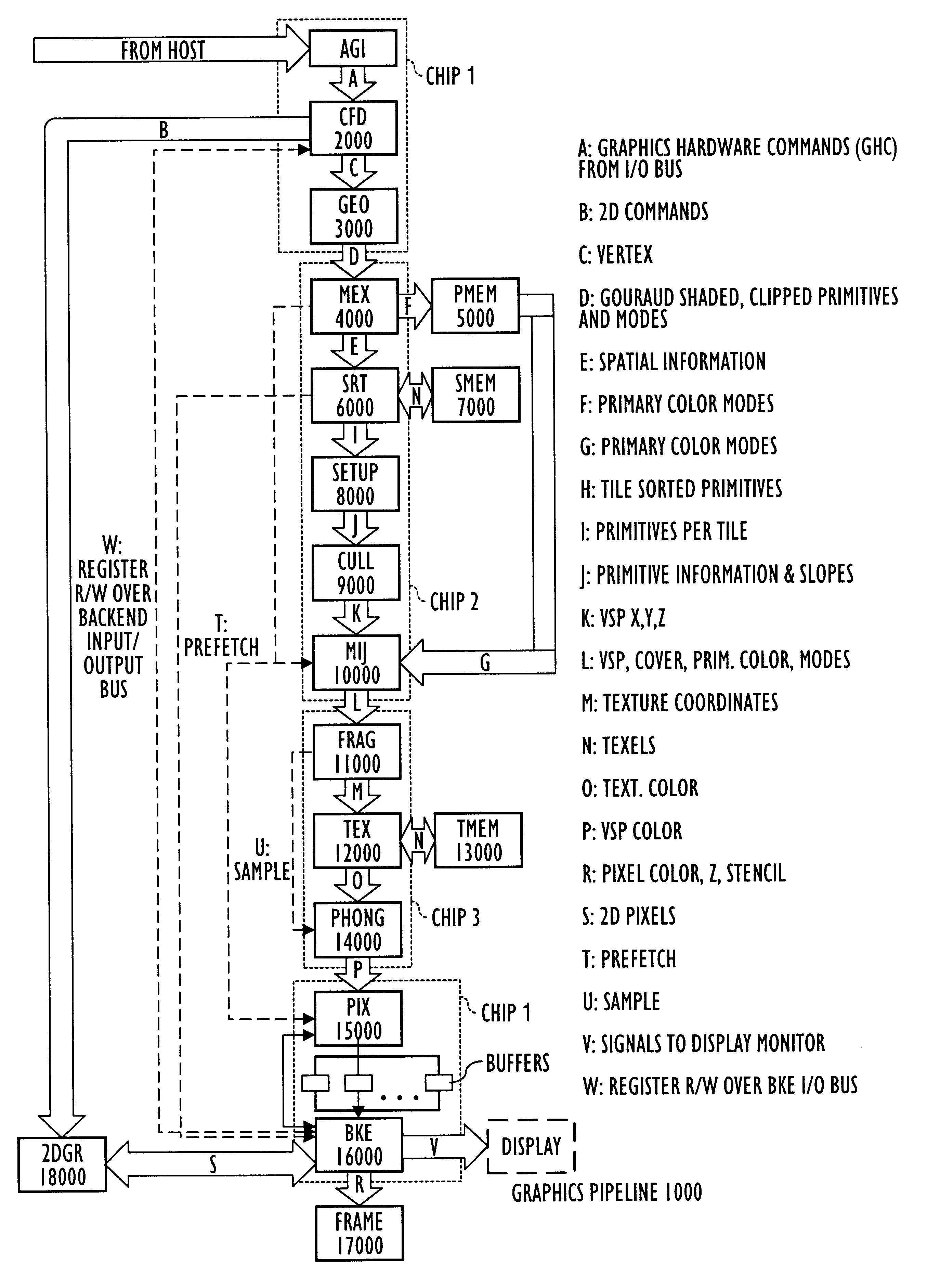

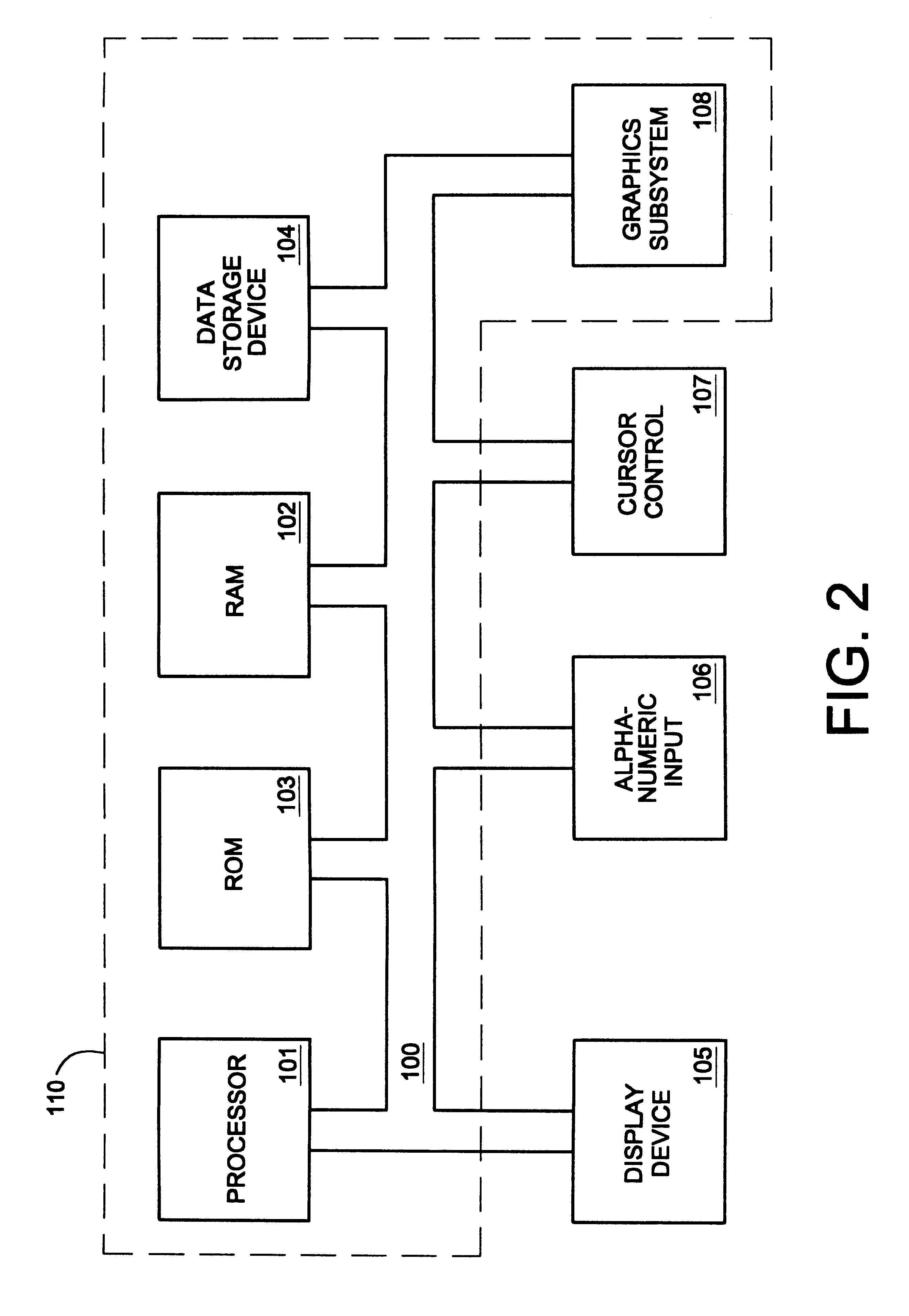

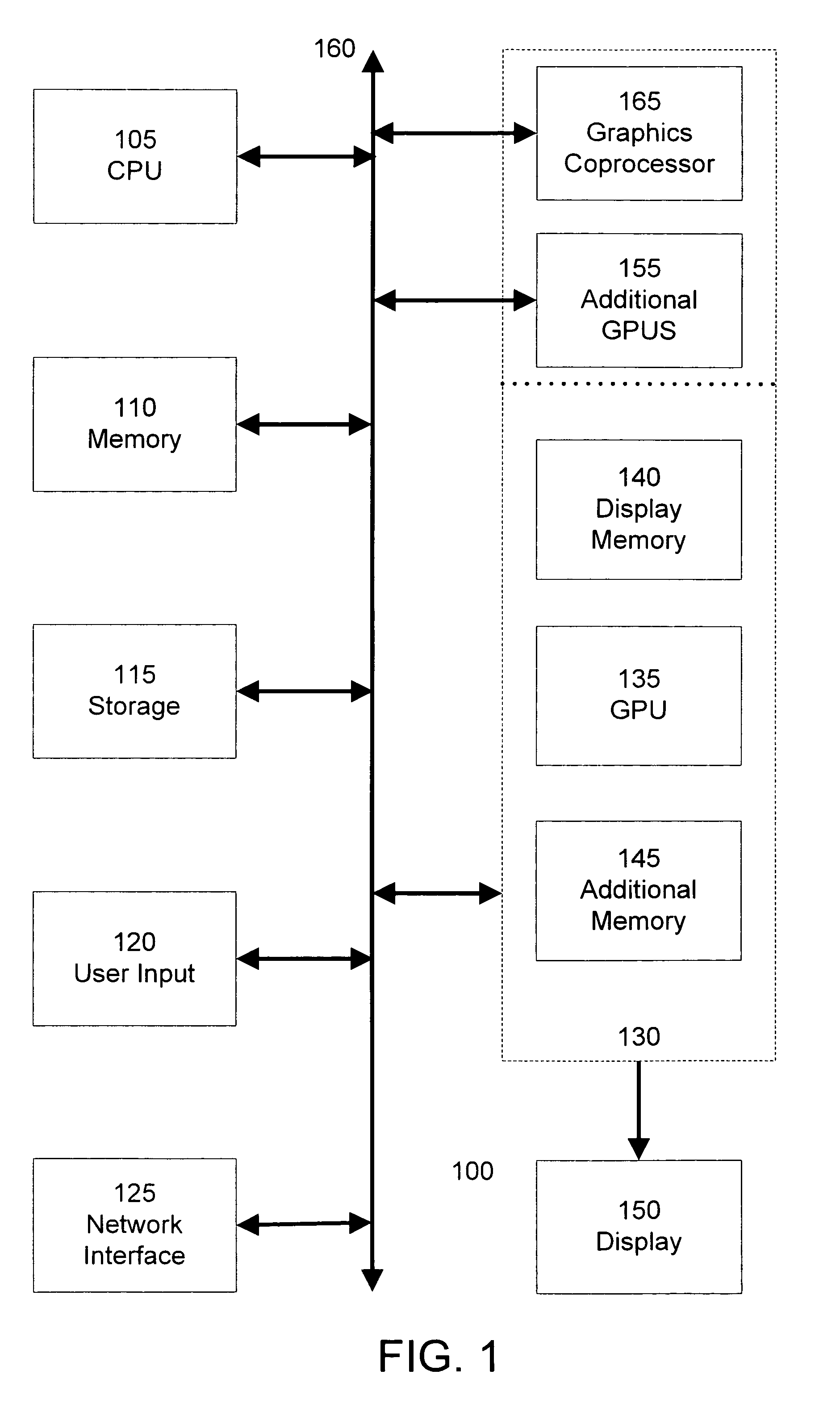

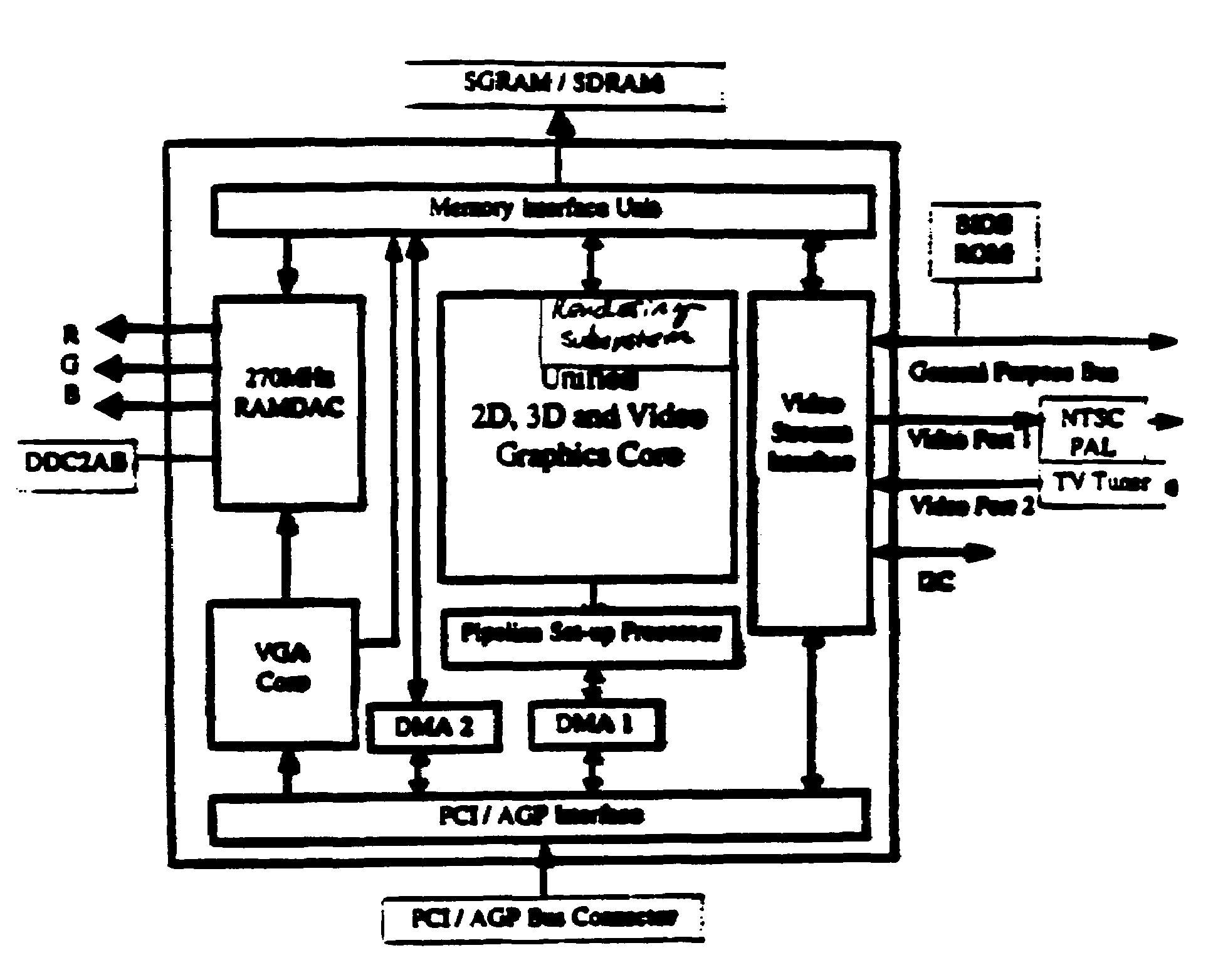

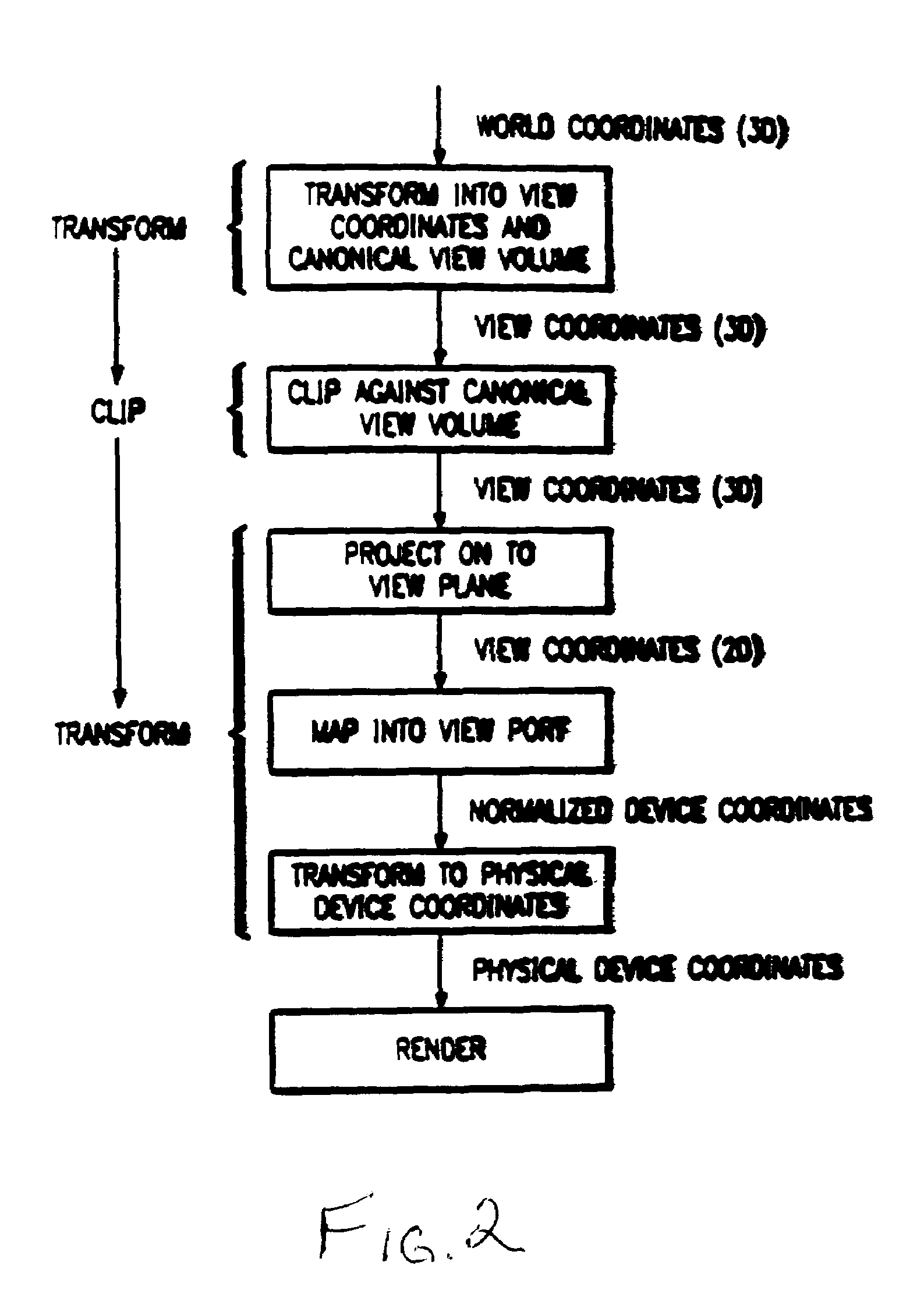

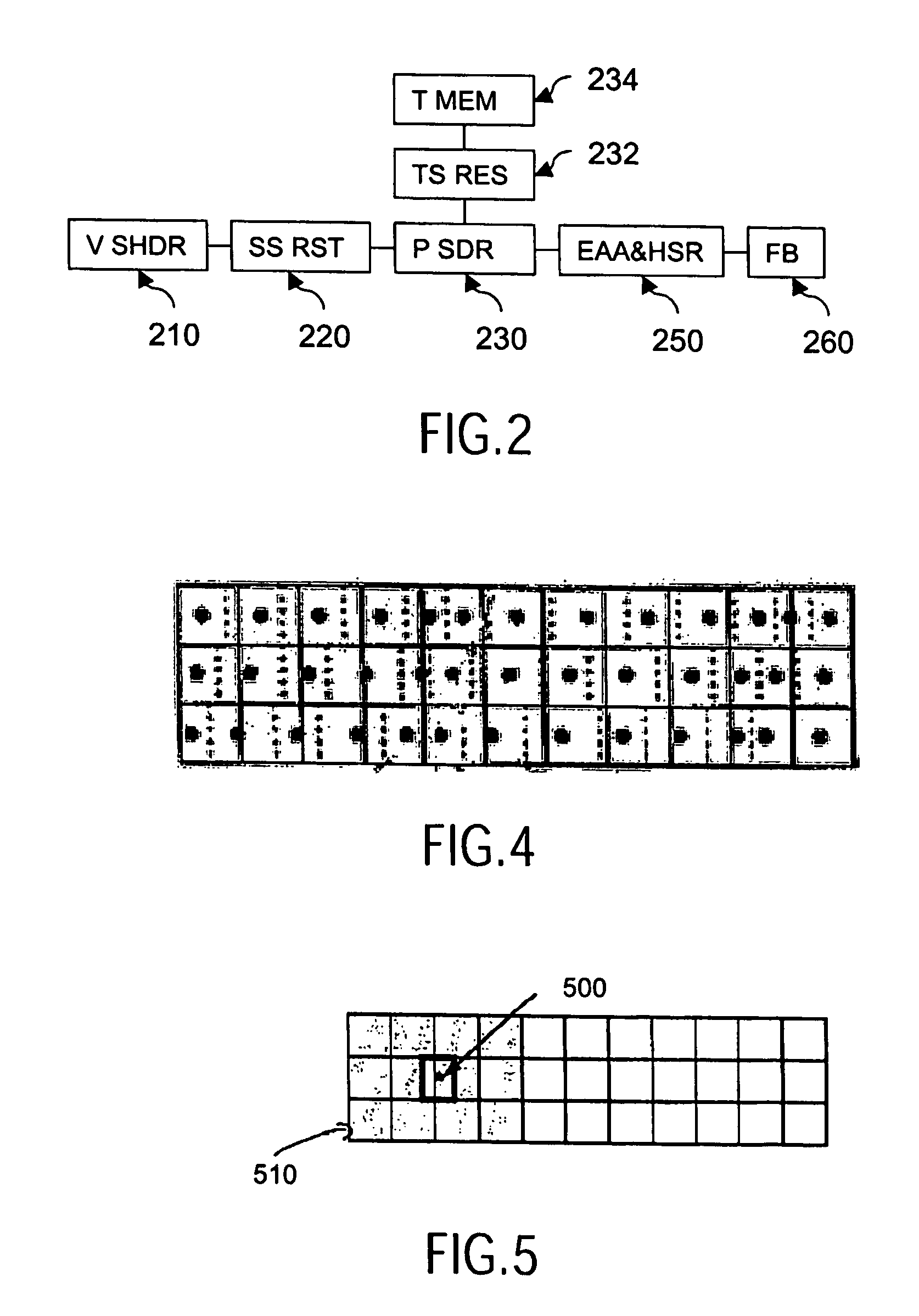

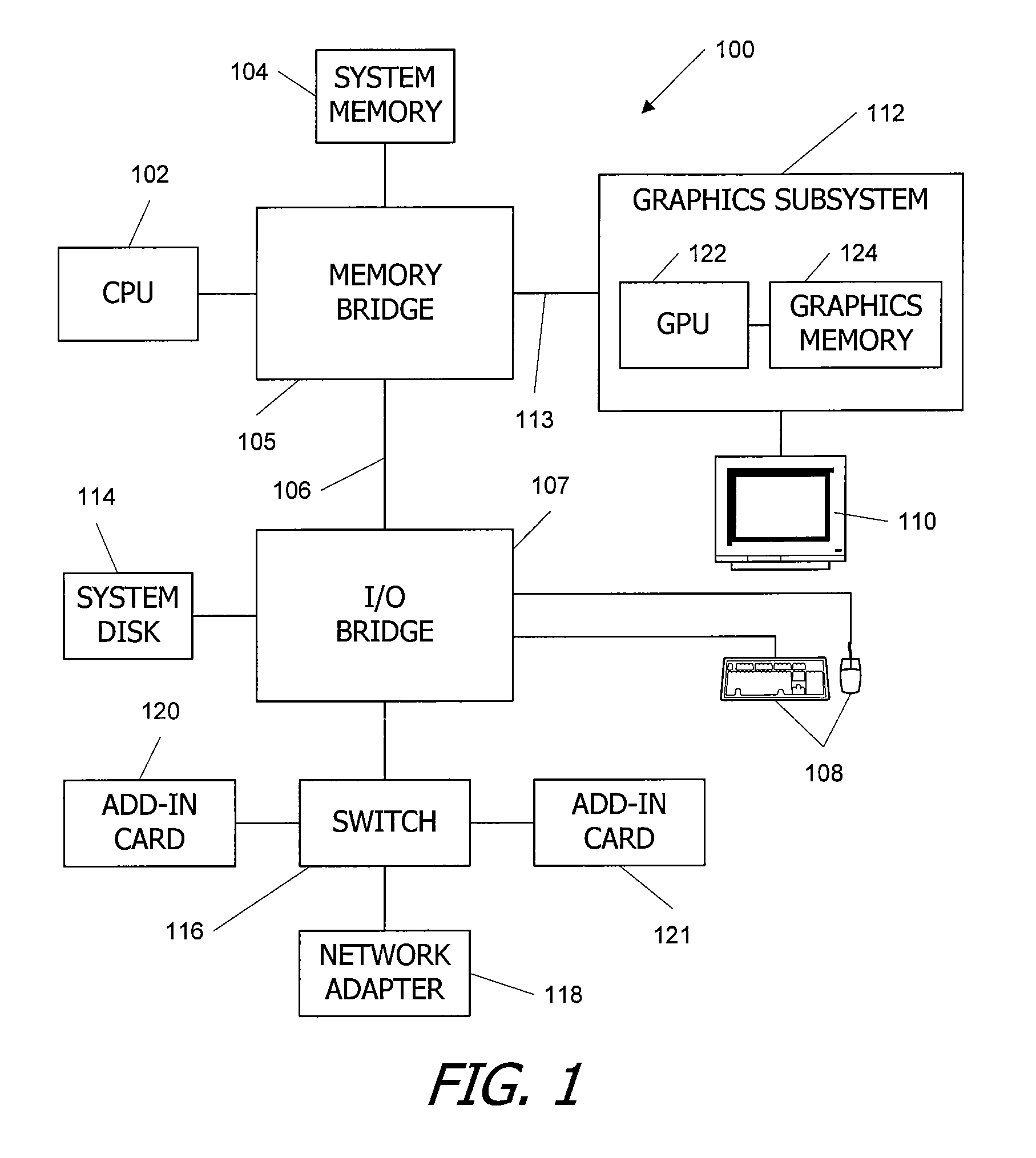

Three-dimensional computer graphics systems and methods and more particularly to structure and method for a three-dimensional graphics processor and having other enhanced graphics processing features. In one embodiment the graphics processor is Deferred Shading Graphics Processor (DSGP) comprising an AGP interface, a command fetch decode (2000), a geometry unit (3000), a mode extraction (4000) and polygon memory (5000), a sort unit (6000) and sort memory (7000), a setup unit (8000), a cull unit (9000), a mode injection (10000), a fragment unit (11000), a texture (12000) and texture memory (13000) a phong shading (14000), a pixel unit (15000), a backend unit (1600) coupled to a frame buffer (17000). Other embodiments need not include all of these functional units, and the structures and methods of these units are applicable to other computational processes and systems as well as deferred and non-deferred shading graphical processors.

Owner:APPLE INC

Deferred shading graphics pipeline processor

InactiveUS6268875B1Attenuation bandwidthTexturing/coloringImage memory managementPhong shadingComputer graphics (images)

Three-dimensional computer graphics systems and methods and more particularly to structure and method for a three-dimensional graphics processor and having other enhanced graphics processing features. In one embodiment the graphics processor is a Deferred Shading Graphics Processor (DSGP) comprising an AGP interface, a command fetch & decode (2000), a geometry unit (3000), a mode extraction (4000) and polygon memory (5000), a sort unit (6000) and sort memory (7000), a setup unit (8000), a cull unit (9000), a mode injection (10000), a fragment unit (11000), a texture (12000) and texture memory (13000) a phong shading (14000), a pixel unit (15000), a backend unit (1600) coupled to a frame buffer (17000). Other embodiments need not include all of these functional units, and the structures and methods of these units are applicable to other computational processes and systems as well as deferred and non-deferred shading graphical processors.

Owner:APPLE INC

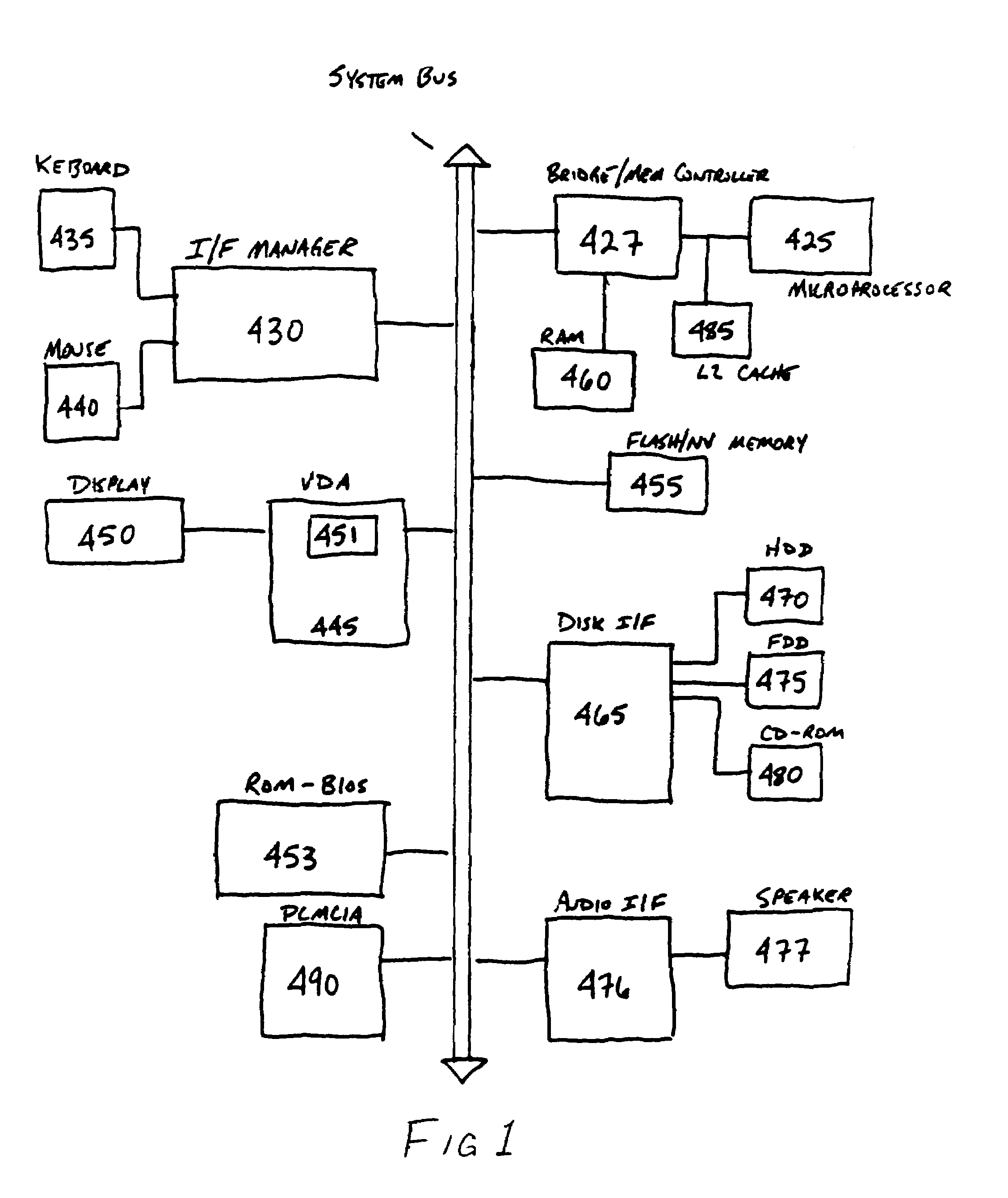

Synchronizing graphics texture management in a computer system using threads

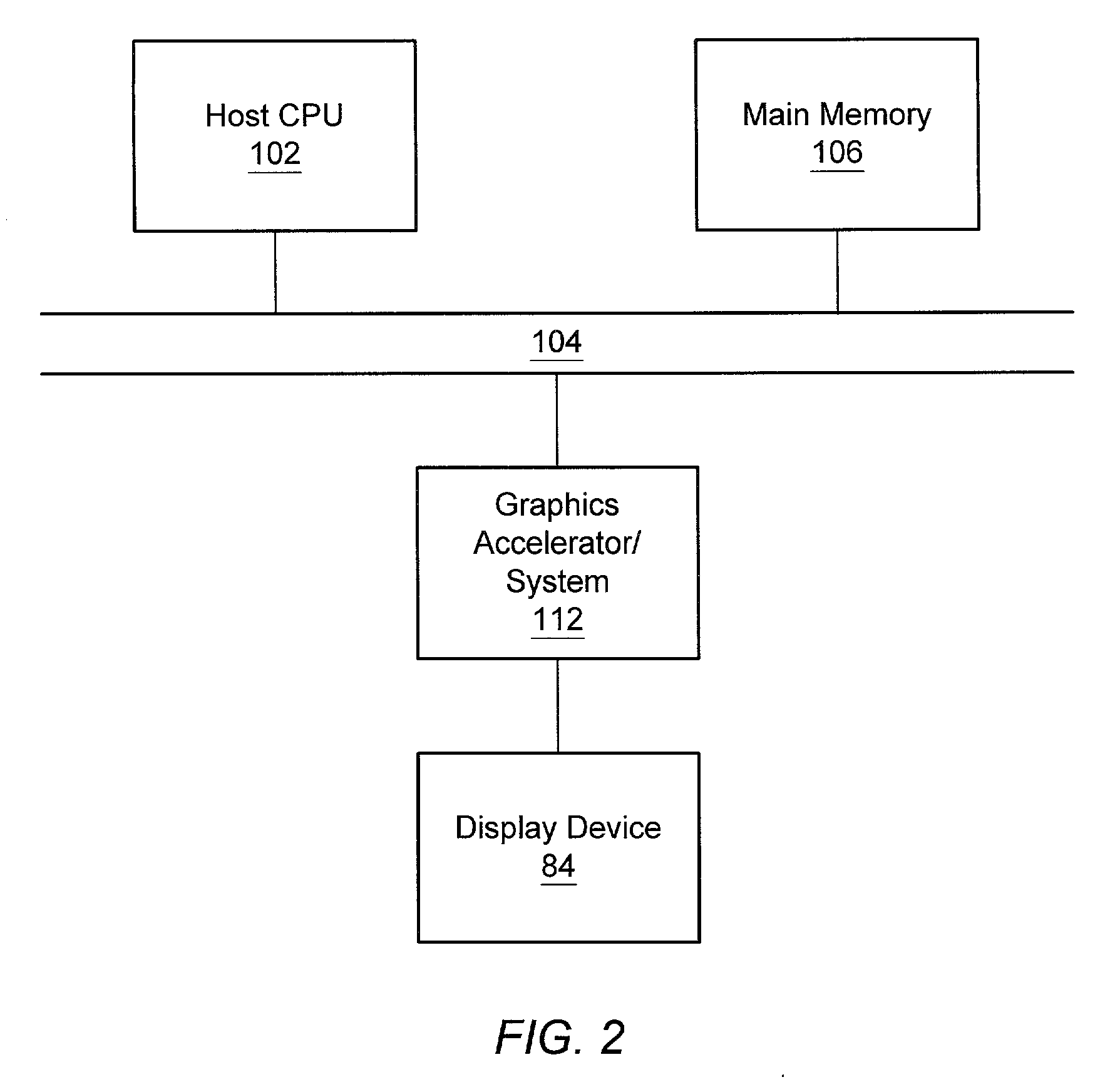

InactiveUS6437788B1Improved context-switchingRemoval is very complexResource allocationCathode-ray tube indicatorsGraphicsOperational system

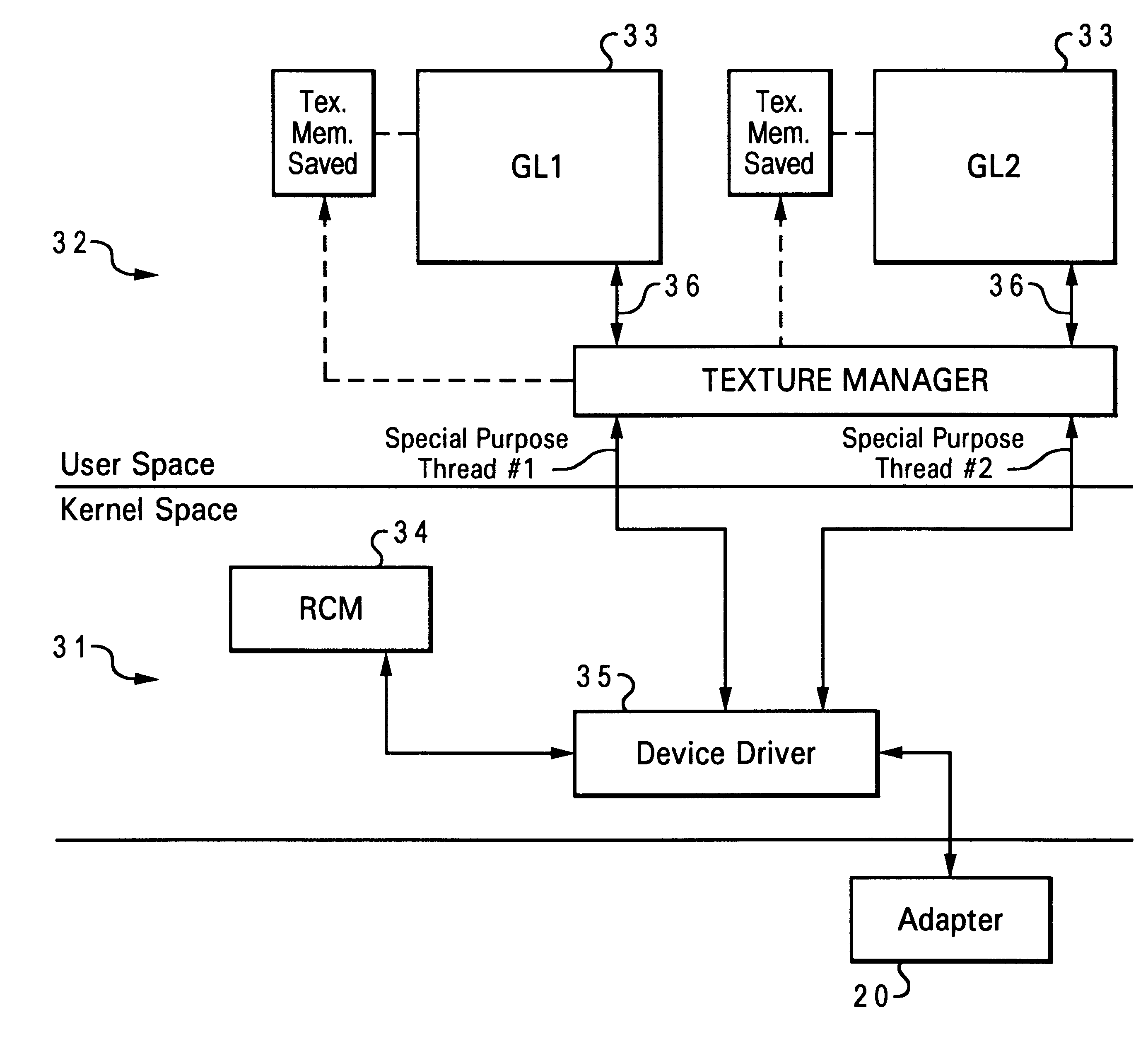

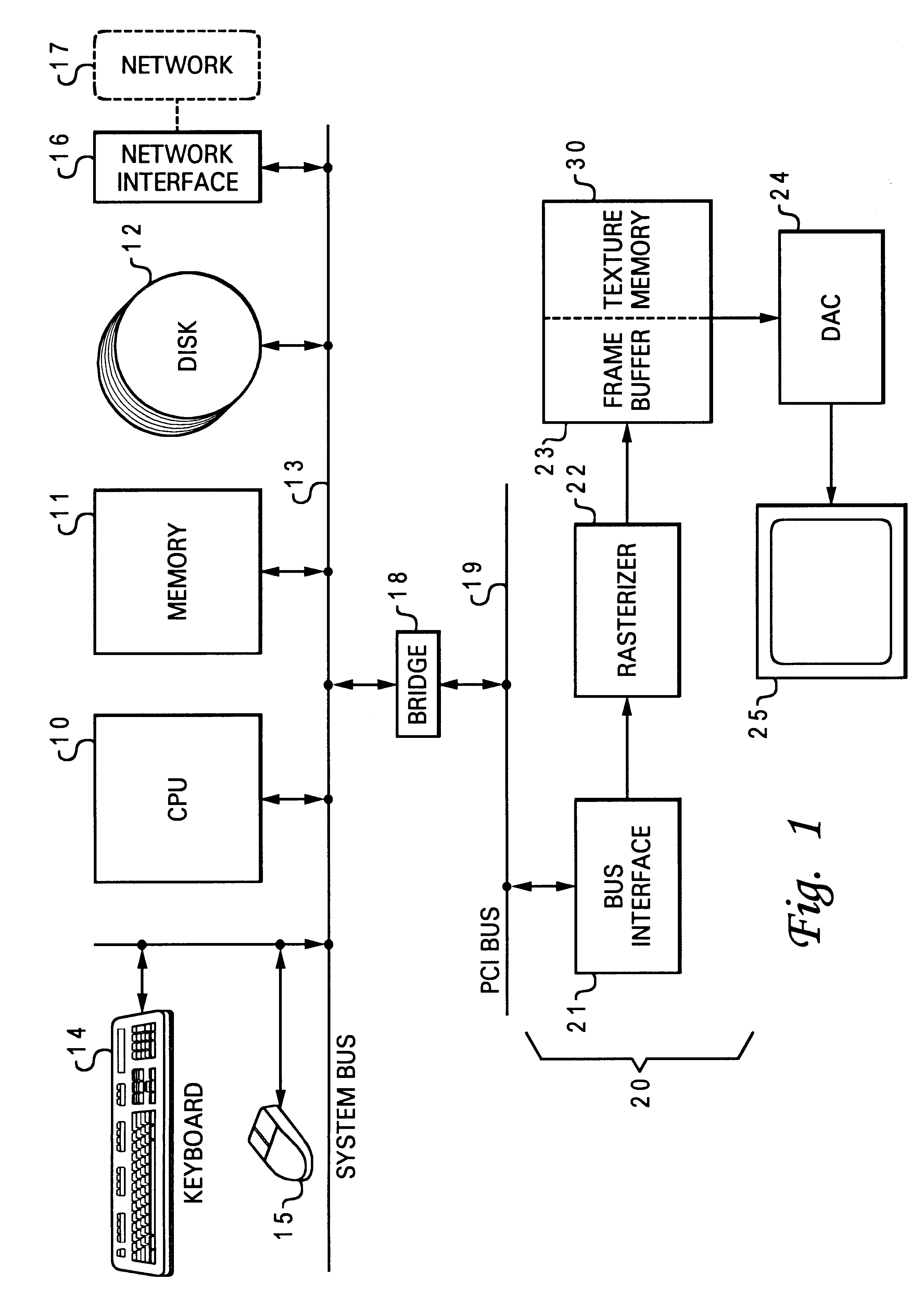

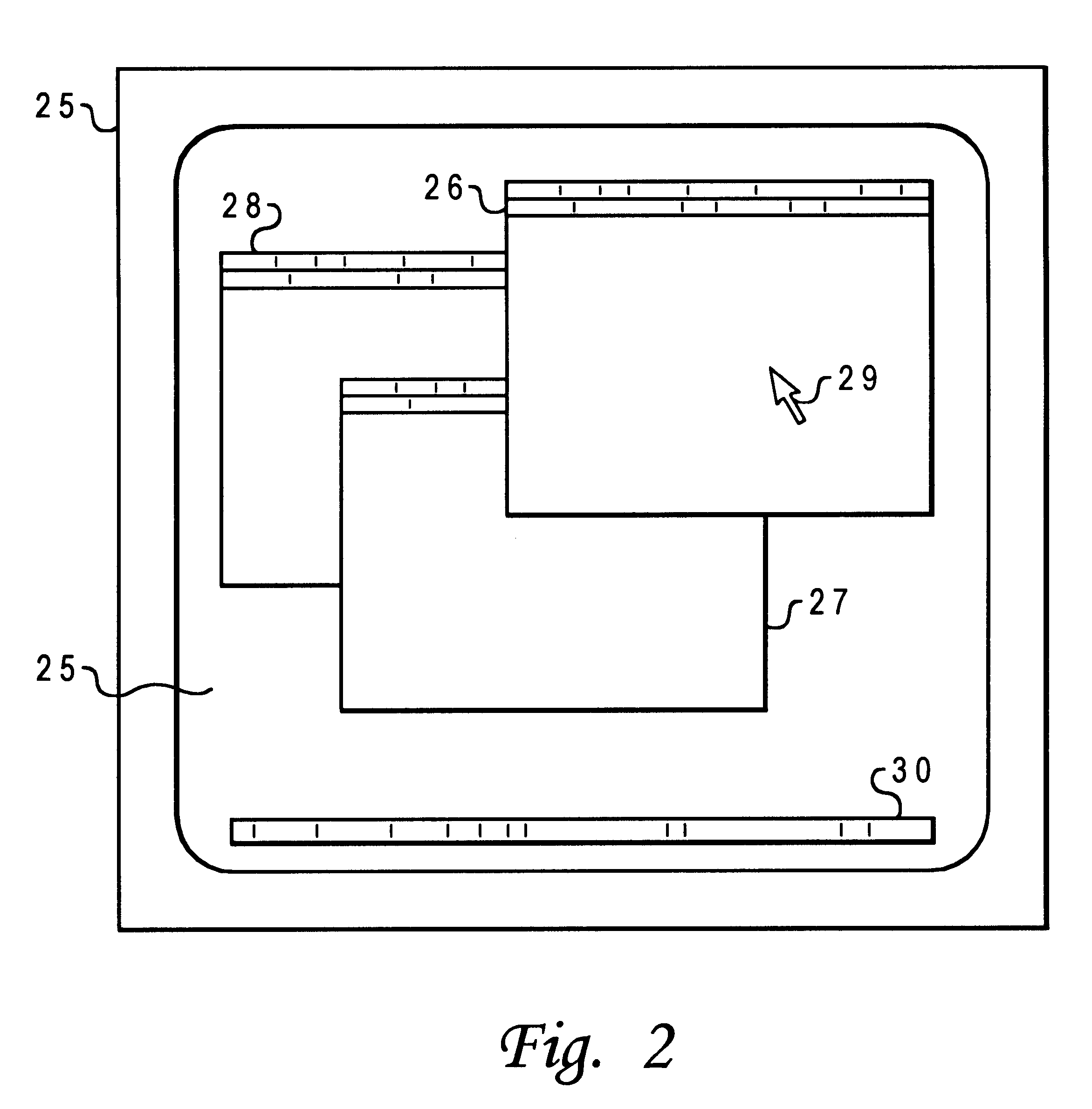

A computer system having a graphics display with texture management employs a graphics adapter with texture memory. The graphics adapter is "virtualized' by the operating system. When making a graphics context switch, the state of the graphics adapter including texture memory is saved. Threads are used to allow rapid and frequent context switches. A graphics process that will use texture memory in the adapter reserves a thread, for use during a graphics context switch. The thread calls into the operating system where it is blocked until a graphics context switch is initiated. At that time, the thread is unblocked to do texture management, such as saving of texture memory. During the save portion of the graphics context switch the graphics driver saves the current hardware state of the adapter, and the special purpose texture thread is unblocked to allow texture memory to be processed, and saves texture memory and calls back into the driver where it is blocked. During the restore portion of the graphics context switch the driver restores the state of the adapter to that of another graphics process, except for texture memory. The special purpose texture thread associated with the new graphics process is unblocked, passed an indication that a restore operation is in progress, and restores textures as required and calls back into the driver where it is blocked in the kernel. The driver completes the context switch and the graphics process is dispatched.

Owner:NVIDIA CORP

Static and dynamic video resizing

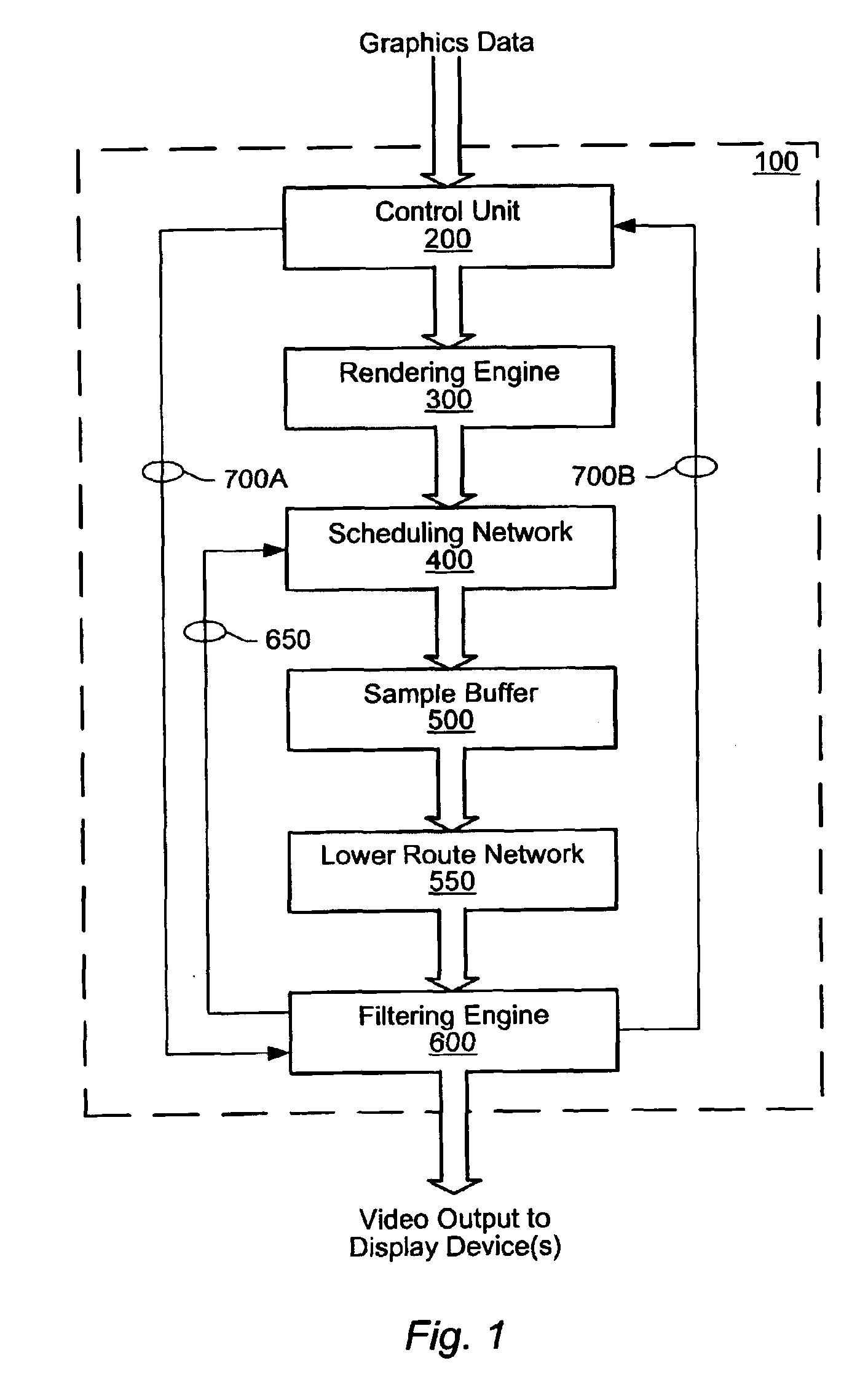

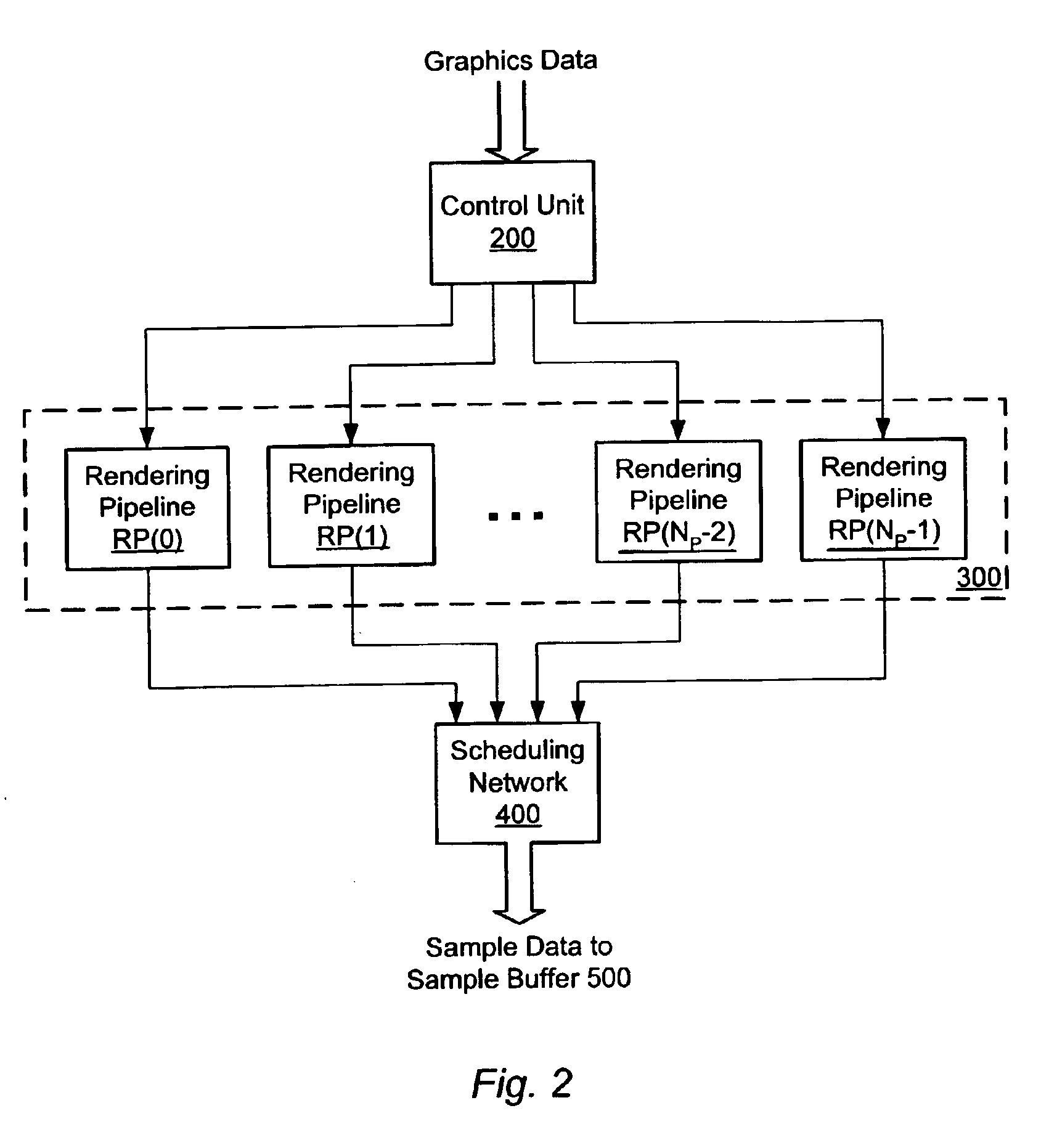

InactiveUS20010048435A1Drawing from basic elementsGeometric image transformationGraphicsGraphic system

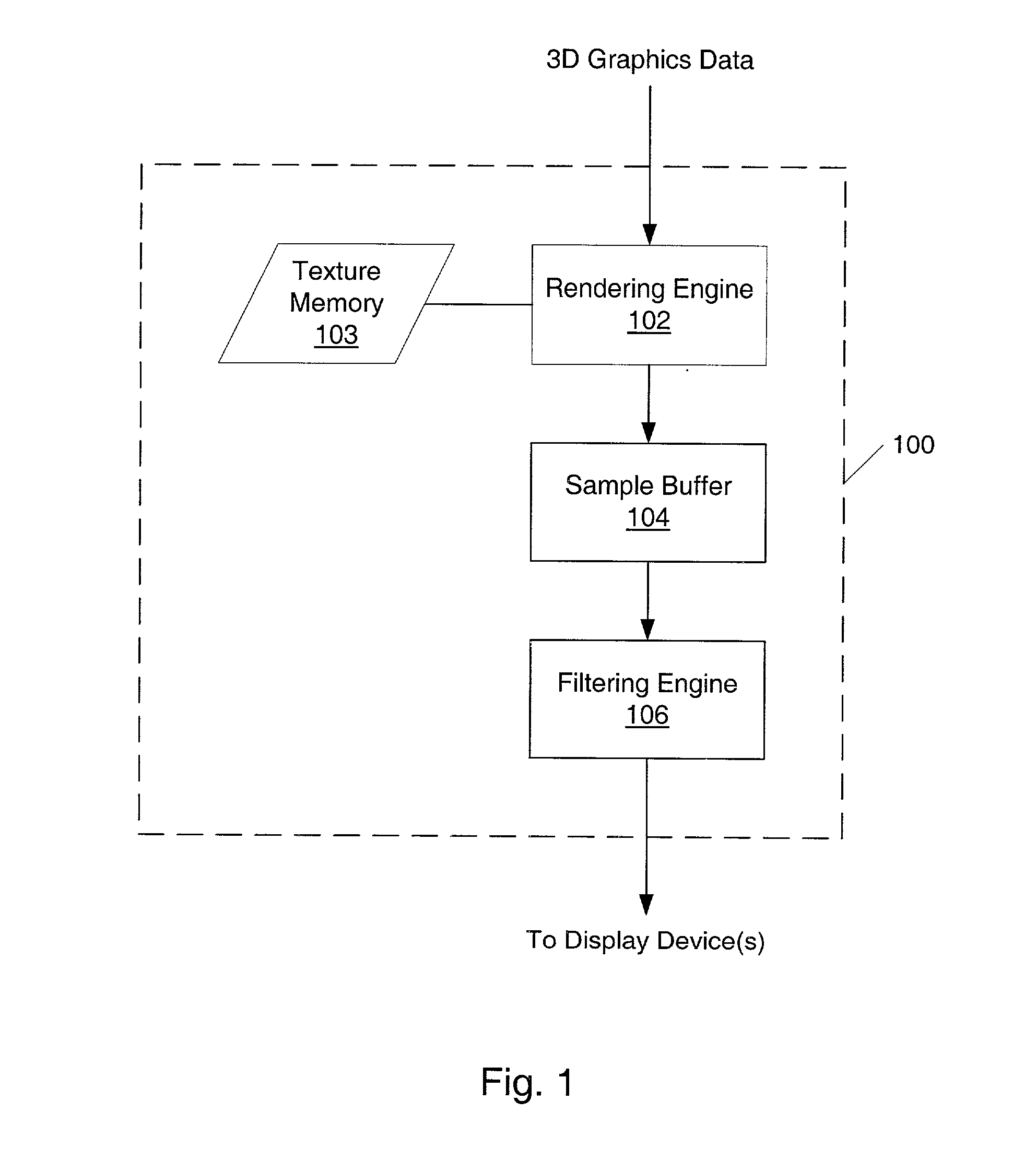

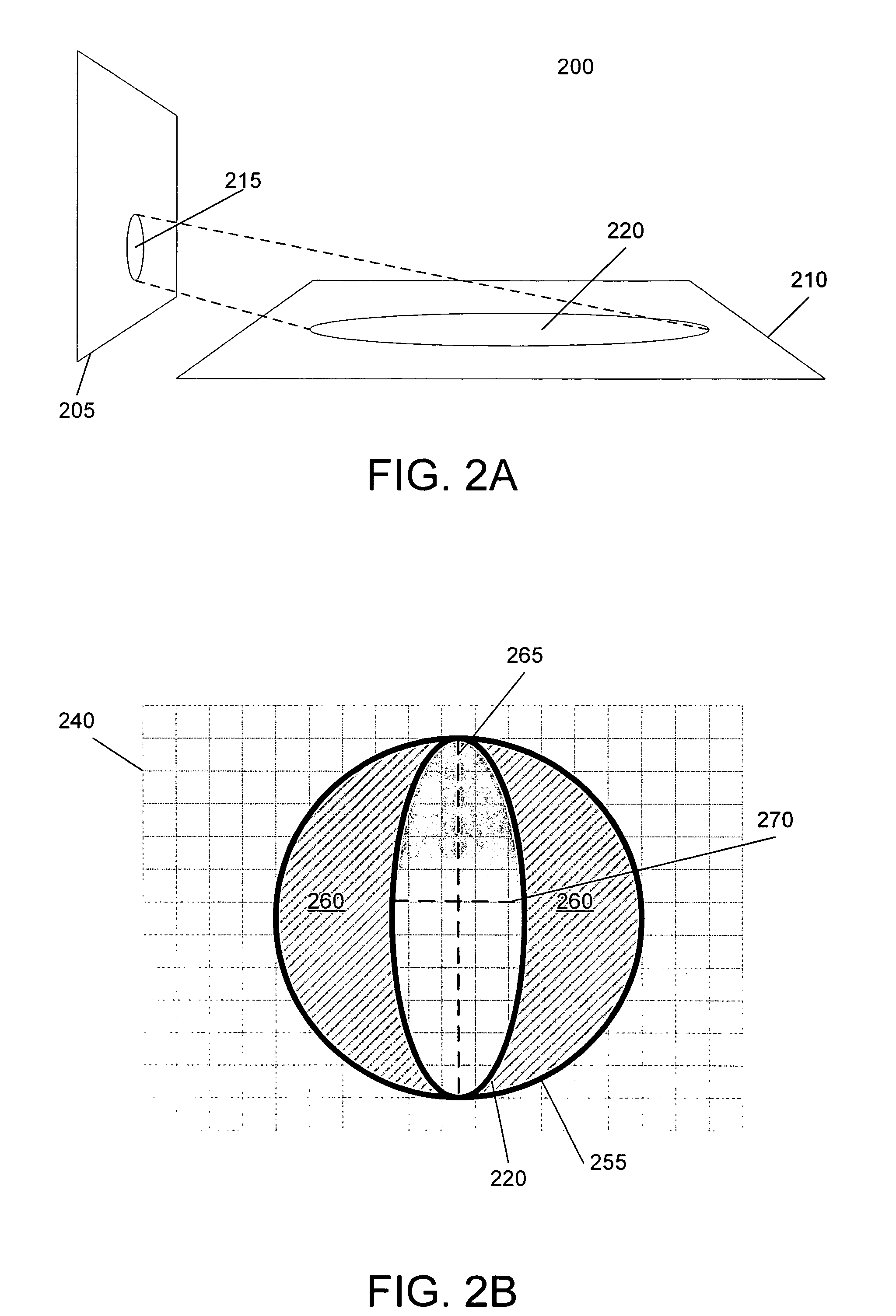

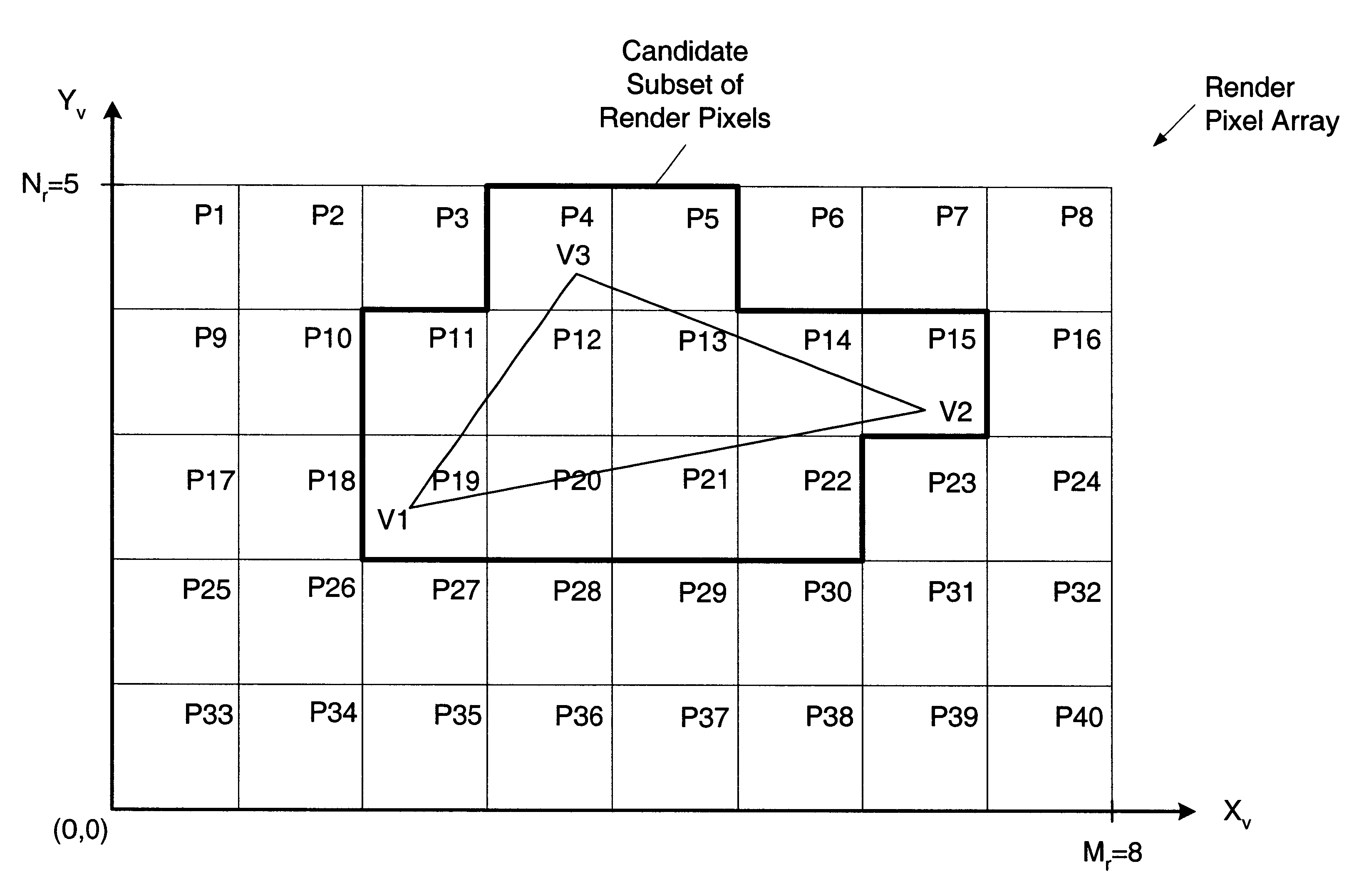

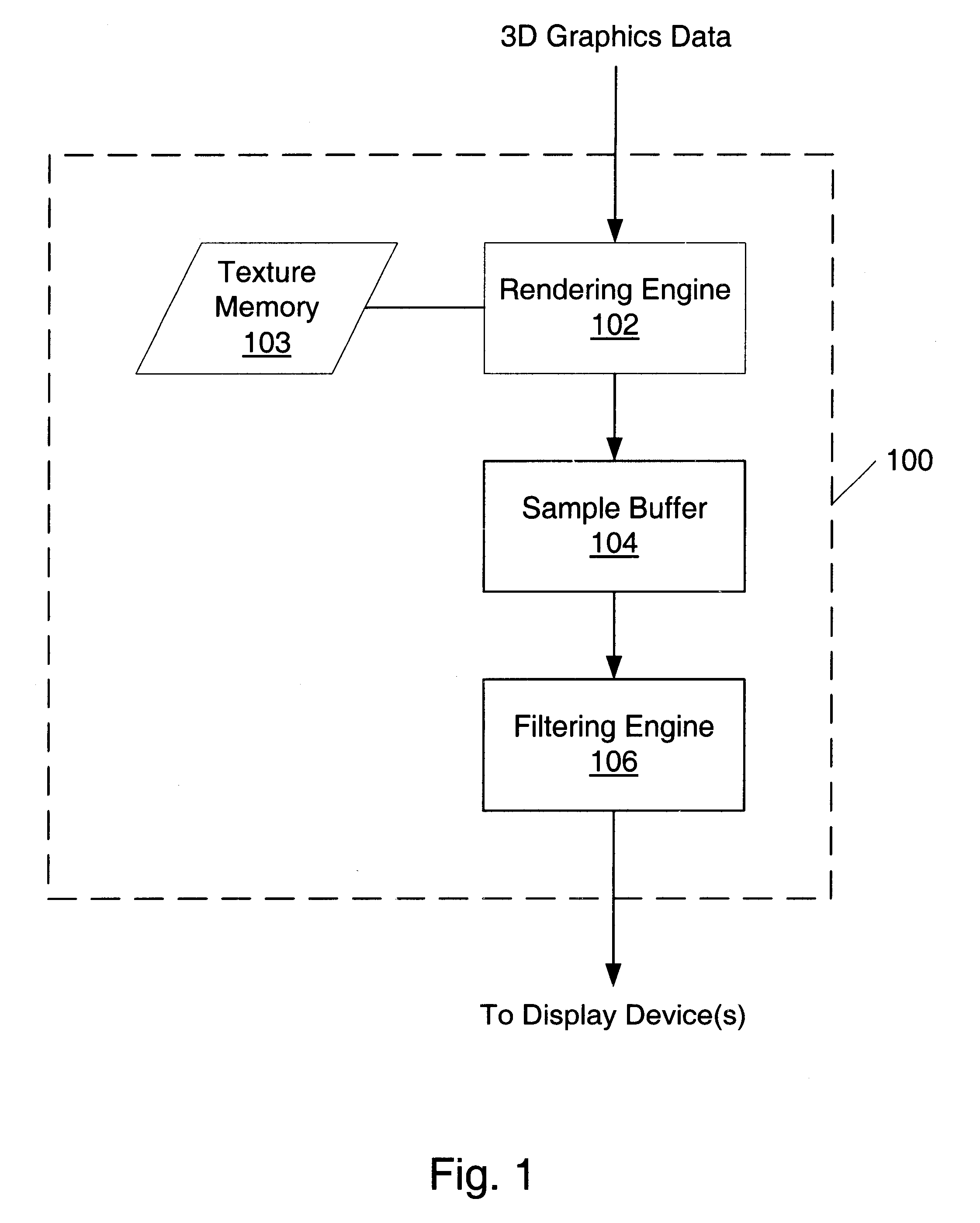

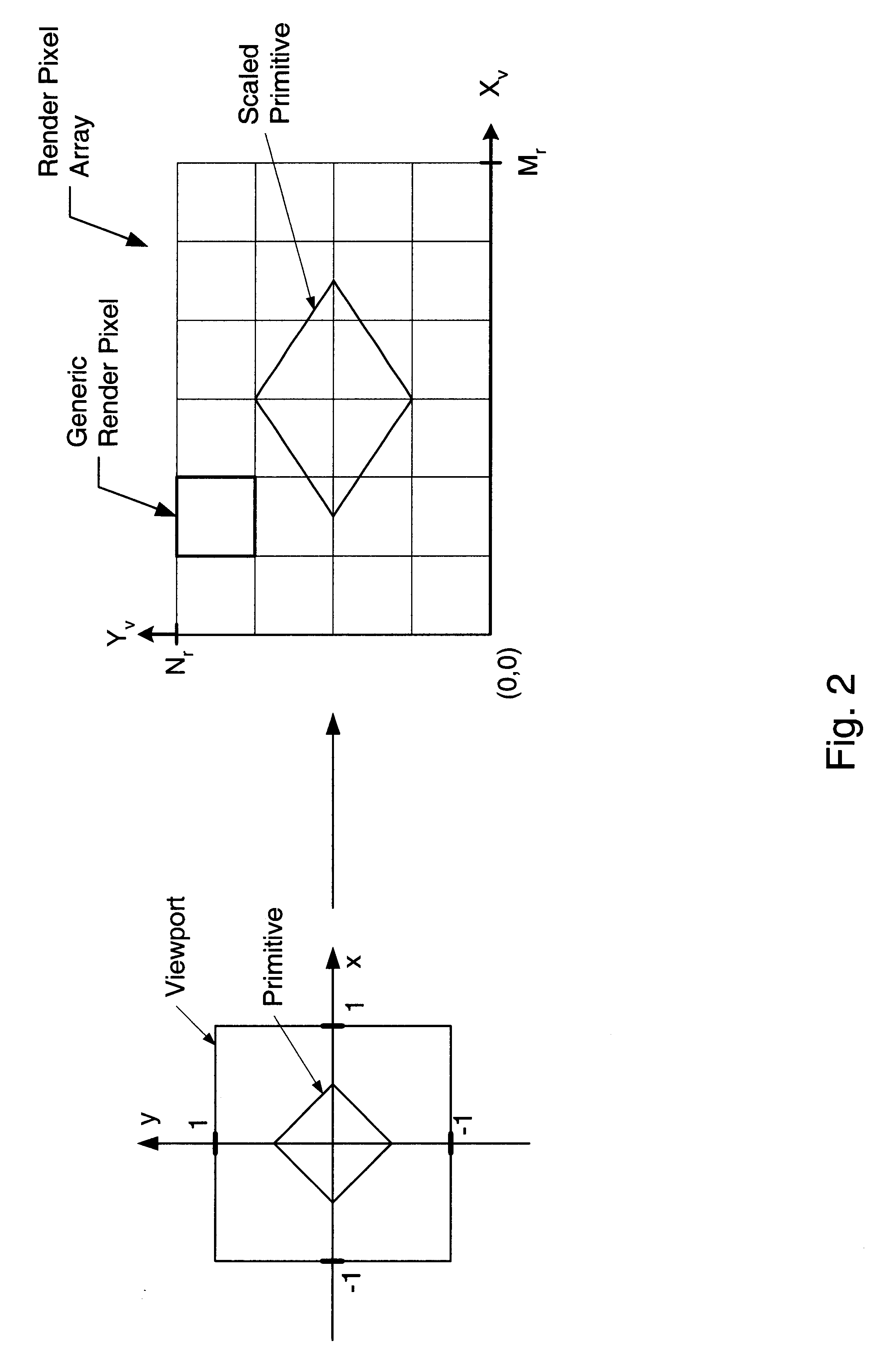

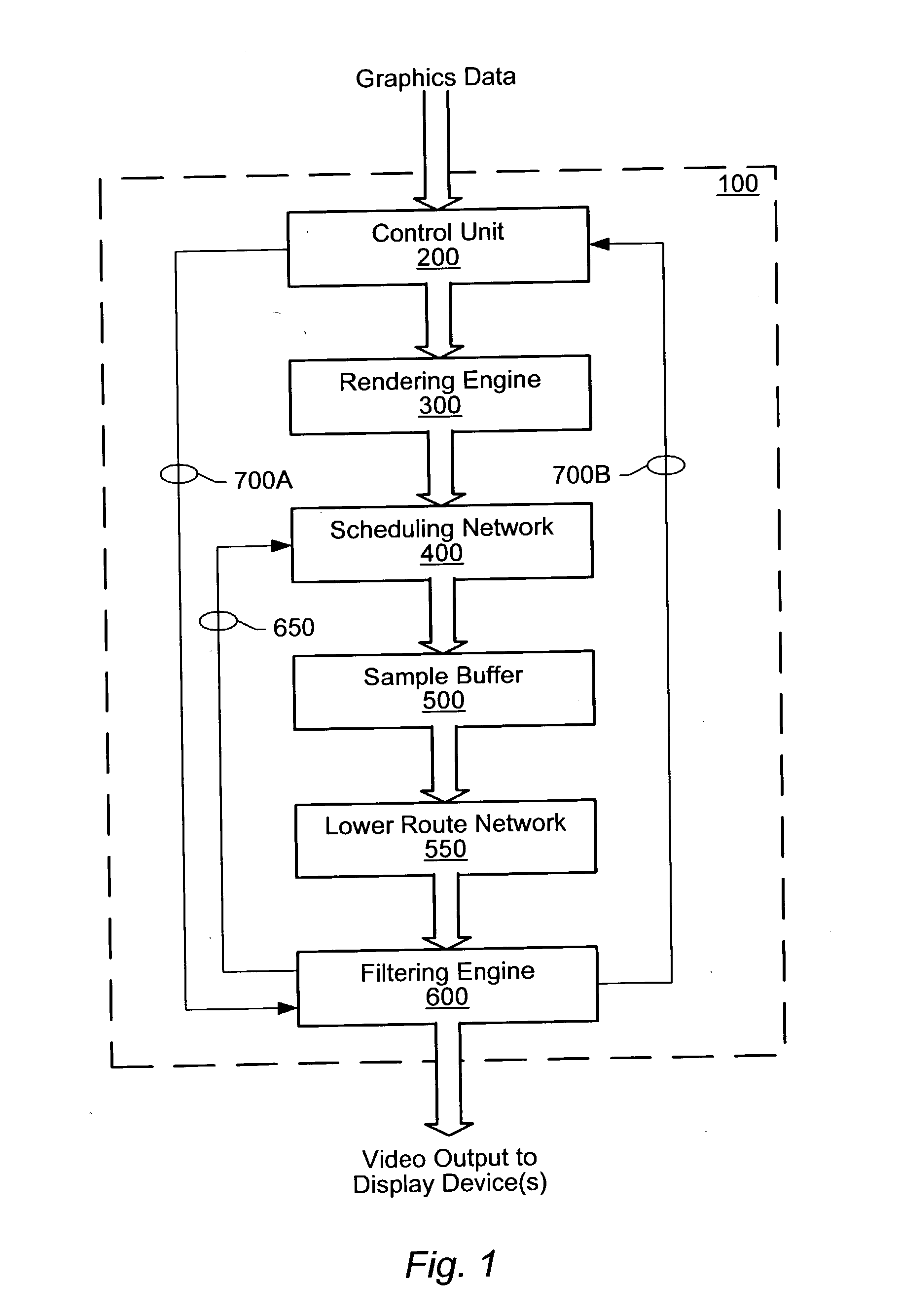

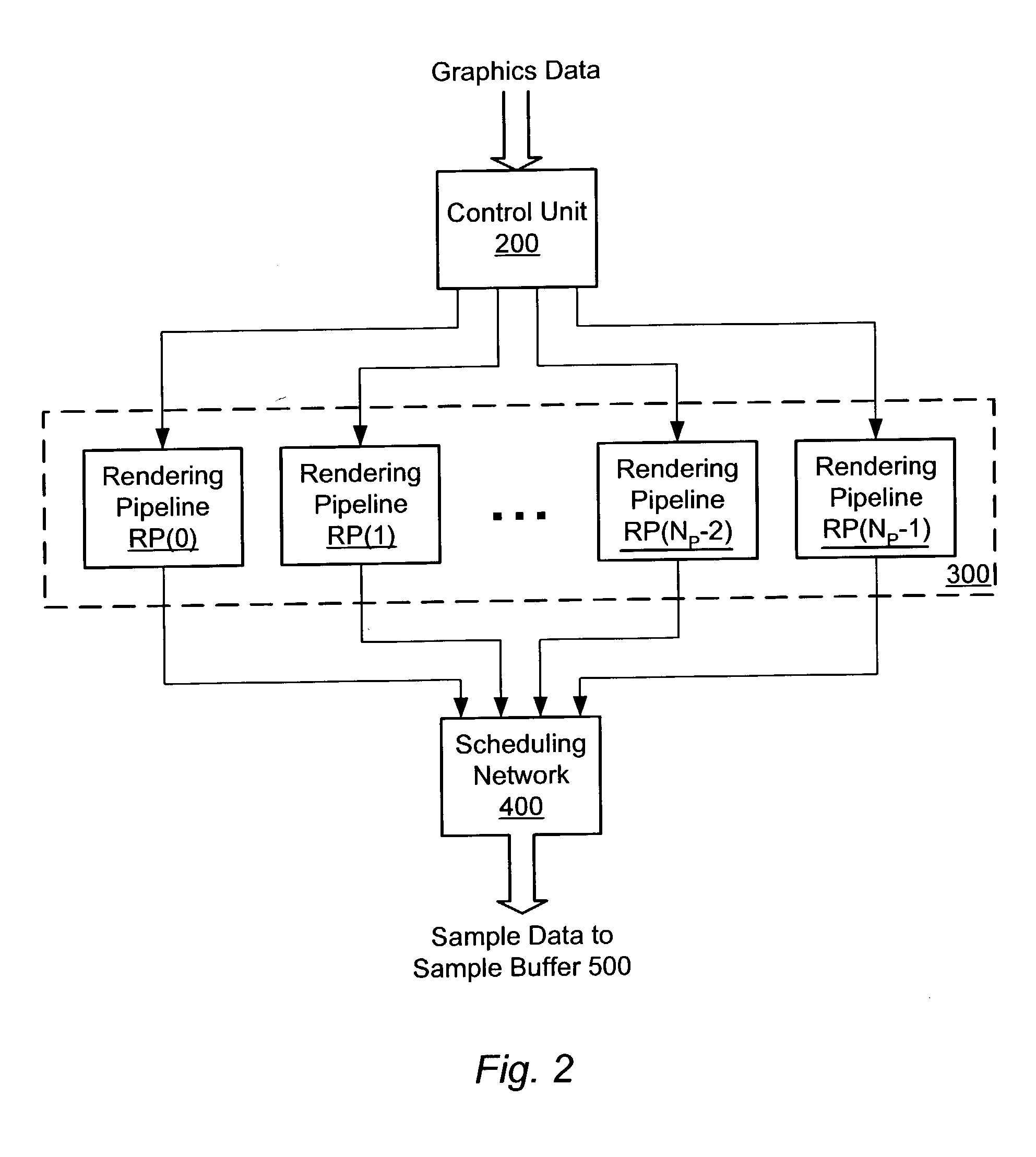

A graphics system comprises a texture memory, a rendering engine, a sample buffer and a filtering engine. The rendering engine renders received primitives based on a render pixel array whose vertical and horizontal resolutions are dynamically programmable. The rendering engine determines render pixels that geometrically intersect a primitive. For each intersecting render pixel, a texture access may be required (if texture processing is turned on) to determine texture values. The texture values may be used to compute sample values at sample positions interior to the sample render pixel and the primitive. A controlling agent may decrease the vertical and horizontal resolutions of the render pixel array to control frame render time. The filtering engine may programmably generate virtual pixel centers covering the render pixel array. Any change in the render pixel resolutions may require an accommodating change in the virtual pixel array parameters.

Owner:ORACLE INT CORP

Hashed direct-mapped texture cache

InactiveUS6233647B1Memory adressing/allocation/relocationCathode-ray tube indicatorsBit fieldParallel computing

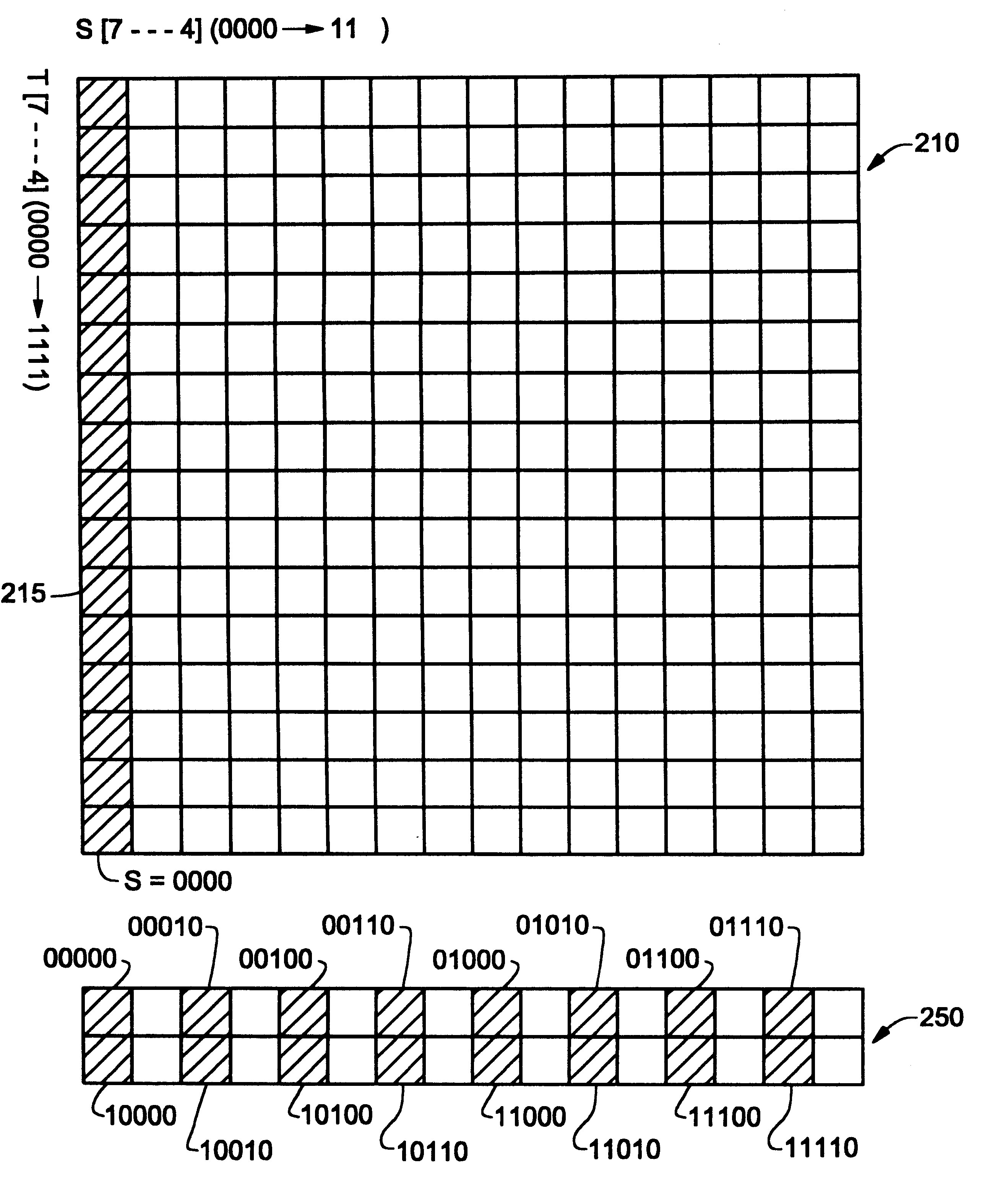

The present invention pertains to an apparatus for and method of mapping texture memory to a texture cache such that cache contention is minimized. Significantly, in one embodiment of the present invention, addresses of the texture memory are mapped to entries of the texture cache according to a predetermined hashing scheme. According to the one embodiment, texture memory is addressed as a virtually contiguous address space by a multi-dimensional index. The multi-dimensional index is further partitioned into a low order bit field and a high order bit field. Low order bits of the multi-dimensional index are directly mapped to low order bits of the cache address. High order bits of the multi-dimensional index are mapped to high order bits of the cache address according to a predetermined address-hashing scheme. Particularly, in one embodiment, high order bits of the multi-dimensional index are selectively "exclusive-or-ed" to generate corresponding addresses of the texture cache.

Owner:MORGAN STANLEY +1

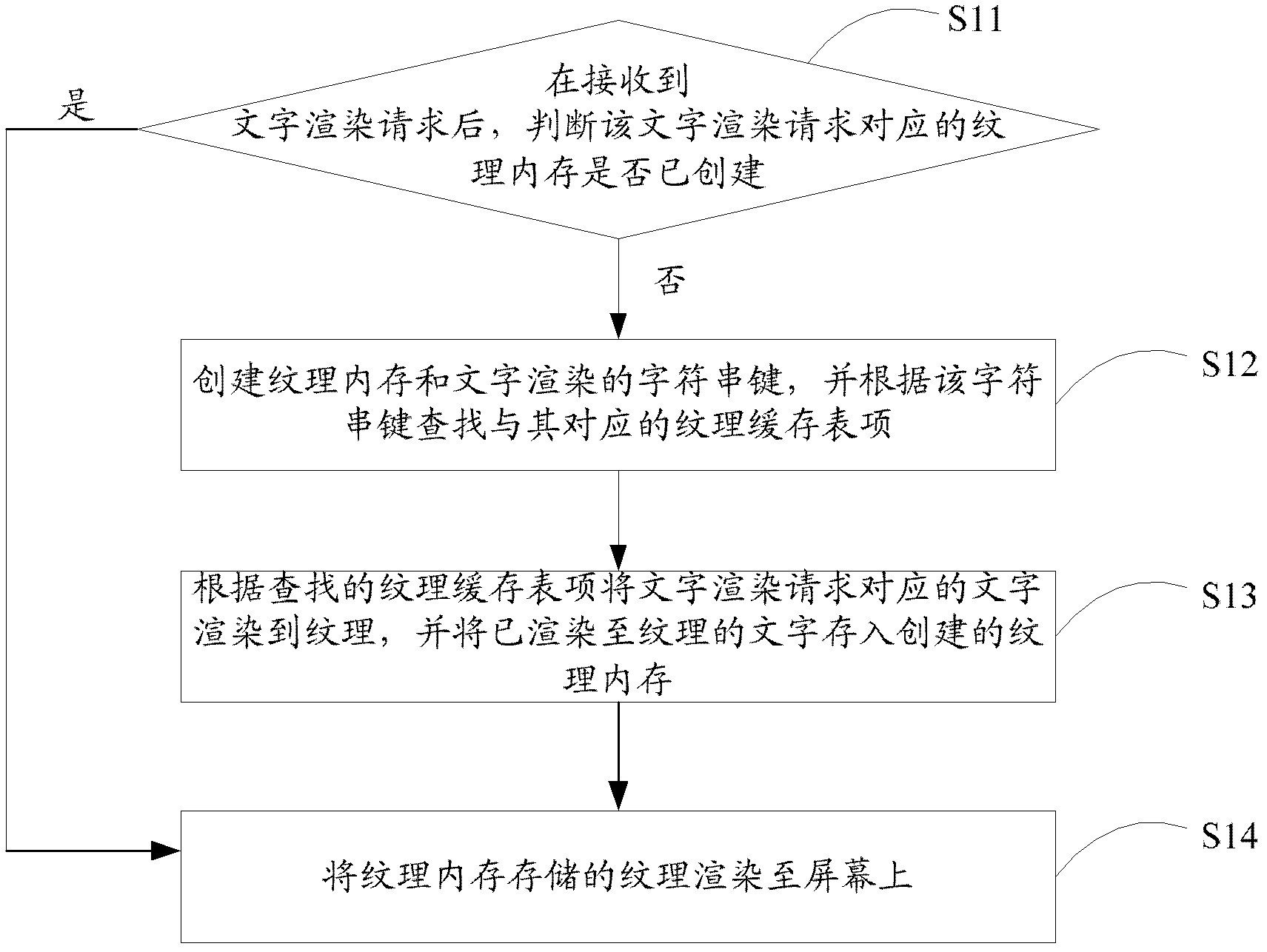

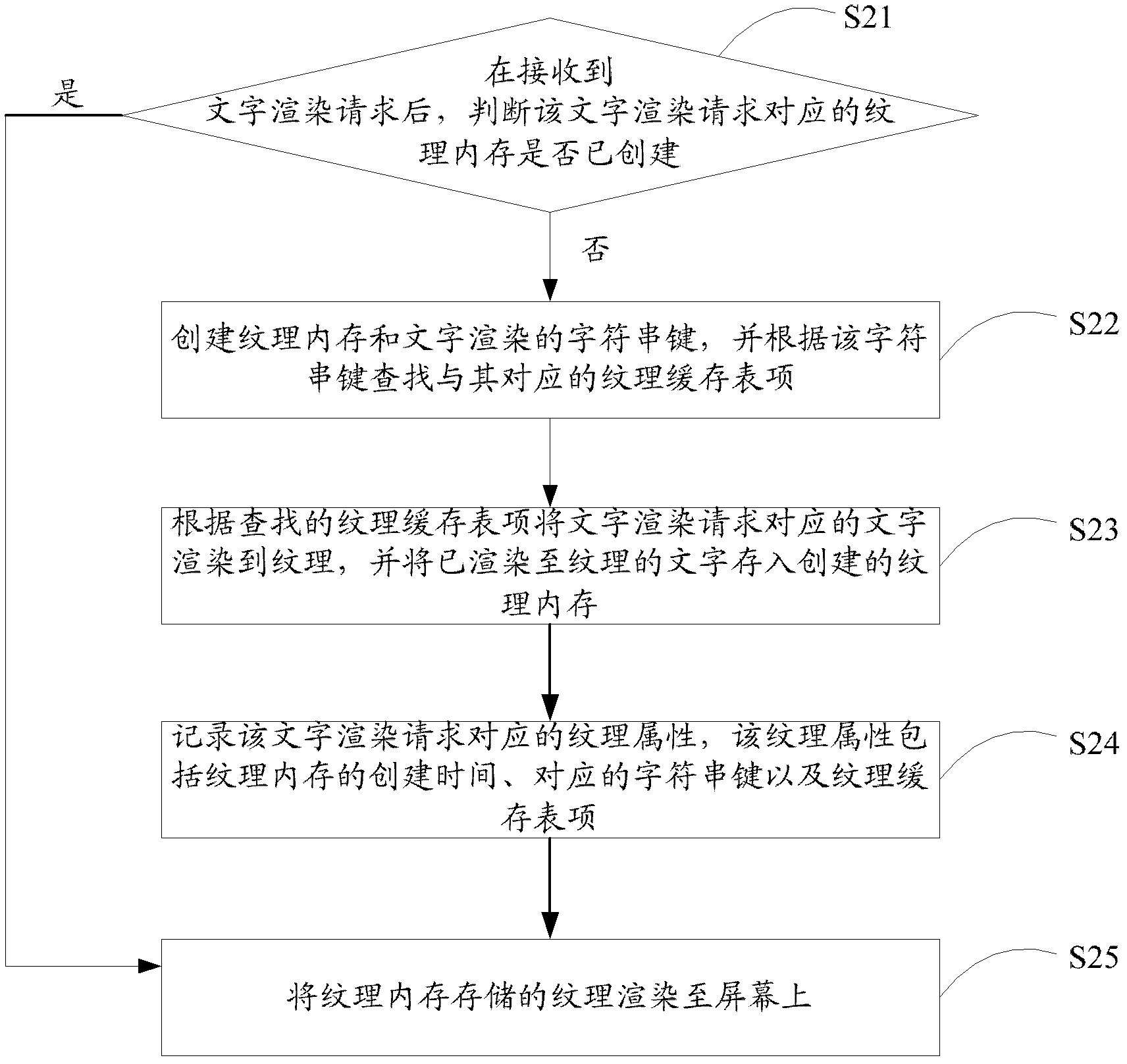

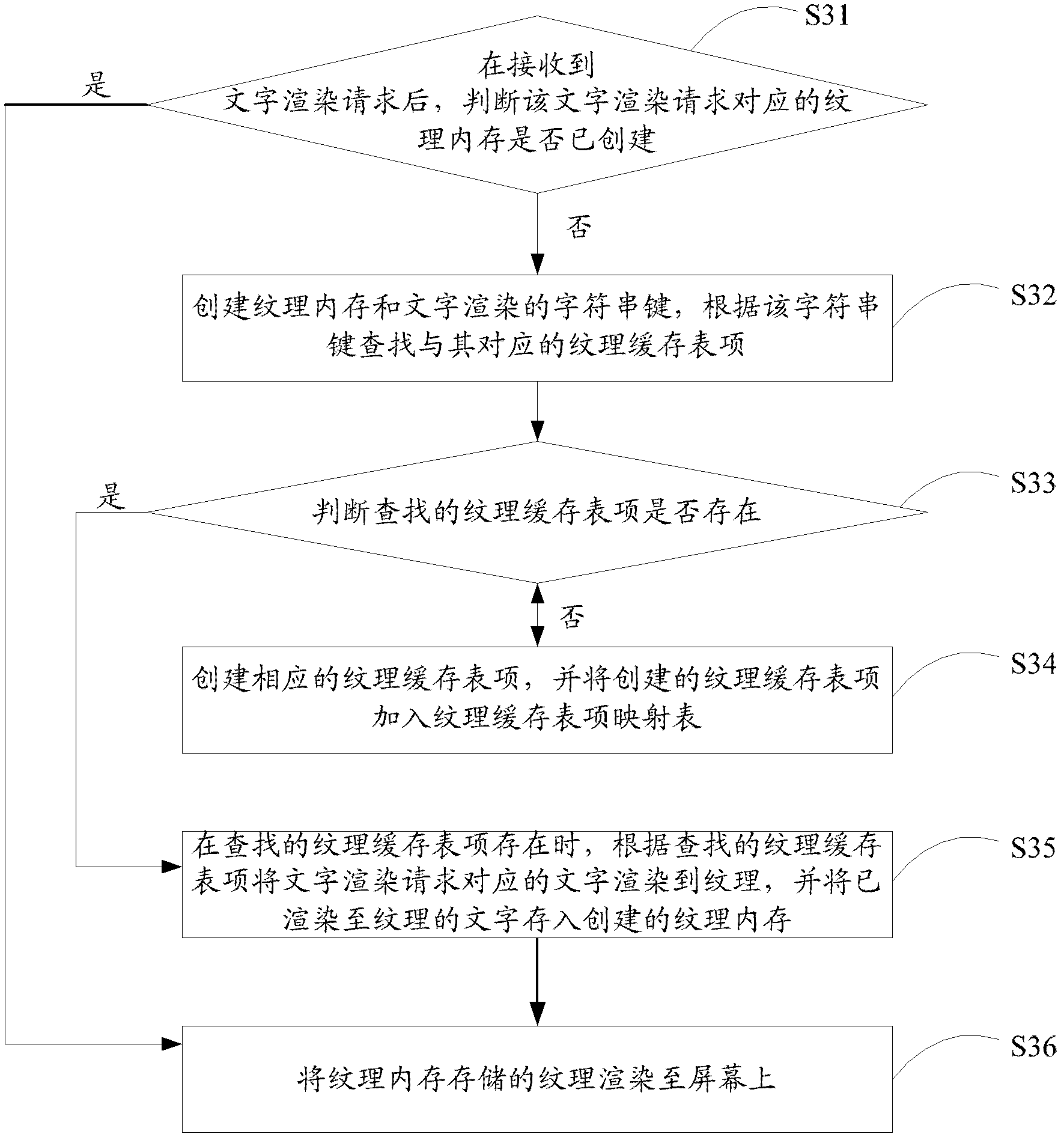

Method and device for rendering characters

ActiveCN103186919AImprove experienceImprove the level of3D-image renderingImaging processingComputer graphics (images)

The invention is applicable to the field of image processing, and provides a method and a device for rendering characters. The method comprises the following steps that whether a texture memory corresponding to a character rendering request is established is judged after the character rendering request is received; if the texture memory is not established, the texture memory and a character string key rendered by the characters are created; a texture cache table entry corresponding to the character string key is searched according to the character string key; the characters corresponding to the character rendering request are rendered to a texture according to the searched texture cache table entry; the characters rendered to the texture are stored in the established texture memory; and if the texture memory is established, the texture stored by the texture memory is rendered onto a screen. According to the method and the device, the characters are rendered to the texture; the texture is rendered onto the screen; a D3D (Dynamic 3-dimensional Display) renders the texture onto the screen by using hardware acceleration, so that fps (frames per second) can be kept at a higher level; and good experience of a user is improved.

Owner:TENCENT TECH (SHENZHEN) CO LTD

On the fly hardware based interdigitation

InactiveUS20070182738A1Image analysisCharacter and pattern recognitionComputer graphics (images)Texture memory

A method of interdigitation for display of an autostereoscopic source image to a screen comprising a plurality of pixels having sub-pixels and sub-pixel components and apparatus for interdigitation is provided. The method comprises generating a texture memory coordinate at each pixel location on the screen of the source image, calculating screen pixel location based on the texture memory coordinate of each pixel, computing view numbers based on screen pixel location, wherein view numbers comprise one value for each sub-pixel component, mapping proportional pixel locations in tiles from multiple tile perspective views of the autostereoscopic image to a resultant image using the view numbers, and extracting one subpixel component from each proportional pixel location to represent color for the pixel in the resultant image.

Owner:REAID INC

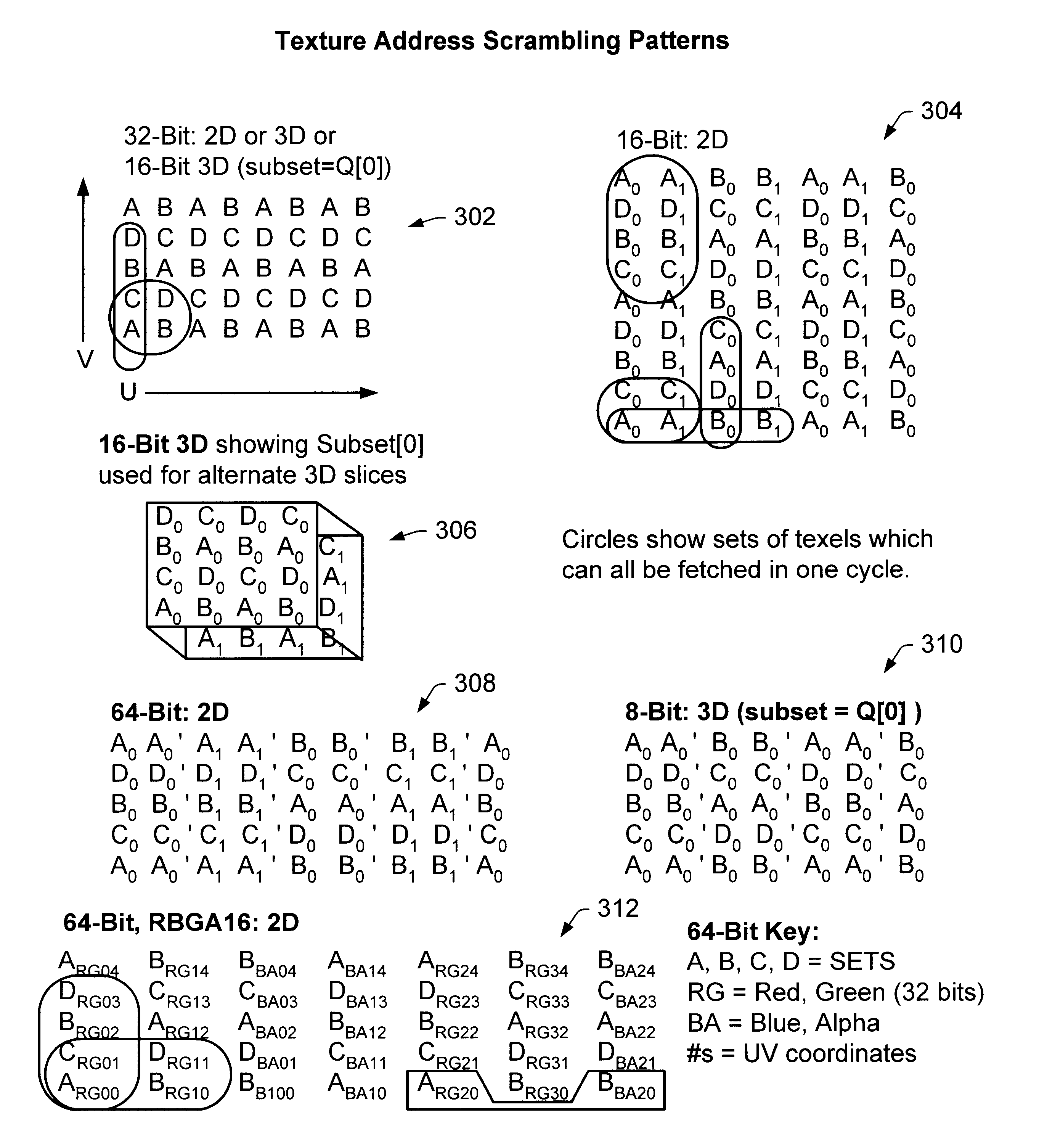

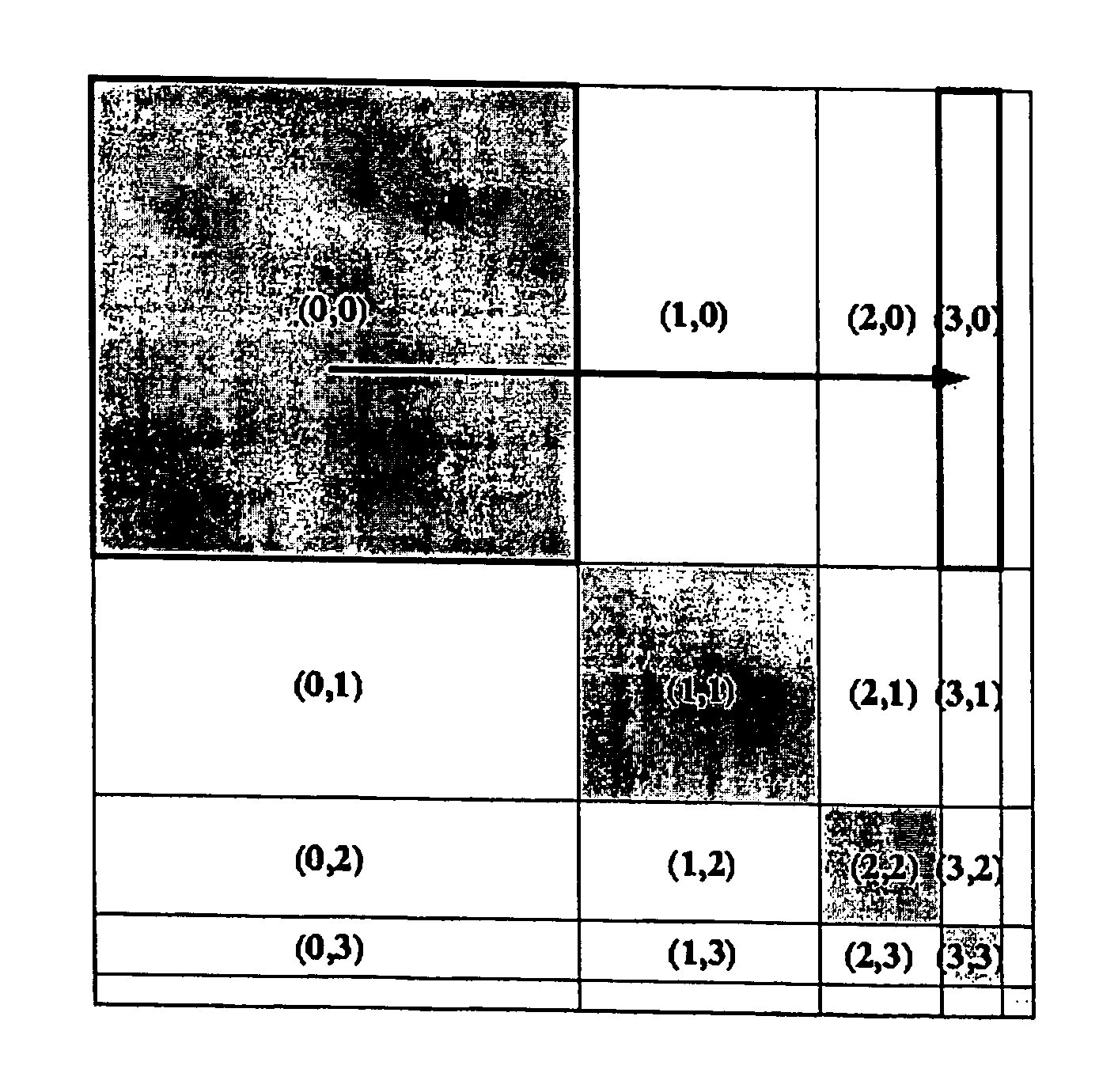

Memory interleaving technique for texture mapping in a graphics system

A graphics system and method for storing and accessing texture maps comprising texels. The graphics system may include a graphics processor and a texture memory comprising a plurality of memory devices for storing the texture maps. The texels (or portions of the texels) may be stored in the memory devices in an interleaved fashion. The texel data is interleaved in the memory devices to guarantee that, no matter which NxM array of texels is accessed, each texel in the array is present in a different memory device or chip and hence are concurrently available. Thus the NxM array of texels may be output concurrently or simultaneously, regardless of which array is accessed, i.e., regardless of which pixel is addressed. Embodiments are also described where the memory devices output arrays of texels for at least two respective neighboring pixels, or a 3D array of texels, in parallel in response to a single read transaction. Also, the body and border portions of the texture map are stored in separate areas of memory (e.g., in different memory address spaces), but texel interleaving is still performed.

Owner:ORACLE INT CORP

Window system 2D graphics redirection using direct texture rendering

ActiveUS20050179691A1Increase ratingsSmall memory footprintImage memory managementCathode-ray tube indicatorsGraphicsTexture rendering

The 3D window system utilizes hardware accelerated window system rendering to eliminate the pixel copy step of 3D window system output redirection. The 3D window system includes a window server that directs the window system device driver graphics routines to render into the texture memory of a graphics device.

Owner:ORACLE INT CORP

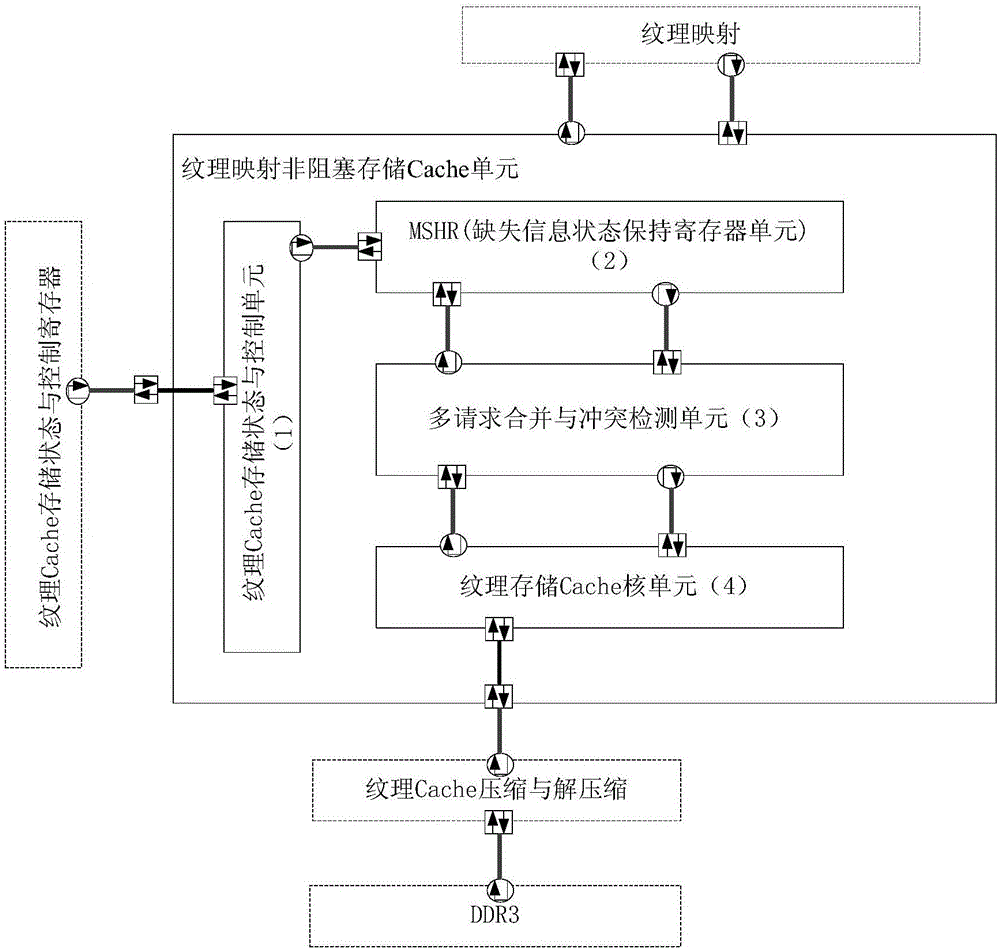

Modeling structure of GPU texture mapping non-blocking memory Cache

ActiveCN106683158AAchieving massive parallelismRealize requirementsImage memory managementProcessor architectures/configurationCollision detectionSignal design

The invention belongs to the field of computer figures, and provides a modeling structure of a GPU texture mapping non-blocking memory Cache. The modeling structure comprises a texture Cache storage status and control unit (1), a missing information status handling register memory cell (MSHR) (2), a multi-request combination and collision detection unit (3), and a texture memory Cache core unit (4). Hardware modeling with accurate periods is conducted on a texture memory Cache access process, parallel processing of texture access request data is realized through a multi-process mode including input request collision detection, request combination and division, multiple ports, multiple Banks and non-blocking flowing, and large-scale parallelism and high throughput demands of texture access data are met effectively. Moreover, the modeling structure effectively avoids configuration of complex circuit signal design and rapid assessment large-scale hardware system, is suitable for system level design and development of circuits in an early age, and provides effective reference for products and functions of the same kind.

Owner:XIAN AVIATION COMPUTING TECH RES INST OF AVIATION IND CORP OF CHINA

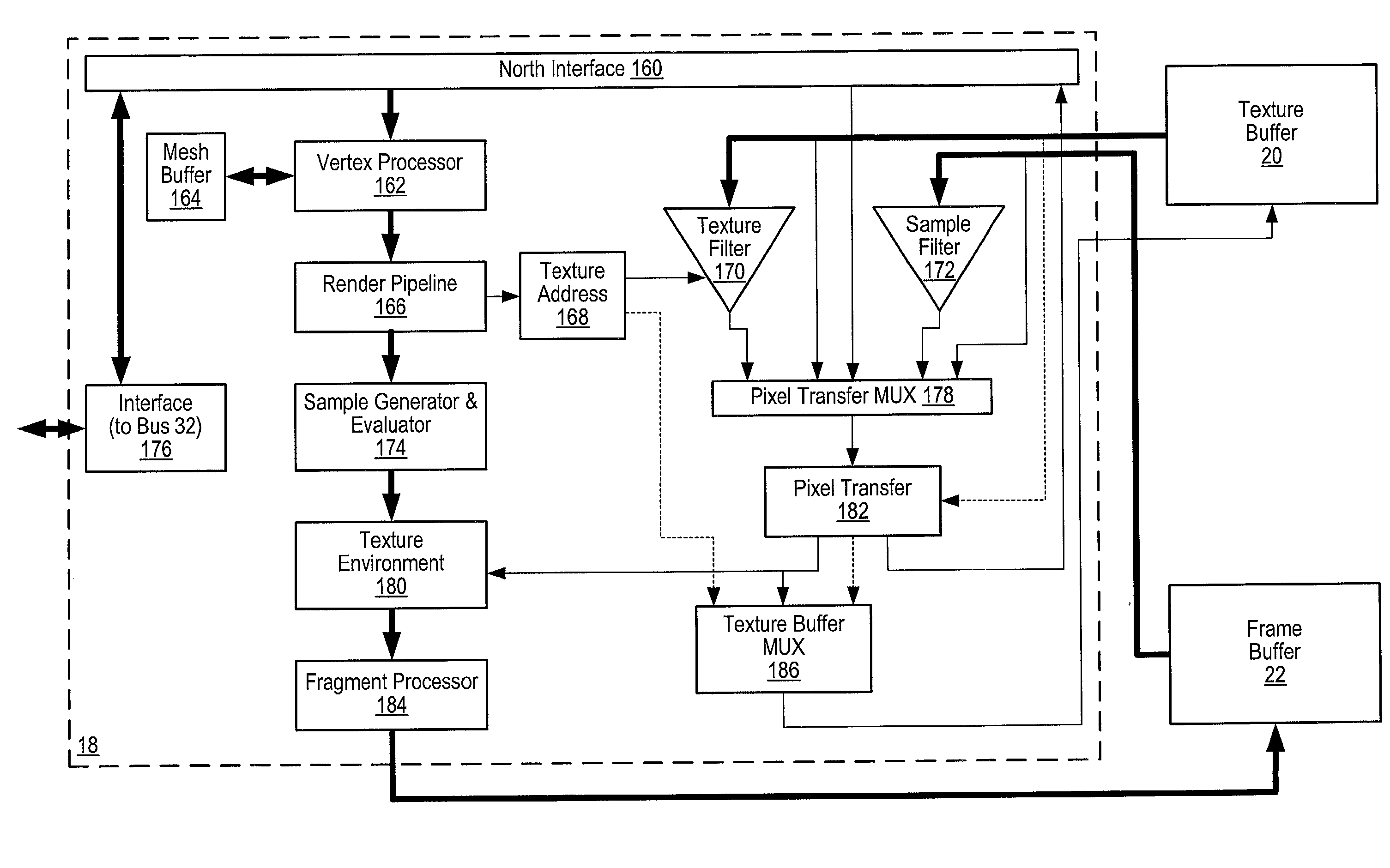

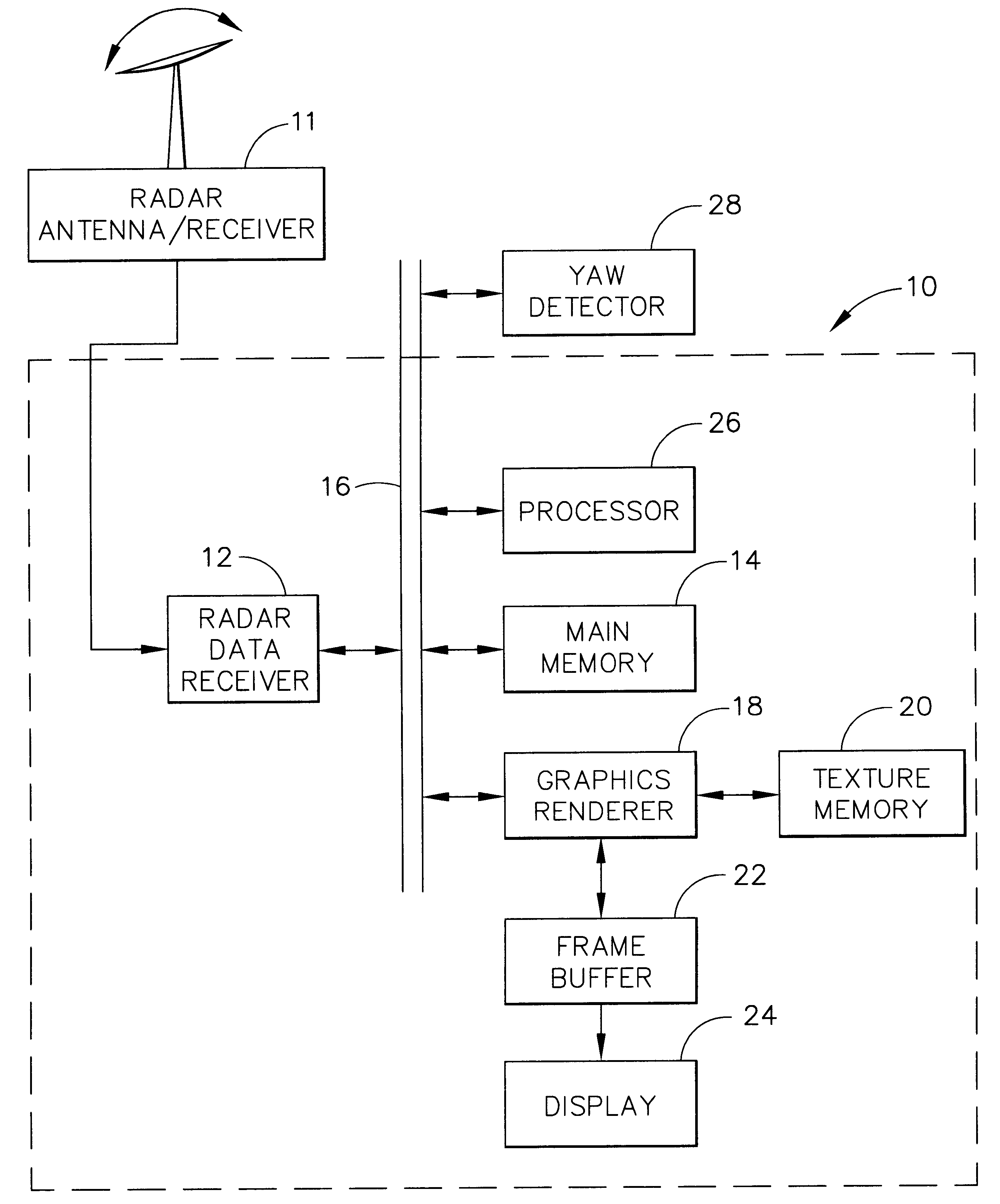

Use of texture memory for WX scan conversion

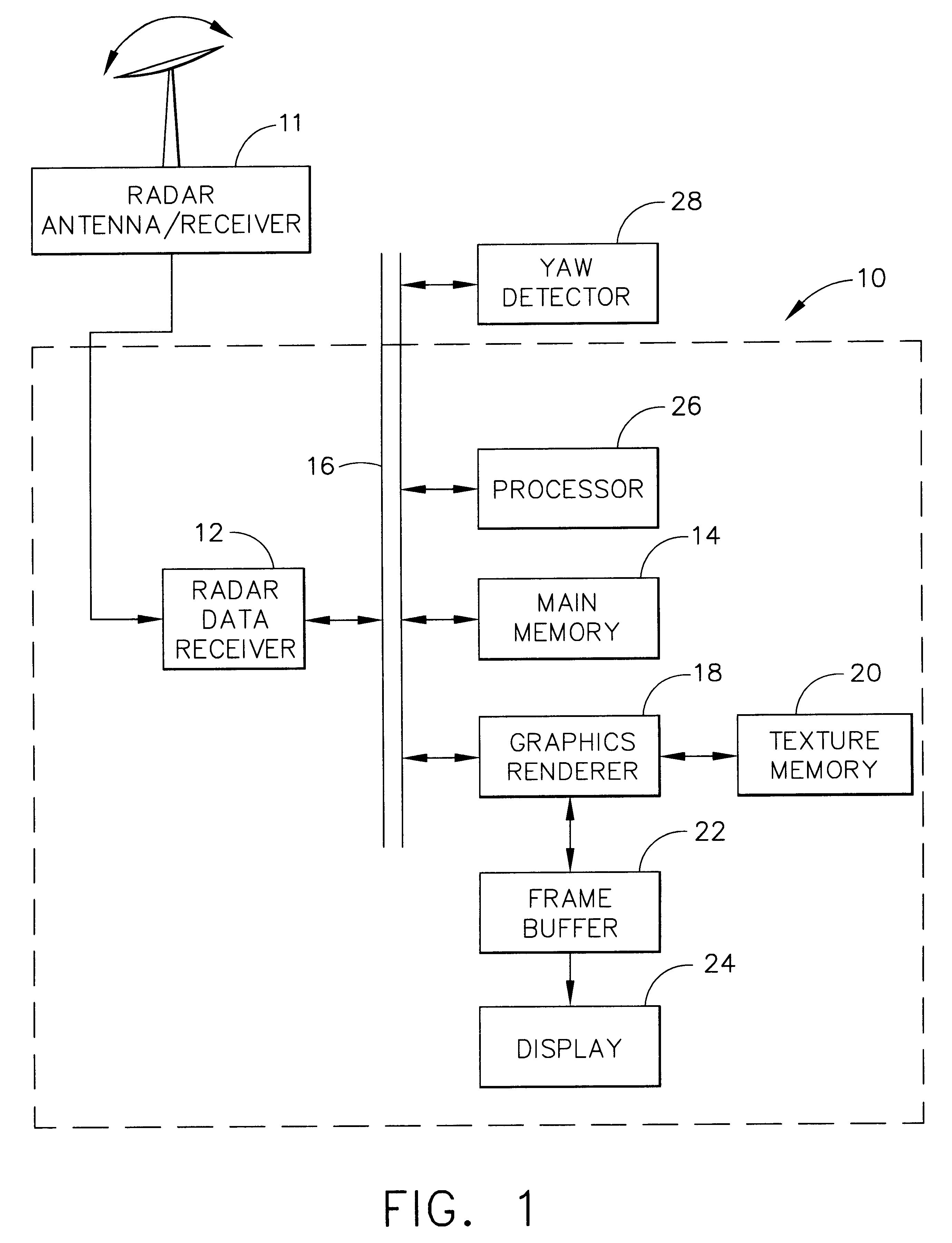

A radar display system (10) according to the present invention generates textured radar display data by utilizing a direct memory access receiver (12) to receive radially scanned radar data, to convert the radially scanned radar data into range bin data sets, and to store the range bin data sets. A graphics renderer (18) stores the set of range bin data sets in a texture memory (20) as a plurality of rectangular textures, and bit maps the rectangular textures to a series of display triangles in a frame buffer (22). The graphics renderer (18) colors the display triangles in accordance with the rectangular textures by performing a bi-linear interpolation of the color and warps the display triangles in accordance with the size of a display (24).

Owner:HONEYWELL INT INC

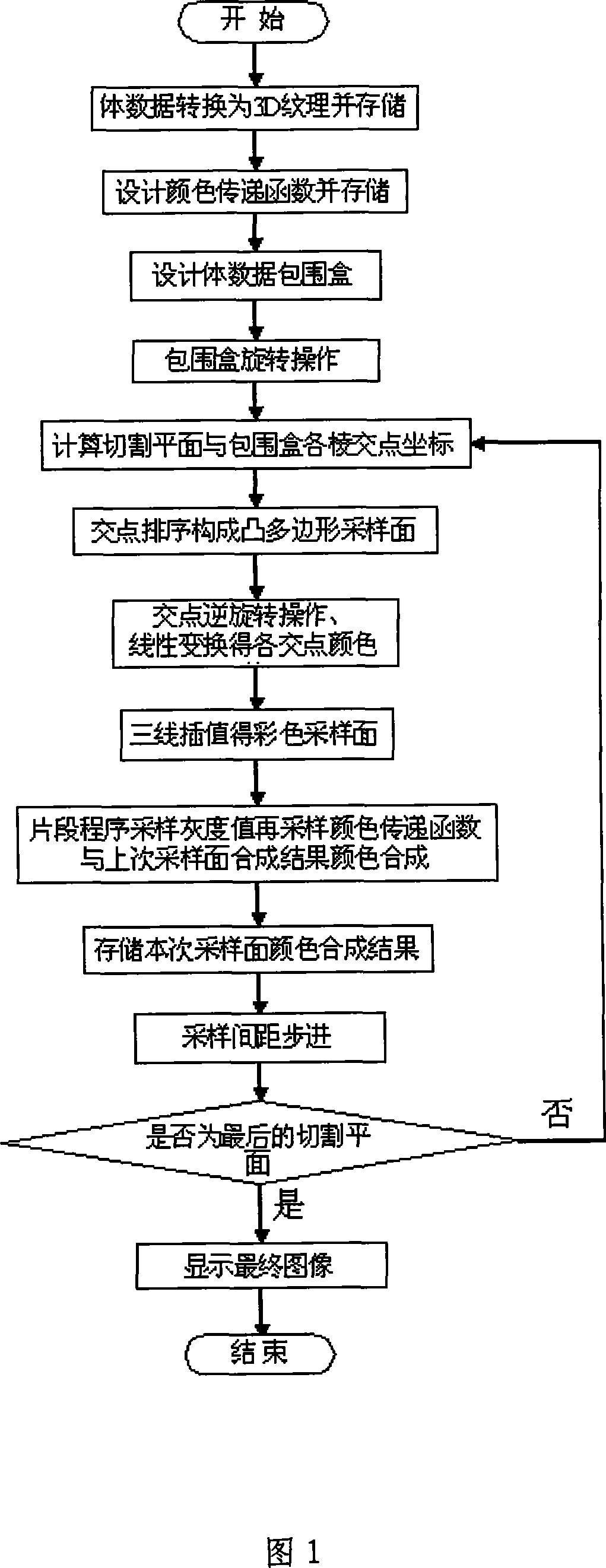

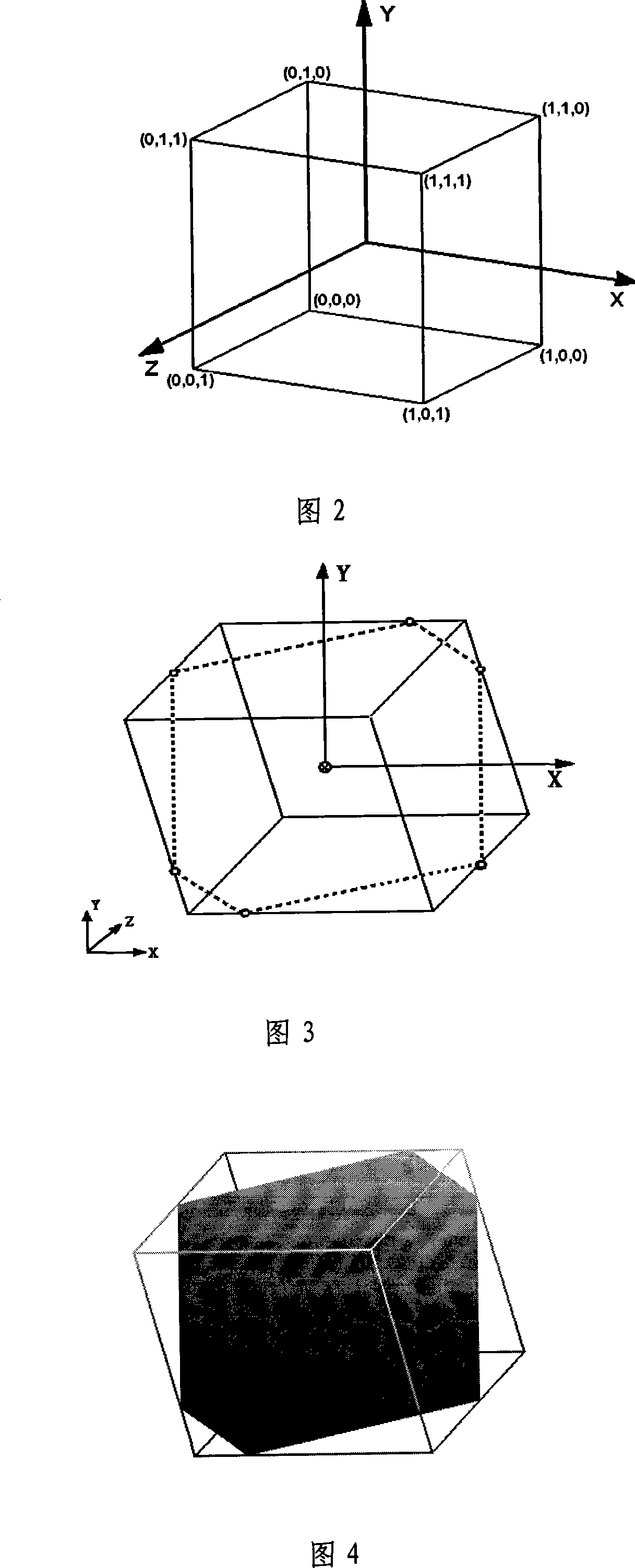

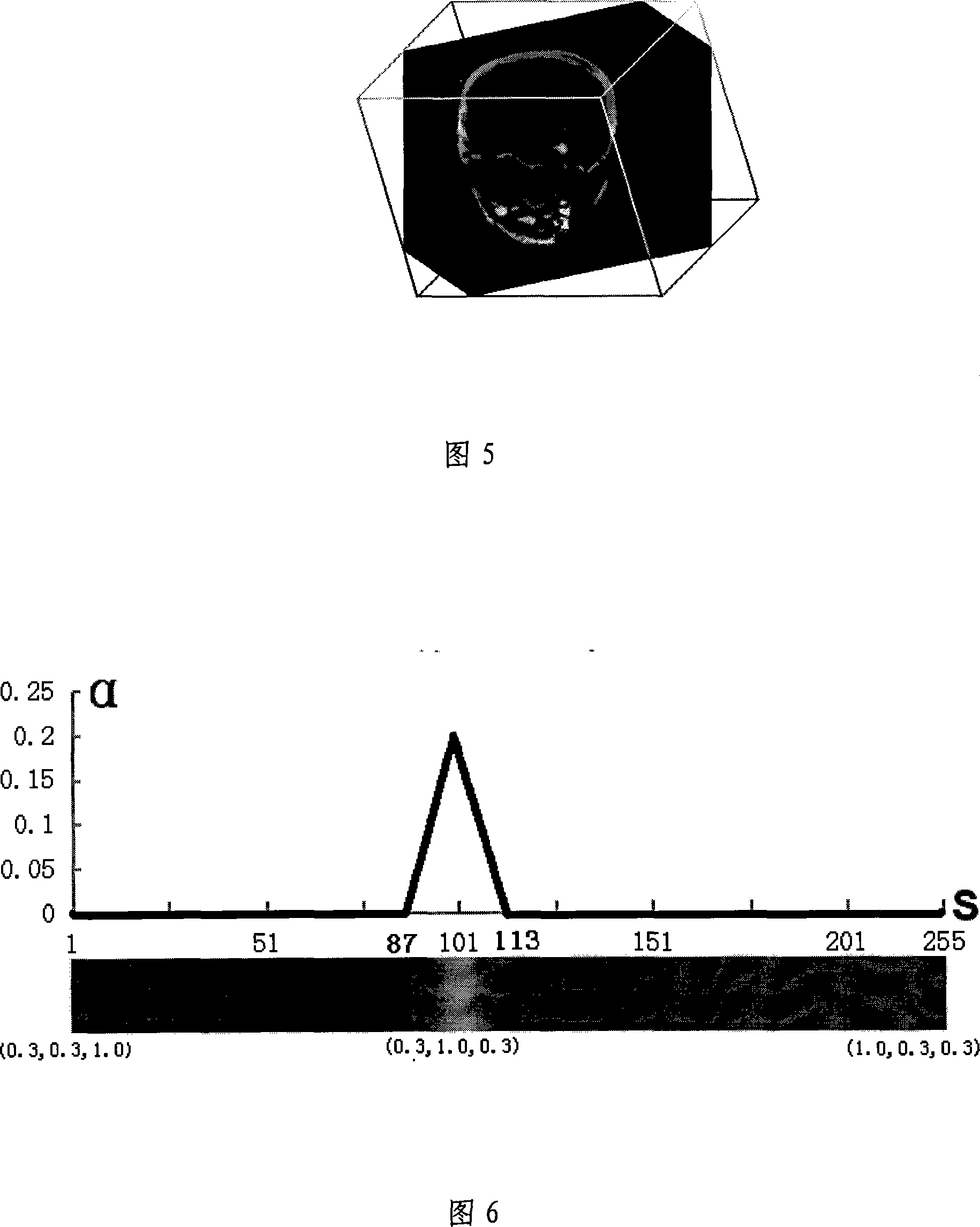

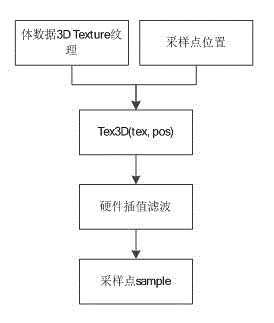

Body drafting visual method based on surface sample-taking

InactiveCN101178816AHigh speedImprove parallelism3D-image renderingRectangular coordinatesComputer graphics (images)

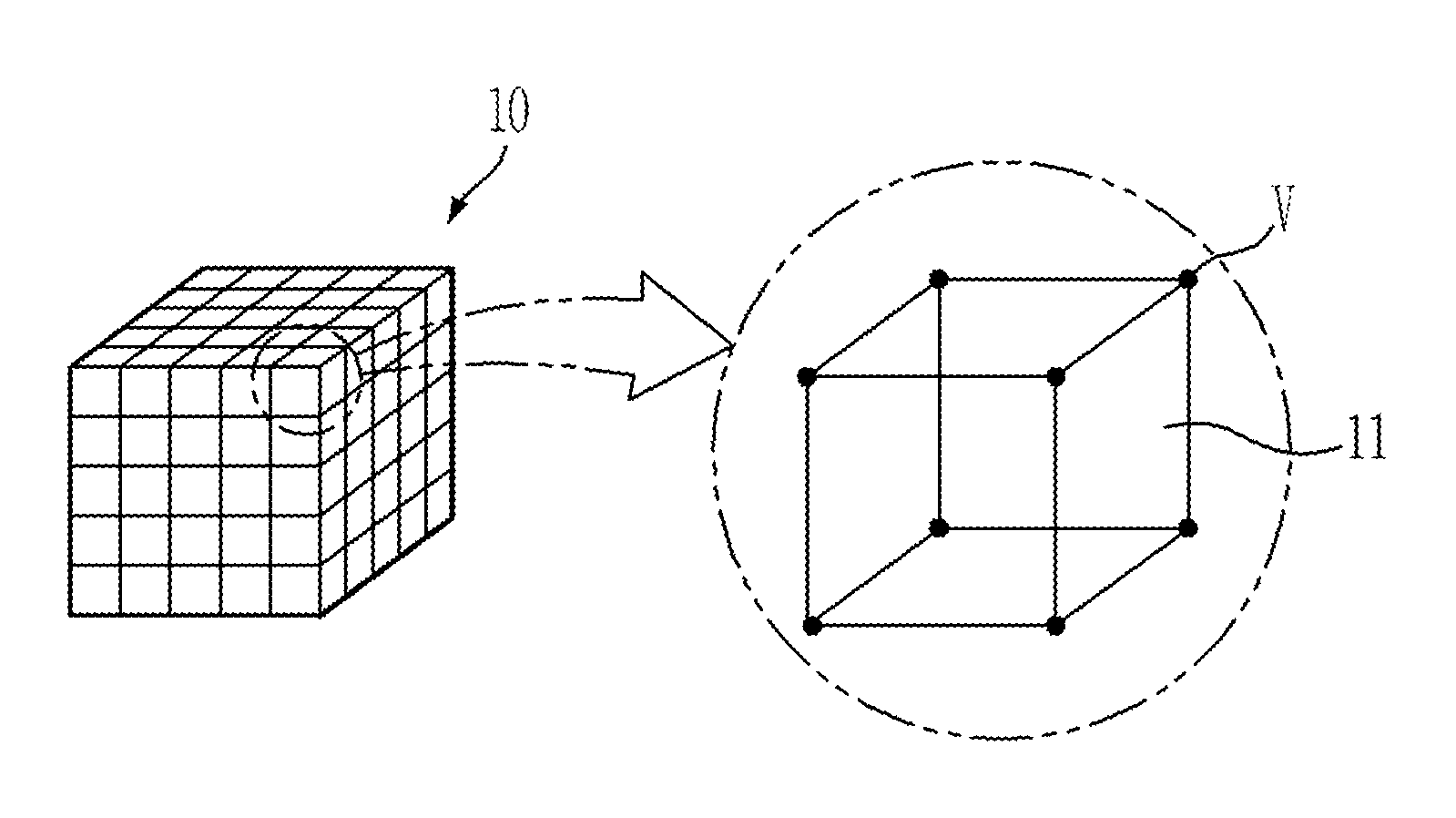

The invention relates to a volume rendering visualization method based on the sampling. Firstly convert the volume data into 3D texture memory; then design a bounding box containing all the volume data with the rectangular coordinate system origin as the center, set the initial corresponding relation of 8 vertex coordinates and color values to have the bounding box rotating around the center and calculate the new coordinates of the bounding box after rotating by the self-defined rotation matrix; after point coordinates inverse rotation and linear transformation to the intersection points of the cutting plane perpendicular to the line of sight and the edges of the bounding box to get the corresponding color values, color convex polygon sampling plane can be obtained through GPU trilinear interpolation calculation; with the color value of each point of the sampling plane as the coordinate, the 3D texture volume data can be sampled to perform the color composition calculation; change the step value to have the cutting plane advancing along the light of sight until the cutting plane does not intersect with the bounding box and draw the final image. The method calculates large amounts of sampling coordinates point of the polygon sampling plane at one time, thus improving the program parallelism, reducing the workload and improving volume rendering speed remarkably.

Owner:GUILIN UNIV OF ELECTRONIC TECH

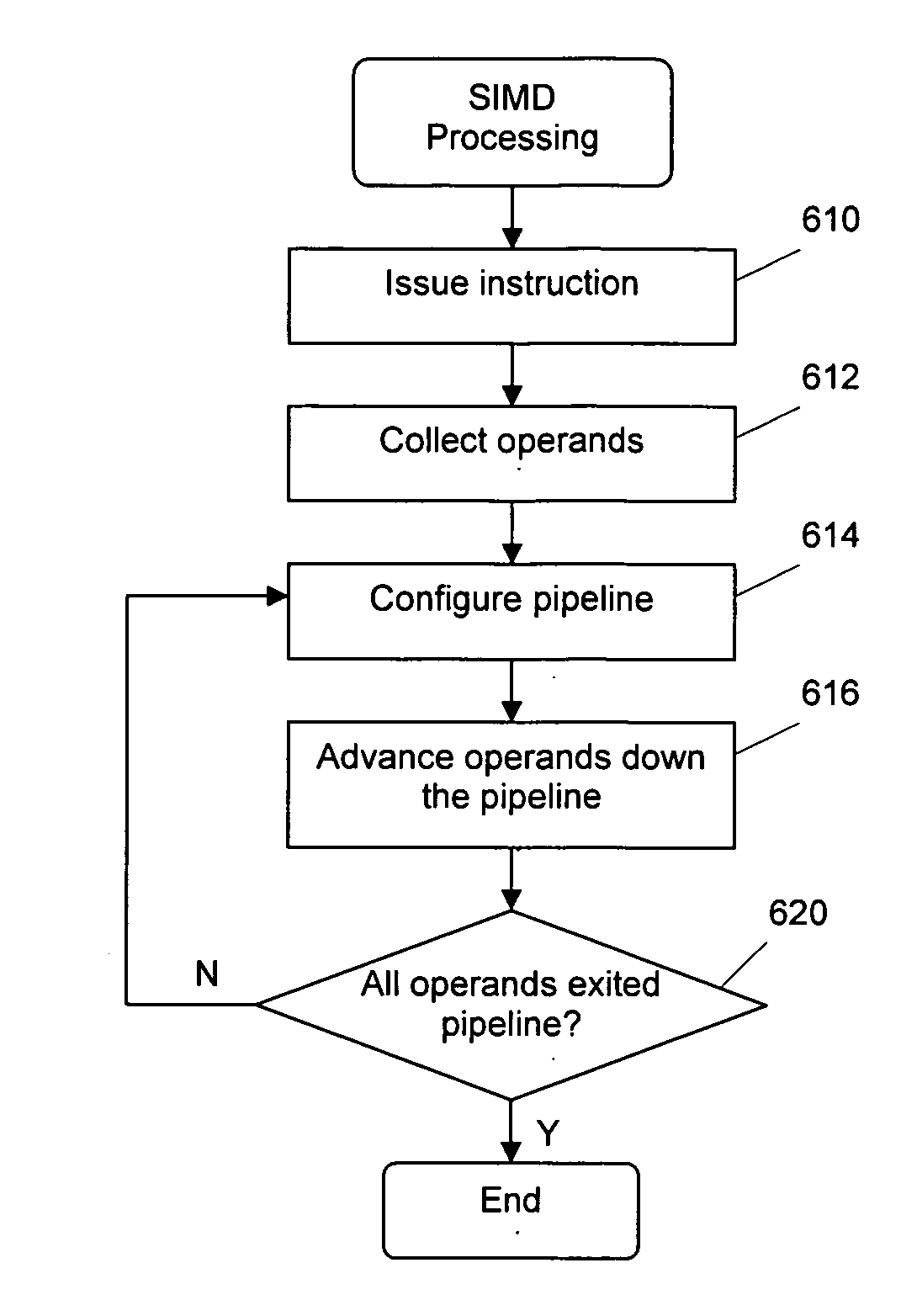

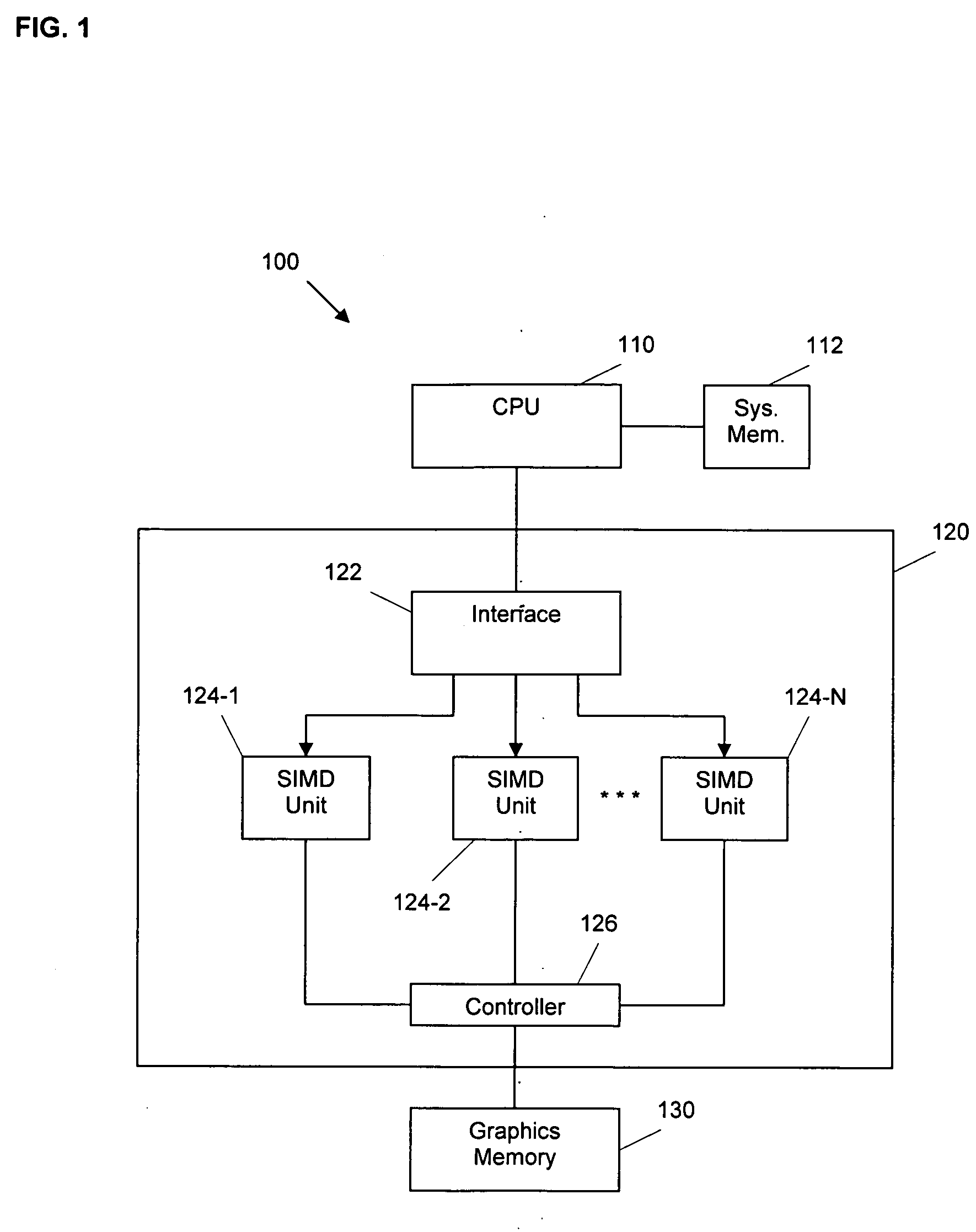

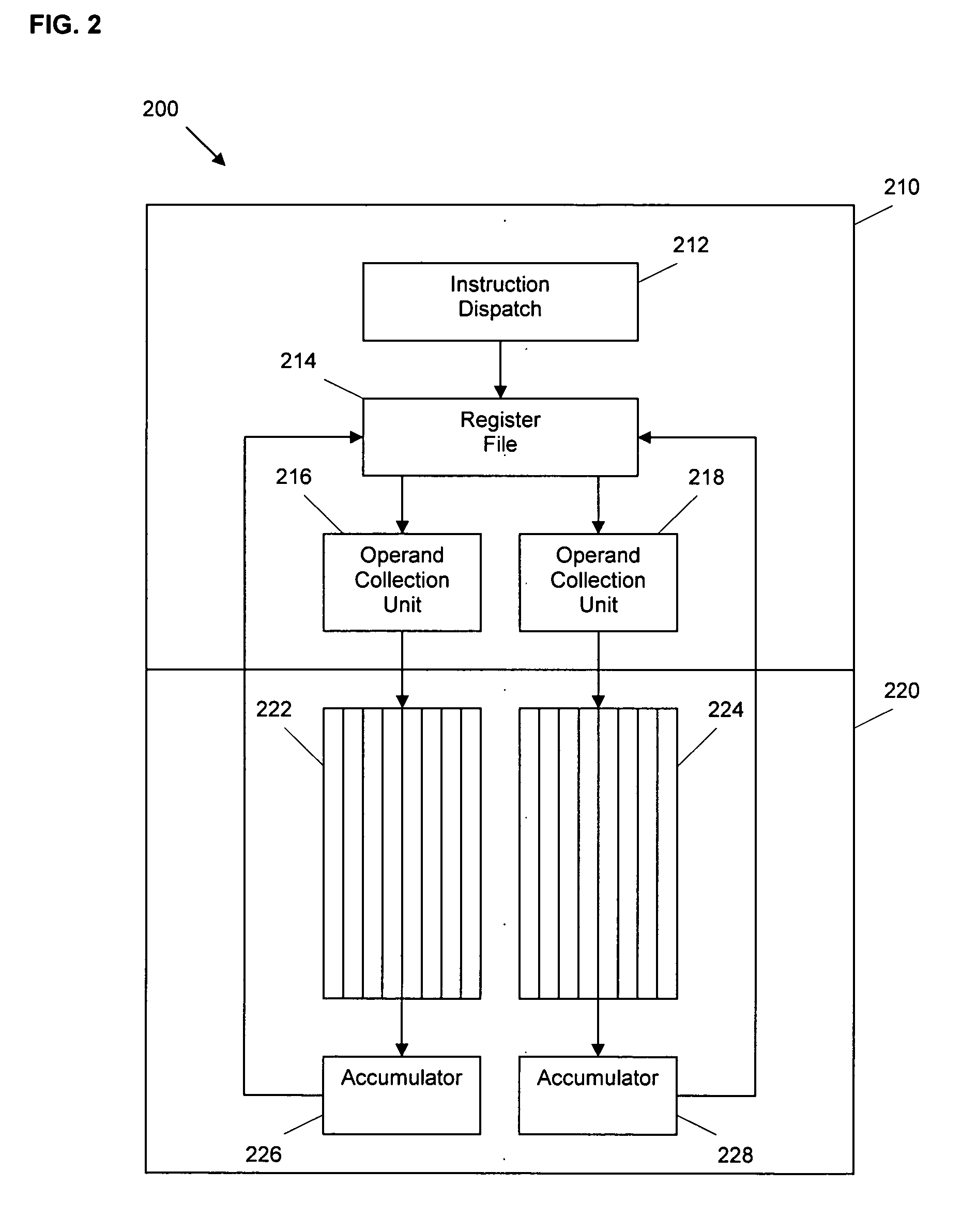

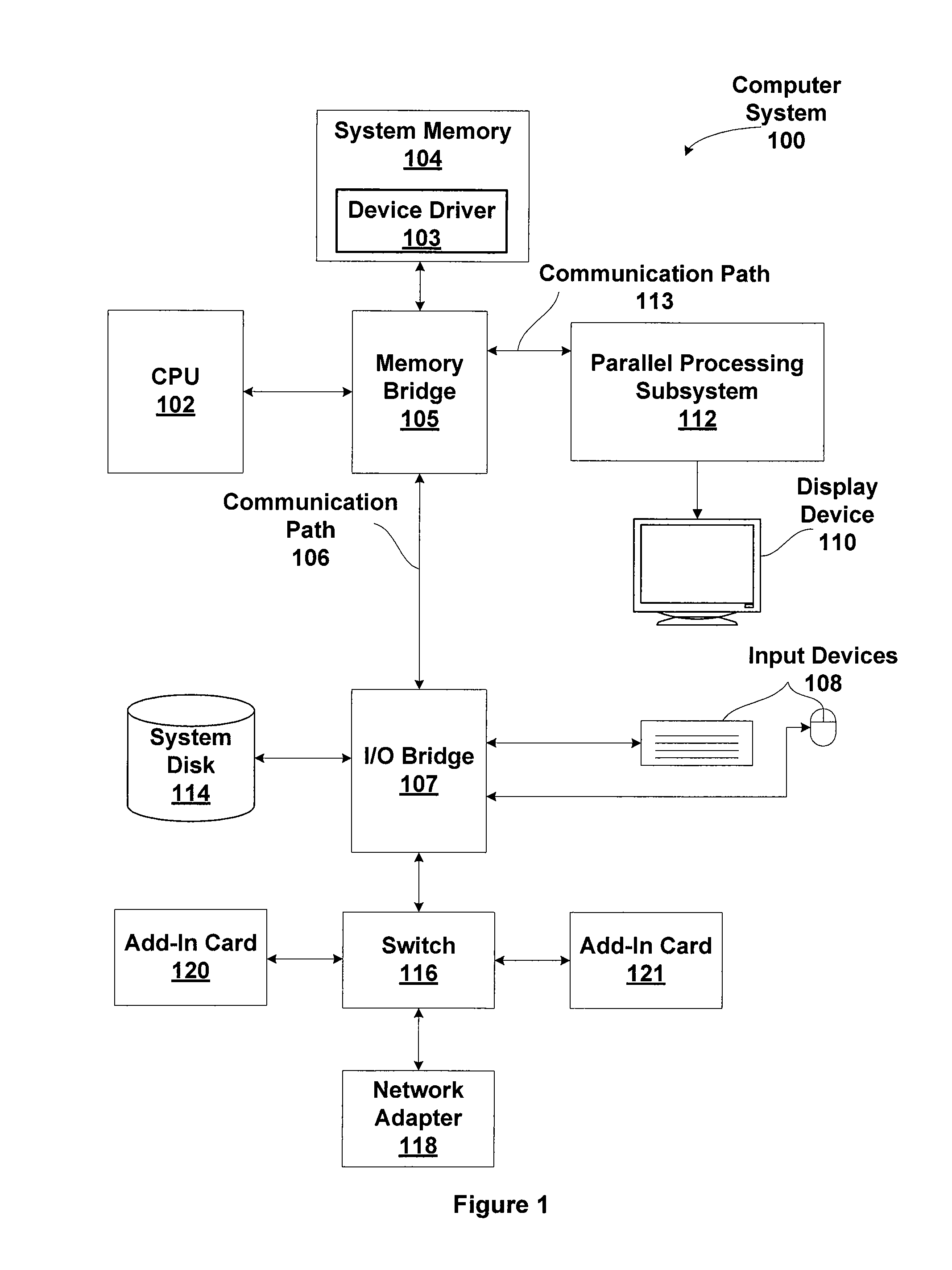

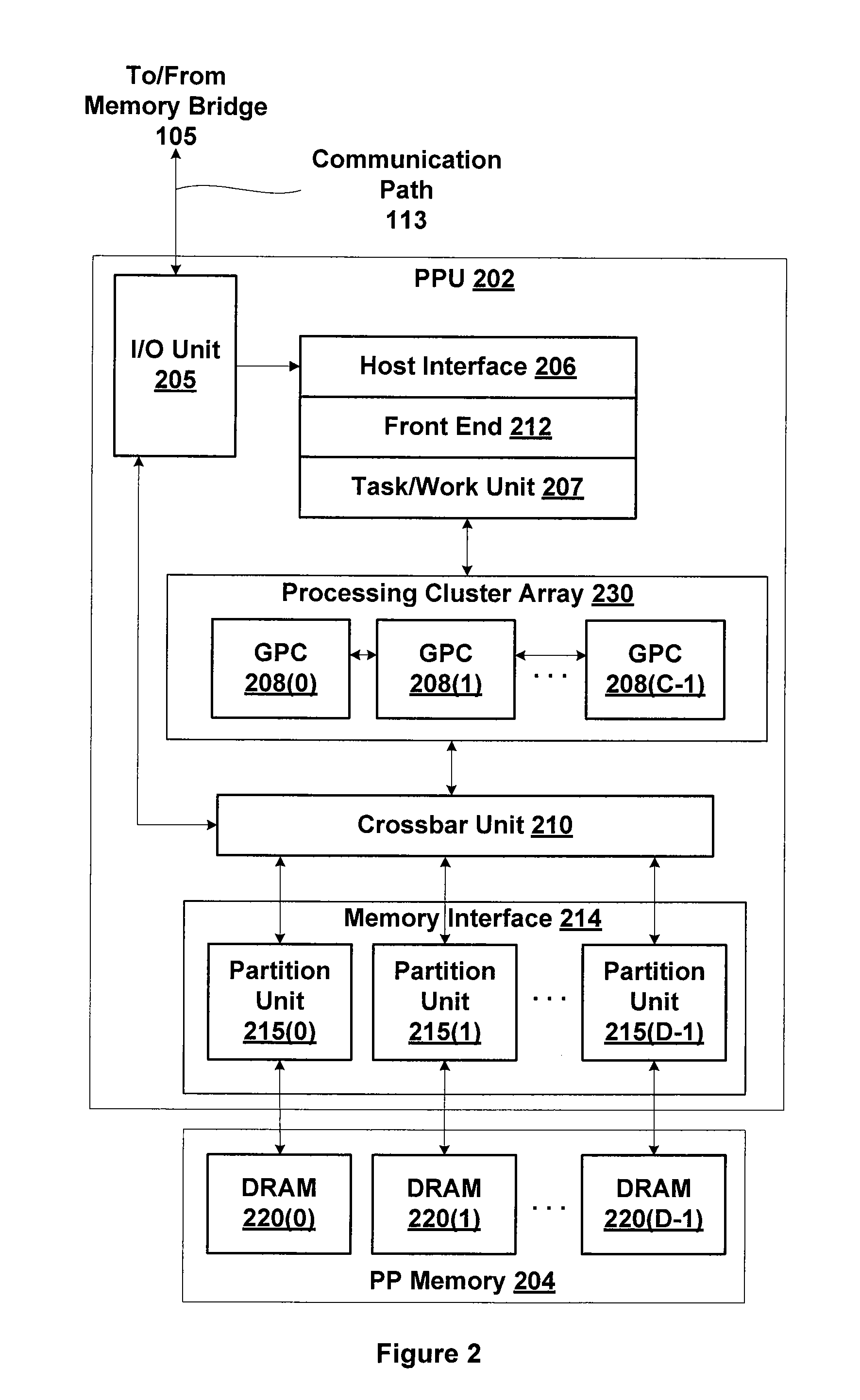

System and method for processing thread groups in a SIMD architecture

ActiveUS20070130447A1Reduce clock frequencyLow hardware requirementsGeneral purpose stored program computerMemory systemsGraphicsDatapath

A SIMD processor efficiently utilizes its hardware resources to achieve higher data processing throughput. The effective width of a SIMD processor is extended by clocking the instruction processing side of the SIMD processor at a fraction of the rate of the data processing side and by providing multiple execution pipelines, each with multiple data paths. As a result, higher data processing throughput is achieved while an instruction is fetched and issued once per clock. This configuration also allows a large group of threads to be clustered and executed together through the SIMD processor so that greater memory efficiency can be achieved for certain types of operations like texture memory accesses performed in connection with graphics processing.

Owner:NVIDIA CORP

Dirt map method and apparatus for graphic display system

InactiveUS7071937B1Improve realismCathode-ray tube indicators3D-image renderingRough surfaceGraphics

A method and system for map based per-pixel specularity modulation of a surface in a real time 3D graphics renderer through the use of interpolated specularity function or environmental map values. One or more functional modules calculate a pair of specular light intensity values or color values. Each specularity value is representative of the specular light reflected by the given pixel at an extreme surface reflectance characteristic, i.e. one may represent reflection from a very smooth surface while the other represents reflection from a very rough surface. A specularity modulation, or dirt map, value is arrived at by either a procedural calculation based on surface offset coordinates or by retrieval from a two-dimensional map contained in a texture memory. The specularity modulation value is then used as a weight to interpolate the pair of specularity values. The resulting interpolated specularity value is then optionally scaled by the modulation value (or a derivative thereof) to produce a final specularity value. This final specularity intensity or color value is then passed to a lighting unit that modulates pixel color appropriately to include the given specular light.

Owner:CCVG

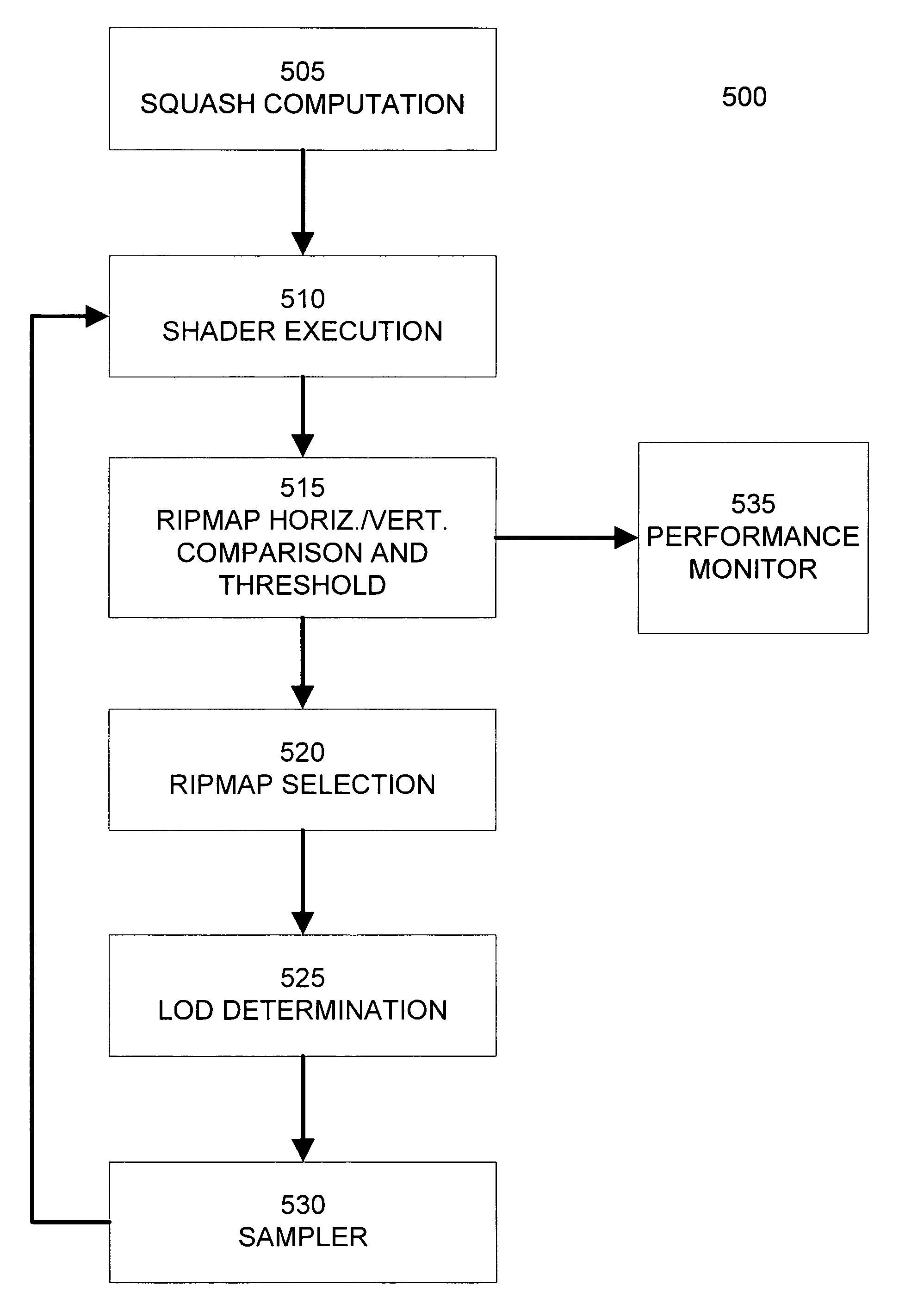

Anisotropic texture prefiltering

ActiveUS7525551B1Optimize anisotropic filteringMaximize anisotropic texture filtering performanceDetails involving antialiasingCathode-ray tube indicatorsPattern recognitionGraphics

Ripmapping and footprint assembly are used to anisotropically filter texture maps. A subset of the set of ripmaps associated with a base texture is created and stored. The subset includes ripmaps selected to maximize anisotropic texture sampling performance and to minimize the texture memory requirements. For pixel footprints not aligned with the anisotropy of ripmaps or requiring a ripmap outside of the subset, footprint assembly is used to perform anisotropic filtering by taking multiple isotropic probes from a mipmap. For texture samples aligned within a tolerance range of the anisotropy of a ripmap, footprint assembly constructs an anisotropic texture sample from one or more samples of a ripmap. Ripmap statistics are collected during texture mapping to dynamically determine an optimal subset of ripmaps, and additional ripmaps can be added to the subset on demand if warranted. A graphics driver can analyze ripmap statistics to determine the subset of ripmaps.

Owner:NVIDIA CORP

Static and dynamic video resizing

Owner:ORACLE INT CORP

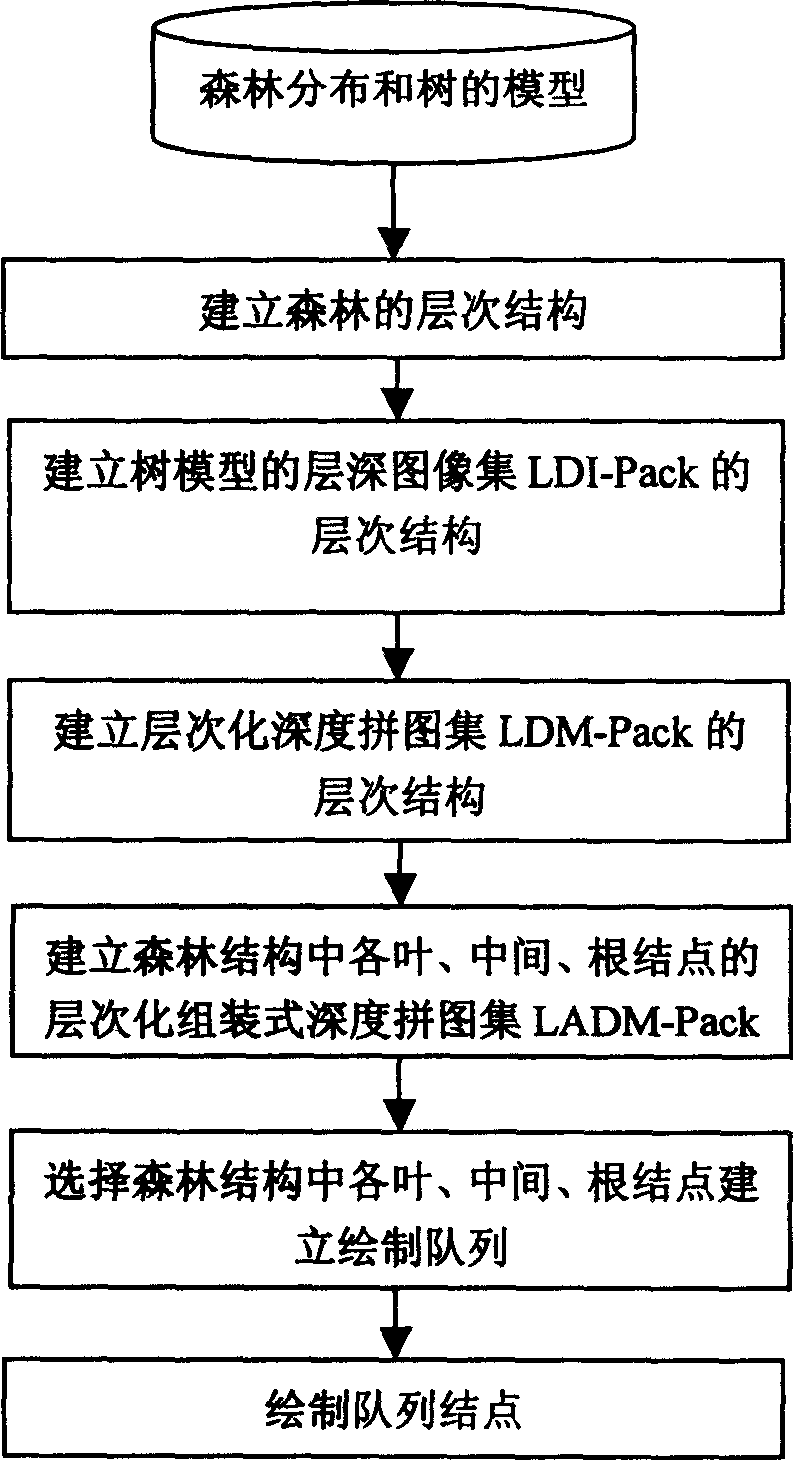

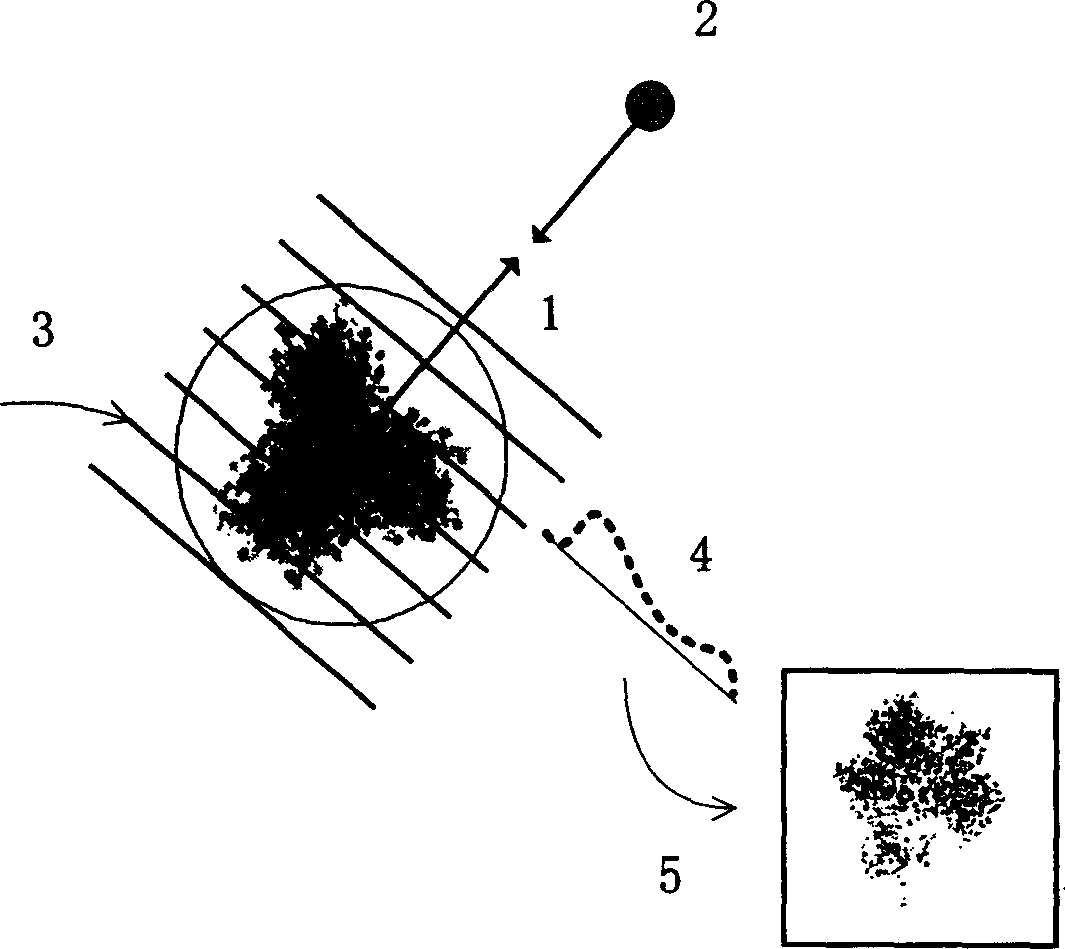

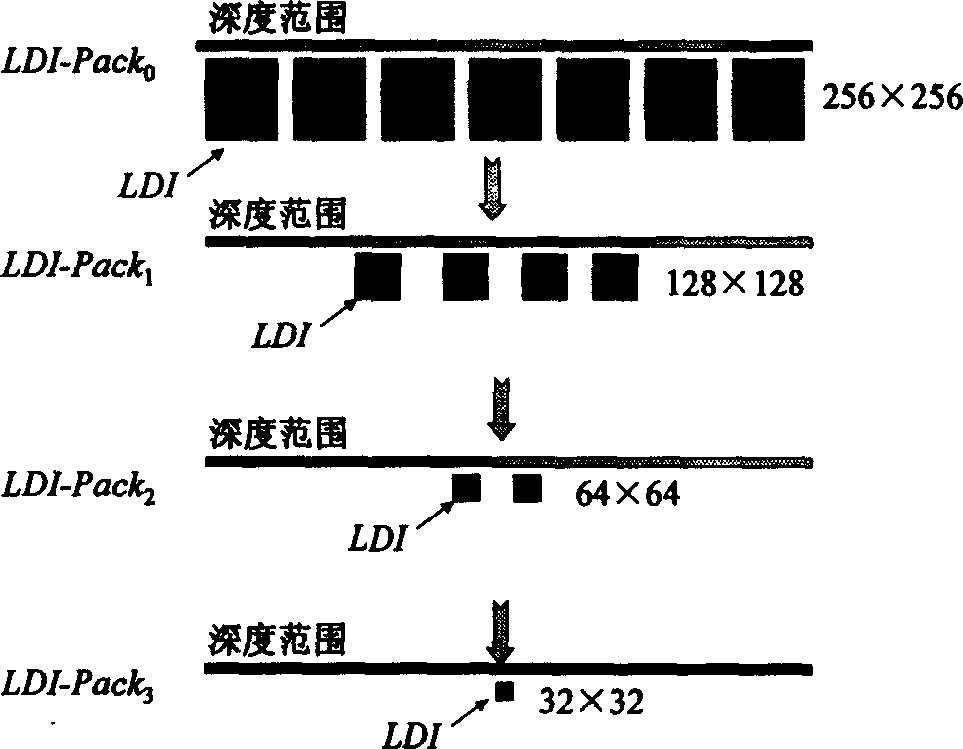

Fast drawing forest method of graded hierarchical assembling depth paste-up atlas

ActiveCN1564203AReduce consumptionImage Quality Balance3D modellingPattern recognitionTexture memory

The invention includes following six steps: hierarchical structure of forest, LDI-Pack structure for tree model, LDM-Pack structure, each node LADM-Pack in structure of forest, plotting queue, and node in plotting queue. Advantages of the method are: referencing LOD, IBR, PBR, and Billboard provides good balance among quality of drawing, plotting performance and storage expense; self-adapting texture compression method reduces expenses for texture memory; confluent method realizes graduating transition. The method is applicable to geo information emulation, virtual scene roam and game engine etc. areas.

Owner:ZHEJIANG UNIV

Load/store operations in texture hardware

ActiveUS20150084975A1Small surface areaReduce power consumptionMemory architecture accessing/allocationImage memory managementParallel computingTexture memory

Approaches are disclosed for performing memory access operations in a texture processing pipeline having a first portion configured to process texture memory access operations and a second portion configured to process non-texture memory access operations. A texture unit receives a memory access request. The texture unit determines whether the memory access request includes a texture memory access operation. If the memory access request includes a texture memory access operation, then the texture unit processes the memory access request via at least the first portion of the texture processing pipeline, otherwise, the texture unit processes the memory access request via at least the second portion of the texture processing pipeline. One advantage of the disclosed approach is that the same processing and cache memory may be used for both texture operations and load / store operations to various other address spaces, leading to reduced surface area and power consumption.

Owner:NVIDIA CORP

Autonomous address translation in graphic subsystem

InactiveUS7050061B1Add visual interestIncrease frame rateMemory adressing/allocation/relocationImage memory managementGraphicsGraphic card

A texture caching controller, located on the graphics card, handles address logical-to-physical translation for texture addresses which are not downloaded to level-1 memory due to low use or dynamically changing values. This offloads texture memory management duties from the host.

Owner:ZIILABS INC LTD A ORGANIZED UNDER THE LAWS OF BERMUDA +2

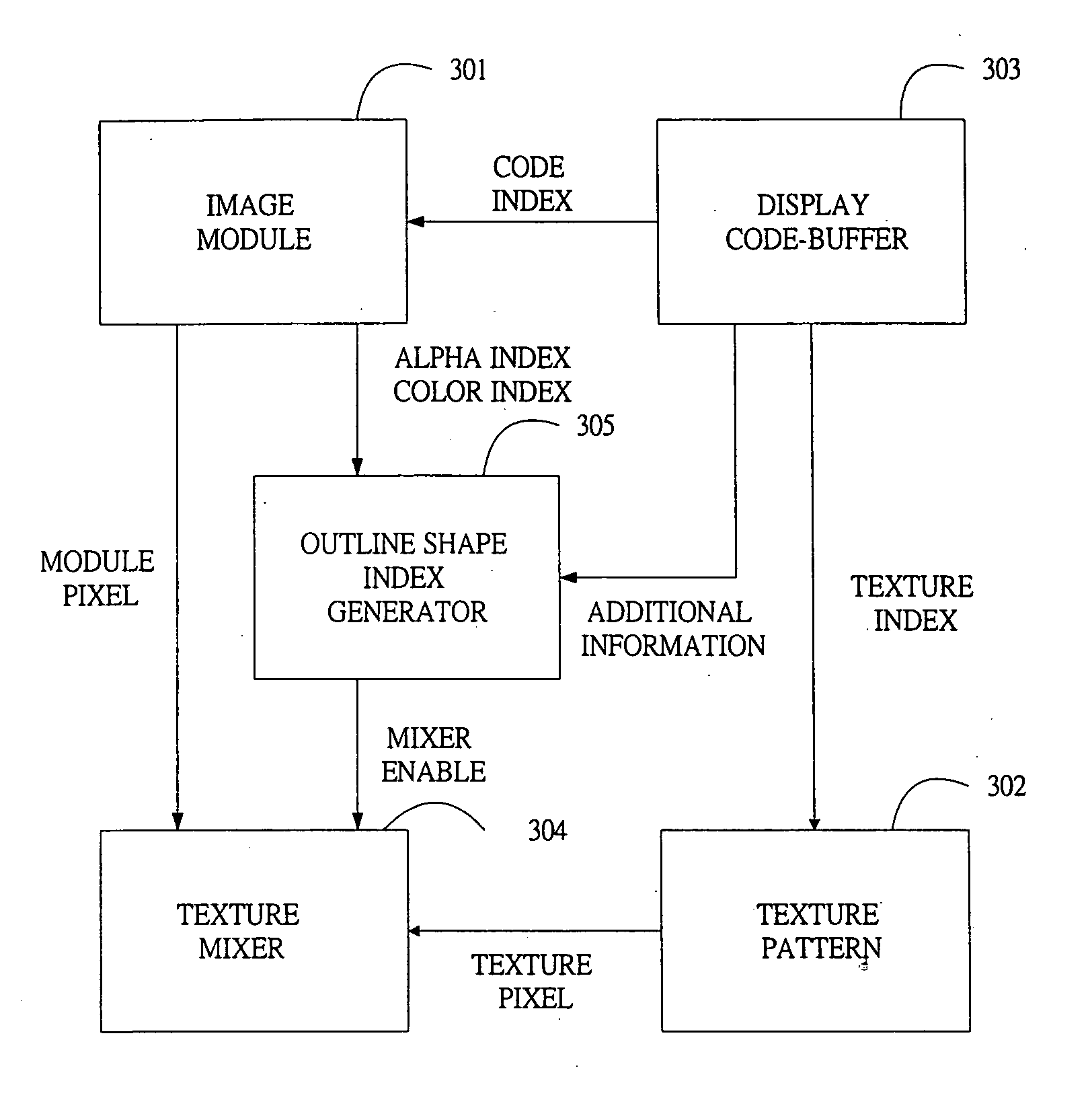

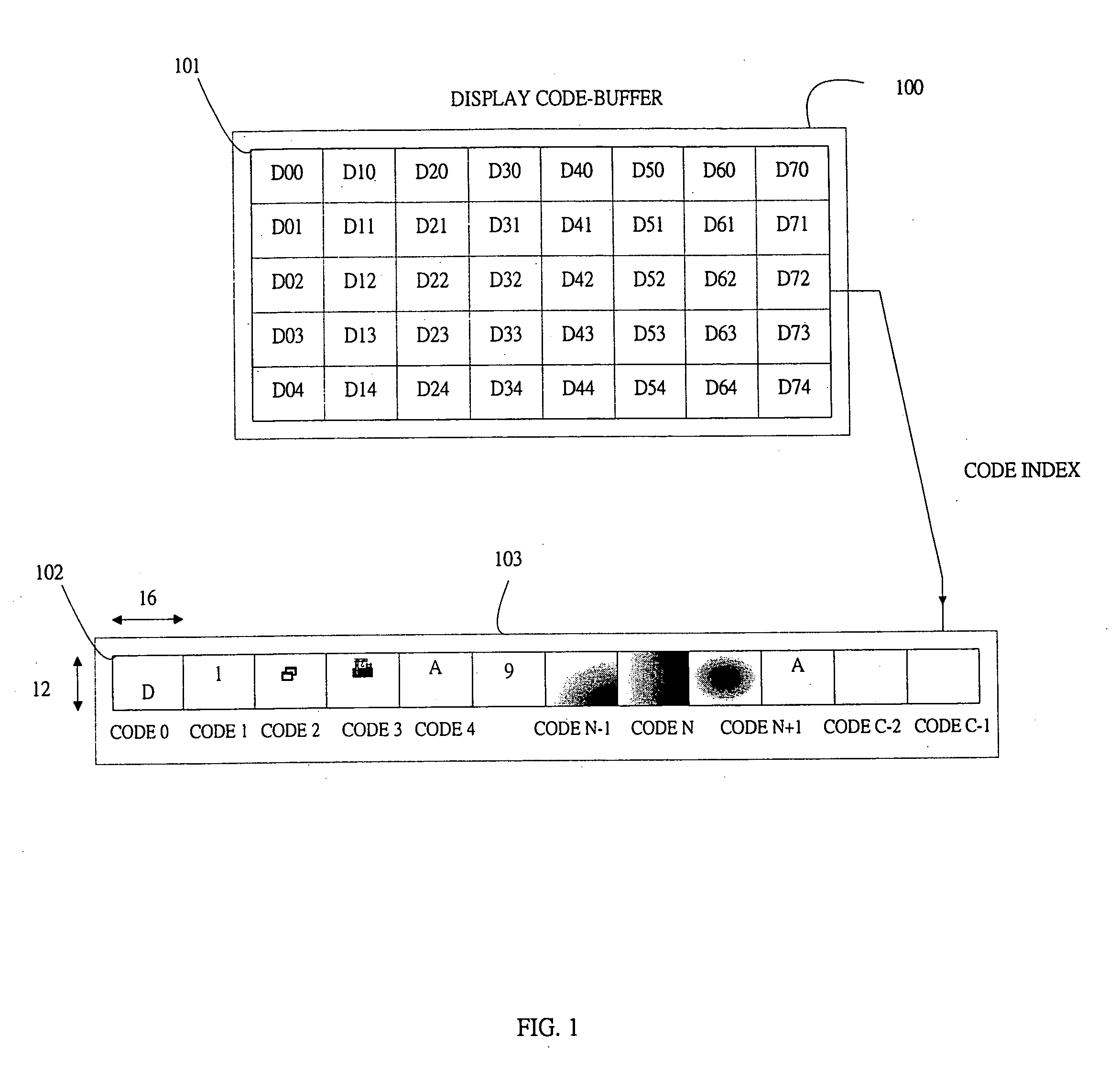

User interface display apparatus using texture mapping method

A low cost user interface display system, like on screen display (OSD), using texture mapping method is presented. The present invention only uses a little texture memory and can generate very fancy user interface display. With the method of texture mapping, even the low cost system can have a colorful, fancy user interface display. A user interface display apparatus using texture-mapping method, comprising a image module, texture patterns, display code-buffer, texture mixer and outline shape index generator to texture-maps the predefined image module in the mixing area with the texture patterns. For some existing OSD devices, the texture-mapping method also can provide a low cost approach to fancy the original OSD display output in the display device. Moreover, changing the texture pattern is very easy to system manufacture, and it can make the user interface looks good and different.

Owner:XUESHAN TECH INC

Memory interleaving technique for texture mapping in a graphics system

A graphics system and method for storing and accessing texture maps comprising texels. The graphics system may include a graphics processor and a texture memory comprising a plurality of memory devices for storing the texture maps. The texels (or portions of the texels) may be stored in the memory devices in an interleaved fashion. The texel data is interleaved in the memory devices to guarantee that, no matter which NxM array of texels is accessed, each texel in the array is present in a different memory device or chip and hence are concurrently available. Thus the NxM array of texels may be output concurrently or simultaneously, regardless of which array is accessed, i.e., regardless of which pixel is addressed. Embodiments are also described where the memory devices output arrays of texels for at least two respective neighboring pixels, or a 3D array of texels, in parallel in response to a single read transaction. Also, the body and border portions of the texture map are stored in separate areas of memory (e.g., in different memory address spaces), but texel interleaving is still performed.

Owner:ORACLE INT CORP

Selection of a mipmap level

InactiveUS20060158451A1Reduce resolutionAttenuation bandwidthCathode-ray tube indicators3D-image renderingGraphicsMagnification

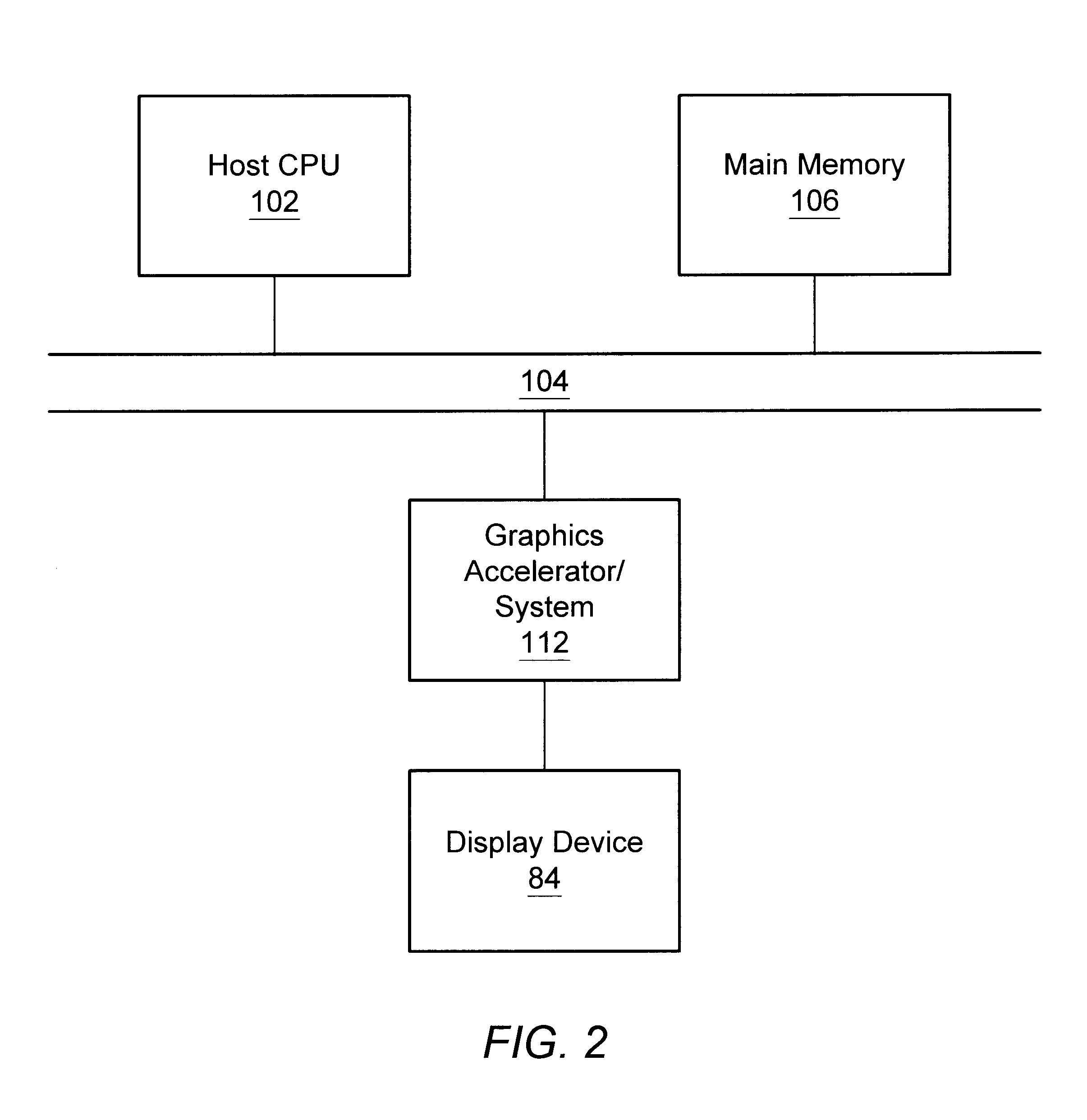

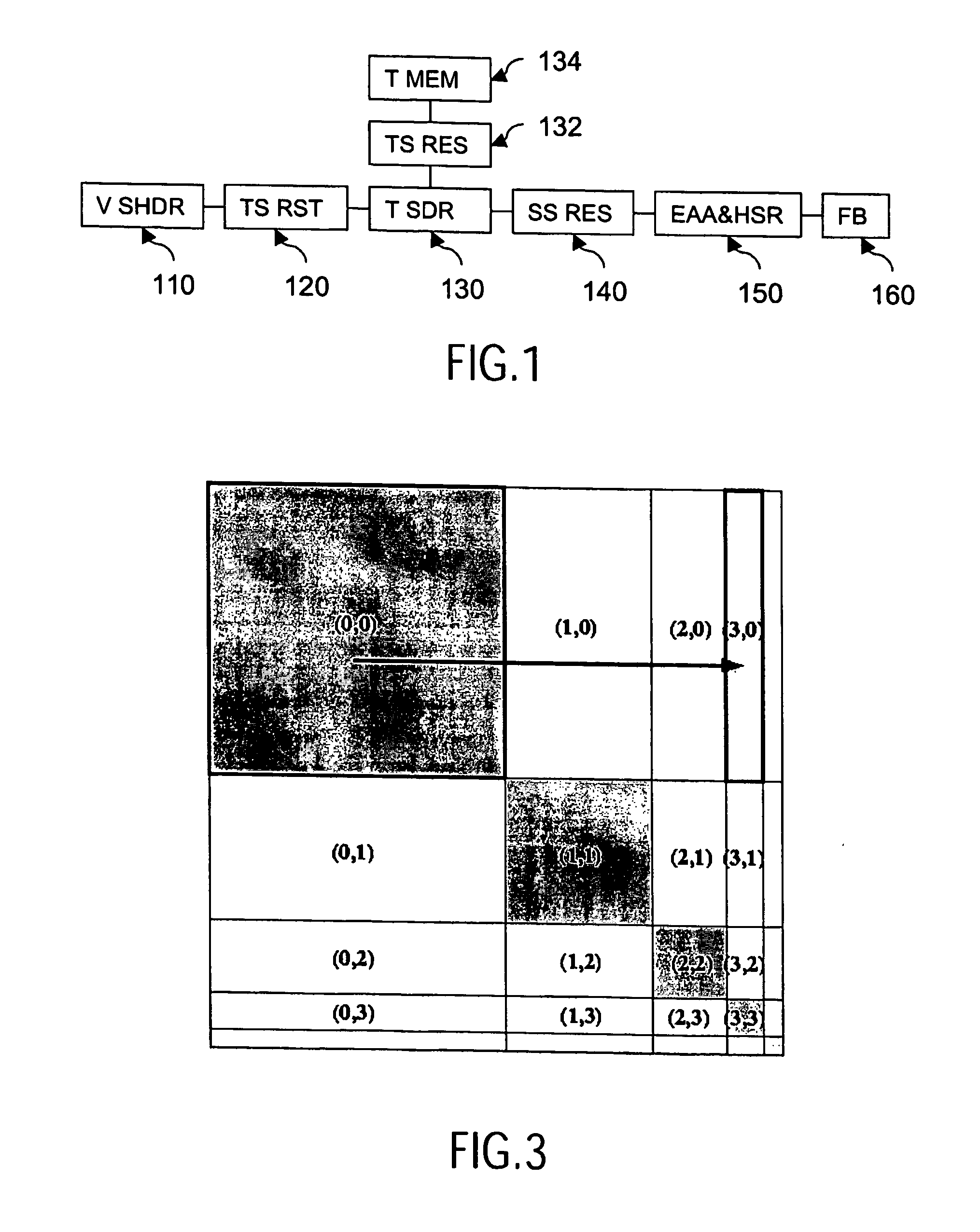

A computer graphics includes a texture memory (134) storing texture maps in a mipmap structure, texels in a texture map being specified by a pair of u and v coordinates. A rasterizer (120) determines for a texel (u, v) corresponding initial 4D mipmap levels (mmlu, mmlv) and a magnification factor representing a magnification that occurs when the texel is mapped to a corresponding pixel position on the display. It then determines final 4D mipmap levels in dependence on the determined initial 4D mipmap levels mmlu, mmlv, and the magnification factor. A texture space resampler (132) obtains texture data from a texture map identified by the pair off final 4D mipmap levels. A texture mapper (140) maps the obtained texture data to corresponding pixel data defining the display image.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

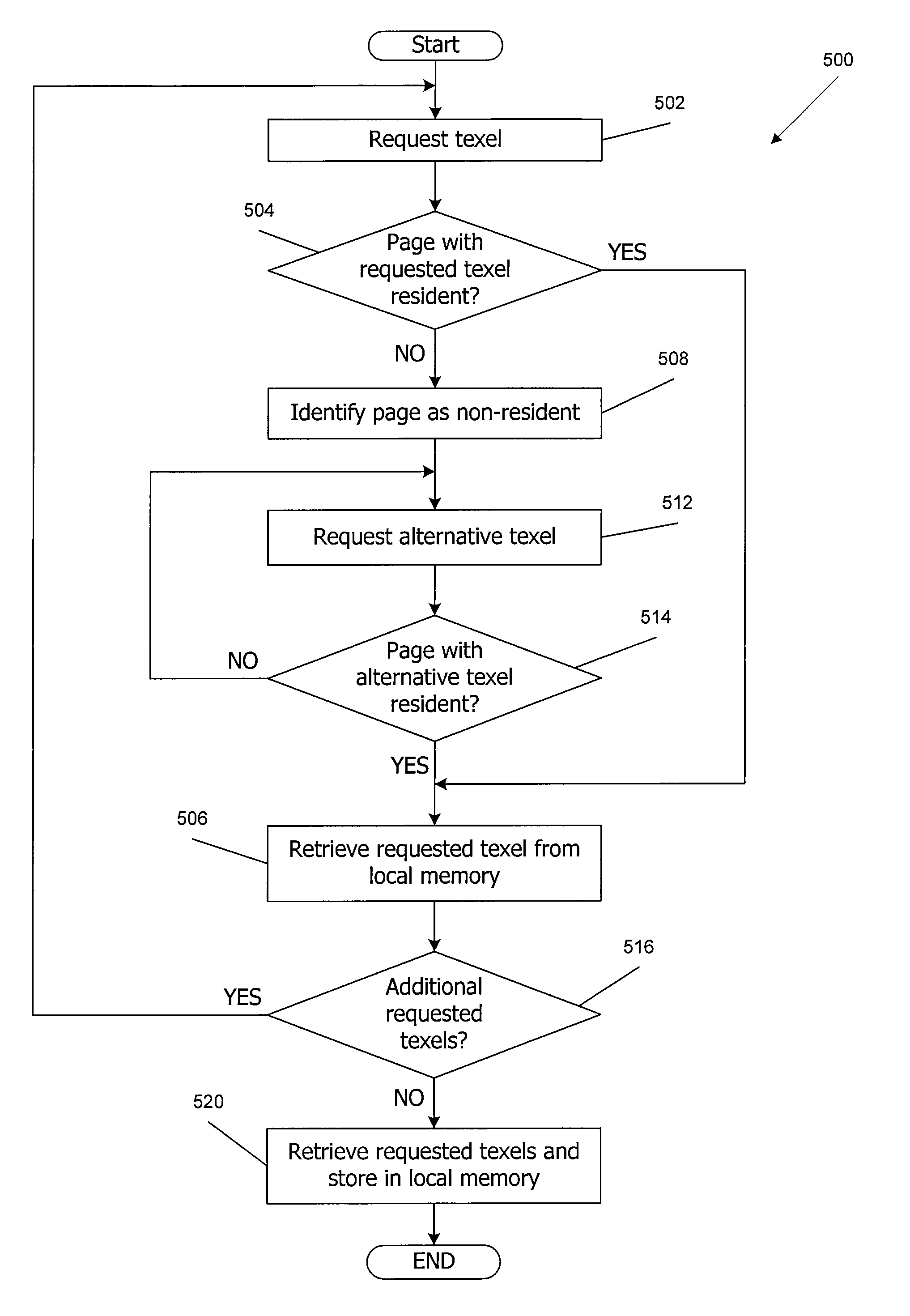

Deferred page faulting in virtual memory based sparse texture representations

A virtually-addressed local texture memory stores selected regions (a sparse representation) of a texture for use by a graphics processor. The graphics processor requests a texel of the texture by referencing a virtual address of the texel. A memory interface references an address map to determine whether the requested texel is in one of the regions of the texture that is resident in the local texture memory. If so, the texel is retrieved from the local memory and used in the rendering operation; if not, an alternative texel that is resident in the local memory is retrieved and used in the rendering operation. Non-resident regions that include requested texels are retrieved from a primary texture data store at regular intervals (e.g., once per frame) and stored in local texture memory for use in a subsequent rendering operation.

Owner:NVIDIA CORP

Method and system for texturing

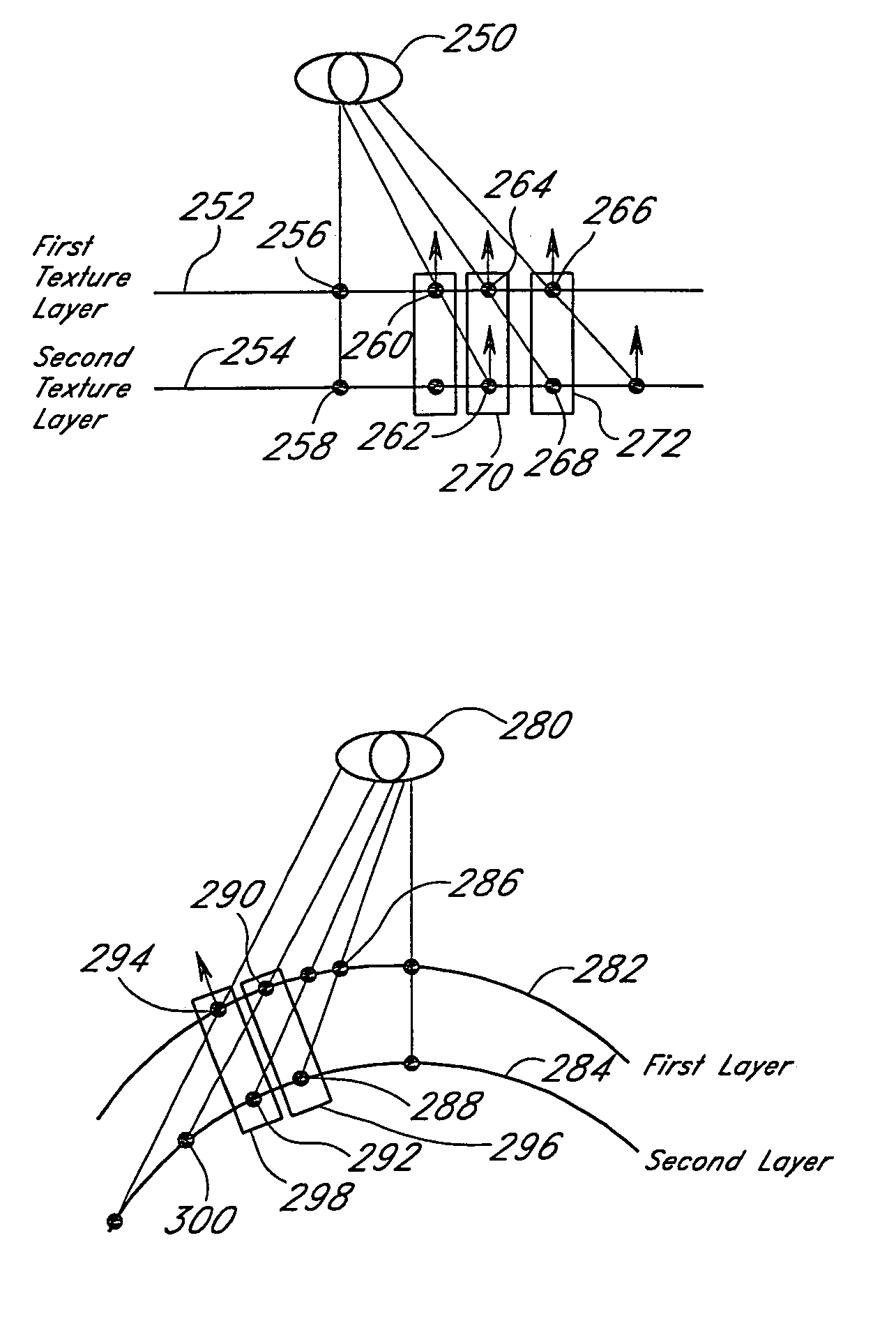

InactiveUS7136069B1Avoid inconvenienceAvoid delayCathode-ray tube indicatorsInput/output processes for data processingPattern recognitionParallax

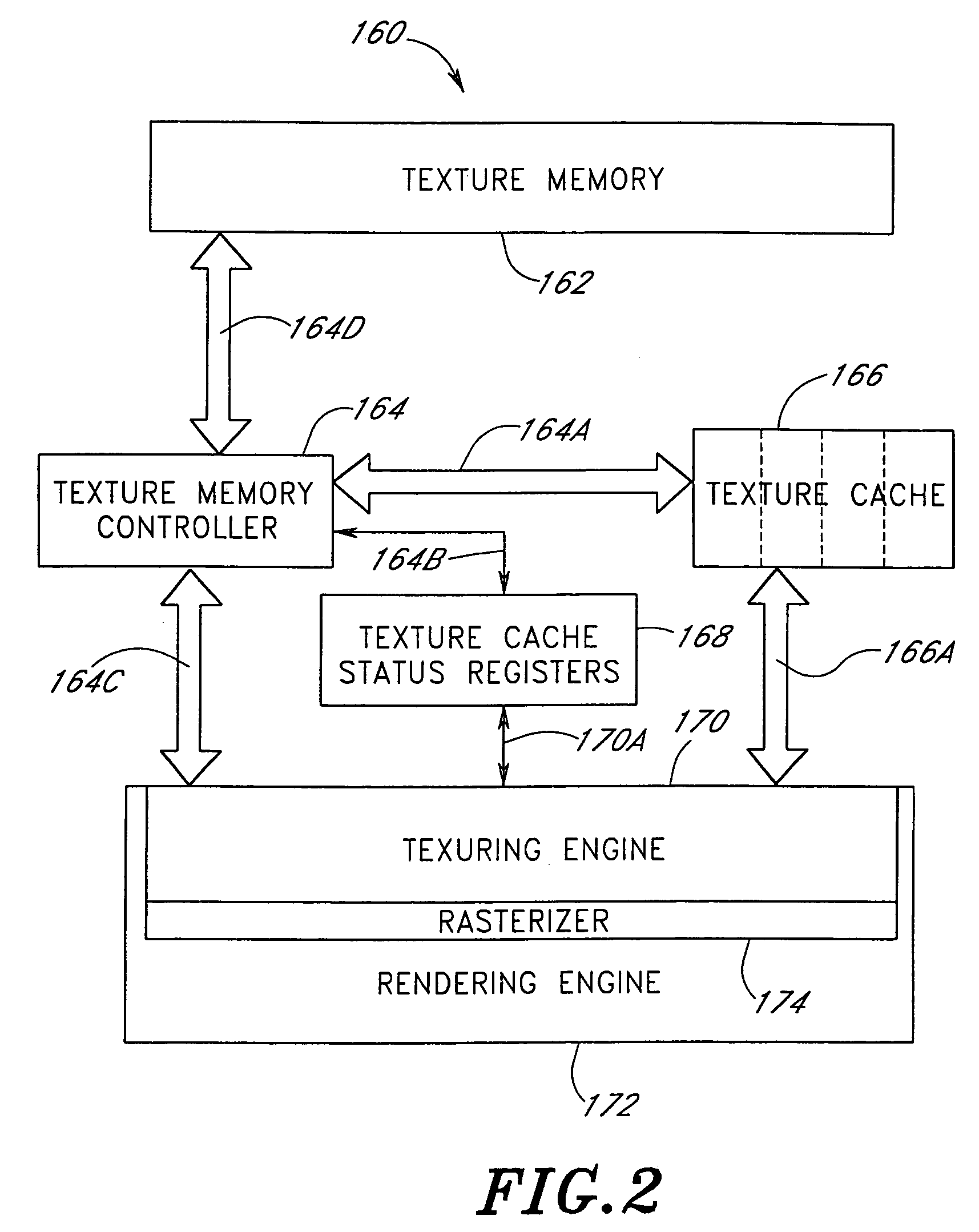

A method and system for texturing. The texturing system is configured to render surfaces that have an apparent thickness, where the upper layers of the surface are partially transparent and sub-surface details show through the upper layers. Interpolated stepping values provide parallax between various texture layers. The texturing system also provides a texture memory configured to store texture data as a plurality of packets. Each packet comprises texture data from at least two texture layers. A texture memory controller is configured to access one or more packets in the texture memory and pass the packets to a texturing engine.

Owner:SONY CORP +1

Design for a non-blocking cache for texture mapping

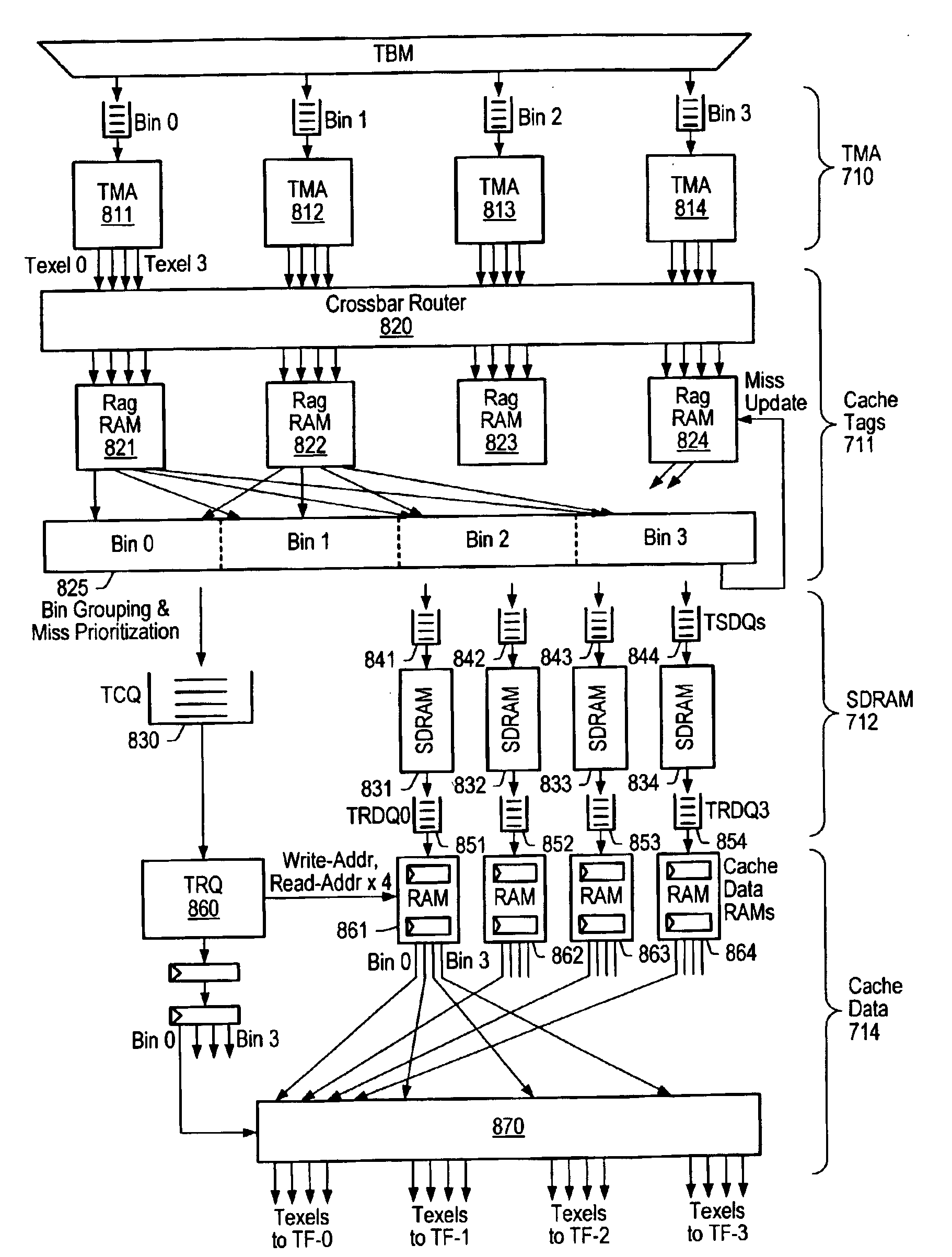

InactiveUS6933945B2More availabilityMemory adressing/allocation/relocationCathode-ray tube indicatorsTexture memoryMemory controller

A non-blocking cache for texture mapping is implemented by separating Cache Tags from Cache Data. Multiple requests for data may be processed in parallel without strict ordering or synchronization. Separating Cache Tags and Cache Data results in a texture memory cache design that preempts stalling which would otherwise occur in case of cache-misses. Multiple Cache Tags with corresponding respective system memory controllers and Data Cache units allow for simultaneous processing of multiple requests without strict ordering. In preferred embodiments the texture memory cache may also be configured to predict cache misses and merge with burst reads from memory, and may equally be configured to minimize memory read-requests necessary during multitexturing, thus maximizing bandwidth.

Owner:ORACLE INT CORP

Novel design for a non-blocking cache for texture mapping

ActiveUS20050052449A1More availabilityMemory adressing/allocation/relocationCathode-ray tube indicatorsMemory controllerTexture memory

A non-blocking cache for texture mapping is implemented by separating Cache Tags from Cache Data. Multiple requests for data may be processed in parallel without strict ordering or synchronization. Separating Cache Tags and Cache Data results in a texture memory cache design that preempts stalling which would otherwise occur in case of cache-misses. Multiple Cache Tags with corresponding respective system memory controllers and Data Cache units allow for simultaneous processing of multiple requests without strict ordering. In preferred embodiments the texture memory cache may also be configured to predict cache misses and merge with burst reads from memory, and may equally be configured to minimize memory read-requests necessary during multitexturing, thus maximizing bandwidth.

Owner:ORACLE INT CORP

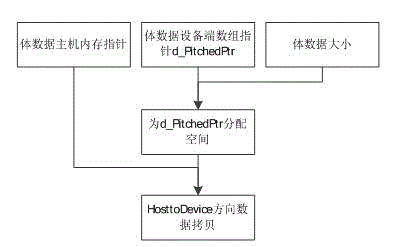

Access memory method for realizing shear wave data three-dimensional visualization by aiming at parallel volume rendering

InactiveCN102750727AAchieve memory access optimization3D-image renderingPlate tectonicsTexture memory

The invention provides an access memory method for realizing shear wave data three-dimensional visualization by aiming at parallel volume rendering. According to the access memory method, four-based access memory optimization strategies including texture memory strategies, global memory strategies, global and share memory strategies, constant memory strategies designed by aiming at a visual angle matrix frequently invoking shear wave data, and rendering quality evaluation method and criterion are provided. Through the access memory method, the rendering efficiency for realizing the shear wave data three-dimensional visualization by adopting a volume rendering method on the basis of a CUDA (compute unified device architecture) can be improved. Therefore, the access memory method perfectly helps scientific research personnel to accurately know the plate tectonics, the dynamics process, the earthquake generation mechanism and the like, and further, the fields of geological exploration, continental plates, seismic interpretation and the like are favorably developed.

Owner:WUHAN UNIV

Graphics processing unit, image processing apparatus including graphics processing unit, and image processing method using graphics processing unit

InactiveUS20140015834A1Improve processing speedTexturing/coloringCathode-ray tube indicatorsGraphicsImaging processing

A graphics processing unit (GPU), an image processing apparatus including the GPU, and an image processing method using the GPU are provided. The graphics processing unit includes a texture memory configured to store a plurality of two-dimensional (2D) slices formed by slicing volume data or 2D texture, a texture mapping unit configured to perform 2D texture mapping on the 2D texture and to perform 2D texture sampling on the plurality of 2D slices, and a calculation processor configured to perform volume rendering using sampling values of the 2D texture sampling.

Owner:SAMSUNG ELECTRONICS CO LTD

Alternative hough forests real time target tracking method based on GPU (graphics process unit)

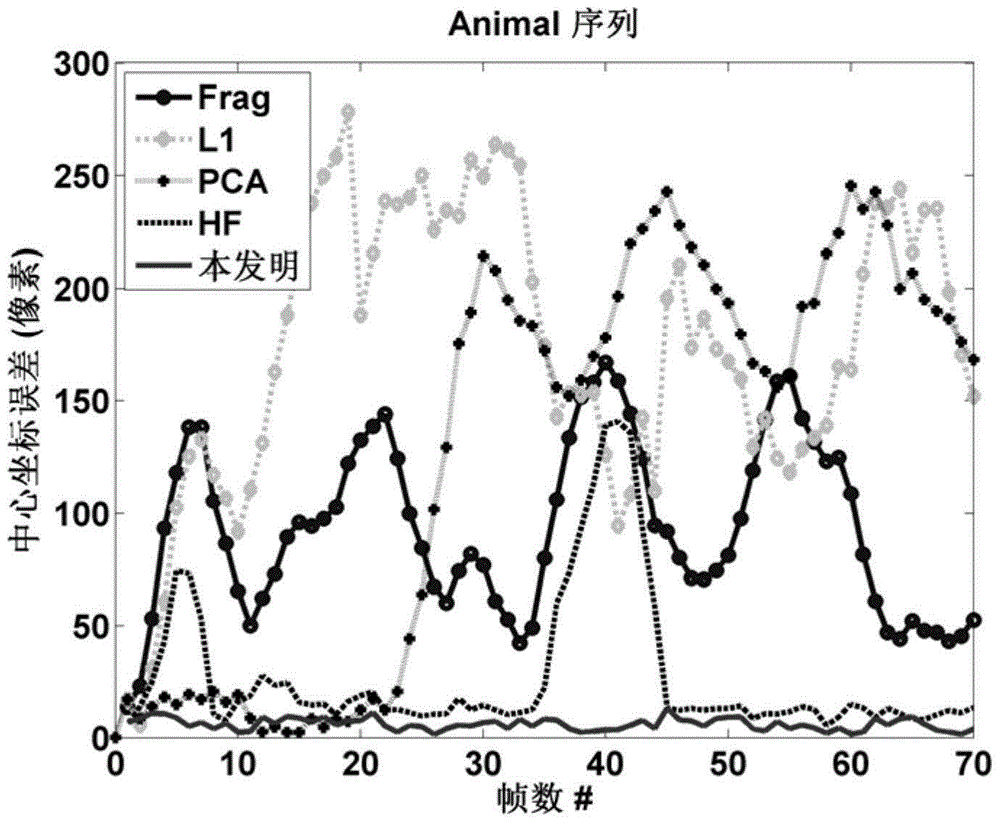

InactiveCN105184220AImprove robustnessHigh precisionCharacter and pattern recognitionPattern recognitionNODAL

An alternative hough forests real time target tracking method based on a GPU (graphics process unit) is provided. The alternative hough forests real time target tracking method based on the GPU comprises: 1) extracting a training sample set according to a video sequence to be tested; 2) setting the number of random trees in the alternative hough forests and the maximum depth of the forests; 3) giving the training samples different weights; 4) initializing root nodes of each random tree; 5) building the alternative hough forests; 6) employing a splitting strategy when the nodes are splitting; 7) storing the alternative hough forests into a texture memory of the GPU; 8) manually determining an object region and an object center of a first frame image in a video, and setting a search radius; 9) detecting a follow-up frame through employing built alternative hough forests in the GPU, and obtaining a confidence map with respect to the object center position; 10) storing the confidence map into the texture memory of the GPU; 11) determining the object position in the present frame through employing the confidence map and combining the object region and the object center of the last frame; and 12) repeating the step 9 and the step 10 until completing the object tracking of all the frames in the video sequence.

Owner:XIAMEN UNIV

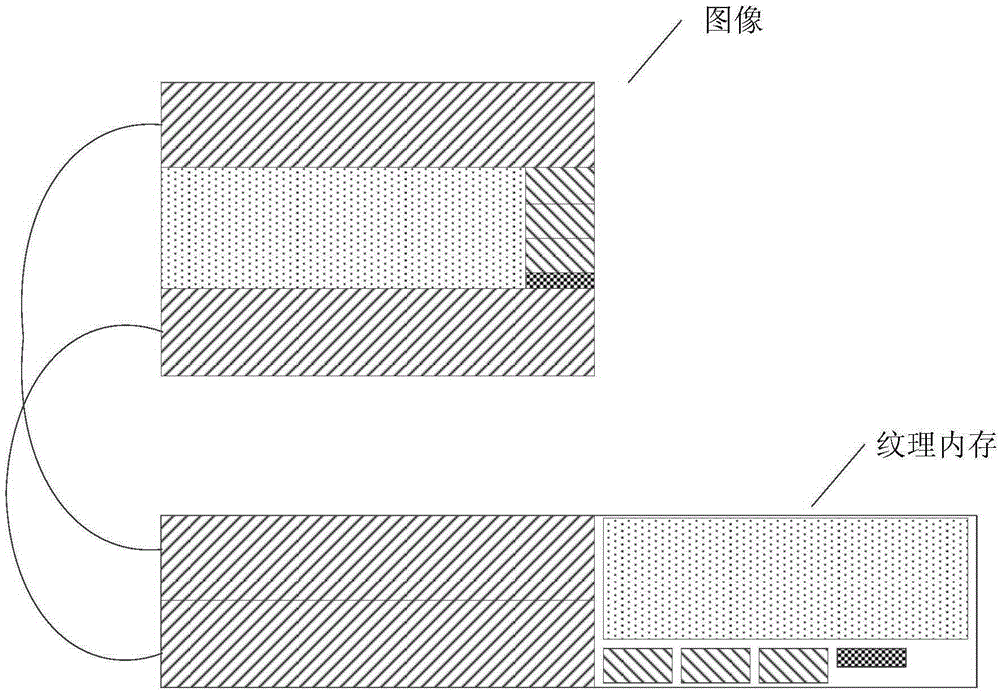

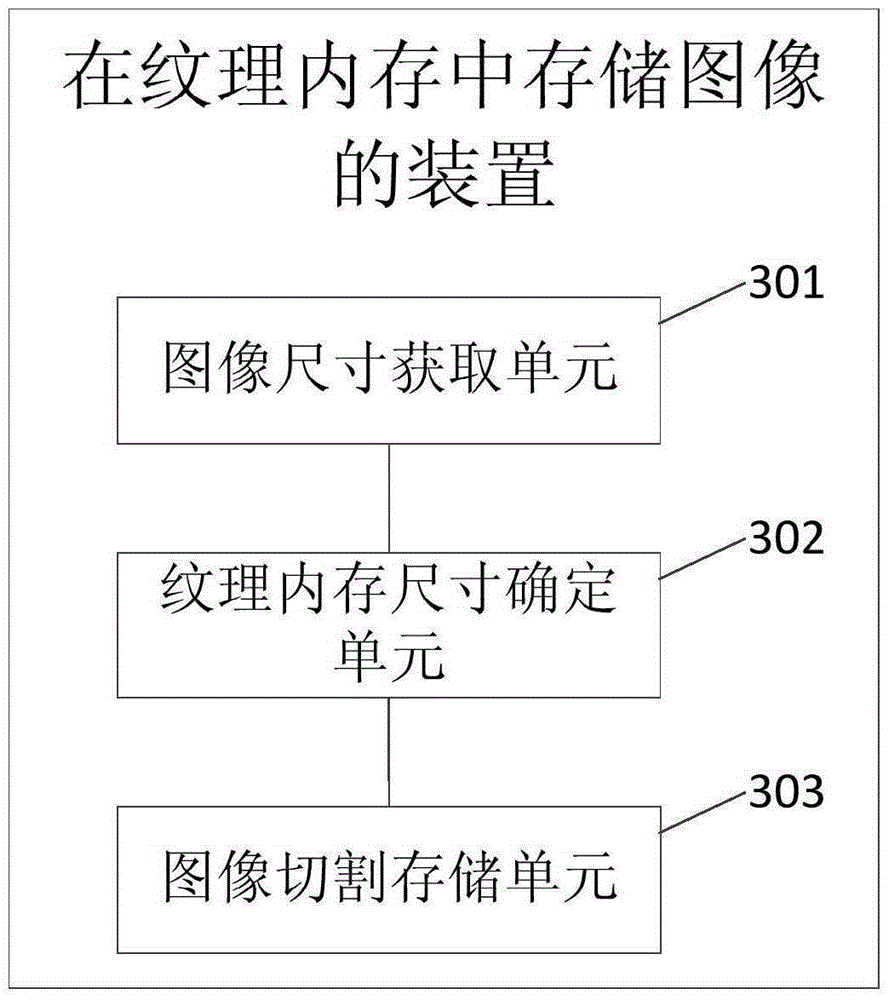

Method and device for storing image in texture memory

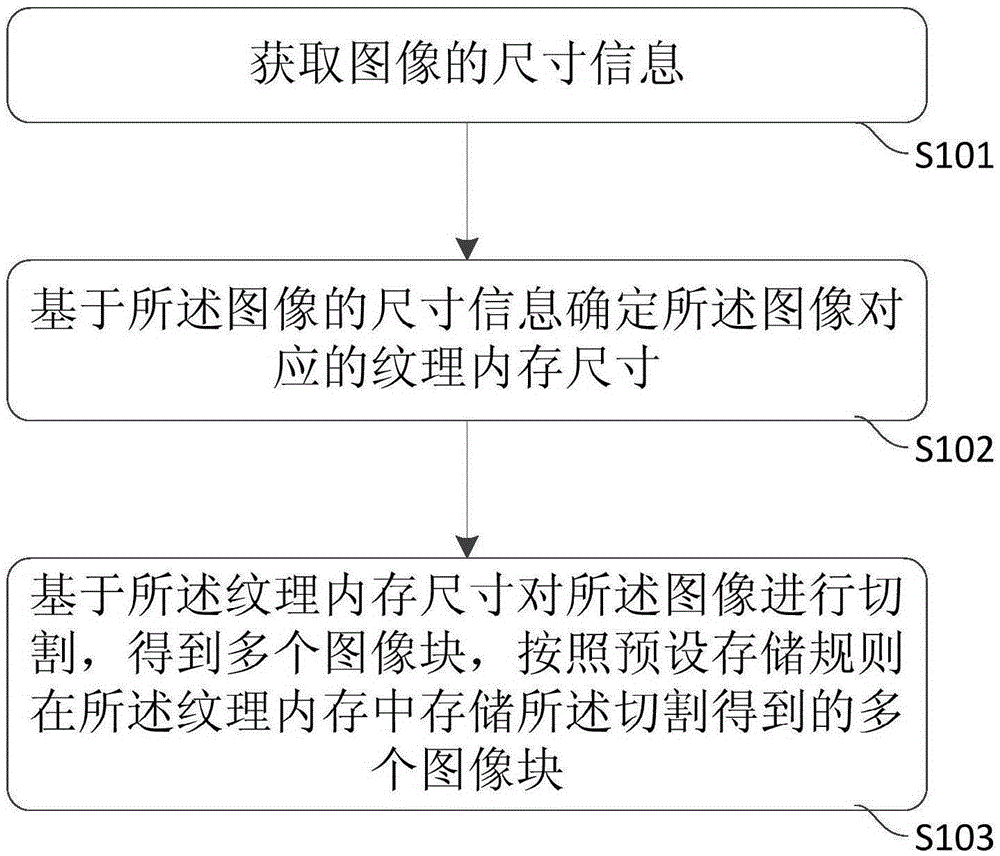

ActiveCN106611401ASave spaceHigh speedImage enhancementImage analysisImaging processingComputer graphics (images)

The embodiment of the invention discloses a method and a device for storing an image in a texture memory. The method comprises the following steps of: obtaining the dimension information of an image; on the basis of the dimension information of the image, determining a texture memory dimension corresponding to the image; and on the basis of the texture memory dimension, segmenting the image to obtain a plurality of image blocks, and storing the plurality of image blocks obtained by segmentation in the texture memory according to a preset storage rule. By use of the method and the device, which are provided by the embodiment of the invention, for storing the image in the texture memory, the memory can be saved, and image processing speed is improved.

Owner:ALIBABA GRP HLDG LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com