Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

128 results about "Level design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Level design, or environment design, is a discipline of game development involving creation of video game levels—locales, stages, or missions. This is commonly done using a level editor, a game development software designed for building levels; however, some games feature built-in level editing tools. Level design is both an artistic and technical process.

Algorithmic electronic system level design platform

InactiveUS20070162268A1CAD circuit designSpecial data processing applicationsElement modelComputer architecture

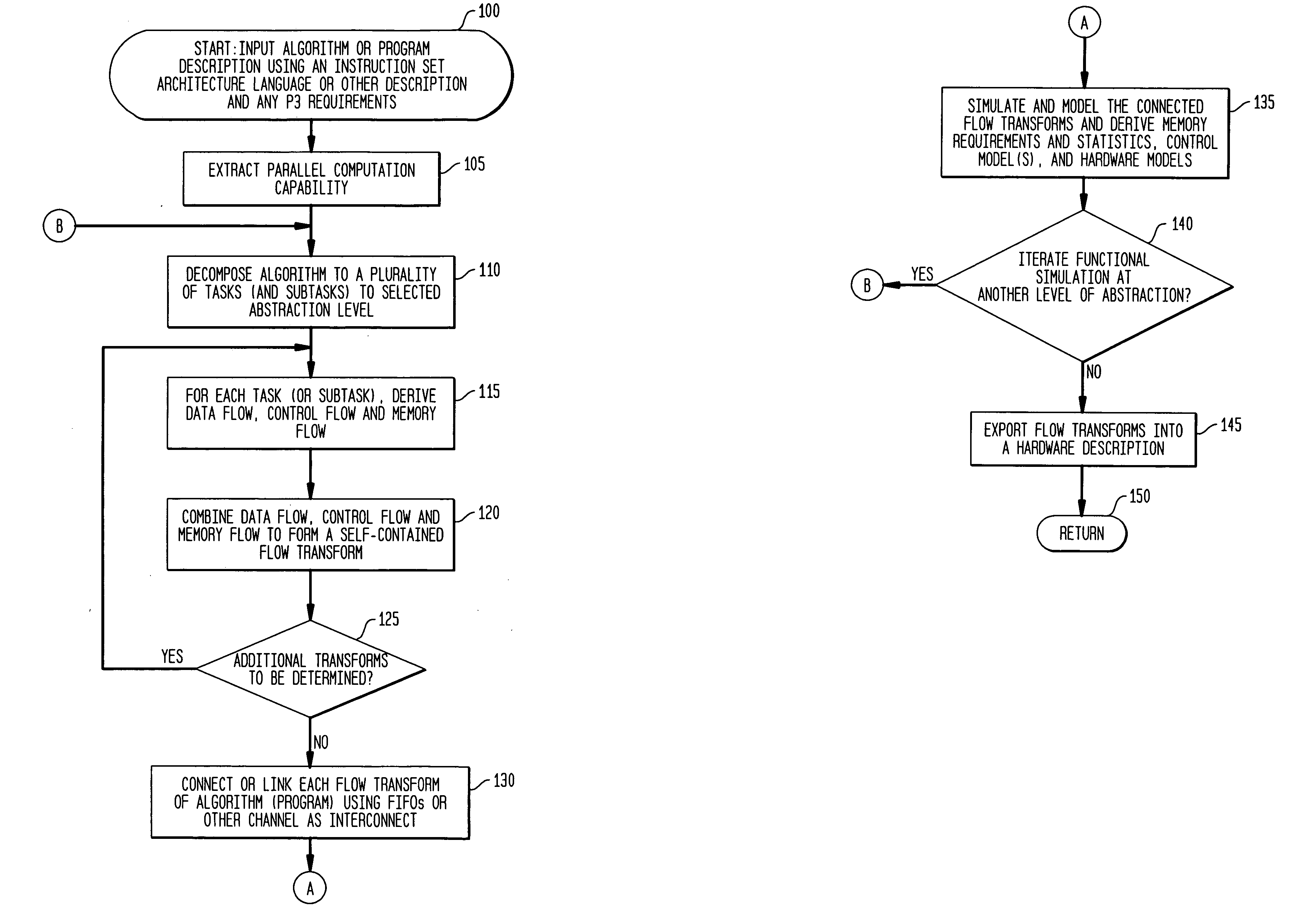

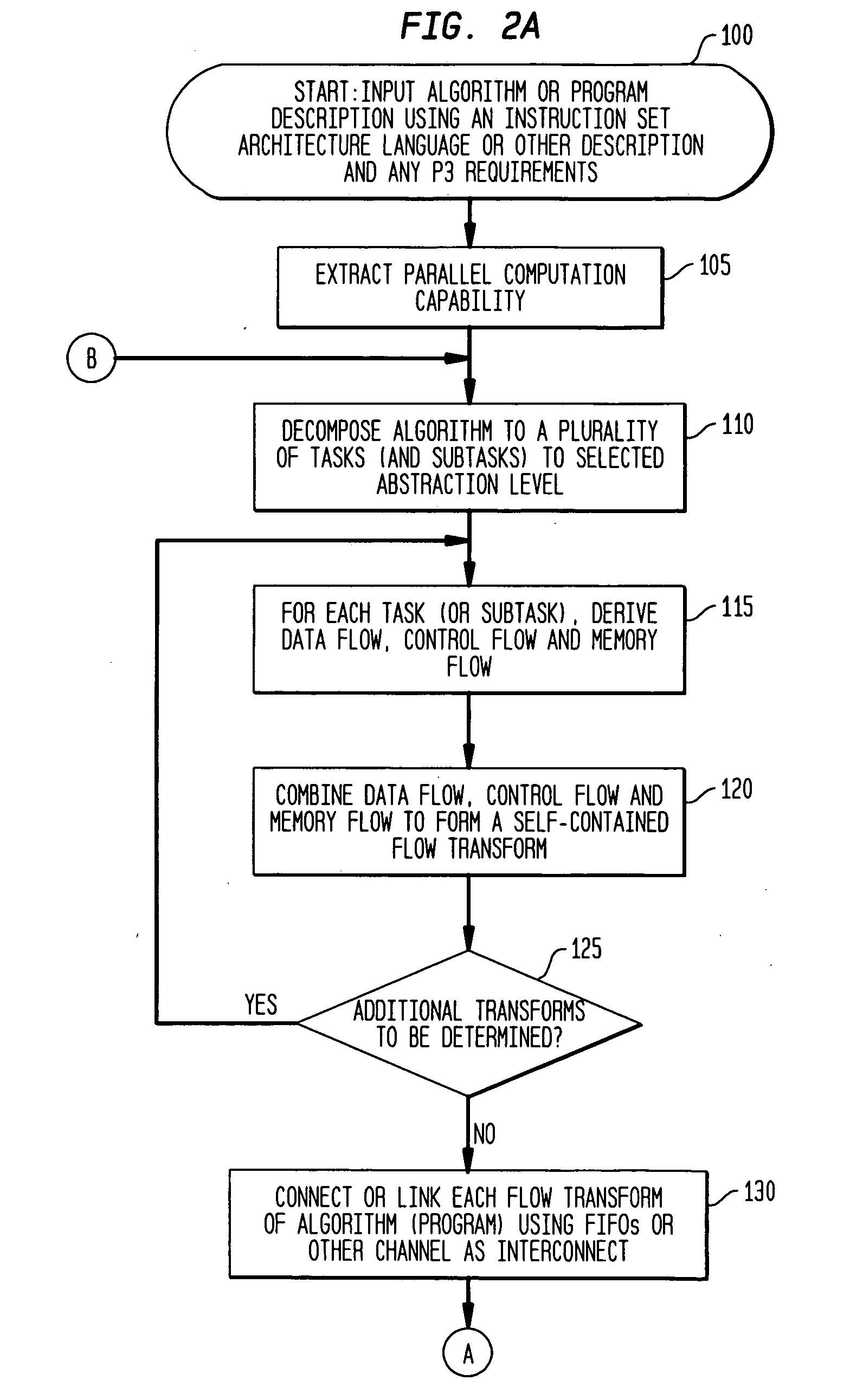

A computing system and method are provided for algorithmic electronic system level design. An exemplary system comprises a plurality of databases for storing a plurality of functional models, a plurality of computational element models, and a plurality of hardware definition representations. An application design processor is adapted to perform a first functional simulation of an algorithm using a plurality of computational element architecture definitions to generate a first selection of a plurality of computational elements and corresponding control code for an implementation of the algorithm. A control and memory modeling processor is adapted to generate a plurality of flow transforms from the algorithm and to convert the plurality of flow transforms into the plurality of plurality of computational element models. A system simulation processor is adapted to convert the plurality of computational element models into the plurality of hardware definition representations and to perform a second functional simulation of the algorithm using the plurality of computational element models corresponding to the first selection and the corresponding control code.

Owner:KOTA BHASKAR +3

Method for tracking and locating container by adopting label sensor network

ActiveCN102325344AComprehensive monitoringImprove access to informationNetwork traffic/resource managementNetwork topologiesRelevant informationTest algorithm

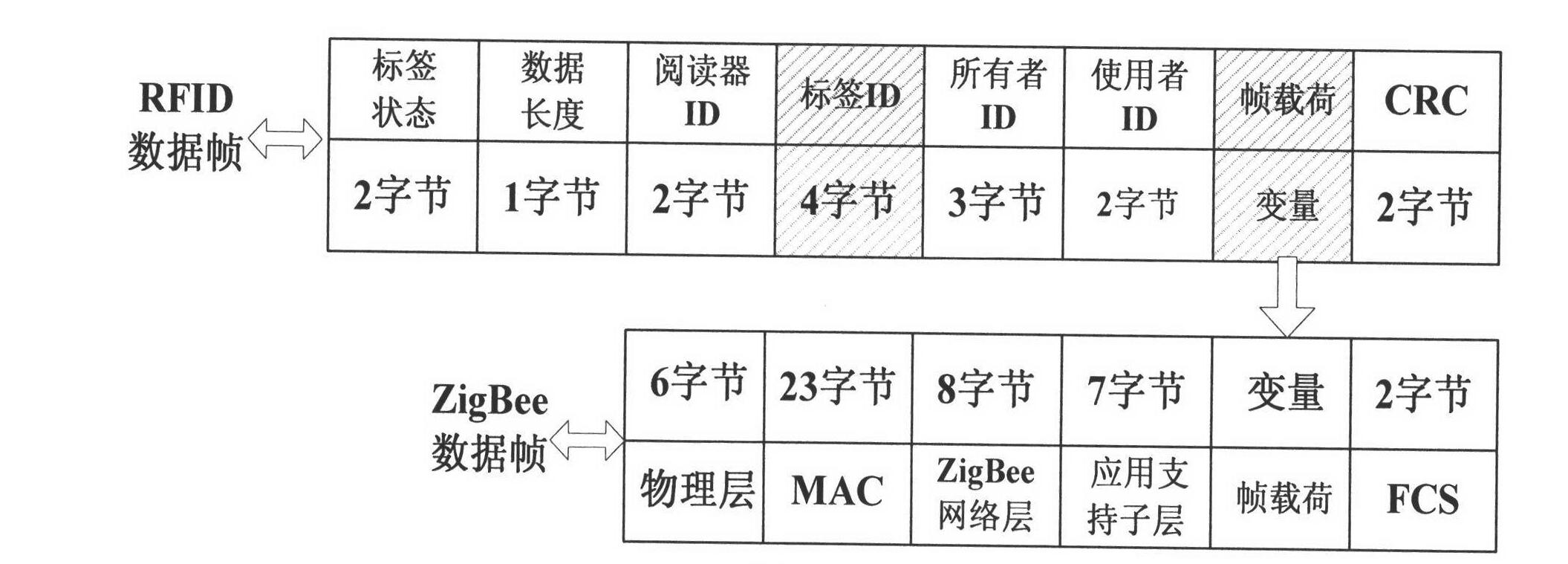

At present, an RFID (Radio Frequency Identification Device) technology is used in the container physical distribution process, however, the application of the RFID technology in the field of container physical distribution tracking and locating is limited due to defects and limitations of an RFID per se. The invention provides a method for tracking and locating a container by adopting a label sensor network, and in the method, the sensor network is fused with an RFID network, so that transmitting various types of radio frequency label data is realized by a ZigBee network through gateway level design, hardware module design, protocol fusion and the like. By using the label sensor network, the transmission radius of the traditional RFID network is increased, and a series of problems such as incapability of sensing object states, poor an-interference performance and the like of the RFID are solved. Positional information of the container is calculated through a subtriangular inner pointer testing algorithm. Relevant information such as a position, a safety condition, humidity and temperature change and the like of the container can be gotten by a shipper or manager through a computer and a mobile phone, and once unforeseen circumstances such as container damage, transportation line change or delay and the like happen, alarm information can be received in time.

Owner:NANJING UNIV OF POSTS & TELECOMM

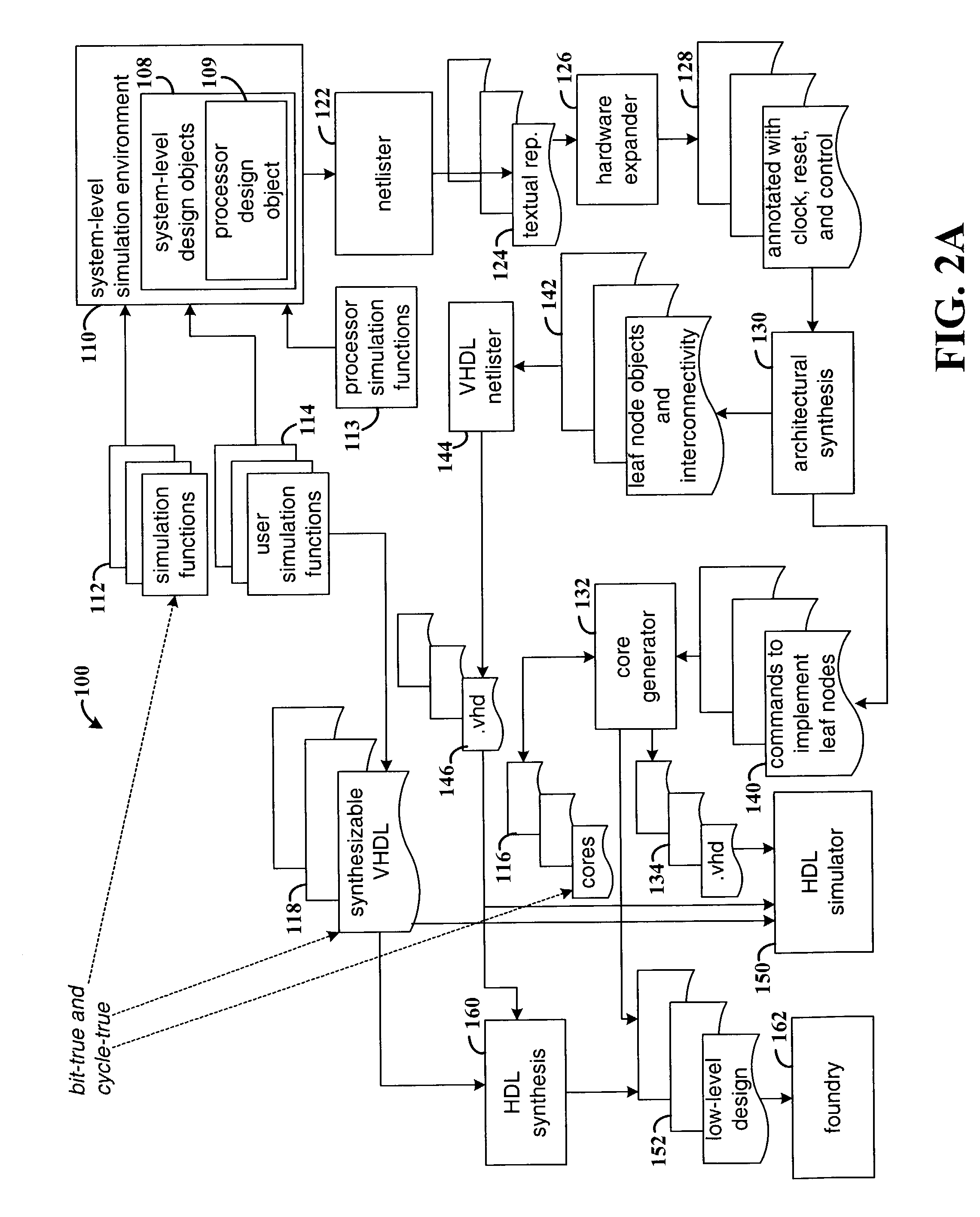

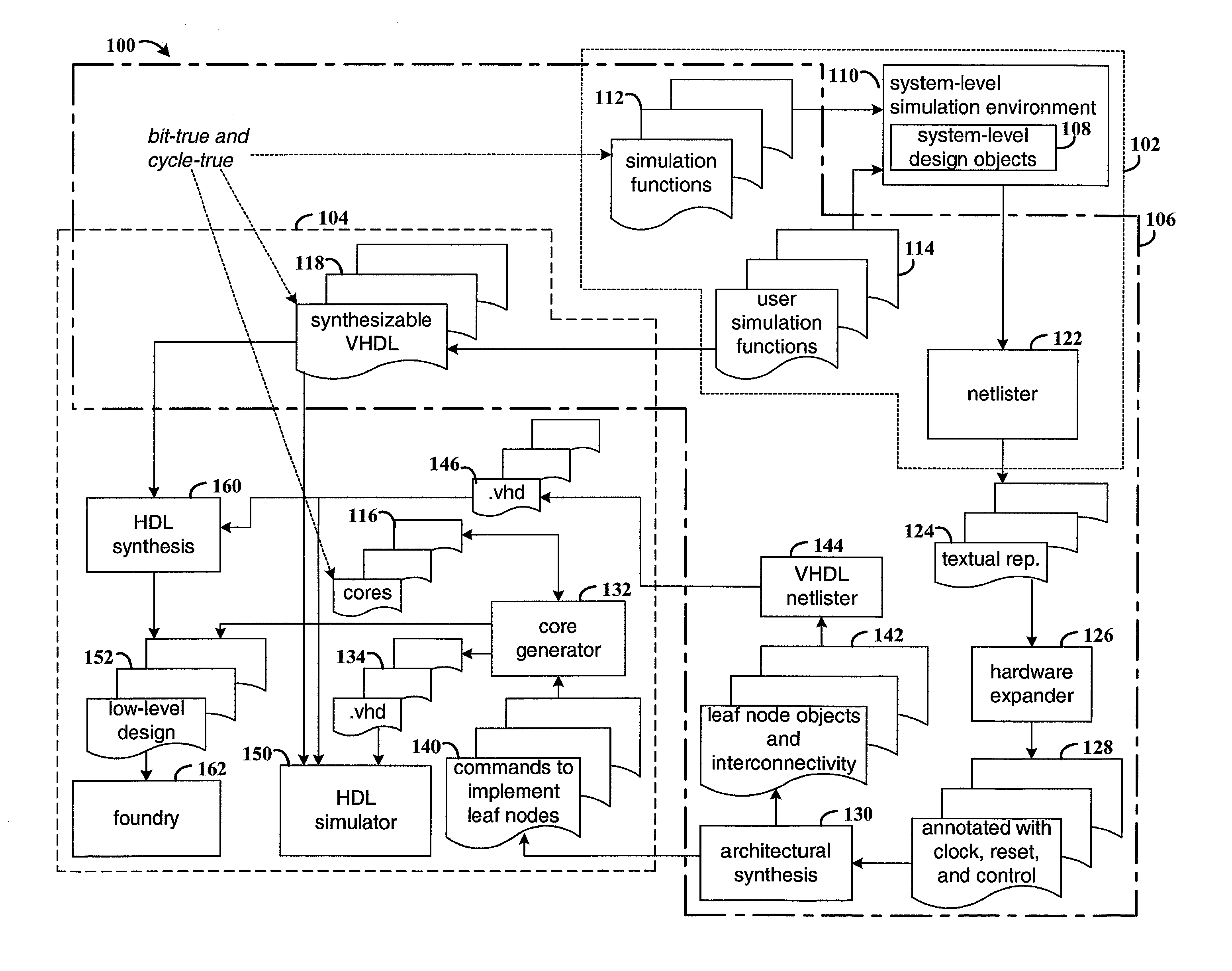

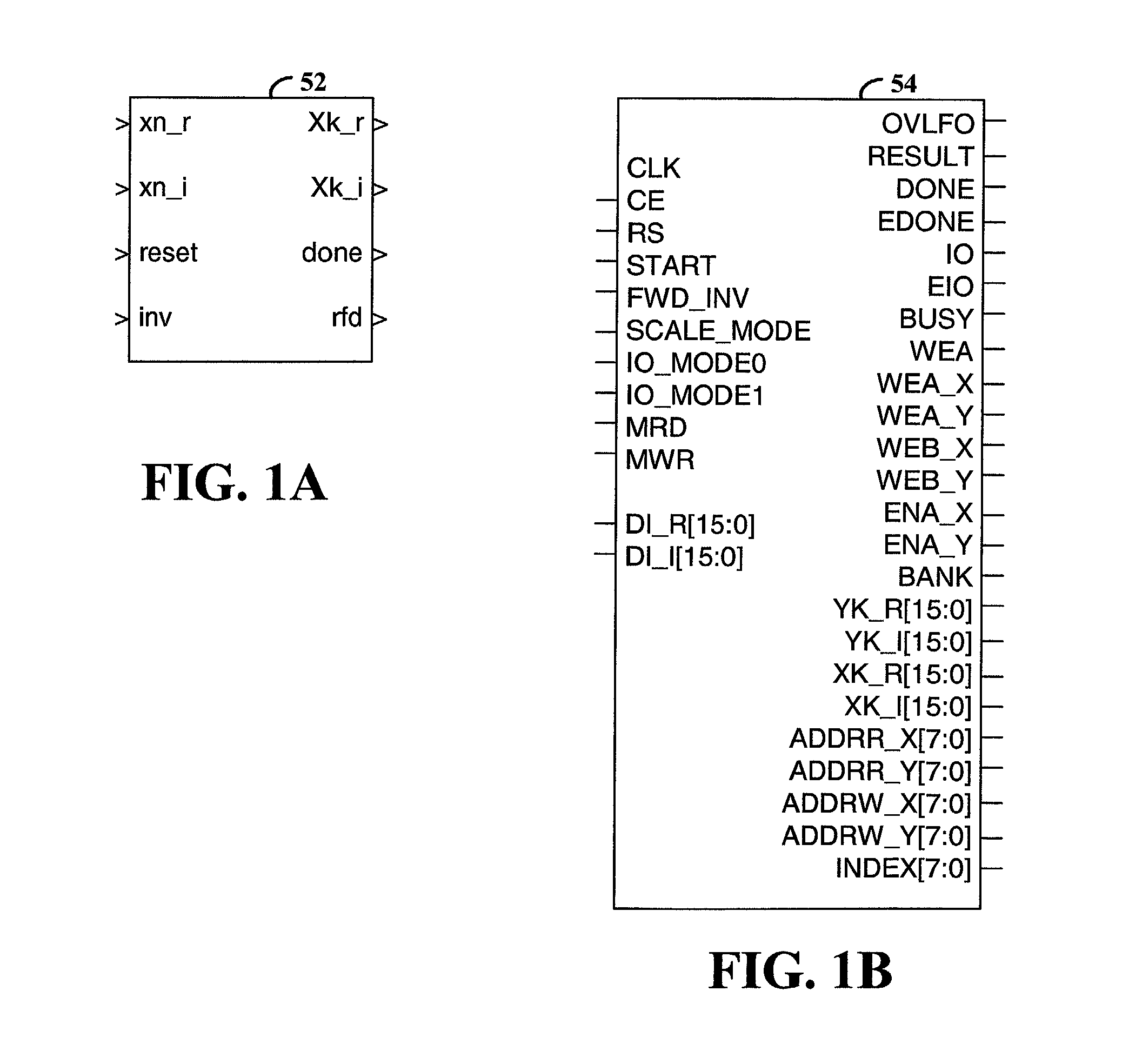

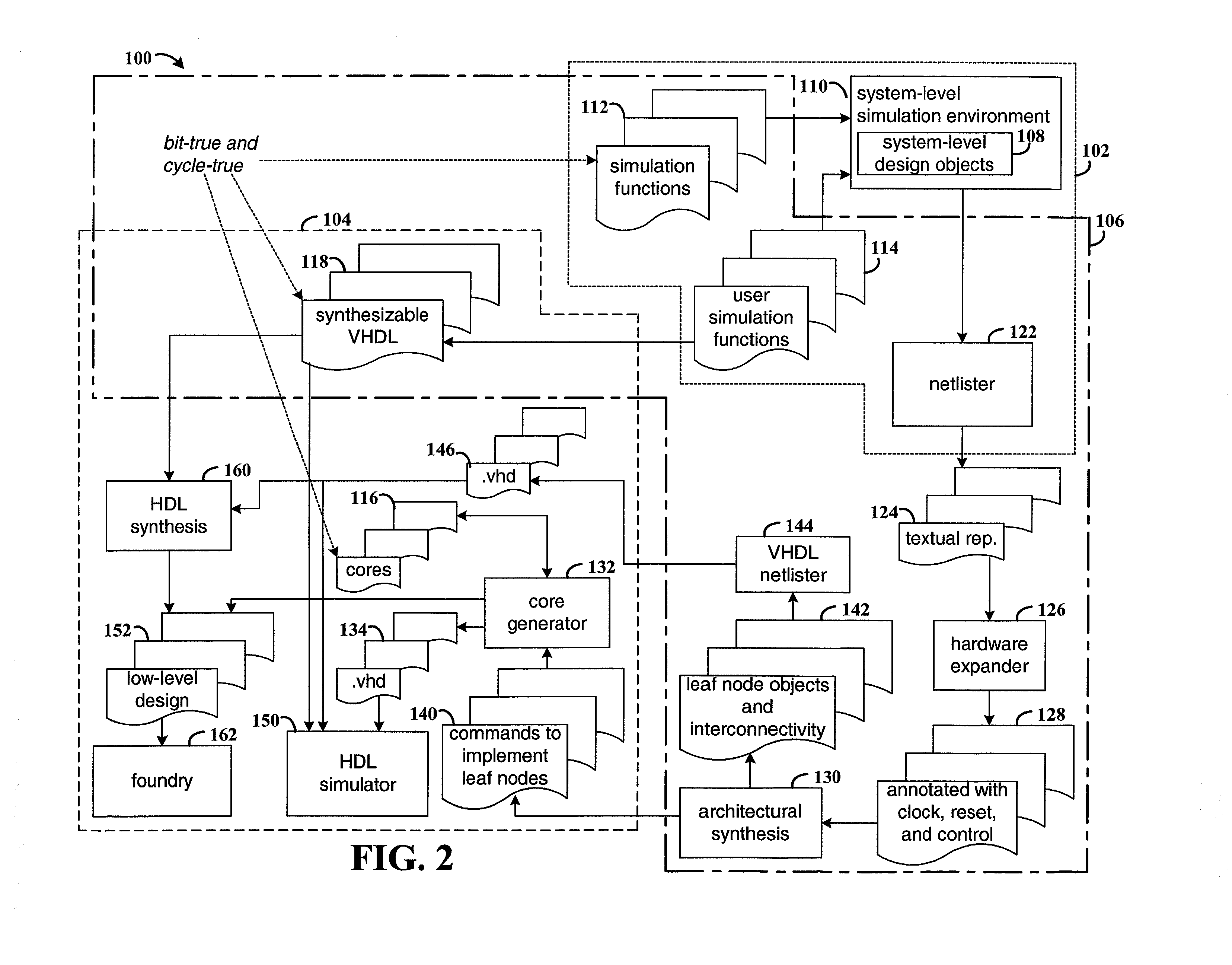

Method and system for modeling and automatically generating an embedded system from a system-level environment

InactiveUS7085702B1Electric pulse generatorAnalogue computers for nuclear physicsLevel designProcessor design

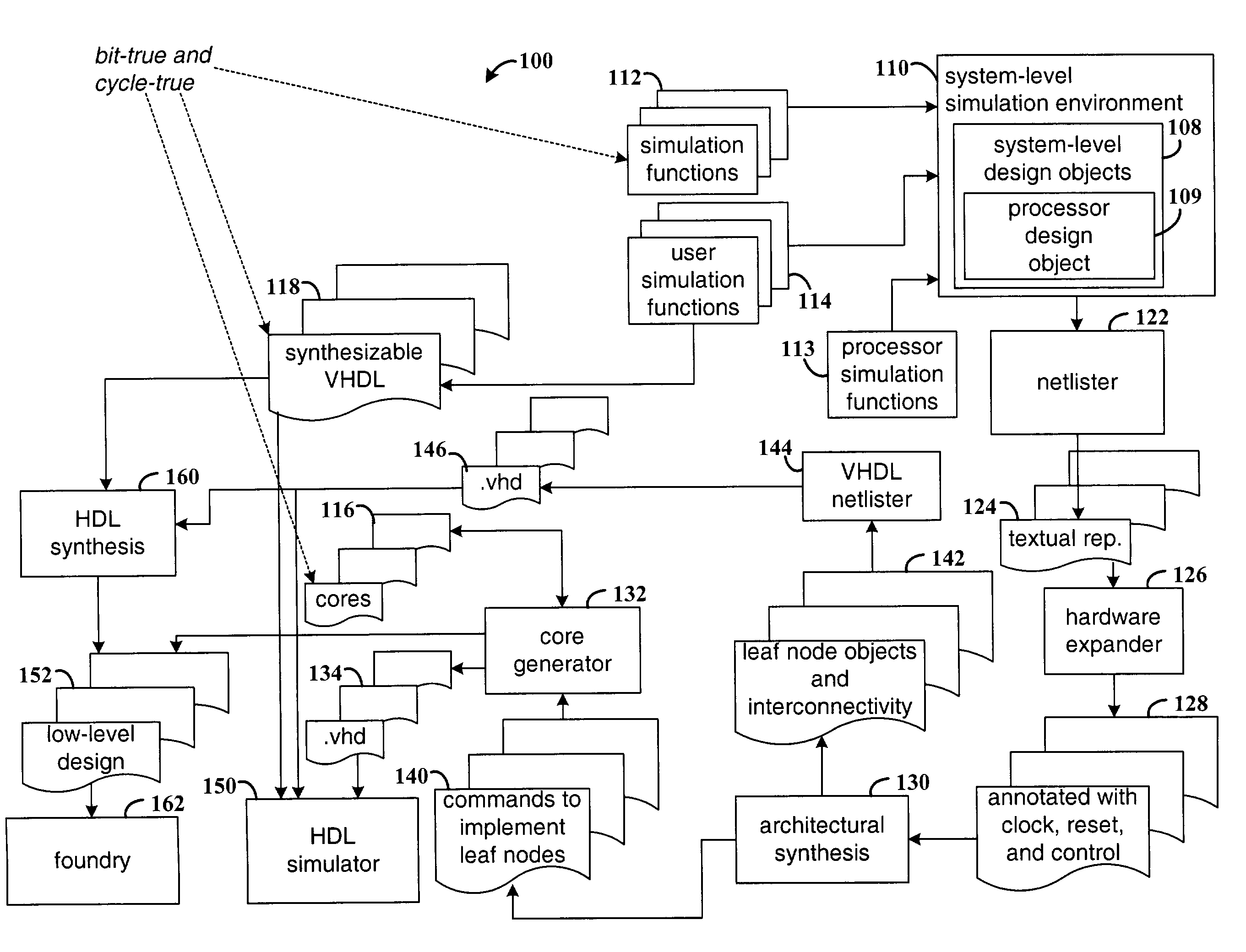

Method and system for modeling and automatically generating an embedded system from a system-level environment. A plurality of user-selectable system-level design objects are provided in the system-level environment. Each system-level design object is defined by a system-level function and is selectable by a system-level designer. A plurality of hardware-level design objects are also provided. Each hardware-level design object is configured to generate a hardware definition of a hardware-level function. Each system-level design object maps to one or more hardware-level design objects. A processor design object is provided which defines a processor. In response to selections made by the designer, a system-level design is instantiated in a system-level design file. The system-level design includes user-selected ones of the system-level and processor design objects. The system simulates behavior of the system-level design consistent with the processor, system-level functions, and behavior of a hardware definition from the hardware-level design objects that implement the user-selected ones of the system-level design objects.

Owner:XILINX INC

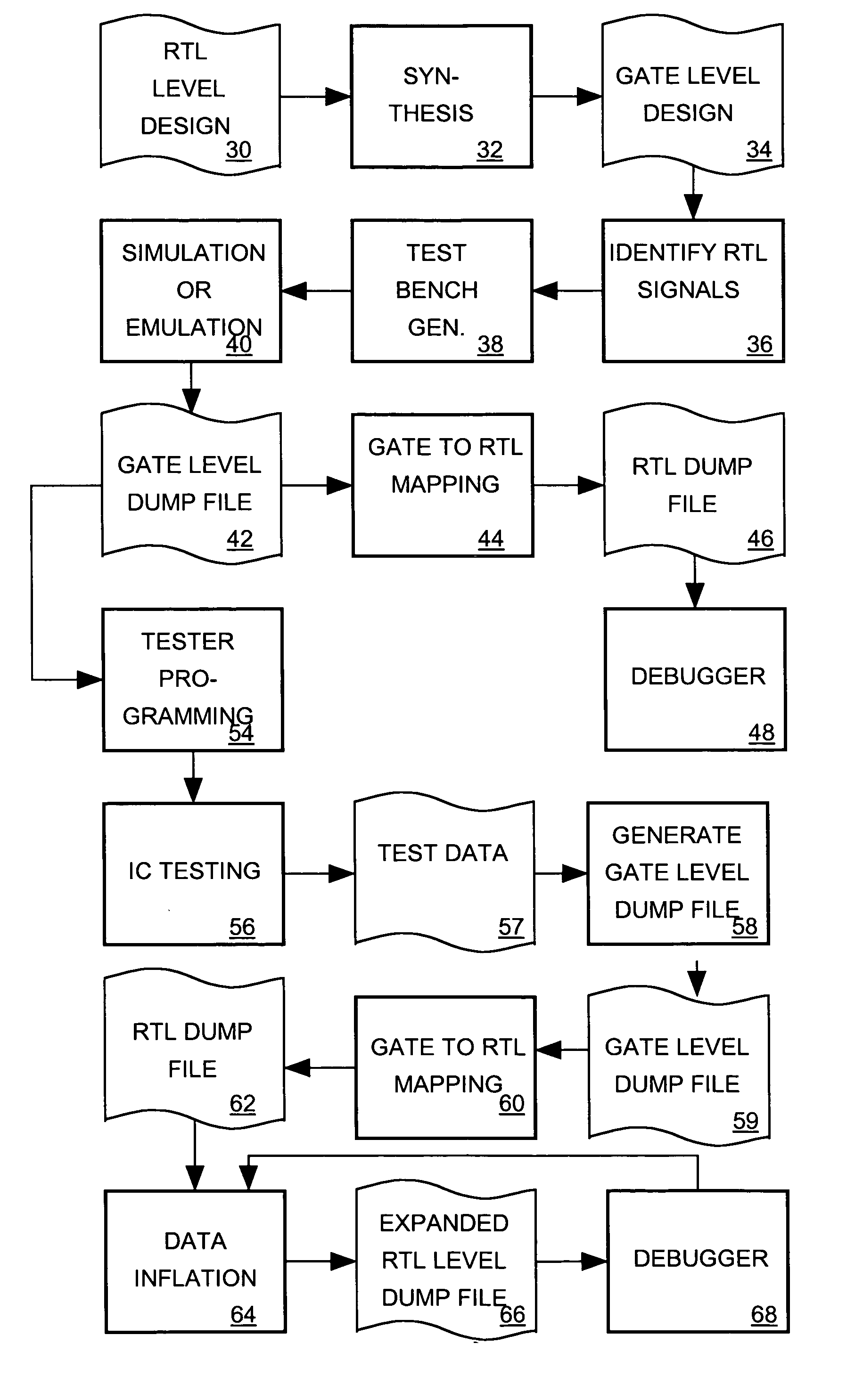

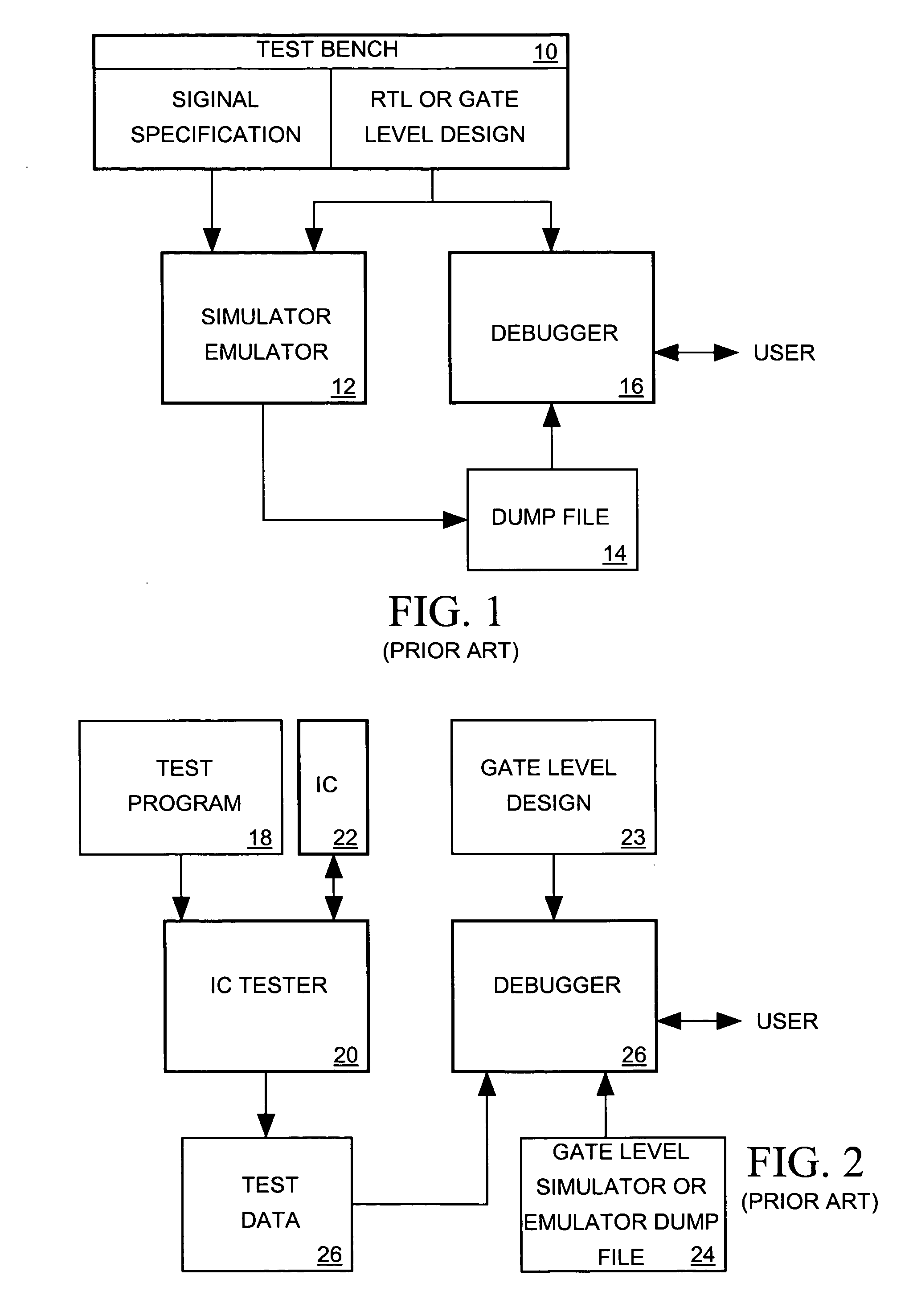

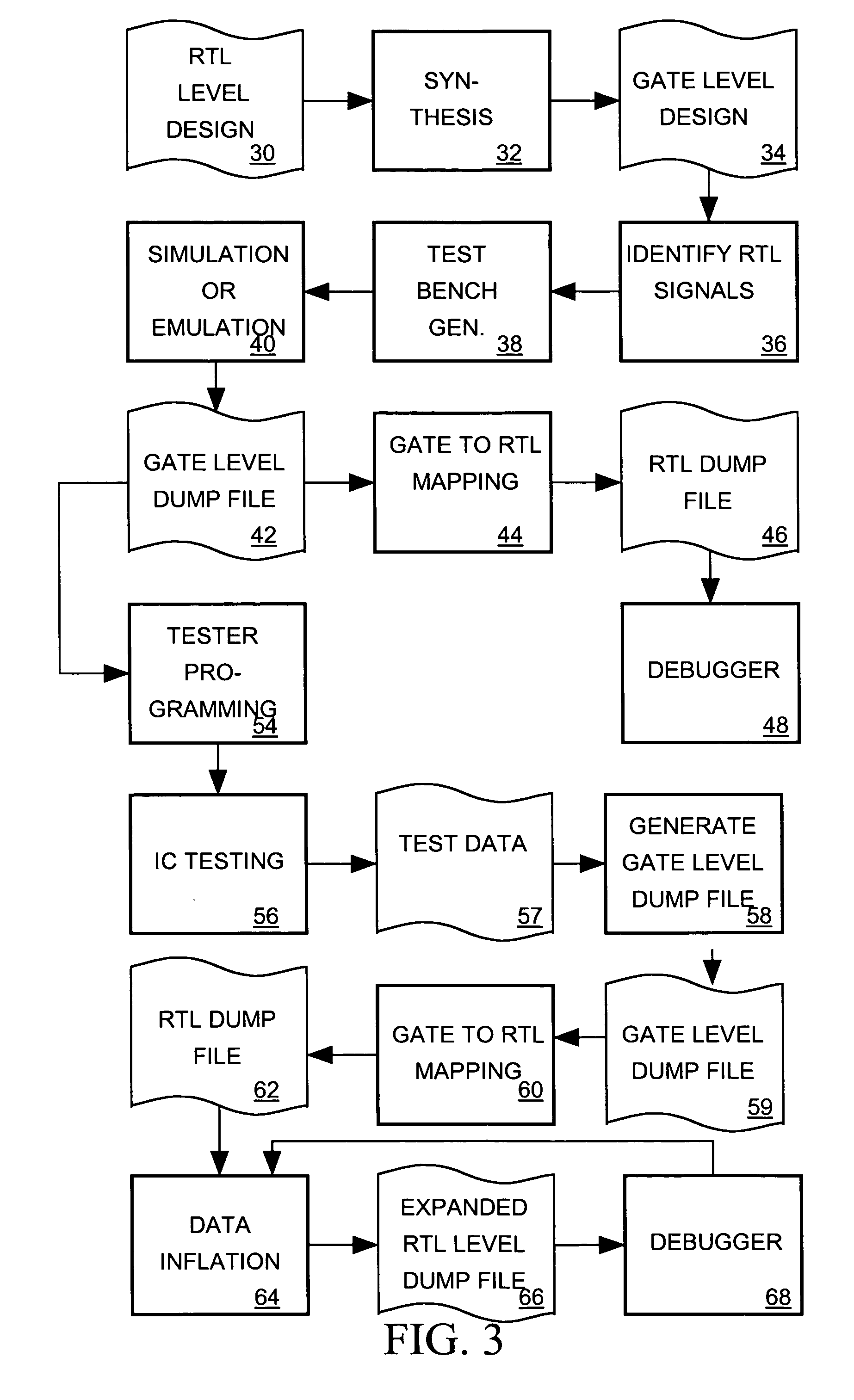

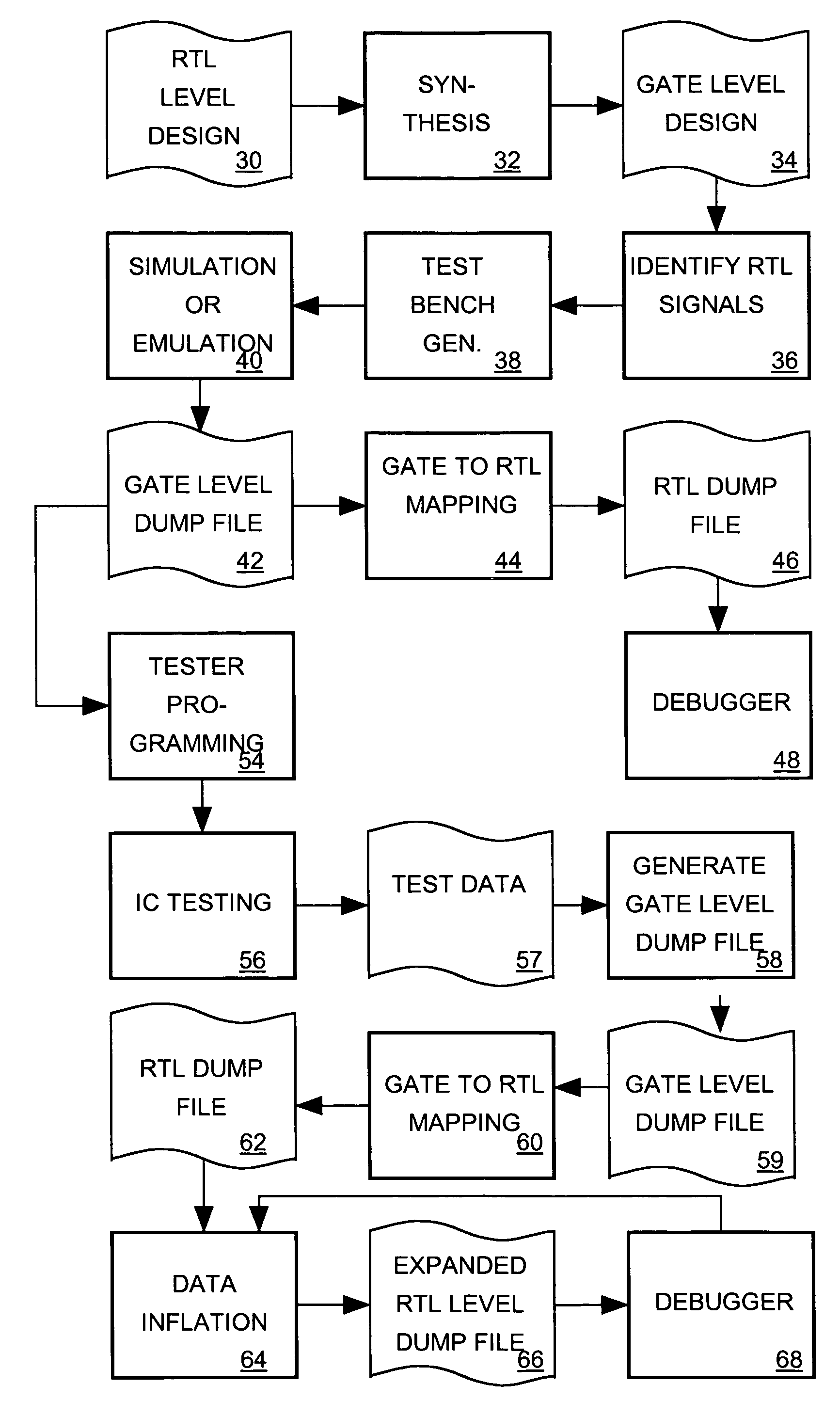

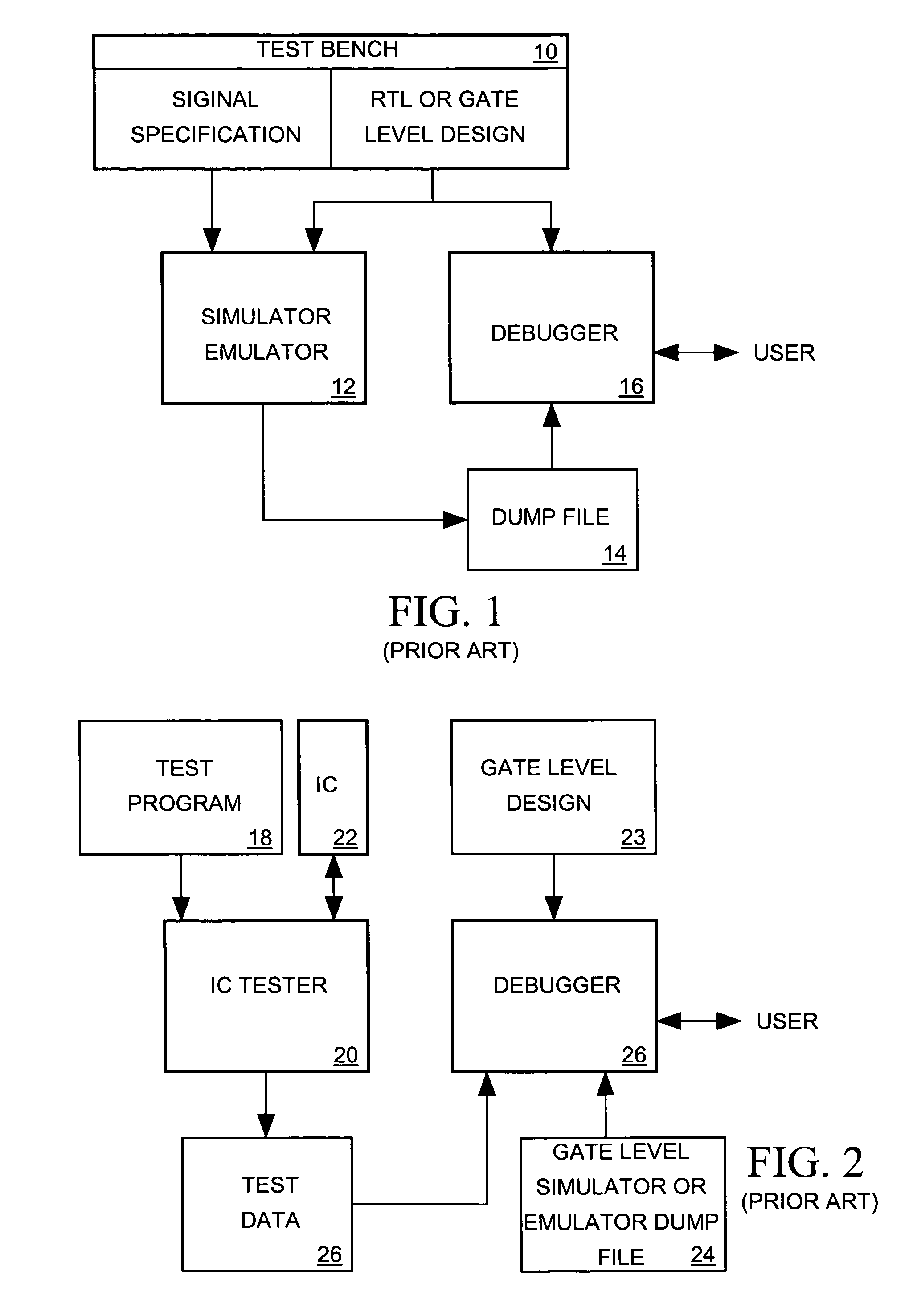

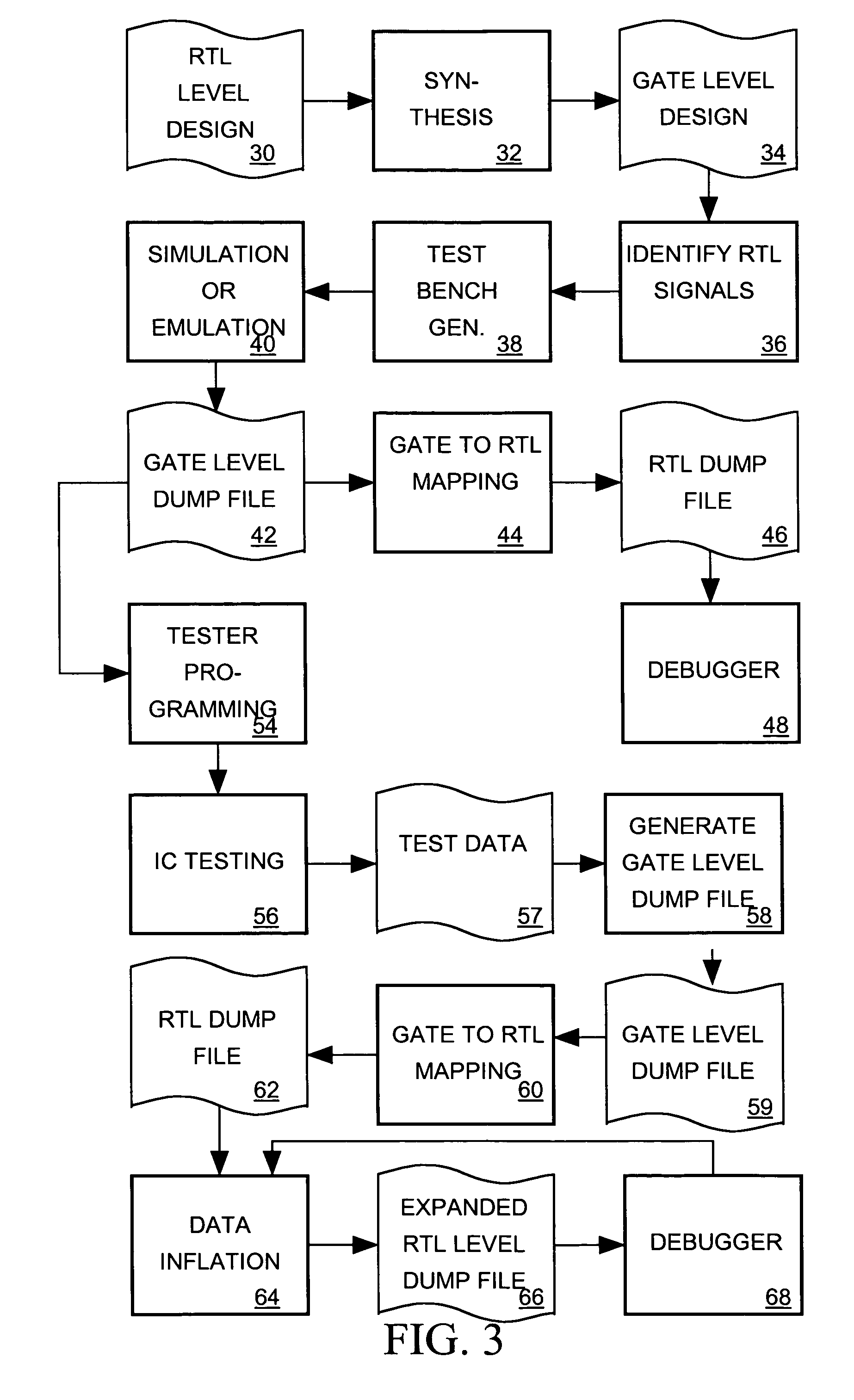

Debugging system for gate level IC designs

ActiveUS20070174805A1Easy to understandSimplify the commissioning processSemiconductor/solid-state device testing/measurementDetecting faulty computer hardwareComputer architectureComputer-aided

A register transfer level (RTL) IC design describing a IC as comprising a plurality of logic blocks communicating via signals and using a high level language to describe the logic blocks according to the logical relationships between signals they receive and signals they generate. A computer-aided synthesizer processes an RTL IC design to produce a gate level design for the IC describing its logic blocks as comprising instances of cells communicating via signals. A synthesizer or emulator processes the gate level design to produce a gate level dump file referencing signals of the gate level design and indicating how those signals behave in response to time-varying signals supplied as inputs to the IC. The gate level dump file is converted into an RTL dump file referencing signals of the RTL design and indicating how those signals behave. A debugger processes the RTL dump file to produce displays depicting the RTL design and behavior of signals indicated by the RTL dump file. Thus while the IC is simulated or emulated at the gate level of the design to produce waveform data for a debugger, the gate level-to-RTL dump file conversion process enables a designer debug the more familiar RTL design based on the gate level simulation or emulation results.

Owner:SYNOPSYS INC

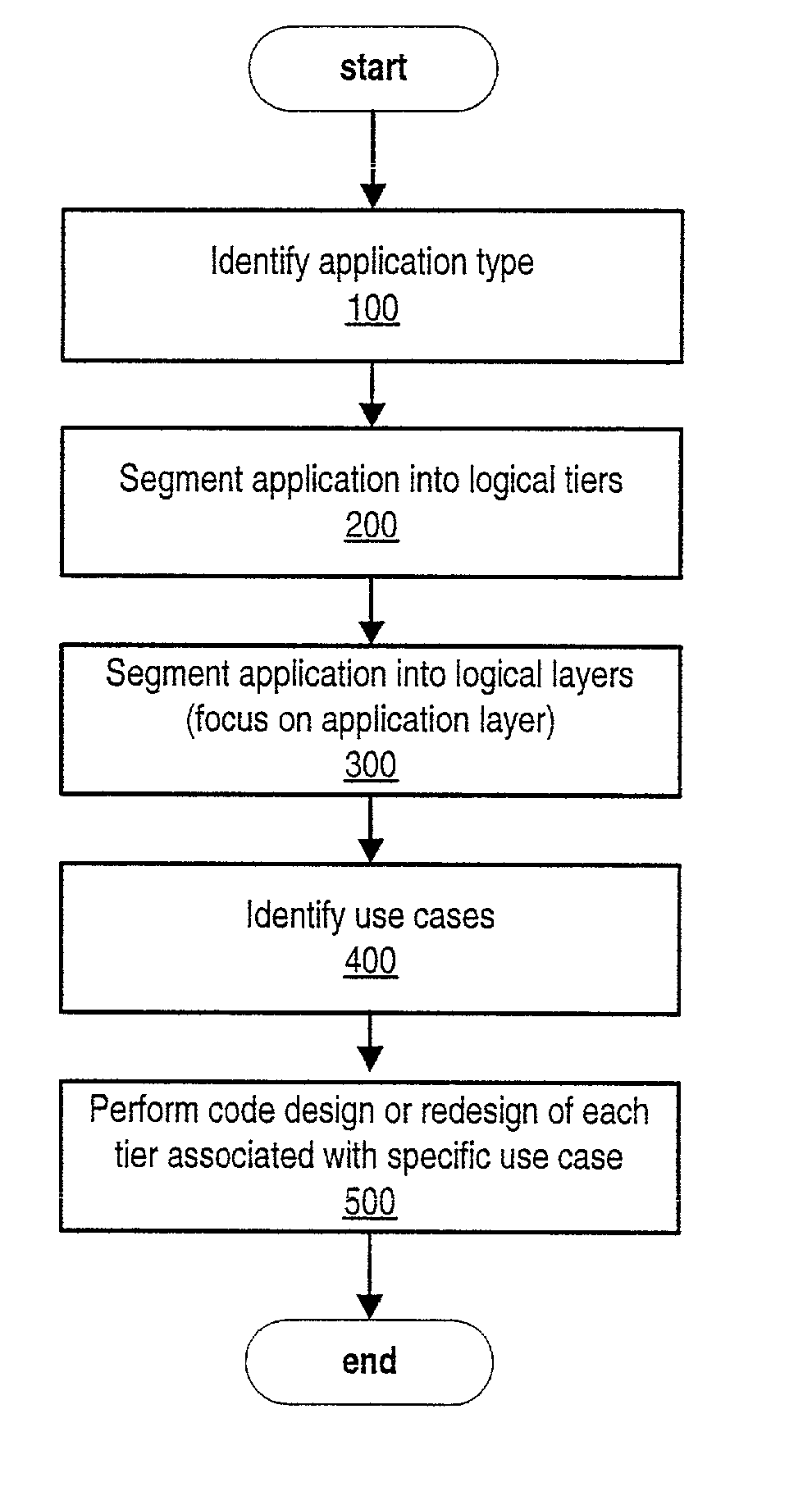

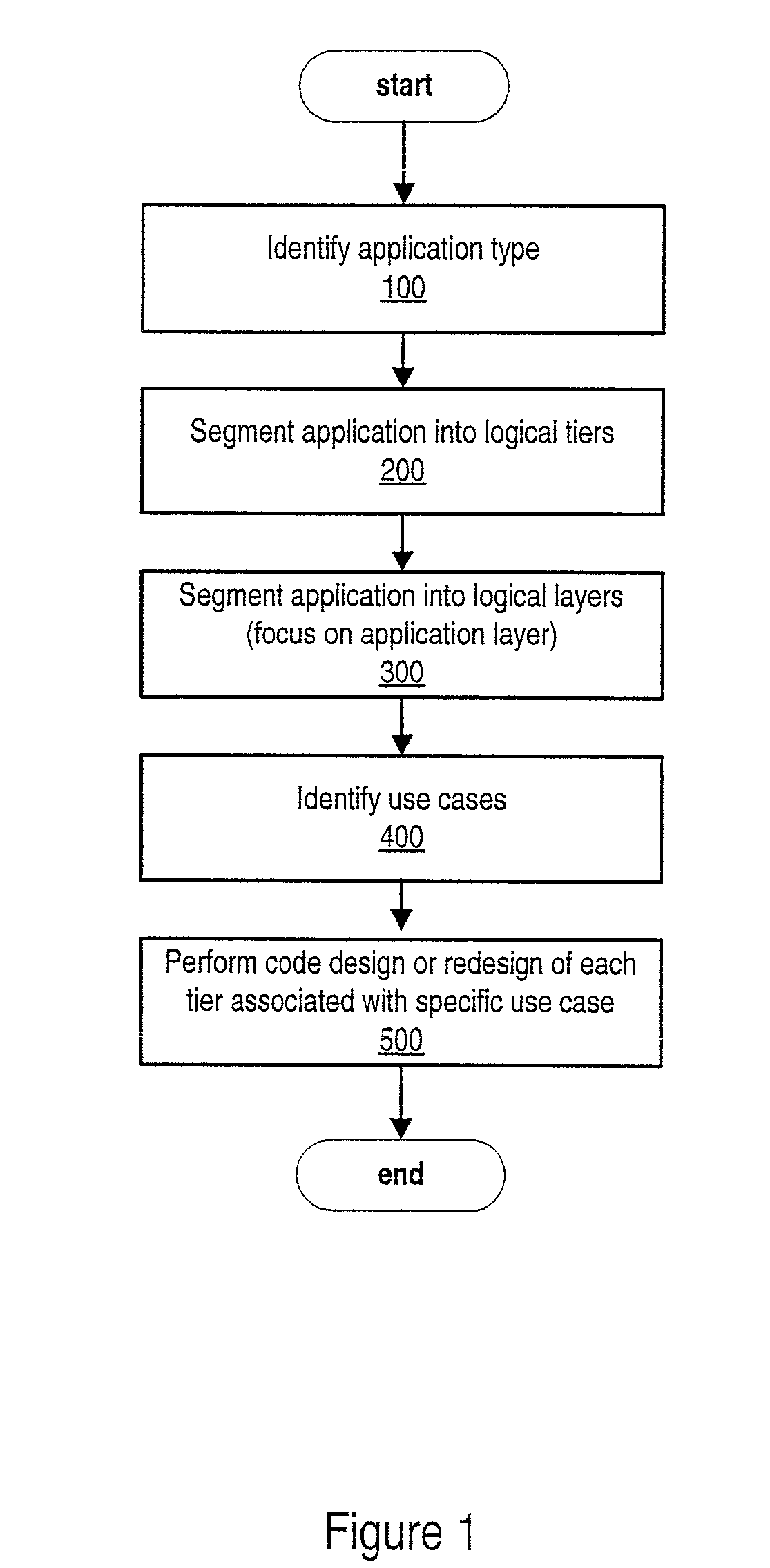

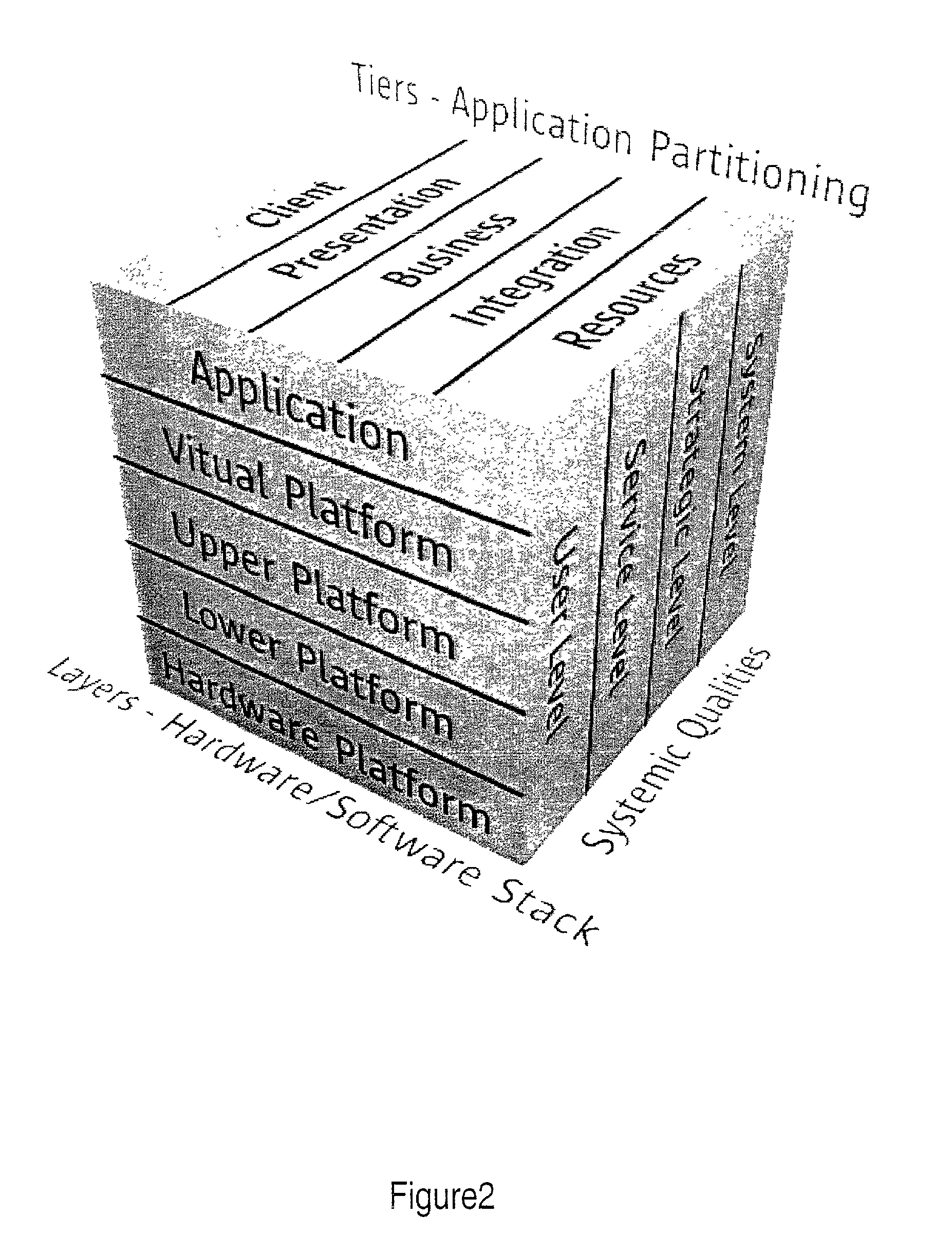

Design and redesign of enterprise applications

An enterprise application may be constructed or reconstructed according to a system and method for designing or redesigning enterprise applications. The design or redesign process may include identification of the application type, in addition to representation of the application type as a decomposition of software components. The design or redesign may focus on reviewing code level component design and utilization. The code level design or redesign may include an analysis of each component within each use case within each tier based on patterns, frameworks, and / or refactoring. The application design or redesign may yield recommendations for code creation or code improvements. The recommendations may include specific application enhancements. The recommendations may include specific code design to be incorporated during construction or reconstruction. The recommendations may include results for guiding the design or redesign phase for an application.

Owner:ORACLE INT CORP

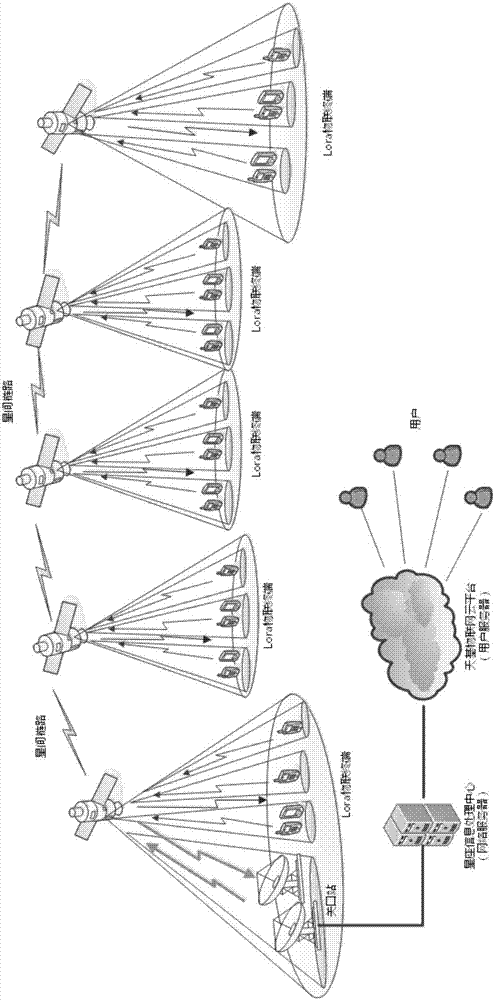

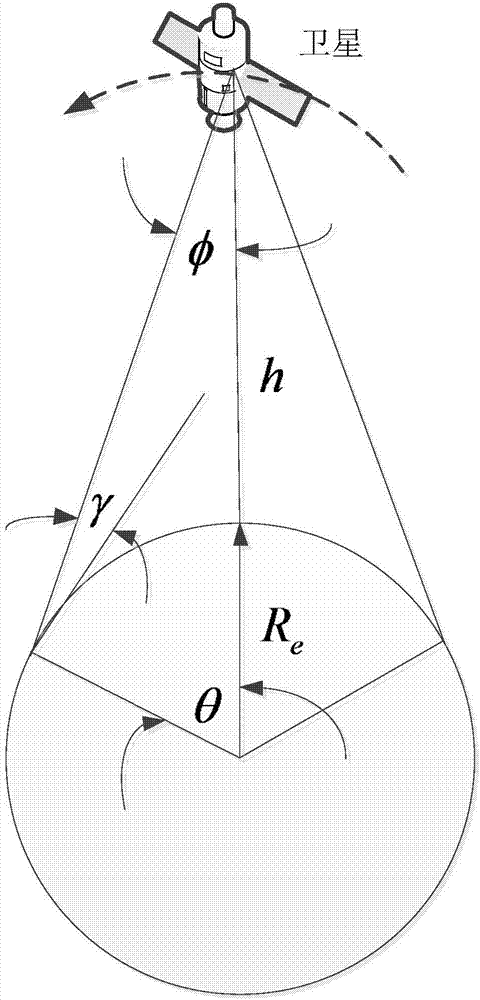

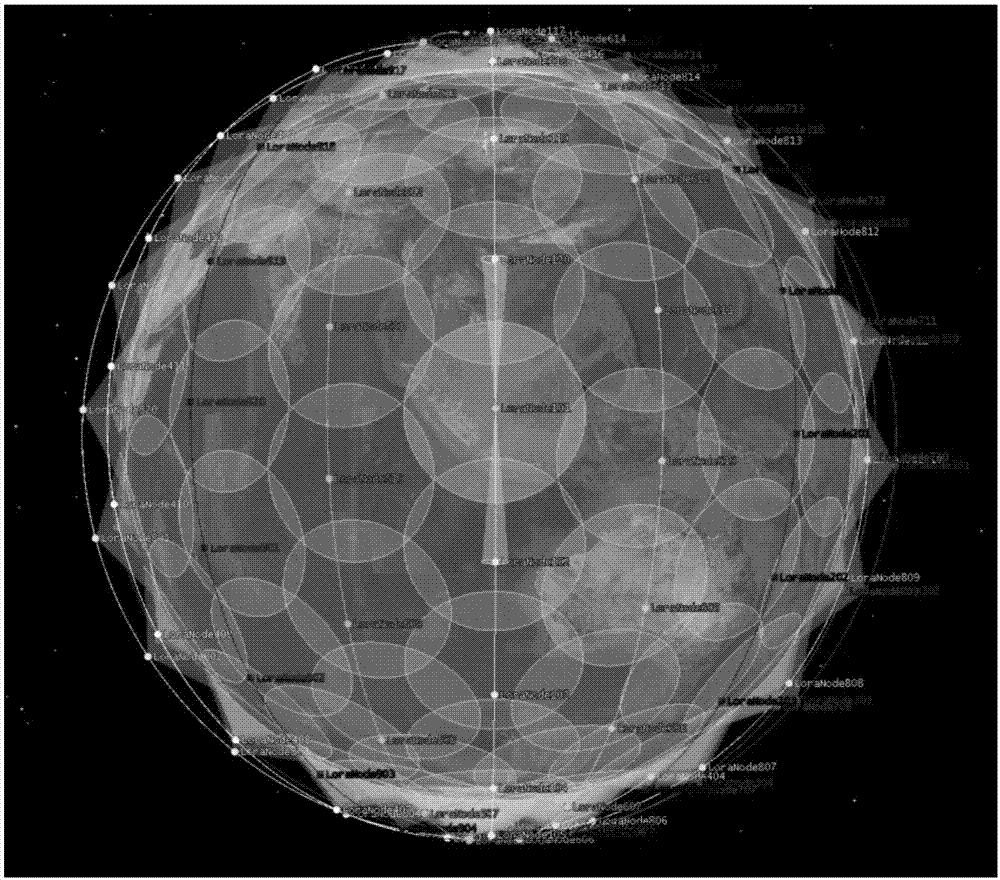

Global real-time internet of things constellation system

ActiveCN108011660AEnable connectivityRealize management abilityRadio transmissionWide areaSensing data

The invention provides a global real-time Internet of things (IOT) constellation system. The system includes a space segment including a plurality of low-orbit satellites that are interconnected through inter-satellite links, a ground segment which is used for completing an operation control function and a data distribution and recovery processing function. The ground segment includes a pluralityof constellation gateway stations. The system also comprises a user segment which is used for collecting sensing data and comprises a plurality of user terminals. The constellation gateway stations ofthe ground segment and the user terminals of the user segment communicate with the low-orbit satellites of the space segment through respective links. The system has the advantages that the system isfor the cloud, network and end system level designs of global wide-area space-based IOT applications, and the IOT new connection and management capabilities of multiple industrial mass applications are achieved.

Owner:湖南鲸瓴智联信息技术有限公司

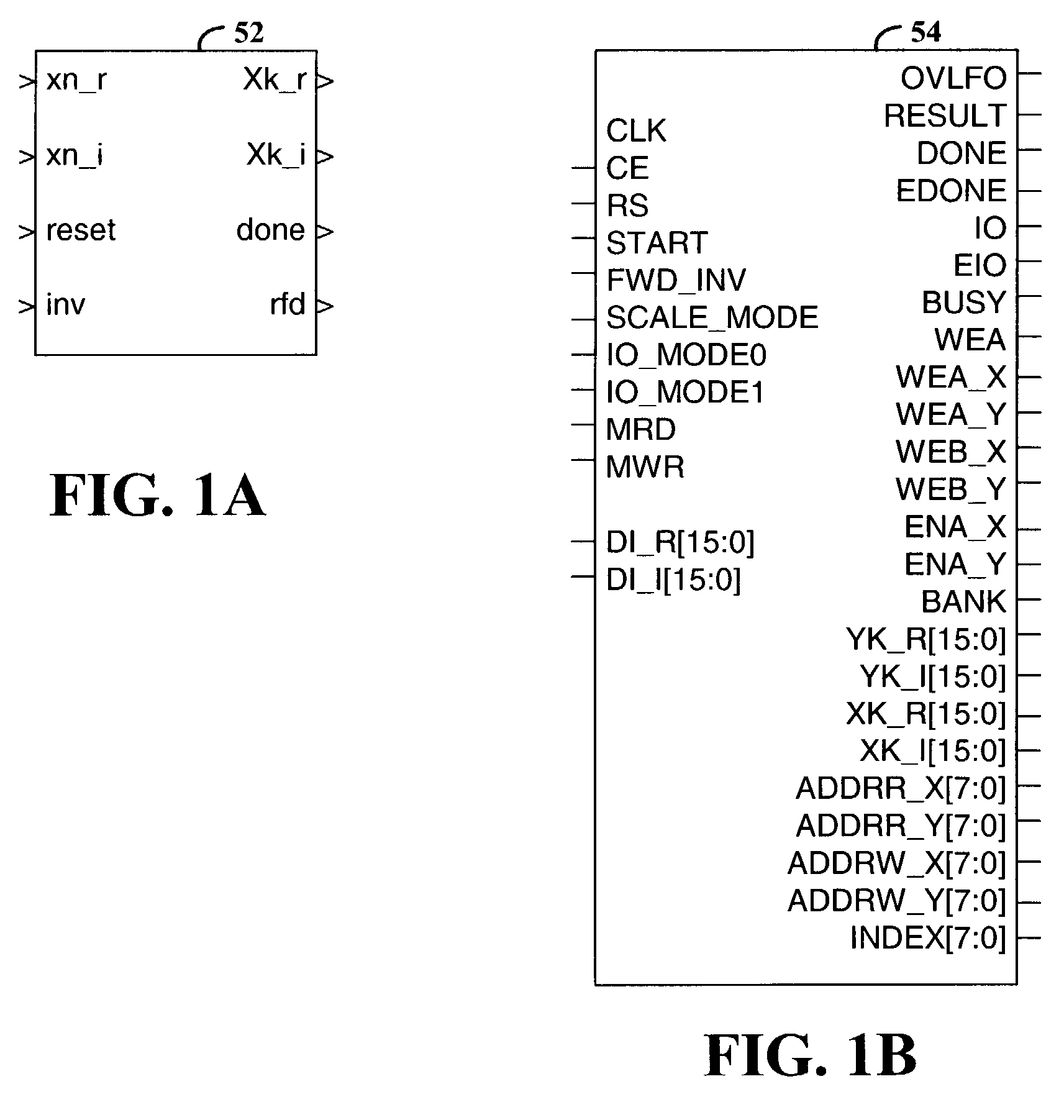

Method and system for modeling and automatically generating an electronic design from a system level environment

ActiveUS7110935B1CAD circuit designSoftware simulation/interpretation/emulationComputer architectureLevel design

Method and system for creating an electronic circuit design from a system-level environment. A plurality of user-selectable system-level design objects are provided in the system-level environment. Each system-level design object is defined by a system-level function and is selectable by a system-level designer. A plurality of hardware-level design objects are also provided. Each hardware-level design object is configured to generate a hardware definition of a hardware-level function. Each system-level design object maps to one or more hardware-level design objects. In response to selections made by the designer, a system-level design is instantiated in a system-level design file. The system-level design includes user-selected ones of the system-level design objects. The system simulates behavior of the system-level design consistent with both the system-level functions and behavior of a hardware definition from the hardware-level design objects that implement the user-selected ones of the system-level design objects.

Owner:XILINX INC

Debugging system for gate level IC designs

ActiveUS7478346B2Easy to understandSimplify the commissioning processSemiconductor/solid-state device testing/measurementDetecting faulty computer hardwareComputer architectureLevel design

A synthesizer or emulator processes a gate level IC design derived from an RTL design to produce a gate level dump file indicating how signals of the gate level design behave. The gate level dump file is converted into an RTL dump file indicating how signals of the RTL design behave. A debugger processes the RTL dump file to produce displays depicting the RTL design and behavior of signals indicated by the RTL dump file. Thus while the IC is simulated or emulated at the gate level of the design to produce waveform data for a debugger, the gate level-to-RTL dump file conversion process enables a designer debug the more familiar RTL design based on the gate level simulation or emulation results. file conversion process enables a designer debug the more familiar RTL design based on the gate level simulation or emulation results.

Owner:SYNOPSYS INC

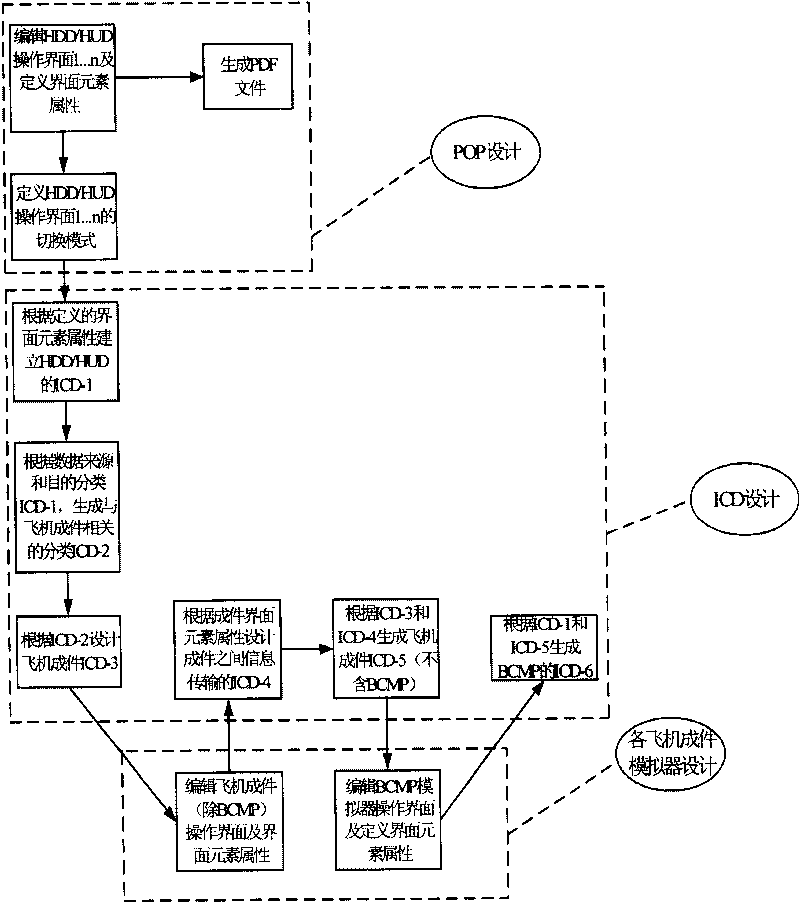

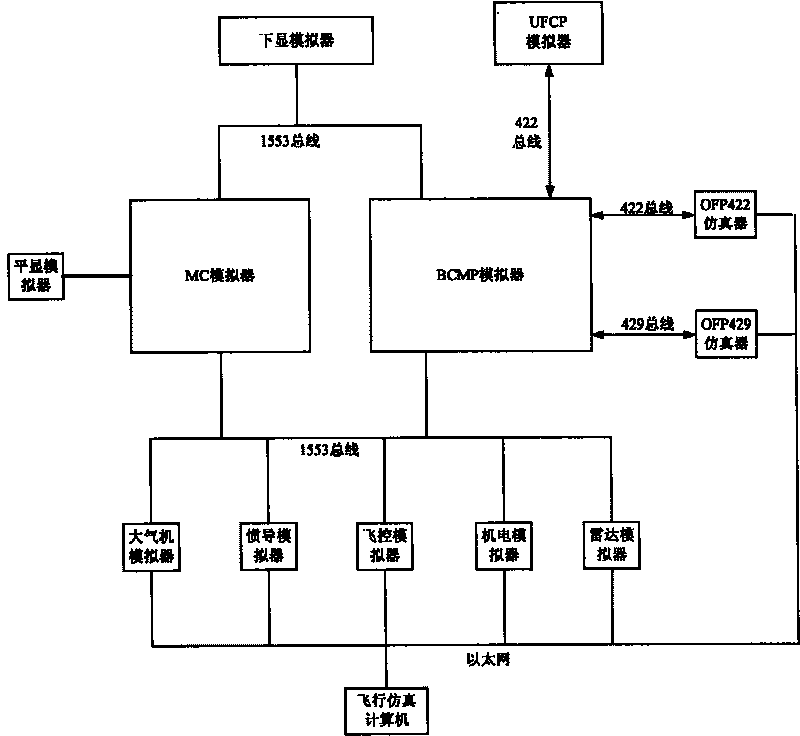

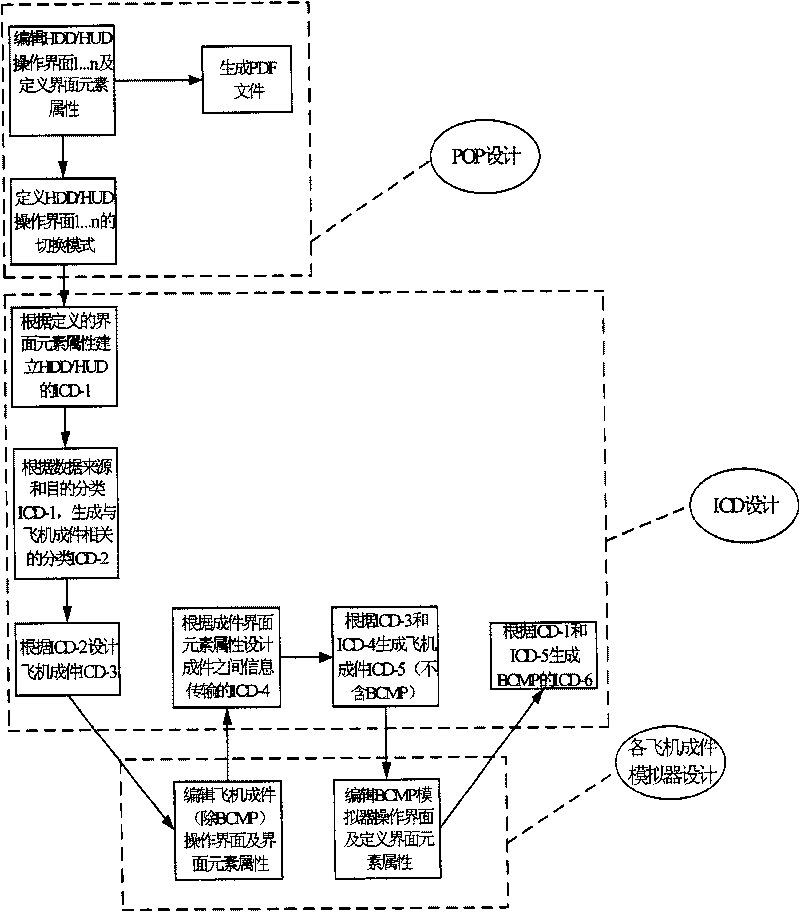

Avionics system digitalized design verification system and method

ActiveCN101763443AChange the measured valueRealize processingSpecial data processing applicationsElectricityDisplay device

The invention relates to an aircraft avionics technology, in particular to an avionics system digitalized design verification system and a method. The system comprises a BCMP simulator, a MC simulator, an aircraft member simulator, a display device simulator and an OFP emulator. The invention comprises the following design steps such as POP design, system ICD design, each aircraft member simulator design and BCMP simulator design and the like, which can provide digitalized design tools for aircraft design stage, verify the top-level design without verification and modification at the uniting and adjustment stage after the aircraft members are developed, and greatly reduce cost and time of the design, verification and modification of the top-level design; moreover, pilots can intervene in advance in the prior period of model number design, thus evaluating the overall design of the avionics system and shortening model number development cycle.

Owner:JIANGXI HONGDU AVIATION IND GRP

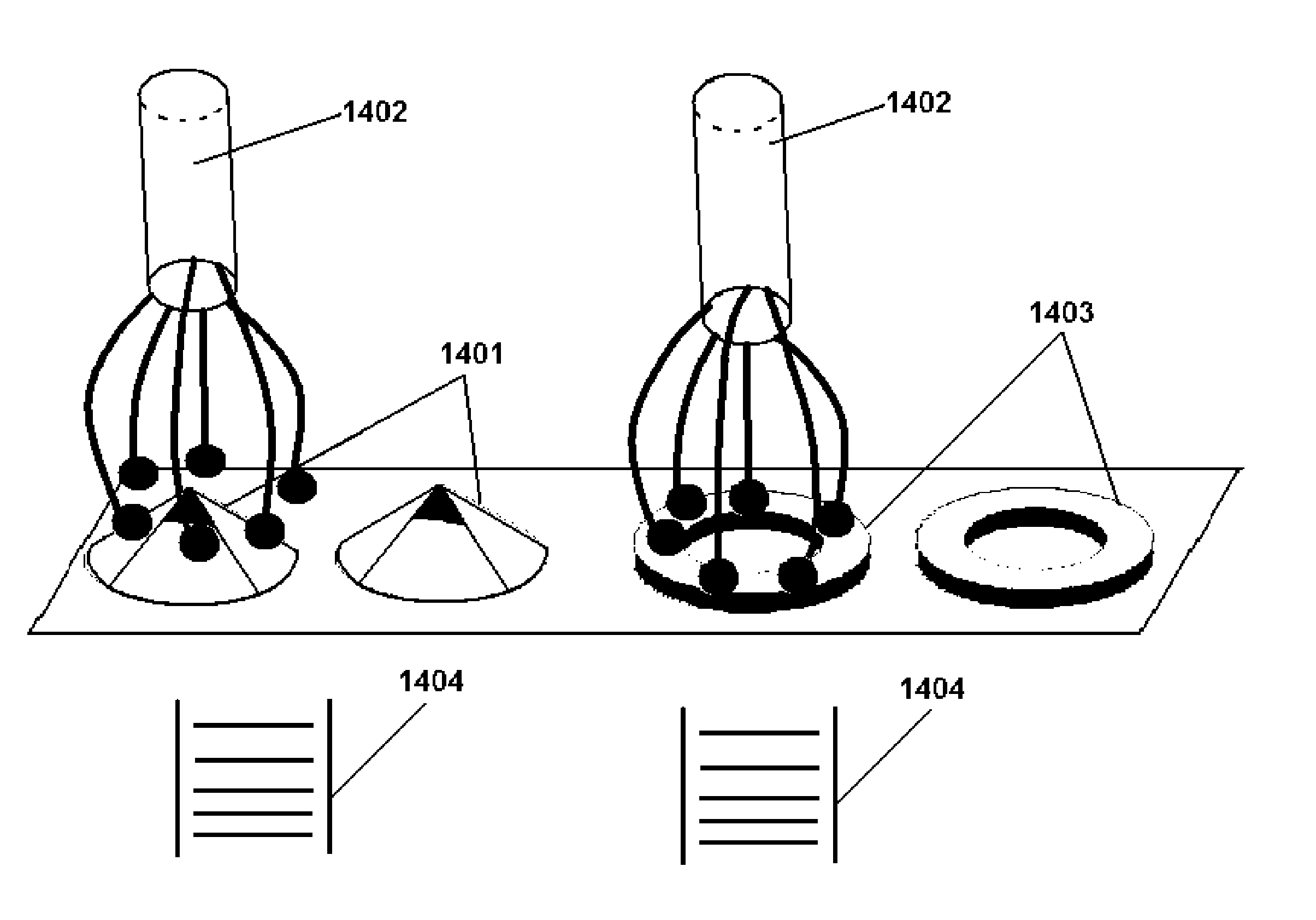

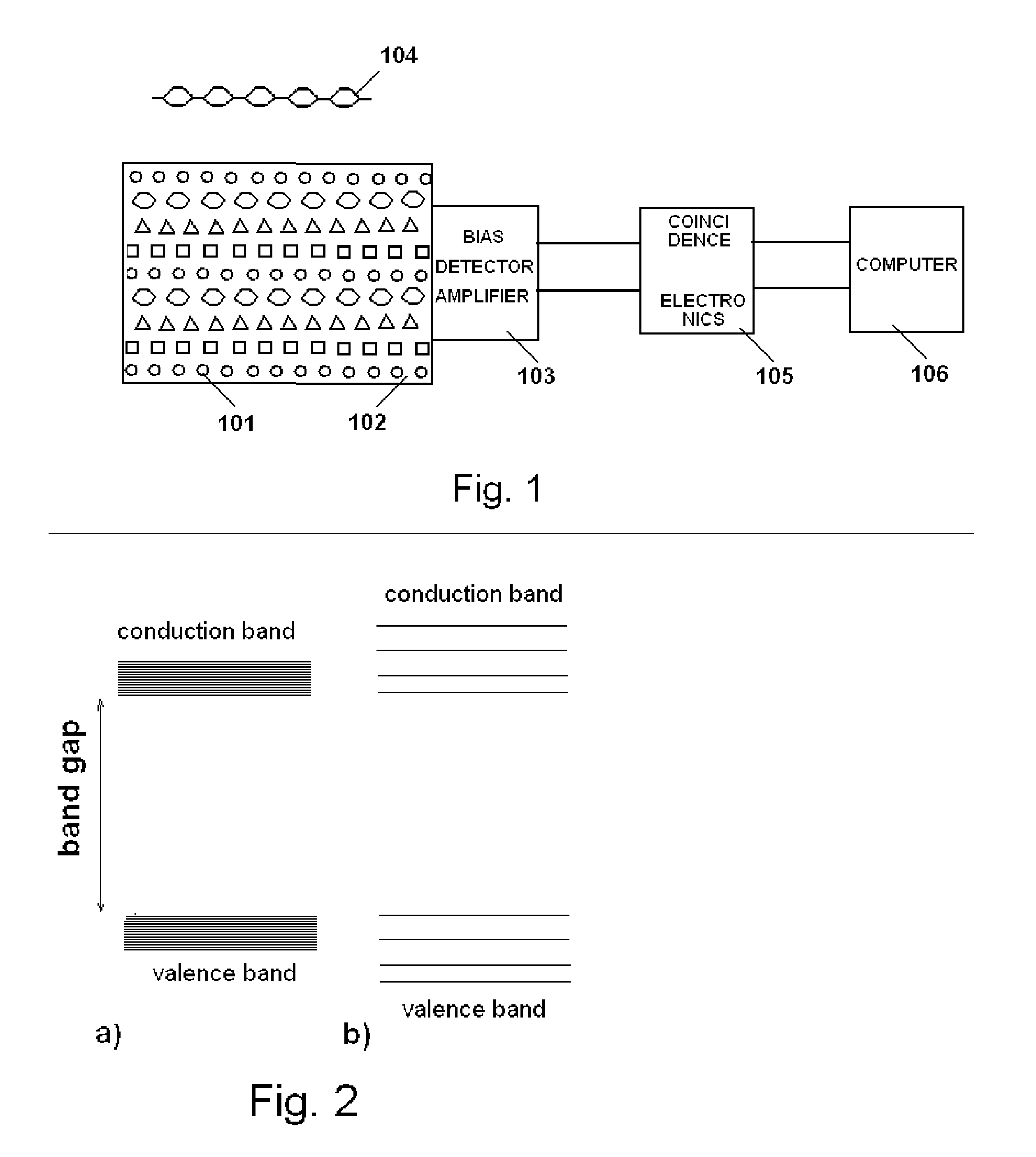

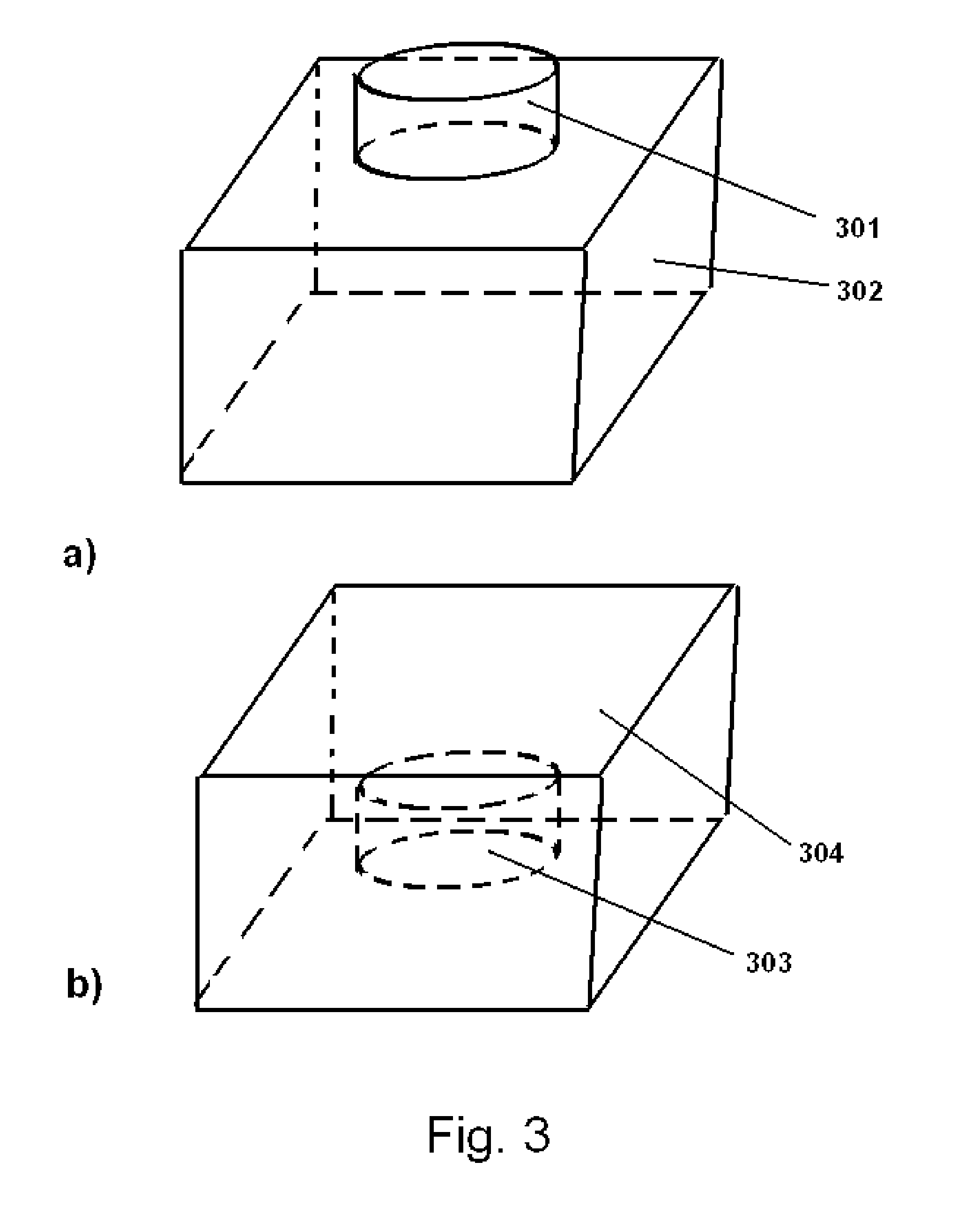

Detection methods and detection devices based on the quantum confinement effects

InactiveUS20090321261A1Easy to detectMiniaturizationOptical radiation measurementBioreactor/fermenter combinationsTarget analysisEnergy transfer

The invention describes detection methods and devices that comprise nanostructures and which detection mechanism is based on the quantum confinement effects. The nanostructures are built to have specific energy levels designed to match the energy levels of the targeted analyte that is to be detected. The analyte species are sensed by measuring charge or / and energy transfer between the species and the nanostructures, which will be proportional to the overlap between the density of states distribution in the nanostructures and the density of states distribution in the targeted analyte species. Different molecular species have different electronic density of states, so the charge or / and energy transfer between the targeted analyte and detector nanostructures will occur only for specific analyte which has the same electronic density of states as the detectors nanostructure. The detection methods, devices, and potential applications include, but are not limited to: chemical, biochemical, biological or biochemical analysis.

Owner:VLAHOVIC DR BRANISLAV +1

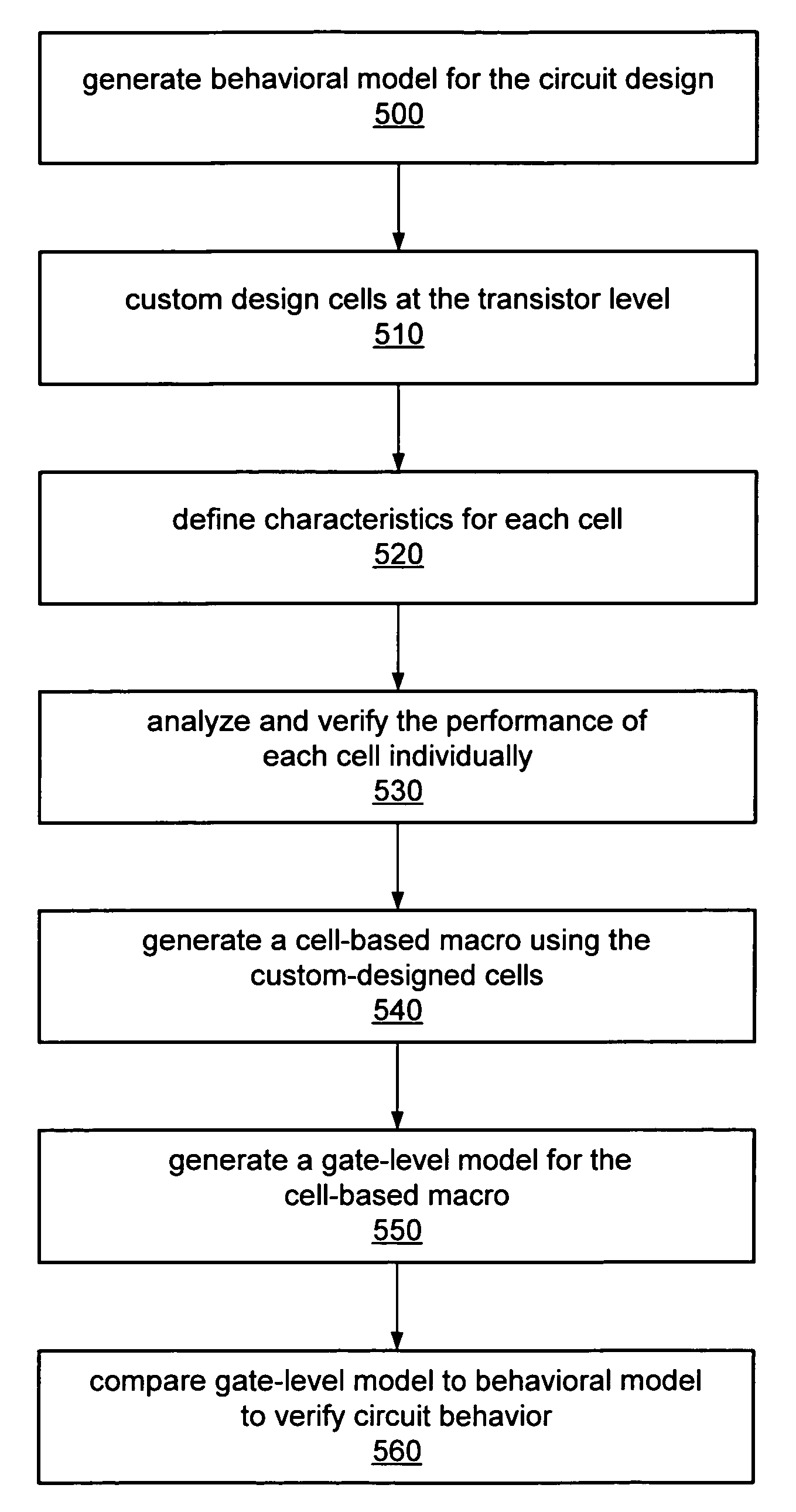

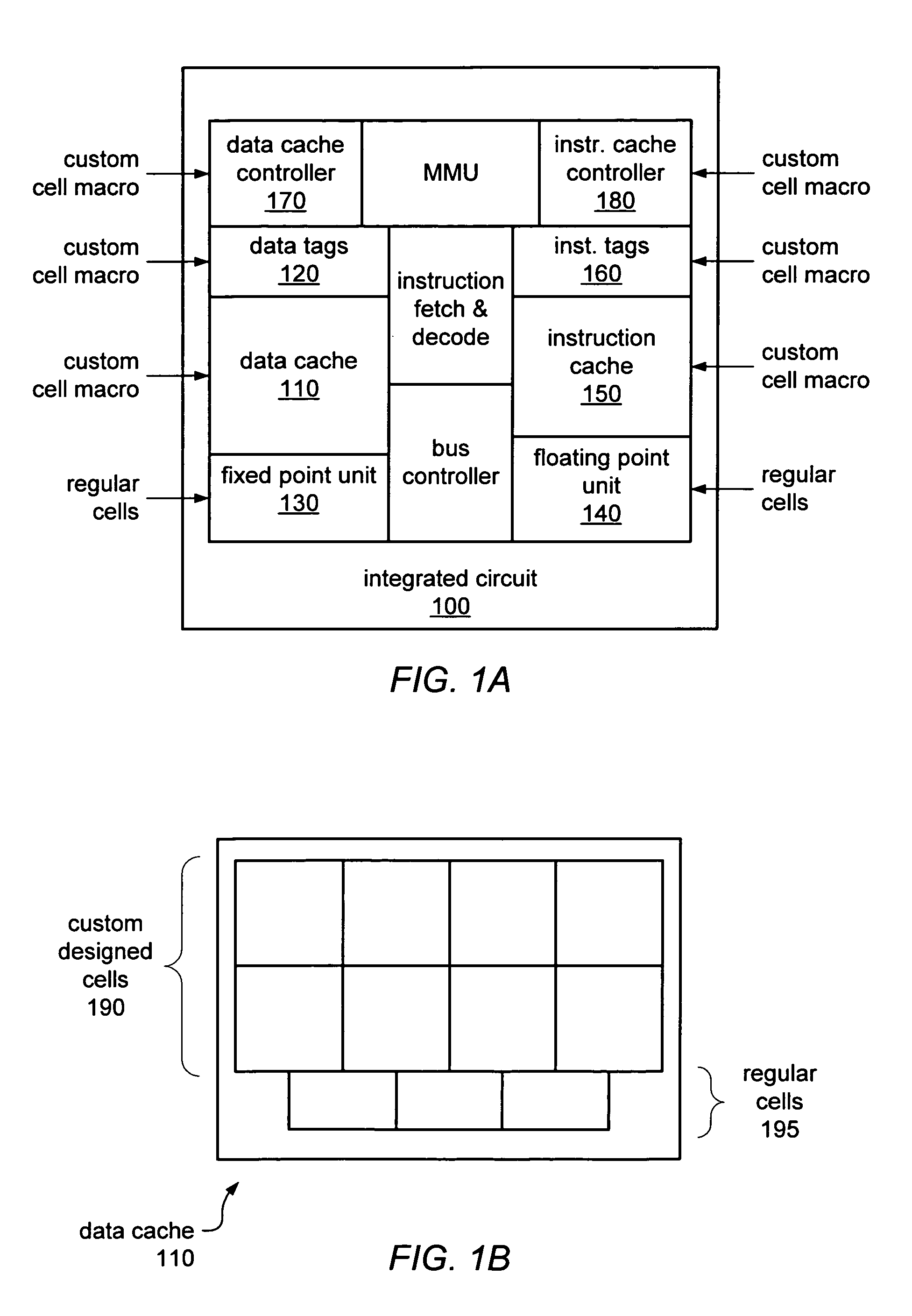

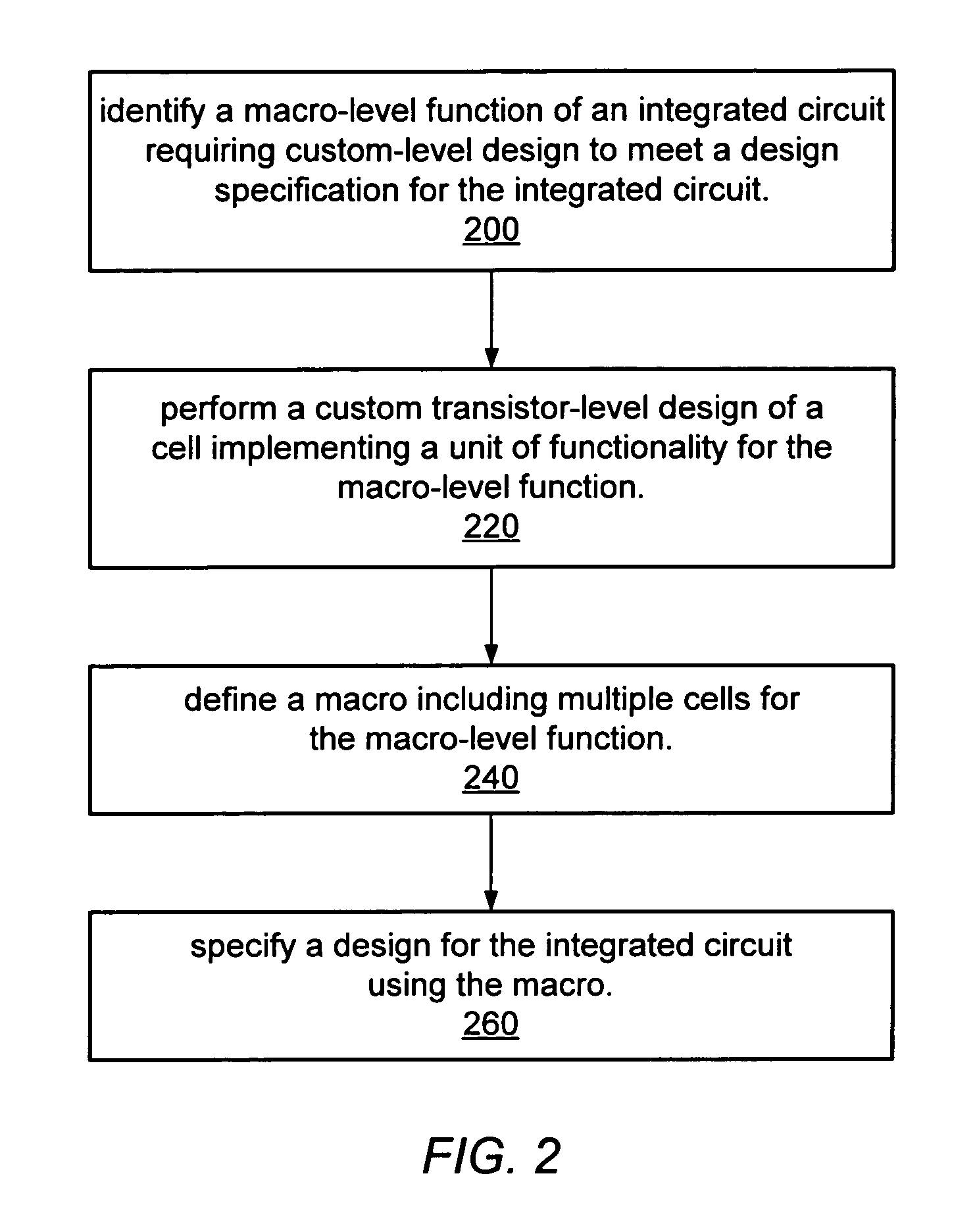

Integrated circuit design with cell-based macros

InactiveUS7401310B1CAD circuit designSoftware simulation/interpretation/emulationStatic timing analysisValidation methods

A method for designing integrated circuits may include custom designing, at the transistor level, individual cells to be incorporated into cell-based macros. A macro-level function of an integrated circuit's design specification requiring custom, transistor-level design may be identified and custom cells may be designed at the transistor-level to meet the design specification. Custom designed cells may be included in cell-based macros, thus allowing cell-based simulation and verification methodologies and tools to be used on the integrated circuit design. Static timing analysis, circuit extraction and other characteristics may be defined for each custom cell and the timing analysis and circuit extraction for cell-based macros may be defined based on the timing and extraction information for the custom cells included in the macro.

Owner:GLOBALFOUNDRIES INC

Congestion management suitable for wideband satellite communication system

ActiveCN101309103AImprove service qualitySimplify Design ComplexityRadio transmissionData switching networksQuality of serviceLevel design

The invention discloses a congestion management method suitable for a broadband satellite communication system, which relates to the congestion management technology of the broadband satellite communication system in telecommunication field. The invention provides the proposal design of the system congestion management function and provides a configuration requirement on the buffer capacity of the satellite equipment from the aspects of satellite-ground congestion management function distribution, bandwidth resource distribution type, priority level design and congestion control measures based on the application and technology characters of broadband satellite communication system. The invention mainly uses pre-arranged bandwidth resource plan and distribution, adopts satellite equipment configured with large buffer to simplify the congestion control measures between satellite equipment and ground equipment, and effectively solves the design conflict between the quality of service of the system and the utilizing ratio of the bandwidth resource. The congestion management method suitable for a broadband satellite communication system of the invention has the advantages of simplifying the complexity of satellite equipment, enhancing the system running stability, and increasing the quality of service and the bandwidth resource utilizing ratio of the system. The congestion management method suitable for a broadband satellite communication system of the invention is especially suitable for the node-interconnected broadband satellite communication system.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP +1

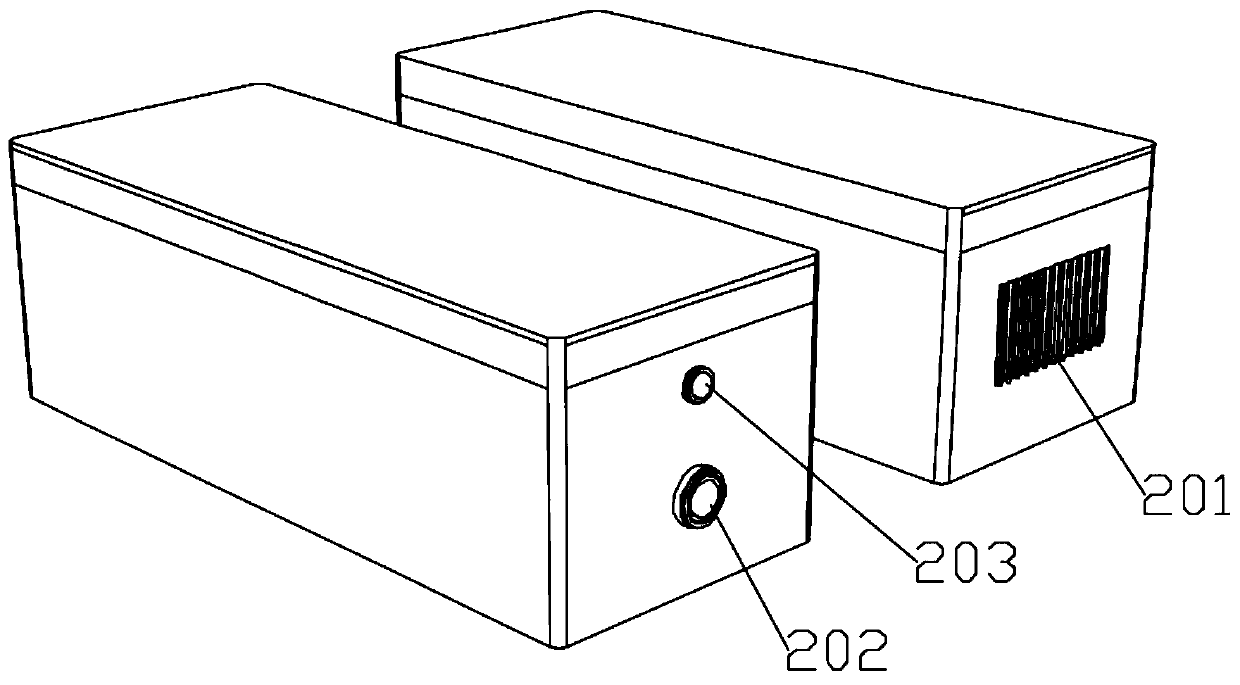

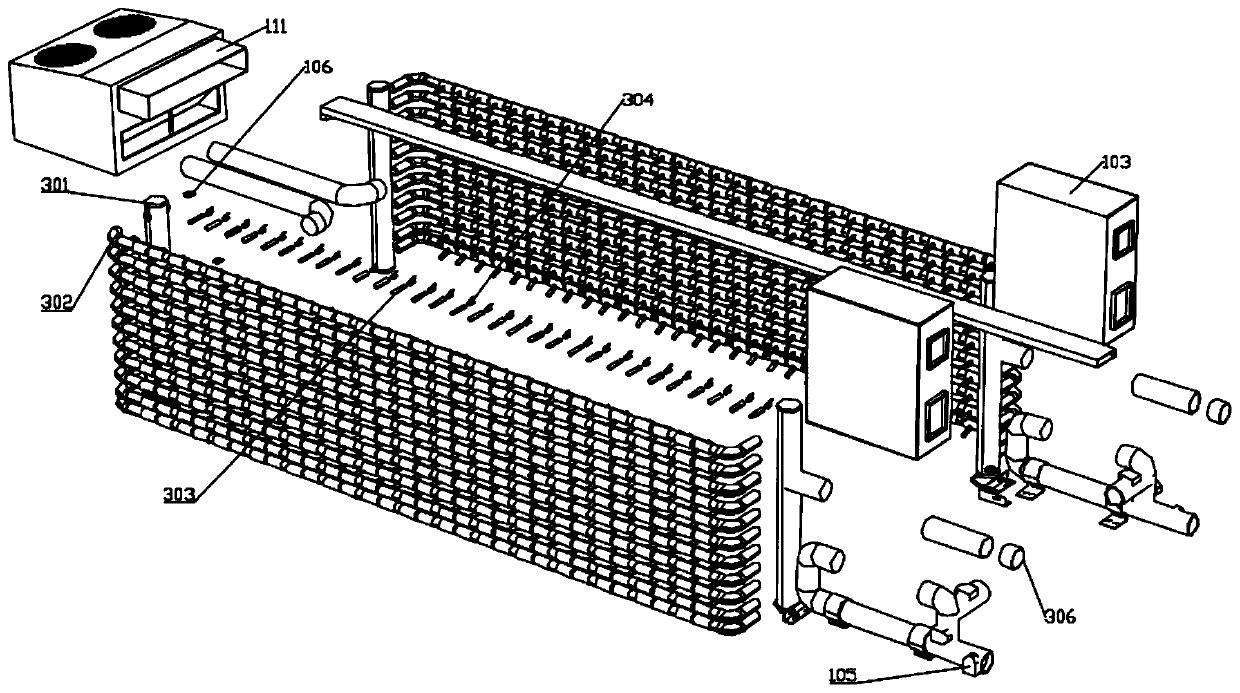

Thermal management and fire-fighting system equipment for electrochemical energy storage square cabin

PendingCN109893802AFix bugsSolve problemsFire rescueCell component detailsElectrical batteryThermal management system

The invention discloses system for thermal management and fire-fighting system equipment for an electrochemical energy storage square cabin, and solves defects existing in a heat management system ora fire-fighting system of an existing energy storage square cabin. The equipment comprises a heat management system, a battery module and a fire fighting system; the heat management system comprises an air cooling pipeline, a refrigerating machine, a total heat exchange unit, a gas monitoring module and a ventilation electromagnetic valve; the fire-fighting system comprises a fire-fighting agent mist spray release pipeline, a fire-fighting agent shower release pipeline, a fire-fighting agent conveying pipeline, a fire-fighting host, a flame detector, a temperature monitoring module and a secondary water fire-fighting connecting pipeline. According to the equipment, through the cooperation of the air cooling pipeline, the refrigerating machine, the temperature monitoring module, the flamedetector, the fire-fighting host and the like, the defects and shortcomings existing in the thermal management system or the fire fighting system of the existing energy storage square cabin are effectively overcome, the safety and the reliability of the energy storage square cabin are guaranteed through the integrated top level design, and the operation risk and the maintenance cost of the energystorage square cabin are reduced.

Owner:SOUTHERN POWER GRID PEAK LOAD & FREQUENCY REGULATION GENERATING CO LTD +2

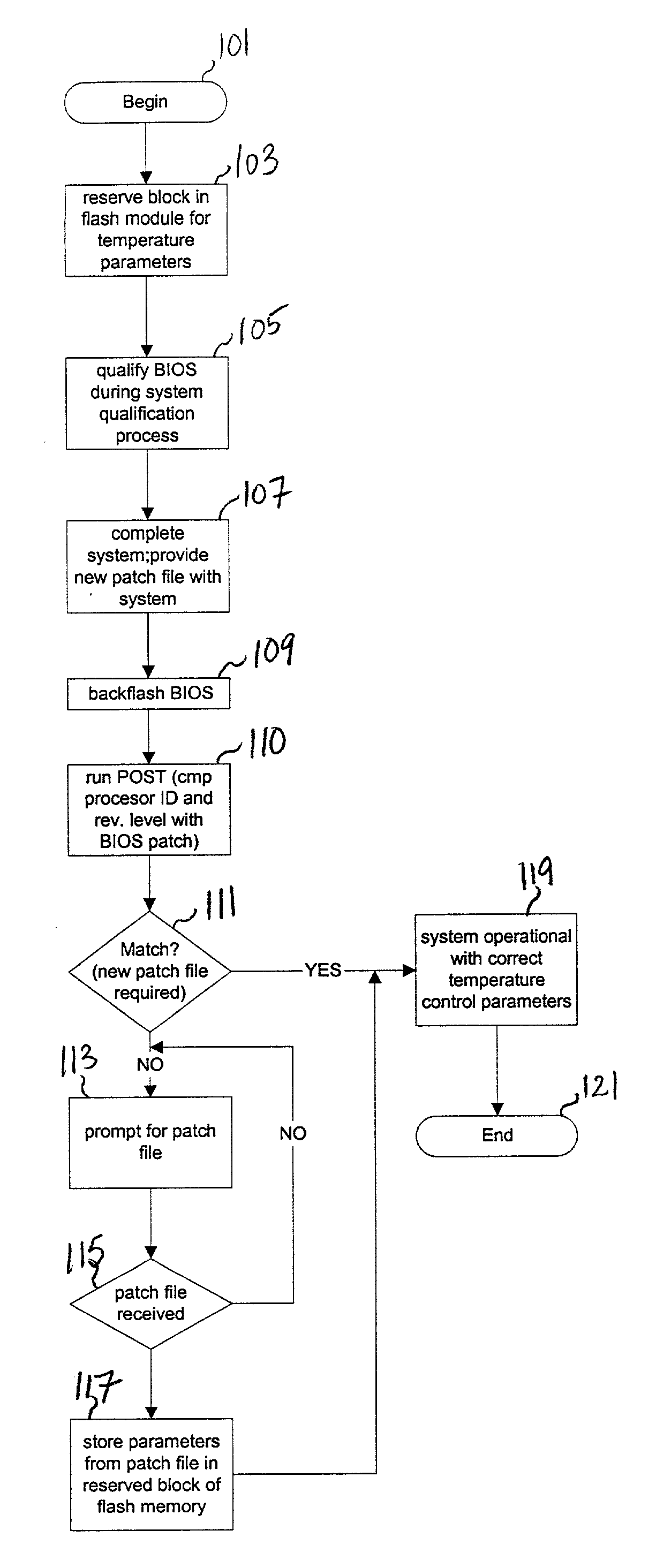

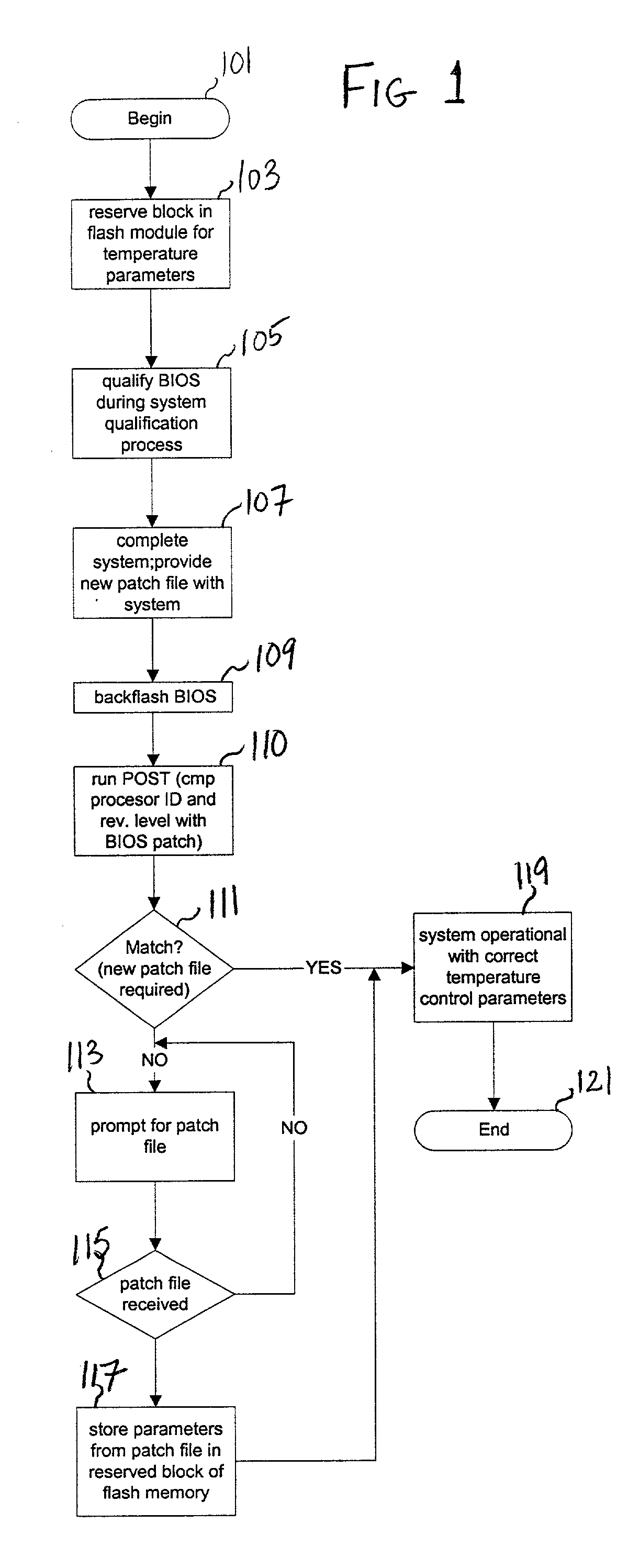

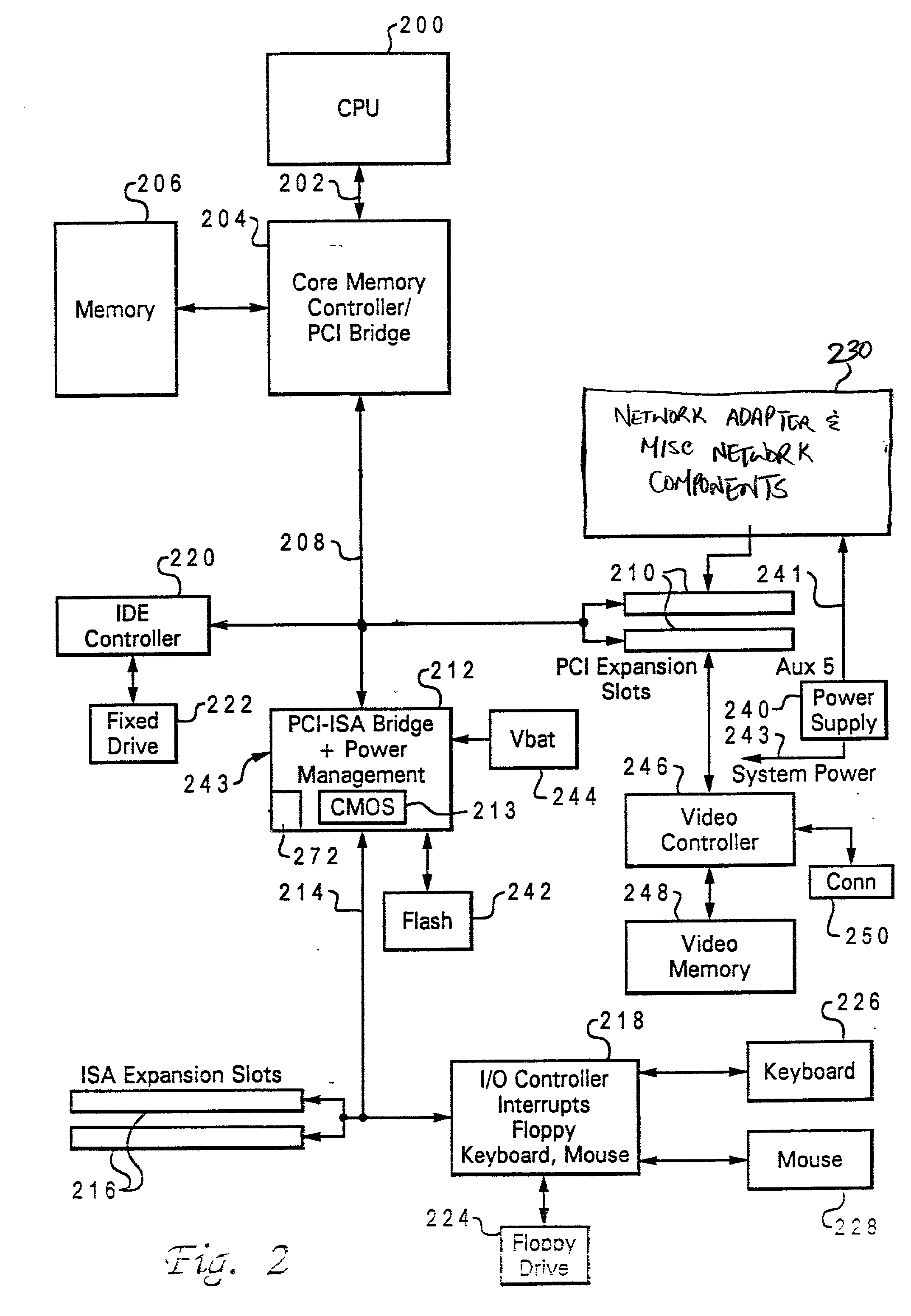

Method and system for providing a flexible temperature design for a computer system

A method and system for providing correct operational parameters for up-level design components utilized within a computer system after a low level basic input / output system (BIOS) code has been qualified. A patch file is created or obtained for a component that is added to a computer system after a BIOS code has been qualified for the computer system. The patch file includes the operating parameters (or profiles) of the component. The flash module is designed with a memory block reserved for holding data from the patch file, which can be updated independently of the rest of the flash module. The Advance Configuration Program Interface (ACPI) or advanced power management (APM) code of the computer system is modified to dynamically read the parameters from this memory block and update their respective functions accordingly. During set up of the computer system, the patch file is flashed into the reserved block of the flash module. The data is merged by the FLASH utility into the existing BIOS so that the computer system has the correct parameters for the particular component.

Owner:LENOVO PC INT

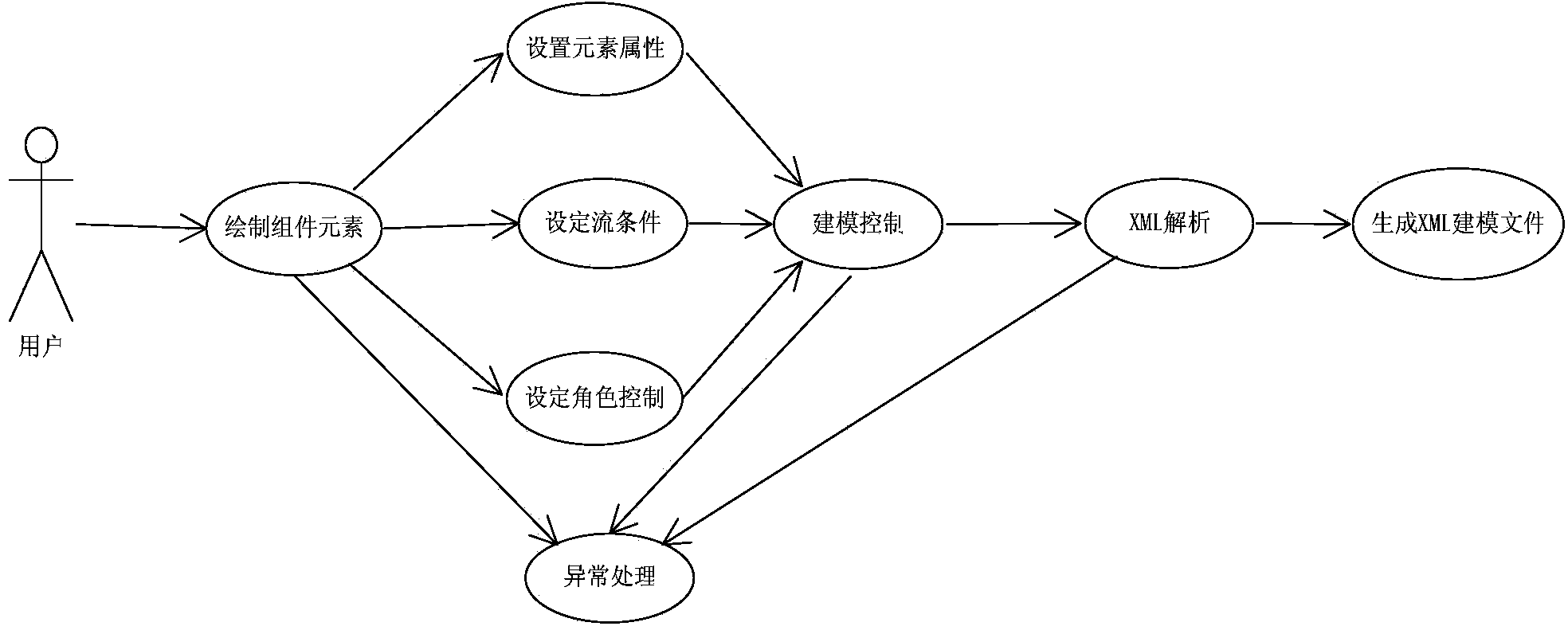

Visual game level editing method and system based on trigger

ActiveCN105653274AShorten development timeImprove maintainabilityVisual/graphical programmingSpecific program execution arrangementsMaintainabilityReusability

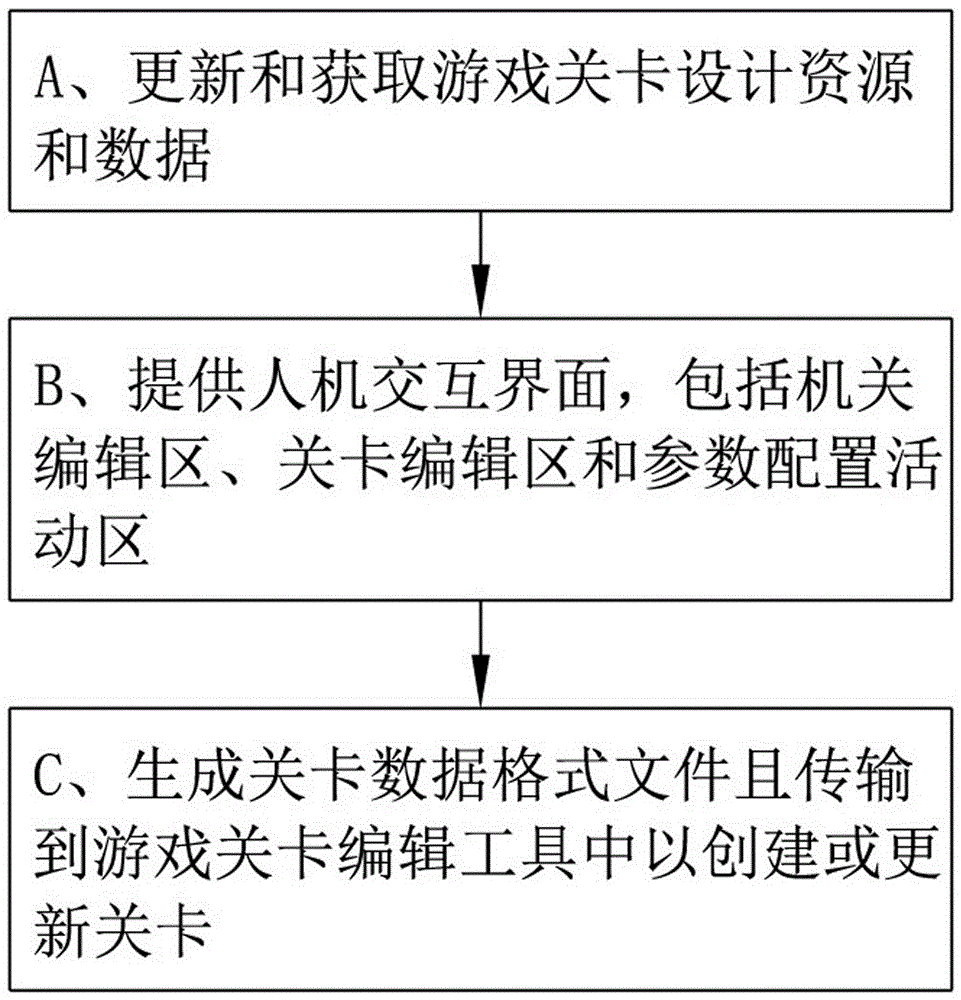

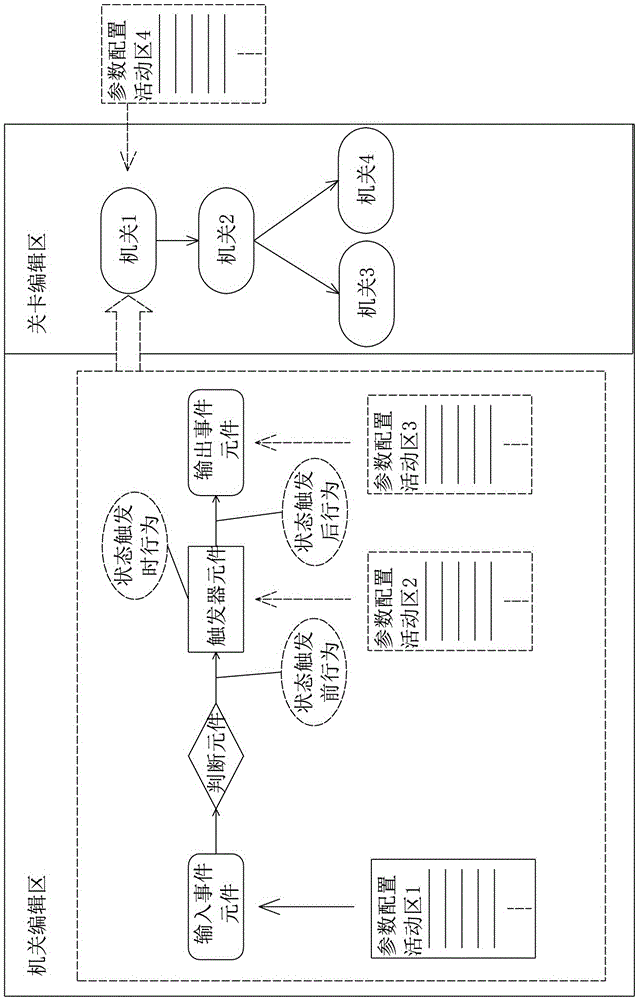

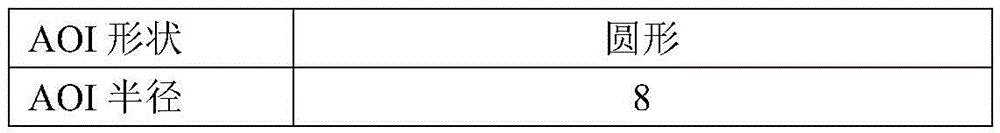

The invention discloses a visual game level editing method and system based on a trigger, wherein the method comprises the following steps of A, accessing a game development database, and updating and obtaining game level design resources and data; B, providing a man-computer interaction interface, wherein the man-computer interaction interface comprises a stratagem editing region, a level editing region and a parameter configuration activity region; C, loading the game level design resources and data into elements in the stratagem editing region and the level editing region configured by a user, and translating at least one tested stratagem combining element into a level data format file and transmitting the level data format file into a game level editing tool to create or updating the level. The system comprises a first module, a second module and a third module, wherein the first module is used for accessing the game development database; the second module is used for providing the man-computer interaction interface; and the third module is used for exporting the level data format file. The method and the system have the advantages that the game level development cost is obviously reduced; the reusability and the maintainability of code are improved.

Owner:ZHUHAI KINGSOFT ONLINE GAME TECH CO LTD +1

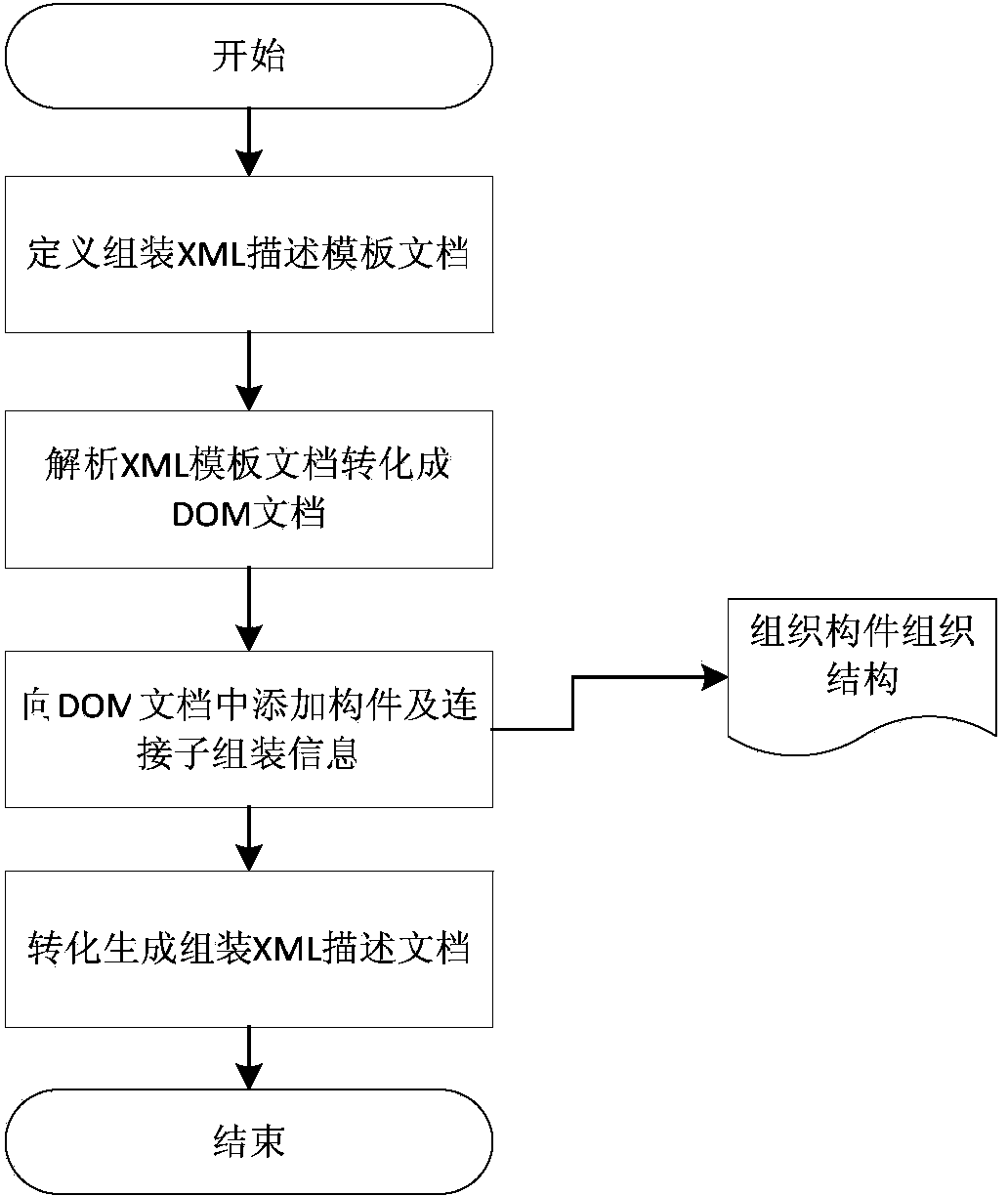

Full life circle development achievement system of intemetware

InactiveCN103645908AImprove scalabilityClear business processSpecific program execution arrangementsFile synchronizationThird party

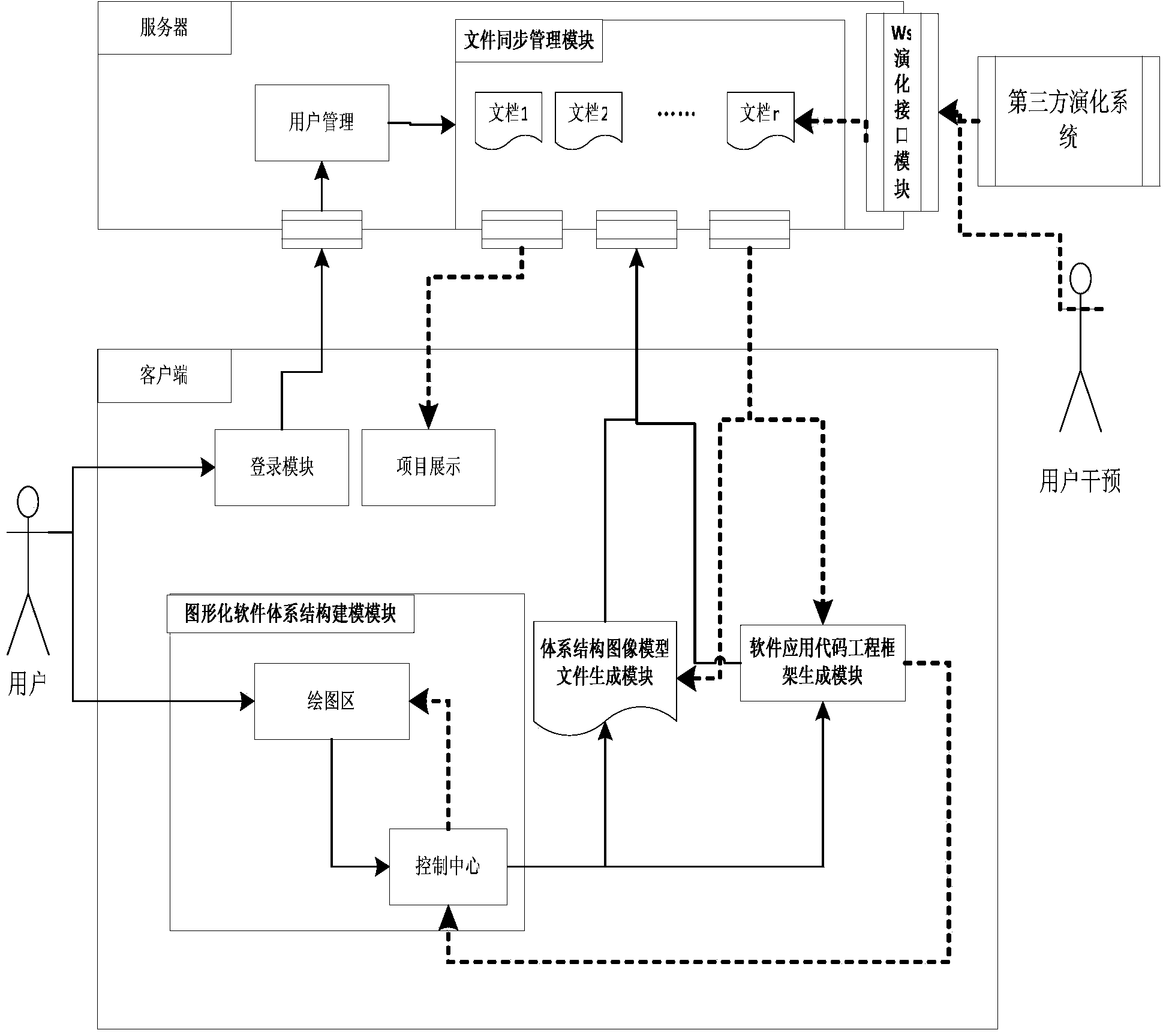

The invention discloses a full life circle development achievement system of intemetware, which is a client and server framework. A client comprises a graphical software system structure modeling module, a system structure image model file generation module and a software application code engineering frame generation module, wherein a server comprises a file synchronization management module and a Web Services evolution interface module. A subscriber generates a code frame through the code engineering framework generation module of the system after graphical modeling of a business layer by collaborative development, so as to remove a barrier from the business layer to a code achievement layer. The overall service component architecture (SCA) has dynamic evolution by leading in an ideal of a CCO model and transforming the SCA, and the dynamic evolution mechanism is encapsulated into an interface to be provided to a third party sensing drive evolution system, so that the overall code frame has the evolution function. By adopting the full life circle development achievement system, a total development target that a top-level design is provided for development of a network large complicated software system, a code generation technology is provided for development of the intemetware, and a supported overall development target is provided for dynamic evolution of the intemetware is achieved.

Owner:INST OF SOFTWARE - CHINESE ACAD OF SCI

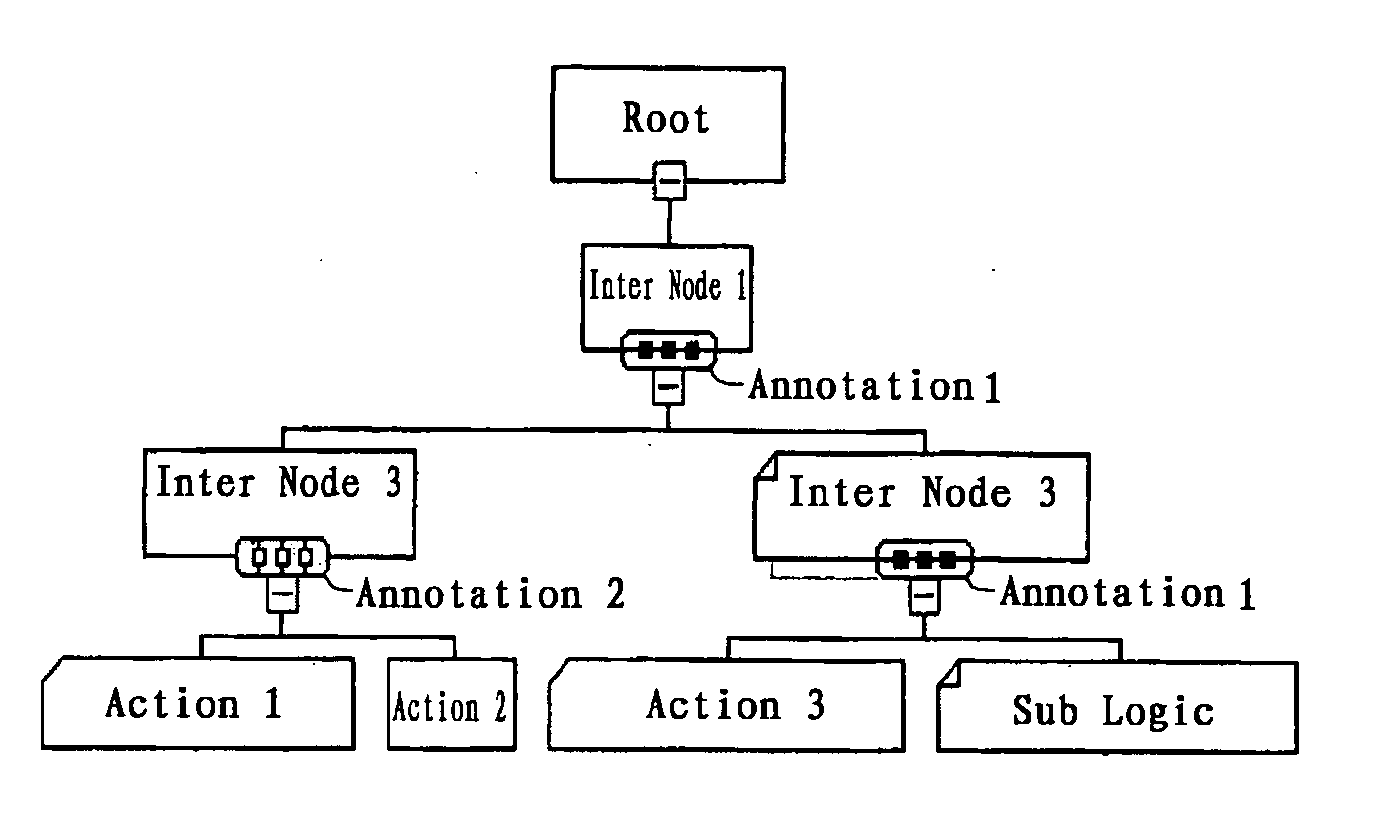

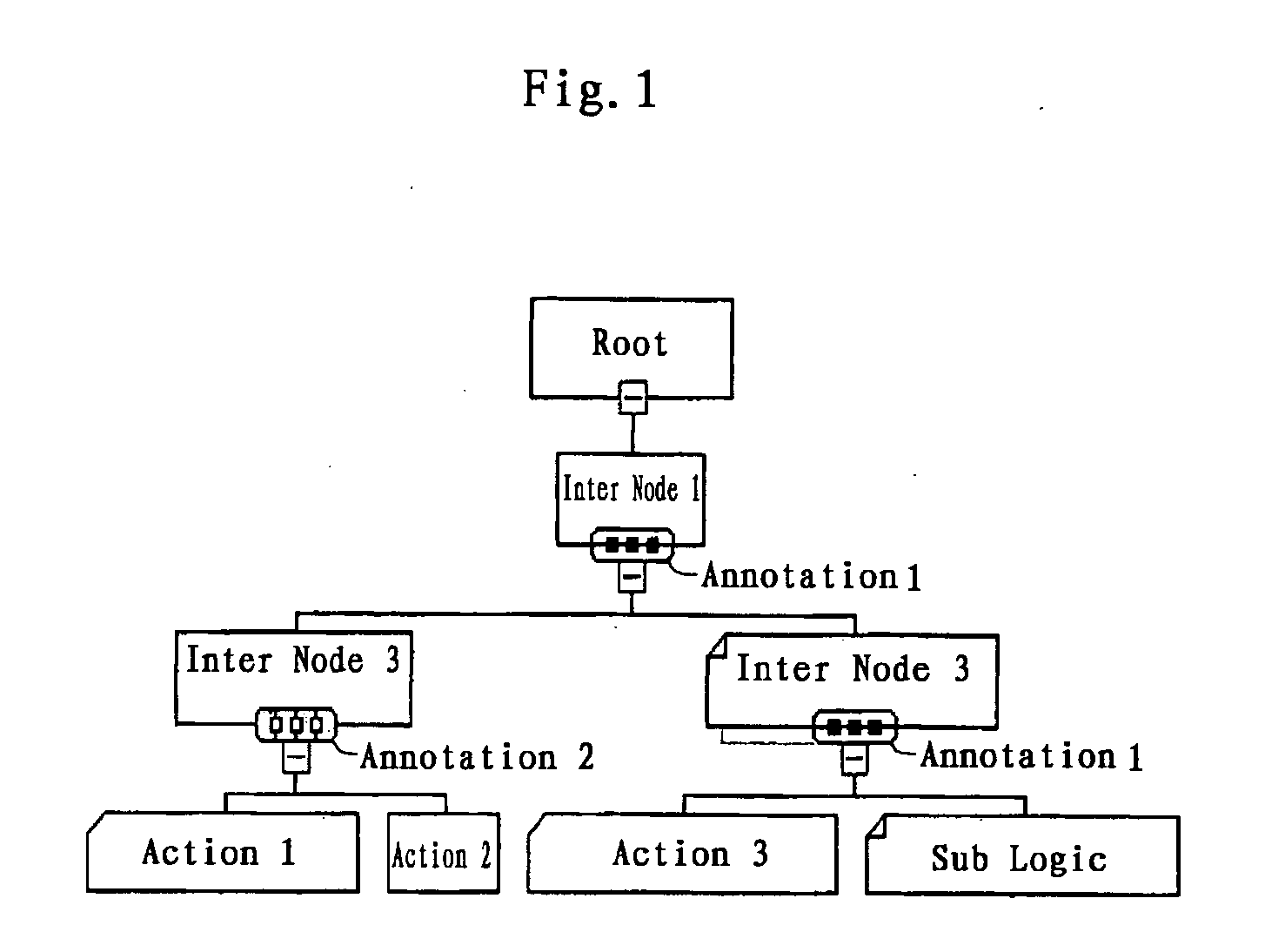

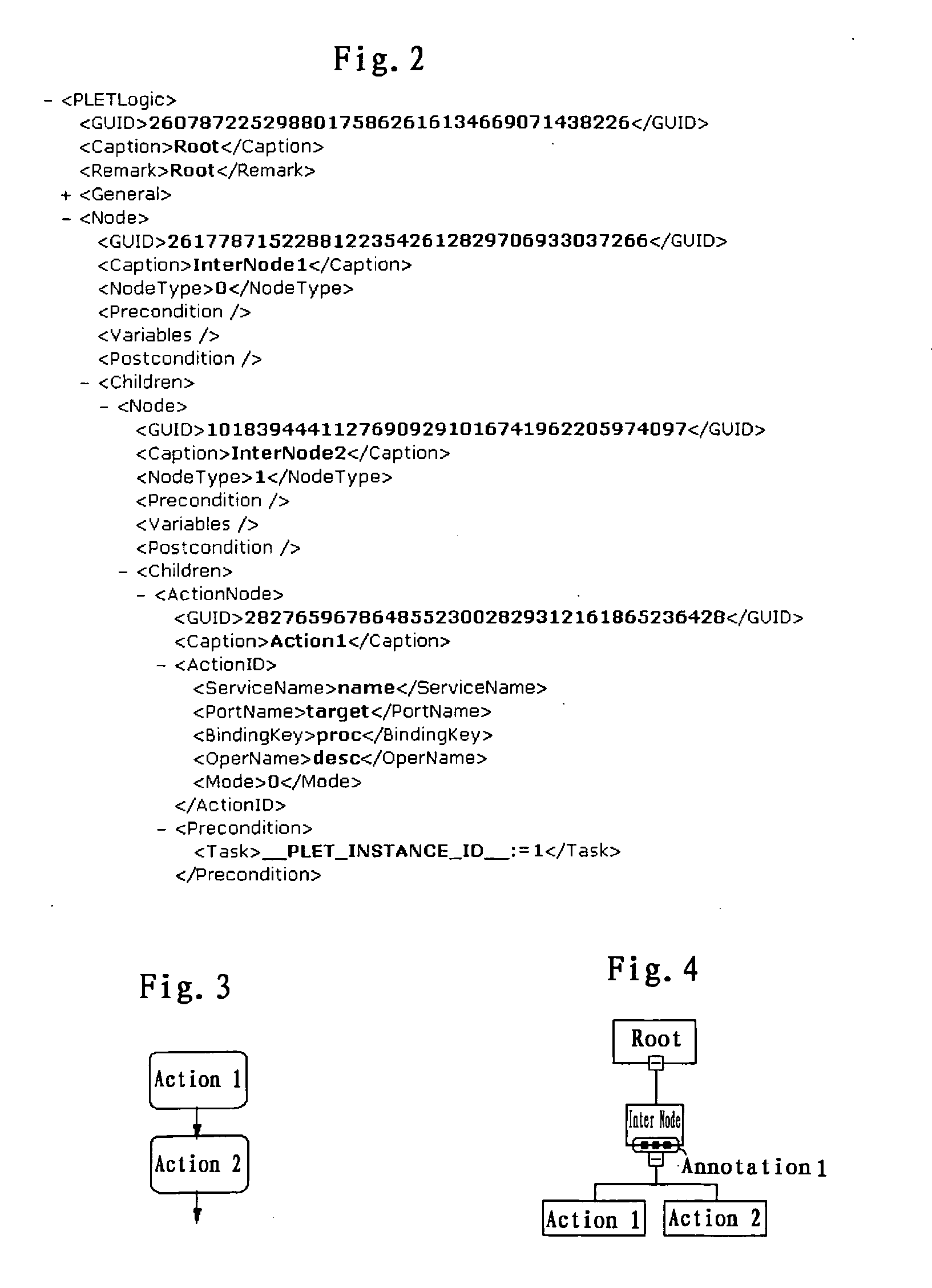

Processing logic modeling and execution

InactiveUS20050289088A1Promote collaborationDigital computer detailsSoftware designAnnotationLevel design

Provides processing logic modeling and executing methods, systems and apparatus. These facilitate collaboration between business analyst and IT staff for process modeling and maintenance of the consistency between business level design and IT implementation design. A task is decomposed into sub-tasks and is represented by a tree. Annotations to the nodes of the tree are used to represent the relations between the sub-tasks. A processing logic is thus completed. When executing the processing logic, traversing the tree follows according to the annotations.

Owner:IBM CORP

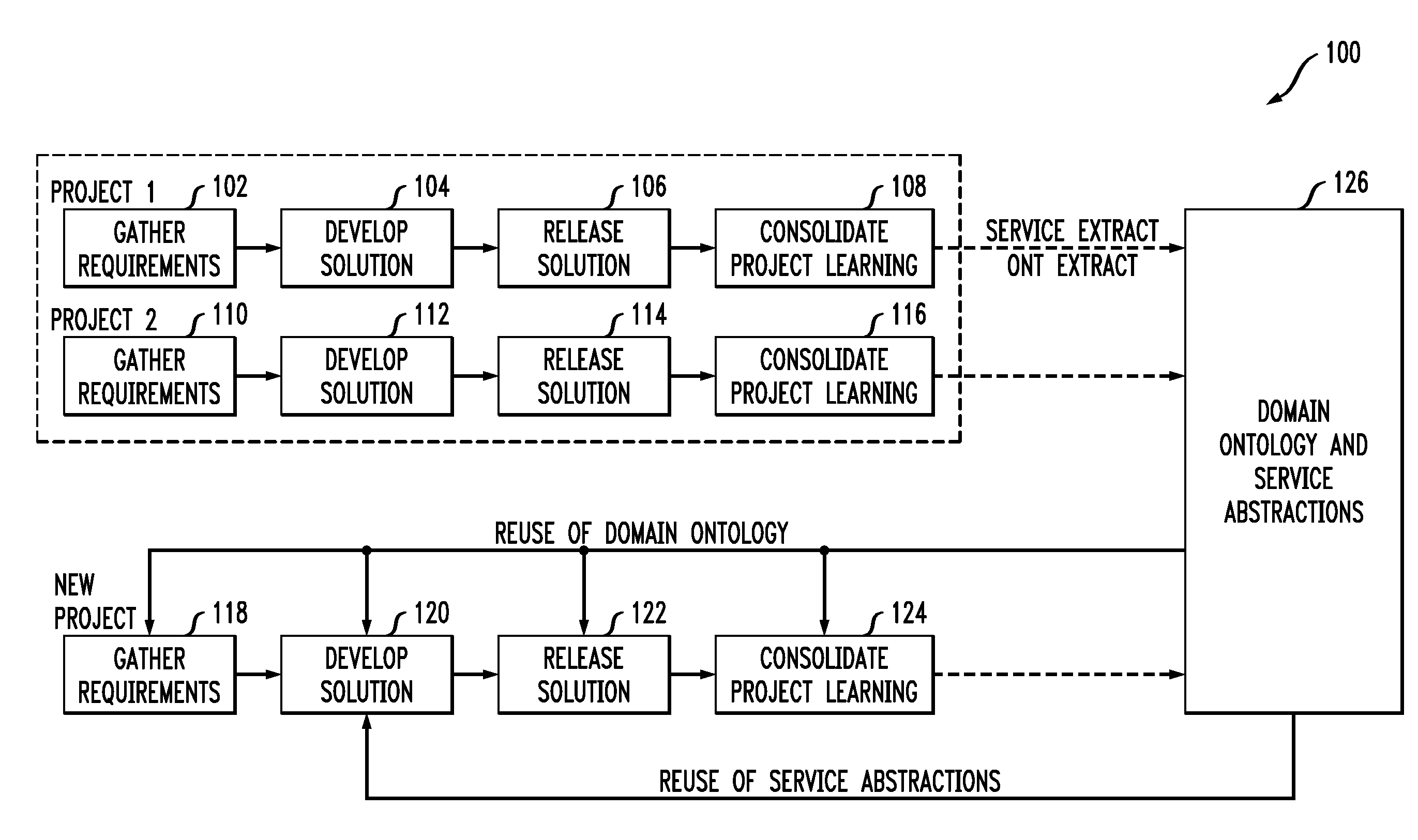

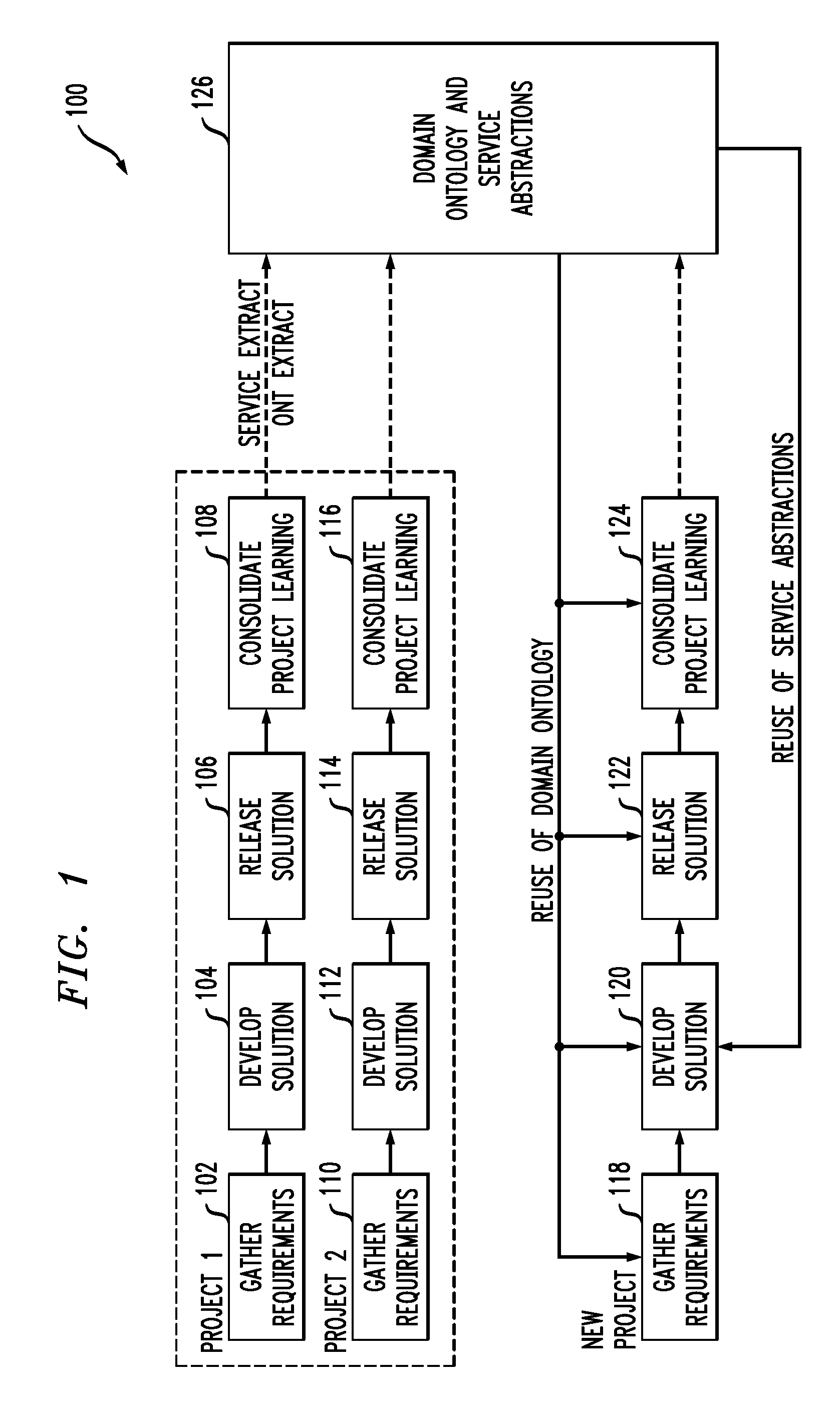

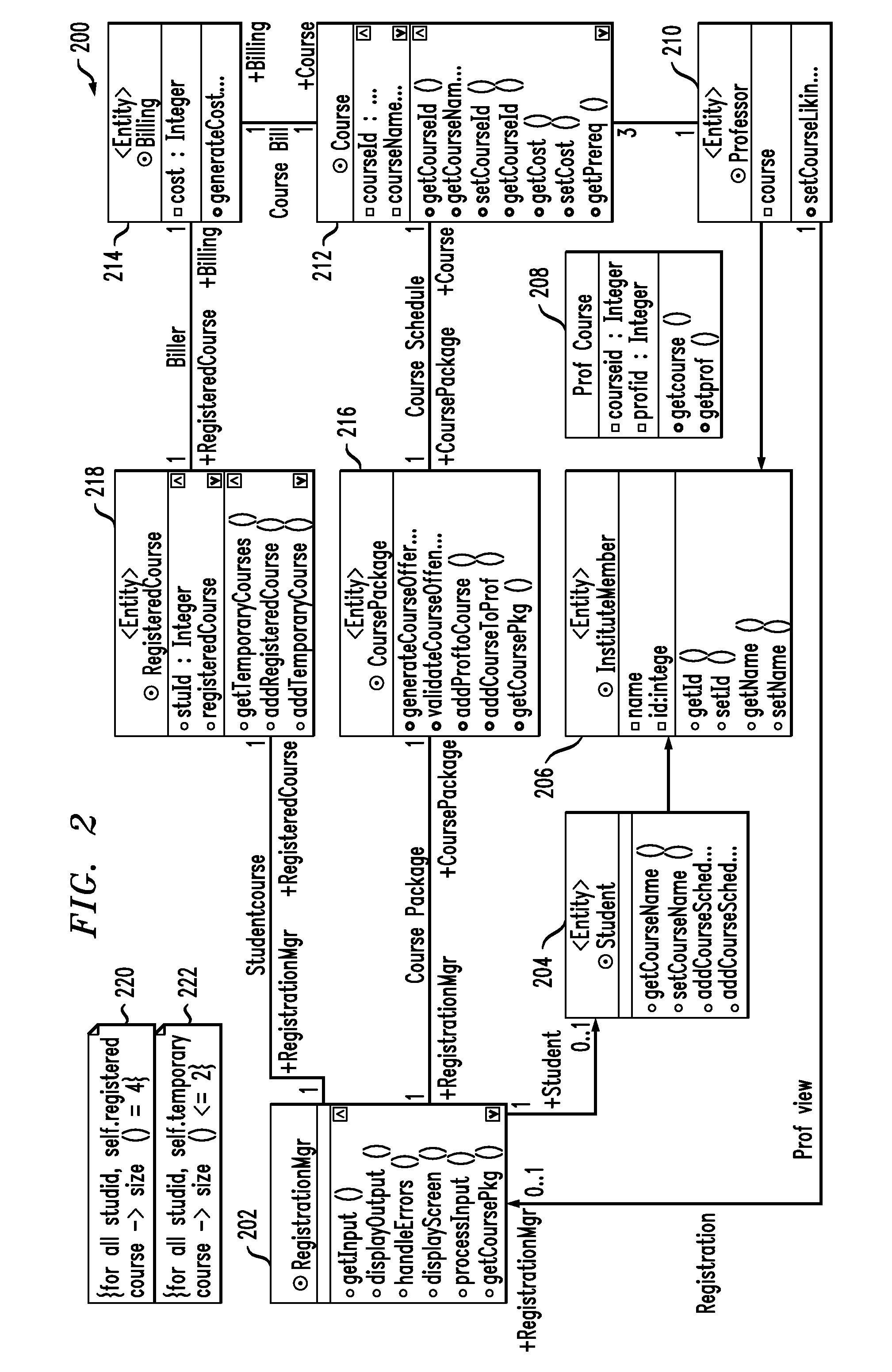

Generating functional artifacts from low level design diagrams

InactiveUS20100122238A1Shorten development timeLess timeRequirement analysisSoftware reuseLevel designClass diagram

At least one design diagram is obtained from at least one previous software project. At least one service abstraction is extracted from the at least one design diagram. The at least one service abstraction is reused in a new software project. In another aspect, requirements are obtained for a current software project; at least one class diagram is obtained from at least one previous software project; a dependency graph is generated from the at least one design diagram, using link analysis; relationships between classes in the dependency graph are analyzed to obtain functional artifacts for the requirements; and the functional artifacts are reused in the new software project.

Owner:IBM CORP

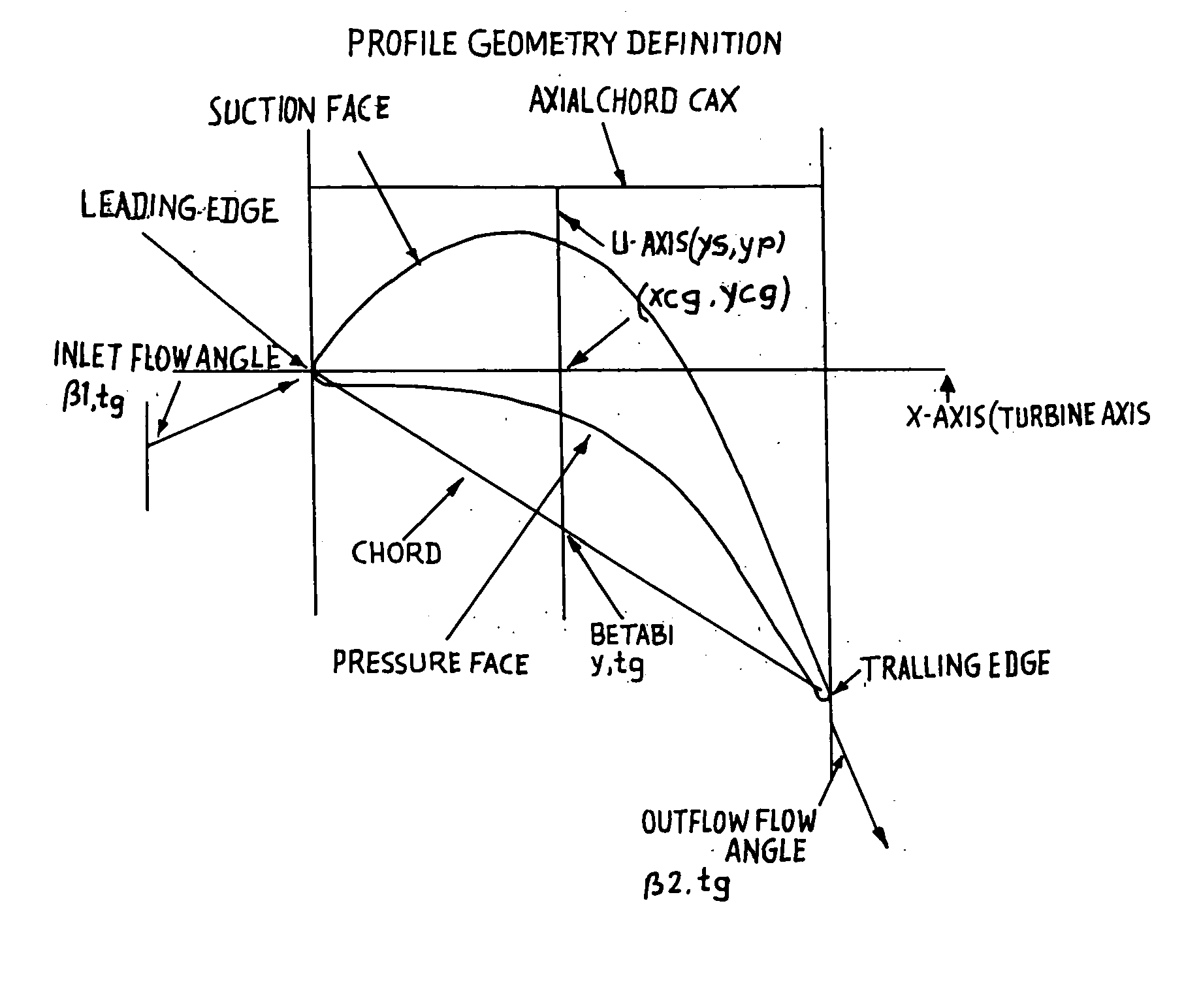

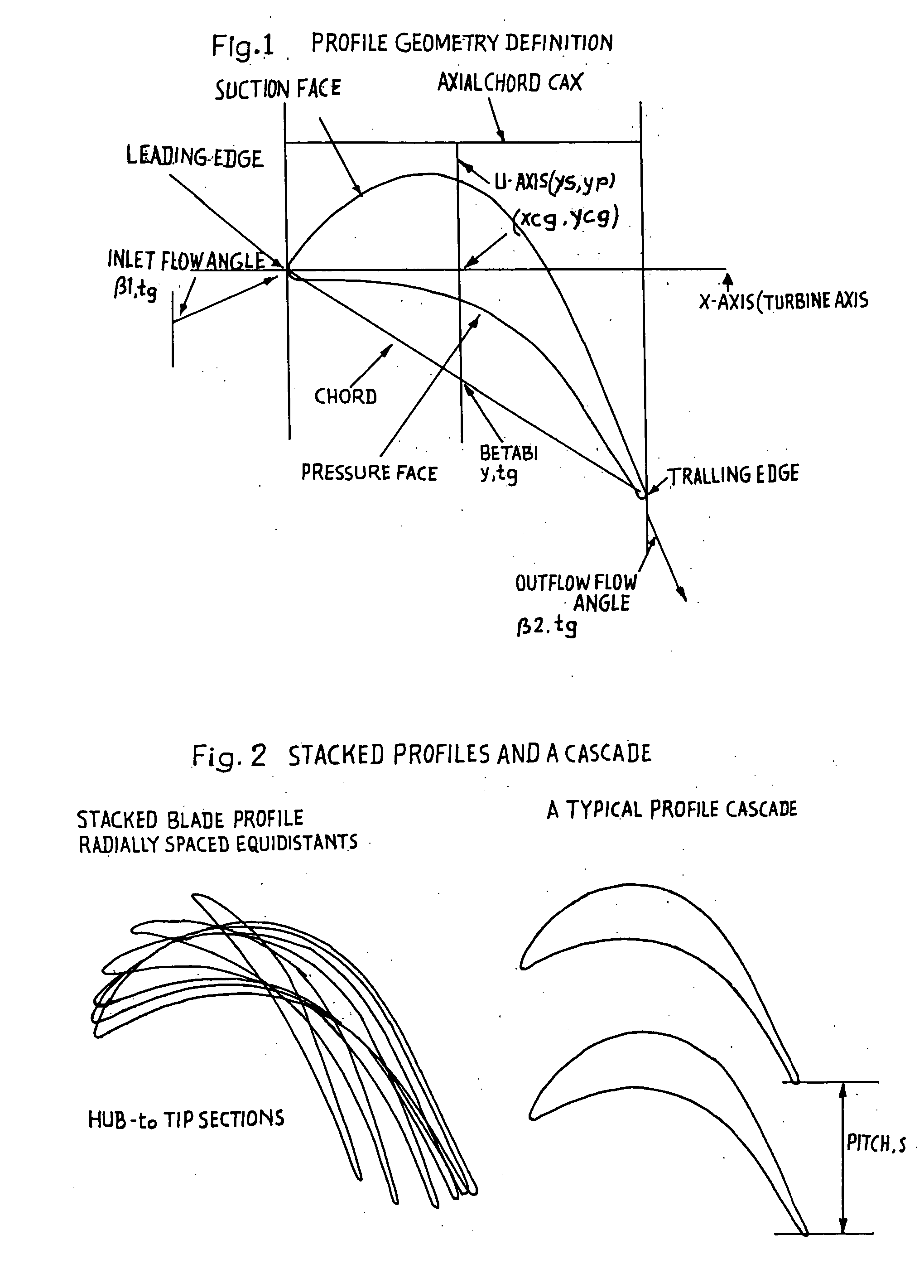

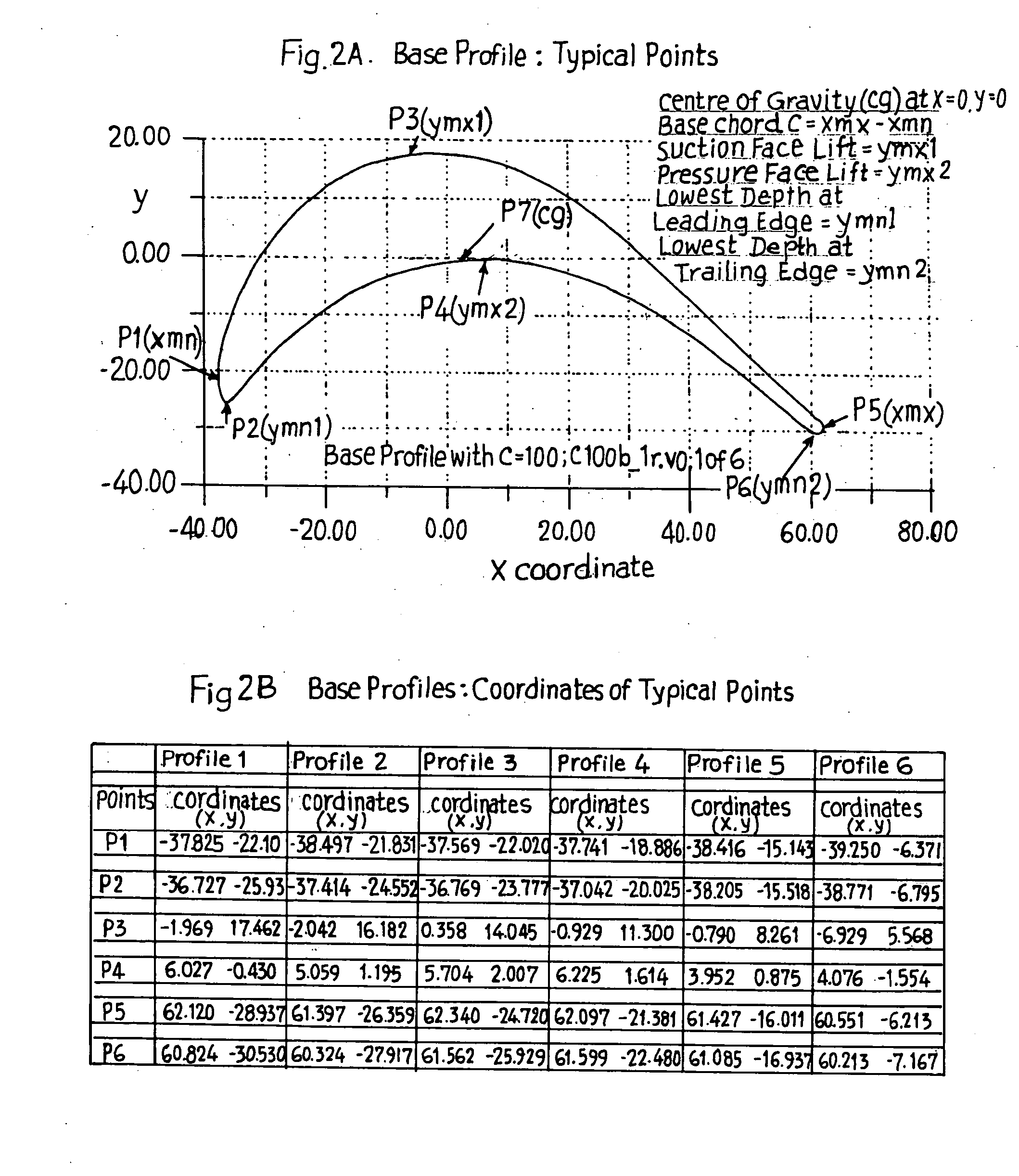

Transonic blade profiles

InactiveUS20050220625A1Taller in heightHigh aspect ratioEngine manufactureOther chemical processesEngineeringNomogram

The present invention relates to the aerodynamic design of moving blades, pertaining to later stages of axial steam turbines where the inlet flow is non-uniform over the blade height. The claim made herein is a set of six invented transonic blade profiles which can be used to develop various type of 3D twisted blades for axial steam turbine. The aerodynamic characteristics of these 6 base profiles are evaluated herein as a function of stagger angle and pitch / chord ratios. The aerodynamic characteristics invented herein is for a group of six base profiles which are to be used for creation of three dimensional blades made of varying cross-sections and twisted over the blade height while ensuring the centers of gravity of these sections lie in a radial line. Each of the blades, sections from hub to tip is twisted differently from desired outlet angle. Thus the nomograms can be used to develop quickly a first level design of a 3D blade making use of 2D base profiles whose performance is shown in the form of nomograms.

Owner:BHARAT HEAVY ELECTRICALS LIMITED

Computing device independent and transferable game level design and other objects

ActiveUS8864583B1Less capabilitySmall sizeStatic indicating devicesGeometric image transformationLevel designComputer science

A system which employs a method of creating transferable map schemas, storing the map schemas to storage devices, receiving target device settings, re-sampling the map schemas to fit the target devices using the target device settings, delivering the re-sampled map schemas to the target devices is described. Thereby providing the innovation that map schemas may be accessed by more than one type of device, the method by which maps are scaled from a created map dimension with given details to either a larger map having the ability to be utilized on a more capable playing device or to a map or a smaller map having the ability to be utilized on a less capable device without losing the important game-specific required data is also described.

Owner:IBM CORP

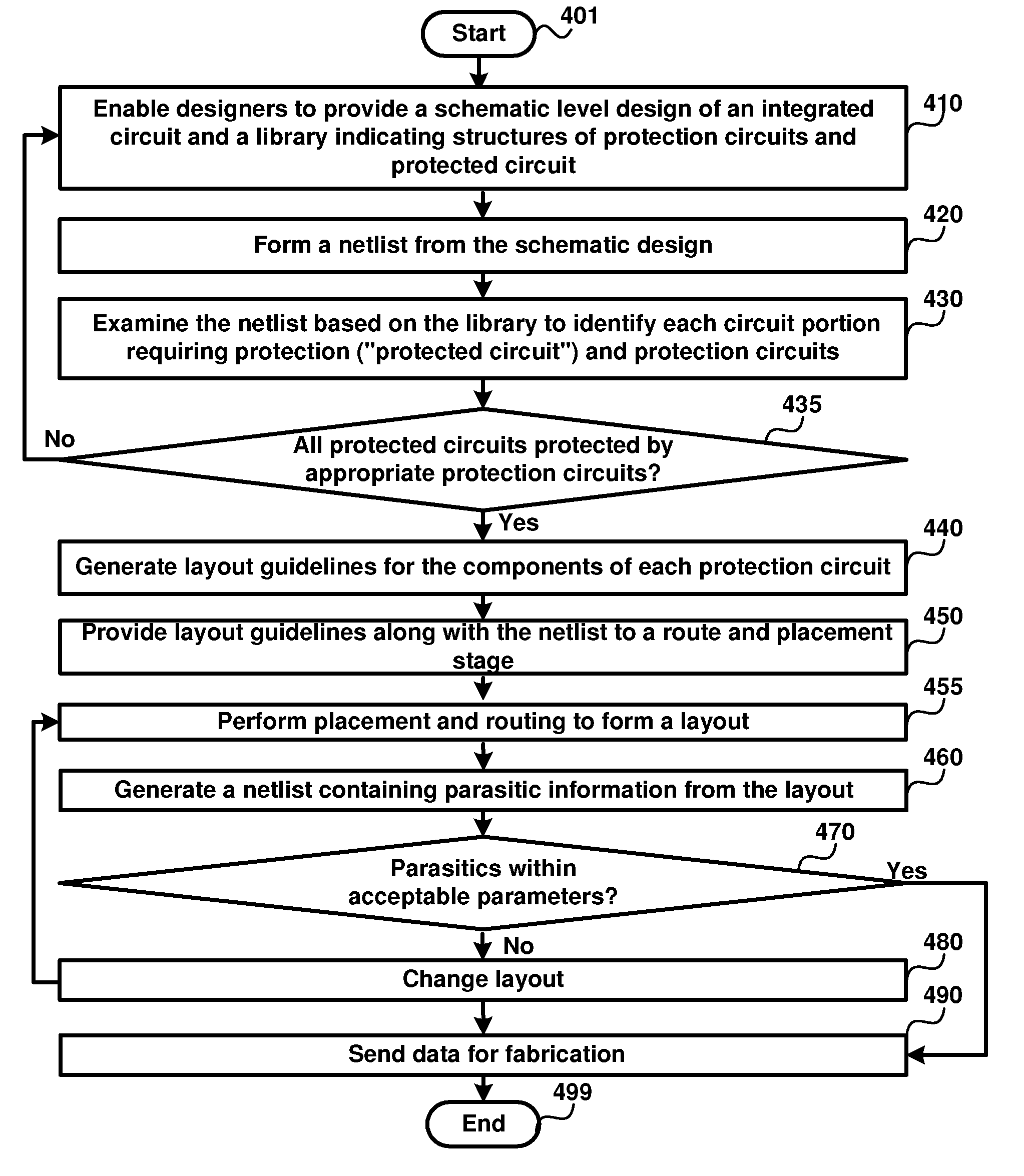

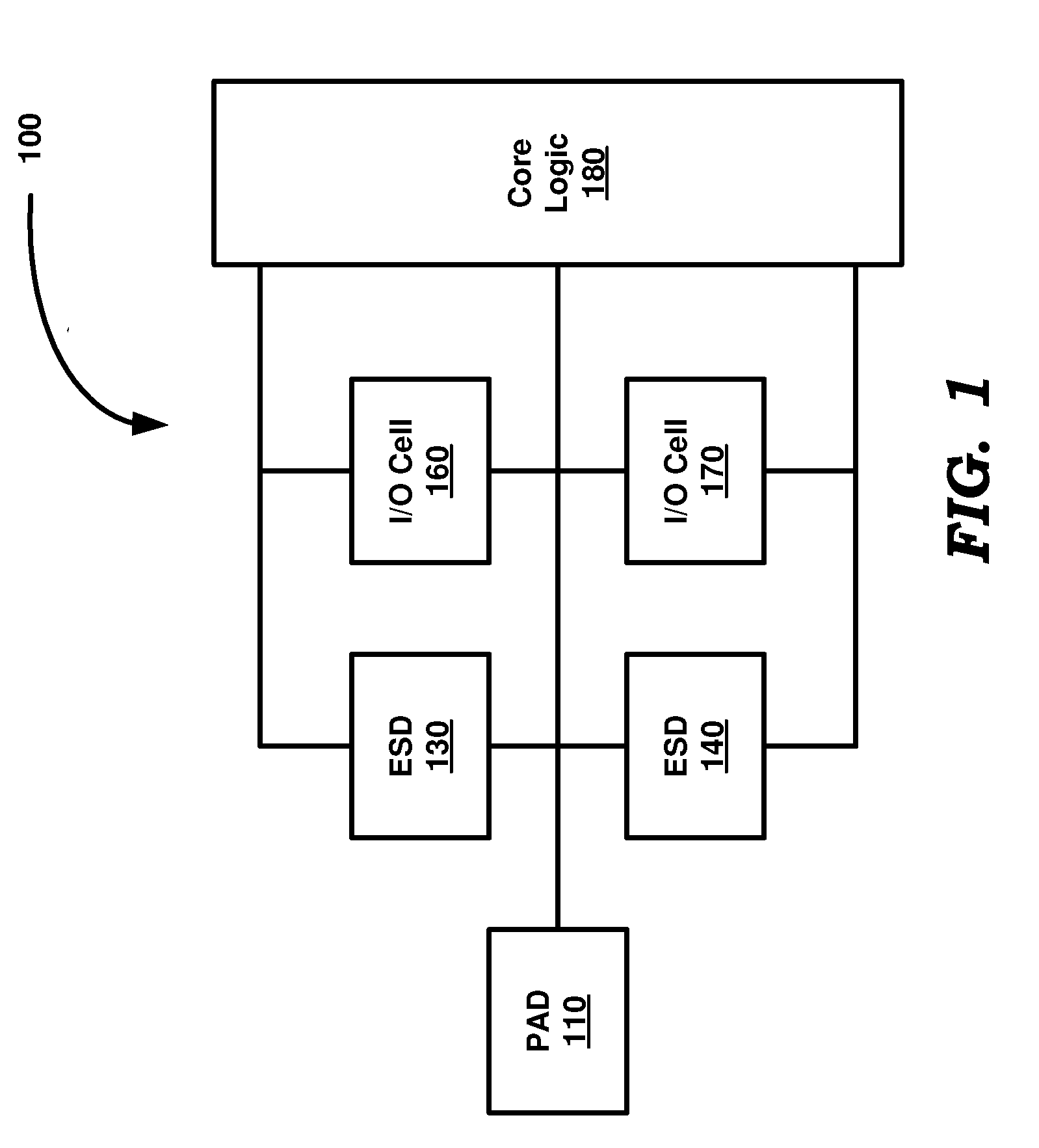

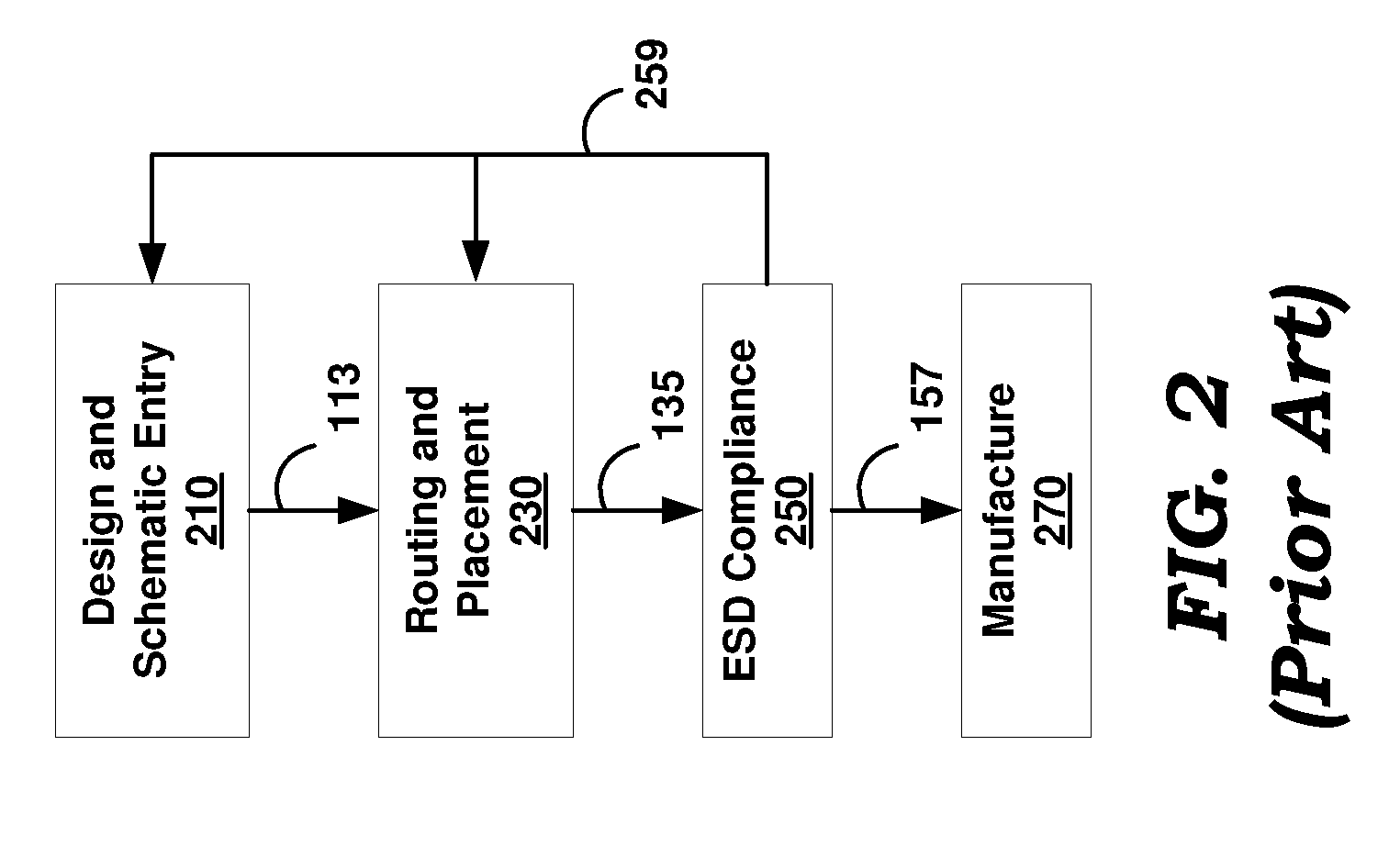

Validation Of An Integrated Circuit For Electro Static Discharge Compliance

An aspect of the present invention validates ESD compliance by examining netlist data generated from a schematic level design of an integrated circuit. Routing and placement may be performed only after confirming that whether each protected circuit (having exposure to ESD current, without the protection circuit) is protected by an appropriate protection circuit. As a result, the design cycle time may be reduced. According to another aspect of the present invention, layout guidelines for each protection circuit is also considered in performing the routing and placement. As a result, the number of iterations in a design cycle may be reduced.

Owner:TEXAS INSTR INC

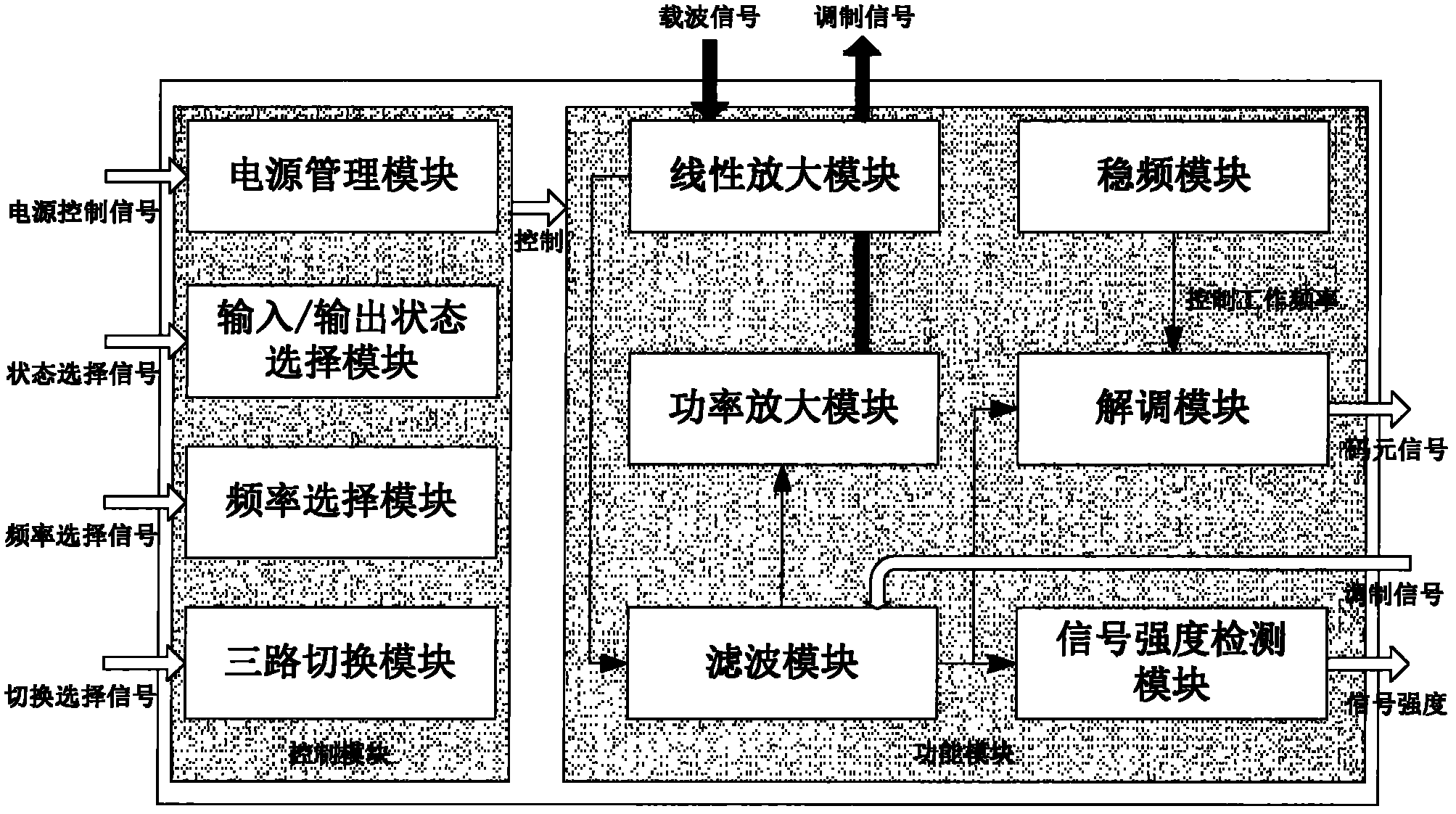

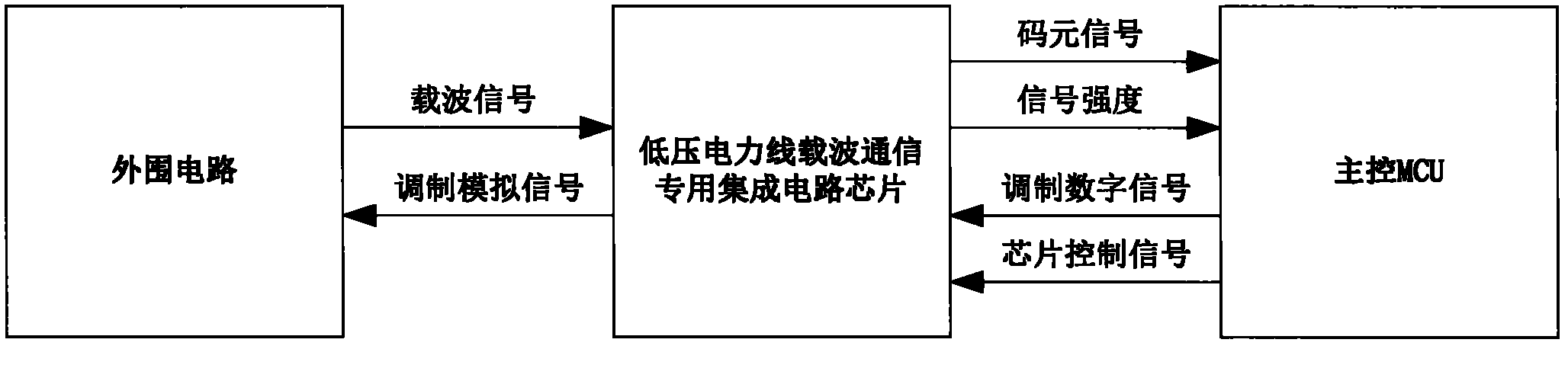

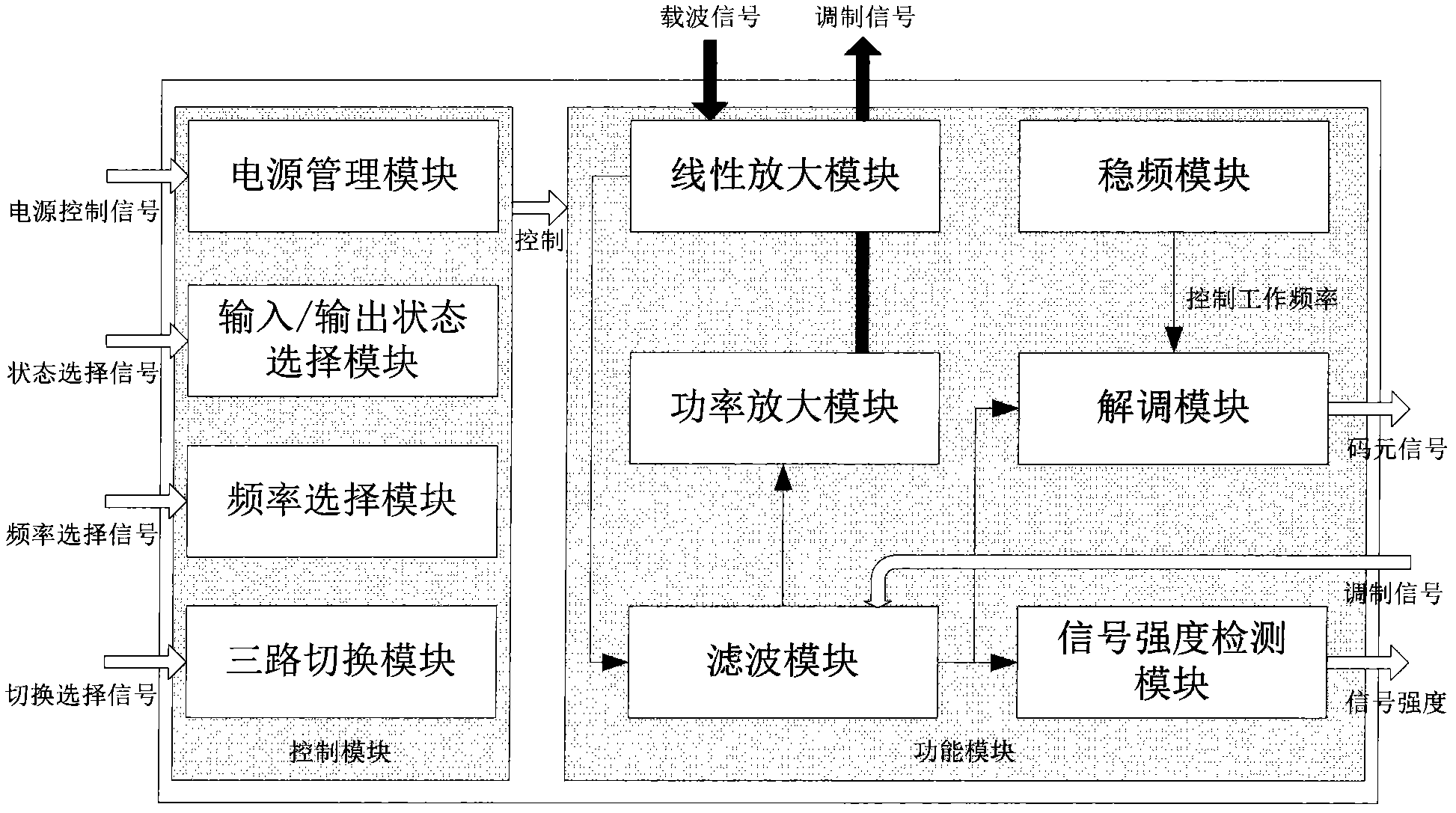

ASIC (application-specific integrated circuit) chip applicable to low-voltage power line carrier communication

ActiveCN102355283AImprove performanceEasy to control power consumptionPower distribution line transmissionFrequency stabilizationSystems design

The invention discloses an ASIC (application-specific integrated circuit) chip applicable to low-voltage power line carrier communication. The ASIC chip comprises a power management module, an input / output state selection module, a frequency selection module, a three-way switching module, a linear amplification module, a filter module, a demodulation module, a frequency stabilization module, a power amplification module and a signal intensity detection module. The chip receives an FSK (frequency shift keying) spread spectrum modulation carrier signal transmitted by a peripheral circuit, and after the FSK spread spectrum modulation carrier signal is subjected to demodulation processing, the equivalent intensity values of a demodulation code element signal and an input signal are output to a MCU (master control unit); the chip receives an FSK spread spectrum modulation digital signal transmitted by the MCU, and after the FSK spread spectrum modulation digital signal is subjected to filtering processing, an FSK spread spectrum modulation analog signal is output to the peripheral circuit; and power supply of the chip can be controlled by the MCU. By using the ASIC chip disclosed by the invention, the board-level design of a system is reduced, the complexity and cost of system design are reduced, and the performance of low-voltage power line carrier communication can be effectively improved, thereby enhancing the application prospect of the low-voltage power line carrier communication technology.

Owner:QINGDAO TOPSCOMM COMM

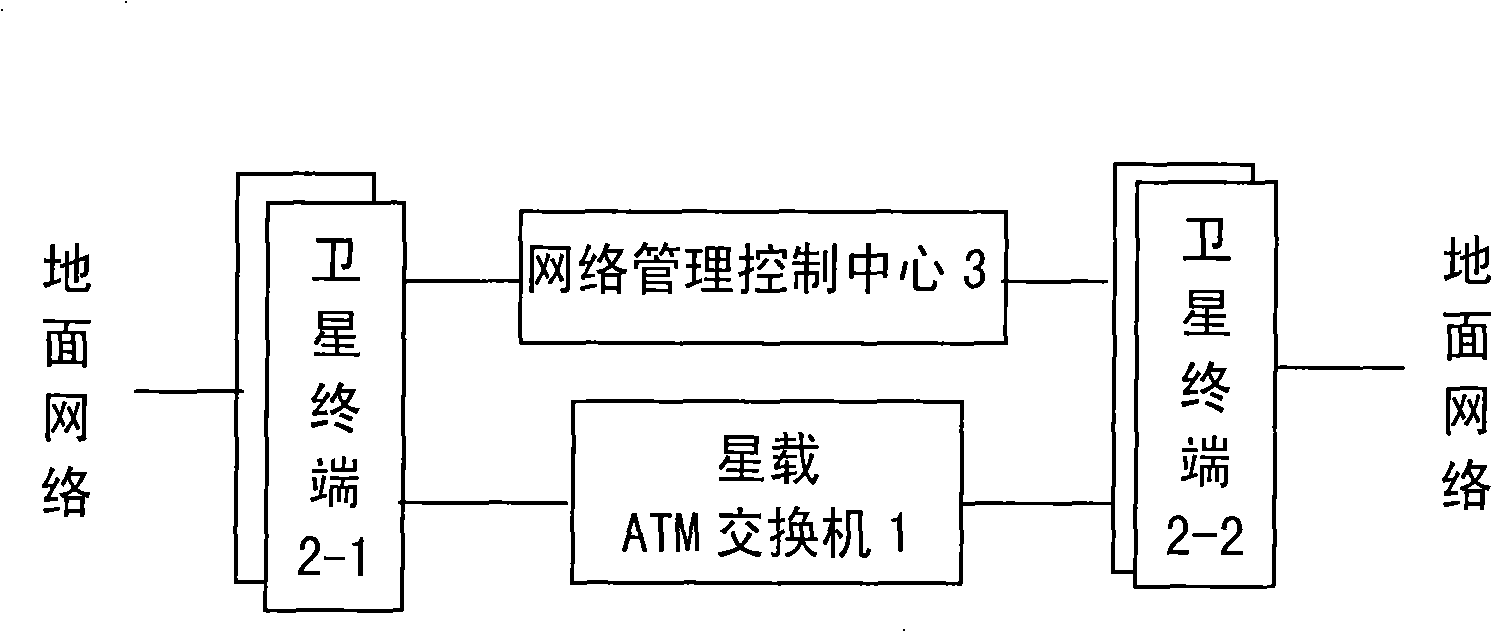

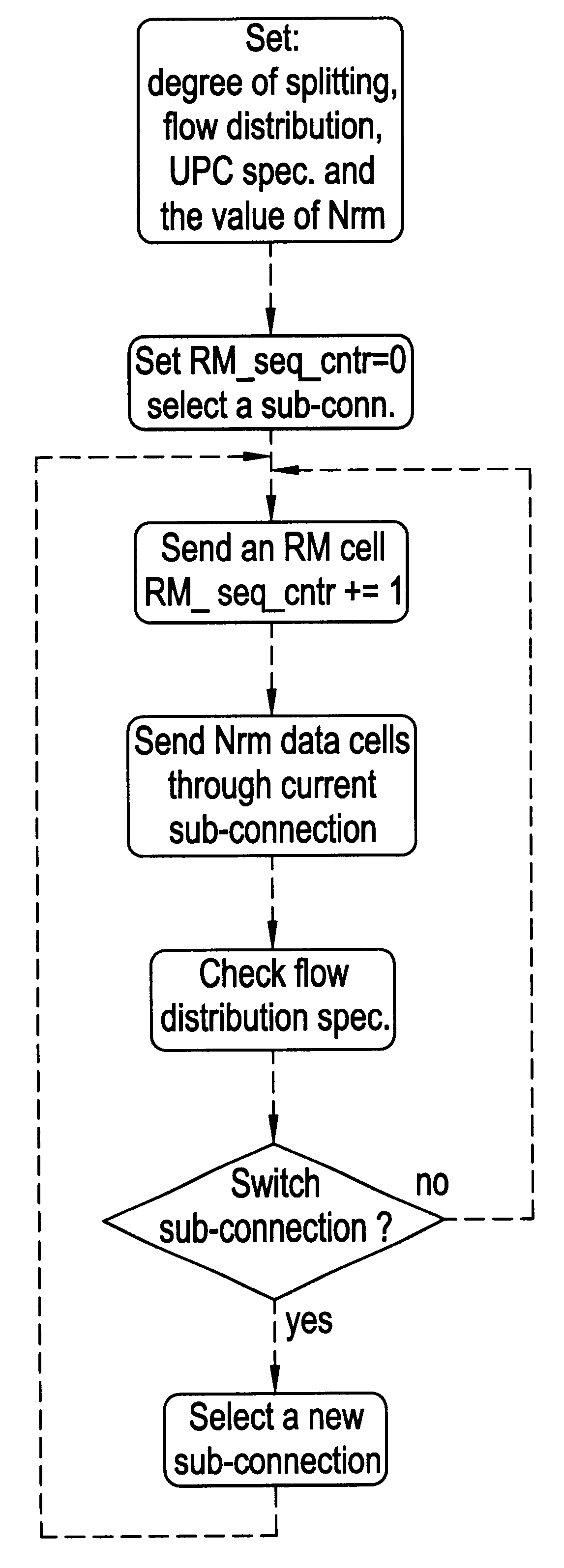

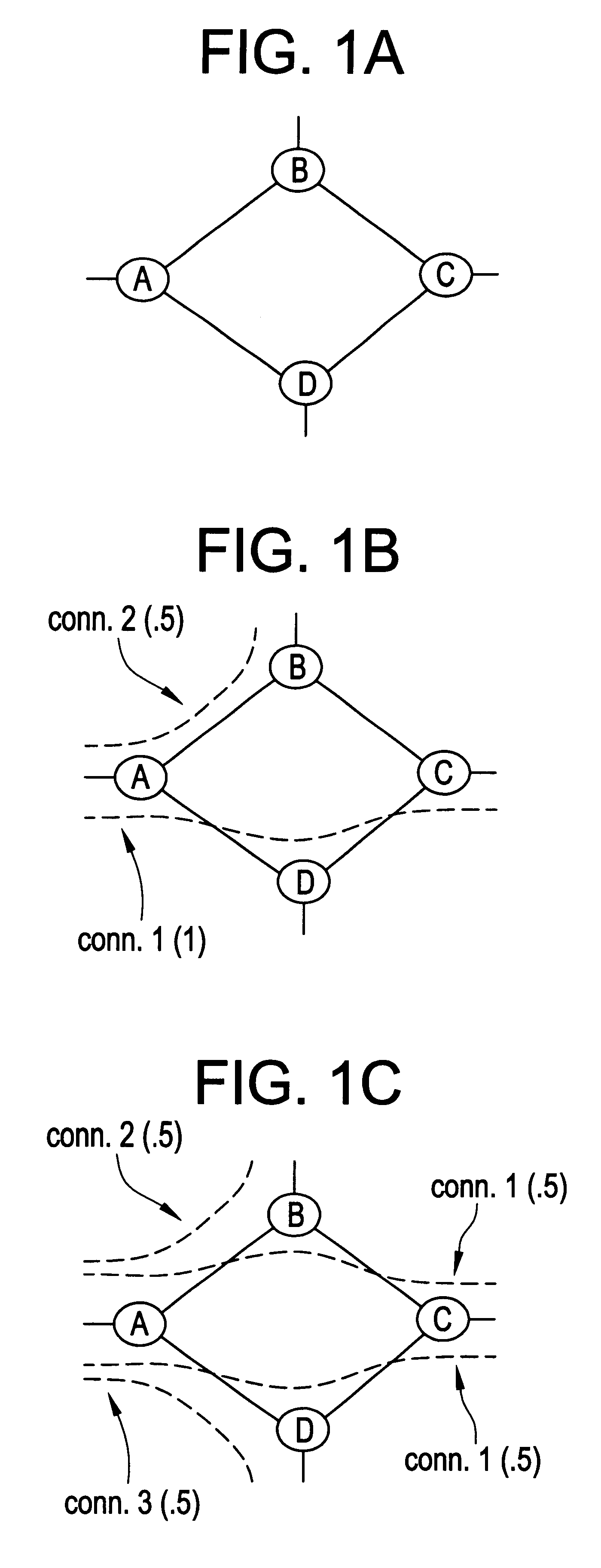

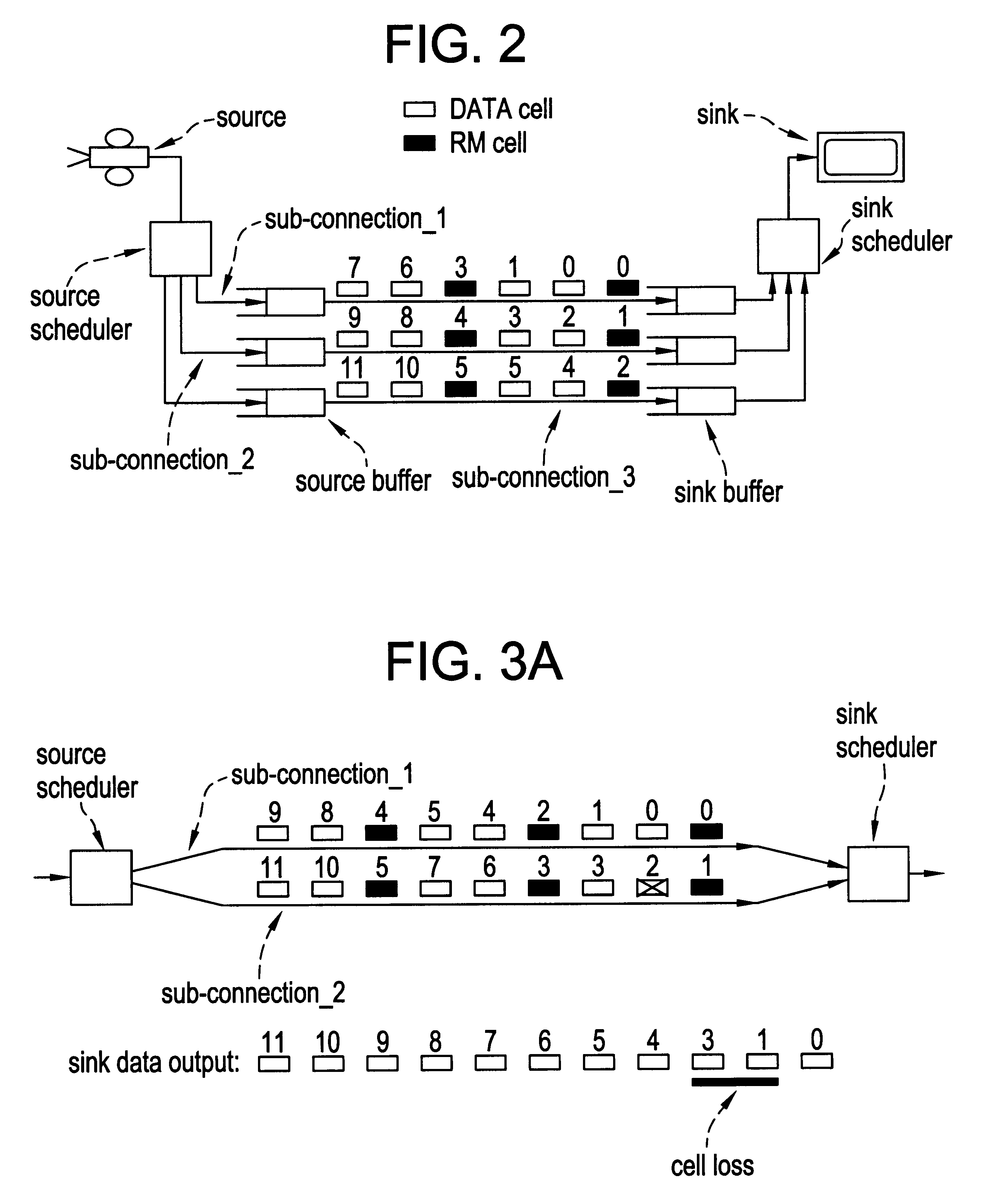

Connection splitting: an efficient way of reducing call blocking in ATM

InactiveUS6535487B1Reduce call blockingLess bandwidth fragmentationError prevention/detection by using return channelFrequency-division multiplex detailsBroadbandLevel design

A technique for reducing ATM call blocking is provided that splits wideband connections into multiple low-bandwidth sub-connections and routing them independently through the network. Fragmented network bandwidth is used for supporting calls which are otherwise blocked by conventional routing. A detailed cell-level design for the split scheduling algorithms is provided. A system for implementing splitting without requiring any protocol changes within the network is provided. Such a system modifies the control plane protocols only within the end-stations.

Owner:NEC CORP

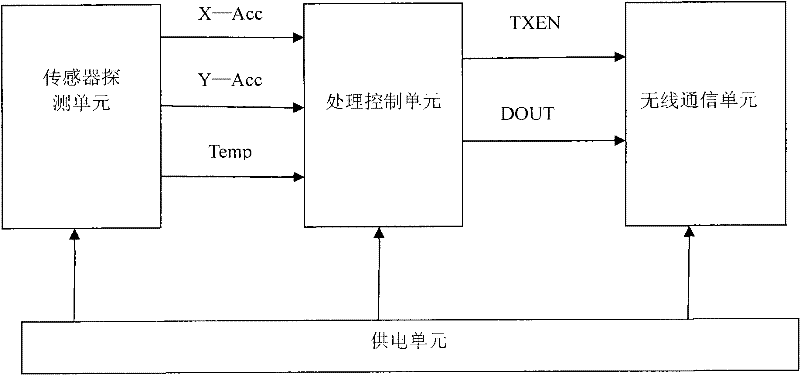

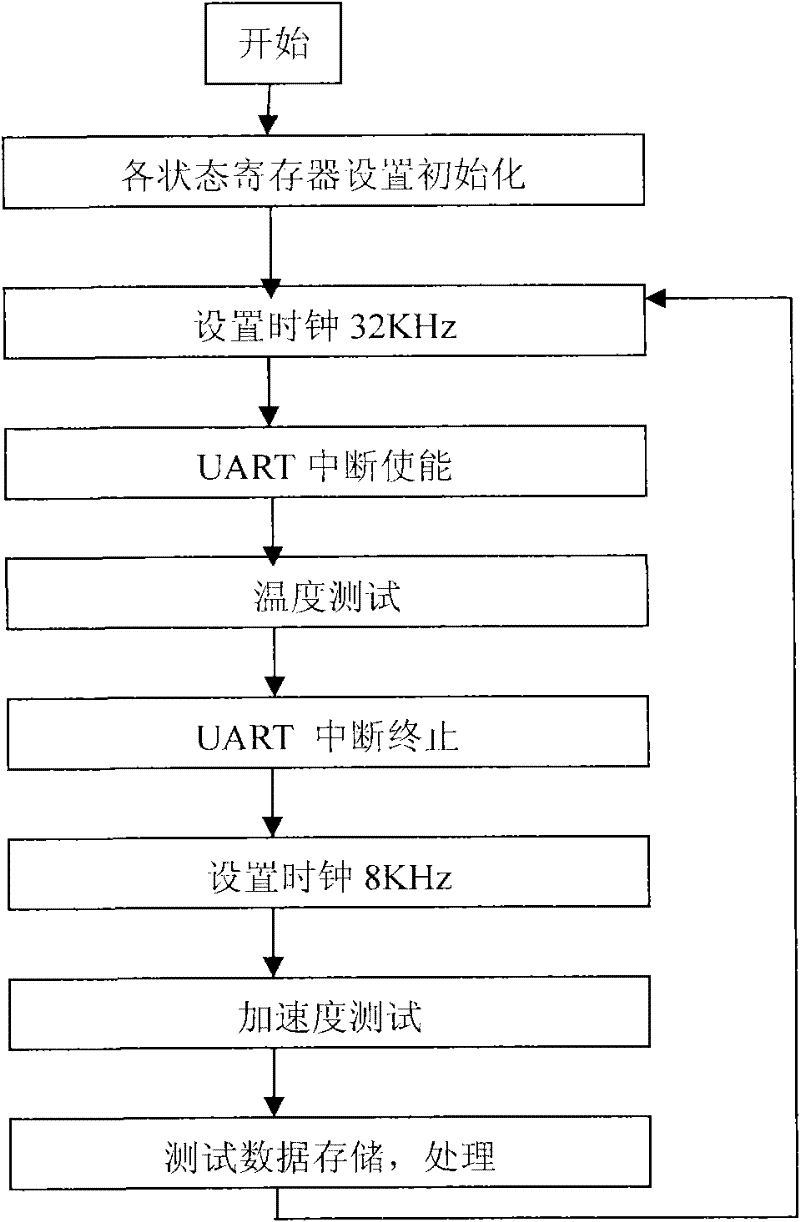

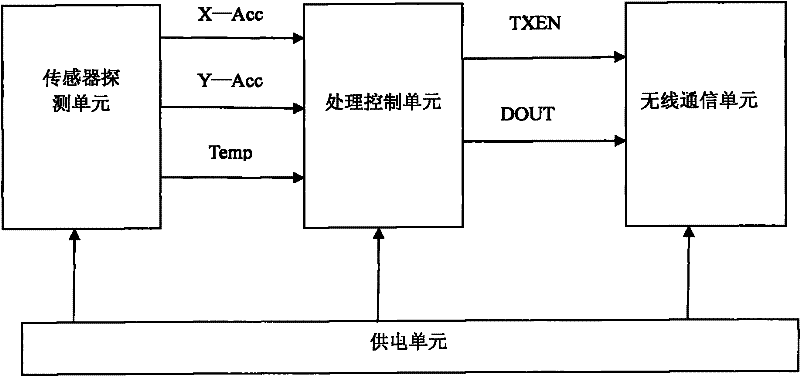

Low power consumption wireless sensor network node

InactiveCN102457932AReduce the number of nodesRealize the positioning of the branch pointPower managementNetwork topologiesLine sensorLevel design

The invention provides a low power consumption wireless sensor network node. Amount of nodes is substantially reduced. The node is suitable for realization of signal monitoring in an area in a special environment. According to a wireless sensor network, branch node positioning can be solved, time synchronization technology is realized, and a user application interface is realized. The wireless sensor network node comprises a sensing detection unit, a processing control unit, a radio communication unit and a power supply unit. C language programming is employed by wireless sensor network node software, effective data is packaged in design, and formats are a lead code, an address, an effective data load and a check code. To an nRF403 chip, using 0x55FF as the lead code in a UART mode is supported. The address is identifiers of different response points. The effective data load comprises a data packet satisfying an upper level design protocol format. The check code is added at an end of the data packet, and validity of the data can be verified. Data packaging and processing are all realized by the processing control unit.

Owner:高旭

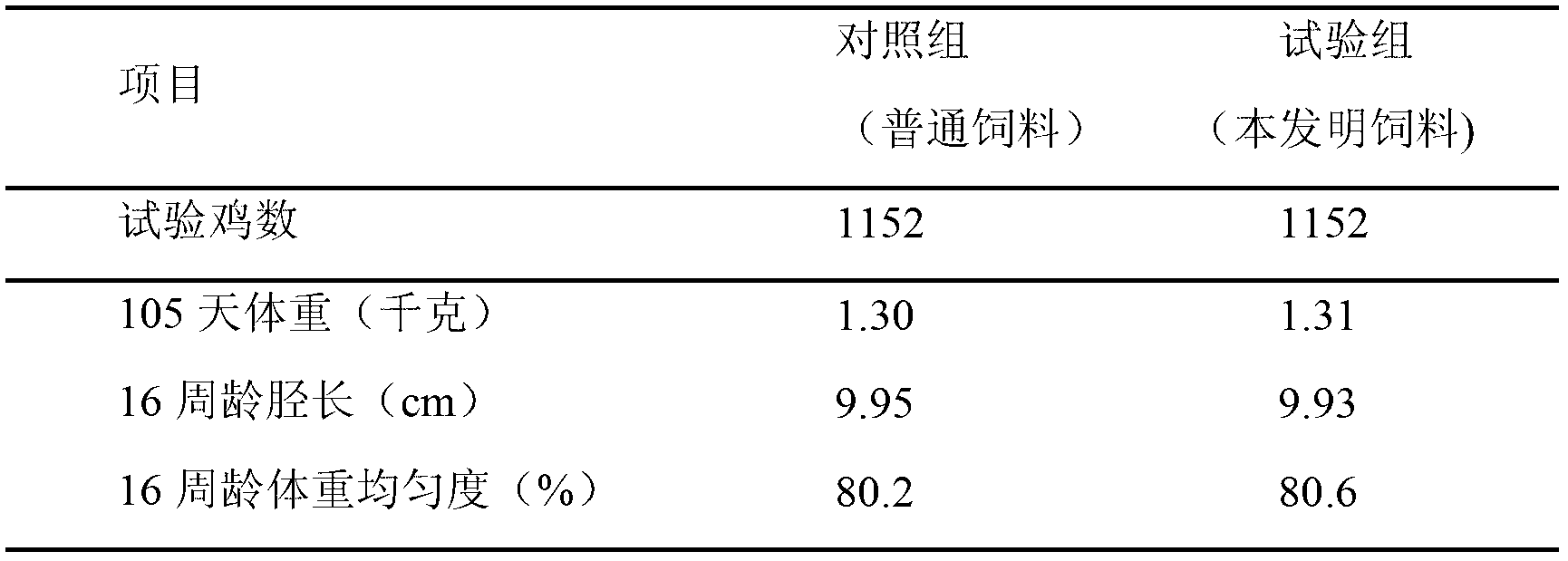

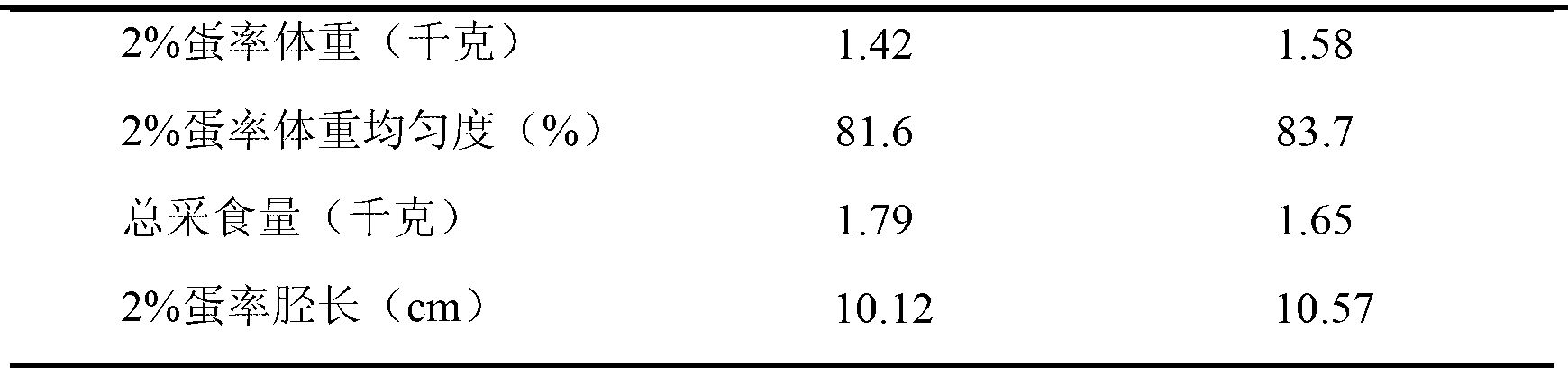

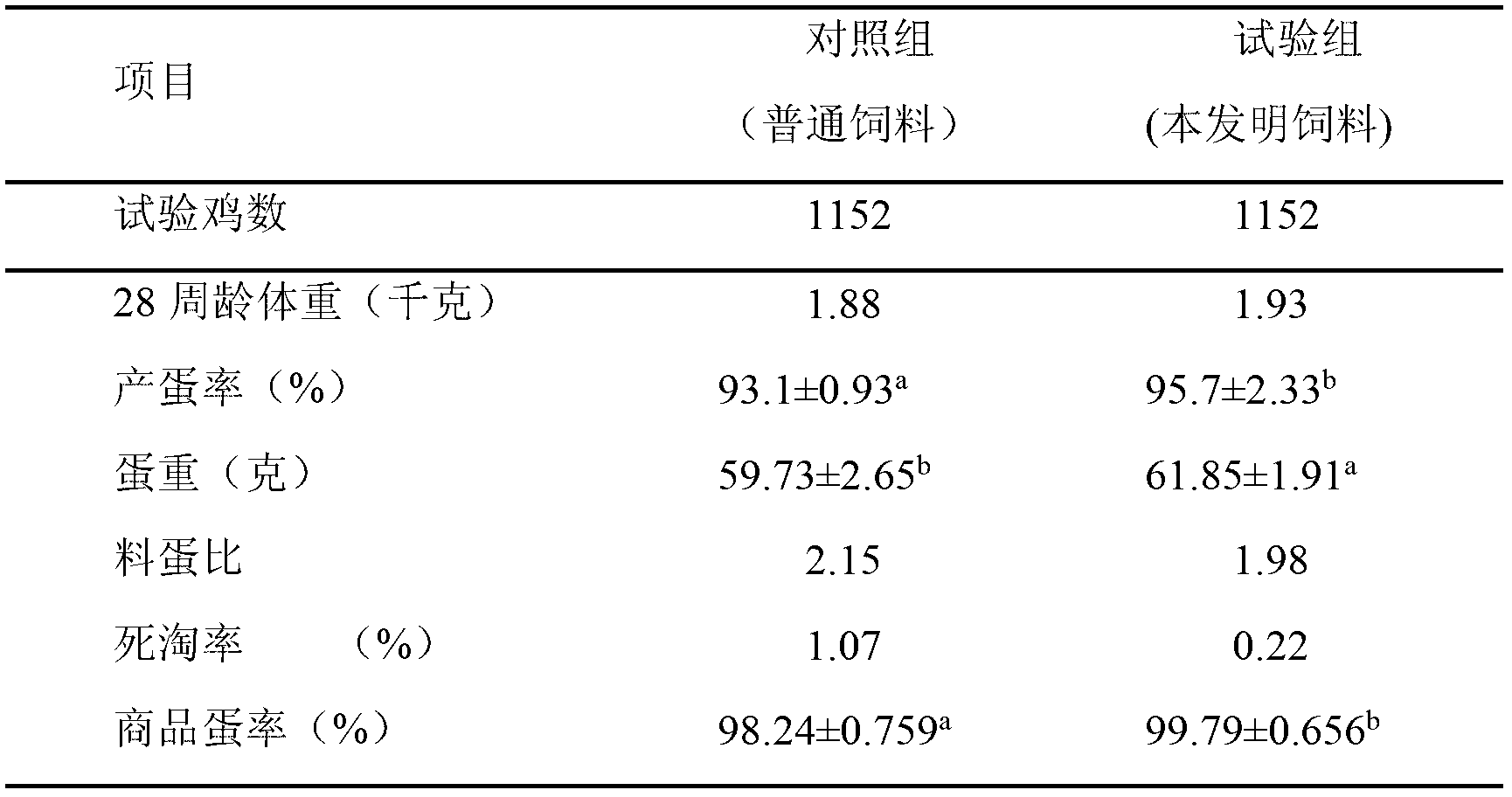

Uniform-crowning high-egg-yield laying hen nutritional set feed application method and feed thereof

ActiveCN103250678ASatisfy developmentMeet weight gainAnimal feeding stuffLevel designReproductive organ

The invention discloses a uniform-crowning high-egg-yield laying hen nutritional set feed application method and feed thereof, and belongs to the field of feed compositions and feeding. By repeated demonstrations and laying hen laboratory screening, the feed mainly comprising corn, wheat, corn gluten meal, soybean meal, sunflower seed meal, corn by-products, soybean oil, enzyme preparations, microbial preparations, vitamin E, organic selenium, organic chromium, organic zinc and the like is developed. The set feed is divided into two stages, one ranges from crowning period 16 weeks to 2% laying rate, the other ranges from early laying peak with 2% laying rate to 28 weeks, nutritional levels designed for the two stages are different, the two stages have certain differences in raw materials, requirements for reproductive organ development, weight growth and high egg yield are met sufficiently, and the average egg weight in 28 weeks is 61.3 grams and is 3.03% higher than the average; laying rate reaches above 95%; egg yield is increased from 48.2grams / per egg / per day to 50.1grams / per egg / per day; death and culling rate of the stage from 16 weeks to 28 weeks is decreased to 0.75%; every hen lays three more eggs; and more economic benefit of 18,000 RMB is created by 10,000 hens.

Owner:扶余禾丰牧业有限公司

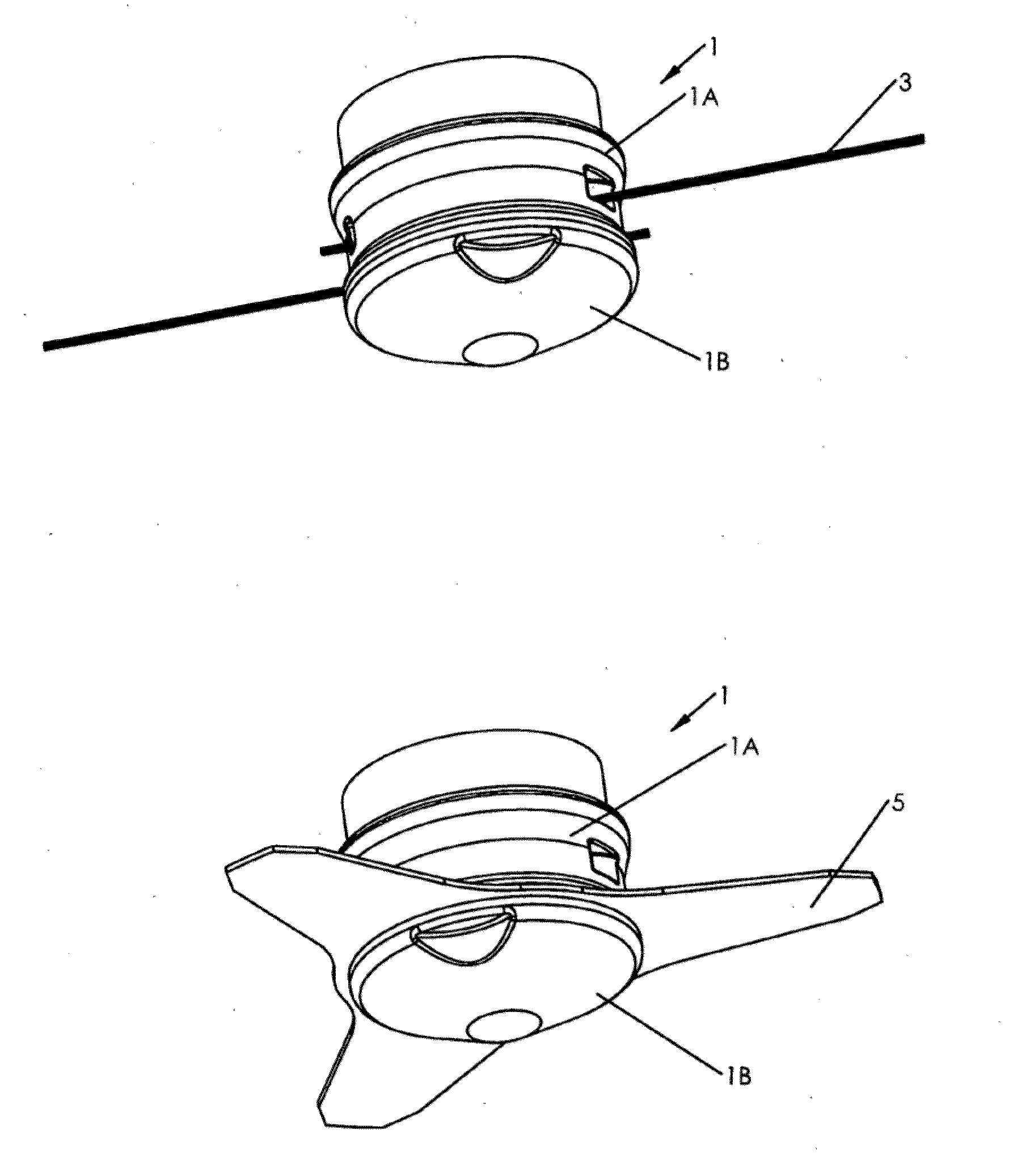

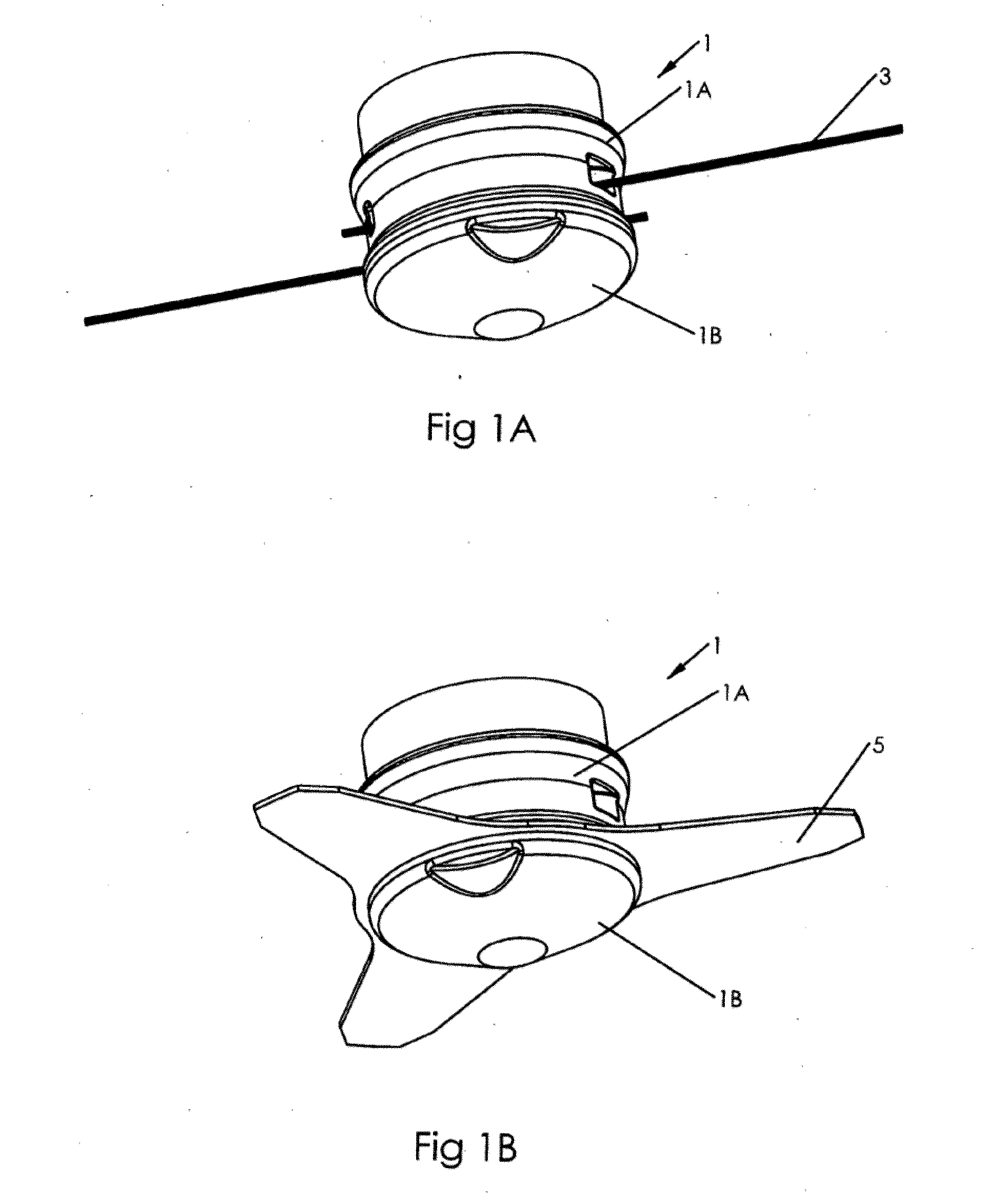

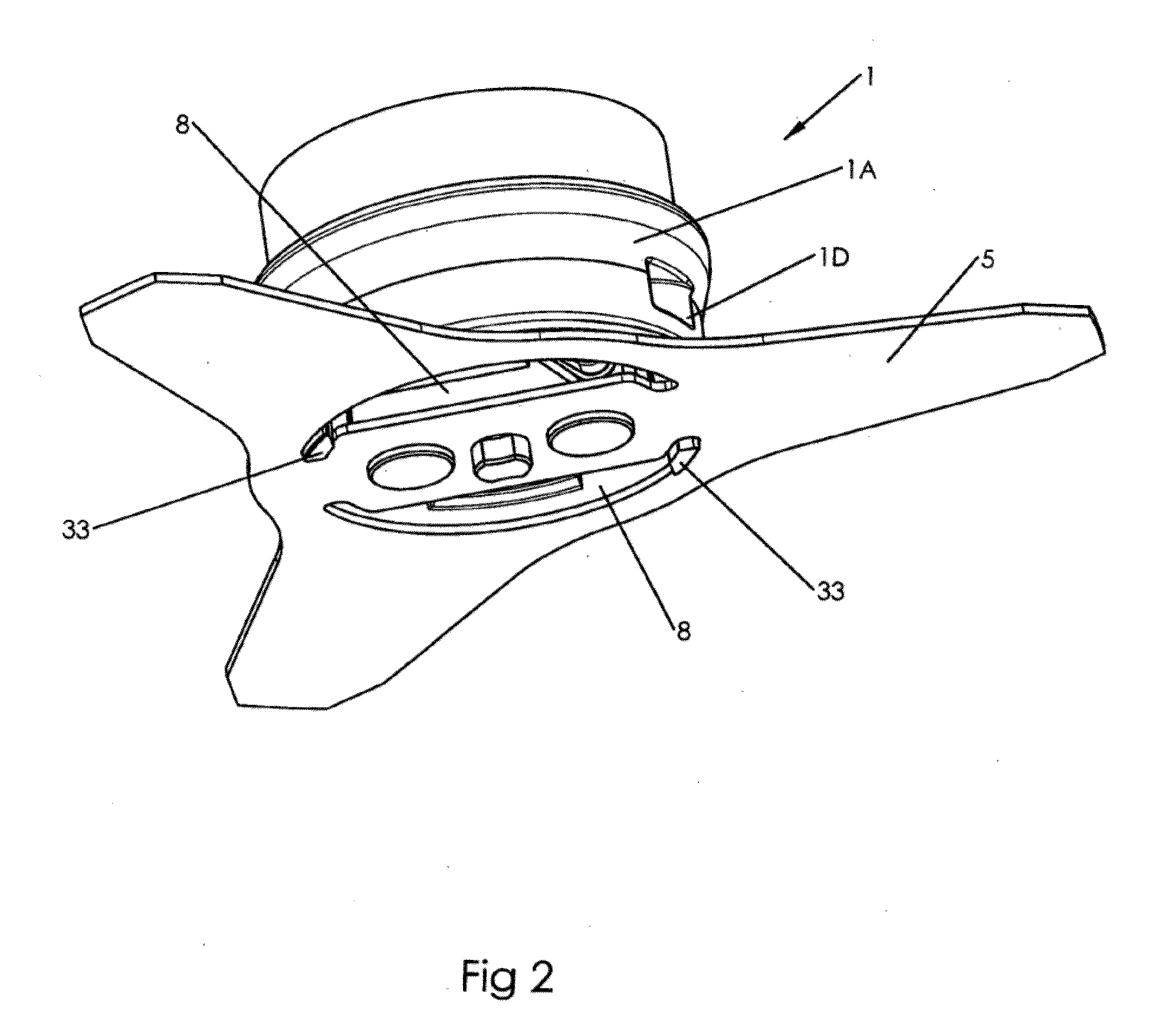

Multifunctional rotary cutting head for cutting devices, and portable devices comprising such a cutting head

A multifunctional rotary cutting head is provided for cutting devices as well as portable devices equipped with such a cutting head. The cutting head comprises a rotary housing that has at least a top part and a bottom part and accommodates a support for one or more cutting elements or tools. The support is penetrated by an axial drive shaft on which the support is mounted. The support for the cutting element(s)or tool(s) has two leads to selectively mounting the cutting element(s) or tool(s), i.e. a first level designed to mount strands of cutting wire and a second level designed to mount an interchangeable cutting blade.

Owner:PELLENC SA

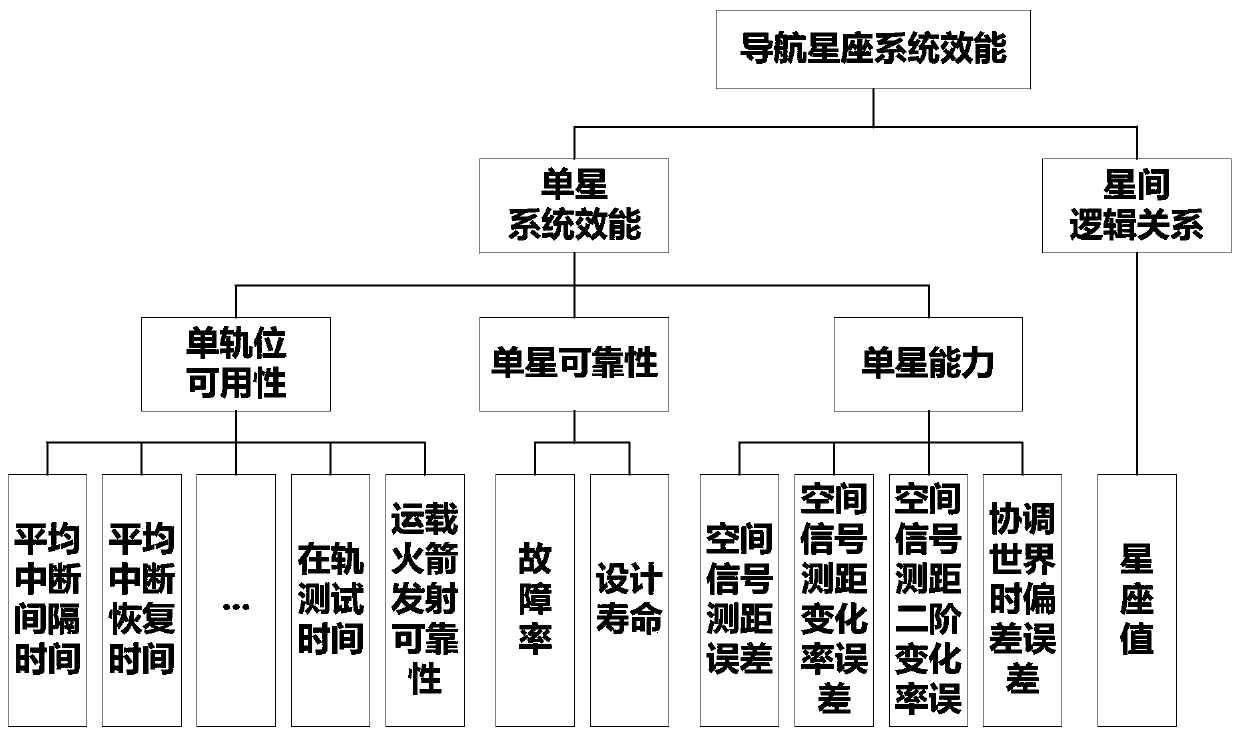

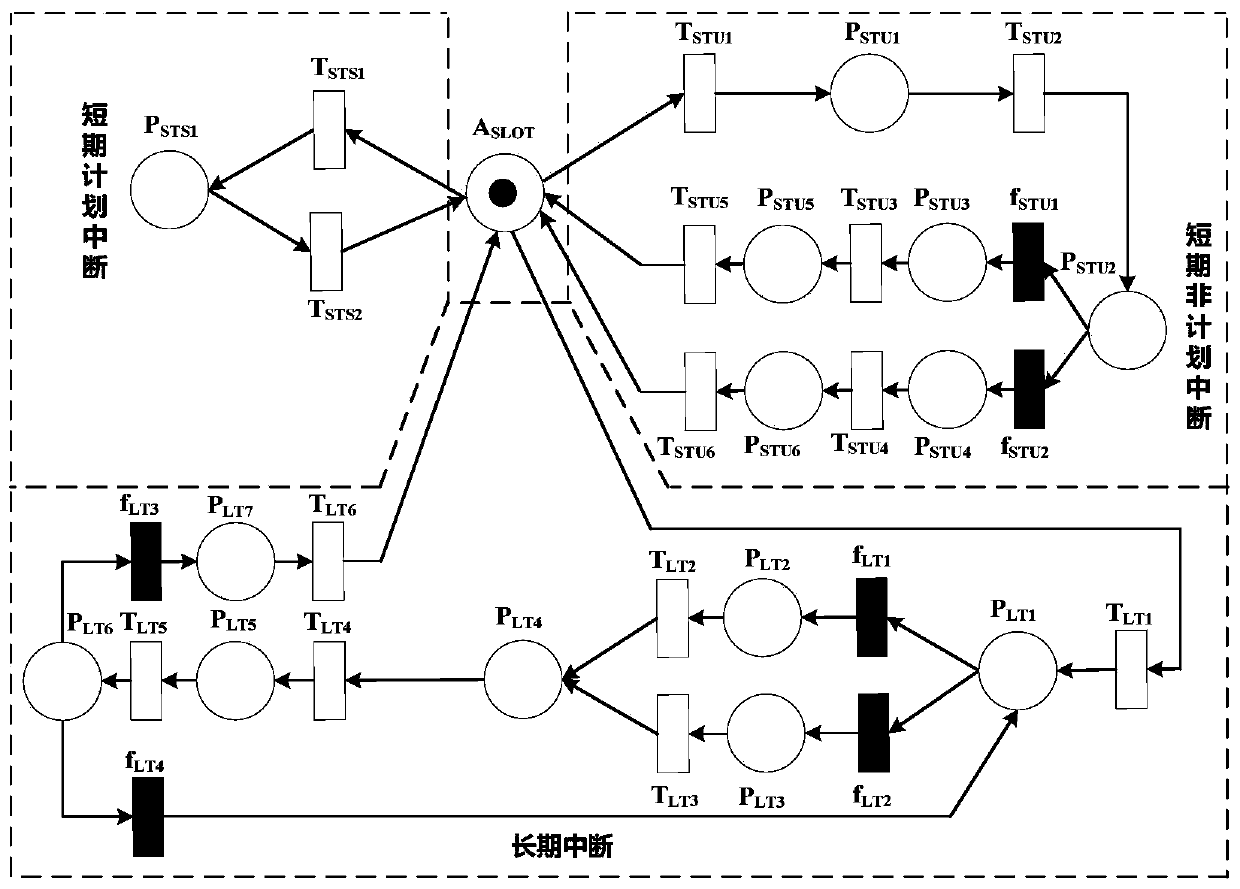

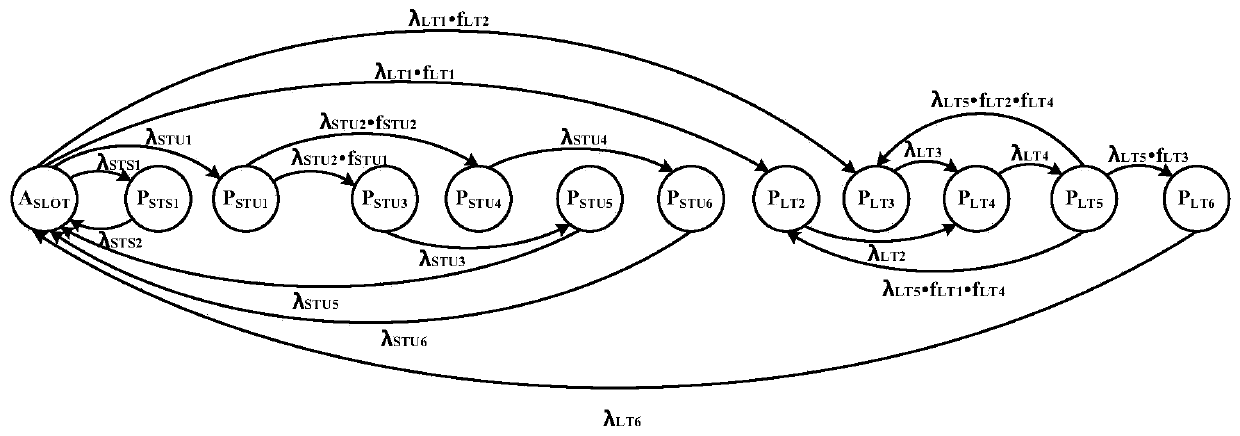

System efficiency comprehensive evaluation method for navigation constellation

InactiveCN110031872ARealization of comprehensive system performance evaluationImprove interactivitySatellite radio beaconingSimulationRocket

The invention discloses a system efficiency comprehensive evaluation method of a navigation constellation, which comprehensively considers different interruption types such as short-term planned interruption, short-term unplanned interruption, long-term interruption and the like, and various factors such as average interruption interval time of a satellite, satellite development time, reliabilityof a carrier rocket, inter-satellite logic relation, spatial signal precision and the like, utilizes a generalized random Petri network to construct a single-rail availability model, utilizes random faults and loss faults to construct a single-satellite multi-parameter reliability model, utilizes a combined weighting method based on a game theory to construct a single-satellite capability model, utilizes a weighted product method to construct a single-satellite system efficiency model, comprehensively considers single-satellite system efficiency and inter-satellite logic relation, and utilizesa Bayesian network to develop navigation constellation system efficiency modeling, so that the system efficiency comprehensive evaluation of the navigation constellation can be realized; and the system efficiency comprehensive evaluation method of a navigation constellation method can provide quantitative basis for top-level design and running state evaluation of the satellite navigation system,and can be expanded to be applied to series constellations such as communication, remote sensing and the like.

Owner:中国航天系统科学与工程研究院

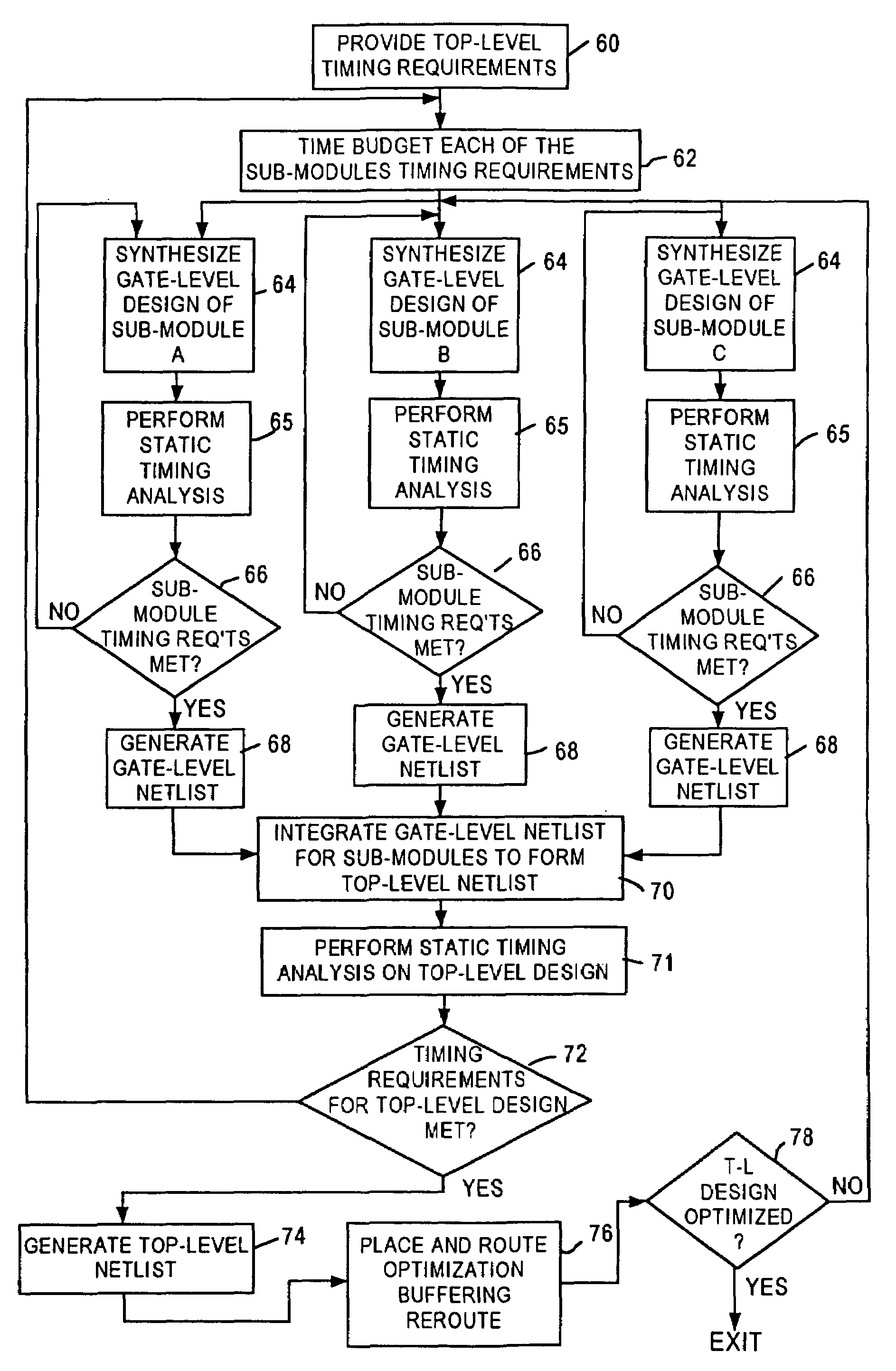

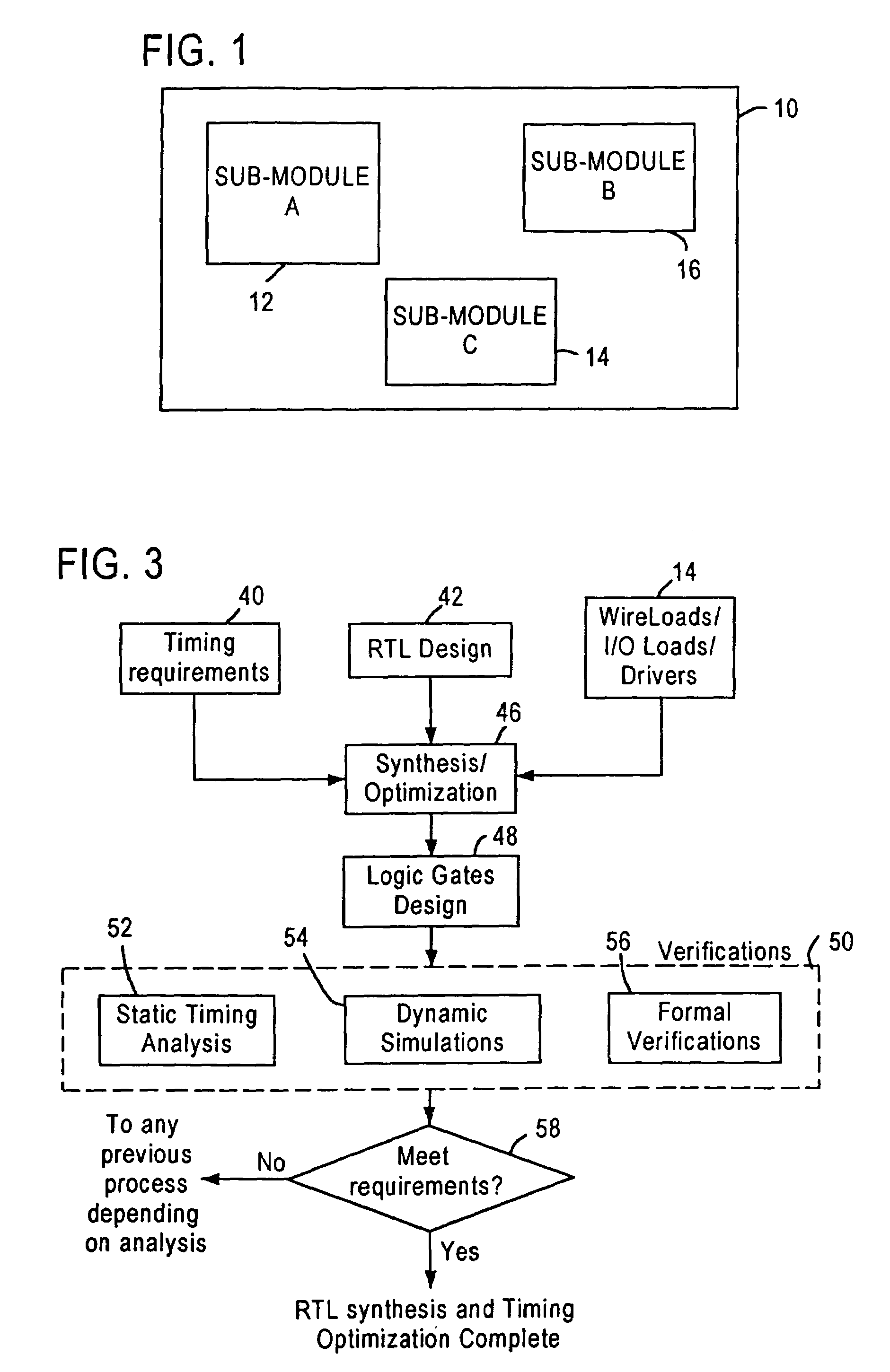

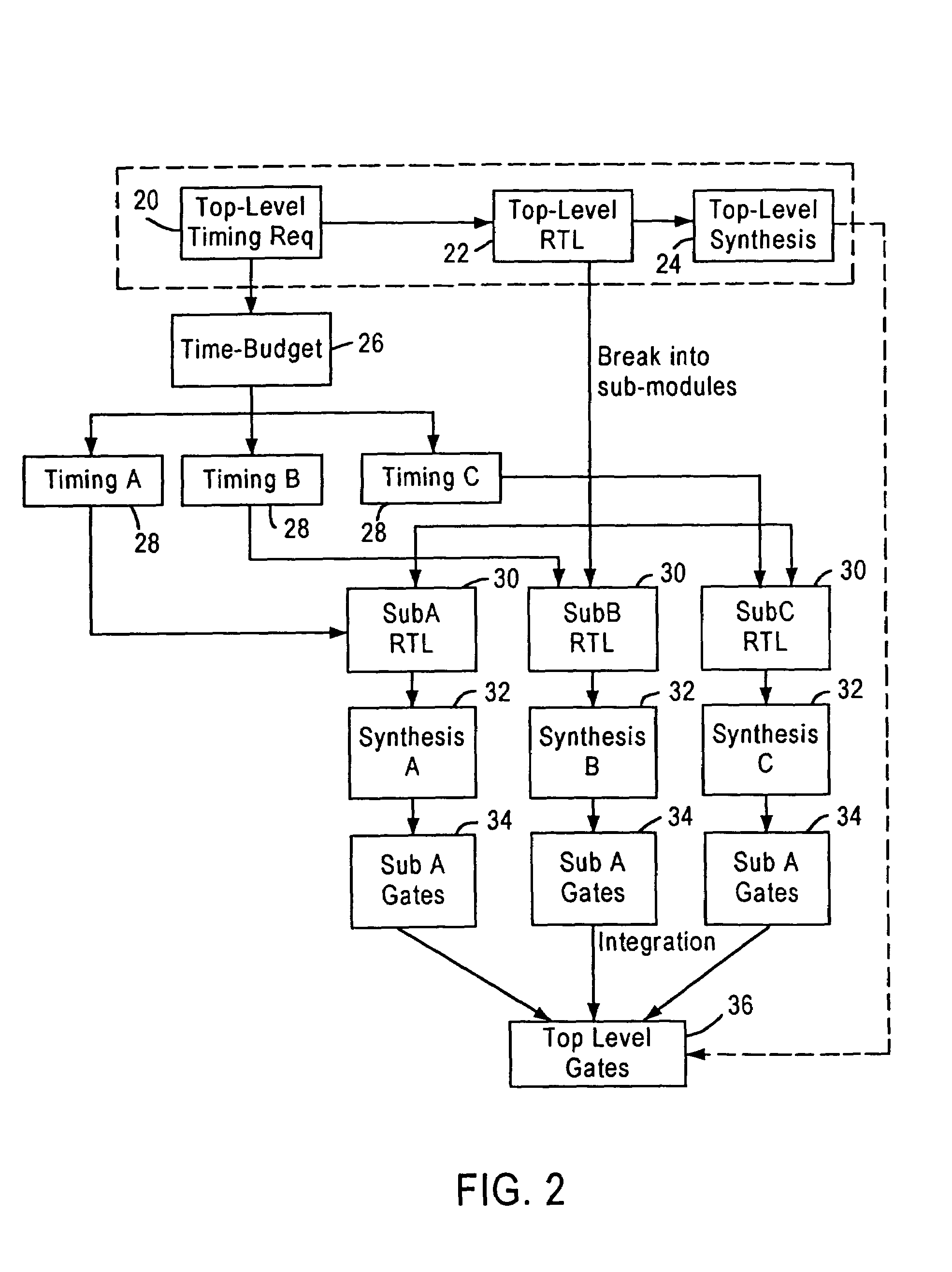

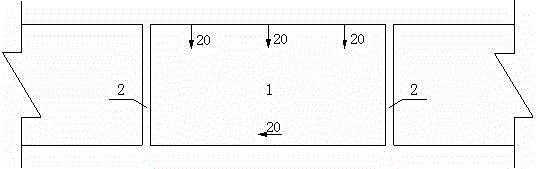

Bottom-up approach for synthesis of register transfer level (RTL) based design

InactiveUS7010774B1Increase the areaFaster time-to-marketMetal-working drilling toolsCutting toolsFormal requirementsProcessor register

A method for synthesizing a register transfer level (RTL) based design employs a bottom-up approach to generate a final top-level design. The top-level design is divided into a plurality of sub-modules. Each of the sub-modules is then independently synthesized using an RTL based design approach and independently adapted to conform to timing requirements produced for each of the sub-modules using time budgets that are based on the top-level timing requirements. Once the sub-modules are synthesized and pass individual timing requirements specific for those sub-modules, the sub-modules are integrated to form a top-level design. The top-level design may then be verified for timing requirements and other formal requirements.

Owner:ADVANCED MICRO DEVICES INC

High-pile wharf horizontal bearing capacity and static-dynamic characteristic in-situ overall detecting method

ActiveCN104614020ASimple and fast operationOperating economyElectrical/magnetic solid deformation measurementUsing optical meansStructural dynamicsRelevant information

The invention discloses a high-pile wharf horizontal bearing capacity and static-dynamic characteristic in-situ overall detecting method. The method is used for a horizontal movement detecting a state of loads, including horizontal load applied to measure the deformation of rubber fenders detection or horizontal loads, pier structure under horizontal load deformation force and displacement detection, static and dynamic traits and so on. And based on the test data, combined with the raw survey data to determine the design of the ship pier design, level design, loading docks and other relevant information and data base to determine the ability to work in a high - pile under lateral loads, structural dynamic behavior, assess the high-pile wharf structural quality and usage. Is one of the most direct and most reliable test method, it can more accurately assess the actual level of the active marina pier on static and dynamic load capacity and operating characteristics of the pier inspection, safety assessment, repair and reinforcement and renovation work provide a scientific basis.

Owner:SOUTHEAST UNIV

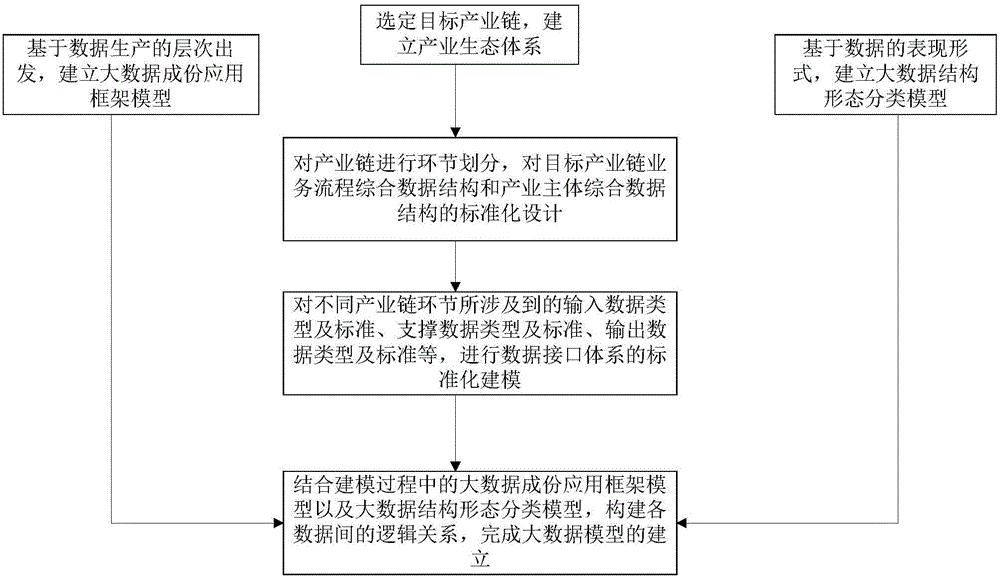

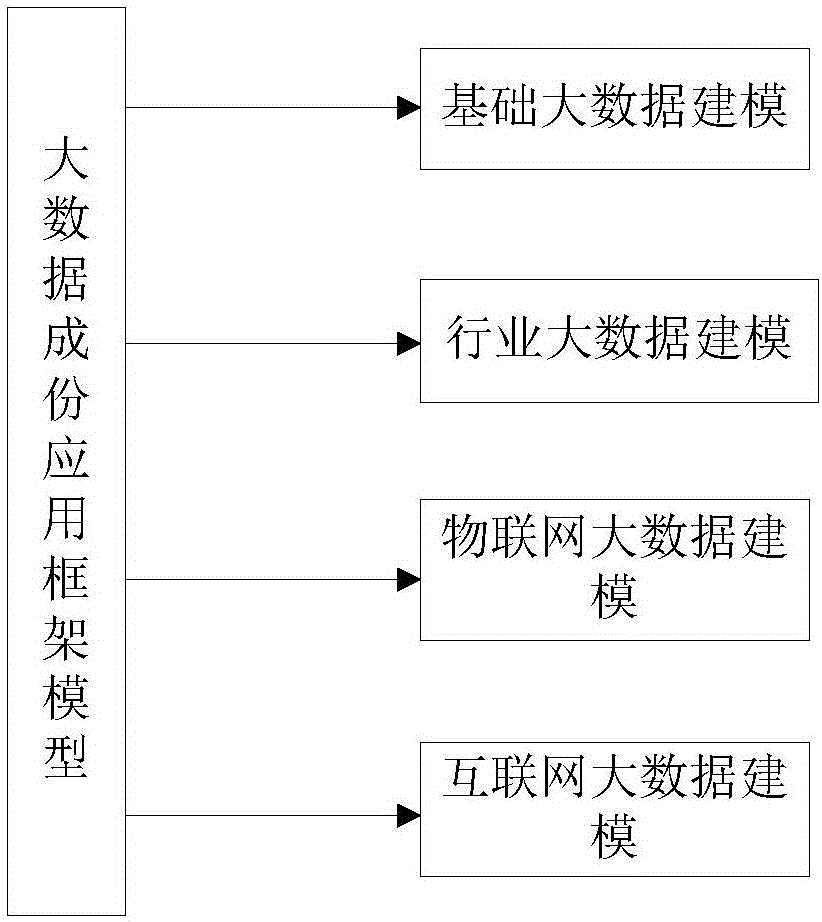

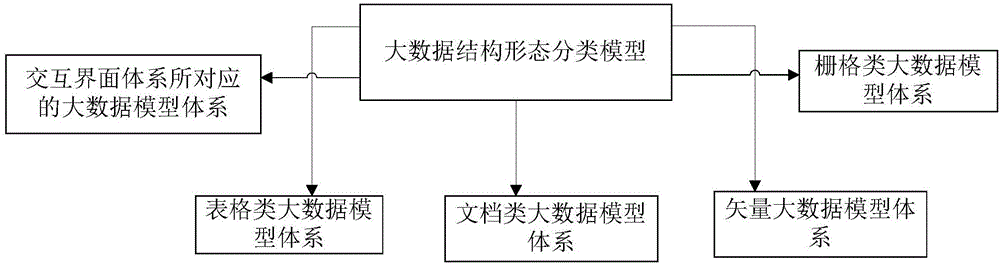

Modeling method of industry chain ecological big data model and the application thereof

InactiveCN106355535AOptimizing the Synthetic Structural ModelOvercome the lack of logical association of industrial processesData processing applicationsSynthetic dataLevel design

The invention discloses a modeling method of industry chain ecological big data model, comprising selecting a target industry chain, establishing an industry ecological system, establishing a big data component application framework model, establishing a big data structural form classification model, implementing link division for the industry chain based on the industry ecological system and according to the features of the industry ecological system where the target industry chain belongs, implementing standard design for the business process comprehensive data structure of the target industry chain and the comprehensive data structure of the industrial subject, meanwhile, implementing standard modeling of data interface system for the input data type and standard etc., related to different industry chain links, constituting the logical relationship among various data, and finishing big data modeling. The modeling method of industry chain ecological big data model is according to the requirements of the whole industry ecological system formed on the basis of the vertical industry chain and the horizontal correlative industry chain, and comply with the top-level design principle, and achieves automation, systematization and modeling of the big data model.

Owner:鼎天智(北京)大数据科技有限公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com