ASIC (application-specific integrated circuit) chip applicable to low-voltage power line carrier communication

A low-voltage power line and carrier communication technology, which is applied in the distribution line transmission system and other directions, can solve the problems of demodulation, inability to carry out different carrier communication frequency points, and poor consistency of peripheral filter circuits, so as to reduce complexity and cost and increase modulation Digital signal filter output function, the effect of simplifying board-level design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] In order to make the purpose, technical solutions and advantages of the present invention clearer, the technical solutions in the embodiments of the present invention will be further clearly and completely described below in conjunction with the accompanying drawings of the embodiments of the present invention. Obviously, the described embodiments are the embodiment of the present invention. One, but not all, embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

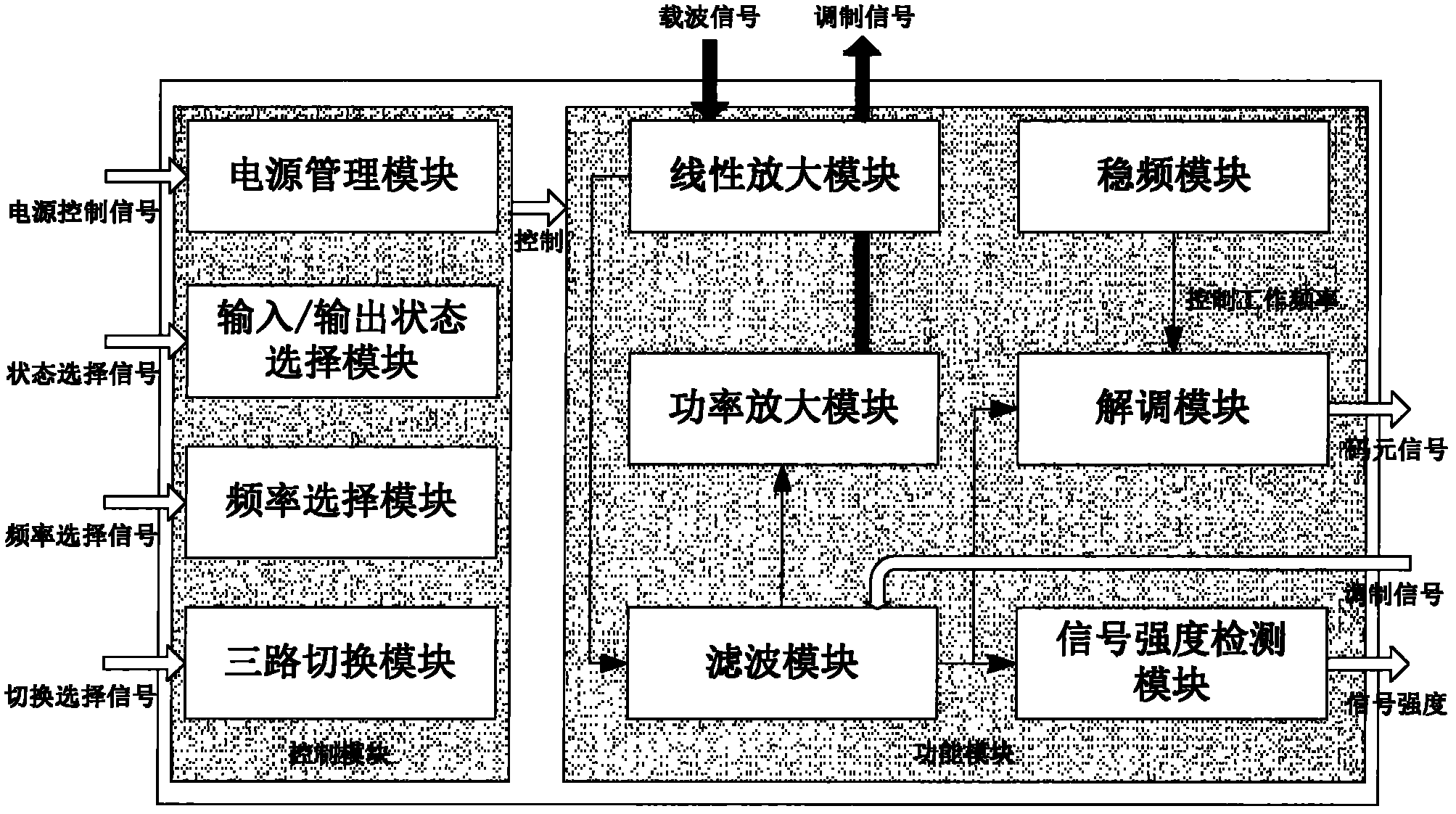

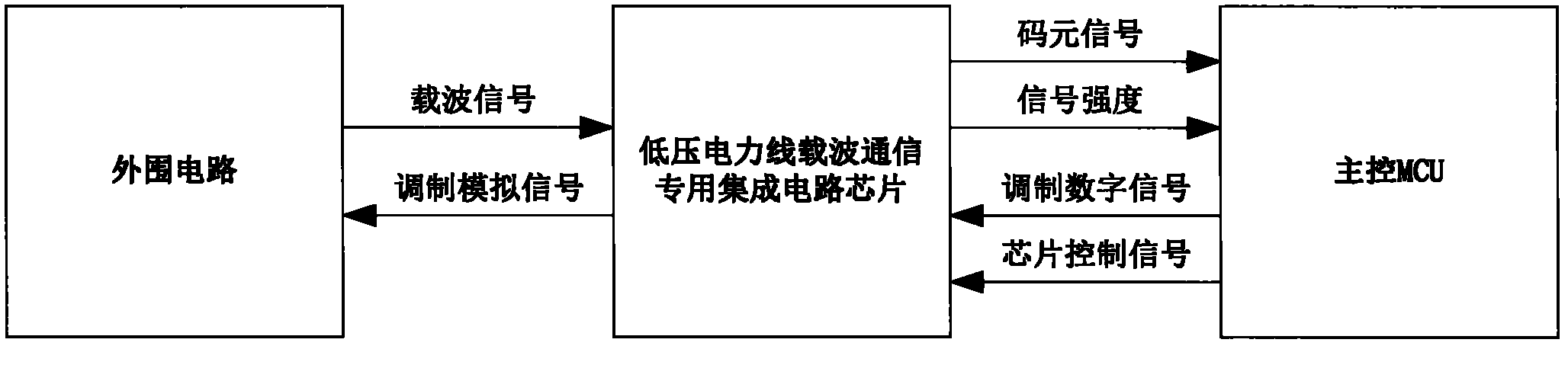

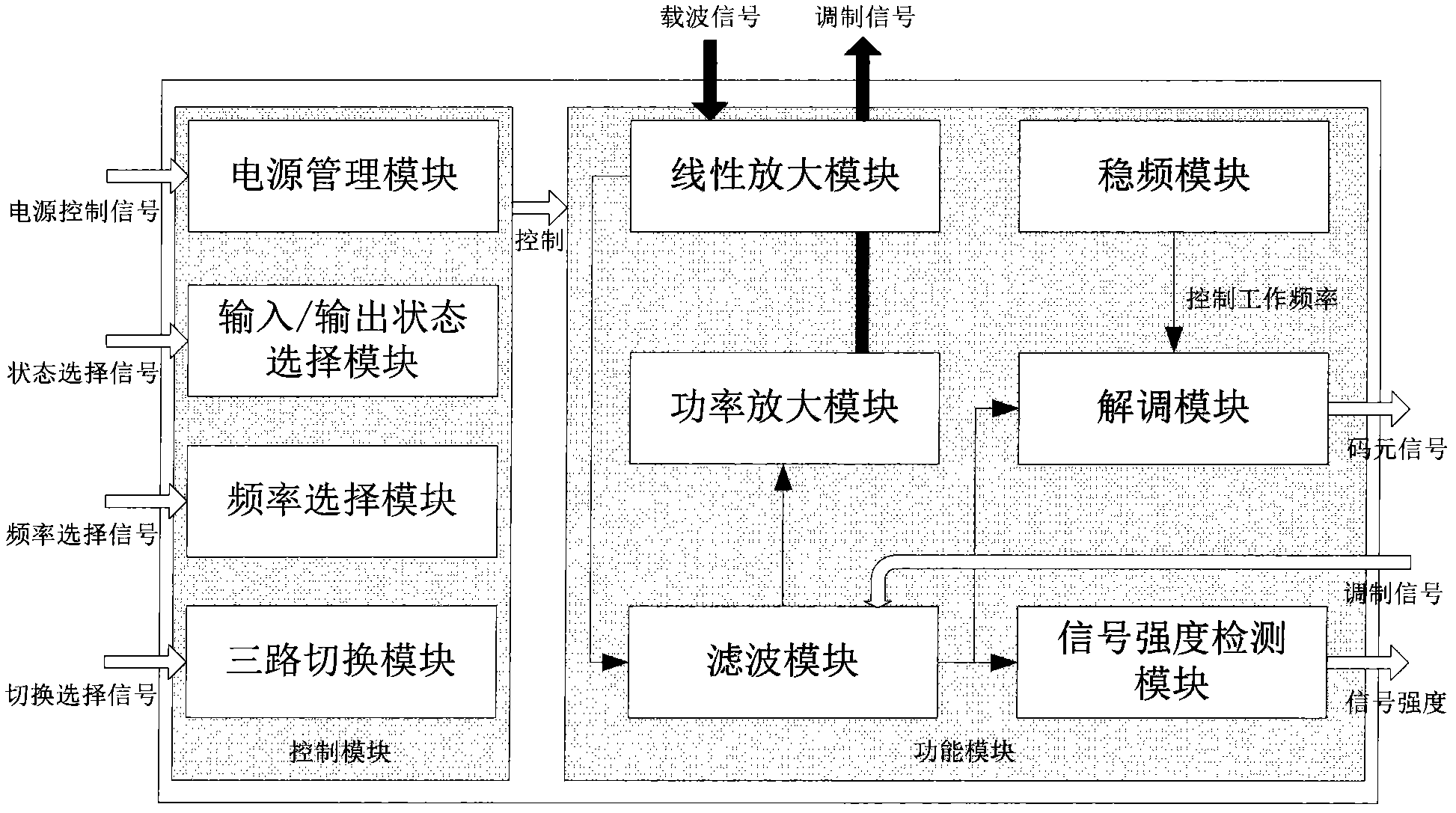

[0015] figure 1 It is an internal structure diagram of an embodiment of an ASIC chip suitable for low-voltage power line carrier communication of the present invention. The chip completes the three functions of input demodulation, output filtering, and signal strength detection in low-voltage power line carrier communication, and the power consump...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com