Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

37 results about "Carry propagation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

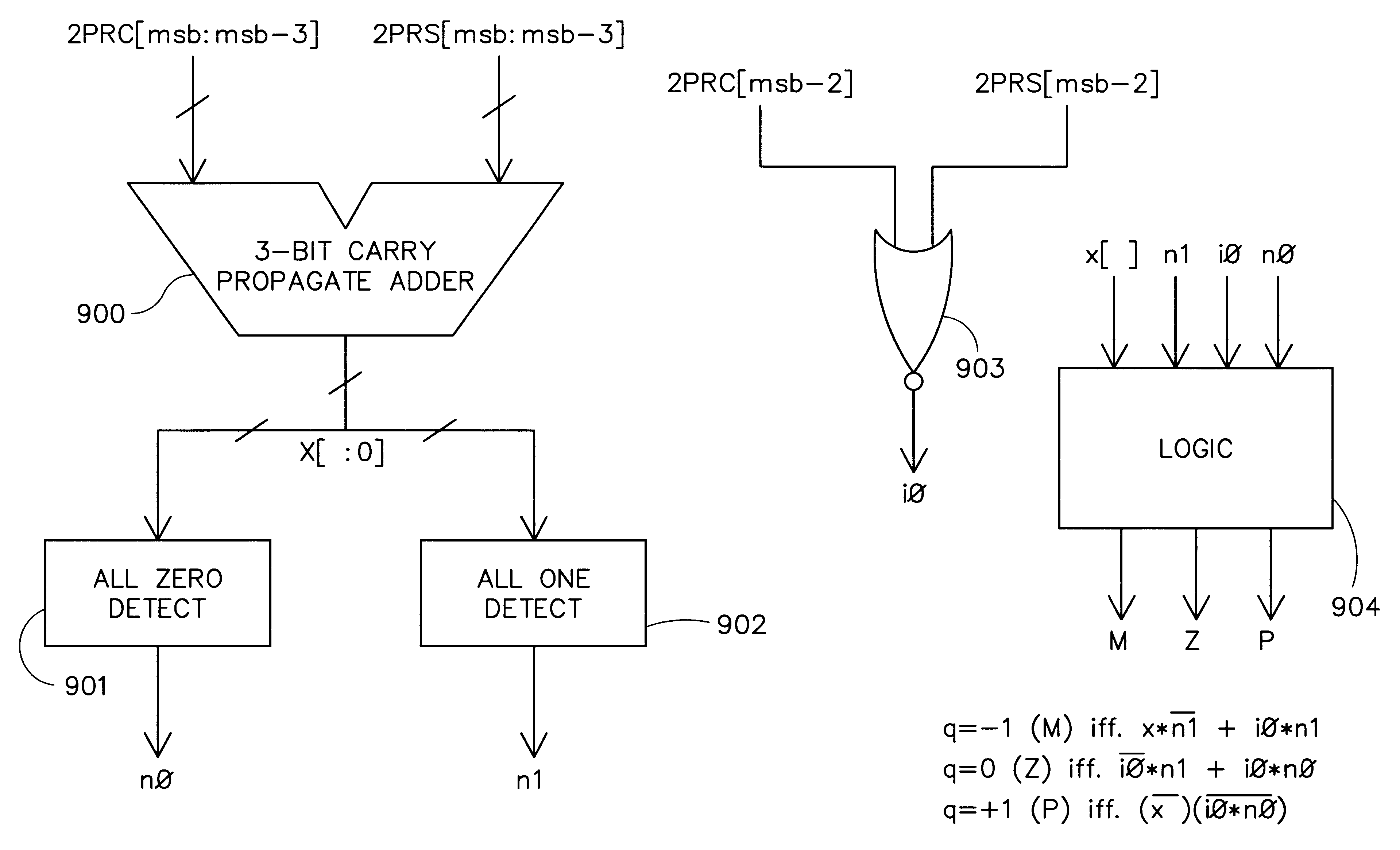

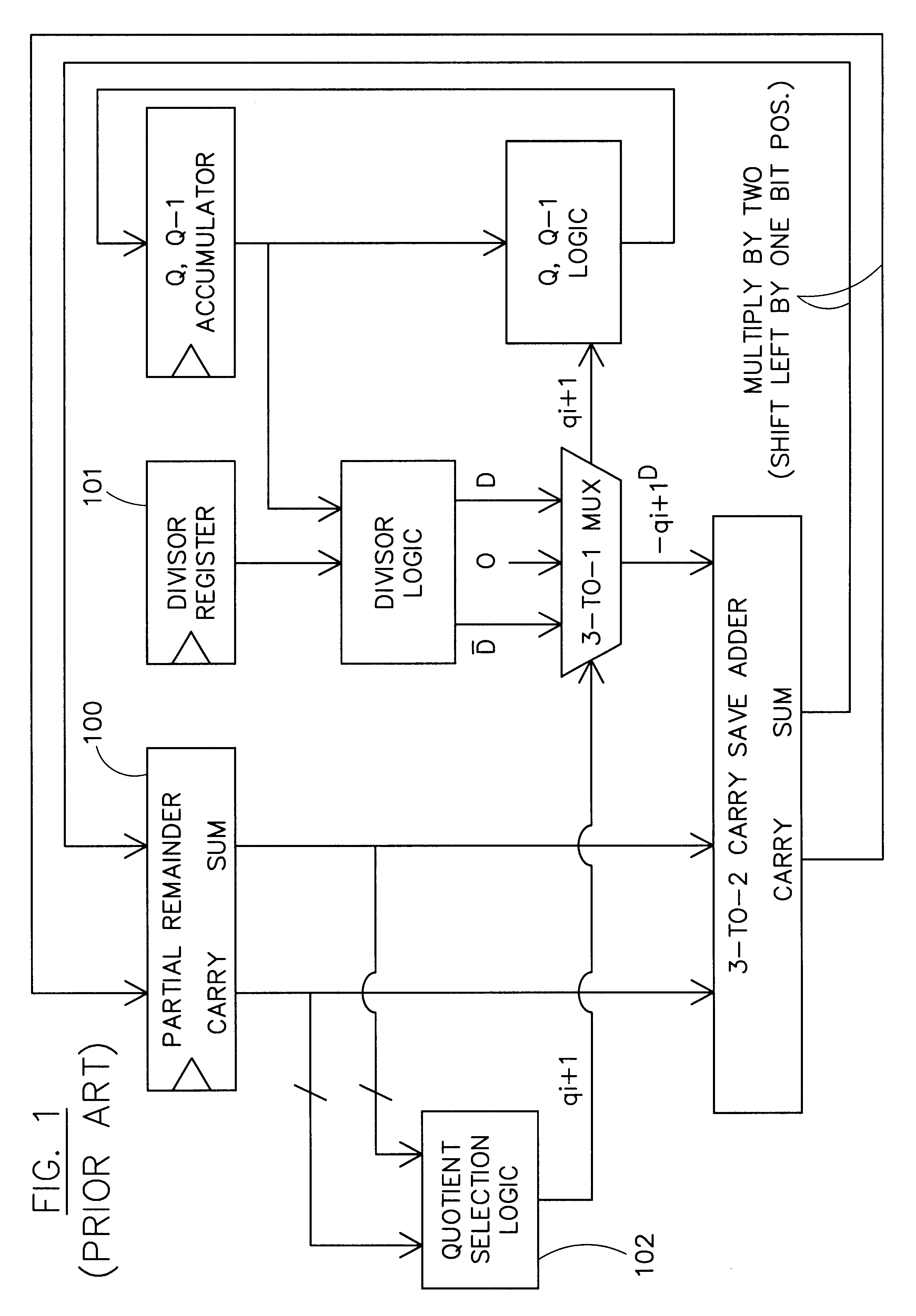

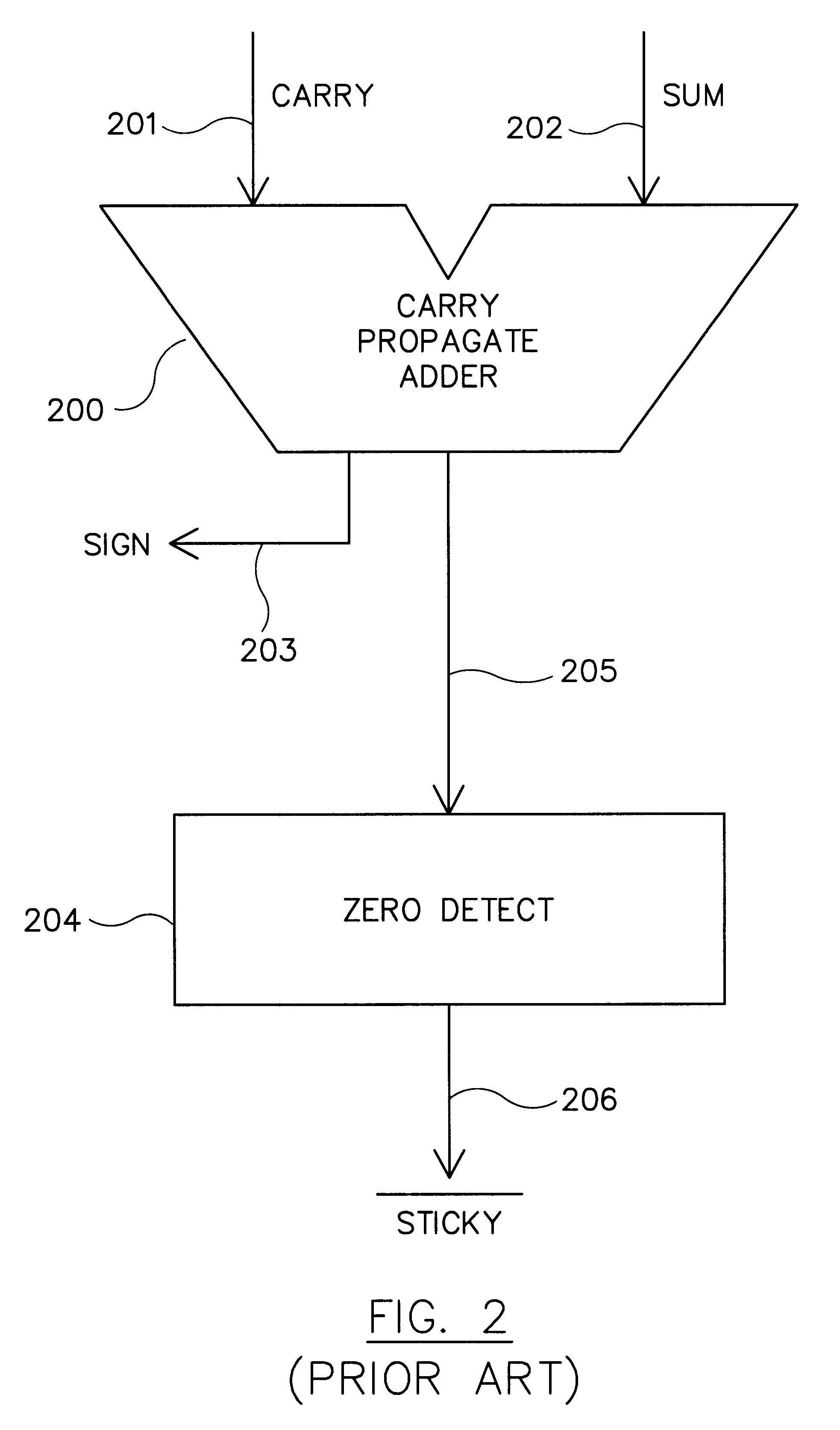

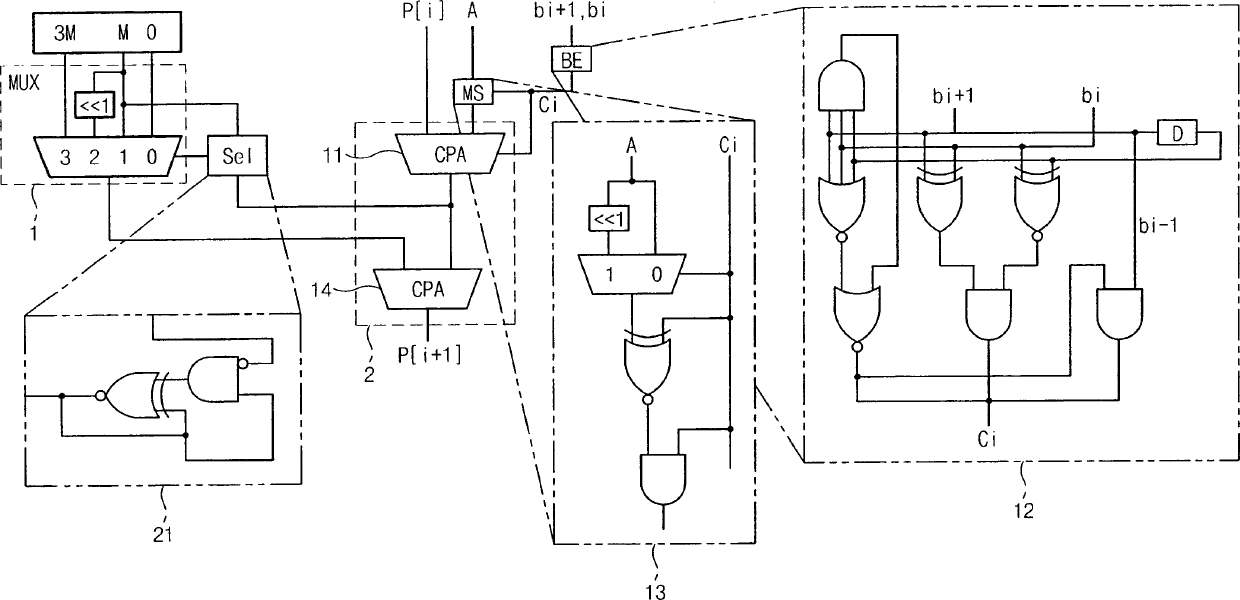

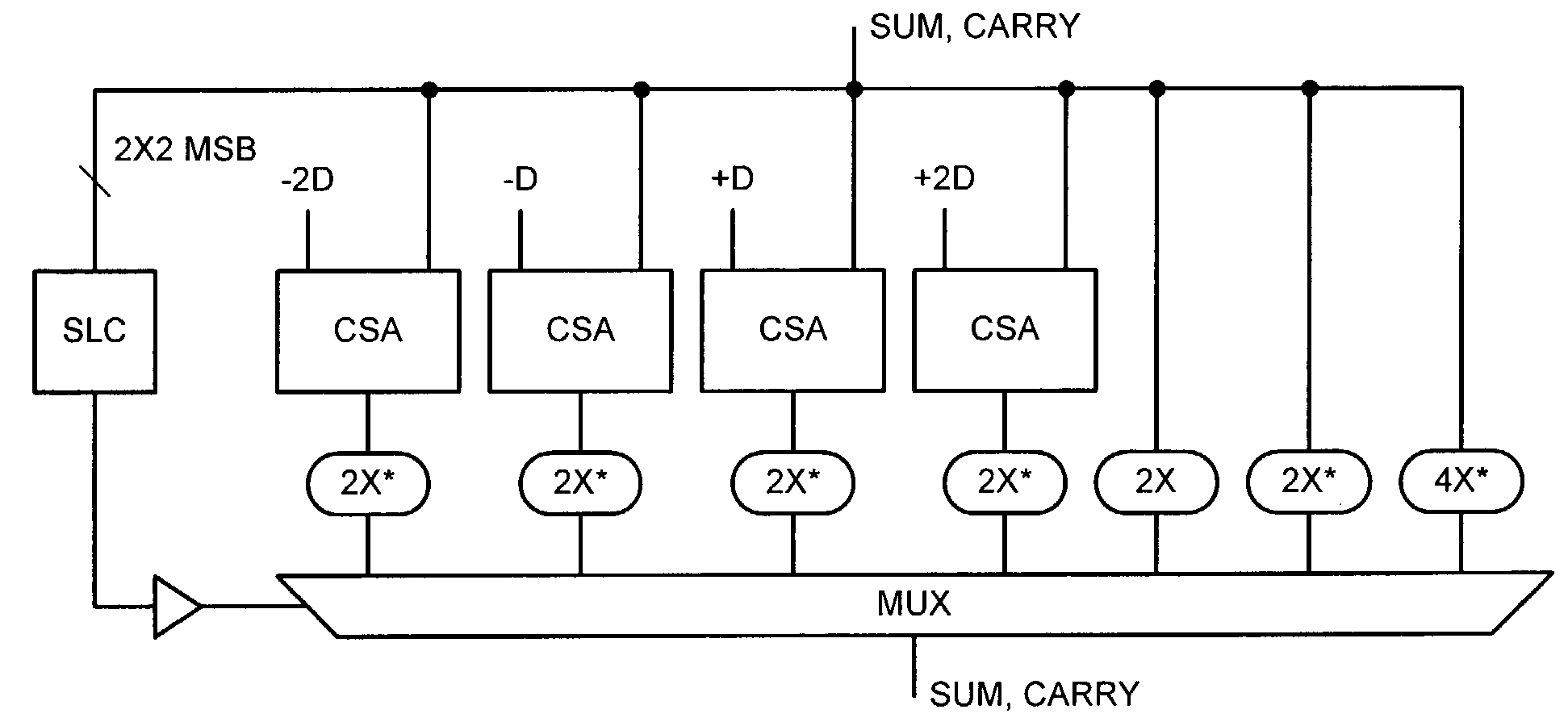

Quotient digit selection logic for floating point division/square root

InactiveUS6594681B1Computations using contact-making devicesComputation using non-contact making devicesCarry propagationAlgorithm

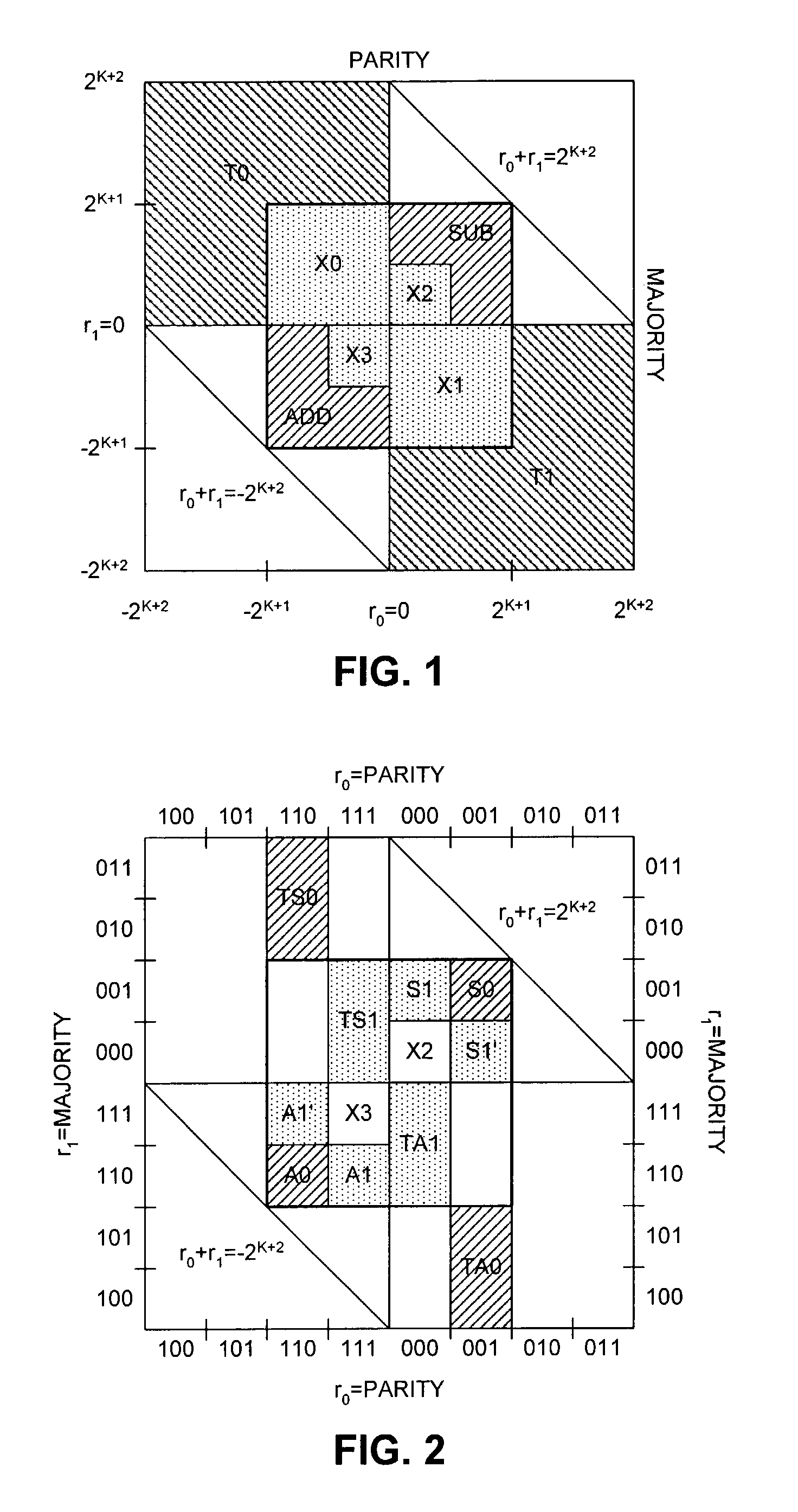

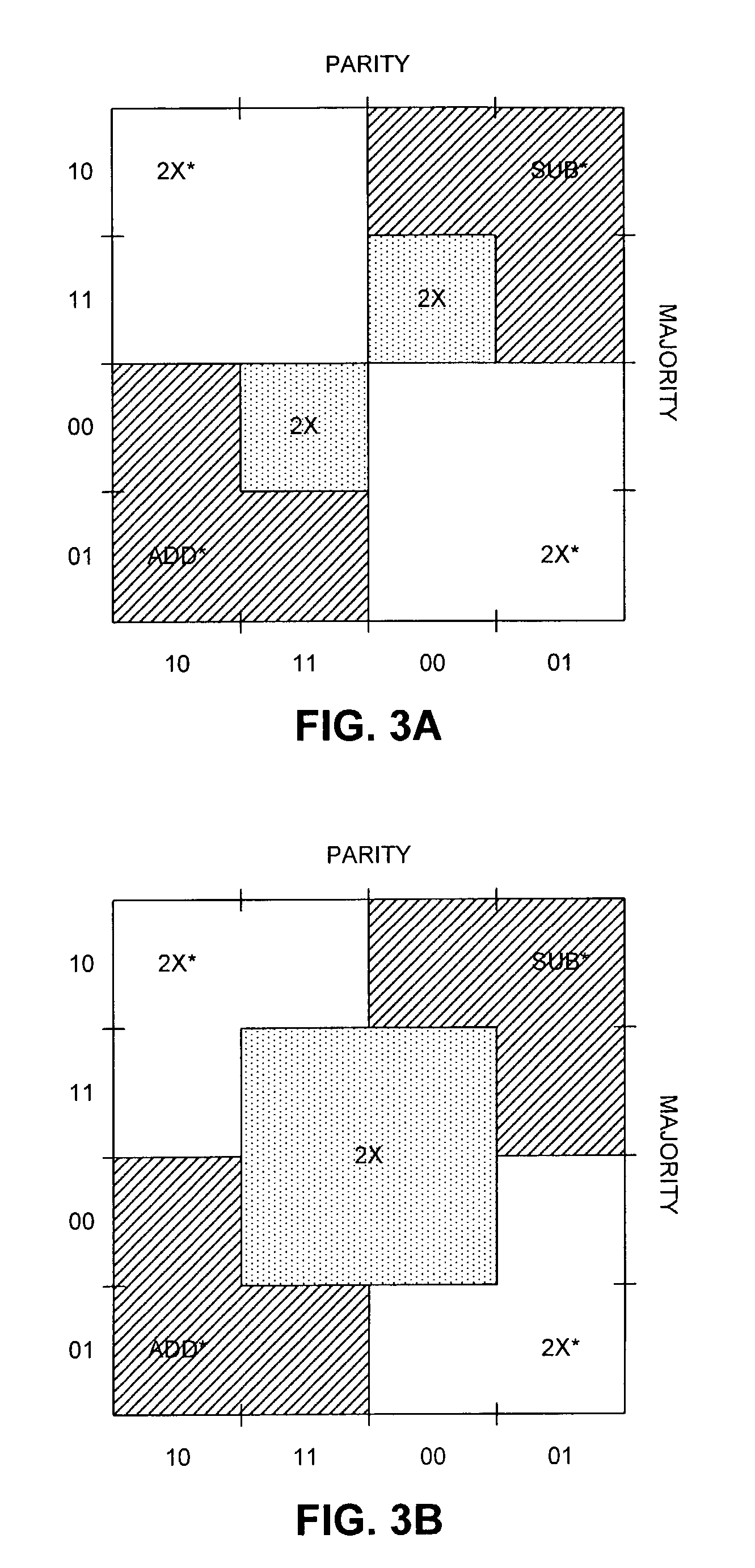

Quotient digit selection logic using a three-bit carry propagate adder is presented. An enhanced quotient digit selection function prevents the working partial remainder from becoming negative if the result is exact. The enhanced quotient digit selection logic chooses a quotient digit of zero instead of a quotient digit of one when the actual partial remainder is zero. Using a four bit estimated partial remainder where the upper four bits are zero, a possible carry propagation into fourth most significant bit is detected. This can be accomplished by looking at the fourth most significant sum and carry bits of the redundant partial remainder. If they are both zero, then a carry propagation out of that bit position into the least significant position of the estimated partial remainder is not possible, and a quotient digit of zero is chosen. This provides a one cycle savings since negative partial remainders no longer need to be restored before calculating the sticky bit. Extra hardware is eliminated because it is no longer necessary to provide any extra mechanism for restoring the preliminary final partial remainder. Latency is improved because no additional cycle time is required to restore negative preliminary partial remainders. In an alternative embodiment, where the upper three bits of the estimated partial remainder are ones while the fourth most significant bit is zero, a quotient digit of negative one is chosen. This alternative embodiment allows correct exact results in all rounding modes including rounding toward plus or minus infinity.

Owner:ORACLE INT CORP

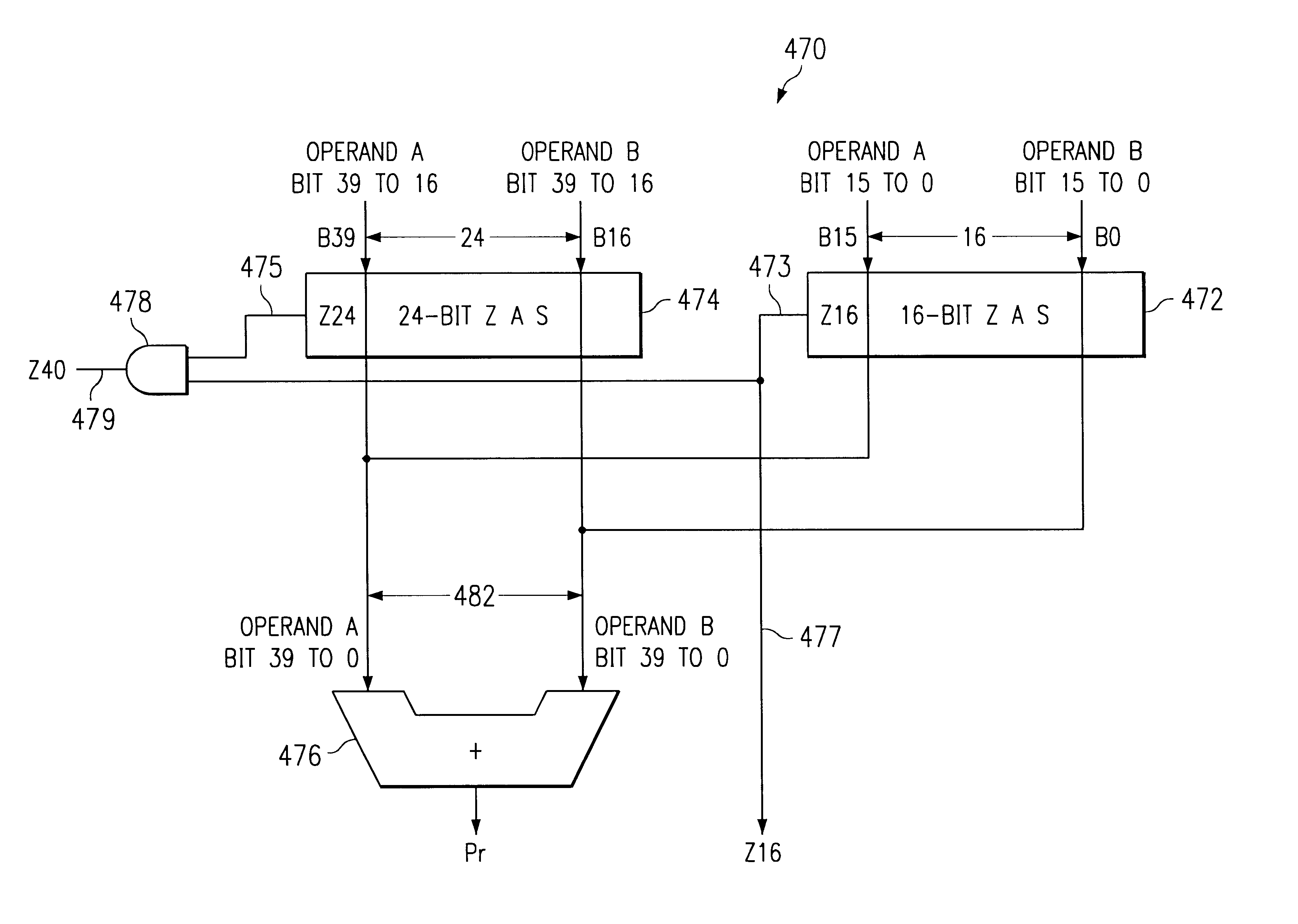

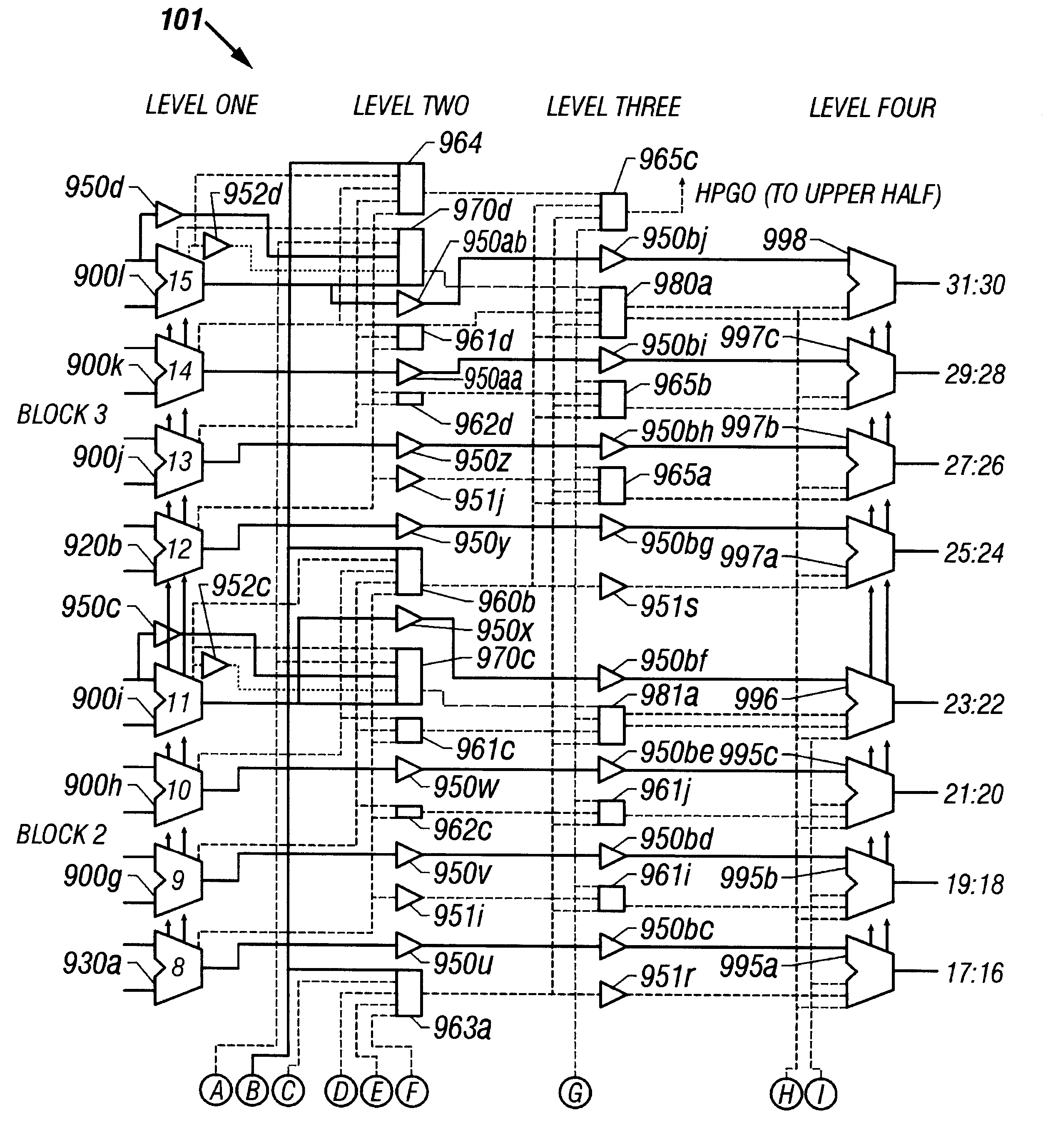

Rounding mechanisms in processors

InactiveUS7047272B2Efficient hardware implementationComputation using non-contact making devicesDigital computer detailsRoundingAlgorithm

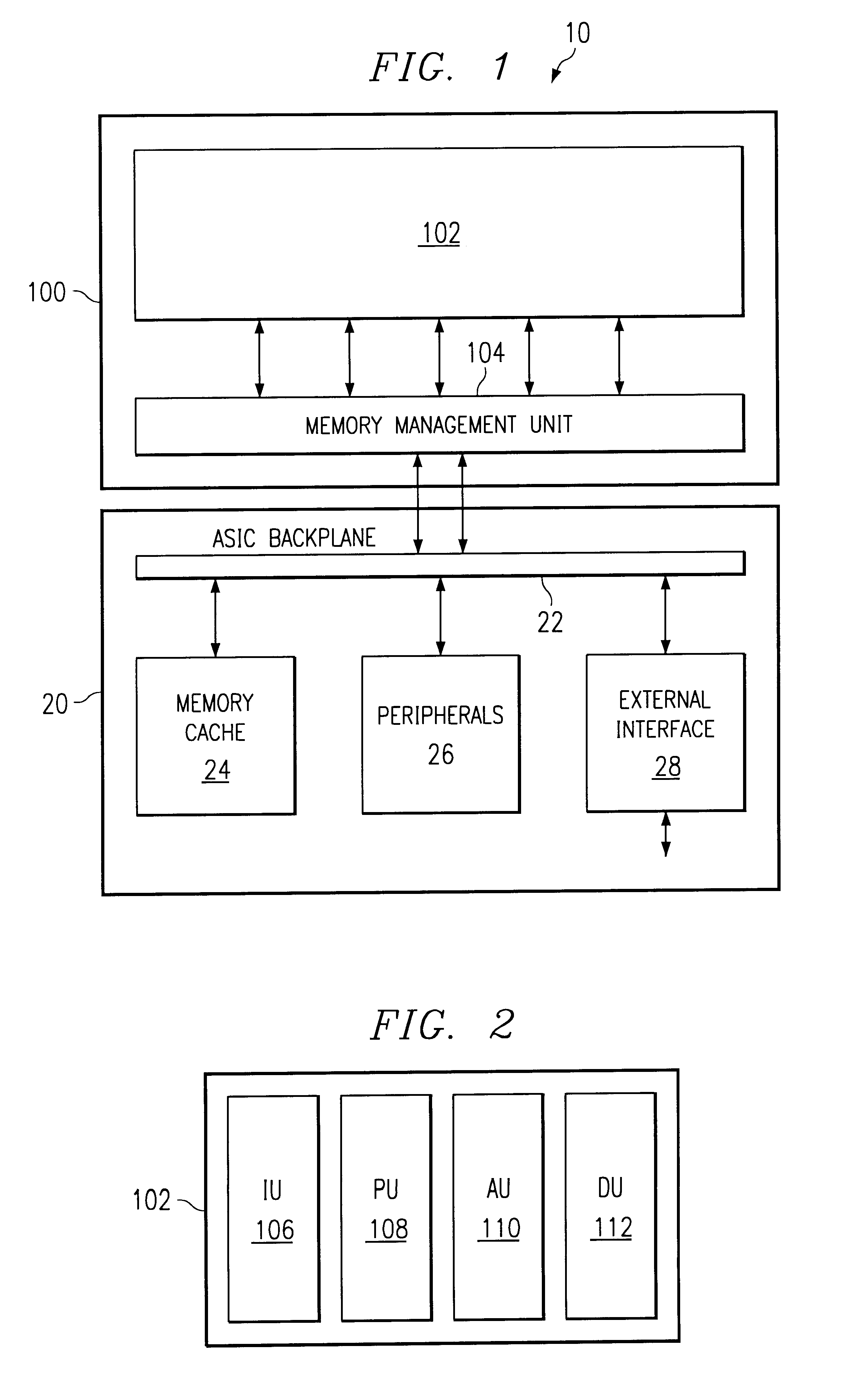

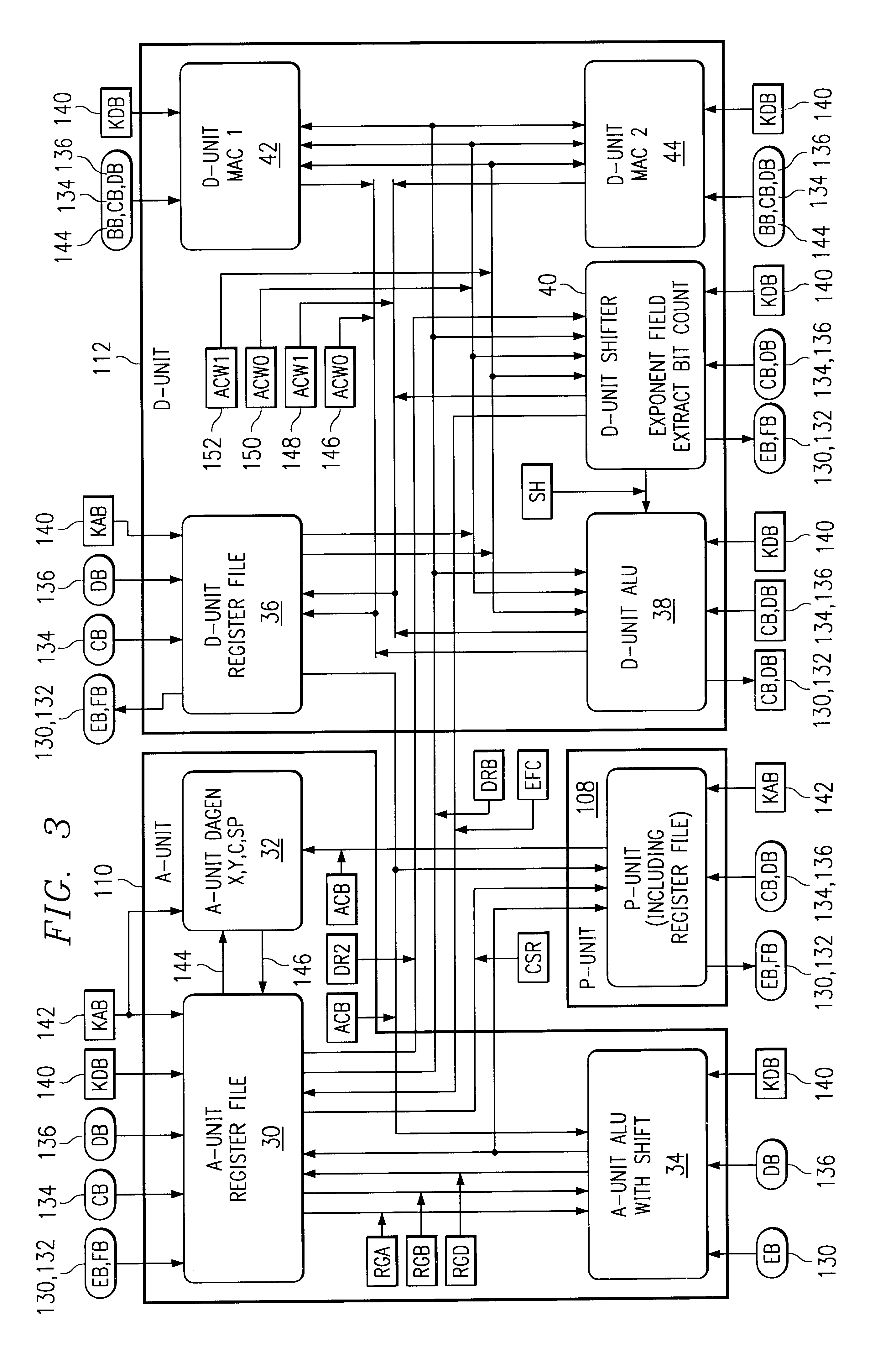

An arithmetic unit, for example a multiply and accumulate (MAC) unit 42, for a processing engine includes a partial product reduction tree 480. The partial product reduction tree will generate carry results and provides a final output to a final adder 470 connected to the partial production reduction tree. Unbiased rounding logic 476 is provided. A carry propagation tree is responsive to the carry results for anticipating a zero on each of N least significant bits of the final adder. When zero is anticipated on each of N least significant bits of the final adder, the carry propagation tree is operable to generate an output signal 477 which is used by the unbiased rounding stage to force the (N+1)th least significant bit of the final adder to zero. Through the use of a carry propagation tree to predict, or anticipate zeros on the N least significant bits, unbiased rounding can be effected without a time penalty in that a carry propagation tree can be configured to be at least a rapid as the carry propagation of the final adder. Where a zero anticipation function is provided, this can also be mapped onto the carry propagation tree, thus providing an efficient hardware implementation through sharing of that hardware between functions.

Owner:TEXAS INSTR INC

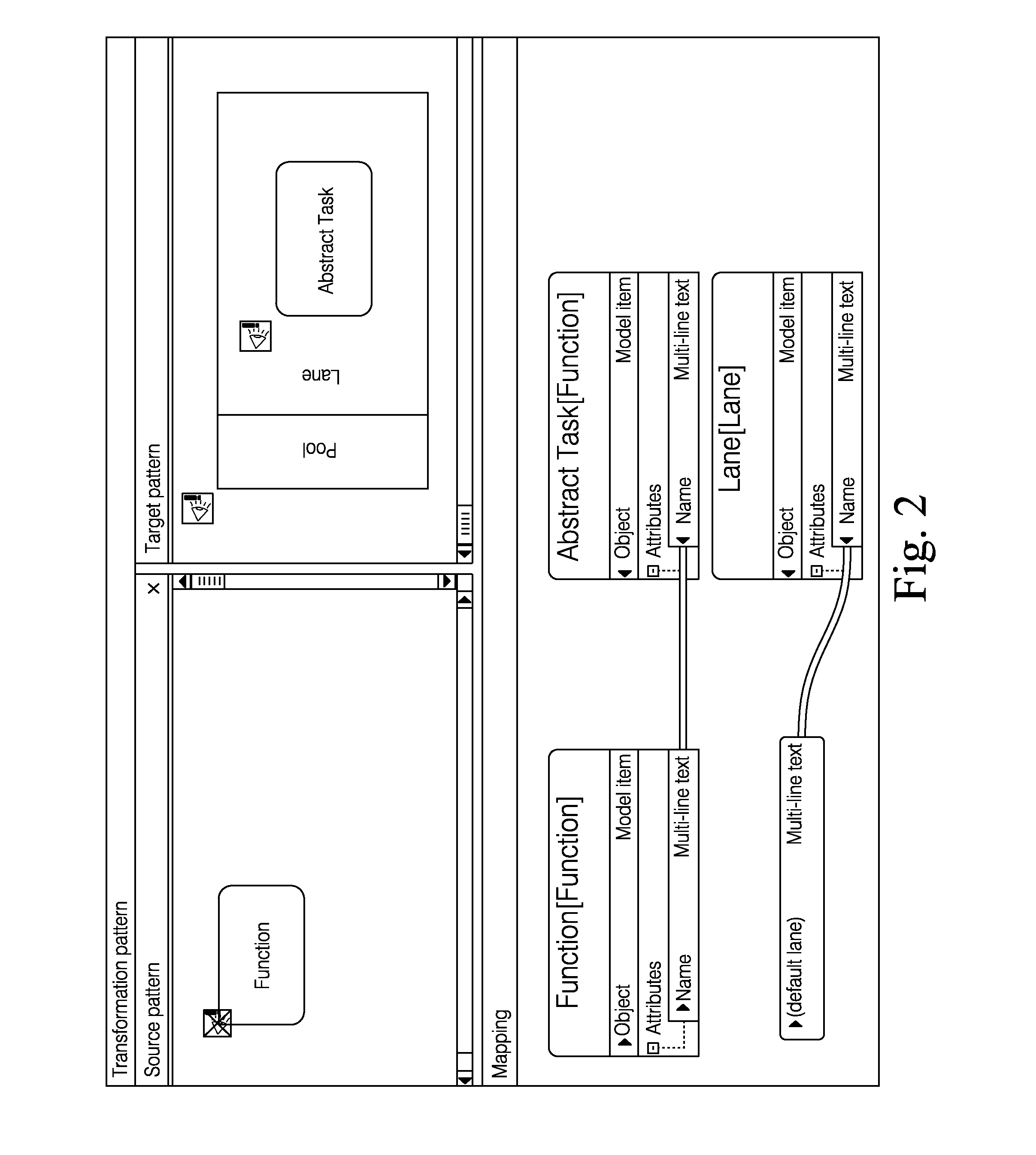

Selective change propagation techniques for supporting partial roundtrips in model-to-model transformations

ActiveUS20130104099A1Easy to resolveResolve them easily and quicklyResourcesRequirement analysisCarry propagationComputer science

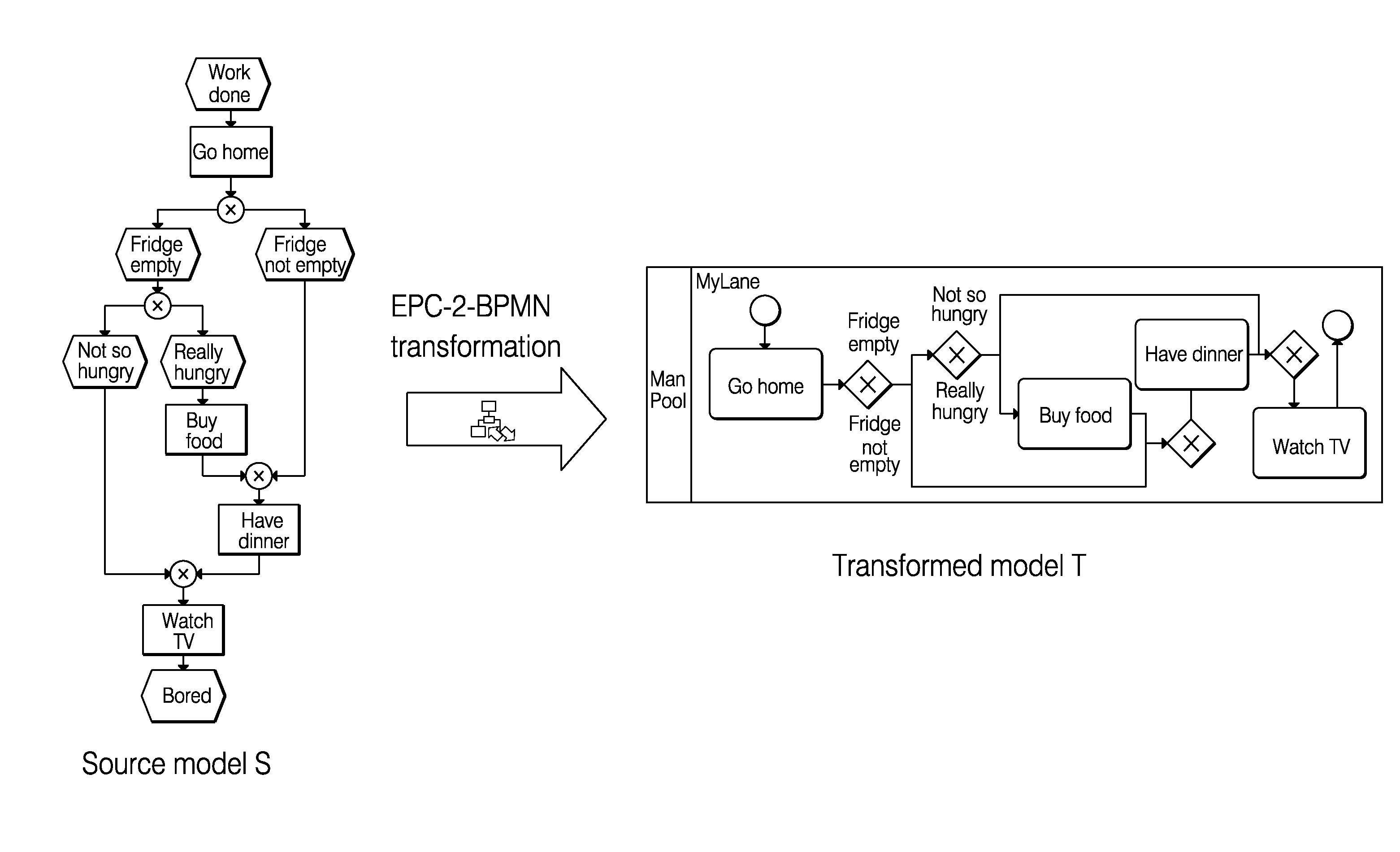

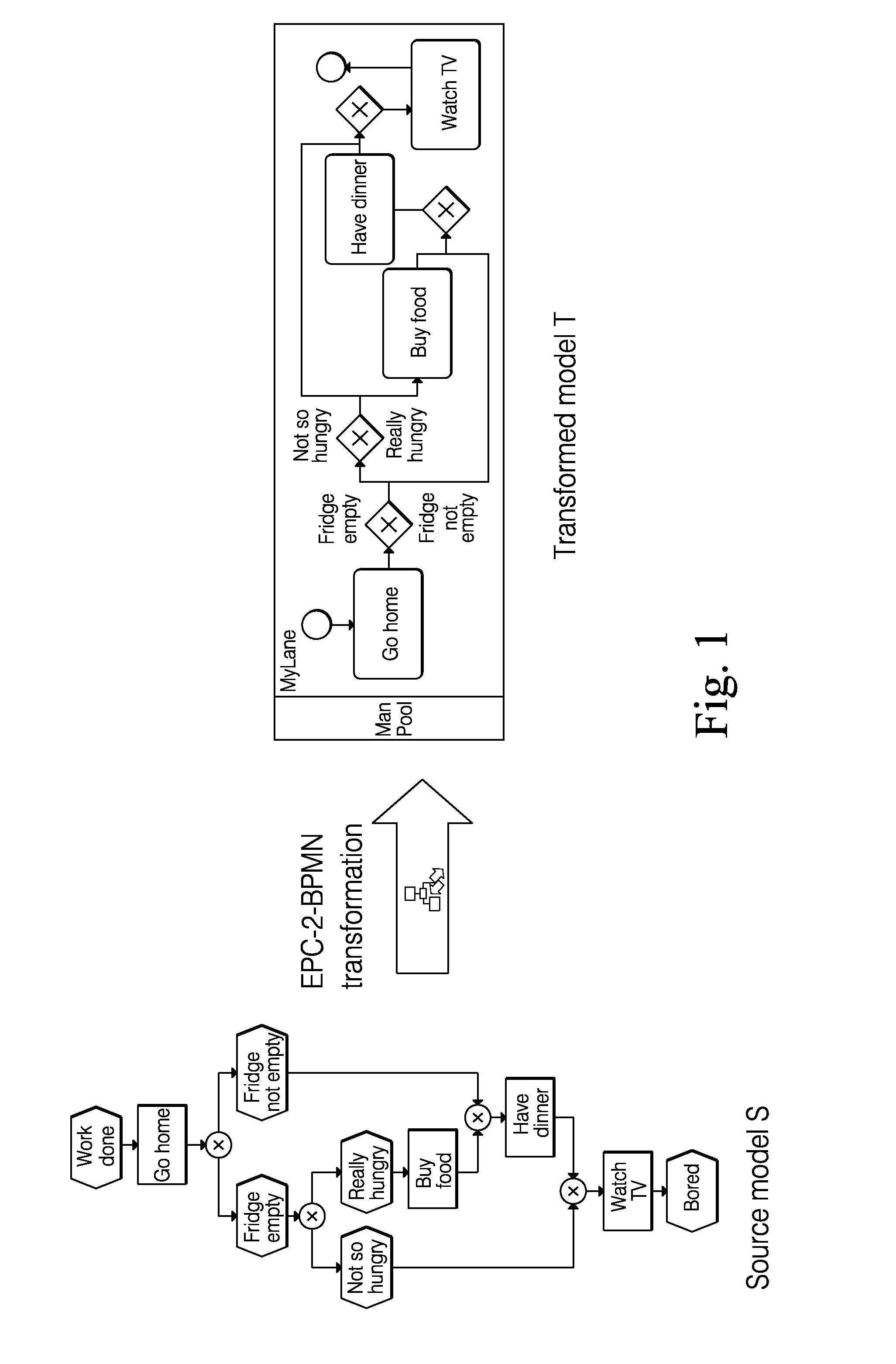

Certain example embodiments relate to selective change propagation techniques for supporting partial roundtrips in model-to-model transformations. In certain example embodiments, enablement checking is performed to determine whether a propagation operation can be performed for an object. If the object passes enablement checking, the propagation is executed by, for example, creating the object(s) in a business-oriented (e.g., EPC) model; updating relevant internal attributes of technical (e.g., BPMN) objects that allow for the successful merge; optionally correcting user-introduced errors in the technical model; and properly connecting the pulled-up objects with their surroundings. The connecting is performed so that the objects advantageously appear as if the current business-oriented model was used for the merge. According to certain example embodiments, the connecting may be deterministic, e.g., such that the result will be the same regardless of order or sequence in which the propagations are made.

Owner:SOFTWARE AG

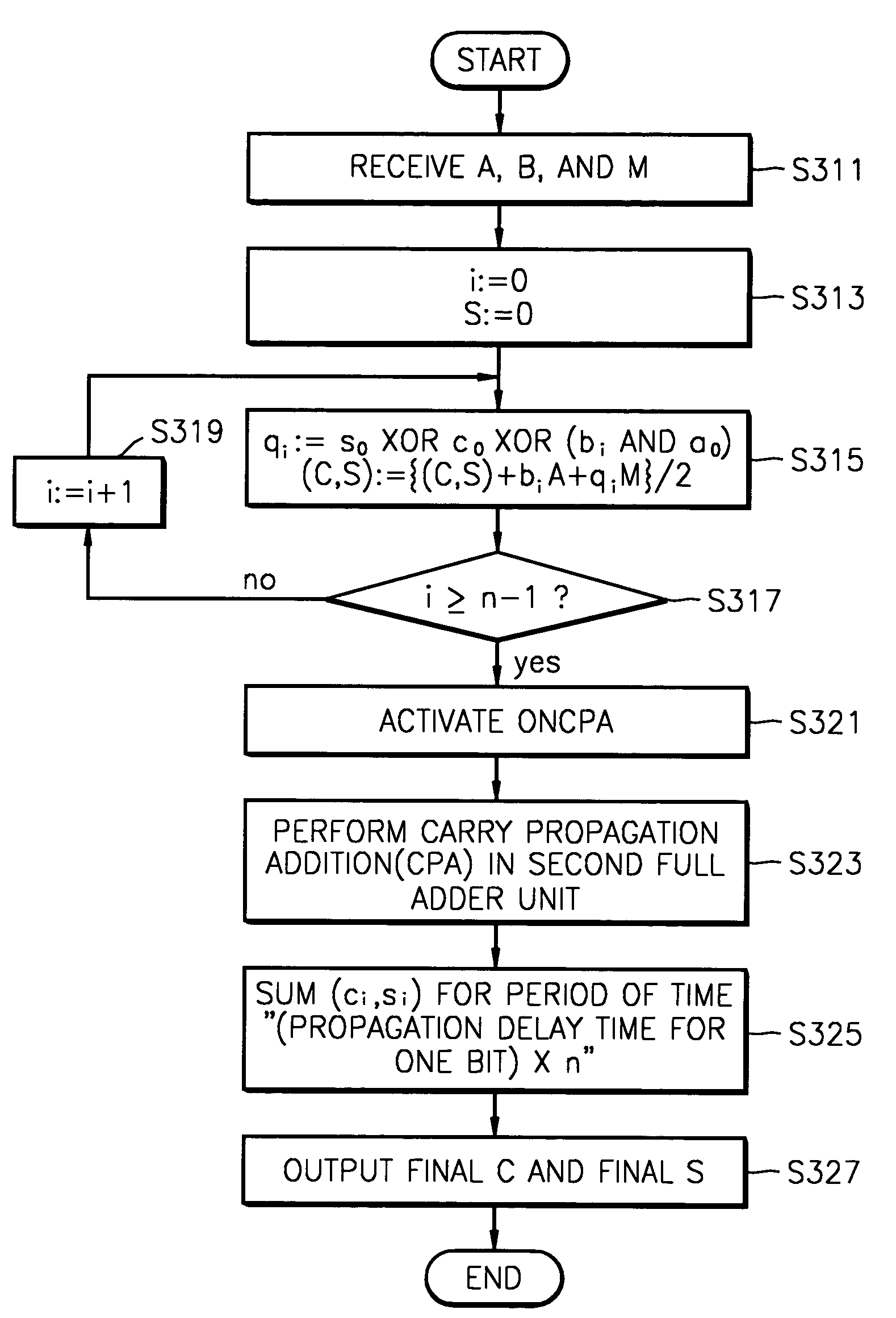

Montgomery modular multiplier and method thereof using carry save addition

InactiveUS7543011B2Reduce power consumptionIncrease speedComputation using non-contact making devicesDigital computer detailsCarry propagationModular multiplier

A method of reducing power consumption and / or enhancing computation speed in the modulus multiplication operation of a Montgomery modulus multiplication module. A coding scheme reduces the need for an adder or memory element for obtaining multiple modulus values, and the use of carry save addition with carry propagation addition enhances the computational speed of the multiplication module.

Owner:SAMSUNG ELECTRONICS CO LTD

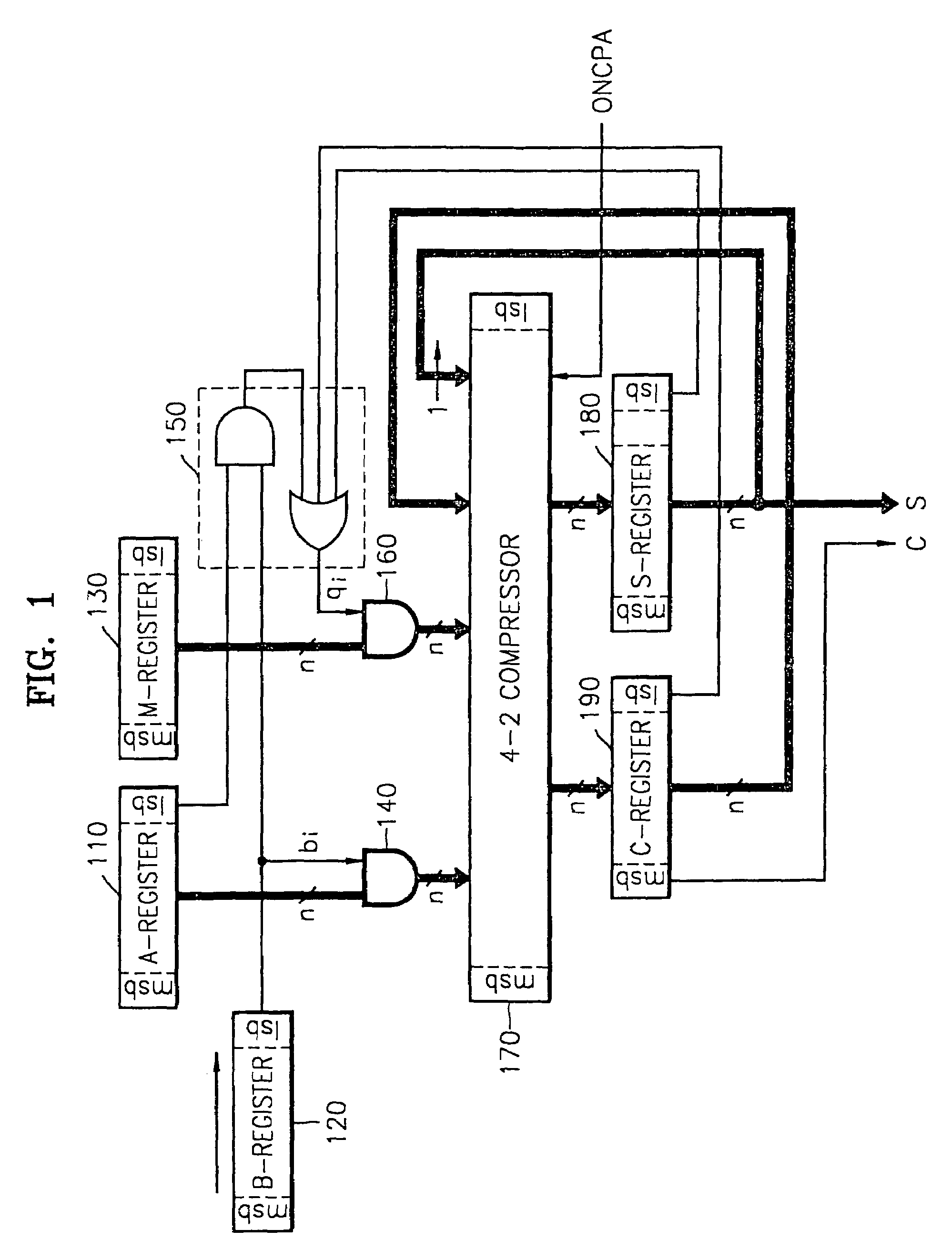

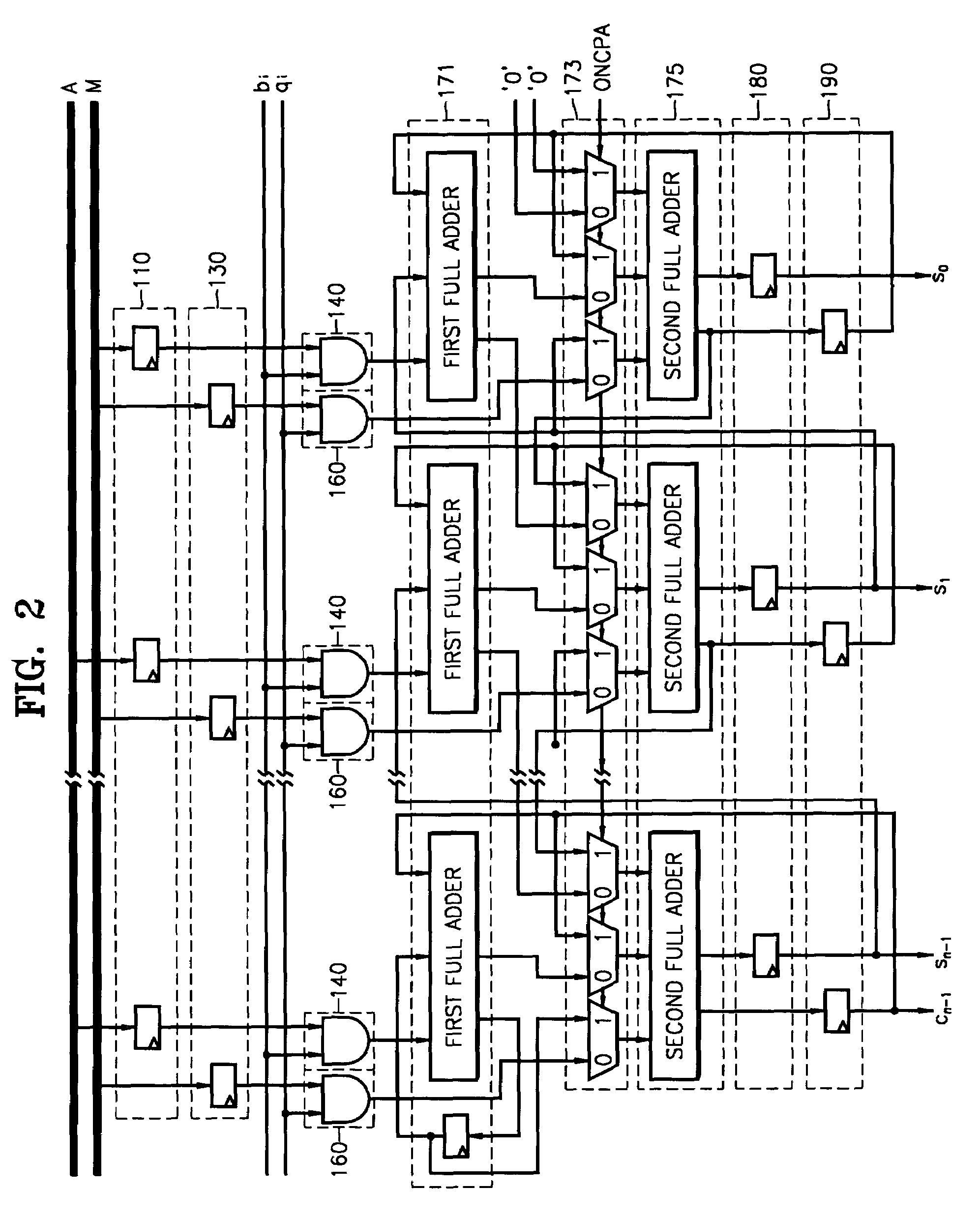

Montgomery modular multiplier using a compressor and multiplication method

ActiveUS20040125948A1Easy to disassembleHigh speedPublic key for secure communicationComputation using non-contact making devicesCarry propagationModular multiplier

A Montgomery modular multiplier receiving a multiplicand (A), a modulus (M), and a multiplier (B), using a t-s compressor, where t>3 and s>1, and a multiplication method performed in the same. In response to a carry propagation adder signal, the t-s compressor performs additions on the carry C and the sum Sand obtains the final results in a carry propagation adder structure.

Owner:SAMSUNG ELECTRONICS CO LTD

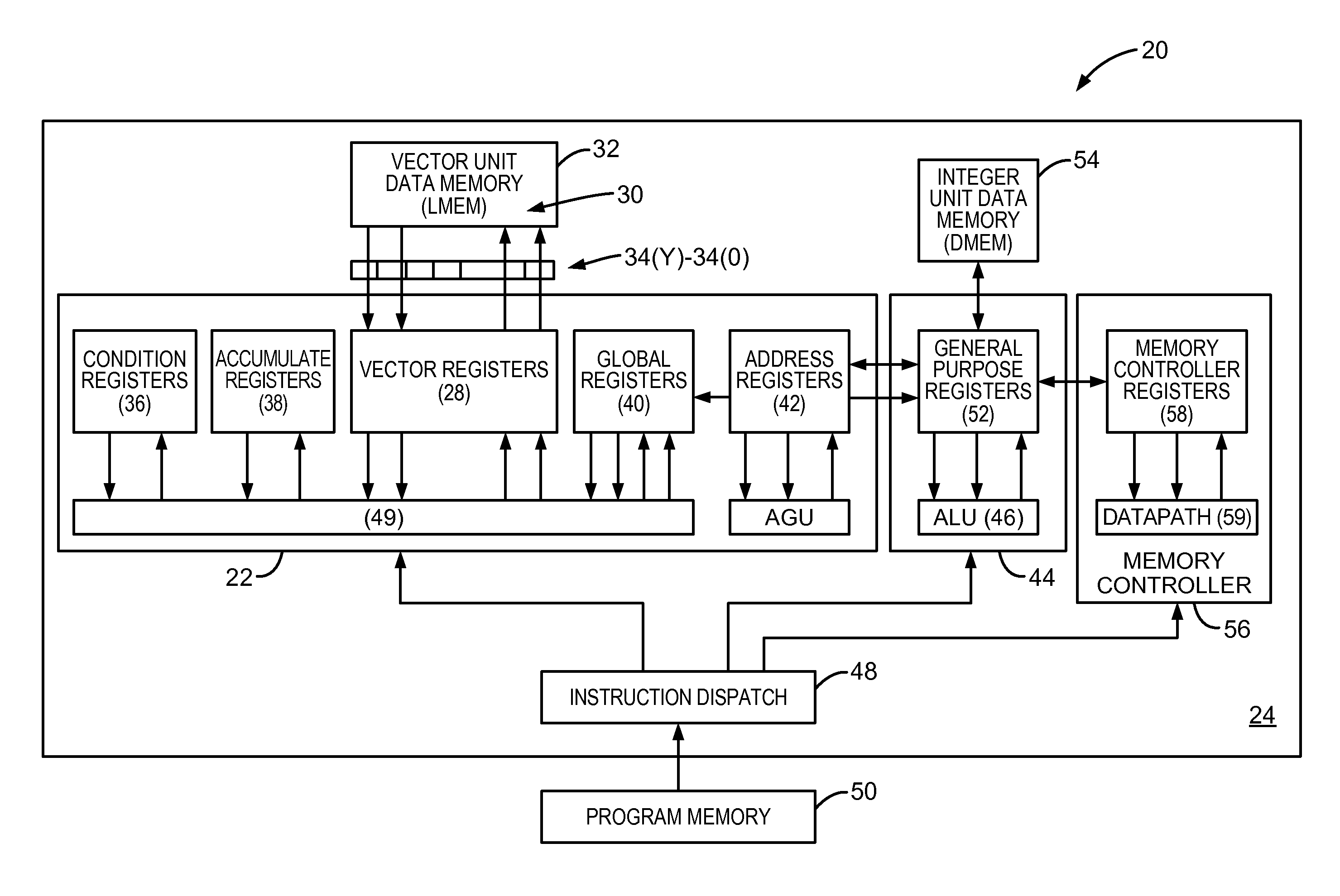

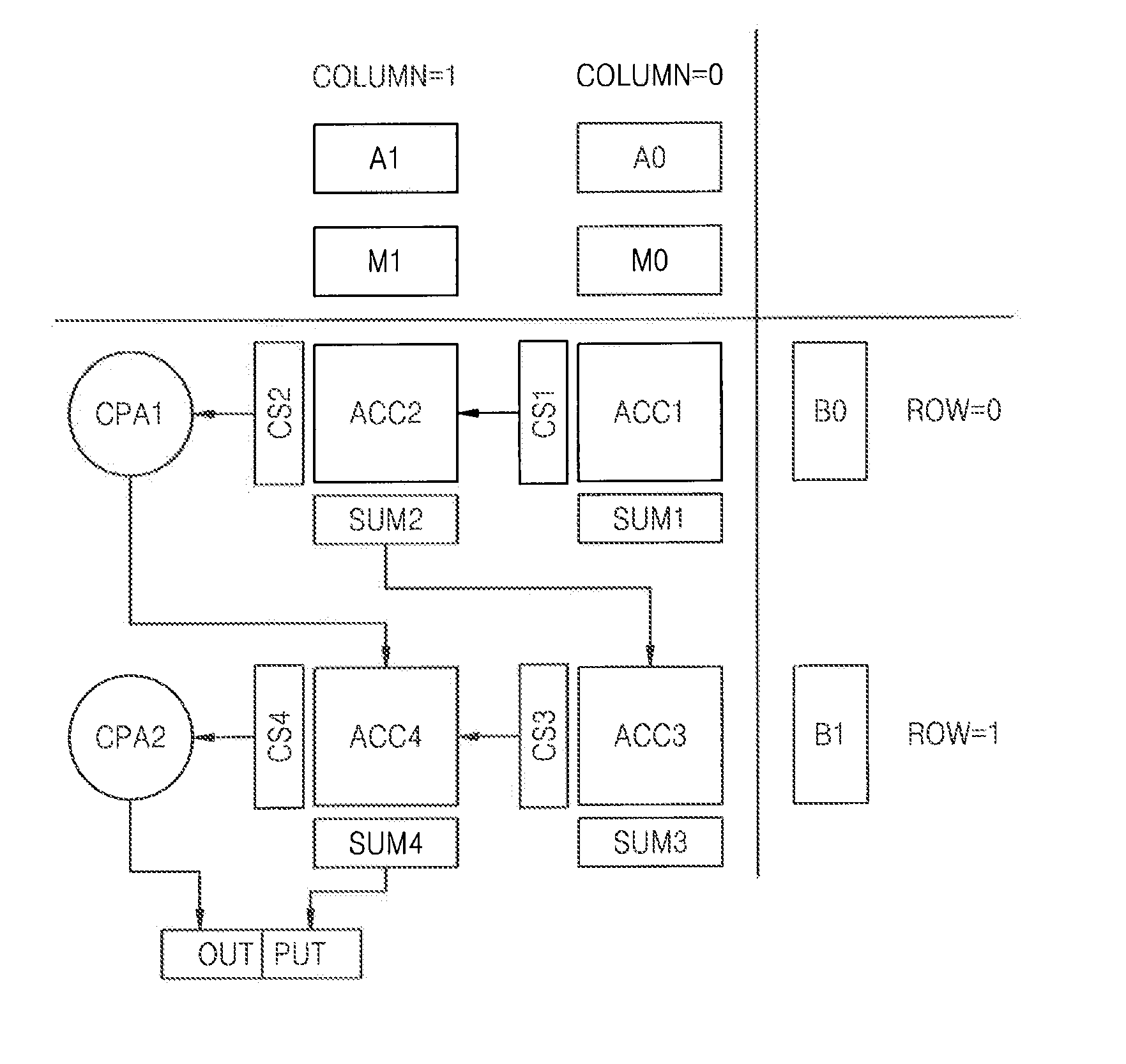

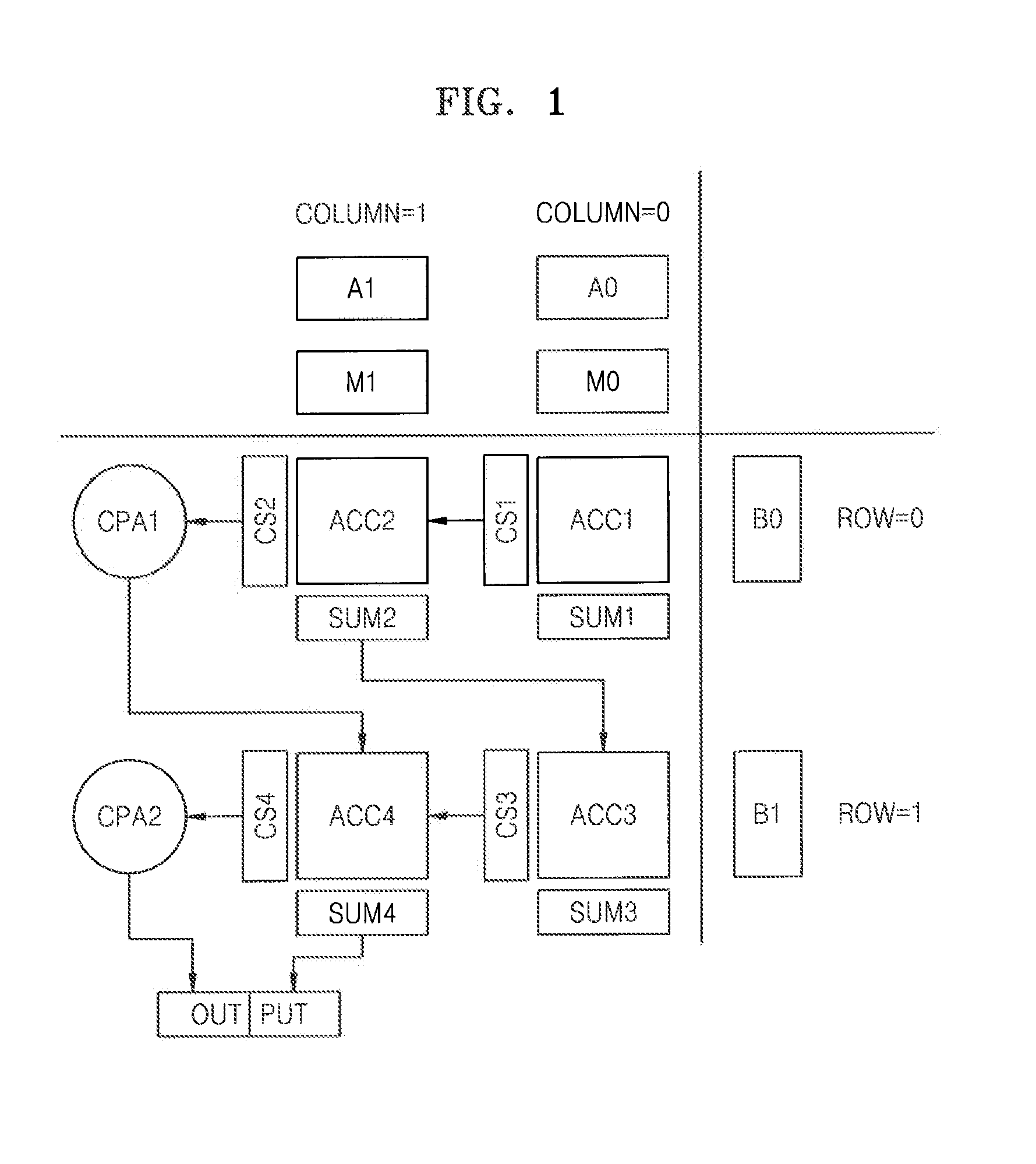

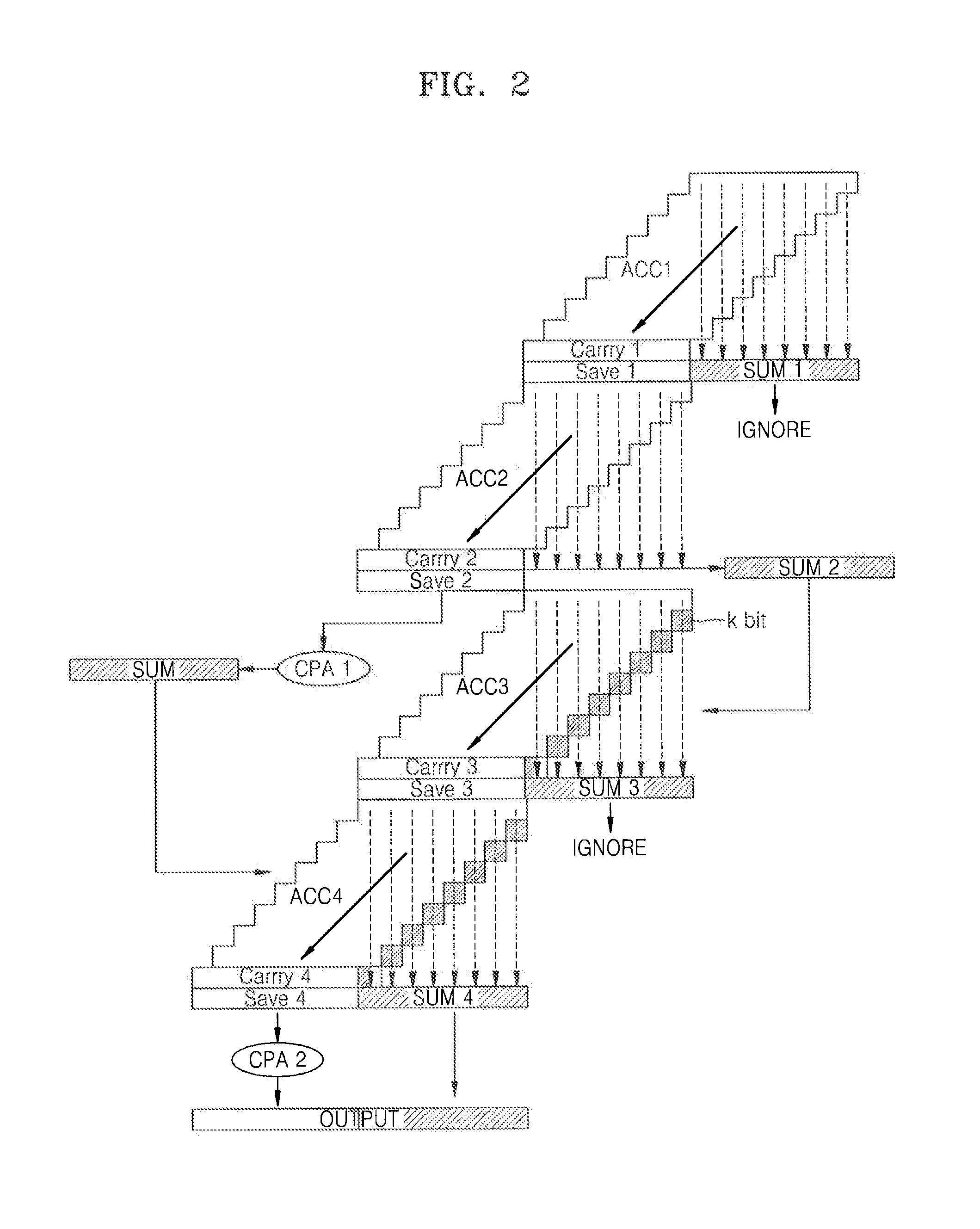

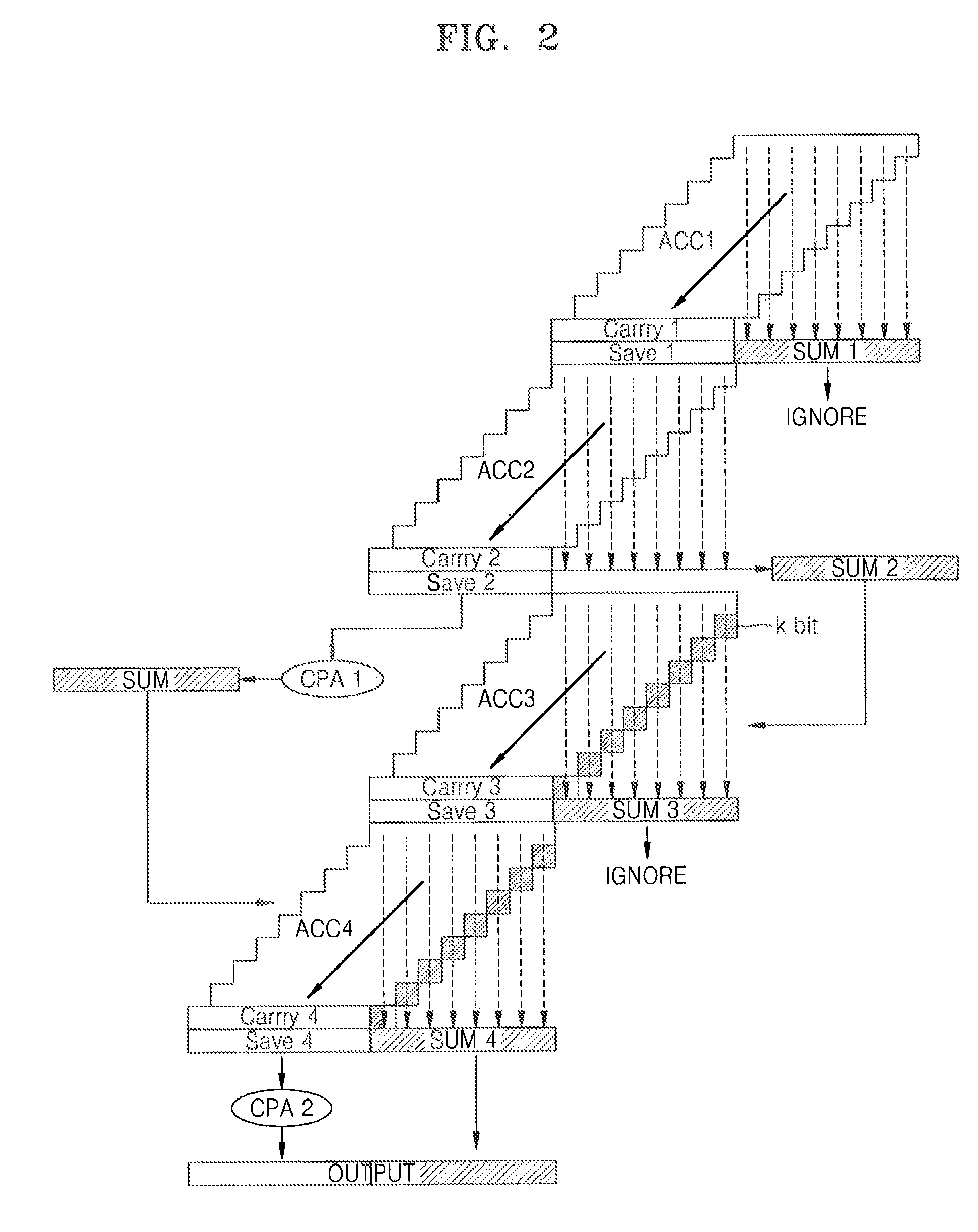

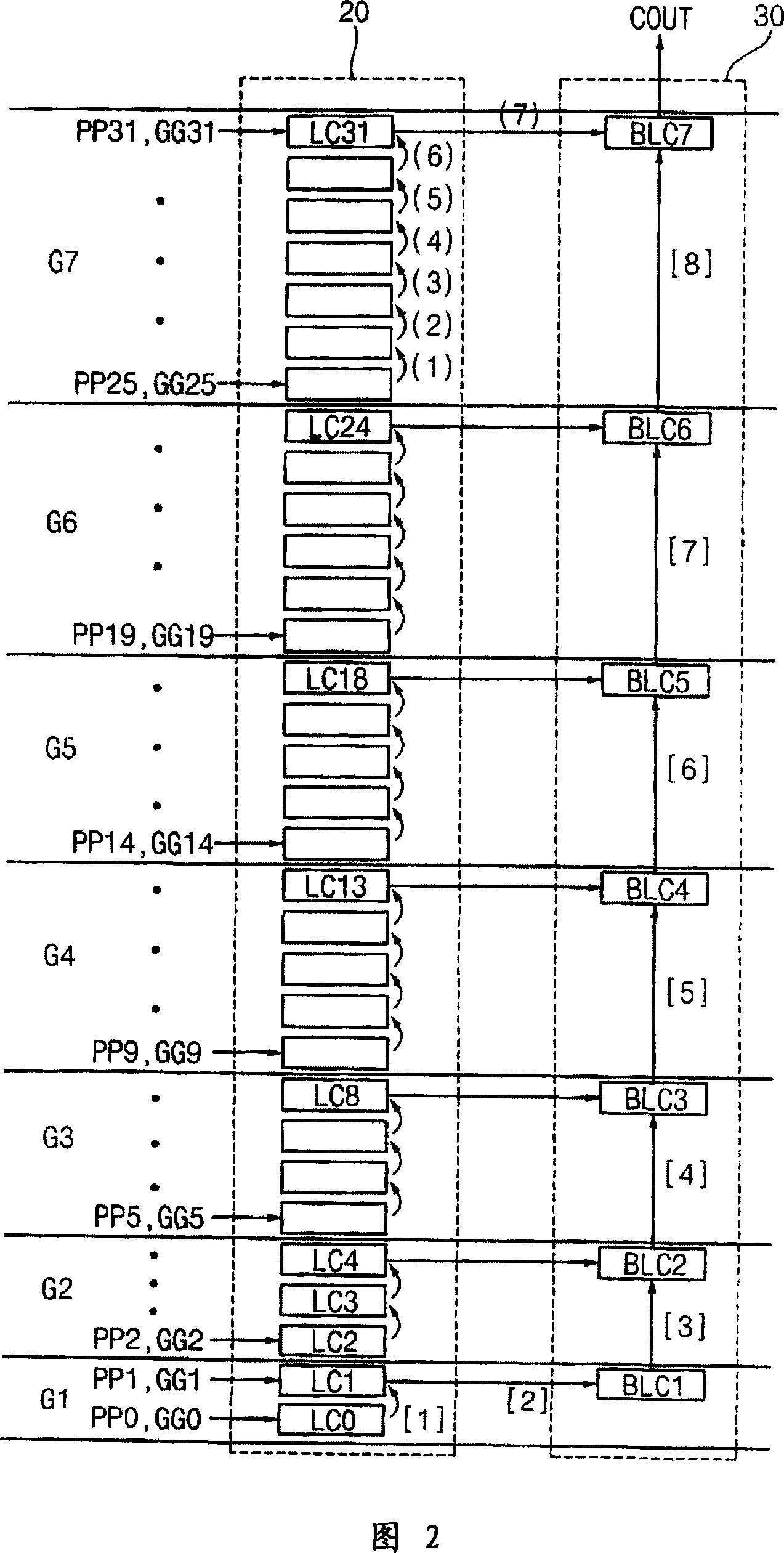

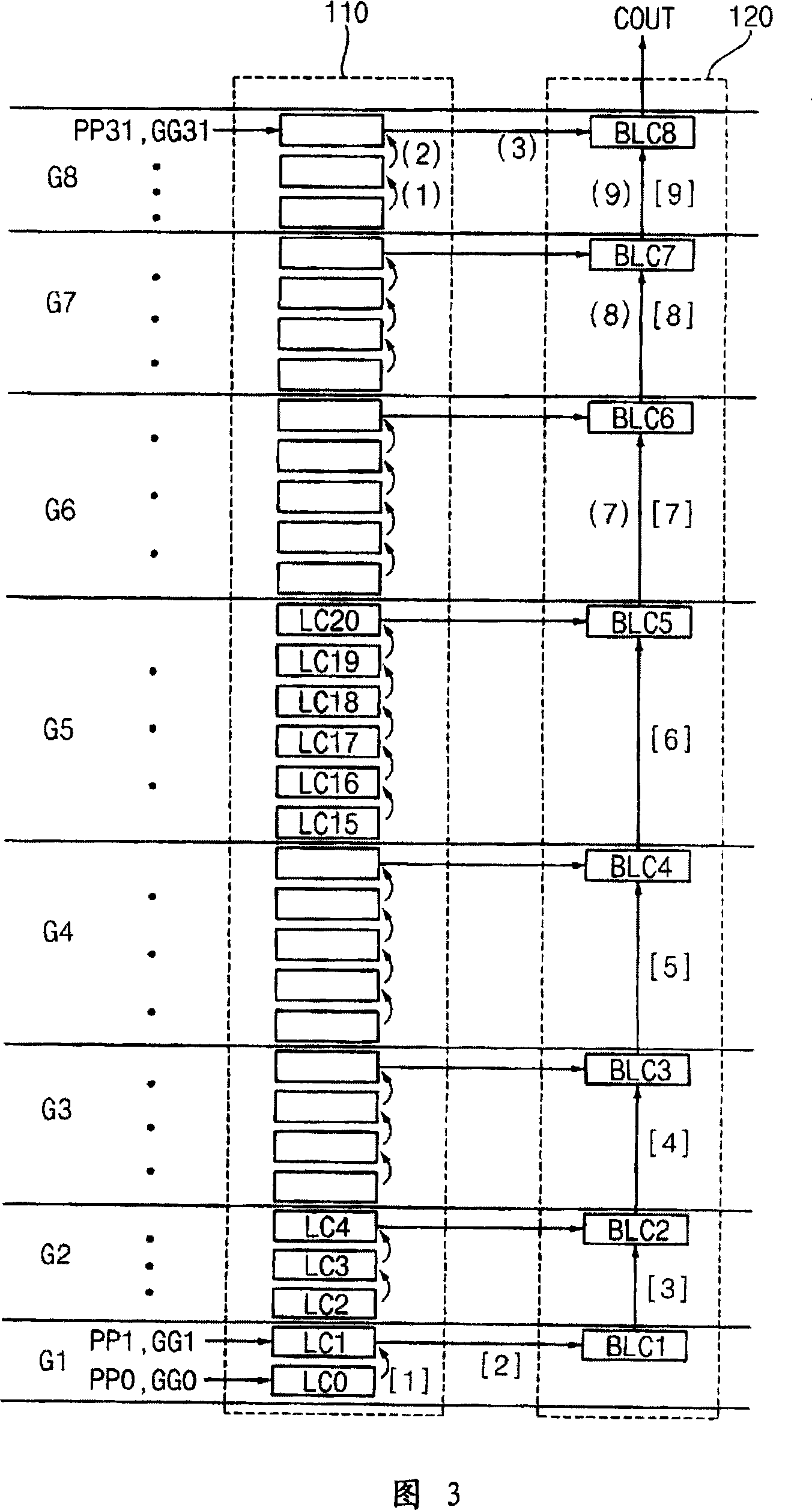

Vector processing carry-save accumulators employing redundant carry-save format to reduce carry propagation, and related vector processors, systems, and methods

InactiveUS20140280407A1Reduce carry propagationDecrease their propagationComputation using non-contact making devicesDigital computer detailsCarry propagationAND gate

Embodiments disclosed herein include vector processing carry-save accumulators employing redundant carry-save format to reduce carry propagation. The multi-mode vector processing carry-save accumulators employing redundant carry-save format can be provided in a vector processing engine (VPE) to perform vector accumulation operations. Related vector processors, systems, and methods are also disclosed. The accumulator blocks are configured as carry-save accumulator structures. The accumulator blocks are configured to accumulate in redundant carry-save format so that carrys and saves are accumulated and saved without the need to provide a carry propagation path and a carry propagation add operation during each step of accumulation. A carry propagate adder is only required to propagate the accumulated carry once at the end of the accumulation. In this manner, power consumption and gate delay associated with performing a carry propagation add operation during each step of accumulation in the accumulator blocks is reduced or eliminated.

Owner:QUALCOMM INC

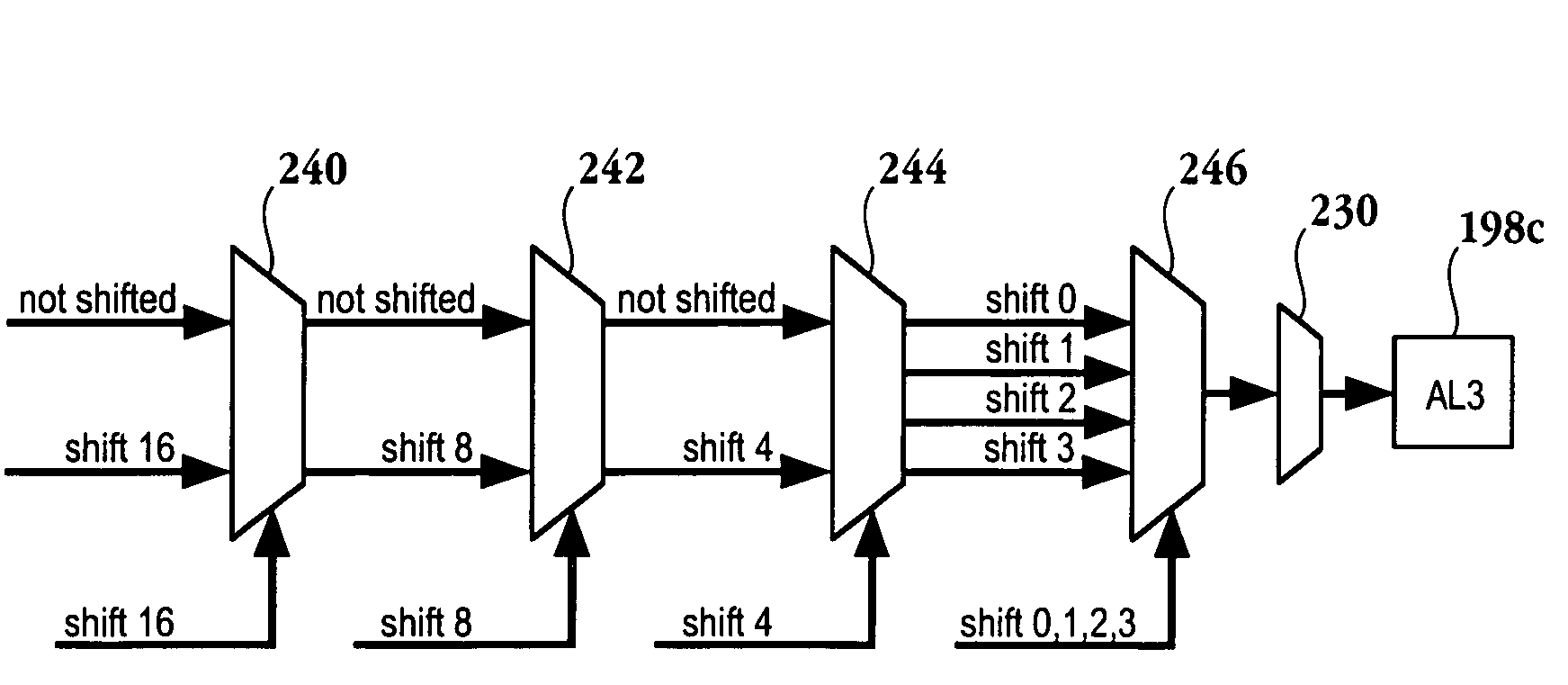

Method and apparatus for aligning operands for a processor

InactiveUS7320013B2Efficient processingDigital data processing detailsDigital computer detailsCarry propagationLeast significant bit

A method for transparently presenting different size operands to be processed is provided. The method initiates with providing a first operand having a first bit-width. Then, a bit width of a second operand associated with a processor is determined. The second operand has a greater bit width than the first operand. Next, the first operand is transformed by aligning a least significant bit of the first operand to a lowest bit position of a transformed operand having a bit size equal to the second operand. Then, the bits of the transformed operand are sign extended and padded in a manner to allow carry propagation. Next, the transformed operand is transmitted to the processor. A method for shifting operands and a processor are also provided.

Owner:RPX CORP

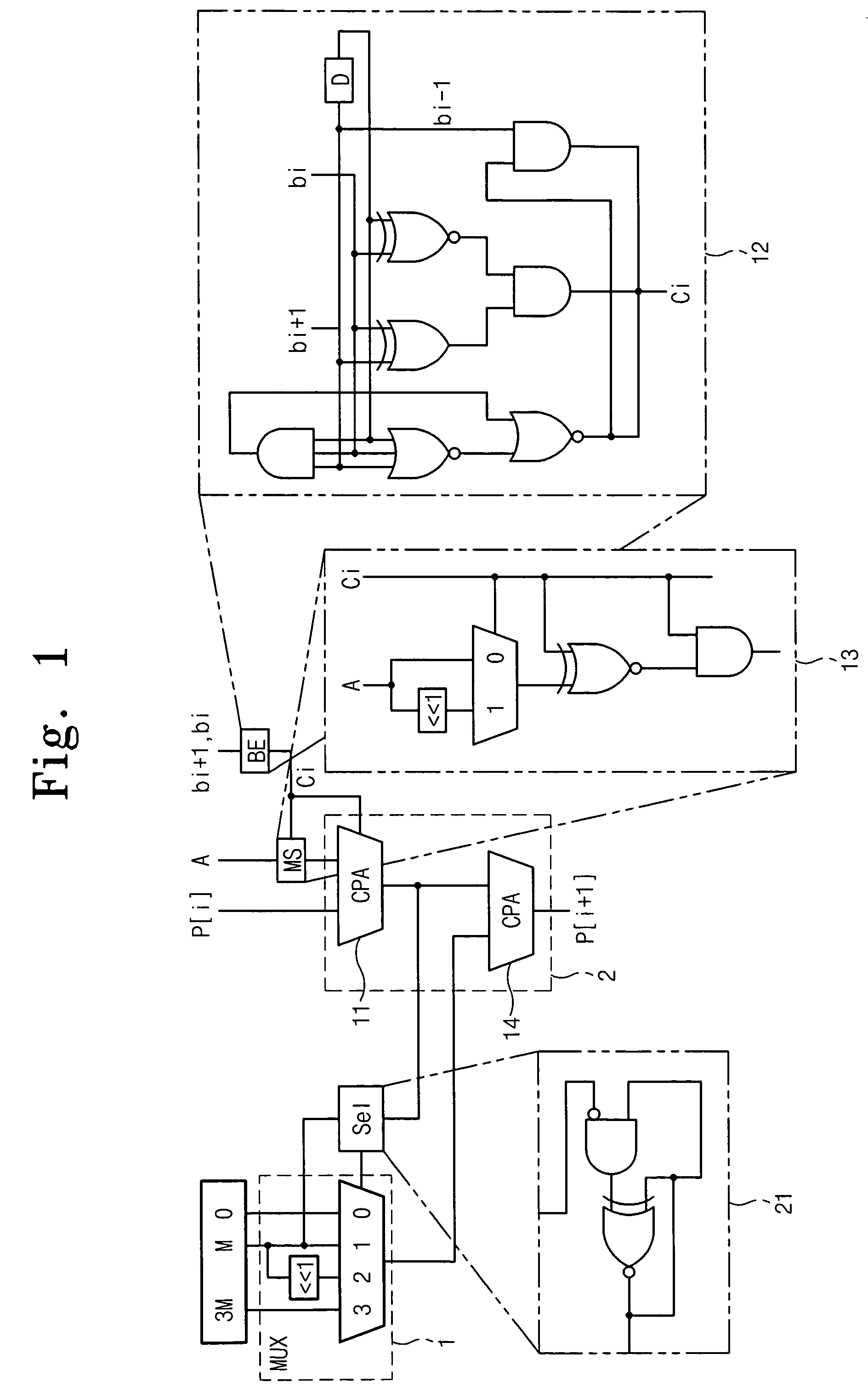

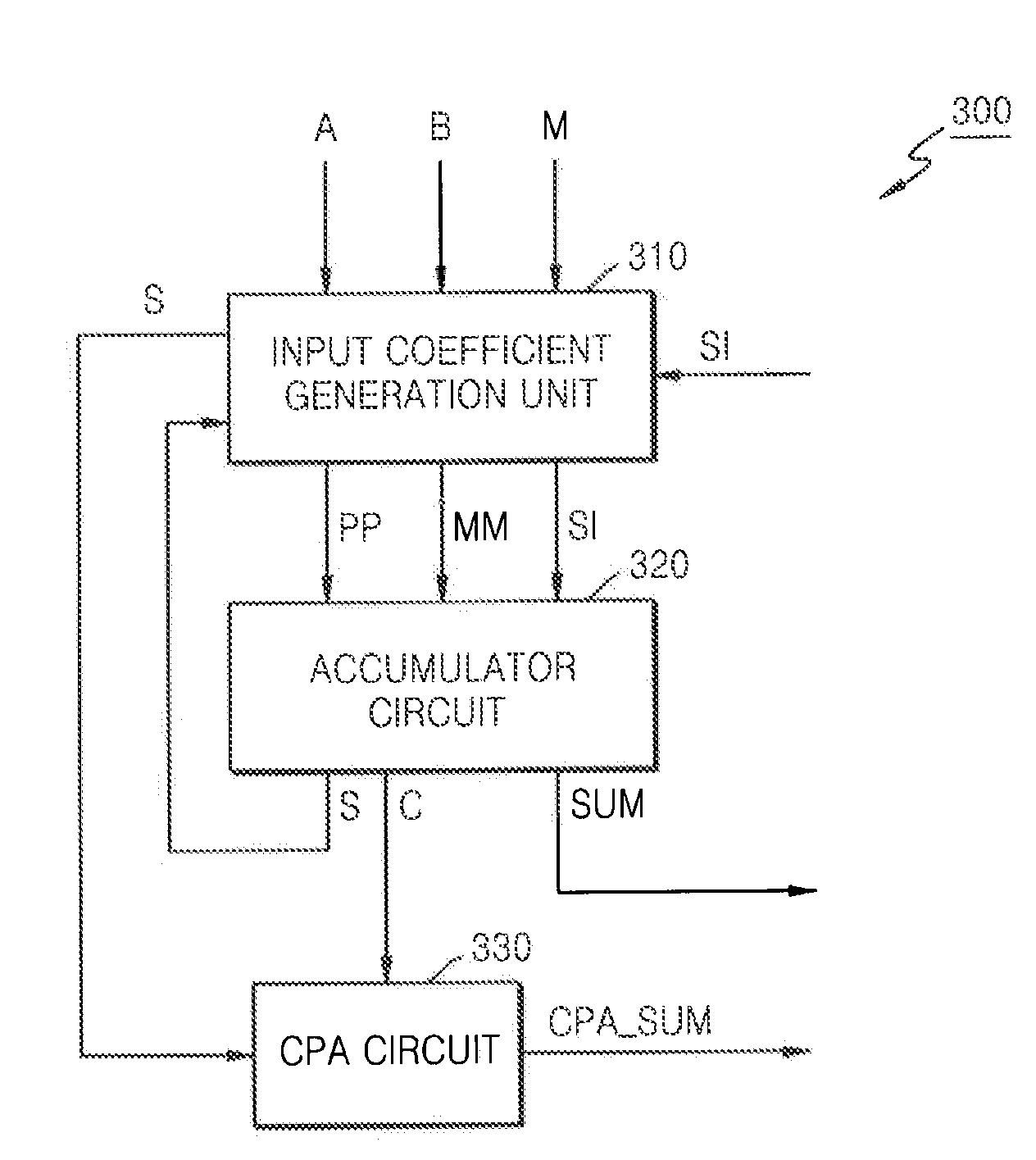

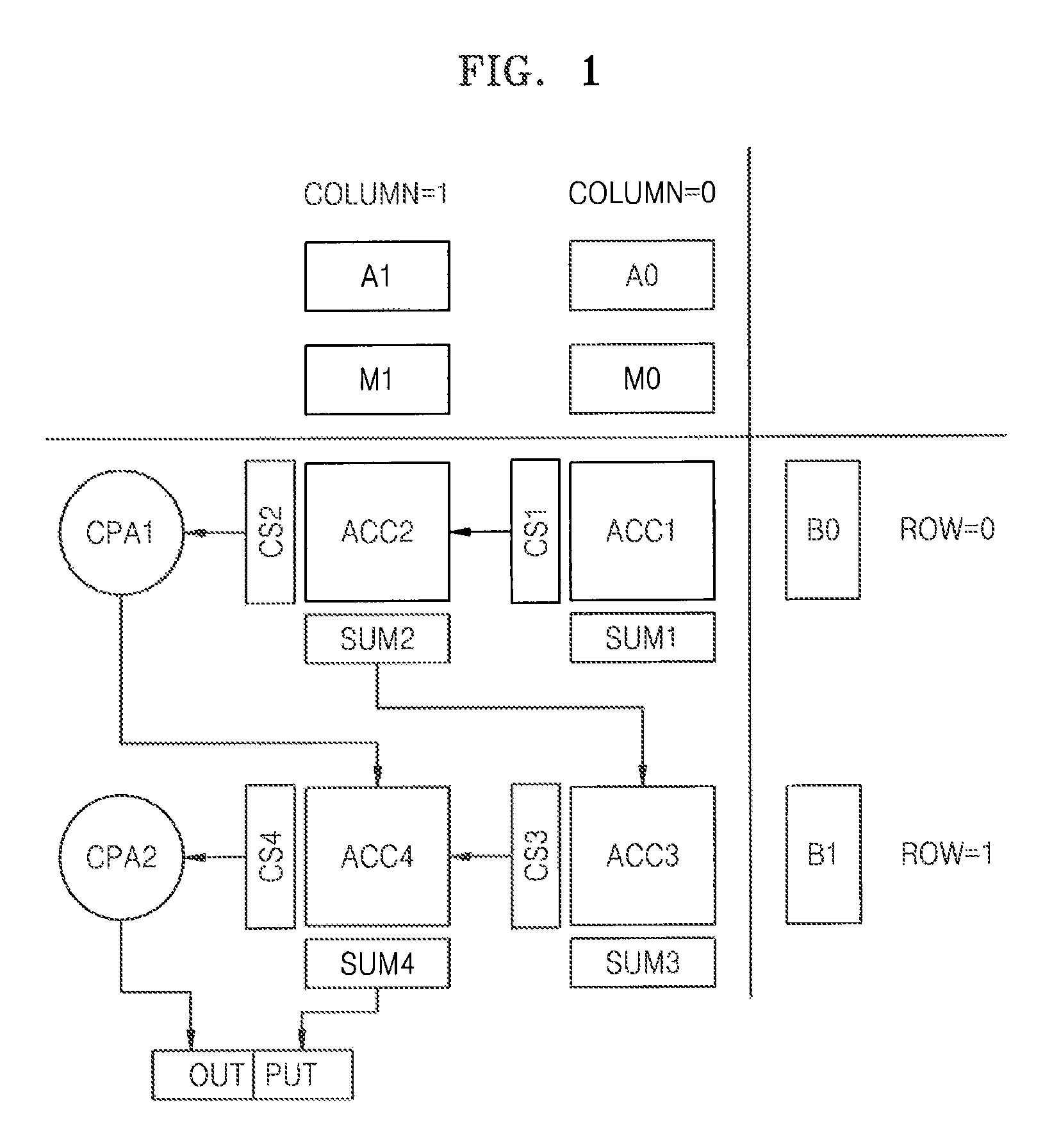

Montgomery multiplier having efficient hardware structure

ActiveUS20110231467A1Reduce countReduce hardware complexityComputation using denominational number representationHardware structureBinary multiplier

A radix-2k Montgomery multiplier including an input coefficient generation unit to receive a multiplier, a multiplicand, a modulus, a sum and a previous sum, to generate and to output a partial product and a multiple modulus by using at least one of the multiplier, the multiplicand, the modulus and the sum, and to divide and to output the received previous sum into units of k bits, an accumulator circuit to receive the partial product, the multiple modulus and k bits of the previous sum from the input coefficient generation unit, and to generate and to output a carry and a sum by summing the partial product, the multiple modulus and the previous sum, and a carry propagation adder (CPA) circuit to generate and to output an ultimate sum by using the carry and the sum.

Owner:SAMSUNG ELECTRONICS CO LTD

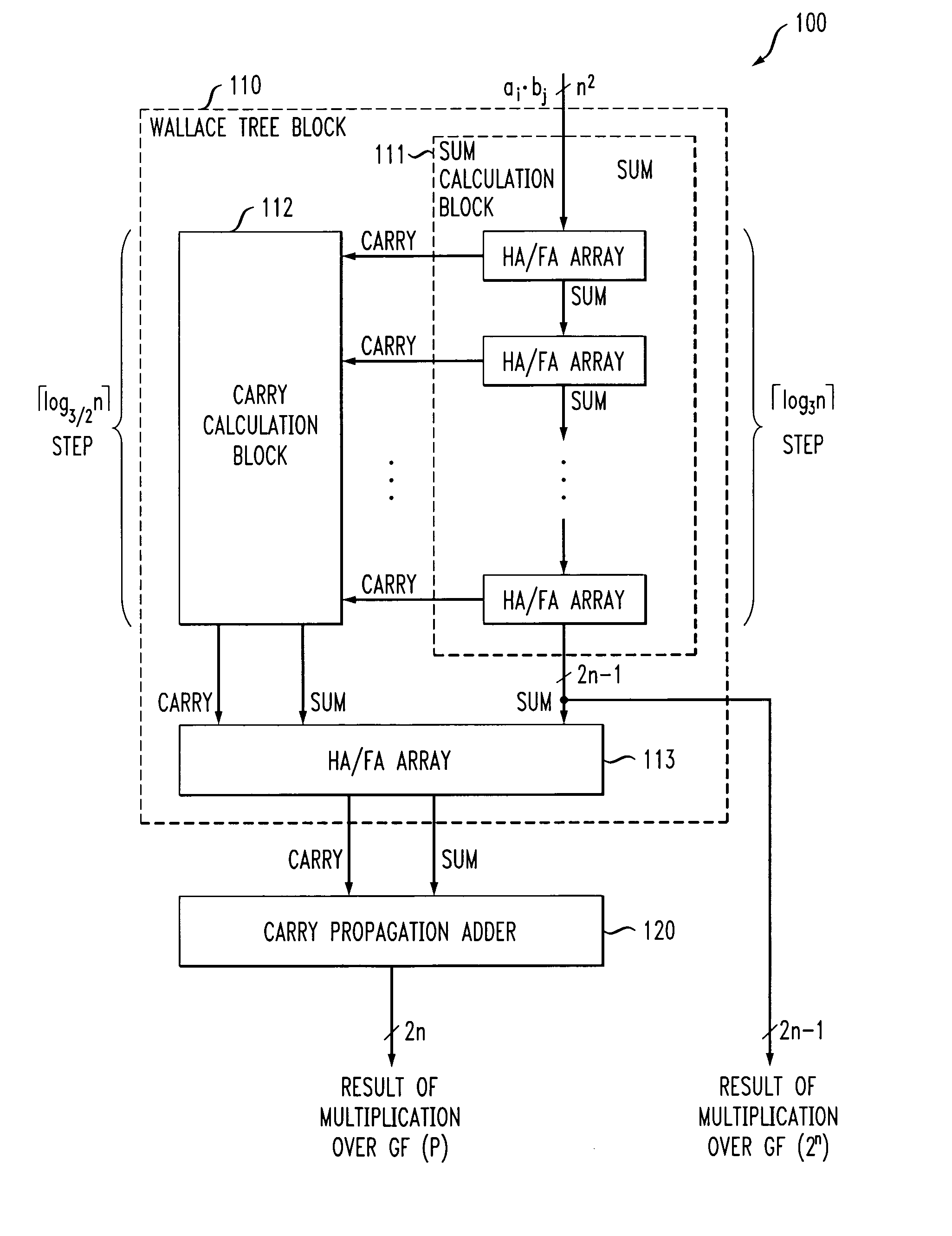

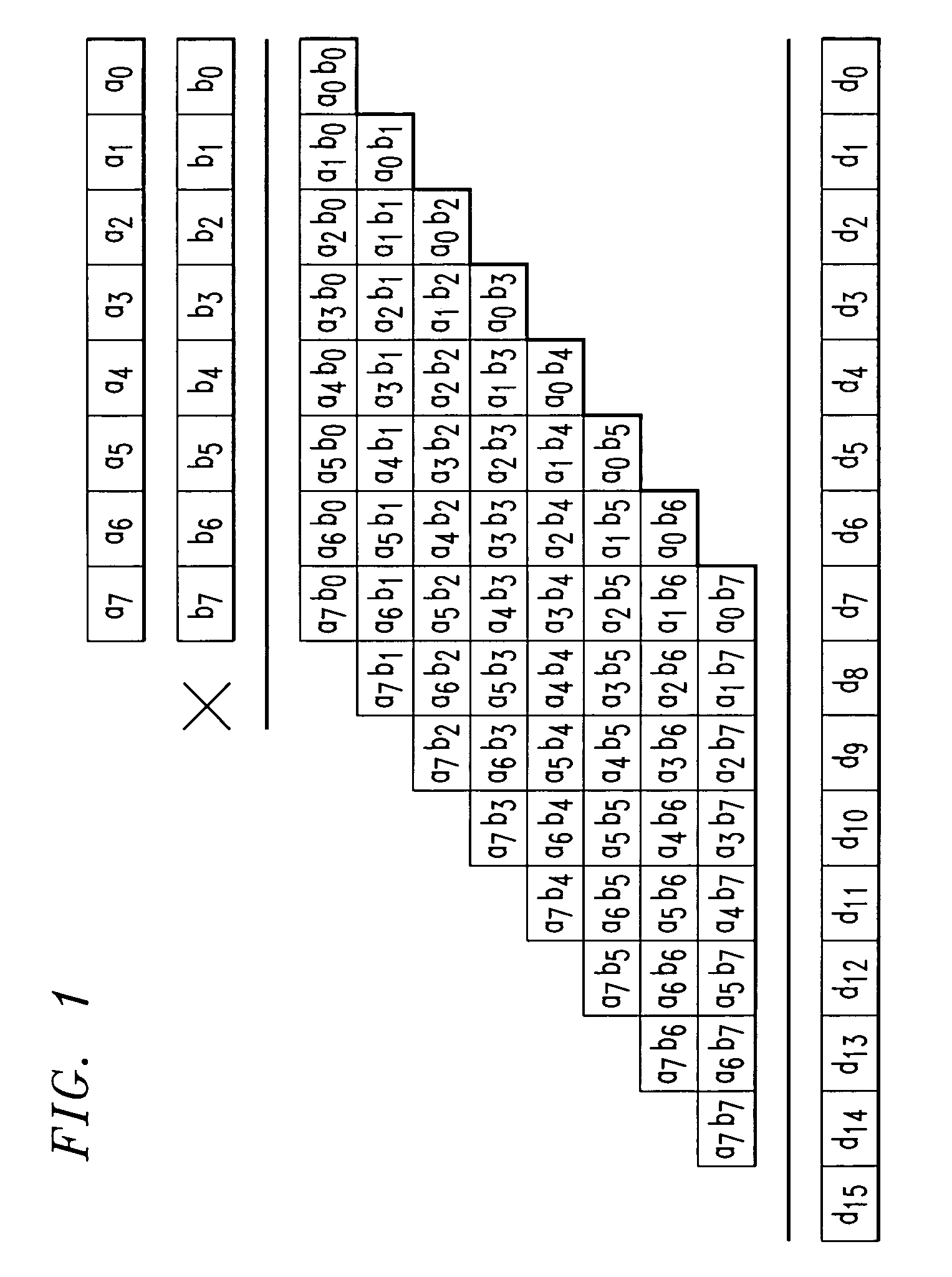

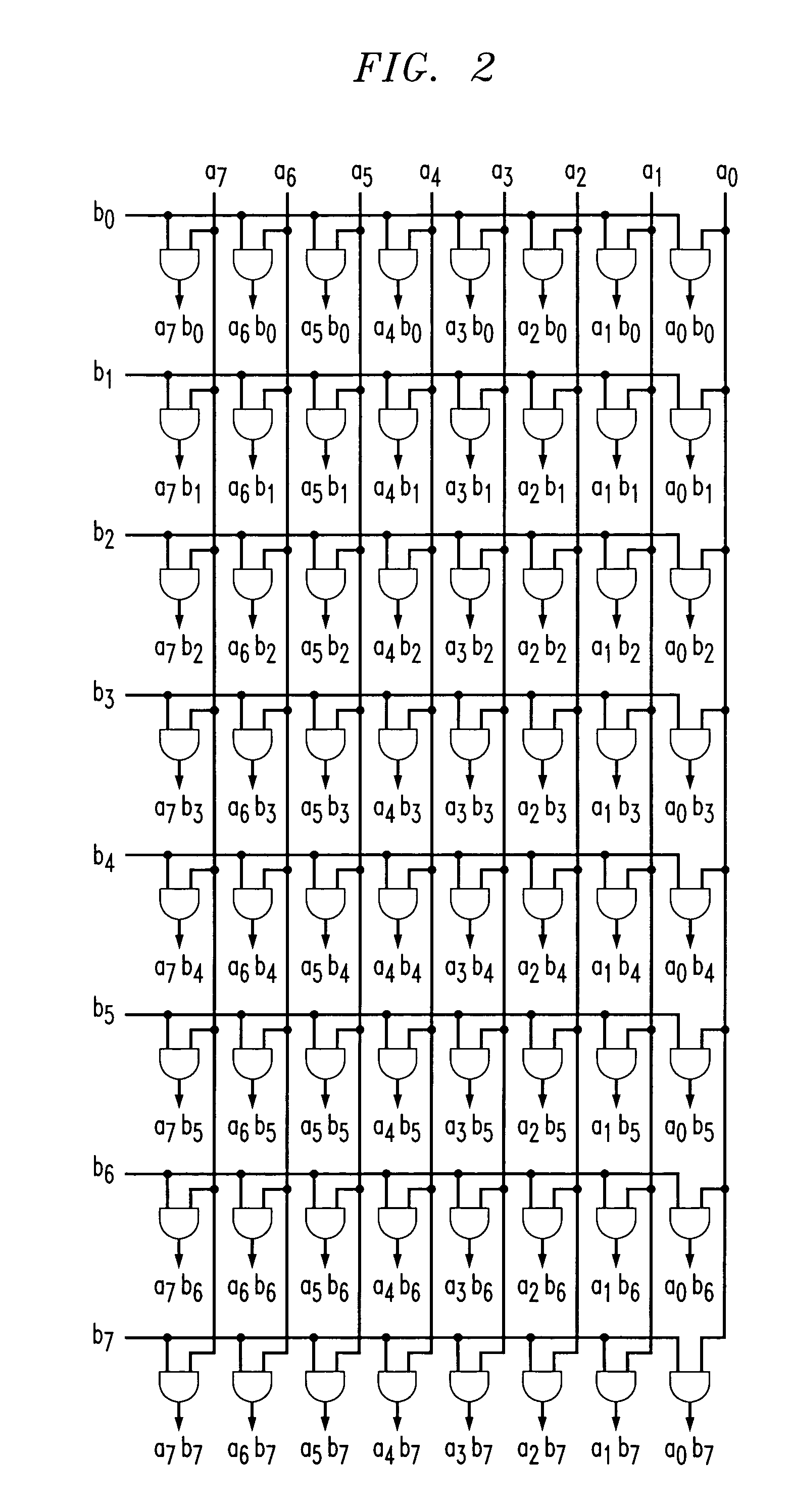

Multiplier and cipher circuit

InactiveUS8244790B2Increase in circuit sizeComputation using non-contact making devicesDigital computer detailsWallace treeCarry propagation

A multiplier circuit is disclosed including a Wallace tree block and a carry propagation adder. The Wallace tree block includes a sum calculation block adding partial products for each digit and a carry calculation block adding carries obtained in the addition by the sum calculation block. In the case of multiplication over an extension field (finite field GF(2n)) of two, a result of calculation by the sum calculation block is outputted. The carry propagation adder adds the result of calculation by the sum calculation block and a result of calculation by the carry calculation block. In the case of multiplication for integers (finite field GF(p)), a result of calculation by the carry propagation adder is outputted.

Owner:IBM CORP

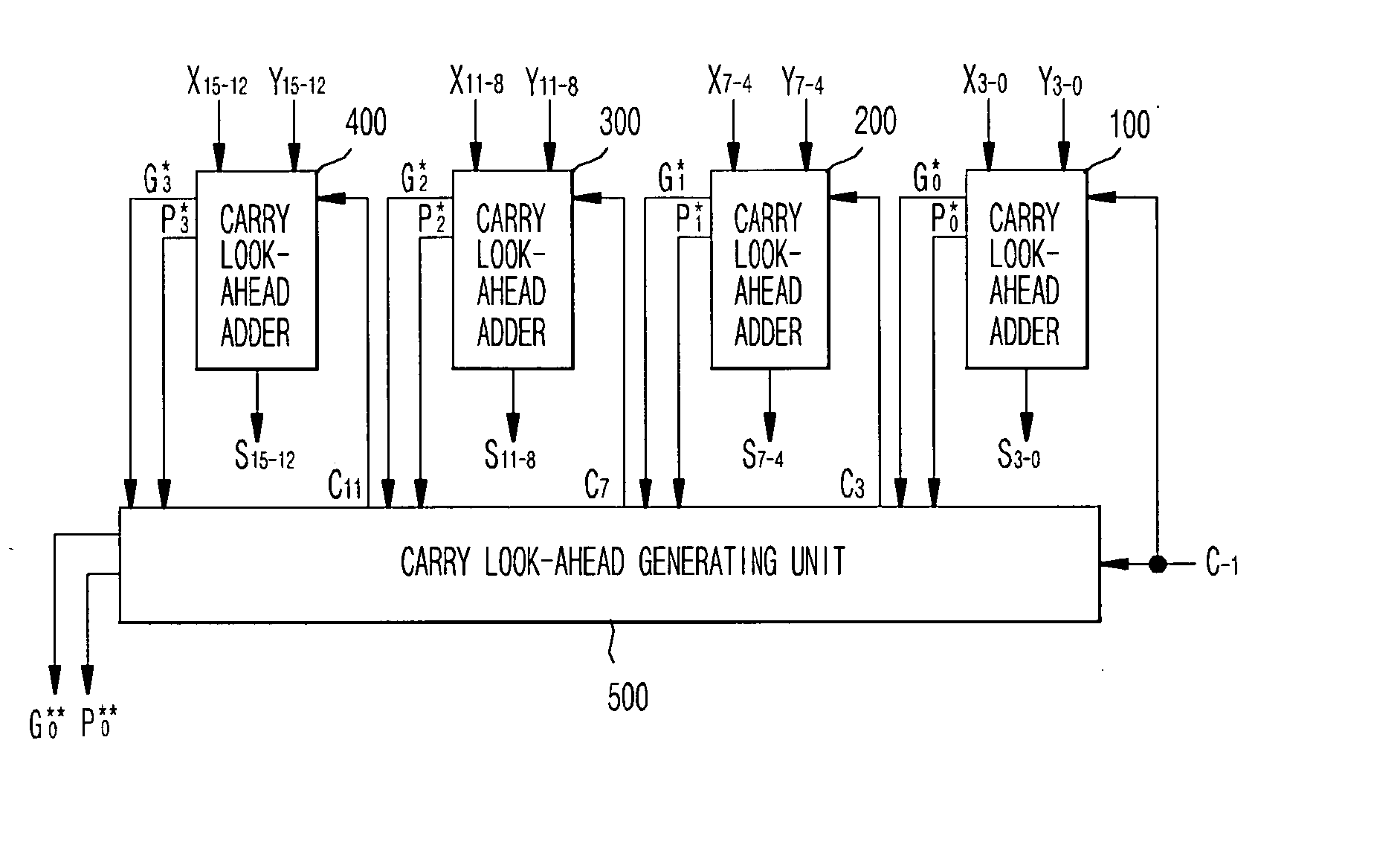

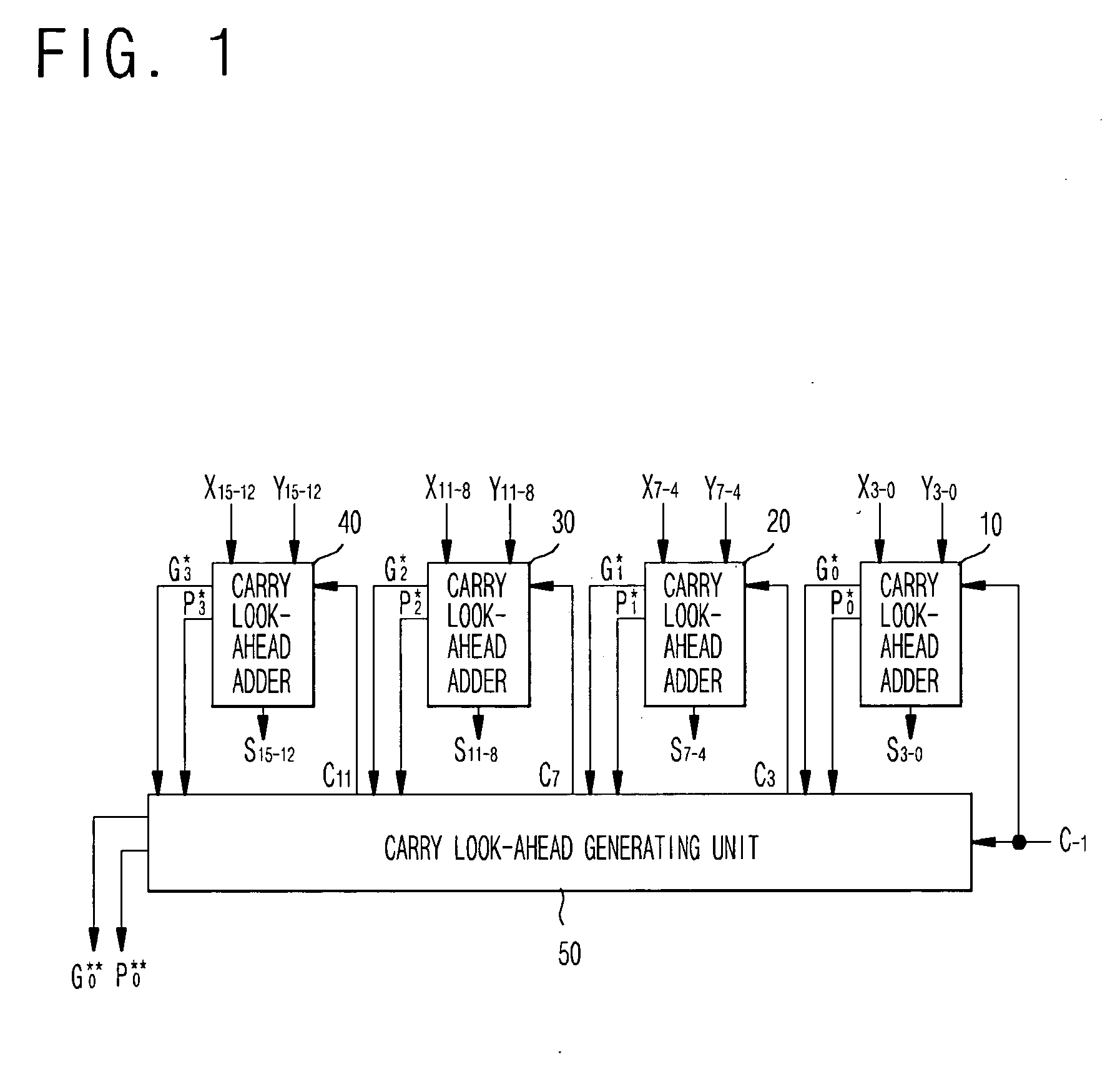

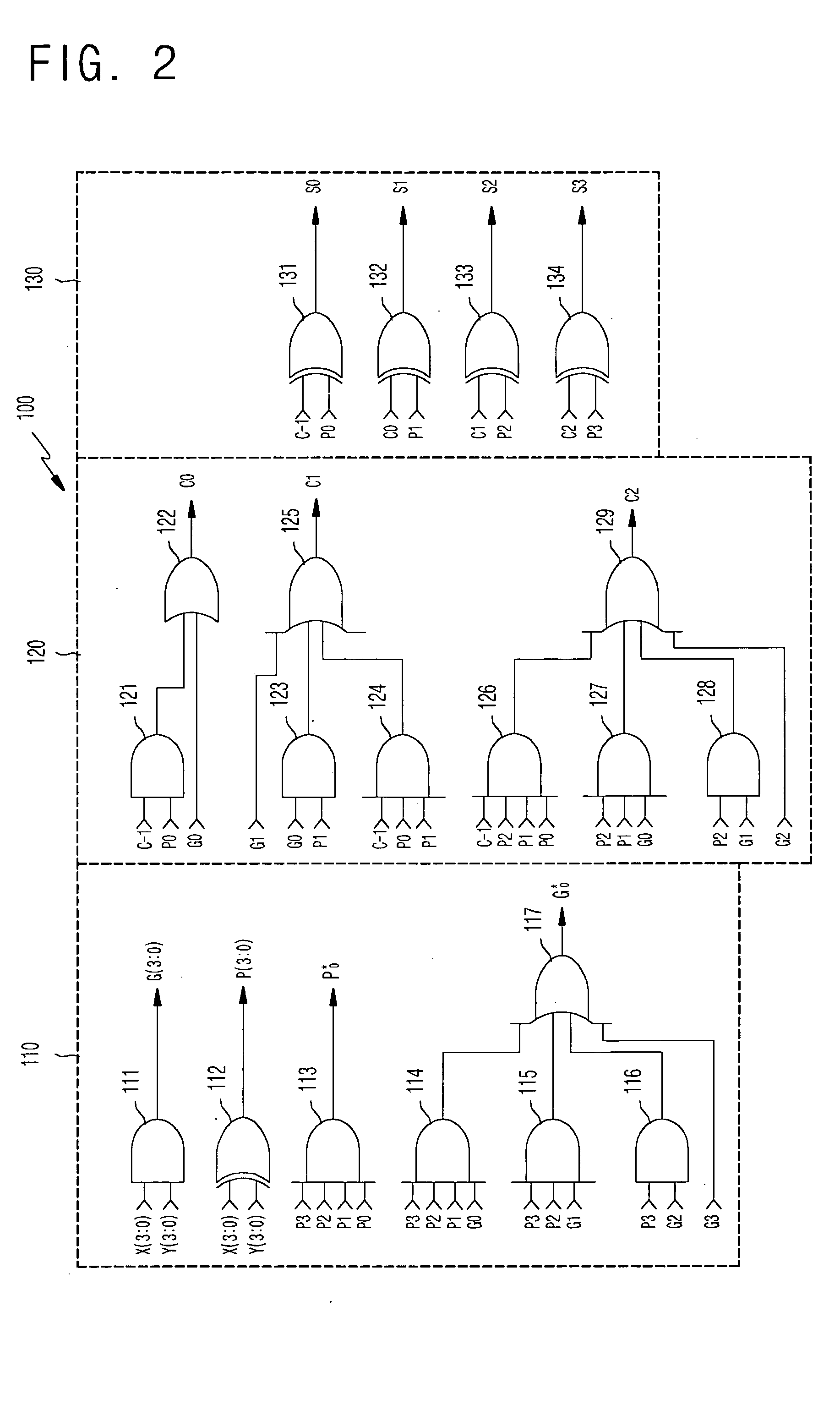

Carry look-ahead adder having a reduced area

InactiveUS20050091299A1Reduce areaReduce the numberComputation using non-contact making devicesPropagation delayCarry propagation

The present invention relates to a carry look-ahead adder. The carry look-ahead adder is configured in 4-bit units in general. Each 4-bt carry look-ahead adder is combined with a carry look-ahead generating unit to constitute a carry look-ahead adder that can process input signals of larger size. The carry look-ahead adder according to the embodiment of the present invention calculates carry of each bit sequentially not by using any carry generation function or any carry propagation function but by using previous bit when generating an internal carry in the adder, so that propagation delay is allowed a little but the logic gate circuit can be simplified.

Owner:ELECTRONICS & TELECOMM RES INST

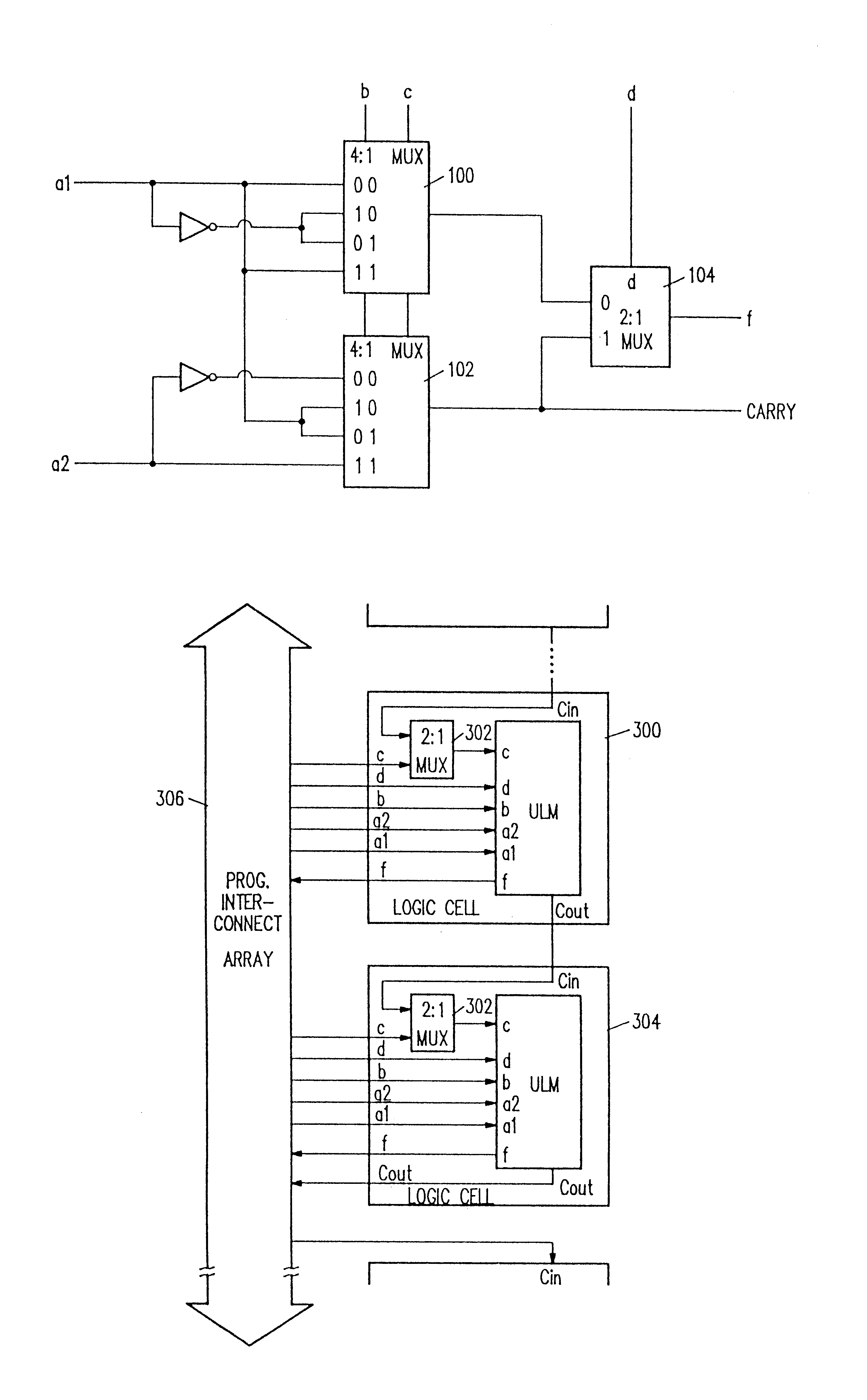

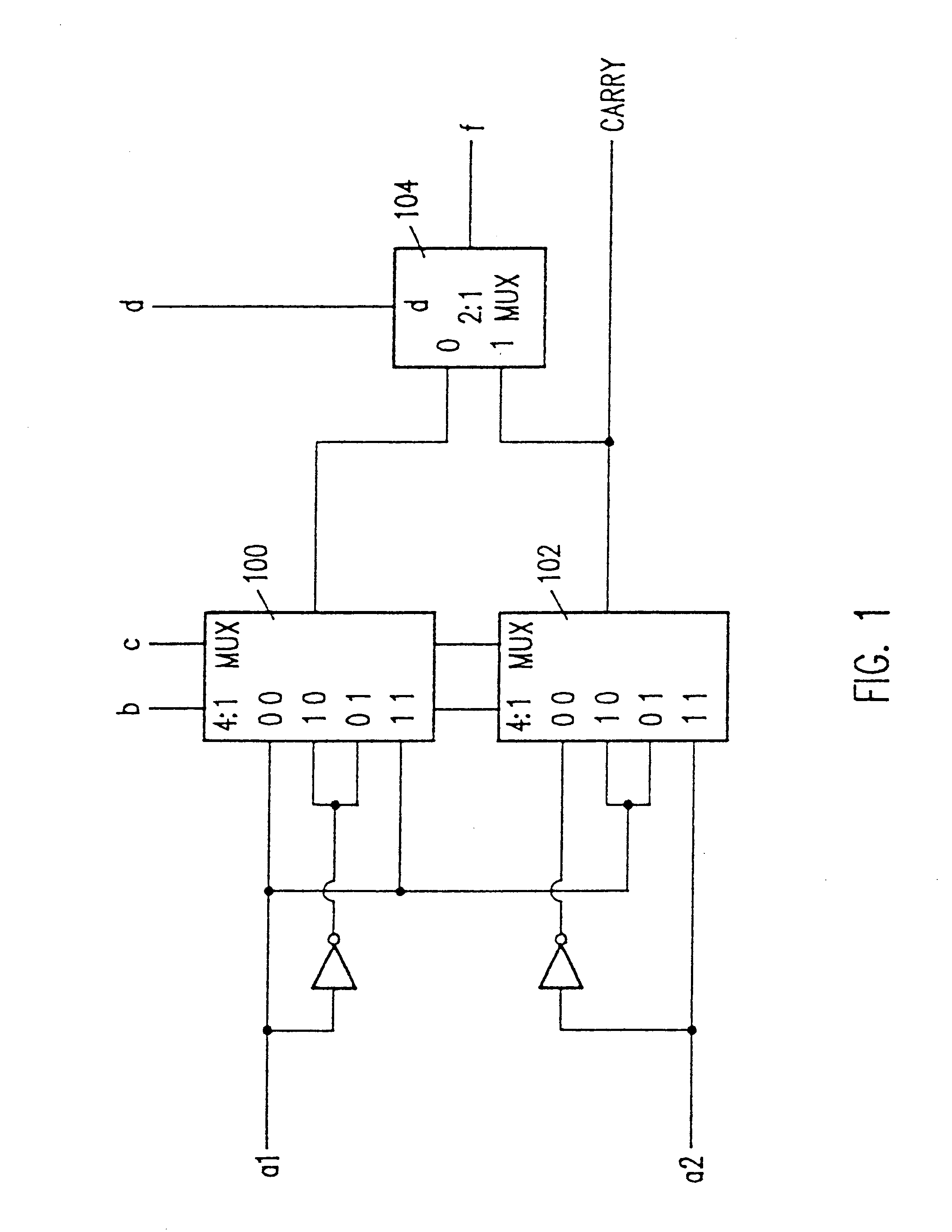

Universal logic module with arithmetic capabilities

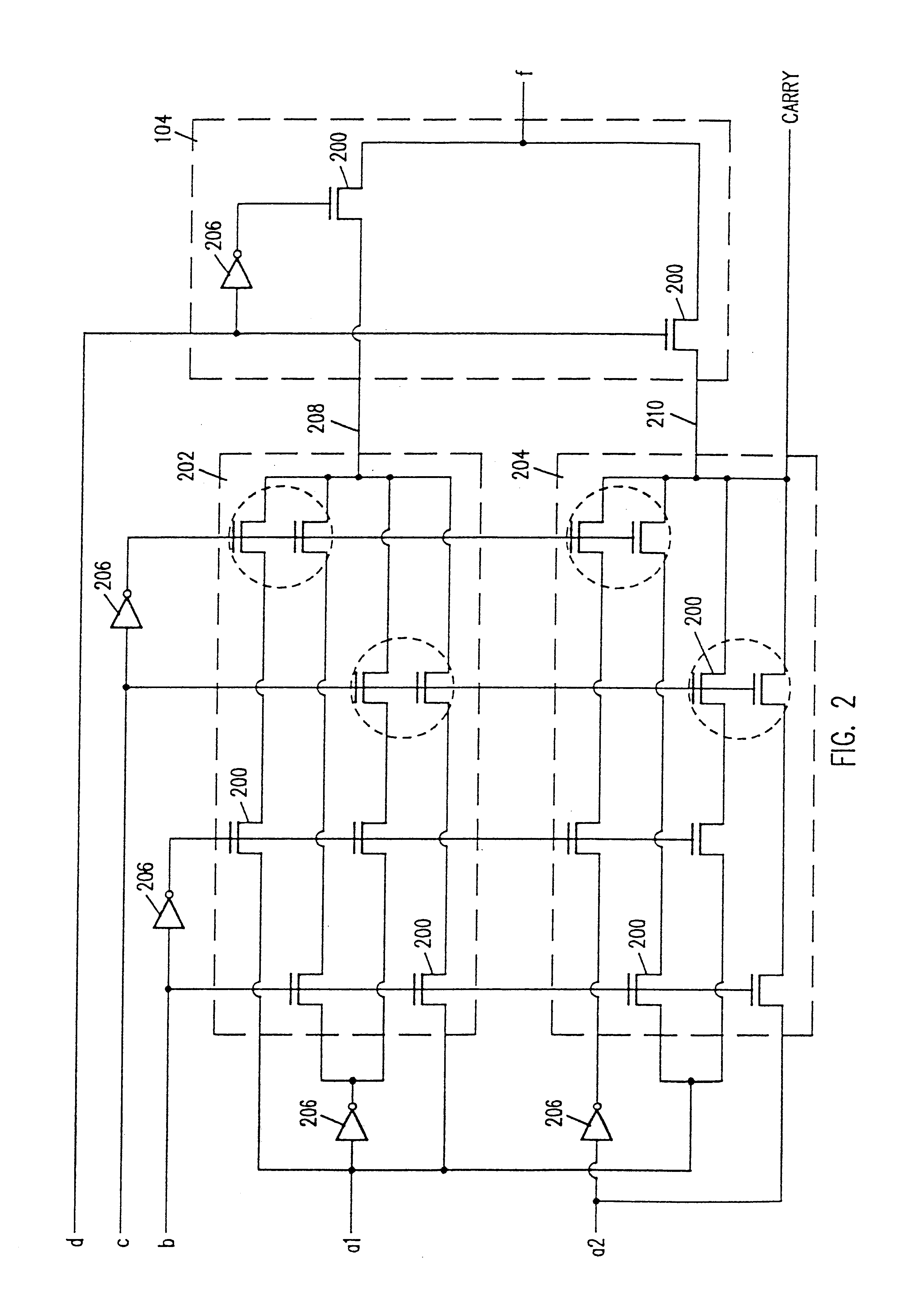

InactiveUSRE38451E1Computation using non-contact making devicesSolid-state devicesCarry propagationProgrammable logic device

A universal logic module for use in a programmable logic device, capable of generating all logical functions of three variables or less. The universal logic module also implements a full adder with carry propagation.

Owner:ALTERA CORP

Montgomery modular multiplier and method thereof using carry save addition

InactiveCN1570848AGuaranteed normal operationApplicability is clearComputation using non-contact making devicesComputations using residue arithmeticCarry propagationModular multiplier

A method of reducing power consumption and / or enhancing computation speed in the modulus multiplication operation of a Montgomery modulus multiplication module. A coding scheme reduces the need for an adder or memory element for obtaining multiple modulus values, and the use of carry save addition with carry propagation addition enhances the computational speed of the multiplication module.

Owner:SAMSUNG ELECTRONICS CO LTD

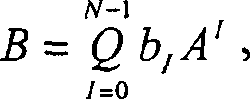

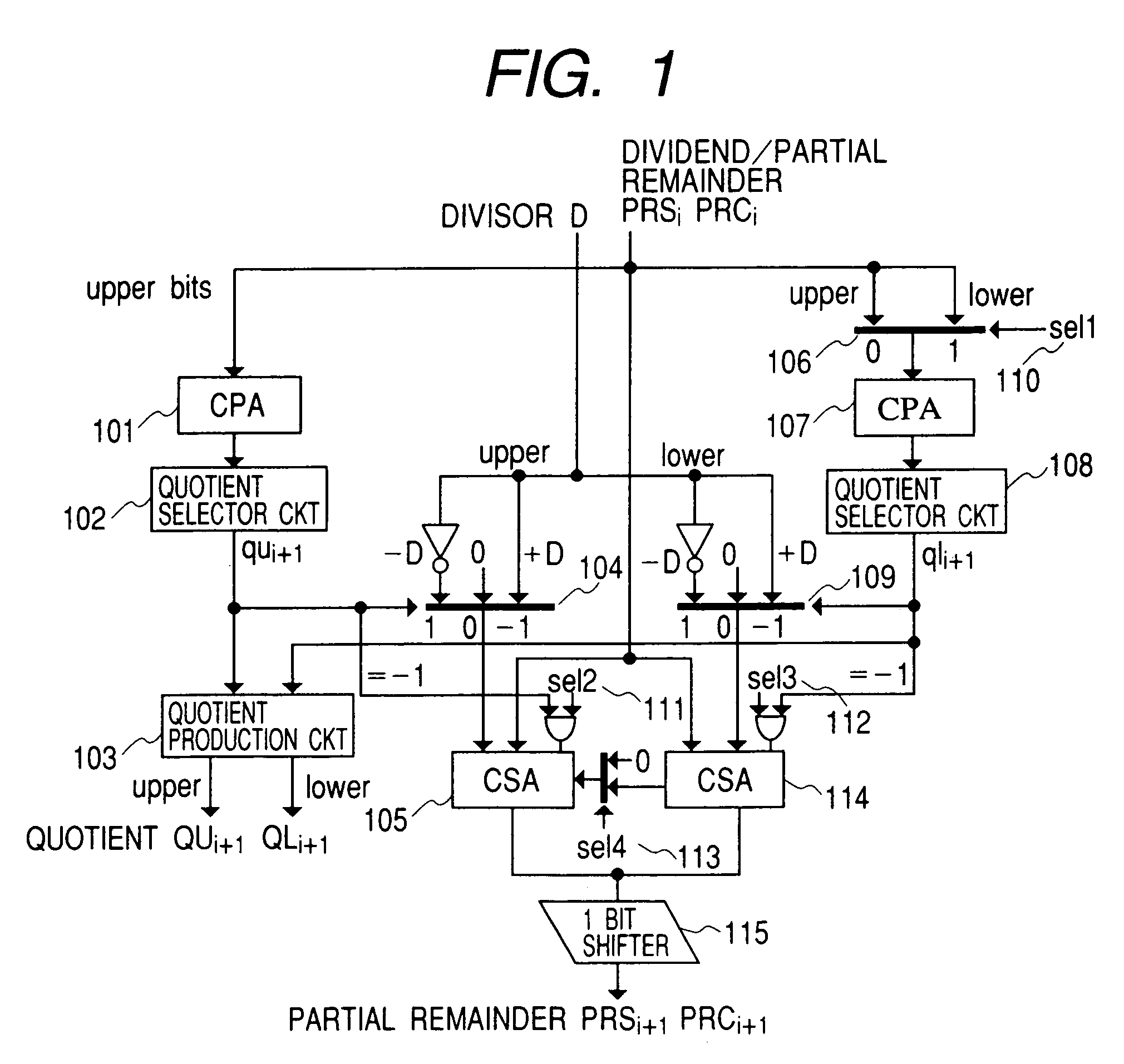

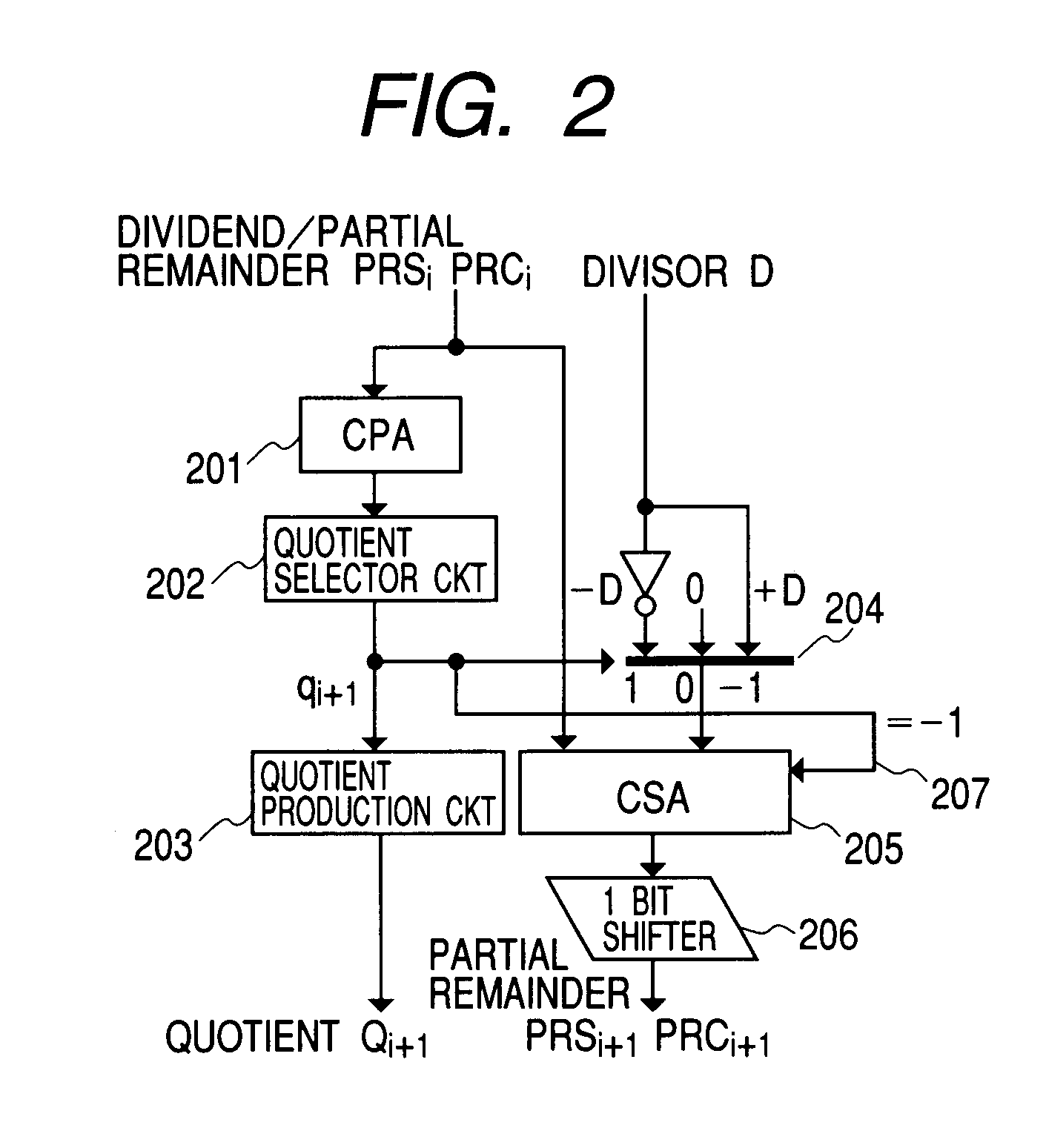

Floating point computing unit

A Sweeney Robertson Tocher (SRT) divider and a square root extractor of floating point double-precision bit width, including a selector of single-precision and double-precision, a carry propagation adder (CPA) for conducting carry propagation of a partial remainder, a quotient digit selector circuit for making selection on a quotient digit, and a selector of a divisor or a partial square root extractor circuit, in a lower side thereof. A selector for selecting the propagation of carry between a carry save adder (CSA) in the upper side and the lower side thereof is provided, and a selector of a starting position within a quotient production circuit is provided, thereby enabling the execution of two (2) calculations, such as, division or square root extraction of the floating point single-precision, at the same time, but without increasing the bit width of a computing unit. Also, with the square root extraction, it is possible to execute two (2) calculations of single-precision in parallel, in a similar manner, by adding a partial square root extraction circuit thereinto.

Owner:RENESAS ELECTRONICS CORP

Montgomery modular multiplier using a compressor and multiplication method

ActiveUS7412474B2Reduce latencyEasy to disassemblePublic key for secure communicationComputation using non-contact making devicesCarry propagationModular multiplier

A Montgomery modular multiplier receiving a multiplicand (A), a modulus (M), and a multiplier (B), using a t-s compressor, where t>3 and s>1, and a multiplication method performed in the same. In response to a carry propagation adder signal, the t-s compressor performs additions on the carry C and the sum S and obtains the final results in a carry propagation adder structure.

Owner:SAMSUNG ELECTRONICS CO LTD

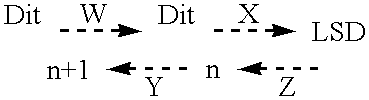

Method and apparatus for interruption of carry propagation on partition boundaries

InactiveUS6272514B1Versatile high-performance adder/subtractorComputation using non-contact making devicesCarry propagation16-bit

An apparatus and method that perform partitionable carry-lookahead logic on two N-nary operands. The operands may be selectably partitioned into 8-bit, 16-bit, 32-bit, or 64-bit operands. The present invention performs carry-lookahead logic to calculate a block carry-lookahead indicator for a grouping, or block, of bits. The present invention forces the block indicator to a "Halt" value if the block comprises the most significant block within a partition, thus interrupting the carry propagation chain on partition boundaries. The present invention supports interruption of the carry propagation chain for both addition and subtraction.

Owner:APPLE INC

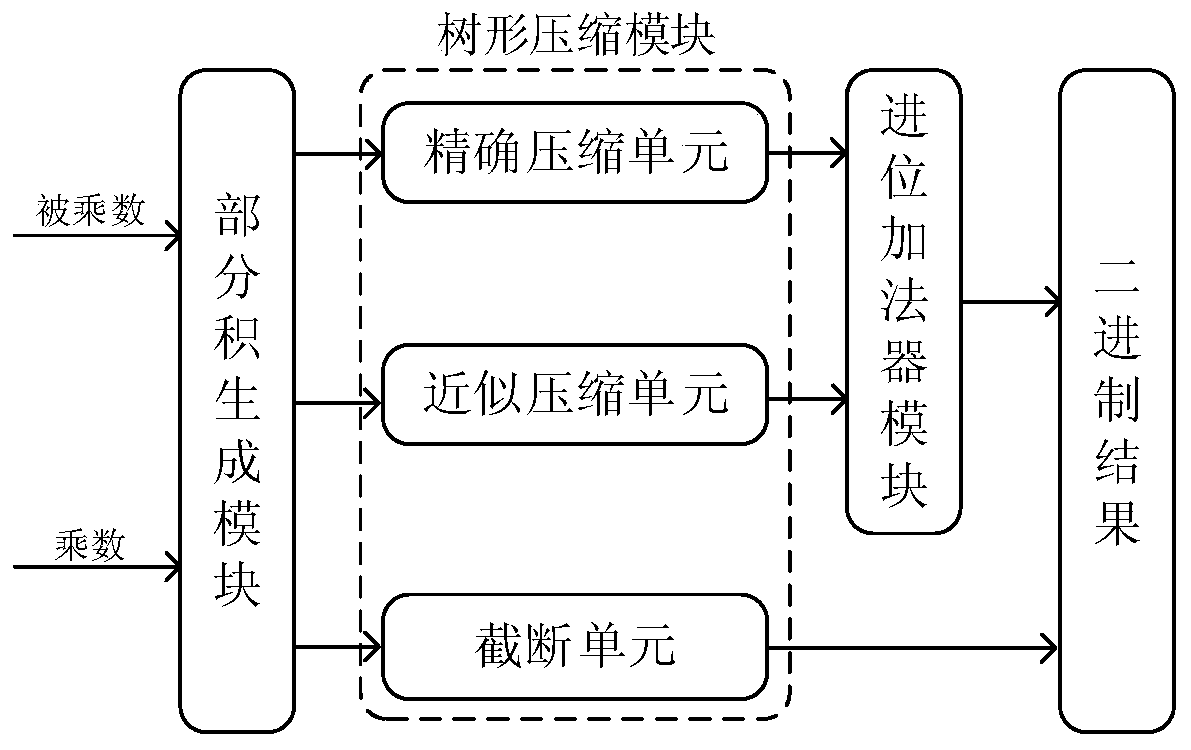

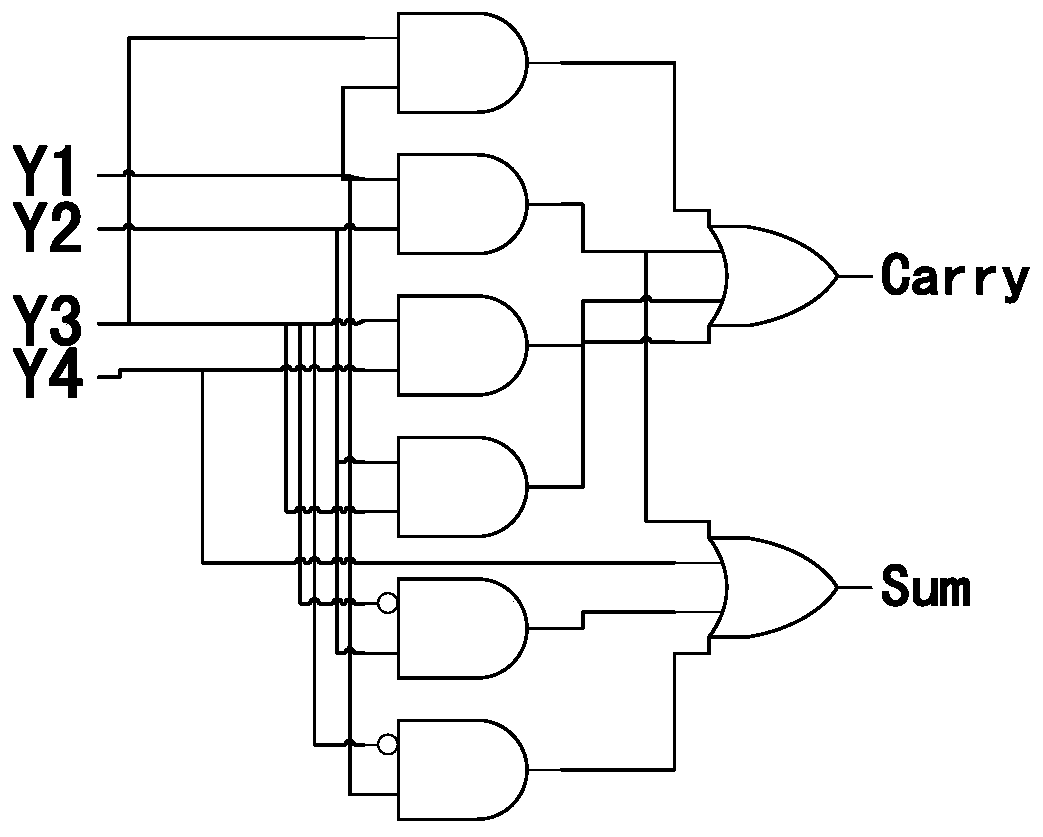

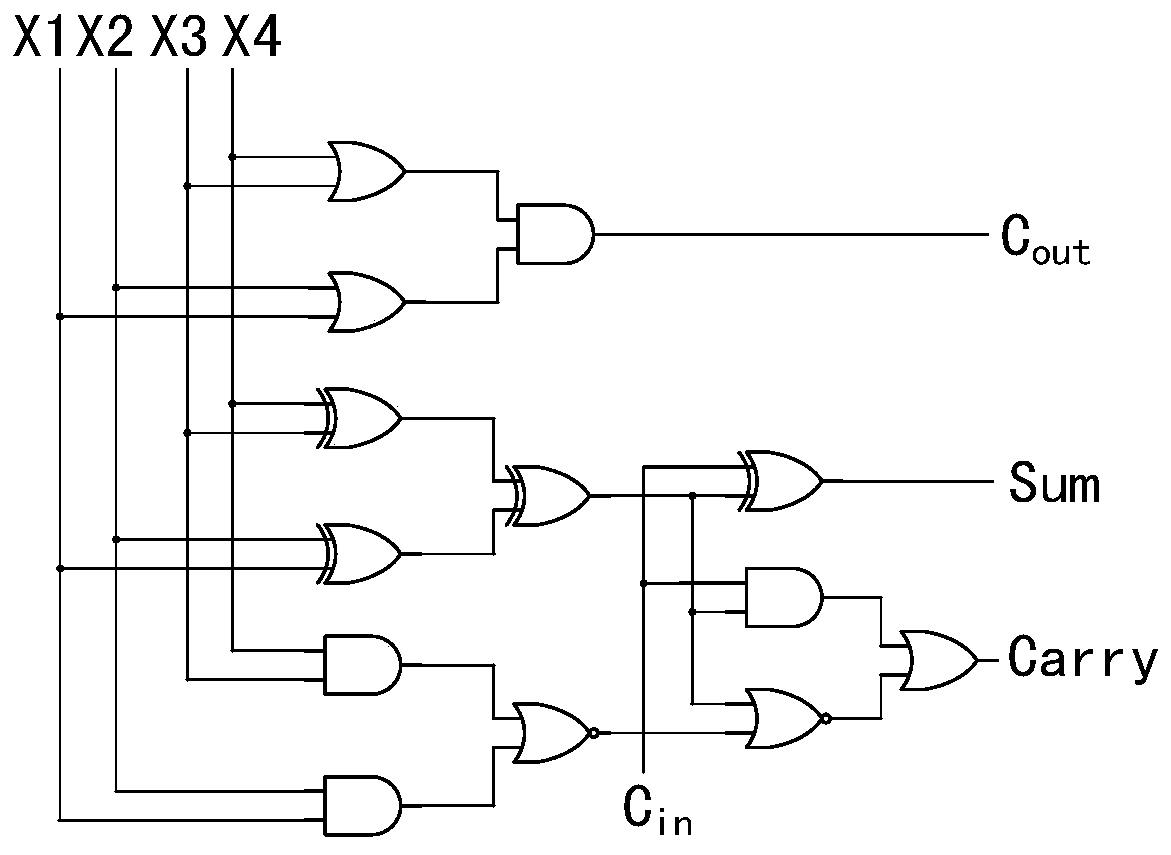

Approximate multiplier based on approximate 6-2 and 4-2 compressors and calculation method

ActiveCN111221499ALower latencyLow power consumptionDigital data processing detailsBinary multiplierCarry propagation

The invention provides an approximate multiplier based on approximate 6-2 and 4-2 compressors and a calculation method. The approximate multiplier comprises a partial product generation module, a partial product tree-shaped compression module and a carry adder module. The partial product generation module is an AND gate array, and each bit of a multiplier and a multiplicand is subjected to AND operation to obtain a corresponding partial product; the partial product tree compression module comprises an accurate compression unit, an approximate compression unit and a truncation unit; and the carry propagation adder is used for combining an output signal obtained by adding output signals of the precise compression unit and the approximate compression unit with an output signal of the truncation unit to obtain a result. According to the invention, the area cost, time delay and power consumption of the multiplier can be greatly reduced, so that the performance of the multiplier is improvedand the energy consumption is reduced.

Owner:HEFEI UNIV OF TECH

Method and apparatus for performing a carry-save division operation

ActiveUS7660842B2Speeds up the division operationEliminate needComputation using non-contact making devicesCarry propagationComputer science

One embodiment of the present invention provides a system that performs a carry-save division operation that divides a numerator, N, by a denominator, D, to produce an approximation of the quotient, Q=N / D. The system approximates Q by iteratively selecting an operation to perform based on higher order bits of a remainder, r, and then performing the operation, wherein the operation can include, subtracting D from r and adding a coefficient c to a quotient calculated thus far q, or adding D to r and subtracting c from q. These subtraction and addition operations maintain r and q in carry-save form, which eliminates the need for carry propagation and thereby speeds up the division operation. Furthermore, the selection logic is simpler than previous SRT division implementations, which provides another important speed up.

Owner:ORACLE INT CORP

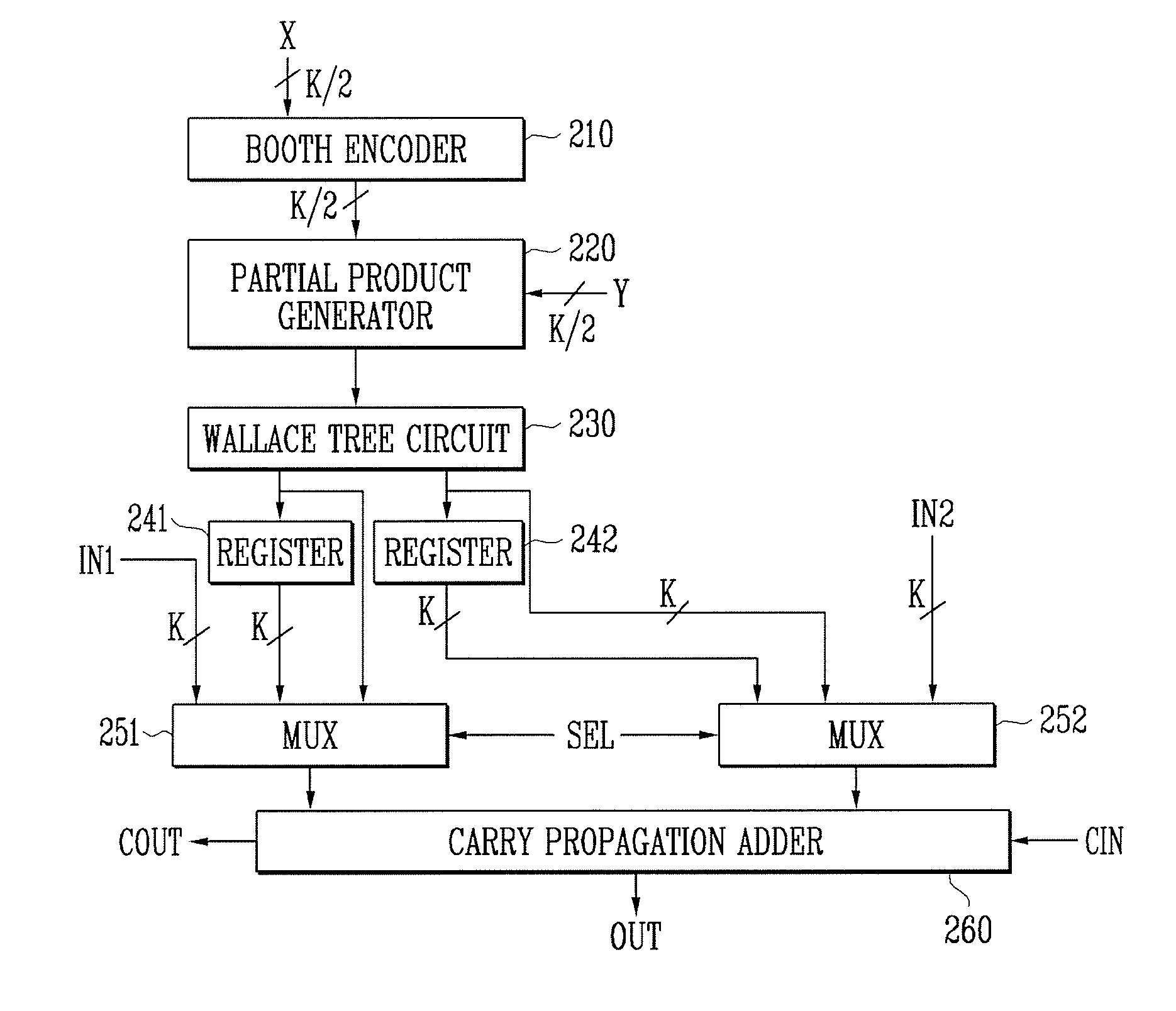

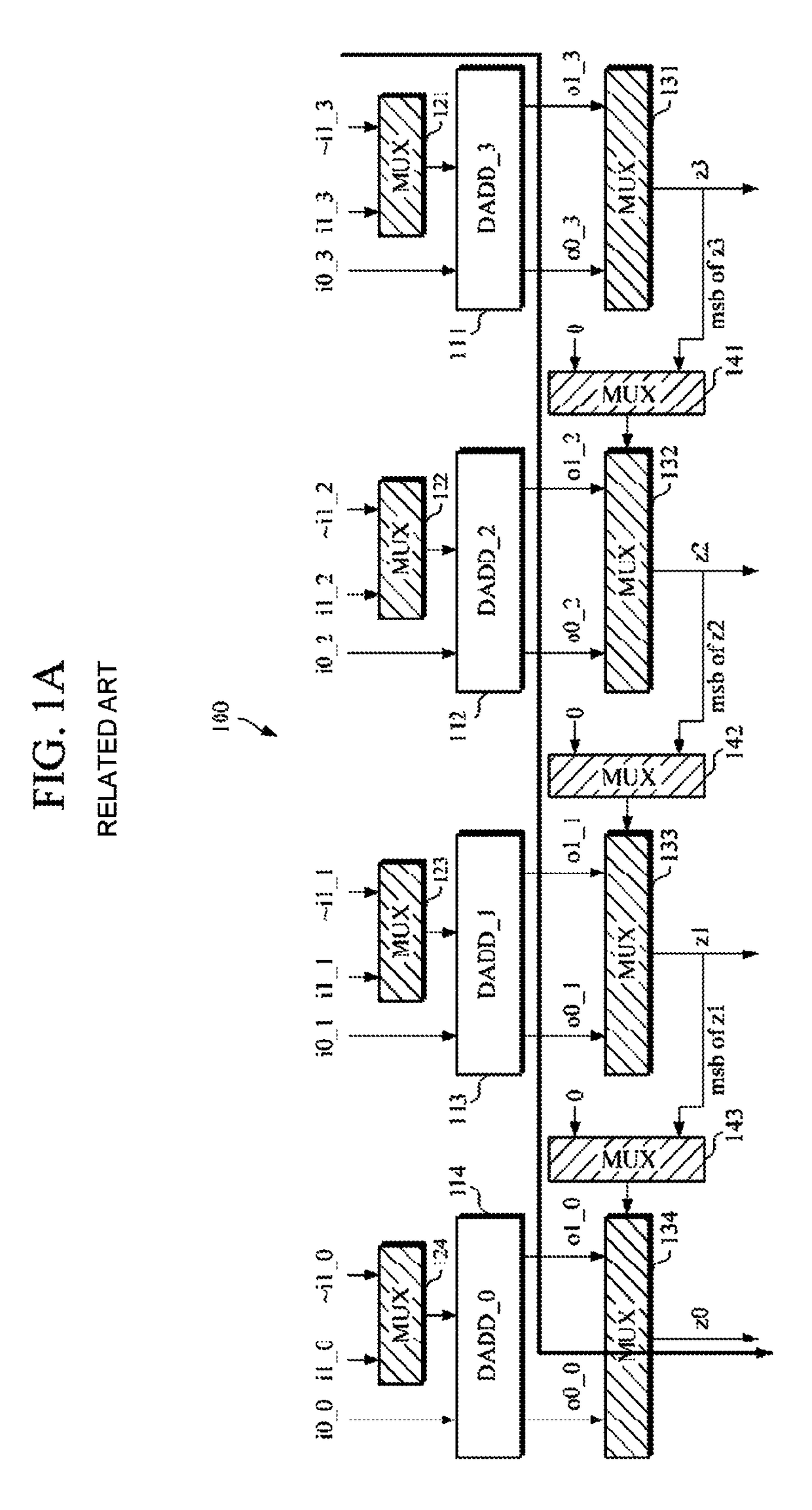

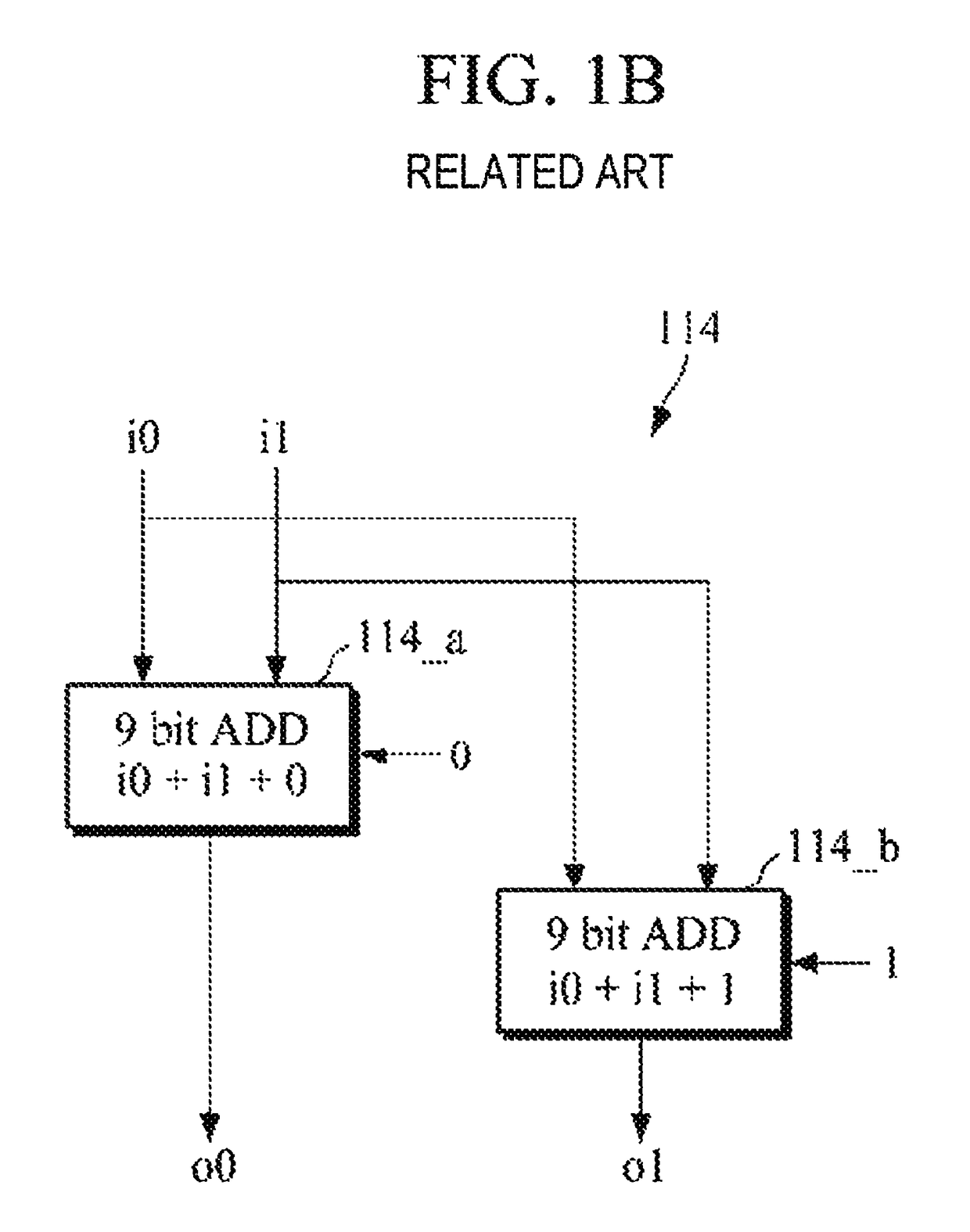

Reconfigurable arithmetic unit and high-efficiency processor having the same

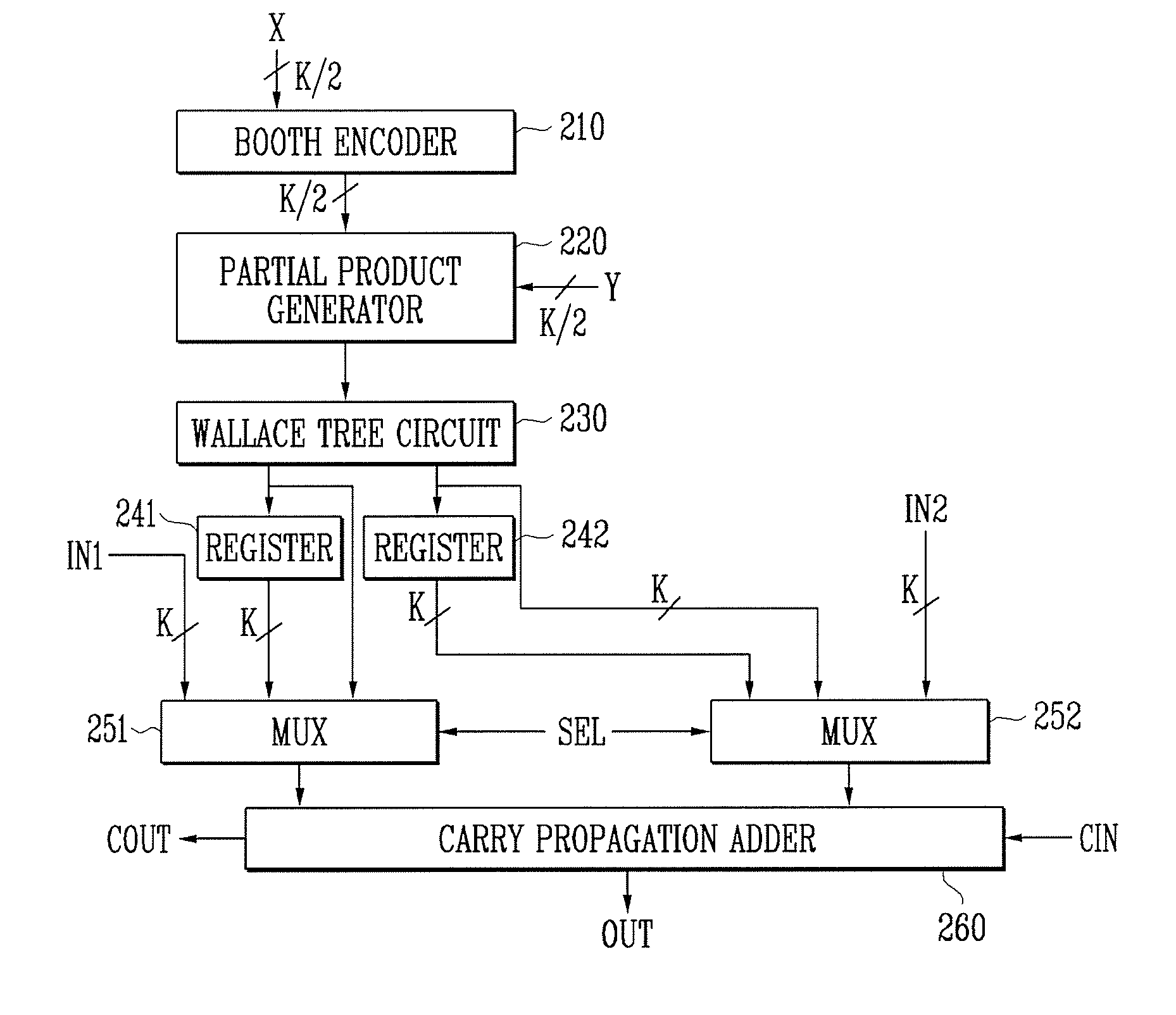

ActiveUS20090150471A1High degree of useImprove energy efficiencyComputation using non-contact making devicesComplex mathematical operationsWallace treeBinary multiplier

Provided are a reconfigurable arithmetic unit and a processor having the same. The reconfigurable arithmetic unit can perform an addition operation or a multiplication operation according to an instruction by sharing an adder. The reconfigurable arithmetic unit includes a booth encoder for encoding a multiplier, a partial product generator for generating a plurality of partial products using the encoded multiplier and a multiplicand, a Wallace tree circuit for compressing the partial products into a first partial product and a second partial product, a first Multiplexer (MUX) for selecting and outputting one of the first partial product and a first addition input according to a selection signal, a second MUX for selecting and outputting one of the second partial product and a second addition input according to the selection signal, and a Carry Propagation Adder (CPA) for adding an output of the first MUX and an output of the second MUX to output an operation result. The arithmetic unit can operate as an adder or a multiplier according to an instruction, and thus can increase the degree of use of entire hardware.

Owner:ELECTRONICS & TELECOMM RES INST

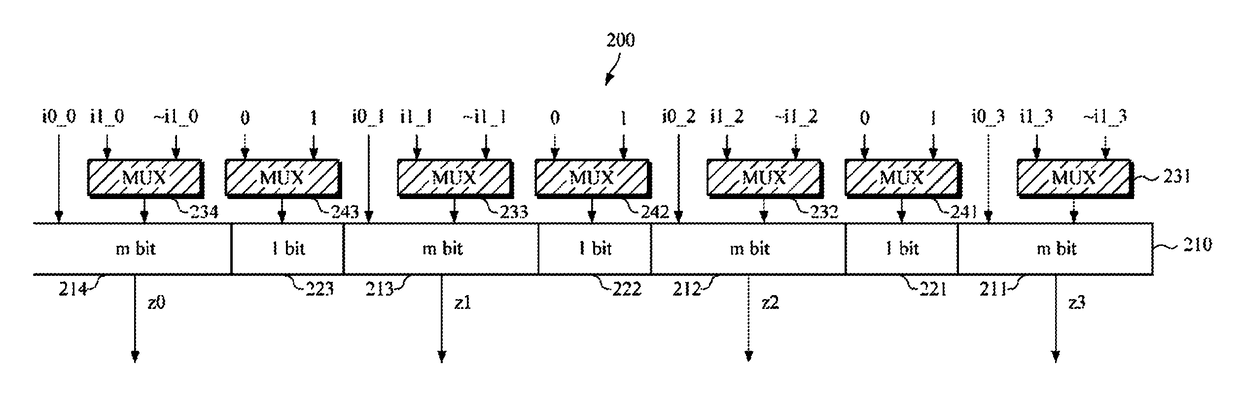

Adder capable of supporting addition and subtraction of up to n-bit data and method of supporting addition and subtraction of a plurality of data type using the adder

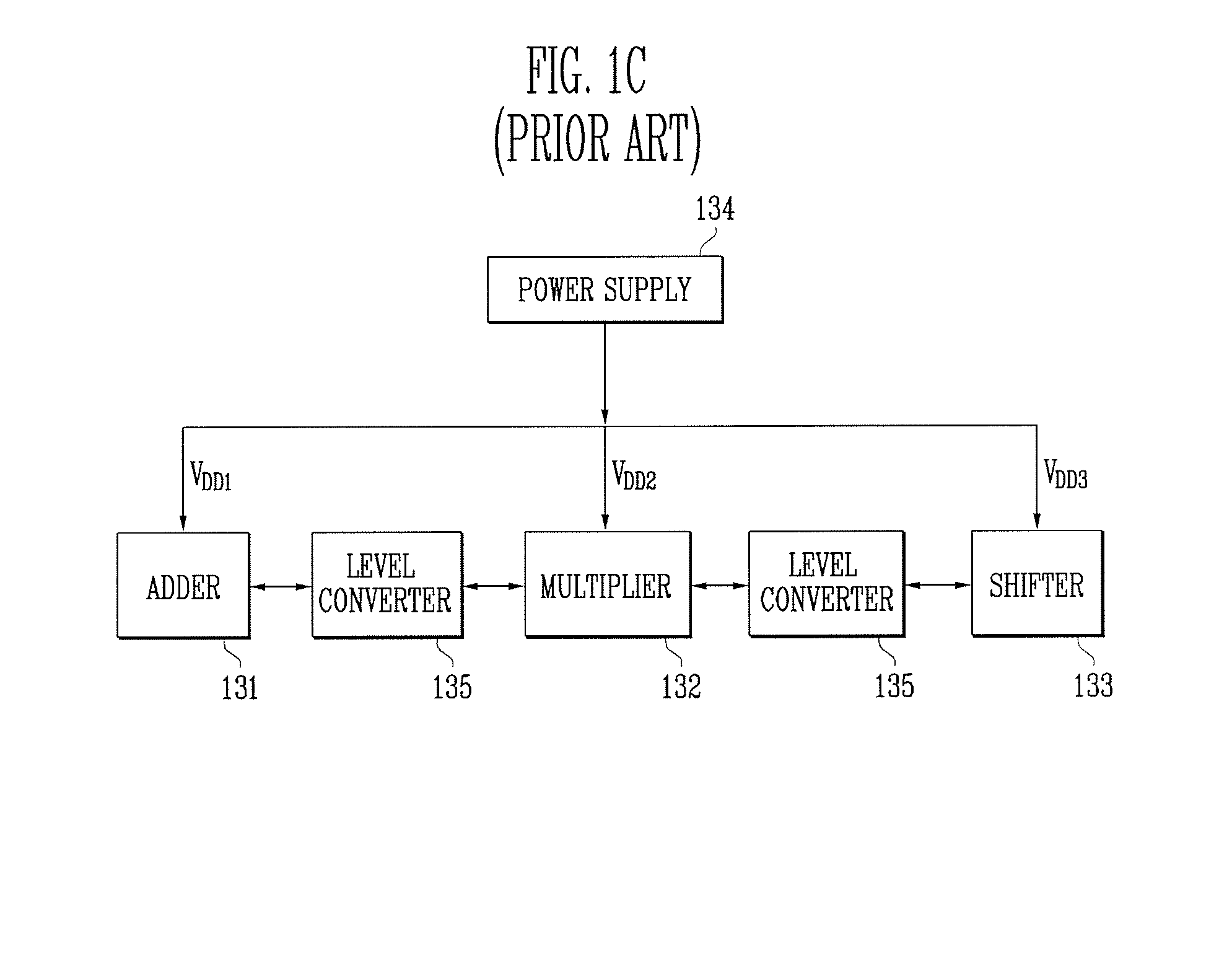

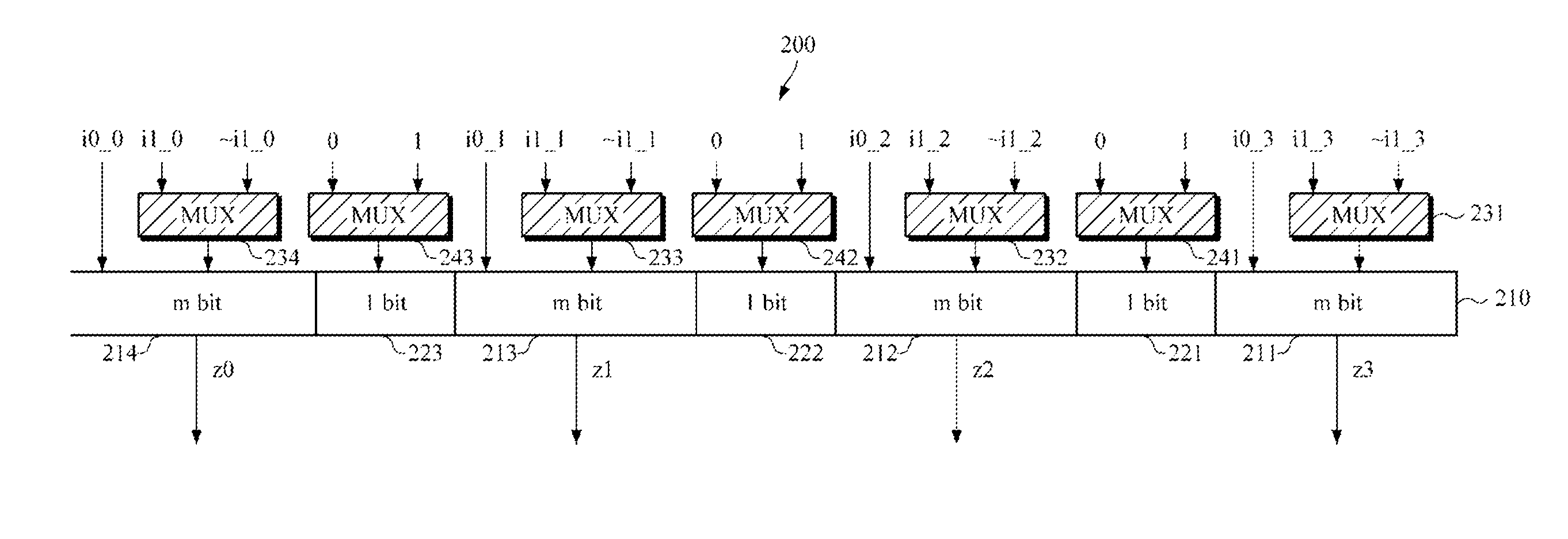

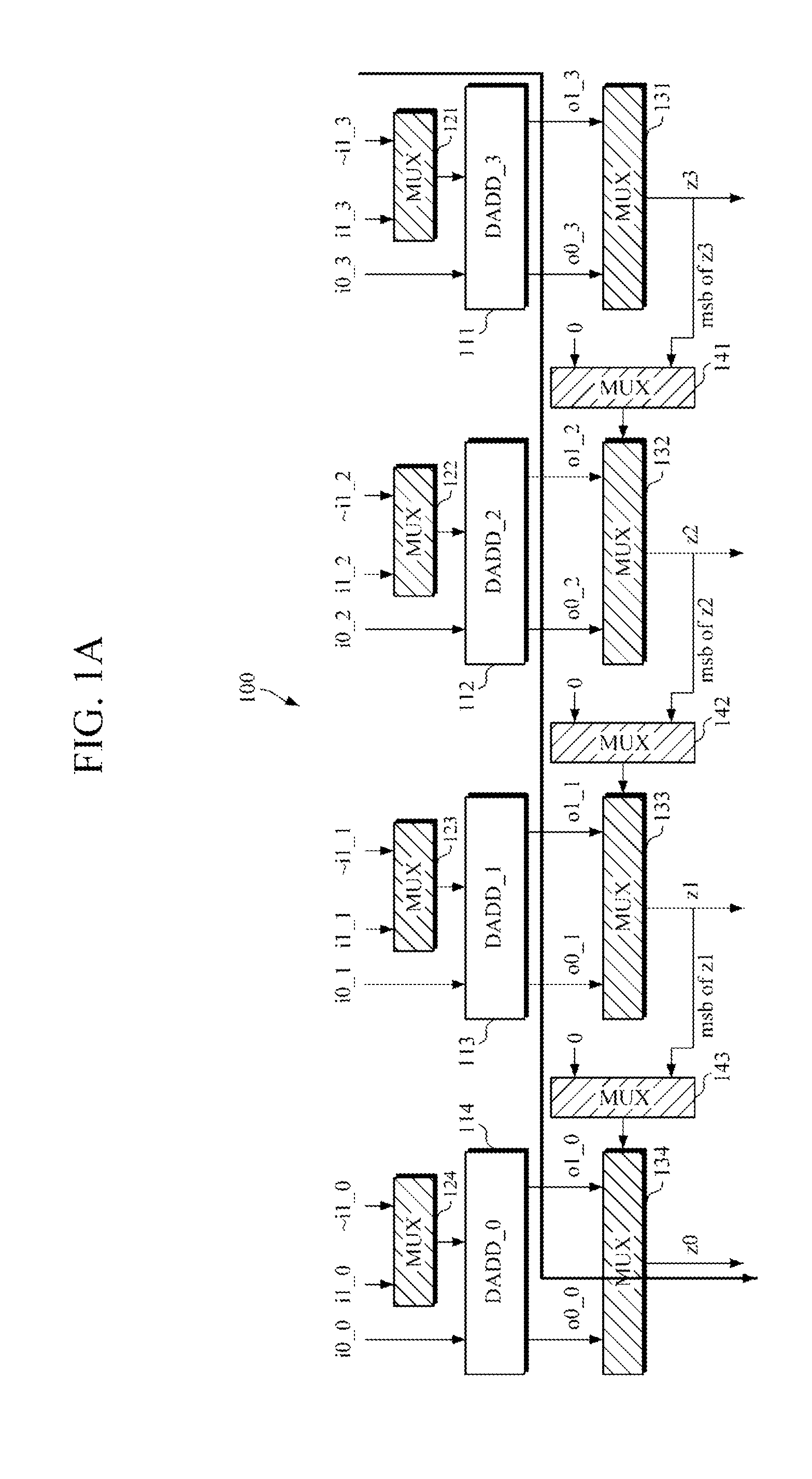

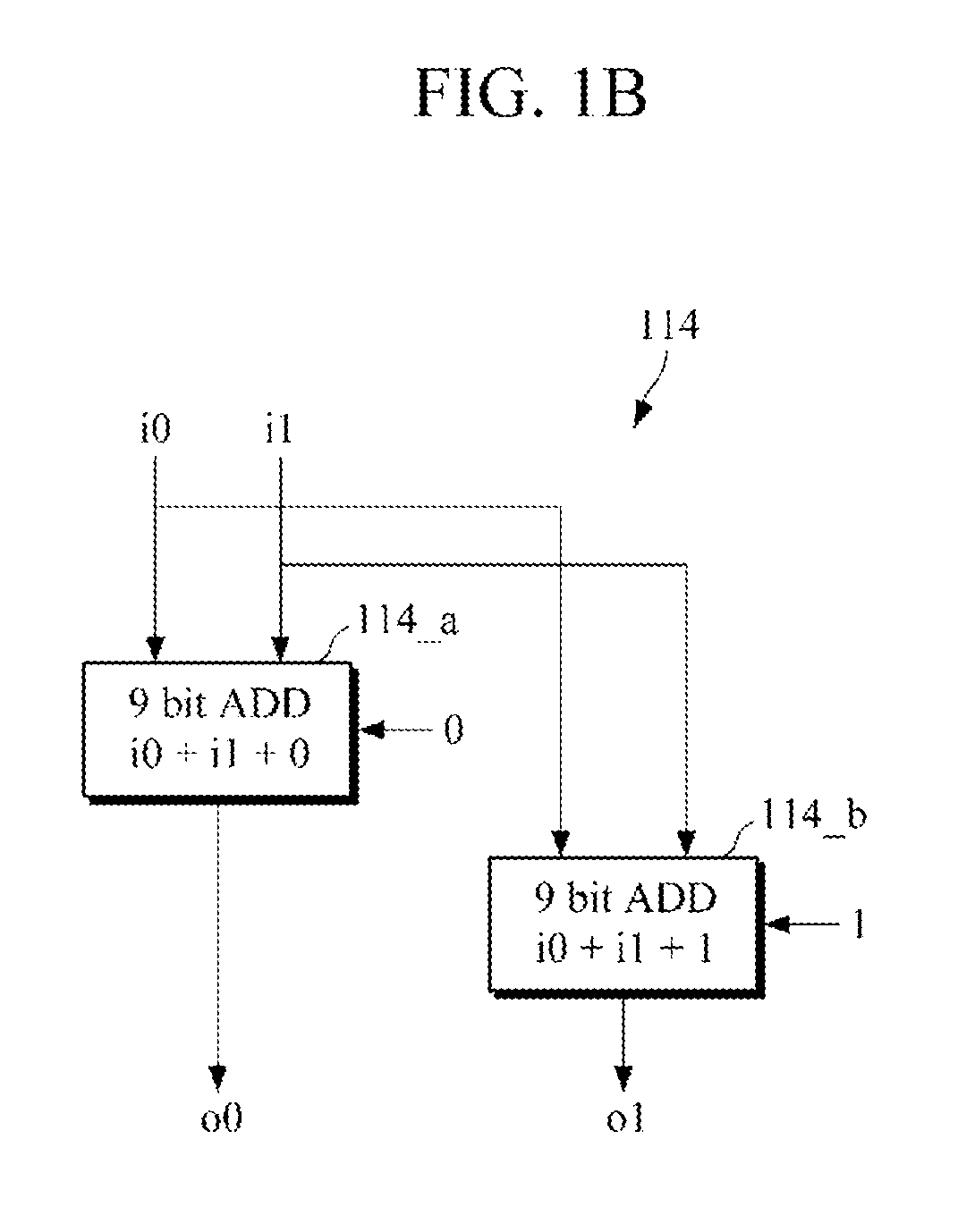

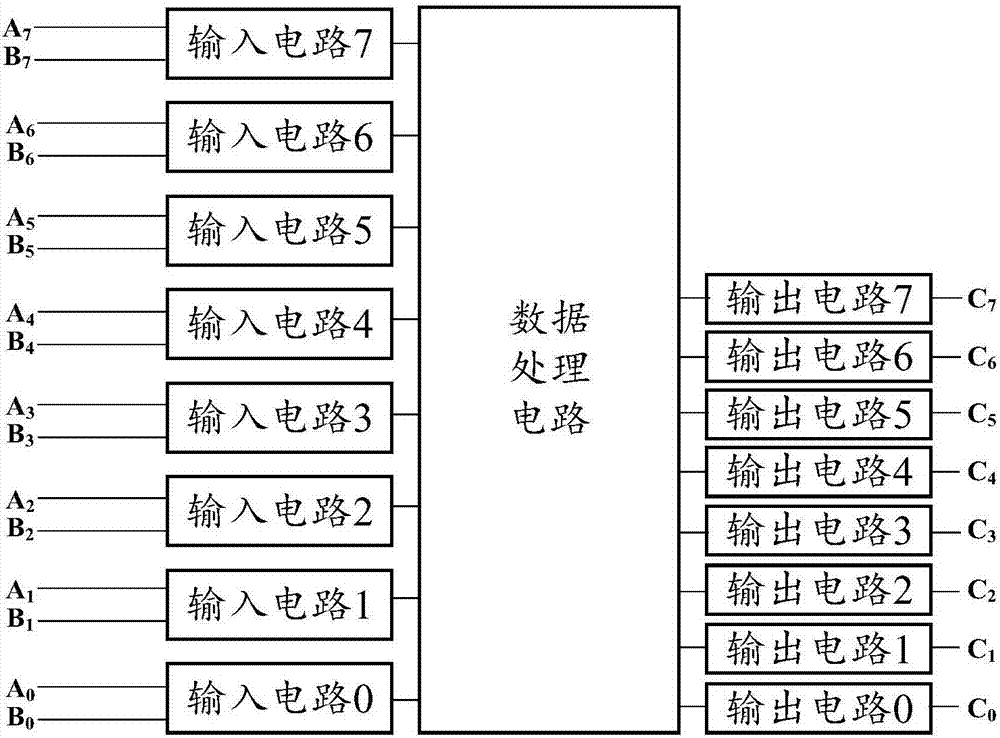

ActiveUS20140214913A1Computations using contact-making devicesComputation using non-contact making devicesCarry propagationControl data

An adder for supporting multiple data types by controlling a carry propagation is provided. The adder includes a plurality of first addition areas configured to receive pieces of incoming operand data, wherein each of the plurality of first addition areas includes a predetermined unit number of bits, and a plurality of second addition areas configured to receive pieces of control data based on a type of the operand data and an operation type, wherein the plurality of second addition areas are alternately arranged between the plurality of first addition areas.

Owner:SAMSUNG ELECTRONICS CO LTD

Reconfigurable arithmetic unit and high-efficiency processor having the same

ActiveUS8150903B2High degree of useImprove energy efficiencyComputation using non-contact making devicesWallace treeBinary multiplier

Provided are a reconfigurable arithmetic unit and a processor having the same. The reconfigurable arithmetic unit can perform an addition operation or a multiplication operation according to an instruction by sharing an adder. The reconfigurable arithmetic unit includes a booth encoder for encoding a multiplier, a partial product generator for generating a plurality of partial products using the encoded multiplier and a multiplicand, a Wallace tree circuit for compressing the partial products into a first partial product and a second partial product, a first Multiplexer (MUX) for selecting and outputting one of the first partial product and a first addition input according to a selection signal, a second MUX for selecting and outputting one of the second partial product and a second addition input according to the selection signal, and a Carry Propagation Adder (CPA) for adding an output of the first MUX and an output of the second MUX to output an operation result. The arithmetic unit can operate as an adder or a multiplier according to an instruction, and thus can increase the degree of use of entire hardware.

Owner:ELECTRONICS & TELECOMM RES INST

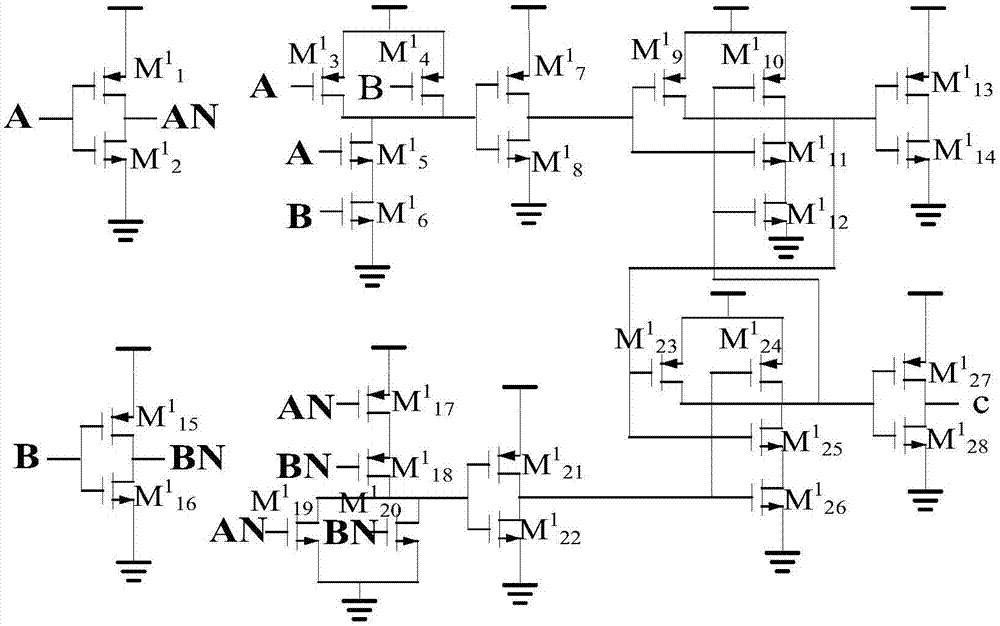

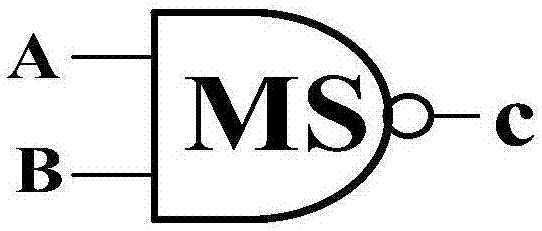

Subthreshold anti-noise full adder circuit

InactiveCN107425846ALow working voltageImprove noise immunityLogic circuits characterised by logic functionDigital data processing detailsCarry propagationComputer module

The invention provides a subthreshold anti-noise full adder circuit comprising a data input circuit module, wherein the data input circuit module comprises a logic AND gate and a logic exclusive-OR gate and is used for generating a carry signal and a carry propagation signal through an input signal; a data processing circuit module, wherein the data processing circuit module comprises a logic AND gate and a selector and is used for performing logic operation on the carry signal and the carry propagation signal; a data output circuit module, wherein the data output circuit module comprises a logic exclusive-OR gate and is used for outputting a summarization signal and the carry propagation signal generated by the data processing circuit module, wherein the logic AND gates in the data input circuit module and the data output circuit module are Markov AND gates, and the logic exclusive-OR gates are Markov exclusive-OR gates. The subthreshold anti-noise full adder circuit can make the working voltage of the full adder be lower and meanwhile improve the anti-noise performance.

Owner:SHANGHAI JIAO TONG UNIV +1

Montgomery multiplier having efficient hardware structure

ActiveUS8756268B2Reduce complexityReduce countComputations using residue arithmeticComputation using denominational number representationHardware structureBinary multiplier

A radix-2k Montgomery multiplier including an input coefficient generation unit to receive a multiplier, a multiplicand, a modulus, a sum and a previous sum, to generate and to output a partial product and a multiple modulus by using at least one of the multiplier, the multiplicand, the modulus and the sum, and to divide and to output the received previous sum into units of k bits, an accumulator circuit to receive the partial product, the multiple modulus and k bits of the previous sum from the input coefficient generation unit, and to generate and to output a carry and a sum by summing the partial product, the multiple modulus and the previous sum, and a carry propagation adder (CPA) circuit to generate and to output an ultimate sum by using the carry and the sum.

Owner:SAMSUNG ELECTRONICS CO LTD

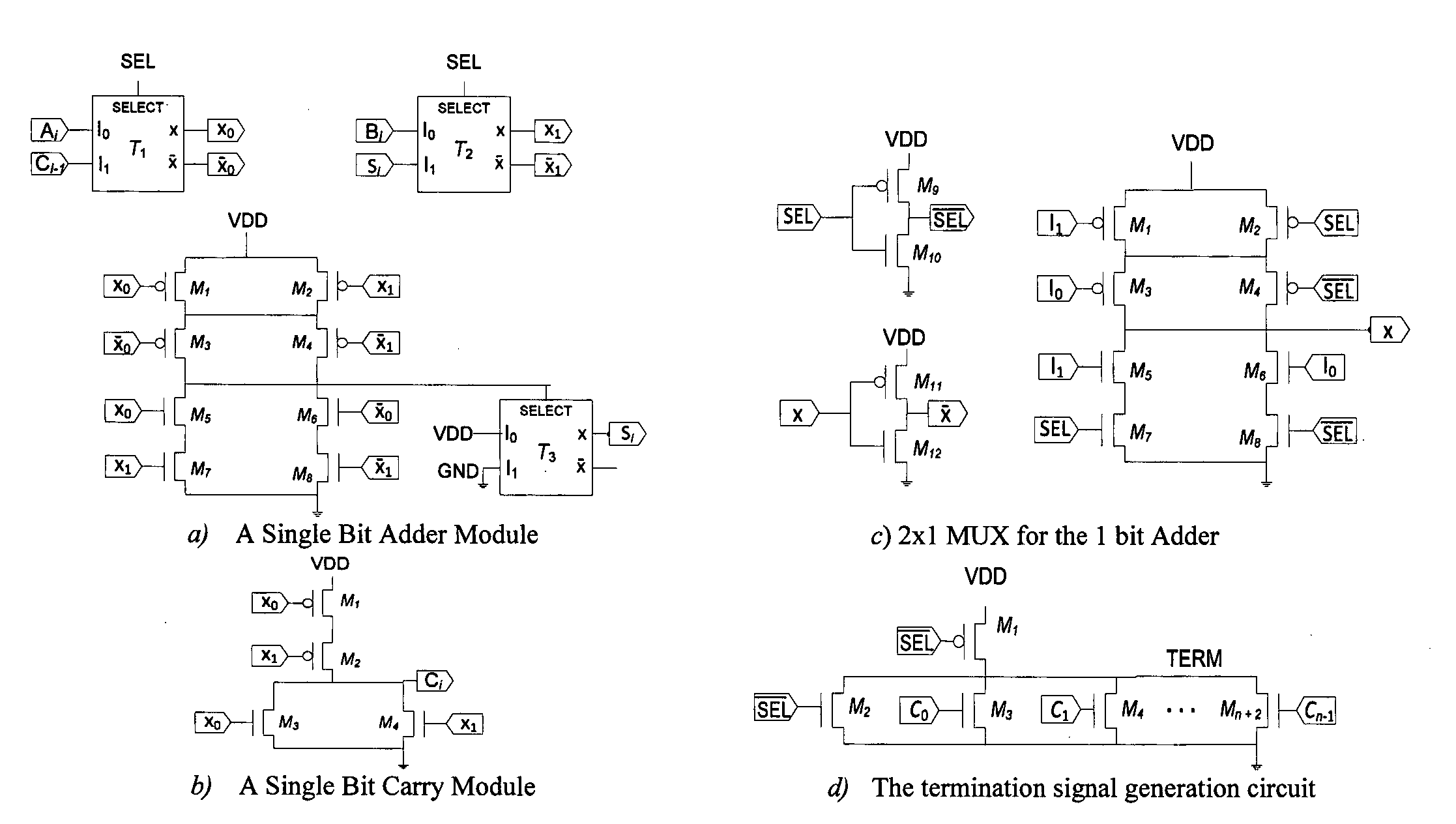

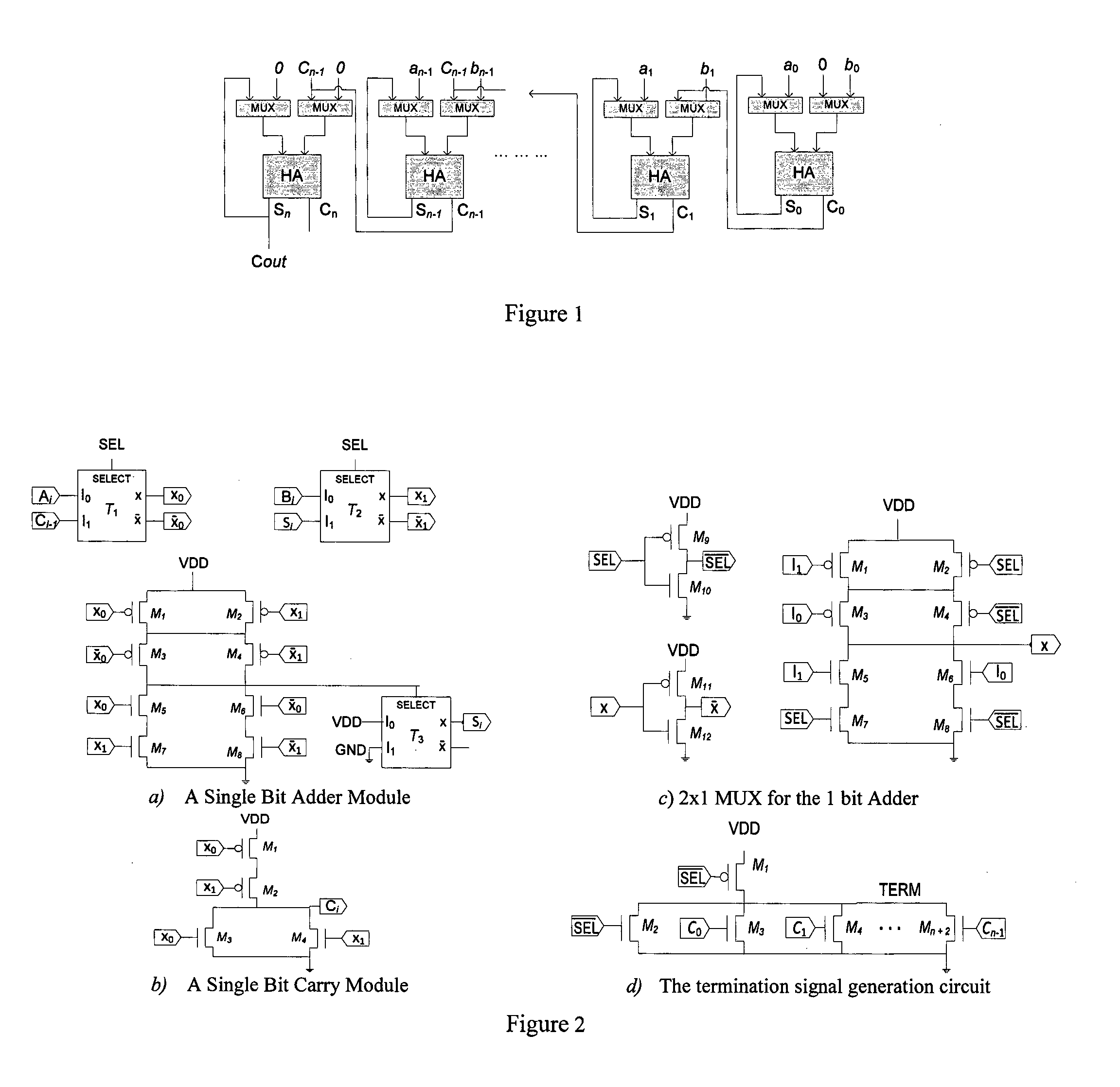

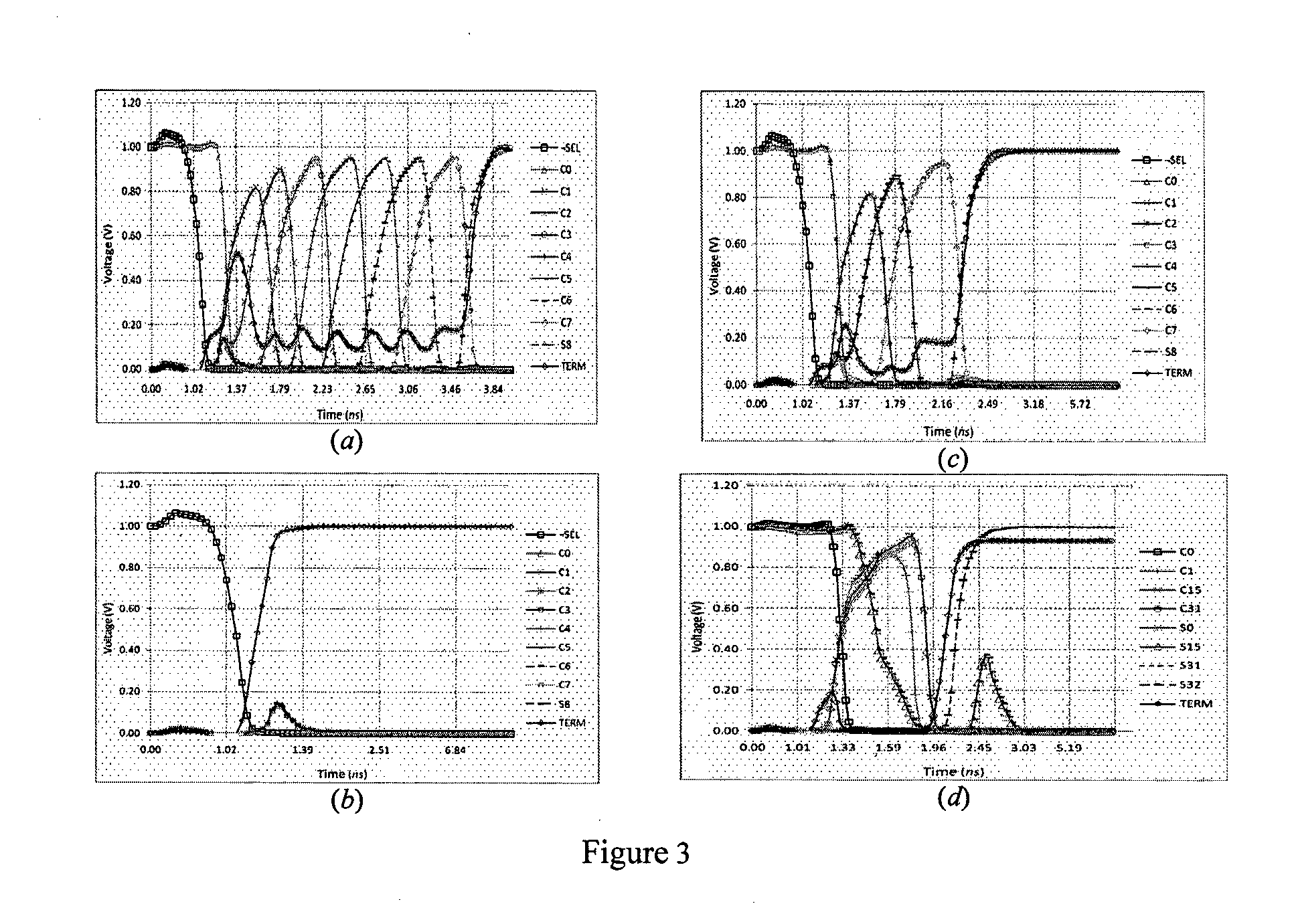

Parallel self-timer adder (PASTA)

InactiveUS20130117345A1Fast and area/interconnection efficient parallel adderComputation using non-contact making devicesComplex mathematical operationsComputational scienceCMOS

A parallel self-timed adder (PASTA) is disclosed. It is based on recursive formulation and uses only half adders for performing multi-bit binary addition. Theoretically the operation is parallel for those bits that do not need any carry chain propagation. Thus the new approach attains logarithmic performance without any special speed-up circuitry or look-ahead schema. The corresponding CMOS implementation of the design along with completion detection unit is also presented. The design is regular and does not have any practical limitations of fan-ins or fan-outs or complex interconnections. Thus it is more suitable for adoption in fast adder implementation in high-performance processors. The performance of the implementation is tested using SPICE circuit simulation tool by linear technology. Simulation results show its superiority over cascaded circuit adders. A constant time carry propagation is also achieved using the proposed implementation by tuning the CMOS parameters.

Owner:UNIVERSITI MALAYA

System and method for long addition and long multiplication in associative memory

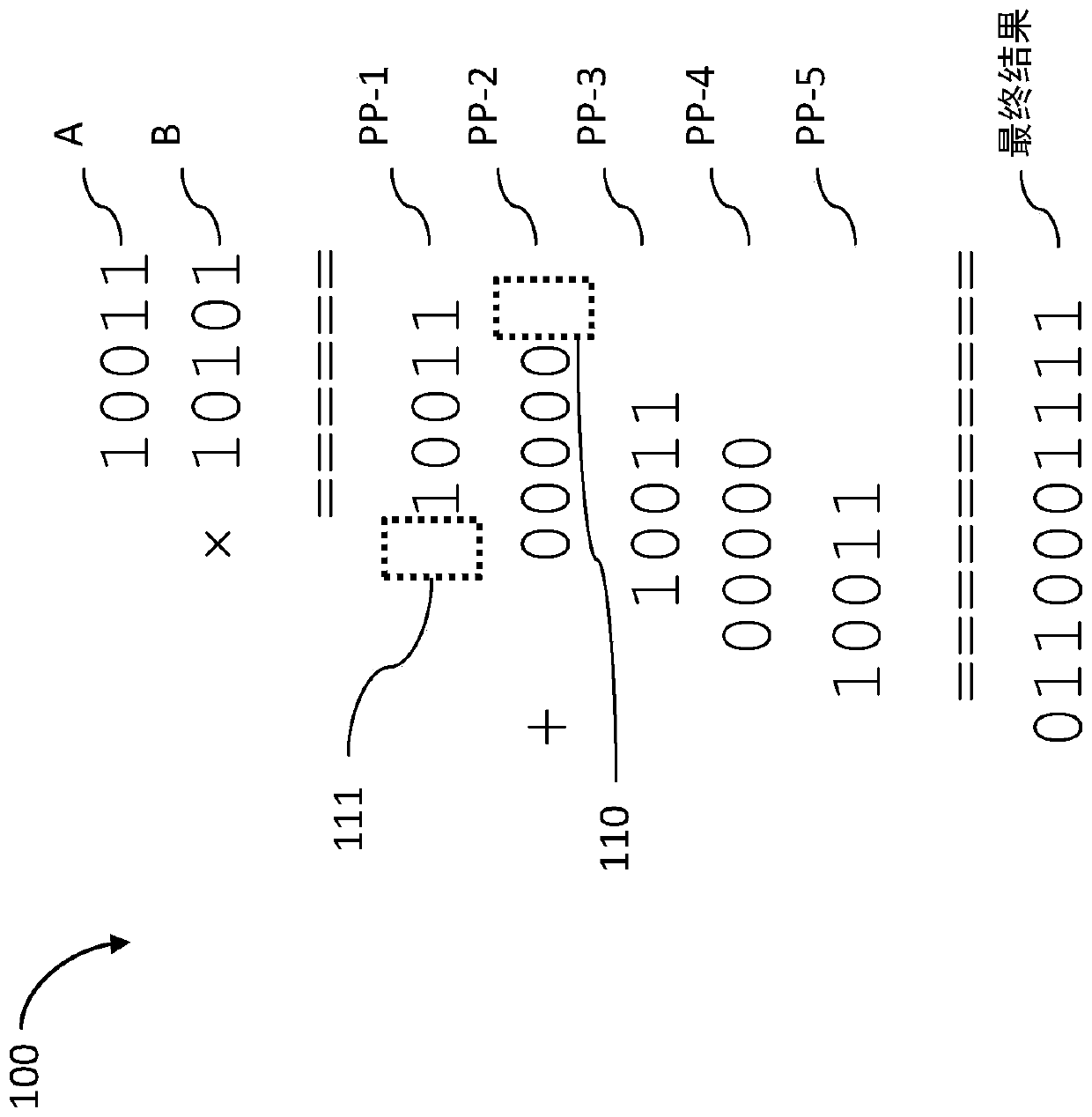

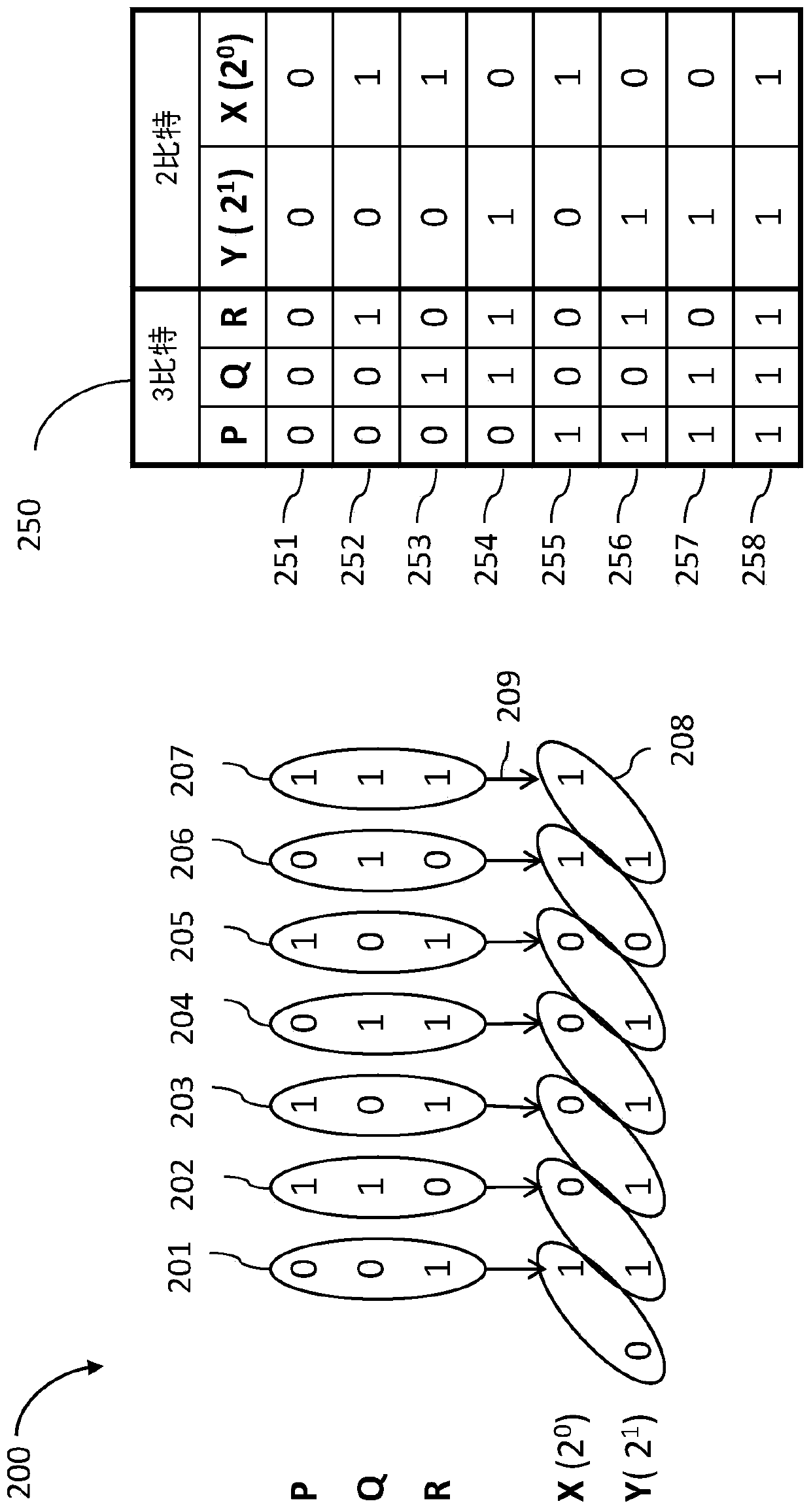

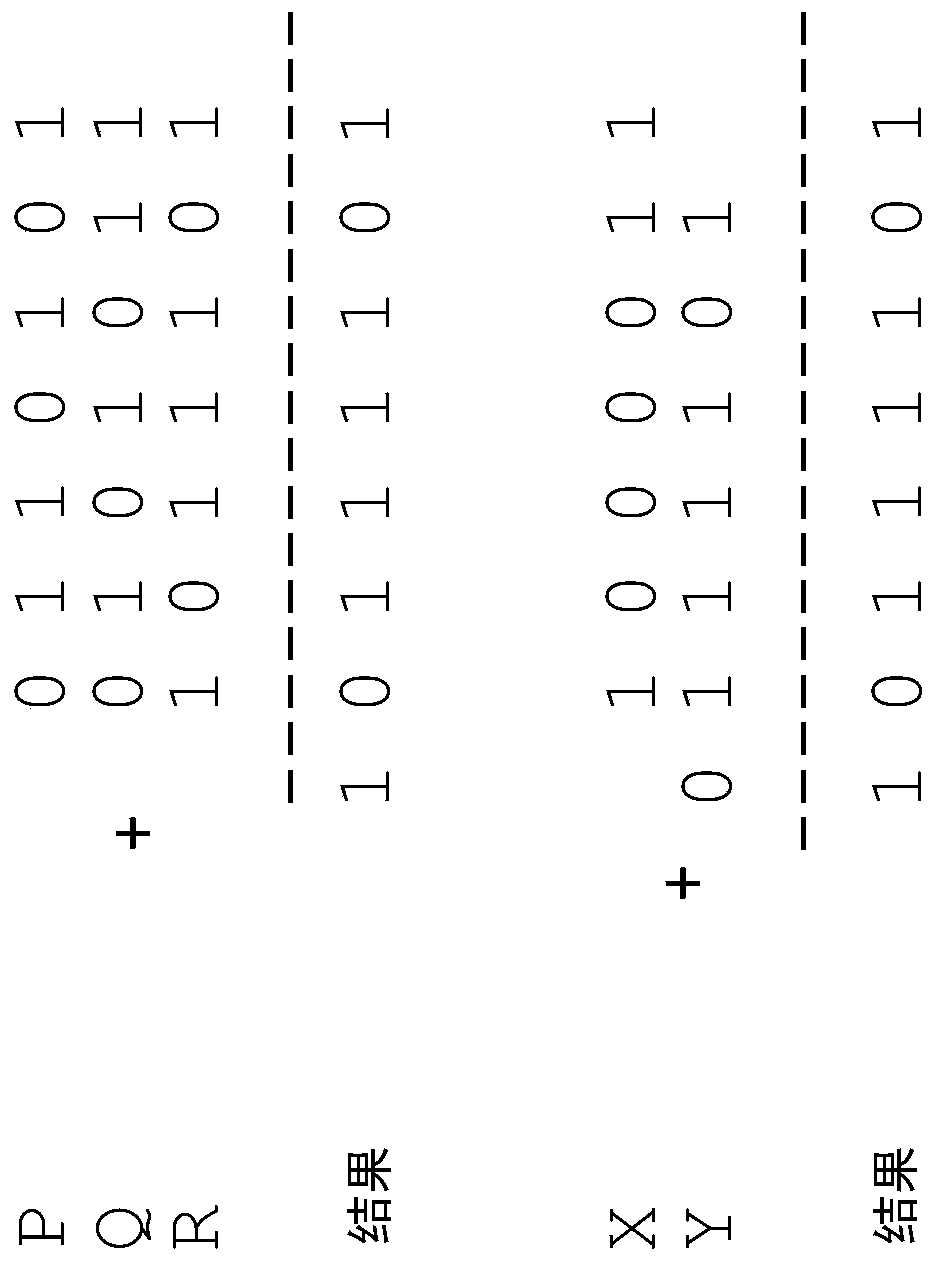

A method for an associative memory device includes replacing a set of three multi-bit binary numbers P, Q and R, stored in the associative memory device, with two multi-bit binary numbers X and Y, also stored in the associative memory device, wherein a sum of the binary numbers P, Q and R is equal to a sum of the binary numbers X and Y. A system includes an associative memory array having rows and columns and a multi-bit multiplier. Each column of the array stores two multi-bit binary numbers to be multiplied. The multi-bit multiplier multiplies, in parallel, the two multi-bit binary numbers per column by concurrently processing all bits of partial products generated by the multiplier. The multiplier performs the processing without any carry propagation delay when adding all but the last two partial products.

Owner:GSI TECH

Conditional selection adder and method of conditional selection adding

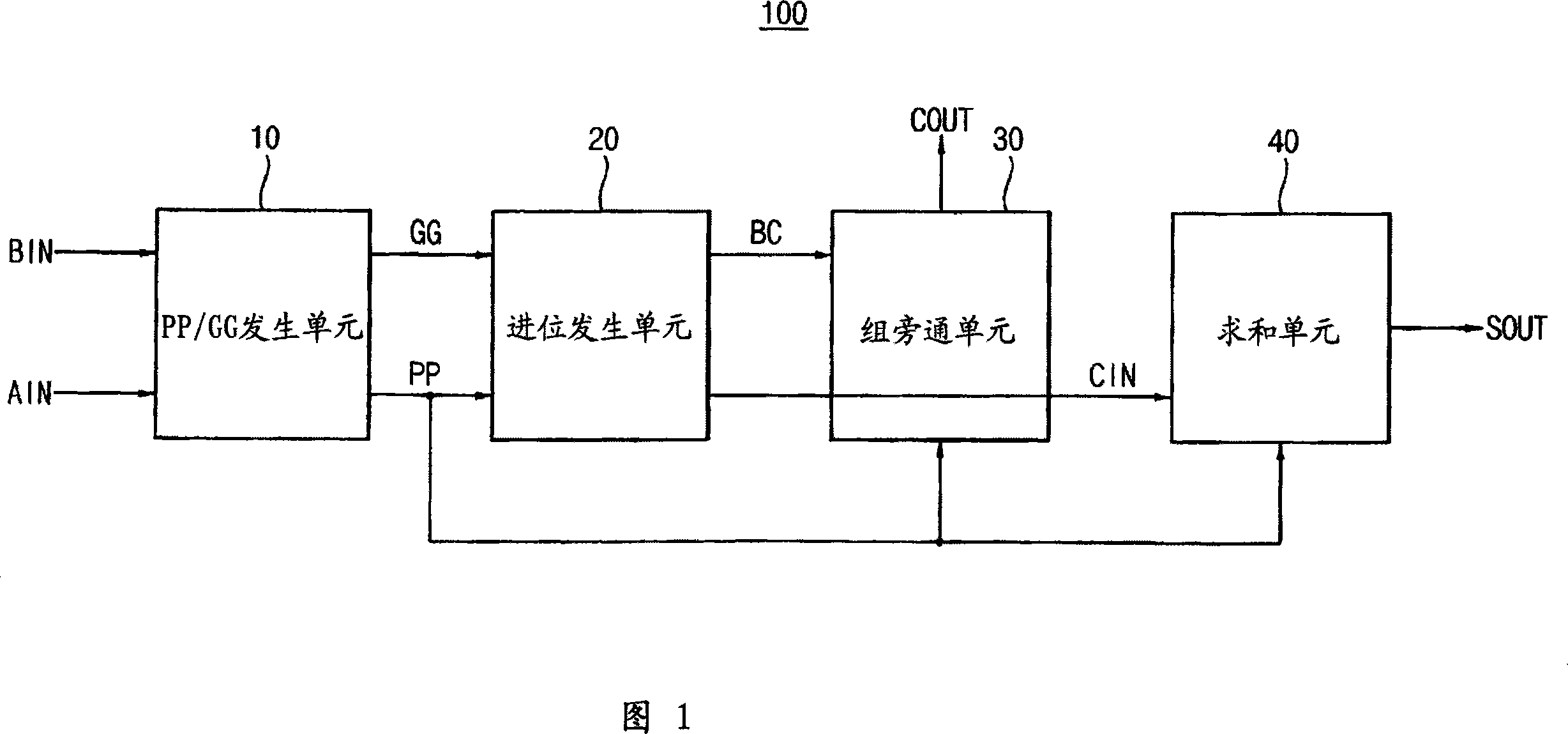

Conditional selection adders include first and second signal generators and a summation circuit. The first signal generator is configured to generate a carry generation signal and a carry propagation signal in response to a pair of operands to be added. The second signal generator is configured to generate a carry input signal and a block carry signal in response to the carry generation signal and the carry propagation signal. This second signal generator includes a plurality of groups of leaf-cells arranged in ascending order from a first group containing the fewest number of leaf-cells to a second group containing a largest number of leaf-cells. The summation circuit is configured to generate a sum of the pair of operands in response to the block carry signal, the carry propagation signal and the carry input signal. The summation circuit may include a group bypass circuit and a summation unit.

Owner:SAMSUNG ELECTRONICS CO LTD

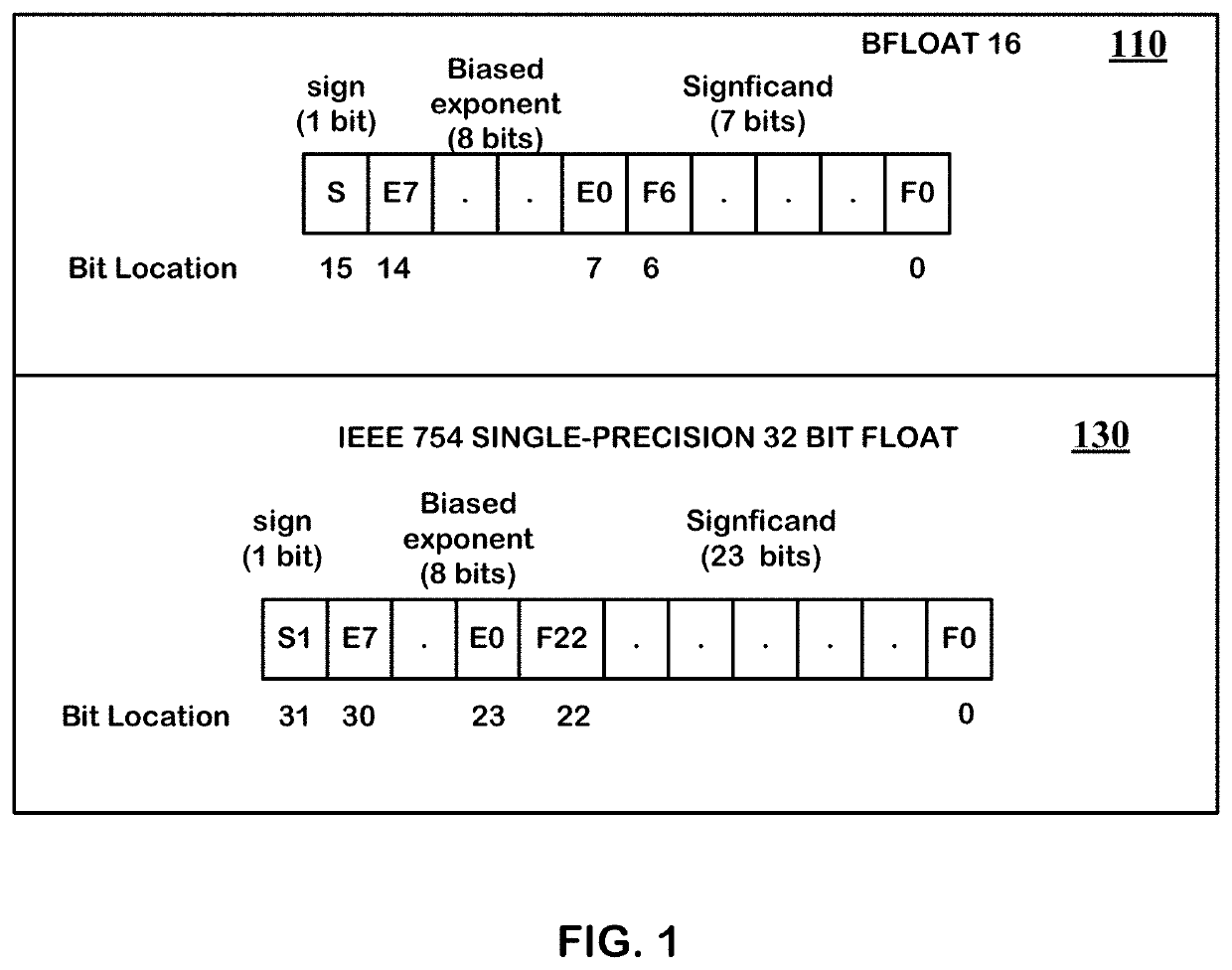

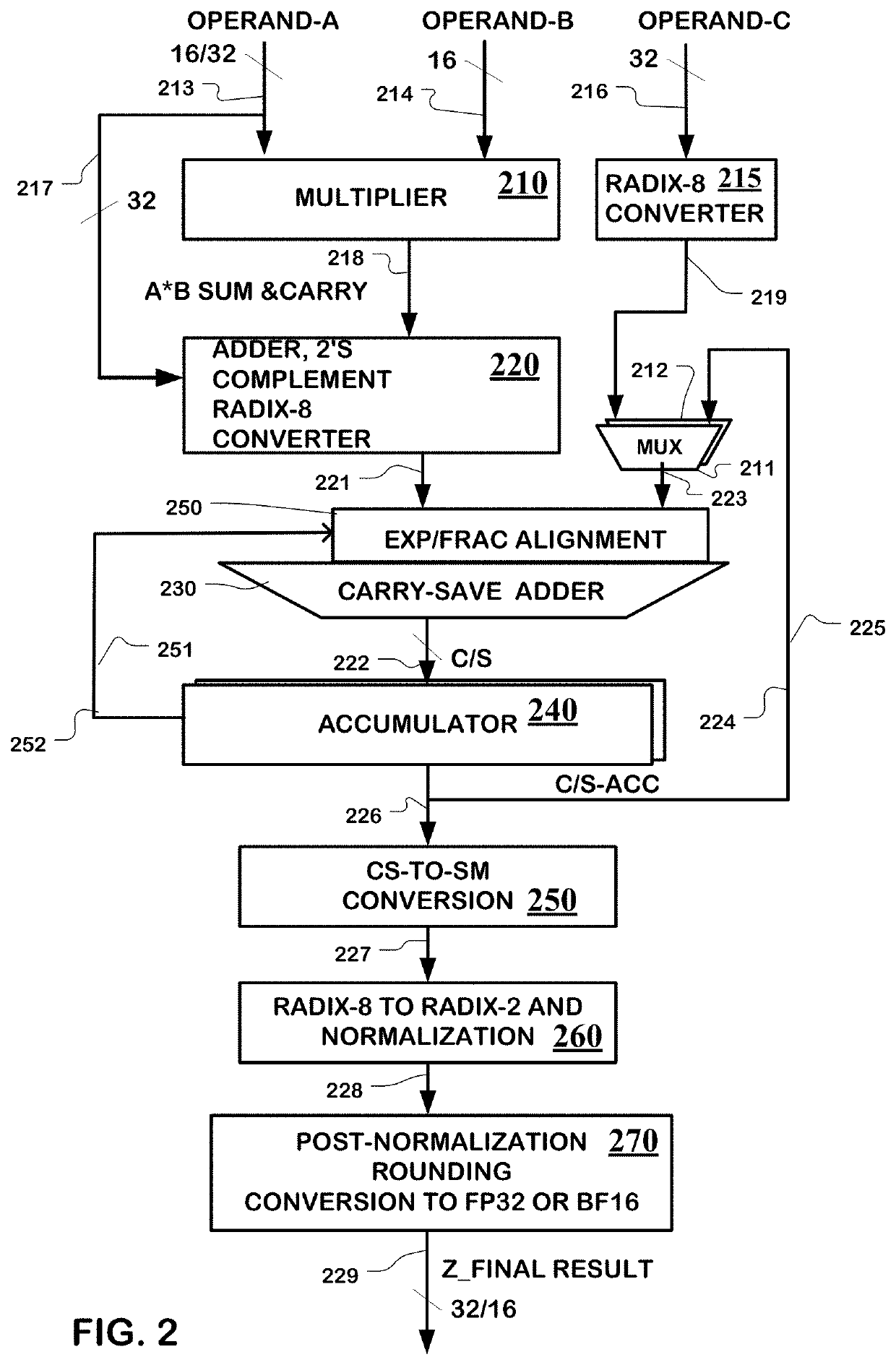

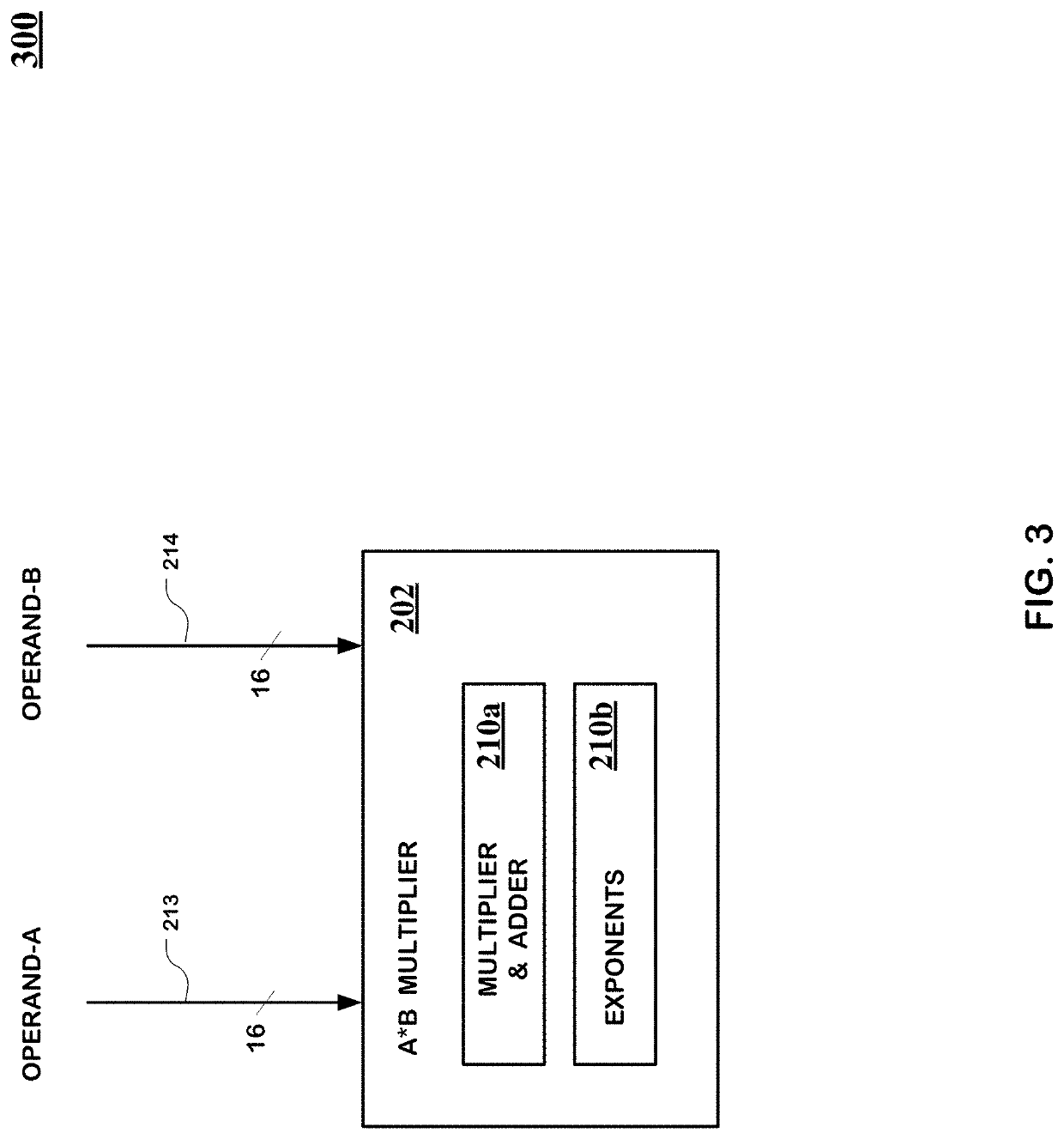

Floating point multiply-add, accumulate unit with combined alignment circuits

Floating point Multiply-Add, Accumulate Unit, supporting BF16 format for Multiply-Accumulate operations, and FP32 Single-Precision Addition complying with the IEEE 754 Standard. The Multiply-Accumulate unit uses higher radix and longer internal 2's complement significand representation to facilitate precision as well as comparison and operation with negative numbers. The addition can be performed using Carry-Save format to avoid long carry propagation and speed up the operation. The circuit uses early exponent comparison to shorten the accumulate pipeline stage. Operations including overflow detection, zero detection and sign extension are adopted for 2s complement and Carry-Save format.

Owner:SAMBANOVA SYST INC

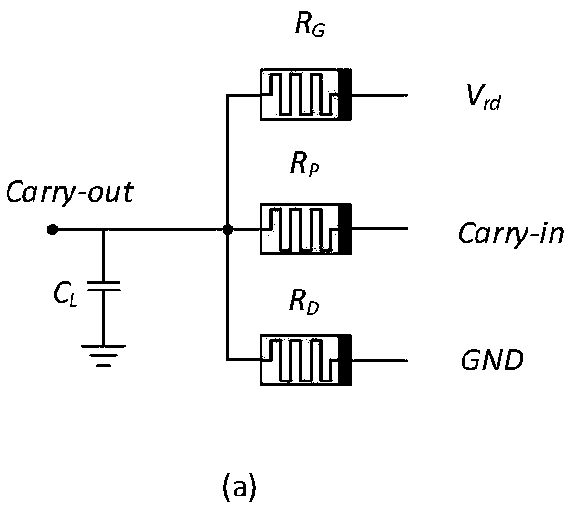

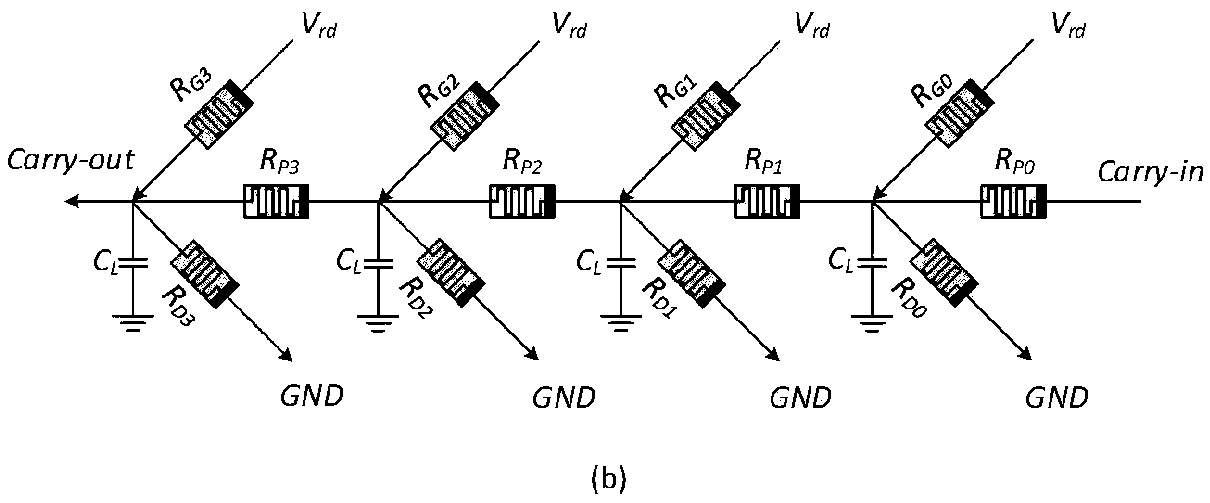

A fast algorithm for calculating the undercurrent path of an adder based on a memristor array

ActiveCN109521993AImprove computing powerArea cost increaseDigital data processing detailsCarry propagationFast algorithm

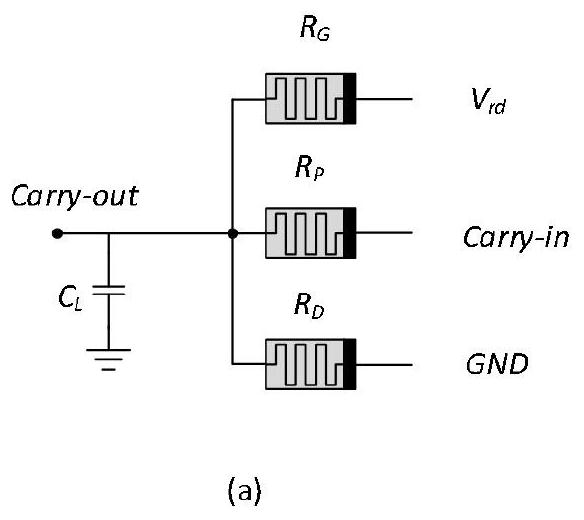

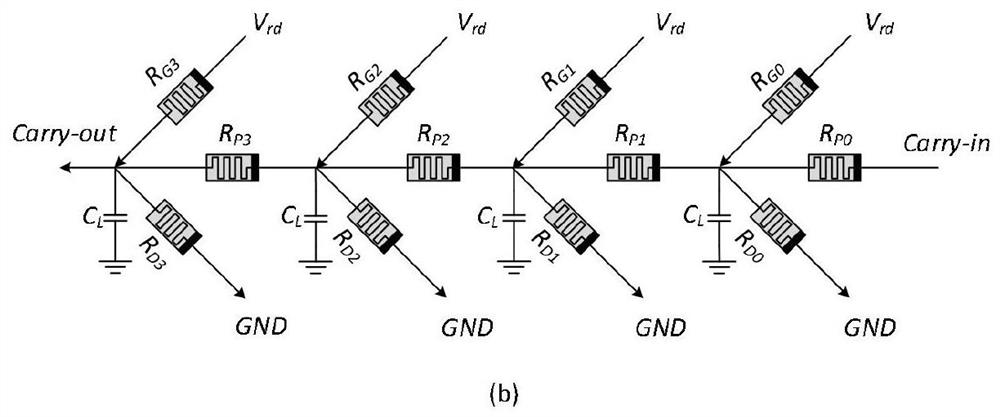

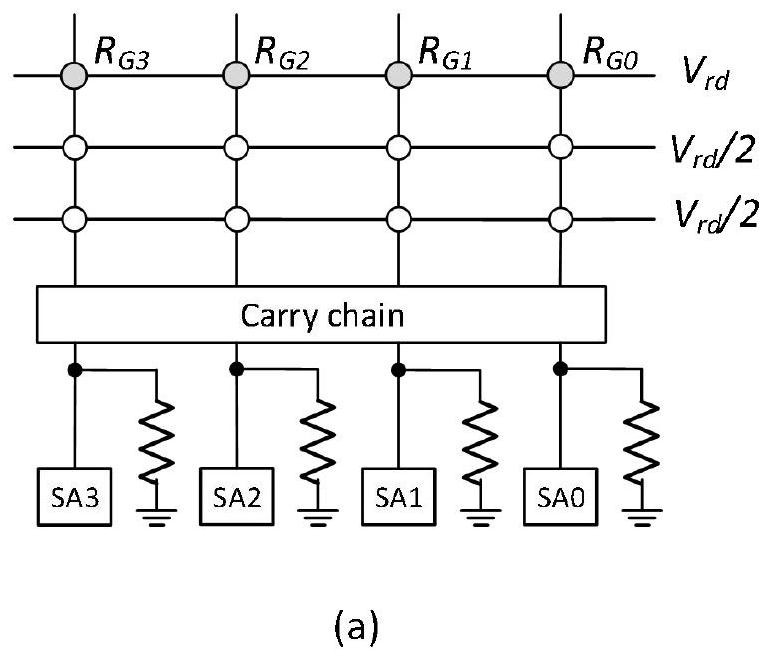

The invention discloses a fast algorithm for calculating the undercurrent path of an adder based on a memristor array, comprising the following steps: 1) carrying subsurface current path mapping, calculating the states of RG, RD and RP in advance, and determining the carrying calculation paths of different bits; 2) constructing a serial carry chain, and as a transmission path cannot be formed by the array structure, a carry propagation path control by the RP needs to be customized to cope with the RP in step 1); 3) after that carry calculation of the summation calculation bits is completed, completing the summation calculation of all the bits in parallel through the corresponding logic. The invention is based on the design of the adder of the memristor memory array, and utilizes HSPICE anda novel non-volatile memory simulation tool NVSim to test the design, so as to remarkably improve the computational performance, the area overhead and the power consumption overhead.

Owner:SHANGHAI JIAO TONG UNIV

Adder capable of supporting addition and subtraction of up to n-bit data and method of supporting addition and subtraction of a plurality of data type using the adder

ActiveUS9842085B2Computations using contact-making devicesComplex mathematical operationsCarry propagationControl data

An adder for supporting multiple data types by controlling a carry propagation is provided. The adder includes a plurality of first addition areas configured to receive pieces of incoming operand data, wherein each of the plurality of first addition areas includes a predetermined unit number of bits, and a plurality of second addition areas configured to receive pieces of control data based on a type of the operand data and an operation type, wherein the plurality of second addition areas are alternately arranged between the plurality of first addition areas.

Owner:SAMSUNG ELECTRONICS CO LTD

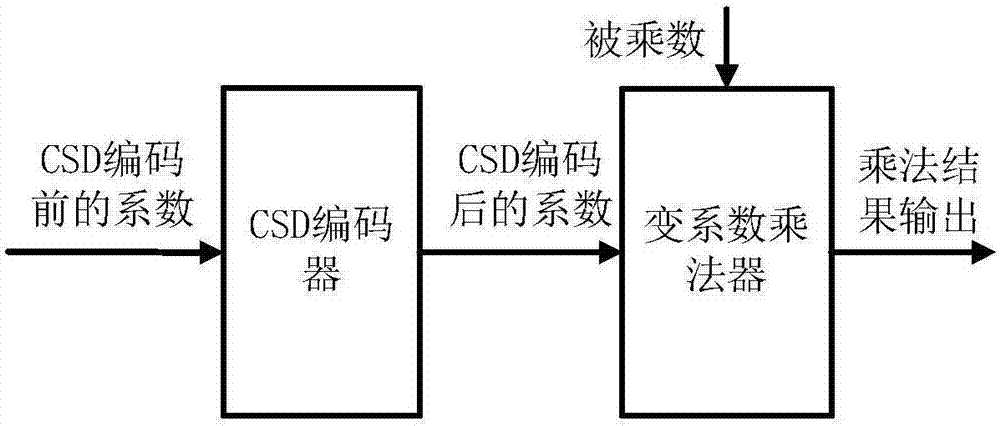

A Parallel Pseudo-CSD Encoder for Variable Coefficient Multipliers

InactiveCN104536719BFast operationImprove data throughputComputation using non-contact making devicesBinary multiplierCarry propagation

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

A Fast Calculation Method of Adder Based on Undercurrent Path of Memristor Array

ActiveCN109521993BImprove computing powerArea cost increaseDigital data processing detailsPathPingCarry propagation

The invention discloses a fast calculation method for an adder based on a memristor array undercurrent path, comprising the following steps: 1) mapping the carry undercurrent path, and calculating R in advance G , R D and R P 2) Constructing a serial carry chain, since the array structure cannot form a carry propagation path, it is necessary to customize a path by R P Controlled carry propagation path to cope with R in step 1) P 3) Summation calculation After the carry calculation of each bit is completed, the summation calculation of all bits is completed in parallel through the corresponding logic implementation. The present invention is based on the design of the adder of the memristor storage array, uses HSPICE and a new non-volatile memory simulation tool NVSim to test the design, and has significant improvements in computing performance, area overhead and power consumption overhead.

Owner:SHANGHAI JIAO TONG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com