Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

399 results about "Logic implementation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Logic gates implementation or logic representation of Boolean functions is very simple and easy form. The implementation of Boolean functions by using logic gates involves in connecting one logic gate’s output to another gate’s input and involves in using AND, OR, NAND and NOR gates.

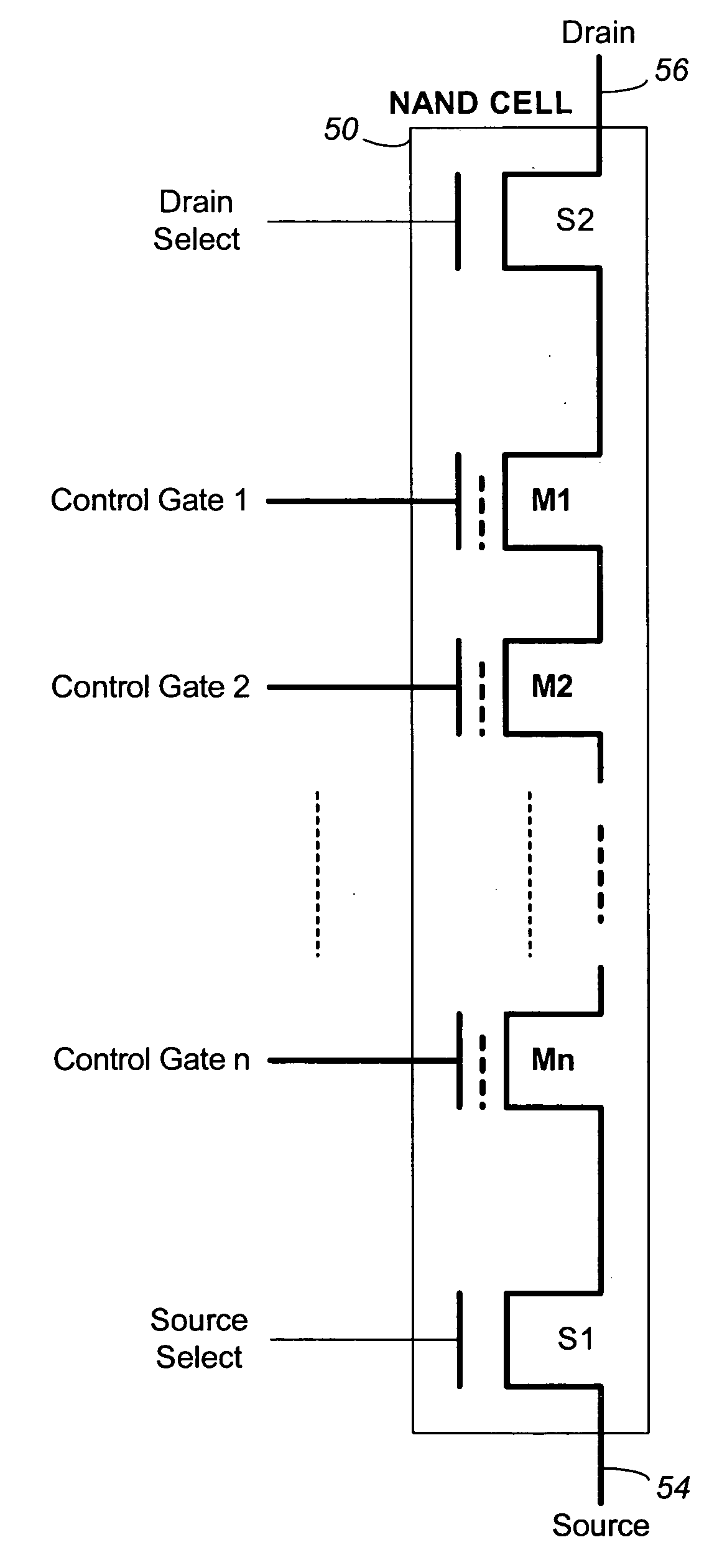

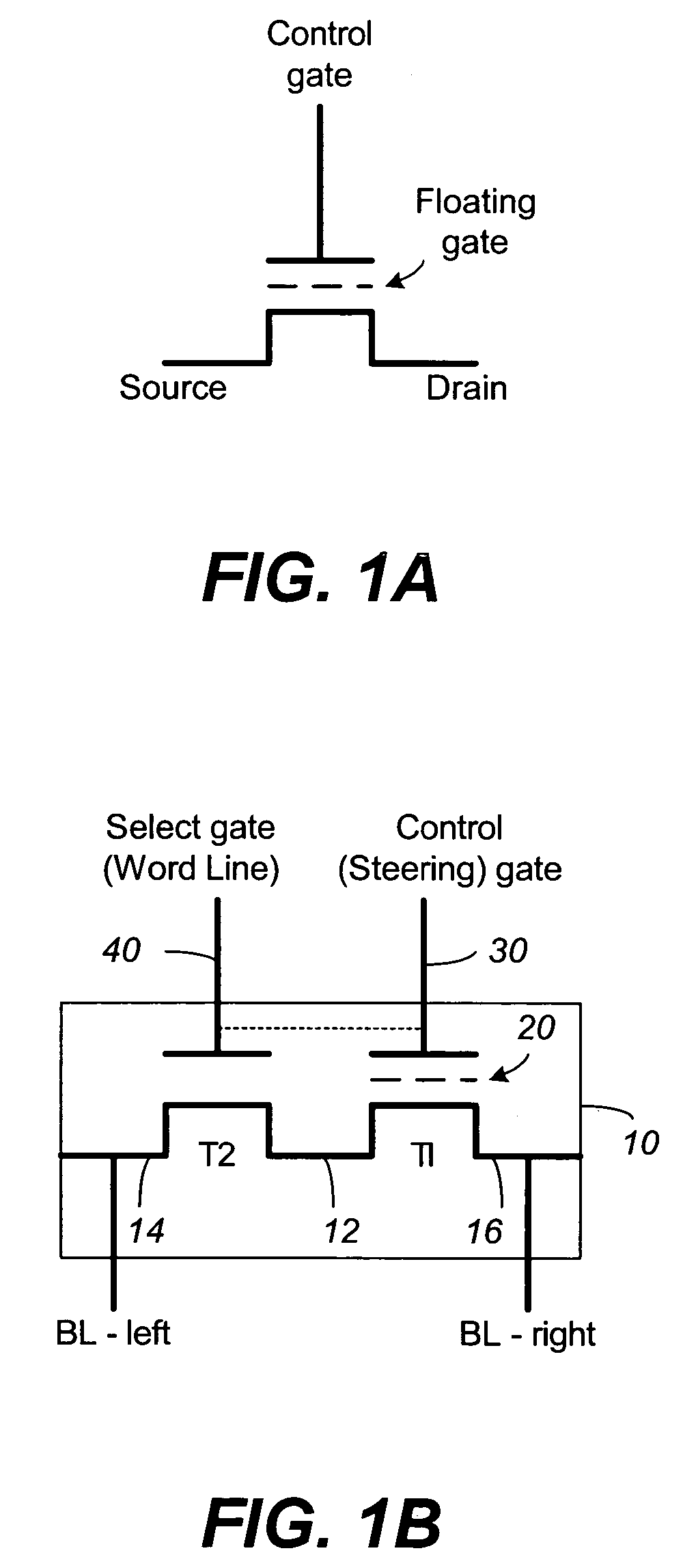

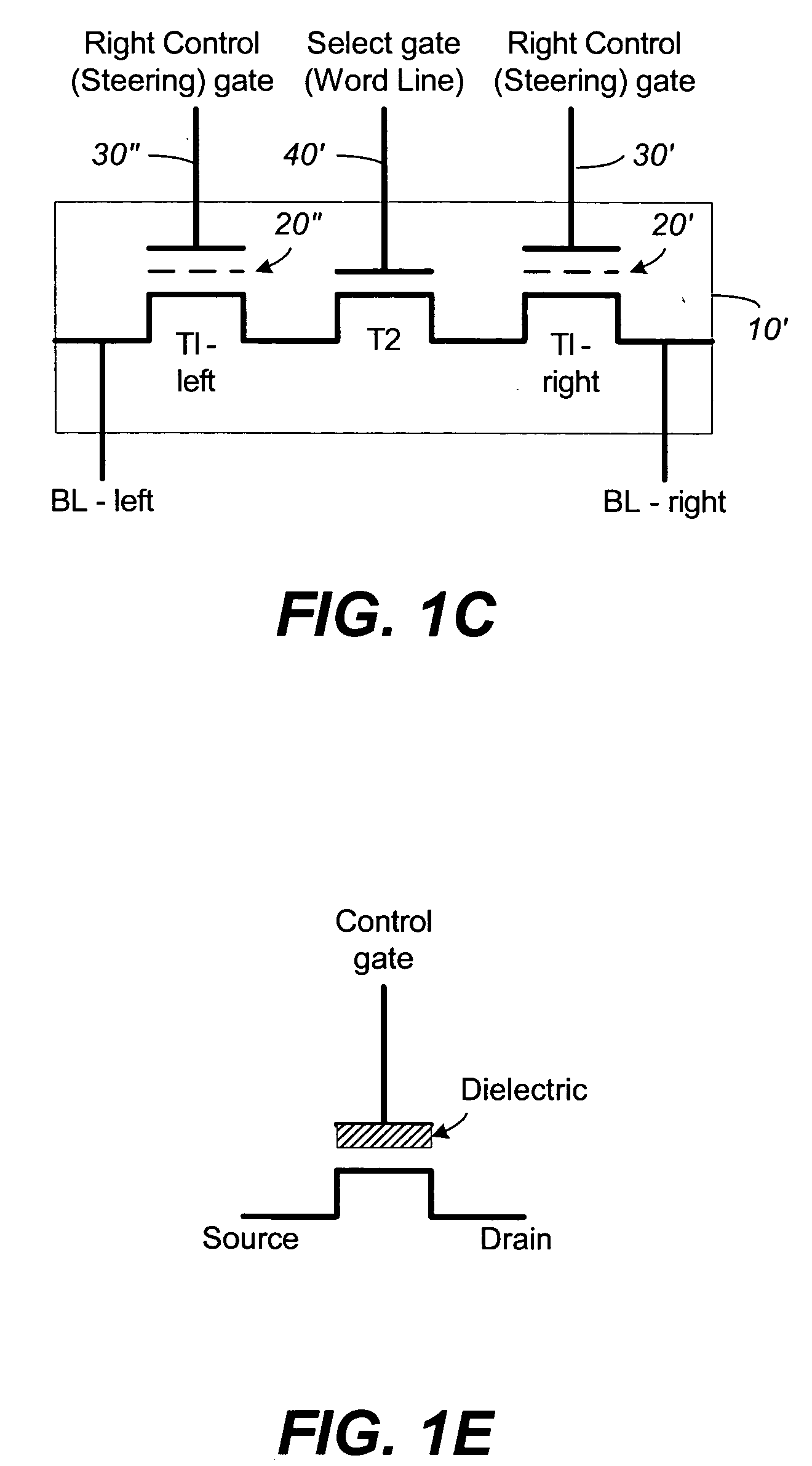

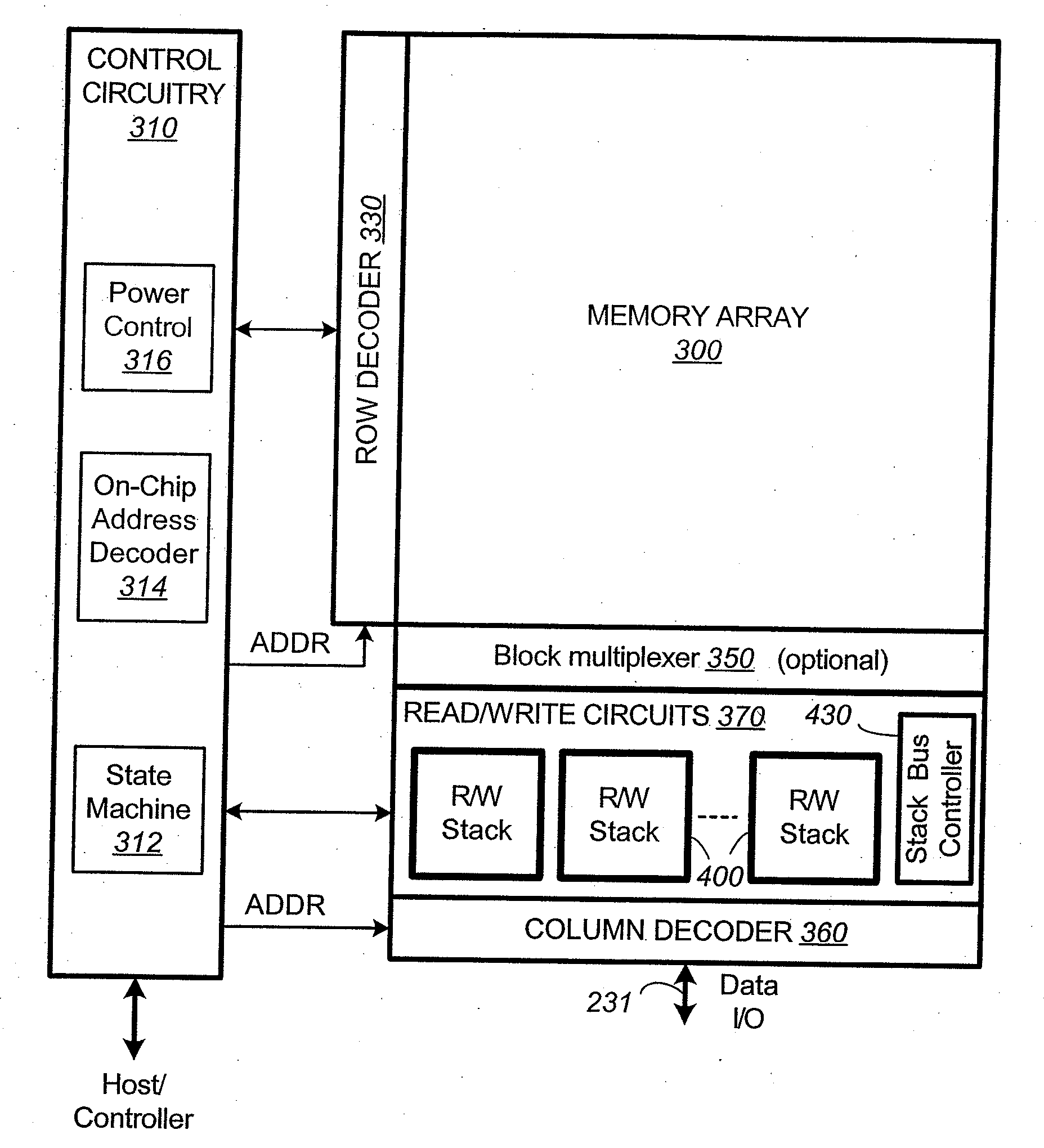

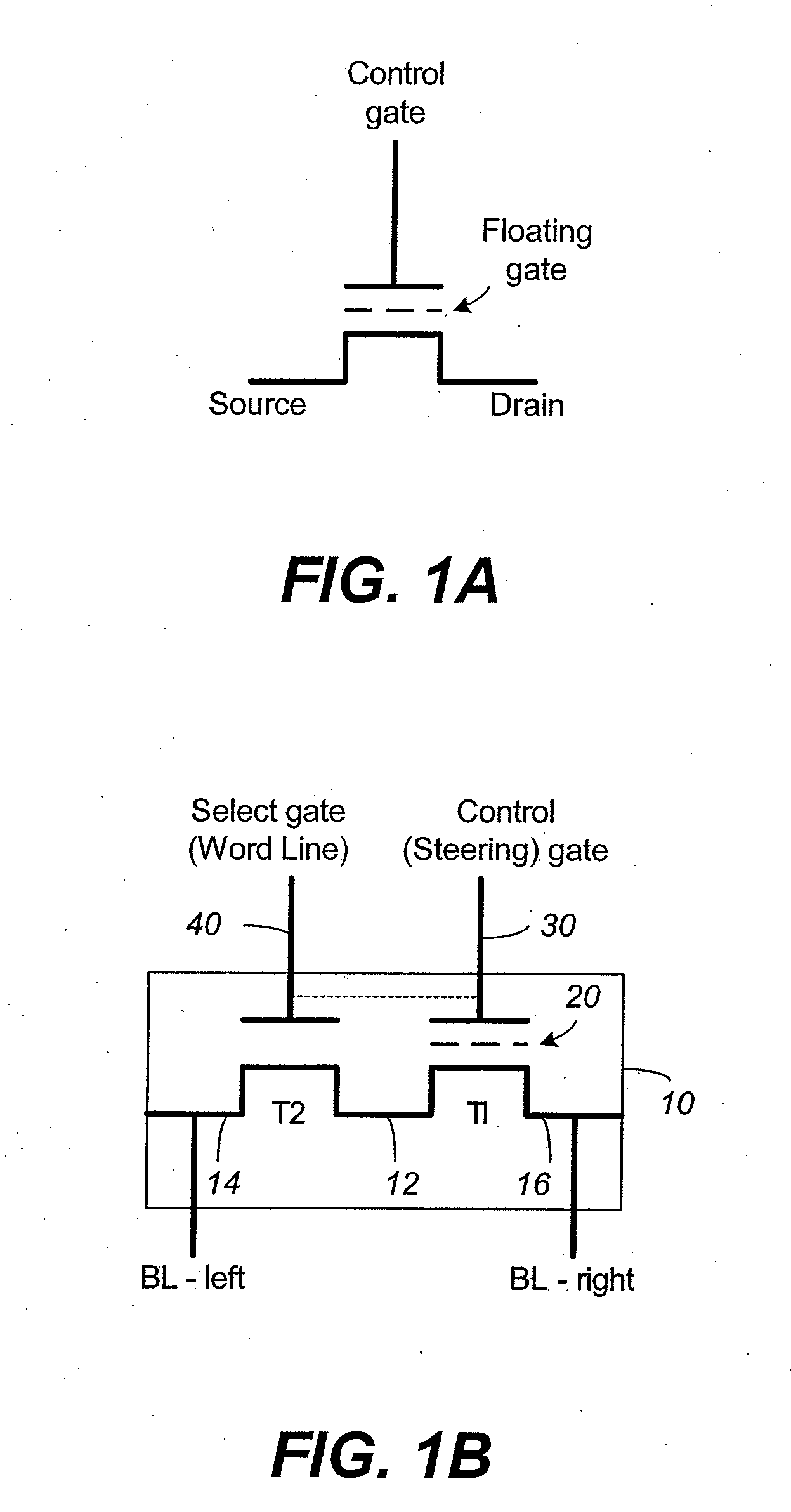

Non-volatile memory and method with shared processing for an aggregate of read/write circuits

InactiveUS20060140007A1Maximum versatilityMinimal componentRead-only memoriesDigital storageAudio power amplifierAssociative processor

A non-volatile memory device capable of reading and writing a large number of memory cells with multiple read / write circuits in parallel has an architecture that reduces redundancy in the multiple read / write circuits to a minimum. The multiple read / write circuits are organized into a bank of similar stacks of components. Redundant circuits such as a processor for processing data among stacks each associated with multiple memory cells are factored out. The processor is implemented with an input logic, a latch and an output logic. The input logic can transform the data received from either the sense amplifier or the data latches. The output logic further processes the transformed data to send to either the sense amplifier or the data latches or to a controller. This provides an infrastructure with maximum versatility and a minimum of components for sophisticated processing of the data sensed and the data to be input or output.

Owner:SANDISK TECH LLC

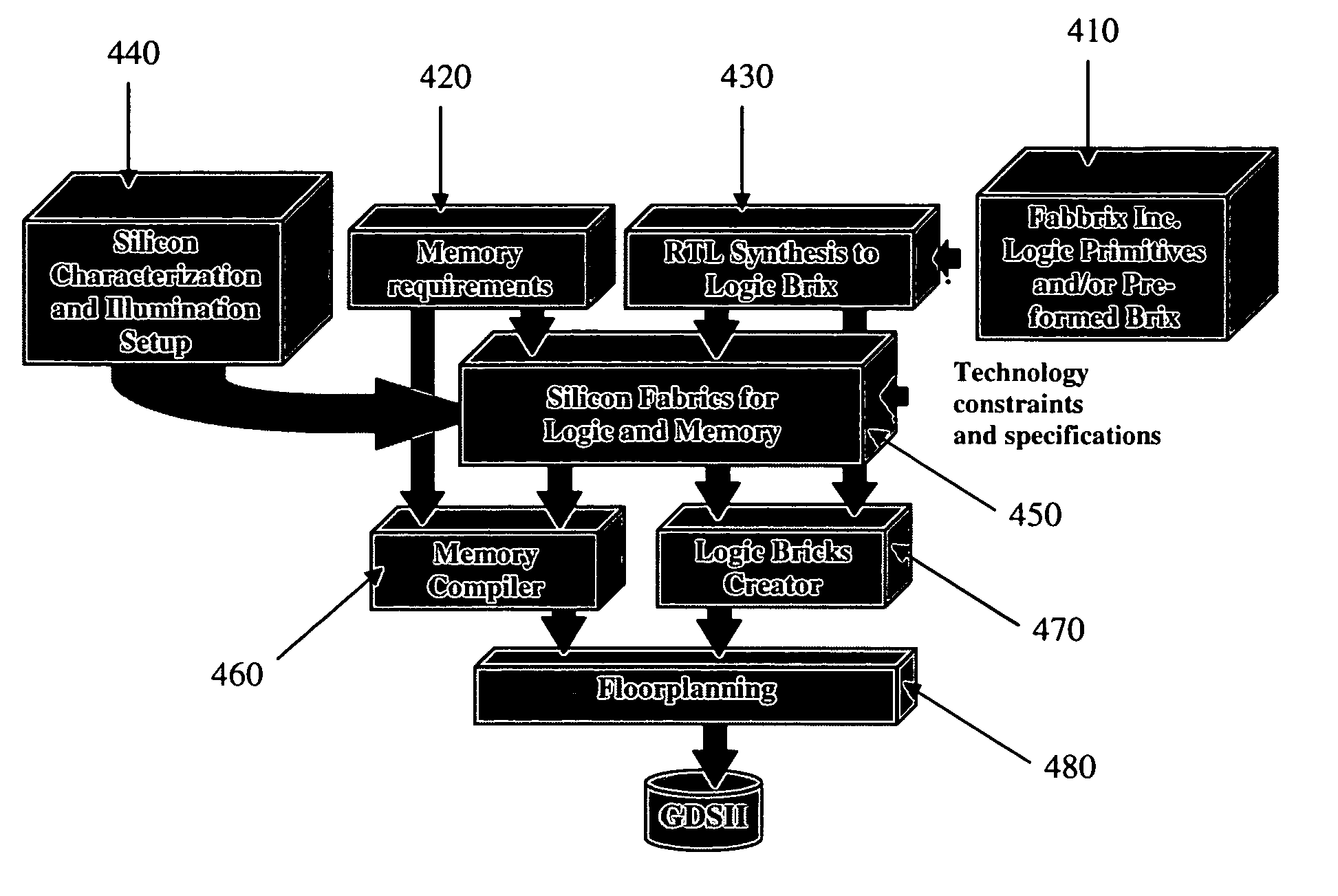

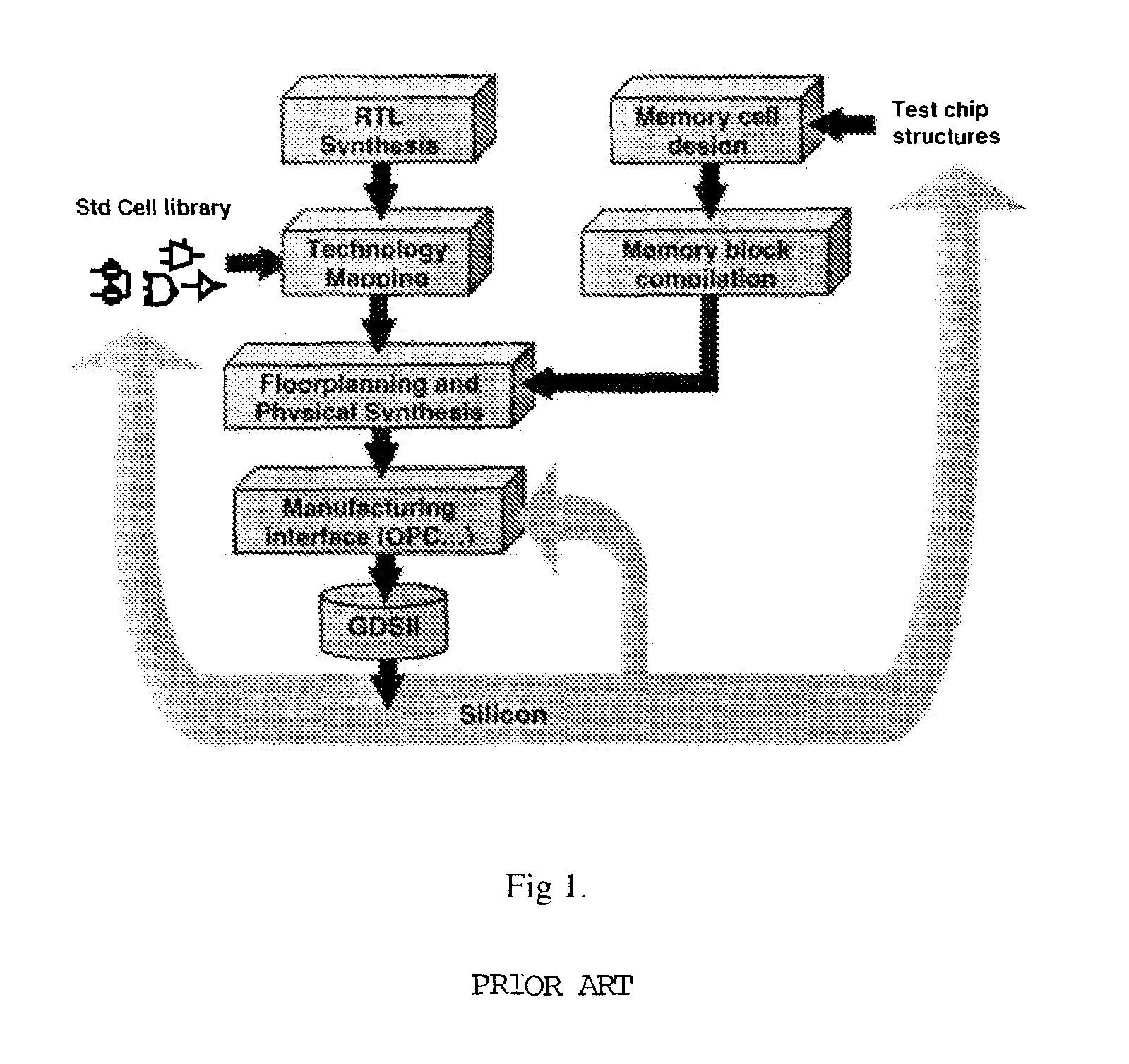

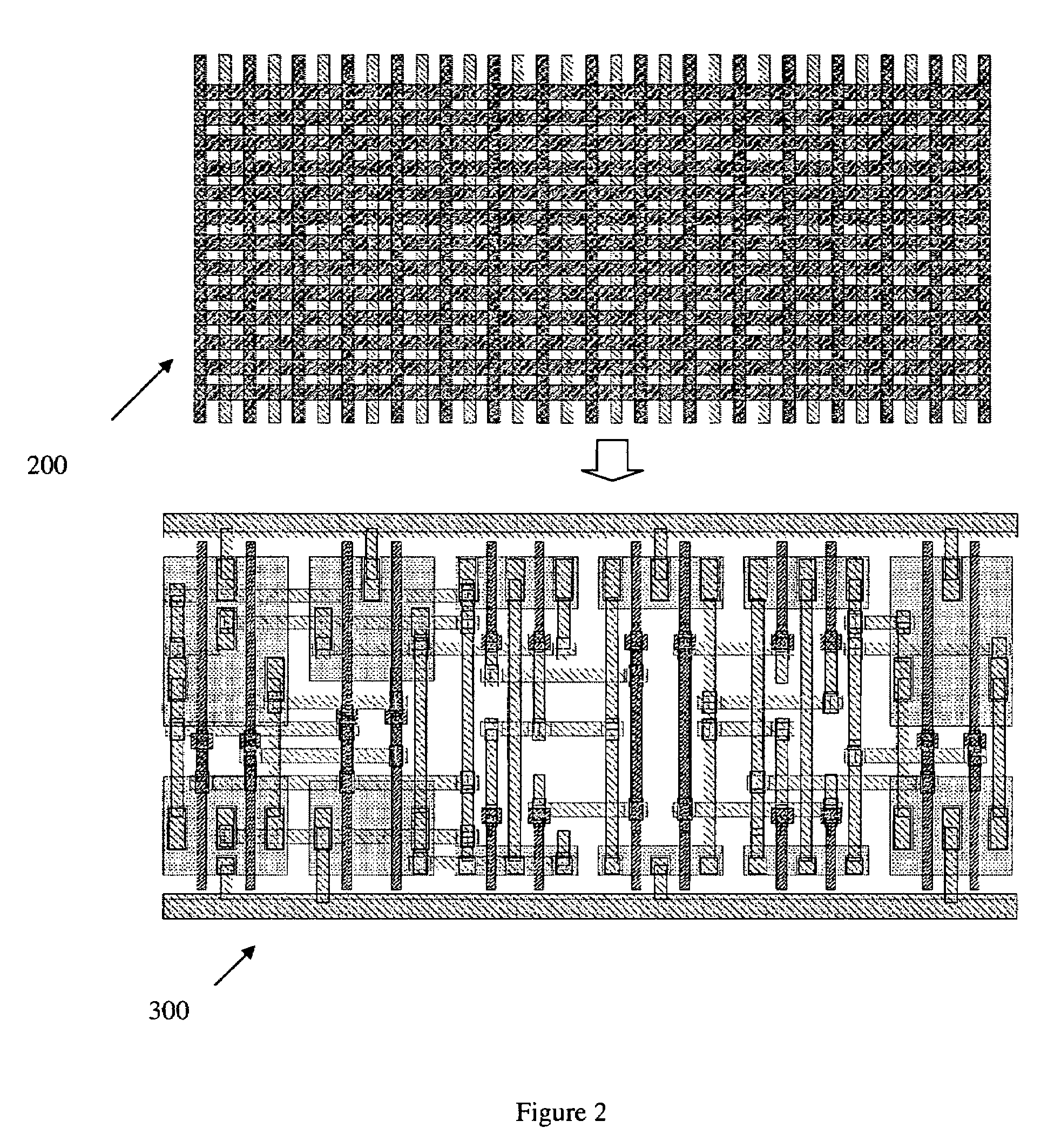

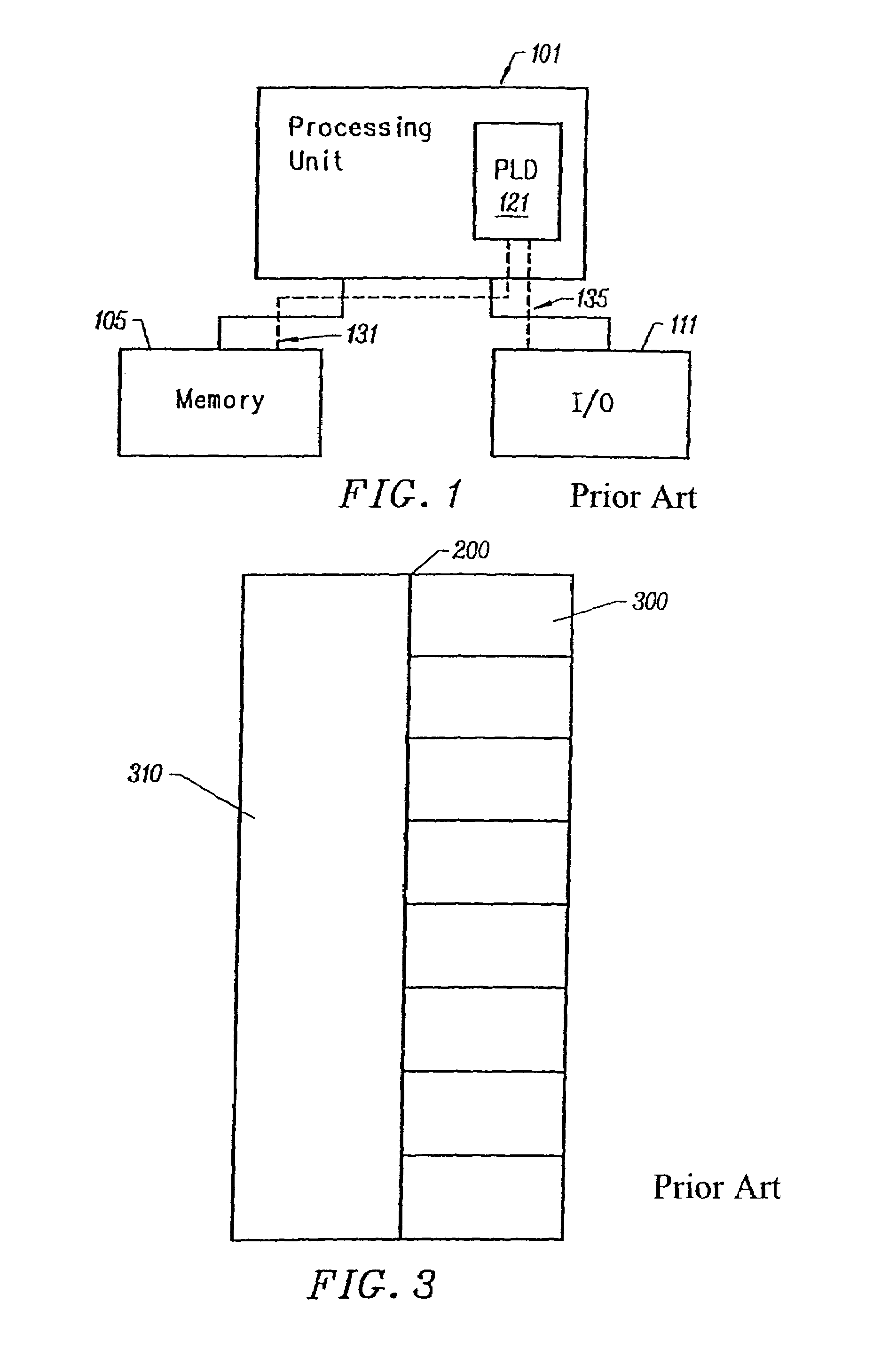

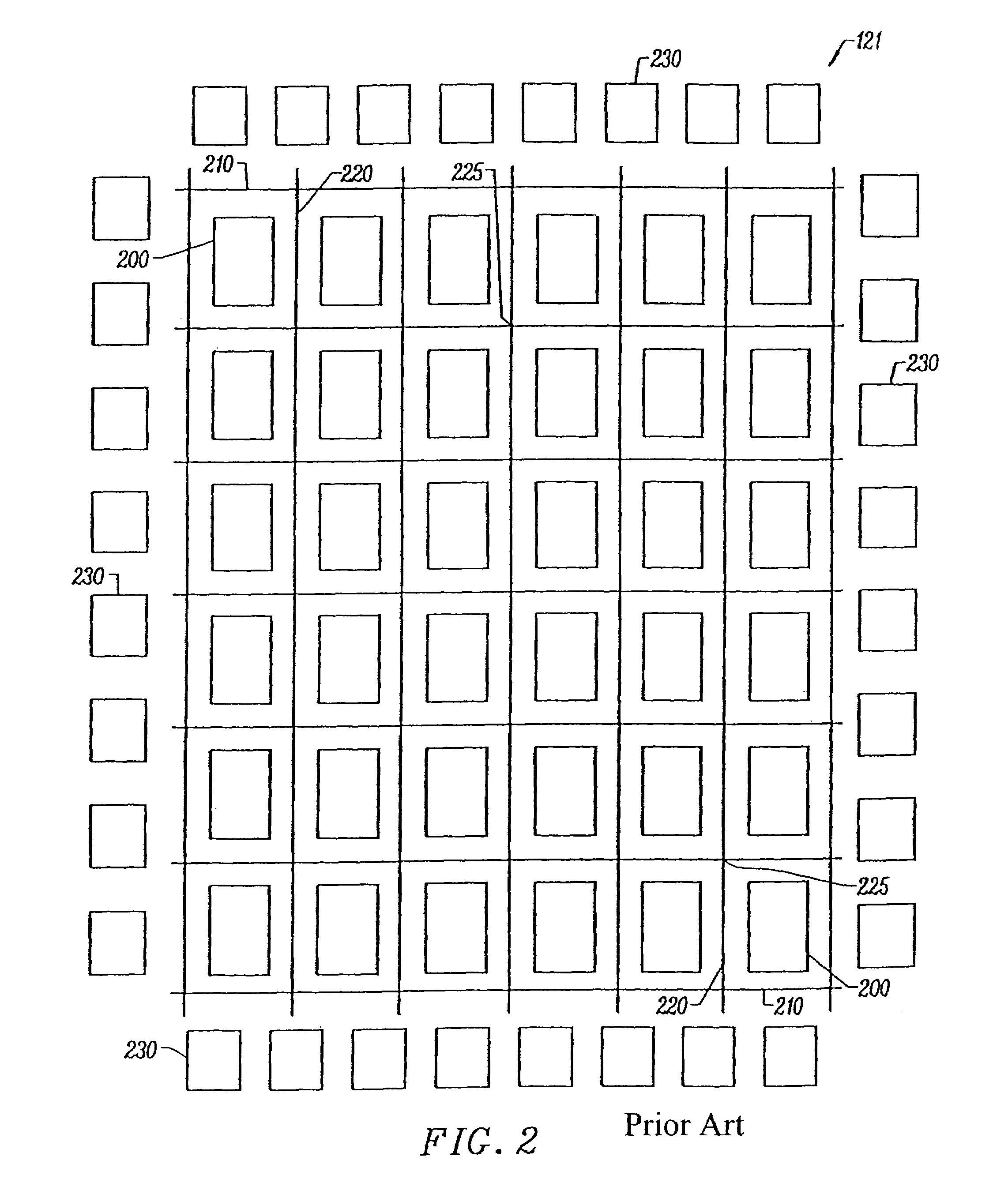

Method and process for design of integrated circuits using regular geometry patterns to obtain geometrically consistent component features

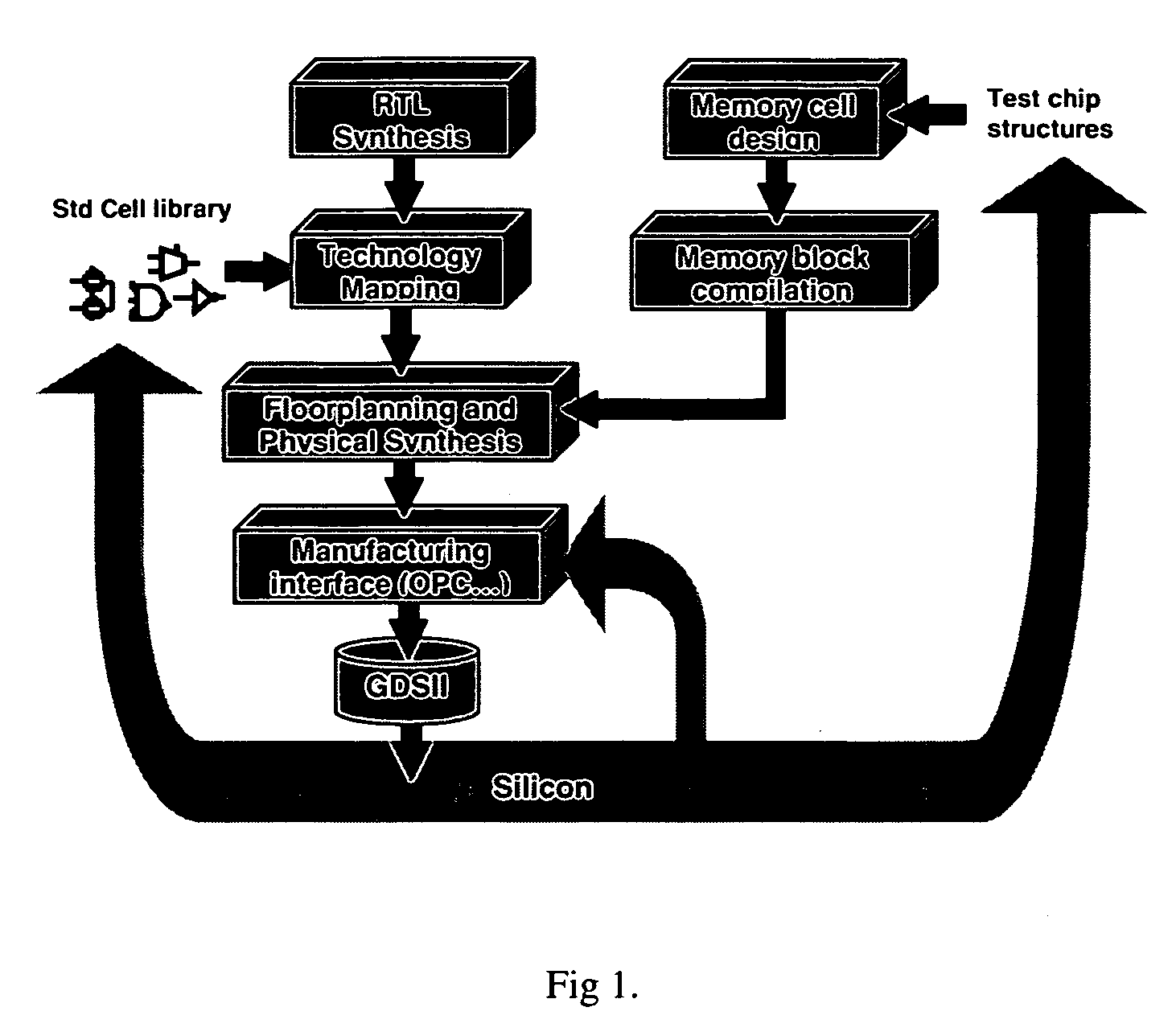

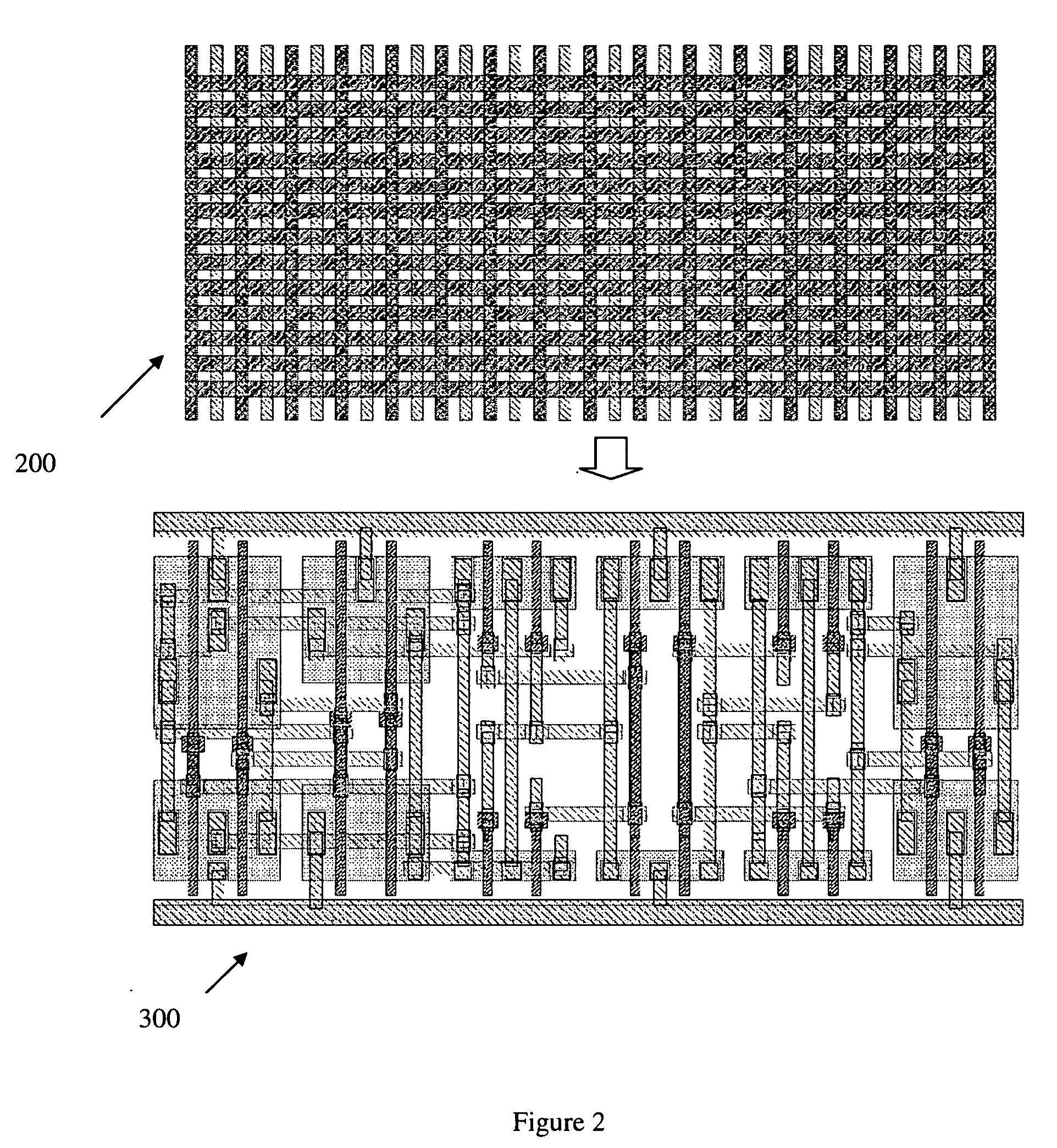

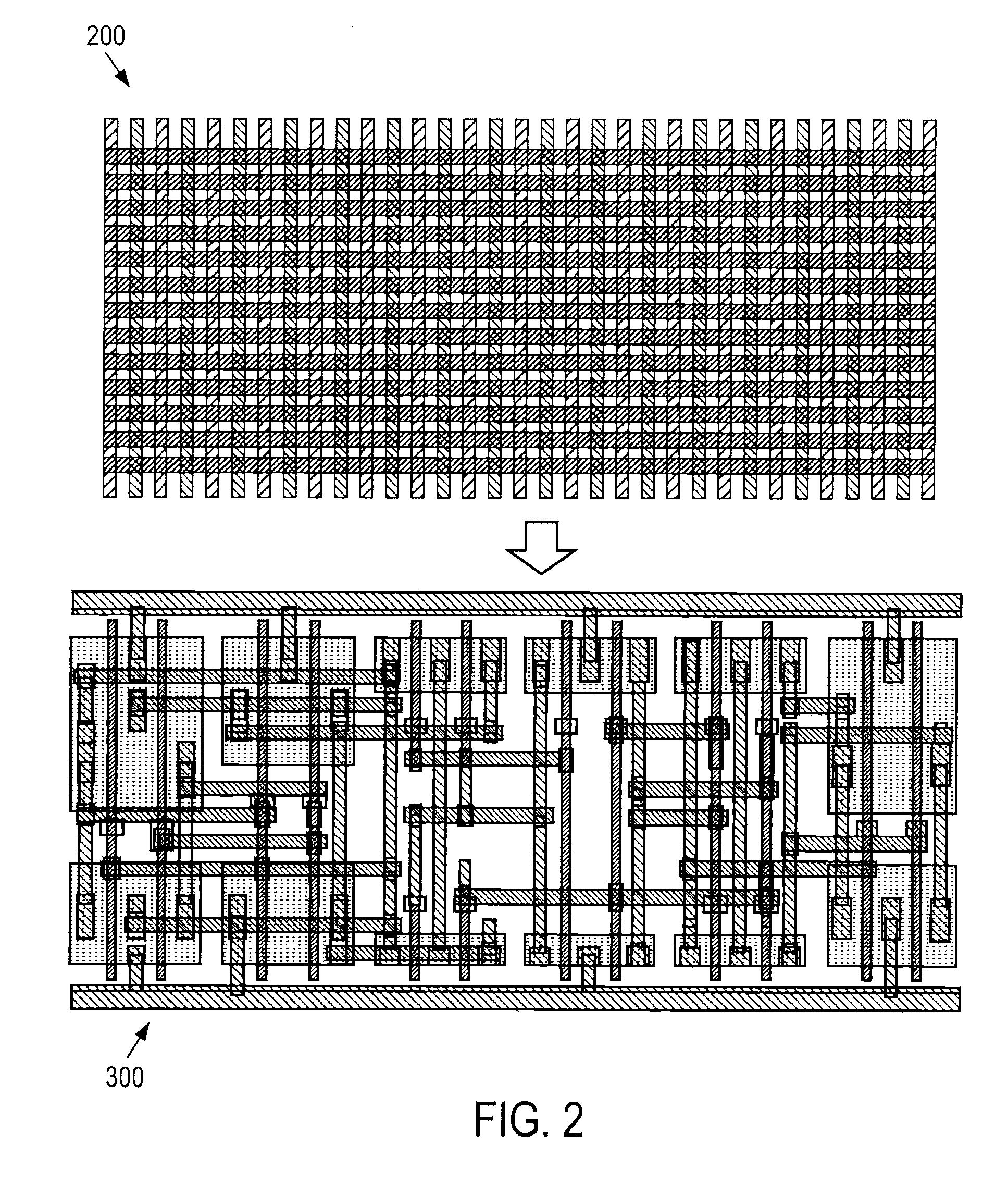

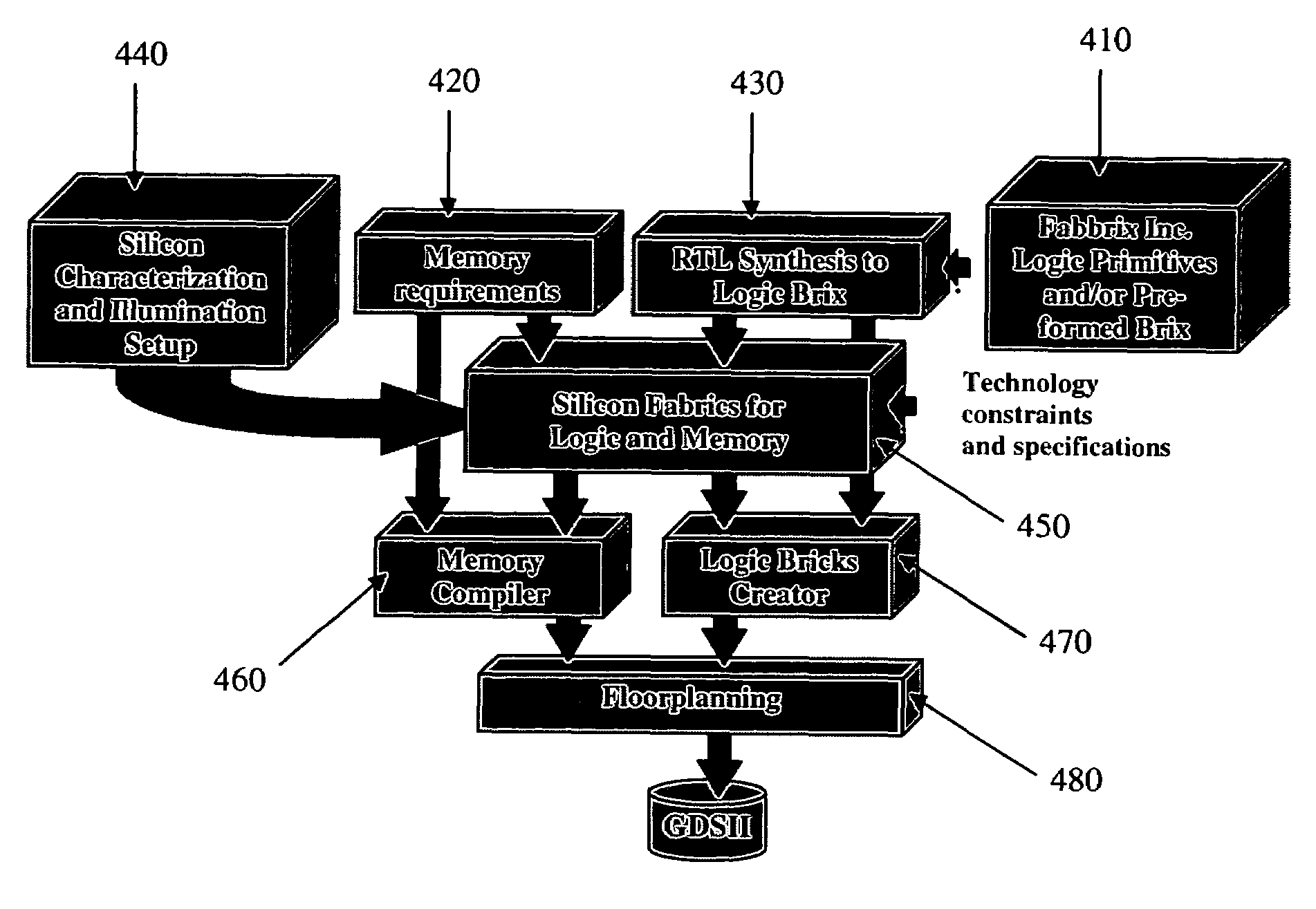

ActiveUS20060112355A1CAD circuit designSpecial data processing applicationsComputer architectureBrick

The invention provides a method and process for designing an integrated circuit based on using the results from both 1) a specific set of silicon test structure characterizations and 2) the decomposition of logic into combinations of simple logic primitives, from which a set of logic bricks are derived that can be assembled for a manufacturable-by-construction design. This implementation of logic is compatible with the lithography settings that are used for implementation of the memory blocks and other components on the integrated circuit, particularly by implementing geometrically consistent component features. The invention provides the ability to recompile a design comprised of logic and memory blocks onto a new geometry fabric to implement a set of technology-specific design changes, without requiring a complete redesign of the entire integrated circuit.

Owner:PDF SOLUTIONS INC

Method and process for design of integrated circuits using regular geometry patterns to obtain geometrically consistent component features

InactiveUS20080098334A1CAD circuit designOriginals for photomechanical treatmentComputer architectureBrick

The invention provides a method and process for designing an integrated circuit based on using the results from both 1) a specific set of silicon test structure characterizations and 2) the decomposition of logic into combinations of simple logic primitives, from which a set of logic bricks are derived that can be assembled for a manufacturable-by-construction design. This implementation of logic is compatible with the lithography settings that are used for implementation of the memory blocks and other components on the integrated circuit, particularly by implementing geometrically consistent component features. The invention provides the ability to recompile a design comprised of logic and memory blocks onto a new geometry fabric to implement a set of technology-specific design changes, without requiring a complete redesign of the entire integrated circuit.

Owner:PDF SOLUTIONS INC

Method and process for design of integrated circuits using regular geometry patterns to obtain geometrically consistent component features

The invention provides a method and process for designing an integrated circuit based on using the results from both 1) a specific set of silicon test structure characterizations and 2) the decomposition of logic into combinations of simple logic primitives, from which a set of logic bricks are derived that can be assembled for a manufacturable-by-construction design. This implementation of logic is compatible with the lithography settings that are used for implementation of the memory blocks and other components on the integrated circuit, particularly by implementing geometrically consistent component features. The invention provides the ability to recompile a design comprised of logic and memory blocks onto a new geometry fabric to implement a set of technology-specific design changes, without requiring a complete redesign of the entire integrated circuit.

Owner:PDF SOLUTIONS INC

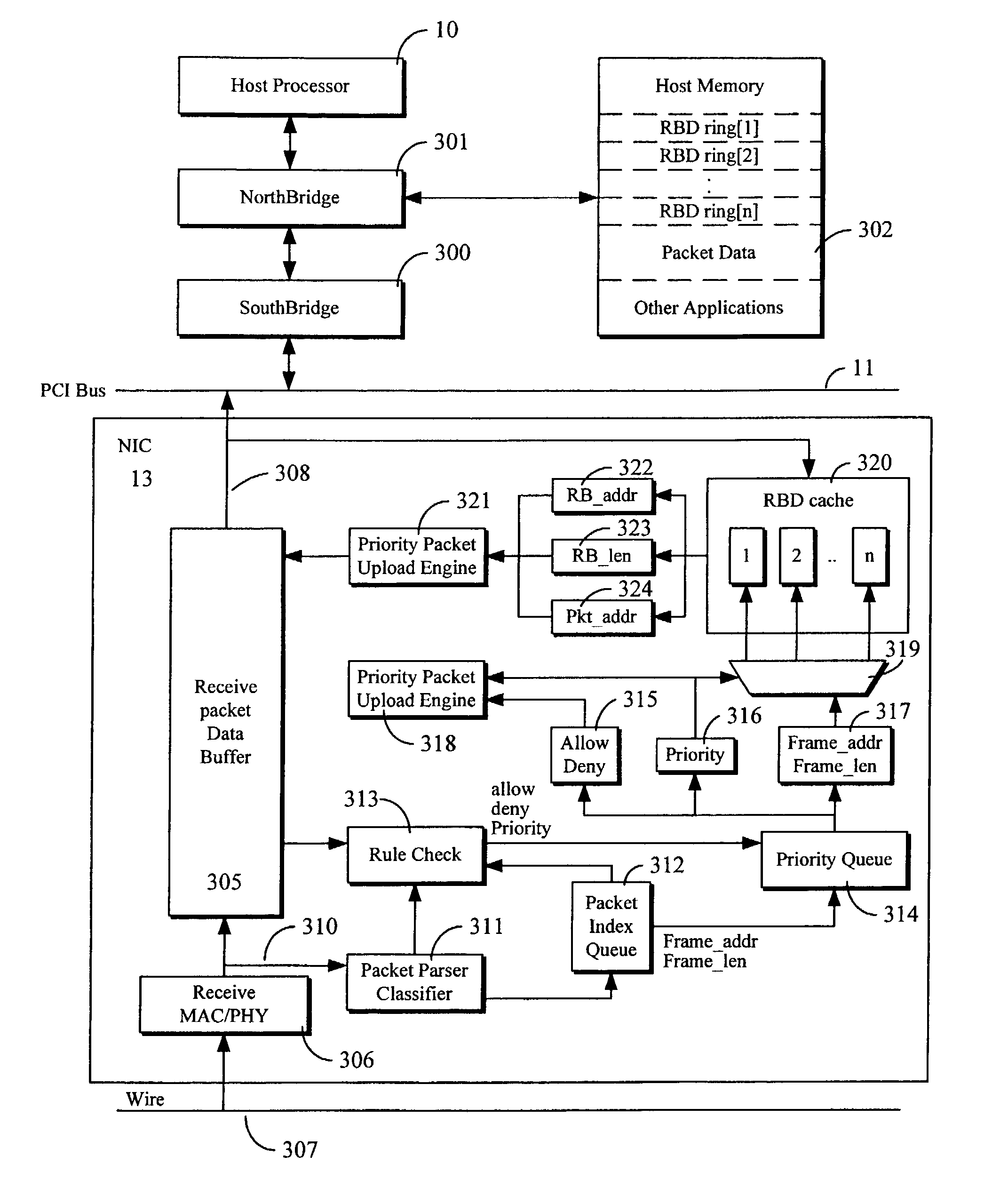

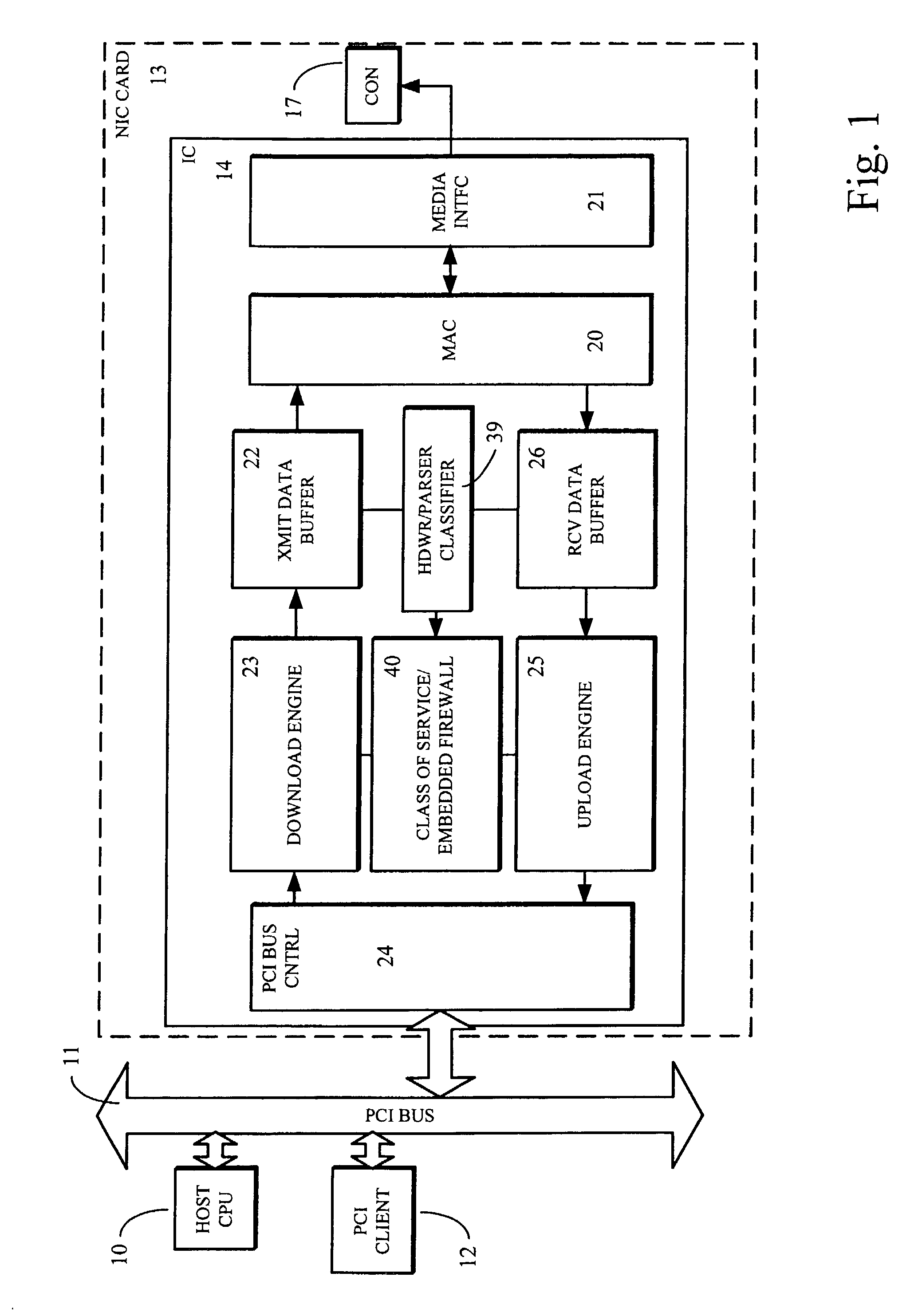

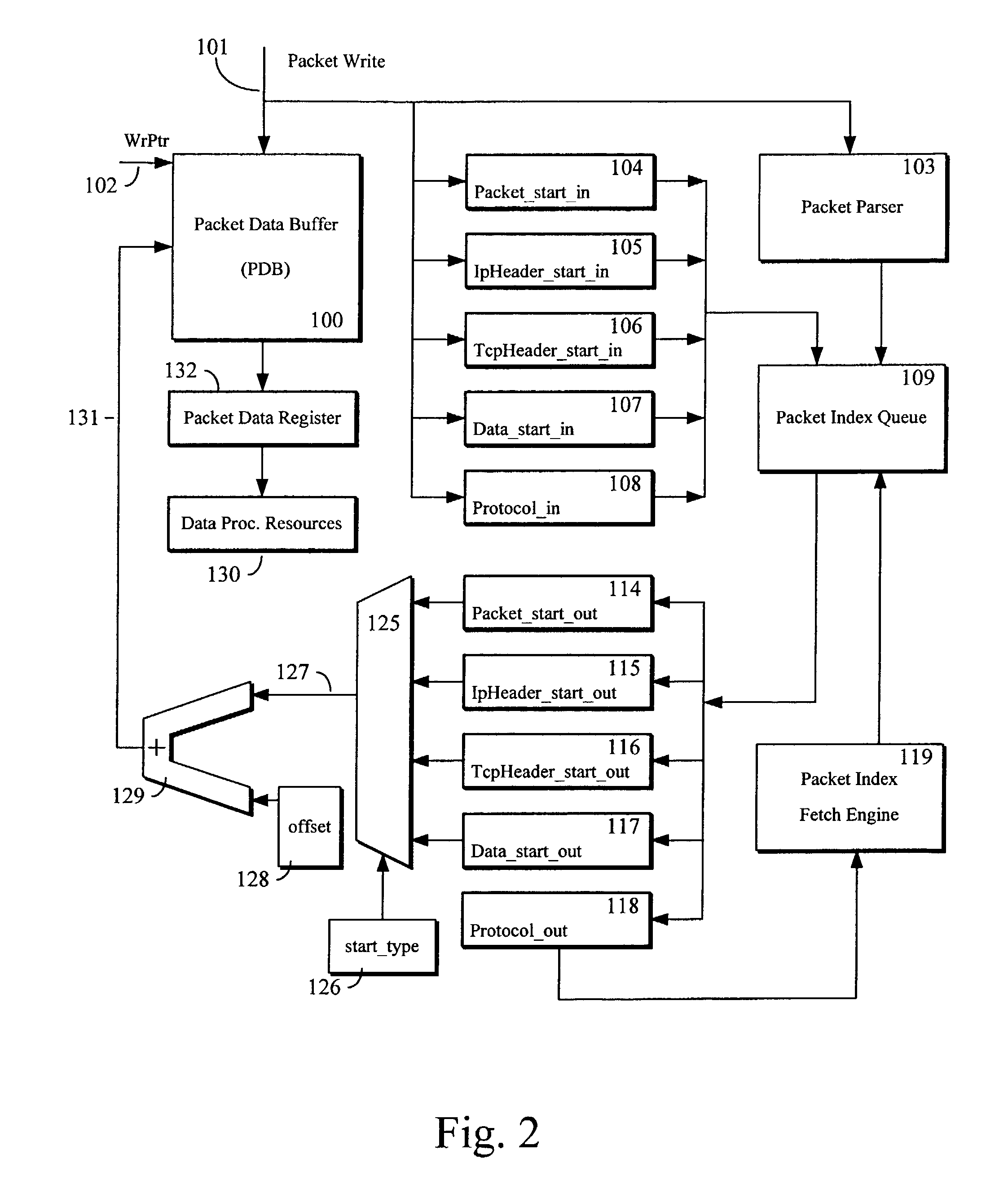

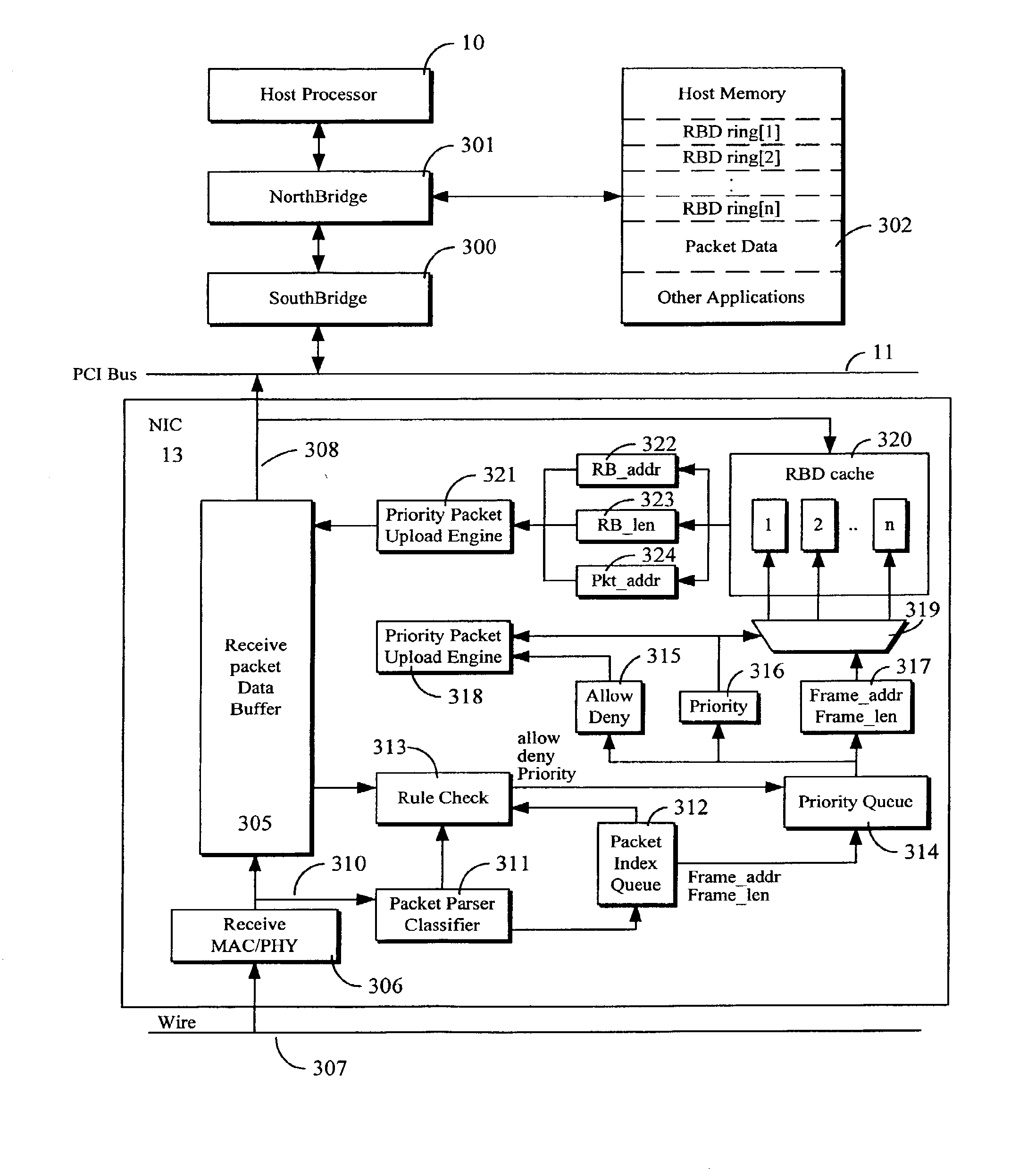

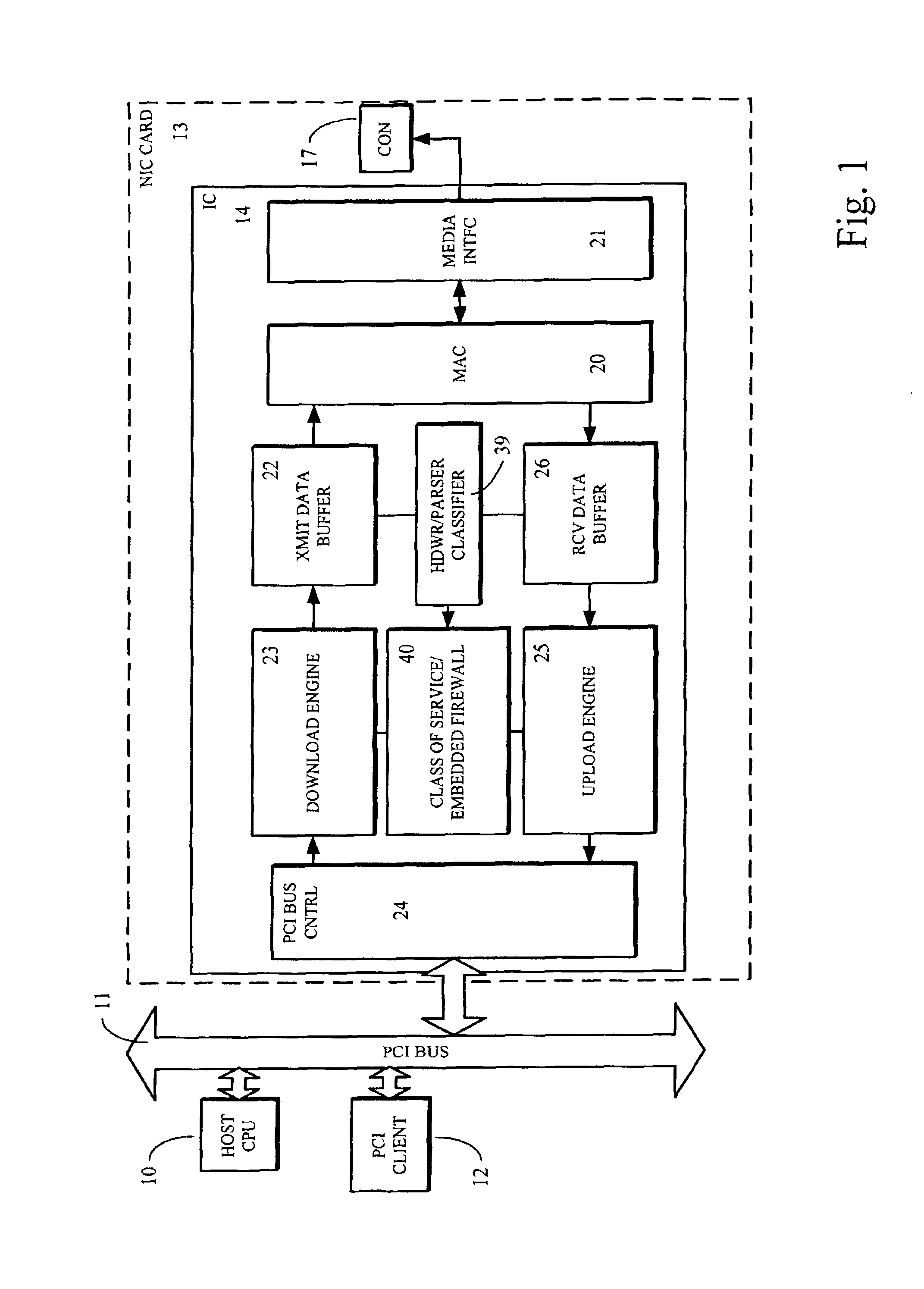

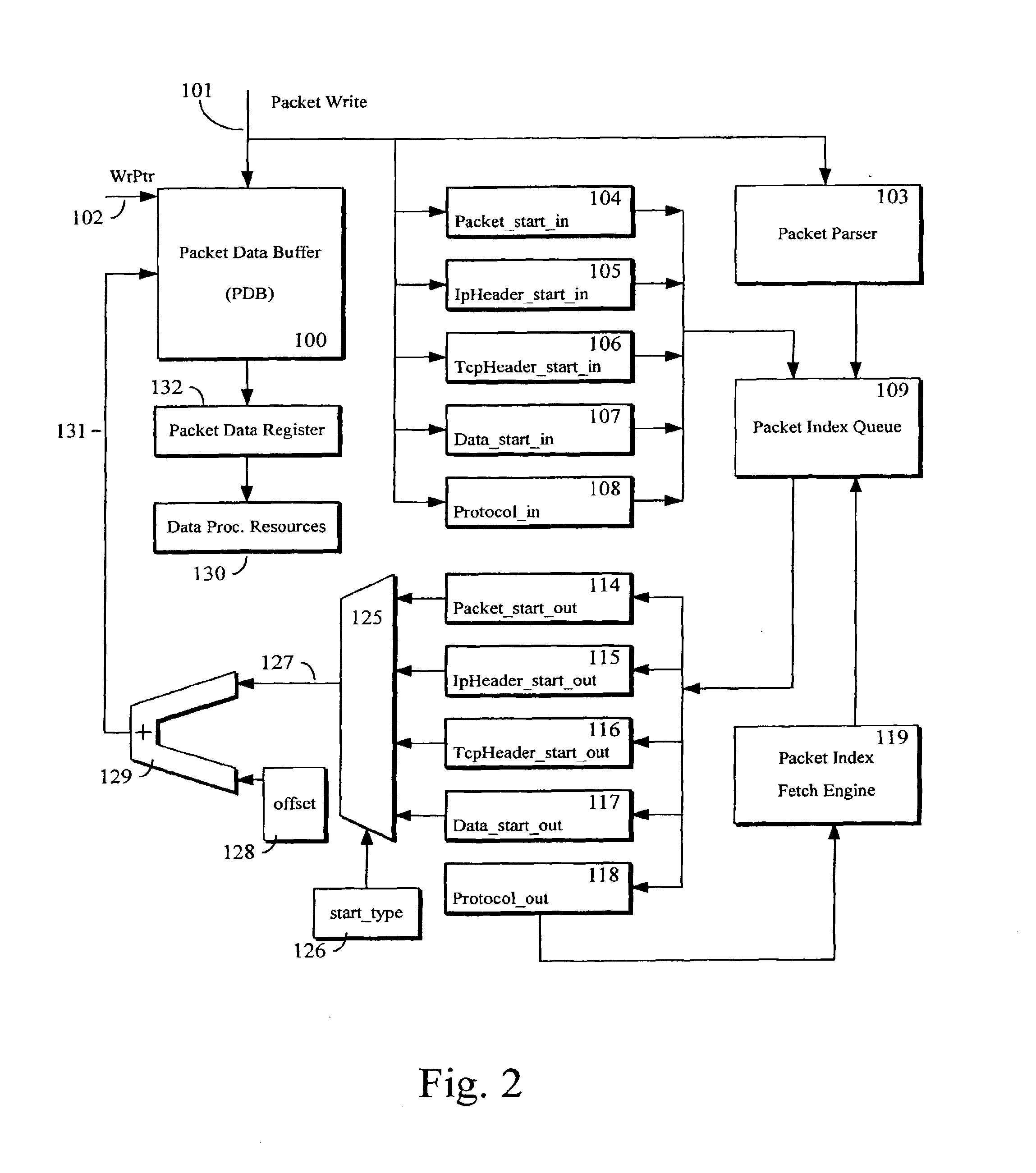

Computer system and network interface supporting class of service queues

ActiveUS7724740B1Increase data rateIncrease speedDigital computer detailsTime-division multiplexClass of serviceData field

A data processing system adapted for high-speed network communications, a method for managing a network interface and a network interface for such system, are provided, in which processing of packets received over the network is achieved by embedded logic at the network interface level. Incoming packets on the network interface are parsed and classified as they are stored in a buffer memory. Functional logic coupled to the buffer memory on the network interface is enabled to access any data field within a packet in a single cycle, using pointers and packet classification information produced by the parsing and classifying step. Results of operations on the data fields in the packets are available before the packets are transferred out of the buffer memory. A data processing system, a method for management of a network interface and a network interface are also provided by the present invention that include an embedded firewall at the network interface level of the system, which protects against inside and outside attacks on the security of data processing system. Furthermore, a data processing system, a method for management of a network interface and a network interface are a provided by the present invention that support class of service management for packets incoming from the network, by applying priority rules at the network interface level of the system.

Owner:VALTRUS INNOVATIONS LTD +1

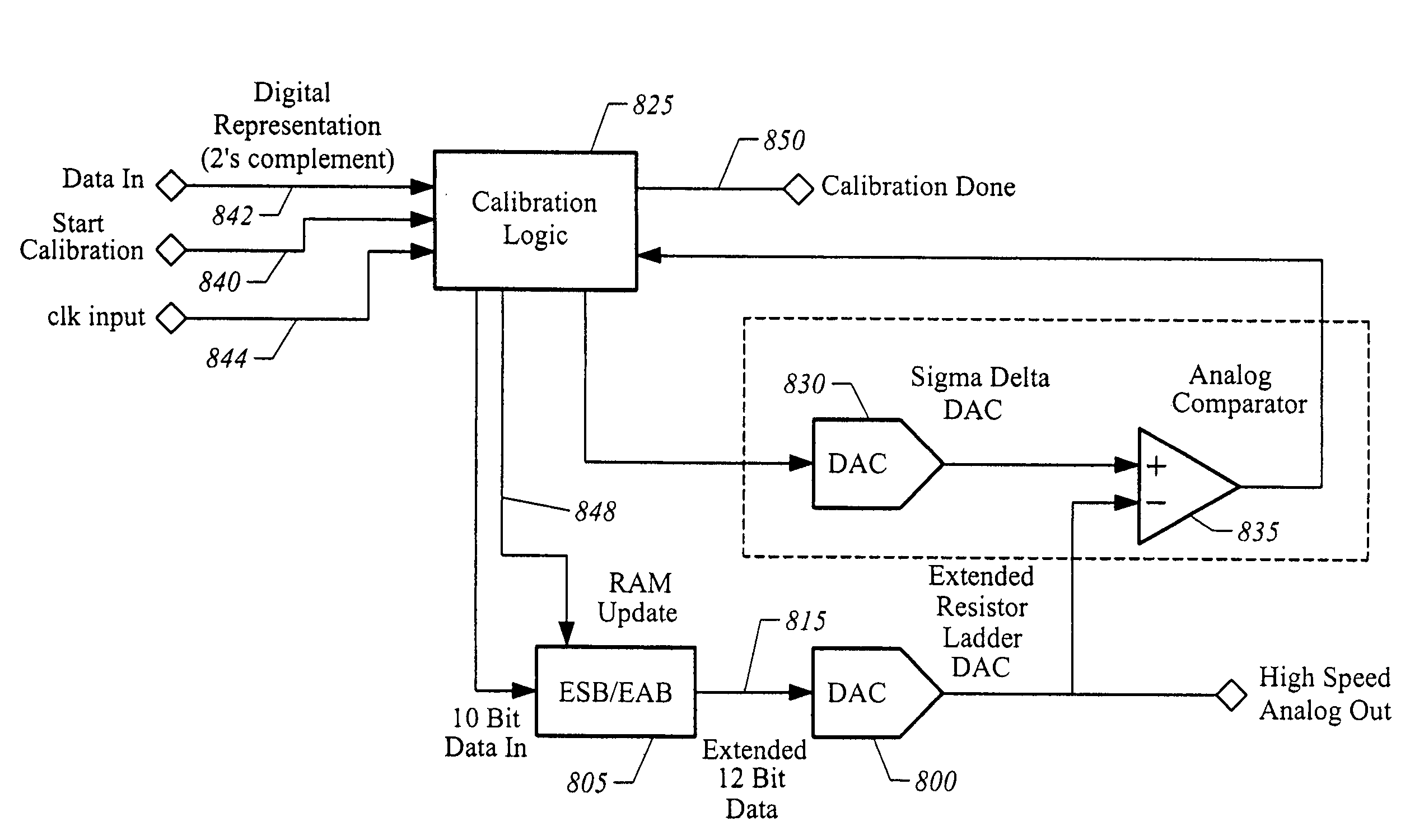

Analog-to-digital converter for programmable logic

InactiveUS6956512B1Electric signal transmission systemsResistance/reactance/impedenceProgrammable logic deviceLogic cell

Digital-to-analog and analog-to-digital conversion are implemented in or using programmable logic. The DAC and ADC circuits may be hardwired in a programmable logic integrated circuit or may be implemented using an intellectual property (IP) core. The IP core would be a series of bits to configure the logic cells and other programmable logic of an integrated circuit to include one or more DACs or ADC, or both on the same integrated circuit. The DAC may be a sigma-delta-modulator-based implementation or a resistor-ladder-based implementation.

Owner:ALTERA CORP

Digital routing switch matrix for digitized radio-frequency signals

InactiveUS7362125B2Efficient executionPrecise processingElectronic switchingSubstation equipmentMulti bandTransceiver

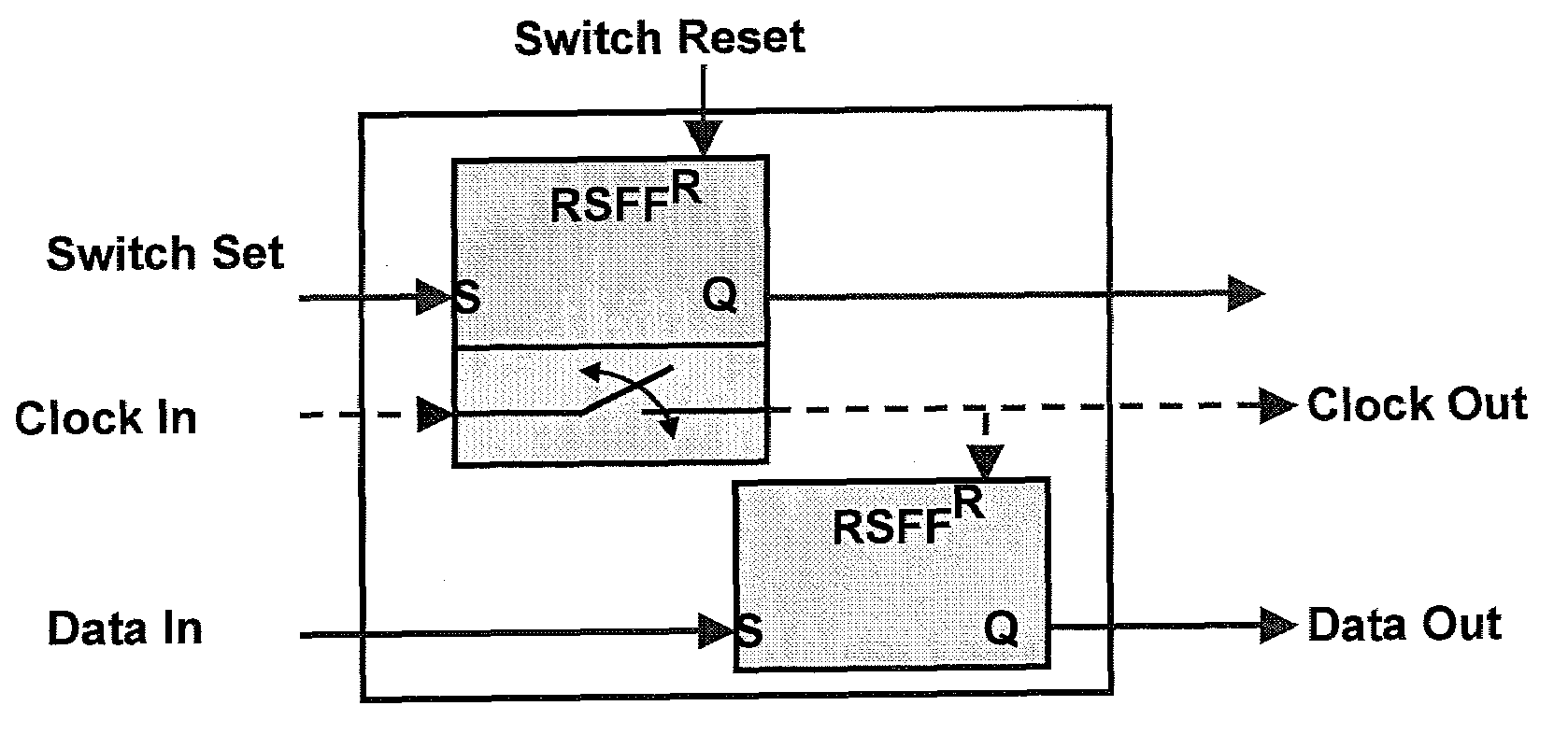

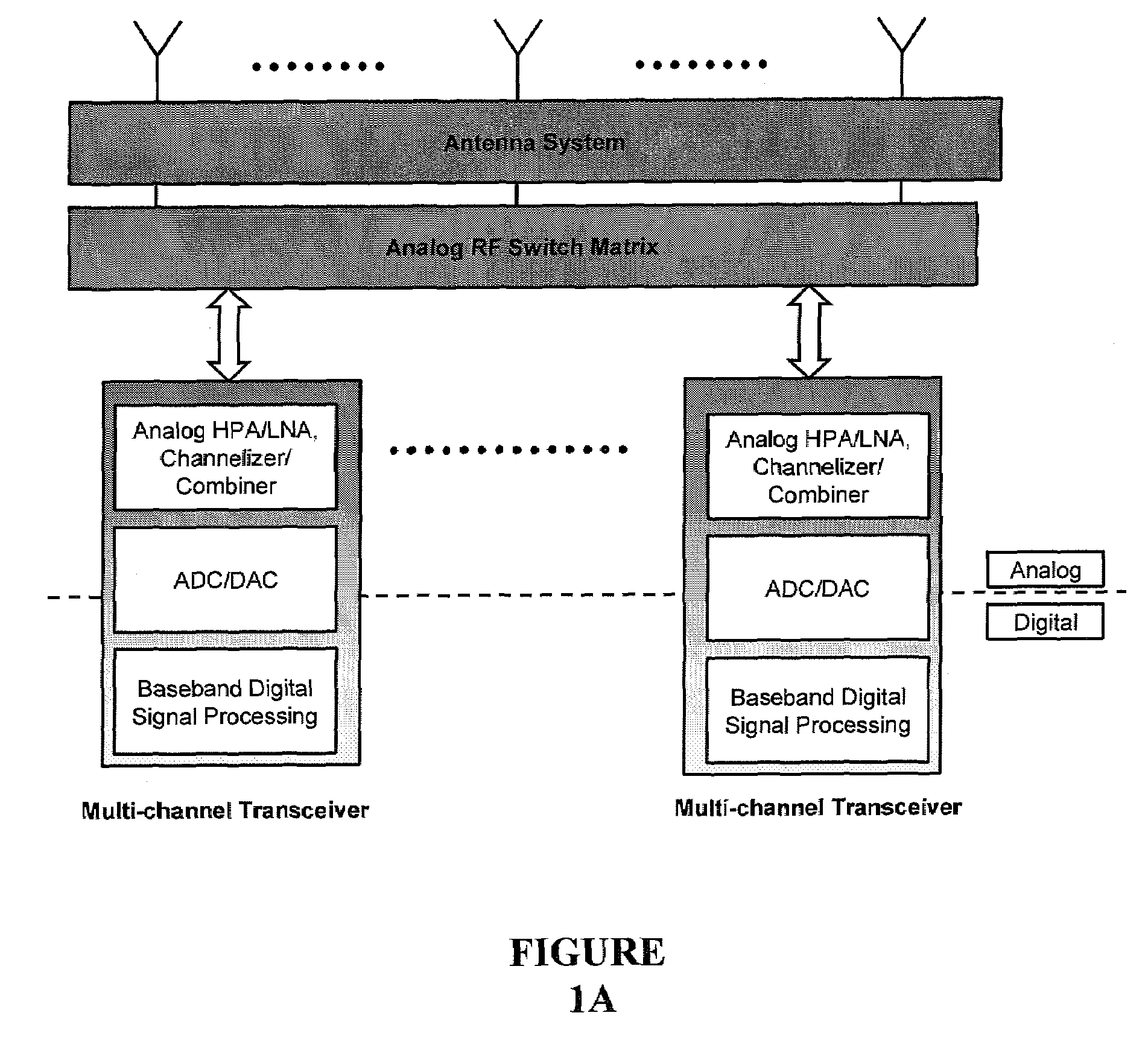

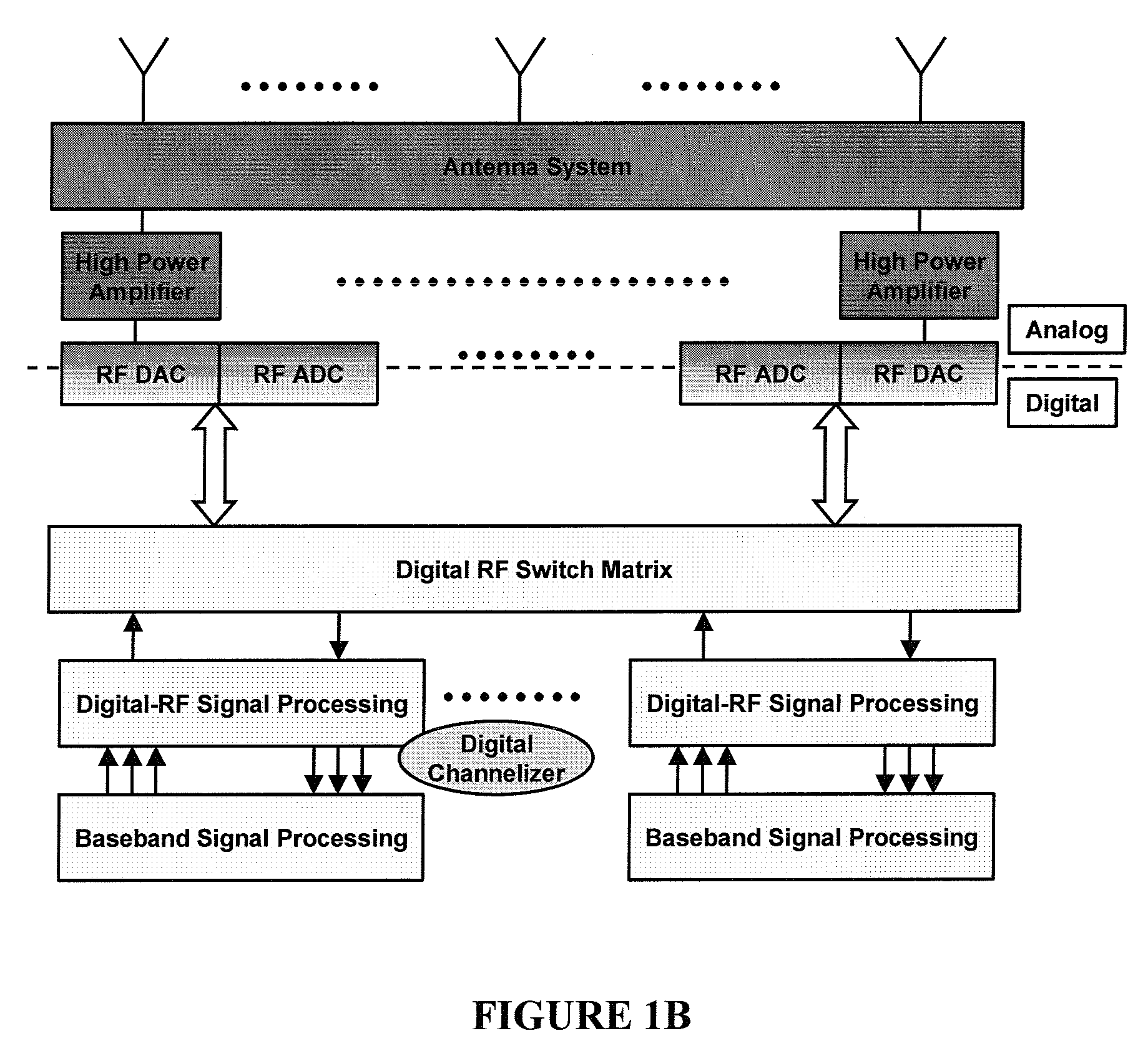

Routing and distribution of radio-frequency (RF) signals is commonly achieved in the analog domain. However, improved performance and simplified circuit architectures may be obtained by first digitizing the RF signal, and then carrying out all routing in the digital domain. A new generation of scalable digital switches has been developed, which routes both the data and clock signals together, this being necessary to maintain the integrity of the digitized RF signal. Given the extremely high switching speeds necessary for these applications (tens of GHz), this is implemented using Rapid-Single-Flux-Quantum (RSFQ) logic with superconducting integrated circuits. Such a digital switch matrix may be applied to either the receiver or transmitter components of an advanced multi-band, multi-channel digital transceiver system, and is compatible with routing of signals with different clock frequencies simultaneously within the same switch matrix.

Owner:HYPRES

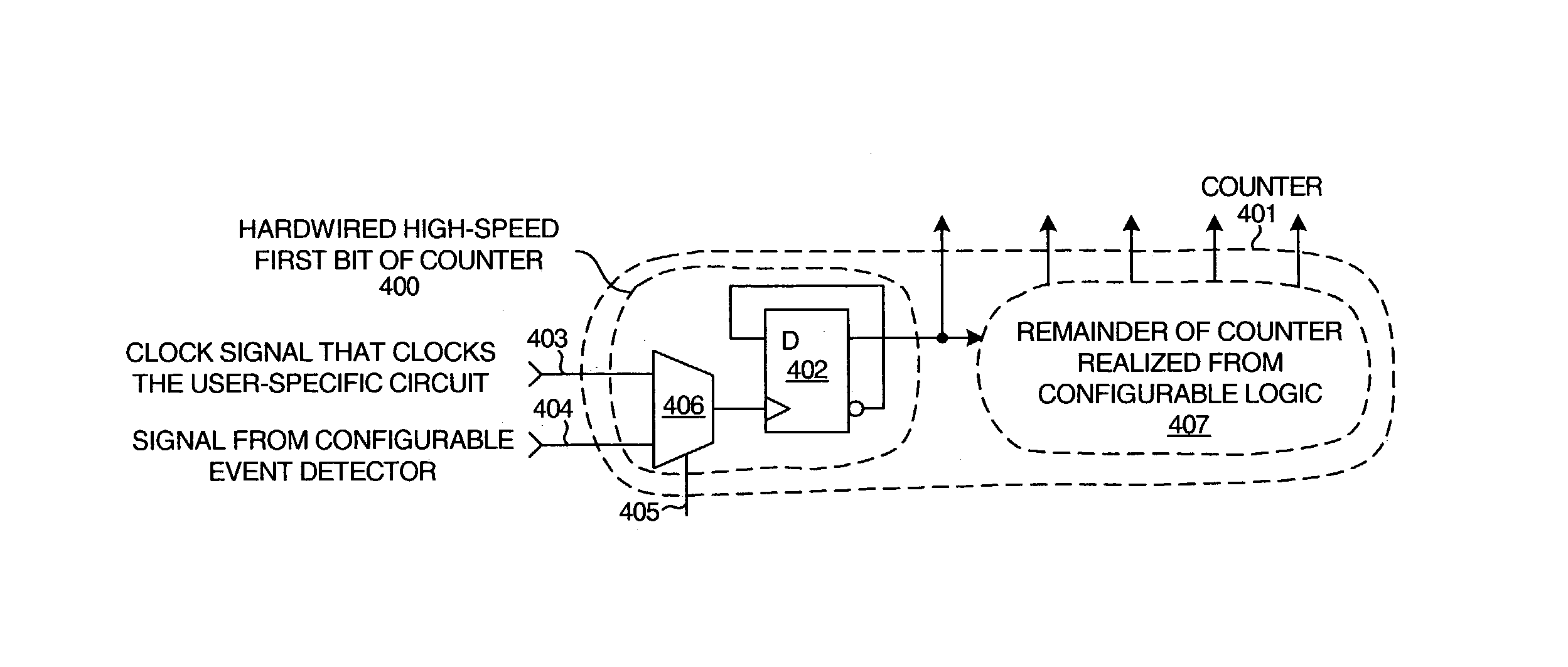

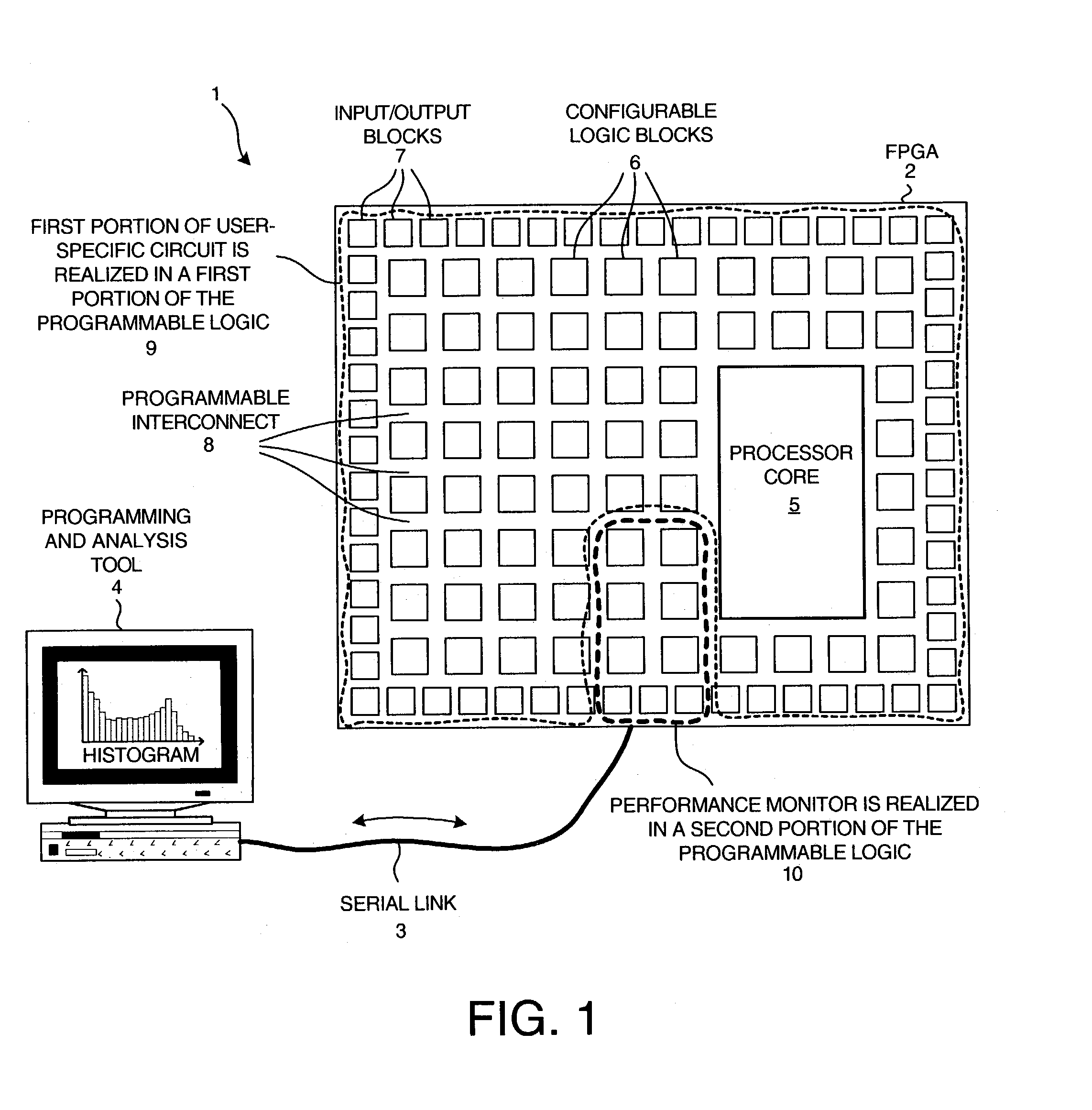

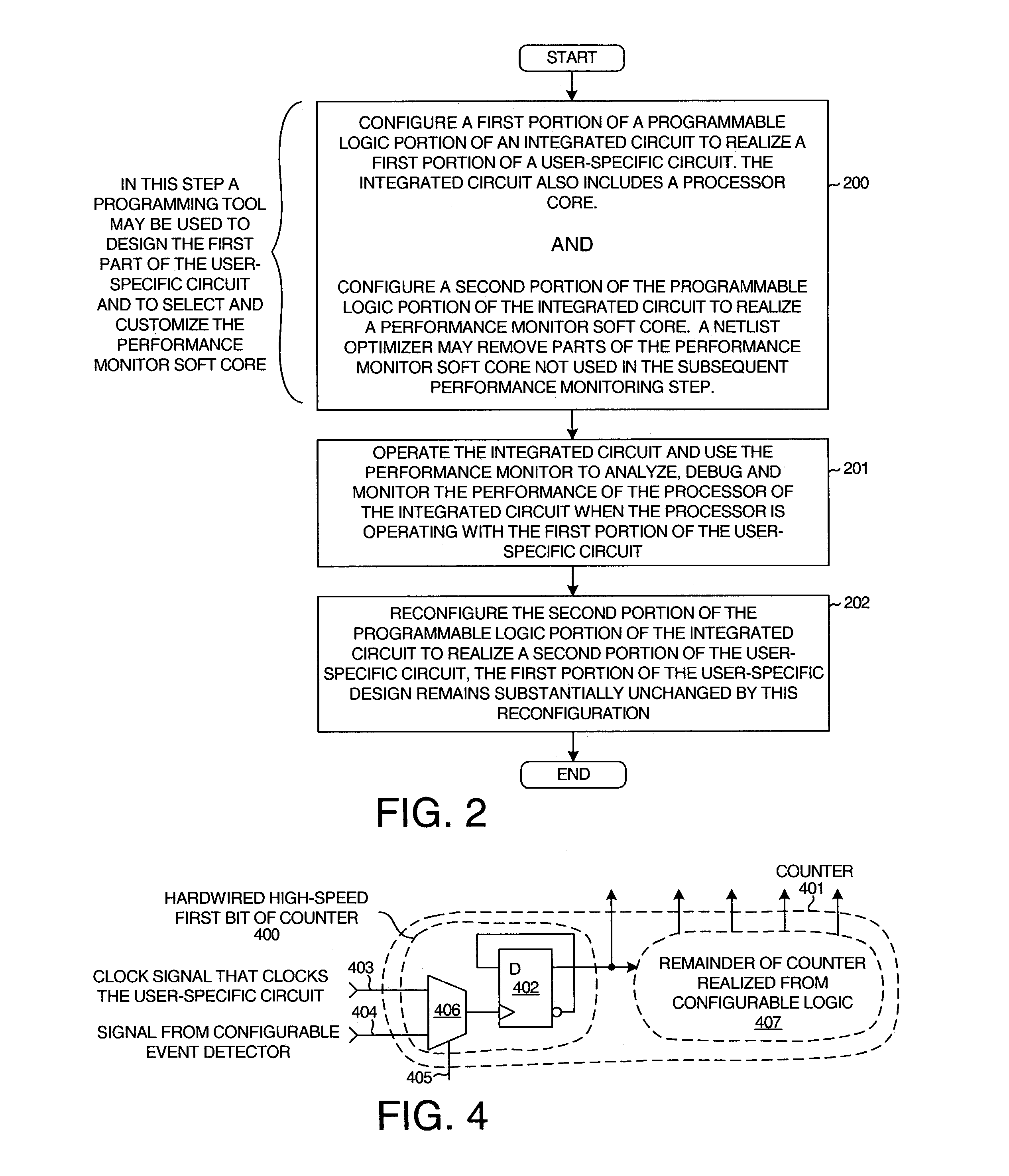

Methods and circuits for realizing a performance monitor for a processor from programmable logic

ActiveUS7308564B1Low costDigital computer detailsHardware monitoringProgrammable logic deviceLogical part

A performance monitor is realized from programmable logic on the same integrated circuit as a processor. A user may use a programming and analysis tool to select a performance monitor soft core and to program it into the integrated circuit. The performance monitor is used to debug and / or monitor operation of the processor. After the debugging and / or performance monitoring, the portion of the programmable logic used to realize the performance monitor can be reconfigured and used to realize another portion of the user-specific circuit. Because the portion of the integrated circuit used to realize the performance monitor can be later used in the user-specific design, the cost of having to provide a no-longer-desired performance monitor in each integrated circuit used in the user's design is avoided. Because the performance monitor is realized from programmable logic, the performance monitor is more flexible than a conventional hardwired configurable performance monitor.

Owner:XILINX INC

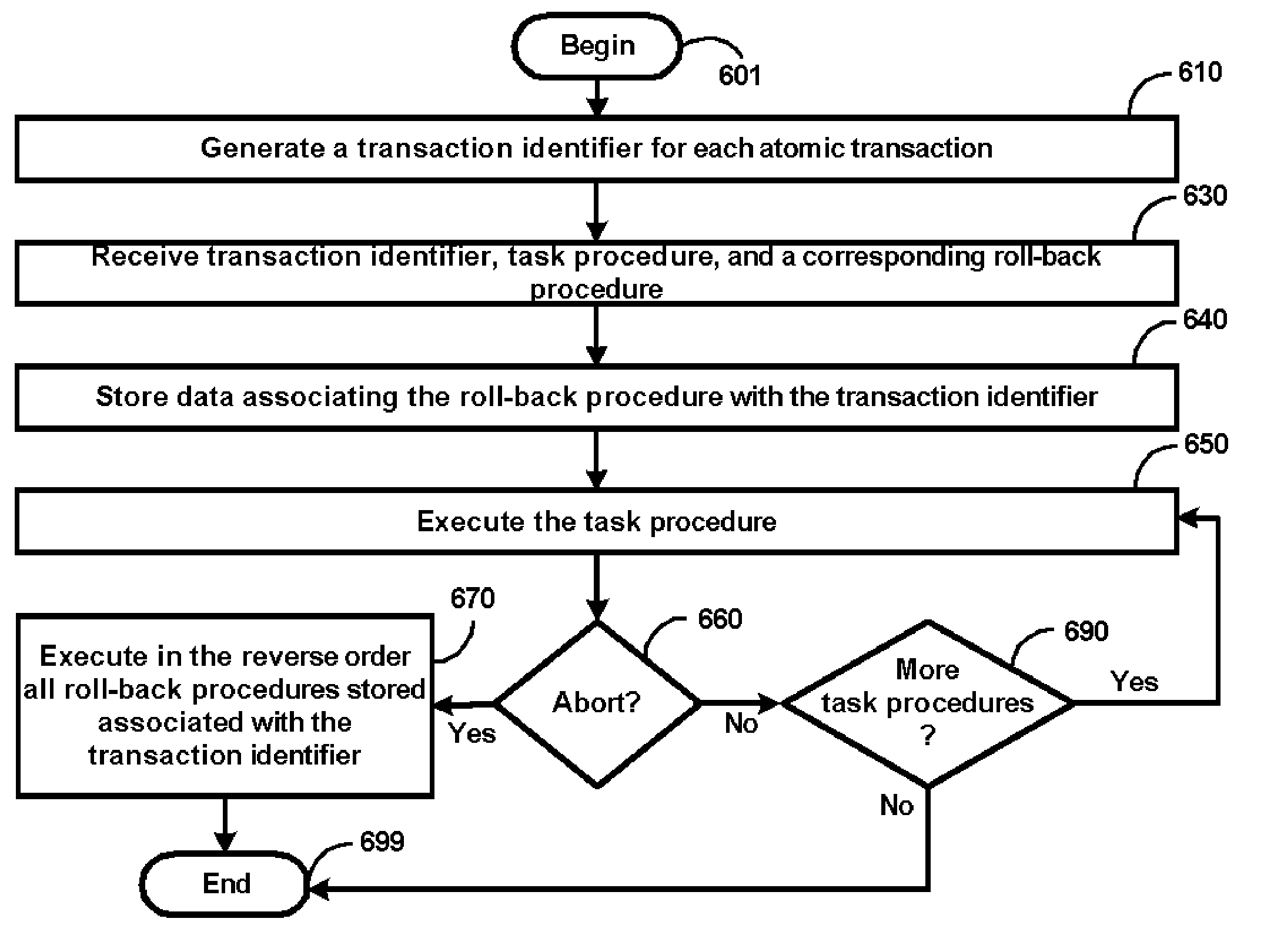

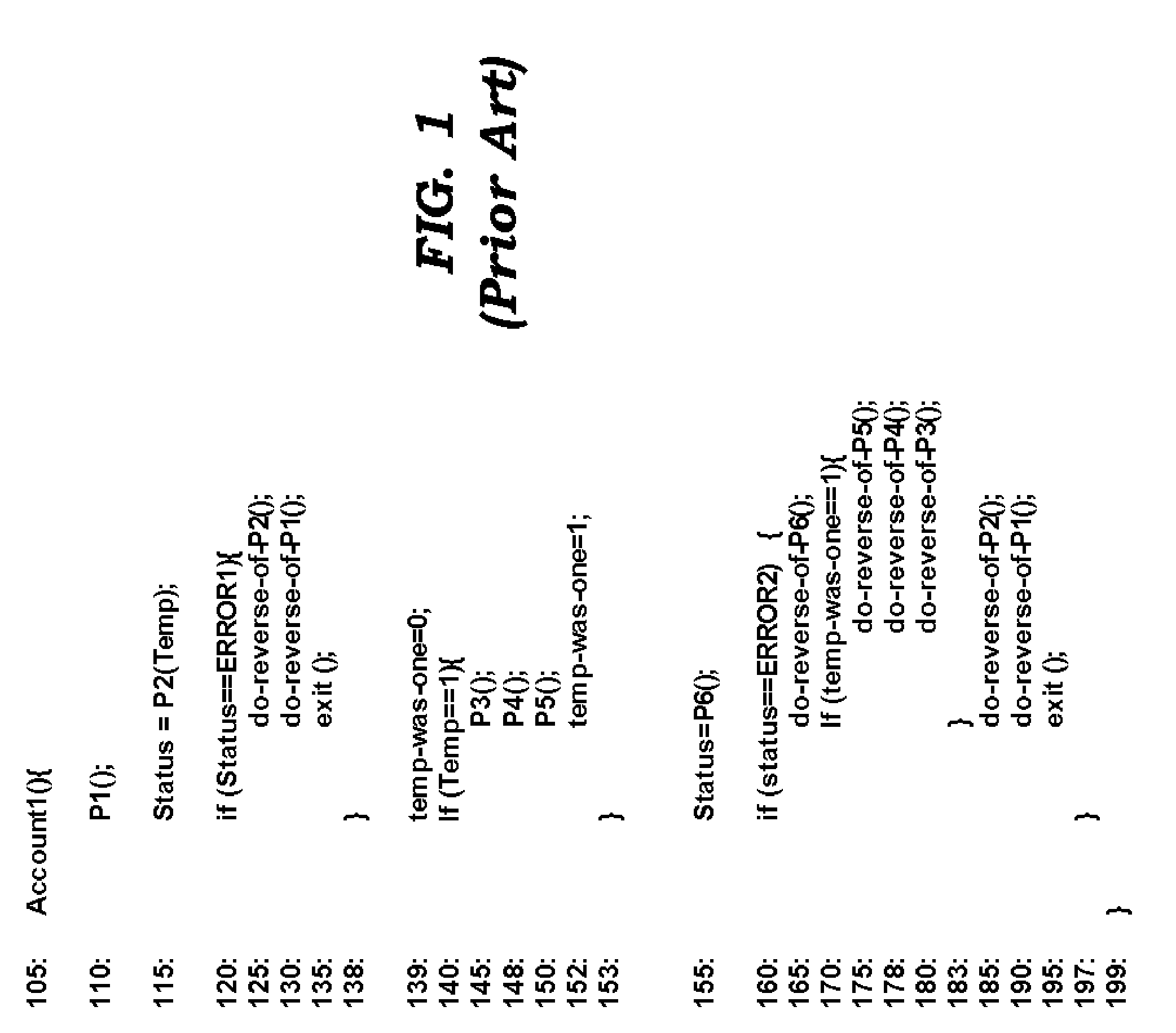

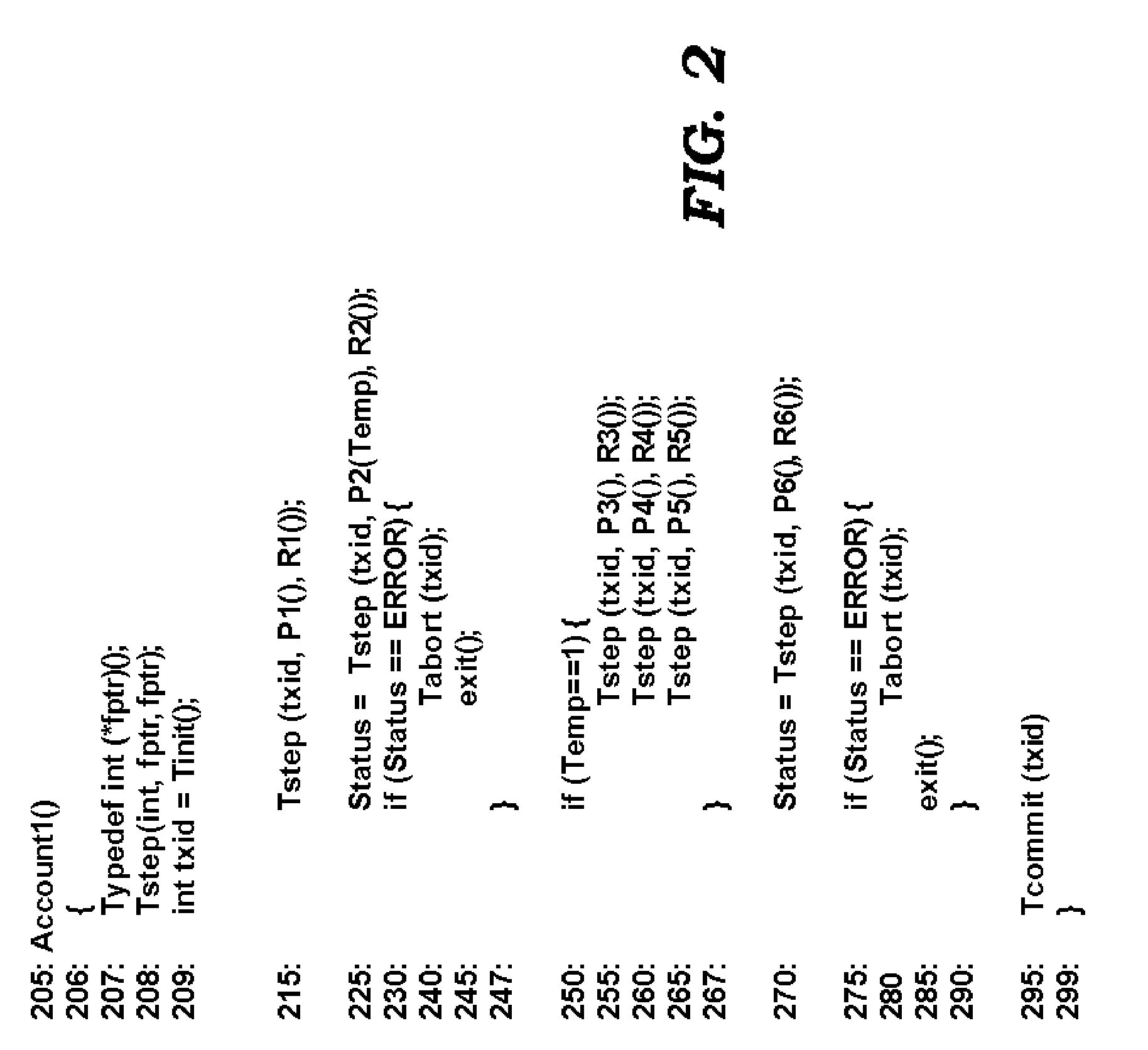

Custom Atomic Transactions in Programming Environments

ActiveUS20060004882A1Error identificationSpecial data processing applicationsProgram logicBack procedures

An aspect of the present invention simplifies the implementation of custom atomic transactions. A program logic (implementing a custom atomic transaction) may request a unique transaction identifier from a programming environment. The program logic may then specify a task procedure, corresponding roll-back procedures, and the transaction identifier using an interface provided by the programming environment. The programming environment keeps track of the specified roll-back procedures. The information maintained by the programming environment may be used to execute the roll-back procedures if the atomic transaction is to be aborted. As the programming environment keeps track of the roll-back procedures to be executed, the implementation of atomic transactions may be simplified.

Owner:ORACLE INT CORP

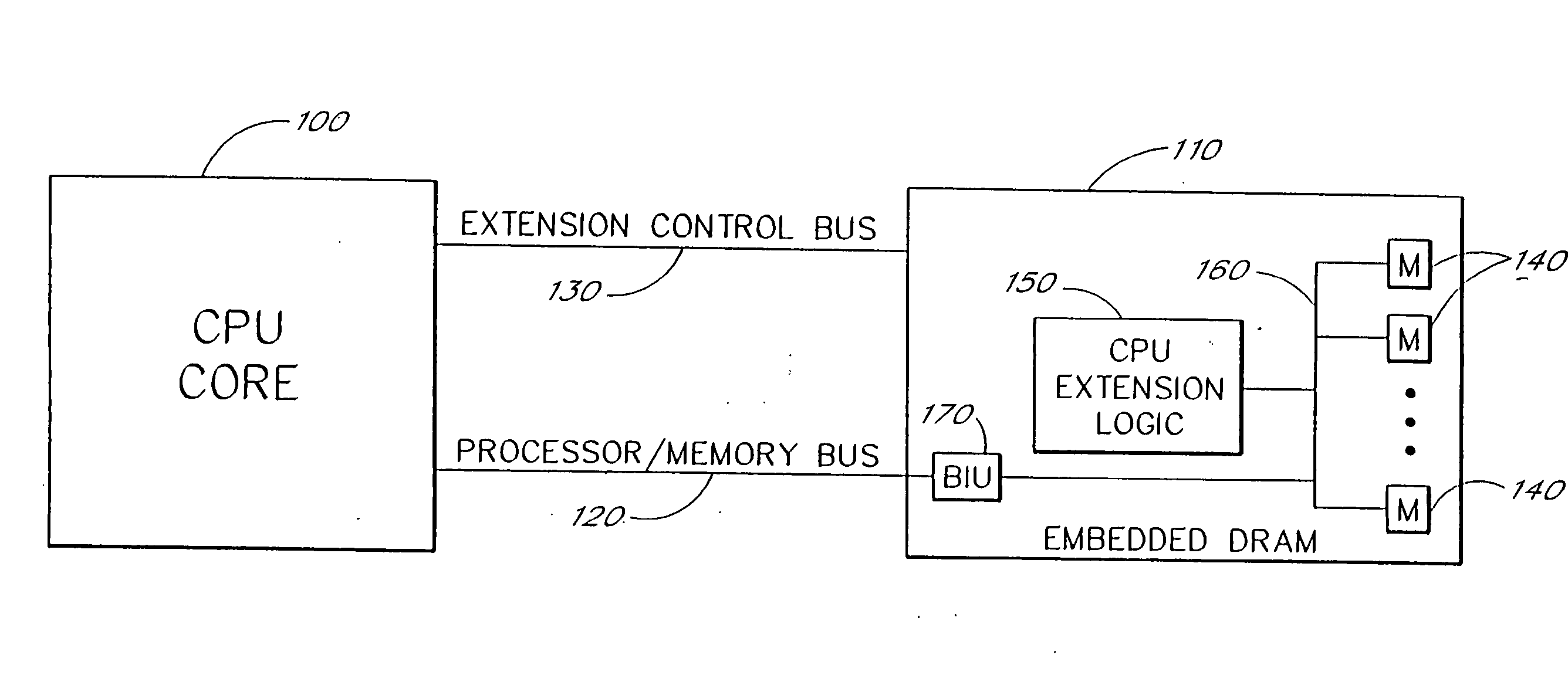

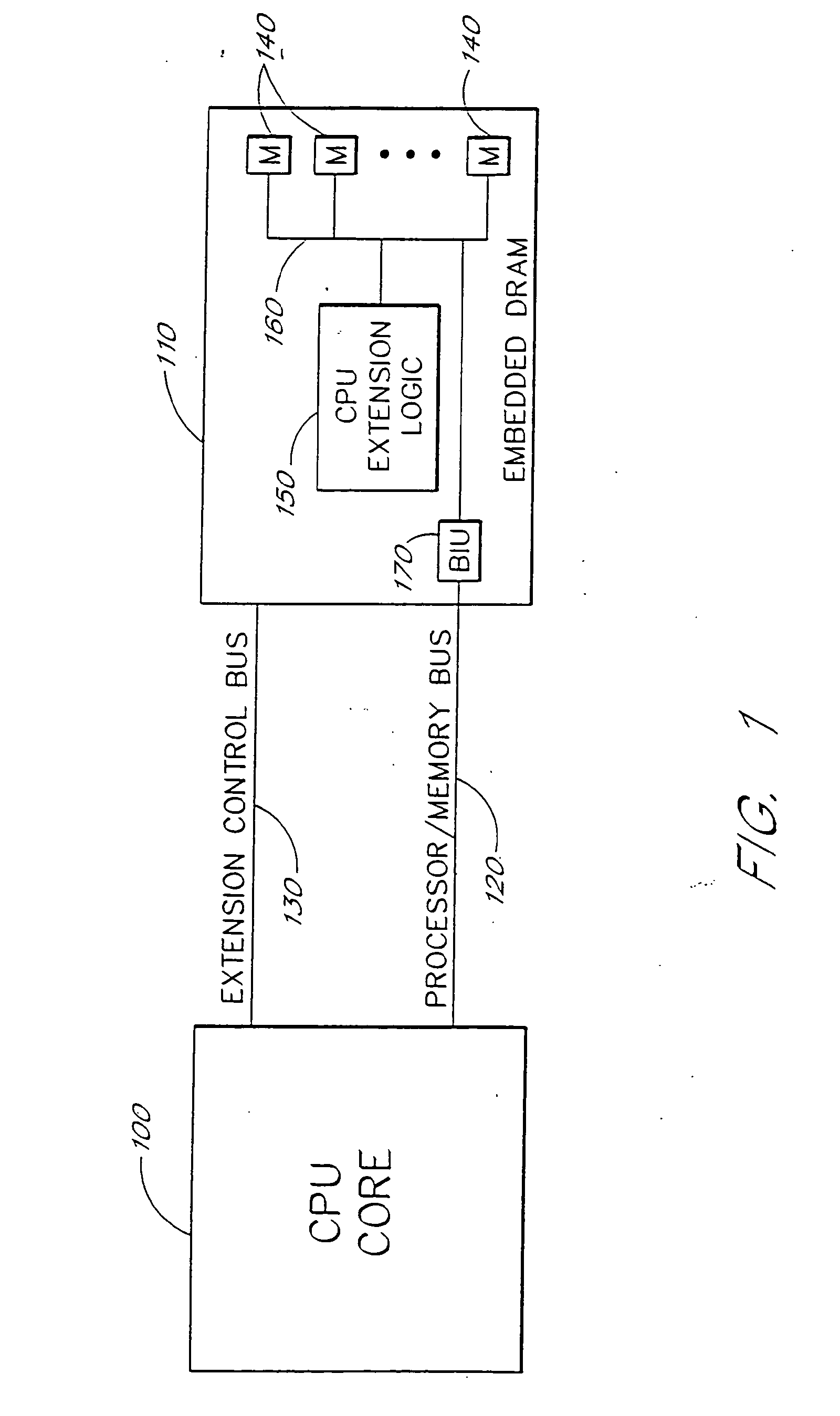

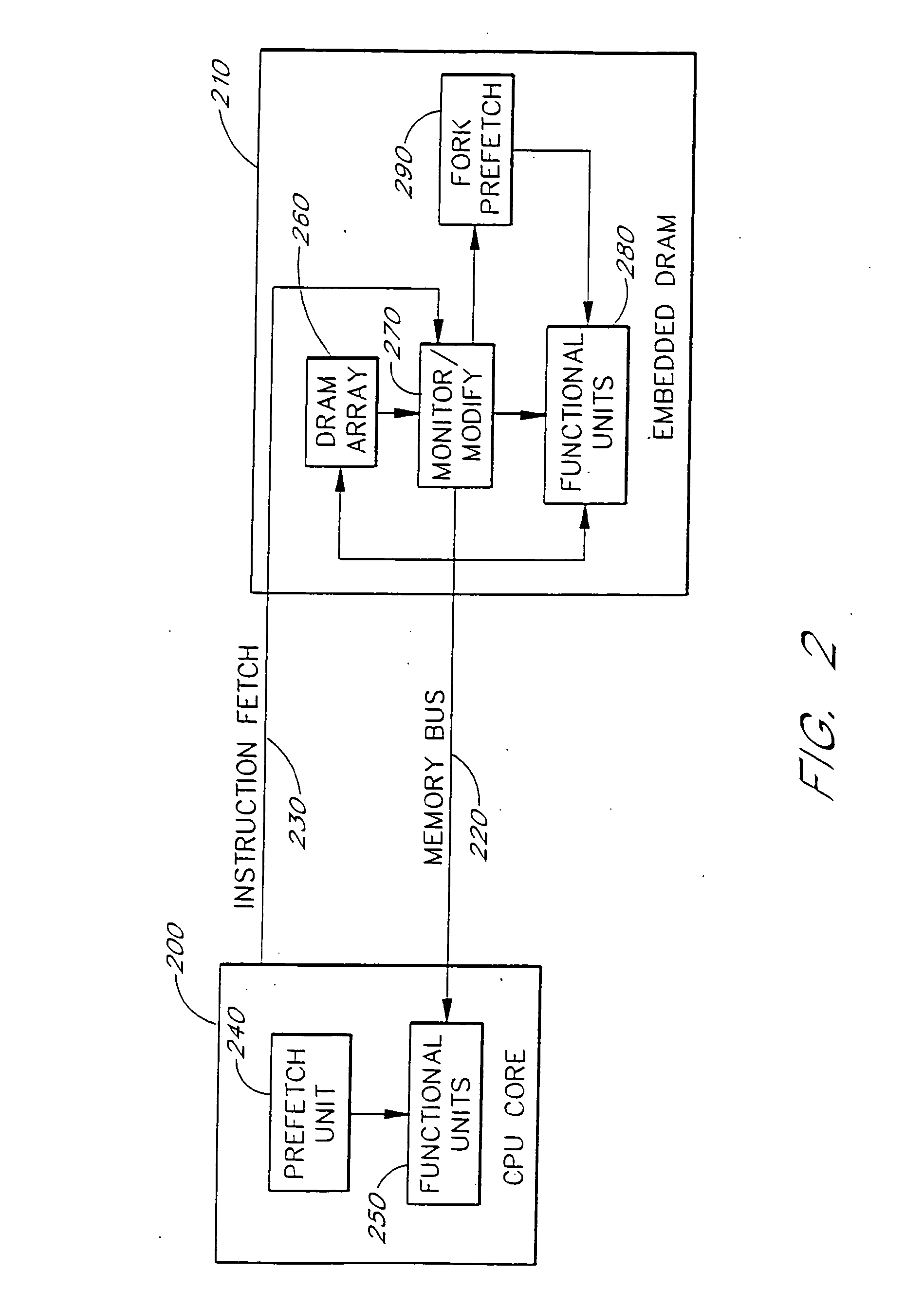

Split Embedded DRAM Processor

InactiveUS20080180450A1Effective cachingTraffic minimizationMultiple digital computer combinationsConcurrent instruction executionTraffic capacityGraphics

A processing architecture includes a first CPU core portion coupled to a second embedded dynamic random access memory (DRAM) portion. These architectural components jointly implement a single processor and instruction set. Advantageously, the embedded logic on the DRAM chip implements the memory intensive processing tasks, thus reducing the amount of traffic that needs to be bussed back and forth between the CPU core and the embedded DRAM chips. The embedded DRAM logic monitors and manipulates the instruction stream into the CPU core. The architecture of the instruction set, data paths, addressing, control, caching, and interfaces are developed to allow the system to operate using a standard programming model. Specialized video and graphics processing systems are developed. Also, an extended very long instruction word (VLIW) architecture implemented as a primary VLIW processor coupled to an embedded DRAM VLIW extension processor efficiently deals with memory intensive tasks. In different embodiments, standard software can be accelerated either with or without the express knowledge of the processor.

Owner:ROUND ROCK RES LLC

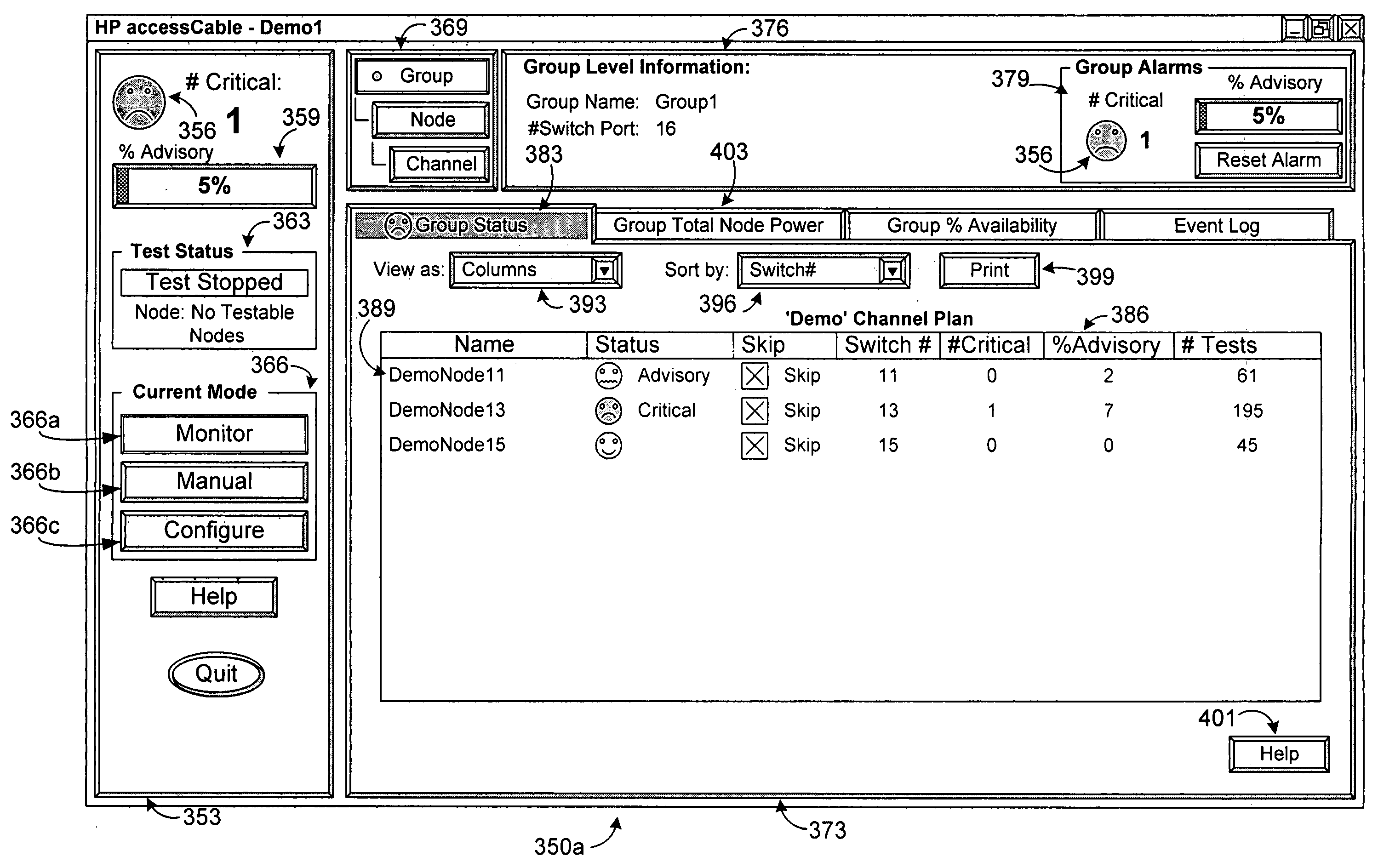

Monitoring system and method implementing warning interface logic

InactiveUS7080398B1Effective monitoringQuick and efficientTwo-way working systemsSelective content distributionSpectrum analyzerDisplay device

Channel and test plans are implemented in connection with a plurality of nodes that communicate signals. The channel plan enables a monitoring system to, among other things, conduct automatic periodic test plans, comprising tests, on the nodes, based upon the predefined data specified in the channel plan. The monitoring system includes a controller controlling a spectrum analyzer and a node interface switch. Notably, the controller also enables user friendly plan set-up and warning interface logic implementation. The warning interface logic generates a channel percent advisory indicator on the display device within a channel level interface component upon an occurrence of an advisory event in a channel associated therewith and generates a channel critical alarm indicator on the display device within a channel level interface component upon an occurrence of a critical event in a channel associated therewith.

Owner:VIAVI SOLUTIONS INC

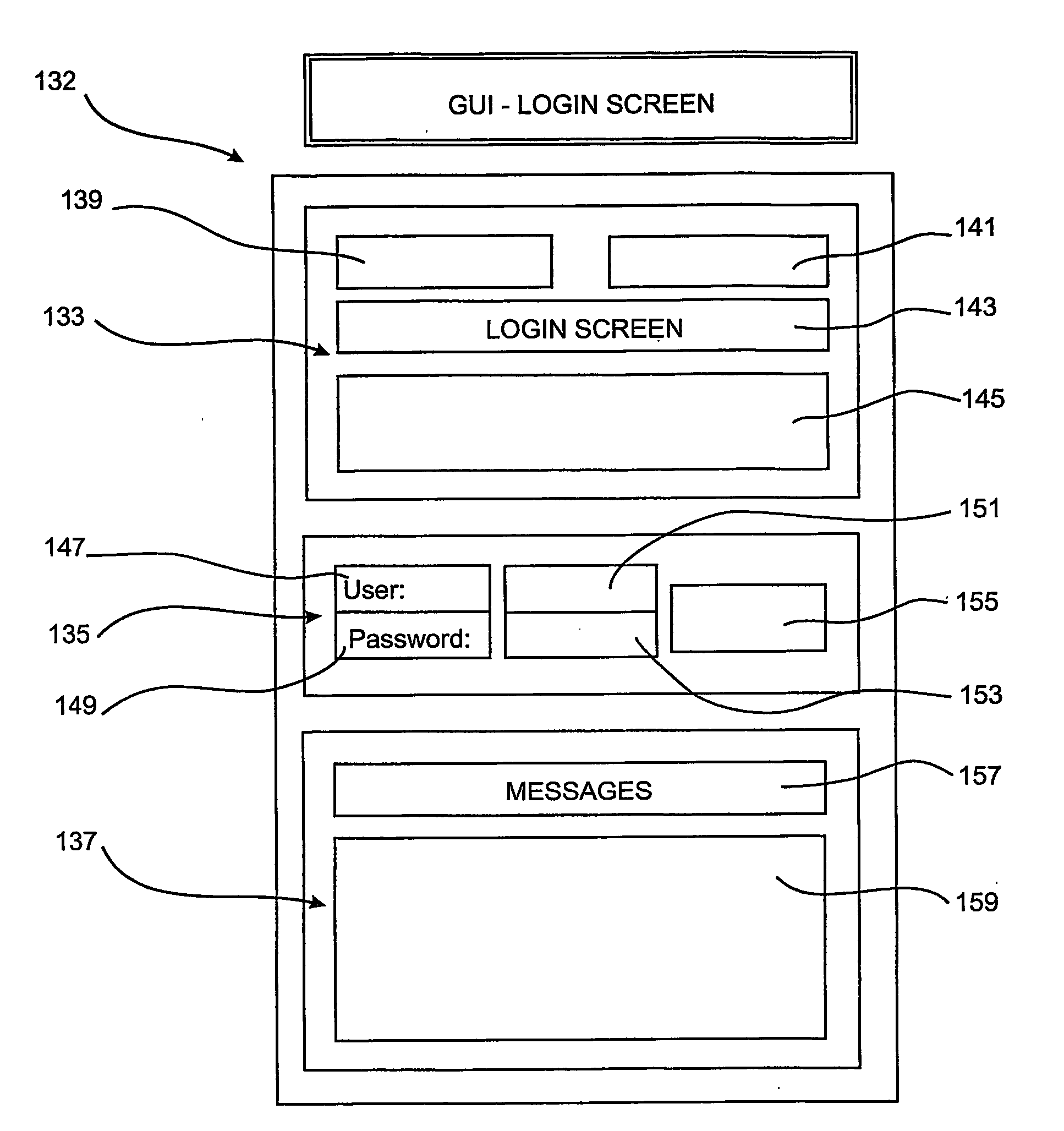

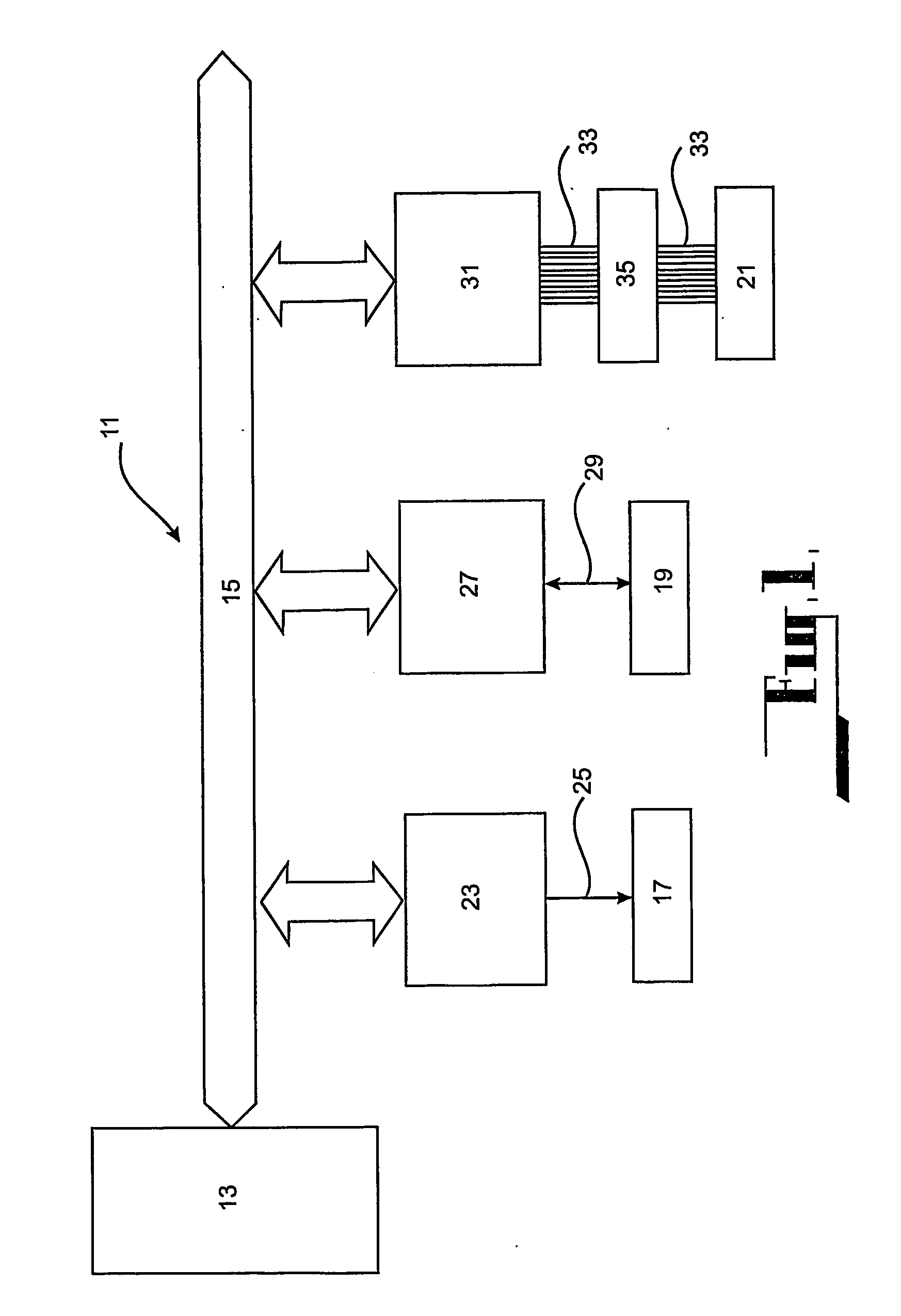

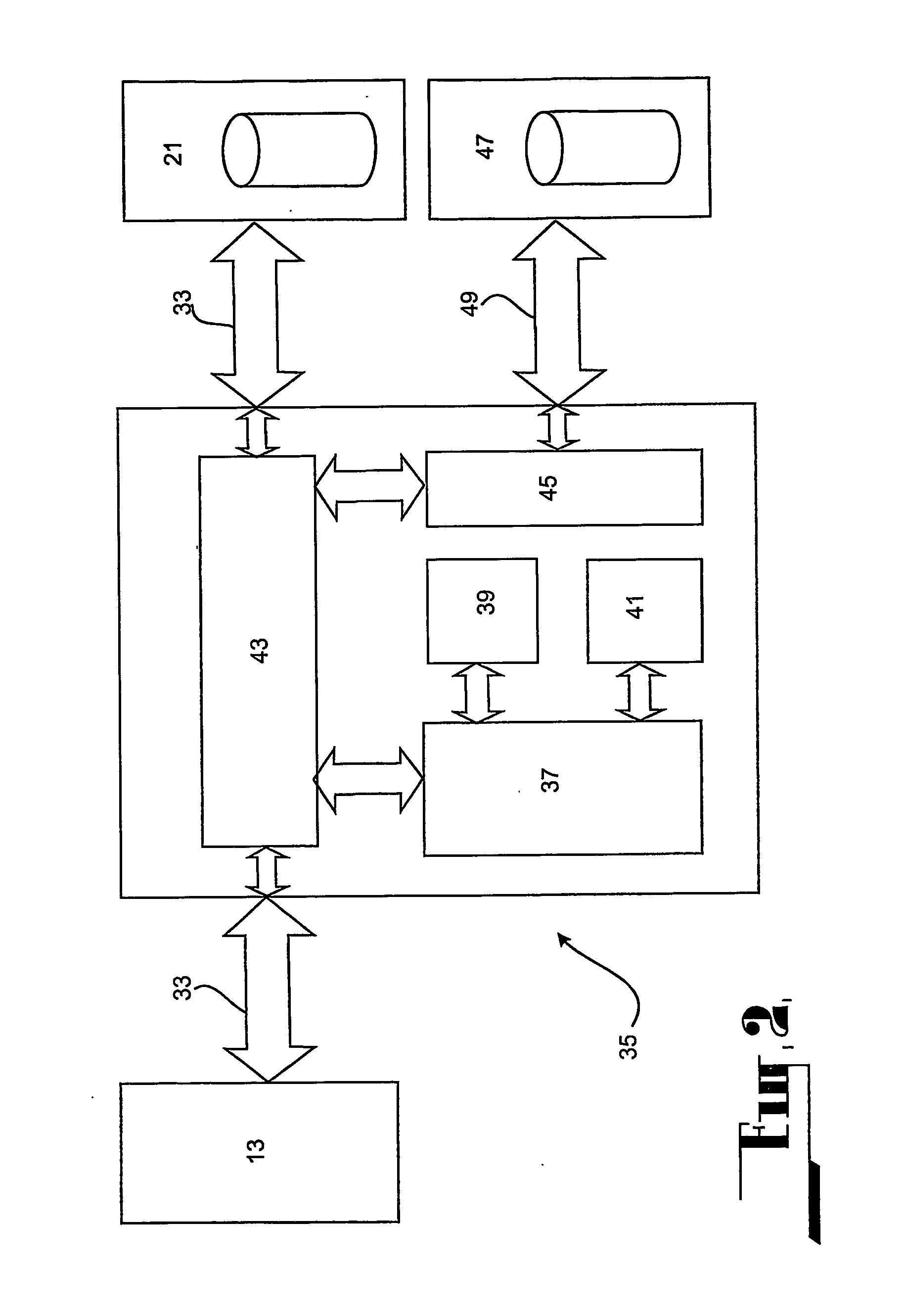

Bus bridge security system and method for computers

InactiveUS20070028292A1Improve protectionPrevent unauthorized accessDigital data processing detailsUser identity/authority verificationData accessComputer memory

A computer security system comprising security logic that is independent of the host CPU (13) for controlling access between the host CPU (13) and the storage device (21). A program memory (41) that is independent of the computer memory unalterably stores and provides computer programs for operating the processor (37) in a manner so as to control access to the storage device (21). The security logic comprises logic in bus bridge circuitry . The bus bridge circuitry can be embodied in the south bridge circuit (326) of a computer system (11) or alternatively in a SOC circuit (351) of a HDD. All data access by the host CPU (13) to the data storage device (21) is blocked before initialisation of the security system and is intercepted immediately after the initialisation under the control of the security logic. The security logic effects independent control of the host CPU (13) and configuration of the computer (11) to prevent unauthorised access to the storage device (21) during the interception phase. All users of the computer (11) are authenticated with a prescribed profile of access to the storage device (21) and data access to the storage device remains blocked until a user of the computer (11) is correctly authenticated.

Owner:SECURE SYST LTD

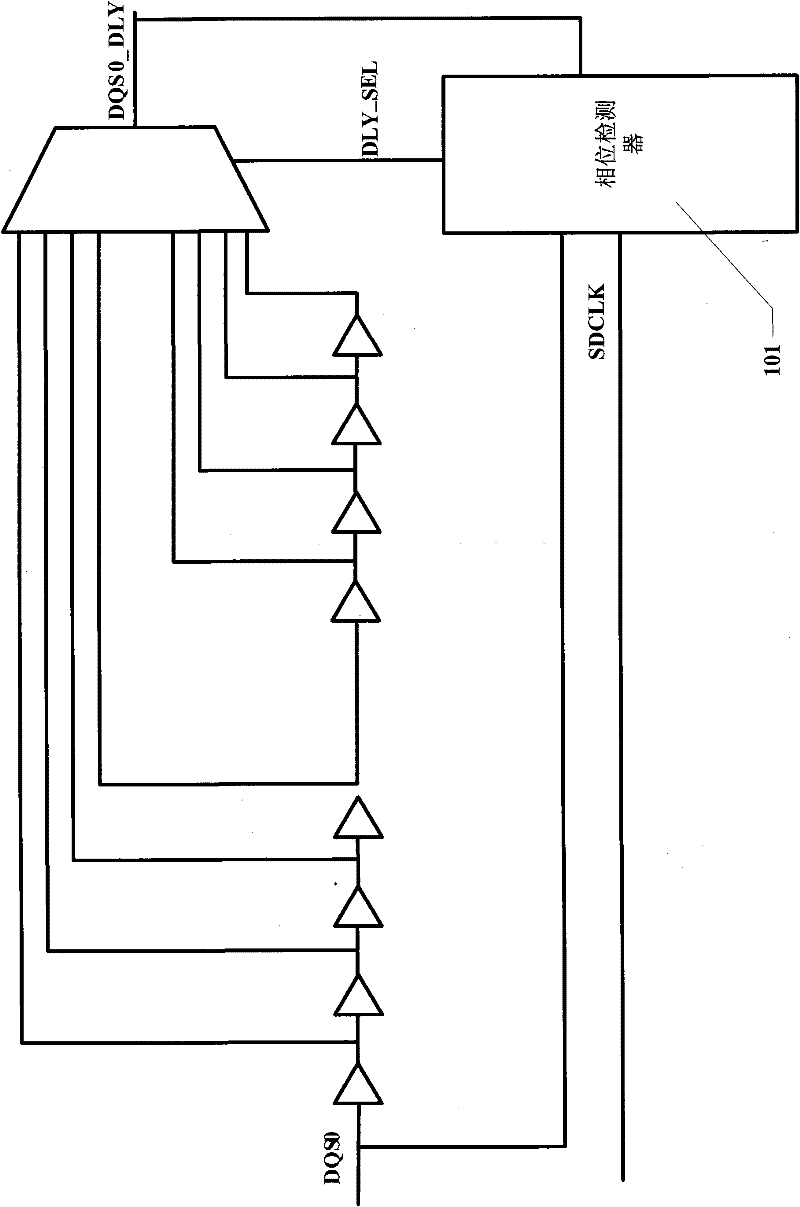

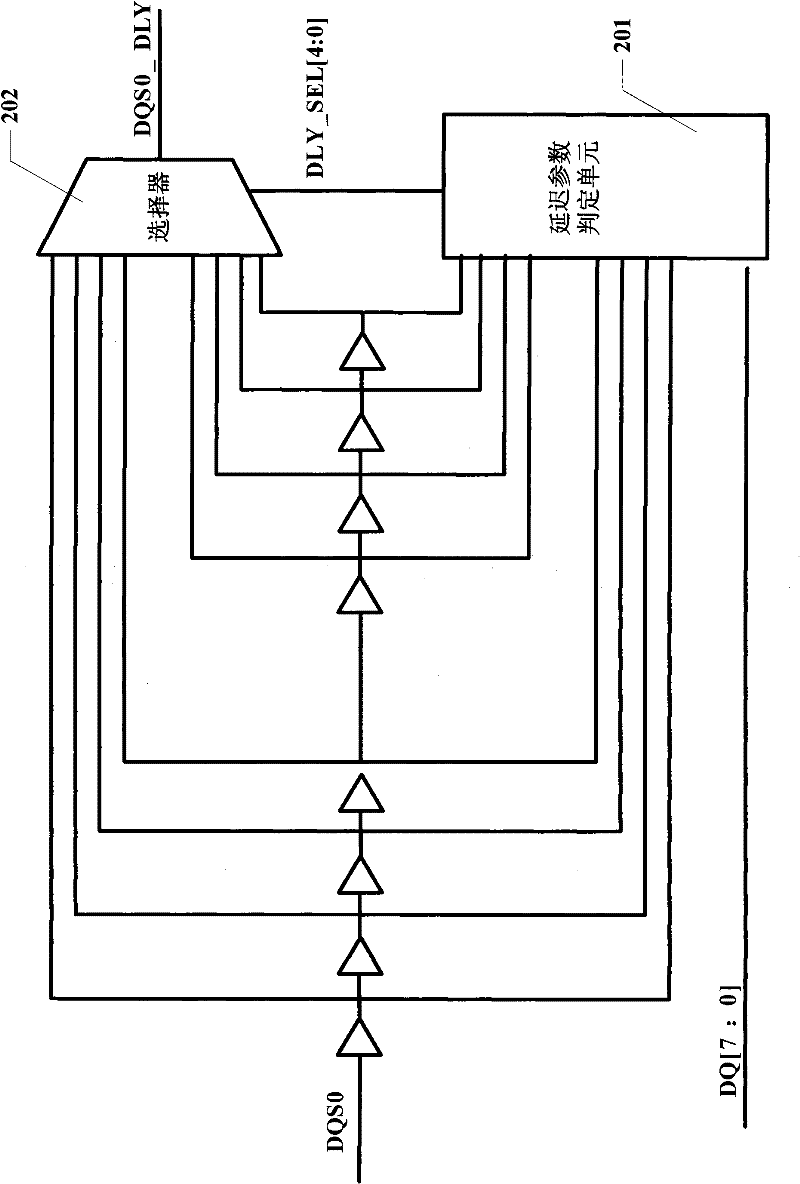

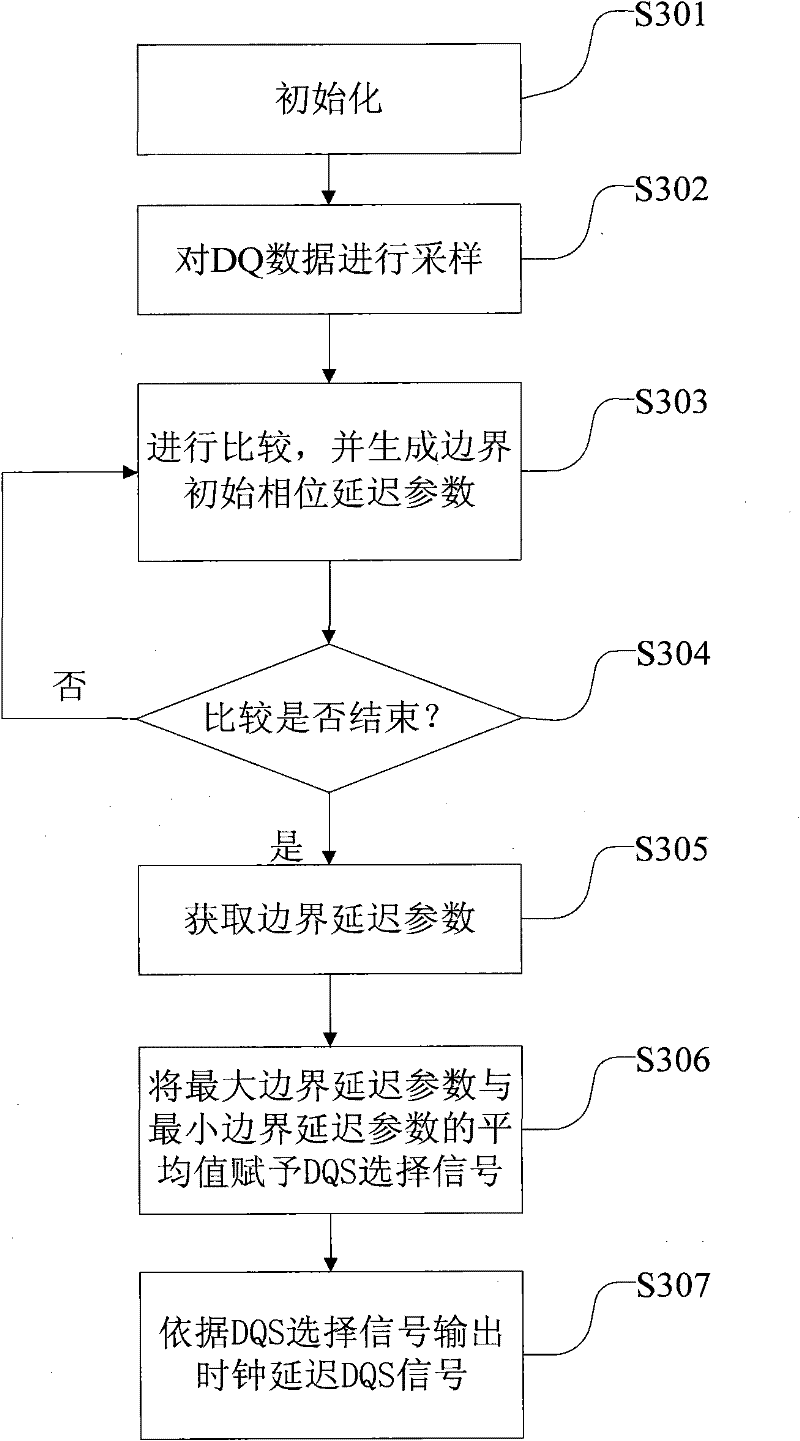

Method for calibrating phase of DQS (bidirectional data strobe) delay for DDR (double data rate) controller and apparatus thereof

ActiveCN102347081AImprove stabilityImprove anti-interference abilityStatic storageDouble data rateScreening method

The invention discloses a phase calibration method of the DQS delay for a DDR controller and an apparatus thereof. The method comprises the following steps: 1, sampling DDR data DQ according to trigger signals after different grade delays of a DQS signal; 2, comparing the data DQ acquired by sampling with a preset self-check datum in byte, and acquiring a minimum boundary delay parameter and a maximum boundary delay parameter through delaying for two beats; 3, endowing a mean value of the minimum boundary delay parameter and the maximum boundary delay parameter to a DQS selection signal; and 4, delaying the DQS signal according to the output clock of the DQS selection signal to obtain a DQS signal at the center of an effective datum window. According to the invention, the phase calibration of the DQS delay is realized through adopting a delay parameter determination unit and hardware in a delay parameter output circuit, and the delayed DQS can accurately fall on the center of the effective datum window through a datum screening method with the delay parameter determination unit, thereby the stability, the accuracy and the interference immunity of datum sampling are enhanced.

Owner:LEADCORE TECH

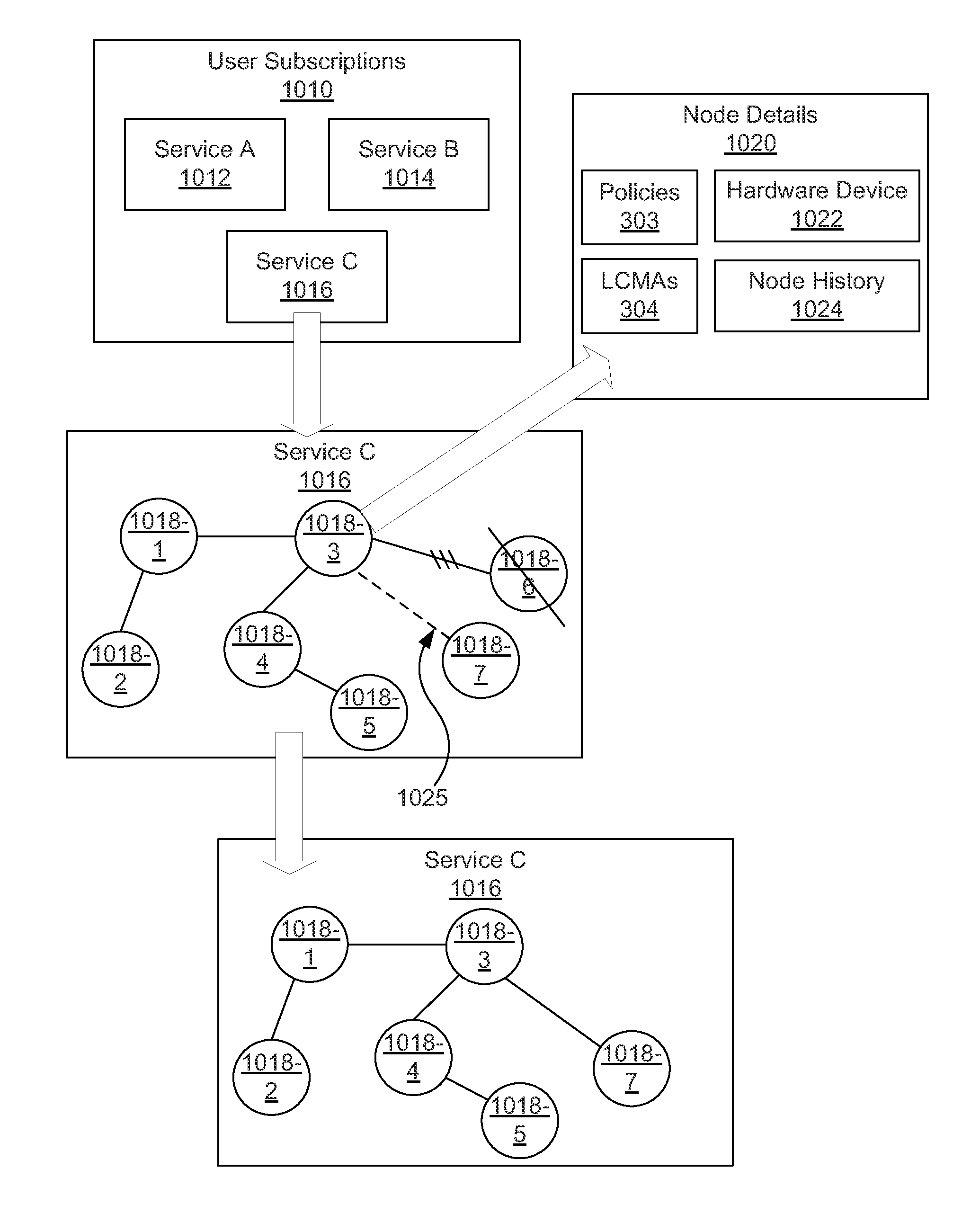

Modifying realized topologies

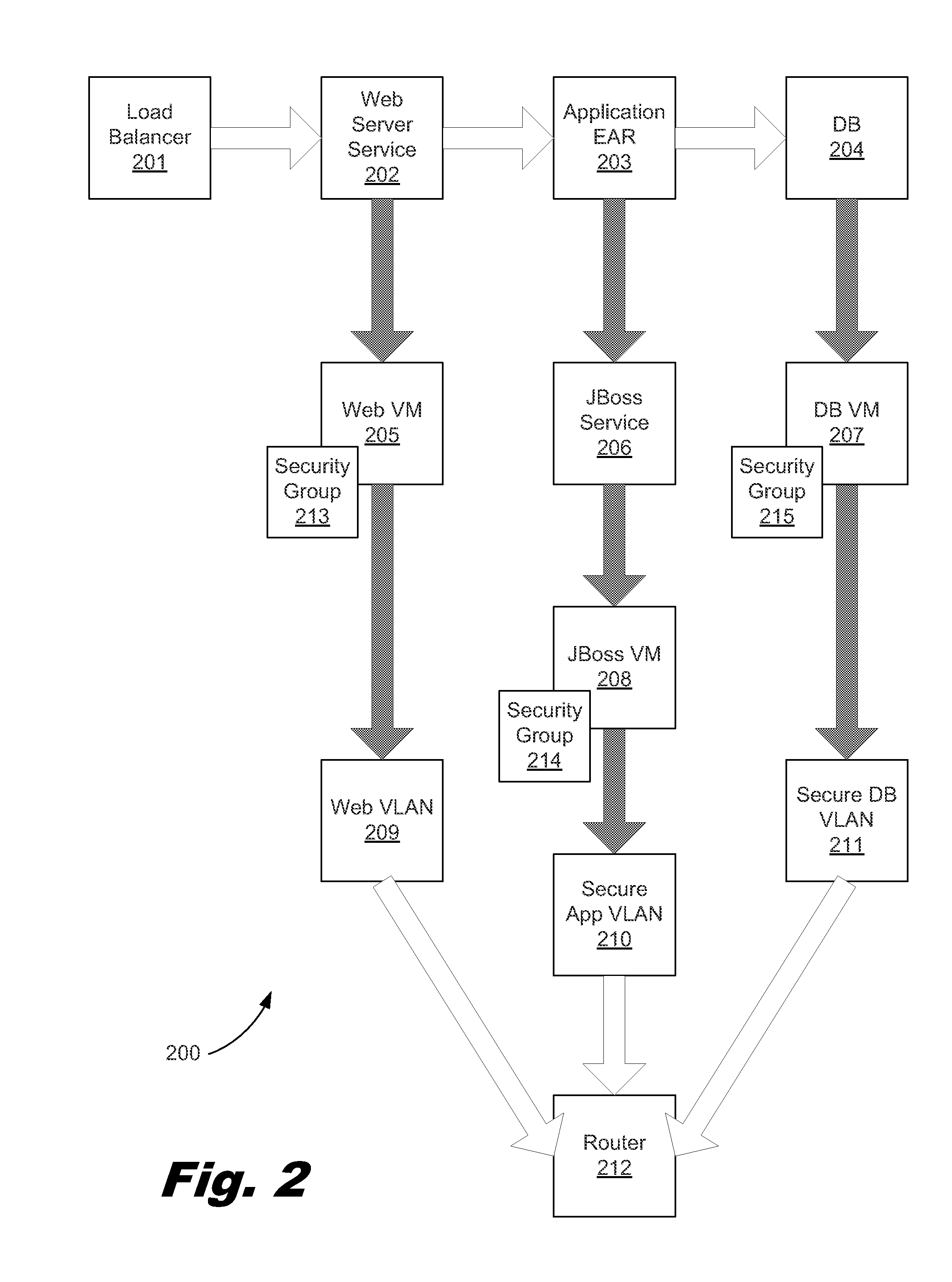

ActiveUS20160234073A1Database updatingDatabase distribution/replicationGraphicsGraphical user interface

A method of updating and editing realized topologies, comprising presenting a realized topology to a user, receiving input indicating modification of portions of the realized topology, and with a processor, executing logic associated with the modified portions based on a number of lifecycle management actions (LCMAs) of the realized topology. A system to update and edit a realized topology, comprising a processor and a graphical user interface (GUI) communicatively coupled to the processor, in which the GUI presents to a user a graphical representation of the realized topology, and in which the system receives input indicating modification of portions of the realized topology, and with a processor, executes logic associated with the modified portions based on a number of lifecycle management actions (LCMAs) of the realized topology.

Owner:MICRO FOCUS LLC

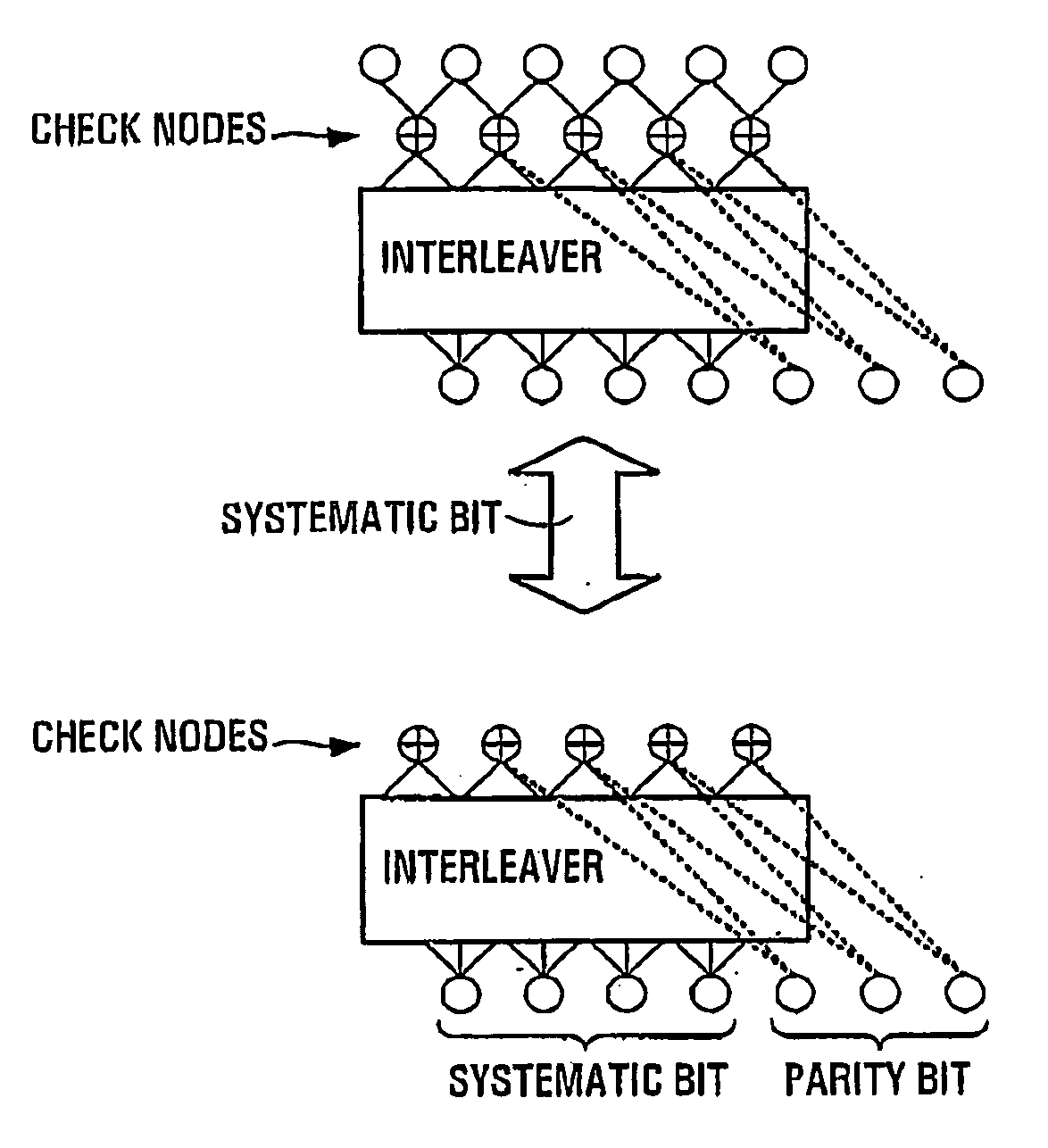

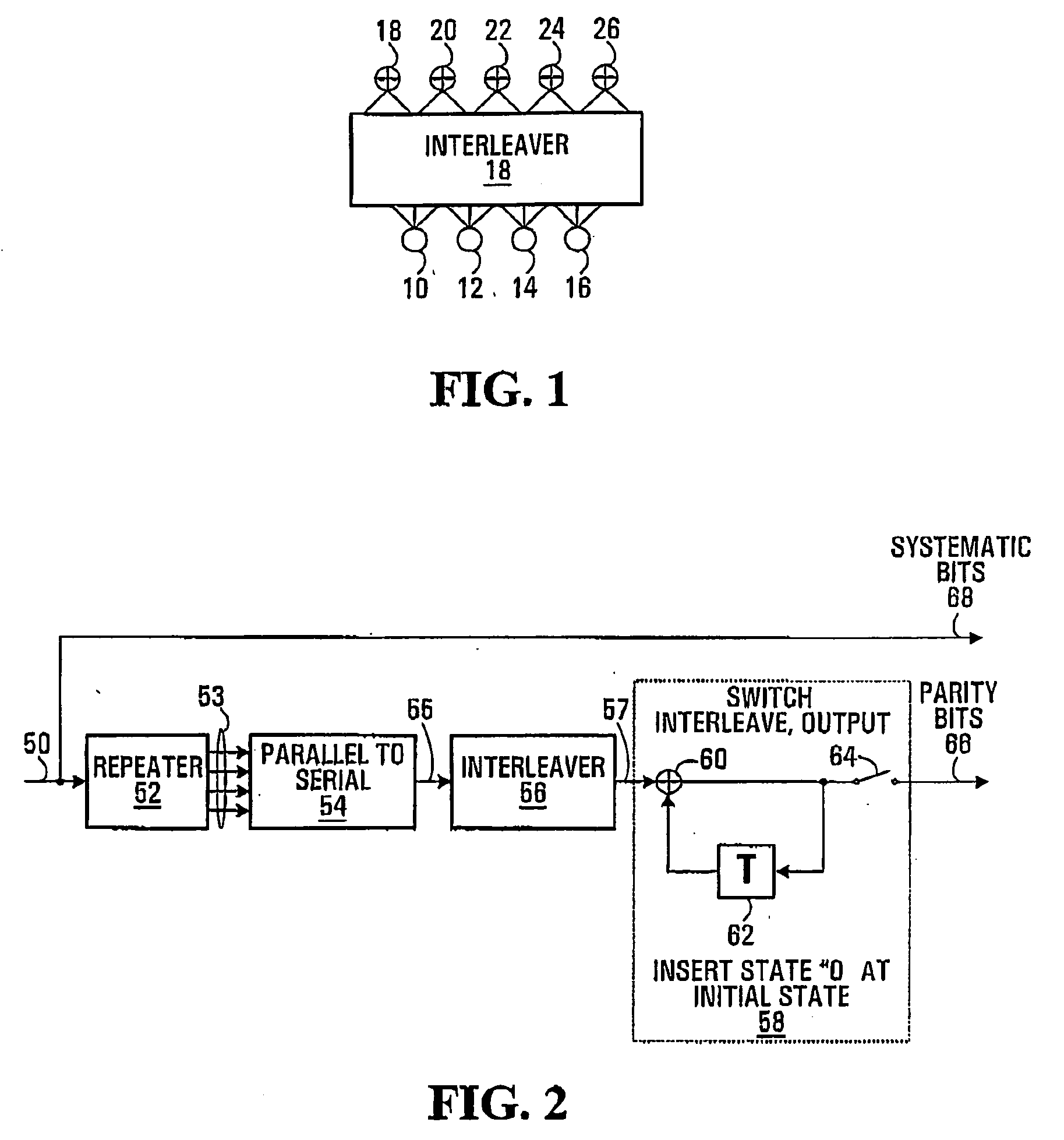

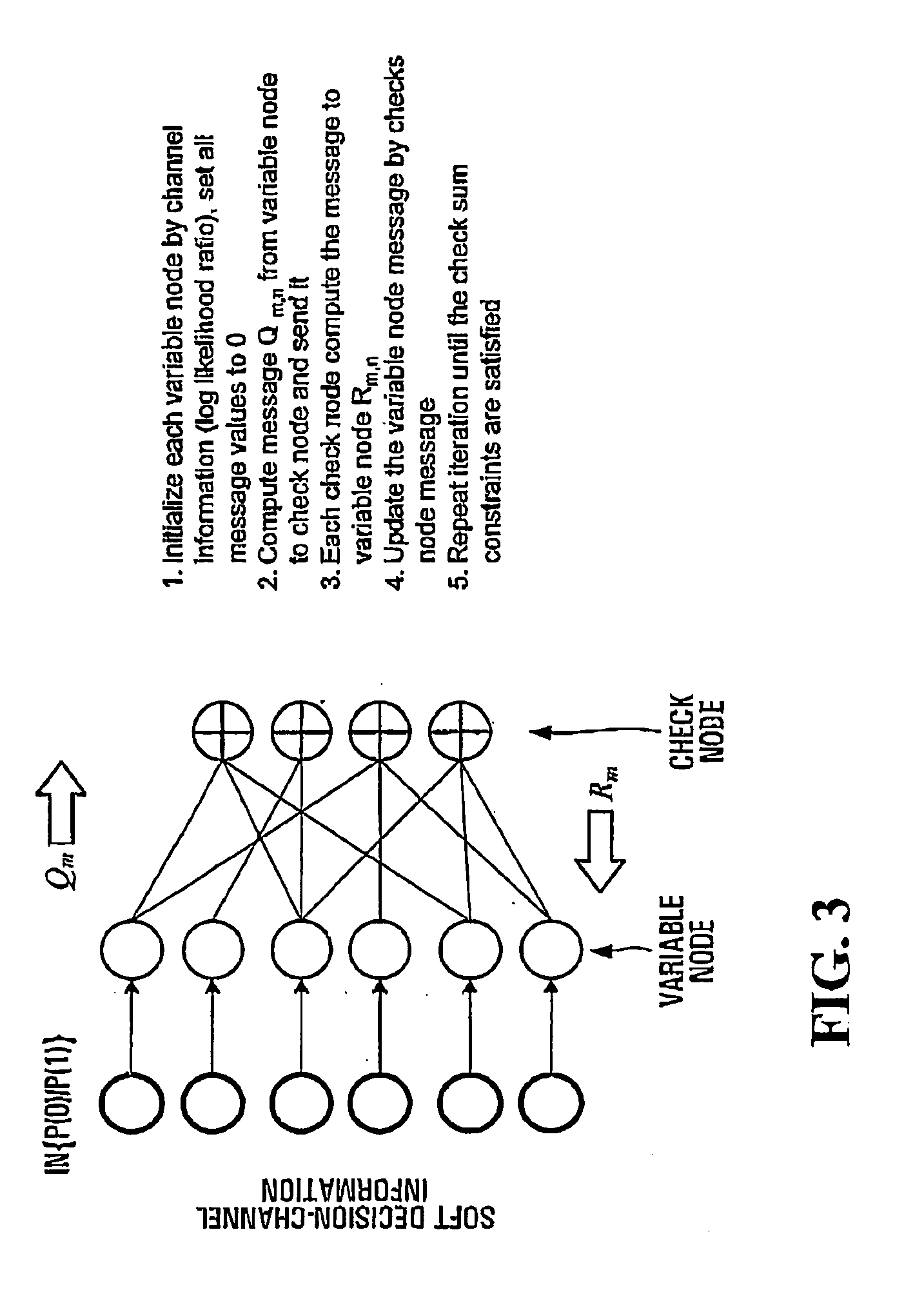

Ldpc encoders, decoders, systems and methods

ActiveUS20090083604A1Fault responseError correction/detection using multiple parity bitsLogic implementationRepeat pattern

An LDPC encoder with a complexity that increases linearly as a function of block size is provided. They arc implementable with simple logic consisting of a repeater with an irregular repeat pattern, an interleaver, and an accumulator that performs irregular accumulations.

Owner:ALLLE INC

Non-Volatile Memory and Method with Shared Processing for an Aggregate of Read/Write Circuits

ActiveUS20070263450A1Maximum versatilityMinimal componentRead-only memoriesDigital storageAudio power amplifierAssociative processor

A non-volatile memory device capable of reading and writing a large number of memory cells with multiple read / write circuits in parallel has an architecture that reduces redundancy in the multiple read / write circuits to a minimum. The multiple read / write circuits are organized into a bank of similar stacks of components. Redundant circuits such as a processor for processing data among stacks each associated with multiple memory cells are factored out. The processor is implemented with an input logic, a latch and an output logic. The input logic can transform the data received from either the sense amplifier or the data latches. The output logic further processes the transformed data to send to either the sense amplifier or the data latches or to a controller. This provides an infrastructure with maximum versatility and a minimum of components for sophisticated processing of the data sensed and the data to be input or output.

Owner:SANDISK TECH LLC

Heterogeneous multi-core infrared image processing system and method

InactiveCN103412619AEliminate Bandwidth BottlenecksImprove real-time processing performanceDigital data processing detailsSpecific program execution arrangementsOperational systemParallel computing

The invention discloses a heterogeneous multi-core infrared image processing system and method. The method mainly includes: 1, utilizing programmable logic of a Zynq to realize a driving schedule of a detector to complete collection and caching of an infrared image; 2, utilizing a CPU0 (central processing unit 0) of the Zynq to operate a Linux operating system to write a Qt-based display and control interface; 3, utilizing a CPU1 of the Zynq to respond to a serial port command in real time, and setting a system parameter and a video driving chip online; 4, utilizing the programmable logic to realize algorithmic hardware acceleration and a driving schedule of a video chip. The heterogeneous multi-core infrared image processing system and method has the advantages that a structure of ARM+FPGA in an all programmable platform Zynq chip is utilized to develop the heterogeneous multi-core infrared image processing system, design difficulty of hardware is remarkably reduced, a system bandwidth chokepoint brought by interconnection of conventional framework chip levels is removed, simplicity and flexibility in design and integration of a user IP (internet protocol) are realized, and high universality is realized.

Owner:SHANGHAI INST OF TECHNICAL PHYSICS - CHINESE ACAD OF SCI

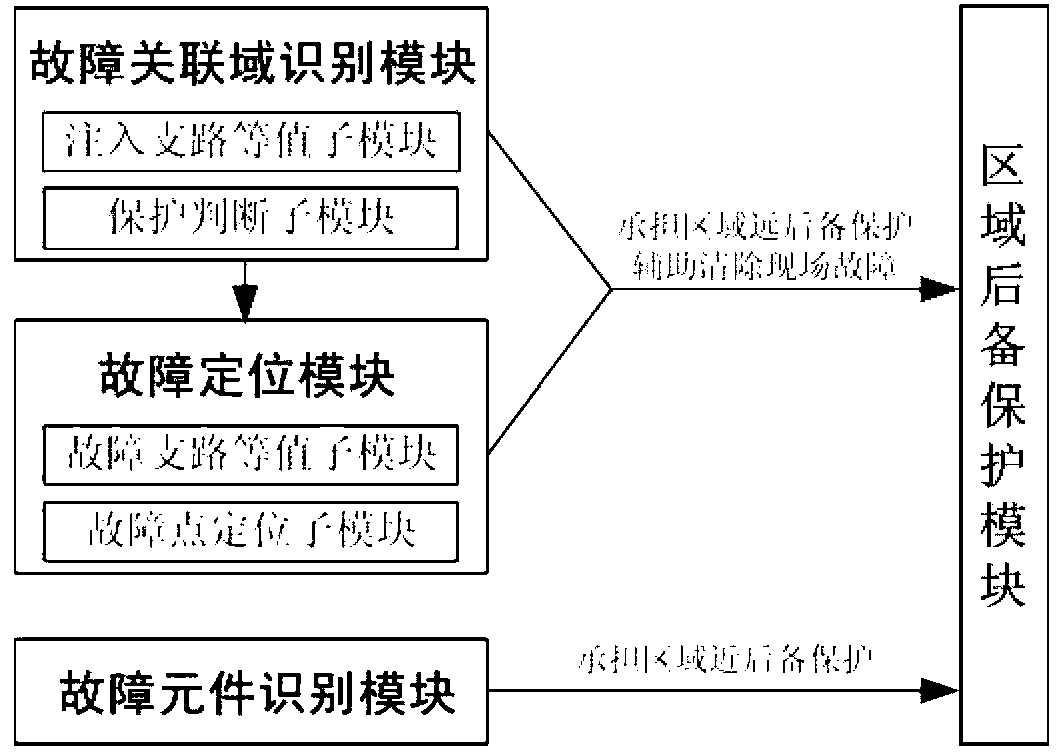

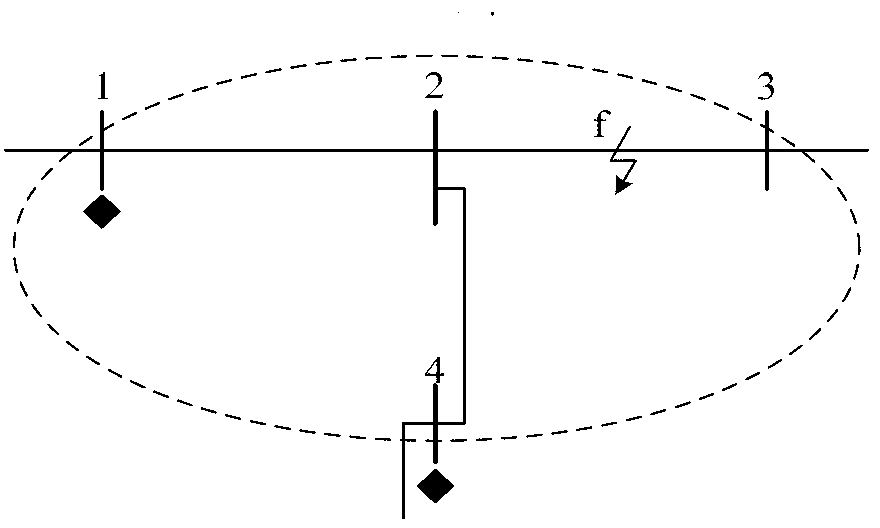

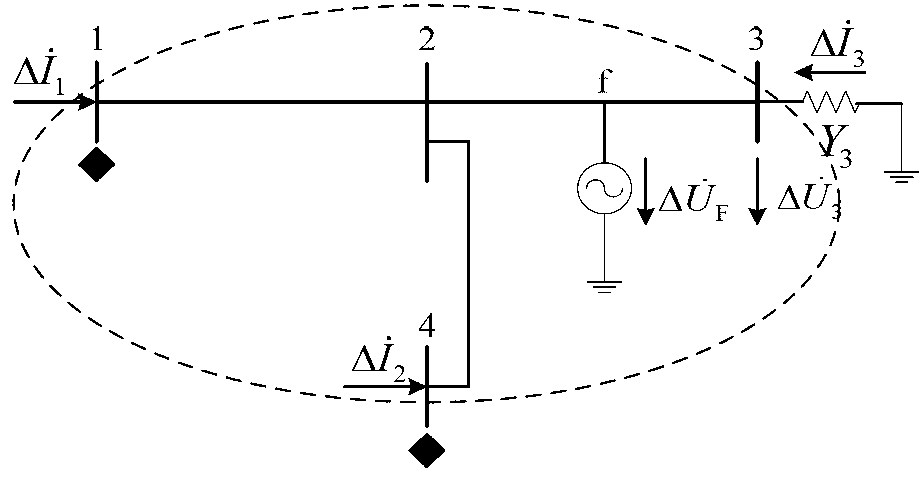

System and method for grid fault identification based on random point distribution PMU

ActiveCN103323742AReduce dependencyMeet the needs of backup protection applicationsEmergency protective circuit arrangementsFault locationGrid faultElectric power system

The invention discloses a system and method for grid fault identification based on a random point distribution PMU and belongs to the technical field of power system fault identification. The system comprises a fault relative domain identification module, a fault locating module, a fault component identification module and a domain backup protection module. A grid structure changing characteristic is evolved to a branch current difference by the fault relative domain identification module, so that fault relative domain identification is achieved; overall traversal is conducted on a relative domain by the fault locating module, so that accurate location of a fault point is achieved based on a node voltage matching condition; based on virtual current differential, protecting criteria are constructed through an opposite terminal calculated current and a home terminal actually detected current by the fault component identification module, so that fault component identification is achieved; according to domain backup protection operation logic, the near backup tripping function and the far backup tripping function are achieved by the domain backup protection module. Complete domain backup protection under the environment of random PMU point distribution is achieved and the dependence degree on synchronous data of protection is reduced to a great extent.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING)

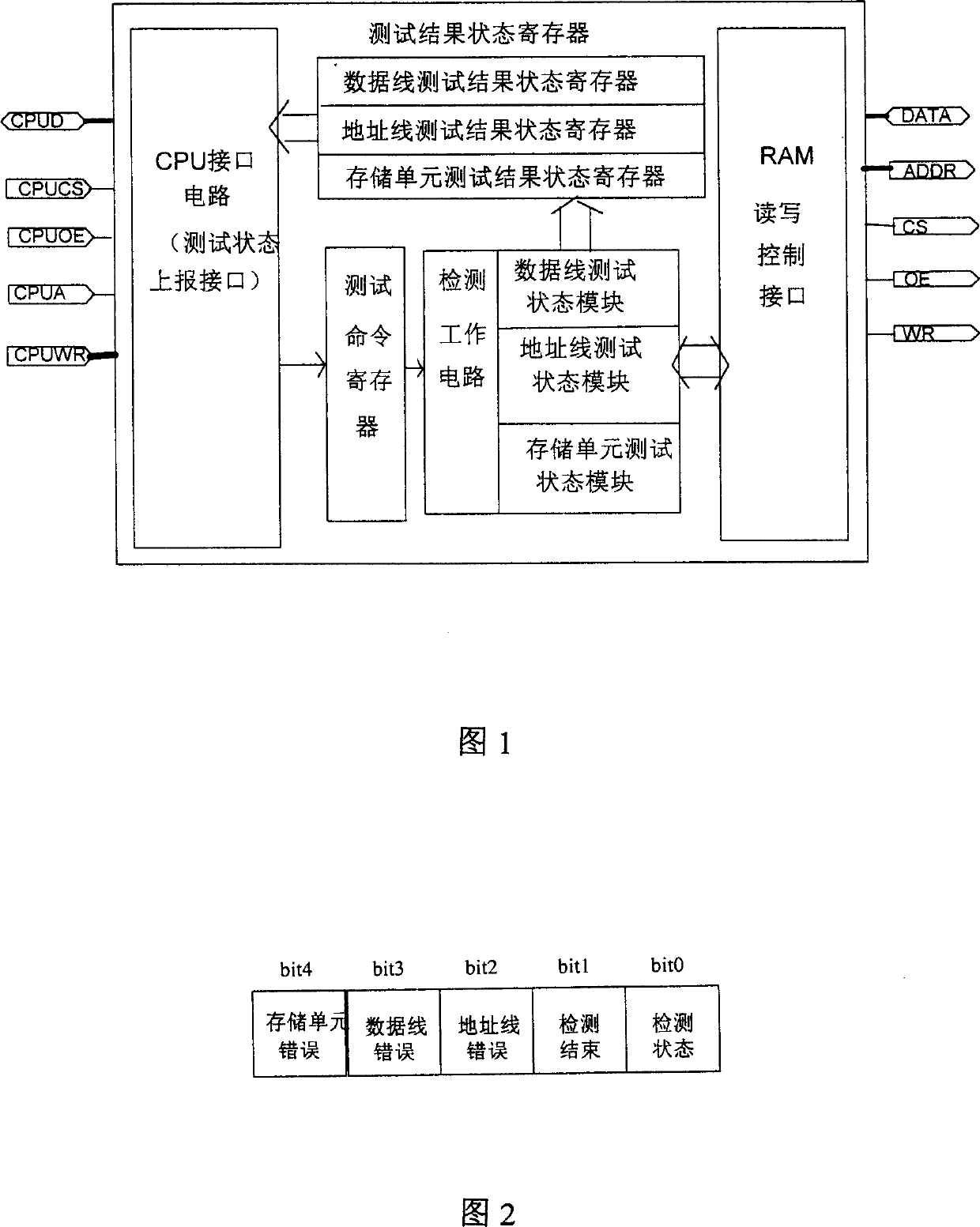

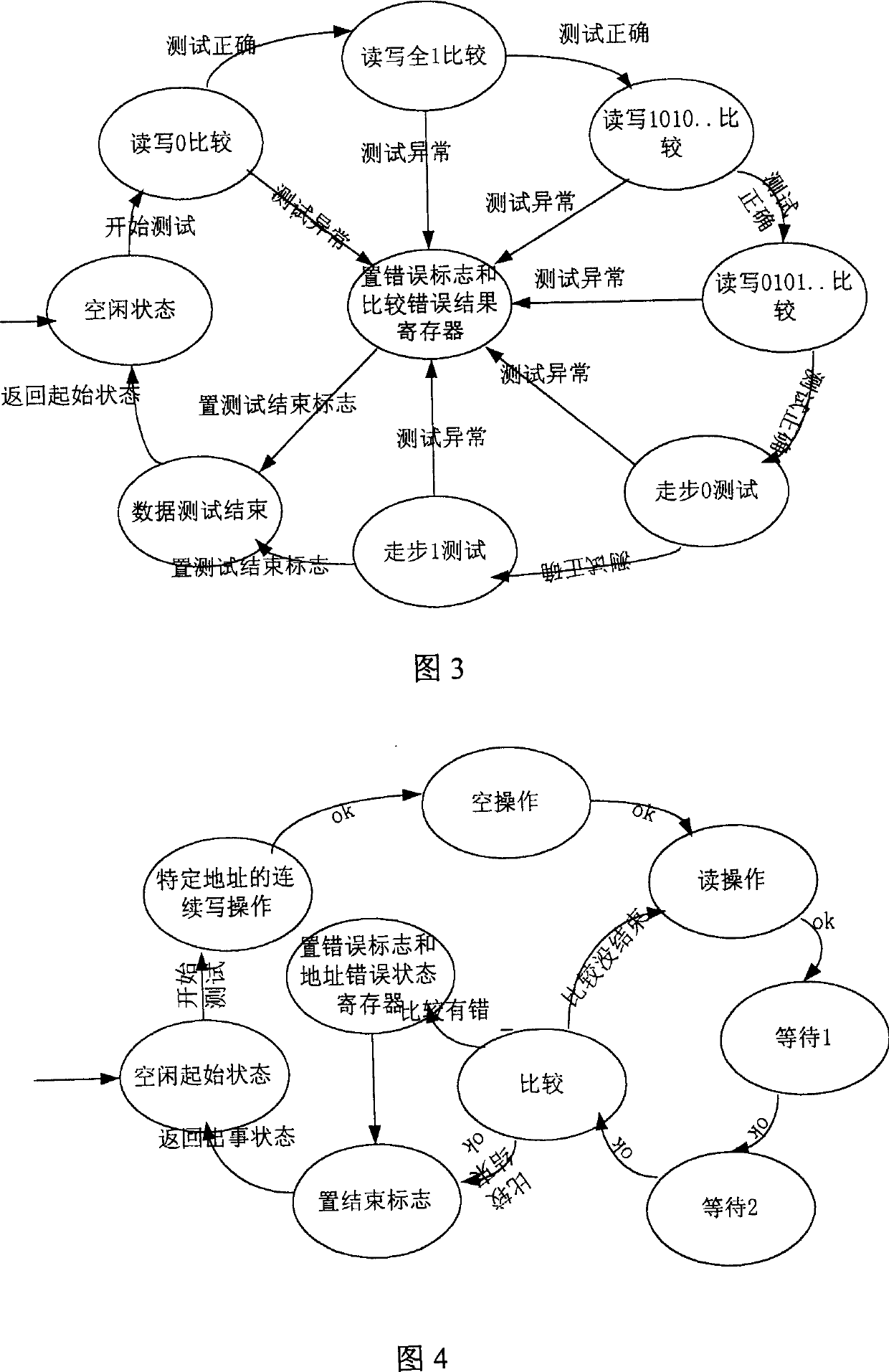

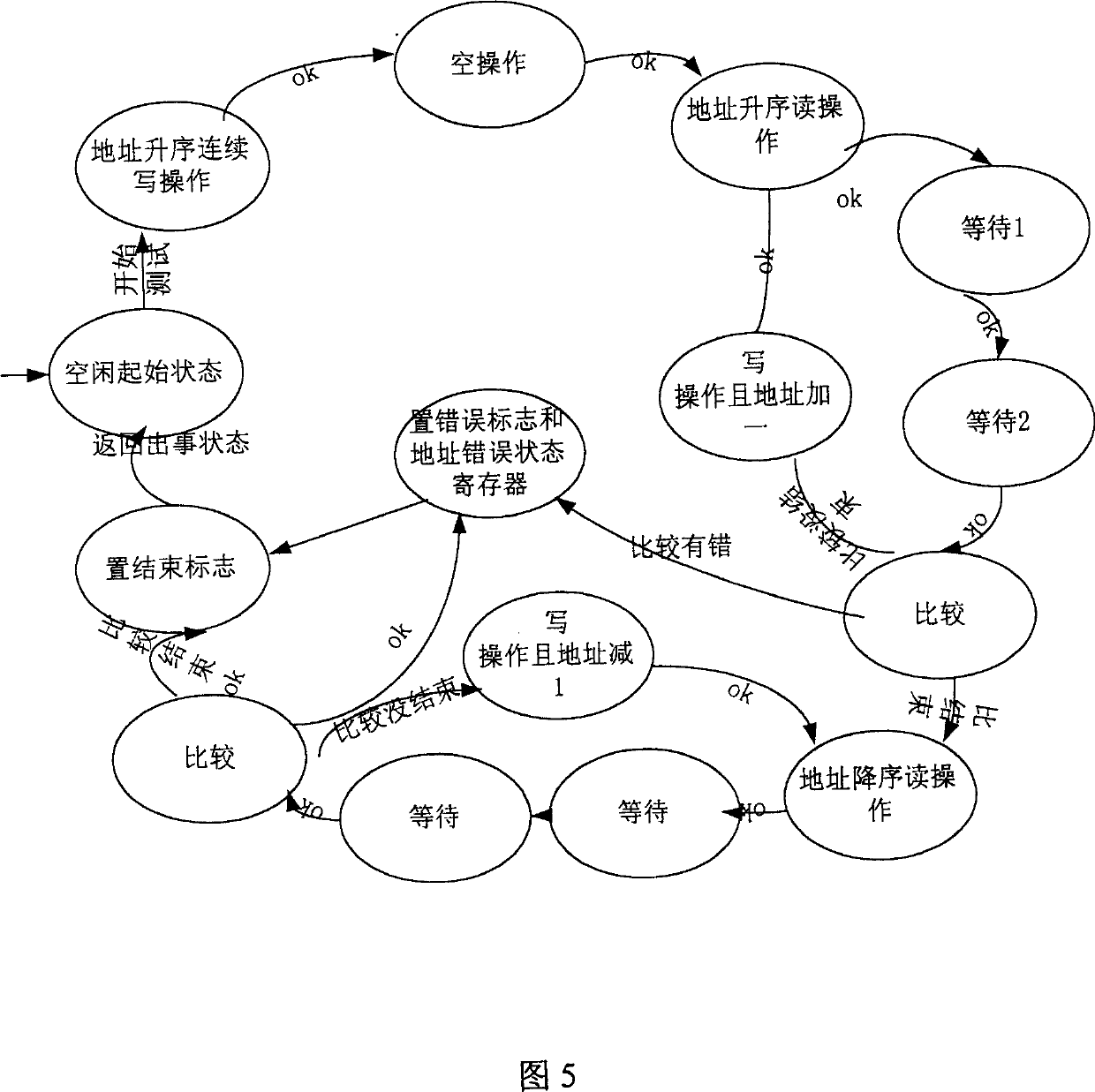

RAM high speed test control circuit and its testing method

InactiveCN1427420AEfficient detectionComprehensive testSemiconductor/solid-state device testing/measurementElectronic circuit testingTest typesStep test

A control circuit for high-speed test of RAM is disclosed, which is based on hardware logic for correct location of failure and high test efficiency. Its test method includes such steps as setting up the state of test command register, choosing test type, strobing test register, testing data lines by comparison, testing address lines by comparison, step test of memory units, and analyzing error type by reading state registers.

Owner:HUAWEI TECH CO LTD

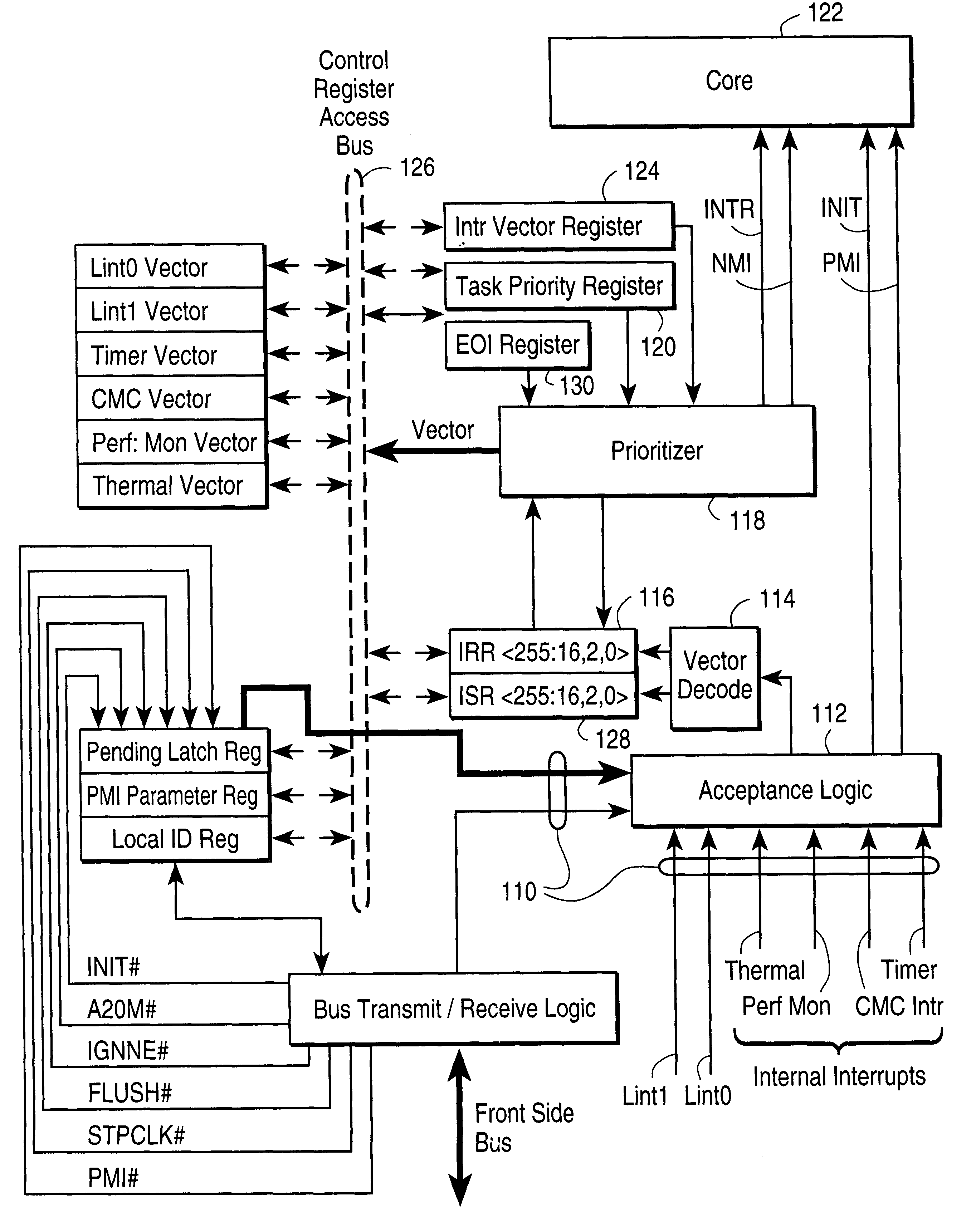

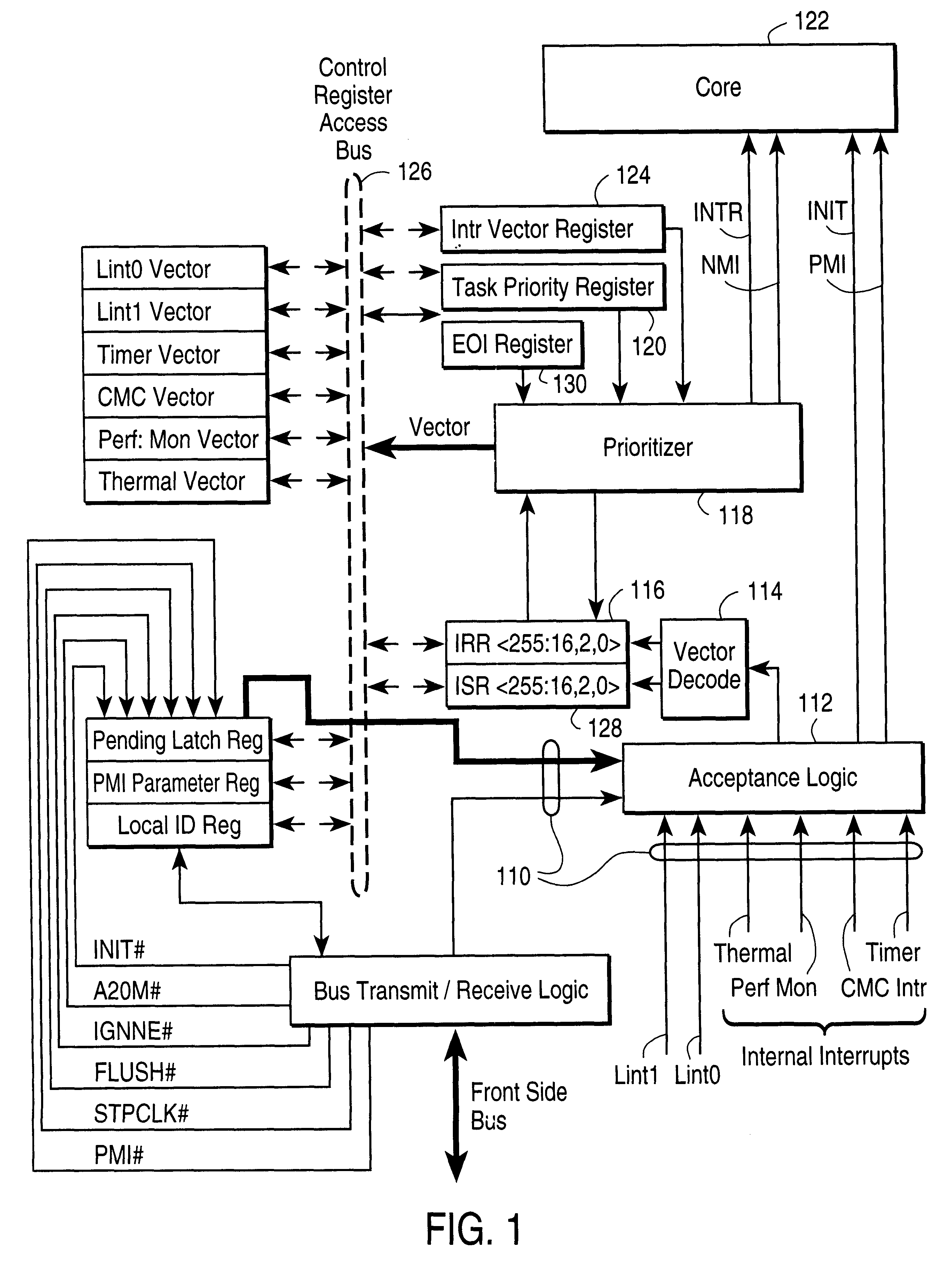

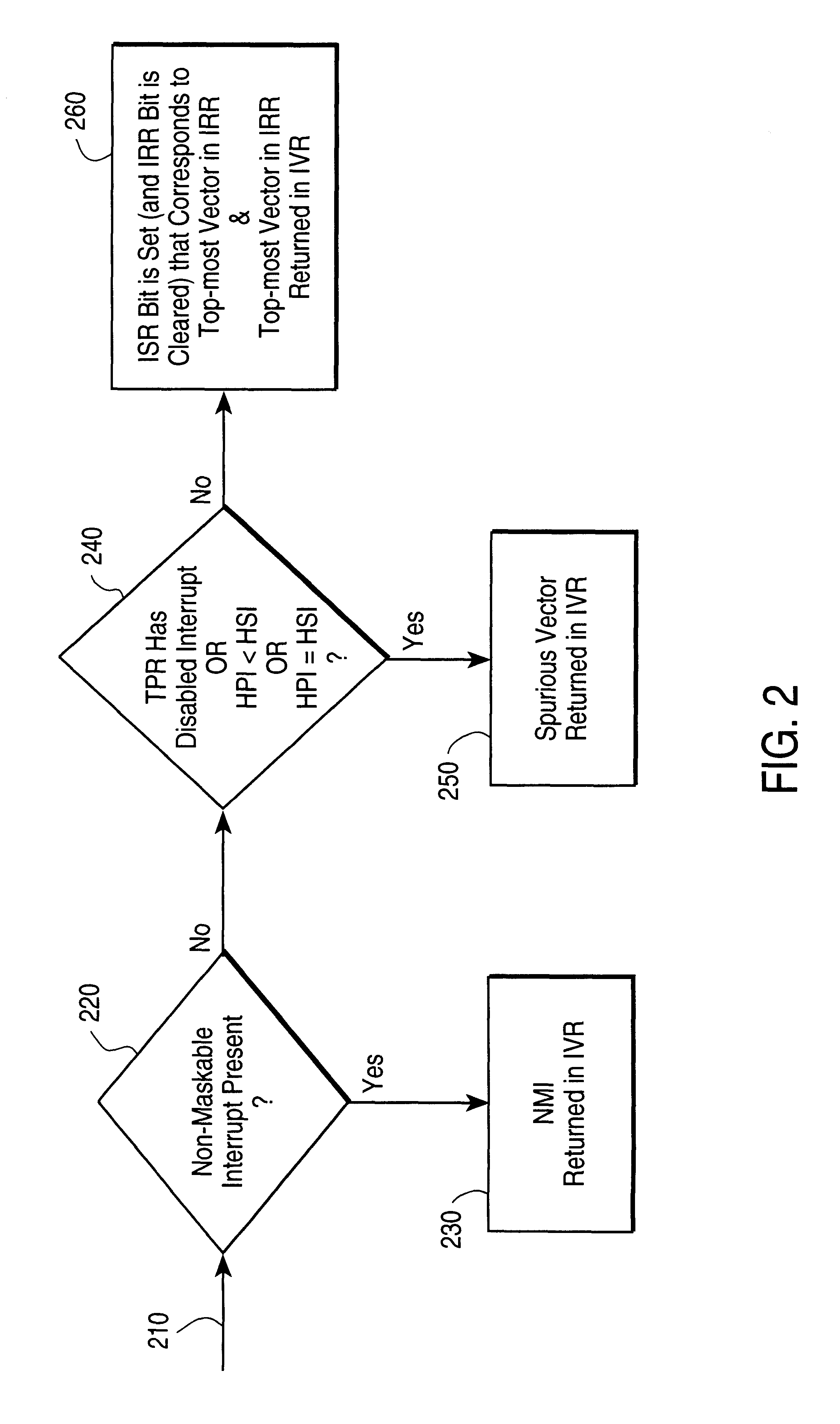

Apparatus and method for initiating hardware priority management by software controlled register access

InactiveUS6298410B1Increased latencyEasy to changeGeneral purpose stored program computerElectric digital data processingProcessor registerControl register

An apparatus and method for controlling interrupts in a computer are disclosed, in which programmable software operates to control when data concerning the interrupt having highest priority is to be provided, and hardware logic operates to control how that data is provided. An interrupt vector register is included in the computer CPU. The interrupt vector register does not act like the typical register. It is not a physical register, and cannot be written to. A read to this register by the programmable software, triggers the hardware logic. Once triggered, this logic performs certain control tasks, the end result of which is returning to the programmable software, a vector corresponding to the interrupt having highest priority. The programmable software can implement various software policies, in addition to the hardware policy implemented by the hardware logic.

Owner:INTEL CORP

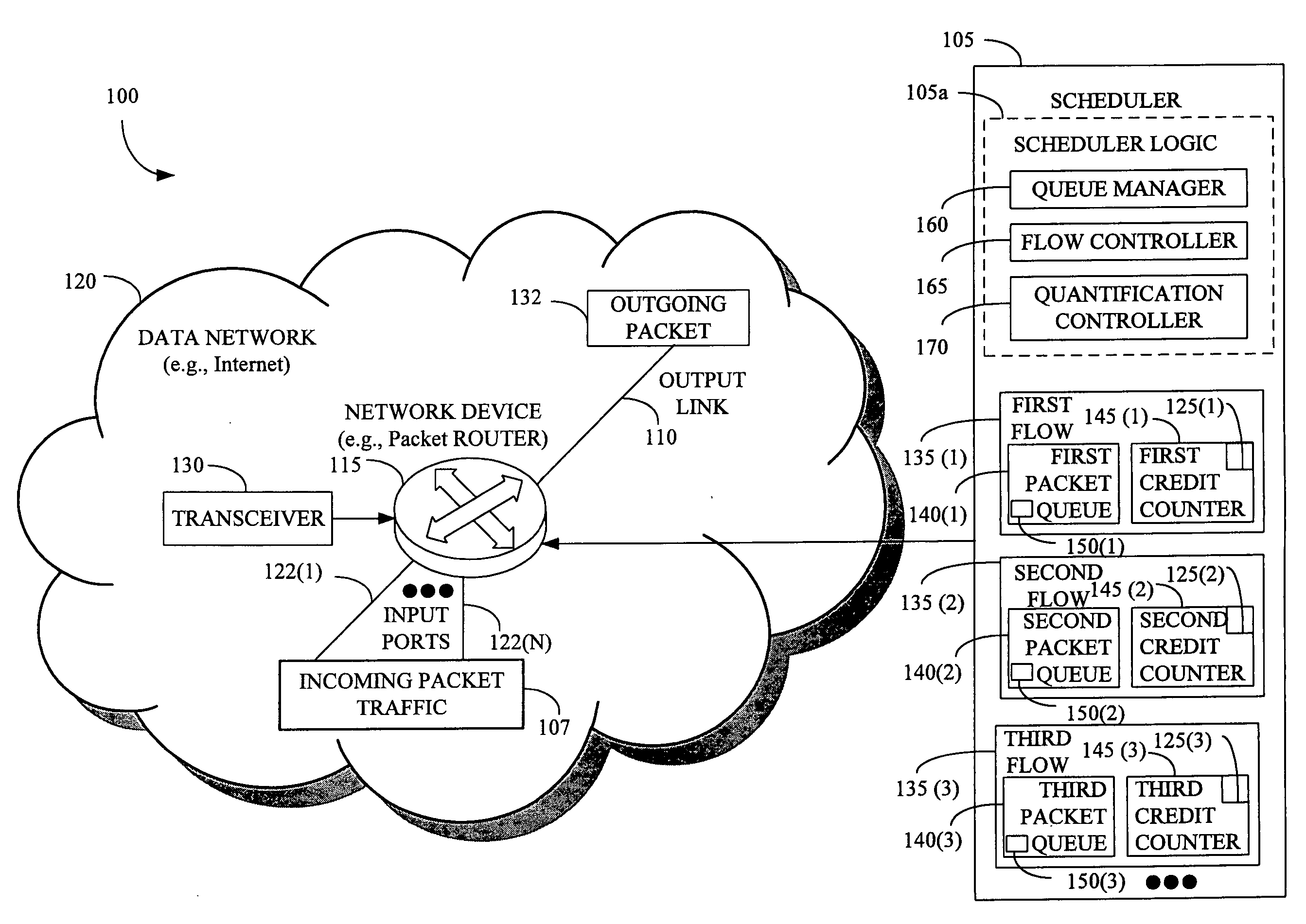

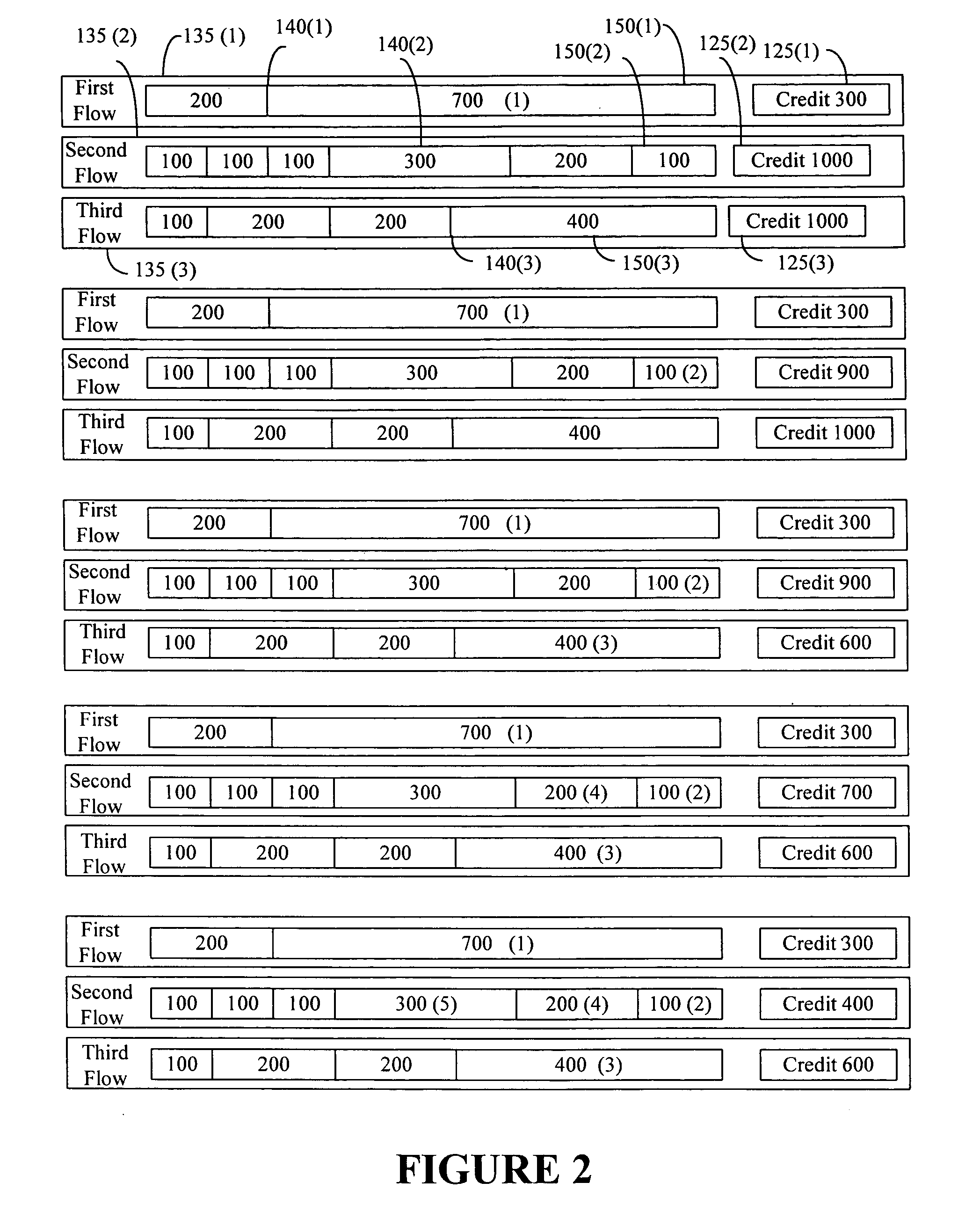

Scheduling incoming packet traffic on an output link of a network device associated with a data network

The present invention provides a method and an apparatus for scheduling a flow on an output link among a plurality of flows of incoming packet traffic at a network device associated with a data network. A scheduler comprises scheduler logic that uses a credit counter per flow to keep track of the service difference received between two or more flows and selects the flow for service next that has the maximum credit value. The scheduler logic decrements the current credit value by the amount of service received based on either the packet size or a ratio of the packet size and a weight value of the front-end packet of the next flow of outgoing packet stream selected for service and is being currently served. To specify a minimum guaranteed bandwidth for a specific flow, the scheduler logic selectively updates the corresponding indication of serving an outgoing packet on the output link for the plurality of flows of outgoing packet stream including the first and second indications based on the update value for the larger indication. When a current credit value drops below a threshold value, regardless of a state of a particular flow, the credit counters of all the flows in the plurality of flows of outgoing packet stream may be updated. The scheduler logic implements a fair scheduling algorithm with characteristics approximating the characteristics of timestamp schedulers but without their computational complexity. A relatively reduced calculation complexity of the scheduler logic with low bounded delay enables use thereof in high-speed networks devices, such as a packet router.

Owner:LUCENT TECH INC

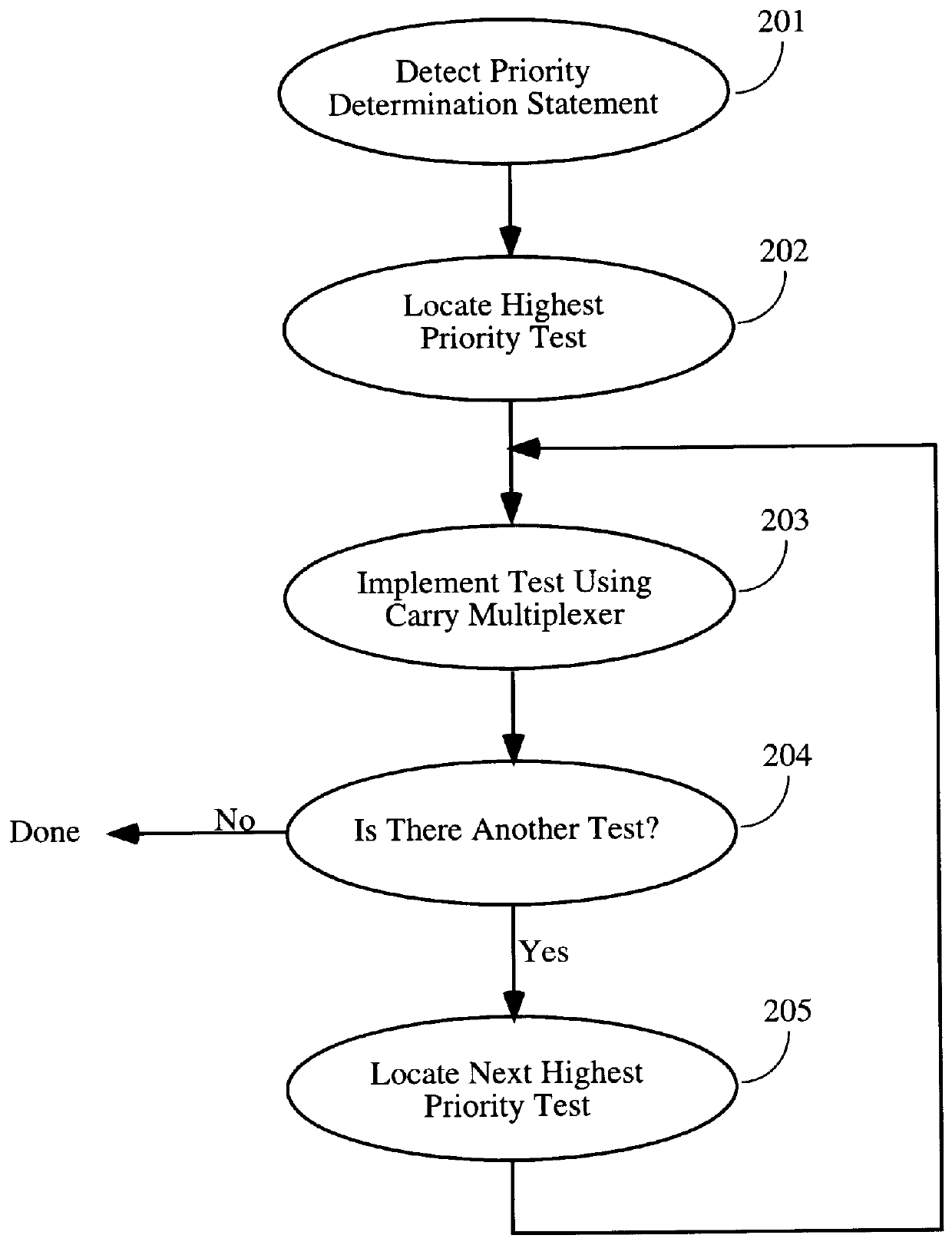

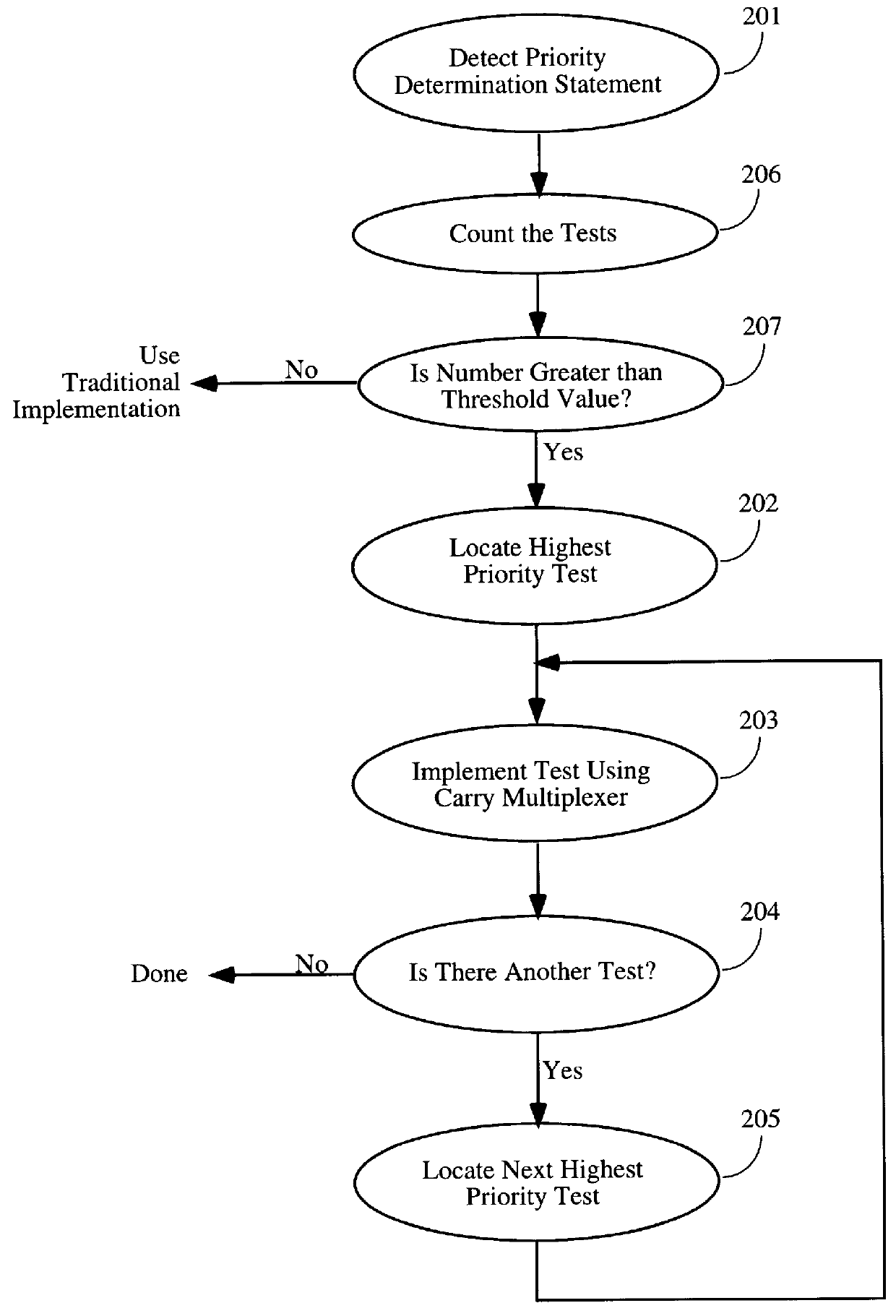

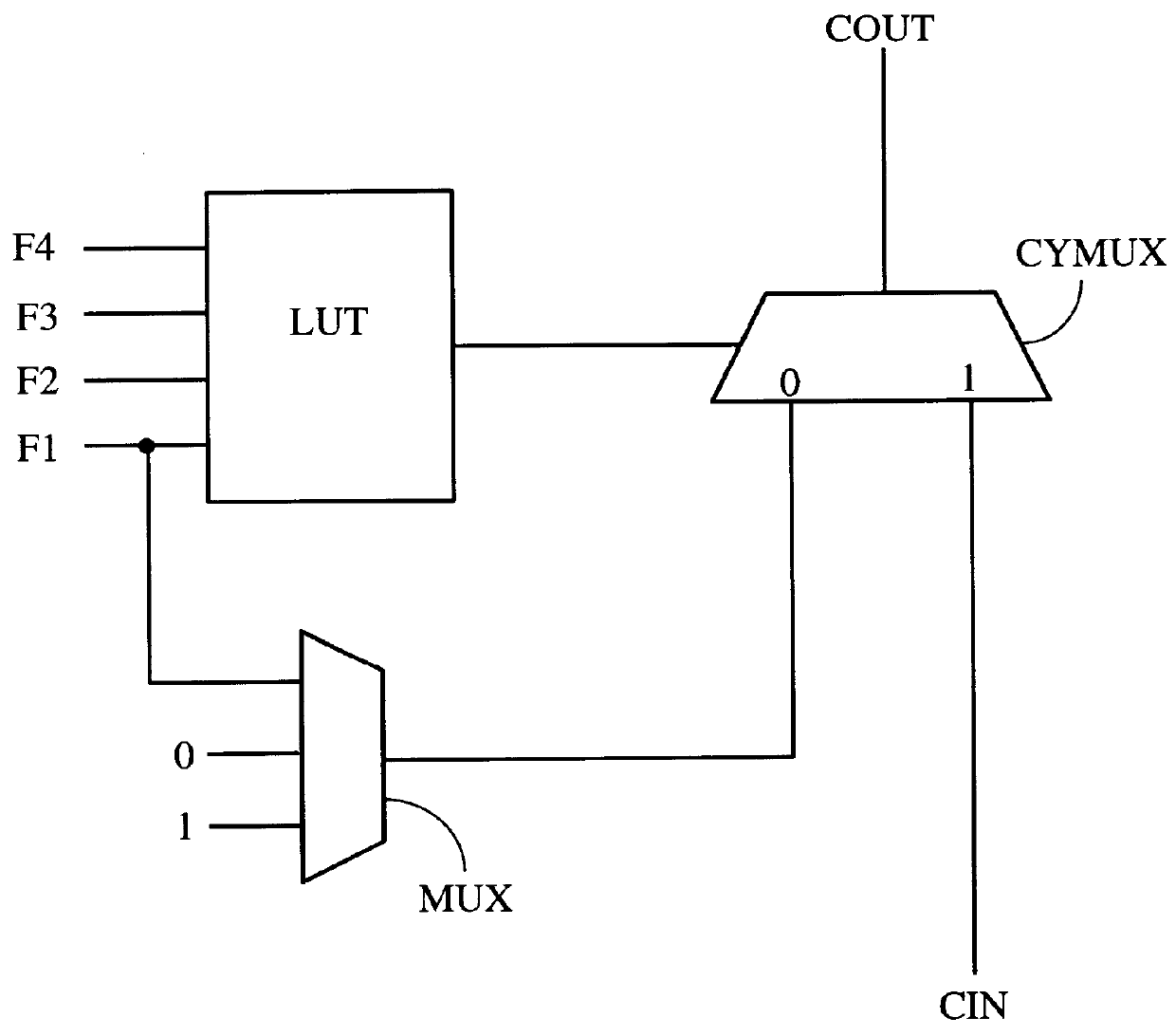

Method for implementing priority encoders using FPGA carry logic

The invention provides a method for implementing an HDL-specified priority encoder as carry logic in an FPGA. A first embodiment of the method includes the steps of: 1) detecting an priority determination statement in the HDL code; 2) implementing the highest priority test in the statement using a first carry multiplexer; and 3) implementing the next highest priority test in the statement using another carry multiplexer that accepts the output of the preceding carry multiplexer as a carry input; and 4) repeating step 3 until each test in the statement has been implemented. Another embodiment of the invention includes the additional steps of: 1) counting the number of tests performed in the priority determination statement; and 2) comparing the number of tests to a set threshold criterion, to determine whether it is appropriate to implement the statement using carry logic.

Owner:XILINX INC

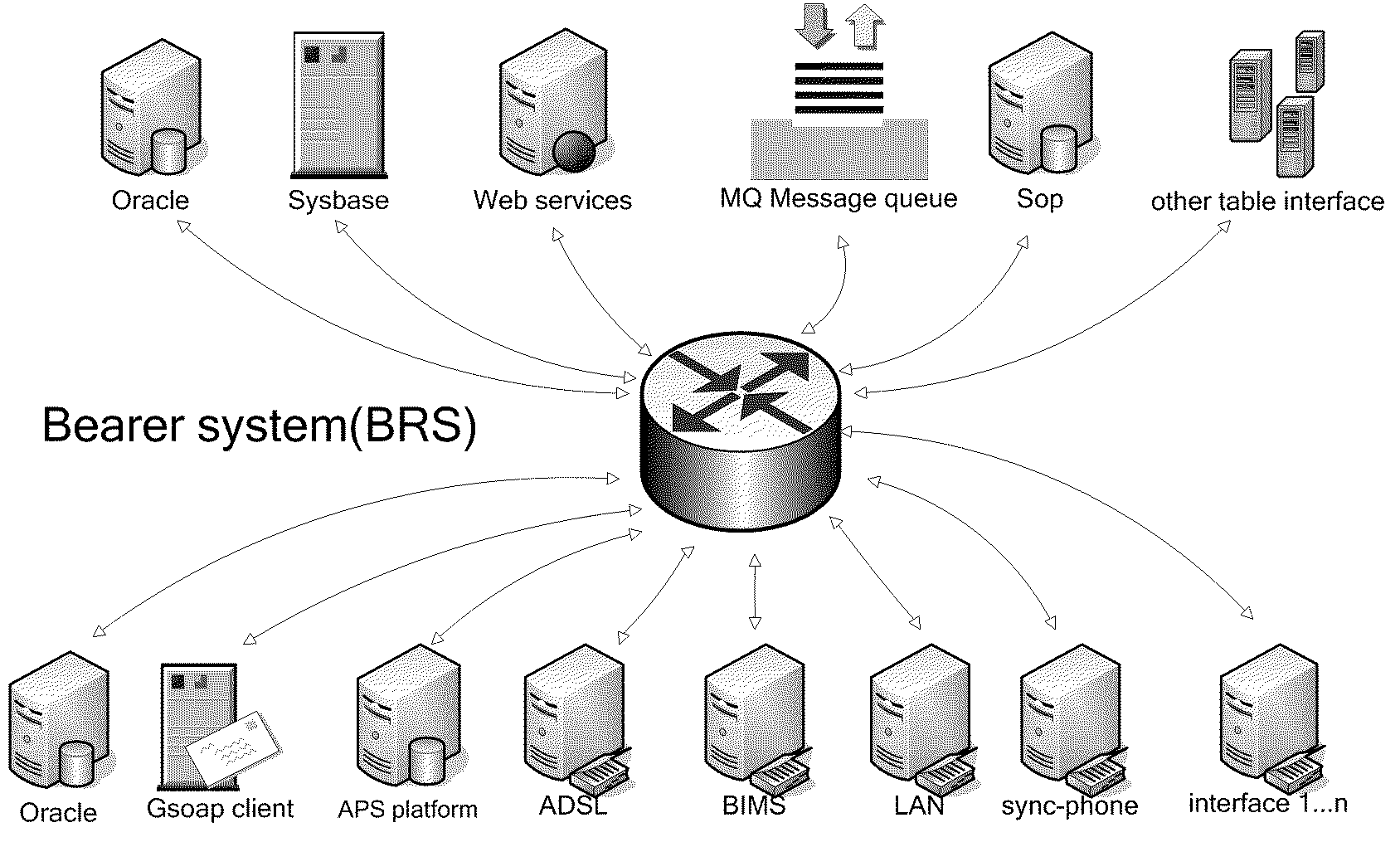

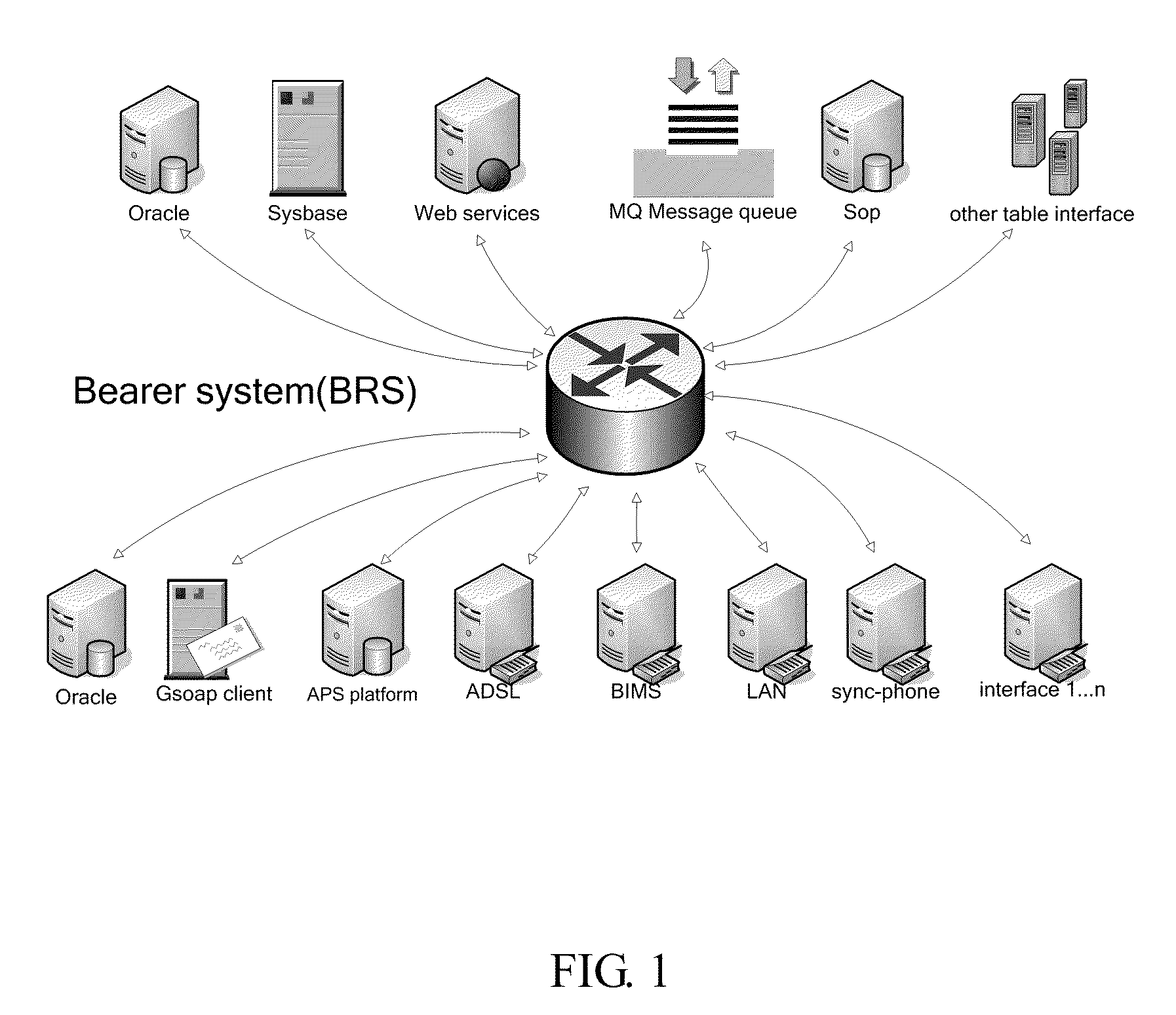

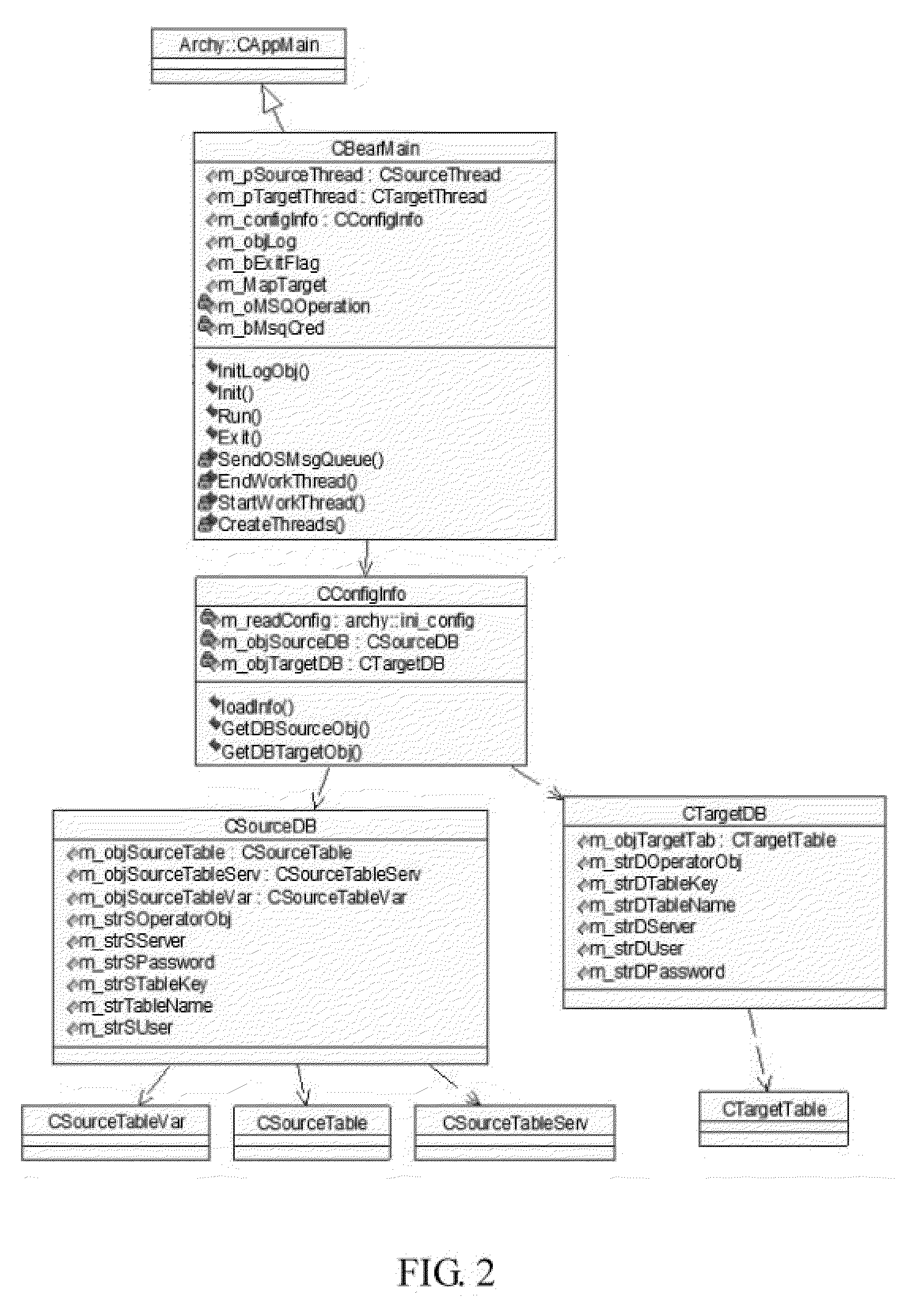

MAP-Queue-Based Data Transfer Method

InactiveUS20100179967A1Reduces abundant cost of development and maintenanceImprove abilitiesDigital data processing detailsTransmissionComputer compatibilityOracle database

As for the data transfer method based on MAP, adopts a MAP data structure during the data transferring process and configures it using SOID (Standard of Interface Department) syntax after encapsulation; the definition of MAP data structure; one system consists of many matching and individual source ends and target ends, one source end just accesses to its matching target end, and vice versa, all member methods of source and target end adopt MAP structure to transfer data, logic implementation steps are shown as below: data processing of database is the most basic and most featured part of BRS system which adopts SOID syntax, if a table is not simply imported into another Oracle database, it should be treated by another process, that is, generate a derived class directly, and then rewrite “Key process”; data transfer method based on MAP bring excellent compatibility. It nearly supports all kinds of existing platforms, protocols, businesses and manufacturers.

Owner:LINKAGE TECH GROUP

Computer system and network interface with hardware based packet filtering and classification

ActiveUS9479464B1Increase speedIncrease data rateData switching by path configurationData fieldClass of service

A data processing system adapted for high-speed network communications, a method for managing a network interface and a network interface for such system, are provided, in to which processing of packets received over the network is achieved by embedded logic at the network interface level. Incoming packets on the network interface are parsed and classified as they are stored in a buffer memory. Functional logic coupled to the buffer memory on the network interface is enabled to access any data field within a packet in a single cycle, using pointers and packet classification information produced by the parsing and classifying step. Results of operations on the data fields in the packets are available before the packets are transferred out of the buffer memory. A data processing system, a method for management of a network interface and a network interface are also provided by the present invention that include an embedded firewall at the network interface level of the system, which protects against inside and outside attacks on the security of data processing system. Furthermore, a data processing system, a method for management of a network interface and a network interface are a provided by the present invention that support class of service management for packets incoming from the network, by applying priority rules at the network interface level of the system.

Owner:VALTRUS INNOVATIONS LTD +1

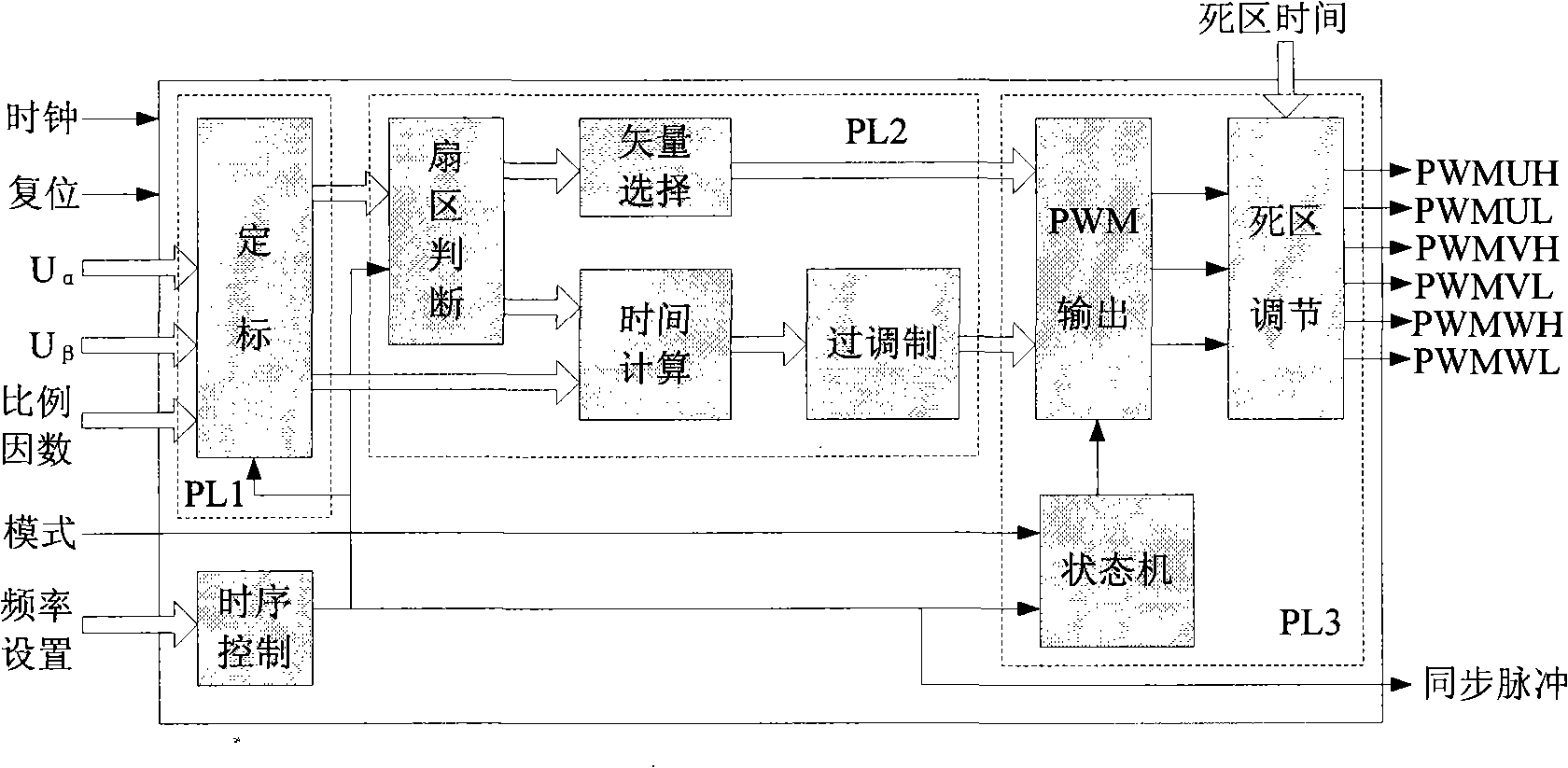

Space vector width pulse modulation method based on FPGA

InactiveCN101272123AAvoid complex calculationsFlexible programmingElectronic commutation motor controlAC motor controlModularityModular design

The invention provides a realizing scheme of a space vector pulse width modulating arithmetic based on FPGA. The scheme divides a space vector pulse width modulating (SVPWM) adjustor into nine modules according to an FPGA modular design philosophy which are: picketage, time-oriented sequential control; sector judging, a state machine, vector selection, time calculation, over modulation, PWM output and dead area adjusting modules. The scheme fully utilizes the parallel processing characteristic of the FPGA as well as the logic realizing and hardware multiplier resources and mainly adopts logical judgment and a plurality of multiplication calculations, thus avoiding the complex calculations like arc tangent and trigonometric function. The scheme supports the modes of over modulation, dead area adjusting, symmetrical PWM and non- symmetrical PWM.

Owner:JIANGNAN UNIV

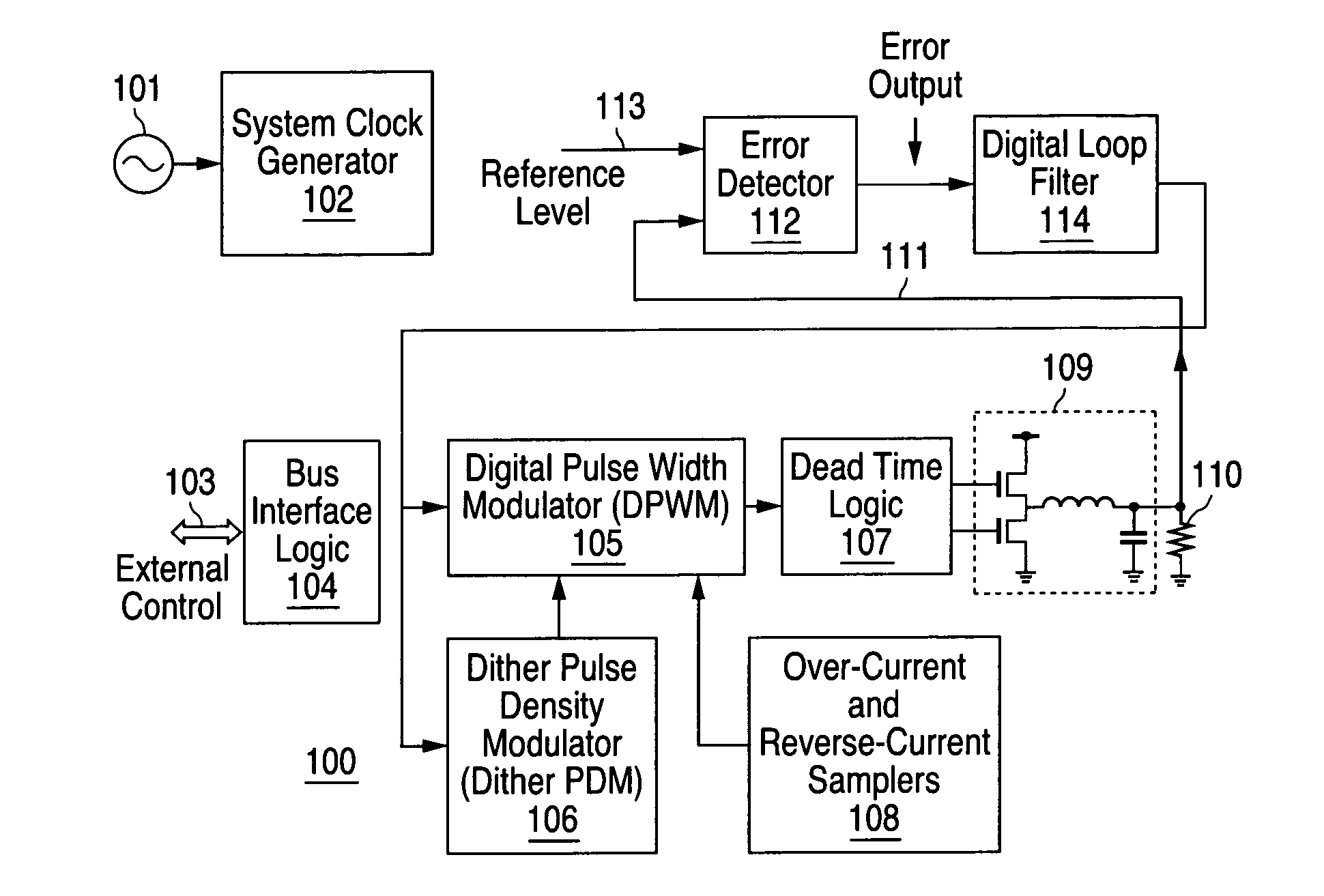

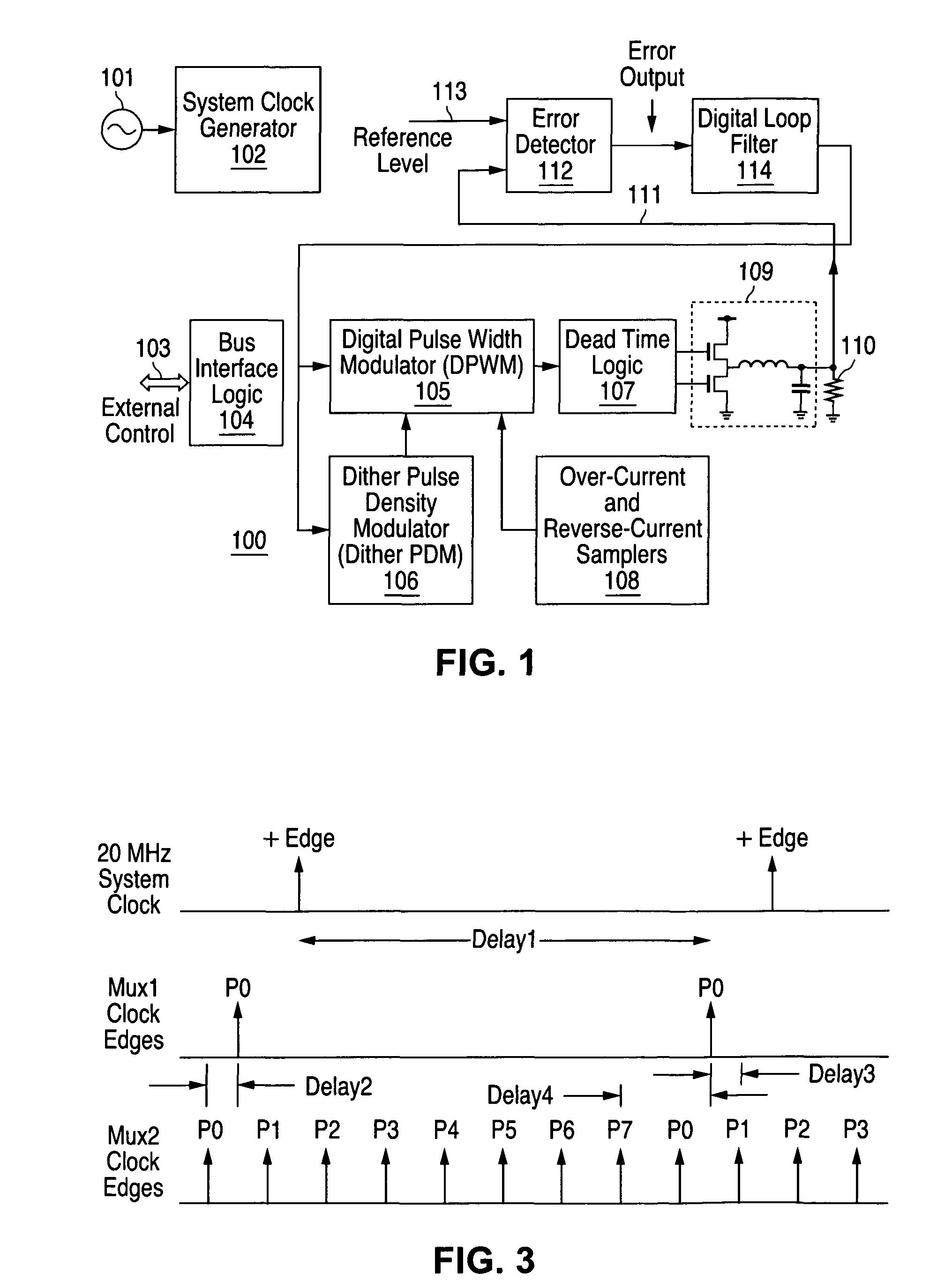

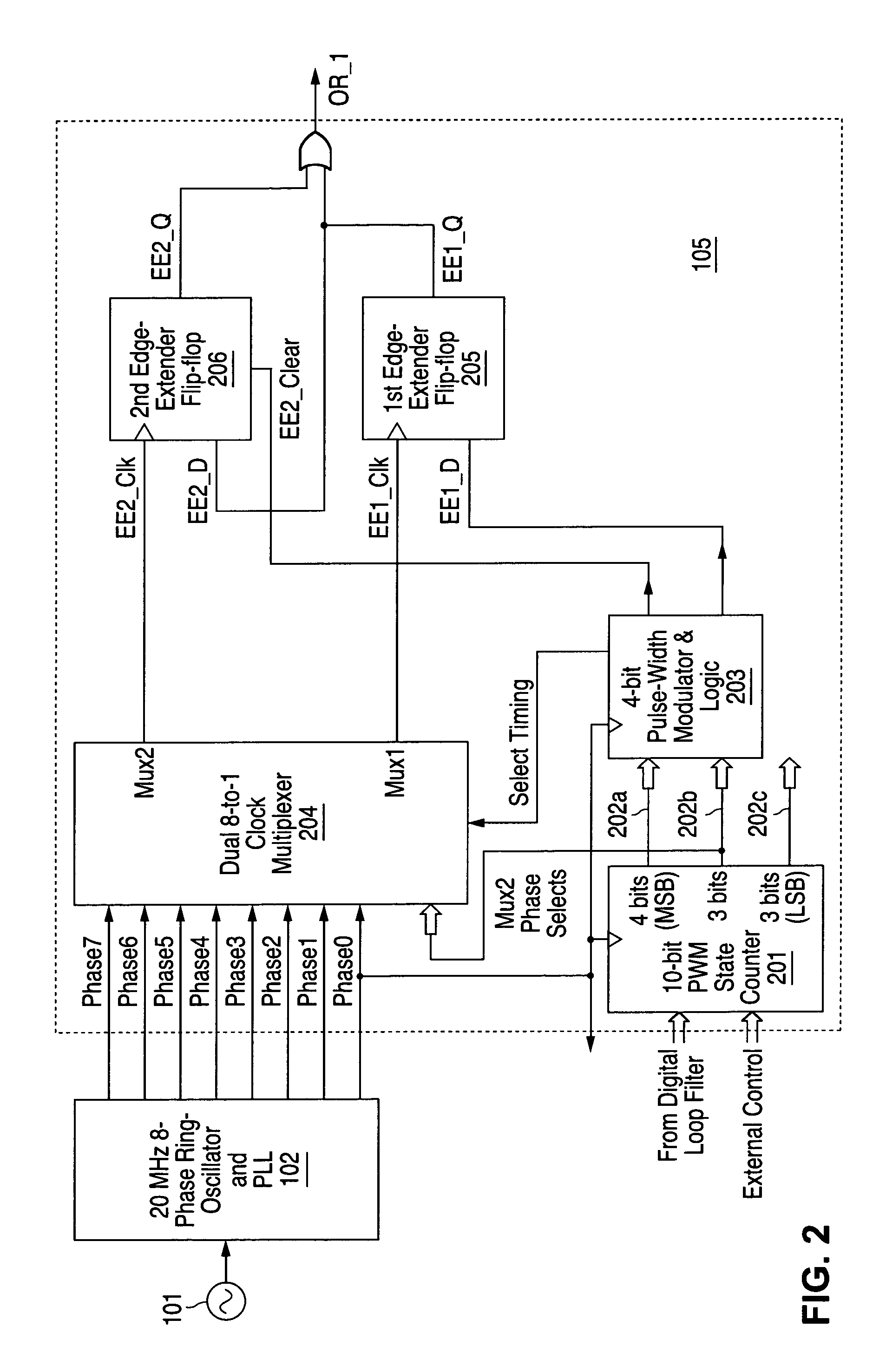

Fine-resolution edge-extending pulse width modulator

Fine resolution pulse width modulation is achieved through feed-forward edge extending logic. A ring-oscillator produces phase-shifted versions of a system clock and two latches operate in parallel with the system clock output from the multiplexer clocking a first latch and a selected phase-shifted version of the system clock from the multiplexer clocking the second latch. The first latch receives a coarse output pulse equal to a selected number of clock periods as an input, while the second latch receives the output of the first latch as an input. A logic gate combines outputs from the latches to produce the output pulse having a trailing edge extended by a selected number of phase divisions.

Owner:NAT SEMICON CORP

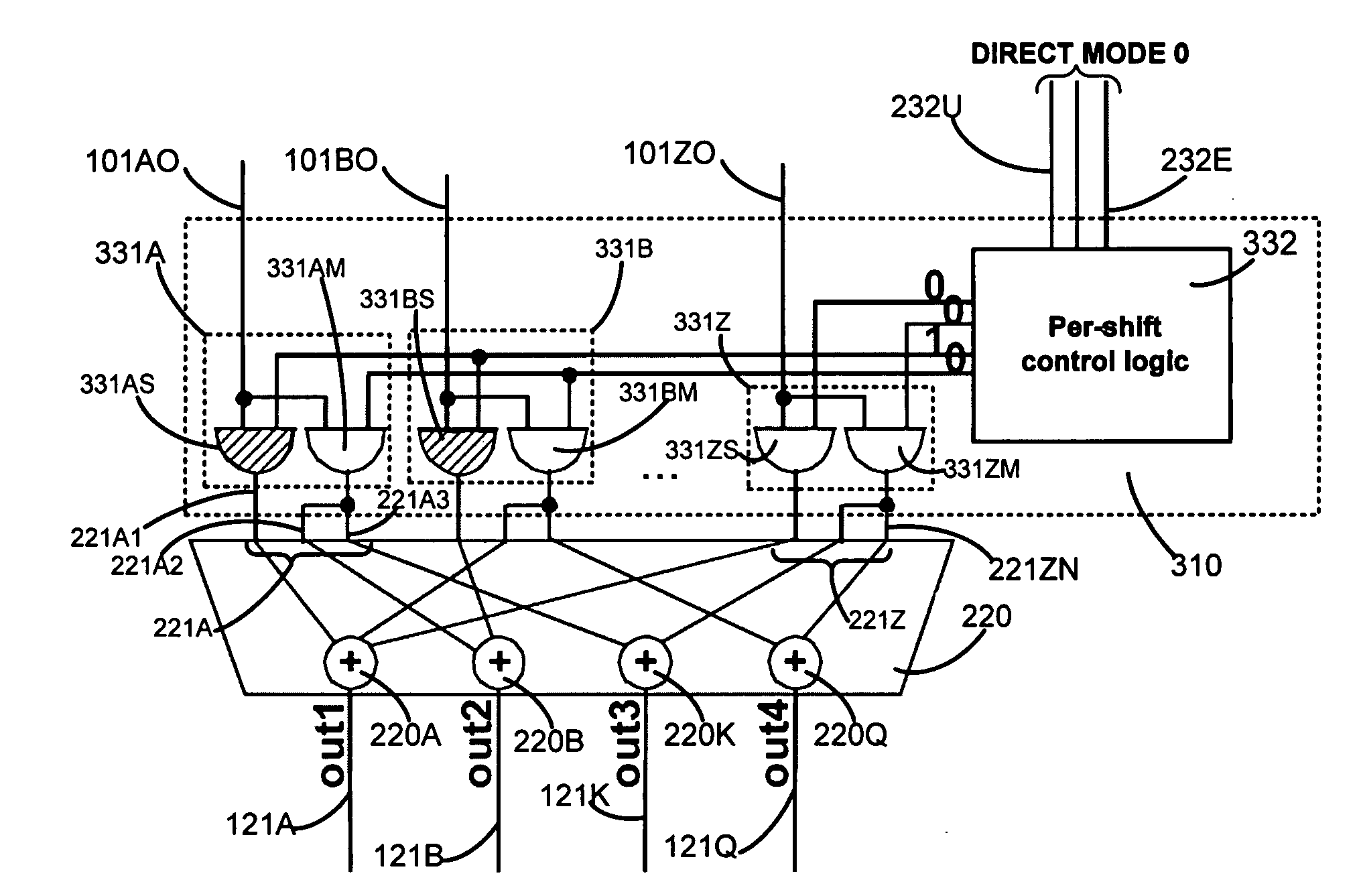

Scan compression circuit and method of design therefor

A scan-based circuit includes a selector that is implemented by multiple observation logics. Each observation logic is coupled to a scan chain to receive data to be supplied to a combinational compressor. Each observation logic is also coupled to a single input line in a corresponding group of input lines of the combinational compressor, to selectively supply data from the coupled scan chain. Each observation logic may be coupled to additional input lines (if present) in the corresponding group. The selector is operable on a per-shift basis in (a) transparent mode wherein data is supplied to all input lines and (b) several direct modes wherein data from only one scan chain is supplied at each compressor output without overlap.

Owner:SYNOPSYS INC

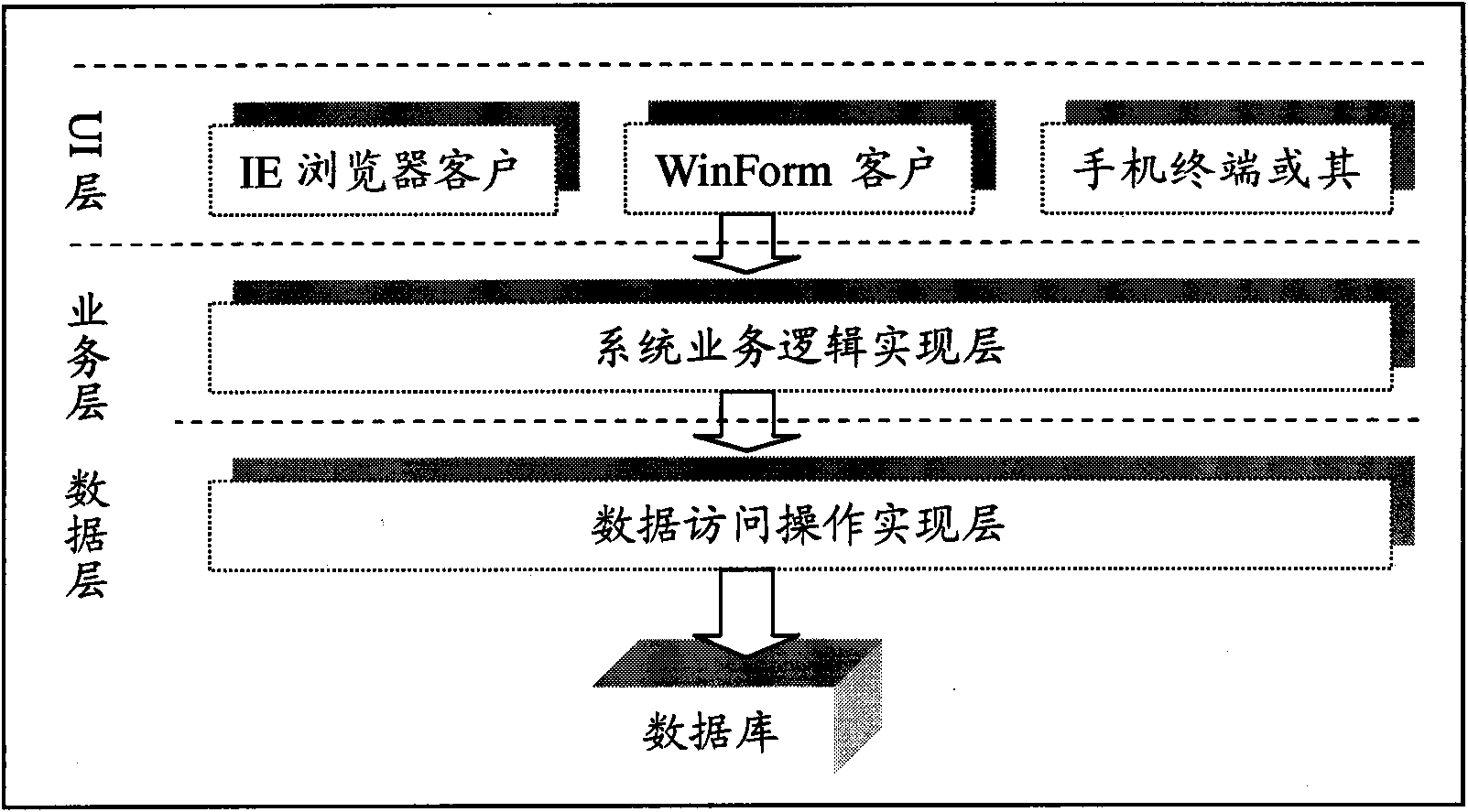

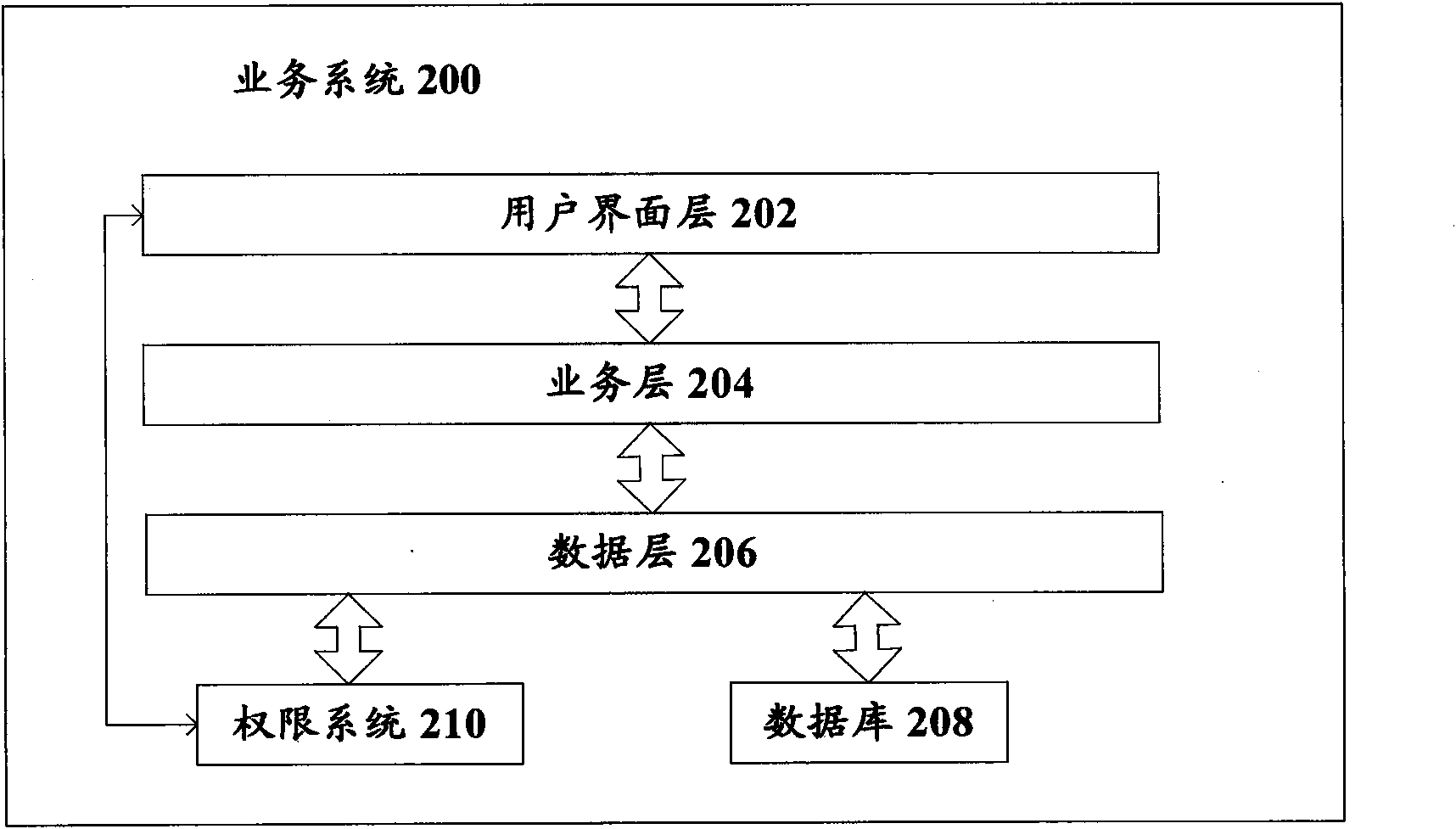

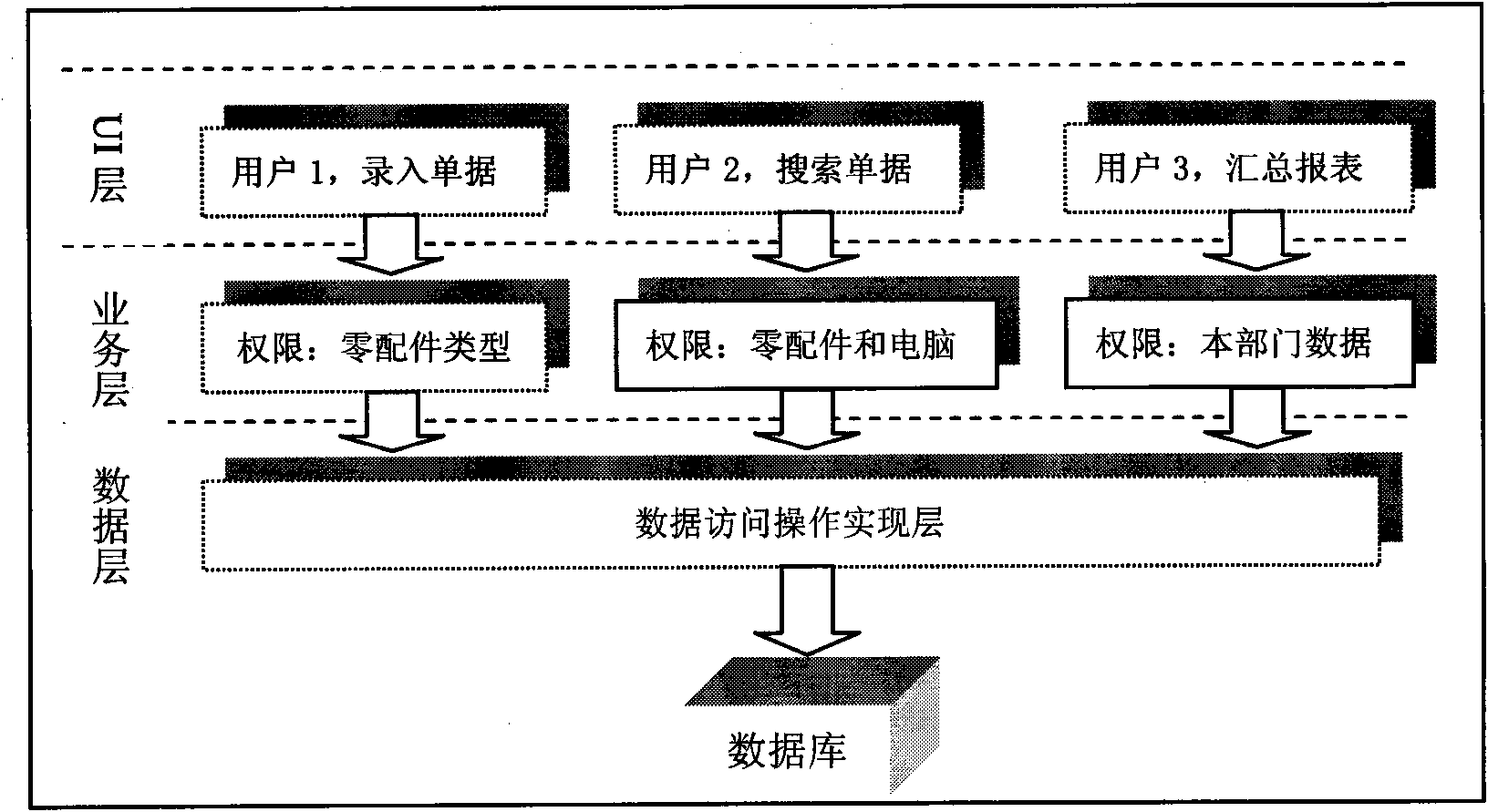

Service system, authority system and data authority control method for service system

InactiveCN101587439AIntegrity guaranteedReduce workloadSpecific program execution arrangementsMemory systemsUser inputAuthority control

The present invention provides a service system comprising a user interface, wherein, the user inputs instructions by the user interface; a service layer, wherein, the corresponding system service logic can be implemented according to the instructions inputted by the user; a data layer for implementing the access operations of the data according to the system service logic; a database for storing the data required by the service system; an authority system which is isolated with the service layer for providing the authority control of the data layer by the authority regulation. The invention not only implements the data layer authority control facing to the service object, but also processes the service object and the data authority of associated service object, keeps the integrality of the object data, the authority control is unite completed by the core part of the invention, the service program developing personnel need not focus on the authority regulation any longer, when the program is programmed, only the concrete service logic needs to be completed.

Owner:YONYOU NETWORK TECH

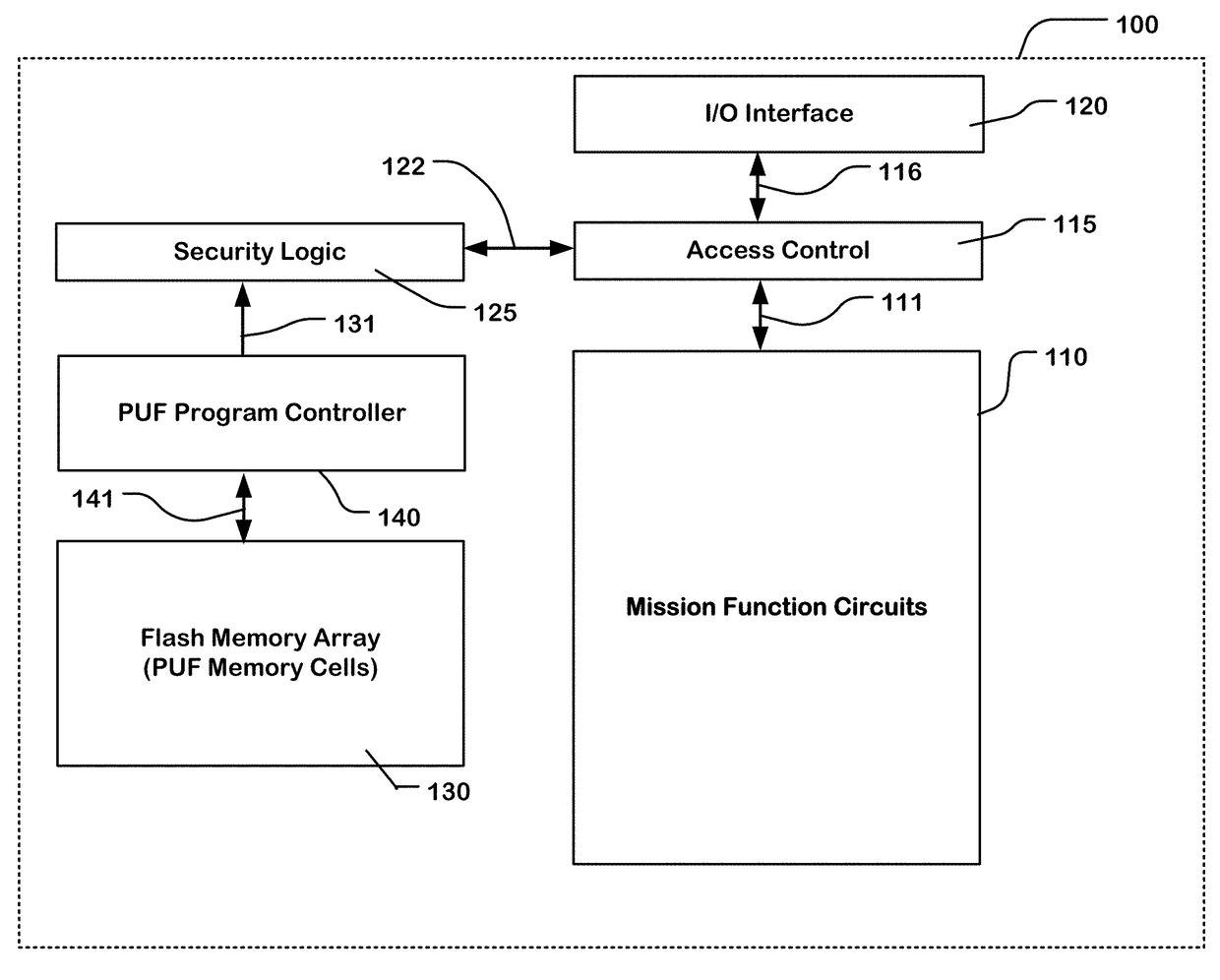

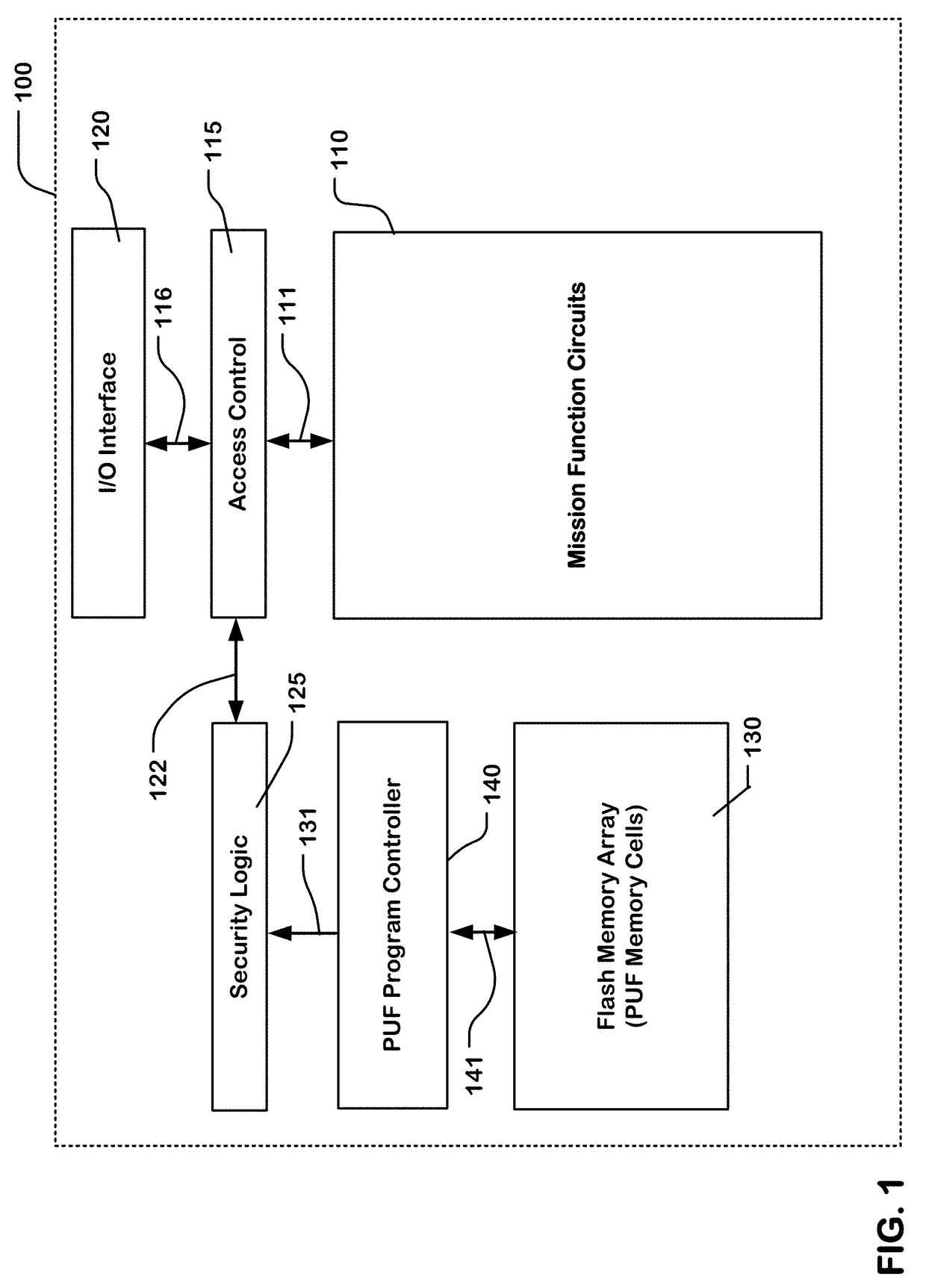

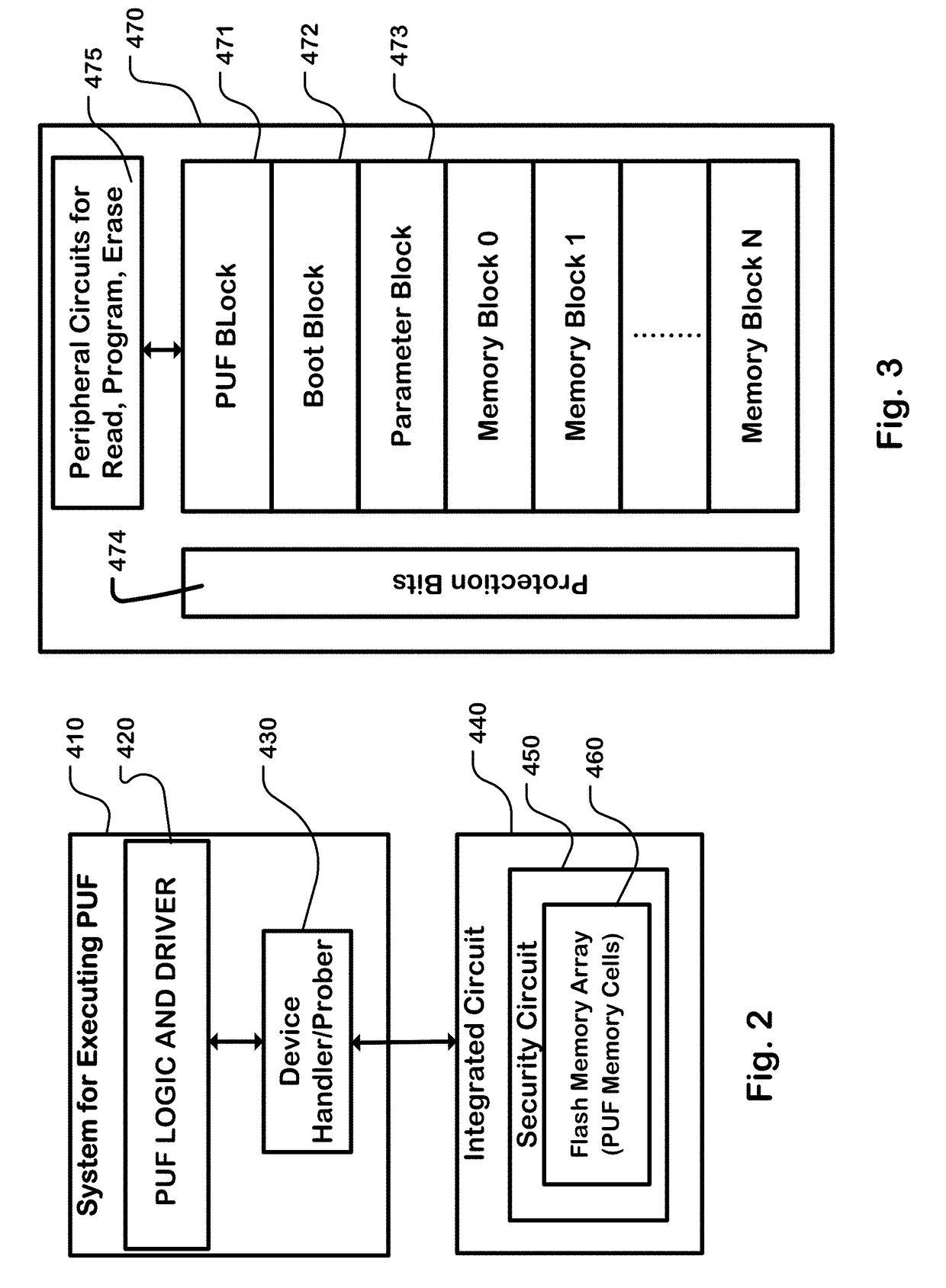

Non-volatile memory with security key storage

ActiveUS20180039581A1Increase flexibility and reliabilitySuitable for useMemory architecture accessing/allocationKey distribution for secure communicationData setKey storage

A system and method for utilizing a security key stored in non-volatile memory, and for generating a PUF-based data set on an integrated circuit including non-volatile memory cells, such as flash memory cells, are described. The method includes storing a security key in a particular block in a plurality of blocks of the non-volatile memory array; utilizing, in a security logic circuit coupled to the non-volatile memory array, the security key stored in the particular block in a protocol to enable access via a port by external devices or communication networks to data stored in blocks in the plurality of blocks; and enabling read-only access to the particular block by the security logic for use in the protocol, and preventing access to the particular block via the port.

Owner:MACRONIX INT CO LTD

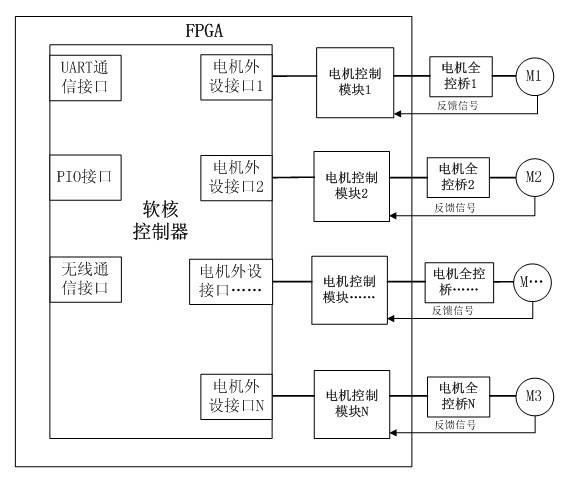

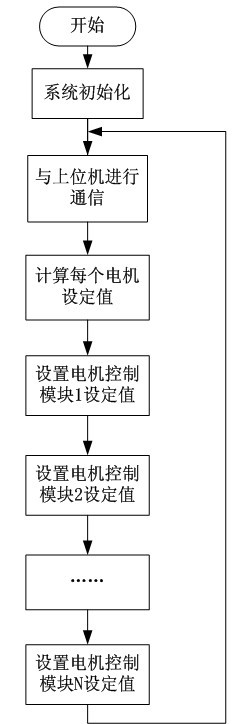

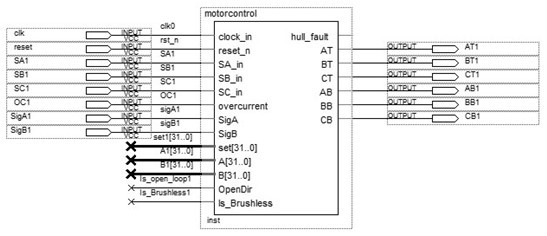

A fpga-based high-precision multi-motor control method

InactiveCN102291062AFast operationImprove performanceMultiple motor speed/torque controlControl systemMiniaturization

The invention belongs to the field of motor control, and in particular relates to a high-precision multi-motor control method. The present invention is a high-precision multi-motor control method based on FPGA. The control system includes an embedded CPU soft core and a motor control module implemented by hardware logic. , A motor control peripheral driver interface that connects the CPU and the motor control module in accordance with the avalon bus protocol. The present invention provides a multi-motor control method capable of accurate measurement, real-time control and miniaturization. The method can adjust the number of motor control modules according to the number of motors required; configure the parameters of the motor control modules according to the types and characteristics of the motors; Configure the peripheral modules of the embedded CPU according to the additional functions of the system, and all the control functions of the system will be realized on one FPGA chip.

Owner:ZHEJIANG UNIV

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com