Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

480 results about "Construction design" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Method and process for design of integrated circuits using regular geometry patterns to obtain geometrically consistent component features

ActiveUS20060112355A1CAD circuit designSpecial data processing applicationsComputer architectureBrick

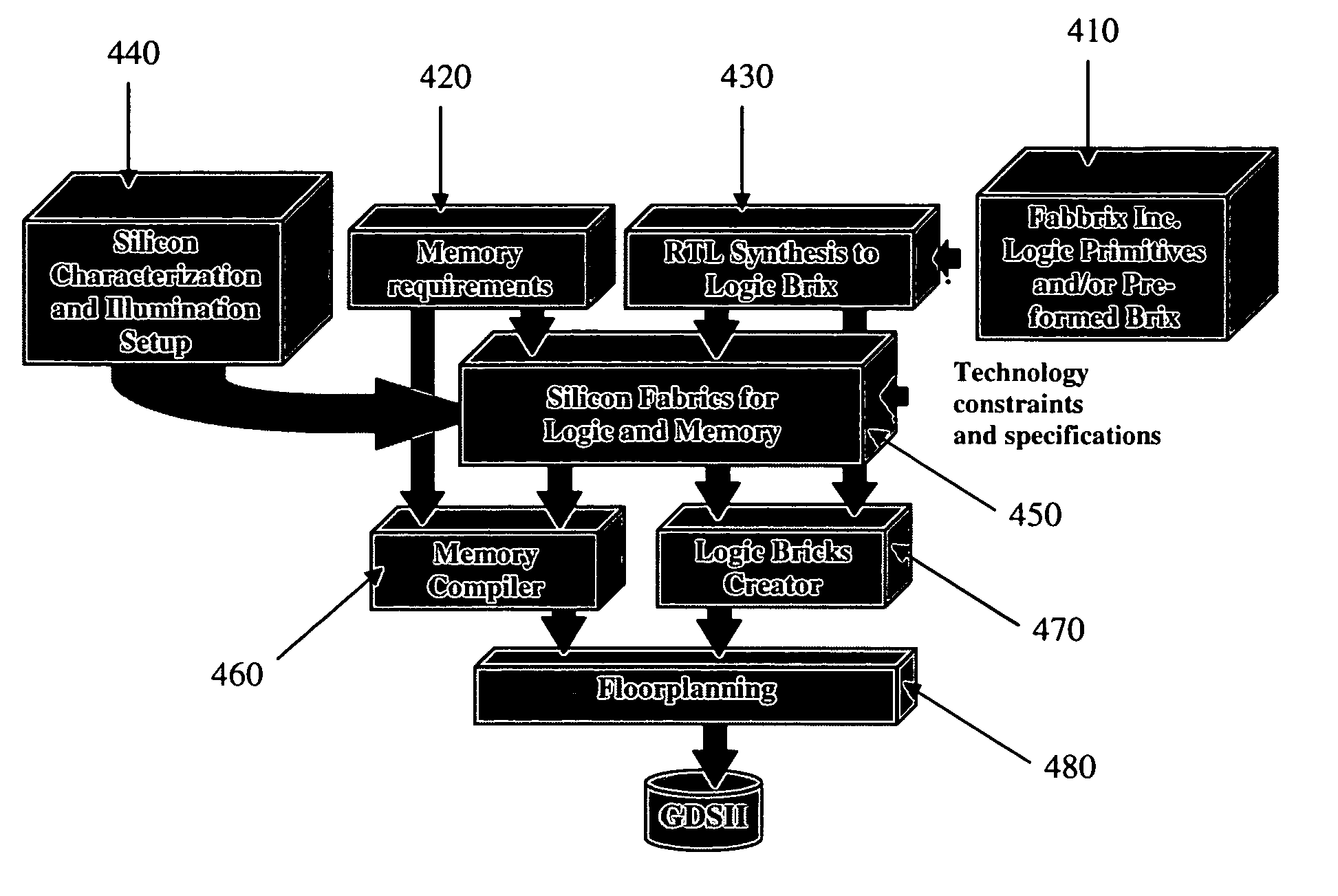

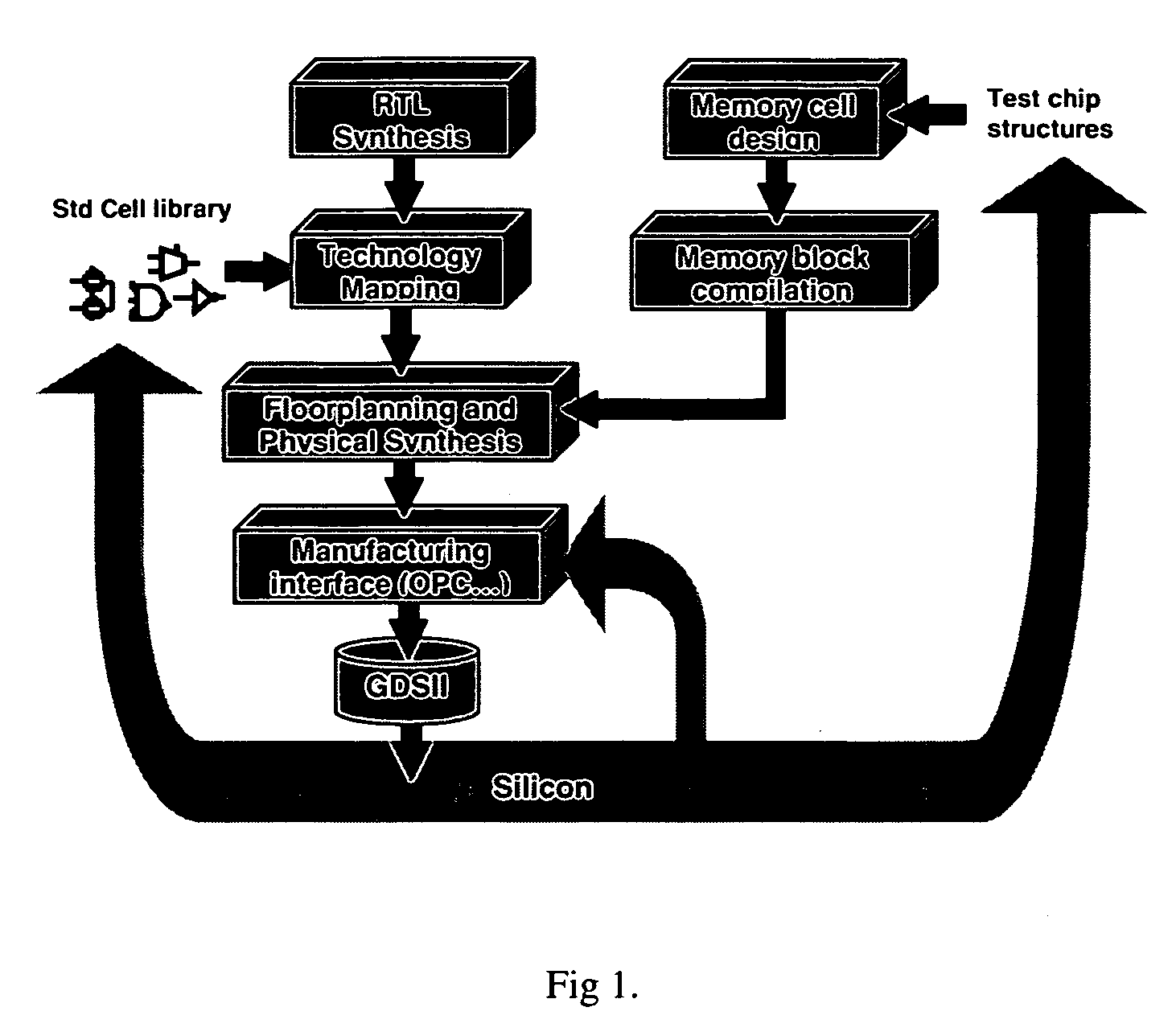

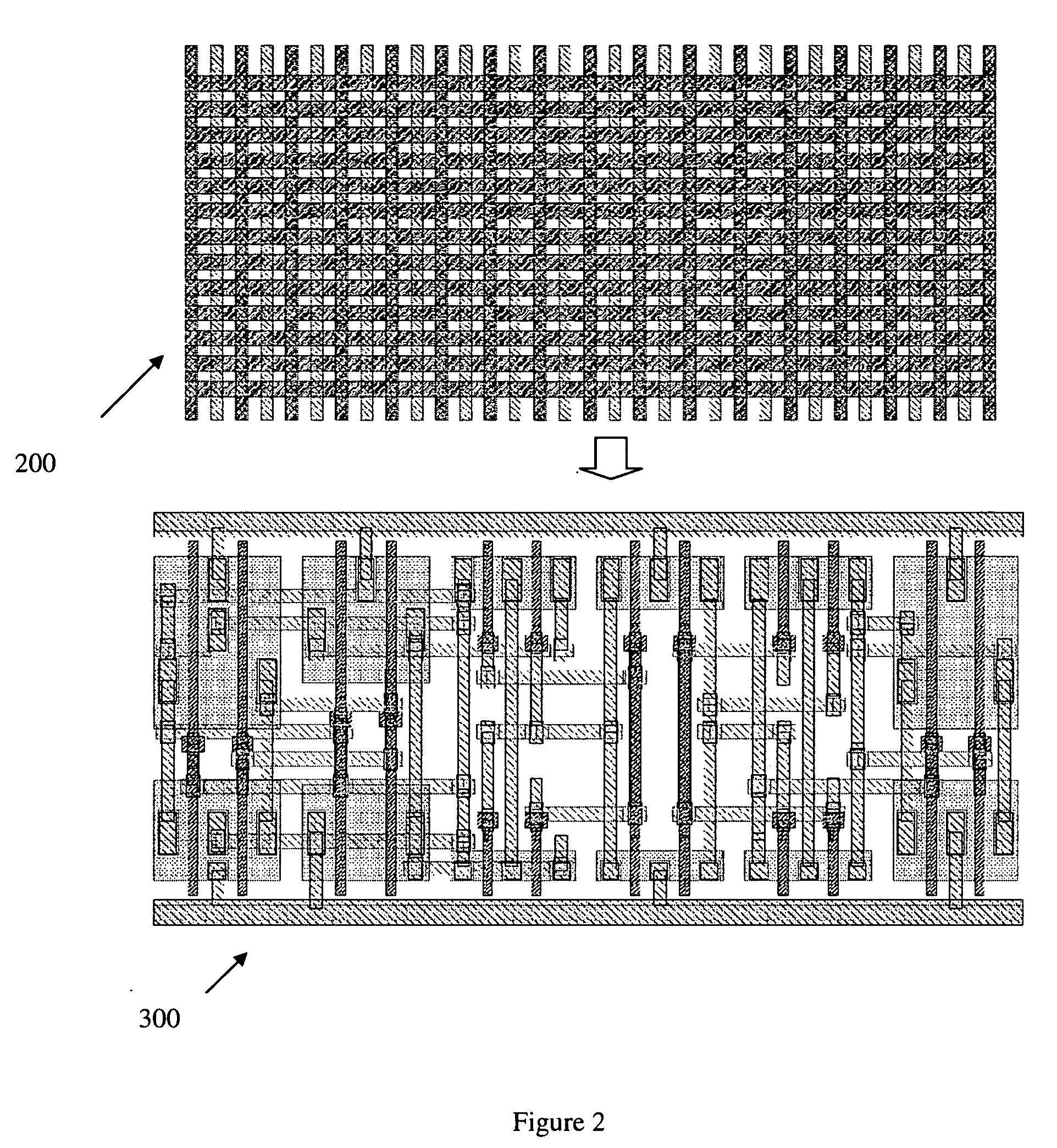

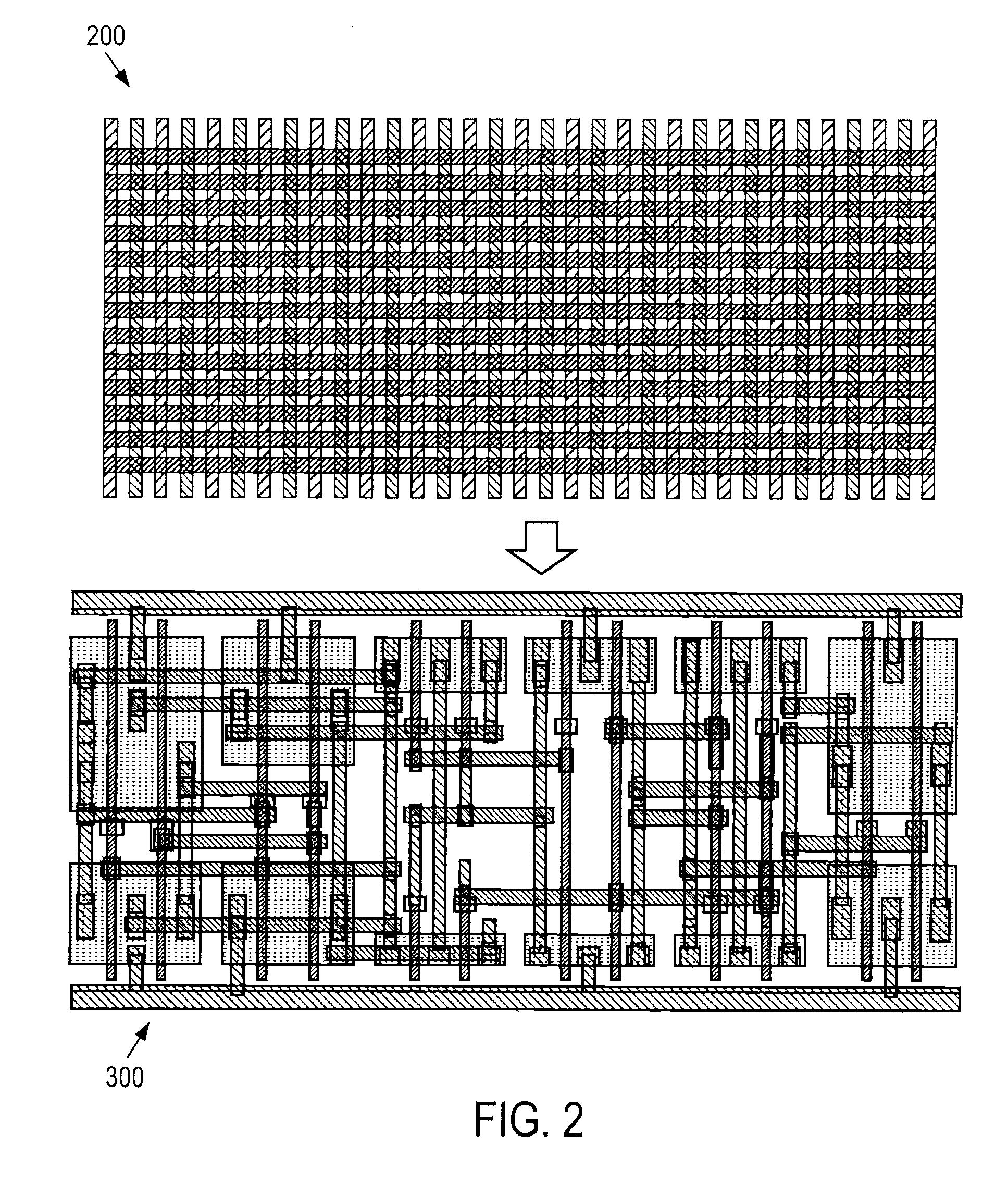

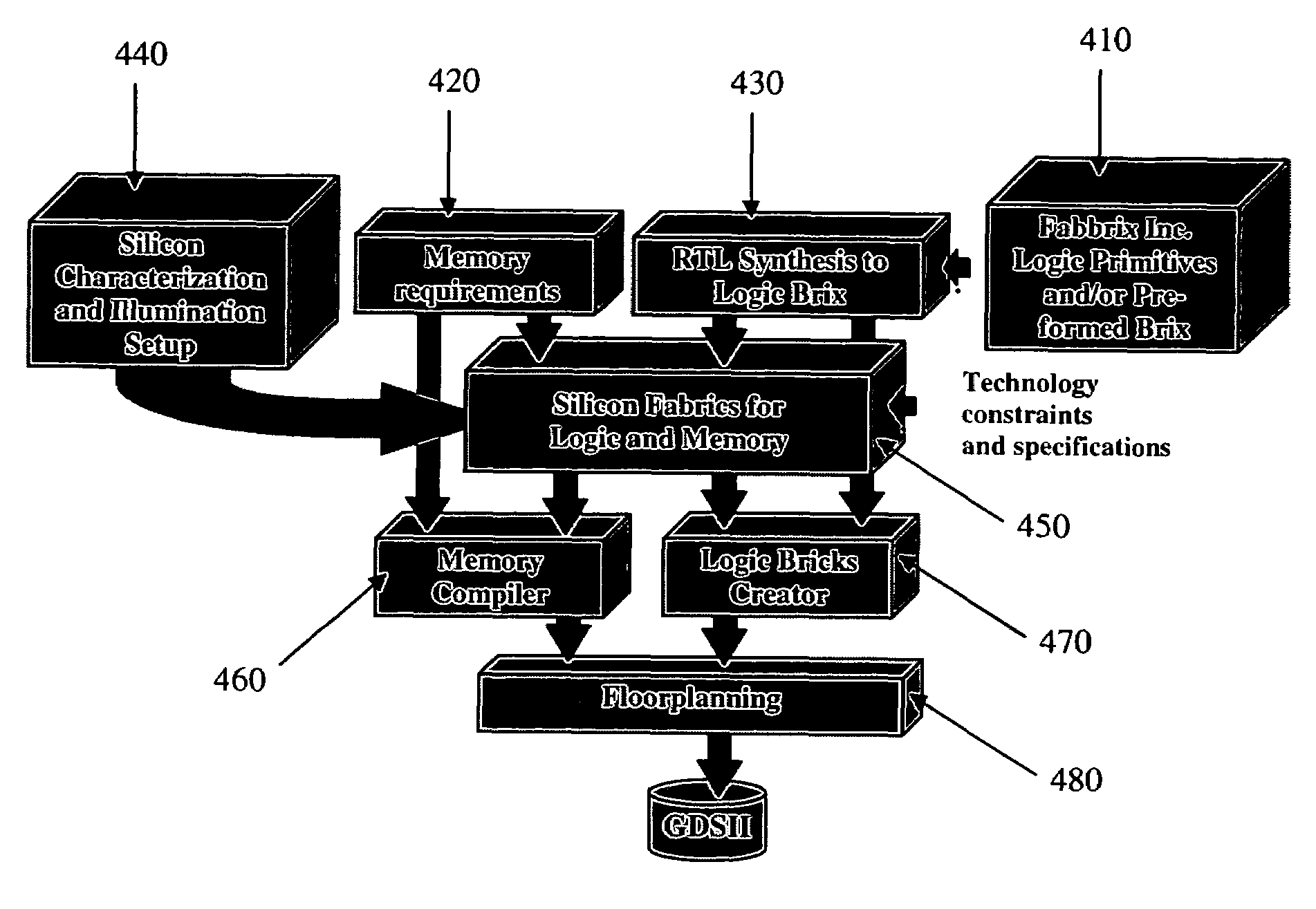

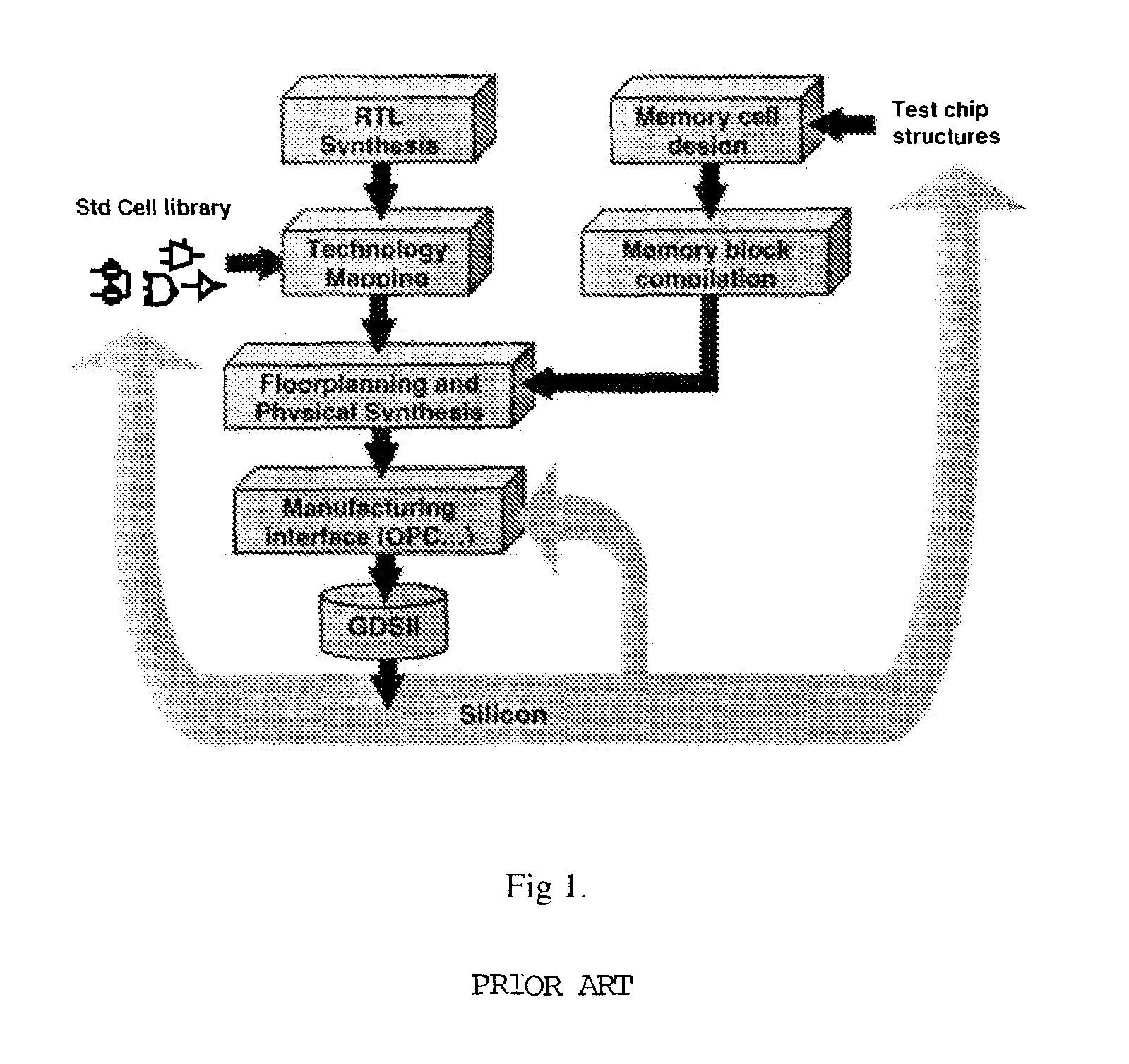

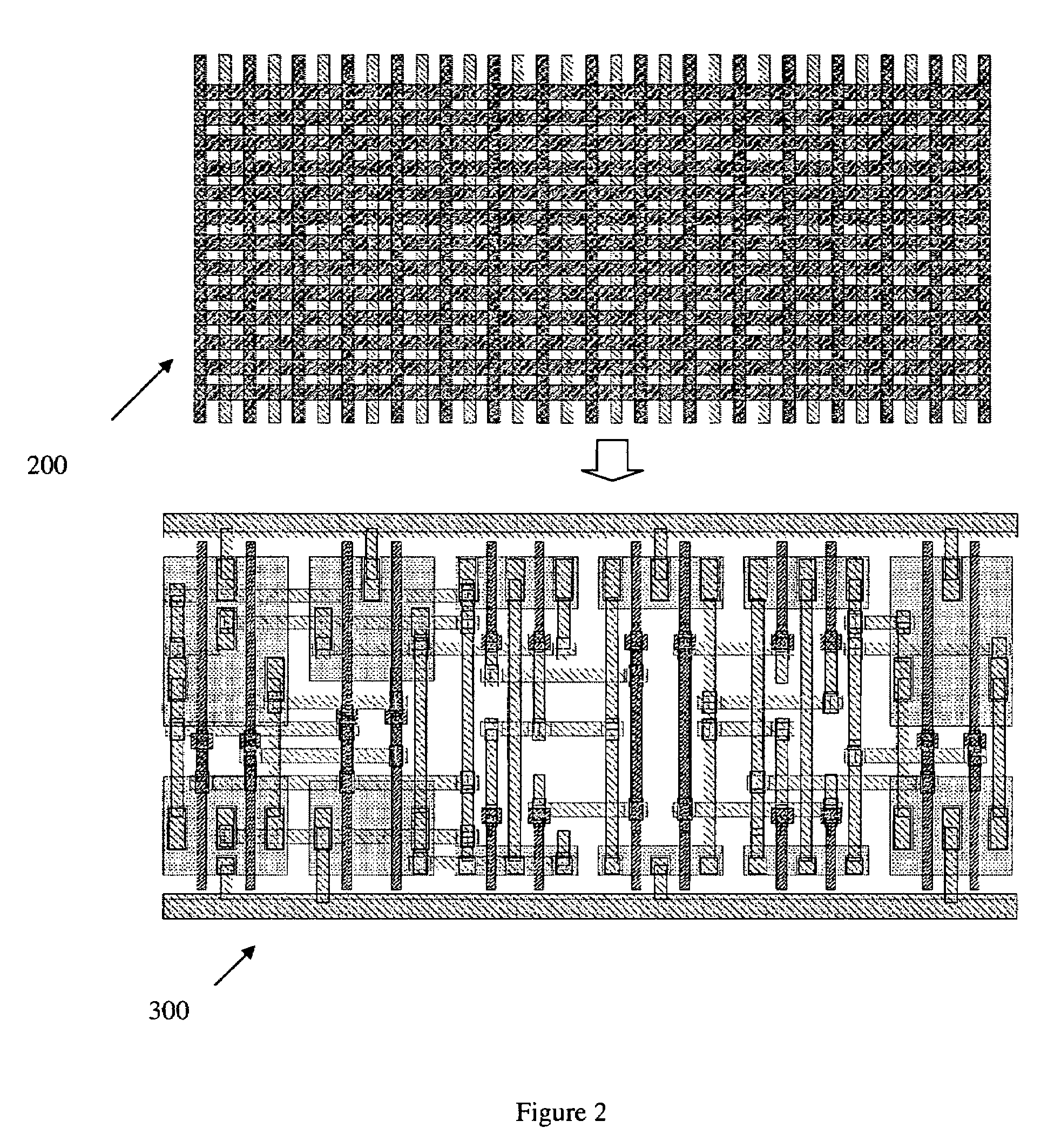

The invention provides a method and process for designing an integrated circuit based on using the results from both 1) a specific set of silicon test structure characterizations and 2) the decomposition of logic into combinations of simple logic primitives, from which a set of logic bricks are derived that can be assembled for a manufacturable-by-construction design. This implementation of logic is compatible with the lithography settings that are used for implementation of the memory blocks and other components on the integrated circuit, particularly by implementing geometrically consistent component features. The invention provides the ability to recompile a design comprised of logic and memory blocks onto a new geometry fabric to implement a set of technology-specific design changes, without requiring a complete redesign of the entire integrated circuit.

Owner:PDF SOLUTIONS INC

Method and process for design of integrated circuits using regular geometry patterns to obtain geometrically consistent component features

InactiveUS20080098334A1CAD circuit designOriginals for photomechanical treatmentComputer architectureBrick

The invention provides a method and process for designing an integrated circuit based on using the results from both 1) a specific set of silicon test structure characterizations and 2) the decomposition of logic into combinations of simple logic primitives, from which a set of logic bricks are derived that can be assembled for a manufacturable-by-construction design. This implementation of logic is compatible with the lithography settings that are used for implementation of the memory blocks and other components on the integrated circuit, particularly by implementing geometrically consistent component features. The invention provides the ability to recompile a design comprised of logic and memory blocks onto a new geometry fabric to implement a set of technology-specific design changes, without requiring a complete redesign of the entire integrated circuit.

Owner:PDF SOLUTIONS INC

Method and process for design of integrated circuits using regular geometry patterns to obtain geometrically consistent component features

The invention provides a method and process for designing an integrated circuit based on using the results from both 1) a specific set of silicon test structure characterizations and 2) the decomposition of logic into combinations of simple logic primitives, from which a set of logic bricks are derived that can be assembled for a manufacturable-by-construction design. This implementation of logic is compatible with the lithography settings that are used for implementation of the memory blocks and other components on the integrated circuit, particularly by implementing geometrically consistent component features. The invention provides the ability to recompile a design comprised of logic and memory blocks onto a new geometry fabric to implement a set of technology-specific design changes, without requiring a complete redesign of the entire integrated circuit.

Owner:PDF SOLUTIONS INC

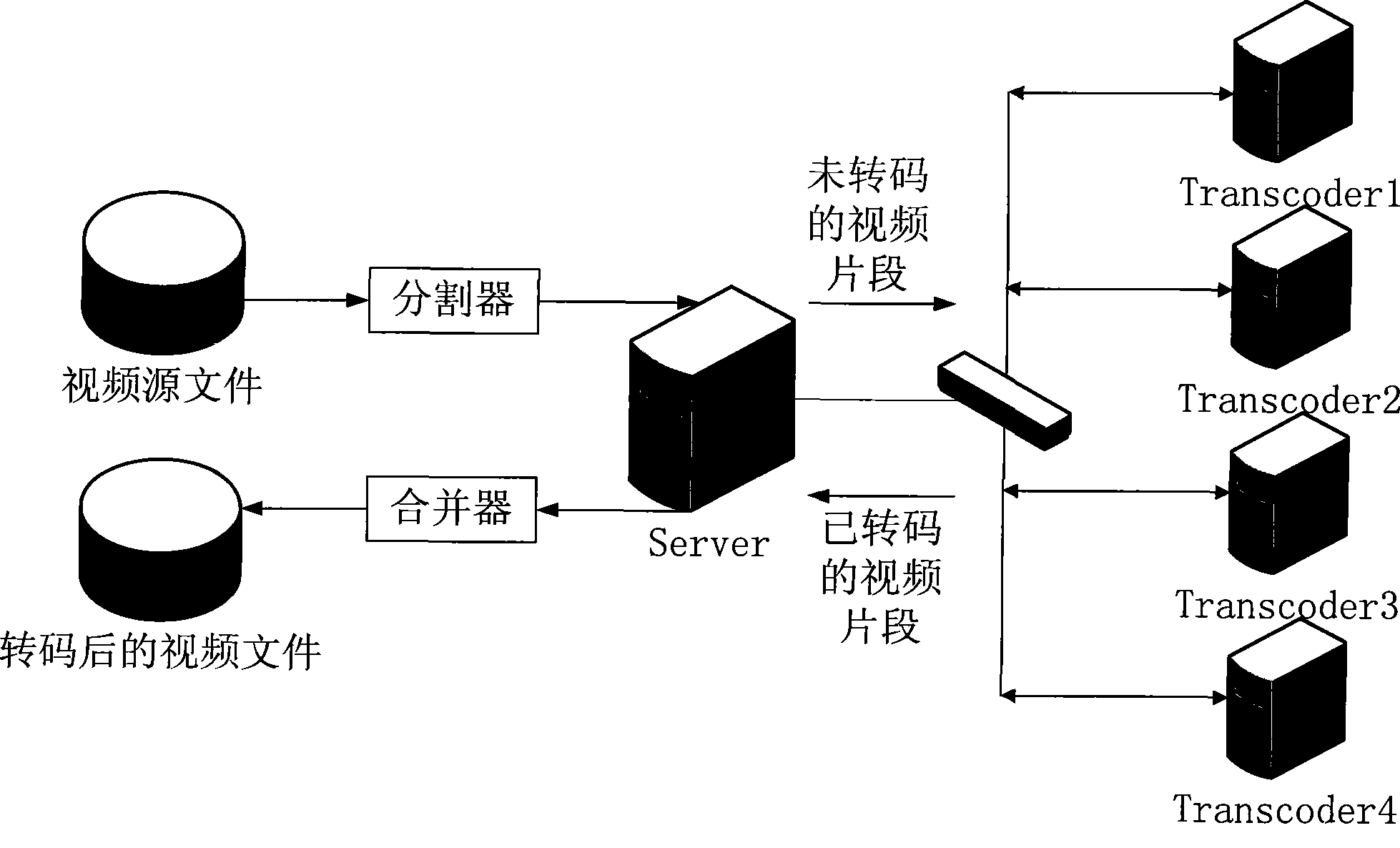

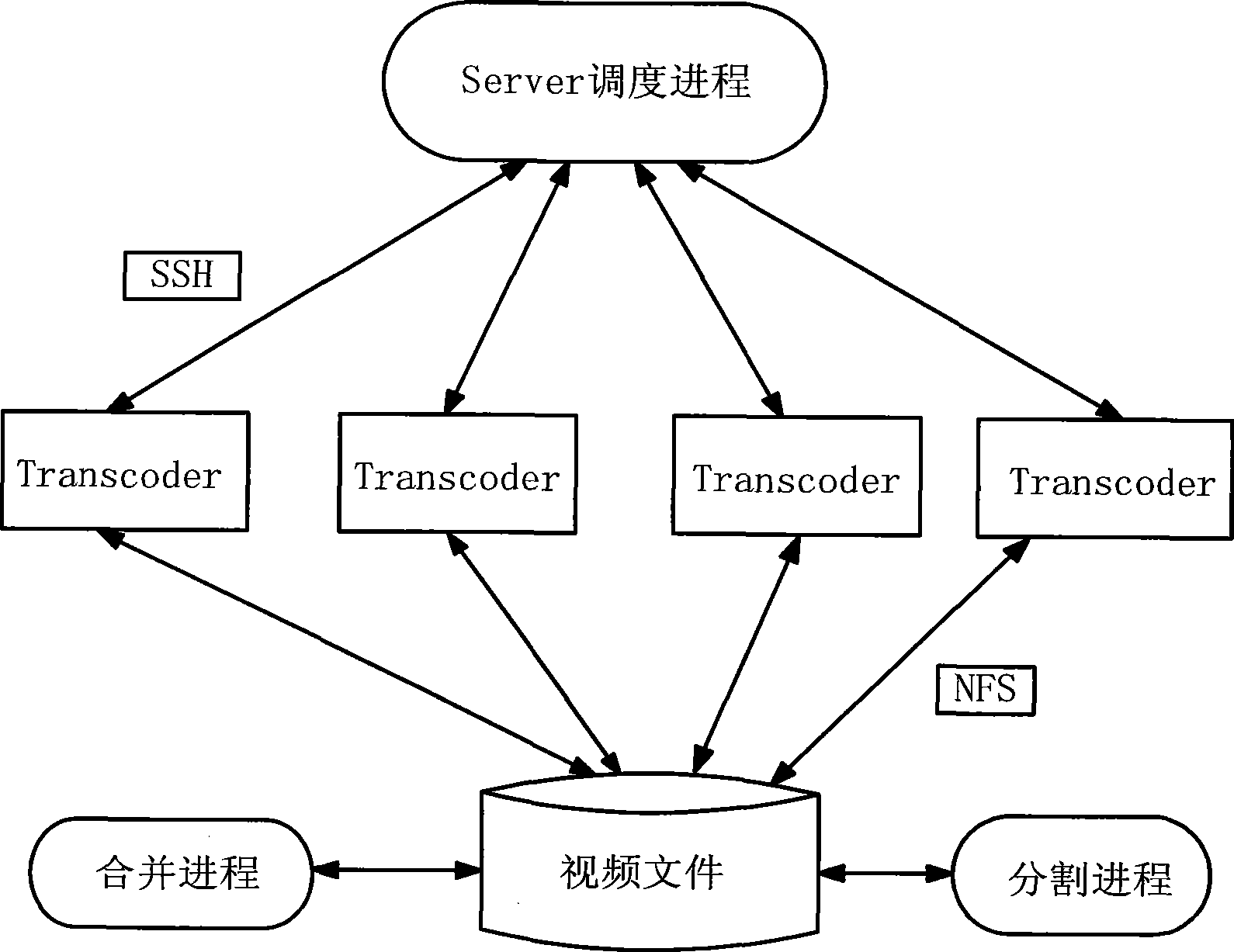

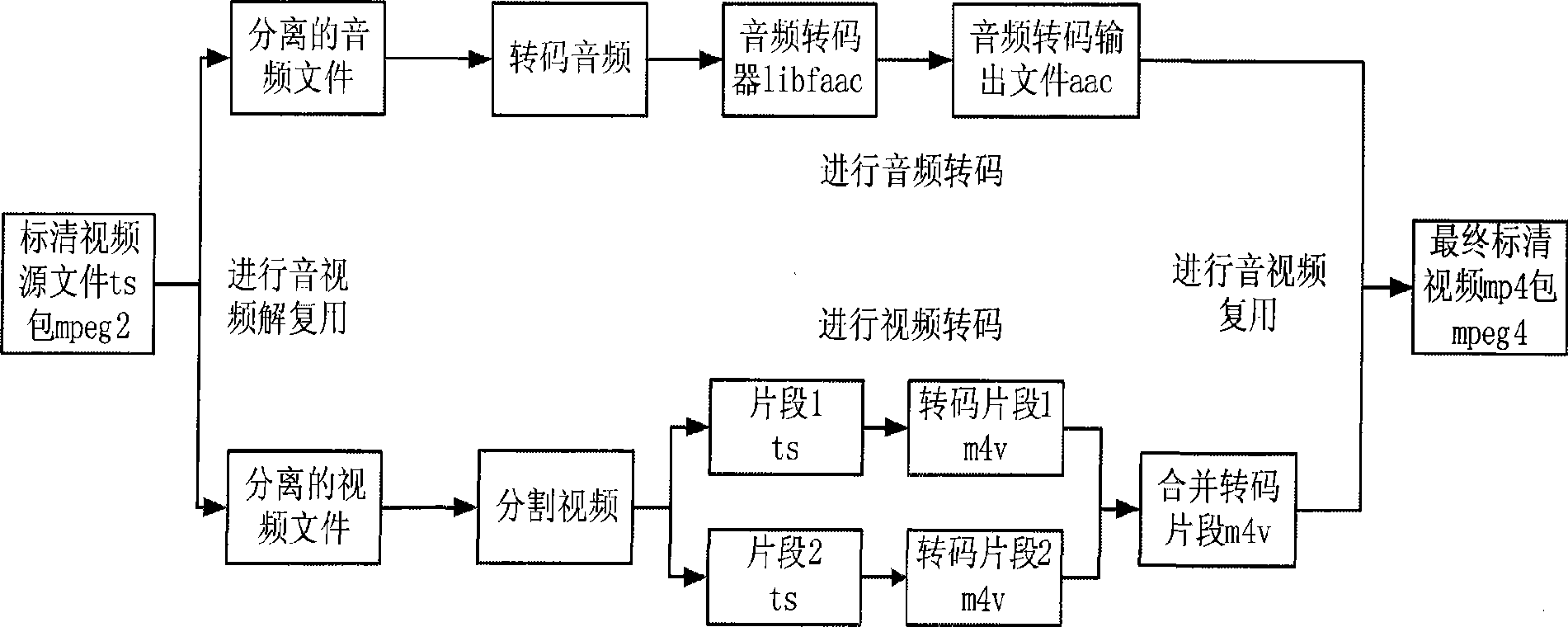

Distributed multi-format digital video transcoding construction design method

InactiveCN101459848AIncrease transcoding rateIncrease the rate of transcodingTelevision systemsDigital video signal modificationDigital videoTranscoding

The invention discloses a method for designing a distributed type multiformat video transcoding structure, which comprises the following steps: rapidly dividing a video in a seamless mode after de-multiplexing an original video file, transmitting video segments and audio files to each of transcoding PCs for carrying out rapid multiformat transcoding through a dynamic scheduler process, the decoding only needs once after inputting the video with a certain format, then various formats of code screams can be output, and the code rate control can be carried out to the output code stream well, finally collecting the video segments after the transcoding to carry out a seamless splitting and multiplexing with the audio files after the transcoding. The invention improves the transcoding rate of a pixel area cascade decoder, which increases the quality of the video after the transcoding.

Owner:XI AN JIAOTONG UNIV

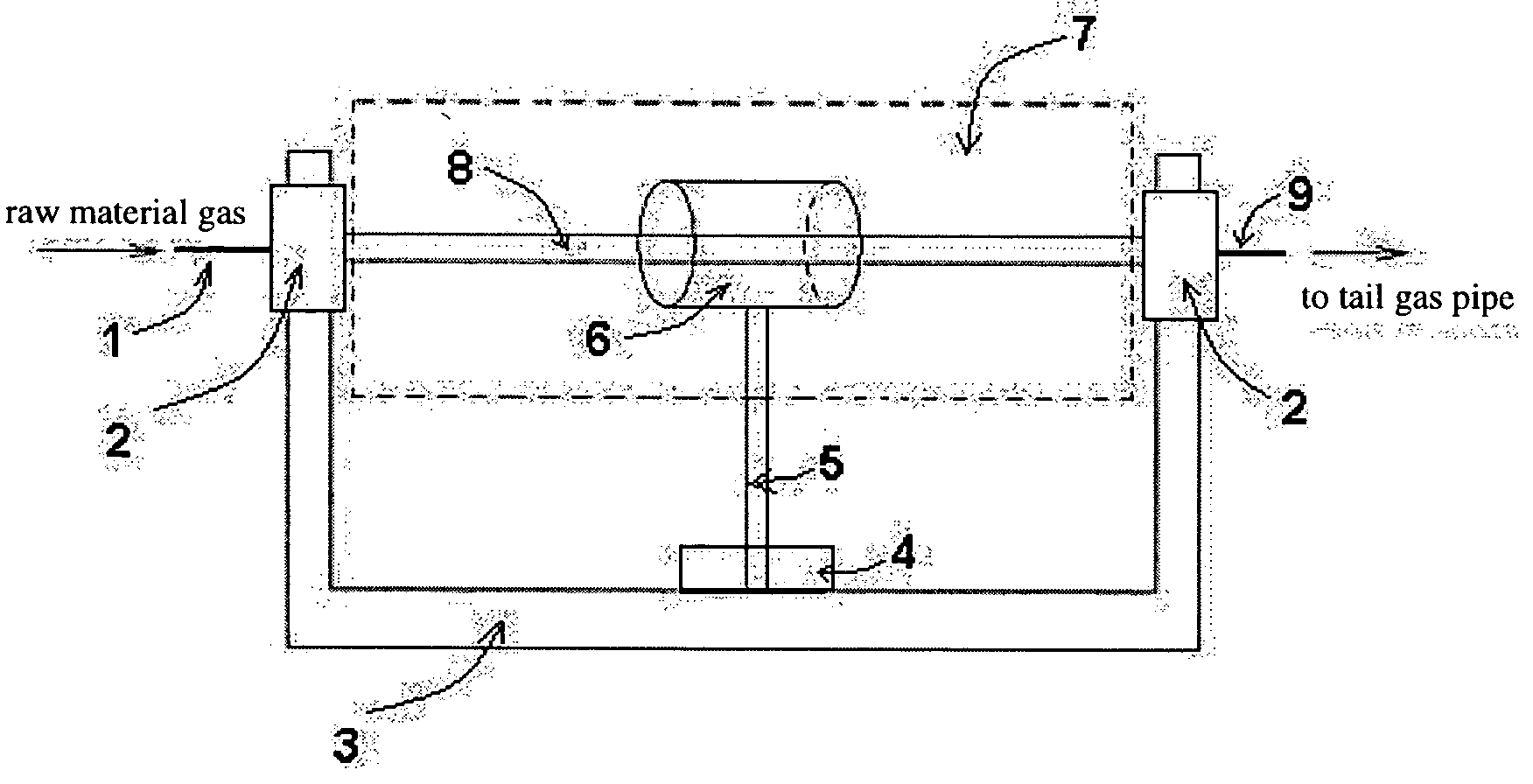

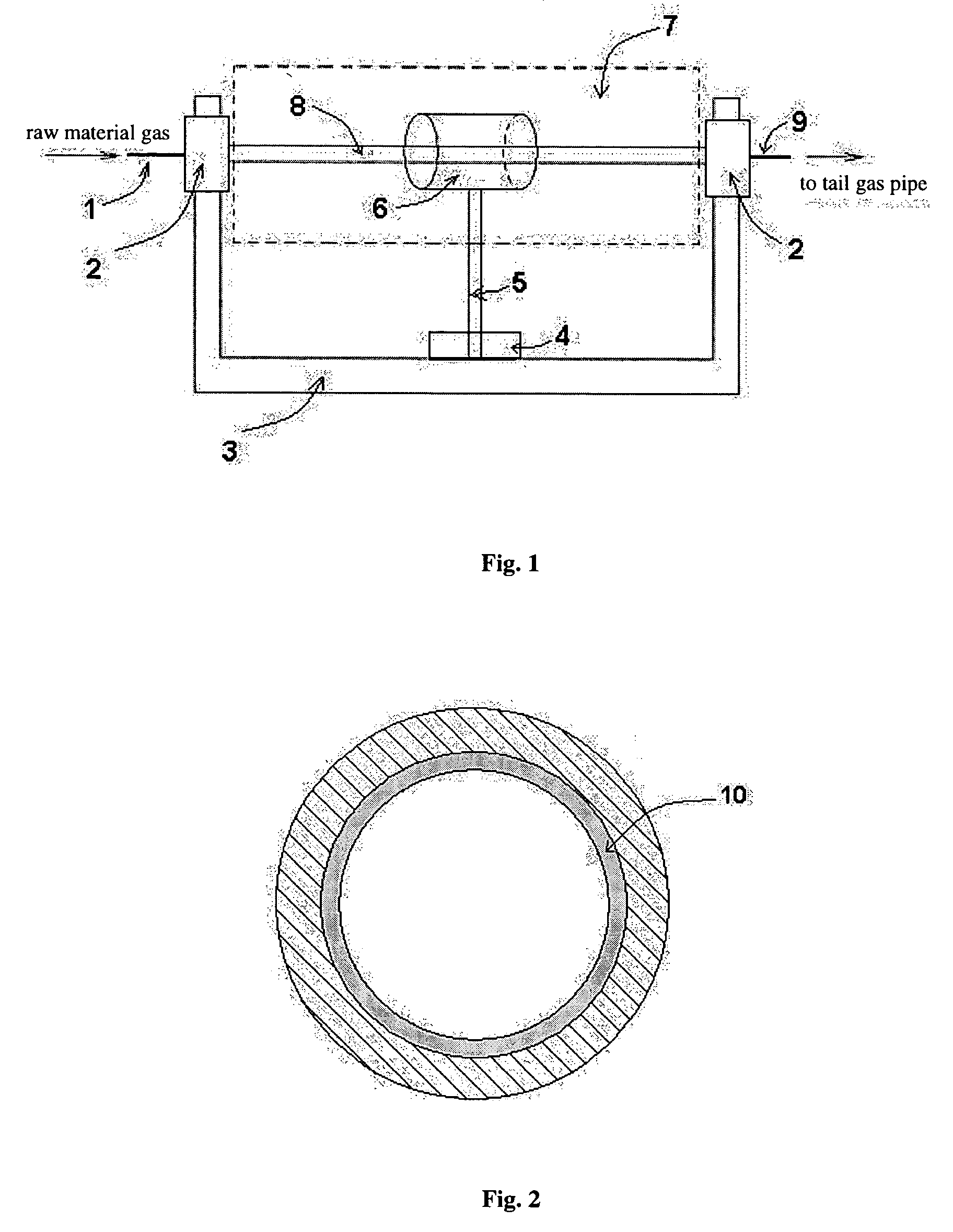

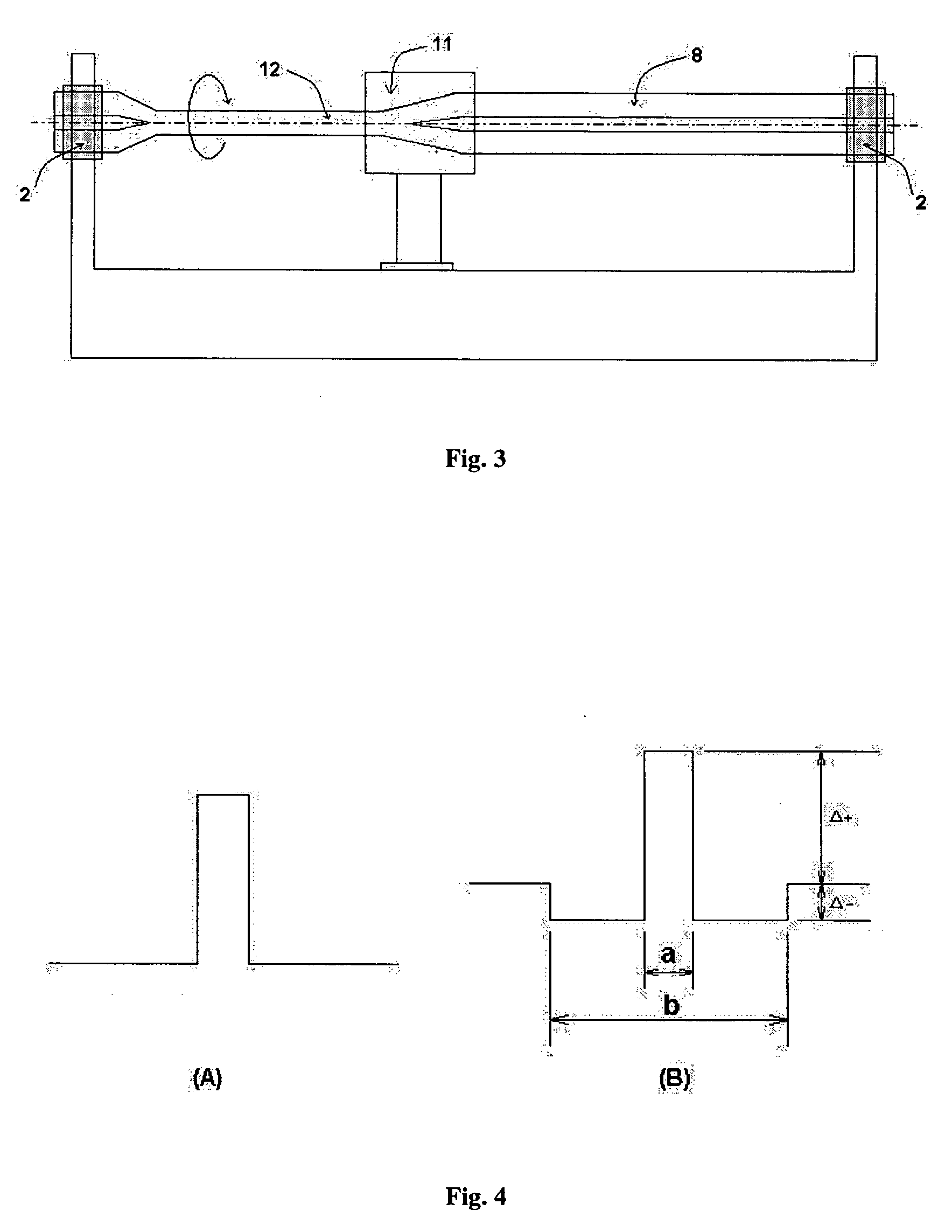

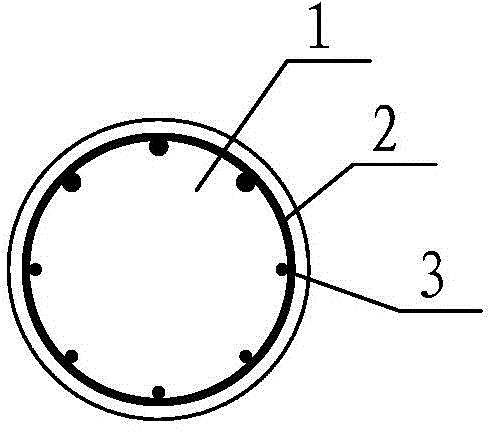

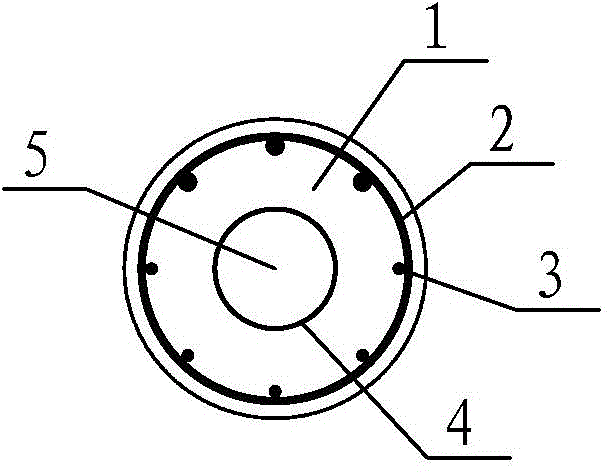

Method of manufacture of low water peak single mode optical fiber

The present invention directs to a method of manufacturing low water peak single mode optical fiber, which comprises performing deposition in a substrate tube using PCVD technology, whereby a deposited layer of a certain construction design is formed on the inner wall of the substrate tube, melt contracting the substrate tube into a solid core rod according to melt contraction technology, producing an optical fiber preform by combining the core rod and a jacket tube of low hydroxyl content by means of RIT technology or by depositing an outer cladding on the outer surface of the core rod using OVD technology, sending the optical fiber preform into a fiber drawing furnace to draw it into an optical fiber, wherein: in the PCVD technology, the content of impurities in a gas mixture of raw materials, which is characterized by the infrared spectrum transmissivity thereof, is required to a transmissivity of 90% or greater, the water content in O2 is 100 ppb or less, the water content in C2F6 is 1000 ppb or less, the hydroxyl content of the substrate tube is 1000 ppb or less, the dynamic leak rate of a deposition machine is 1.0×10−5 mbar·l / s or less; during melt contraction of the substrate tube, the dynamic leak rate of a melt contraction machine is 1.0×10−5 mbar·l / s or less; the hydroxyl content of the jacket tube of low hydroxyl content is required to be 10 ppm or less; the relative humidity of environment during the process of manufacture is 25% or less; the ratio of the cladding diameter to the core layer diameter (b / a value) in the waveguide structure of the optical fiber is from 2.0 to 7.0.

Owner:YANGTZE OPTICAL FIBRE & CABLE CO LTD

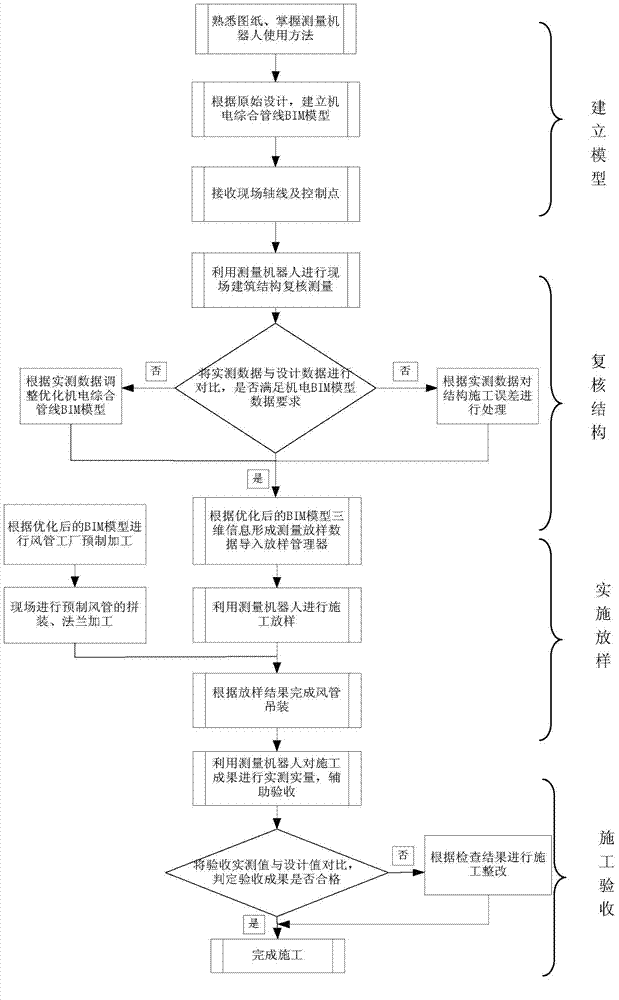

Mechanical and electrical installation engineering construction method based on BIM platform and measuring robot

ActiveCN104499714AAccurate Construction StakeoutBuilding material handlingQuality levelArchitectural engineering

The invention relates to a mechanical and electrical installation engineering construction method based on a BIM (Building Information Modeling) platform and a measuring robot. According to the method, a mechanical and electrical integral pipeline BIM model and the measuring robot are used. The method has the main characteristics that 1, a design result is optimized, and the actual dimension condition of an on-site building structure is fed back into the mechanical and electrical integral pipeline BIM model in a three-dimensional data form, so that the construction design is optimized, and the construction mistake is reduced; 2, precise and efficient positioning and sampling of on-site mechanical and electrical pipeline and equipment installation is performed through the measuring robot by using three-dimensional data information in the mechanical and electrical integral pipeline BIM model, so that the construction process is optimized, the construction efficiency is improved, and meanwhile, high construction quality is ensured; and 3, the construction site data is collected by using the measuring robot, the auxiliary construction acceptance can be realized through the comparison between measured data and design data, and the quality level of the construction result is enabled to meet the design requirements.

Owner:THE SECOND CONSTR ENG CO LTD OF CHINA CONSTR THIRD ENG BUREAU

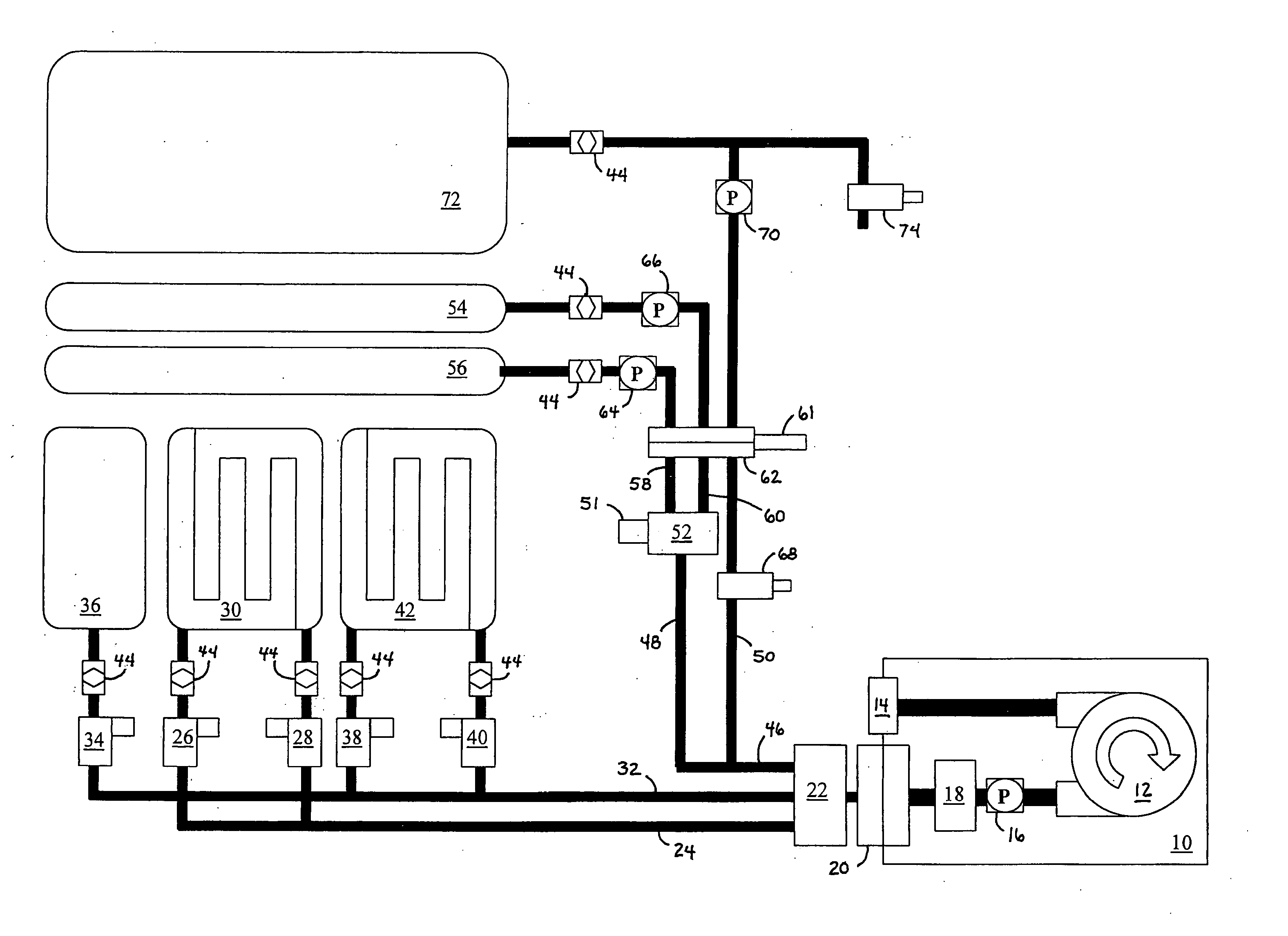

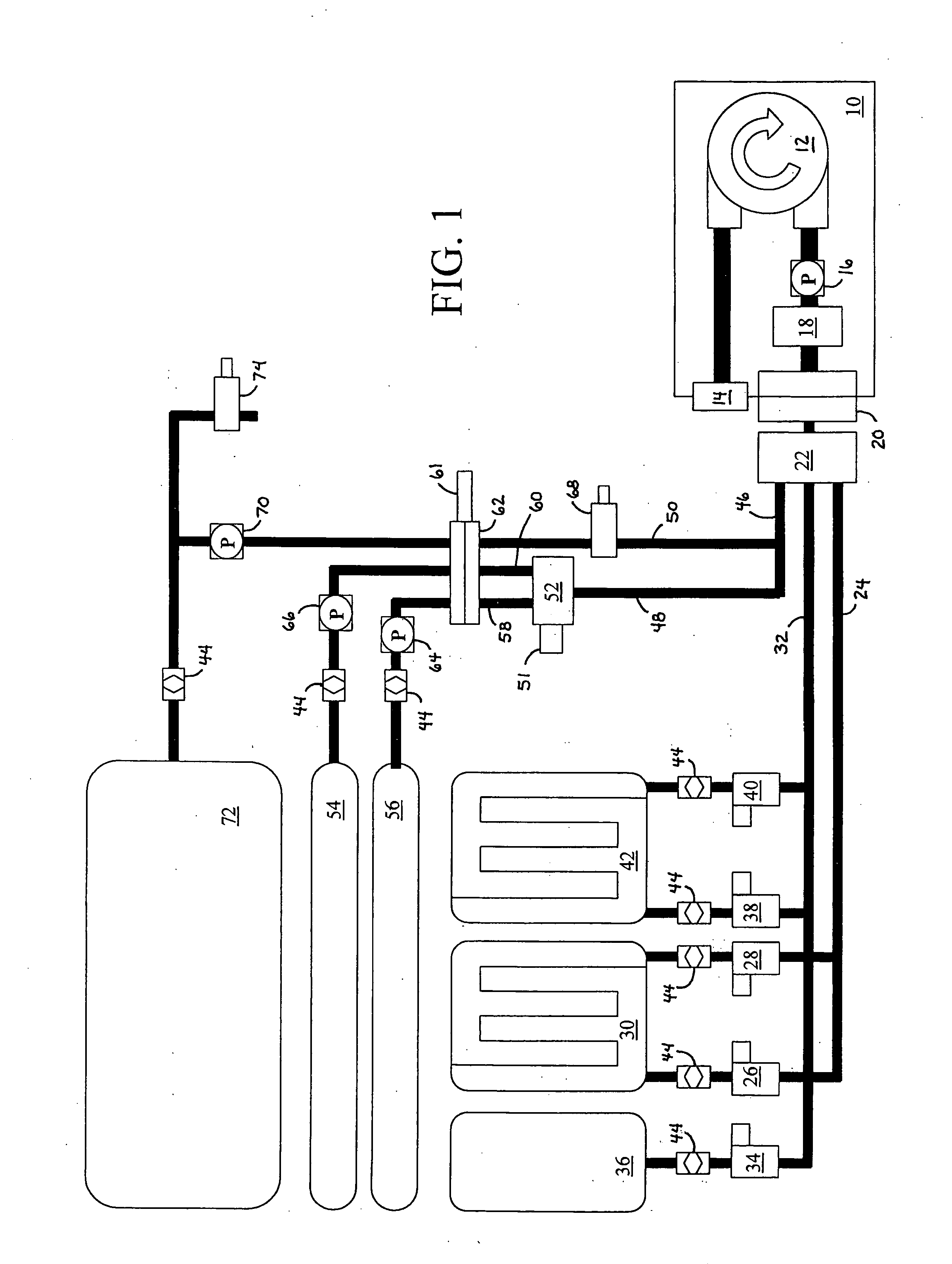

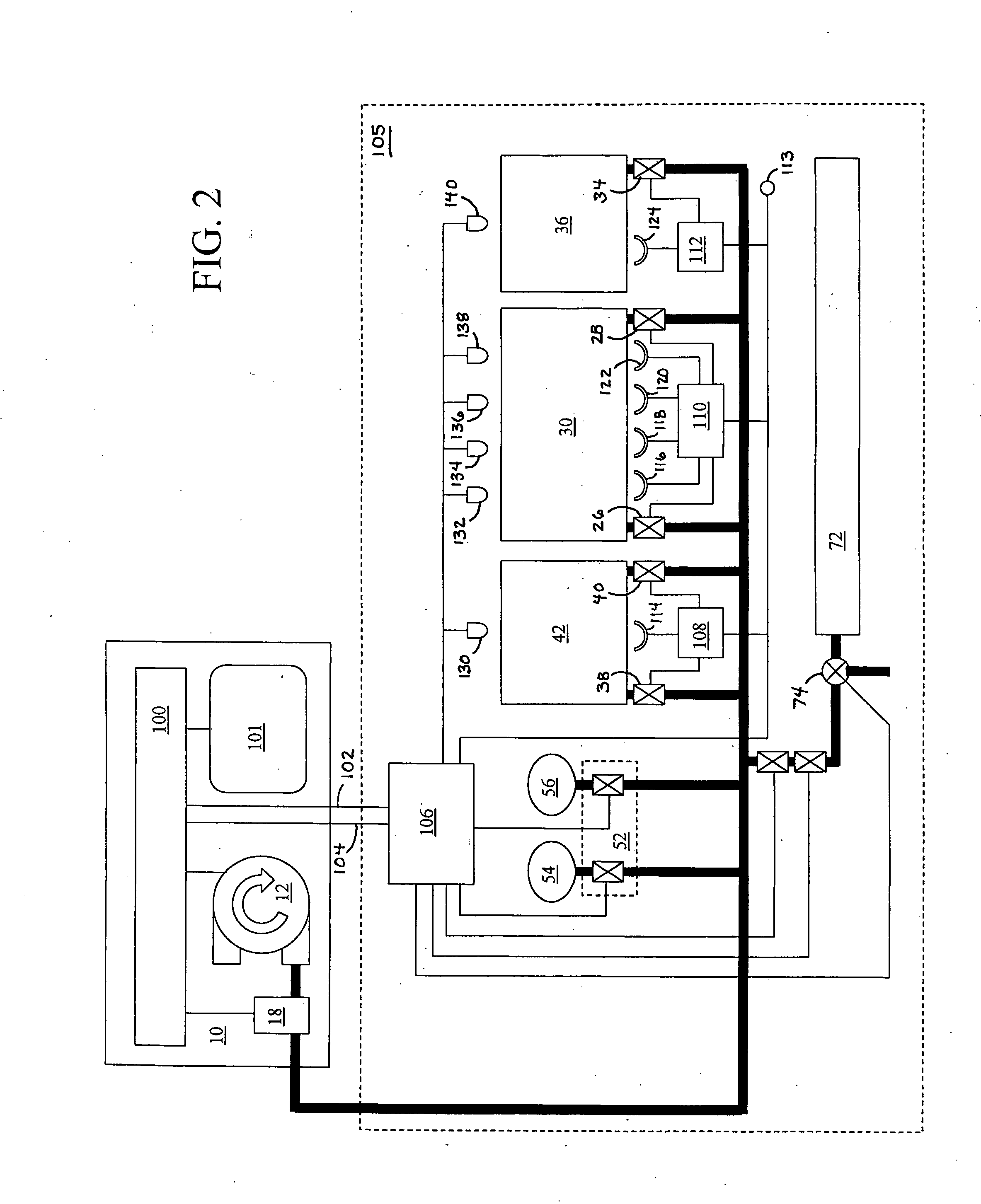

System and method for maintaining air inflatable mattress configuration

ActiveUS20060179579A1Easy maintenanceReduce crosstalkStuffed mattressesSpring mattressesFoot cushionControl system

A system and method for maintaining an air inflation mattress configuration sufficient for patient support and comfort. Infrared illumination levels are measured within individual or groups of inflated mattress chambers. A staggered approach to illumination monitoring of chambers or sections to eliminate crosstalk between the infrared sensors is carried out. Distributed microprocessor controllers established in a network configuration utilizing controller network protocols reduces the wiring and connections necessary for the assembled system. Various mattress cushion construction techniques, such as sewing and or RF welding methods, are used for the creation of individual chambers utilizing specific types of IR translucent, transparent or reflective materials. The construction of the cushions and bladders in the system includes the use of various types of fabrics with low to high air loss qualities as required. The overall mattress assembly, including the control systems and the methodologies associated with such control systems, provide a unique approach to the maintenance of a consistently comfortable patient support surface. The use of a handheld unit for both programming the system and downloading information about the operation of the system is also anticipated. The specific cushion construction designs associated with the head, body, and foot cushion components of the mattress are tailored to operate specifically with the control capabilities (sensors and air flow regulators) of the invention.

Owner:HUNTLEIGH TECH LTD

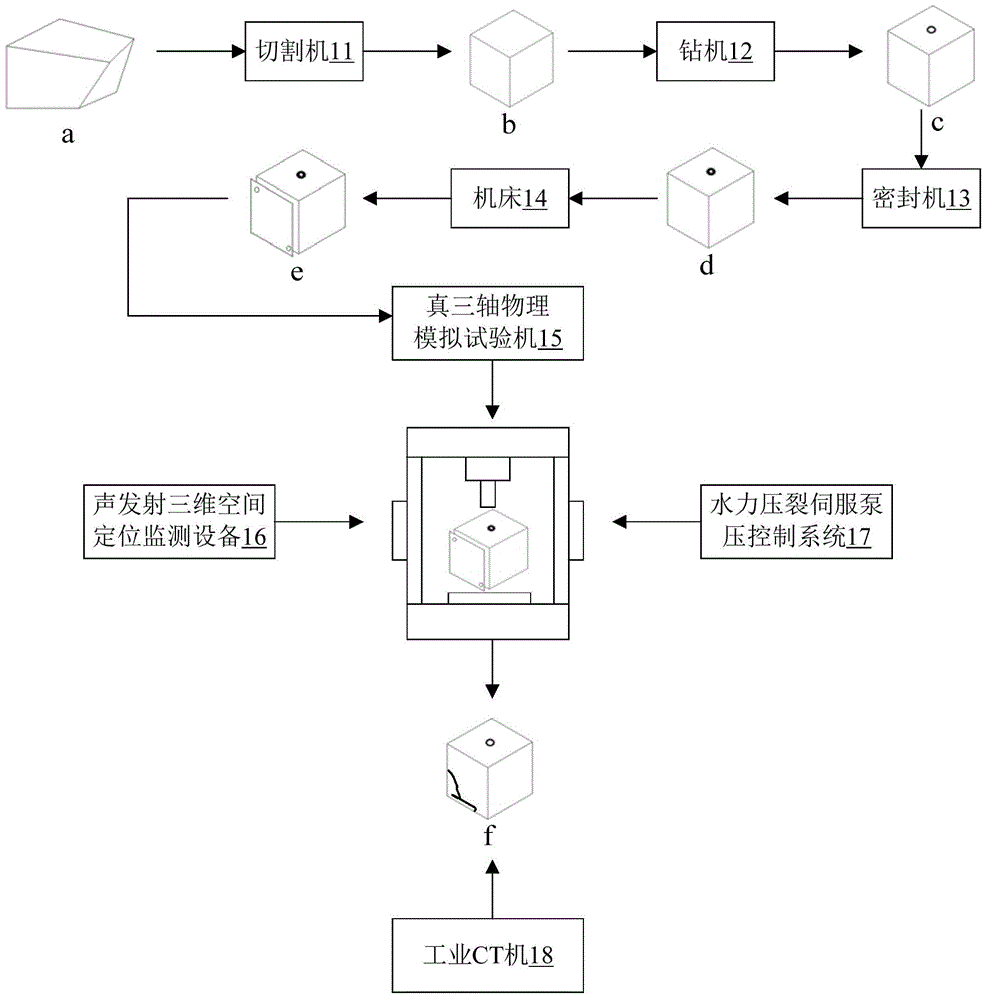

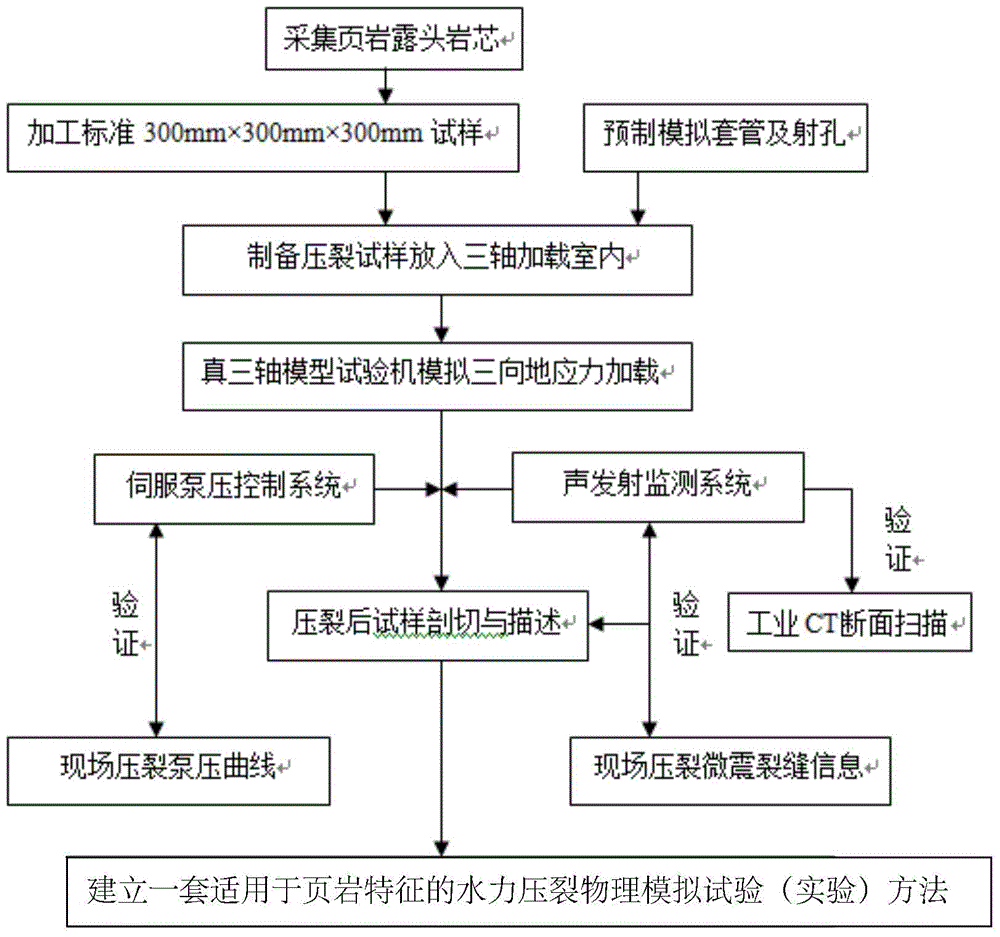

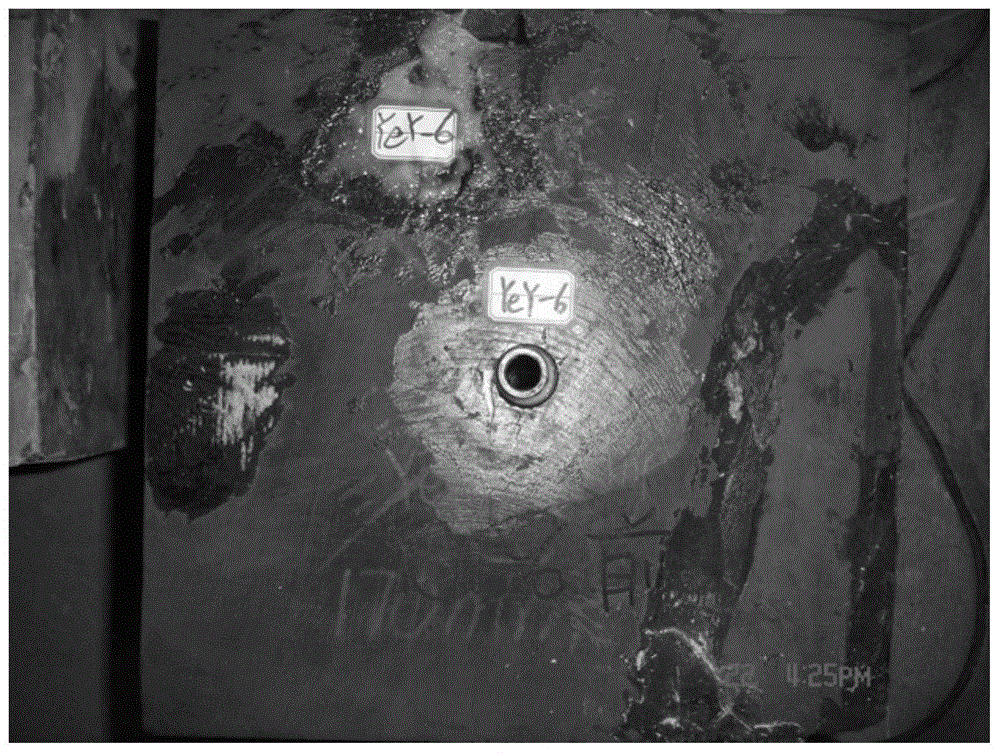

Physical simulation system and method for fracture propagation in shale

InactiveCN105756645AAccurate discriminationTo achieve the purpose of increasing productionFluid removalFracturing fluidHydraulic fracturing

The invention discloses a physical simulation system and method for fracture propagation in shale. The system comprises a drilling rig, a sealing machine, a machine tool, a true triaxial physical simulation testing machine, a hydraulic fracturing servo pump pressure control system, acoustic emission three-dimensional space location monitoring equipment and an industrial CT (computed tomography) machine, wherein the drilling rig, the sealing machine and the machine tool are jointly used for processing acquired shale into a fracturing sample; the true triaxial physical simulation testing machine is used for loading simulated three-dimensional ground stress to the fracturing sample; the hydraulic fracturing servo pump pressure control system is used for providing a fracturing fluid for the fracturing sample, so that a hydraulic fracturing process can be simulated; the acoustic emission three-dimensional space location monitoring equipment is used for monitoring the simulated hydraulic fracturing process in real time; the industrial CT machine is used for preforming tomography scanning on the fracturing sample before and after hydraulic fracturing. The physical simulation system for fracture propagation in the shale can be used for researching fracture initiation, expansion and extension laws of anisotropic shale in the hydraulic fracturing process, so that fracture information can be distinguished more accurately, high-precision basic data are provided for fracturing construction design, technical support is provided for site fracturing construction, and the yield is increased.

Owner:CHINA PETROLEUM & CHEM CORP +1

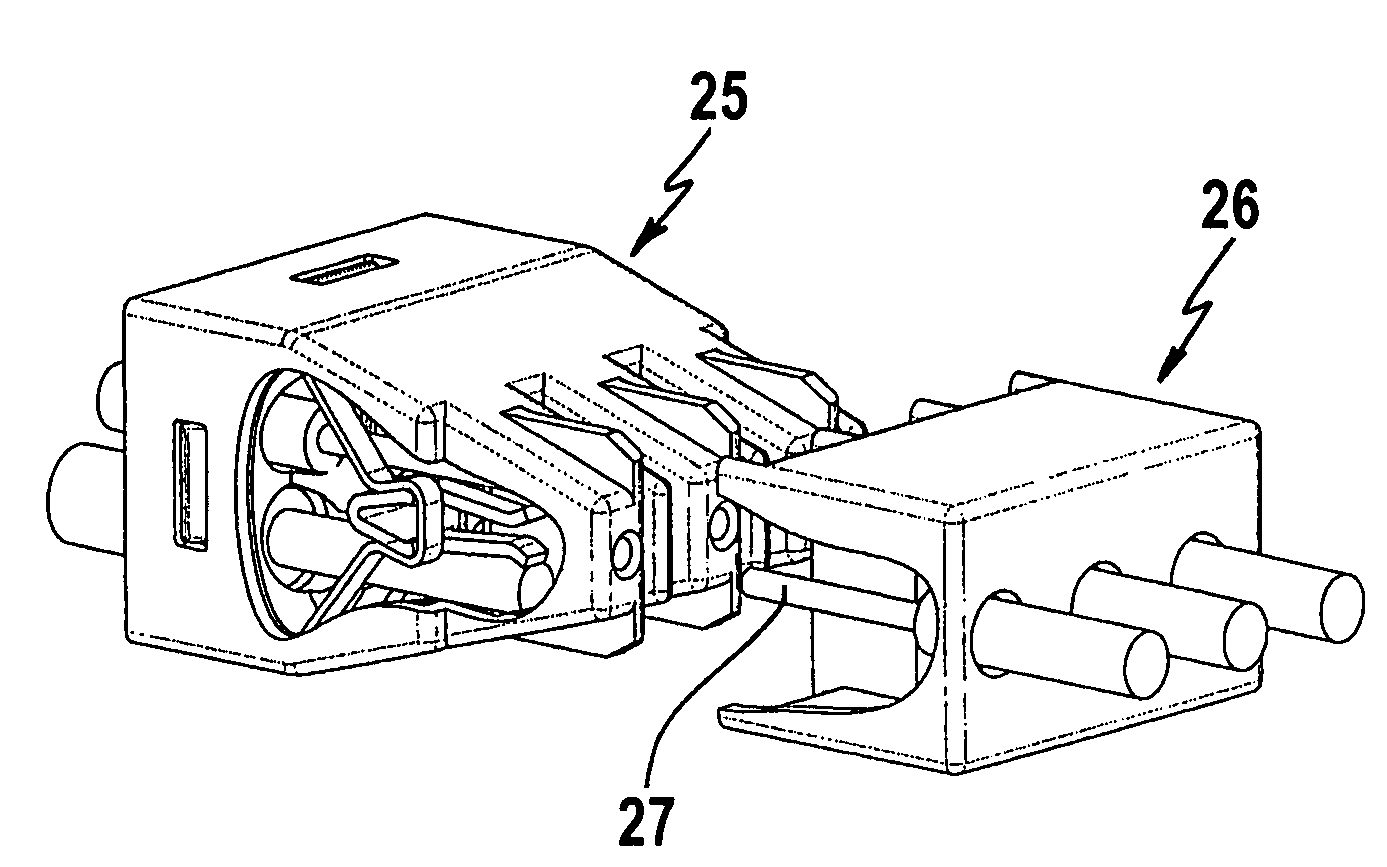

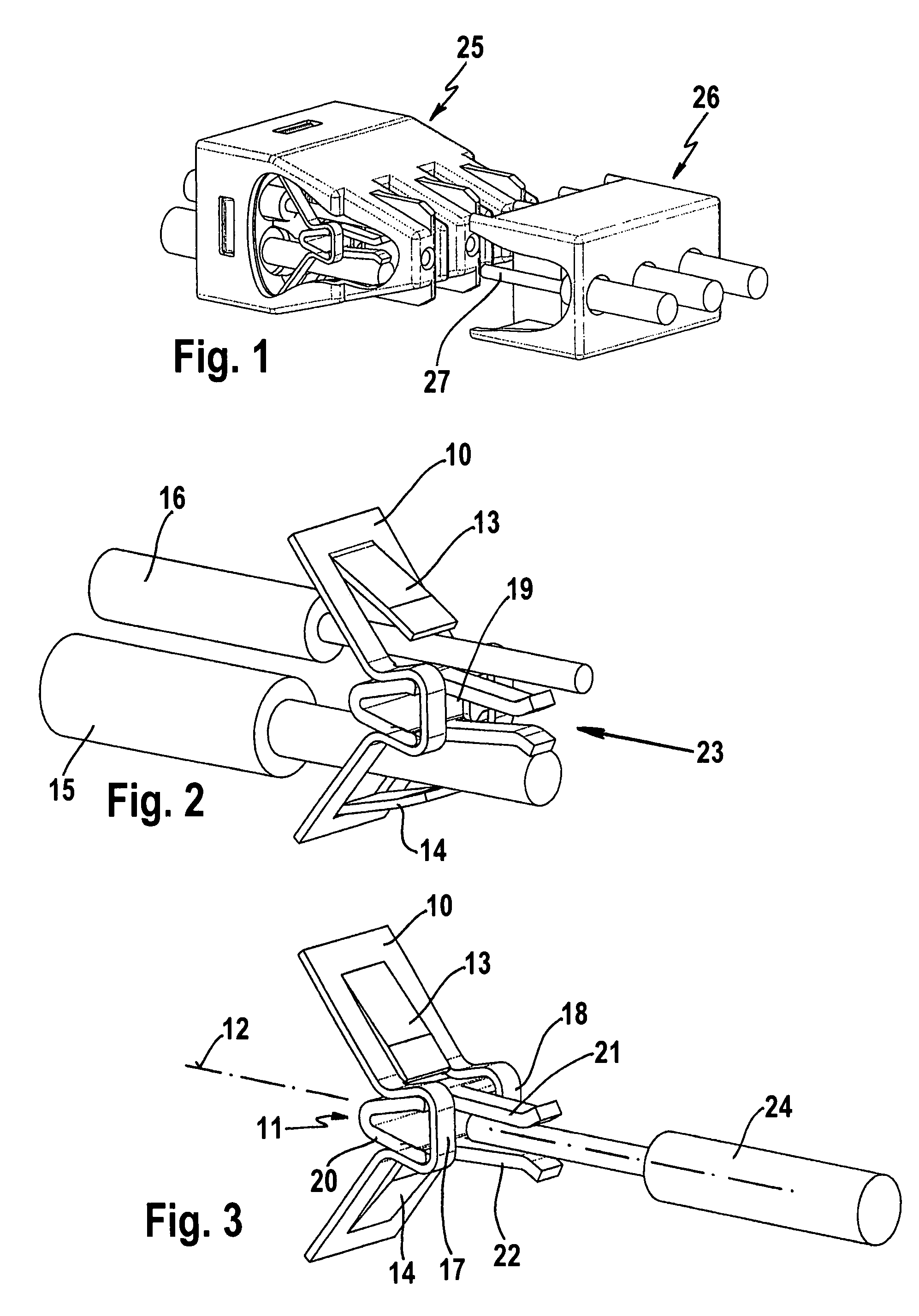

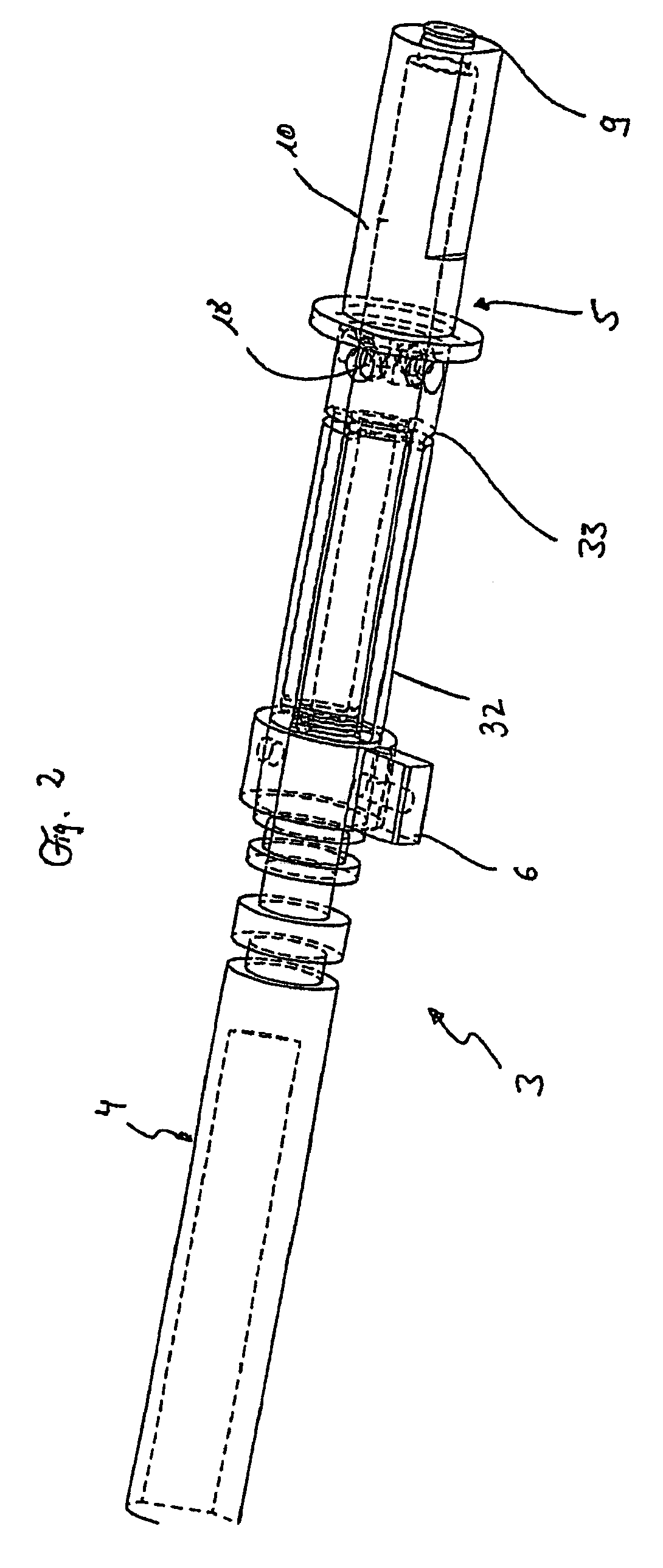

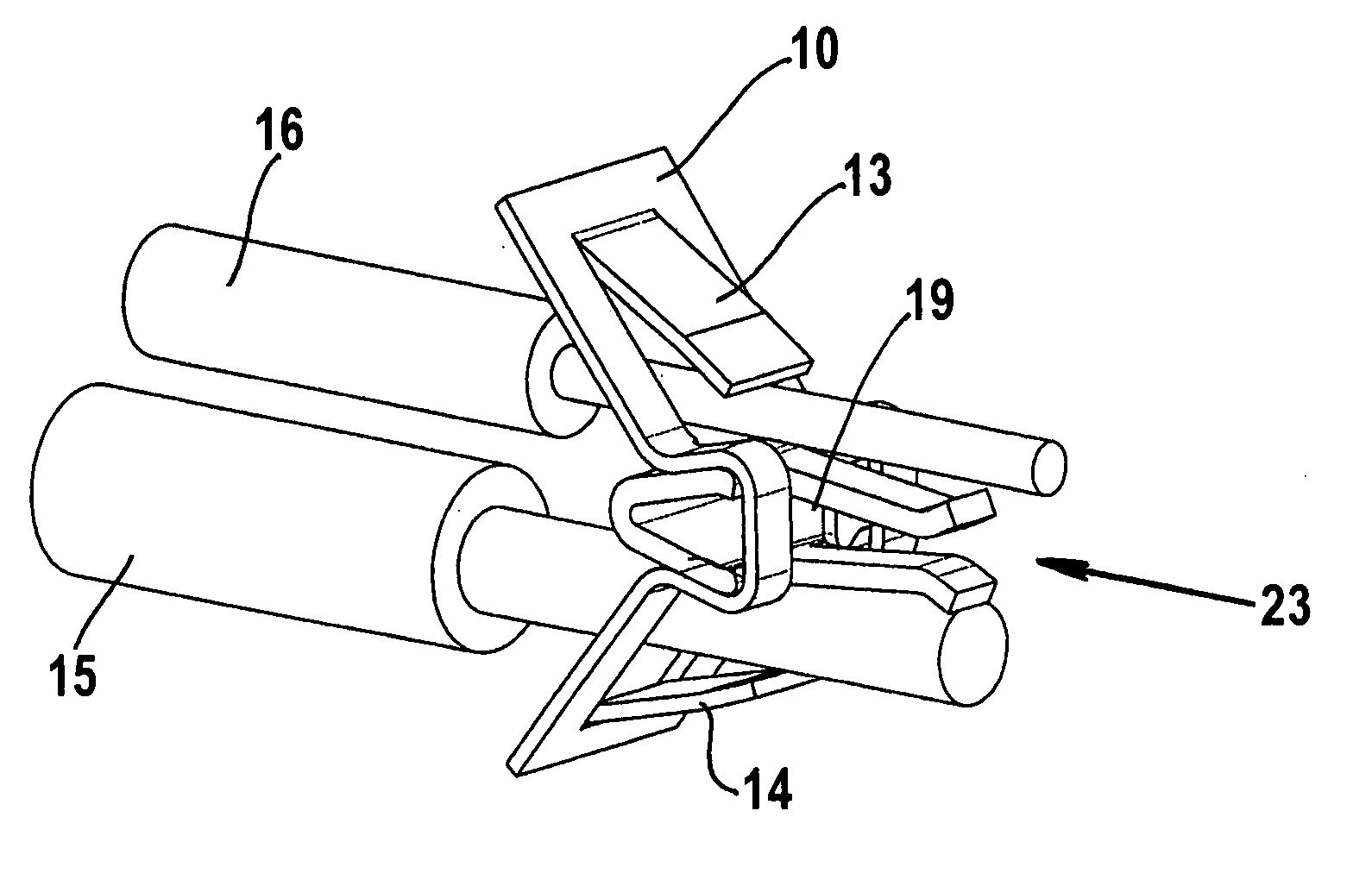

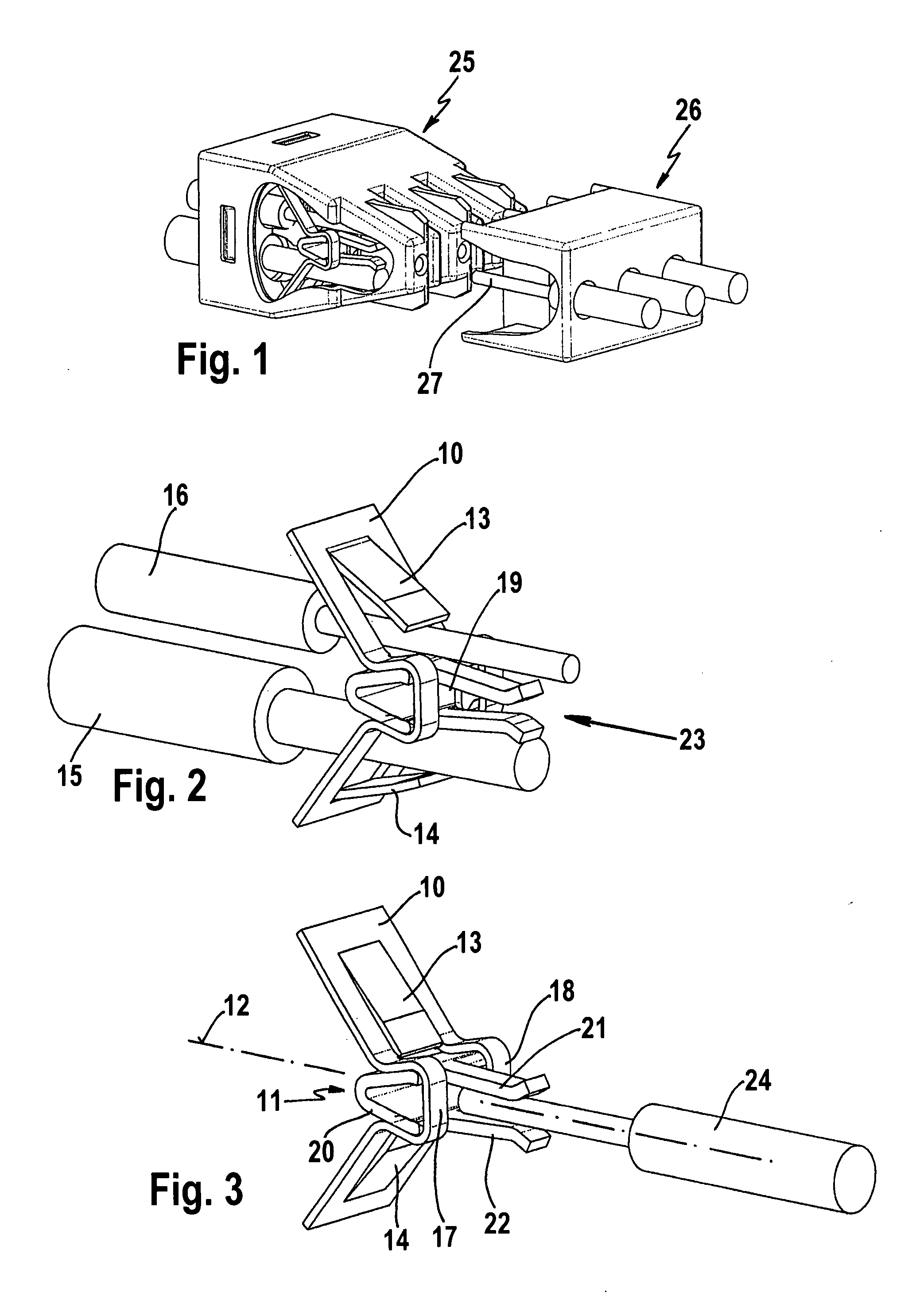

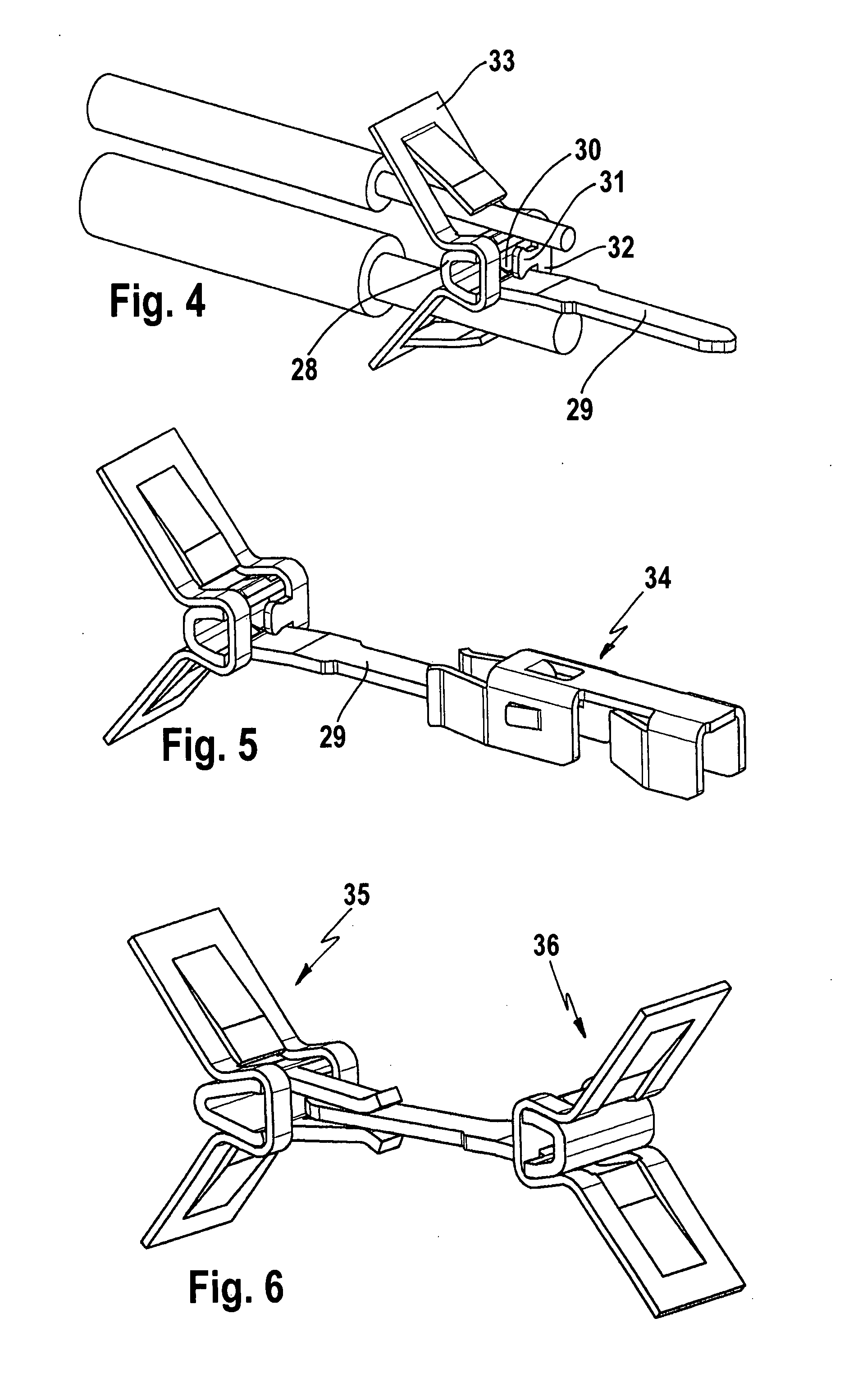

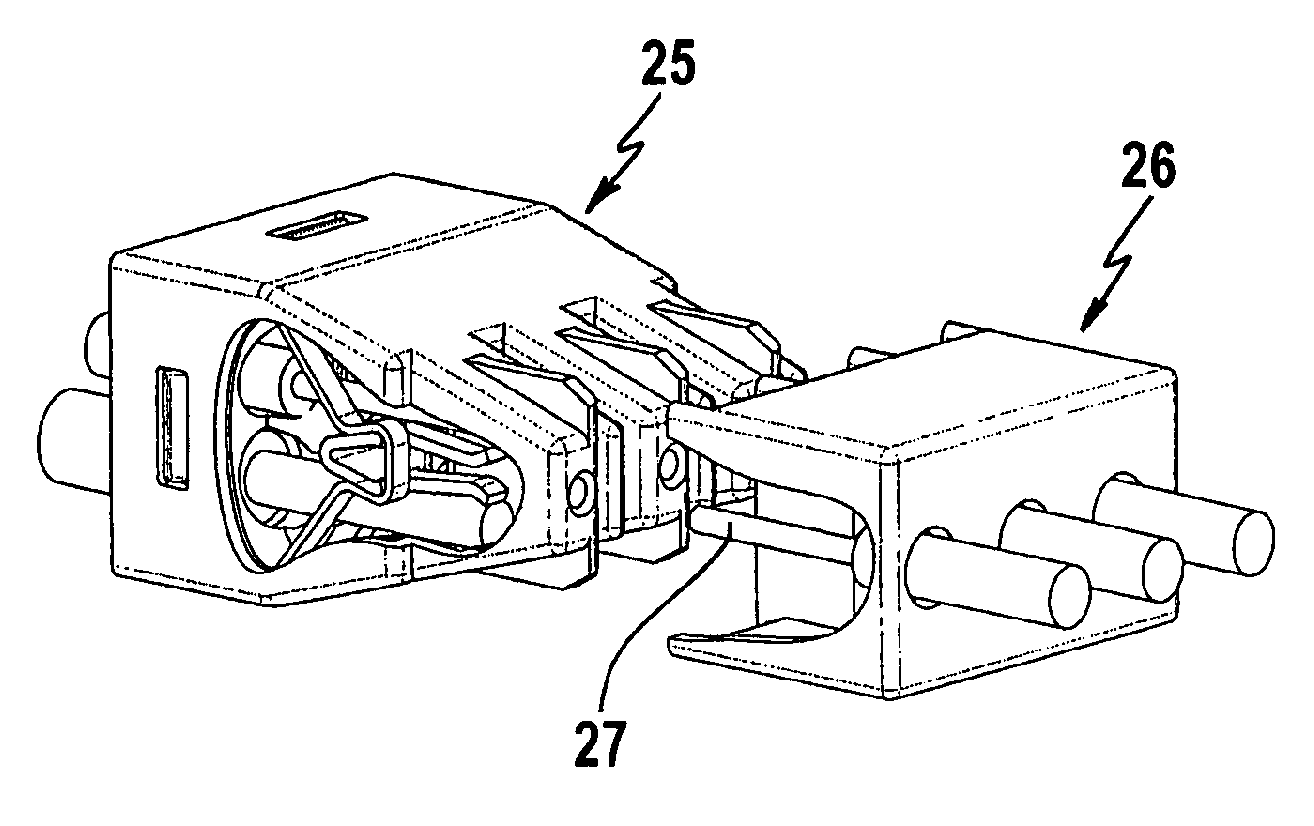

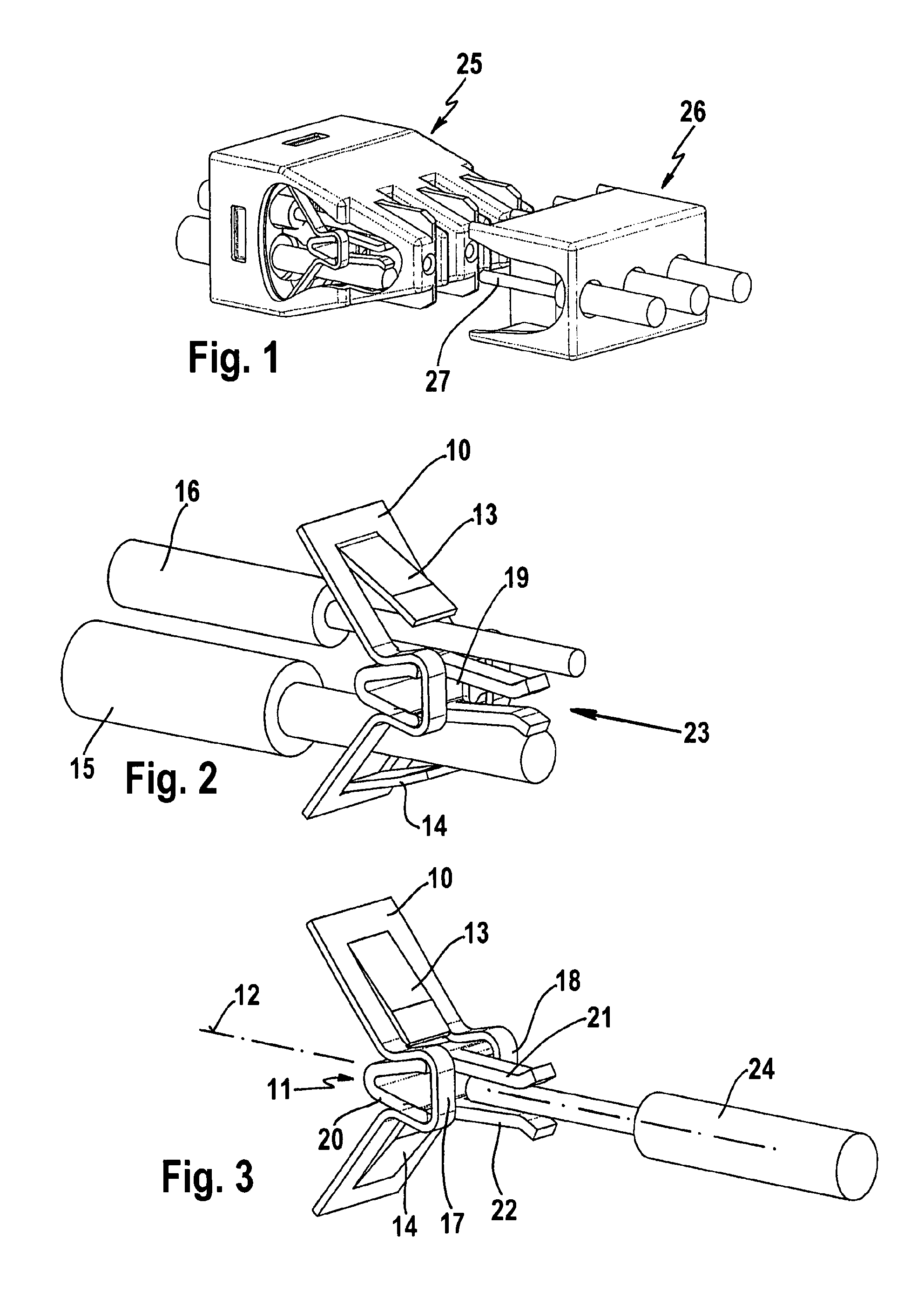

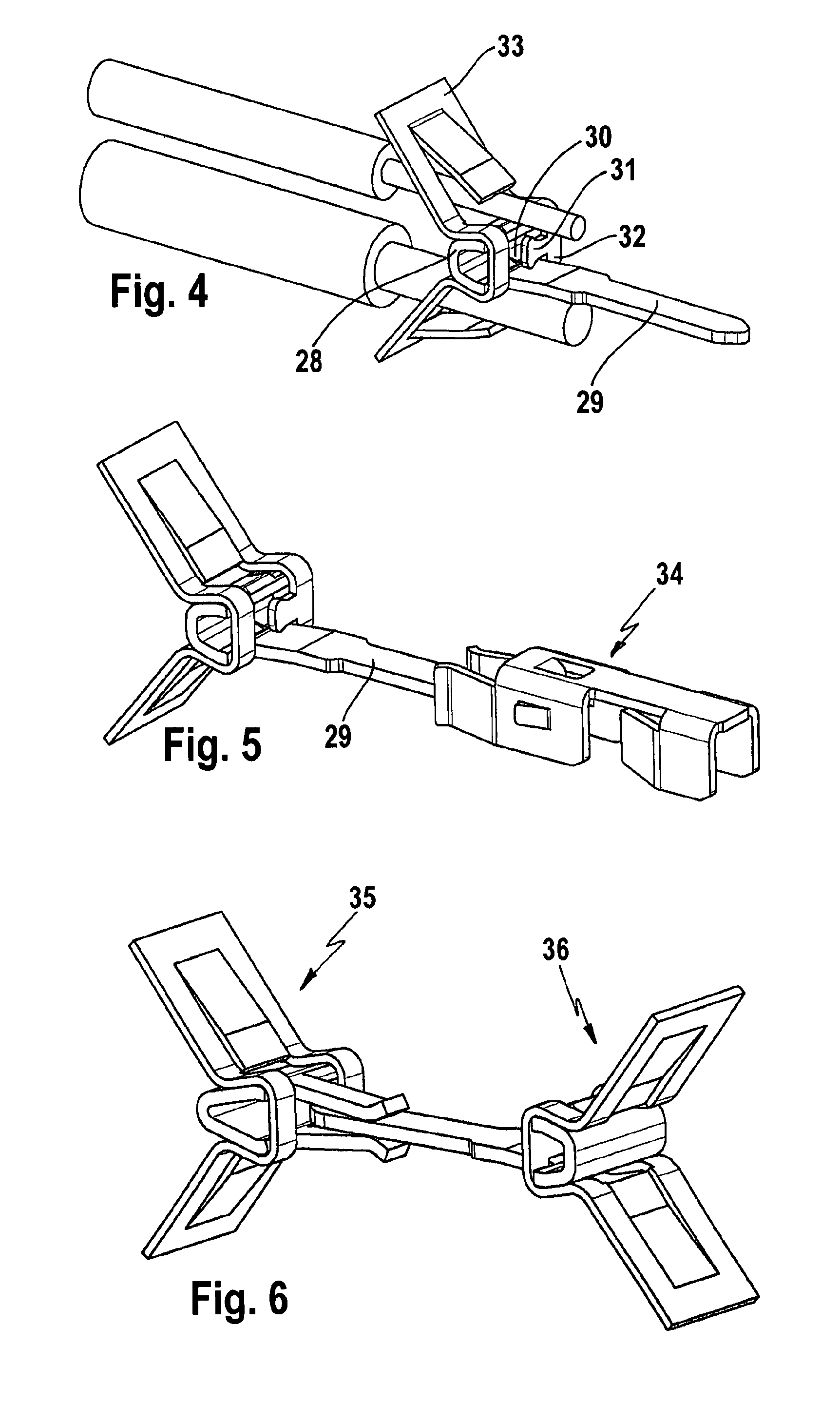

Electrical clamp connector and connecting terminal

InactiveUS7384319B2Contact member manufacturingCoupling contact membersElectrical conductorEngineering

The invention relates to an electrical clamp connector and connecting terminal that, per pole, has at least two conductor terminal connections oriented in the same direction and an additional connecting contact on the opposite-lying side, which serves for connecting a countercontact external to the terminal. It is proposed for such a terminal to use the especially small-construction design features of a terminal that is produced from a single piece of spring steel sheet and a busbar rod, and to combine these with the new features that the busbar rod has one or two cross projections, which project through the free opening in the spring steel sheet and form the additional connecting contact, which, for example, may be constructed in the form of a socket contact or in the form of a plug-in contact.

Owner:WAGO VERW GMBH

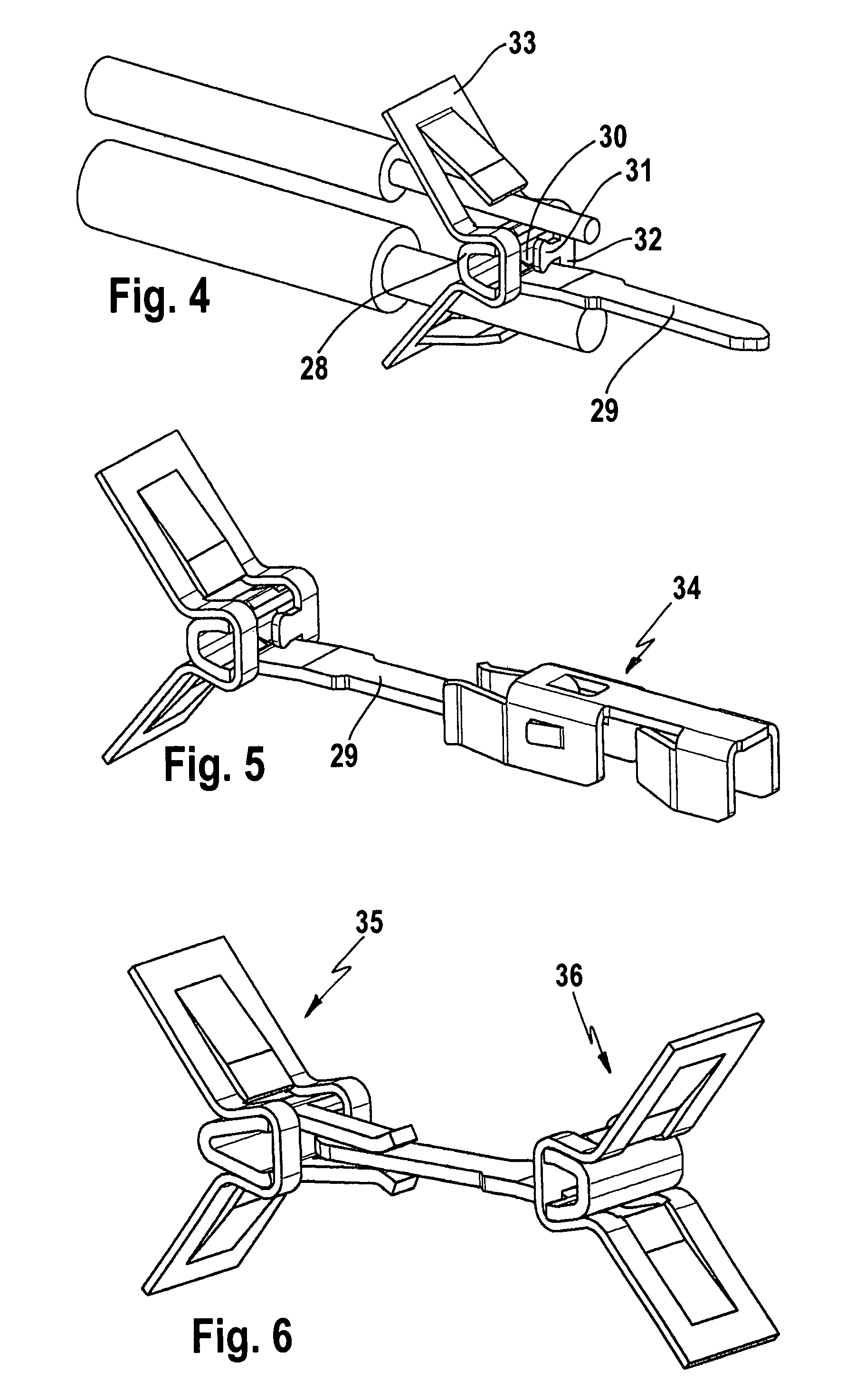

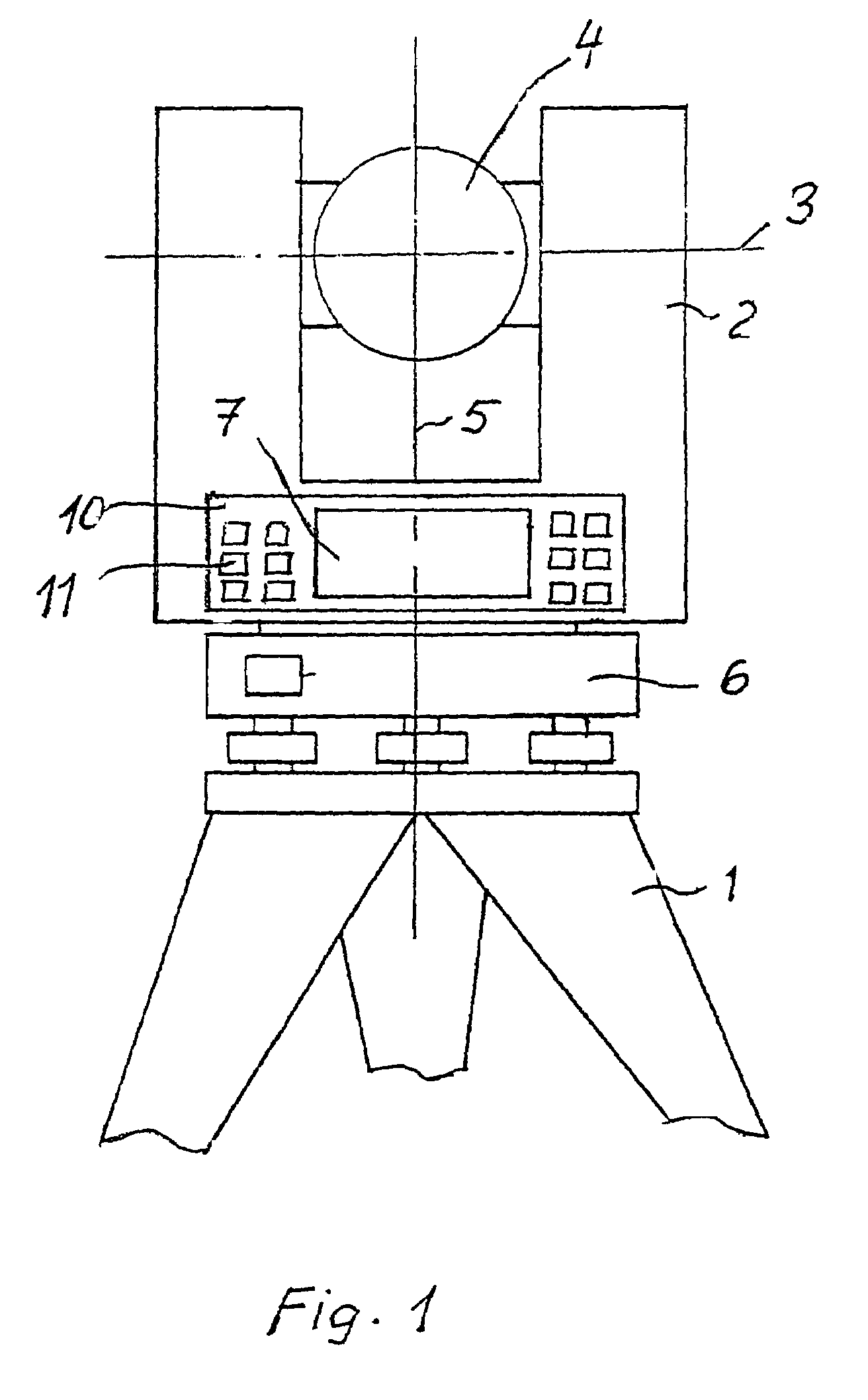

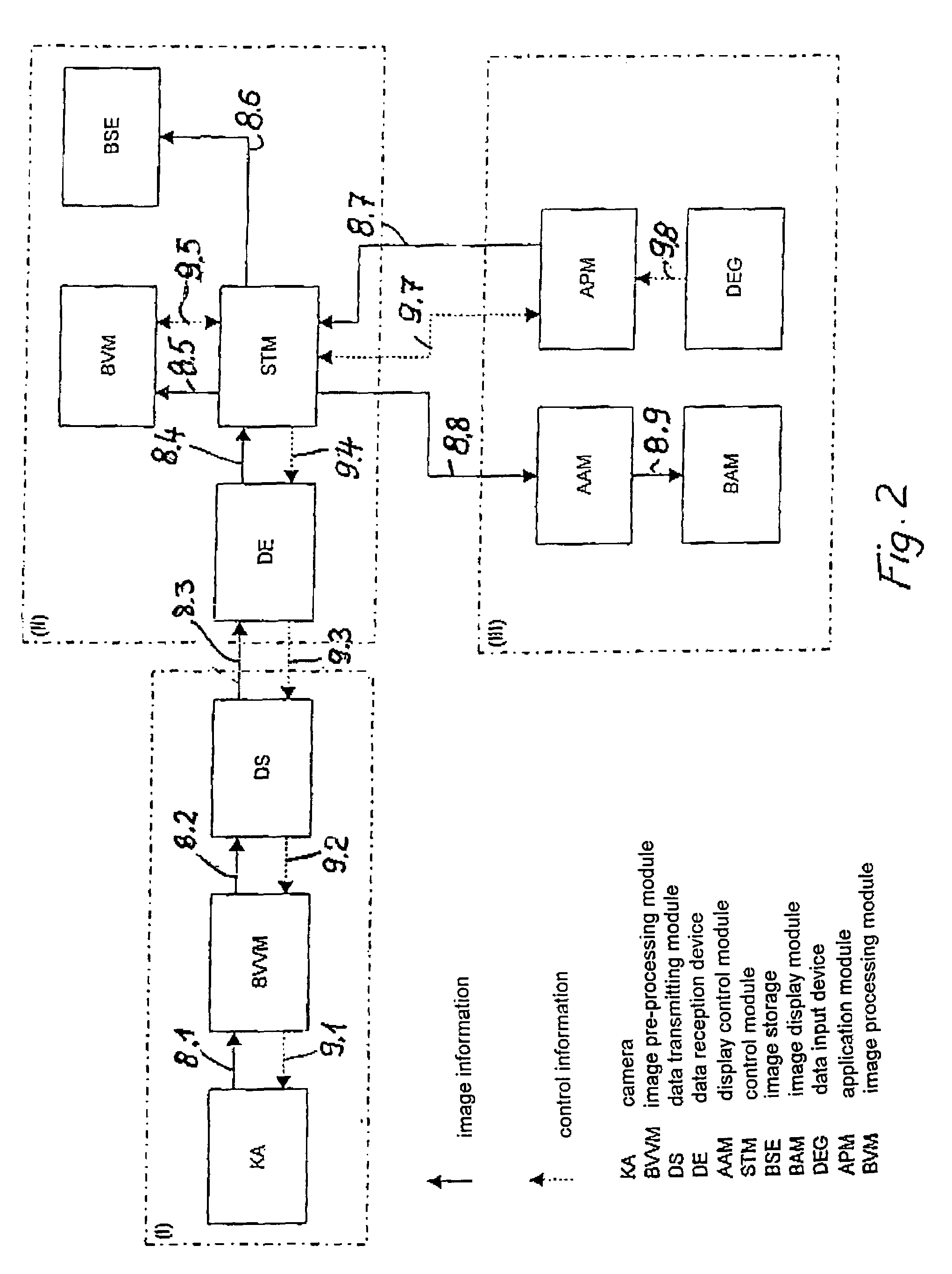

Method and arrangement for carrying out an information flow and data flow for geodetic instruments

ActiveUS7339611B2Compact structureTelevision system detailsSurveying instrumentsImaging processingData stream

A method and an arrangement for carrying out an information flow and data flow in a geodetic instrument with image processing is disclosed. For this purpose, the data flow and information flow needed for image processing are distributed to a plurality of function modules which are arranged in the instrument and which comprise function groups and are carried out by means of these function groups. The arrangement includes a plurality of function groups which are arranged in the instrument at locations determined by its construction design. These function groups are composed of a plurality of function modules.

Owner:TRIMBLE JENA

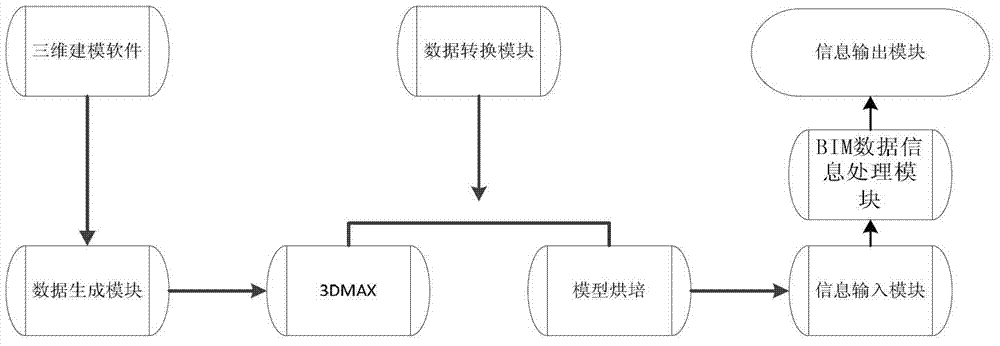

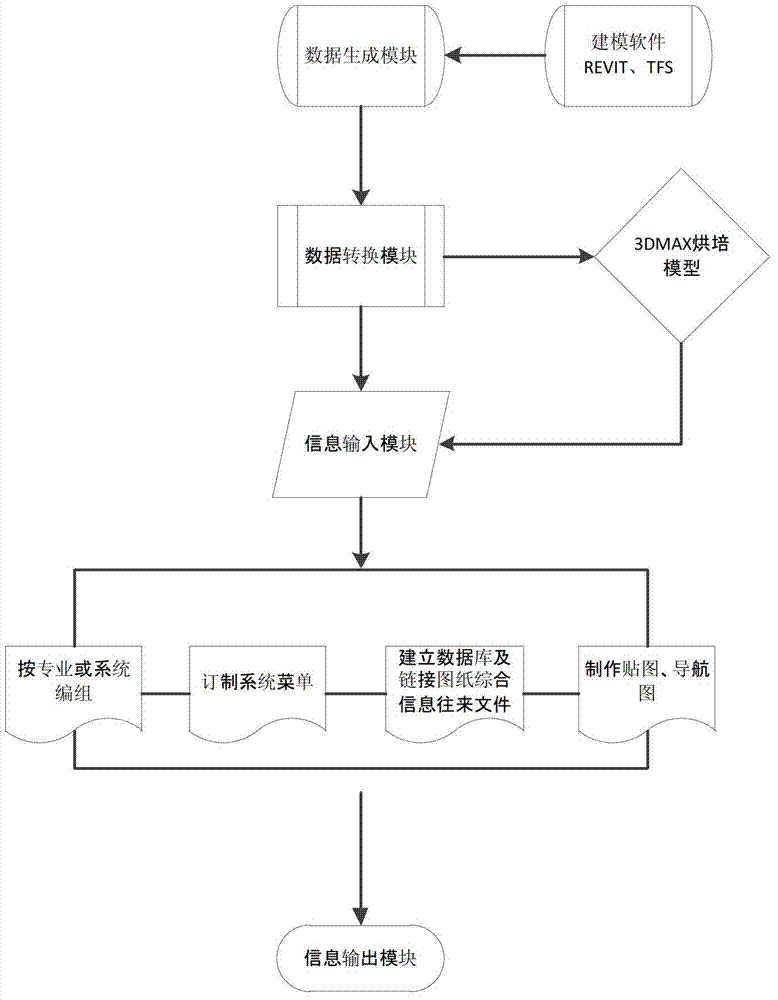

Information management method and system based on electromechanical integrated BIM (building information model)

Owner:CHINA CONSTR IND & ENERGY ENG GRP CO LTD

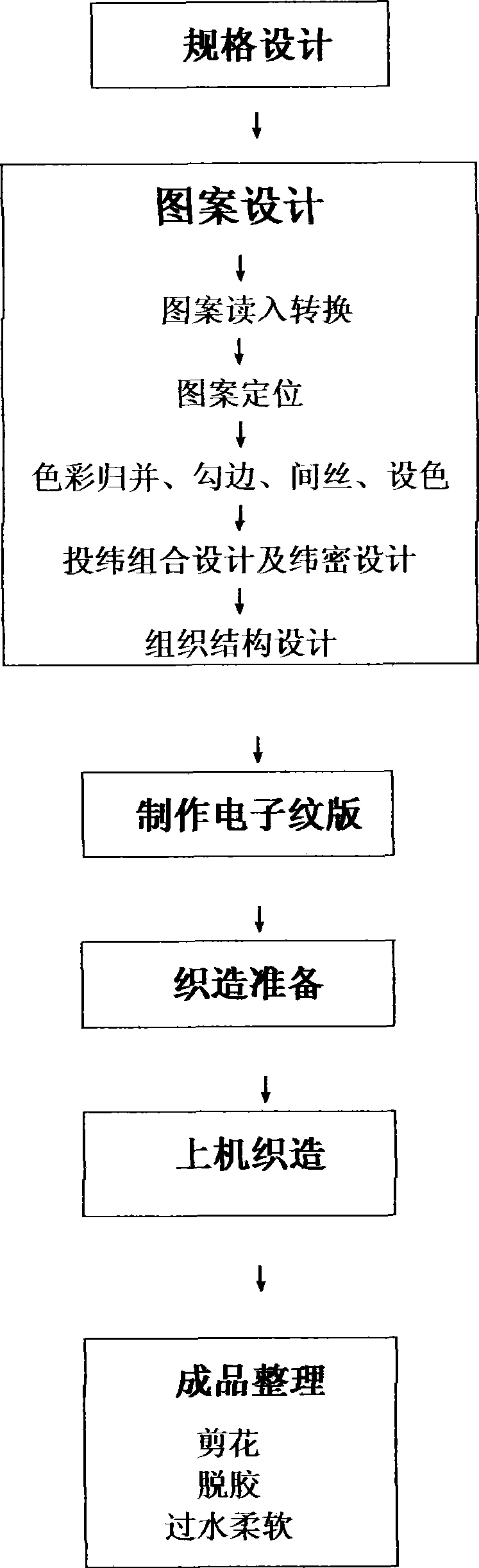

Production method of figured cloth different from embroidery characteristics

ActiveCN101423998AFeel goodStrong three-dimensional senseCard-punching apparatusSwivel-woven fabricsWork in processVolumetric Mass Density

The invention discloses a method for manufacturing jacquard fabrics different from embroidering properties, which comprises the following steps of specification design, pattern design, weaving preparation, weaving on a machine, and sorting of finished products, wherein the step of pattern design is to read target patterns of the jacquard fabrics to be manufactured into a computer, to adjust and position the position of the patterns on the fabrics according to the dimension of the finished products, to set a plurality of colors for the patterns, to merge the colors, and to manufacture an electronic pattern card through picking combinational design, longitude and latitude density design and weave construction design; and the step of sorting of the finished products is to perform trimming on the floating length of weft threads on the reverse side of semifinished products which are off the machine. The jacquard fabrics produced by the method have good hand feeling, strong third dimension, high ornamental value, and distinct contrast between rugged figured pattern and refined bottom plates, achieve the embroidering style after being subjected to two procedures of jacquard weaving and jacquard trimming, is accurate to position the patterns, are more suitable to be used as family spinning fabrics such as curtains and back cushions compared with the prior jacquard fabrics, and have the characteristics of short manufacturing time and low production cost.

Owner:DALI SILK ZHEJIANG

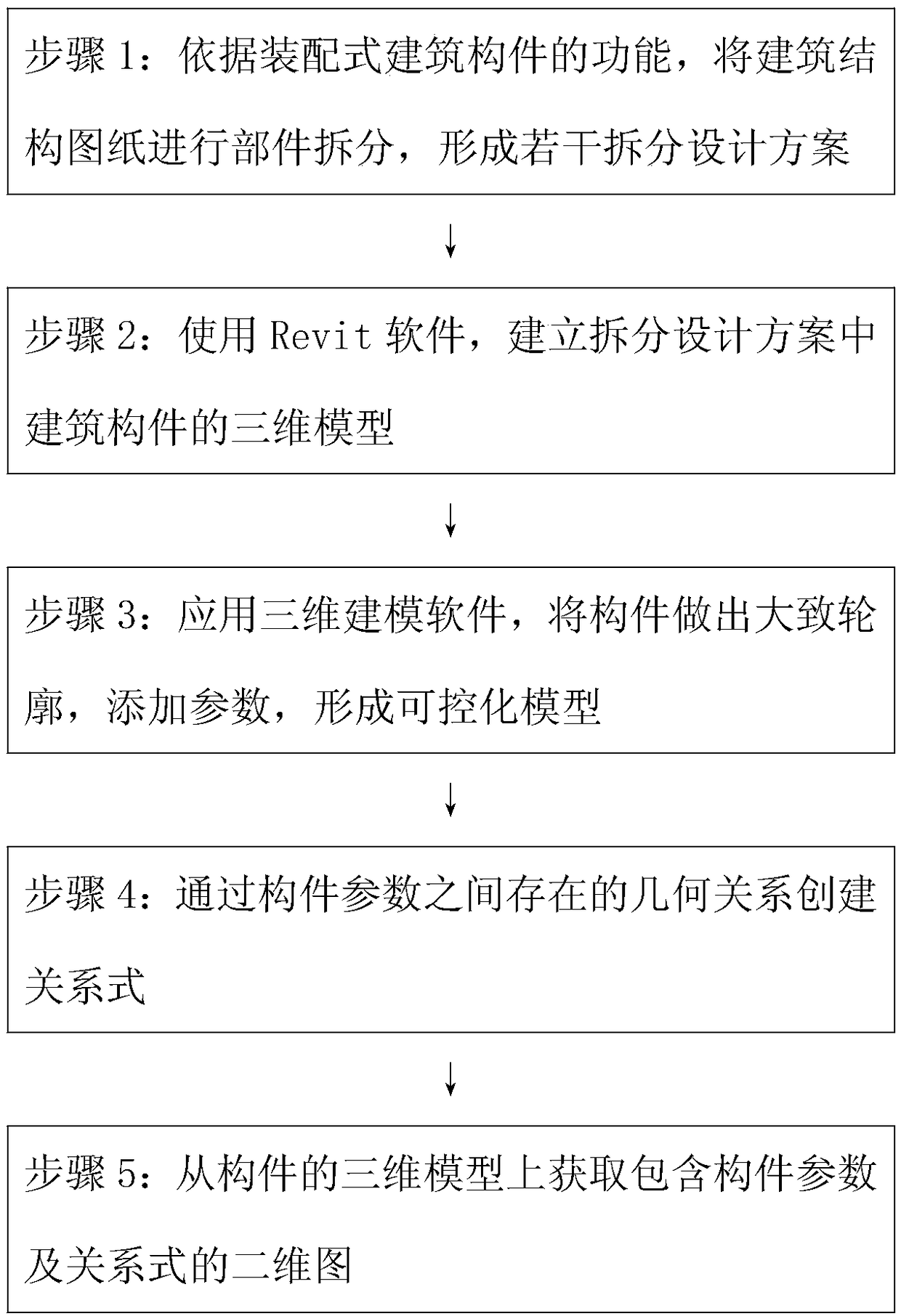

BIM-based fabricated member parametrization design method

InactiveCN108664697AFast and accurate generationMeet factory productionGeometric CADDesign optimisation/simulationTwo-dimensional graphDimensional modeling

The invention provides a BIM-based fabricated member parametrization design method. The method comprises the steps of 1: according to functions of fabricated building members, performing component disassembly on a building structure drawing to form a plurality of disassembly design schemes, wherein the schemes are specifically expressed in a form of "total construction design + BIM issued component disassembly drawing"; 2: by using Revit software, establishing three-dimensional models of the building members in the disassembly design schemes; 3: by applying three-dimensional modeling software,making rough profiles of the members, adding parameters, and forming controllable models; 4: through a geometric relationship between the parameters of the members, creating a relational expression;and 5: from the three-dimensional models of the members, obtaining a two-dimensional graph comprising the parameters of the members and the relationship expression. According to the design, the drawing needed by factory production is quickly and accurately generated, and the material requirement amount can be automatically calculated and summarized according to the parameters in the drawing.

Owner:山东住工装配建筑有限公司

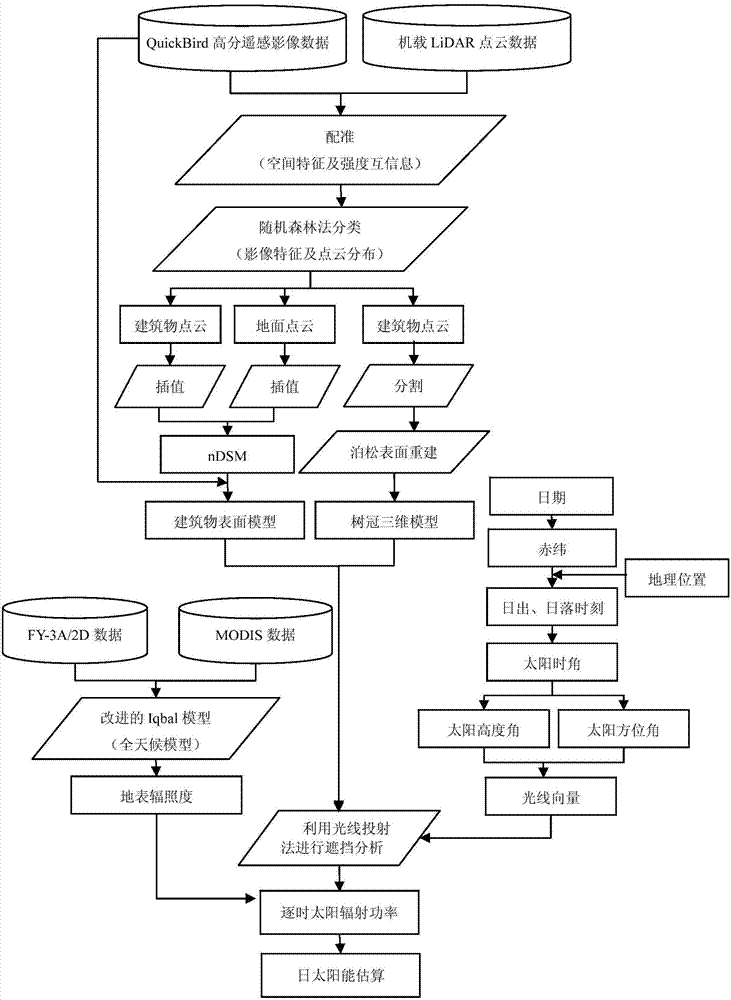

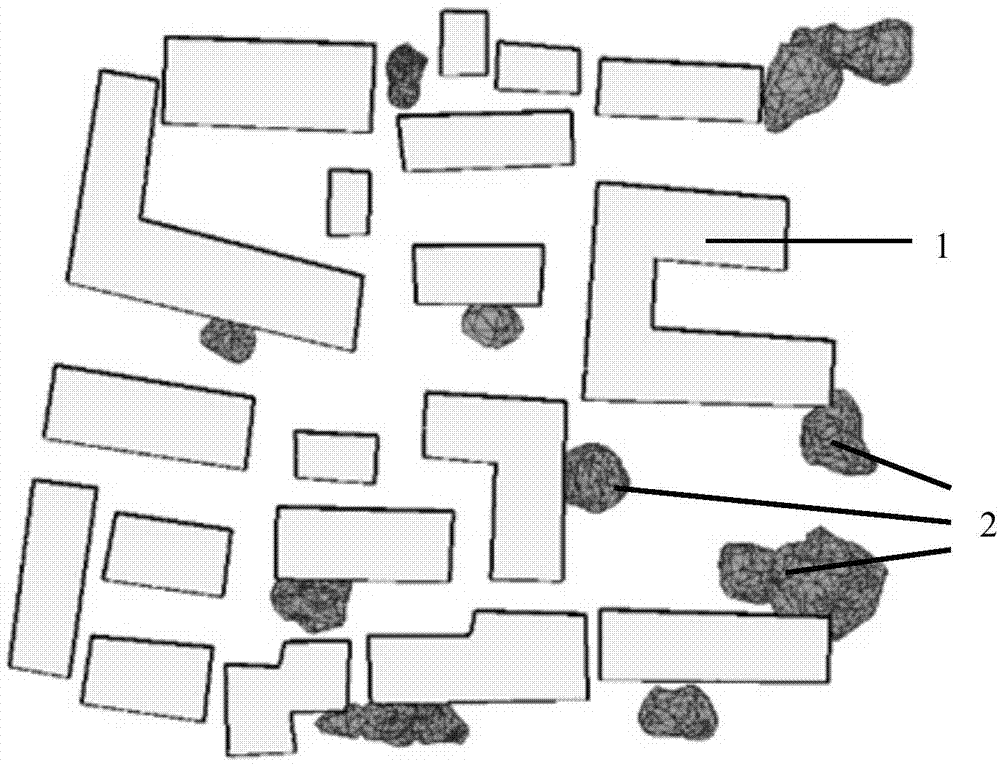

Rapid estimation method for solar energy in construction size

ActiveCN103942420APreserve morphological informationDetails change description idealCharacter and pattern recognitionSpecial data processing applicationsUrban regionBuilding design

The invention discloses a rapid estimation method for solar energy in a construction size. The method includes the steps that by the comprehensive utilization of LiDAR data and high-resolution remote sensing image data, and three-dimension digital surface modeling is performed on objects such as urban constructions and trees; through simulation analysis of the attenuation effect, on direct solar radiation to the ground, of the atmosphere and the sheltering influence, on direct solar radiation energy obtained by construction surfaces including roofs and wall faces, by the urban objects, the solar energy obtained by the roofs and the wall faces of the urban constructions and dynamic estimated values are obtained. The rapid estimation method is suitable for specific application of using solar energy resources in the construction size in an urban region, wherein the specific application includes optimal configuration of energy resources, installation of solar photovoltaic equipment, design of green and environment-friendly constructions and the like.

Owner:PEKING UNIV

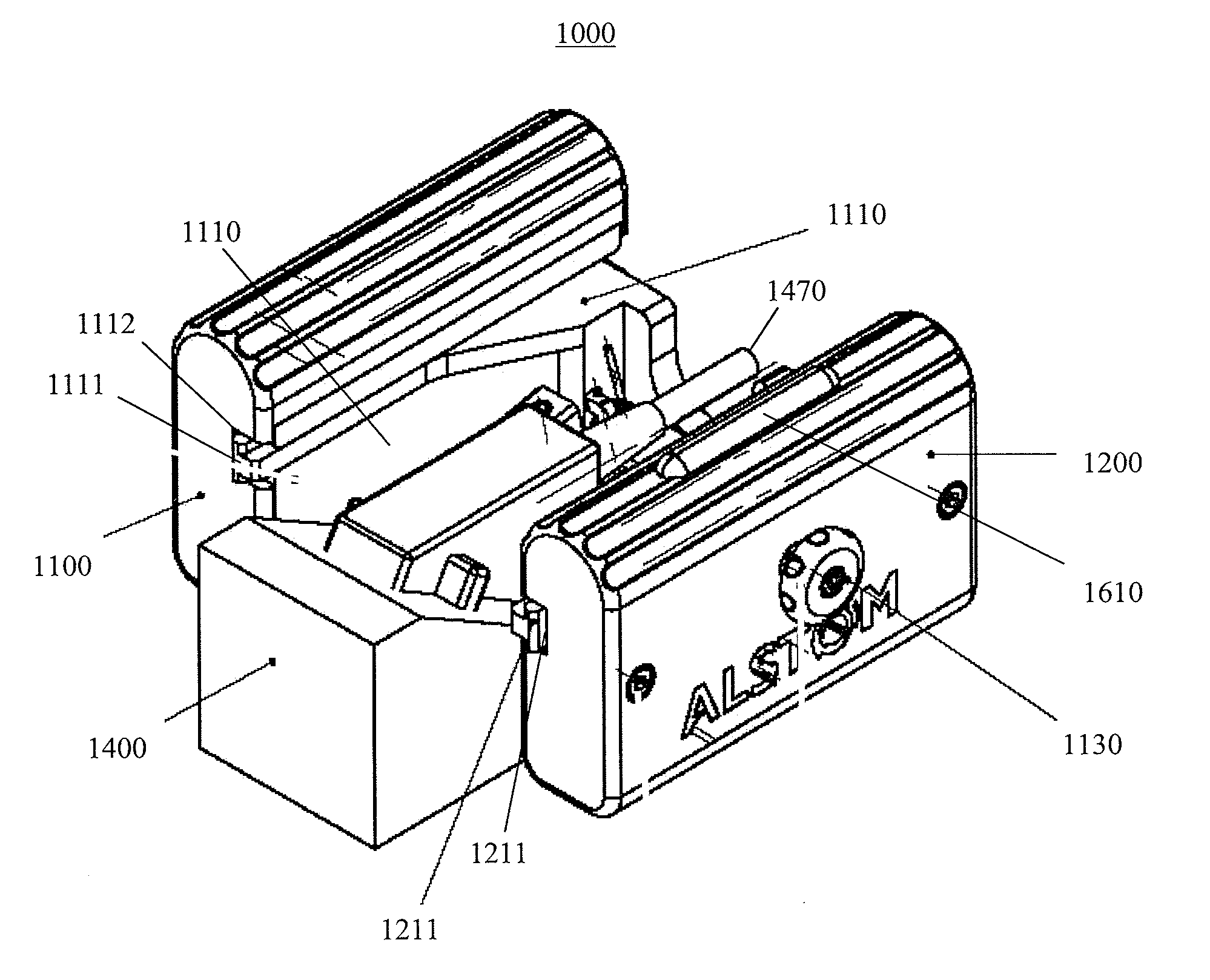

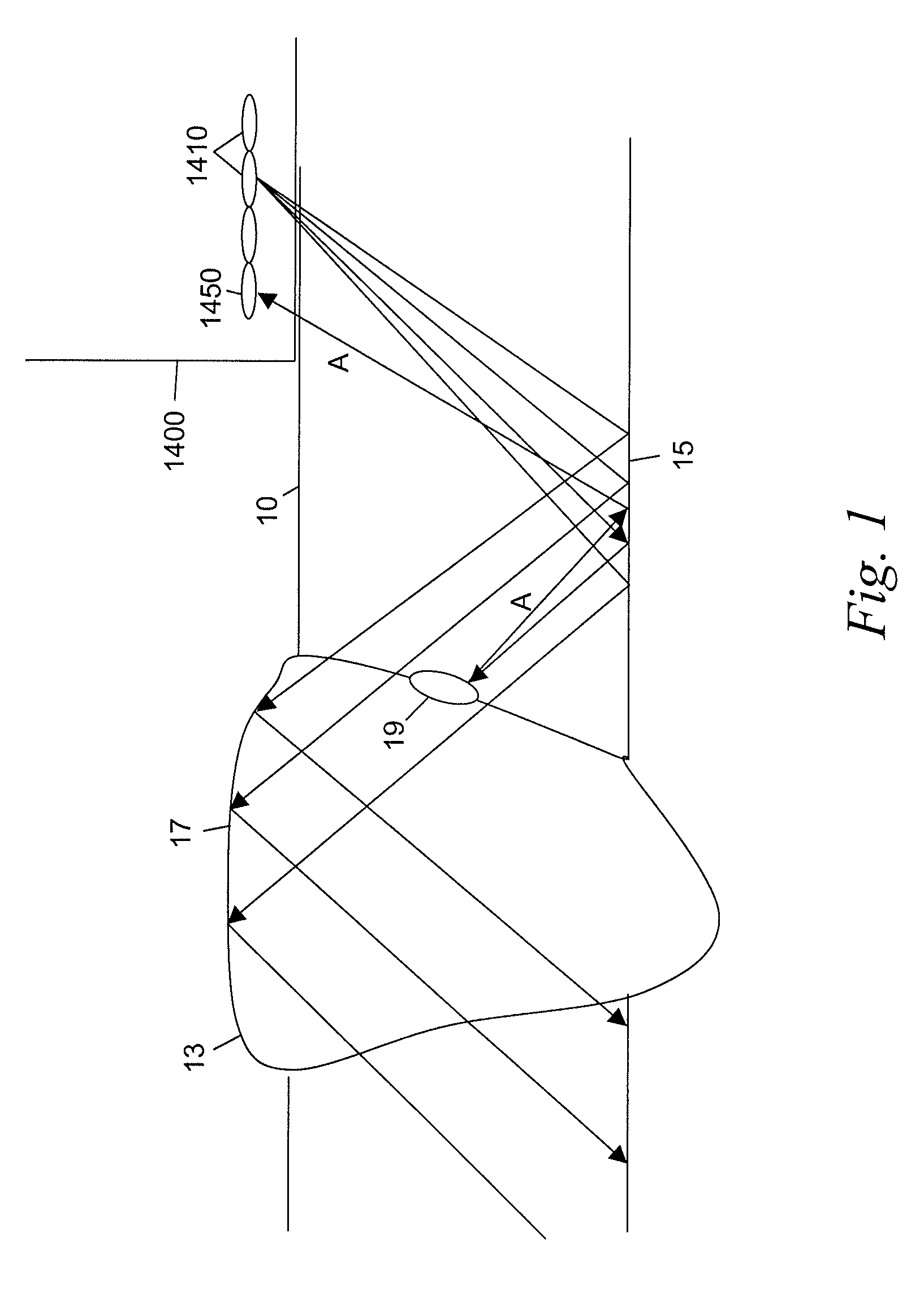

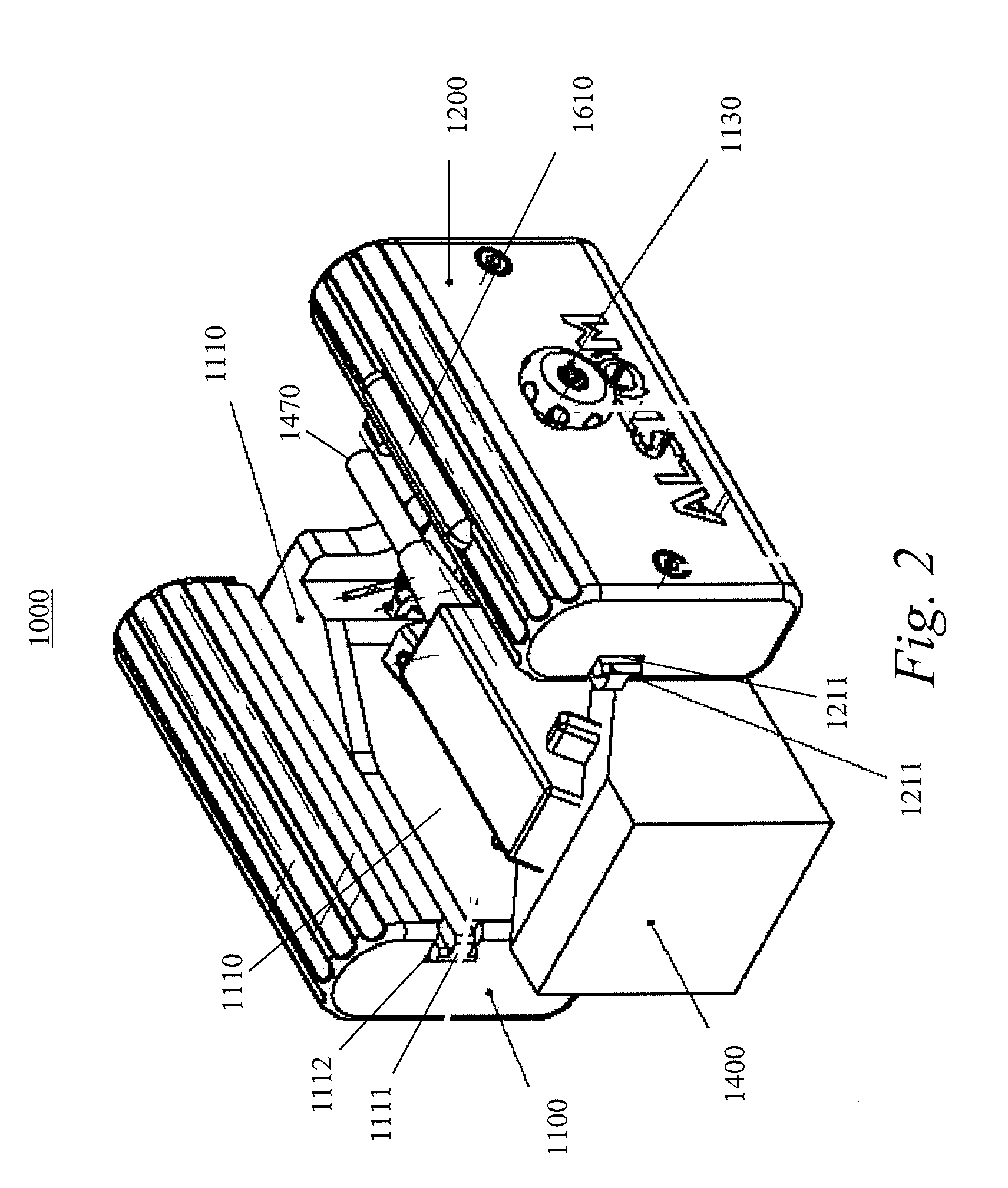

Low profile ultrasound inspection scanner

ActiveUS20100224001A1Analysing solids using sonic/ultrasonic/infrasonic wavesUsing subsonic/sonic/ultrasonic vibration meansEngineeringConstruction design

An inspection scanner [1000] is described that has a low profile construction designed to fit into tight spaces and inspect structures [10] such as weld joints [13]. Wheel frame assemblies [1100, 1200] carry a probe holder assembly [1110] with an ultrasonic (US) array [1400] that emits US beams through the structure [10] and receives reflected sound waves. The probe holder assembly [1110] extends and US beam is angled away to inspect in tight locations. The wheel frame assemblies [1100, 1200] roll on wheels [1140, 1240] that drive an encoder [1250]. Encoder [1250] provides the specific locations for the received sound waves with respect to the weld. The locations and received sound waves are used to reconstruct a signal showing imperfections inside of structure [10]. The wheels [1140, 1240] may be magnetic to hold it to the structure [10] being inspected. A brake system [1600] may be employed to hold the inspection scanner [1000] at a given location.

Owner:GENERAL ELECTRIC TECH GMBH +1

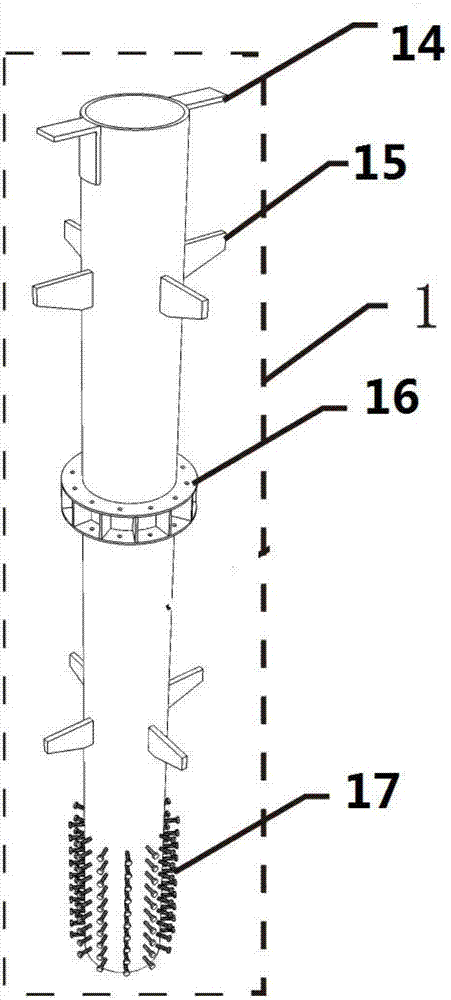

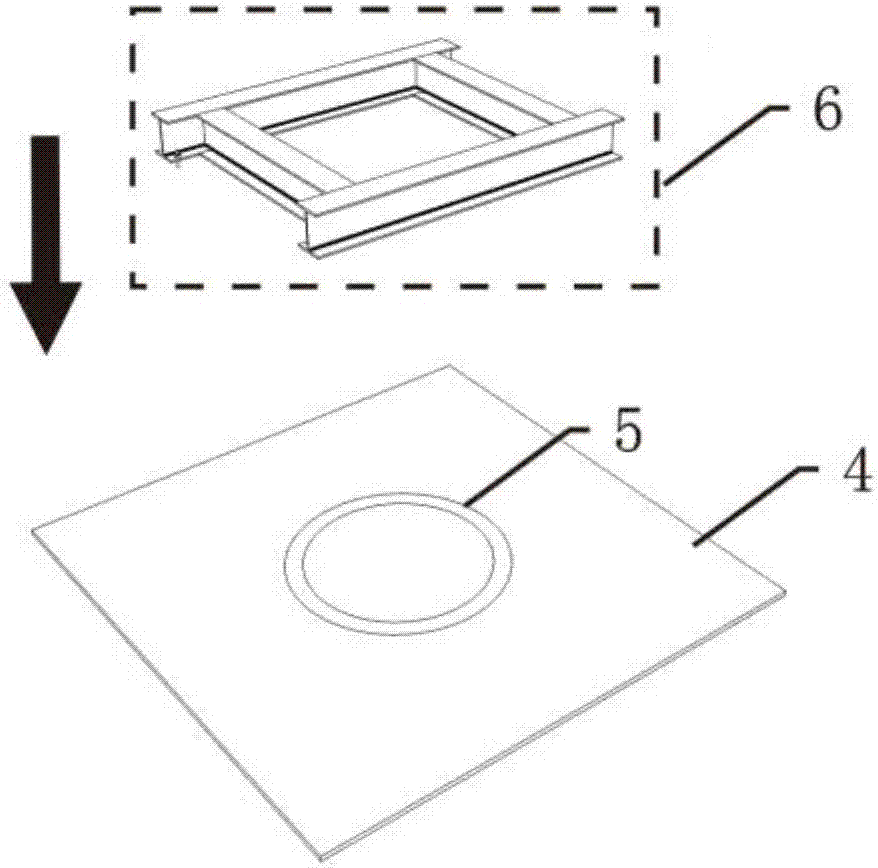

Steel pipe column verticality adjusting device and pile column integrated construction technology by using steel pipe column verticality adjusting device in reverse construction

InactiveCN107288357AImprove installation accuracyLow costBuilding material handlingBulkheads/pilesEconomic benefitsBuilding design

The invention provides a steel pipe column verticality adjusting device and a pile column integrated construction technology by using the steel pipe column verticality adjusting device in a reverse construction technology. Pile column integrated construction in the reverse construction can be met, complicated steel pipe column verticality adjusting and positioning equipment can be omitted, the perpendicularity of a steel pipe column in the reverse construction is dramatically improved, the construction period is shortened, and the project cost is reduced. According to the steel pipe column verticality adjusting device, the structure is simple, adjustment is convenient, the verticality adjusting effect is audio-visual, repeated using can be achieved, the construction cost is effectively reduced, and the economic benefit is dramatically improved; and through organic coordinating working of each built-up section of the verticality adjusting device, it is ensured that the steel pipe column can vertically meet the demands of building design, the safe structure is achieved, and using function is satisfied.

Owner:YUNNAN CONSTR INVESTMENT HLDG GRP CO LTD

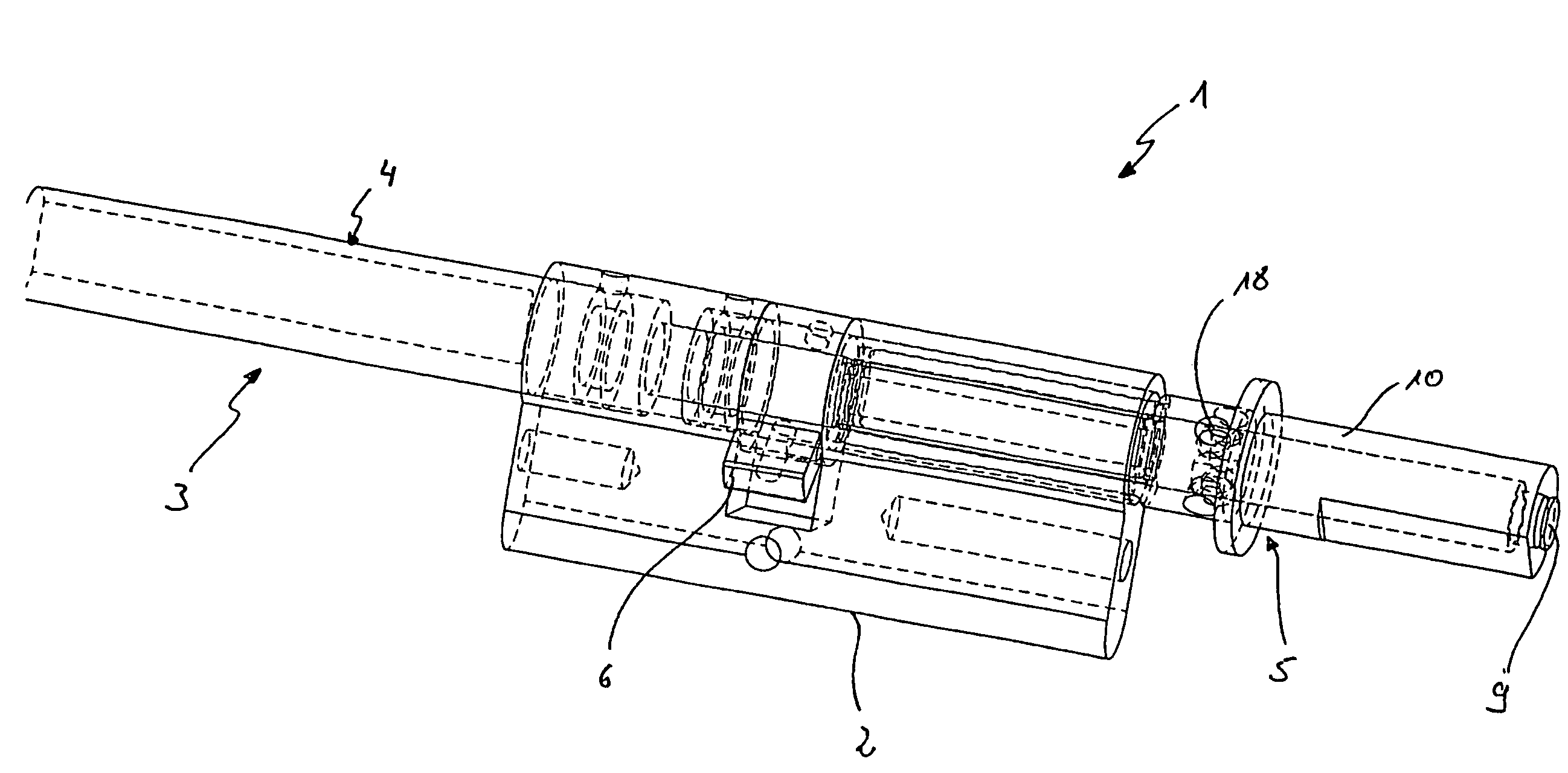

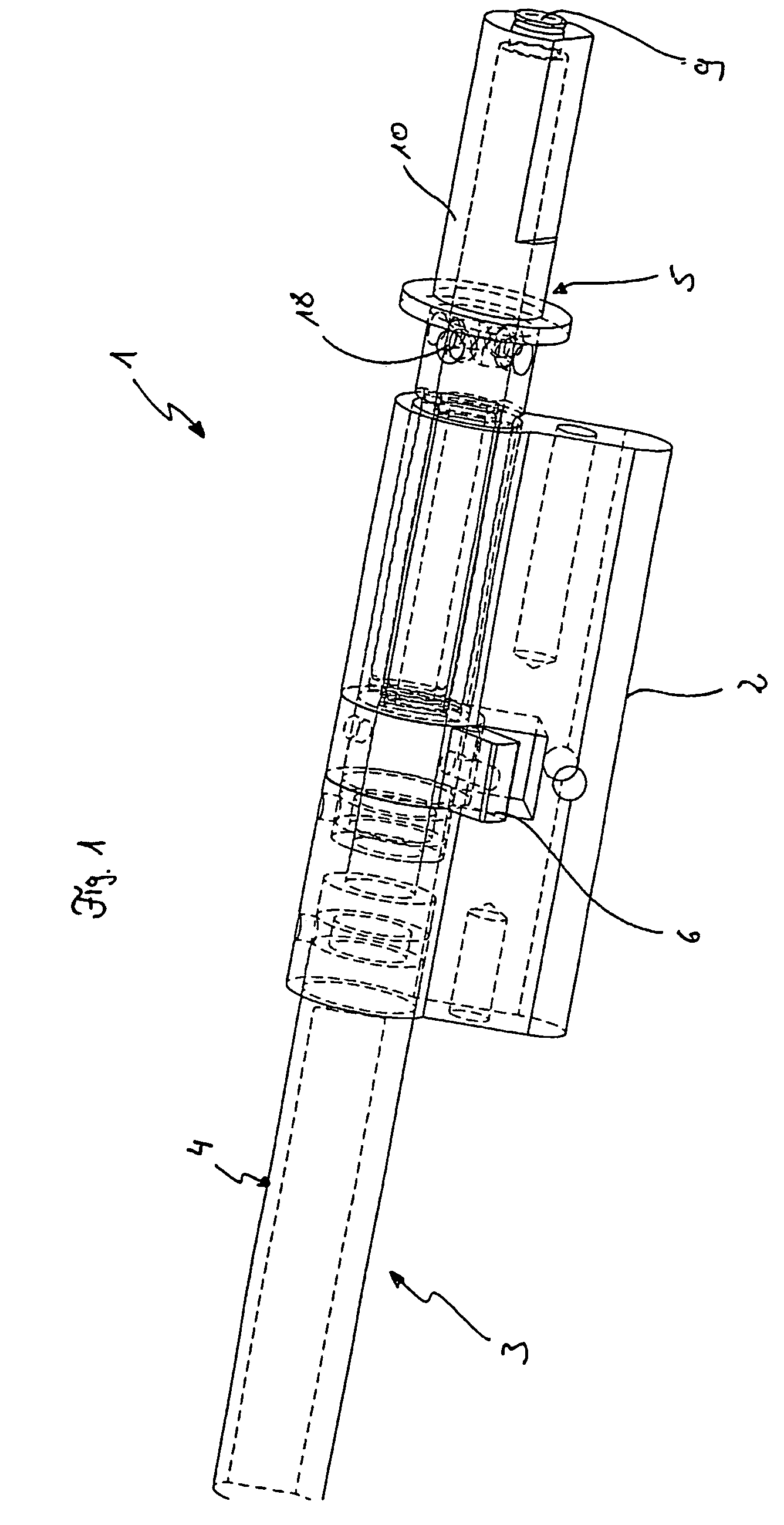

Lock

InactiveUS7275402B2Simple and reliable and low-energy actuationAnti-theft cycle devicesAnti-theft devicesCouplingLocking mechanism

A lock, such as a mortise lock, for a door. The lock comprises a locking cylinder that can be inserted into a door leaf and a shaft having two sections, each section of the shaft having a handle at the end, preferably a rotary knob or a standard door handle and being actively interconnected by a coupling after recognition of an authorisation code. The lock can be used for various applications as a result of its construction design, with a standard locking cylinder in various doors and that it allows, a simple, reliable, low-energy actuation of the locking mechanism. To achieve this, the coupling (11) comprises at least two, preferably four or more rolling members (17) that are guided in recesses (18) of a second part (10) of a first section (5) of the shaft (3). The rolling members can be pushed into cavities (20) that run around the periphery of the first part (9) of the first section (5) of the shaft (3), in order to actively connect a first part (9) and the second part (10) of the first section (5) of the shaft (3), using a radially or axially displaceable sliding element (22).

Owner:BURG WACHTER

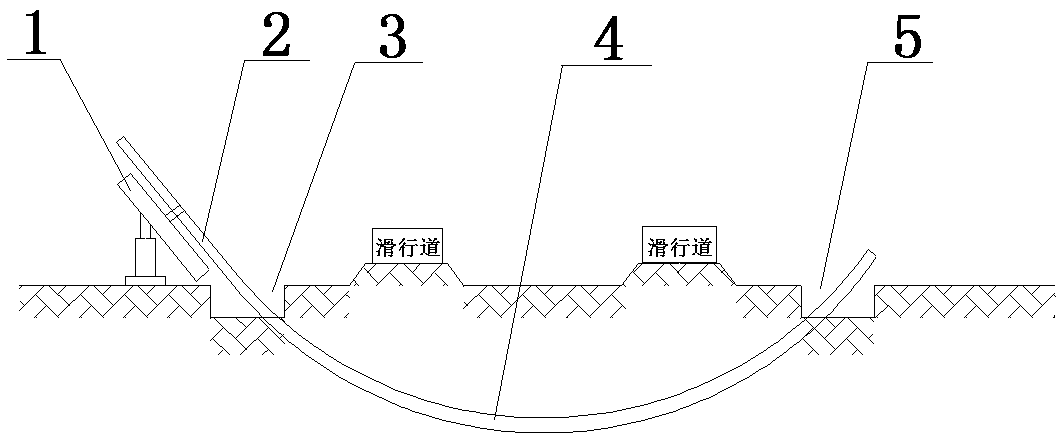

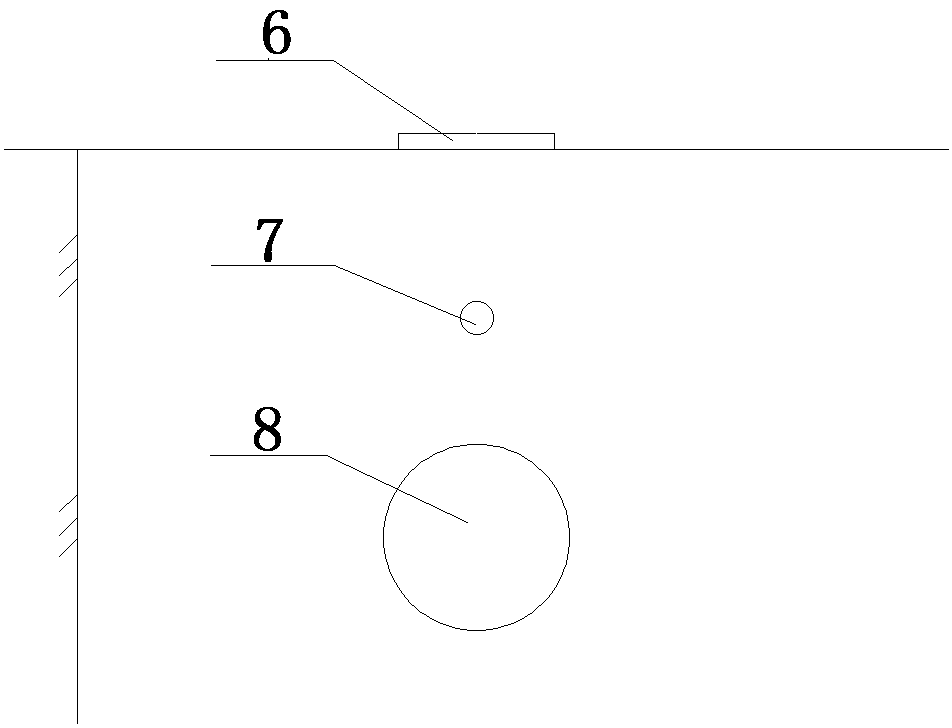

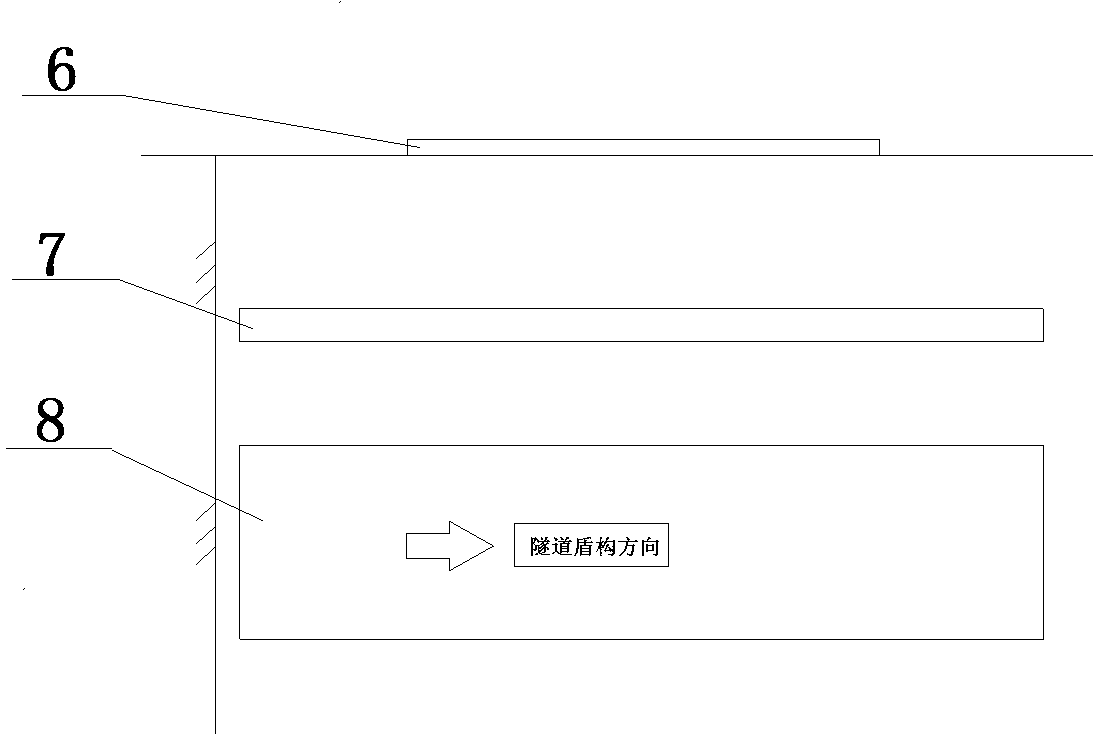

Real-time monitoring method for displacement of underground deep-layer soil body

ActiveCN102995615AEffective monitoring of settlementHigh precisionIn situ soil foundationDynamic monitoringConstruction design

The invention relates to the field of underground construction monitoring, and particularly relates to a real-time monitoring method for displacement of an underground deep-layer soil body. The real-time monitoring method comprises the following steps of: burying an inclination measuring pipe at the position under the surface of the existing building, distributing a plurality of inclinometer probes in the inclination measuring pipe, and connecting the plurality of inclinometer probes together by cables; then statically monitoring settlement displacement data at the position in real time by utilizing all the inclinometer probes, sending the data to a computer on the ground by a cable, carrying out data processing, and obtaining settlement information. The real-time monitoring method has the advantages that the settlement of the underground deep-layer soil body of the building along the vertical direction in construction is effectively monitored, the real-time static monitoring area is large, the accuracy of measured data is high, the labor cost for dynamic monitoring is reduced, and a solid foundation is laid for construction design, progress scheduling and avoiding measures and the like.

Owner:SHANGHAI URBAN CONSTRUCTION MUNICIPAL ENGINEERING (GROUP) CO LTD

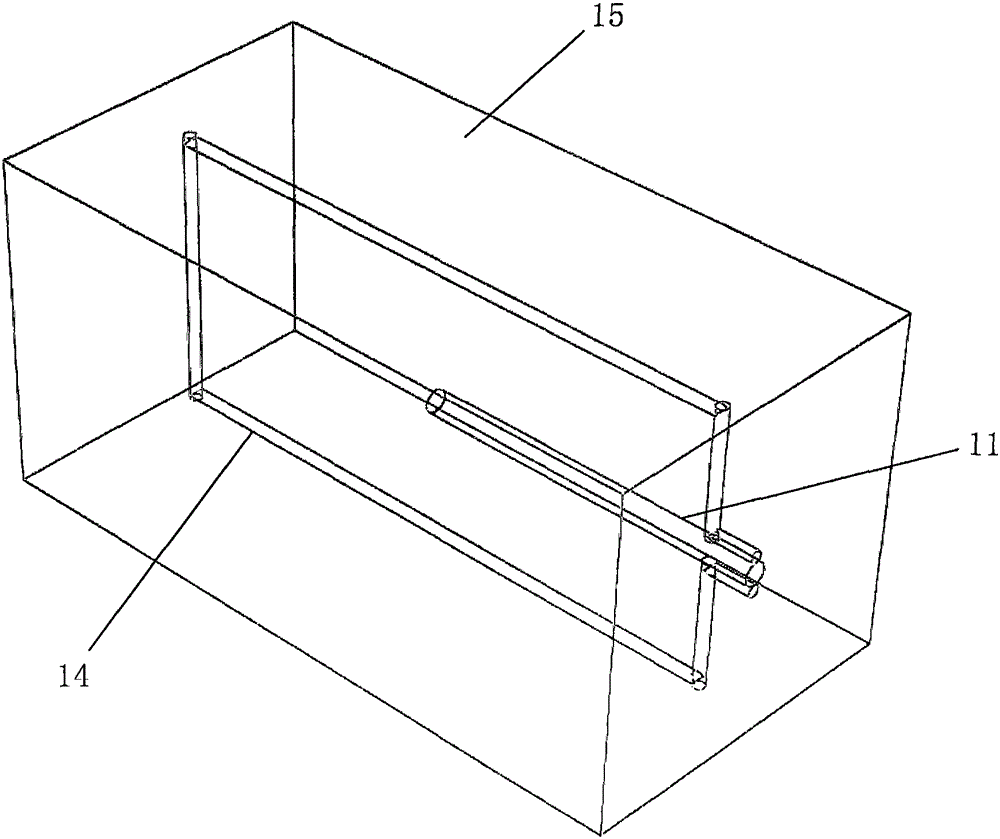

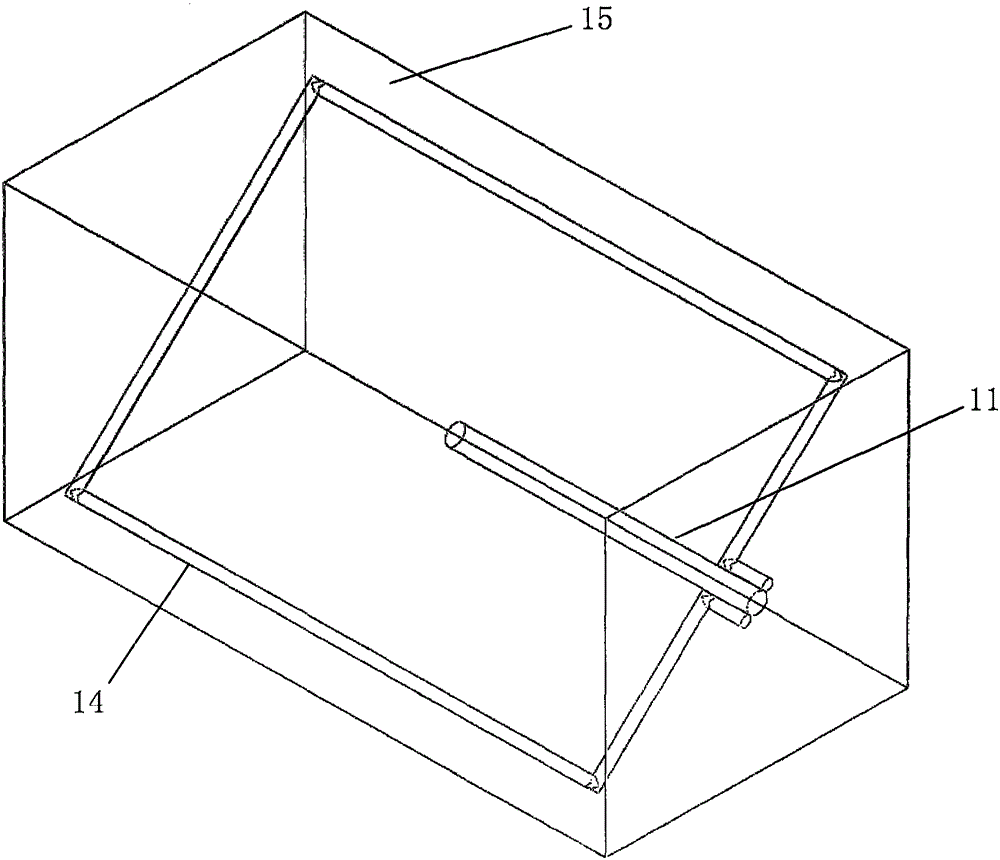

Experimental device for simulating hydrofracture action mechanism in steam assisted gravity drainage (SAGD) process

The invention discloses an experimental device for simulating a hydrofracture action mechanism in the steam assisted gravity drainage (SAGD) process. The experimental device comprises a true triaxial stress loading device, a steam heating device, a fracture device and an acoustic emission monitoring device. The true triaxial stress loading device can apply stress in three directions to an experimental rock sample through a pressure chamber. The steam heating device locally heats the experimental rock sample through a hot steam circulation pipeline prefabricated in the experimental rock sample and monitors the temperature of the experimental rock sample through a temperature sensor arranged on the surface of the experimental rock sample. The fracture device injects fracturing fluid into the experimental rock sample through a shaft prefabricated in the experimental rock sample. The acoustic emission monitoring device monitors acoustic emission signals generated inside the experimental rock sample and determines the crack spatial position through a corresponding positioning algorithm. By the adoption of the experimental device, the SAGD hydrofracture process under a high-temperature and high-pressure condition is simulated, and thus true and effective evaluation and reference are provided for hydrofracture construction design of a thickened-oil oilfield.

Owner:CHINA UNIV OF PETROLEUM (BEIJING)

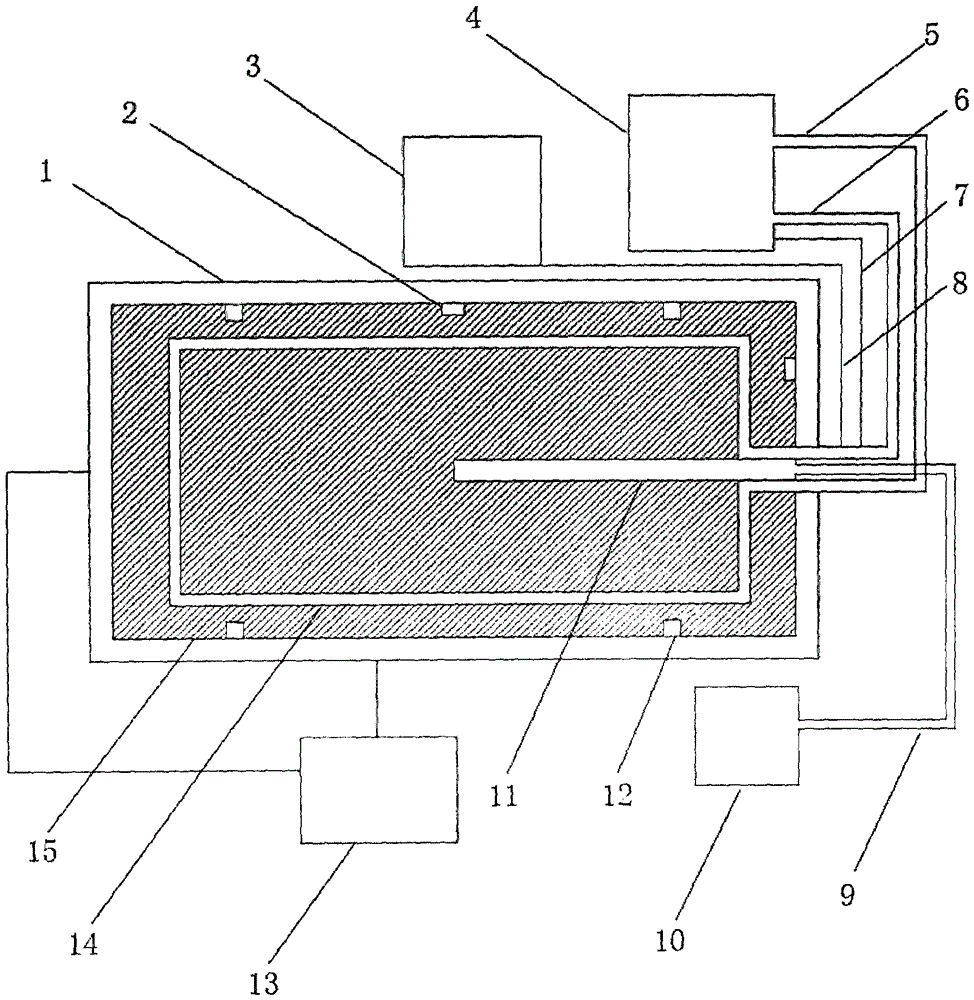

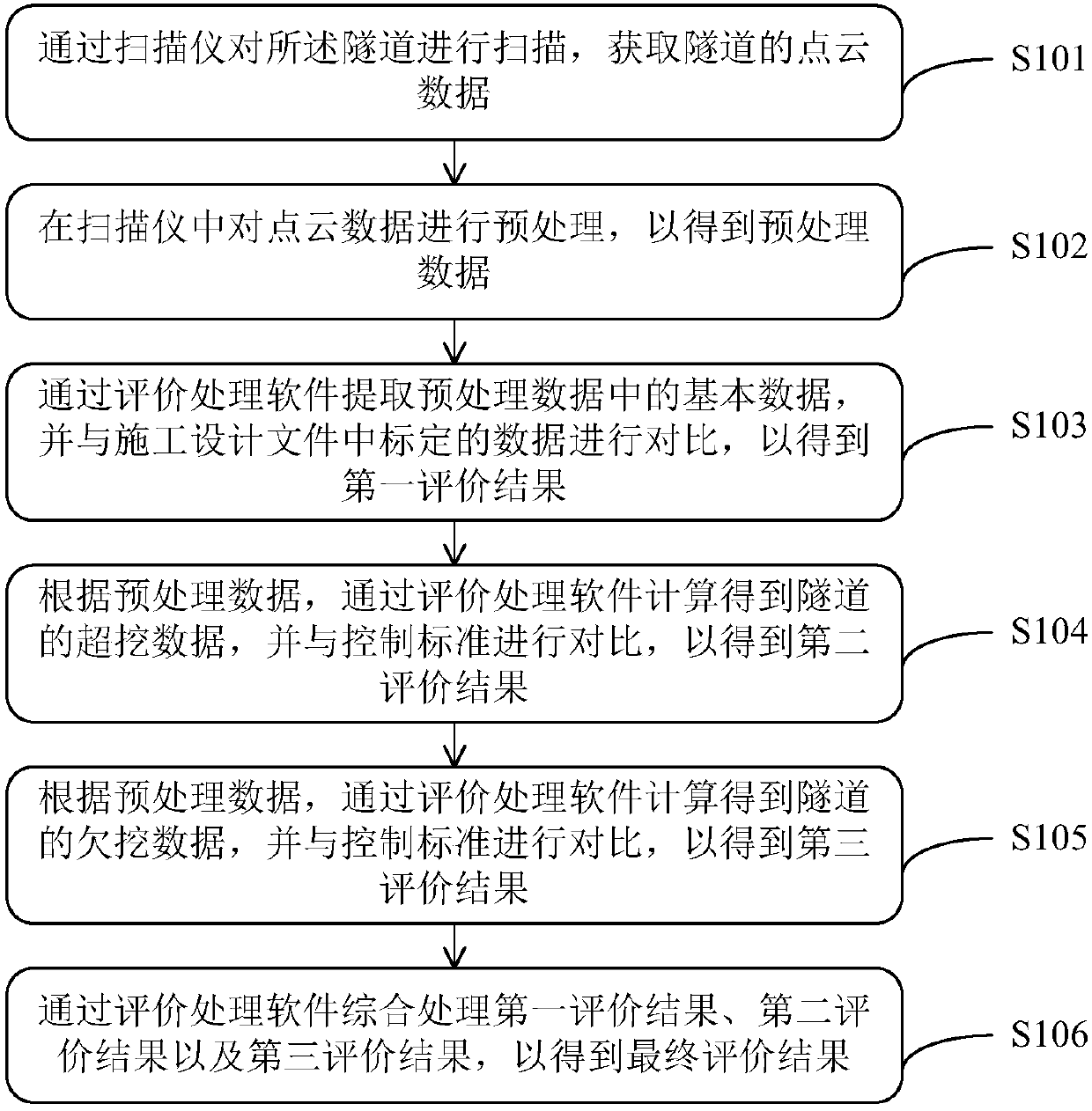

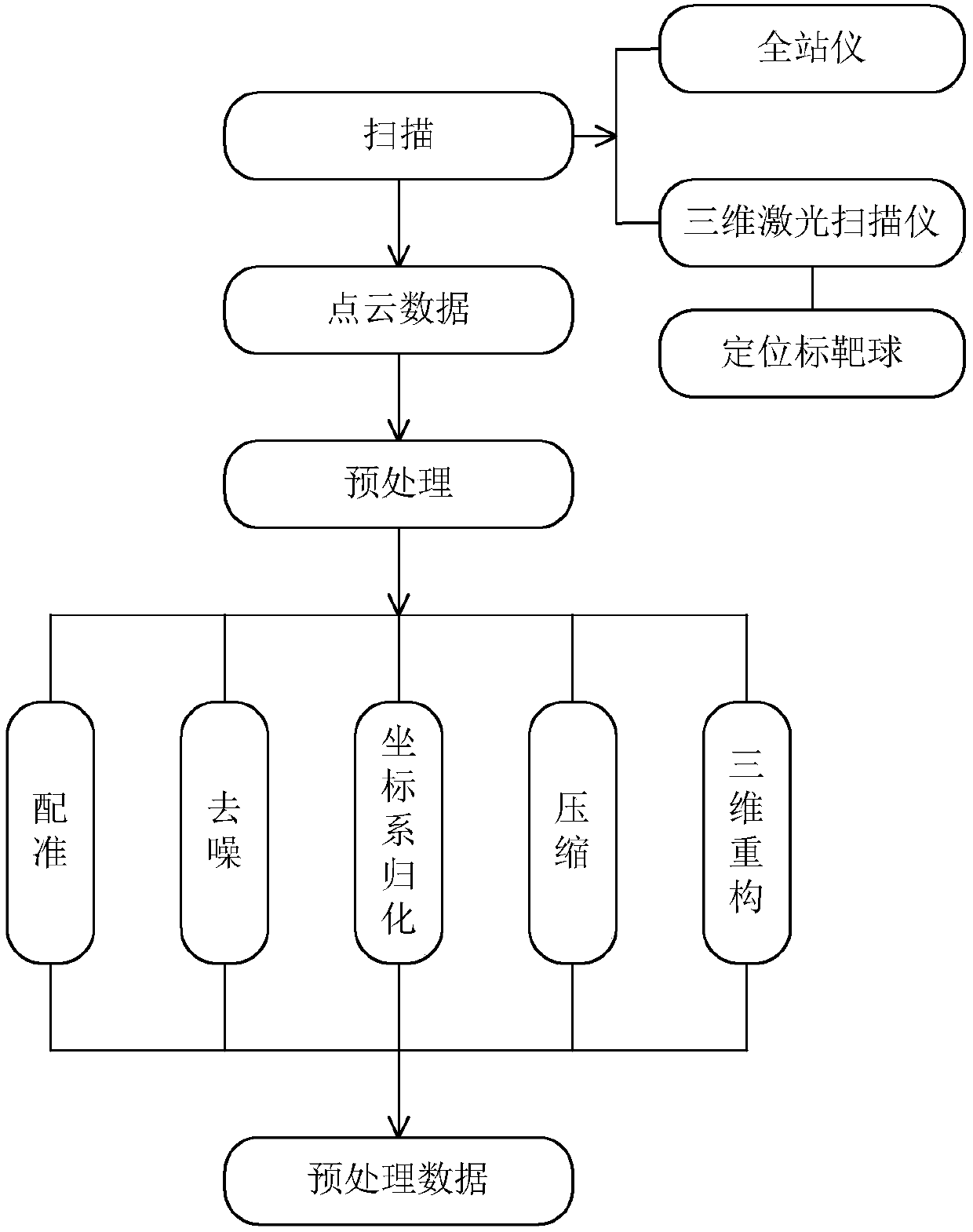

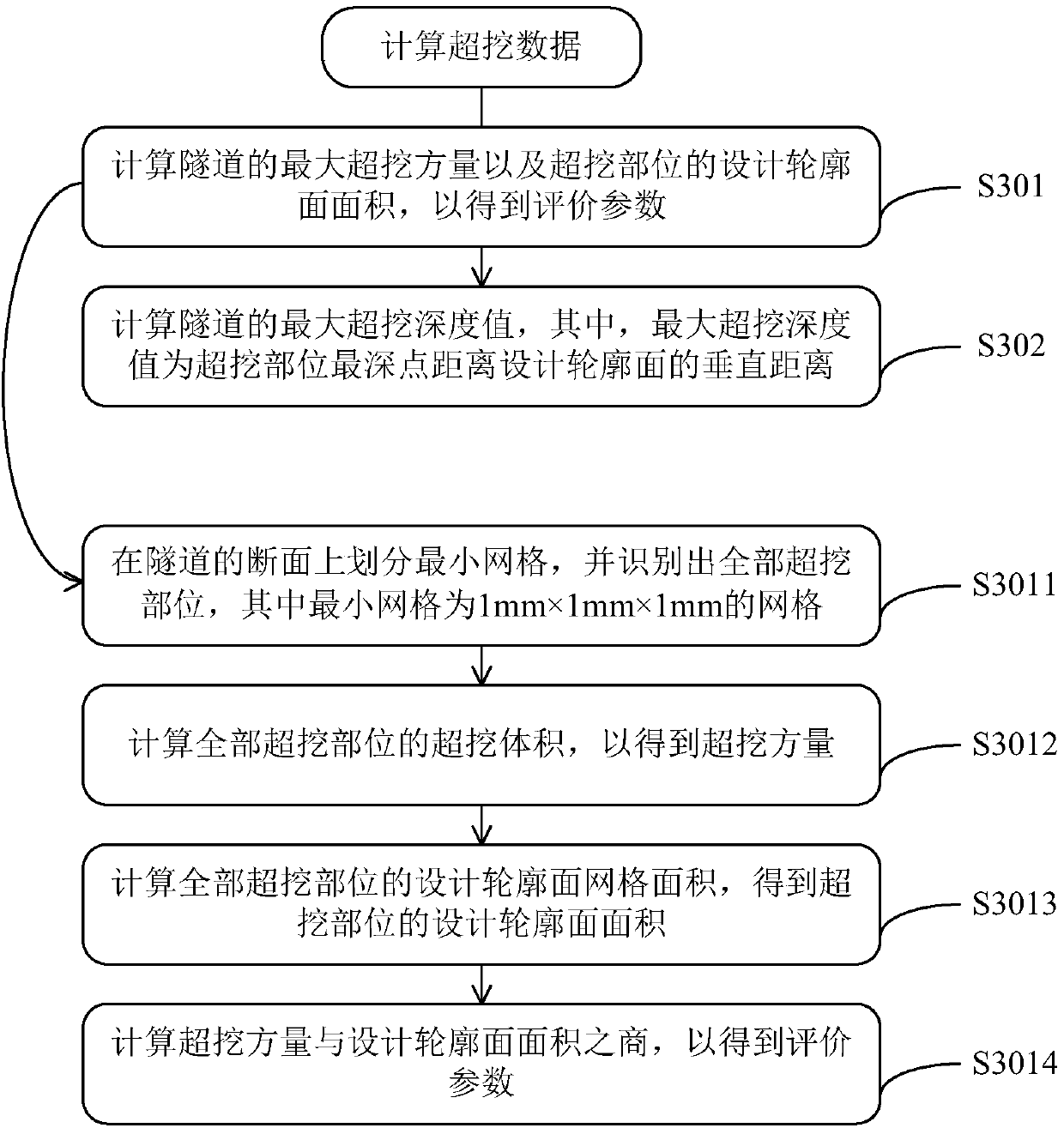

Method and system used for evaluating overbreak and underbreak of tunnel

ActiveCN107762559AShort cycle timeEasy to operateMining devicesData processing applicationsEvaluation resultPoint cloud

The present invention provides a method for evaluating overbreak and underbreak of a tunnel. The method comprises the following steps that the tunnel is scanned, point cloud data of the tunnel is obtained, and the point cloud data is preprocessed so as to obtain preprocessed data; basic data in the preprocessed data is extracted and compared with calibrated data in a construction design document,and the first evaluation result is obtained; overbreak data of the tunnel are calculated and obtained according to the preprocessed data and compared with the control standard, and the second evaluation result is obtained; according to the preprocessed data, the underbreak data of the tunnel is calculated and obtained and compared with the control standard, and the third evaluation result is obtained; the first evaluation result, the second evaluation result and the third evaluation result are comprehensively processed so as to obtain the final evaluation result. The method and system used forevaluating overbreak and underbreak of the tunnel can be used for evaluating overbreak and underbreak of the tunnel, the calculated overbreak data and the calculated underbreak data are compared withthe control standard, and tunnel engineering is evaluated.

Owner:RAILWAY ENG RES INST CHINA ACADEMY OF RAILWAY SCI +1

Electrical clamp connector and connecting terminal

InactiveUS20070259574A1Contact member manufacturingCoupling contact membersElectrical conductorSpring steel

The invention relates to an electrical clamp connector and connecting terminal that, per pole, has at least two conductor terminal connections oriented in the same direction and an additional connecting contact on the opposite-lying side, which serves for connecting a countercontact external to the terminal. It is proposed for such a terminal to use the especially small-construction design features of a terminal that is produced from a single piece of spring steel sheet and a busbar rod, and to combine these with the new features that the busbar rod has one or two cross projections, which project through the free opening in the spring steel sheet and form the additional connecting contact, which, for example, may be constructed in the form of a socket contact or in the form of a plug-in contact.

Owner:WAGO VERW GMBH

Project management system

InactiveCN106408172ASimple monitoring processEasy to judgeGeometric image transformationResourcesProject completionMonitoring system

A project management system is disclosed and comprises a project progress database, a project progress sketch map, a project progress monitoring system, a project standard template picture which is generated via a project construction design drawing, a project implementation site imaging system, an implementation site processing system and a remote monitoring terminal. Via the project management system, a project implementation site can be monitored remotely; monitoring operation can be conducted in a simple, convenient and direct manner; manpower resources can be saved. Feedback on construction conditions of an implementation site can be given timely due to real time monitoring operation, convenience of determining operation can be realized, and high result accuracy can be achieved. Project progress can be automatically adjusted and monitored according to change of implementation conditions via the project management system, and project completion time can be effectively monitored.

Owner:广东达安项目管理股份有限公司

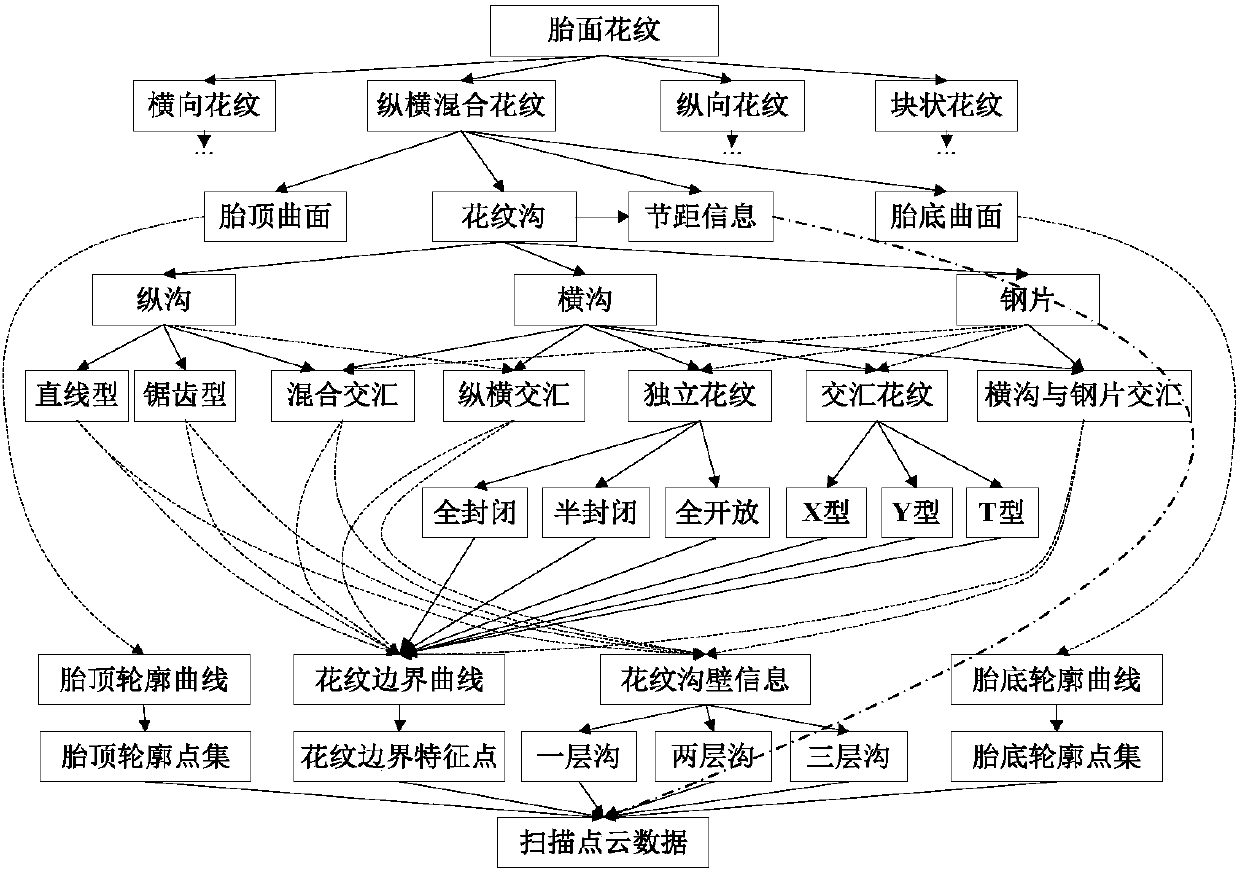

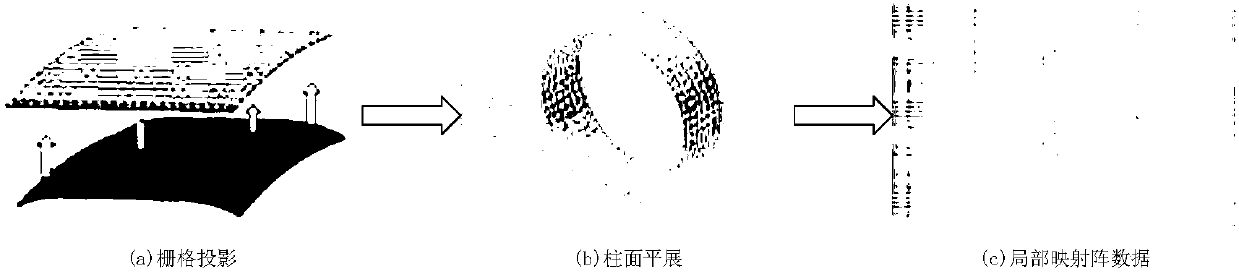

Reverse modeling method for structural design parameters of tread patterns

InactiveCN107657130AReduce operating process timeReduce waiting timeGeometric CADSpecial data processing applicationsConstruction designAnalysis data

The invention relates to a reverse modeling method for structural design parameters of tread patterns. The reverse modeling method comprises the steps that point cloud data attributes of a tire are obtained, the data attributes are analyzed, and a model reconstruction system is built; the conversion from 3D tread point cloud to a point cloud mapping matrix is conducted with the tread point cloud obtained through optimized segmentation as an object and a grid as a primary unit; according to the point cloud mapping matrix, the point cloud of a tire tread is segmented and extracted; the pattern boundary feature information is extracted, a pattern profile curve is constructed; according to the pattern profile curve, the permissible approximate error and the length and the number of segments ofmachining features are adjusted, so that pattern reconstruction optimization is achieved. By means of the reverse modeling method, the pattern construction design information can be quickly and efficiently recovered, the intelligence degree of the structural design of the tread patterns is improved, the types of basic patterns in a pattern rule base are perfected, and it is very instructive to complete the synergetic improvement in the multidimensional characteristics of the tire by improving the pattern structure forms.

Owner:GITI RADIAL TIRE (ANHUI) CO LTD +1

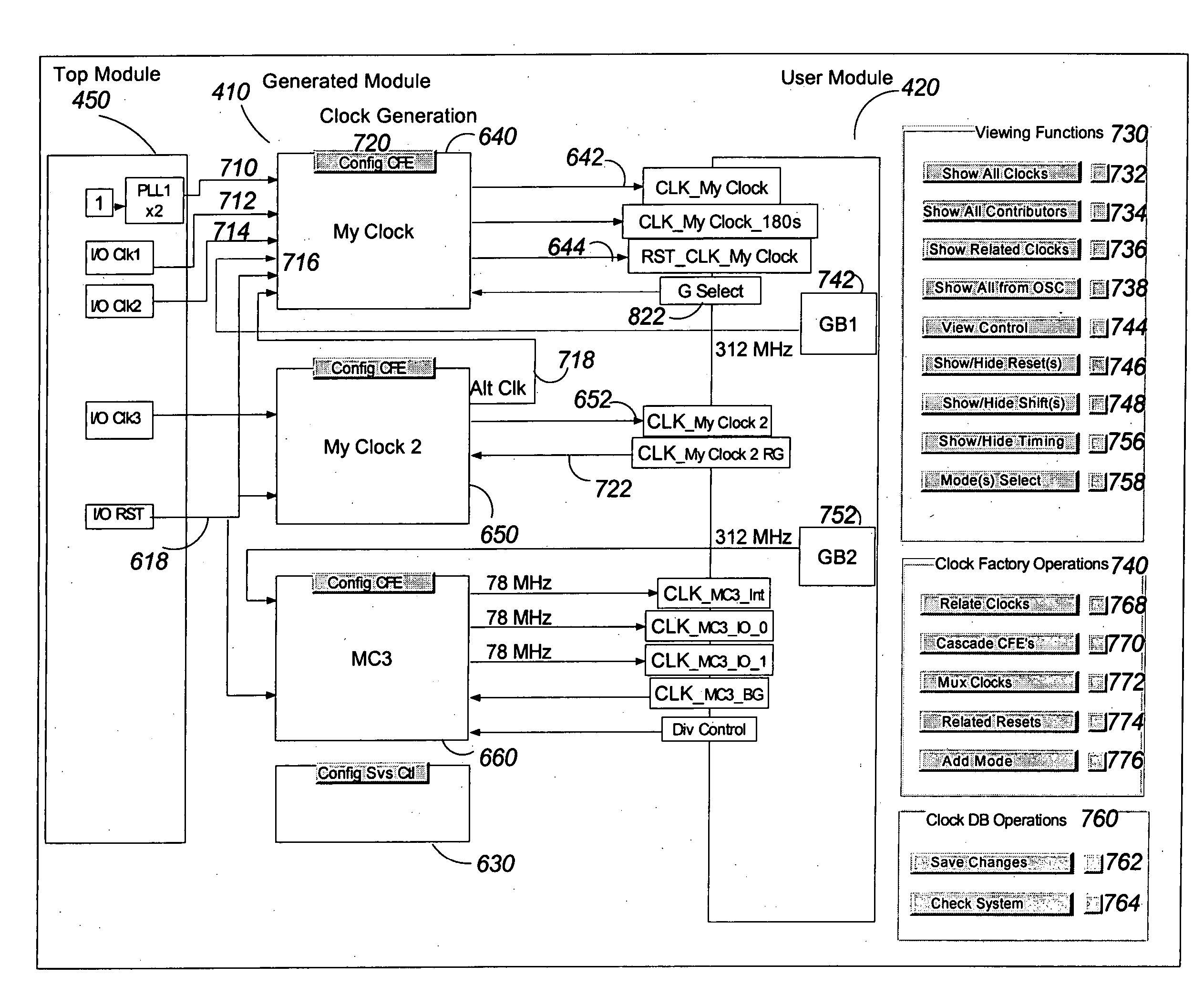

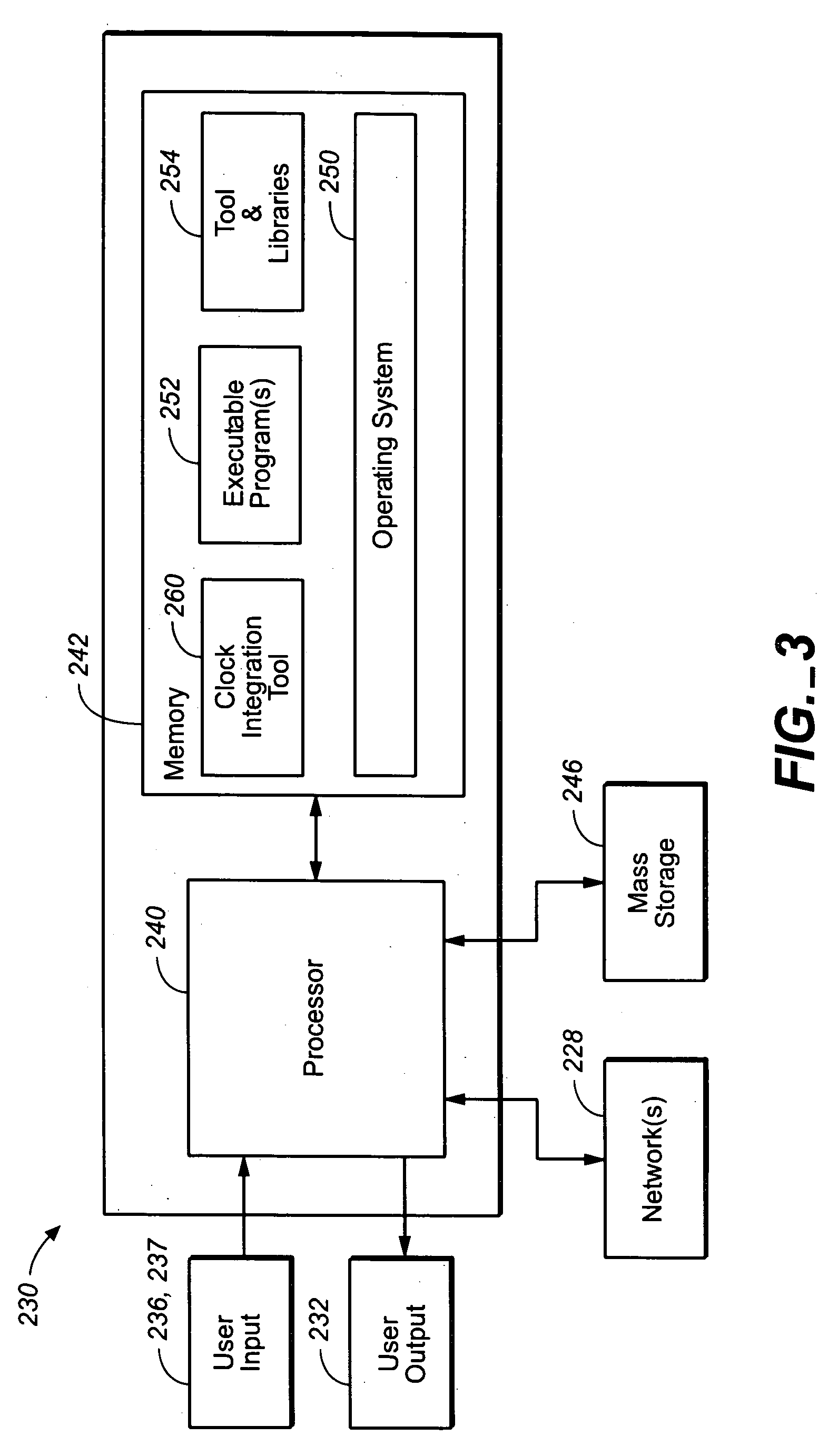

Guided capture, creation, and seamless integration with scalable complexity of a clock specification into a design flow of an integrated circuit

InactiveUS20050273738A1Generating/distributing signalsExecution for user interfacesMultiplexingMultiple context

A clock integration method, tool, and a computer program product that captures, creates, and seamlessly integrates a clock specification to achieve a correct-by-construction design flow of a semiconductor product, such as an ASIC, from a partially manufactured semiconductor platform. The clocking elements of the design flow are combined and displayed to a chip designer in a plurality of context-driven user interfaces and views. Within each view, the details of the clock specification are presented in the context of the information to guide a chip designer to make relevant and correct determinations, e.g., if the context is a high level overview of the logic of the intended semiconductor product, then only the high level parameters, such as source, frequency, path of the clocks signals through the high level modules, etc. are seen. When a chip designer wants more or less detailed information, she / he need only zoom in / zoom out through the plurality of views of the design flow. Each view can combine the logical, structural, architectural, cost, timing, and other features of the clock in a particular context. A user can zoom in all the way to select and manipulate the circuit elements of a PLL, a clock factory element, etc. as in the creation or generation of a clock for the intended semiconductor product. The user can then zoom out and the clock integration method and tool herein determines how changes in selected muxed clock signals and / or elements affect other clocks in the same or other modules and / or the same clock in other modules. Creating, inserting, and integrating clocks for a complex integrated circuit has never been easier.

Owner:BELL SEMICON LLC

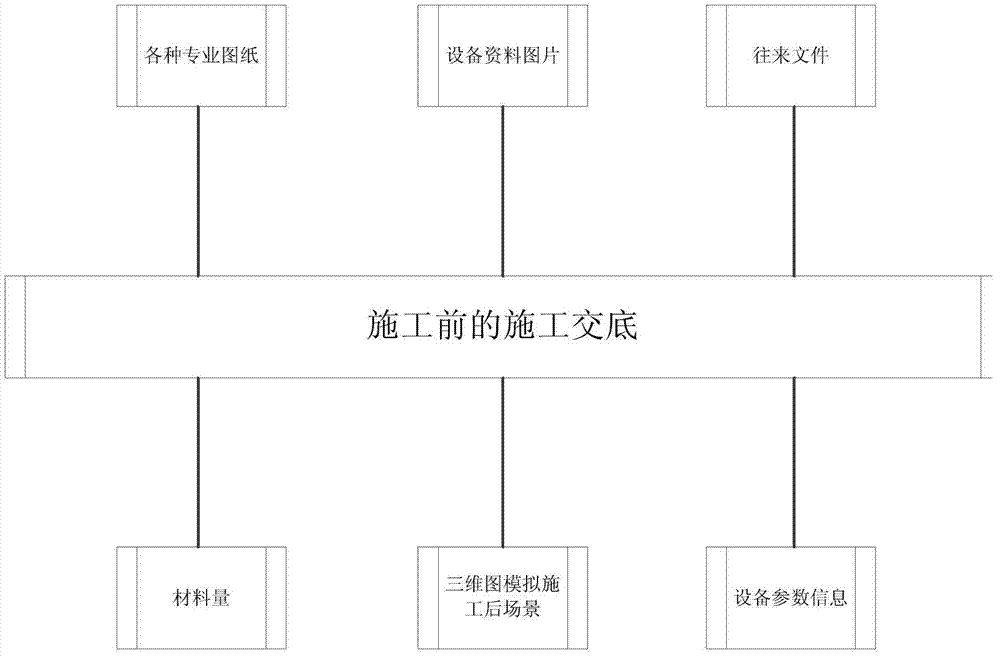

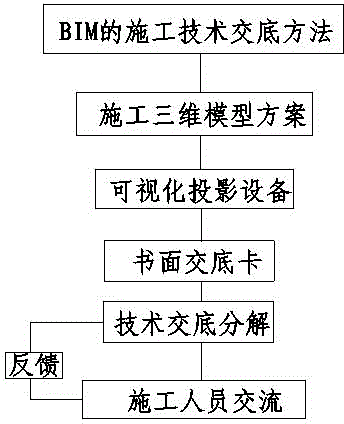

Pre-construction technical disclosure method based on BIM

InactiveCN104573254AImprove construction efficiencyGuarantee the construction qualityData processing applicationsSpecial data processing applicationsDevice placementConstruction design

The invention discloses a pre-construction technical disclosure method based on BIM. The method includes the following steps: building a construction BIM three-dimensional model according to construction design and marking relevant technical parameters in the model; manufacturing a construction scheme disclosure written card; placing the construction BIM three-dimensional model on a communication screen through a visual device. The method further includes that a designer breaks down the BIM three-dimensional model through the communication screen and explain technical parameters to constructors to conduct technical disclosure, and the constructors feed back opinions through the technical disclosure. The method has the advantages of being visual, quick and capable of improving construction efficiency, enabling the constructors to learn construction steps and various construction requirements and ensuring construction quality.

Owner:CHINA MCC17 GRP

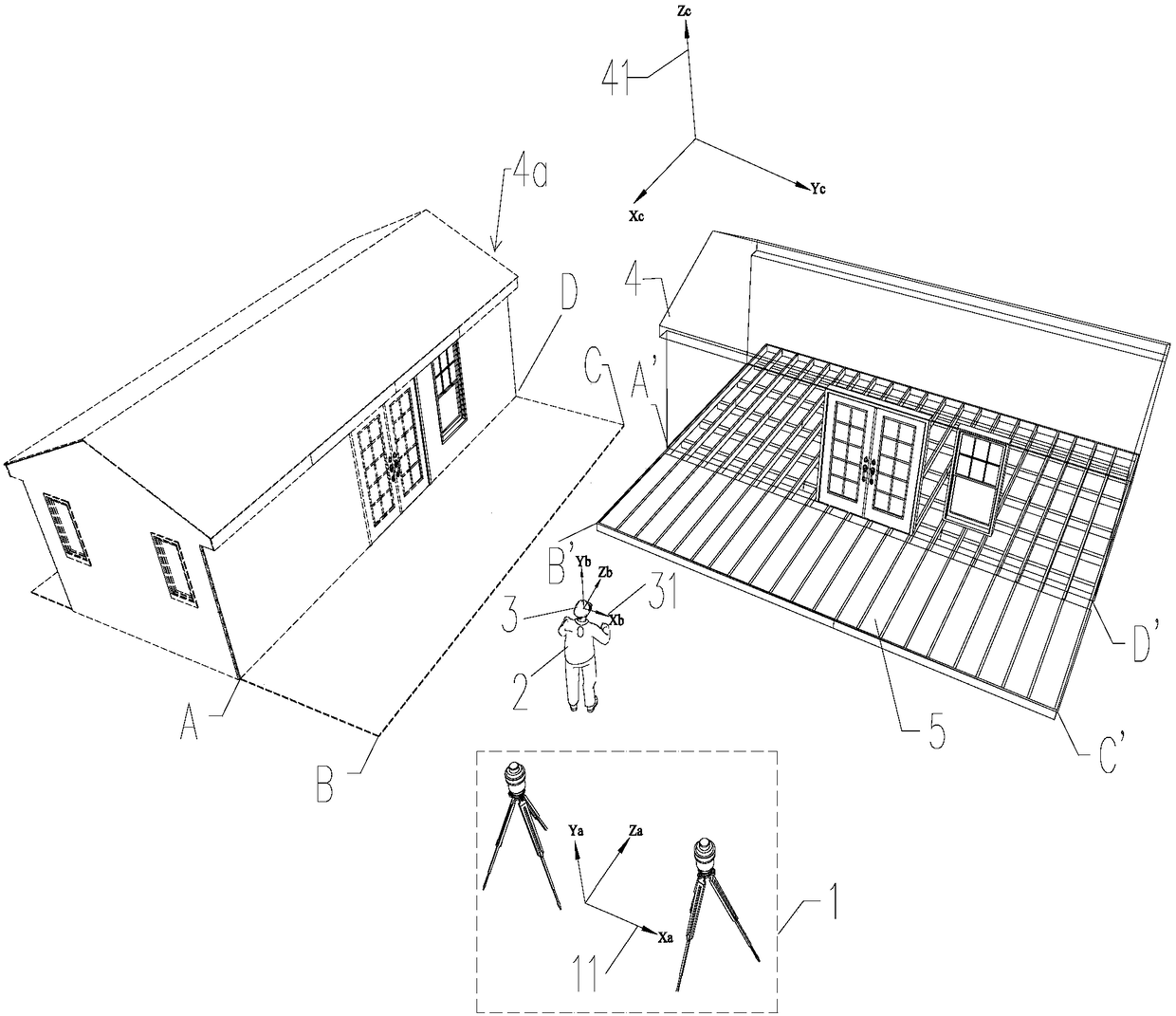

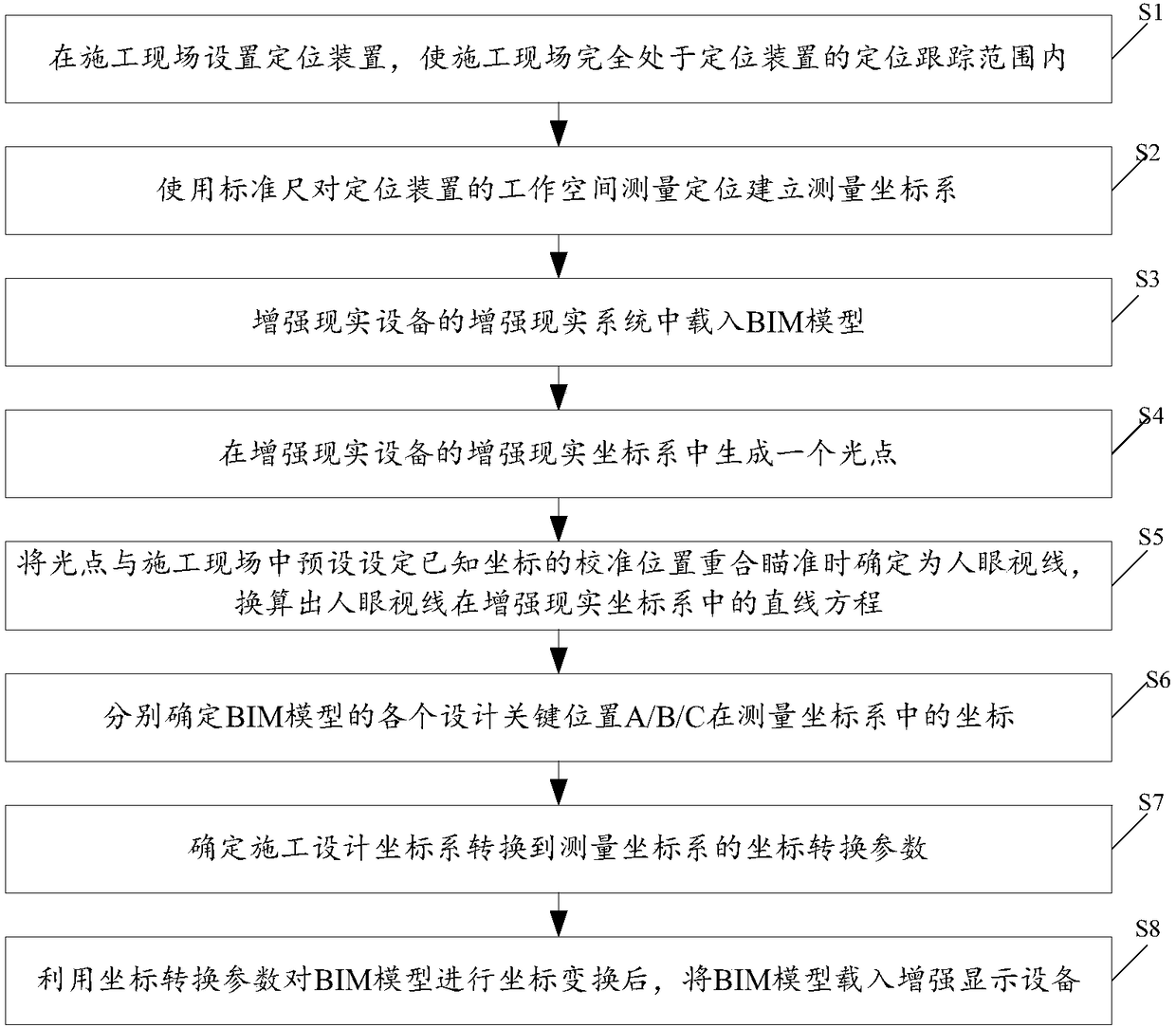

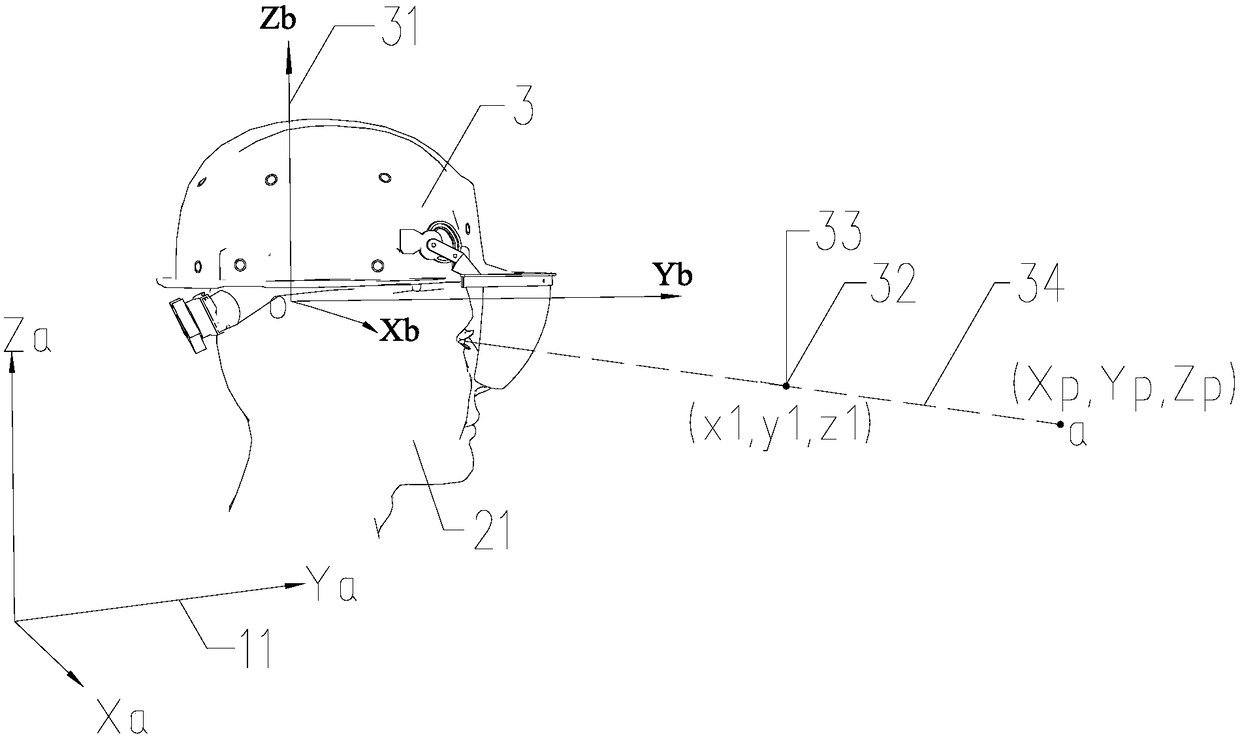

Augmented reality lofting system and implementation method based on BIM technology

ActiveCN108227929AEasy to superviseAvoid misunderstandingInput/output for user-computer interactionData processing applicationsTransformation parameterCritical position

The invention discloses an augmented reality lofting system and method based on a BIM technology. The method comprises the steps that a construction site is located in a positioning and tracking rangeof a positioning device, and a standard ruler is used for measuring and positioning the working space of the positioning device and establishing a measurement coordinate system; coordinates of key design positions A / B / C in the measurement coordinate system are determined respectively; coordinate transformation parameters of a construction design coordinate system which is converted to the measurement coordinate system are determined; the coordinate conversion parameters are utilized to conduct coordinate transformation on a BIM model, then the BIM model after subjected to coordinate transformation is loaded into augmented reality equipment, and when a user wears the augmented reality equipment on the head to observe the construction site, the BIM model is displayed in the construction site and all the key design positions of the BIM model overlap with all key construction positions of the construction site one to one respectively. By means of the method, the mapping relationship of the construction site and the BIM model can be accurately determined so that a BIM three-dimensional design result of a design unit can be accurately superimposed on the construction site by using an augmented reality technology.

Owner:廖卫东 +2

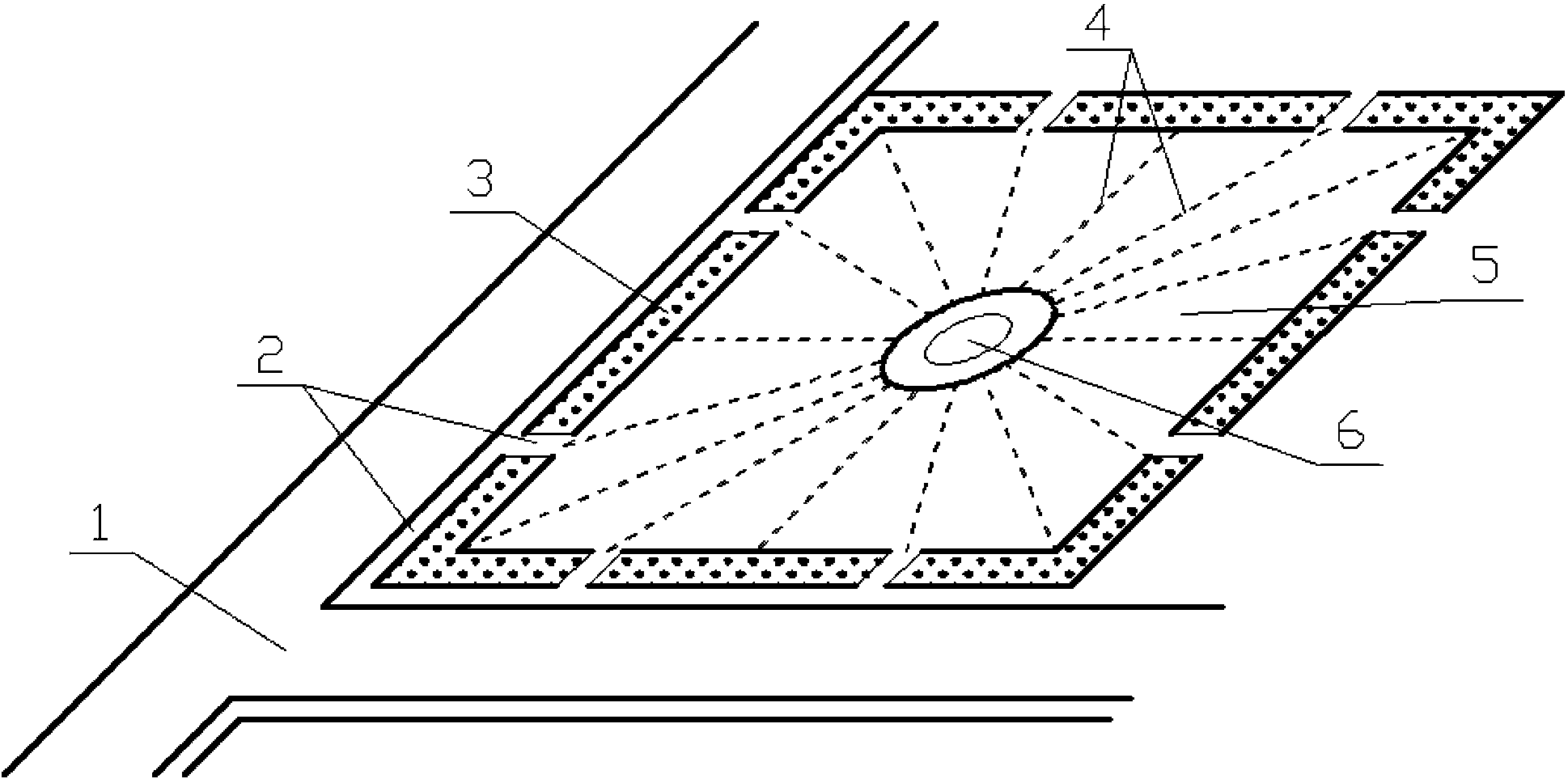

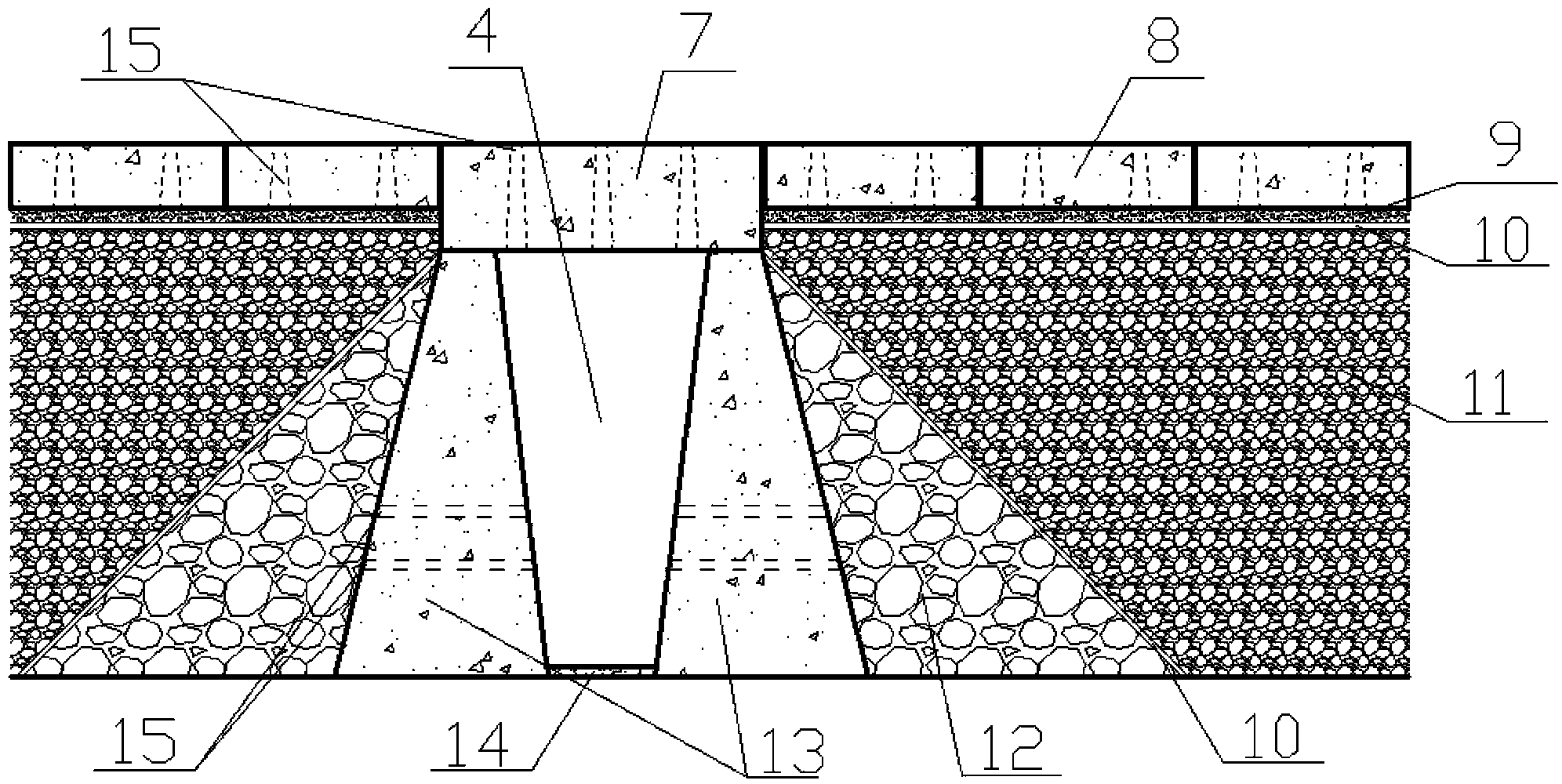

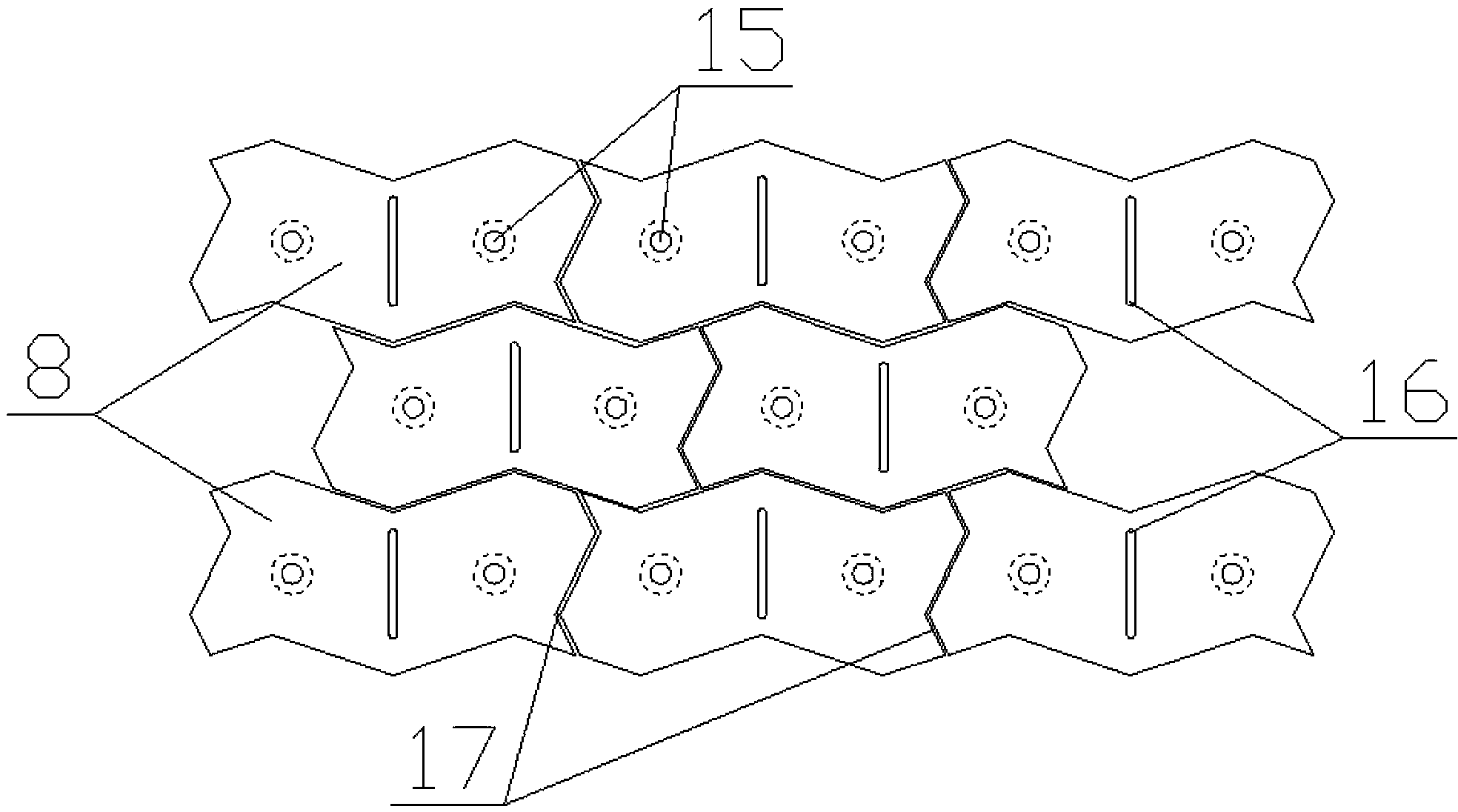

Rainwater penetration collection device based on concrete-sand-based water-permeable bricks

InactiveCN103352411AHigh strengthIncreased durabilityGround-workGeneral water supply conservationBrickAdhesive

The invention relates to a rainwater penetration collection device based on concrete-sand-based water-permeable bricks. The invention belongs to the field of construction design. The invention is characterized in that: pedestrian walkways and squares are paved by using concrete-sand-based water-permeable bricks; rainwater enters the concrete-sand-based pavement water-permeable bricks and cover-plate water-permeable bricks, and is filtered by a gravel bedding layer and a crushed stone bedding layer; rainwater enters a rainwater collection ditch through the water-permeable bricks of a ditch wall of a rainwater-collection thin ditch side wall; the rainwater is then gathered to a water storage tank on the square and is used as a landscape or used for irrigation. The device is characterized in that screened and processed desert sand is used as a main aggregate; high-grade cement is adopted as an adhesive; and proper additives are added. Frustum-shaped water-permeation holes are provided on brick bodies, and anti-slip stripes are arranged on the brick body. The device provided by the invention has the advantages that: desert sand is sufficiently utilized; the strength is high, and cost is low; the water permeability is good, and the water-permeation holes are prevented from blockage; the device is safe and comfortable; a good rainwater collection plane which is the square is sufficiently utilized; and rainwater processing is simple and feasible.

Owner:DALIAN UNIV OF TECH

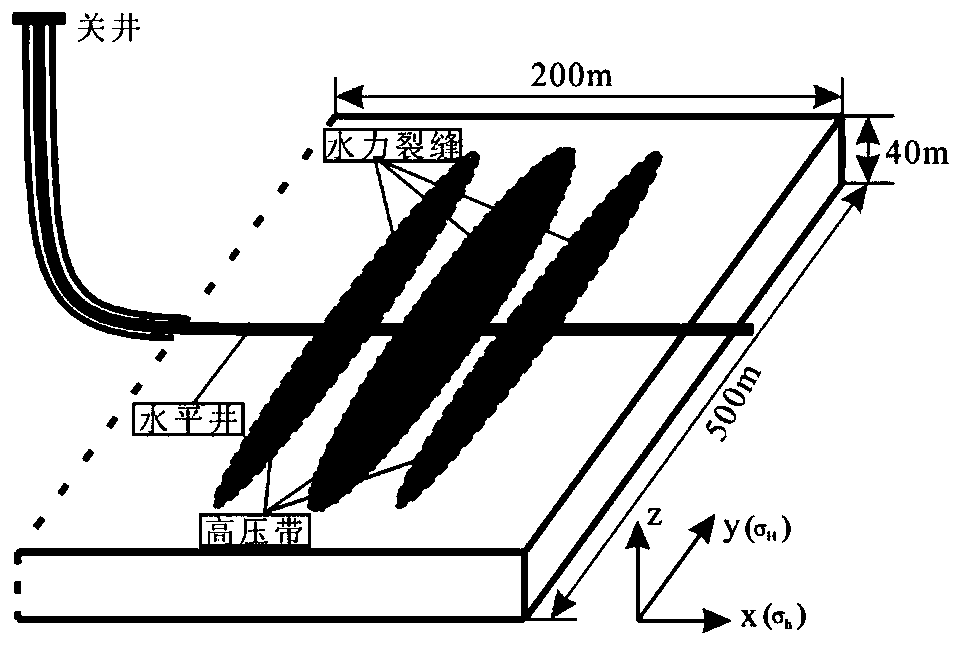

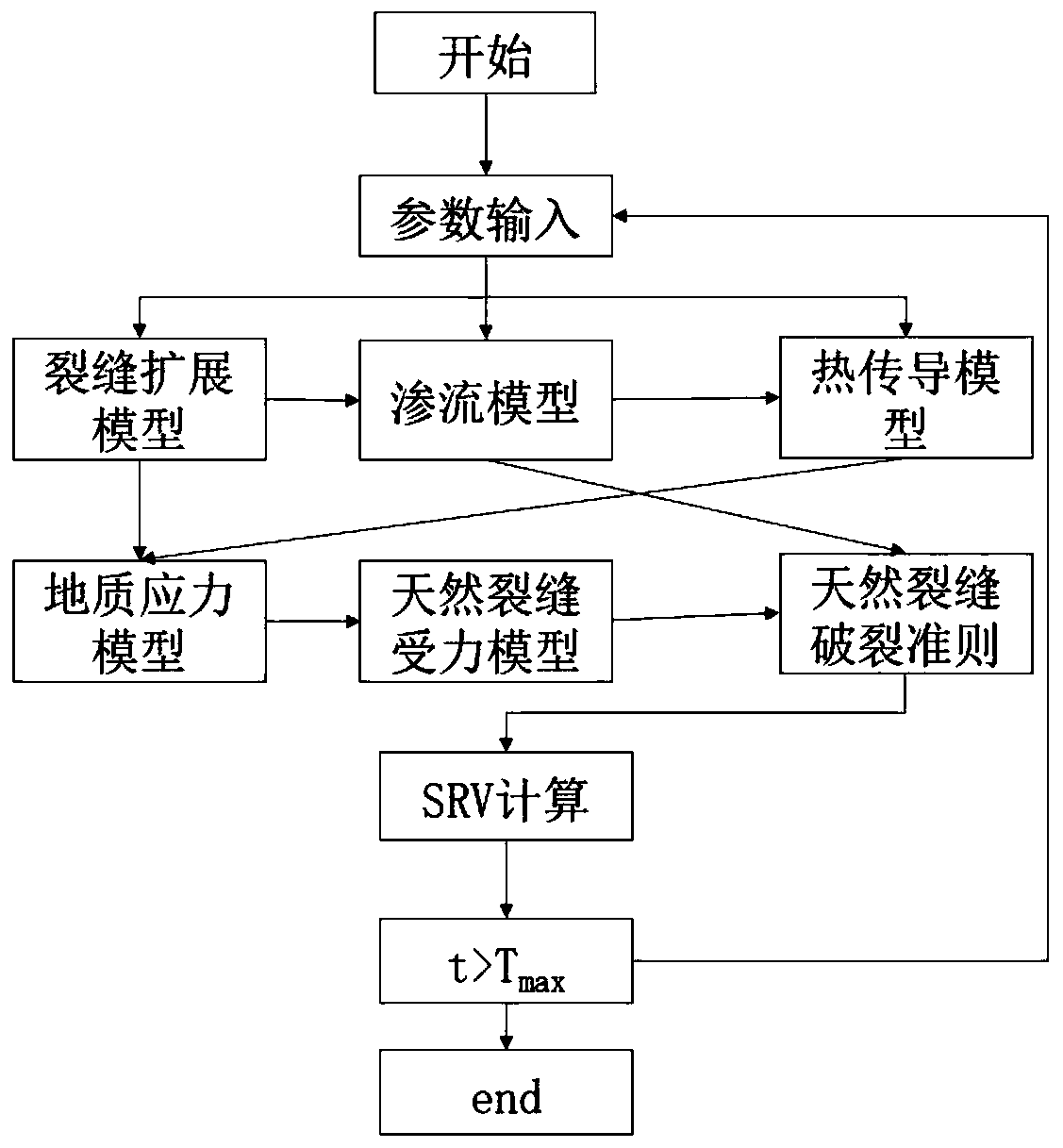

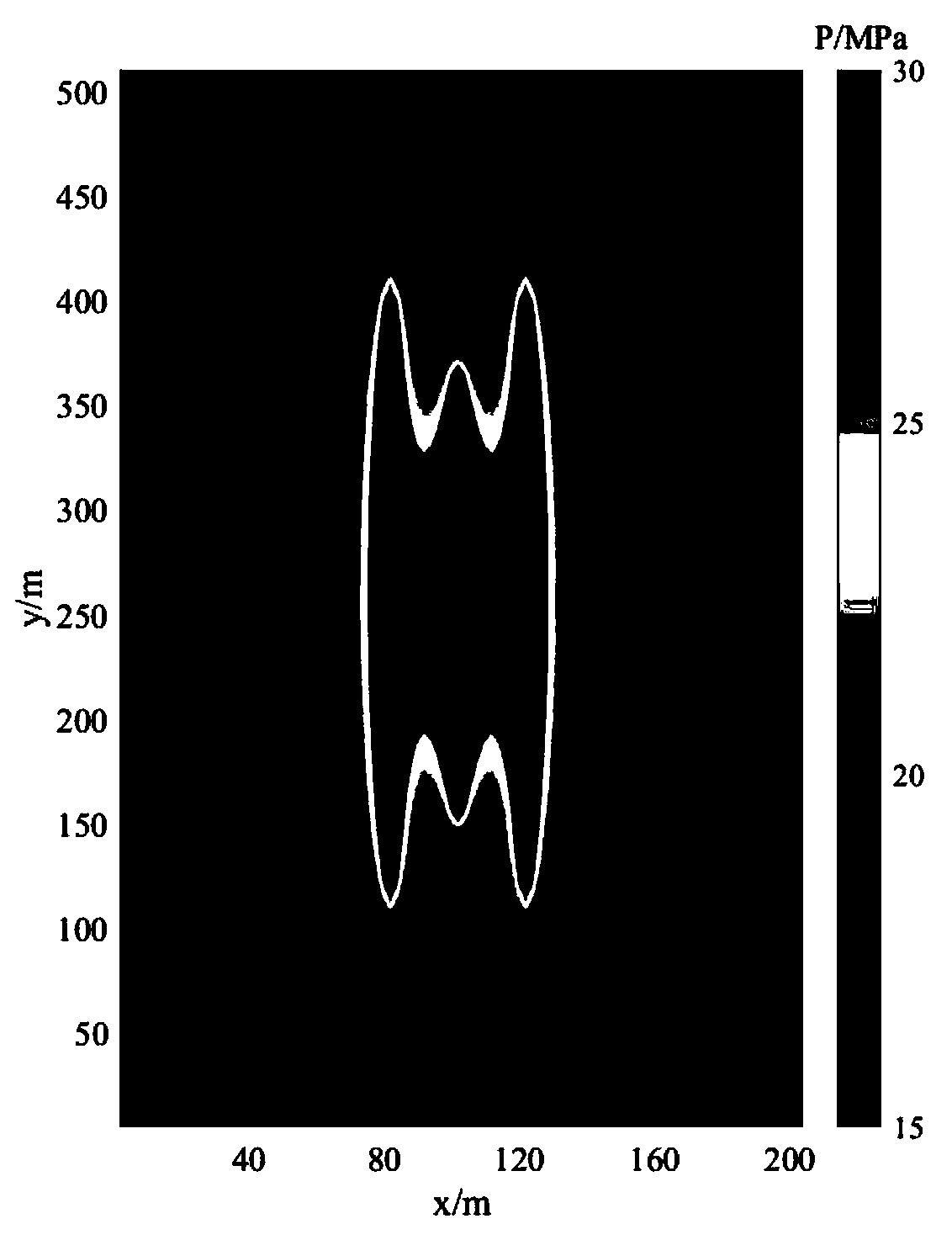

Ultra-deep sandstone fracture network transformation evaluating method based on heat-fluid-solid coupling effect

ActiveCN110005389AEnrich the evaluation theory of retrofit volumeReduce induced stressSurveyFluid removalStress distributionPorosity

The invention discloses an ultra-deep sandstone fracture network transformation evaluating method based on a heat-fluid-solid coupling effect. The ultra-deep sandstone fracture network transformationevaluating method comprises the following steps that physical parameters of a reservoir are obtained; distribution of fluid pressure in a fracture, the fracture length, the fracture width and the quantity of fluid filtered to the reservoir are calculated; reservoir pore pressure distribution after the unit discrete time is calculated; temperature distribution in the reservoir is calculated; stressdistribution after full coupling is calculated; the porosity and the permeability after the stress effect are solved through stress distribution; meanwhile, by combining the conversion relation of the stress to normal stress and shear stress of a natural fracture face, the force-bearing condition of the natural fracture face is obtained; and finally, whether the natural fracture is damaged or notand the kind of damage are analyzed. The ultra-deep sandstone fracture network transformation evaluating method is suitable for evaluating the fracturing transformation volume of an ultra-deep densesandstone gas reservoir fracture network, the blank aiming at numerical simulation study for evaluating the transformation volume of the ultra-deep dense sandstone gas reservoir fracture network is filled up, and a reliable prediction and evaluation method is provided for fracturing construction design of the ultra-deep dense sandstone reservoir fracture network.

Owner:SOUTHWEST PETROLEUM UNIV

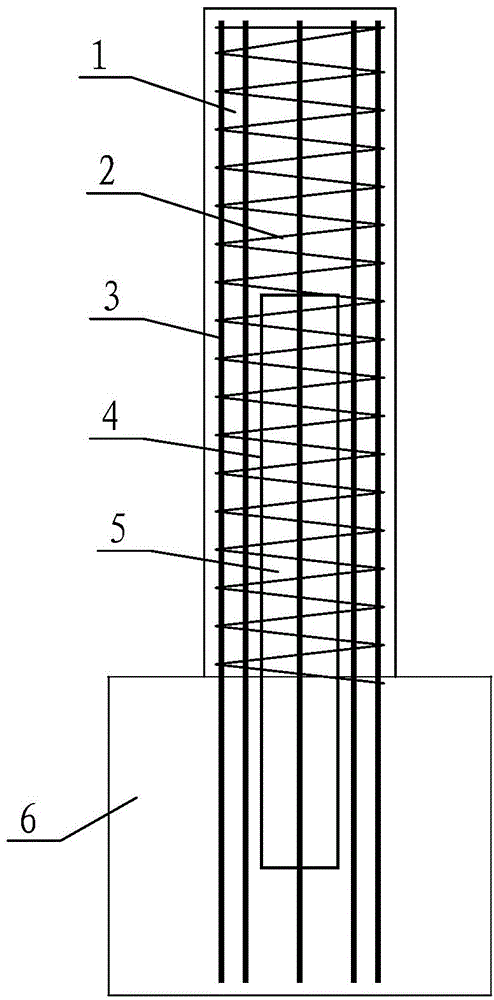

Locally-embedded steel pipe concrete column type aseismatic bridge pier

InactiveCN104562922AReduced shear reinforcementImprove construction qualityBridge structural detailsBridge materialsNormal strength concreteReinforced concrete

The invention provides a locally-embedded steel pipe concrete column type aseismatic bridge pier, and belongs to the technical field of structural design of bridges. The aseismatic bridge pier comprises longitudinal ribs, stirrups, steel pipes, common strength concrete, high strength concrete and a bridge pier foundation. According to the bridge pier, a steel pipe concrete column is locally embedded to the reinforced concrete bridge pier, the advantage of high ductility of the common strength concrete bridge pier and the advantages of high pressure resistance, high shear resisting, high bearing capacity and high ductility of the steel pipe high strength concrete are fully utilized, and therefore, the shear resistance, the pressure resistance, the bearing capacity, the ductility and the energy consumption capacity of the bridge pier can be improved, the bridge pier can be avoided shearing damaging and bending conquassation, and as a result, the aseismatic performance of the reinforced concrete bridge pier can be effectively improved; the steel pipe concrete column is embedded in the local maximum force bearing range of the bridge pier, so that the purpose of the improving the aseismatic performance of the bridge pier is achieved, and the purpose of minimizing the cost of the bridge pier and the construction difficulty can be reached. The bridge pier can be widely applied to the field of bridge construction design.

Owner:DALIAN UNIV OF TECH

Electrical clamp connector and connecting terminal

ActiveUSRE44490E1Contact member manufacturingCoupling contact membersElectricityElectrical conductor

The invention relates to an electrical clamp connector and connecting terminal that, per pole, has at least two conductor terminal connections oriented in the same direction and an additional connecting contact on the opposite-lying side, which serves for connecting a countercontact external to the terminal. It is proposed for such a terminal to use the especially small-construction design features of a terminal that is produced from a single piece of spring steel sheet and a busbar rod, and to combine these with the new features that the busbar rod has one or two cross projections, which project through the free opening in the spring steel sheet and form the additional connecting contact, which, for example, may be constructed in the form of a socket contact or in the form of a plug-in contact.

Owner:WAGO VERW GMBH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com