Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

228 results about "Negation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In logic, negation, also called the logical complement, is an operation that takes a proposition P to another proposition "not P", written ¬P, which is interpreted intuitively as being true when P is false, and false when P is true. Negation is thus a unary (single-argument) logical connective. It may be applied as an operation on notions, propositions, truth values, or semantic values more generally.

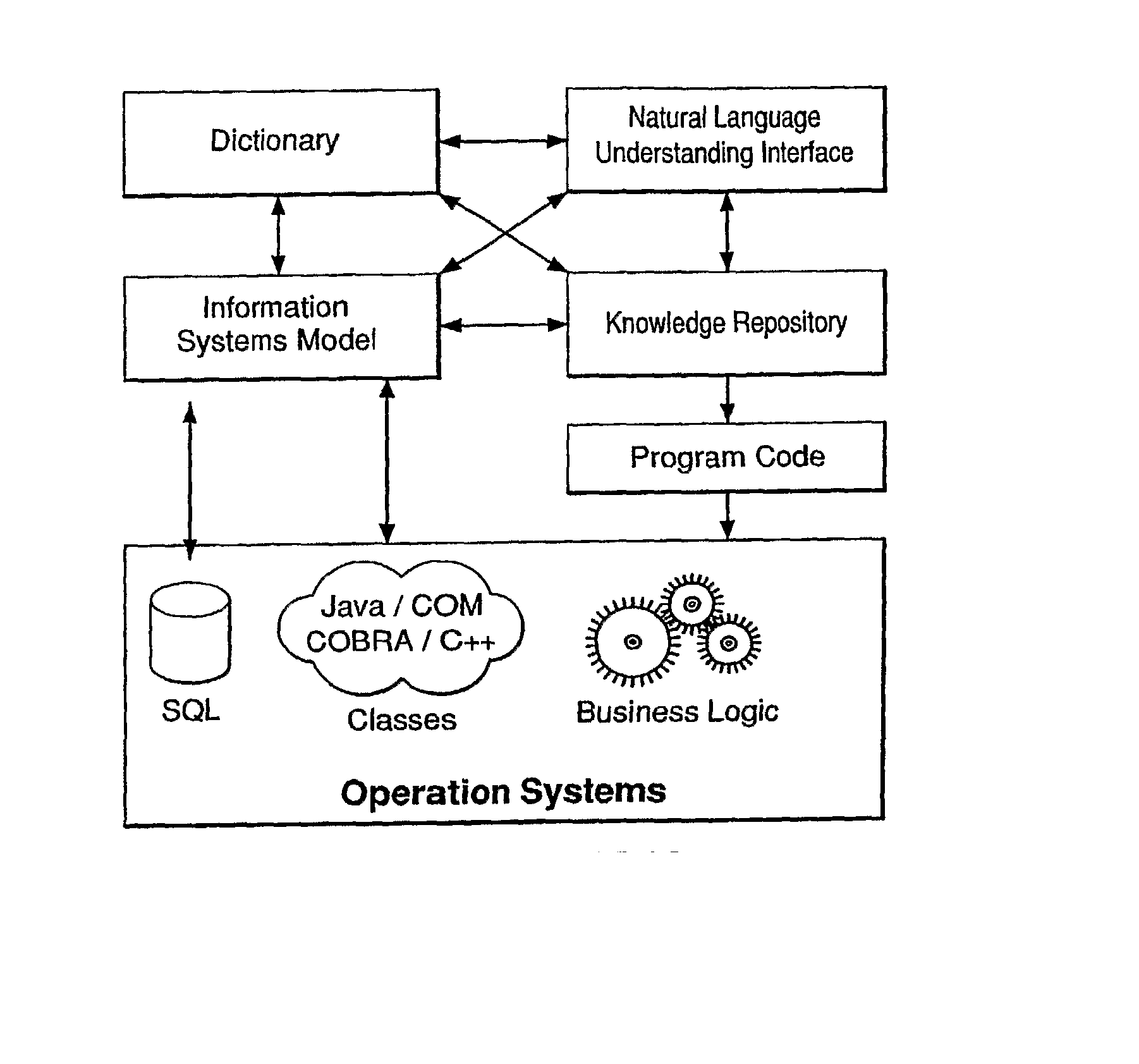

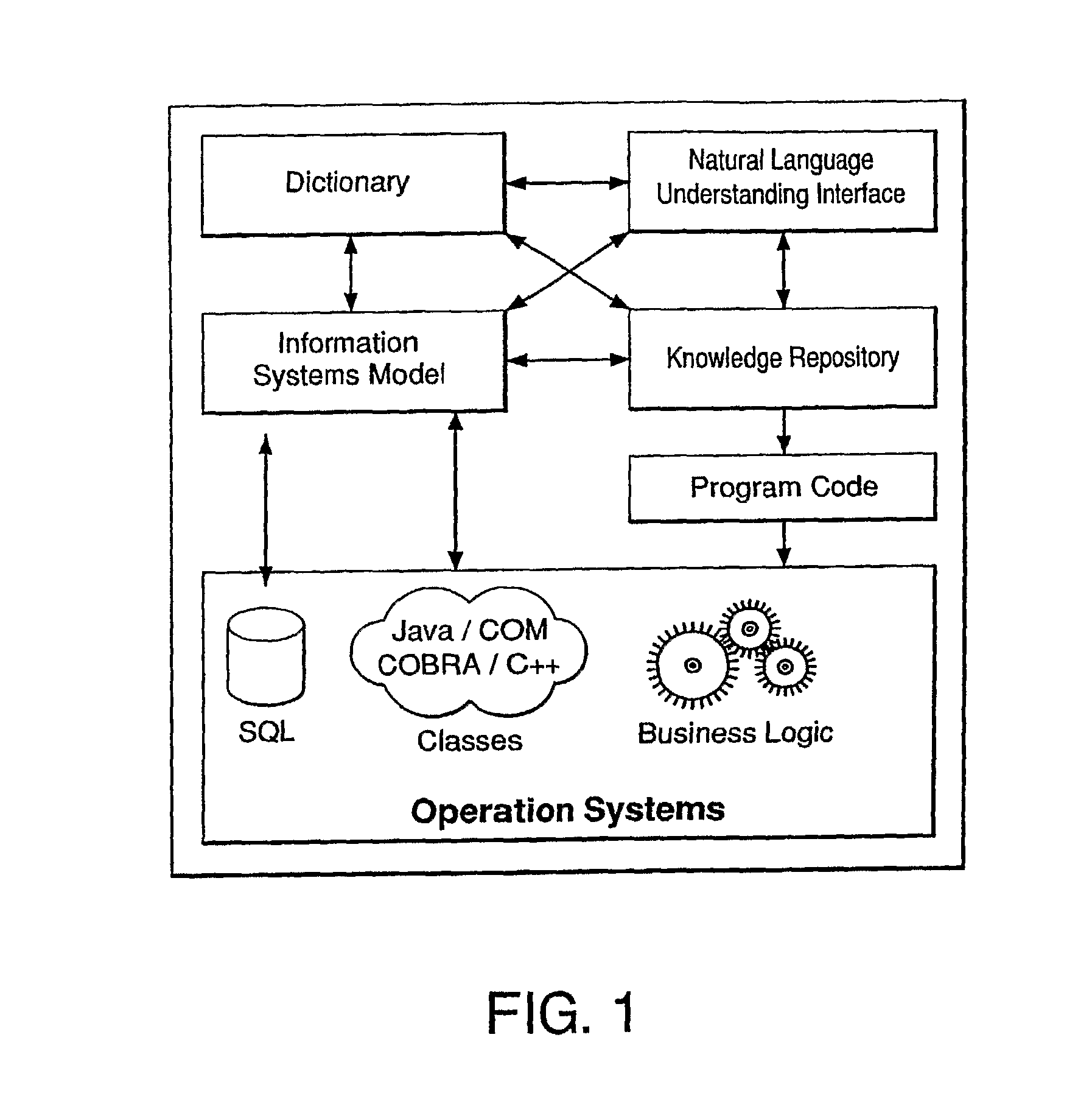

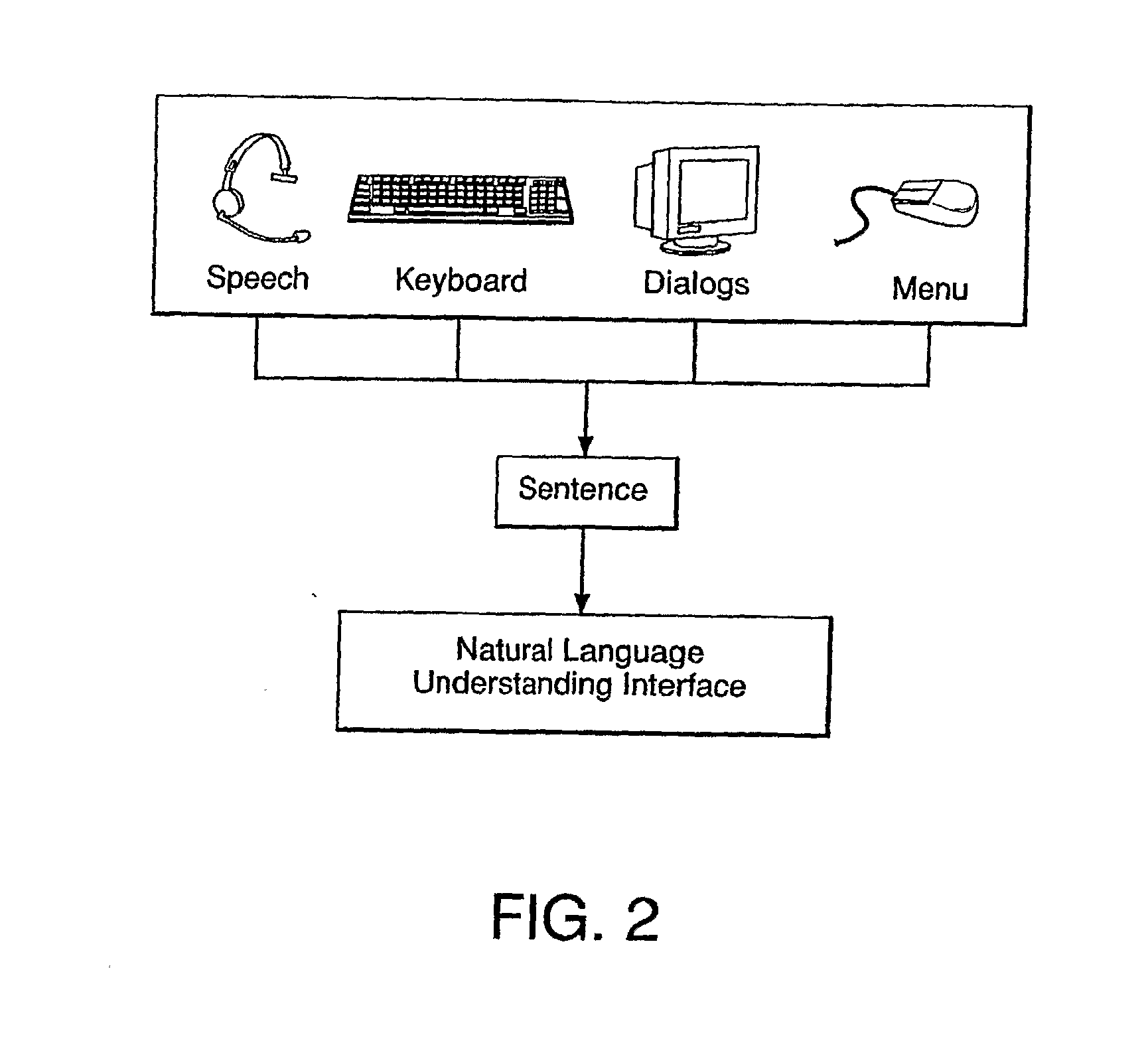

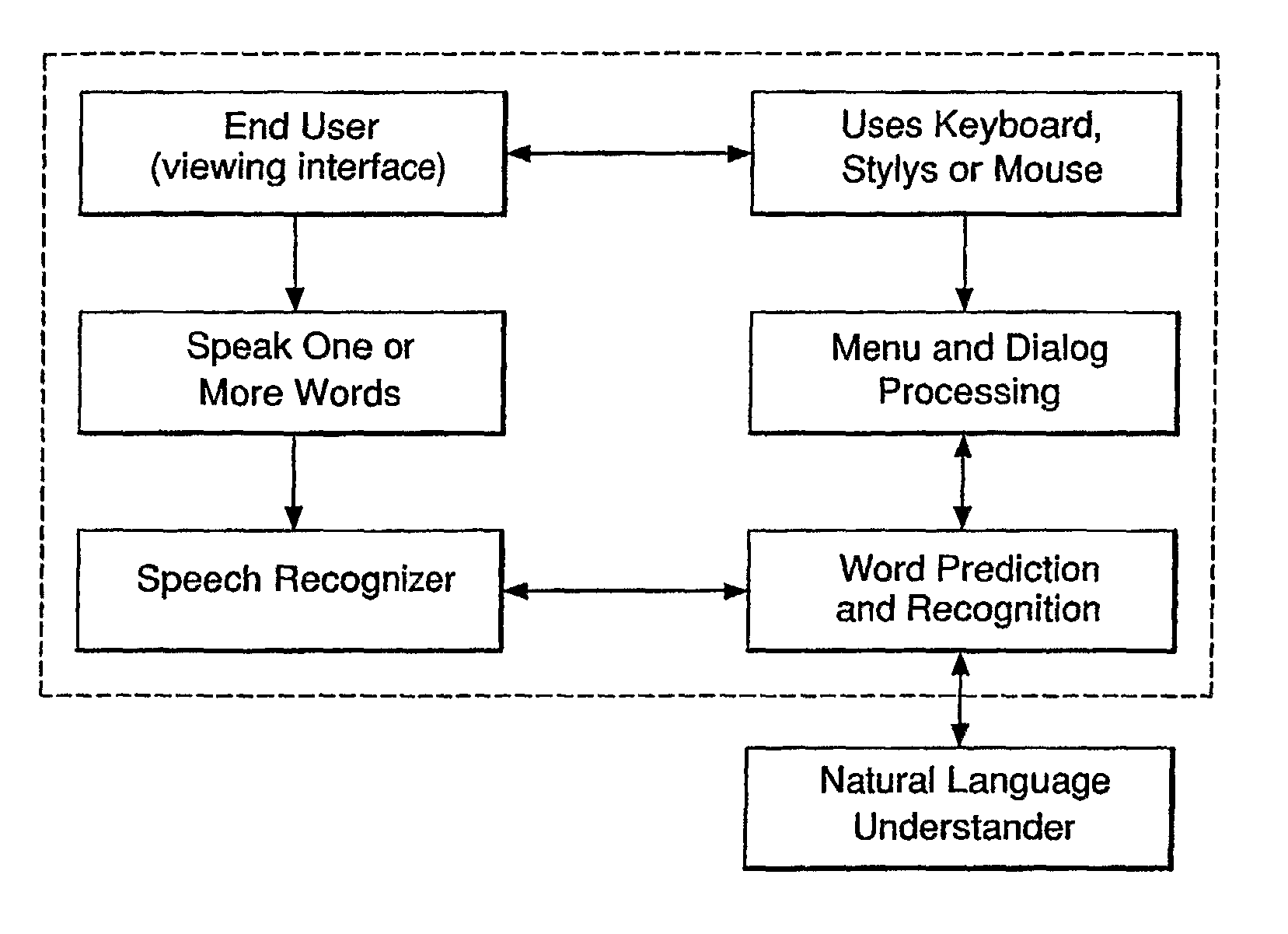

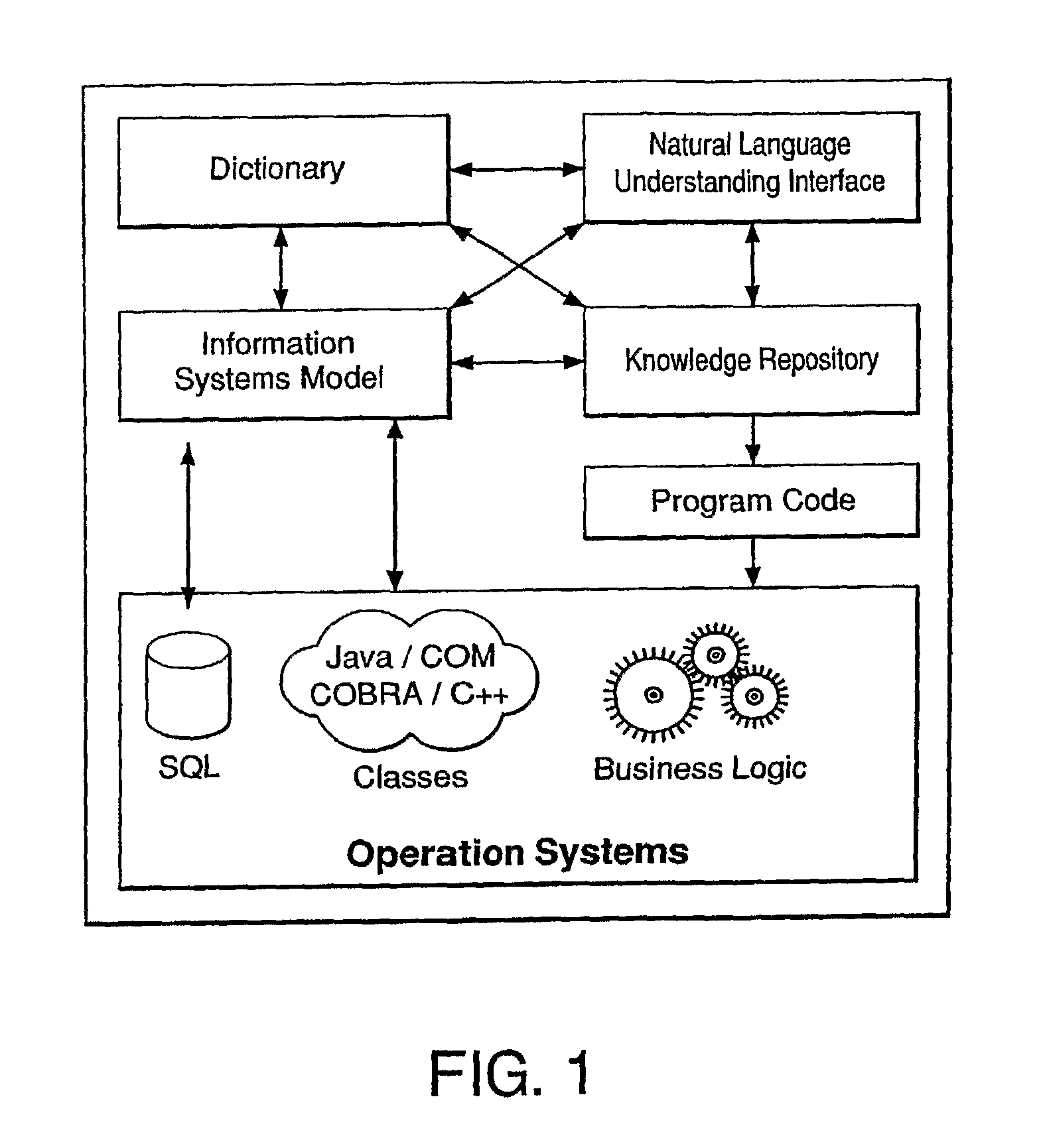

System for Enterprise Knowledge Management and Automation

ActiveUS20080097748A1Easy to useDigital data information retrievalSemantic analysisFirst-order predicateSoftware design

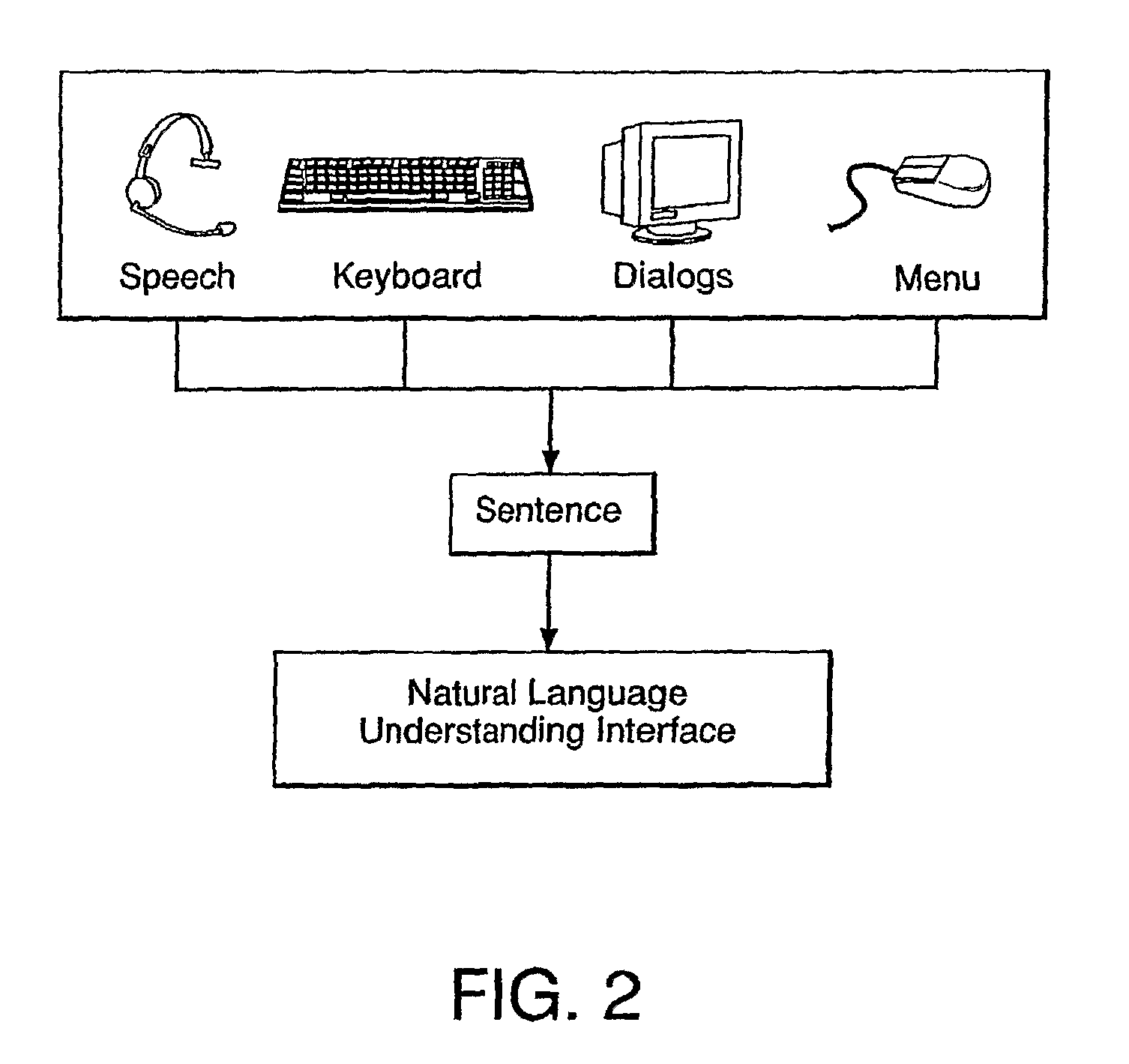

The present invention is directed to a system for managing business knowledge expressed as statements, preferably sentences using a vocabulary, where such statements may be automated by the generation of programming language source code or computer program instructions. As such, the present invention also manages software design specifications that define, describe, or constrain the programming code it generates or programs with which it or the code it generates is to integrate. The present invention facilitates the creation of composite sentences. In one embodiment, the present invention also interprets a composite sentence as a logical formula in first order predicate calculus or similar logic formalism supporting conjunction, disjunction, and negation as well as existentially and universally quantified variables. The invention further interprets natural language, including singular common count noun phrases and connectives, as variables in formal logic. Further, the invention then implements the logical interpretations as rules.

Owner:ORACLE INT CORP

Microblog sentiment analysis method based on large-scale corpus characteristic learning

ActiveCN104899298ALow costFast trainingData processing applicationsWeb data indexingFeature vectorNerve network

The invention discloses a microblog sentiment analysis method based on large-scale corpus characteristic learning. The method is characterized in that microblog texts is used to train a neural network based on Word2Vec, the neural network completes training by inputting the microblog texts, the neural network maps the input microblog to a corresponding word vector according to grammar contents, emotional tendency of current contents, and whether words are denied or not, and a matrix formed by word vectors corresponding to the words in the microblog is obtained. Synthesis of word vectors is performed on the matrix, so as to further obtain a feature vector corresponding to the microblog. Through applying the feature vector to training and prediction of a sentiment classification device, a relatively accurate microblog sentiment analysis is obtained. Compared with the prior art, the method is low in cost and high in analysis accurate rate, and is especially suitable for large-scale corpus, and is fast in training speed. Combining with grammar contents and emotional tendency, the method effectively processes negation relations, and improves accurate rate of sentiment analysis.

Owner:EAST CHINA NORMAL UNIV

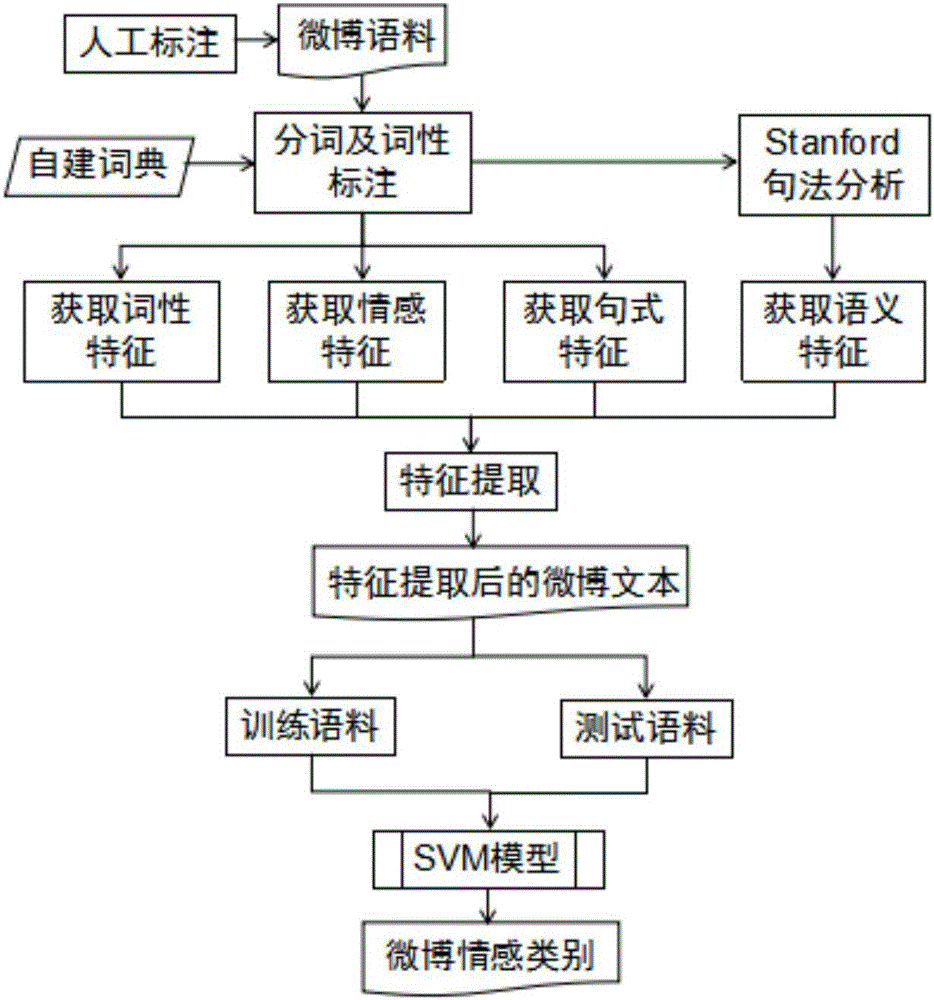

SVM based micro-blog emotion classification method fusing various kinds of emotion resources

PendingCN106503049AImprove accuracyAccurate acquisitionNatural language data processingSpecial data processing applicationsPart of speechStructure analysis

The invention discloses an SVM based micro-blog emotion classification method fusing various kinds of emotion resources. The method includes the following steps: constructing relevant dictionaries including an emotion dictionary, a negation dictionary, and a degree adverb dictionary; performing pretreatment on different corpora, performing word segmentation and part-of-speech tagging on the corpora, and performing sentence structure analysis; comparing the segmented words and positive and negative dictionaries to acquire initial word polarity, comparing words ahead of emotion words and the word degree grade dictionary and the negation dictionary to acquire modifier weight, and multiplying the initial word polarity by the modifier weight to acquire emotion scores of each micro-blog; extracting features such as nouns, verbs, adjectives, positive and negative emotion words, degree adverb weights, emotion scores, privatives and specific symbols from part-of-speech features, emotion features, sentence pattern features, and semantic features; and inputting the extracted features into an Libsvm to perform model training so as to acquire a training model. The method can achieve emotion 5-grade classification of micro-blogs, and can accurately and roundly acquire emotion tendency of netizens.

Owner:NANJING UNIV OF SCI & TECH

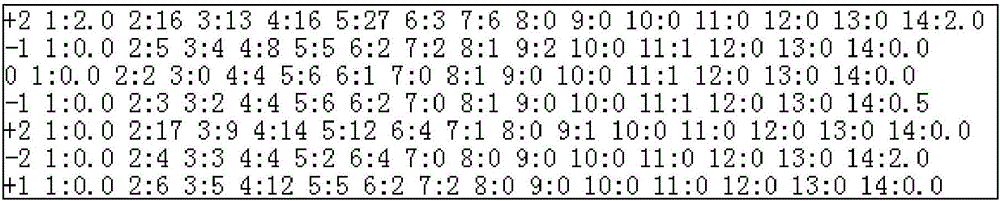

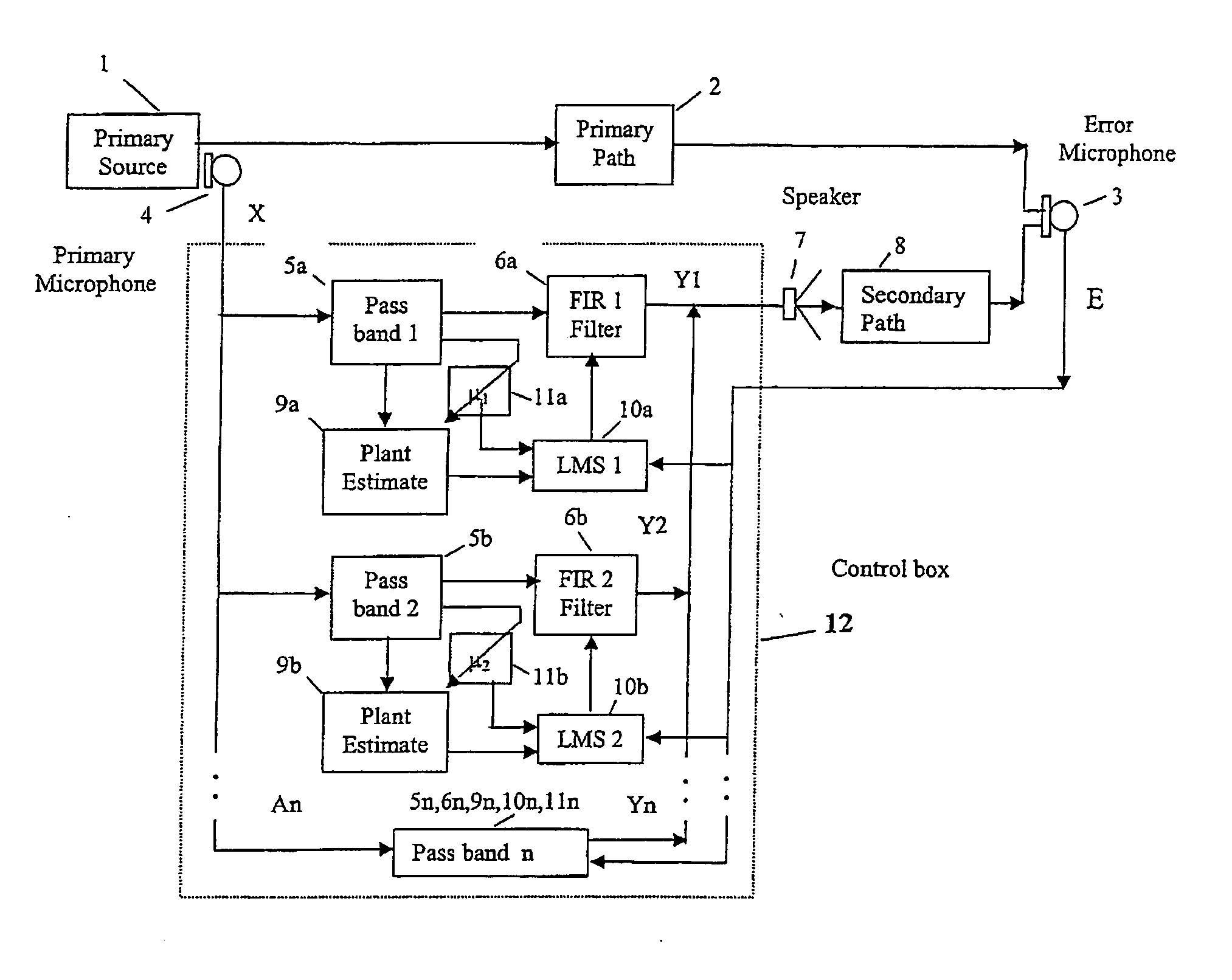

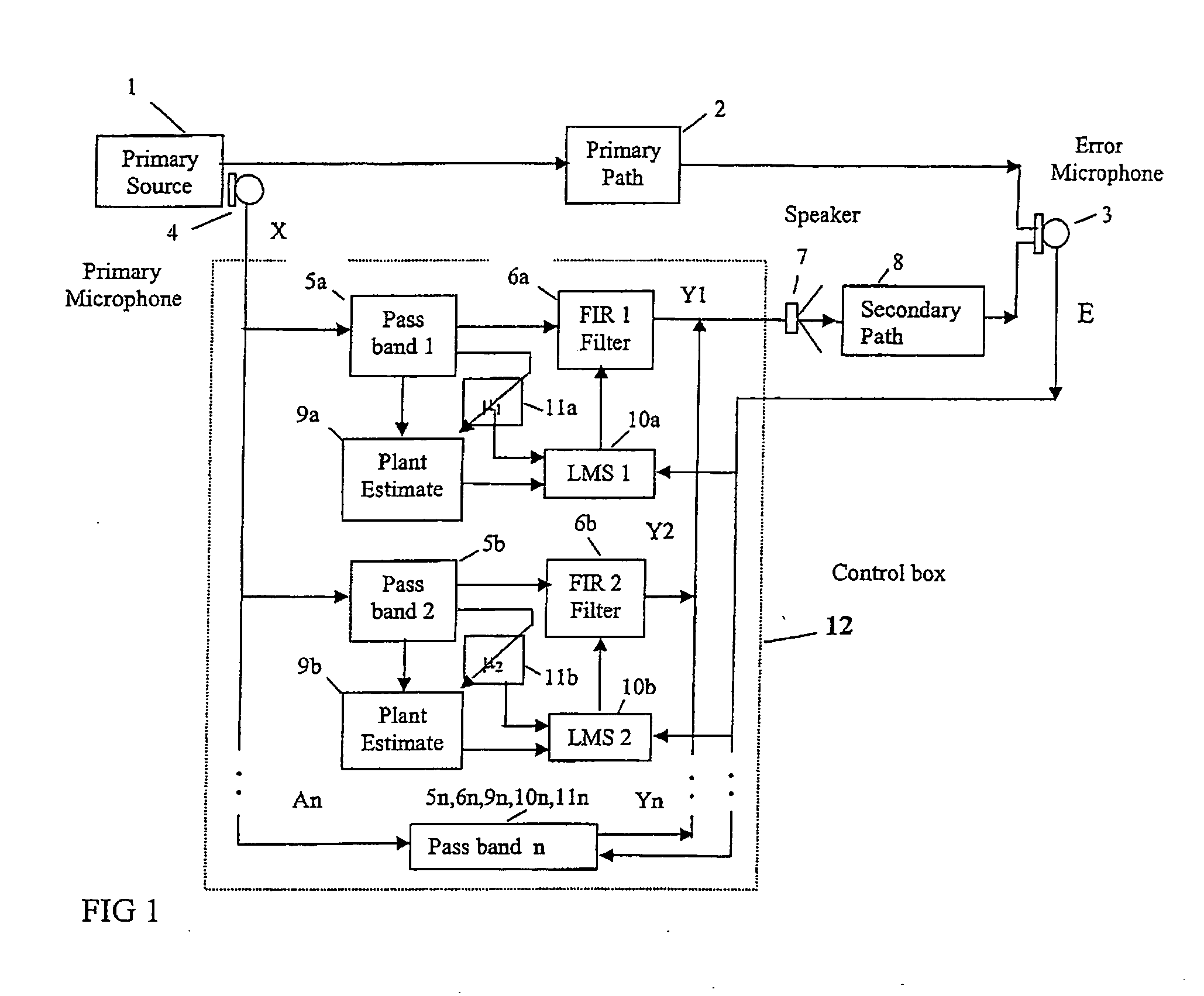

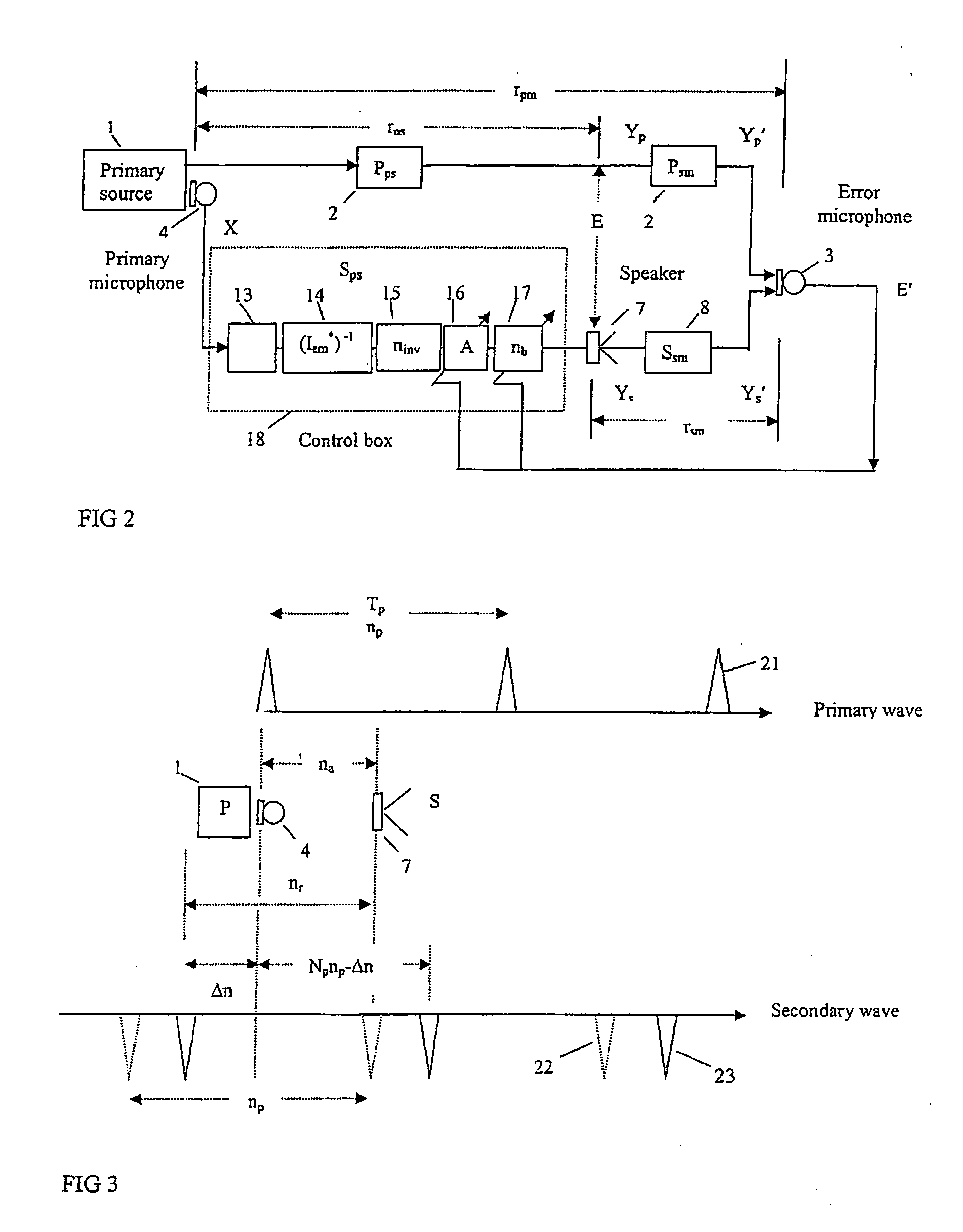

Active noise control system in unrestricted space

The adaptive speed to changes in a primary source noise is increased through a noise detecting means feeding parallel multi-passband means and multi-transverse adaptive filter means, where each adaptive filter has its own individual adaptive step size means adjusted automatically according to the signal strength at each passband output. The output from each of the multi-adaptive filter means drives a secondary canceling source generating means where each multi-adaptive filter means is automatically adjusted to produce minimum sound in its passband at an error detecting means. Alternatively, the output from the noise detecting means is negated through a negation means, passed through a plant neutralization inverse means and an inverse delay means before driving the secondary source generating means. The secondary source output is aligned and match in amplitude to that of the primary sources, through a delay buffer means and an amplitude regulator means, which are adjusted successively until the output at the error detector means is a minimum.

Owner:WRIGHT COMPANY

System and method for product configuration using numerical clauses and inference procedures

InactiveUS7003360B1Lower performance requirementsConstraint-based CADKnowledge representationTruth valueNegation

A system and method for product configuration represents a product using a configuration model having numerical clauses. Features of the product are associated with literals in the numerical clauses. The numerical clauses may specify a number of literals to determine whether the numerical clause is satisfied, satisfiable, or unsatisfiable. Numerical clauses represent constraints that govern the configuration of the product. Resolving numerical clauses and user choices involves one or more inference procedures. In one embodiment, unit clauses represent user choices, and a configuration engine asserts the unit clause and performs numerical unit resolution between the unit clause and all numerical clauses containing the complement (generally a negation) of the unit clause. Complementary literals are eliminated from the current state of the configuration model. In one embodiment, if the uneliminated literals in a numerical clause causes the clause to be satisfied, the uneliminated literals are recursively asserted. The configuration engine then performs numerical unit resolution between the recursively asserted, uneliminated literals and numerical clauses containing the complements of the uneliminated literals. Numerical clauses may also function as literals. Numerical clauses may include negations of consumer literals and positive provider literals. If a user chooses a consumer feature, by knowing the consumer and provider weights, the configuration engine can determine which provider literals should be included, excluded, or remain selectable. Embodiments of the invention can implement a logic-based truth maintenance system and numerical unit resolution.

Owner:VERSATA DEV GROUP

Method for embedding and extracting watermark in English texts

InactiveCN1700205AImprove privacyImprove securityDigital data processing detailsSpecial data processing applicationsNatural language processingNegation

The invention relates to a method for embedding and extracting water spot from English text in the field of text copyright protection technique. It has the following steps: changing the copyright information into binary bit string, reading in the text and filtering special characters and indent and then operating the character string and copyright person's private key to obtain integer number Z, if Z can divide embedding ratio exactly, the next sentence is water spot information sentence, using Z to do negation with copyright information binary bit string to ascertain the information bit of bided embedding water spot, using Z to do negation with the number of the characters of water spot information sentence to ascertain the location of the water spot information bit so that 0, 1 which can represent the relation of the adjacent alpha codes are uniform with bided embedding water spot information bit until finish text. The process of extracting water spot information is a reverse process of embedding it.

Owner:TSINGHUA UNIV

Software behavior detection system based on symbolic execution technology and detection method thereof

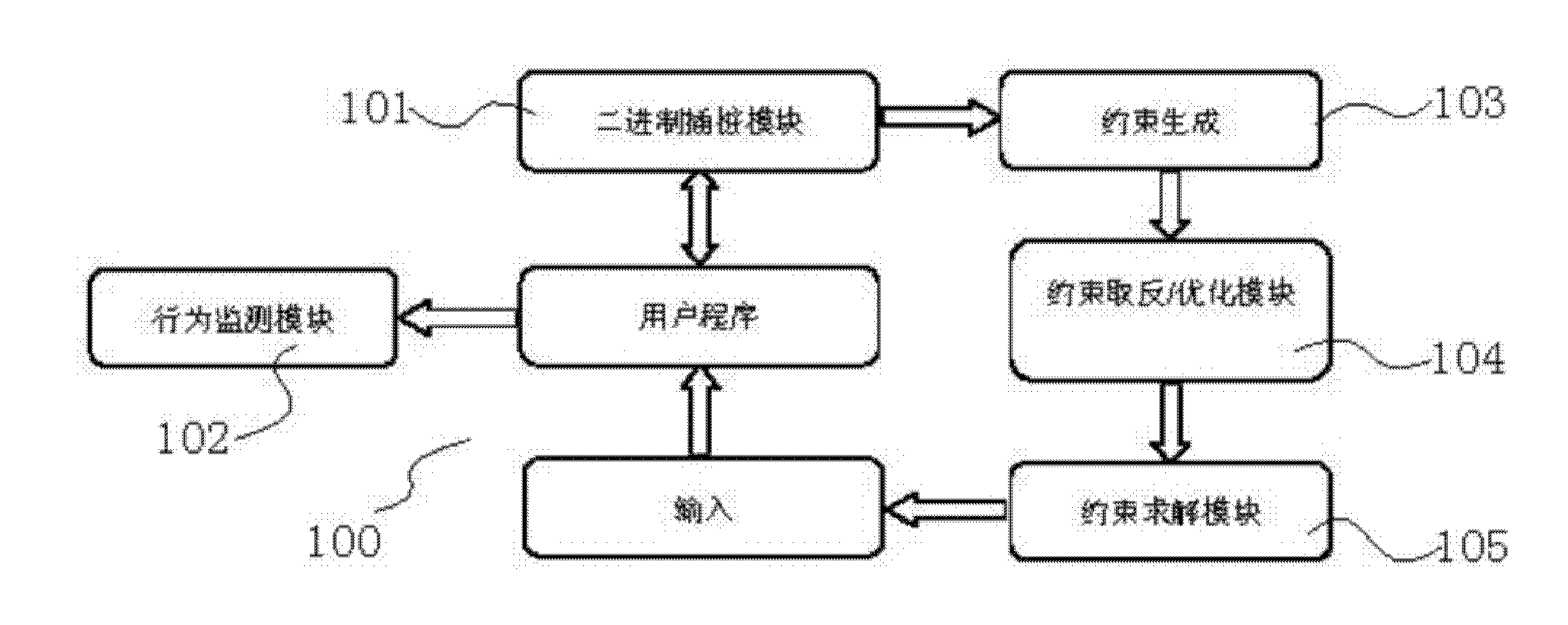

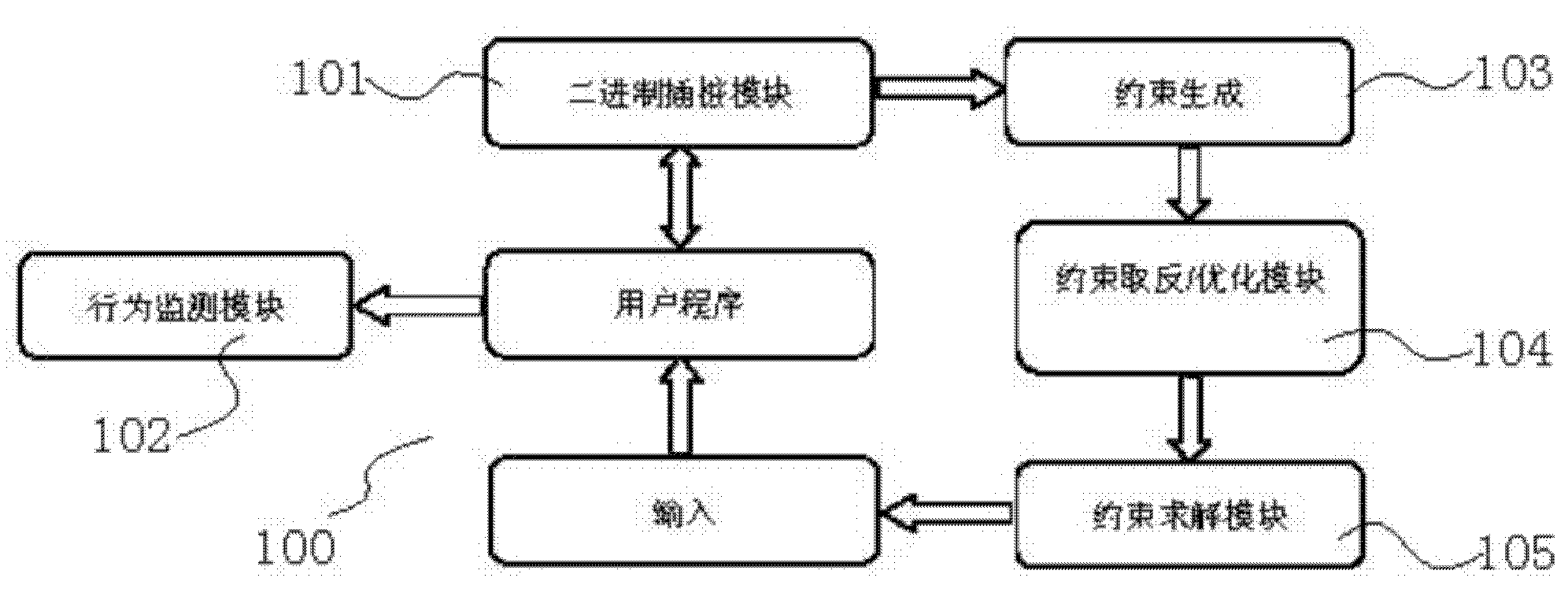

InactiveCN102222035AImprove accuracyIncrease diversityHardware monitoringSoftware testing/debuggingNegationTheoretical computer science

The invention discloses a software behavior detection system based on symbolic execution technology and a detection method thereof, wherein the detection system consists of a constraint generation module, a constraint negation / optimization module, a constraint solution module, a binary code pile pitching module and a behavior monitor module; and the method specifically comprises the following steps of: monitoring software behavior in the actual execution process of a program, collecting information relevant to the behavior, and providing certain essential data for behavior analysis; and simultaneously, collecting the constraint condition of the current path; after the program execution is finished, negating a certain constraint condition in the set of collected path constraint conditions so as to acquire a new patch constraint set, and solving the newly generated new patch constraint set by using a solver so as to determine whether a path can be achieved; and if the preconditions traversing the patch can be met, triggering a new software behavior by traversing the path. The system and the method can efficiently improve the precision and comprehensiveness of behavior detection.

Owner:THE THIRD RES INST OF MIN OF PUBLIC SECURITY

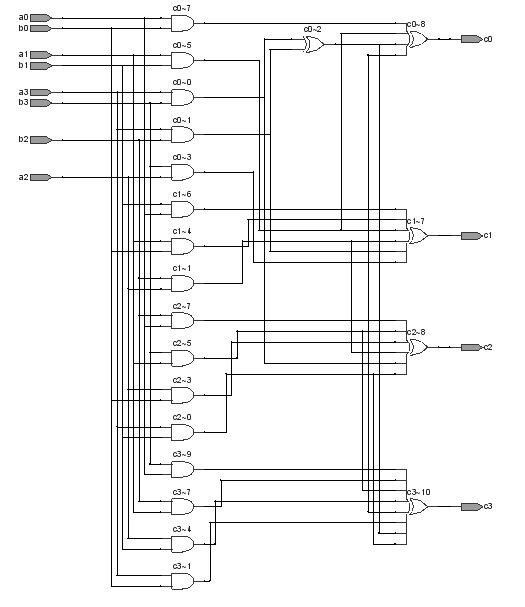

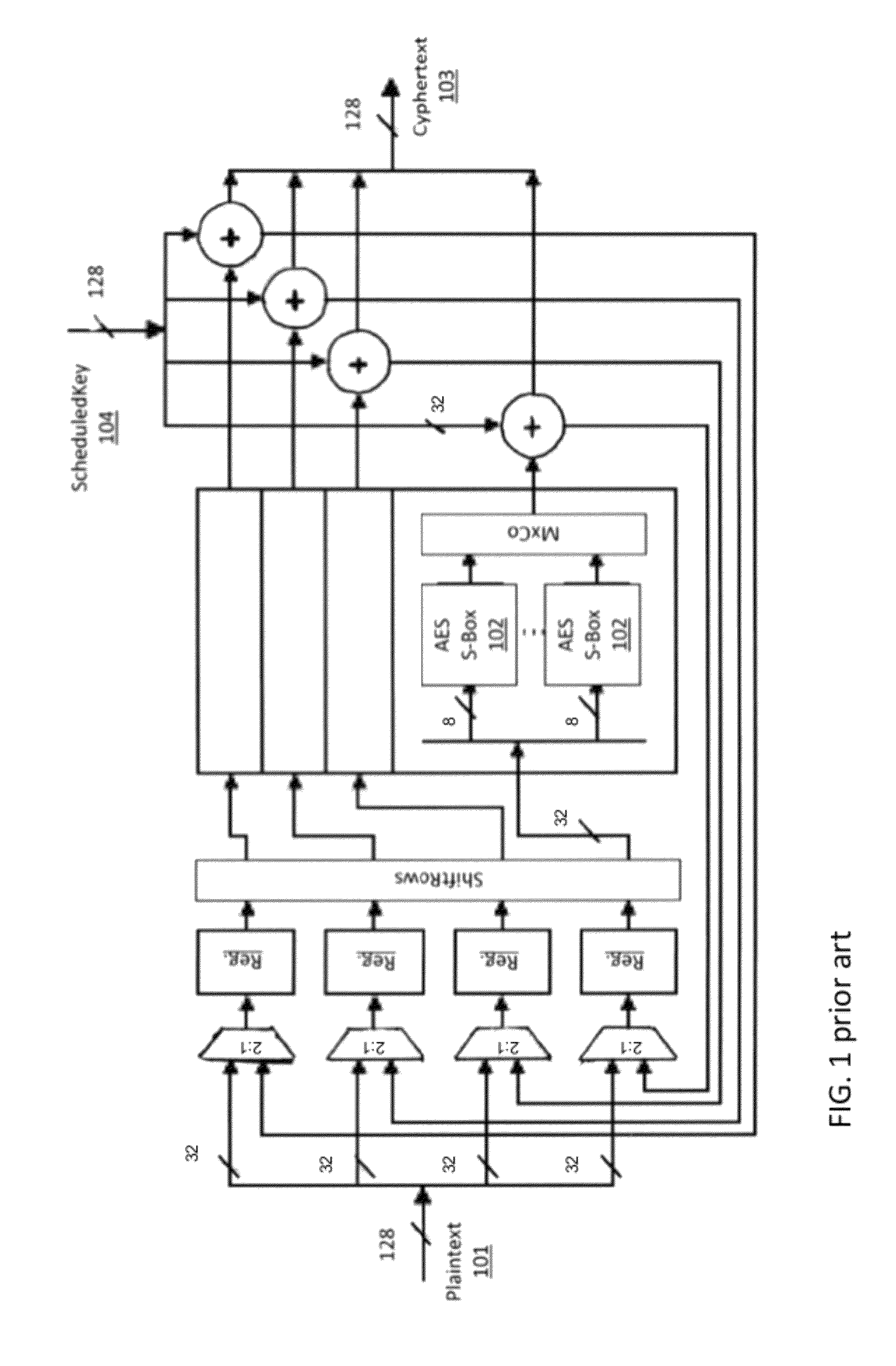

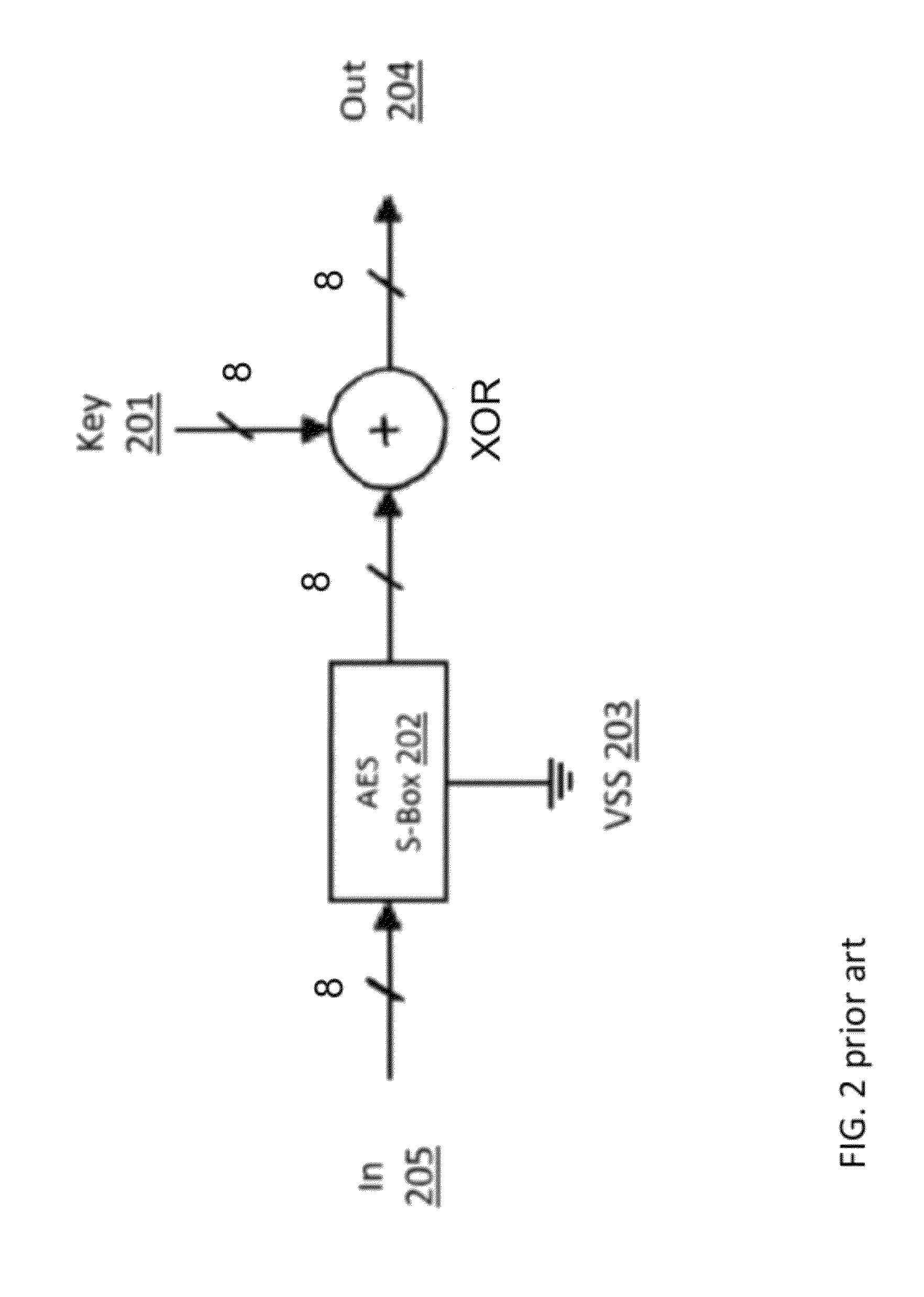

S box applicable to hardware realization and circuit realization method thereof

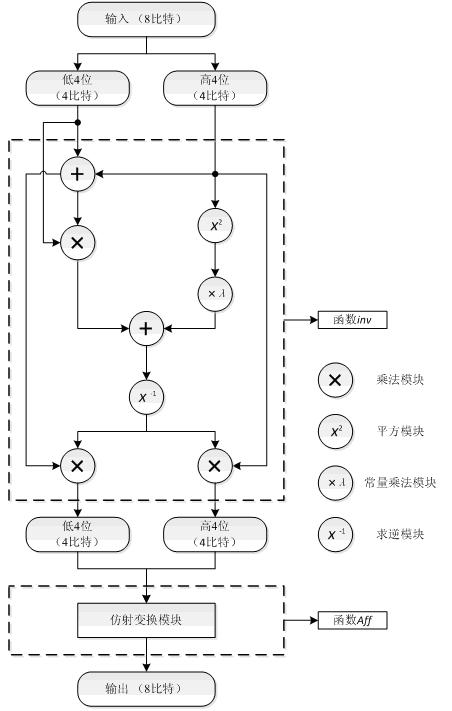

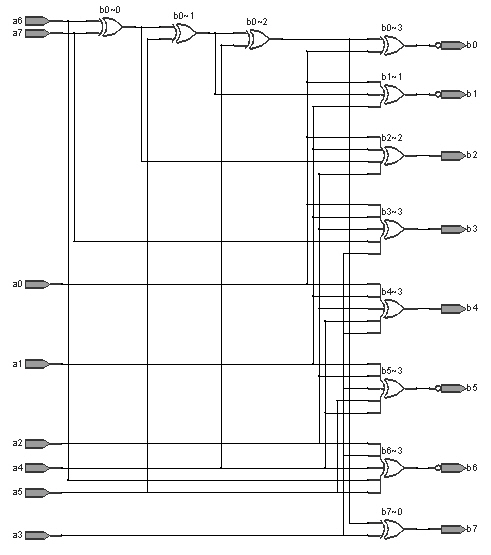

InactiveCN101938349AStrong nonlinearityStrongly Differential Propagation ProbabilitySecuring communicationS-boxNegation

The invention provides an 8*8 S box applicable to hardware realization and a circuit realization method thereof. The S box is compounded by using an inversion operation on a finite field GF (((22)2)2) and affine transformation of GF (2)8 and has stronger nonlinearity, difference transmission probability, snowslide performance, algebra complexity and other cryptological properties. Compared with other Galois fields comprising 28 elements, the field GF (((22)2)2) selected by the invention can reduce the complexity of the inversion operation, and the selection of polynomials generated by various levels of field extension further reduces the expense of subfield operations. The invention also provides a hardware realization mode of the S box, the entire calculation process of the S box can be fully converted into the operations of XOR, AND and negation of bits, and the hardware realization mode can be realized by using a simple logic gate circuit. The entire process does not require table lookup, so that the overall realization expense of hardware is reduced.

Owner:BEIHANG UNIV

Memristor-based multivalued logic device and operating method thereof

ActiveCN105761750AImplement storageRealize computingDigital storageElectrical resistance and conductanceNegation

The invention discloses a memristor-based nonvolatile multivalued logic device and an operating method thereof. The method provides an operating method for negation and dextrorotation of three-valued logic and multivalued T gate logic, which realizes an exhaustive set of multivalued logic, such as three-valued logic based on the multi-resistance state transition characteristic of a memristor. All the logic operation results are stored in the device in a nonvolatile resistance state, such that a logic operation function and a data storage function are realized simultaneously in the device, i.e., storage and calculation are fused; therefore, a device basis is laid for going beyond the limitation from an information device Moore's law and breaking through the Von Neumann bottleneck in a computer architecture. The memristor-based multivalued logic device disclosed by the invention can be applied to a novel solid-state memory, a logic-arithmetic unit, a programmable gate array, an on-chip system and other fields as a basic unit, and provides a new path for boosting novel computer architecture.

Owner:HUAZHONG UNIV OF SCI & TECH

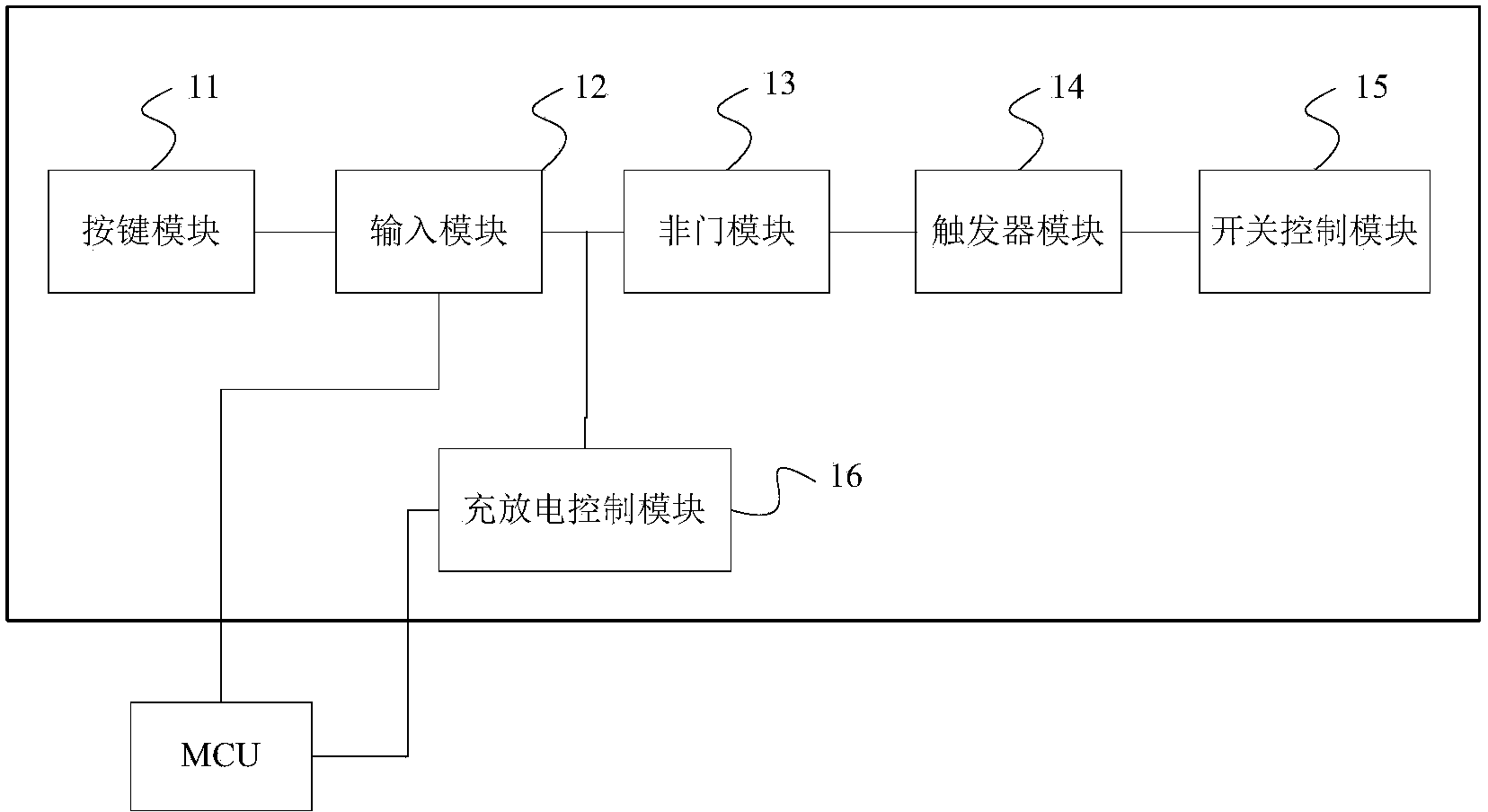

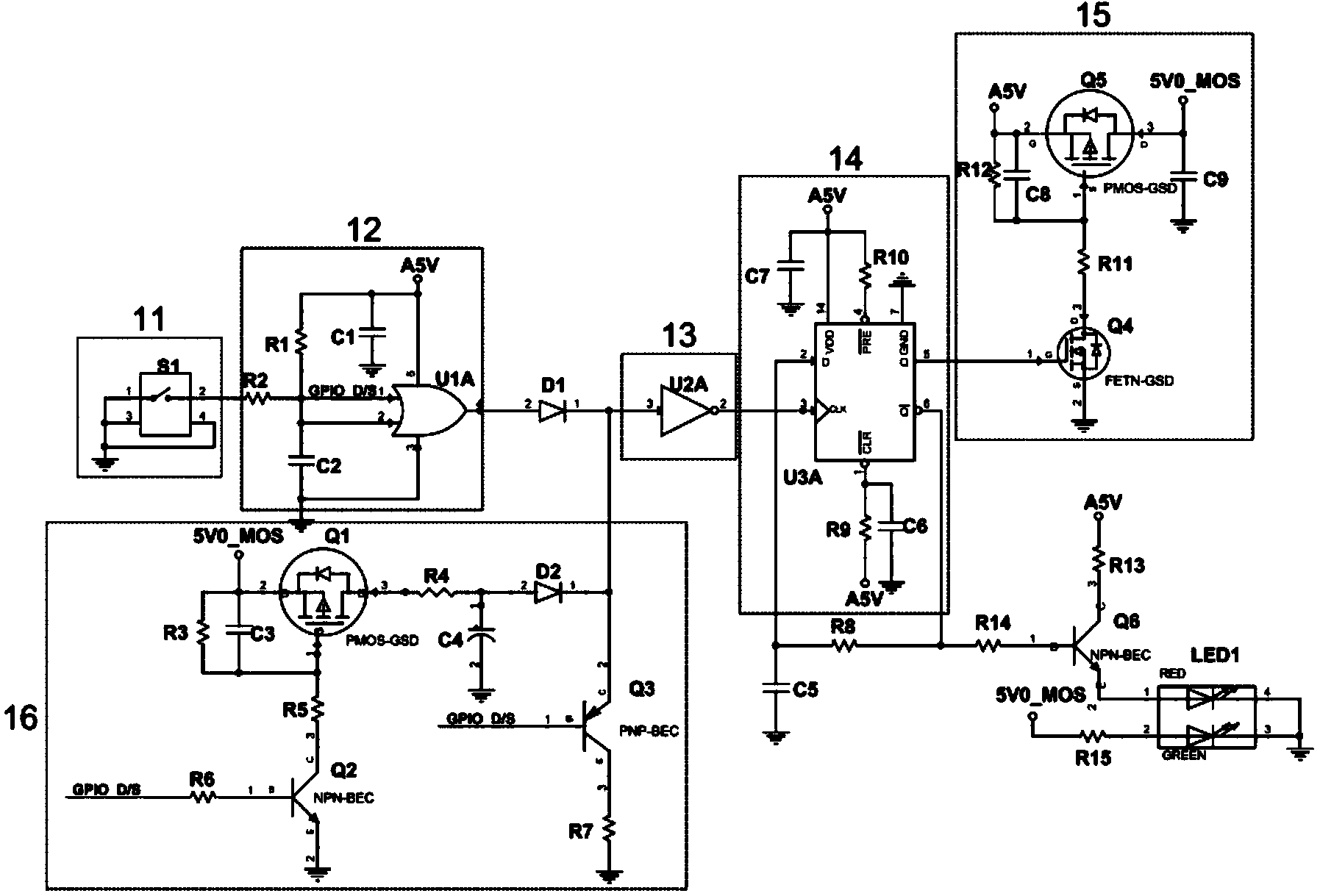

Startup and shutdown machine circuit

The embodiment of the invention provides a startup and shutdown machine circuit. The circuit comprises a key module, an input module, a charging and discharging control module, a non-gate module, a trigger module and a startup and shutdown control module, wherein the key module is used for inputting key signals, the input module is used for outputting pulse signals according to the key signals and control signals output by an MCU, the charging and discharging control module is used for performing charging and discharging control and controlling the logic state of the non-gate module to be turned over, the non-gate module is used for performing negation on the pulse signals output by the input module, the trigger module is used for outputting startup and shutdown signals to the startup and shutdown control module according to the pulse signals after negation, and the startup and shutdown control module is used for outputting power supply signals to a terminal according to startup and shutdown signals so as to control the terminal to be started up or shut down. The circuit can achieve the aims of starting up and shutting down the terminal in the key pressing process and storing data in the shutting down process, and due to the fact that each module in the startup and shutdown machine circuit is composed of some independent simple components, and a single chip microcomputer is not needed, the cost of the startup and shutdown machine circuit is reduced.

Owner:HISILICON (SHANGHAI) TECH CO LTD

Server resource management, analysis, and intrusion negation

InactiveUS7353538B2Reduce usageMemory loss protectionDigital data processing detailsNegationResource management

Owner:PALO ALTO NETWORKS INC

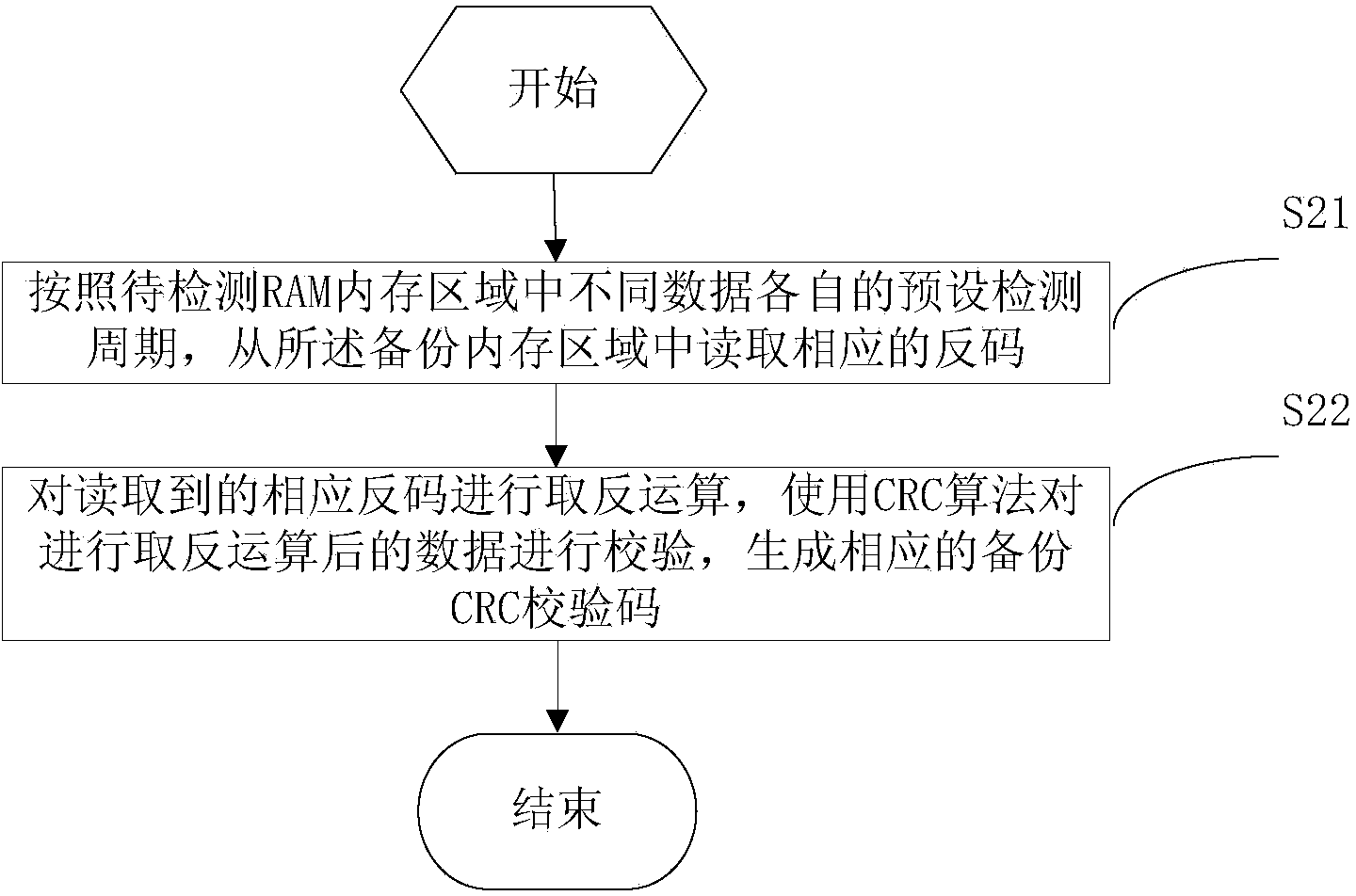

RAM internal storage detection method and device

InactiveCN103678028ARedundant data error correctionRedundant operation error correctionNegationData lines

The invention provides an RAM internal storage detection method. The method includes the steps that it is determined that data in an RAM internal storage area to be detected are true codes; one's complement codes generated after negation is conducted on the true codes are stored into a backup internal storage area; if same data exist in the true codes and the one's complement codes, it is judged that physical damages exist in the data in the true codes, or else negation operation is conducted on the one's complement codes read from the backup internal storage area, a CRC algorithm is utilized to check data on which the negation operation is conducted, and then backup CRC check codes are generated; original CRC check codes corresponding to the true codes and the backup CRC check codes are compared, whether the original CRC check codes corresponding to the true codes and the backup CRC check codes are consistent or not is judged, if yes, it is judged that a data line relevant to the RAM internal storage area to be detected is not damaged or the data in the true codes are not tampered, and if not, it is judged that the data line relevant to the RAM internal storage area to be detected is damaged or the data in the true codes are tampered. Consequently, by the adoption of the RAM internal storage detection method and device, the reason for causing incorrect data storage can be detected.

Owner:CHONGQING CHUANYI AUTOMATION

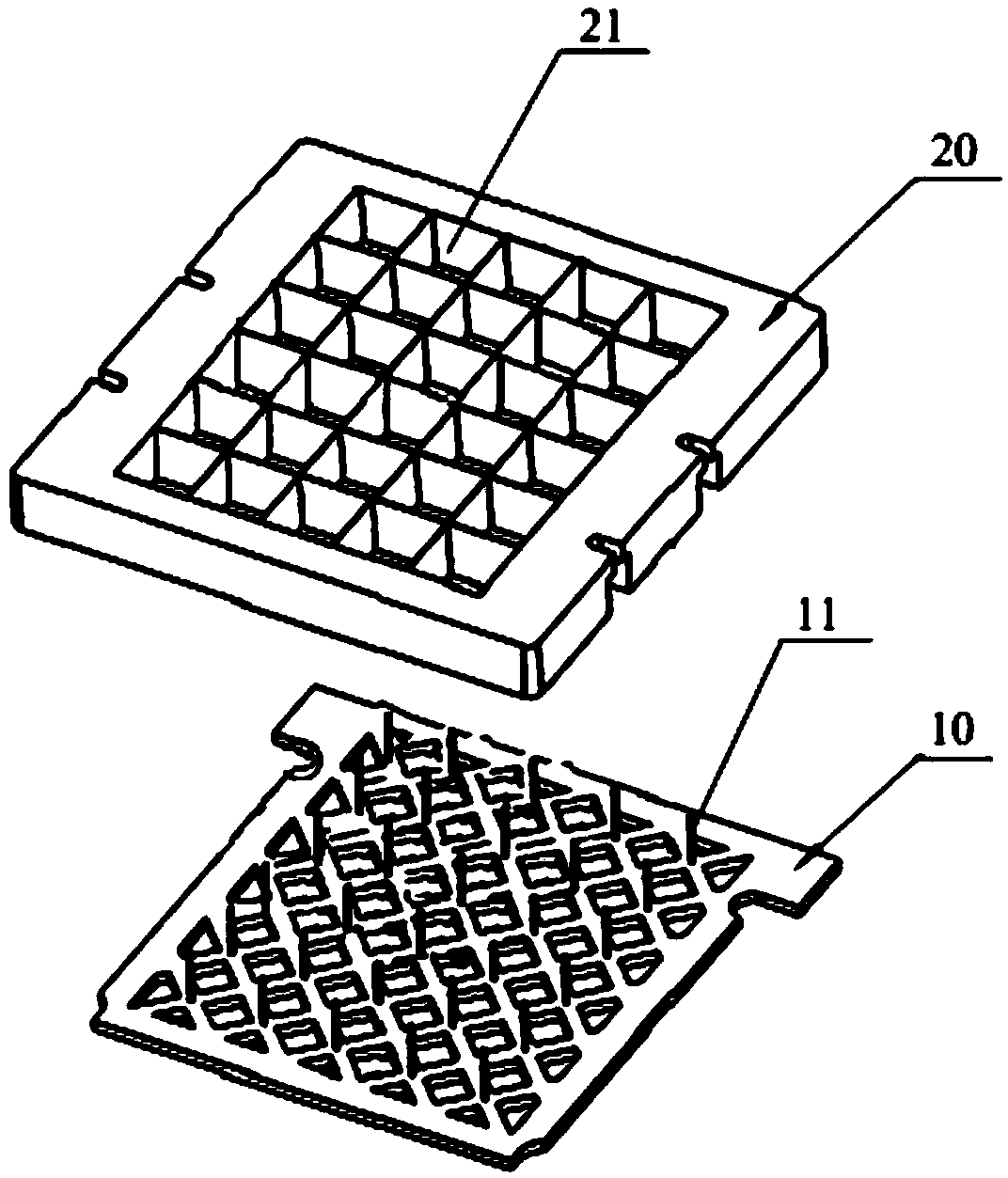

Combined electronic air purification device

InactiveCN103438512AHigh performance purificationAvoid the problem of not being able to collectLighting and heating apparatusDeodrantsElectric dischargeEngineering

The invention discloses a combined electronic air purification device. The combined electronic air purification device comprises an anode plate and a cathode plate, wherein the anode plate is connected with a positive high-voltage power supply; the cathode plate is connected with a negative high-voltage power supply; dust collection and ventilation holes are distributed in the anode plate; the cathode plate is provided with electric discharge pins which are arranged at the parts corresponding to the dust collection and ventilation holes in the anode plate and extend into the dust collection and ventilation holes, so that the electric discharge pins on the cathode plate discharge negative electricity, and dust and ions in air around the electric discharge pins are provided with negative charge, and are adsorbed on the anode plate. The method integrates the characteristics of high-voltage static electricity sterilization and dust collection, plasma sterilization and dust collection and multi-point negative ion emission, prevents the problems that the static electricity generated in the high-voltage static electricity method is harmful to the health of people, and dust particles are difficult to collect in plasma purification, achieves the effect of emitting negation ions by a plurality of electric discharge pins, and can be used for purifying air with high efficiency.

Owner:杨春红

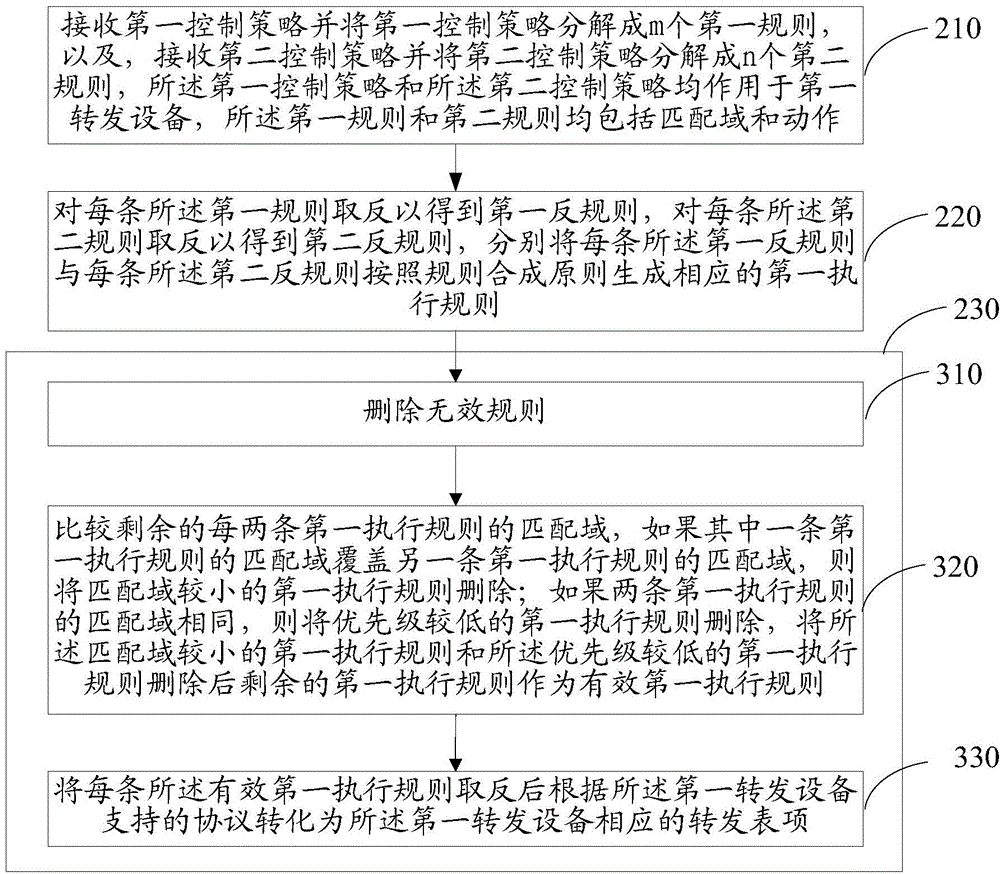

Strategy conflict solution method and device

ActiveCN104104615AAvoid Conflicting Rule SituationsResolving Policy ConflictsData switching networksNegationComputer science

The invention discloses a strategy conflict solution method and device. The method includes the steps of receiving a first control strategy, resolving the first control strategy into m first rules, receiving a second control strategy, resolving the second control strategy into n second rules, conducting negation on each first rule to obtain a first reversed rule, conducting negation on each second rule to obtain a second reversed rule, generating a corresponding first execution rule through each first reversed rule and the corresponding second reversed rule according to the rule synthesis principle, deleting the invalid rules, enabling the rest of the first execution rules to serve as the valid first execution rules, conducting negation on each valid first execution rule, and then converting the valid first execution rules into forwarding table items corresponding to a first forwarding device according to the protocol supported by the first forwarding device. By means of the method, strategy conflicts can be solved.

Owner:HUAWEI TECH CO LTD

Large scale phased array difference beam forming system based on sub-array division

ActiveCN108051782AOvercoming differential beam zero depth sizeOvercome positionWave based measurement systemsNegationArray element

The invention provides a large scale phased array difference beam forming system based on sub-array division, and aims to provide a difference beam forming device that can approach to the performanceof array element level difference beams and mono-pulse tracking precision. The system comprises N*M serially connected radio frequency processing modules corresponding to antenna array elements, a digital pretreatment module, a primary sub-array inner beam forming module, and a secondary difference beam sub-array cross-regional splitting and weighting-synthesizing module. The system comprises a designed azimuth dimension and pitching dimension sub-array cross-regional splitting unit and following cascaded units: a sub-array symmetrical positive azimuth difference beam weighting processing unit, a sub-array symmetrical negative azimuth difference beam weighting processing unit, a sub-array symmetrical positive pitching difference beam weighting processing unit, a sub-array symmetrical negative pitching difference beam weighting processing unit, and an azimuth difference and azimuth difference beam synthesizing unit. An add-subtract treatment is carried out in an azimuth-pitching coordinate area division symmetrical negation mode to obtain the azimuth difference and pitching difference beams.

Owner:10TH RES INST OF CETC

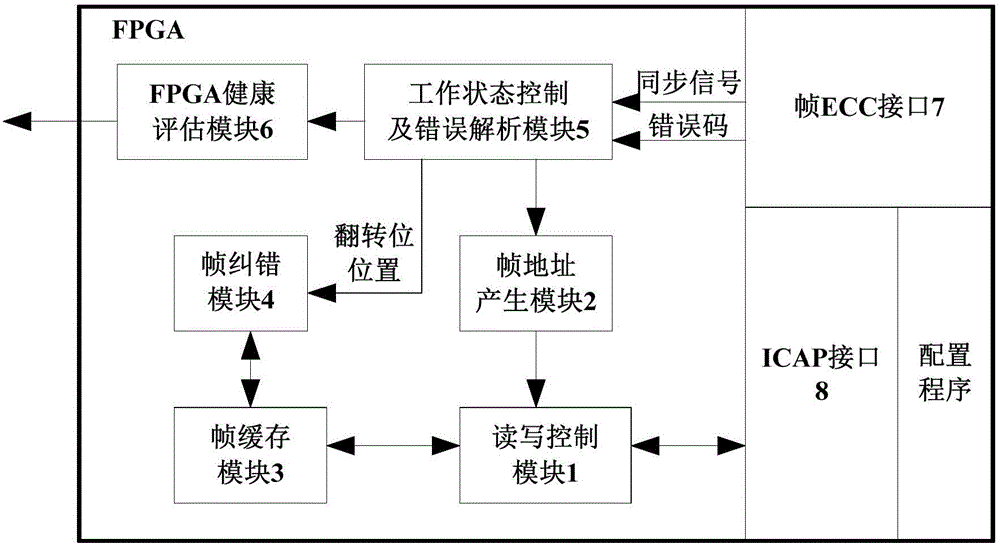

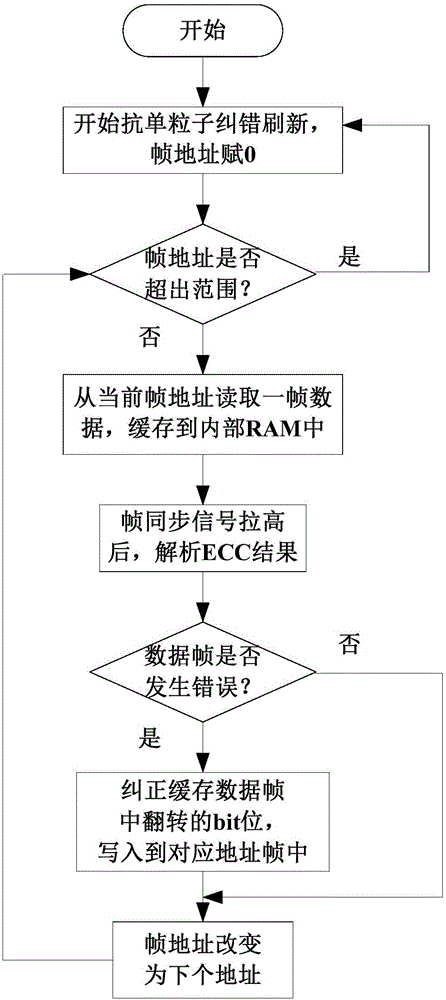

SEU (single event upset)-resistant fast refreshing circuit and method applied to FPGA (field programmable gate array) and based on ECCs (error correcting codes)

ActiveCN106293991ARefresh fastRefresh rate intelligent adjustmentRedundant data error correctionNegationComputer module

The invention relates to an SEU (single event upset)-resistant fast refreshing circuit and method applied to an FPGA (field programmable gate array) and based on ECCs (error correcting codes). The method comprises steps as follows: for any one frame address generated by a frame address generation module, a read-write control module reads data frames through an ICAP (internal configuration access port) of the FPGA, only reads frame data of the current frame address every time and writes the read data frame into a frame caching module; after a frame synchronization signal received by a working state control and error analysis module from a frame ECC interface of the FPGA becomes higher from lower, the ECCs of the current data frame are read, and the upset position in the data frame is calculated; a frame error correction module reads a segment of SEU data from the frame caching module according to the upset position and performs negation on the upset position, correct data after error correction is obtained and is written into the frame caching module again, the correct data frame is written into the current frame address of the FPGA again by the read-write control module, and accordingly, SEU-resistant error correction of the FPGA is completed.

Owner:SHANGHAI RADIO EQUIP RES INST

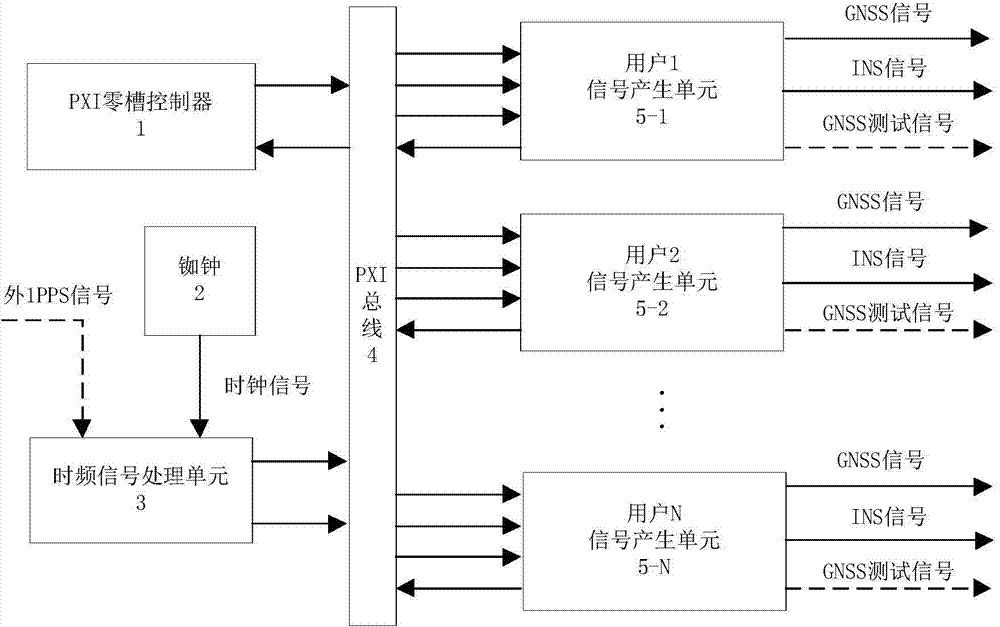

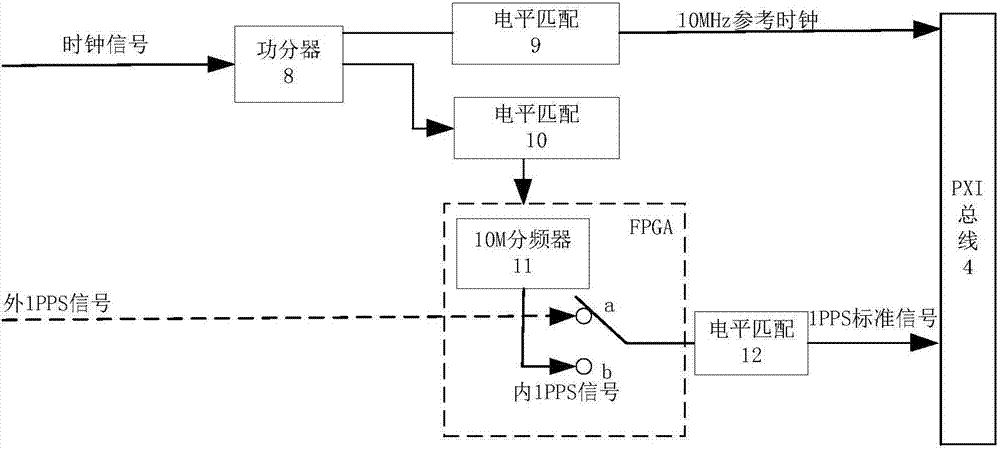

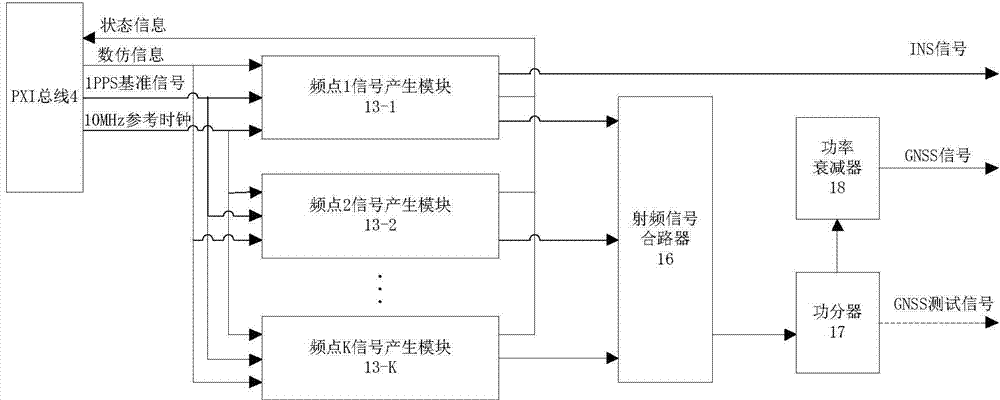

Real-time GNSS/INS (global navigation satellite system/inertial navigation system) combined navigation signal simulator based on PXI (PCI extensions for instrumentation) bus

ActiveCN104730541AIncrease flexibilityStrong configurabilitySatellite radio beaconingExtensibilityNegation

The invention discloses a real-time GNSS / INS (global navigation satellite system / inertial navigation system) combined navigation signal simulator based on a PXI (PCI extensions for instrumentation) bus and relates to a real-time GNSS / INS combined navigation signal simulator in the navigation field. The simulator comprises a time-frequency signal processing unit, a user signal generating unit, the PXI bus, a PXI slot-0 controller, a rubidium clock and the like; the user signal generating unit is composed of multiple frequency-point signal generating modules, a radiofrequency signal combiner, a power divider, a power attenuator and the like. The PXI bus technique is used in system structuring, configurability and extensibility are excellent, the simulator is imparted multi-navigation system multi-frequency GNSS / INS navigation signal simulation capacity by selecting parts, especially the multi-user GNSS / INS combined negation signal simulation output capacity, and the need of the navigation field for real-time testing of GNSS, INS and GNSS / INS combined navigation signals is fully met.

Owner:NO 54 INST OF CHINA ELECTRONICS SCI & TECH GRP

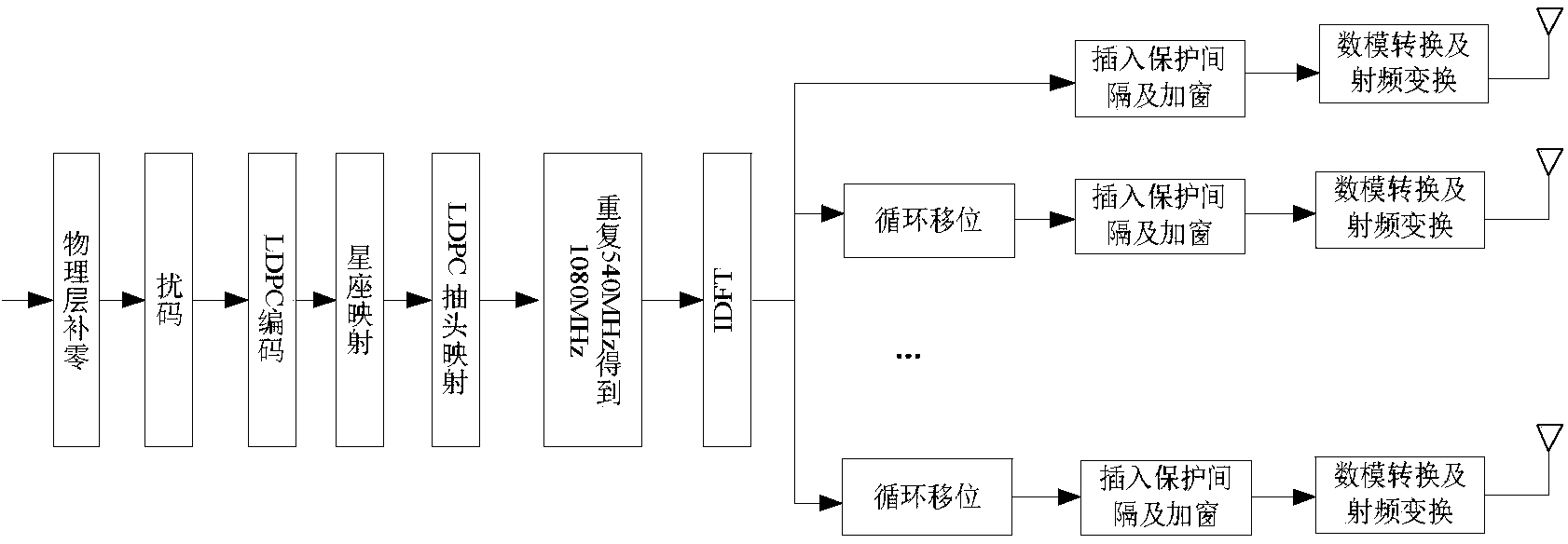

Method and device for improving robustness of signaling frame transmission

ActiveCN103957083AImprove transmission robustnessImprove transmission reliabilityError preventionNegationForward error correction

The invention discloses a method and device for improving robustness of signaling frame transmission. The method includes the steps that before forward error correction encoding, a scrambled signaling frame is repeated, or repeating and negation are carried out, or a position filling 0 in the signaling frame is changed after repetition, the position filling 0 in the signaling frame can be changed after repeating and negation, and accordingly a new signal frame is generated. The device comprises a processing system, the processing system is used for repeating the scrambled signaling frame, or carrying out repeating and negation, or changing the position filling 0 in the signaling frame after repetition or changing the position filling 0 in the signaling frame after repeating and negation to generate the new signaling frame before forward error correction encoding and to transmit the new signaling frame to an encoding module of a transmitter; a receiver receives the signaling frame, decodes the signaling frame, and then restores a signaling frame b of an L bit according to the method of repetition or repeating and negation and the position filling 0 in sending. According to the method, diversity gain brought due to the fact that the signaling frame with a short bit is mapped into forward error correction encoding and input with a long bit, and reliability of signaling frame transmission is improved.

Owner:南京易太可通信技术有限公司

System for enterprise knowledge management and automation

ActiveUS8135576B2Facilitates productive useDigital data information retrievalSemantic analysisFirst-order predicateSoftware design

Owner:ORACLE INT CORP

Complex multiplication method and apparatus with phase rotation

ActiveUS20040267860A1Computation using non-contact making devicesTransmissionNegationComputer science

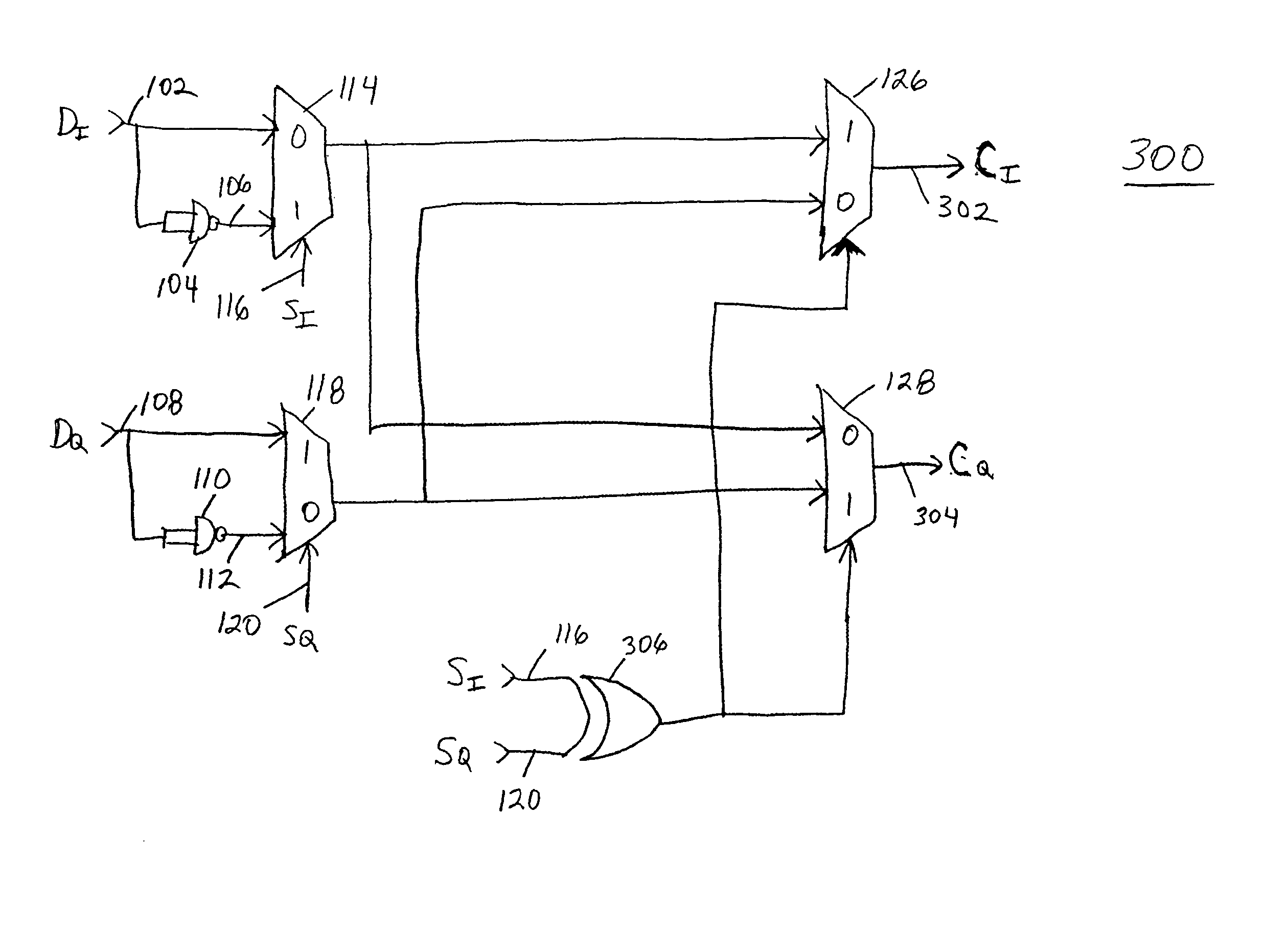

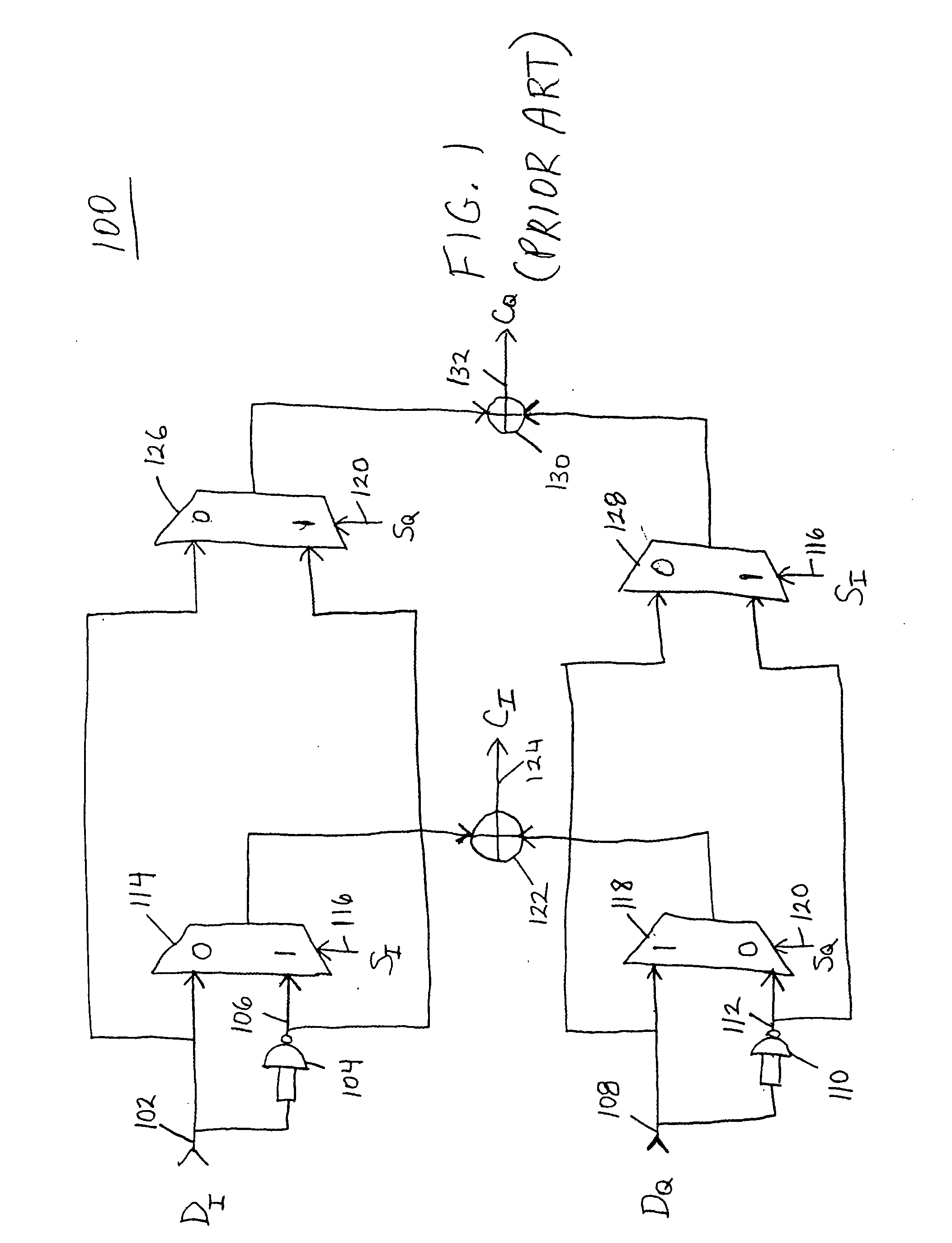

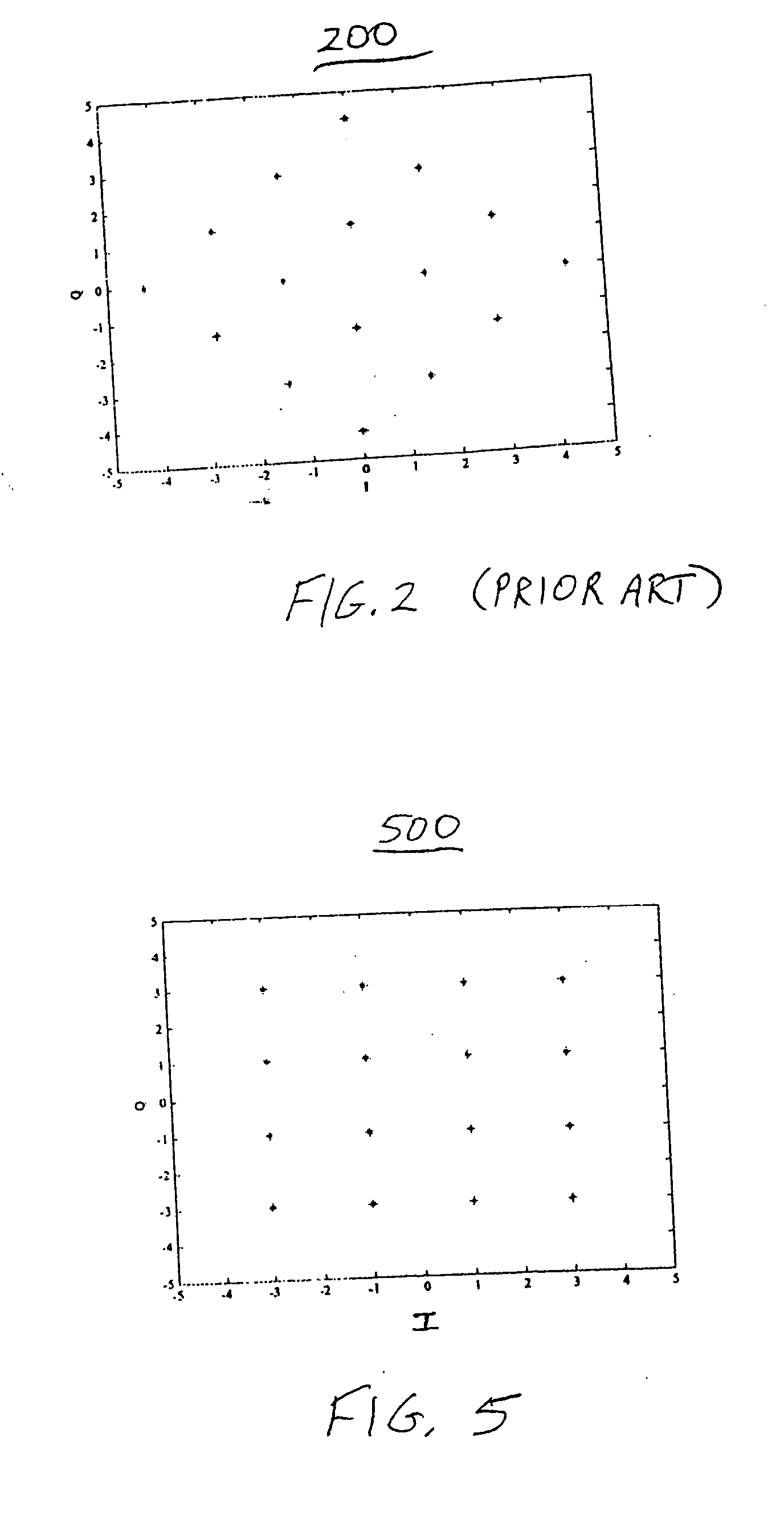

A method and apparatus for complex multiplication includes steps of: (a) receiving a complex multiplicand having a real value and an imaginary value (704); (b) generating a negation of the real value of the complex multiplicand (706); (c) generating a negation of the imaginary value of the complex multiplicand (708); (d) receiving a complex multiplier (710); and (e) selecting a phasor constant having a value wherein a complex product of the complex multiplicand times the complex multiplier times the phasor constant has a real value equal to one of the real value of the complex multiplicand, the imaginary value of the complex multiplicand, the negation of the real value of the complex multiplicand, and the negation of the imaginary value of the complex multiplicand (712).

Owner:GOOGLE TECH HLDG LLC

Encoding method, decoding method, related device and storage medium

ActiveCN110086575AImprove transmission qualitySolve the problem of uncodedForward error control useComputer hardwareNegation

The embodiment of the invention discloses an encoding method, a decoding method, a related device and a storage medium. The encoding method comprises the following steps: acquiring a first bit streamof original encoded data; performing a preset logic operation according to the first bit stream to obtain a second bit stream, with the number of bits of the second bit stream being greater than the number of bits of the first bit stream; whether the logic values of the last two bits in the second bit stream are the same or not is judged, if so, subjecting the logic value of at least one of the last two bits to negation processing, and acquiring a third bit stream; and inverting the target bit in the third bit stream, and inserting the inverted target bit as a flag bit into the first bit of the third bit stream to obtain target coded data. According to the embodiment of the invention, the problem of no code in the channel transmission process of the information is solved, so that the signal transmission quality is improved.

Owner:SHENZHEN CHINA STAR OPTOELECTRONICS TECH CO LTD

Real-time on-line system-based field leaf image edge extraction method and system

ActiveCN101964108APrecise positioningGood denoisingImage enhancementImage analysisNegationGray level

The invention relates to a real-time on-line system-based field leaf image edge extraction method and a real-time on-line system-based field leaf image edge extraction system. The method comprises the following steps of: 1, performing gray-level mapping processing on segmentation area sub-images; 2, performing smoothening and noise removing, thresholding, edge detection and preliminary optimization on the images processed by the step 1, and judging whether a target area has a leaf shape; 3, performing smoothening and noise removing, thresholding negation, edge detection and preliminary optimization on the images processed by the step 1, and judging whether the target area has a leaf shape; 4, performing smoothening and noise removing, thresholding, thresholding negation, edge detection, preliminary optimization and area combination on the images processed by the step 1, and judging whether the target area has a leaf shape; and 5, performing further optimization and closed operation onthe images processed by the steps 2, 3 and 4 to obtain edge-closed edge images. Through the method and the system, complete, enclosed and accurately positioned target boundary curve images can be acquired, and the segmentation success rate is high.

Owner:CHINA AGRI UNIV

Ultra-lightweight RFID mutual authentication method

ActiveCN103716164AEasy to hideGuaranteed forward securityUser identity/authority verificationCo-operative working arrangementsNegationReader writer

The invention discloses an ultra-lightweight RFID mutual authentication method, and belongs to the technical field of RFID. With a negation cyclic displacement operation processing tag and data stored by a rear-end database, secret data are greatly hidden. According to the authentication method, tag authentication is firstly performed, then a stage of mutual authentication is performed, and information stored by a reader-writer and an electronic tag is updated after success of mutual authentication so that forward security is guaranteed. New and old authentication information stored by the electronic tag is combined with resistance replay aggression data M which are designed in the authentication process by utilizing secret key information of the new and old authentication information so that non-synchronous aggression and replay aggression are effectively resisted.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

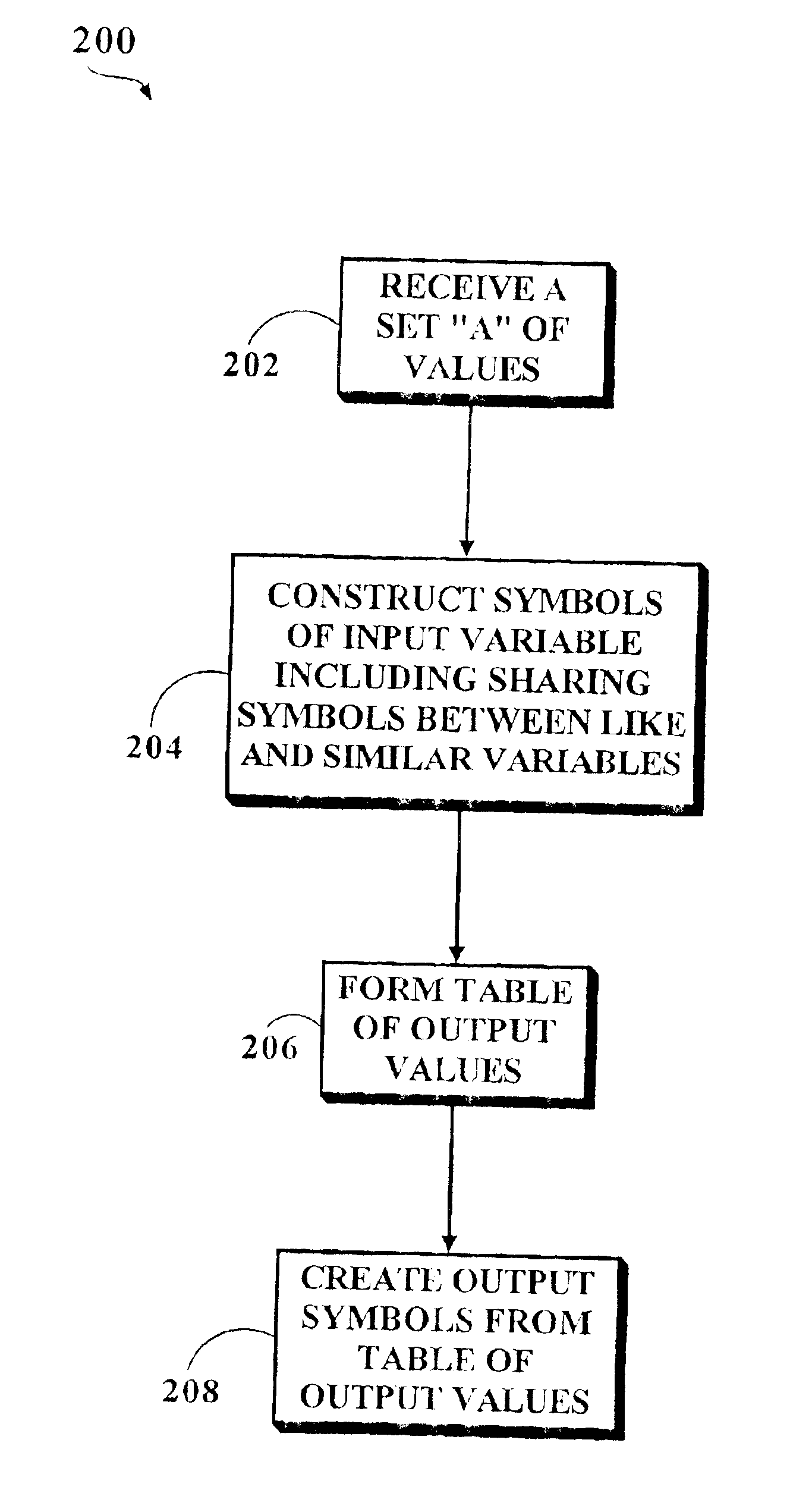

Symbolic simulation driven netlist simplification

InactiveUS6842750B2Data processing applicationsDigital data processing detailsSymbolic simulationNegation

The present invention is directed to a simplification method for an arbitrary library. In aspects of the present invention, the method does not rely on specific properties of the library elements and has linear complexity. The present invention may be implemented based on a symbolic simulation in an alphabet which contains 0, 1, symbols of variables, and negations of the variables' symbols. In an aspect of the present invention, a method for reducing redundancy in a simulation through use of a symbolic simulation utilizing an arbitrary library includes receiving a set A of values, the set A including input variables which are elements of the set A. Symbols of the input variables are constructed in which like and similar variables share a like symbol and a similar symbol respectively. A table of output values computed from a table of a Boolean operator employing the constructed symbols of the input variable is formed, the constructed symbols formed to reduce redundancy.

Owner:BELL SEMICON LLC

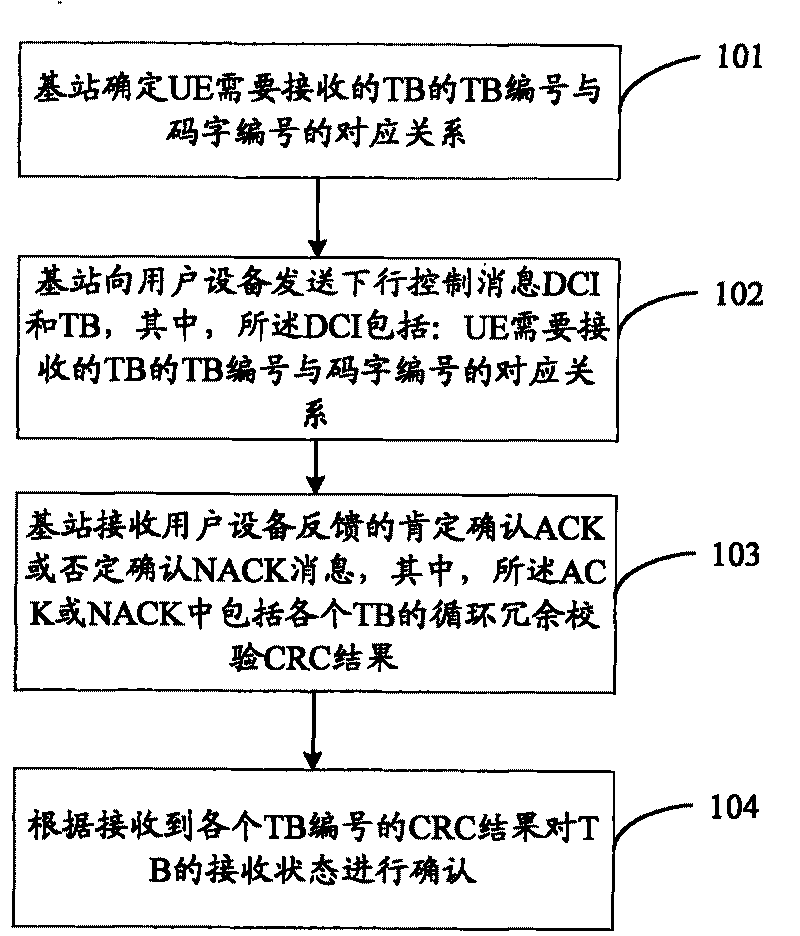

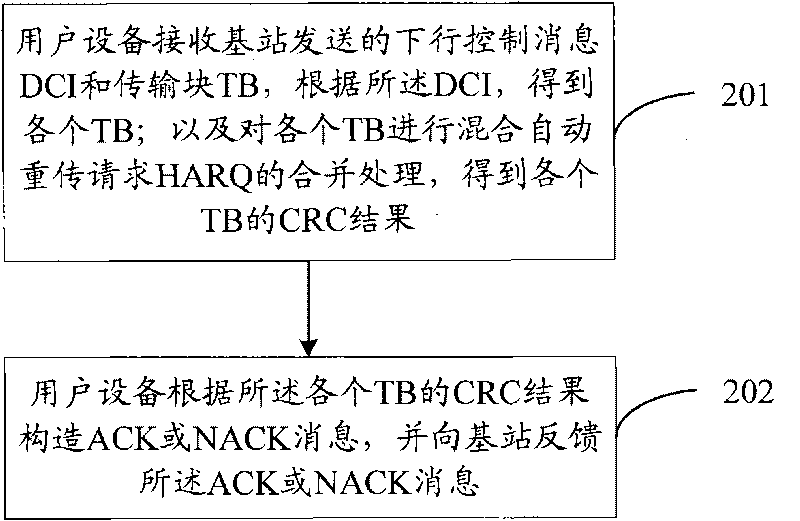

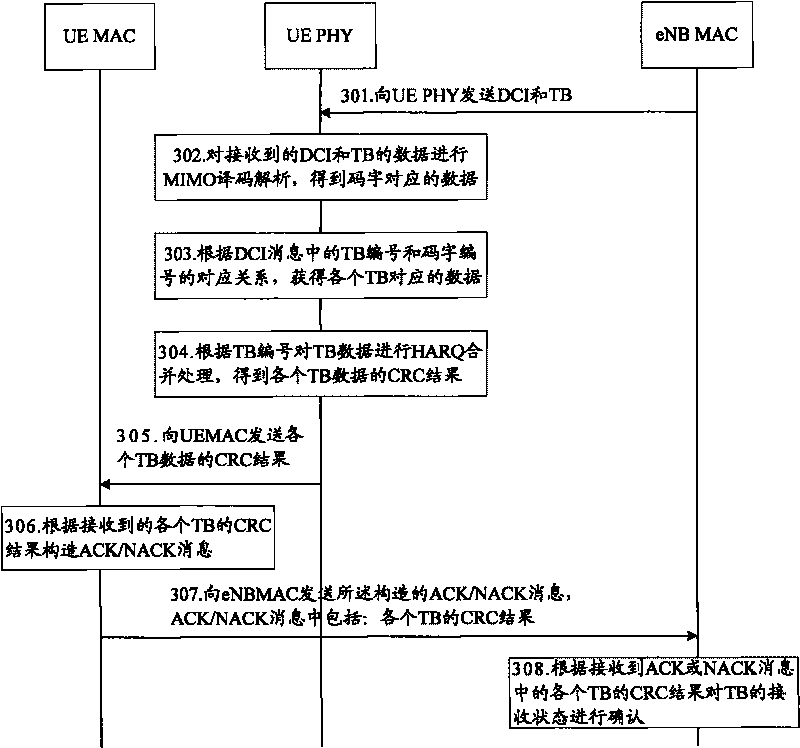

Data transmission method, user equipment, base station and data transmission system

ActiveCN101699780AReduce memory usageError prevention/detection by using return channelNegationUser equipment

The invention relates to a data transmission method, user equipment, a base station and a data transmission system, and the method comprises the following steps: determining the corresponding relationship between TB number and code word number of the user equipment; sending downlink control messages of DCI and TB to the user equipment, wherein the DCI comprises the corresponding relationship between the TB number of the TB which needs to be received by the UE and the code word number; receiving a confirmation ACK message or a negation NACK message fed back by the user equipment, wherein, the ACK or the NACK comprises cyclic redundancy check CRC results of various TB; and confirming the receiving state to the TB according to the CRC results of the various TB. The invention can reduce the TB number-code word number conversion problem in the prior art, as well as the problem that as a network side caches the corresponding relationship between the TB number of the TB which needs to be received by all UE and the code word number, a memory is occupied.

Owner:SHANGHAI HUAWEI TECH CO LTD

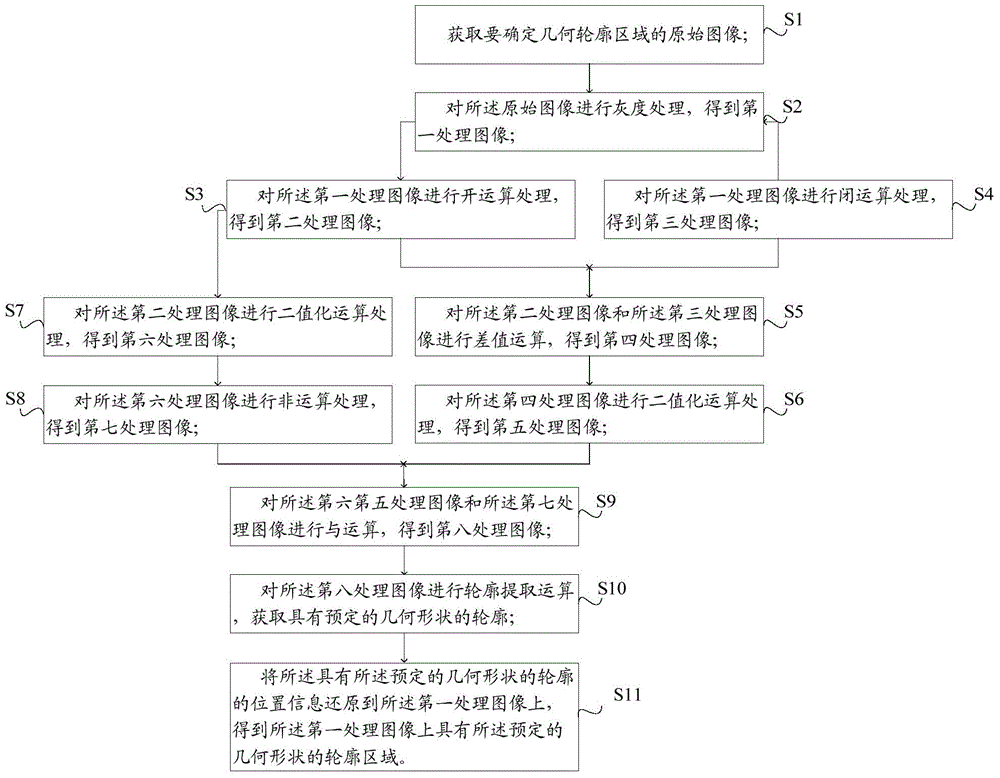

Method and system for determining geometric outline area on image

ActiveCN104156941ABrightness Differential EnhancementImage analysisCharacter and pattern recognitionNegationComputer vision

The invention discloses a method and system for determining a geometric outline area on an image, and the position of a predetermined geometric outline area on the image can be more accurately determined. The method for determining the geometric outline area on the image includes the steps of conducting gray processing for an original image to obtain a first processing image; respectively conducting open operation processing and closing operation processing for the first image to obtain a second processing image and a third processing image respectively; conducting margin calculation for the second and third processing images to obtain a fourth processing image; conducting binarization calculation for the fourth processing image to obtain a fifth processing image; conducting binarization calculation for the second processing image to obtain a sixth processing image; conducting negation operation processing for the sixth processing image to obtain a seventh processing image; conducting AND operation for the fifth processing image and the seventh processing image to obtain an eighth processing image; conducting contour extraction operation for the eighth processing image to obtain a contour with a predetermined geometry; and restoring position information of the contour to the first processing image to obtain a contour area with the predetermined geometry on the first processing image. The invention is suitable for use in occasions requiring accurate positioning of geometric contour area on an image.

Owner:北京致胜宏达科技有限公司

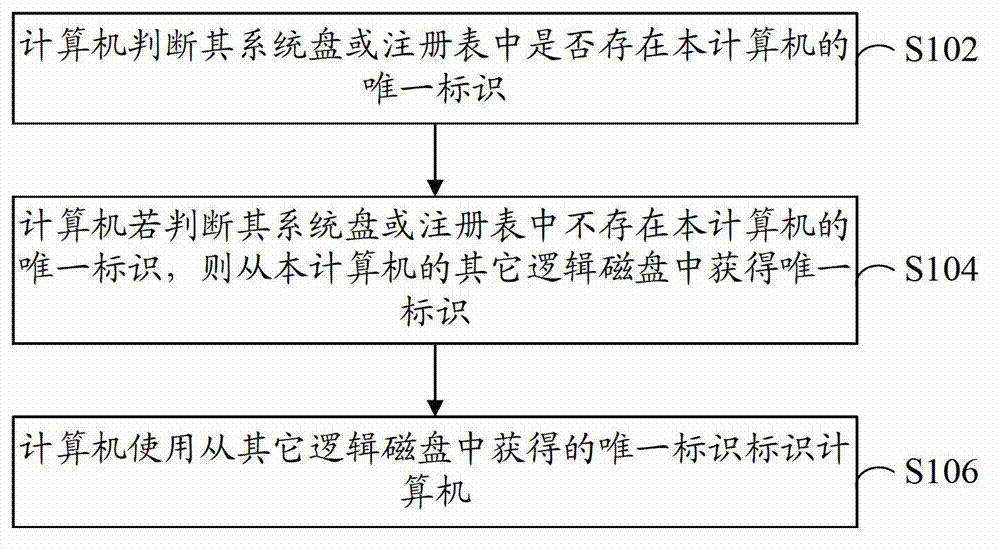

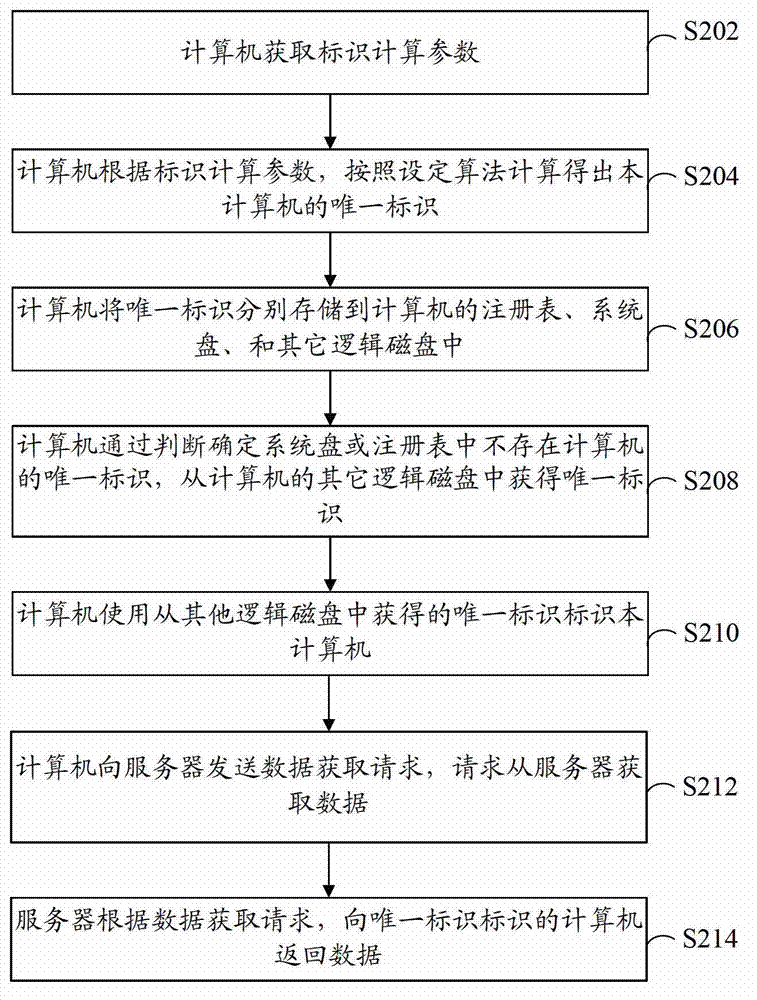

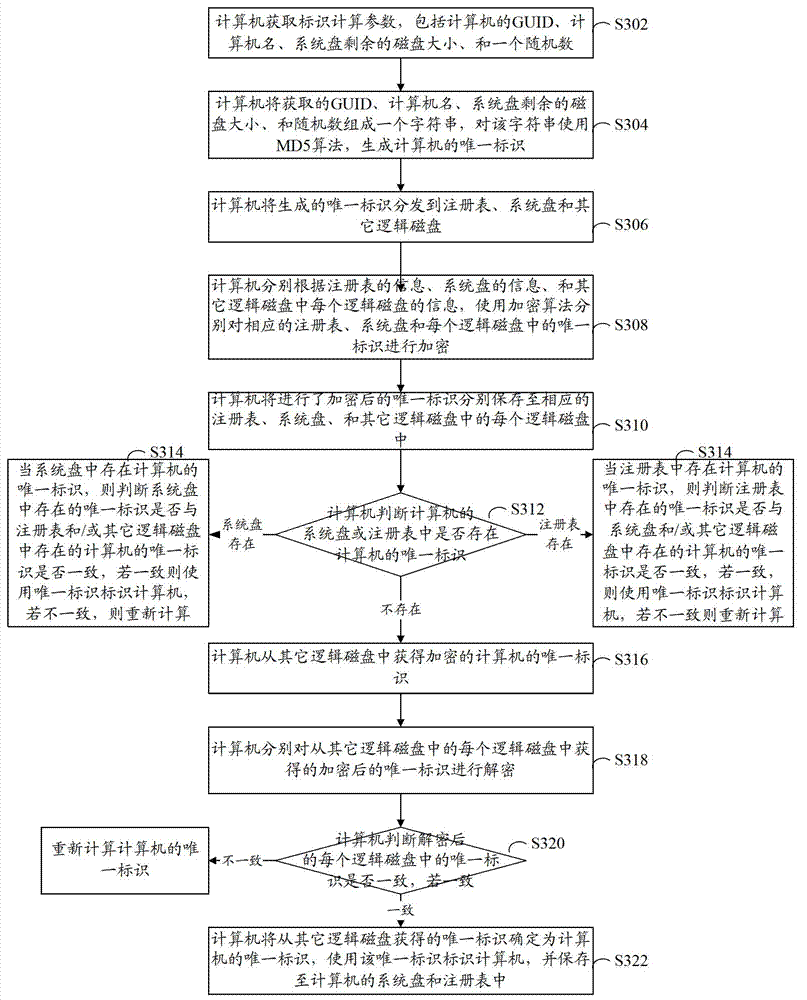

Computing device identifying method and device

ActiveCN102930230AAccurate identificationGuaranteed stabilityInternal/peripheral component protectionNegationData acquisition

The invention provides a computing device identifying method and a computing device identifying device. The computing device identifying device comprises a judgment module, a negation module, an identifying module and an interaction module, wherein the interaction module is used for transmitting a data acquisition request to a server after the identifying module utilizes an exclusive identifier which is acquired from other logic disks to identity a computing device, and the data acquisition request carries the exclusive identifier; and the interaction module is used for acquiring the data which is transmitted by the server according to the data acquisition request to the computing device identified with the exclusive identifier. Through the method and the device, the effect of accurately identifying the computing device is achieved.

Owner:BEIJING QIANXIN TECH

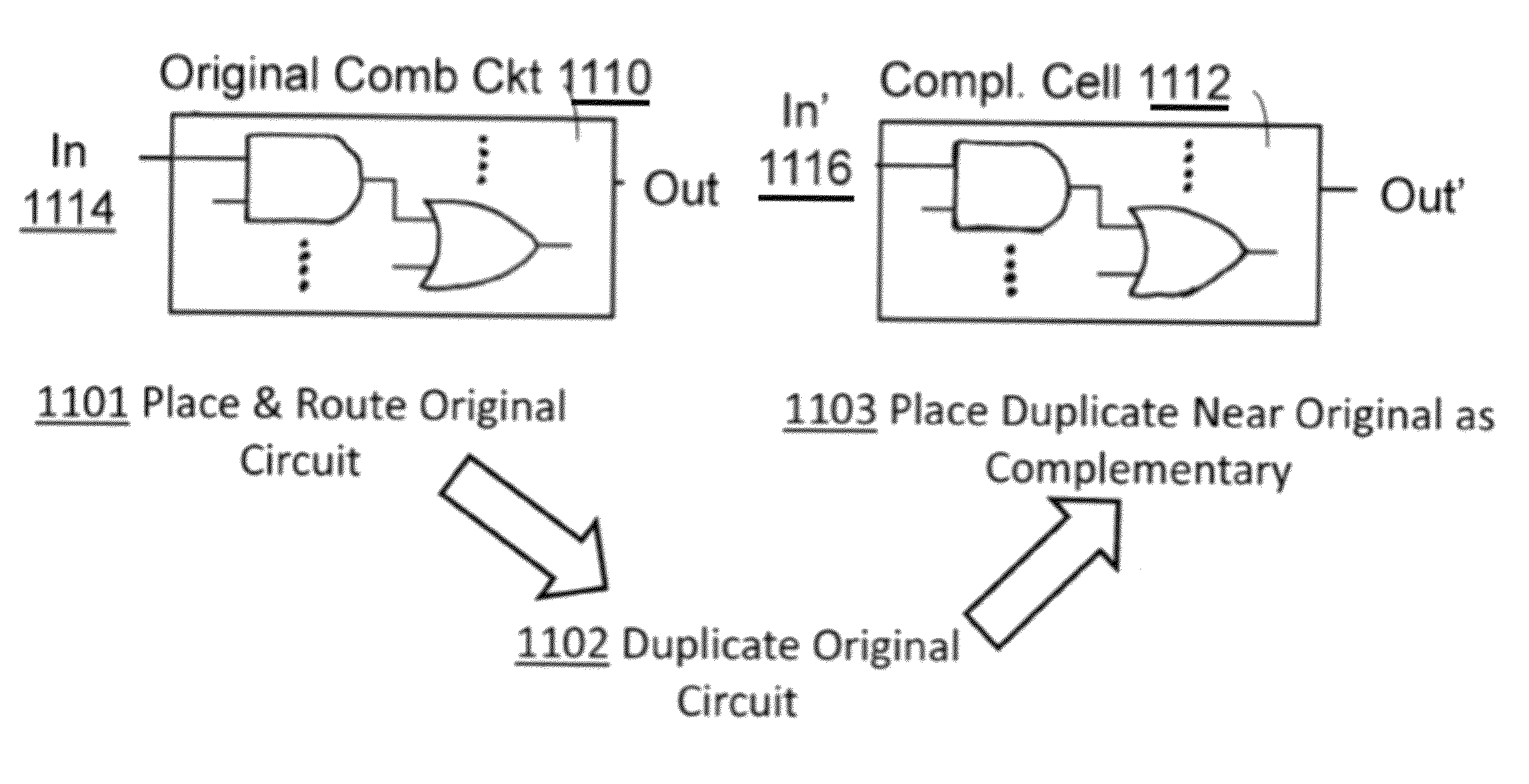

Homogeneous dual-rail logic for DPA attack resistive secure circuit design

ActiveUS8395408B2Reliability increase by circuit redundancySpecial data processing applicationsNegationPrimary cell

Homogenous dual-rail logic for DPA attack resistive secure circuit design is disclosed. According to one embodiment, an HDRL circuit comprises a primary cell and a complementary cell, wherein the complementary cell is an identical duplicate of the primary cell. The HDRL circuit comprises a first set of inputs and a second set of inputs, wherein the second set of inputs are a negation of the first set of inputs. The HDRL circuit has a differential power at a level that is resistive to DPA attacks.

Owner:RGT UNIV OF CALIFORNIA

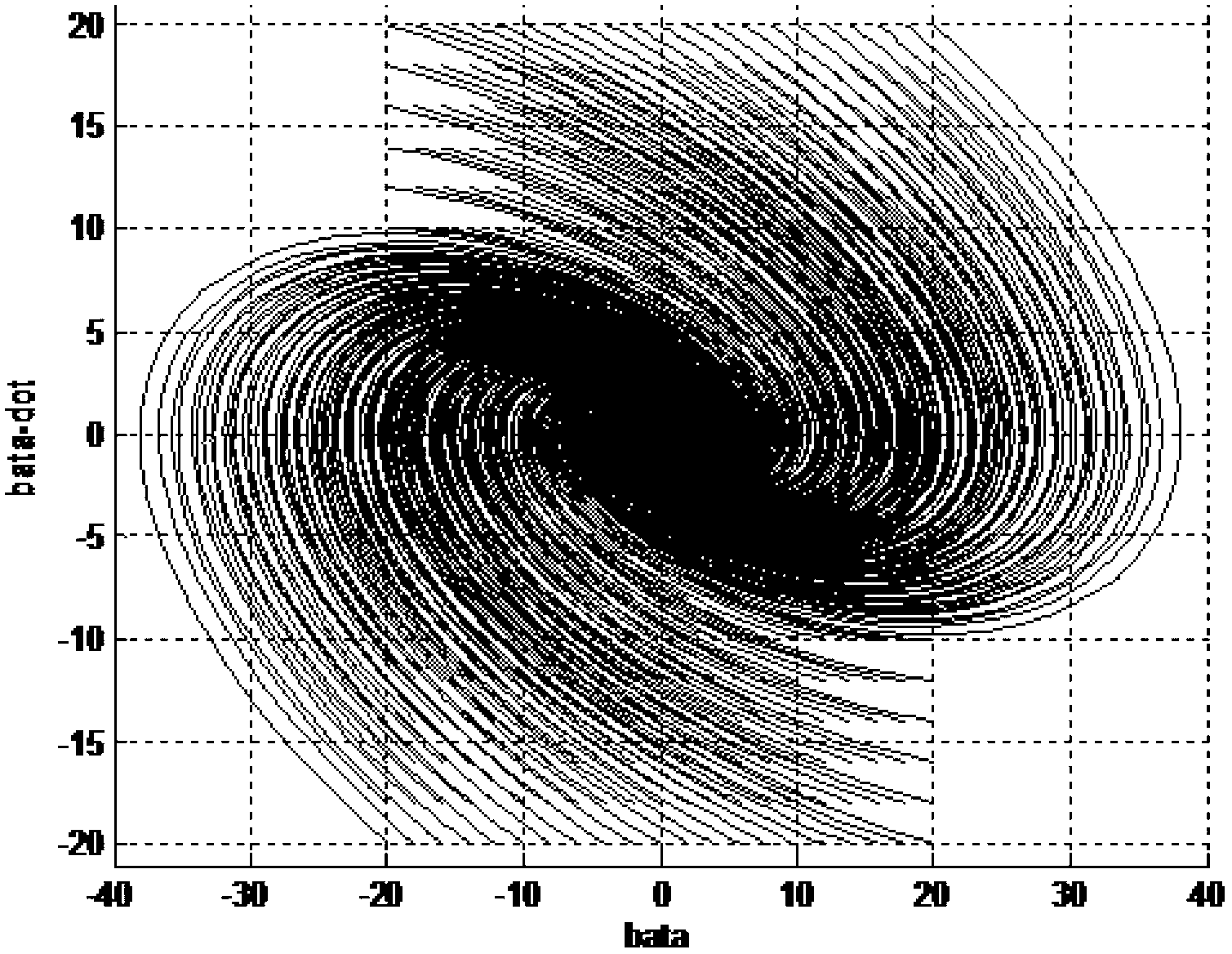

Conventional aircraft model-based lateral-directional controller area design method

InactiveCN102707723AGuaranteed stabilityAvoid incorrect approximations such as ignoring aerodynamic effectsAdaptive controlPosition/course control in three dimensionsAngle of incidenceEngineering

The invention discloses a conventional aircraft model-based lateral-directional controller area design method, which is used for solving the technical problem of incapability of directly determining the whole stability of a given flight area by the conventional controller design method. According to the method, a trimming control plane, an angle of incidence of airflow and an angle of sideslip for the stable circling under a given turning radius when the altitude and mach number of a control target are given are obtained through aerodynamic force and a moment equation, the area stability of a system is determined by adopting a phase plane analysis model, and the structure and parameters of a feedback controller are determined on the basis of the area stability to directly control the lateral-directional movement of an aircraft, so that inaccurate approximation such as the negation of aerodynamic action in the moment equation is avoided, the controller can ensure the stability of the aircraft in the whole design area, and the problems of instable and unsafe flight and the like caused by the analysis model can be reduced and even solved.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

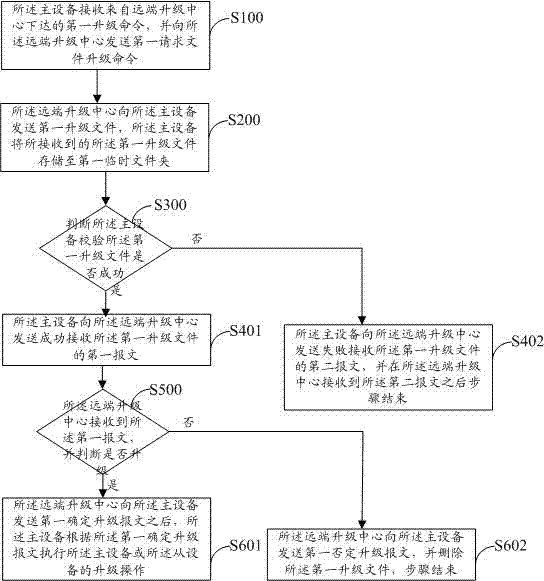

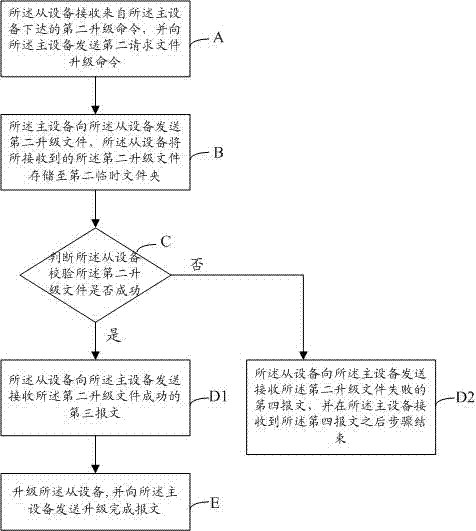

Remote upgrade method and device based on main and auxiliary equipment

The invention discloses a remote upgrade method and a device based on main and auxiliary equipment. The method includes that main equipment receives first upgrade commands issued from a remote upgrade center and sends the first demand file upgrade commands; the main equipment stores a first upgrade file into a first temporary file; whether the main equipment verifies the first upgrade file successfully is judged, if the main equipment verifies the first upgrade file successfully, a first message successfully receiving the first upgrade file is sent to the remote upgrade center, if not, a second message unsuccessfully receiving the first upgrade file is sent to the remote upgrade center, and the step is finished after the second message is received; and the remote upgrade center receives the first message, whether upgrade is judged, if the upgrade is performed, a second affirmation upgrade message is sent to the main equipment, upgrade operations of the main and auxiliary equipment are performed respectively, if not, a negation upgrade message is sent to the main equipment, the first upgrade message is deleted, and the step is finished. According to the remote upgrade method and the device based on main and auxiliary equipment, the problem that equipment is inconvenient to maintain is solved, and the cost is reduced.

Owner:AEROSPACE SCI & IND SHENZHEN GROUP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com