SEU (single event upset)-resistant fast refreshing circuit and method applied to FPGA (field programmable gate array) and based on ECCs (error correcting codes)

An anti-single event, error-correcting code technology, applied in the field of FPGA circuit reliability design, can solve the problems of increasing the difficulty of program design and not being able to provide the position of single event flipping in data frames, etc., to overcome dynamic refresh circuit, compact structure, The effect of intelligent adjustment of refresh rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

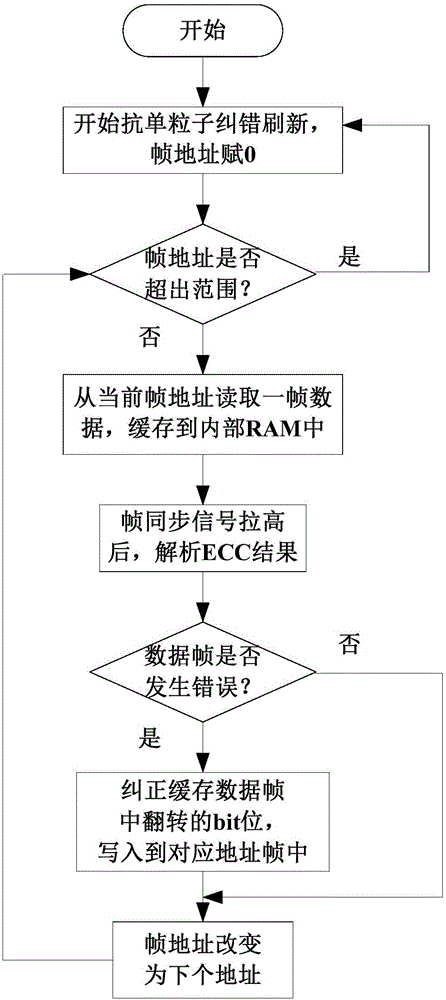

[0043] Hereinafter, a preferred embodiment of the FPGA anti-single event upset fast refresh circuit based on ECC error correction codes involved in the present invention will be described with reference to the accompanying drawings.

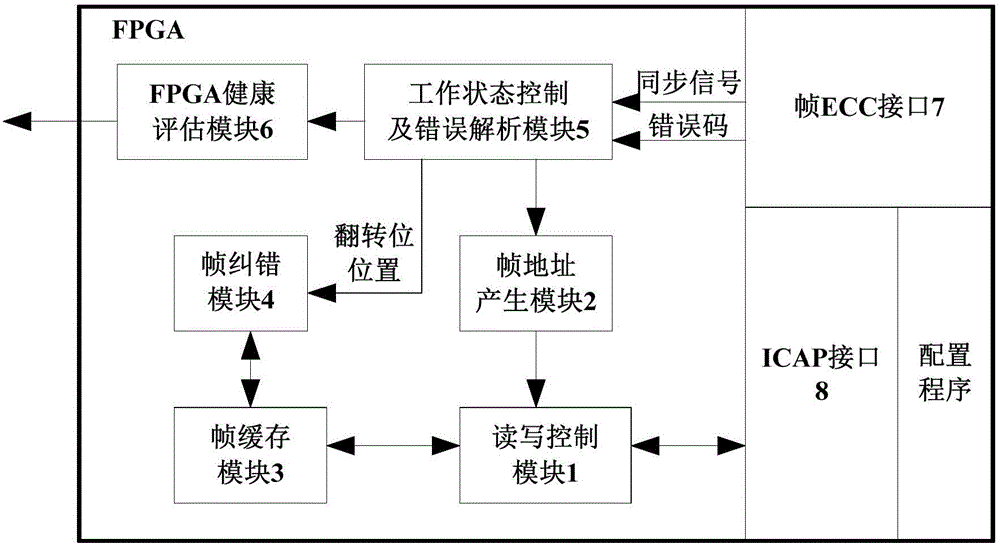

[0044] figure 1 It is a schematic diagram showing the circuit involved in the present invention. figure 1 The circuit in the circuit includes: read and write control module 1, frame address generation module 2, frame buffer module 3, frame error correction module 4, working state control and error analysis module 5 and FPGA health assessment module 6.

[0045] Among them, the frame address generation module 2 generates a corresponding frame address according to the FPGA structure, which can be obtained through the frame address analysis circuit; the frame buffer module 3 stores a frame of data read, if there is a bit flip in the data frame, after error correction Afterwards, it will be written to the corresponding frame address; the frame error ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com