S box applicable to hardware realization and circuit realization method thereof

An implementation method and circuit technology, applied in the field of information security, to achieve the effects of reducing complexity, strong nonlinearity, and reducing overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The present invention will be further described below in conjunction with specific examples.

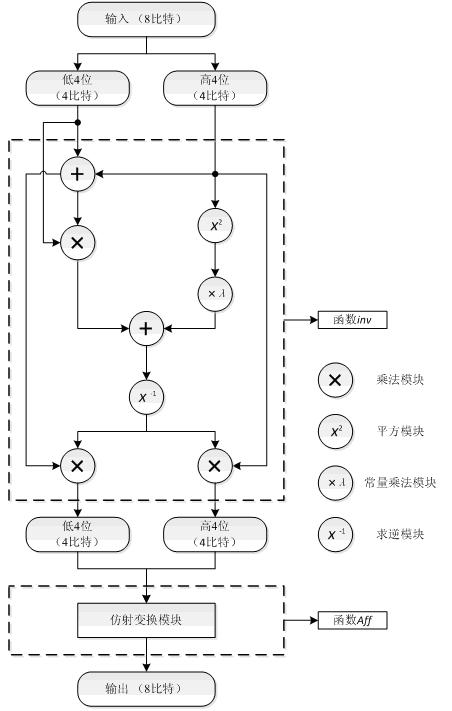

[0036] S box of the present invention is as follows to the processing procedure of 8 bit data:

[0037] 1. The input 8-bit data As a parallel connection of two 4-bit data, record the upper 4 bits as , the lower 4 bits are , , in the sense of finite fields, the representations are respectively , .

[0038] 2. in In (the same below) calculation

[0039] 3. Calculate , (can be parallelized);

[0040] 4. Calculate

[0041] 5. in Zhongqiu inverse of

[0042] 6. Calculate , ;

[0043] 7. Will and paralleled into an 8-bit number , its high and low 4 bits are and 4 bits of

[0044] (The results obtained from the calculation process from step 1 to step 7 satisfy )

[0045] 8. Calculate ;(function The calculation formula has been given above).

[0046] 9. Output 8-bit data

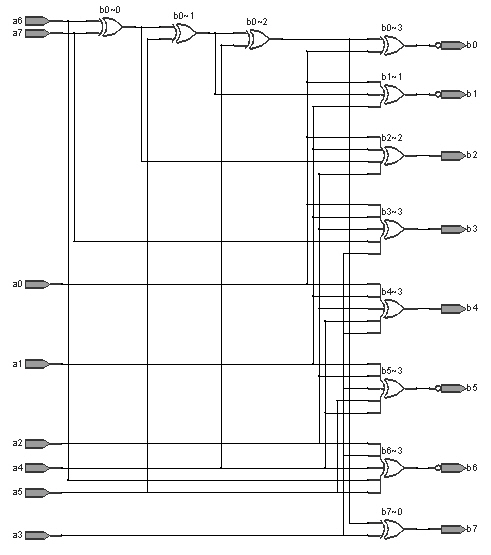

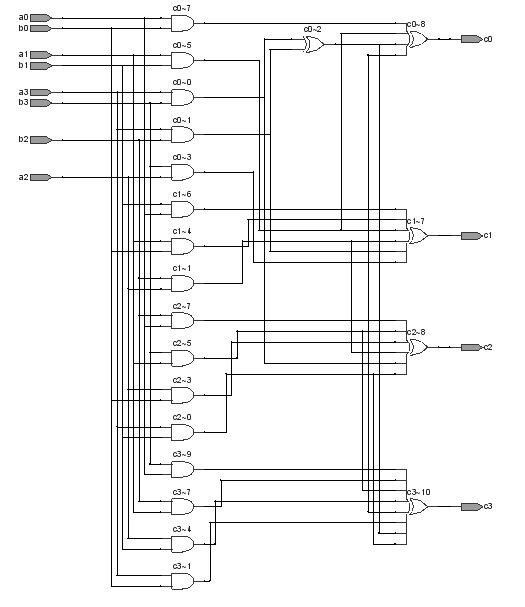

[0047] The above operation involves the domain The op...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com