Fault simulation system and fault analysis method for single event upset

A single-event flipping and fault simulation technology, applied in the field of single-event flipping fault simulation systems and analysis, can solve problems such as slow simulation speed, and achieve the effects of flexible use, fast simulation speed, and improved simulation speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

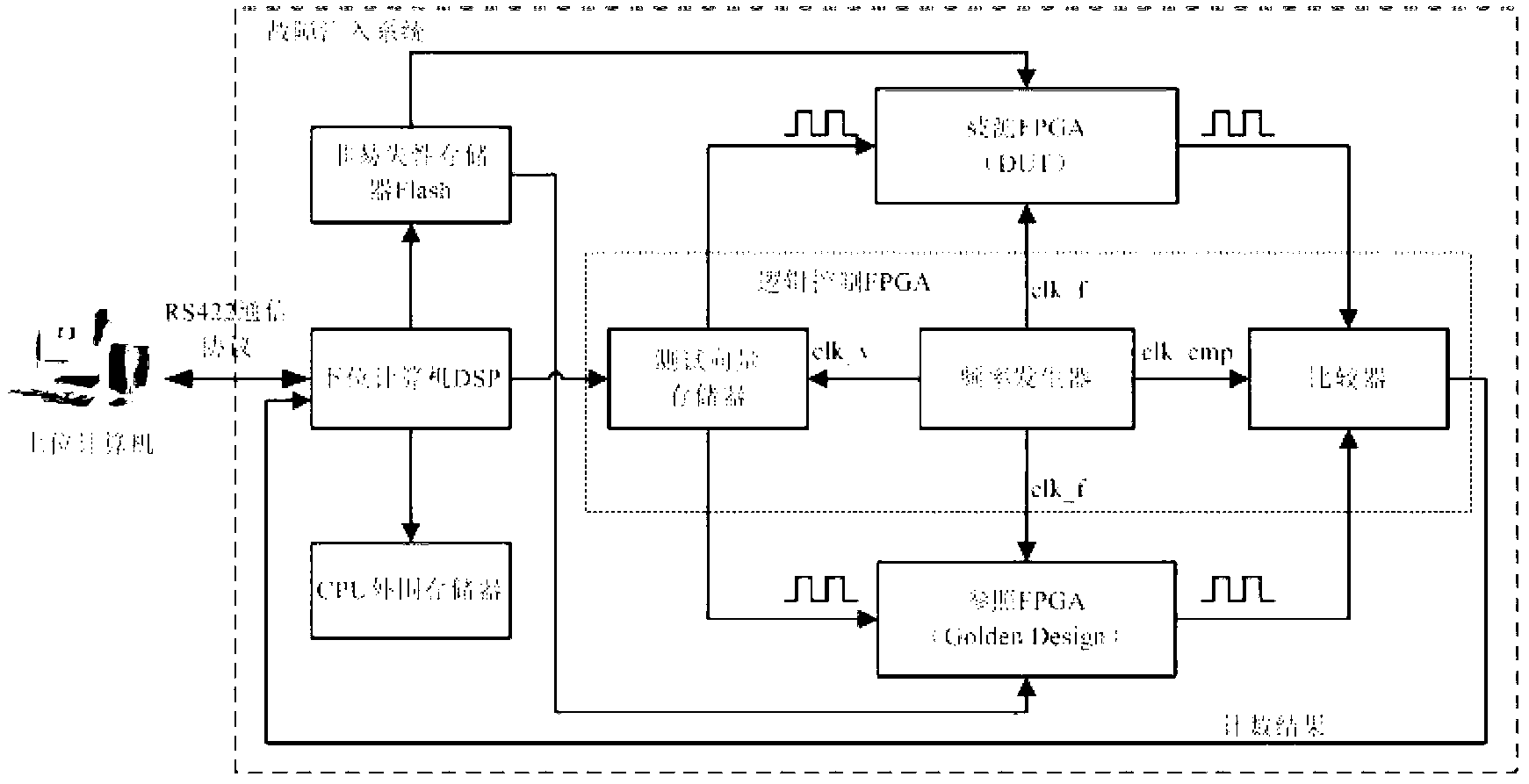

[0050] figure 2 It is a schematic diagram of the hardware structure of the fault injection system in the present invention. The main frame of the system is composed of a host computer and a control board, and the serial port communication protocol RS422 is used for communication between the host computer and the control board. The lower computer adopts TI’s 2000 series DSP TMS320LF2407, which is mainly responsible for receiving commands and data from the upper computer, returning the test data obtained from the test board to the computer, reading and writing Flash, and controlling timing and logic control of the FPGA pair. The FPGA under test is configured and read back.

[0051] The timing and logic control circuit is realized by the Spartan-II series FPGA of Xilinx Company, which is mainly responsible for the realization of the timing and logic control circuit, including: generating the clock signal of the system, such as the synchronous clock of two FPGAs, the output clock...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com