Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

1012 results about "Major and minor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In German music terminology, major and minor are also called "groß" and "klein" as synonyms for "Dur" and "Moll". In Western music, the adjectives major and minor can describe a musical composition, movement, section, scale, key, chord, or interval.

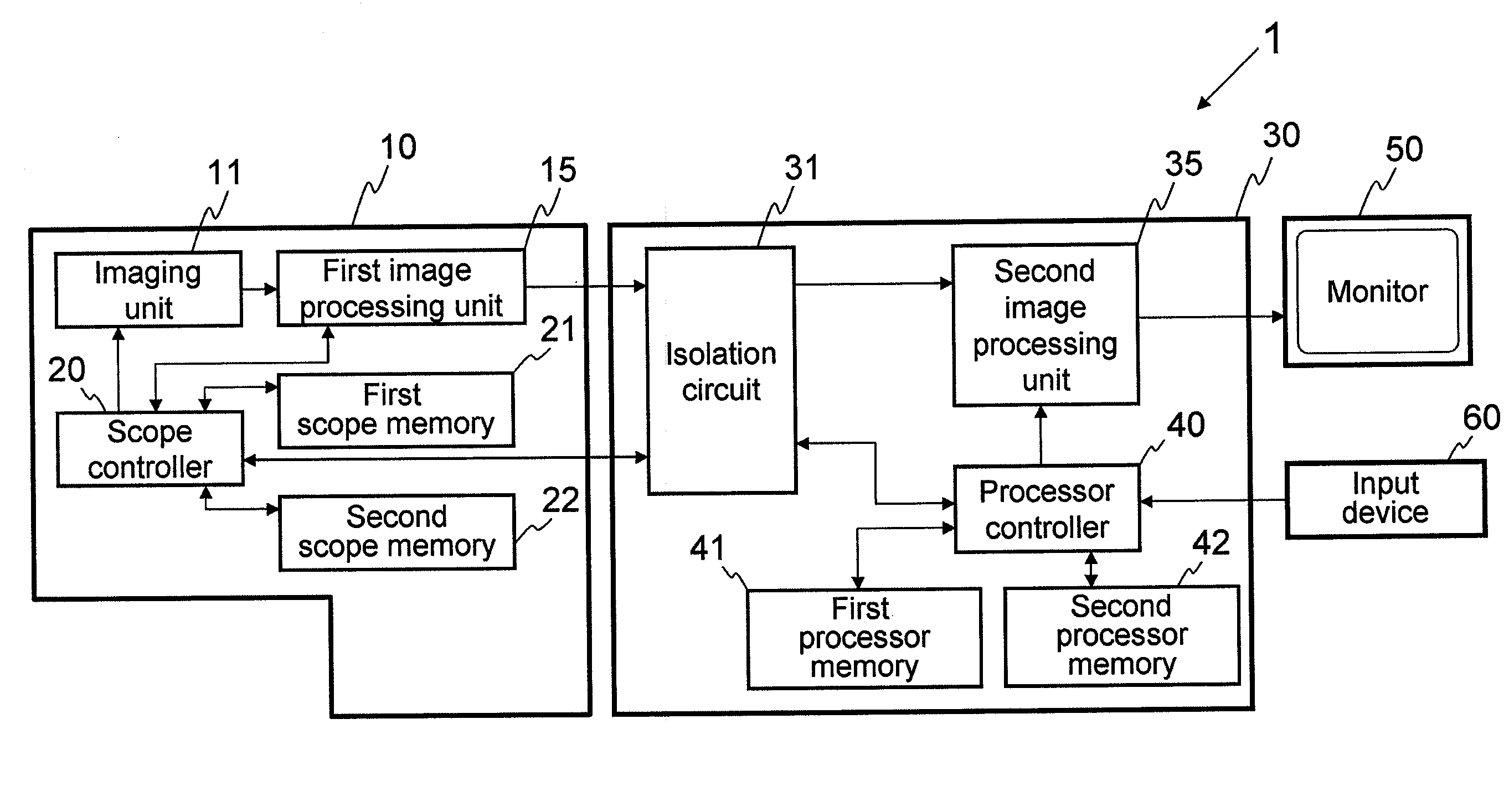

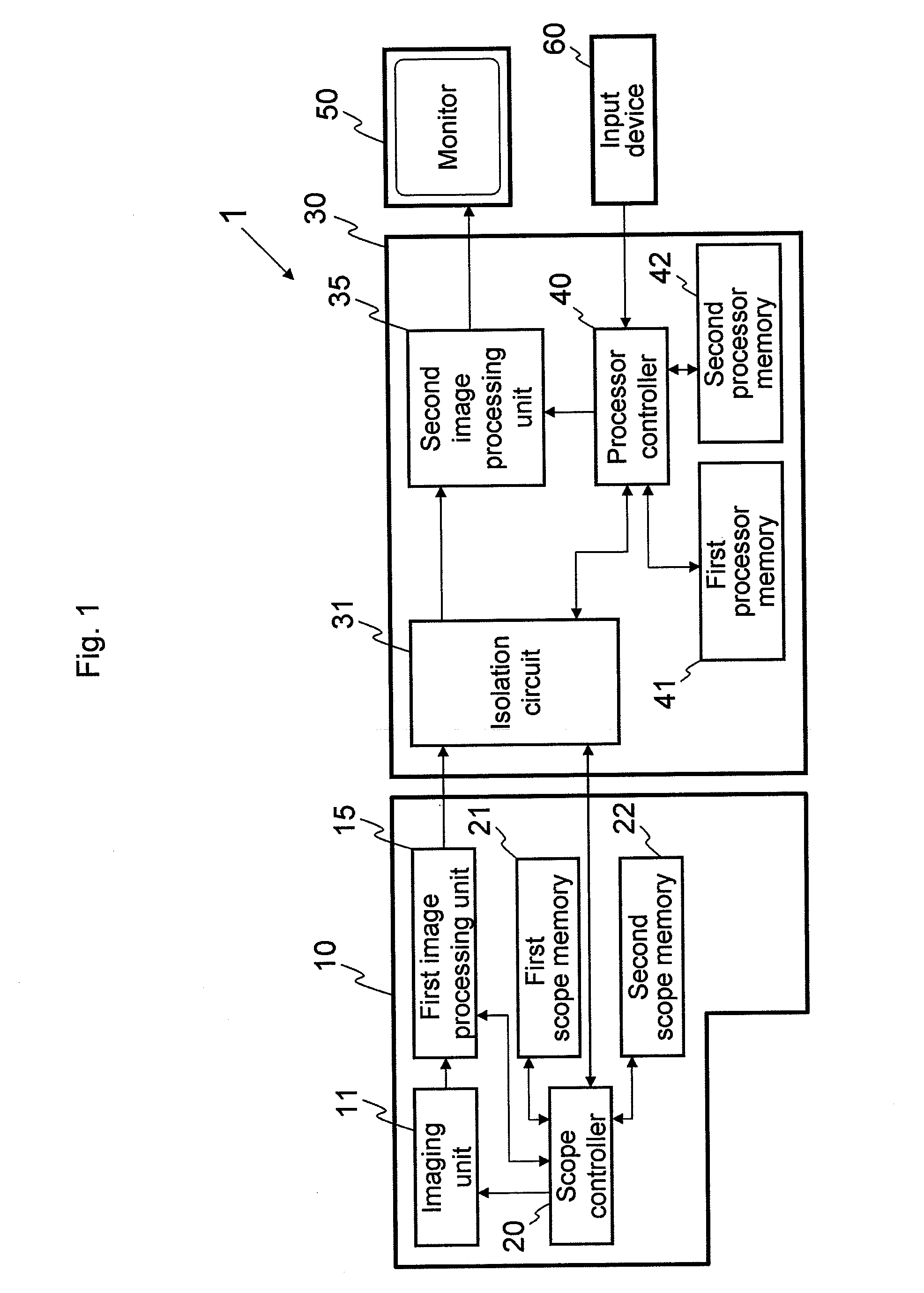

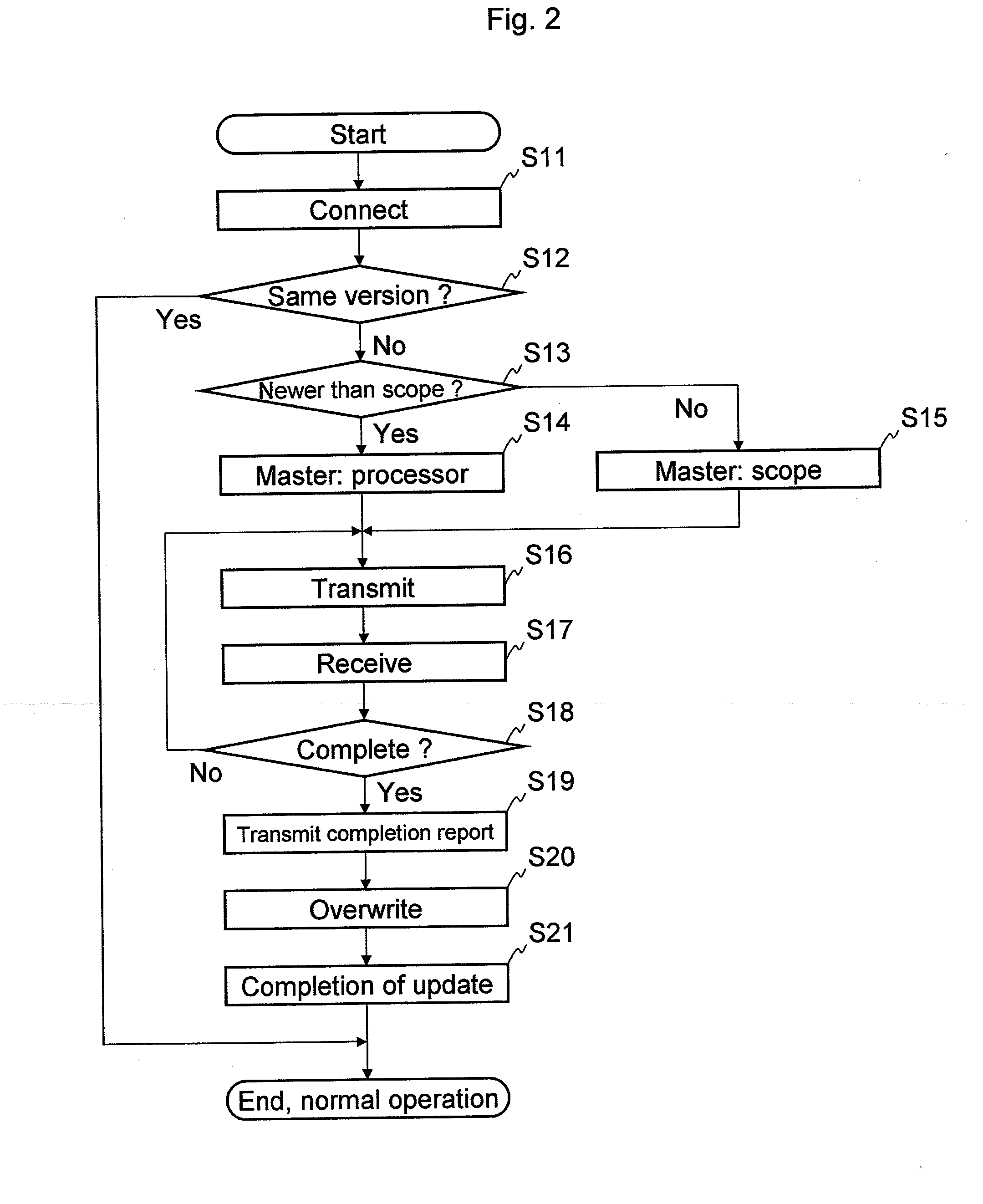

Endoscope system

InactiveUS20090290016A1Easy to updateEndoscopesColor television detailsImaging processingParallel computing

An endoscope system comprises a scope and a processor. The scope has an imaging sensor, a first image-processing unit that performs primary image processing, a first memory, and a second memory. The first and second memories are non-volatile. The processor has a second image-processing unit that performs secondary image processing, and a processor memory that is non-volatile. The first memory stores an system data that includes parameters for the primary and secondary image processing. The processor memory stores the system data. The second memory is used for storing the system data stored in the processor memory when it is determined that the system data stored in the first memory is older than the system data stored in the processor memory. The system data stored in the second memory is overwritten onto the first scope memory after the system data is stored in the second memory.

Owner:HOYA CORP

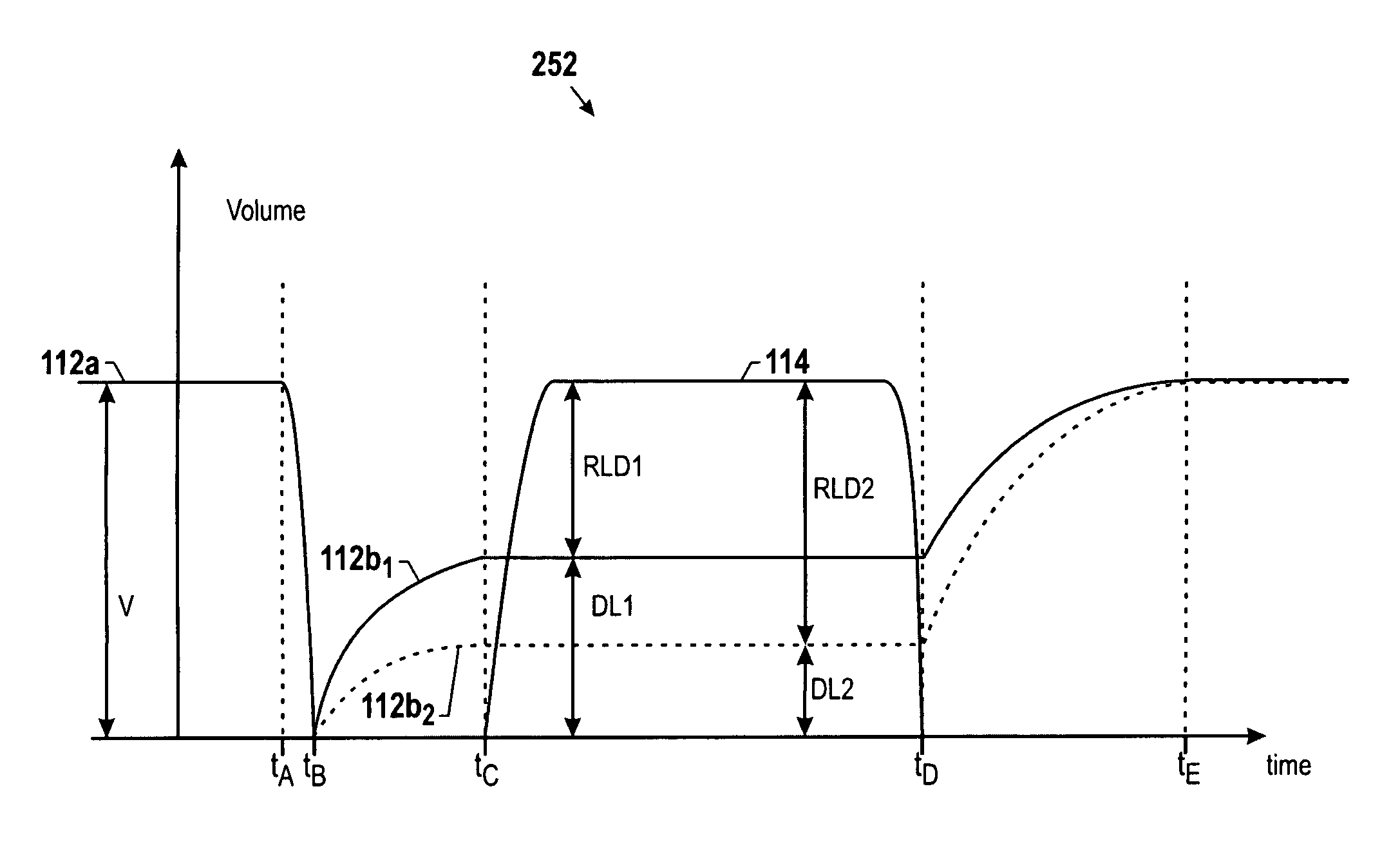

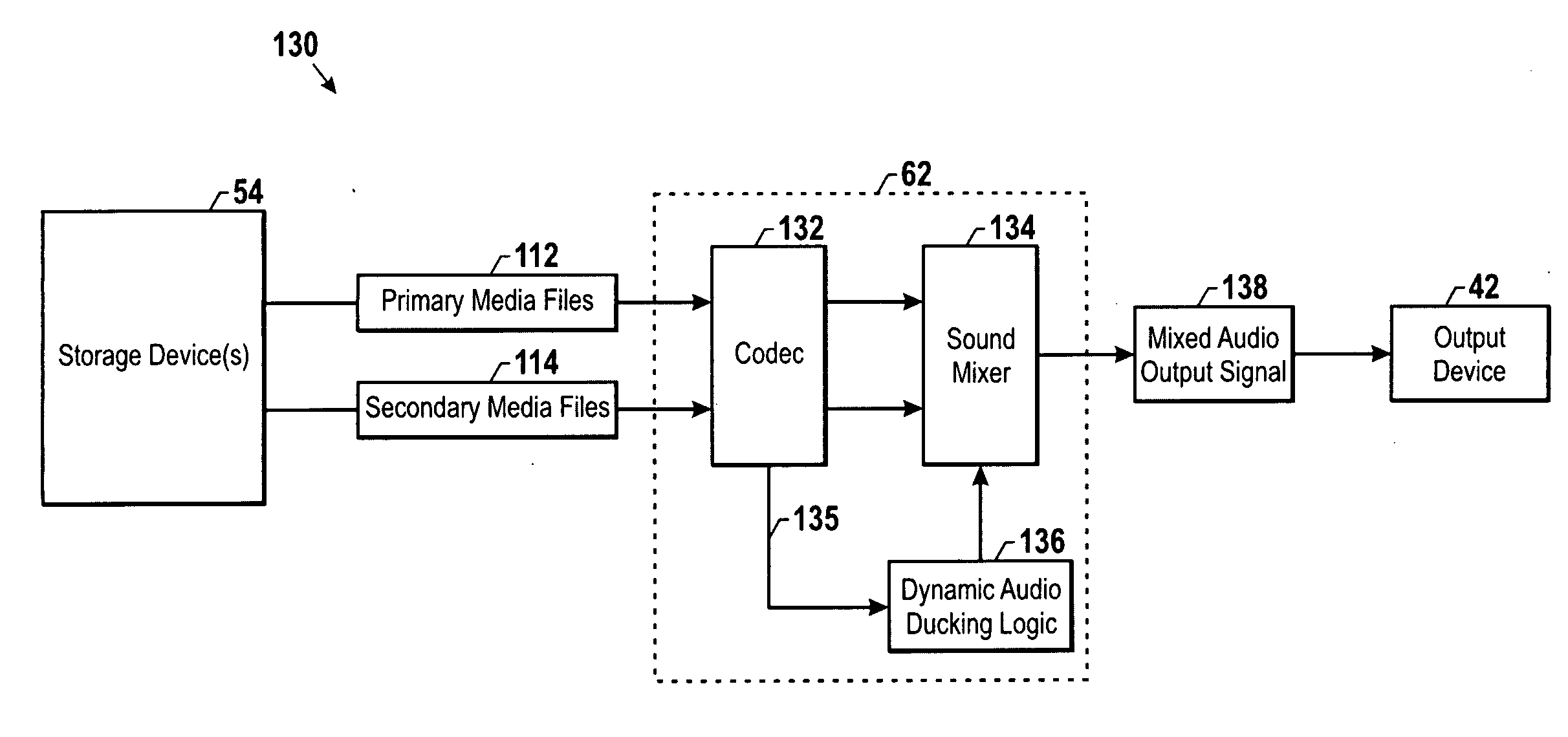

Dynamic audio ducking

Various dynamic audio ducking techniques are provided that may be applied where multiple audio streams, such as a primary audio stream and a secondary audio stream, are being played back simultaneously. For example, a secondary audio stream may include a voice announcement of one or more pieces of information pertaining to the primary audio stream, such as the name of the track or the name of the artist. In one embodiment, the primary audio data and the voice feedback data are initially analyzed to determine a loudness value. Based on their respective loudness values, the primary audio stream may be ducked during the period of simultaneous playback such that a relative loudness difference is generally maintained with respect to the loudness of the primary and secondary audio streams. Accordingly, the amount of ducking applied may be customized for each piece of audio data depending on its loudness characteristics.

Owner:APPLE INC

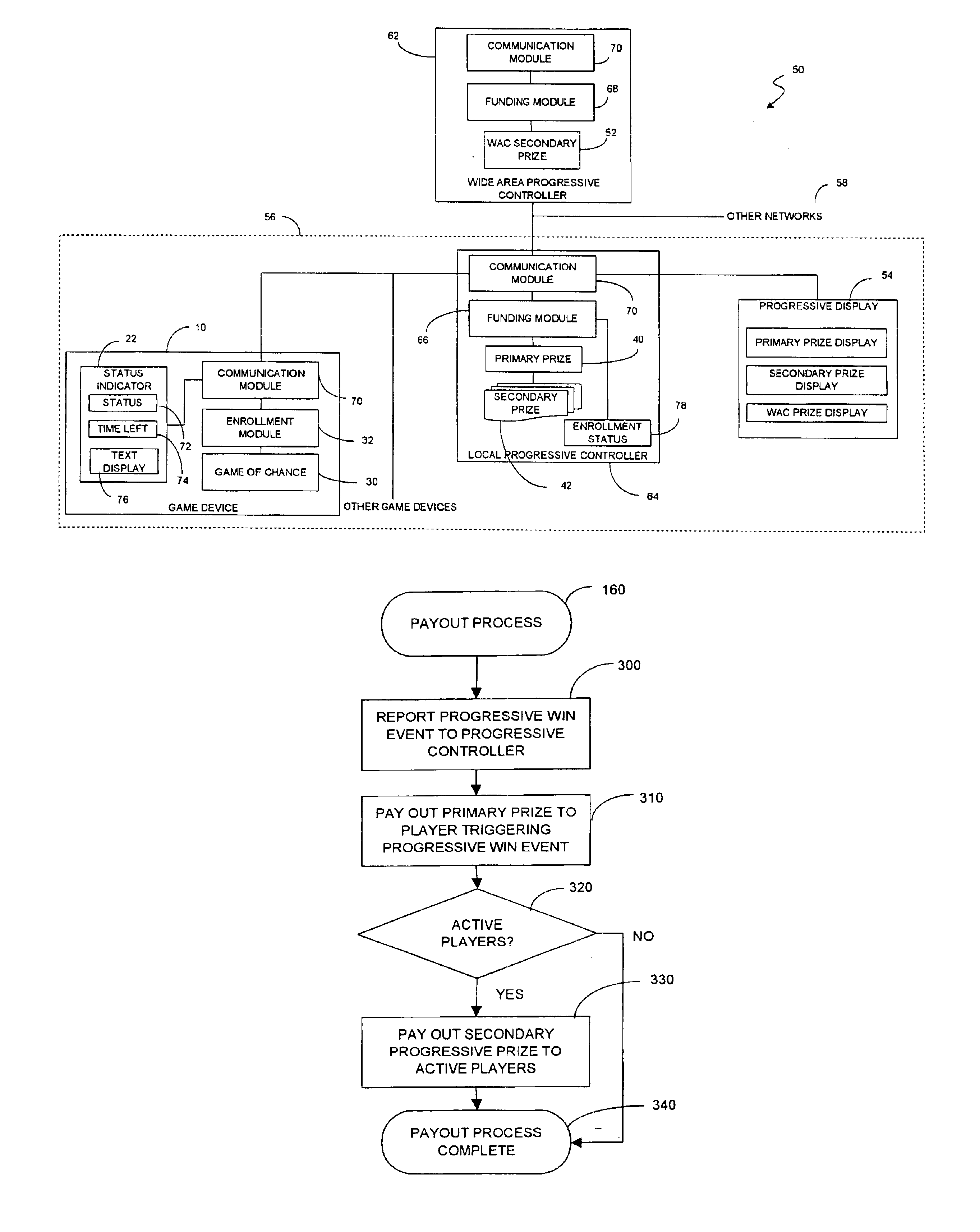

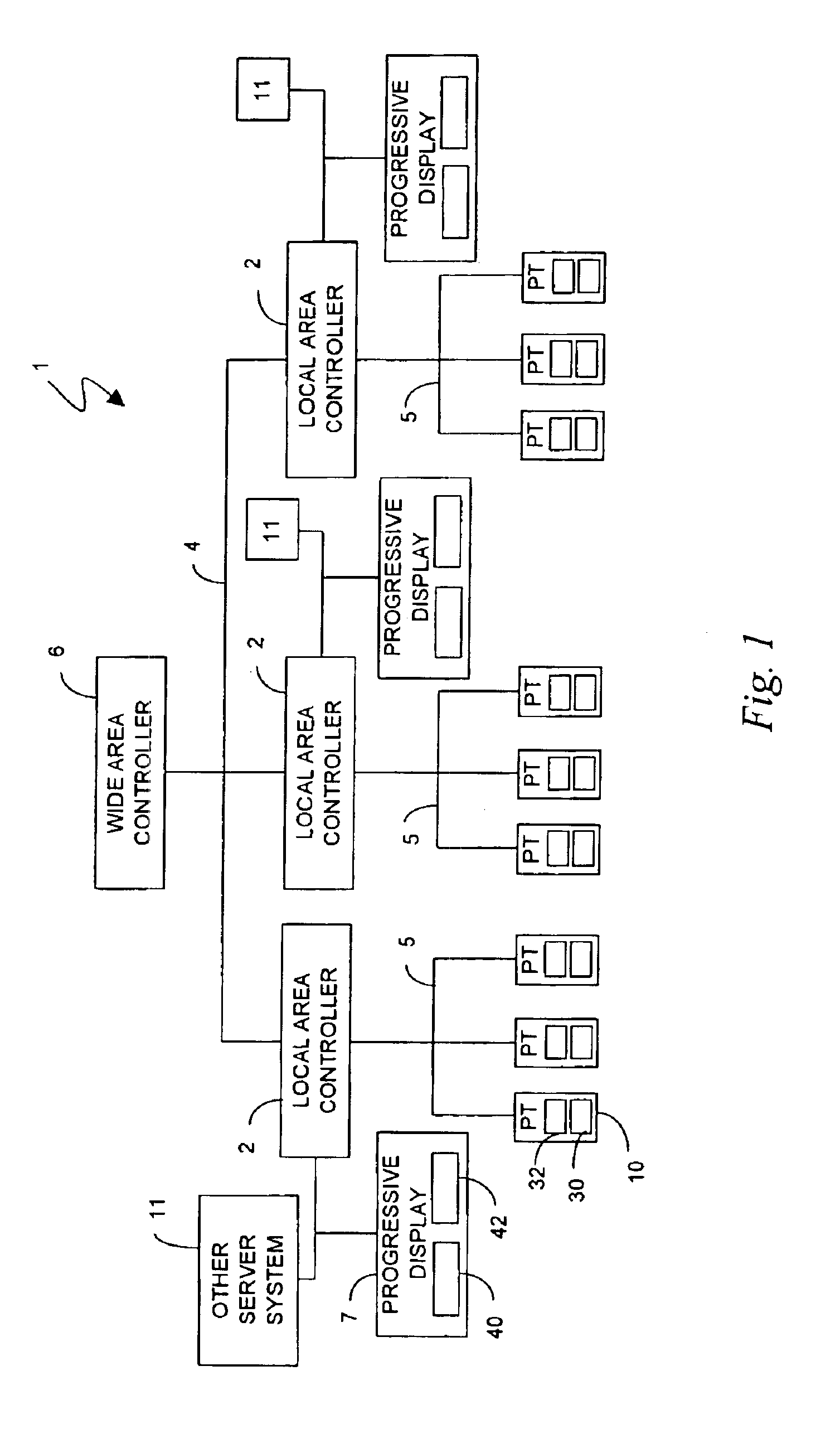

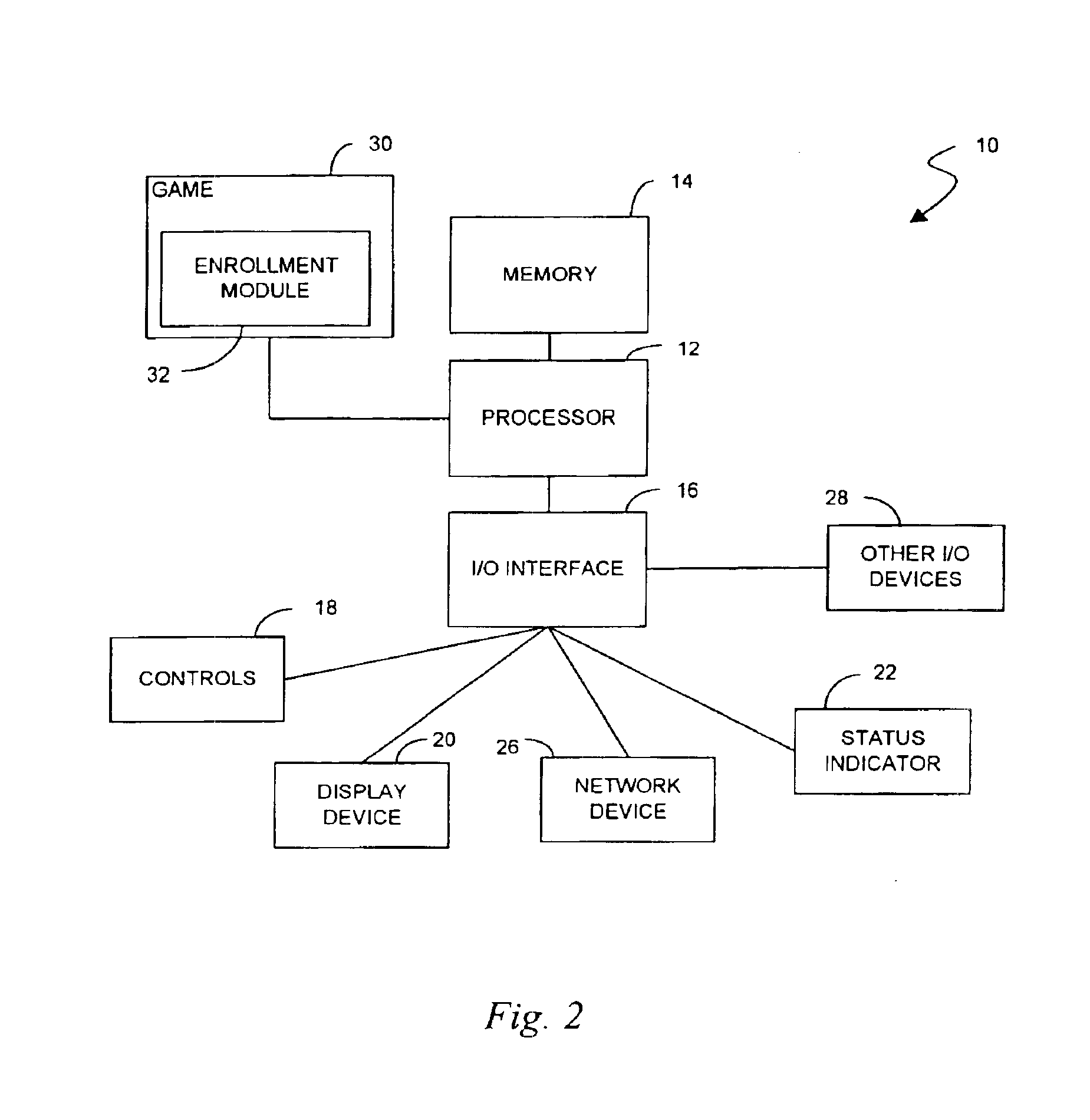

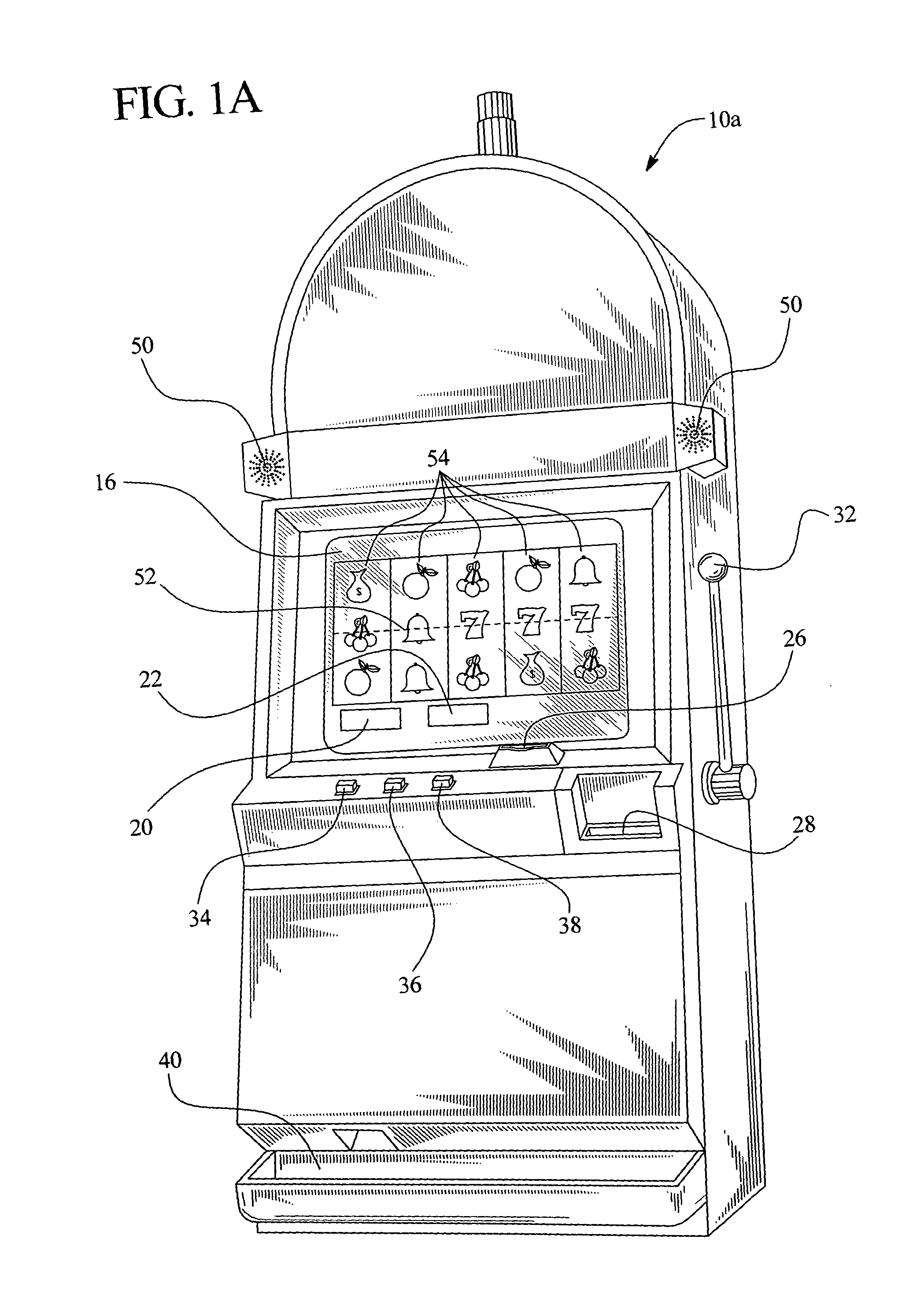

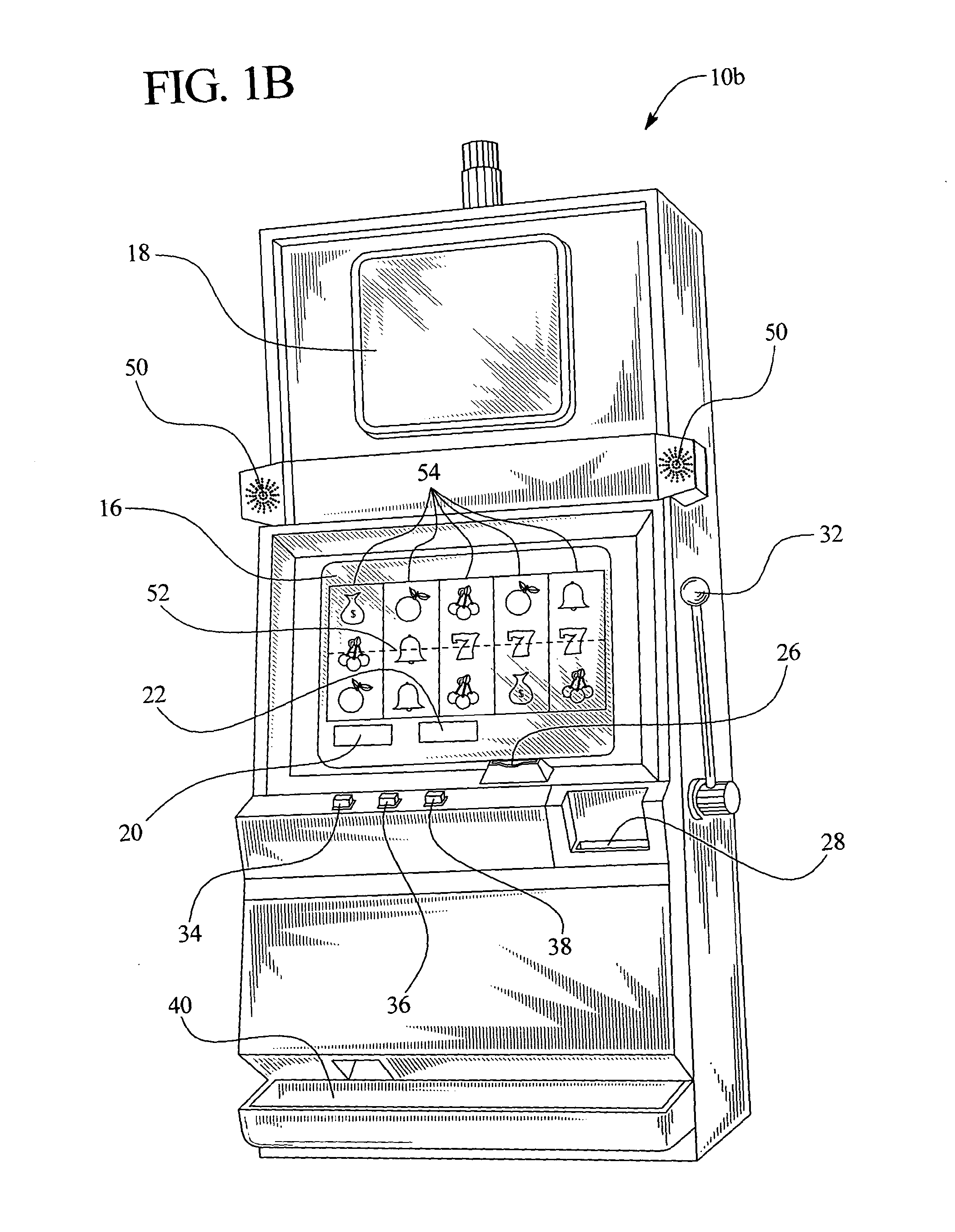

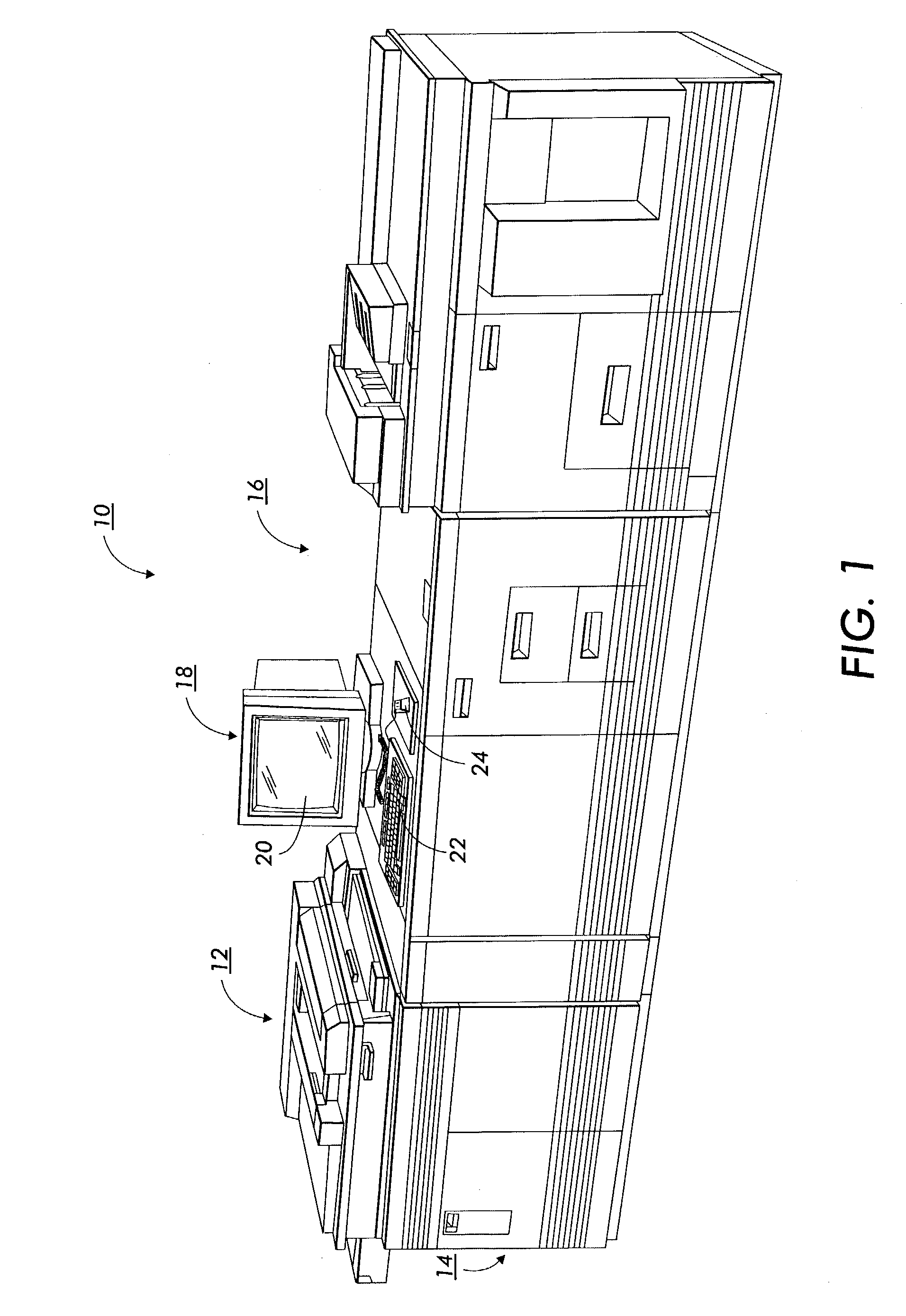

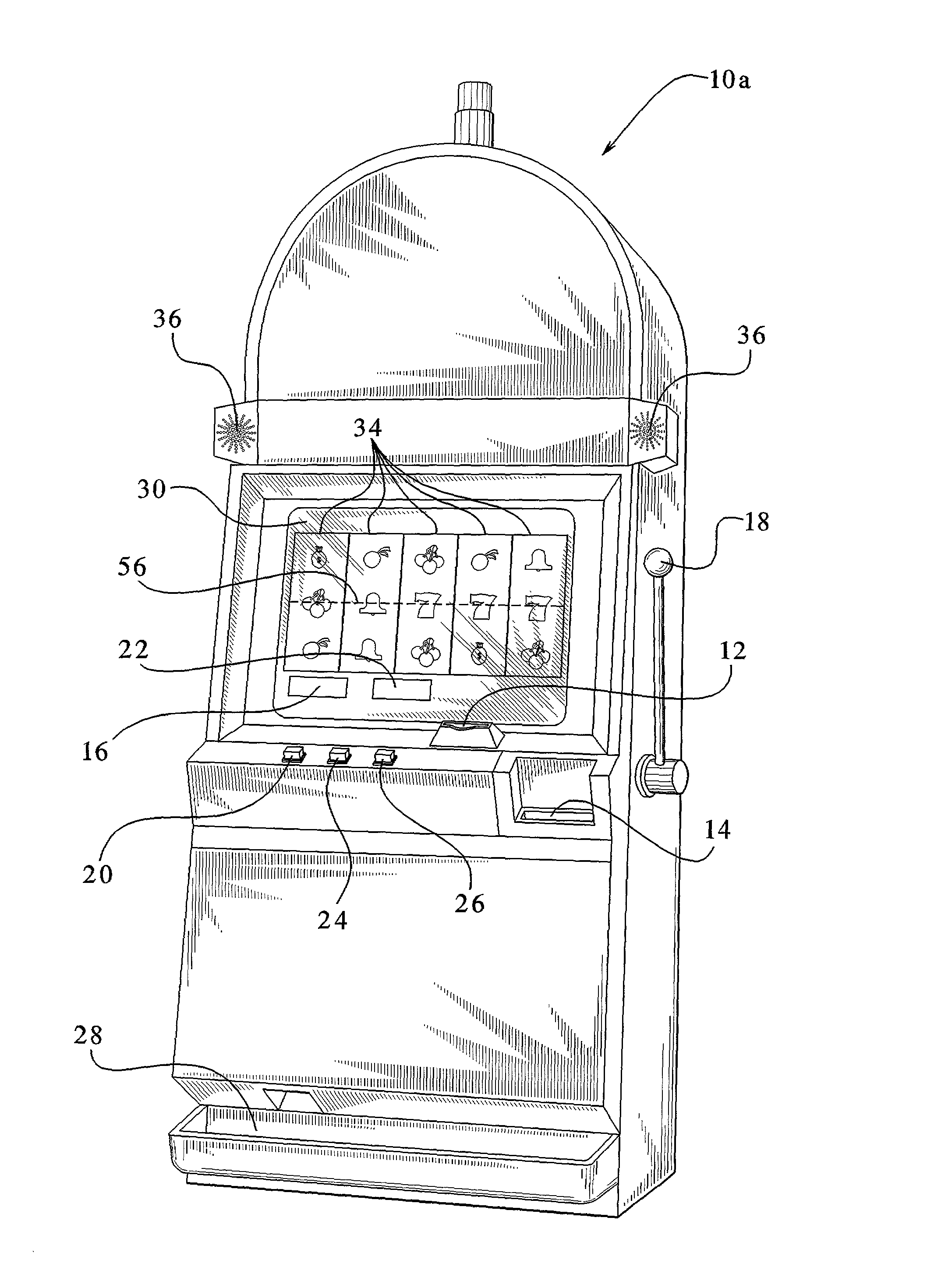

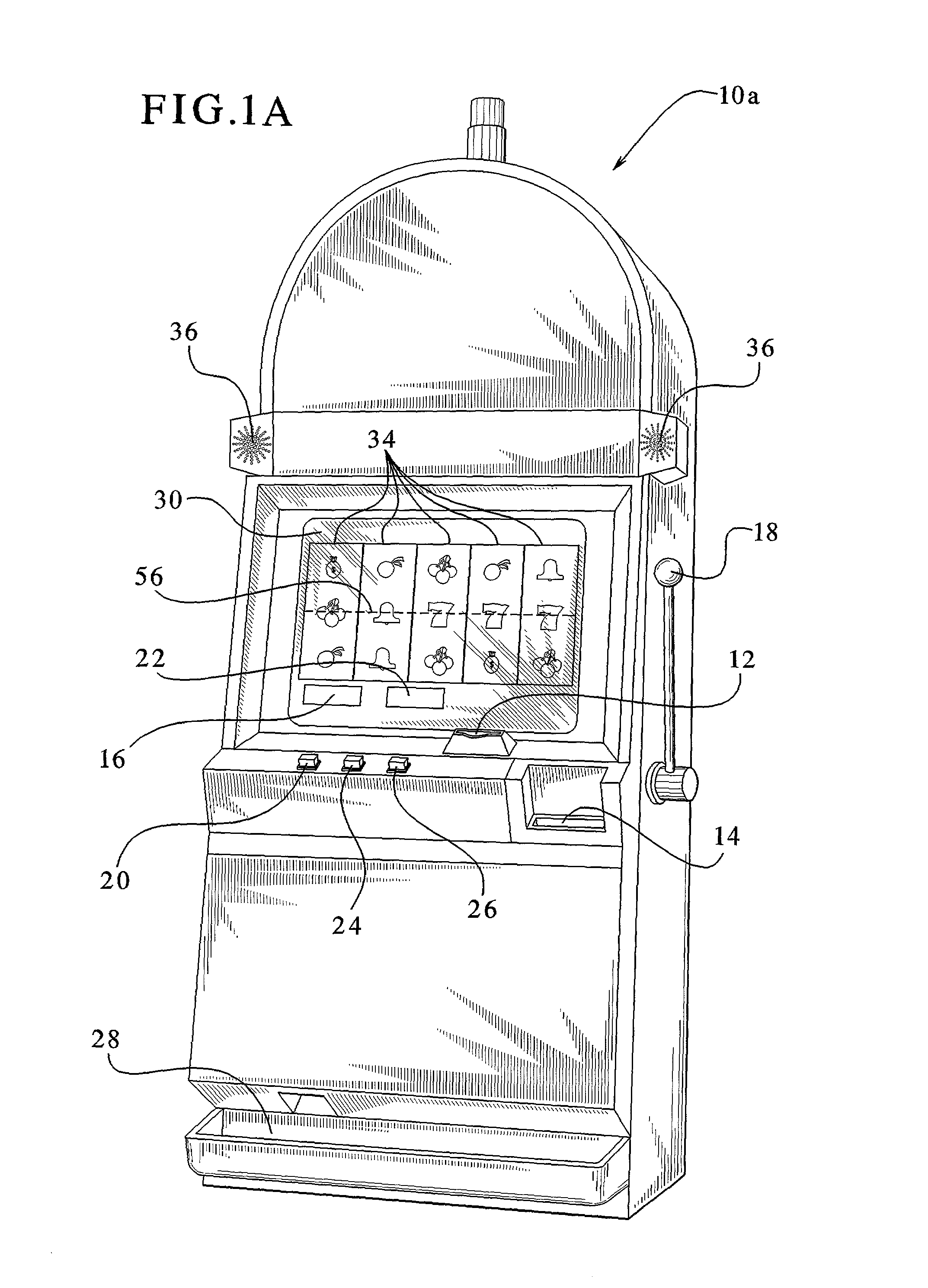

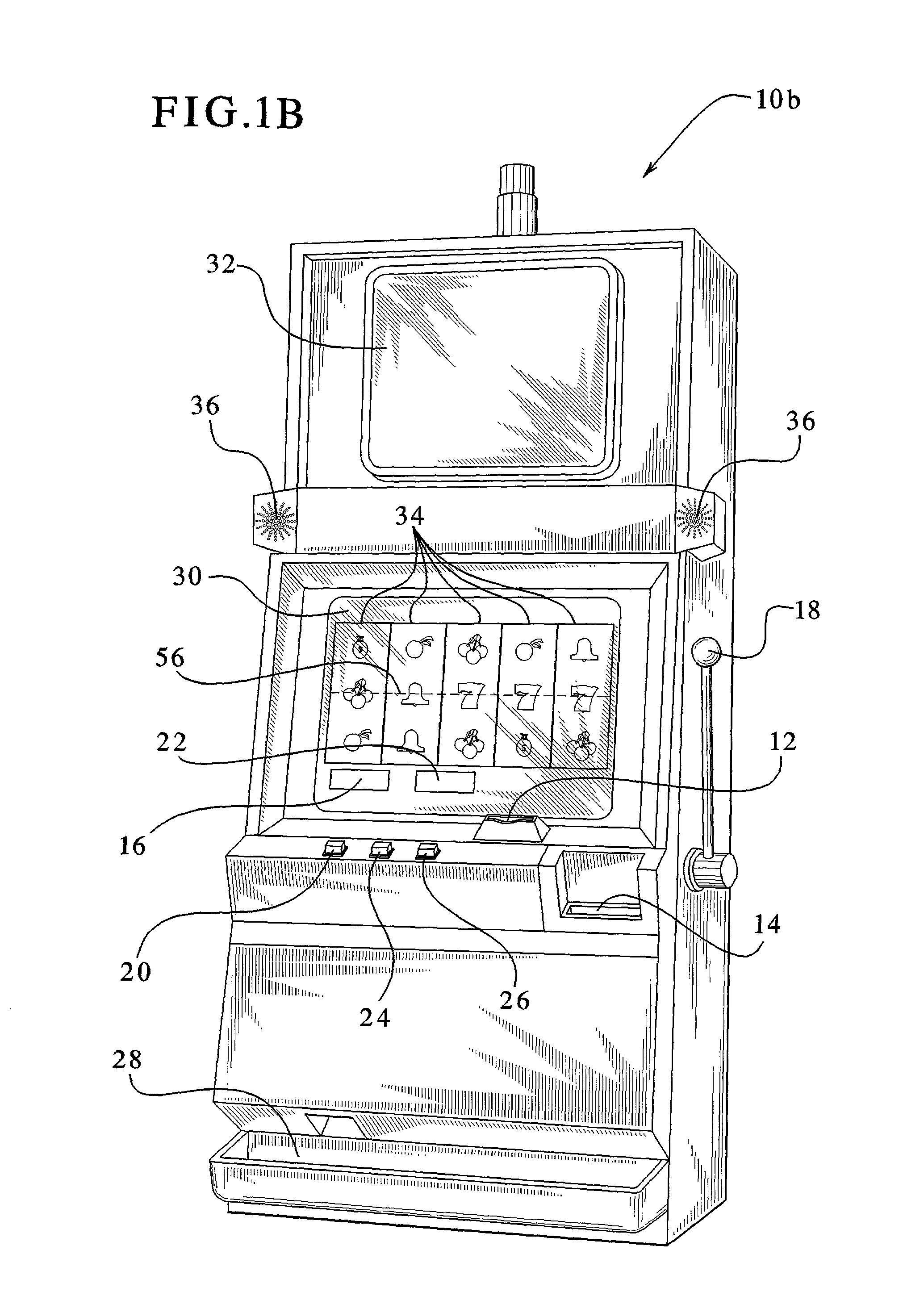

Shared progressive gaming system and method

InactiveUS6887154B1Apparatus for meter-controlled dispensingVideo gamesState variationSufficient time

A progressive system (local and wide) where a primary and secondary progressive meter is maintained is disclosed. When a progressive win event occurs, there are two payouts: the first payout (defined by the primary meter) is paid to the player triggering the progressive payout event; the second payout (defined by the secondary meter) is paid to other players (or game devices) having “active” or “enrolled” status at the time of the primary payout event. The present invention provides a method for automating the “shared” win, including means for readily determining “active” players. A countdown meter may be used to enable the player a sufficient amount of time to continue play and be considered “active.” Additionally display meters may be used to indicate the status of the player or to warn the player of an imminent change in status. The progressive prizes may be funded using traditional methods (e.g., percentage of wagers, marketing budget). The progressive prizes may also be funded using expired prizes which have expired or lapsed.

Owner:BALLY GAMING INC

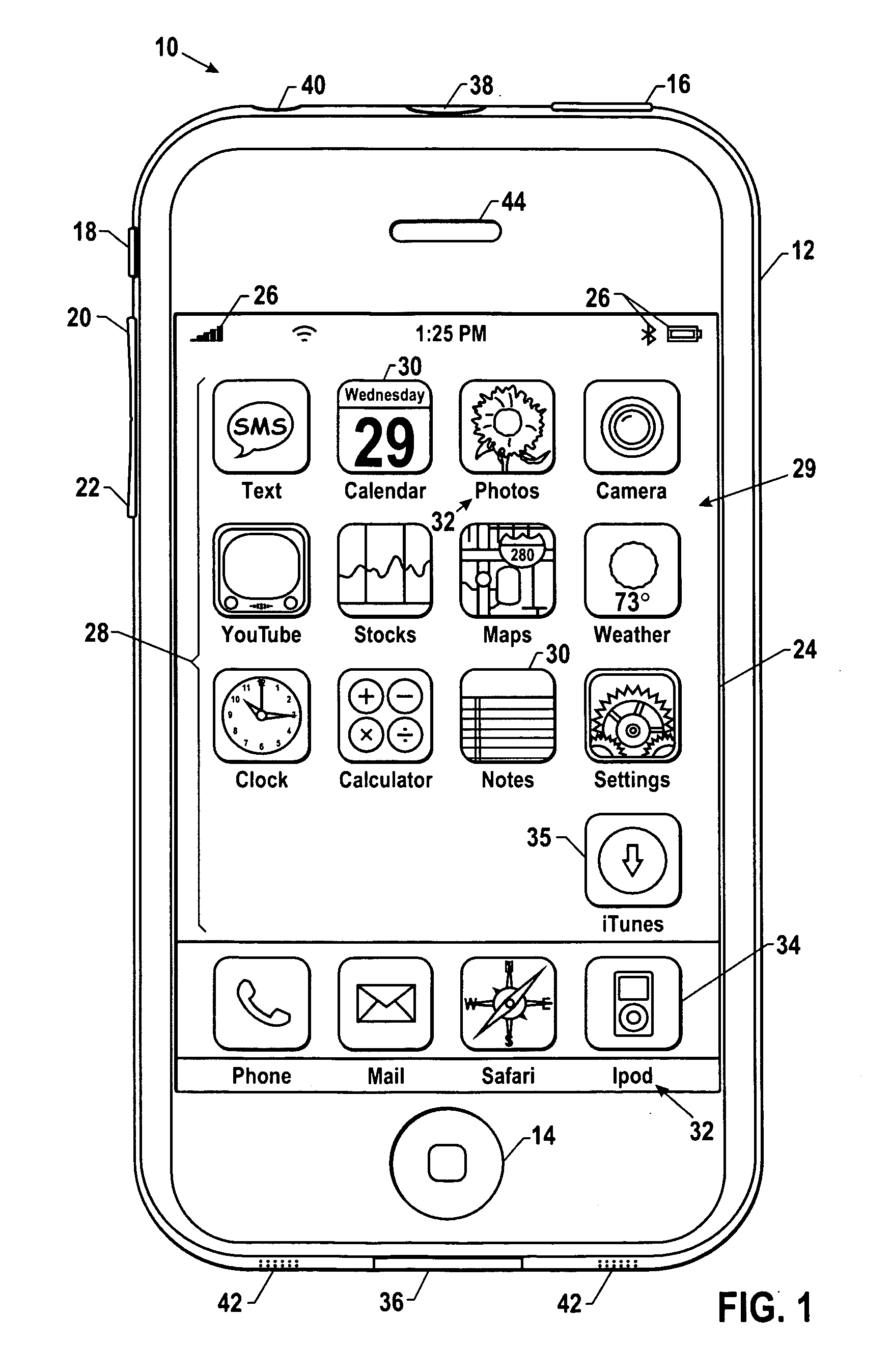

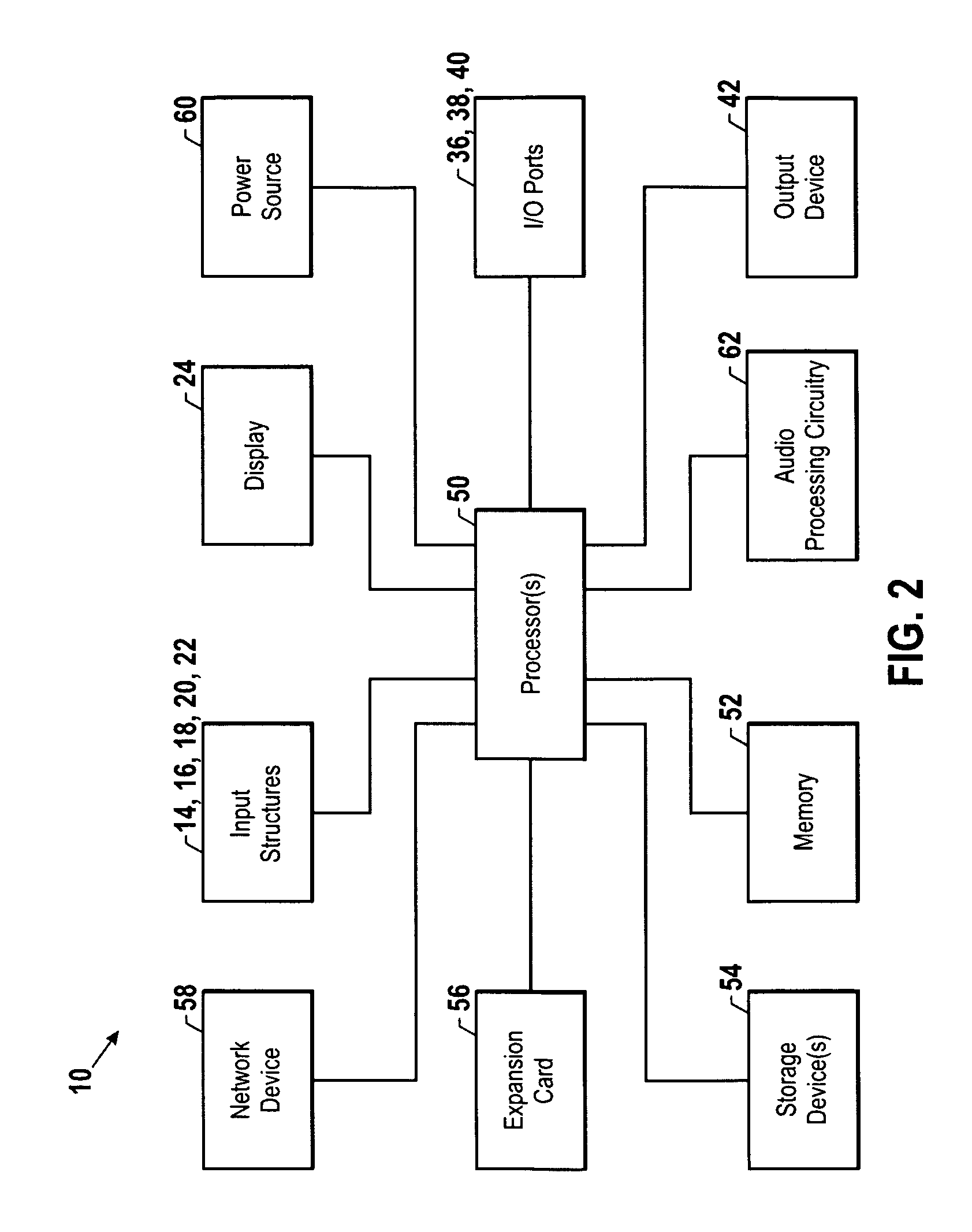

Dynamic audio ducking

Various dynamic audio ducking techniques are provided that may be applied where multiple audio streams, such as a primary audio stream and a secondary audio stream, are being played back simultaneously. For example, a secondary audio stream may include a voice announcement of one or more pieces of information pertaining to the primary audio stream, such as the name of the track or the name of the artist. In one embodiment, the primary audio data and the voice feedback data are initially analyzed to determine a loudness value. Based on their respective loudness values, the primary audio stream may be ducked during the period of simultaneous playback such that a relative loudness difference is generally maintained with respect to the loudness of the primary and secondary audio streams. Accordingly, the amount of ducking applied may be customized for each piece of audio data depending on its loudness characteristics.

Owner:APPLE INC

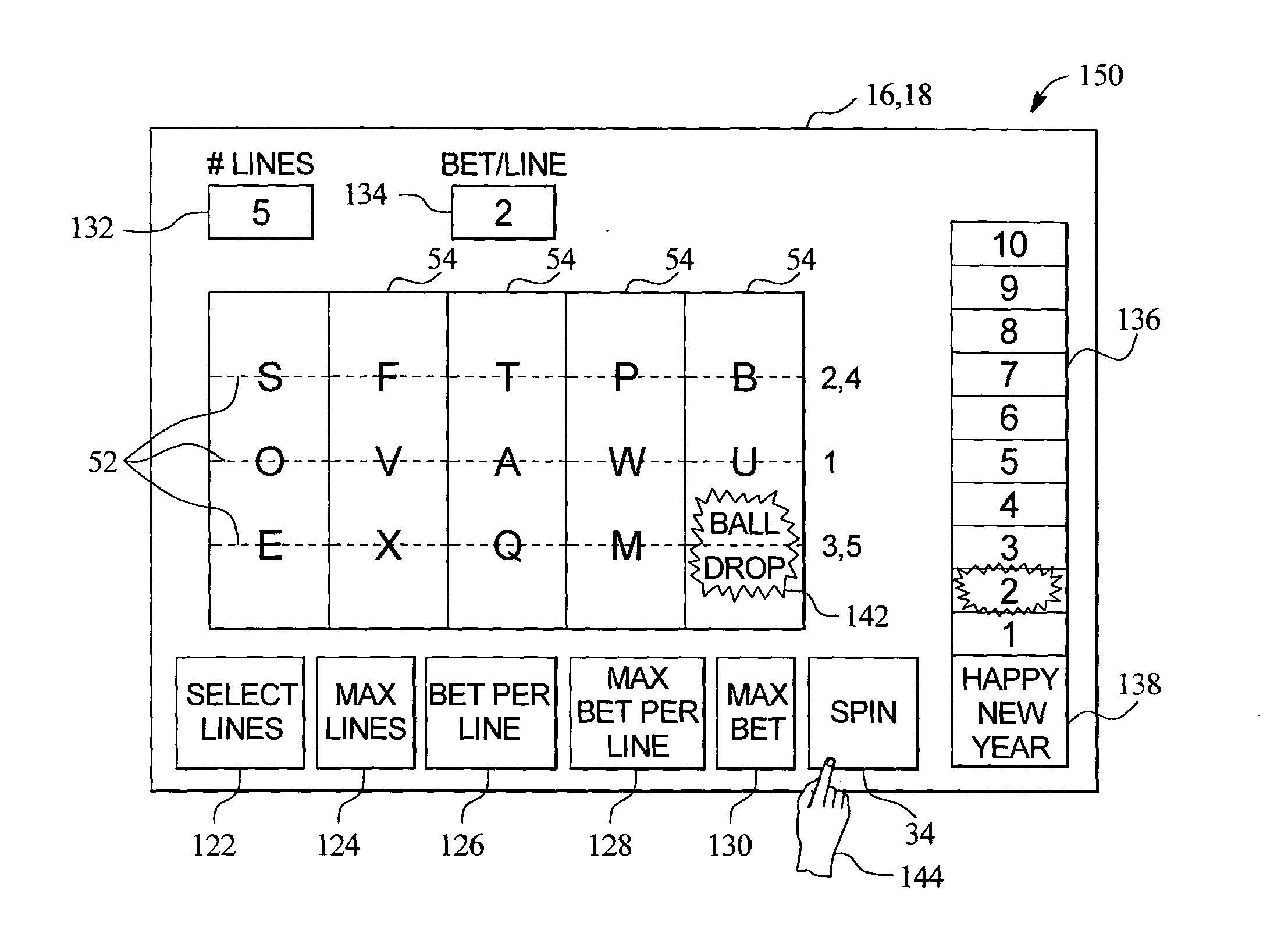

Gaming device having bonus game dependent upon variable wager component selection

A primary and secondary game for a wagering gaming machine. In one embodiment, the number of lines wagered or a slot machine makes the player eligible for a bonus game, and a wager made per payline effects how many moves or positions on a meter the player advances upon achieving the bonus triggering symbol or combination of symbols. When the player advances the meter to the end, the gaming device displays a payout event. The payout event can be any type of bonus gaming event that potentially provides an award to the player.

Owner:IGT

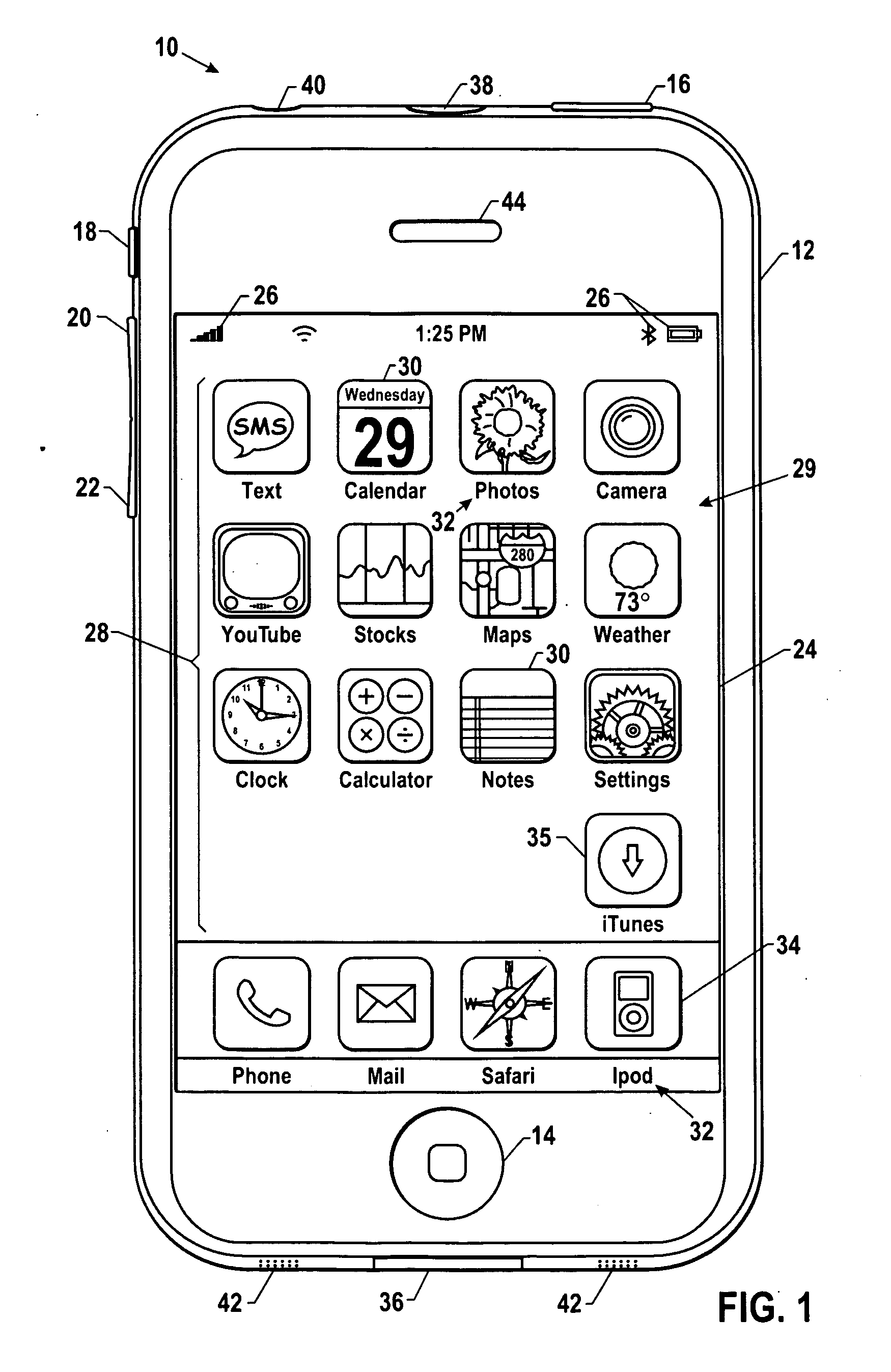

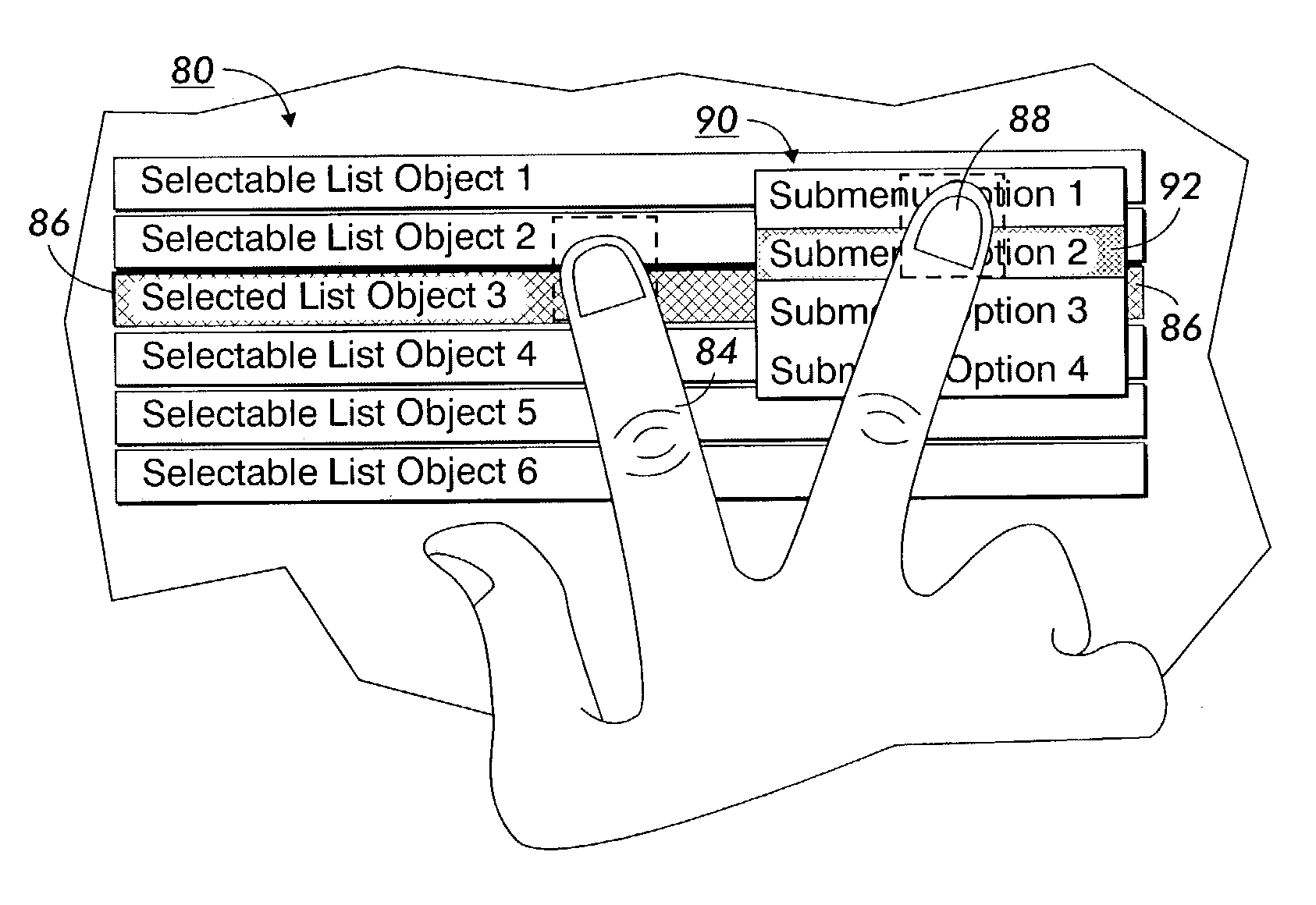

Secondary touch contextual sub-menu navigation for touch screen interface

ActiveUS7158123B2Cathode-ray tube indicatorsElectrographic process apparatusContact positionTouchscreen

A touch sensitive user interface of the type having a display screen for displaying images representative of menus and selectable list objects, for example; control logic responsive to the touch sensitive user interface for determining the contact position of a first probe and a second probe, such as two separate fingers, thereon, displaying menus including list objects representing primary and secondary features or functions respectively, so that a user may touch a selection on the primary menu with the first probe and subsequently touch an area on the display screen where a contextually related secondary menu is displayed for selection of contextually related features or functions.

Owner:TAHOE RES LTD

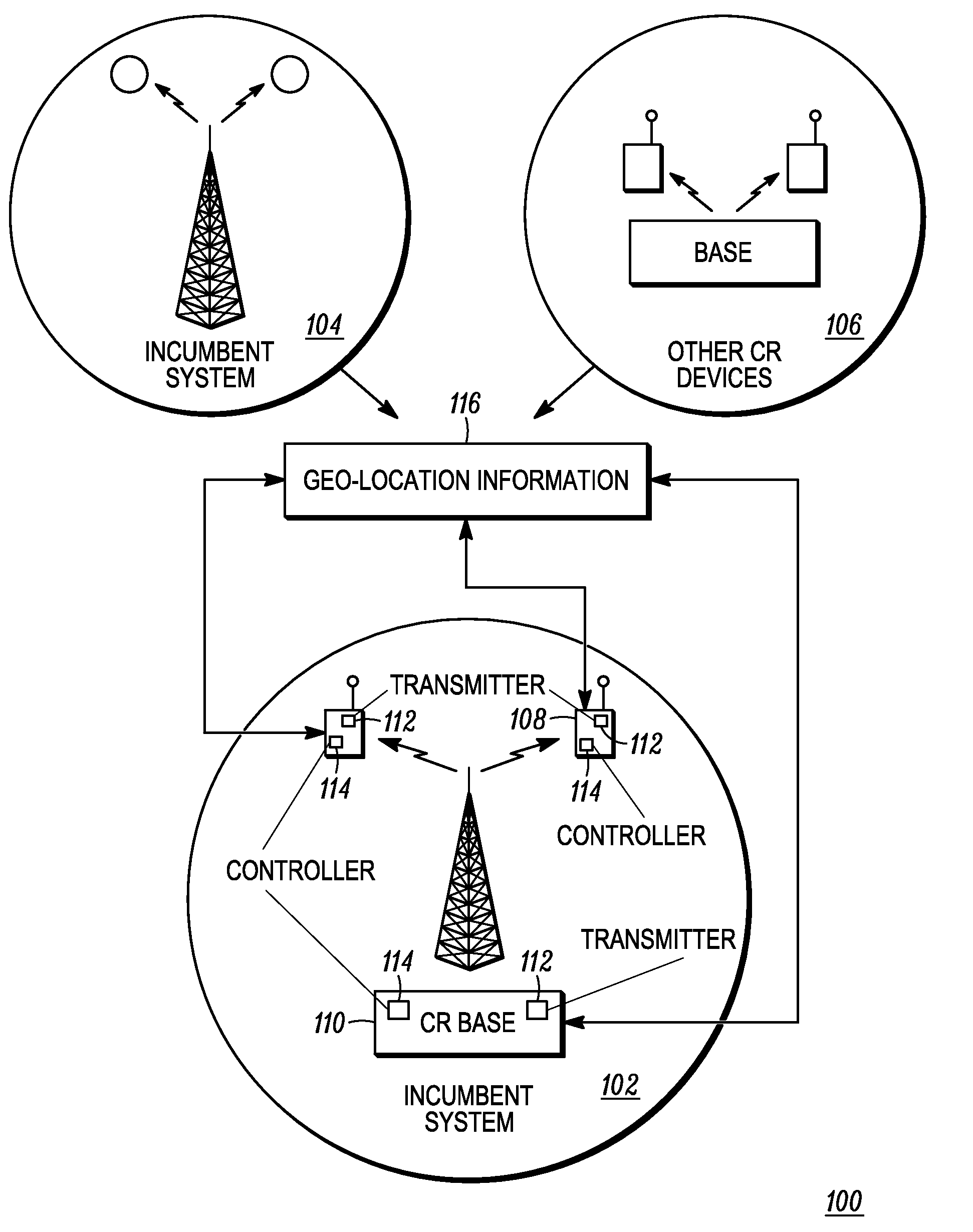

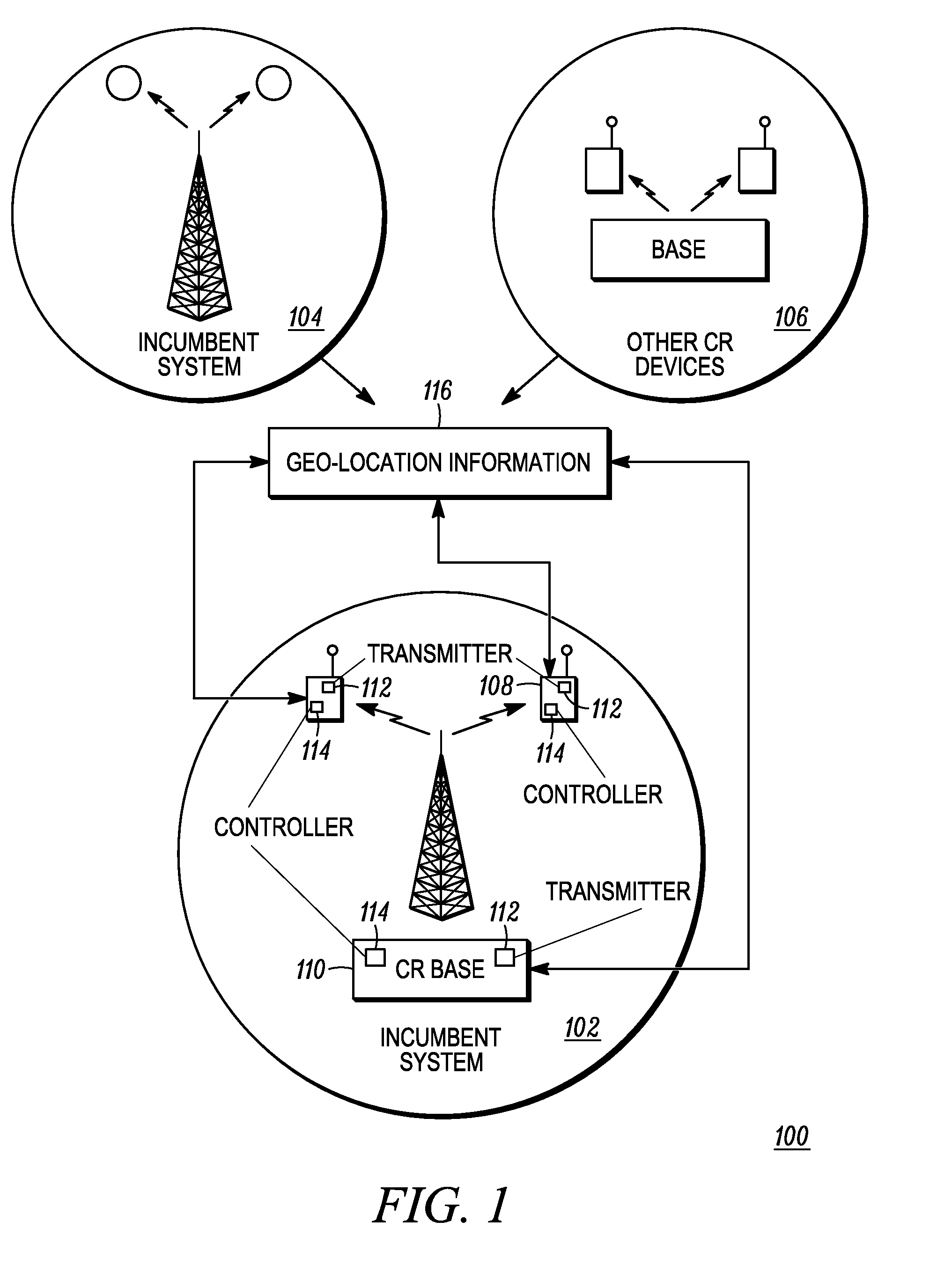

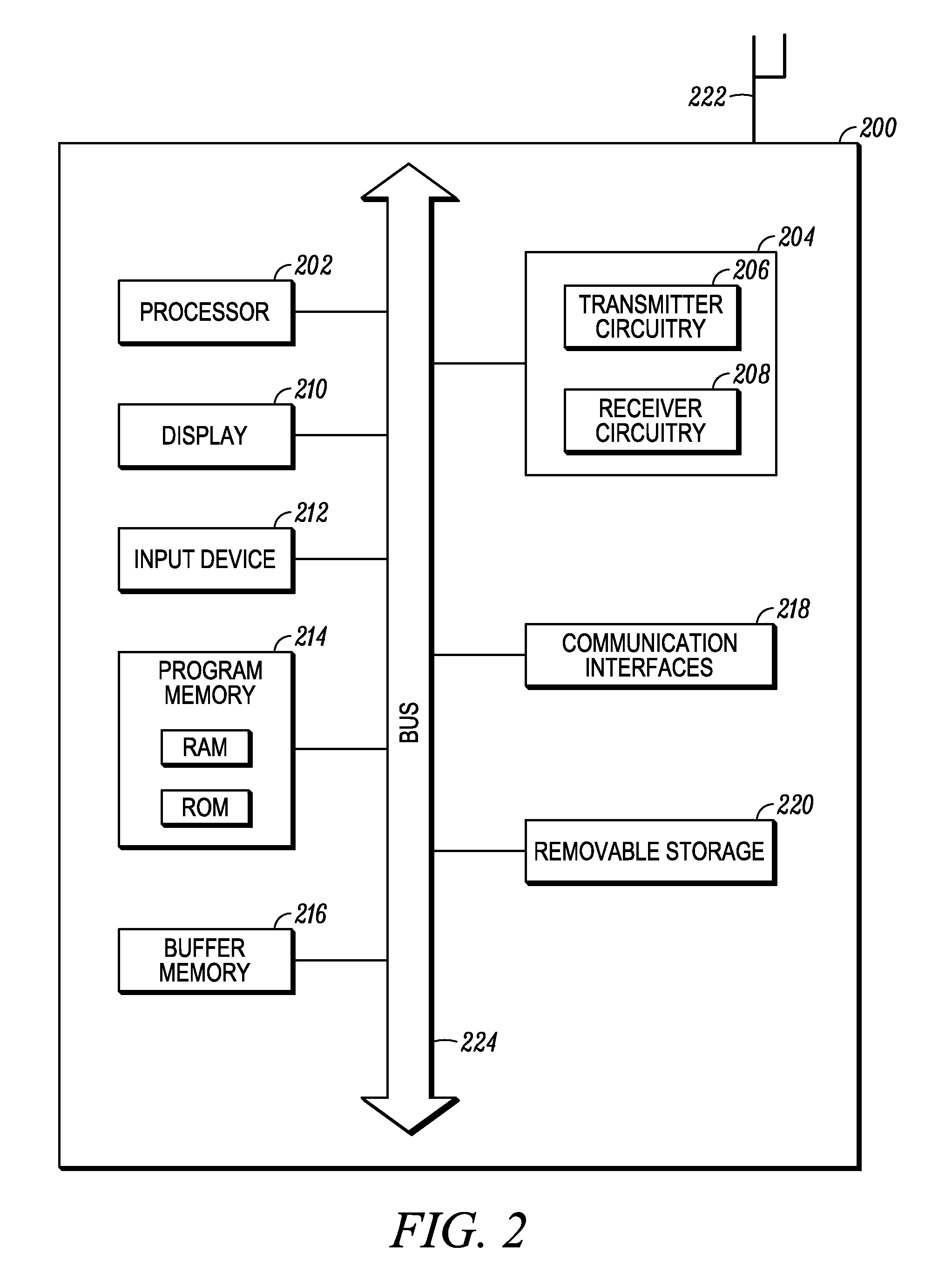

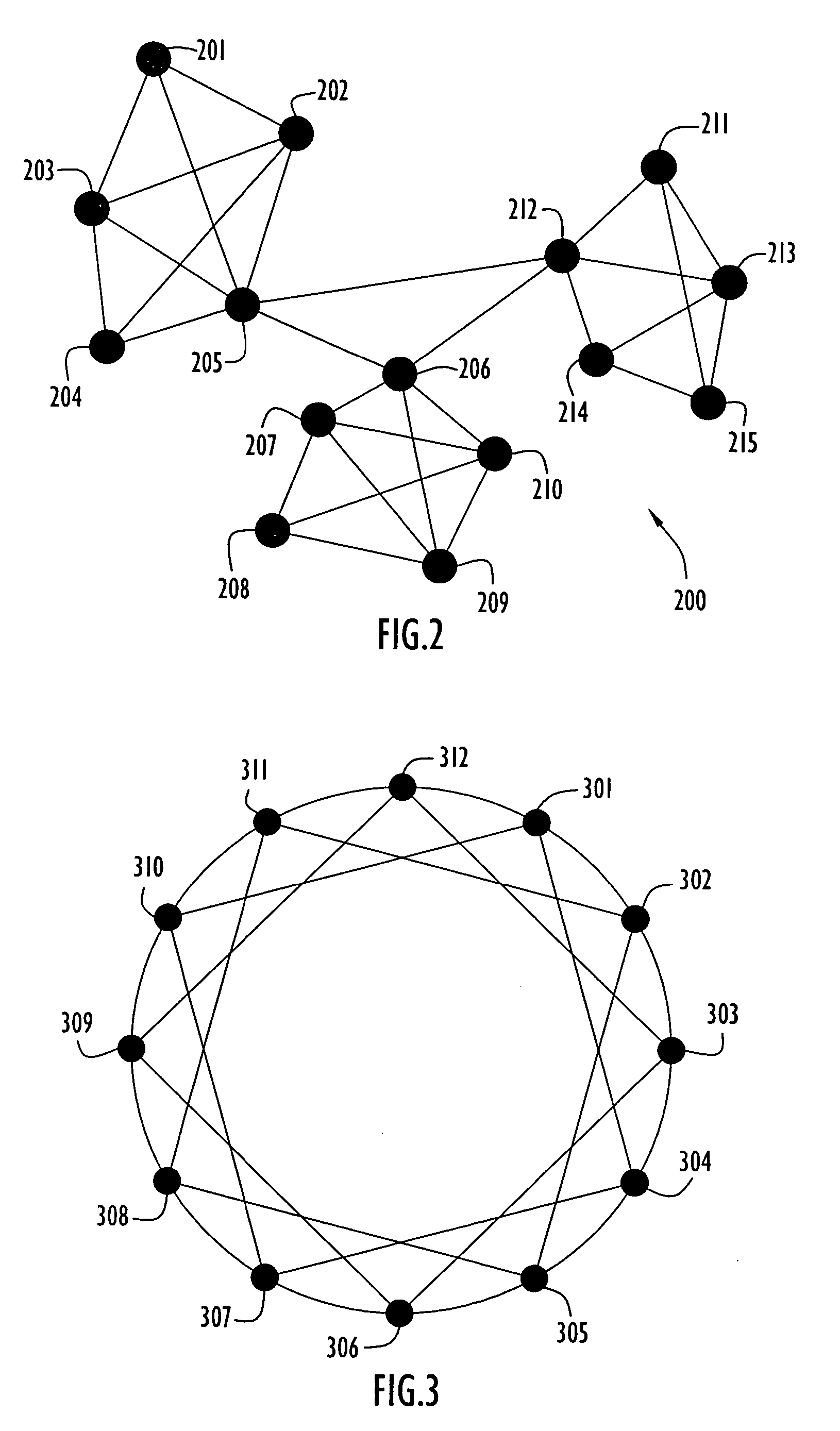

Method for database driven channel quality estimation in a cognitive radio network

ActiveUS20100330919A1Power managementTransmission monitoringCo-channel interferenceGeolocation database

A method of determining operating parameters for a secondary system transmitter is described. The transmitter characteristics, including location and operating frequency band, are provided to a geo-location database. The database determines the maximum allowable transmission power that meets various specifications for different channels and conveys the power and channel(s) to the transmitter. The database estimates channel incumbent signal strengths based on the transmitter location and primary and higher-priority secondary incumbent systems, estimates the splatter levels, determines whether adjacent and co-channel interference protection ratios are met, and adjusts the allowable power level accordingly. The database also estimates aggregate co- and adjacent channel primary and secondary incumbent system interference levels at the transmitter location and predicts channel quality for each allowable channel. The estimated levels are updated using measurements of actual levels at the transmitter location. The database dynamically allocates channels using the secondary system priorities.

Owner:MOTOROLA SOLUTIONS INC +1

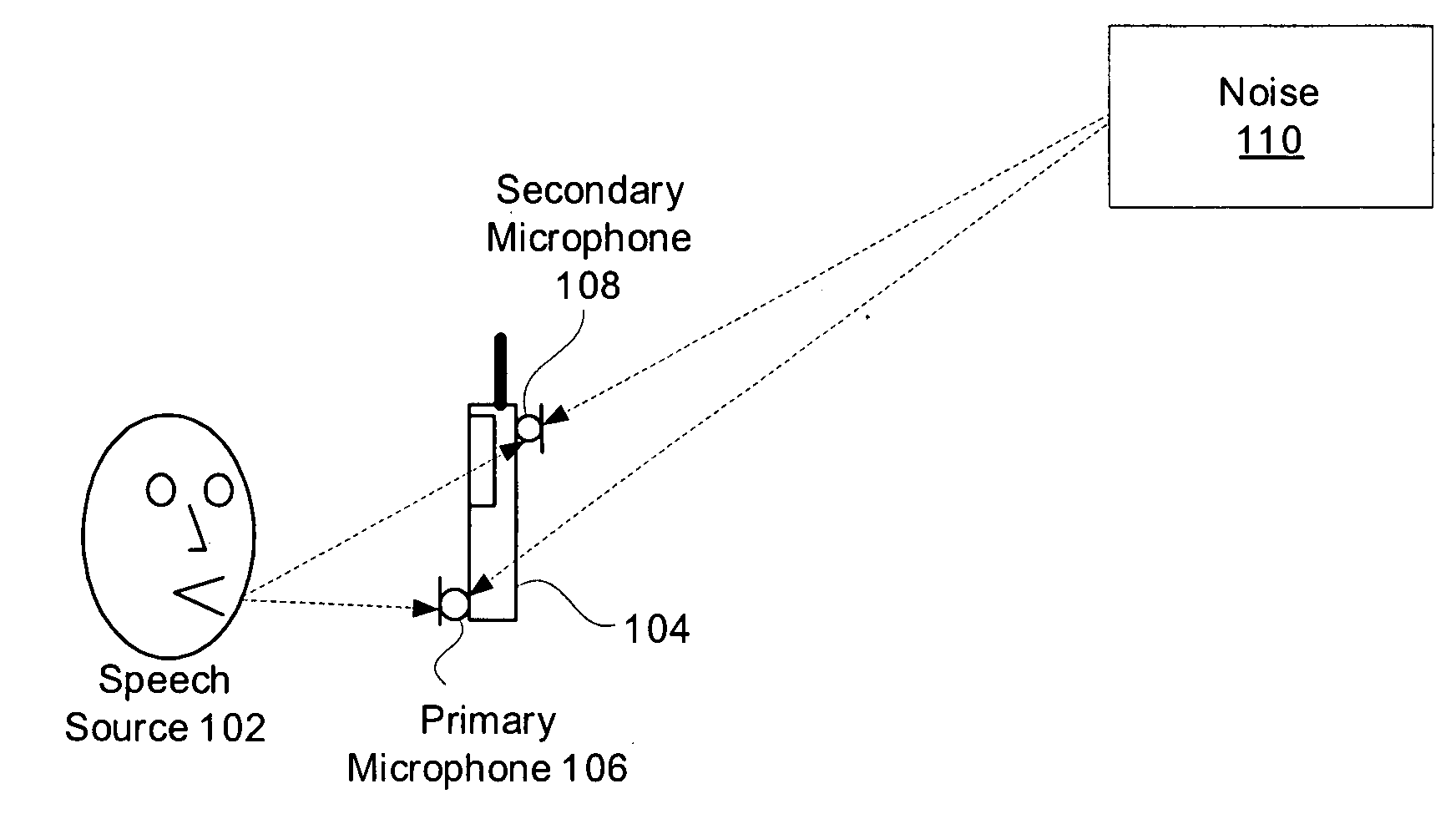

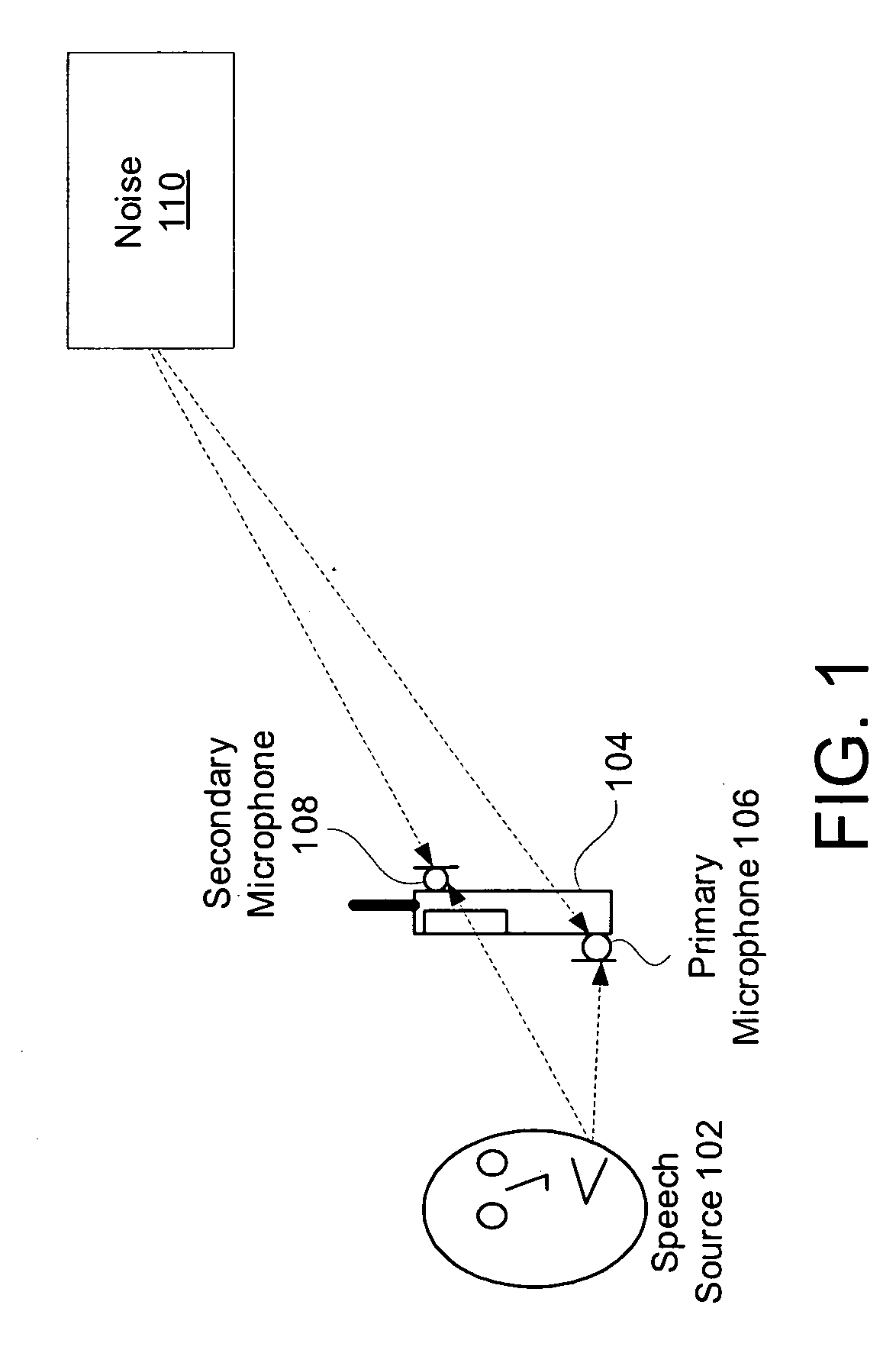

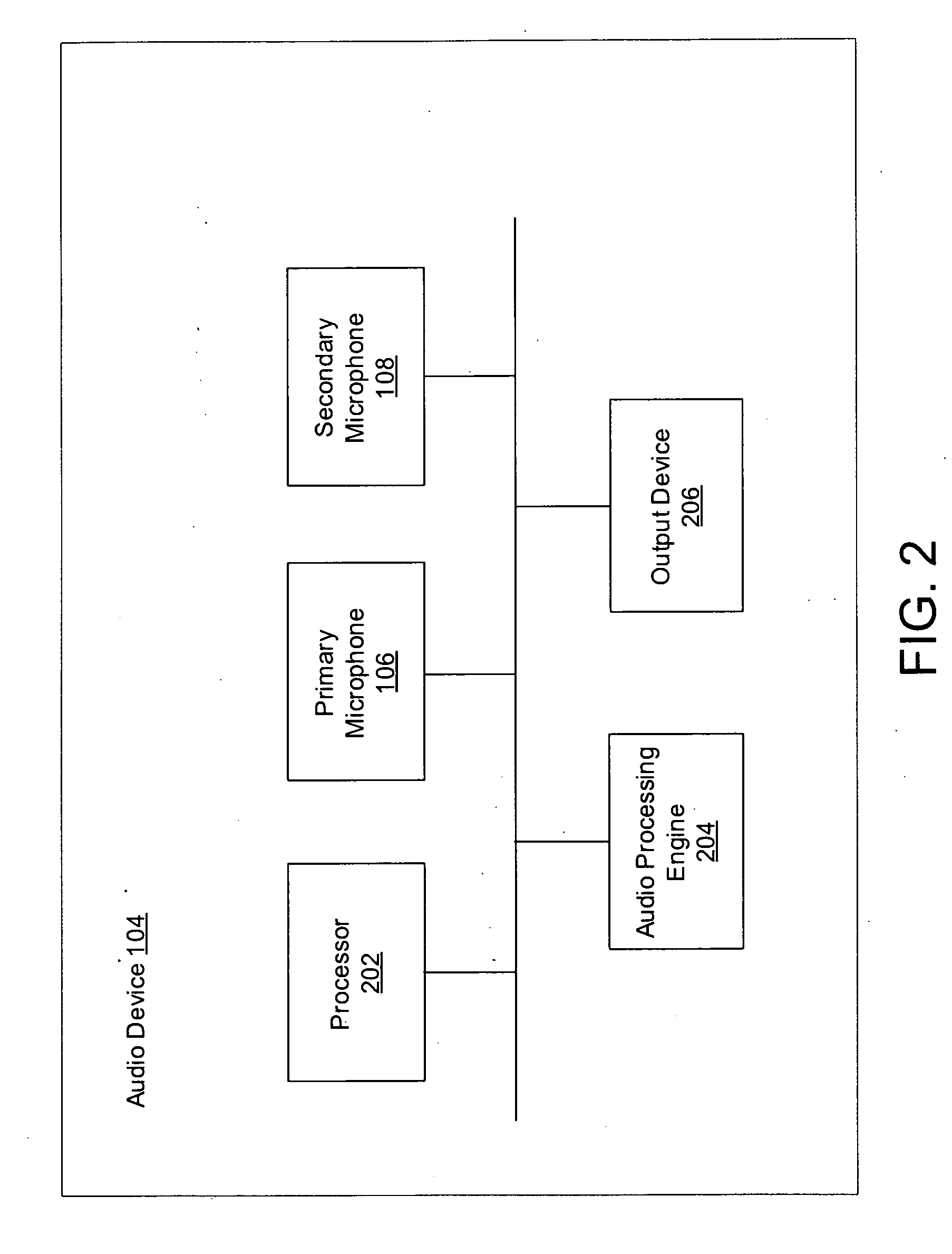

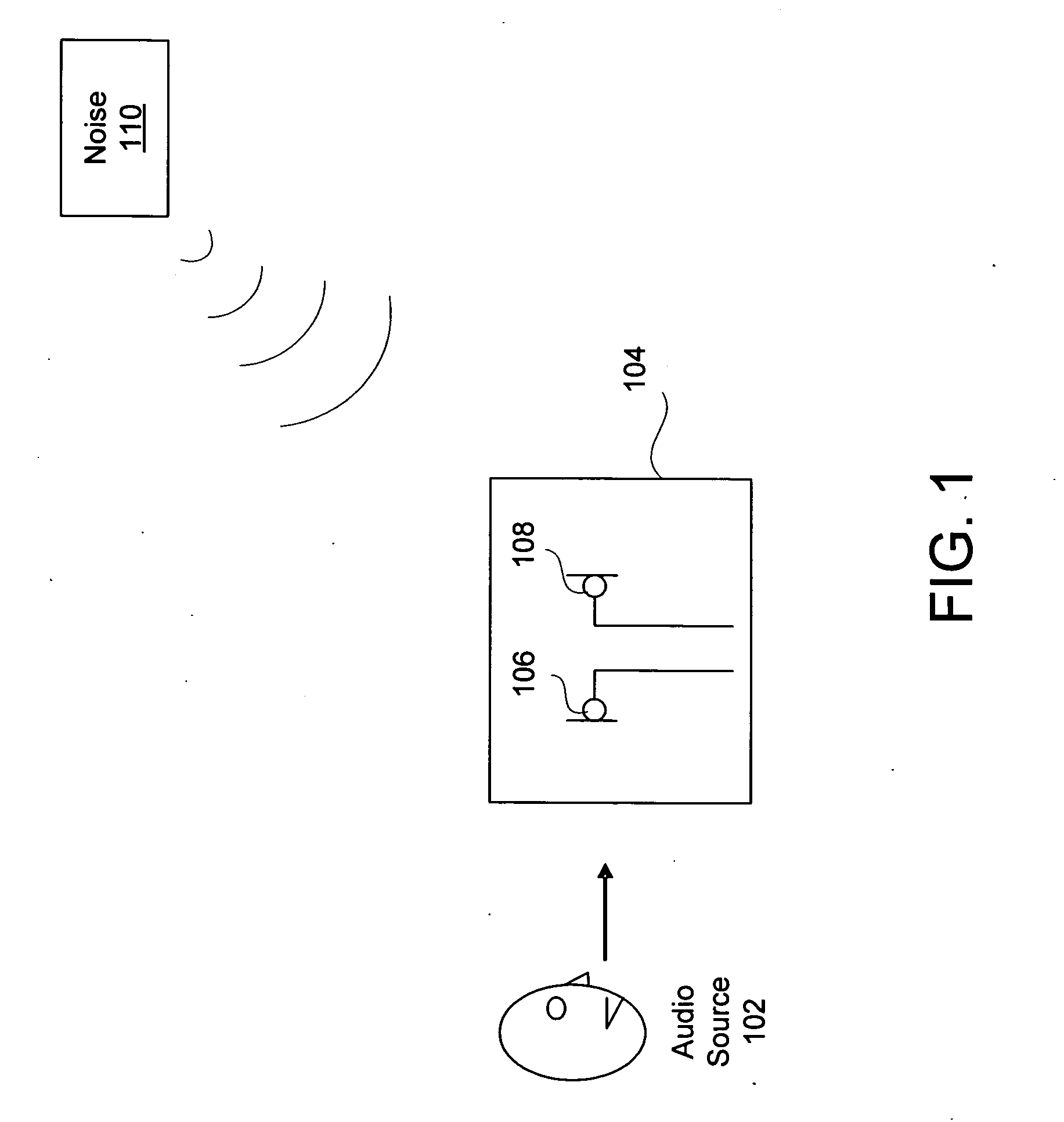

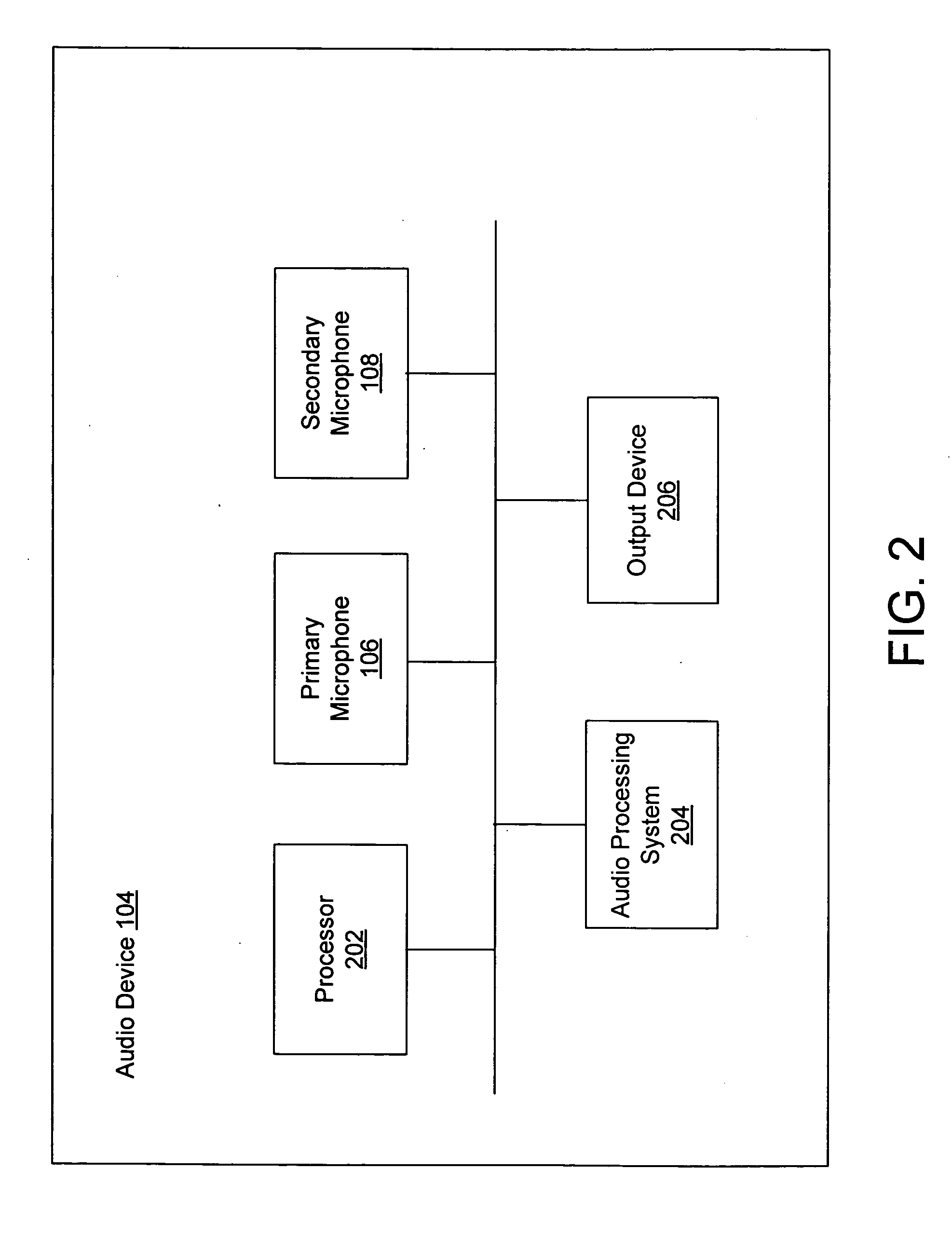

System and method for providing single microphone noise suppression fallback

Systems and methods for providing single microphone noise suppression fallback are provided. In exemplary embodiments, primary and secondary acoustic signals are received. A single microphone noise estimate may be generated based on the primary acoustic signal, while a dual microphone noise estimate may be generated based on the primary and secondary acoustic signals. A combined noise estimate based on the single and dual microphone noise estimates is then determined. Using the combined noise estimate, a gain mask may be generated and applied to the primary acoustic signal to generate a noise suppressed signal. Subsequently, the noise suppressed signal may be output.

Owner:KNOWLES ELECTRONICS INC

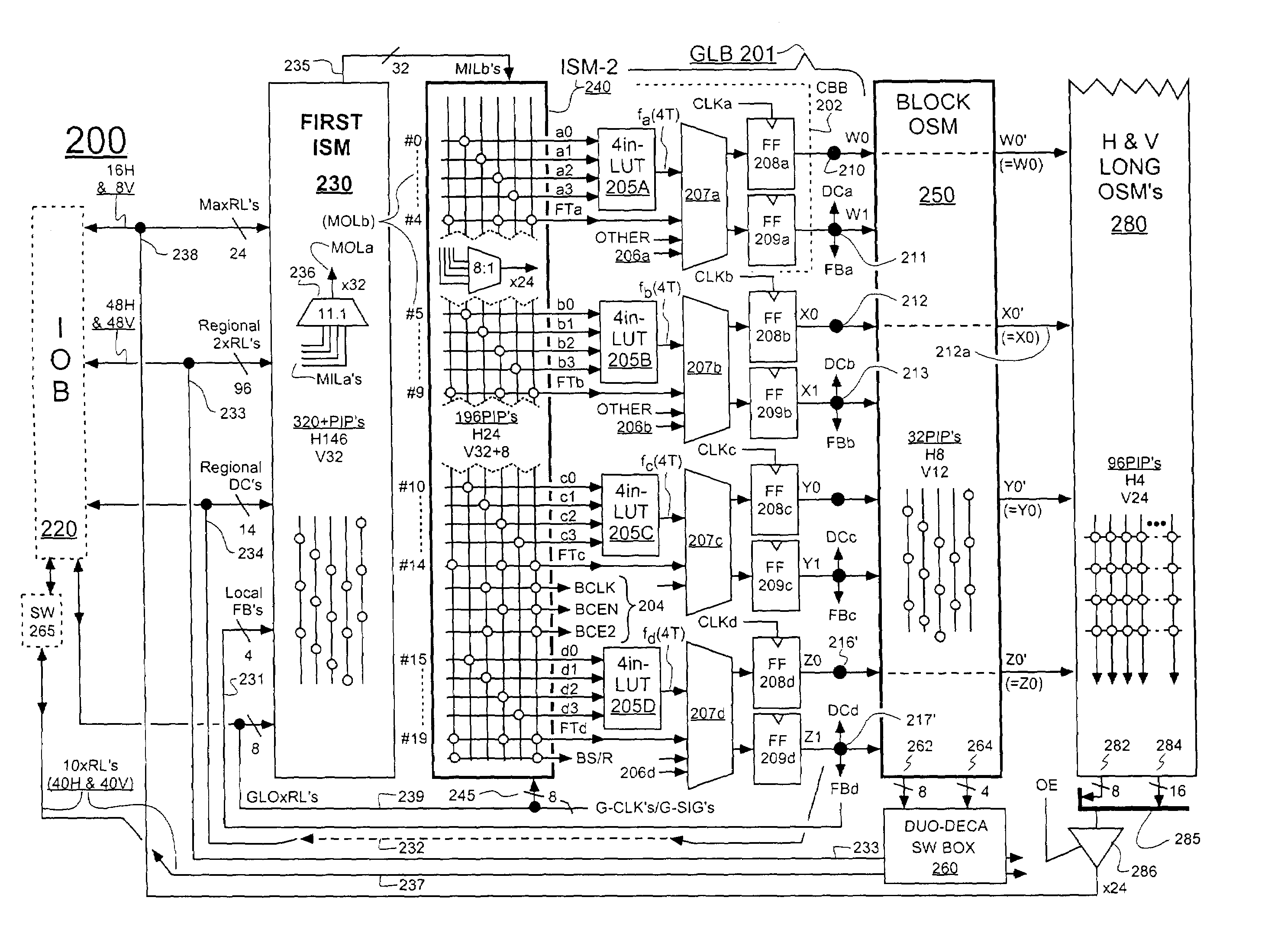

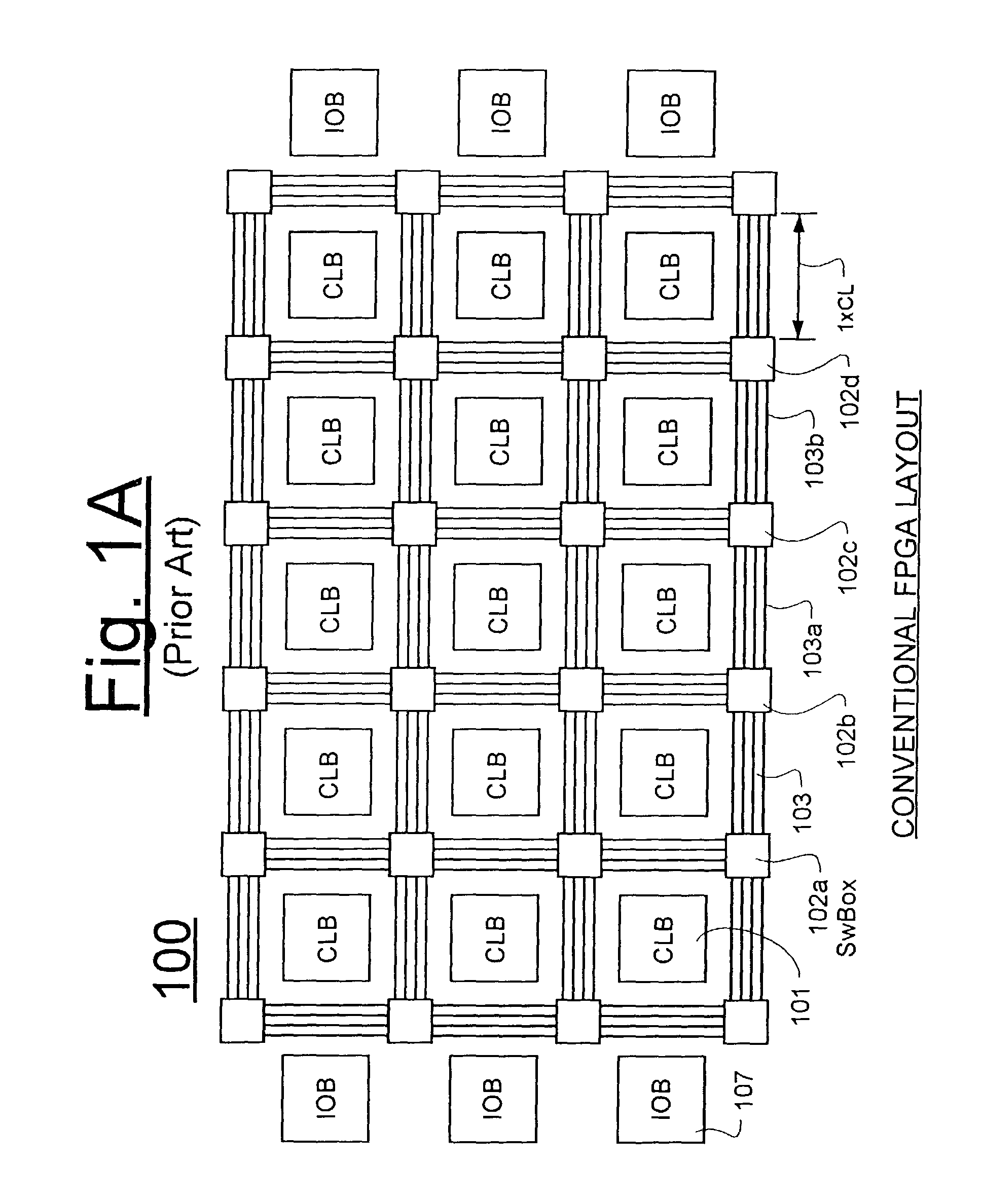

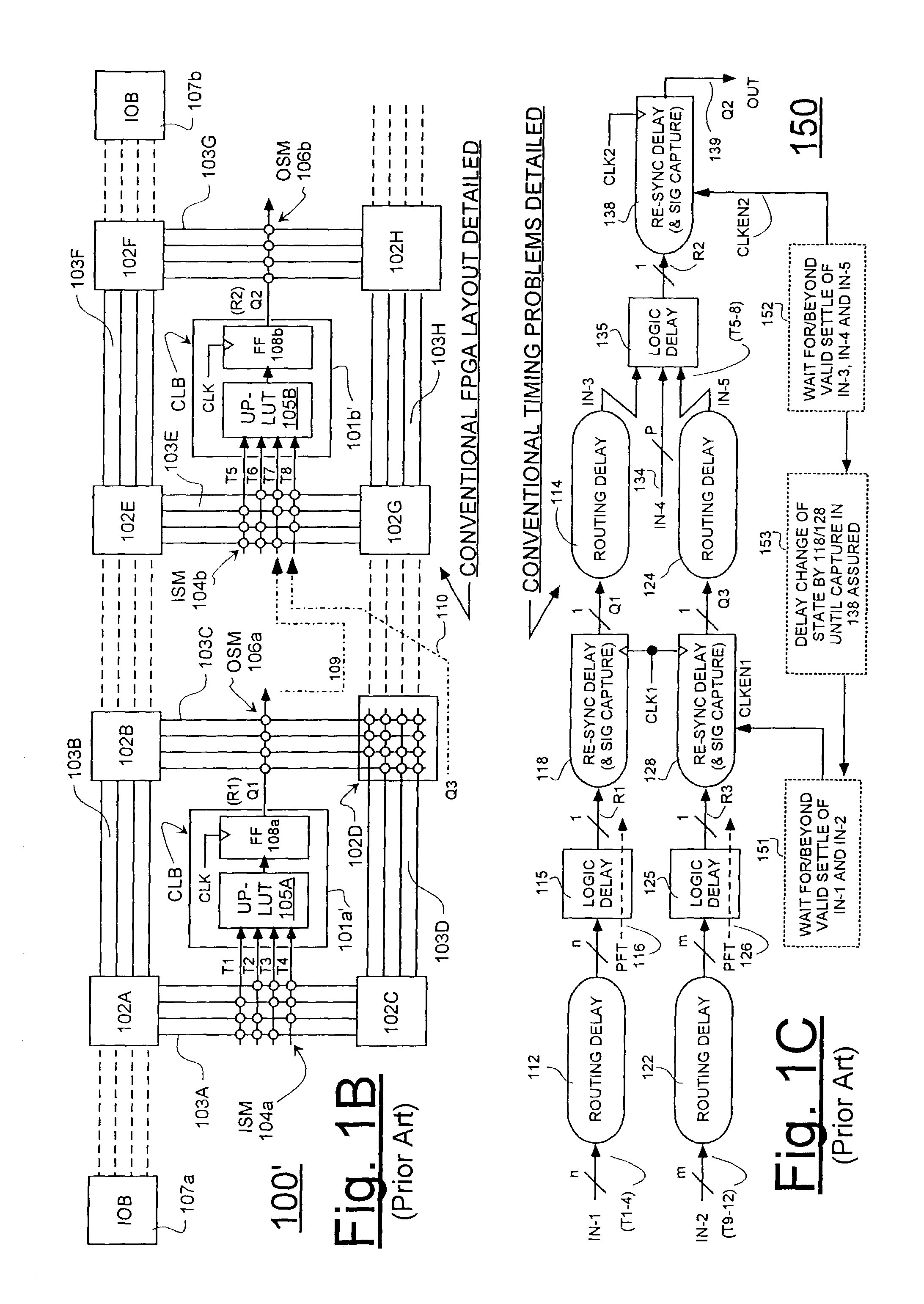

FPGA with register-intensive architecture

ActiveUS7028281B1Minimize resourceReduce consumptionSolid-state devicesCAD circuit designProcessor registerMultiplexer

Field programmable gate arrays (FPGA's) may be structured in accordance with the disclosure to have a register-intensive architecture that provides, for each of plural function-spawning LookUp Tables (e.g. a 4-input, base LUT's) within a logic block, a plurality of in-block accessible registers. A register-feeding multiplexer means may be provided for allowing each of the plural registers to equivalently capture and store a result signal output by the corresponding, base LUT of the plural registers. Registerable, primary and secondary feedthroughs may be provided for each base LUT so that locally-acquired input signals of the LUT may be fed-through to the corresponding, in-block registers for register-recovery purposes without fully consuming (wasting) the lookup resources of the associated, base LUT. A multi-stage, input switch matrix (ISM) may be further provided for acquiring and routing input signals from adjacent, block-interconnect lines (AIL's) and / or block-intra-connect lines (e.g., FB's) to the base LUT's and / or their respective, registerable feedthroughs. Techniques are disclosed for utilizing the many in-block registers and / or the registerable feedthroughs and / or the multi-stage ISM's for efficiently implementing various circuit designs by appropriately configuring such register-intensive FPGA's.

Owner:LATTICE SEMICON CORP

Control System For and Method of Combining Materials

An apparatus and method for combining multiple materials. The multiple materials may include both a major material and one or more minor materials. The major and minor materials are added at transient or steady state flow rates, depending upon a command from a control signal. The actual flow rates track the commanded flow rates, but deviate by an error. The claimed arrangement provides an instantaneous and time-based error believed to be unobtainable in the prior art.

Owner:PROCTER & GAMBLE CO

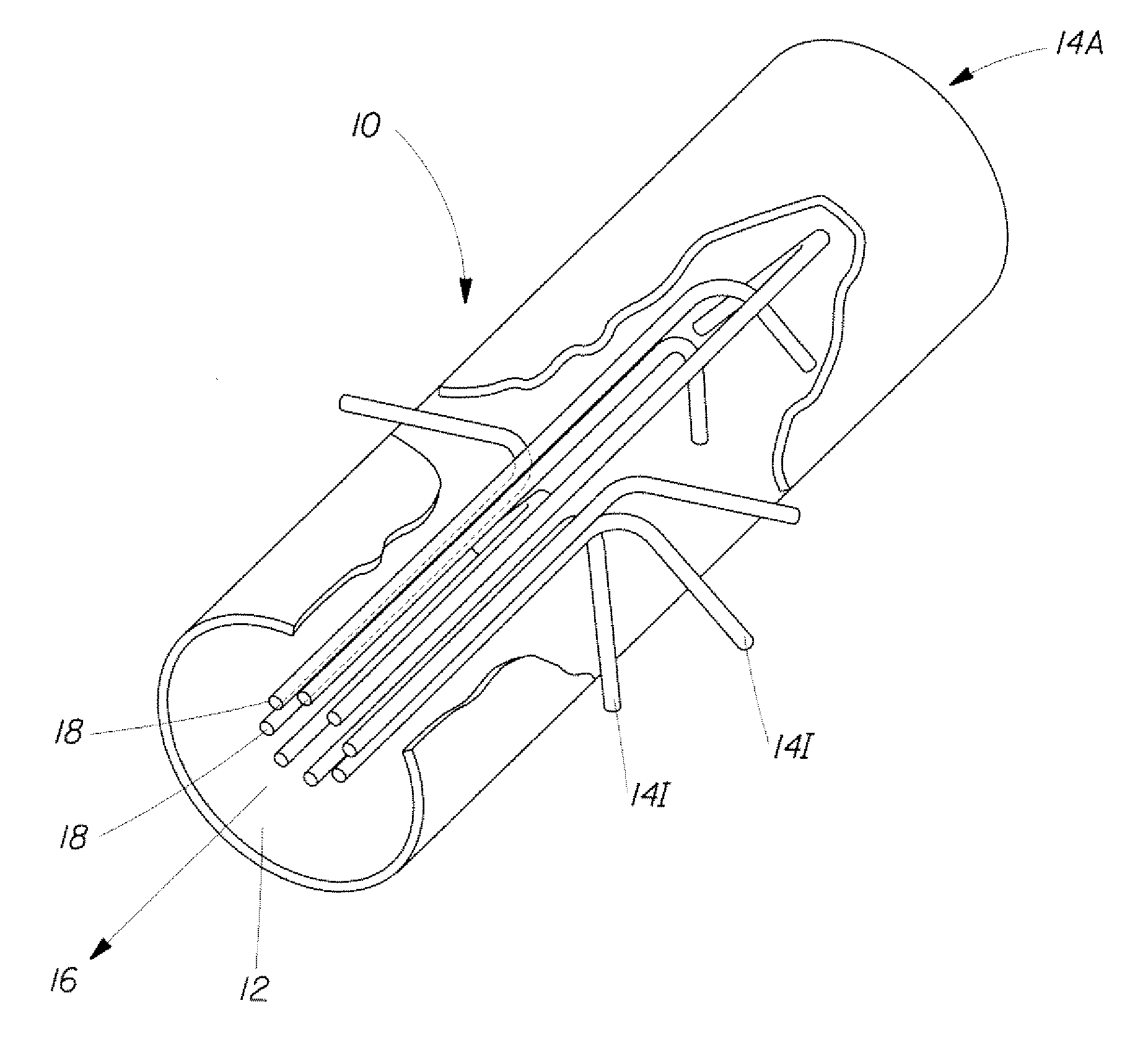

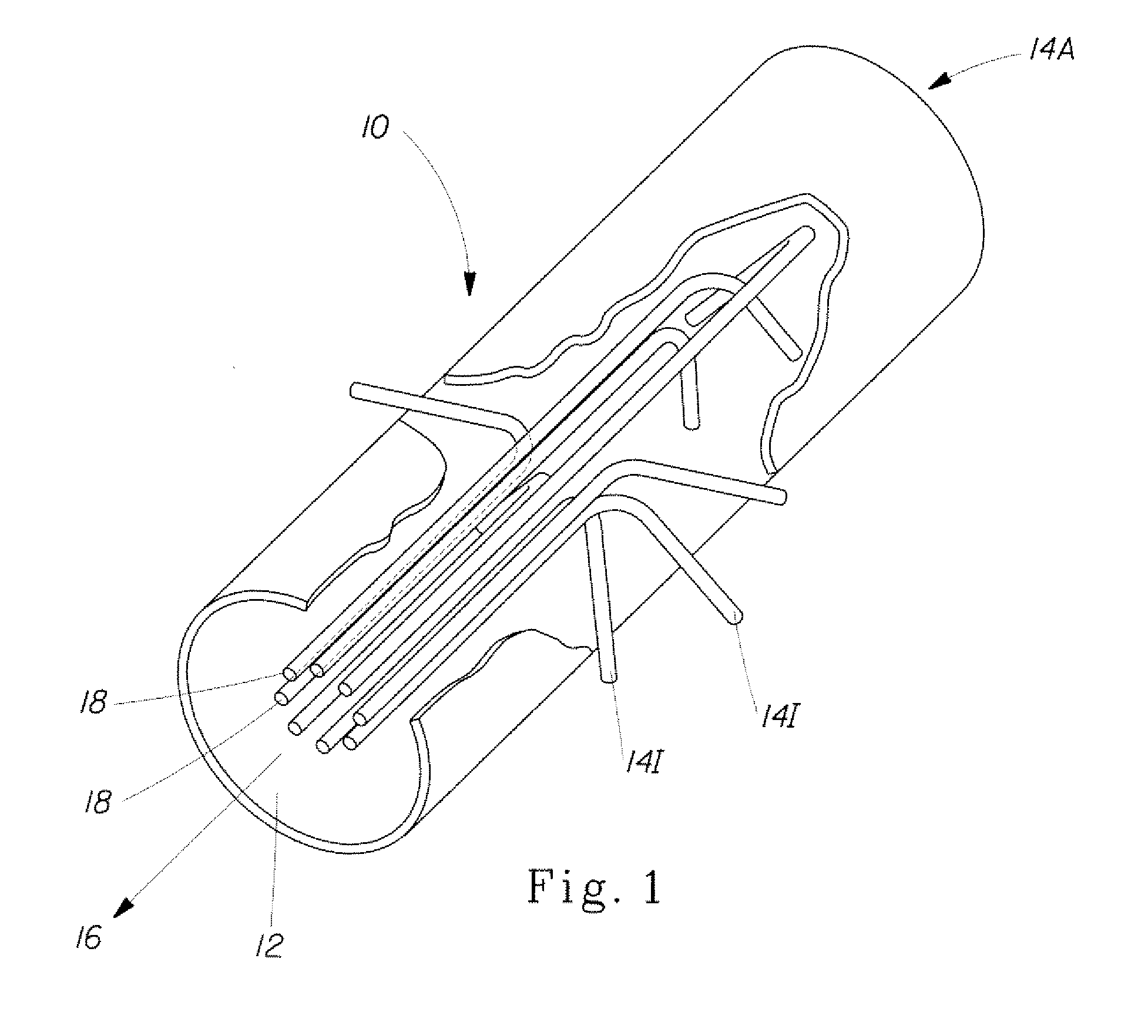

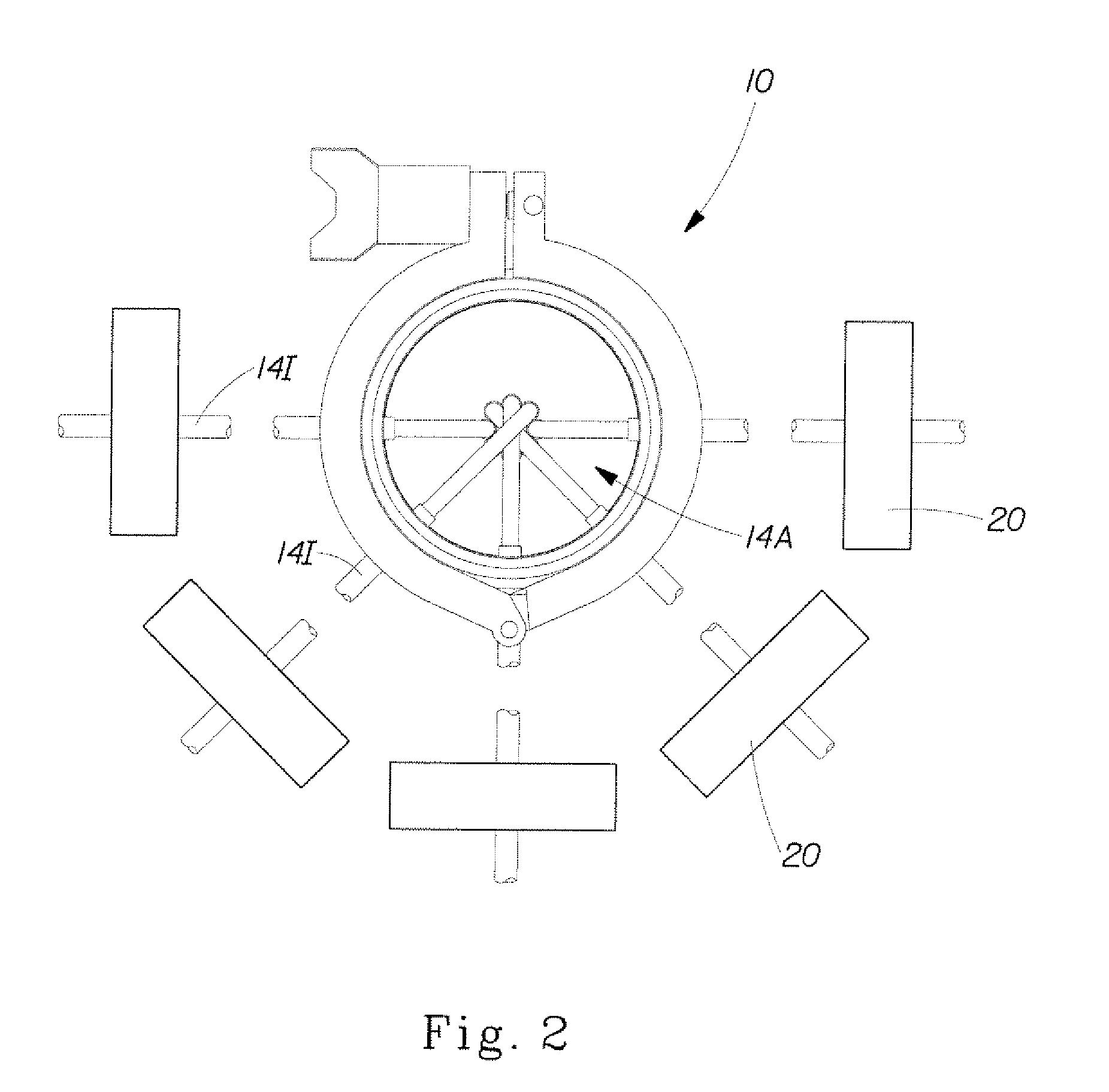

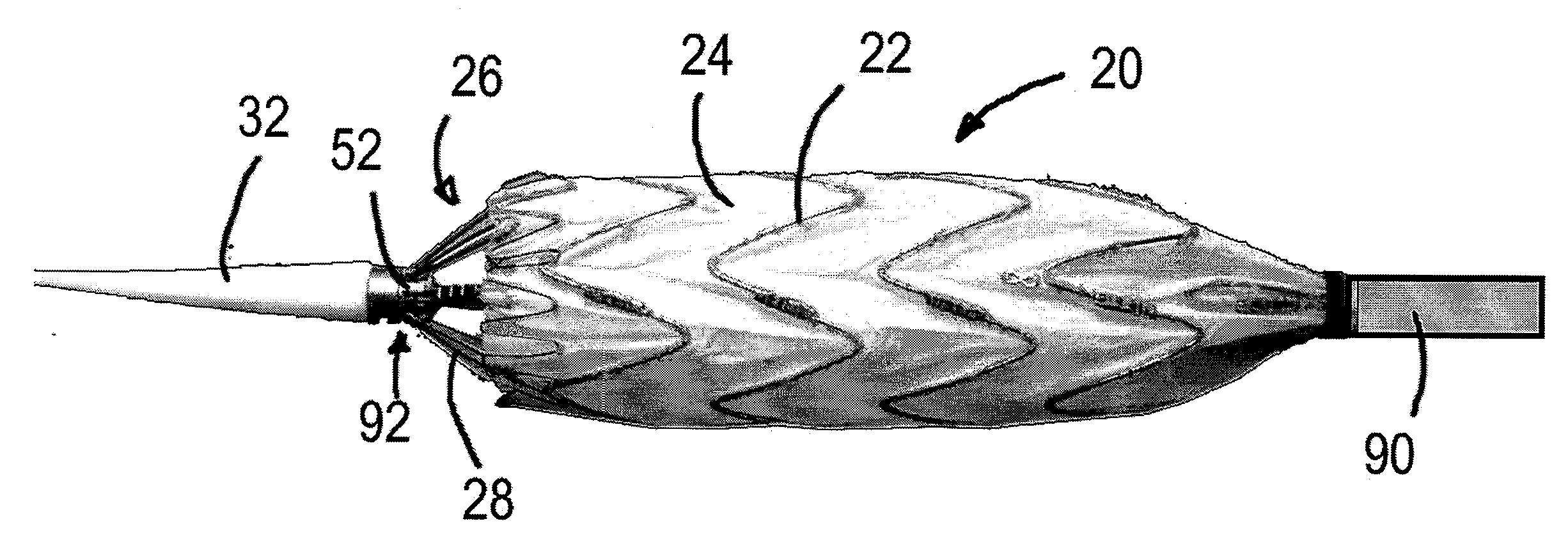

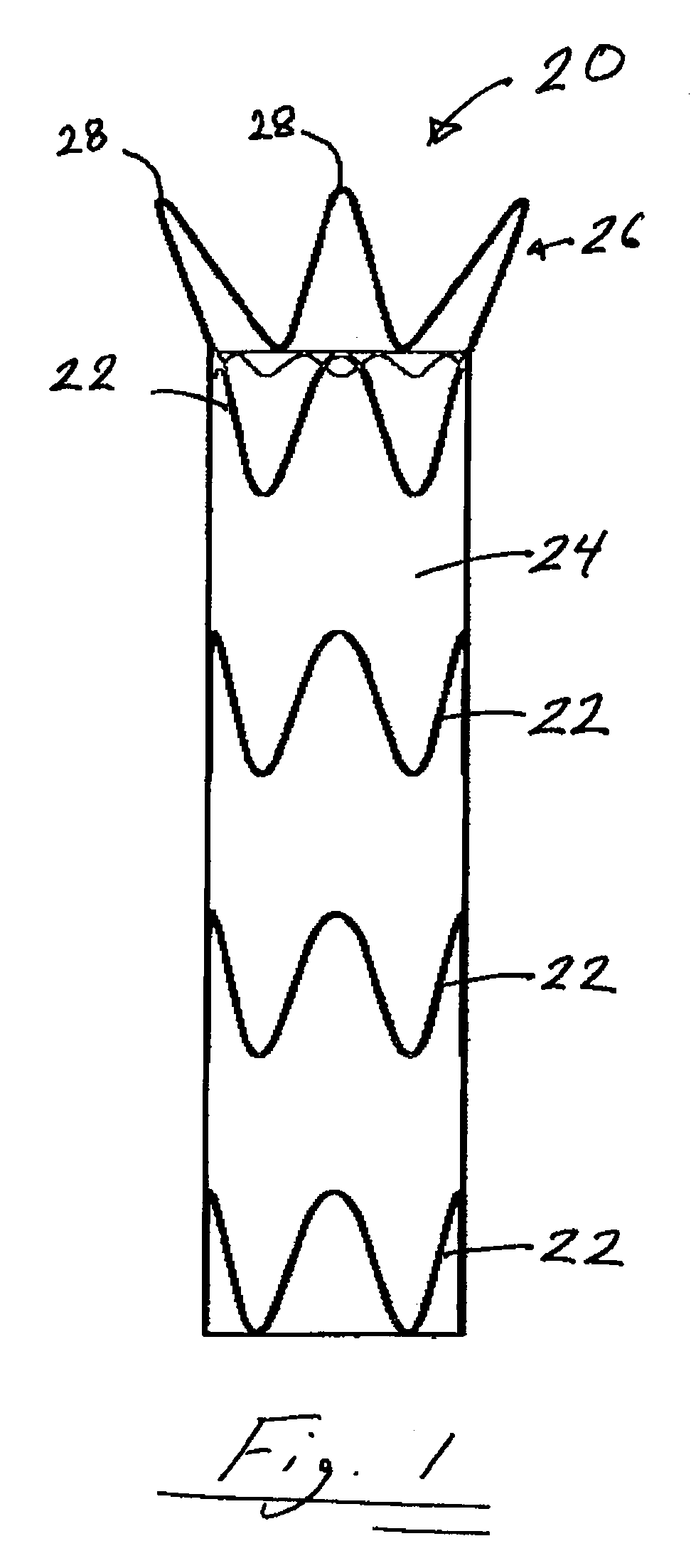

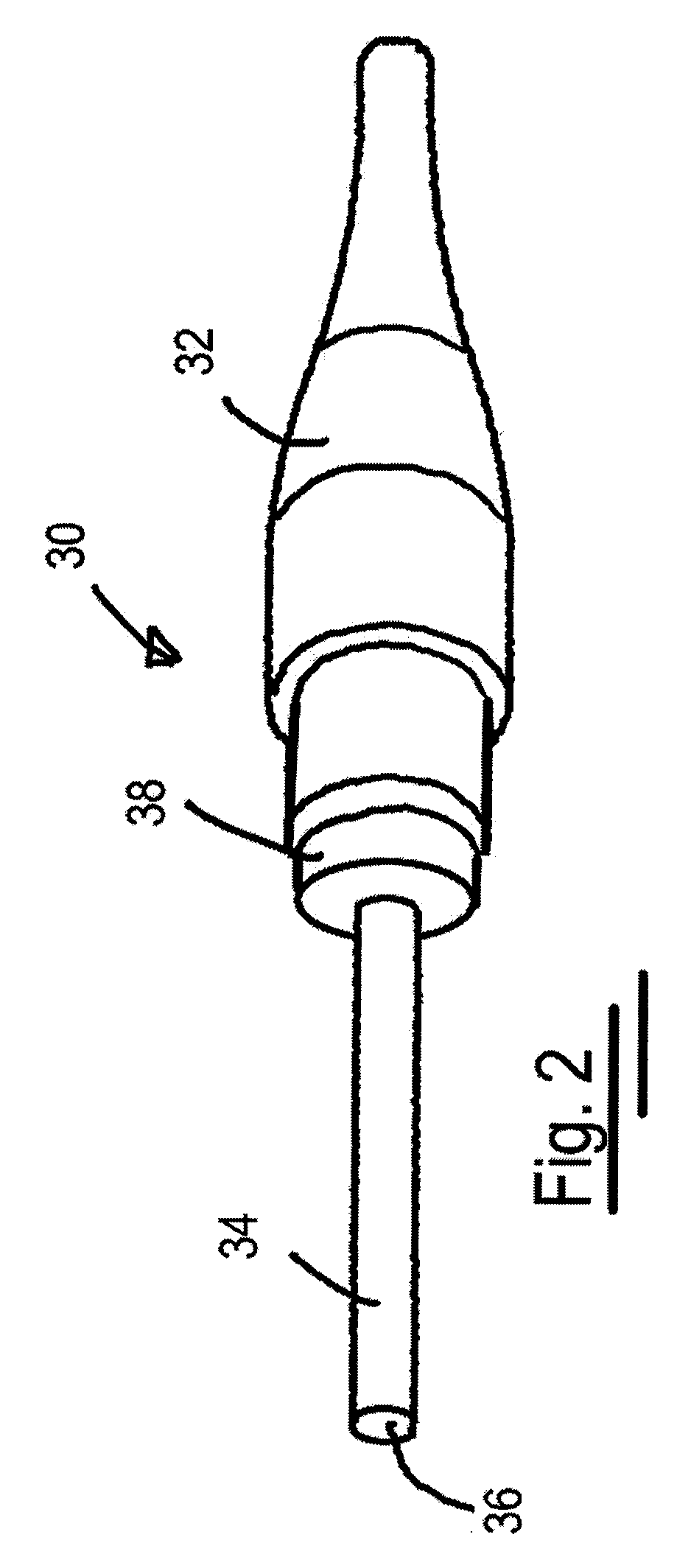

Stent Graft Delivery System and Method of Use

A stent graft delivery system and method of use including a delivery system for a stent graft including a nosecone assembly having a nosecone and a nosecone shaft; a spindle assembly defining a spindle assembly lumen through which the nosecone shaft can slide, the spindle assembly having a spindle fitting and a spindle shaft; and a stent capture assembly defining a stent capture assembly lumen through which the spindle shaft can slide, the stent capture assembly having a stent capture fitting and a stent capture shaft. The spindle fitting is slidably mateable with the stent capture fitting to retain an end of the stent graft at a delivery diameter. A stent graft delivery system with an end stent capture configuration providing both a primary and a secondary deployment procedure facilitated by the threaded connection between a bare stent crown spindle fitting and a system nosecone.

Owner:MEDTRONIC VASCULAR INC

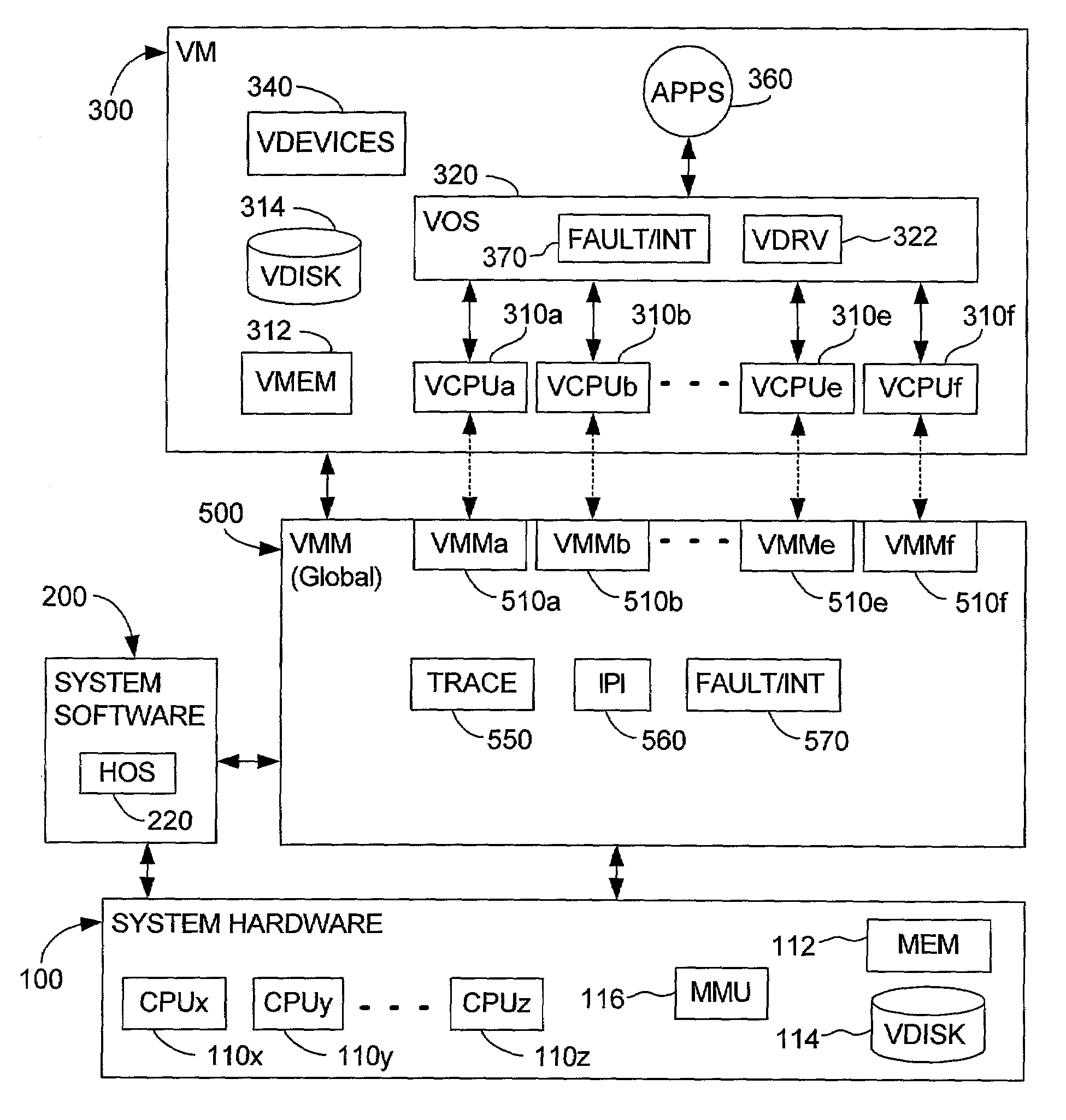

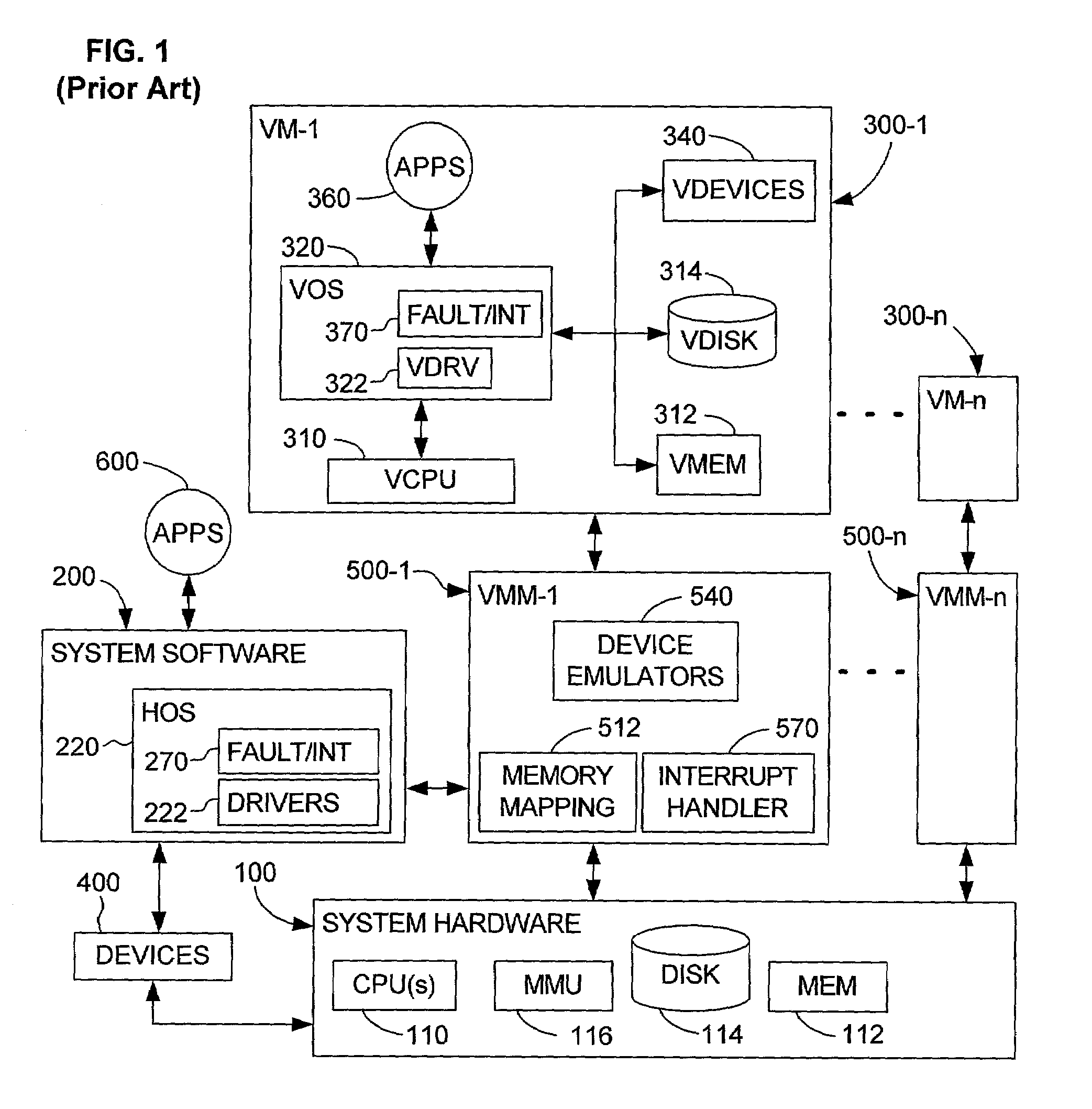

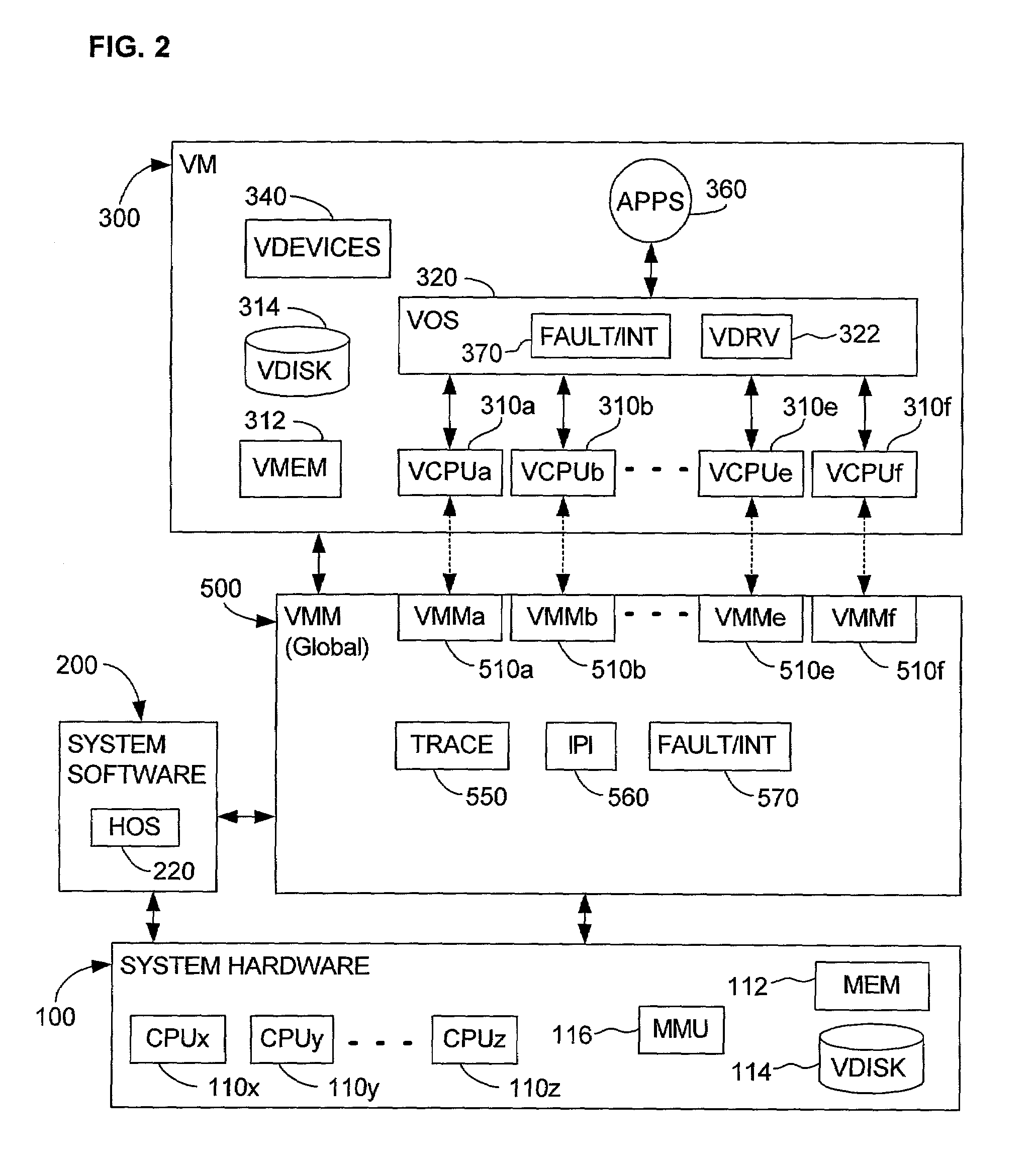

System and method for detecting access to shared structures and for maintaining coherence of derived structures in virtualized multiprocessor systems

A computer system includes at least one virtual machine that has a plurality of virtual processors all running on an underlying hardware platform. A software interface layer such as a virtual machine monitor establishes traces on primary structures located in a common memory space as needed for the different virtual processors. Whenever any one of the virtual processors generates a trace event, such as accessing a traced structure, then a notification is sent to at least the other virtual processors that have a trace on the accessed primary structure. In some applications, the VMM derives and maintains secondary structures corresponding to the primary structures, such as where the VMM converts, through binary translation, original code intended to run on a virtual processor into code that can be run on an underlying physical processor of the hardware platform. In these applications, the VMM may rederive or invalidate the secondary structures as needed upon receipt of the notification of the trace event. Different semantics are provided for the notification, providing different choices of performance versus guaranteed consistency between primary and secondary structures. In the preferred embodiment of the invention, a dedicated sub-system is included within the VMM for each virtual processor; each sub-system establishes traces, senses trace events, issues the notification, and performs other operations relating specifically to its respective virtual processor.

Owner:VMWARE INC

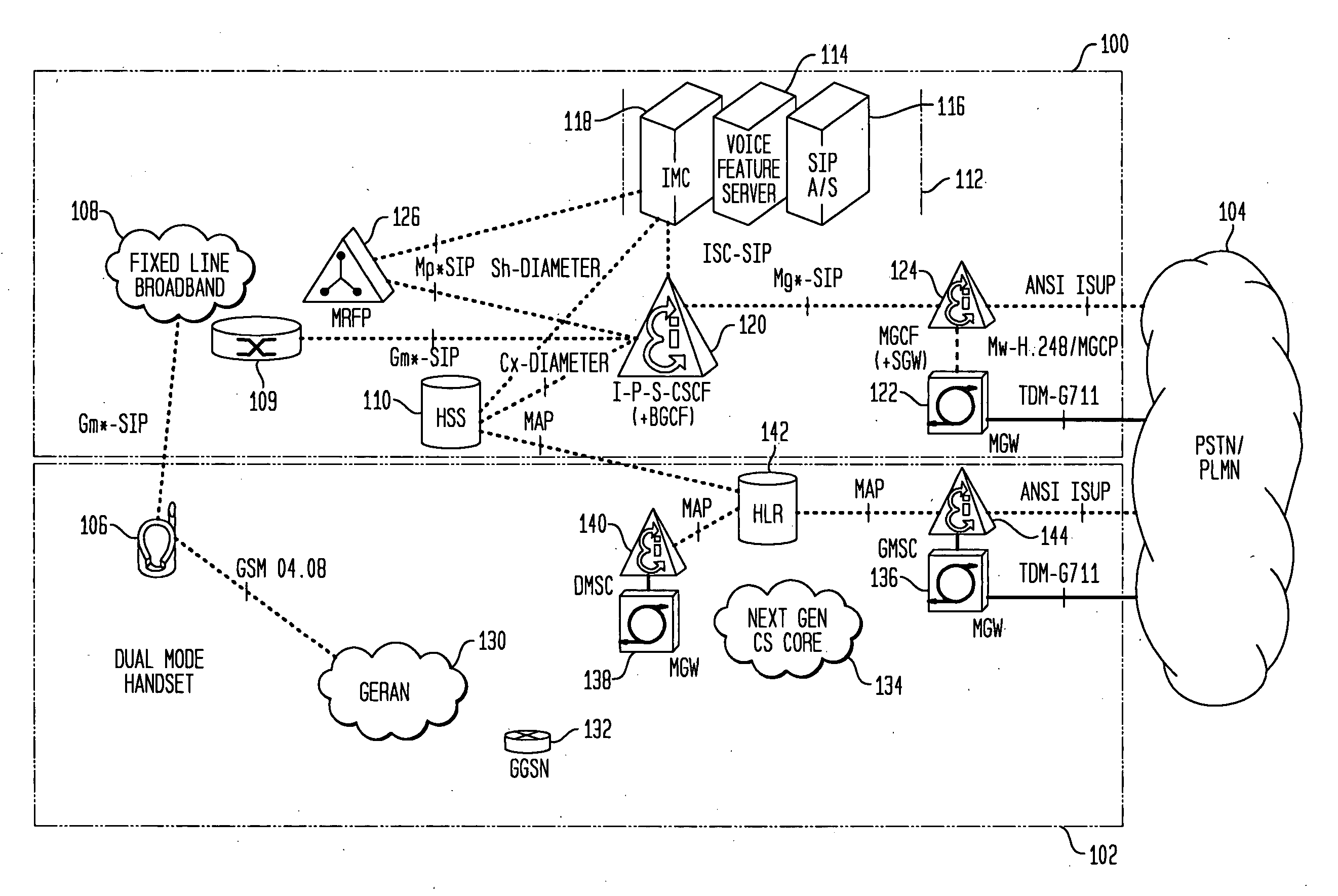

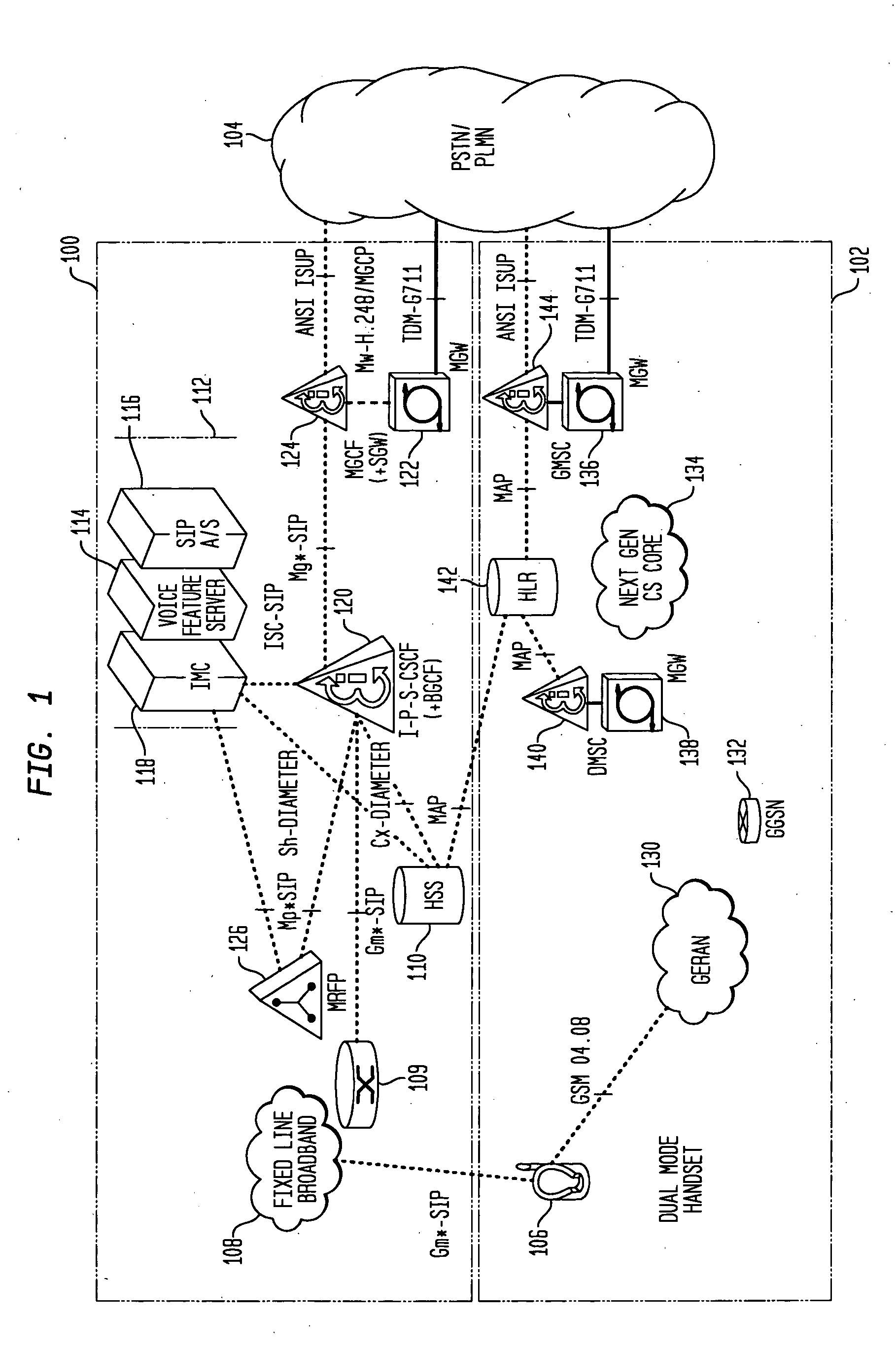

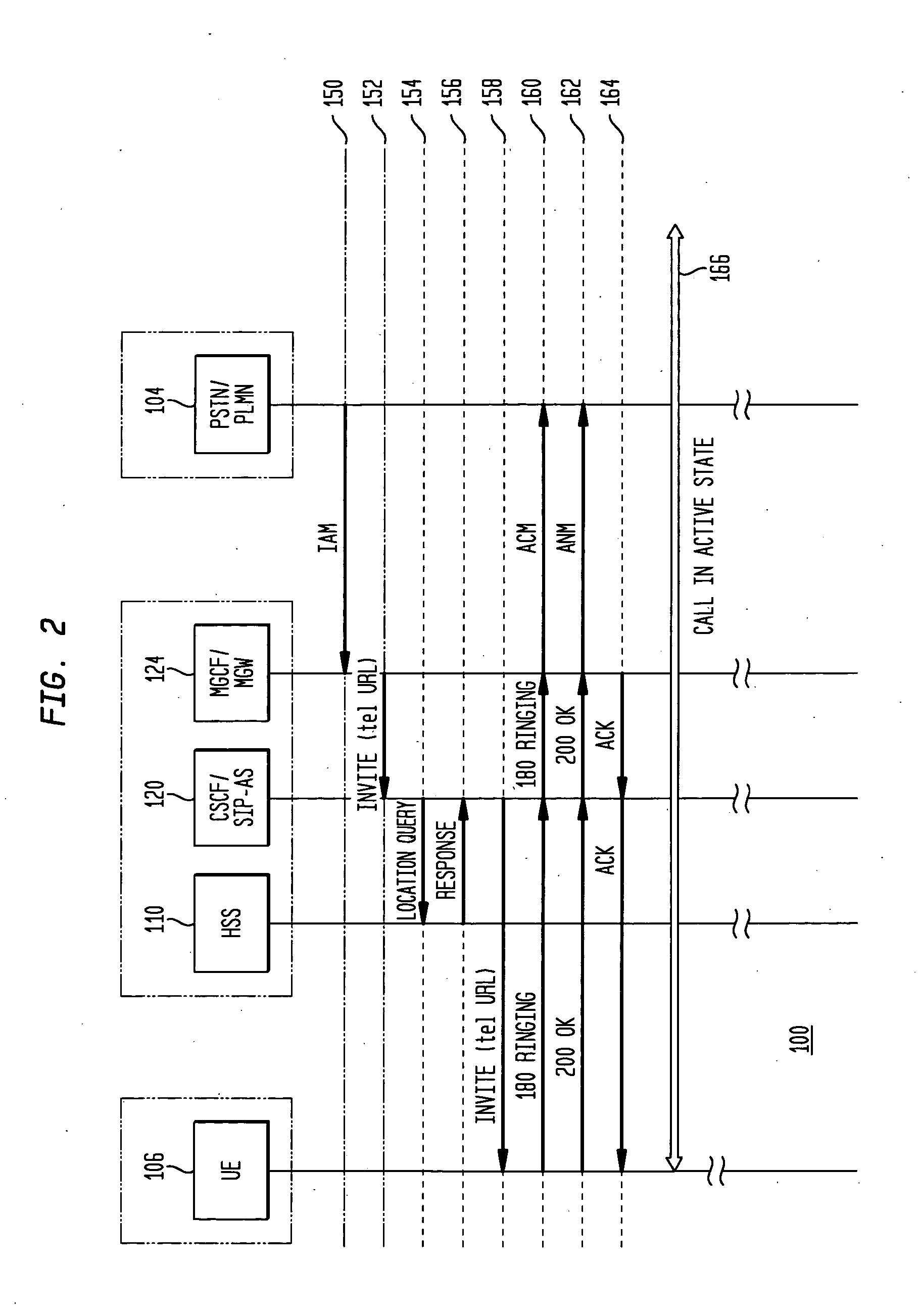

Pseudo number portability in fixed-mobile convergence with one number

InactiveUS20060079236A1Facilitate effectivelyImprove efficiencyRadio/inductive link selection arrangementsNetwork connectionsTelecommunicationsUser equipment

A Fixed-Mobile Convergence (FMC) network and method of handling calls in a FMC network. Registration is maintained for FMC User Equipment (UE) with at least two (a primary and a secondary) networks, e.g., a mobile network and a fixed network with a wireless connection capability. The primary network maintains subscribers numbers with each FMC UE being assigned one of the subscribers numbers. Calls to FMC UE are routed to the primary network and, if the UE is not present in the primary network, forwarded to the secondary network. A preferred FMC network may be implemented in existing fixed and mobile networks without requiring that one be integrated into the other.

Owner:SIEMENS COMMUNICATIONS INC

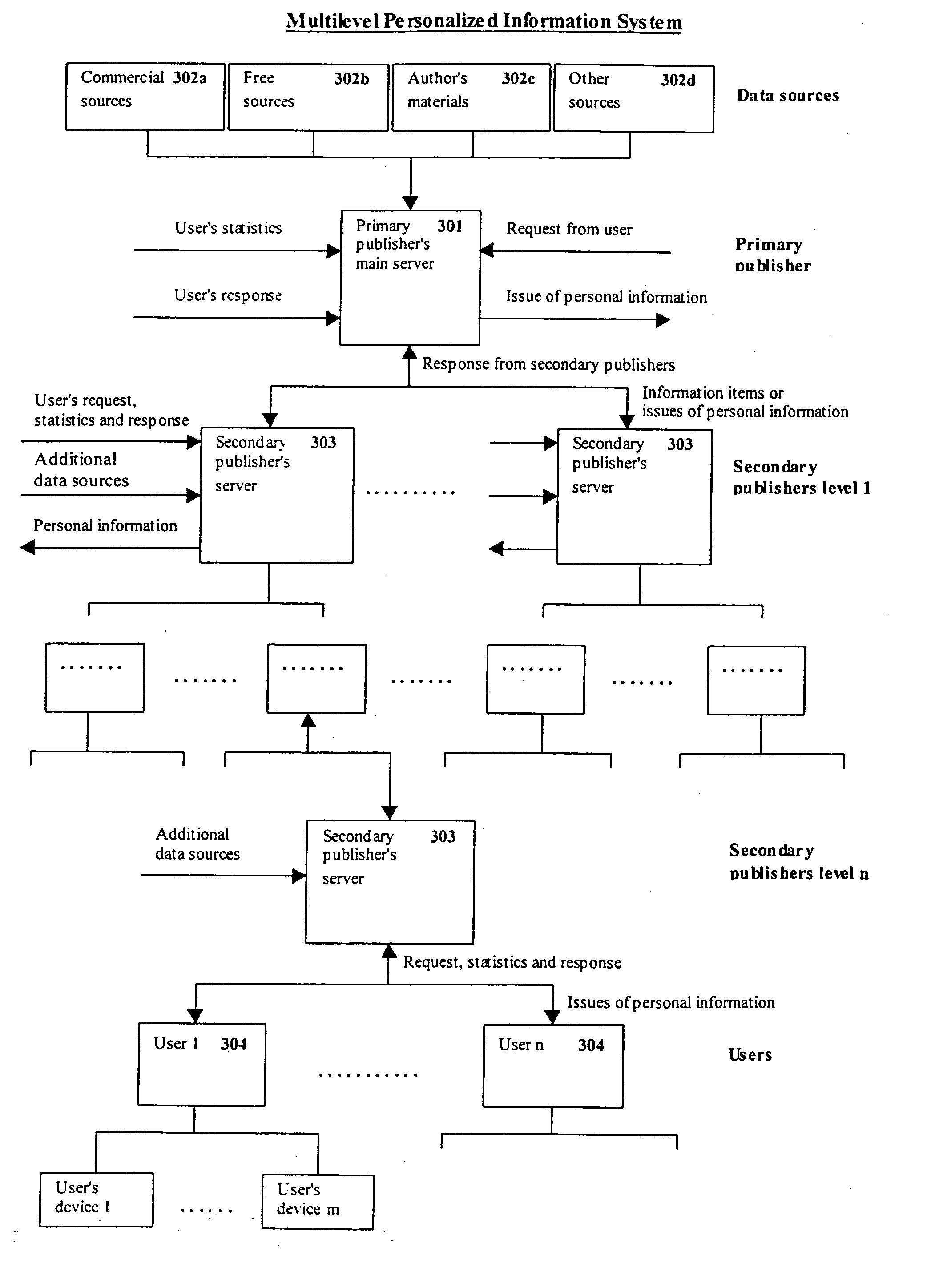

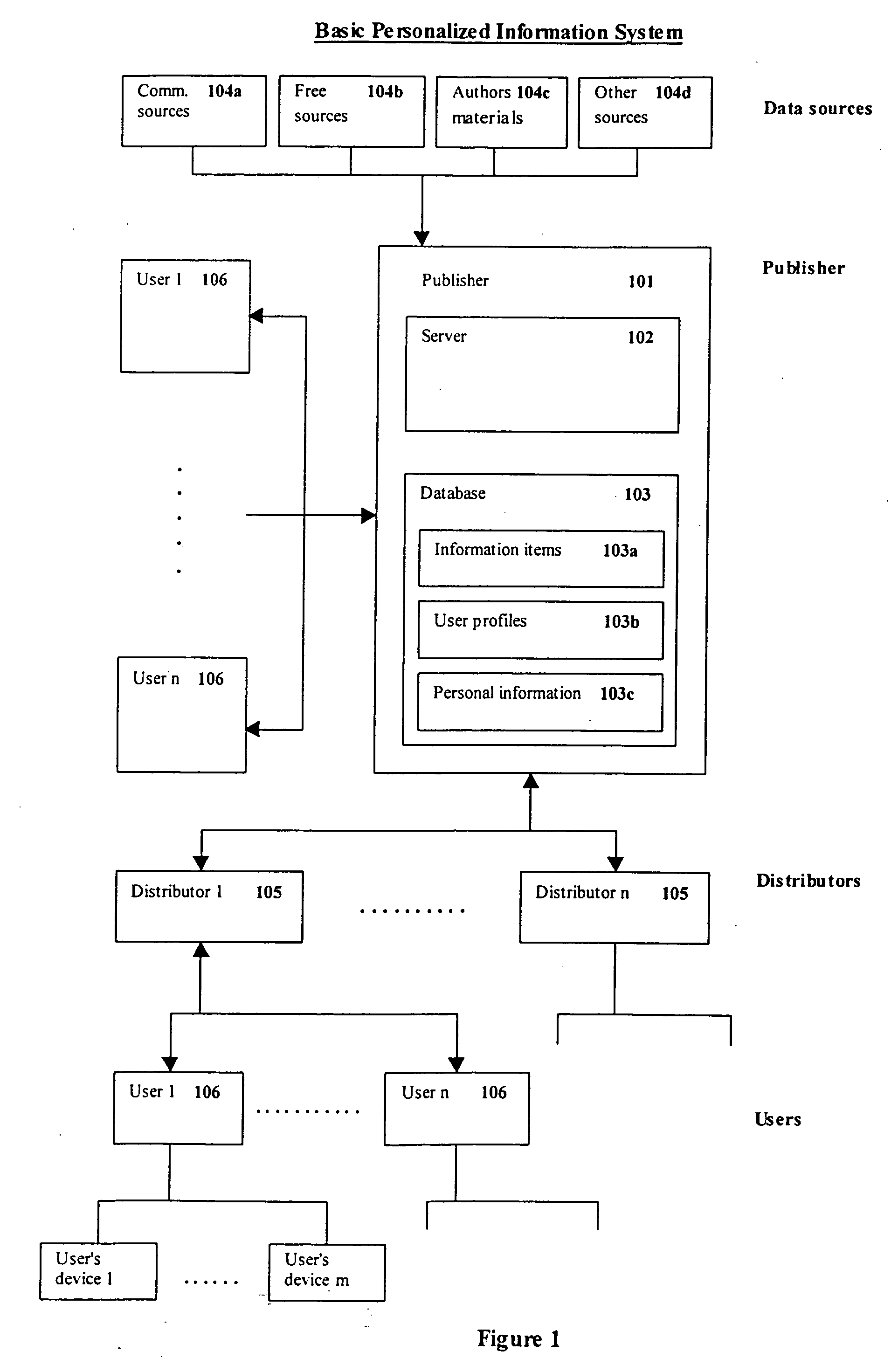

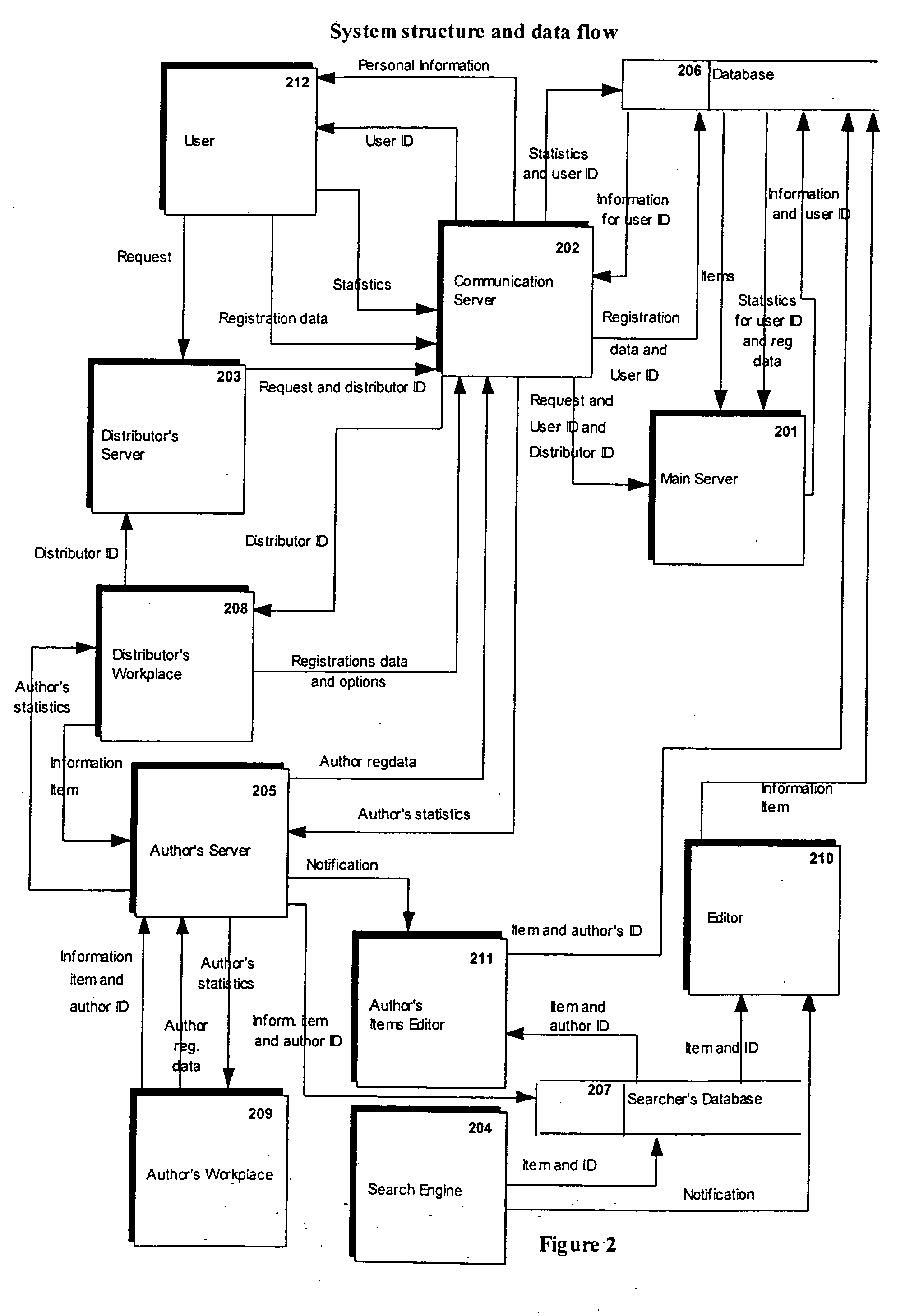

Interactive personal information system and method

InactiveUS20060031114A1Increase profitMarket predictionsDigital data information retrievalPersonalizationUser profile

The interactive personal information system and method delivers personalized information to users by having a publisher, or a multilevel structure of primary and secondary publishers, collect information items into at least one database for periodic delivery of collections of information items to users as personalized information. The collections are selected based on user profiles that are refined based on collecting and analyzing subjective responses from the users. The personalized information can be delivered in various formats and can include various interactive tools to increase its utility. Different levels of publishers can provide information items and response analysis to other publishers. Information items can be sought by publishers based on user requests and response analysis.

Owner:ZOMMERS OLEG

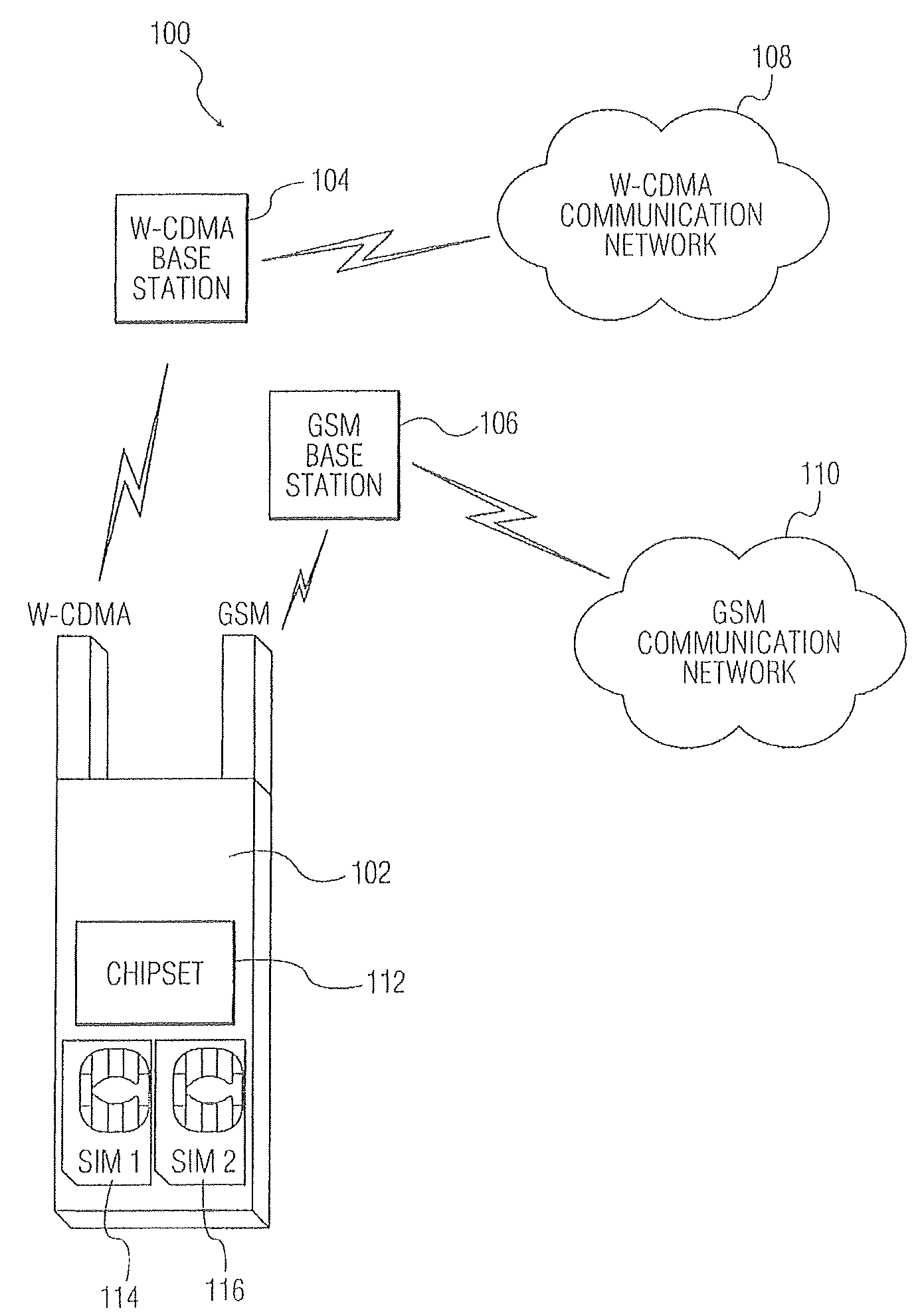

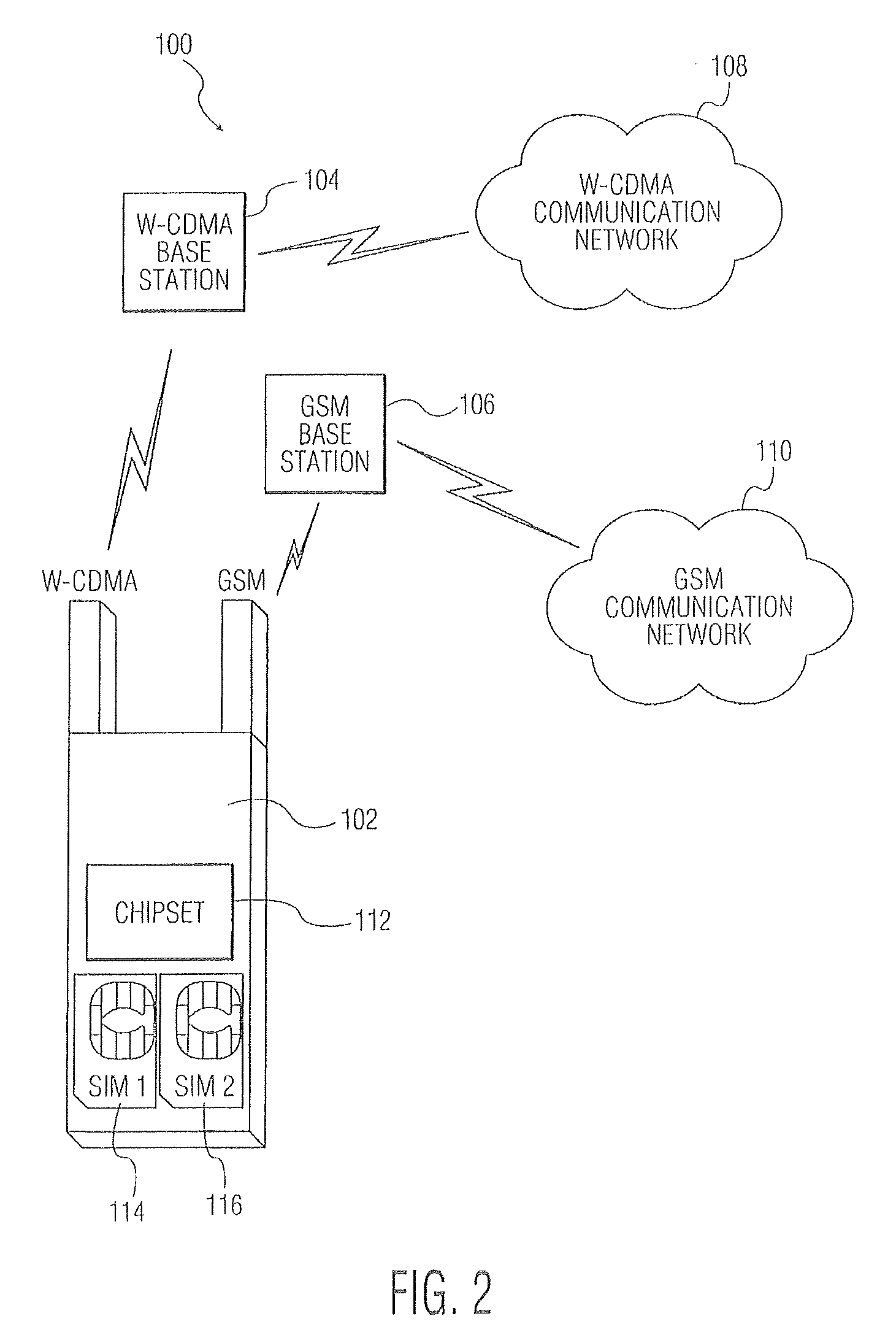

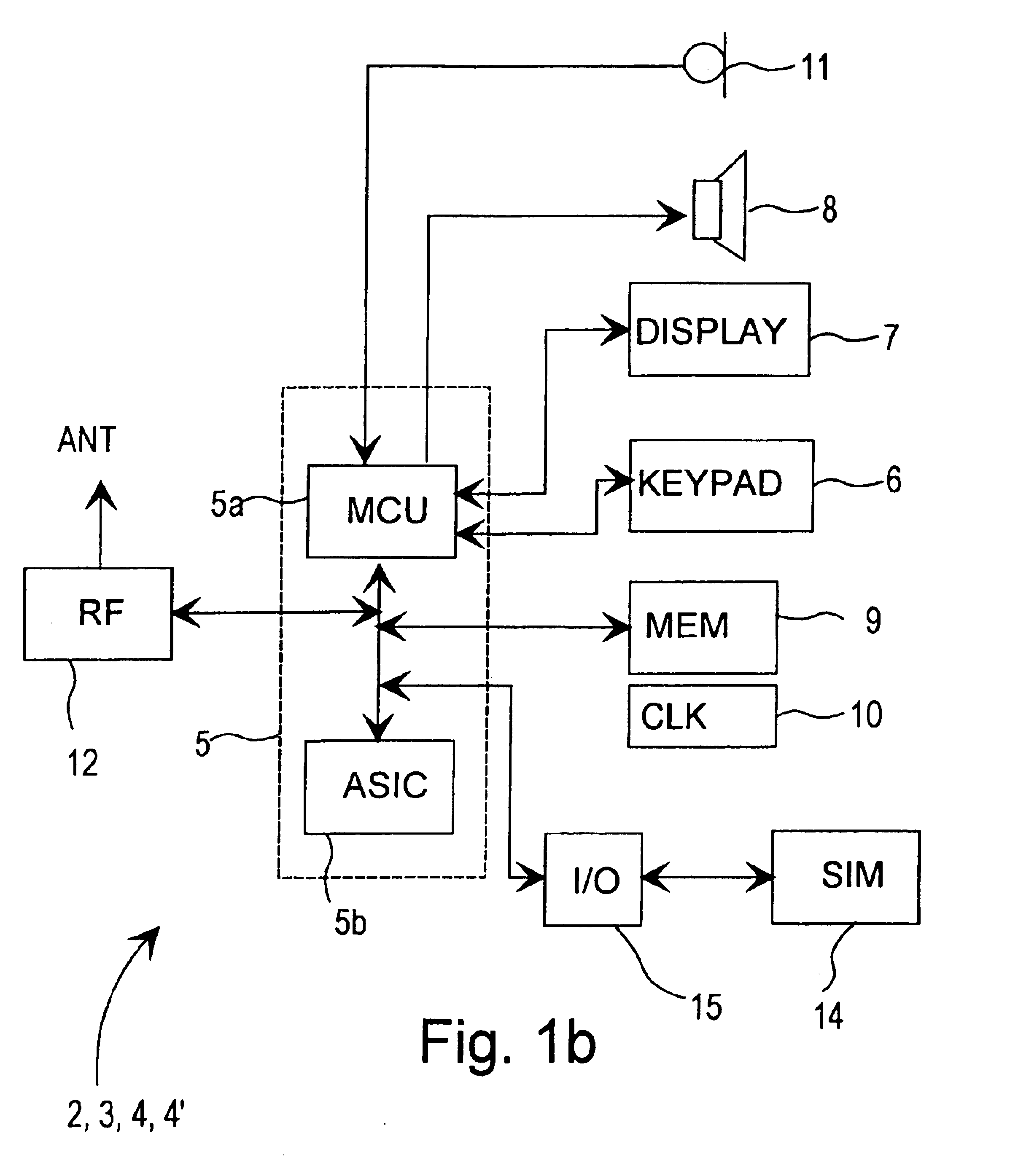

Method and system for enabling dual standby state in a wireless communications system

ActiveUS20090131054A1Facilitate a dual standby featurePower managementConnection managementCommunications systemMaster controller

A system and method having a multimode wireless communication terminal with at least two SIM card slots for use with at least two phone numbers simultaneously online (dual standby). The system includes a main controller, a primary mode module, a secondary mode module, and an inter-system measurement module. The main controller operates the multimode wireless communication terminal in single standby or dual standby state. The primary mode module enables the primary mode of operation for the multimode wireless communication terminal. The primary mode of operation is a default mode of operation. The secondary mode module enables the secondary mode of operation for the multimode wireless communication terminal. Paging information for the primary mode of operation and the secondary mode of operation are monitored at their respective monitoring rates using a TDM method. Switching between the primary and secondary modes of operation is executed by an inter-system handover module. During the dual standby state, both the inter-system measurement and handover are initiated by the terminal itself. The multimode wireless communication terminal is used in a multimode wireless communication system.

Owner:TELEFON AB LM ERICSSON (PUBL)

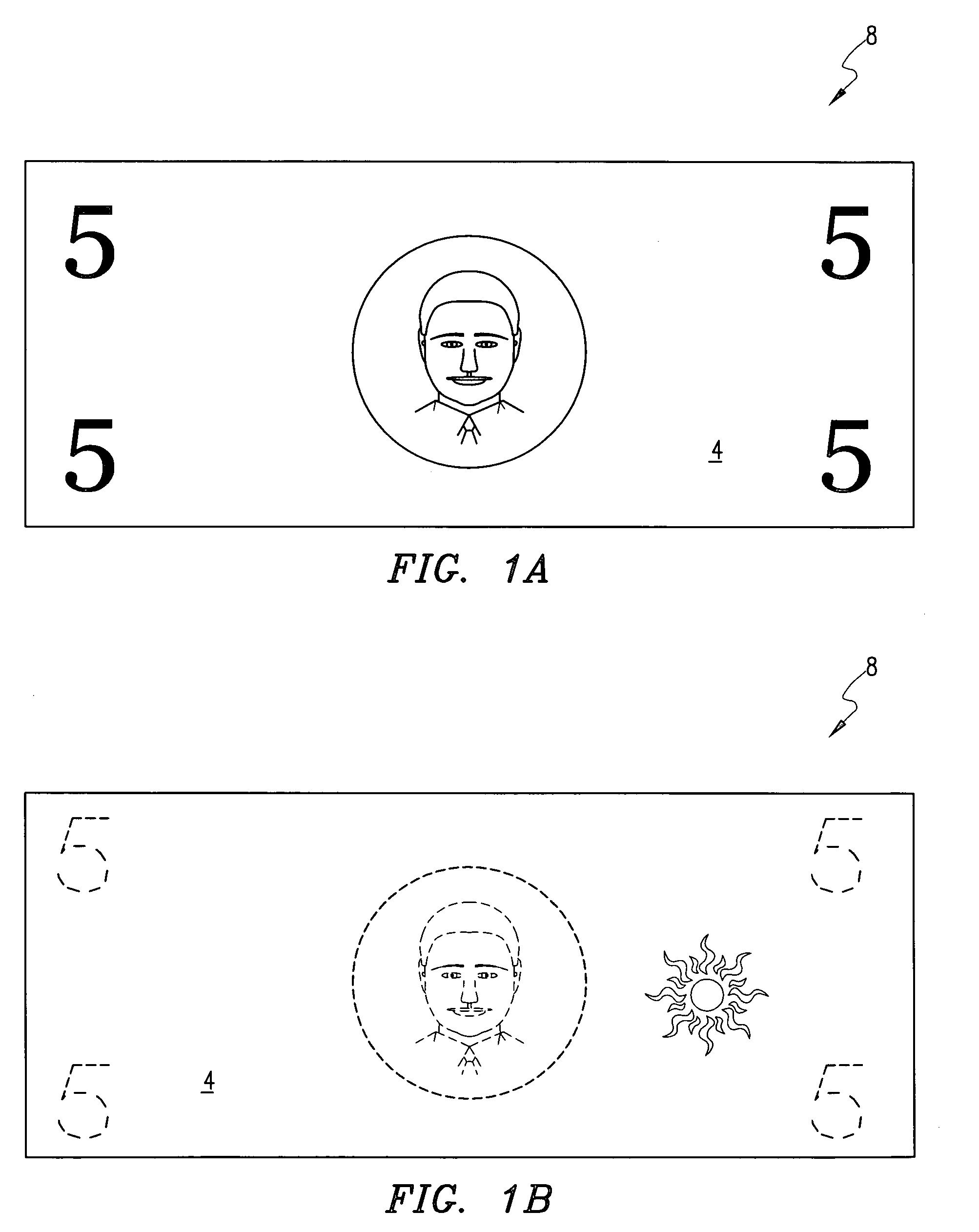

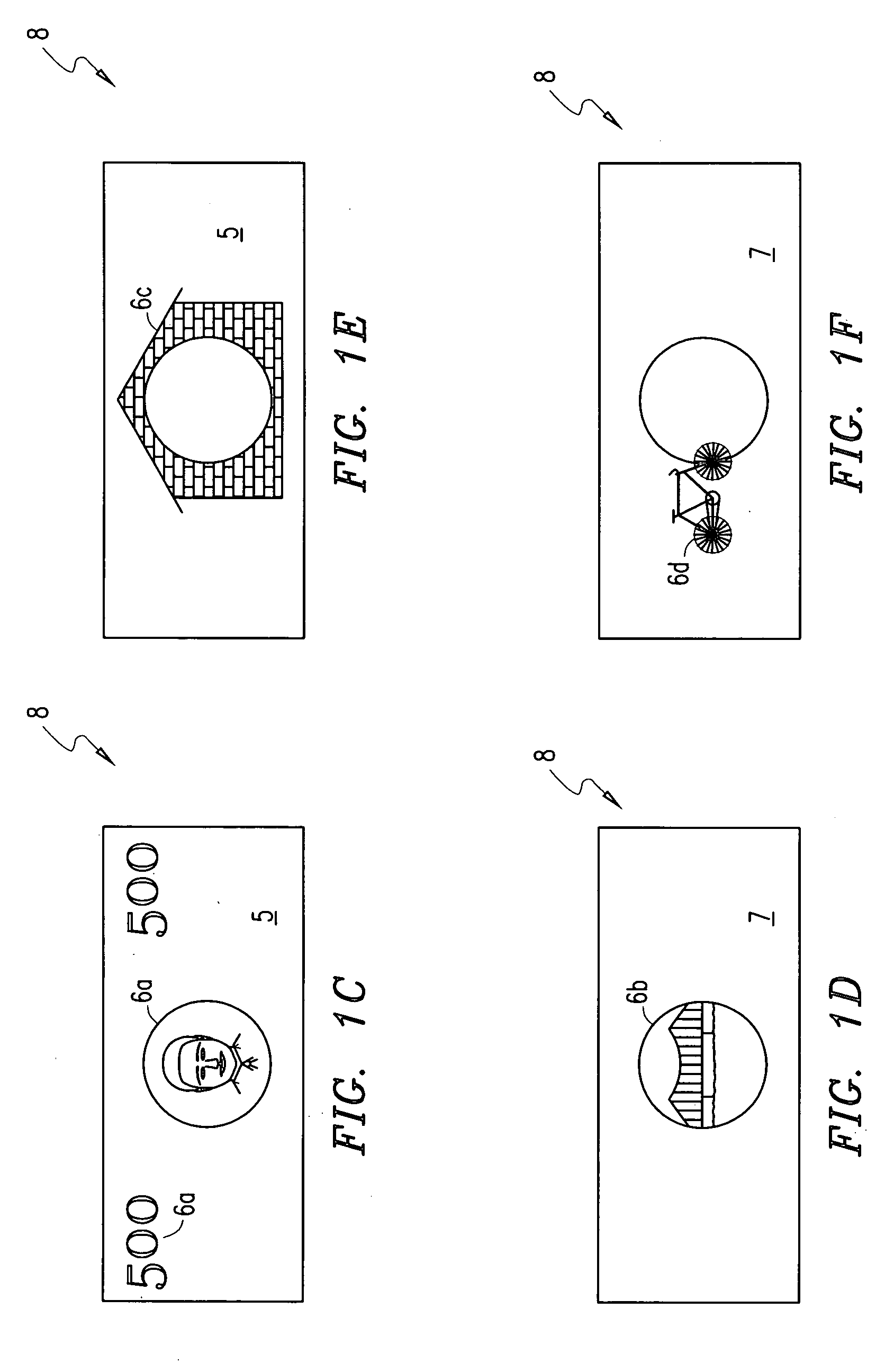

Document processing system using primary and secondary pictorial image comparison

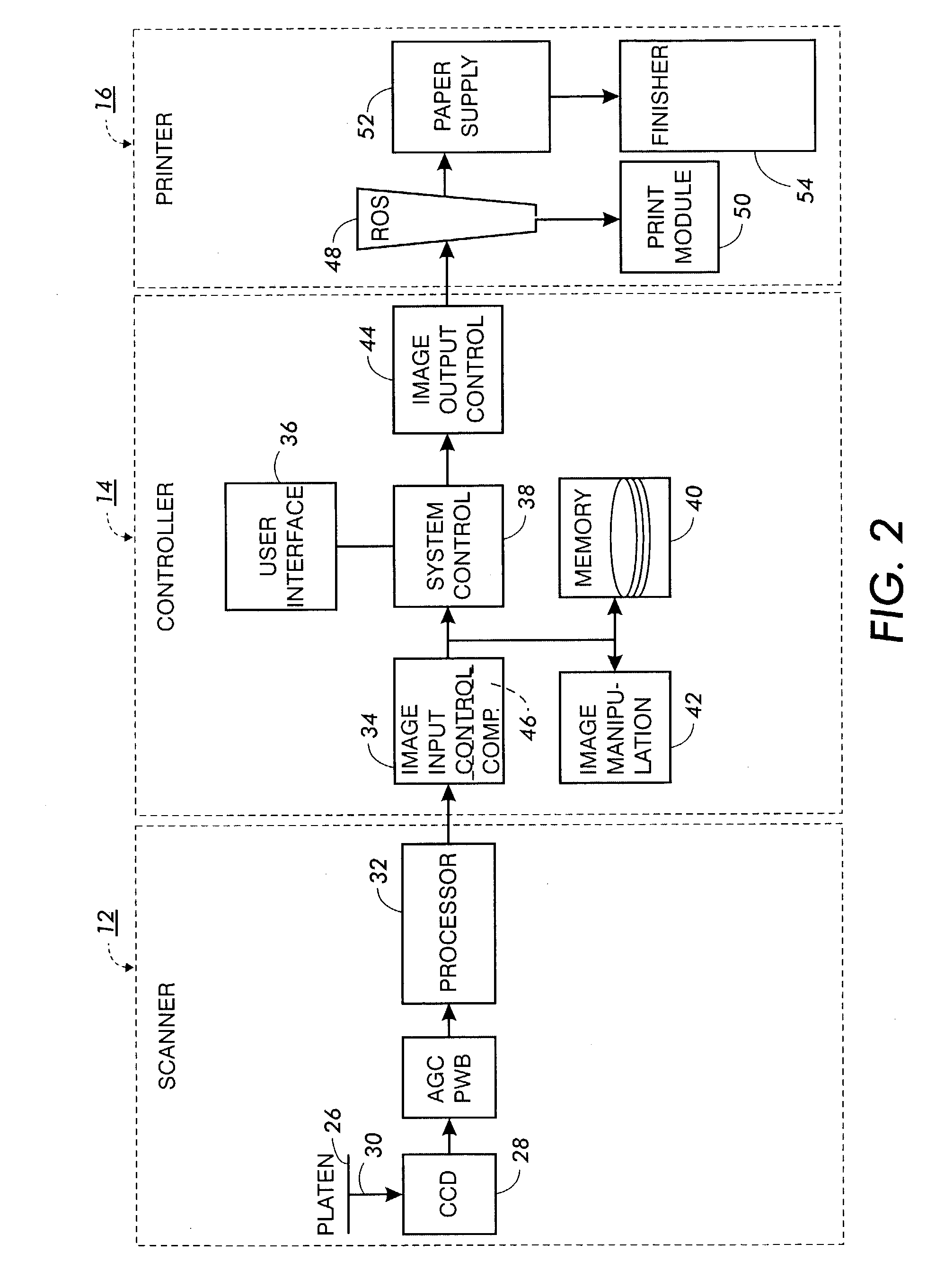

InactiveUS20050169511A1Precise processingManner is significantPaper-money testing devicesCharacter and pattern recognitionComputer graphics (images)Paper document

A document identification system having an input and output receptacle, a transport path, and an image scanner. Primary visible pictorial images and secondary invisible pictorial images are captured by the image scanner. A processor compares the primary and secondary captured pictorial images with master primary and secondary pictorial images to determine the identity of the document, such as denomination or authentication.

Owner:CUMMINS-ALLISON CORP

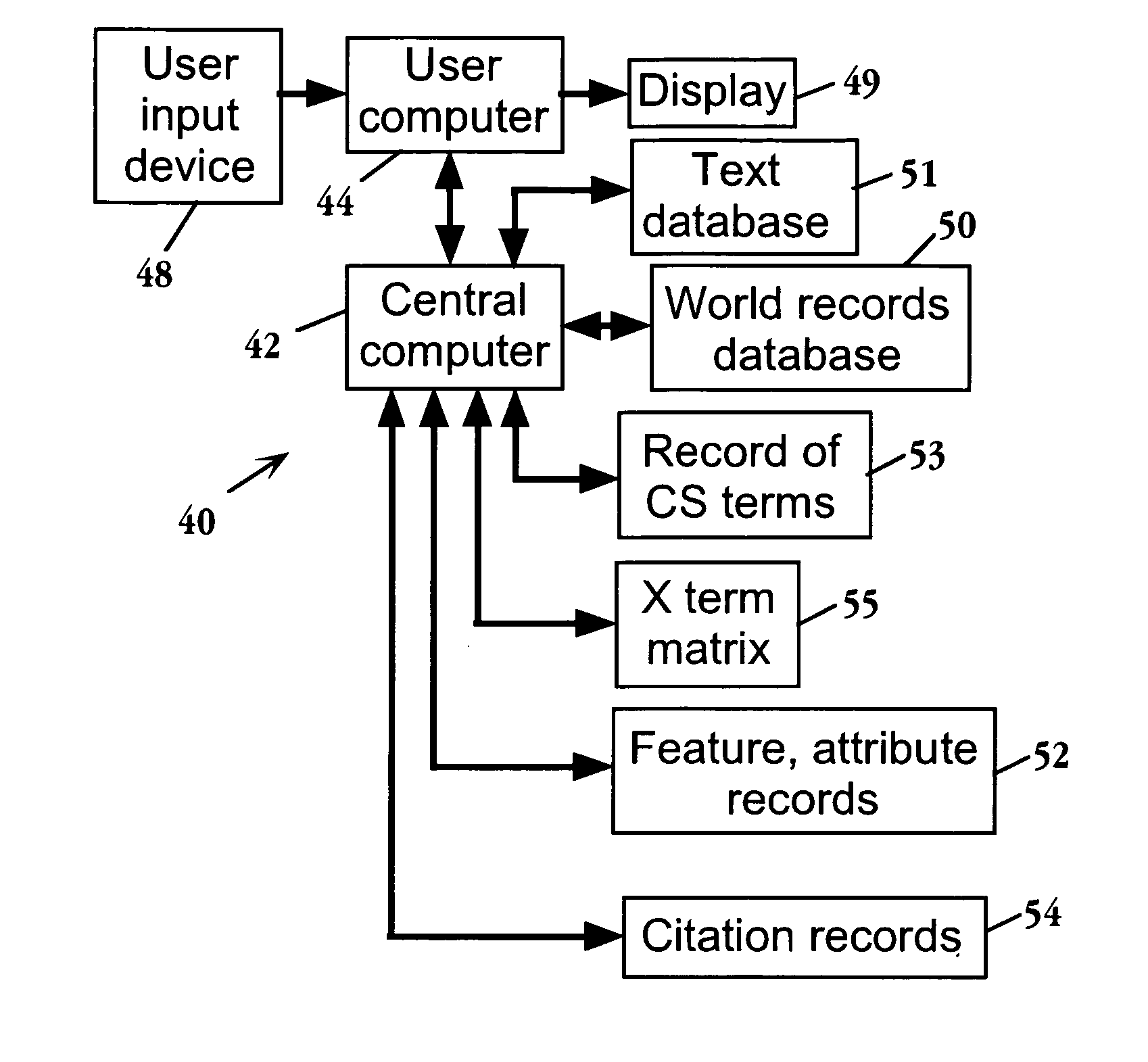

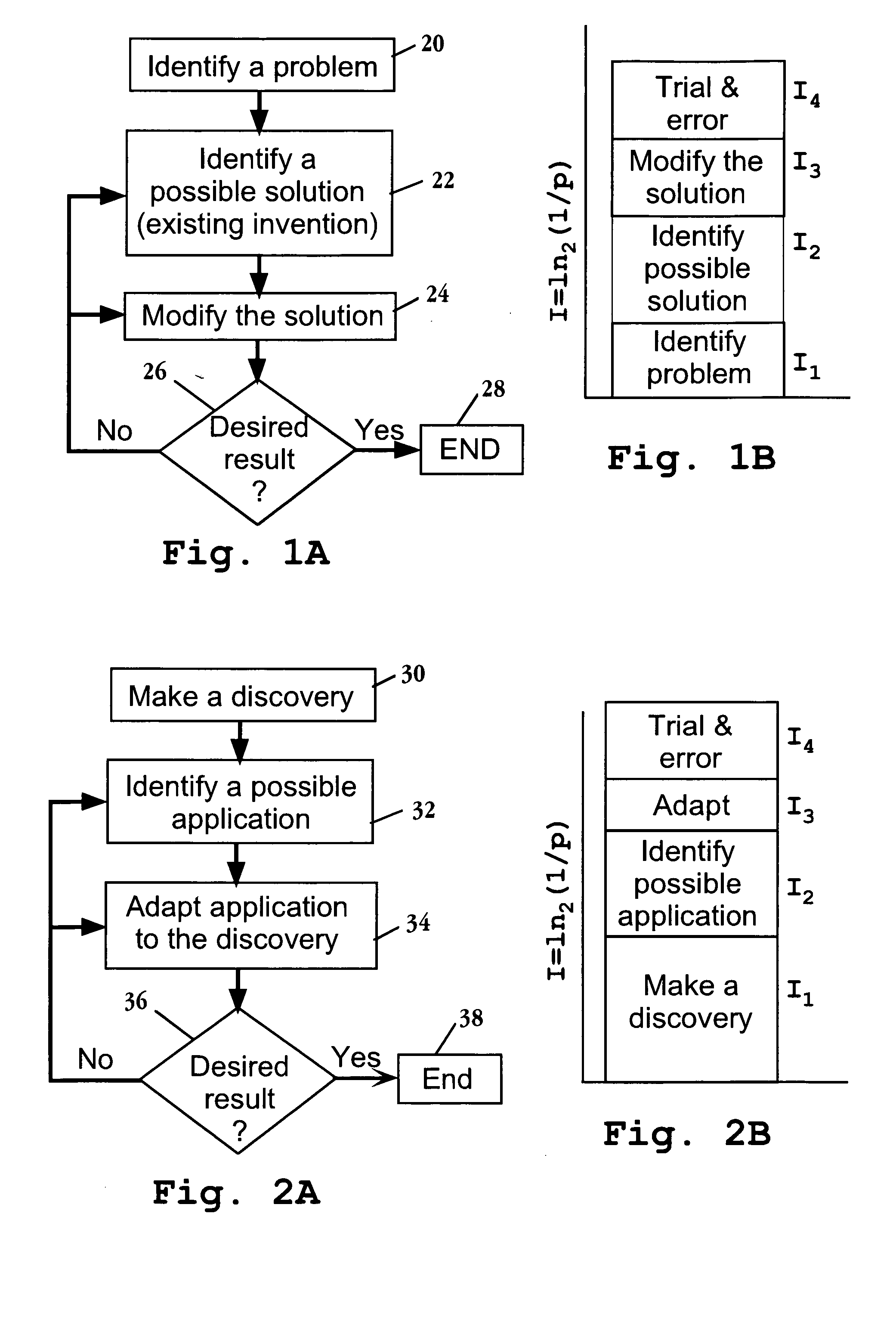

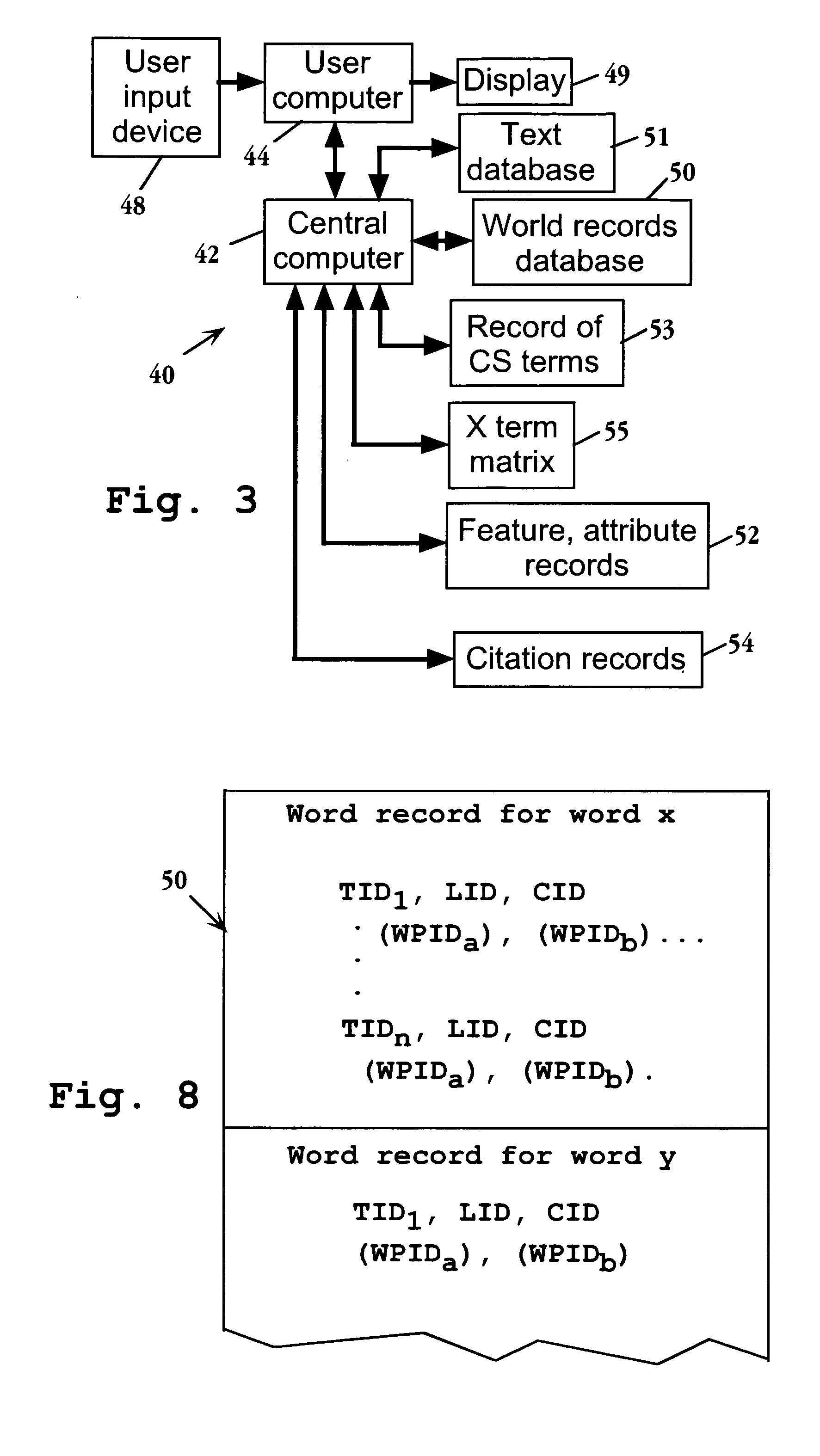

Code, system, and method for generating concepts

InactiveUS20050198026A1High occurrence rateNatural language translationSpecial data processing applicationsAlgorithmGenetic algorithm

Disclosed are a computer-readable code, system and method for generating candidate novel concepts in one or more selected fields. The system operates to generate strings of terms composed of combinations of word and optionally, word-group terms that are descriptive of concept elements in such field(s), and uses a genetic algorithm to find one or more high fitness strings, based on the application of a fitness metric which quantifies, e.g., the number occurrence of pairs of terms in texts in a selected library of texts. The highest- score string or strings are then applied in a database search to identify one or more pairs of primary and secondary texts whose terms overlap with those of a high fitness string.

Owner:WORD DATA

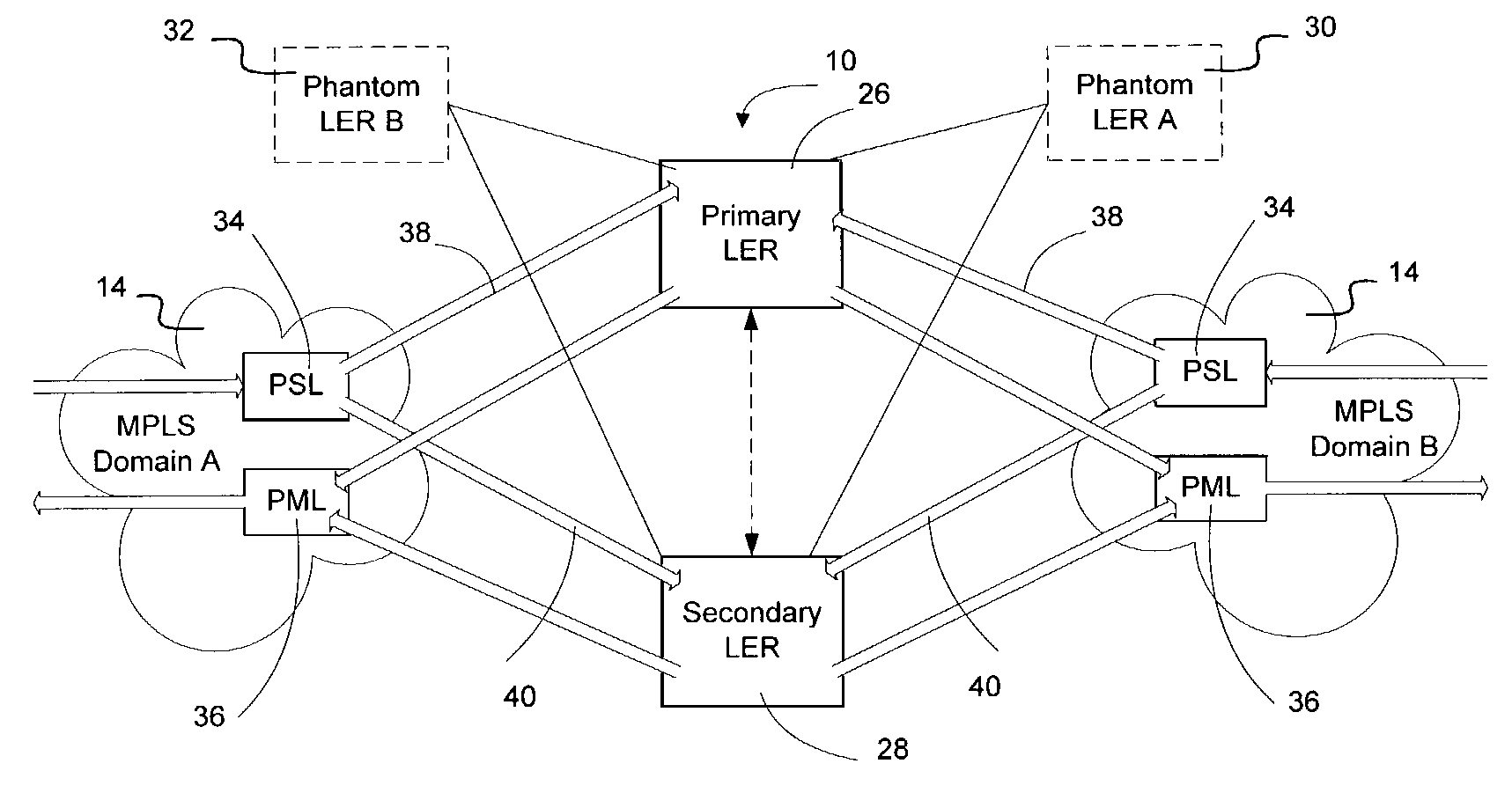

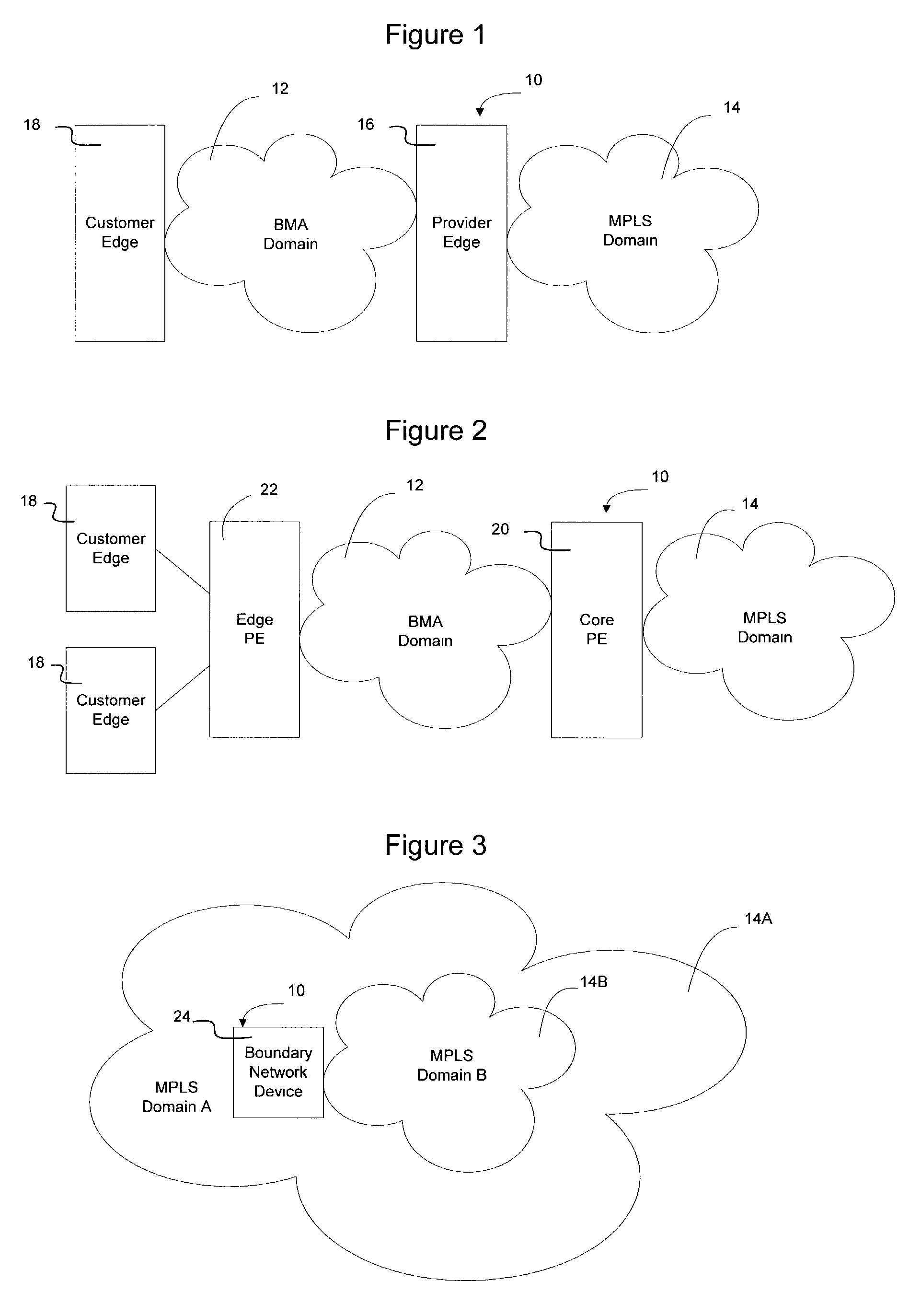

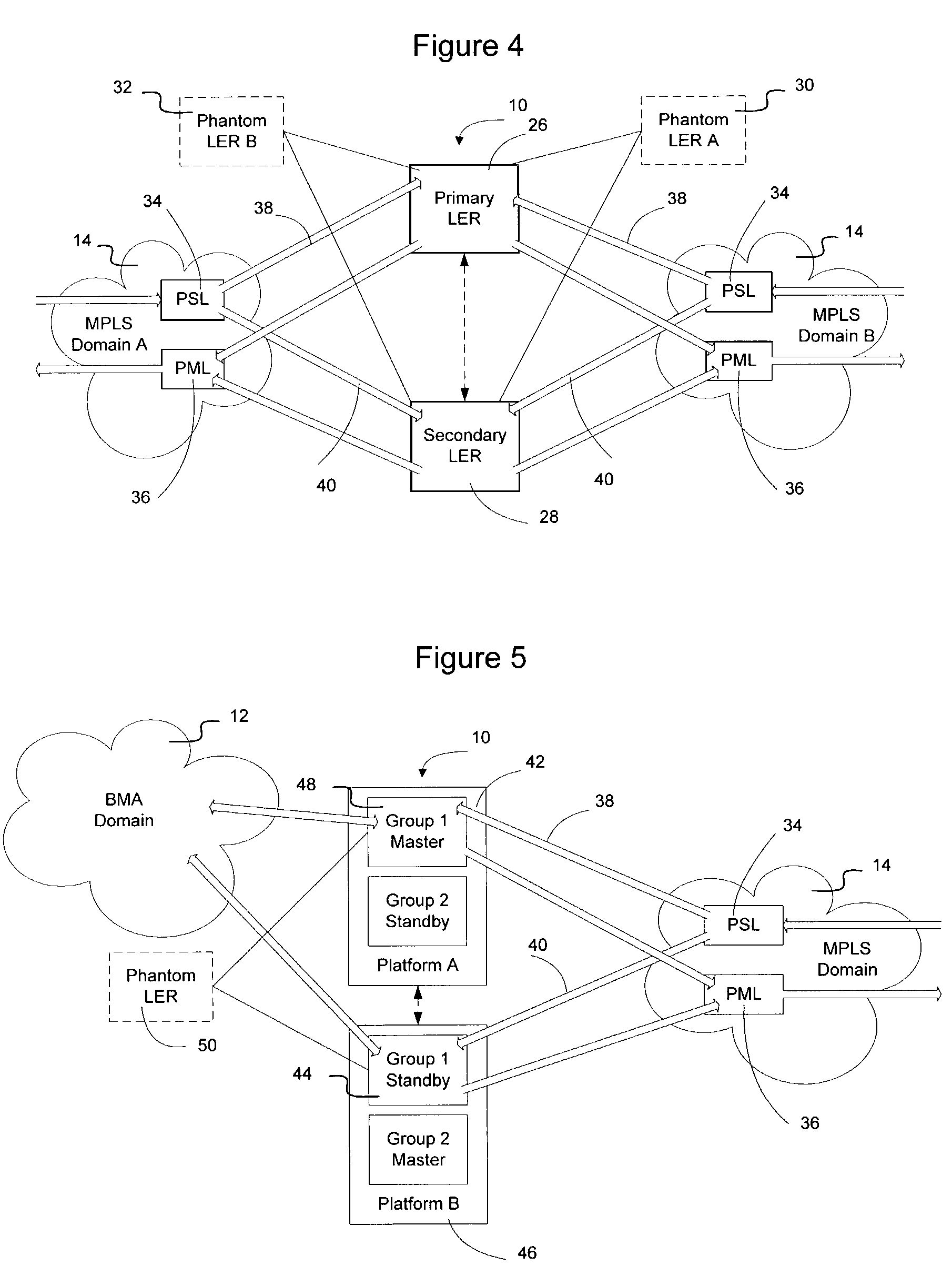

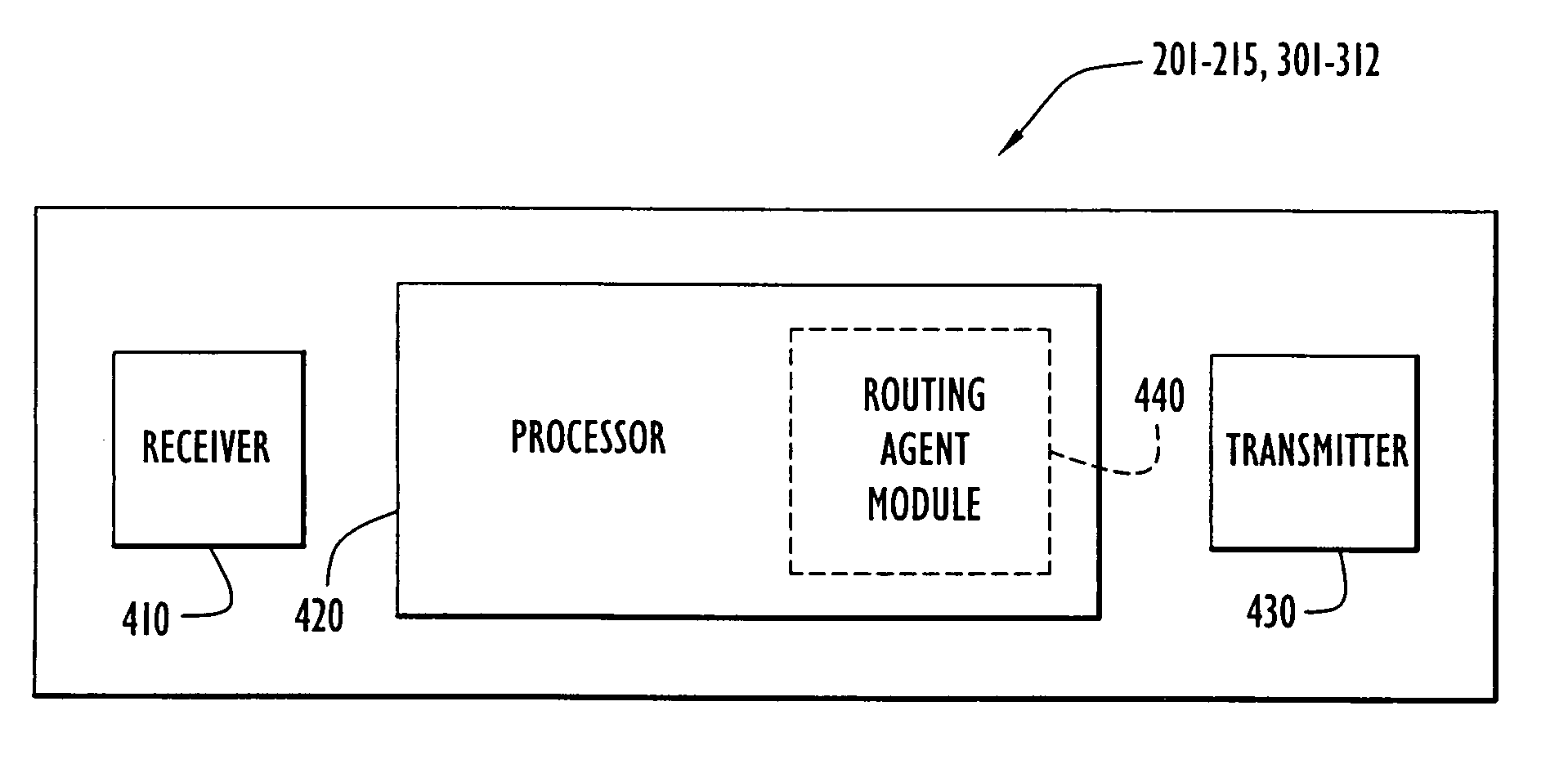

Method and apparatus for achieving transparent redundancy at a hierarchical boundary

InactiveUS7269132B1Achieve redundancyIncrease elasticityError preventionFrequency-division multiplex detailsTraffic volumeMajor and minor

Transparent redundancy may be achieved at a MPLS-MPLS hierarchical boundary or a BMA-MPLS hierarchical boundary by utilizing local repair mechanisms extant in each domain to select automatically the same boundary network devices as the primary and secondary boundary network devices. In the MPLS domain, two LERs advertise the ability to forward traffic to a phantom LER and map all traffic originated into that domain as having been on a path originating at the phantom LER. This will cause the LERs to appear as being one hop away from the phantom LER, causing MPLS to assume the real LERs are part of a LSP terminating at the phantom LER. MPLS local repair will thus establish one of the LERs as the primary LER and the other LER as the secondary LER. In an Ethernet domain, each boundary network device is treated analogously to a router in the VRRP scheme for routers.

Owner:RPX CLEARINGHOUSE

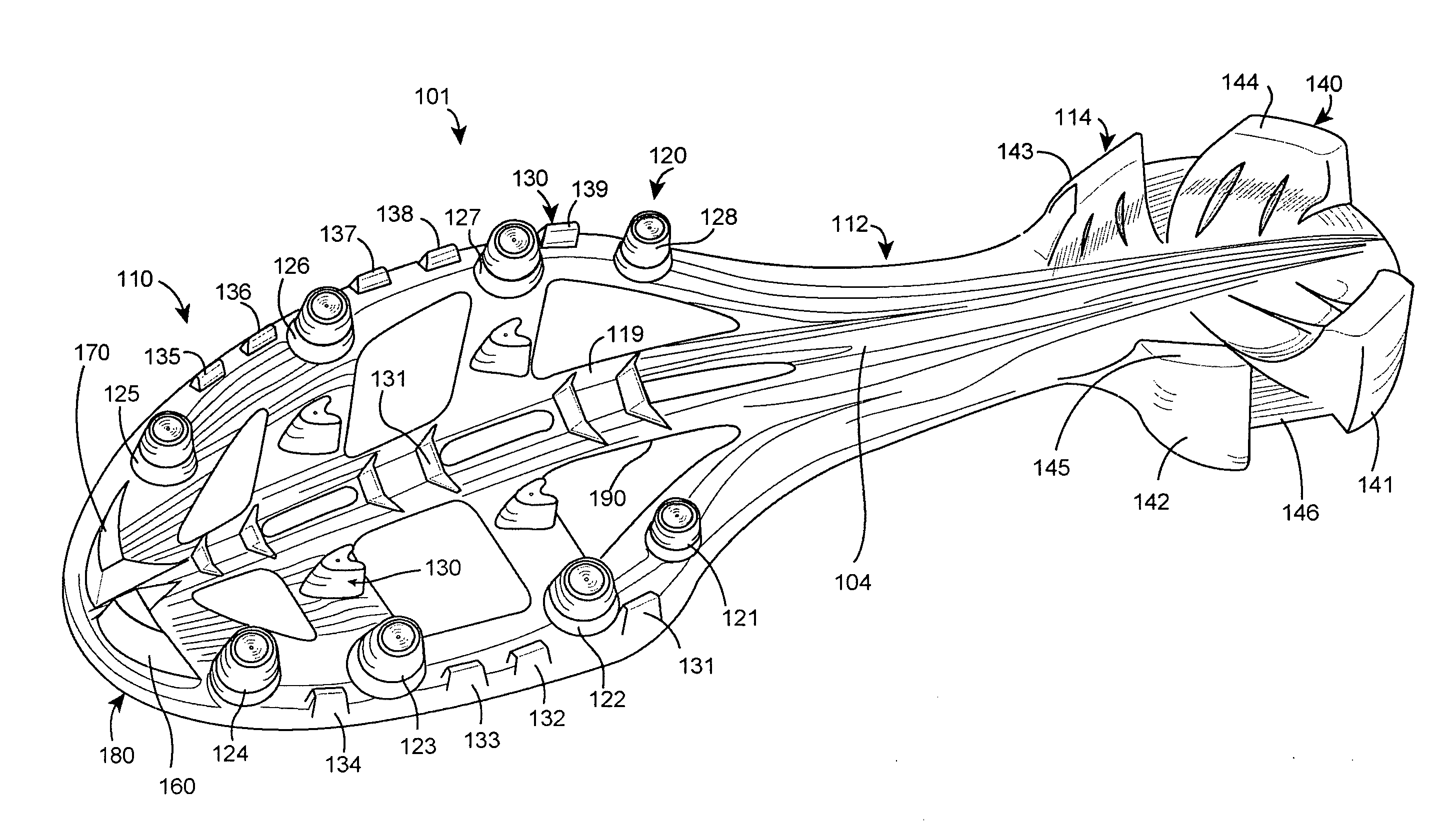

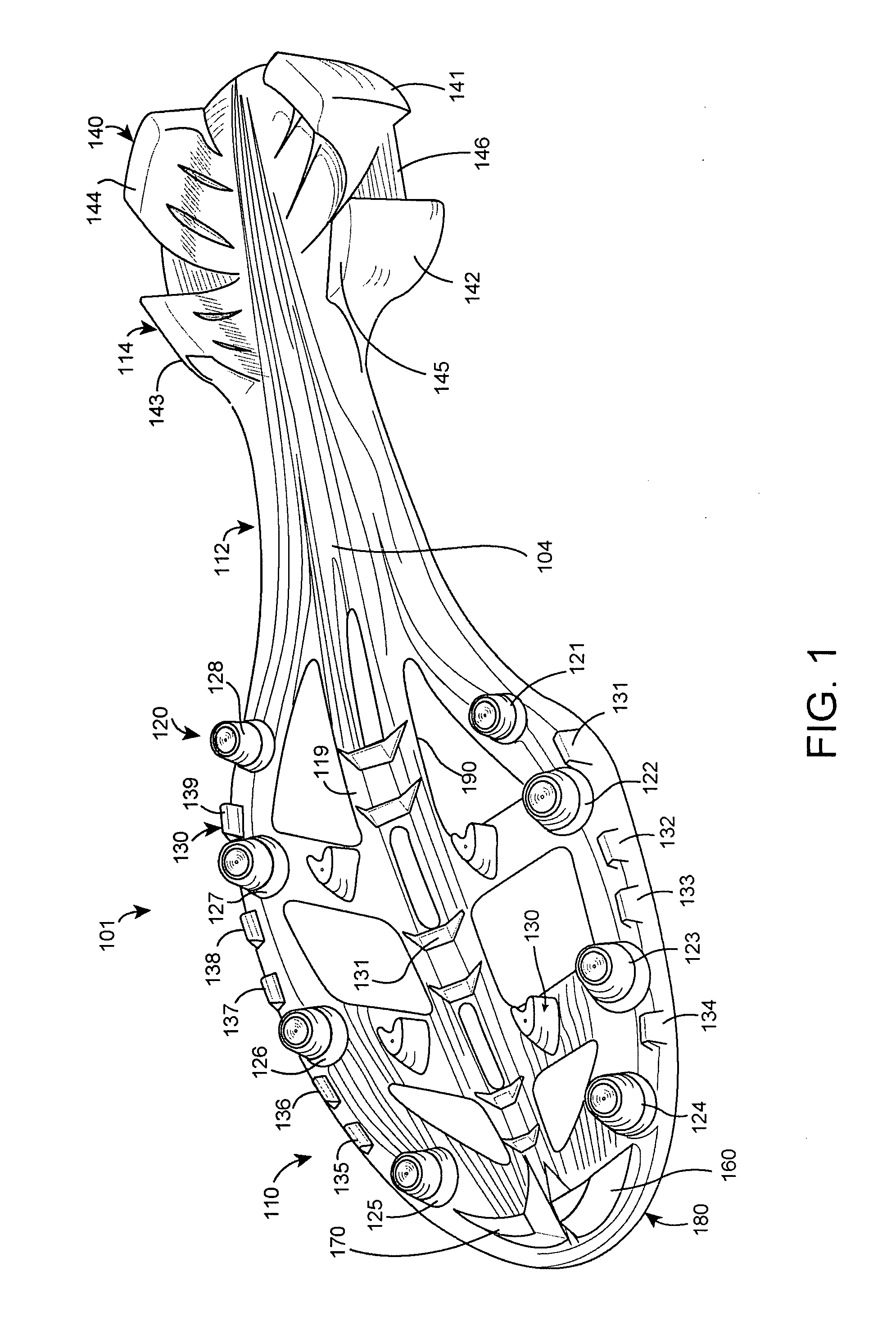

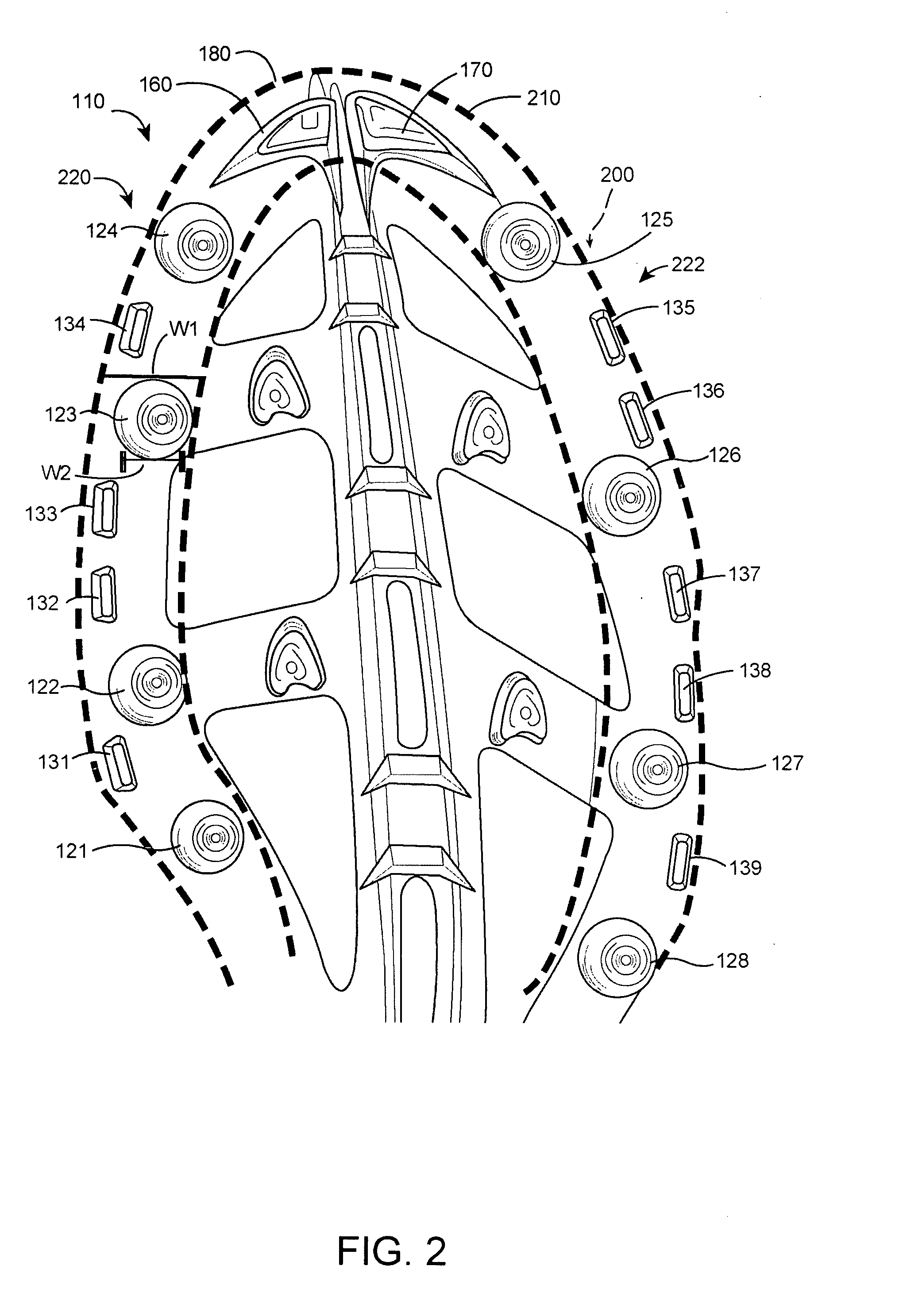

Article of Footwear with Walled Cleat System

An article of footwear with primary cleats and secondary cleats is disclosed. The primary and secondary cleats are preferably disposed on an outer peripheral zone of a forefoot portion of a sole and present a walled cleat system on a portion of the outer peripheral zone. The article of footwear also includes bladed toe cleats.

Owner:NIKE INC

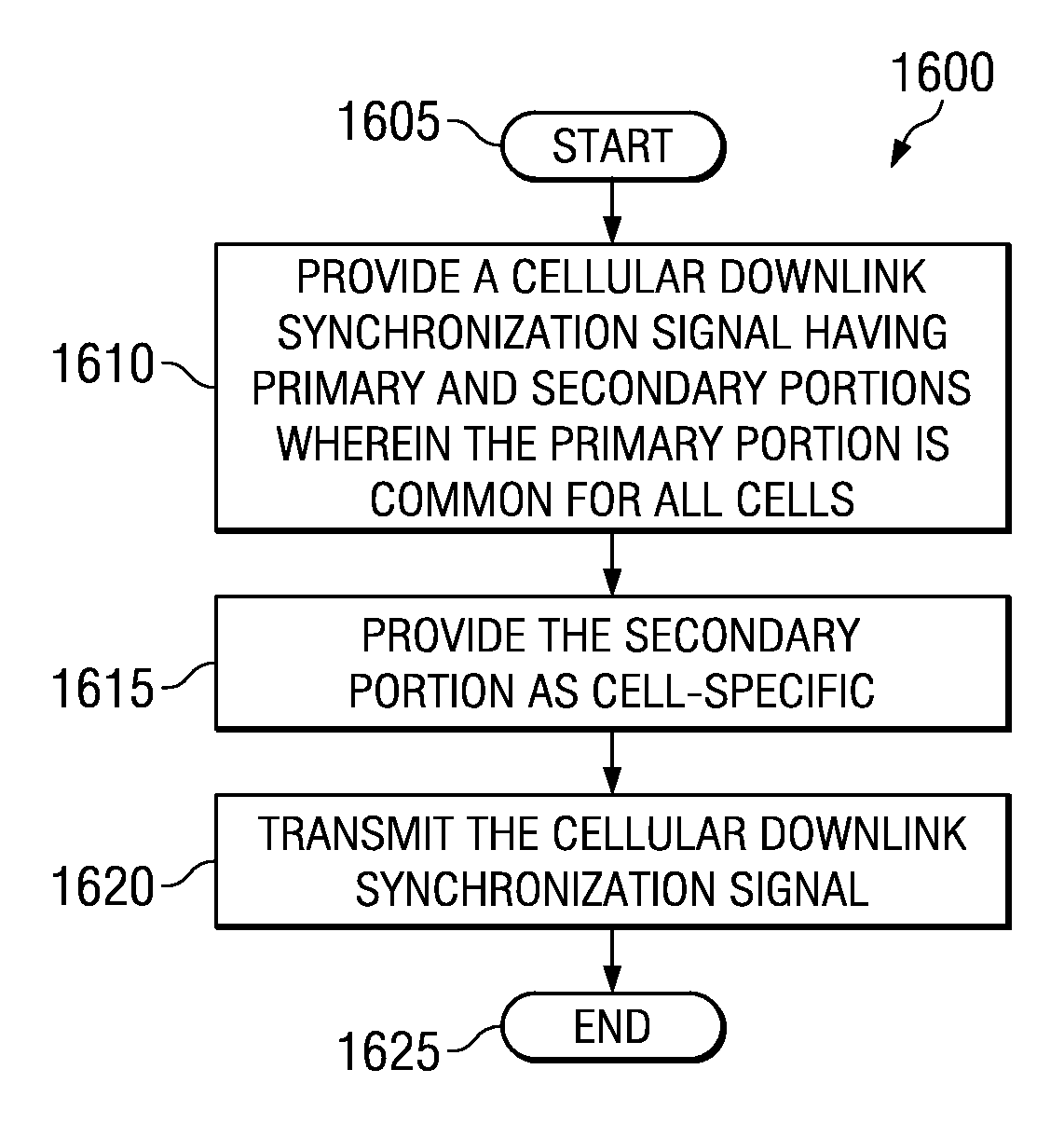

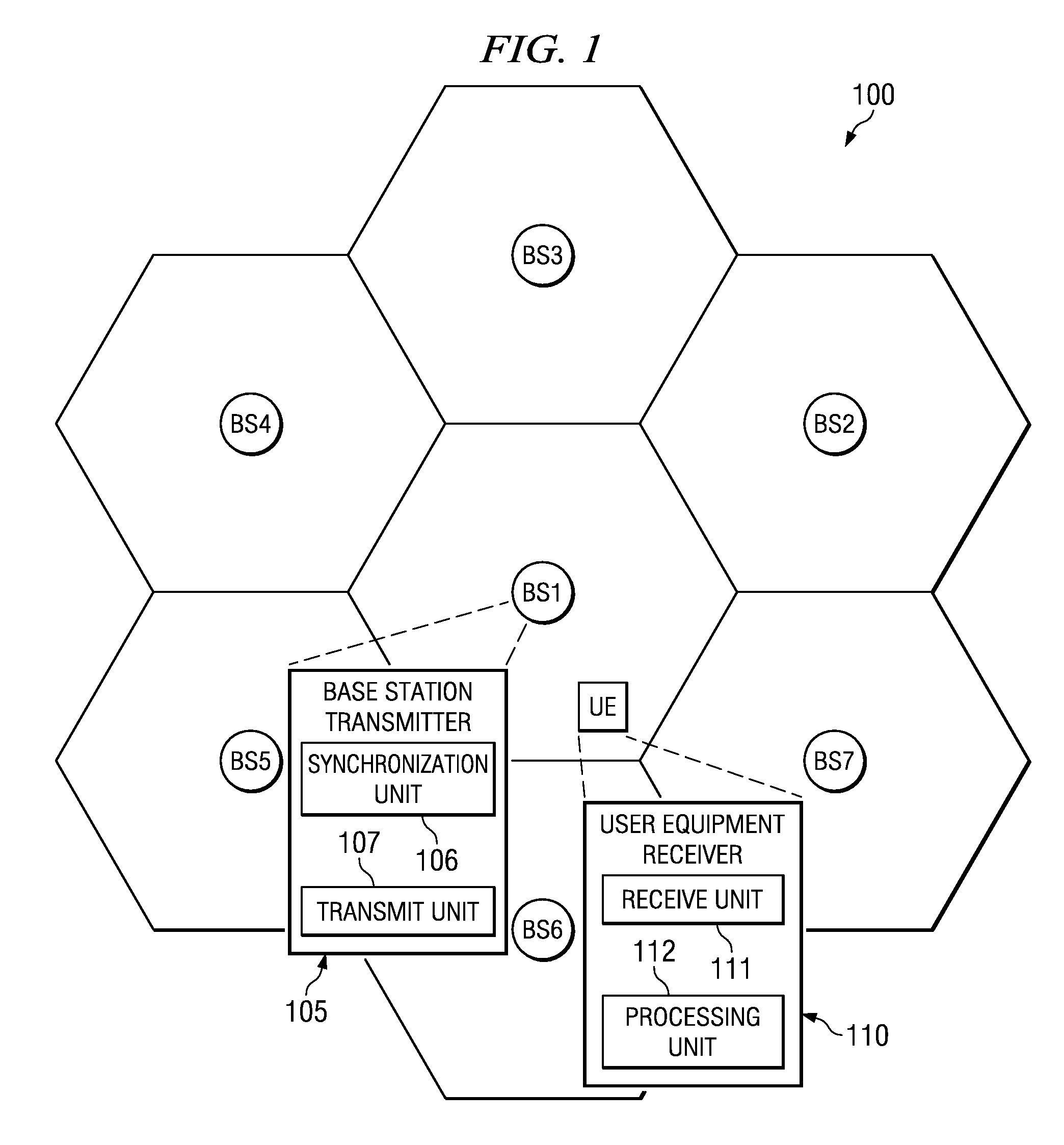

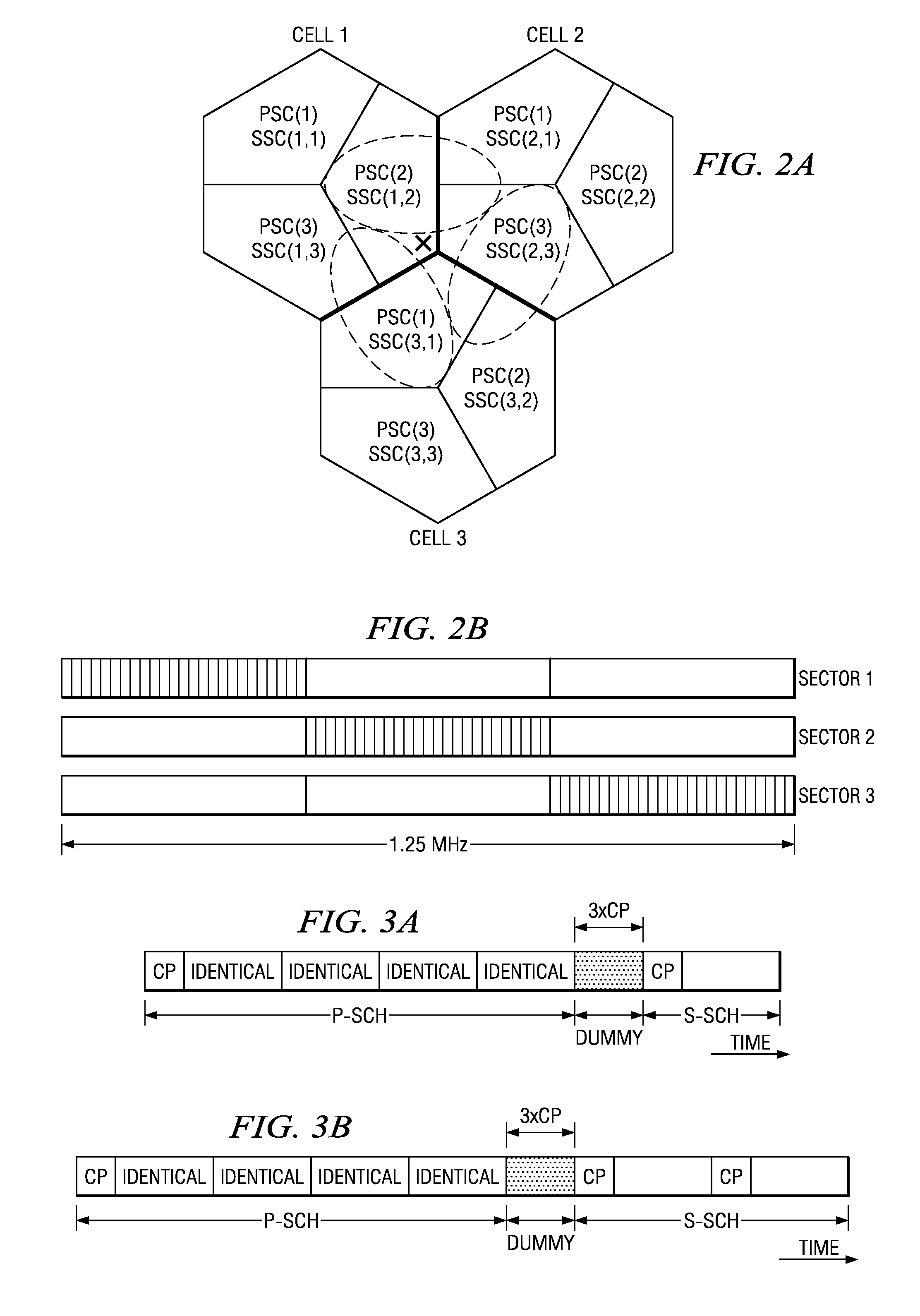

Downlink synchronization for a cellular OFDM communication system

ActiveUS20080019350A1Modulated-carrier systemsTransmission path divisionCell specificOfdm communication system

The present invention provides a method of operating a base station transmitter. In one embodiment, the method includes providing a cellular downlink synchronization signal having primary and secondary portions, wherein the primary portion is common for all cells and the secondary portion is cell-specific and transmitting the cellular downlink synchronization signal. In another embodiment, the method includes providing a cellular downlink synchronization signal having primary and secondary portions wherein the primary portion employs a corresponding one of a plurality of different primary signals allocated to adjoining transmission cells. The method also includes further providing cell-specific information in the secondary portion and transmitting the cellular downlink synchronization signal. The present invention also provides a method of operating user equipment. The method includes receiving a cellular downlink synchronization signal having primary and secondary portions wherein the secondary portion provides cell-specific parameters and identifying and extracting the secondary portion.

Owner:TEXAS INSTR INC

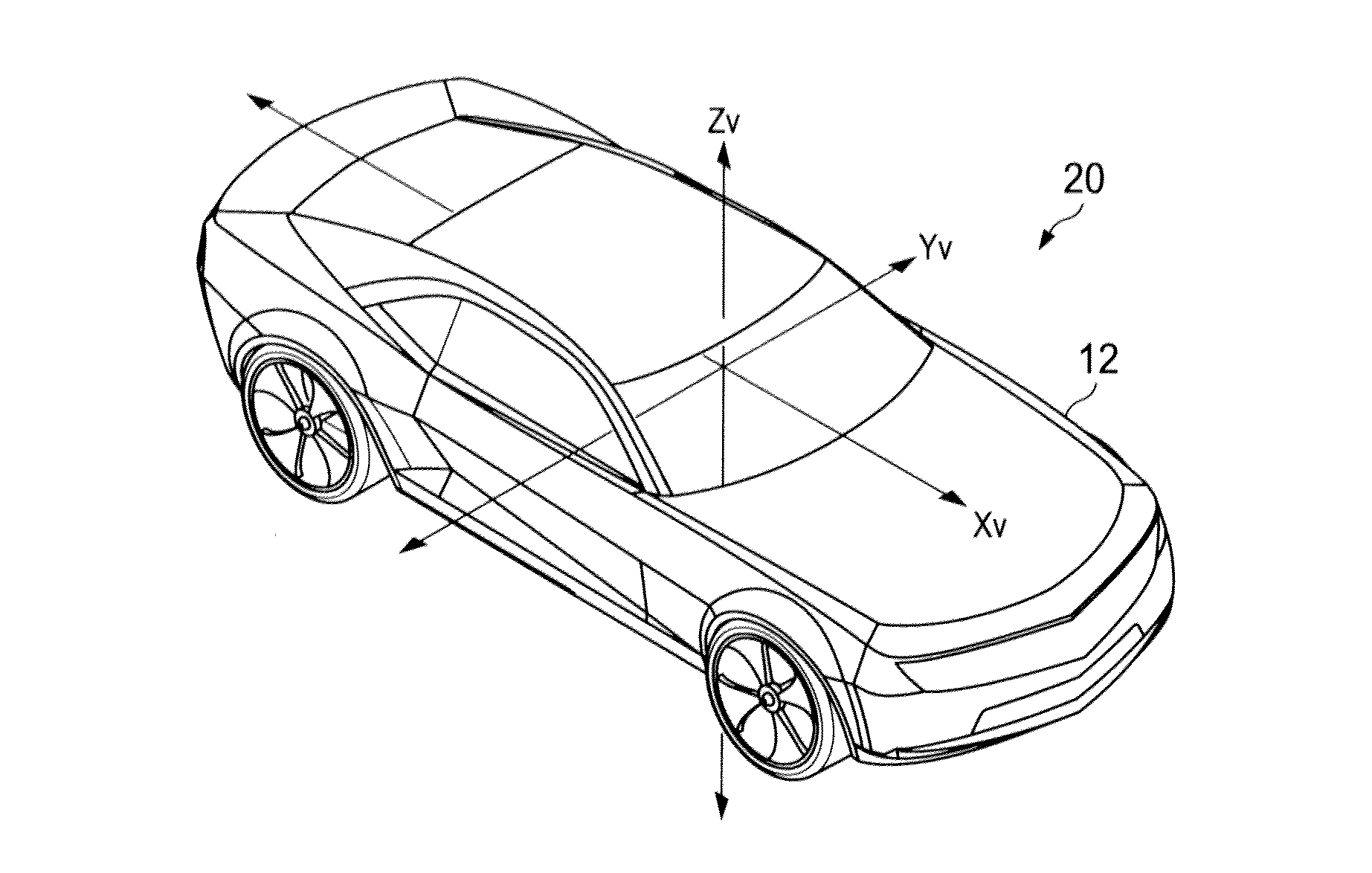

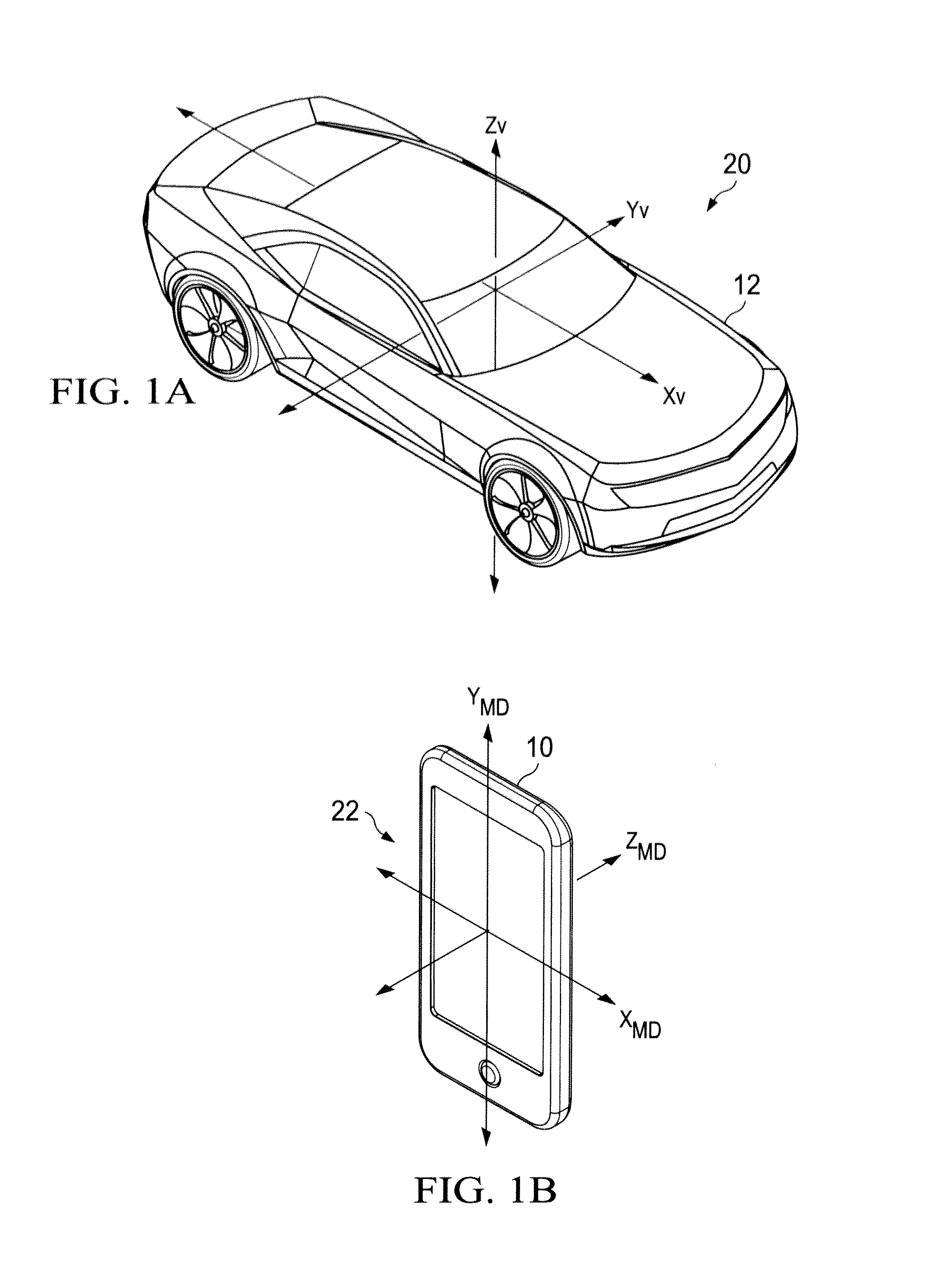

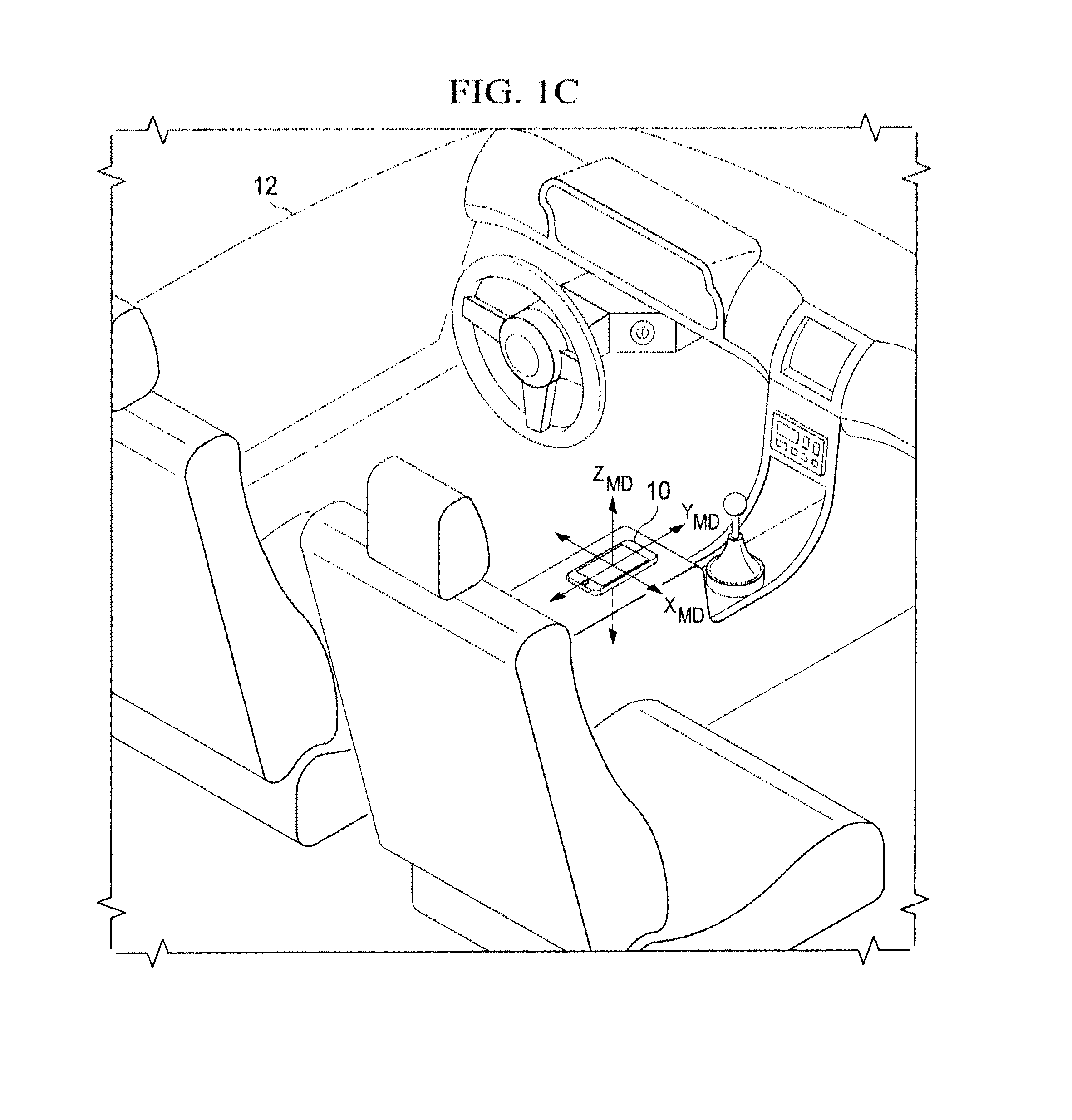

System and Method for Auto-Calibration and Auto-Correction of Primary and Secondary Motion for Telematics Applications via Wireless Mobile Devices

InactiveUS20140149145A1Improve accuracyEasy to collectFinanceDigital computer detailsTransformation algorithmWireless mobile devices

A mobile device for capturing motion data of a vehicle when the mobile device is travelling with the vehicle, the mobile device comprising: at least one sensor; a processor; a non-transitory storage medium; and an orientation algorithm comprising a set of computer readable instructions stored in the non-transitory storage medium and when executed by the processor configured to allow the mobile device to determine an orientation of the mobile device relative to an orientation of the vehicle; and a transformation algorithm comprising a set of computer readable instructions stored in the non-transitory storage medium and when executed by the processor configured to allow the mobile device to transform motion sensor data to remove secondary movement of the mobile device, which corresponds to the relative movement of the mobile device within the vehicle, and retain primary movement of the mobile device, which corresponds to the motion of the vehicle.

Owner:STATE FARM INSURANCE

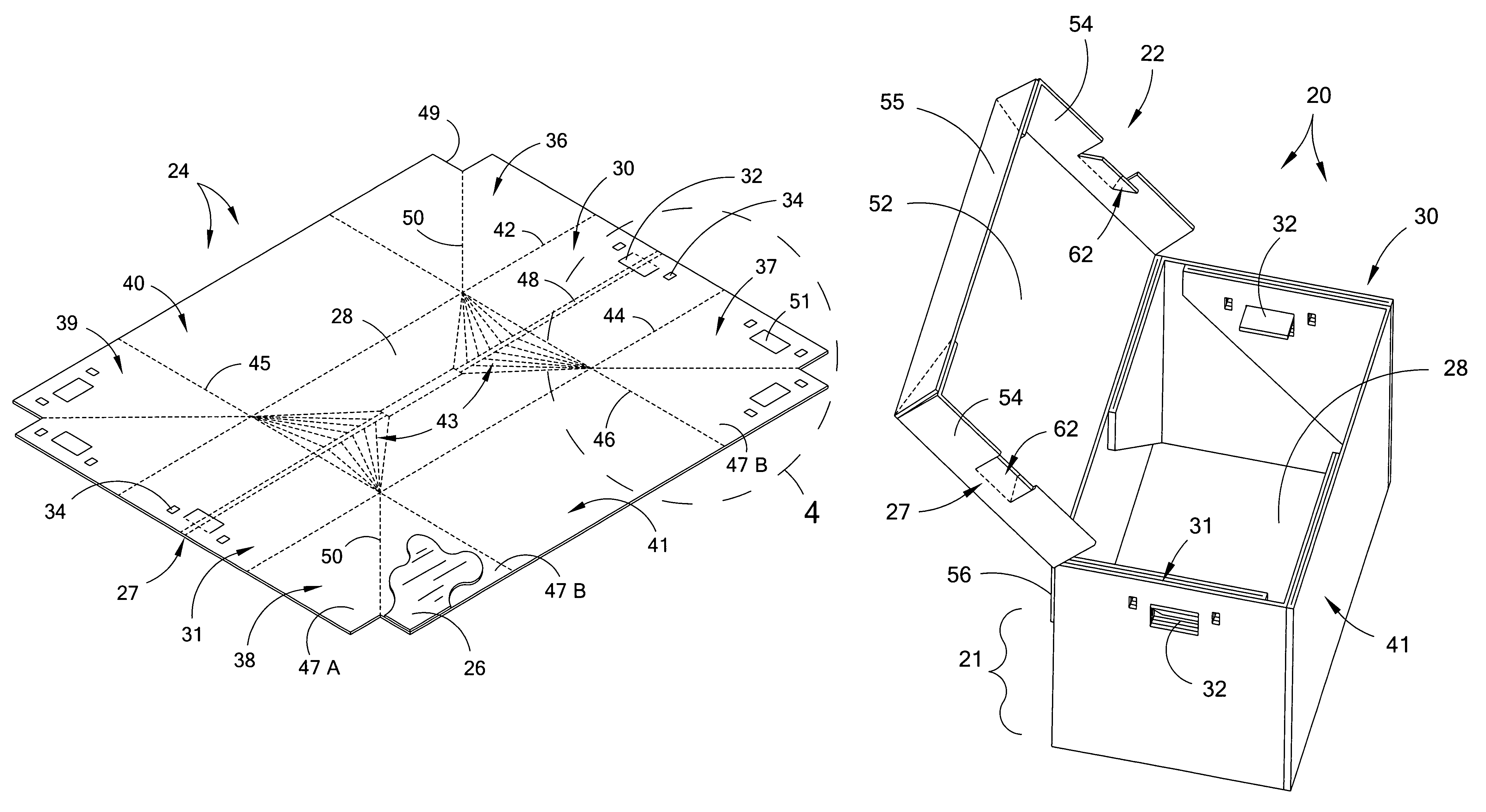

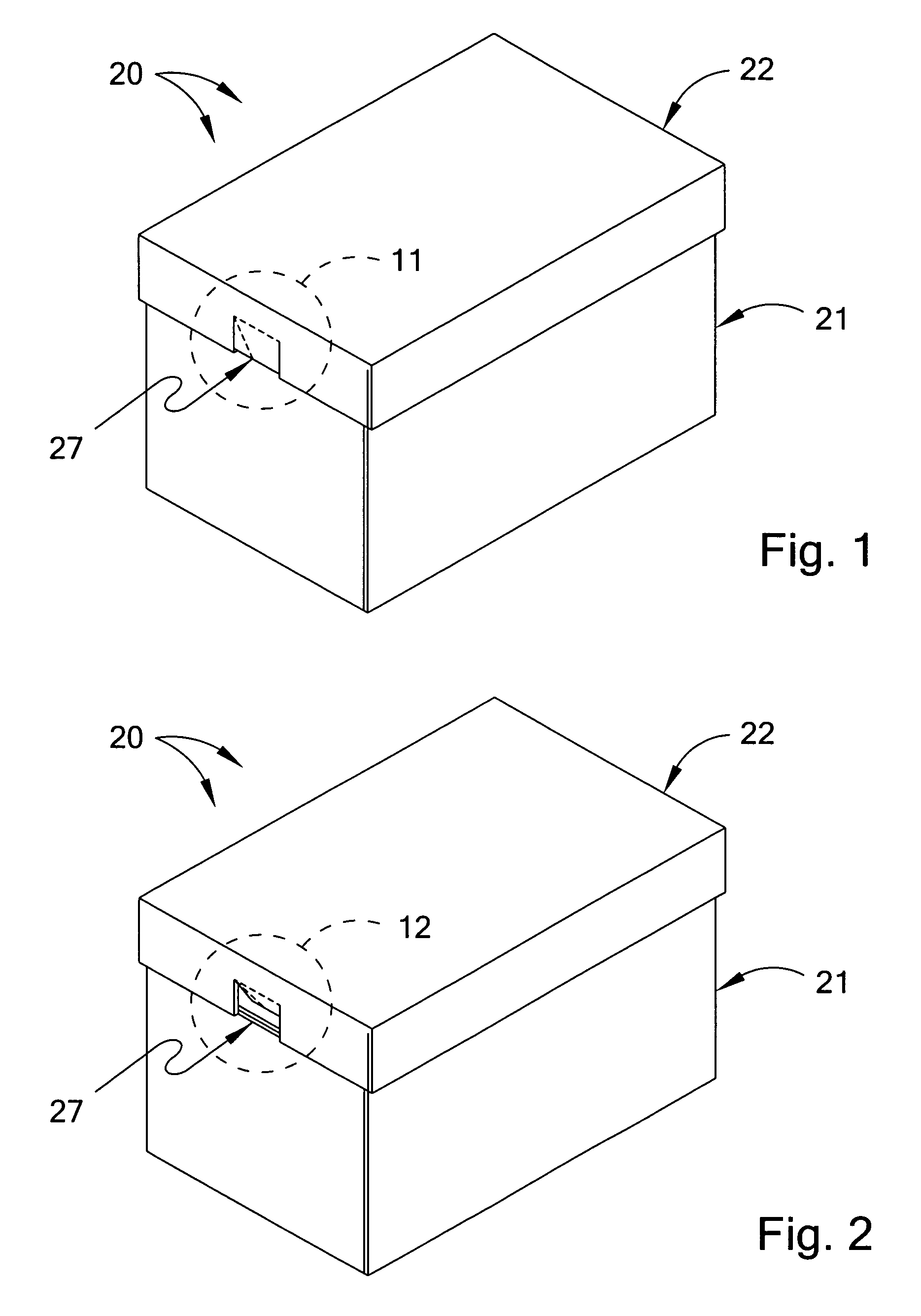

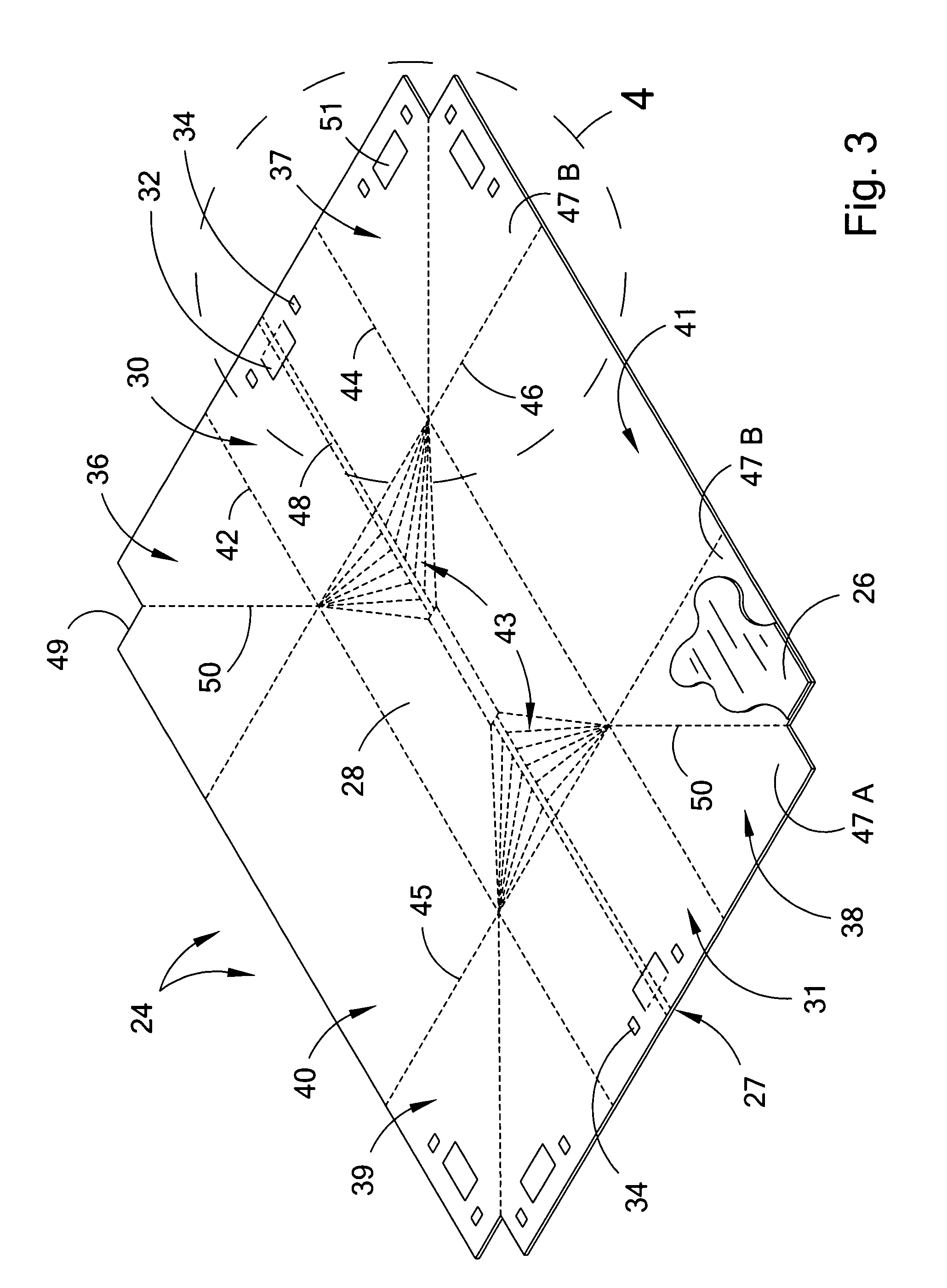

Folded corrugated container with reinforced quick-locking handles

A container comprises a knockdown carton made from a flat blank of corrugated material, and a knockdown lid. The carton comprises a center panel, foldable end panels, foldable side panels, and foldable corner panels. A pair of diametrically opposed corner panels are folded inwardly into contact with opposed end panels. The end panels comprise rectangular cutout holes surrounding foldable flaps. The lid has a central panel that is divided from integral end panels and integral side panels. A lid side panel extending vertically downwardly is coupled to the carton. Lid end panels have elliptical orifices that register with carton cutout regions and adjoining slots that align with handle anchor orifices. An alternative lid has flaps comprising major and minor segments separated by a diagonal fold line. The minor segment has an apex that releasably biases the flap in engagement with the end panel, yieldably locking the lid.

Owner:PRATT CORRUGATED HLDG

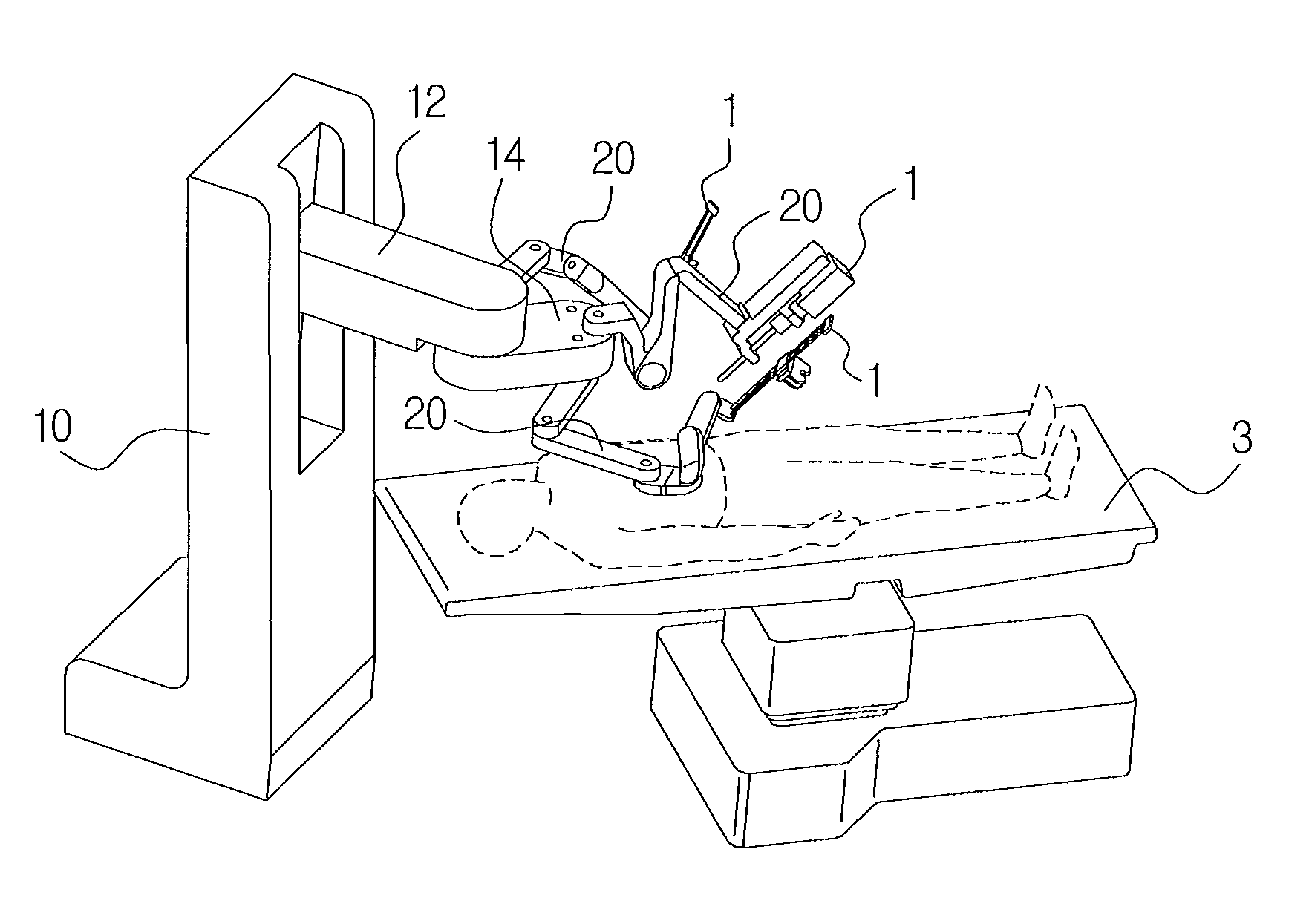

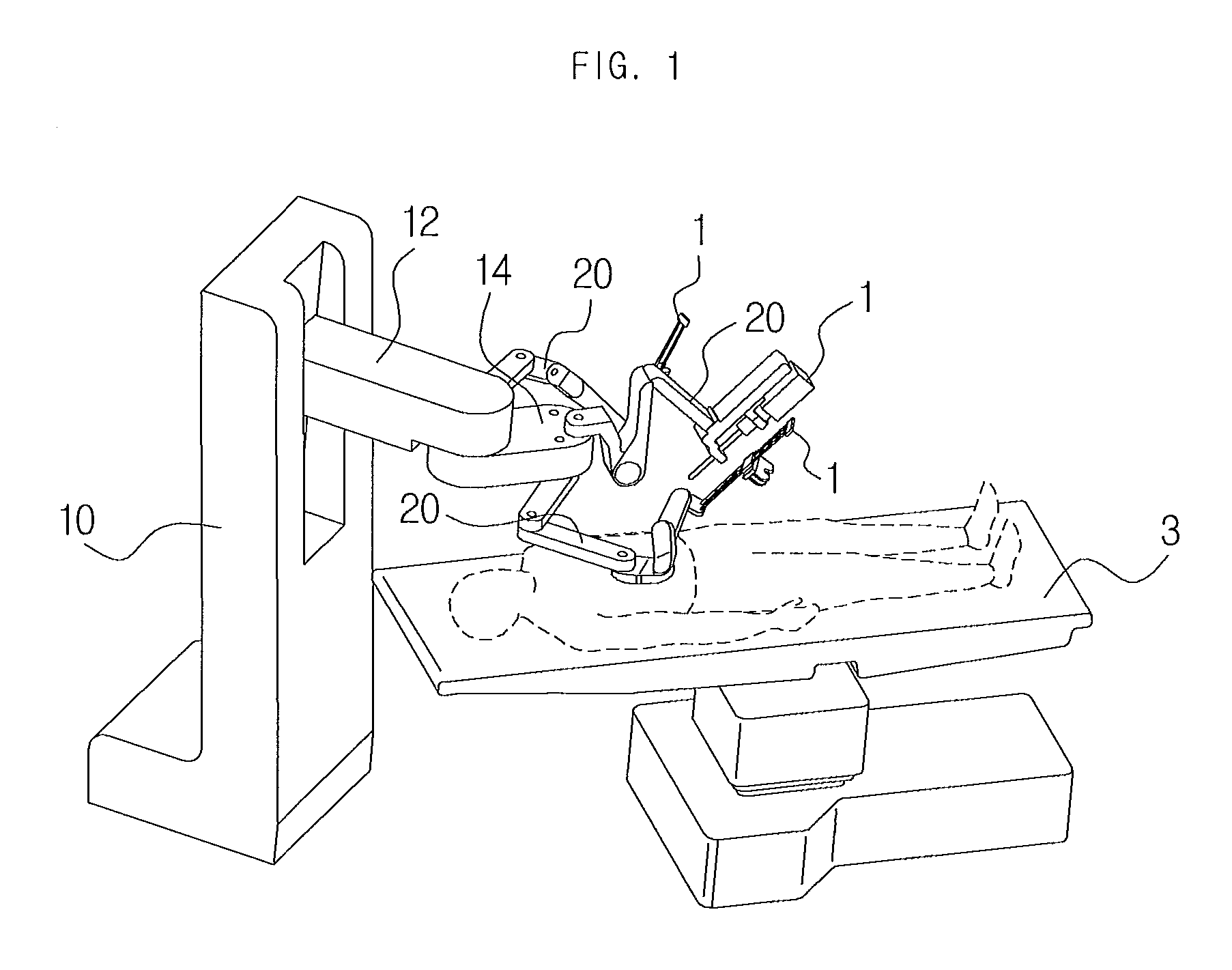

Surgical slave robot

ActiveUS7954397B2Functionality precisionExact strengthMechanical apparatusJointsSurgical operationSurgical robot

Owner:MEERECO

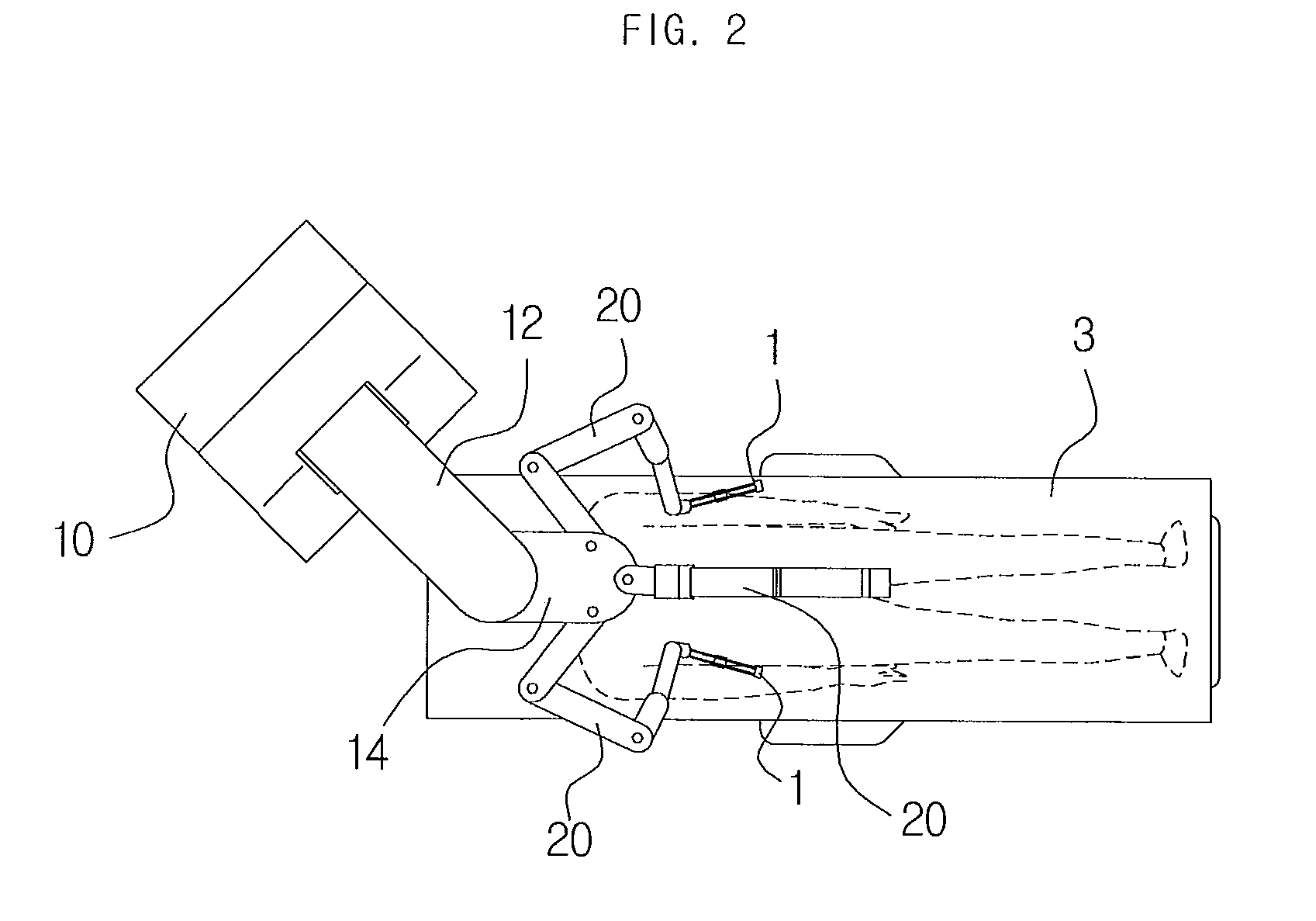

Method and system for transferring data in a communications network using redundant communication paths

ActiveUS20060256768A1Improve delivery reliabilityDecrease packet delivery timeData switching by path configurationMultiple digital computer combinationsReliable transmissionTransport layer

A communication node of the present invention automatically transmits original and duplicate packets over different paths in a communications network to improve delivery reliability of the packet and to decrease packet delivery time. A packet is typically marked for reliable transmission by the application layer of a source node, while a routing agent module within the node IP layer processes the marked packets. The marked packets are transmitted over redundant (e.g., primary and secondary) network paths from the source node to the destination node. The primary path is usually the shortest path between the source and destination nodes, while the secondary path is selected to avoid overlap with the primary path. The application or transport layer of the destination node filters or removes plural copies of received packets.

Owner:HARRIS GLOBAL COMMUNICATIONS INC

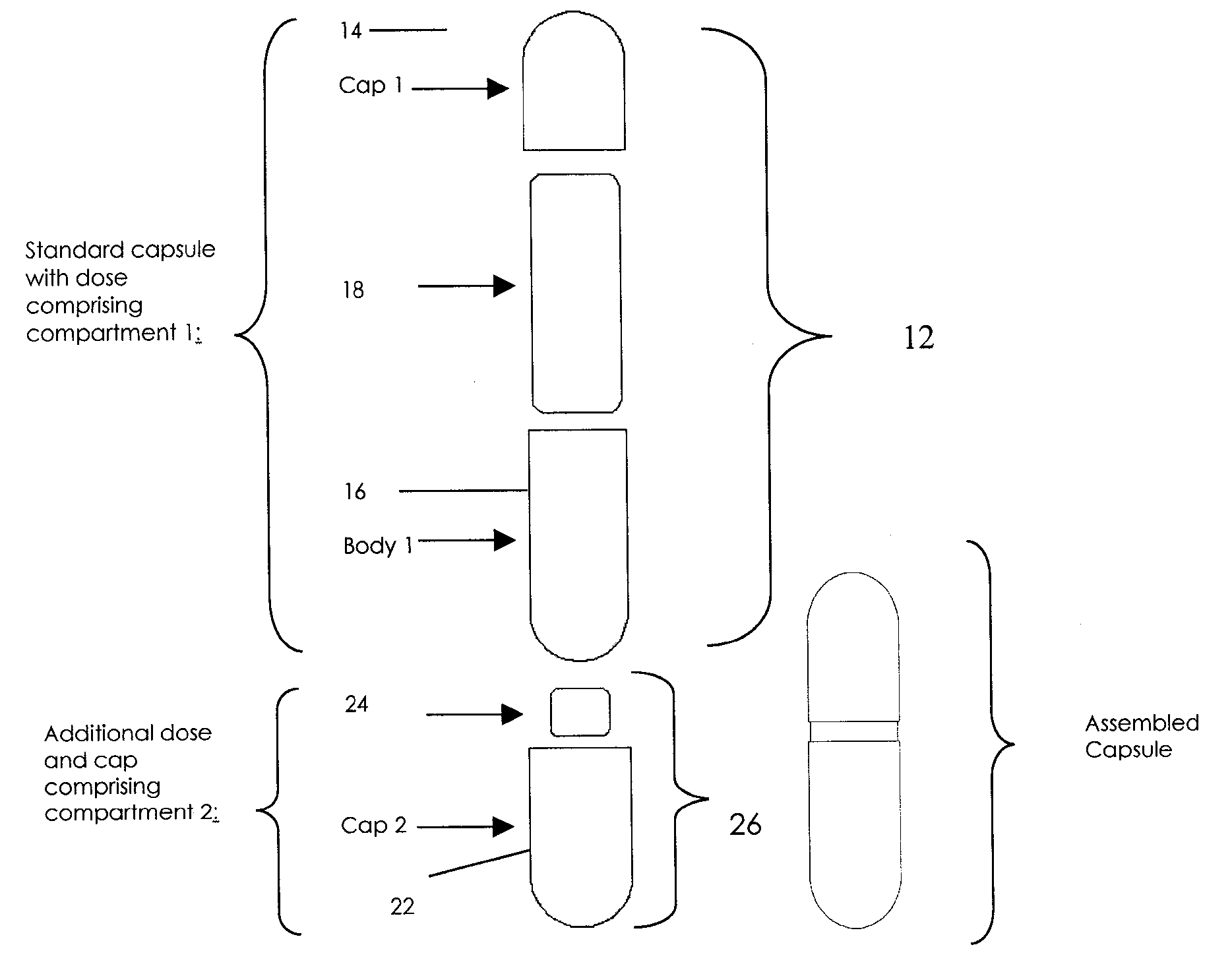

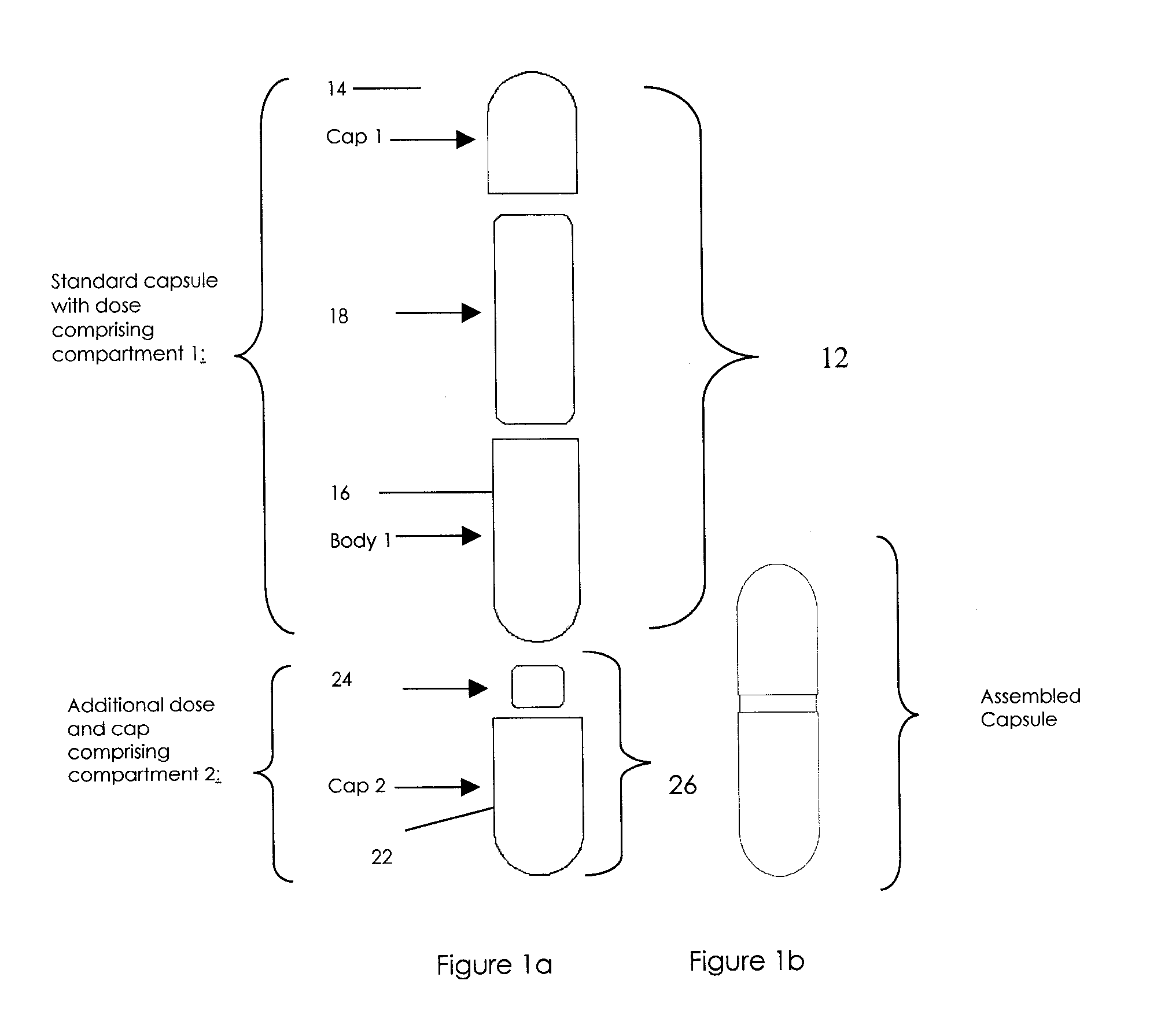

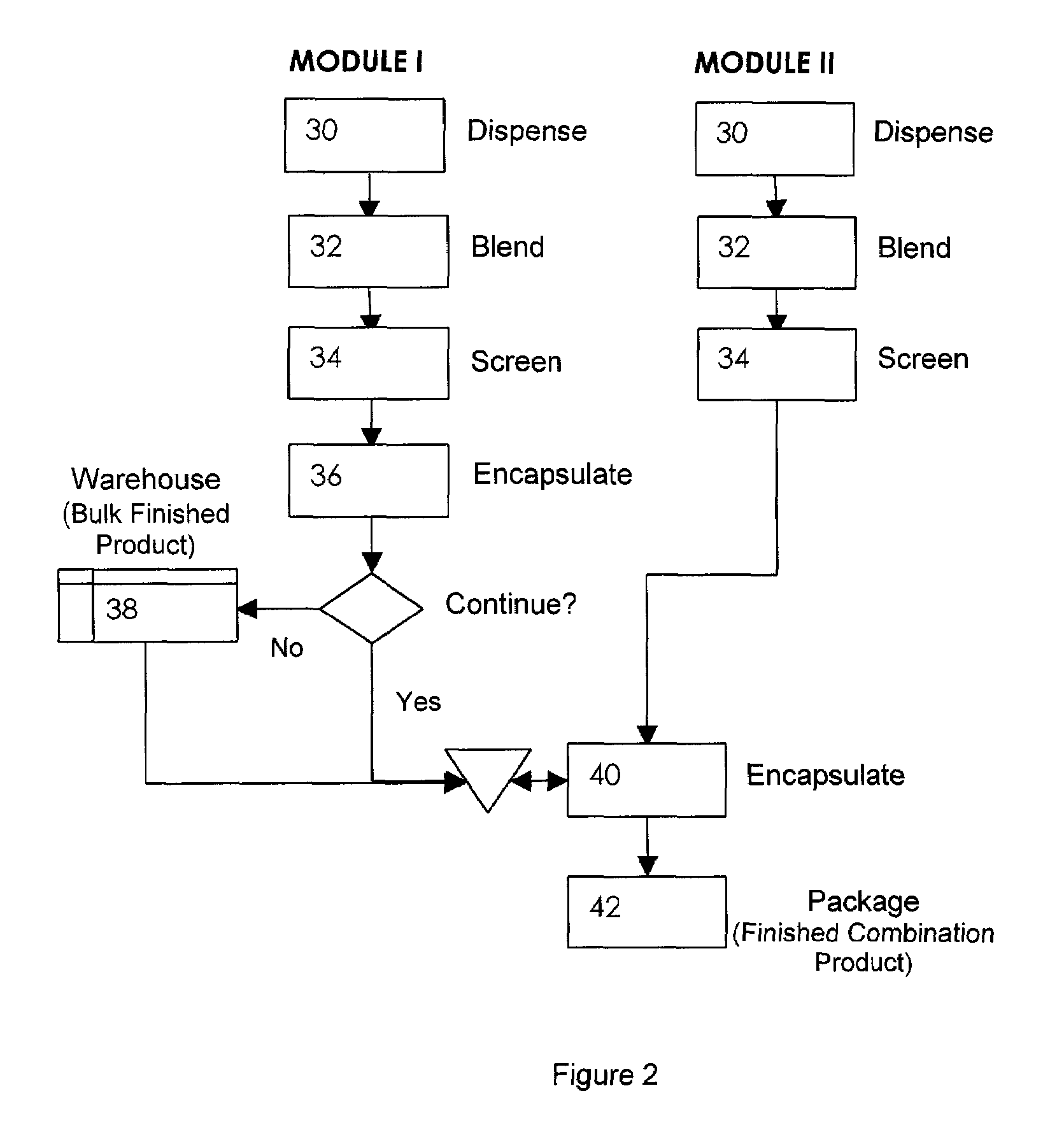

Oral dosage combination pharmaceutical packaging

InactiveUS20090087483A1Overall design flexibilityIncreased riskAntibacterial agentsBiocideMedicinePharmaceutical packaging

Pharmaceutical fixed dose combination products are formed by merging a fixed dose of a first pharmaceutical formulation from primary module, with a fixed dose of a second pharmaceutical formulation from a secondary module. In a preferred embodiment the first and second pharmaceutical formulations are separated from one another in a three piece capsule, a capsule-in-a-capsule or a tablet-in-a-capsule, and the primary and secondary modules are interchangeable.

Owner:MICRODOSE THERAPEUTX INC

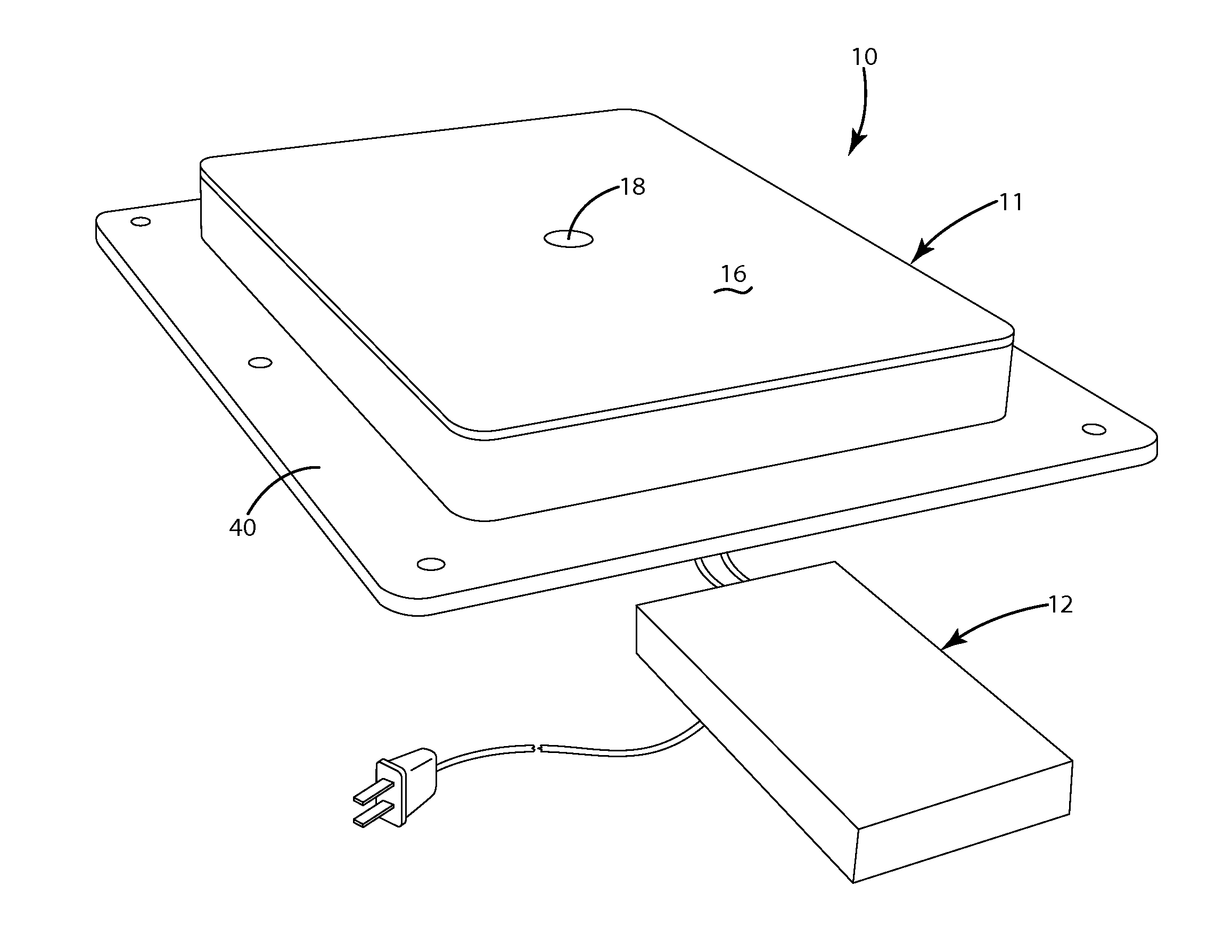

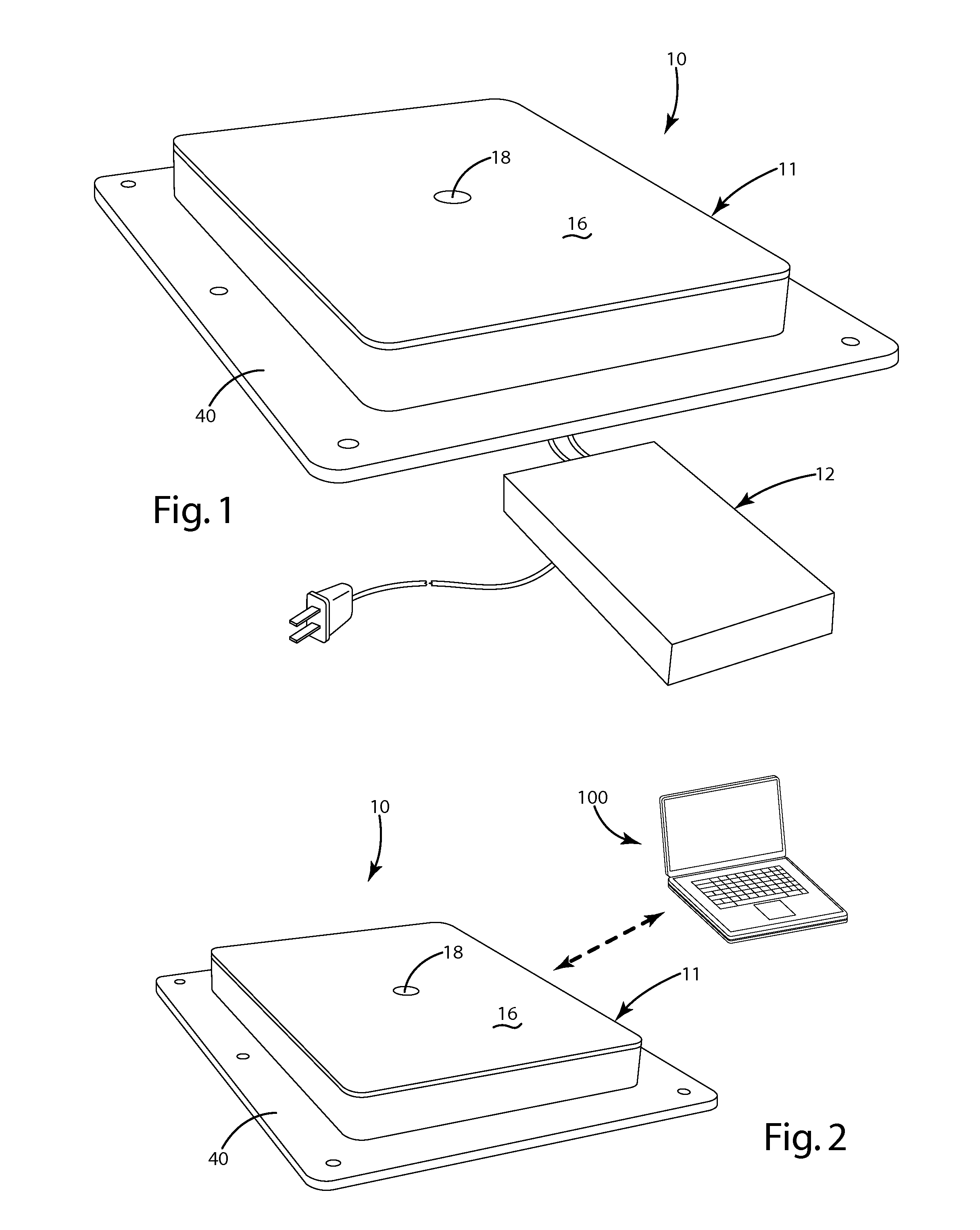

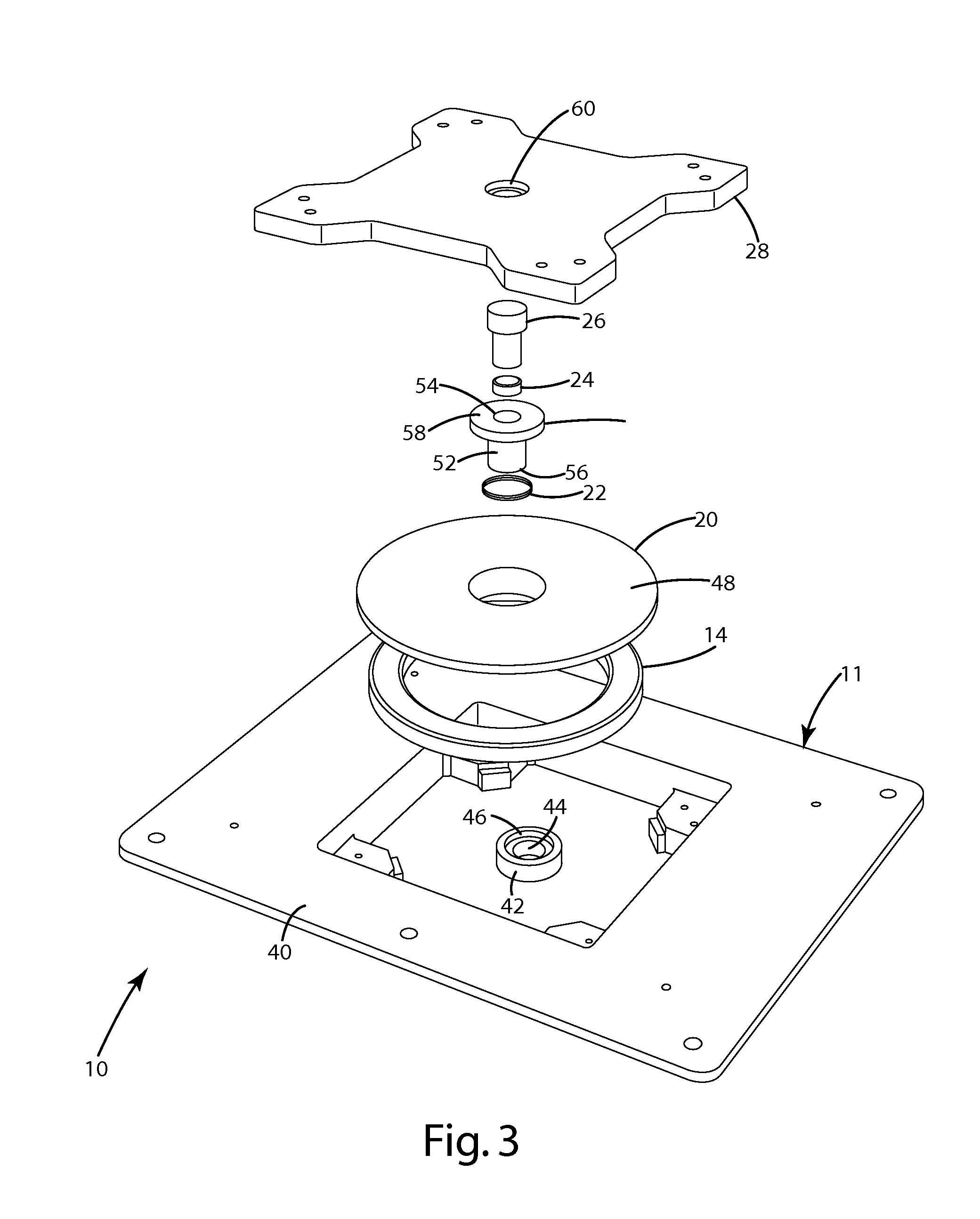

Inductive power supply

ActiveUS8373310B2Reduced footprintSimple mechanical structureBatteries circuit arrangementsElectromagnetic wave systemCharging stationMajor and minor

In one aspect, the present invention provides a wireless power supply having a plunger for mechanically interconnecting a remote device with the power supply. The plunger may be extendable / retractable to interfit with the remote device. In a second aspect, the present invention provides a wireless power supply with a movable primary that allows for close alignment between the primary and the secondary when the remote device is disposed within a range of different positions with respect to the charging surface. The movable primary may, for example, be coupled to the remote device by a peg, a plunger or a magnet. Alternatively, the position of the movable primary may be adjusted manually. In a third aspect, the present invention provides a charging bowl having a plurality of charging stations disposed about a common axis. Each charging station may include a movable primary that permits some freedom in positioning of the remote device on the charging surface. In a fourth aspect, the present invention provides a wireless power supply having a manually movable primary.

Owner:PHILIPS IP VENTURES BV

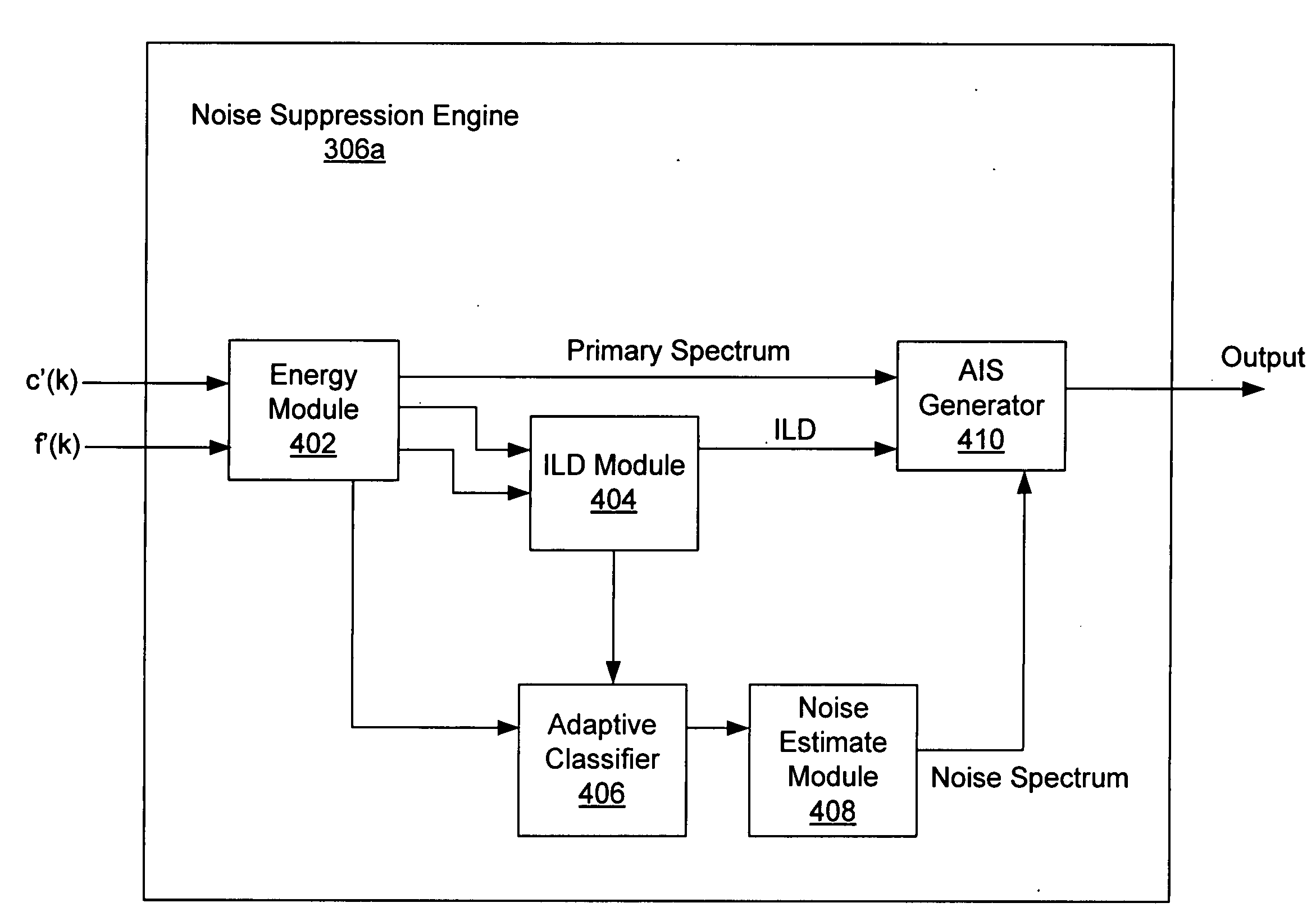

System and method for providing noise suppression utilizing null processing noise subtraction

Systems and methods for noise suppression using noise subtraction processing are provided. The noise subtraction processing comprises receiving at least a primary and a secondary acoustic signal. A desired signal component may be calculated and subtracted from the secondary acoustic signal to obtaining a noise component signal. A determination may be made of a reference energy ratio and a prediction energy ratio. A determination may be made as to whether to adjust the noise component signal based partially on the reference energy ratio and partially on the prediction energy ratio. The noise component signal may be adjusted or frozen based on the determination. The noise component signal may then be removed from the primary acoustic signal to generate a noise subtracted signal which may be outputted.

Owner:KNOWLES ELECTRONICS INC

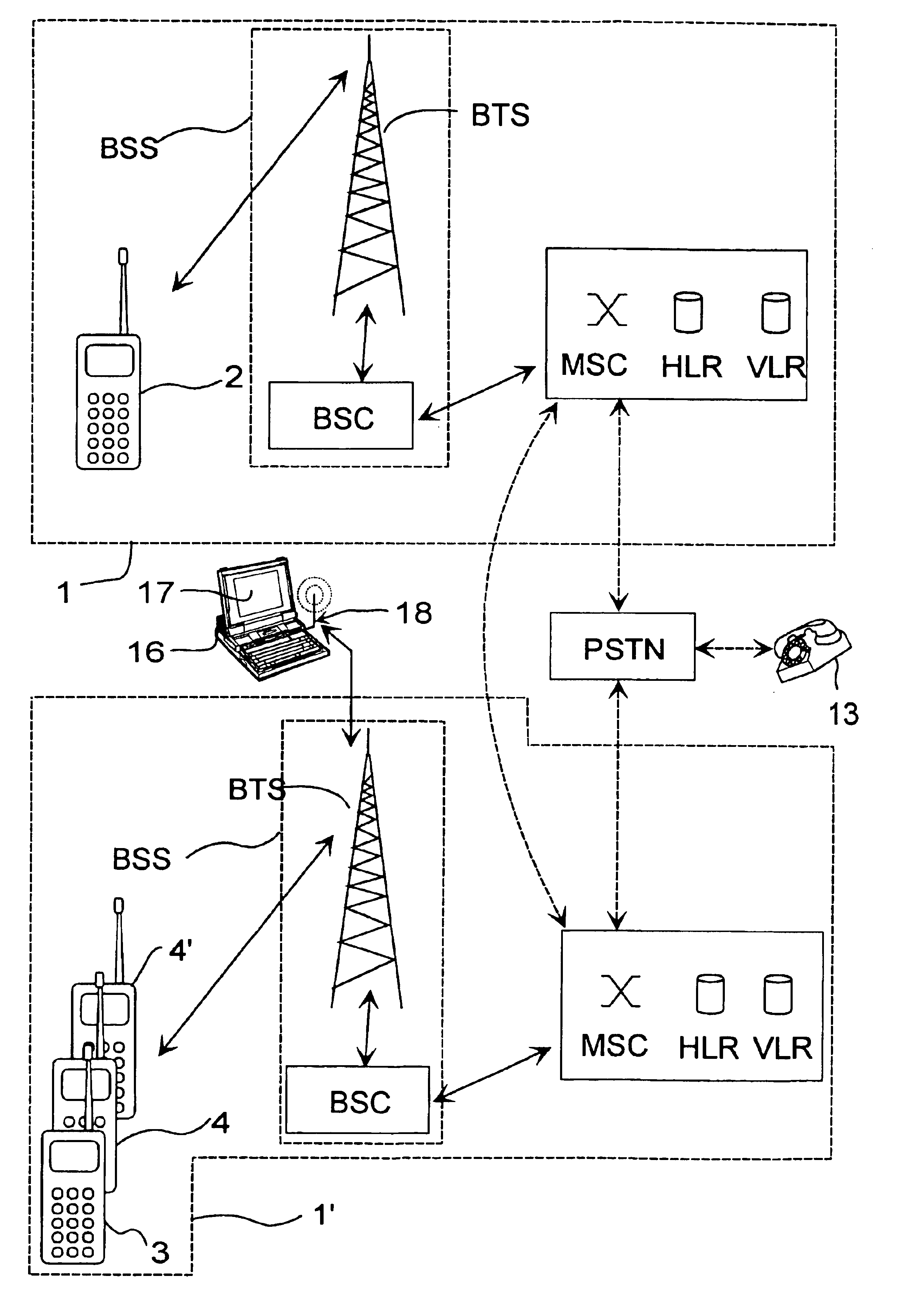

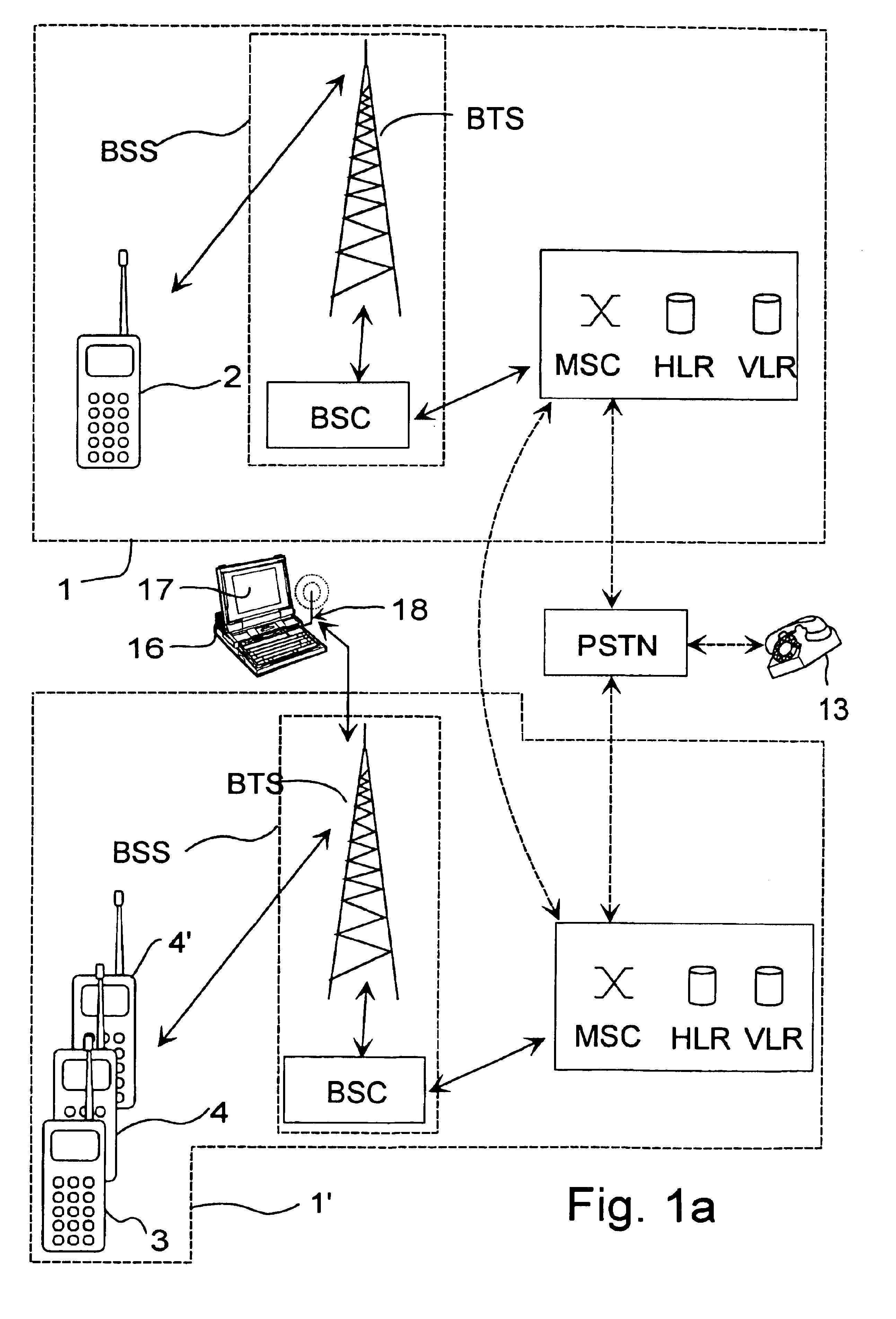

Selective message service to primary and secondary mobile stations

InactiveUS6892074B2Special service for subscribersCommmunication supplementary servicesTelecommunicationsMobile station

The invention relates to a method for the transmission of messages by using a message service to a recipient who uses at least a primary mobile station (3), in which there is at least the possibility to receive calls and messages, and at least one secondary mobile station (4, 4′), in which there is at least the possibility to receive messages. The messages addressed to the primary mobile station (3) can be directed to any of the secondary mobile stations (4, 4′) of the recipient, irrespective of calls.

Owner:CELLULAR COMM EQUIP LLC

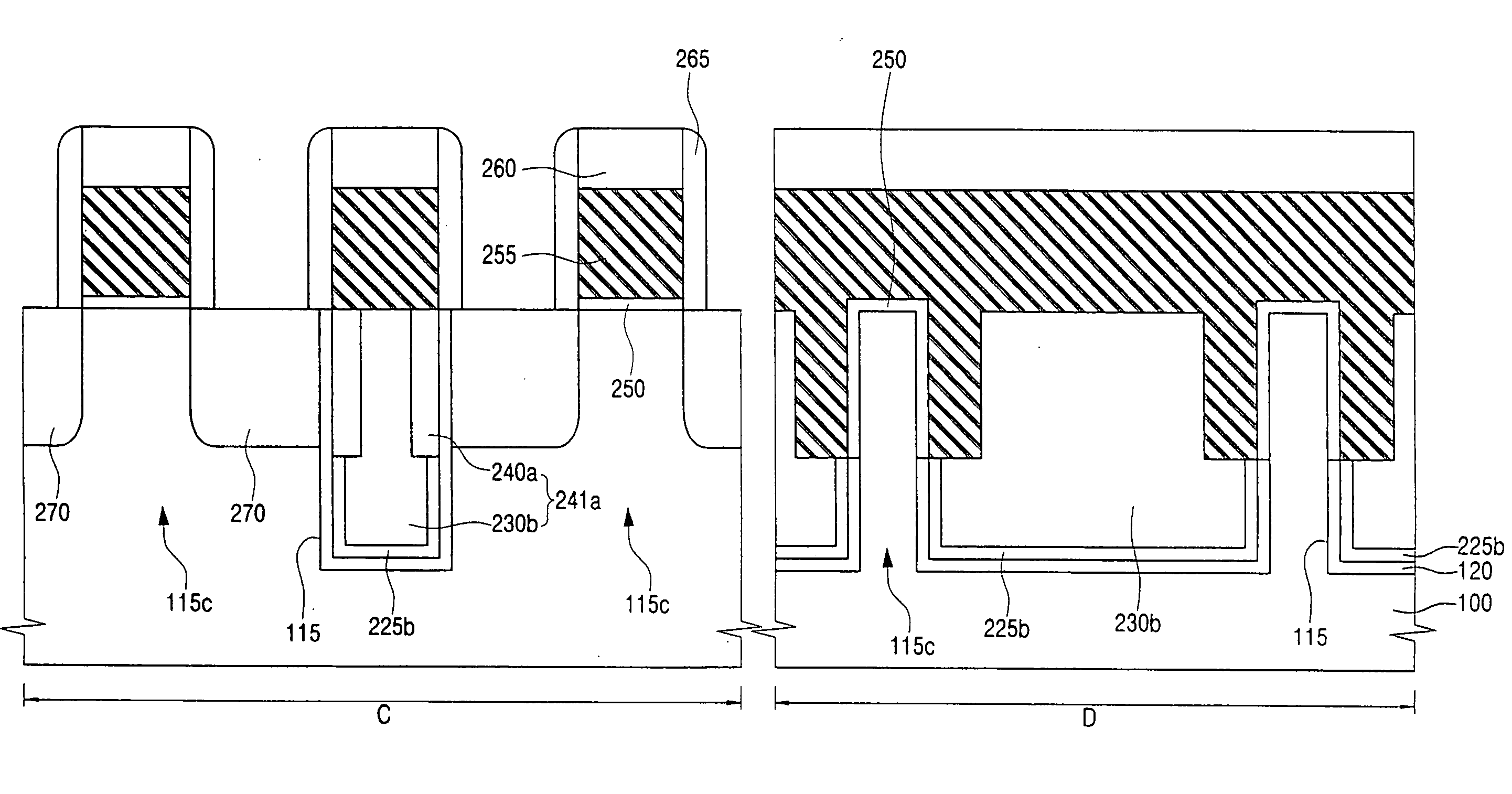

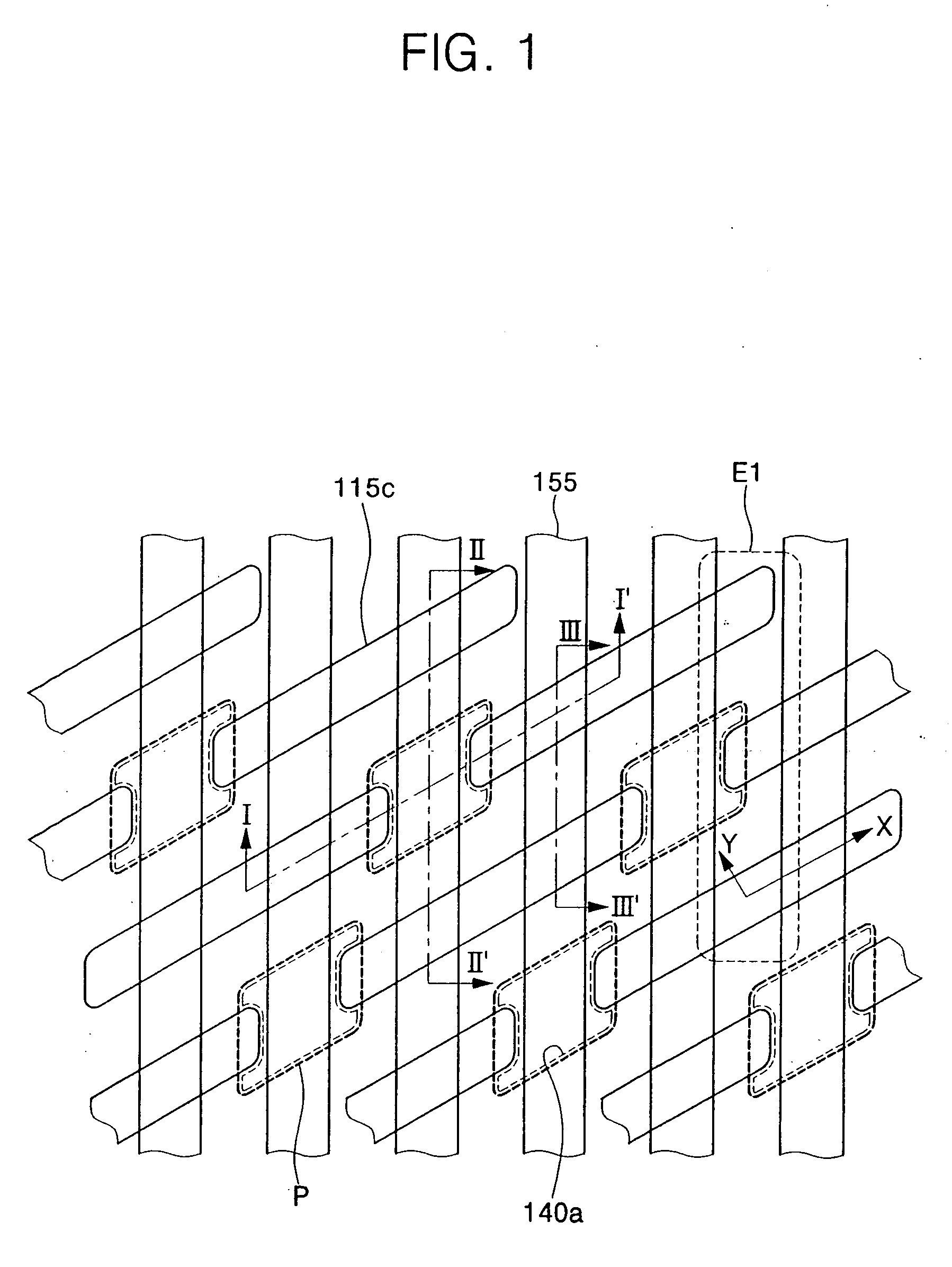

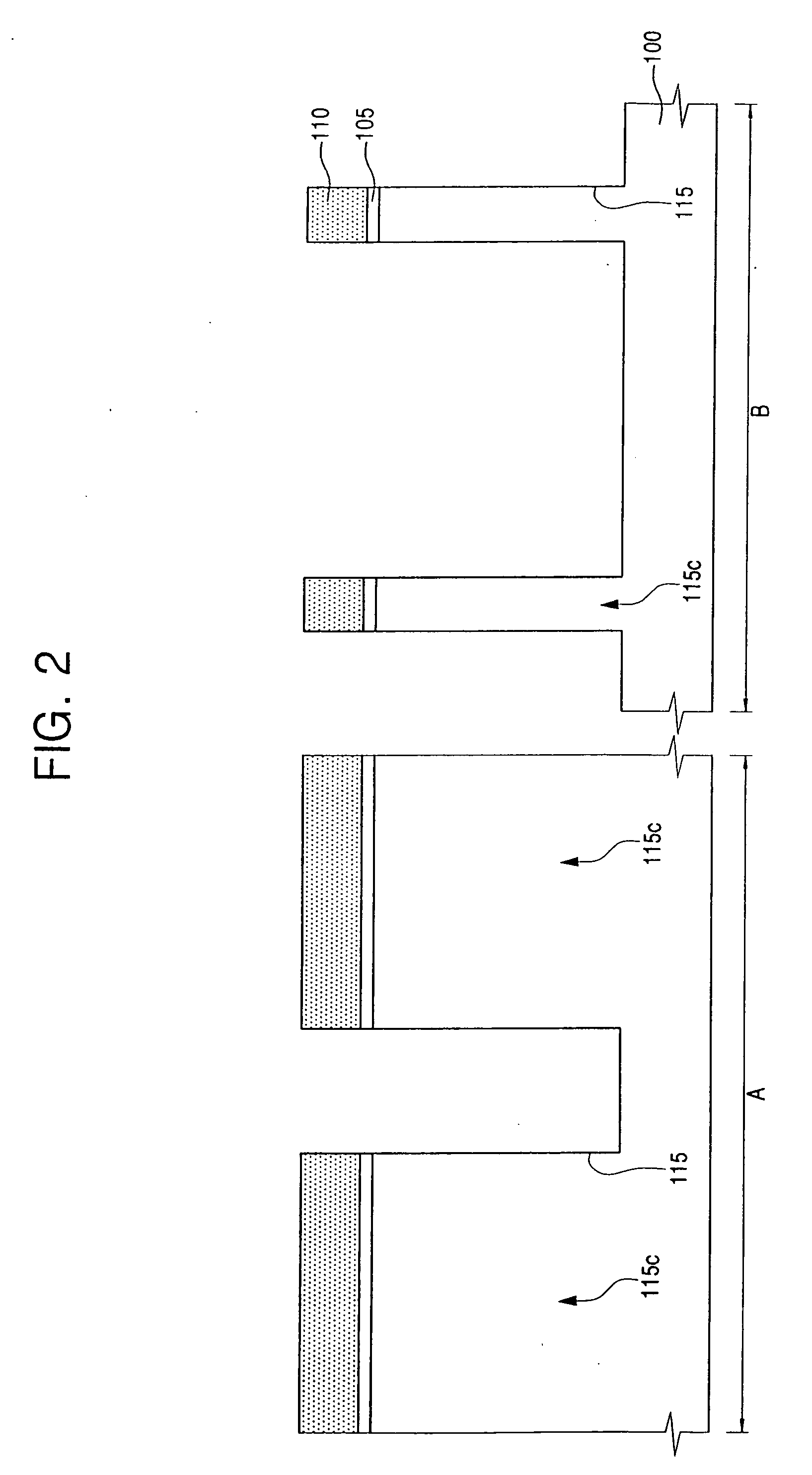

Isolation method of defining active fins, method of fabricating semiconductor device using the same and semiconductor device fabricated thereby

InactiveUS20070134884A1Semiconductor/solid-state device manufacturingSemiconductor devicesDevice materialIsolation layer

An isolation method of defining active fins, a method of fabricating a semiconductor device using the same, and a semiconductor device fabricated thereby are provided. The method of fabricating a semiconductor device includes: preparing a semiconductor substrate; and forming a plurality of active fins having major and minor axes and two-dimensionally arrayed on the semiconductor substrate in directions of the major and minor axes. A liner pattern is formed on lower sidewalls of the active fins. An isolation layer is formed on the semiconductor substrate having the liner pattern, and the isolation layer exposes top surfaces of the active fins and a part of the active fins' sidewalls substantially parallel to the major axis. Parallel gate lines are formed to cover the top surfaces and the exposed sidewalls of the active fins, cross over the active fins, and run on the isolation layer.

Owner:SAMSUNG ELECTRONICS CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com