Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

876results about "Printed resistor incorporation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

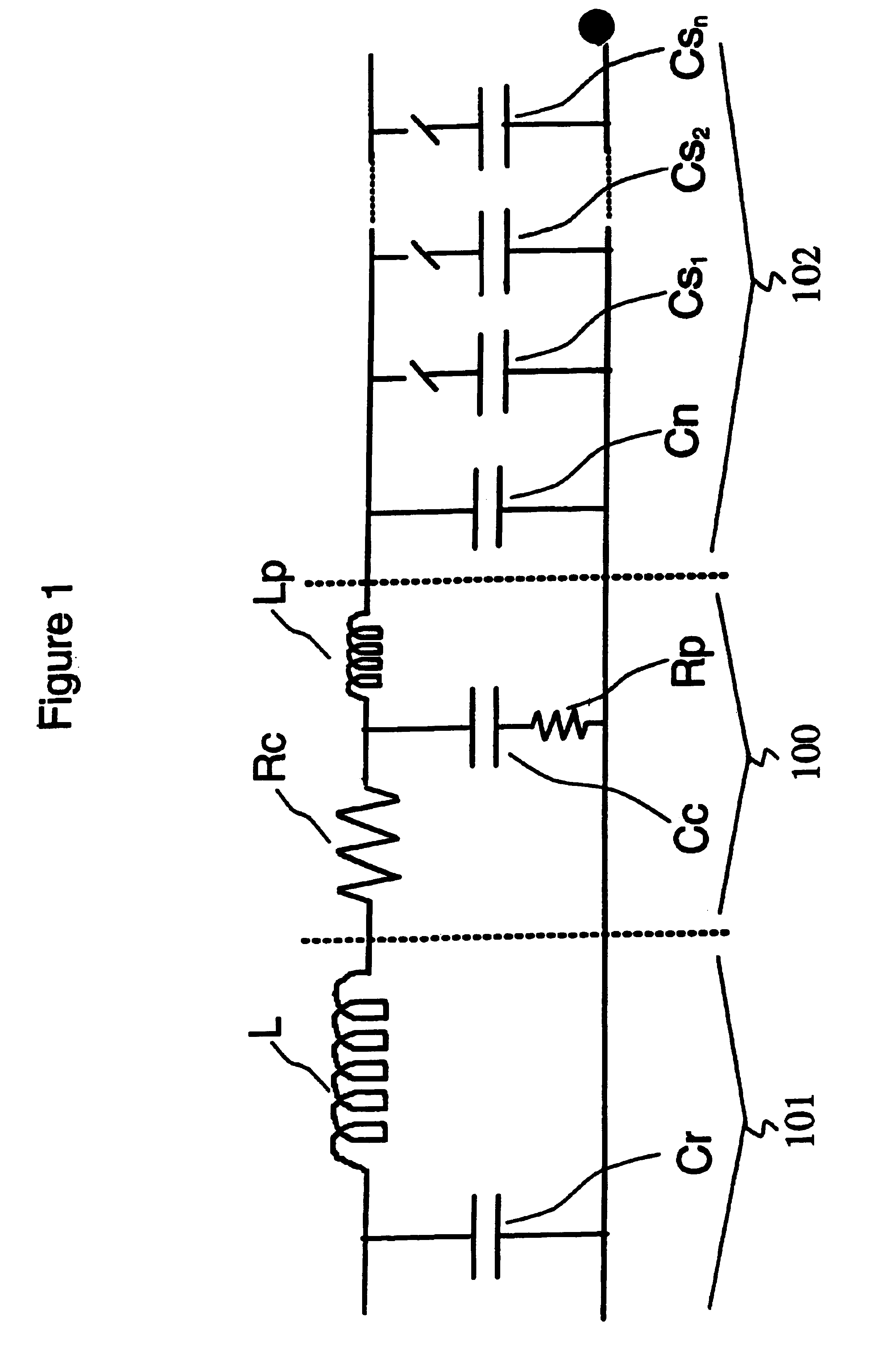

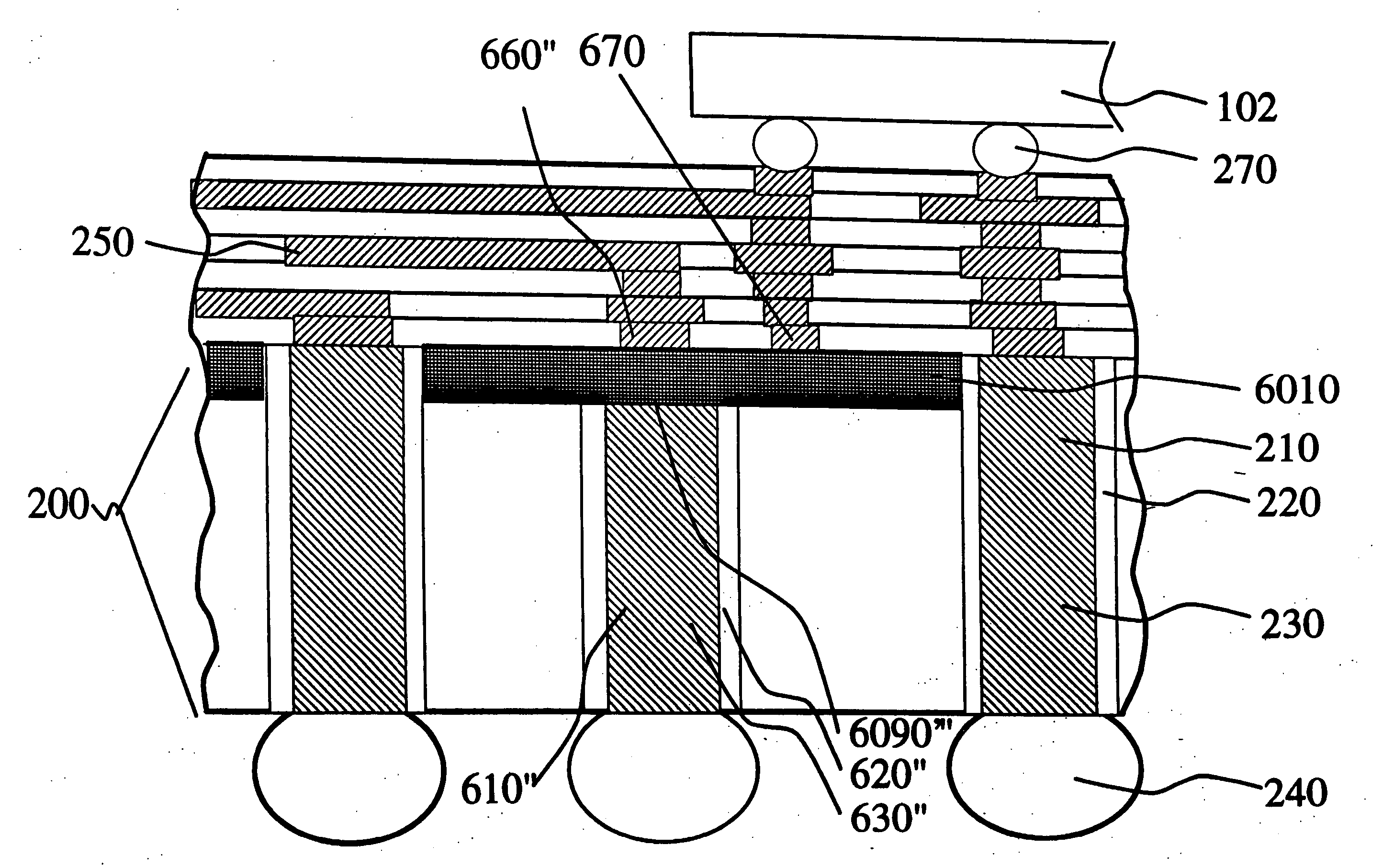

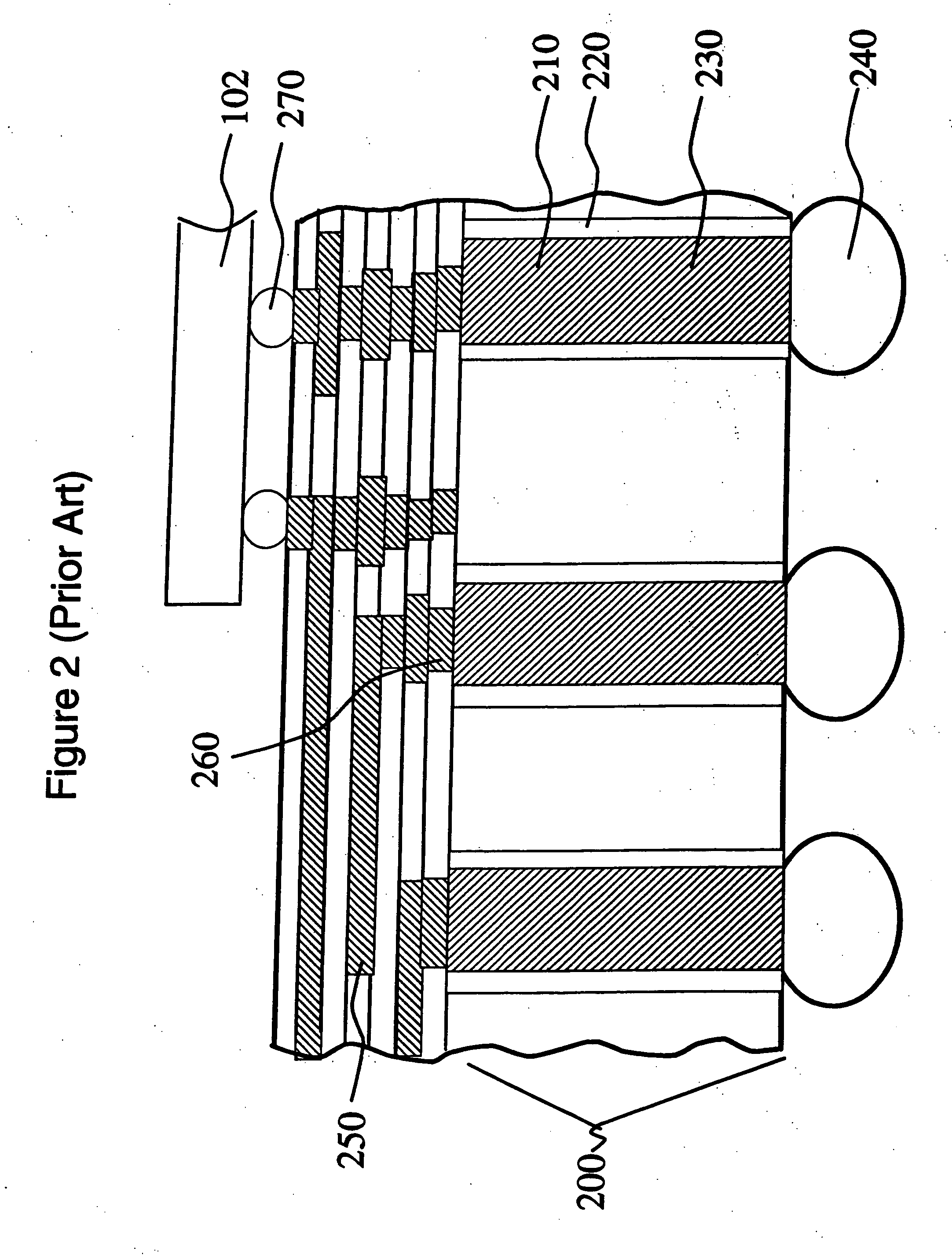

High density chip carrier with integrated passive devices

InactiveUS6962872B2Reduce inductanceEasy accessSemiconductor/solid-state device detailsPrinted circuit aspectsHigh densityEngineering

Owner:GLOBALFOUNDRIES U S INC

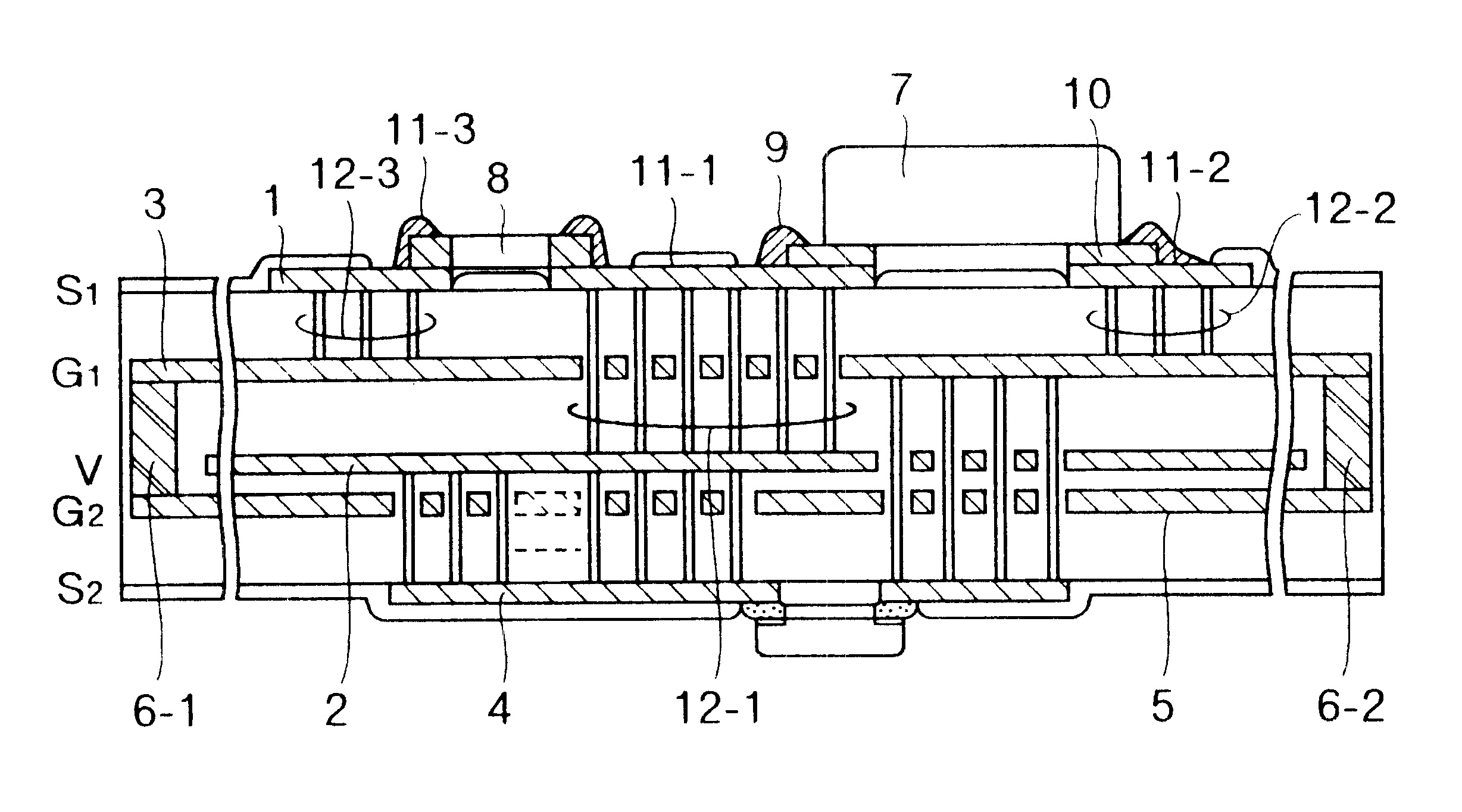

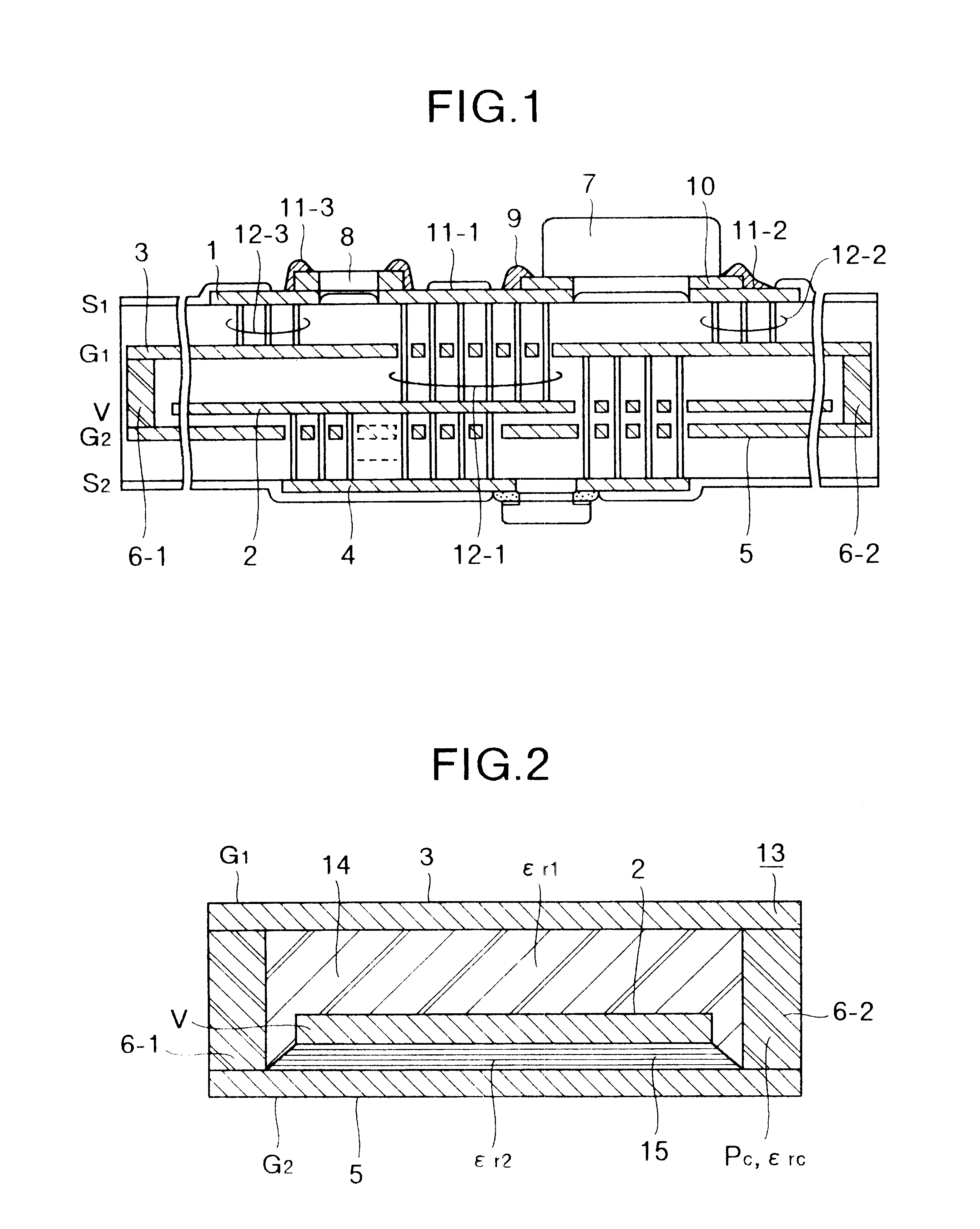

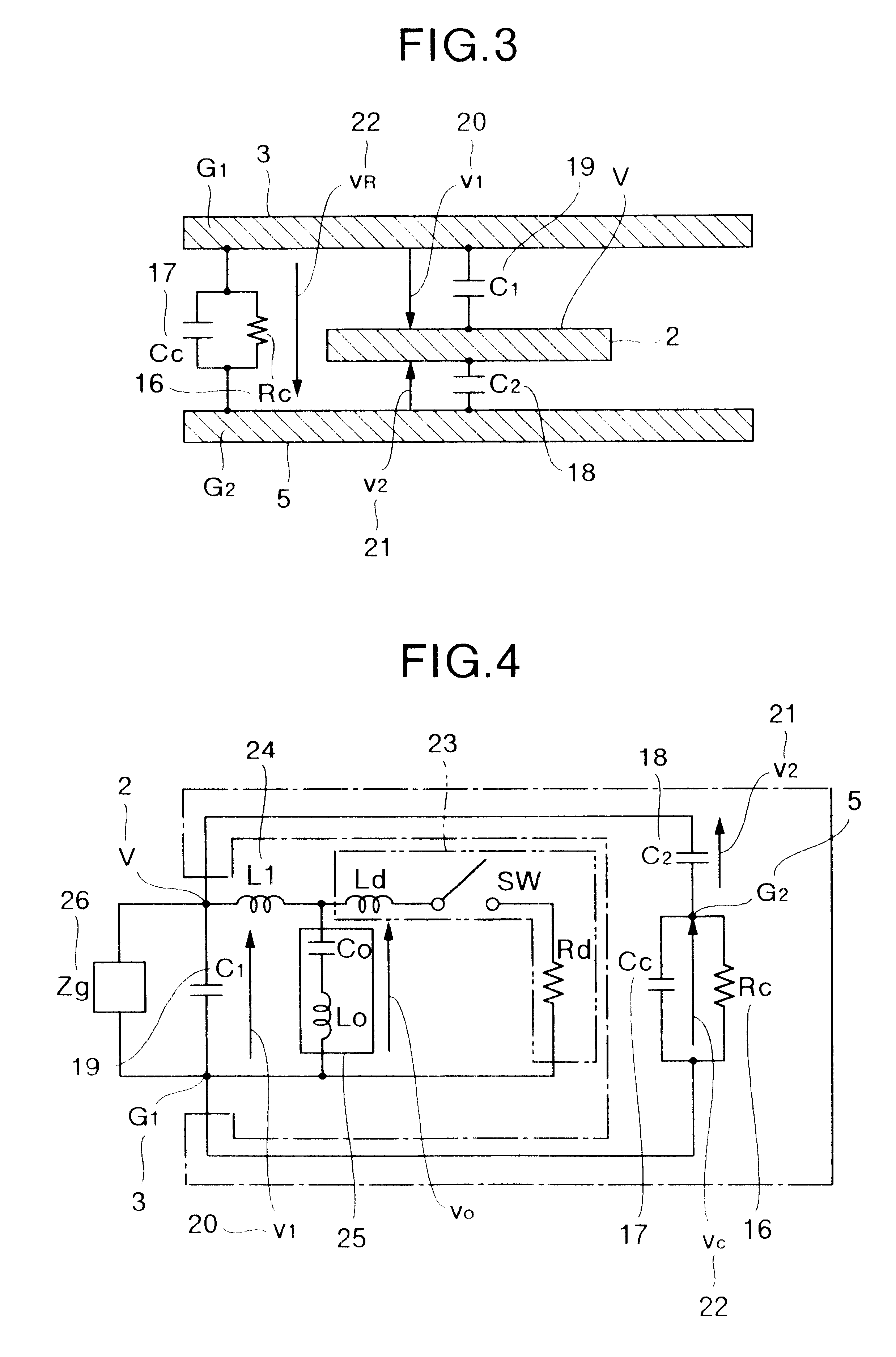

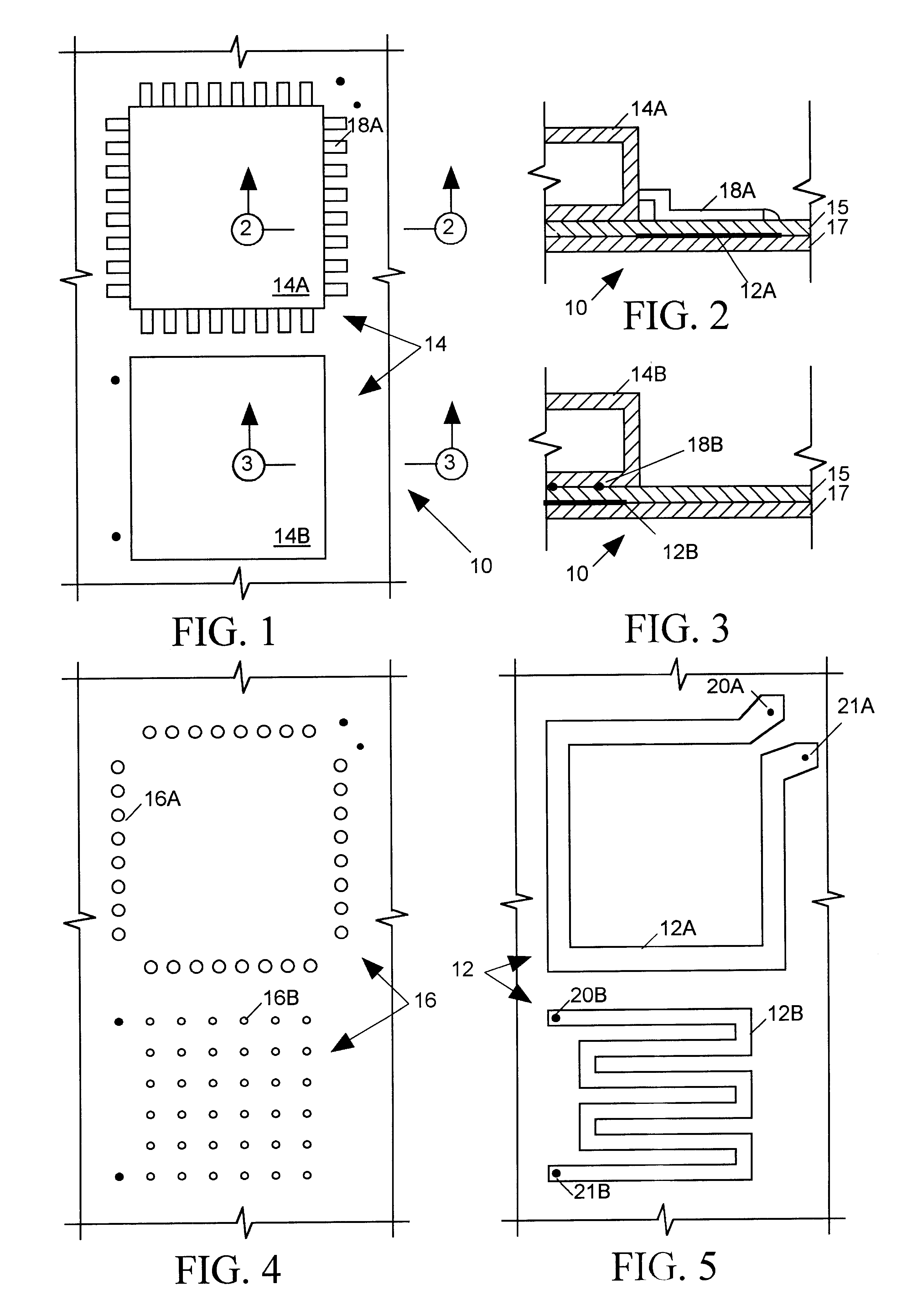

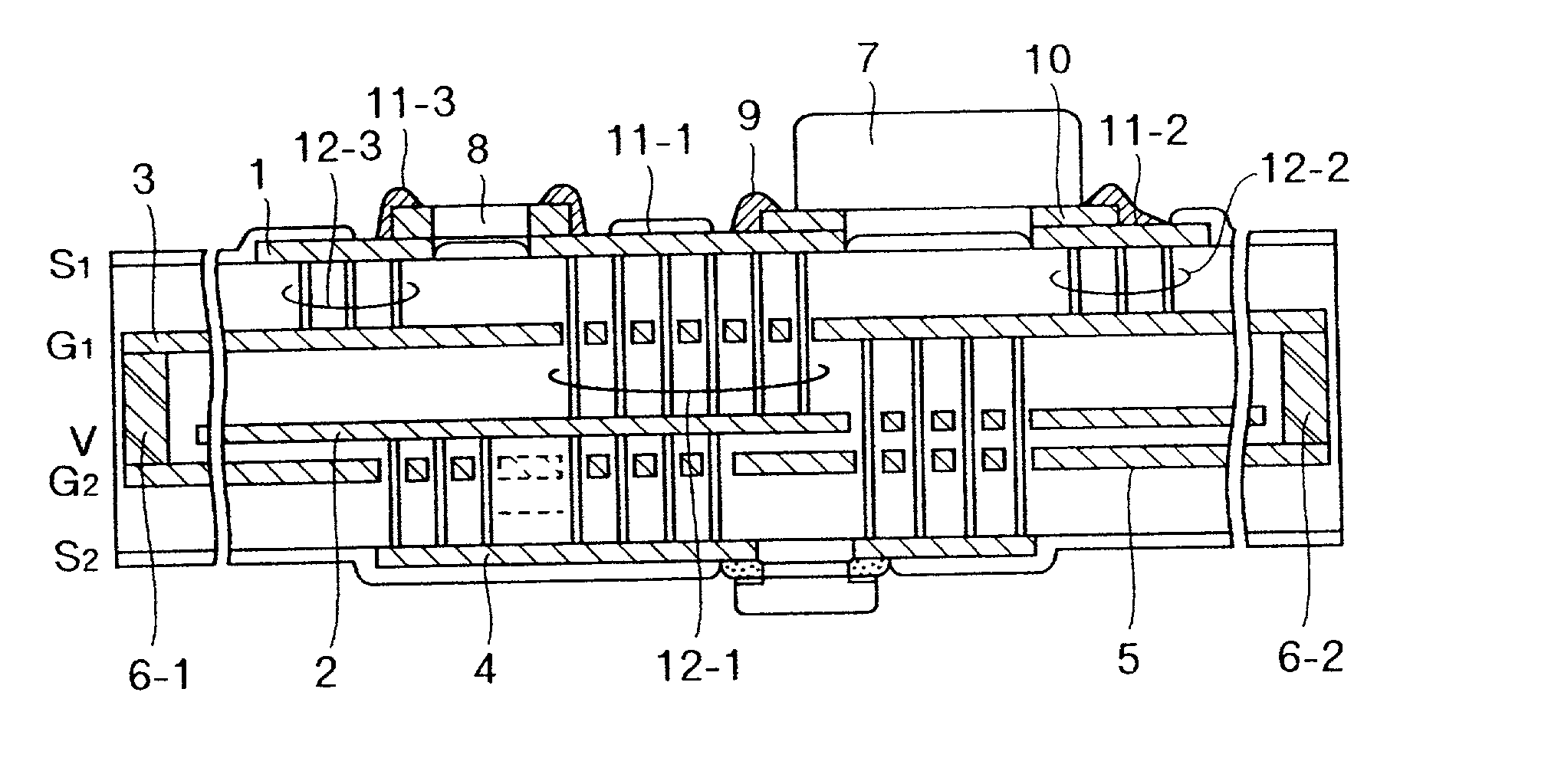

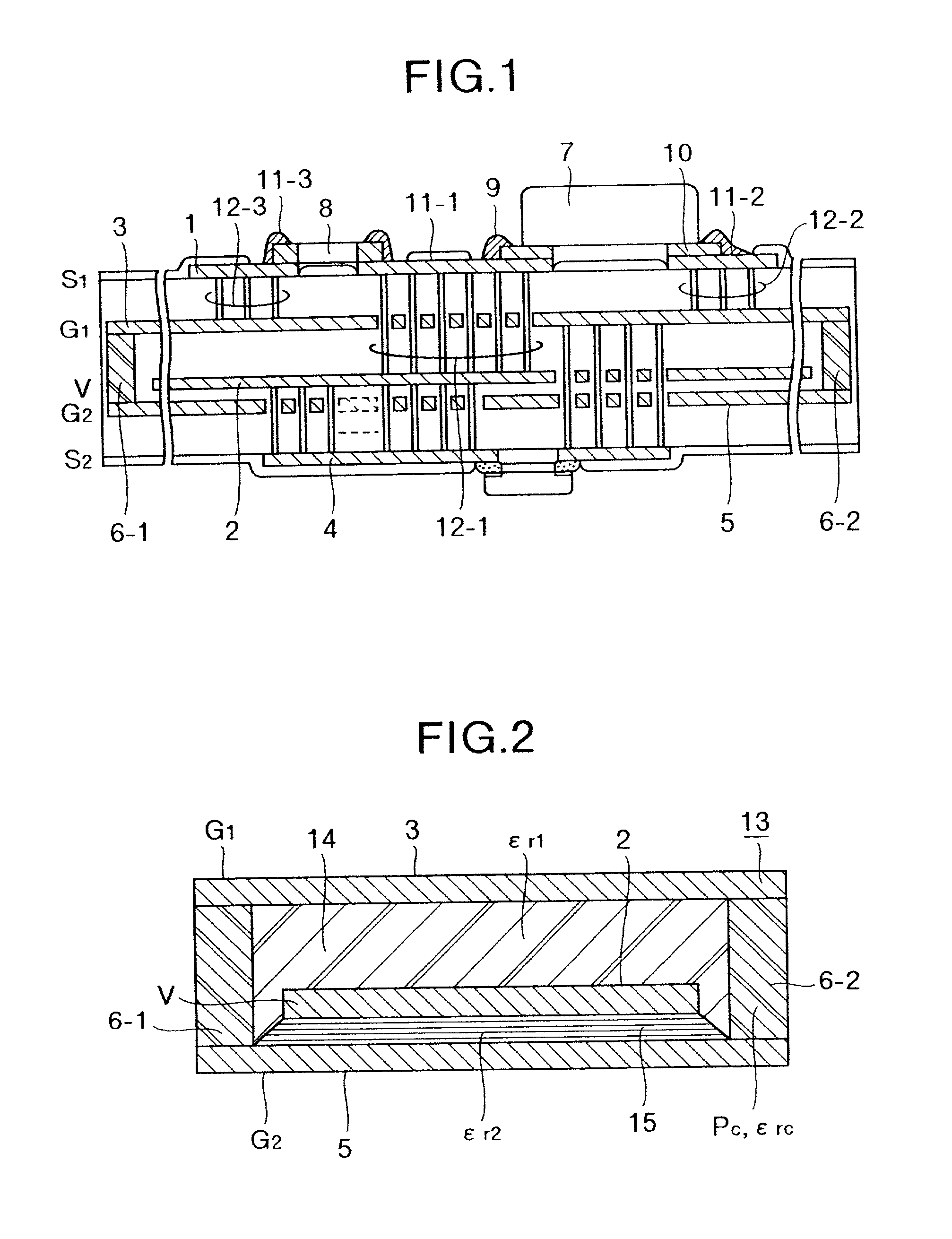

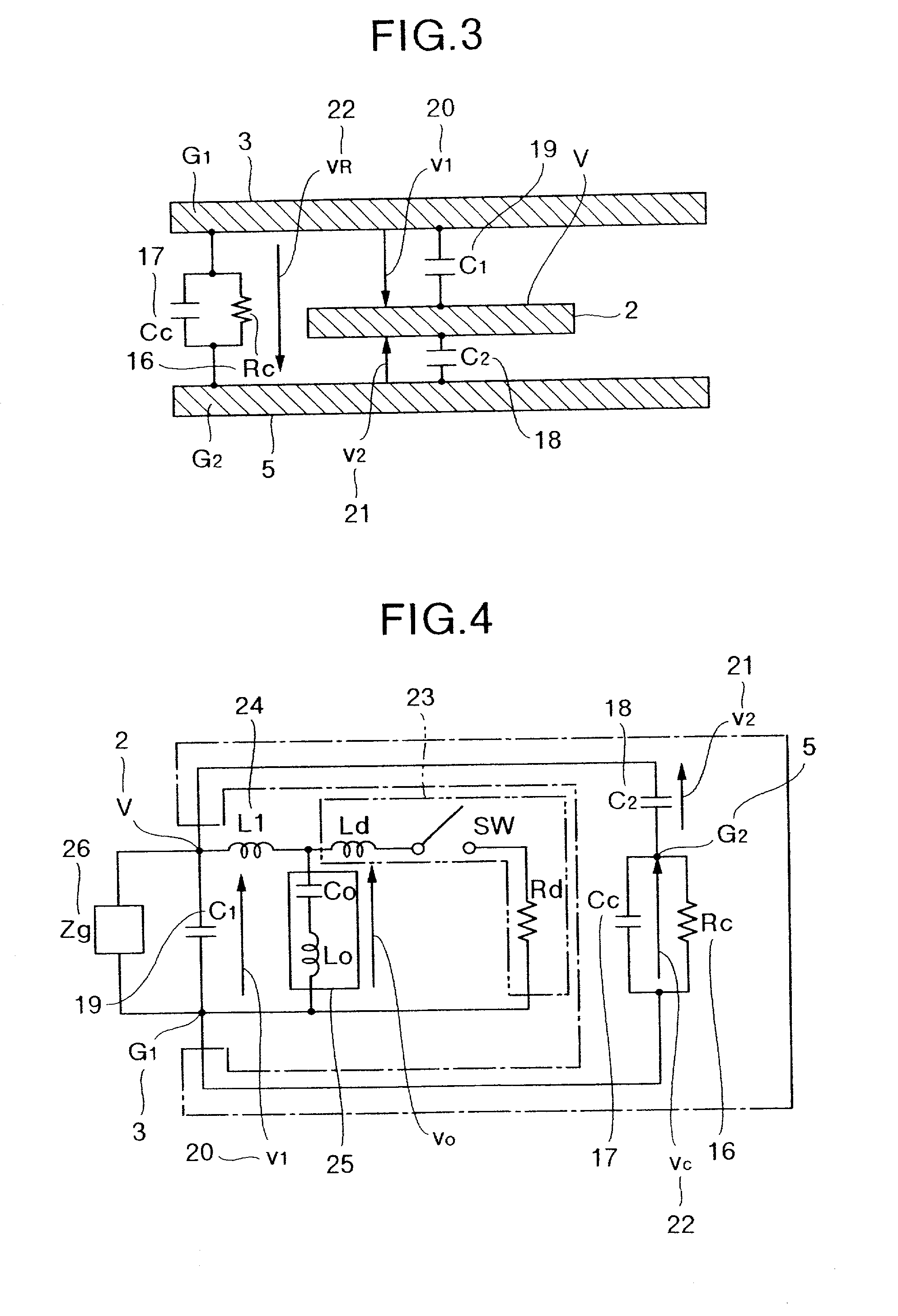

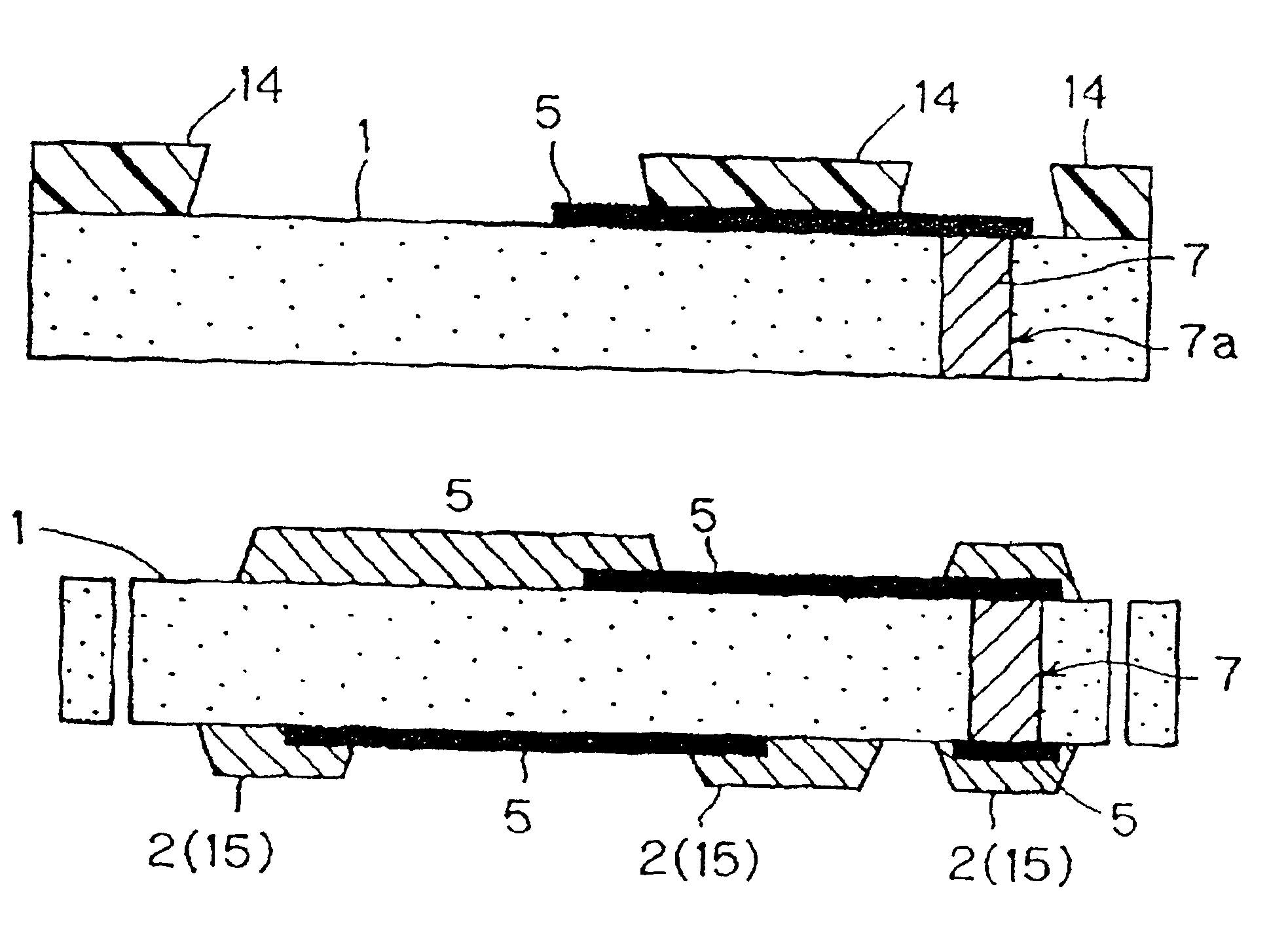

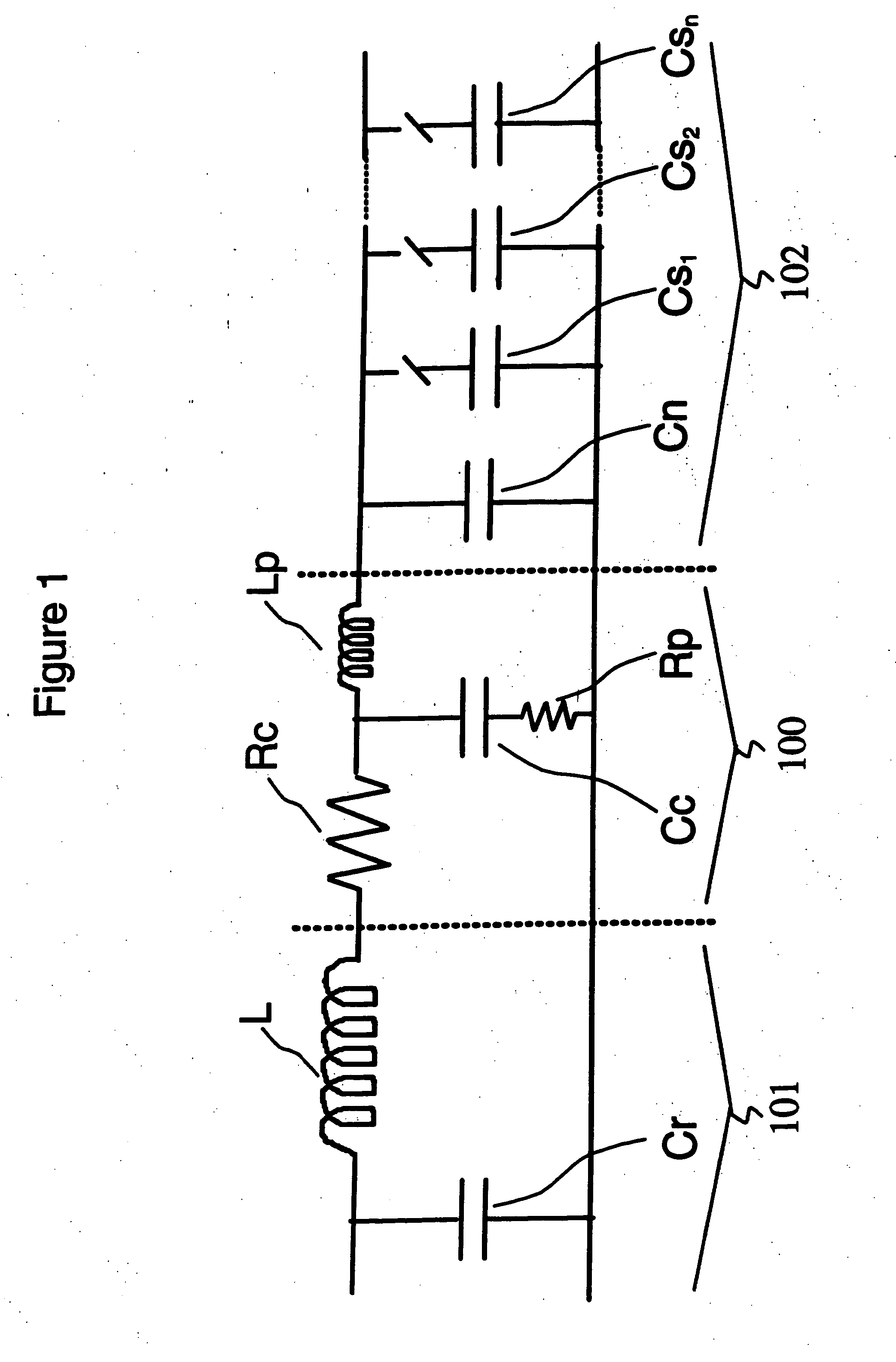

Low-EMI electronic apparatus, low-EMI circuit board, and method of manufacturing the low-EMI circuit board.

InactiveUS6353540B1Radiation suppressionHigh packageMagnetic/electric field screeningFinal product manufactureCapacitanceCountermeasure

Owner:HITACHI LTD

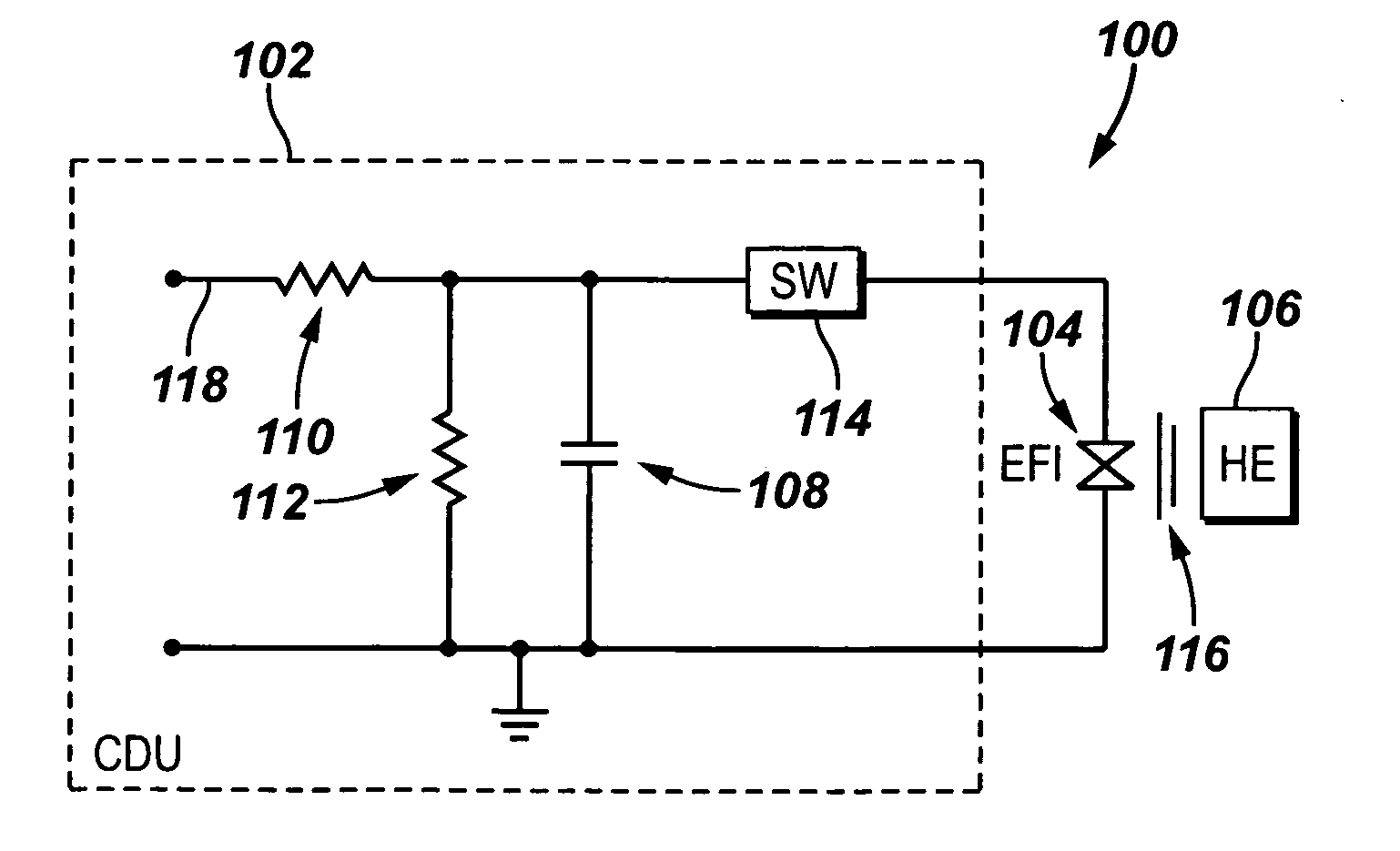

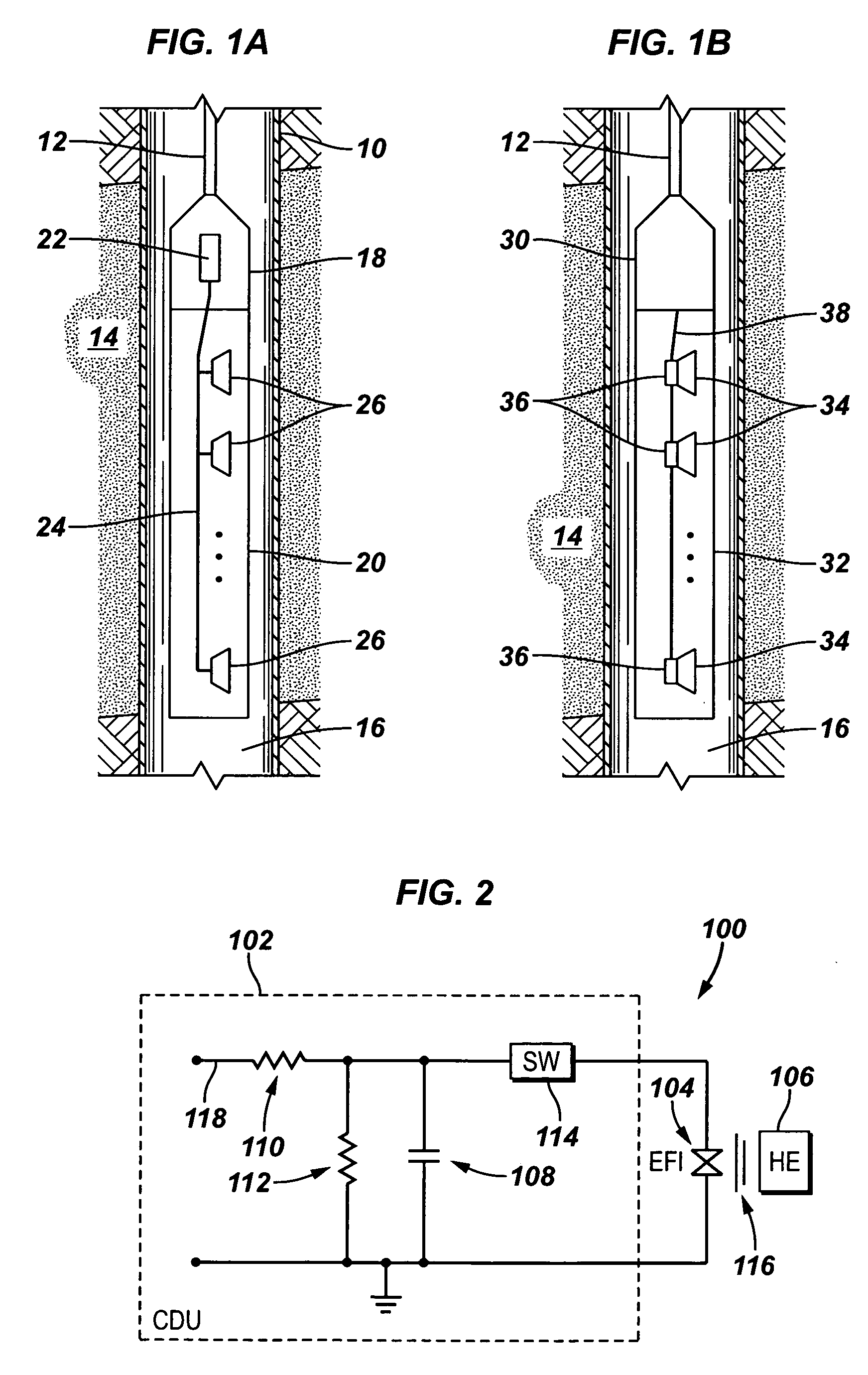

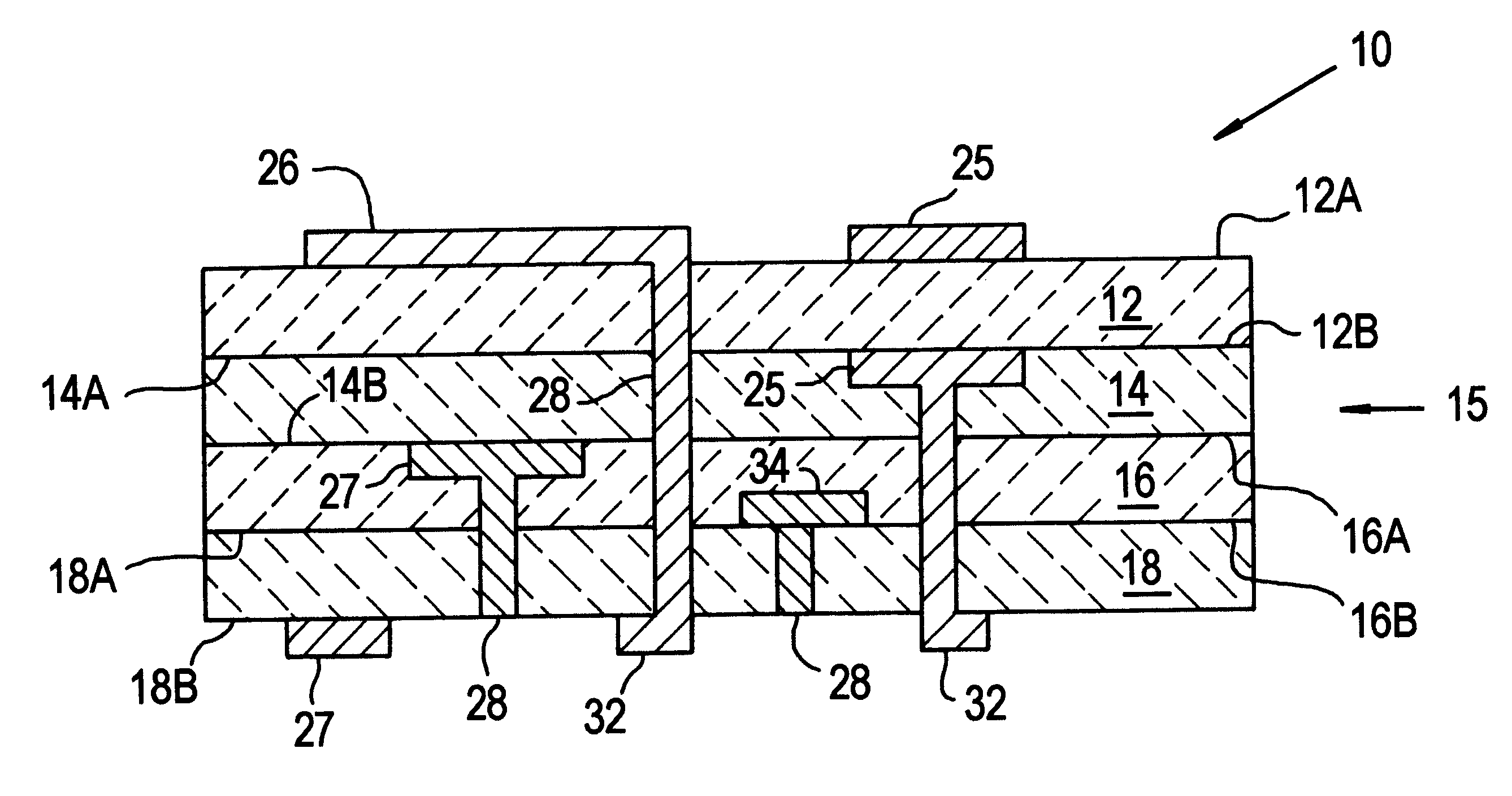

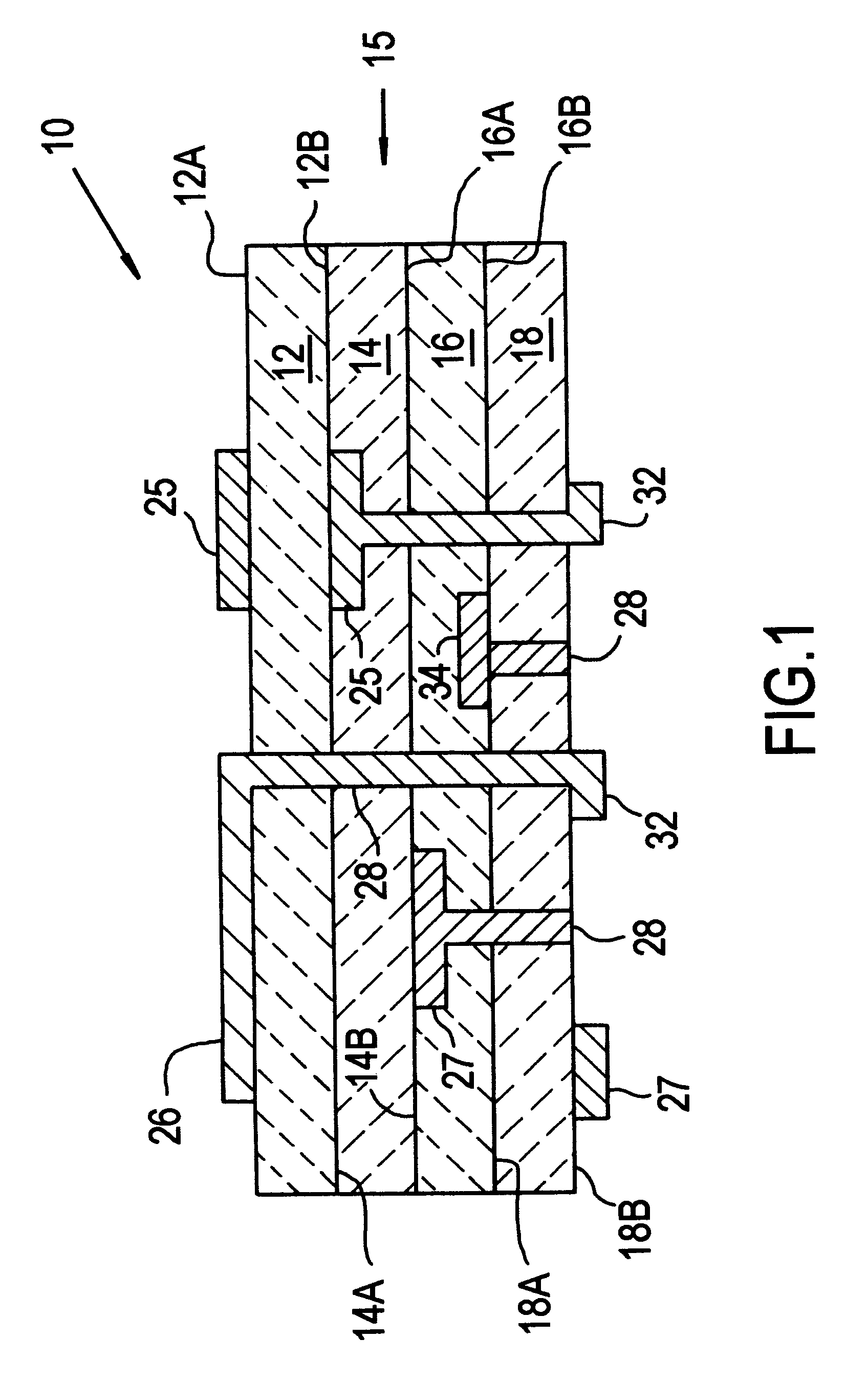

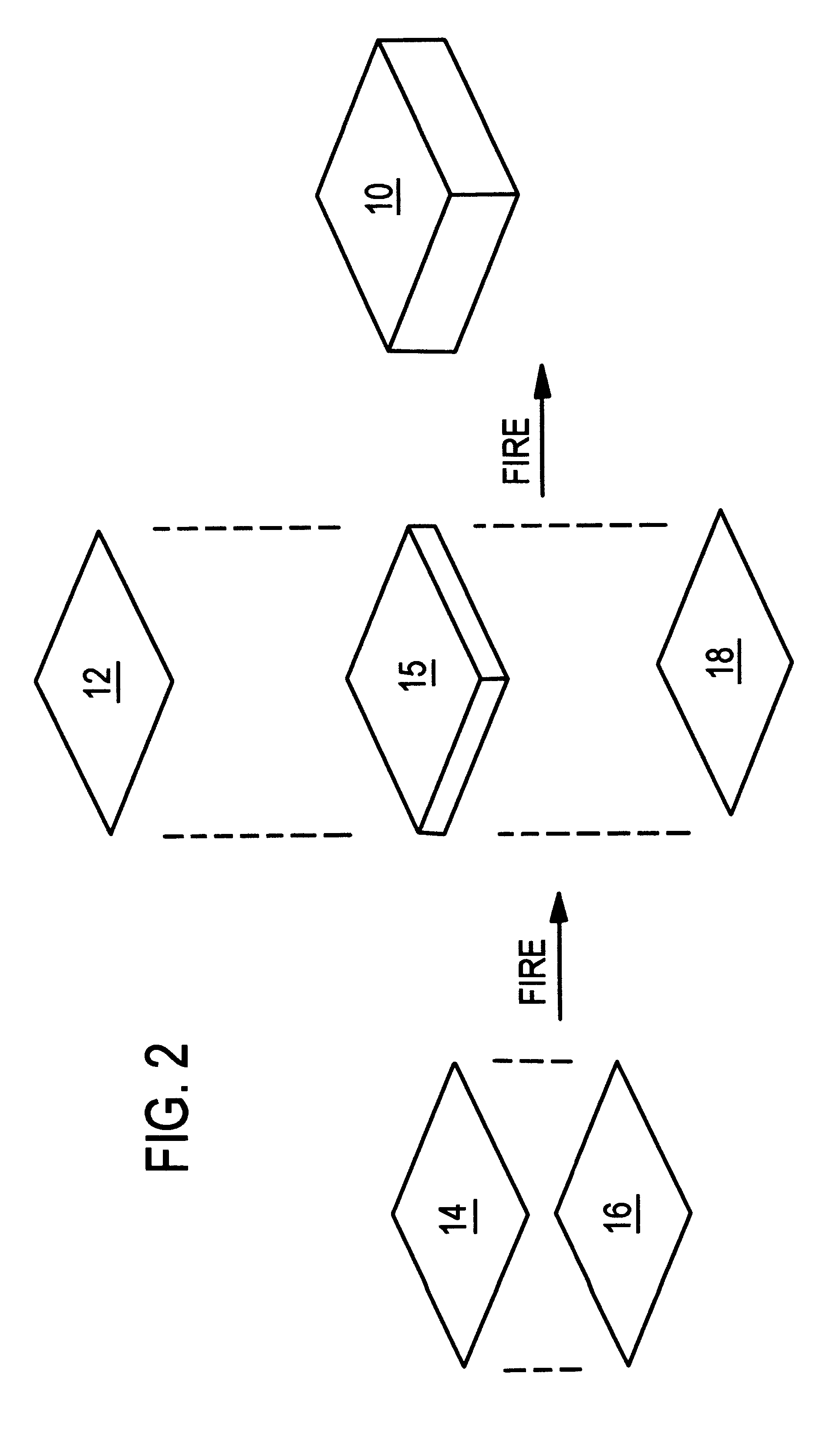

Integrated detonators for use with explosive devices

A detonator assembly is provided for use in oilfield operations to detonate an explosive downhole including a capacitor discharge unit and initiator electrically connected together to form a single unit. It is emphasized that this abstract is provided to comply with the rules requiring an abstract, which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:SCHLUMBERGER TECH CORP

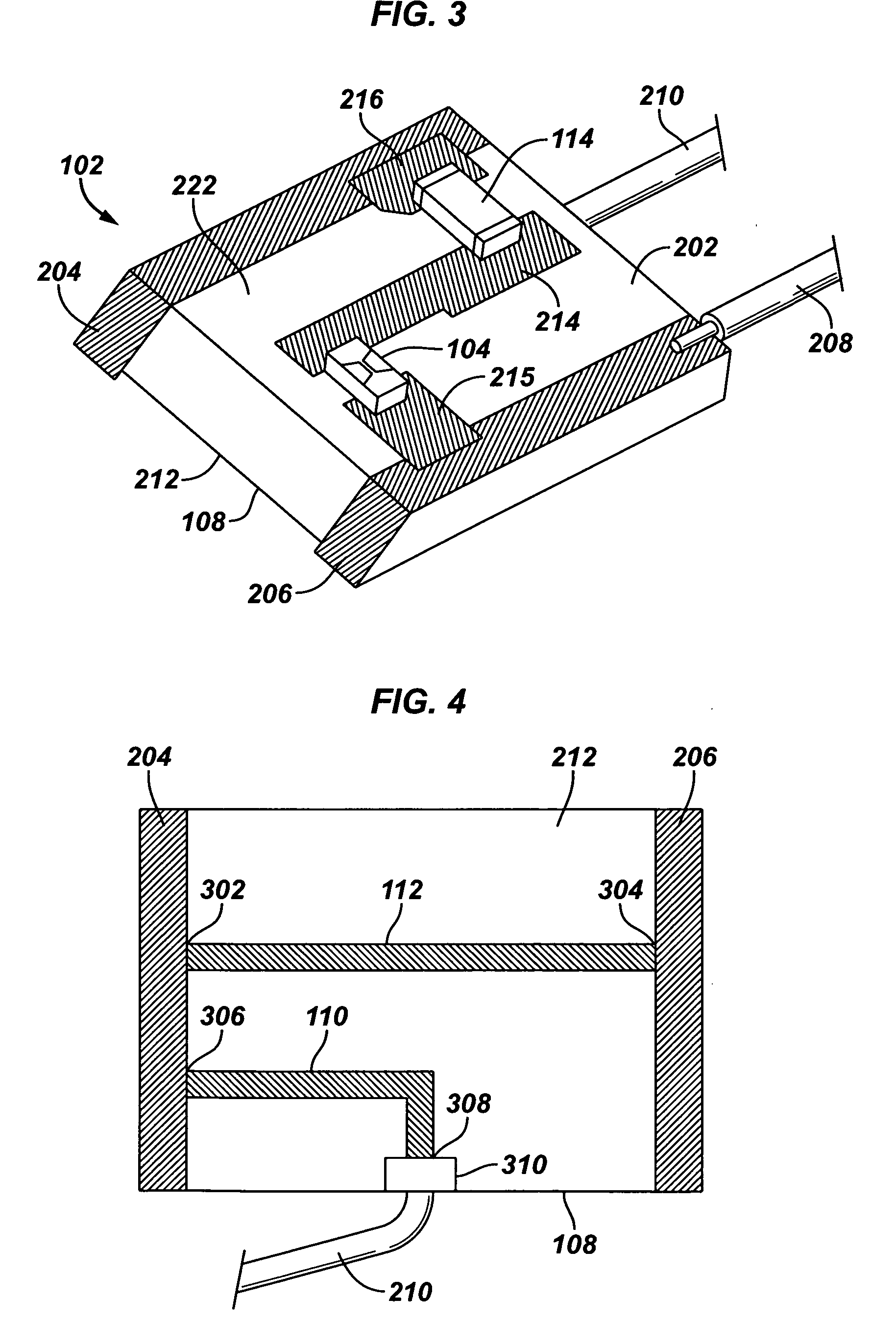

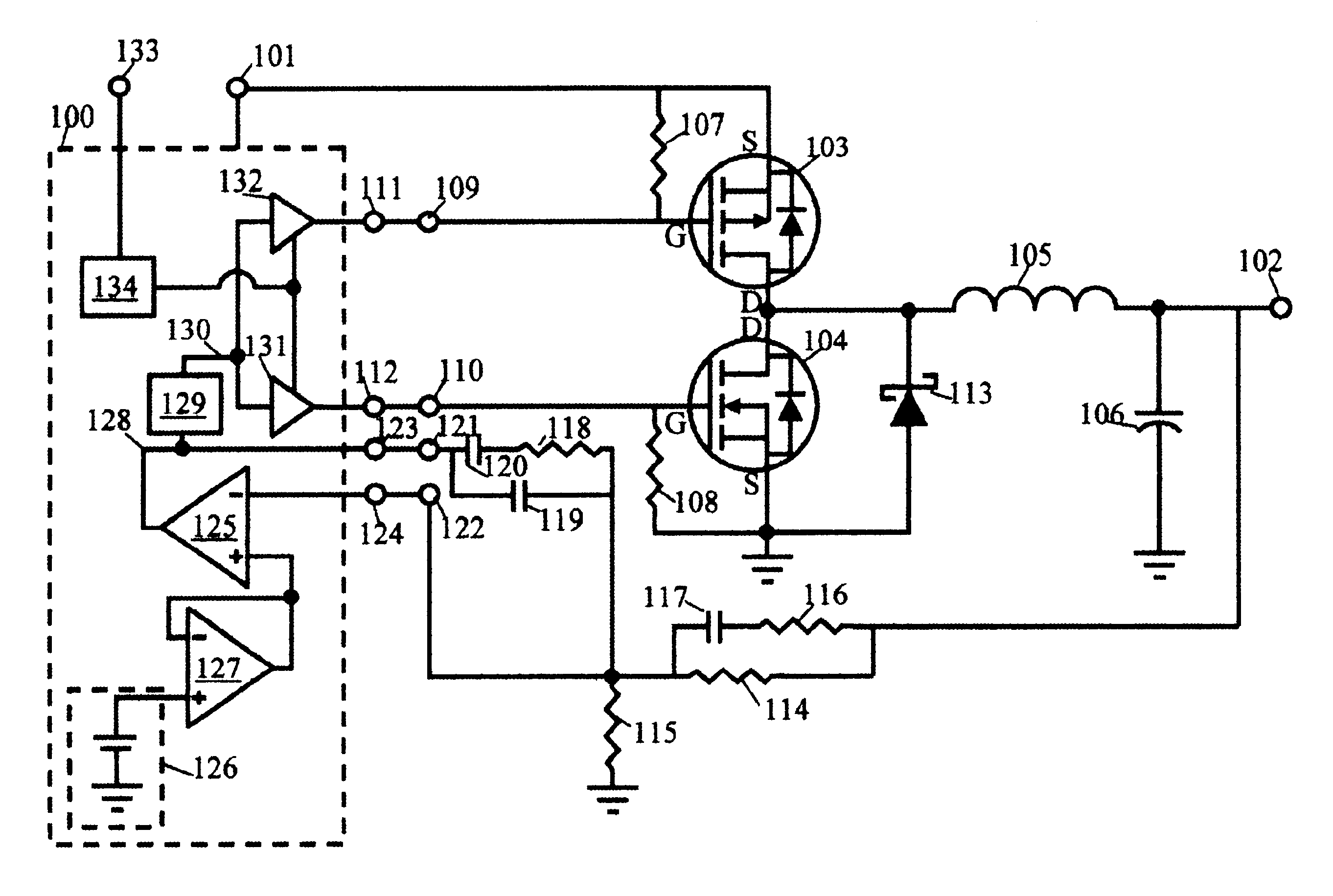

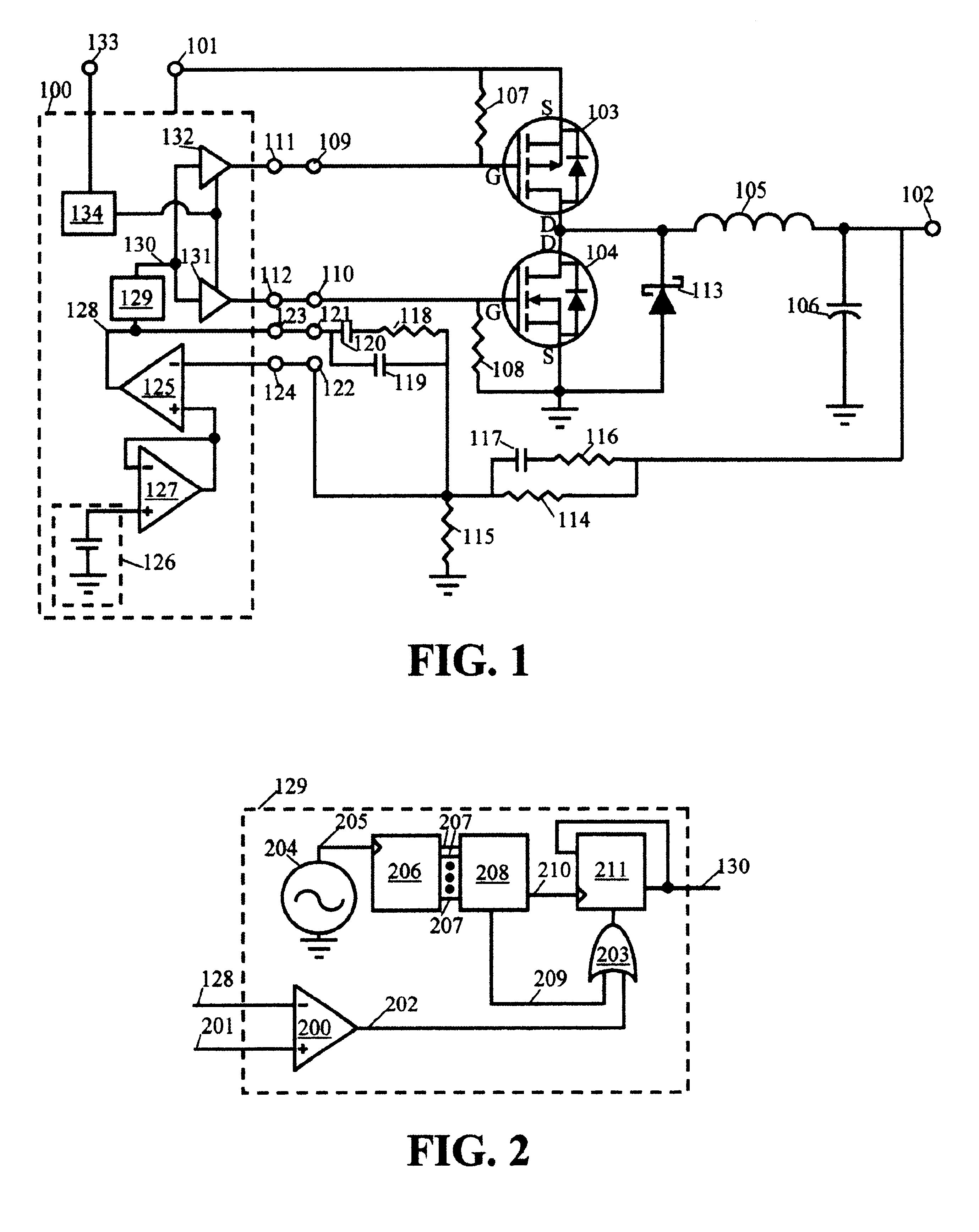

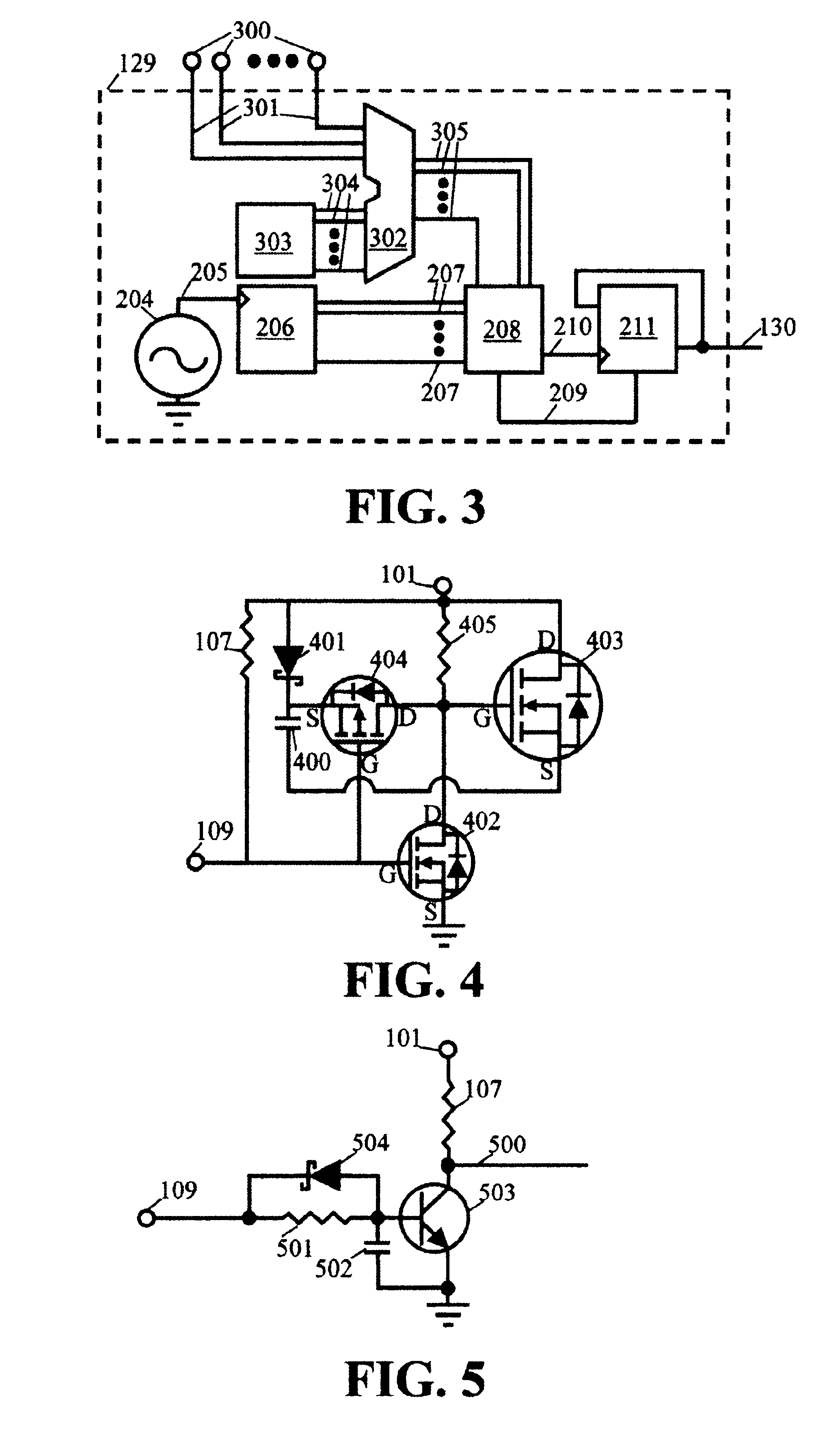

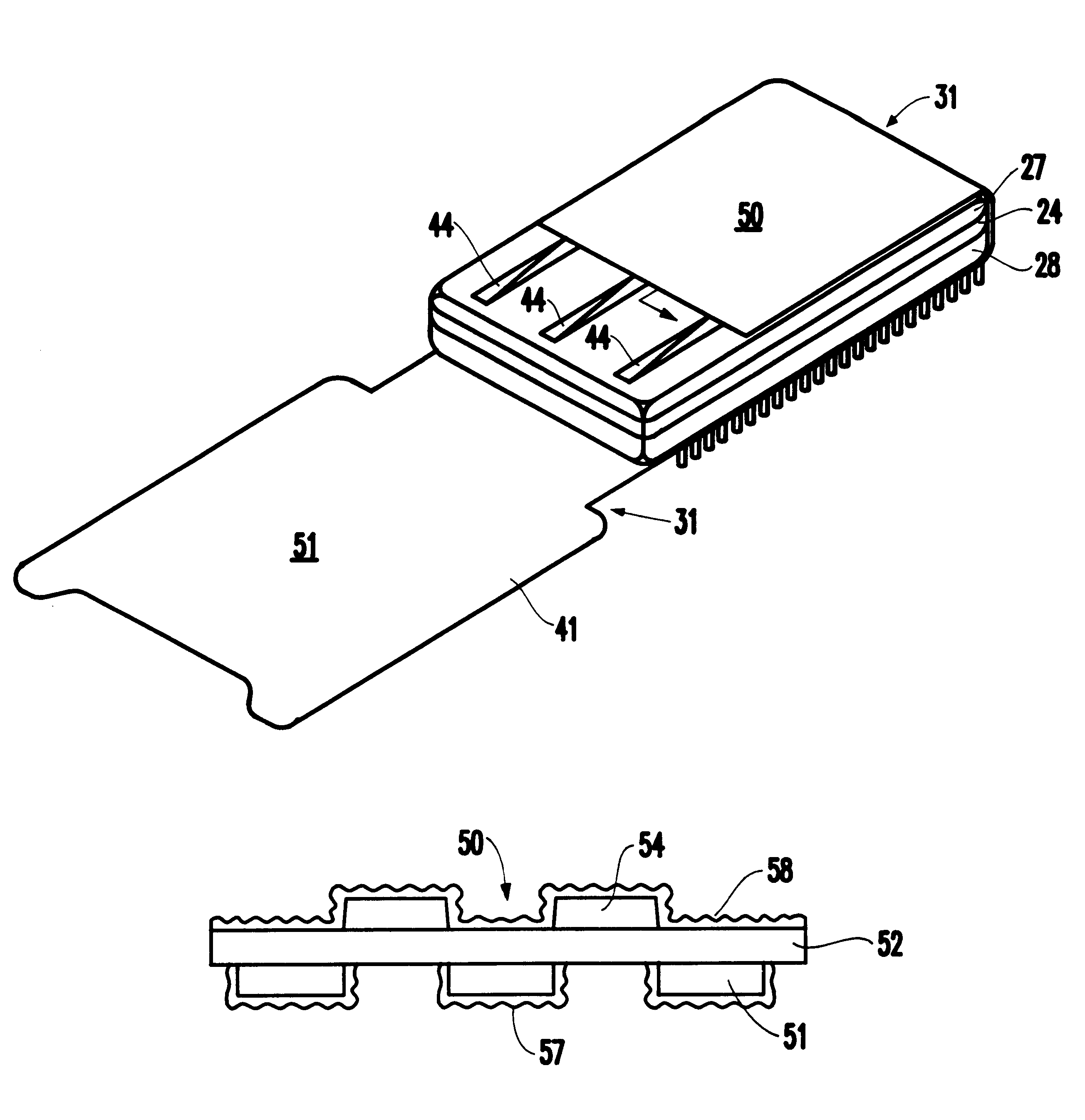

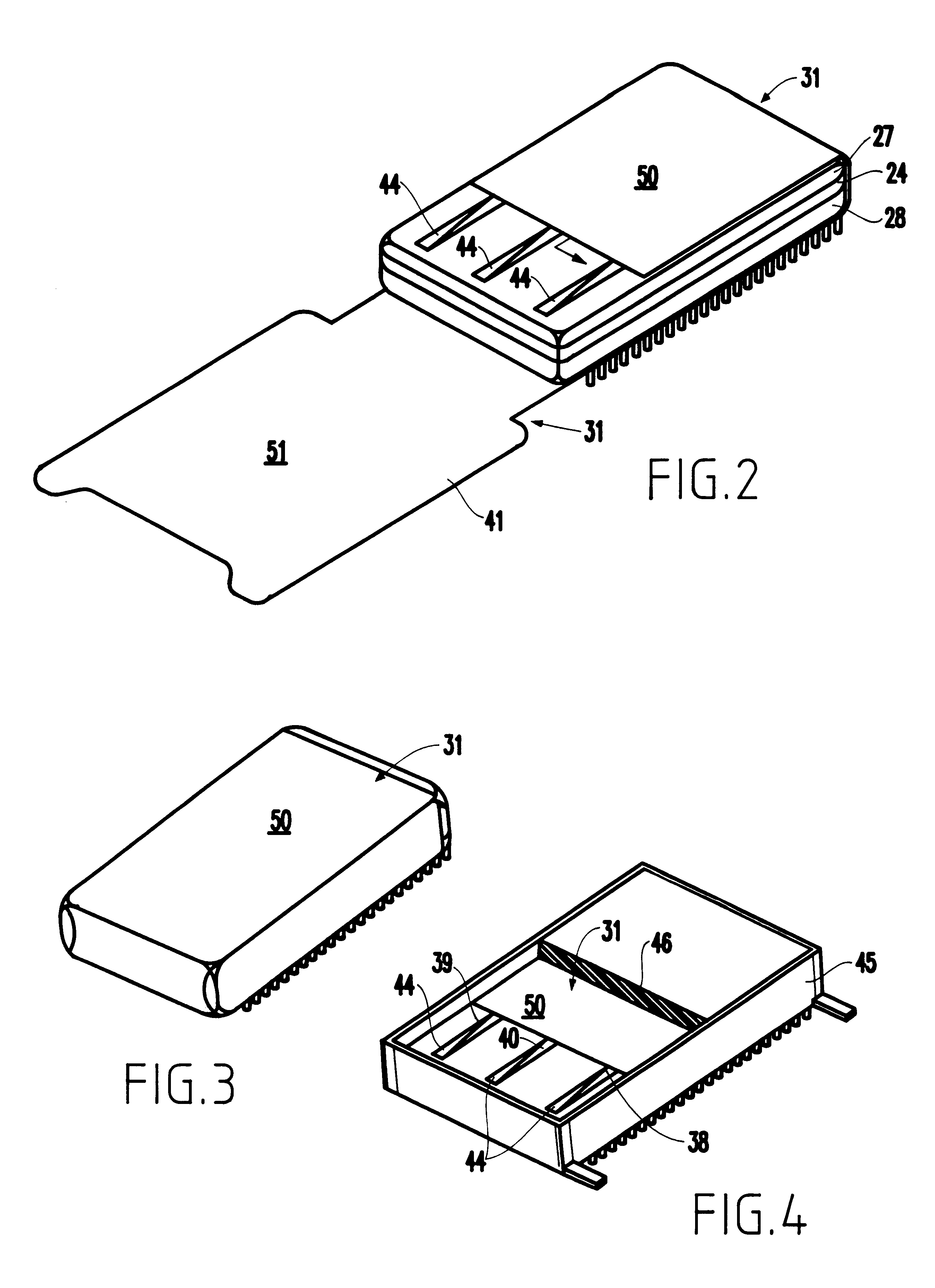

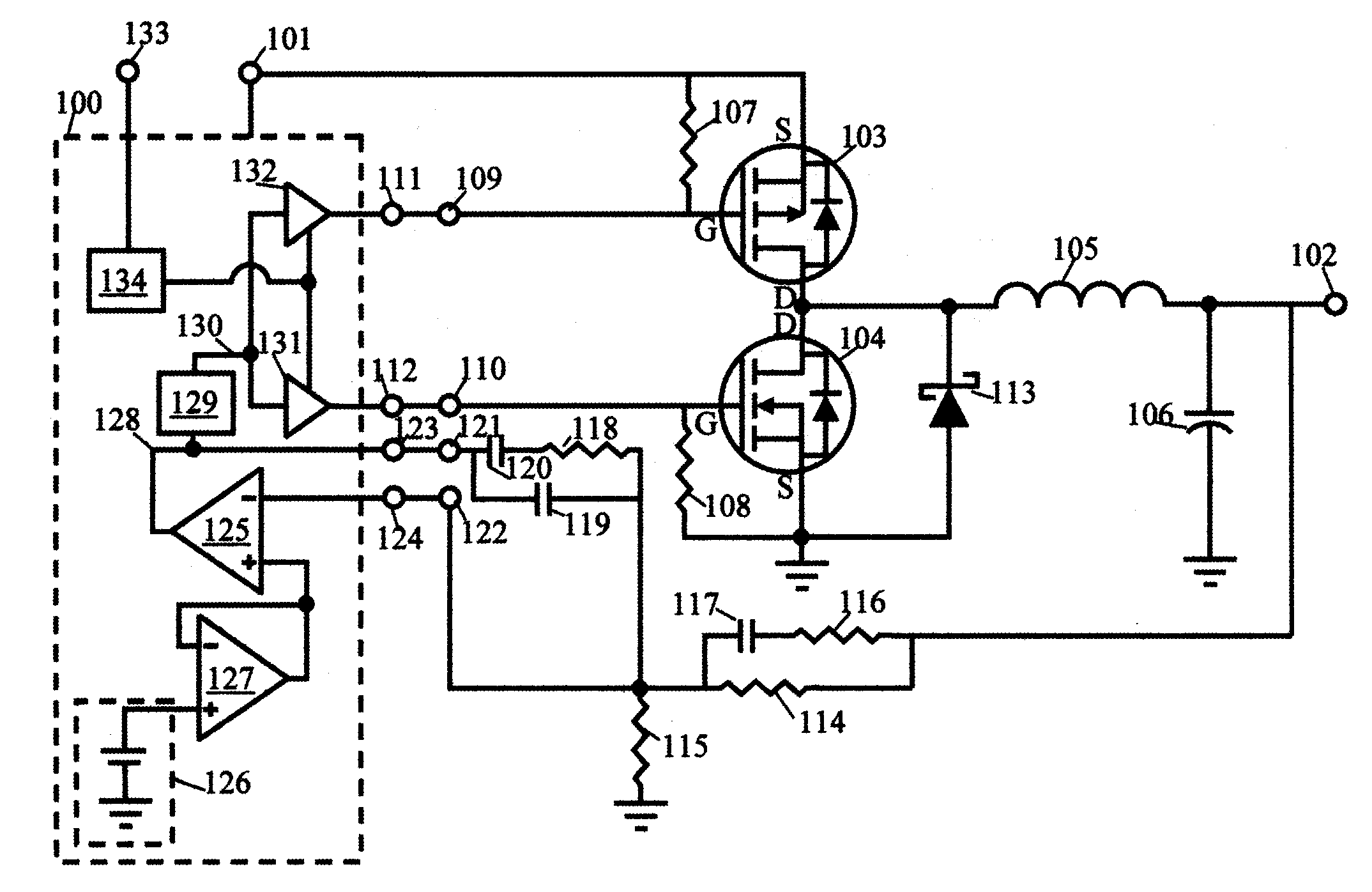

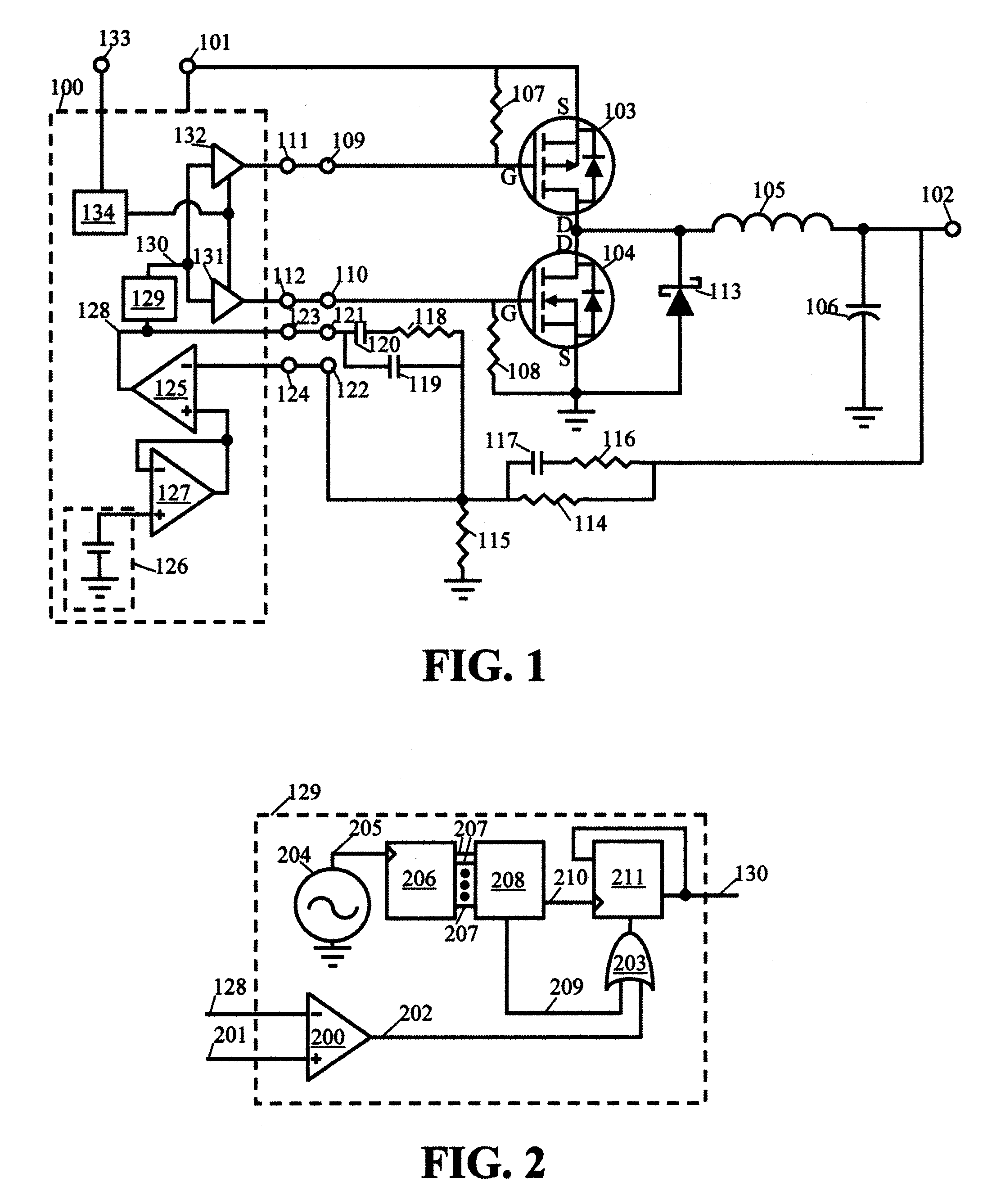

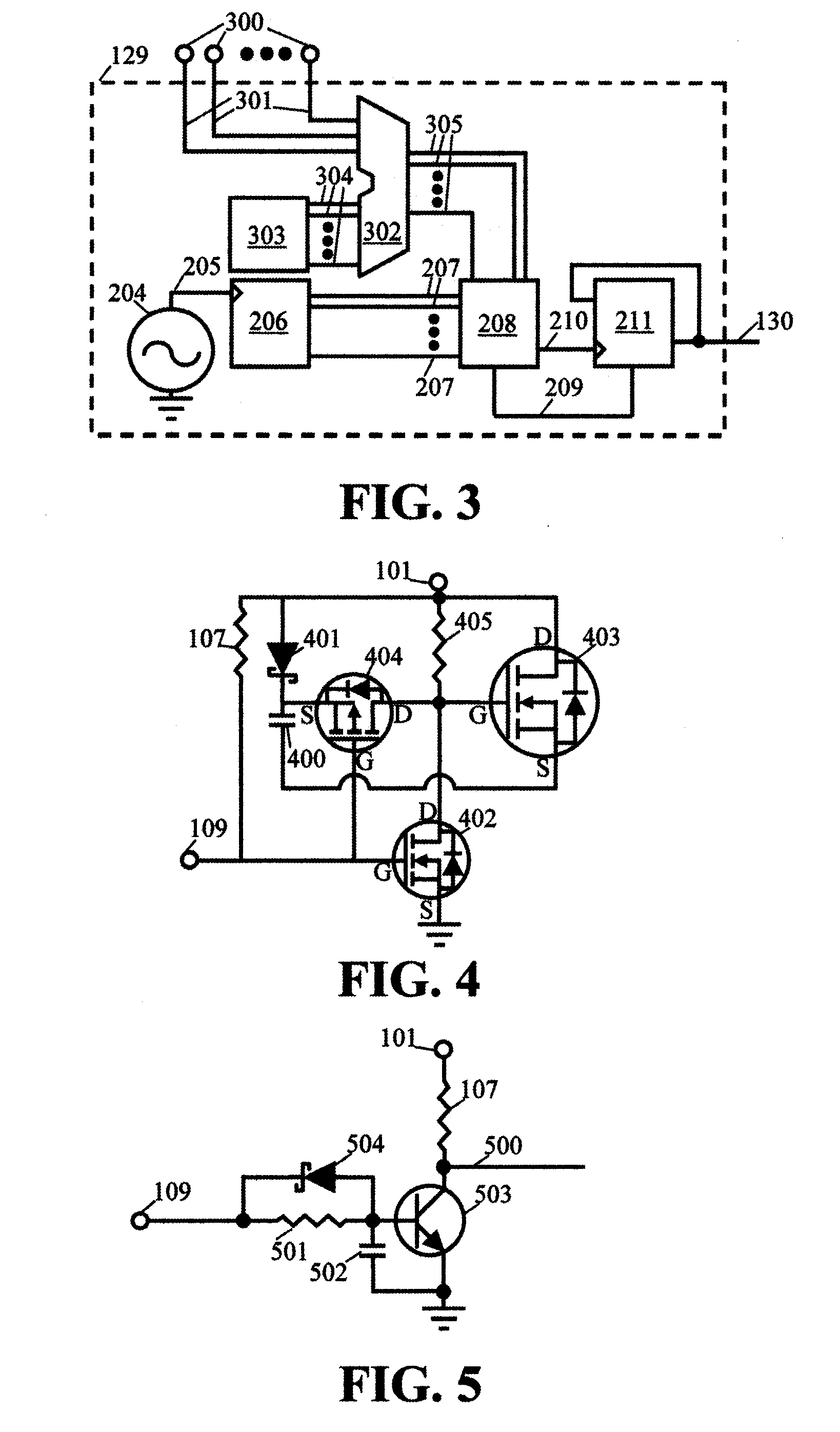

System and method for integrating a digital core with a switch mode power supply

InactiveUS6940189B2Improve powerMinimal costVolume/mass flow measurementSolid-state devicesVoltage converterPower switching

A digital core embodied within a semiconductor die that requires plural separate power supply voltage domains is situated within any of a variety of integrated circuit packaging technologies. Within the integrated circuit package including this semiconductor die also exists a switch mode DC-to-DC voltage converter, preferably a synchronous step-down regulator powering the entire integrated circuit from one supply voltage. The components contained within the integrated circuit package along with the semiconductor die include the switch mode power supply's power switching transistors, inductor core and windings, digital open-loop output voltage fixing circuitry, output capacitors and substrate for mounting said components when integrated within a packaging technology that does not already include a substrate.

Owner:CUFER ASSET LTD LLC

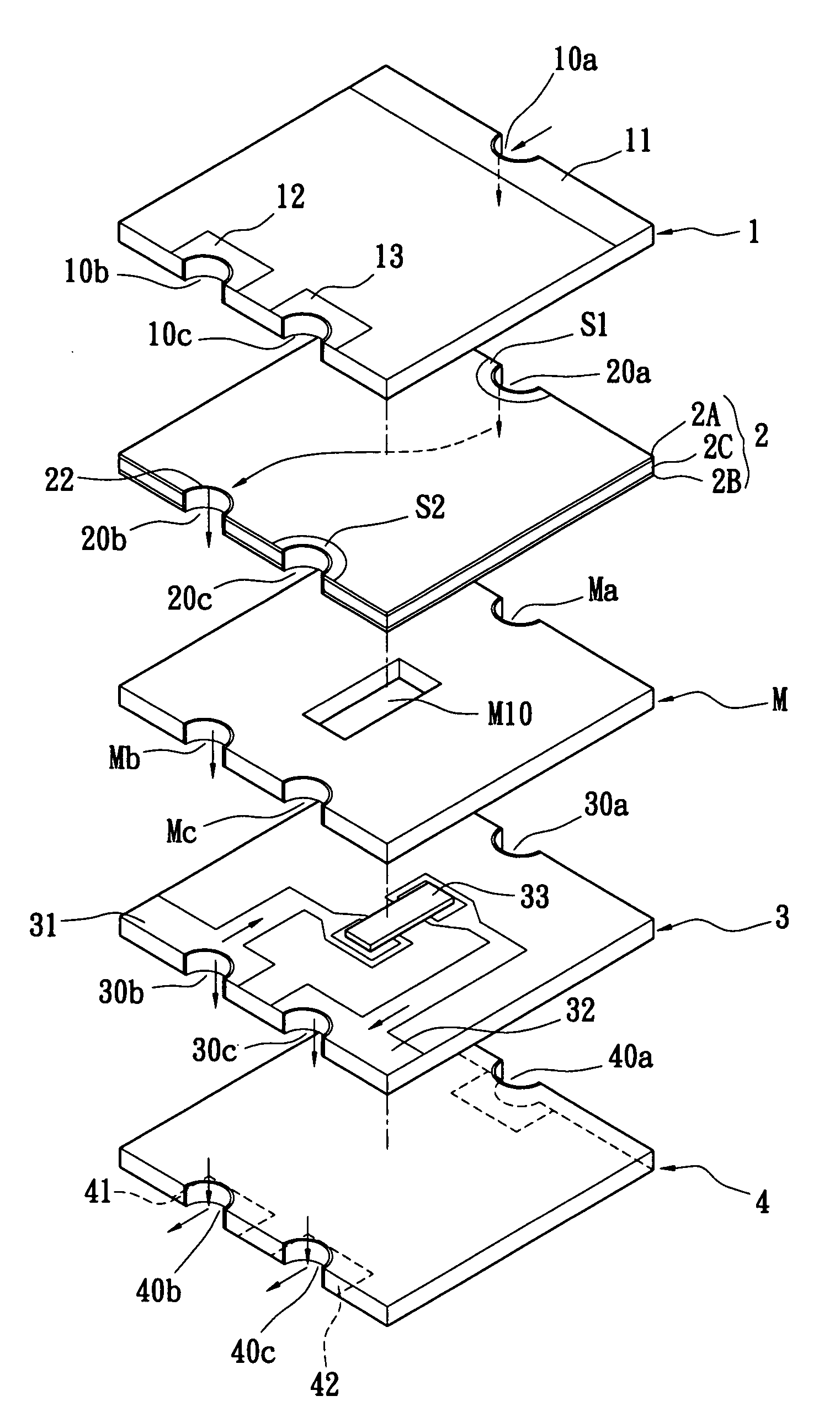

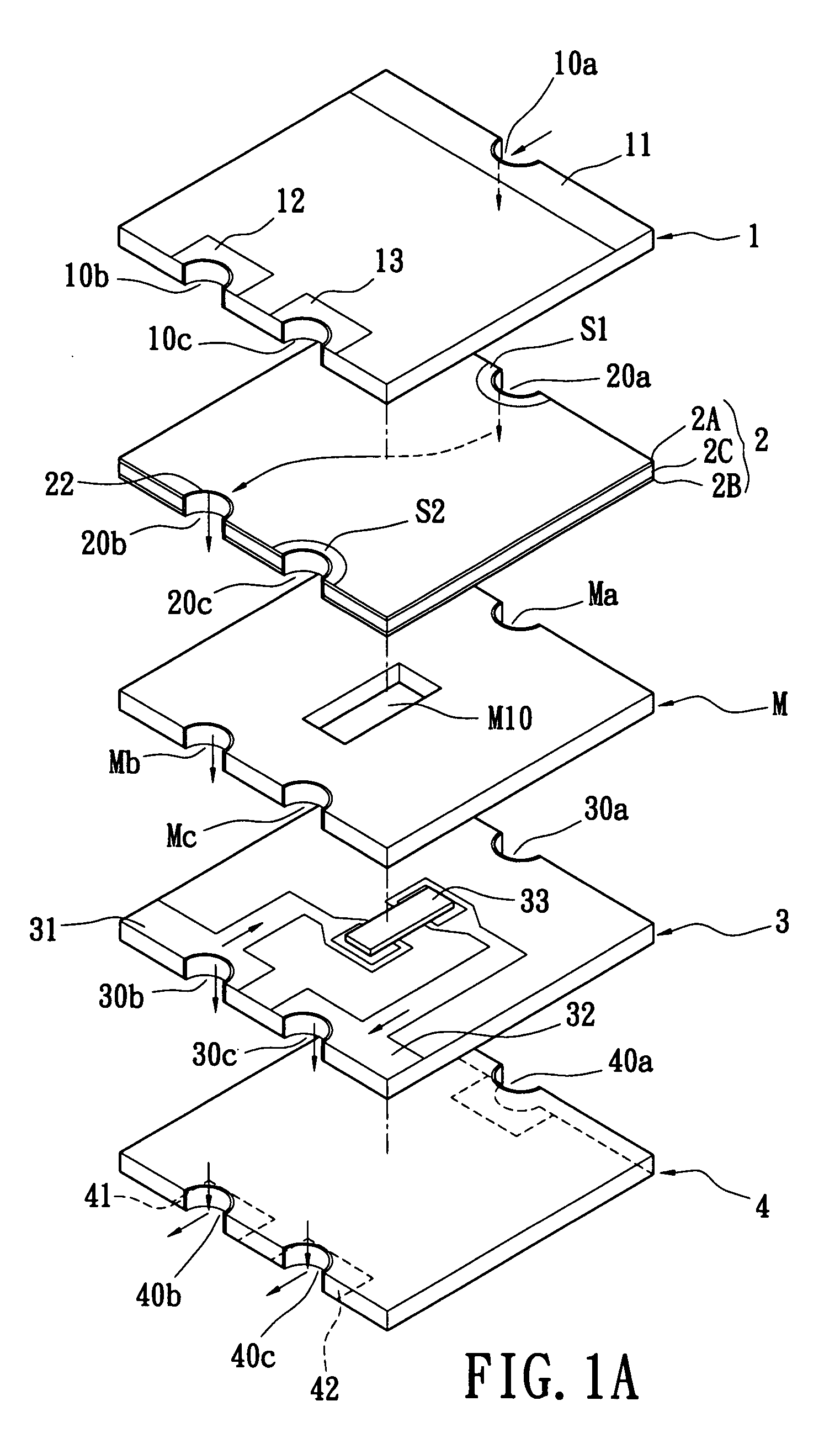

Methods for Fabricating Three-Dimensional All Organic Interconnect Structures

InactiveUS20070267138A1High frequency and high bandwidth applicationsSemiconductor/solid-state device detailsSolid-state devicesLiquid crystallineMaterials science

The present invention includes methods for making liquid crystalline polymer (LCP) interconnect structures using a high temperature and low temperature single sided LCP, where both the high and low temperature LCP are provided with a z-axis connection. The single sided conductive layer is a bus layer to form z-axis conductive stud within the high and low temperature LCP. High and low temperature LCP layers are etched or built up to form circuit patterns and subsequently bonded together to form final multilayer circuit pattern where the low temperature LCP melts to form both dielectric to dielectric bond to high temperature LCP circuit layer, and dielectric to conductive bond.

Owner:GEORGIA TECH RES CORP

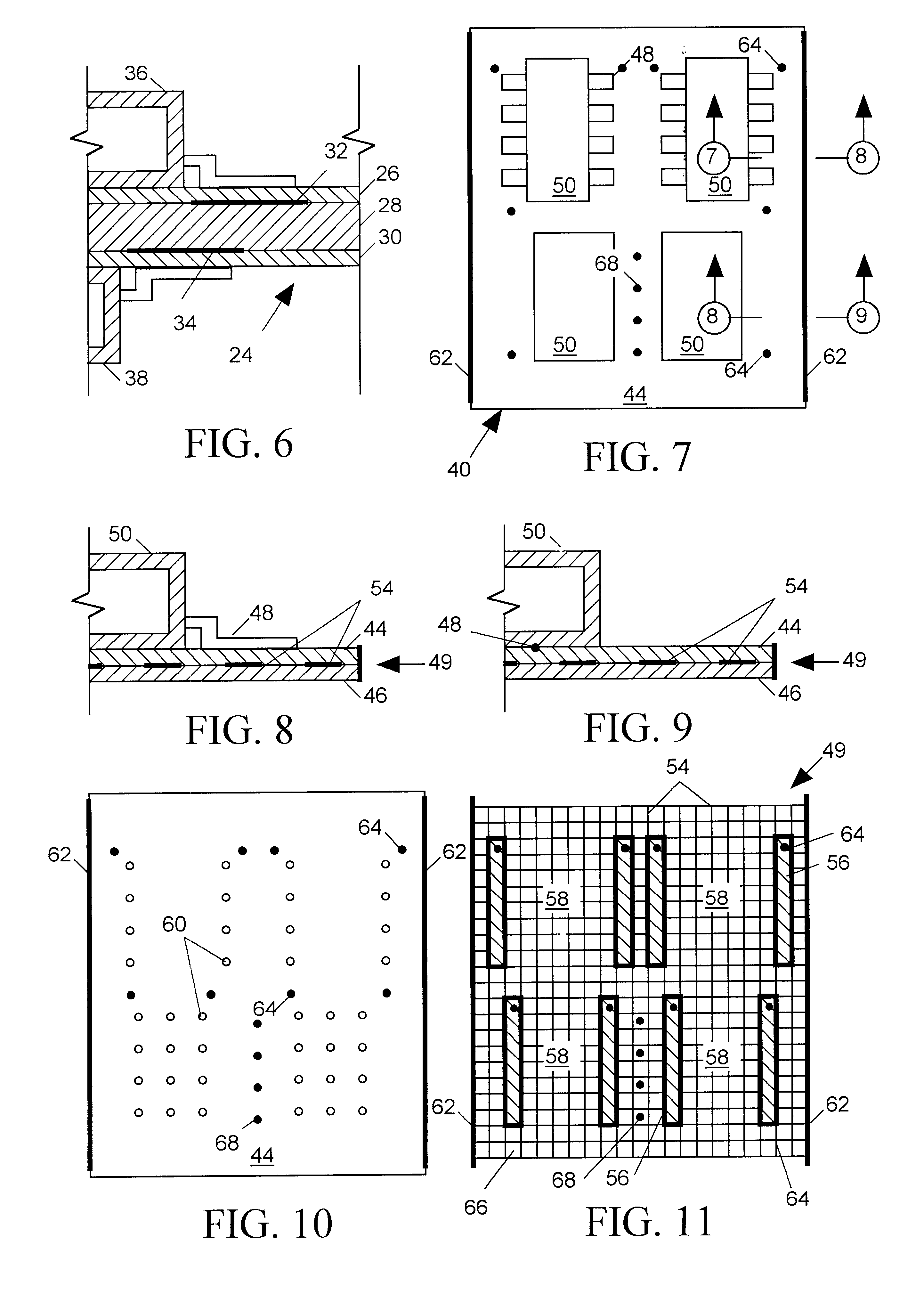

Tamper-responding encapsulated enclosure having flexible protective mesh structure

InactiveUS6686539B2Avoid Information LeakageDigital data processing detailsSemiconductor/solid-state device detailsDielectricNetwork on

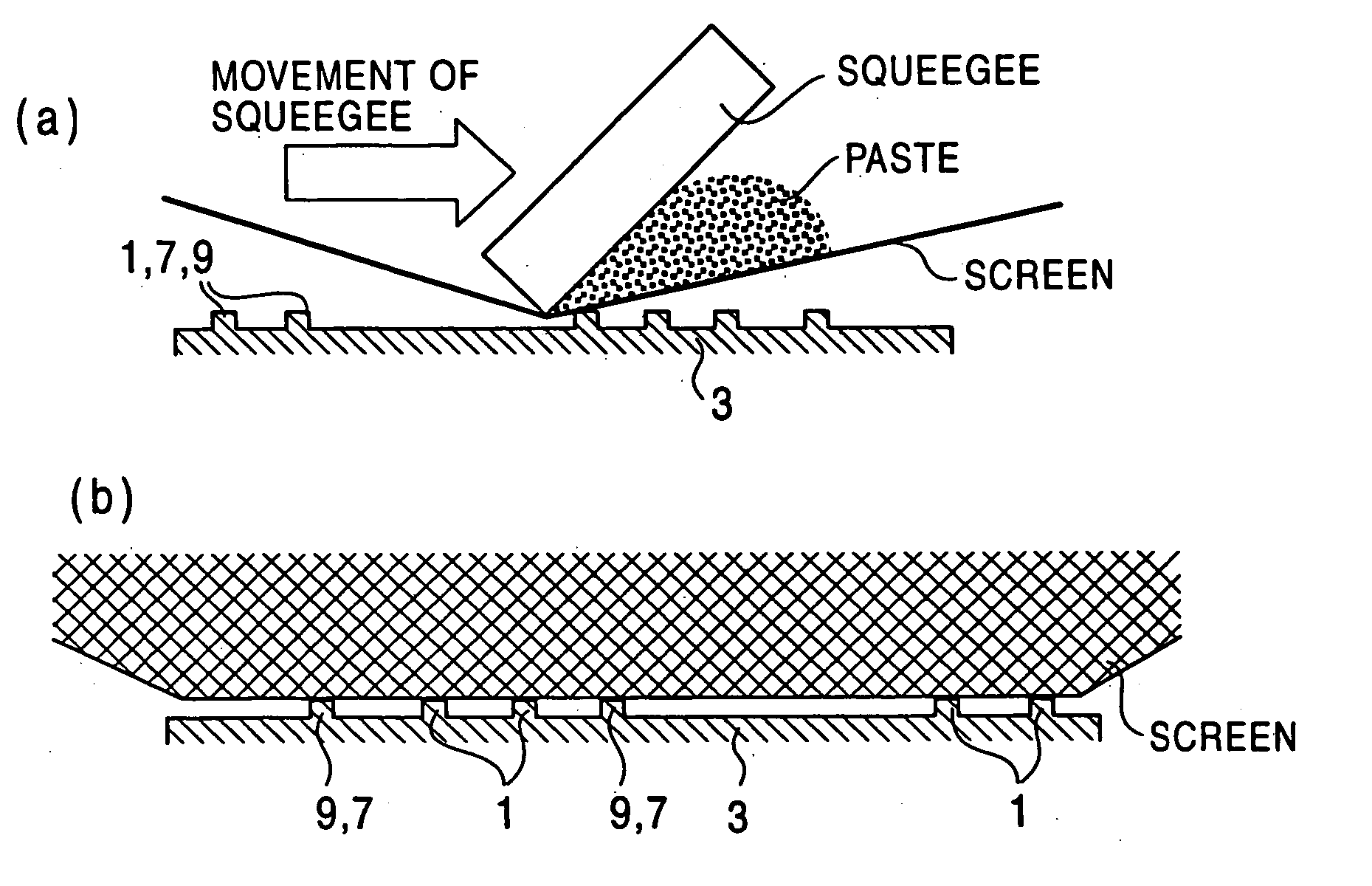

A structure and method for forming a tamper respondent electronic circuit enclosure that includes an integrated circuit structure, a mesh structure surrounding the integrated circuit structure, and a sealed enclosure surrounding the mesh structure. The mesh structure includes a layer of flexible dielectric having a first side and a second side, a screen-printed pattern of flexible electrically conductive first circuit lines forming a first resistor network on the first side, and a photo lithographically-formed pattern of flexible electrically conductive second circuit lines forming a second resistor network on the second side.

Owner:IBM CORP

Low temperature co-fired ceramic with improved registration

InactiveUS6205032B1Semiconductor/solid-state device detailsSolid-state devicesHigh densityMetallurgy

A low temperature co-fired ceramic assembly (LTCC) with a constraining core to minimize shrinkage of outer ceramic layers during firing. The outer ceramic layers have high density circuit features. A ceramic core includes several ceramic layers. Several via holes are located in the first and second ceramic layers. Several low density circuit features are located on the ceramic layers that make up the core. Outer ceramic layers are placed top and bottom of the ceramic core. The outer ceramic layers have via holes and high density circuit features. The circuit features patterned on the ceramic layers include resistors, capacitors, circuit lines, vias, inductors, or bond pads. The ceramic core is fired first in a furnace. The outer layers are then laminated to the ceramic core and fired. The ceramic core controls the shrinkage rate of the outer ceramic layers during firing allowing higher density circuit features on the outer layers.

Owner:CTS CORP ELKHART

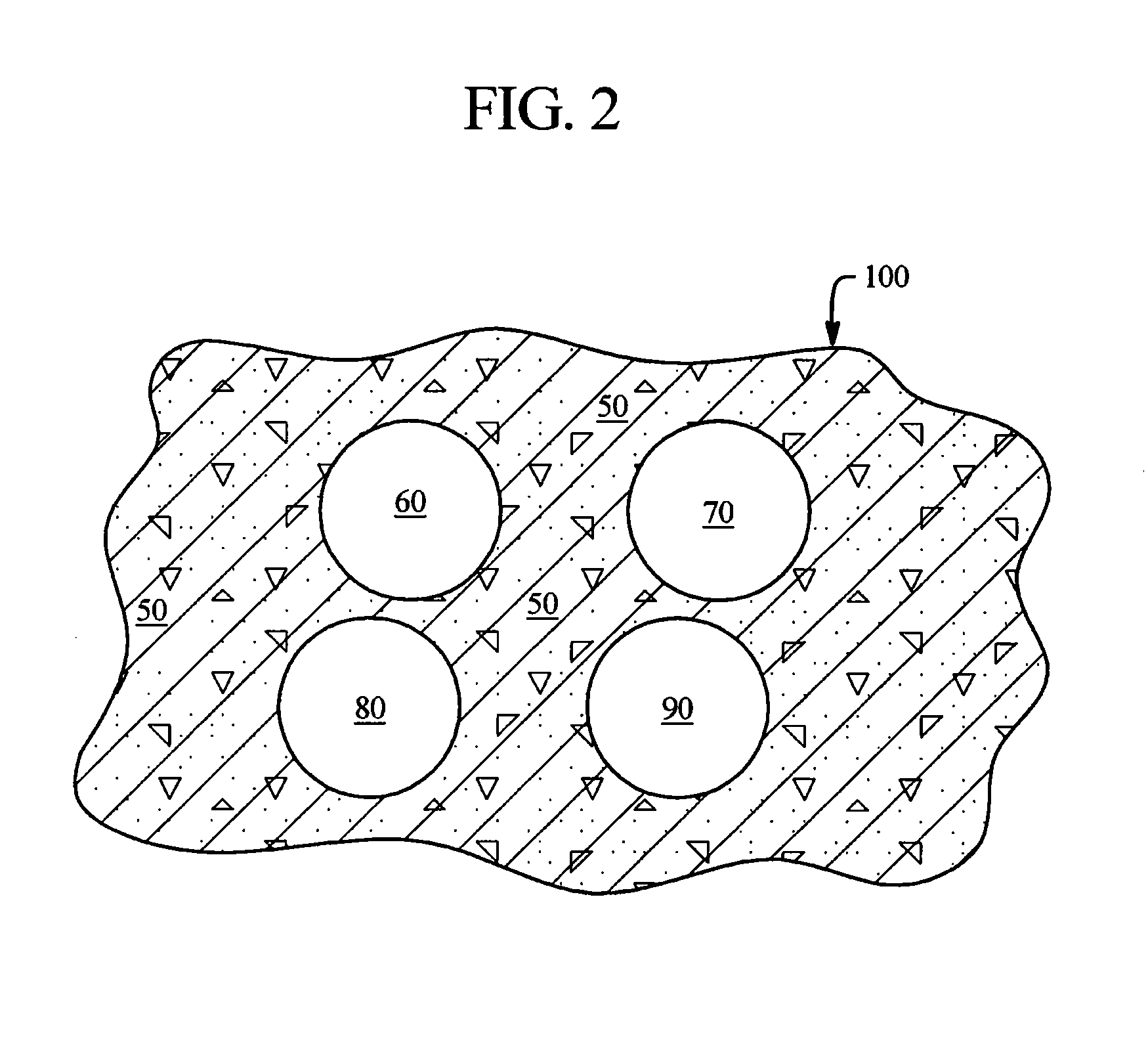

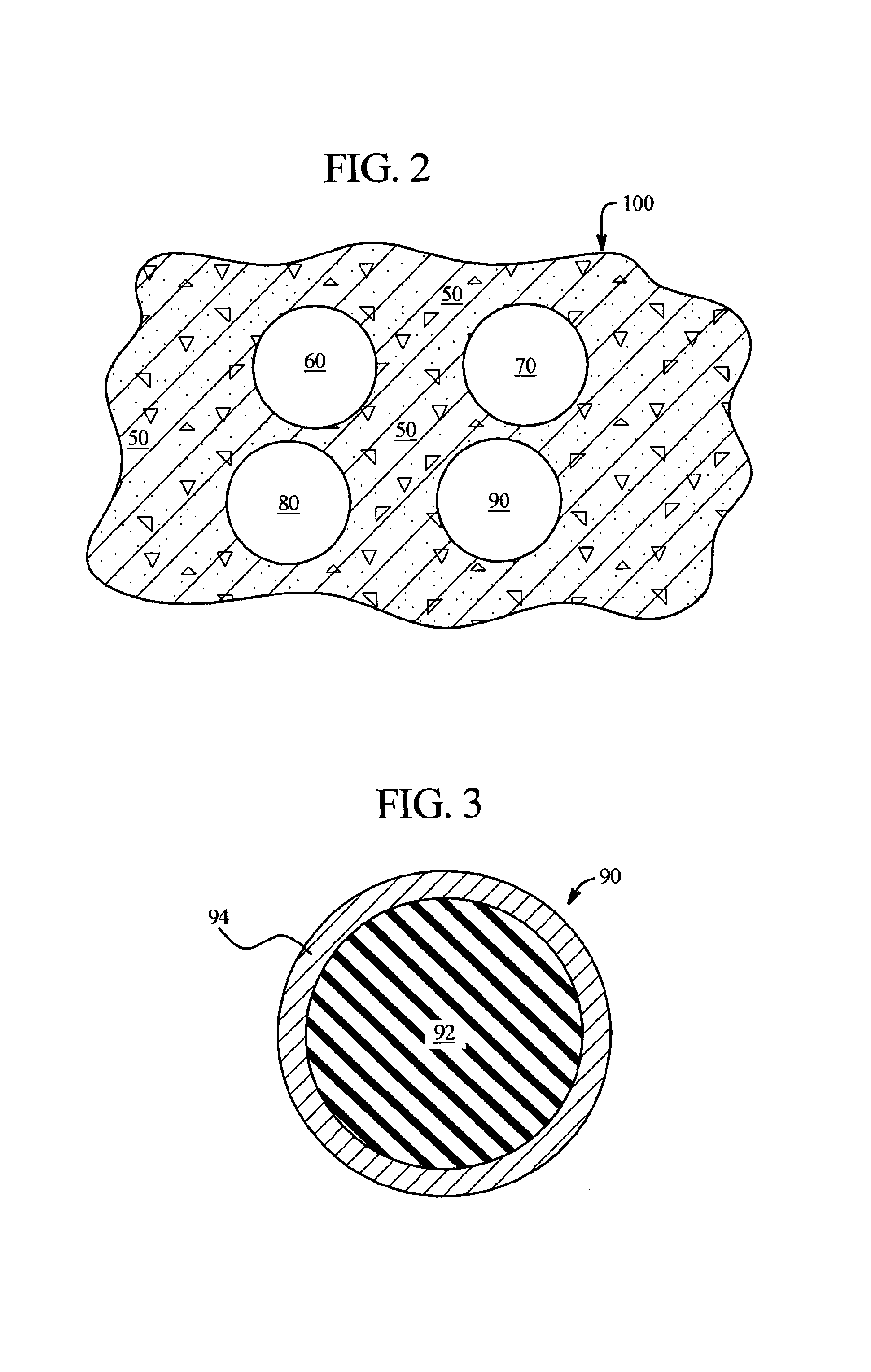

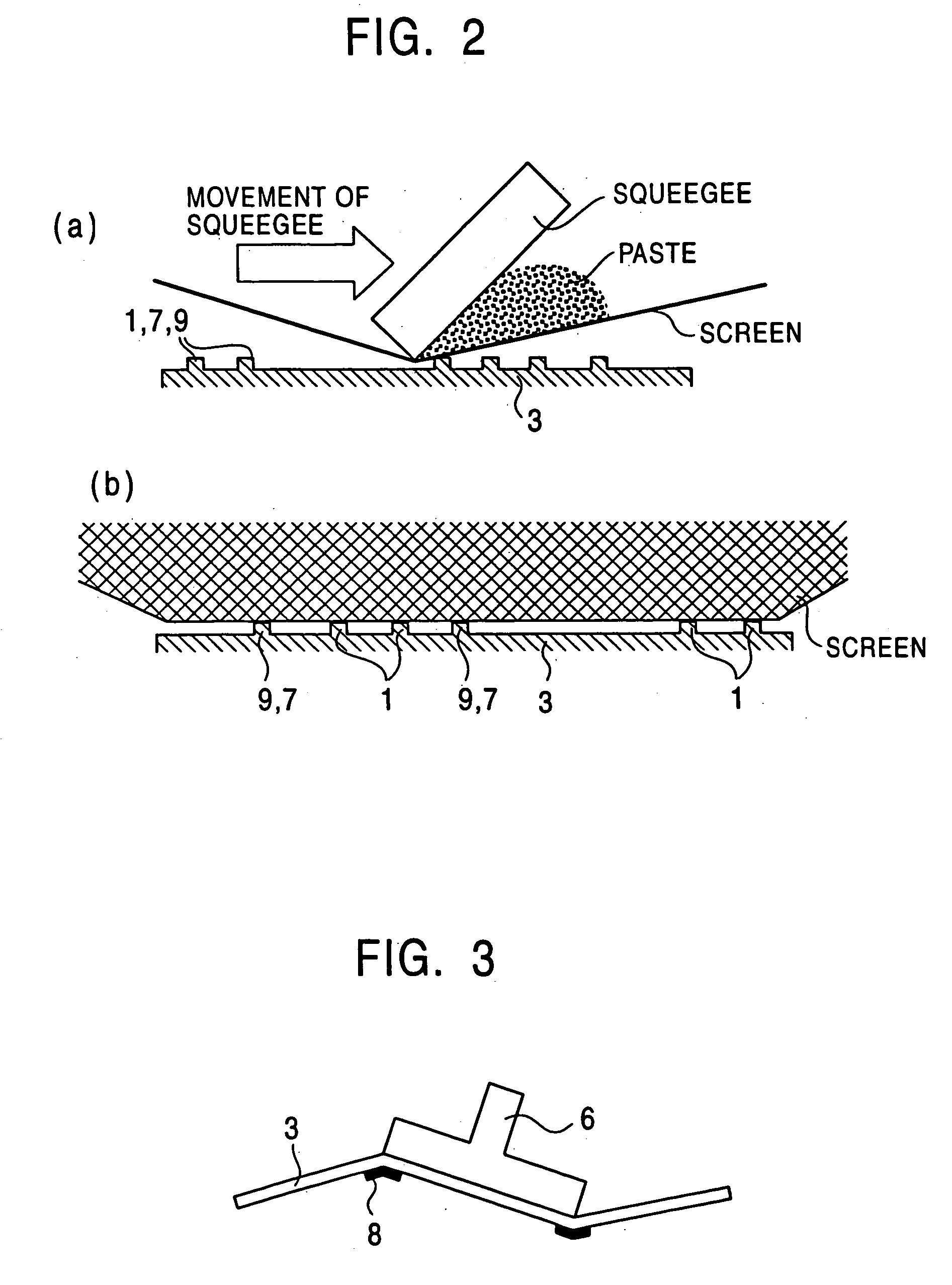

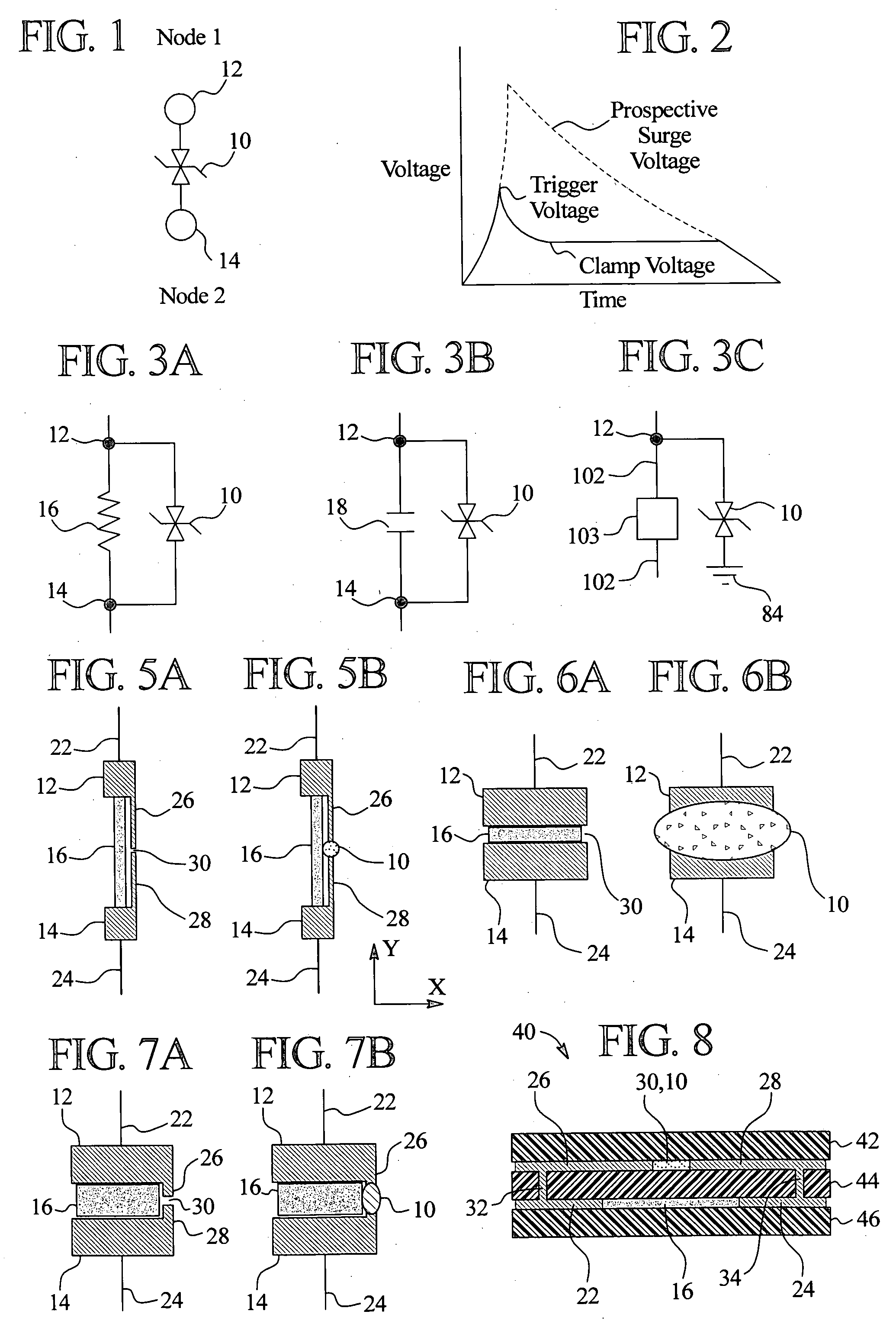

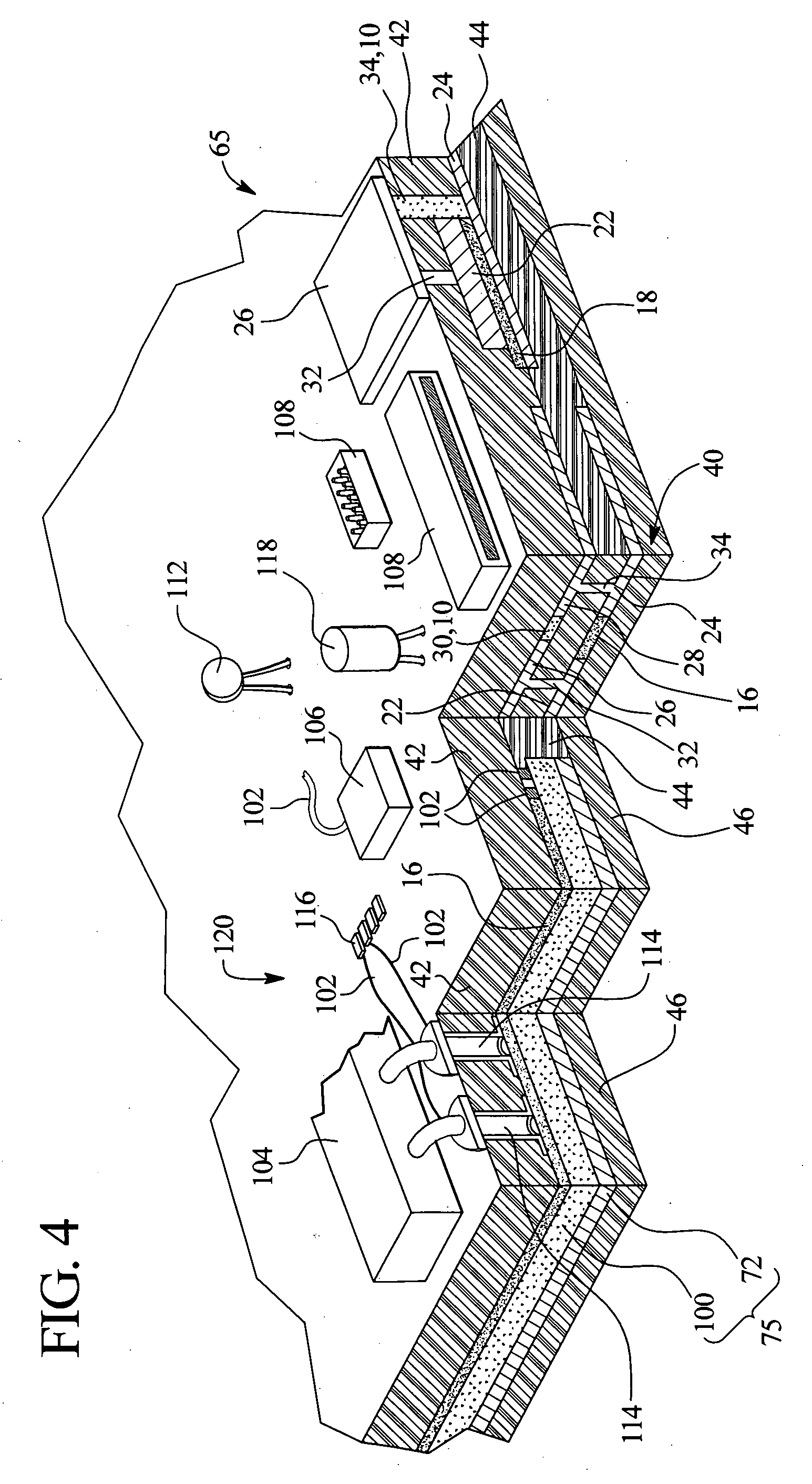

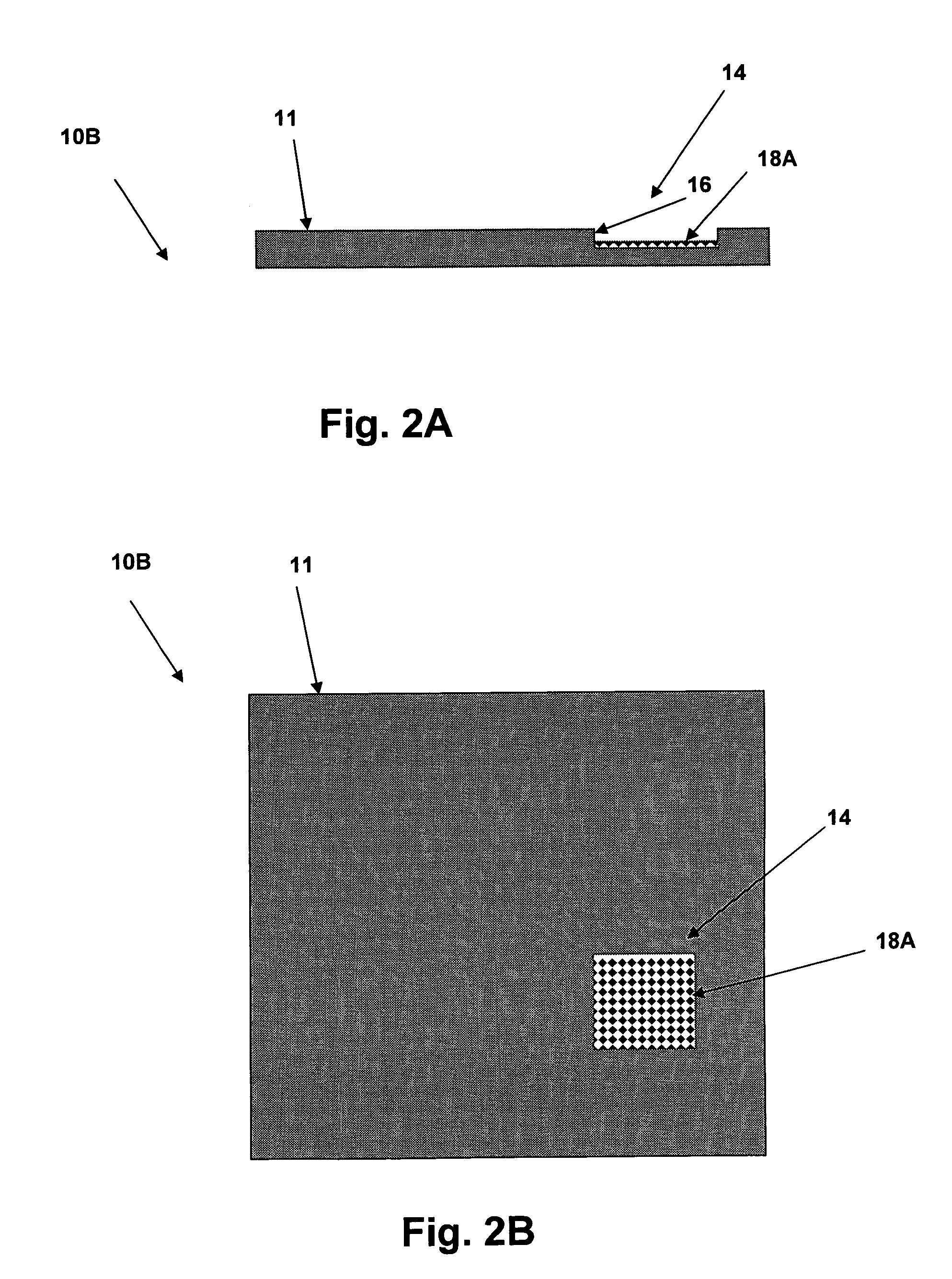

Direct application voltage variable material, devices employing same and methods of manufacturing such devices

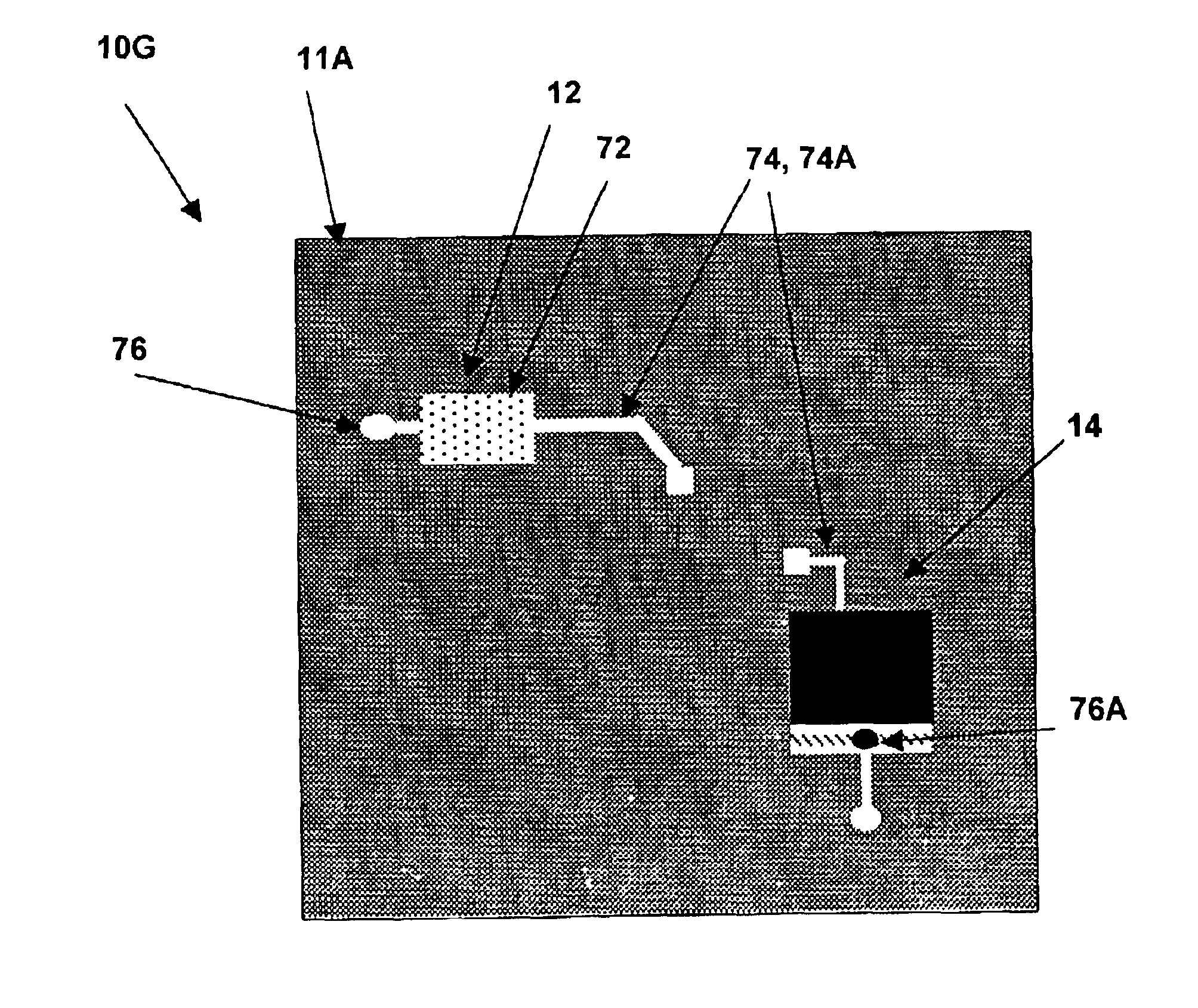

ActiveUS20050057867A1Directly appliedCurrent responsive resistorsPrinted circuit aspectsStencil printingMechanical engineering

A voltage variable material (“VVM”) including an insulative binder that is formulated to intrinsically adhere to conductive and non-conductive surfaces is provided. The binder and thus the VVM is self-curable and applicable in a spreadable form that dries before use. The binder eliminates the need to place the VVM in a separate device or to provide separate printed circuit board pads on which to electrically connect the VVM. The binder and thus the VVM can be directly applied to many different types of substrates, such as a rigid FR-4 laminate, a polyimide, a polymer or a multilayer PCB via a process such as screen or stencil printing. In one embodiment, the VVM includes two types of conductive particles, one with a core and one without a core. The VVM can also have core-shell type semiconductive particles.

Owner:LITTELFUSE INC

Methods for fabricating three-dimensional all organic interconnect structures

InactiveUS20040000425A1Semiconductor/solid-state device detailsSolid-state devicesLiquid crystallineAdhesive

The present invention comprises methods for making three-dimensional (3-D) liquid crystalline polymer (LCP) interconnect structures using a high temperature singe sided liquid crystalline polymer, and low temperature single sided liquid crystalline polymer, whereas both the high temperature LCP and the low temperature LCP are drilled using a laser or mechanical drill or mechanically punch to form a z-axis connection. The single sided Conductive layer is used as a bus layer to form z axis conductive stud conductive stud within the high temperature and low temperature LCP, followed by deposition of a metallic capping layer of the stud that serves as the bonding metal between the conductive interconnects to form the z-axis electrical connection. High temperature and low temperature LCP circuit layers are etched or built up to form circuit patterns and subsequently bonded together to form final 3-D multilayer circuit pattern whereas the low temperature LCP melts to form both dielectric to dielectric bond to high temperature LCP circuit layer, and dielectric to conductive bond, whereas, metal to metal bonding occurs with high temperature metal capping layer bonding to conductive metal layer. The resultant structure is then packaged using two metallized organic cores that are laminated onto either side of the device using a low temperature adhesive with similar electrical properties and subsequently metallized to form the input output terminals and EM shielding.

Owner:GEORGIA TECH RES CORP

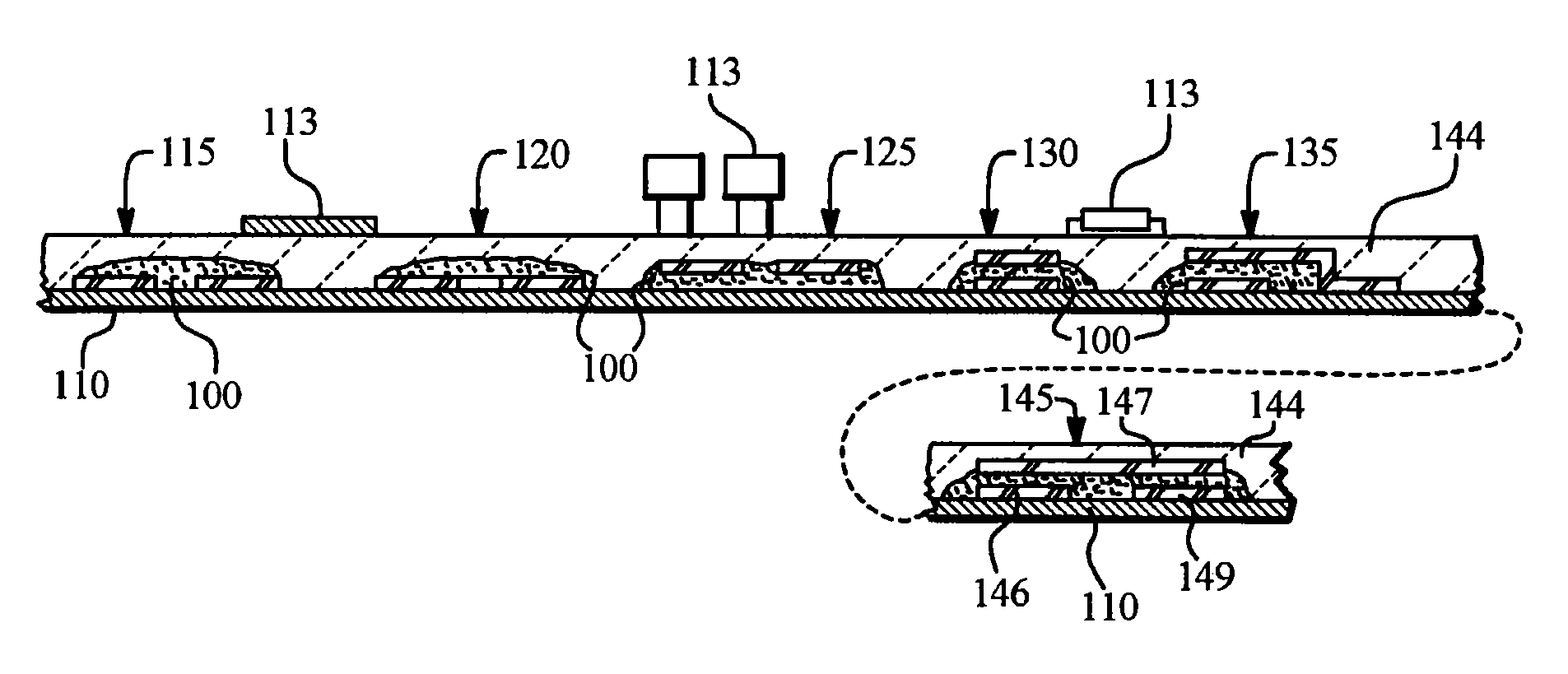

Self-heating circuit board

InactiveUS6396706B1Inexpensive and convenientSemiconductor/solid-state device detailsSolid-state devicesVoltage pulseAdhesive

Separate heating elements are embedded in a printed circuit board near integrated circuit (IC) packages or other parts mounted on the circuit board. Each heating element supplies heat to the part residing near it in response to an input voltage pulse. The heating elements are used to selectively melt solder or adhesives attaching the parts to the circuit board so that they can be easily removed or to temporarily melt solder or cure adhesive when the parts are mounted on the circuit board. The heating elements are also used to supply heat to IC packages for regulating their operating temperatures.

Owner:MA ZHONGXIN +1

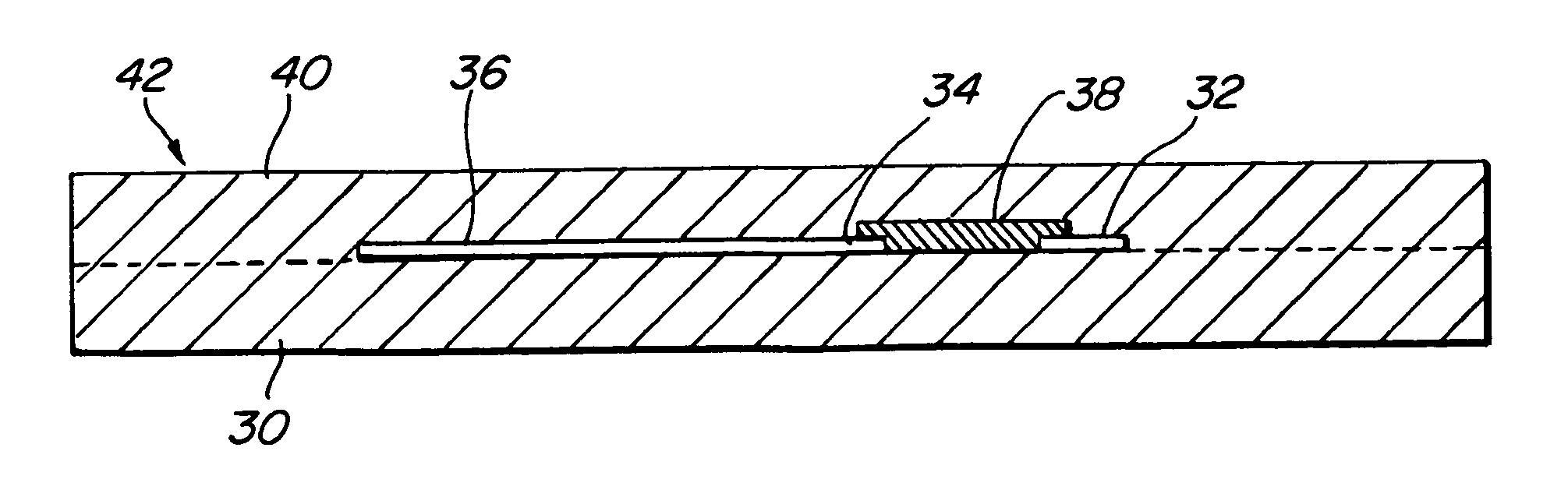

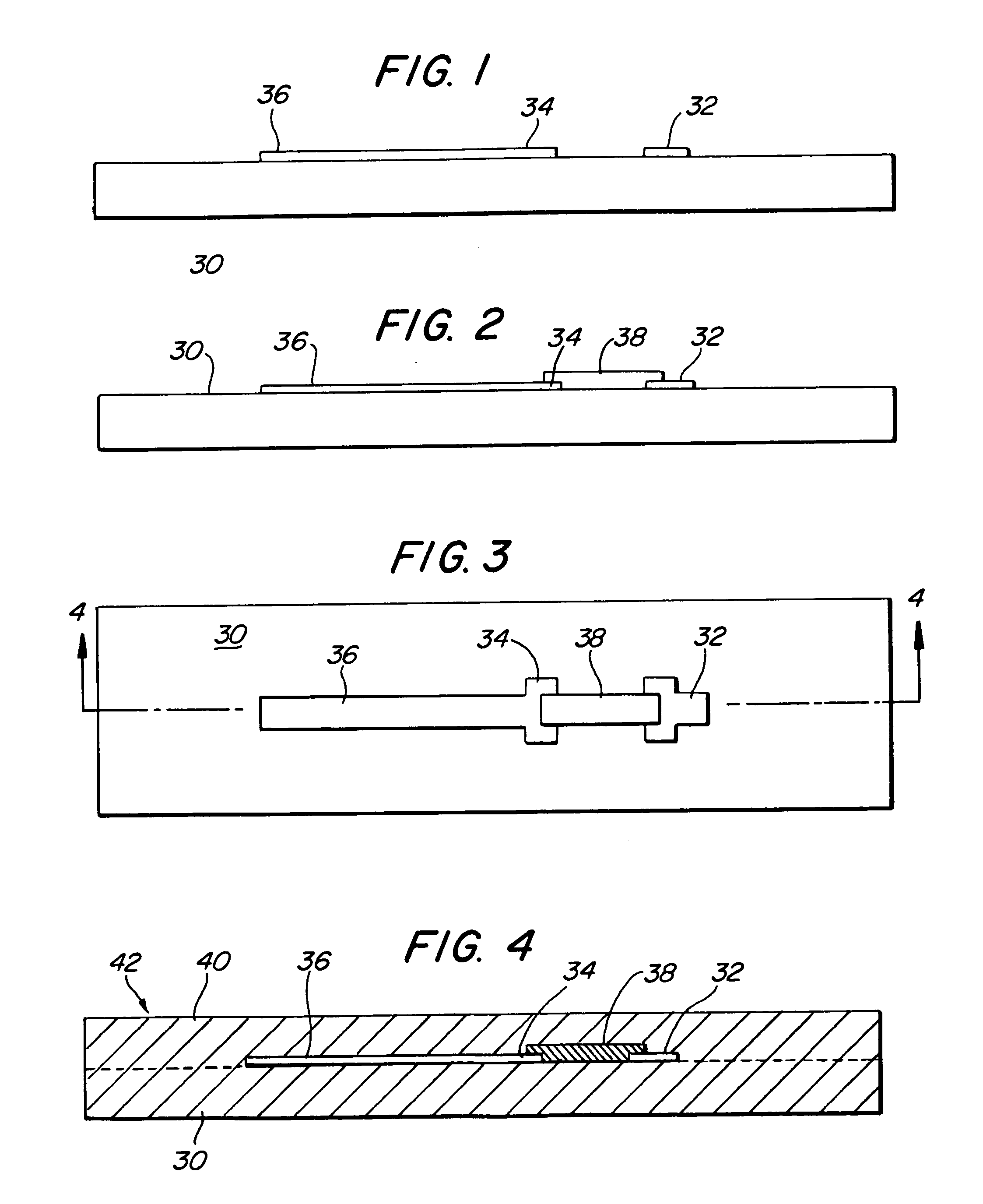

Electronic pressure sensitive transducer apparatus and method for manufacturing same

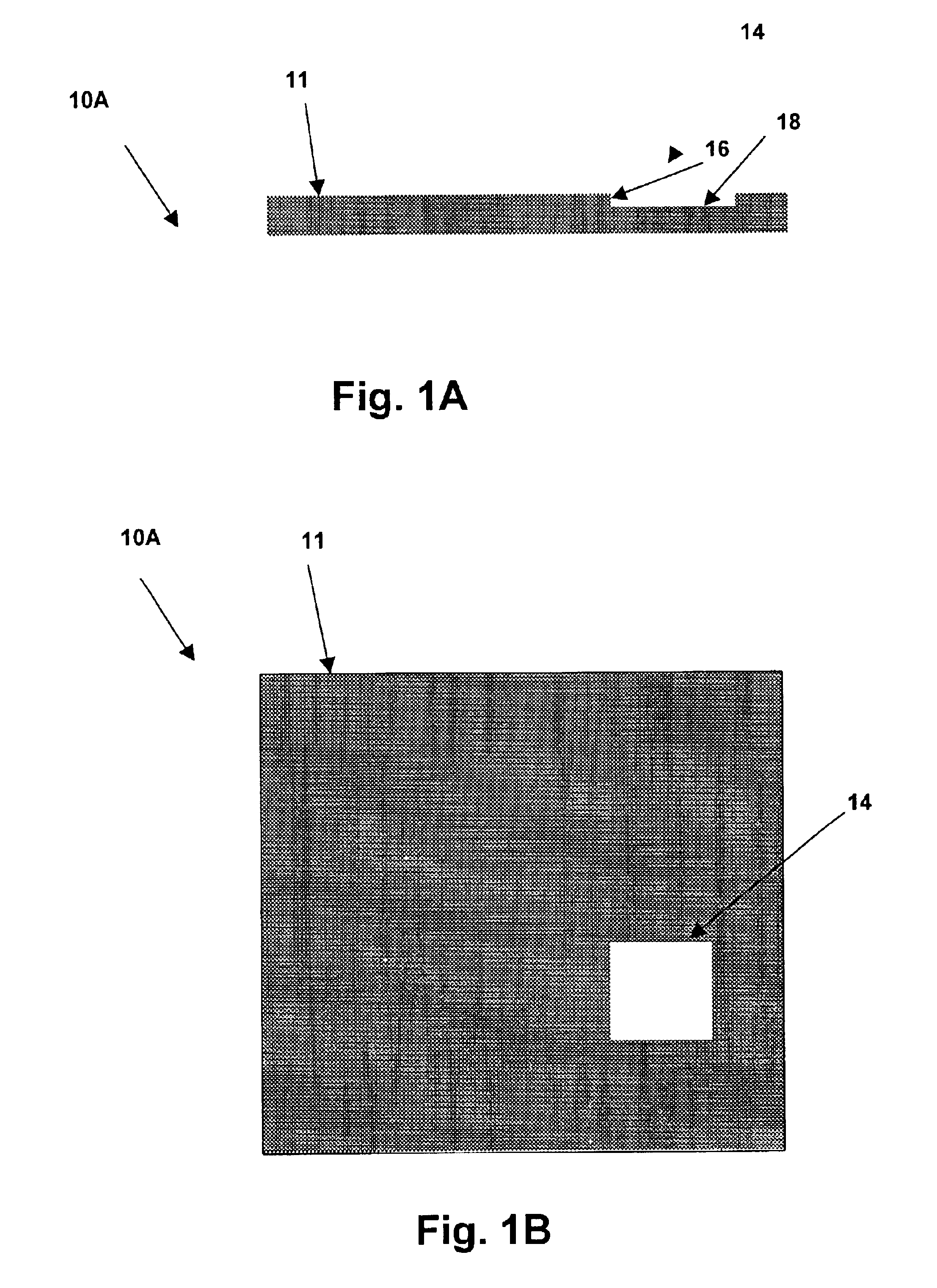

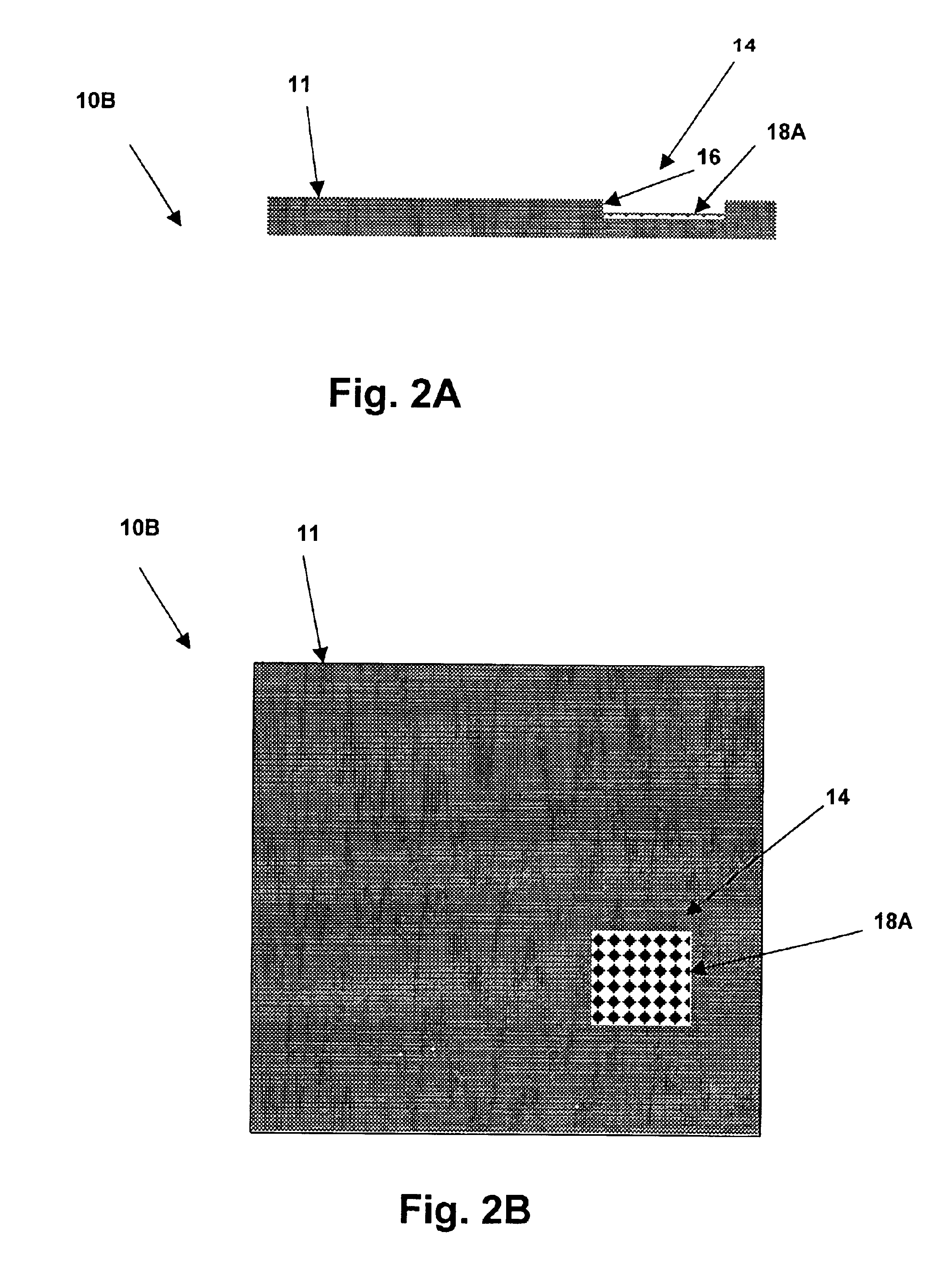

InactiveUS6909354B2Low costReduce complexityPrinted circuit assemblingPrinted circuit aspectsTransducerEngineering

The cost and complexity of an electronic pressure sensitive transducer are decreased by constructing such a transducer directly on a printed circuit board containing support electronics. Conductive traces are formed on the printed circuit board to define a contact area. A flexible substrate having an inner surface is positioned over the contact area. An adhesive spacer, substantially surrounding the contact area, attaches the flexible substrate to the printed circuit board. At least one resistive layer is deposited on the flexible substrate inner surface. In use, the resistive layer contacts at least two conductive traces in response to pressure applied to the flexible substrate to produce an electrical signal indicative of applied pressure.

Owner:INTERLINK ELECTRONICS

Direct application voltage variable material, devices employing same and methods of manufacturing such devices

InactiveUS7183891B2Directly appliedCurrent responsive resistorsPrinted circuit aspectsScreen printingStencil printing

A voltage variable material (“VVM”) including an insulative binder that is formulated to intrinsically adhere to conductive and non-conductive surfaces is provided. The binder and thus the VVM is self-curable and applicable in a spreadable form that dries before use. The binder eliminates the need to place the VVM in a separate device or to provide separate printed circuit board pads on which to electrically connect the VVM. The binder and thus the VVM can be directly applied to many different types of substrates, such as a rigid FR-4 laminate, a polyimide, a polymer or a multilayer PCB via a process such as screen or stencil printing. In one embodiment, the VVM includes two types of conductive particles, one with a core and one without a core. The VVM can also have core-shell type semiconductive particles.

Owner:LITTELFUSE INC

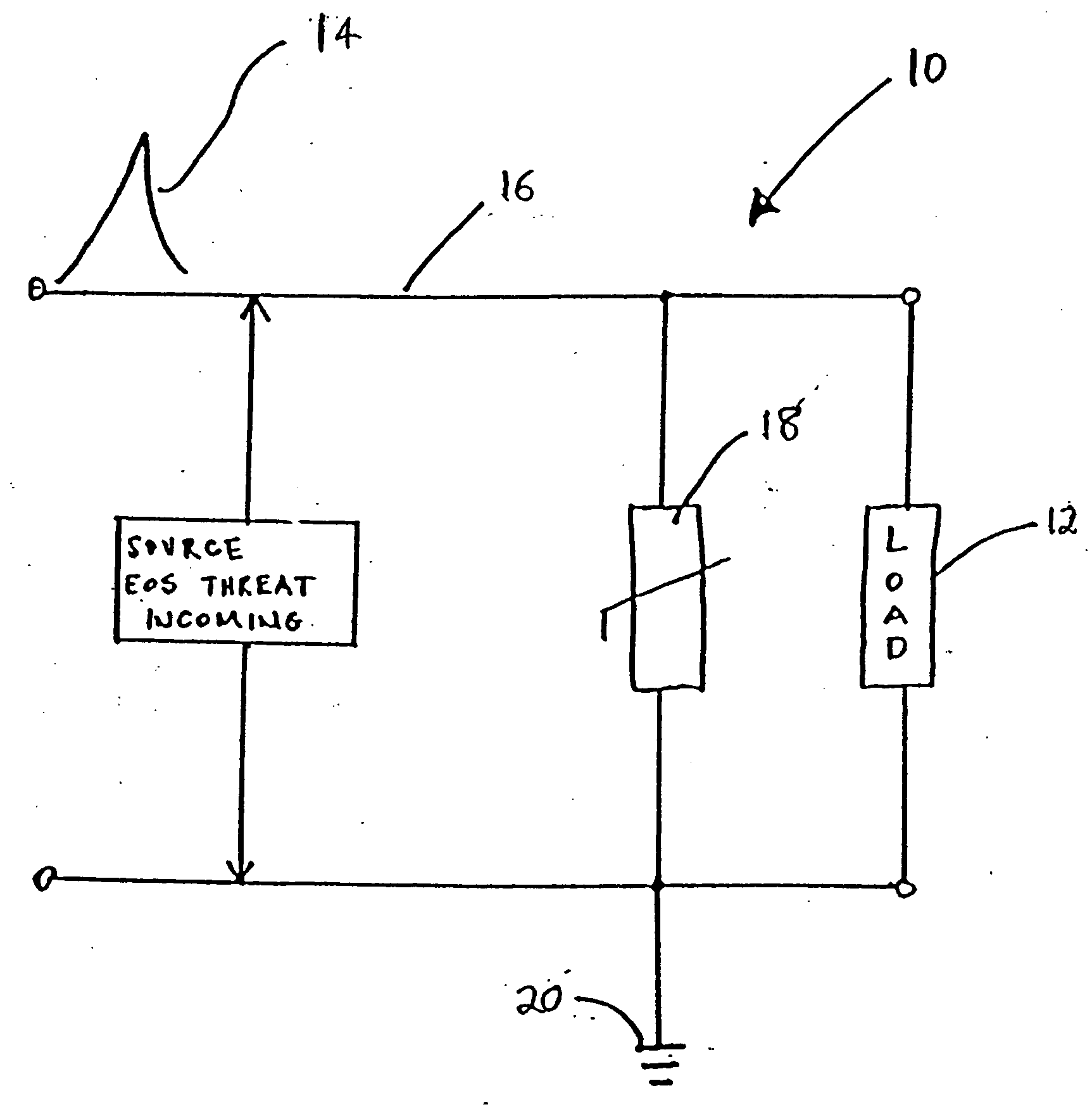

Voltage variable material for direct application and devices employing same

InactiveUS7202770B2Directly appliedSemiconductor/solid-state device detailsSolid-state devicesOvervoltagePolymer

The present invention provides overvoltage circuit protection. Specifically, the present invention provides a voltage variable material (“VVM”) that includes an insulative binder that is formulated to intrinsically adhere to conductive and nonconductive surfaces. The binder and thus the VVM is self-curable and may be applied to an application in the form of an ink, which dries in a final form for use. The binder eliminates the need to place the VVM in a separate device or for separate printed circuit board pads on which to electrically connect the VVM. The binder and thus the VVM can be directly applied to many different types of substrates, such as a rigid (FR-4) laminate, a polyimide or a polymer. The VVM can also be directly applied to different types of substrates that are placed inside a device.

Owner:LITTELFUSE INC

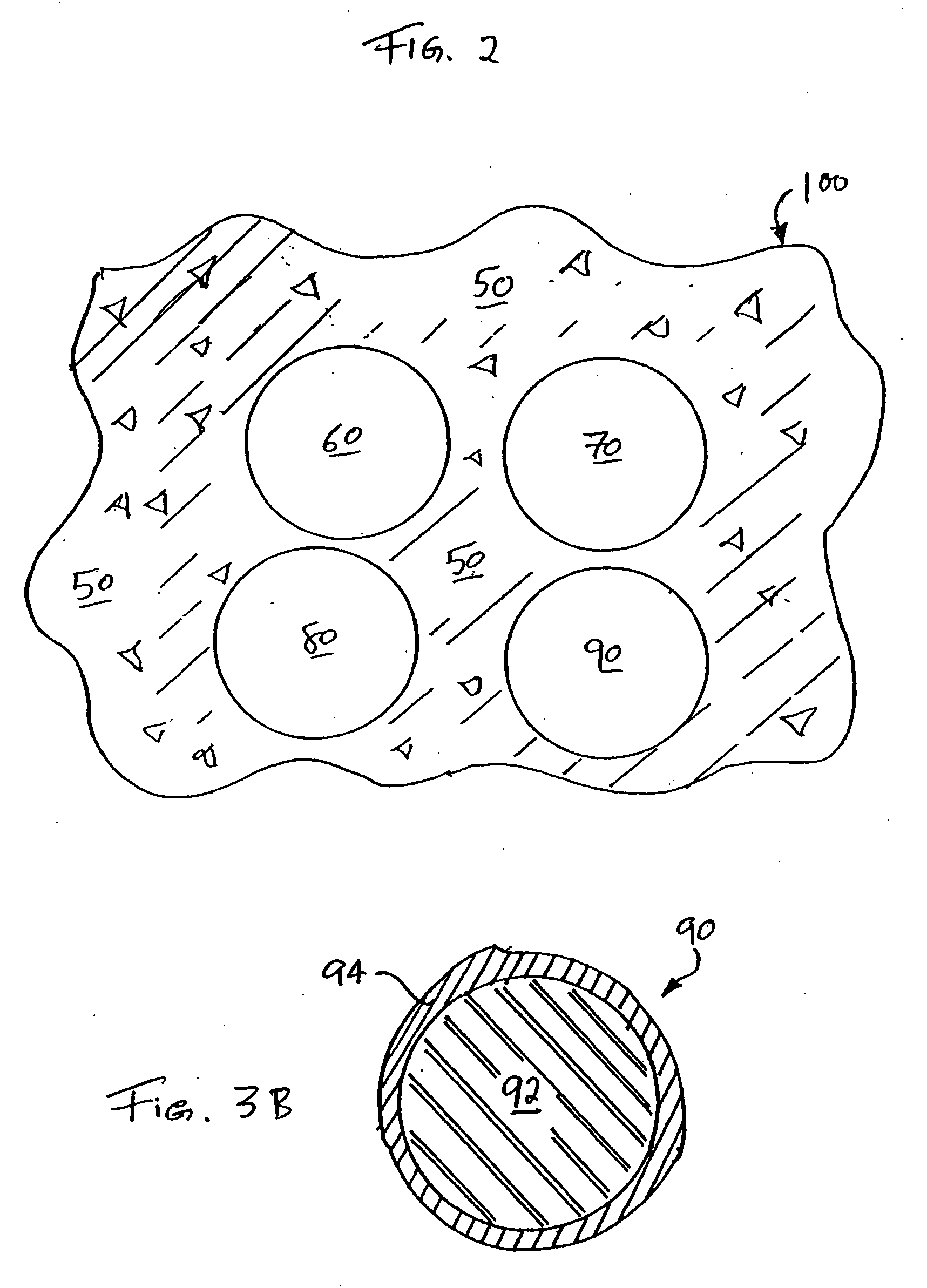

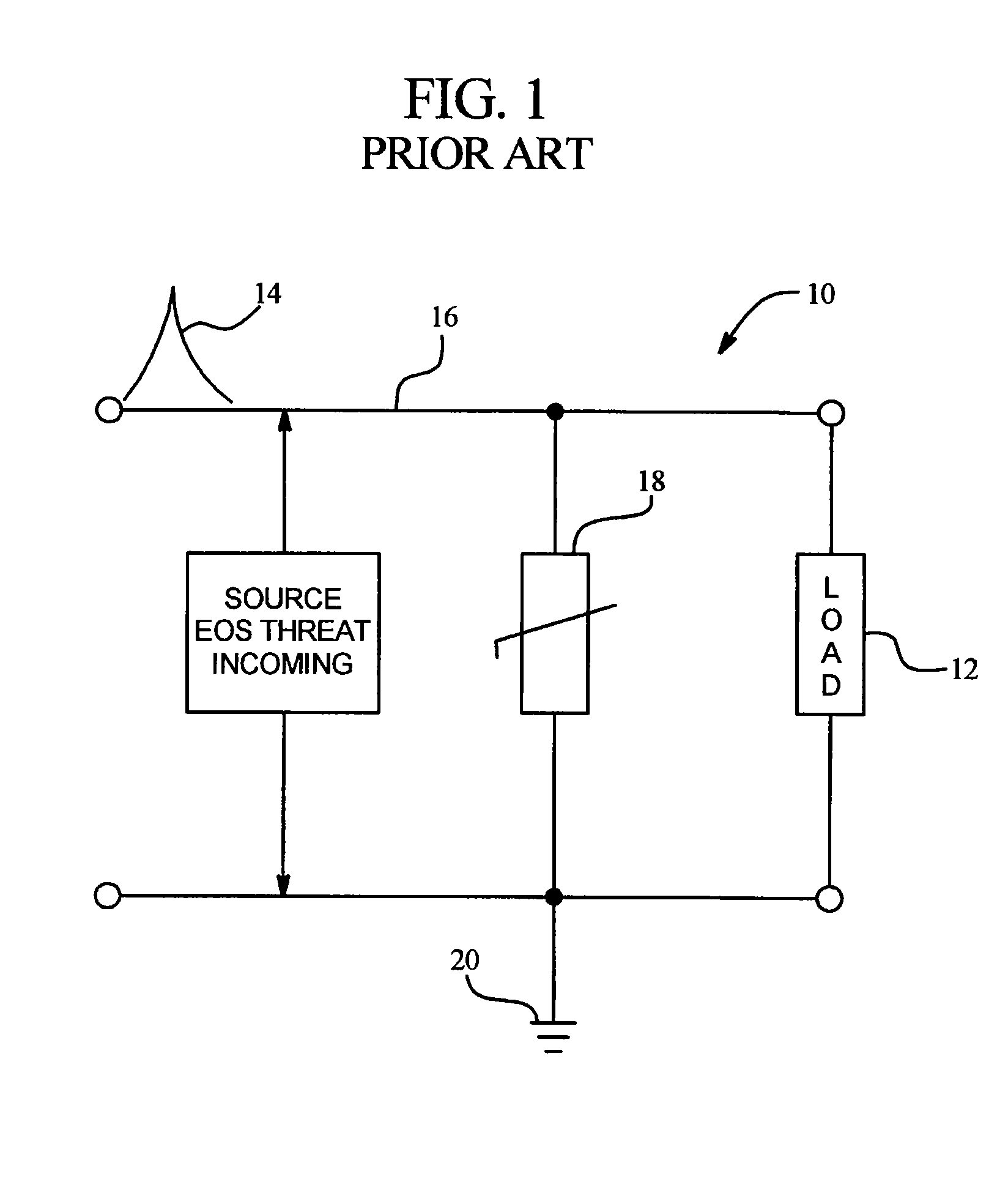

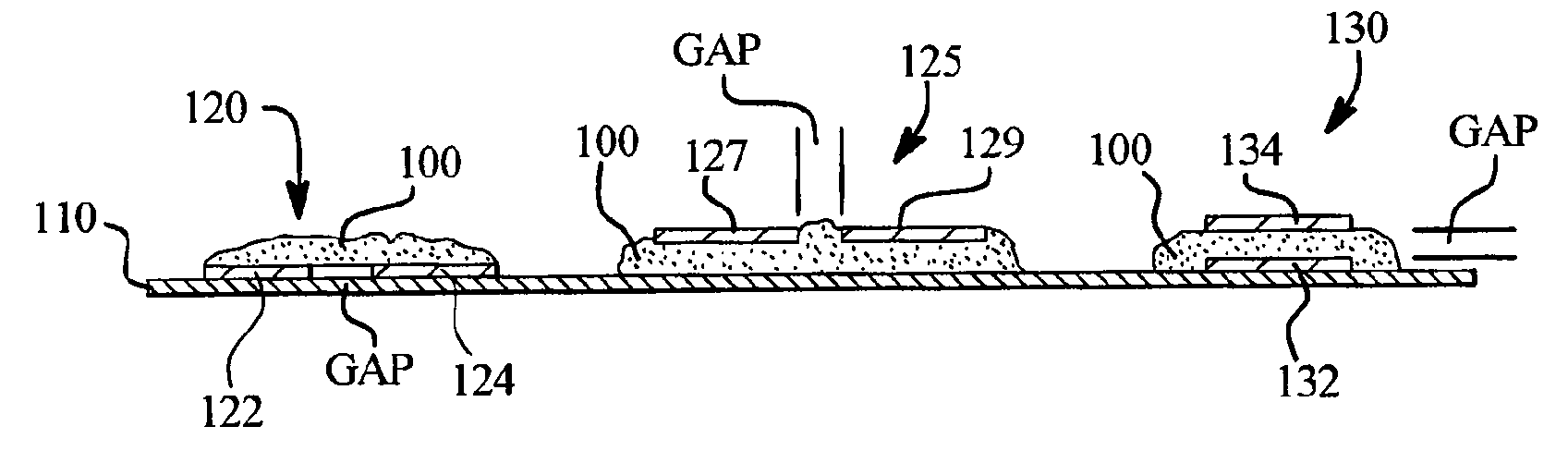

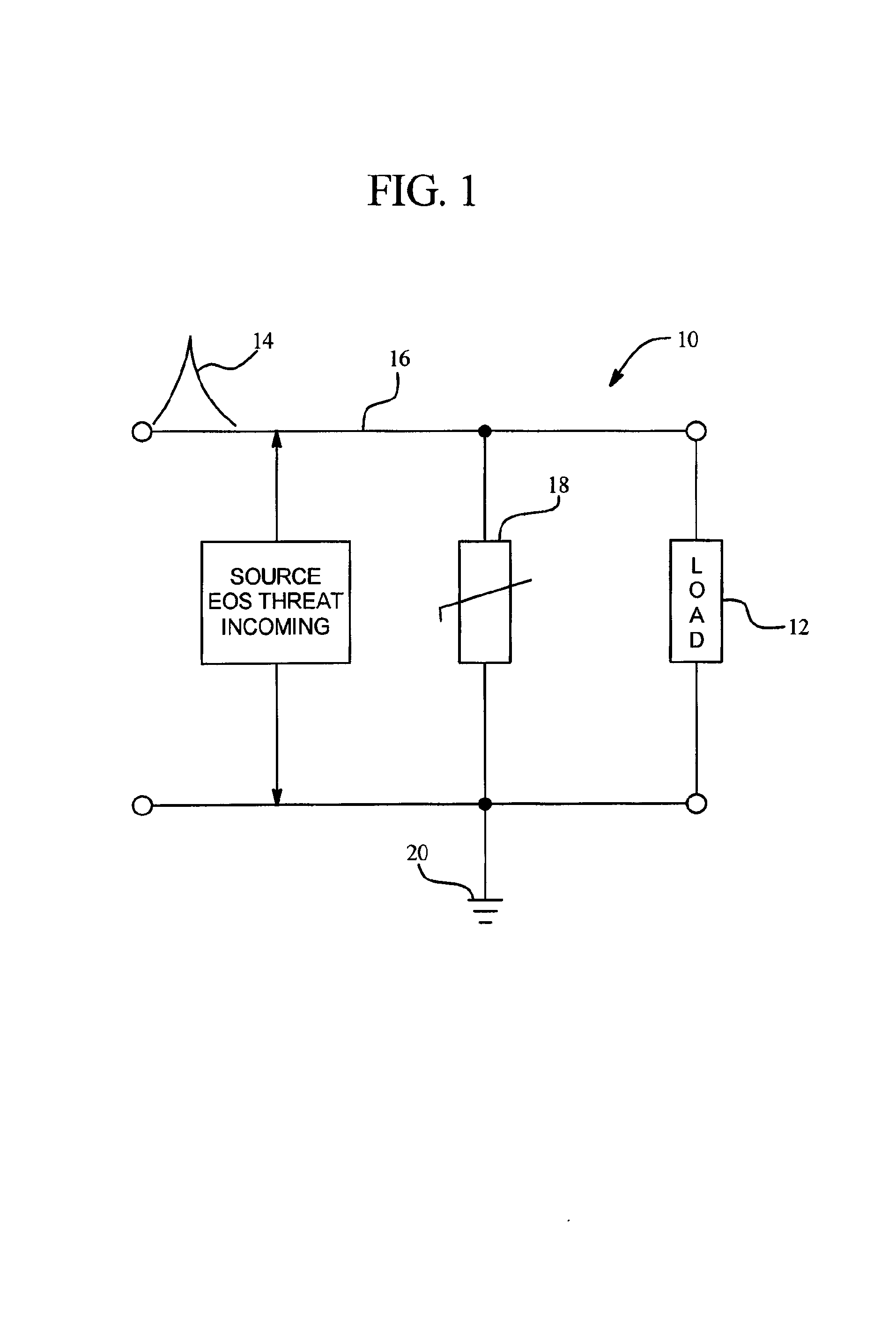

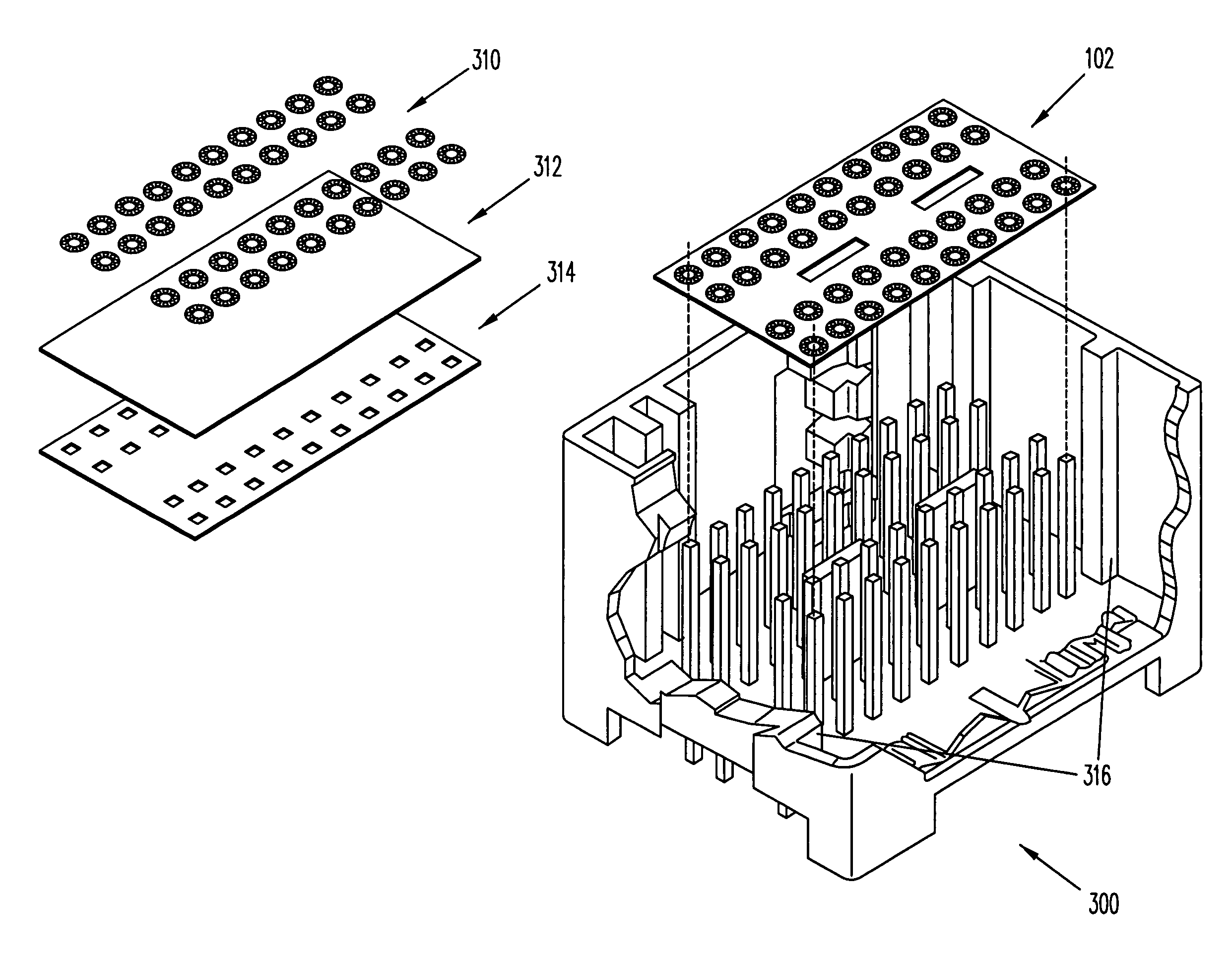

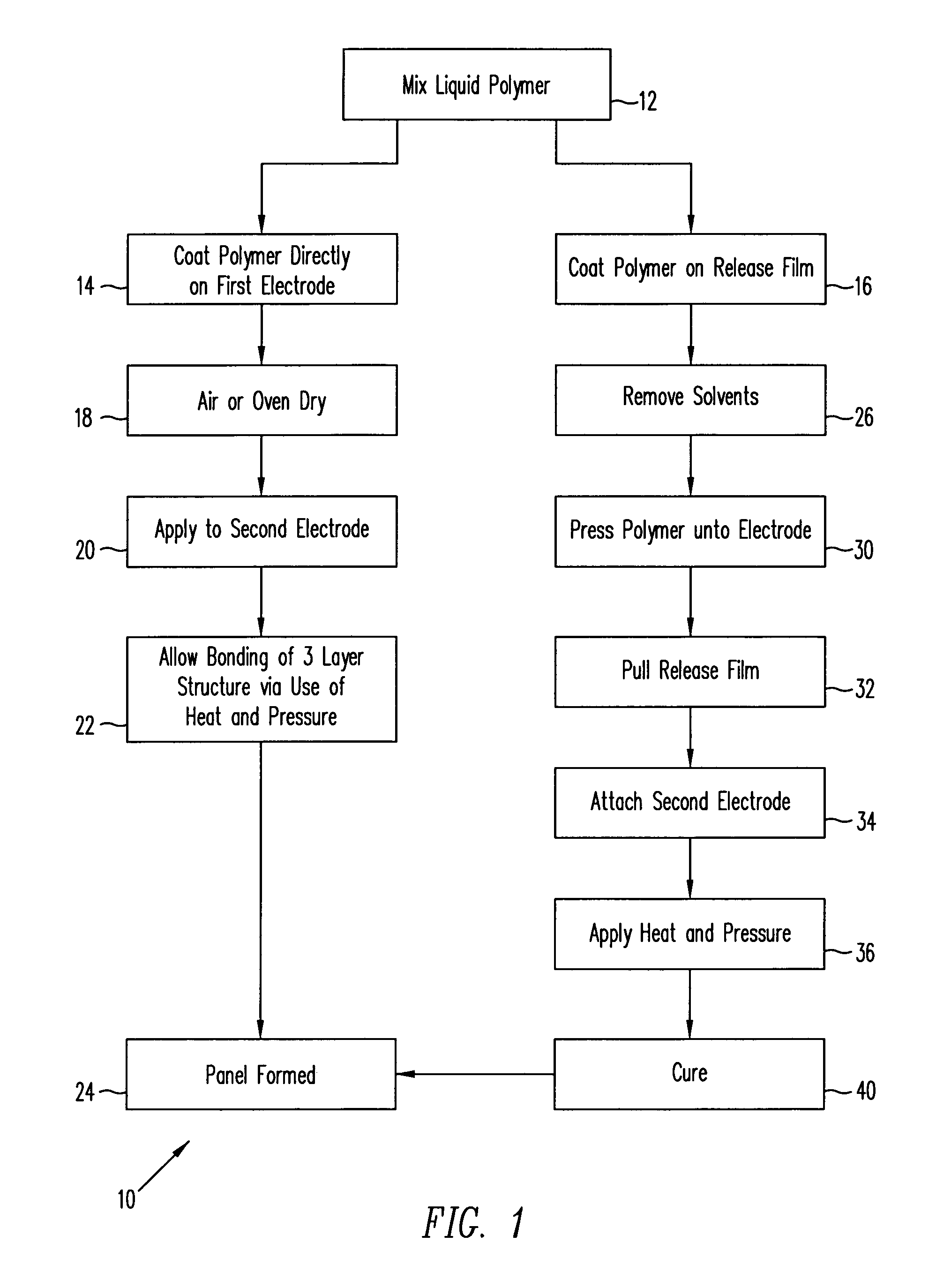

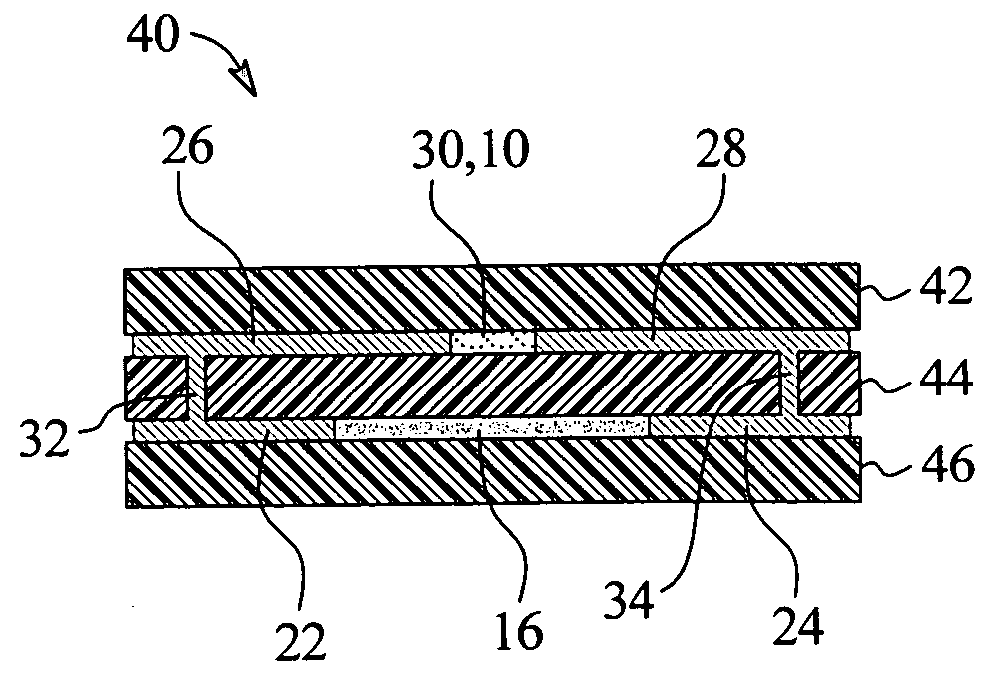

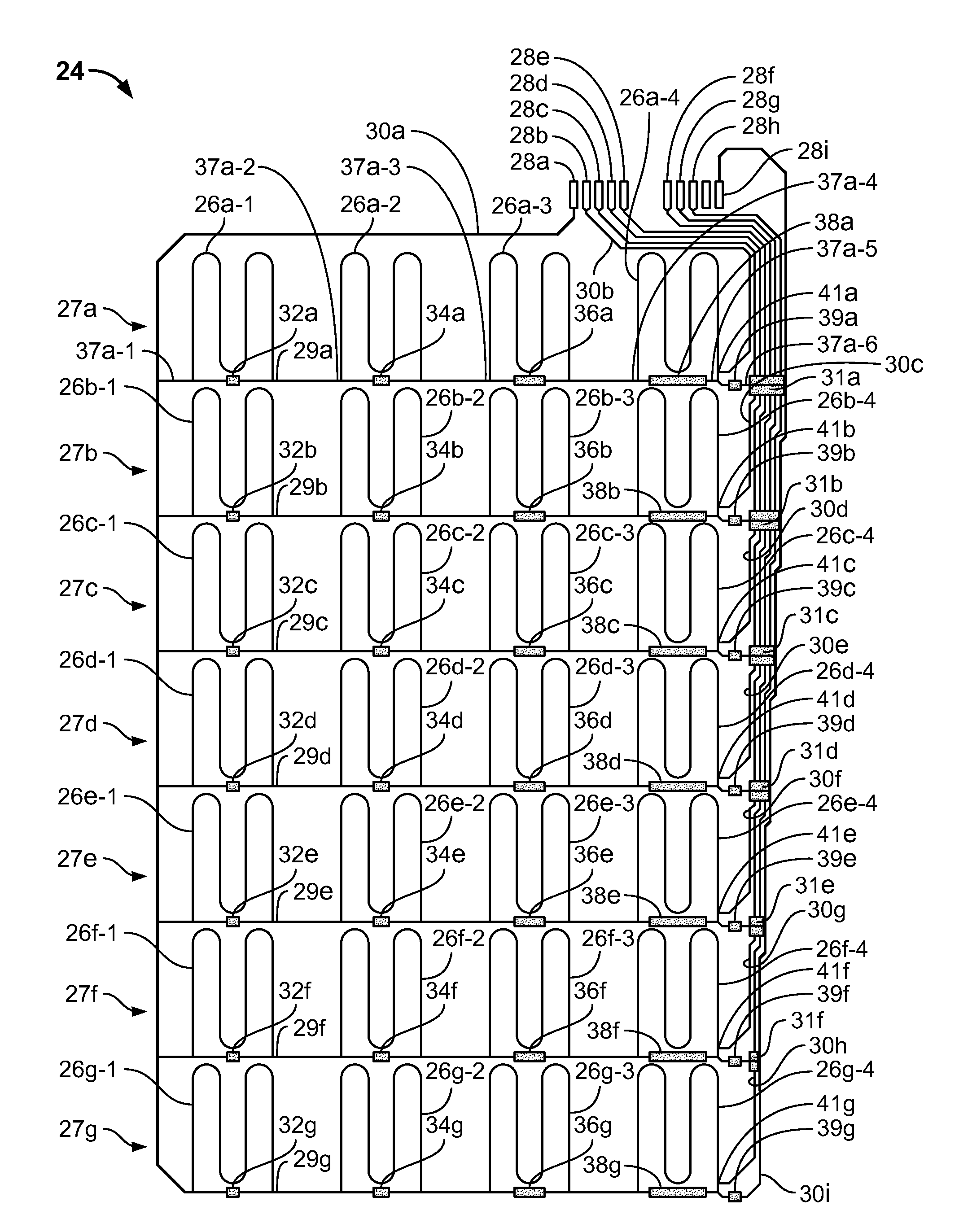

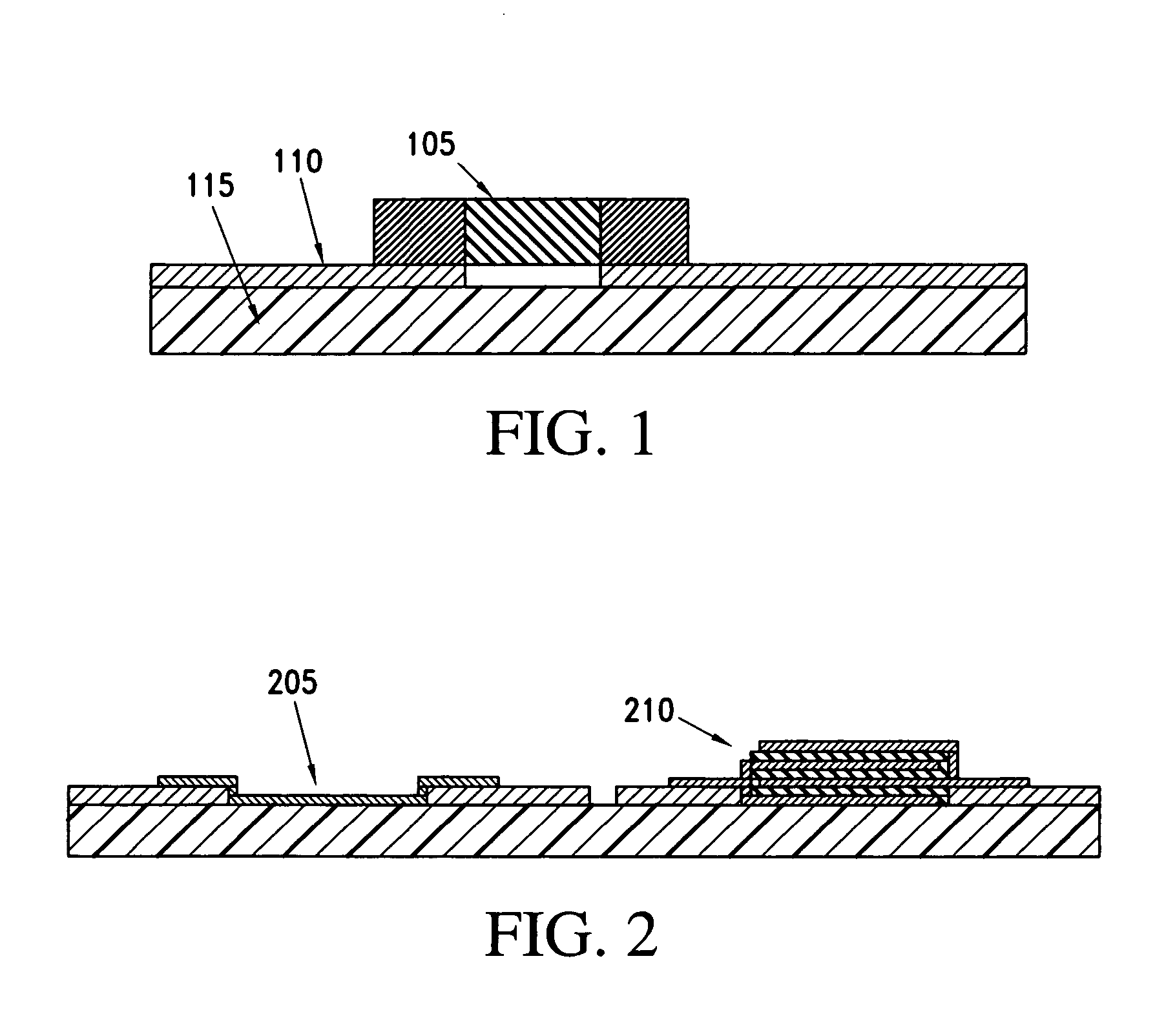

Method of manufacturing devices to protect election components

InactiveUS6981319B2Easy to customizeMake fastFuse device manufactureInsulating layers/substrates workingManufacturing technologyElectronic component

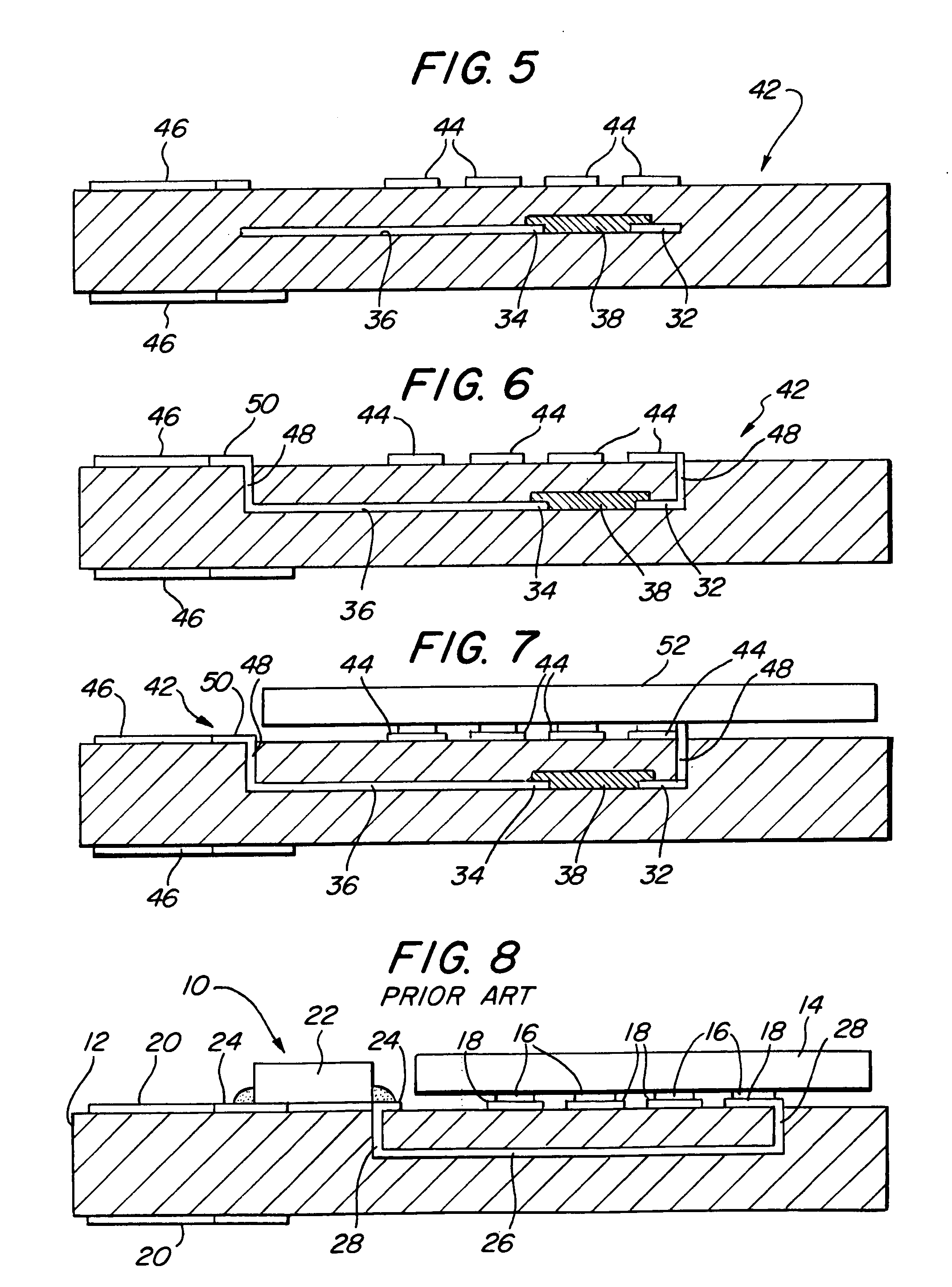

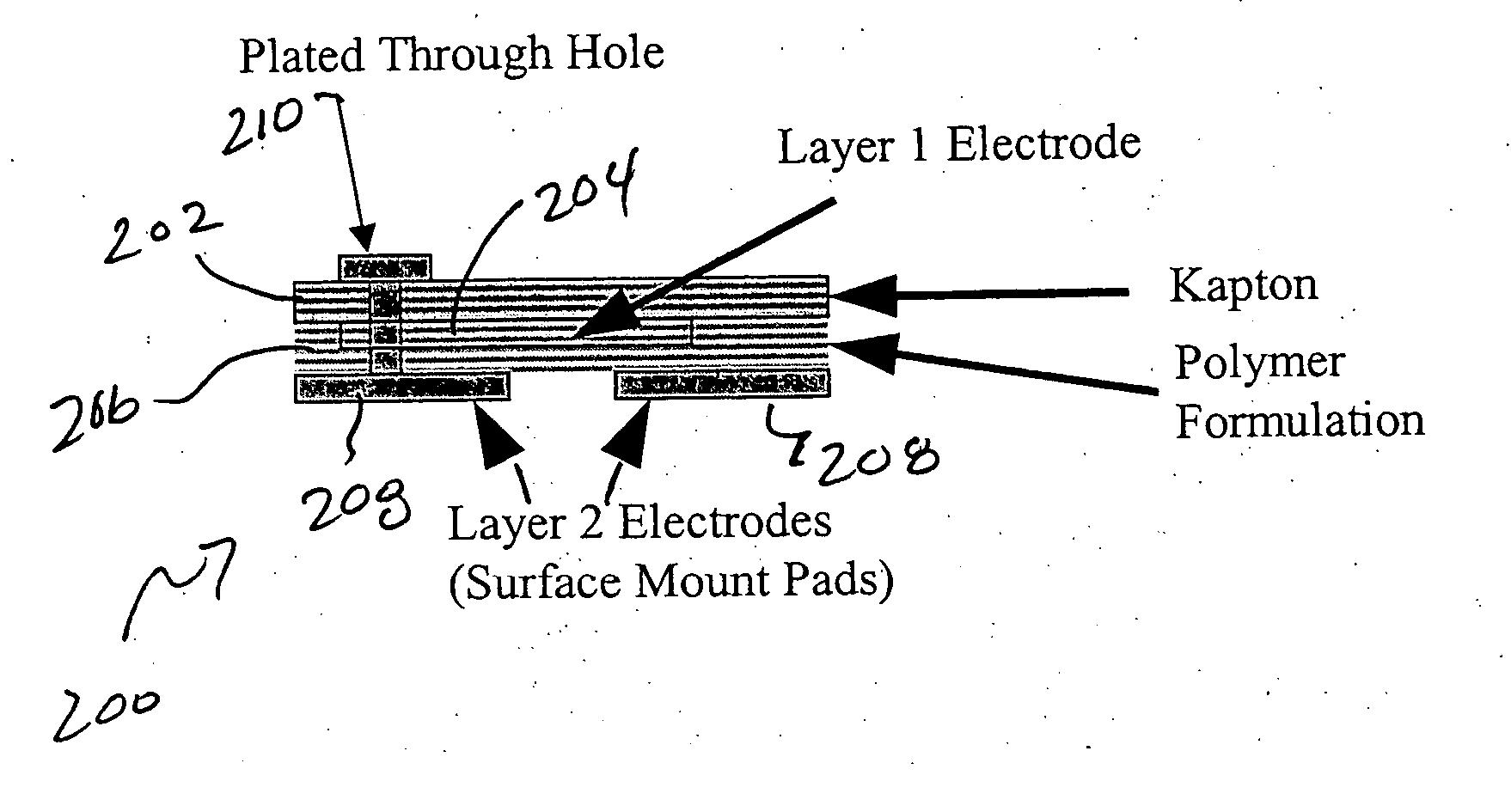

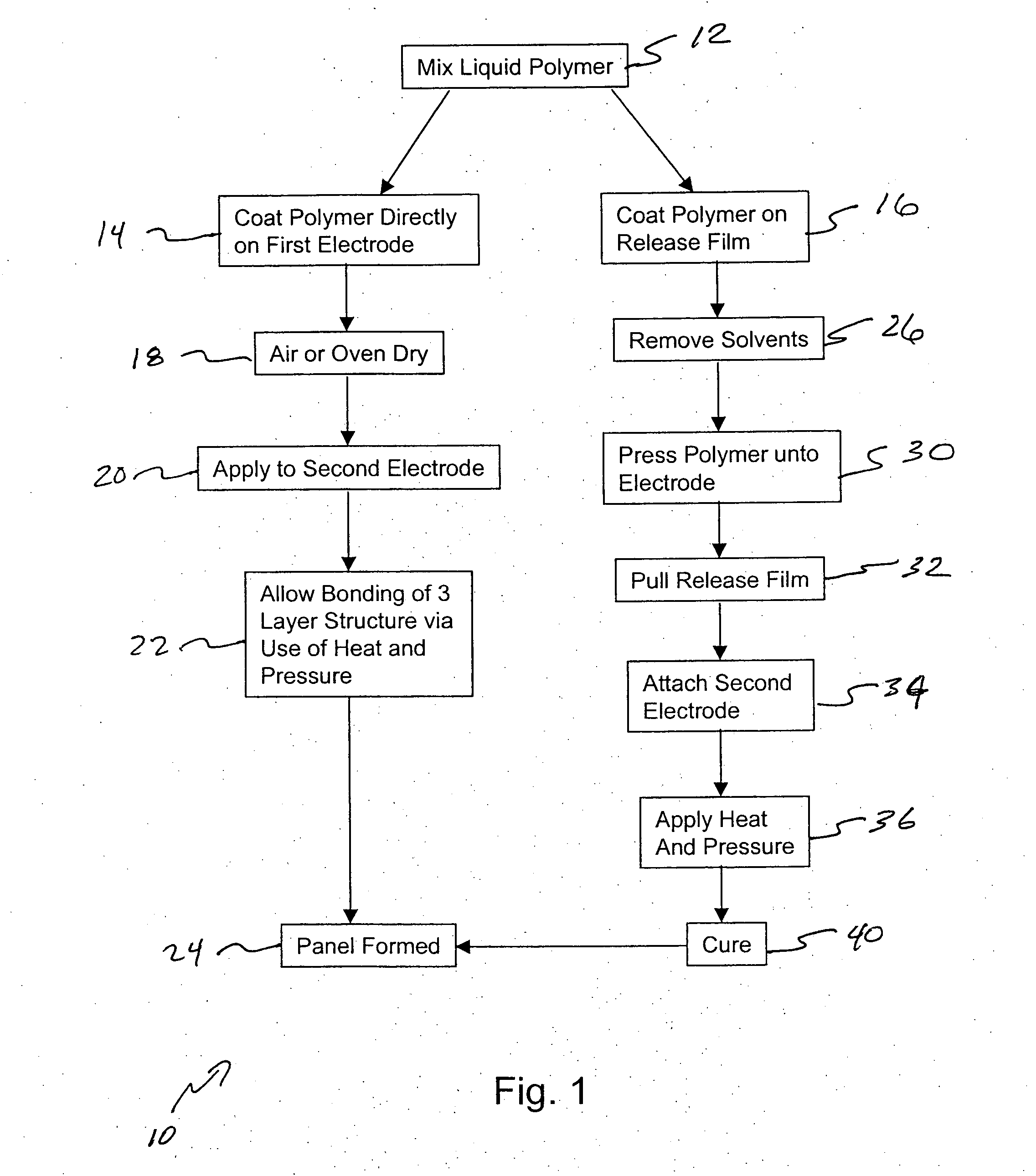

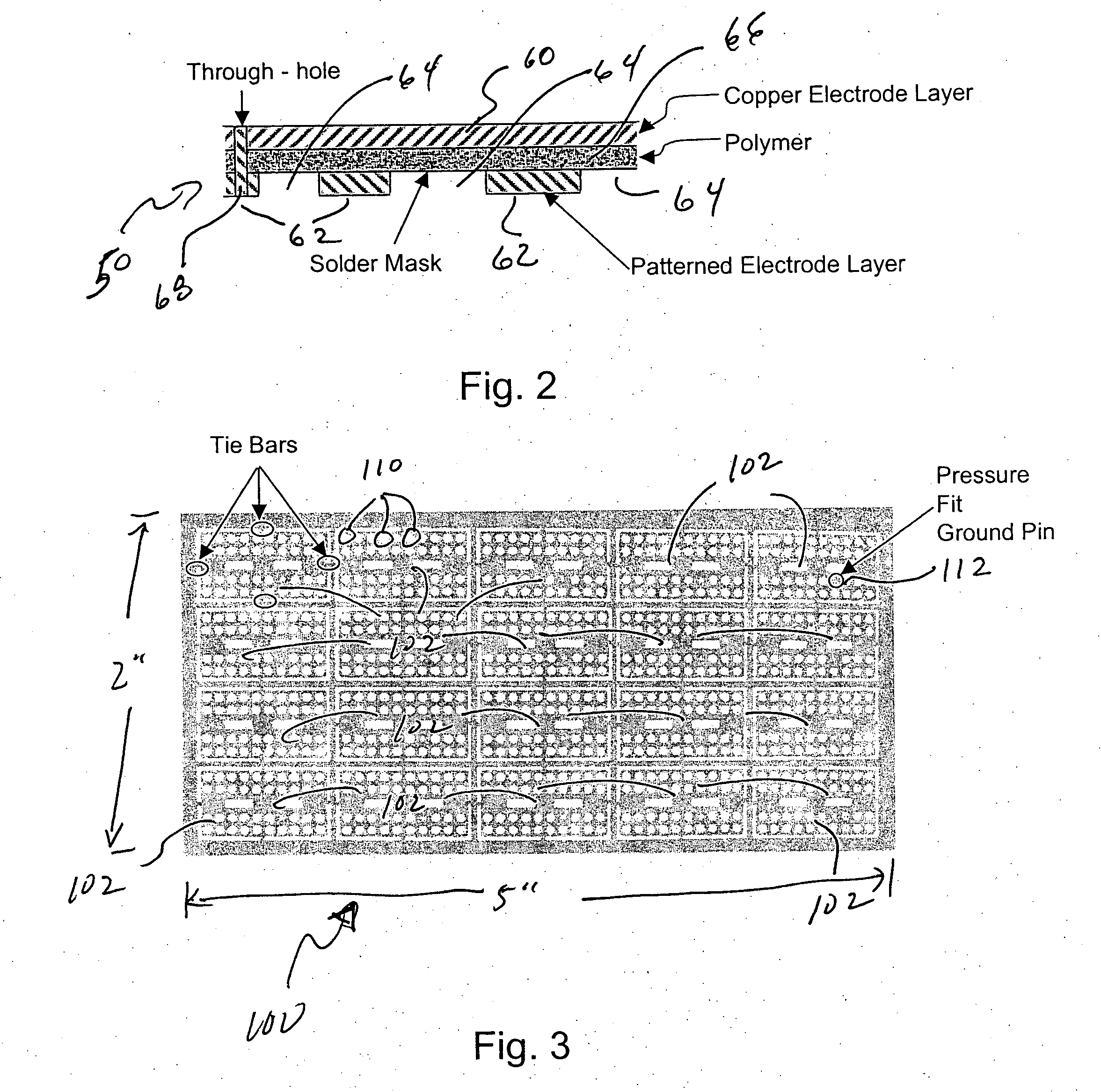

Devices capable of protecting electronic components during the occurrence of a disturbance event using printed circuit board manufacturing techniques. A three (3) layer structure is formed comprising a polymer-based formulation sandwiched between two electrode layers. The devices can be manufactured in panel form providing high quantities of devices which can be removed from the panel and applied directly to the component to be protected. Desired patterns can be formed on either one of the electrode layers by photo-etch techniques thereby providing a process that can be tailored to a large number of applications.

Owner:ELECTRONICS POLYMERS NEWCO

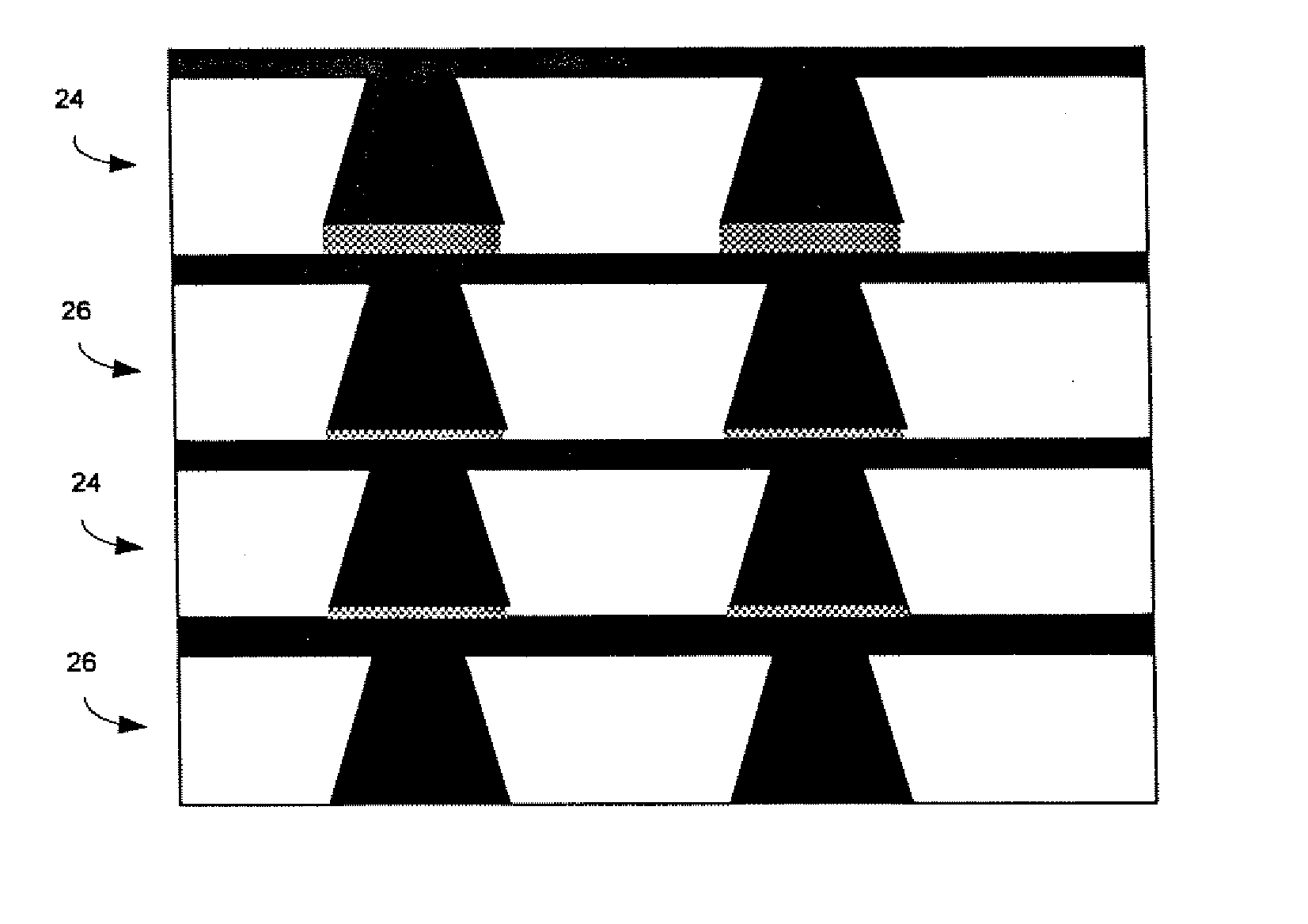

Low-EMI electronic apparatus, low-EMI circuit board, and method of manufacturing the low-EMI circuit board

InactiveUS20020015293A1Suppress spurious radiationIncrease costMagnetic/electric field screeningFinal product manufactureCapacitanceCountermeasure

A low-EMI circuit which realizes a high mounting density by converting the potential fluctuation of a power supply layer with respect to a ground layer which occurs on switching an IC device etc., into Joule's heat in the substrate without using any parts as a countermeasure against the EMI. Its structure, a circuit board using it, and a method of manufacturing the circuit board are also disclosed. Parallel plate lines in which the Q-value of the stray capacitance between solid layers viewed from the power supply layer and ground layer is equivalently reduced and which are matchedly terminated by forming a structure in which a resistor (resistor layer) and another ground layer are provided in addition to the power supply layer and the ground layer on a multilayered circuit board. A closed shield structure is also disclosed. This invention can remarkably suppress unwanted radiation by absorbing the potential fluctuation (resonance) which occurs in a power supply loop by equivalently reducing the Q-value of the stray capacitance, absorbing the standing wave by the parallel plate lines matchedly terminated and, closing and shielding the parallel plate lines.

Owner:SUMITOMO RUBBER IND LTD

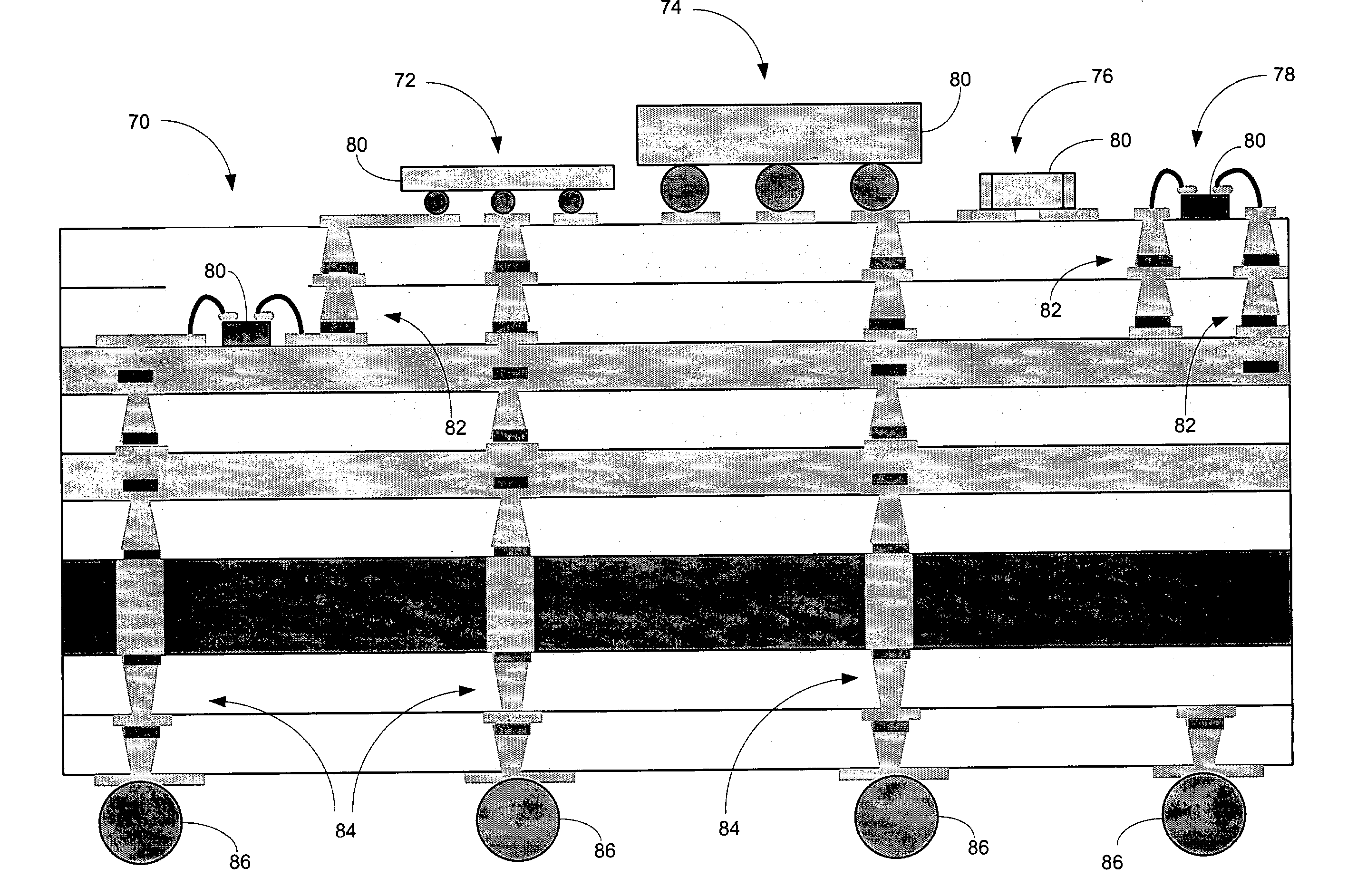

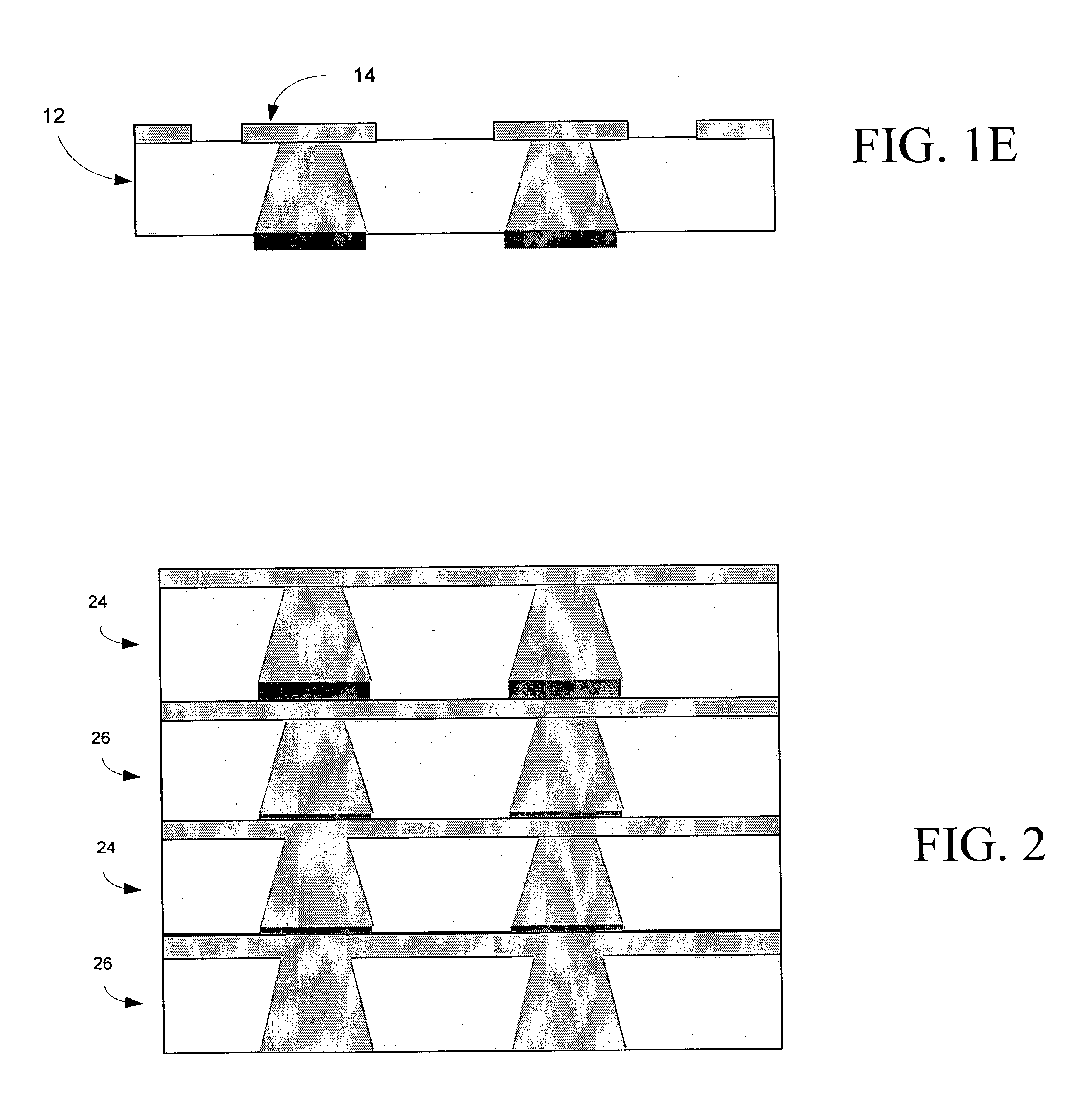

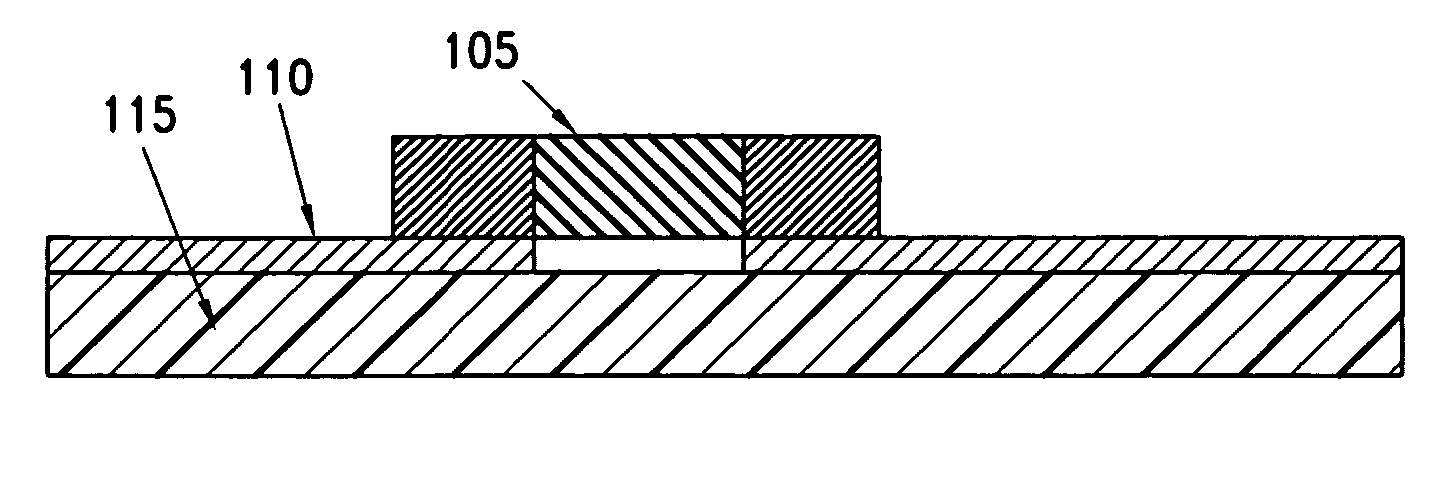

Printed circuit board memory module with embedded passive components

InactiveUS20050094465A1Minimize overall surface areaLess noisySemiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorComputer module

A memory module includes a plurality of memory components mounted on a printed circuit board, and a plurality of passive components embedded within the board directly underneath the memory components to minimize the space occupied by the passive components and the lengths of the required conductive traces. The passive components and the memory components are connected by conductor-filled vias between the contacts of the embedded components and the memory components mounted above them on the board surface. The passive components may be thick film resistors, either series damping resistors or differential damping resistors. By embedding the resistors directly beneath the memory components, there is enough space on the board to provide a set of termination resistors for each of the several memory components on the board, thereby eliminating the need for a single resistor to be shared by two or more memory components, resulting in more precise output signals.

Owner:NETLIST INC

ESD protection devices and methods of making same using standard manufacturing processes

ActiveUS20050083163A1Easy to customizeMinimal effortInsulating layers/substrates workingPrinted resistor incorporationManufacturing technologyElectronic component

Devices capable of protecting electronic components during the occurrence of a disturbance event using printed circuit board manufacturing techniques. A three (3) layer structure is formed comprising a polymer-based formulation sandwiched between two electrode layers. The devices can be manufactured in panel form providing high quantities of devices which can be removed from the panel and applied directly to the component to be protected. Desired patterns can be formed on either one of the electrode layers by photo-etch techniques thereby providing a process that can be tailored to a large number of applications.

Owner:ELECTRONICS POLYMERS NEWCO

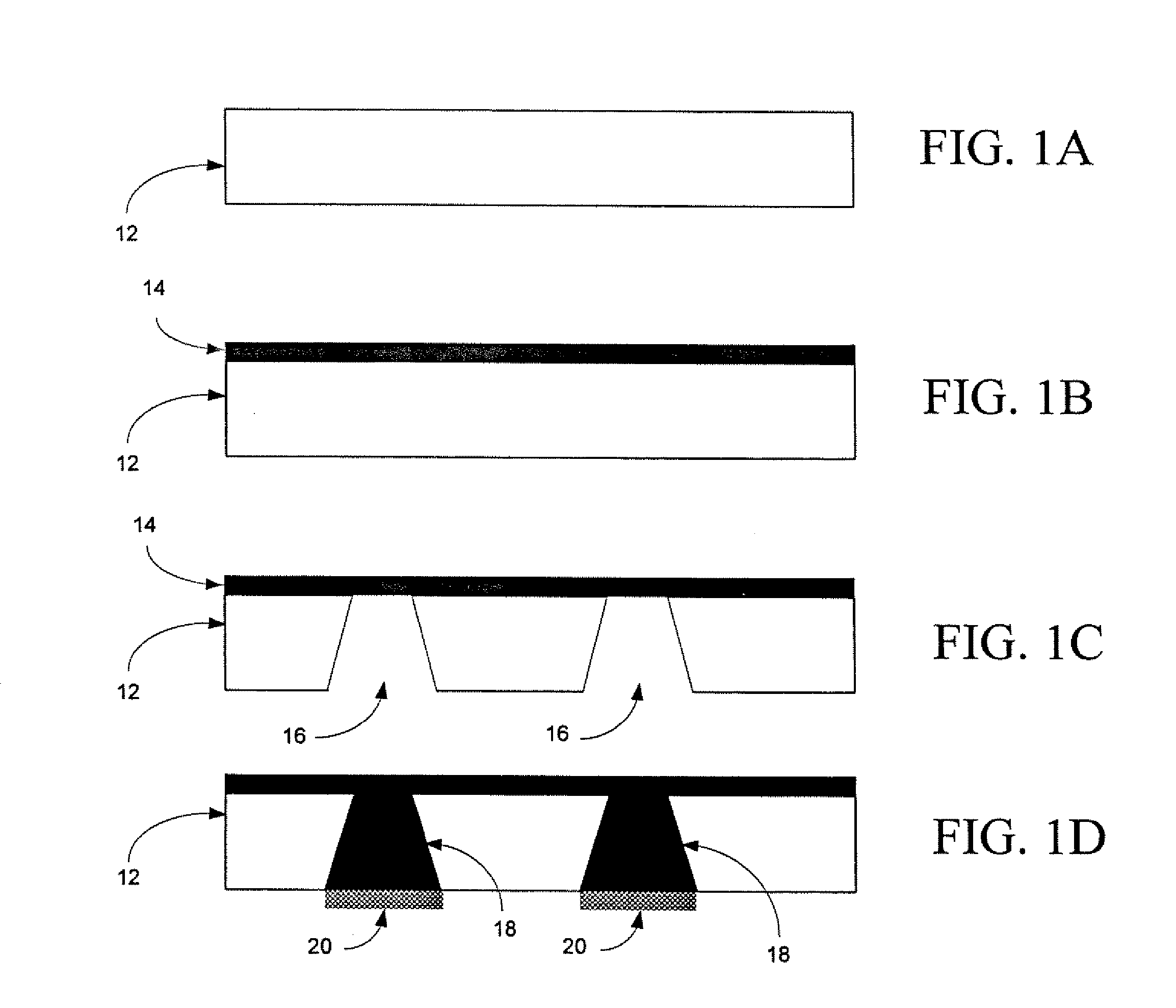

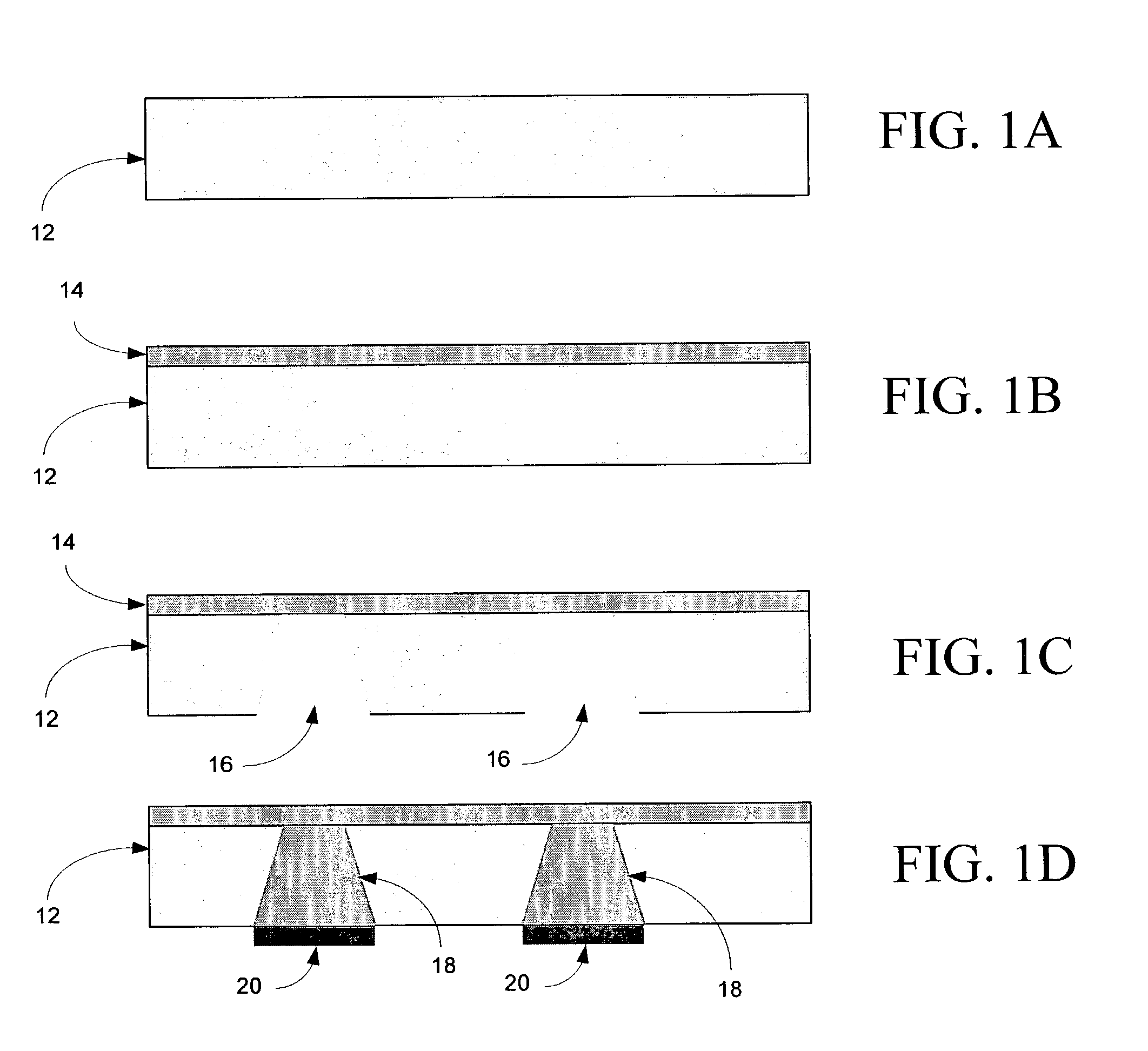

Integrated circuit substrate having embedded passive components and methods therefor

InactiveUS6987661B1Incremental costMultiple fixed capacitorsFixed capacitor dielectricConductive pasteConductive materials

An integrated circuit substrate having embdedded passive components provides a reduced cost and compact package for a die and one or more passive components. An insulating layer of the substrate is embossed or laser-ablated to generate apertures for insertion of a paste forming the body of the passive component. A resistive paste is used to form resistors and a dielectric paste is used for forming capacitors. A capacitor plate may be deposited at a bottom of the aperture by using a doped substrate material and activating only the bottom wall of the aperture, enabling plating of the bottom wall without depositing conductive material on the side walls of the aperture. Vias may be formed to the bottom plate by using a disjoint structure and conductive paste technology. Connection to the passive components may be made by conductive paste-filled channels forming conductive patterns on the substrate.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

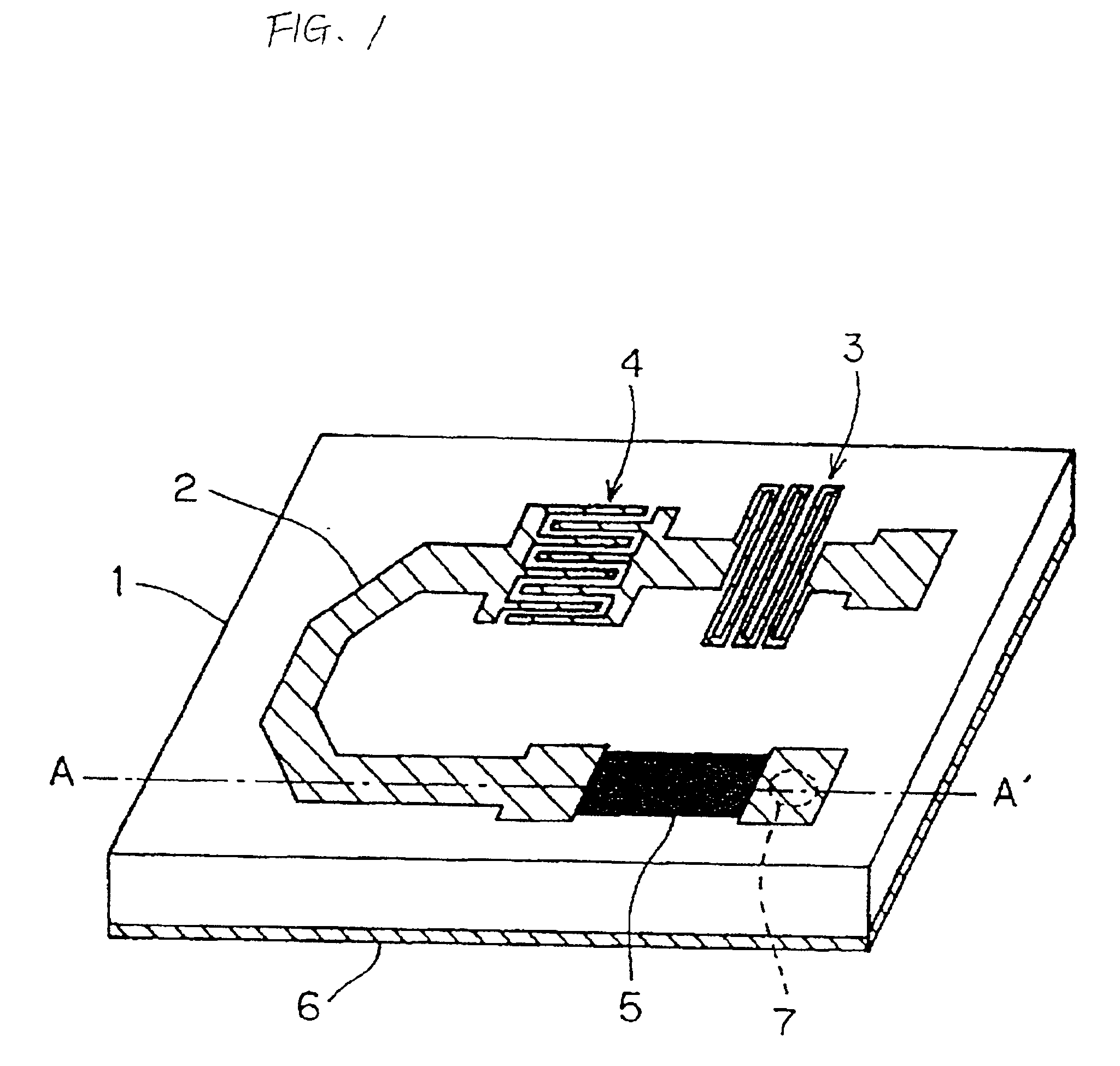

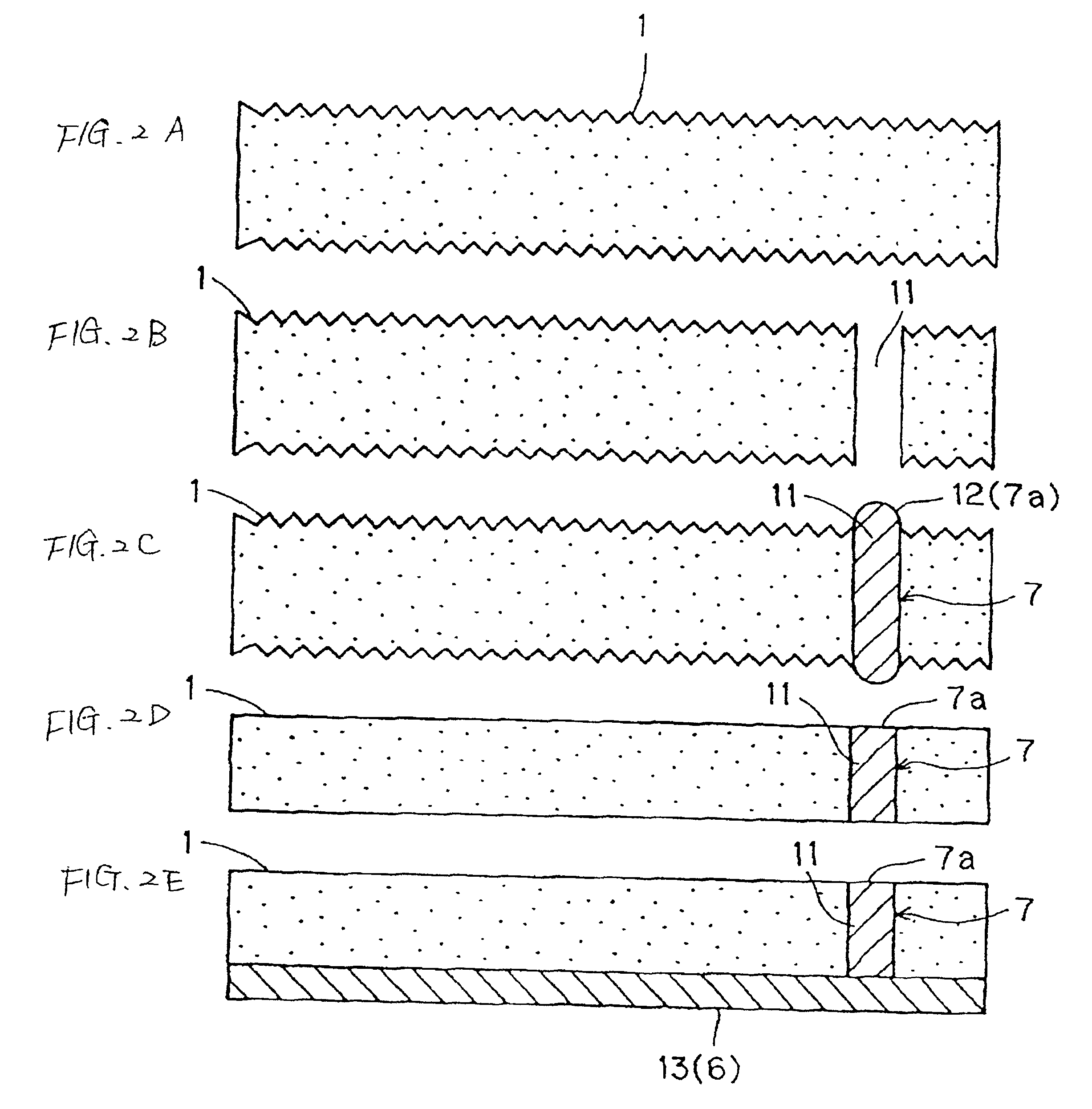

Resistor element, stress sensor, and method for manufacturing them

InactiveUS20060218779A1Easily and elastically changedPrinted circuit aspectsForce measurementElectrical resistance and conductanceScreen printing

A stress sensor in which the direction and magnitude of a stress being applied to a post bonded to or integrated with an insulating board can be grasped from variation in the resistance of resistor elements being stimulated by application of the stress while suppressing variation in the shape of each resistor. The resistor element comprises a resistor formed, by screen print, between a pair of electrodes for the resistor element, i.e. circuit pattern electrodes, arranged on the surface of the insulating board. The electrode is connected, through a conductor, with a board terminal part arranged at one end of the insulating board. The electrode and the conductor or a print accuracy adjusting member have a constant height from the surface of the insulating board. Arrangement of the conductor, electrode and print accuracy adjusting member is entirely identical or similar for the resistor elements in the vicinity thereof.

Owner:ELAN MICROELECTRONICS CORPORATION

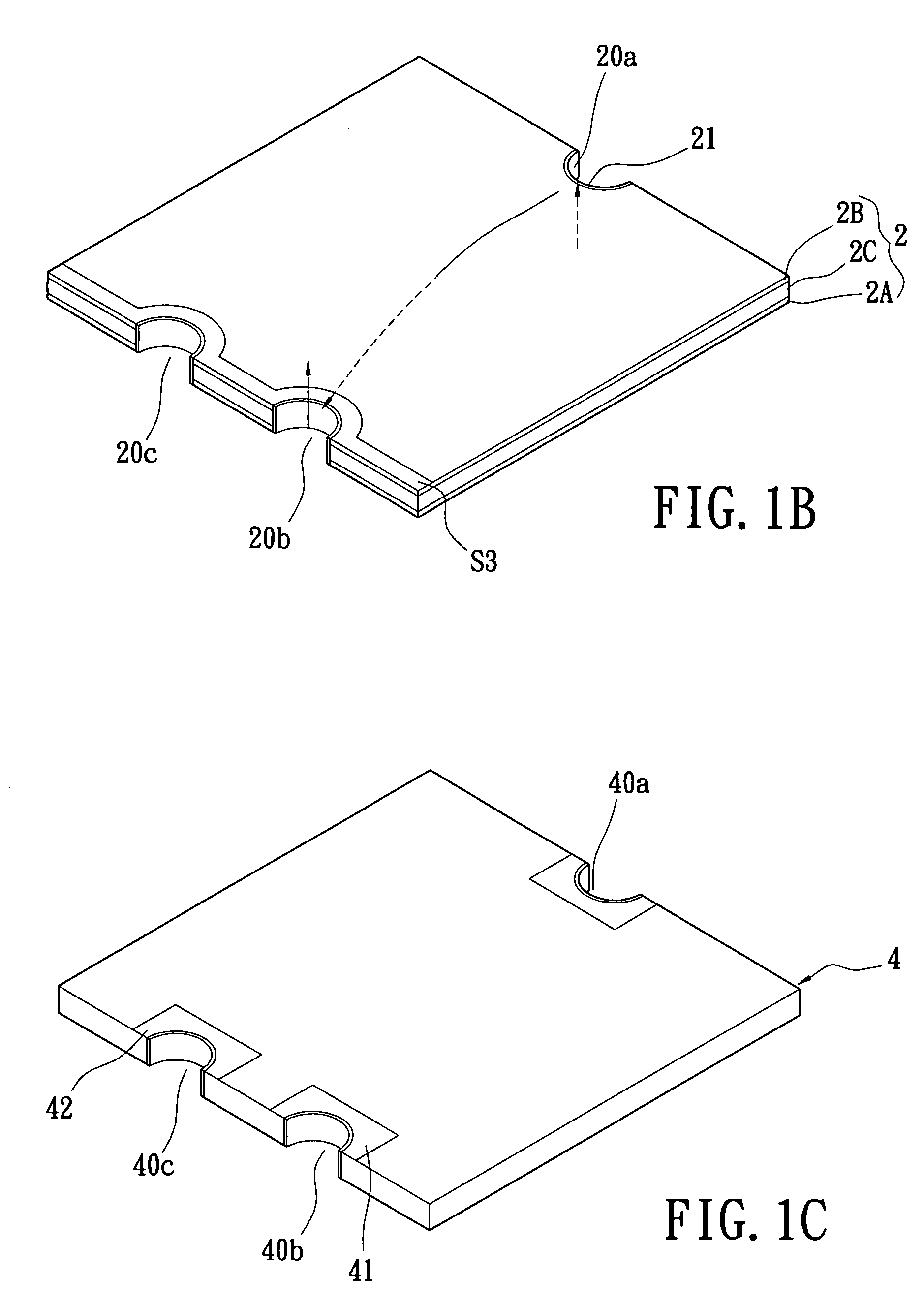

Embedded type multifunctional integrated structure and method for manufacturing the same

InactiveUS20090130369A1Function increaseSmall sizeLayered productsCross-talk/noise/interference reductionEngineeringElectrical and Electronics engineering

Owner:INPAQ TECH

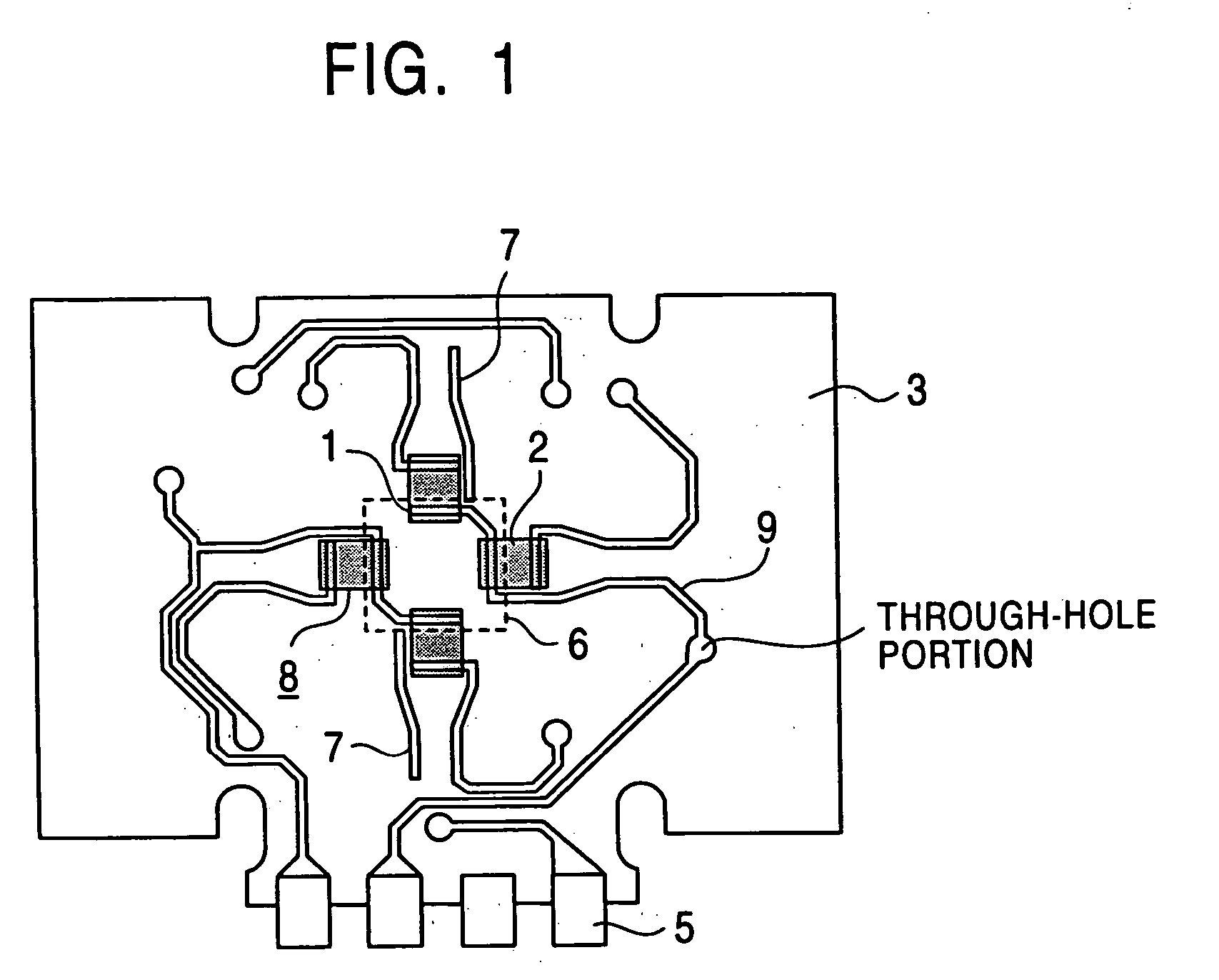

High frequency circuit chip and method of producing the same

InactiveUS6838377B2Small sizeEfficient productionSemiconductor/solid-state device detailsPrinted circuit aspectsMaterial PerforationElectrical and Electronics engineering

In the production of a high frequency circuit chip in which a wiring pattern is disposed on a substrate having a through-hole, a connecting electrode of the through-hole is formed by filling electrically conductive paste into a perforation and firing it, and the wiring pattern is formed by a lift-off method. Moreover, at least the surface of the substrate for the wiring pattern to be formed thereon is mirror-polished, and thereafter, the wiring pattern is formed on the mirror-polished surface by the lift-off method.

Owner:MURATA MFG CO LTD

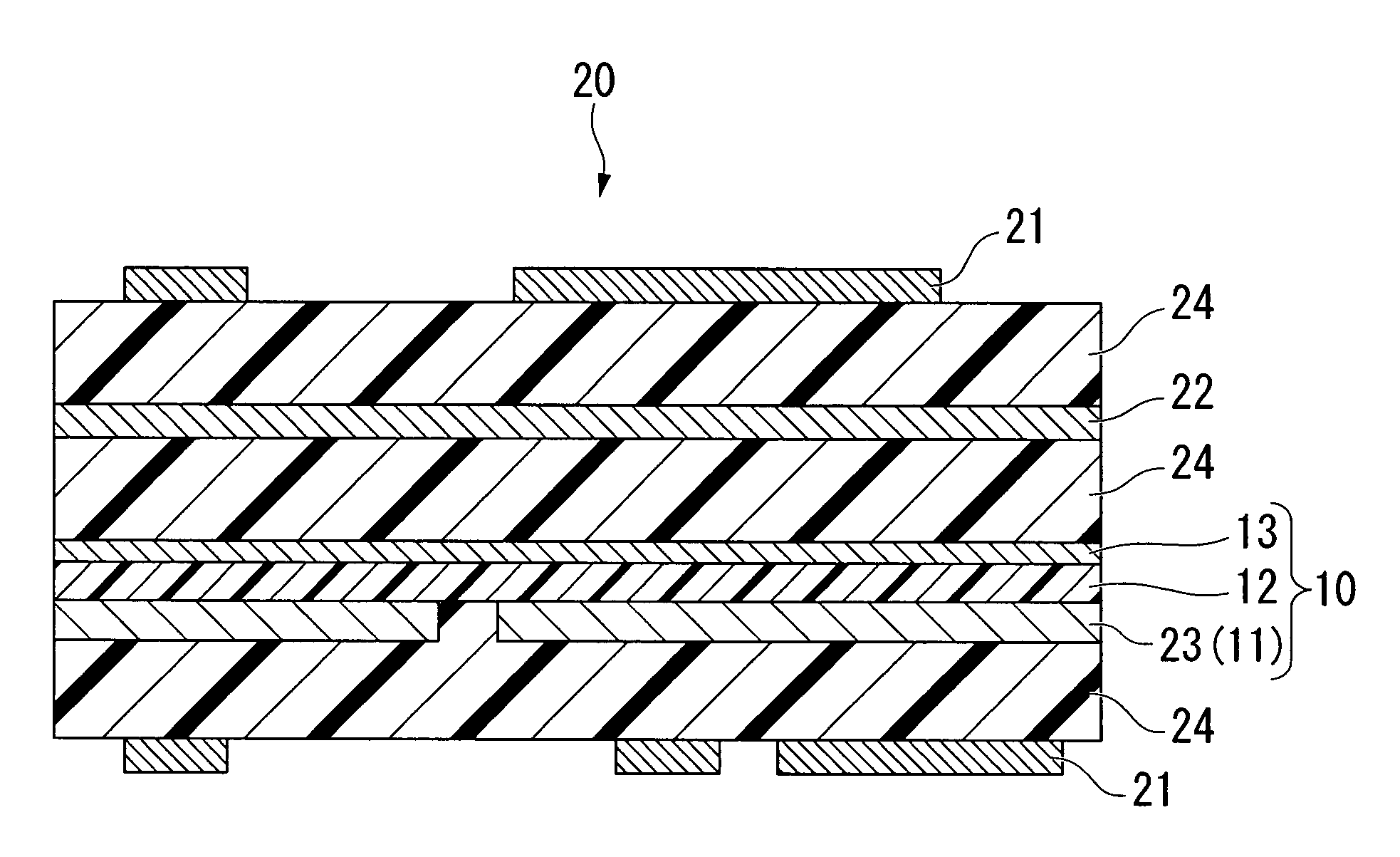

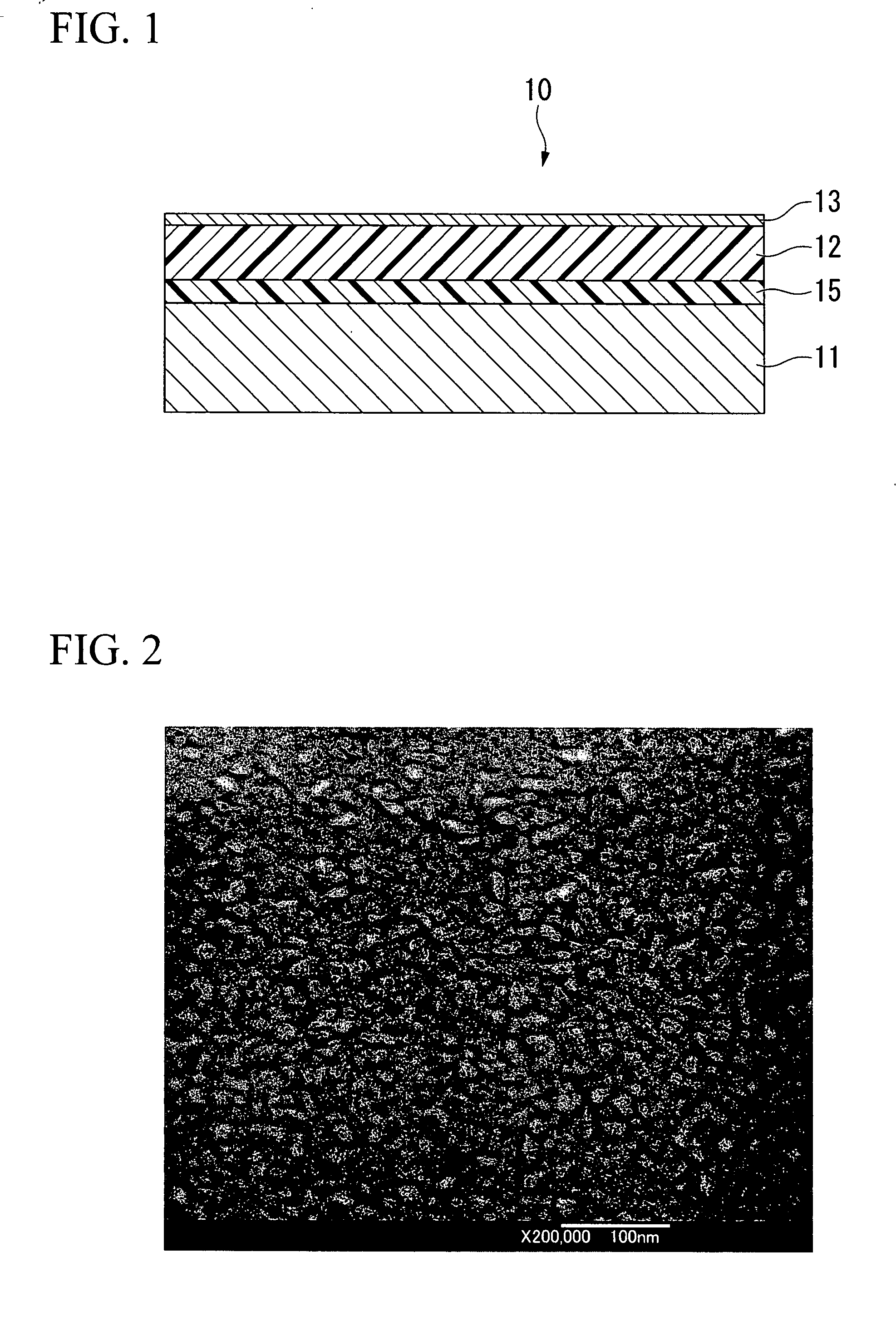

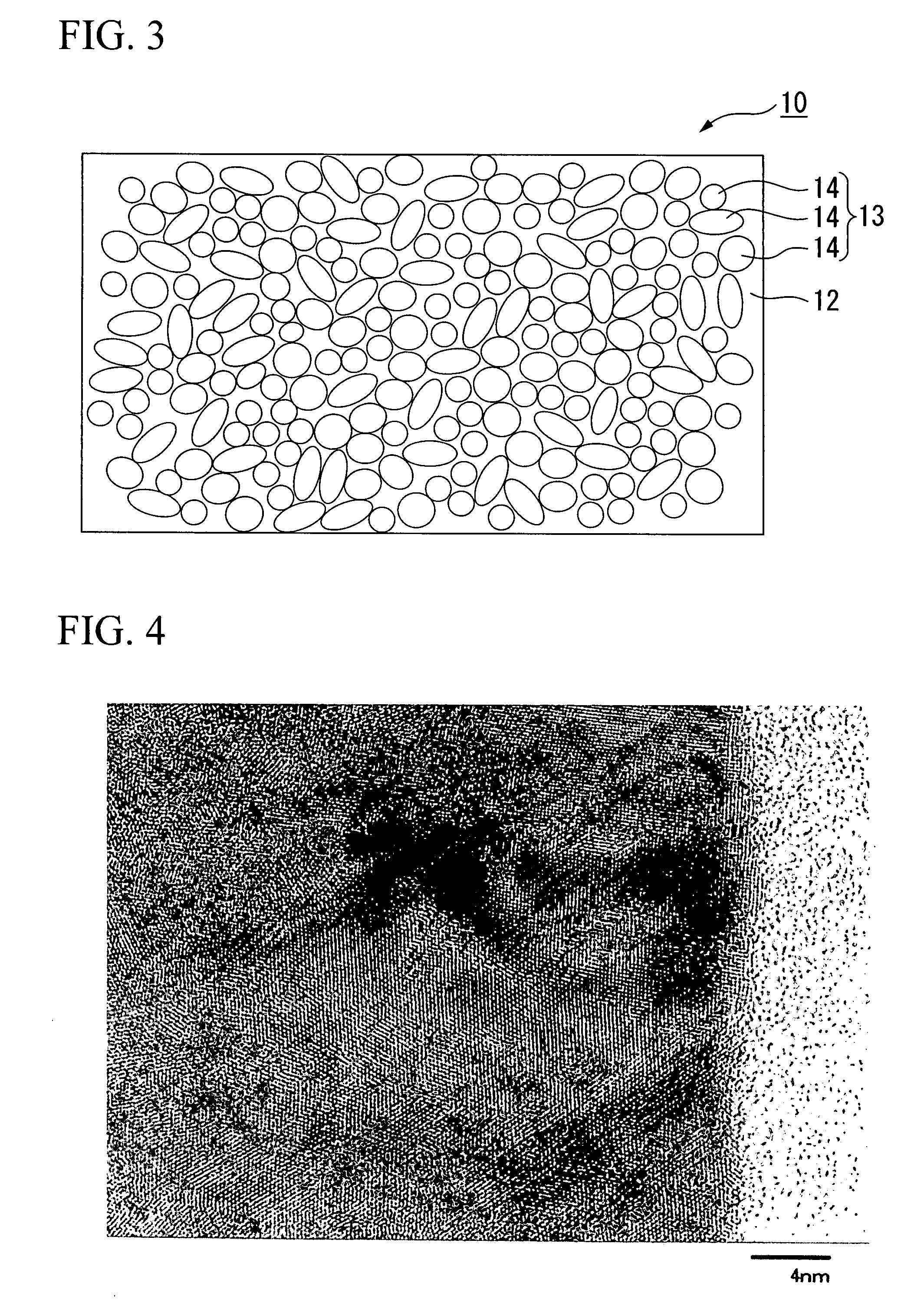

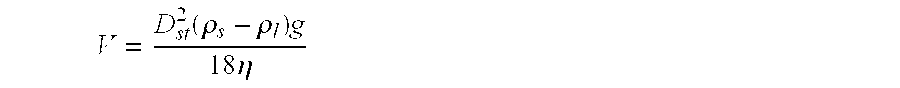

Noise-suppressing wiring-member and printed wiring board

ActiveUS20080049410A1Reduce the amount requiredMagnetic/electric field screeningCross-talk/noise/interference reductionMetallic materialsSurface roughness

The present invention relates to a wiring member including: a copper foil layer having a smooth surface with a surface roughness Rz of 2 μm or less; a noise suppressing layer containing a metallic material or a conductive ceramic and having a thickness of 5 to 200 nm; and an insulating resin layer provided between the smooth surface of the copper foil layer and the noise suppressing layer, and also relates to a printed wiring board equipped with the wiring member. Moreover, the present invention relates to a noise suppressing structure including: a first conductive layer; a second conductive layer; a noise suppressing layer provided between the first conductive layer and the second conductive layer, the noise suppressing layer being to be electromagnetically-coupled with the first conductive layer, the noise suppressing layer comprising a metallic material or a conductive ceramic, and the noise suppressing layer having a thickness of 5 to 300 nm; a first insulating layer provided between the first conductive layer and the noise suppressing layer; and a second insulating layer provided between the second conductive layer and the noise suppressing layer; wherein the noise suppressing structure has: a region (I) in which the noise suppressing layer and the first conductive layer face each other; and a region (II) in which the noise suppressing layer and the first conductive layer do not face each other but the noise suppressing layer and the second conductive layer face each other, the regions (I) and (II) neighboring each other.

Owner:SHIN-ETSU POLYMER CO LTD

Precursor compositions and methods for the deposition of passive electrical components on a substrate

InactiveUS7524528B2Conductive materialSemiconductor/solid-state device manufacturingElectronic componentViscosity

Precursor compositions for the deposition of electronic features such as resistors and dielectric components and methods for the deposition of the precursor compositions. The precursor compositions have a low viscosity, such as not greater than about 1000 centipoise and can be deposited using a direct-write tool. The precursors also have a low conversion temperature, enabling the formation of electronic features on a wide variety of substrates, including low temperature substrates.

Owner:CABOT CORP

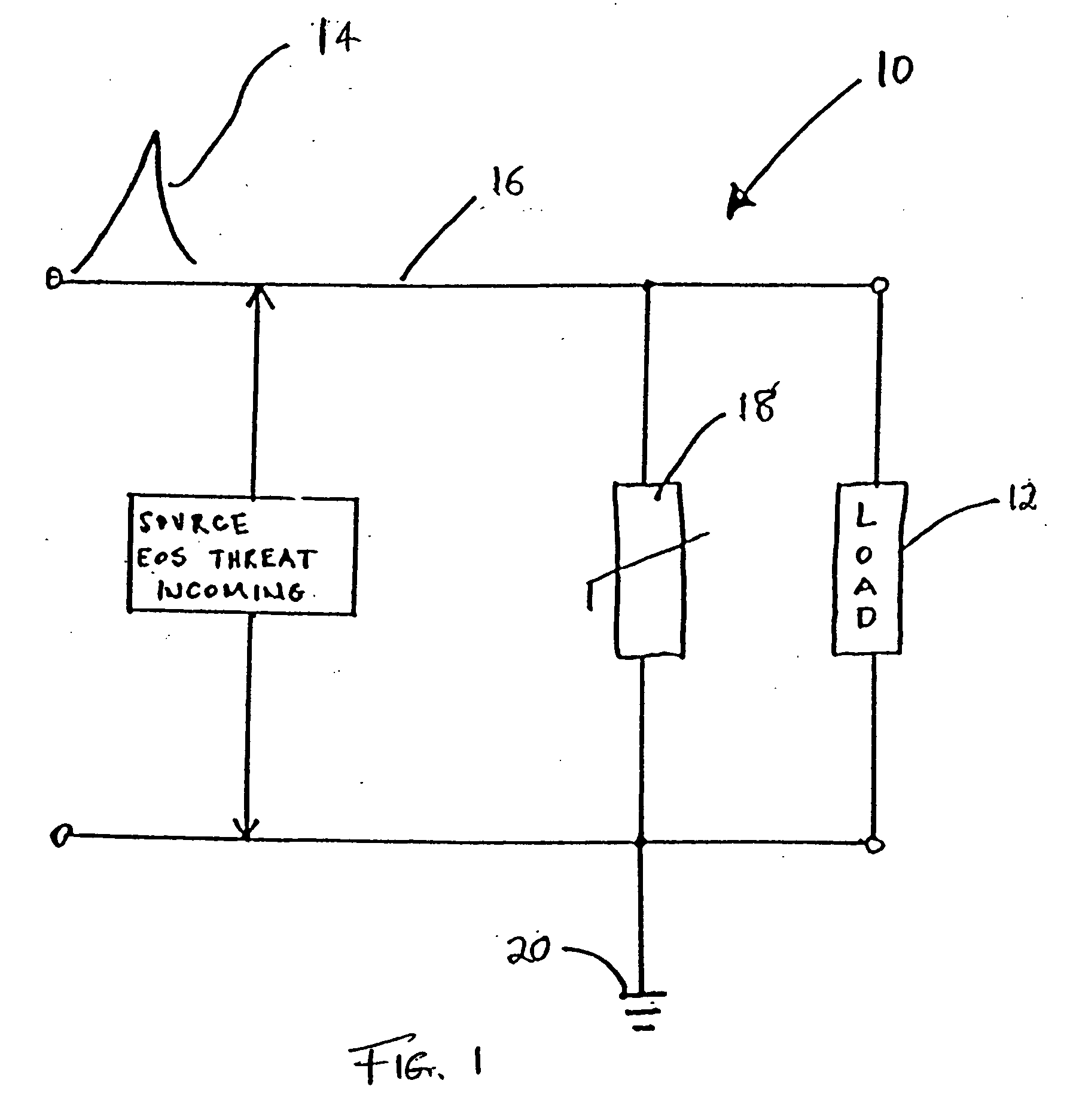

Electrostatic discharge protection for embedded components

InactiveUS20060152334A1Protection elementLow costPrinted circuit aspectsHigh voltage circuit adaptationsCapacitanceElectrical resistance and conductance

An improved electrical circuit that includes an embedded electrical component and an embedded voltage variable material (“VVM”) is provided. In one embodiment, the embedded VVM is provided as a voltage variable substrate, which is used in combination with an embedded electrical component, such as an embedded resistive material or an embedded capacitive material.

Owner:LITTELFUSE INC

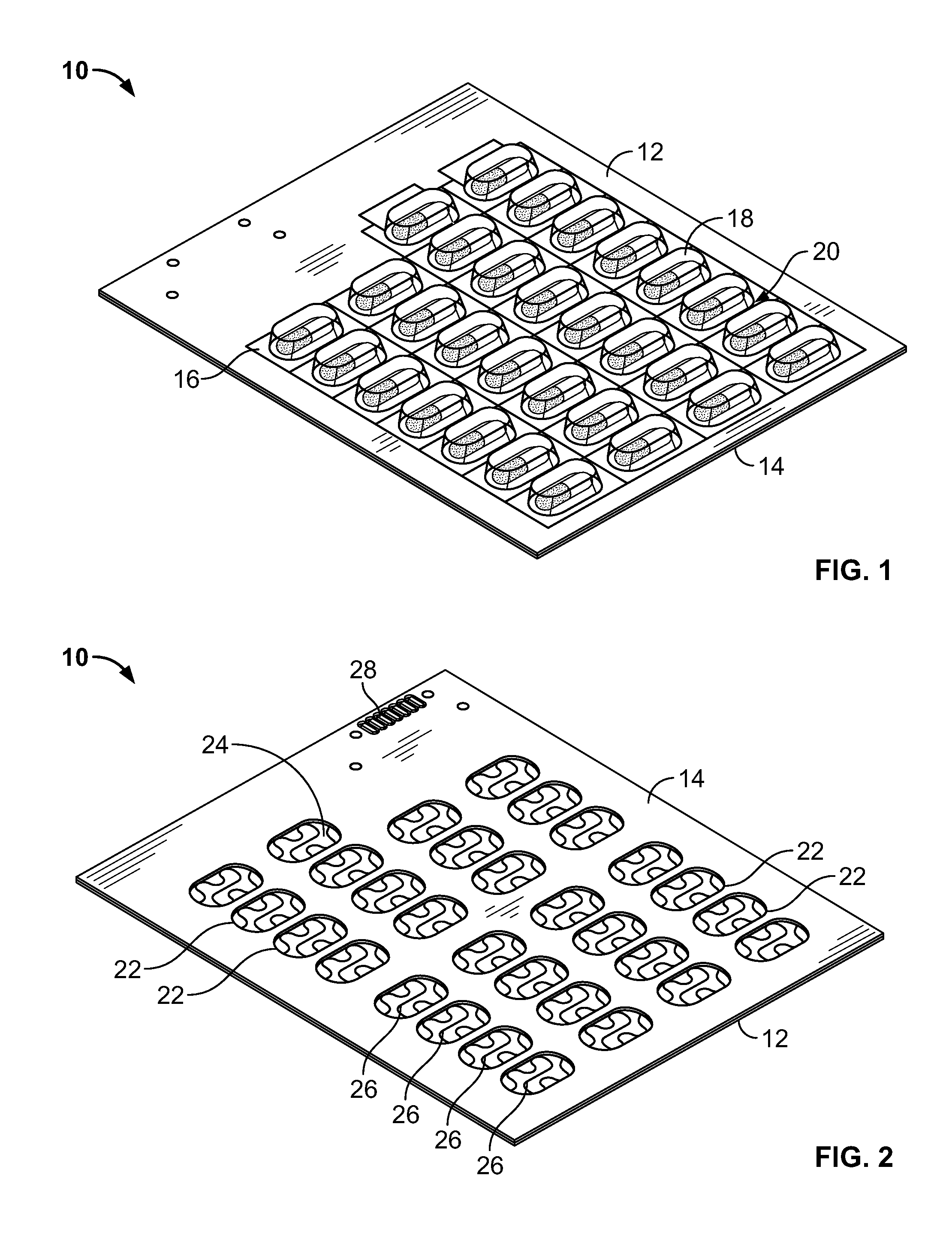

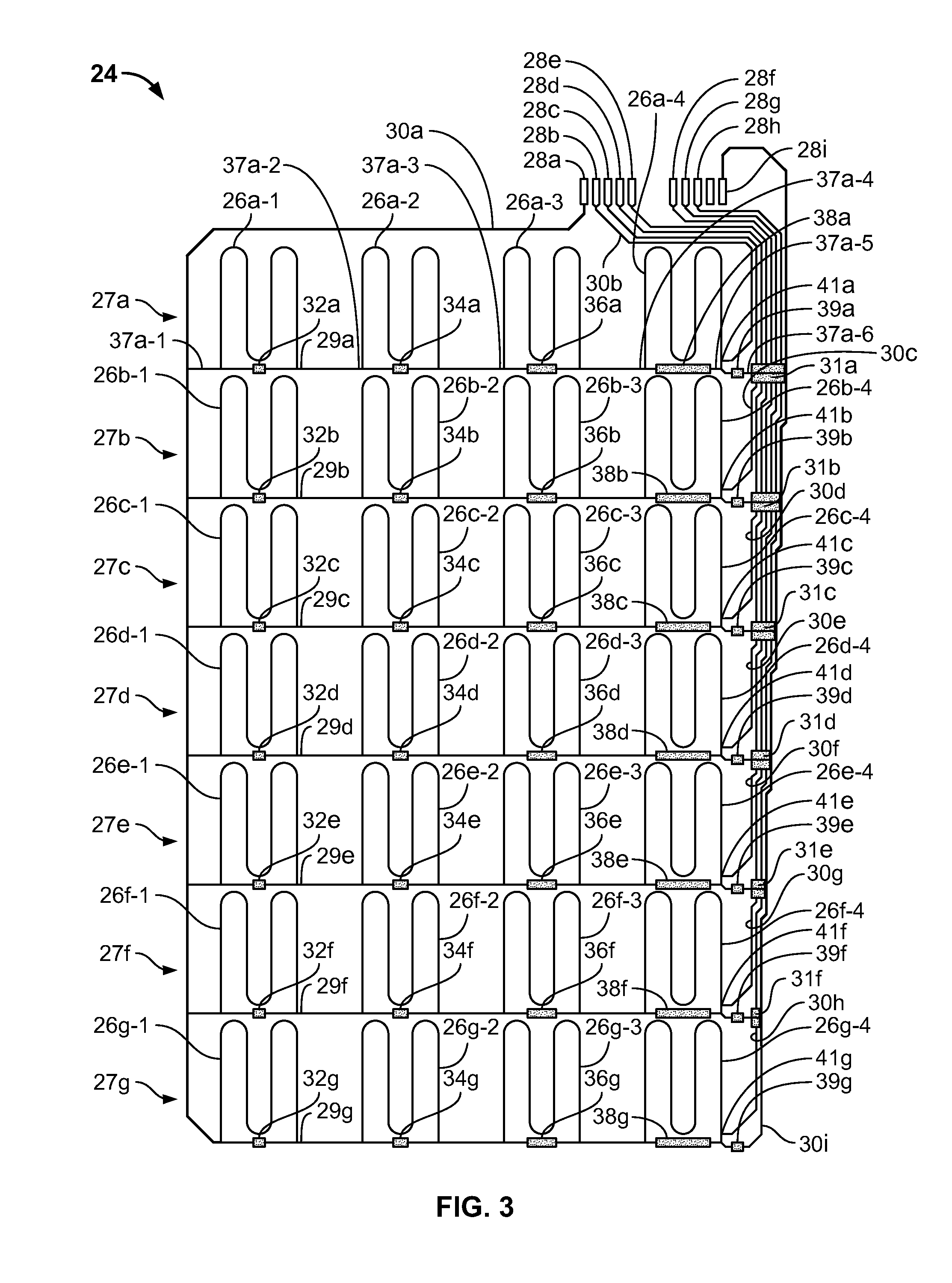

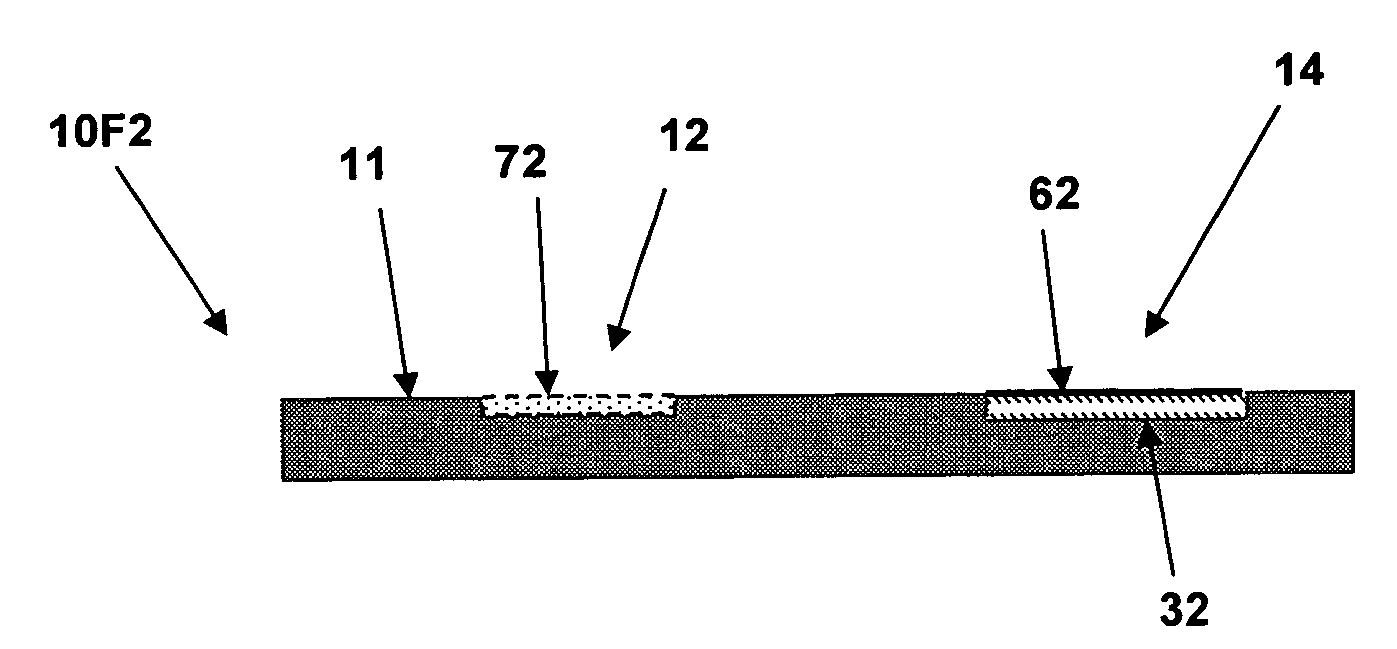

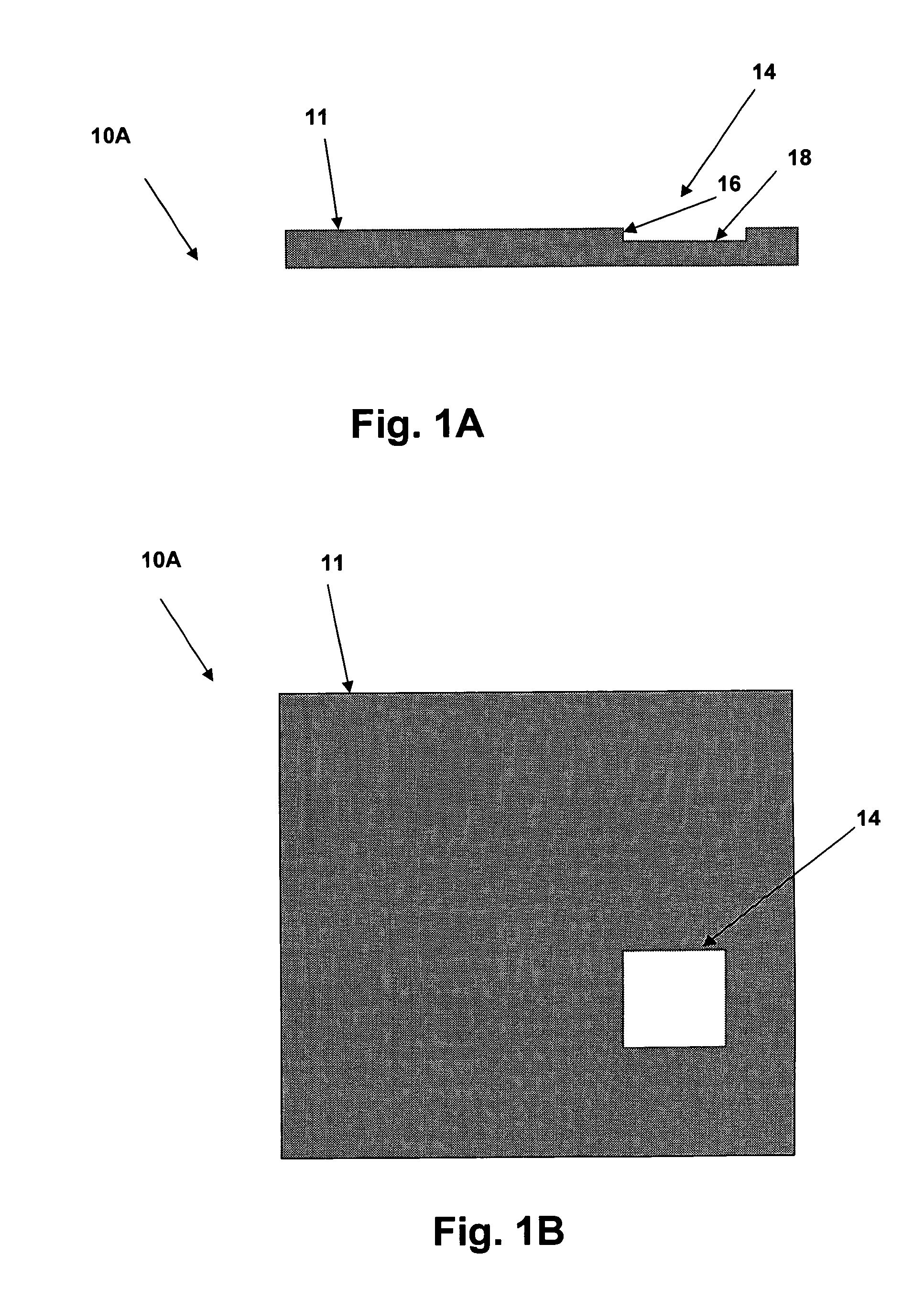

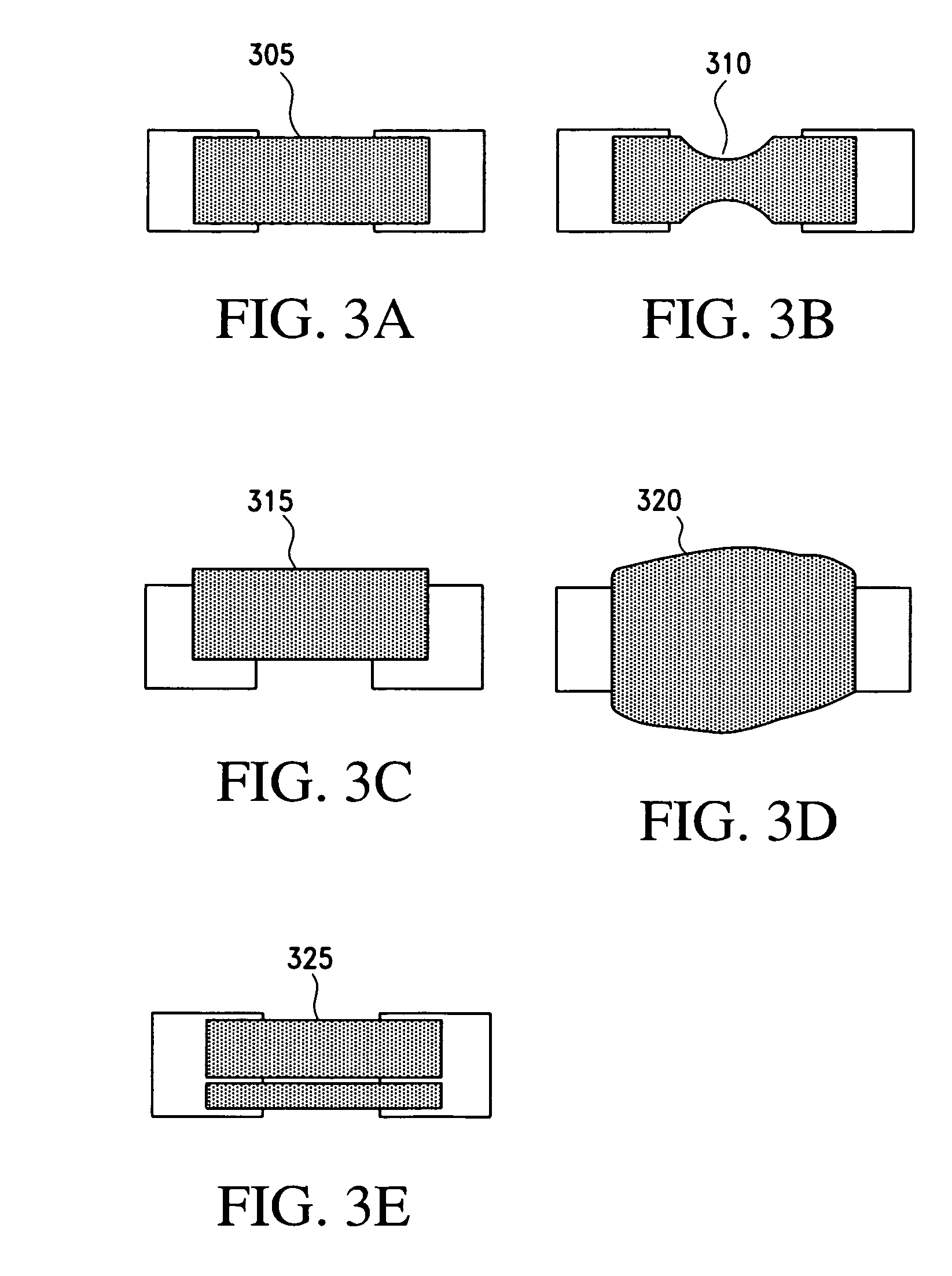

Dosage form package and a frangible electrical circuit sheet therefor

A frangible electrical circuit sheet for a dosage form package includes a first plurality of electrically conductive trace subnetworks interconnected with one another to form a network of electrically conductive traces and disposed on the sheet. The sheet further includes a second plurality of circuit elements connected to the network of electrically conductive traces such that each circuit element is associated with one of the subnetworks. At least some of the circuit elements have element values that differ from one another.

Owner:MTS MEDICATION TECH

Method for making an integrated circuit substrate having embedded passive components

InactiveUS7334326B1Low incremental costIncremental costPrinted circuit assemblingElectrolytic capacitorsConductive pasteConductive materials

A method for making an integrated circuit substrate having embedded passive components provides a reduced cost and compact package for a die and one or more passive components. An insulating layer of the substrate is embossed or laser-ablated to generate apertures for insertion of a paste forming the body of the passive component. A resistive paste is used to form resistors and a dielectric paste is used for forming capacitors. A capacitor plate may be deposited at a bottom of the aperture by using a doped substrate material and activating only the bottom wall of the aperture, enabling plating of the bottom wall without depositing conductive material on the side walls of the aperture. Vias may be formed to the bottom plate by using a disjoint structure and conductive paste technology. Connection to the passive components may be made by conductive paste-filled channels forming conductive patterns on the substrate.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

Replacement of passive electrical components

A process of fabricating a passive electrical component, such as a resistor, a capacitor, or an inductor, is provided. The process includes the step of ink-jet printing at least one electronic ink onto a substrate in a predetermined pattern. The step of ink-jet printing may include the steps of: a) selecting at least one electronic ink having at least one electrical characteristic when cured; b) determining a positional layout for a plurality of droplets of the at least one electronic ink such that, when the at least one electronic ink has been cured, the positional layout provides a desired response for the electrical component; c) printing each of the plurality of droplets of the at least one electronic ink onto the substrate according to the positional layout using an ink-jet printing process; and d) curing the at least one electronic ink.

Owner:CABOT CORP

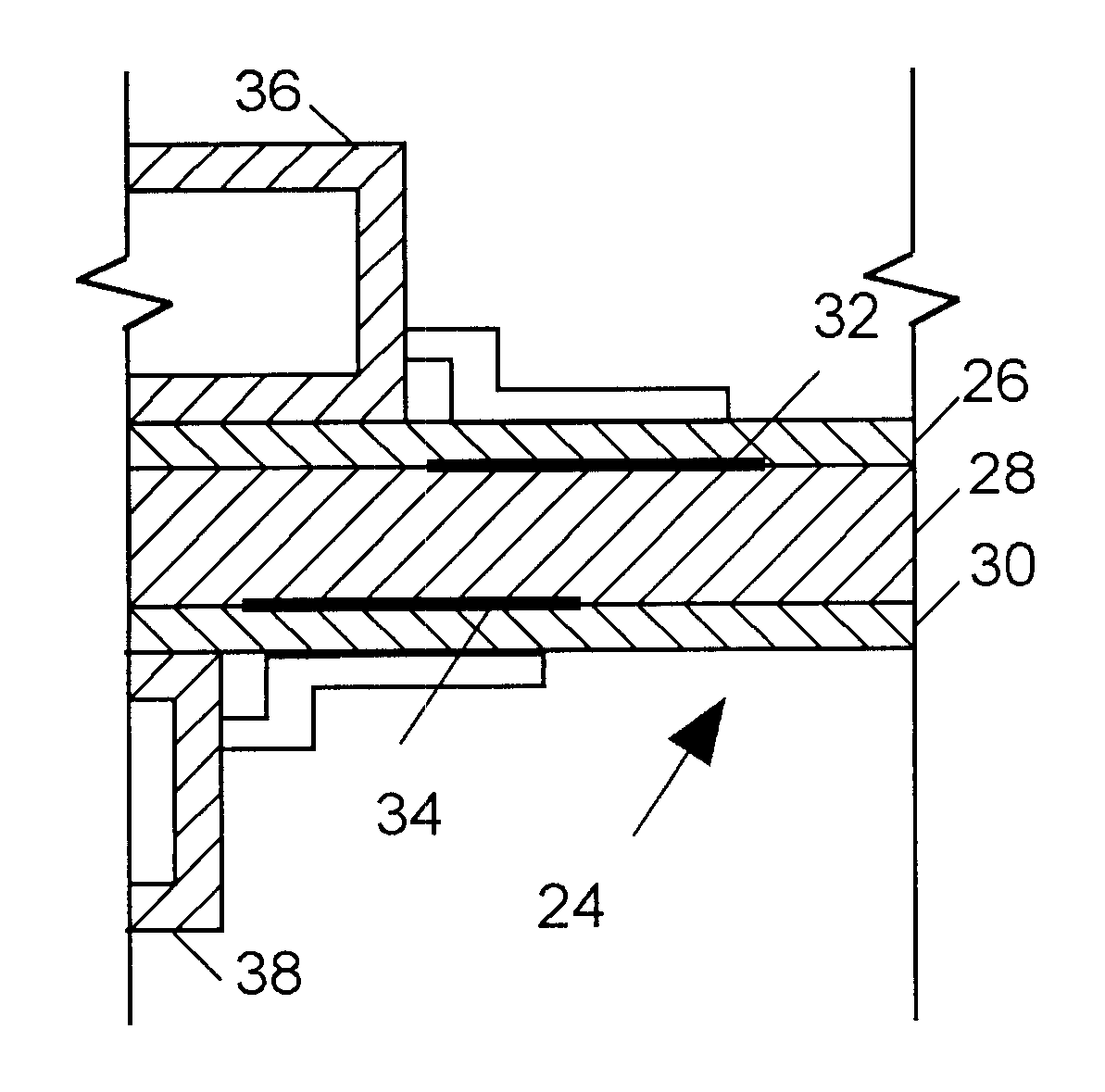

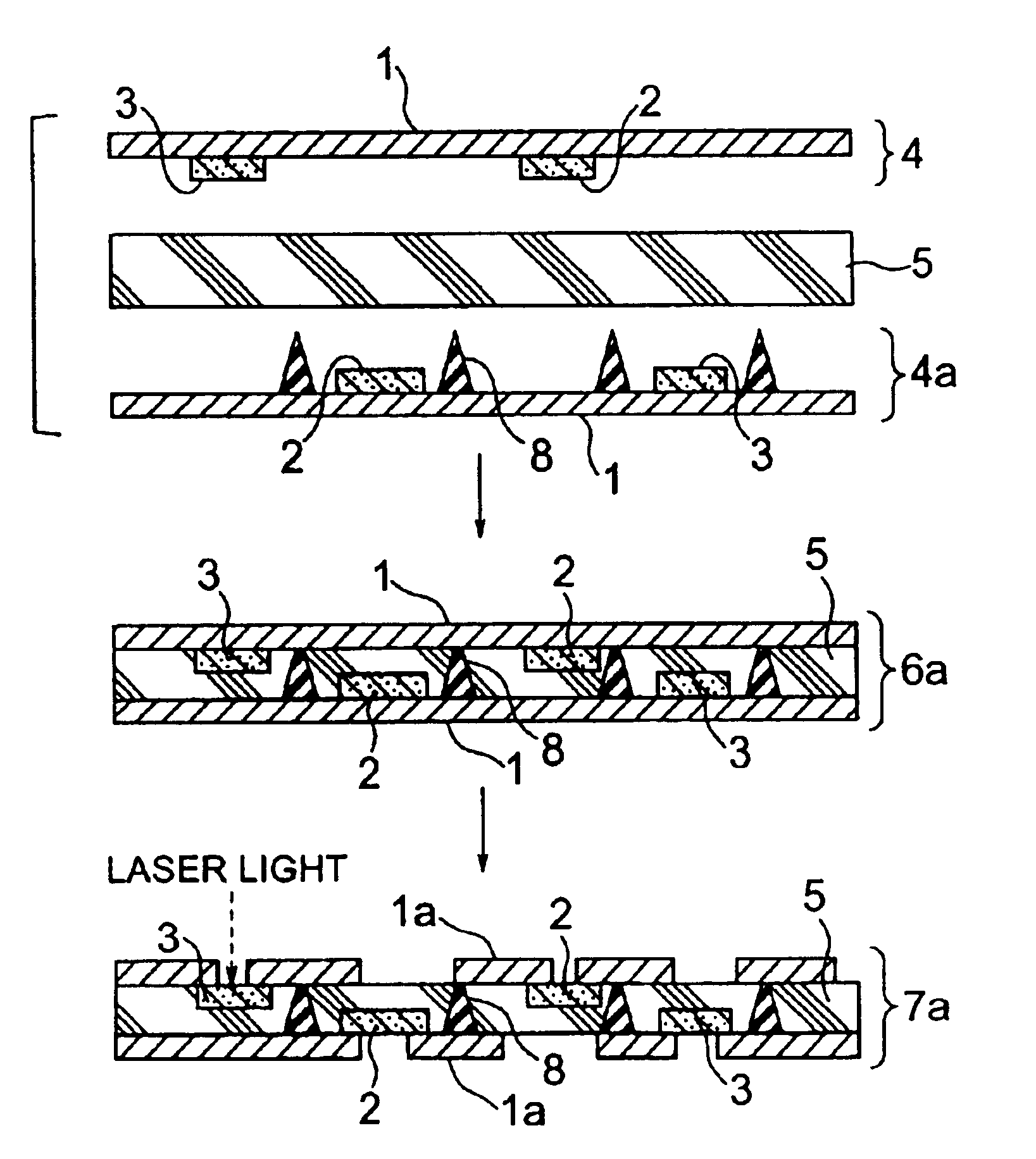

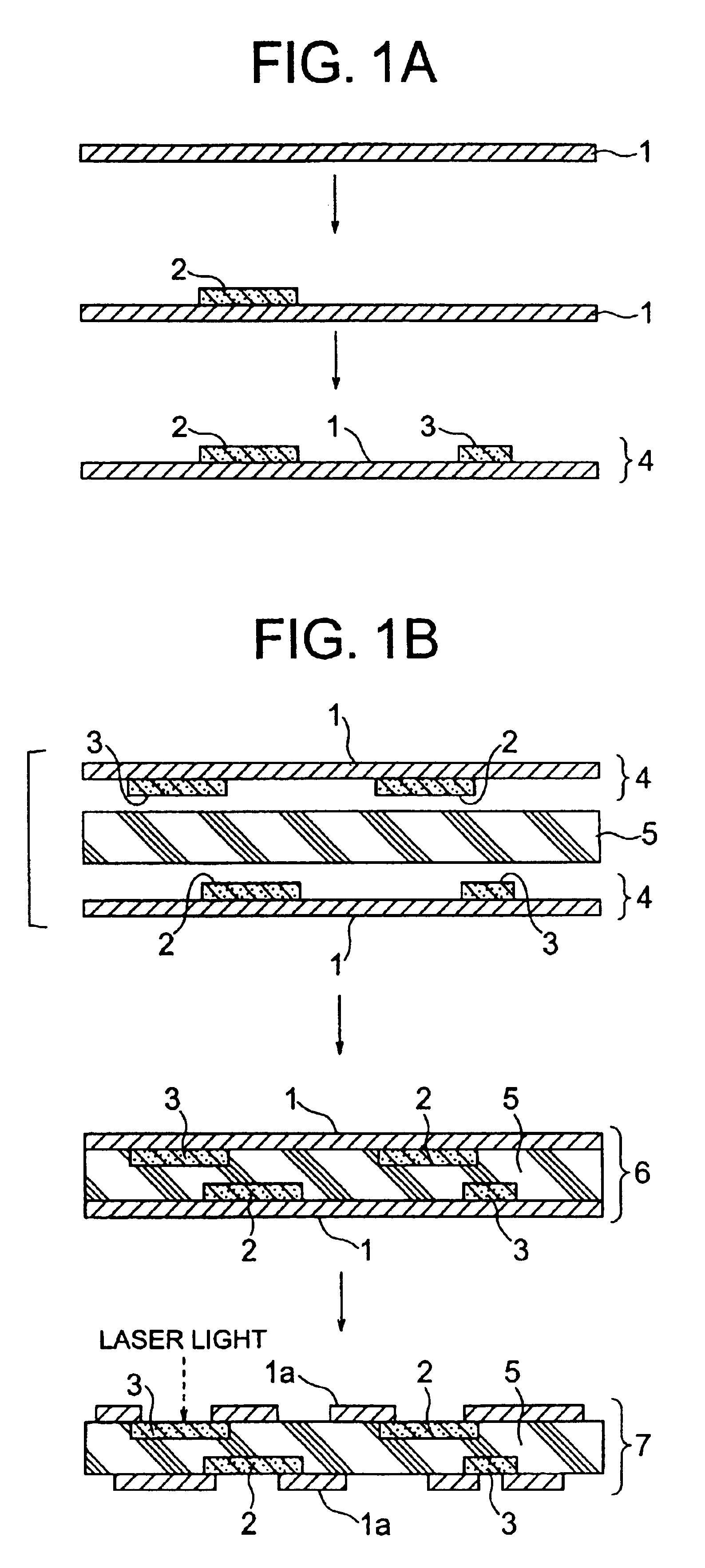

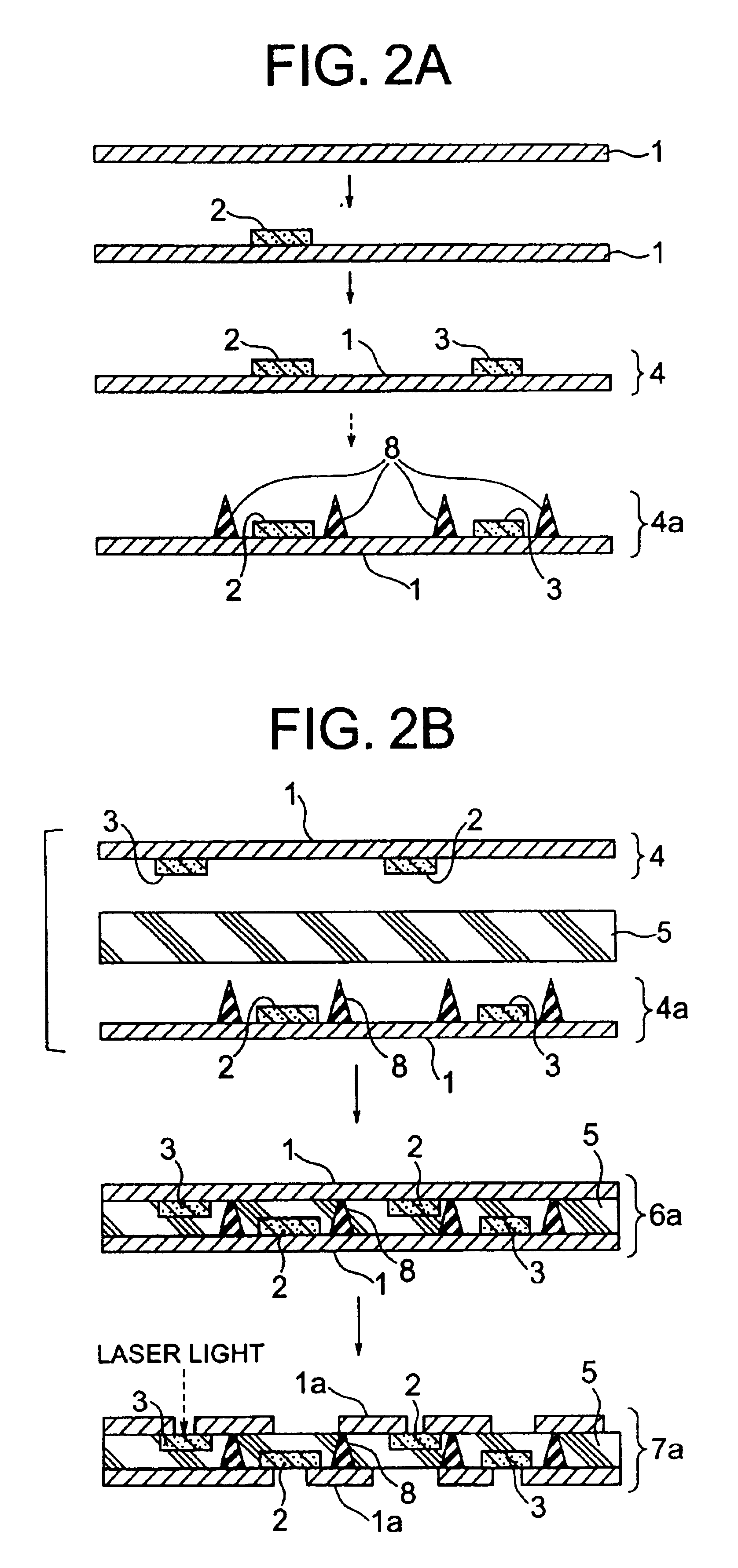

Wiring board provided with passive element and cone shaped bumps

InactiveUS6872893B2Improve featuresPrinted resistor incorporationElectrical connection printed elementsMetal foilPower strip

A fabricating method of a wiring board provided with passive elements is disclosed. The fabricating method includes coating one or both of resistive paste and dielectric paste on at least any one of first surfaces of a first metal foil and a second metal foil each of which has a first surface and a second surface; arranging an insulating board having thermo-plasticity and thermo-setting properties so as to face the first surface of the first metal foil, and arranging the first surface side of the second metal foil so as to face a surface different from a surface to which the first metal foil faces of the insulating board; forming a double-sided wiring board by stacking, pressurizing and heating the arranged first metal foil, insulating board, and second metal foil, and thereby integrating these; and patterning the first metal foil and / or the second metal foil.

Owner:DAI NIPPON PRINTING CO LTD

System and method for integrating a digital core with a switch mode power supply

InactiveUS20050024908A1Good power savingMinimal costDigital data processing detailsDc-dc conversionCapacitanceEngineering

A digital core embodied within a semiconductor die is situated within any of a variety of integrated circuit packaging technologies including but not limited to Ball Grid Array or Quad Flat Pack surface mount technology. Said semiconductor die is of the variety that requires plural separate power supply voltage domains such as a digital core supply of differing voltage than the input / output pad ring supply voltage. Within the integrated circuit package including said semiconductor die also exists a high efficiency DC-to-DC voltage converter of type commonly known as a chopper or a switch mode power supply. In the preferred embodiment this switch mode power supply would be of the highest efficiency, a synchronous step-down regulator, thus to enable powering the entire integrated circuit from one supply voltage. The components contained within the integrated circuit package along with the semiconductor die include the majority if not the totality of the components comprising the switch mode power supply, which could include the power switching transistors; an inductor core and windings; the output voltage fixing circuitry; the output capacitor; and the substrate for mounting said components when integrated within a packaging technology that does not already include a substrate such as within the periphery of a lead frame for leaded devices.

Owner:CUFER ASSET LTD LLC

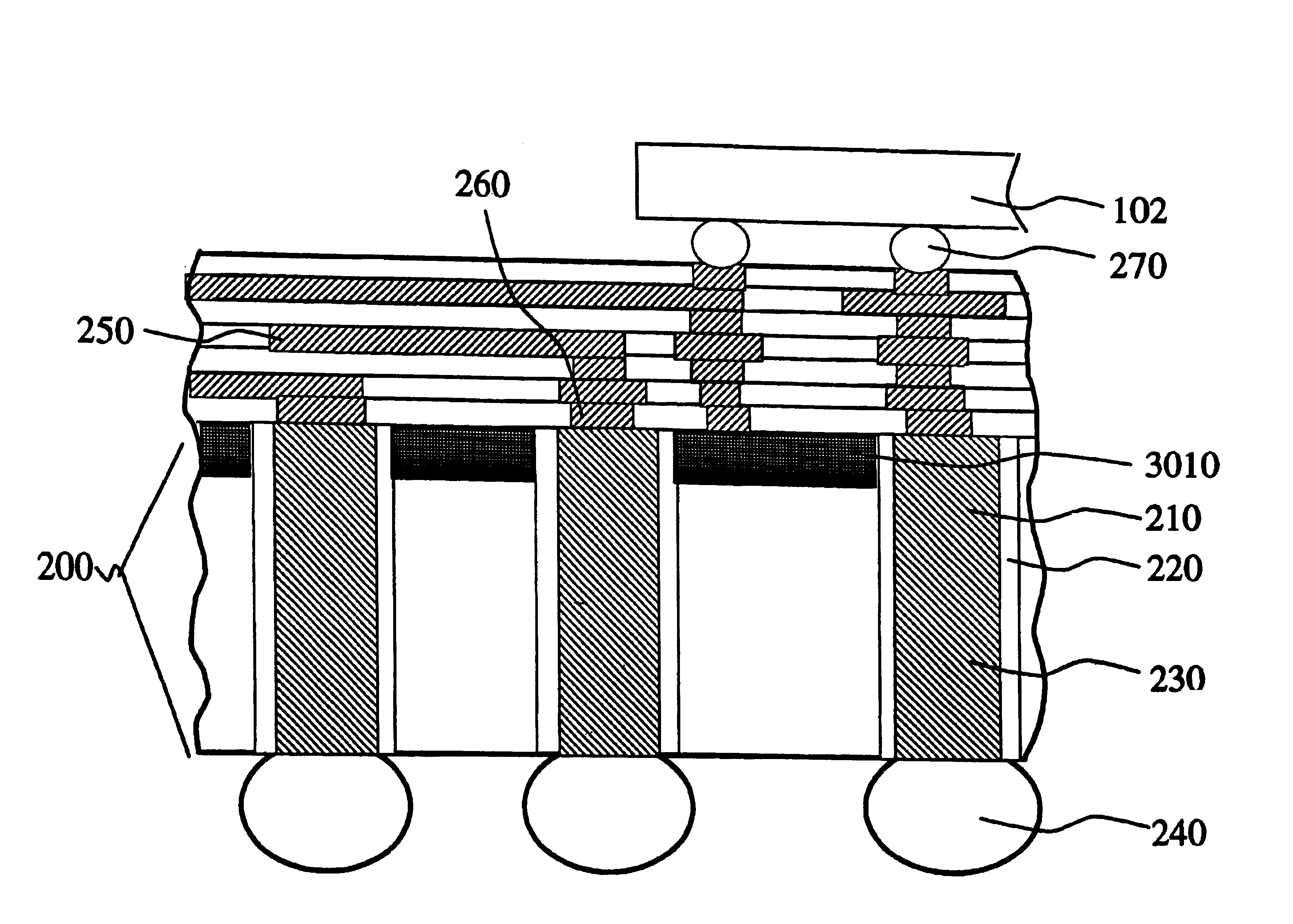

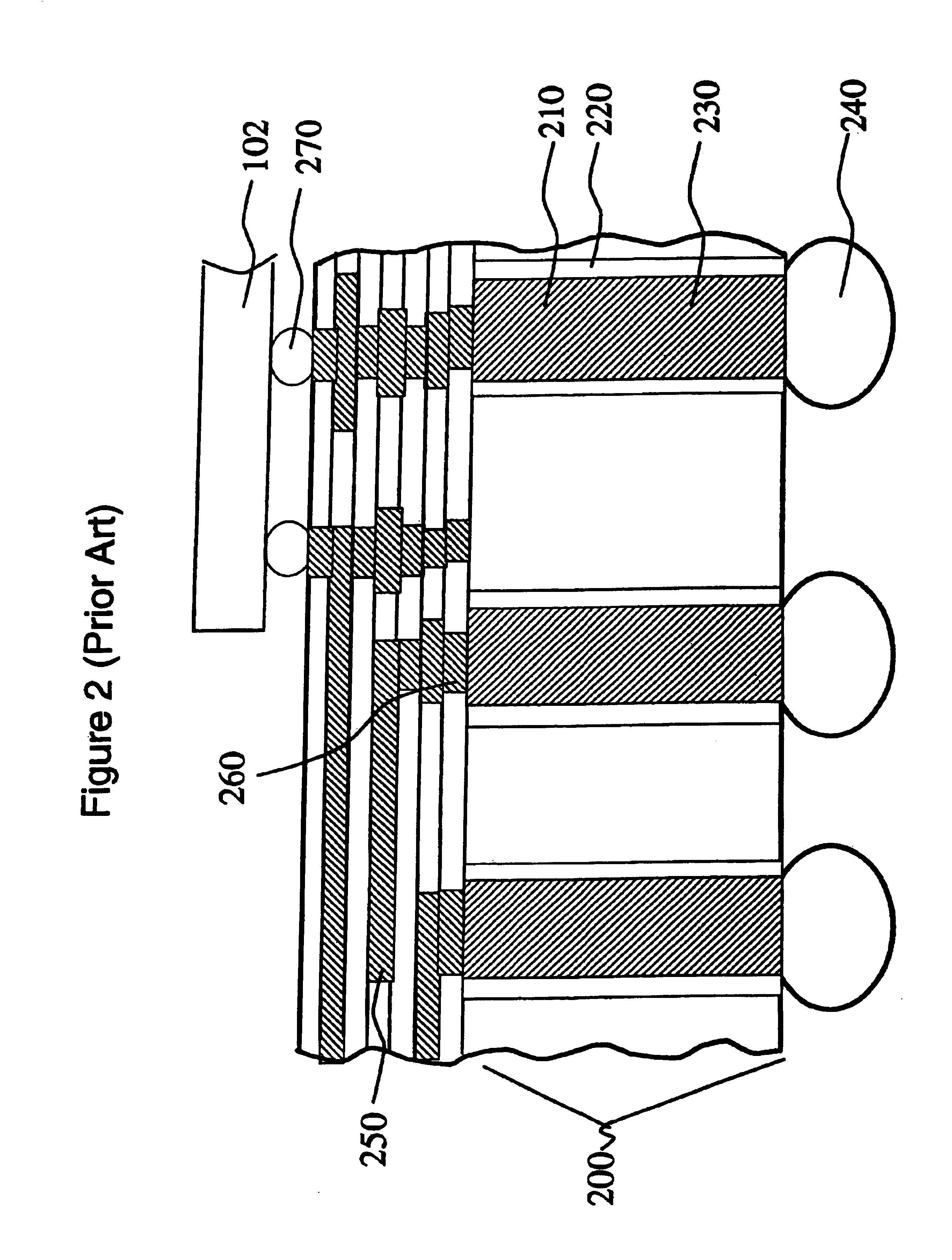

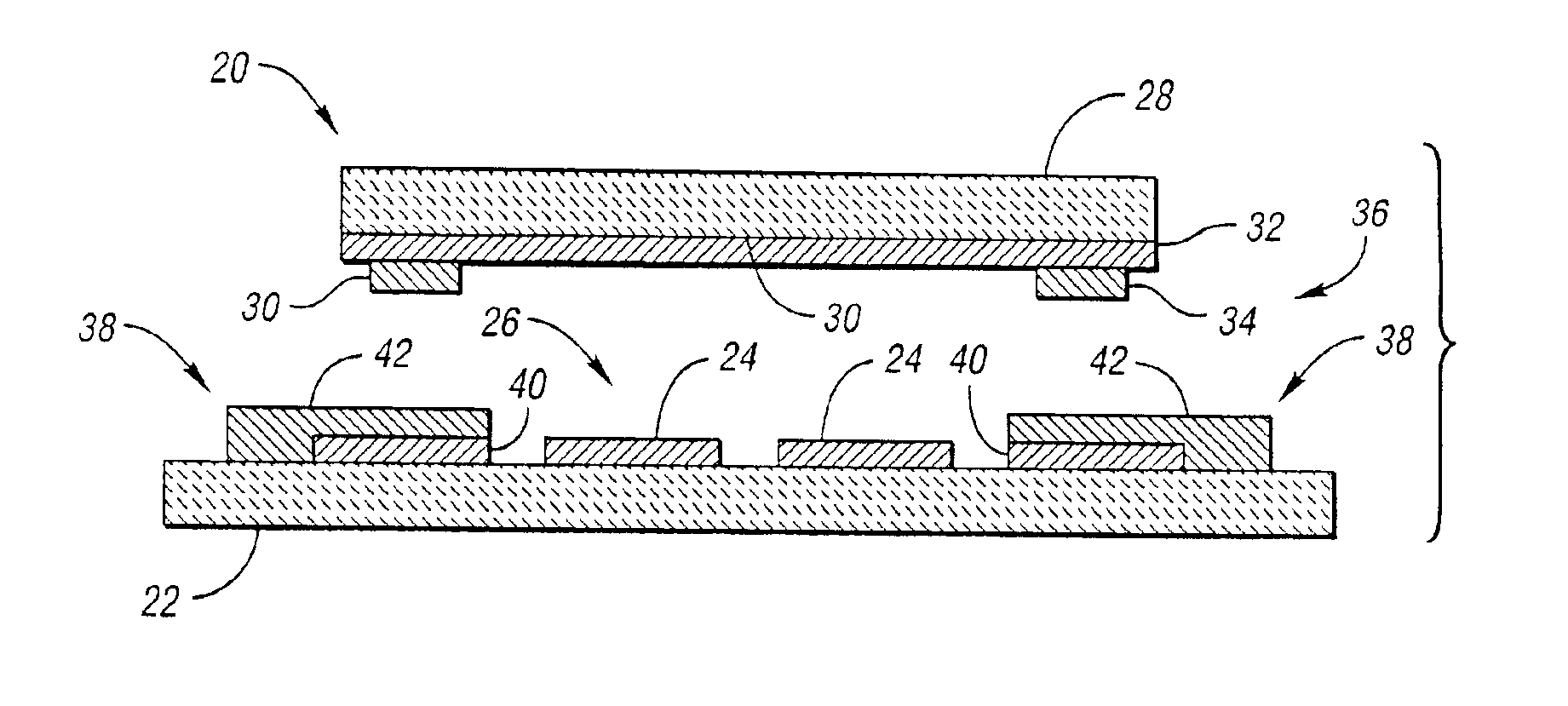

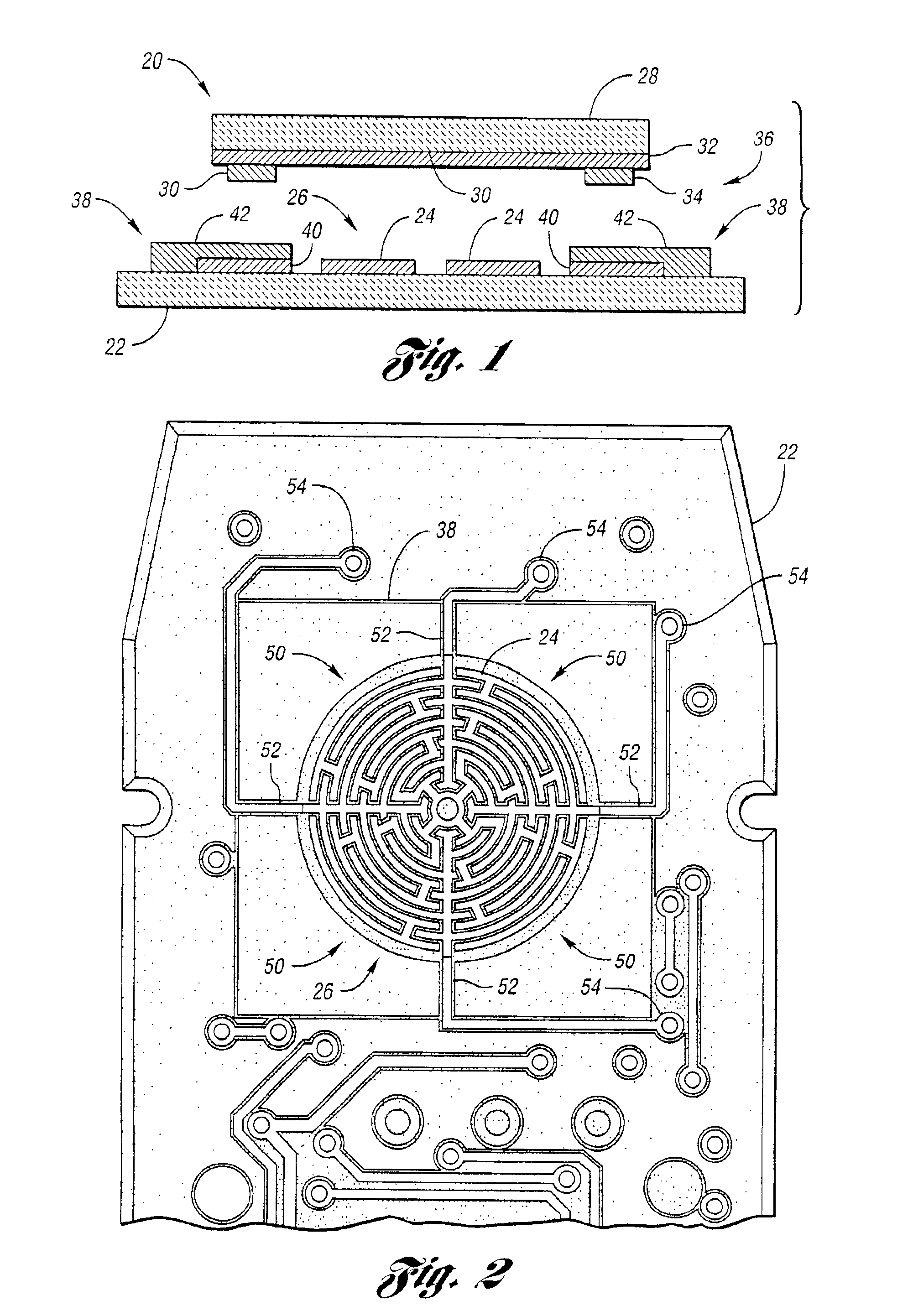

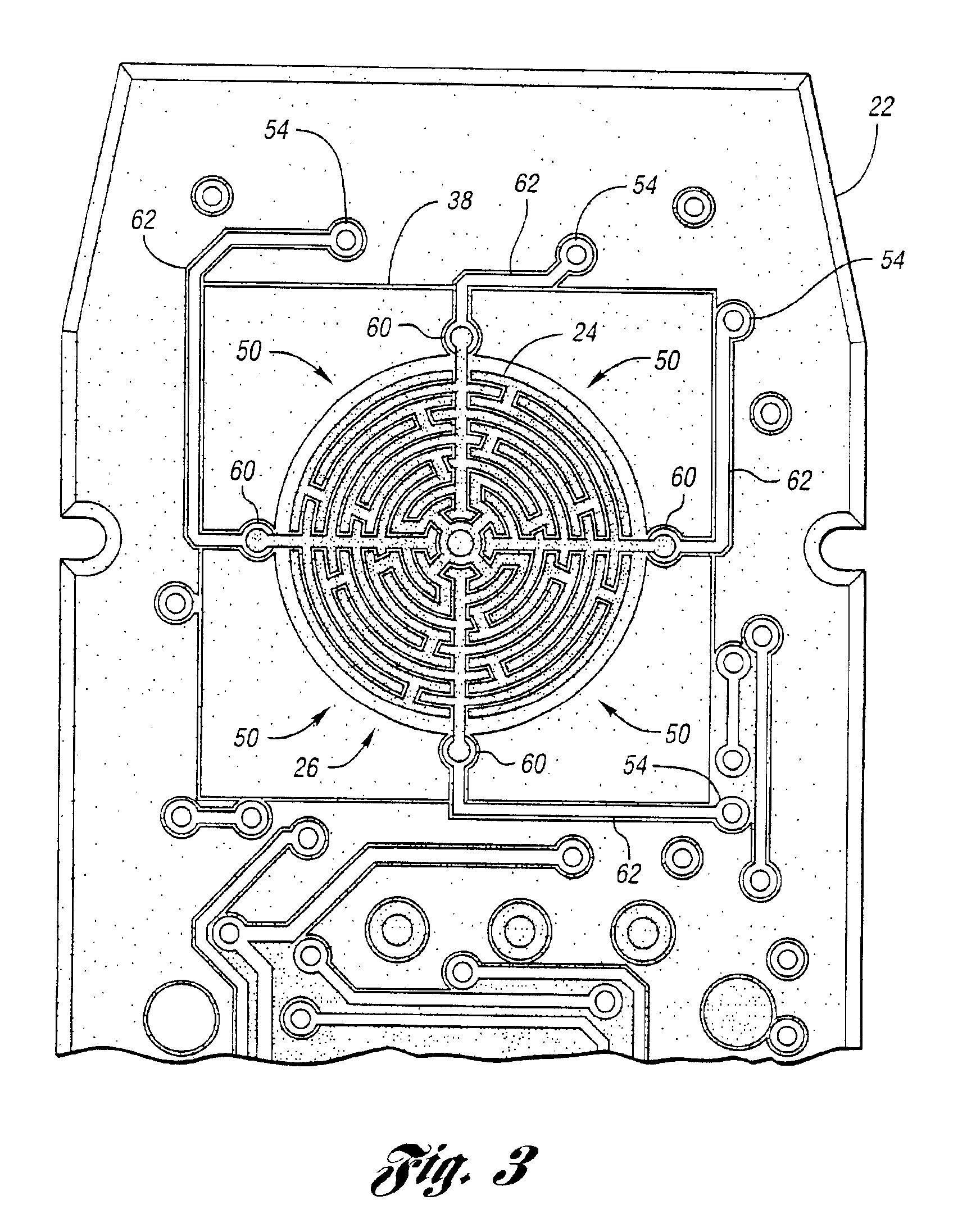

High density chip carrier with integrated passive devices

InactiveUS20050023664A1Fast electrical accessReduce inductanceSemiconductor/solid-state device detailsPrinted circuit aspectsHigh densityChip carrier

A carrier for a semiconductor component is provided having passive components integrated in its substrate. The passive components include decoupling components, such as capacitors and resistors. A set of connections is integrated to provide a close electrical proximity to the supported components.

Owner:GLOBALFOUNDRIES US INC

Popular searches

Printed capacitor incorporation Multilayer circuit manufacture Semiconductor devices Electrical apparatus contructional details Printed circuits structural associations Circuit susbtrate materials Metallic pattern materials Printed element electric connection formation Current interference reduction Conductive pattern formation

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com