Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

53results about How to "Reduce charge accumulation" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

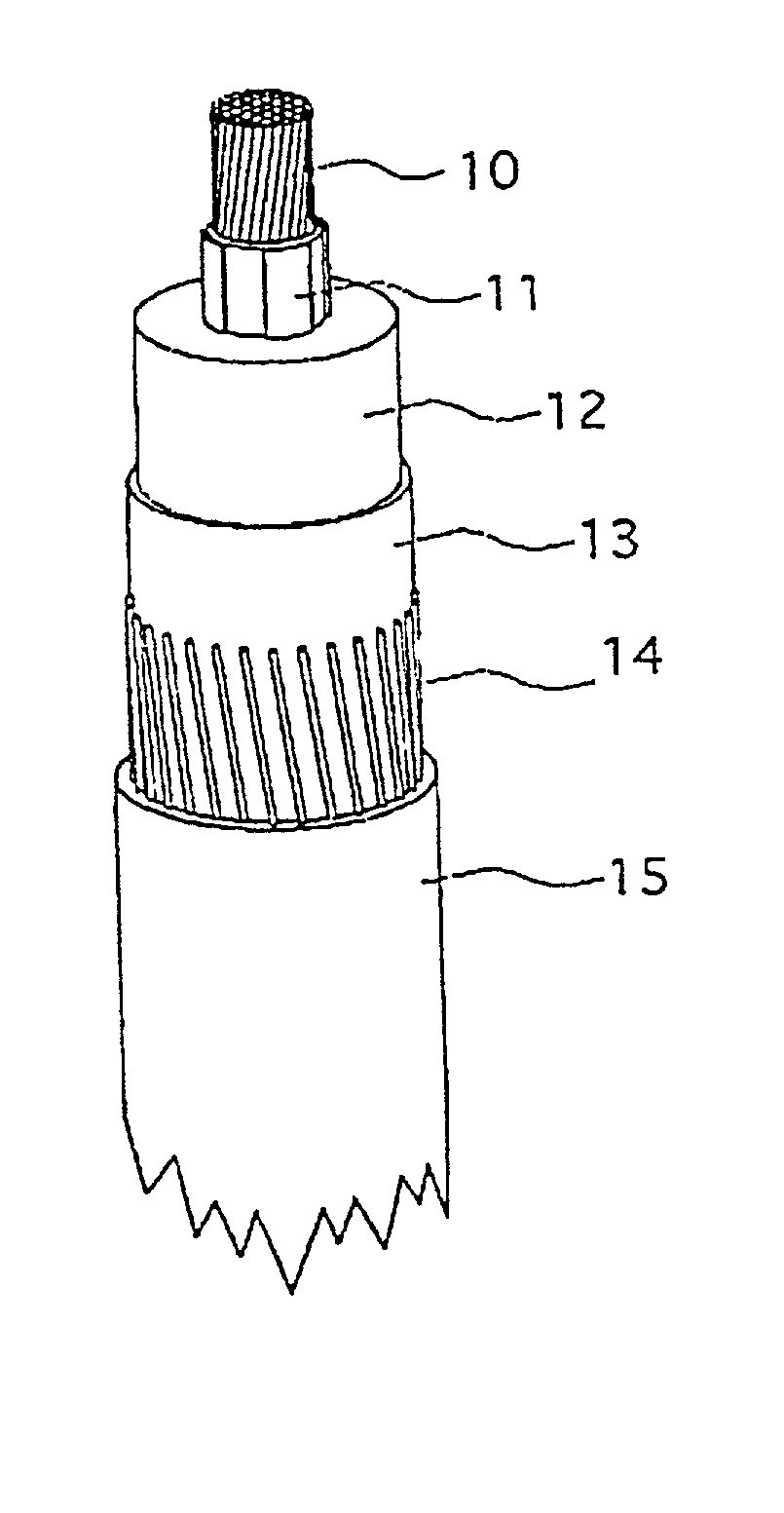

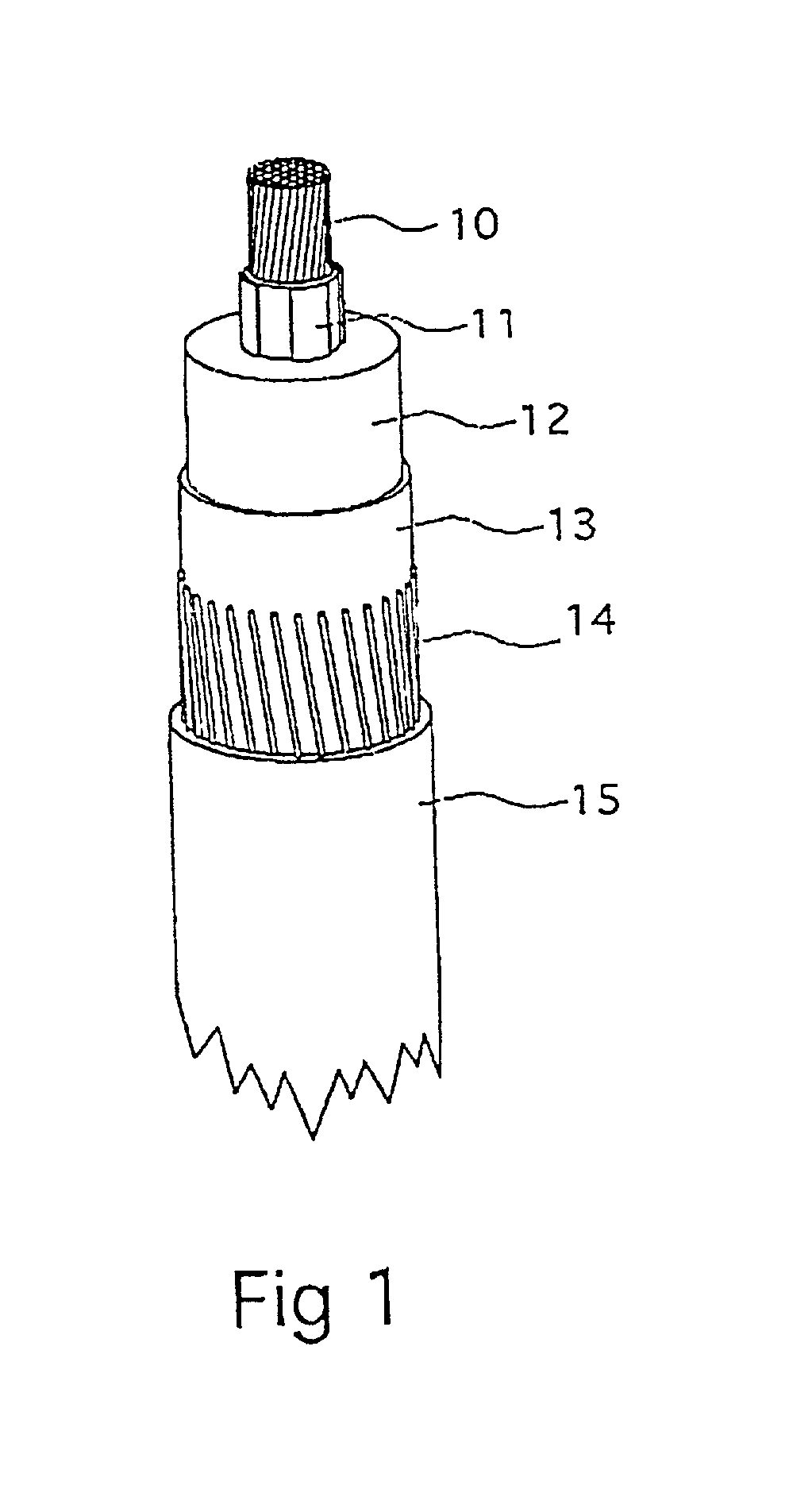

Electric DC-cable with an insulation system

InactiveUS20020039654A1Shorten production timeLow production costPlastic/resin/waxes insulatorsYarnCross-linkElectrical conductor

An insulated DC-cable and method for production of an insulated DC-cable with an insulating system comprising an extruded cross-linked polyethylene based insulation disposed around the conductor. The extruded polyethylene based compound comprises additives such as cross-linking agent, scorch retarding agent and antioxidant. The scorch retarding agent comprises a compound (D), 2,4-diphenyl-4-methyl-pentene-1 and the antioxidant comprises a compound (C), a diester of 3-(3,5-di-tert-butyl-4-hydroxyphenyl)propionicacid and thiodiglycol. The compounded polyethylene based resin composition is extruded and cross-linked at a temperature and for a period of time sufficient enough to cross link the insulation. The temperature and the period of time upon extrusion and cross-linking are limited so as to substantially suppress or essentially avoid undesired polar by-products being formed in the cross-linked composition.

Owner:GUSTAFSSON BILL +7

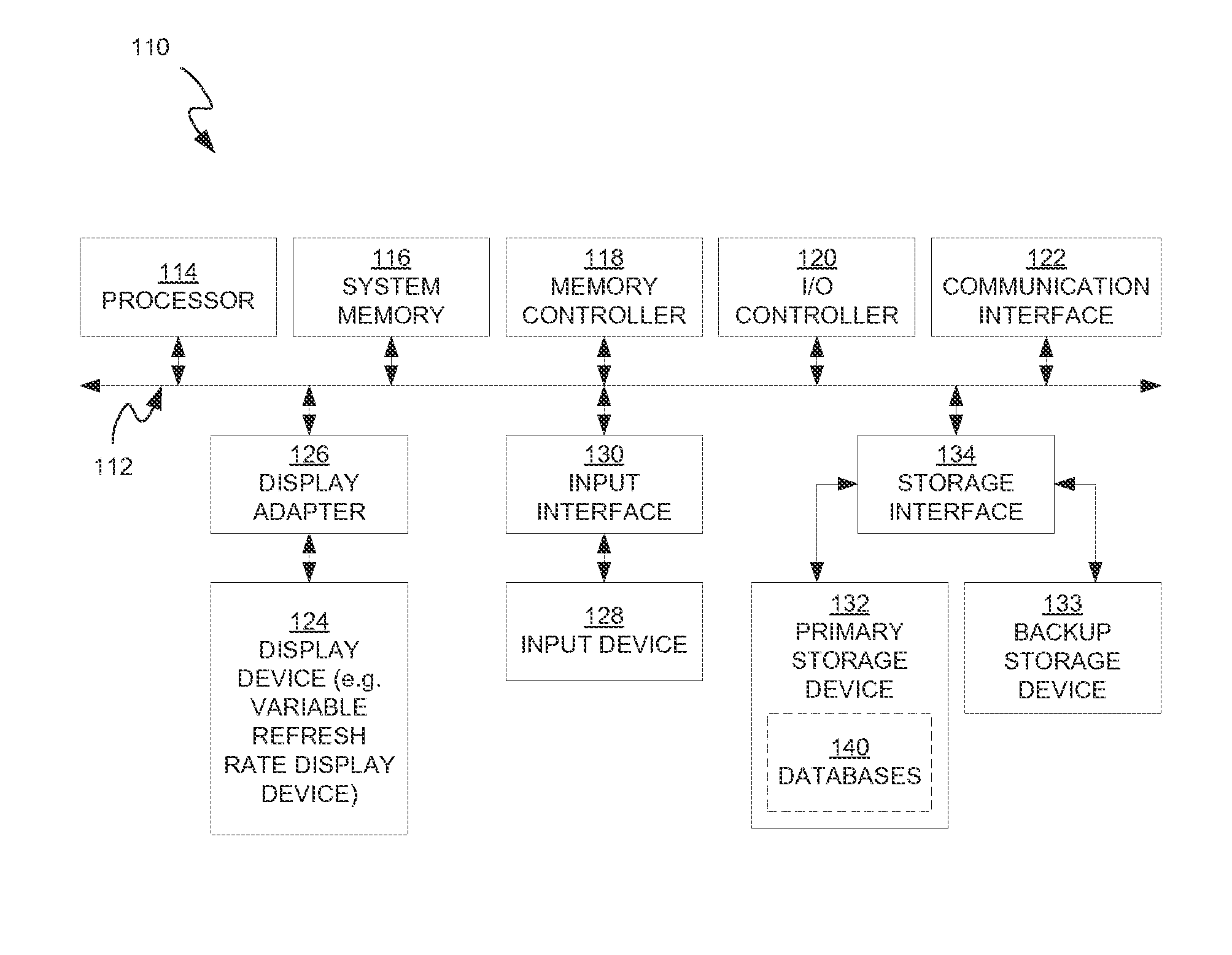

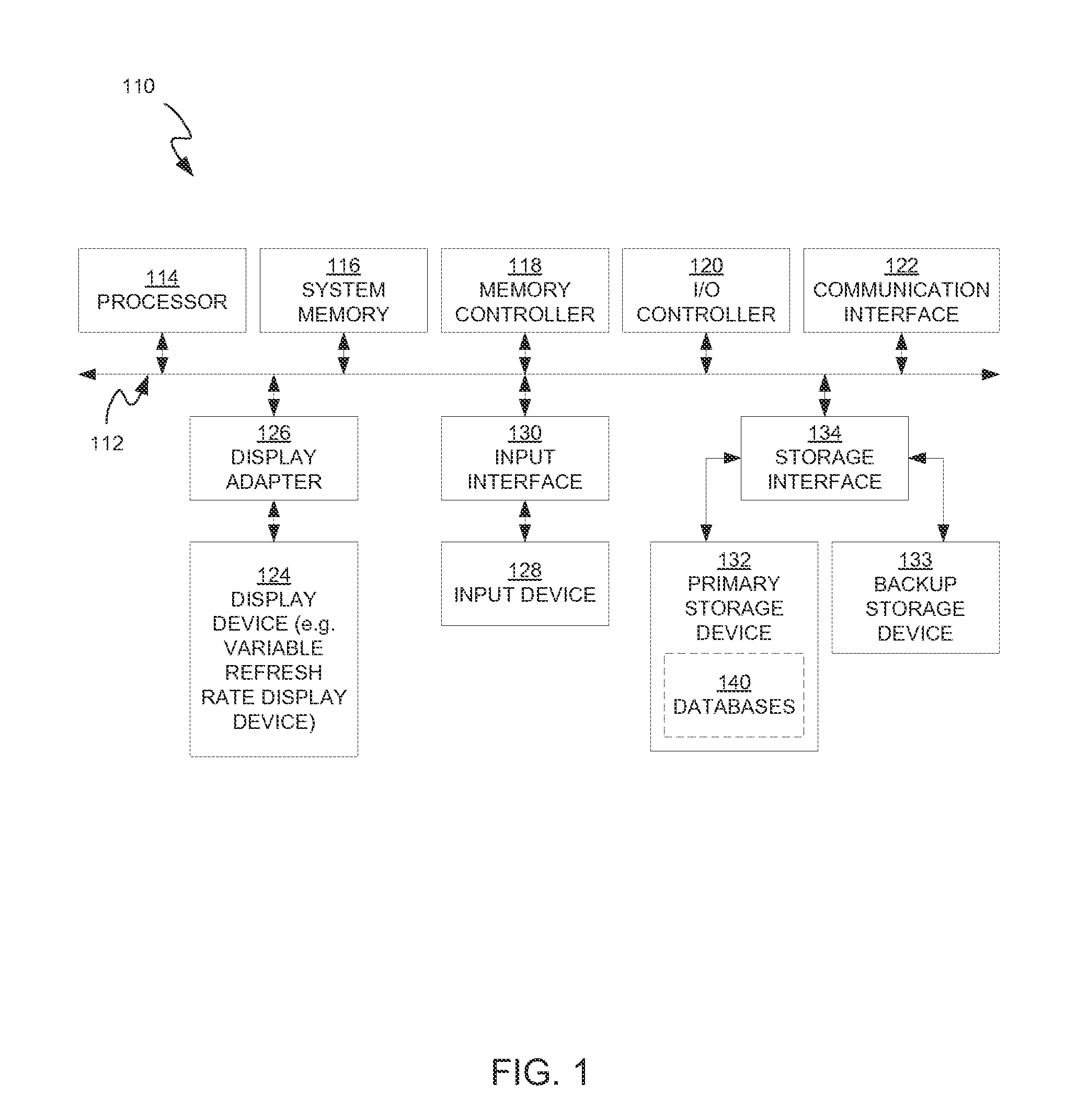

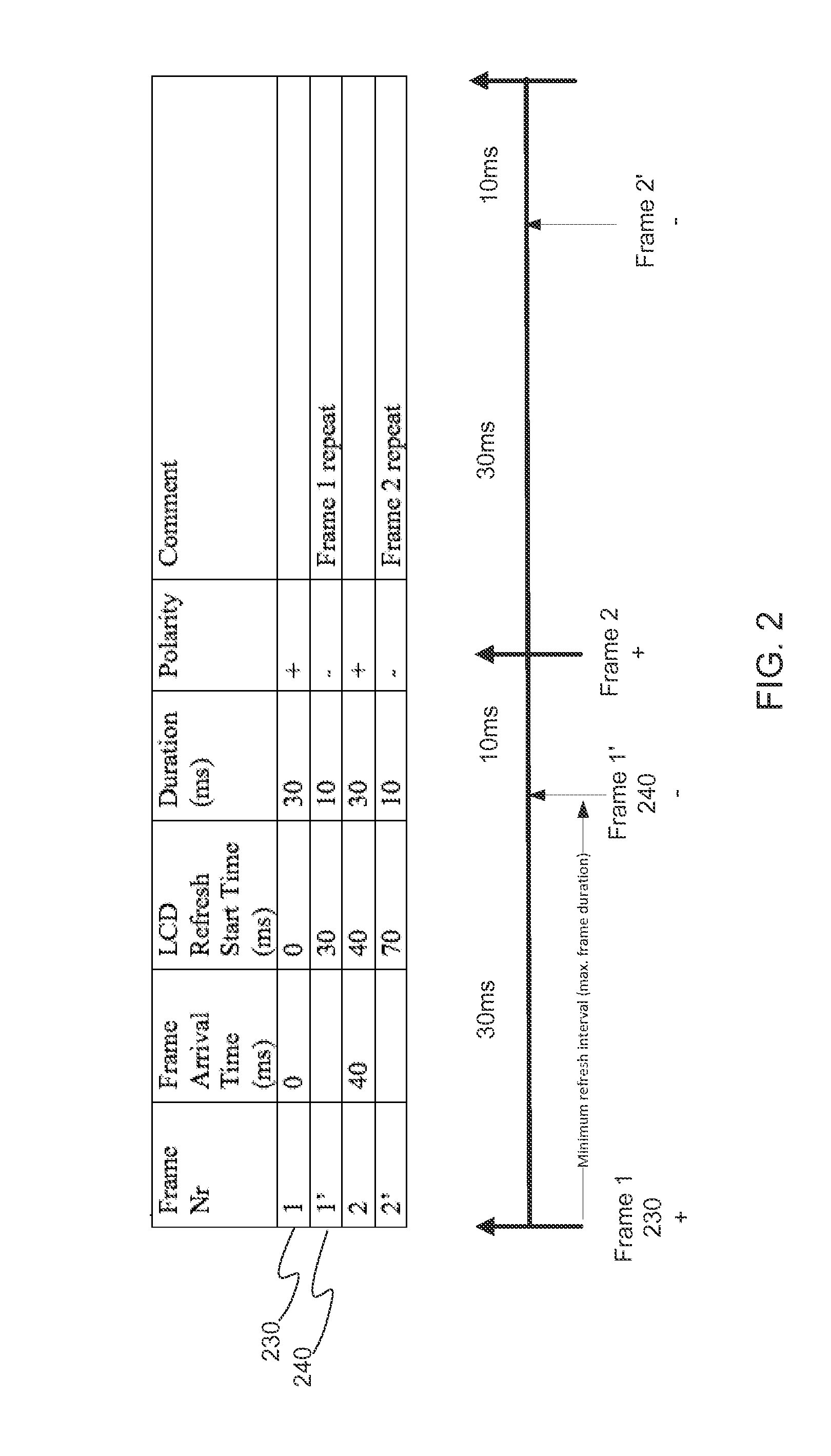

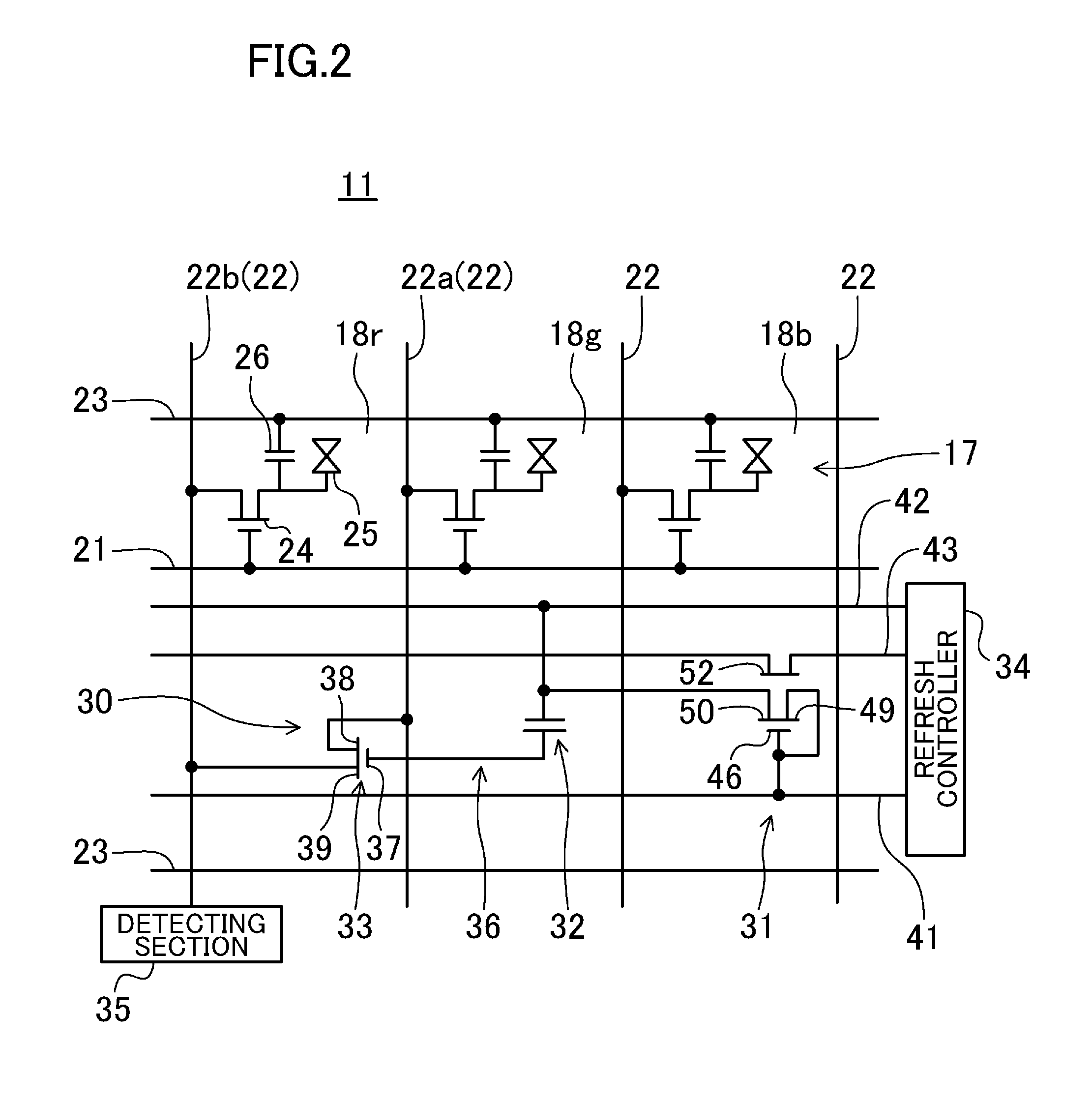

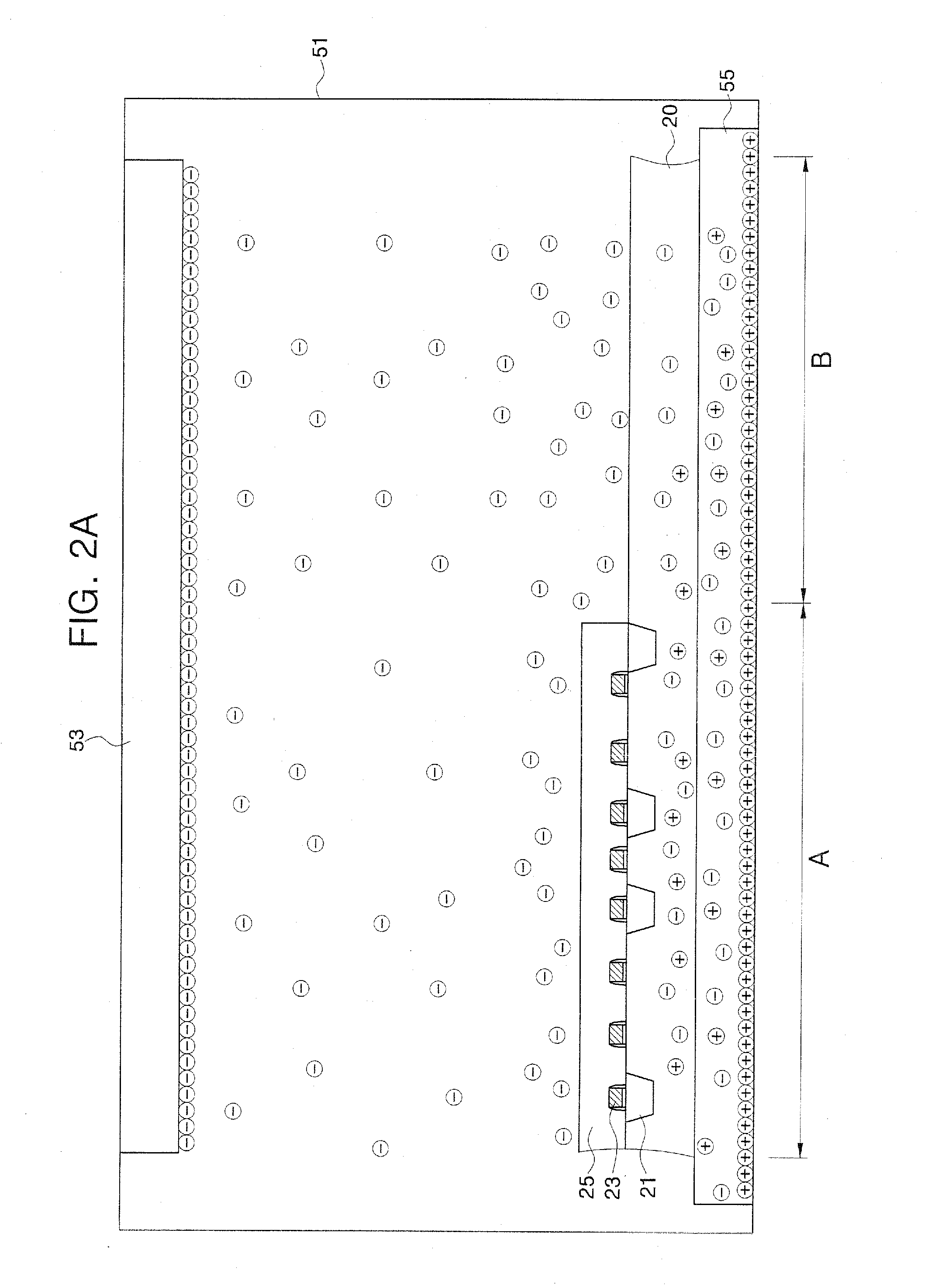

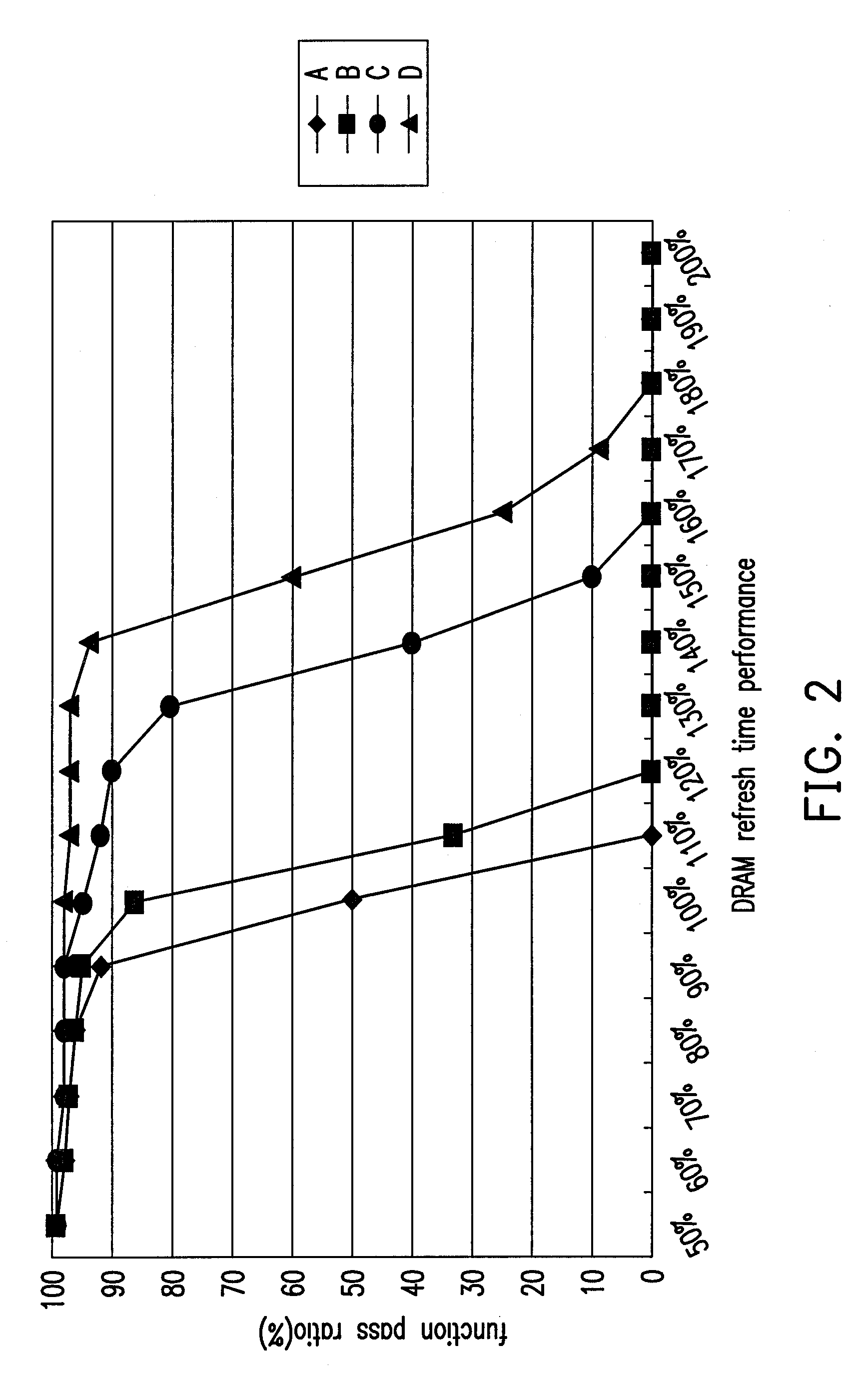

Techniques for avoiding and remedying DC bias buildup on a flat panel variable refresh rate display

ActiveUS20150243234A1Avoid accumulationAvoid artifactsStatic indicating devicesDisplay deviceRefresh rate

A method for driving a display panel having a variable refresh rate is disclosed. The method comprises receiving a current input frame from an image source. It also comprises determining a first number of re-scanned frames to insert between the current input frame and a subsequent input frame, wherein the re-scanned frames repeat the current input frame, and wherein the determining depends on a minimum refresh interval (MRI) of the display panel. Further, it comprises calculating intervals to insert the first number of re-scanned frames between the current input frame and the subsequent input frame. Further, it comprises scanning the current input frame for display on the display panel. Finally it comprises inserting the first number of re-scanned frames at the respective intervals between the current input frame and the subsequent input frame from the image source, wherein the inserting is operable to reduce charge accumulation in the display panel.

Owner:NVIDIA CORP

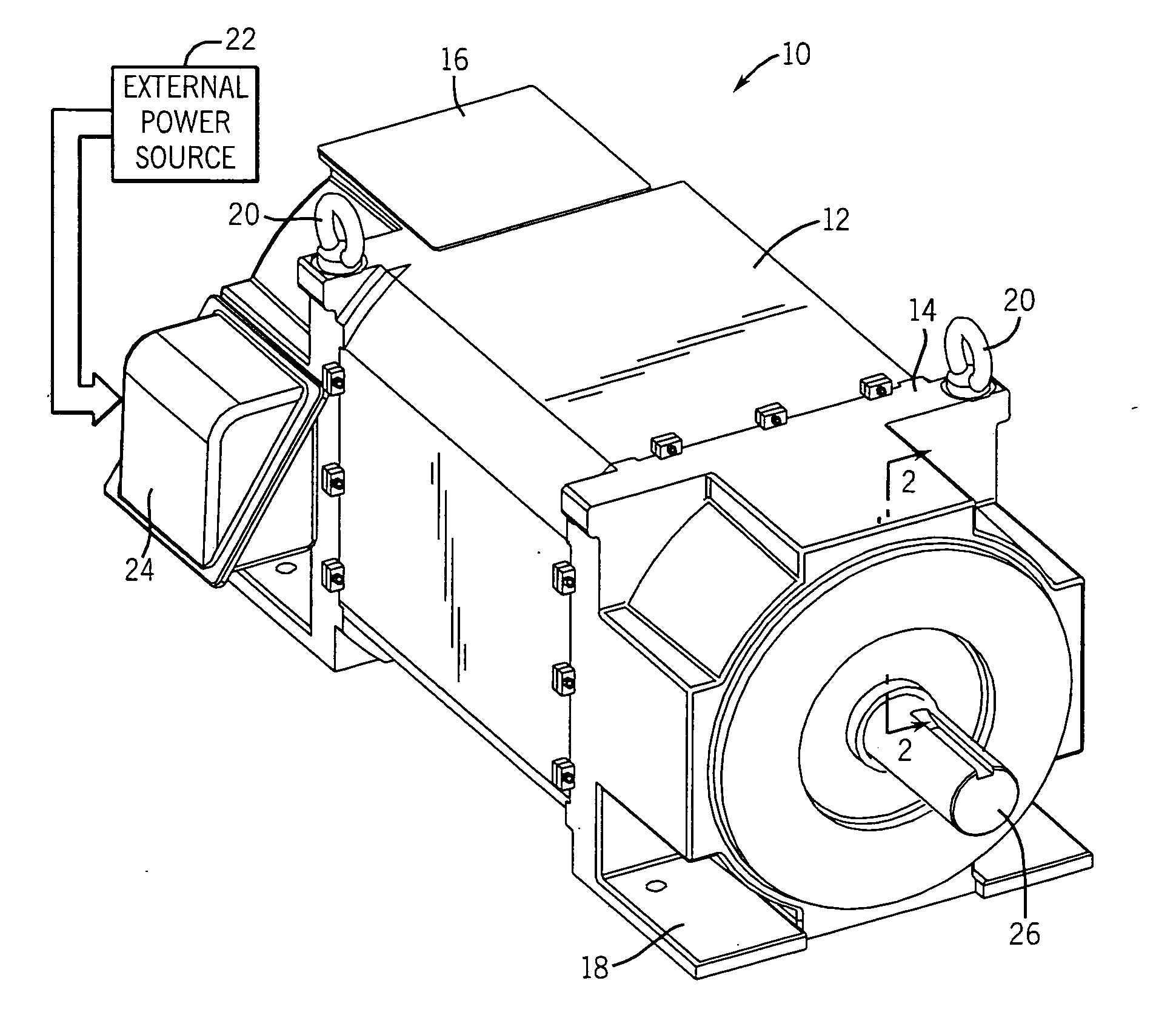

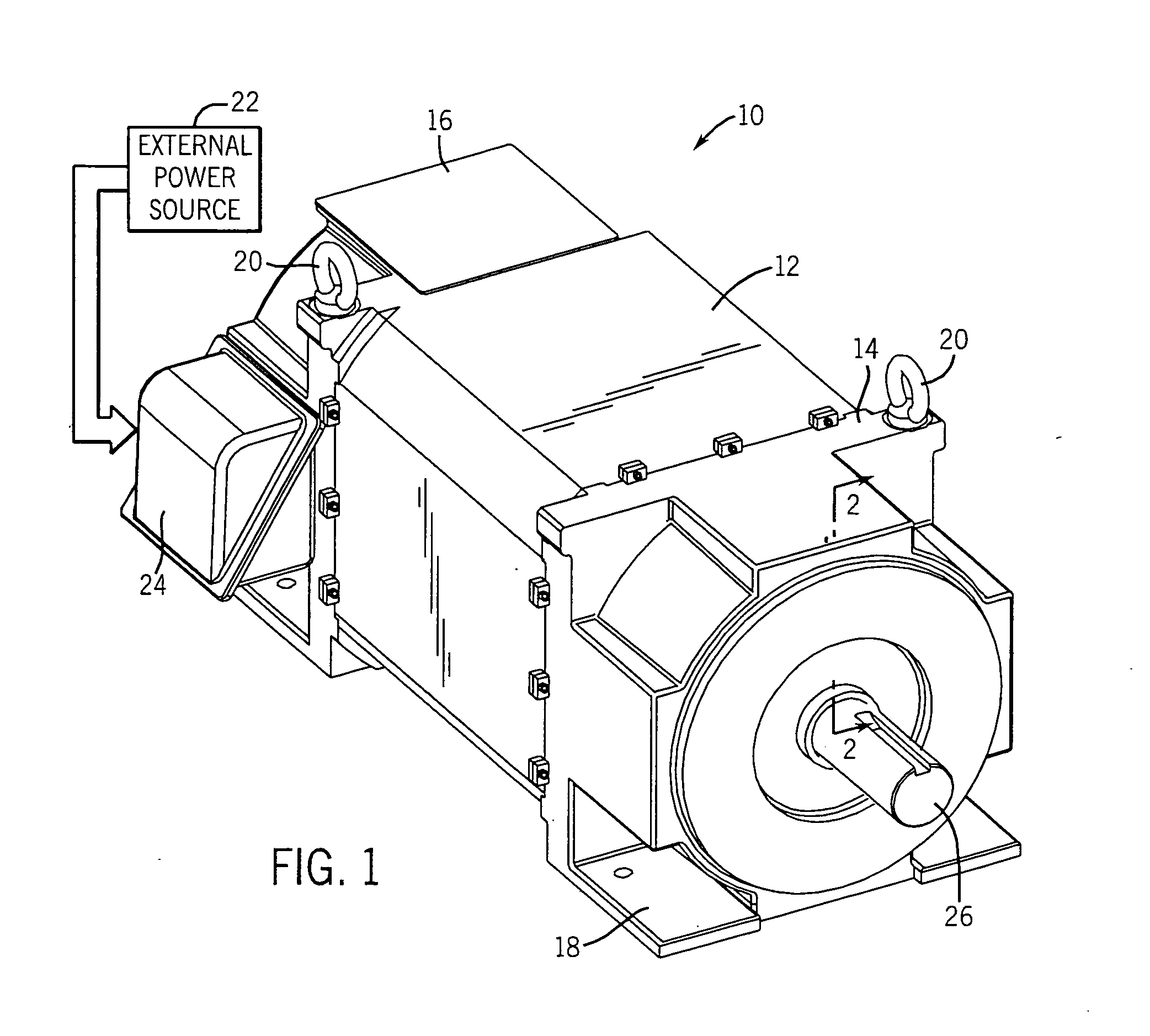

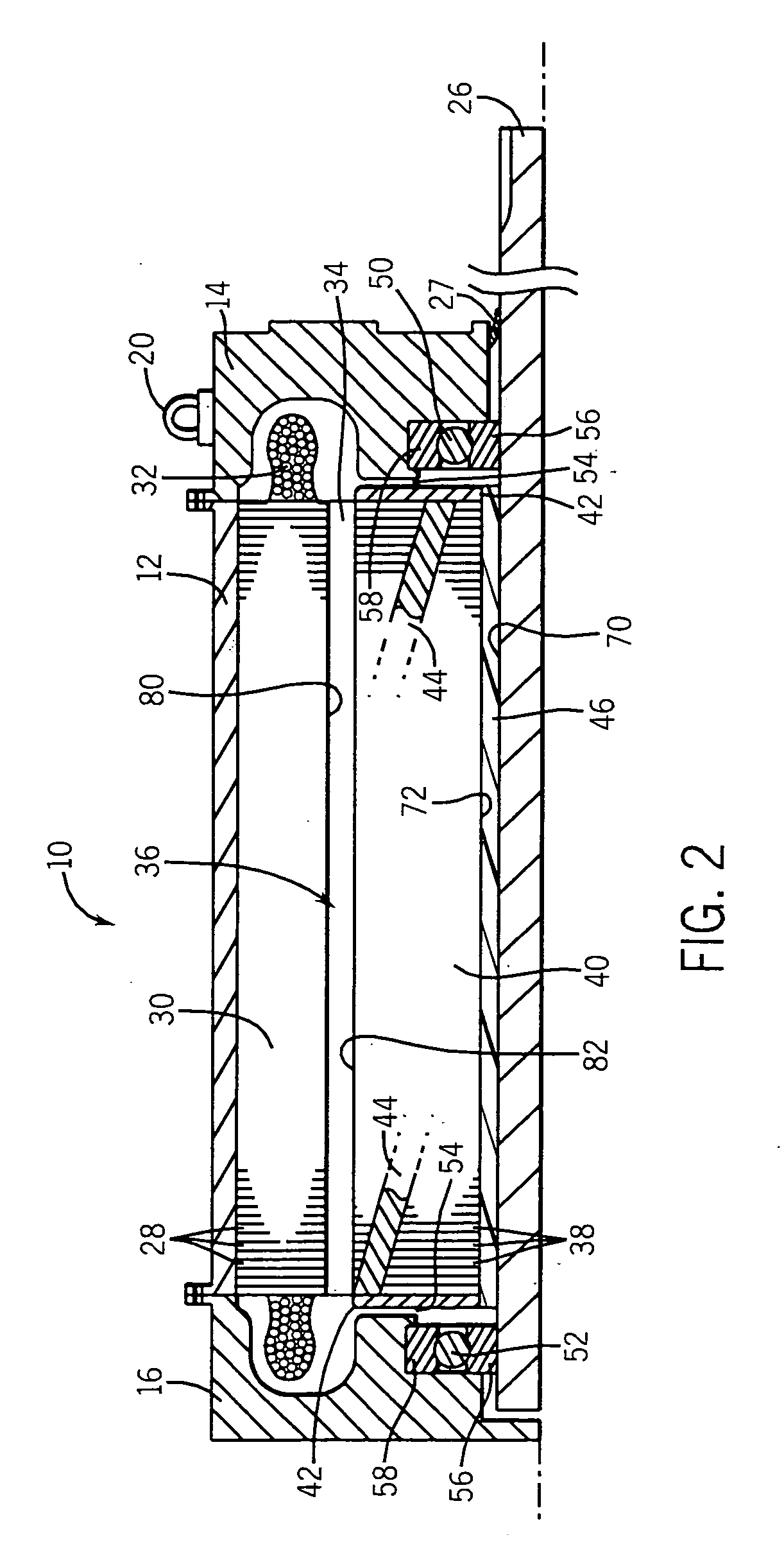

Apparatus and method for reducing shaft charge

InactiveUS20050253480A1Reduces build-up of chargeReduce build-upMagnetic circuit rotating partsManufacturing stator/rotor bodiesEngineeringDielectric layer

According to an exemplary embodiment, the present invention provides a rotatable element, such as a rotor for an electric motor. The exemplary rotatable element has a core with a generally circular cross-section and a channel that extends through the core along an axial centerline of the core. The element also includes a shaft that is secured to the core and that is disposed in the channel. Additionally, the element includes a dielectric layer disposed between the shaft and the core that electrically insulates the core and shaft with respect to one another. Accordingly, the dielectric layer prevents current from flowing between the core and the shaft. In turn, the dielectric layer reduces the development of charge in the shaft.

Owner:RELIANCE ELECTRIC TECH

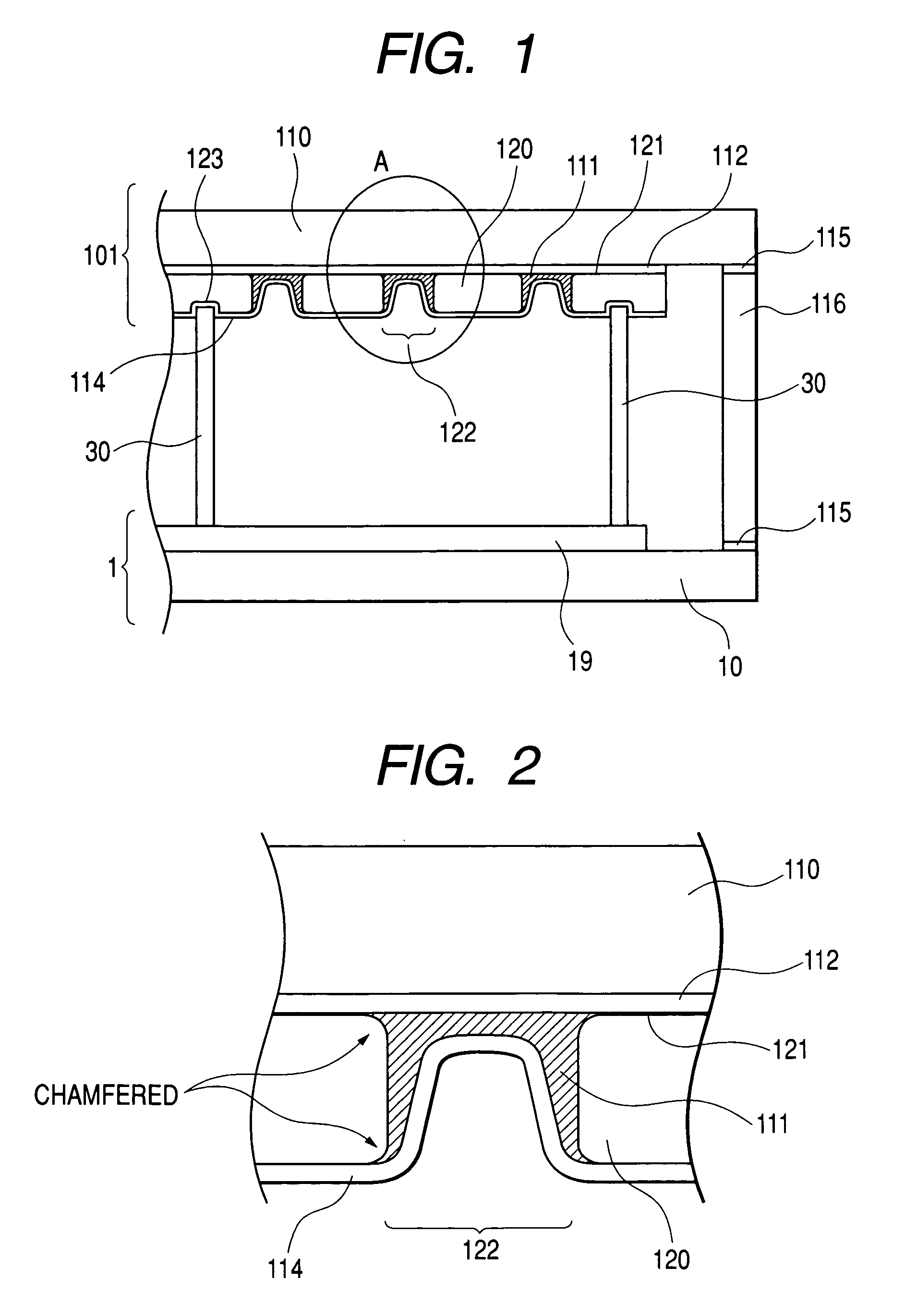

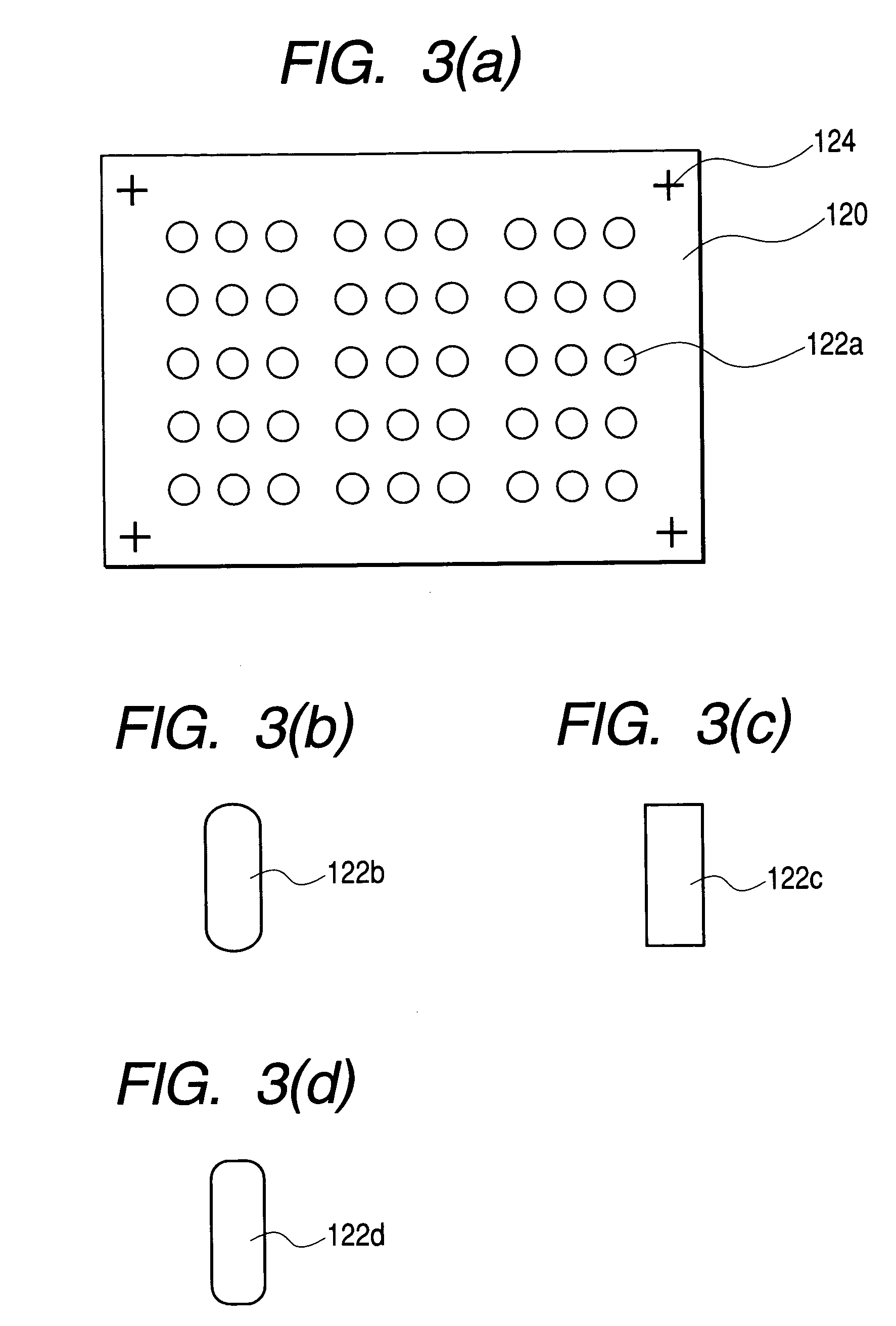

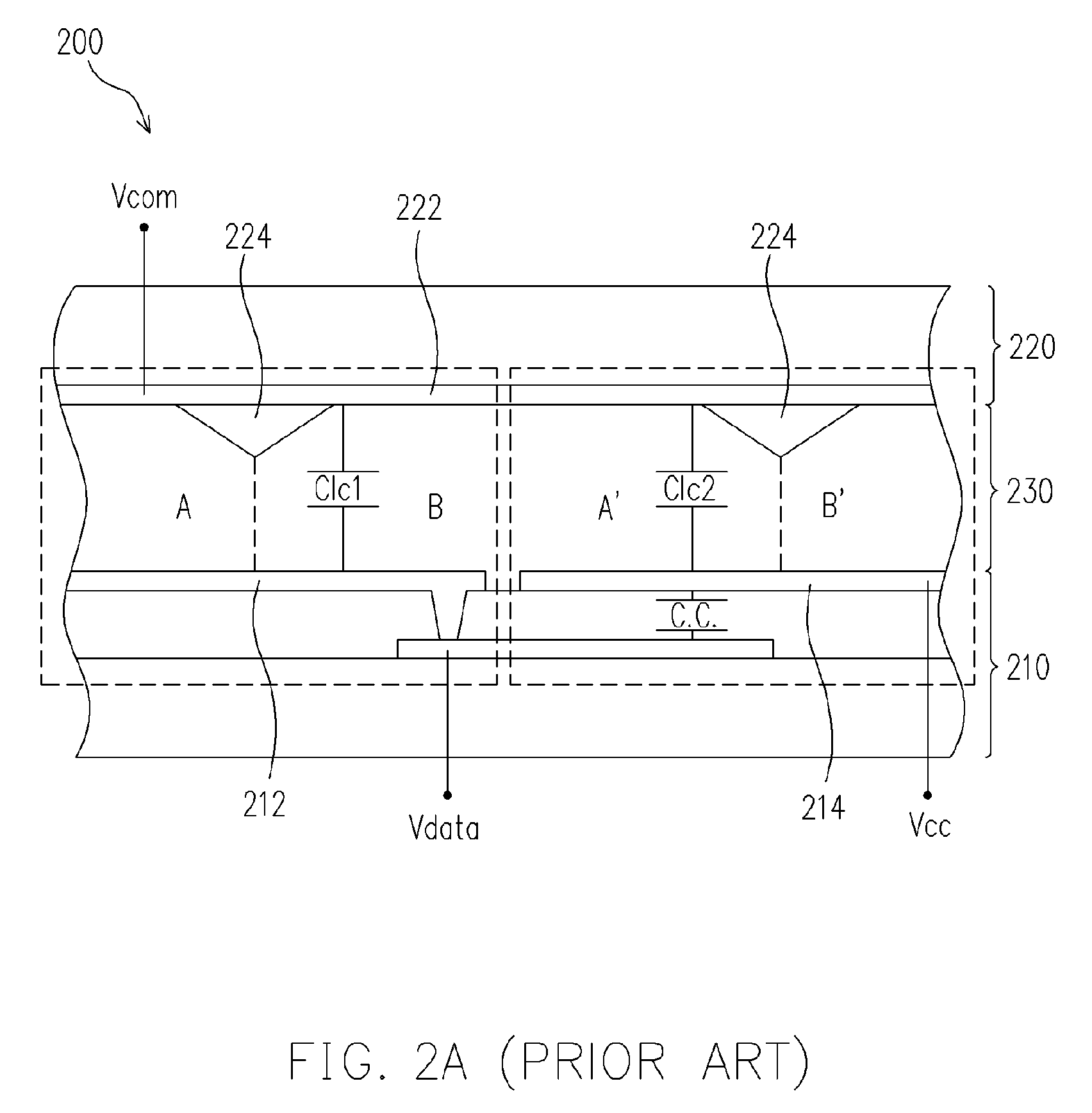

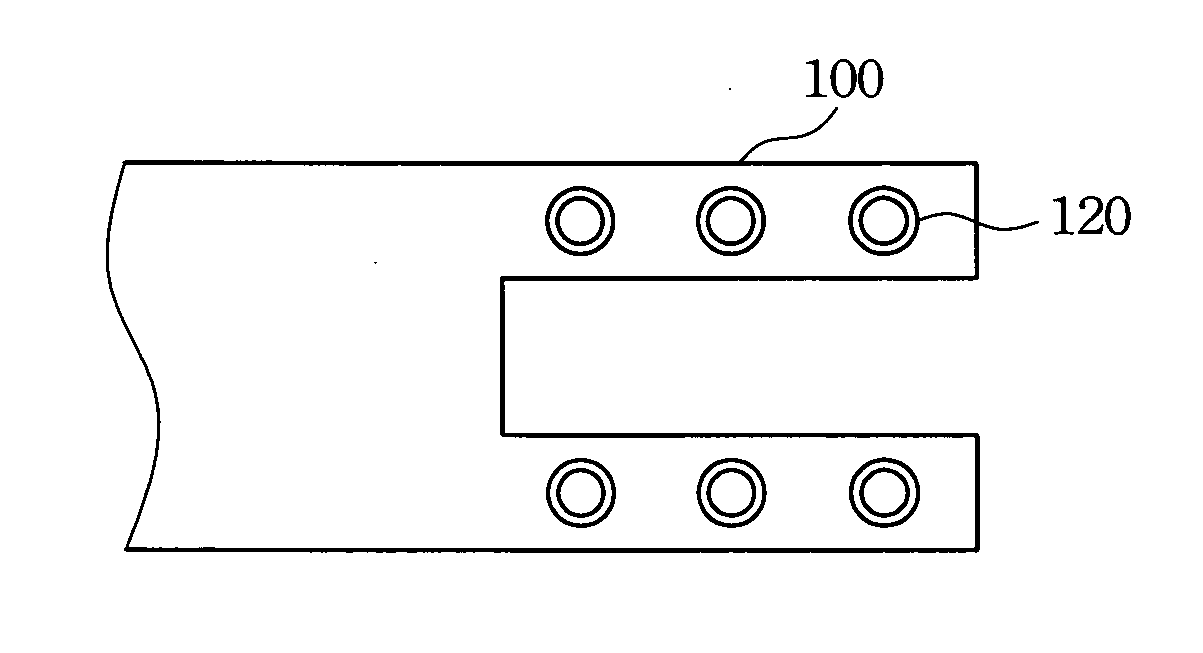

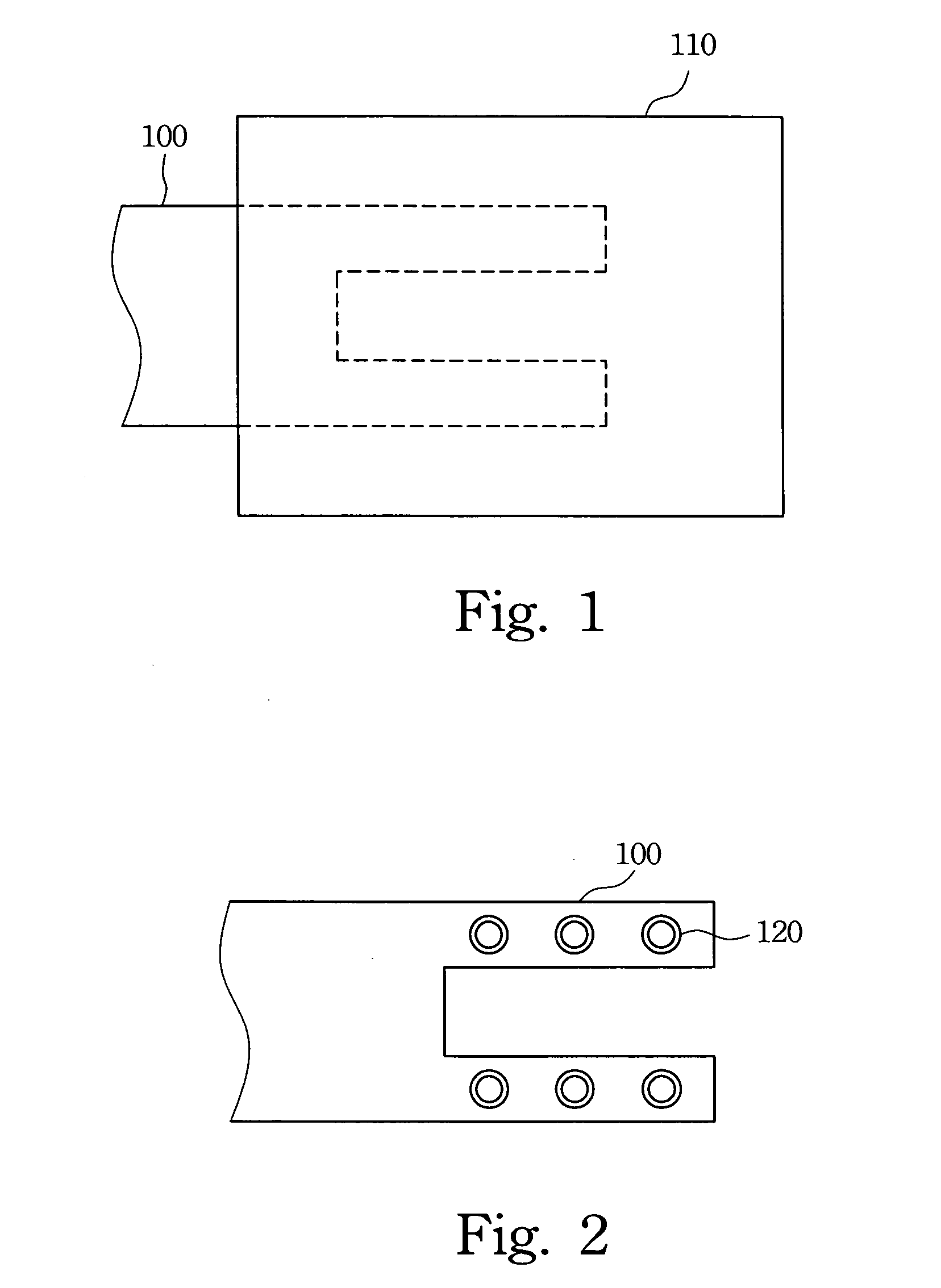

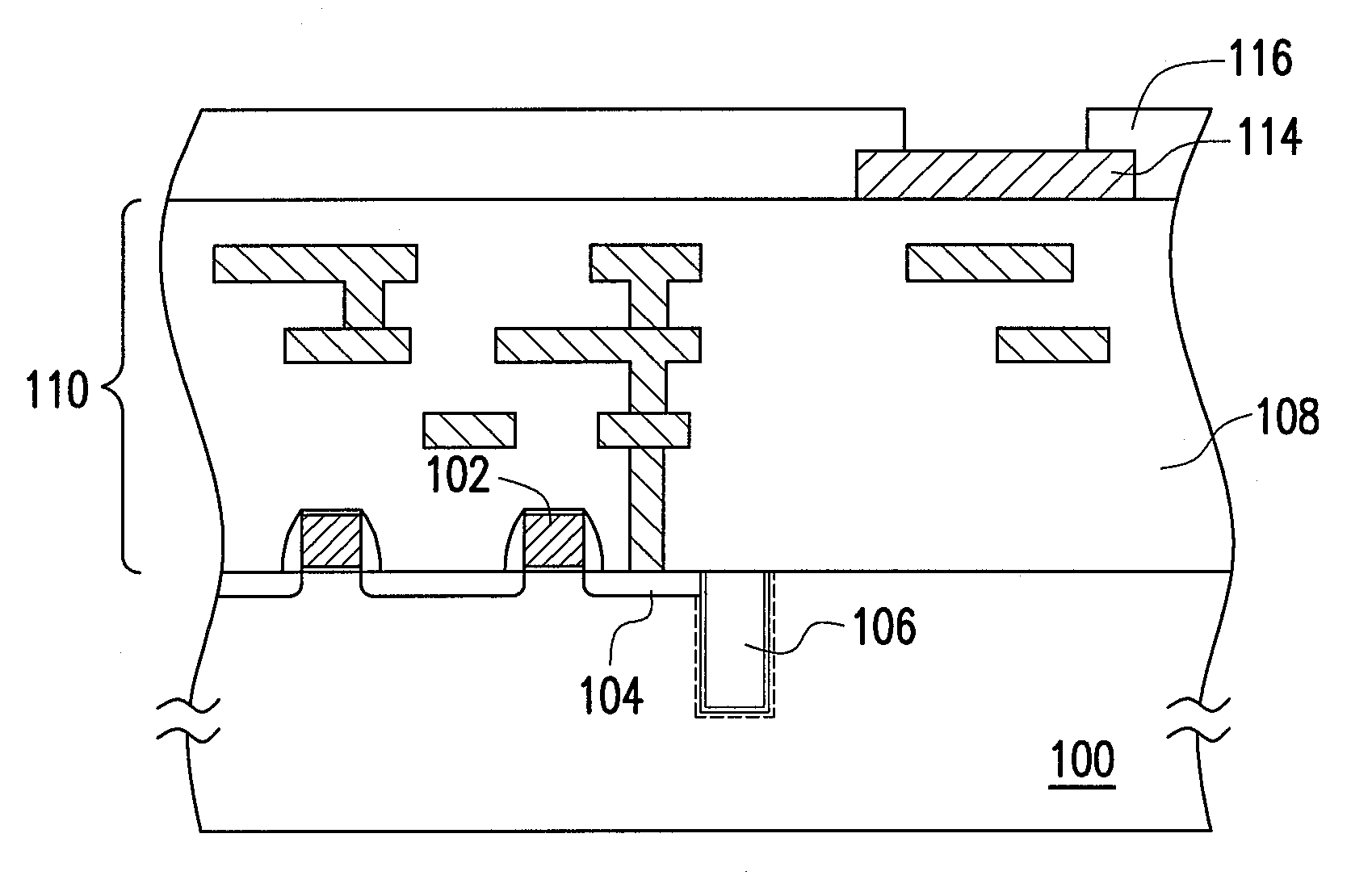

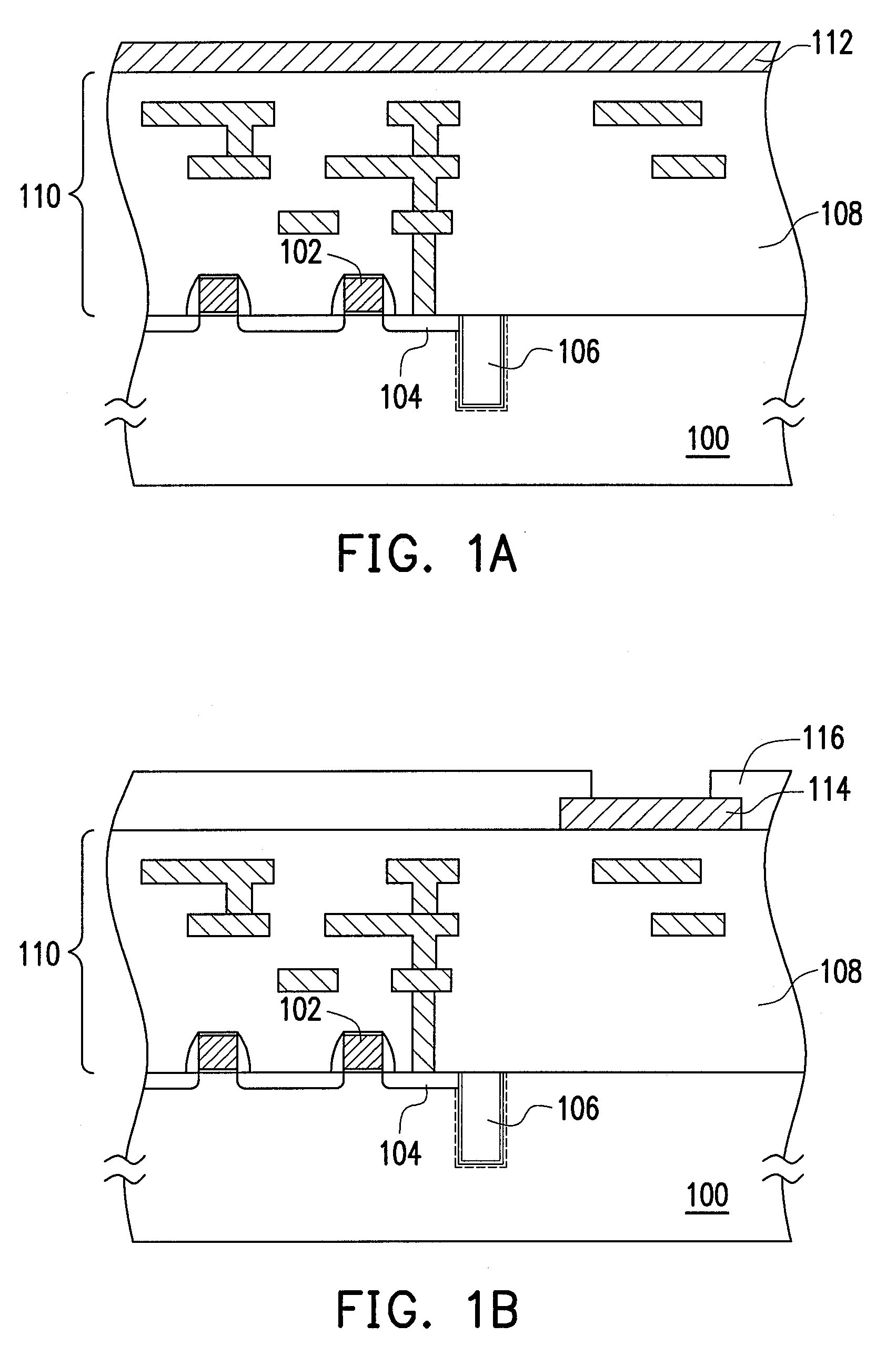

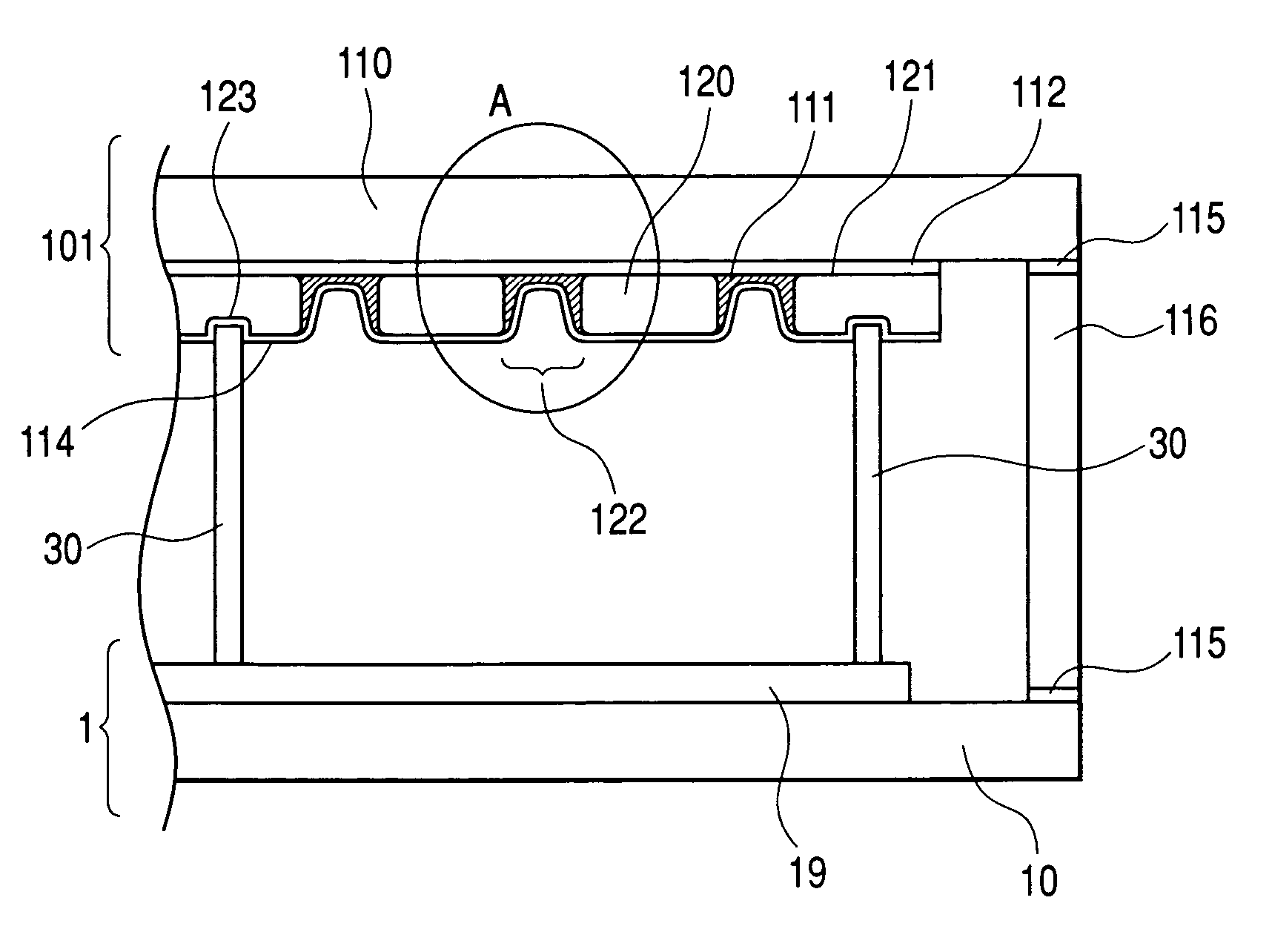

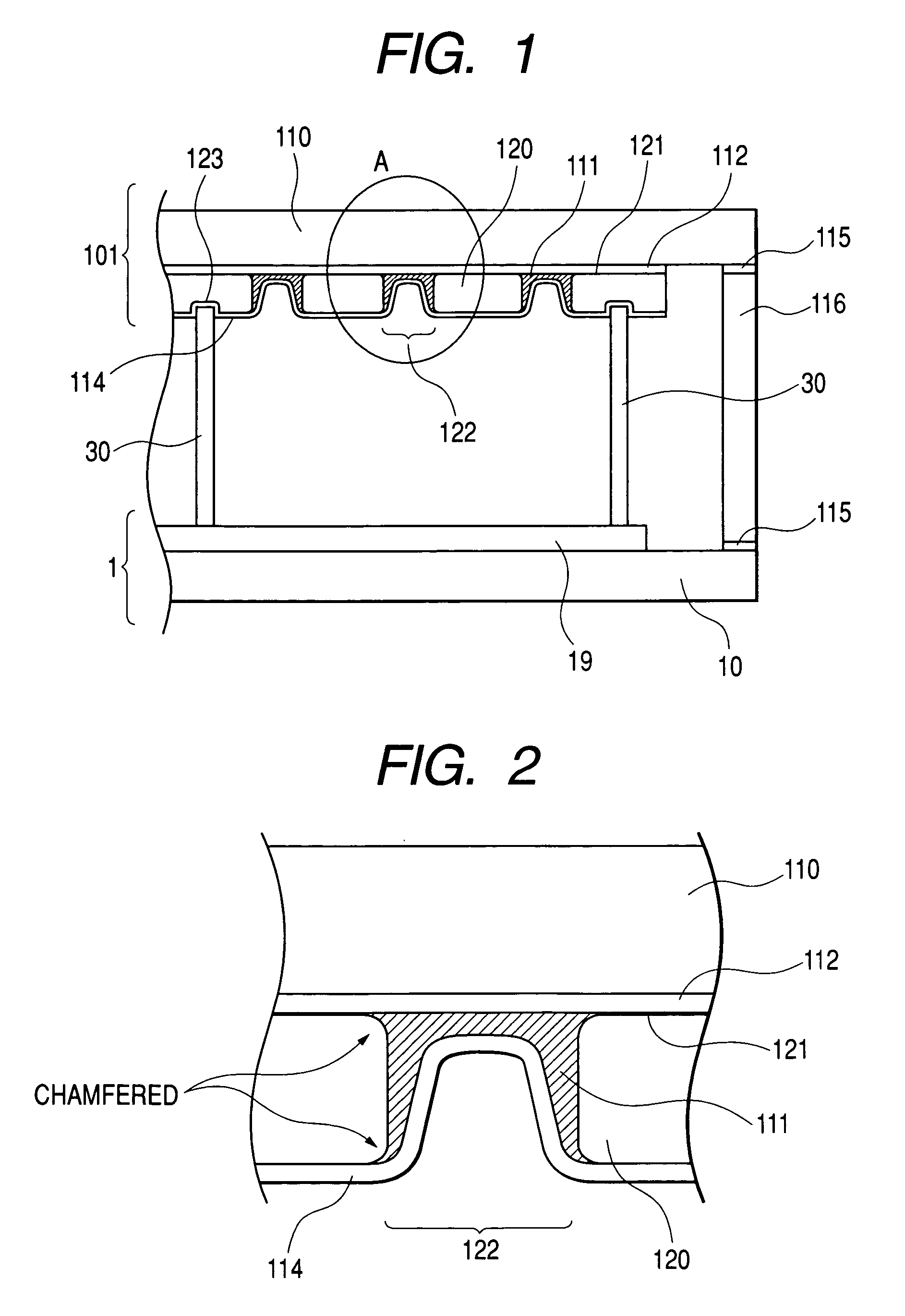

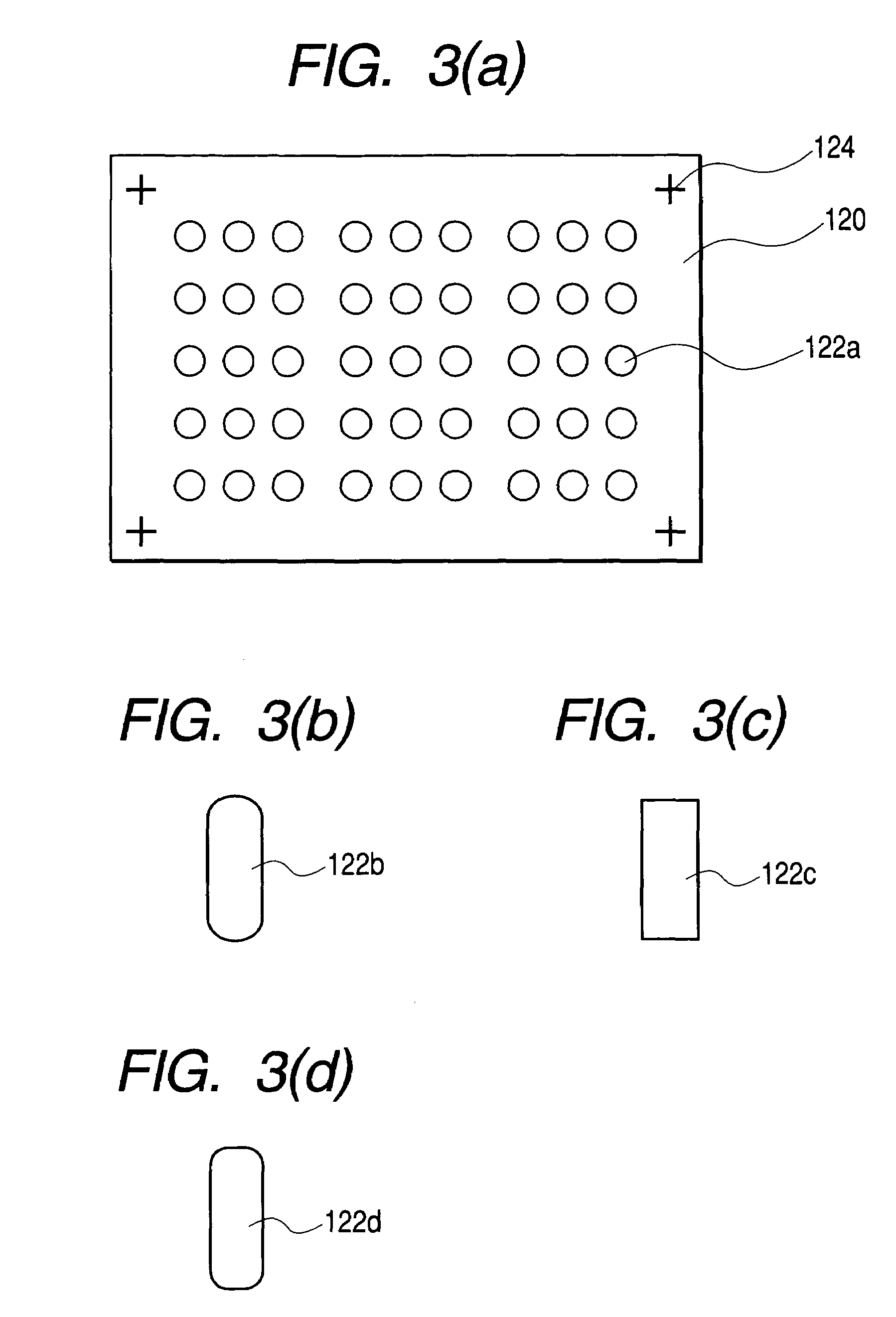

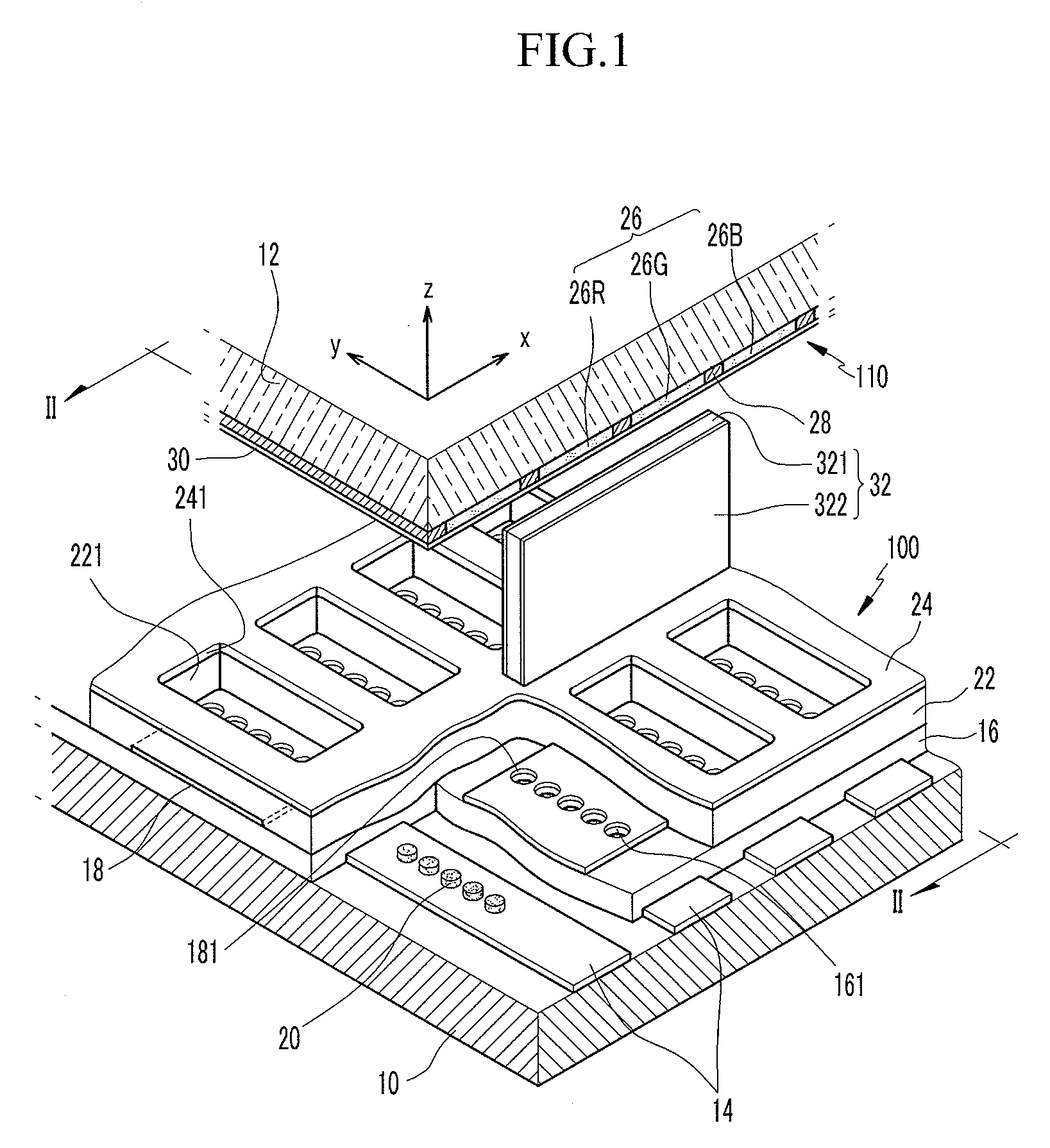

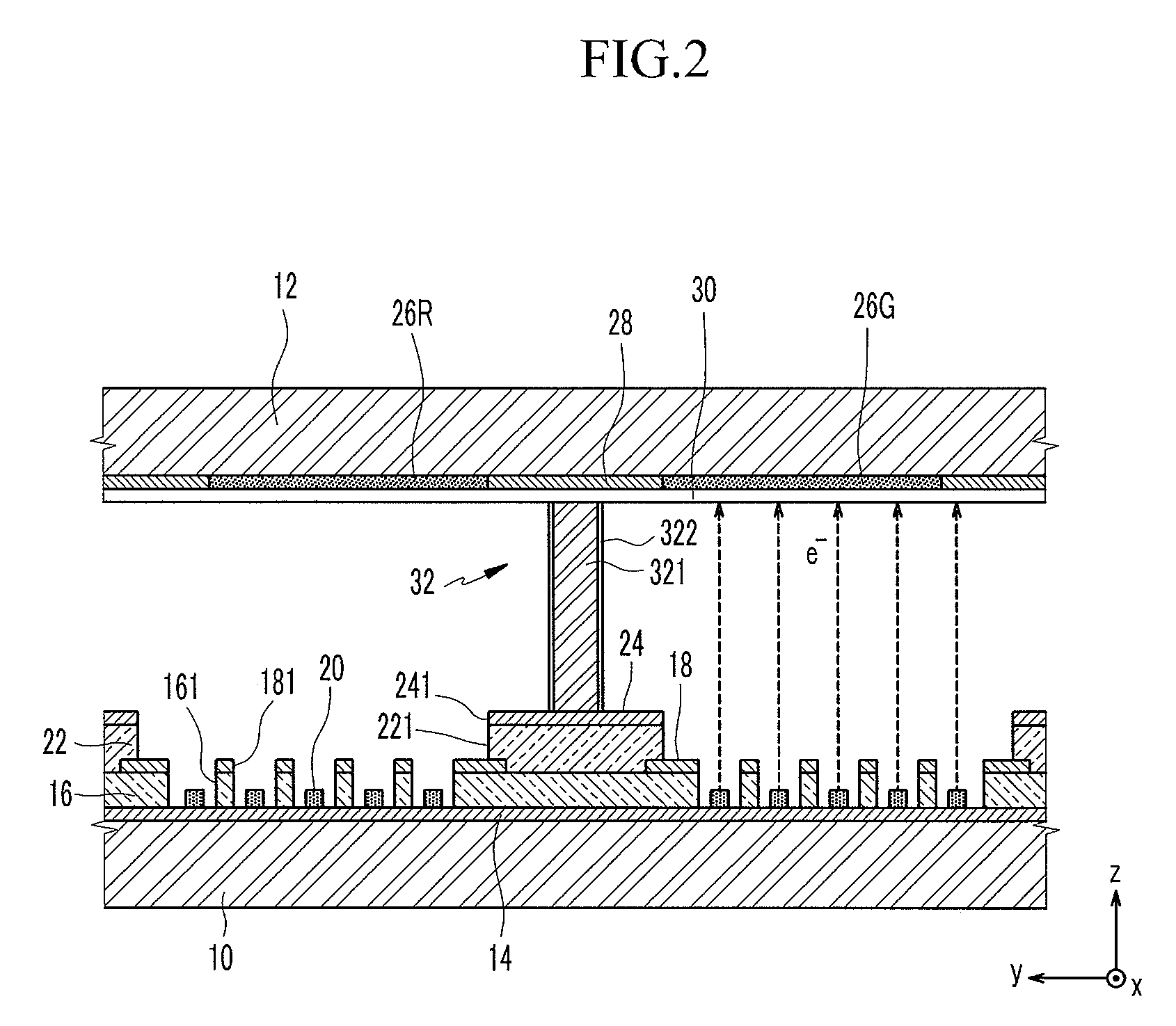

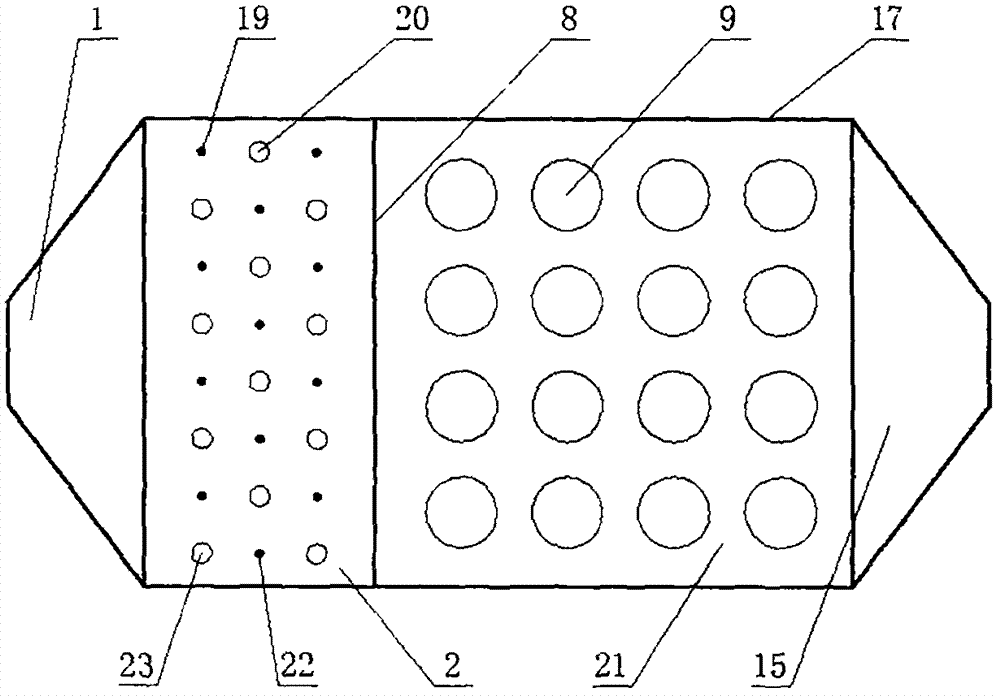

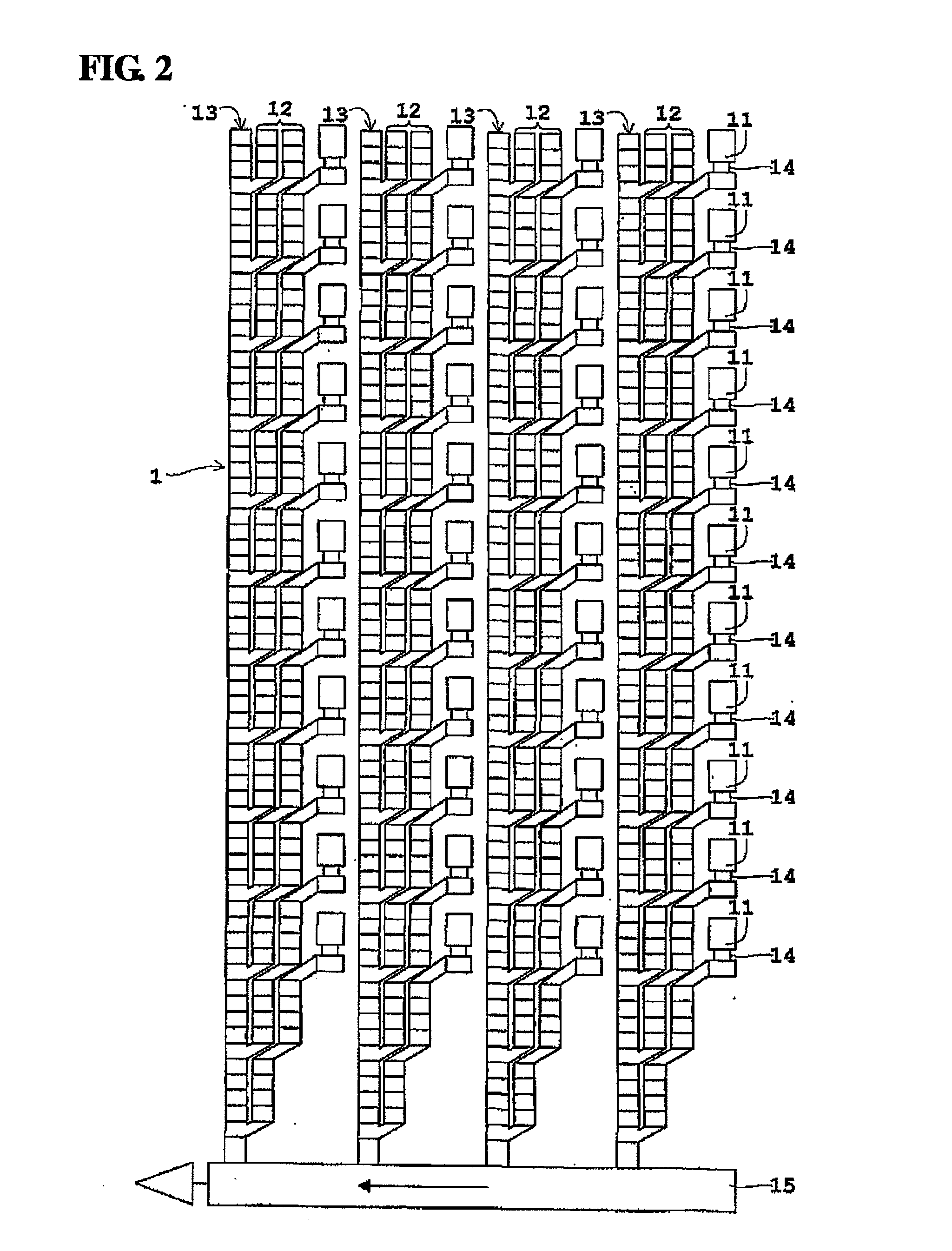

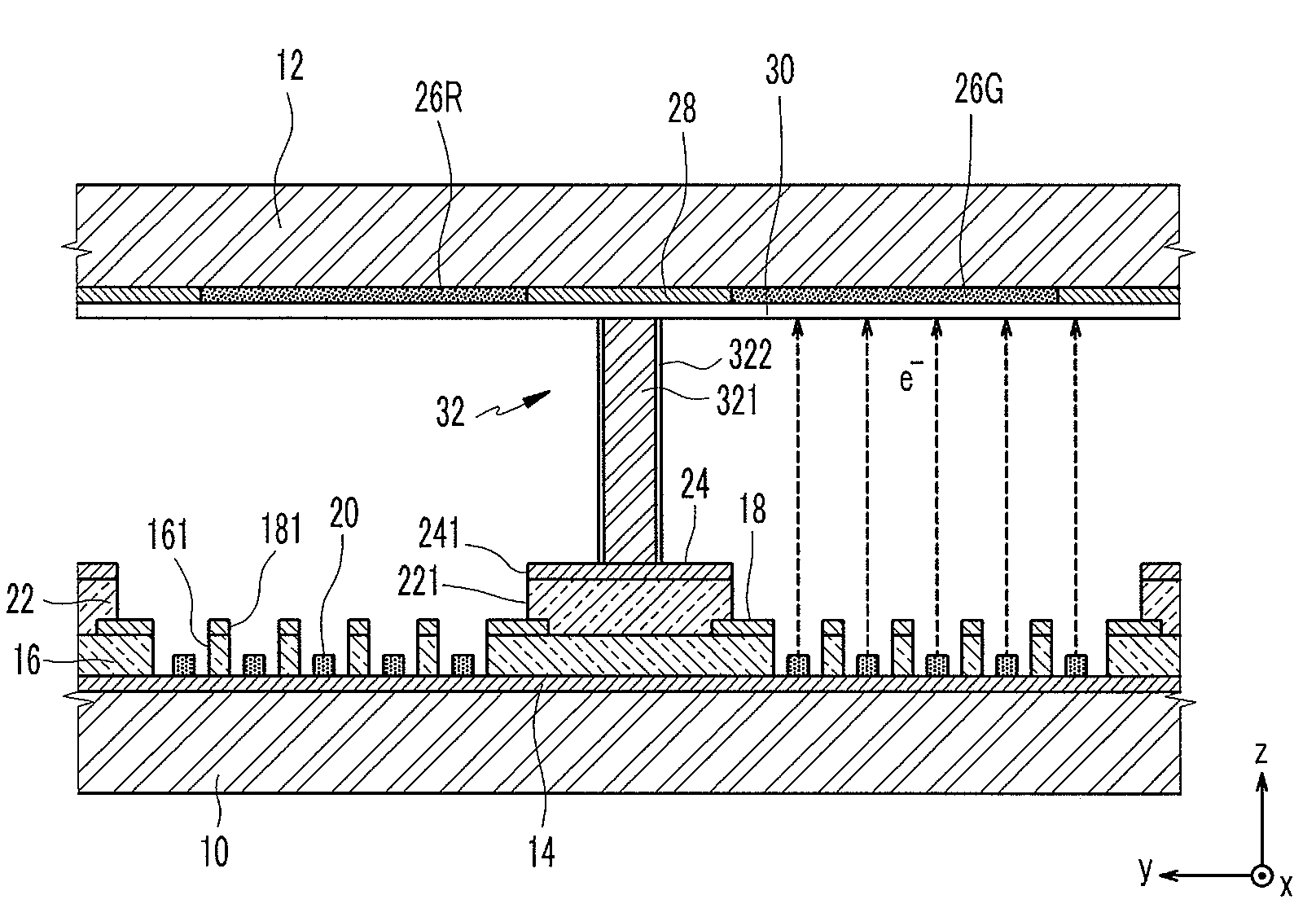

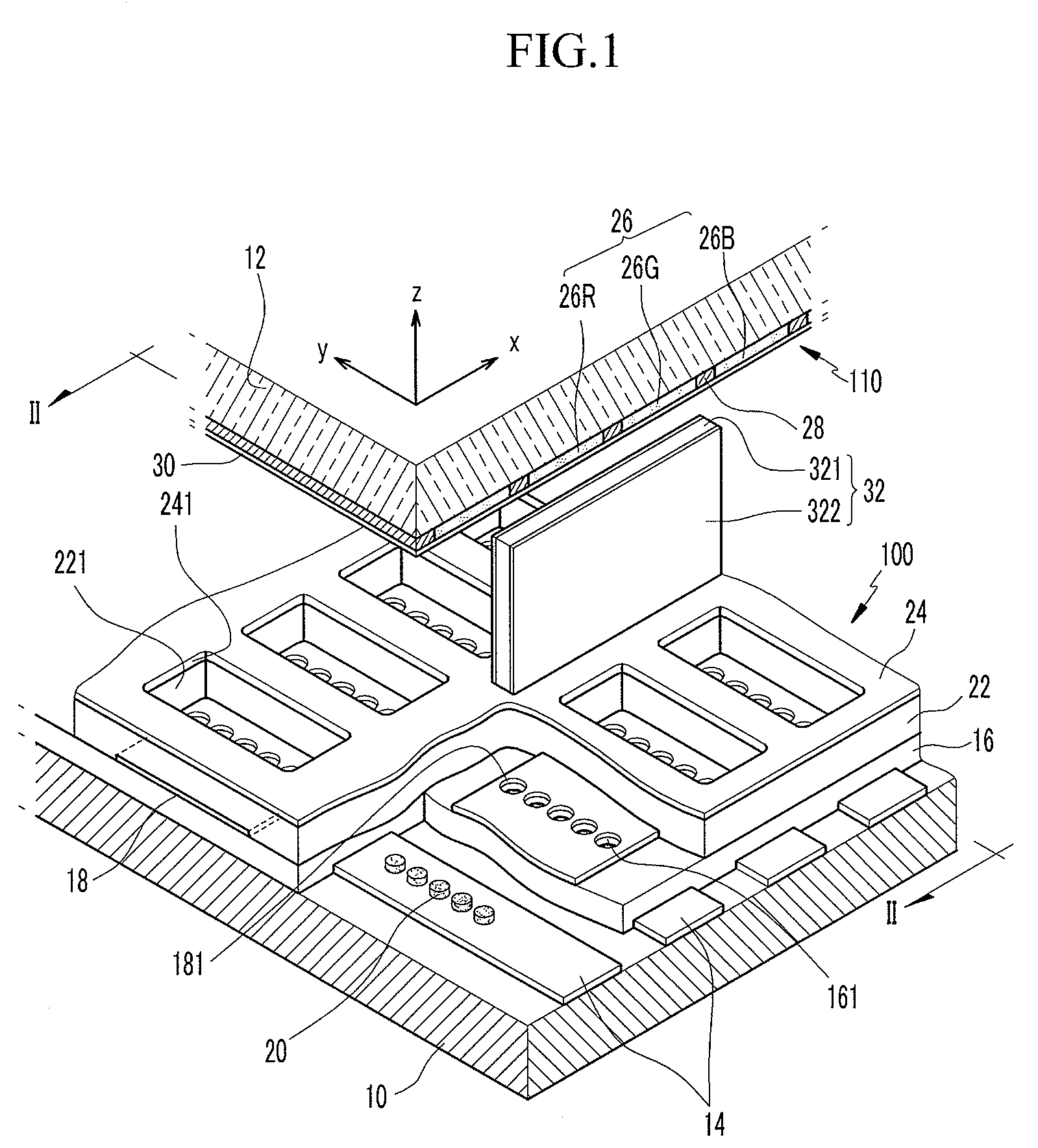

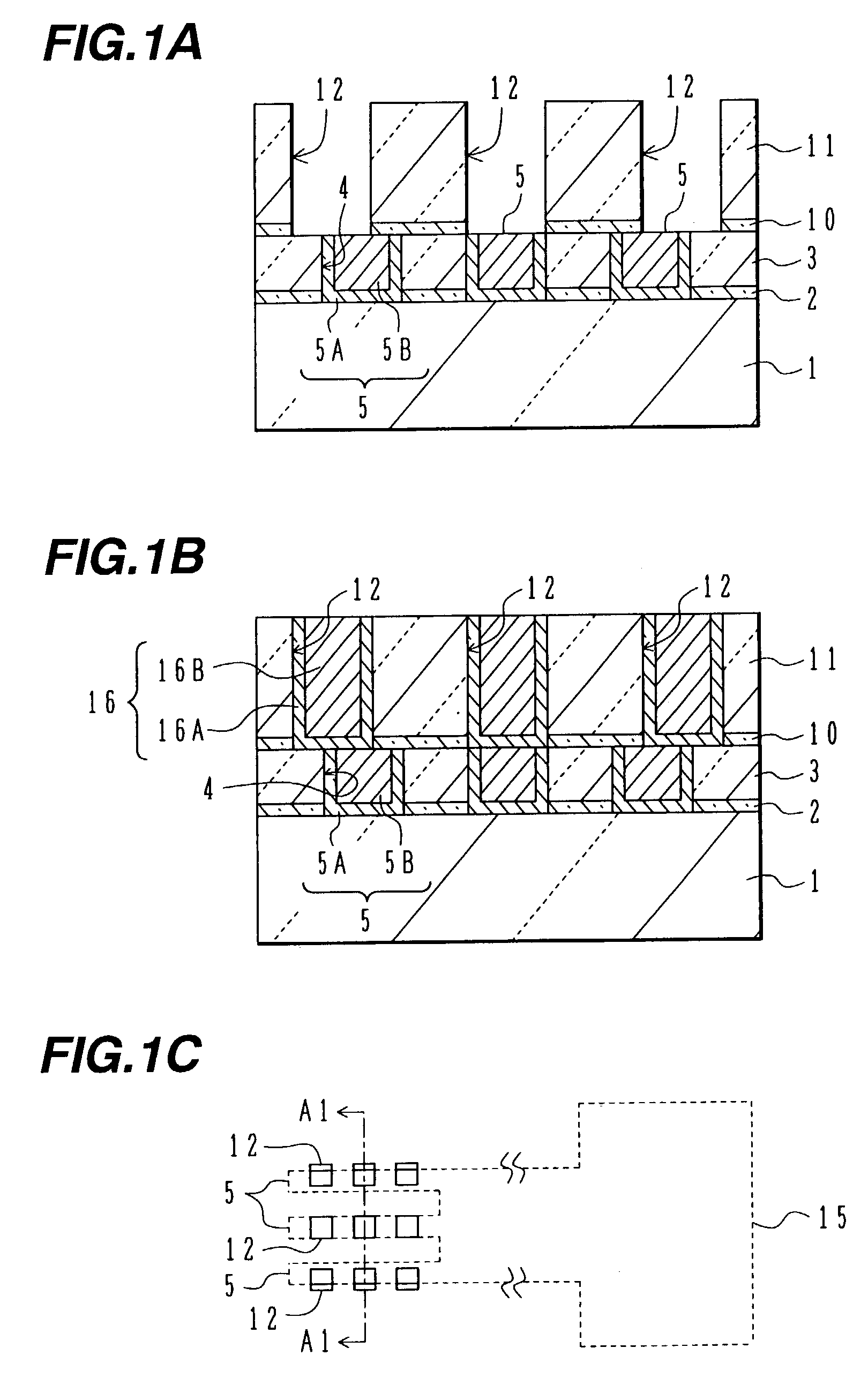

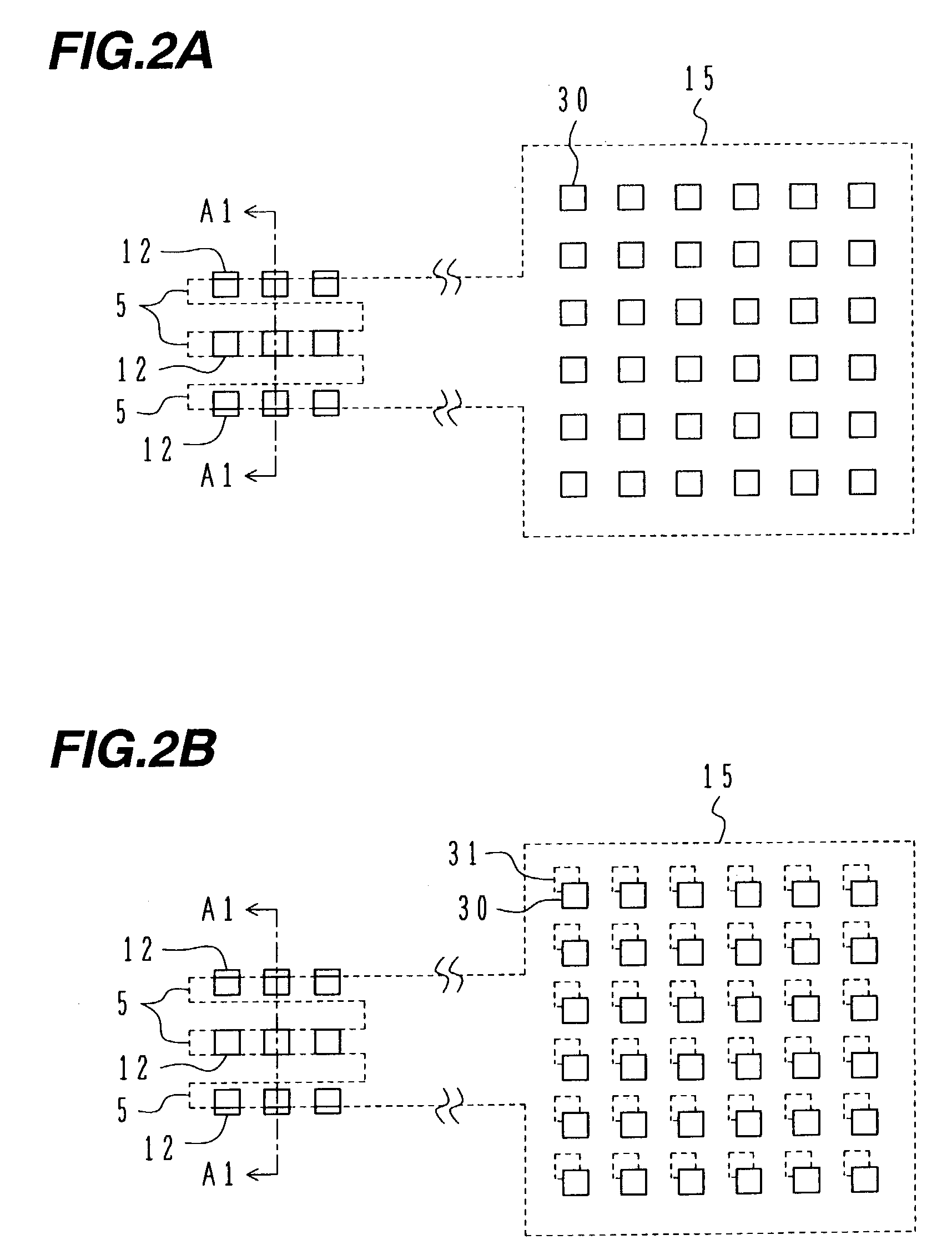

Flat panel display device

InactiveUS20040174114A1Low costReducing light emissionElectrode assembly support/mounting/spacing/insulationIncadescent body mountings/supportFlat panel displayEngineering

There is disclosed a flat panel display device capable of reducing charging of phosphors and disposing spacers easily and accurately. The flat panel display device has a rear substrate 1 including an insulating substrate 10 provided with many cold cathode elements 19 for emitting electrons, a display substrate 101 including a light-transmissive substrate 110 disposed to face the rear substrate 1, and phosphors 111 disposed on the light-transmissive substrate for generating light when excited by electron beams from the cold cathode elements 19, and a peripheral frame member 116. A space enclosed by the rear substrate 1, the display substrate 101 and the peripheral frame member 116 is made vacuum tight. Provided on the light-transmissive substrate 110 is a metal sheet 120 perforated with plural fine holes 122 arranged in a matrix configuration and having the phosphors 111 disposed therewithin to form a light-emissive region.

Owner:MAXELL HLDG LTD

Surface grafted metal oxide particles and compositions comprising the same

ActiveUS7153574B2Improve business performanceIncreased residual potentialSynthetic resin layered productsCellulosic plastic layered productsElectron acceptorMetal

Owner:XEROX CORP +1

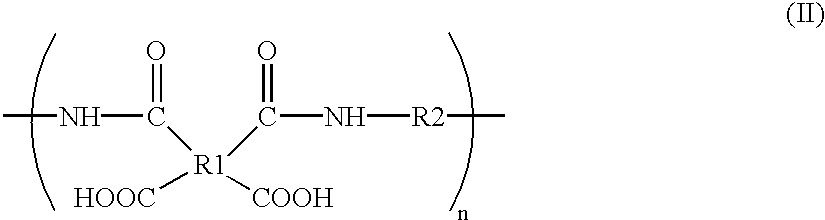

Liquid crystal orientating agent and liquid crystal display element using it

InactiveUS20060142538A1Excellent liquid crystal alignmentHigh voltage retention characteristicLiquid crystal compositionsThin material handlingCrystallographyReduced contrast volume

To provide a liquid crystal aligning agent useful to obtain a liquid crystal alignment film excellent in liquid crystal alignment properties, alignment controlling power and rubbing resistance, having high voltage retention characteristics and having reduced charge accumulation, and a liquid crystal display device which is less susceptible to display failure, to lowering of contrast or to image persistence. A liquid crystal aligning agent comprising a low resistance polyimide precursor having a volume resistivity of from 1×1010 to 1×1014 Ωcm when formed into a film, and a high alignment polyimide precursor or polyimide having a specific structure, and a liquid crystal display device employing this liquid crystal aligning agent.

Owner:NISSAN CHEM IND LTD

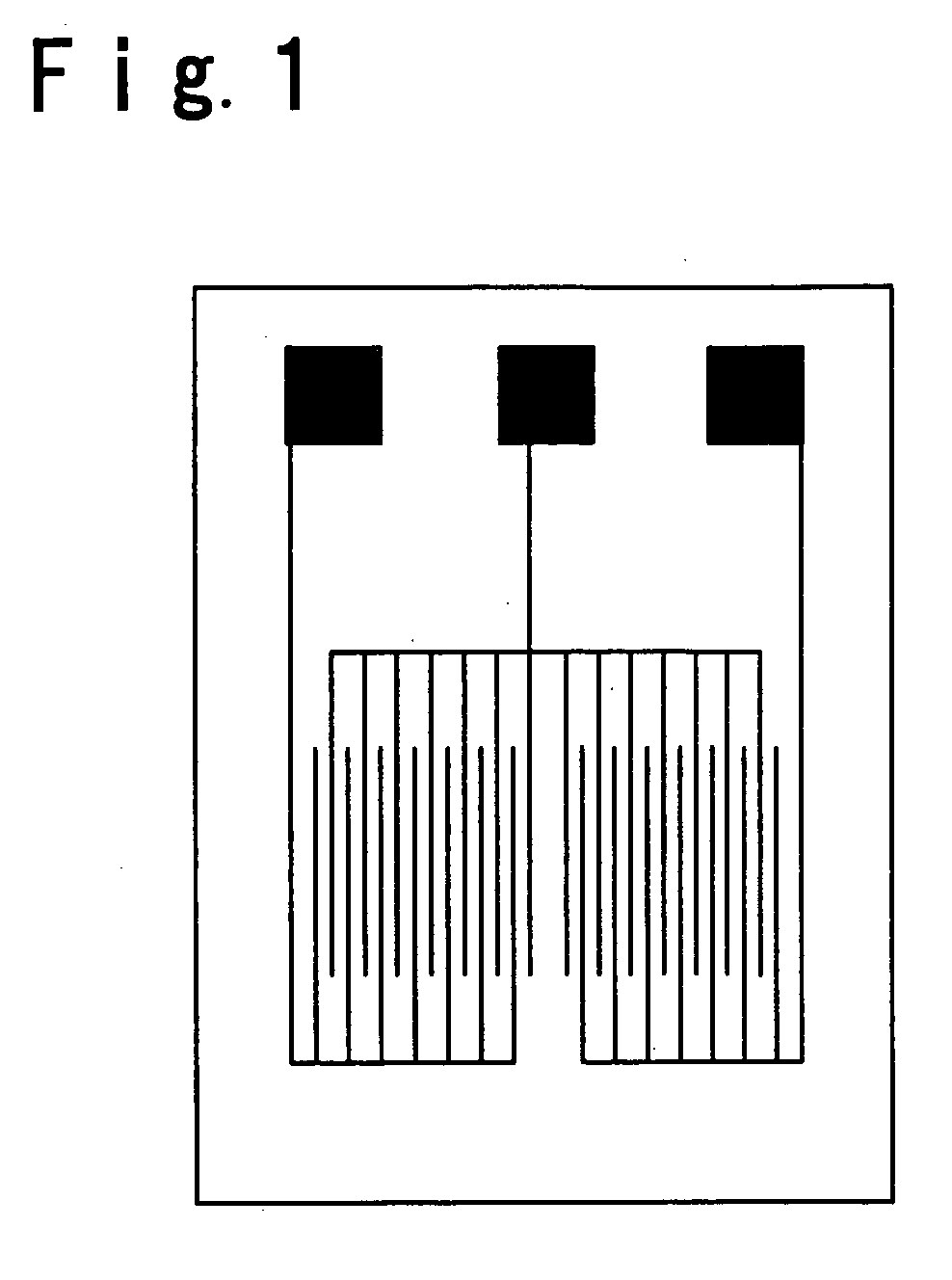

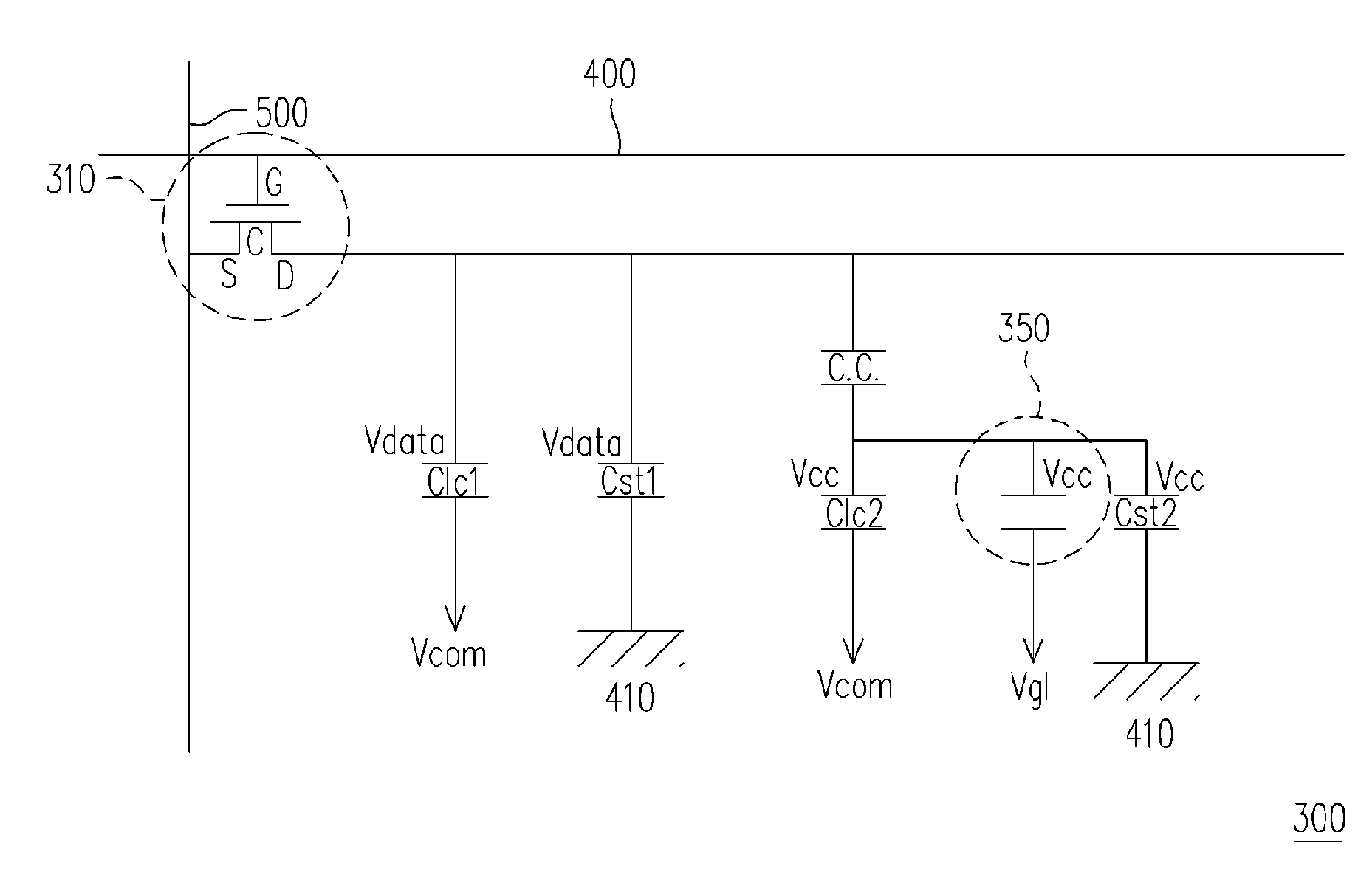

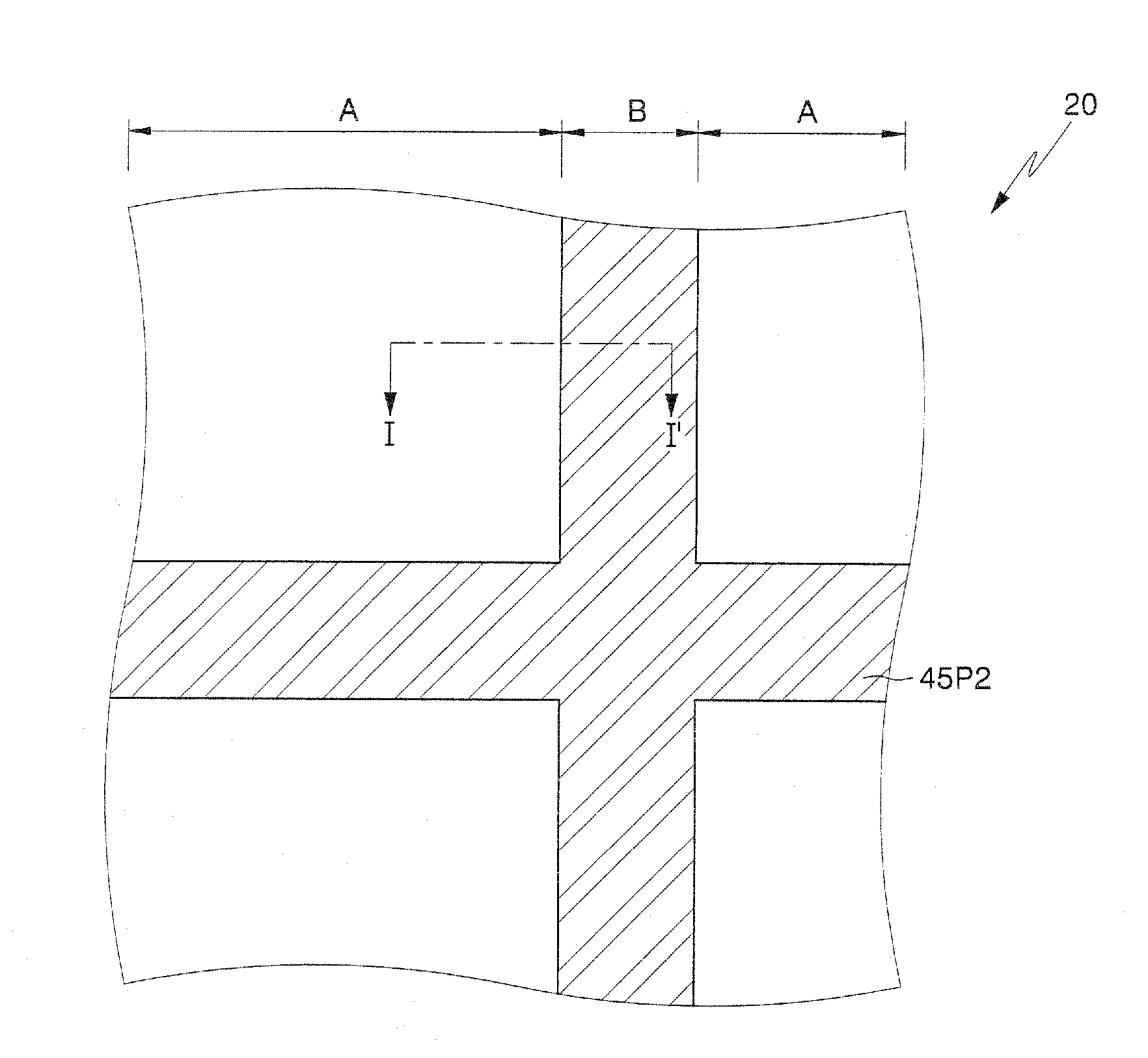

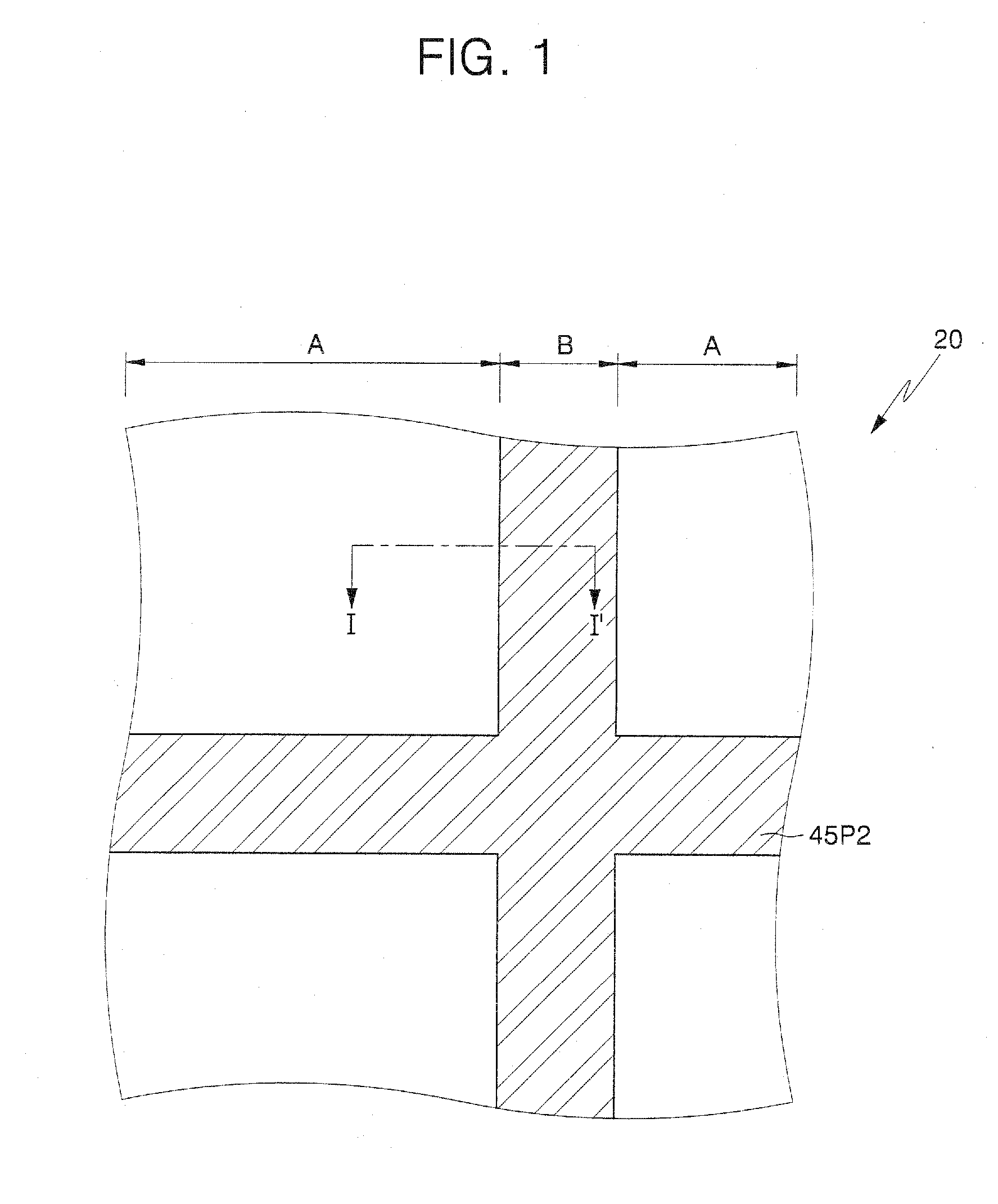

Pixel structure and active matrix substrate

ActiveUS7518687B2Prevent image retentionReduce charge accumulationSolid-state devicesNon-linear opticsElectricityCoupling

A pixel structure electrically connected to a scan line and a data line, includes an active device, a first pixel electrode, a second pixel electrode, a capacitor coupling electrode and a charge releasing device. The active device is electrically connected to the scan line and the data line. The second pixel electrode is electrically isolated from the first pixel electrode. The capacitor coupling electrode is disposed under the second pixel electrode and electrically connected to the data line through the active device. The charge releasing device is electrically connected to the second pixel electrode. The above-described pixel structure is able to effectively solve the image sticking problem. In addition, further provides an active matrix substrate which is able to avoid the image sticking effect.

Owner:AU OPTRONICS CORP

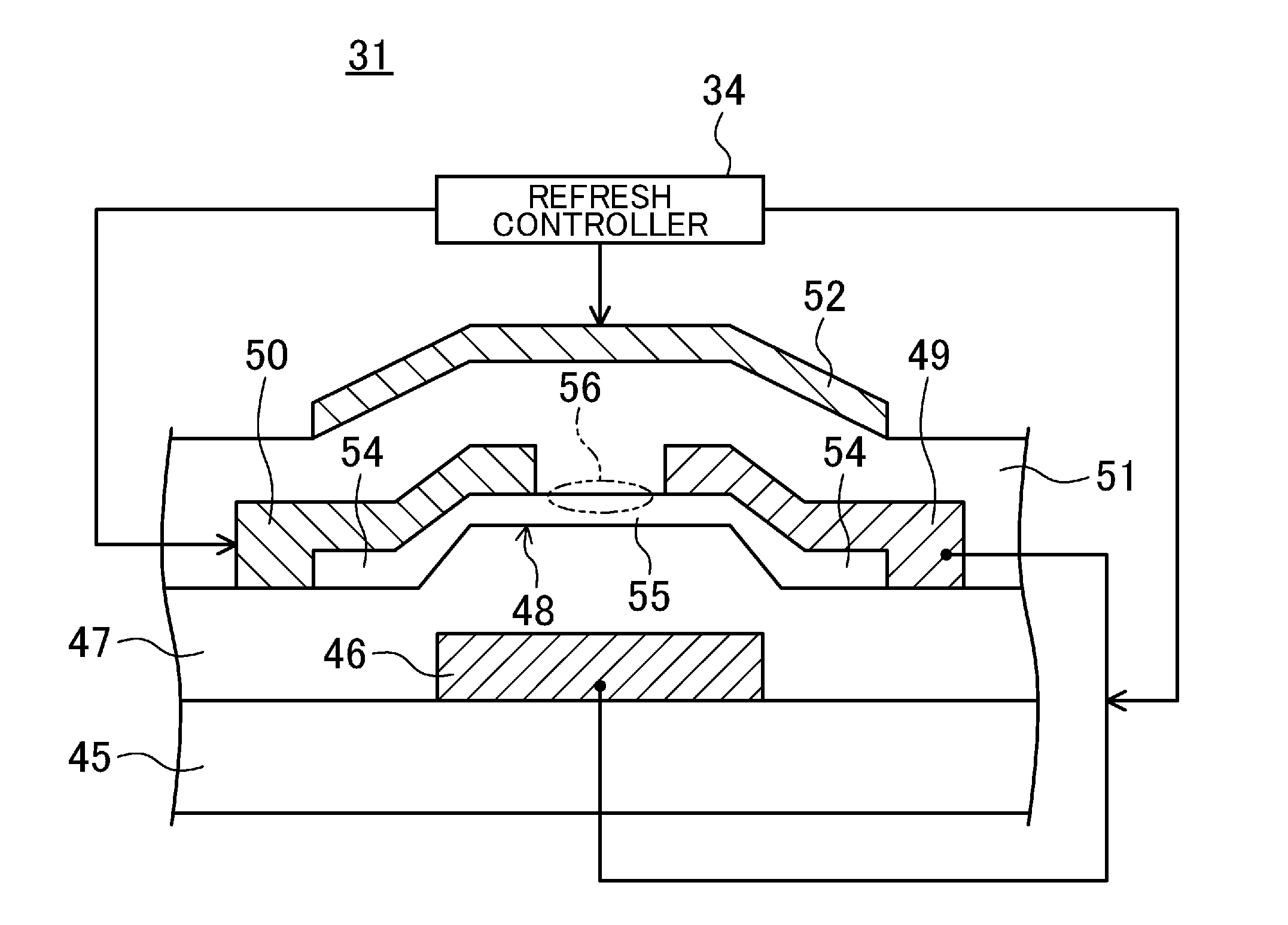

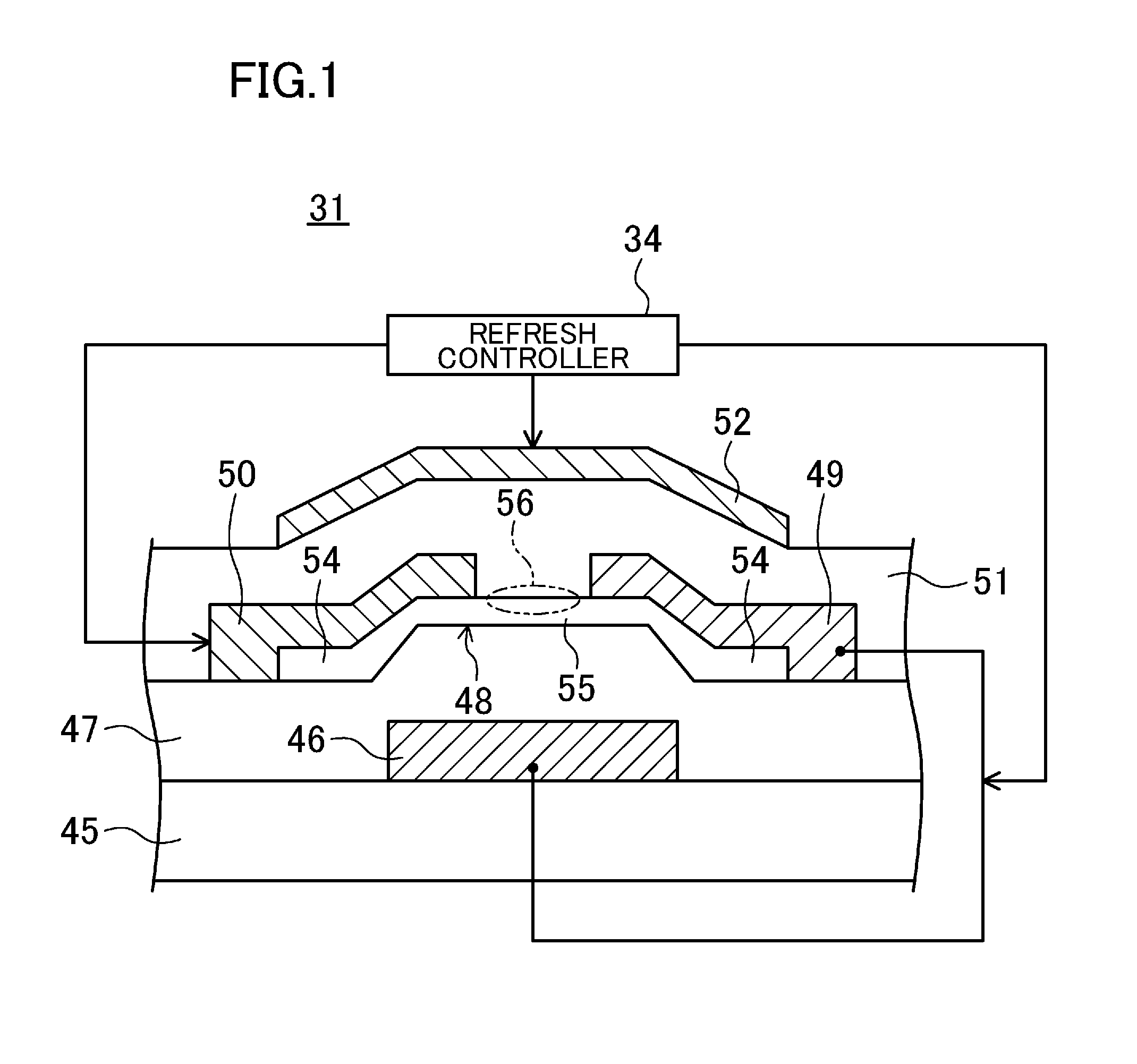

Phototransistor and display device including the same

InactiveUS20120074474A1Reduce charge accumulationImprove featuresTransistorSolid-state devicesDisplay deviceEngineering

A phototransistor includes a source electrode and a gate electrode which have the same electric potential, a transparent electrode formed on a surface of an interlayer insulating film so as to be located above a channel region, and a refresh controller for reducing a charge accumulated in a portion of the channel region, the portion facing the transparent electrode, by applying a voltage between the transparent electrode, and the gate electrode and the source electrode.

Owner:SHARP KK

Surface grafted metal oxide particles and compositions comprising the same

ActiveUS20060014020A1Improve business performanceIncreased residual potentialSynthetic resin layered productsCellulosic plastic layered productsMetalElectron acceptor

Owner:XEROX CORP +1

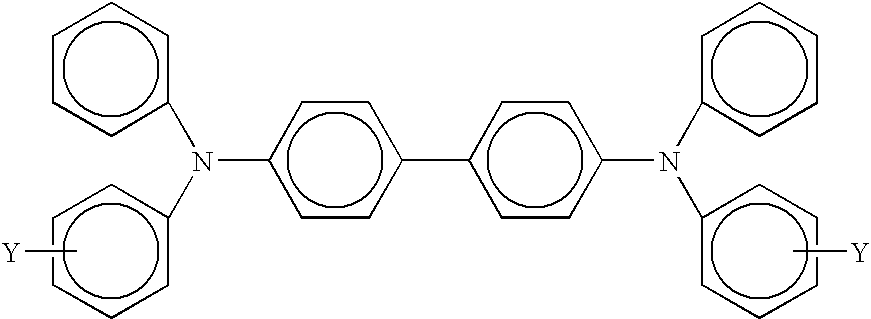

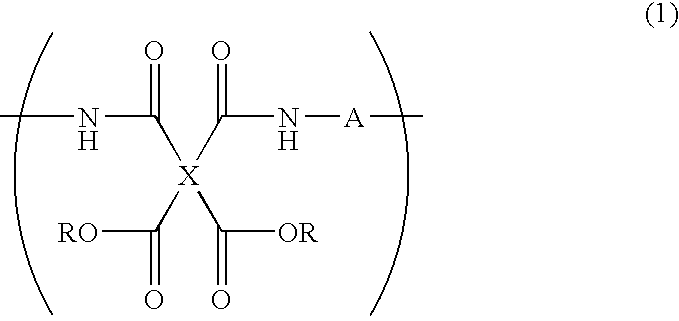

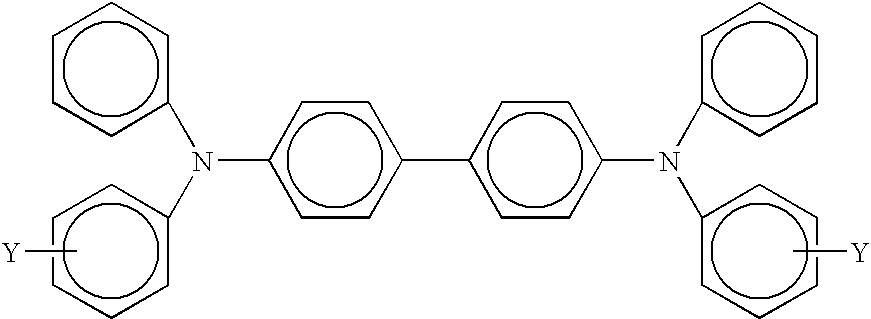

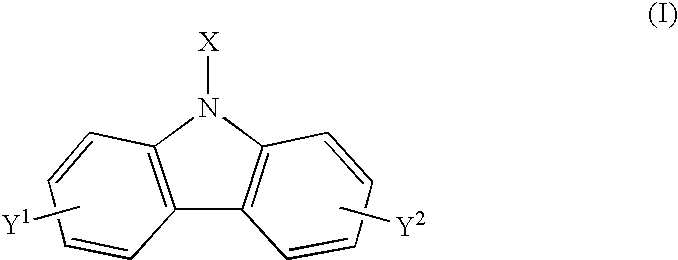

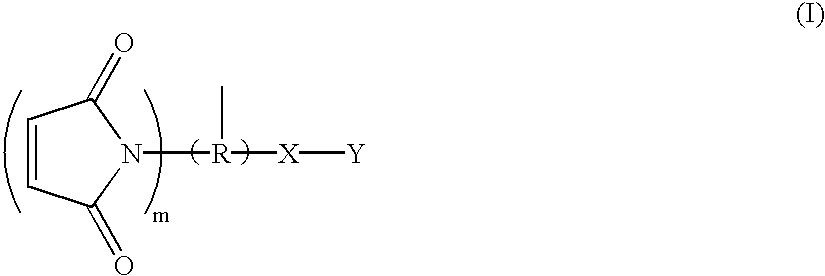

Aligning agent for liquid crystal and liquid-crystal display element

InactiveUS20060024452A1Excellent voltage retentionReduce charge accumulationLiquid crystal compositionsThin material handlingCrystallographyLiquid-crystal display

To provide a liquid crystal alignment treating agent to obtain a liquid alignment film of polyamide type which, in its applications to various display devices employing nematic liquid crystal, is excellent in voltage retention, has a reduced charge accumulation and is excellent in durability against rubbing treatment, and a liquid crystal display device employing it. A liquid crystal alignment treating agent to obtain an alignment film for nematic liquid crystal by rubbing treatment after forming a coating film, characterized in that it comprises at least one polymer selected from a polyamic acid obtained by reacting one or more tetracarboxylic dianhydrides with one or more diamines comprising at least one diamine having a structure represented by the following formula (I), and a polyimide obtained by cyclodehydration of such a polyamic acid; and a liquid crystal display device obtained by applying the liquid crystal alignment treating agent to a pair of substrates having electrodes, to form coating films, rubbing the coating film surfaces to form liquid crystal alignment films, and sandwiching nematic liquid crystal between the liquid crystal alignment films formed on the pair of substrates: wherein X is a hydrogen atom or a monovalent organic group, and each of Y1 and Y2 is a primary amino group or a monovalent organic group having one primary amino group.

Owner:NISSAN CHEM IND LTD

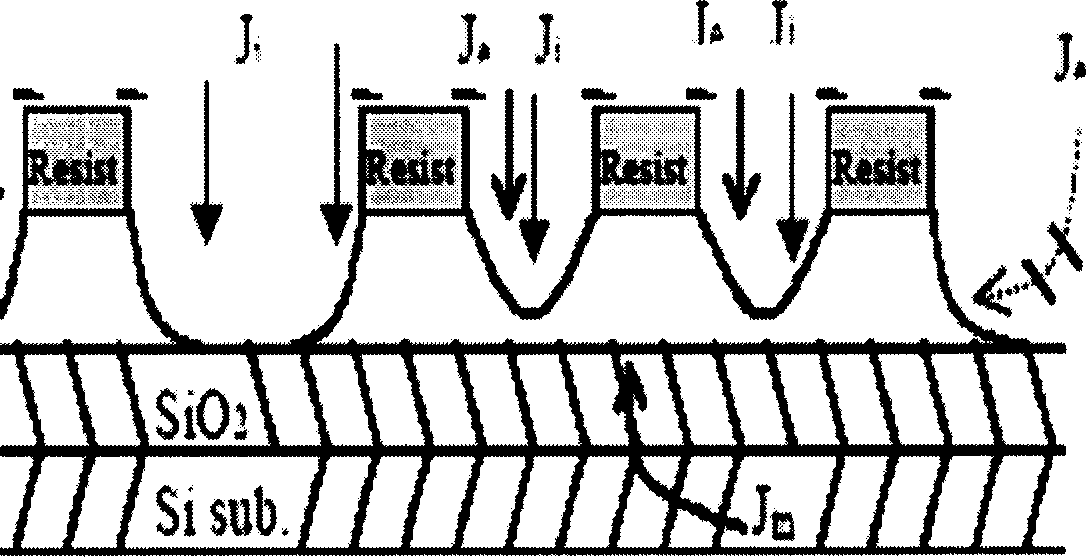

Method for preventing charge-up in plasma process and semiconductor wafer manufactured using same

InactiveUS20070039923A1Reduce charge accumulationAvoid chargingDecorative surface effectsSolid-state devicesSemiconductor chipPlasma etching

A method for preventing plasma charge-up of a semiconductor wafer includes defining a semiconductor chip region and a scribe line region on a semiconductor wafer, forming an interlayer insulating layer pattern on the wafer, the interlayer insulating layer pattern exposing the scribe line region, plasma etching the interlayer insulating layer pattern to form a contact hole that exposes the semiconductor chip region, and during the plasma etching, discharging an electric charge generated by the plasma etching through the scribe line region.

Owner:SAMSUNG ELECTRONICS CO LTD

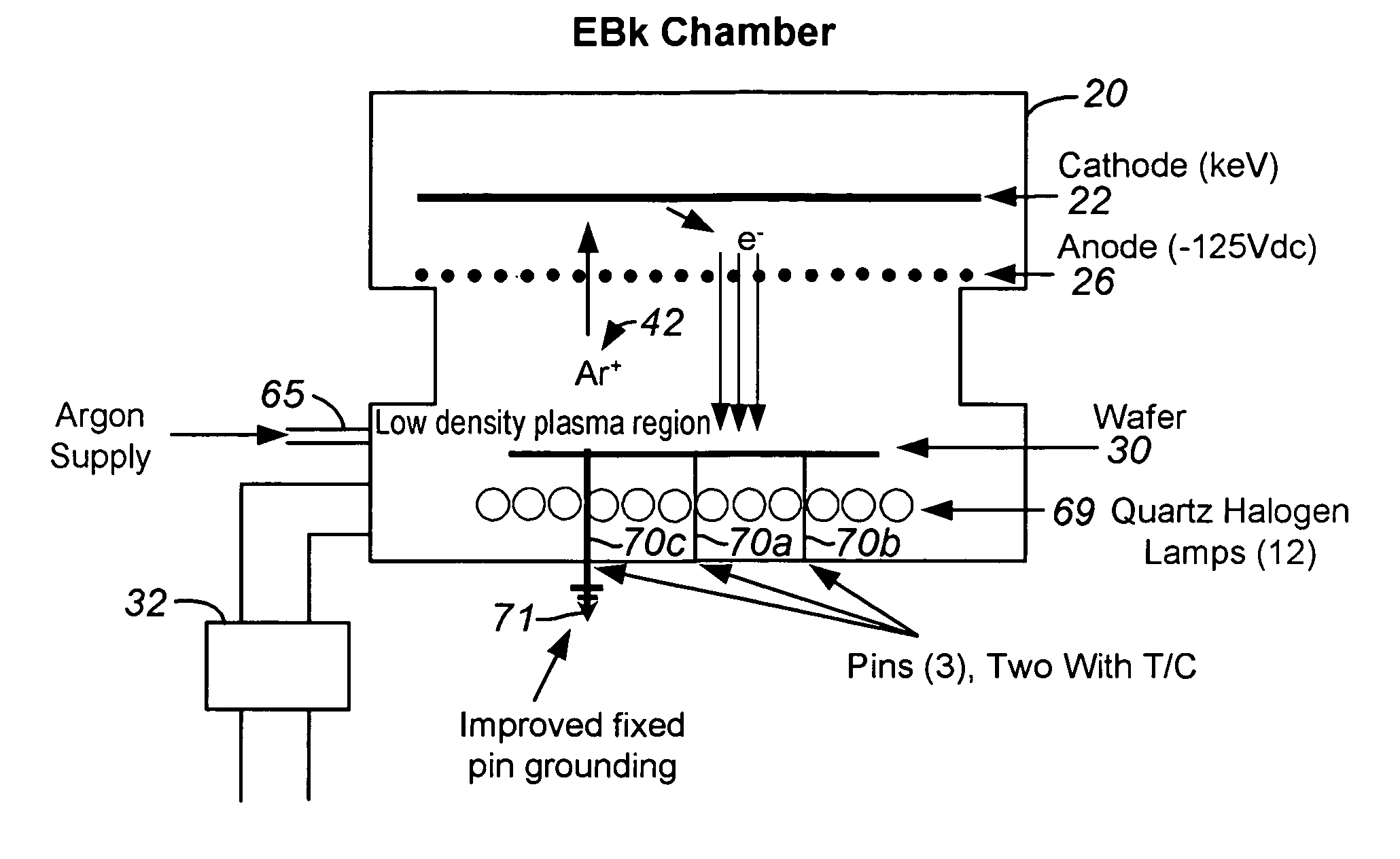

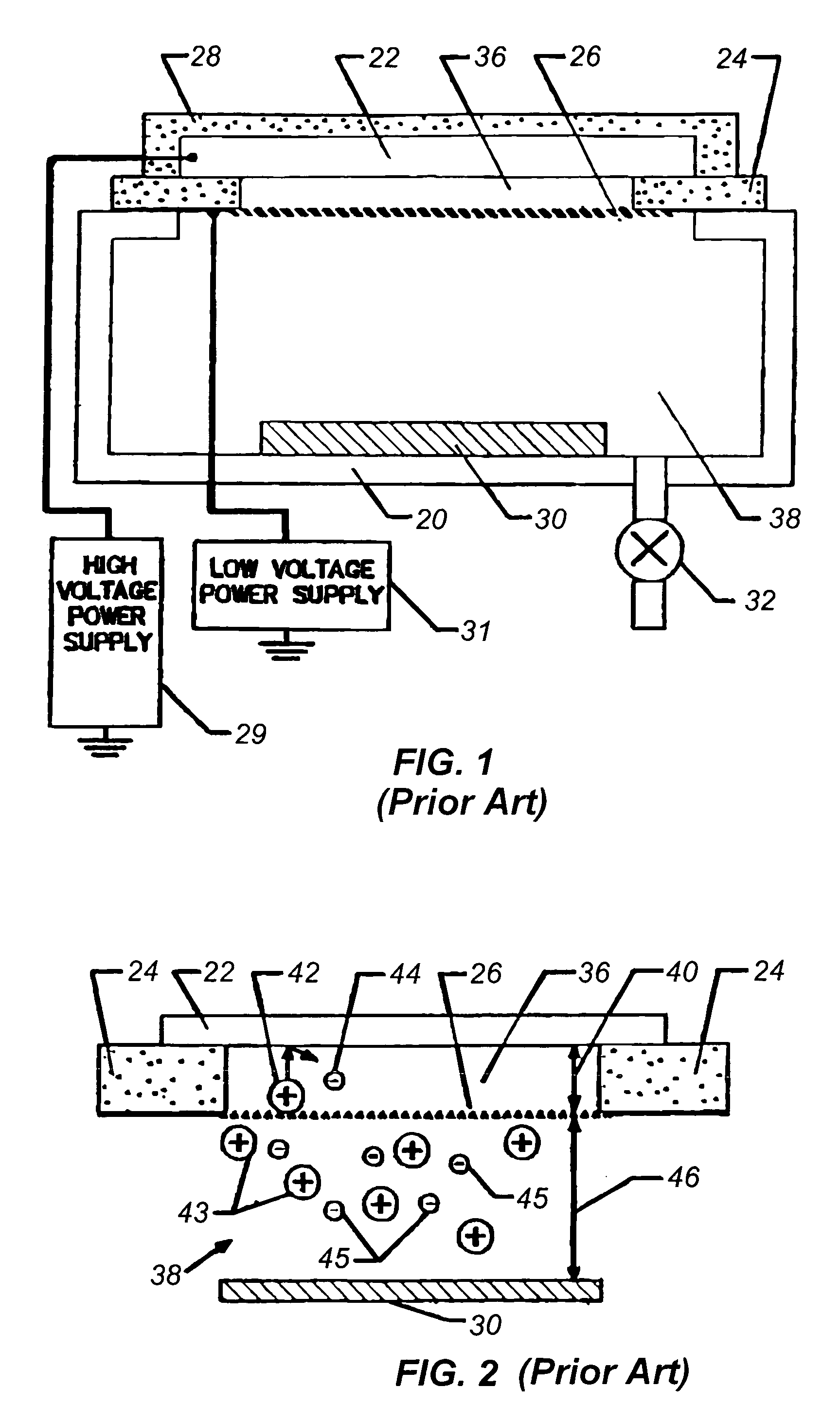

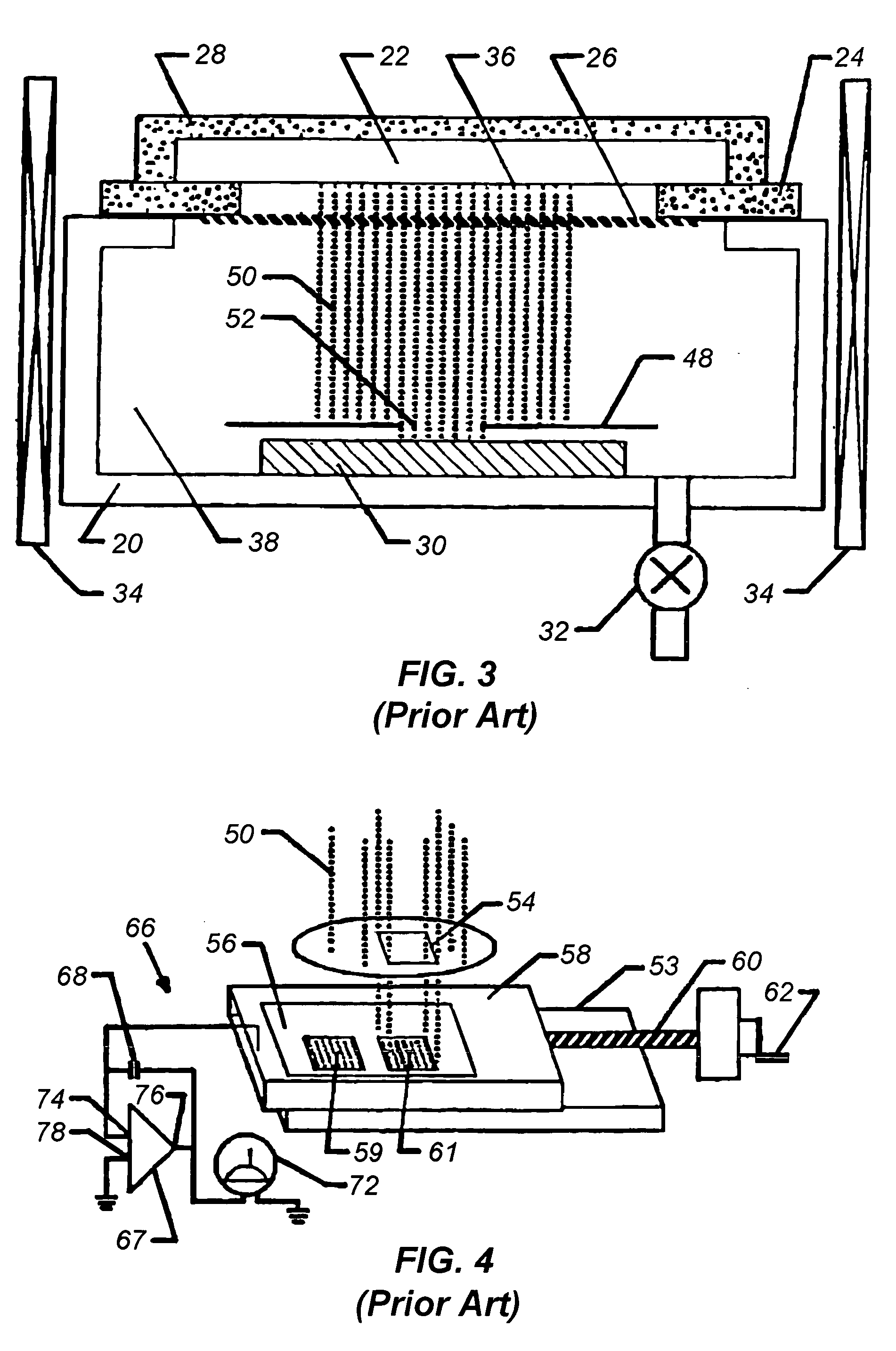

Method and apparatus for reducing charge density on a dielectric coated substrate after exposure to a large area electron beam

InactiveUS20060192150A1Avoid damageReduce voltageElectric discharge tubesIrradiation devicesBeam sourceAnode voltage

Embodiments in accordance with the present invention relate to a number of techniques, which may be applied alone or in combination, to reduce charge damage of substrates exposed to electron beam radiation. In one embodiment, charge damage is reduced by establishing a robust electrical connection between the exposed substrate and ground. In another embodiment, charge damage is reduced by modifying the sequence of steps for activating and deactivating the electron beam source to reduce the accumulation of charge on the substrate. In still another embodiment, a plasma is struck in the chamber containing the e-beam treated substrate, thereby removing accumulated charge from the substrate. In a further embodiment of the present invention, the voltage of the anode of the e-beam source is reduced in magnitude to account for differences in electron conversion efficiency exhibited by different cathode materials.

Owner:APPLIED MATERIALS INC

Hyperbranched polymer-SiO2 modified epoxy resin insulating material and preparation method thereof

InactiveCN110776806APolymer branching degreeReduced effectivenessNon-macromolecular adhesive additivesEpoxy resin adhesivesPolymer sciencePolymer modified

The invention relates to the technical field of epoxy resin adhesives, and discloses a hyperbranched polymer-SiO2 modified epoxy resin insulating material and a preparation method thereof. The hyperbranched polymer-SiO2 modified epoxy resin insulating material is prepared from the following formula materials: hyperbranched polymer, nanosilicon dioxide, a silane coupling agent, a catalyst, dodecylsuccinic anhydride and epoxy resin. A three-dimensional net-like spherical structure of the hyperbranched polymer has a high degree of molecular branching, so that nano-SiO2 is uniformly dispersed on the huge specific surface of the hyperbranched polymer, nano-SiO2 agglomeration is reduced, nano-SiO2 reduces the effective charge and charge accumulation in a coating interface area, the diffusion rate of a carrier is reduced, the formation of conductive paths is suppressed, the breakdown characteristics of epoxy resin coatings are improved, the hyperbranched polymer has excellent elastic expansion structure and good structural stability, the crosslinking density of the epoxy resin is increased, the mobility of a molecular segment of the epoxy resin is suppressed, and the impact cross sectioncaused by the stress expansion of the resin is reduced.

Owner:王利玲

Robotic arm for preventing electrostatic damage

InactiveUS20050001438A1Avoid electrostatic damageReduce charge accumulationSemiconductor/solid-state device manufacturingCharge manipulationRobotic armEngineering

A robotic arm that has a main body and pads thereon can prevent electrostatic damage. These pads are used to carry substrates between and in processing machines. A material of these pads is the same as or similar to the material of the substrate to lower the amount of the electrostatic charges produced during the manufacturing process. Therefore, the electrostatic charges cannot damage the electronic devices on the substrate.

Owner:CHUNGHWA PICTURE TUBES LTD

Semiconductor process

ActiveUS20110014784A1Improve device performanceReduce the possibilitySemiconductor/solid-state device detailsSolid-state devicesCopperMetal

A semiconductor process is provided. First, a substrate having a dielectric layer formed thereon is provided. Thereafter, an interconnection structure including copper is formed in the dielectric layer. Afterwards, a metal layer is formed on the dielectric layer. The metal layer is then patterned to form a pad. An annealing process is performed, wherein the gas source for the annealing process includes hydrogen in a concentration of 50% to 90%.

Owner:UNITED MICROELECTRONICS CORP

Flat panel display device

InactiveUS7095169B2Reduce charge accumulationEasily and accuratelyElectrode assembly support/mounting/spacing/insulationIncadescent body mountings/supportPhosphorCold cathode

A flat panel display device capable of reducing charging of phosphors and disposing spacers easily and accurately. The flat panel display device has a rear substrate including an insulating substrate provided with many cold cathode elements for emitting electrons, a display substrate including a light-transmissive substrate disposed to face the rear substrate, and phosphors disposed on the light-transmissive substrate for generating light when excited by electron beams from the cold cathode elements, and a peripheral frame member. Provided on the light-transmissive substrate is a metal sheet perforated with plural fine holes arranged in a matrix configuration and having the phosphors disposed therewithin to form a light-emissive region.

Owner:MAXELL HLDG LTD

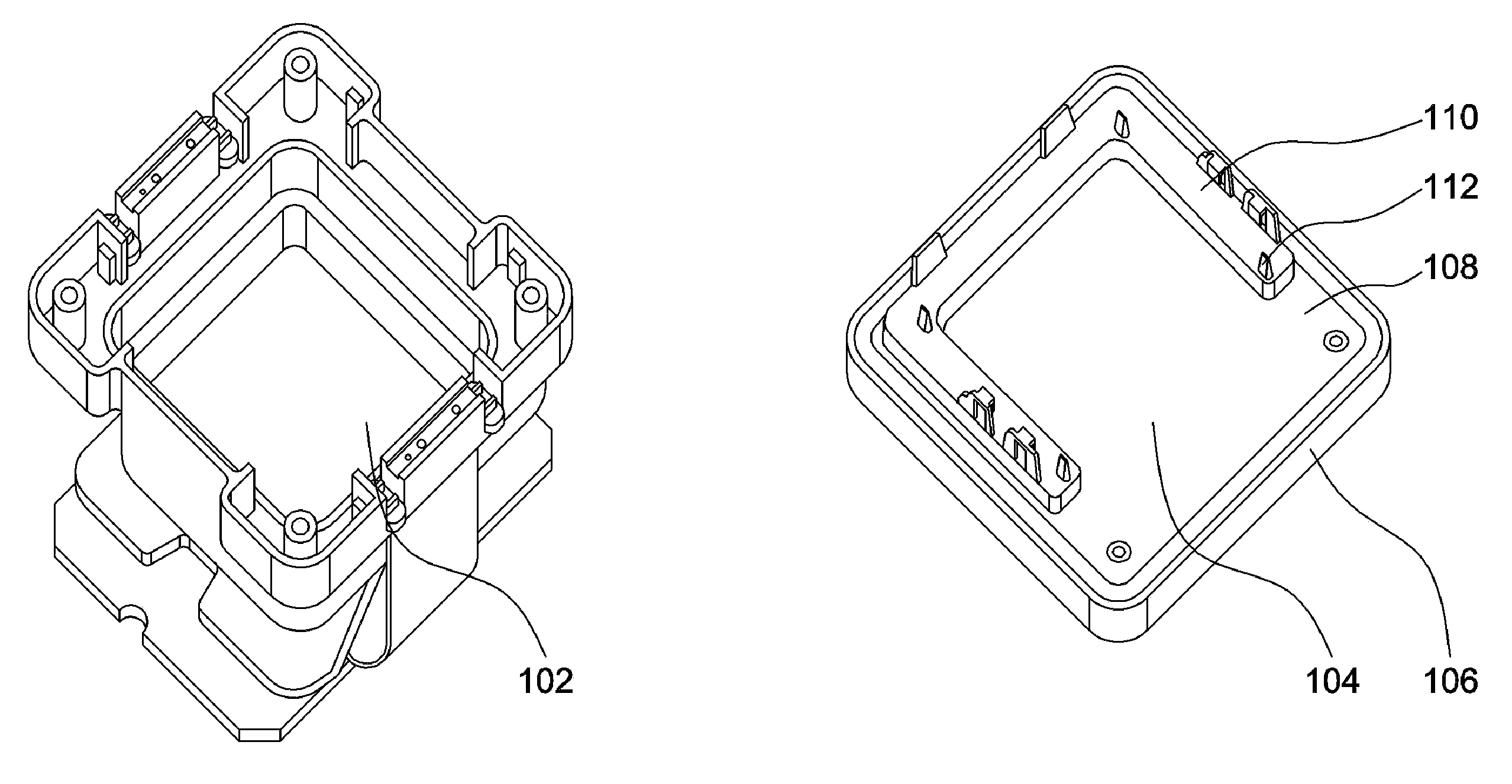

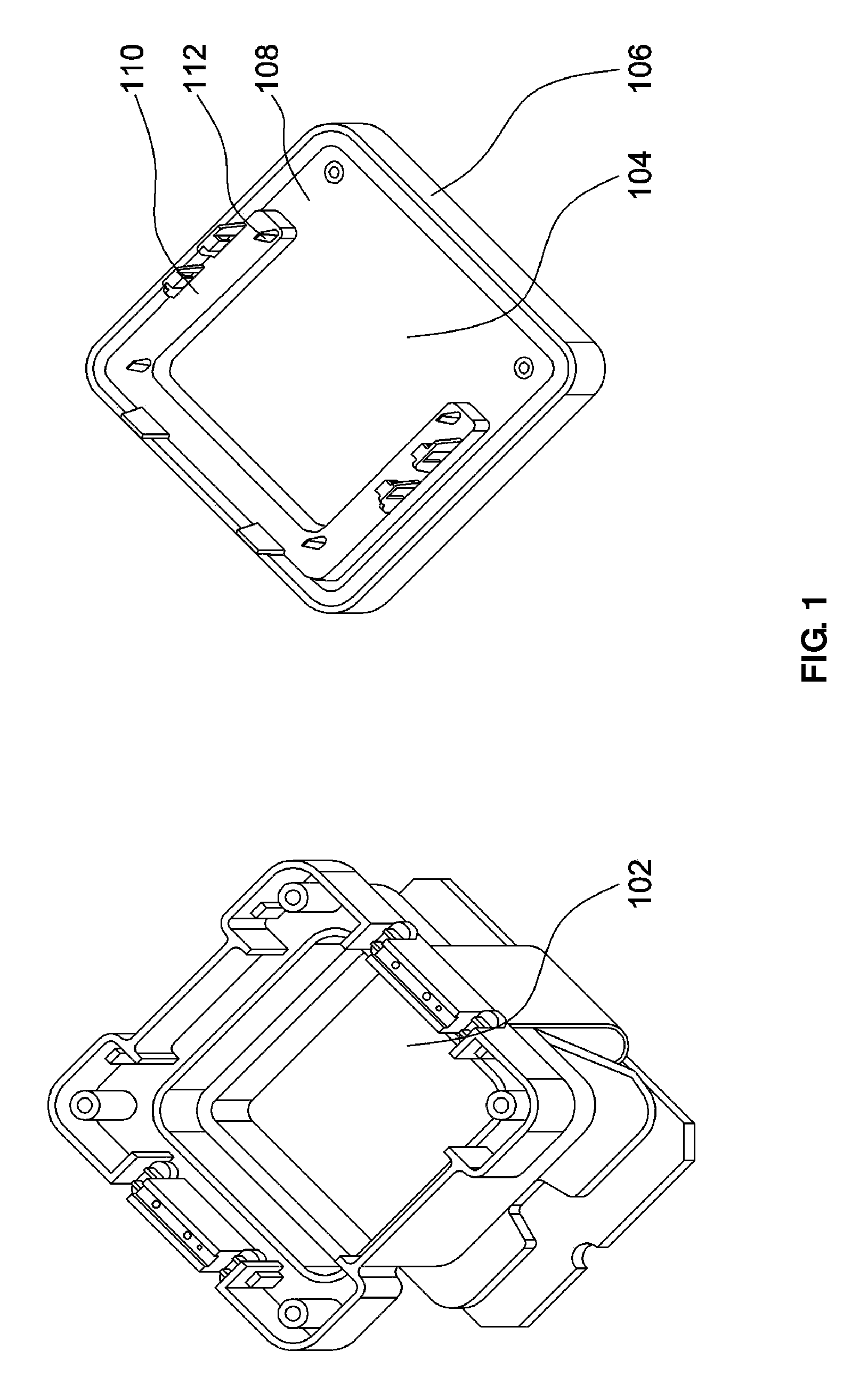

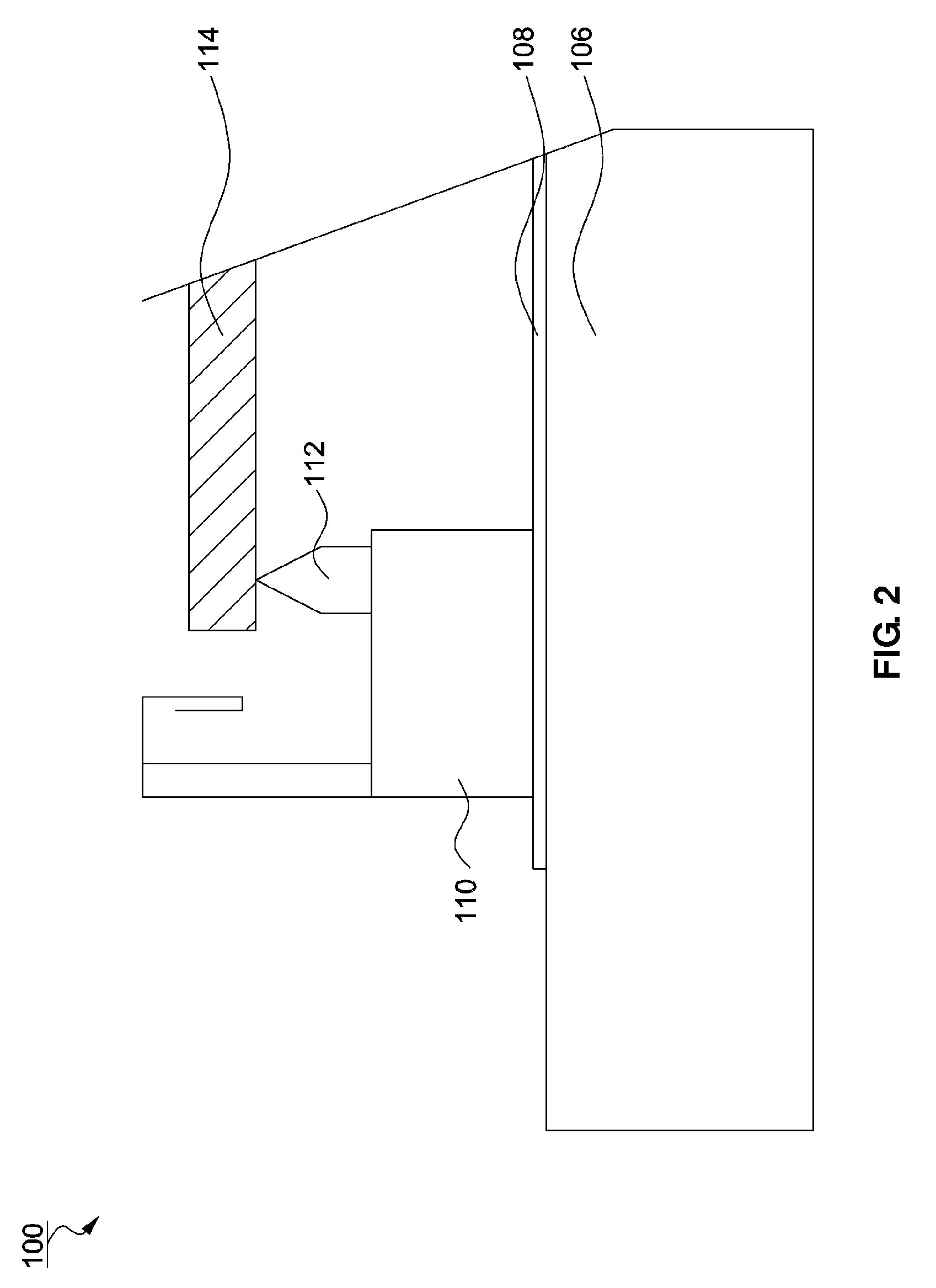

Photomask pod, photomask transport pod and supporter thereof

InactiveUS20090038985A1Eliminate accumulationReduce charge accumulationPhotomechanical apparatusSemiconductor/solid-state device manufacturingEngineeringPhotomask

A photomask pod and a photomask transport pod are provided for preventing particles in the environment from defiling a photomask as well as charge accumulation on the photomask from causing ESD damage. The photomask pod comprises two covers and the supporters or retainers on at least one of the two covers are made of a static dissipative material, which facilitates reducing charge accumulation and protecting the photomask from ESD damage.

Owner:GUDENG PRECISION IND CO LTD

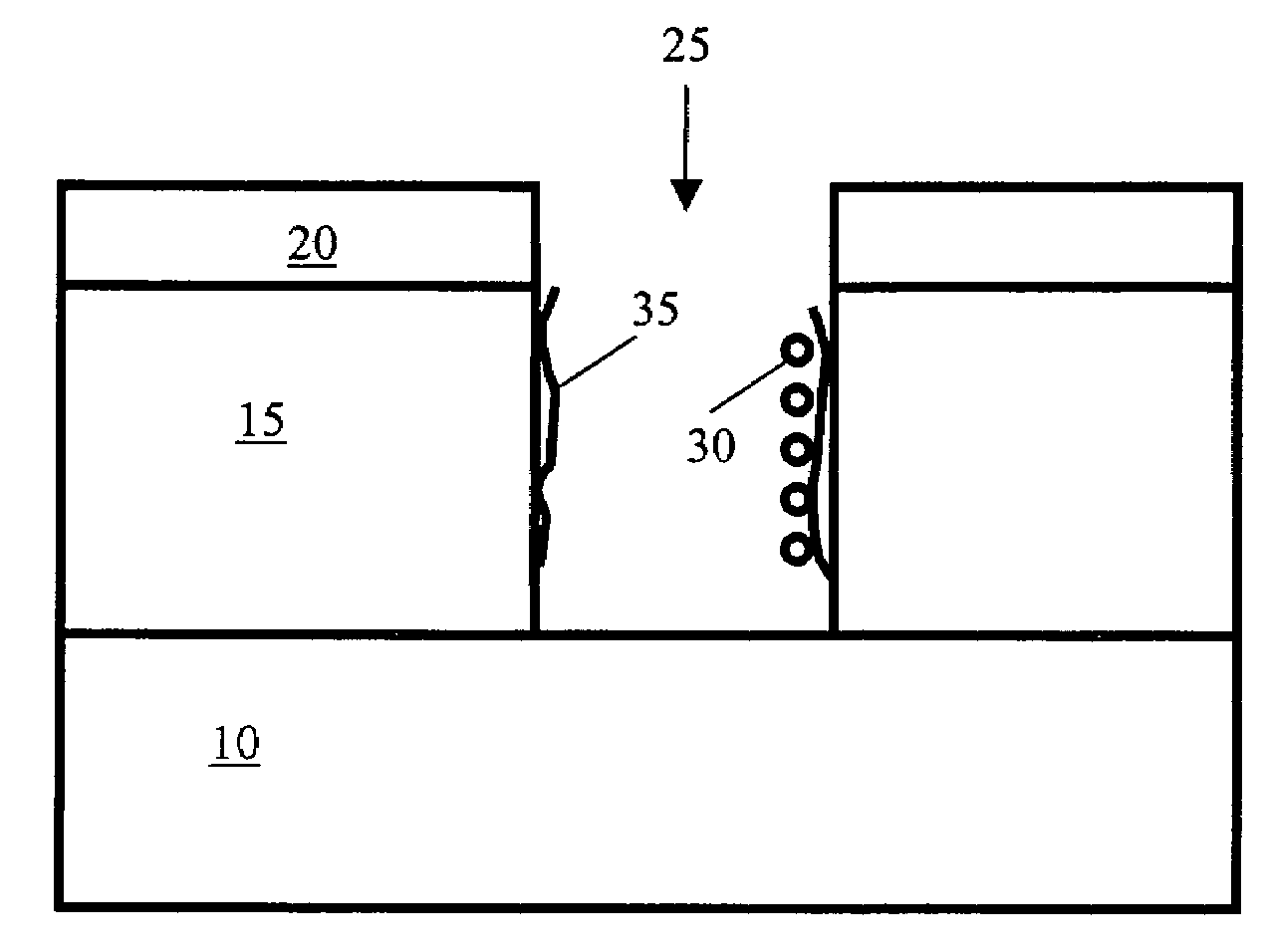

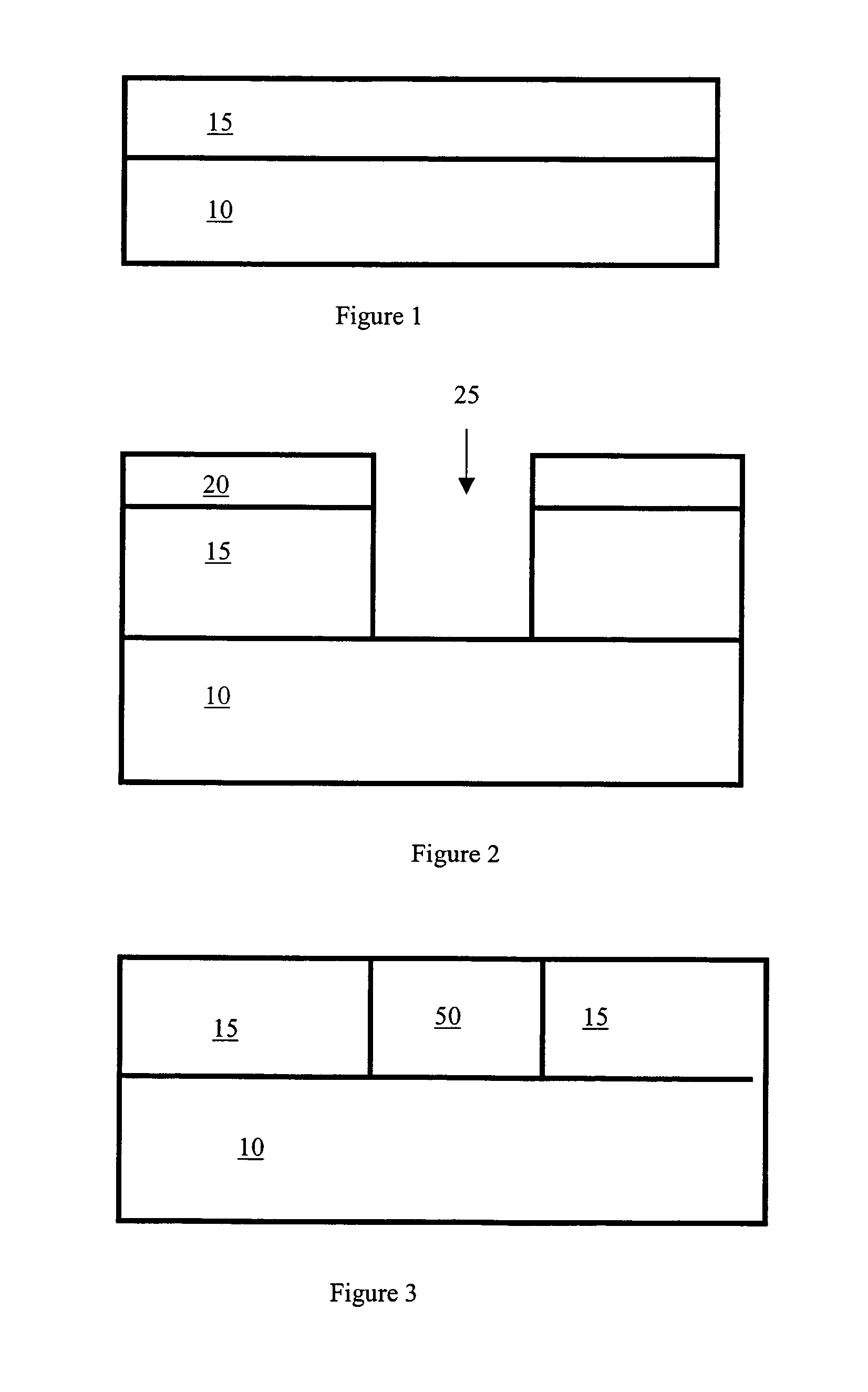

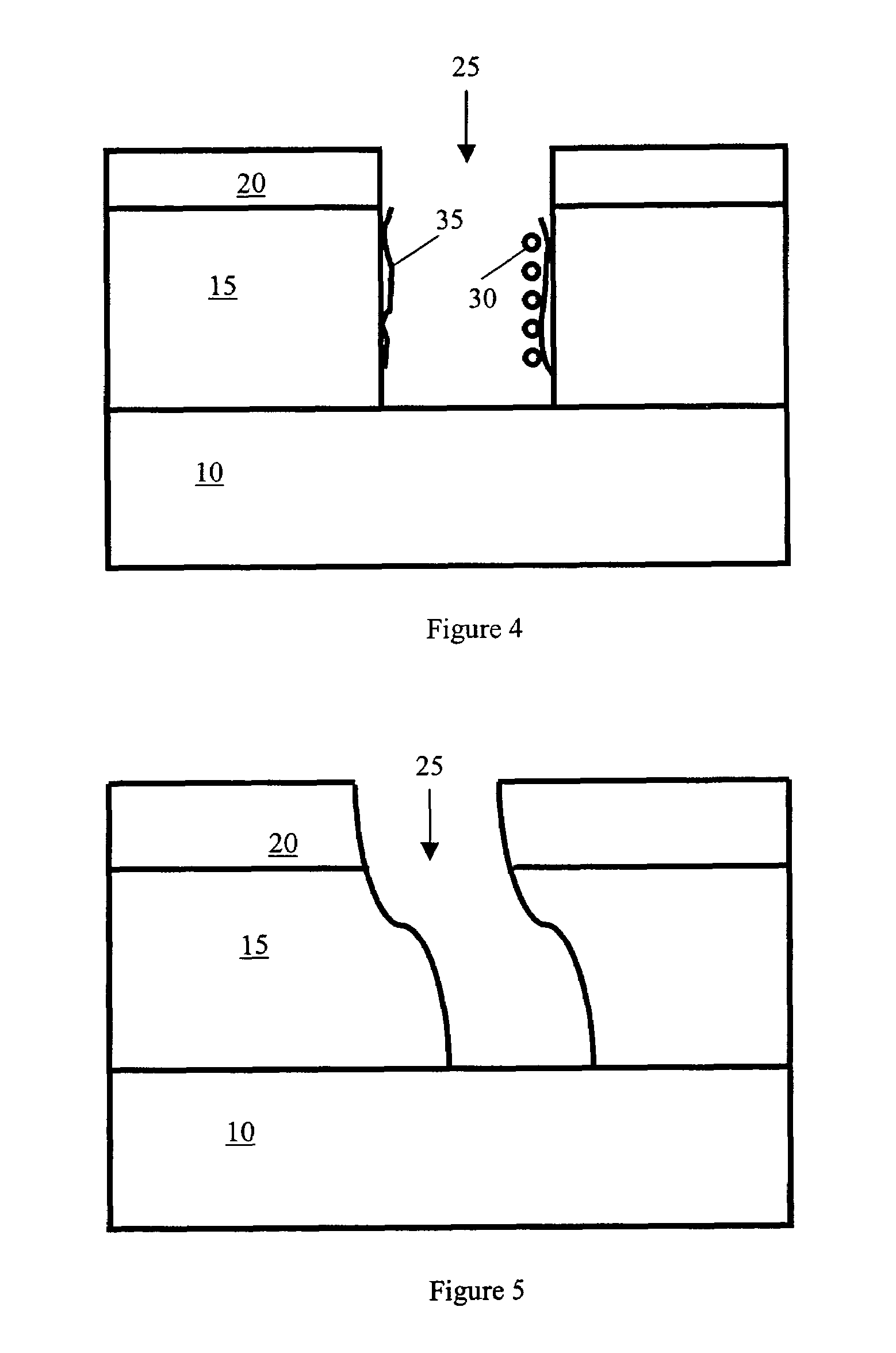

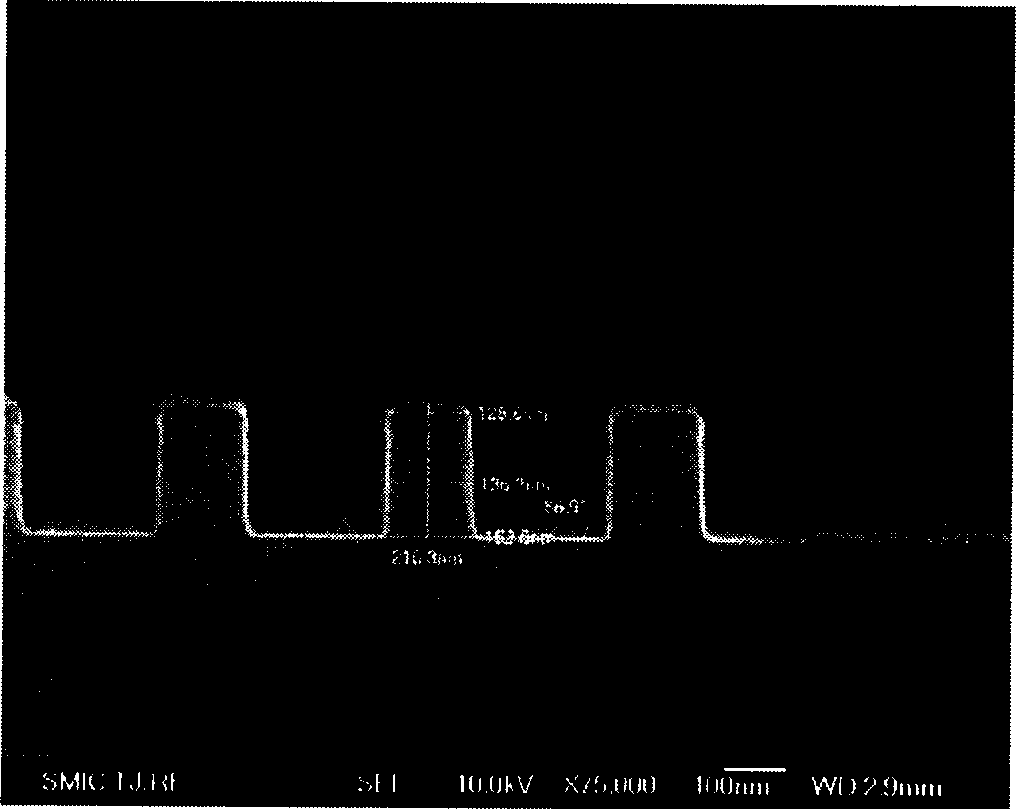

Method to reduce charge buildup during high aspect ratio contact etch

ActiveUS7344975B2Reduce charge accumulationAvoid distortionSemiconductor/solid-state device manufacturingSemiconductor devicesDopantCarbon chain

A method of high aspect ratio contact etching a substantially vertical contact hole in an oxide layer using a hard photoresist mask is described. The oxide layer is deposited on an underlying substrate. A plasma etching gas is formed from a carbon source gas. Dopants are mixed into the gas. The doped plasma etching gas etches a substantially vertical contact hole through the oxide layer by doping carbon chain polymers formed along the sidewalls of the contact holes during the etching process into a conductive state. The conductive state of the carbon chain polymers reduces the charge buildup along sidewalls to prevent twisting of the contact holes by bleeding off the charge and ensuring proper alignment with active area landing regions. The etching stops at the underlying substrate.

Owner:MICRON TECH INC

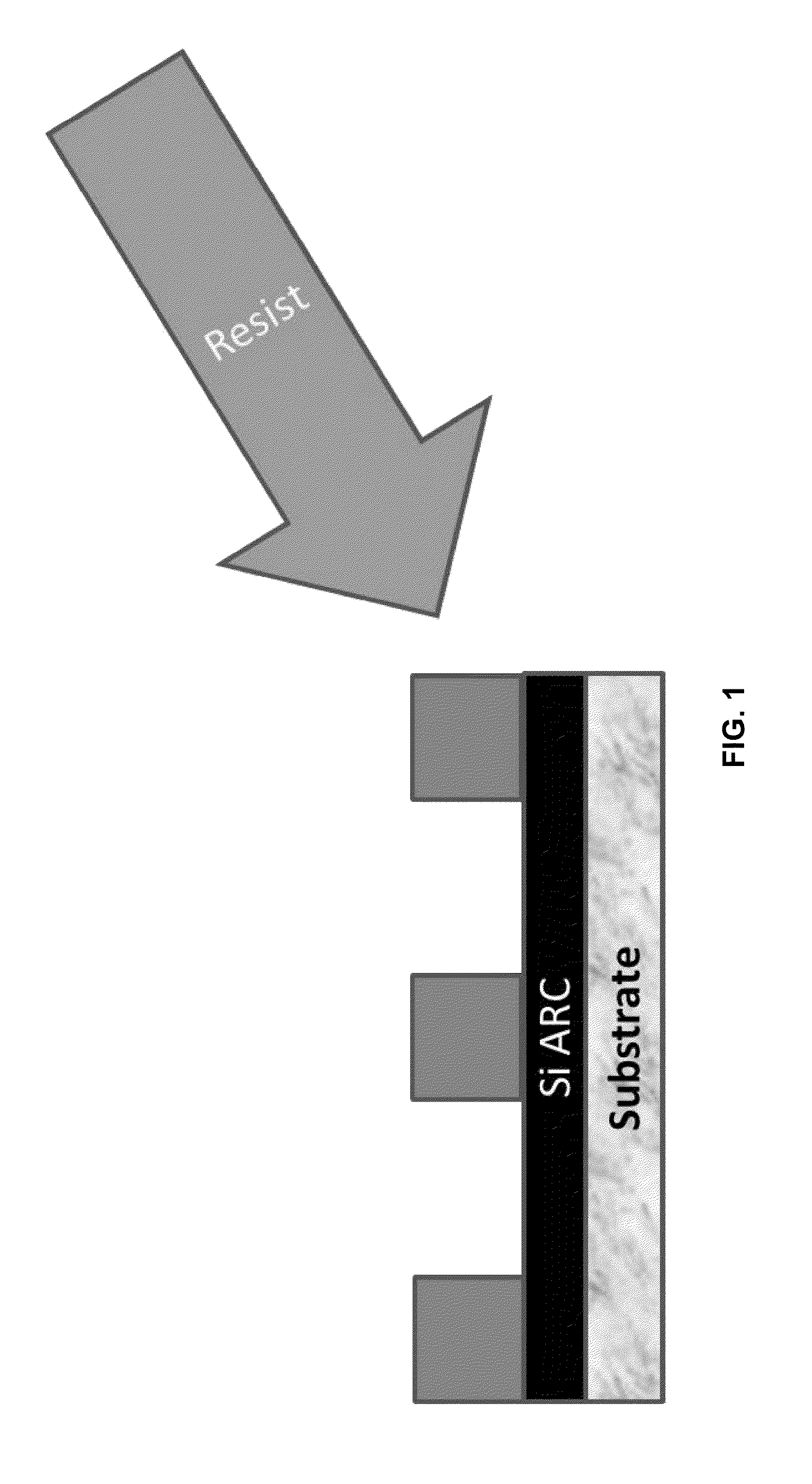

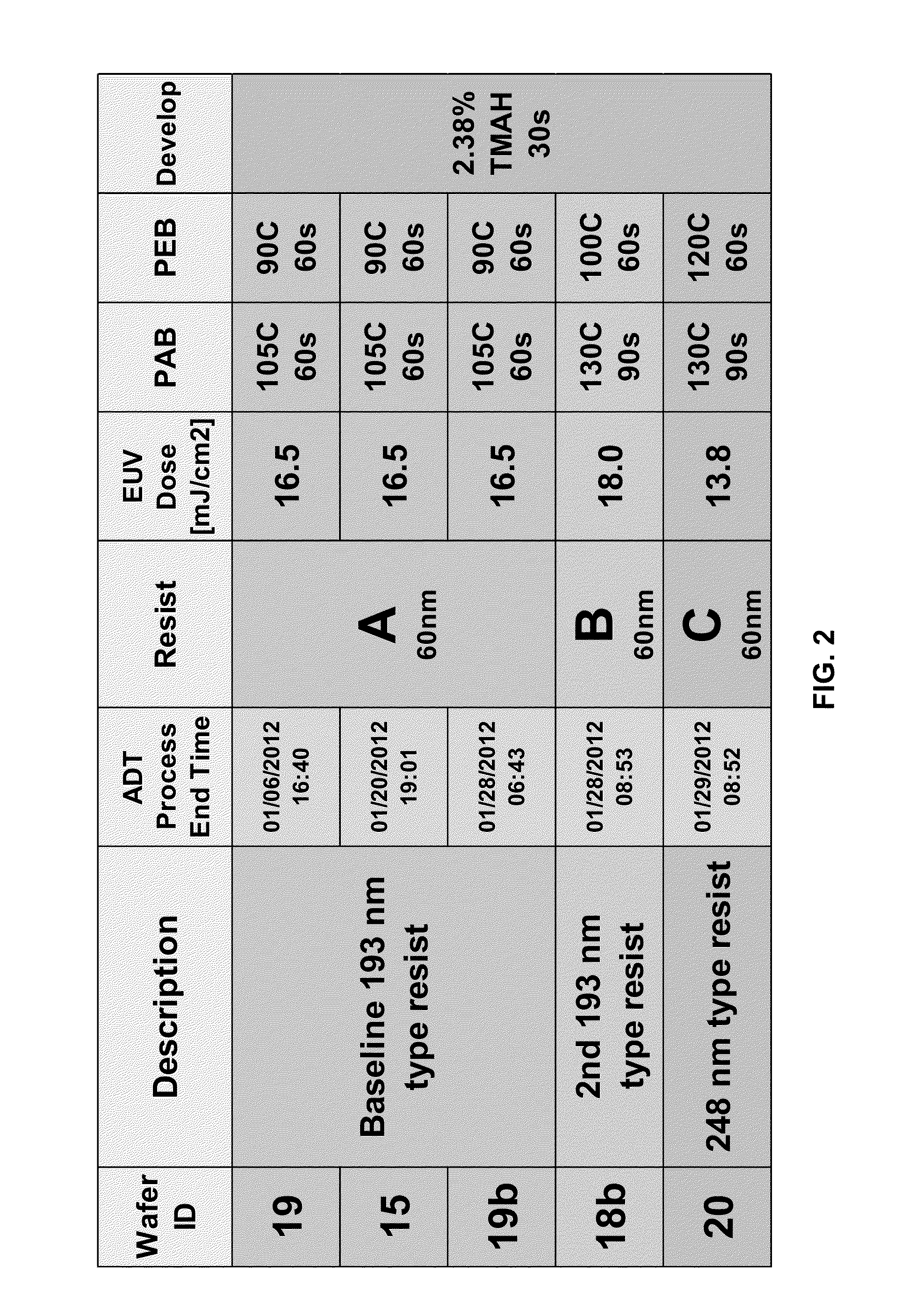

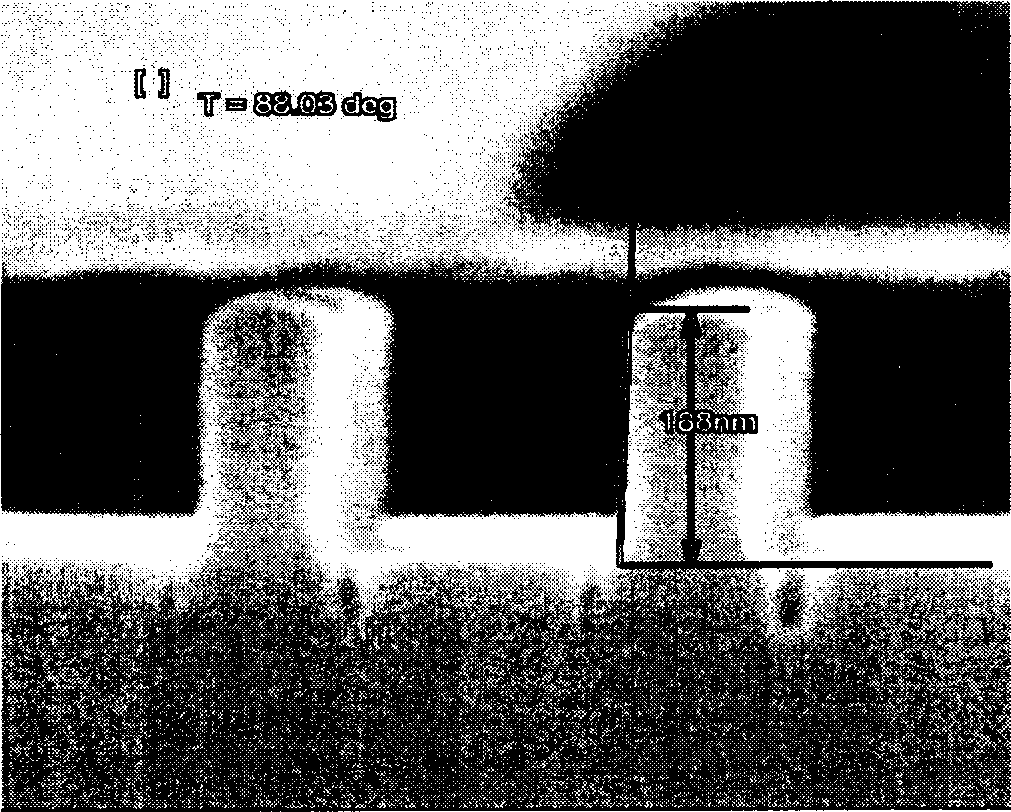

Method for reducing charge in critical dimension-scanning electron microscope metrology

InactiveUS20140206112A1Reduce charge accumulationReduce the impactMaterial analysis using wave/particle radiationSiliconLithographic artistMetrology

Methods and compositions are provided for reducing or eliminating charge buildup during scanning electron microscopy (SEM) metrology of a critical dimension (CD) in a structure produced by lithography. An under layer is utilized that comprises silicon in the construction of the structure. When the lithography structure comprising the silicon-comprising under layer is scanned for CDs using SEM, the under layer reduces or eliminates charge buildup during SEM metrological observations.

Owner:THE RES FOUND OF STATE UNIV OF NEW YORK +1

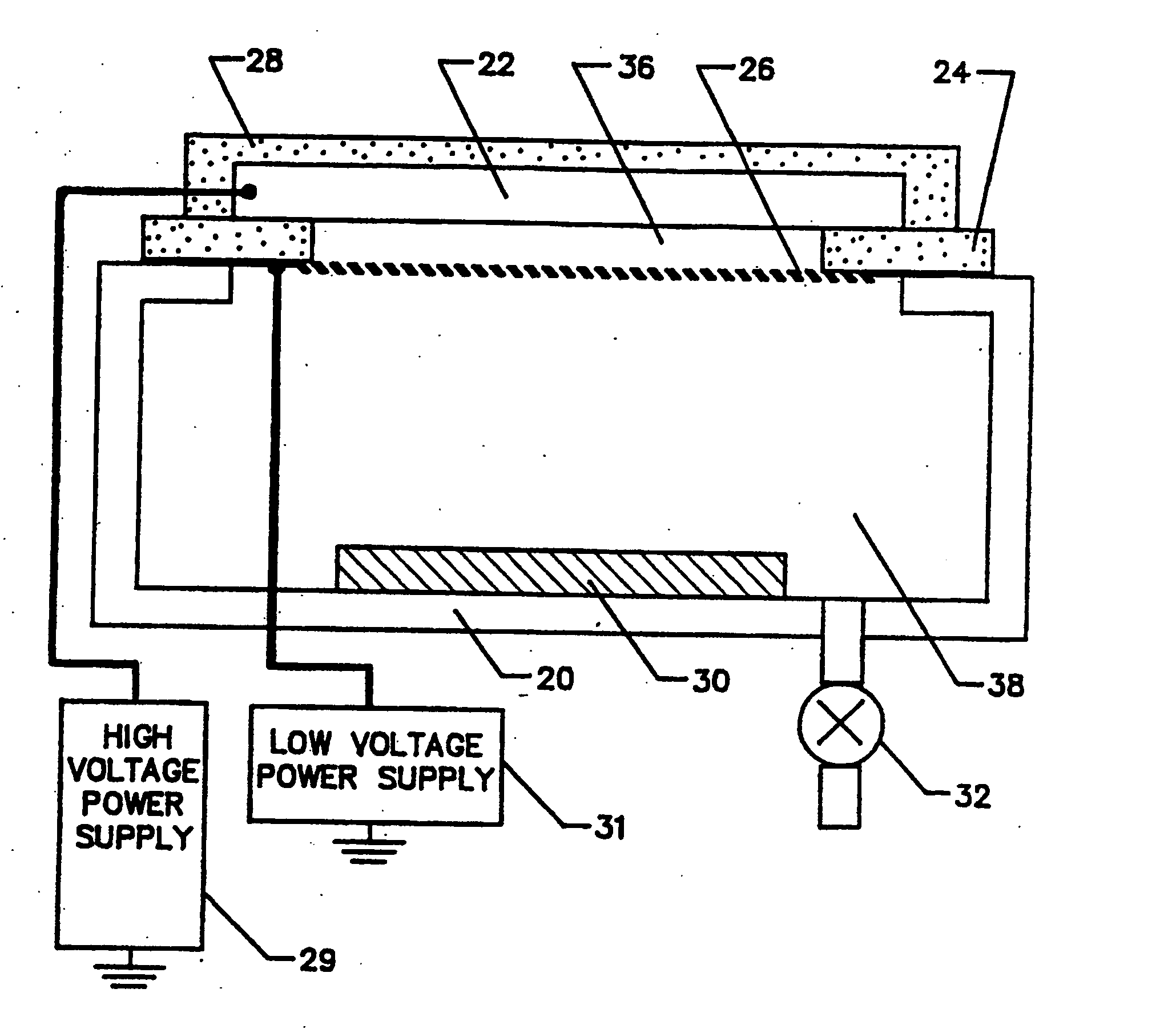

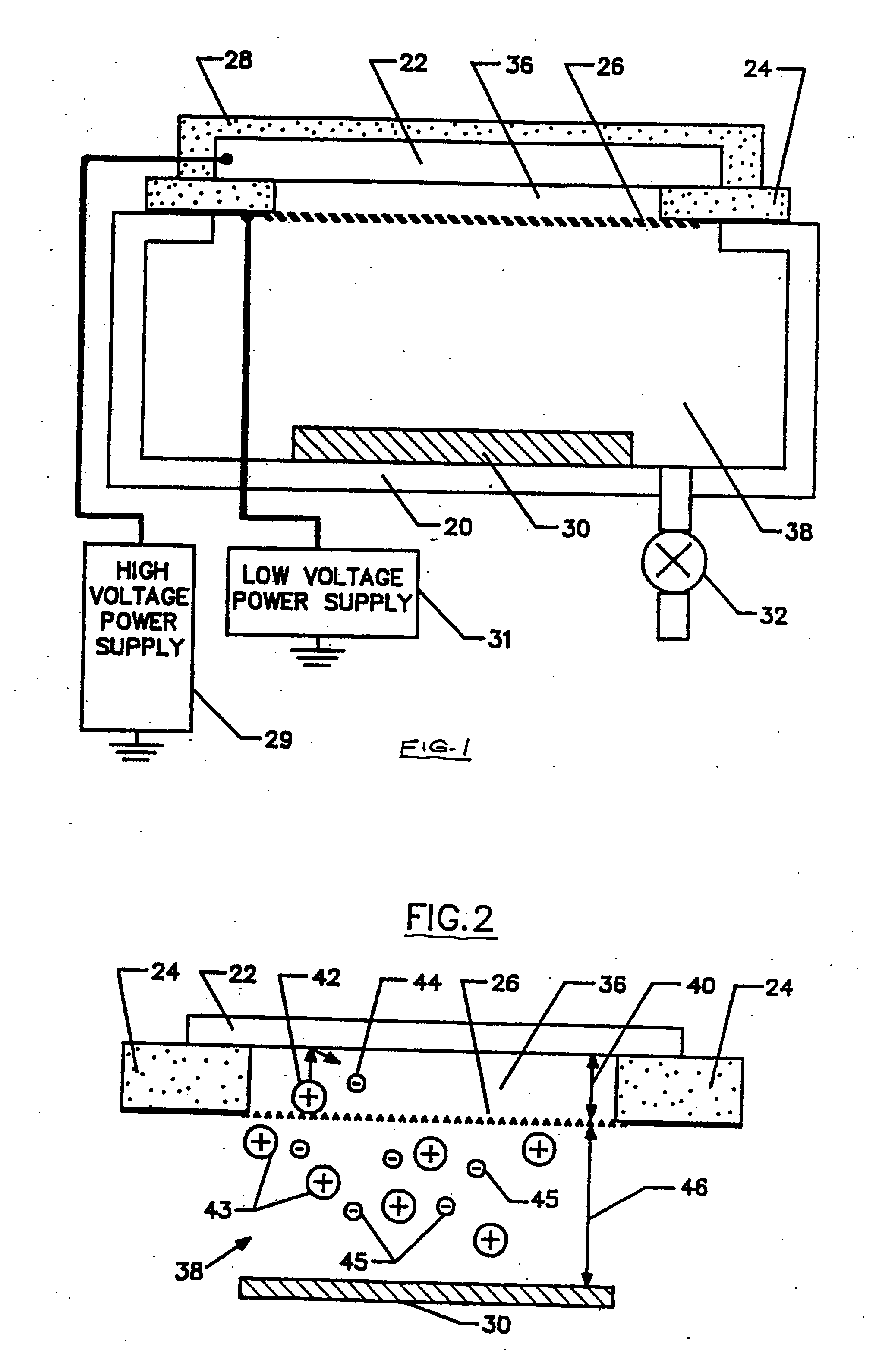

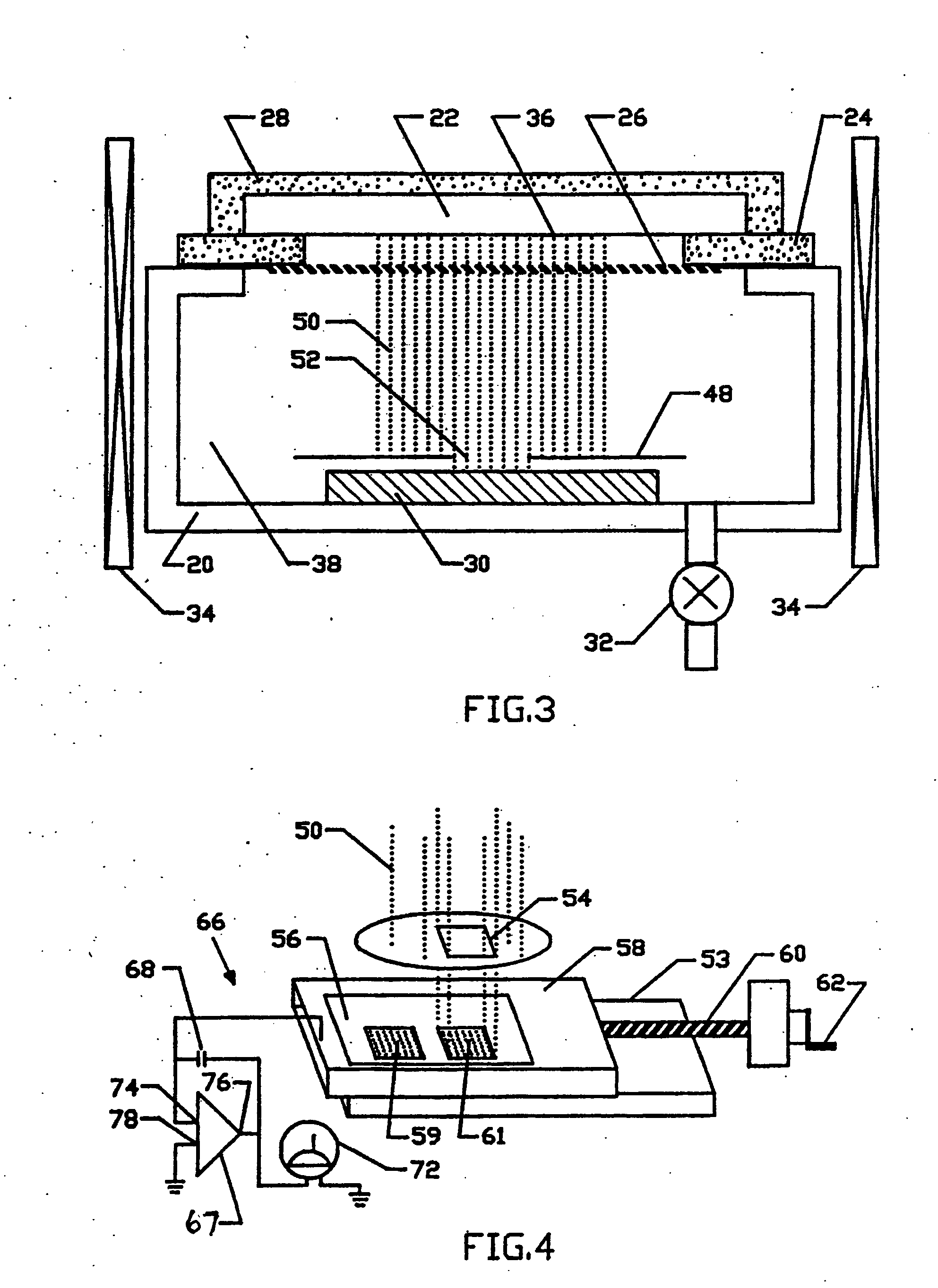

Method and apparatus for reducing charge density on a dielectric coated substrate after exposure to large area electron beam

InactiveUS20050224722A1Charge damage be reduceReduce charge accumulationElectric discharge tubesRadiation therapyAnode voltageVoltage

Embodiments in accordance with the present invention relate to a number of techniques, which may be applied alone or in combination, to reduce charge damage of substrates exposed to electron beam radiation. In one embodiment, charge damage is reduced by establishing a robust electrical connection between the exposed substrate and ground. In another embodiment, charge damage is reduced by modifying the sequence of steps for activating and deactivating the electron beam source to reduce the accumulation of charge on the substrate. In still another embodiment, a plasma is struck in the chamber containing the e-beam treated substrate, thereby removing accumulated charge from the substrate. In a further embodiment of the present invention, the voltage of the anode of the e-beam source is reduced in magnitude to account for differences in electron conversion efficiency exhibited by different cathode materials.

Owner:APPLIED MATERIALS INC

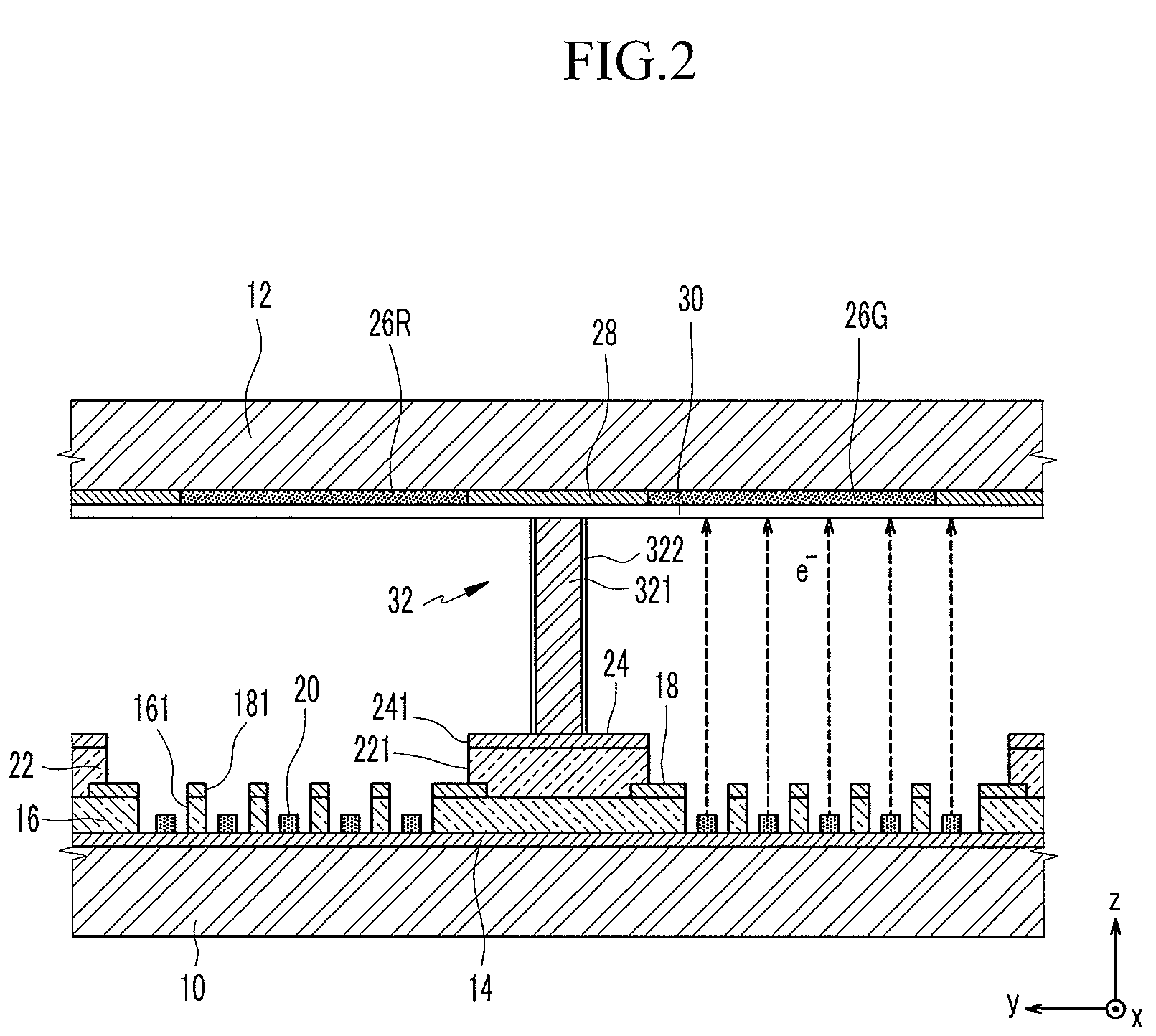

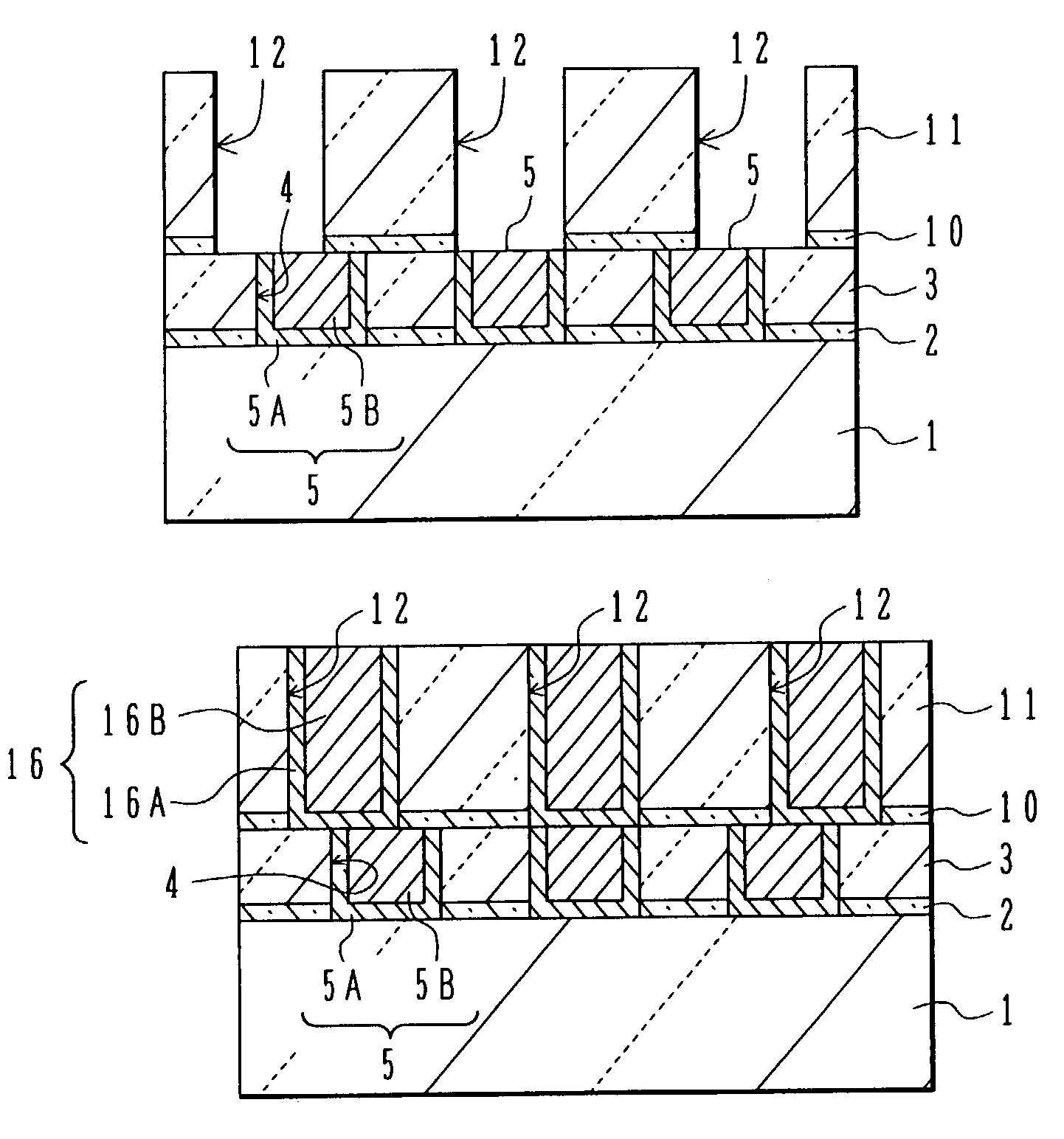

Electron emission display

InactiveUS20080106184A1Improve color accuracySuppress in appearanceIncadescent body mountings/supportElectrode assembly support/mounting/spacing/insulationTemperature coefficientDisplay device

Owner:SAMSUNG SDI CO LTD

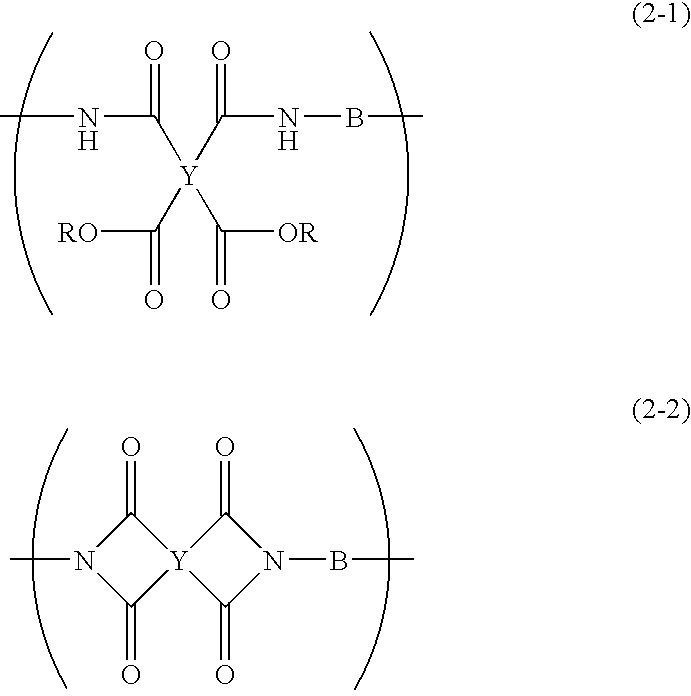

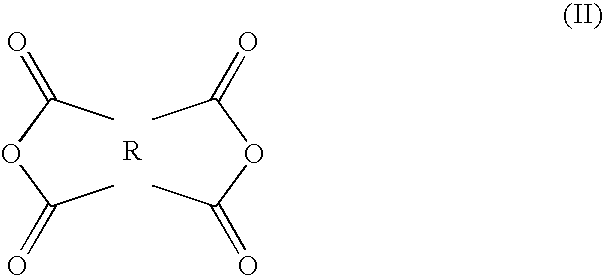

Liquid crystal aligning film

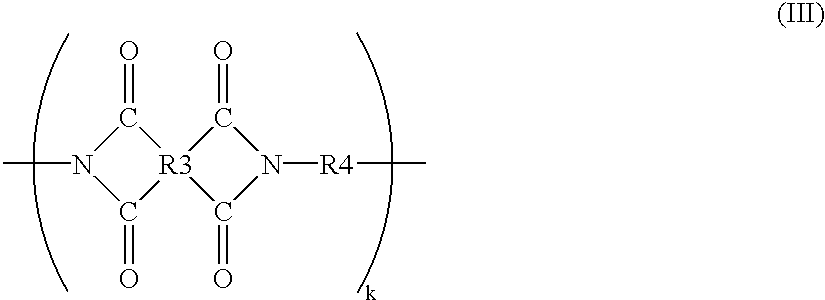

InactiveUS20030036624A1High voltage retentionReduce charge accumulationLiquid crystal compositionsSynthetic resin layered productsCrystallographyOligomer

The present invention provides a kind of liquid crystal aligning film composition used for liquid crystal display (LCD), in which the liquid crystal aligning film composition used for LCD is a polyimide resin oligomer (A) having the structural formula (I) as shown in the following: wherein m is an interger of 1, 2, and 3, R is selected one of from aromatic and cyclicaliphatic, X is selected from the group containing amide, ester, and ether etc., Y is the group of containing cholesterol structure; this polyimide resin oligomer (A) and the second reagent (B) are mixed together, through an induced process (C), to produce a thin film for aligning liquid crystal molecule.

Owner:IND TECH RES INST

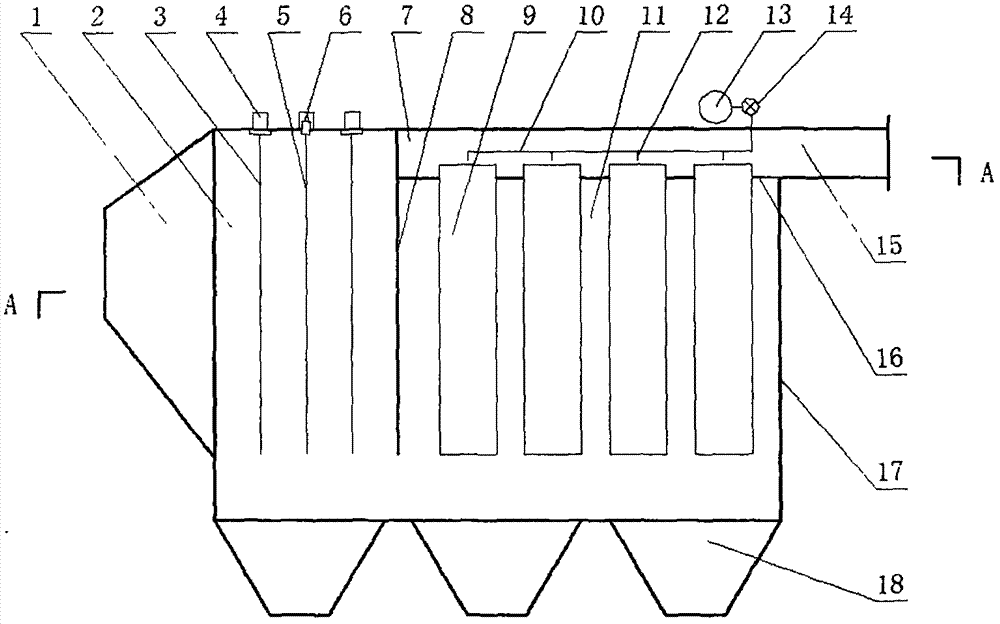

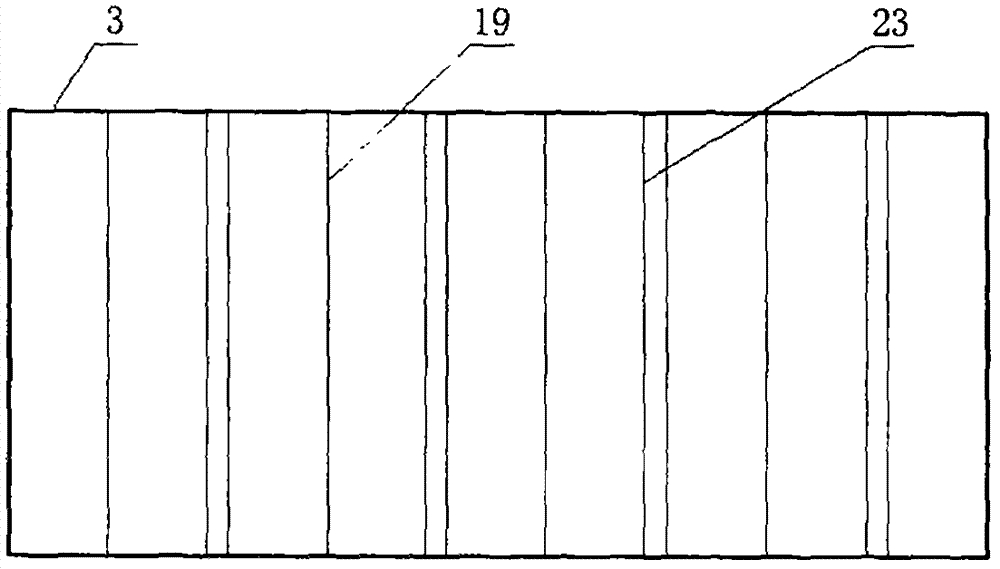

Transverse bipolar electric-bag composite dust collector

InactiveCN107149982AImprove dust collection efficiencyAvoid accumulationExternal electric electrostatic seperatorEngineeringDust collector

The invention relates to a transverse bipolar electric-bag composite dust collector. According to the technical scheme adopted by the invention, a gas inlet box (1) is connected with an inlet end of a dust collector body (17); a gas outlet box (15) is connected with an outlet end of the dust collector body (17); an anode corona wire (19) and an anode tube (23) are fixedly arranged on an anode framework (3) alternatively at equal distance; and a cathode tube (20) and a cathode corona wire (22) are fixedly arranged on a cathode framework (5) alternatively at equal distance. The anode framework (3) and the cathode framework (5) are alternatively arranged at equal distance in a direction perpendicular to a gas inlet direction. In the inlet flow direction, the cathode corona wire is opposite to the anode tube (23), and the anode corona wire (19) is opposite to the cathode tube (20). Positive ions are generated between the anode corona wire (19) and the cathode tube (20), and negative ions are generated between the cathode corona wire (22) and the anode tube (23). The transverse bipolar electric-bag composite dust collector is beneficial for promoting dust cleaning efficiency of the electric-bag composite dust collector, strengthening electrostatic coagulation of charged dust and improving dust removal efficiency.

Owner:WUHAN UNIV OF SCI & TECH +1

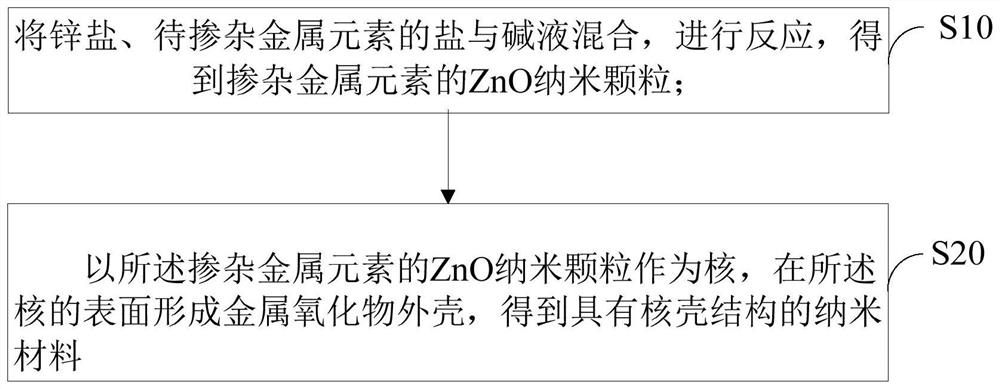

Nano material, preparation method thereof and quantum dot light-emitting diode

PendingCN113948647ABalance injectionImprove efficiencyMaterial nanotechnologyZinc oxides/hydroxidesLight-emitting diodeMaterials science

The invention discloses a nano material, a preparation method thereof and a quantum dot light emitting diode. The nano material has a core-shell structure, and the core of the nano material comprises ZnO nano particles and metal elements doped in the ZnO nano particles; and the shell of the nanometer material comprises a metal oxide. By doping other metal elements in the zinc oxide nanoparticles and wrapping a layer of metal oxide shell, the energy level structure and the electron transmission efficiency of the whole nano material can be adjusted, so that the energy levels of the quantum dots and the nano material in the device are more matched, and the quantum dots and the nano material are more uniform. Transfer of electrons in the quantum dot light-emitting layer to the electron transport layer is reduced, and the electron-hole recombination efficiency of the quantum dot light-emitting layer is improved; electron hole injection of the device is more balanced, charge accumulation of the quantum dot light-emitting layer is reduced, Auger recombination is inhibited, and the radiative recombination efficiency of electron holes is improved; therefore, the zinc oxide nanoparticles are more stable, and the overall stability of the device is improved.

Owner:TCL CORPORATION

Compound material with high energy density and preparation method thereof

The invention relates to the technical field of high polymer compound materials, in particular to a compound material with high energy density and a preparation method thereof. The compound material with high energy density is mainly obtained by mixing titanate particles of a core-shell structure with a high polymer; the titanate particles of the core-shell structure is obtained by coating silicondioxide on the surface of the titanate particles. According to the compound material with the high energy density and the preparation method thereof, the silicon dioxide serving as an insulating layer is coated on the surface of ultra-fine barium titanate particles to form the titanate of the core-shell structure, the local electric field concentration and electric charge accumulation can be effectively weakened, the formation of a leakage current passage is prevented, the dielectric loss is reduced, the voltage resistant performance of the material is wholly improved, and the homogeneous dispersion of titanate and high-interface compatibility brought by a silicon dioxide layer can improve the puncture of thin film; the titanate of the core-shell structure compounds with the high polymer,and the compound material with excellent energy storage performance can be obtained under the condition of lower filling quantity.

Owner:BEIJING UNIV OF POSTS & TELECOMM

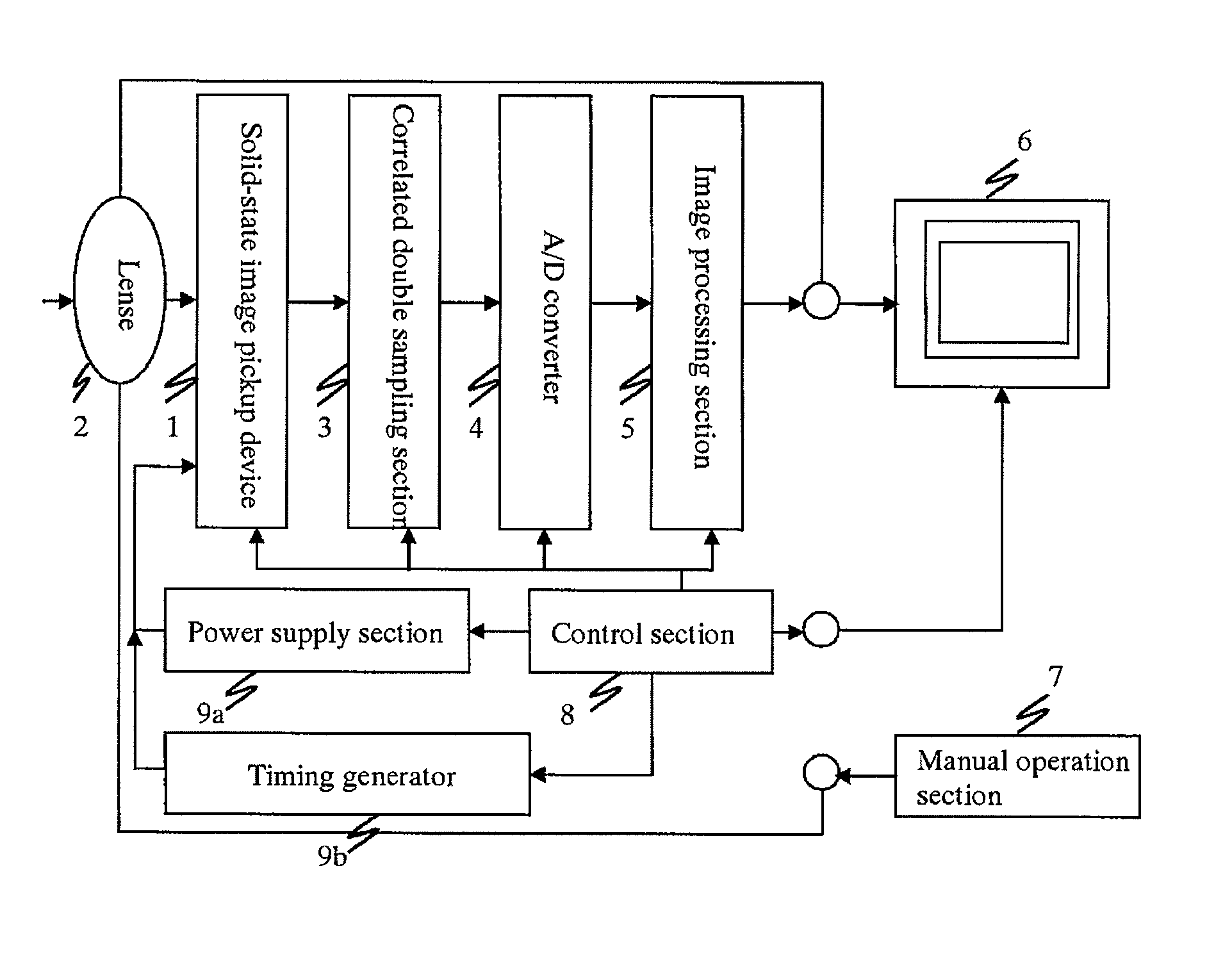

Image pickup device and imaging apparatus using the same

InactiveUS20080117322A1Increase flexibilityInhibit deteriorationTelevision system detailsTelevision system scanning detailsImaging equipmentPhotodiode

Disclosed are an image pickup device and an imaging apparatus using the image pickup device. The image pickup device a photodiode for converting incident light to electric charge and generate a signal charge corresponding to an intensity of the incident light, a CCD cell for accumulatively storing respective signal charges generated from the photodiode, and transferring the signal charges to outside. In the image pickup device, a light-receptor board formed with the photodiode and a CCD-cell board formed with the CCD cell are arranged separately from each other and electrically connected to each other.

Owner:SHIMADZU CORP

Electron emission display including spacers with layers

InactiveUS7772758B2Suppress in appearanceSuppression of distortionIncadescent body mountings/supportElectrode assembly support/mounting/spacing/insulationDisplay deviceLight emission

An electron emission display includes first and second substrates opposing each other, an electron emission unit that is provided on an inner surface of the first substrate, a light emission unit that is provided on an inner surface of the second substrate, and a spacer that is located between the first and second substrate. The spacer includes a main body containing a material whose temperature-coefficient-of-resistance is less than or equal to 3% / ° C.

Owner:SAMSUNG SDI CO LTD

Semiconductor device manufacturing method capable of reliable inspection for hole opening and semiconductor devices manufactured by method

InactiveUS7211448B2Reduce charge accumulationClear imageSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device detailsSecondary electronsSurface layer

A substrate defining an insulating surface layer portion and formed with a wiring groove filled with a wiring line the wiring line is electrically connected to a conductive member. The conductive member occupies an area larger than an area of the wiring line as viewed along a line parallel to a normal to the first surface. An insulating first film is formed on the first surface. A via hole is formed through the first film. The via hole is formed so that a boundary between the wiring line and the insulating surface layer portion passes through the inside of the via hole. The bottom of the via hole is observed with an apparatus for obtaining image information by utilizing secondary electrons and reflection electrons, to judge whether a state of the bottom of the via hole is accepted or rejected.

Owner:FUJITSU SEMICON LTD

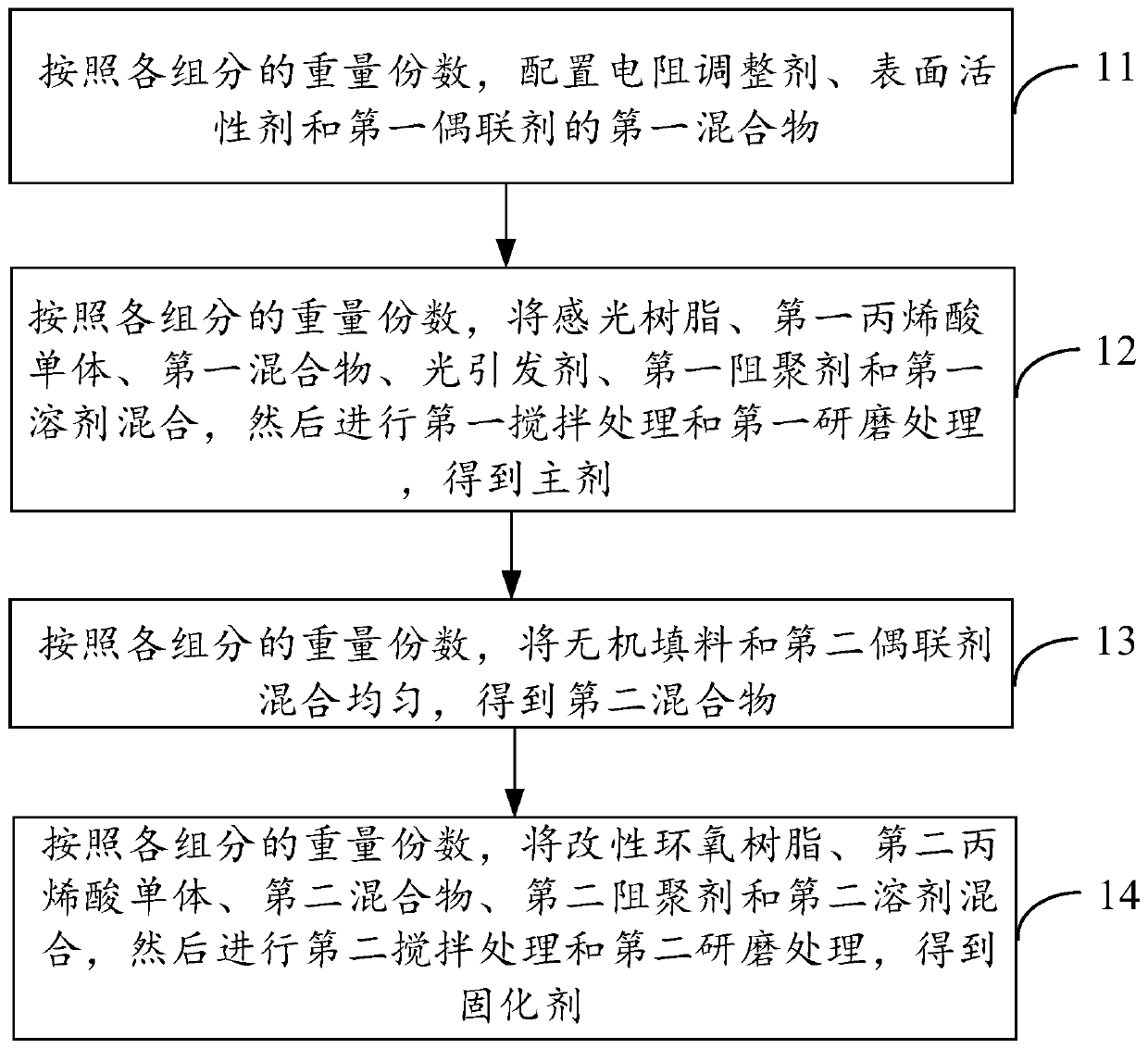

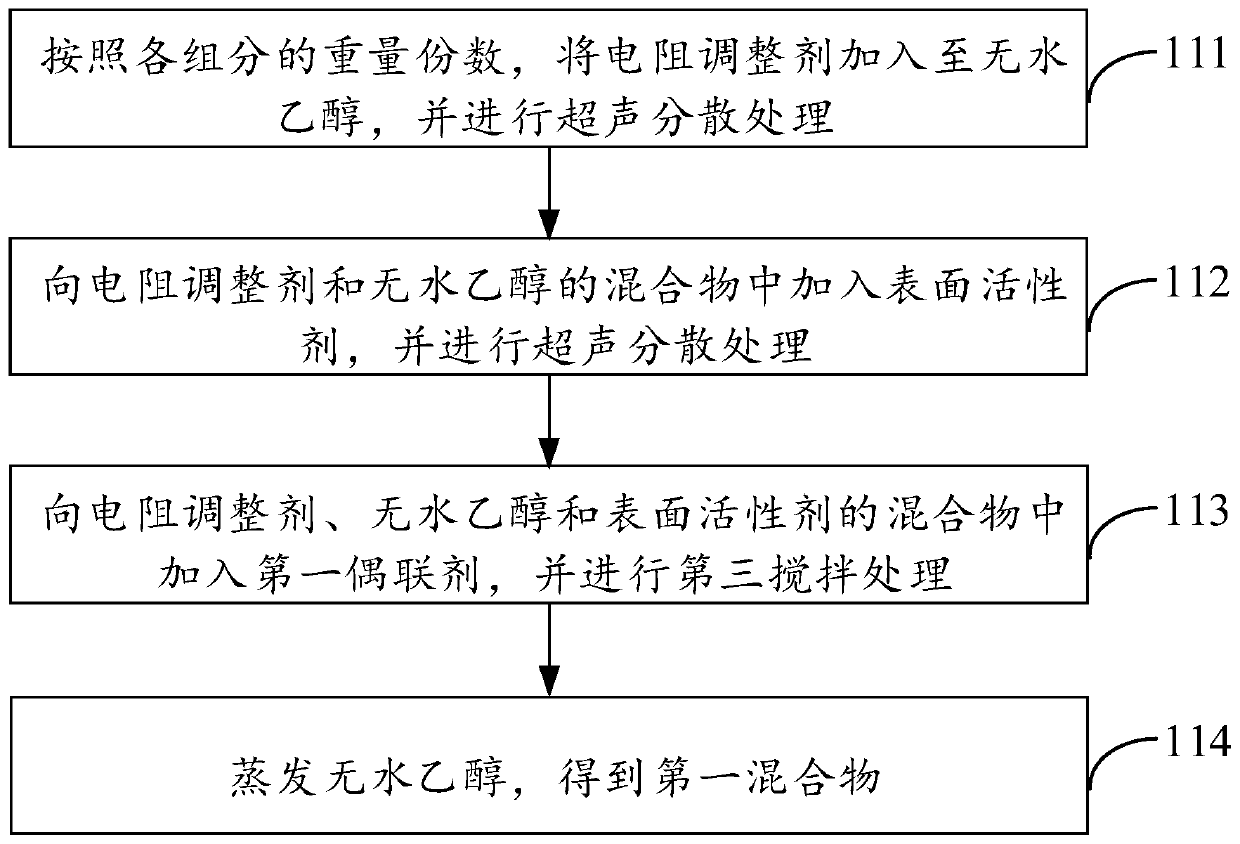

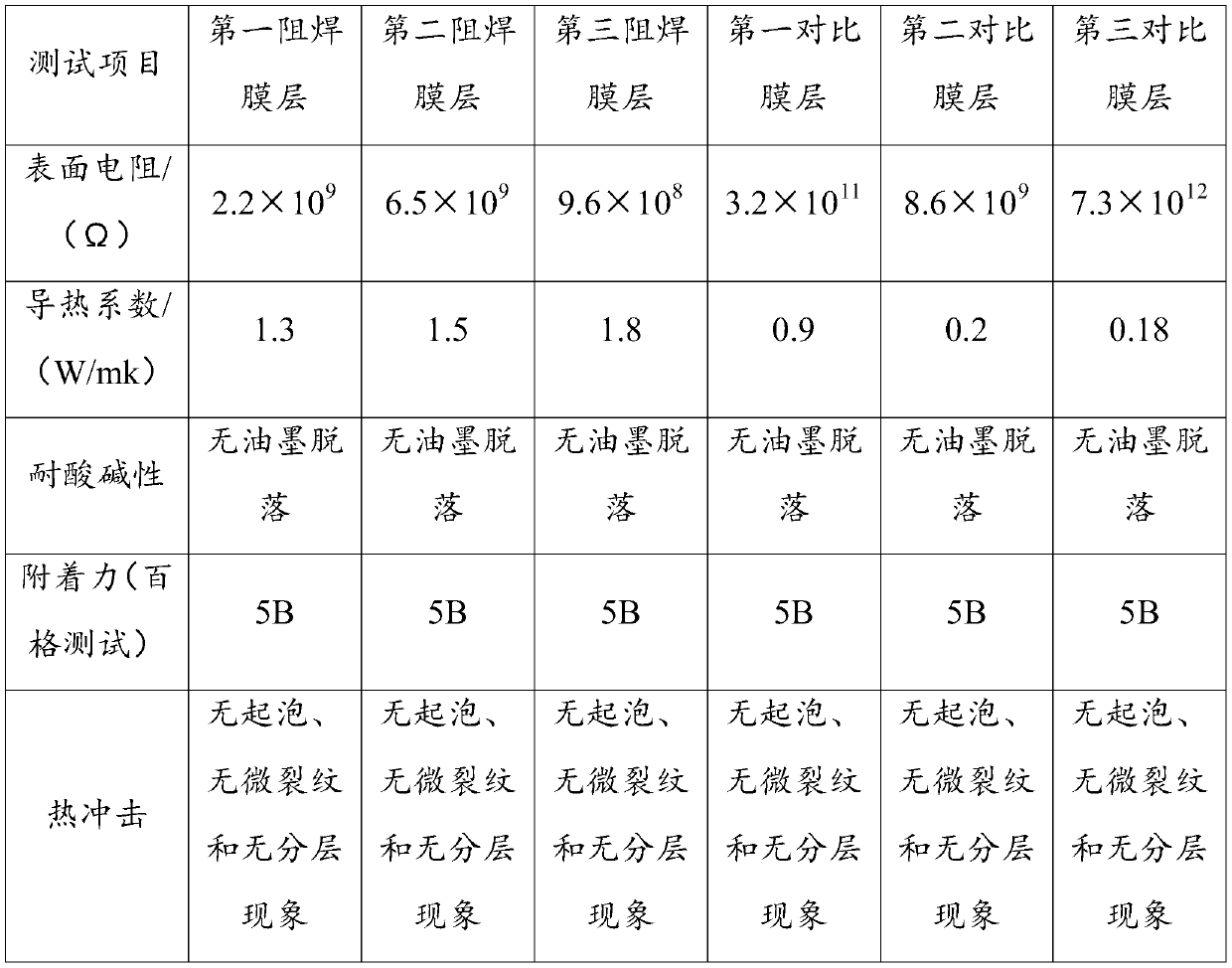

Photosensitive solder resist ink and preparation method thereof, printed circuit board and electronic equipment

InactiveCN111440478AReduce charge accumulationGood anti-static performancePhotomechanical apparatusInksPhotoinitiatorActive agent

The invention provides photosensitive solder resist ink and a preparation method thereof, a printed circuit board and electronic equipment. The photosensitive solder resist ink comprises a main agentand a curing agent according to a mass ratio of 2-4:0.5-1.5. The main agent comprises the following components in parts by weight: 50-100 parts of photosensitive resin, 7-20 parts of a first acrylic monomer, 0.5-5 parts of a resistance regulator, 6-12 parts of a photoinitiator, 0.01-0.2 parts of a first polymerization inhibitor, 0.5-5 parts of a first coupling agent, 0.1-2 parts of a surfactant and 10-25 parts of a first solvent. The curing agent comprises the following components in parts by weight: 40-100 parts of modified epoxy resin, 7-20 parts of a second acrylic monomer, 8-20 parts of aninorganic filler, 0.01-0.2 parts of a second polymerization inhibitor, 0.5-5 parts of a second coupling agent and 10-25 parts of a second solvent. A solder resist film layer formed by the photosensitive solder resist ink has the good antistatic performance, heat conduction performance and heat dissipation performance.

Owner:GUANGZHOU SHIYUAN ELECTRONICS CO LTD

Polysilicon etching technology capable of preventing device from plasma damage

ActiveCN1851880AAvoid accumulationReduce charge accumulationSemiconductor/solid-state device manufacturingSilicon chipPolycrystalline silicon

This invention provides a polysilicon etching technology for preventing damage to plasmas of devices including a through step, a main etching step, a settle step, an over etching step and a silicon chip downloading step, which reduces the charge accumulation on the surface of silicon chips to reduce damage to plasmas.

Owner:BEIJING NAURA MICROELECTRONICS EQUIP CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com