Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

120 results about "Logical element" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

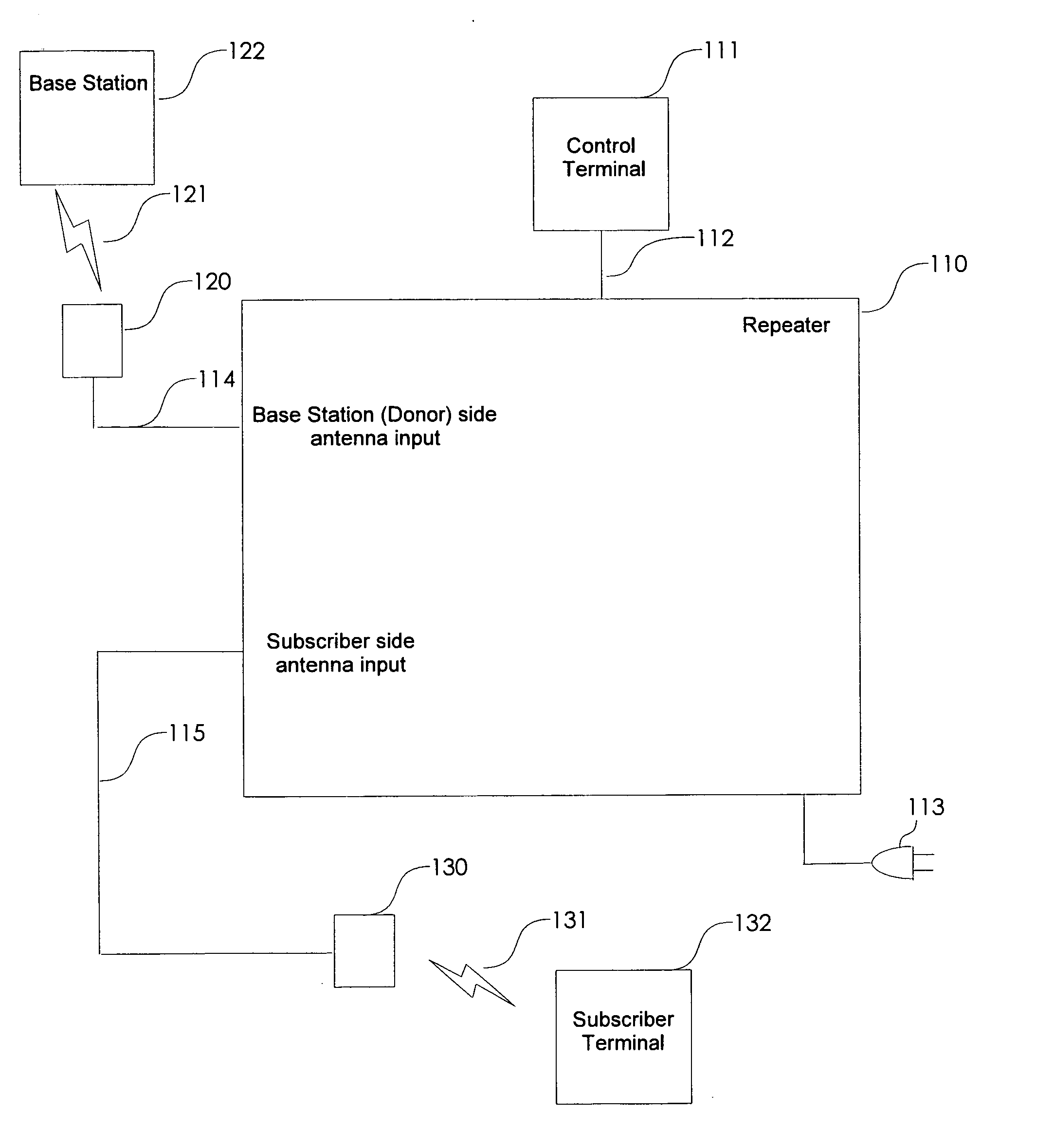

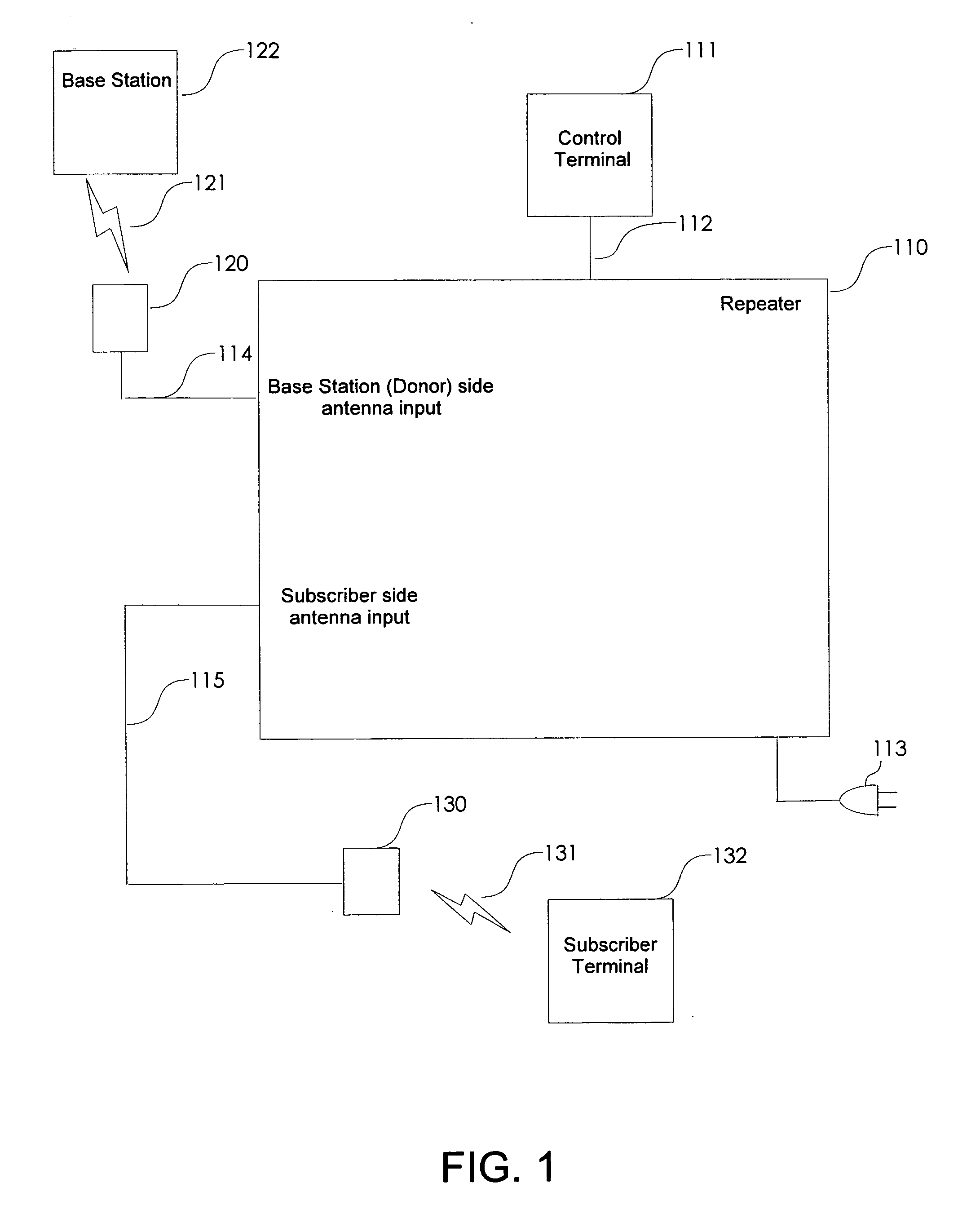

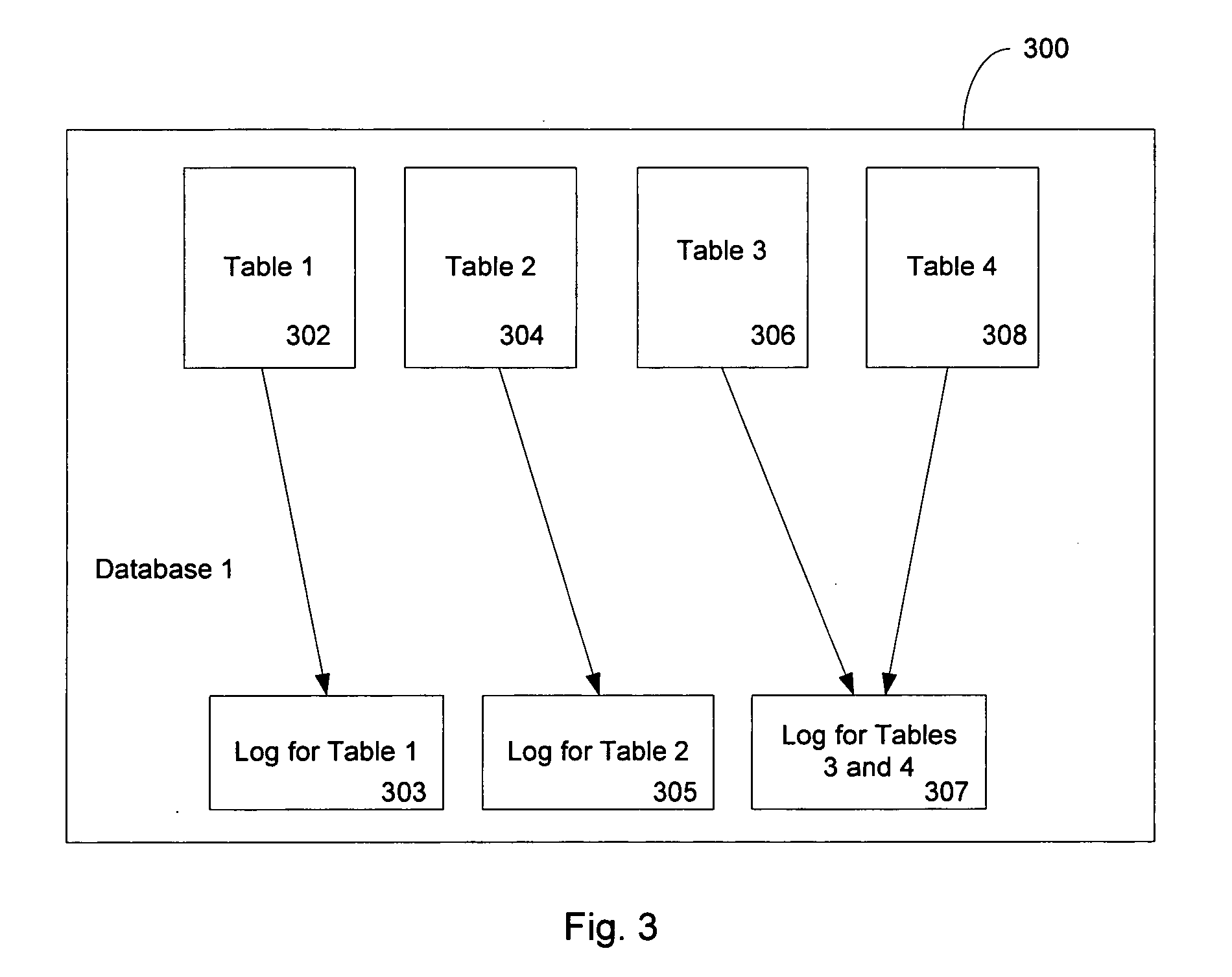

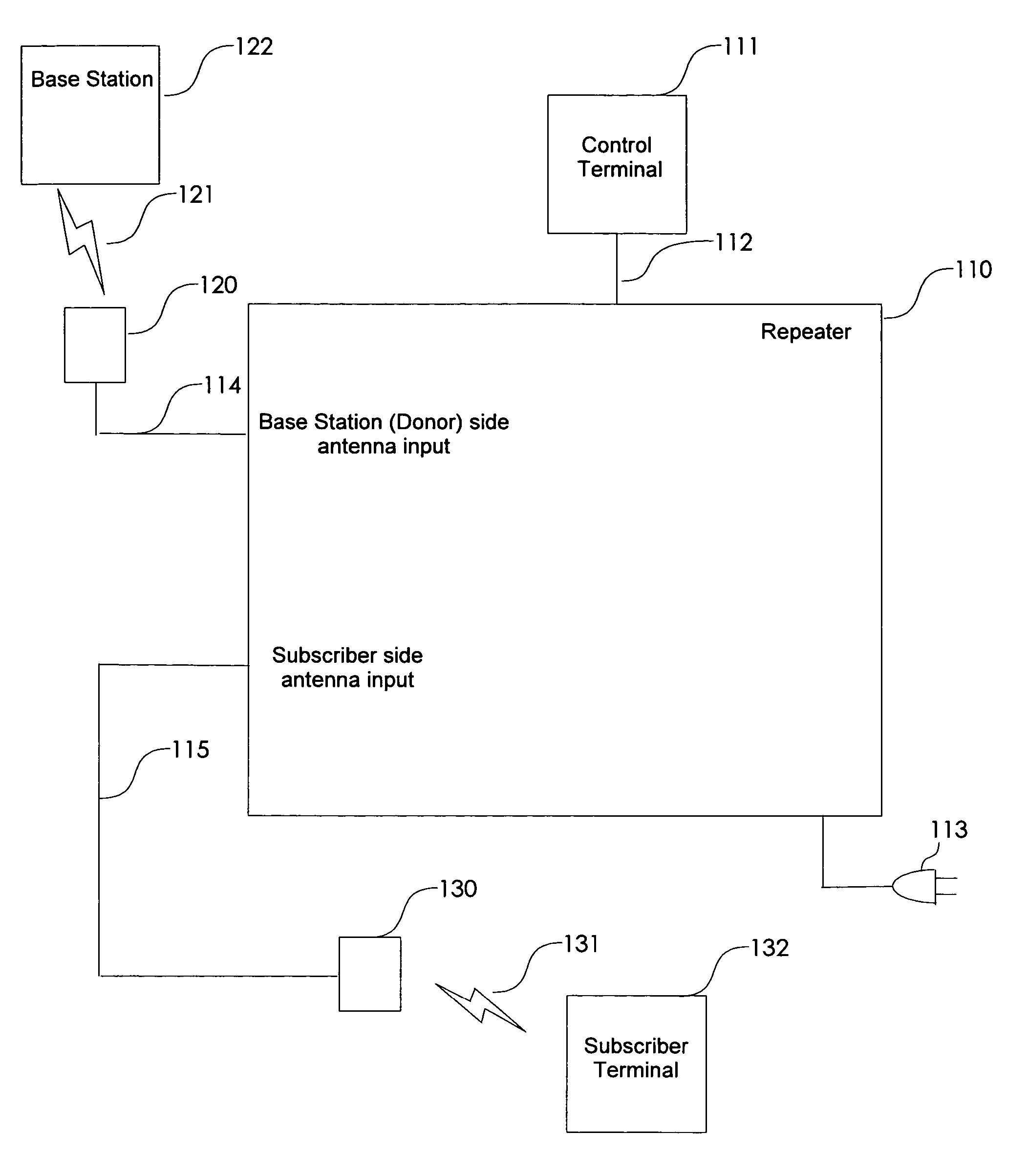

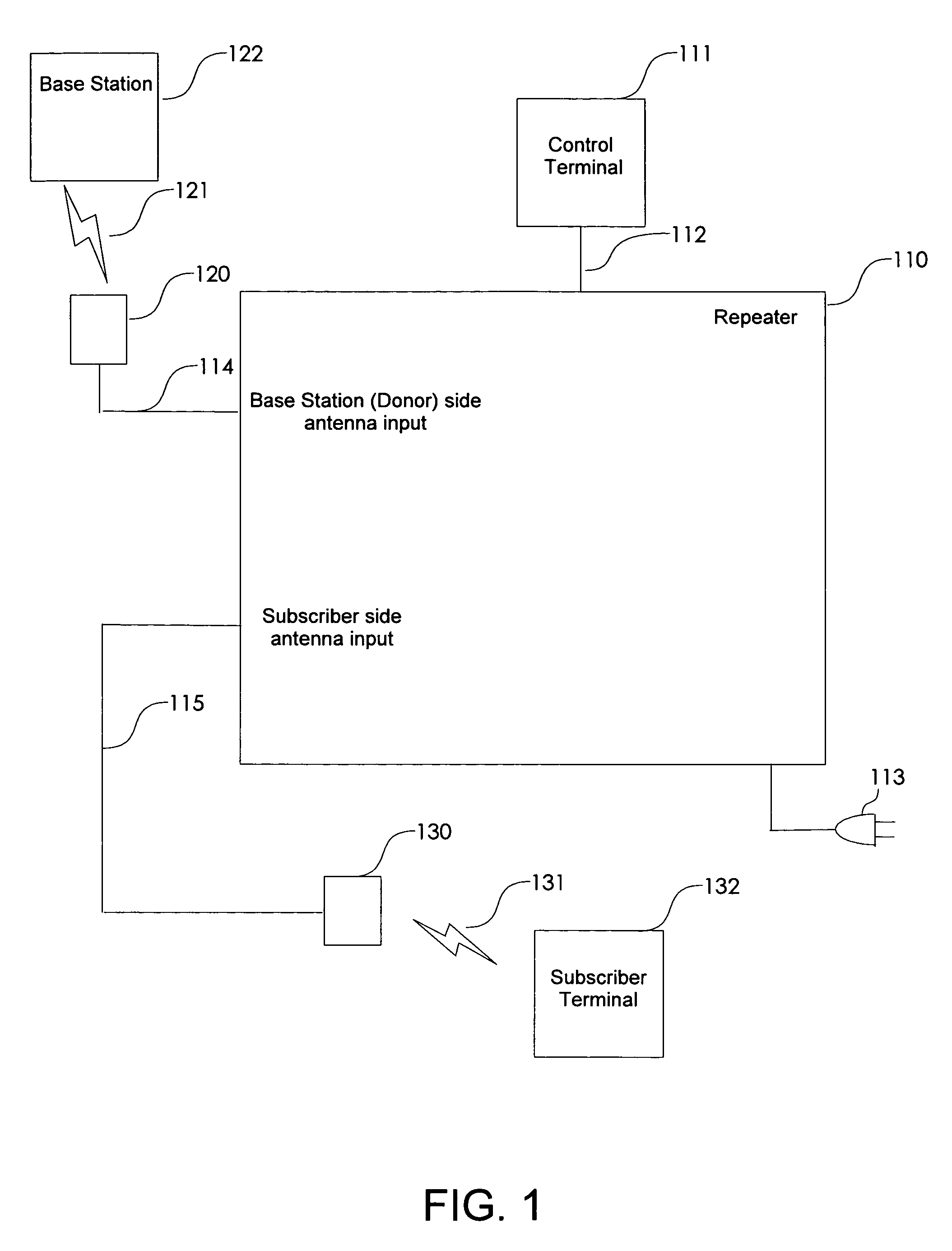

Non-frequency translating repeater with detection and media access control

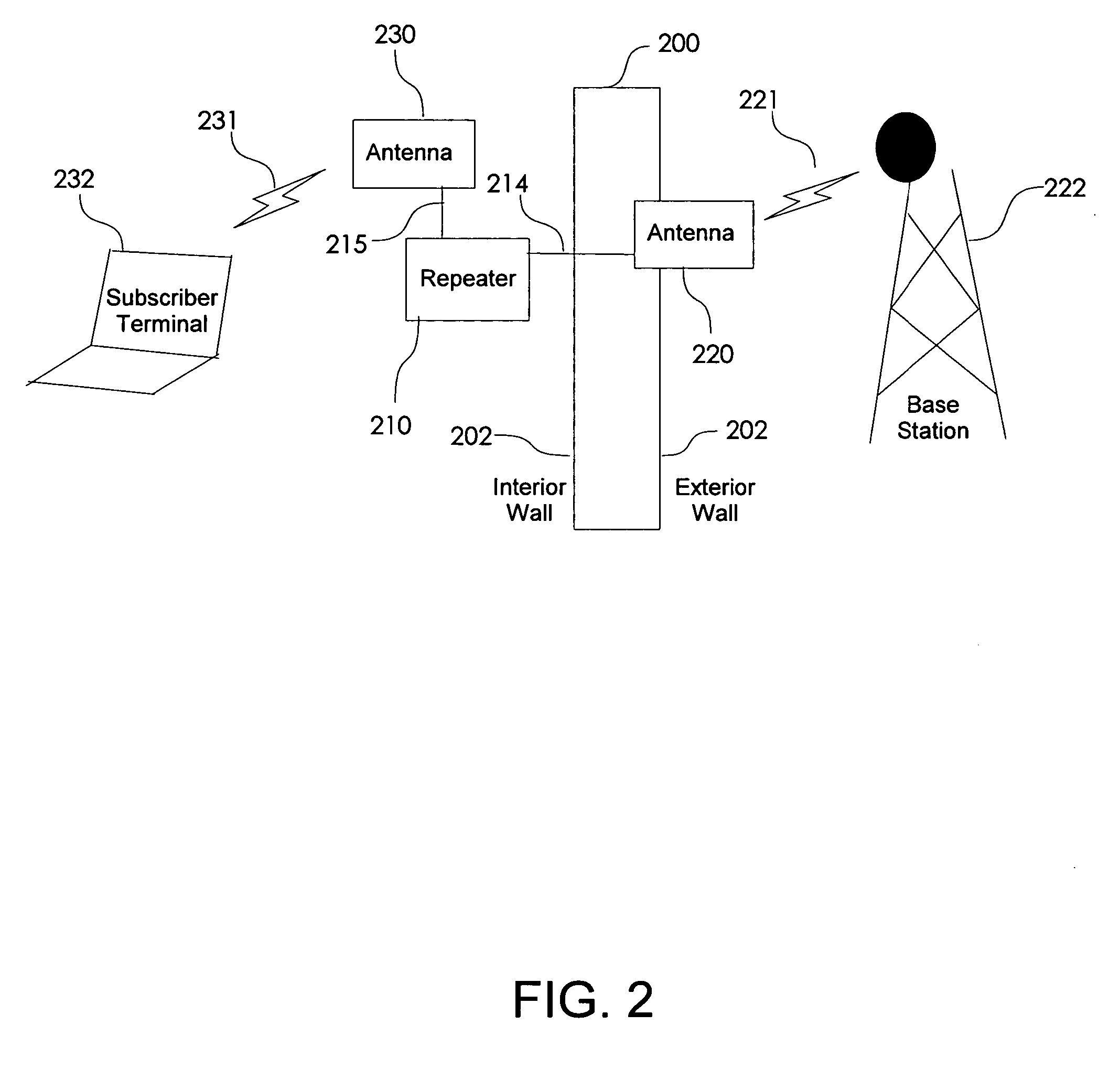

A non-frequency translating repeater (110, 210, 300) for use in a time division duplex (TDD) radio protocol communications system includes detection retransmission and automatic gain control. Detection is performed by detectors (309, 310) and a processor (313). Detection can be overridden by processor (313) using logic elements (314). Antennae (220, 230) having various form factors can be used to couple a base station (222) to a subscriber terminal (232) which can be located in a sub-optimal location such as deep inside a building or the like.

Owner:QUALCOMM INC

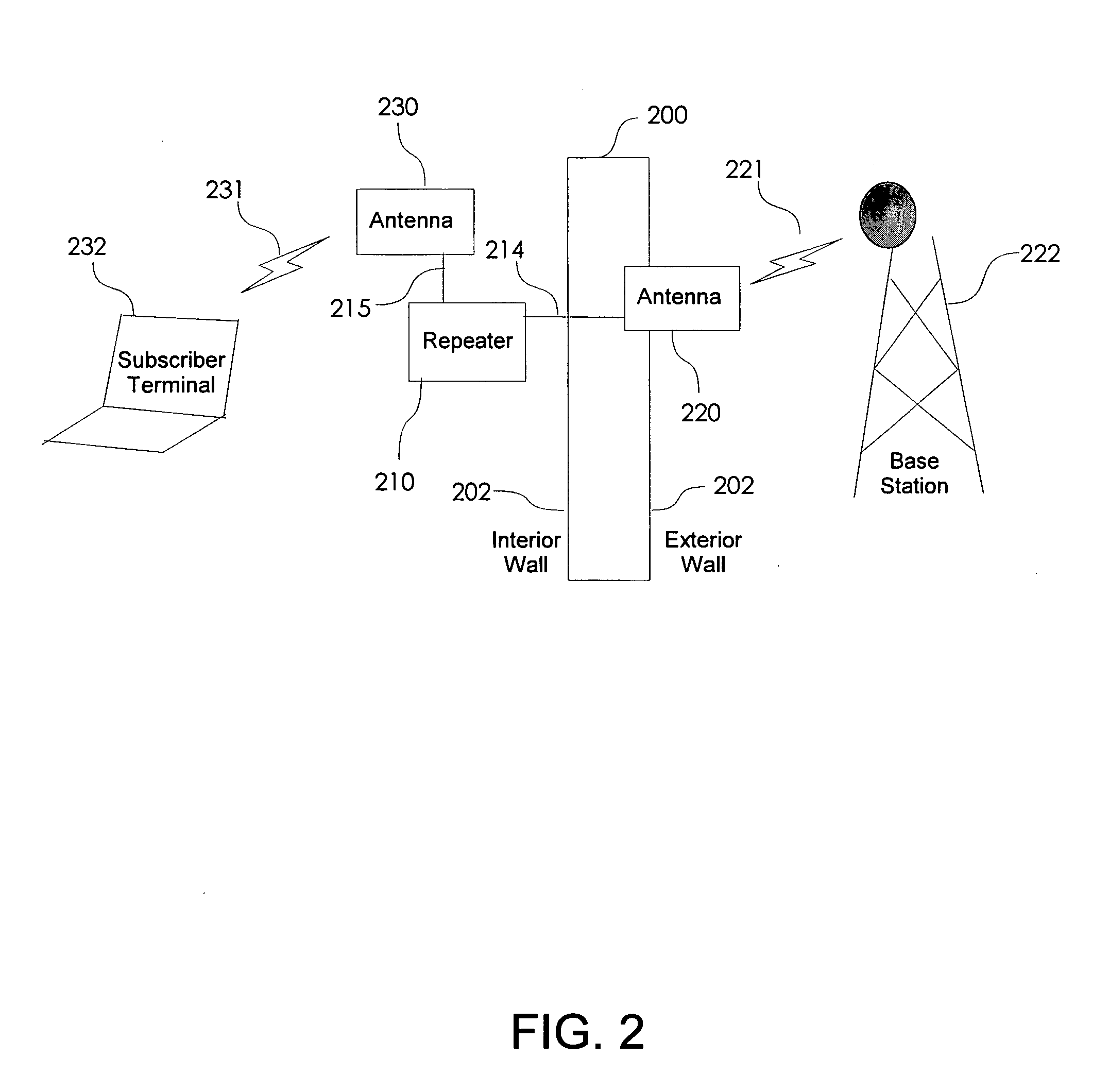

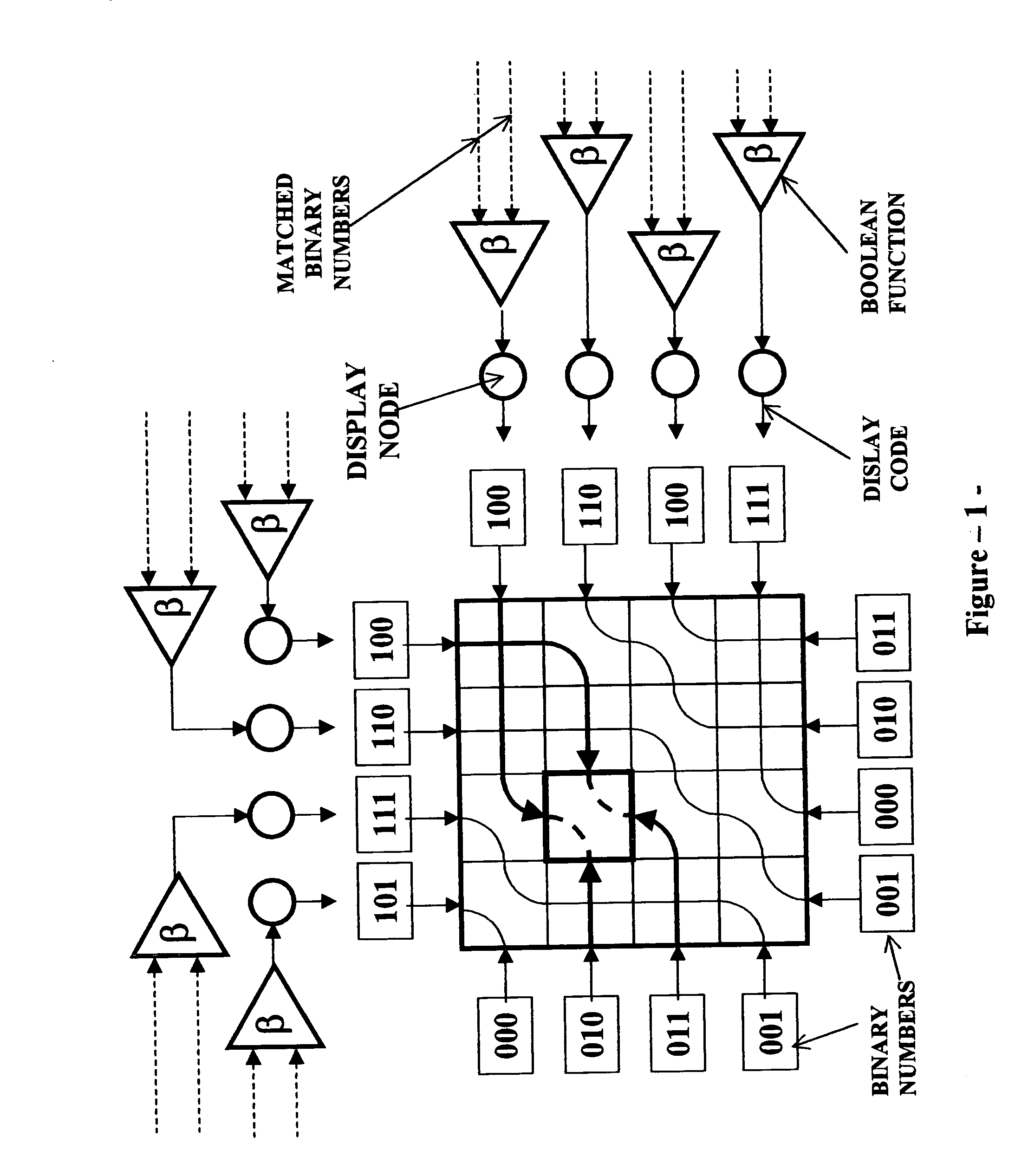

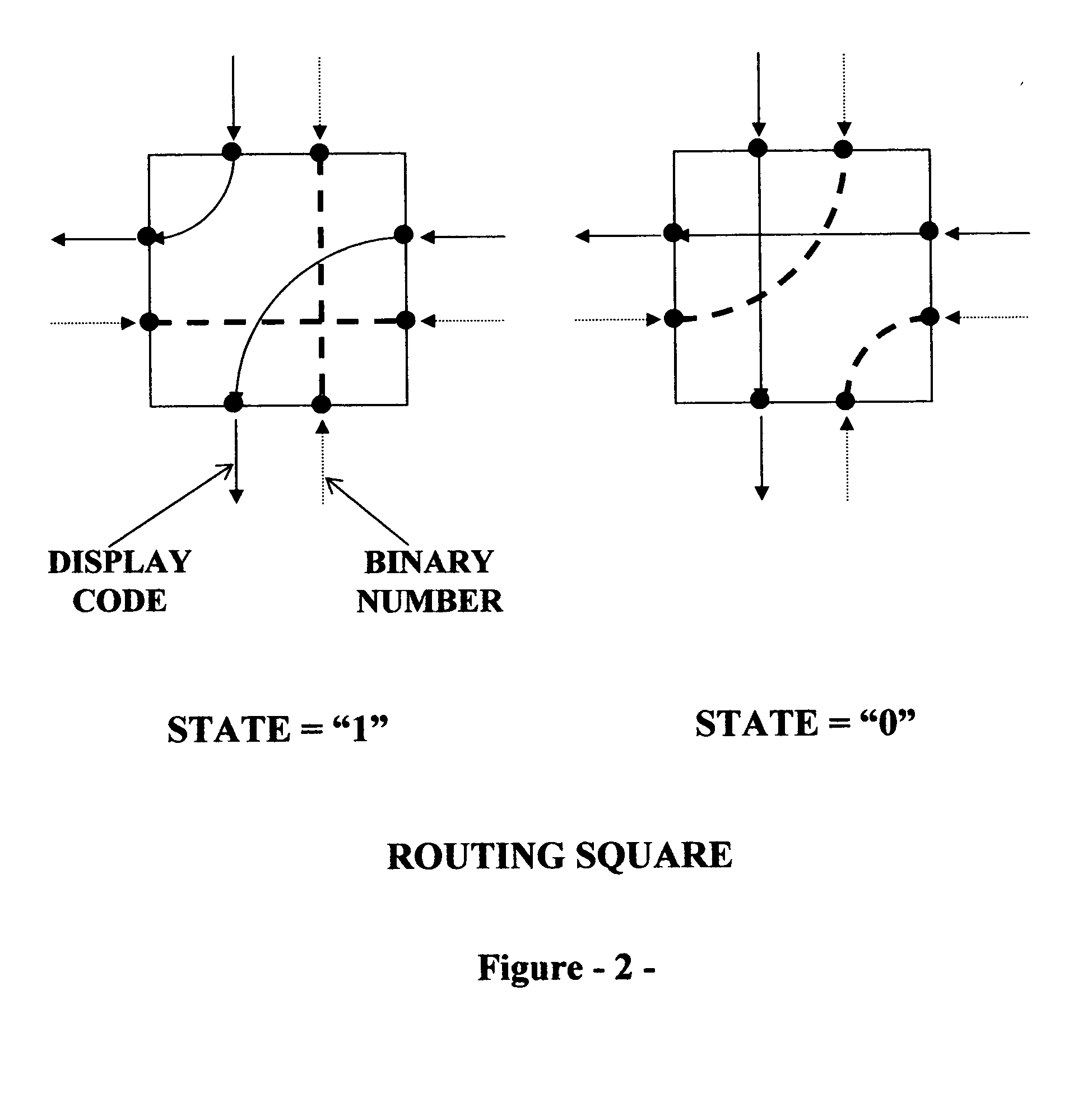

Interactive gaming device

ActiveUS20050164764A1Evenly distributedReduce probabilityApparatus for meter-controlled dispensingVideo gamesLogical elementInput control

An interactive gaming device, method and apparatus, is disclosed which includes means to assign binary numbers to playing positions. Each of said playing positions includes an indicator and a logical element to select and route pairs of the binary numbers to each other. Each playing position may also include an input control mechanism to enable a player to manually interact with the gaming device. Upon a random or a manual activation of a logical element, the matched pairs of binary numbers are used to generate a plurality of display codes. The device then assigns these display codes to the playing positions in order to produce colors or images at the indicators. A determination is then made if a winning display combination has occurred. A plurality of sound and visual effects are also provided to heighten the enjoyment of using the device.

Owner:GHALY NABIL N

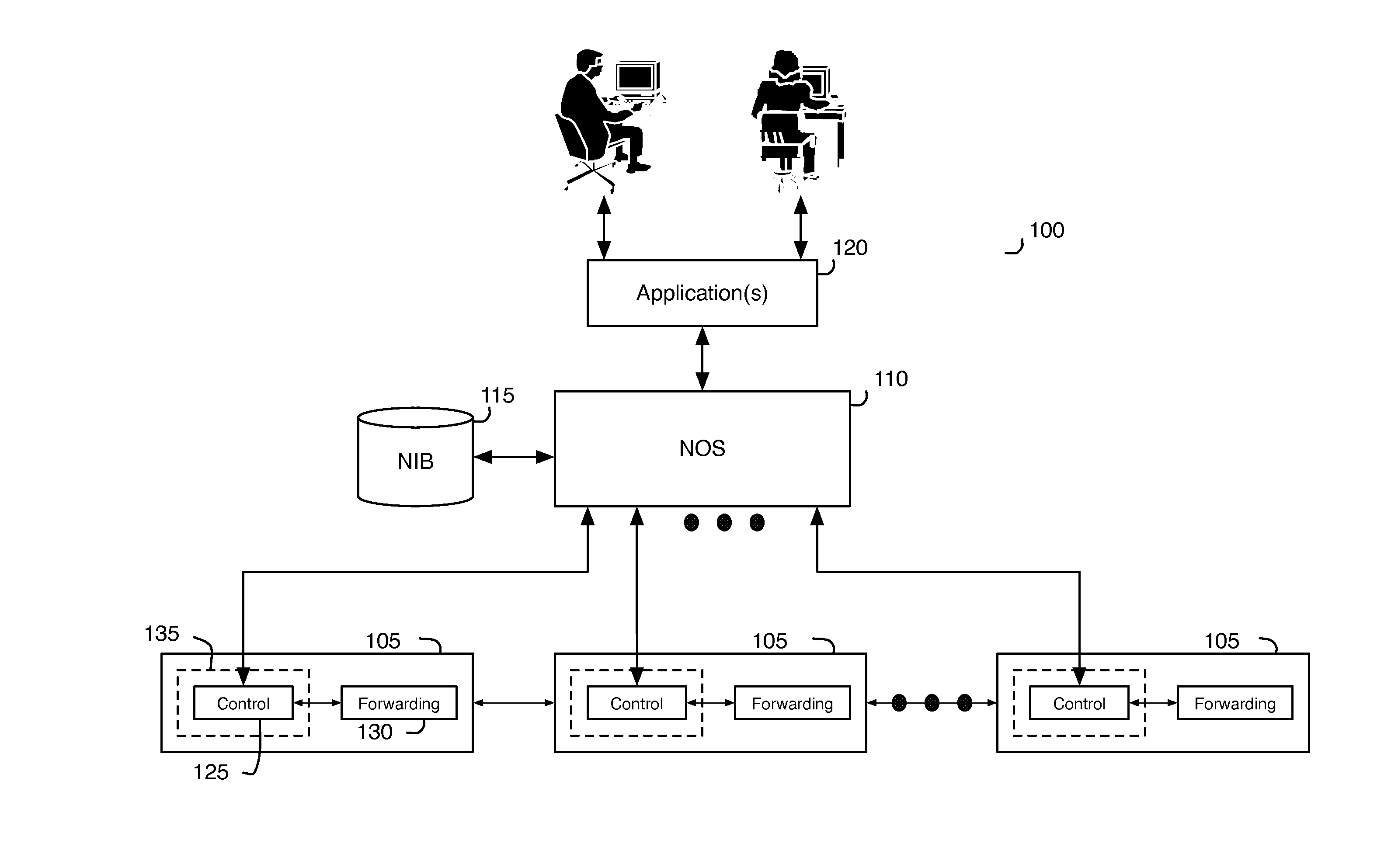

Network control apparatus and method with port security controls

Port security in some embodiments is a technique to apply to a particular port of a logical switching element such that the network data entering and existing the logical switching element through the particular logical port have certain addresses that the switching element has restricted the logical port to use. For instance, a logical switching element may restrict a particular logical port to one or more certain network addresses. To enable a logical port of a logical switch for port security, the control application of some embodiments receives user inputs that designate a particular logical port and a logical switch to which the particular logical port belongs. The control application in some embodiments formats the user inputs into logical control plane data specifying the designation. The control application in some embodiments then converts the logical control plane data into logical forwarding data that specify port security functions.

Owner:NICIRA

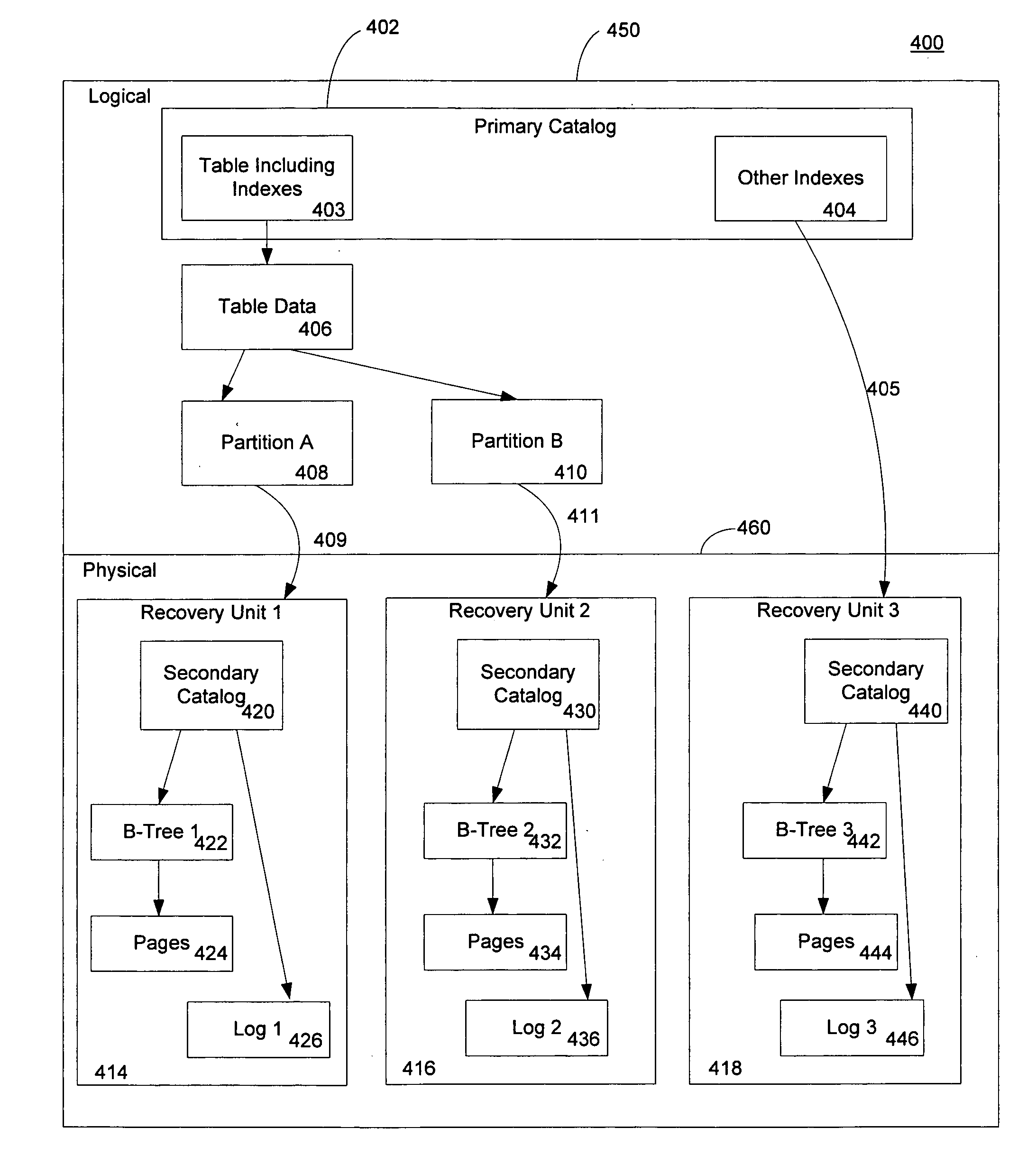

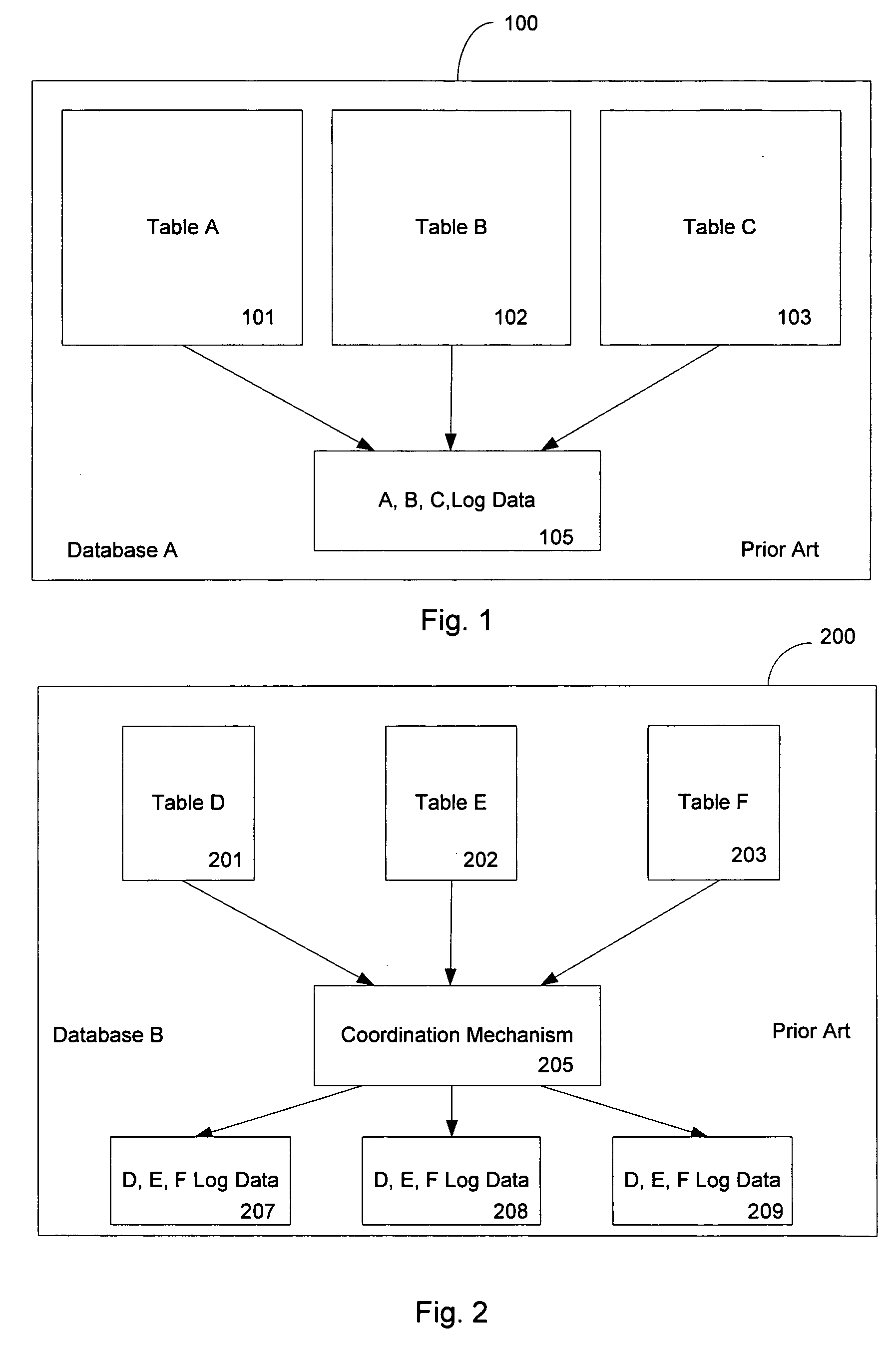

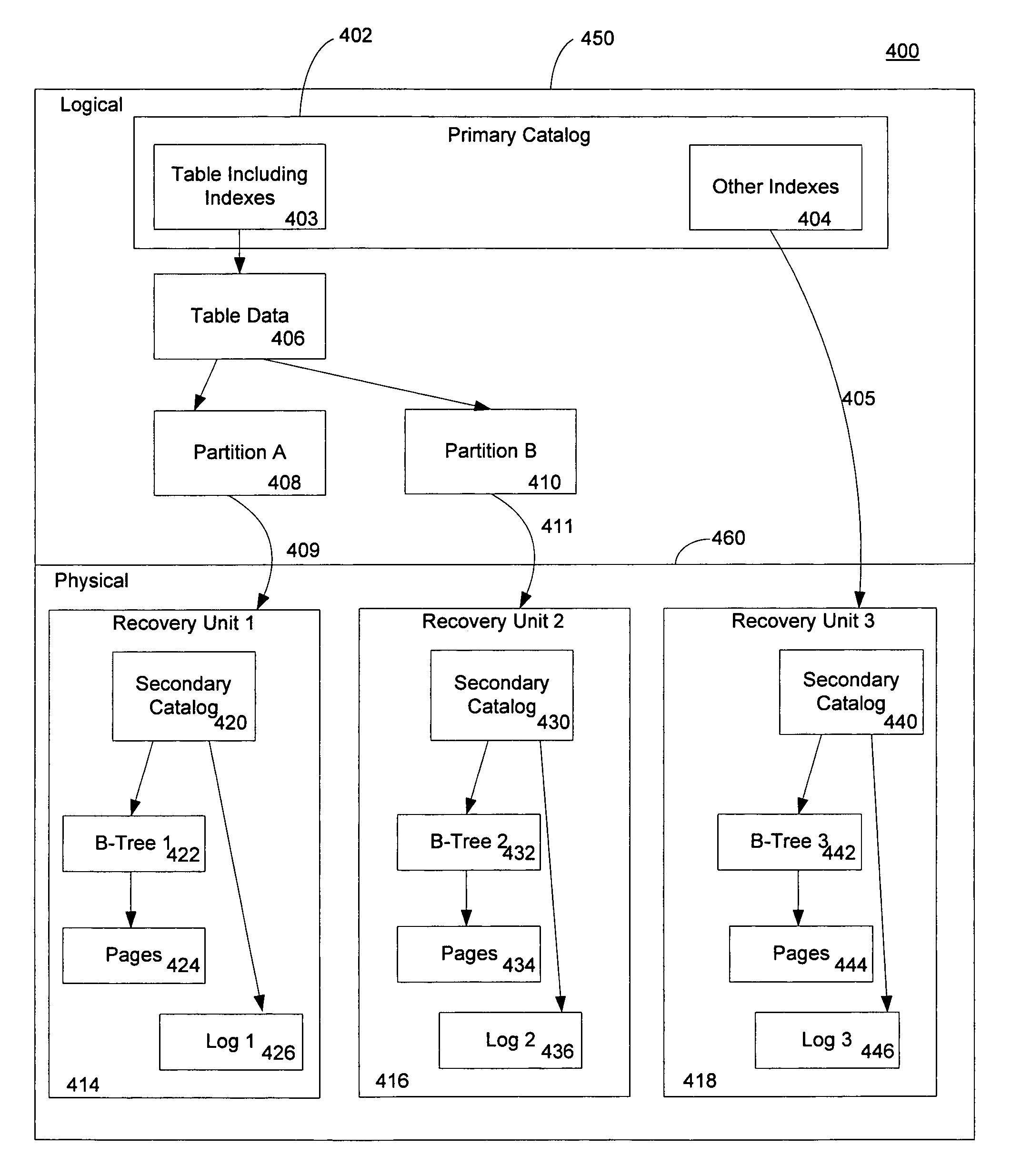

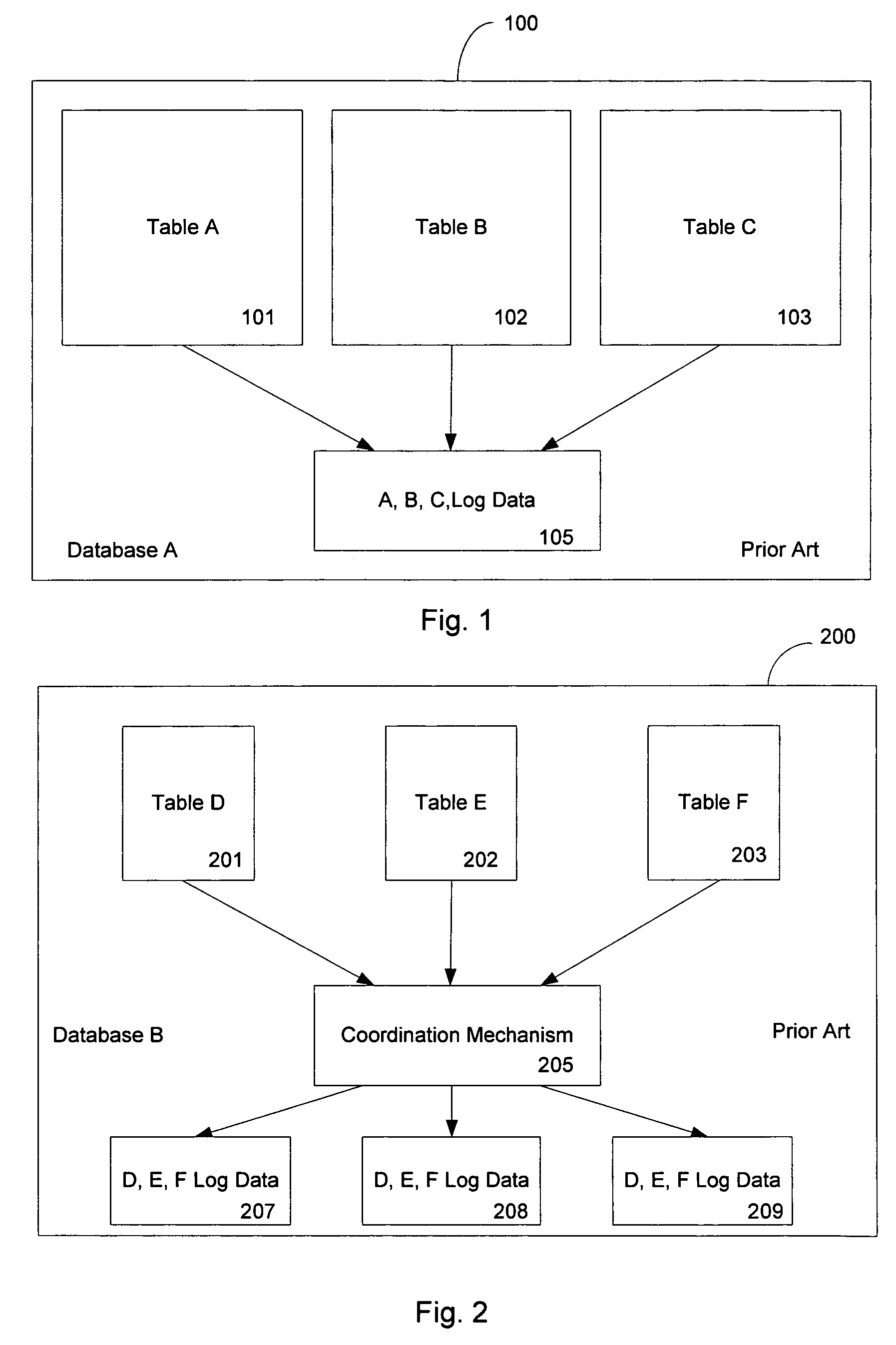

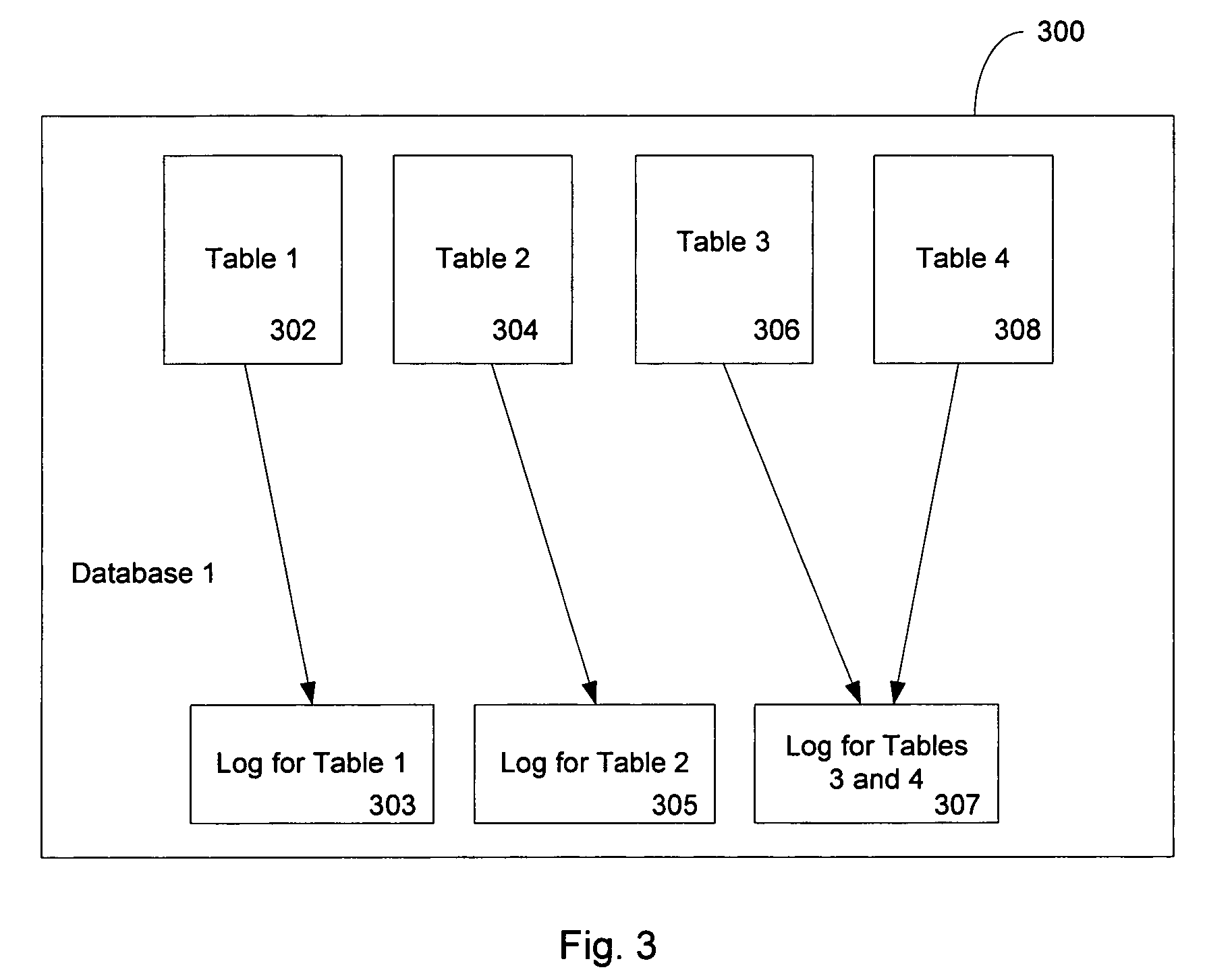

System and method for recovery units in databases

InactiveUS20050193035A1Increase profitEasy to operateData processing applicationsError detection/correctionLogical elementPhysical element

The creation of multiple recoverable units within a database allows a database partition to be reconstructed during maintenance and disaster recovery operations. A method of creating a recovery unit includes partitioning a database into at least two recovery units. A primary catalog of metadata relating to the logical elements of a database such as tables, indexes, and file groups is created. A secondary catalog of metadata relating to the physical elements of a database such as pages, files, B-Trees, and log streams is created for each recovery unit. The primary and secondary metadata catalogs are linked such that only one log stream is associated with any one recovery unit. A single recovery unit may then be exercised to perform recovery or maintenance operations while the remaining recovery units of the database remain online.

Owner:MICROSOFT TECH LICENSING LLC

Non-frequency translating repeater with downlink detection for uplink and downlink synchronization

ActiveUS20070066220A1Network topologiesActive radio relay systemsLogical elementCommunications system

A non-frequency translating repeater (110, 210, 300) for use in a time division duplex (TDD) radio protocol communications system includes detection retransmission and automatic gain control. Detection is performed by detectors (309, 310) and a processor (313). Detection can be overridden by processor (313) using logic elements (314). Antennae (220, 230) having various form factors can be used to couple a base station (222) to a subscriber terminal (232) which can be located in a sub-optimal location such as deep inside a building or the like.

Owner:QUALCOMM INC

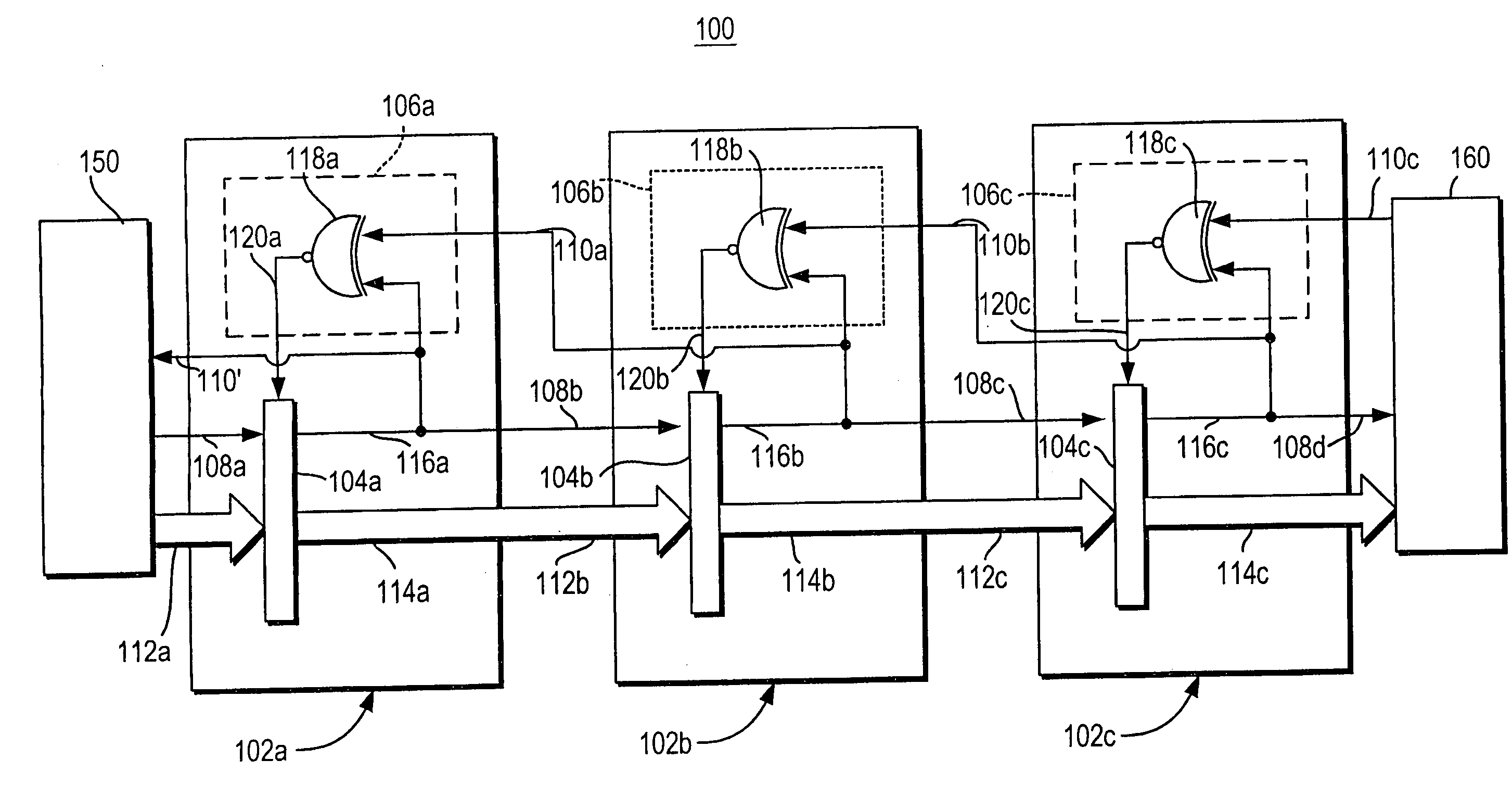

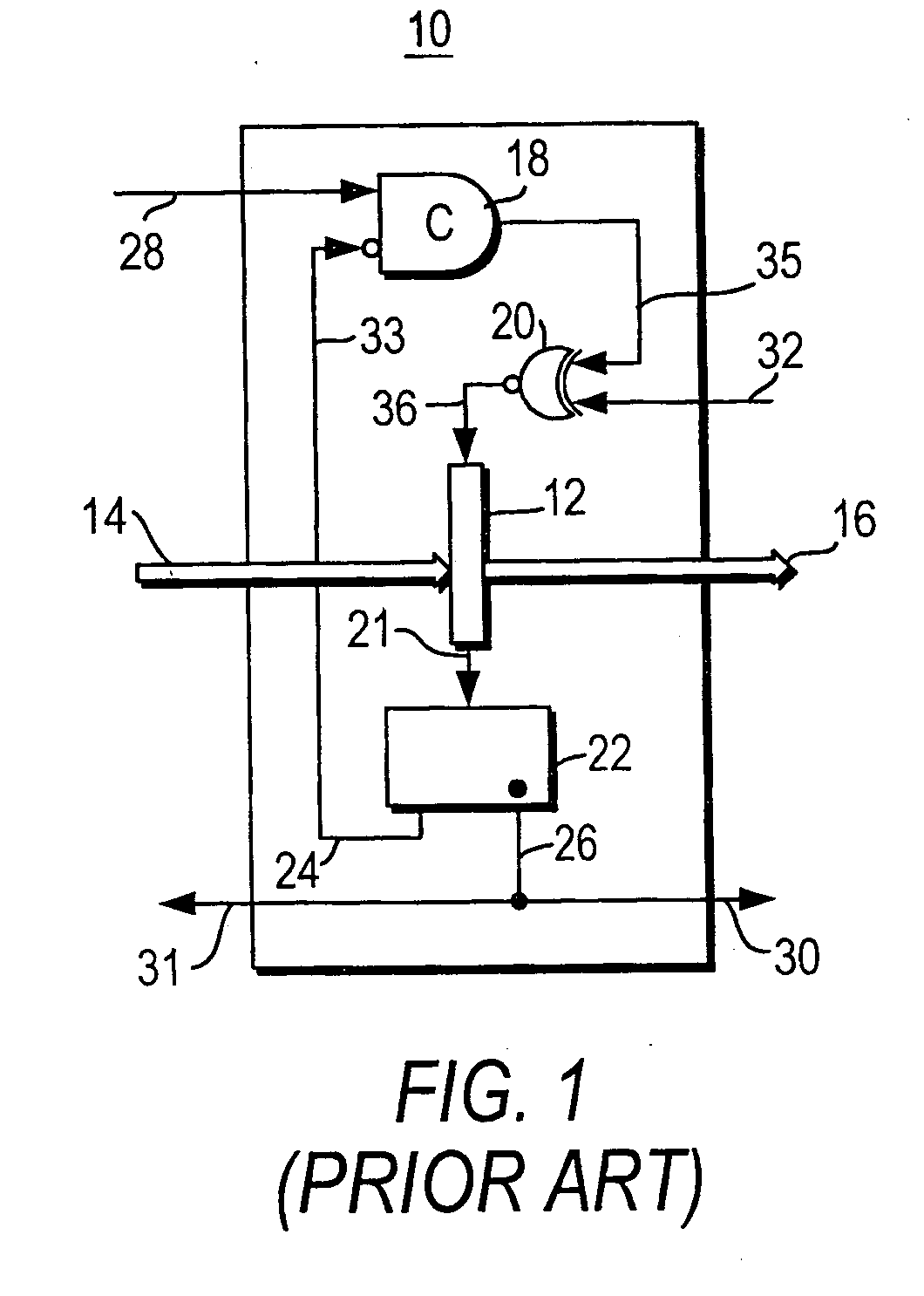

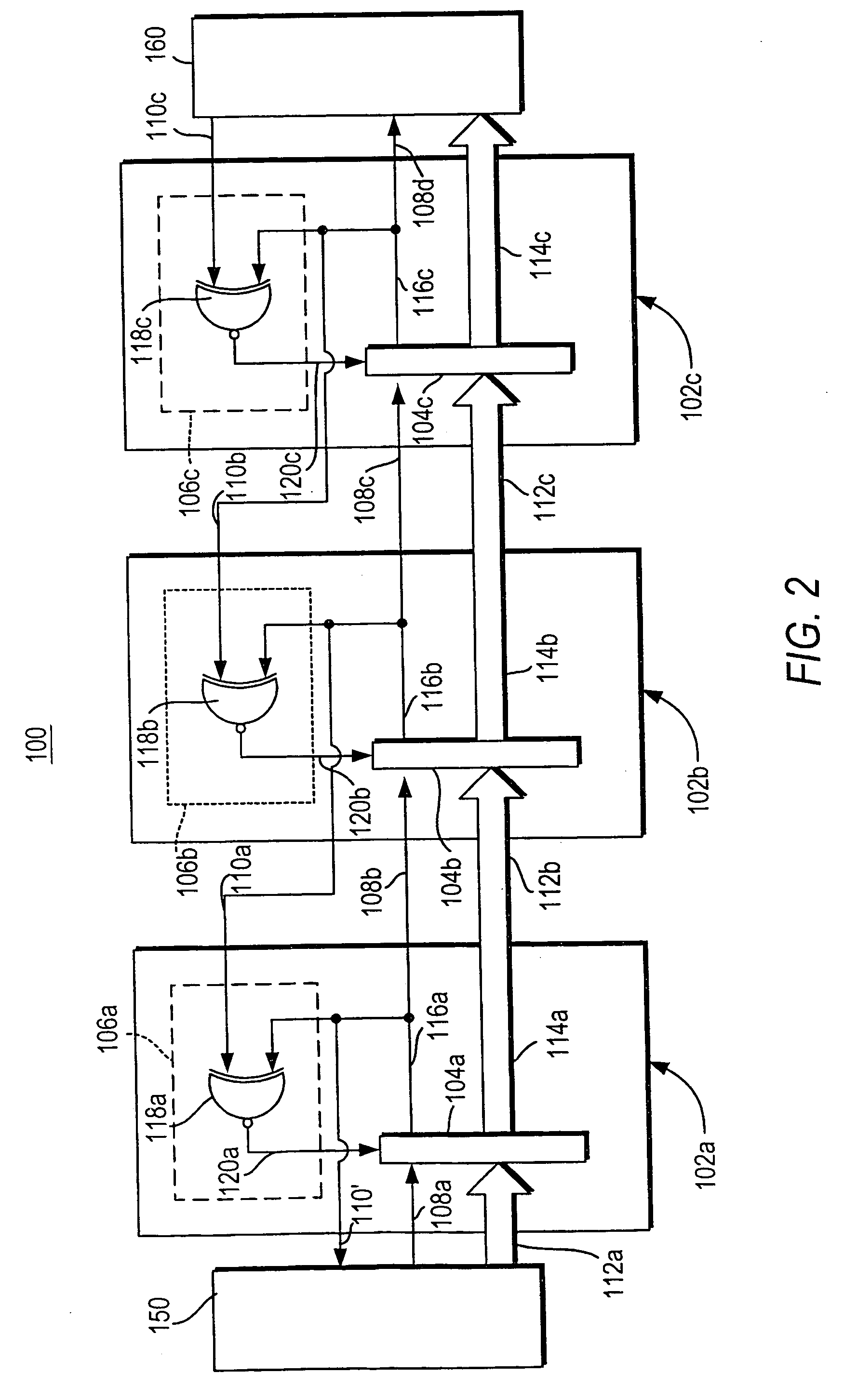

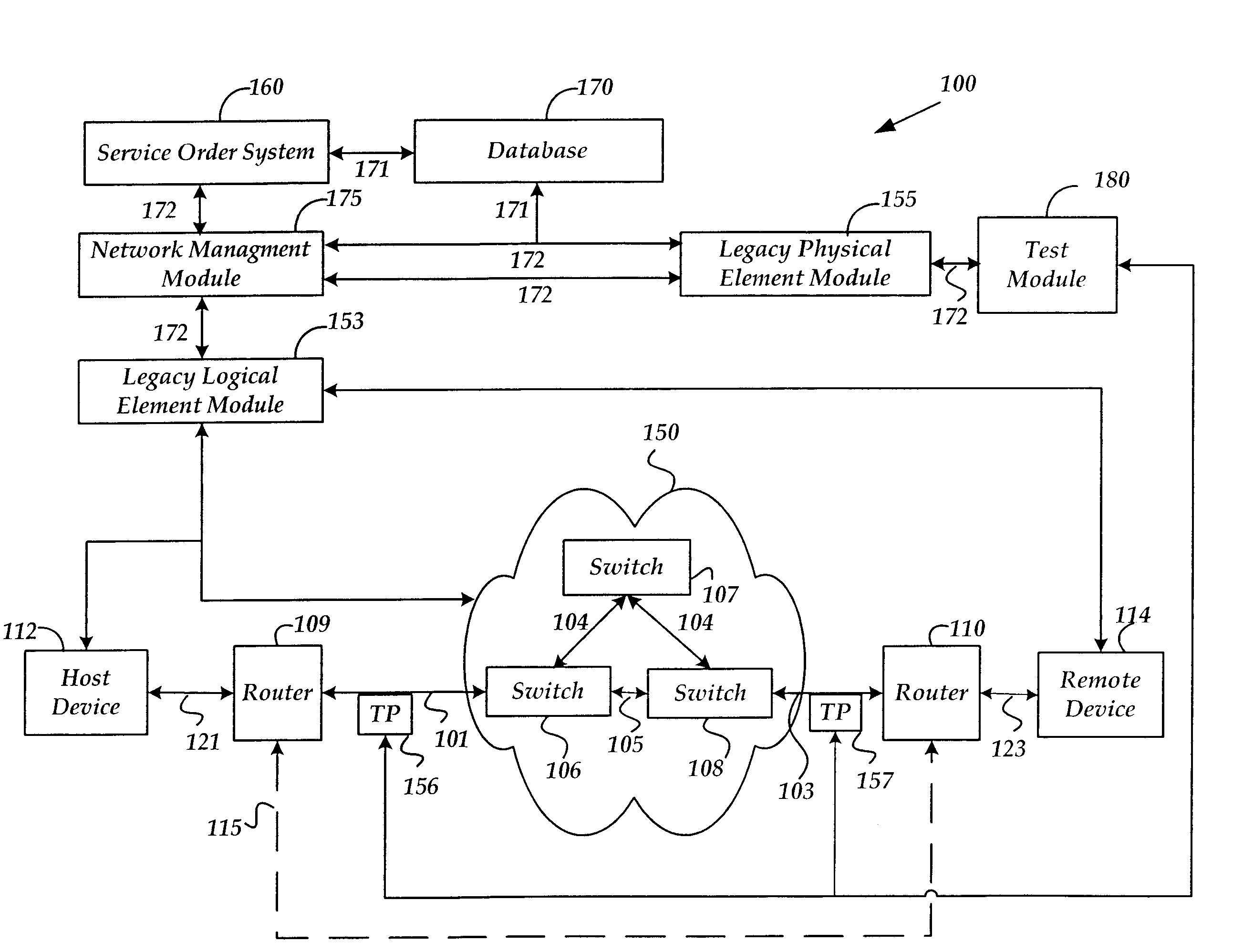

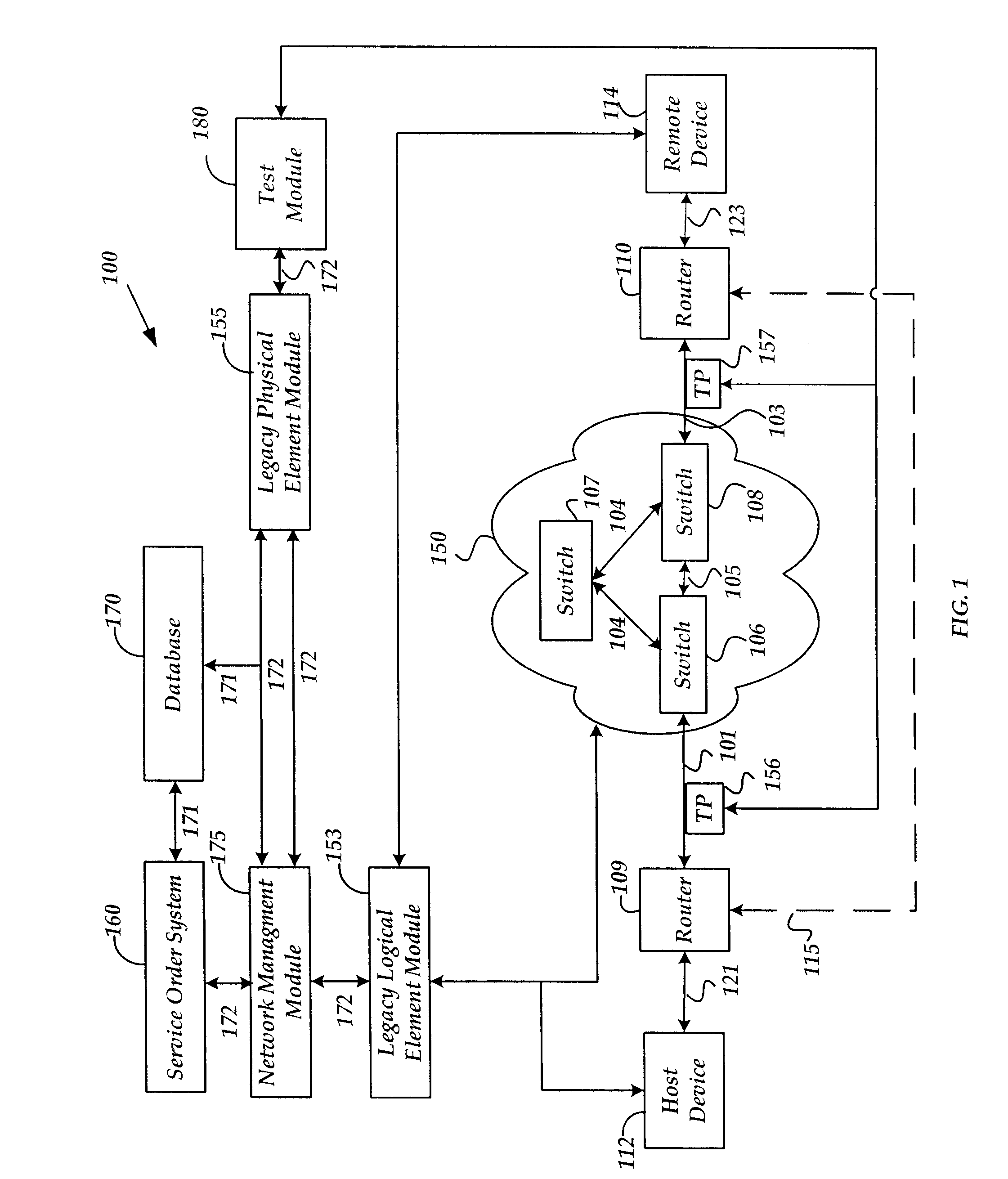

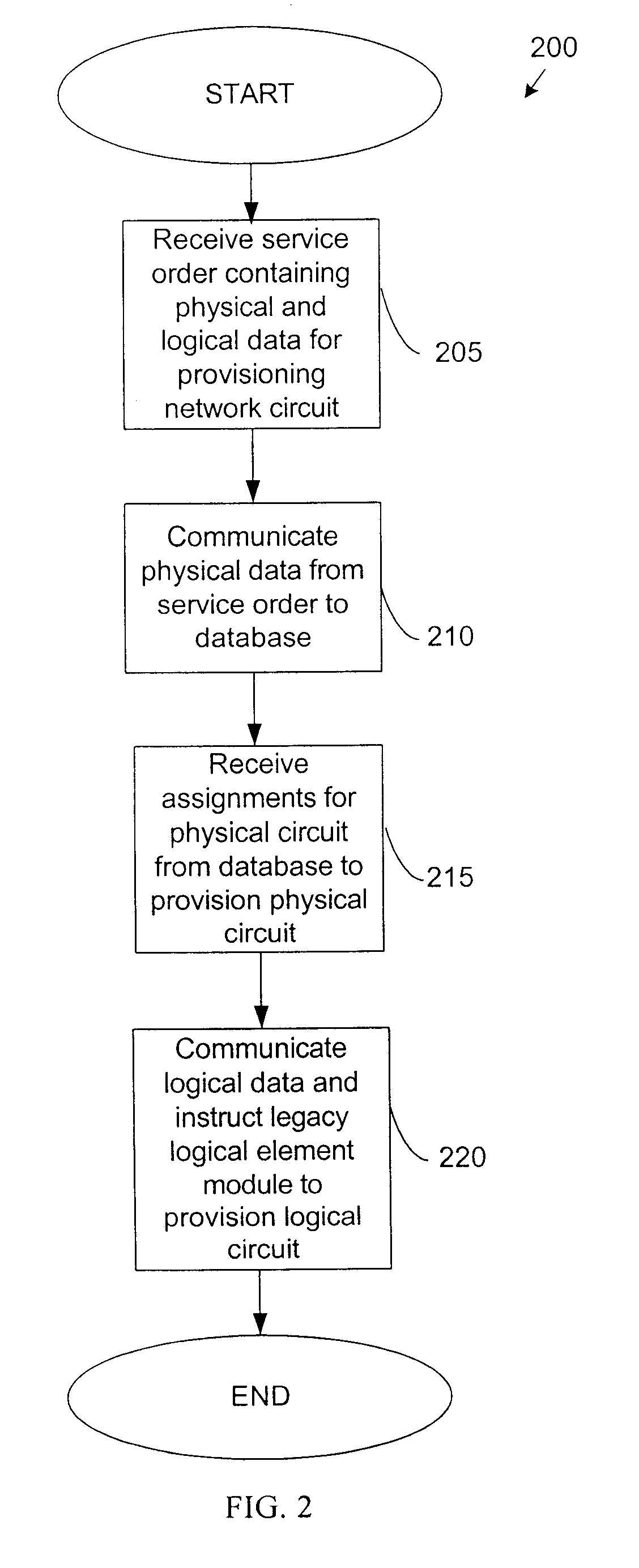

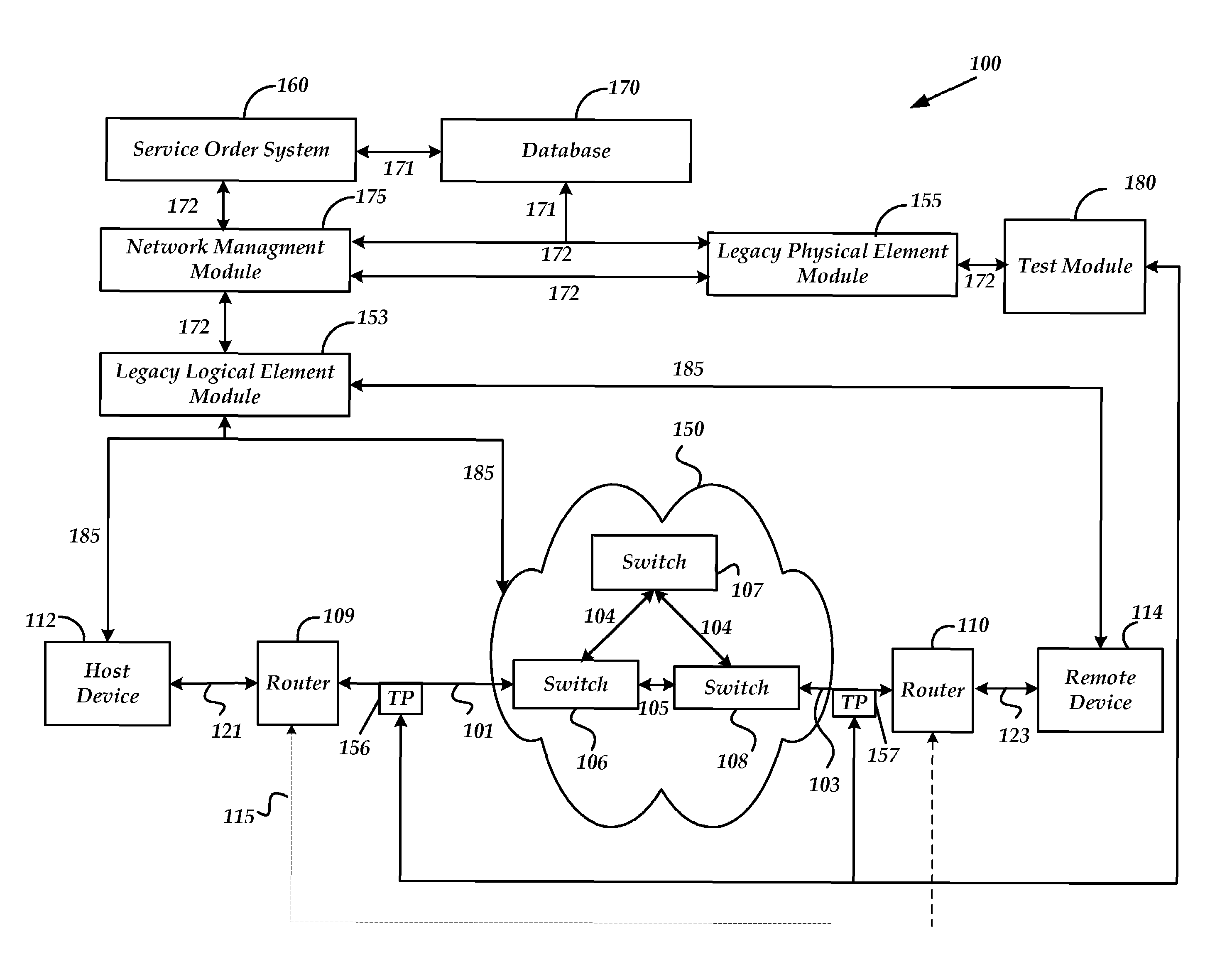

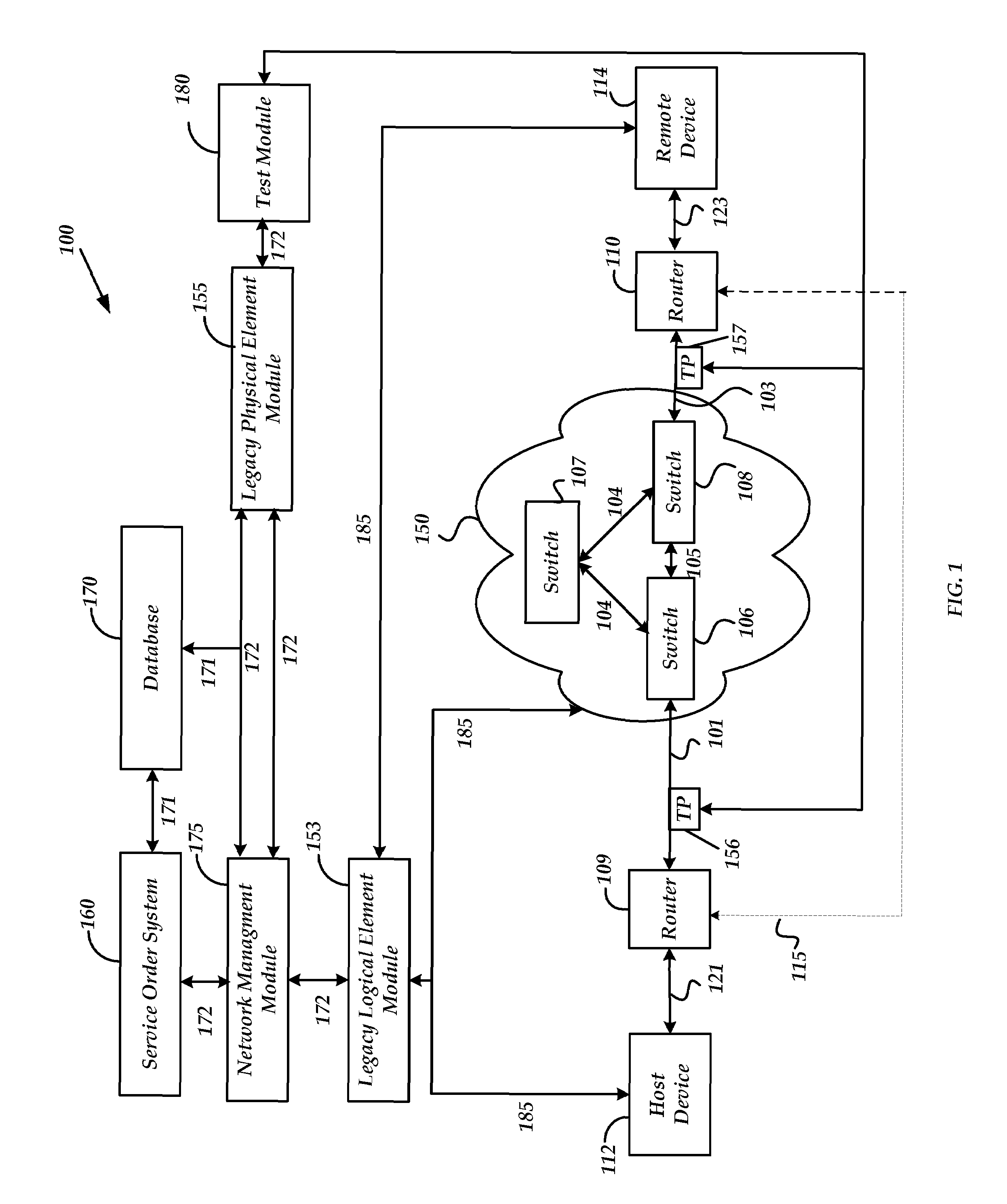

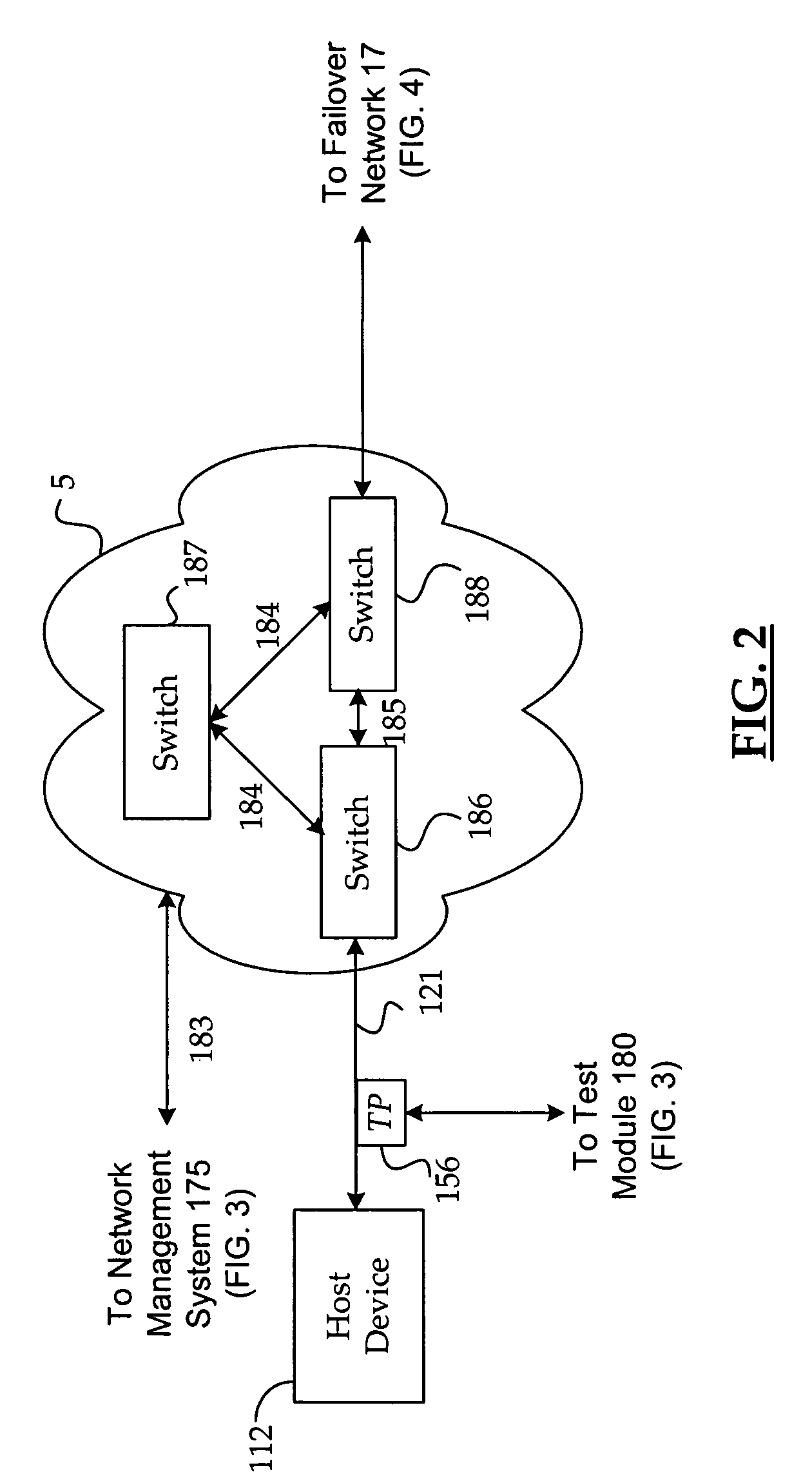

Method and system for provisioning and maintaining a circuit in a data network

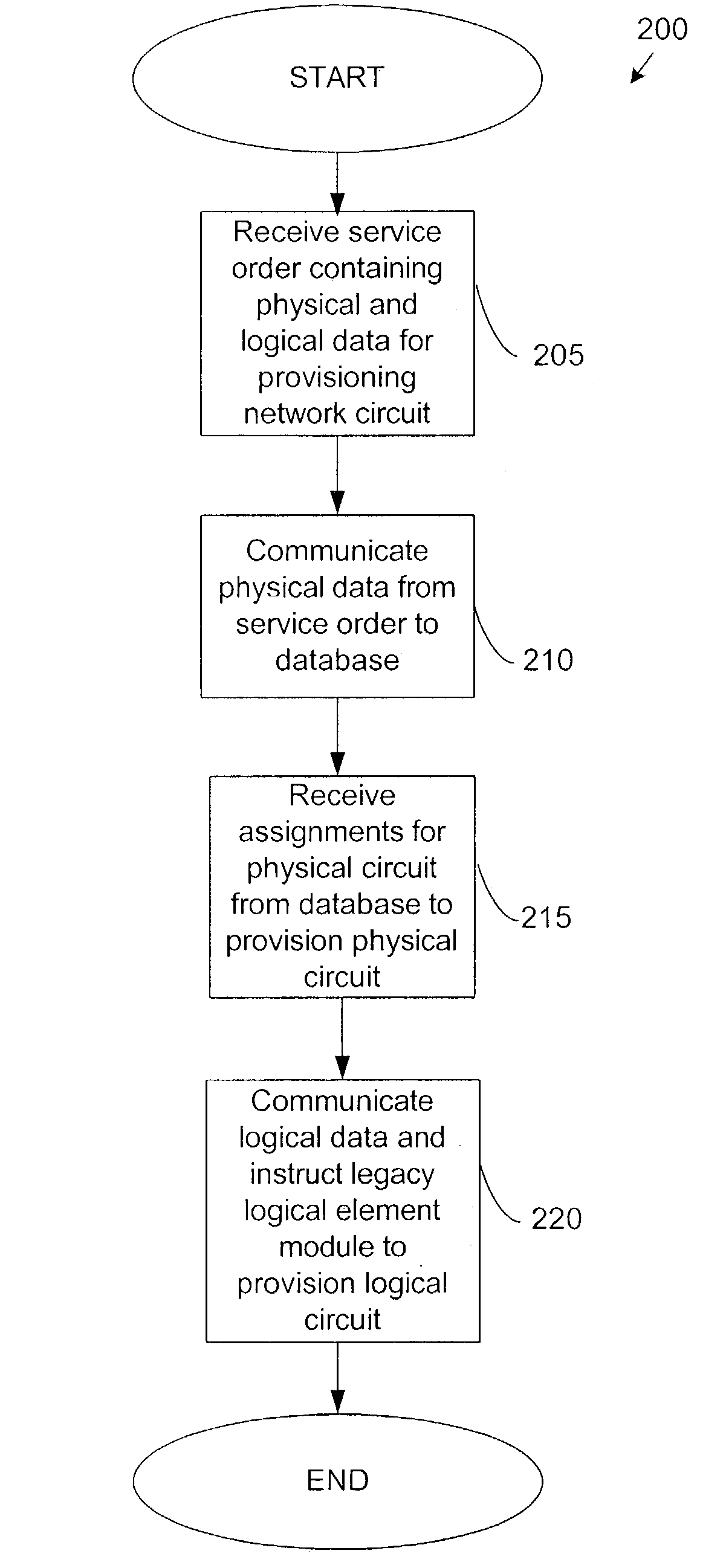

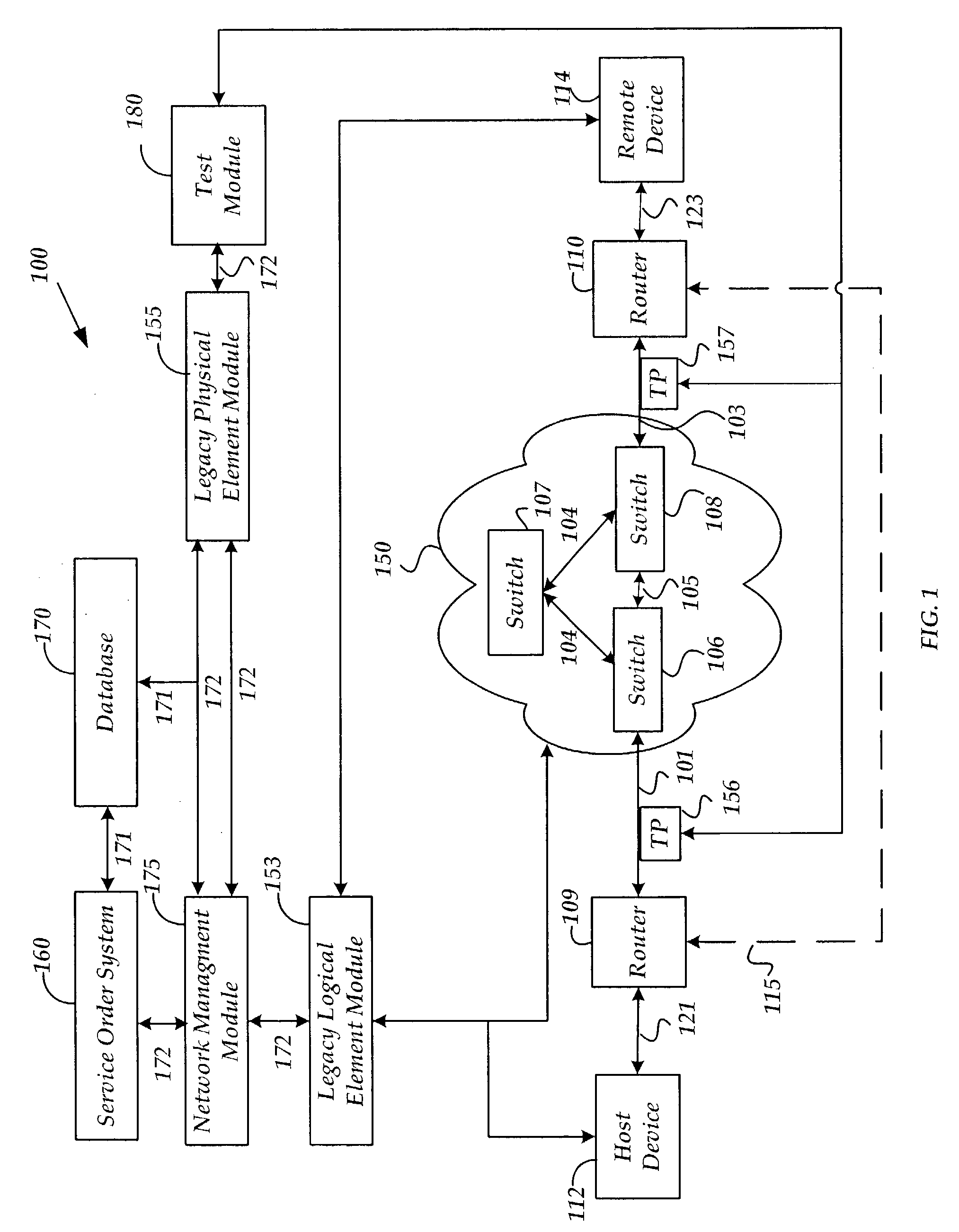

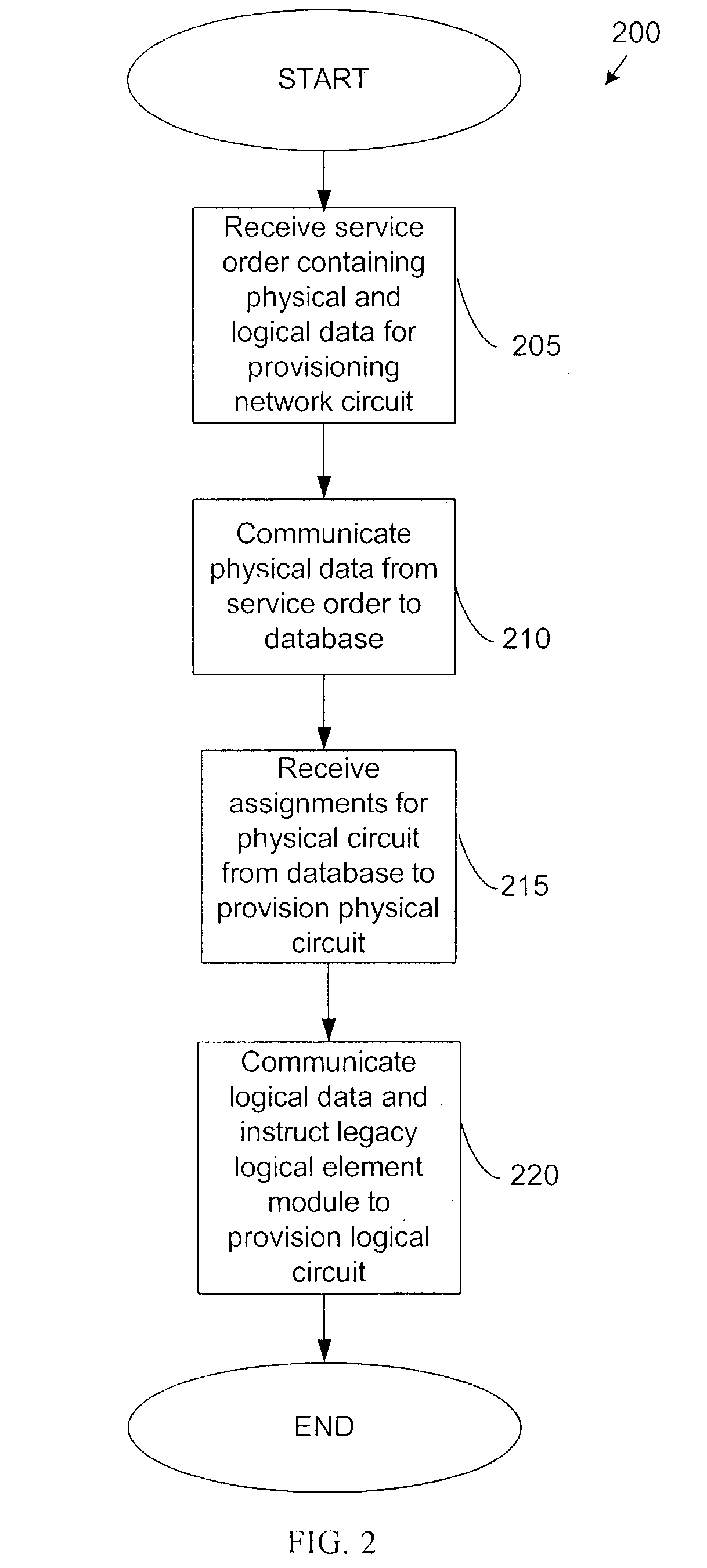

A method and system are provided for provisioning a circuit in a data network without manual intervention. A network management module receives an order for provisioning the circuit and then, based on the order, transmits a request to a legacy logical element module to configure a logical circuit in one or more network devices in the network. The network device may be a switch. The circuit may be a frame relay circuit or an ATM circuit. A method and system are also provided for maintaining a network circuit in a data network. The network circuit includes both a logical circuit and a physical circuit. A legacy physical element module sends a request for logical circuit data to a legacy logical element module through a network management module in communication with the legacy physical element module and the legacy physical element module. Based on the request, the legacy logical element module retrieves the logical circuit data from one or more network devices in the network and transmits the data to the legacy physical element module through the network management module. Upon receiving the logical circuit data, the legacy physical element module troubleshoots the physical circuit to maintain the network circuit.

Owner:AT&T INTPROP I L P

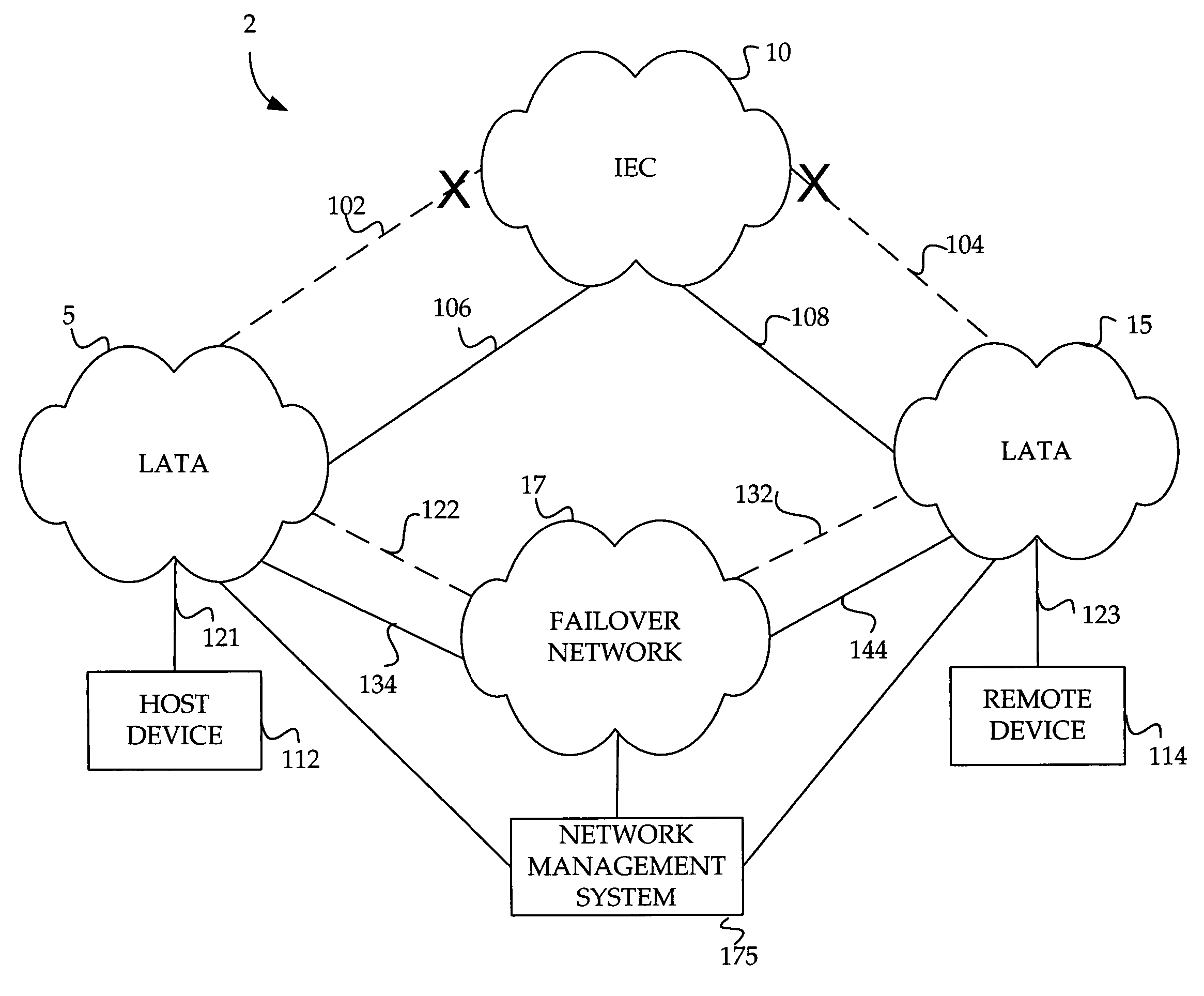

Method and system for fail-safe renaming of logical circuit identifiers for rerouted logical circuits in a data network

A method and system are provided for fail-safe renaming of logical circuit identifiers for rerouted logical circuits in a data network. A network management module is provided for accessing a network device provisioned for routing data over a first logical circuit in the data network. The network management module is further utilized for deleting the first logical circuit in the network device upon detecting a failure in the first logical circuit and provisioning a second logical circuit in the network device for rerouting the data from the first logical circuit. In provisioning the second logical circuit, the network management module is utilized to assign a second logical circuit identifier to identify the second logical circuit. The network management module is further utilized for renaming a first logical circuit identifier to the second logical circuit identifier and renaming a logical circuit label for the first logical circuit in a logical element module in communication with the network management module. The renamed logical circuit label includes the first logical circuit identifier and may be utilized to indicate that the logical circuit data from the failed logical circuit has been rerouted.

Owner:BELLSOUTH INTPROP COR

Asynchronous pipeline with latch controllers

An asynchronous pipeline for high-speed applications uses simple transparent latches in its datapath and small latch controllers for each pipeline stage. The stages communicate with each other using request signals and acknowledgment signals. Each transition on the request signal indicates the arrival of a distinct new data item. Each stage comprises a data latch that is normally enabled to allow data to pass through, and a latch controller that enables and disables the data latch. The request signal and the data are inputs to the data latch. Once the stage has latched the data, a done signal is produced, which is sent to the latch controller, to the previous stage as an acknowledgment signal, and to the next stage as a request signal. The latch controller disables the latch upon receipt of the done signal, and re-enables the data latch upon receipt of the acknowledgment signal from the next stage. For correct operation, the request signal must arrive at the stage after the data inputs have stabilized. The asynchronous pipeline may incorporate logic elements to combine data, as well as matched delay elements for the request, acknowledgment, and done signals. The asynchronous pipeline may also incorporate clocked CMOS logic gates. Fork and join structures are also provided by the asynchronous pipeline design.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

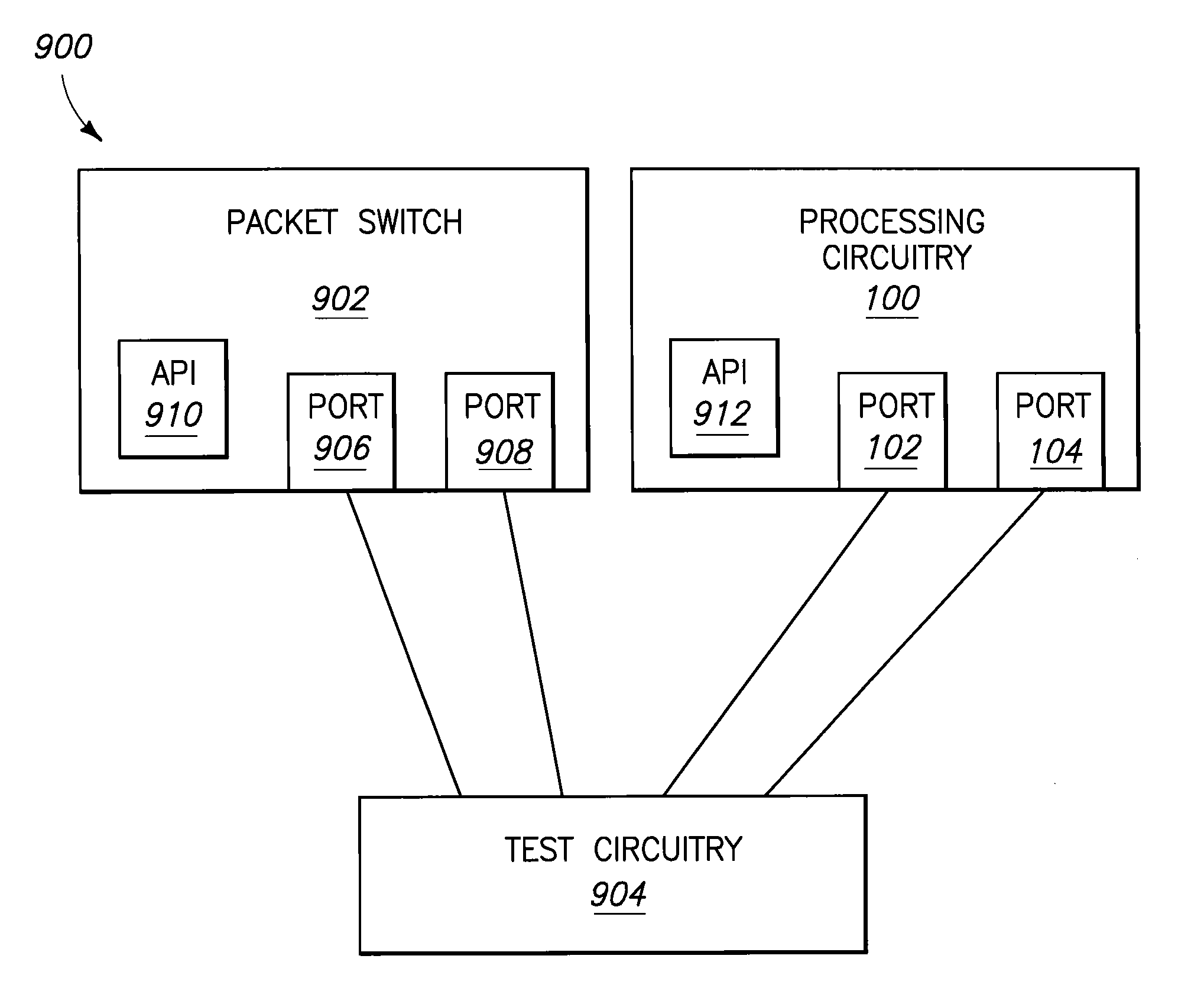

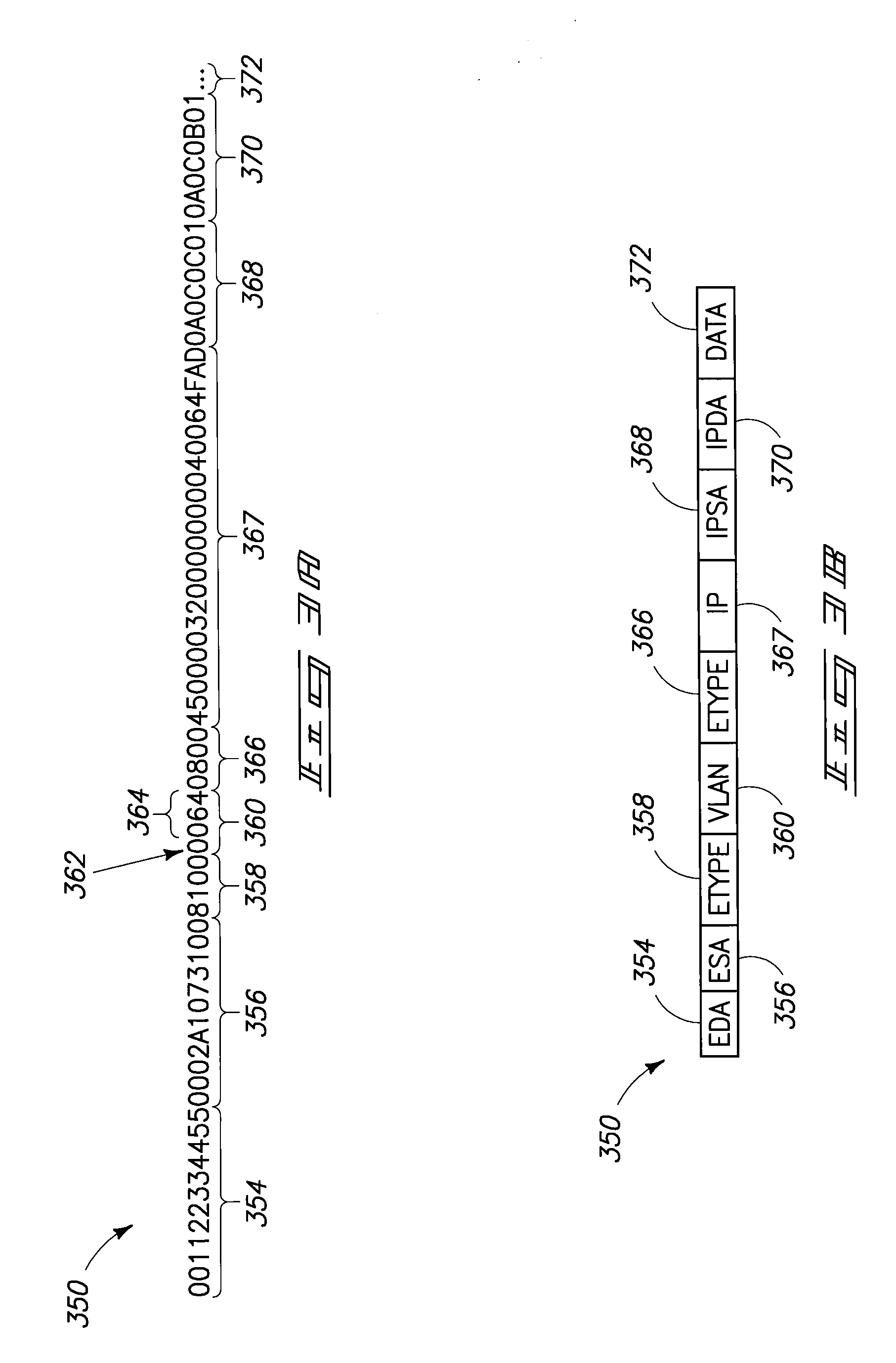

Packet Switch Modeling and Using a Packet Switch Model to Test a Packet Switch

Packet switch test methods include receiving a first packet from a packet switch, receiving a second packet from processing circuitry configured to model expected behavior of the packet switch, comparing the first packet to the second packet, and, based on the comparing, determining whether the packet switch is operating according to the expected behavior. Packet switch modeling methods include identifying functionality of a packet switch to be modeled, creating, in a packet switch model, a plurality of nodes representing physical and / or logical elements of the packet switch, the nodes being configured to process packet data structures and to respectively model different portions of the functionality of the packet switch relative to one another, and, in the packet switch model, connecting the nodes with pathways by which the packet data structures may be forwarded between the nodes.

Owner:CIENA

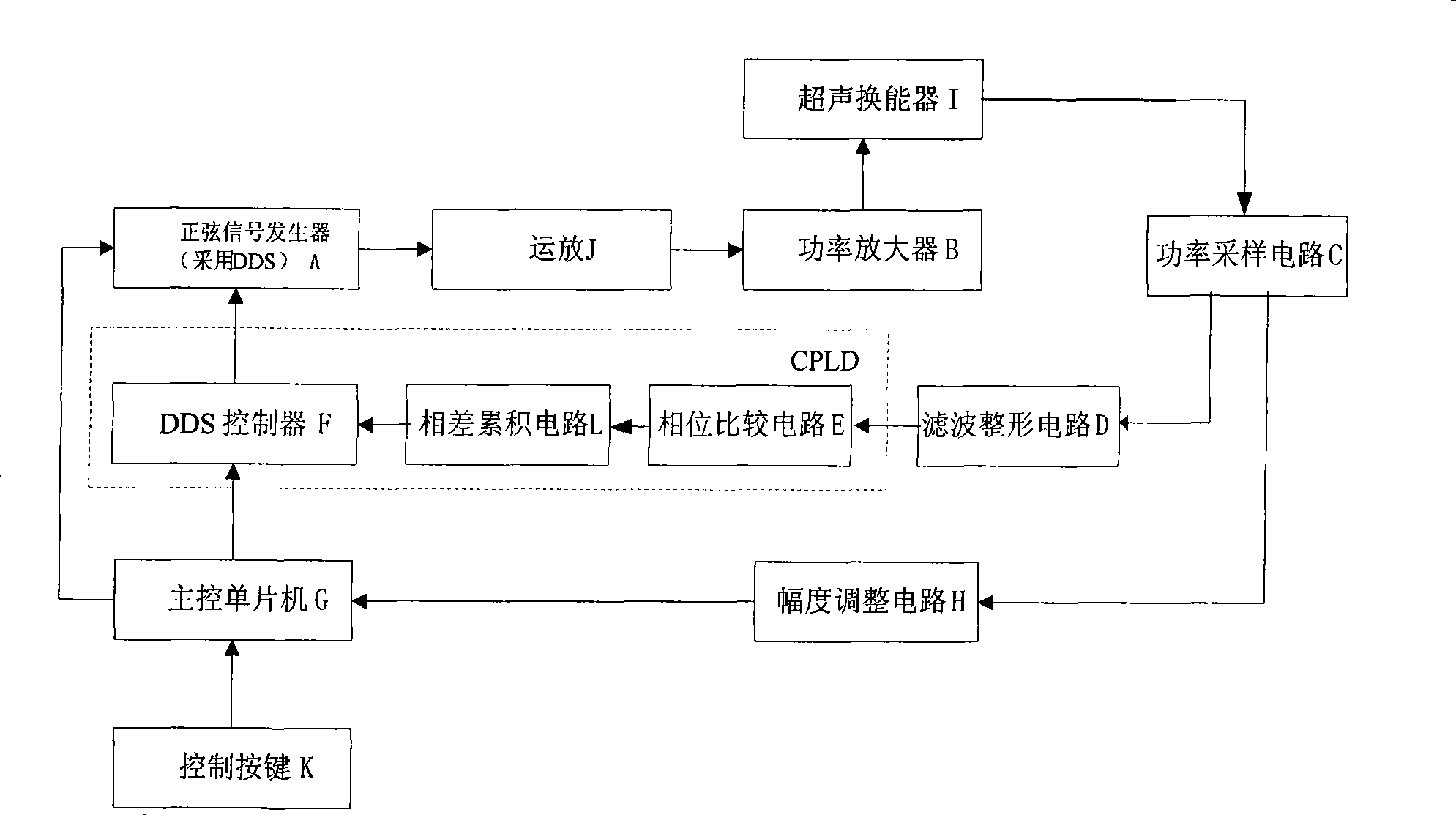

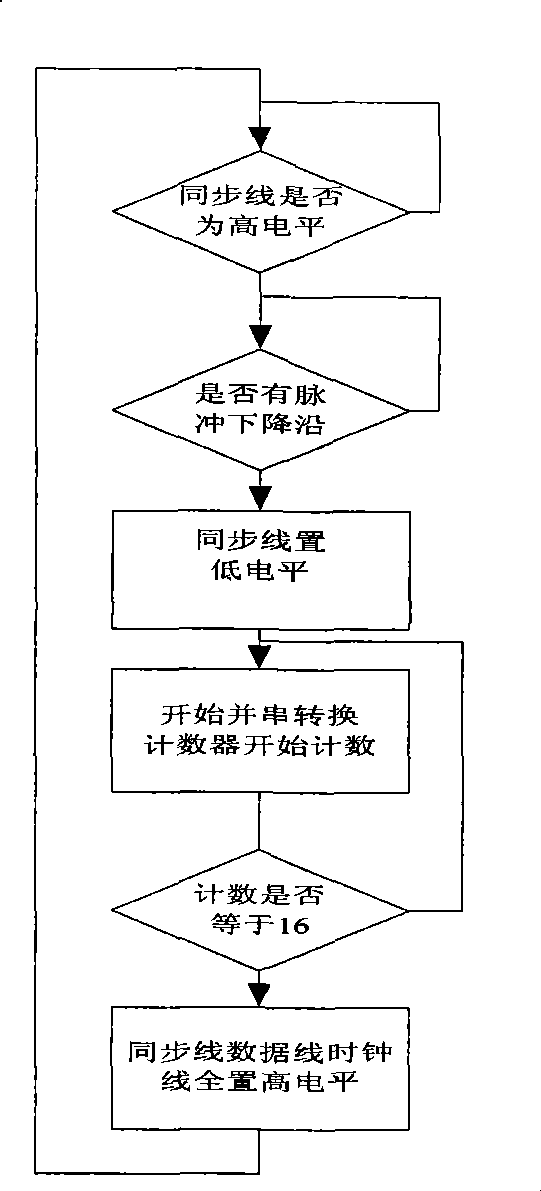

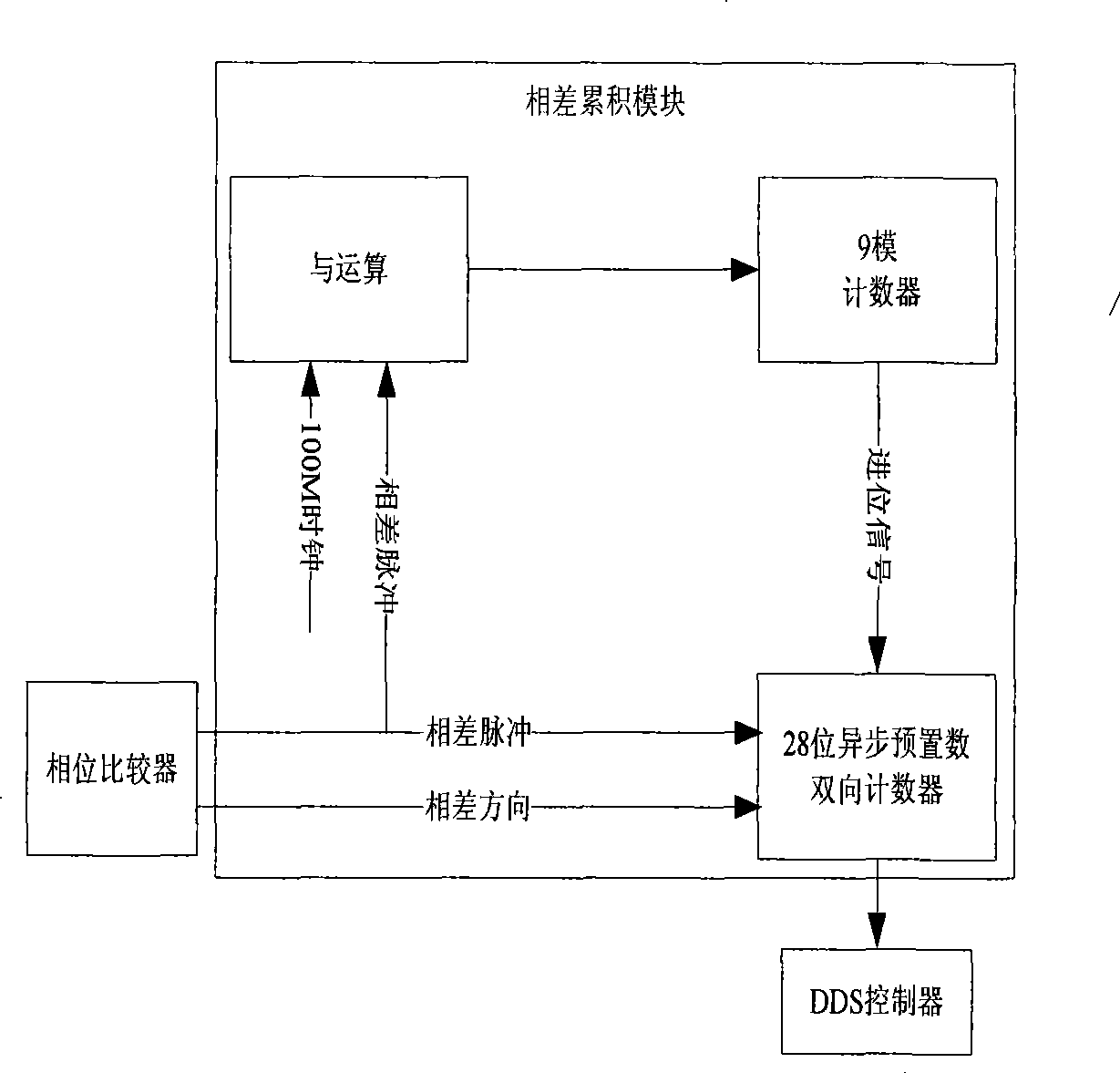

Automatic frequency tracking method of supersonic transducer and system thereof

ActiveCN101468347ARealize digital controlWork reliablyMechanical vibrations separationLogical elementUltrasonic sensor

The invention relates to an automatic frequency tracking method and a system for an ultrasonic transducer. A direct digital frequency synthesizer is used as a signal source, wherein the direct digital frequency synthesizer can be an independent integrated chip and also be achieved by the method that a digital part of a DDS is integrated in a site programmable logical element FPGA and then a digital-analog converter is additionally added. The design of the invention adopts a frequency sweeping and tracking policy, and an automatic frequency controller achieved by the programmable element controls the output frequency of the DDS according to a feedback signal sampled from the self transducer end so as to achieve the full digitization automatic frequency tracking and ensure that the ultrasonic transducer work near a resonance point all the time to obtain the optimal efficiency. A phase comparator utilizes a trigger to give out the arriving time difference of two riser edge signals of two input signals I ph and V ph aiming to the sensitive characteristics of the riser edge signals, and the sequence of the riser edge signals of the two input signals I ph and V ph is given out by a Dirrect pin.

Owner:BEIJING ANHEJIALIER TECH CO LTD

Method and system for provisioning and maintaining a circuit in a data network

A method and system are provided for provisioning a circuit in a data network without manual intervention. A network management module receives an order for provisioning the circuit and then, based on the order, transmits a request to a legacy logical element module to configure a logical circuit in one or more network devices in the network. The network device may be a switch. The circuit may be a frame relay circuit or an ATM circuit. A method and system are also provided for maintaining a network circuit in a data network. The network circuit includes both a logical circuit and a physical circuit. A legacy physical element module sends a request for logical circuit data to a legacy logical element module through a network management module in communication with the legacy physical element module and the legacy physical element module. Based on the request, the legacy logical element module retrieves the logical circuit data from one or more network devices in the network and transmits the data to the legacy physical element module through the network management module. Upon receiving the logical circuit data, the legacy physical element module troubleshoots the physical circuit to maintain the network circuit.

Owner:AT&T INTPROP I L P +1

User interface automation framework classes and interfaces

InactiveUS7644367B2Television system detailsAnalogue secracy/subscription systemsLogical elementClient-side

A method and system providing a client with user interface information are described. The method and system implement a set of application program interfaces for providing user interface information to a client through an accessibility system. The accessibility system includes a mechanism for transferring user interface information from a provider side to the client side and a logical tree for selectively revealing user interface information. The application program interface system includes client side application program interfaces for assisting the client in obtaining user interface information. The client side application program interfaces include an automation class, a logical element class, a raw element class, control pattern classes, and an input class. The provider side application program interfaces include a provider automation class, a provider automation interface, a raw element interface, and control pattern provider interfaces.

Owner:MICROSOFT TECH LICENSING LLC

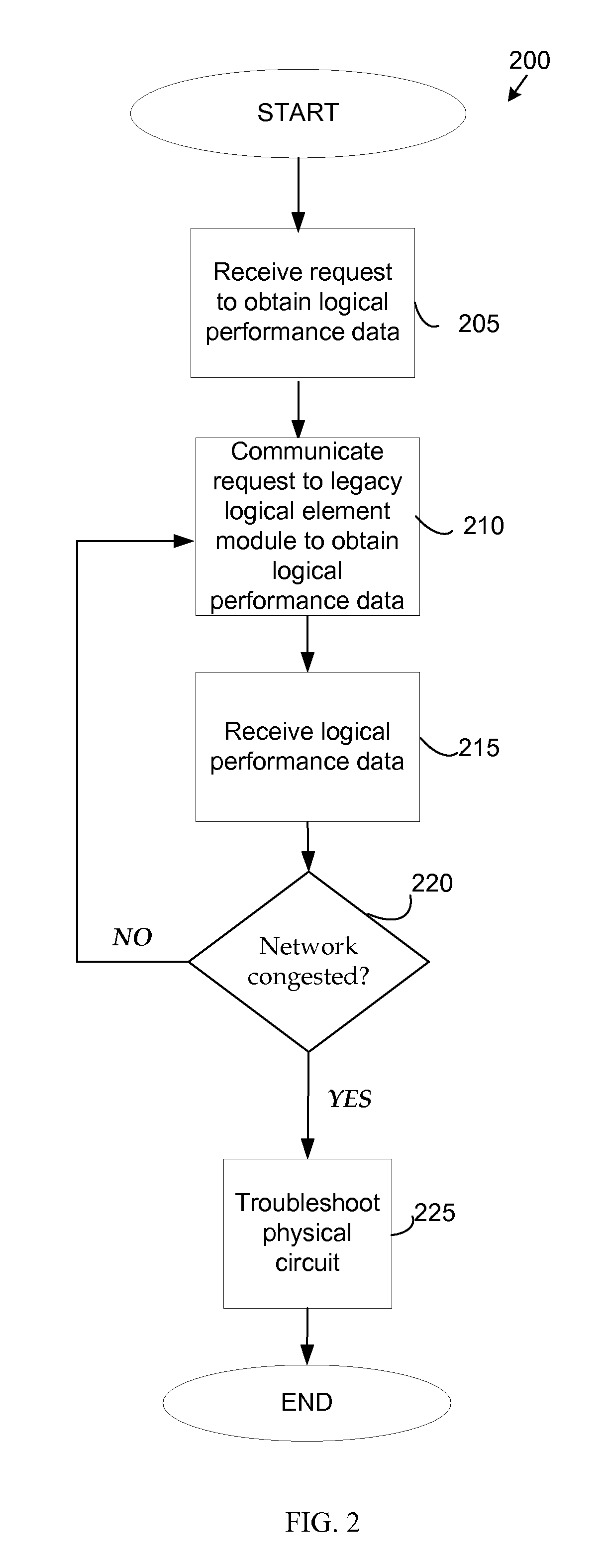

Method and system for obtaining logical performance data for a circuit in a data network

A method and system are provided for obtaining logical performance data for a network circuit in a data network. The network circuit includes both a logical circuit and a physical circuit. A legacy physical element module sends a request for logical performance data to a logical element module through a network management module in communication with the legacy physical element module and the legacy physical element module. Based on the request, the logical element module retrieves the logical performance data from one or more network devices in the network and transmits the data to the legacy physical element module through the network management module. Upon receiving the logical performance data, the legacy physical element module uses the performance data to troubleshoot the physical circuit. The network device may be a switch. The circuit may be a frame relay circuit or an ATM circuit.

Owner:AT&T INTPROP I L P

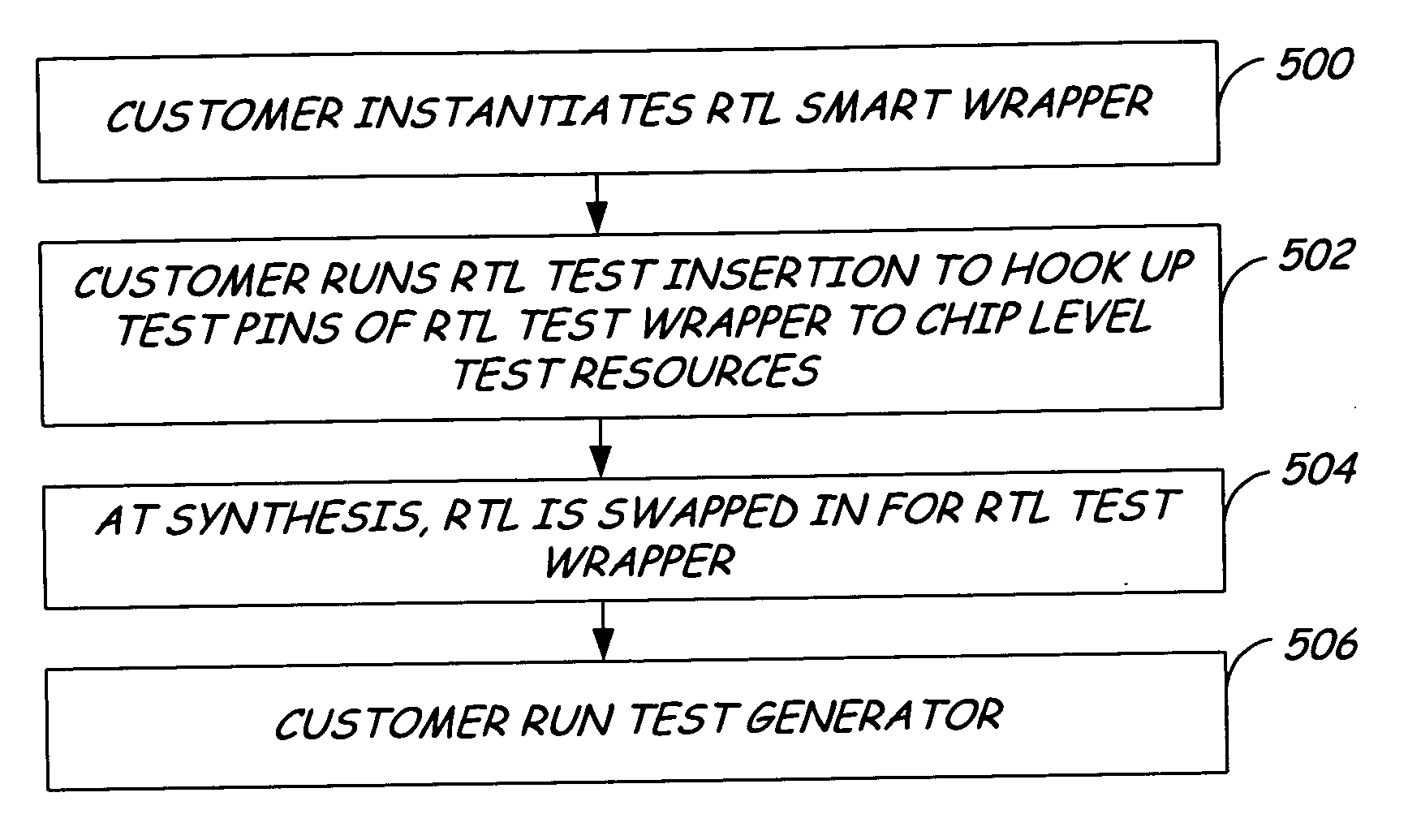

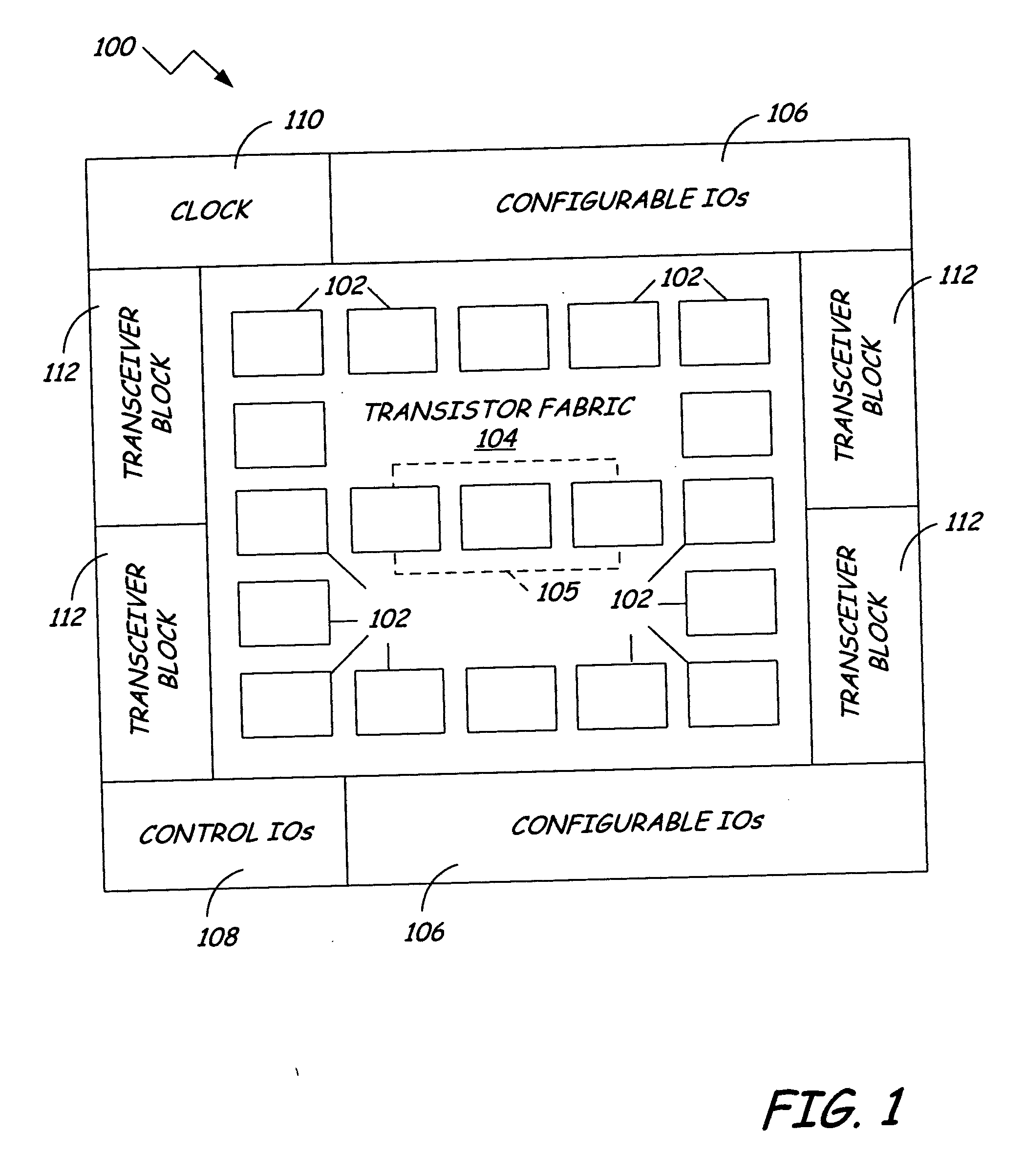

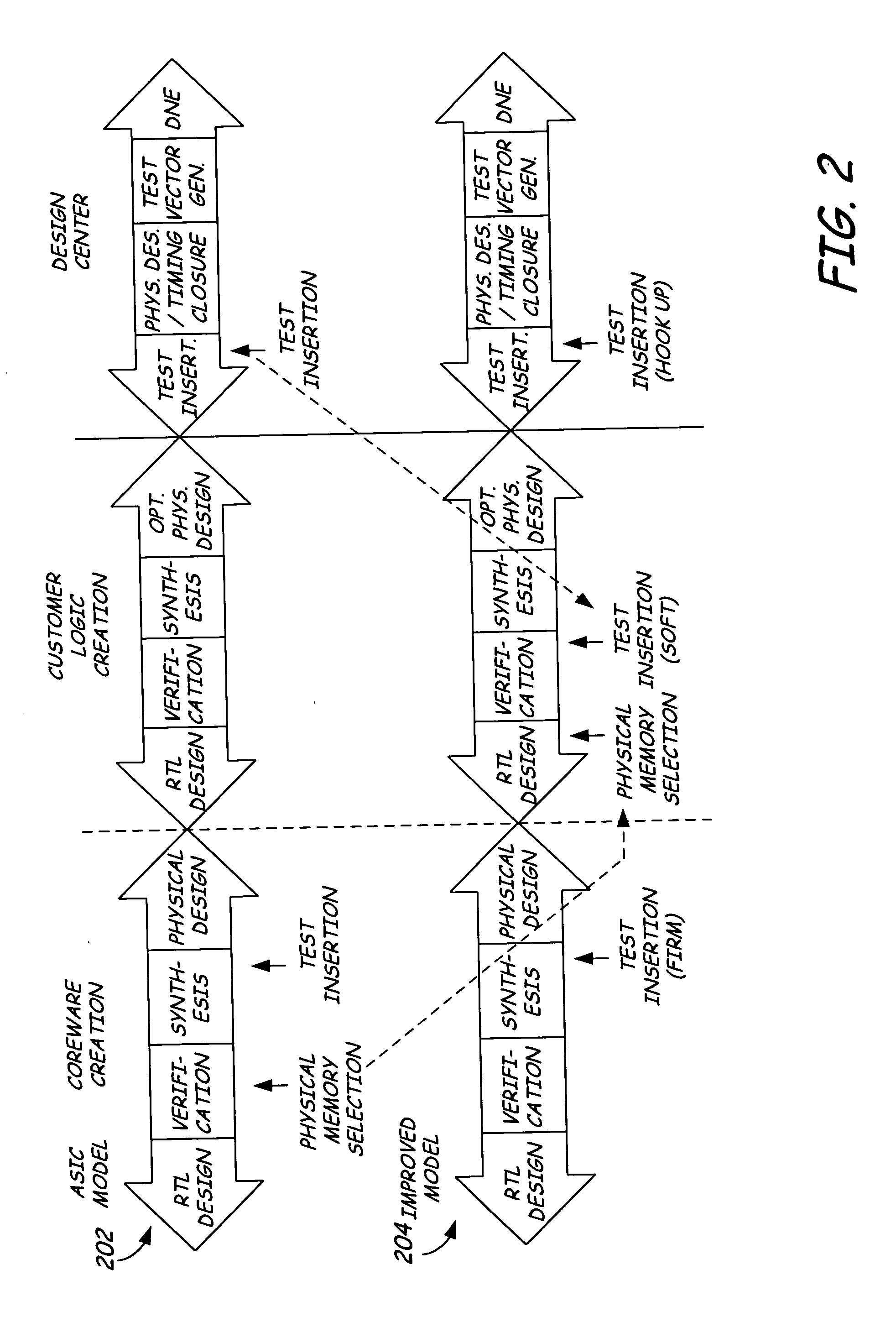

Method for abstraction of manufacturing test access and control ports to support automated RTL manufacturing test insertion flow for reusable modules

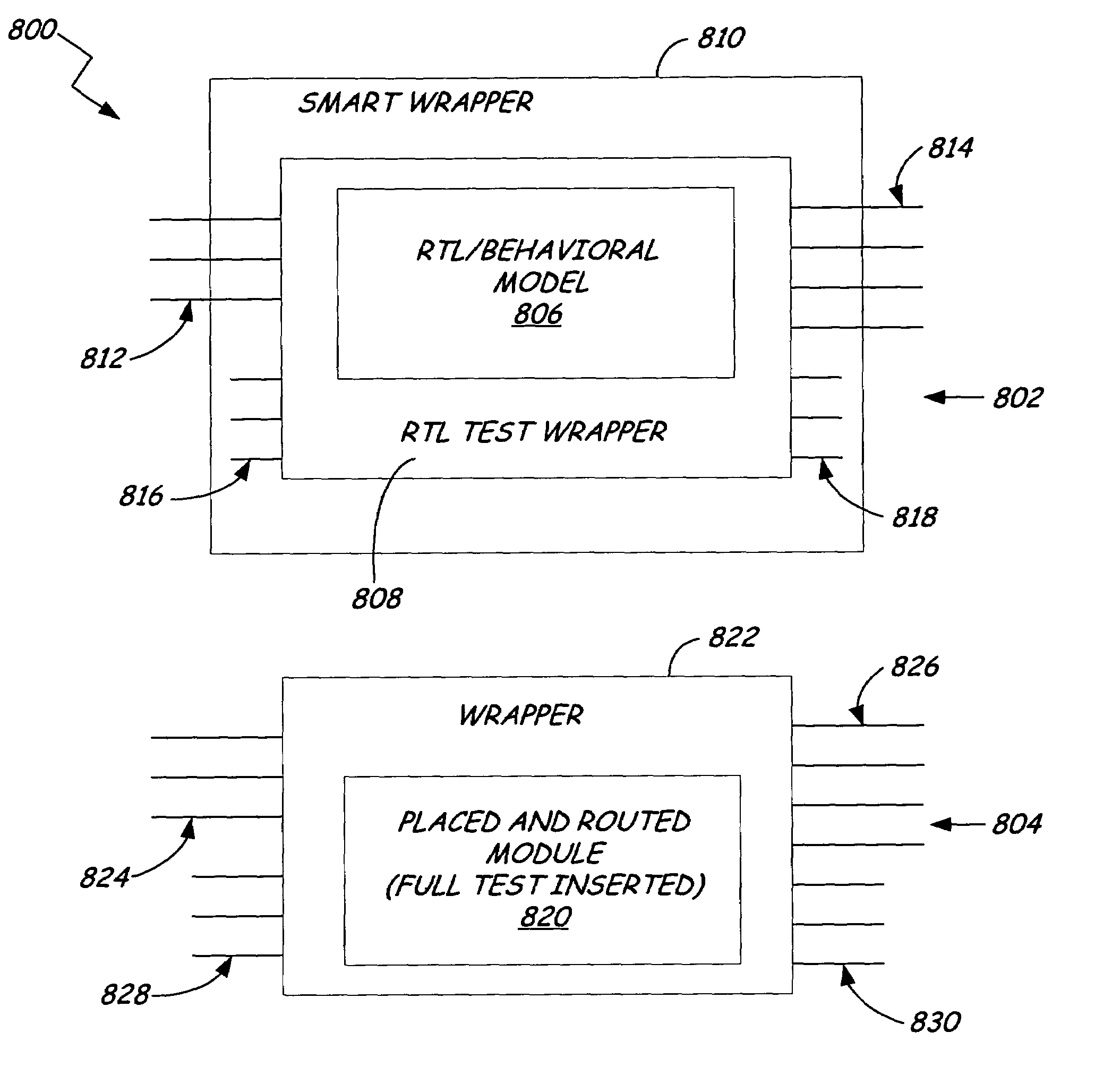

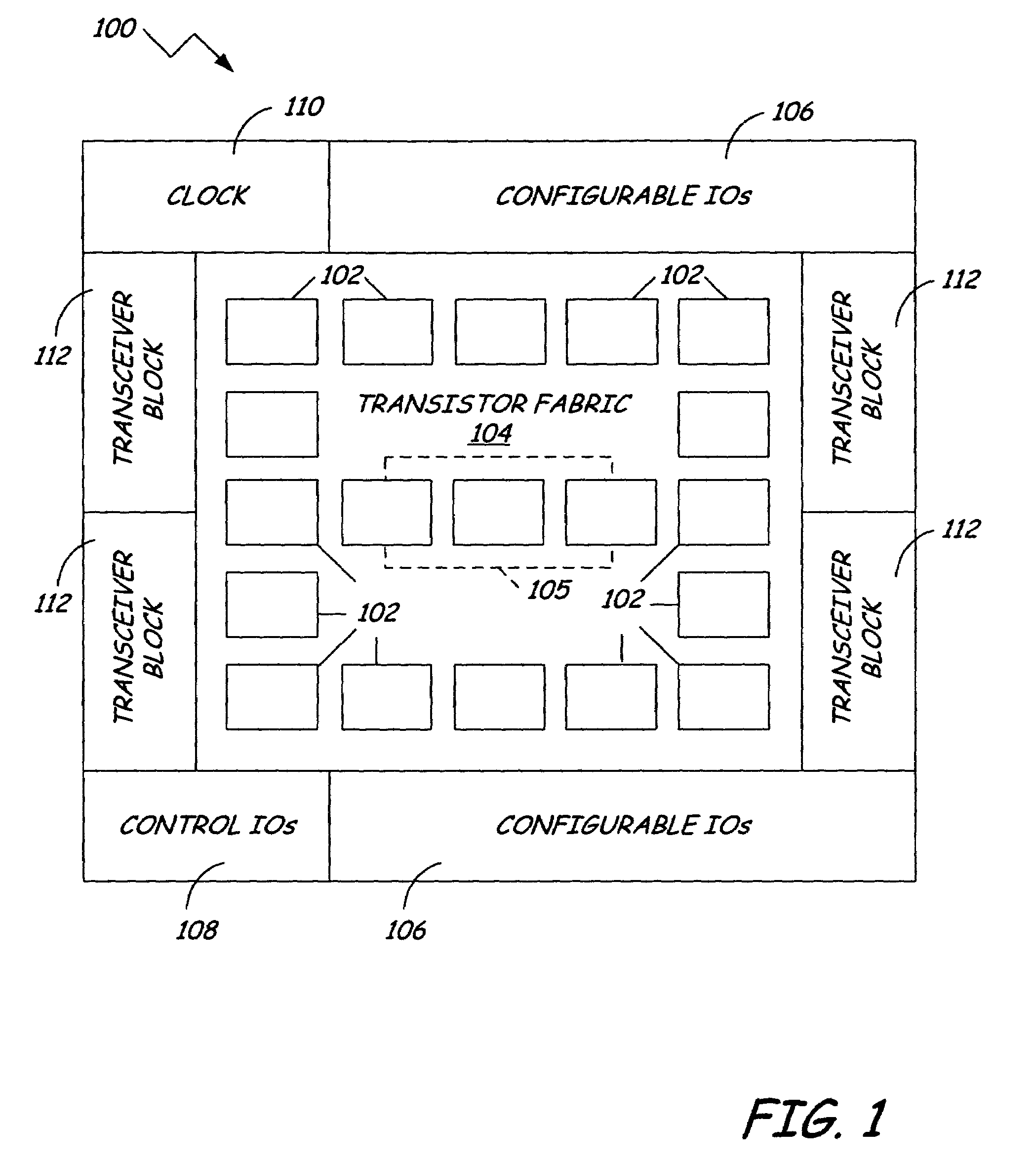

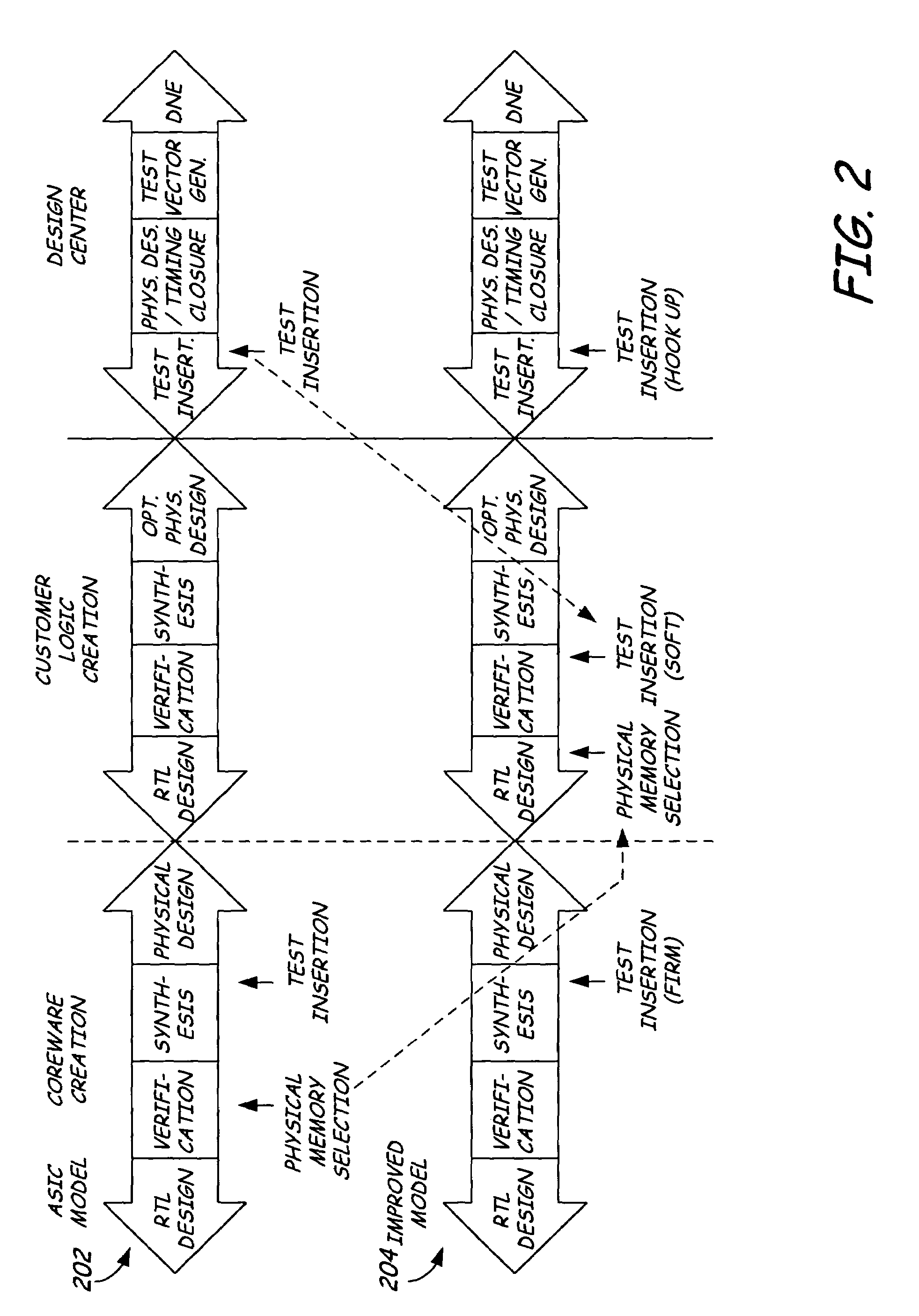

A system for RTL test insertion in an integrated circuit layout pattern includes a core module, a test wrapper, and a smart wrapper. The core module describes a function defined by logical elements, interconnections between logical elements, input pins and output pins. The test wrapper is adapted to encapsulate the core module and to create test pins representing the core module. The smart wrapper is adapted to encapsulate the test wrapper and to assign the test pins to a non-asserted state. The smart wrapper is adapted to place an assertion on one or more of the test pins for static or dynamic testing of the integrated circuit layout pattern.

Owner:BELL SEMICON LLC

Method and system for fail-safe renaming of logical circuit identifiers for rerouted logical circuits in a data network

A method and system are provided for fail-safe renaming of logical circuit identifiers for rerouted logical circuits in a data network. A network management module is provided for accessing a network device provisioned for routing data over a first logical circuit in the data network. The network management module is further utilized for deleting the first logical circuit in the network device upon detecting a failure in the first logical circuit and provisioning a second logical circuit in the network device for rerouting the data from the first logical circuit. In provisioning the second logical circuit, the network management module is utilized to assign a second logical circuit identifier to identify the second logical circuit. The network management module is further utilized for renaming a first logical circuit identifier to the second logical circuit identifier and renaming a logical circuit label for the first logical circuit in a logical element module in communication with the network management module. The renamed logical circuit label includes the first logical circuit identifier and may be utilized to indicate that the logical circuit data from the failed logical circuit has been rerouted.

Owner:BELLSOUTH INTPROP COR

Method for abstraction of manufacturing test access and control ports to support automated RTL manufacturing test insertion flow for reusable modules

A system for RTL test insertion in an integrated circuit layout pattern includes a core module, a test wrapper, and a smart wrapper. The core module describes a function defined by logical elements, interconnections between logical elements, input pins and output pins. The test wrapper is adapted to encapsulate the core module and to create test pins representing the core module. The smart wrapper is adapted to encapsulate the test wrapper and to assign the test pins to a non-asserted state. The smart wrapper is adapted to place an assertion on one or more of the test pins for static or dynamic testing of the integrated circuit layout pattern.

Owner:BELL SEMICON LLC

Form processing method, form processing device, and computer product

InactiveUS20080025618A1Solve problemsCharacter and pattern recognitionOffice automationLogical elementAlgorithm

A form processing apparatus extracts layout information and character information from a form document. A candidate extracting unit extracts word candidates from the character information. A frequency digitizing unit calculates emission probability of a word candidate from each element. A relation digitizing unit calculates transition probability that relationship between word candidates is established. An evaluating unit calculates an evaluation value indicative of a probability of appearance of word candidates in respective logical elements. A determining unit determines the element and a word candidate thereof as the element and a character string thereof in the form document, based on the evaluation value.

Owner:FUJITSU LTD

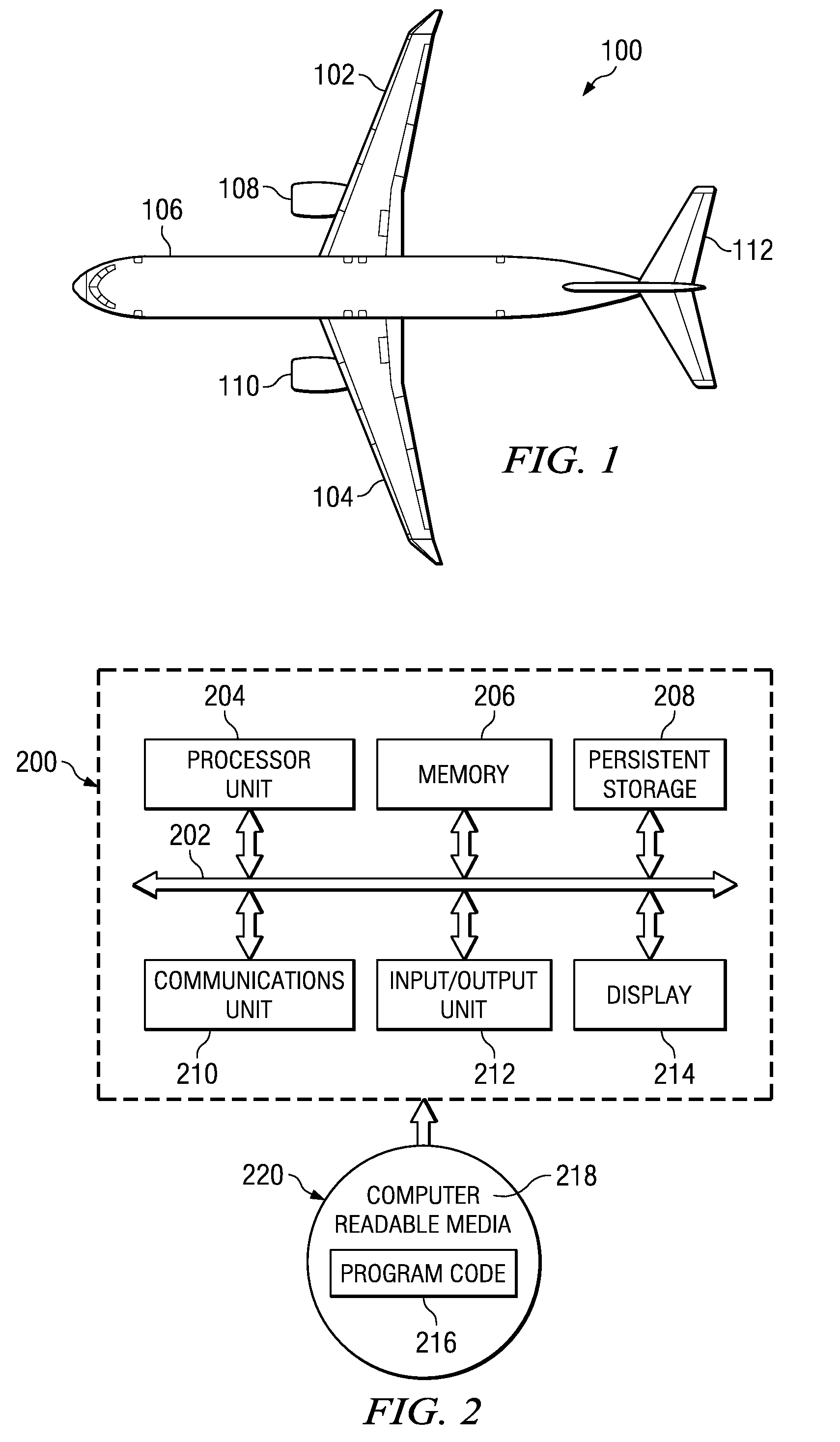

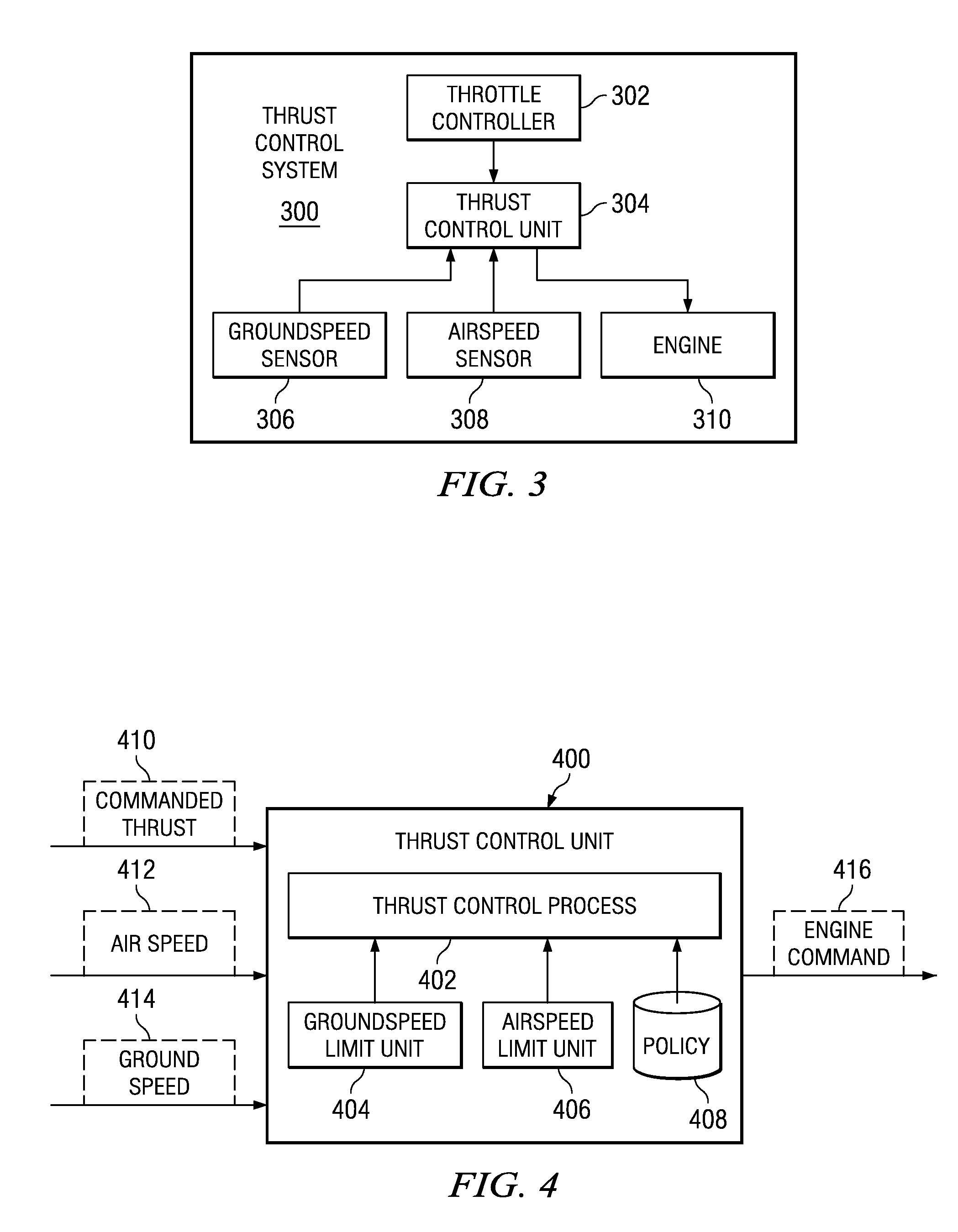

Progressive takeoff thrust ramp for an aircraft

A method is presented for controlling thrust generated by aircraft engines. Engine thrust is controlled based on aircraft groundspeed and airspeed during the initial part of takeoff. Limiting thrust at low groundspeed during the initial phase of takeoff has significant benefits that reduce engine stress during this brief but critical phase leading to flight. Logical elements combine both groundspeed and airspeed in such a way that the operator perceives a smooth progressive thrust increase consistent with normal engine operation.

Owner:THE BOEING CO

Method and system for generating a bitstream view of a design

ActiveUS7343578B1CAD circuit designSpecial data processing applicationsLogical elementComputer architecture

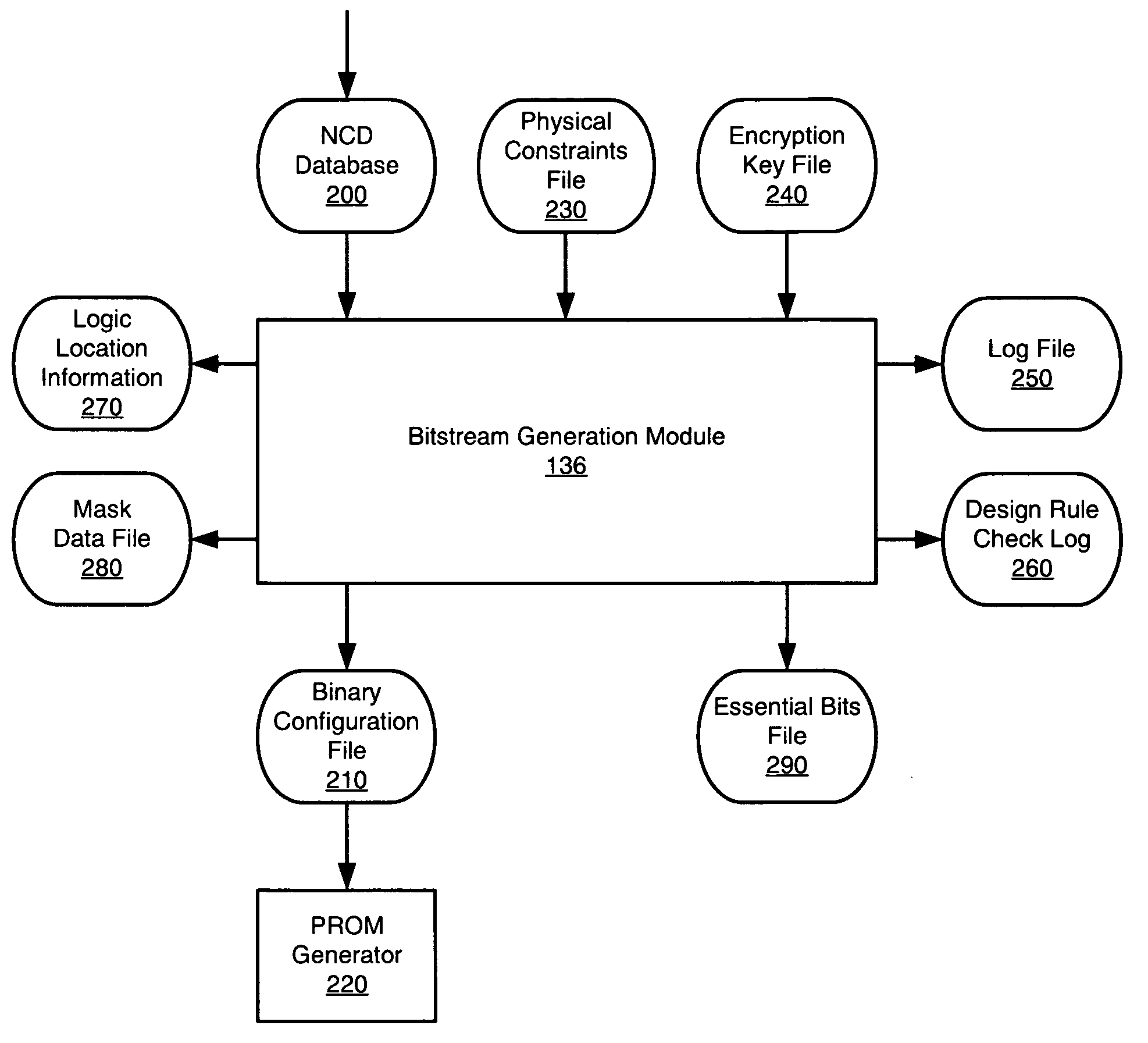

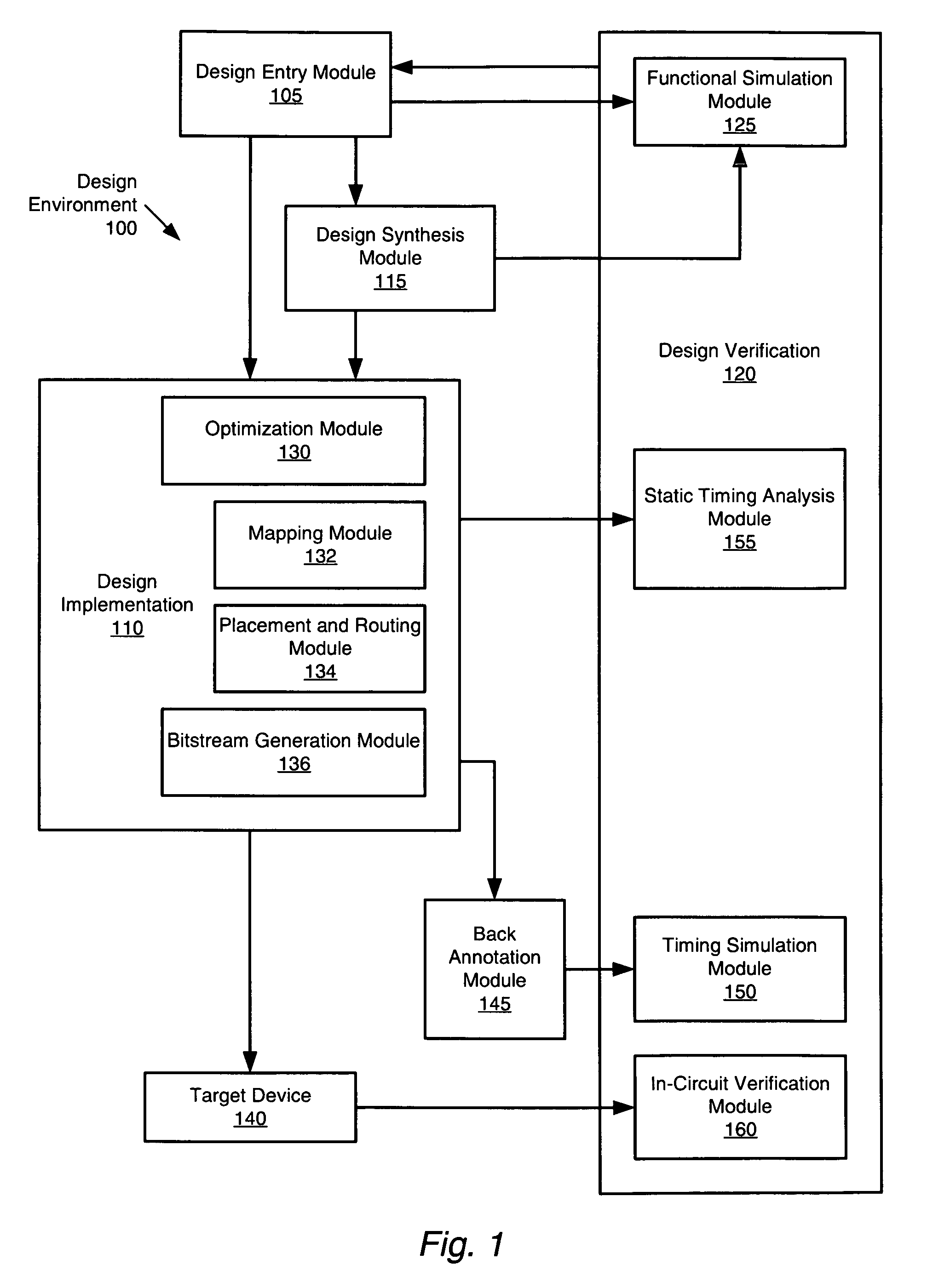

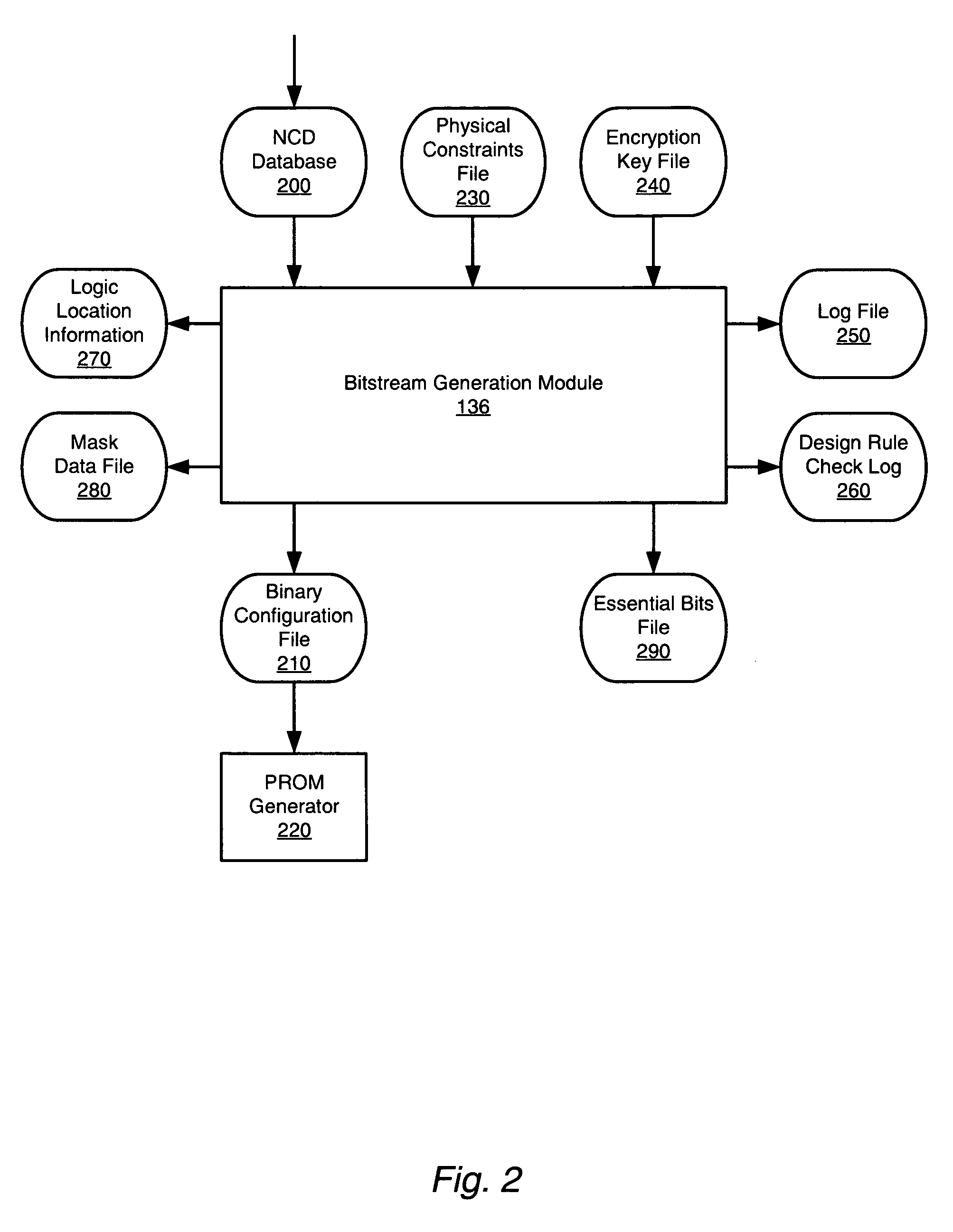

A method and system for generating a bitstream view of a programmable logic device (PLD) design are disclosed. The present invention allows for the correlation of a physical circuit description (e.g., one or more of a PLD design's essential configuration bits) and a logical circuit description (e.g., one or more of the logic elements that make up a PLD design), which can also be viewed as correlating one or more of the physical elements of the design's implementation in the PLD with one or more of the design's logical elements.

Owner:XILINX INC

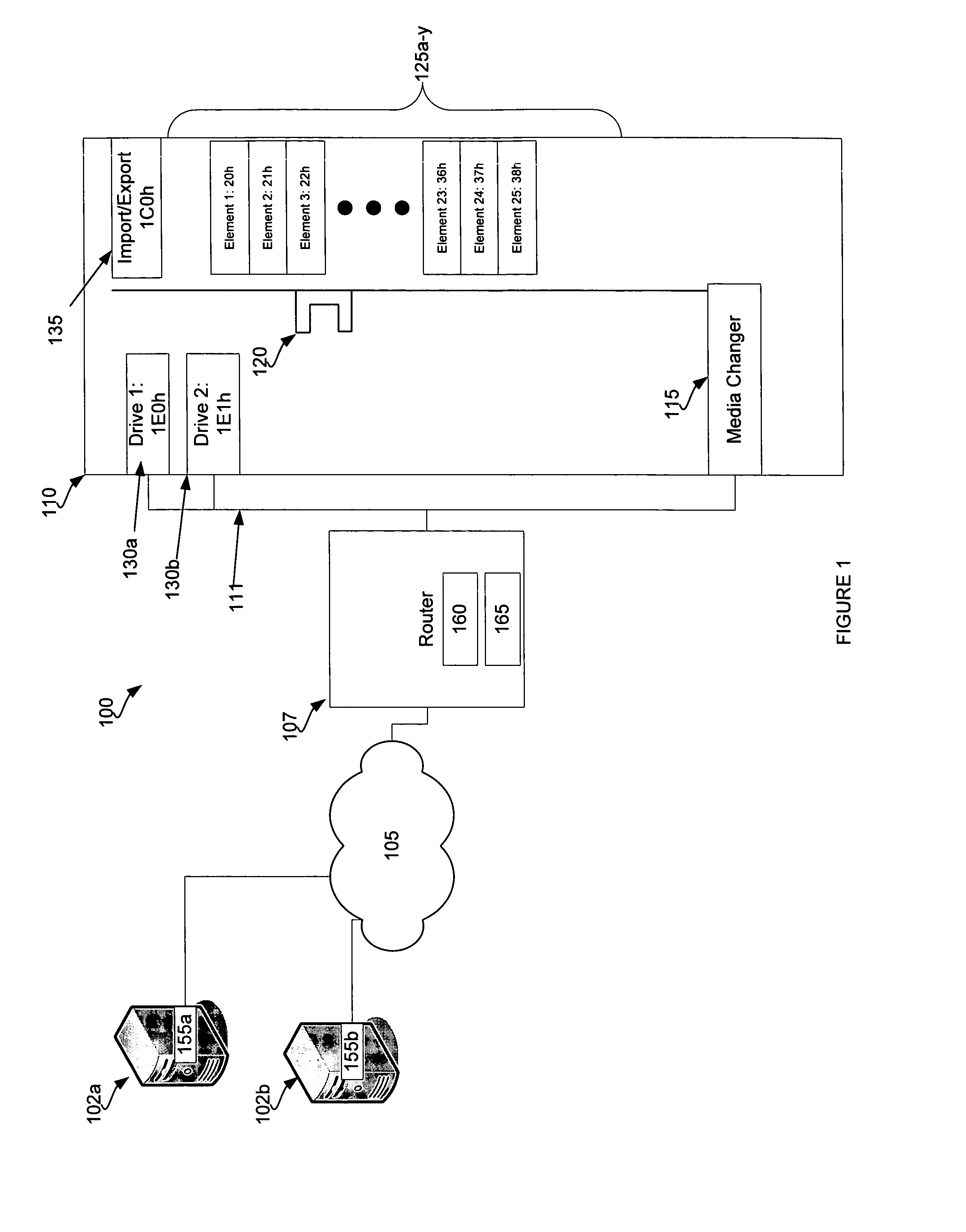

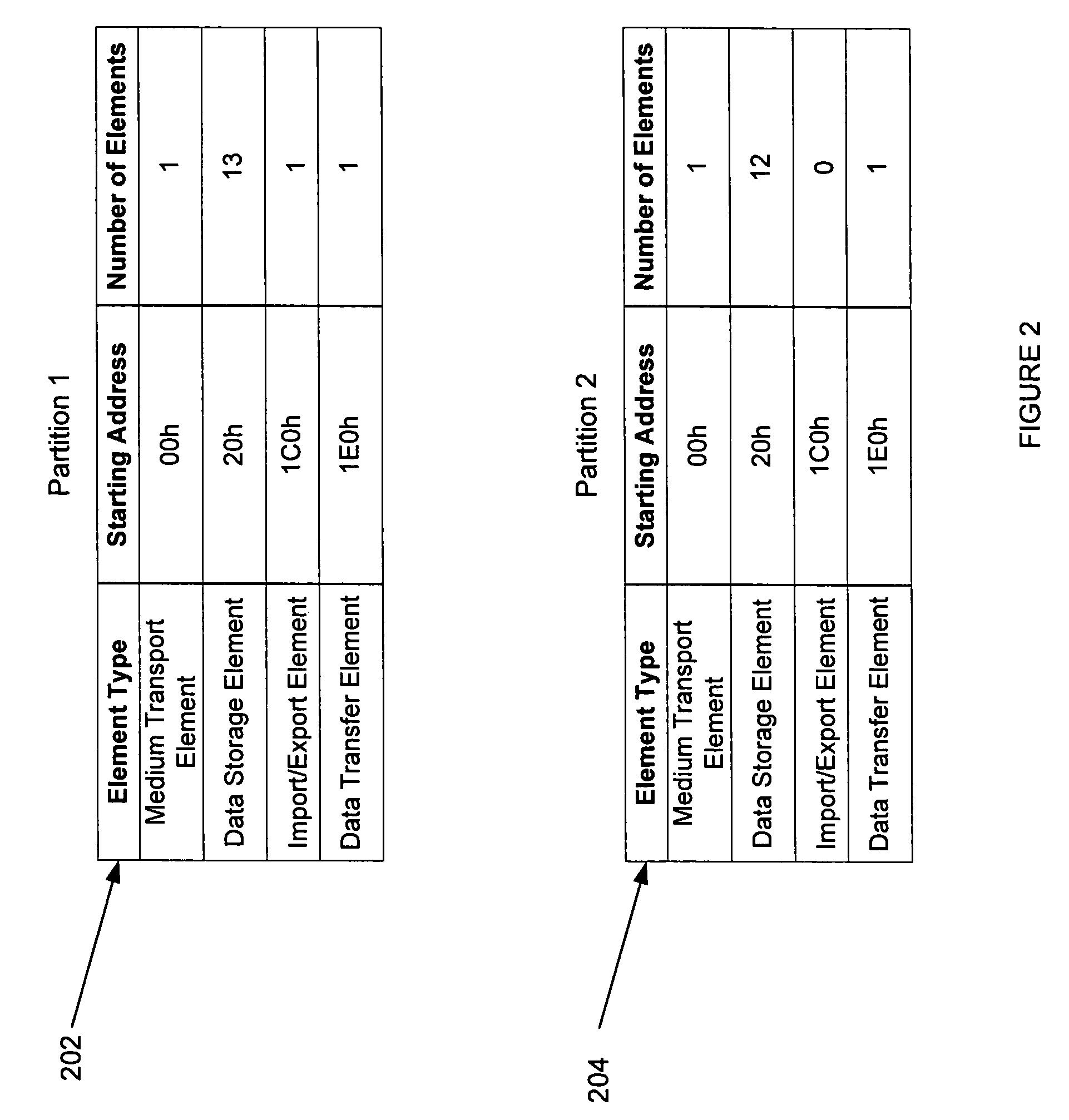

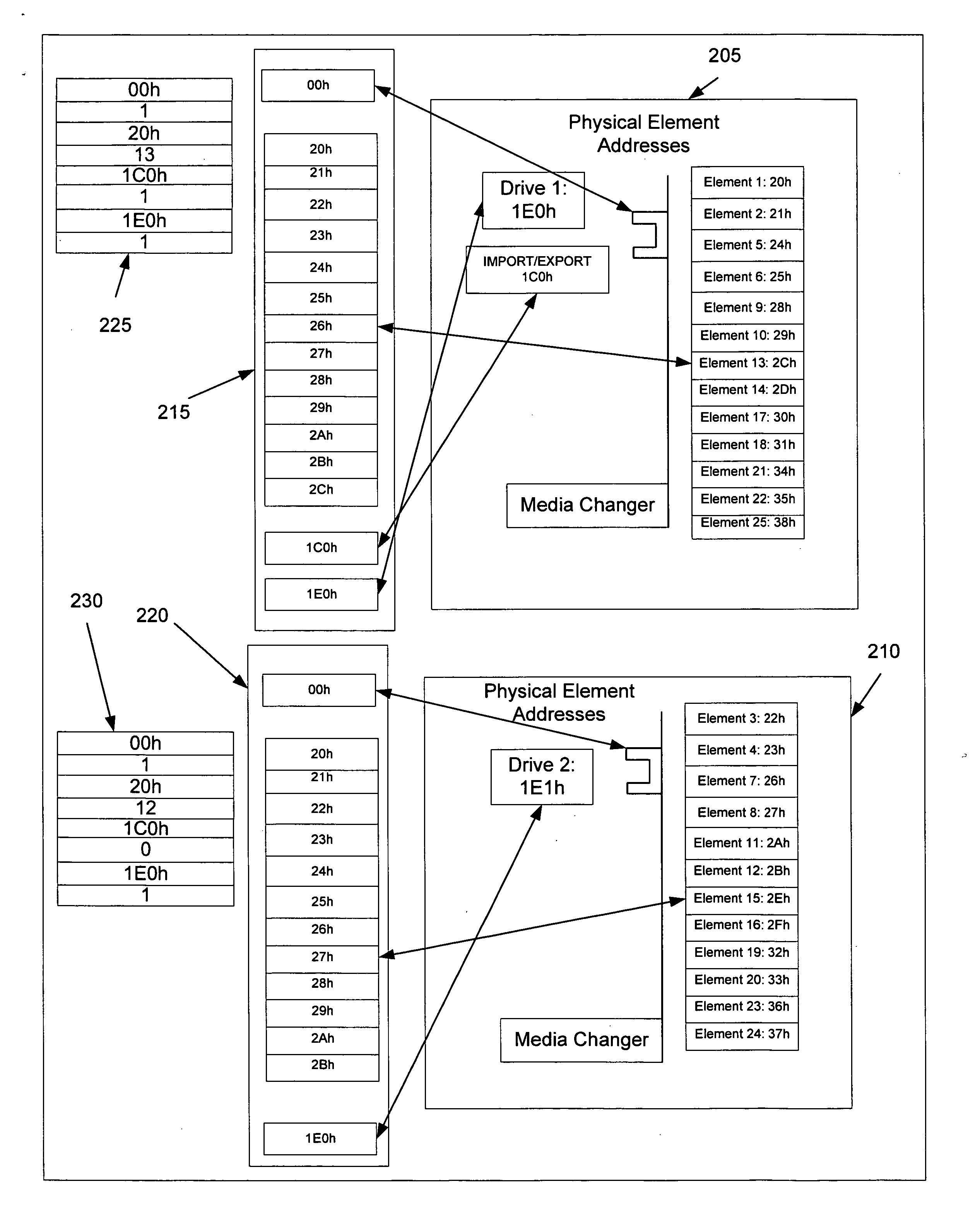

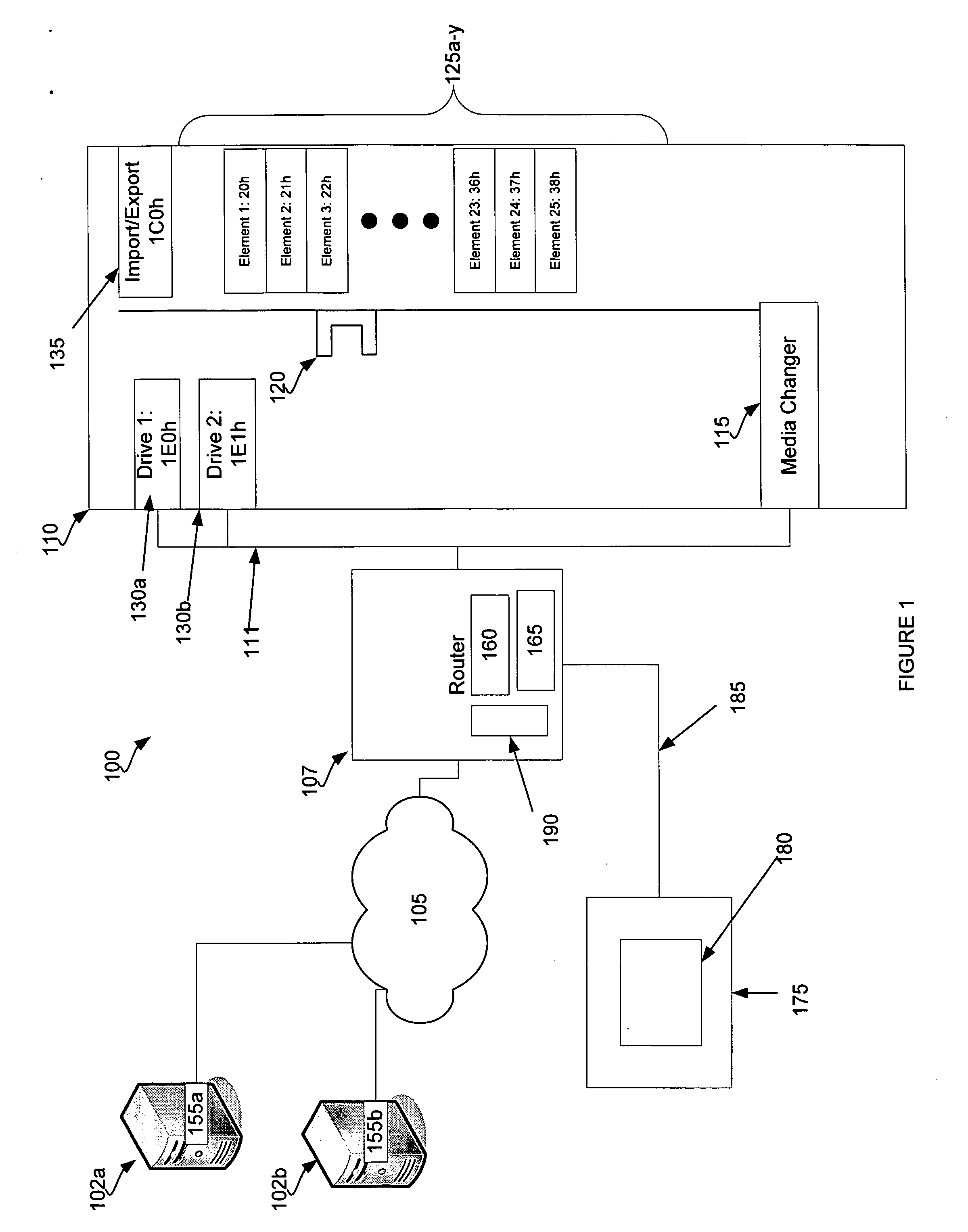

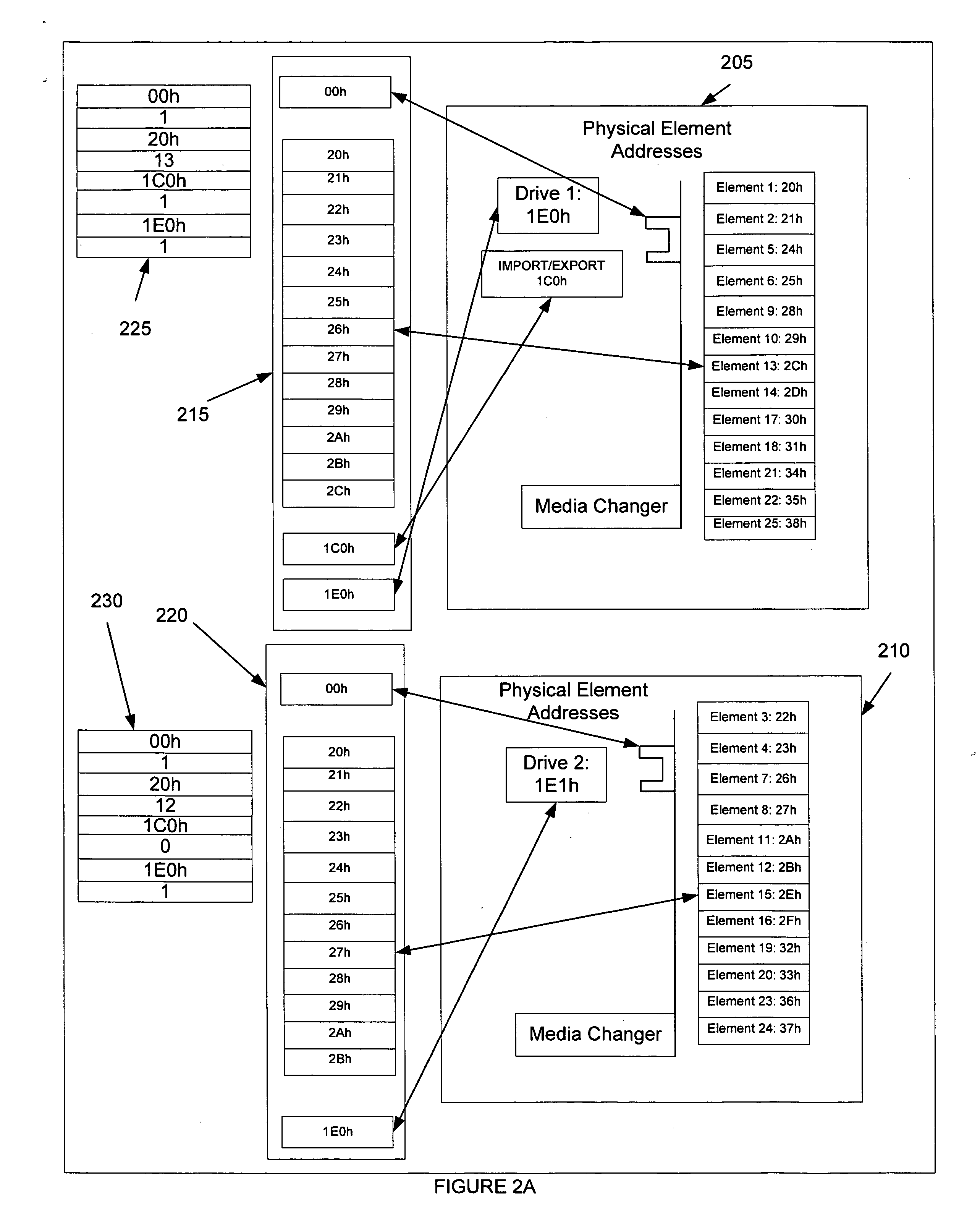

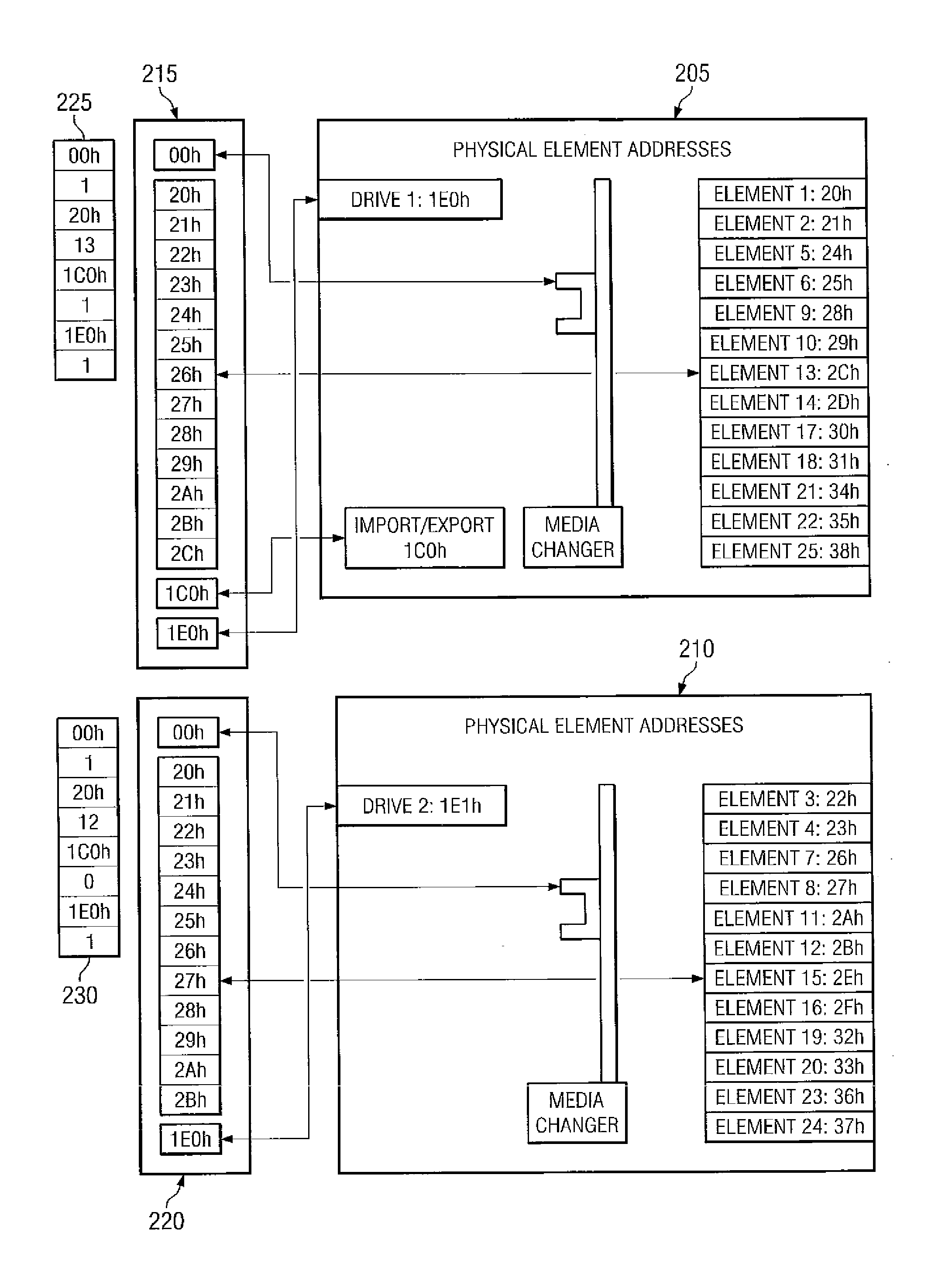

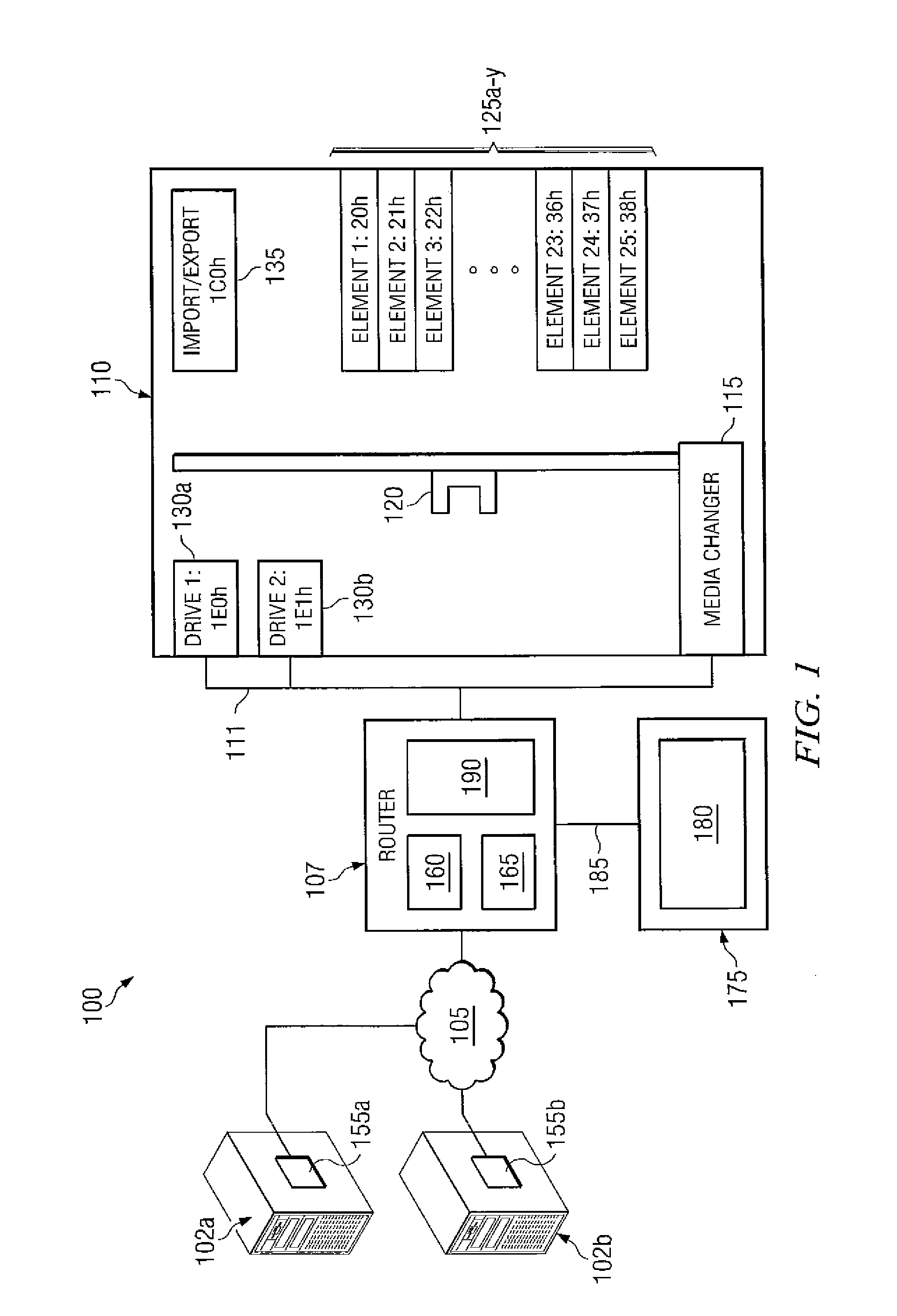

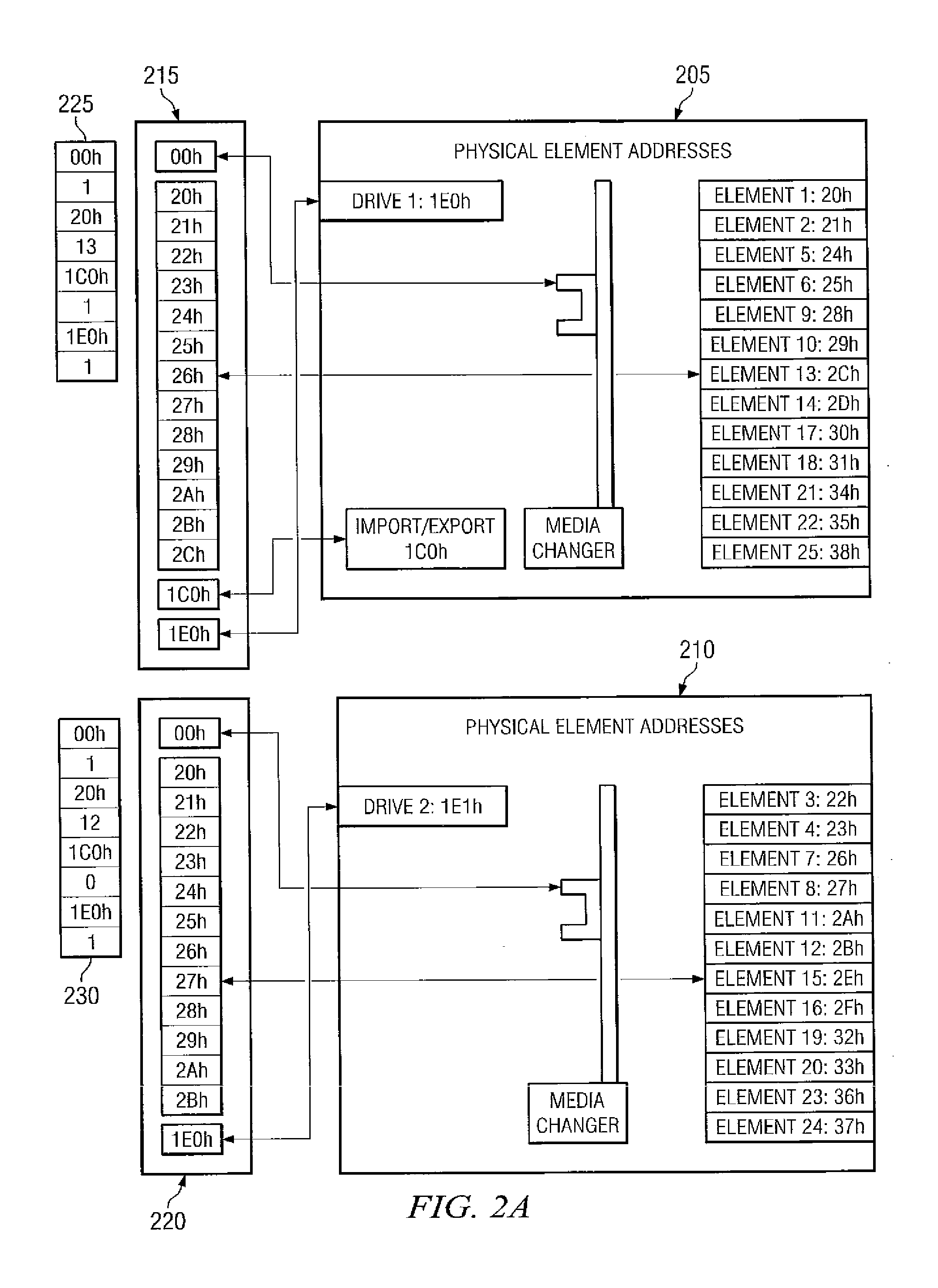

Method and system for presenting contiguous element addresses for a partitioned media library

InactiveUS7370173B2Flat record carrier combinationsRecording carrier detailsLogical elementPhysical element

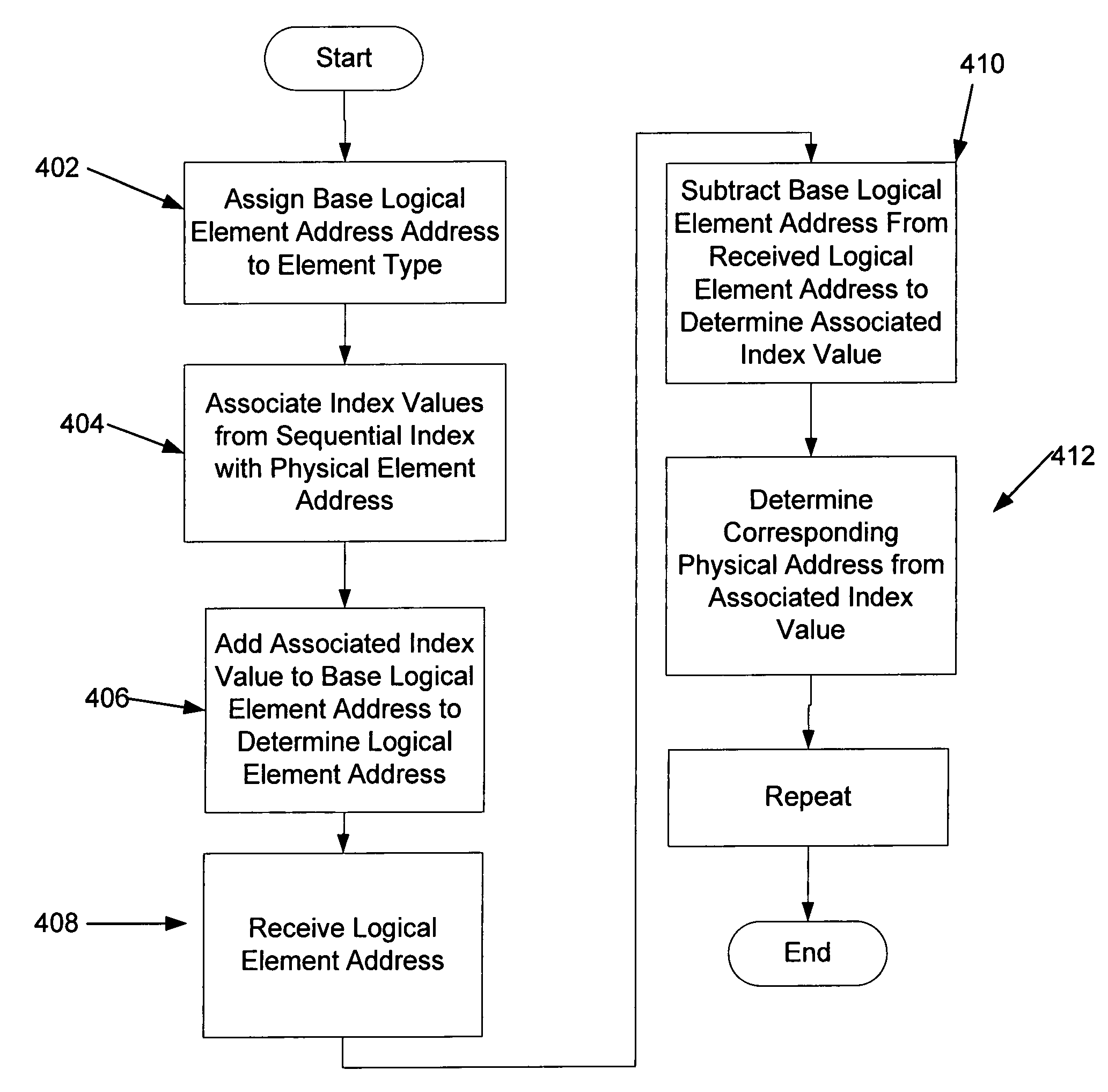

According to one embodiment of the present invention, a controller that partitions a media library for multiple host applications can, for each partition, assign a base element address for an element type and associate physical element addresses for elements of an element type with an index value. For a partition, the logical element address corresponding to a physical element address for an element can be determined by adding the index number associated with the physical element address to the base element address for that element type. The physical element address corresponding to a logical element address for an element can be determined by subtracting the base element address for the element type from the logical element address for the element. The result of subtracting the base element address from the logical element address is an index value for which the associated physical element address can be found.

Owner:CF DB EZ +1

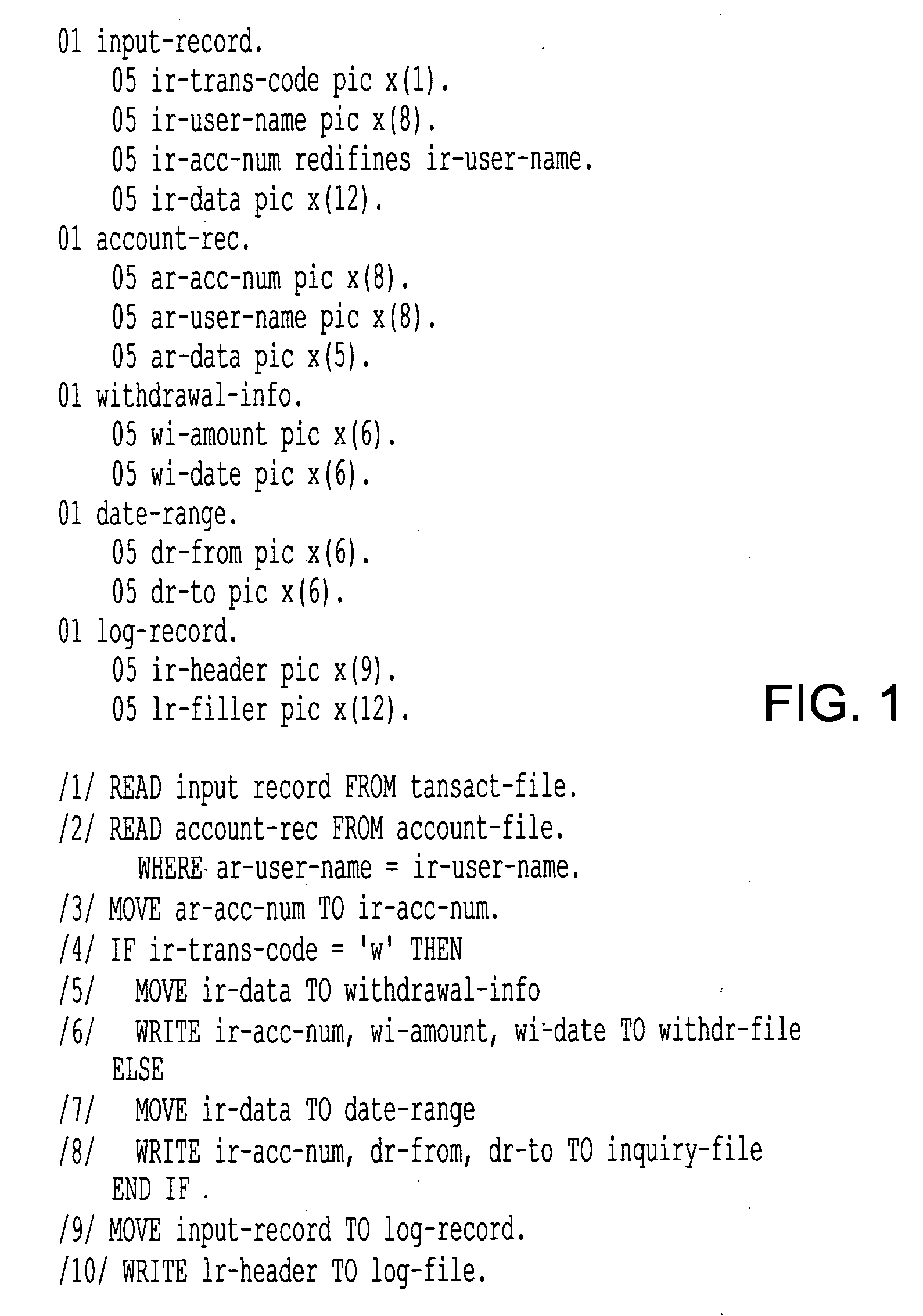

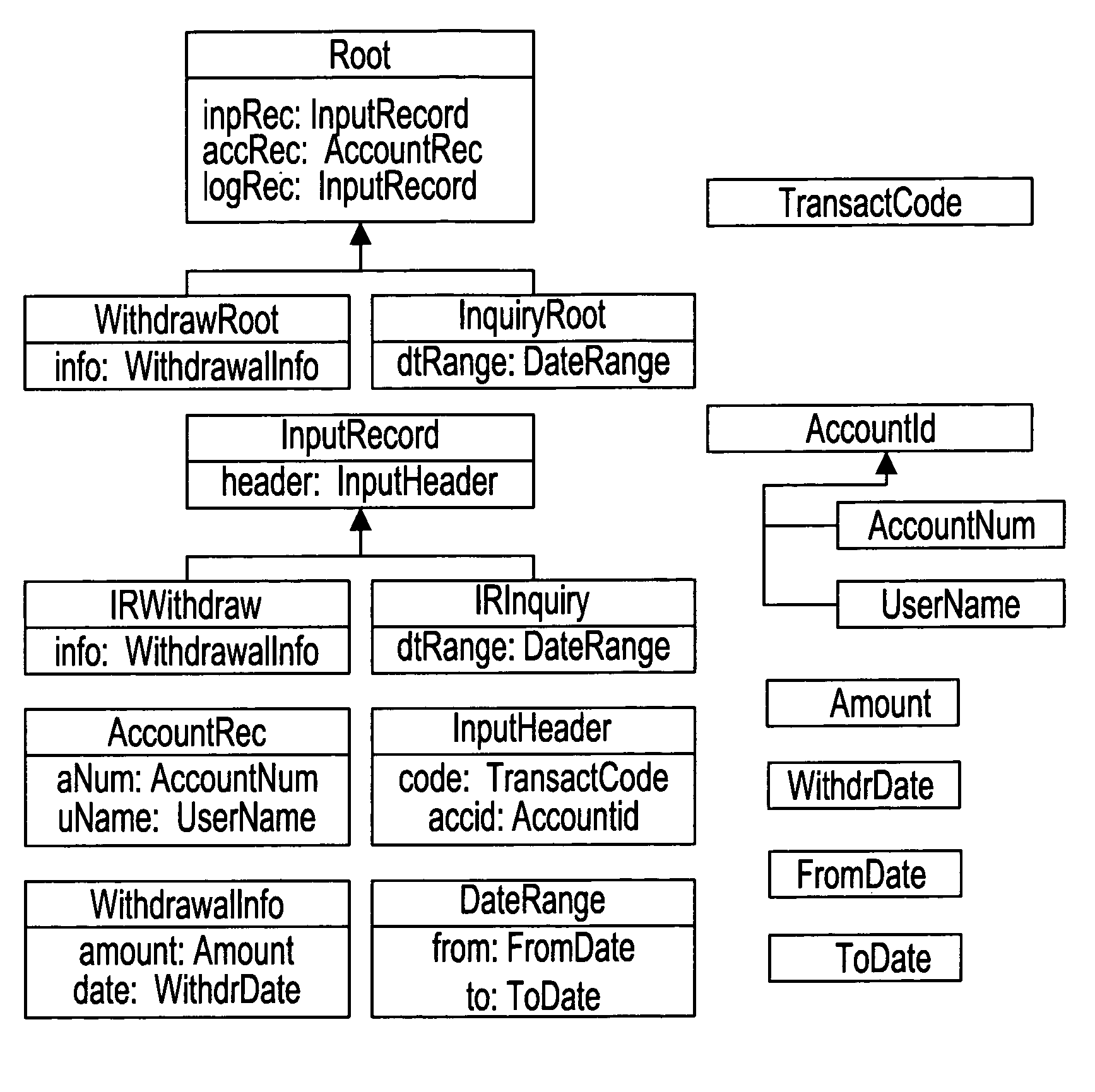

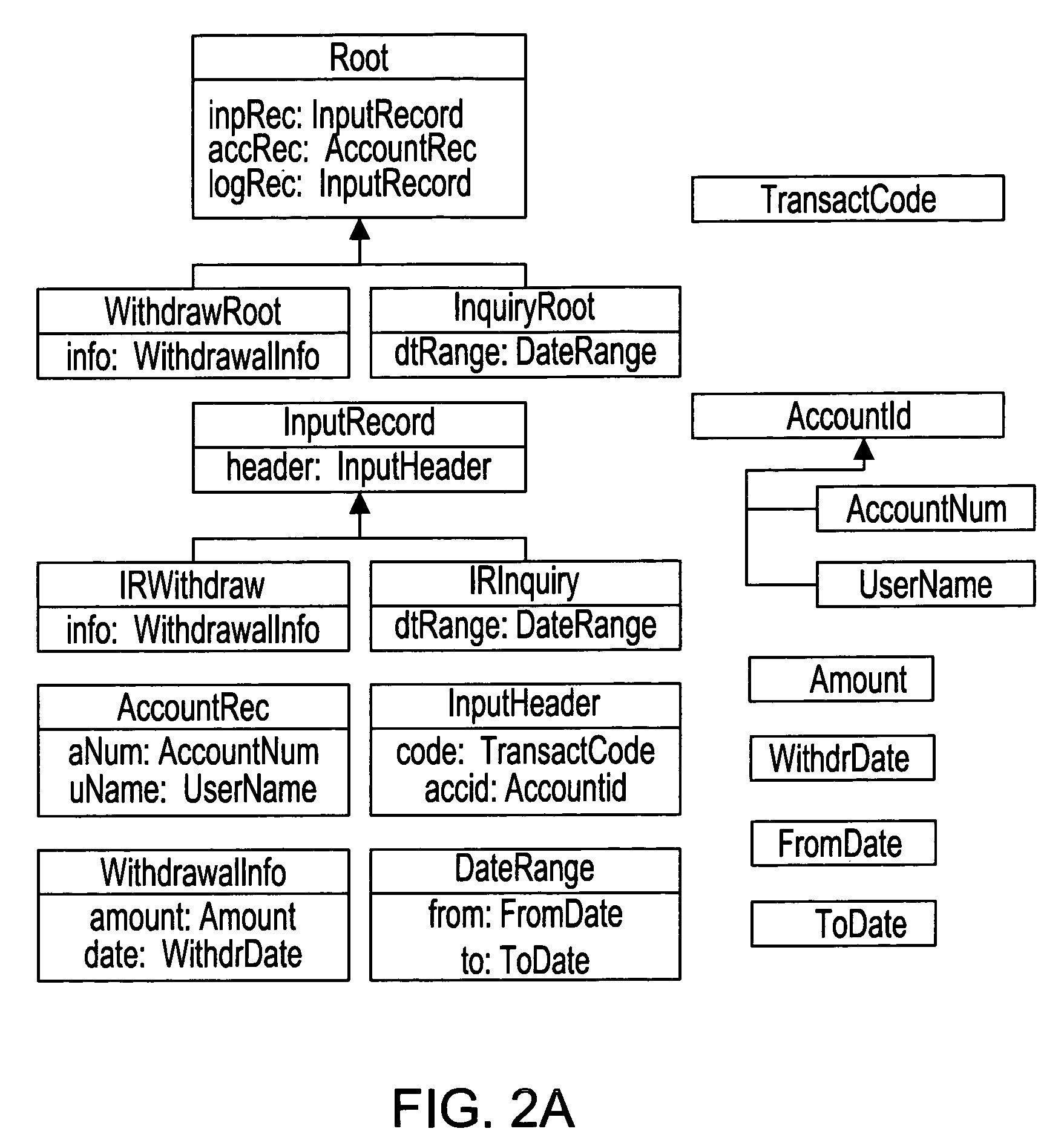

System and method for a logical-model based application understanding and transformation

InactiveUS20070240109A1Reverse engineeringFuzzy logic based systemsLogical elementRelational database

Disclosed is a method of and a system for establishing a logical-model based understanding of a legacy application. The method comprises the steps of providing a physical data model of the legacy application, said physical data model having a plurality of physical elements; establishing a logical data model for the legacy application, said logical data model having a plurality of logical model elements; and establishing links between said logical model elements and said physical elements. One of said physical or logical elements is selected, and said links are used to identify all of the physical or logical elements that are linked to said selected one of said elements. The preferred system may include a component for browsing and navigating the physical data model, logical data model, or the links between them, a component to answer queries about the application expressed using the logical data model, and a component to create a relational data model to support the migration of data stored in legacy databases (including flat files) to relational databases.

Owner:IBM CORP

System and method for recovery units in databases

InactiveUS7334002B2Easy to operateData processing applicationsError detection/correctionLogical elementPhysical element

The creation of multiple recoverable units within a database allows a database partition to be reconstructed during maintenance and disaster recovery operations. A method of creating a recovery unit includes partitioning a database into at least two recovery units. A primary catalog of metadata relating to the logical elements of a database such as tables, indexes, and file groups is created. A secondary catalog of metadata relating to the physical elements of a database such as pages, files, B-Trees, and log streams is created for each recovery unit. The primary and secondary metadata catalogs are linked such that only one log stream is associated with any one recovery unit. A single recovery unit may then be exercised to perform recovery or maintenance operations while the remaining recovery units of the database remain online.

Owner:MICROSOFT TECH LICENSING LLC

System and method for mode select handling for a partitioned media library

One embodiment of the present invention includes a method for handling status commands direct to a partitioned media library that comprises establishing a set of initial logical element addresses for a set of physical element addresses with each initial logical element address corresponding to a physical element address of an element assigned to a library partition, assigning a set of new logical element addresses for the set of physical element addresses in response to a command from a host application (e.g., a MODE SELECT command) and determining a corresponding physical address for a received element address based on the set of new logical element addresses.

Owner:CF DB EZ +1

Displaying Physical Signal Routing in a Diagram of a System

Displaying physical signal routing of a system. A diagram of the system may be displayed. The system may include physical components connected via physical connections and logical components implemented on various ones of the physical components. The diagram may include a plurality of icons connected by wires. At least a first subset of the icons may represent logical elements of the system and wires between the first subset of icons may represent logical connections between corresponding logical elements. User input requesting signal routing information of the system may be received. In response, a signal route corresponding to a first logical connection between a first logical element and a second logical element may be visually indicated.

Owner:NATIONAL INSTRUMENTS

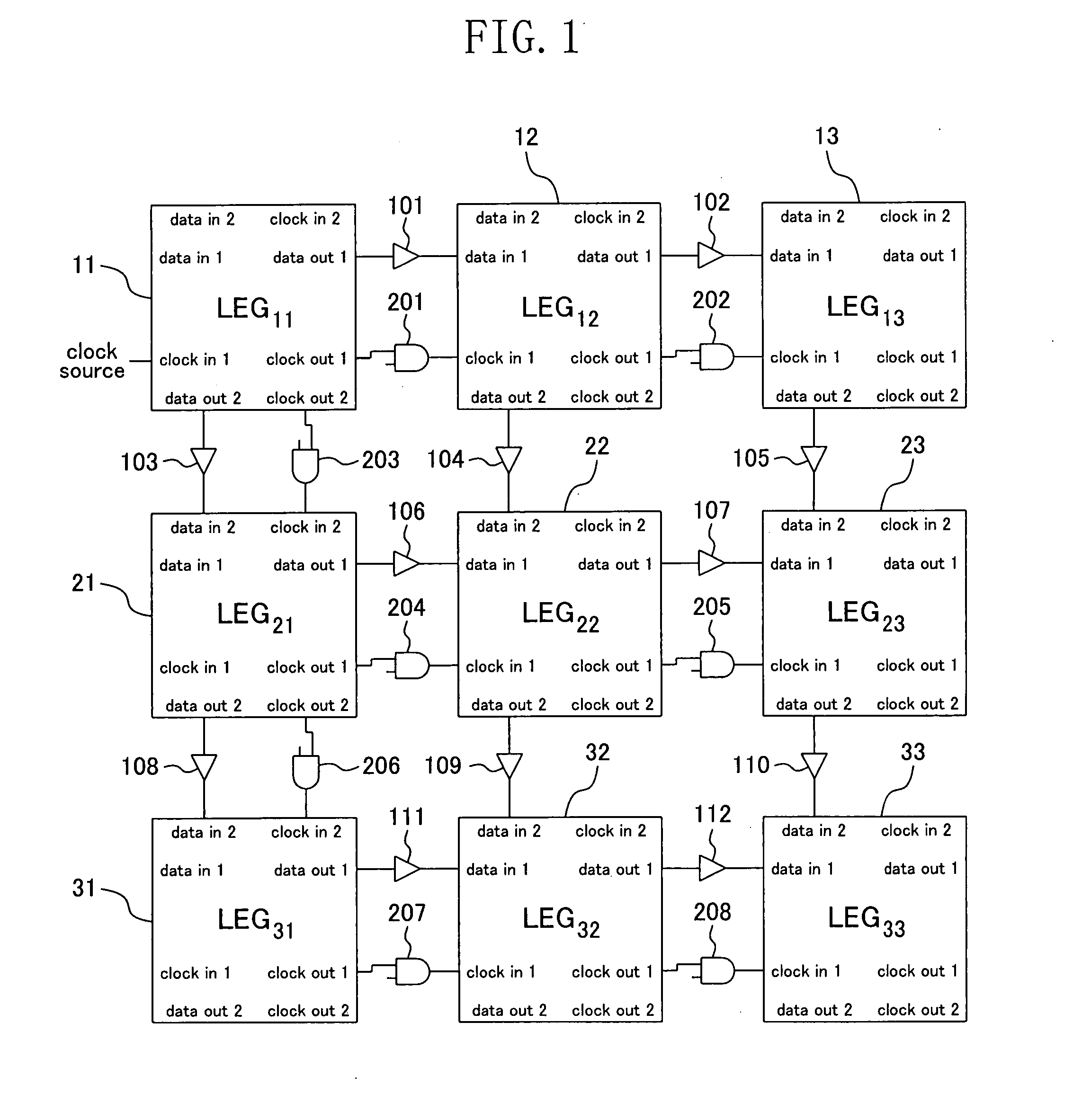

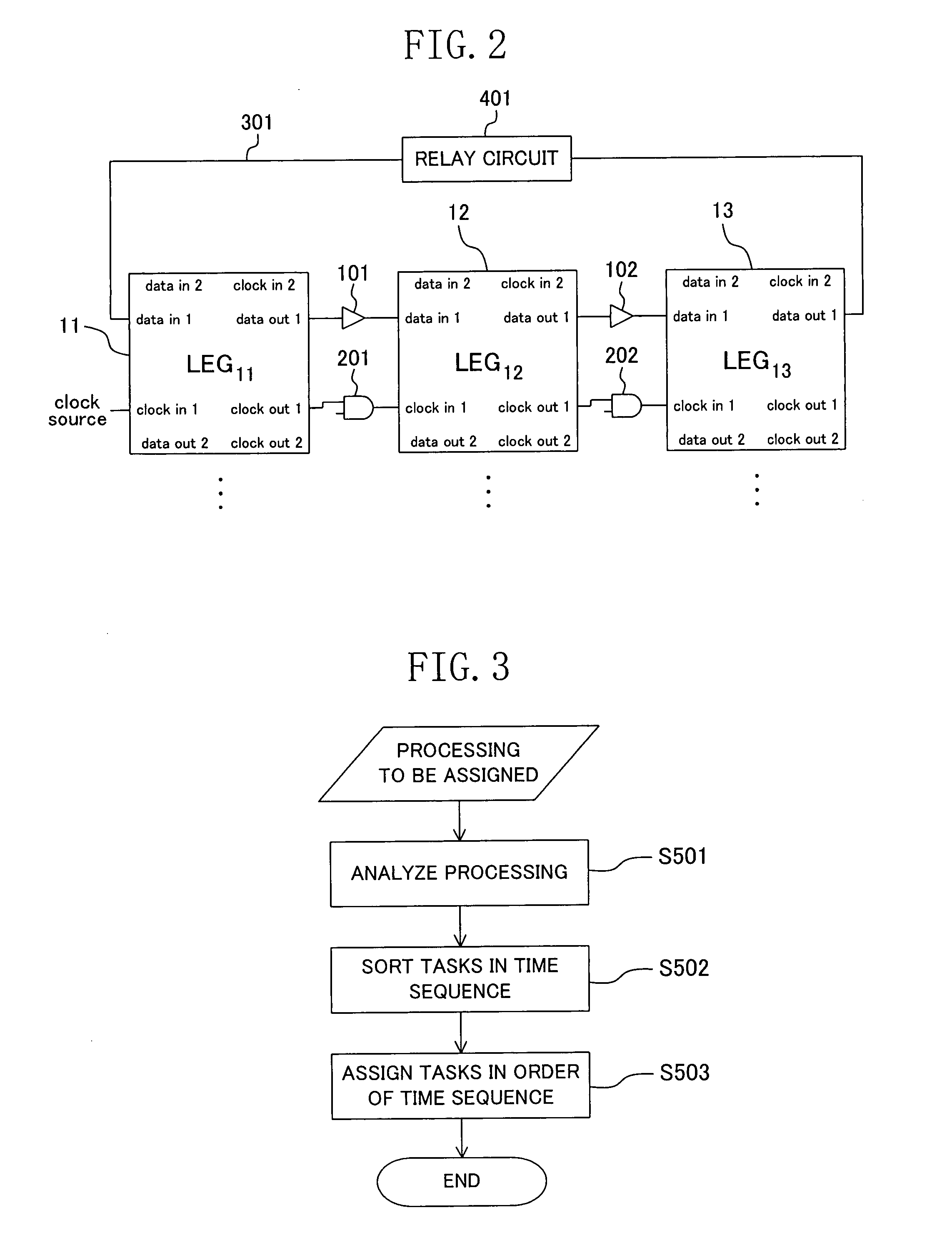

Reconfigurable semiconductor intergrated circuit and processing assignment method for the same

InactiveUS20080061834A1Shorten design timeNew designSolid-state devicesCAD circuit designLogical elementData transmission

A plurality of logic element groups LEG11 to LEG33 respectively include at least one logic element as a component of a reconfigurable semiconductor integrated circuit. Between any logic element groups engaging in data transmission / reception, e.g., LEG11 and LEG12, clock out terminal and clock in terminal are connected via a line while data out terminal and data in terminal are connected via a delay element 101. The logic element groups LEG11 to LEG33 are therefore independent of one another in terms of timing design. Thus, if redesign is necessary for a semiconductor integrated circuit completed with a plurality of logic element groups, only a new circuit may be designed and connected to an existing circuit, or an unnecessary logic element group may just be removed, to complete a new semiconductor integrated circuit.

Owner:SOCIONEXT INC

Progressive takeoff thrust ramp for an aircraft

A method is presented for controlling thrust generated by aircraft engines. Engine thrust is controlled based on aircraft groundspeed and airspeed during the initial part of takeoff. Limiting thrust at low groundspeed during the initial phase of takeoff has significant benefits that reduce engine stress during this brief but critical phase leading to flight. Logical elements combine both groundspeed and airspeed in such a way that the operator perceives a smooth progressive thrust increase consistent with normal engine operation.

Owner:THE BOEING CO

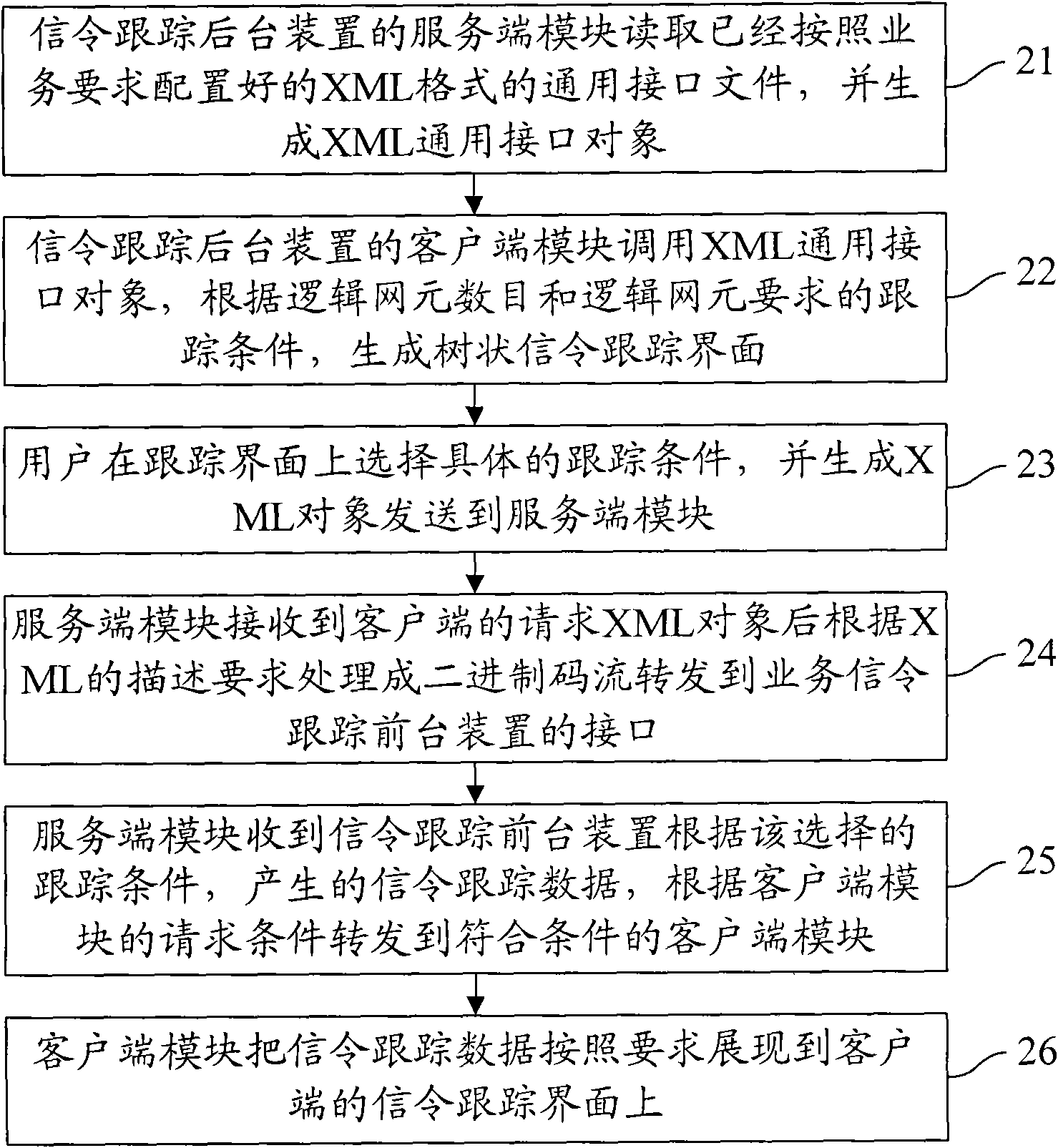

Signaling tracking method, signaling tracking background device and tracking system

InactiveCN101631261AEasy maintenanceReduce maintenance workloadSupervisory/monitoring/testing arrangementsSelection arrangementsLogical elementSignal tracking

The invention provides a signaling tracking method, a signaling tracking background device and a tracking system, wherein the method comprises: the signaling tracking background device acquires a universal interface document which comprises tracking condition of logical element location of a signaling tracking foreground device; the signaling tracking background device processes the universal interface document, so as to generate a signaling tracking interface; the signaling tracking background device displays signaling tracking data meeting the selected tracking condition on the signaling tracking interface. The scheme leads signaling tracking background module codes to be unified and reduces the maintenance workload of developers.

Owner:GLOBAL INNOVATION AGGREGATORS LLC

System and method for mode select handling for a partitioned media library

One embodiment of the present invention includes a method for handling status commands direct to a partitioned media library that comprises establishing a set of initial logical element addresses for a set of physical element addresses with each initial logical element address corresponding to a physical element address of an element assigned to a library partition, assigning a set of new logical element addresses for the set of physical element addresses in response to a command from a host application (e.g., a MODE SELECT command) and determining a corresponding physical address for a received element address based on the set of new logical element addresses.

Owner:CF DB EZ +1

System and method for a logical-model based application understanding and transformation

Disclosed is a method of and a system for establishing a logical-model based understanding of a legacy application. The method comprises the steps of providing a physical data model of the legacy application, said physical data model having a plurality of physical elements; establishing a logical data model for the legacy application, said logical data model having a plurality of logical model elements; and establishing links between said logical model elements and said physical elements. One of said physical or logical elements is selected, and said links are used to identify all of the physical or logical elements that are linked to said selected one of said elements. The preferred system may include a component for browsing and navigating the physical data model, logical data model, or the links between them, a component to answer queries about the application expressed using the logical data model, and a component to create a relational data model to support the migration of data stored in legacy databases (including flat files) to relational databases.

Owner:INT BUSINESS MASCH CORP

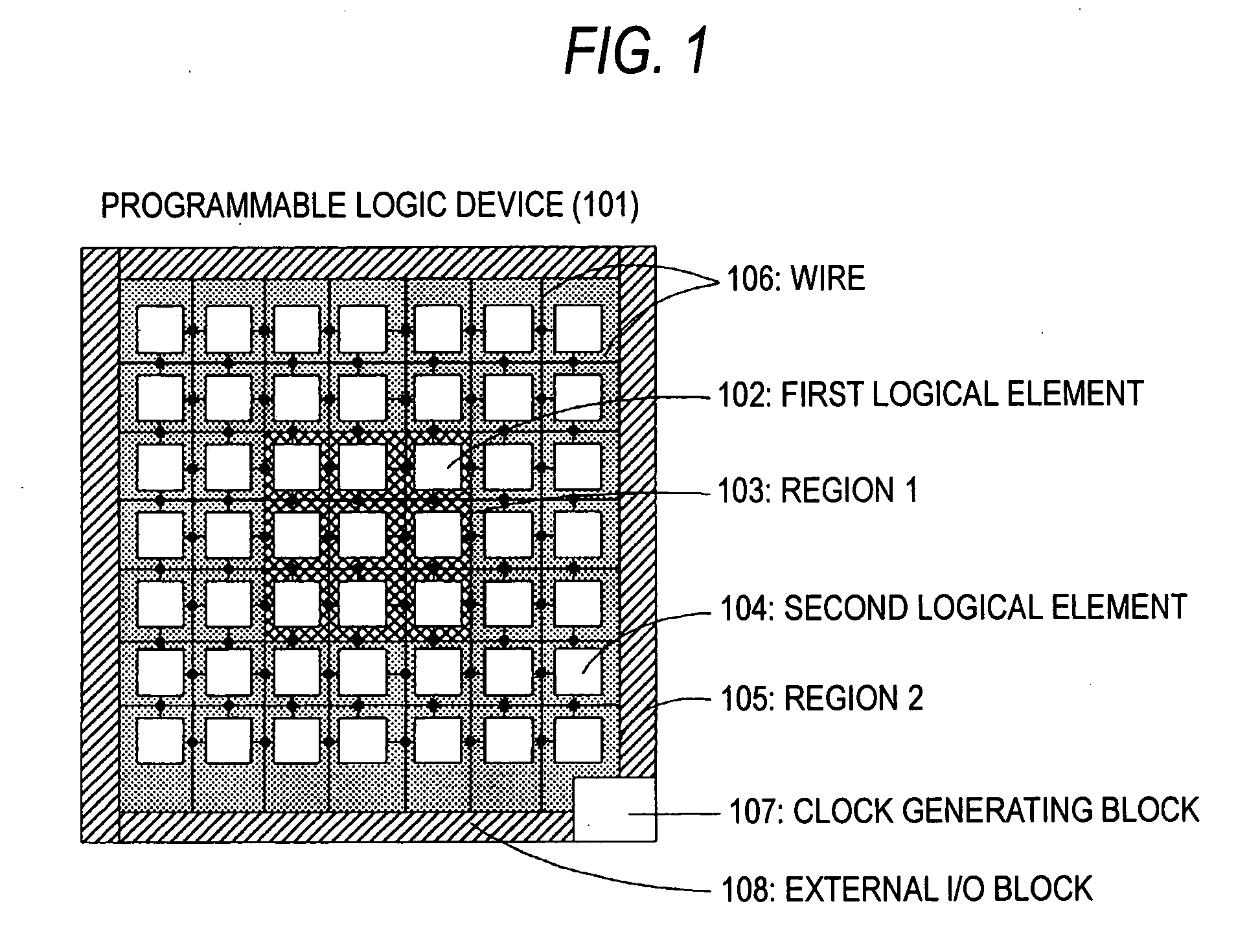

Programmable Logic Device and Method for Designing the Same

InactiveUS20080042687A1Reduce areaReduce power consumptionTransistorSolid-state devicesLogical elementProgrammable logic device

The power consumption and area of a programmable logic device formed from programmable logical elements can be reduced.In a programmable logic device 101 formed from programmable logical elements, there are provided first logical elements 102 and second logical elements 104 having the same logic as the first logical elements 102 but having an upper limit of operating speed designed to be lower than that of the first logical elements 102.

Owner:SOCIONEXT INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com