Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

208results about How to "Avoid short channel effects" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

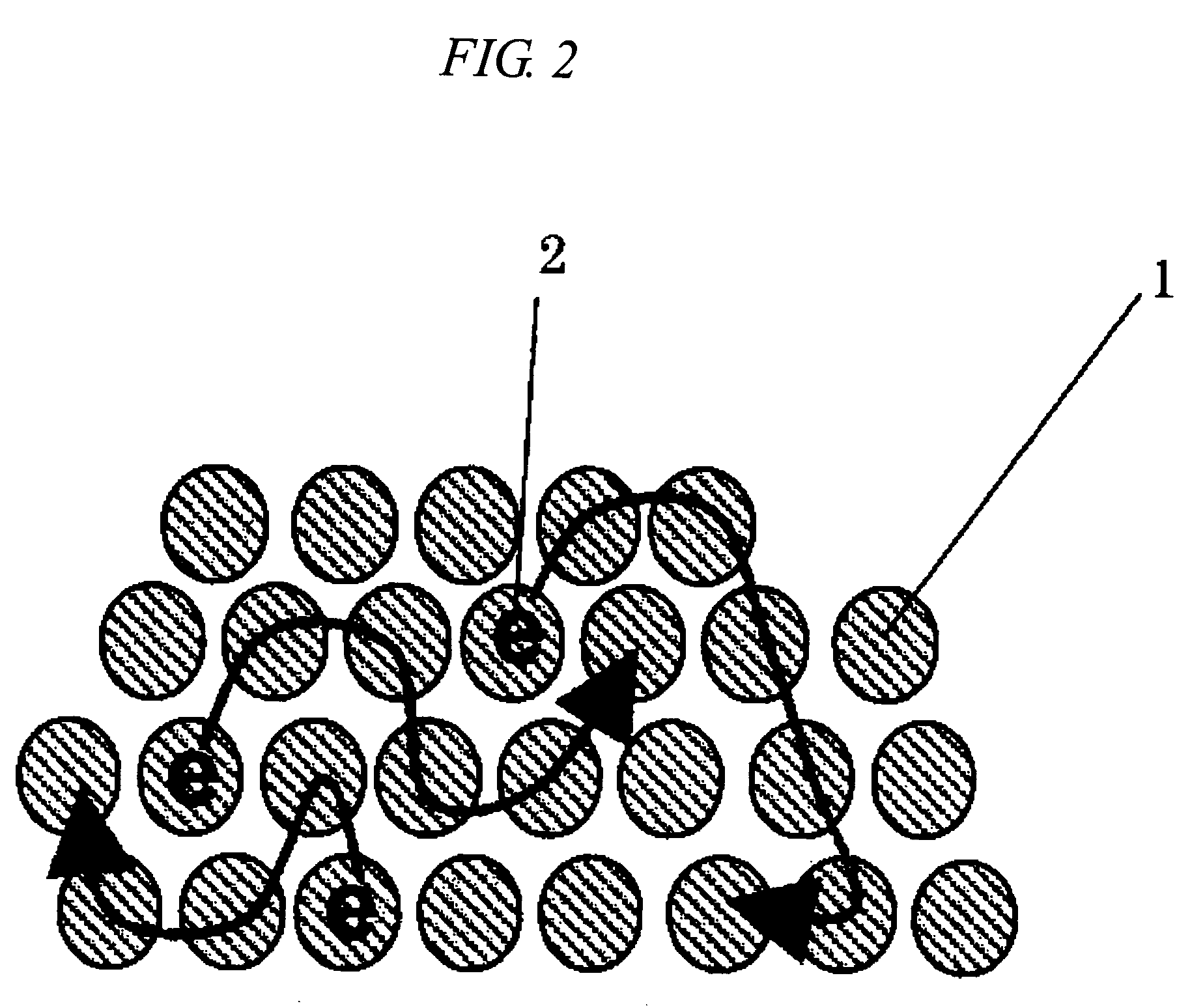

Method of manufacturing semiconductor device, and semiconductor device

ActiveUS20070254414A1Sufficient carrier mobilityImpurity will diffuseSemiconductor/solid-state device manufacturingSemiconductor devicesSurface layerConcentration gradient

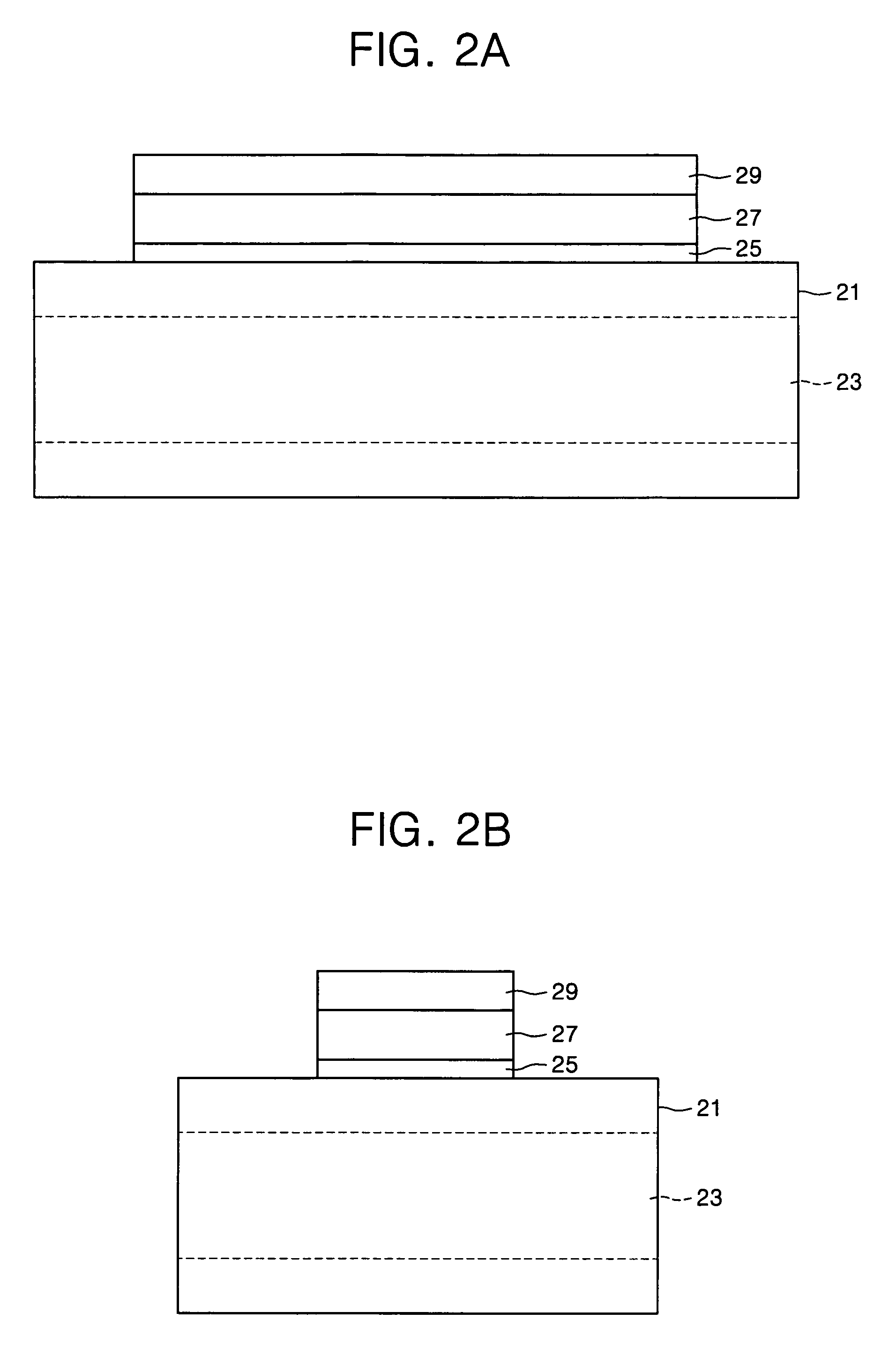

A method of manufacturing a semiconductor device includes: the first step of forming a gate electrode over a silicon substrate, with a gate insulating film; and the second step of digging down a surface layer of the silicon substrate by etching conducted with the gate electrode as a mask. The method of manufacturing the semiconductor device further includes the third step of epitaxially growing, on the surface of the dug-down portion of the silicon substrate, a mixed crystal layer including silicon and atoms different in lattice constant from silicon so that the mixed crystal layer contains an impurity with such a concentration gradient that the impurity concentration increases along the direction from the silicon substrate side toward the surface of the mixed crystal layer.

Owner:SONY CORP

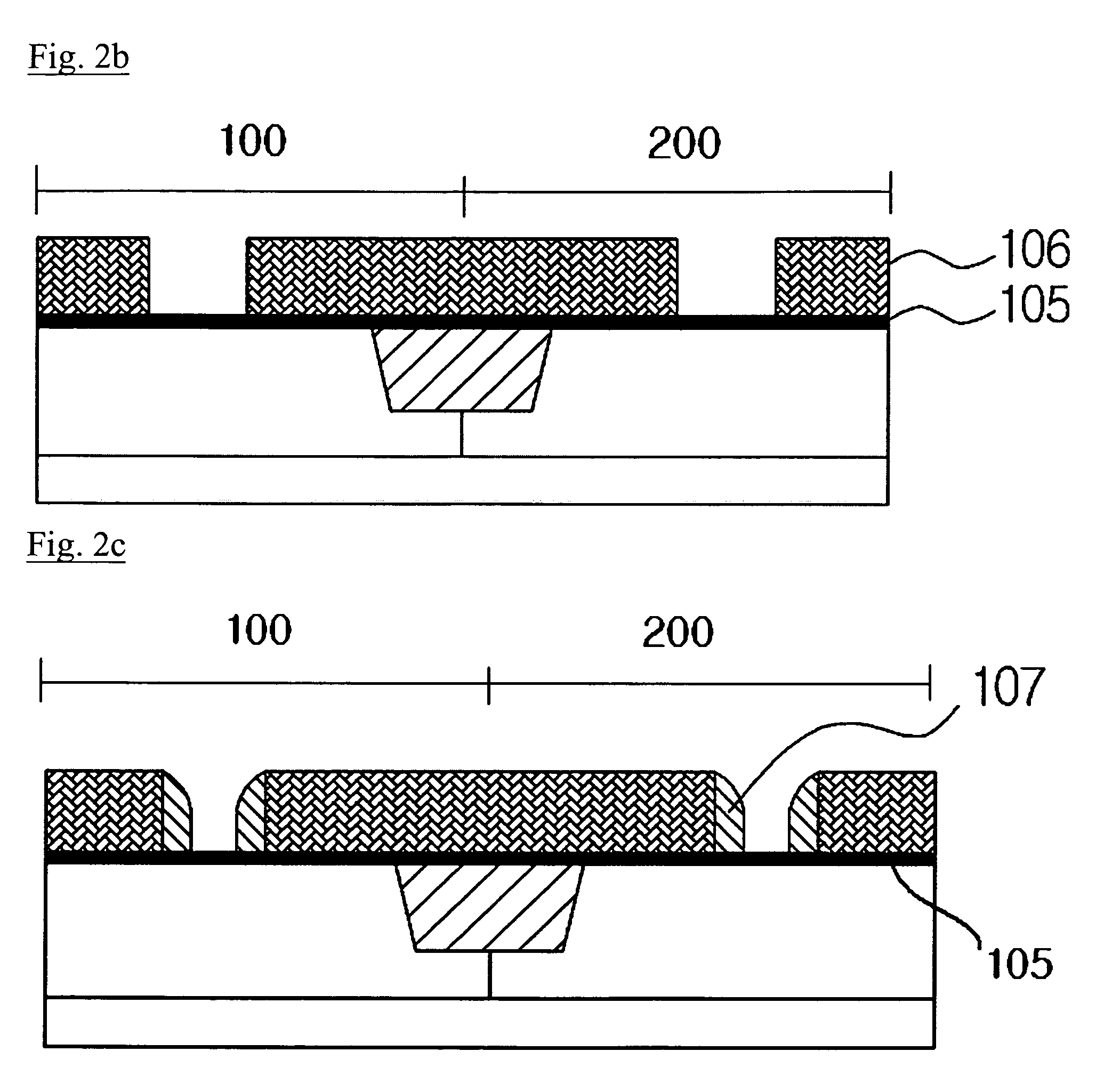

Semiconductor device fabricating method

ActiveUS20050266631A1High speedImprove channel mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesDevice materialSemiconductor

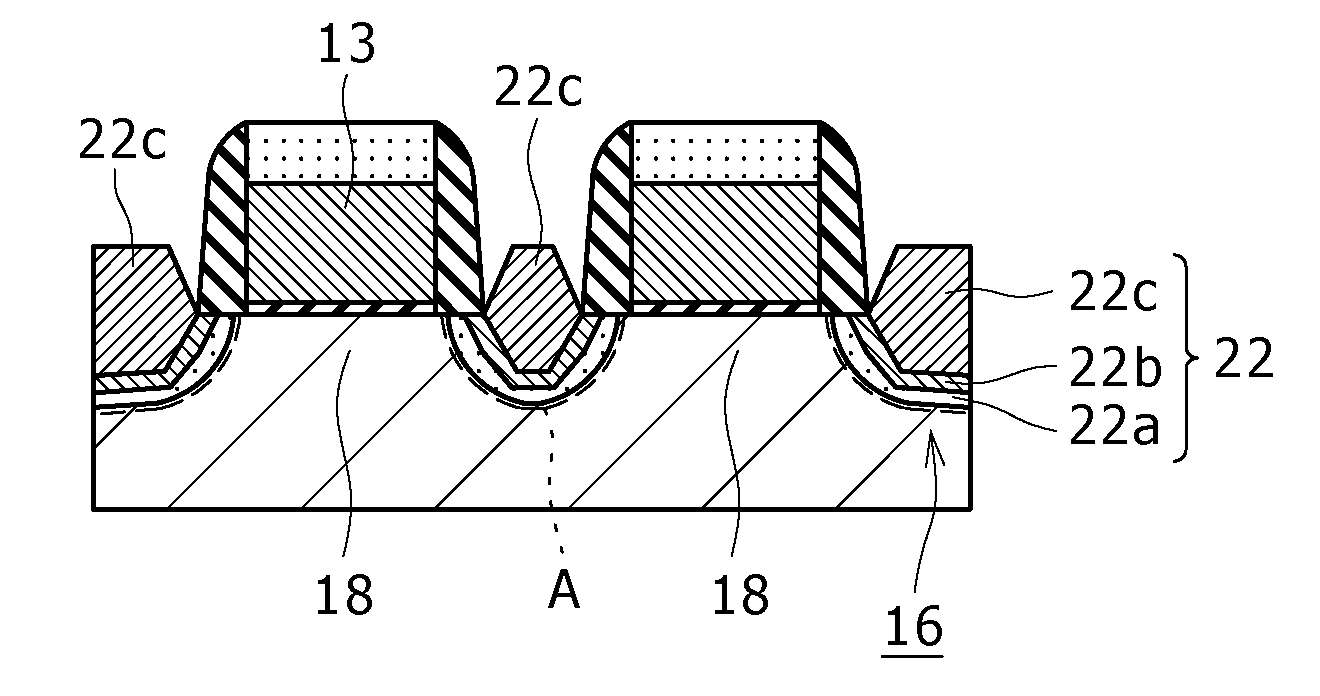

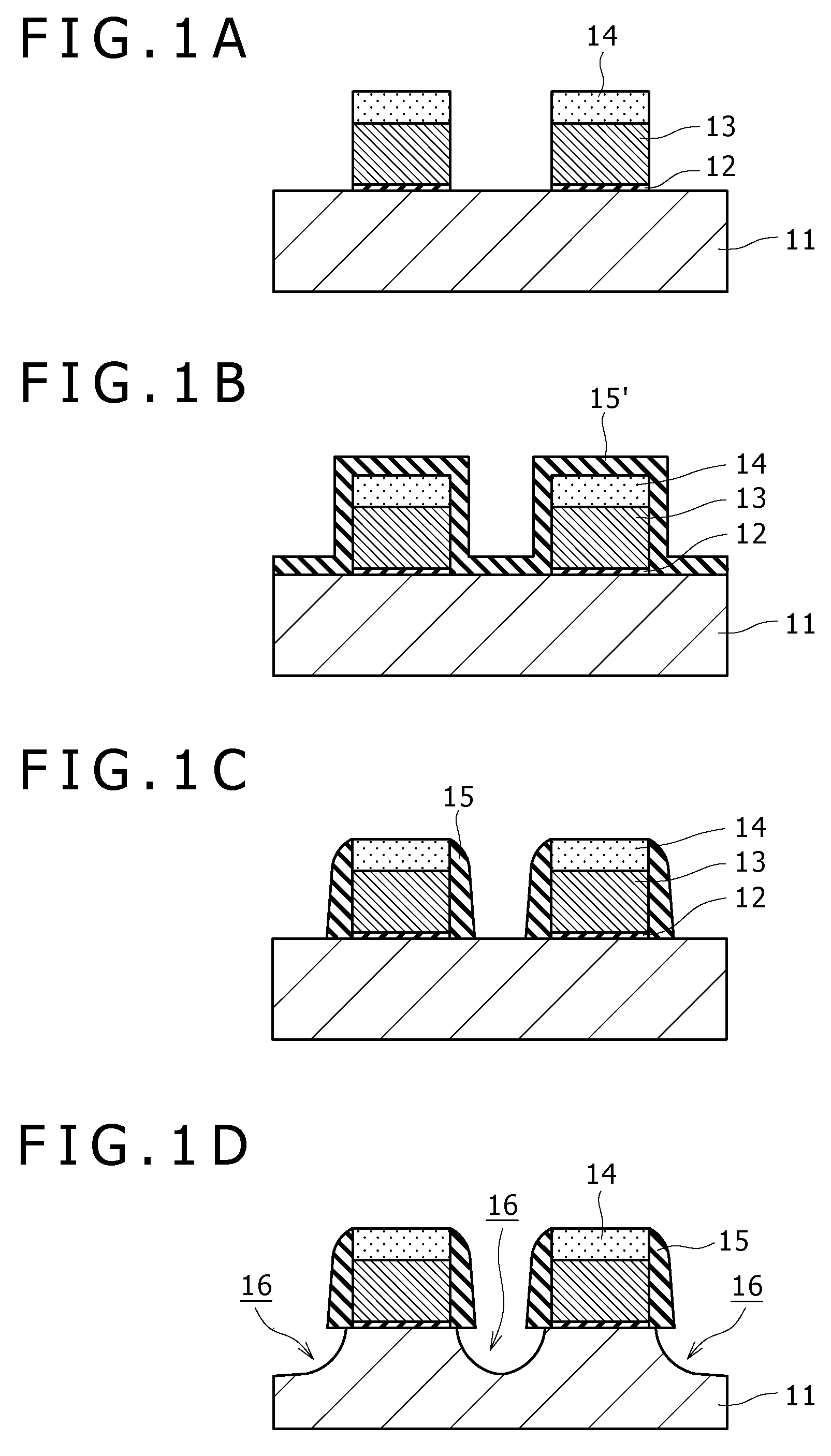

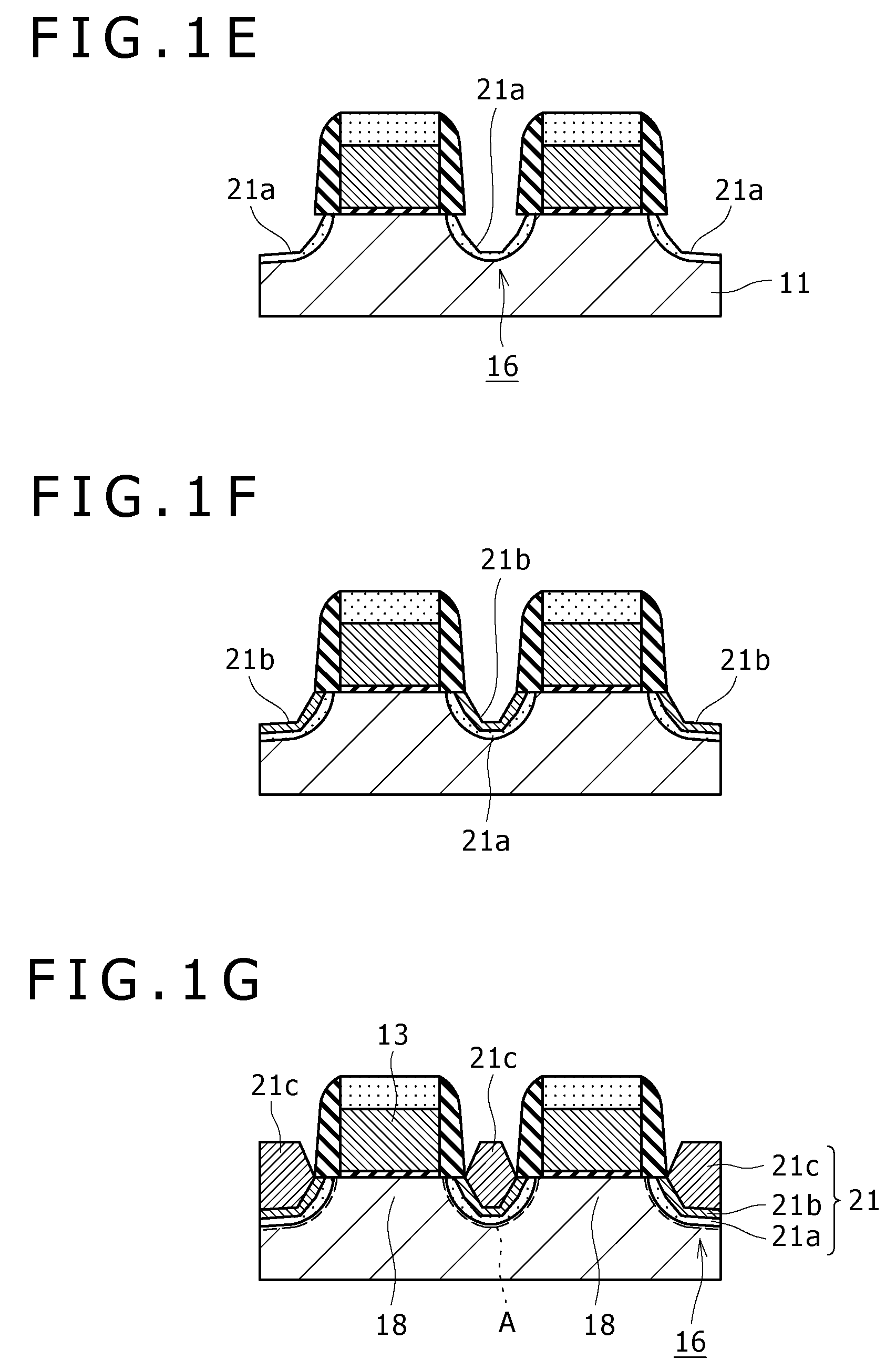

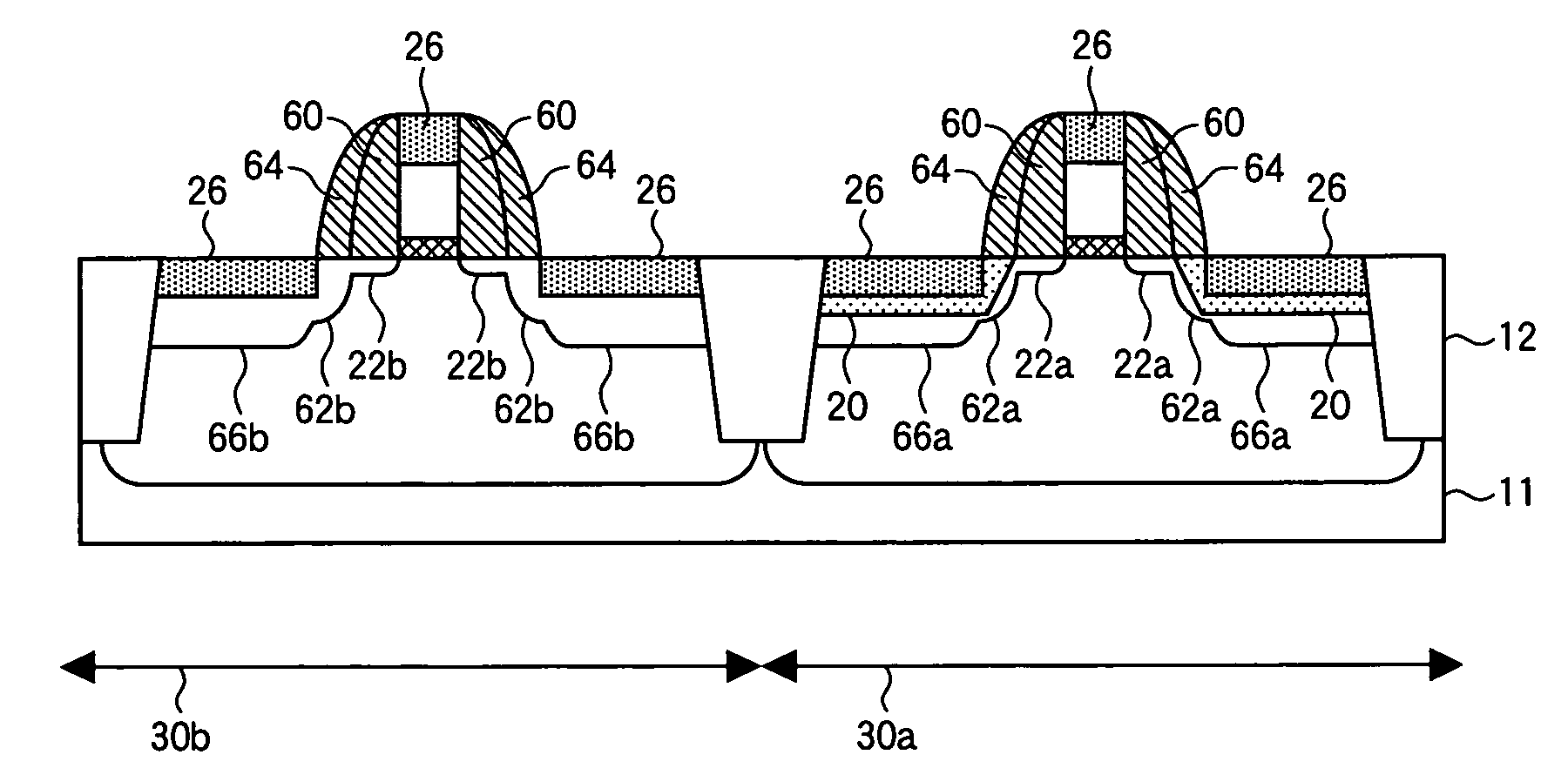

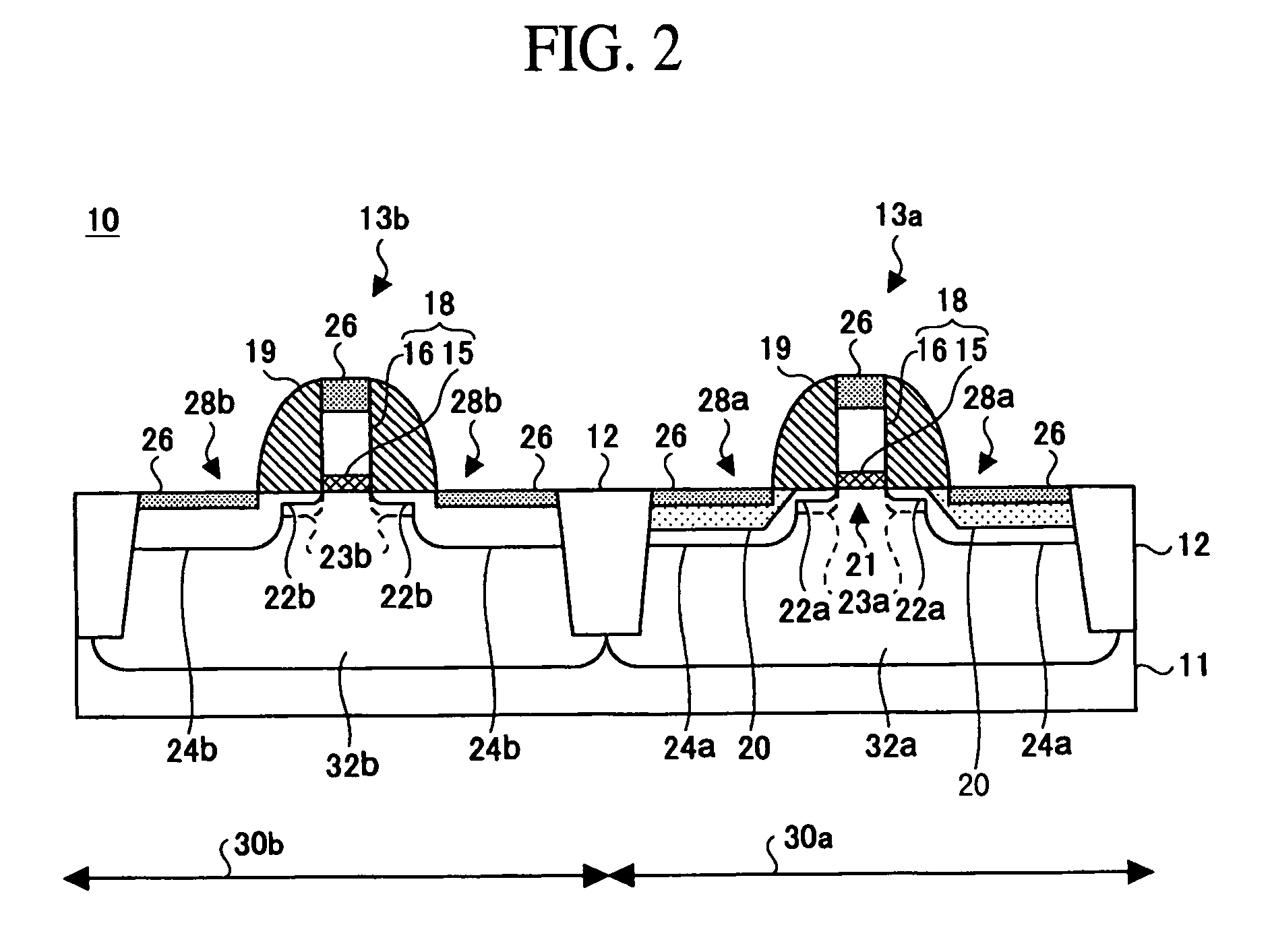

Compression stress applying portions 20 of SiGe film are formed in the source / drain regions of the p-MOSA region 30a. Then, impurities are implanted in the p-MOS region 30a and the n-MOS region 30b to form shallow junction regions 22a, 22b and deep junction regions 23a, 23b. The impurity in the shallow junction regions 22a, 22b is prevented from being diffused immediately below the gate insulation film 15 by the thermal processing in forming the SiGe film, the short channel effect is prevented, and the hole mobility of the channel region of the p-MOS transistor 14a. The operation speed of the p-MOS transistor 13a is balanced with that of the n-MOS transistor, whereby the operation speed of the complementary semiconductor device 10 can be increased. The semiconductor device fabricating method can increase and balance the operation speed of a p-transistor with that of an n-transistor.

Owner:FUJITSU SEMICON LTD

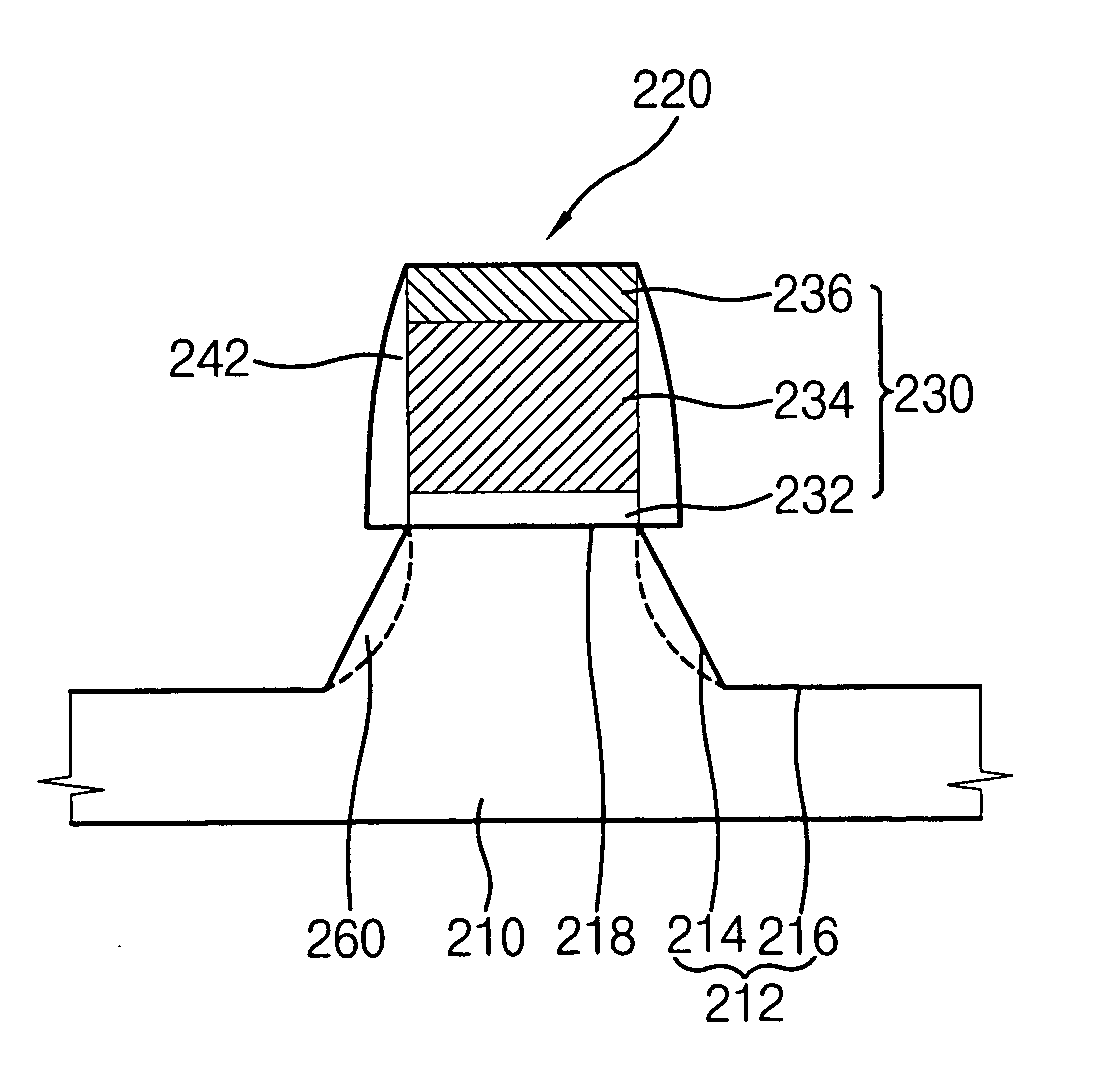

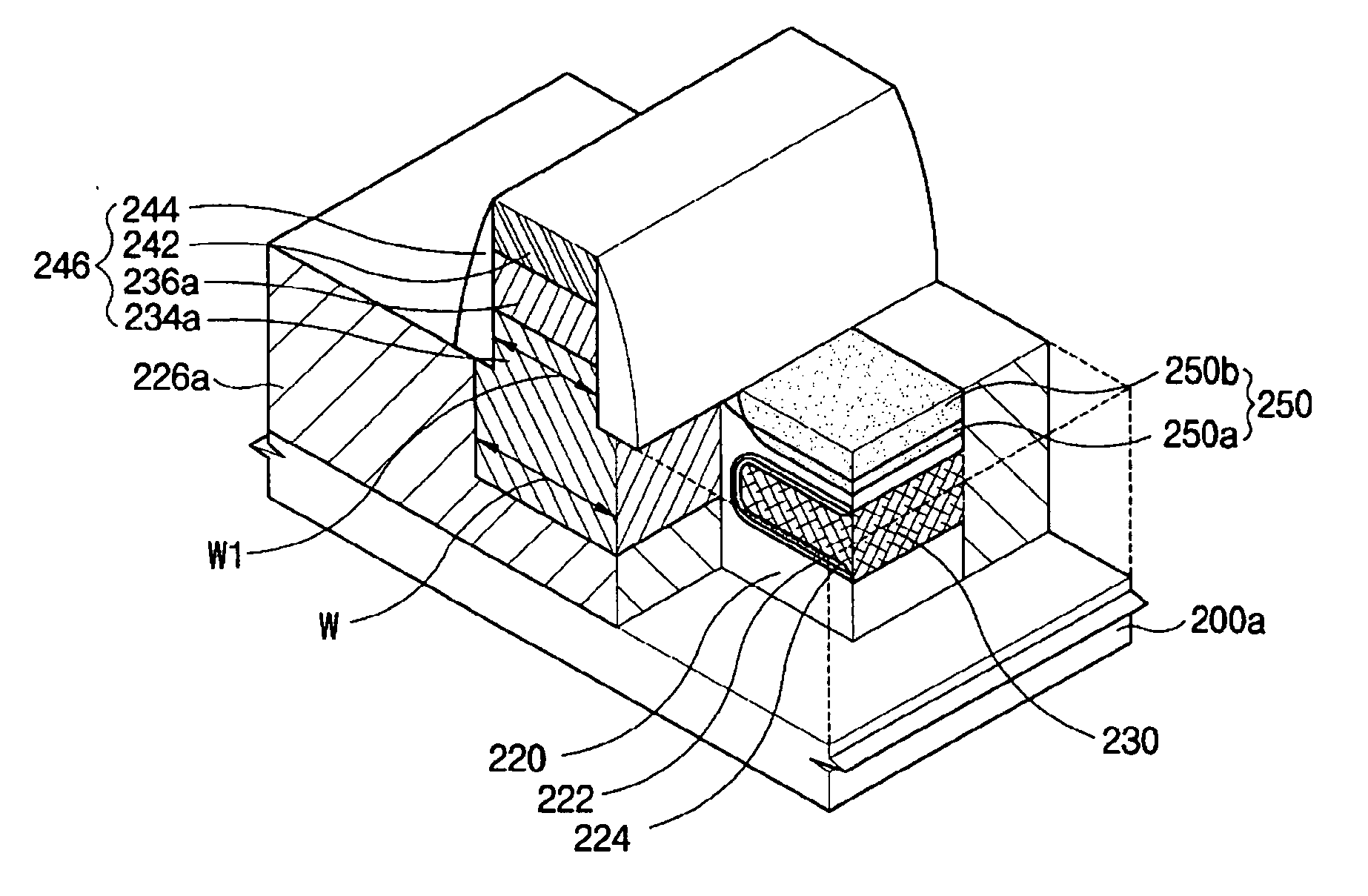

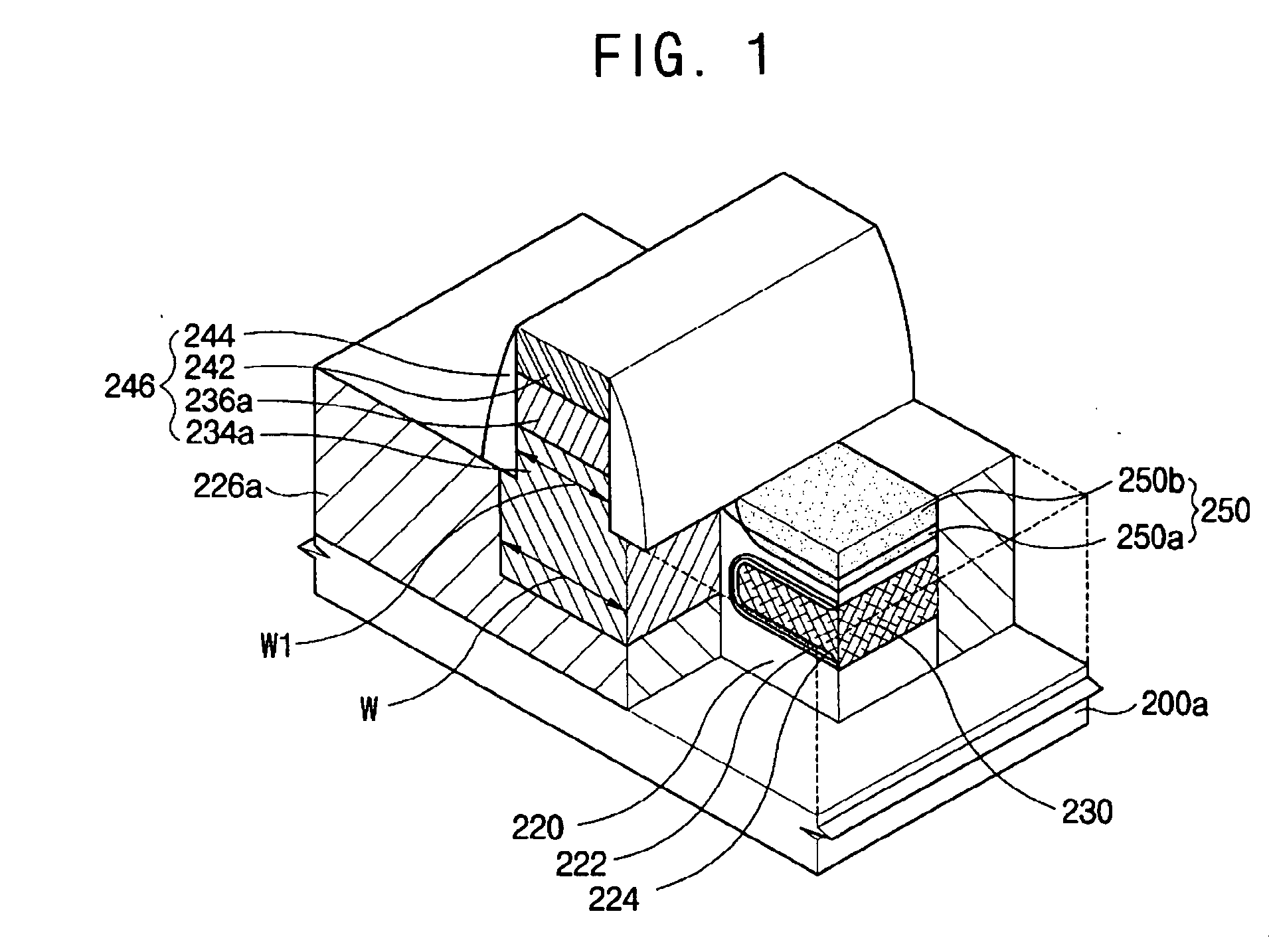

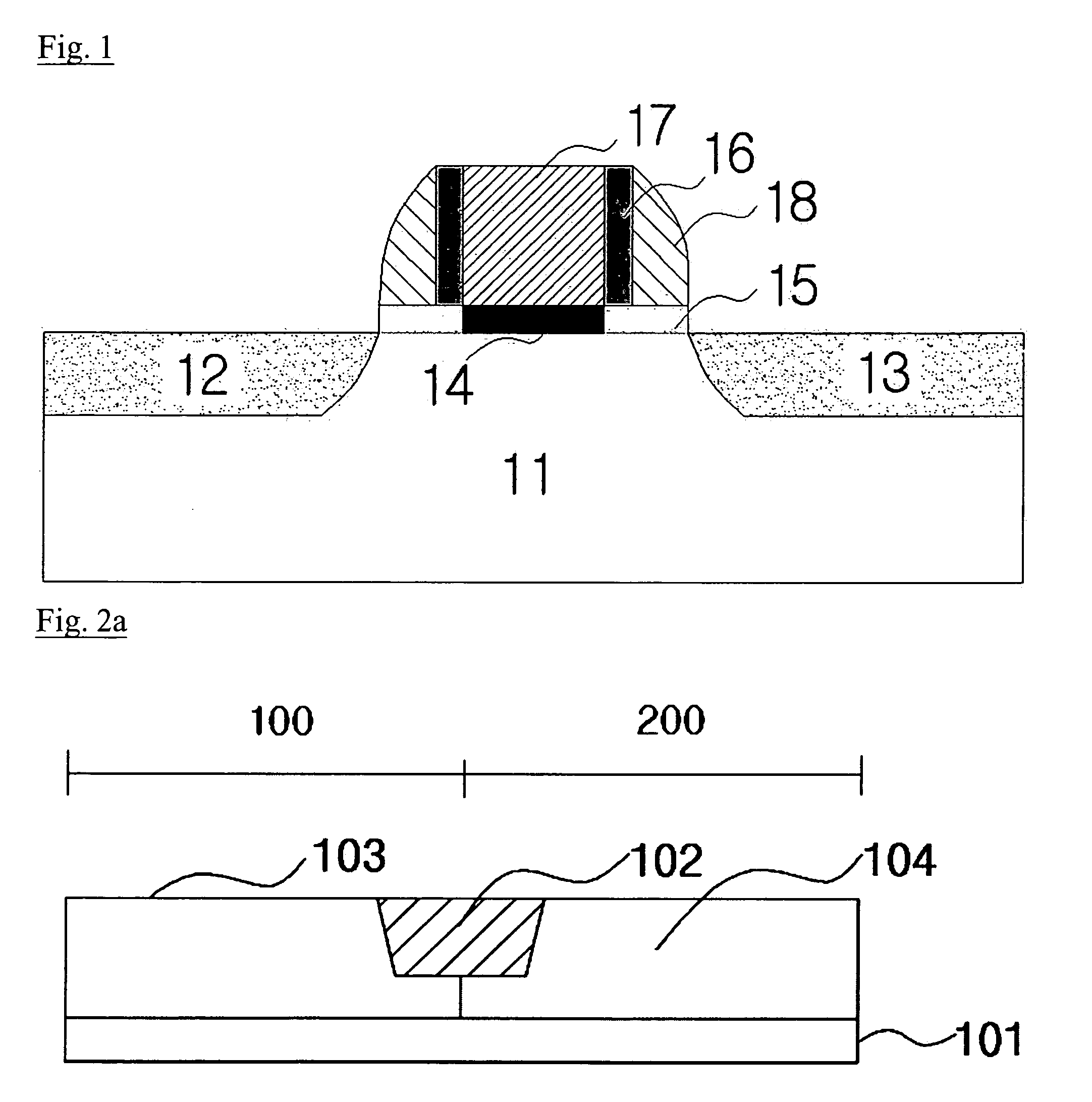

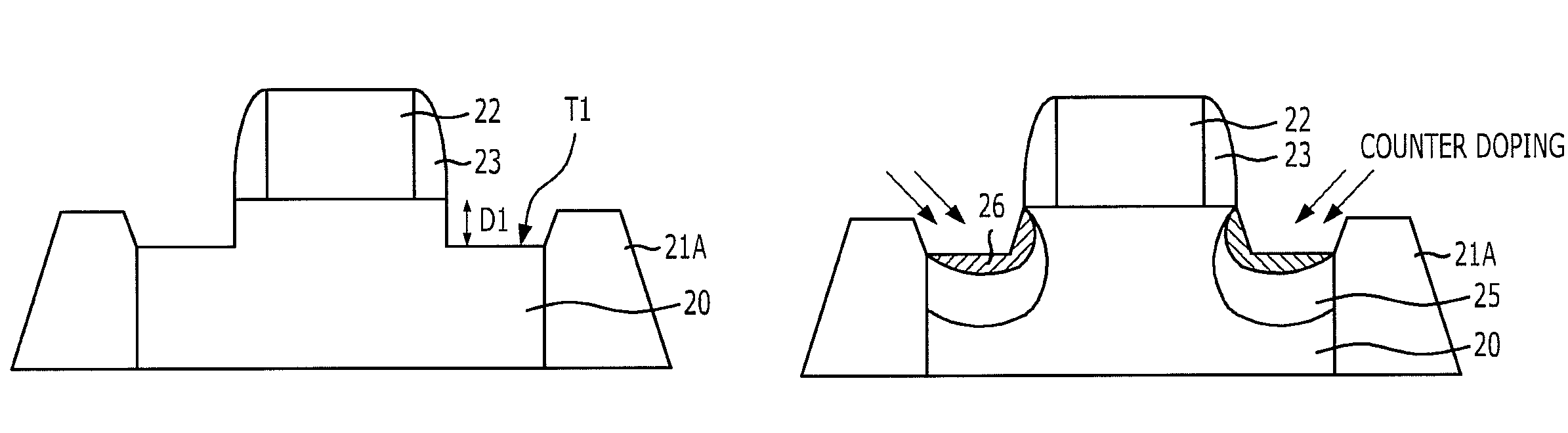

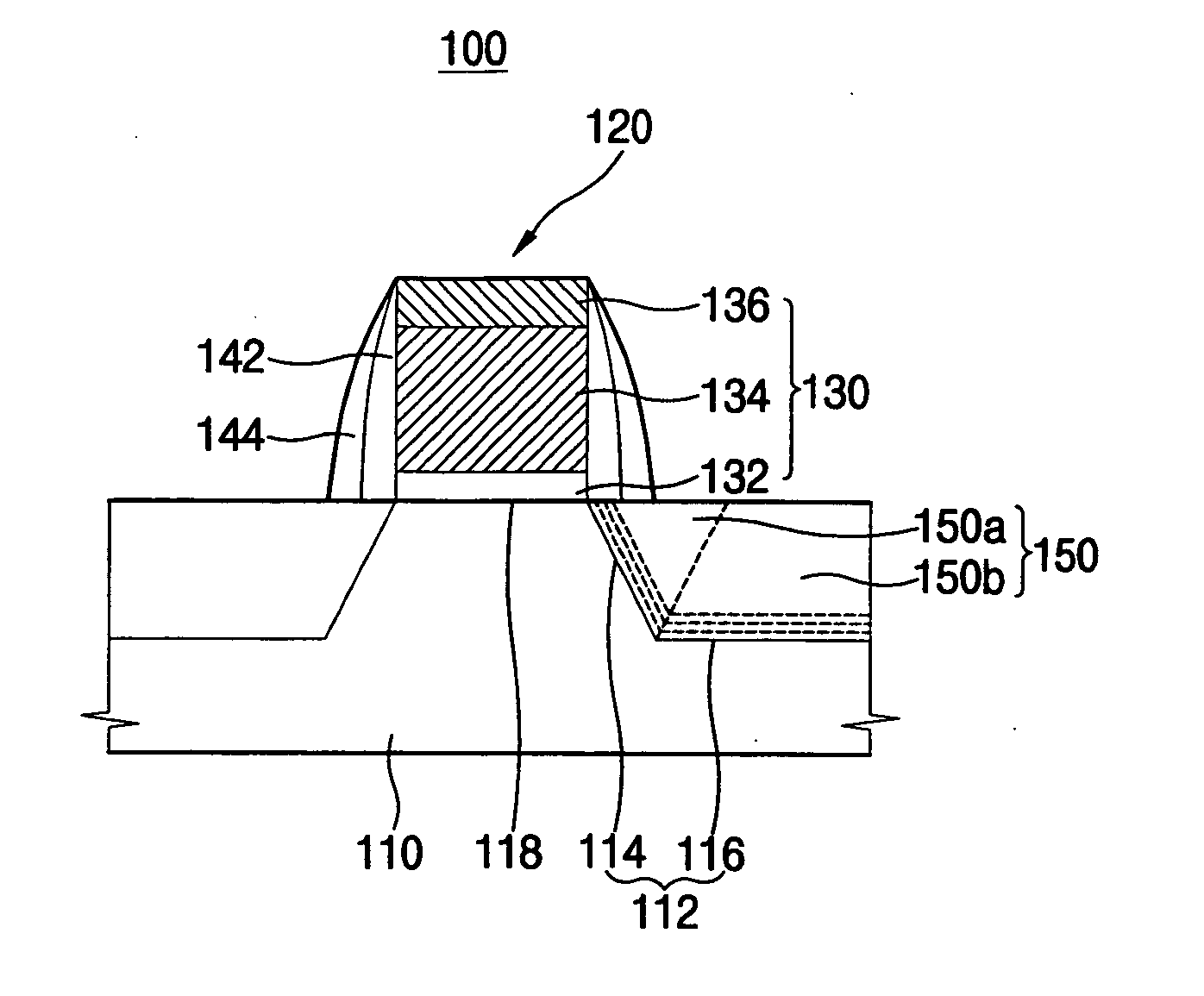

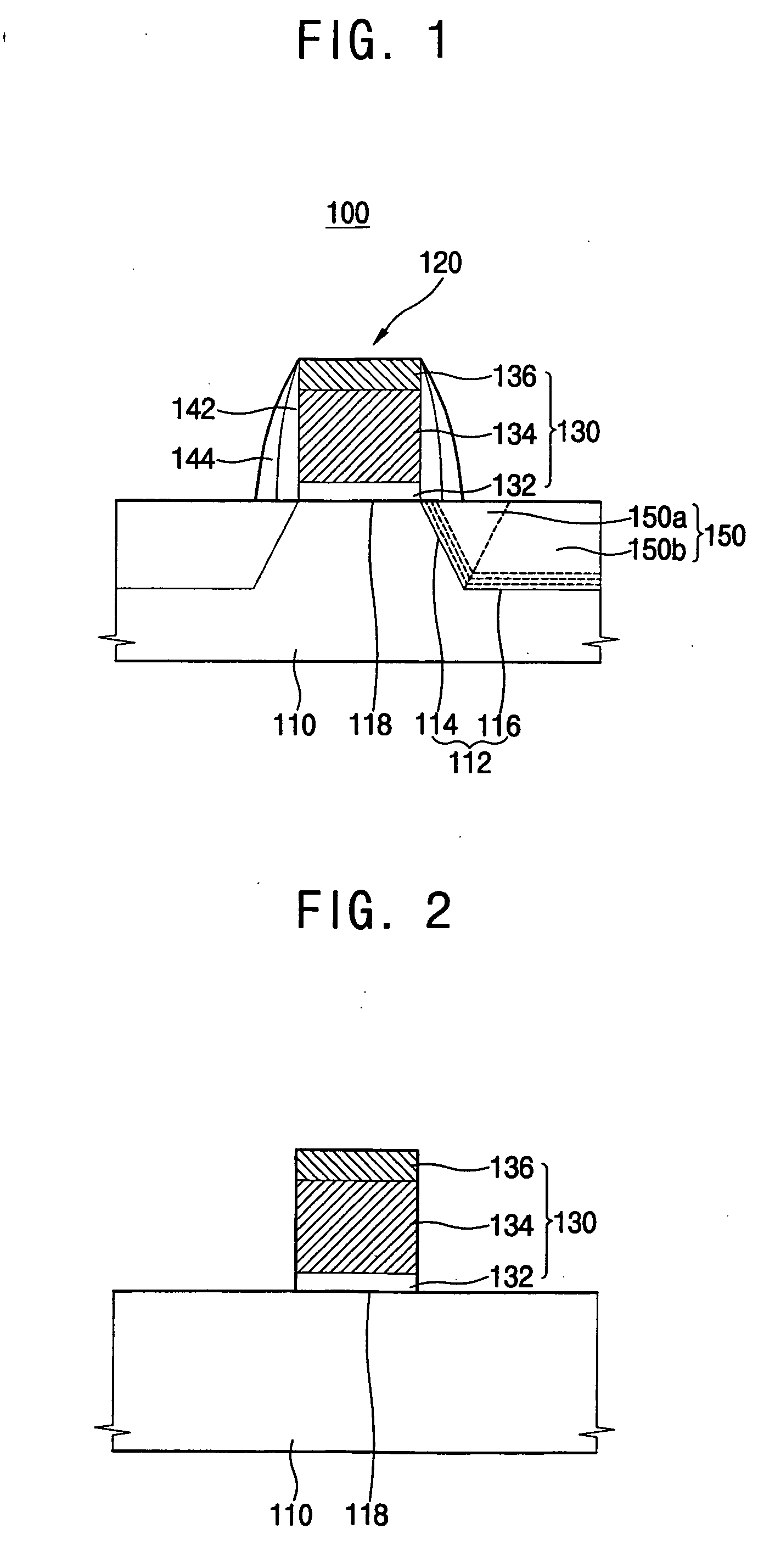

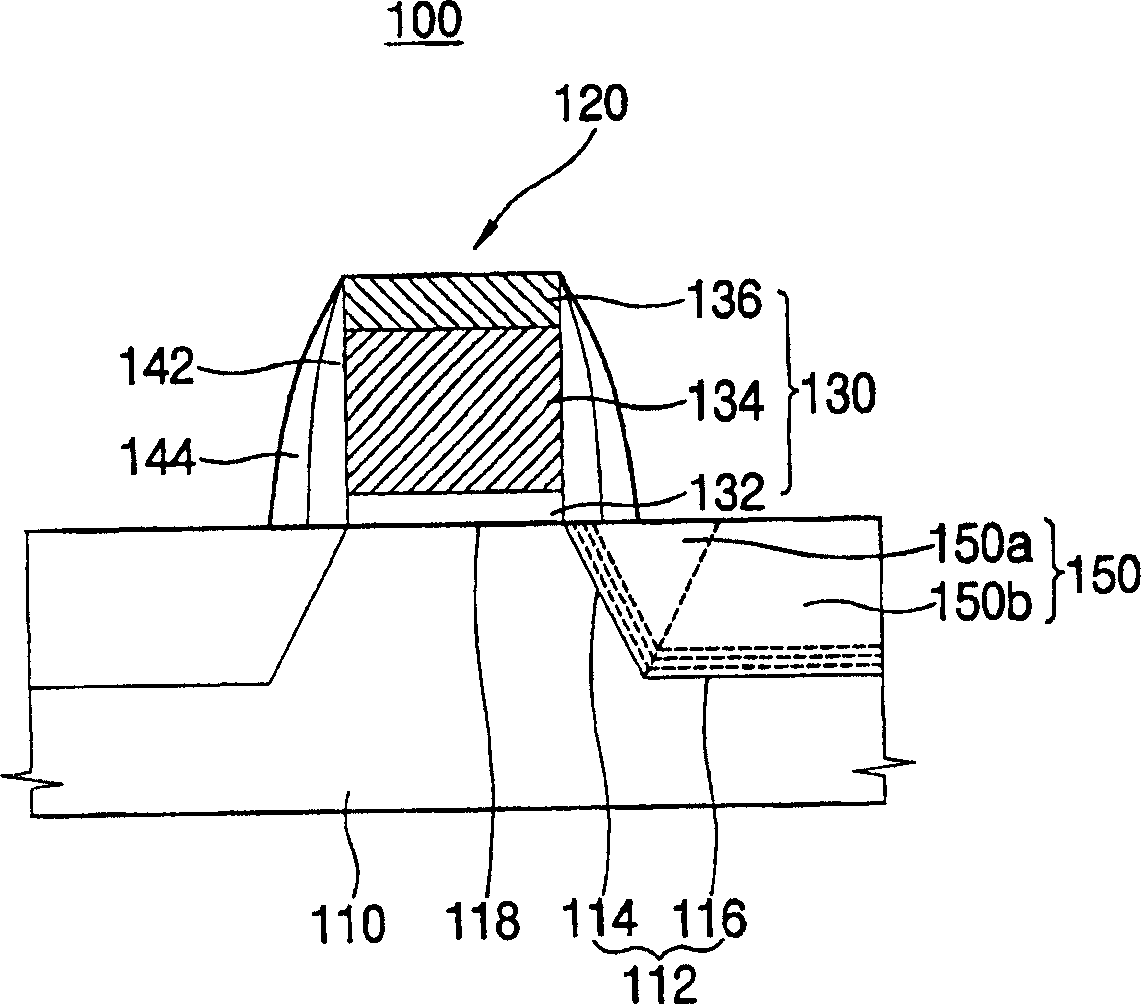

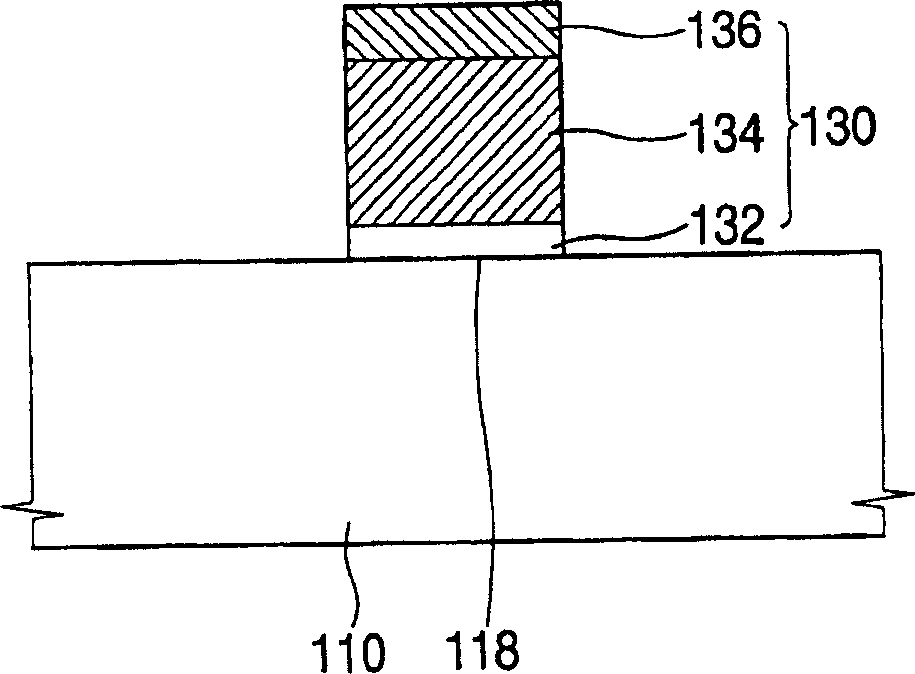

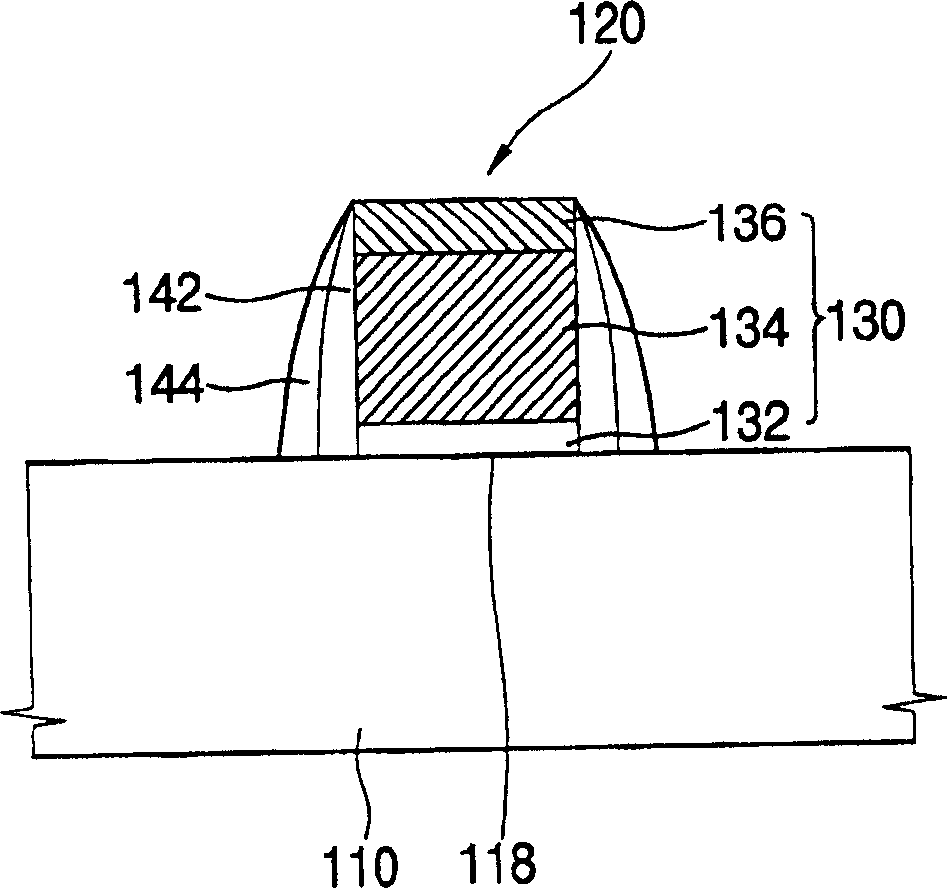

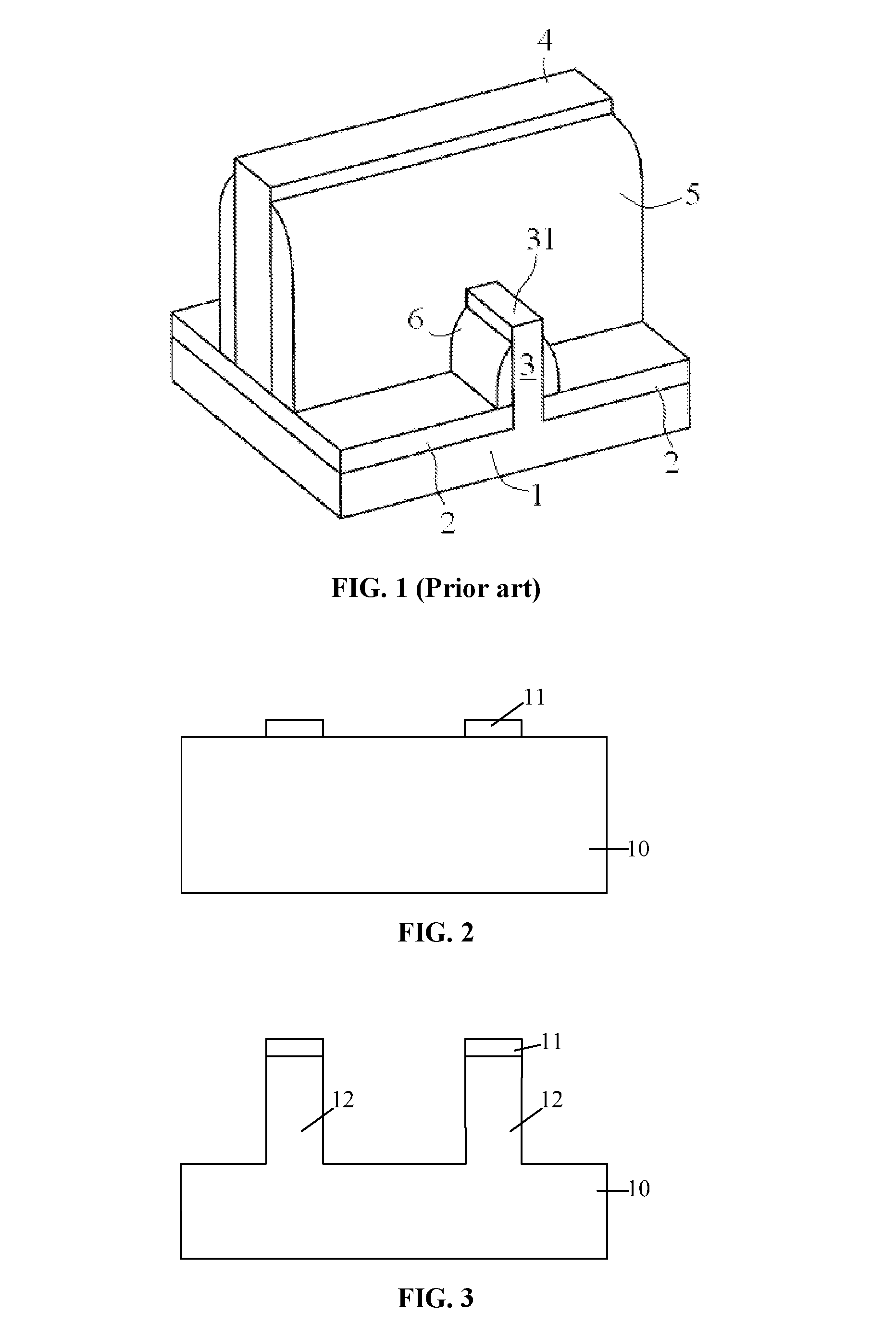

Transistor and method of manufacturing the same

ActiveUS20060038230A1Improved structureExcellent electrical characteristicTransistorSolid-state devicesCrystal planeShort-channel effect

A transistor includes a semiconductor substrate that has a first surface of a {100} crystal plane, a second surface of the {100} crystal plane having a height lower than that of the first surface, and a third surface of a {111} crystal plane connecting the first surface to the second surface. First heavily doped impurity regions are formed under the second surface. A gate structure is formed on the first surface. An epitaxial layer is formed on the second surface and the third surface. Second heavily doped impurity regions are formed at both sides of the gate structure. The second heavily doped impurity regions have side faces of the {111} crystal plane so that a short channel effect generated between the impurity regions may be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

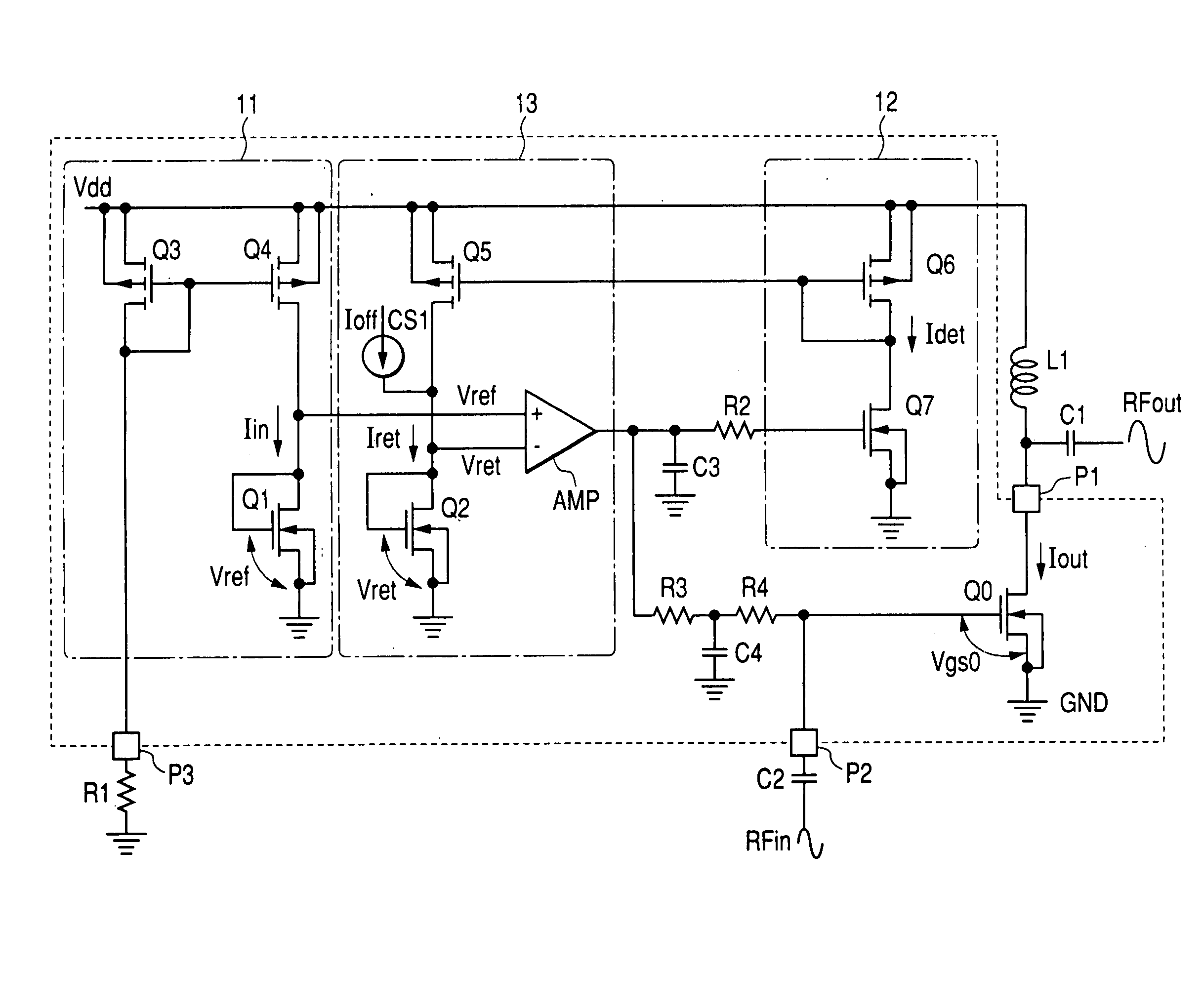

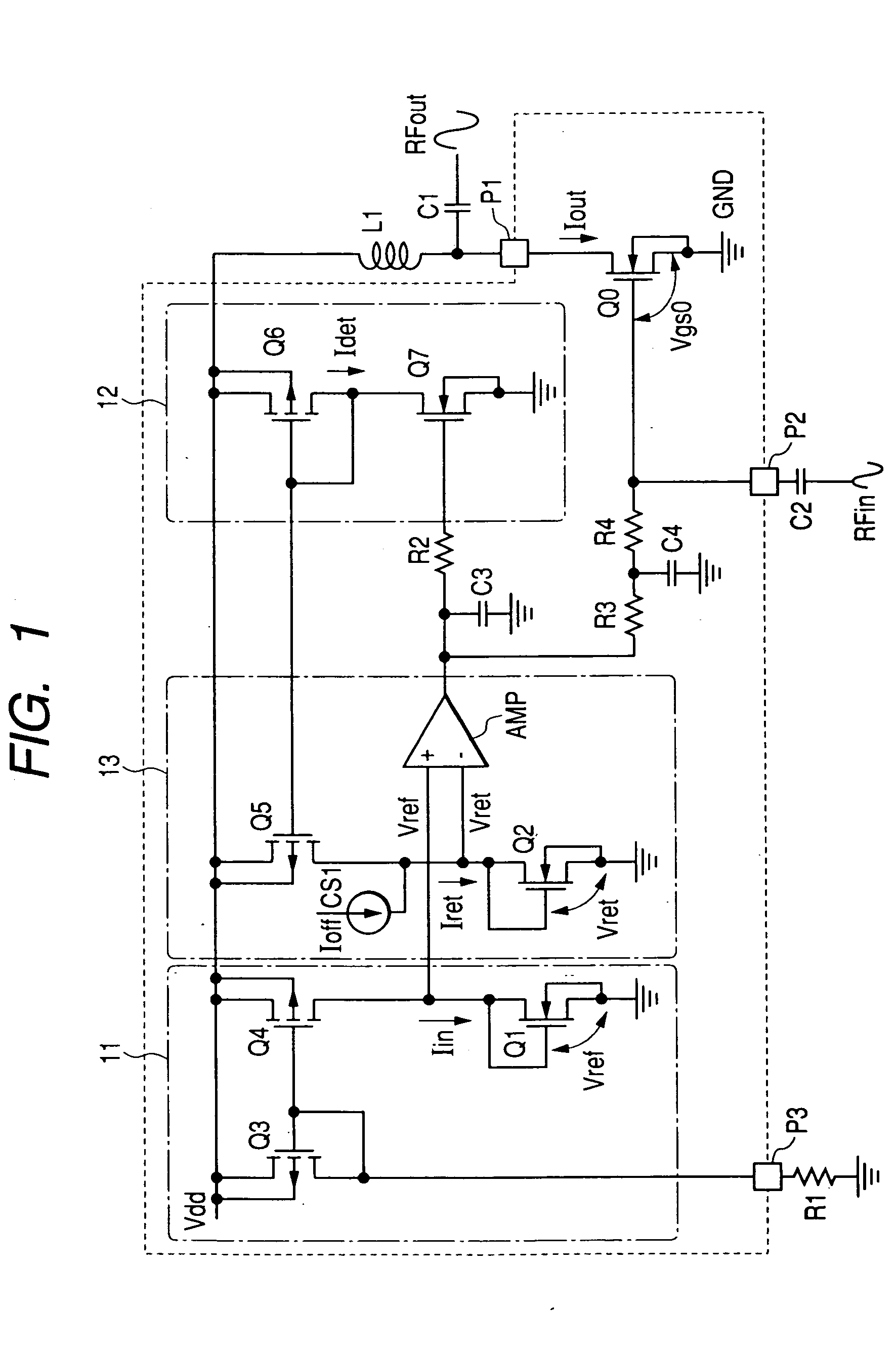

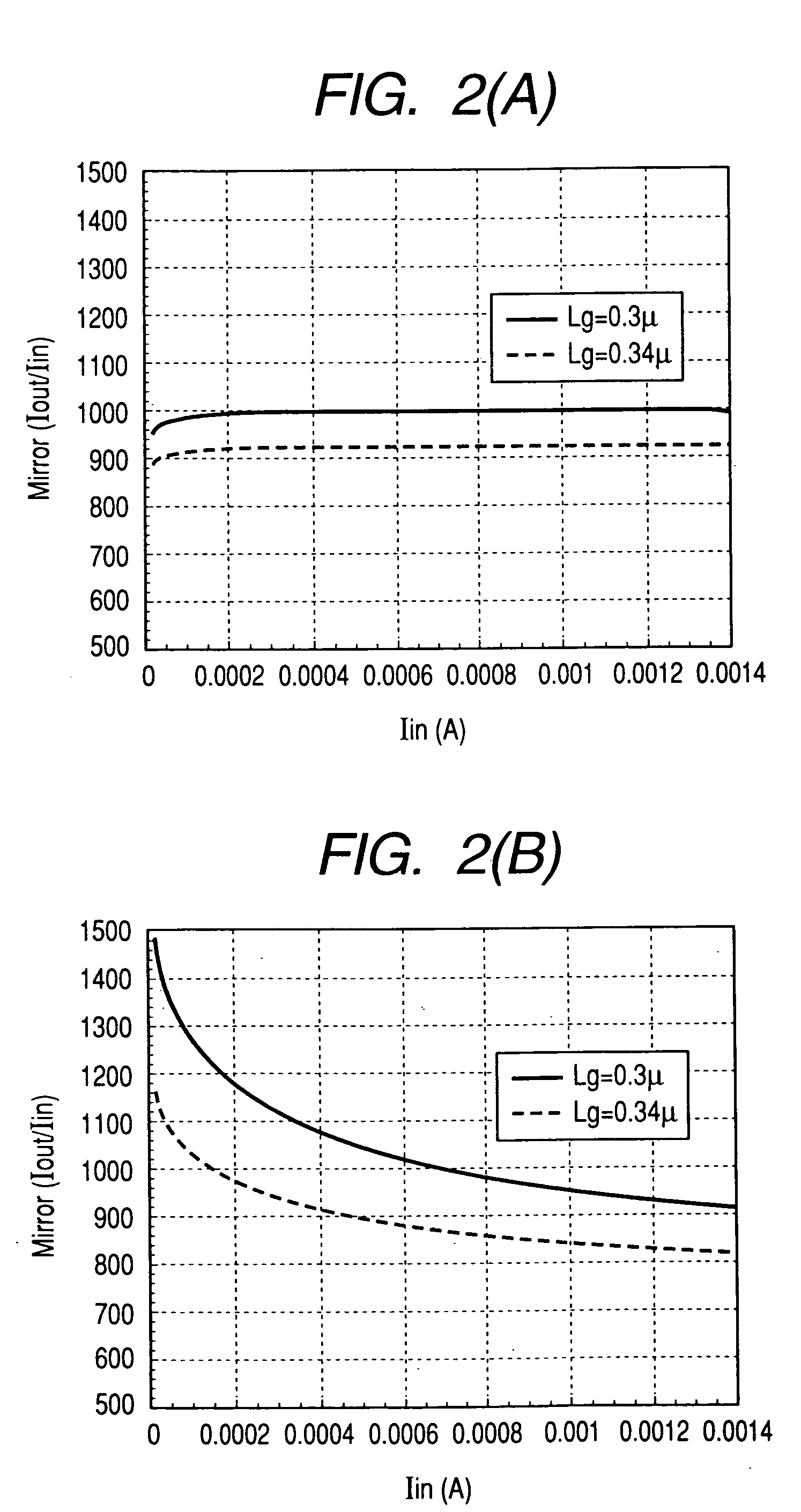

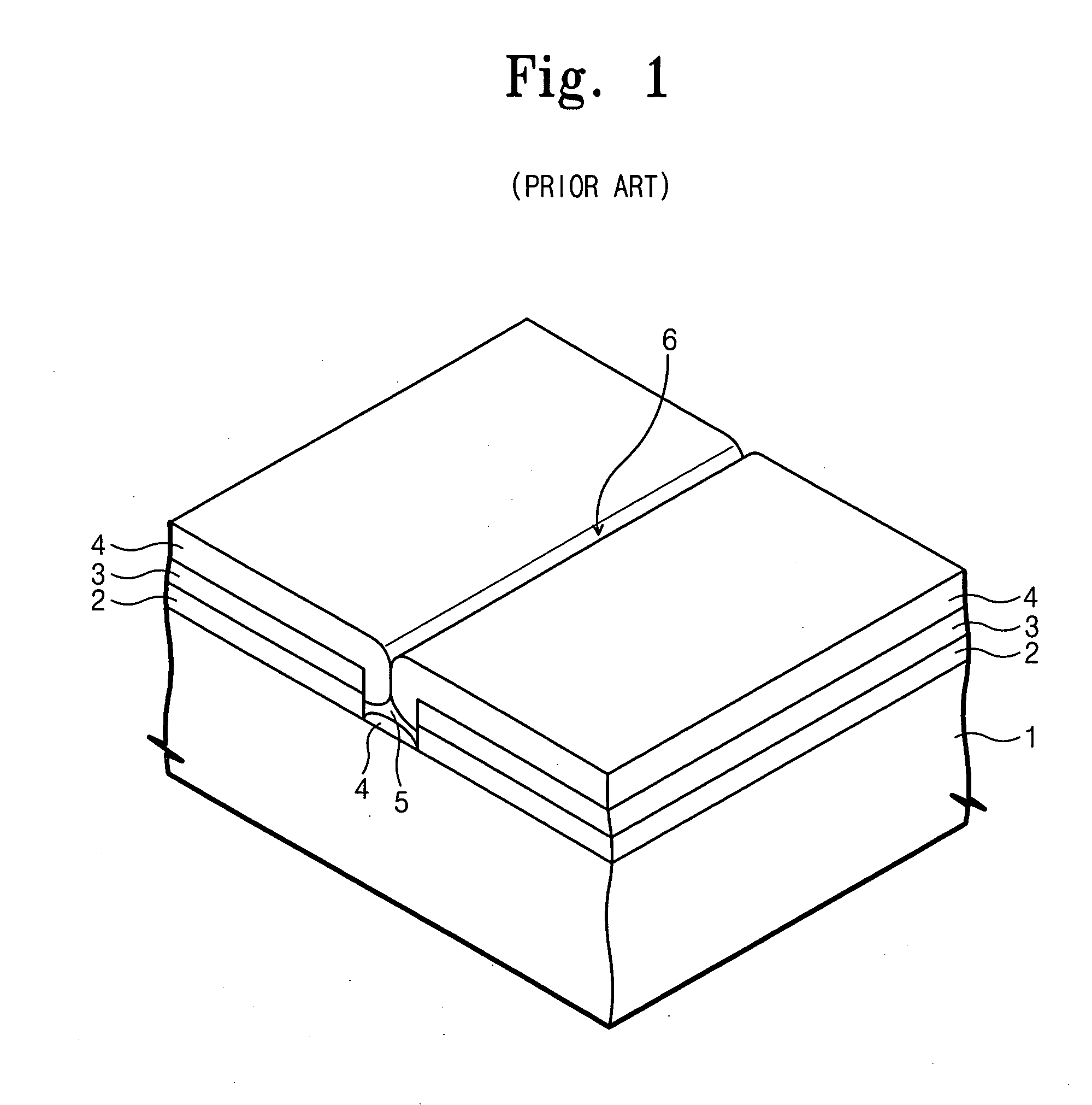

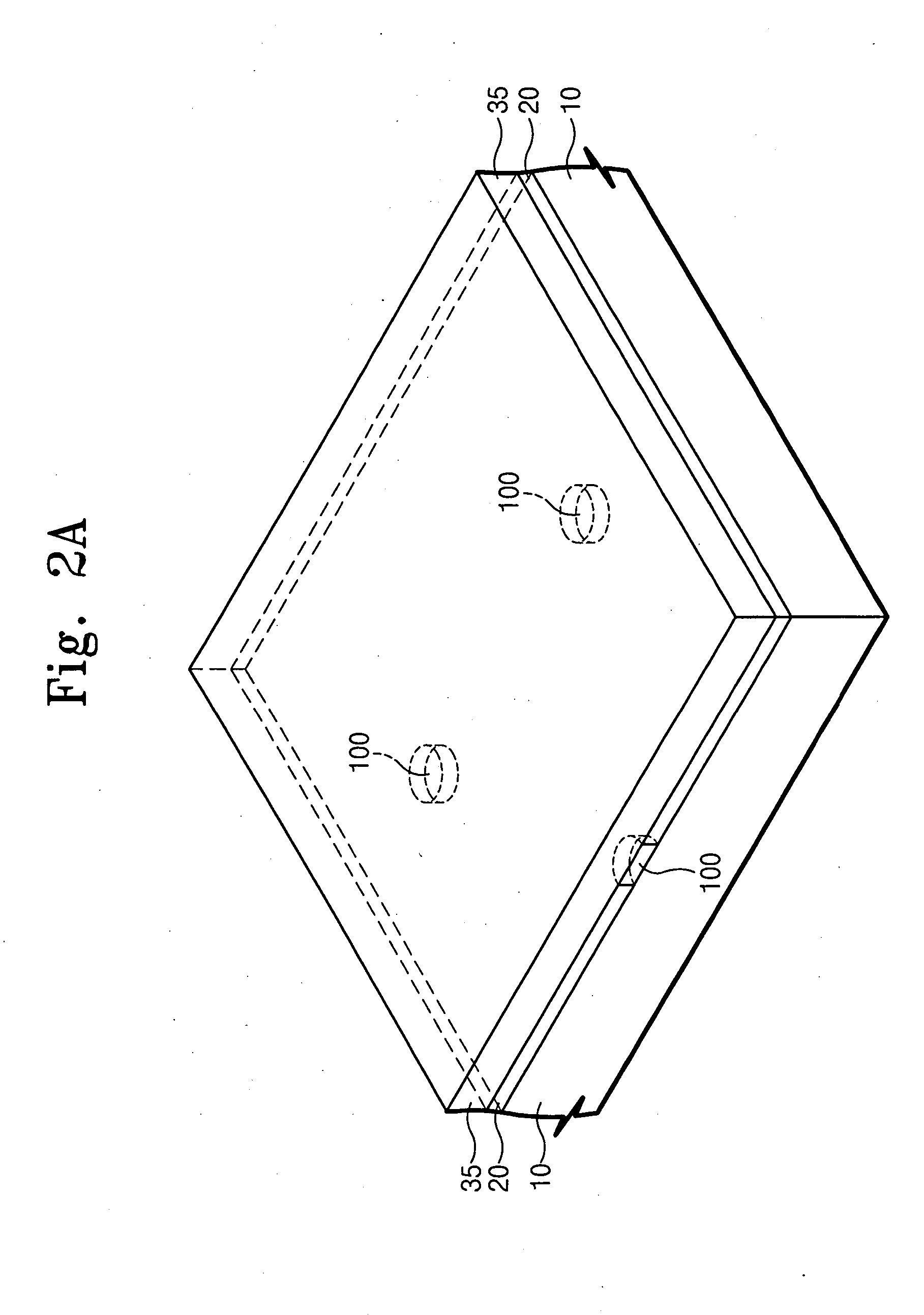

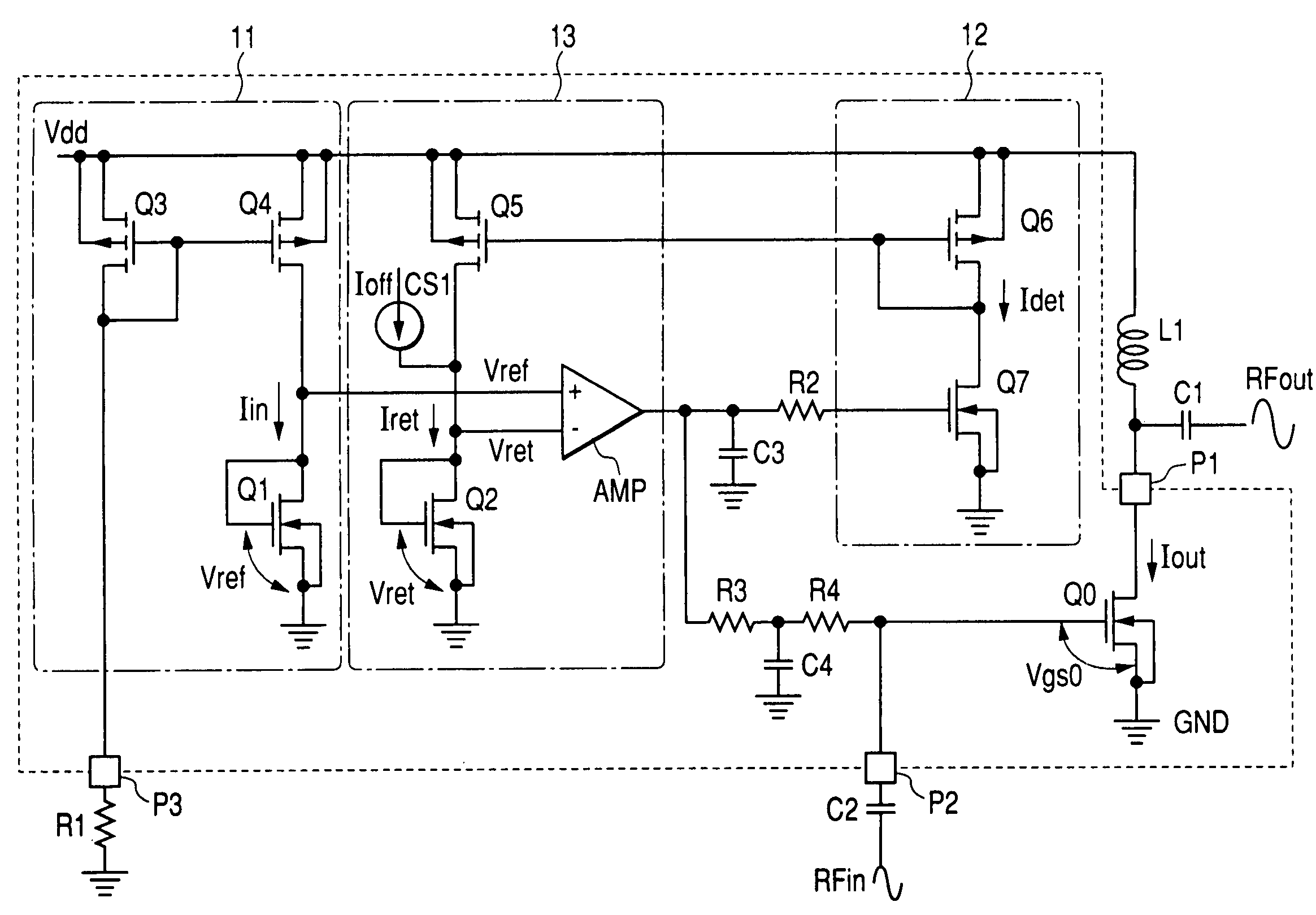

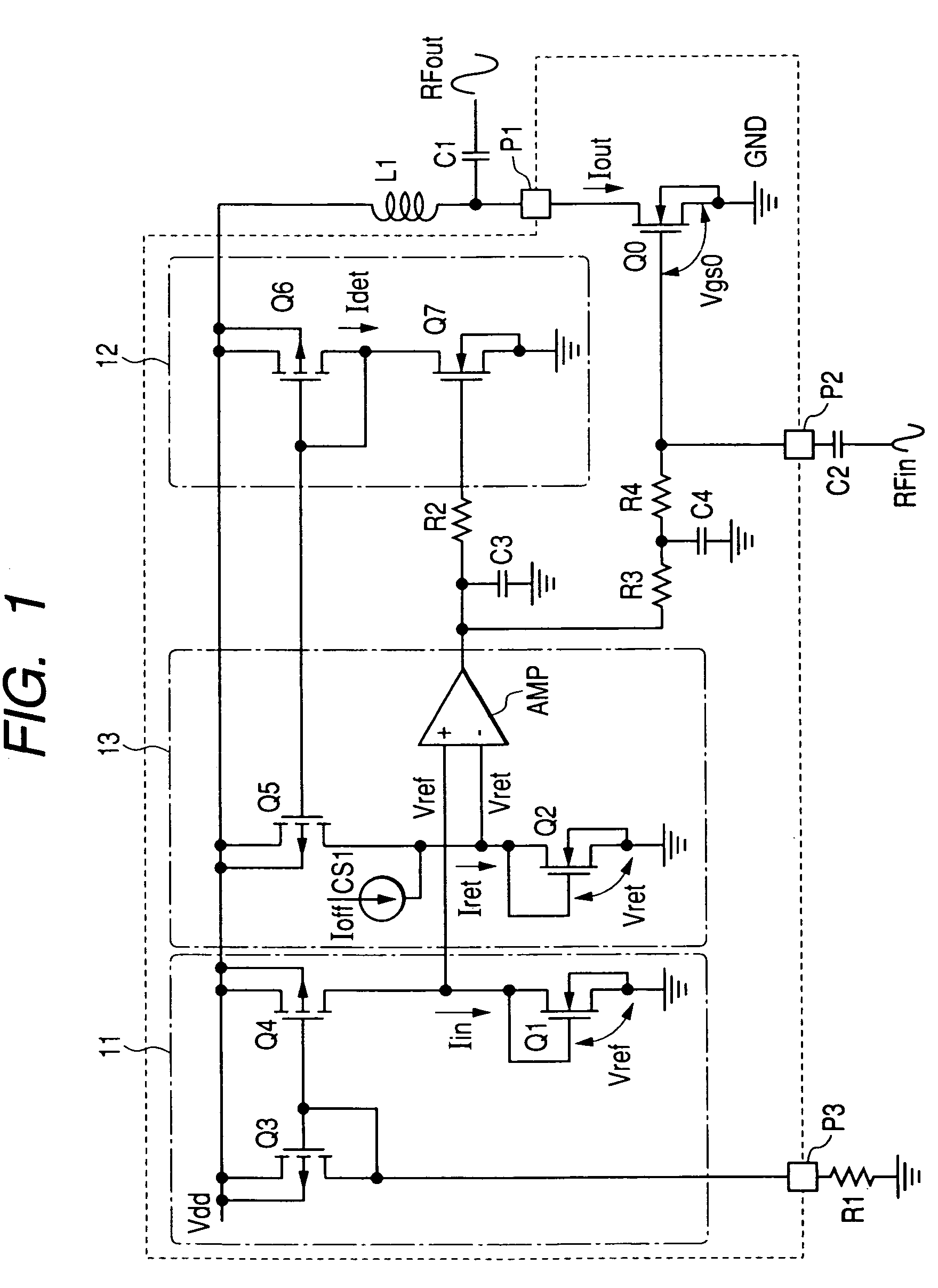

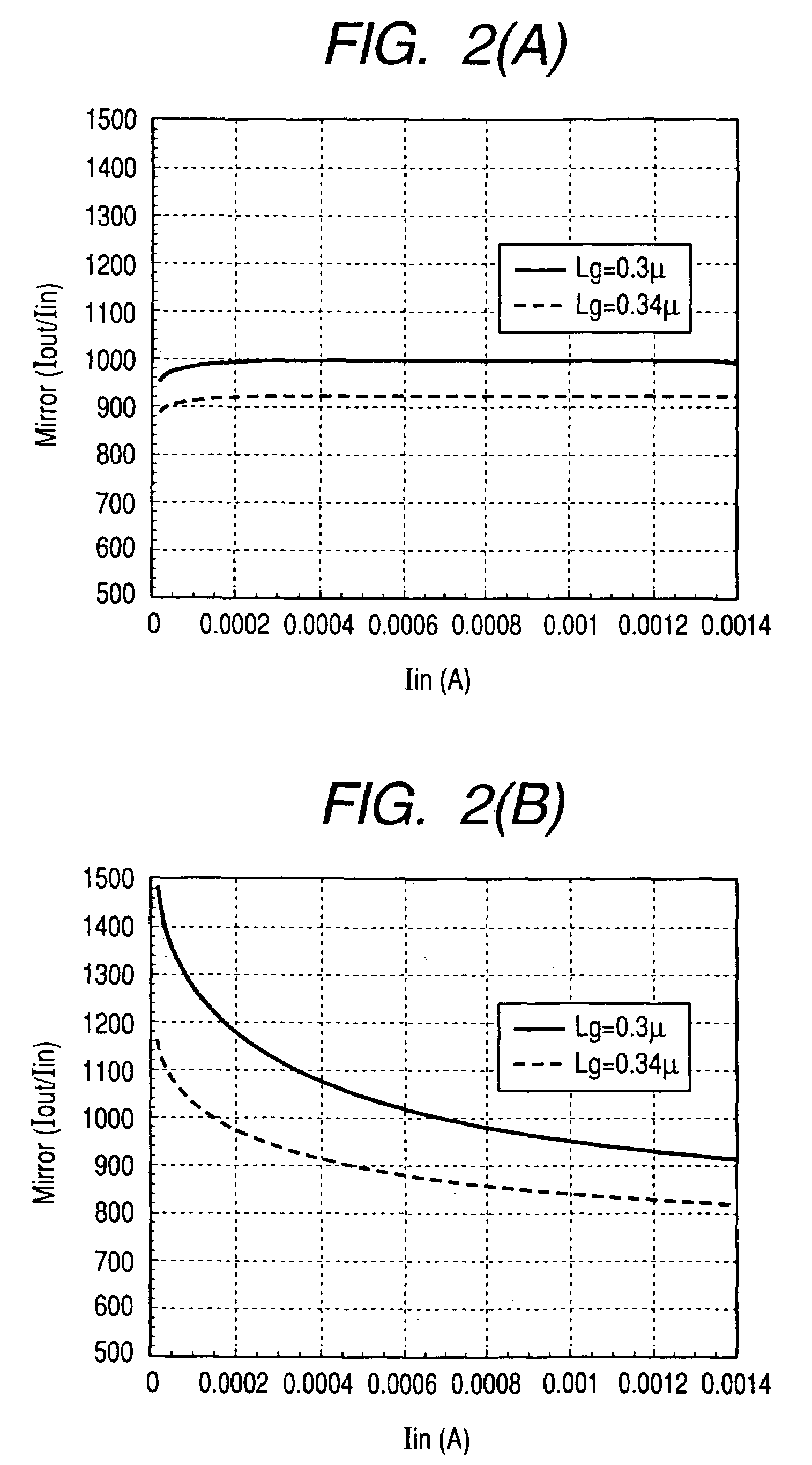

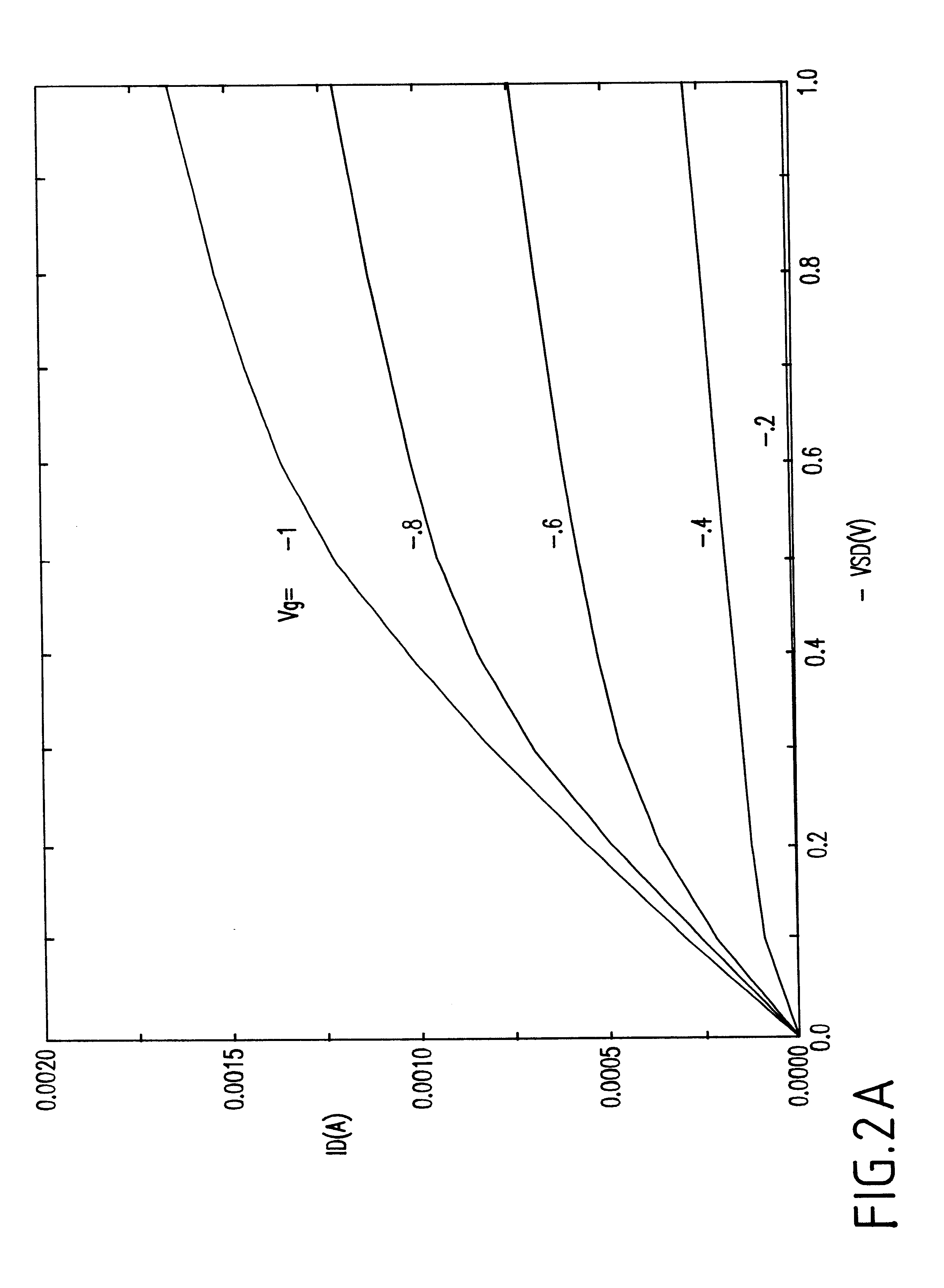

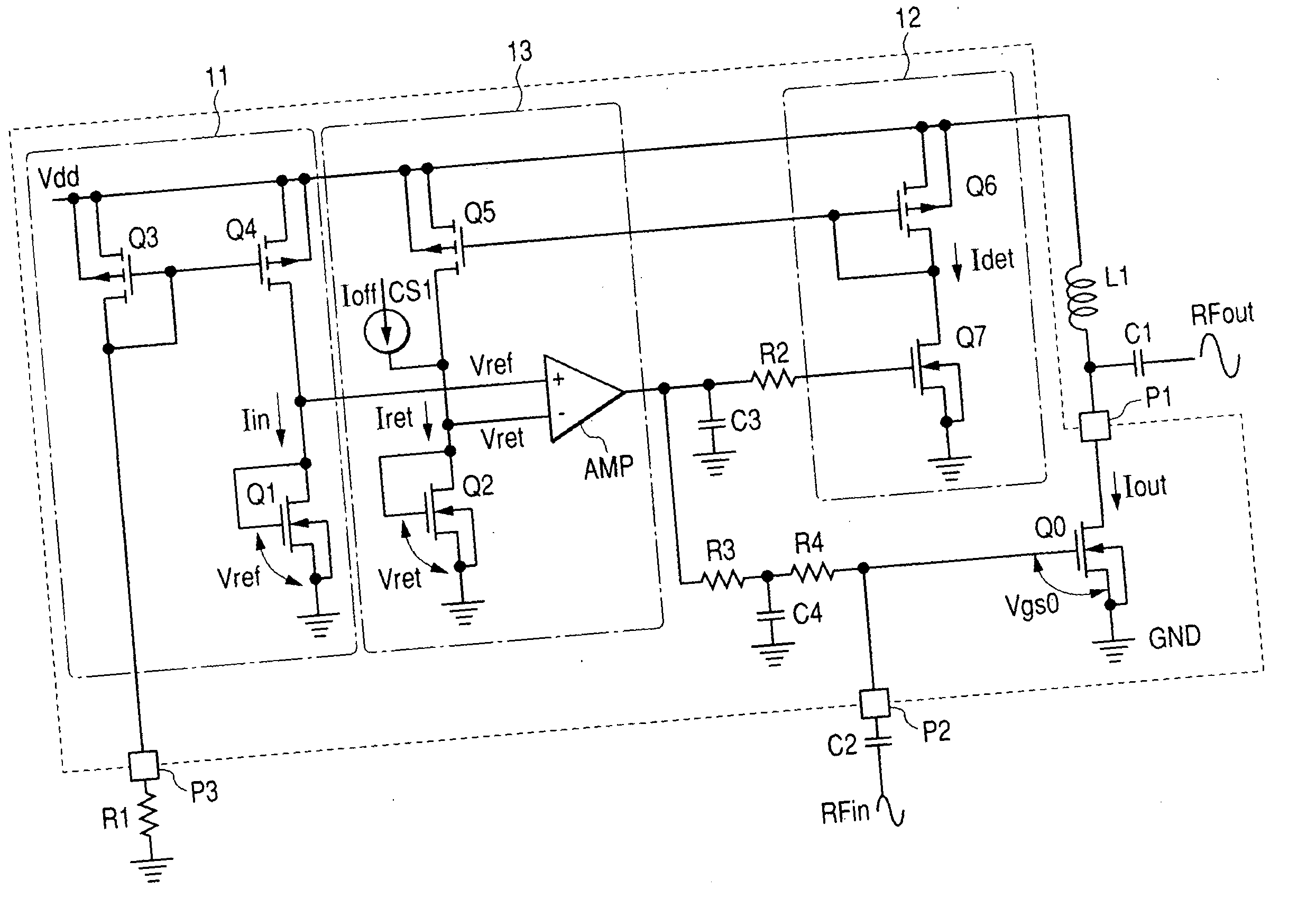

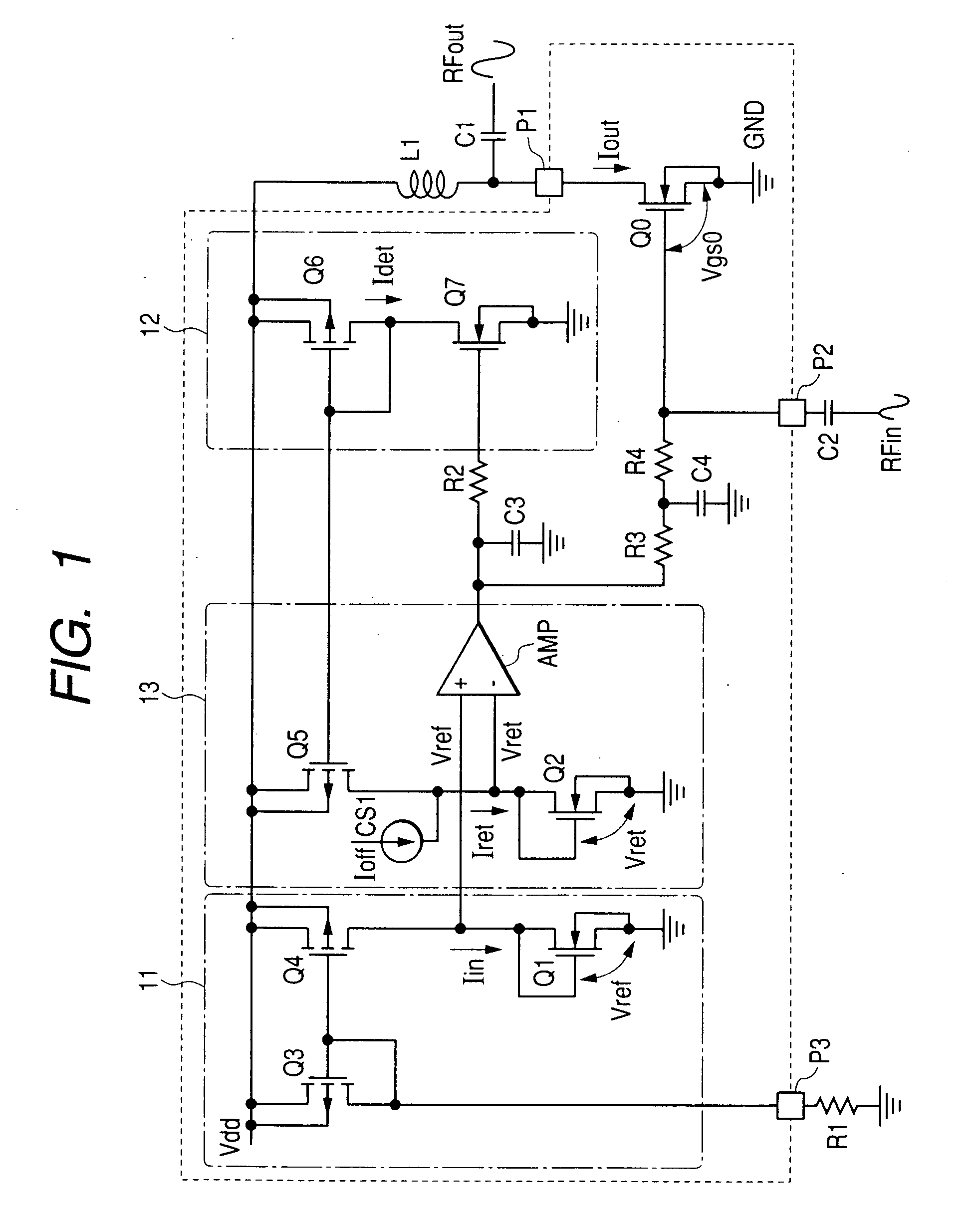

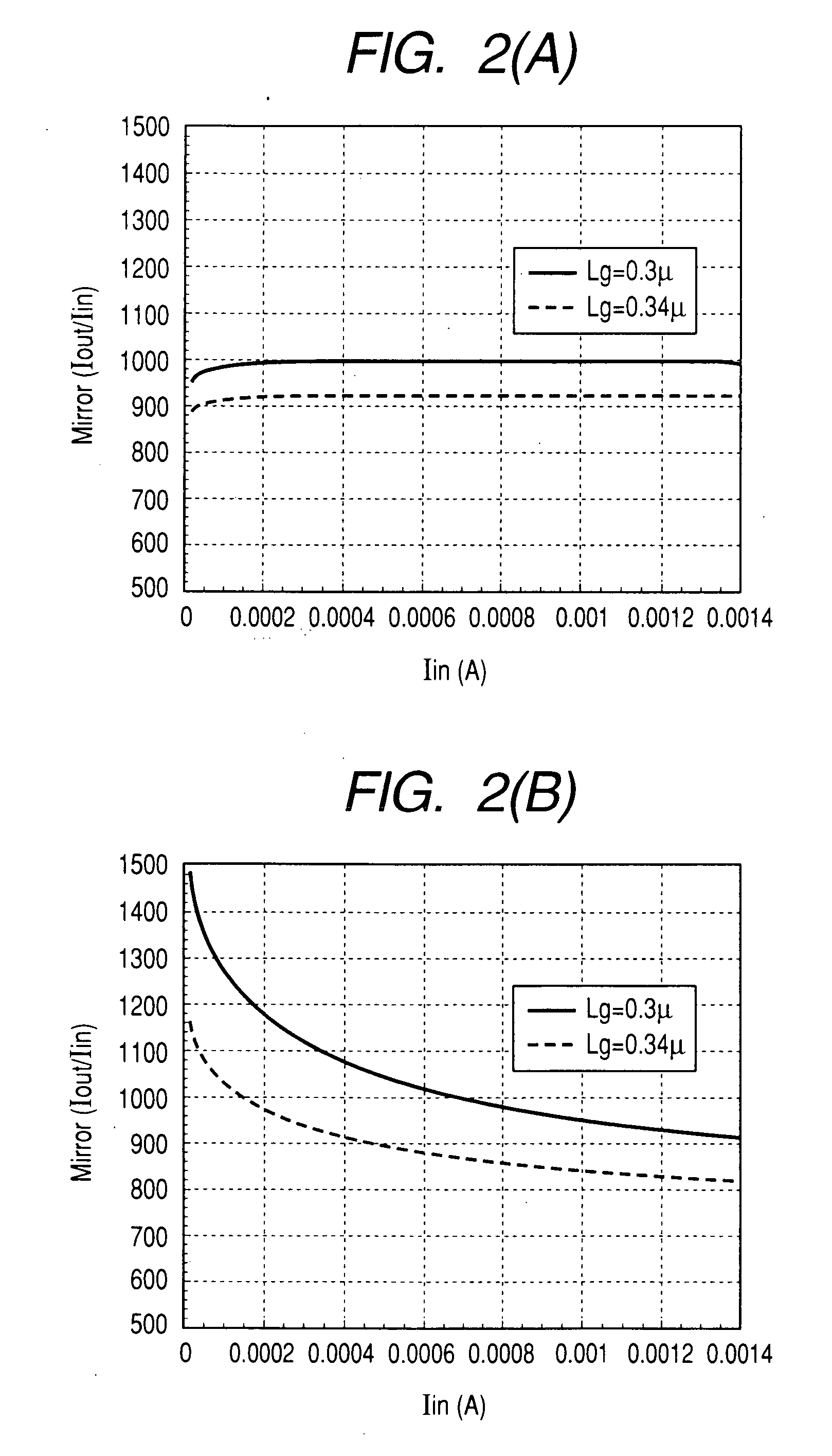

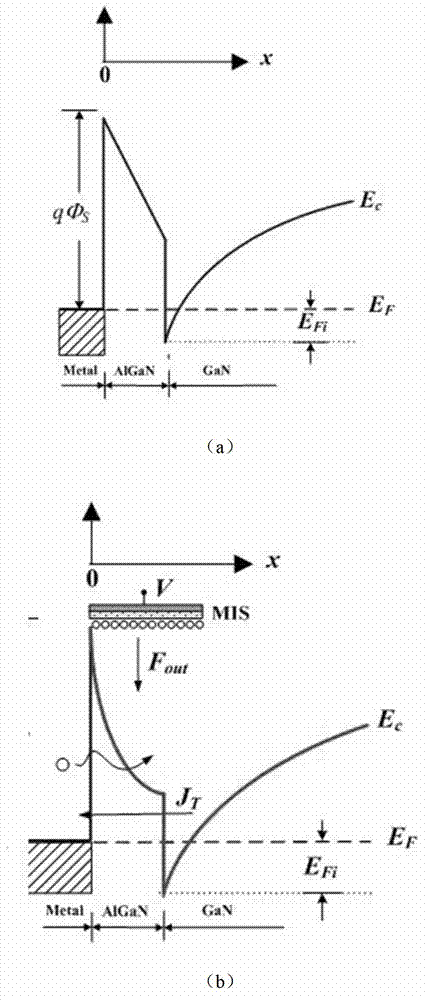

High frequency power amplifier circuit and electronic component for high frequency power amplifier

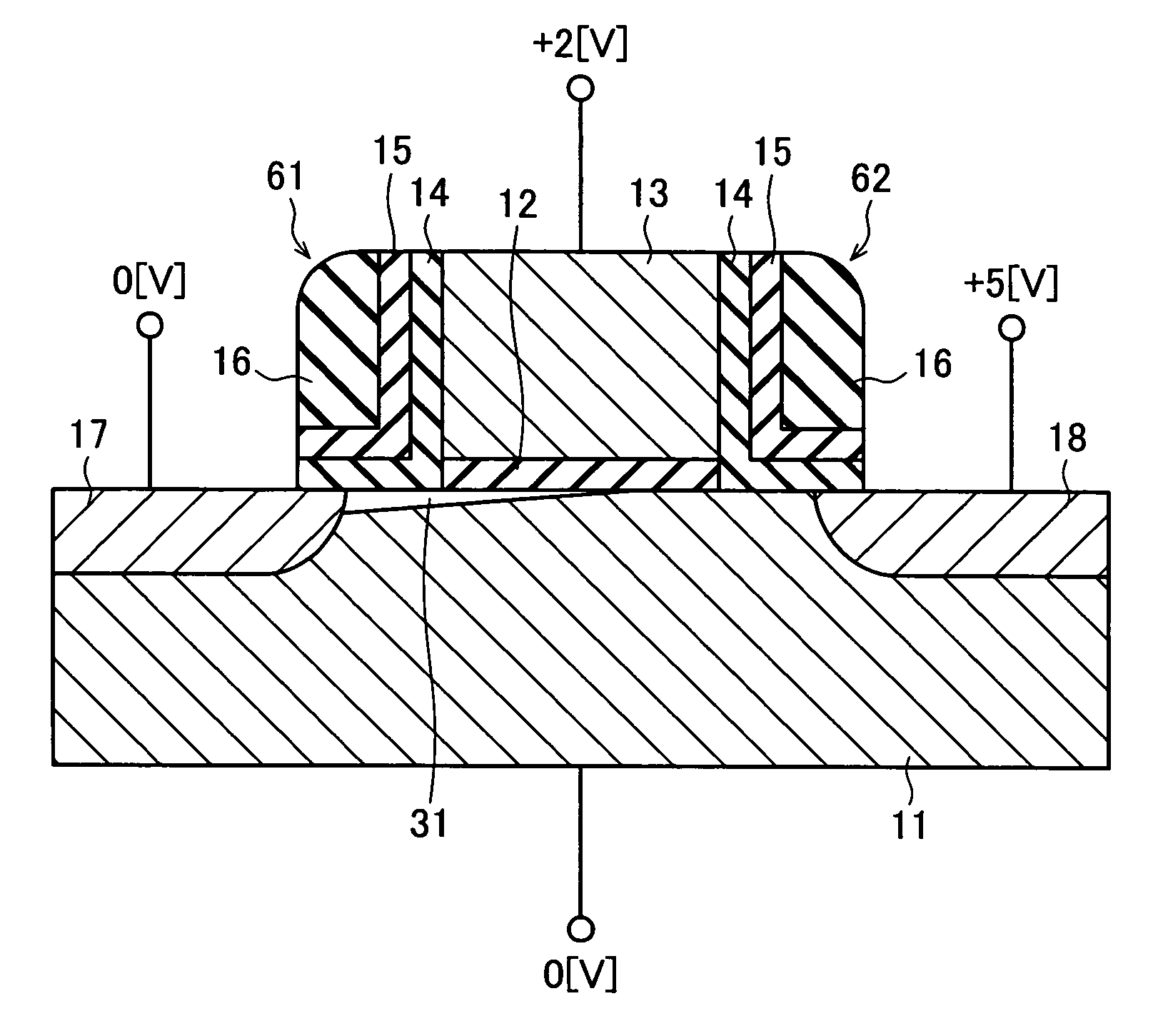

ActiveUS20050083129A1Avoid short channel effectsReduce widthGain controlAmplifier modifications to reduce temperature/voltage variationChannel length modulationAudio power amplifier

In a high frequency power amplifier circuit that supplies a bias to an amplifying FET by a current mirror method, scattering of a threshold voltage Vth due to the scattering of the channel impurity concentration of the FET, and a shift of a bias point caused by the scattering of the threshold voltage Vth and a channel length modulation coefficient λ due to a short channel effect are corrected automatically. The scattering of a high frequency power amplifying characteristic can be reduced as a result.

Owner:MURATA MFG CO LTD

Method of fabricating a complementary semiconductor device having a strained channel p-transistor

ActiveUS7407860B2High speedImprove channel mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductorImpurity

Compression stress applying portions 20 of SiGe film are formed in the source / drain regions of the p-MOSA region 30a. Then, impurities are implanted in the p-MOS region 30a and the n-MOS region 30b to form shallow junction regions 22a, 22b and deep junction regions 23a, 23b. The impurity in the shallow junction regions 22a, 22b is prevented from being diffused immediately below the gate insulation film 15 by the thermal processing in forming the SiGe film, the short channel effect is prevented, and the hole mobility of the channel region of the p-MOS transistor 14a. The operation speed of the p-MOS transistor 13a is balanced with that of the n-MOS transistor, whereby the operation speed of the complementary semiconductor device 10 can be increased. The semiconductor device fabricating method can increase and balance the operation speed of a p-transistor with that of an n-transistor.

Owner:FUJITSU SEMICON LTD

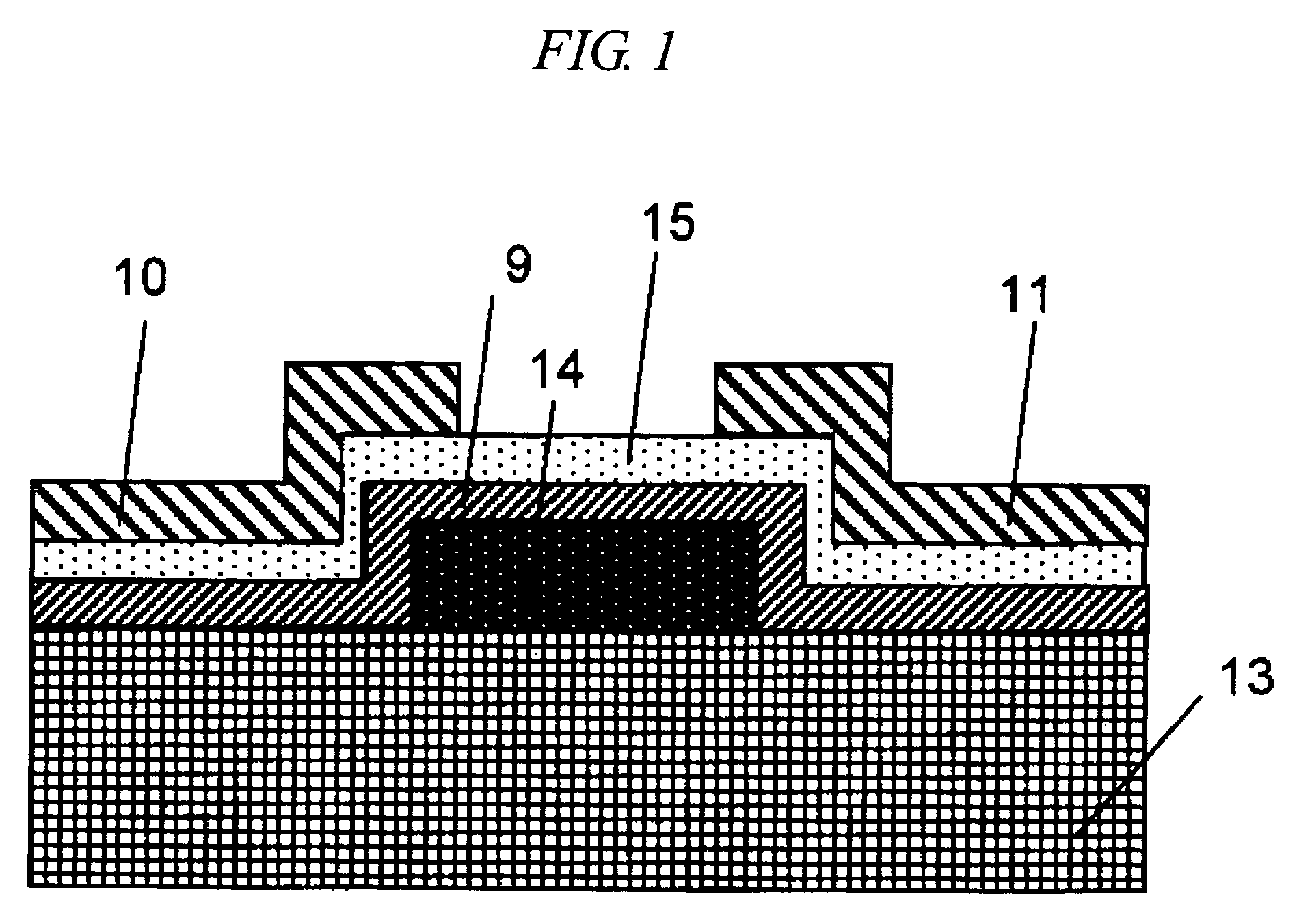

Field effect transistor and manufacturing method thereof

InactiveUS20050139867A1Low costEasily realizedSolid-state devicesSemiconductor/solid-state device manufacturingThermal energyMott transition

The Mott transistor capable of operating at a room temperature can be realized by using a self-organized nanoparticle array for the channel portion. The nanoparticle used in the present invention comprises metal and organic molecules, and the size thereof is extremely small, that is, about a few nm. Therefore, the charging energy is sufficiently larger than the thermal energy kBT=26 meV, and the transistor can operate at a room temperature. Also, since the nanoparticles with a diameter of a few nm are arranged in a self-organized manner and the Mott transition can be caused by the change of a number of electrons of the surface density of about 1012 cm−2, the transistor can operate by the gate voltage of about several V.

Owner:HITACHI LTD

Semiconductor device having partially insulated field effect transistor (PiFET) and method of fabricating the same

ActiveUS20050098094A1Preventing short channel effect and floating body effectAvoid short channel effectsPolycrystalline material growthSolid-state devicesEngineeringField-effect transistor

Embodiments of the invention include a partially insulated field effect transistor and a method of fabricating the same. According to some embodiments, a semiconductor substrate is formed by sequentially stacking a bottom semiconductor layer, a sacrificial layer, and a top semiconductor layer. The sacrificial layer may be removed to form a buried gap region between the bottom semiconductor layer and the top semiconductor layer. Then, a transistor may be formed on the semiconductor substrate. The sacrificial layer may be a crystalline semiconductor formed by an epitaxial growth technology.

Owner:SAMSUNG ELECTRONICS CO LTD

High frequency power amplifier circuit and electronic component for high frequency power amplifier

ActiveUS7304539B2Avoid short channel effectsReduce widthGain controlAmplifier modifications to reduce temperature/voltage variationChannel length modulationHigh frequency power

Owner:MURATA MFG CO LTD

Transistor and method of forming the same

ActiveUS20050194616A1Improve breakdown voltageEffective channel length can be sufficientlySemiconductor/solid-state device manufacturingSemiconductor devicesBreakdown voltageShort-channel effect

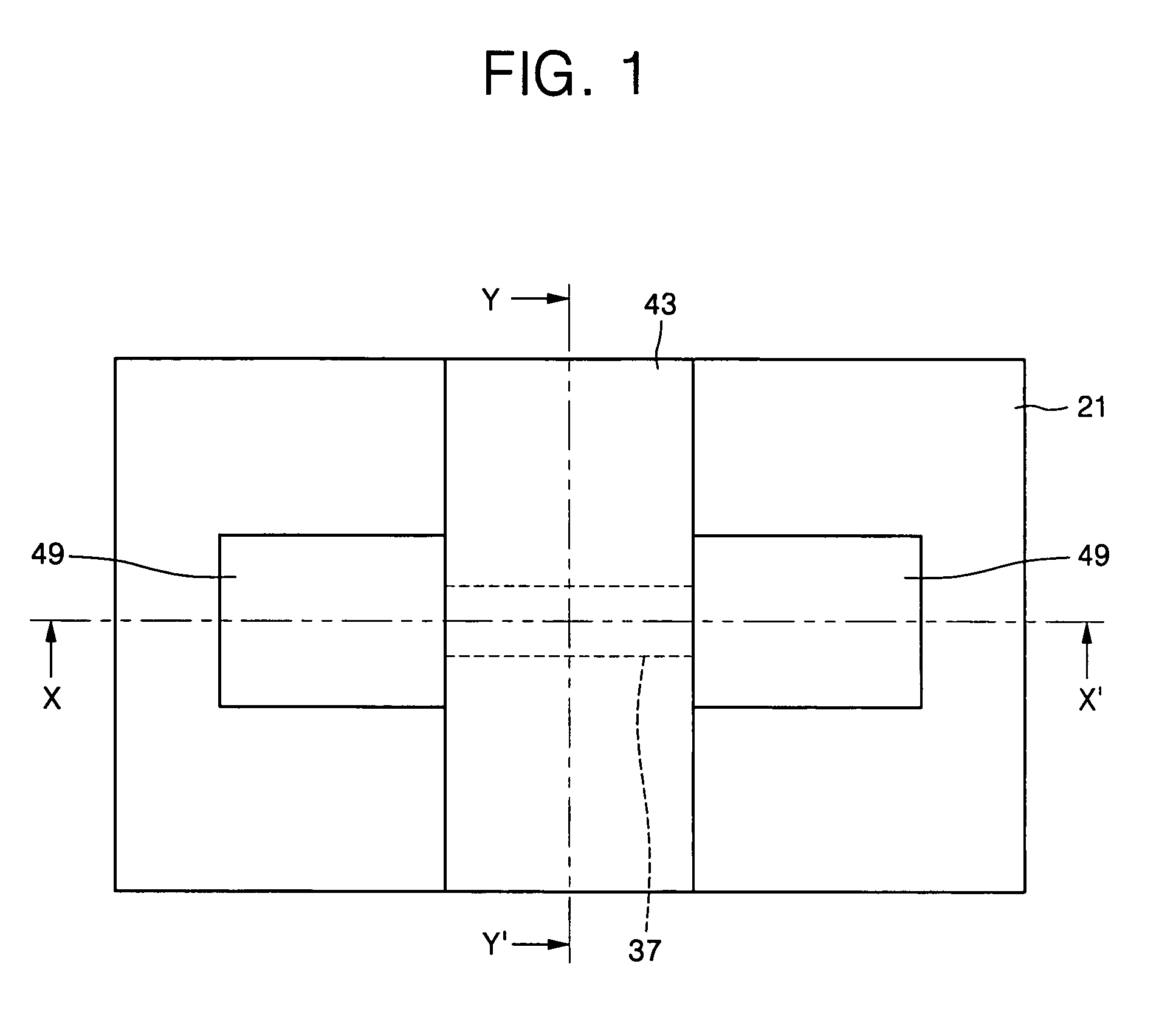

According to some embodiments of the invention, a fin type transistor includes an active structure integrally formed with a silicon substrate. The active structure includes grooves that form blocking regions under source / drain regions. A gate structure is formed to cross the upper face of the active structure and to cover the exposed side surfaces of the lateral portions of the active structure. An effective channel length of a fin type transistor may be sufficiently ensured so that a short channel effect of the transistor may be prevented and the fin type transistor may have a high breakdown voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

Ultrafast nanoscale field effect transistor

InactiveUS6274916B1High densityMinimizes leakage currentSolid-state devicesSemiconductor/solid-state device manufacturingMott insulatorField-effect transistor

A method and structure for a field effect transistor (FET) includes a source region, a drain region, a channel region extending between the source region and the drain region, a gate region, and a gate oxide region separating the gate region from other regions of the FET. The channel region is a Mott insulator. The gate oxide region is thicker than the channel region, and the gate oxide region includes a higher dielectric permittivity than the Mott insulator material.

Owner:IBM CORP

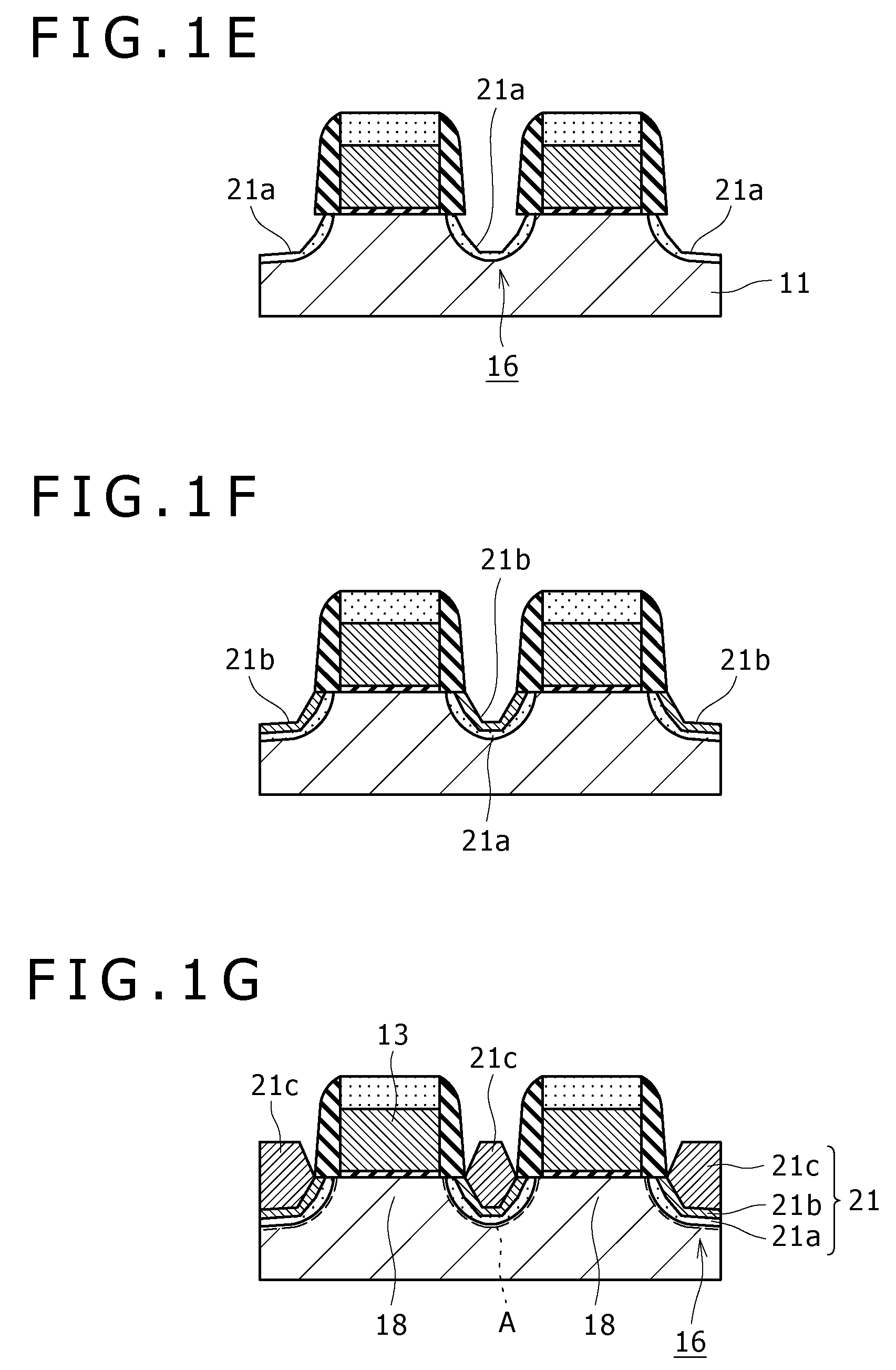

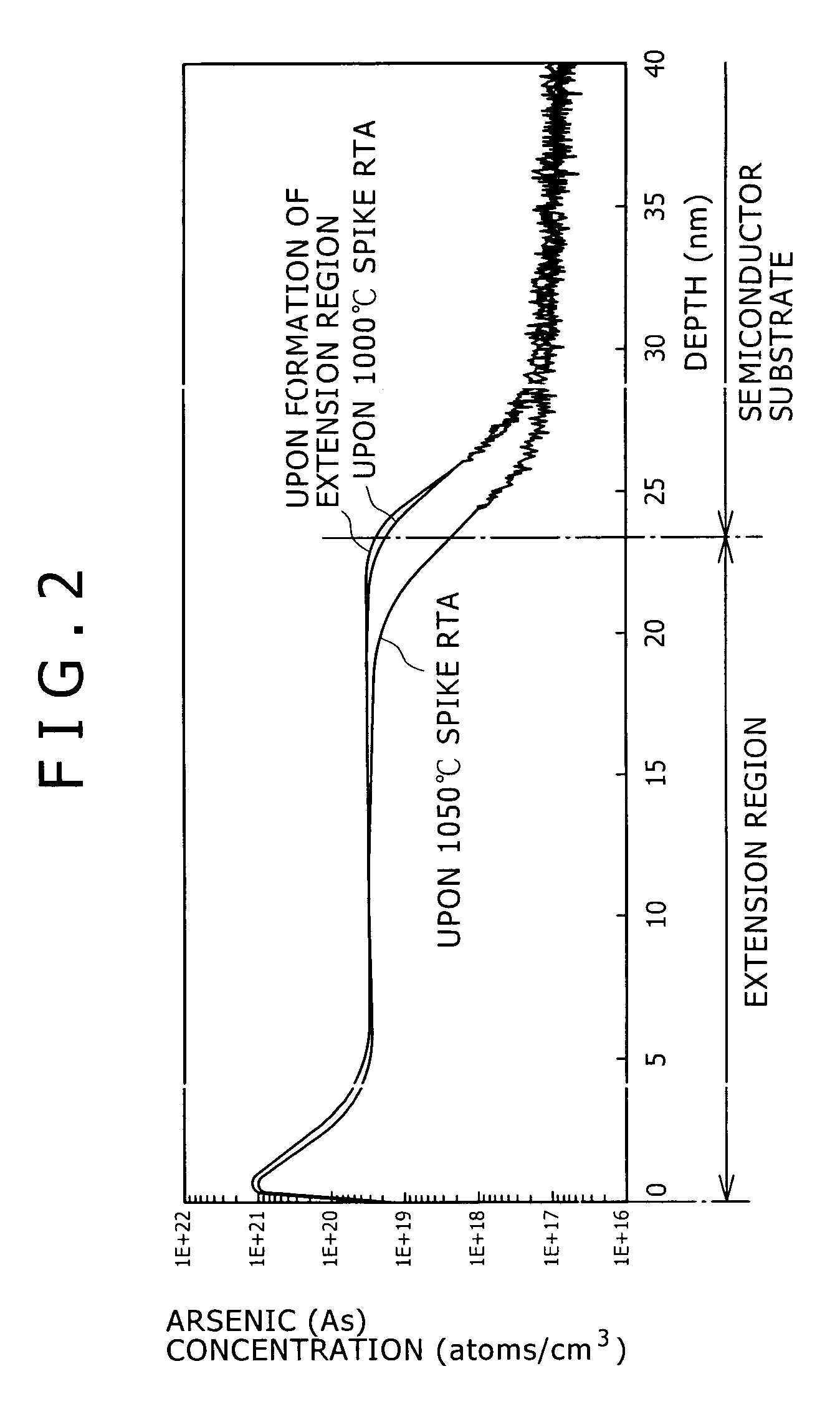

Method of manufacturing semiconductor device, and semiconductor device

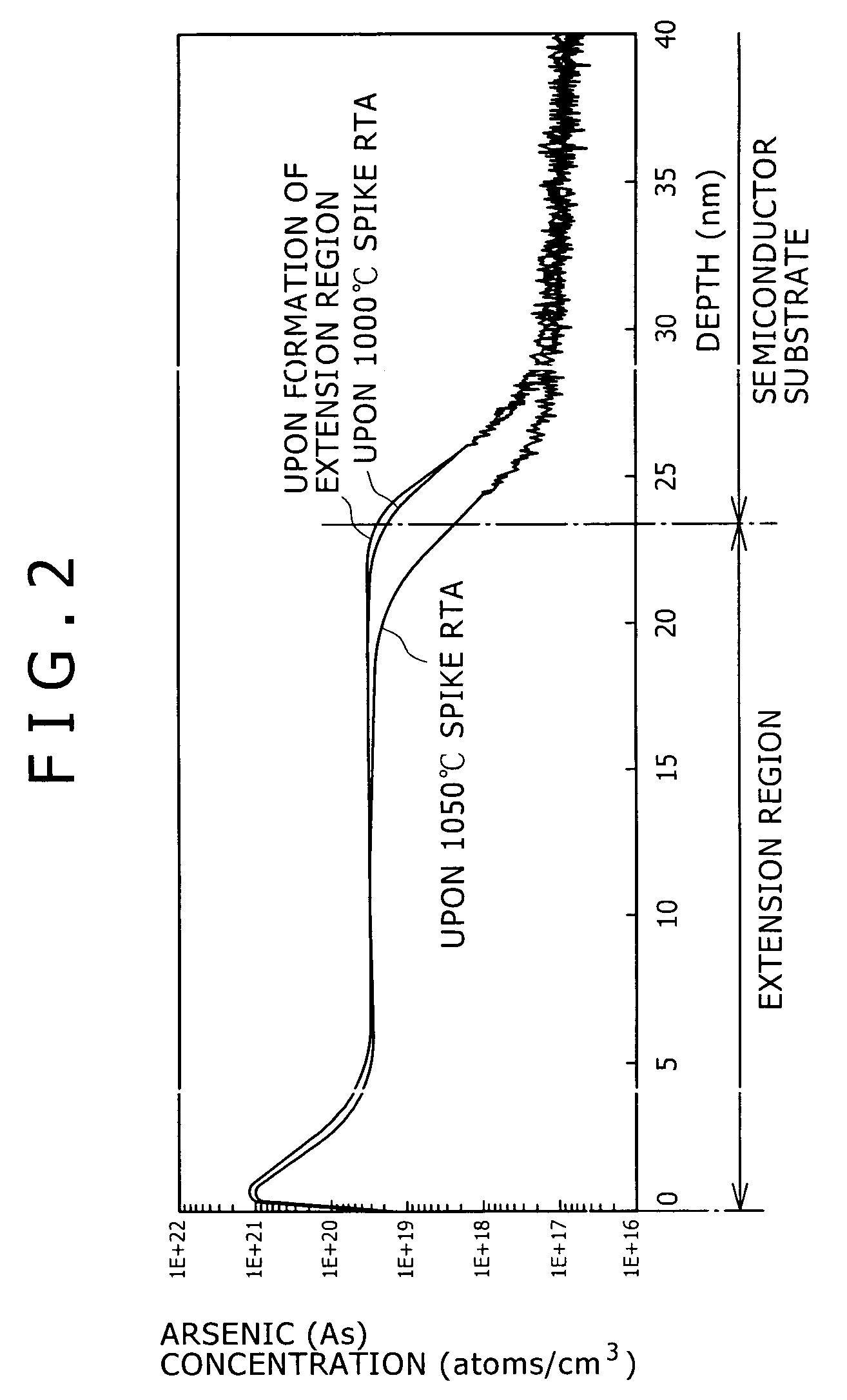

ActiveUS7510925B2Short-channel effectPromote adequate mobilitySemiconductor/solid-state device manufacturingSemiconductor devicesSurface layerConcentration gradient

A method of manufacturing a semiconductor device includes: the first step of forming a gate electrode over a silicon substrate, with a gate insulating film; and the second step of digging down a surface layer of the silicon substrate by etching conducted with the gate electrode as a mask. The method of manufacturing the semiconductor device further includes the third step of epitaxially growing, on the surface of the dug-down portion of the silicon substrate, a mixed crystal layer including silicon and atoms different in lattice constant from silicon so that the mixed crystal layer contains an impurity with such a concentration gradient that the impurity concentration increases along the direction from the silicon substrate side toward the surface of the mixed crystal layer.

Owner:SONY CORP

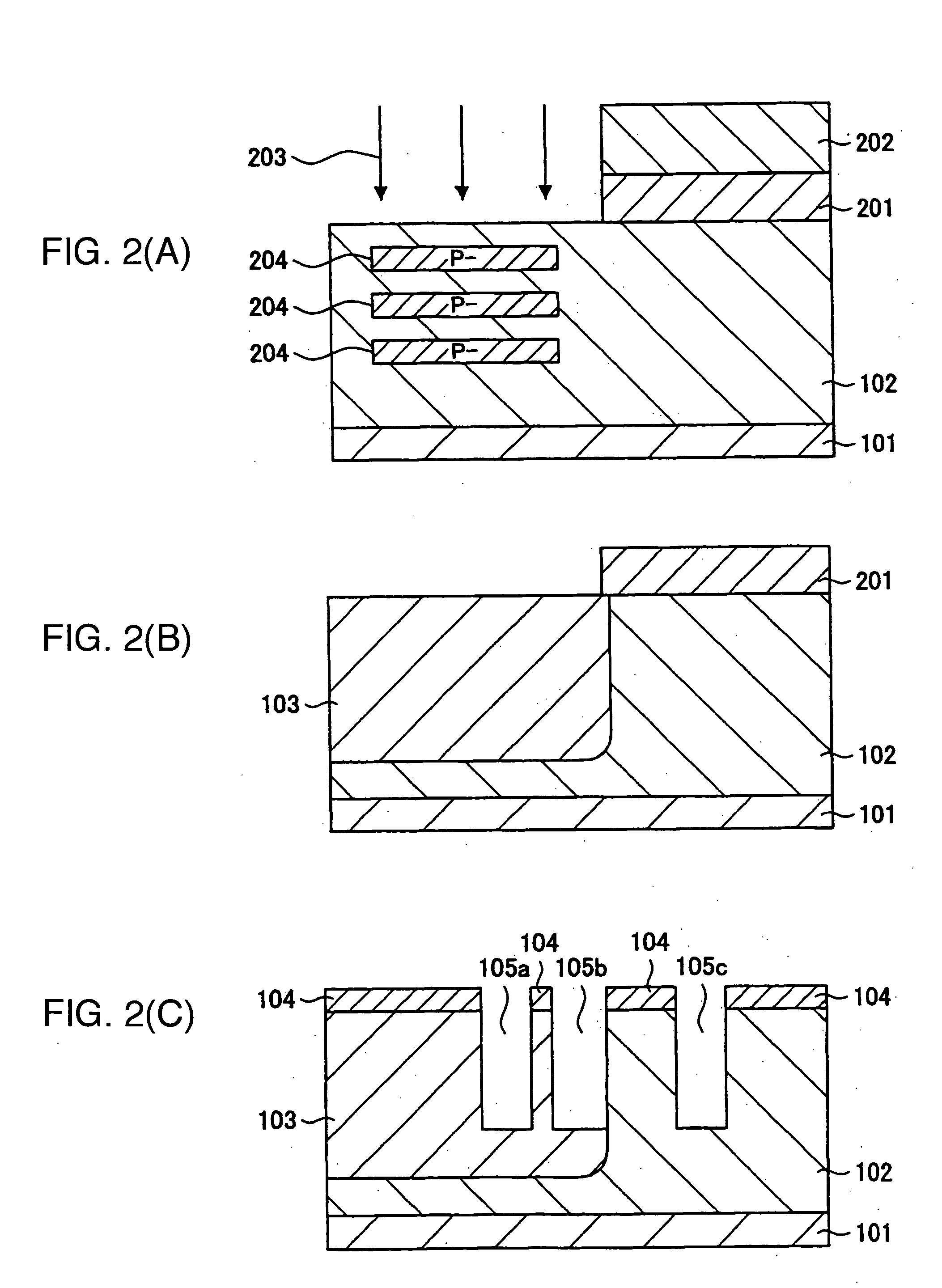

Method for fabricating semiconductor device with vertical channel transistor

ActiveUS20090163017A1Avoid attackReduce lossesSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

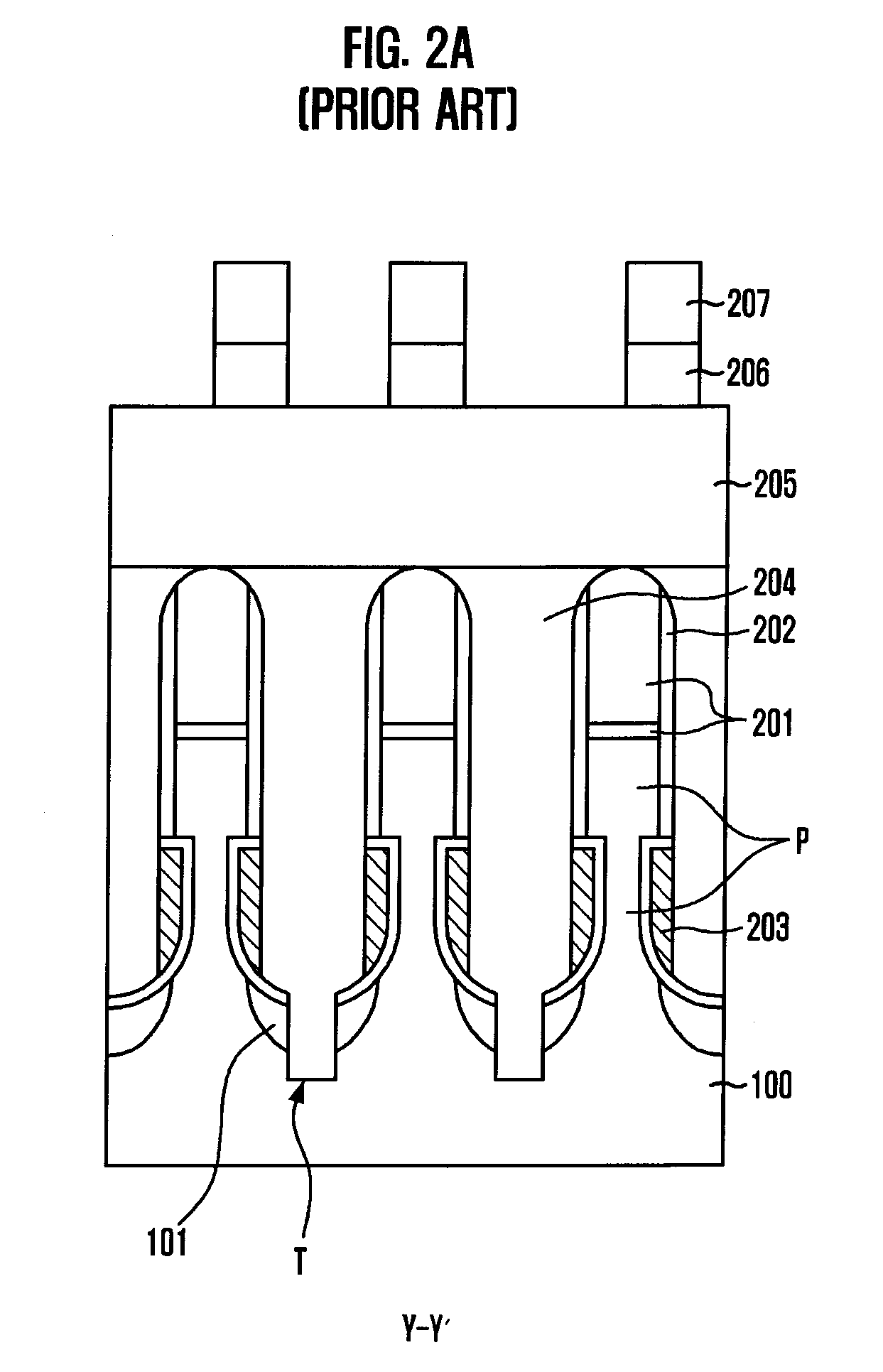

A method for fabricating a semiconductor memory device with a vertical channel transistor includes forming a plurality of pillars each having a hard mask pattern thereon over a substrate, each of the plurality of pillars comprising an upper pillar and a lower pillar; forming a surround type gate electrode surrounding the lower pillar; forming an insulation layer filling a space between the pillars; forming a preliminary trench by primarily etching the insulation layer using a mask pattern for a word line until a portion of the upper pillar is exposed; forming a buffer layer over a resultant structure including the preliminary trench except on a bottom of the preliminary trench; and forming a trench for a word line by secondarily etching the insulation layer until the surround type gate electrode is exposed.

Owner:SK HYNIX INC

Semiconductor device and fabricating method thereof

InactiveUS20050045942A1Avoid short channel effectsReliable semiconductorTransistorSolid-state devicesPolycrystalline siliconOxide

A semiconductor device and a fabricating method thereof are disclosed. The semiconductor device includes polysilicon gate electrodes, a gate oxide layer, sidewall floating gates, a block oxide layer, source / drain areas, and sidewall spacers. In addition, the method includes the steps of: forming a block dielectric layer and a sacrificial layer on a semiconductor substrate; forming trenches by etching the sacrificial layer; forming sidewall floating gates on lateral faces of the trenches; forming a block oxide layer on the sidewall floating gates; forming polysilicon gate electrodes by a patterning process; removing the sacrificial layer; forming source / drain areas by implanting impurity ions into the resulting structure; injecting carriers or electric charges into the sidewall floating gates; and forming spacers on lateral faces of the polysilicon gate electrodes and the sidewall floating gates.

Owner:DONGBU ELECTRONICS CO LTD +1

High frequency power amplifier circuit and electronic component for high frequency power amplifier

ActiveUS20080068086A1Avoid short channel effectsReduce widthGain controlAmplifier modifications to reduce temperature/voltage variationChannel length modulationHigh frequency power

In a high frequency power amplifier circuit that supplies a bias to an amplifying FET by a current mirror method, scattering of a threshold voltage Vth due to the scattering of the channel impurity concentration of the FET, and a shift of a bias point caused by the scattering of the threshold voltage Vth and a channel length modulation coefficient λ due to a short channel effect are corrected automatically. The scattering of a high frequency power amplifying characteristic can be reduced as a result.

Owner:MURATA MFG CO LTD

Method of fabricating transistor for semiconductor device

InactiveUS8062948B2Increase currentAvoid short channel effectsSemiconductor/solid-state device manufacturingSemiconductor devicesDopantSemiconductor

Owner:SK HYNIX INC

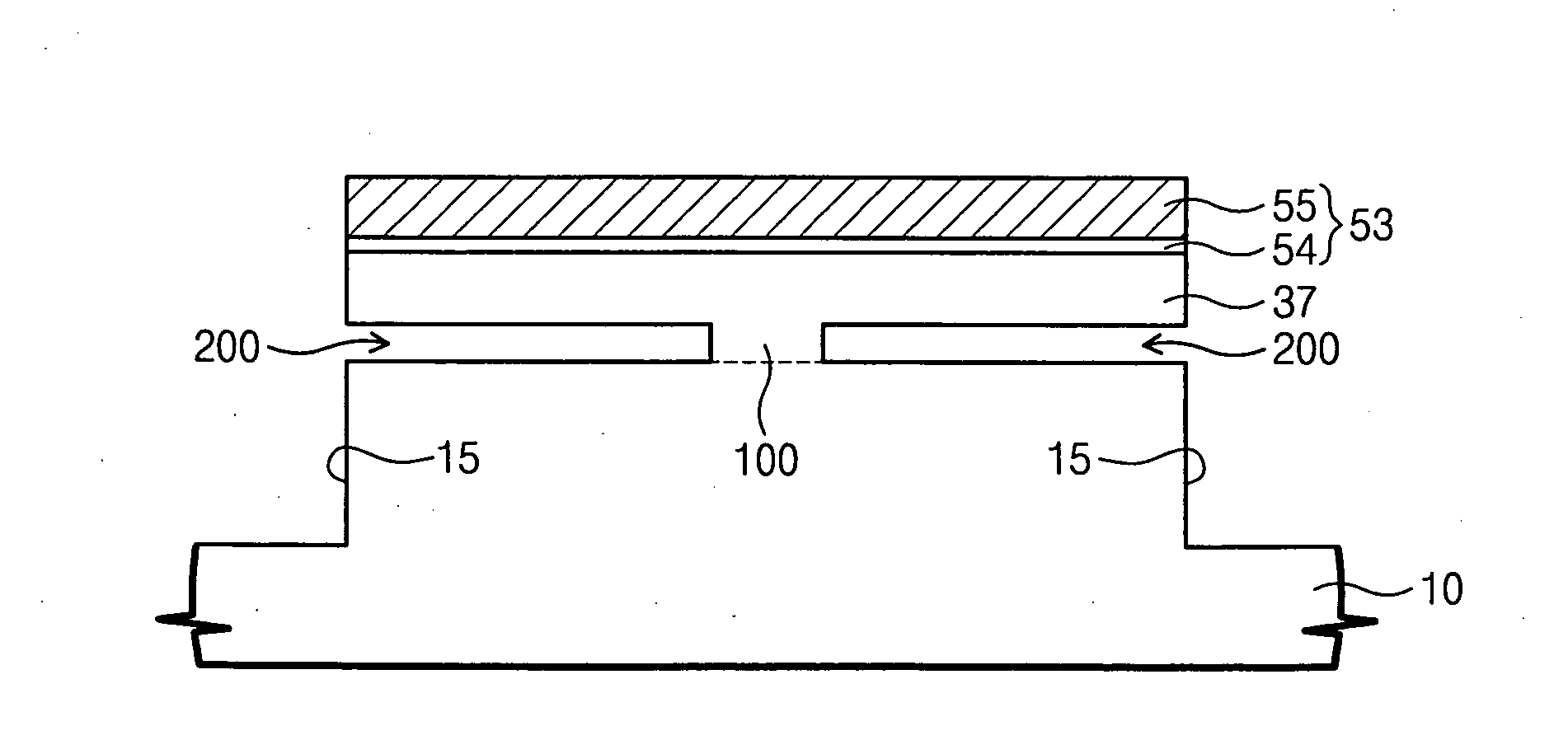

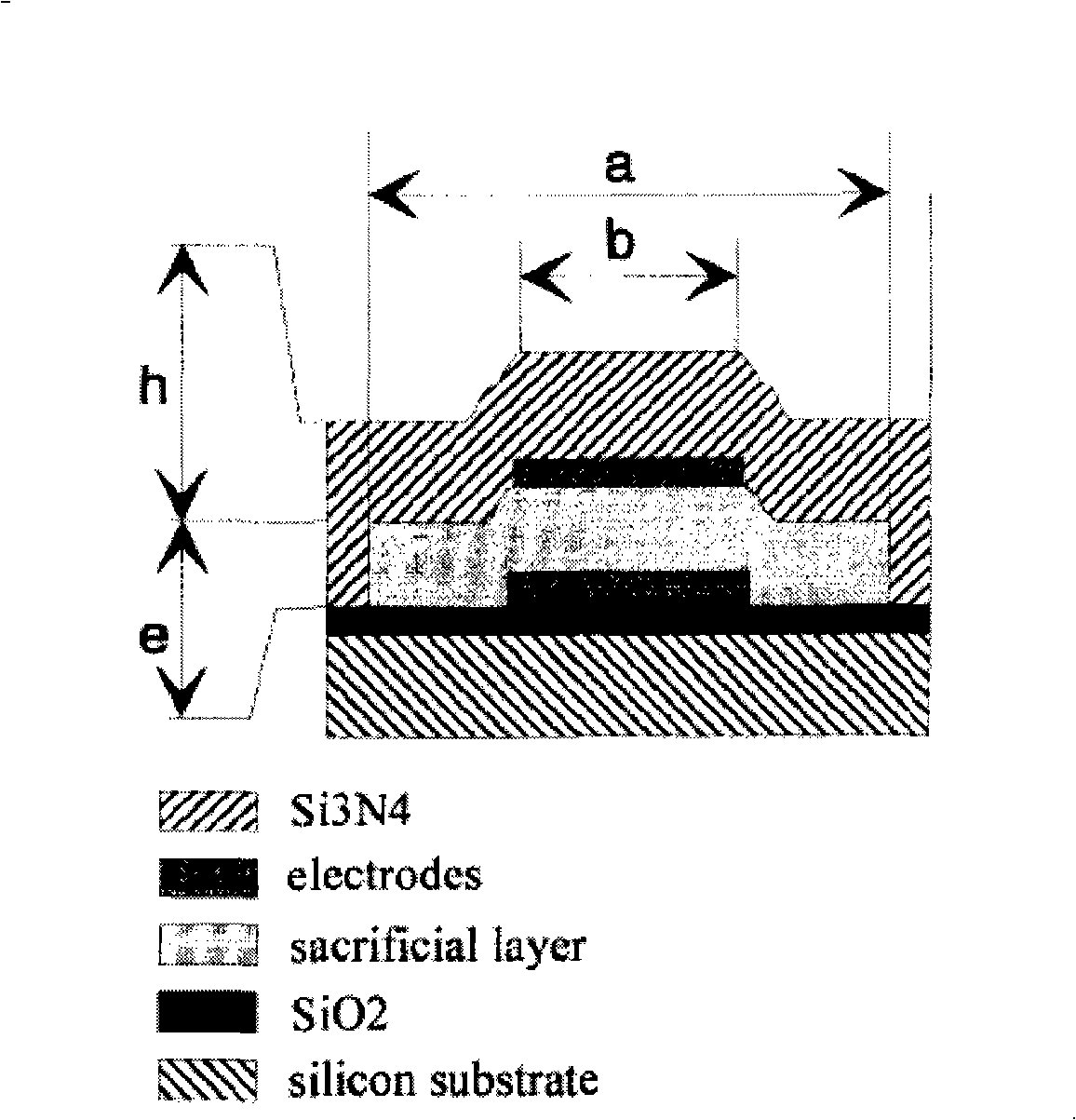

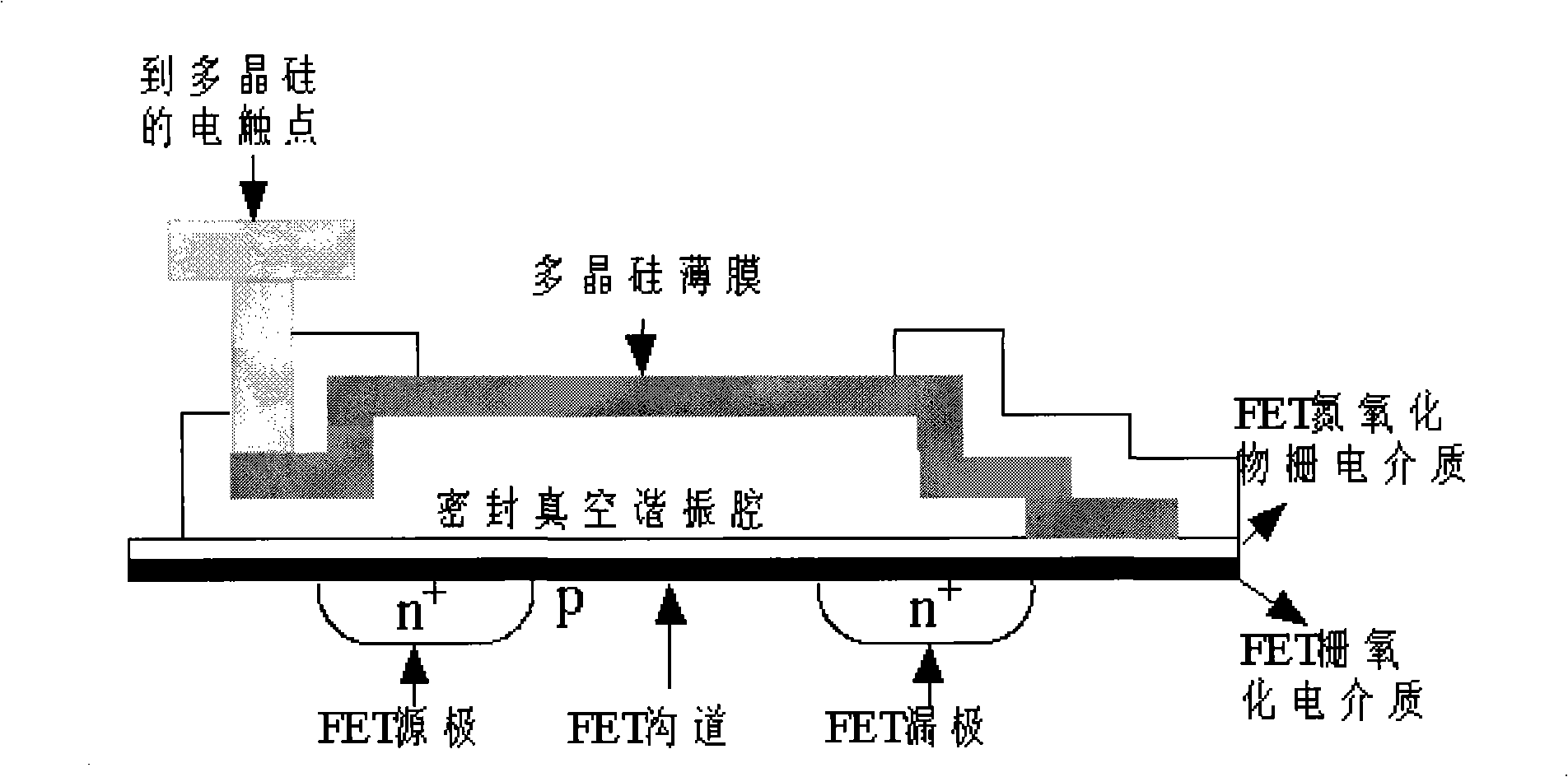

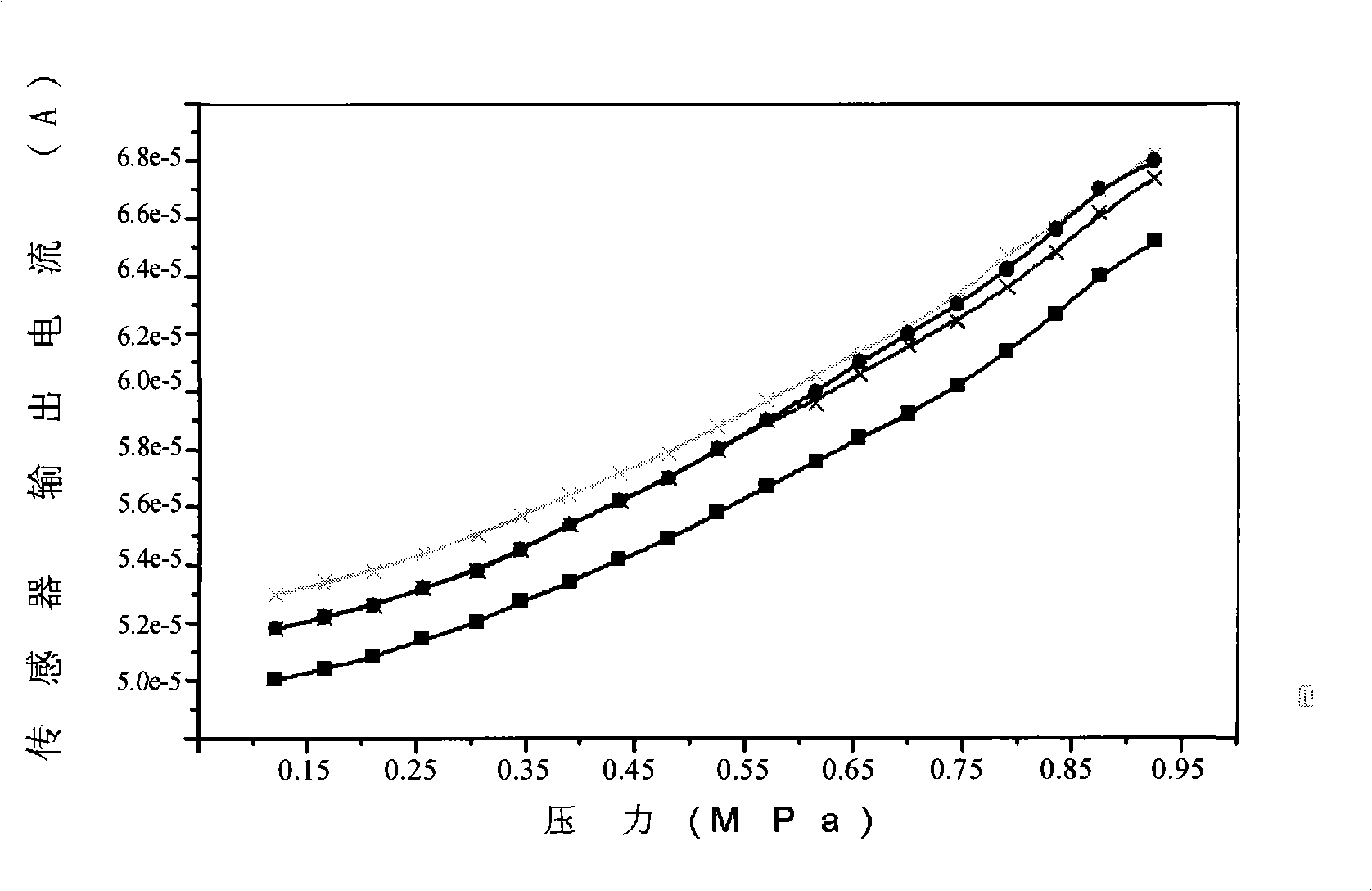

Sensitive large signal output minitype pressure sensor

ActiveCN101303240ALow costAvoid short channel effectsForce measurementConverting sensor output electrically/magneticallyCapacitanceInsulation layer

The embodiment of the invention provides a sensitive and large-signal output minisize pressure sensor, specifically including that a conductive floating layer of capacitance part of the sensor is modified and extended to a gate insulation layer of the MOSFET device to form a floating gate of the MOSFET device, accordingly the capacitance part of the sensor is separated from the MOSFET device therebelow, and the structural dimension of which does not influence the MOSFET device, therefore the MOSFET device can be made into smaller dimension which is suitable to be used in micro / nano system, simultaneously can overcome effectively short channel effect of device, improve simulated attribute of circuit, accomplish signal amplification directly with larger amplification multiple, reduce development and application costs of sensor without using high-dielectric material.

Owner:CHIPONE TECH BEIJINGCO LTD

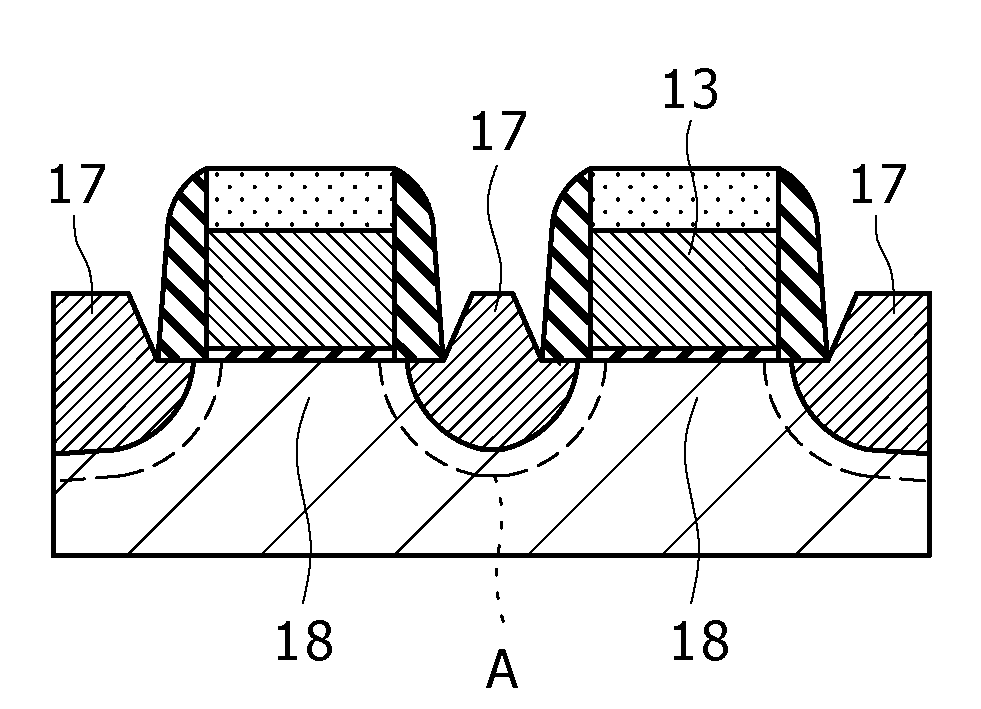

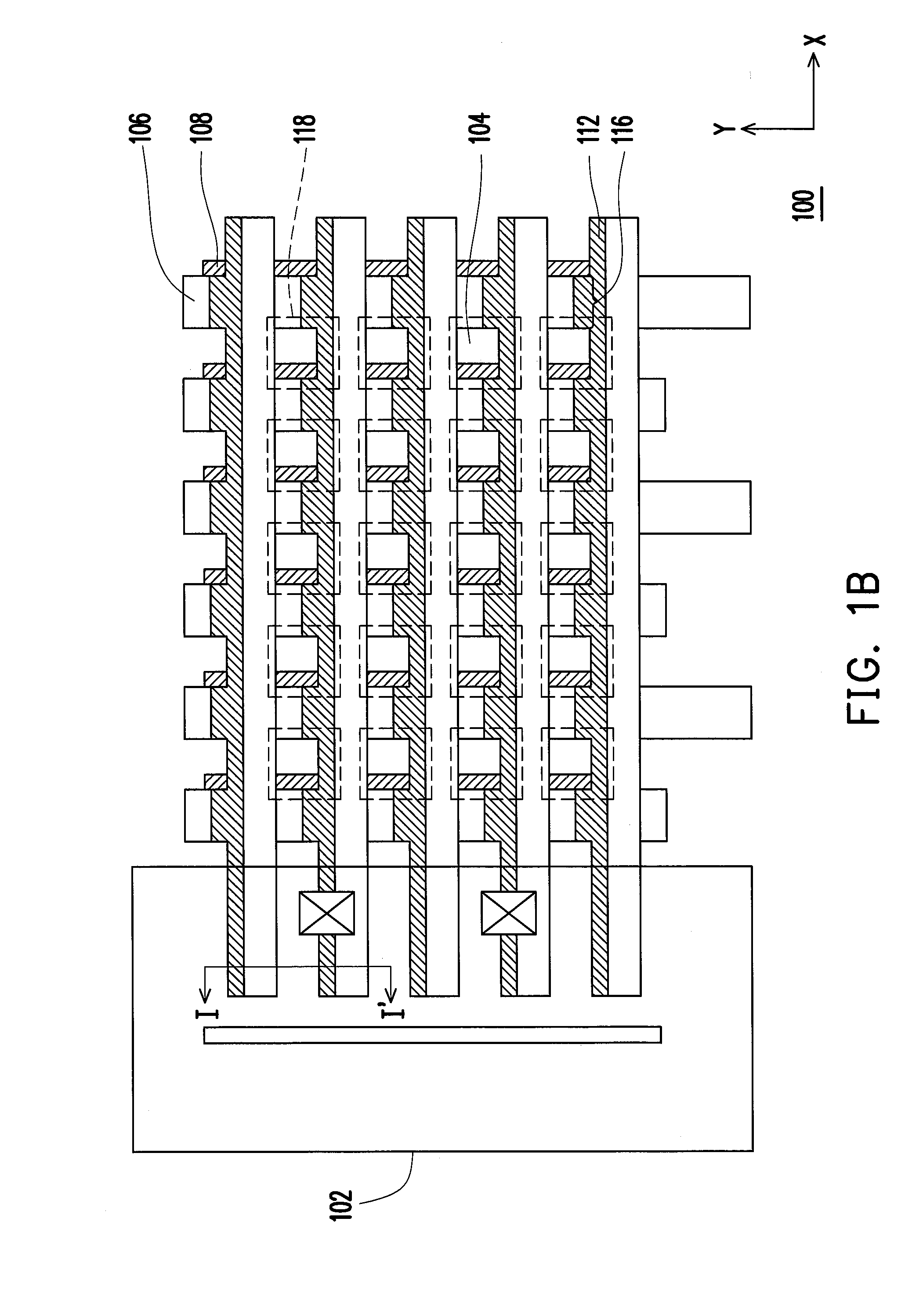

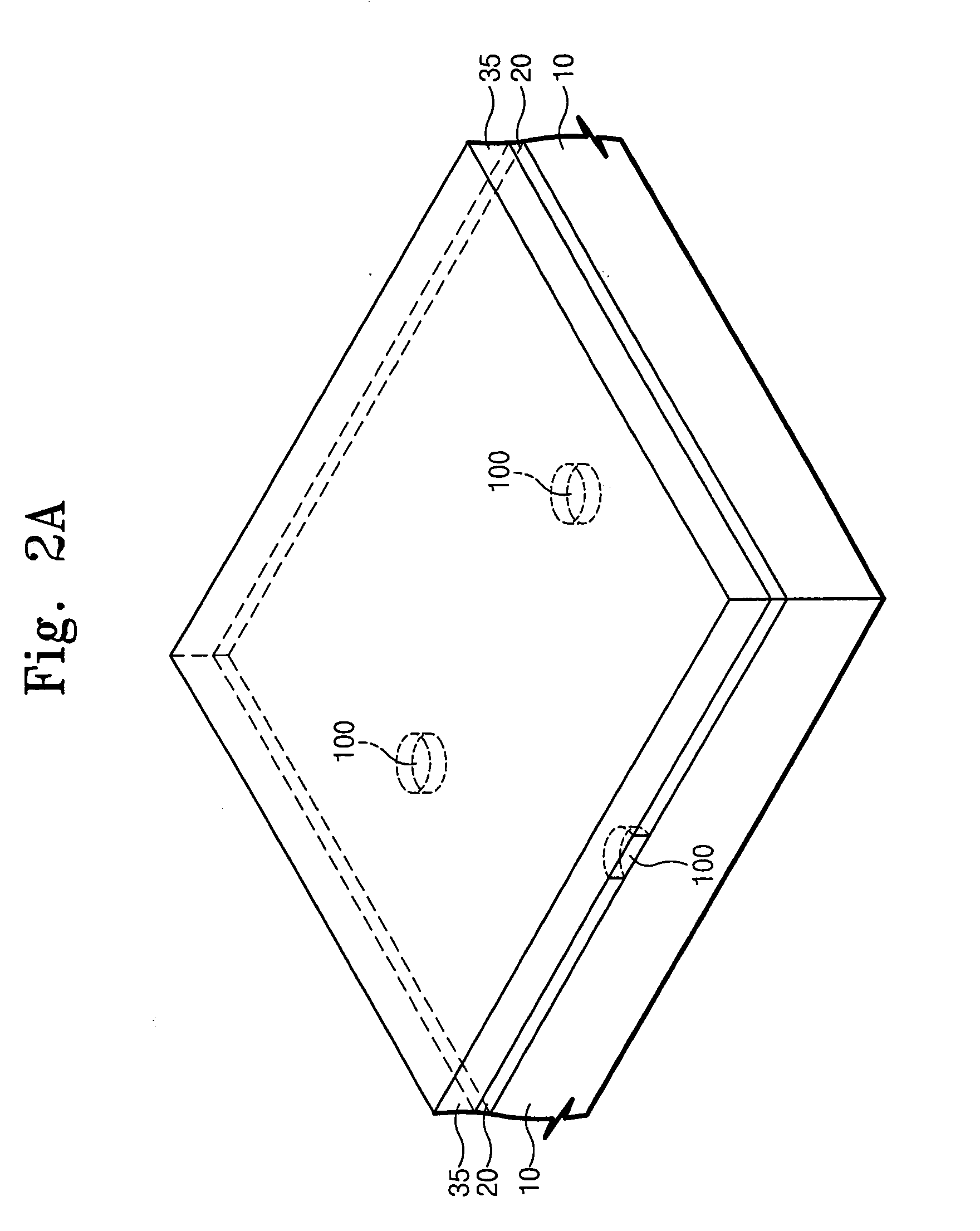

Vertical channel transistor array and manufacturing method thereof

ActiveUS20120181606A1Small sizeImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingTransistor arrayBit line

A vertical channel transistor array includes a plurality of embedded bit lines, a plurality of bit line contacts, a plurality of embedded word lines, and a current leakage isolation structure. An active area of a vertical channel transistor is defined by the semiconductor pillars. The embedded bit lines are disposed in parallel in a semiconductor substrate and extended in a column direction. Each of the bit line contacts is respectively disposed at a side of one of the embedded bit lines. The embedded word lines are disposed in parallel above the embedded bit lines and extended in a row direction. Besides, the embedded word lines and the semiconductor pillars in the same row are connected but spaced by a gate dielectric layer. The current leakage isolation structure is disposed at ends of the embedded bit lines to prevent current leakage between the adjacent bit line contacts.

Owner:POWERCHIP SEMICON MFG CORP

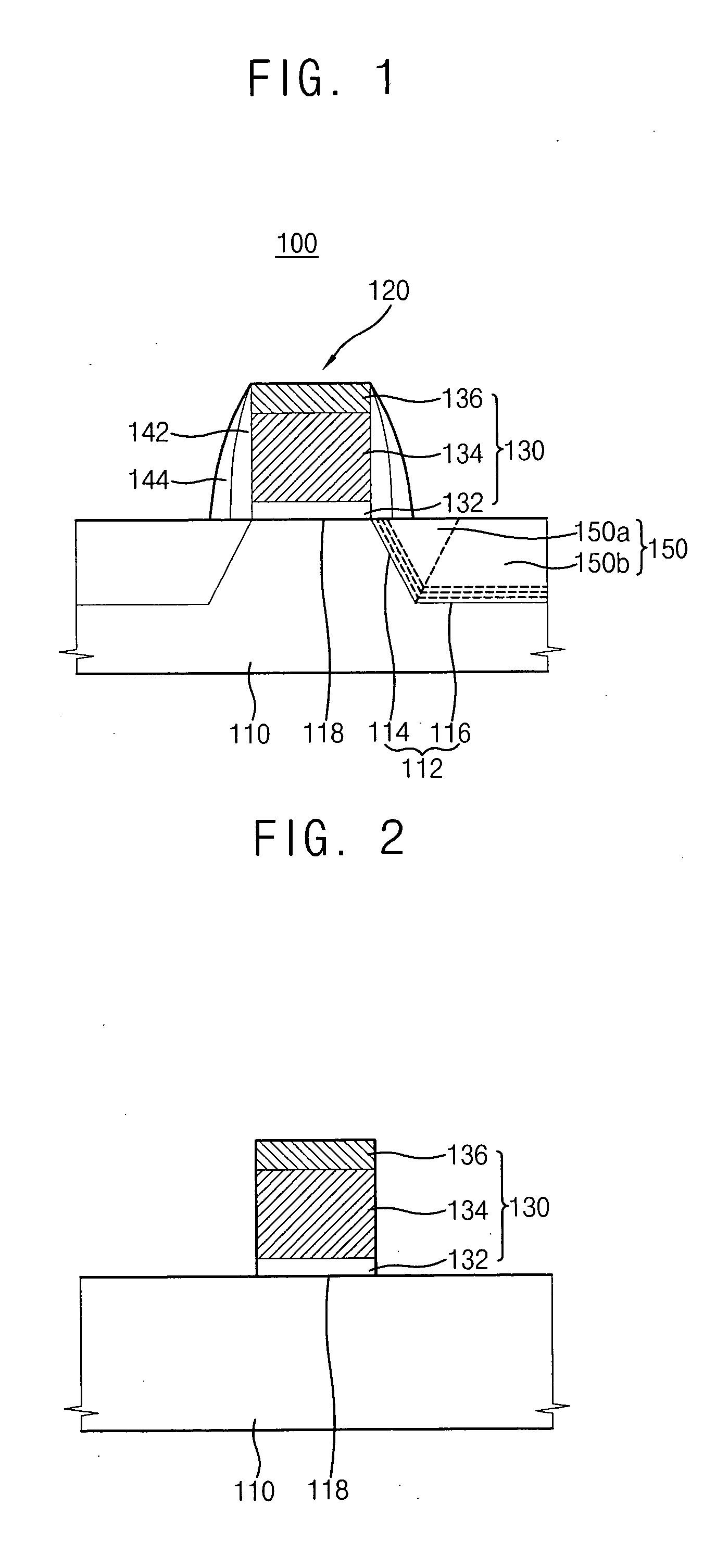

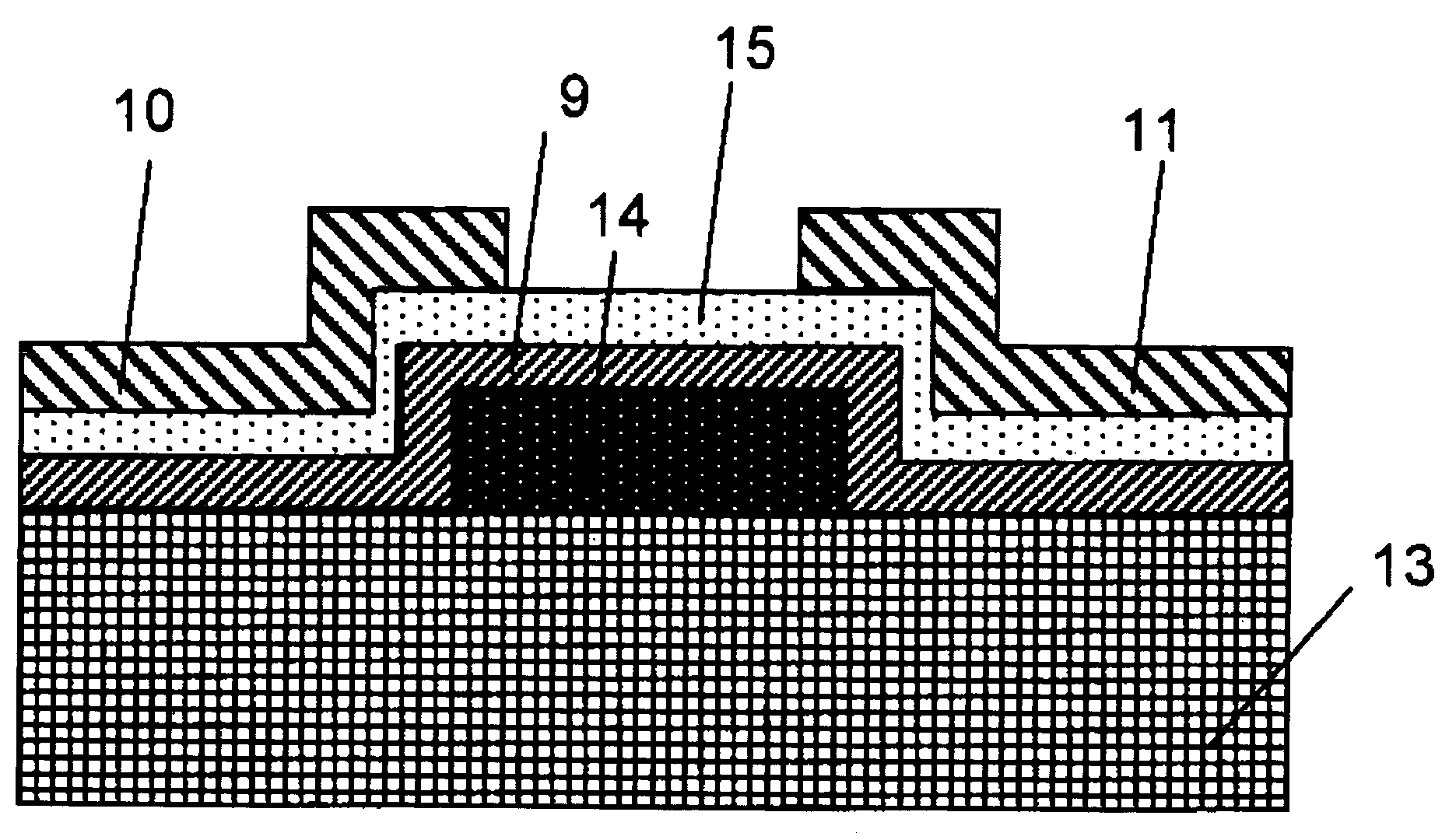

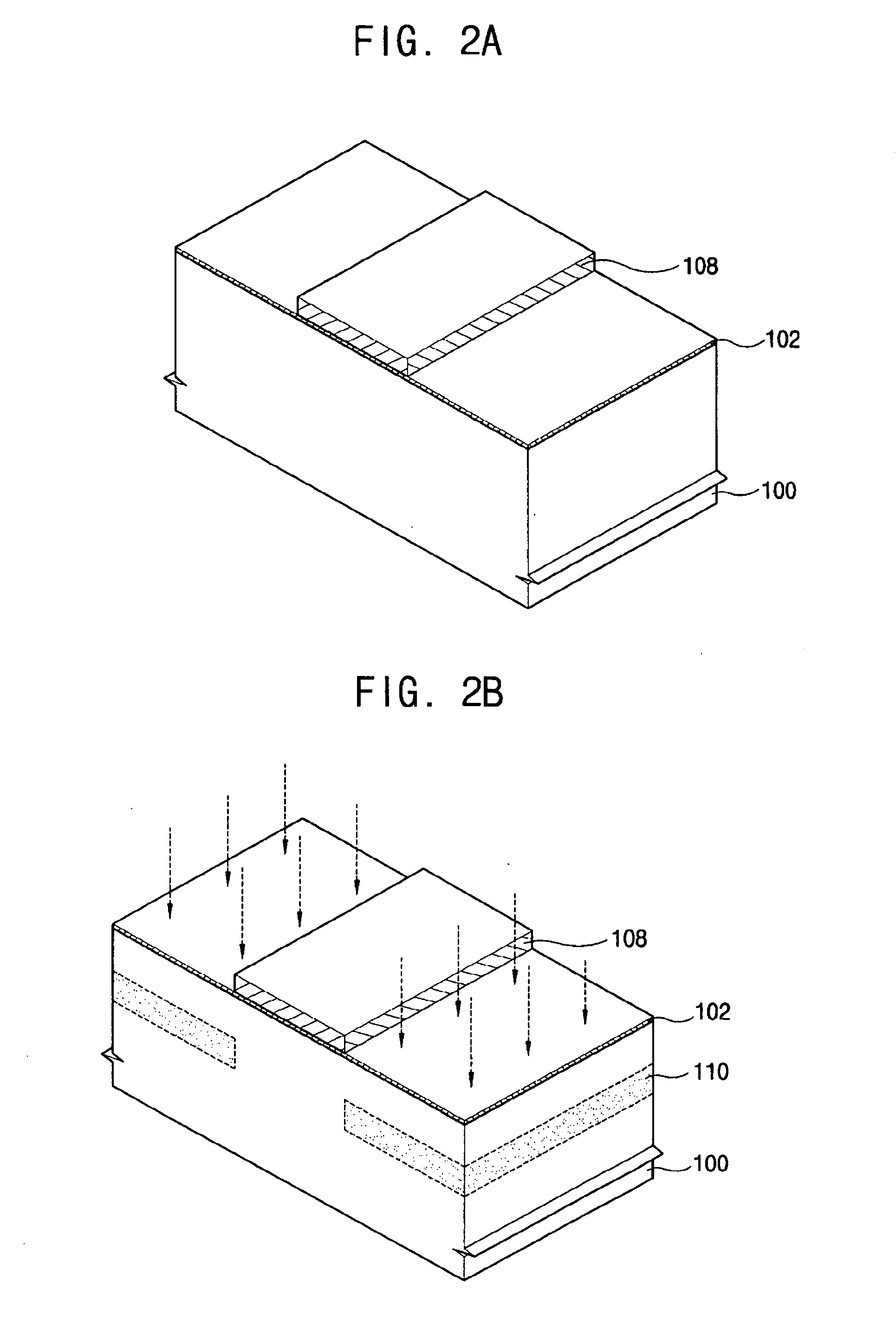

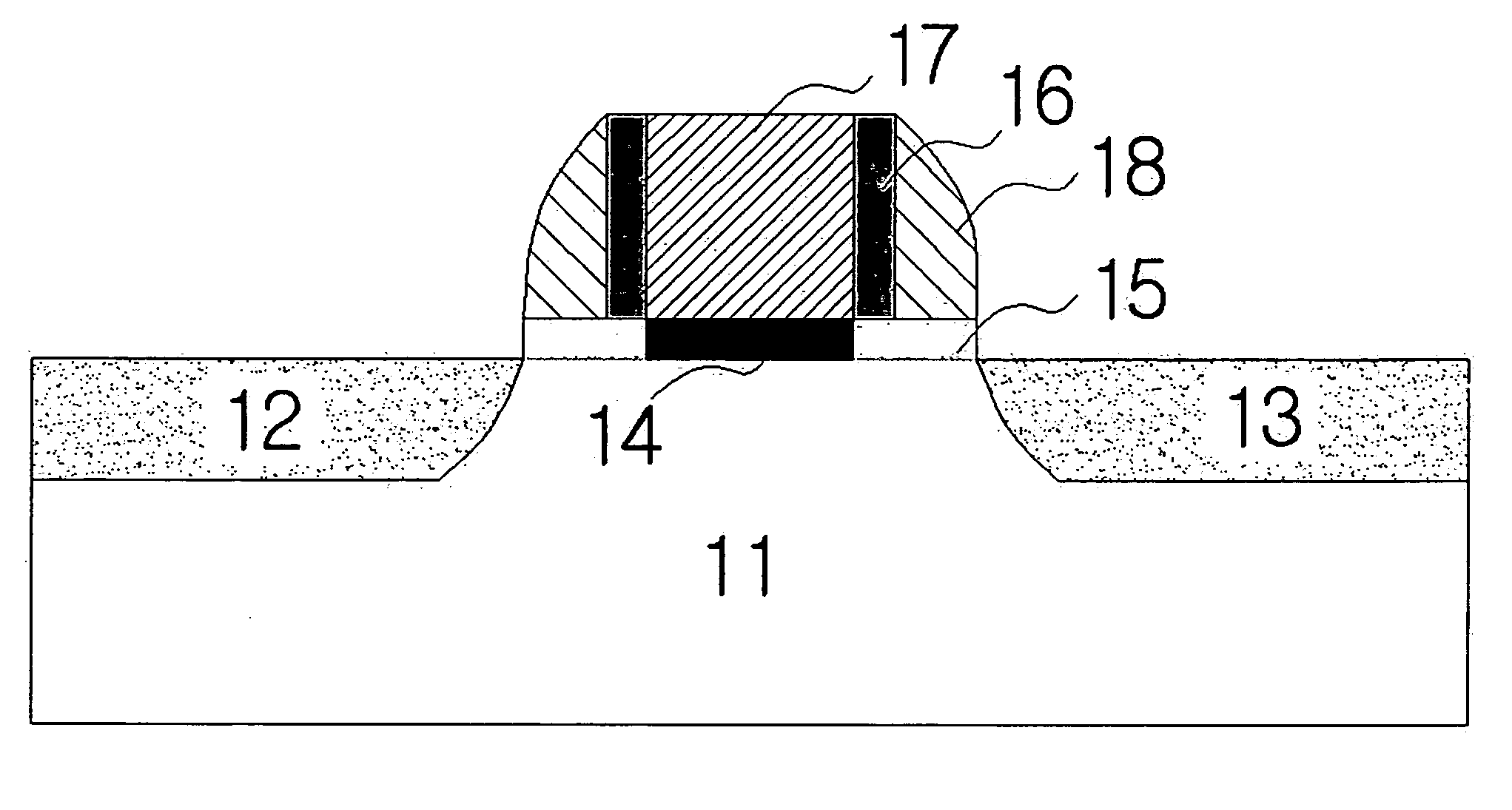

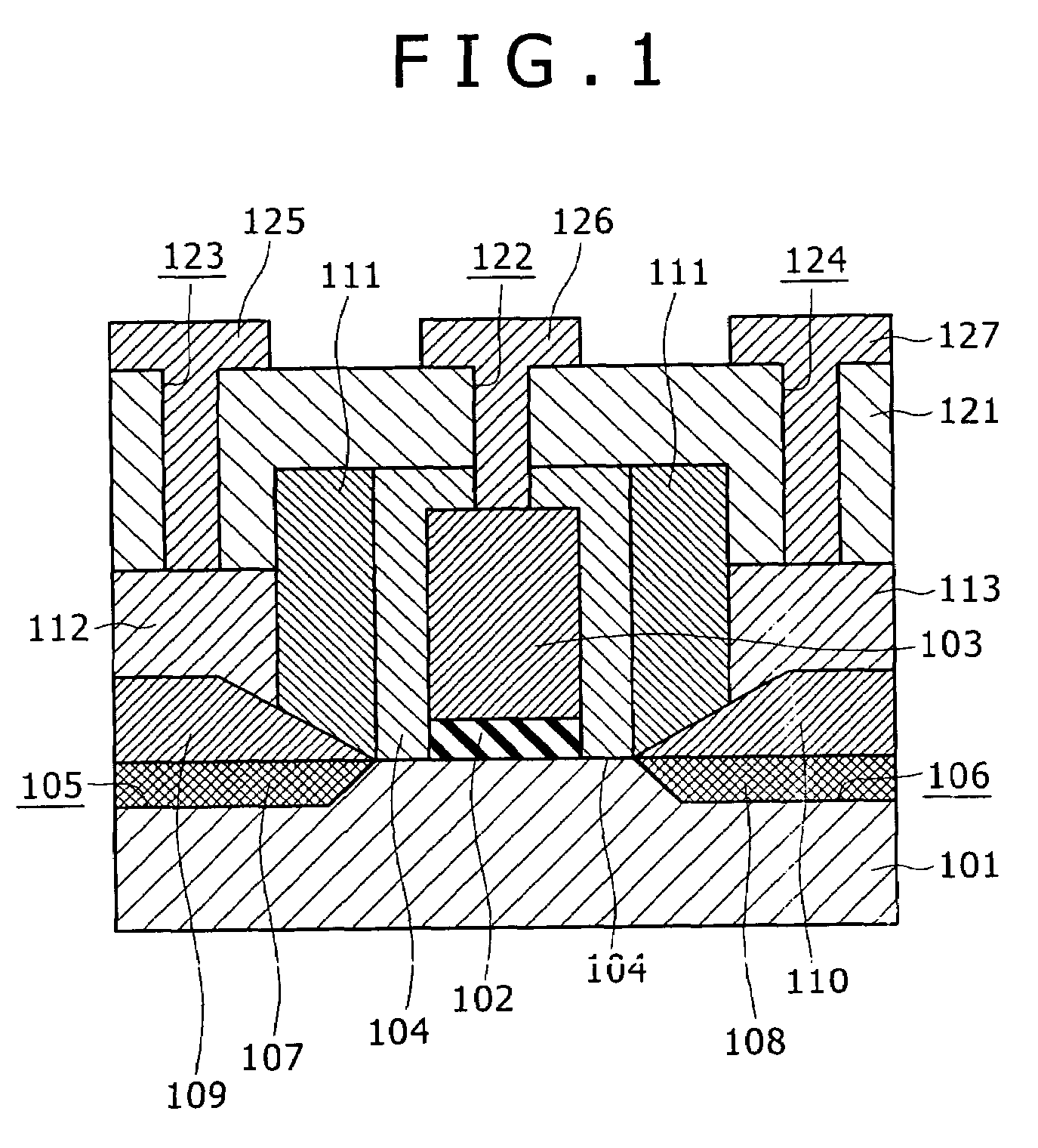

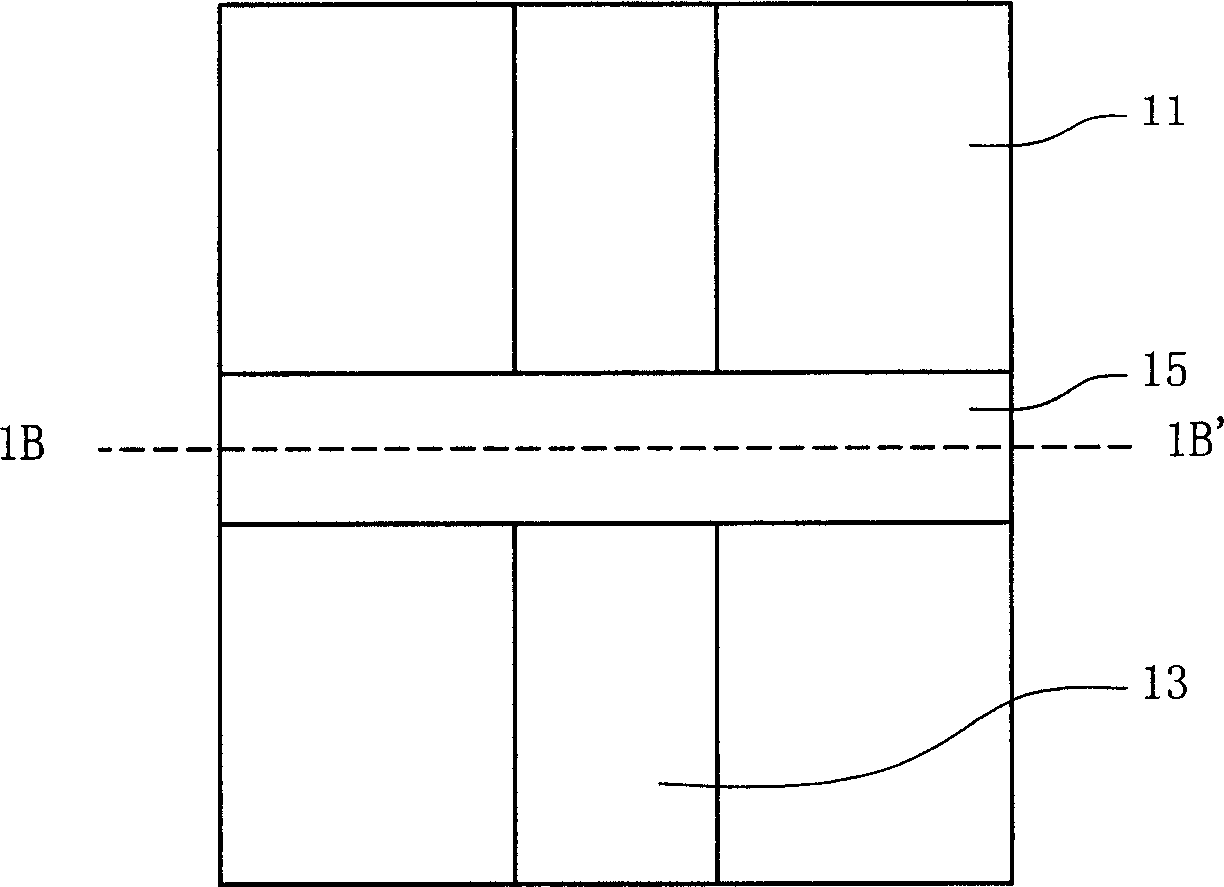

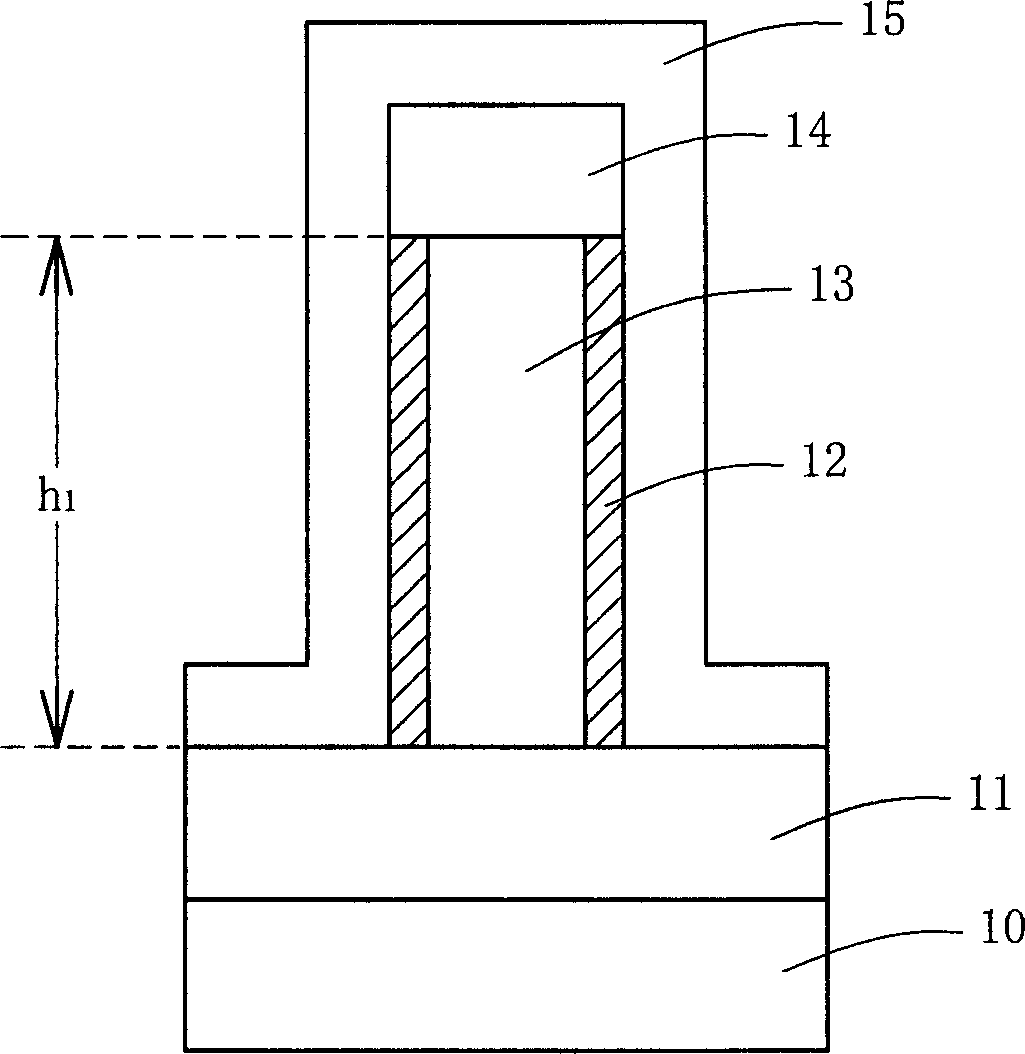

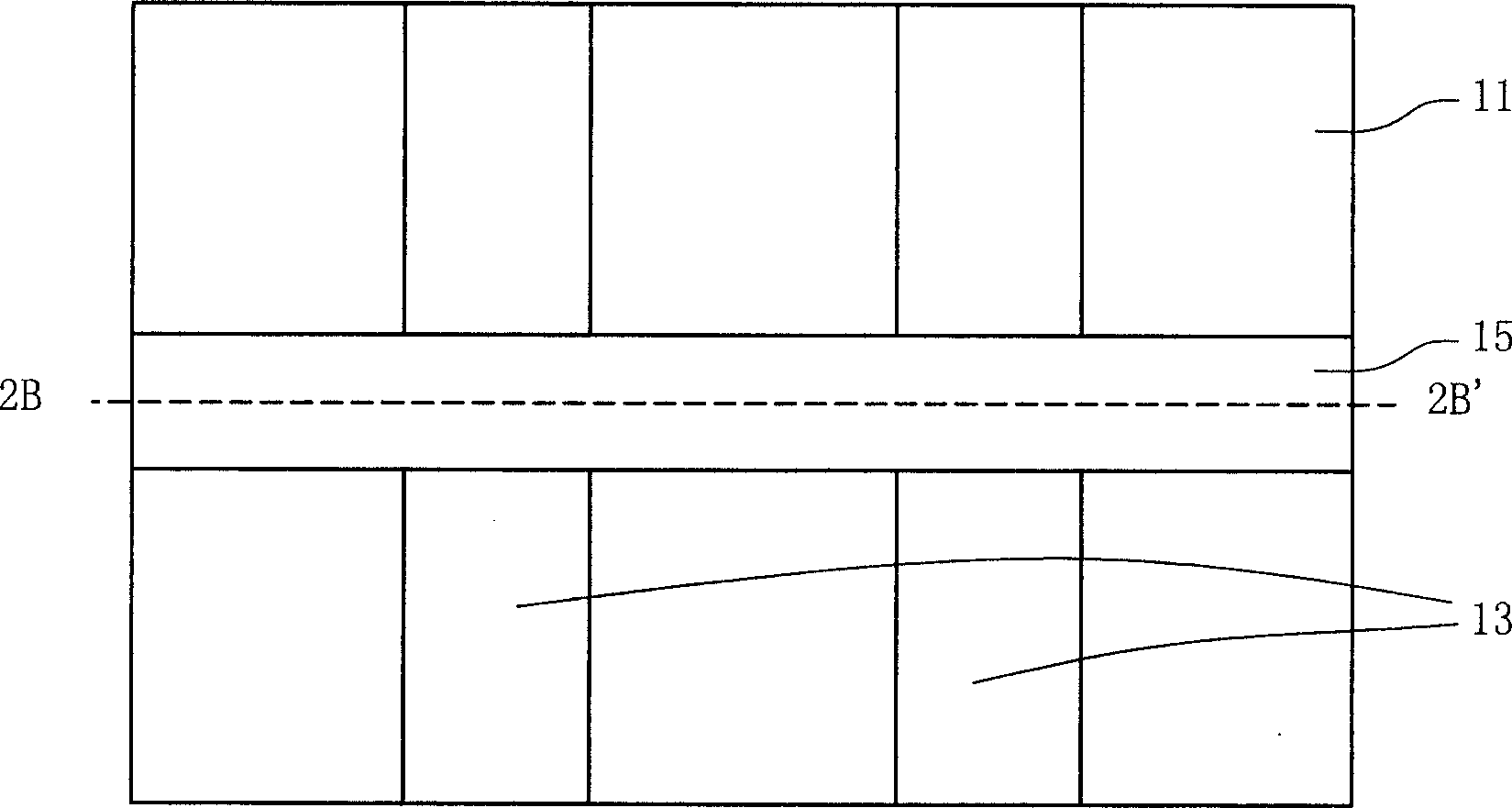

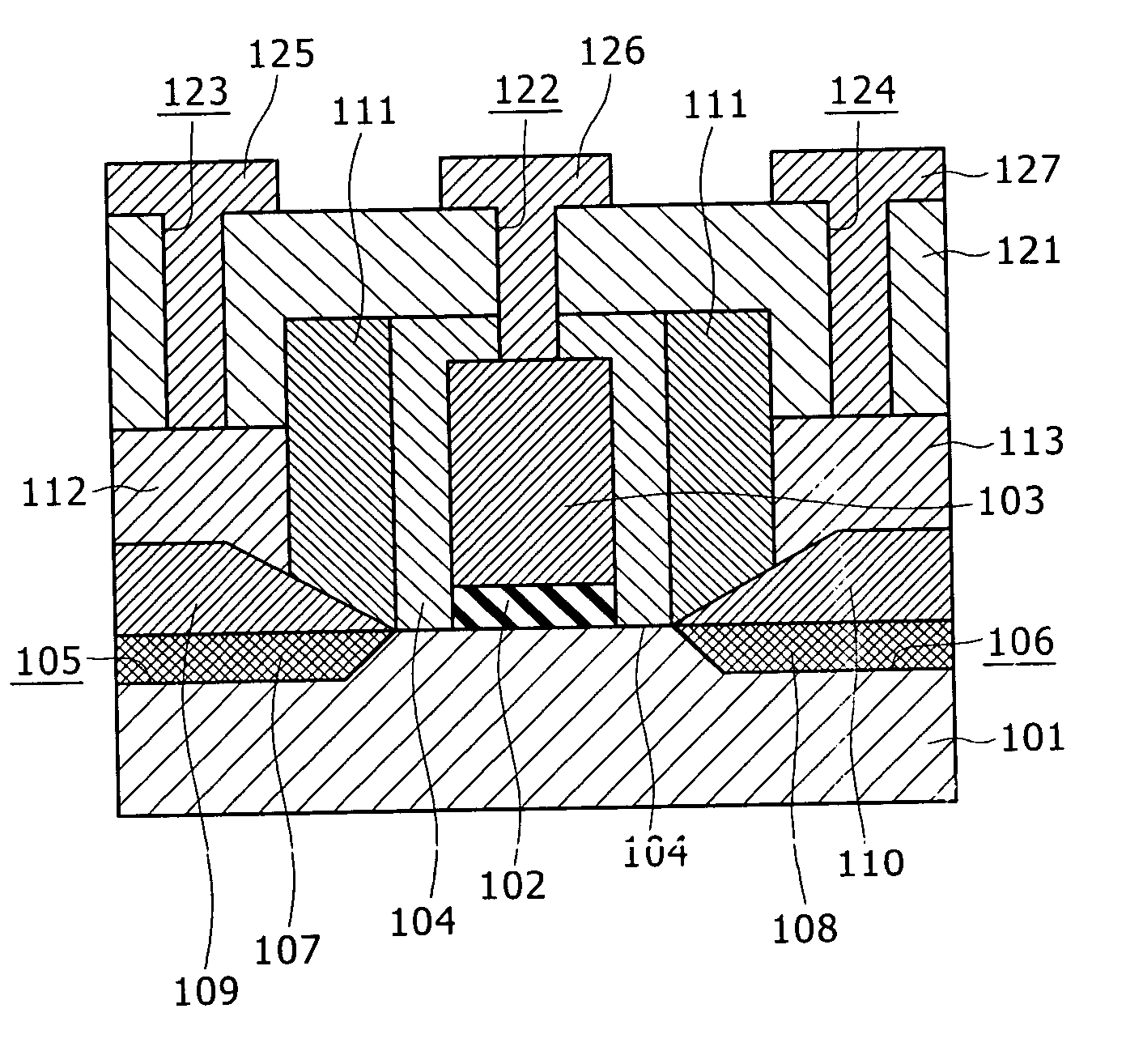

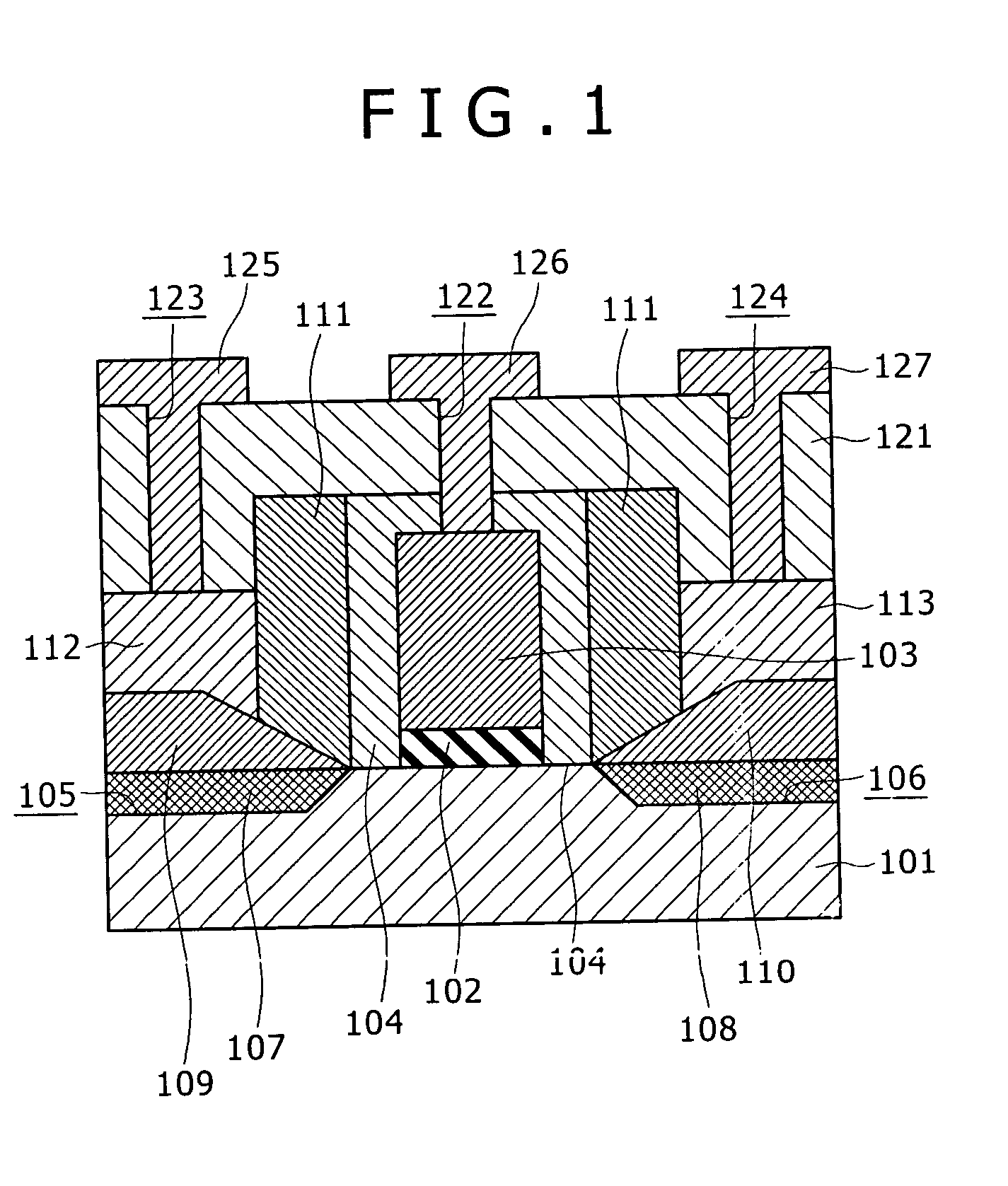

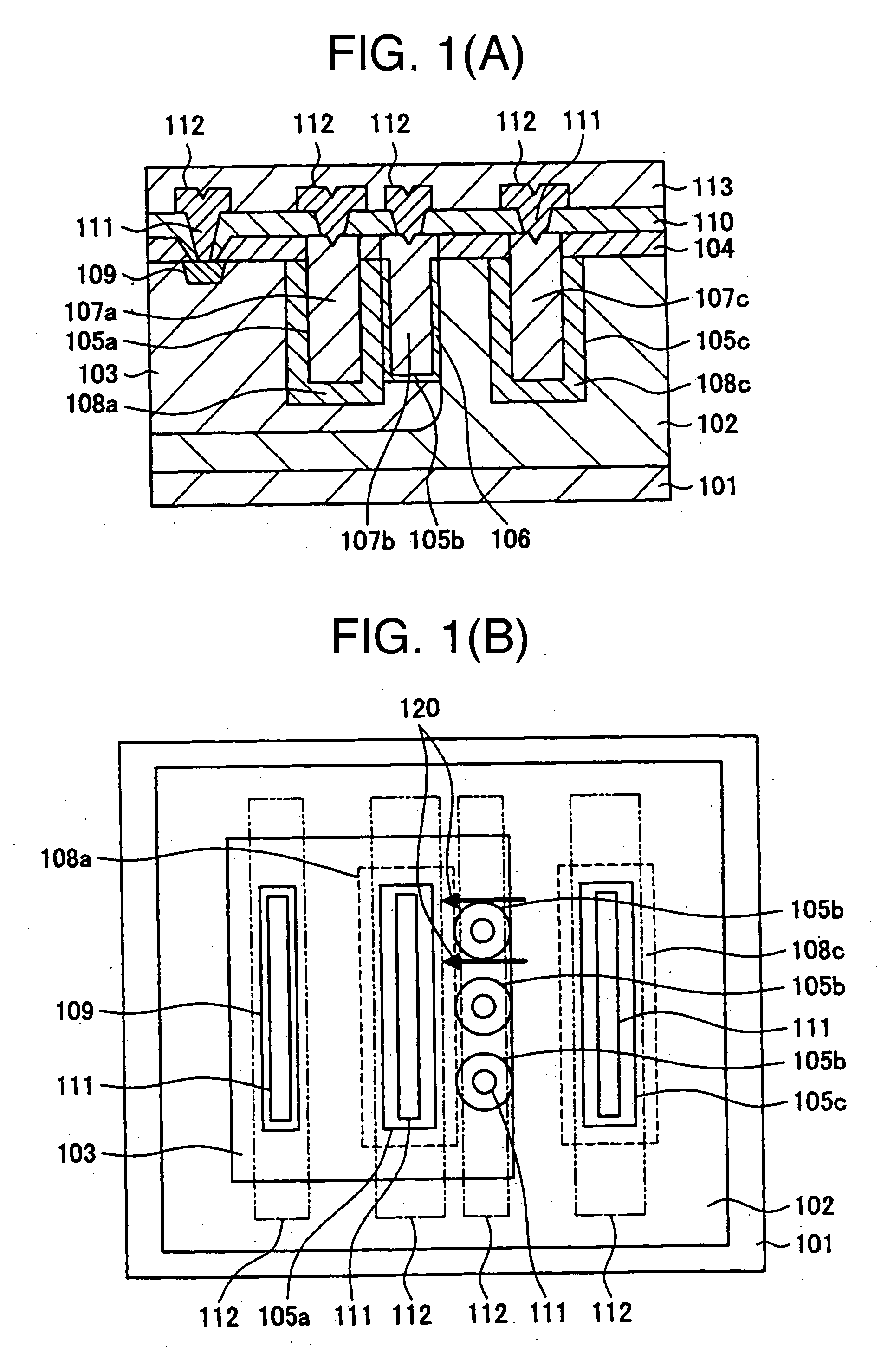

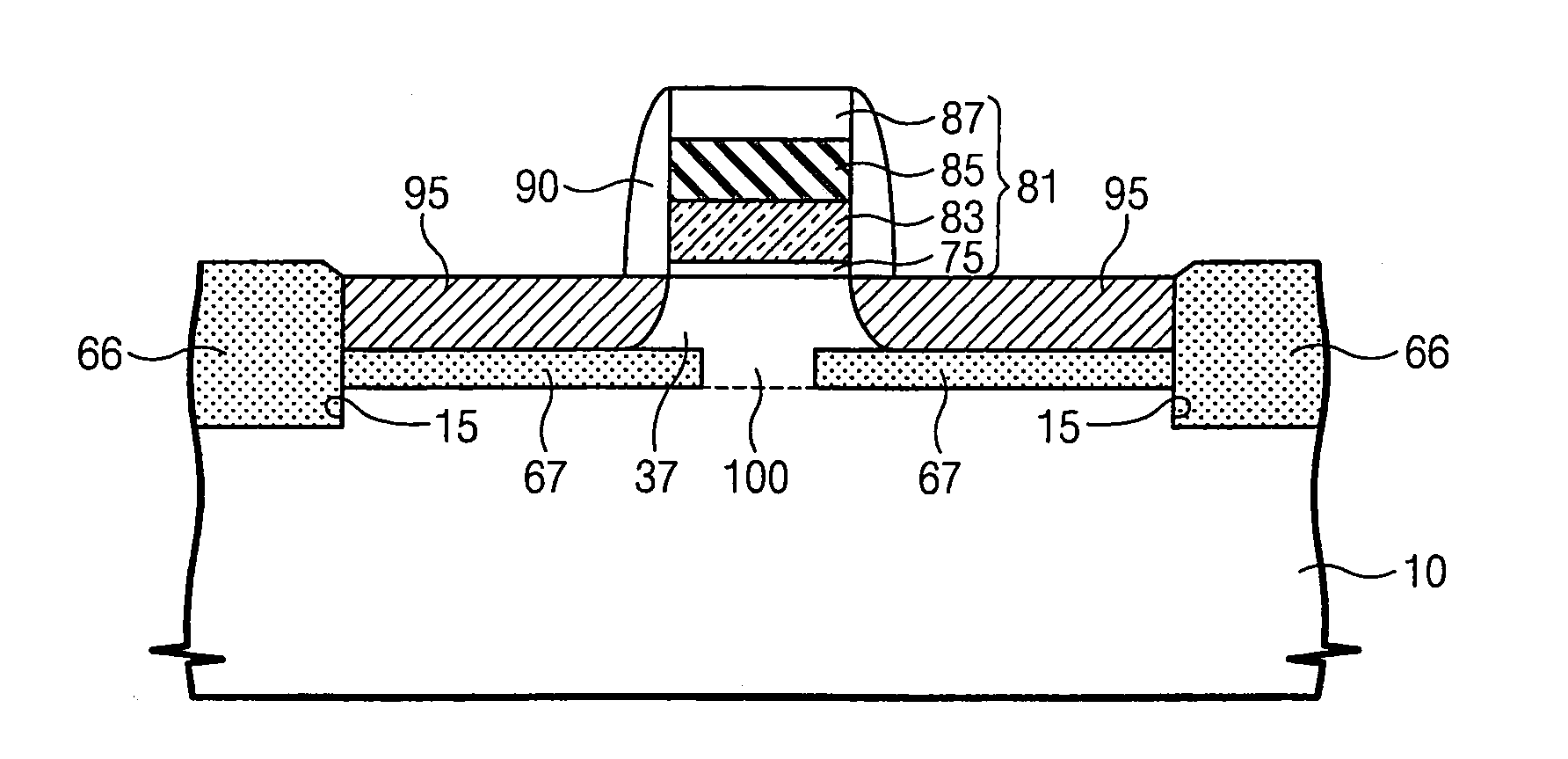

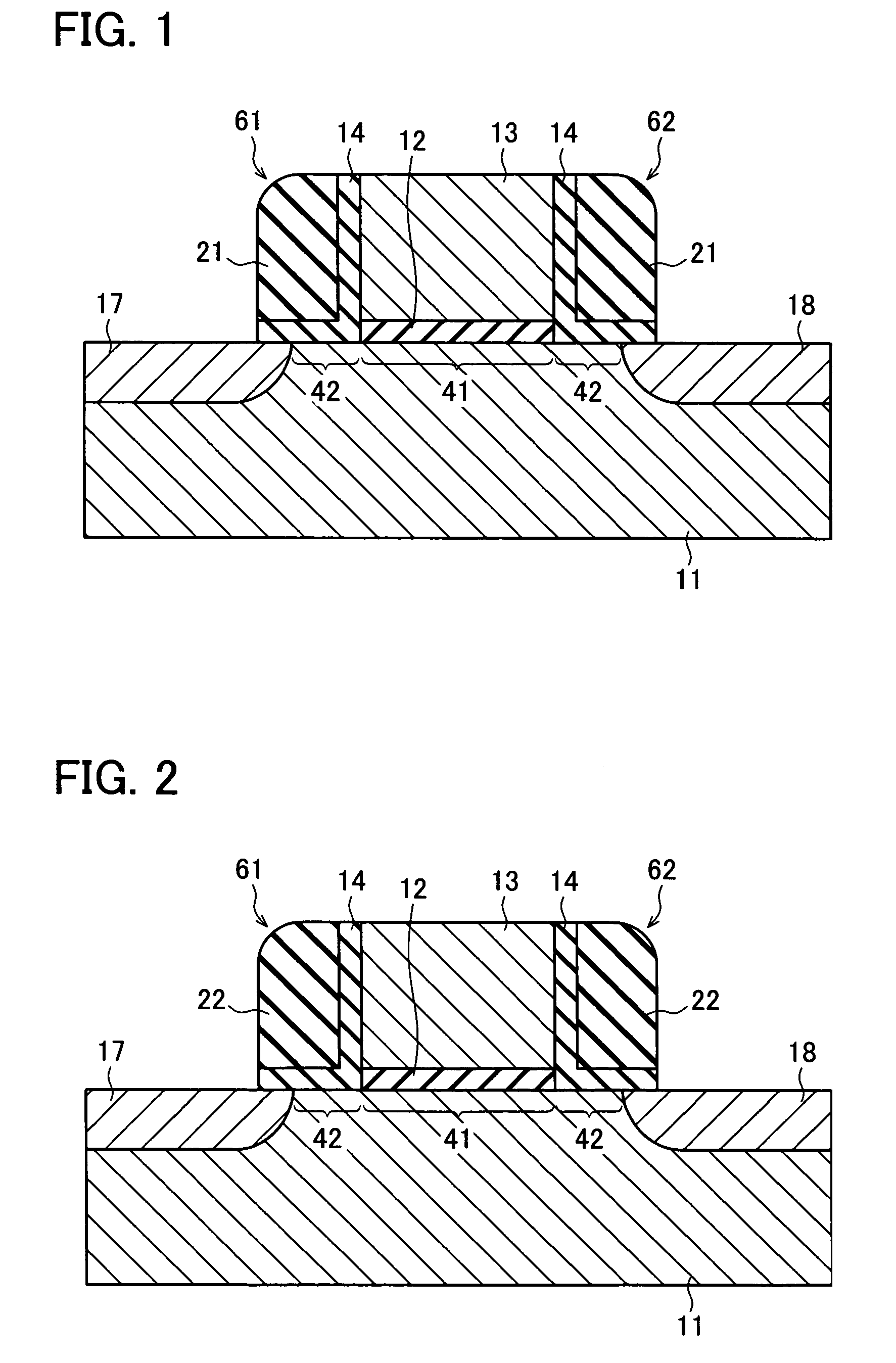

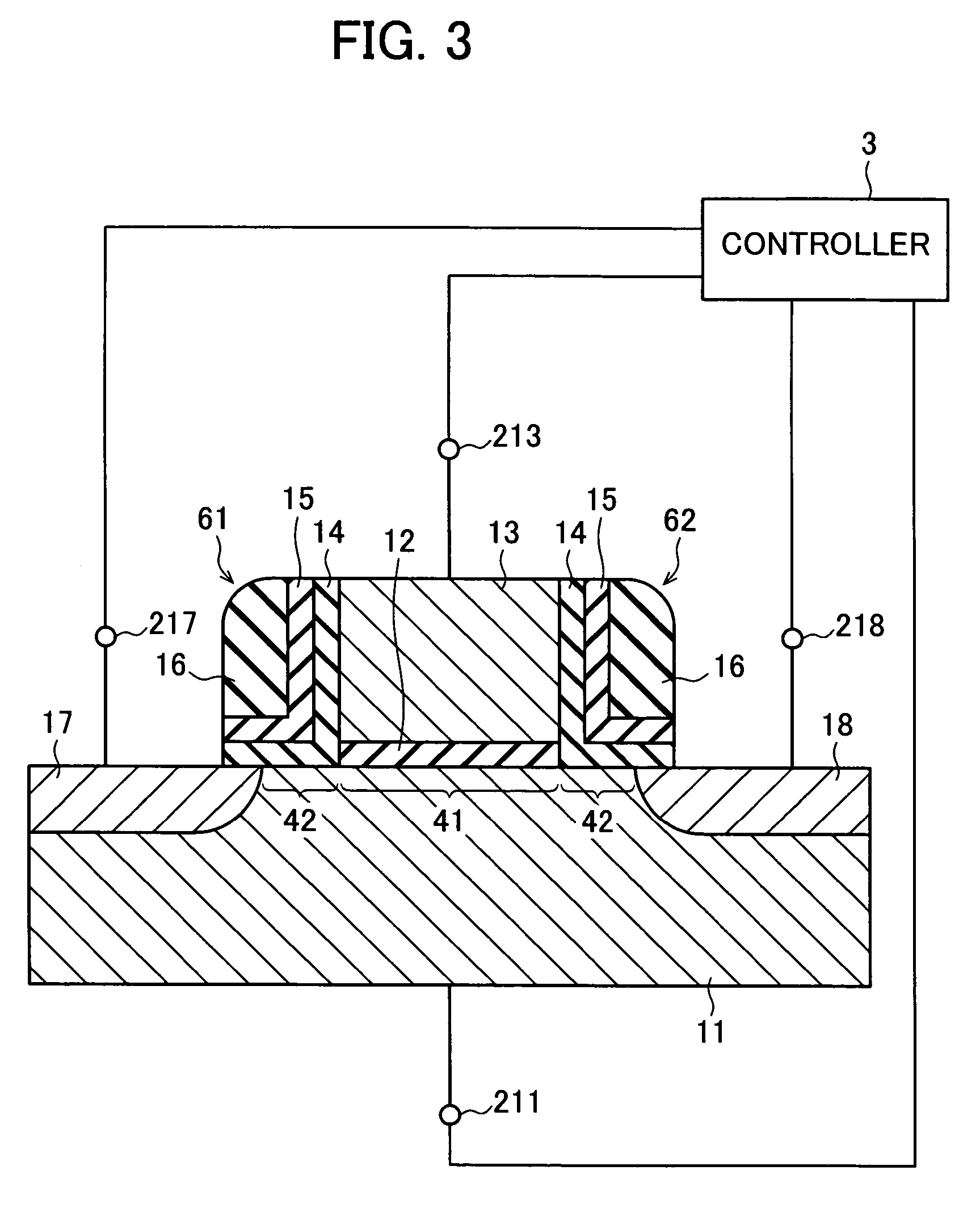

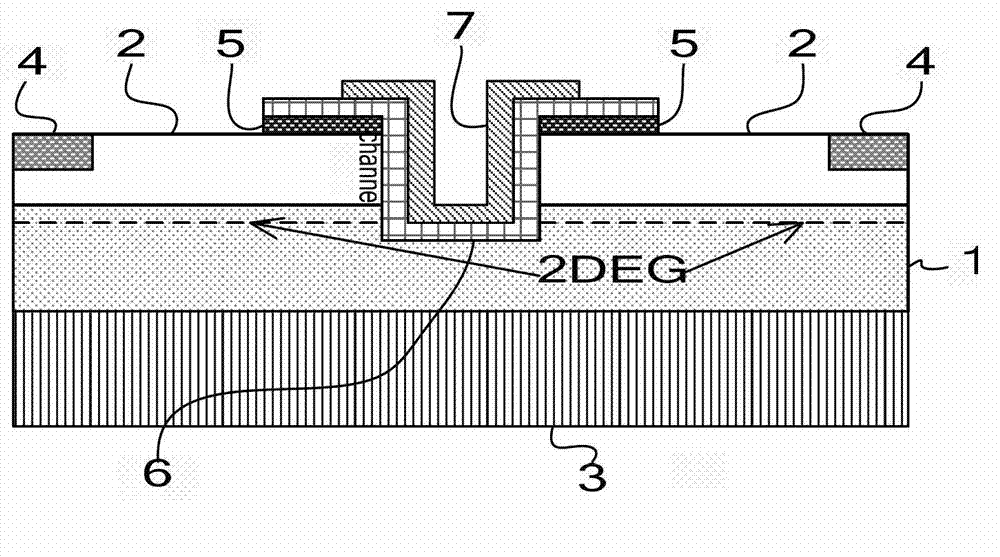

Semiconductor device and method of manufacturing semiconductor device

InactiveUS7557396B2Avoid short channel effectsTransistorSolid-state devicesSemiconductor deviceConduction type

A semiconductor device includes a side wall spacer formed on the side surface of a gate electrode formed on the upper side of a semiconductor substrate with a gate insulation film therebetween, extension regions built up on the semiconductor substrate, and source / drain regions formed on the extension regions, wherein a first epitaxial layer is formed so as to fill up portions, cut out at the time of forming the side wall spacer, of the semiconductor substrate, and the extension regions are formed on the first epitaxial layer from a second epitaxial layer of a conduction type opposite to that of the first epitaxial layer.

Owner:SONY CORP

CMOS transistor inverter with multiple grid transistor

InactiveCN1507063AImprove operational efficiencyAvoid short channel effectsTransistorSolid-state devicesCMOSEngineering

The CMOS transistor inverter includes at least one first multiple grid transistor, which includes one first source connected to the first power source, the first drain connected to the output end and the first grid; at least one second multiple grid transistor, which includes the second source connected to ground, the second drain connected to the output end and the second grid; and one input end contained to the first grid and the second grid.

Owner:TAIWAN SEMICON MFG CO LTD

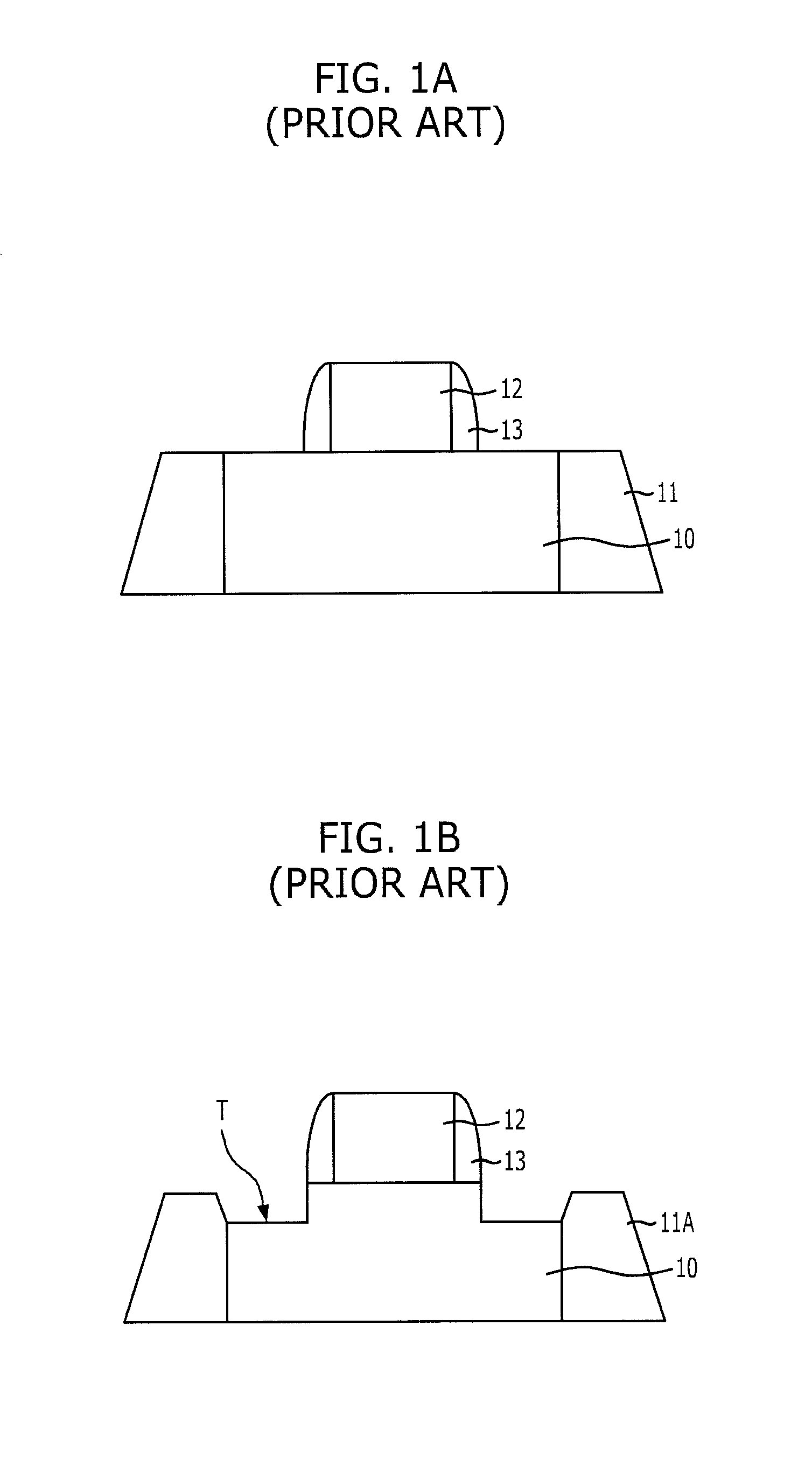

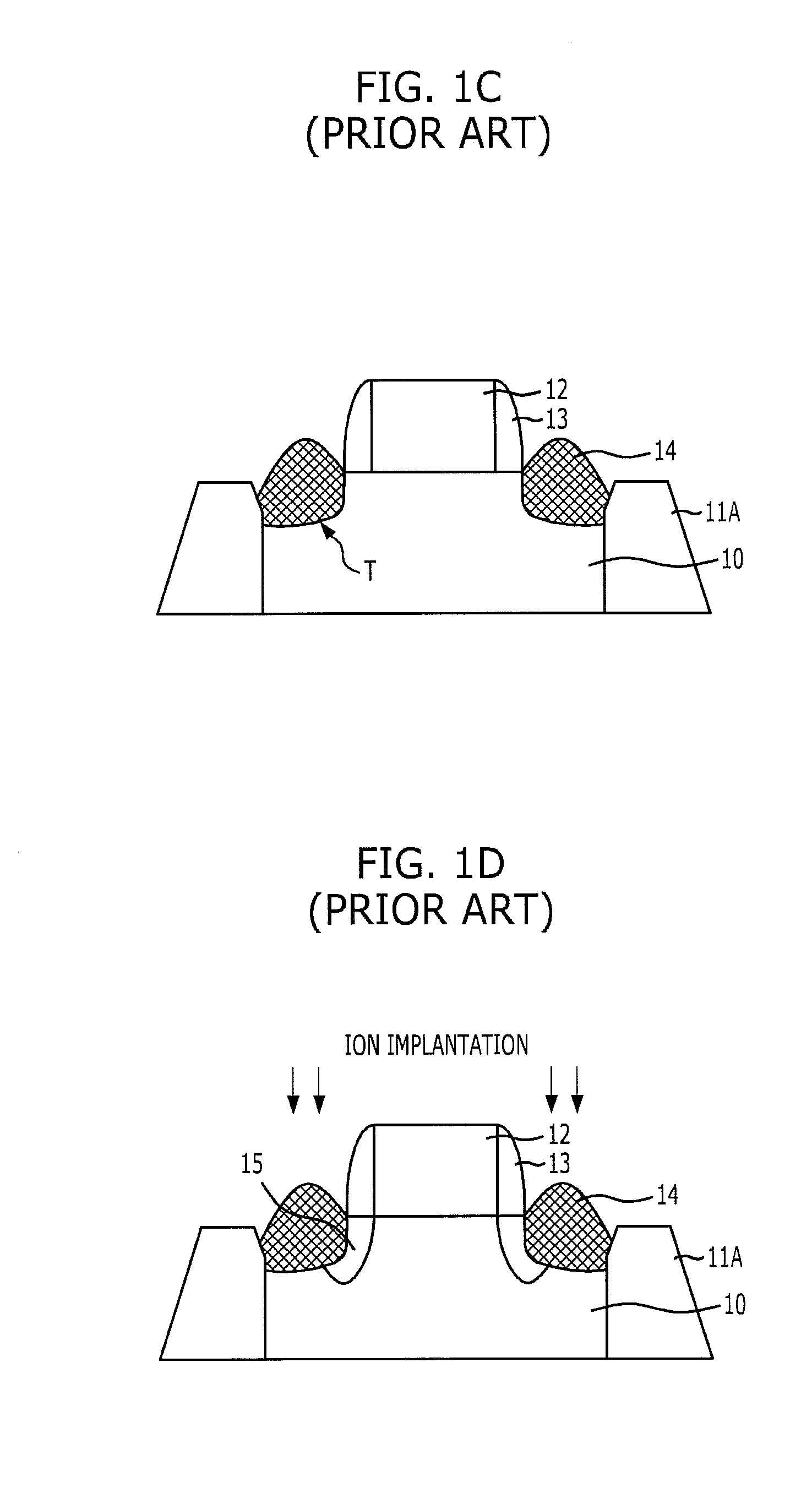

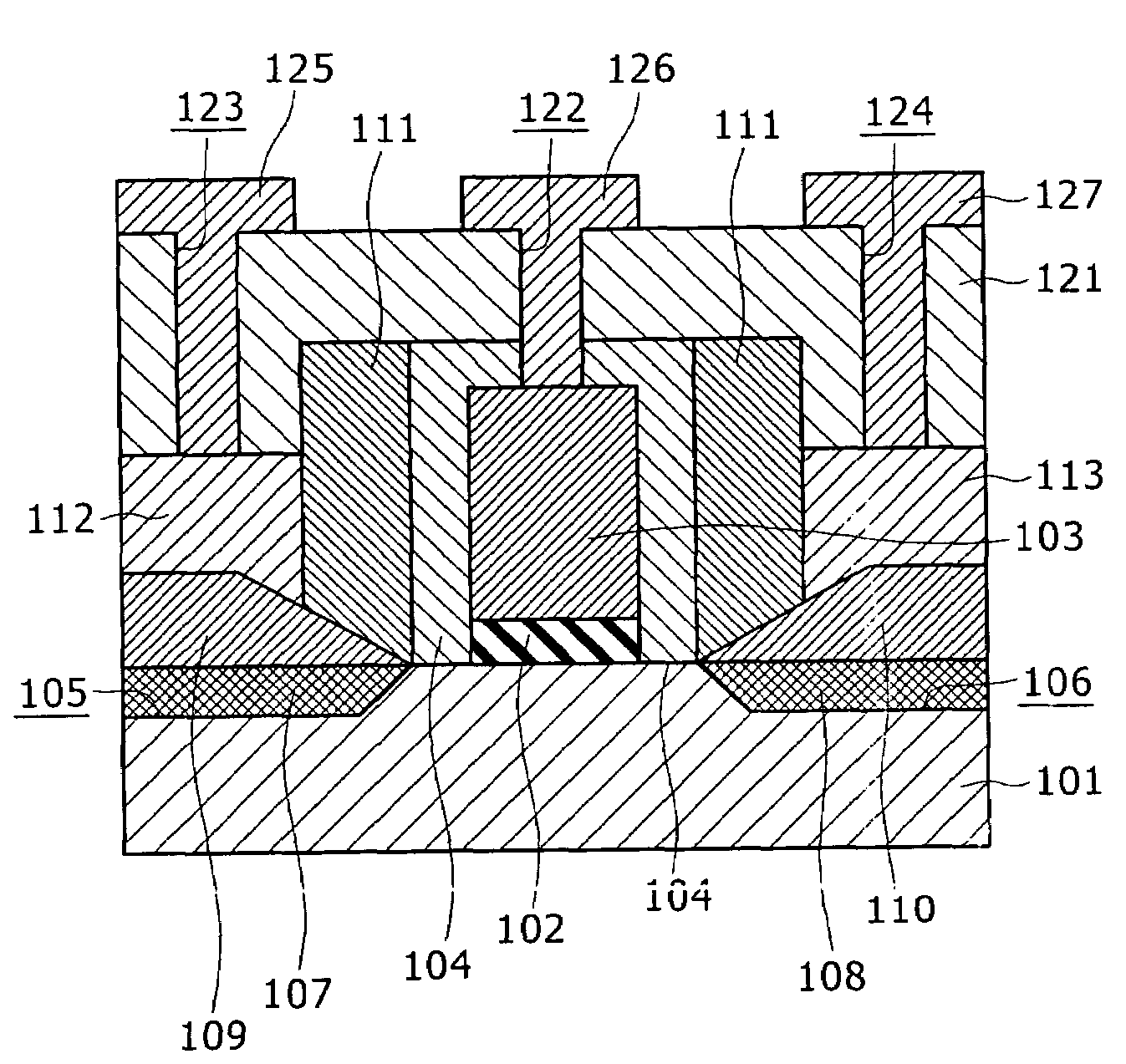

Semiconductor device and method of manufacturing semiconductor device

InactiveUS20060192232A1Avoid short channel effectsTransistorSolid-state devicesDevice materialSemiconductor device

A semiconductor device includes a side wall spacer formed on the side surface of a gate electrode formed on the upper side of a semiconductor substrate with a gate insulation film therebetween, extension regions built up on the semiconductor substrate, and source / drain regions formed on the extension regions, wherein a first epitaxial layer is formed so as to fill up portions, cut out at the time of forming the side wall spacer, of the semiconductor substrate, and the extension regions are formed on the first epitaxial layer from a second epitaxial layer of a conduction type opposite to that of the first epitaxial layer.

Owner:SONY CORP

Transistor and method of manufacturing the same

InactiveUS20060038243A1Simple structureExcellent electrical propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesCrystal planeSemiconductor

A transistor of the present invention includes a semiconductor substrate that has a first surface of the {100} crystal plane, a second surface of the {100} crystal plane having a height lower than that of the first surface, and a side face of the {111} crystal plane connecting the first surface to the second surface. A gate structure is formed on the first surface. An epitaxial layer is formed on the second surface and the side face. Impurity regions are formed adjacent to both sides of the gate structure. The impurity regions have side faces of the {111} crystal plane so that a short channel effect generated between the impurity regions may be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

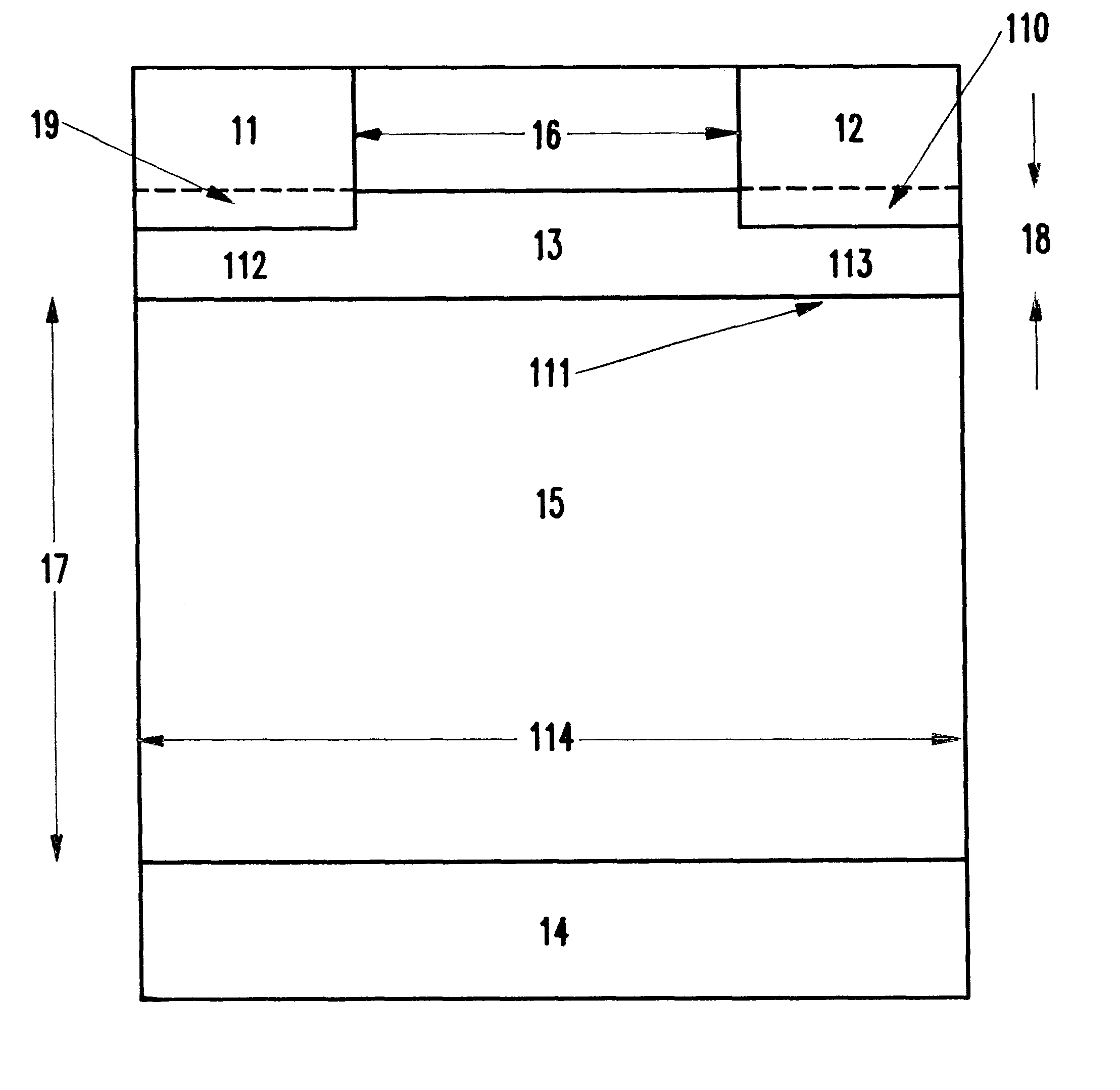

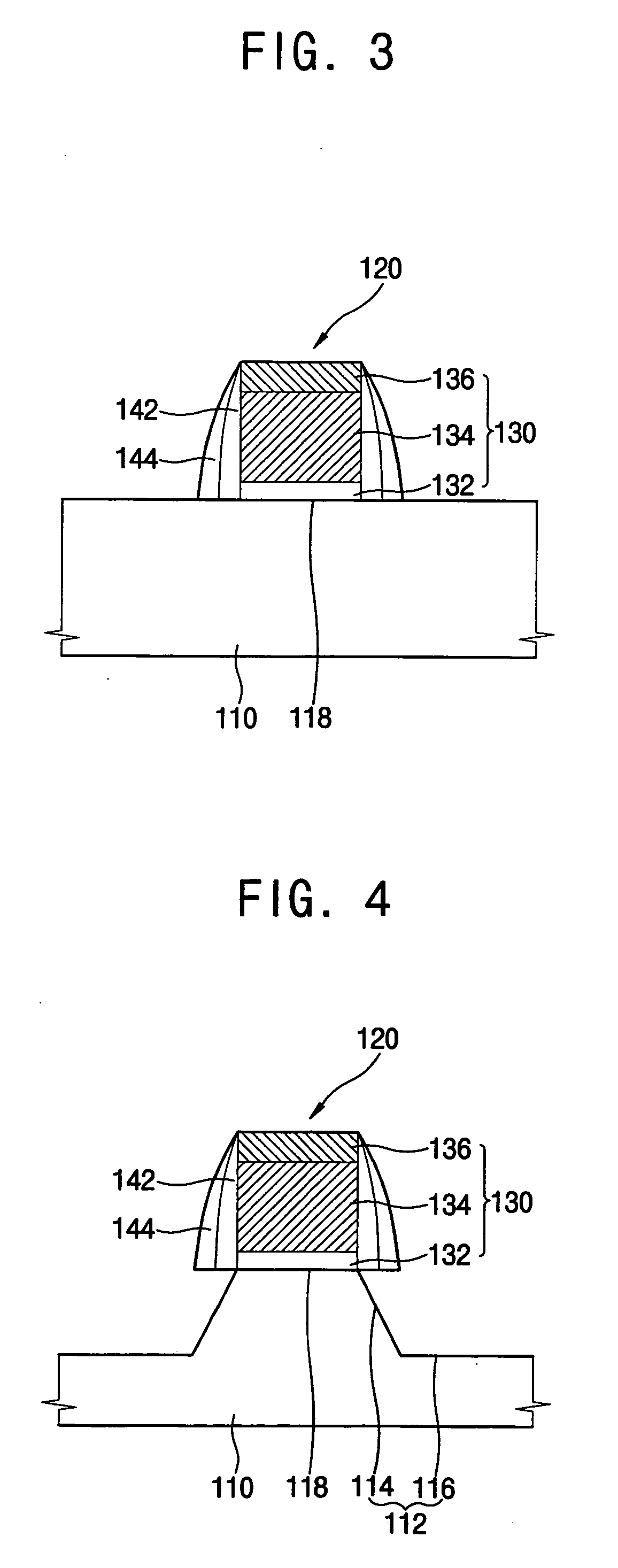

A structure of a lateral diffusion mos transistor in widespread use as a power control device

InactiveUS20050093060A1High currentShort pathTransistorSolid-state devicesDevice materialHigh pressure

There is provided a semiconductor device structured so as to be mounted jointly with other devices on one chip, and capable of controlling a large current in spite of a small device area while having small on-resistance, thereby enabling a high voltage resistance to be obtained. In the case of NLDMOS, the semiconductor device comprises an N well layer, formed on a p-type semiconductor substrate, a P well layer formed in the N well layer, a source electrode formed in a source trench cavity within the P well layer, a gate electrode formed in at least one of gate trench cavities within the P well layer, through the intermediary of an oxide film, and a drain electrode formed in a drain trench cavity within the N well layer, and further, N+ diffused layers are formed around the source trench cavity, the drain trench cavity, respectively.

Owner:LAPIS SEMICON CO LTD

SEMICONDUCTOR DEVICE HAVING PARTIALLY INSULATED FIELD EFFECT TRANSISTOR (PiFET) AND METHOD OF FABRICATING THE SAME

InactiveUS20080145989A1Inhibition effectAvoid short channel effectsSemiconductor/solid-state device manufacturingFrom condensed vaporsDevice materialEngineering

Embodiments of the invention include a partially insulated field effect transistor and a method of fabricating the same. According to some embodiments, a semiconductor substrate is formed by sequentially stacking a bottom semiconductor layer, a sacrificial layer, and a top semiconductor layer. The sacrificial layer may be removed to form a buried gap region between the bottom semiconductor layer and the top semiconductor layer. Then, a transistor may be formed on the semiconductor substrate. The sacrificial layer may be a crystalline semiconductor formed by an epitaxial growth technology.

Owner:SAMSUNG ELECTRONICS CO LTD

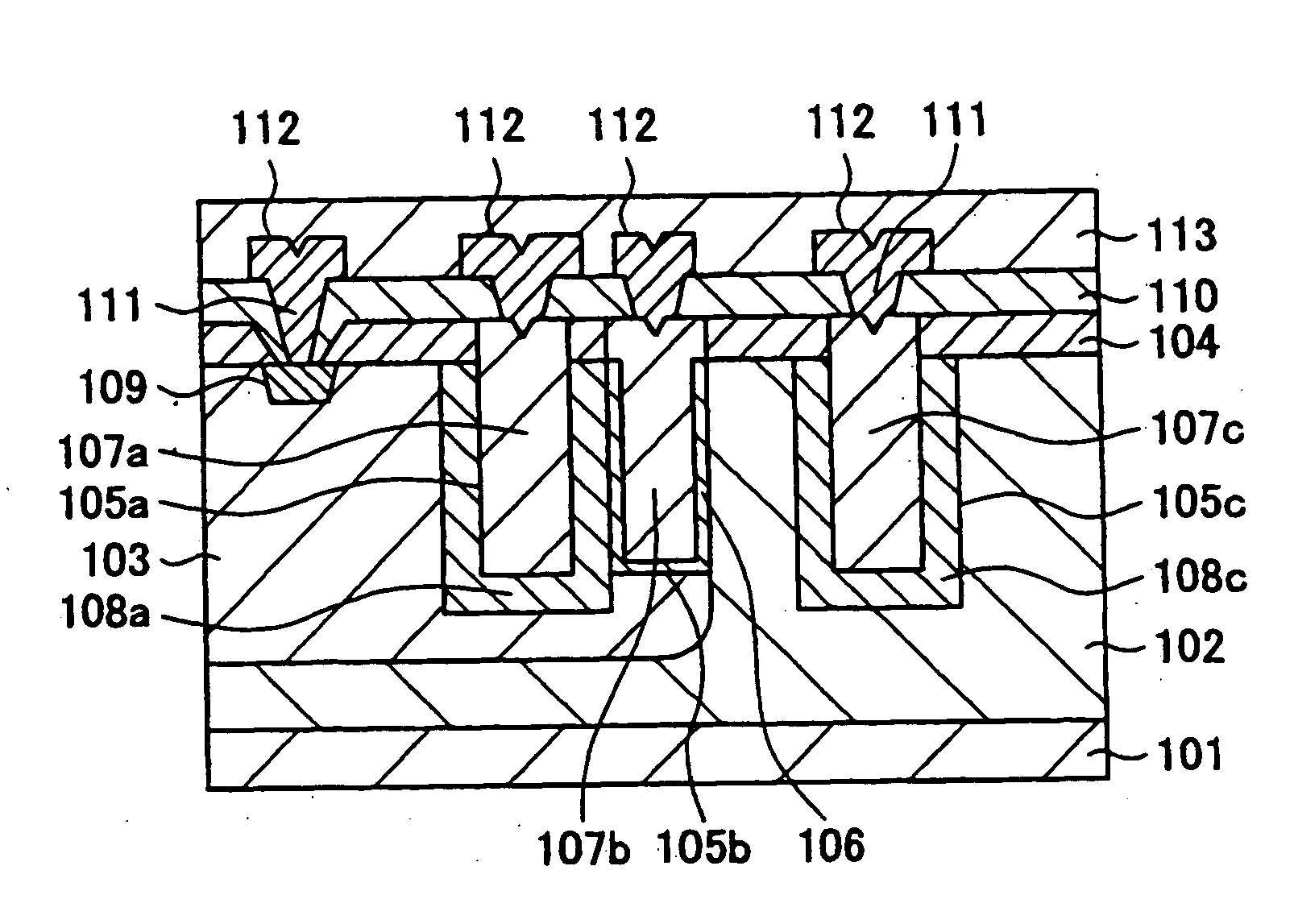

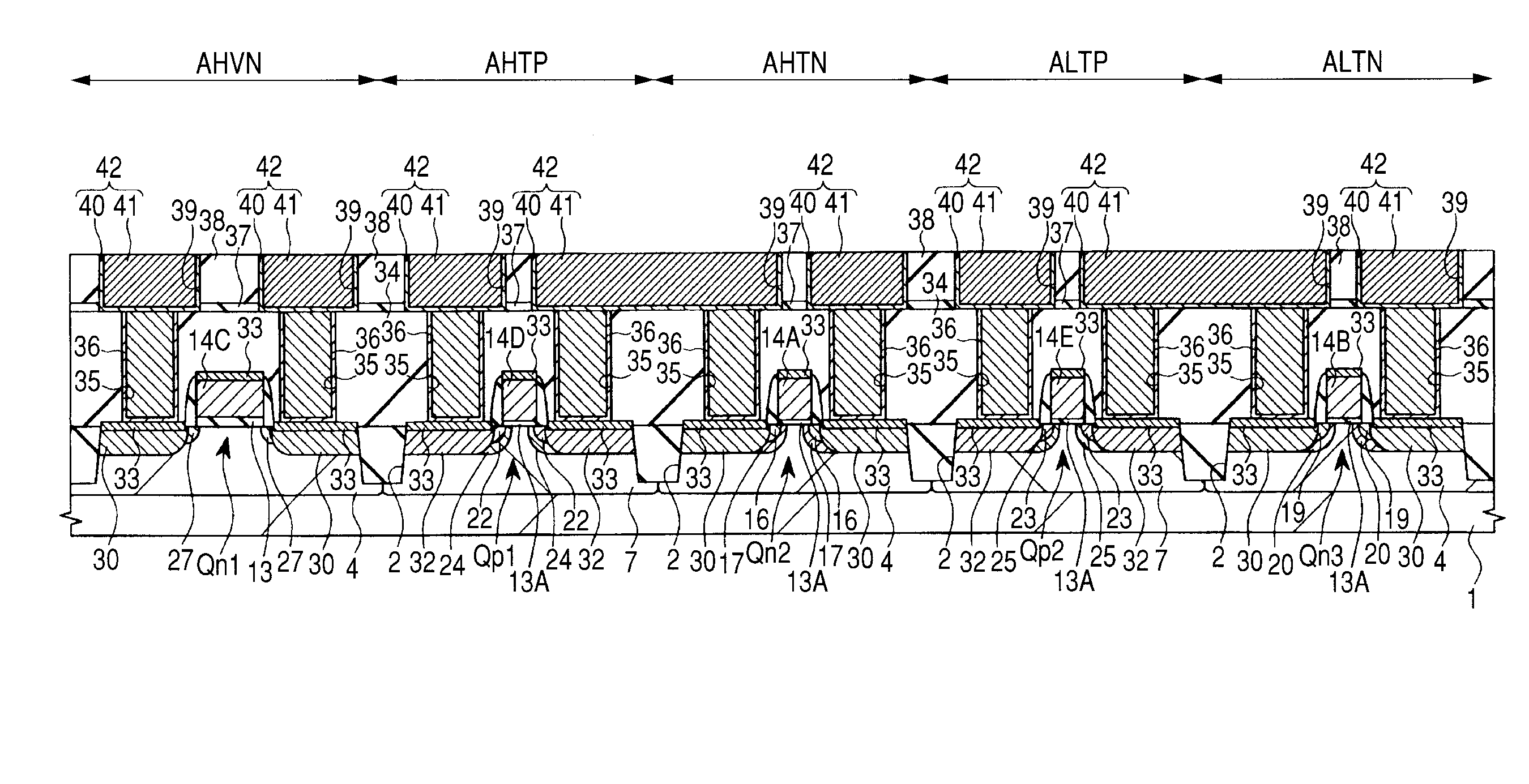

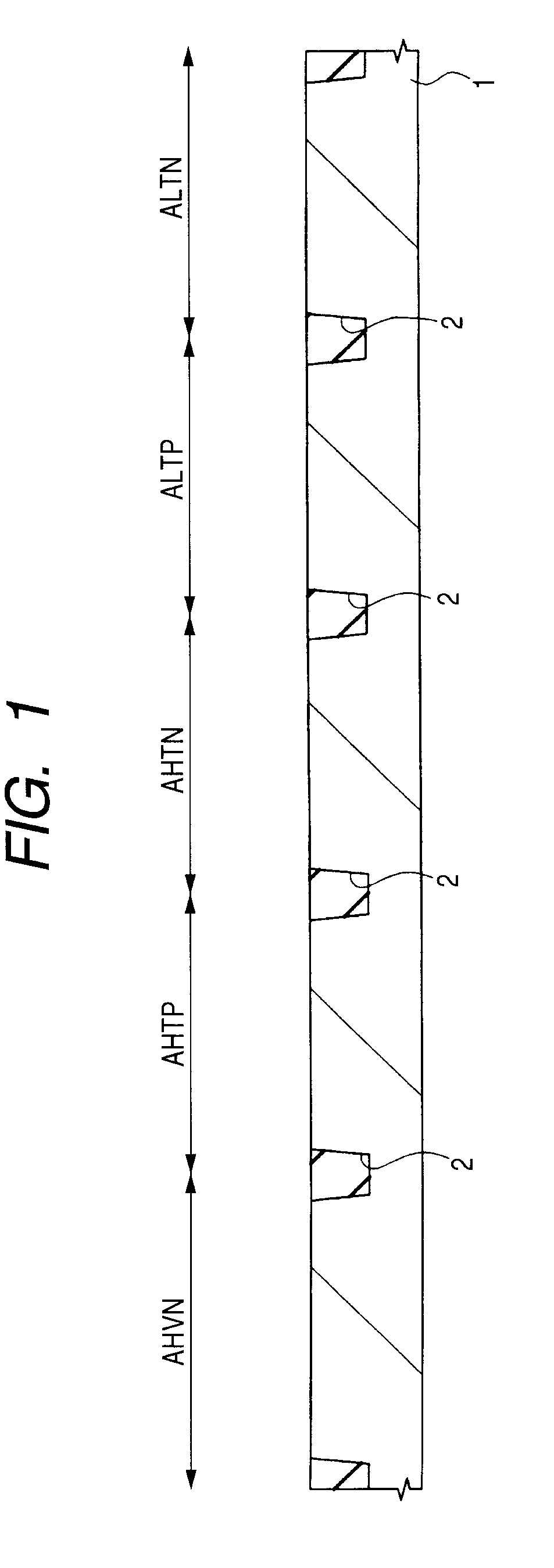

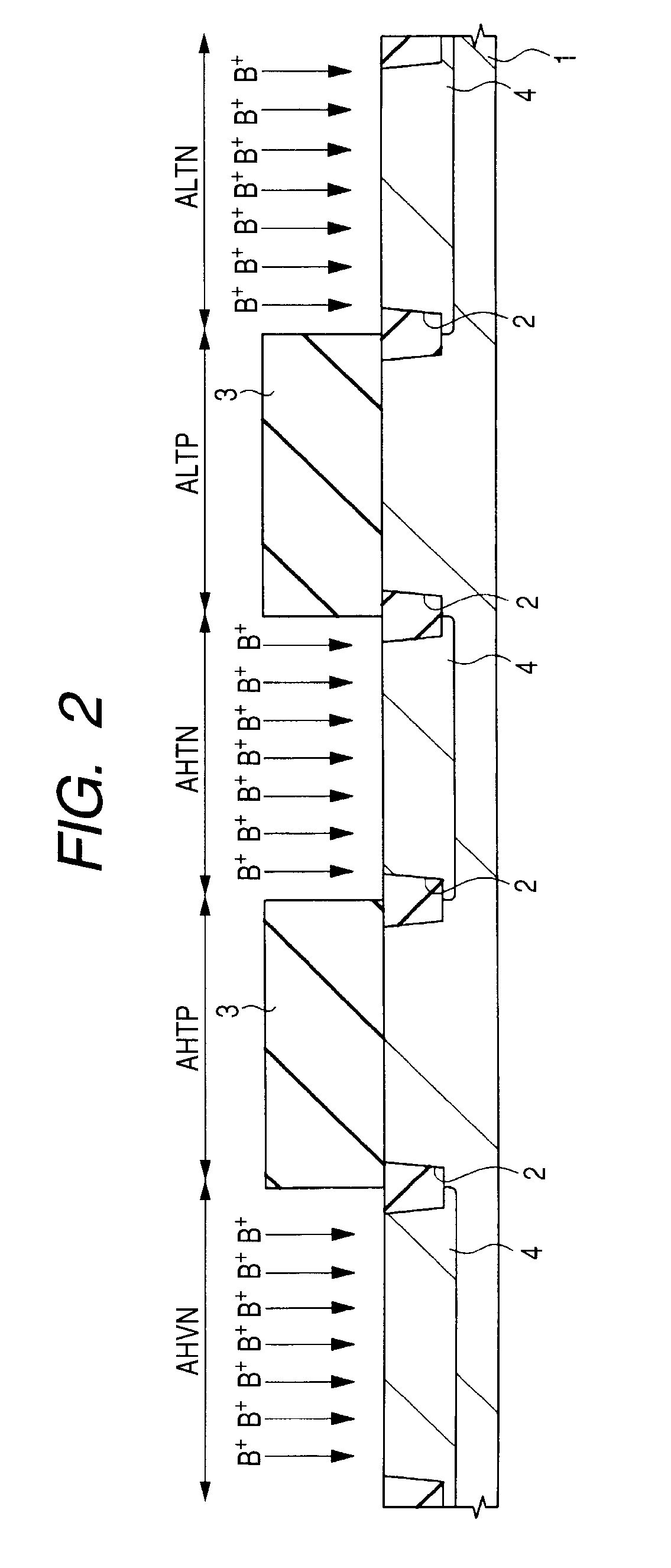

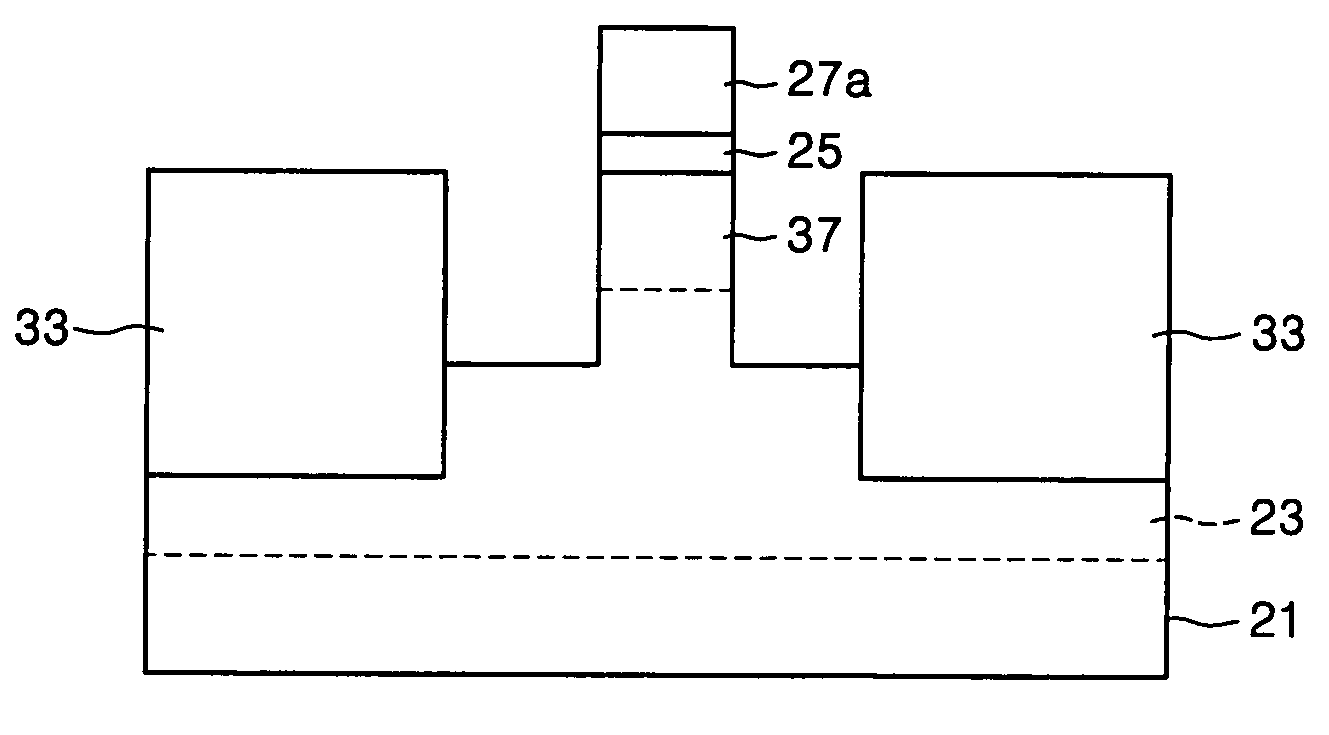

Method of manufacturing a semiconductor integrated circuit device

ActiveUS20080286928A1Avoid short channel effectsSuppress leakage currentSemiconductor/solid-state device manufacturingN channelIntegrated circuit

In the chip with which a plurality of MISFET from which threshold value voltage differs is intermingled, leakage current, such as GIDL current and BTBT current, is suppressed, inhibiting the short channel effect of MISFET. The concentration of the impurity for threshold value voltage adjustment implanted to the region in which n channel type MISFET with relatively low threshold value voltage is formed is made lower than the concentration of the impurity for threshold value voltage adjustment implanted to the region in which n channel type MISFET with relatively high threshold value voltage is formed. Implantation amount of the impurity at the time of forming n− type semiconductor region 19 and punch-through stopper layer 20 in region ALTN is made larger than the implantation amount of the impurity at the time of forming n− type semiconductor region 16 and punch-through stopper layer 17 in region AHTN, respectively.

Owner:RENESAS ELECTRONICS CORP

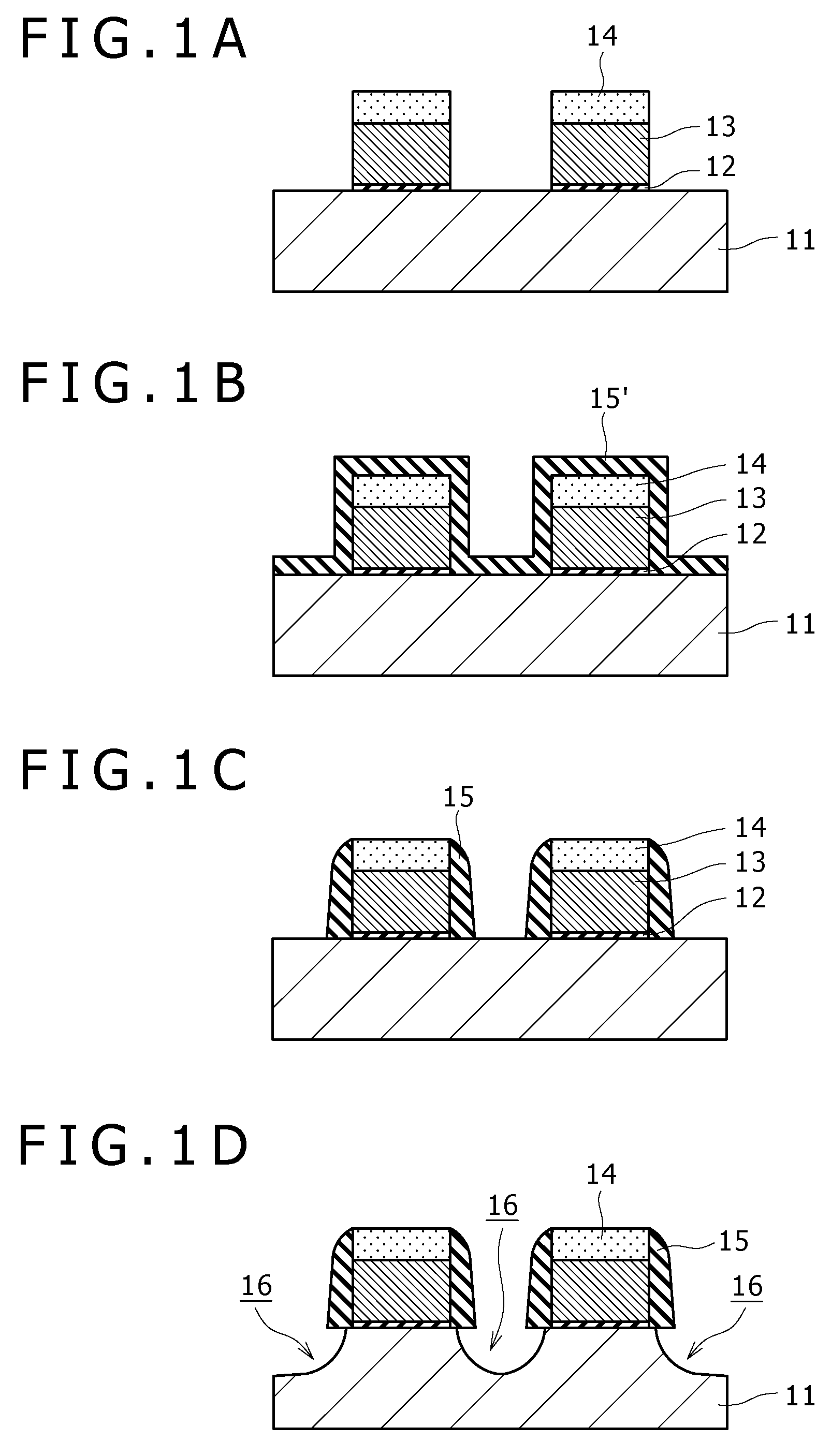

Method of fabricating fin field effect transistor using isotropic etching technique

ActiveUS7153733B2Avoid short channel effectsEasy to integrateTransistorSemiconductor/solid-state device manufacturingEngineeringPhotolithography

Methods of fabricating a fin field effect transistor (FinFET) are disclosed. Embodiments of the invention provide methods of fabricating FinFETs by optimizing a method for forming the fin so that a short channel effect is prevented and high integration is achieved. Accordingly, the fin which has a difficulty in its formation using the current photolithography-etching technique may be readily formed.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for fabricating semiconductor device with vertical channel transistor

ActiveUS7670909B2Avoid short channel effectsIncrease channel lengthSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerEngineering

A method for fabricating a semiconductor memory device with a vertical channel transistor includes forming a plurality of pillars each having a hard mask pattern thereon over a substrate, each of the plurality of pillars comprising an upper pillar and a lower pillar; forming a surround type gate electrode surrounding the lower pillar; forming an insulation layer filling a space between the pillars; forming a preliminary trench by primarily etching the insulation layer using a mask pattern for a word line until a portion of the upper pillar is exposed; forming a buffer layer over a resultant structure including the preliminary trench except on a bottom of the preliminary trench; and forming a trench for a word line by secondarily etching the insulation layer until the surround type gate electrode is exposed.

Owner:SK HYNIX INC

Semiconductor memory having two charge storage sections

InactiveUS7095077B2MiniaturizationEffectively restrained from interfering with each otherTransistorSolid-state devicesMiniaturizationElectric current flow

A semiconductor memory includes: a p-type semiconductor (p-type semiconductor film on a substrate, a p-type well region in a semiconductor substrate, or an insulator); a gate insulating film formed on the p-type semiconductor; a gate electrode formed on the gate insulating film; two charge storage sections formed on side walls of the gate electrode; a channel region provided below the gate electrode; and a first n-type diffusion layer region and a second n-type diffusion layer region provided to sides of the channel region, wherein: the charge storage sections are arranged to change an electric current flow between the first n-type diffusion layer region and the second n-type diffusion layer region under application of a voltage to the gate electrode according to the quantity of electric charges stored in the charge storage sections; and the first n-type diffusion layer region is set to a reference voltage, the other n-type diffusion layer region is set to a voltage greater than the reference voltage, and the gate electrode is set to a voltage greater than the reference voltage. Thus, the semiconductor memory obtained is capable of 2 bit operation and easy to miniaturize.

Owner:SHARP KK

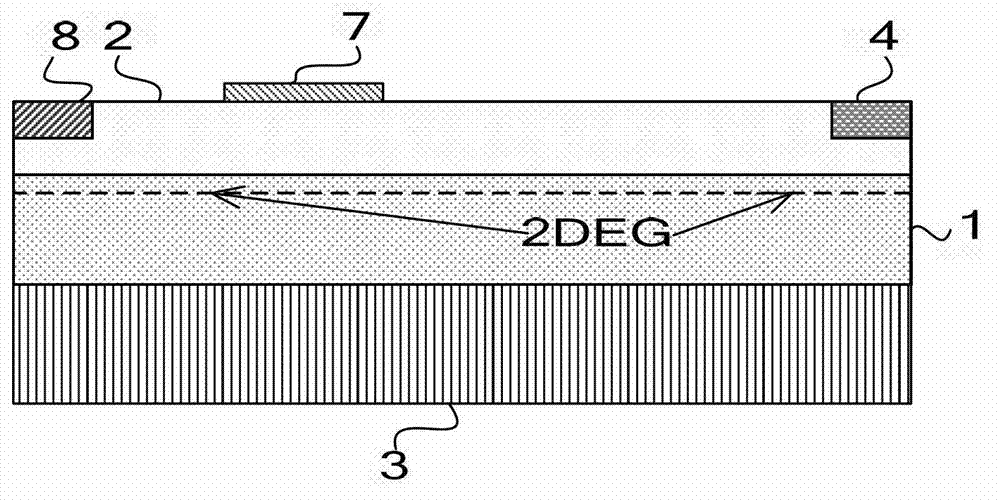

Field-induced tunneling enhanced HEMT (high electron mobility transistor) device

InactiveCN102881716AGood positive characteristicsImprove pressure resistanceSemiconductor devicesSchottky barrierElectron

The invention belongs to the technical field of semiconductor devices, and particularly relates to a field-induced tunneling enhanced HEMT (high electron mobility transistor) device. The field-induced tunneling enhanced HEMT device is different from conventional AlGaN / GaN HEMT devices in that metal sources are in Schottky barrier contact instead of ohm contact in conventional structures; and metal gates are not positioned between the sources and drains but form insulating gate electrodes at the edges, away from the drains, of the sources through etching grooves. Field-control conductive channels are realized by means of the insulating layer and groove technology, field control of the field-control conductive channels is realized by voltage applied to the groove gate electrodes, and electrons subjected to band bending can directly tunnel barriers to be accumulated below the channels in gate modulation when forward voltage is applied to the gate electrodes, so that normally closed channels are realized, and frequency characteristics of the device can be promoted without affecting reverse voltage withstand capability of the device. Meanwhile, the preparation process of the device is compatible to traditional processes, and thereby solid foundation is established for the GaN power integration technology.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Transistor and method of manufacturing the same

InactiveCN1738056AAvoid short channel effectsExcellent electrical propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringCrystal plane

The present invention provides a transistor and a manufacturing method of the transistor.A transistor of the present invention includes a semiconductor substrate that has a first surface of the {100} crystal plane, a second surface of the {100} crystal plane having a height lower than that of the first surface, and a side face of the {111} crystal plane connecting the first surface to the second surface. A gate structure is formed on the first surface. An epitaxial layer is formed on the second surface and the side face. Impurity regions are formed adjacent to both sides of the gate structure. The impurity regions have side faces of the {111} crystal plane so that a short channel effect generated between the impurity regions may be prevented.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor device, finfet transistor and fabrication method thereof

ActiveUS20160351591A1Improve cooling efficiencyAvoid short channel effectsSemiconductor/solid-state device detailsSolid-state devicesInsulation layerDevice material

The present disclosure provides semiconductor devices, fin field-effect transistors and fabrication methods thereof. An exemplary fin field-effect transistor includes a semiconductor substrate; an insulation layer configured for inhibiting a short channel effect and increasing a heat dissipation efficiency of the fin field-effect transistor formed over the semiconductor substrate; at least one fin formed over the insulation layer; a gate structure crossing over at least one fin and covering top and side surfaces of the fin formed over the semiconductor substrate; and a source formed in the fin at one side of the gate structure and a drain formed in the fin at the other side of the gate structure.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com