Method for manufacturing semiconductor device layer

A semiconductor and device layer technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as lattice voids, oxygen-enhanced diffusion, and high concentration of short-channel dopants, and achieve improved performance. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

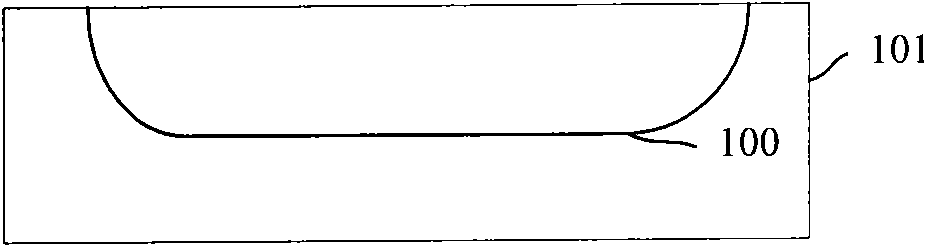

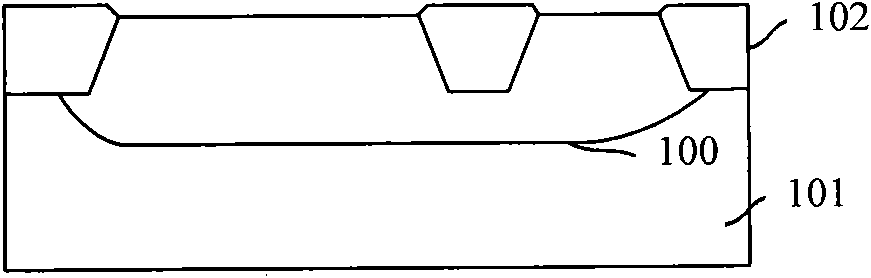

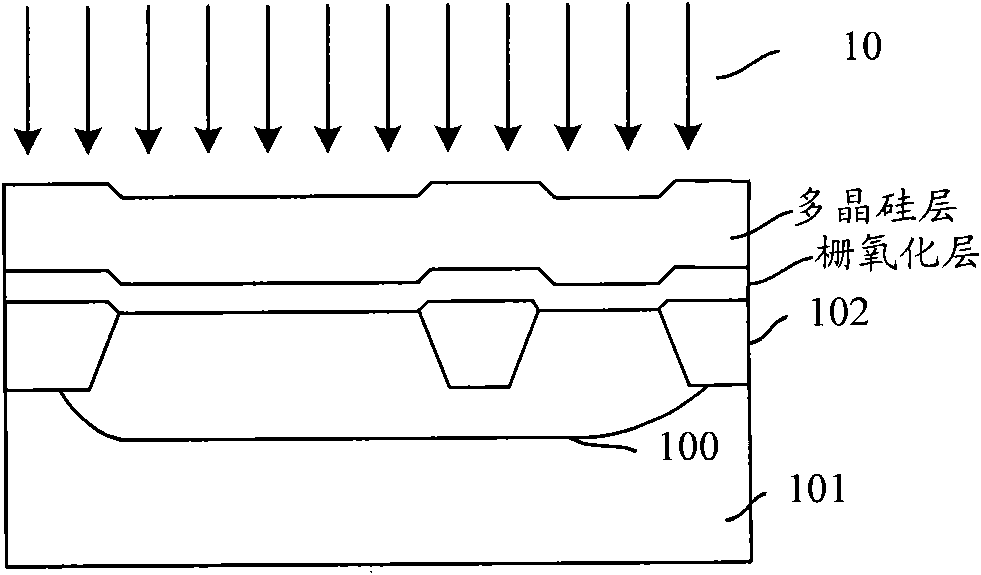

[0042] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below with reference to the accompanying drawings and examples.

[0043]In the prior art, the TED phenomenon during light doping to form a shallow junction is the main cause of SCE and RSCE in the short channel of the semiconductor device, thereby reducing the performance of the final manufactured semiconductor device. To solve this problem, there are three ways. Among them, one way is: reducing the energy of ion implantation or / and reducing the concentration of shallow doping impurities. However, this is at the expense of reducing the performance of the final semiconductor device, and is generally not used; the second method is: during ion implantation in the process of light doping to form a shallow junction, lightly doped impurities and carbon are ion implanted together , so that carbon can fill the gaps between t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com