Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

113 results about "Copper damascene" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

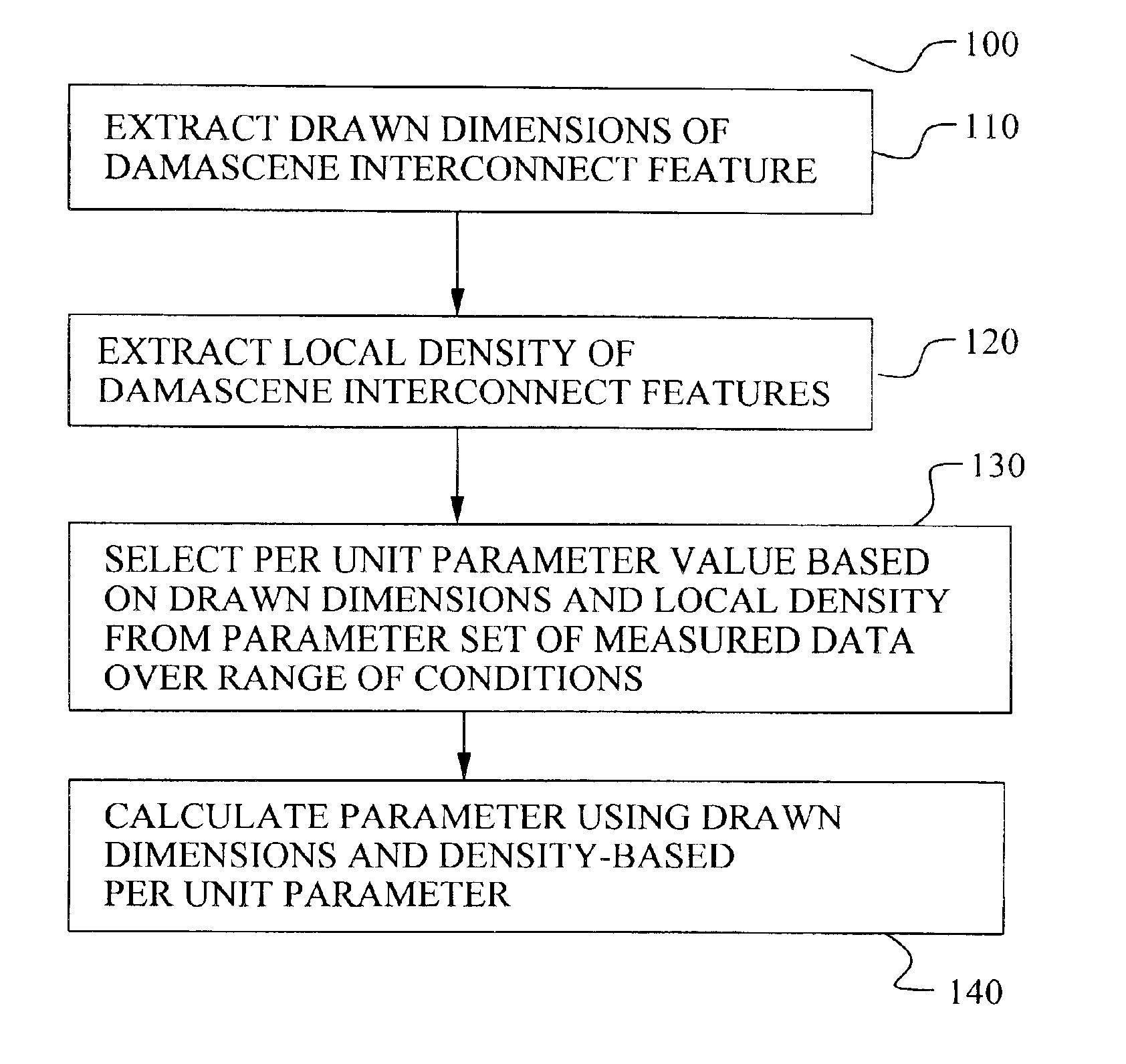

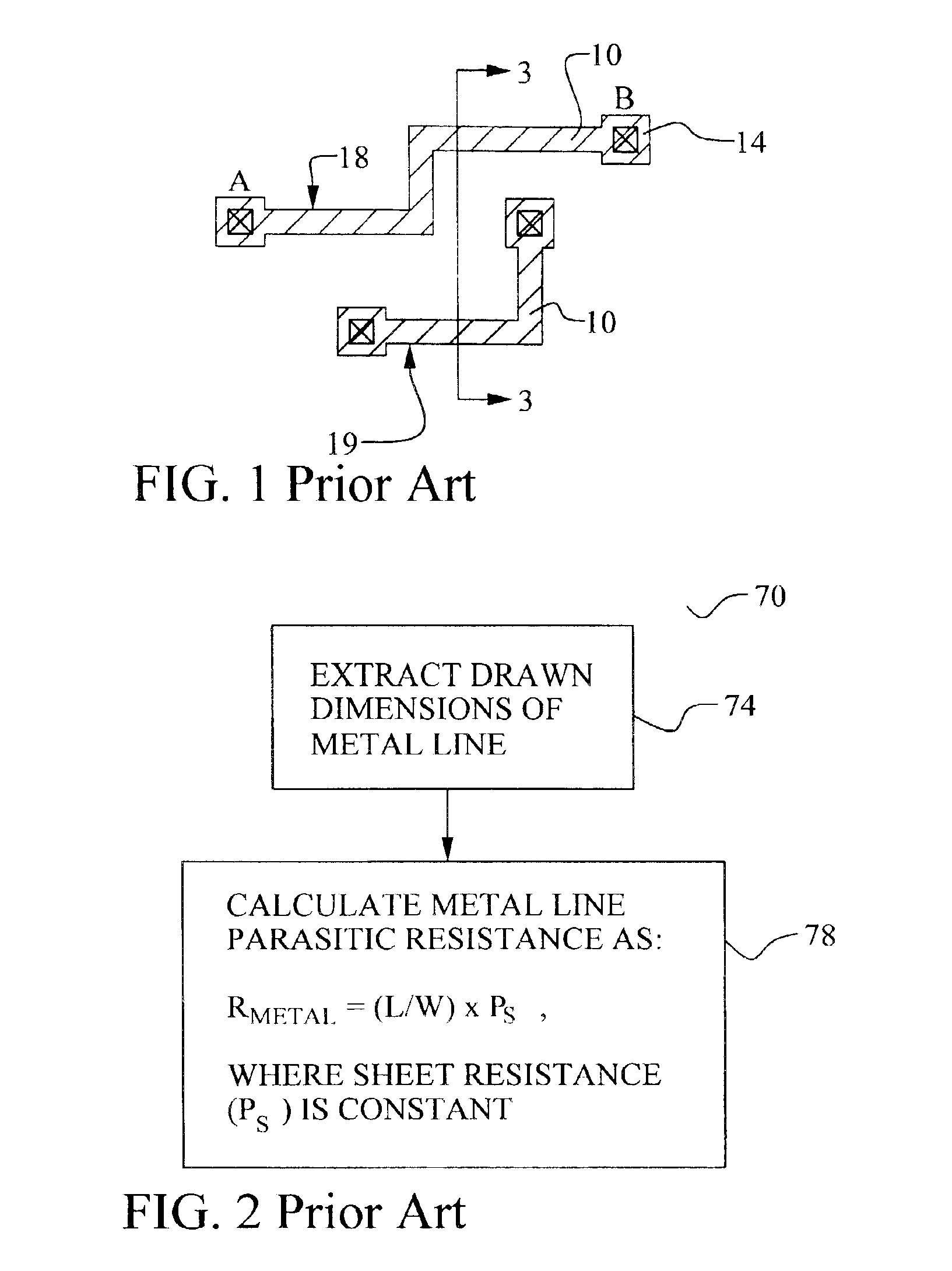

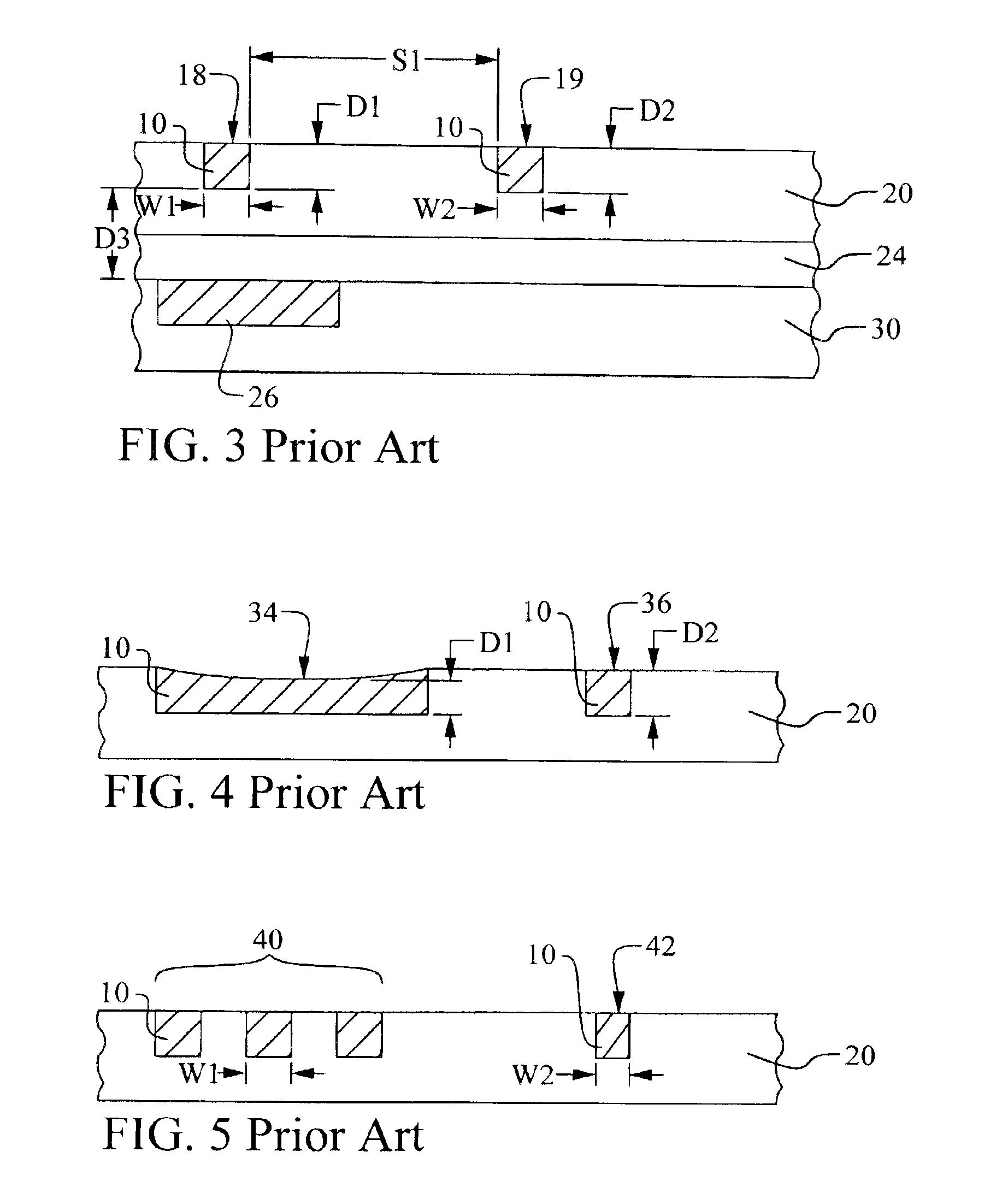

Methodology to characterize metal sheet resistance of copper damascene process

InactiveUS6854100B1Efficiently determinedSemiconductor/solid-state device testing/measurementDetecting faulty computer hardwareCopper damasceneIntegrated circuit

A new method to determine a parameter of a damascene interconnect in an integrated circuit device is achieved. Drawn dimensions and local pattern density of a damascene interconnect are extracted in an integrated circuit device. A parameter of the damascene interconnect is calculating using the drawn dimensions and the local pattern density to select a per unit value from a set of per unit values measured over a range of drawn dimension and pattern density combinations. The method may be used to improve the accuracy of extracted damascene metal line resistance and parasitic capacitance.

Owner:TAIWAN SEMICON MFG CO LTD

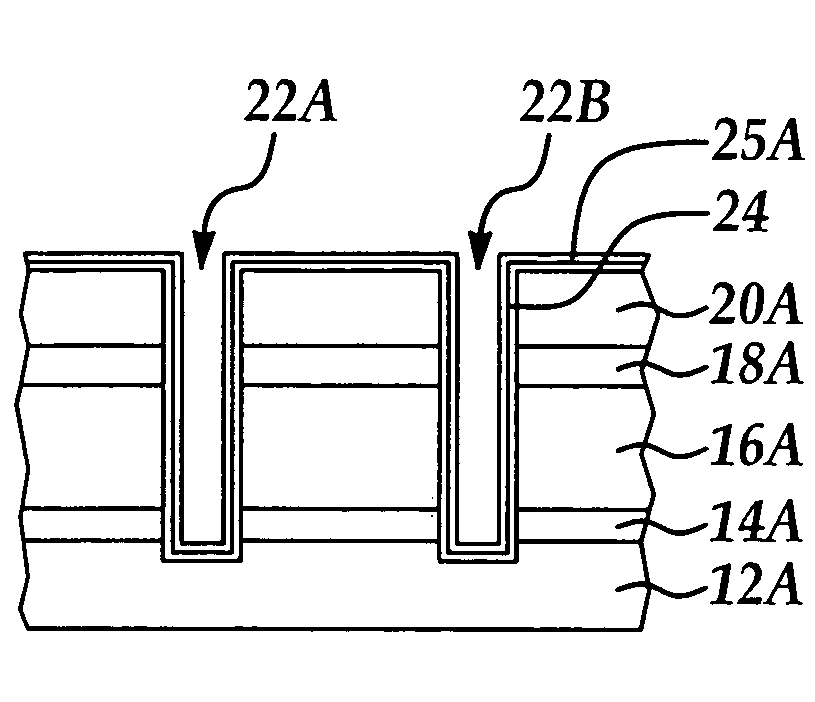

Copper damascene barrier and capping layer

InactiveUS20060024954A1Improve electrical performanceSemiconductor/solid-state device manufacturingAnti-reflective coatingEngineering

A method for forming a damascene with improved electrical properties and resulting structure thereof including providing at least one dielectric insulating layer overlying a first etch stop layer; forming an anti-reflectance coating (ARC) layer prior to a photolithographic patterning process; forming at least one opening extending through a thickness portion of the at least one dielectric insulating layer and first etch stop layer according to said photolithographic patterning and an etching process; blanket depositing a barrier layer including material selected from the group consisting of silicon carbide and silicon oxycarbide to line the at least one opening; blanket depositing a refractory metal liner over the barrier layer; blanket depositing at least one metal layer to fill the at least one opening; and, removing at least the at least one metal layer overlying the at least one opening level according to a chemical mechanical polish (CMP) process.

Owner:WU ZHEN CHENG +3

Metal-insulator-metal capacitor for copper damascene process and method of forming the same

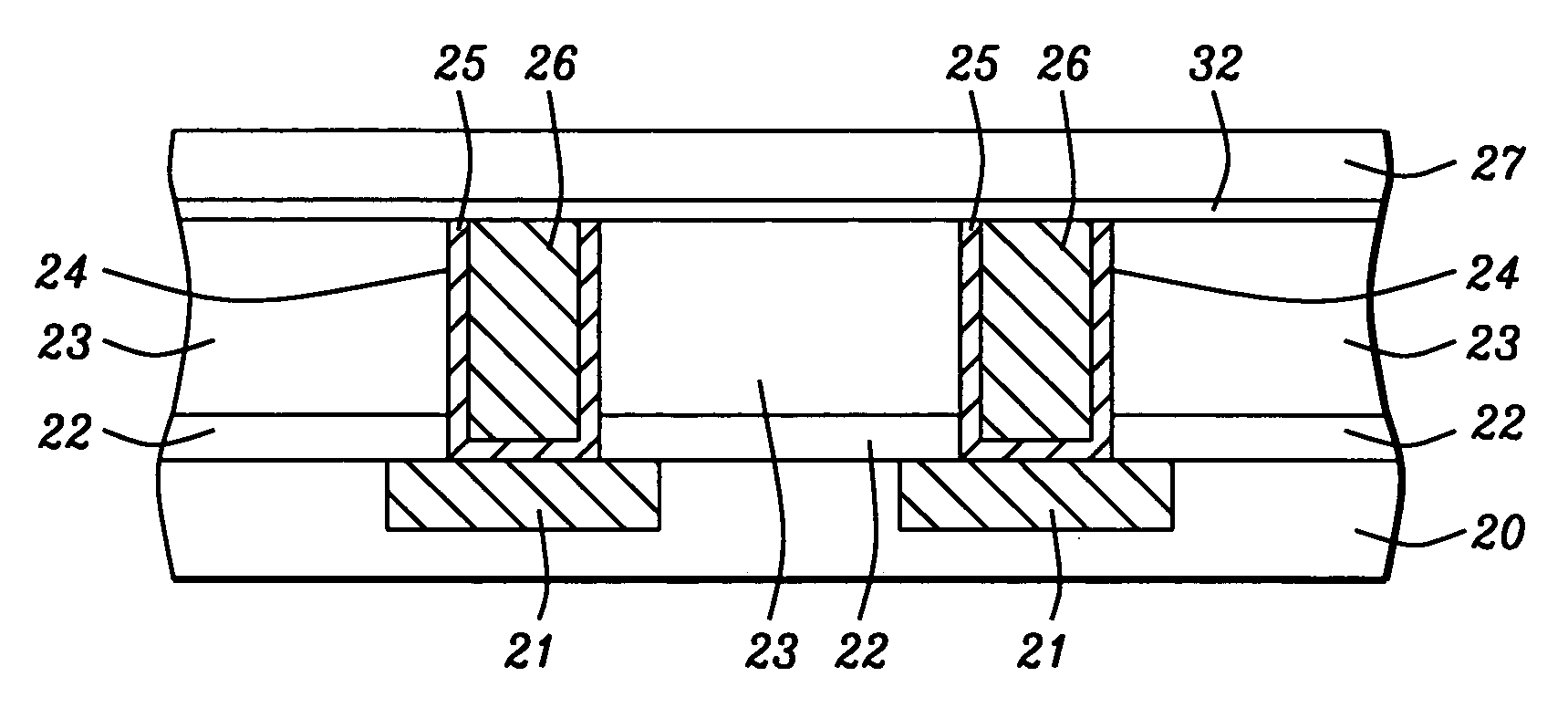

A capacitor structure formed on a semiconductor substrate may include a first interconnect wiring (such as copper damascene) and a first conductive barrier layer in contact with the first interconnect wiring. A first capacitor plate, a capacitor dielectric structure and a second capacitor plate may also be included over the first conductive barrier layer. A second conductive barrier layer may be formed on the second capacitor plate and a second planar insulating structure may be formed over the second capacitor plate. Finally, a second interconnect wiring may be embedded within a second planar insulator structure.

Owner:IBM CORP

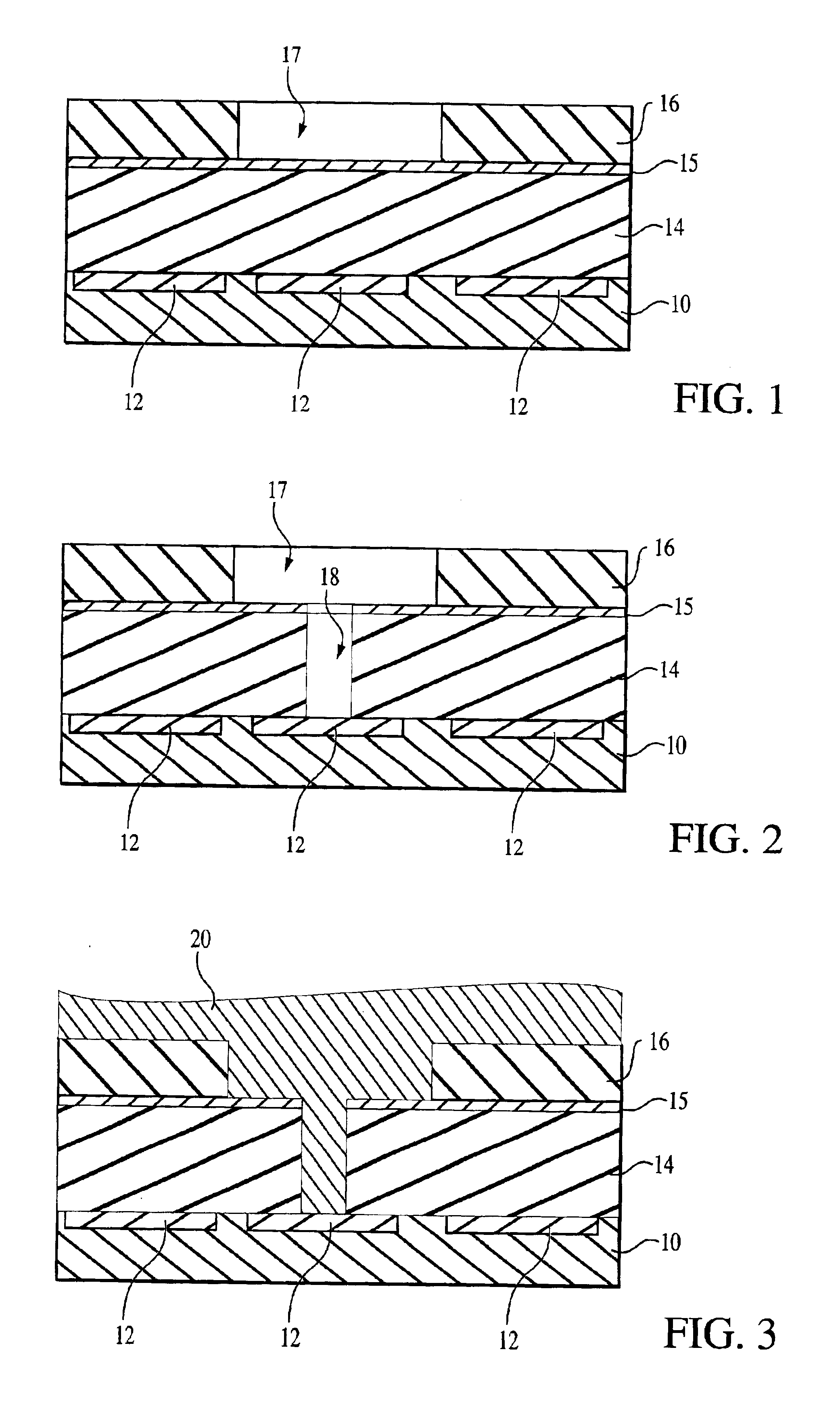

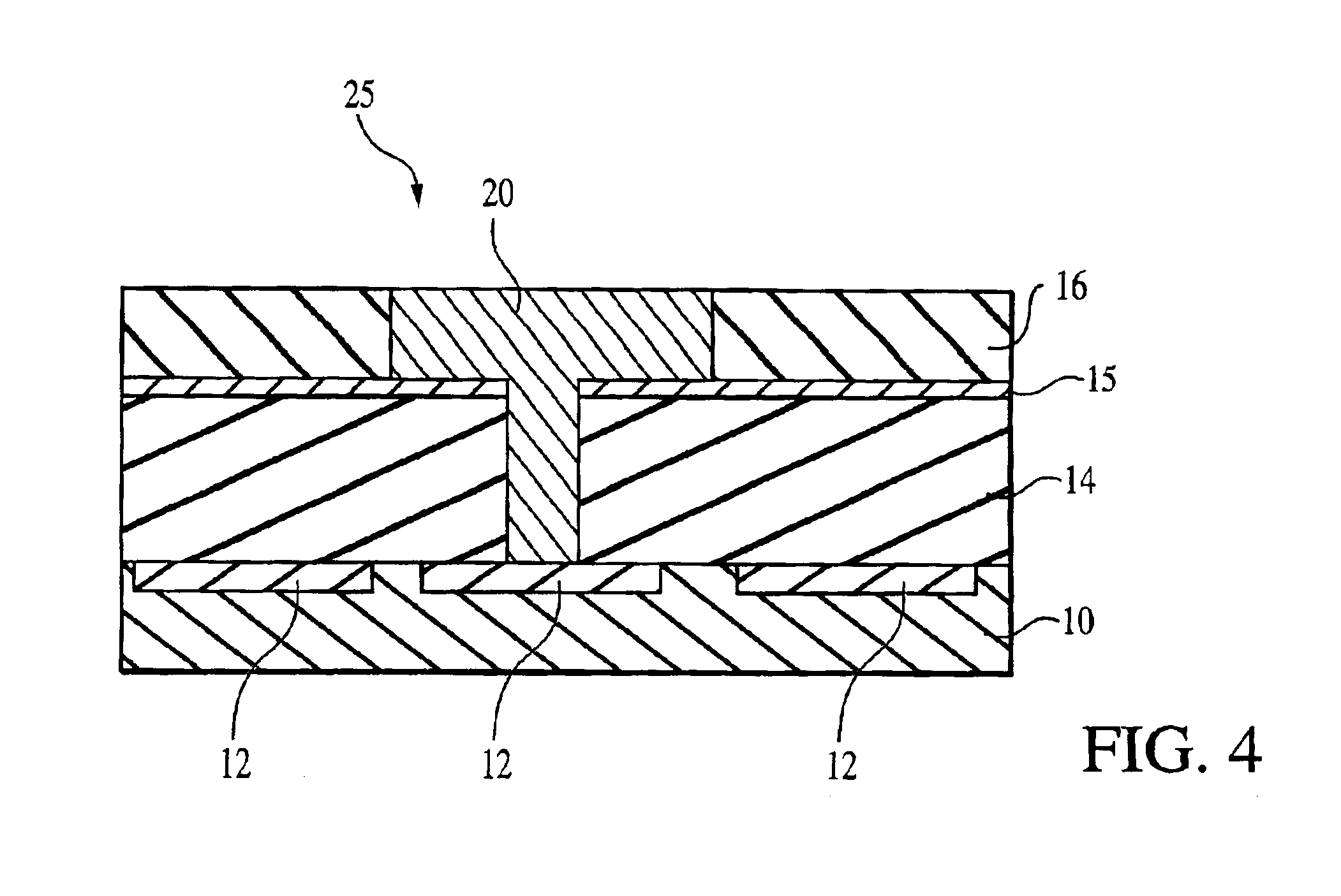

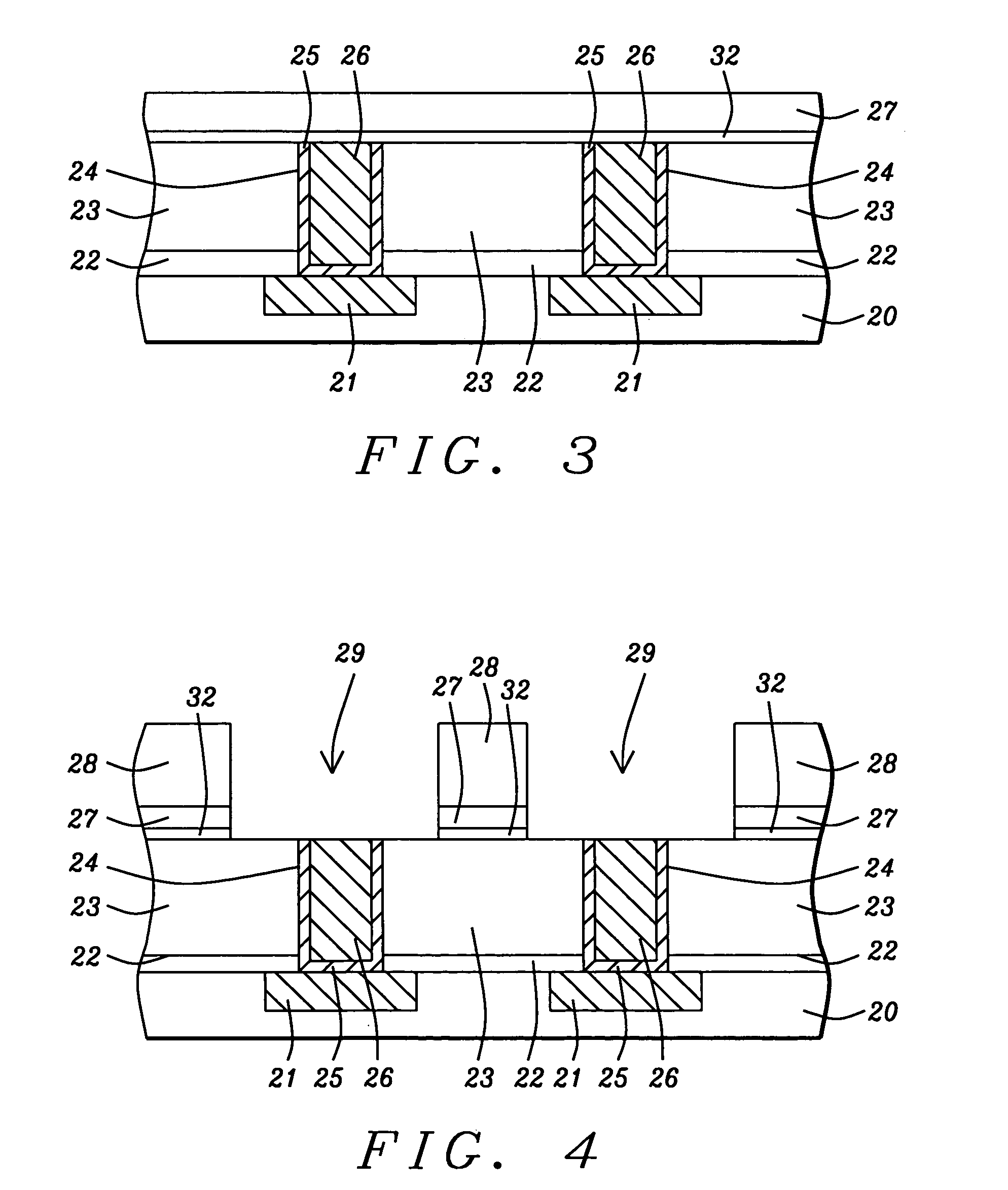

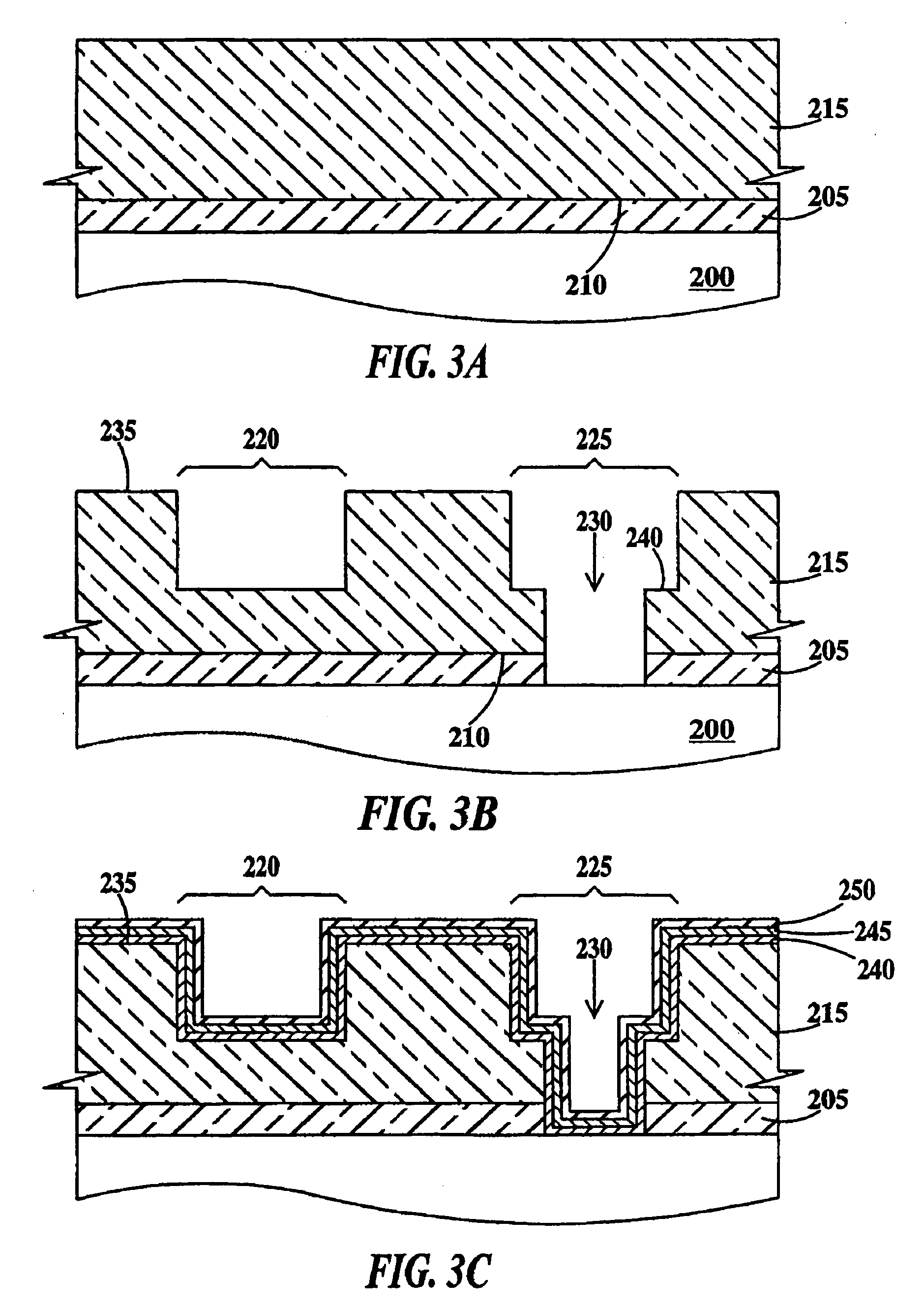

Method and structure for creating ultra low resistance damascene copper wiring

InactiveUS6987059B1Lower resistanceSimple and available process techniqueSemiconductor/solid-state device manufacturingDielectricCopper-wiring

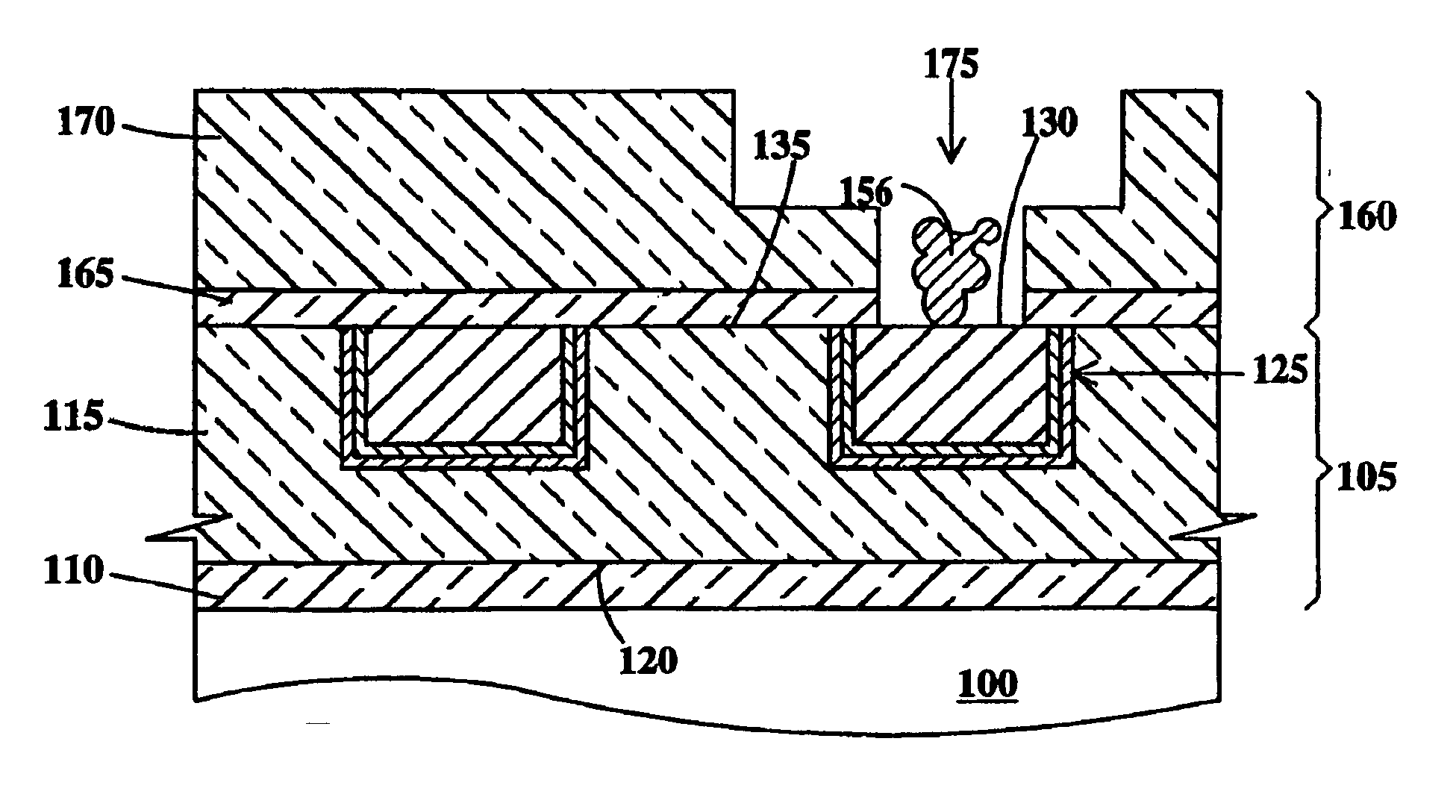

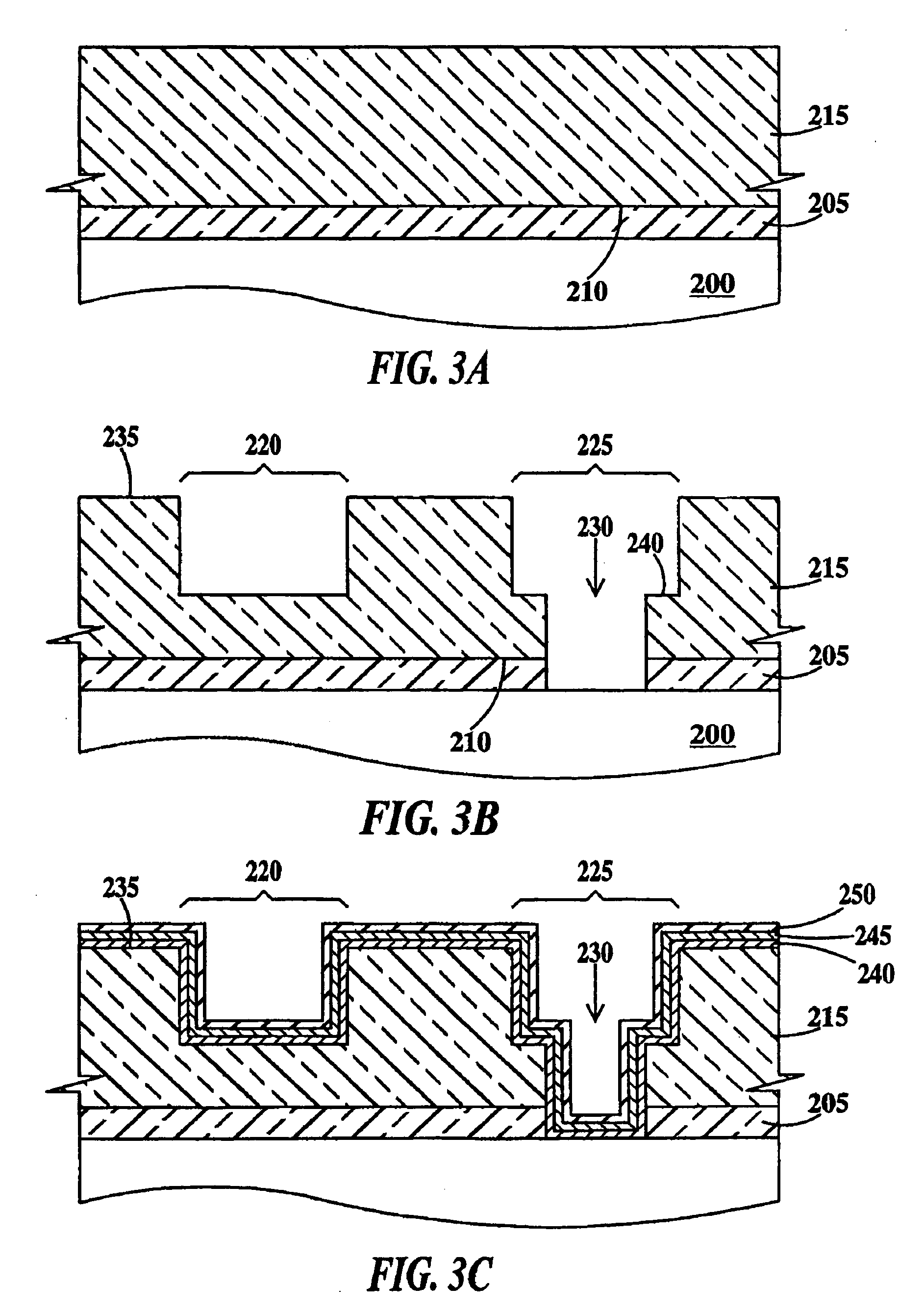

A low resistance copper damascene interconnect structure is formed by providing a thin dielectric film such as SiC or SiOC formed on the sidewalls of the via and trench structures to function as a copper diffusion barrier layer. The dielectric copper diffusion barrier formed on the bottom of the trench structure is removed by anisotropic etching to expose patterned metal areas. The residual dielectric thus forms a dielectric diffusion barrier film on the sidewalls of the structure, and coupled with the metal diffusion barrier subsequently formed in the trench, creates a copper diffusion barrier to protect the bulk dielectric from copper leakage.

Owner:BELL SEMICON LLC

Copper technology for ULSI metallization

InactiveUS6919266B2Reduce diffuseFew process stepsSemiconductor/solid-state device detailsSolid-state devicesTungsten nitrideElectroless deposition

A copper damascene structure formed by direct patterning of a low-dielectric constant material is disclosed. The copper damascene structure includes a tungsten nitride barrier layer formed by atomic layer deposition using sequential deposition reactions. Copper is selectively deposited by a CVD process and / or by an electroless deposition technique.

Owner:MICRON TECH INC

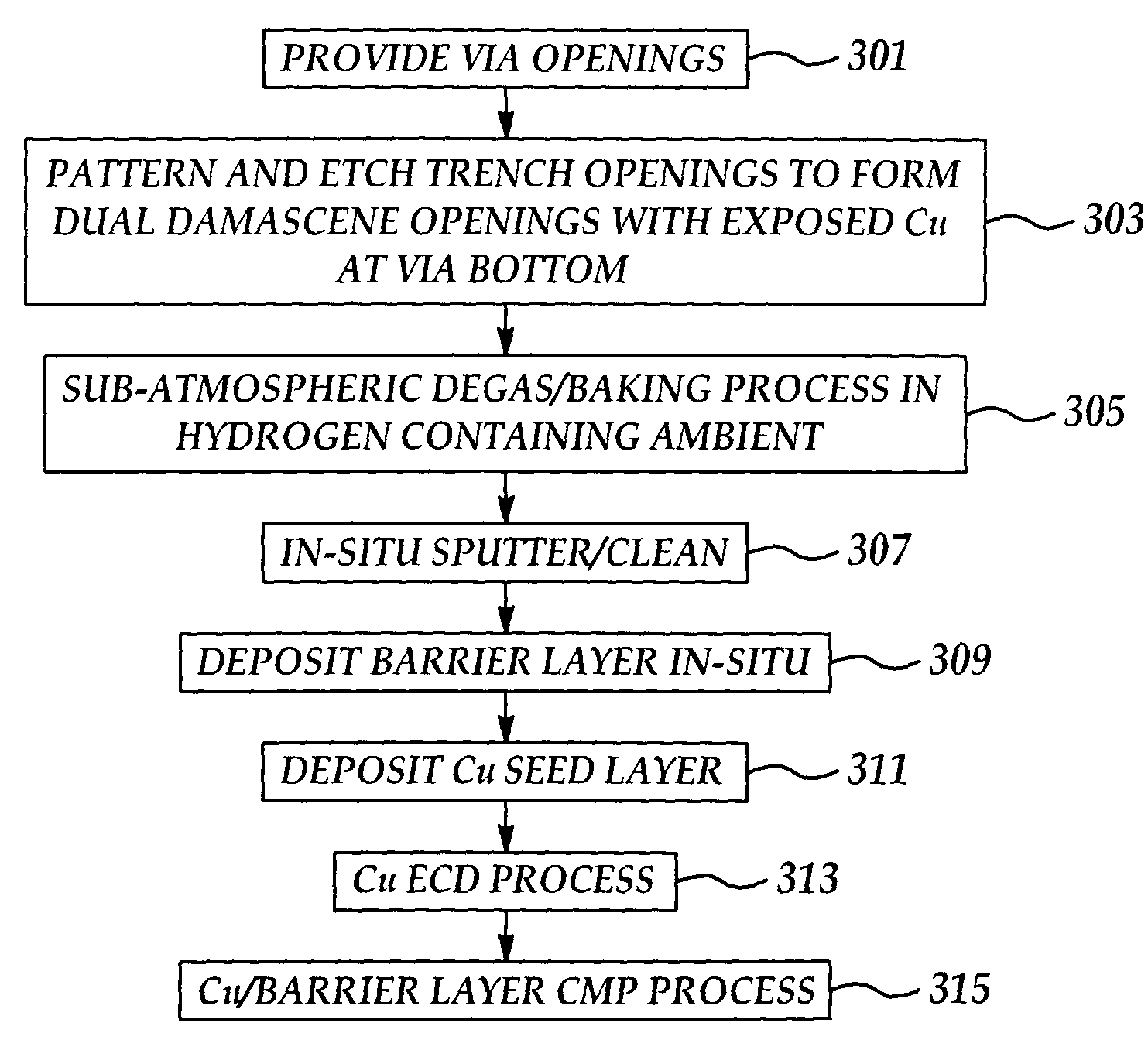

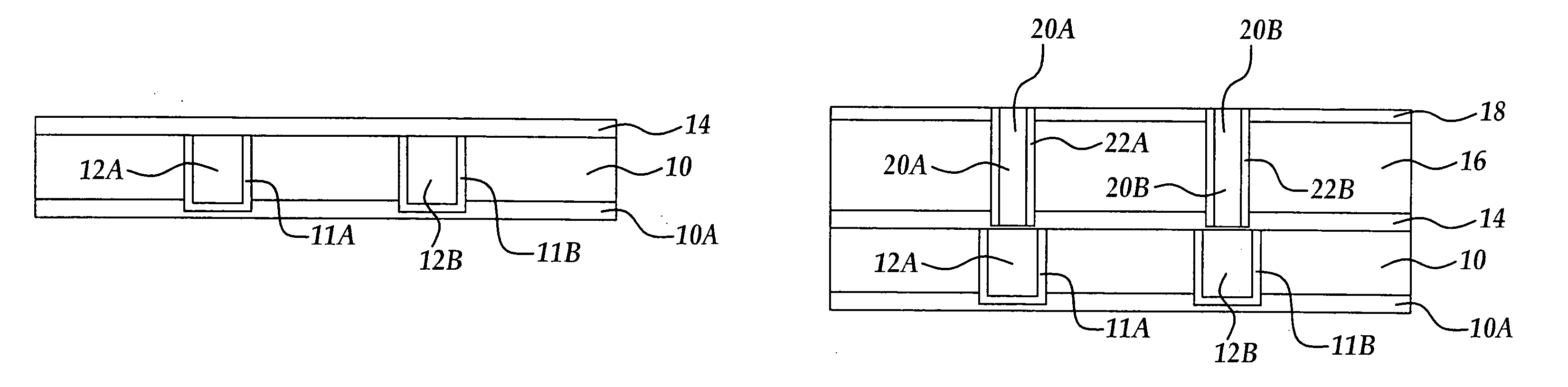

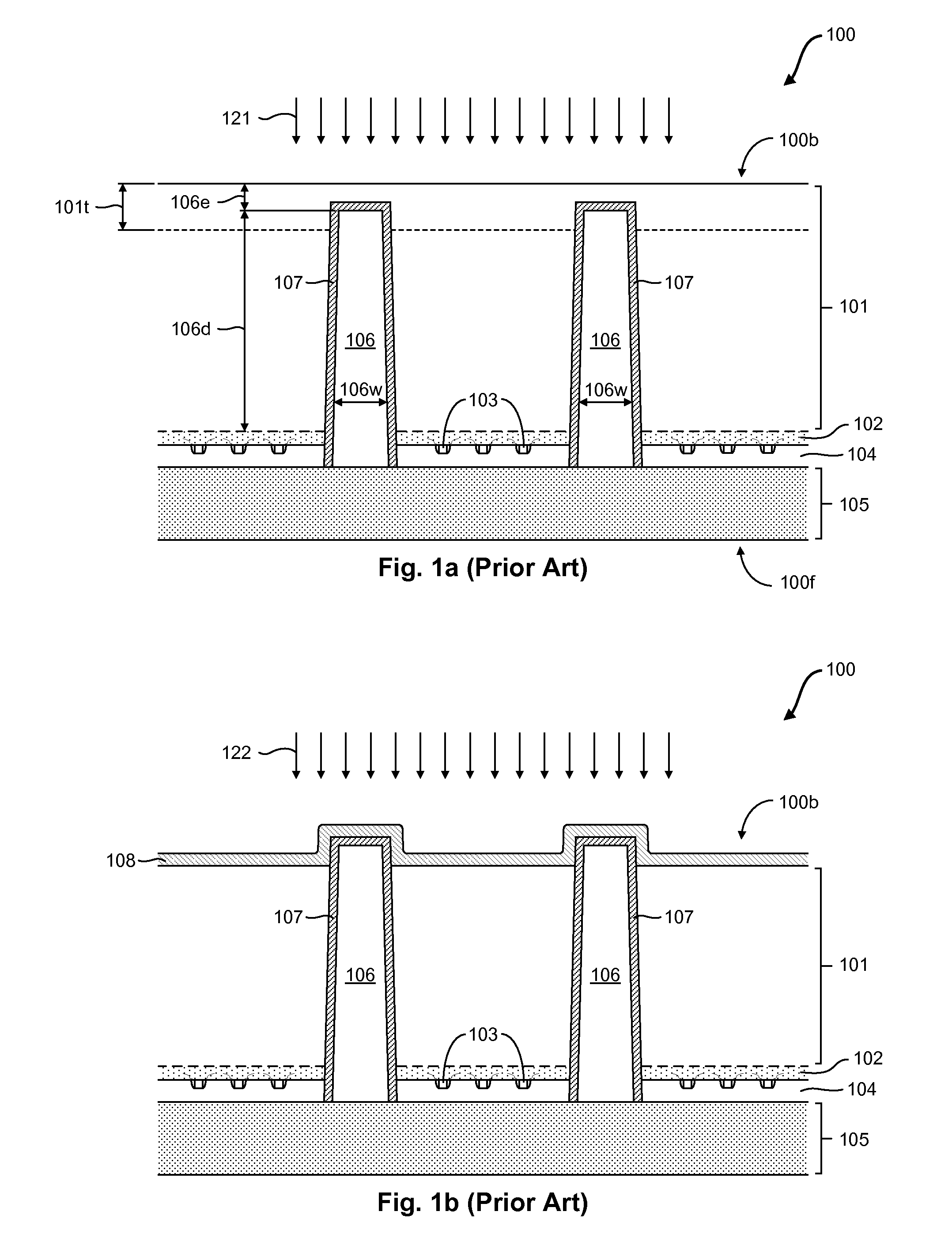

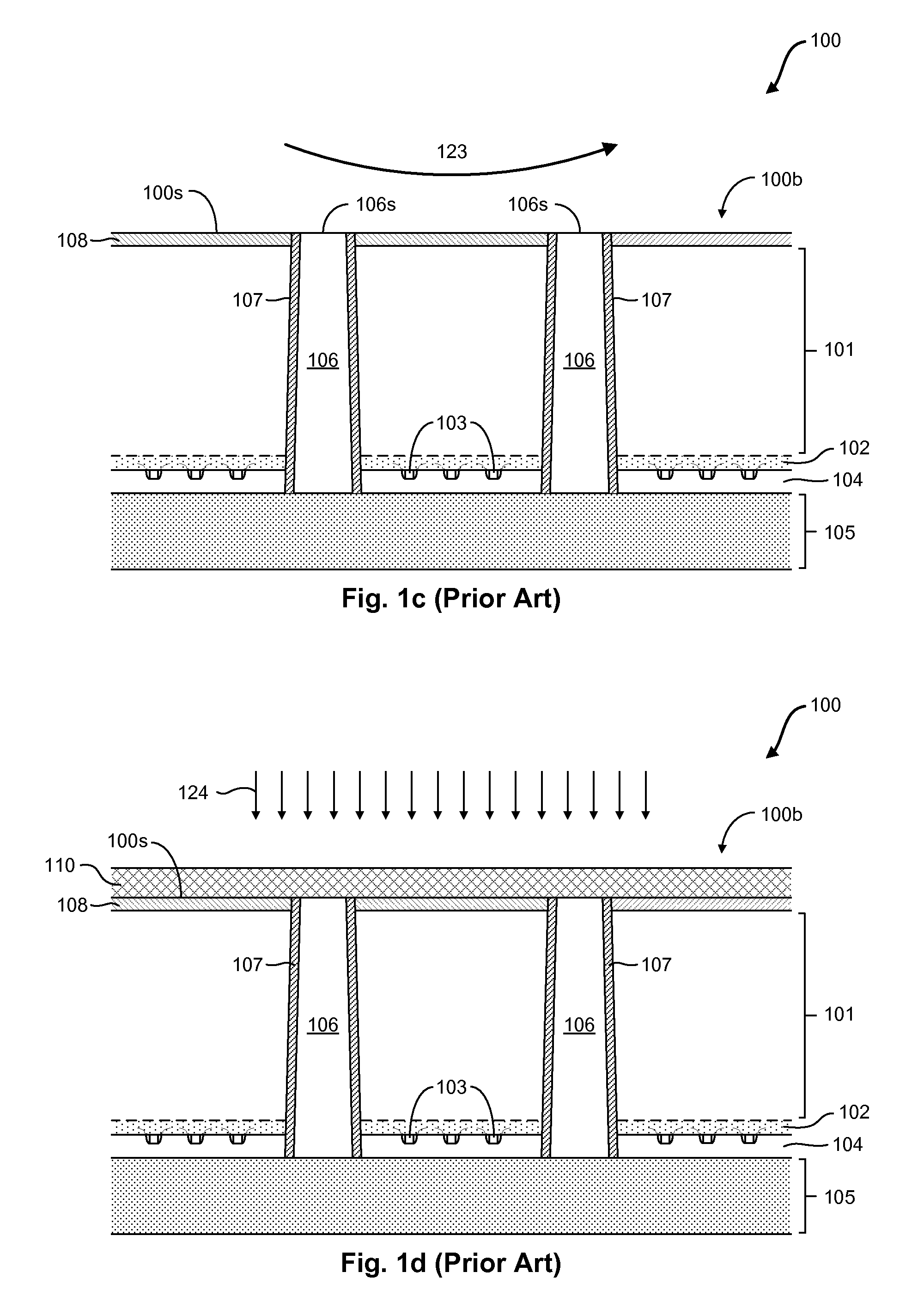

Method for simultaneous degas and baking in copper damascene process

A method for forming a copper damascene feature including providing a semiconductor process wafer including at least one via opening formed to extend through a thickness of at least one dielectric insulating layer and an overlying trench line opening encompassing the at least one via opening to form a dual damascene opening; etching through an etch stop layer at the at least one via opening bottom portion to expose an underlying copper area; carrying out a sub-atmospheric DEGAS process with simultaneous heating of the process wafer in a hydrogen containing ambient; carrying out an in-situ sputter-clean process; and, forming a barrier layer in-situ to line the dual damascene opening.

Owner:TAIWAN SEMICON MFG CO LTD

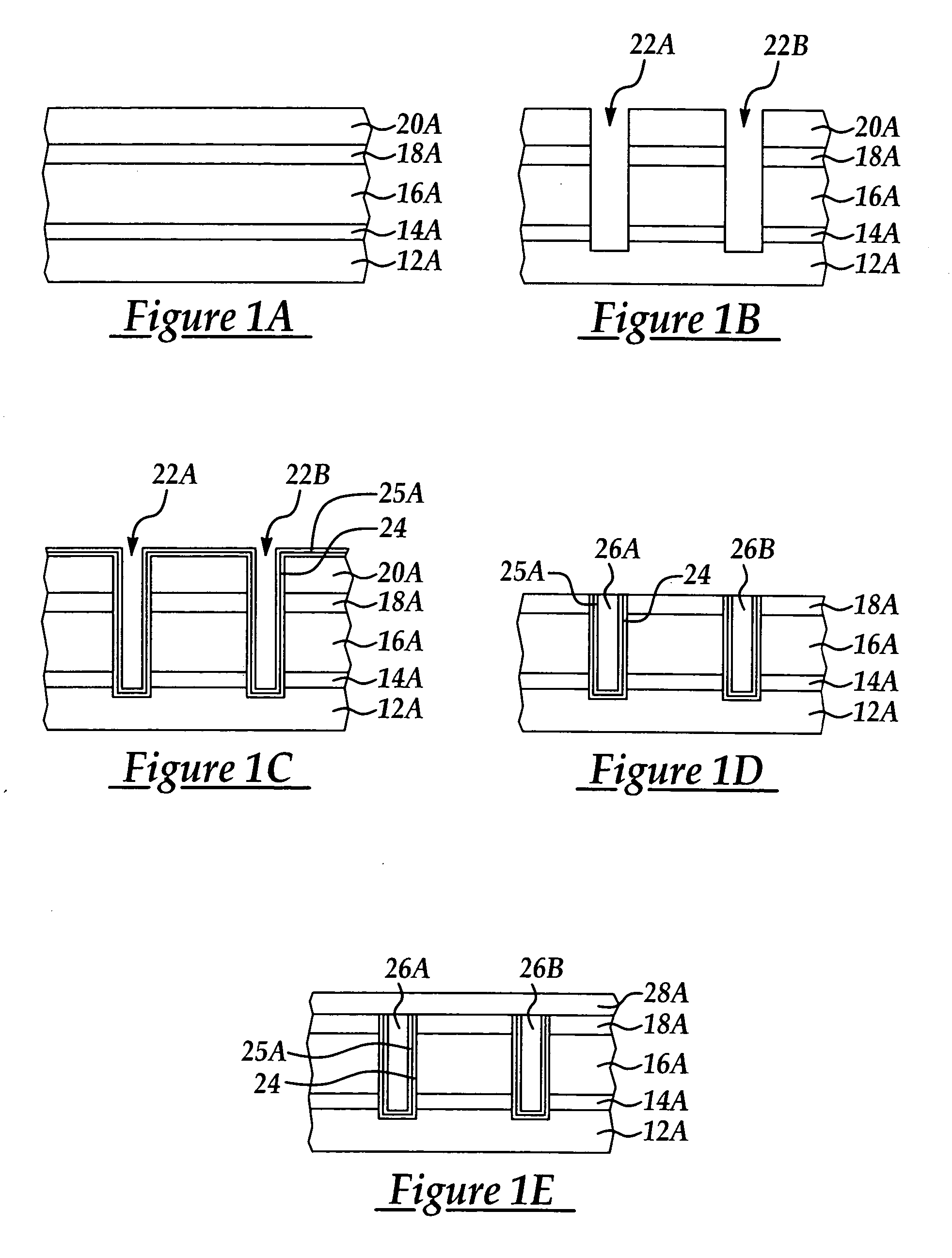

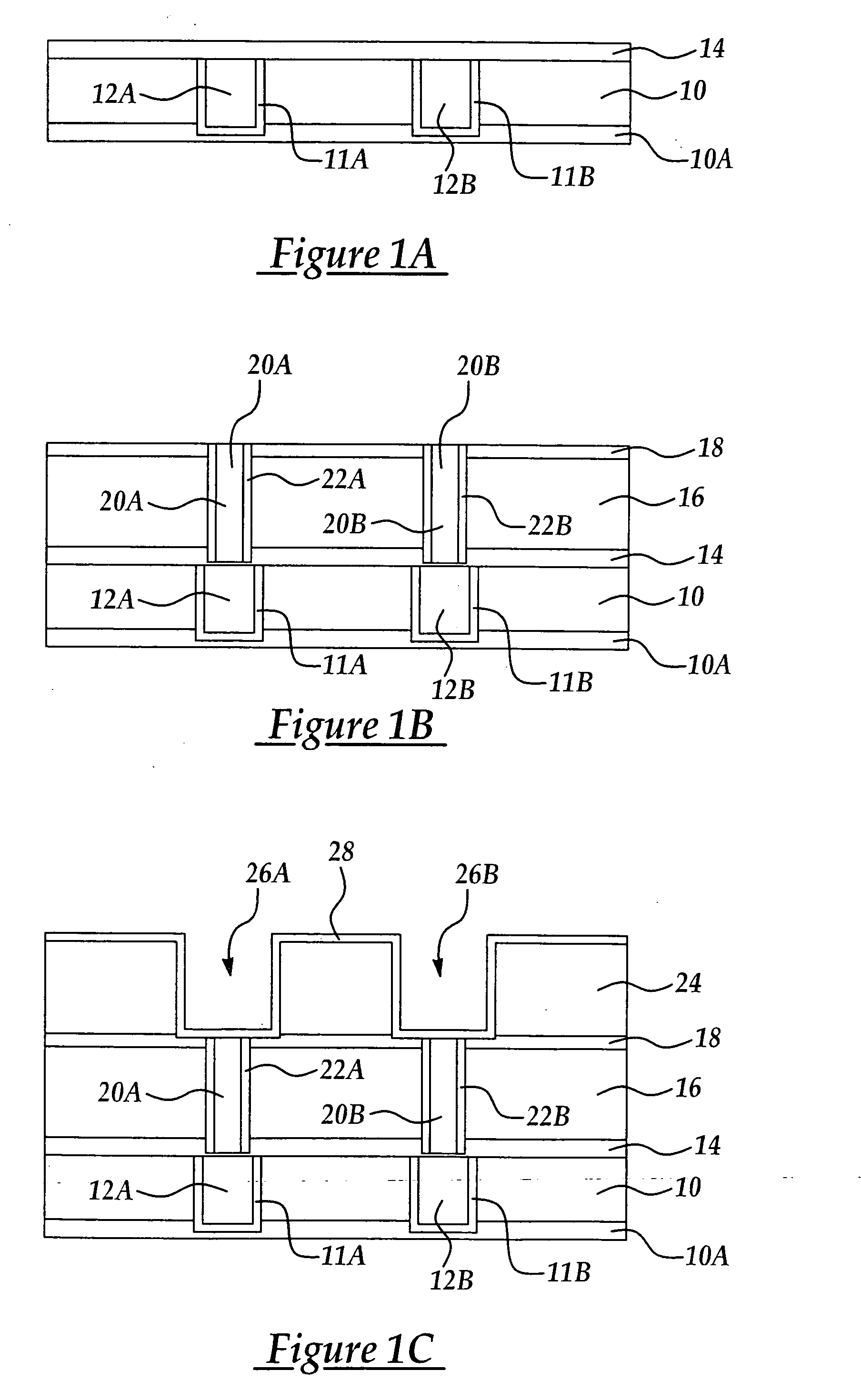

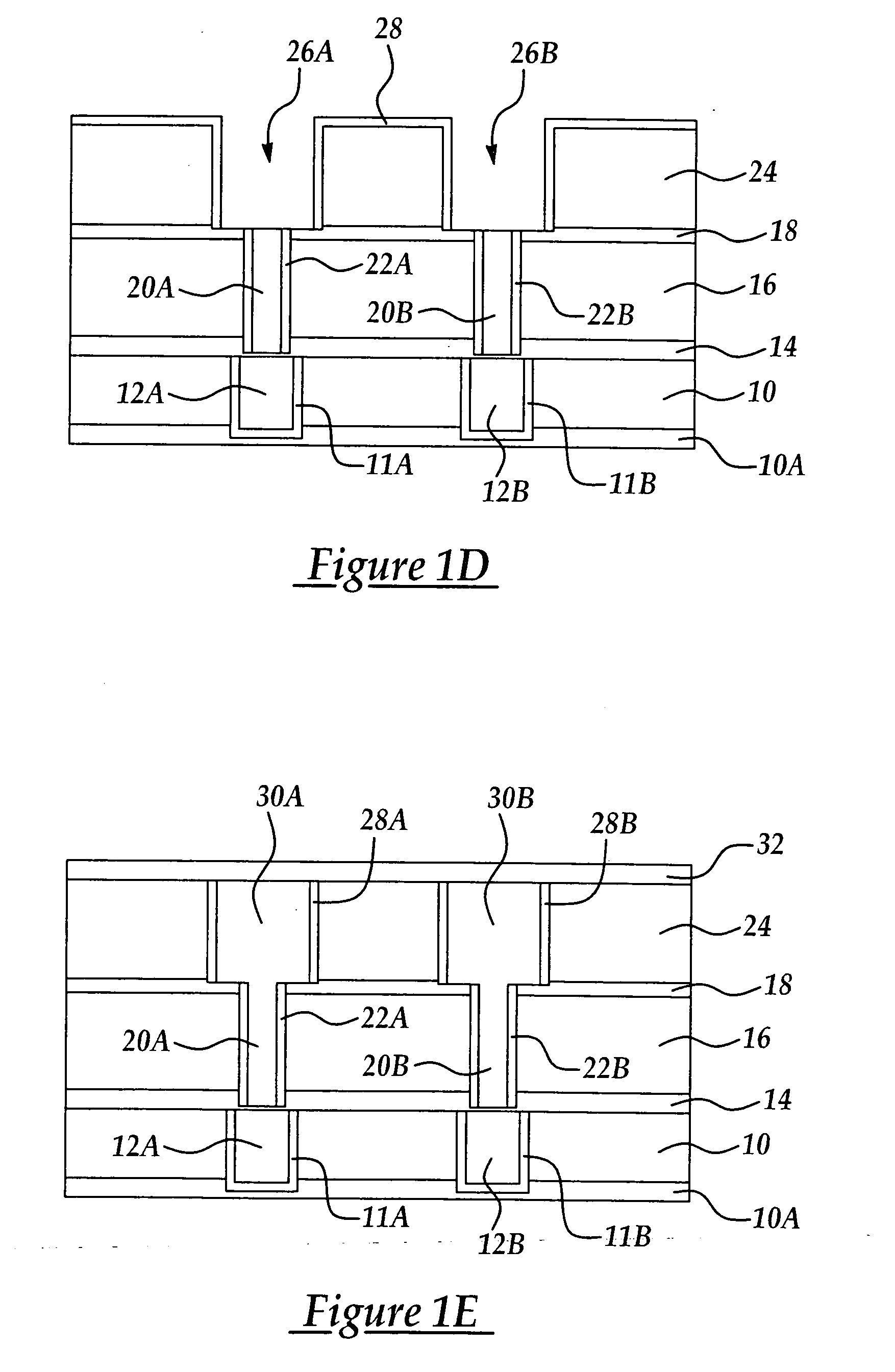

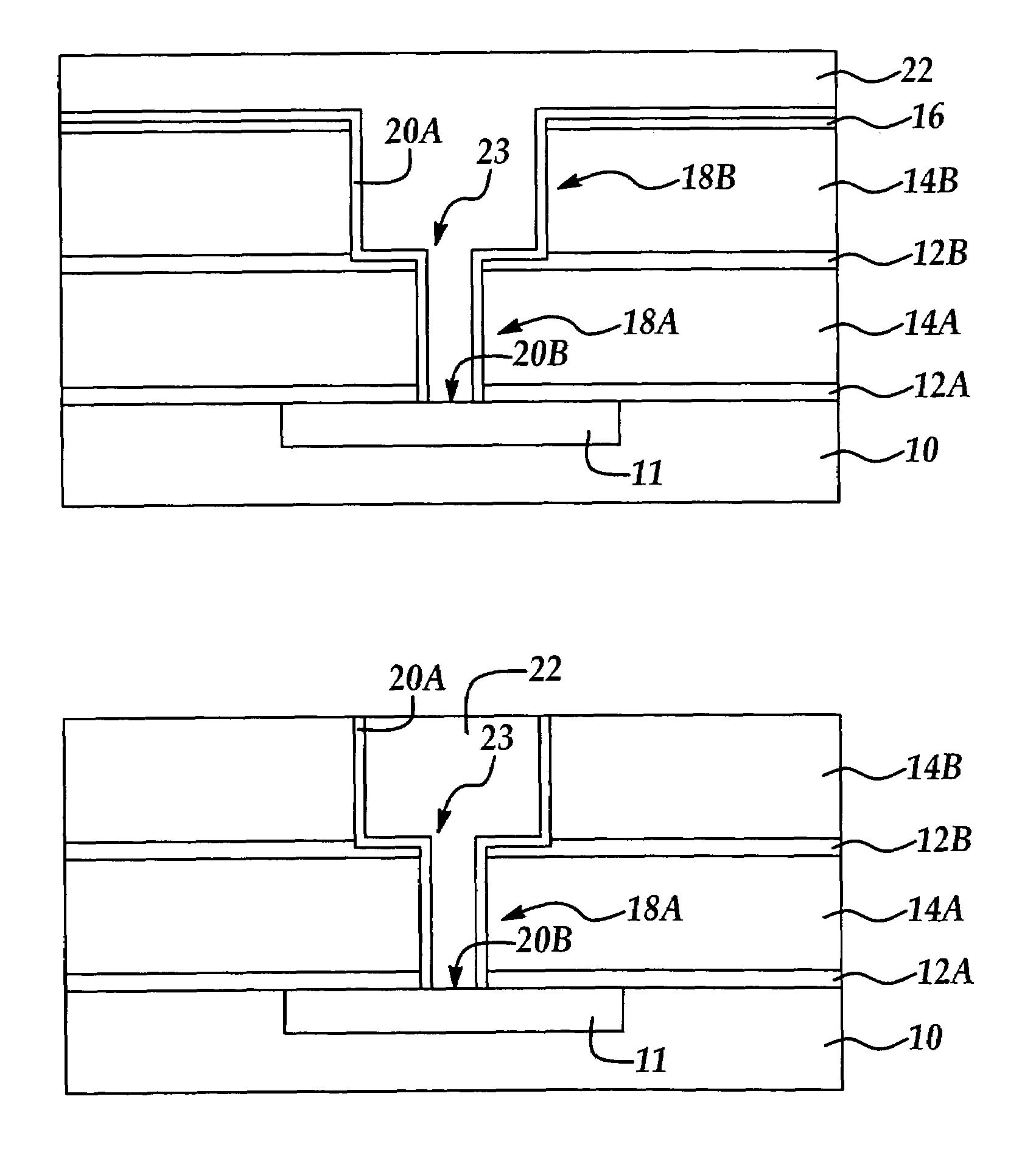

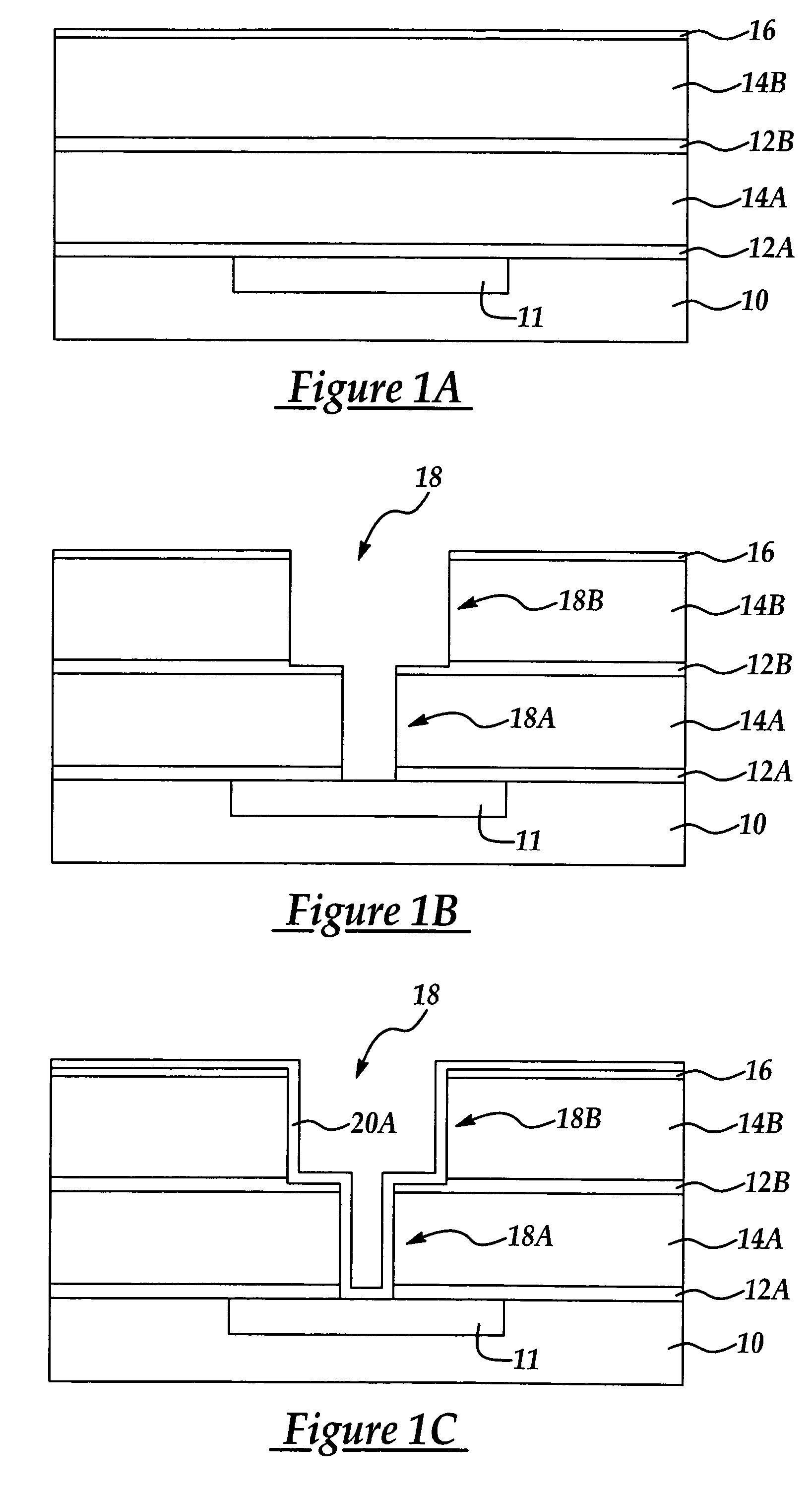

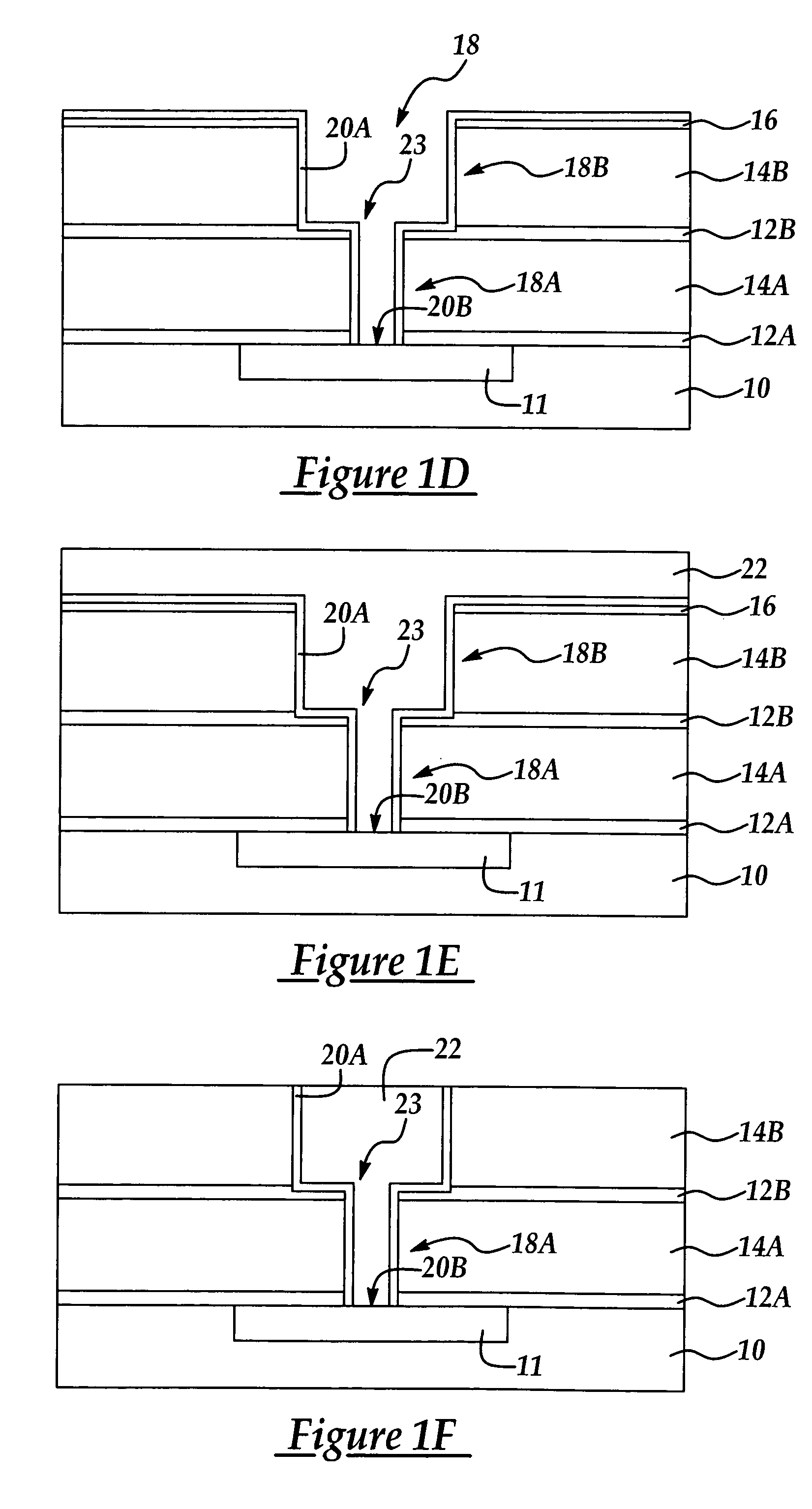

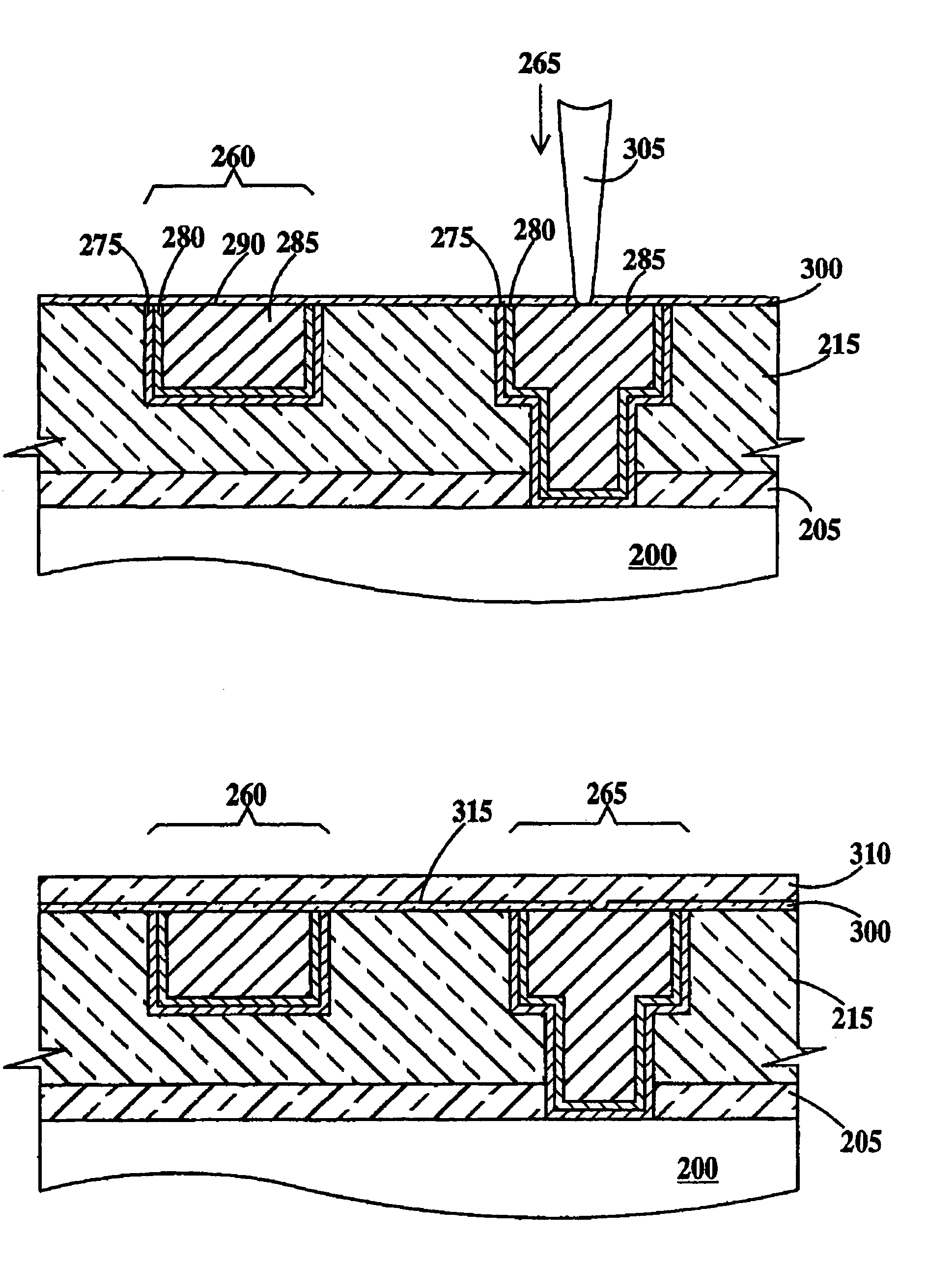

Copper damascene integration scheme for improved barrier layers

A metal filled dual damascene structure with a reduced capacitance contribution and method for forming the same, the method including forming a first metal filled damascene lined with a first metal barrier layer thickness in a first dielectric insulating layer; and, forming a second metal filled damascene lined with a second metal barrier layer thickness overlying the first metal filled damascene in a second dielectric insulating layer.

Owner:TAIWAN SEMICON MFG CO LTD

Differentially metal doped copper damascenes

InactiveUS20060091551A1Improve the immunityAcceptable resistivitySemiconductor/solid-state device detailsSolid-state devicesDopantCopper

A method of forming a copper filled semiconductor feature having improved bulk properties including providing a semiconductor process wafer having a process surface including an opening for forming a semiconductor feature; depositing at least one metal dopant containing layer over the opening to form a thermally diffusive relationship to a subsequently deposited copper layer; depositing said copper layer to substantially fill the opening; and, thermally treating the semiconductor process wafer for a time period sufficient to distribute at least a portion of the metal dopants to collect along at least a portion of the periphery of said copper layer including a portion of said copper layer grain boundaries.

Owner:TAIWAN SEMICON MFG CO LTD

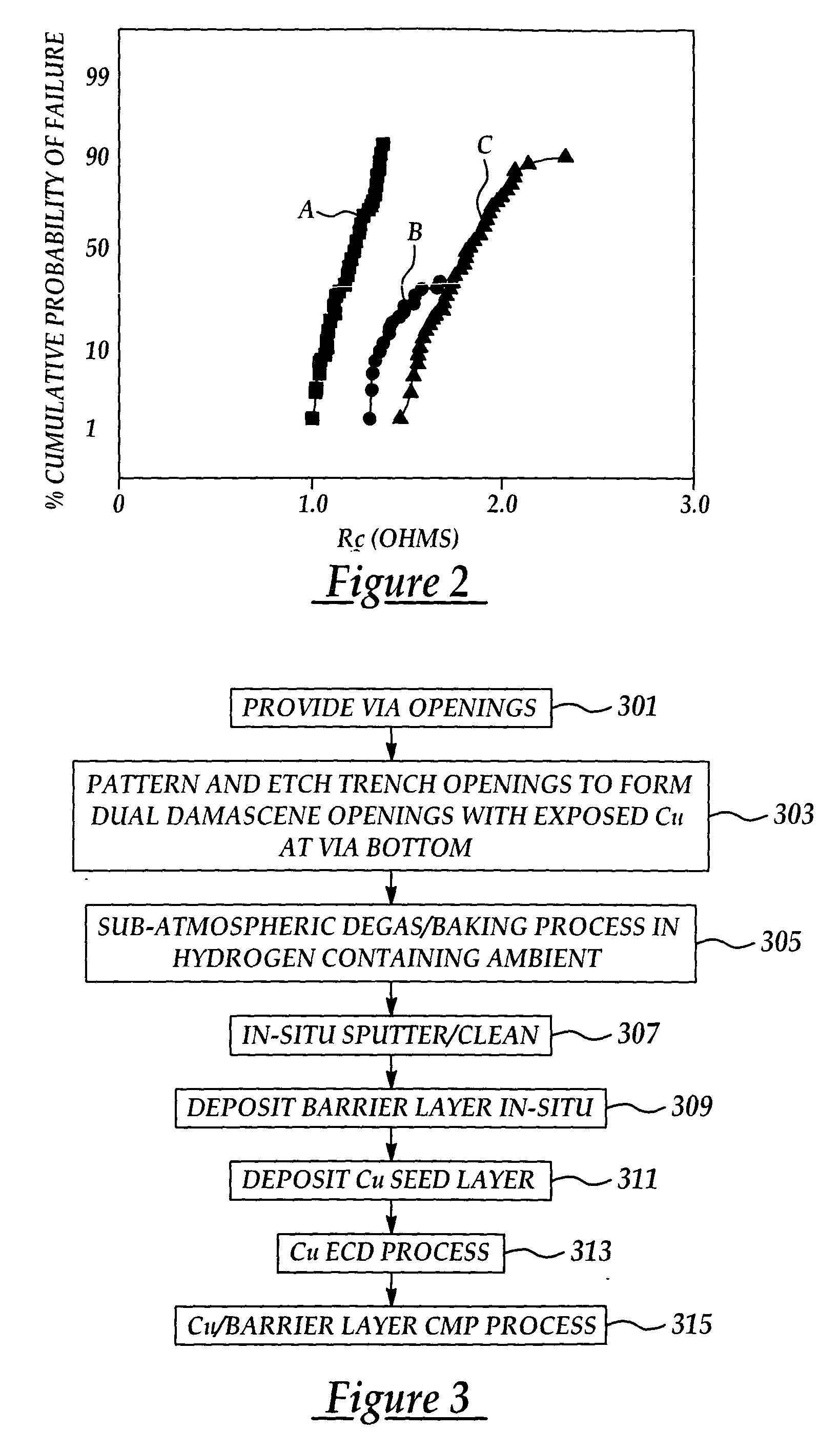

Reliability improvement of SiOC etch with trimethylsilane gas passivation in Cu damascene interconnects

InactiveUS20050245100A1Reduce leakage currentImprove throughputSemiconductor/solid-state device detailsSolid-state devicesTrimethylsilaneLow leakage

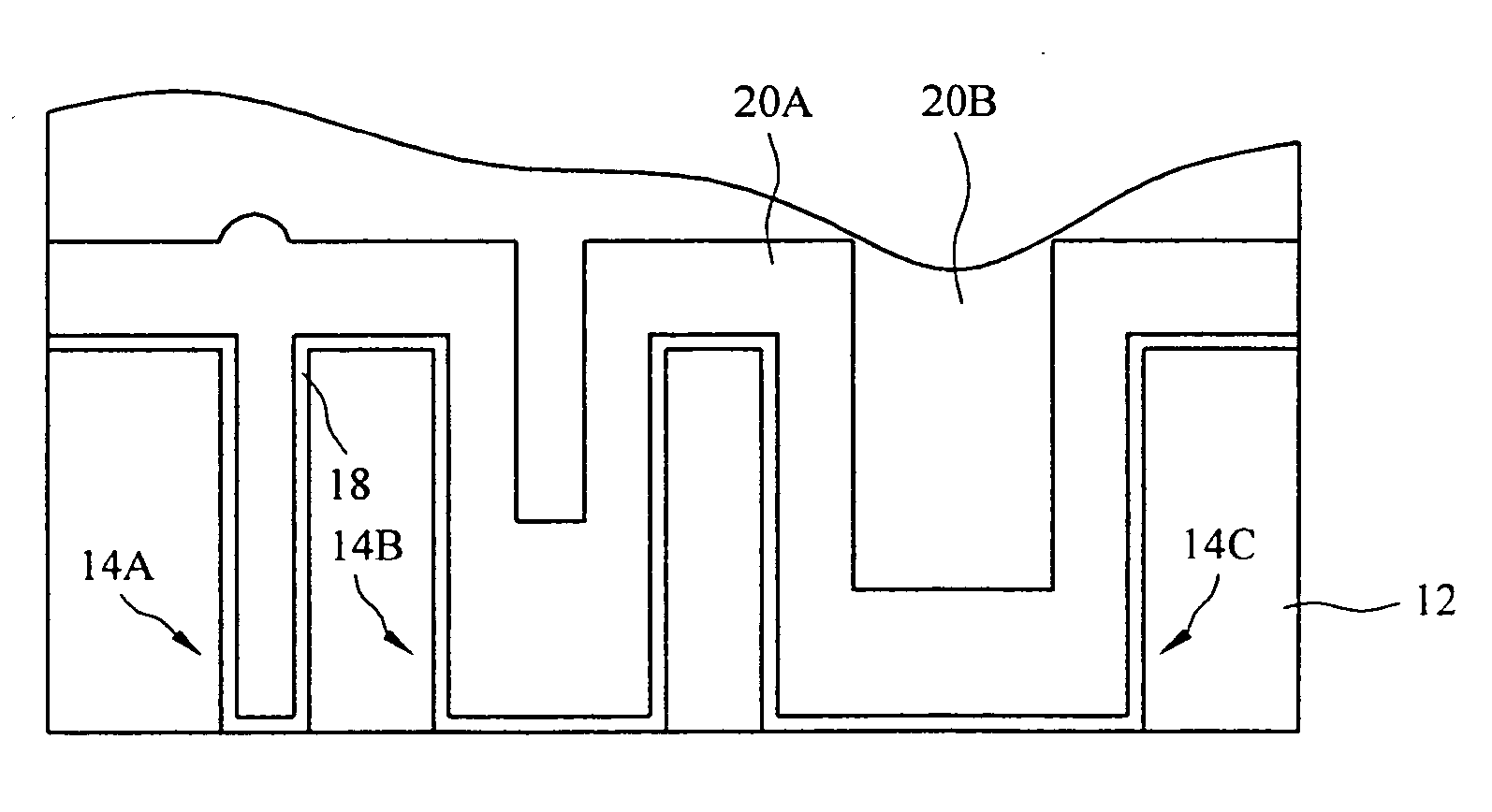

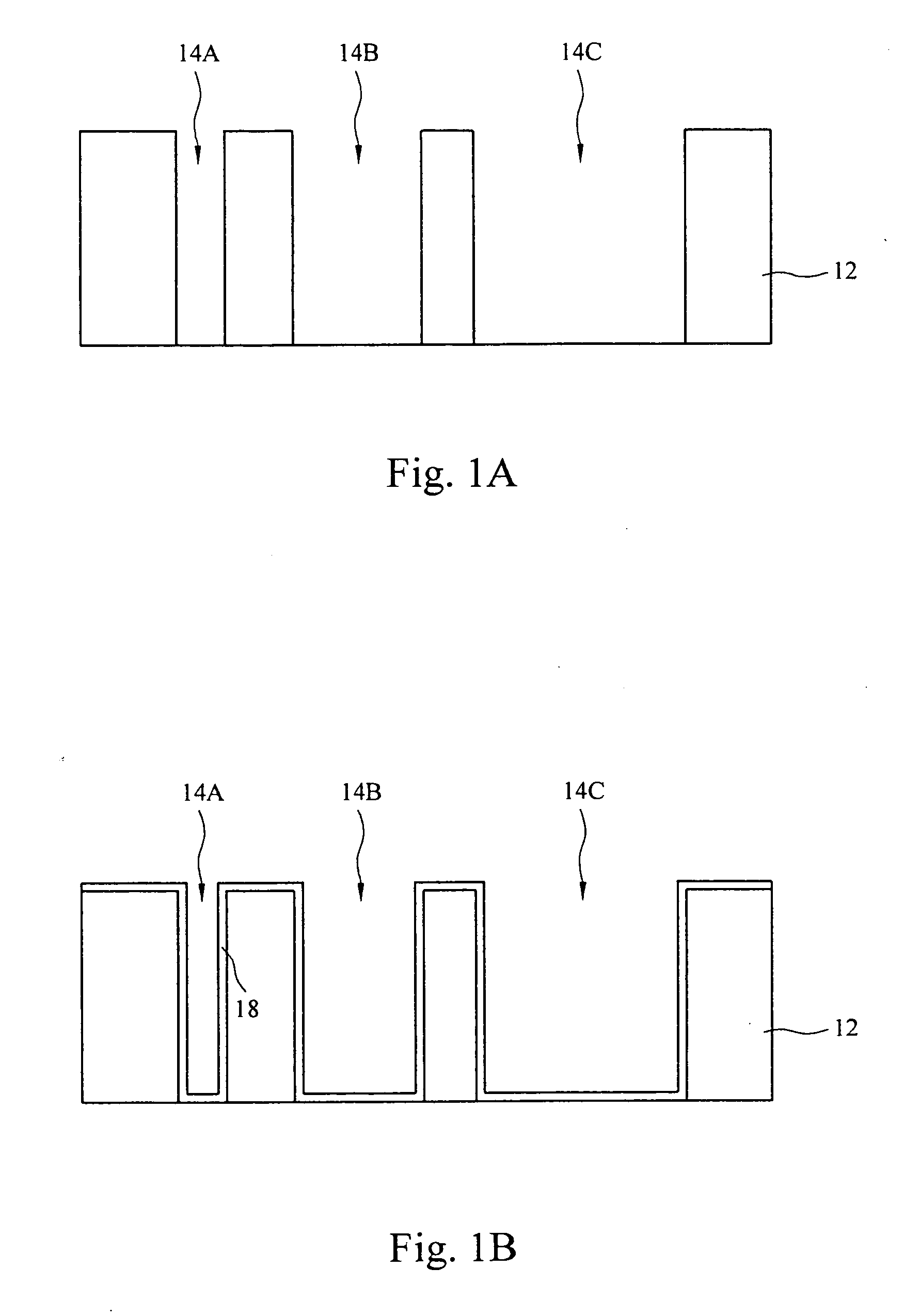

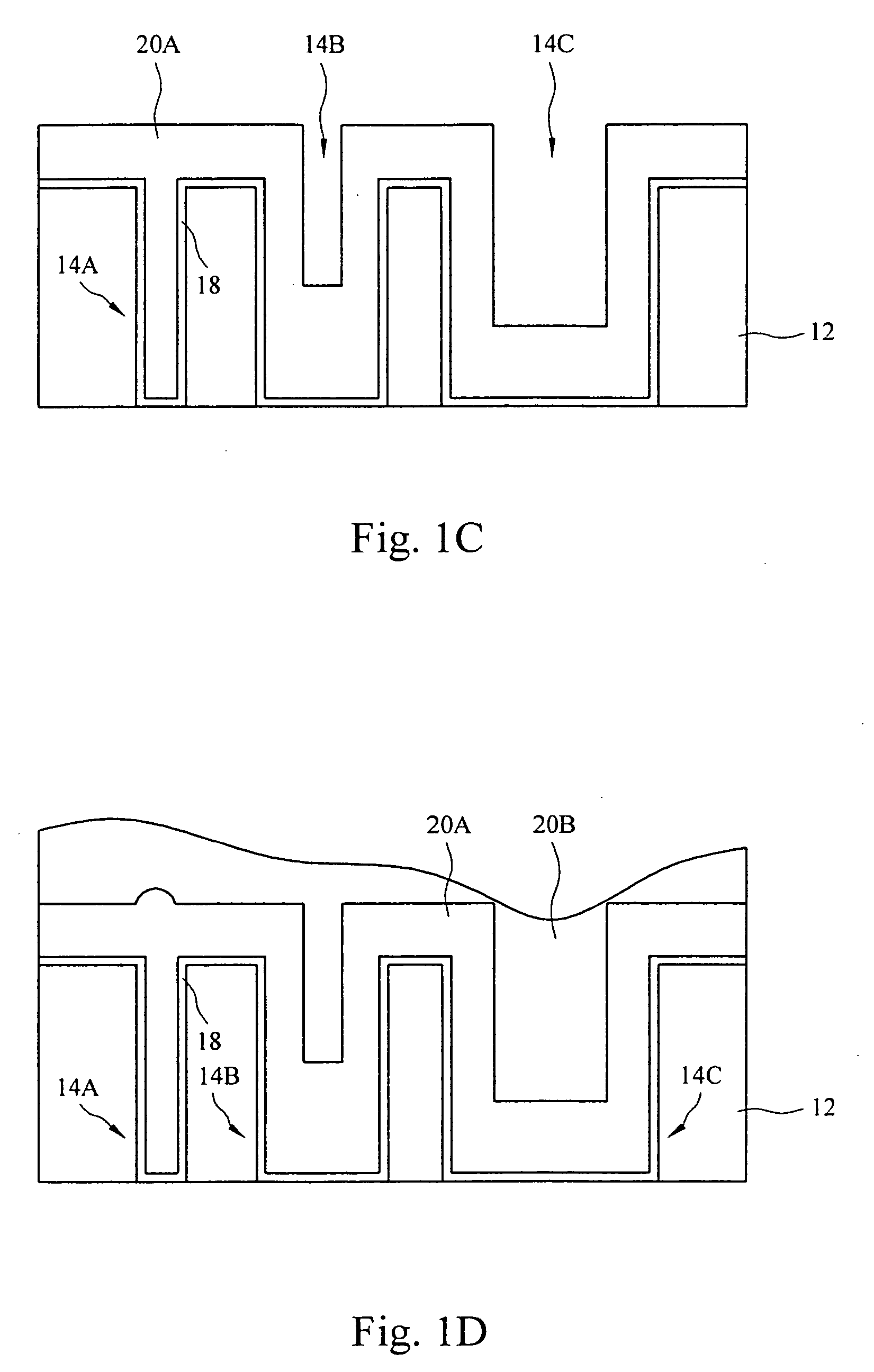

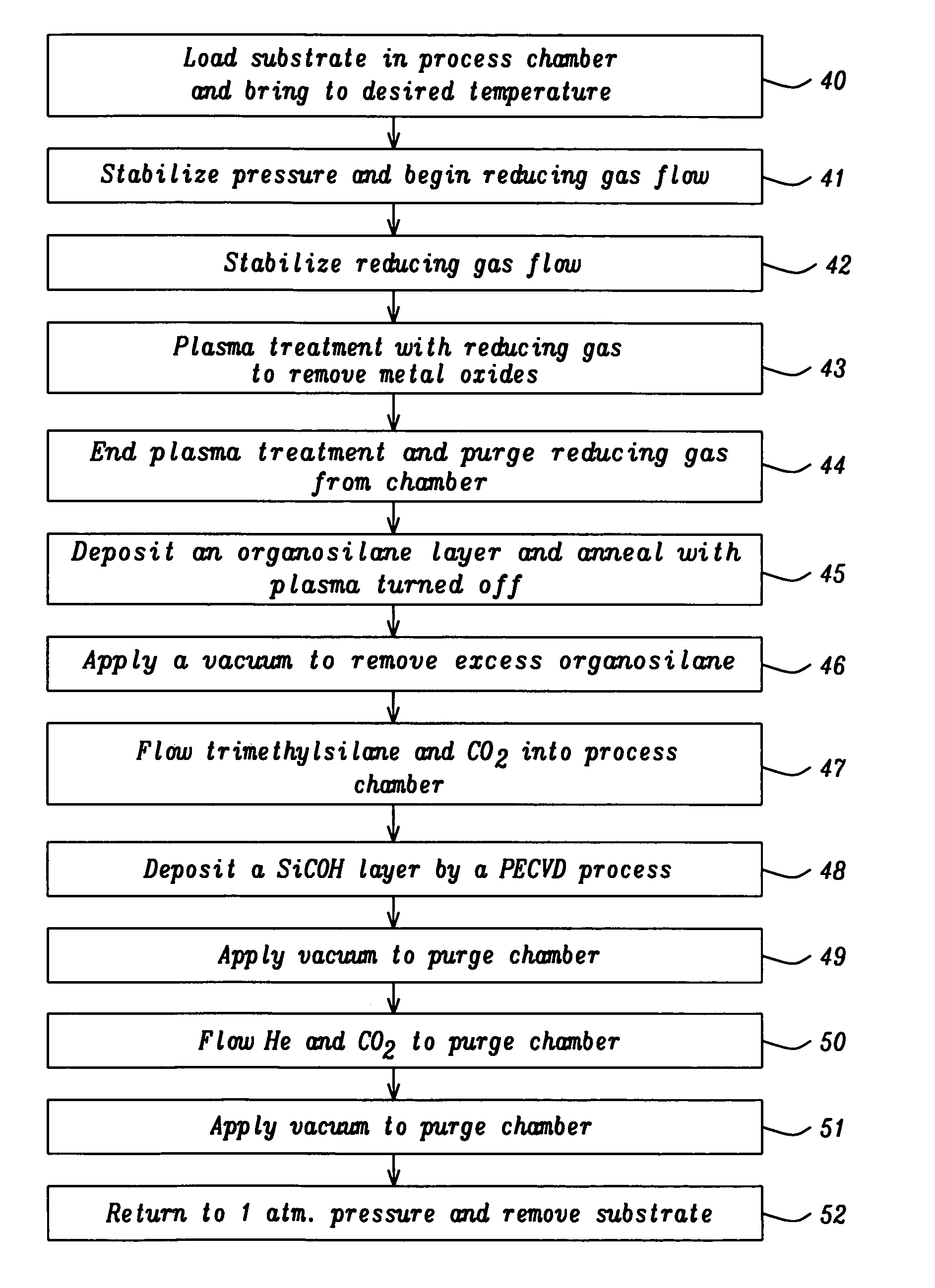

A method of forming a SiCOH etch stop layer in a copper damascene process is described. A substrate with an exposed metal layer is treated with H2 or NH3 plasma to remove metal oxides. Trimethylsilane is flowed into a chamber with no RF power at about 350° C. to form at least a monolayer on the exposed metal layer. The SiCOH layer is formed by a PECVD process including trimethylsilane and CO2 source gases. Optionally, a composite SiCOH layer comprised of a low compressive stress layer on a high compressive stress layer is formed on the substrate. A conventional damascene sequence is then used to form a second metal layer on the exposed metal layer. Via Rc stability is improved and a lower leakage current is achieved with the trimethylsilane passivation layer. A composite SiCOH etch stop layer provides improved stress migration resistance compared to a single low stress SiCOH layer.

Owner:TAIWAN SEMICON MFG CO LTD

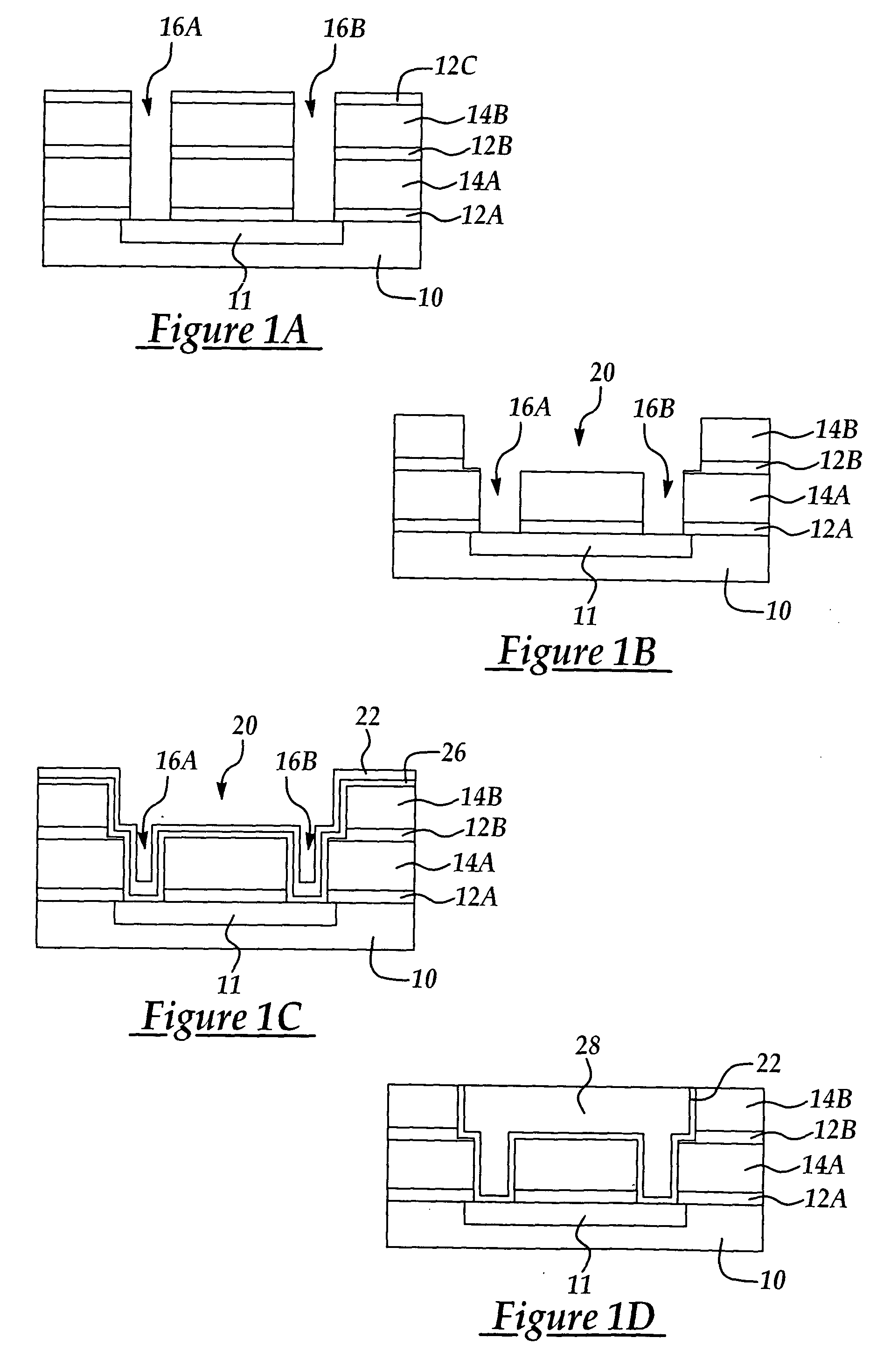

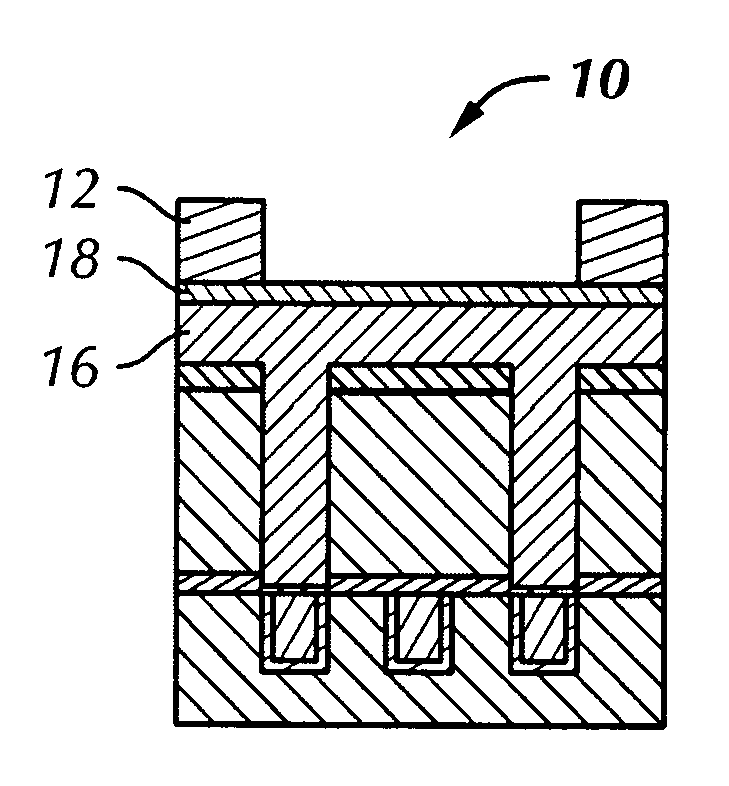

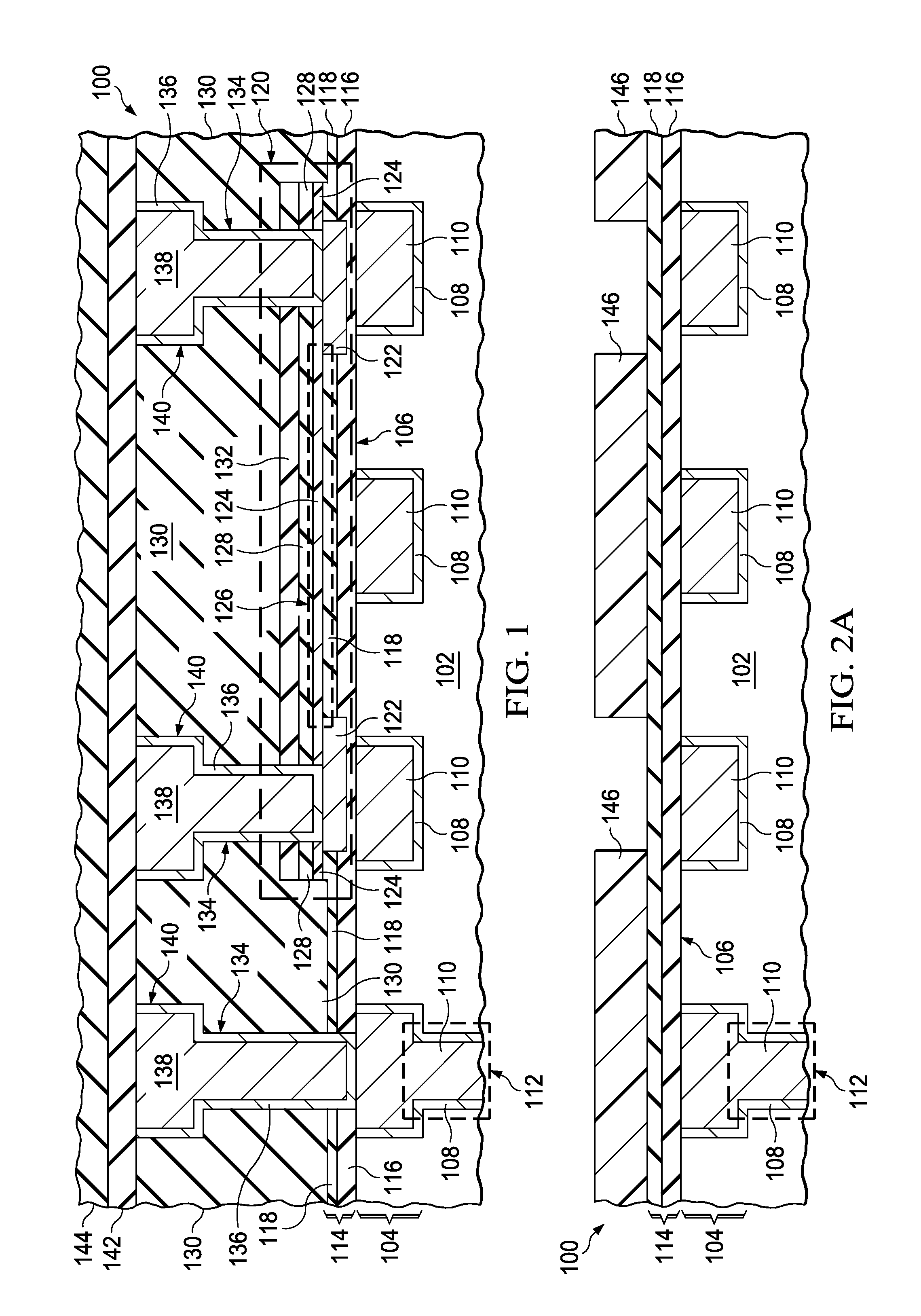

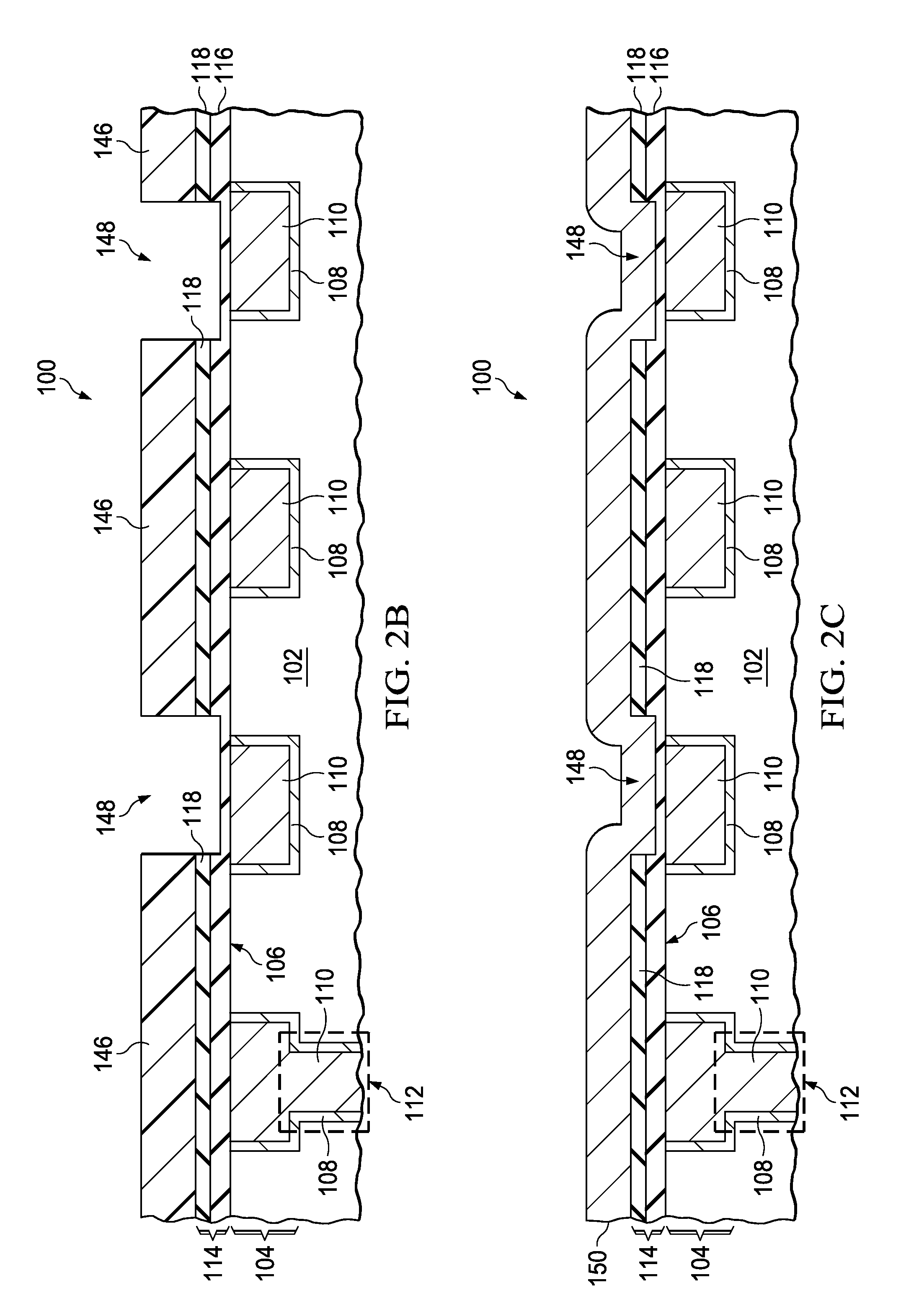

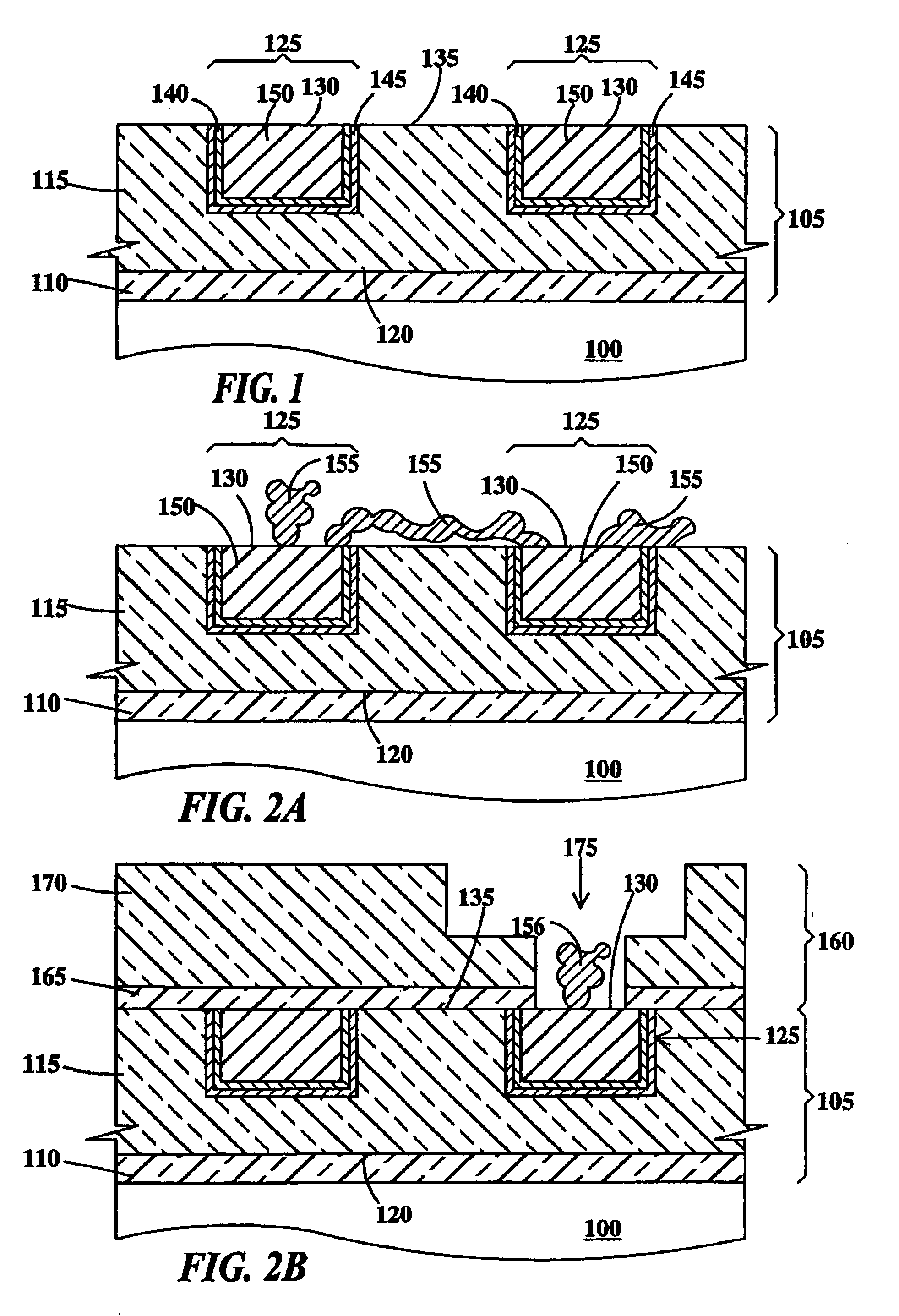

Method of fabricating copper damascene and dual damascene interconnect wiring

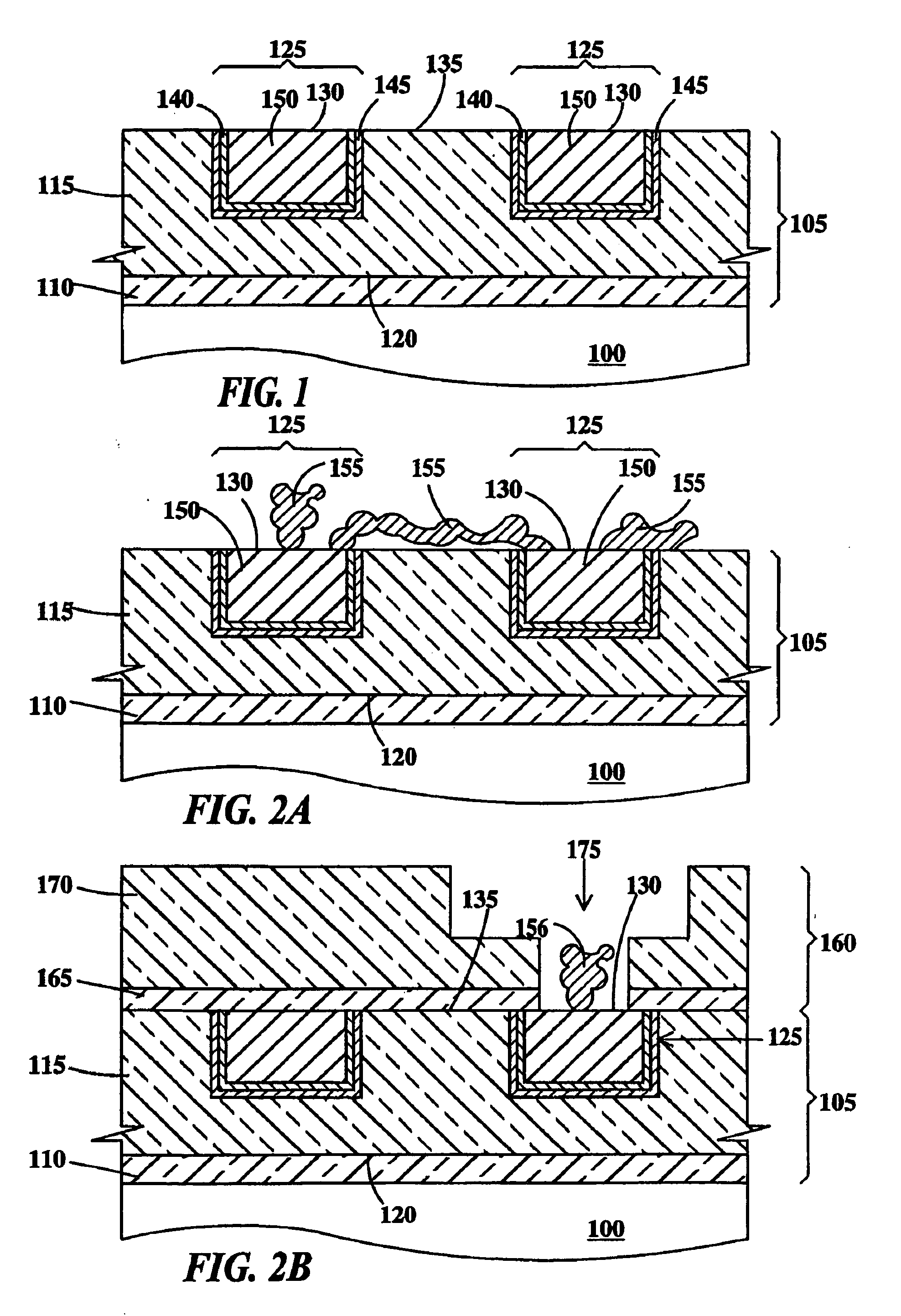

An integrated circuit and a method of manufacturing the integrated circuit, the method including: (a) providing a substrate; (b) forming a copper diffusion barrier layer on the substrate; (c) forming a dielectric layer on a top surface of the copper diffusion barrier layer; (d) forming a copper damascene or dual damascene wire in the dielectric layer, a top surface of the copper damascene or dual damascene wire coplanar with a top surface of the dielectric layer; (e) forming a first capping layer on the top surface of the wire and the top surface of the dielectric layer; (f) after step (e) performing one or more characterization procedures in relation to said integrated circuit; and (g) after step (e) forming a second capping layer on a top surface of the first capping layer.

Owner:AURIGA INNOVATIONS INC

Method of forming barrier layer with reduced resistivity and improved reliability in copper damascene process

ActiveUS20050191855A1Improve the immunityIncreased electrical resistivitySemiconductor/solid-state device manufacturingDielectricRemote plasma

A method for forming a copper dual damascene with improved copper migration resistance and improved electrical resistivity including providing a semiconductor wafer including upper and lower dielectric insulating layers separated by a middle etch stop layer; forming a dual damascene opening extending through a thickness of the upper and lower dielectric insulating layers wherein an upper trench line portion extends through the upper dielectric insulating layer thickness and partially through the middle etch stop layer; blanket depositing a barrier layer including at least one of a refractory metal and refractory metal nitride to line the dual damascene opening; carrying out a remote plasma etch treatment of the dual damascene opening to remove a bottom portion of the barrier layer to reveal an underlying conductive area; and, filling the dual damascene opening with copper to provide a substantially planar surface.

Owner:TAIWAN SEMICON MFG CO LTD

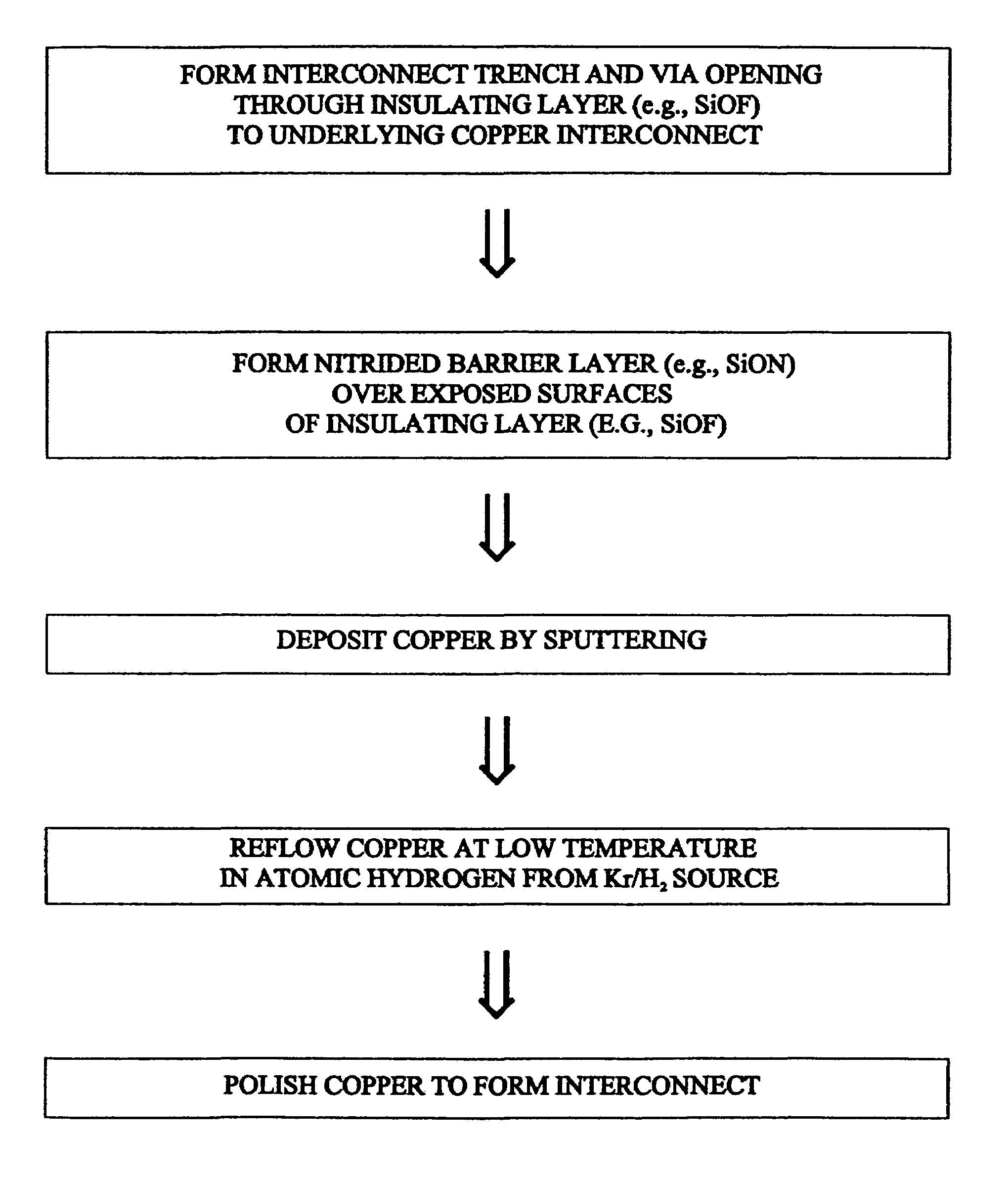

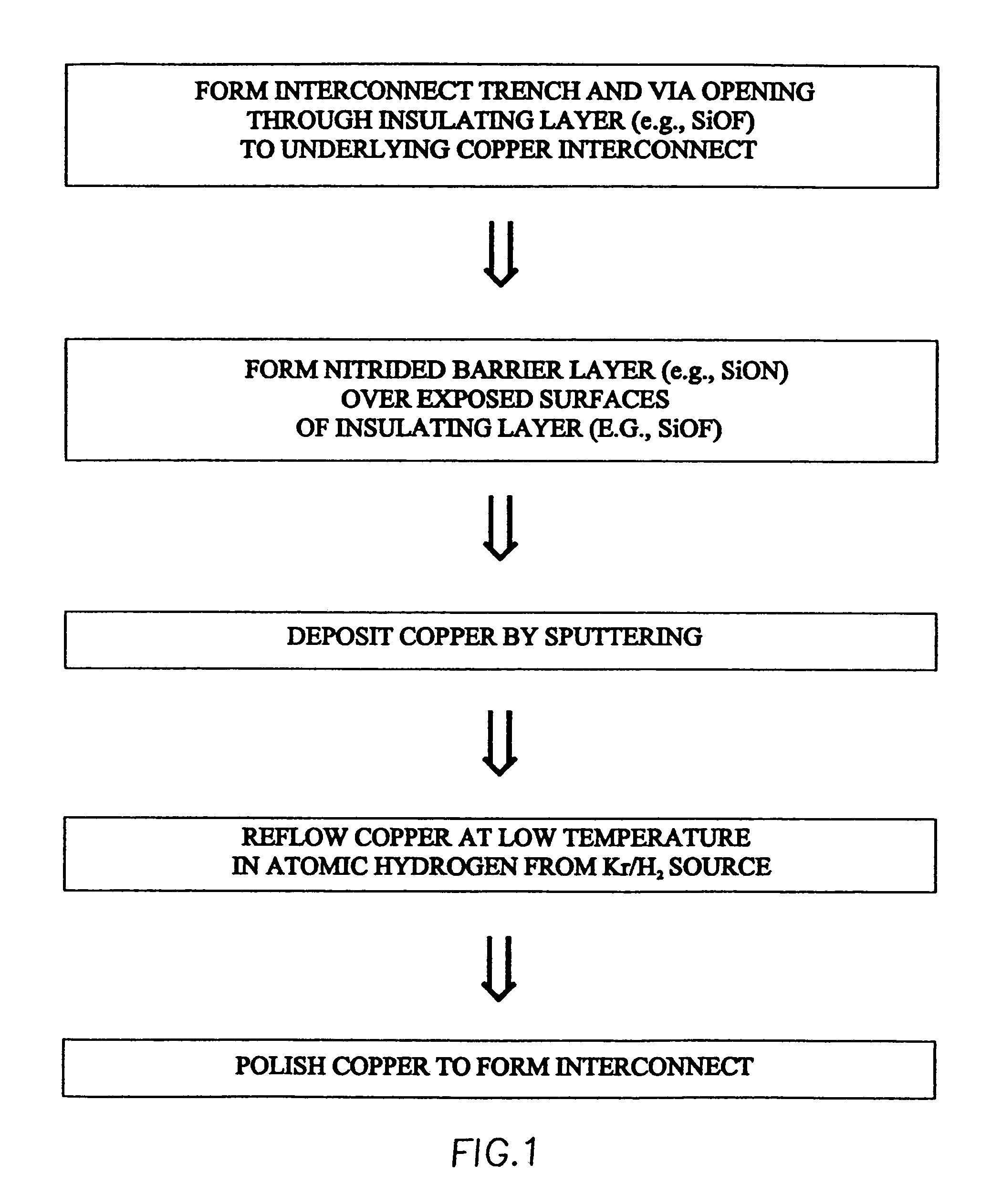

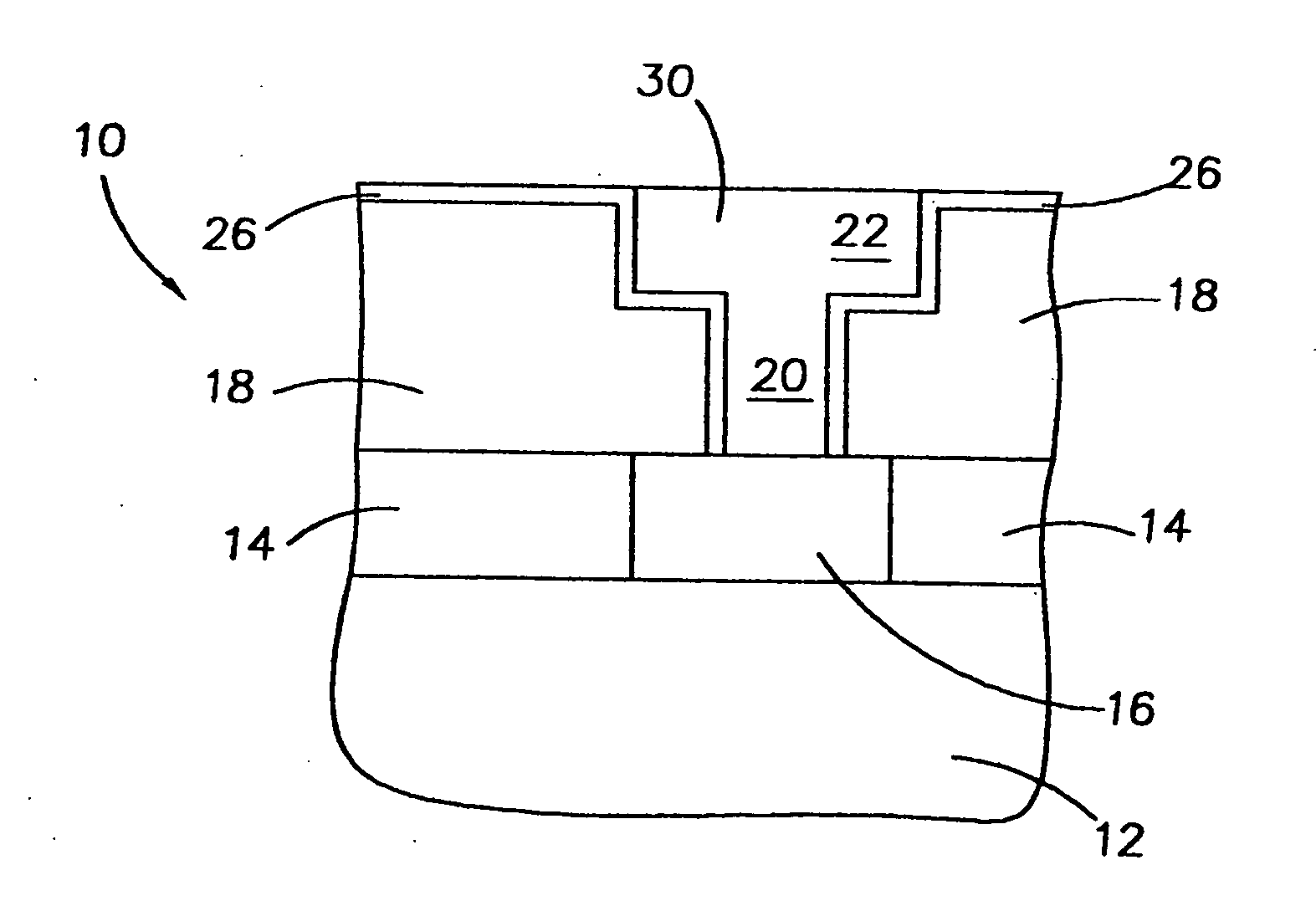

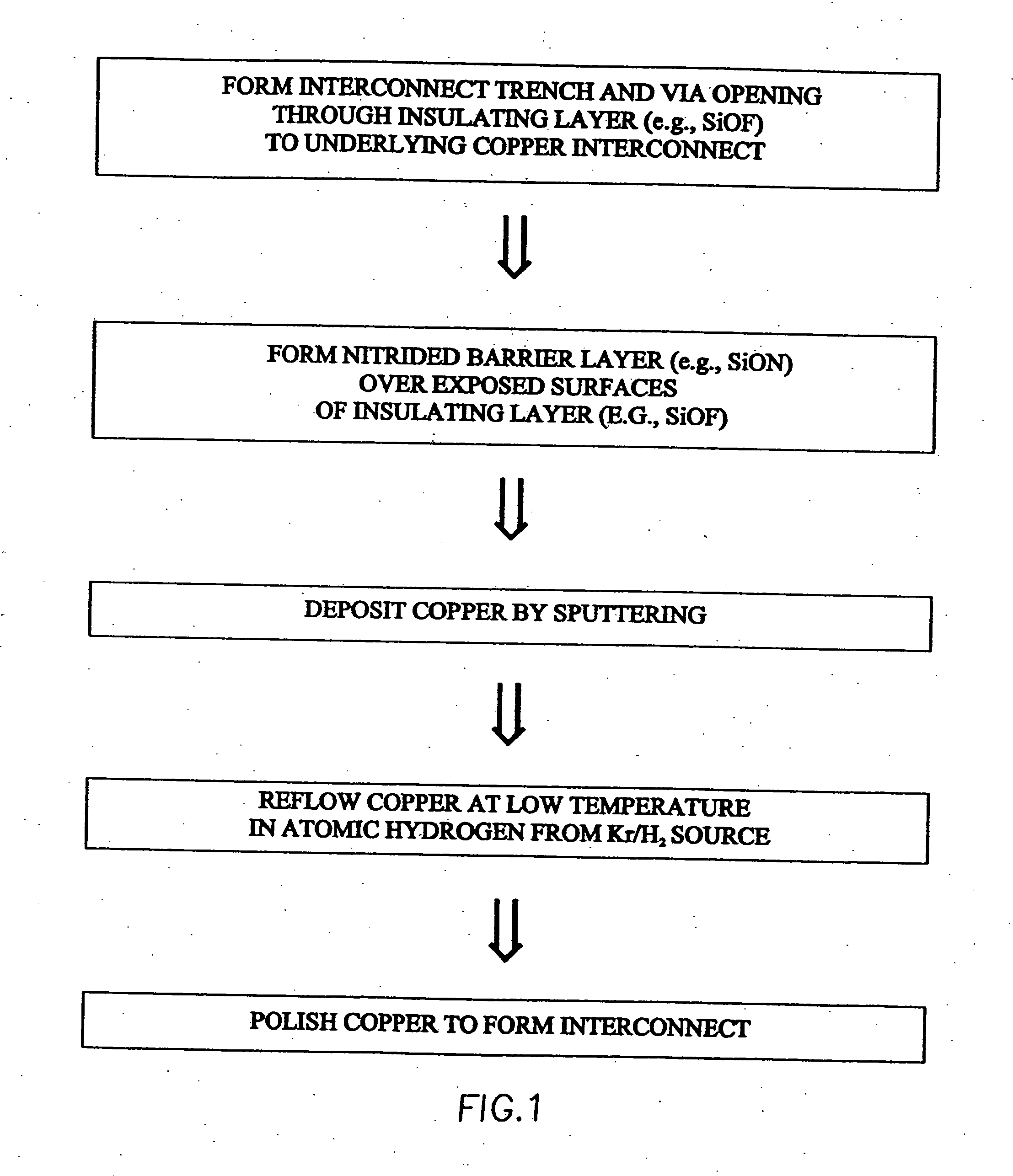

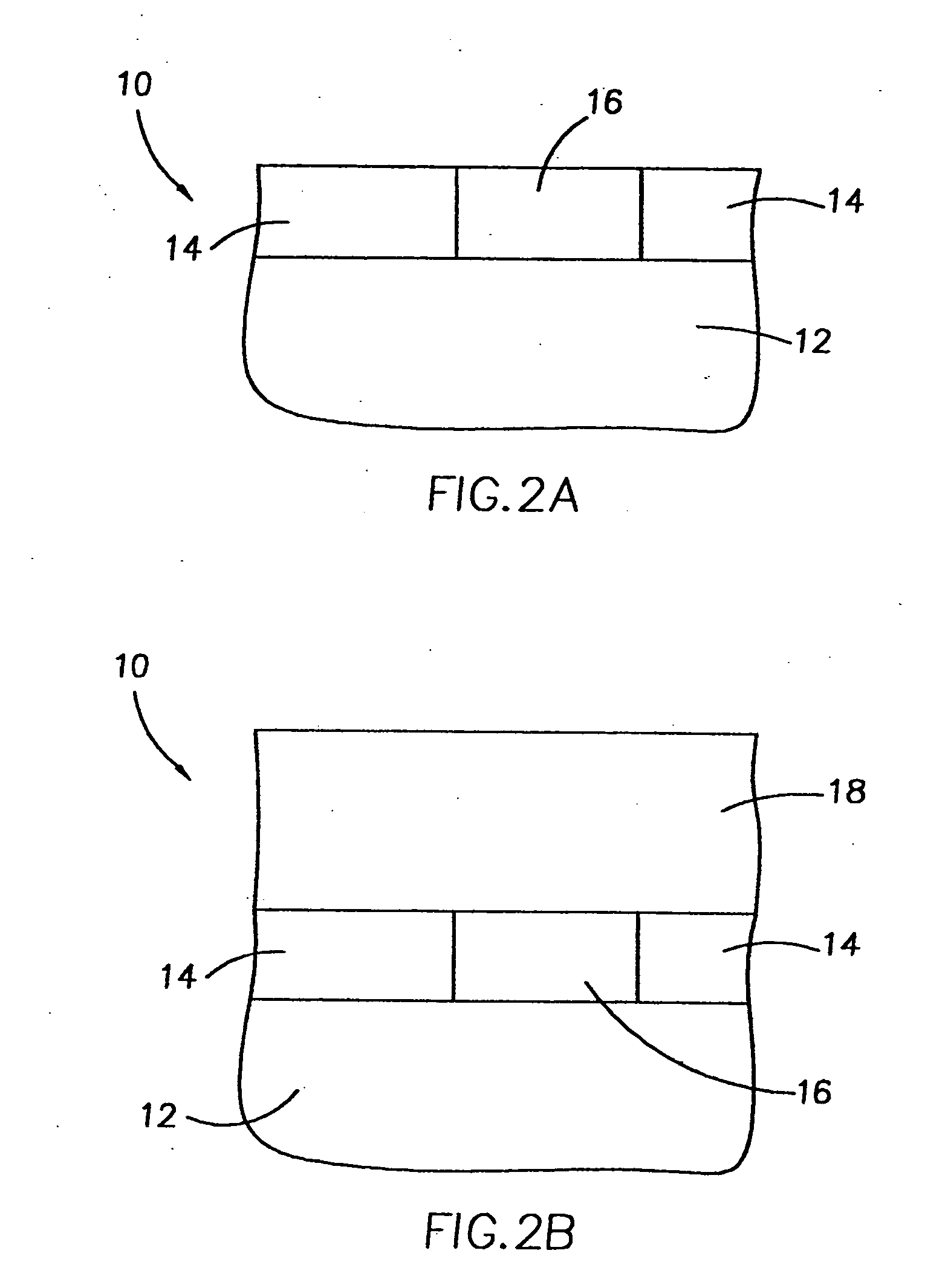

Barrier-metal-free copper damascene technology using atomic hydrogen enhanced reflow

InactiveUS7186643B2Inhibited DiffusionHigh puritySemiconductor/solid-state device detailsSolid-state devicesHydrogenSemiconductor structure

A method for forming conductive contacts and interconnects in a semiconductor structure, and the resulting conductive components are provided. In particular, the method is used to fabricate single or dual damascene copper contacts and interconnects in integrated circuits such as memory devices and microprocessor.

Owner:CONVERSANT INTPROP MANAGEMENT INC

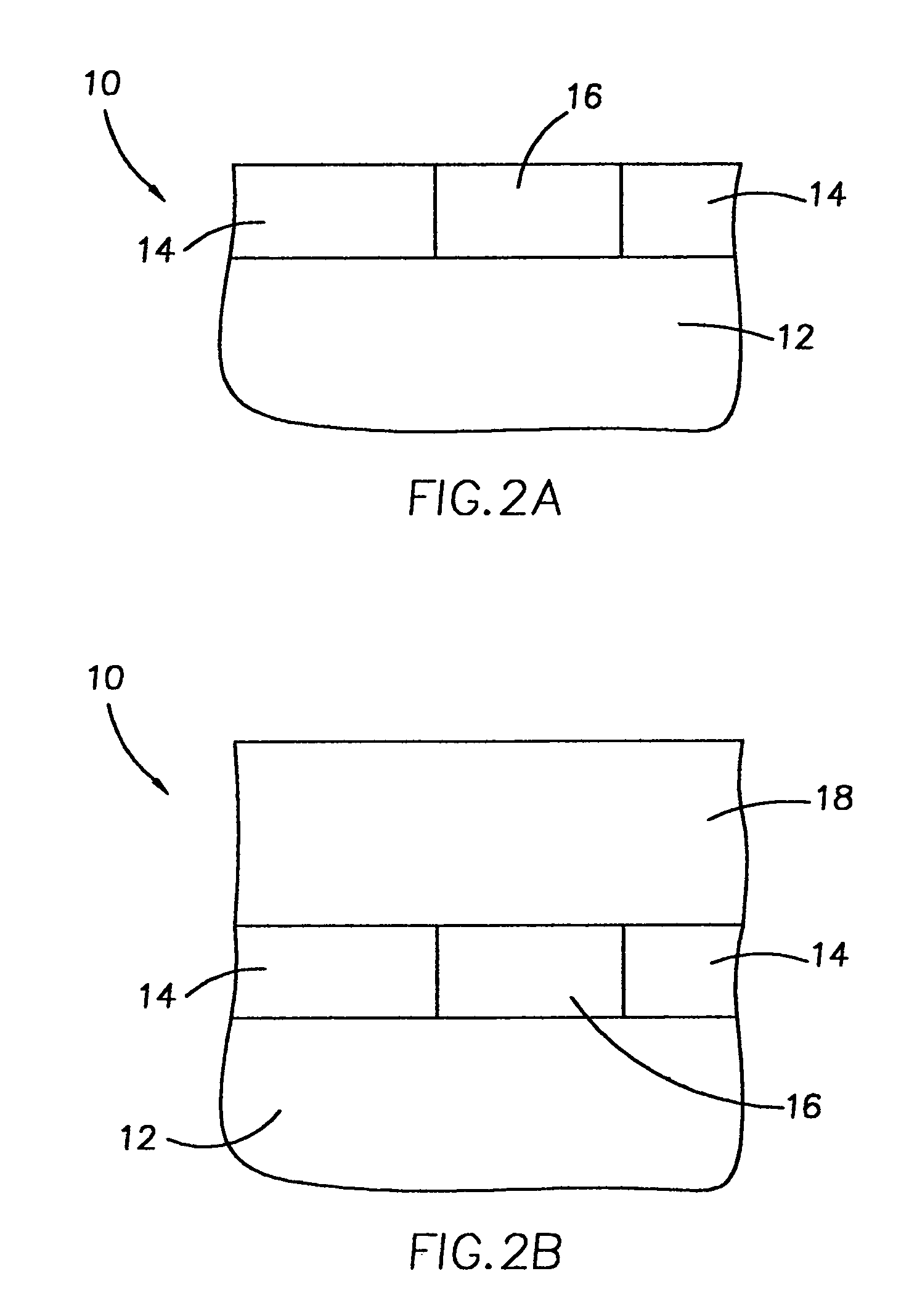

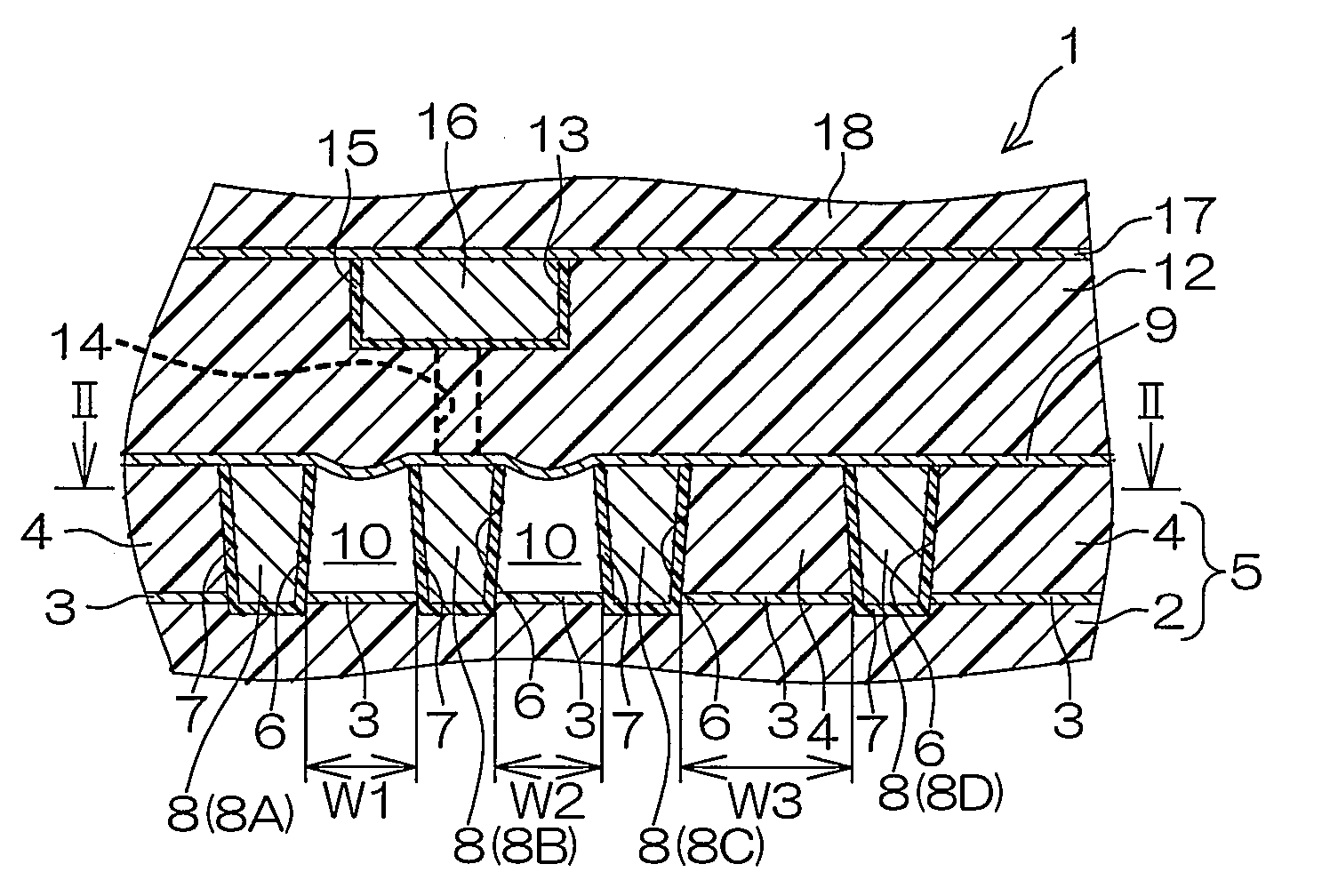

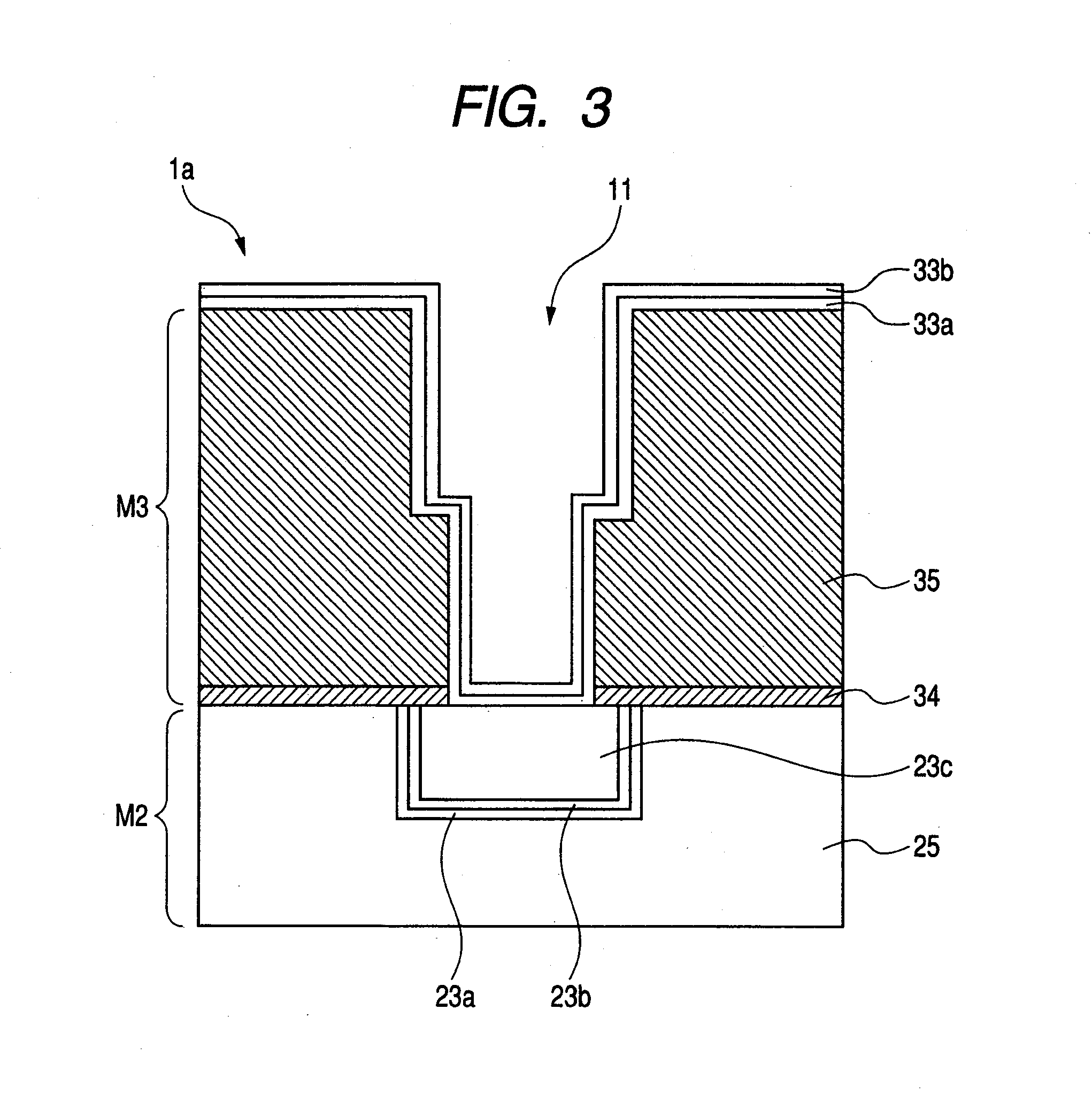

Semiconductor device and method of manufacturing semiconductor device

InactiveUS20090121356A1Inhibited DiffusionPrevent oxidationSemiconductor/solid-state device detailsSolid-state devicesDielectricCopper

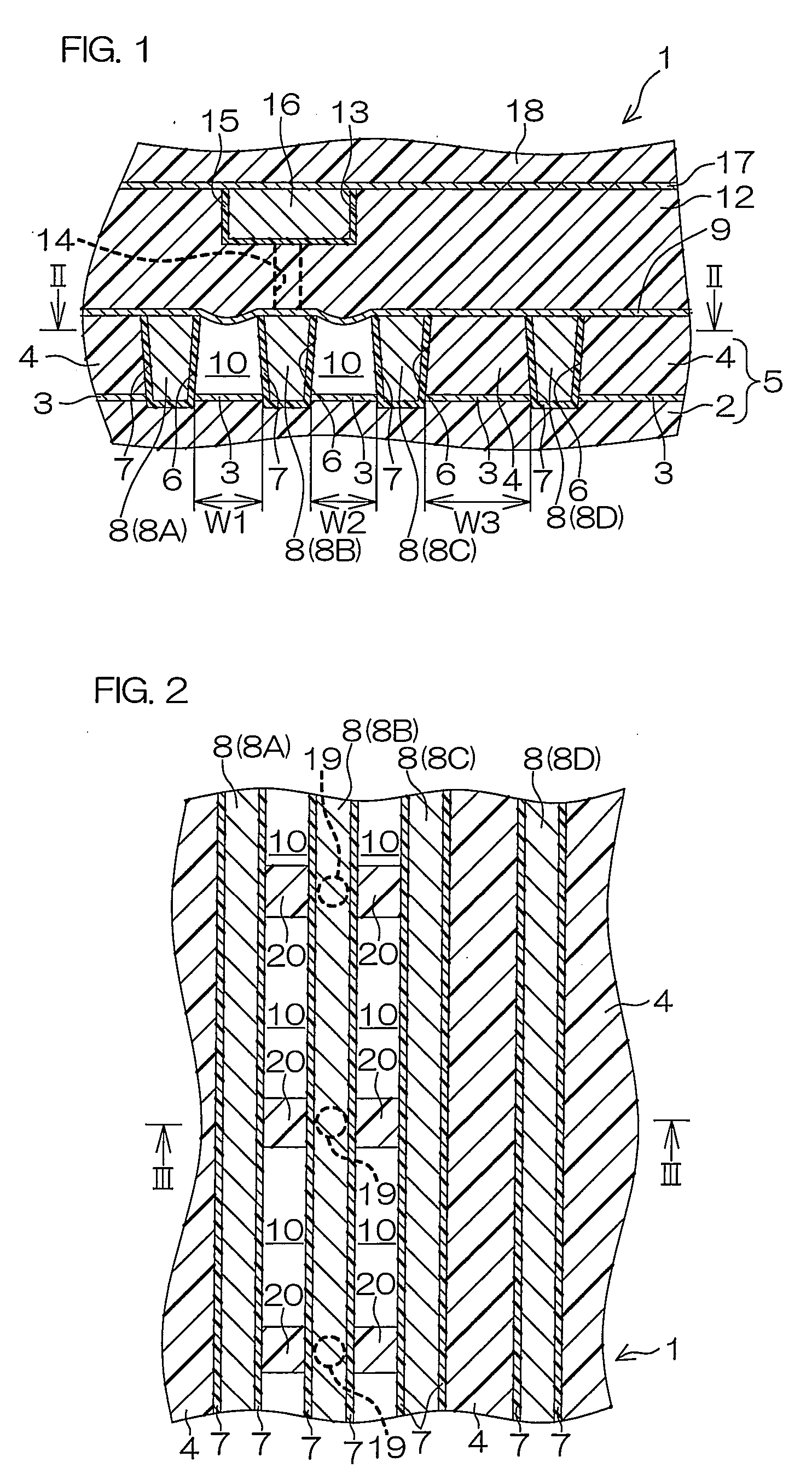

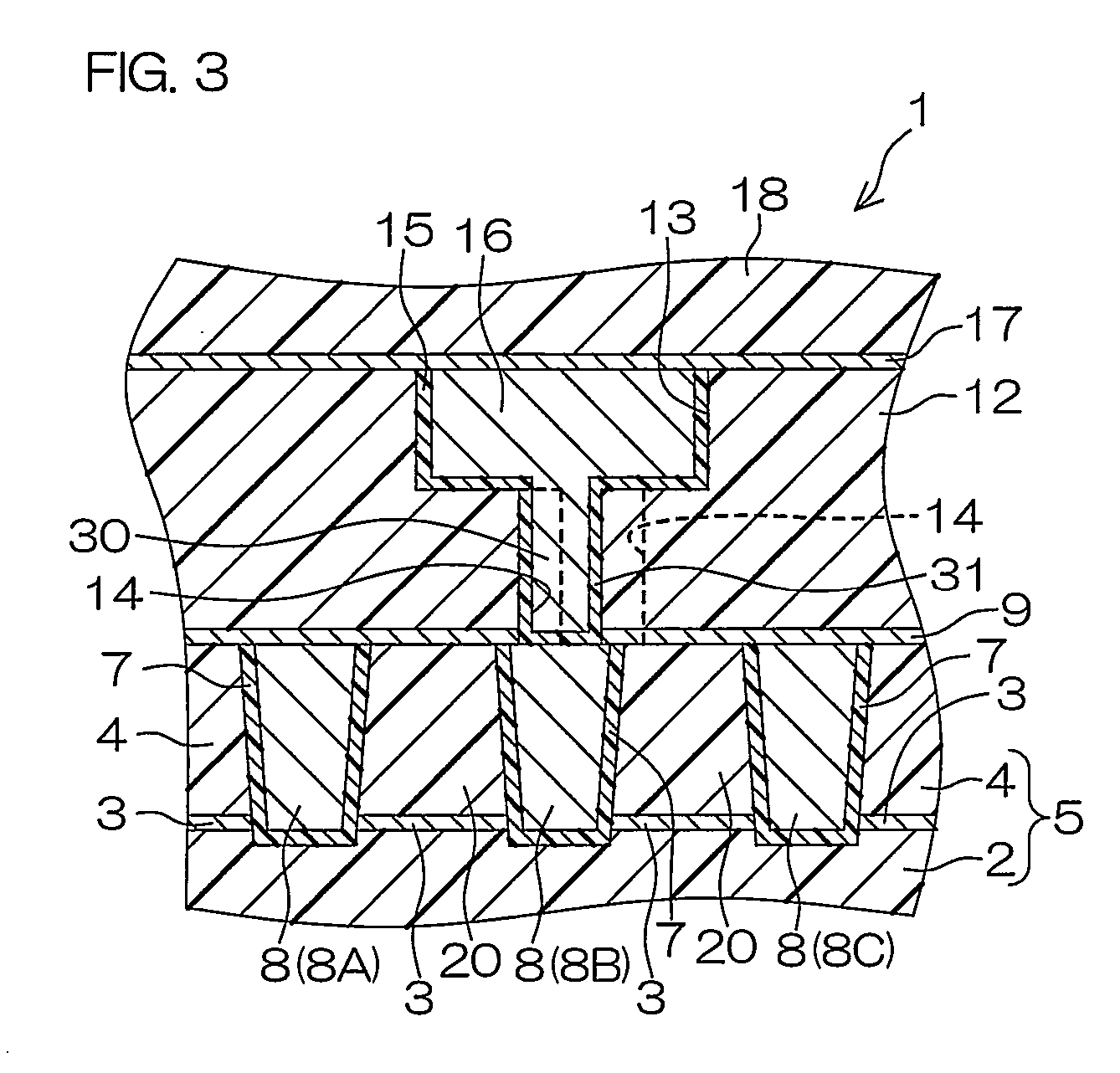

The semiconductor device according to the present invention includes a first interlayer dielectric film, a plurality of copper damascene wires embedded in the first interlayer dielectric film at an interval from each other, and a diffusion preventing film stacked on the first interlayer dielectric film for preventing diffusion of copper contained in the copper damascene wires, while an air gap closed with the diffusion preventing film is formed between the copper damascene wires adjacent to each other by partially removing the first interlayer dielectric film from the space between these copper damascene wires.

Owner:ROHM CO LTD

Reliability improvement of SiOC etch with trimethylsilane gas passivation in Cu damascene interconnects

InactiveUS7193325B2Reduce leakage currentImprove throughputSemiconductor/solid-state device detailsSolid-state devicesTrimethylsilaneLow leakage

A method of forming a SiCOH etch stop layer in a copper damascene process is described. A substrate with an exposed metal layer is treated with H2 or NH3 plasma to remove metal oxides. Trimethylsilane is flowed into a chamber with no RF power at about 350° C. to form at least a monolayer on the exposed metal layer. The SiCOH layer is formed by a PECVD process including trimethylsilane and CO2 source gases. Optionally, a composite SiCOH layer comprised of a low compressive stress layer on a high compressive stress layer is formed on the substrate. A conventional damascene sequence is then used to form a second metal layer on the exposed metal layer. Via Rc stability is improved and a lower leakage current is achieved with the trimethylsilane passivation layer. A composite SiCOH etch stop layer provides improved stress migration resistance compared to a single low stress SiCOH layer.

Owner:TAIWAN SEMICON MFG CO LTD

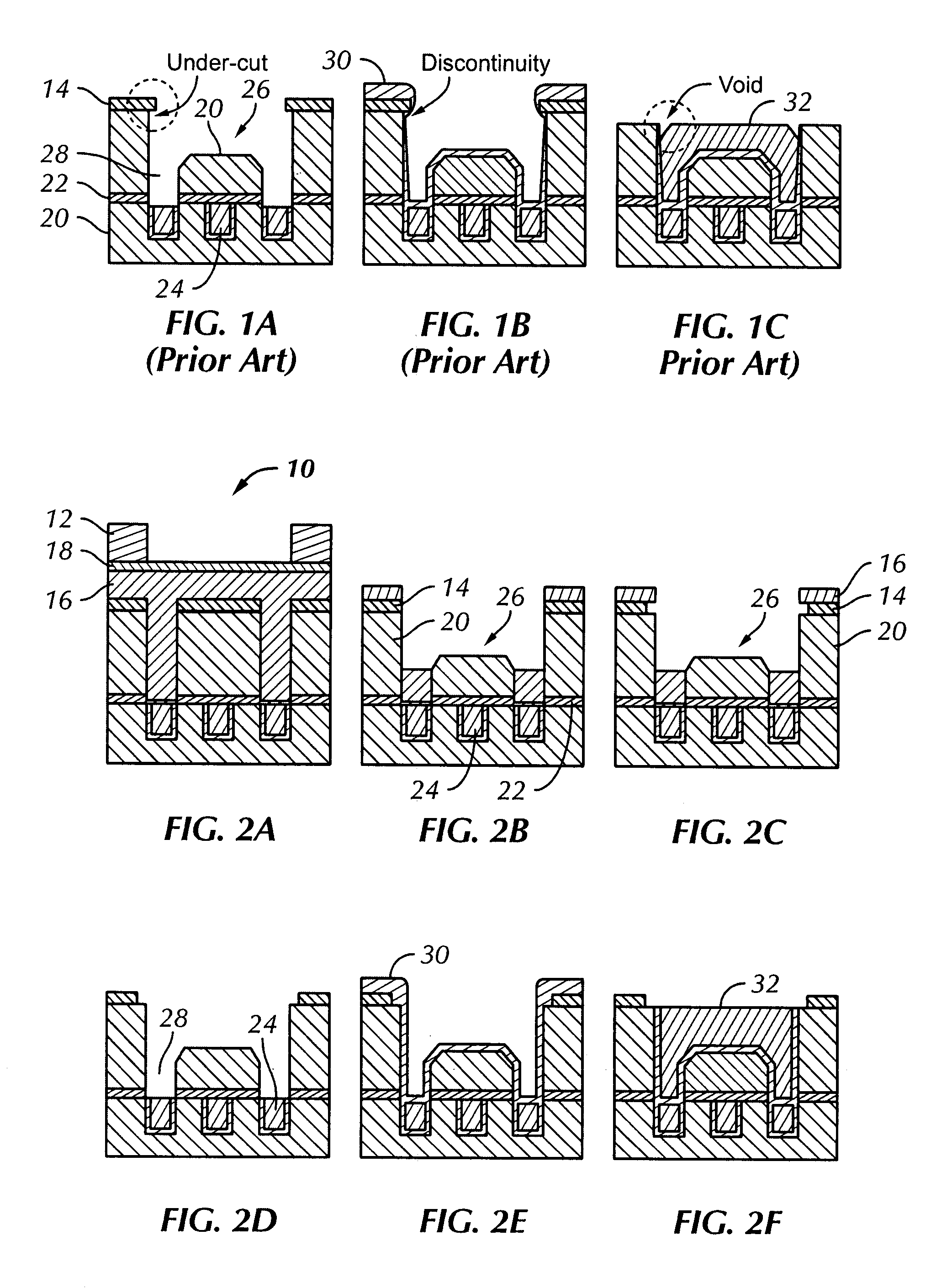

Method for Cu metallization of highly reliable dual damascene structures

InactiveUS7262127B2Speed up the processSemiconductor/solid-state device detailsSolid-state devicesCopperDiffusion barrier

The present invention provides a method for forming a void-free copper damascene structure comprising a substrate having a conductive structure, a first dielectric layer on the substrate, a diffusion barrier layer on the first dielectric layer, and a second dielectric layer on the barrier layer. The method comprises forming via and trench openings developing a photoresist through a first and second hard mask. The first hard mask is laterally etched such that it is eroded to a greater extent from the trench opening with respect to the underlying second dielectric layer. Remaining gap fill layer is removed and the diffusion barrier layer within the via opening is etched to expose the conductive structure. The via and trench openings are plated with a barrier metal and a copper seed layer to obtain copper features that fill the openings and form a void-free copper damascene structure.

Owner:SONY CORP +1

Process for damascene structure with reduced low-k damage

ActiveUS20120252206A1Inhibit migrationImprove electrical performanceSemiconductor/solid-state device manufacturingSemiconductor devicesCopperMetal

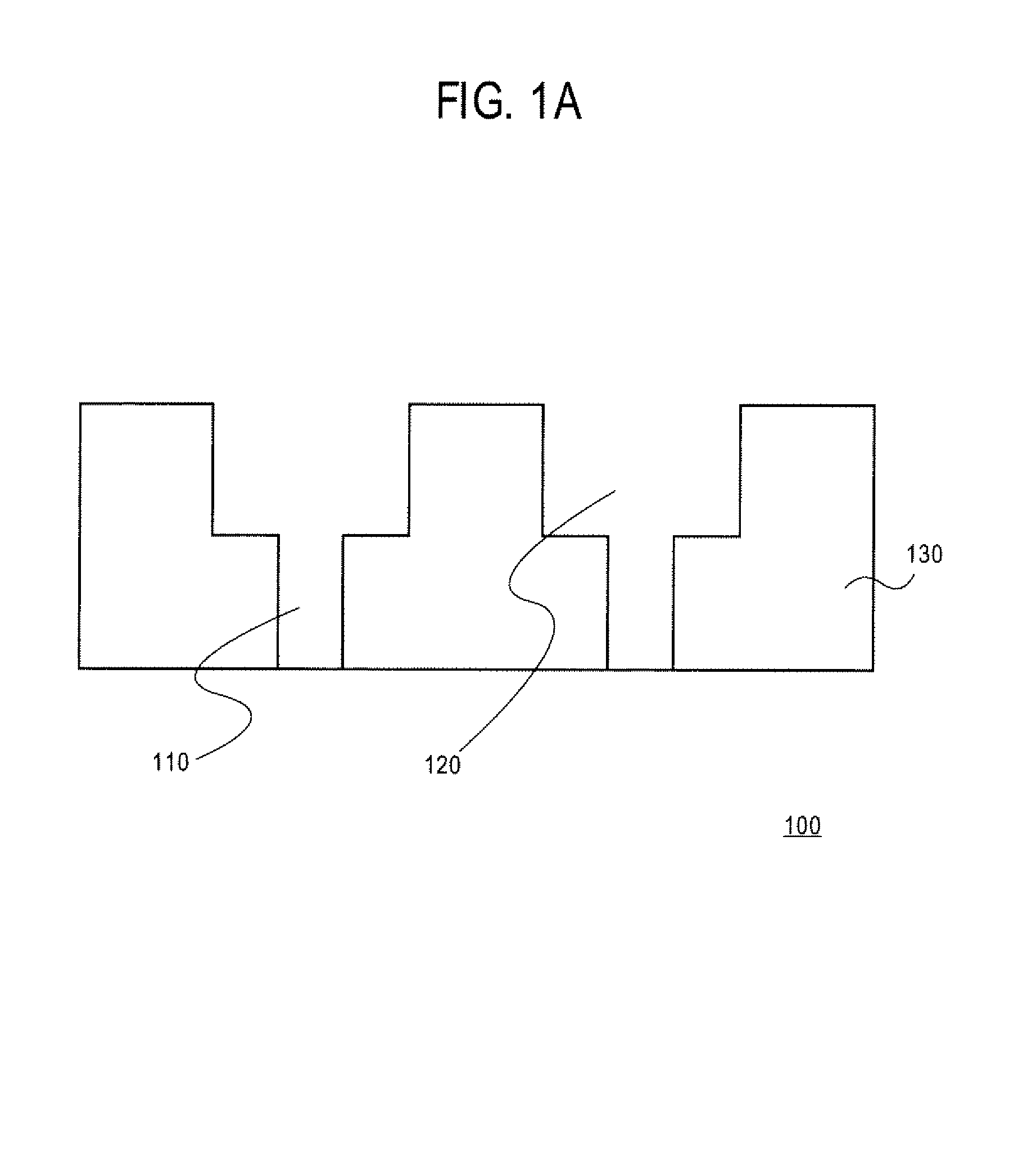

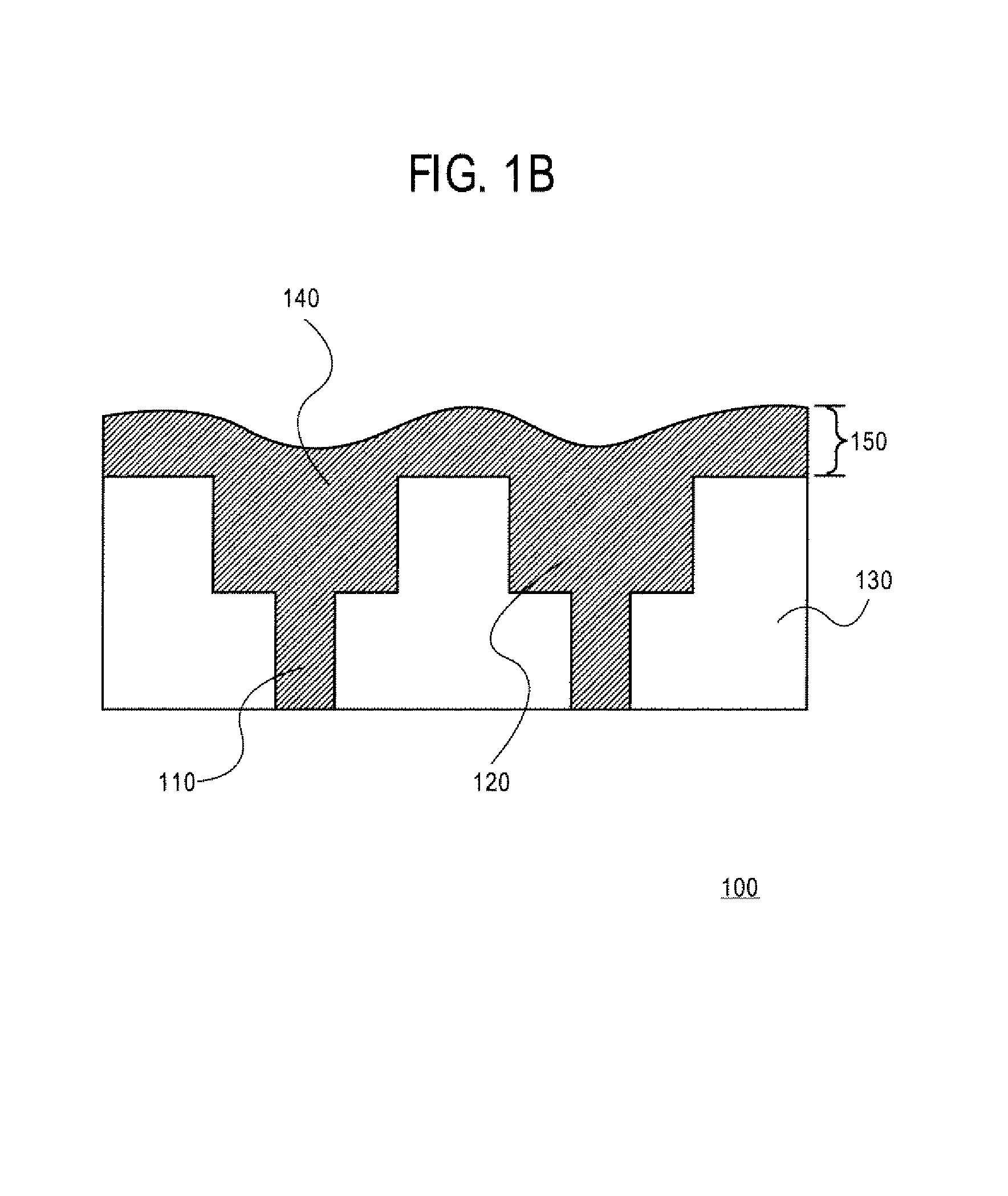

Embodiments described herein generally provide methods for reducing undesired low-k damages during a damascene process using a sacrificial dielectric material and optionally a barrier / capping layer. In one embodiment, a damascene structure is formed through a sacrificial dielectric material deposited over a dielectric base layer. The damascene structure is filled with a suitable metal such as copper. The sacrificial dielectric material filled in trench areas between the copper damascene is then removed, followed by a barrier / cap layer which conformally or selectively covers exposed surfaces of the copper damascene structure. Ultra low-k dielectric materials may then fill the trench areas that were previously filled with sacrificial dielectric material. The invention prevents the ultra low-k material between the metal lines from exposing to various damaging processes during a damascene process such as etching, stripping, wet cleaning, pre-metal cleaning or CMP process.

Owner:APPLIED MATERIALS INC

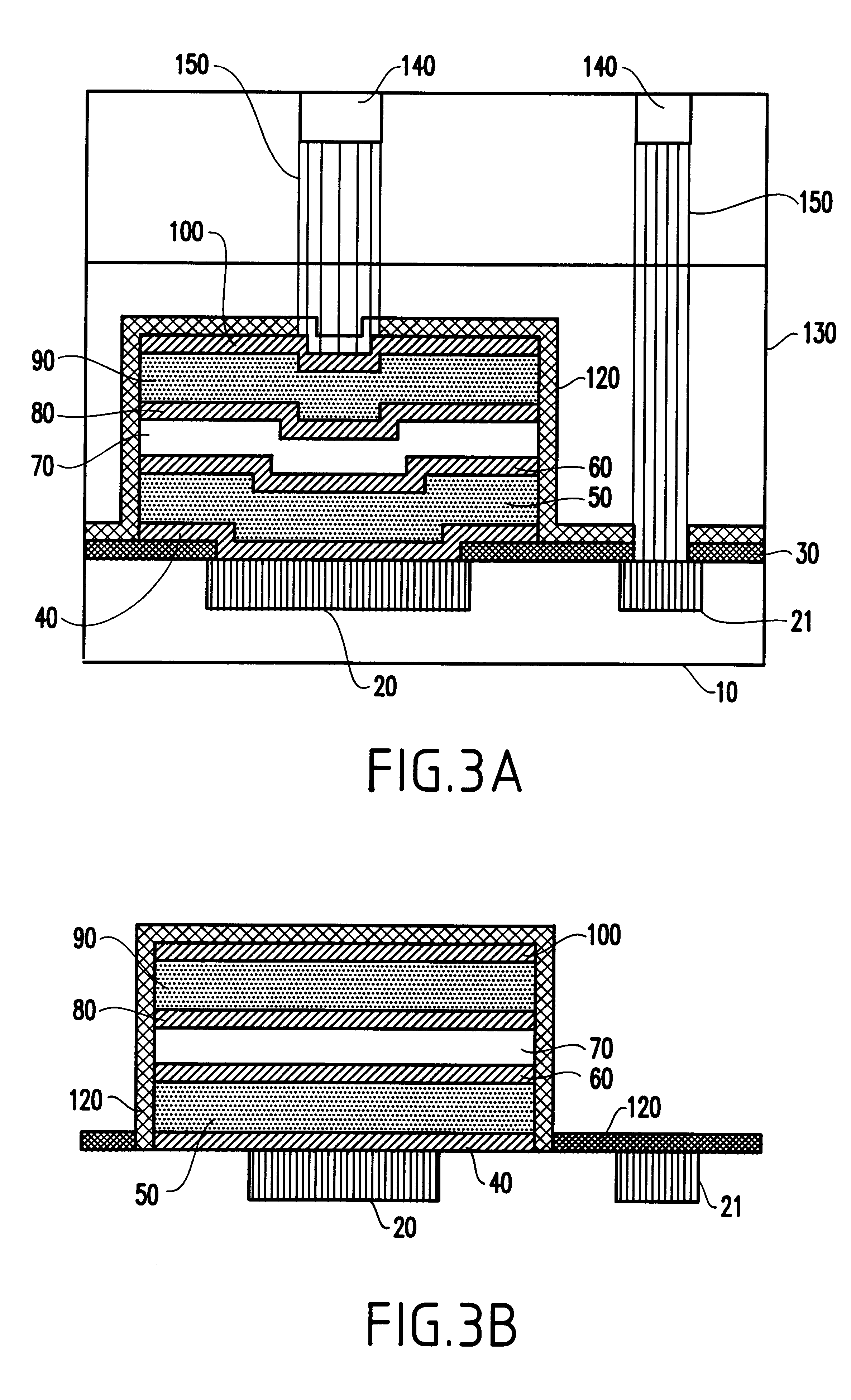

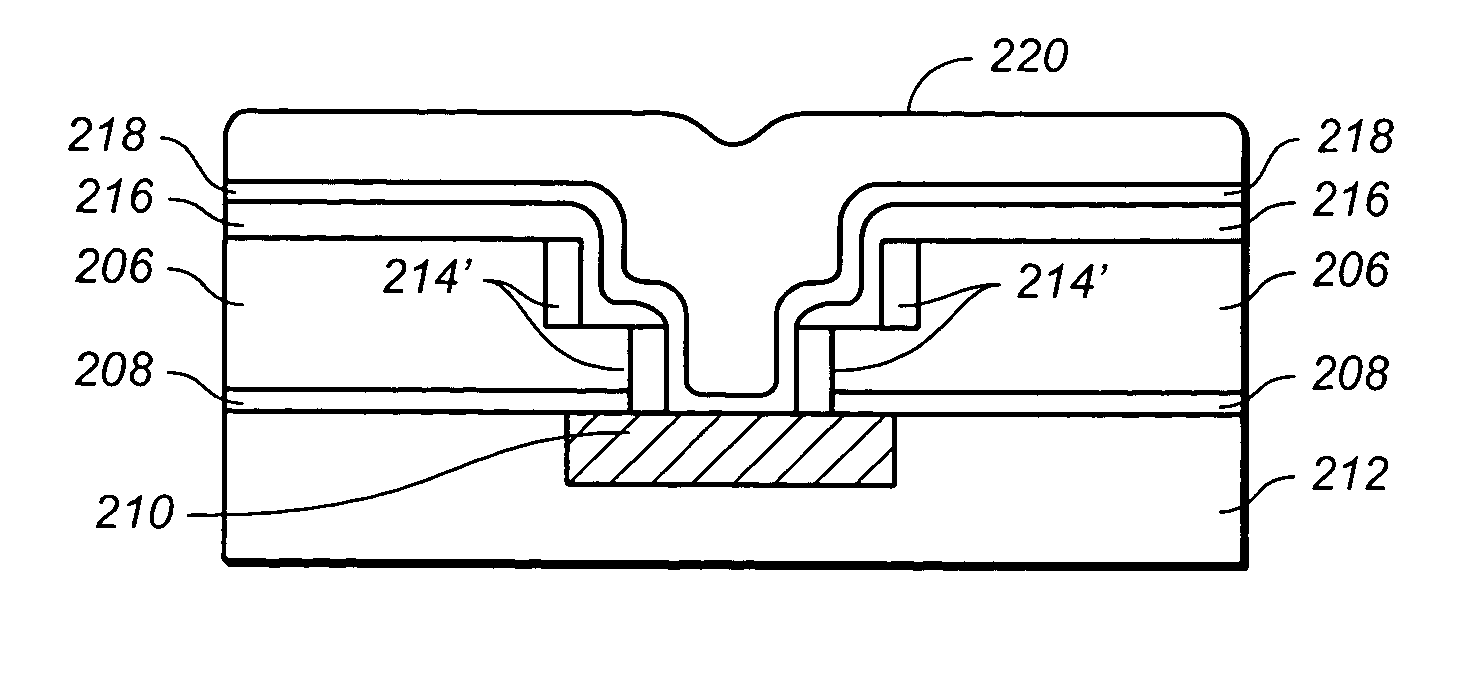

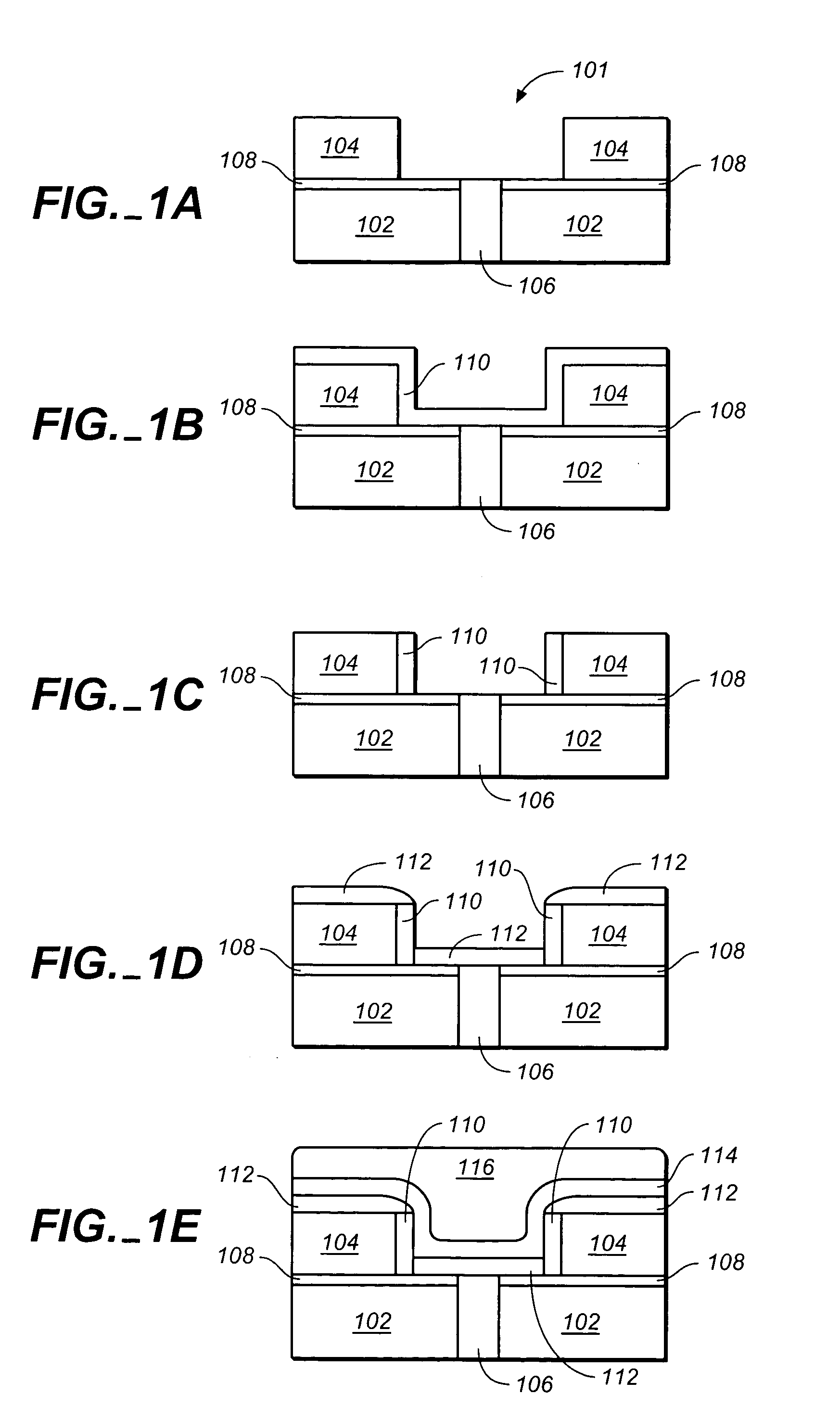

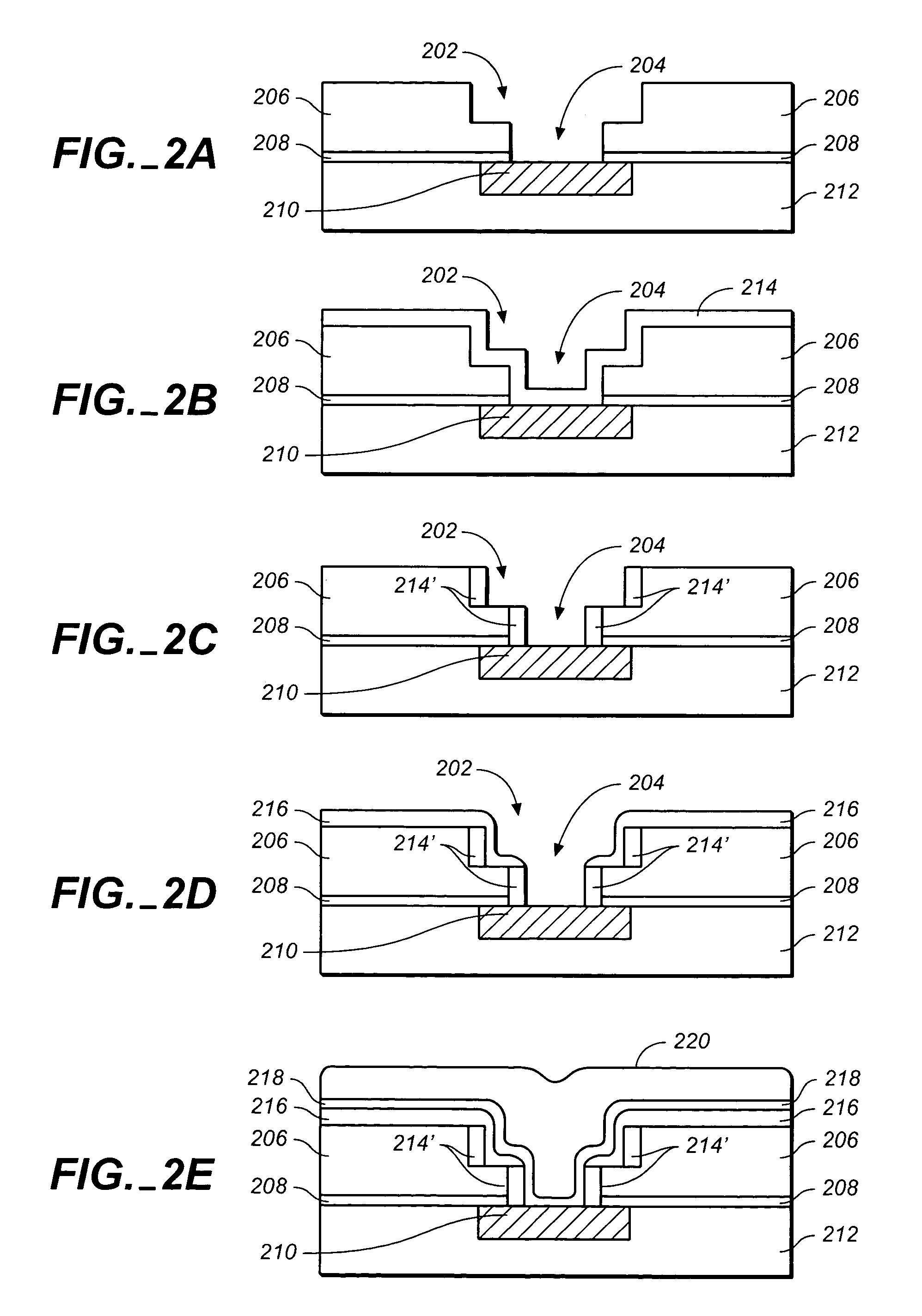

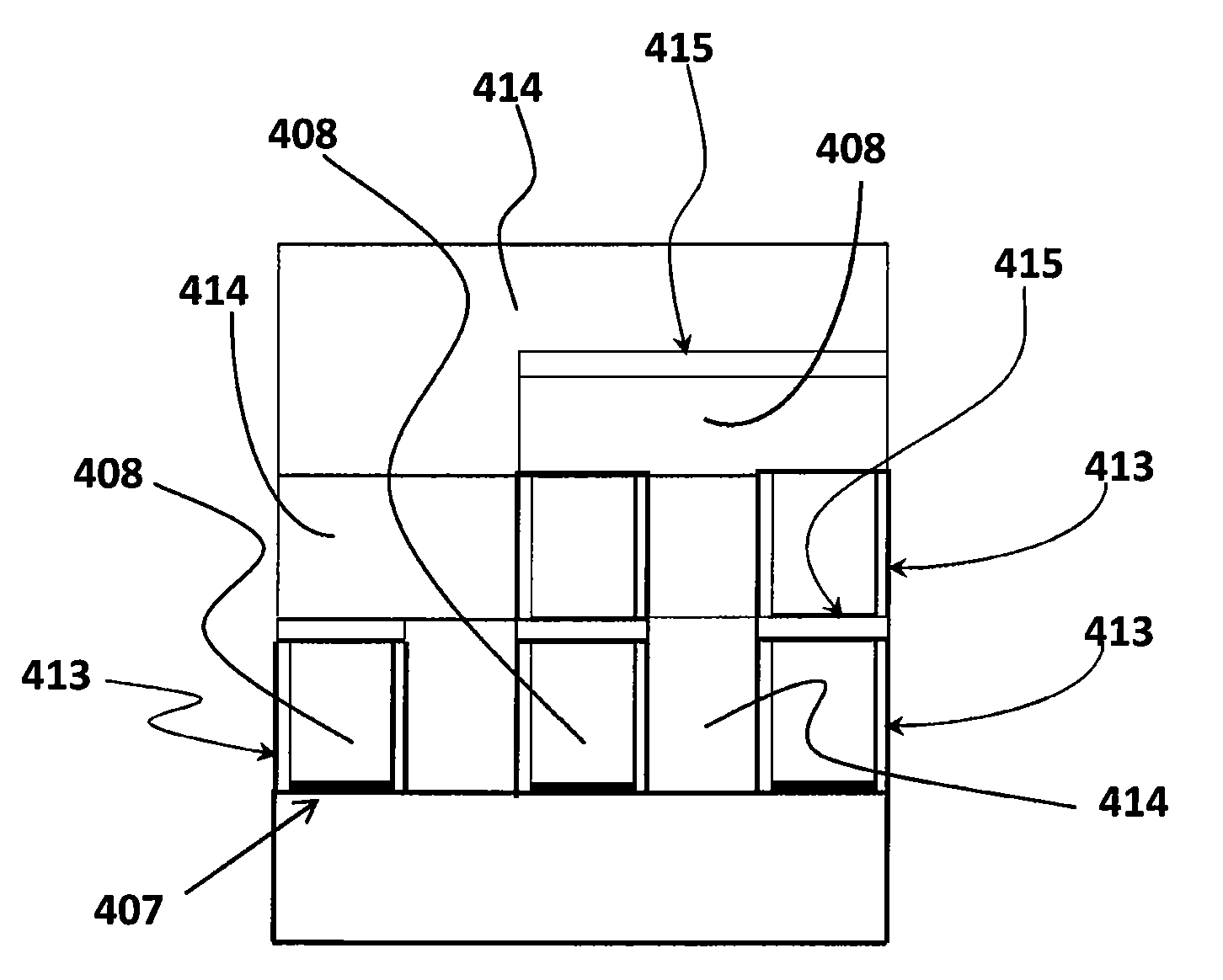

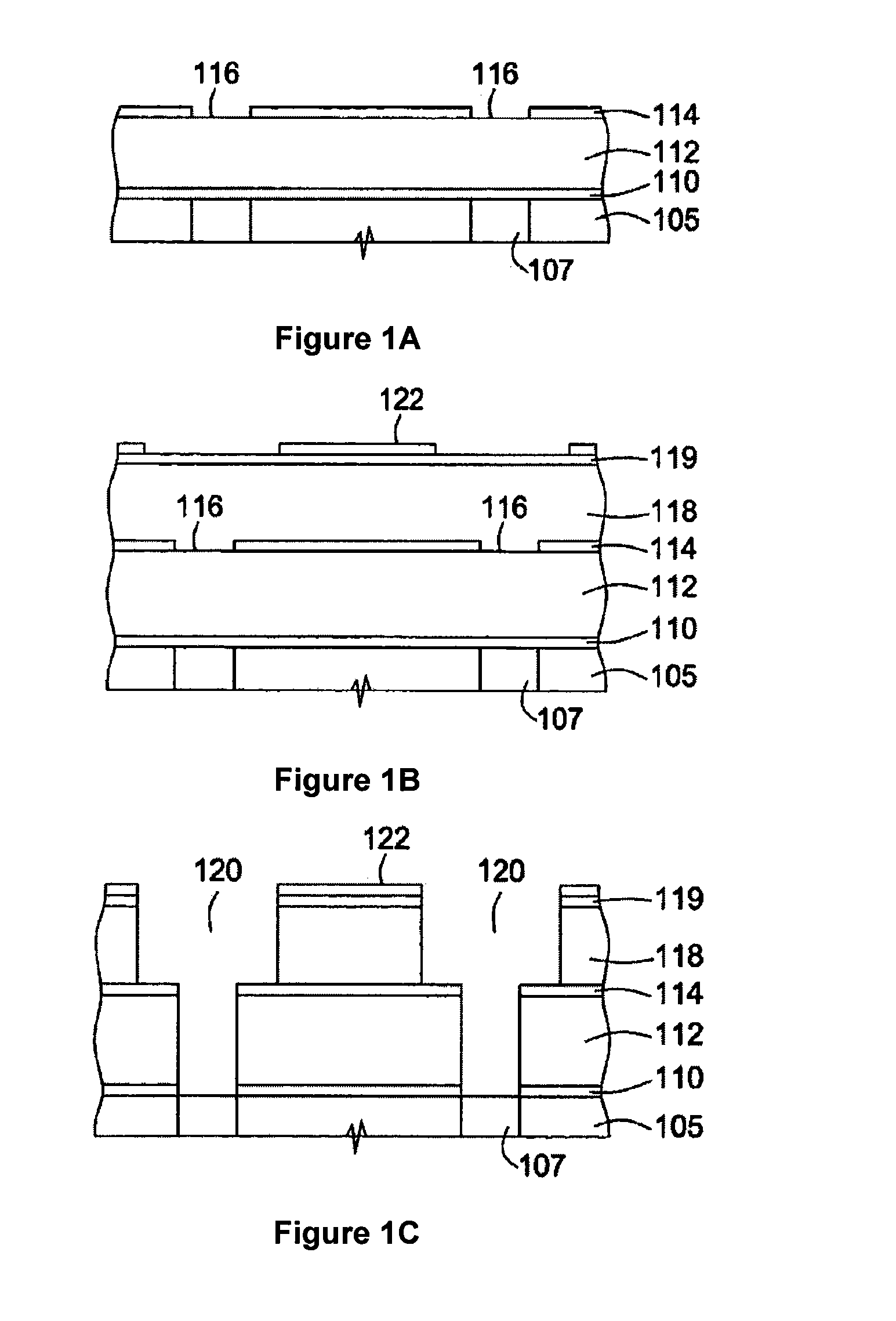

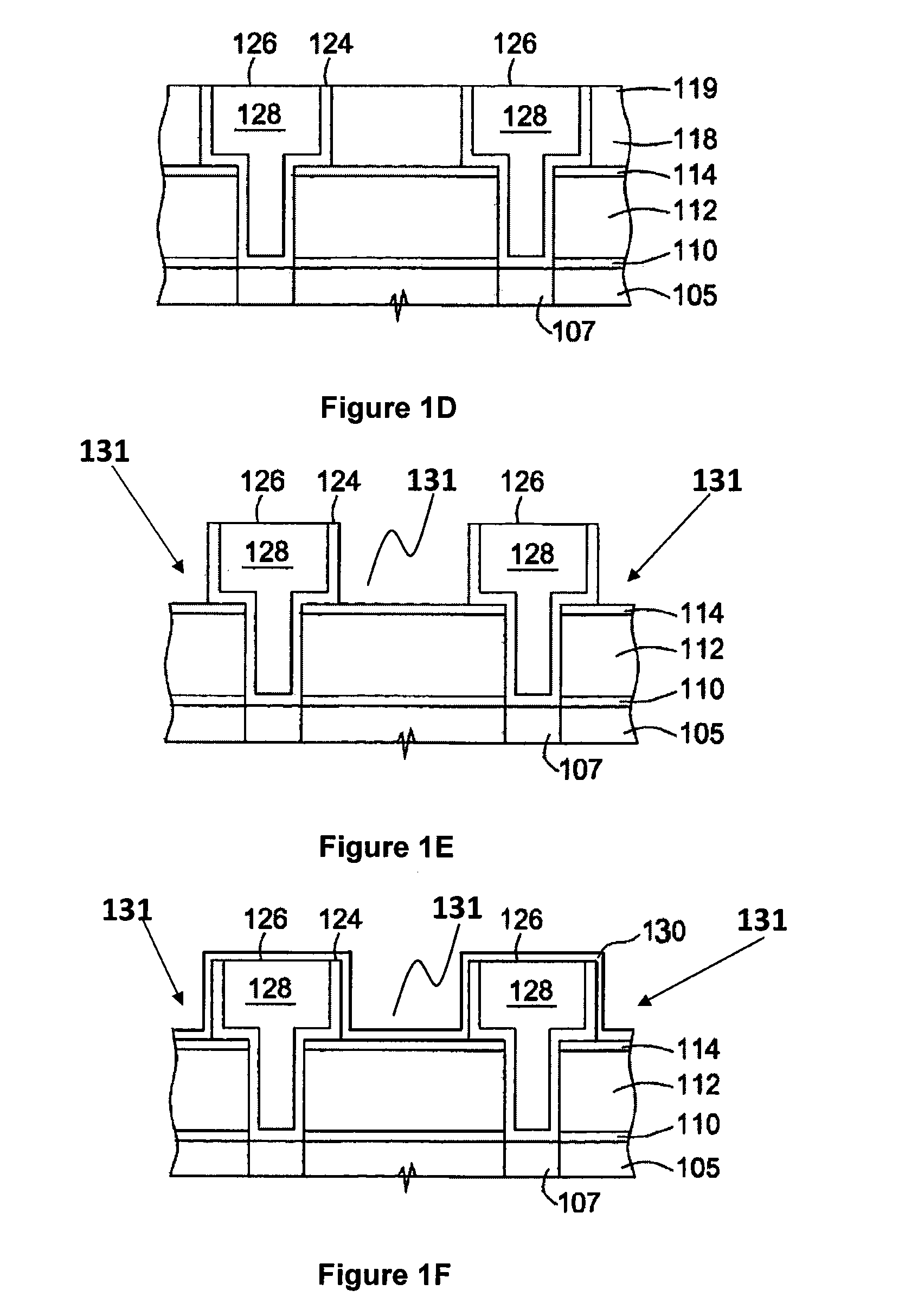

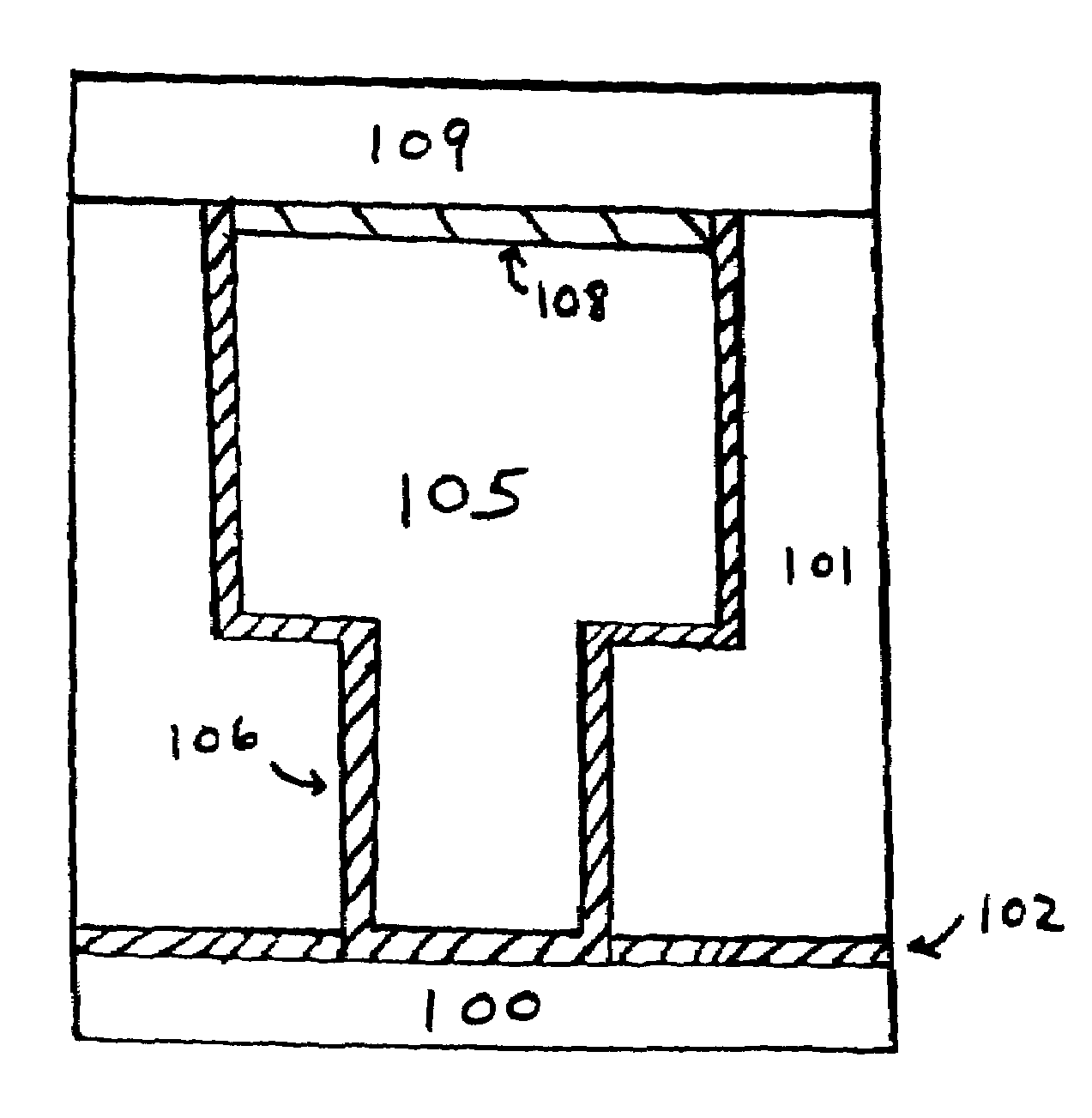

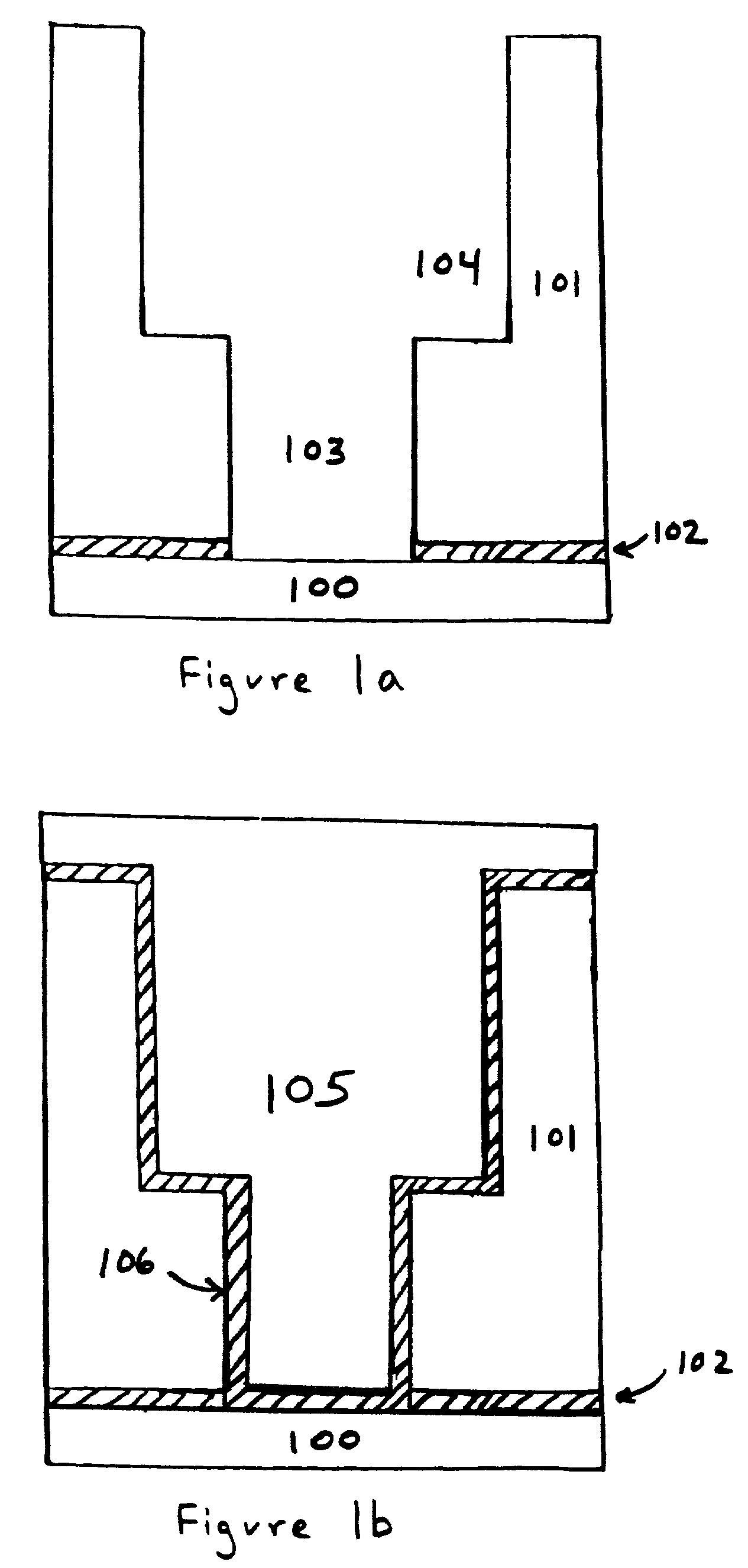

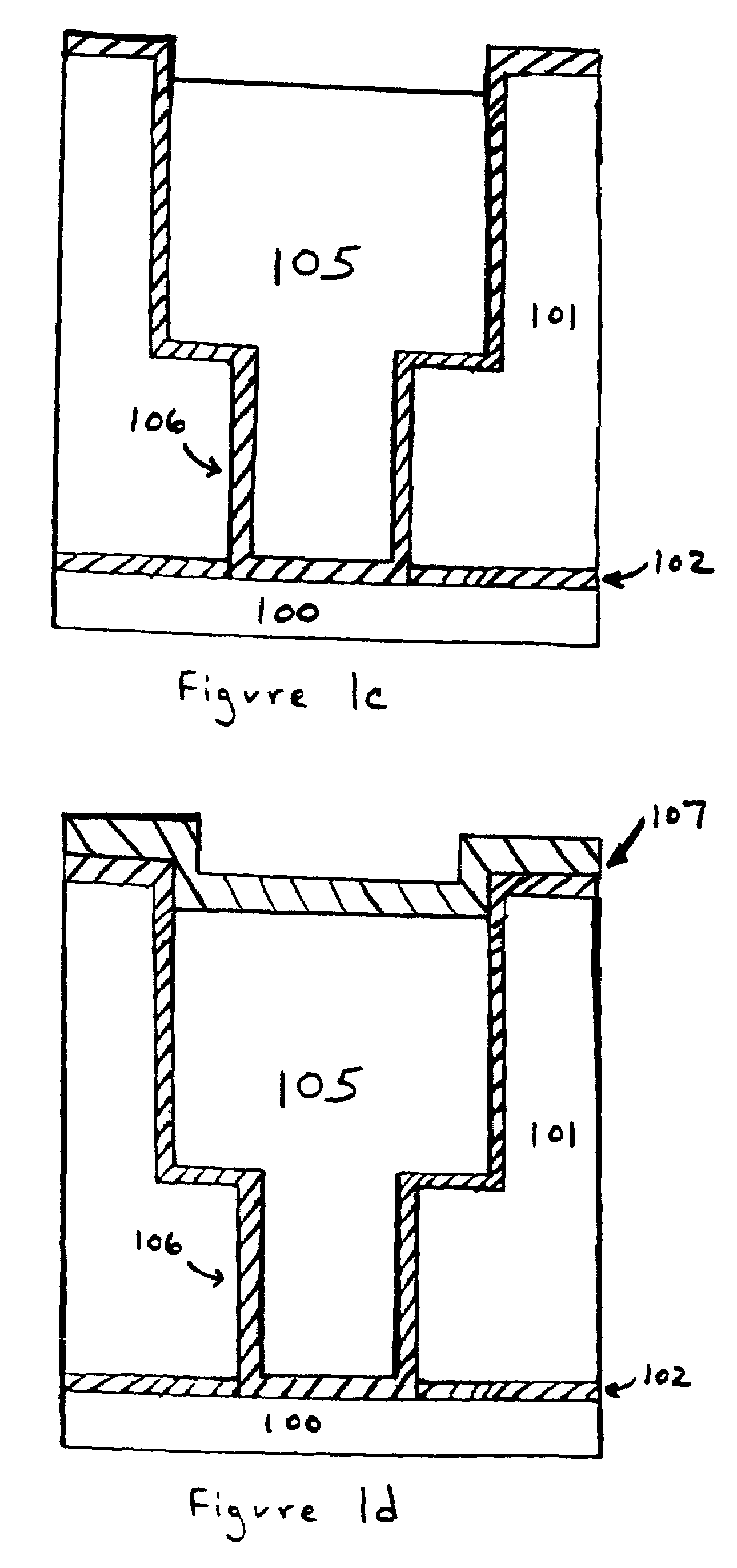

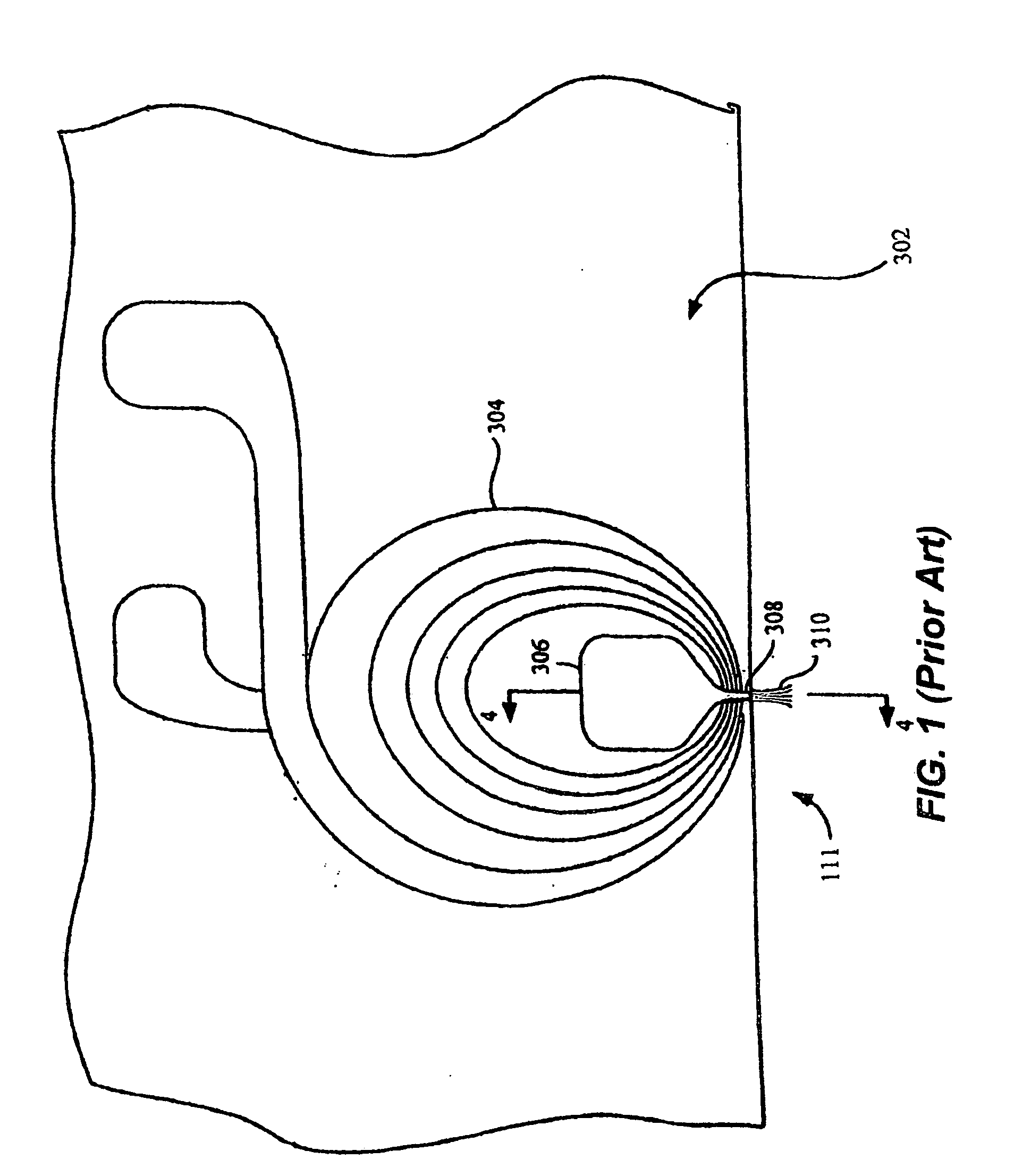

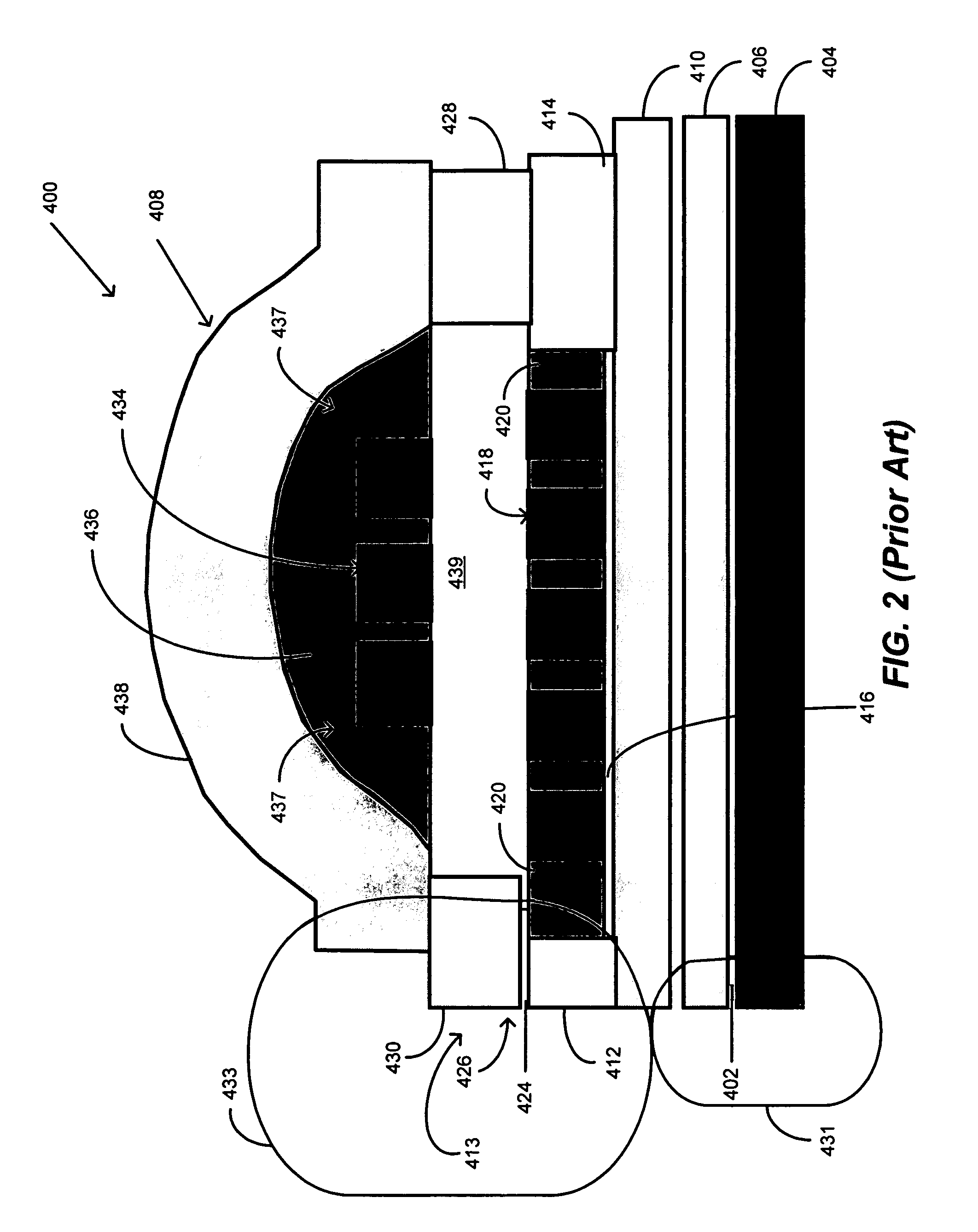

Method of fabricating micro-electromechanical switches on cmos compatible substrates

InactiveCN1575506AElectrostatic/electro-adhesion relaysDecorative surface effectsElectrical conductorEngineering

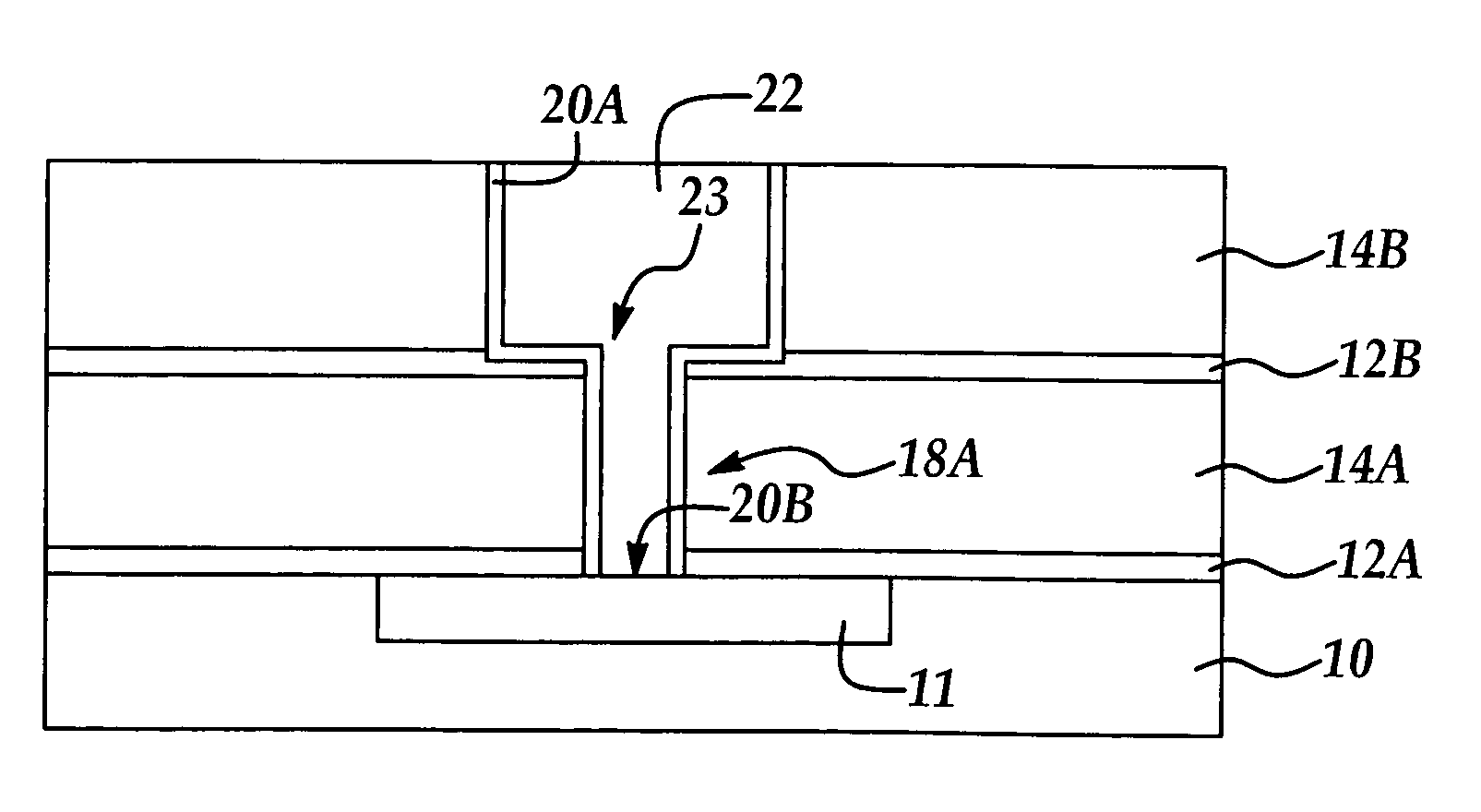

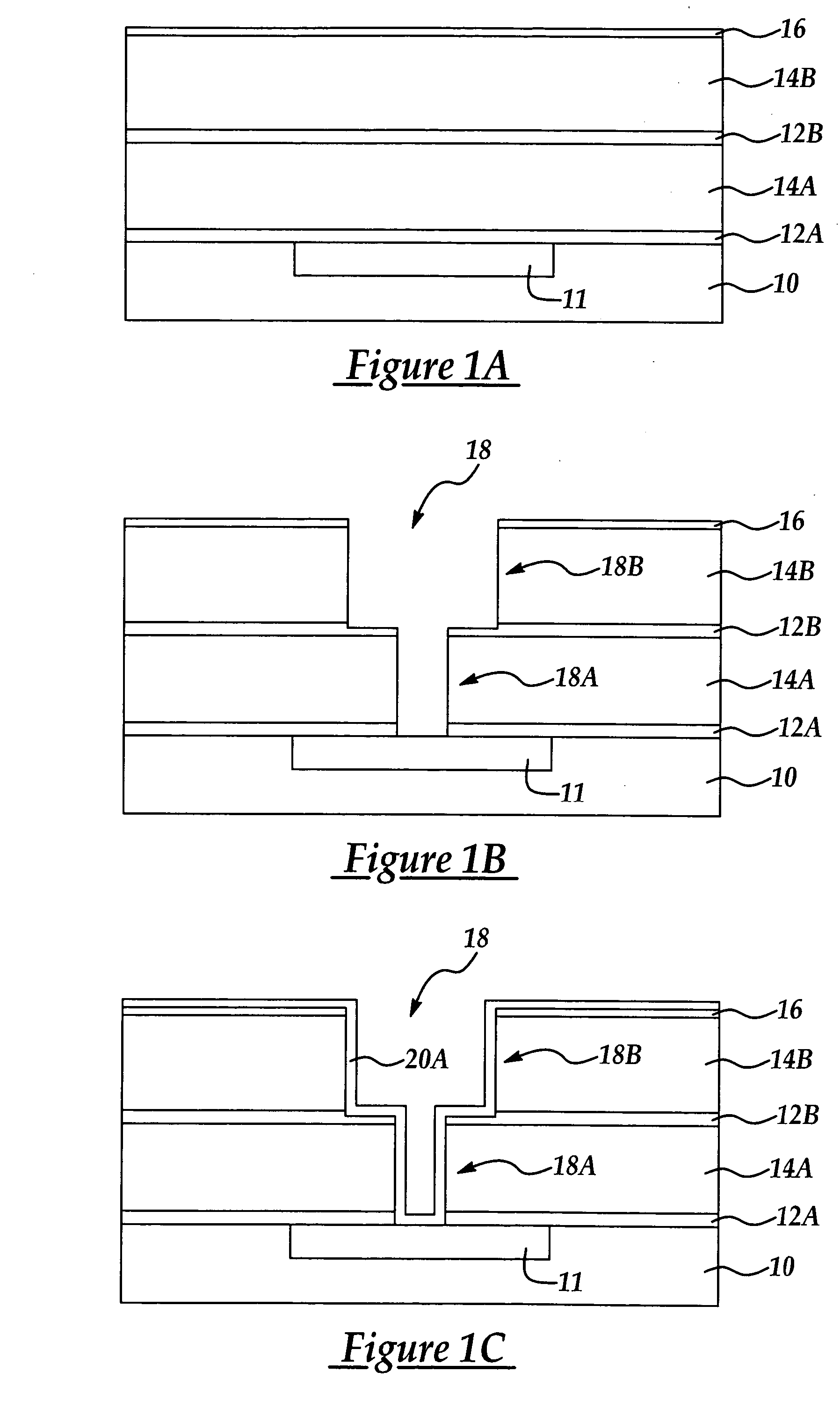

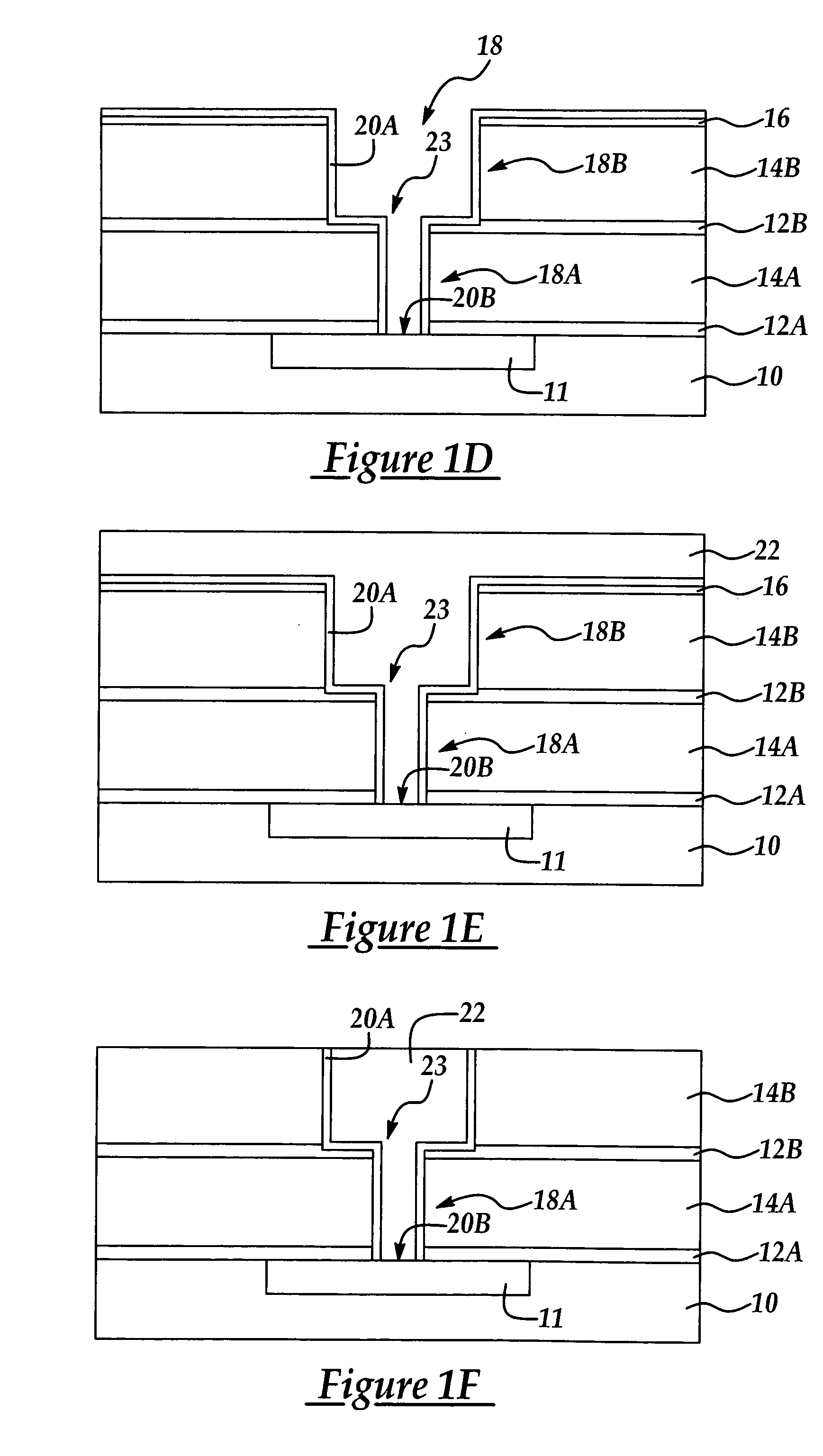

A method of fabricating micro-electromechanical switches (MEMS) integrated with conventional semiconductor interconnect levels, using compatible processes and materials is described. The method is based upon fabricating a capacitive switch that is easily modified to produce various configurations for contact switching and any number of metal-dielectric-metal switches. The process starts with a copper damascene interconnect layer, made of metal conductors inlaid in a dielectric. All or portions of the copper interconnects are recessed to a degree sufficient to provide a capacitive air gap when the switch is in the closed state, as well as provide space for a protective layer of, e.g., Ta / TaN. The metal structures defined within the area specified for the switch act as actuator electrodes to pull down the movable beam and provide one or more paths for the switched signal to traverse. The advantage of an air gap is that air is not subject to charge storage or trapping that can cause reliability and voltage drift problems. Instead of recessing the electrodes to provide a gap, one may just add dielectric on or around the electrode. The next layer is another dielectric layer which is deposited to the desired thickness of the gap formed between the lower electrodes and the moveable beam that forms the switching device. Vias are fabricated through this dielectric to provide connections between the metal interconnect layer and the next metal layer which will also contain the switchable beam. The via layer is then patterned and etched to provide a cavity area which contains the lower activation electrodes as well as the signal paths. The cavity is then back-filled with a sacrificial release material. This release material is then planarized with the top of the dielectric, thereby providing a planar surface upon which the beam layer is constructed.

Owner:格芯公司

Reactive barrier/seed preclean process for damascene process

A method for making a multilayer interconnect electronic component structure, and, in particular, an integrated circuit semiconductor device made using a copper damascene method is provided. The process of the invention uses a method for pre-cleaning exposed copper surfaces in the structure. The method employs a cleaning composition containing a nitrogen containing material and an oxygen containing material and also optionally a hydrogen containing material to remove the copper oxide film on copper surfaces in the structure. The preferred nitrogen material is nitrogen gas and the preferred oxygen material is oxygen gas. The gas mixture is preferably energized to form a plasma which is used to contact and remove the copper oxide and clean the structure. A two-step process may be used employing a nitrogen / oxygen mixture and then a hydrogen containing gas mixture such as Ar / H2. It has also been found that the advantages of the method include not only removal of residue and copper oxide from the structure without significant dielectric shift of the dielectric, but also provides enhanced metal adhesion to the treated dielectric as well as surface passivation of the dielectric.

Owner:NOVELLUS SYSTEMS

Method of forming barrier layer with reduced resistivity and improved reliability in copper damascene process

ActiveUS7071100B2Improve the immunityHigh resistivitySemiconductor/solid-state device manufacturingDielectricRemote plasma

A method for forming a copper dual damascene with improved copper migration resistance and improved electrical resistivity including providing a semiconductor wafer including upper and lower dielectric insulating layers separated by a middle etch stop layer; forming a dual damascene opening extending through a thickness of the upper and lower dielectric insulating layers wherein an upper trench line portion extends through the upper dielectric insulating layer thickness and partially through the middle etch stop layer; blanket depositing a barrier layer including at least one of a refractory metal and refractory metal nitride to line the dual damascene opening; carrying out a remote plasma etch treatment of the dual damascene opening to remove a bottom portion of the barrier layer to reveal an underlying conductive area; and, filling the dual damascene opening with copper to provide a substantially planar surface.

Owner:TAIWAN SEMICON MFG CO LTD

Method of fabricating a copper damascene structure

InactiveUS6660639B2Reducing copper polishing rateRetard the corrosion of said copper linesOther chemical processesSemiconductor/solid-state device manufacturingSlurryCopper

The present invention provides a method of removing copper overlaying a tantalum-based barrier layer during the fabrication of a copper damascene structure having a plurality of copper lines. The method includes providing a chemical-mechanical polishing slurry and polishing the copper layer using the slurry until the tantalum-based barrier layer is exposed. The slurry includes an oxidizing agent that releases free radicals and a non-chelating free radical quencher that retards the corrosion of said copper lines during chemical mechanical polishing. Preferred non-chelating free radical quenchers are ascorbic acid, thiamine, 2-propanol, and alkyl glycols. The present invention also provides copper damascene structures formed according to the method.

Owner:FERRO CORP

Method of making a semiconductor device that has copper damascene interconnects with enhanced electromigration reliability

A method of making a semiconductor device is described. That method includes forming a copper containing layer on a substrate, and forming an alloying layer that includes an alloying element on the copper containing layer. After applying heat to cause an intermetallic layer that includes copper and the alloying element to form on the surface of the copper containing layer, a barrier layer is formed on the intermetallic layer.

Owner:INTEL CORP

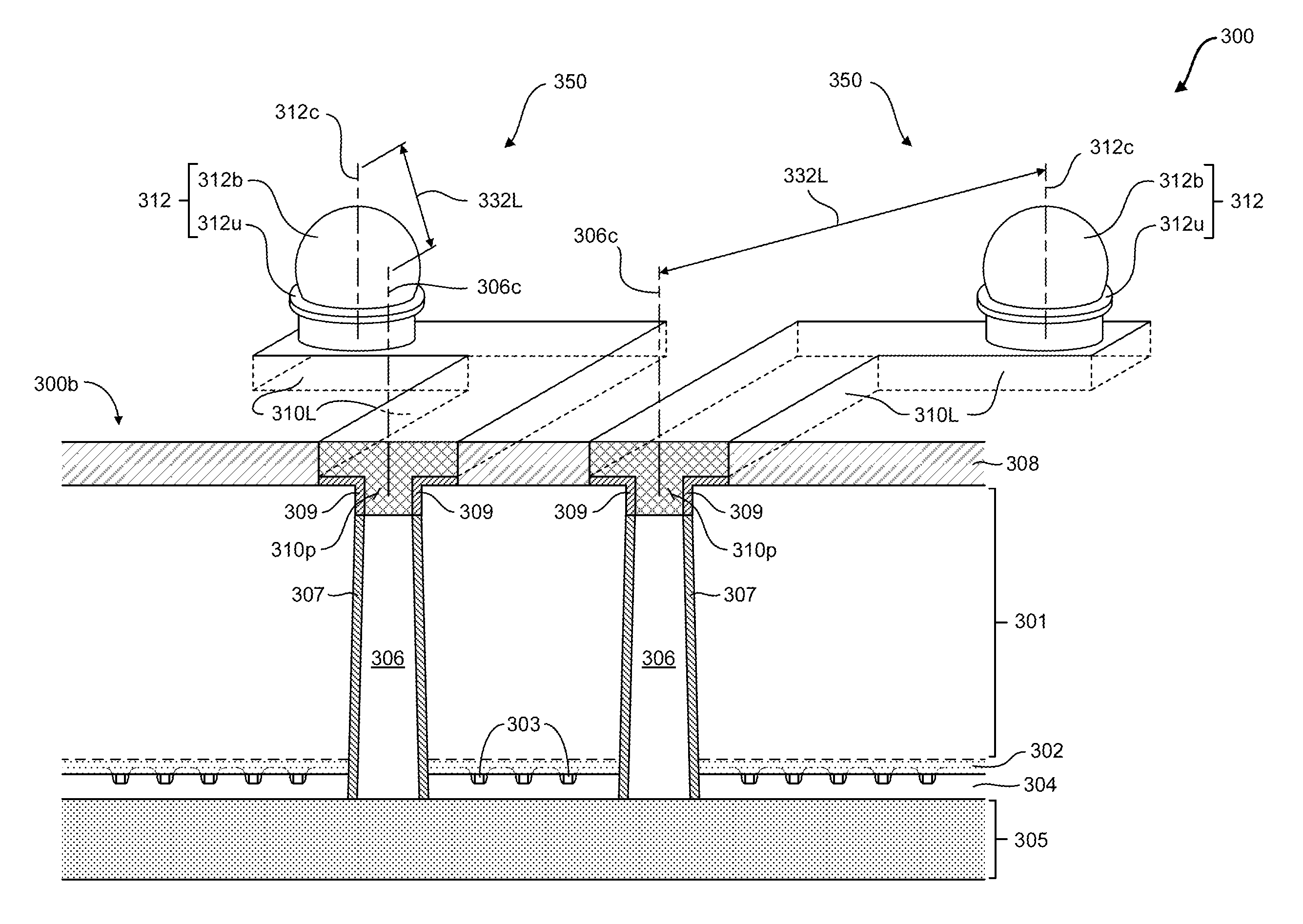

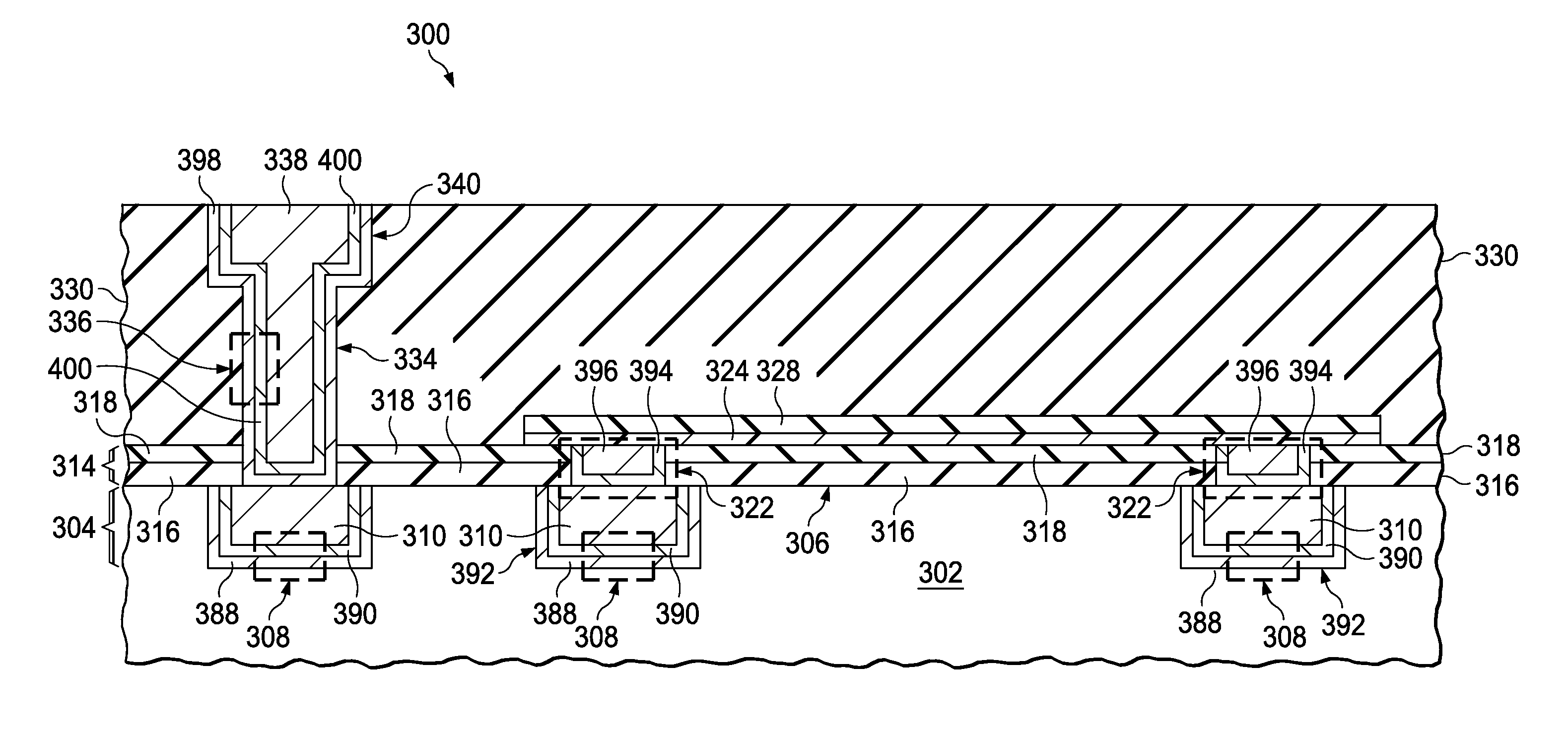

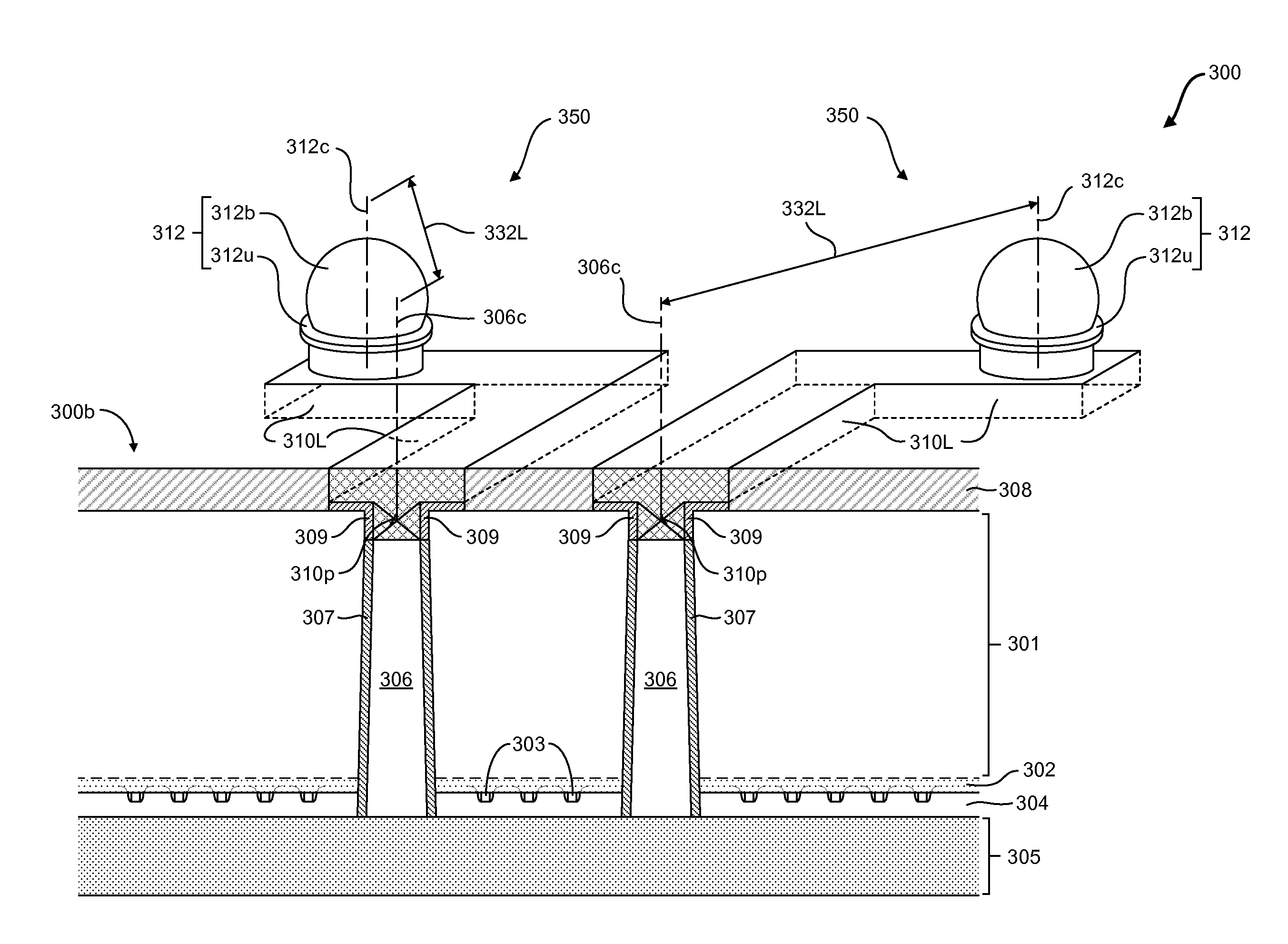

TSV backside processing using copper damascene interconnect technology

ActiveUS8466062B2Semiconductor/solid-state device detailsSolid-state devicesSubject matterSemiconductor chip

Generally, the subject matter disclosed herein relates to interconnect structures used for making electrical connections between semiconductor chips in a stacked or 3D chip configuration, and methods for forming the same. One illustrative method disclosed herein includes forming a conductive via element in a semiconductor substrate, wherein the conductive via element is formed from a front side of the semiconductor substrate so as to initially extend a partial distance through the semiconductor substrate. The illustrative method also includes forming a via opening in a back side of the semiconductor substrate to expose a surface of the conductive via element, and filling the via opening with a layer of conductive contact material.

Owner:GLOBALFOUNDRIES SINGAPORE PTE LTD

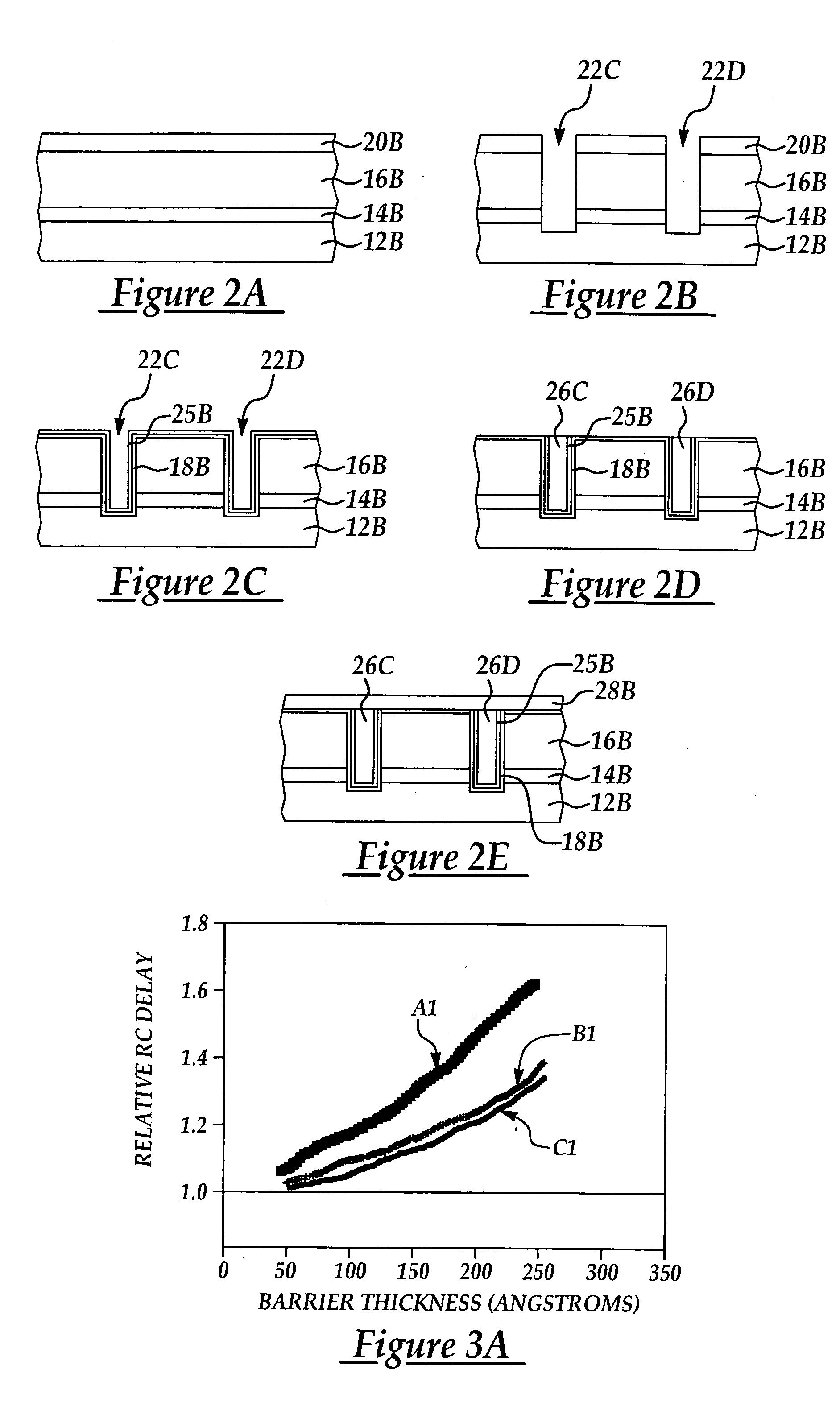

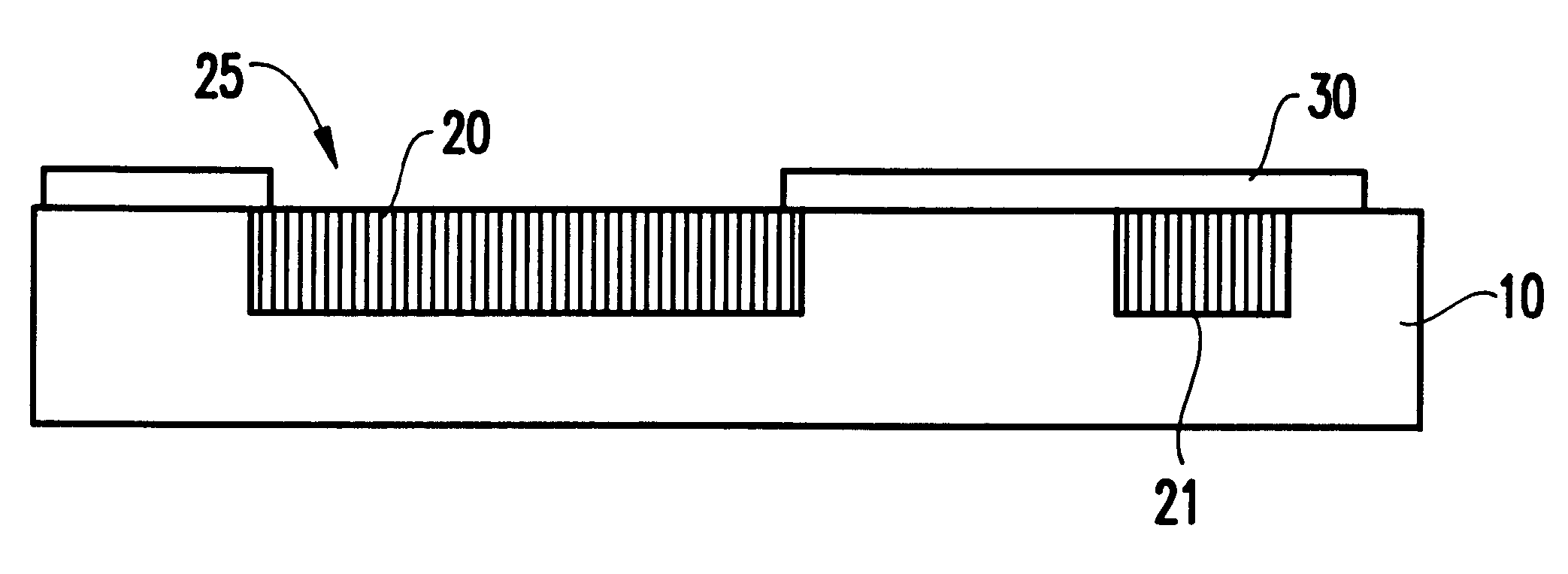

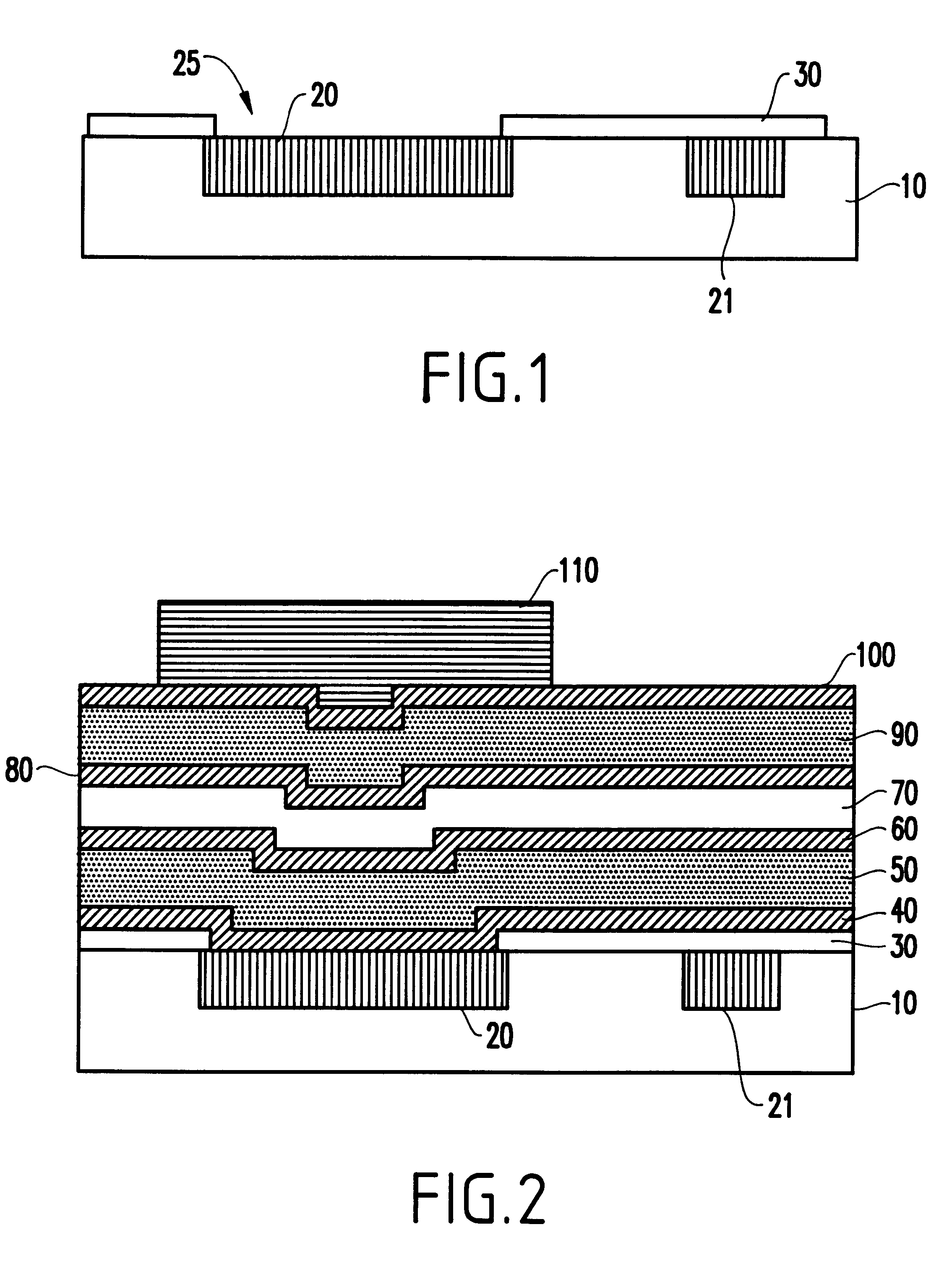

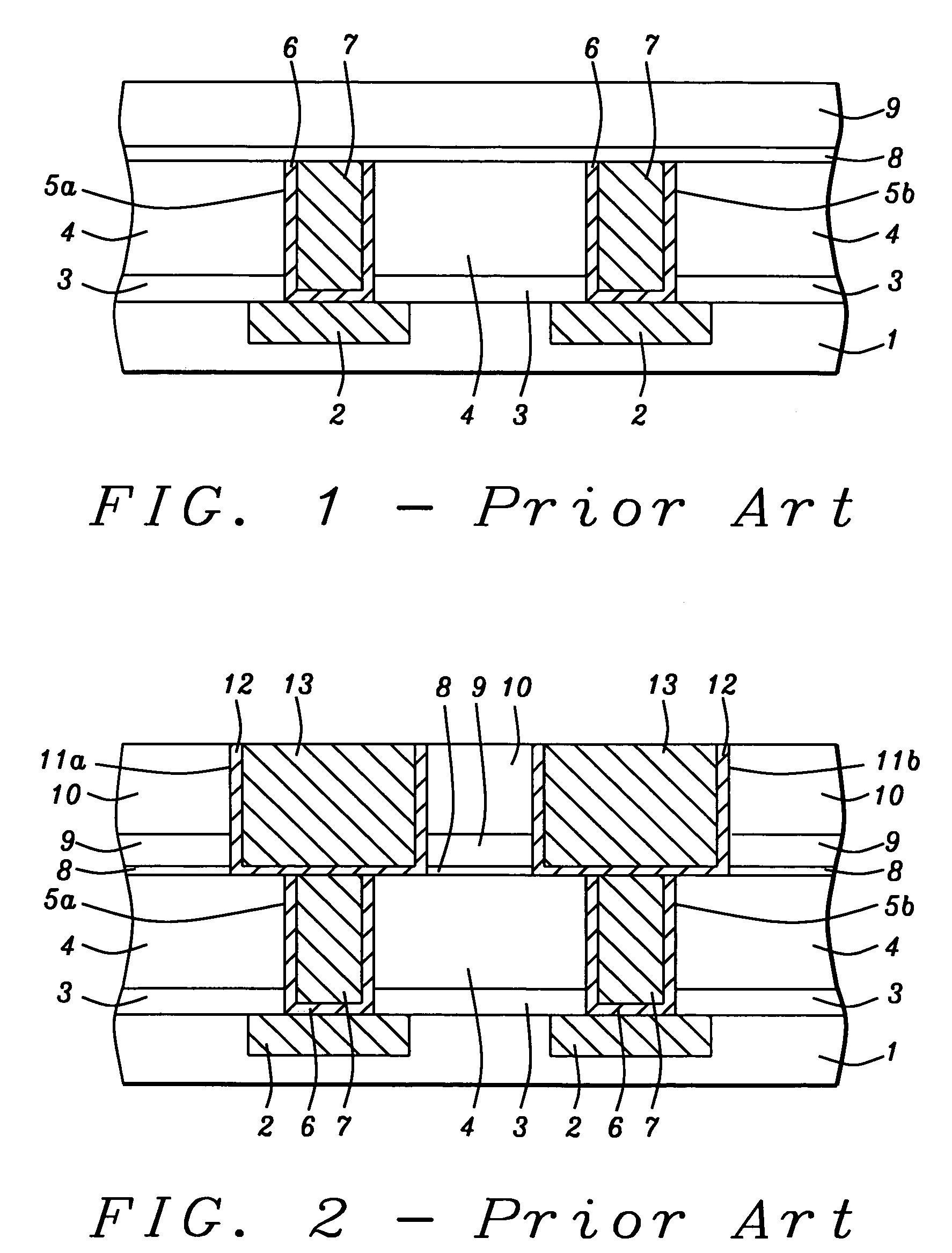

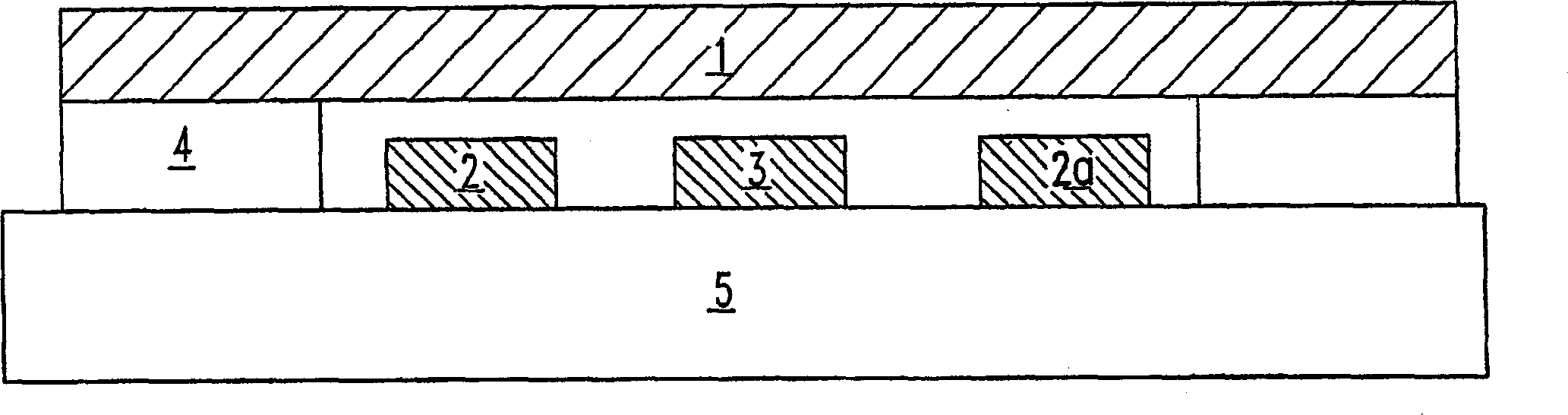

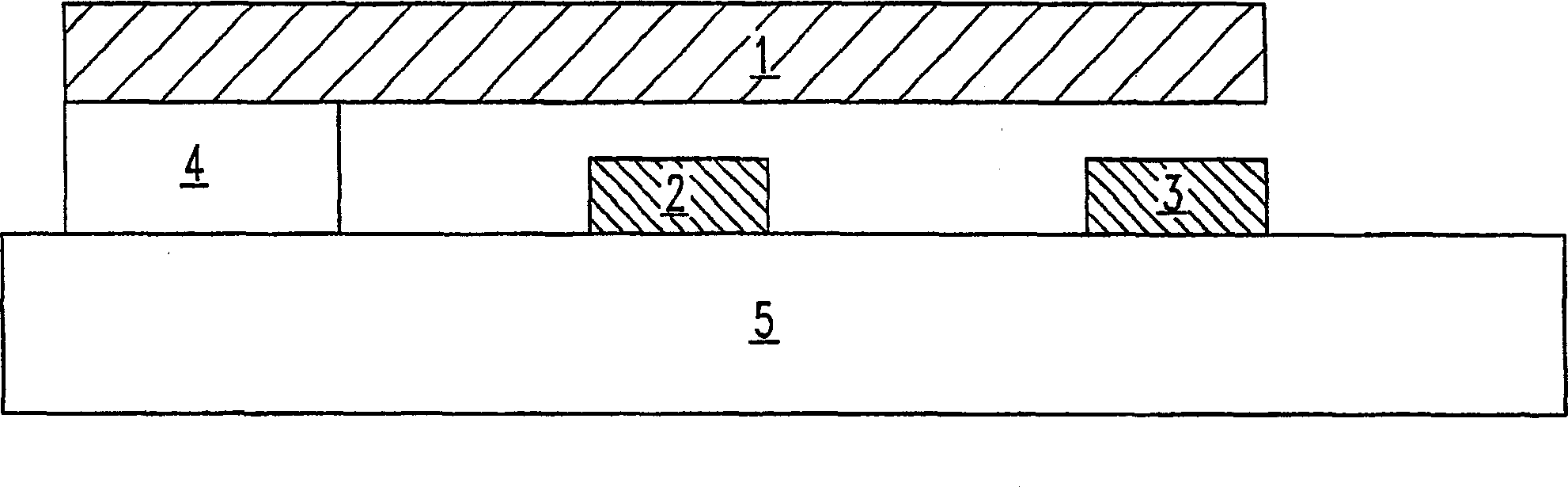

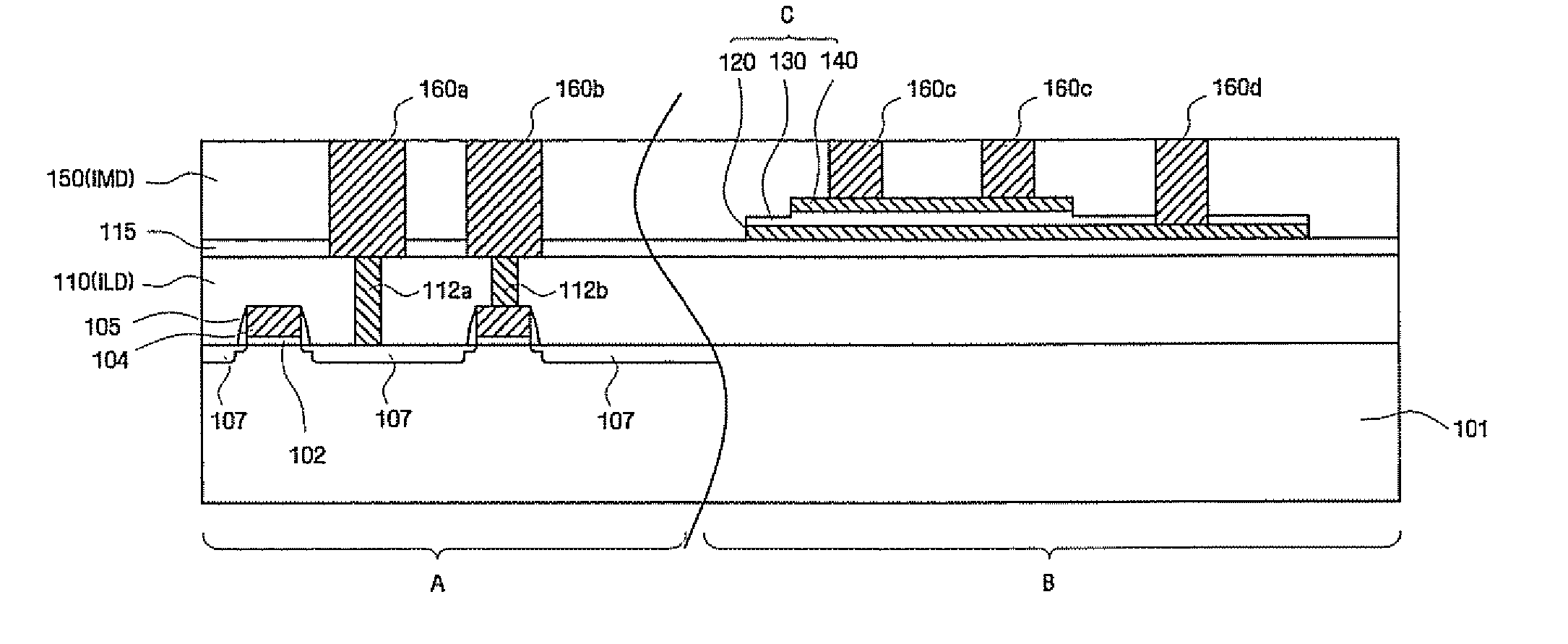

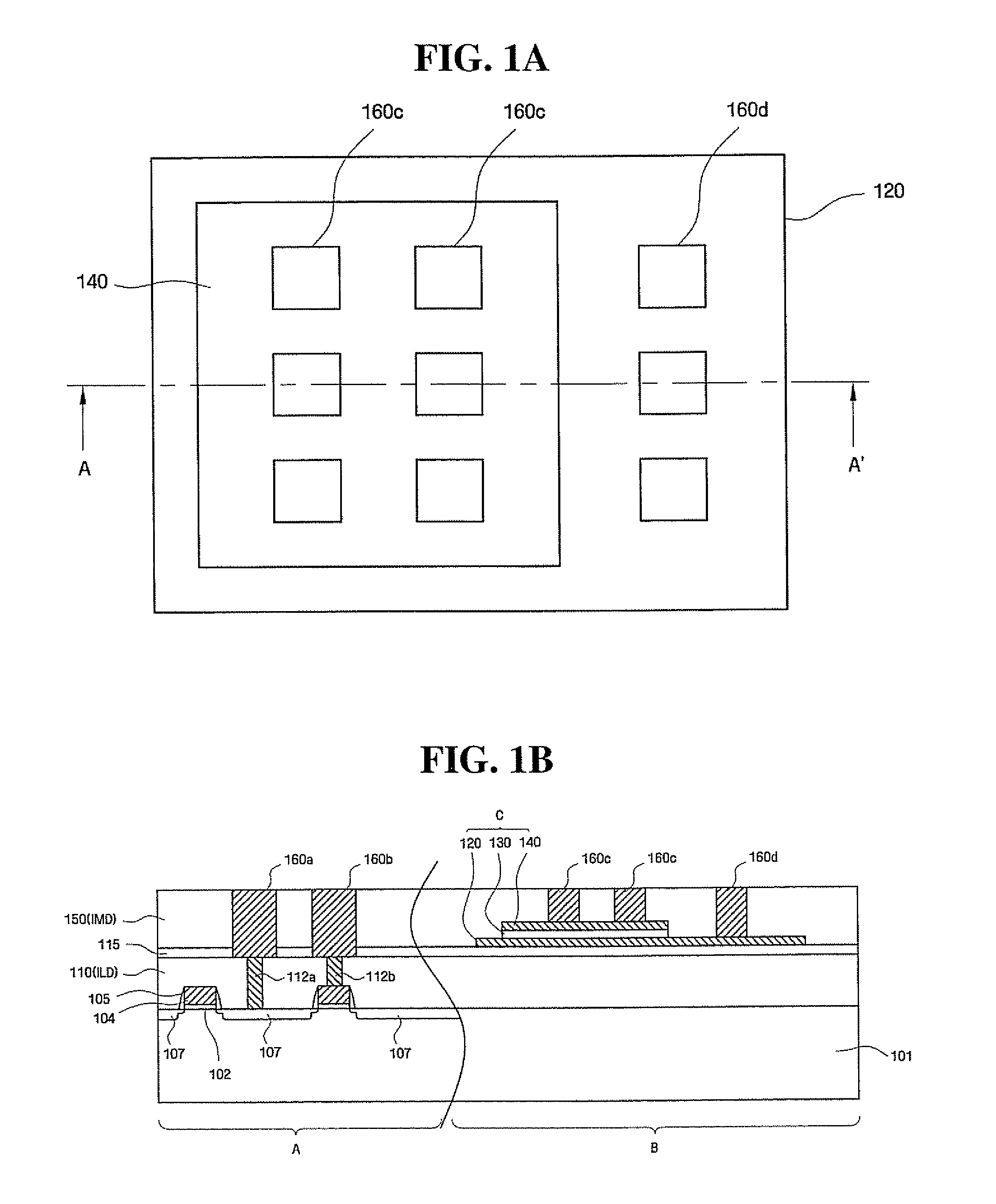

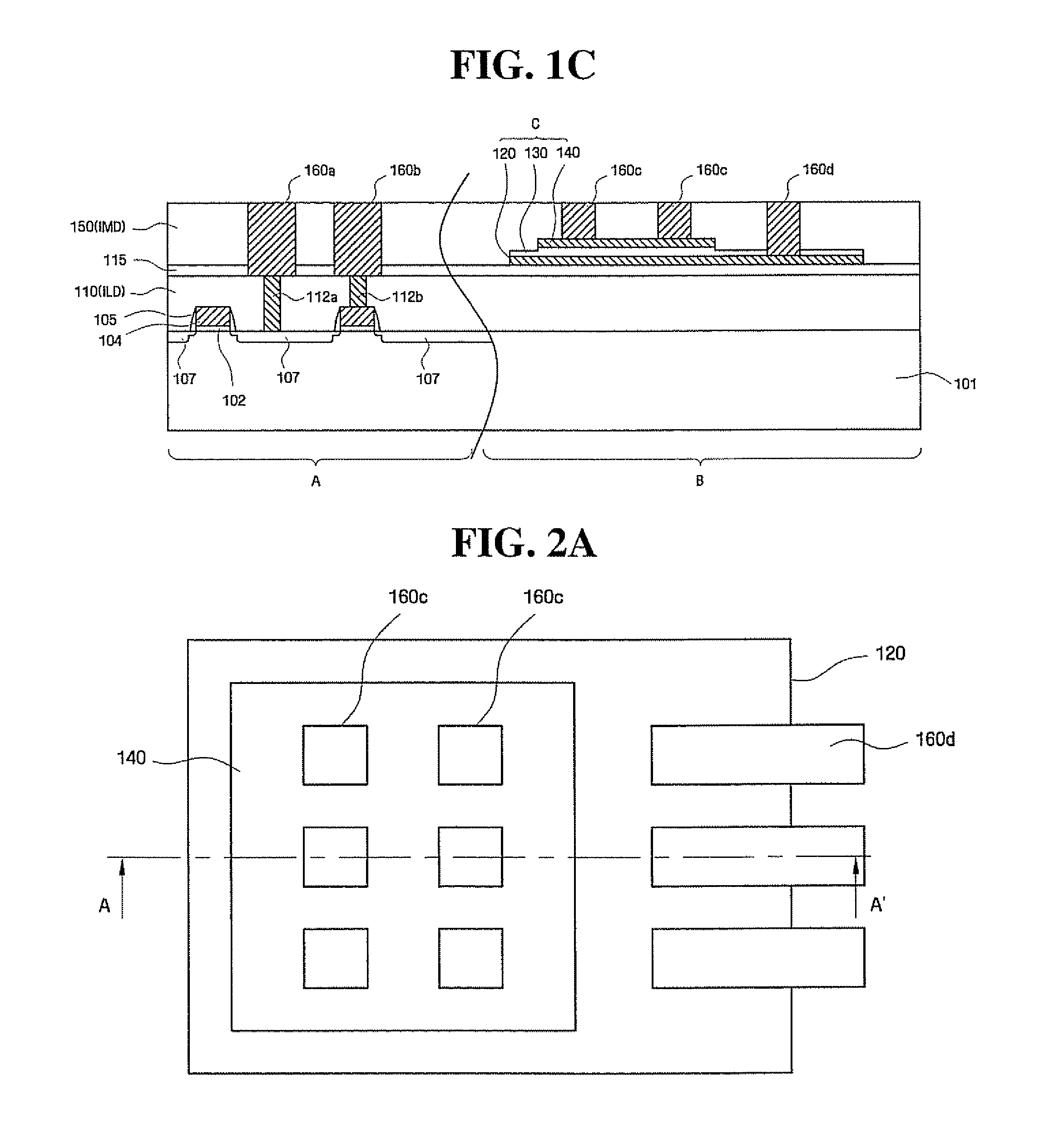

Metal-Insulator-Metal (MIM) Capacitors Formed Beneath First Level Metallization and Methods of Forming Same

InactiveUS20070034988A1Improve leakage current characteristicSufficient durationSemiconductor/solid-state device detailsSolid-state devicesMetal-insulator-metalMetal

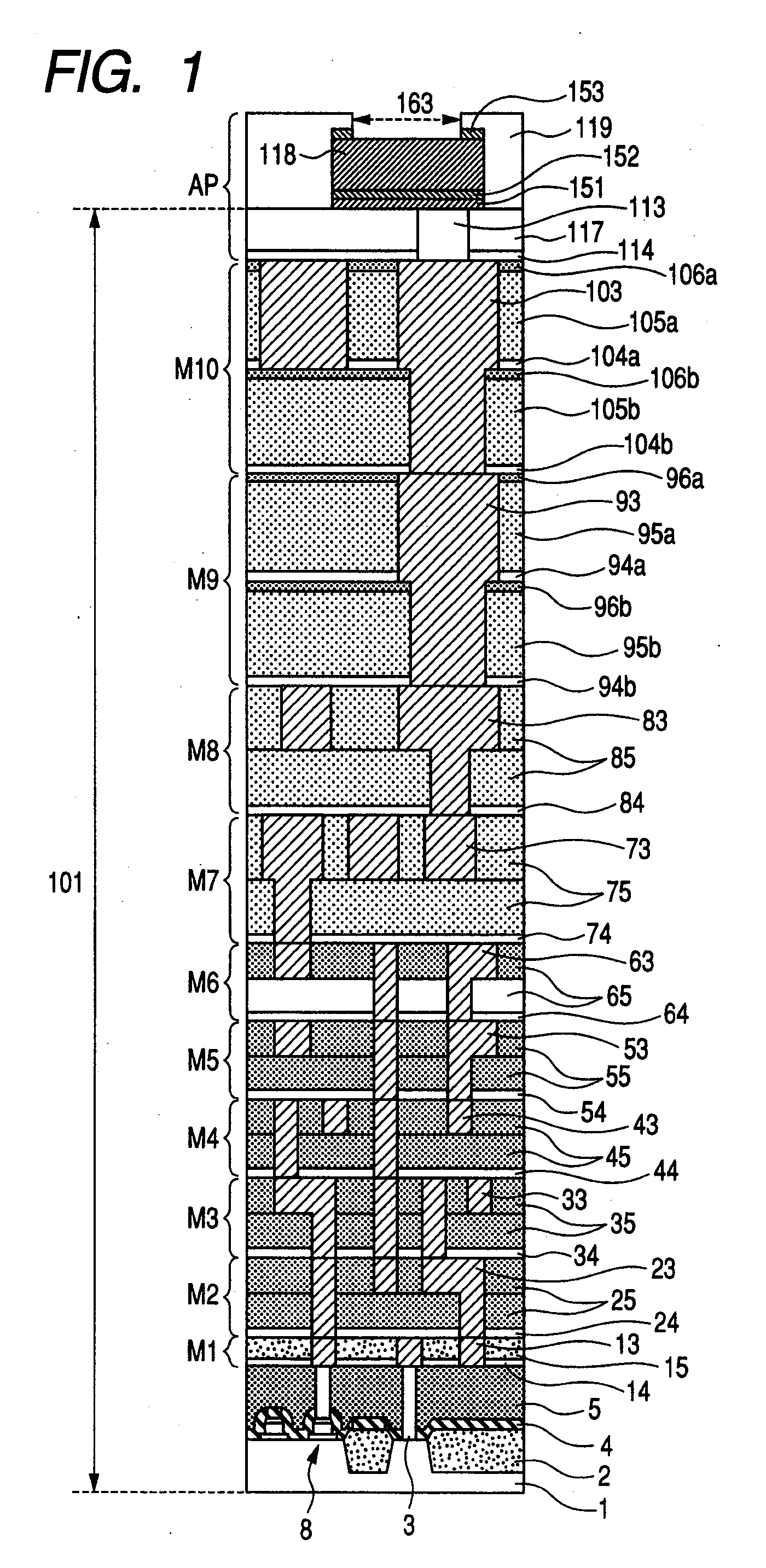

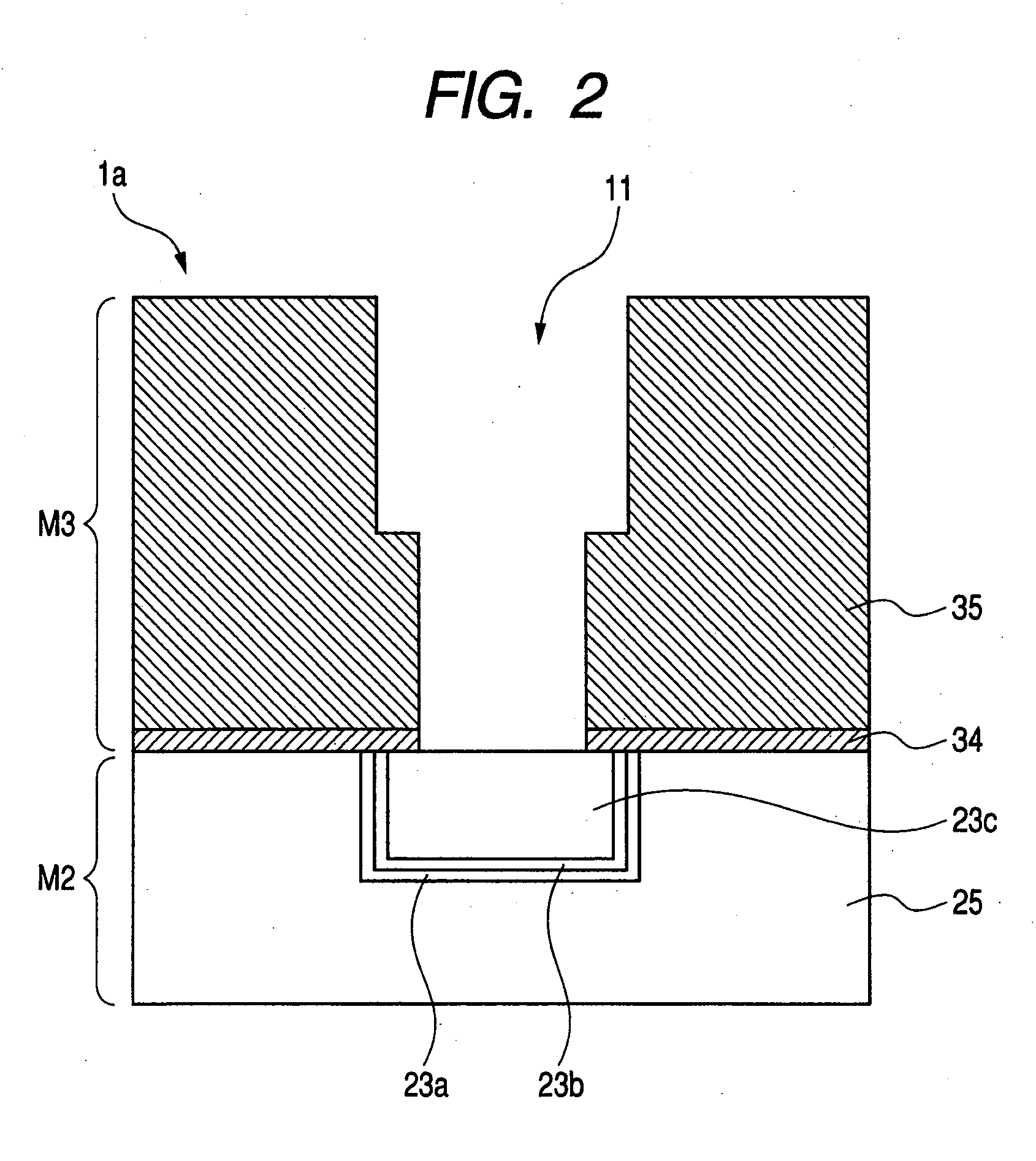

A metal-insulator-metal (MIM) capacitor for an integrated circuit may be provided on the interlayer insulating layer and covered by a inter-metal dielectric (IMD) layer. This IMD layer has at least a first opening therein that exposes an upper surface of a first electrode of the MIM capacitor. This first opening is filled with a first copper damascene interconnect pattern, which may in some embodiments be part of a dual-damascene copper interconnect structure associated with a first and lowermost level of metallization (e.g., M1 wiring layer). This first copper damascene interconnect pattern may have an upper surface that is planar with an upper surface of the IMD layer and a bottom surface that is in contact with the upper surface of the first electrode of the MIM capacitor.

Owner:SAMSUNG ELECTRONICS CO LTD

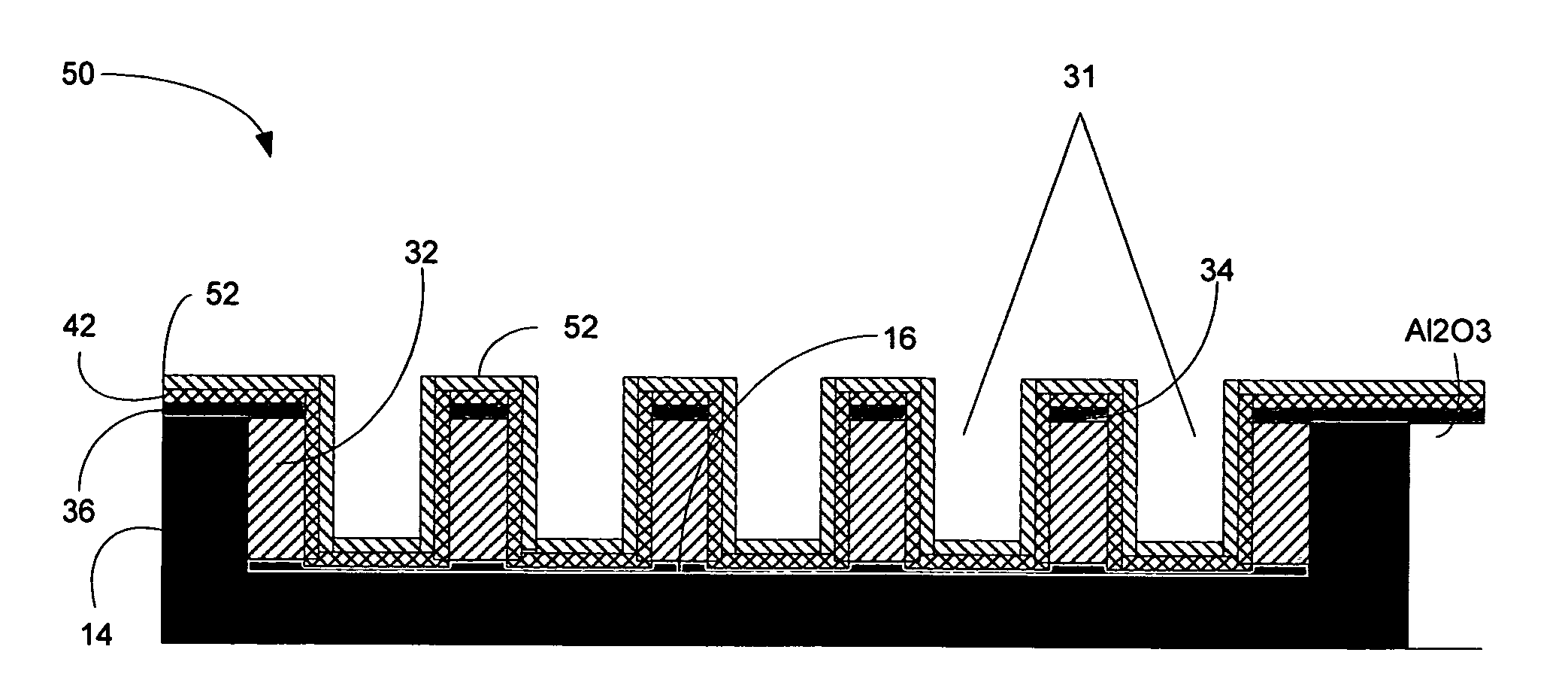

Copper damascene chemical mechanical polishing (CMP) for thin film head writer fabrication

InactiveUS20080096389A1Improve performanceDecorative surface effectsSemiconductor/solid-state device manufacturingSlurryCopper

In one method and embodiment of the present invention, at least one coil layer is formed in a write head, using a two-slurry step of copper damascene chemical mechanical polishing method with a first slurry step removing the undesirable copper that is on top of the tantalum barrier layer and on top of the trenches and a second slurry step removing the remainder of the undesirable copper, the tantalum barrier layer, the silicon dioxide hard mask layer, the hard baked photoresist layer, the magnetic alloy such as NiFe, CoFe, or CoNiFe, and alumina insulating layer for better thin film magnetic head performances.

Owner:HITACHI GLOBAL STORAGE TECH NETHERLANDS BV

Thin film resistor integration in copper damascene metallization

InactiveUS20160218062A1Semiconductor/solid-state device detailsSolid-state devicesCopperDielectric layer

An integrated circuit with copper damascene interconnects includes a thin film resistor. Copper damascene metal lines are formed in a first ILD layer. A dielectric layer including an etch stop layer is formed on the first ILD layer and metal lines. Resistor heads of refractory metal are formed in the dielectric layer so that edges of the resistor heads are substantially coplanar with the adjacent dielectric layer. A thin film resistor layer is formed on the dielectric layer, extending onto the resistor heads. A second ILD layer is formed over the dielectric layer and the thin film resistor layer. Copper damascene vias are formed in the second ILD layer, making contact to the metal lines in the first ILD layer. Connections to the resistor heads are provided by the metal lines and / or the vias.

Owner:TEXAS INSTR INC

Surfactant slurry additives to improve erosion, dishing, and defects during chemical mechanical polishing of copper damascene with low k dielectrics

Slurries and methods for the chemical mechanical polishing of high density copper interconnects in a low k ILD are presented. In a particular embodiment of the present invention, a slurry for polishing copper is formed by combining a surfactant comprising an alkyl ethoxy organic acid such as glycolic acid ethoxylate lauryl ether (GAELE), an abrasive such as silica, an oxidizing agent such as hydrogen peroxide, and a chelating buffer system such as citric acid and potassium citrate dissolved in the mixture. This slurry provides a very low incidence of bent line defects, a low erosion rate, and a low dishing rate on a substrate comprising high density copper interconnects in a low k ILD. Embodiments of methods of the present invention use the disclosed slurries.

Owner:INTEL CORP

Manufacturing method of semiconductor integrated circuit device

InactiveUS20110127158A1Decreasing foreign materialLarge thicknessVacuum evaporation coatingSolid-state devicesTantalum nitrideCopper

In a copper damascene wiring process, a tantalum-based laminated film, which is used as a barrier metal film, is continuously formed in a sputtering deposition chamber. When the continuous deposition process is discontinuously applied to a number of wafers, a tantalum film and a tantalum nitride film which are relatively thin are alternately deposited over an inner surface of a shield in a sputter deposition chamber, which results in a thickness of the deposited film being on the order of several thousand nanometers. The deposited film peels off due to internal stress therein to generate foreign material or particles. To counteract this, a tantalum film, which is much thicker than the tantalum film formed over the wafer at one time, is formed over the substantially inner wall of the chamber at predetermined intervals when repeatedly depositing the tantalum nitride film and the tantalum film in the sputtering deposition chamber.

Owner:RENESAS ELECTRONICS CORP

Barrier-metal-free copper damascene technology using atomic hydrogen enhanced reflow

InactiveUS20060289993A1Inhibited DiffusionHigh puritySemiconductor/solid-state device detailsSolid-state devicesHydrogenSemiconductor structure

Owner:CONVERSANT INTPROP MANAGEMENT INC

Method of fabricating copper damascene and dual damascene interconnect wiring

Owner:AURIGA INNOVATIONS INC

TSV Backside Processing Using Copper Damascene Interconnect Technology

ActiveUS20130105968A1Well formedSemiconductor/solid-state device detailsSolid-state devicesSubject matterSemiconductor chip

Generally, the subject matter disclosed herein relates to interconnect structures used for making electrical connections between semiconductor chips in a stacked or 3D chip configuration, and methods for forming the same. One illustrative method disclosed herein includes forming a conductive via element in a semiconductor substrate, wherein the conductive via element is formed from a front side of the semiconductor substrate so as to initially extend a partial distance through the semiconductor substrate. The illustrative method also includes forming a via opening in a back side of the semiconductor substrate to expose a surface of the conductive via element, and filling the via opening with a layer of conductive contact material.

Owner:GLOBALFOUNDRIES SINGAPORE PTE LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com