Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

235results about How to "Increase line width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Circuit layout methodology using a shape processing application

InactiveUS7188322B2Low costSmall sizeCAD circuit designSpecial data processing applicationsManufacturing technologySoftware engineering

Owner:INT BUSINESS MASCH CORP

Circuit layout methodology

InactiveUS20060195809A1Simplifies design/layout ruleReduce data volumeCAD circuit designSpecial data processing applicationsManufacturing technologyData preparation

A circuit layout methology is provided for eliminating the extra processing time and file-space requirements associated with the optical proximity correction (OPC) of a VLSI design. The methodology starts with the design rules for a given manufacturing technology and establishes a new set of layer-specific grid values. A layout obeying these new grid requirements leads to a significant reduction in data preparation time, cost, and file size. A layout-migration tool can be used to modify an existing layout in order to enforce the new grid requirements.

Owner:IBM CORP

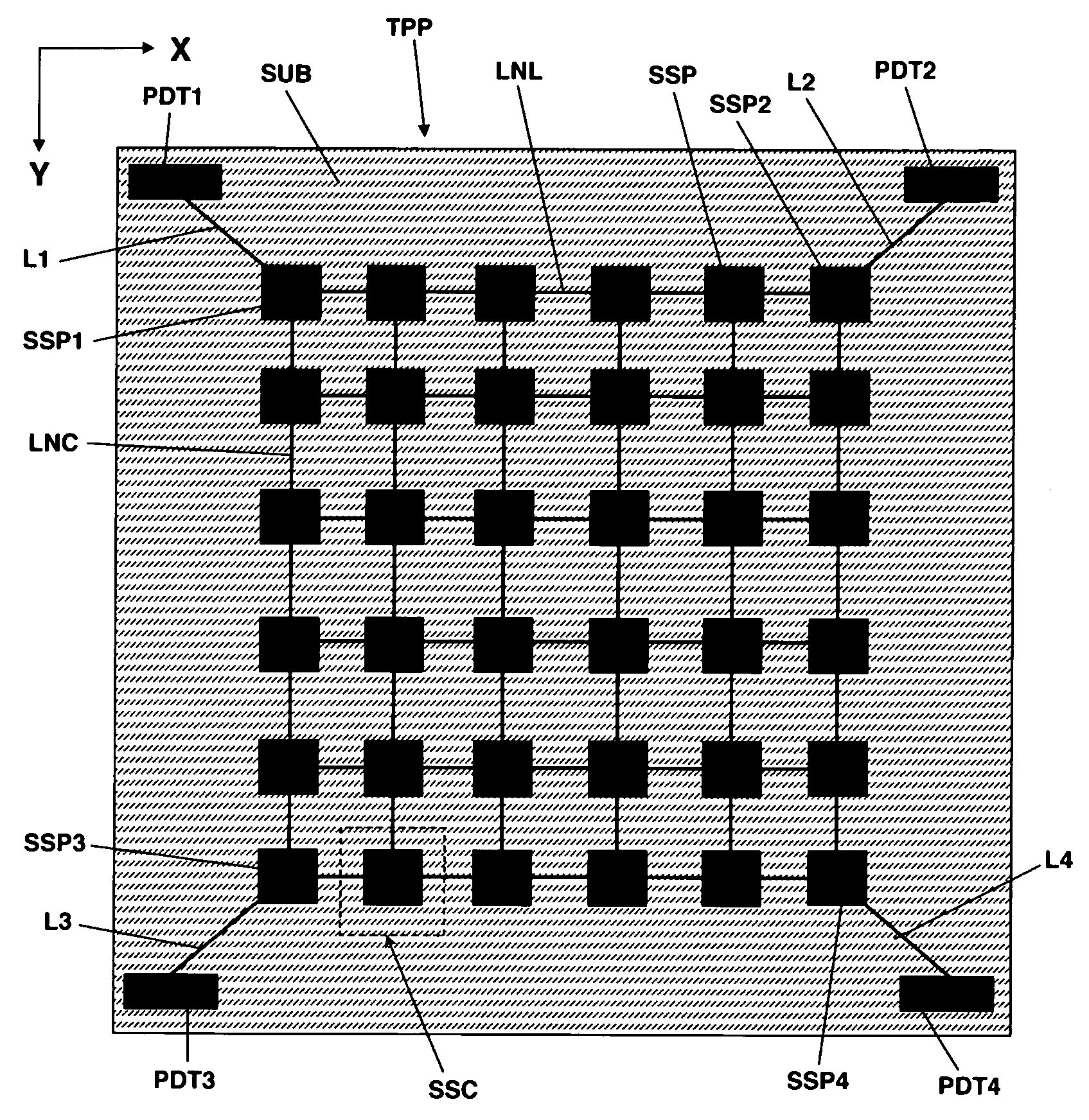

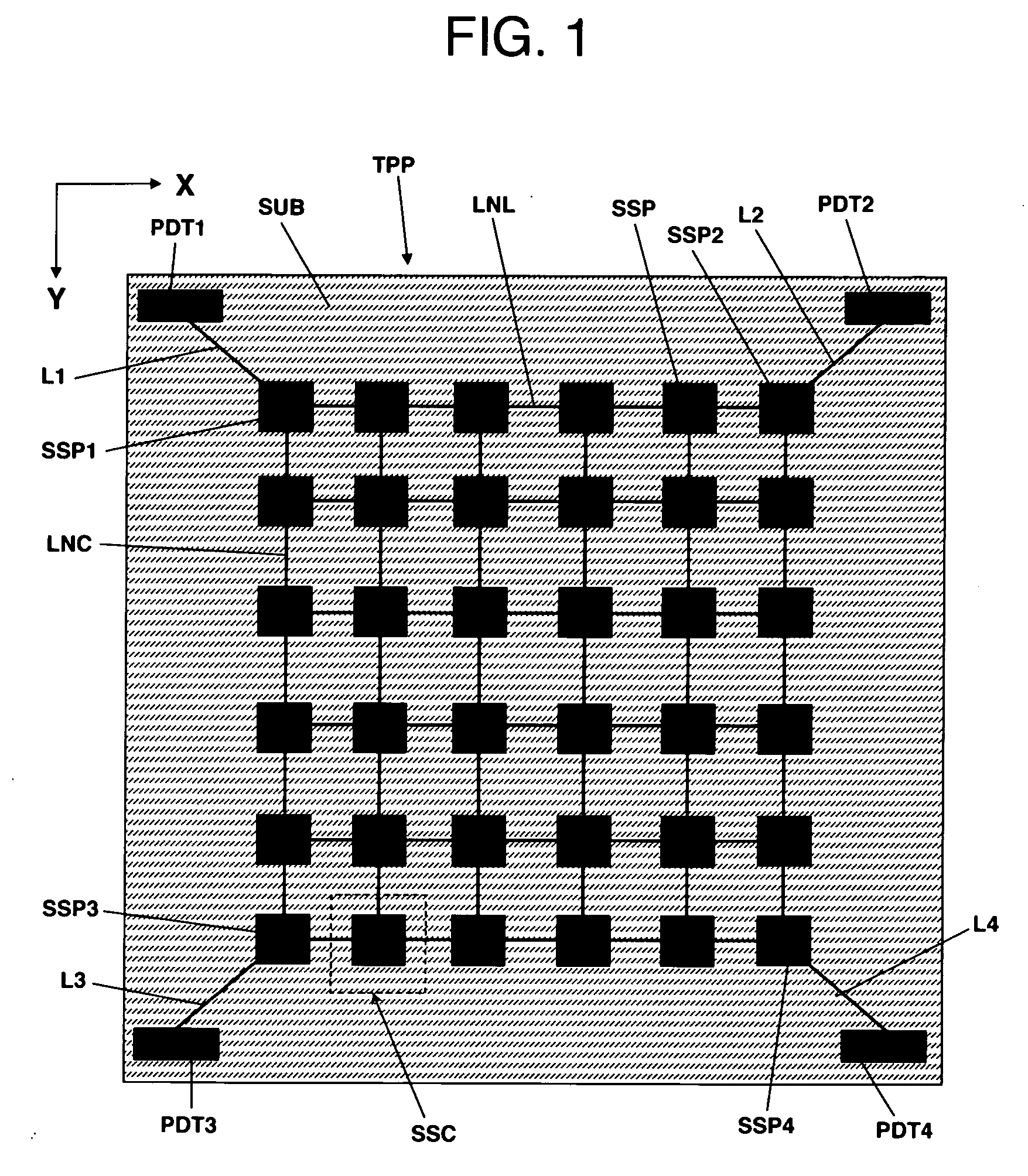

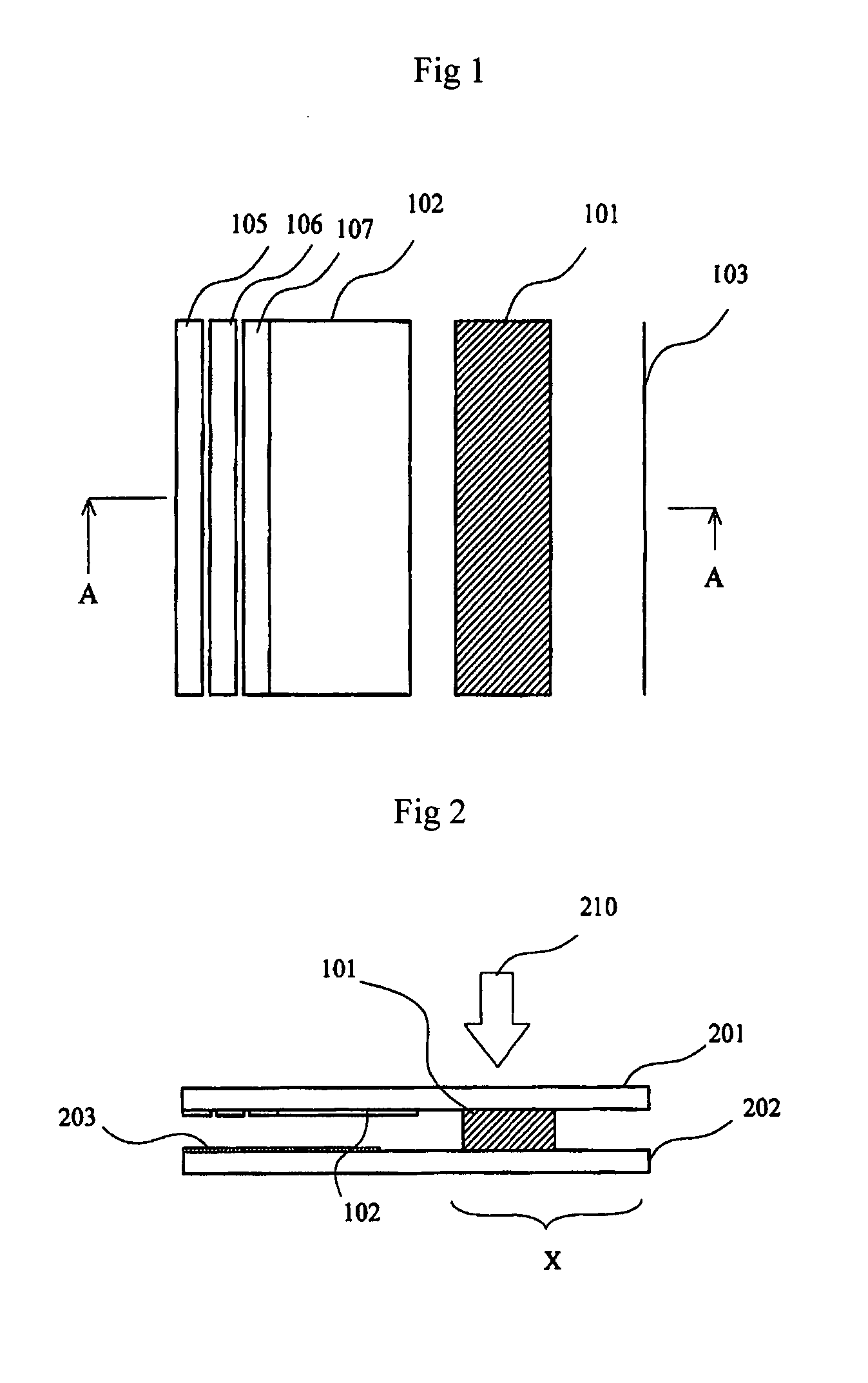

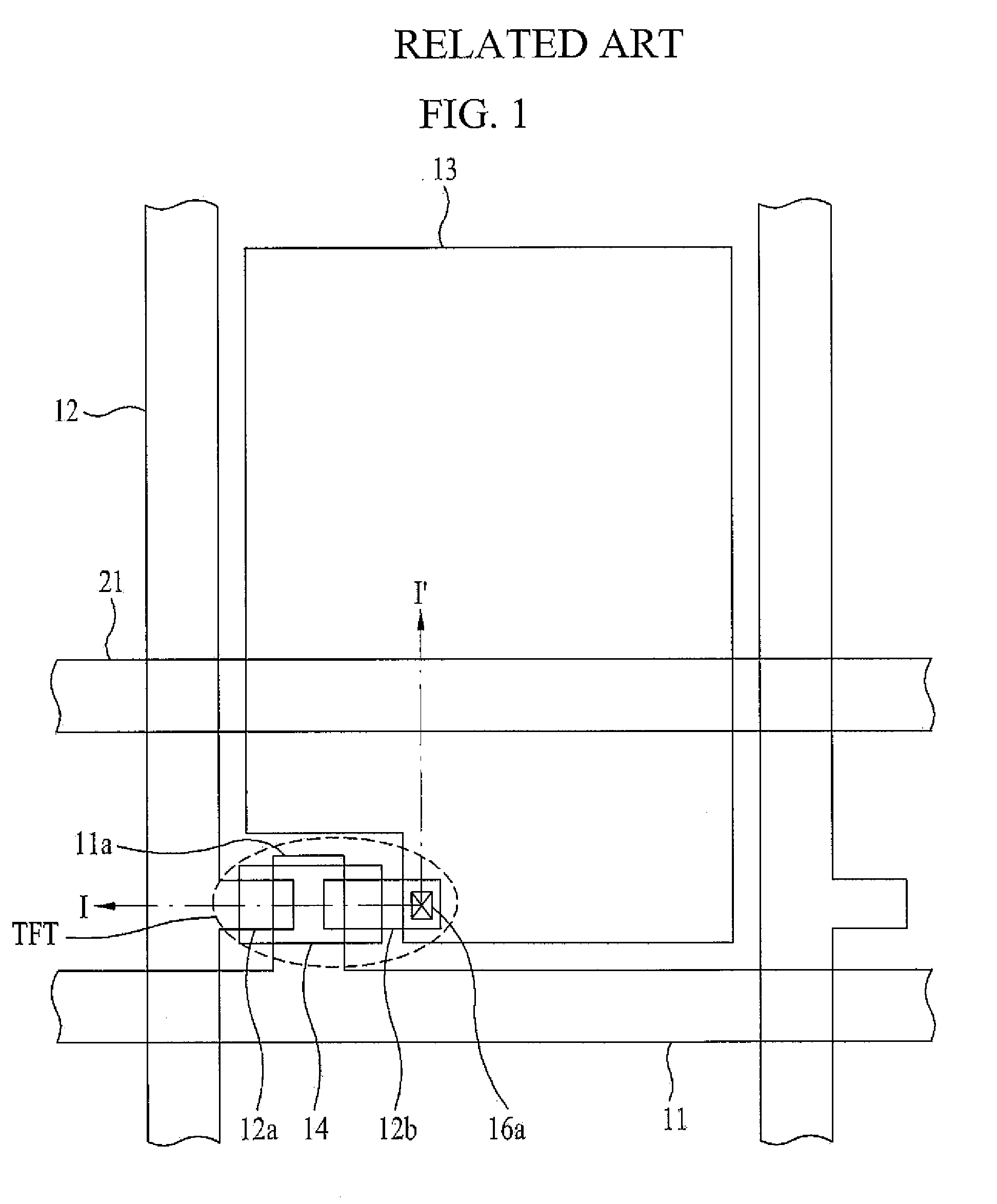

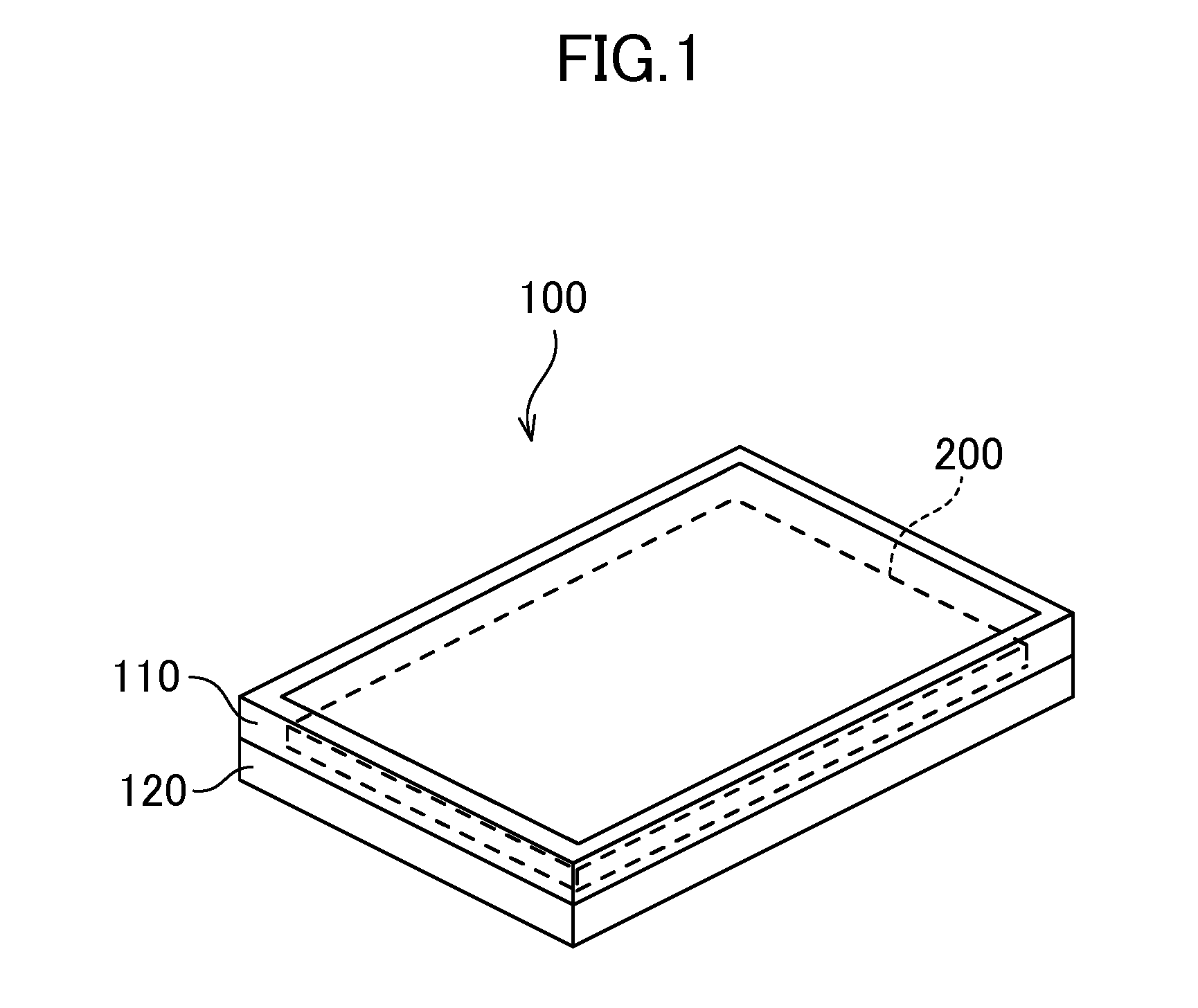

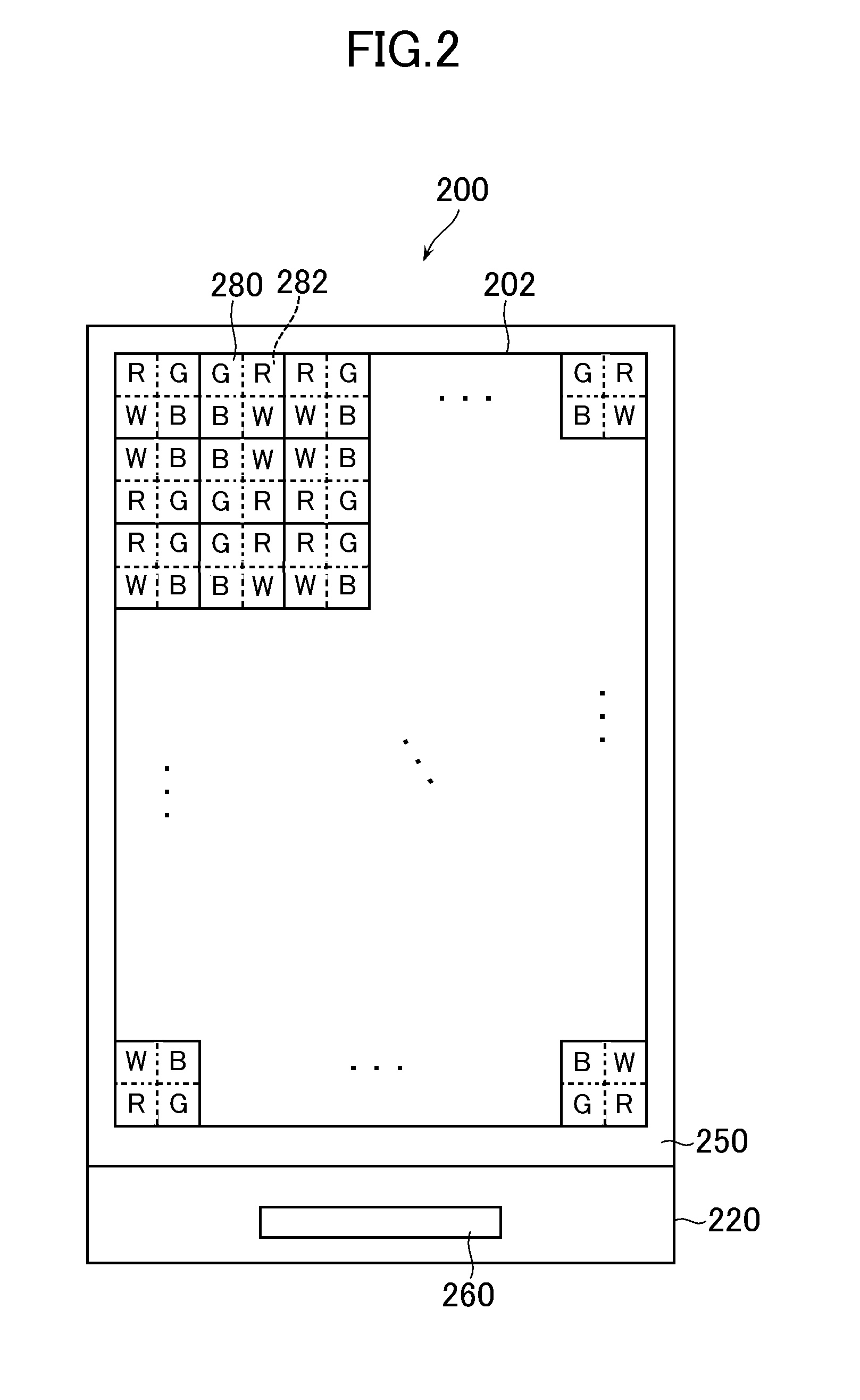

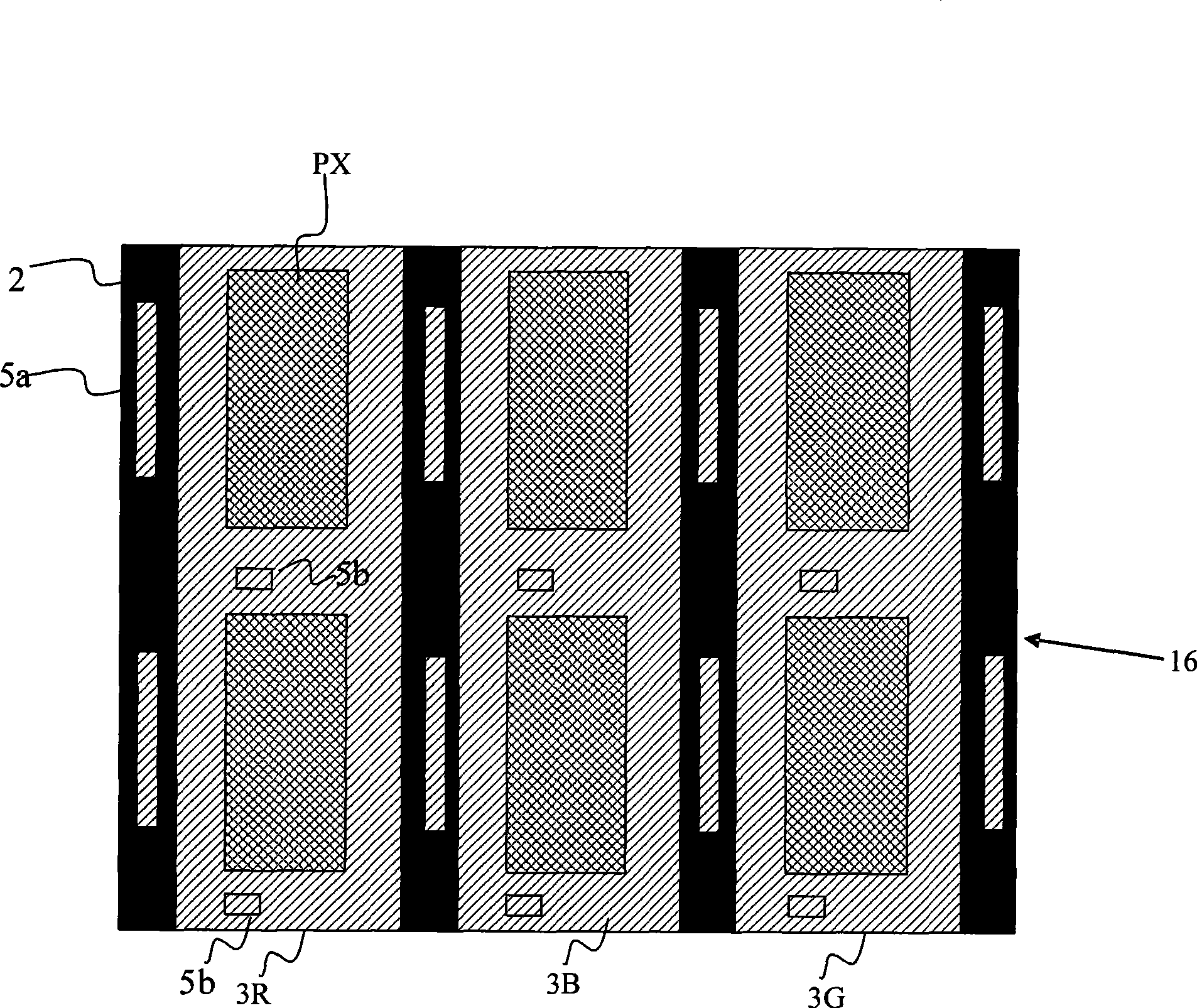

Screen input type image display

InactiveUS20090002338A1Simple structureImprove accuracyInput/output processes for data processingTransparent conducting filmComputer science

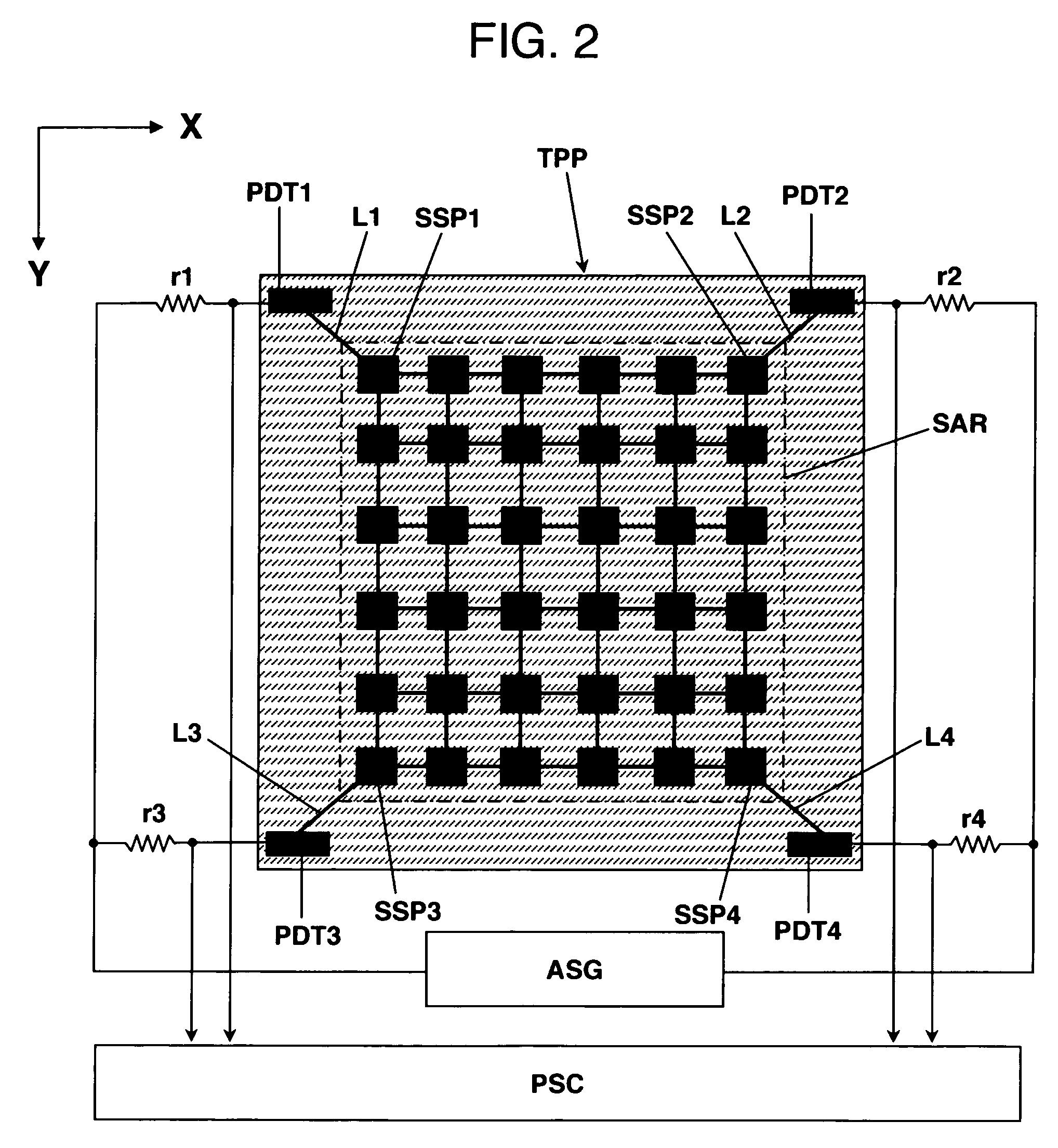

In an image display device incorporating a touch sensor capable of detecting coordinates with simple structure and high precision, a transparent conductive film on a substrate SUB forming a display screen of the image display device is patterned to form detection electrodes taking the shape of a plurality of pad electrodes SSP arranged in a two-dimensional matrix form of rows (X direction) and columns (Y direction). Row connection electrodes LNL and column connection electrodes LNC connecting the detection electrodes in rows and columns of the two-dimensional matrix to each other are formed of the same transparent conductive film as the pad electrodes. By arranging the pad electrodes in the matrix form, the contact area of a finger or the like touching the screen can be made large, resulting in improved detection precision (resolution). The pad electrodes are connected at four corners to coordinate detection terminals PDT1 to PDT4.

Owner:JAPAN DISPLAY INC

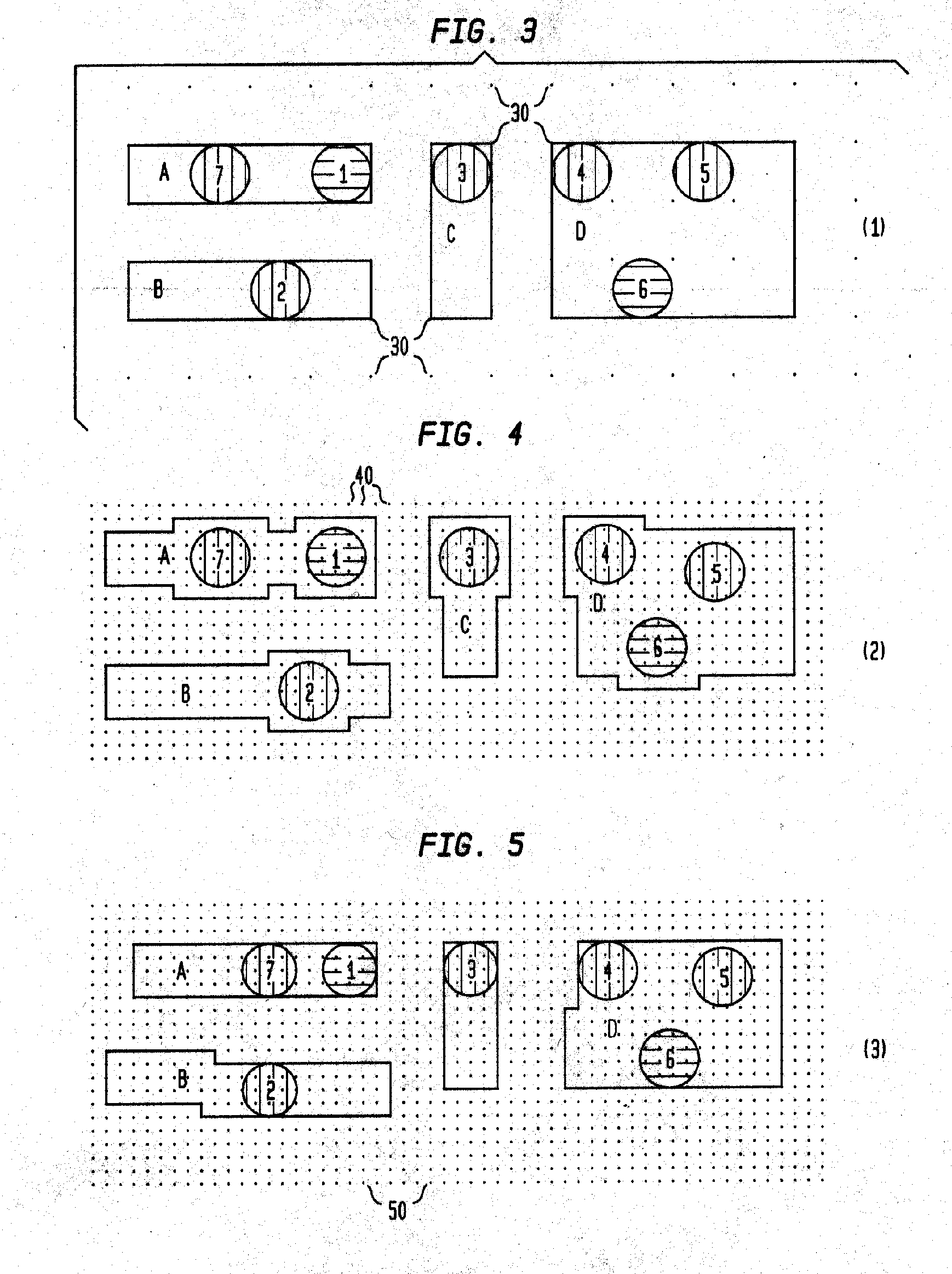

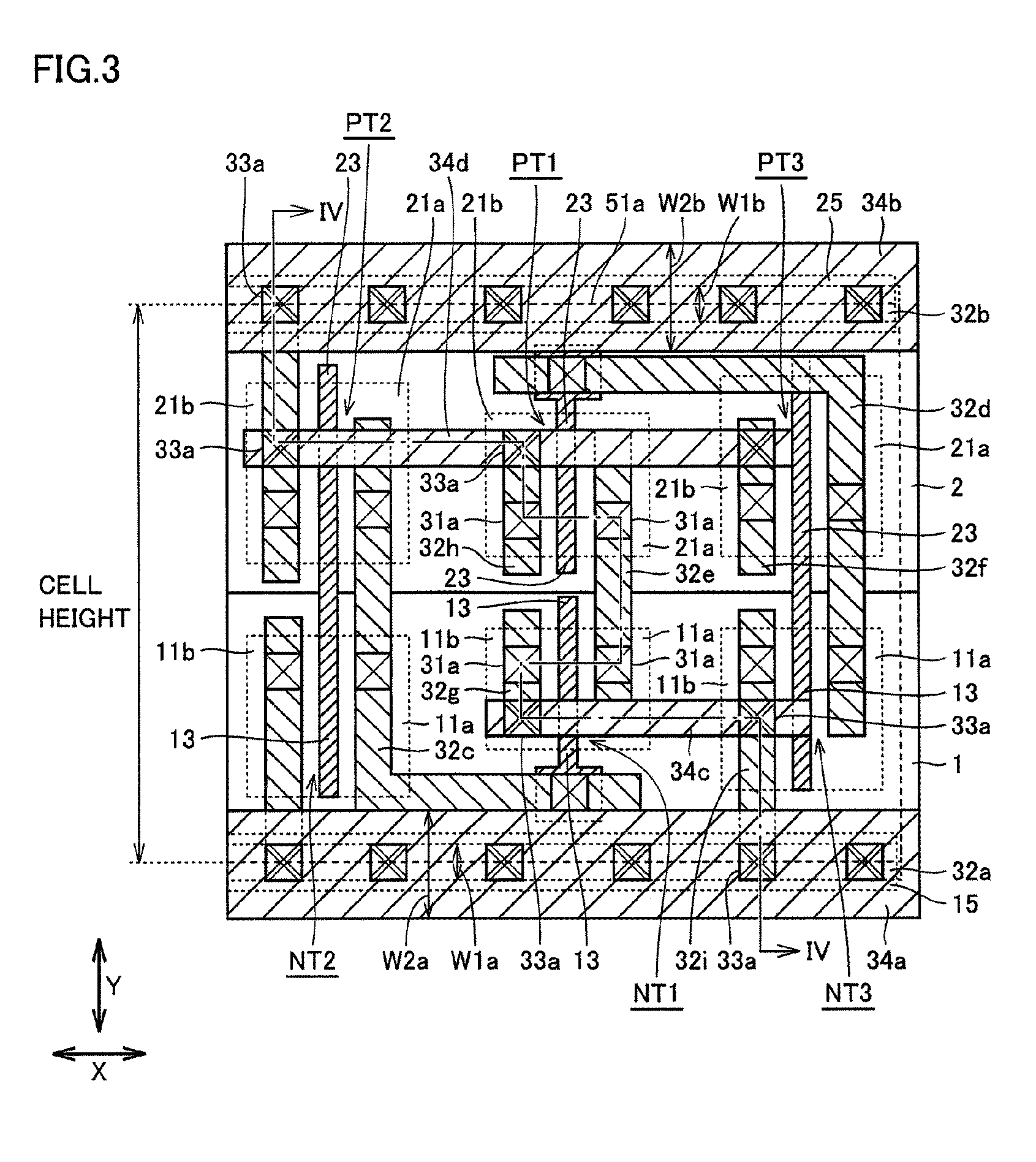

Semiconductor device

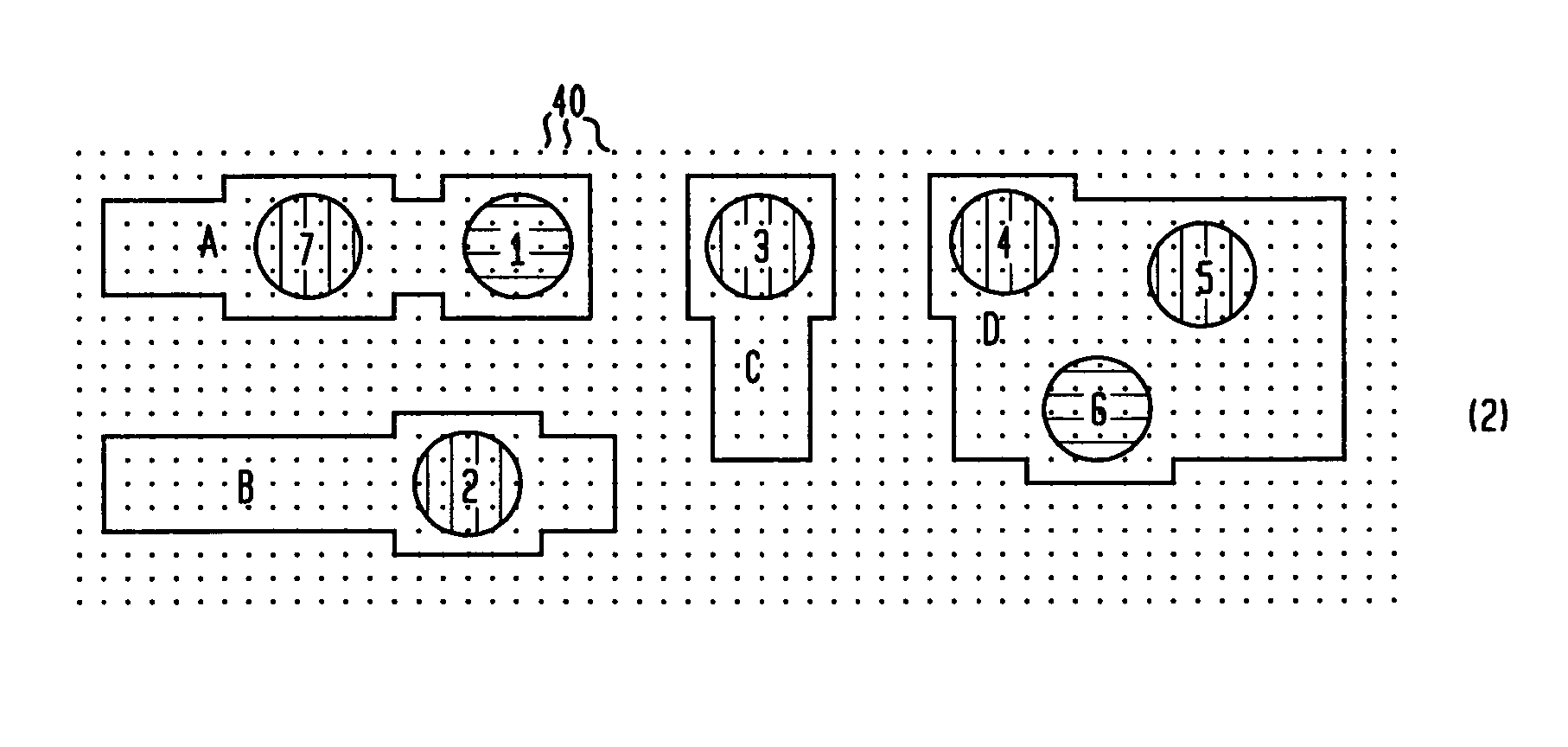

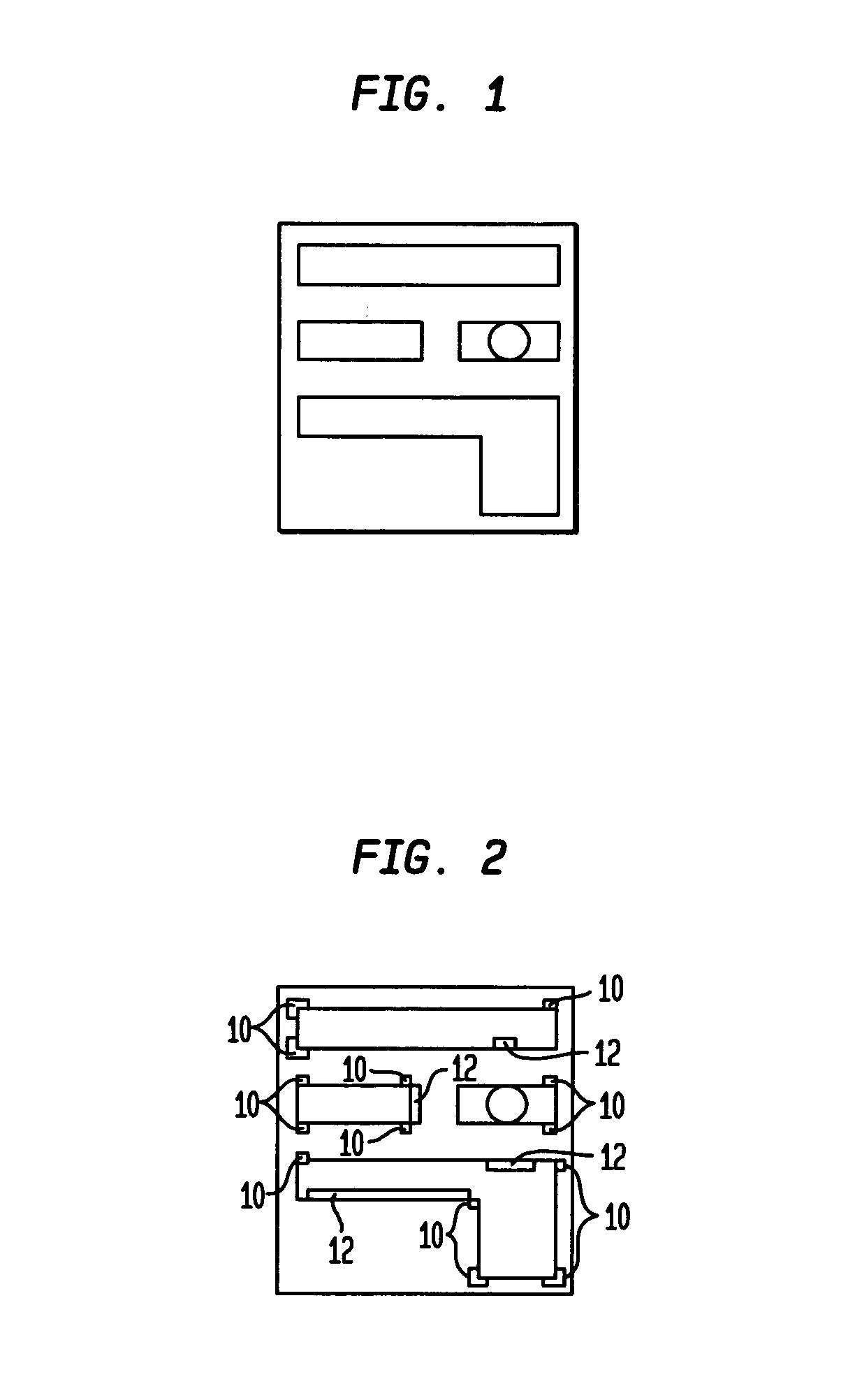

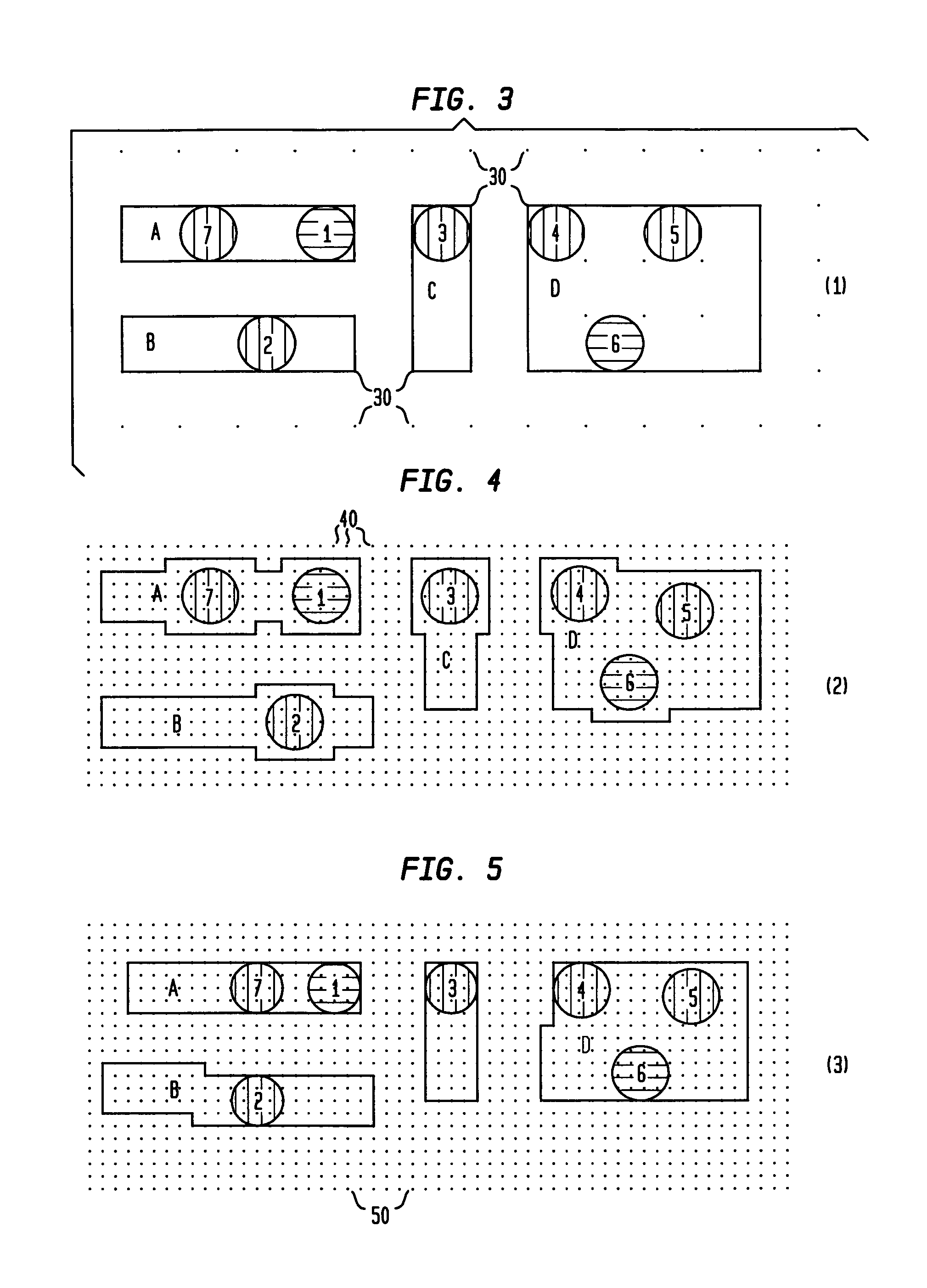

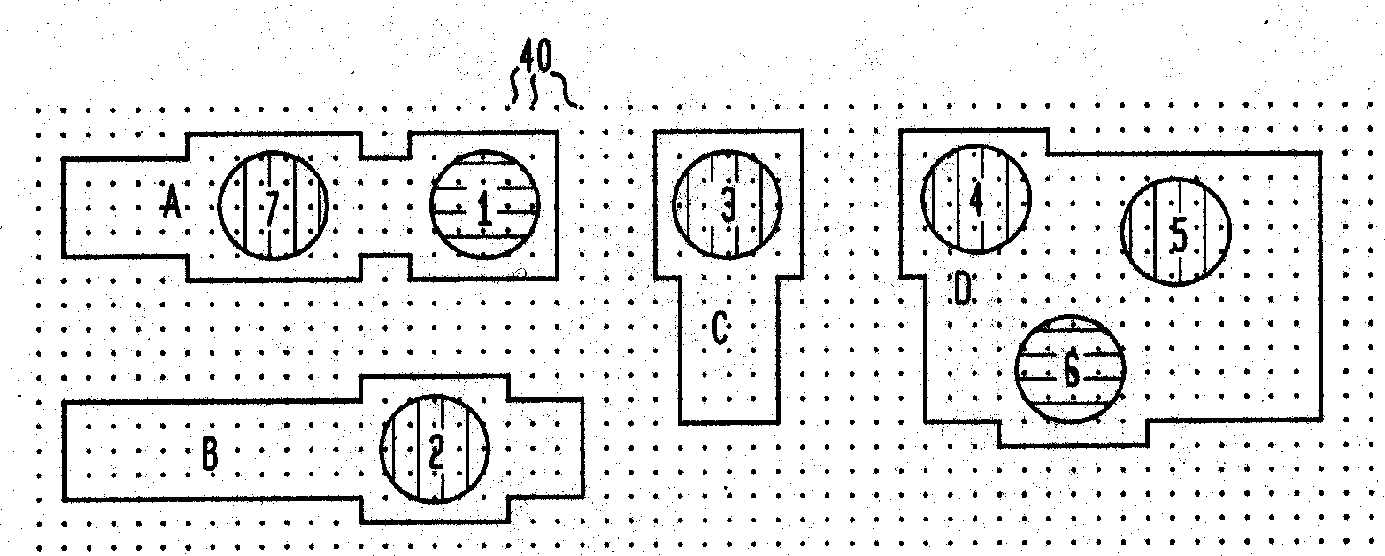

ActiveUS20090026503A1High speedHigh integrationSemiconductor/solid-state device detailsSolid-state devicesCMOSStandard cell

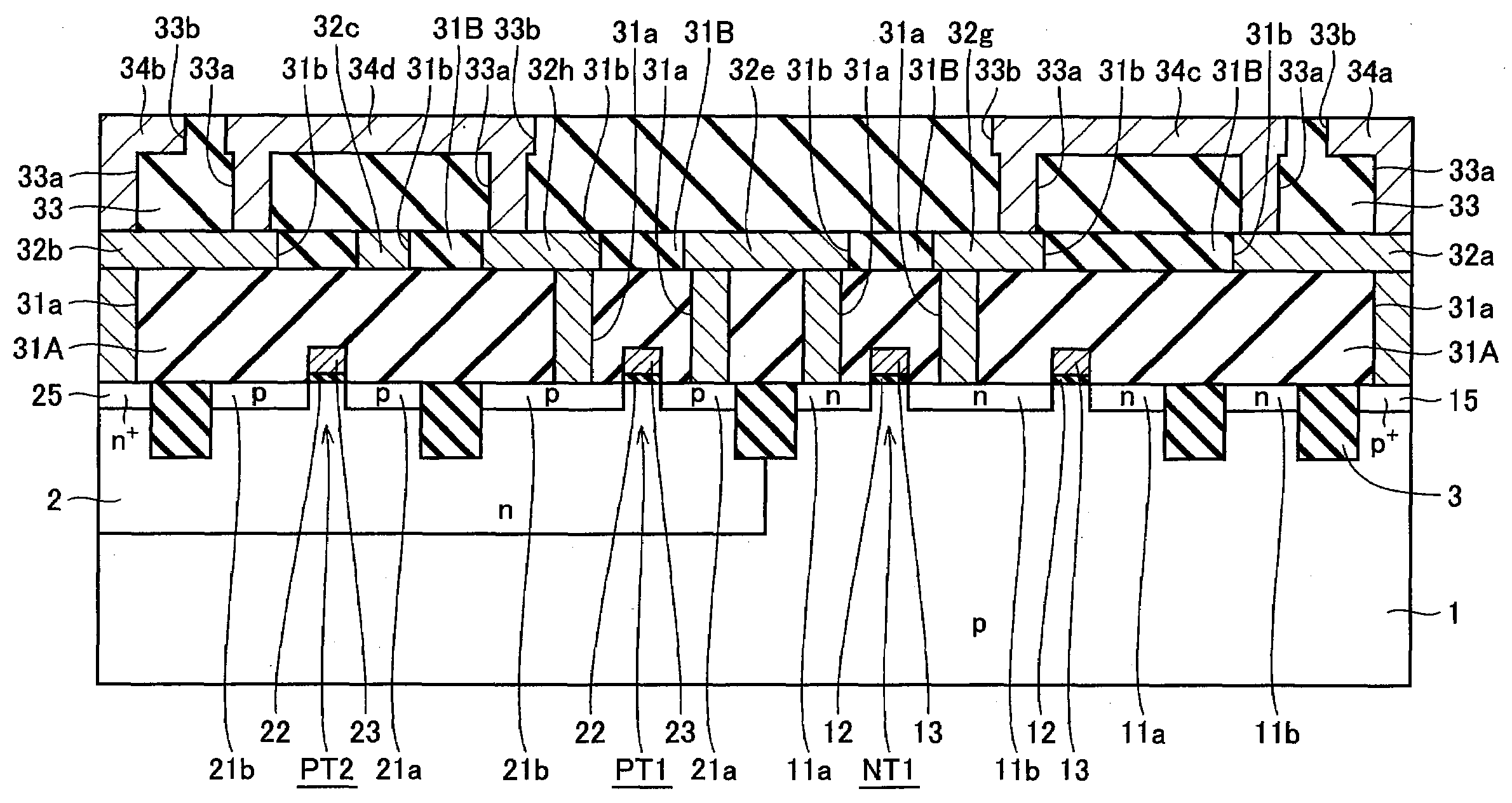

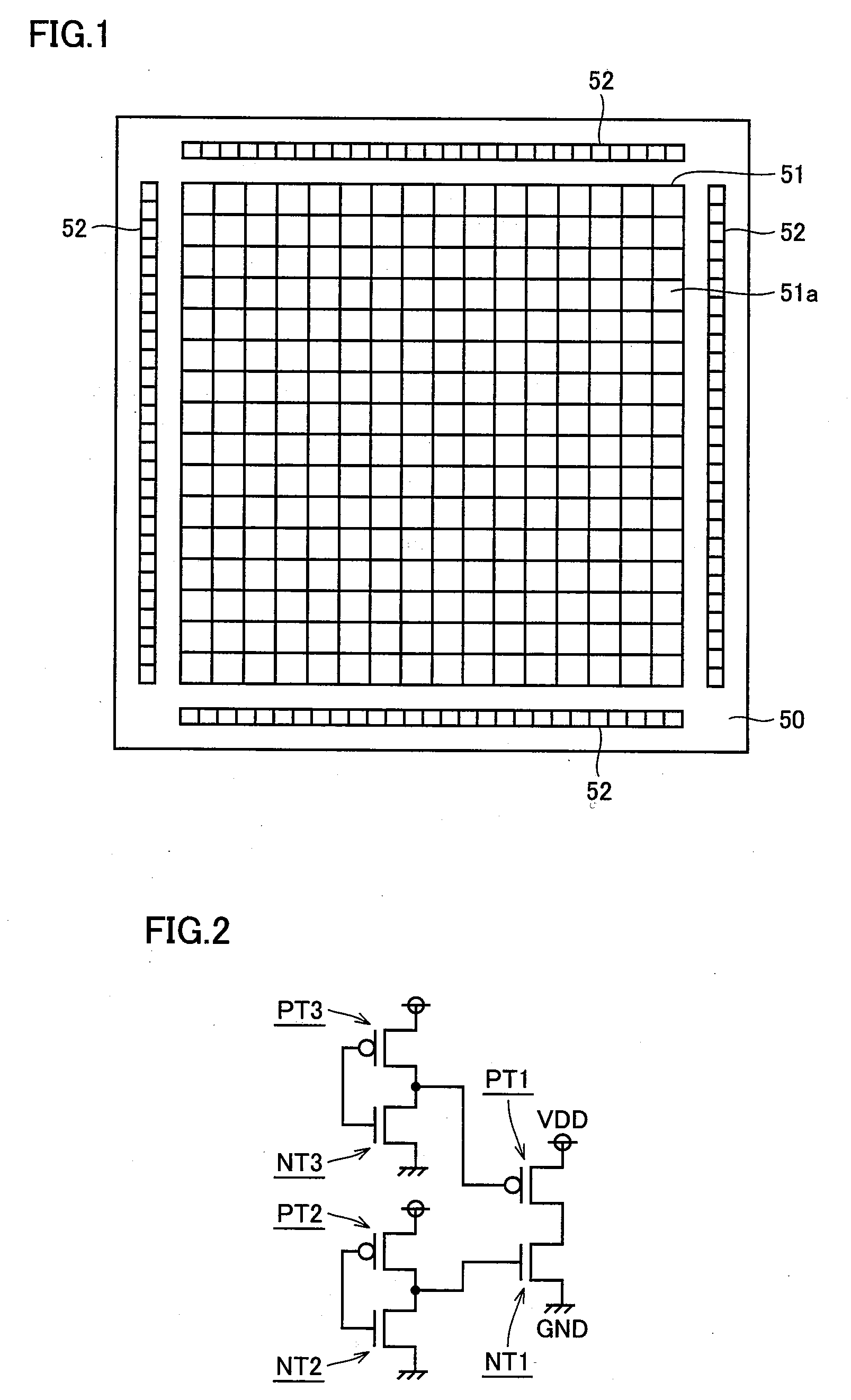

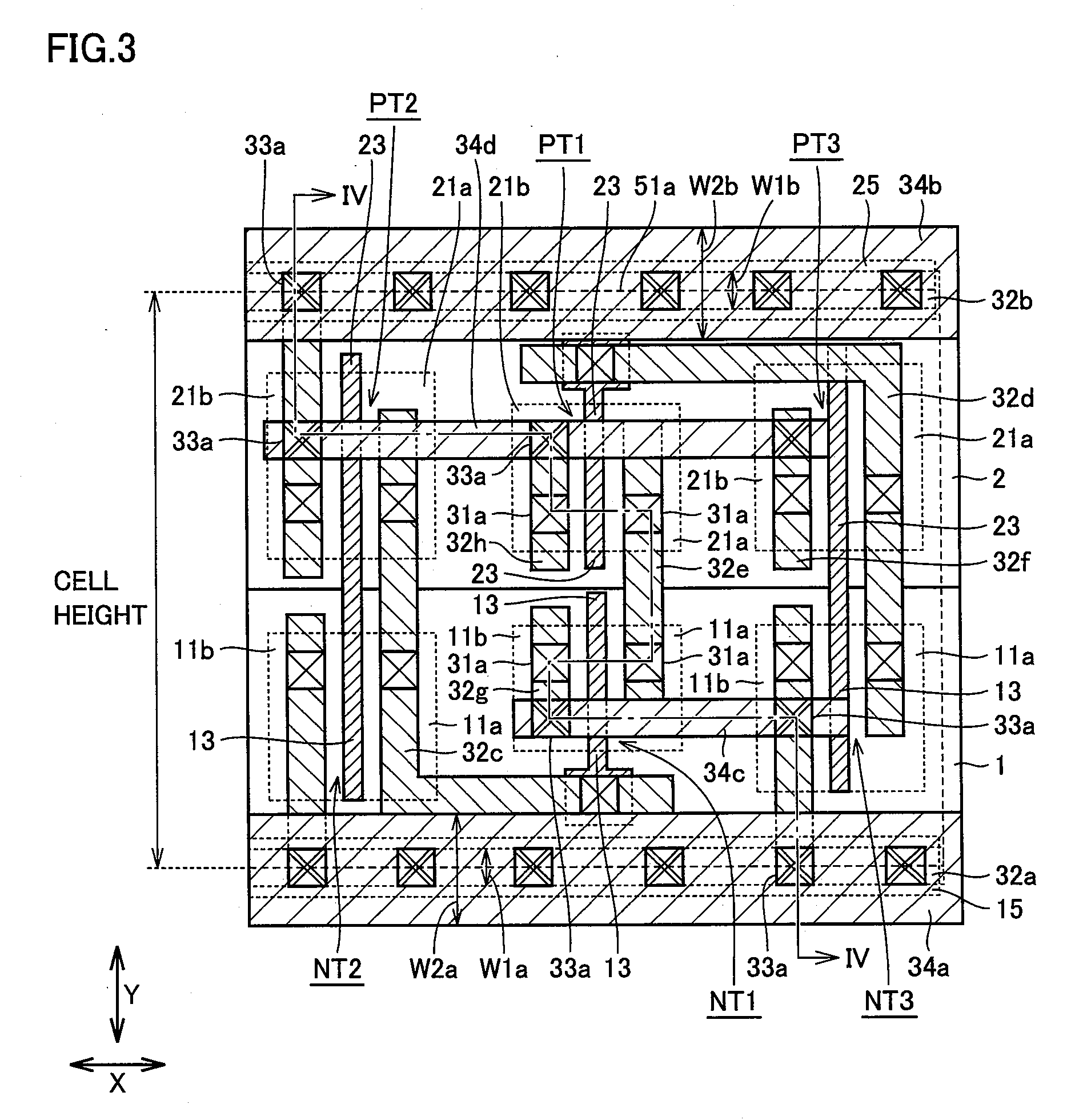

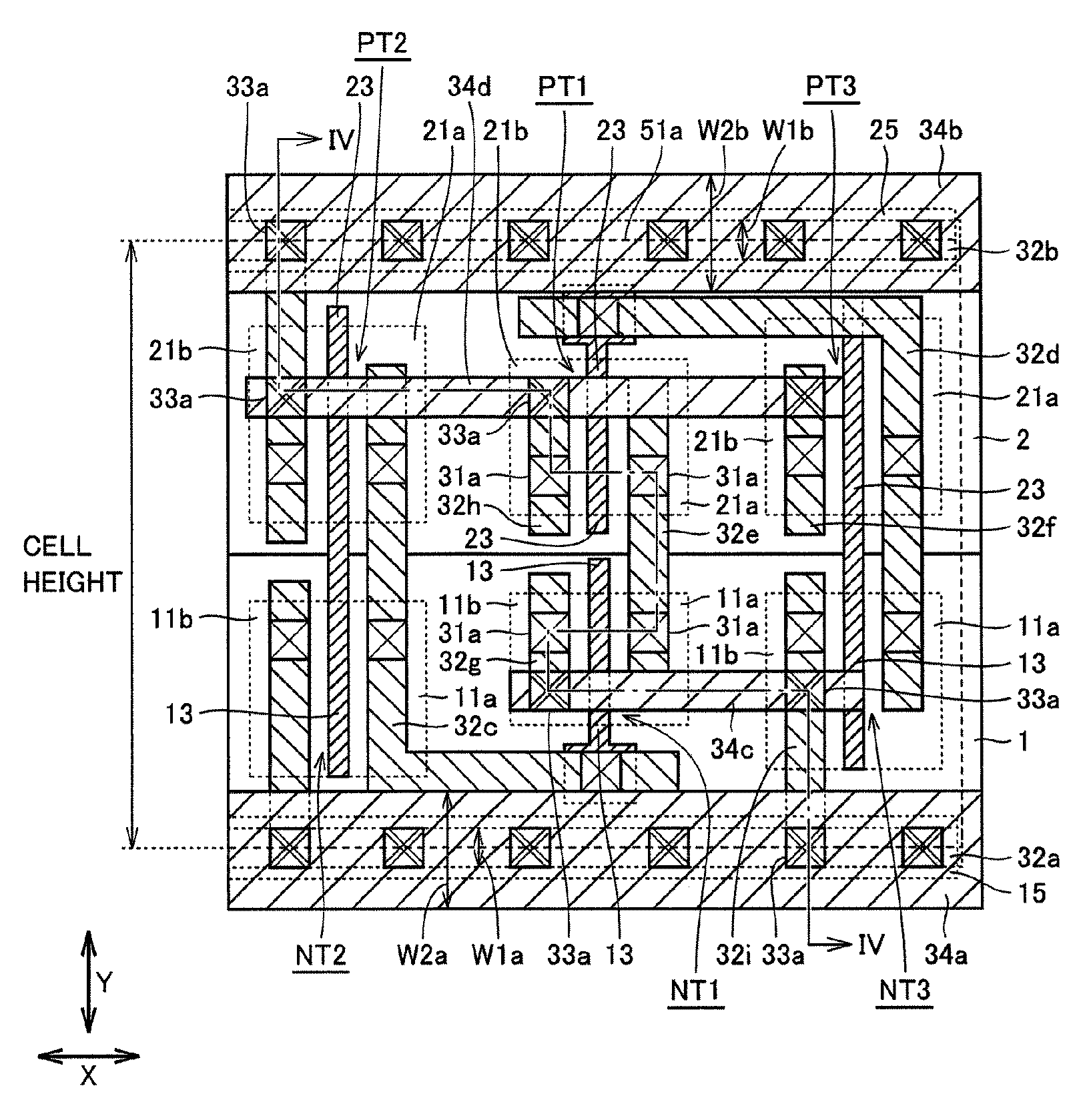

CMOS inverters are included in a standard cell. Power supply lines are electrically connected to CMOS inverters, and include lower layer interconnects and upper layer interconnect. Lower layer interconnects extend along a boundary of standard cells adjacent to each other and on the boundary. Upper layer interconnects are positioned more inside in standard cell than lower layer interconnects, as viewed from a plane. CMOS inverters are electrically connected through upper layer interconnects to lower layer interconnects. Thus, a semiconductor device is obtained that can achieve both higher speeds and higher integration.

Owner:RENESAS ELECTRONICS CORP

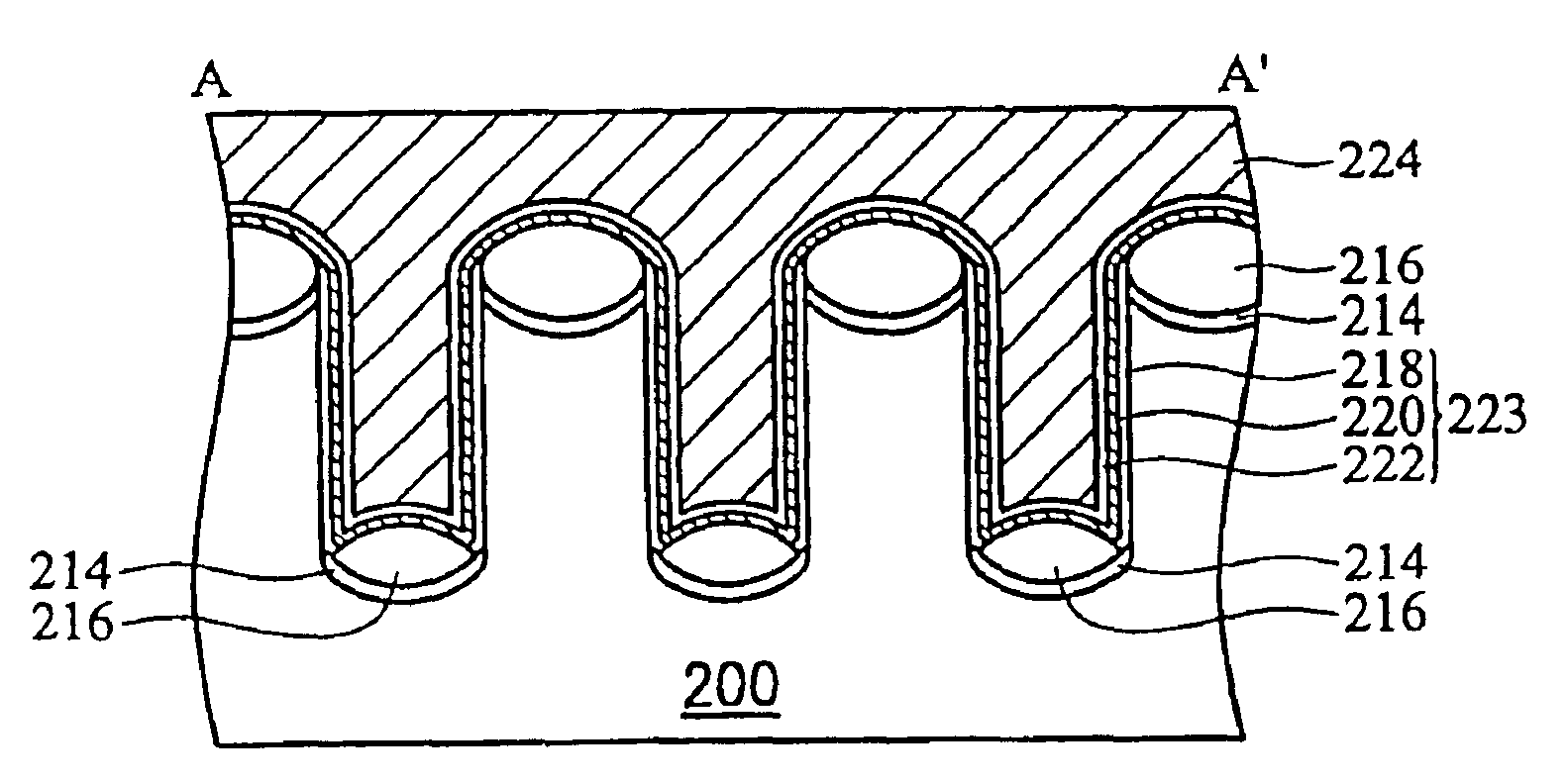

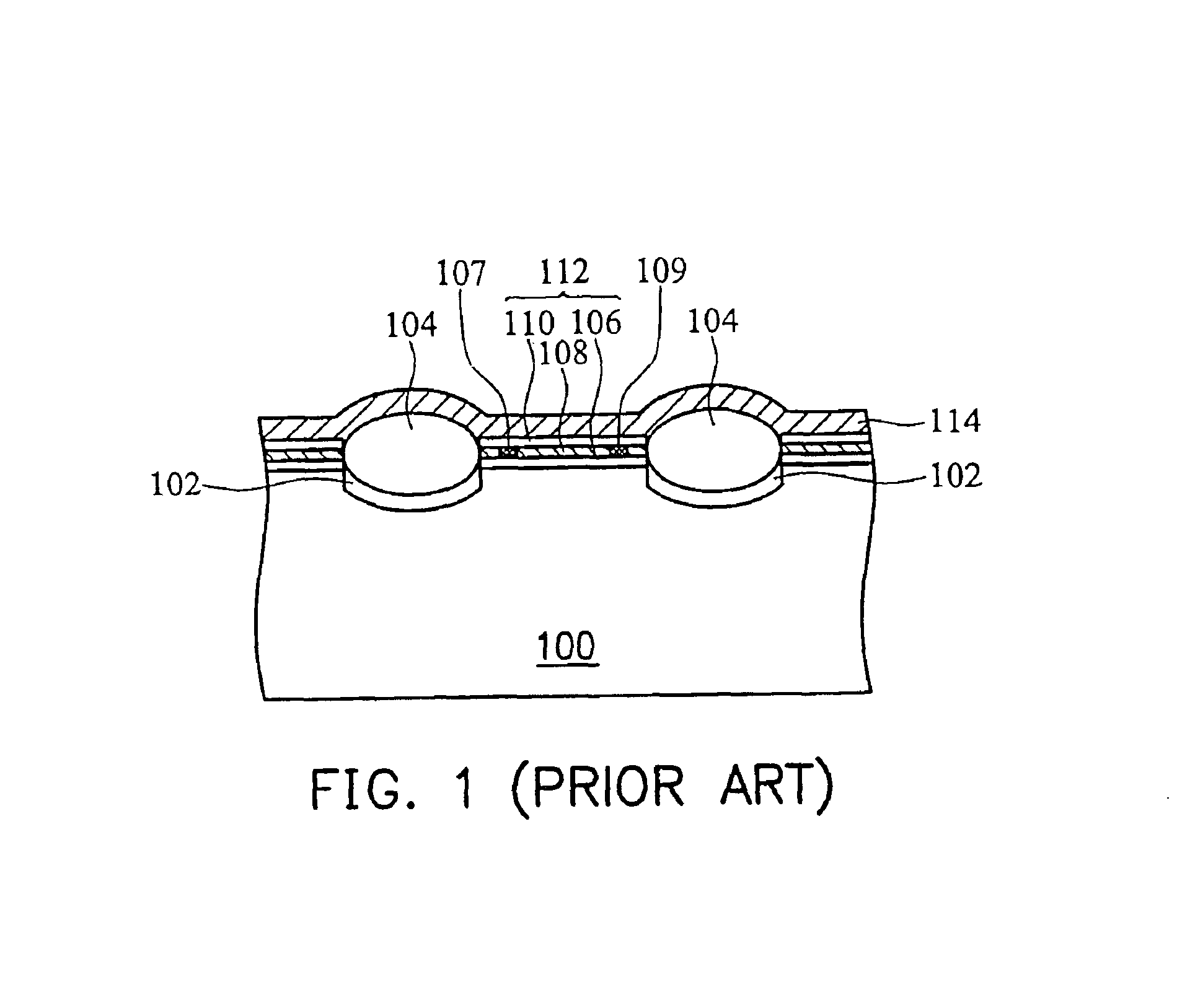

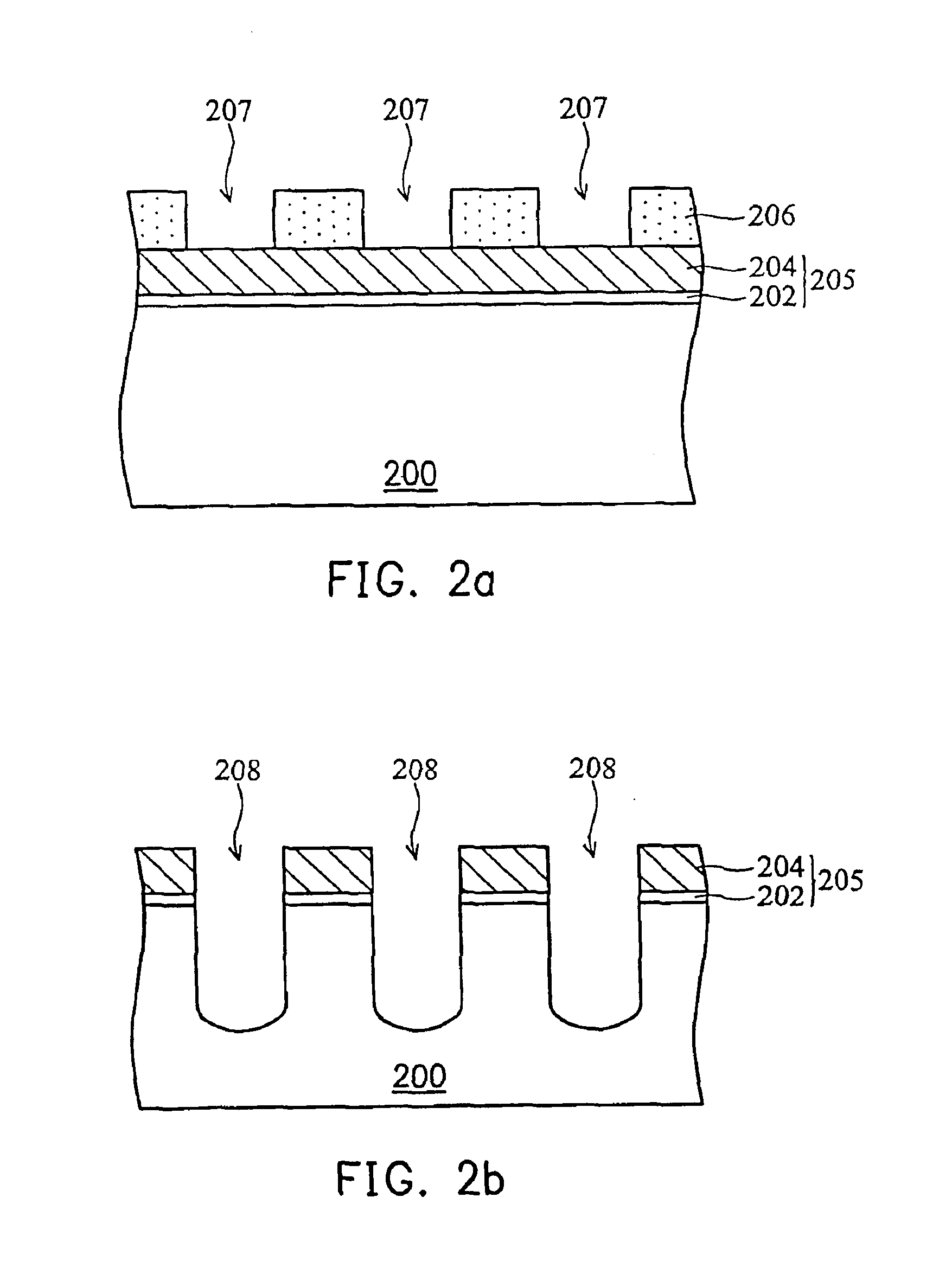

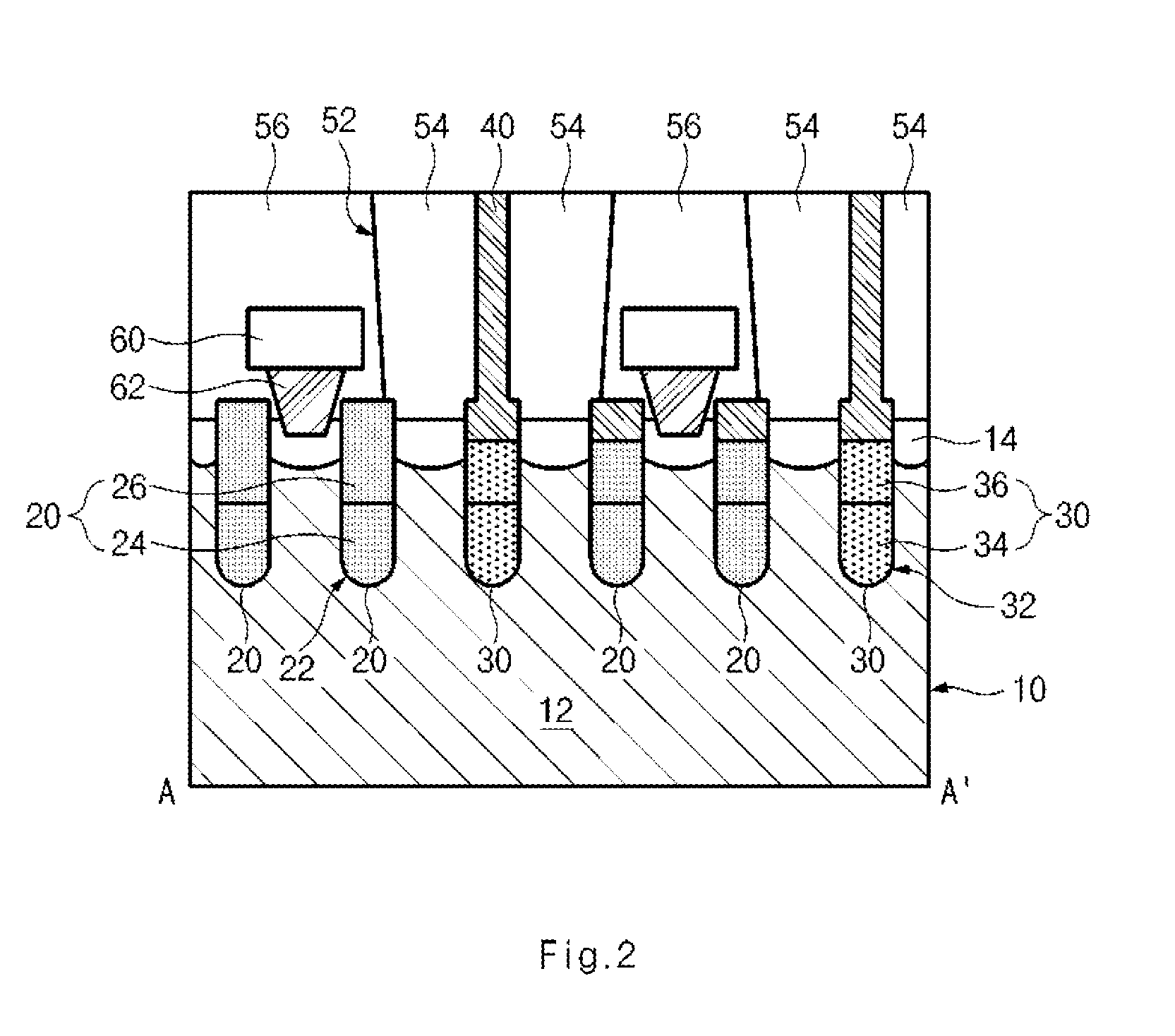

Method for fabricating a vertical NROM cell

InactiveUS6916715B2Reduce resistanceIncreasing bit line widthSolid-state devicesSemiconductor/solid-state device manufacturingBit lineGate dielectric

A method for fabricating a vertical nitride read-only memory (NROM) cell. A substrate having at least one trench is provided. A spacer is formed over the sidewall of the trench. Subsequently, ion implantation is performed on the substrate using the spacer as a mask to form doping areas as bit lines in the substrate near its surface and the bottom of the trench. Bit line oxides are formed over each of the doping areas. After the spacer is removed, a conformable insulating layer as gate dielectric is deposited on the sidewall of the trench and the surface of the bit line oxide. Finally, a conductive layer as a word line is deposited over the insulating layer and fills in the trench.

Owner:NAN YA TECH

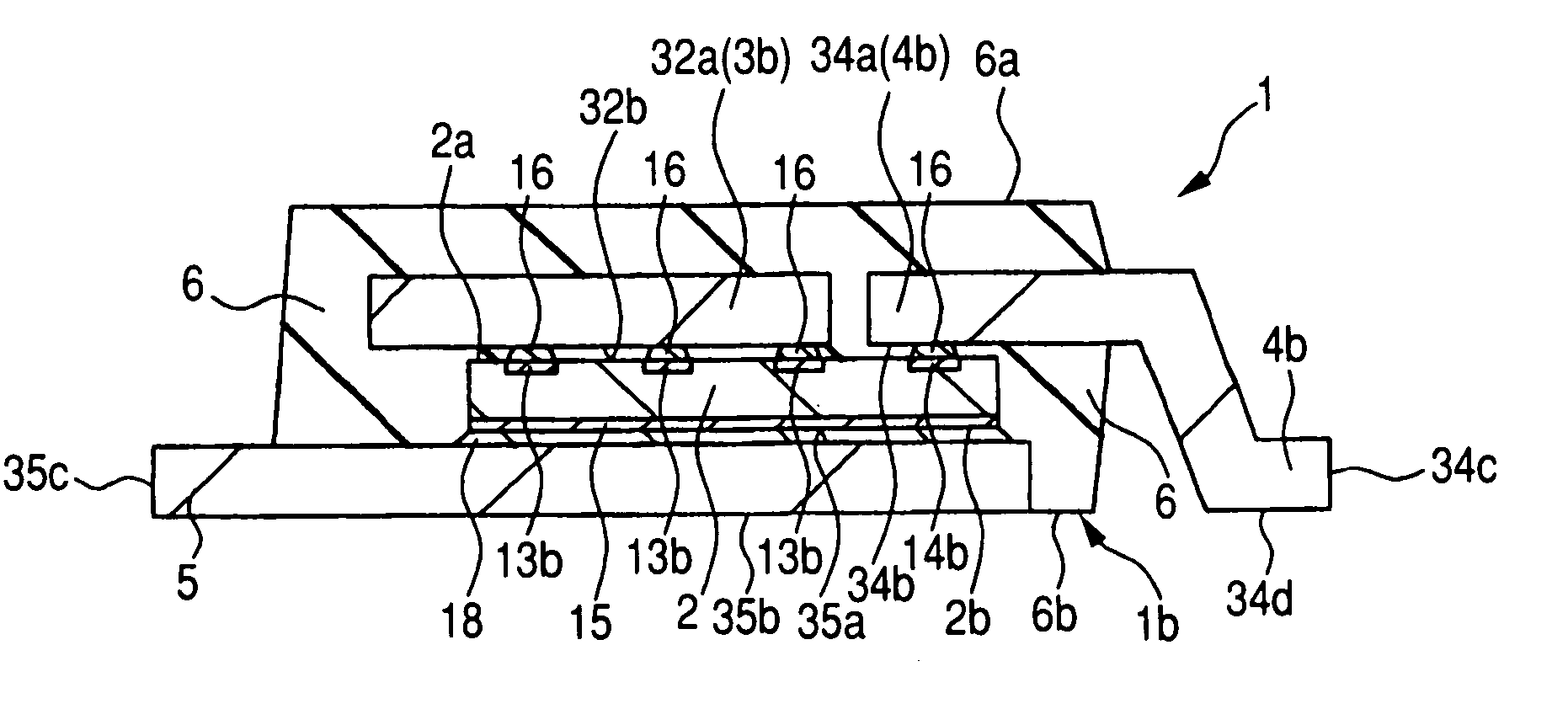

Semiconductor device

InactiveUS20060263988A1Substrate wiring resistant is increasedImprove the immunityTransistorSemiconductor/solid-state device detailsDevice materialSemiconductor chip

Two vertical-type power MISFETs are formed over a semiconductor chip, a common drain electrode formed over a back surface of the semiconductor chip is electrically connected with a drain terminal via a conductive bonding material, source electrodes and gate electrodes formed over a surface of the semiconductor chip are respectively electrically connected with source terminals and gate terminals via bump electrodes, and these components are sealed by a resin sealing portion. The exposed portions of the gate terminals are arranged inside the resin sealing portion, and the exposed portions of the source terminals are arranged outside the resin sealing portion. The source terminals extend over the surface of the semiconductor chip and are connected with the source electrodes which are uniformly arranged over regions of the surface of the semiconductor chip except for gate electrode forming regions and the vicinities of these regions via the bump electrodes.

Owner:RENESAS ELECTRONICS CORP

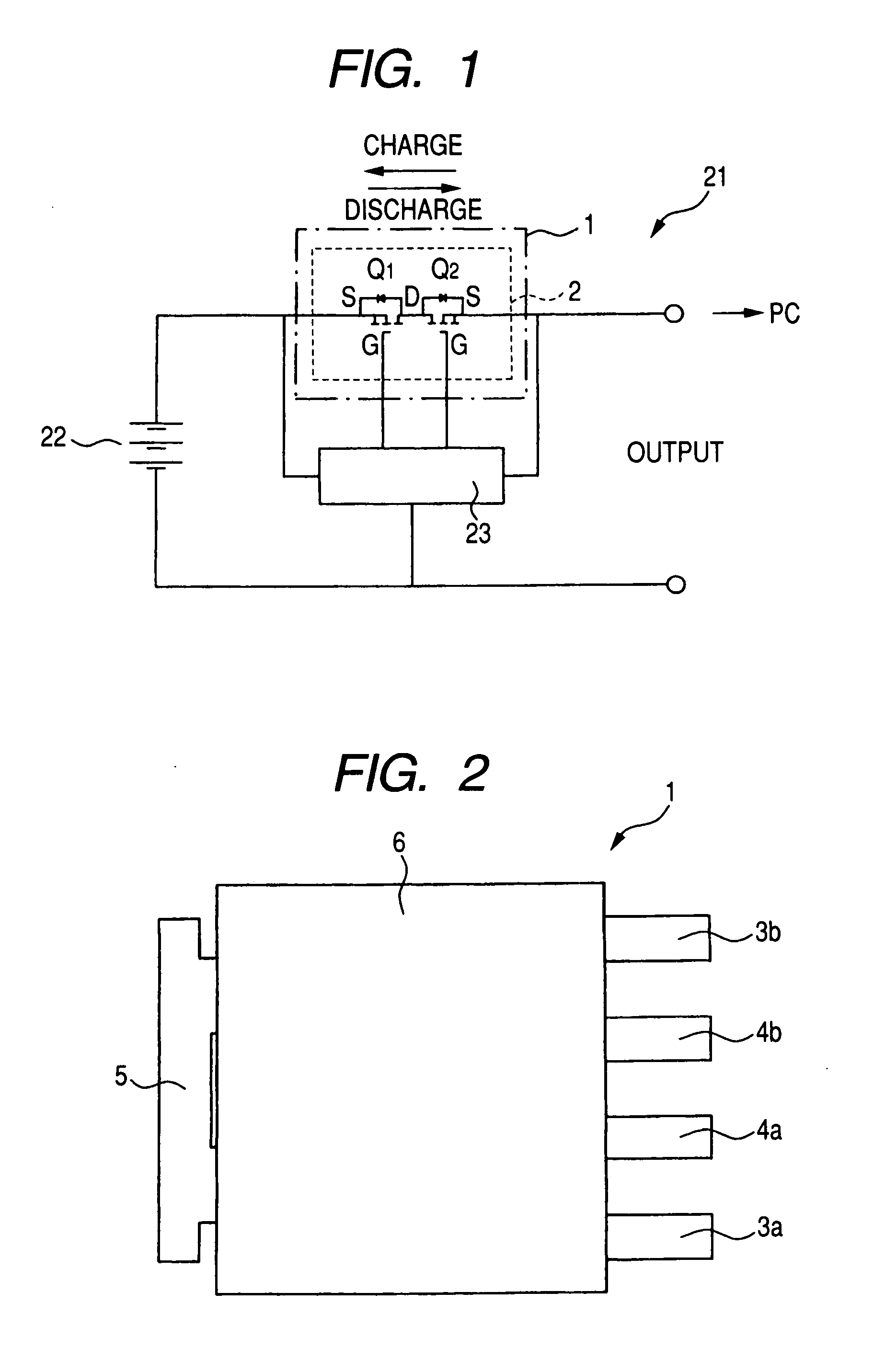

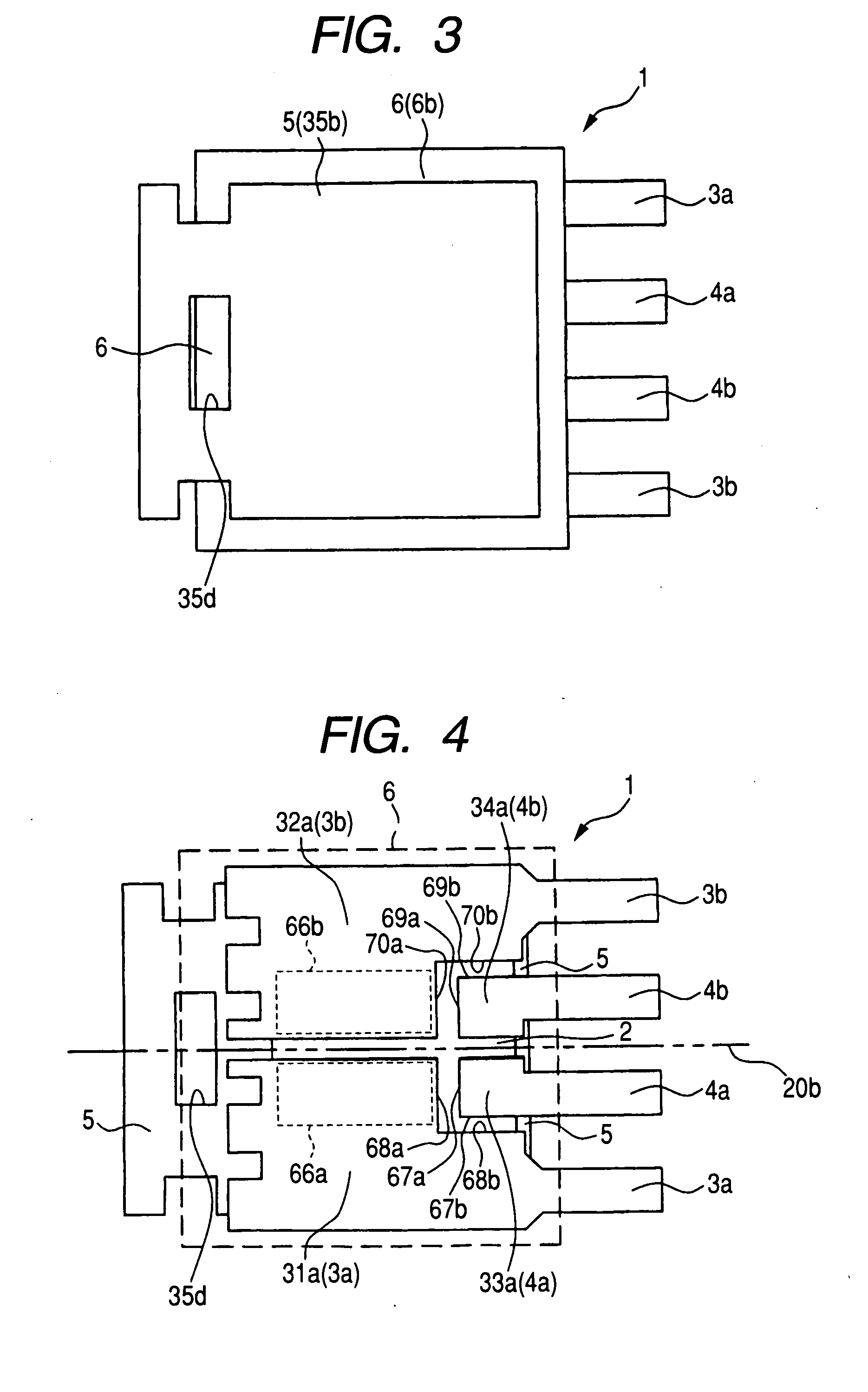

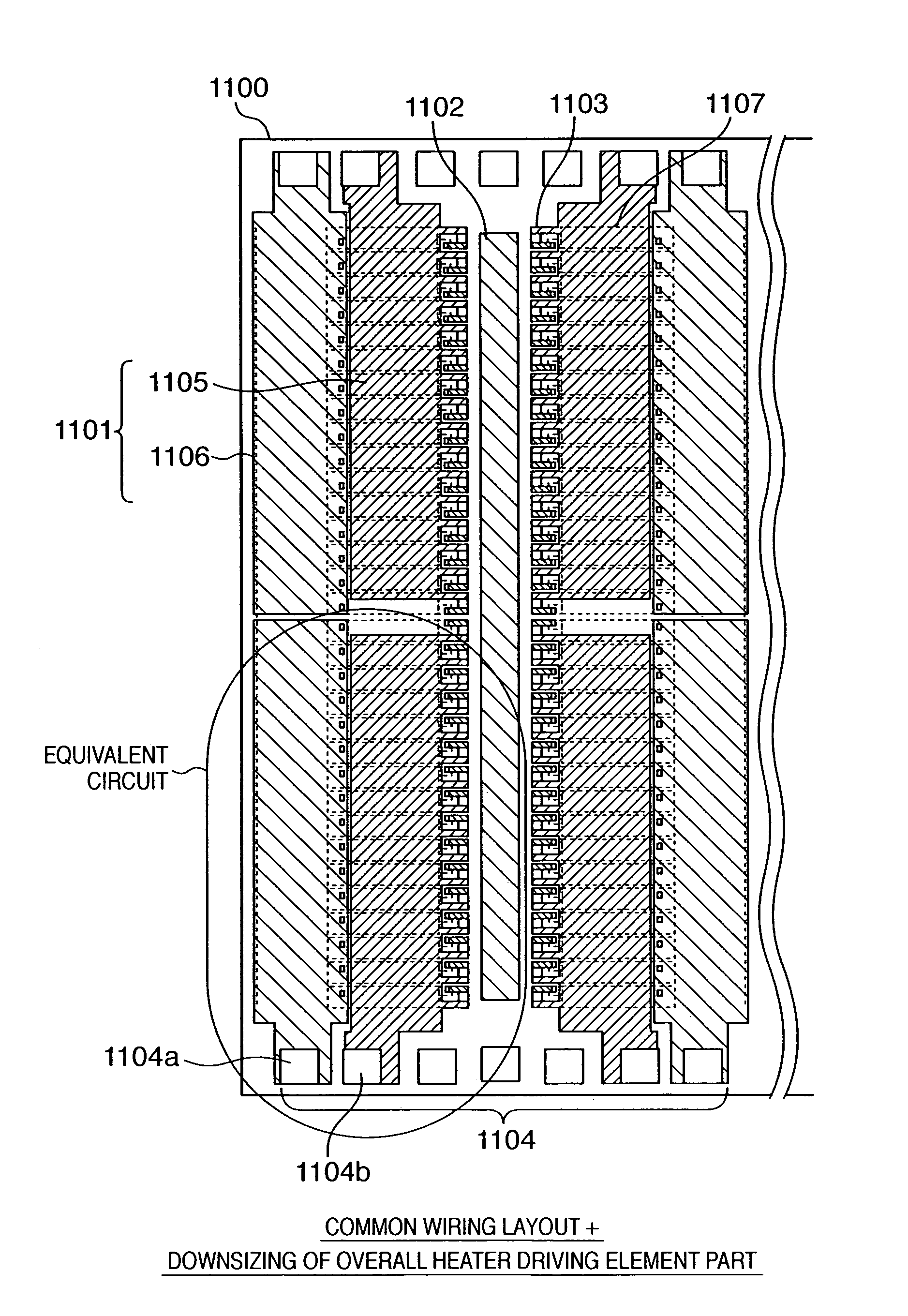

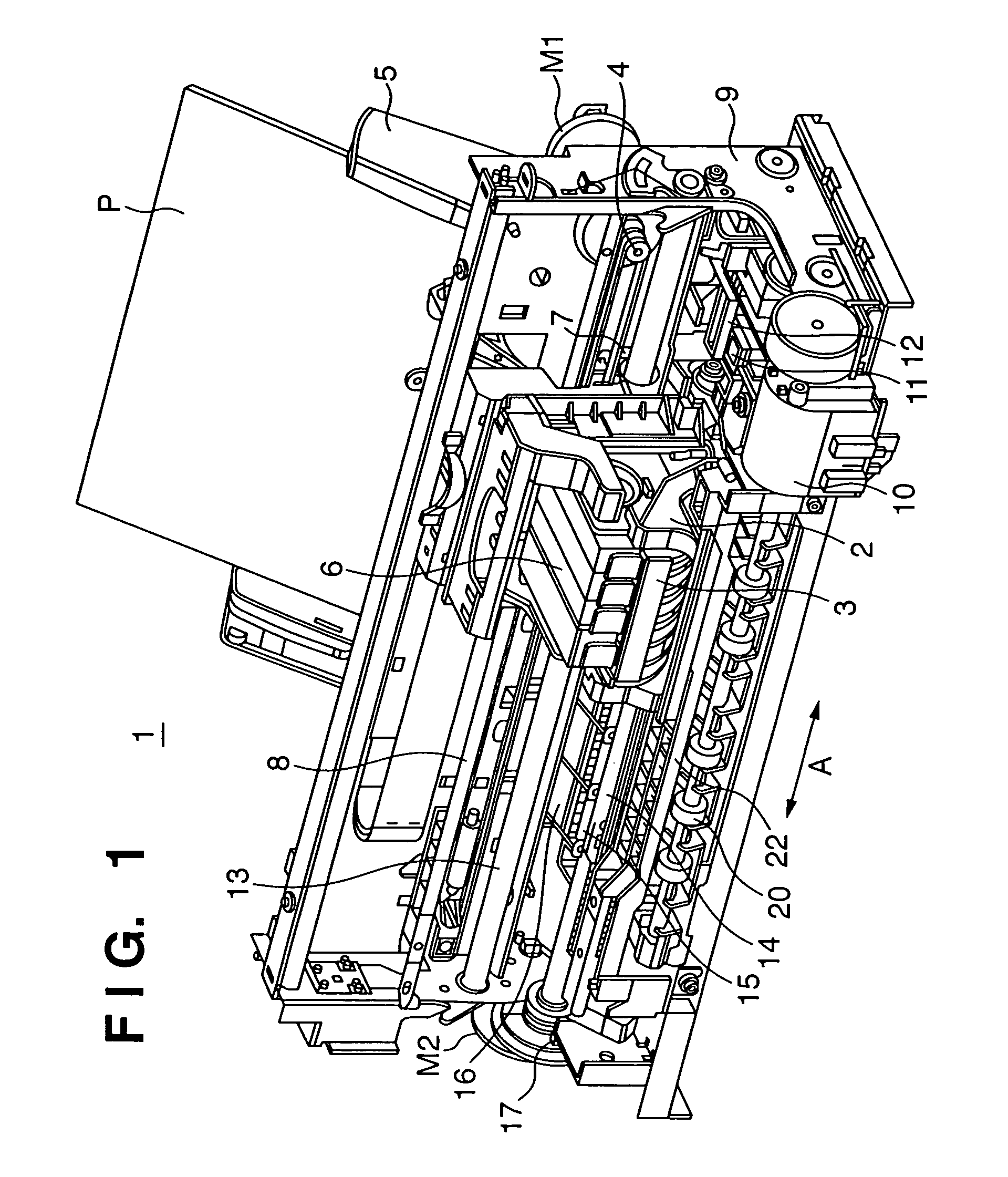

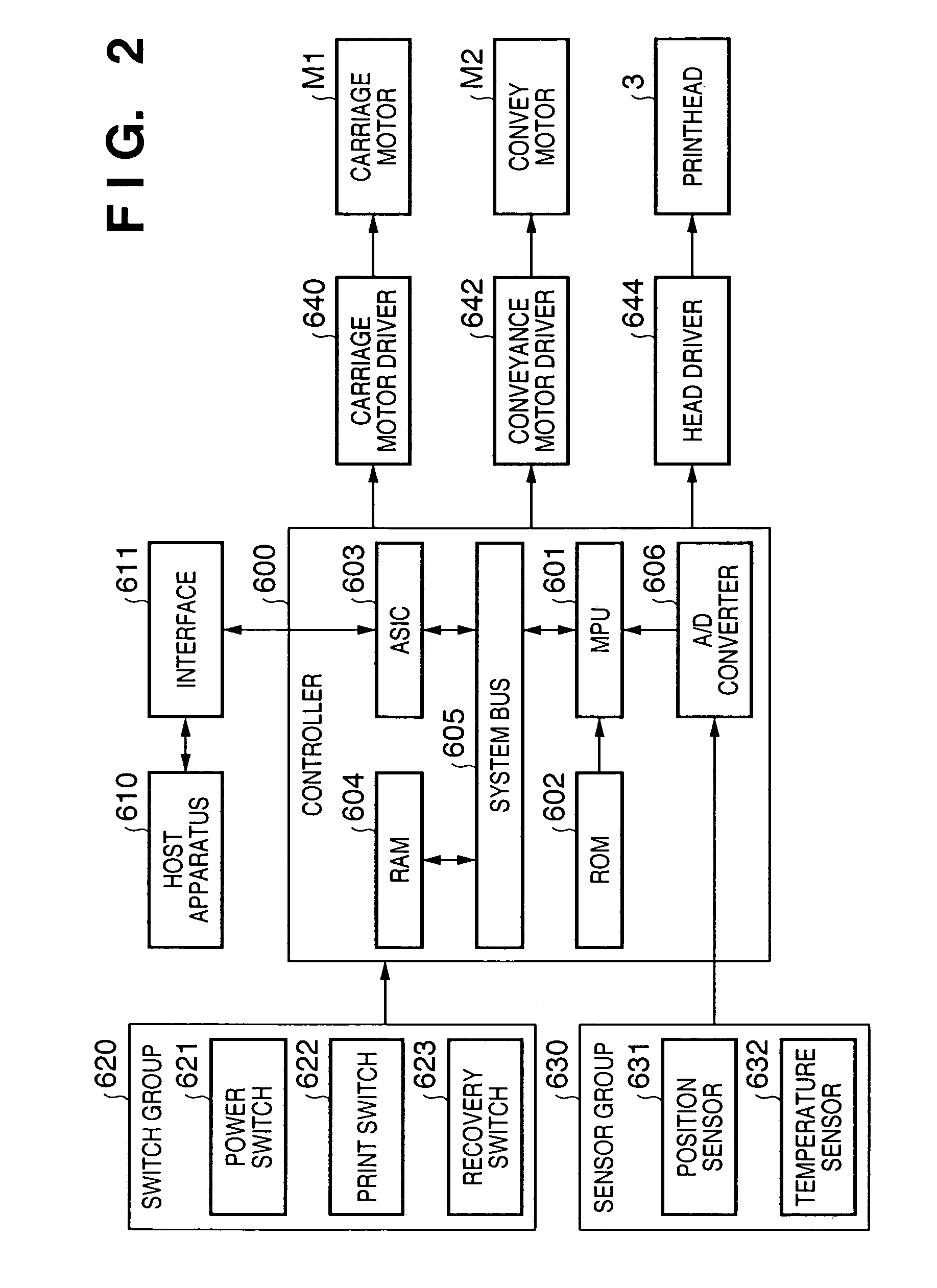

Method of driving a printhead using a constant current and operating MOS transistor in saturation region

InactiveUS7216960B2Increase line widthIncrease the number ofPrintingElectrical resistance and conductanceWire width

This invention relates to a printhead substrate capable of suppressing an increase in wiring width and an increase in the size of a substrate formed by a film forming process while increasing the number of simultaneously driven printing elements in order to improve the printing performance, a printhead using the substrate, and a printing apparatus using the printhead. The wiring lines of the substrate are formed into a common wiring line, and energy applied to a heating resistance element is prevented from deviating from a stable ink discharge range owing to the difference in the number of simultaneously driven heating resistance elements. For this purpose, a driving element is greatly downsized in comparison with a conventional one, and the operation region of a MOS transistor is shifted from the non-saturation region to the saturation region.

Owner:CANON KK

Photoacid generators, photoresist composition including the same and method of forming pattern using the same

InactiveUS20080182203A1Uniform profileIncrease line widthOrganic chemistryOrganic compound preparationPhotoacid generatorSulfonium

A photoresist composition includes about 4% to about 10% by weight of a photoresist resin, about 0.1% to about 0.5% by weight of a photoacid generator having a sulfonium-salt cationic group and a sulfonium-salt anionic group containing a carboxyl group as a hydrophilic site and a remainder of a solvent. The photoresist composition may form a photoresist pattern having a uniform profile.

Owner:SAMSUNG ELECTRONICS CO LTD

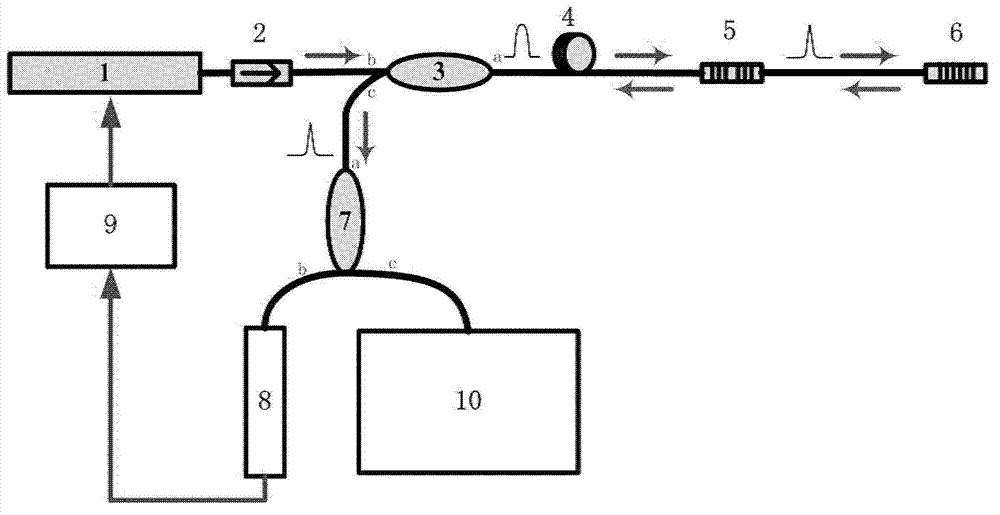

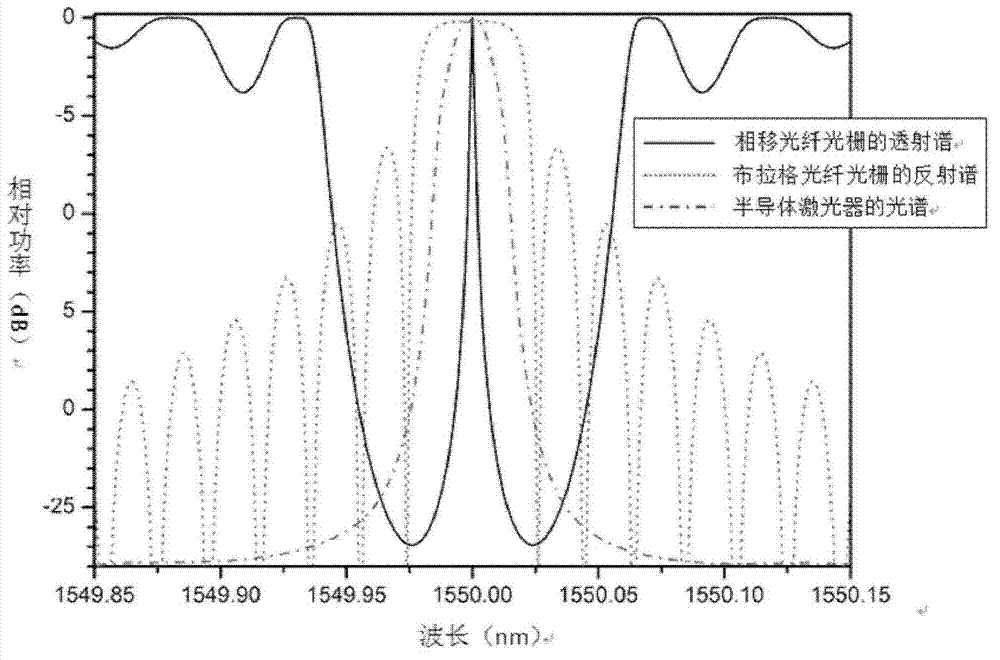

Optical fiber sensing system based on phase-shifted optical fiber grating

ActiveCN102829806ALow costIncrease line widthConverting sensor output opticallyPhase shiftedTunable laser

The invention provides an optical fiber sensing system based on a phase-shifted optical fiber grating. The optical fiber sensing system comprises a semiconductor laser light source, a first coupler, the phase-shifted optical fiber grating, a fiber Bragg grating, a second coupler and a wavelength demodulation instrument, wherein the semiconductor laser light source generates a laser with preset wavelength width; the first coupler is used for coupling the laser with the preset wavelength width to the phase-shifted optical fiber grating and coupling a signal laser reflected back by the fiber Bragg grating to the second coupler; a transmission window of the phase-shifted optical fiber grating changes along with change of external physical quantity of the phase-shifted optical fiber grating, and transmitted portions of the laser passing through the phase-shifted optical fiber grating form the signal laser with wavelength narrower than the preset wavelength; the fiber Bragg grating is used for reflecting the signal laser, and the reflected signal laser is transmitted to the first coupler by the aid of the phase-shifted optical fiber grating; the second coupler is used for coupling the signal laser to the wavelength demodulation instrument; and the wavelength demodulation instrument is used for demodulating the signal laser to obtain the external physical quantity of the phase-shifted optical fiber grating. The optical fiber sensing system based on the phase-shifted optical fiber grating does not need a high-resolution spectrograph or a narrow-linewidth tunable laser, so that cost is greatly saved.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

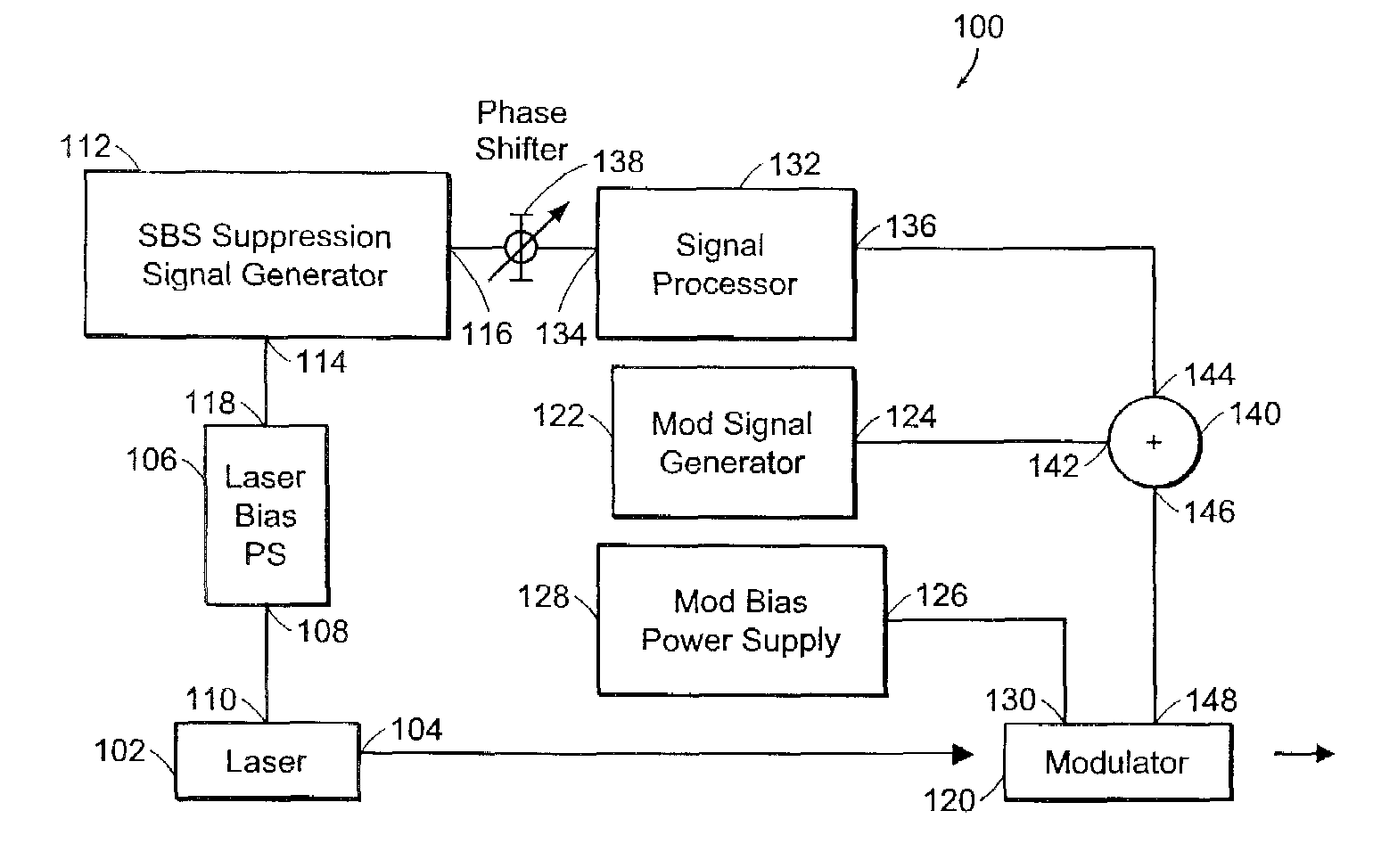

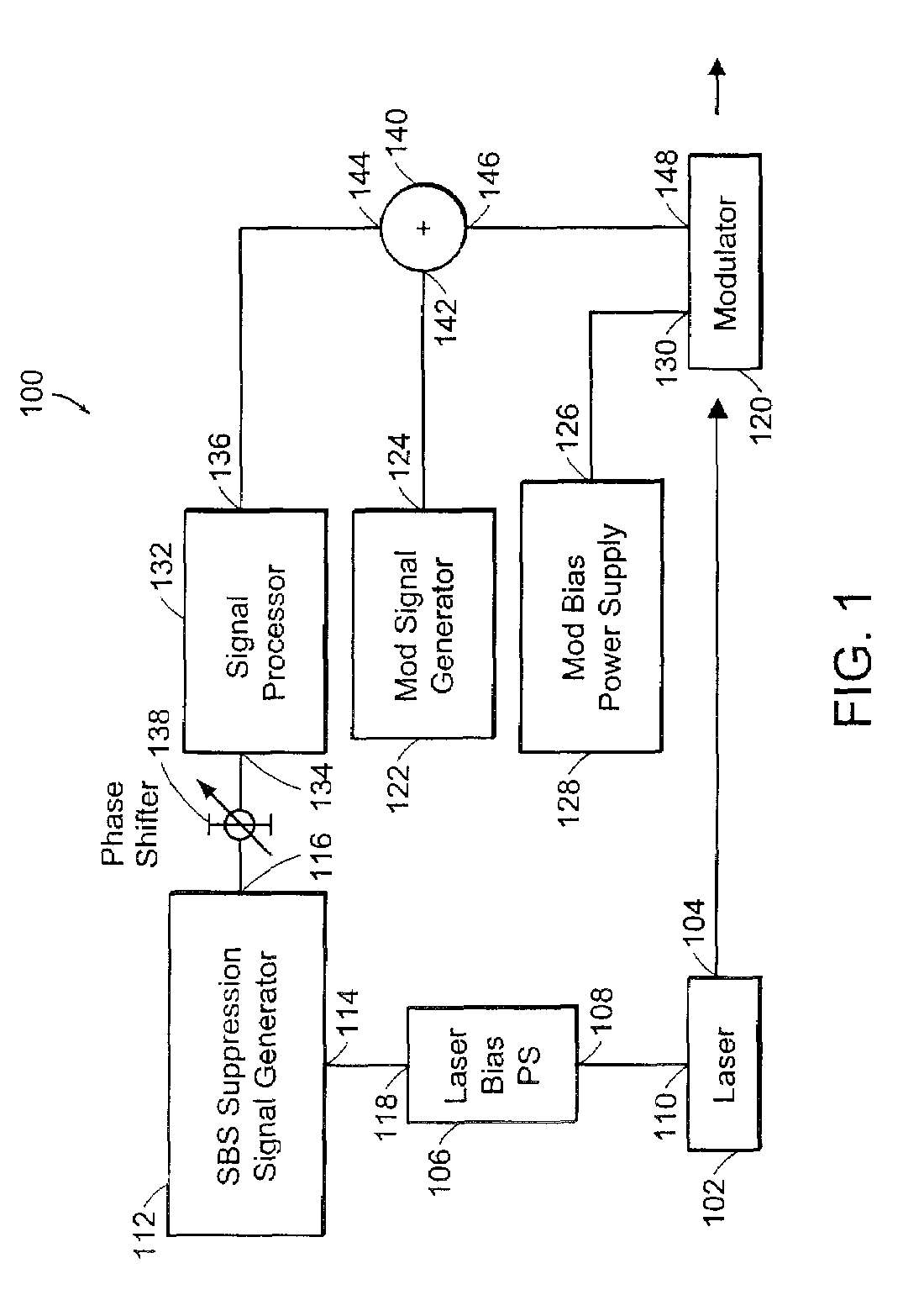

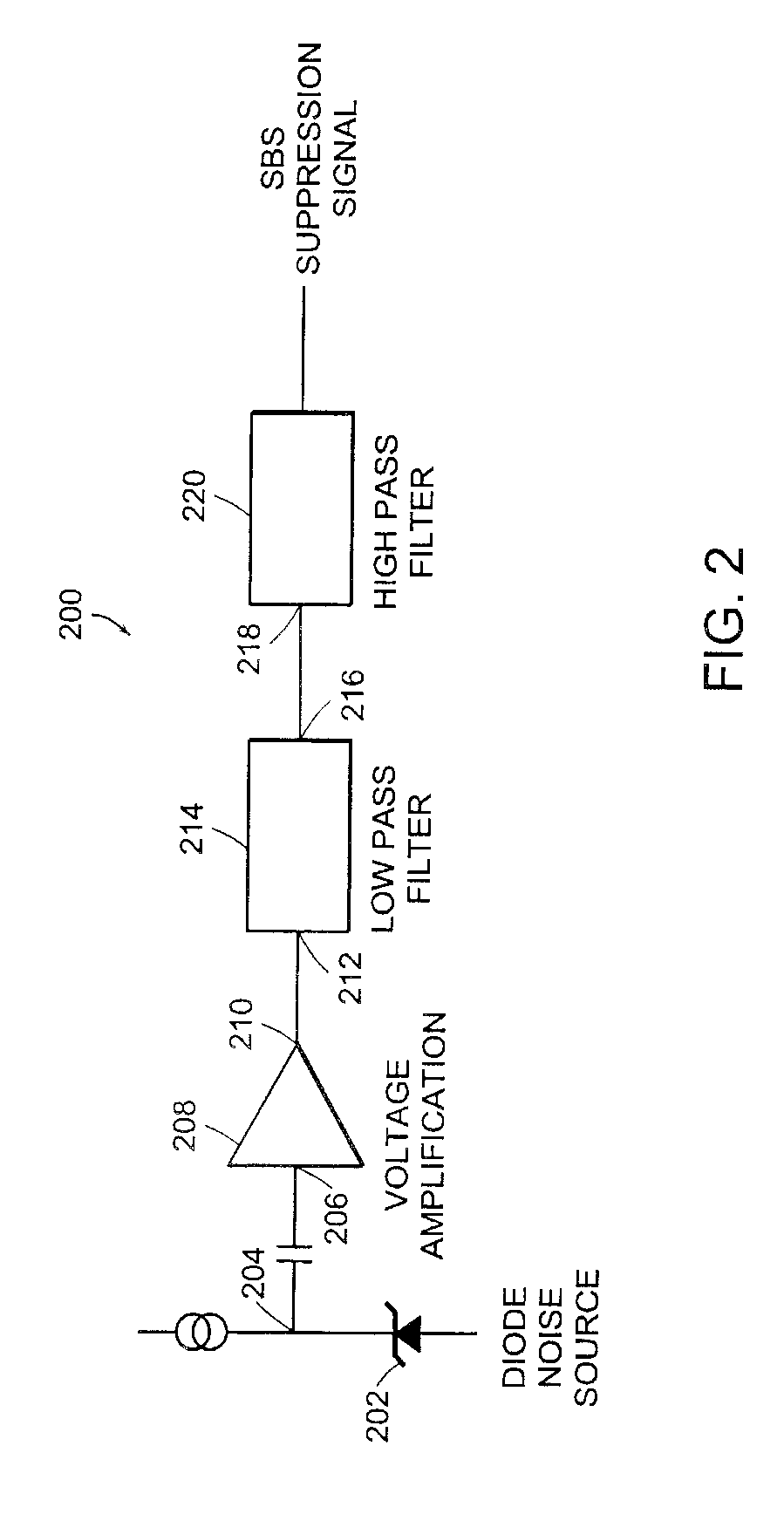

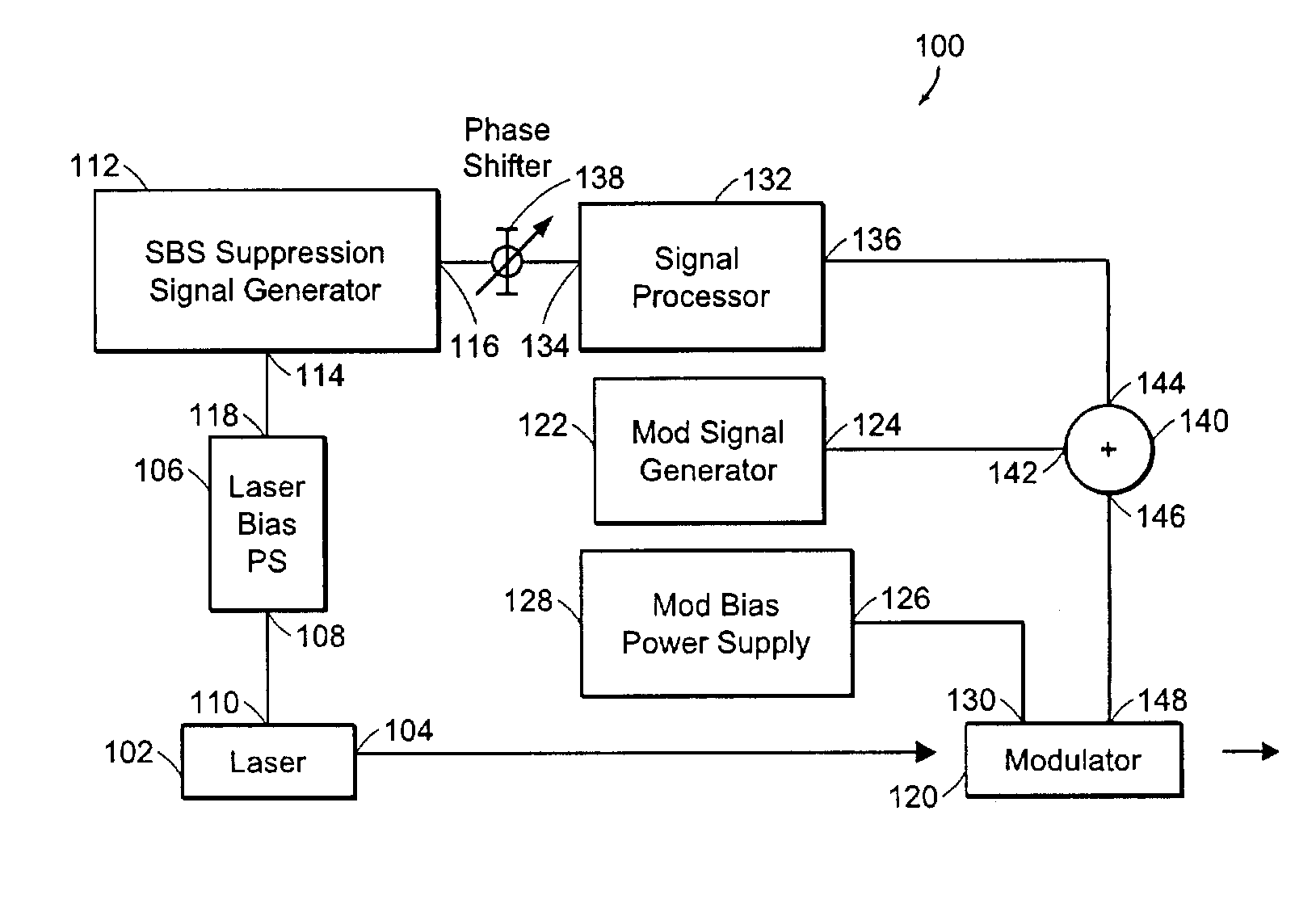

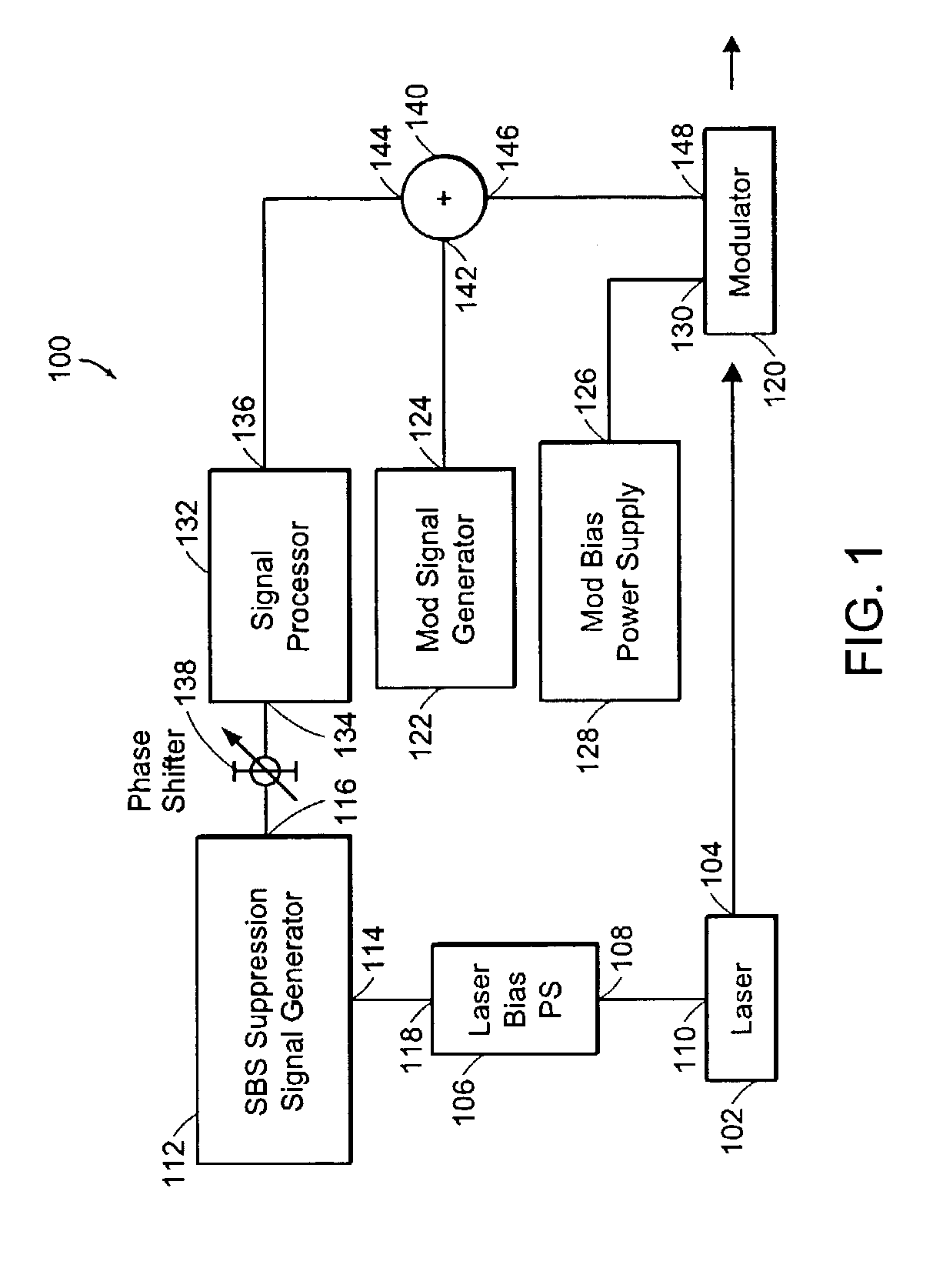

Optical transmitter with SBS suppression

InactiveUS7349637B1Suppression problemHigh bandwidthLaser detailsBrush bodiesLine widthSignal generator

An optical transmitter and methods of generating an optical signal having SBS suppression are described. An optical transmitter having SBS suppression according to the present invention includes a signal generator that generates a SBS suppression signal. A laser generates a line width broadened optical signal having AM noise. A signal processor generates a modified SBS suppression signal from the SBS suppression signal. A modulator modulates the line width broadened optical signal having the AM noise with a payload modulation signal and with the modified SBS suppression signal to generate a payload modulated optical signal having SBS suppression and reduced AM noise.

Owner:II VI DELAWARE INC +1

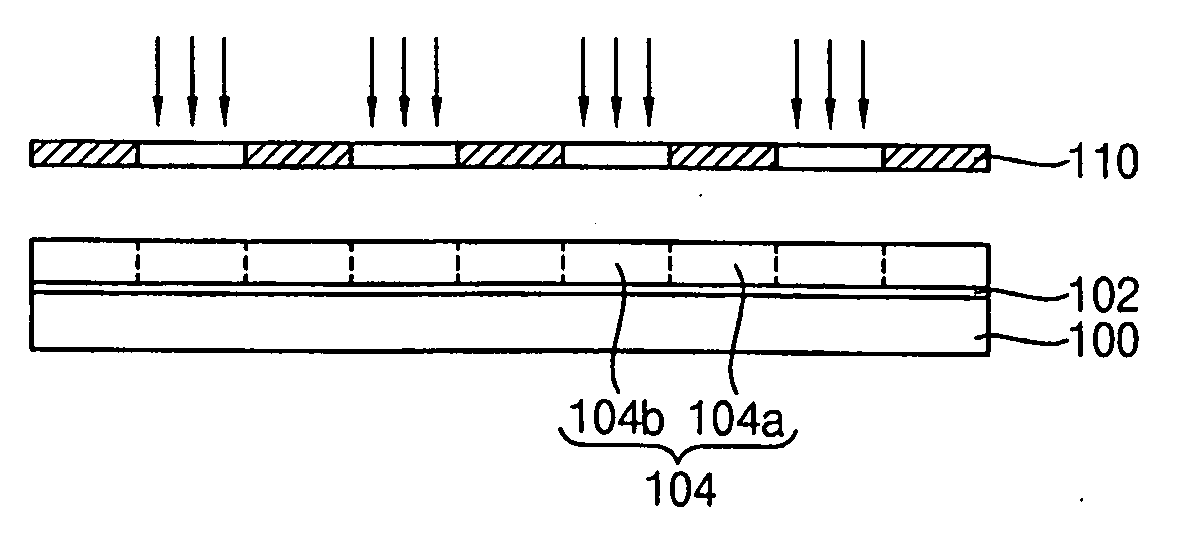

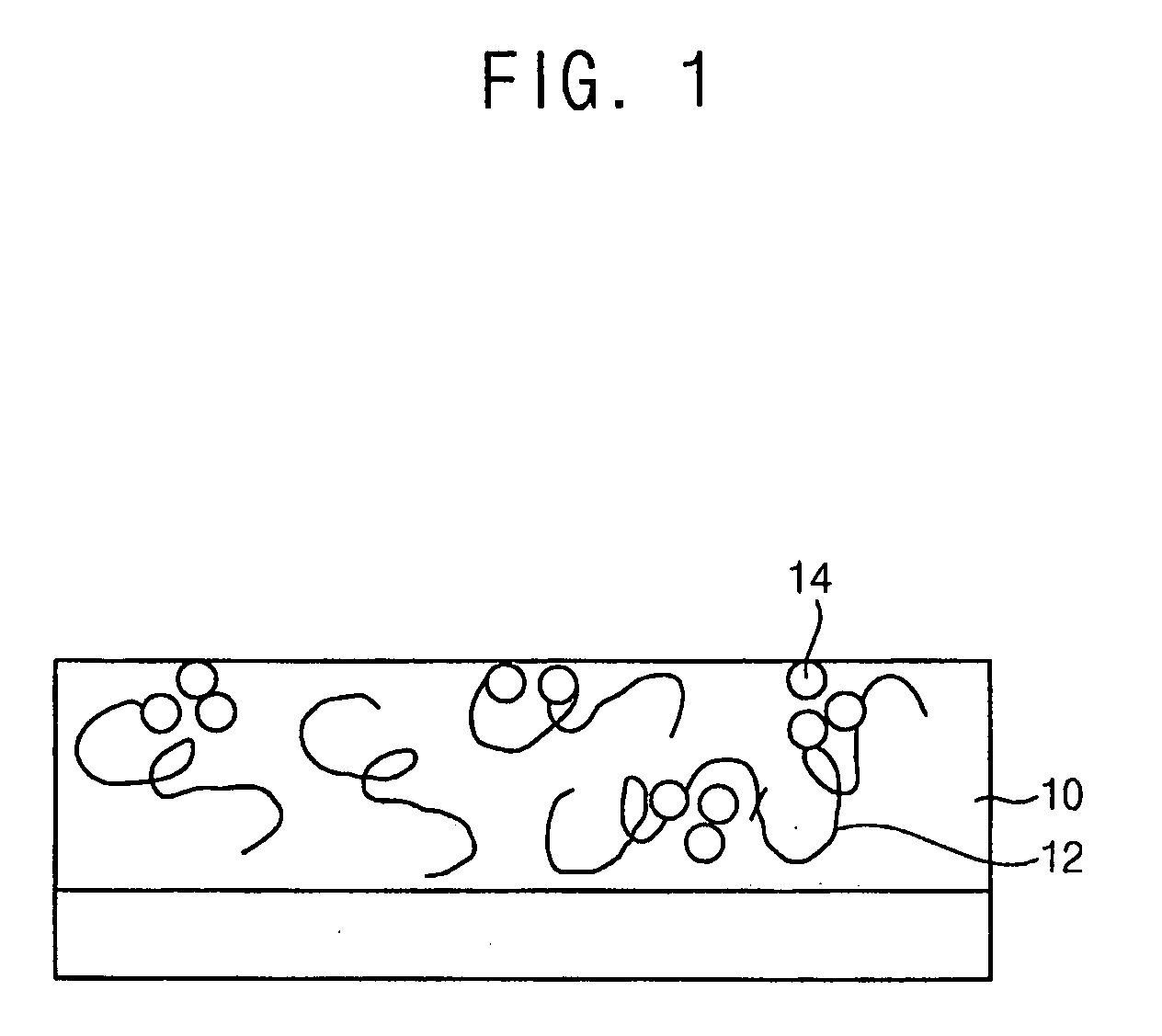

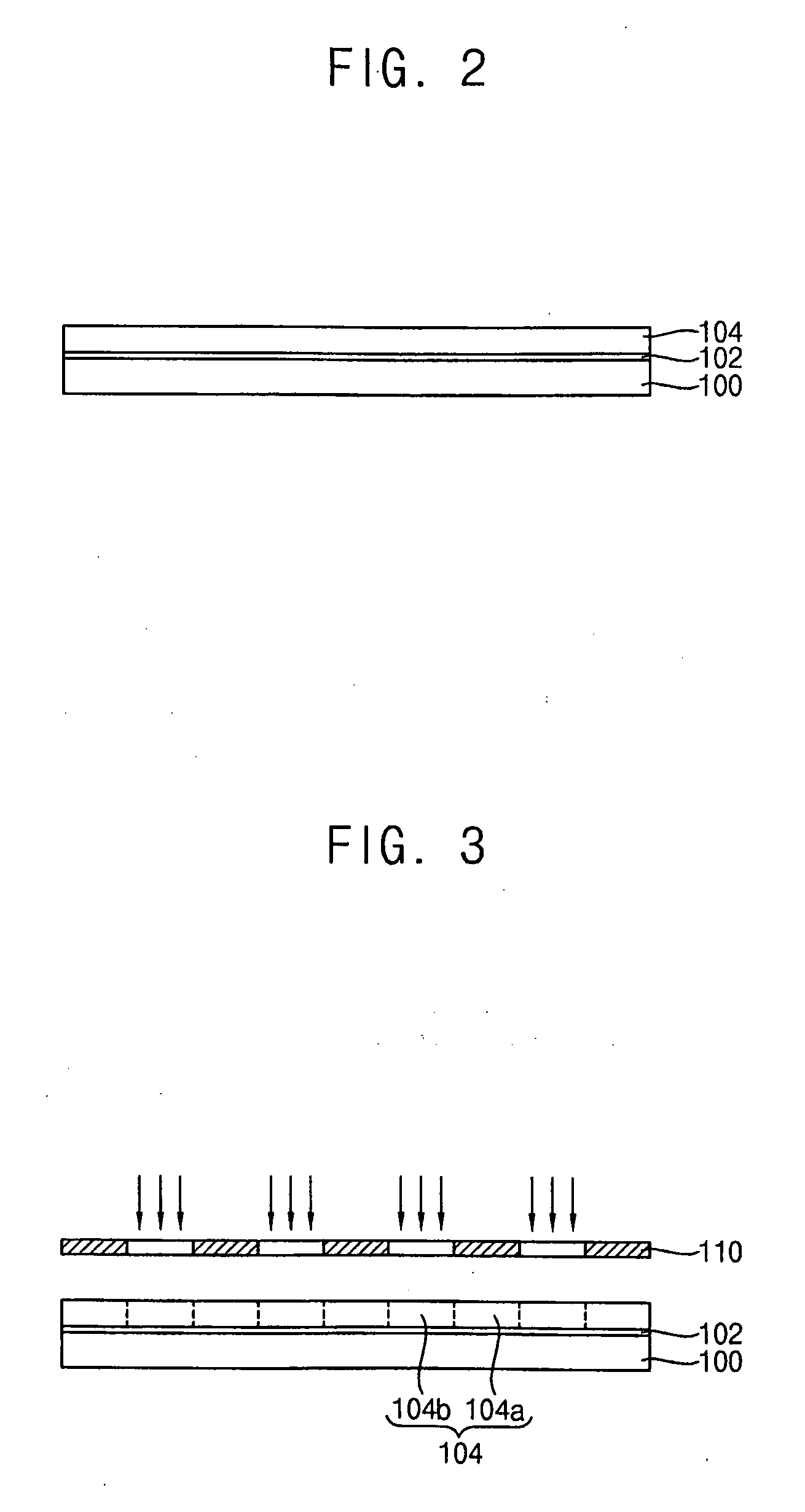

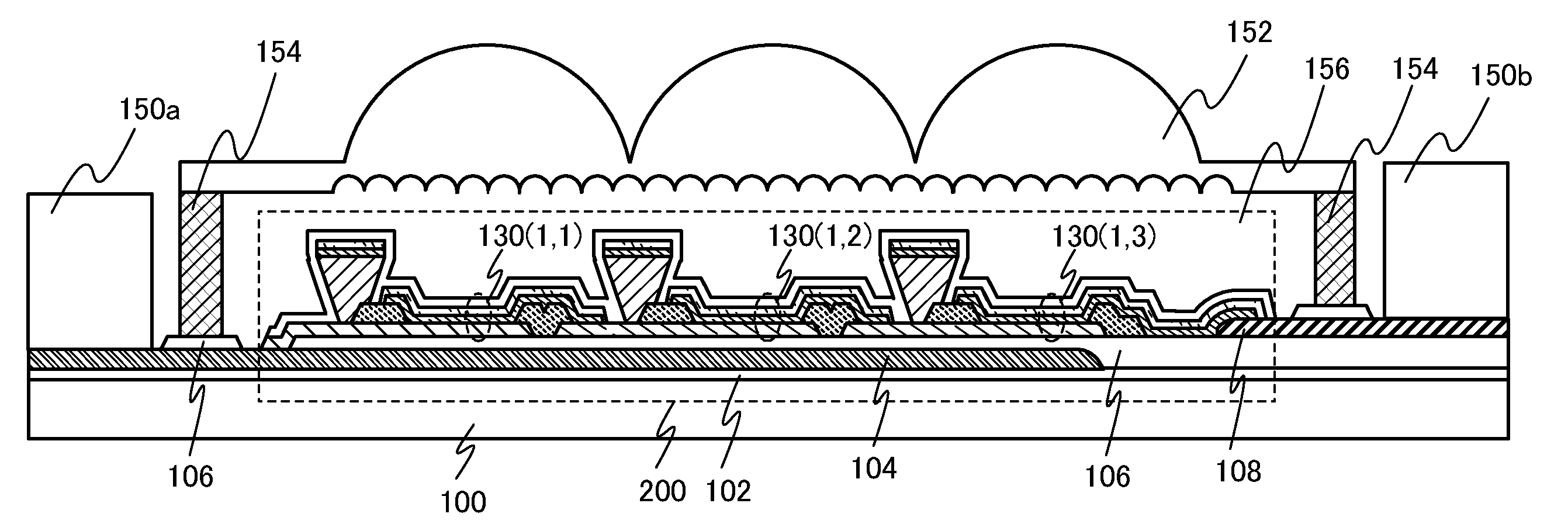

Light-emitting device and lighting device

InactiveUS20120205675A1Improve the immunityIncrease line widthElectroluminescent light sourcesSolid-state devicesSimple Organic CompoundsEngineering

To provide a light-emitting device including the plurality of light-emitting elements having a structure in which a light-emitting area is large and defects in patterning of light-emitting elements are suppressed. To provide a lighting device including the light-emitting device. The light-emitting device includes a first wiring provided over a substrate having an insulating surface, an insulating film provided over the first wiring, a second wiring provided over the insulating film, and a light-emitting element unit including a plurality of light-emitting elements provided over the first wiring with the insulating film provided therebetween. The plurality of light-emitting elements each include a first electrode layer having a light-blocking property, a layer containing an organic compound in contact with the first electrode layer, and a second electrode layer having a light-transmitting property in contact with the layer containing an organic compound. The layers containing an organic compound are separated by a separation layer.

Owner:SEMICON ENERGY LAB CO LTD

Optical transmitter with SBS suppression

An optical transmitter and methods of generating an optical signal having SBS suppression are described. An optical transmitter having SBS suppression according to the present invention includes a signal generator that generates a SBS suppression signal. A laser generates a line width broadened optical signal having AM noise. A signal processor generates a modified SBS suppression signal from the SBS suppression signal. A modulator modulates the line width broadened optical signal having the AM noise with a payload modulation signal and with the modified SBS suppression signal to generate a payload modulated optical signal having SBS suppression and reduced AM noise.

Owner:OPTIUM +1

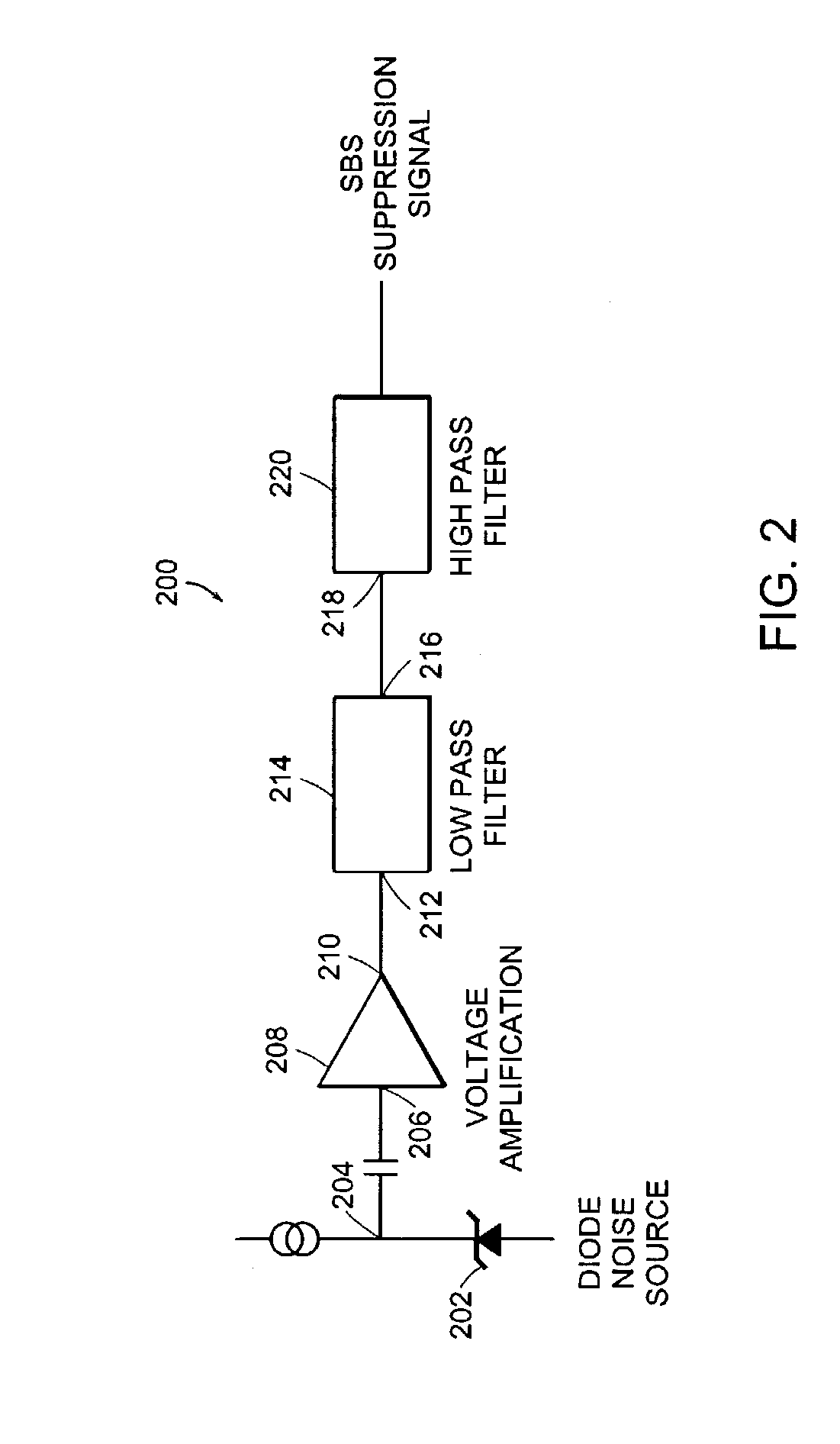

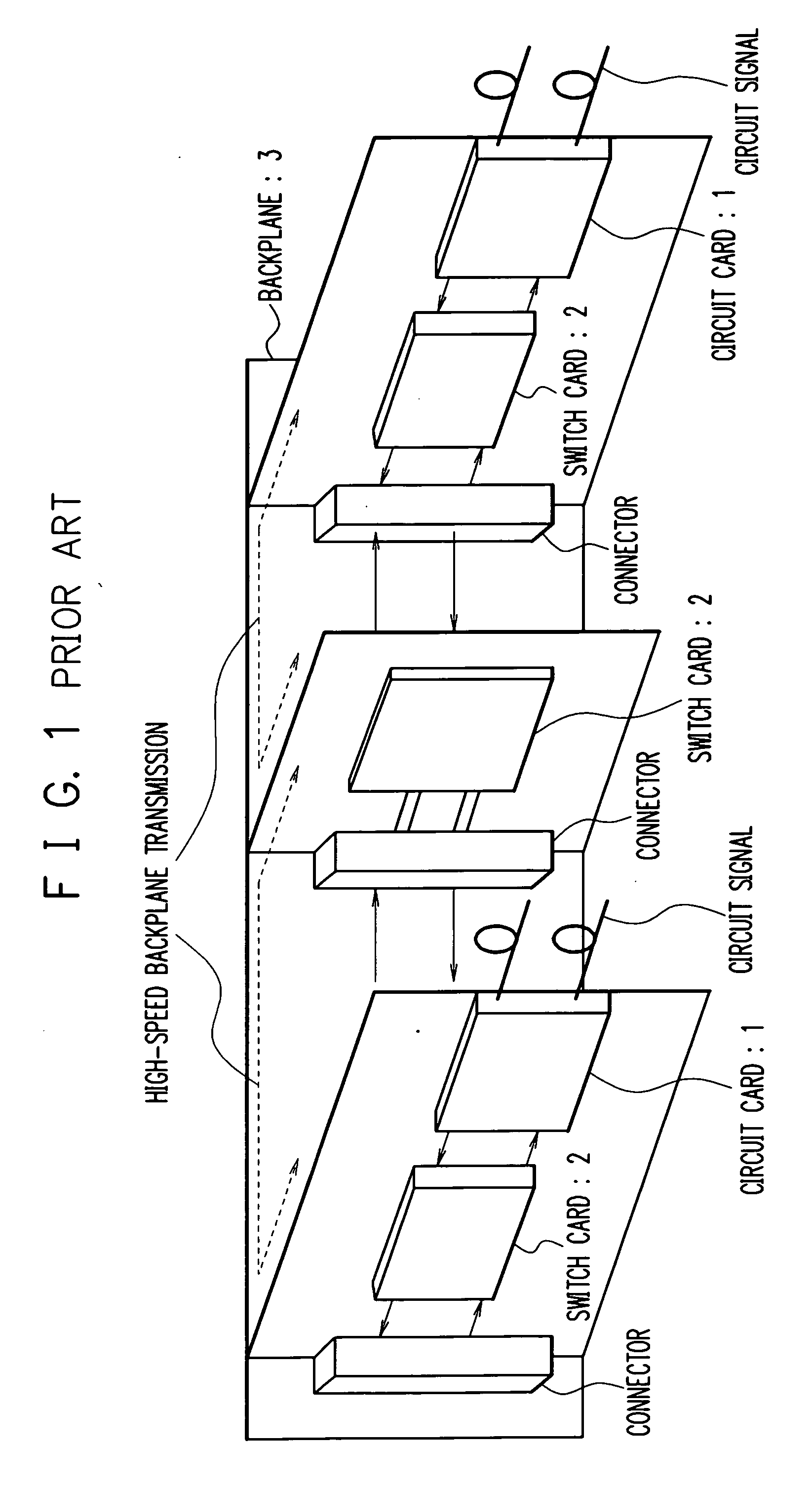

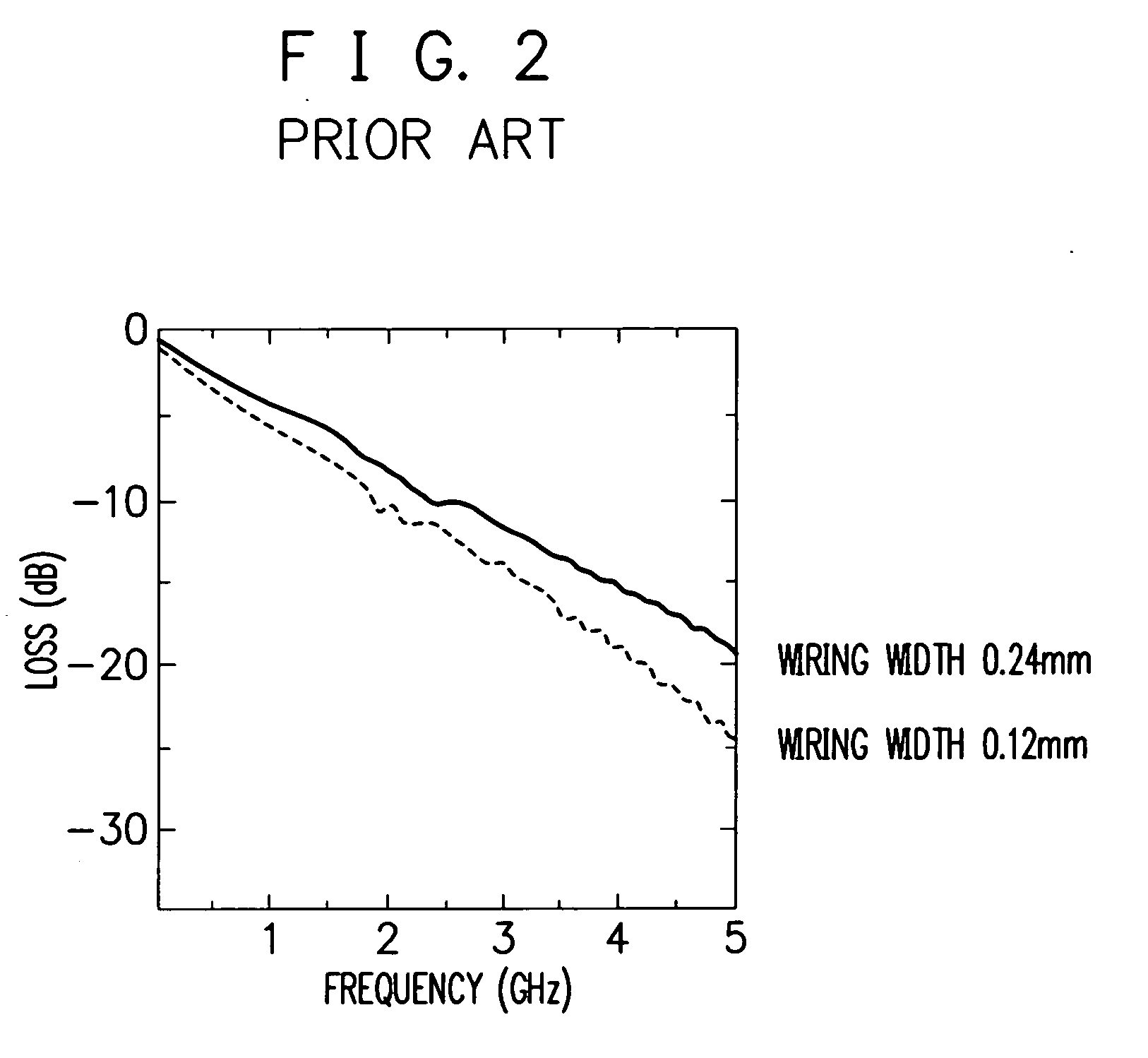

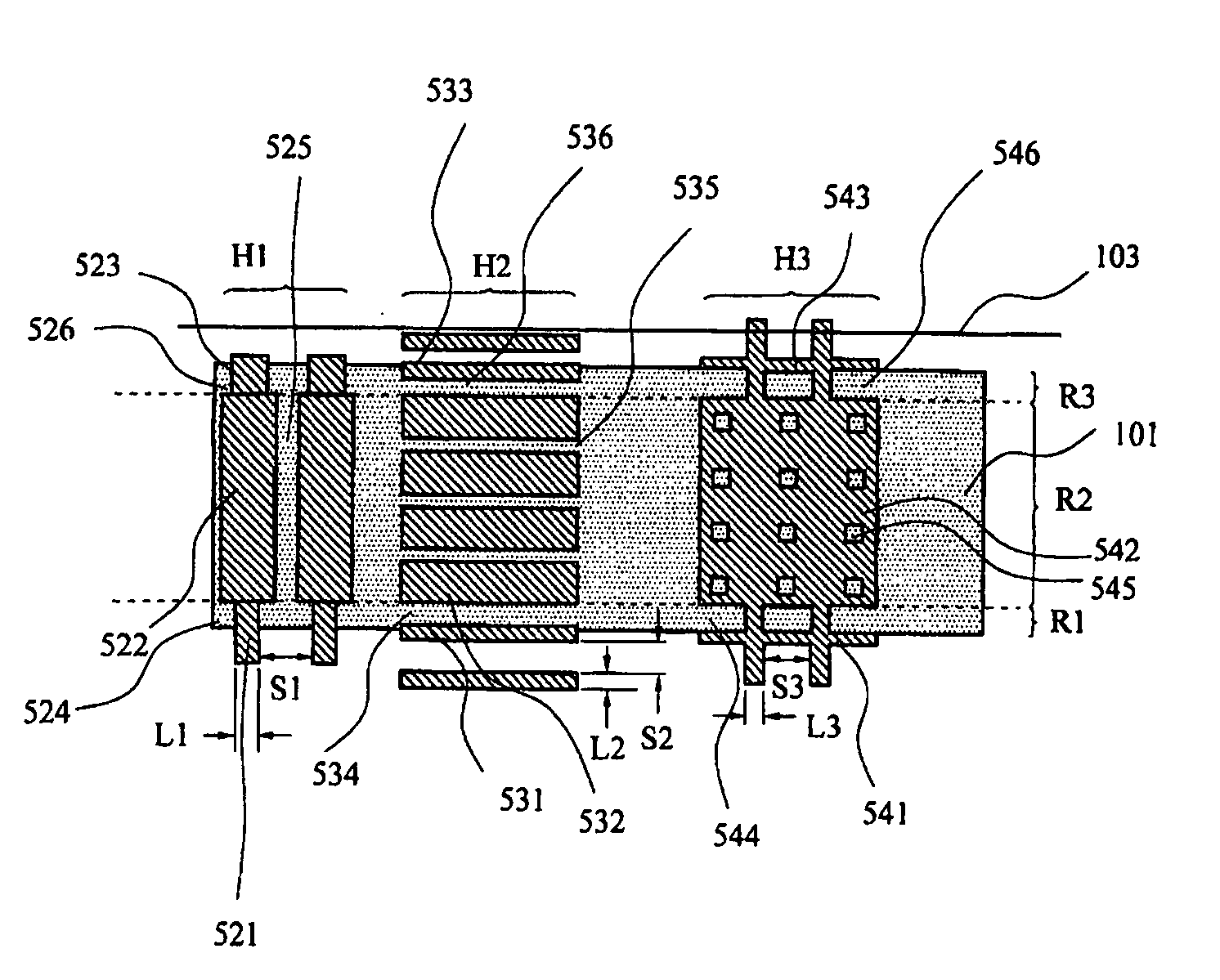

Transmission line and wiring forming method

InactiveUS20060197625A1Reduce the valueIncrease widthMultiple-port networksHigh frequency circuit adaptationsUltrasound attenuationCharacteristic impedance

To provide a transmission line capable of absorbing the reflection caused by mismatching between impedances and restraining the attenuation value of a signal. The following wiring patterns are formed out of a connector mounting area in which a connector is mounted: a wiring pattern designed so as to gradually increase the wiring width and the interval between wirings of a wiring portion (B) and gradually decrease the characteristic impedance of the wiring portion (B) and a wiring pattern designed so as to gradually decrease the wiring width and the interval between wirings of the wiring portion (B′) and gradually amplify the characteristic impedance of the wiring portion (B′).

Owner:NEC CORP

Liquid crystal panel for liquid crystal display device

ActiveUS20080284963A1Downsize frameIncrease widthNon-linear opticsElectrical resistance and conductanceLiquid-crystal display

To utilize effectively the panel space of the liquid crystal panel, this invention has provided a wiring structure, in which the seal material and BM are coated in a superposition and the UV light is irradiated from one side of the TFT substrate; this invention has also provided a wiring structure, in which the seal material can still be irradiated by the UV light with high efficiency, meanwhile, the drop of the resistance value of the metal wiring on the TFT substrate can be restricted to a specific range. The solution is: the liquid crystal dropped is sandwiched between the TFT substrate and the CF substrate, meanwhile the liquid crystal panel is formed by adhering the light cured seal material disposed at the peripheral area of two substrates. In the adhering-formed liquid crystal panel, for the wiring portion, which is the portion of wiring disposed on the TFT substrate superposing the light cured seal material, the wiring structure is formed as follows, that is, the region of the seal material is divided into three regions, an adjacent region, a middle region and an outer region. The function of the respective regions must be held, and the resistance of the metal wiring is minimized under the precondition that the respective function is satisfied sufficiently.

Owner:INFOVISION OPTOELECTRONICS HLDG LTD

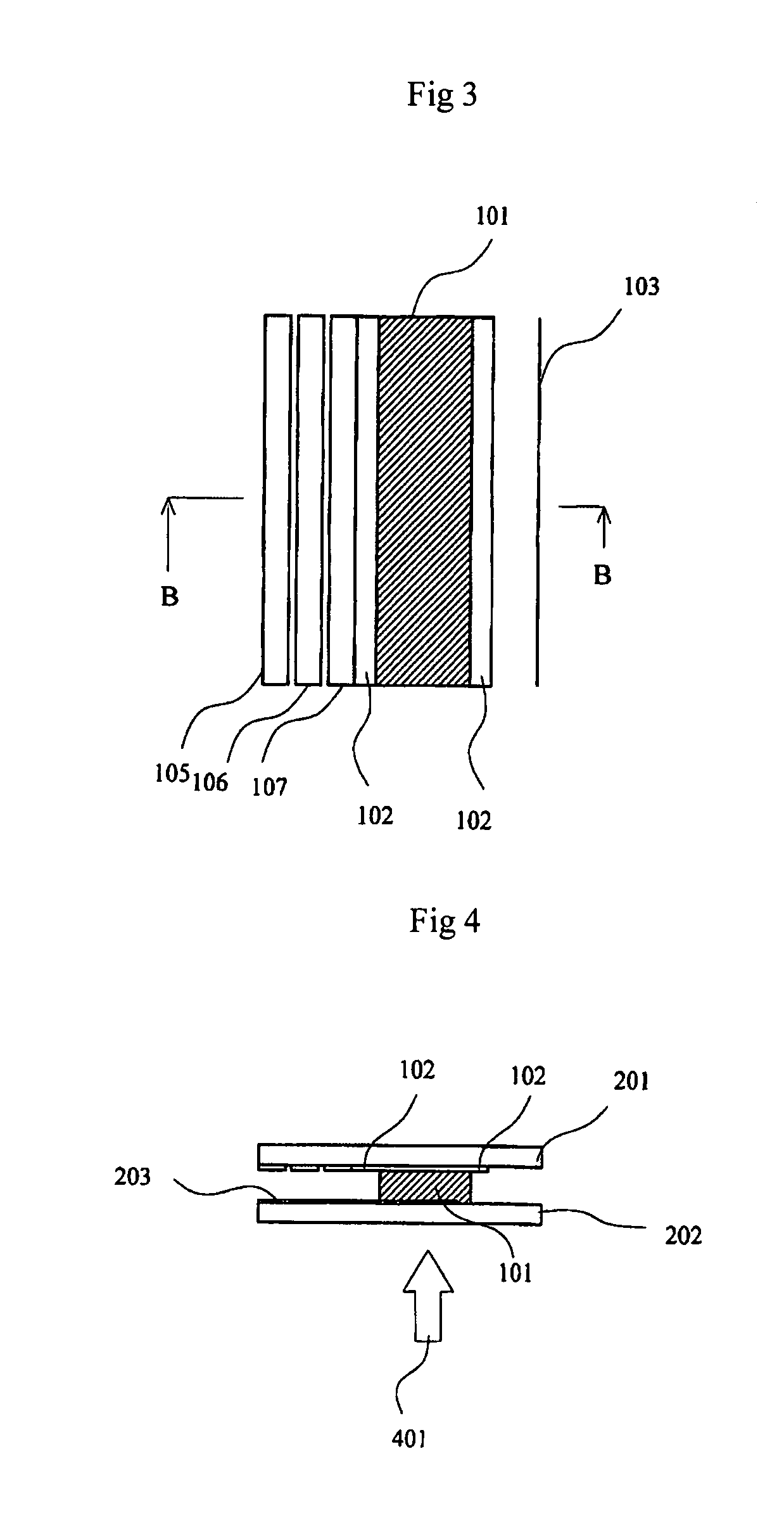

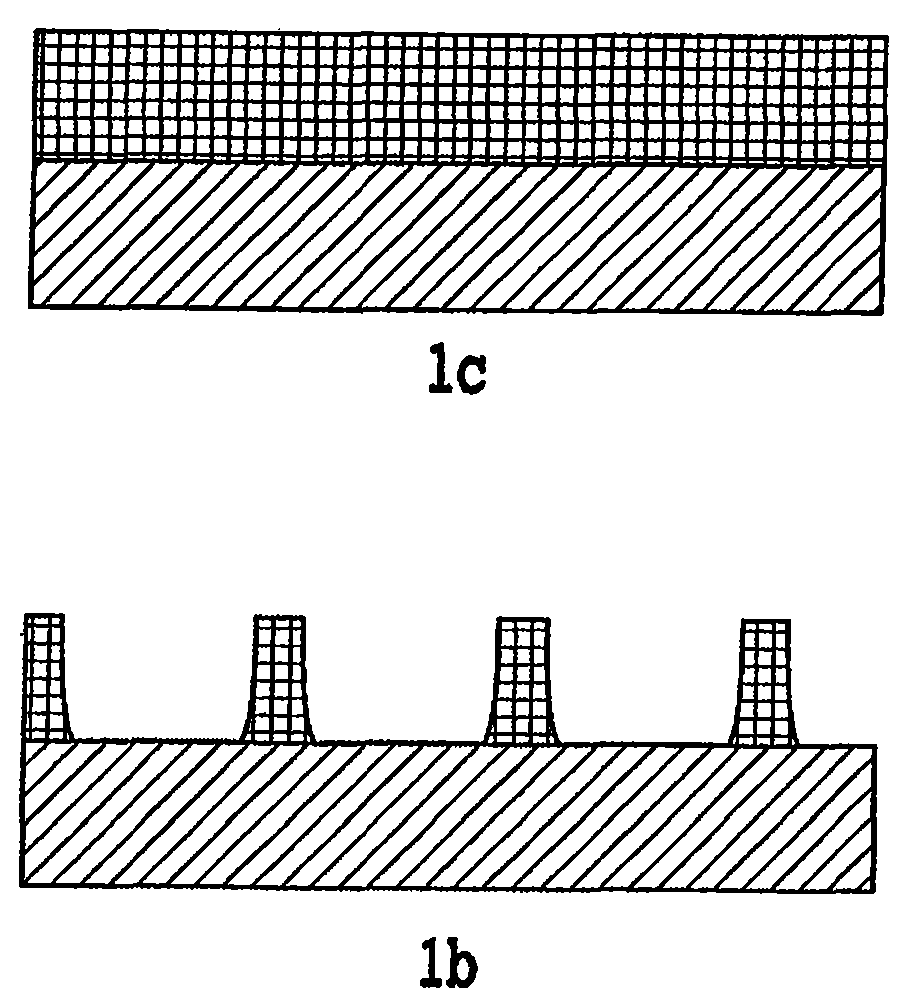

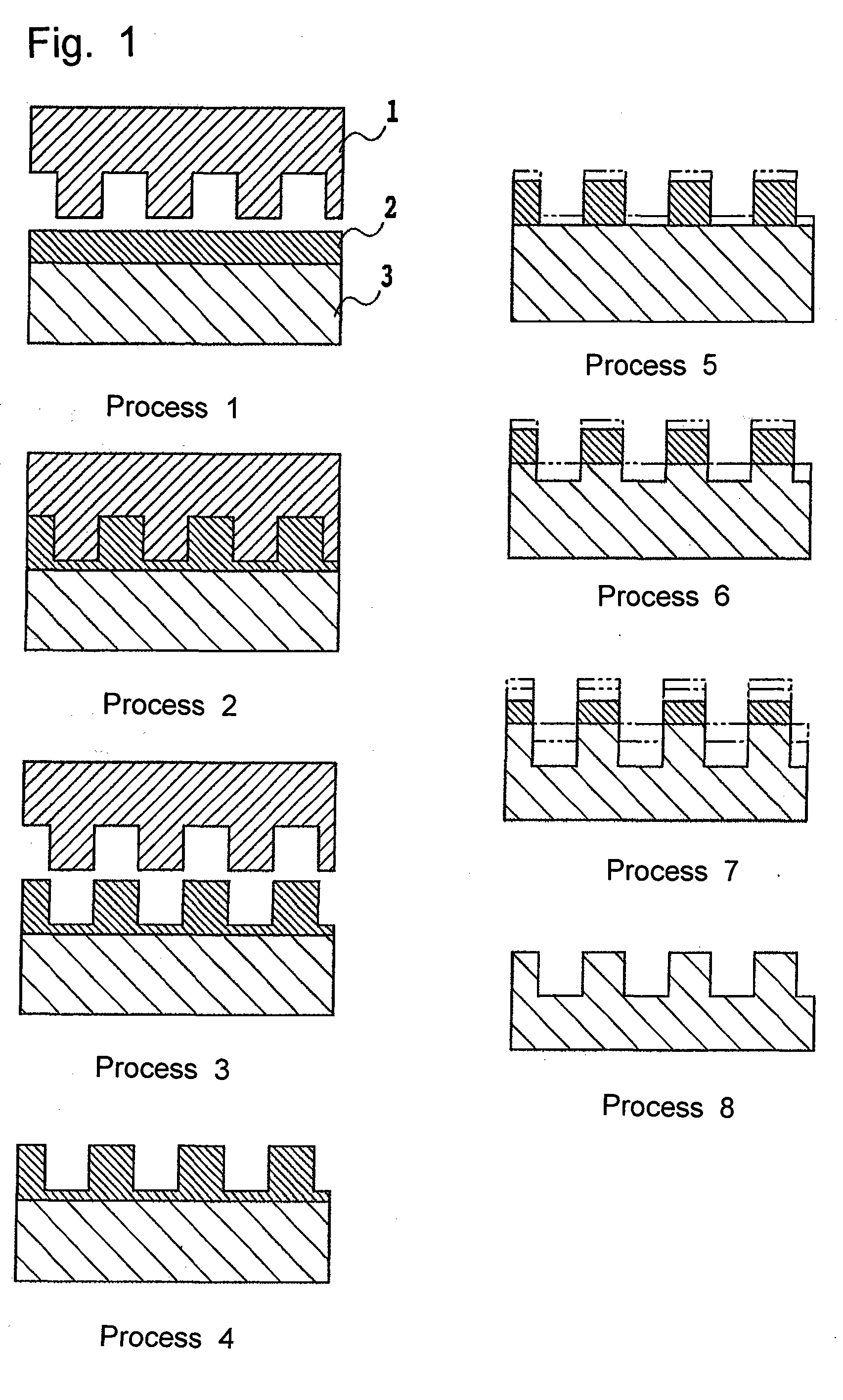

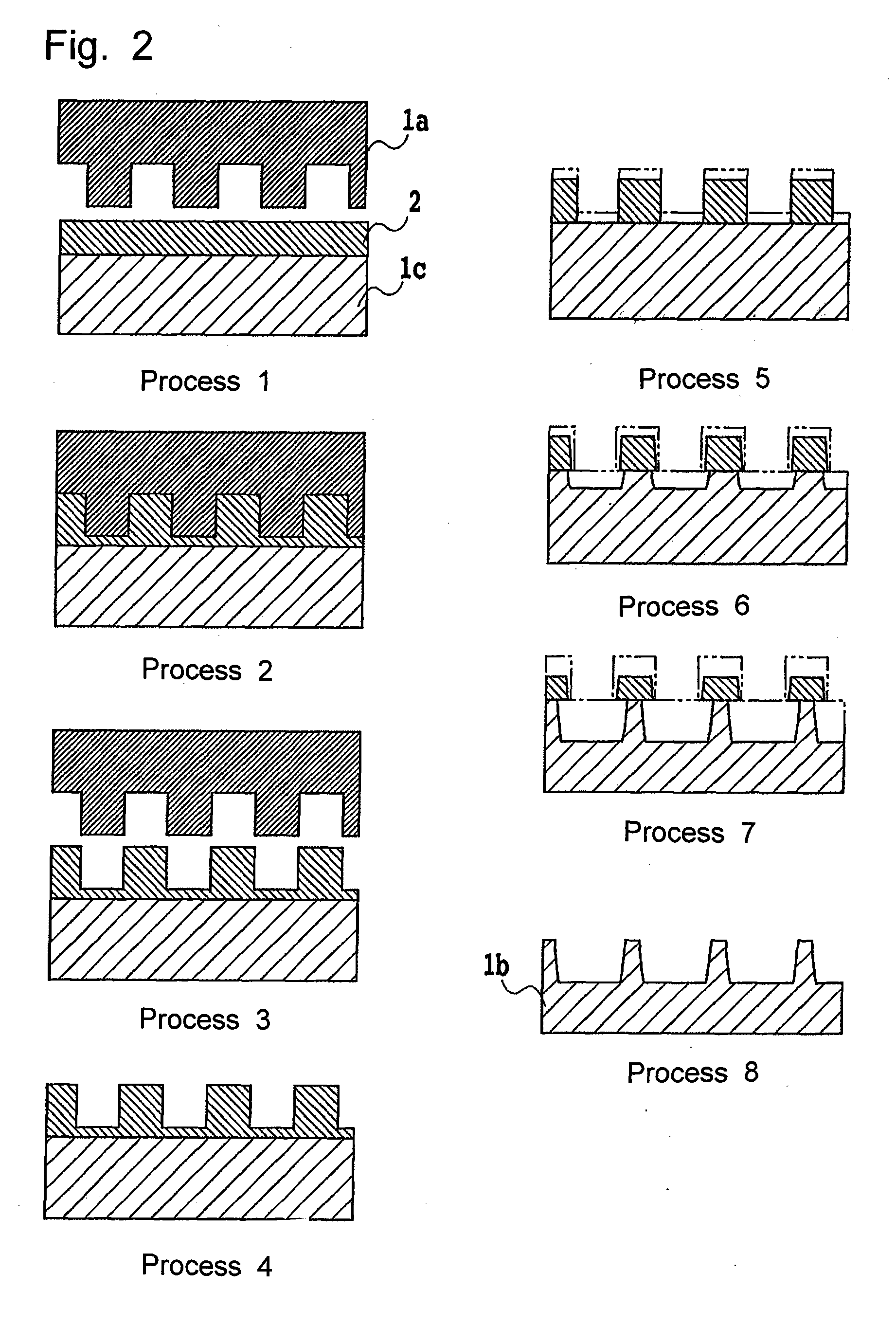

Nano-imprinting mold, method of manufacture of nano-imprinting mold, and recording medium manufactured with nano-imprinting mold

InactiveUS20080187719A1Increase signal strengthRaise the ratioDecorative surface effectsLayered productsResistEtching

A mold is provide which, by using nano-imprinting, enables inexpensive provision of a magnetic recording medium capable of providing signals with a high signal intensity and enabling a high S / N. The method of the mold used in nano-imprinting includes: a transfer process of pressing a parent mold, having a relief pattern, against a resist layer formed on the surface of a substrate, and then releasing the parent mold to transfer the relief pattern to the resist layer; and a relief pattern formation process of exposing a lower substrate in depression portions of the resist in which the relief pattern has been formed by the transfer process, and etching the exposed substrate to form a relief pattern in the substrate, wherein in the relief pattern formation process, side etching of the substrate is performed during substrate etching.

Owner:FUJI ELECTRIC DEVICE TECH CO

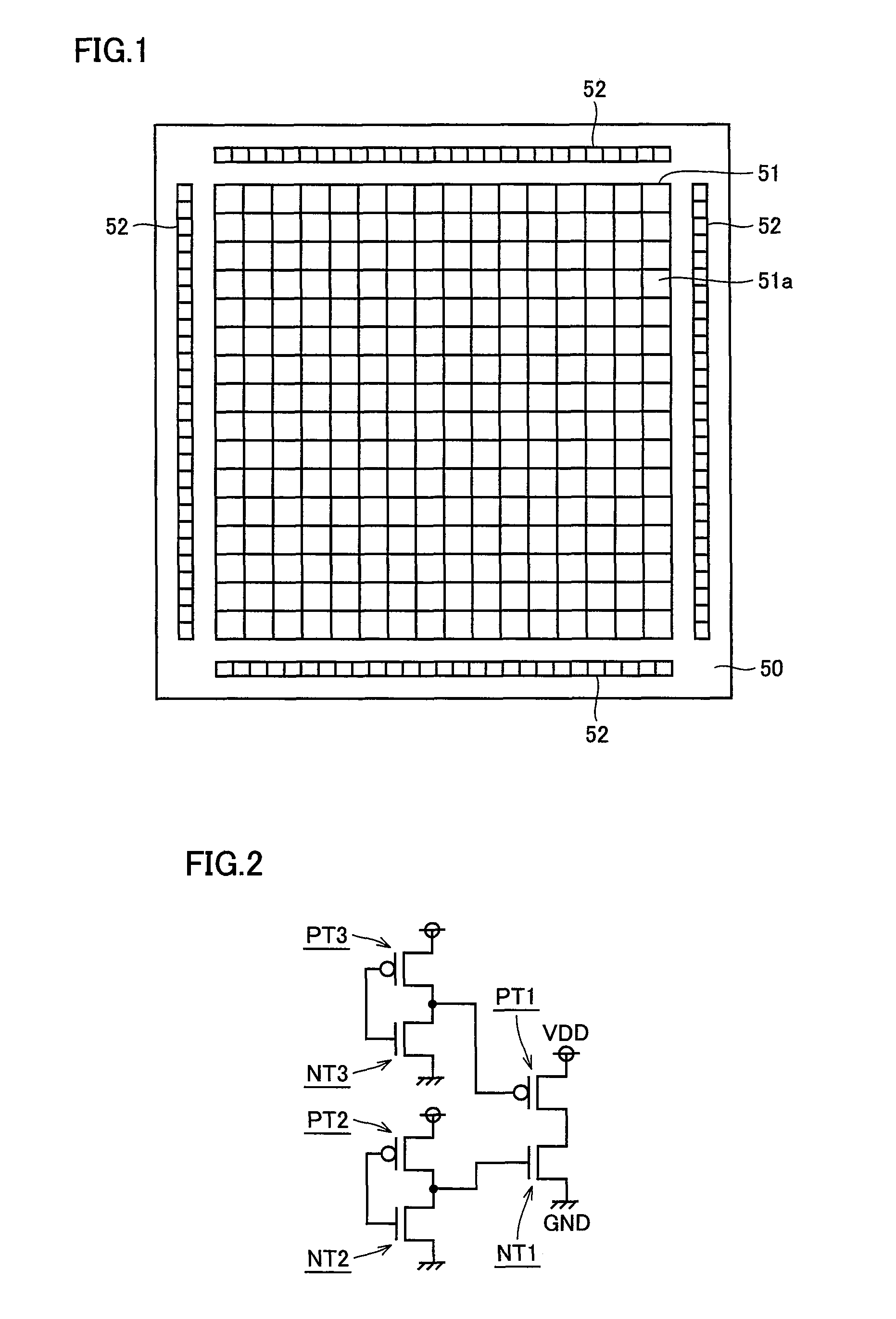

Semiconductor integrated circuit

ActiveUS20060071319A1Decreasing current concentrationLarge wire widthSemiconductor/solid-state device detailsSolid-state devicesSemiconductorIntegrated circuit

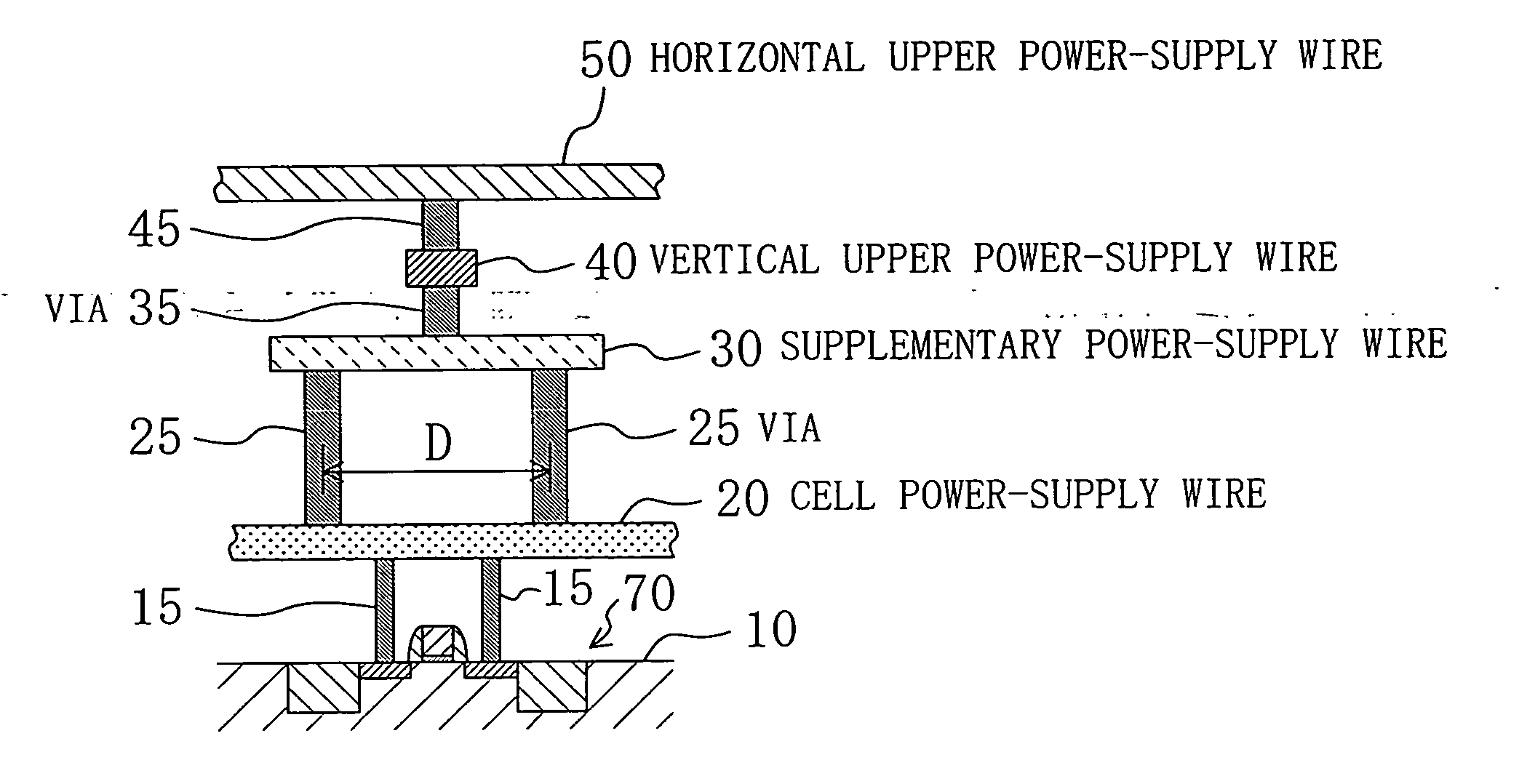

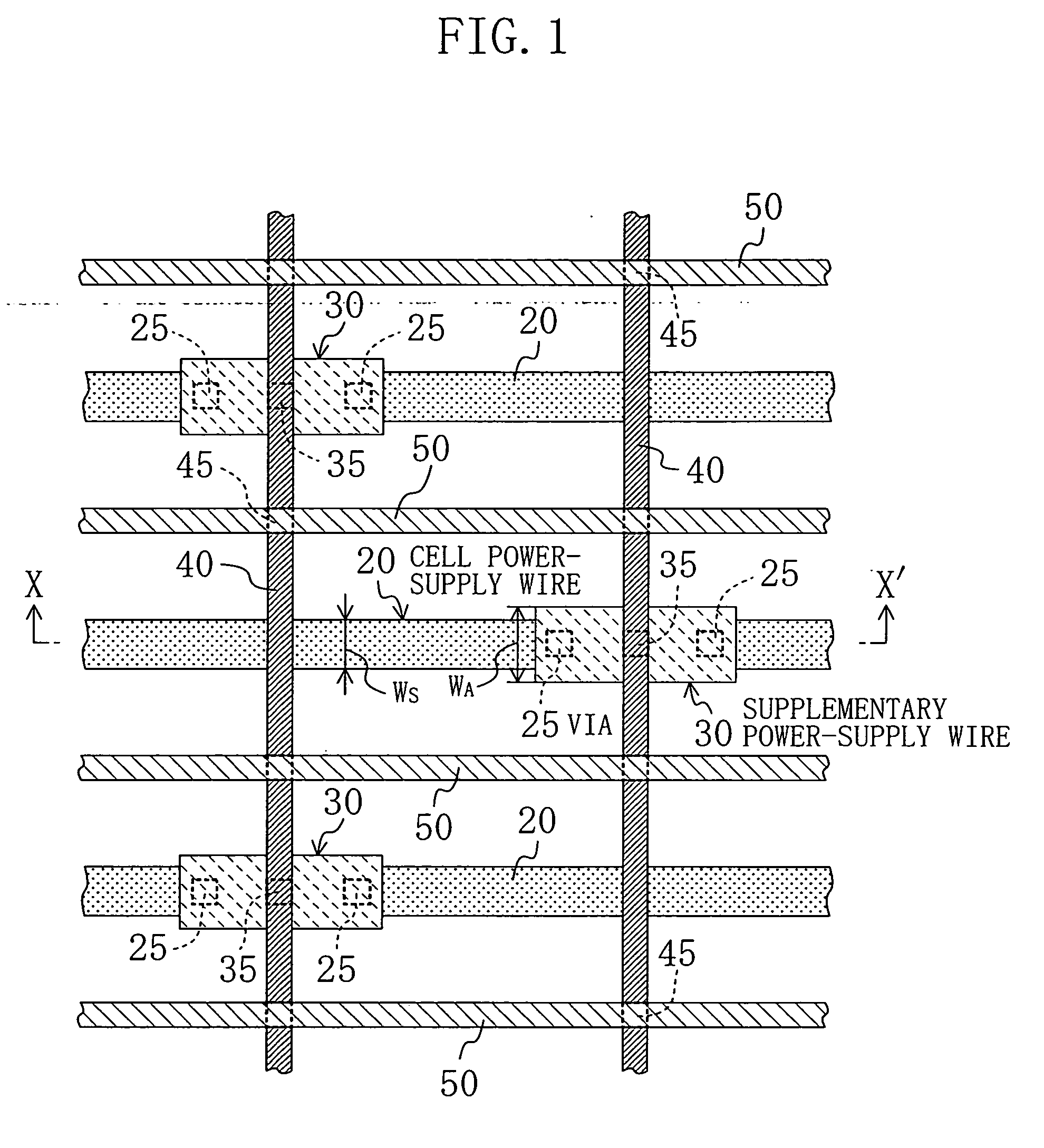

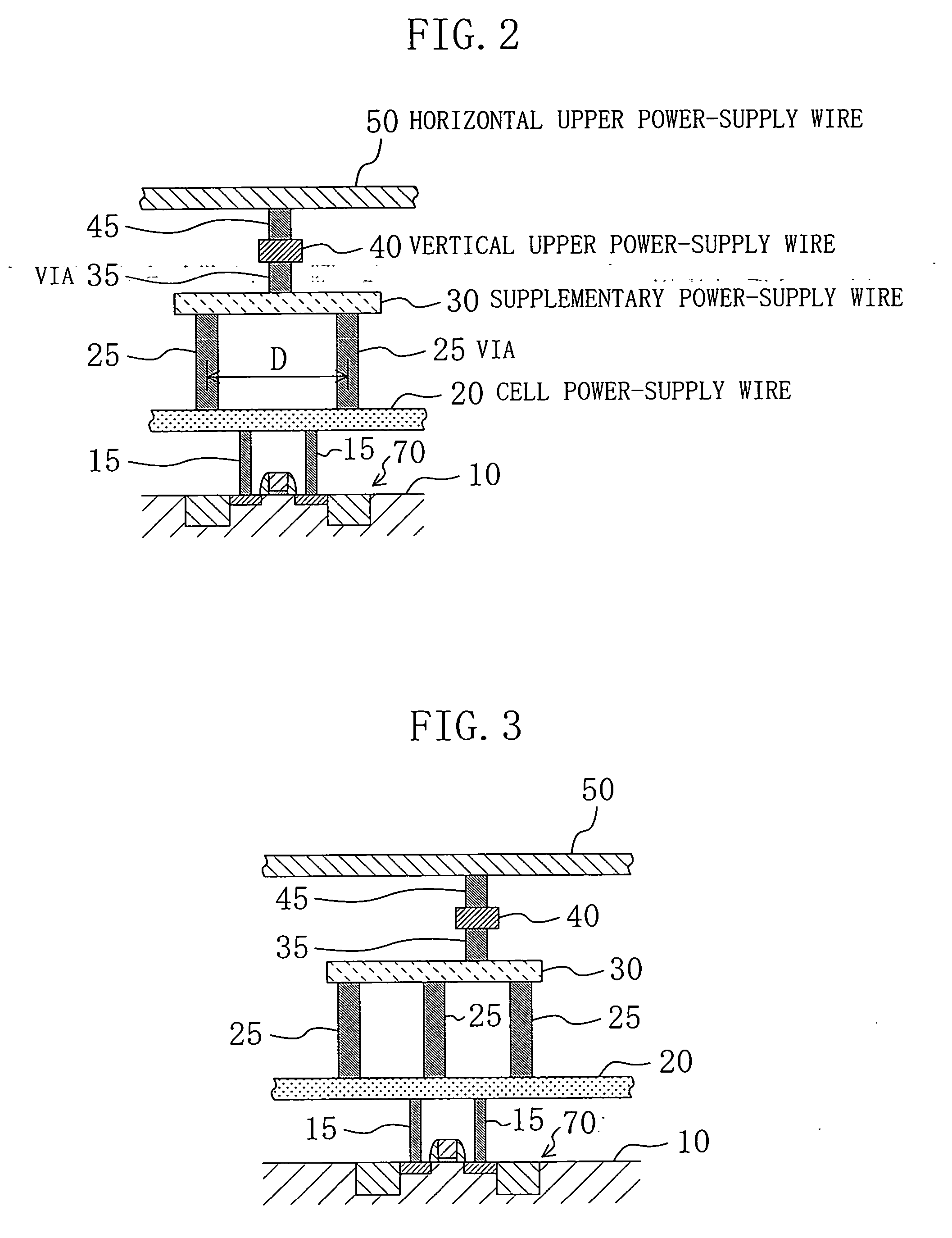

In a semiconductor integrated circuit including a plurality of cells, a supplementary power-supply wire is disposed between a lattice-shaped upper power-supply wire and a lower cell power-supply wire for cases in which power is supplied from the upper power-supply wire to the lower cell power-supply wire. The supplementary power-supply wire and the lower cell power-supply wire are connected by two vias. The supplementary power-supply wire and the upper power-supply wire are connected by a single via. Current from the supplementary power-supply wire is divided by the two vias and then supplied to the lower cell power-supply wire. Therefore, when power is supplied from the upper power-supply wire to the lower cell power-supply wire, current concentration at the connection points of the lower cell power-supply wire to the vias is decreased, thereby reducing wire breaks caused by EM (electro migration).

Owner:III HLDG 12 LLC

Semiconductor device

ActiveUS8063415B2Highly integratedIncrease speedSemiconductor/solid-state device detailsSolid-state devicesPower semiconductor deviceEngineering

Owner:RENESAS ELECTRONICS CORP

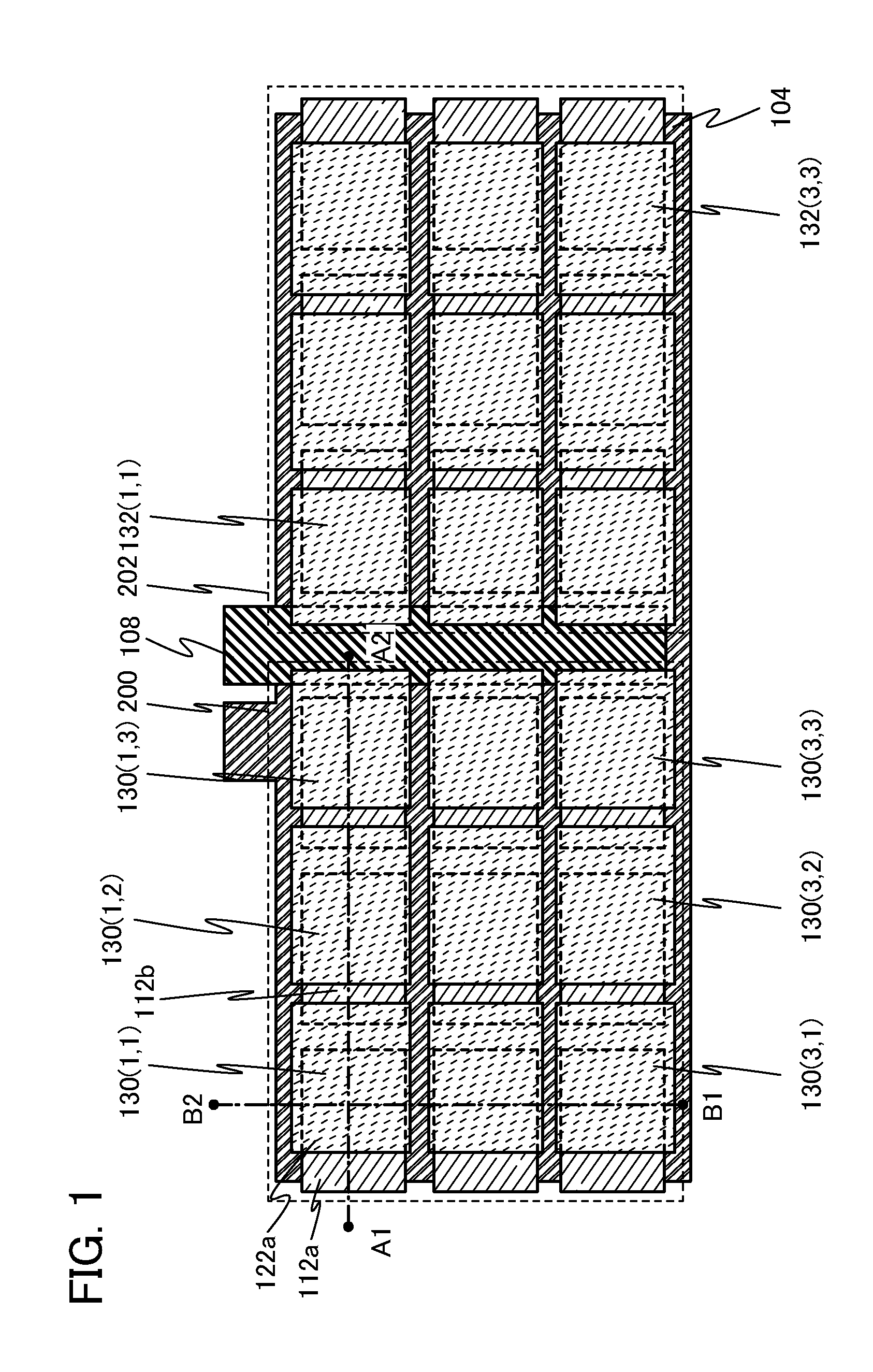

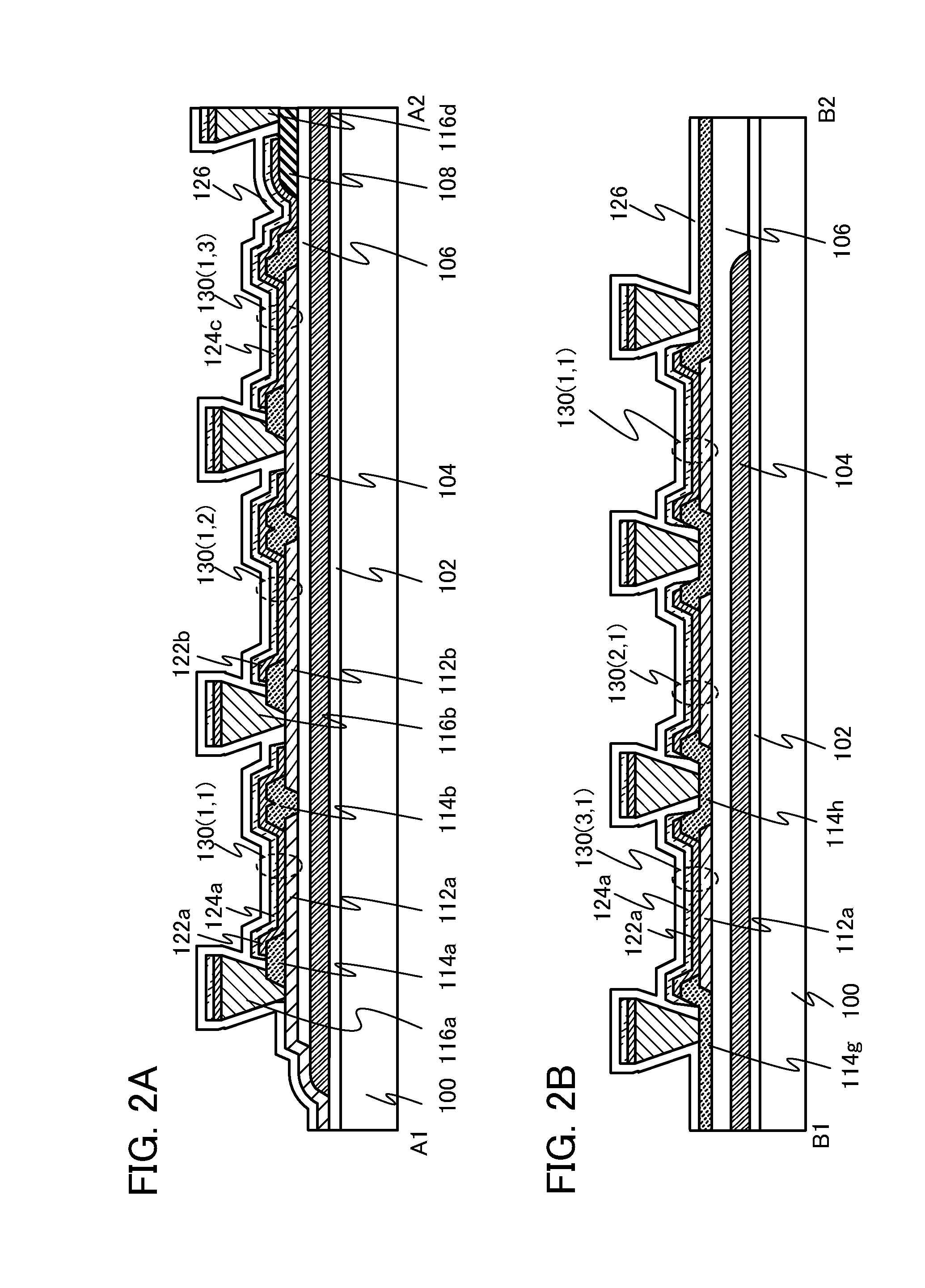

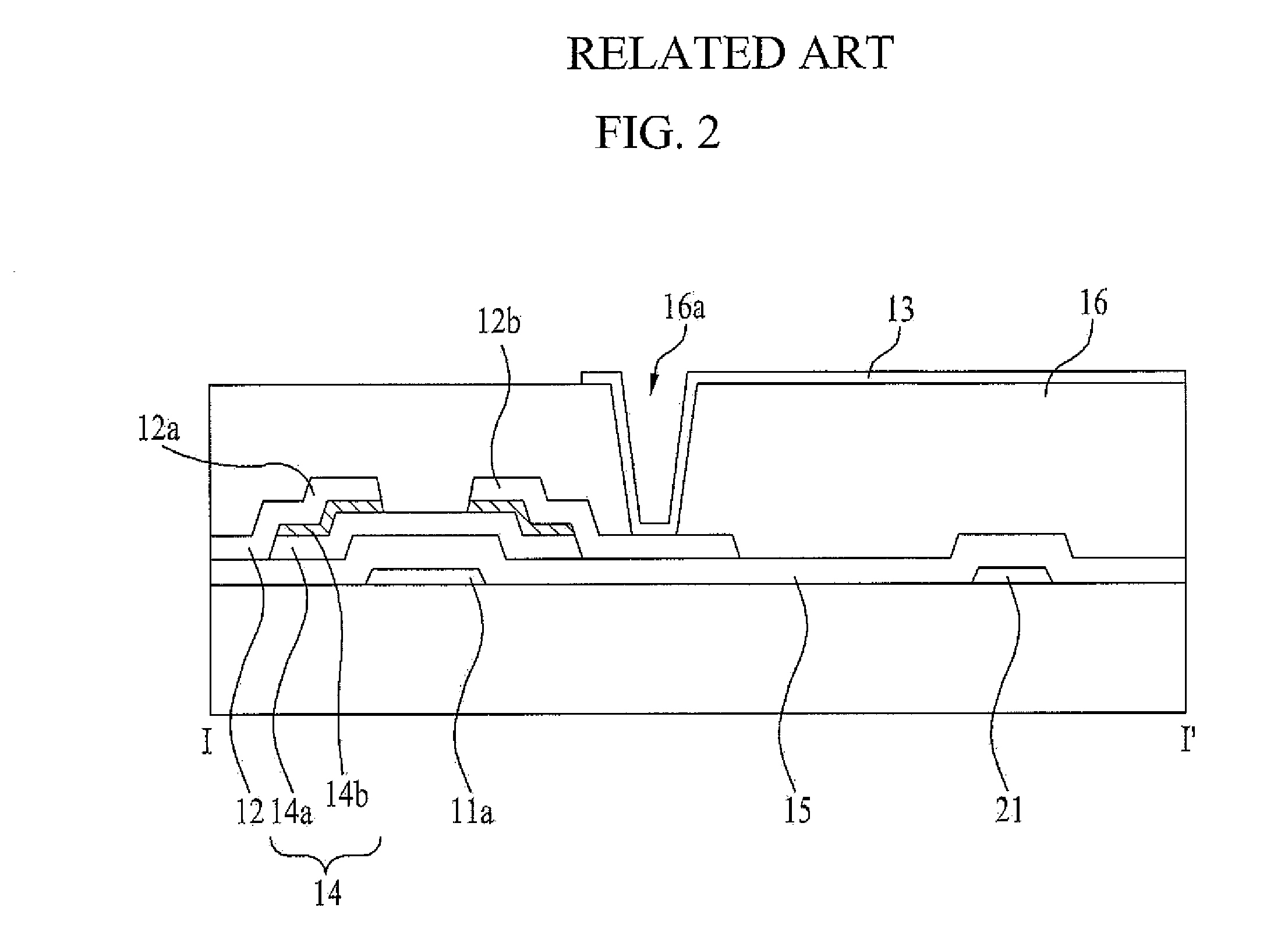

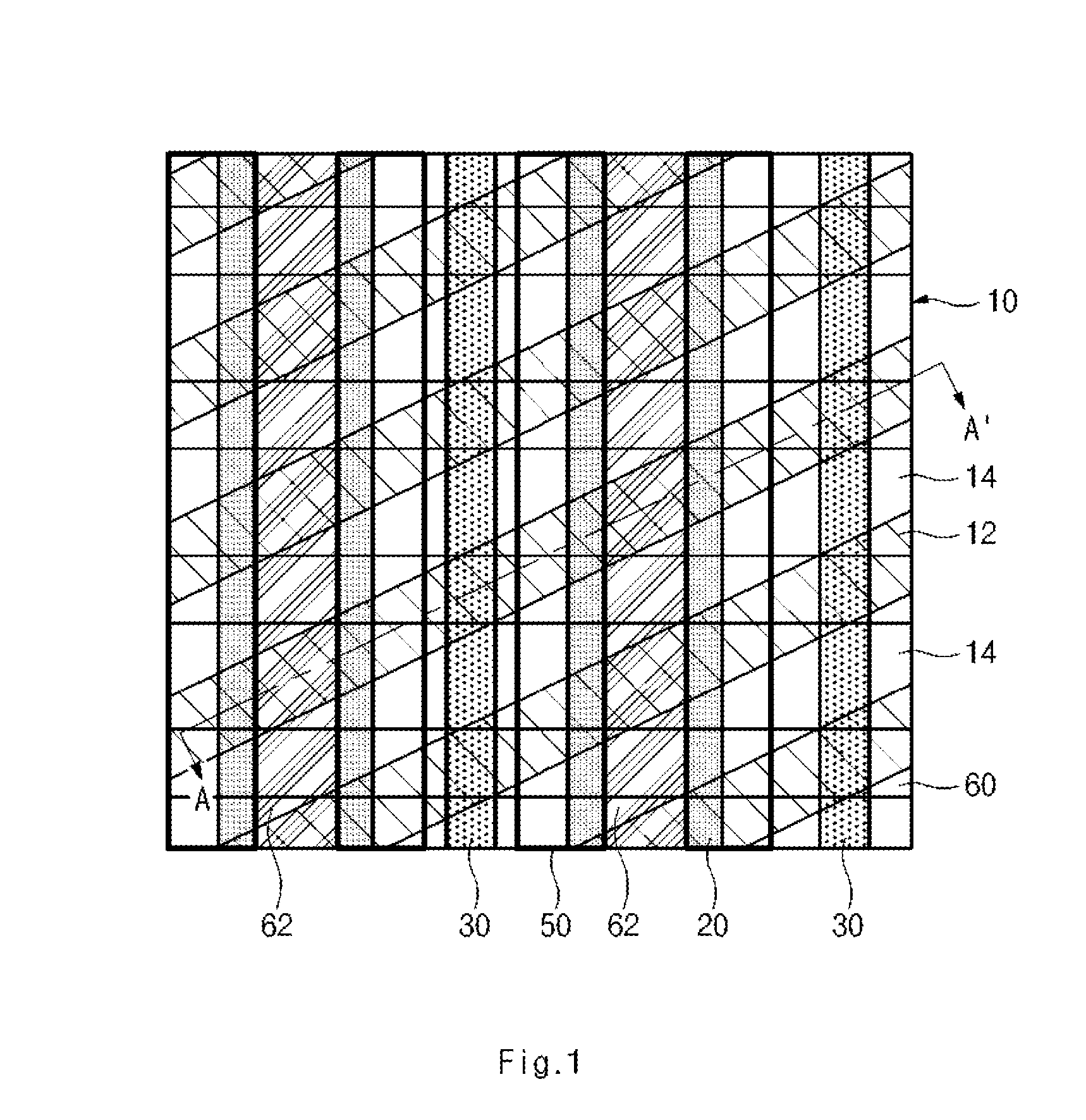

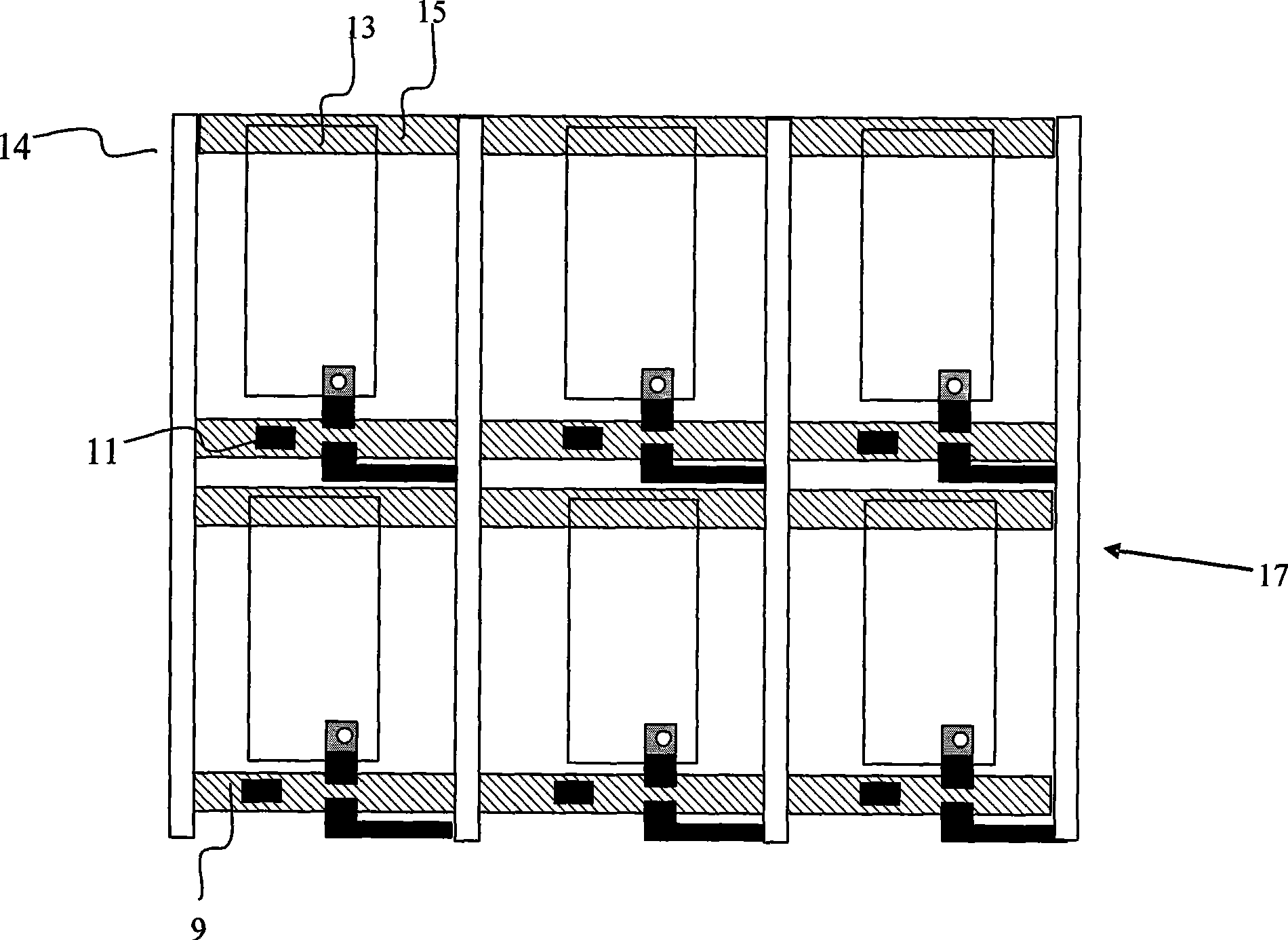

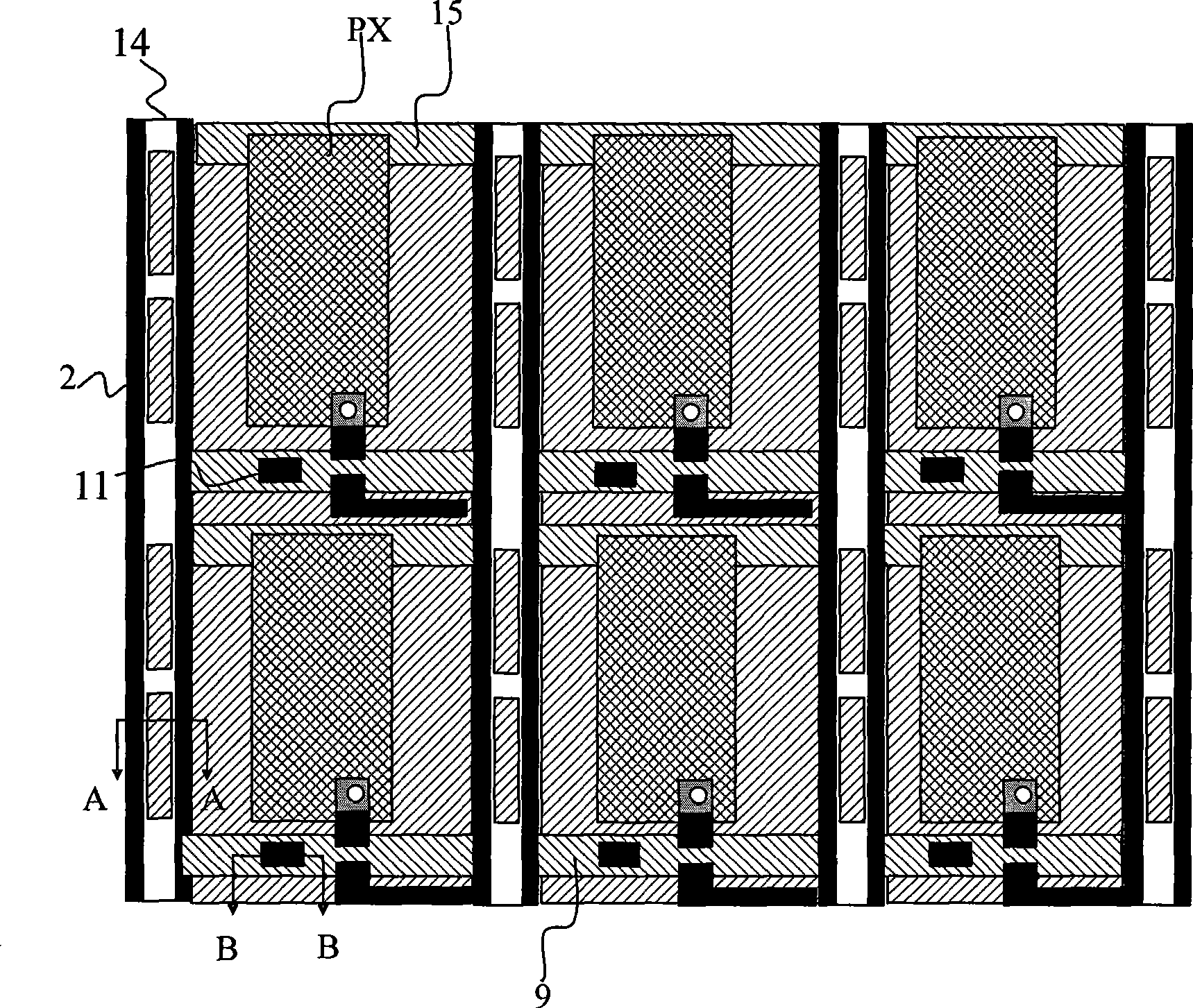

Thin film transistor array substrate and method for manufacturing the same

ActiveUS20090026451A1Increase the aperture ratioReduce resistanceSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringCommon line

A thin film transistor array substrate and a method for manufacturing the same are disclosed. The thin film transistor array substrate includes a plurality of gate lines and a plurality of data lines on a substrate, to define pixel regions crossing each other, thin film transistors, each formed at the intersection of the gate lines and the data lines, and including a gate electrode, a source electrode and a drain electrode, common lines, each including a first pattern formed across the data lines, a second pattern formed adjacent to the data lines on both sides in the pixel region and parallel to the data lines, and a third pattern formed adjacent to the gate lines to connect the second pattern disposed on both the sides in the associated one of the pixel regions, and passing below the drain electrode of the thin film transistors and pixel electrodes formed in the pixel regions.

Owner:LG DISPLAY CO LTD

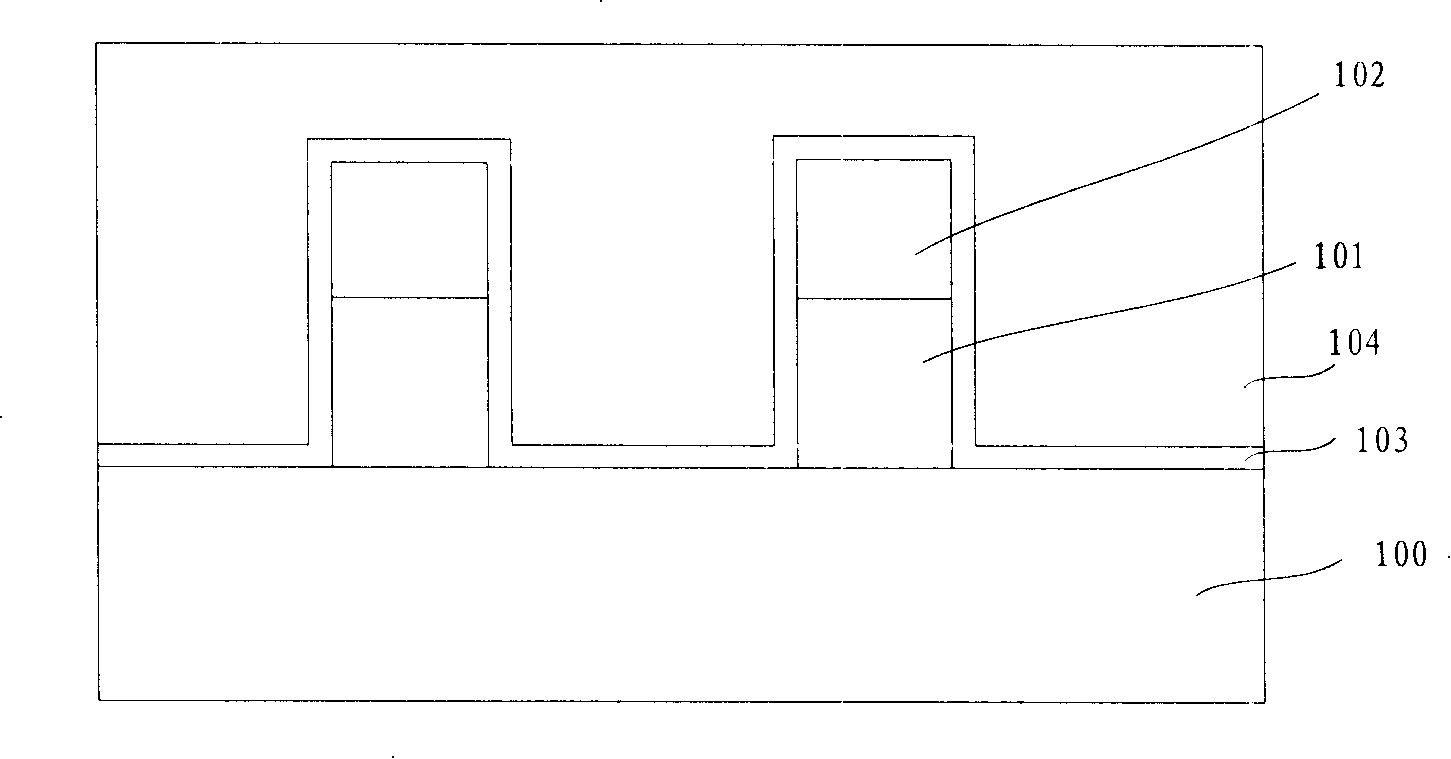

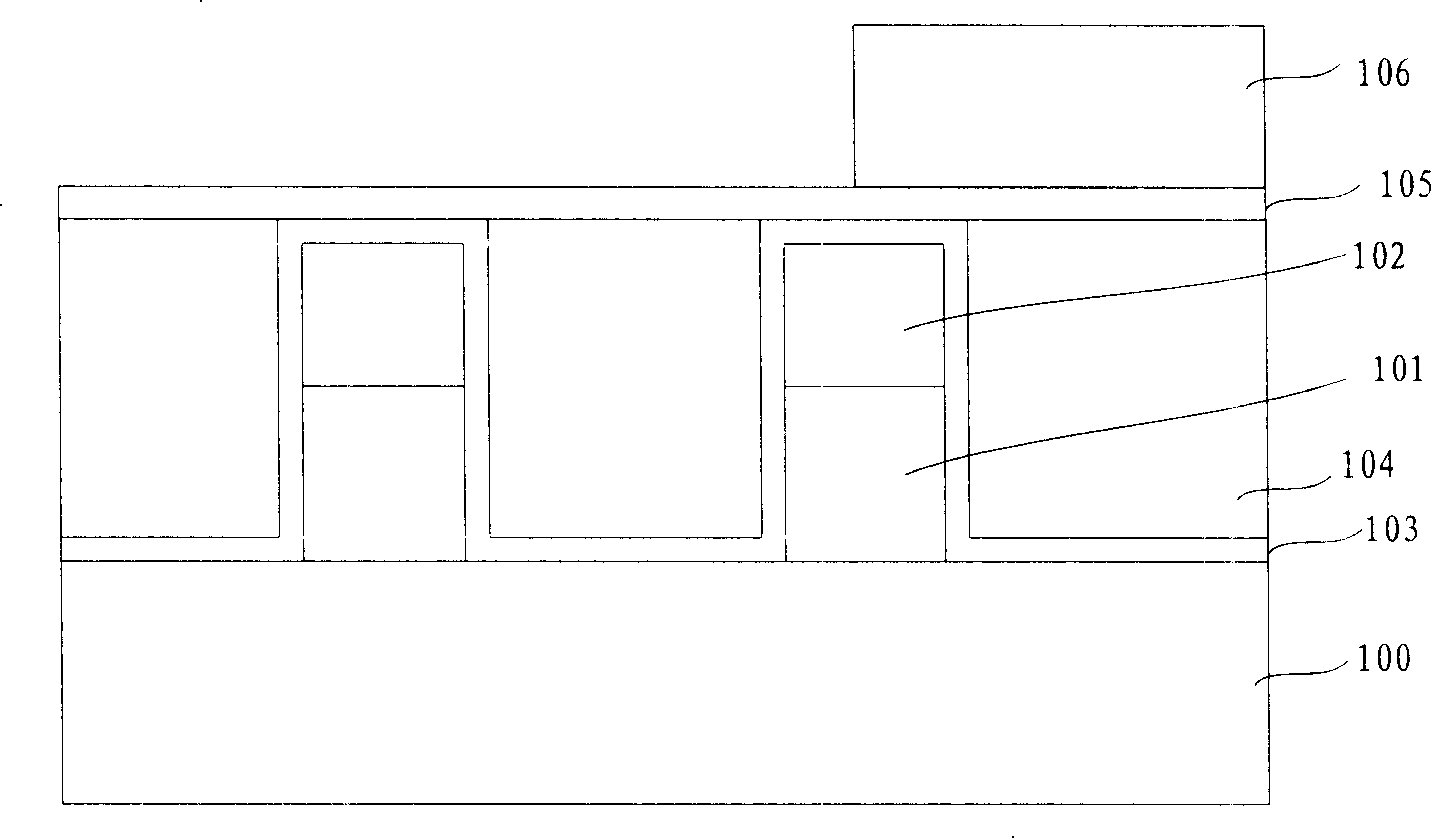

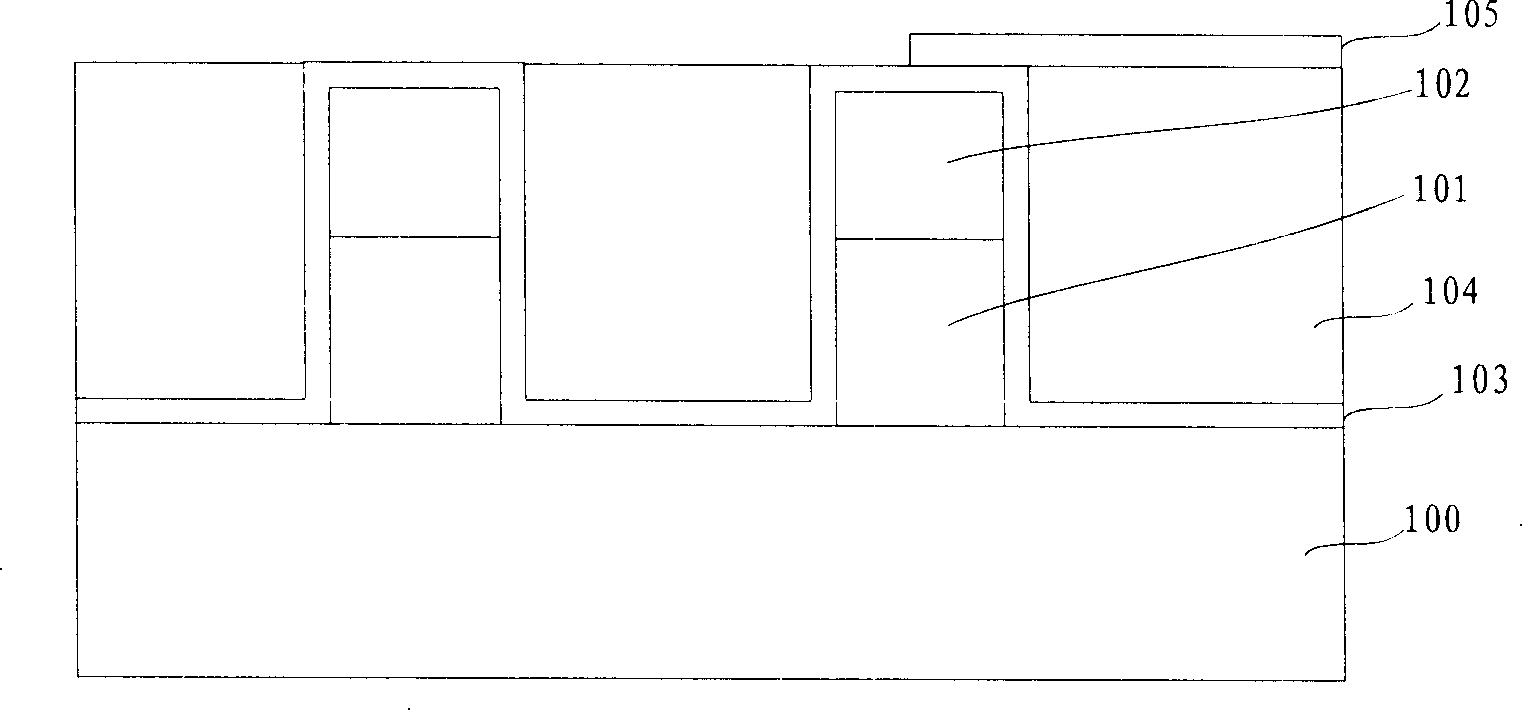

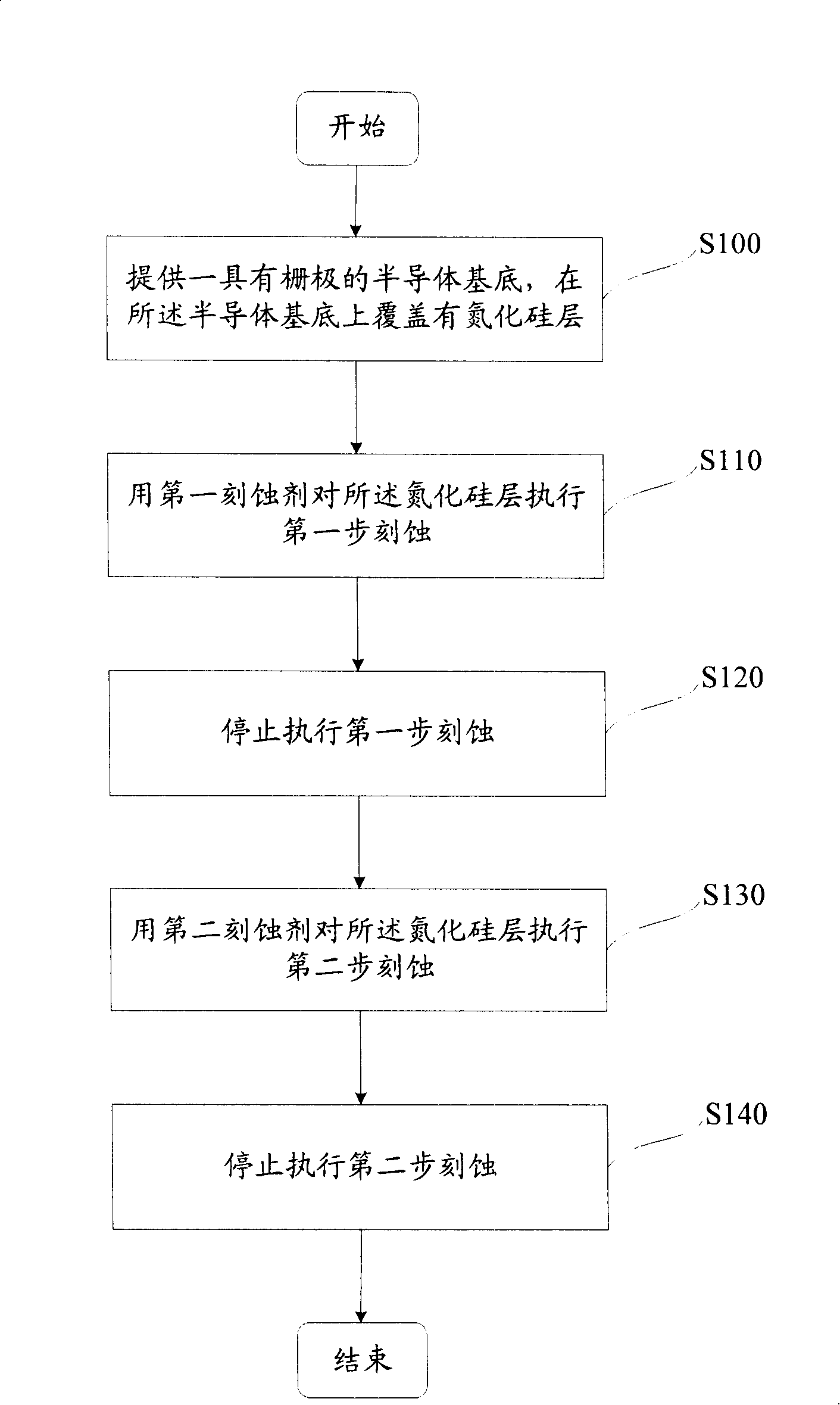

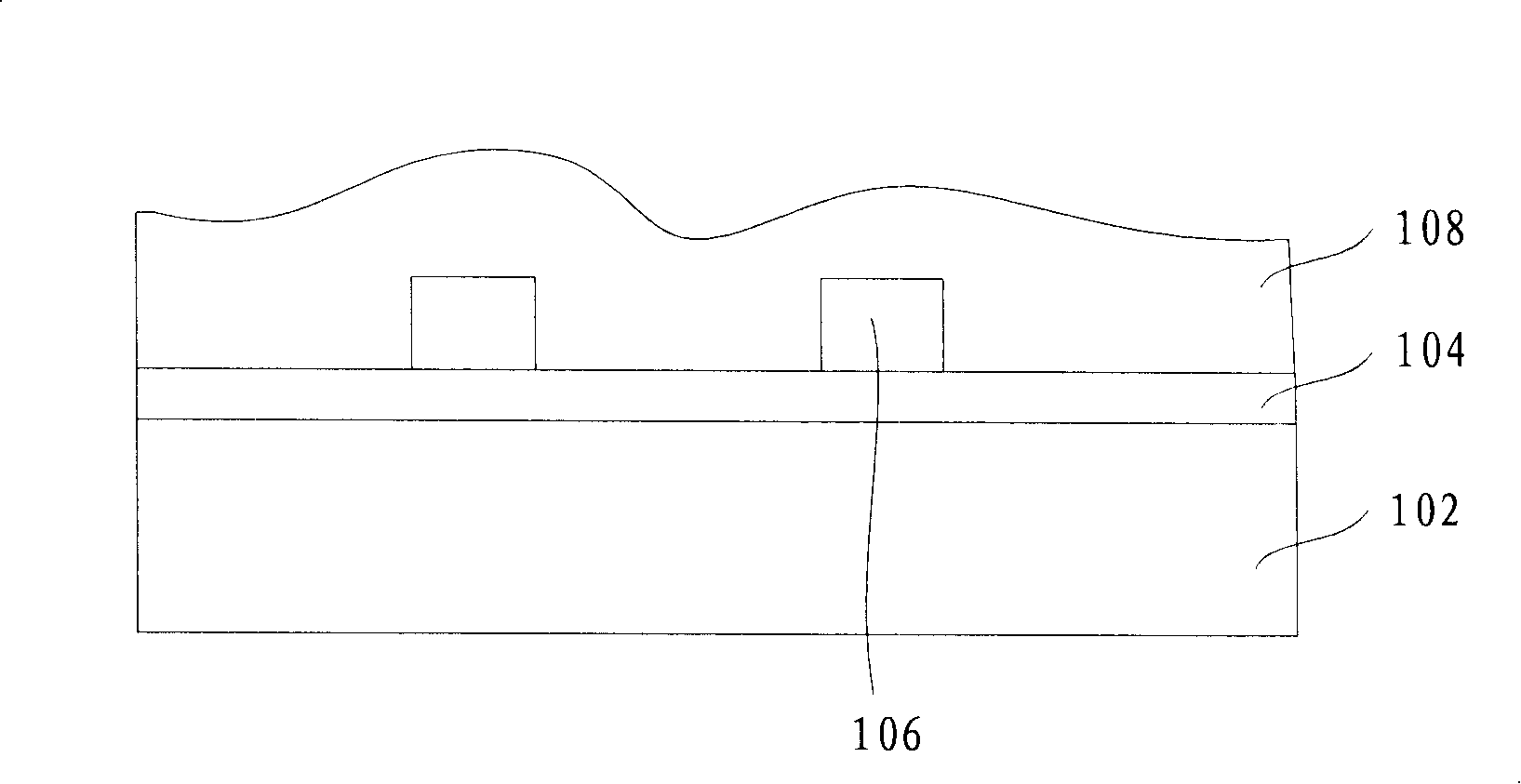

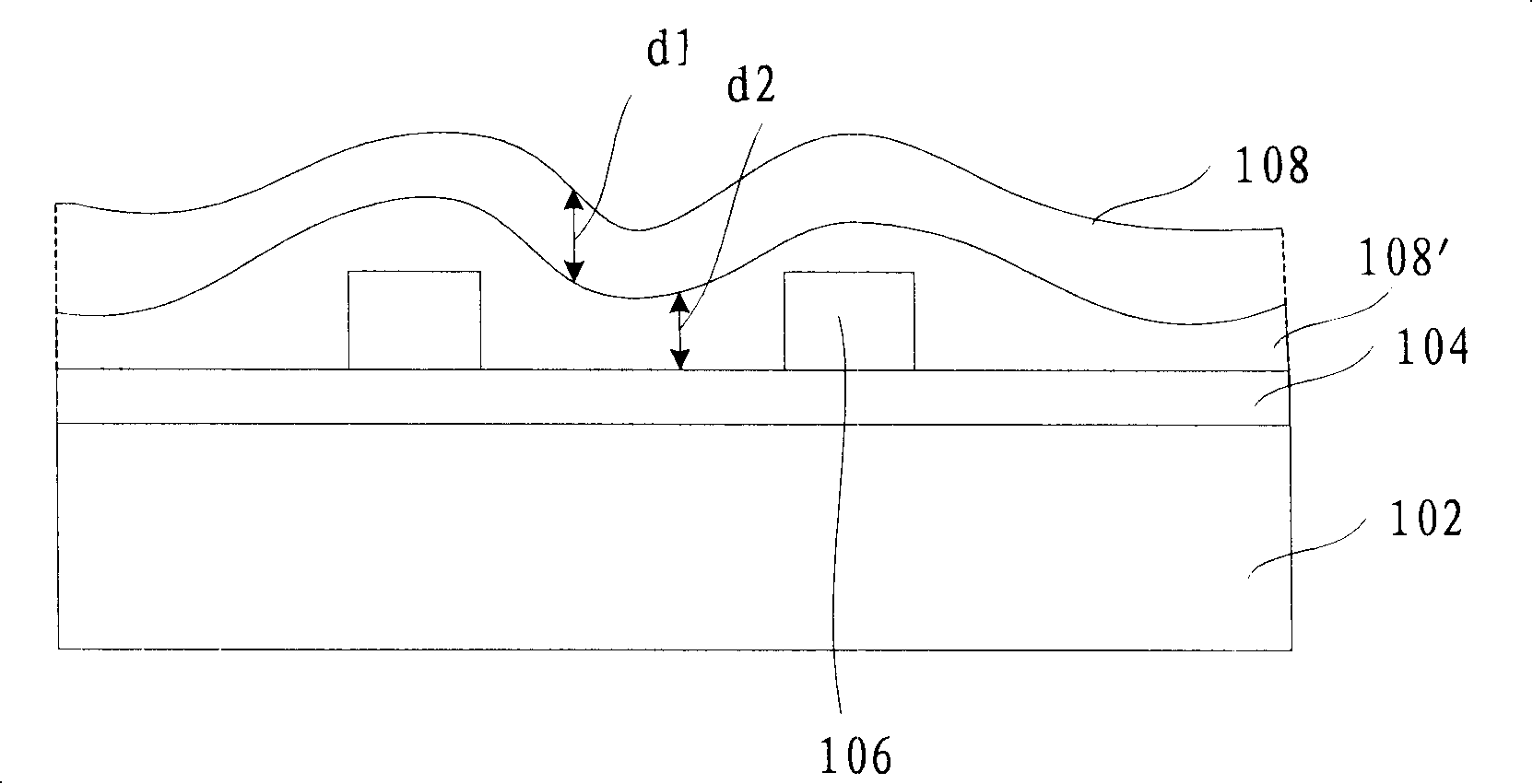

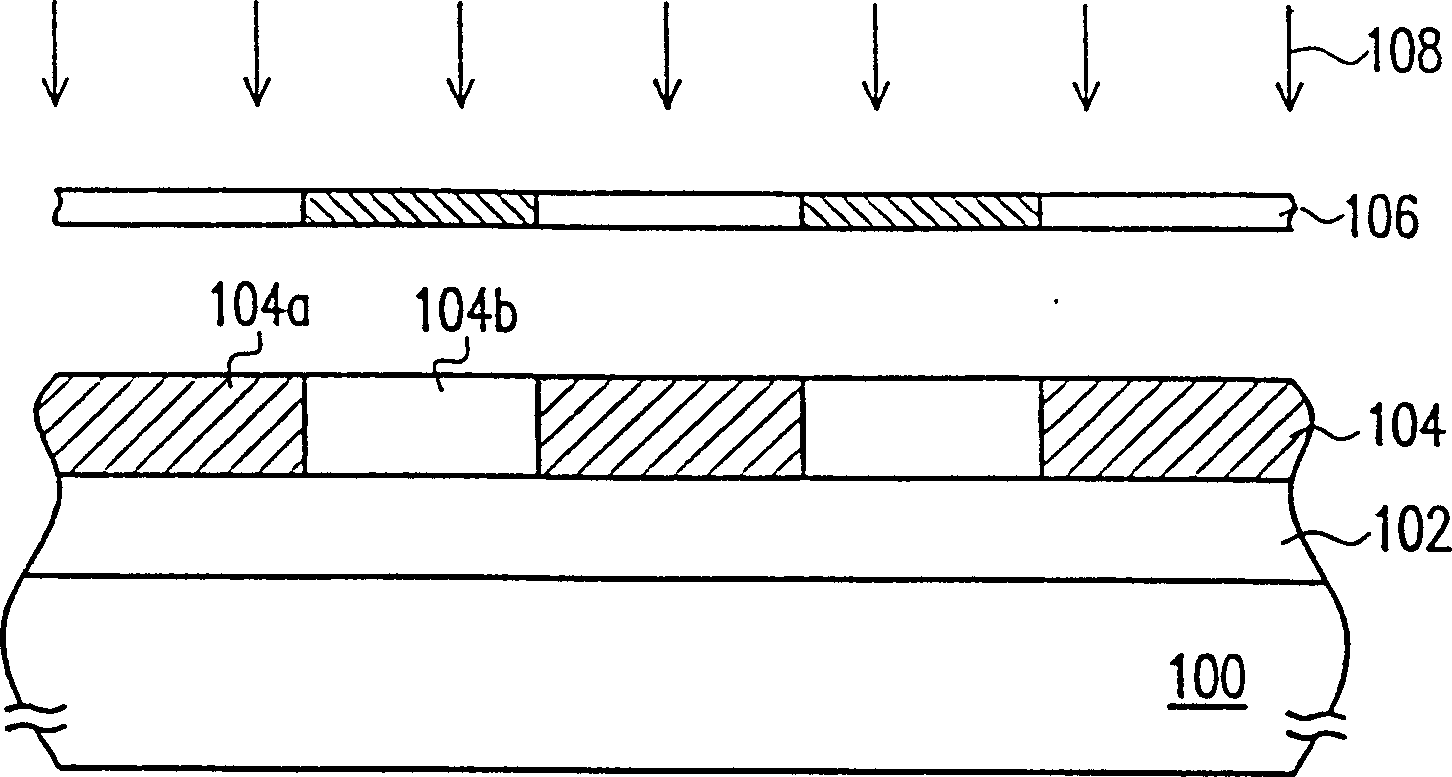

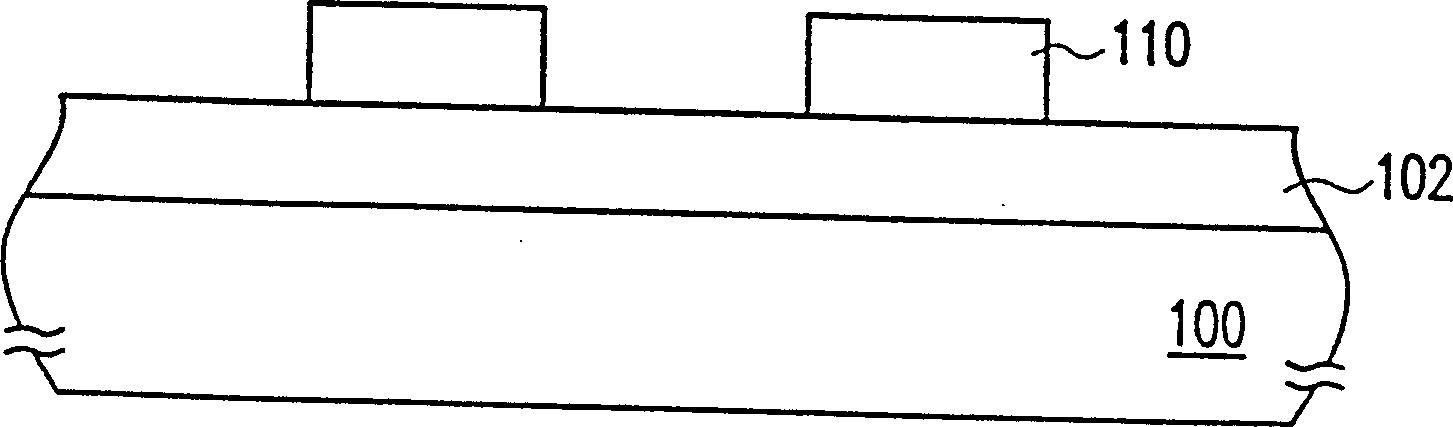

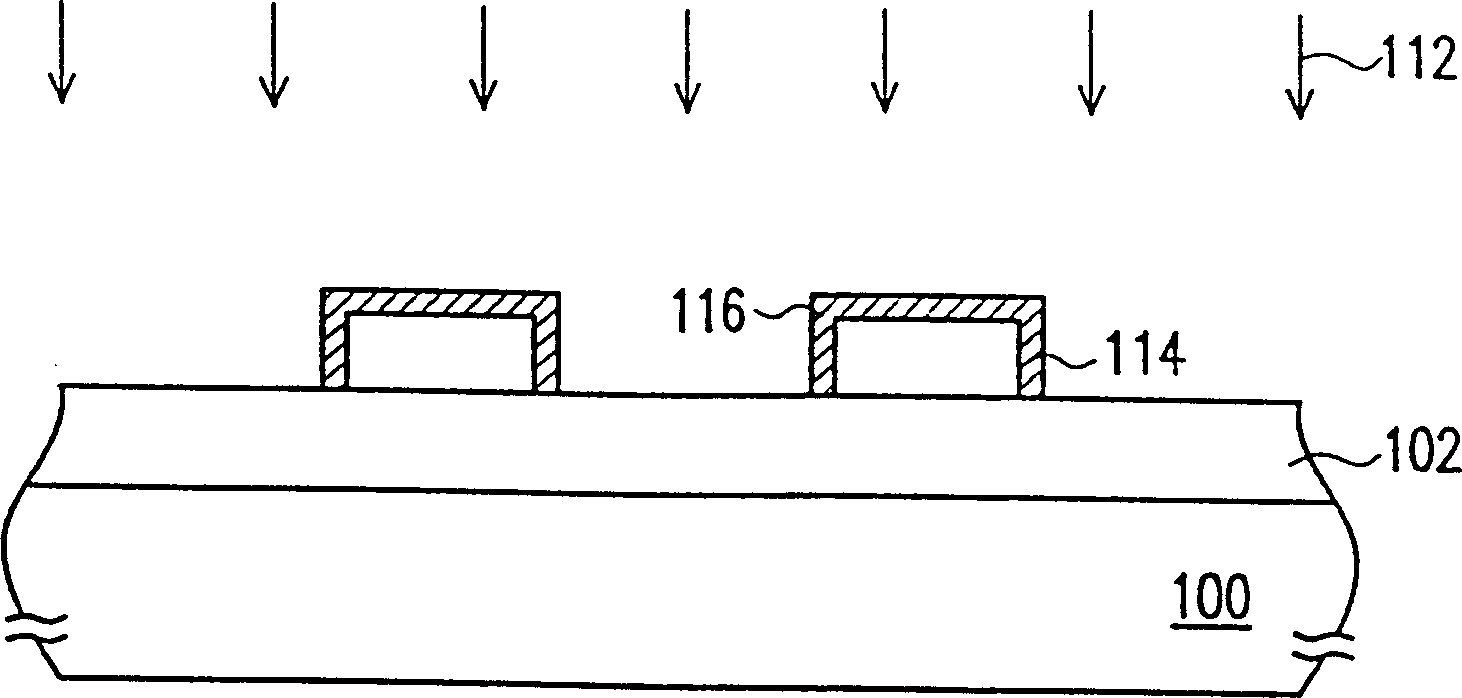

Production method of self-aligning contact hole

ActiveCN101197319AIncrease line widthImprove contourSemiconductor/solid-state device manufacturingElectrical conductorTwo grid

A manufacturing method of self-aligning contact holes comprises the following steps that: a semiconductor substrate is provided; at least two grid electrodes are arranged on the semiconductor substrate; an etching barrier layer is arranged along the surface of the grid electrodes; a medium layer is formed on the etching barrier layer; the top of the medium layer is higher than the top of the grid electrode; a photoresist contact hole pattern is formed on the medium layer and forms a T-shaped opening in the medium layer through etching; the bottom of the opening is arranged between two grid electrodes; the photoresist is removed; the sidewall and the bottom of the opening are cleaned through a wet method; the etching barrier layer on the sidewall and the bottom of the opening is etched and removed. The method can remove or reduce the disadvantages that in the manufacturing method of self-aligning contact holes, the bottom of the contact hole is not opened and the shoulders of the grid electrodes are cut off.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

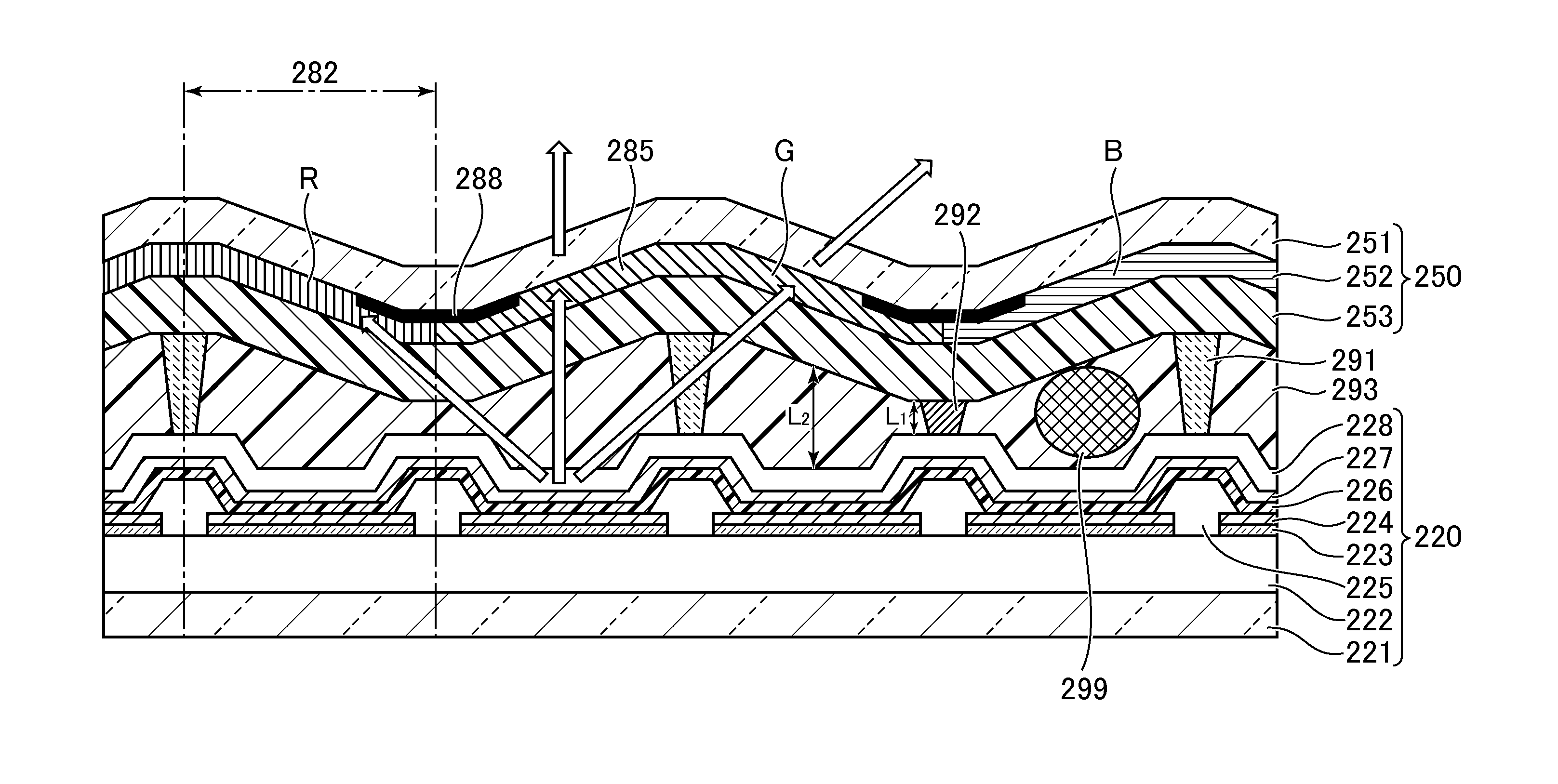

Organic el display device

ActiveUS20150162386A1Large luminous areaColor can be suppressedSolid-state devicesSemiconductor/solid-state device manufacturingColor gelDisplay device

An organic EL display device includes a thin film transistor substrate in which a light-emitting element is provided for each of plural sub-pixels constituting each pixel, a counter substrate provided with a coupled color filter which is a color filter arranged to be extended over plural adjacent sub-pixels and allowing light in one wavelength region to pass through and a light-shielding film which is arranged on a boundary between adjacent color filters to allow lights in different wavelength regions to pass through and shields light, a filler arranged between the thin film transistor substrate and the counter substrate and made of a transparent organic material, and a filler thickness adjustment part which adjusts to cause a thickness of the filler in a region where the light-shielding film is provided to be thinner than a thickness of the filler in a region where the light-emitting element is provided.

Owner:JAPAN DISPLAY INC

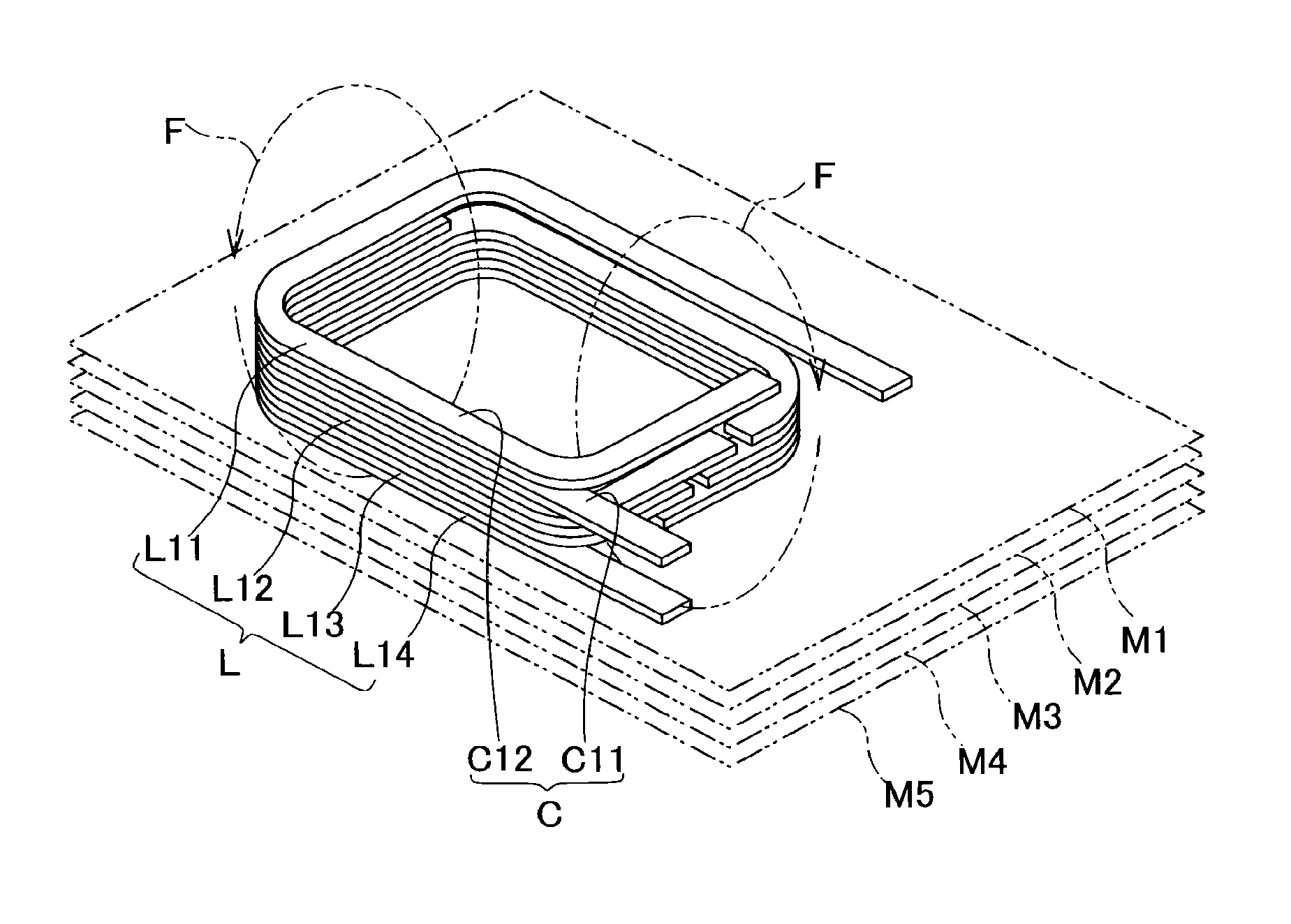

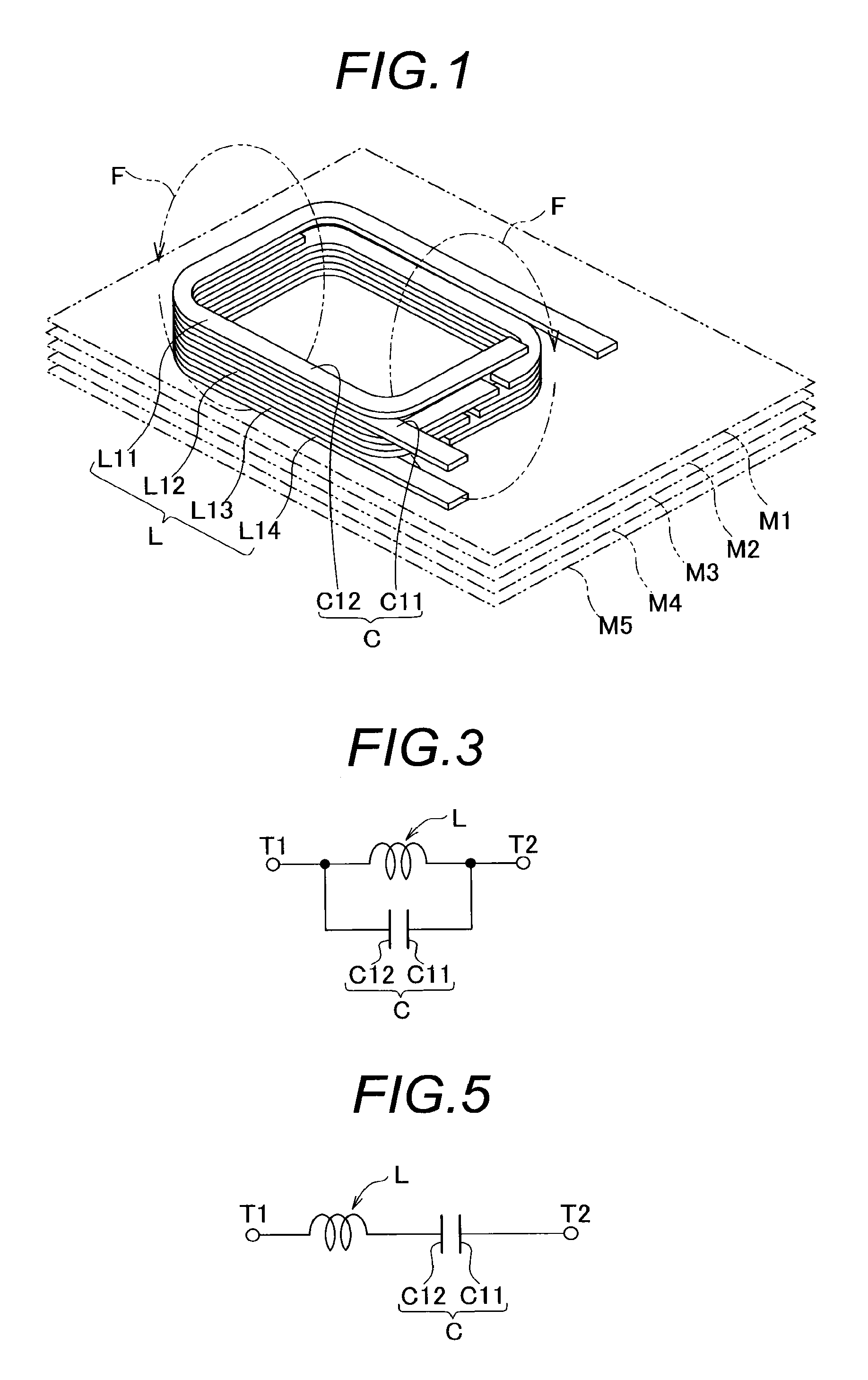

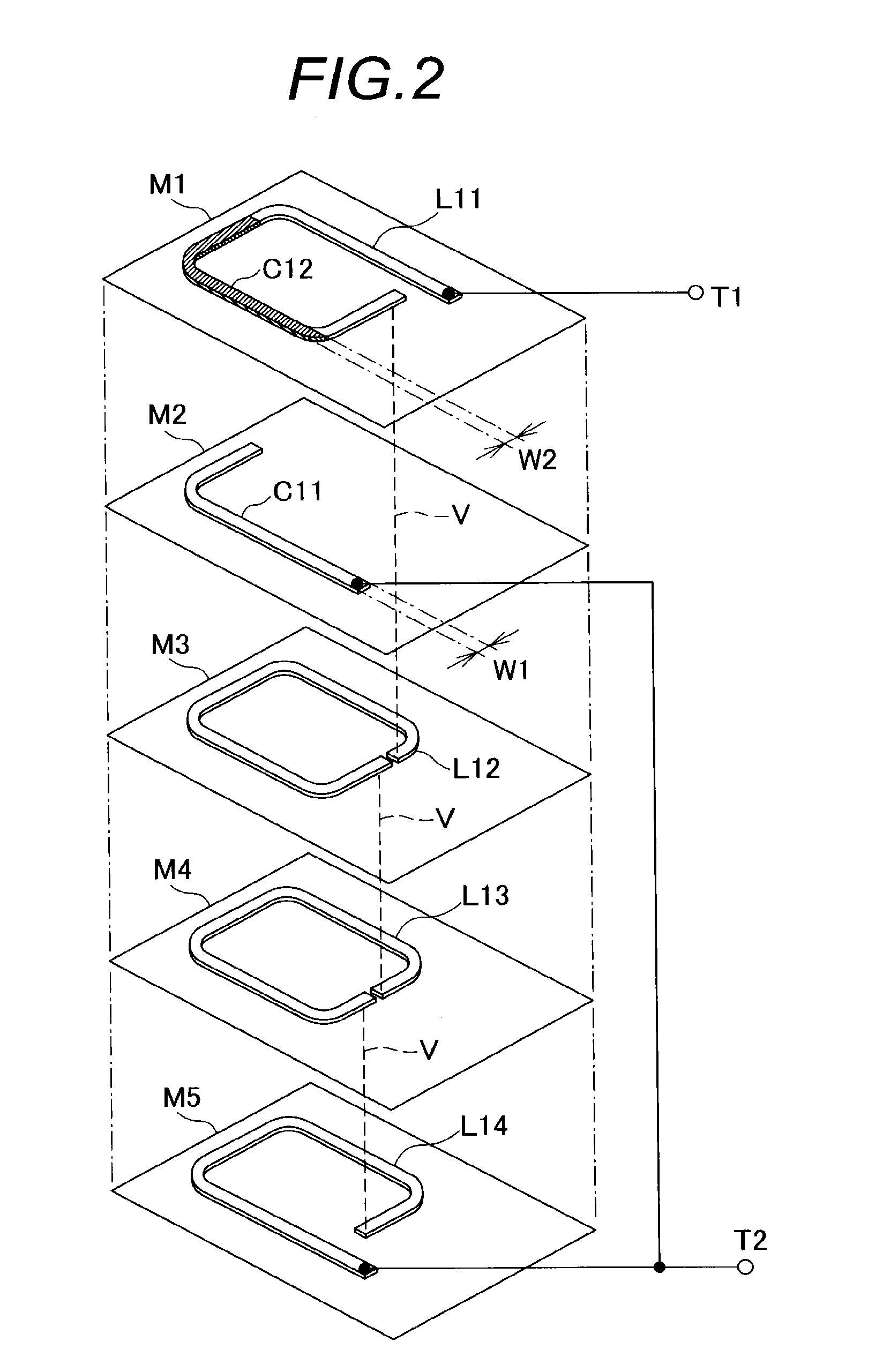

Laminated composite electronic device including coil and capacitor

ActiveUS20160307702A1Reduce the overall heightSmall sizeMultiple-port networksStructural fixed capacitor combinationsElectrical conductorEngineering

A laminated composite electronic device has a circuit including a coil and a capacitor within a laminate having a plurality of conductor layers laminated with an insulating layer interposed between the respective ones of the conductor layers. The device includes a coil conductor arranged on a first conductor layer and forming part of the coil, and a pair of capacitor electrodes for forming the capacitor, one of which is arranged on a second conductor layer such that the one capacitor electrode laps over the coil conductor when viewed from a laminating direction of the laminate, wherein the coil conductor forms part of the coil, and simultaneously serves as the other of the pair of capacitor electrode for forming part of the capacitor.

Owner:TDK CORPARATION

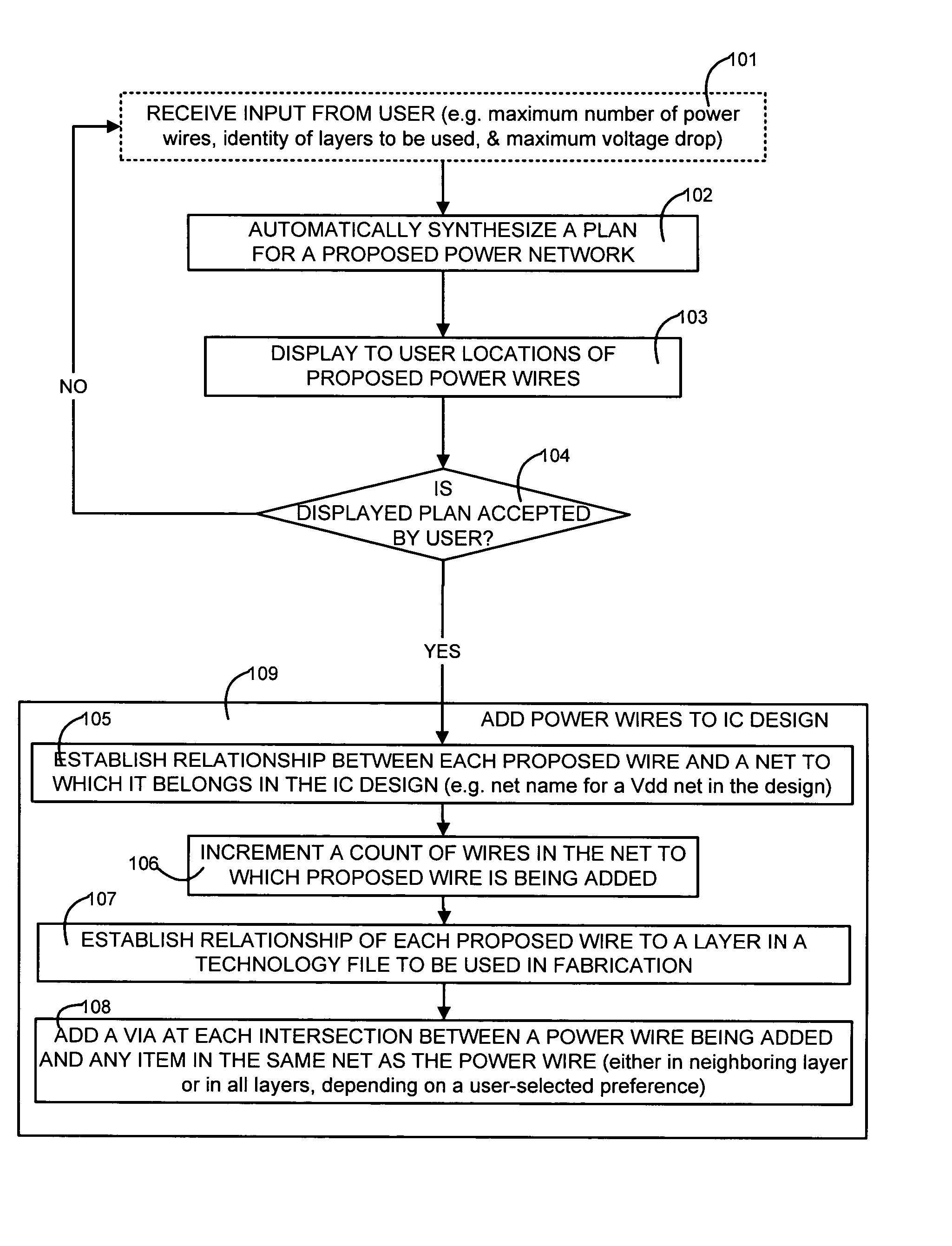

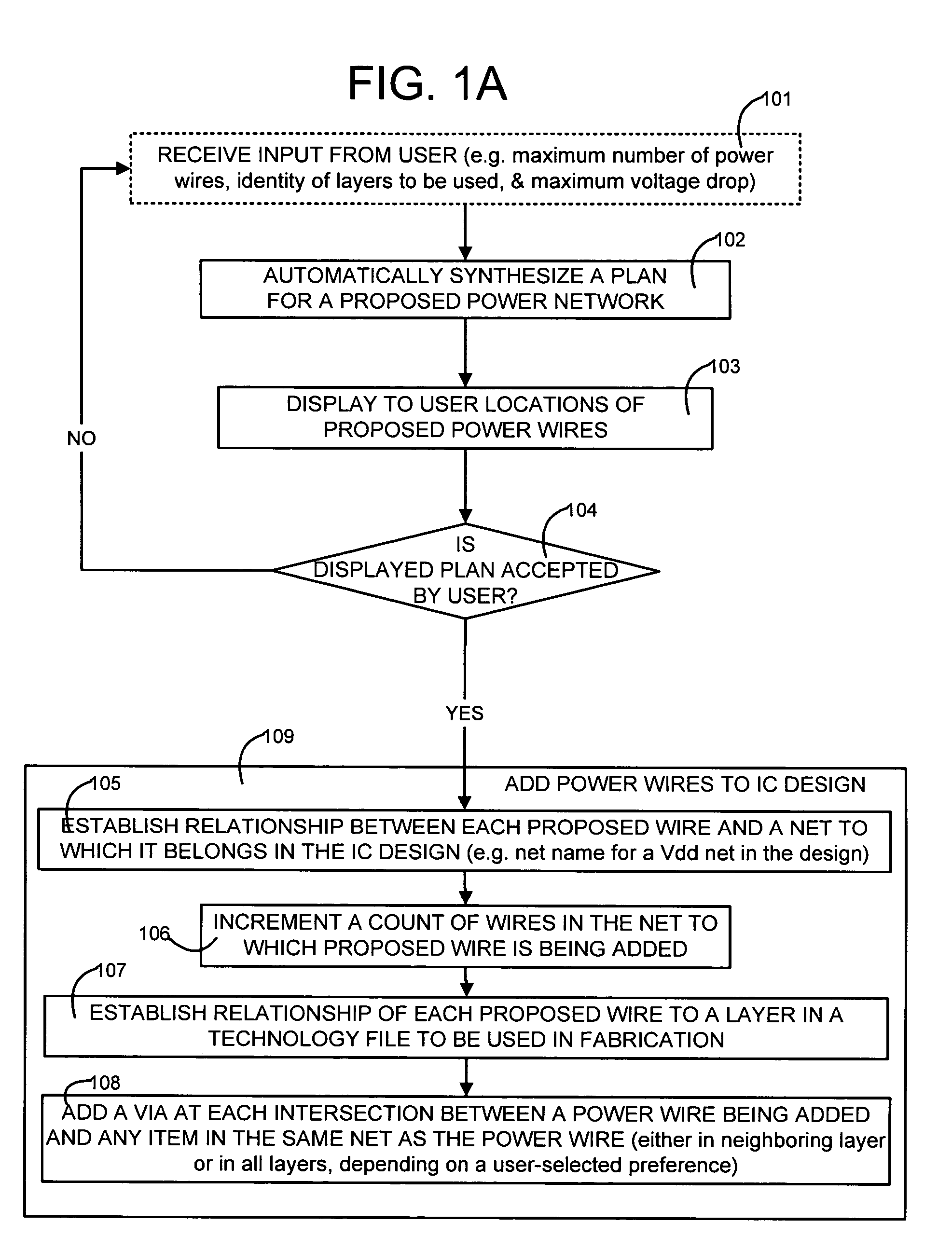

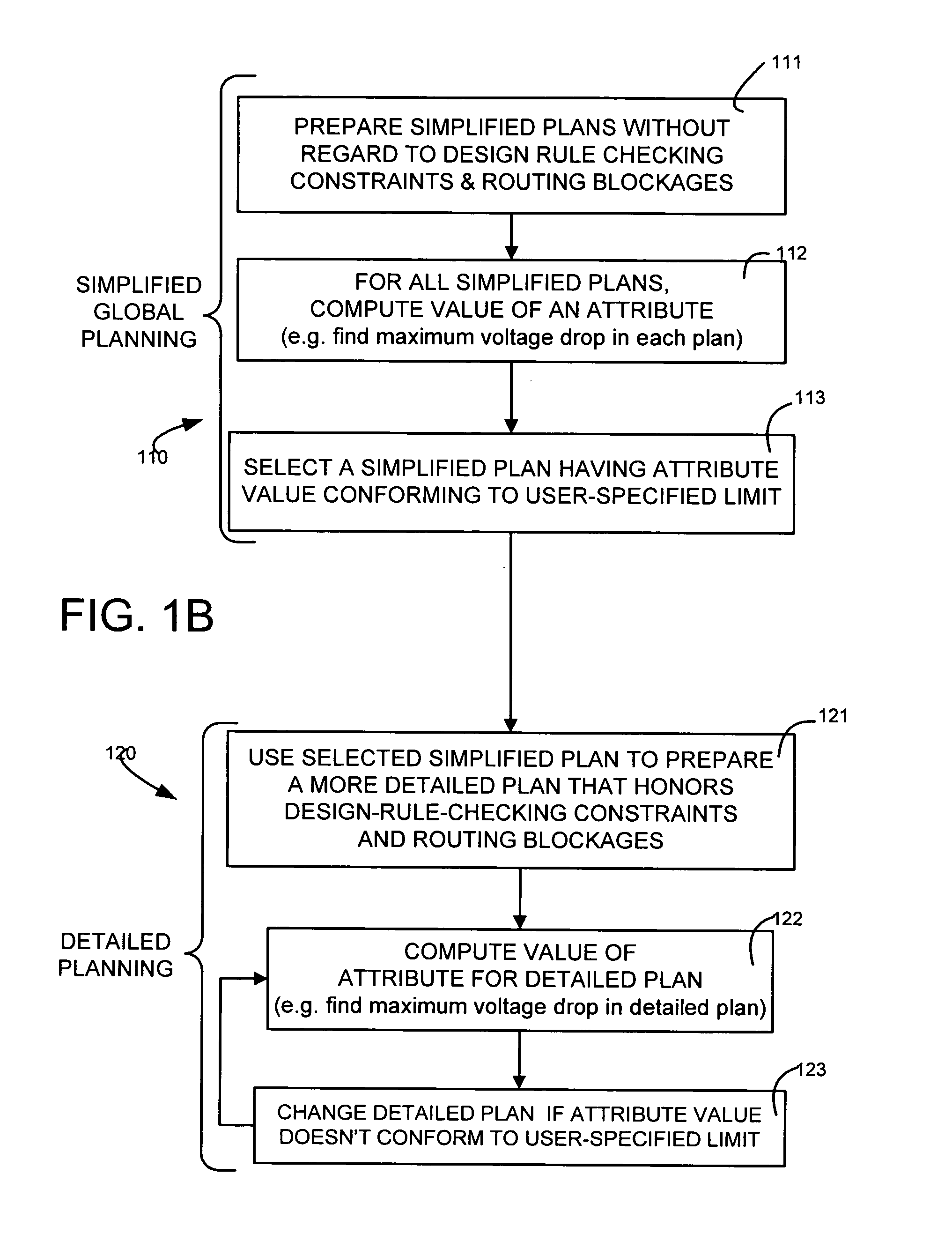

Power network synthesizer for an integrated circuit design

ActiveUS20060095874A1Shorten the timeIncrease line widthComputer aided designSoftware simulation/interpretation/emulationVoltage dropDesign rule checking

A plan for a power network for an integrated circuit device is automatically preparing in two stages. In a first stage, a number of simplified plans are prepared on a global scale, without regard to design rule checking constraints and routing blockages. Next, the simplified plans are evaluated to select a plan that conforms to a user-specified limit for an attribute, such as maximum voltage drop. The selected simplified plan, which identifies a total count of power wires and a width of the power wires, is used in a second stage to prepare a more detailed plan that honors the design rule checking constraints and routing blockages. The detailed plan is evaluated to check for conformance with the user-specified limit on the attribute, and if necessary the detailed plan is changed, e.g. by increasing wire width one or more times, to achieve conformance.

Owner:SYNOPSYS INC

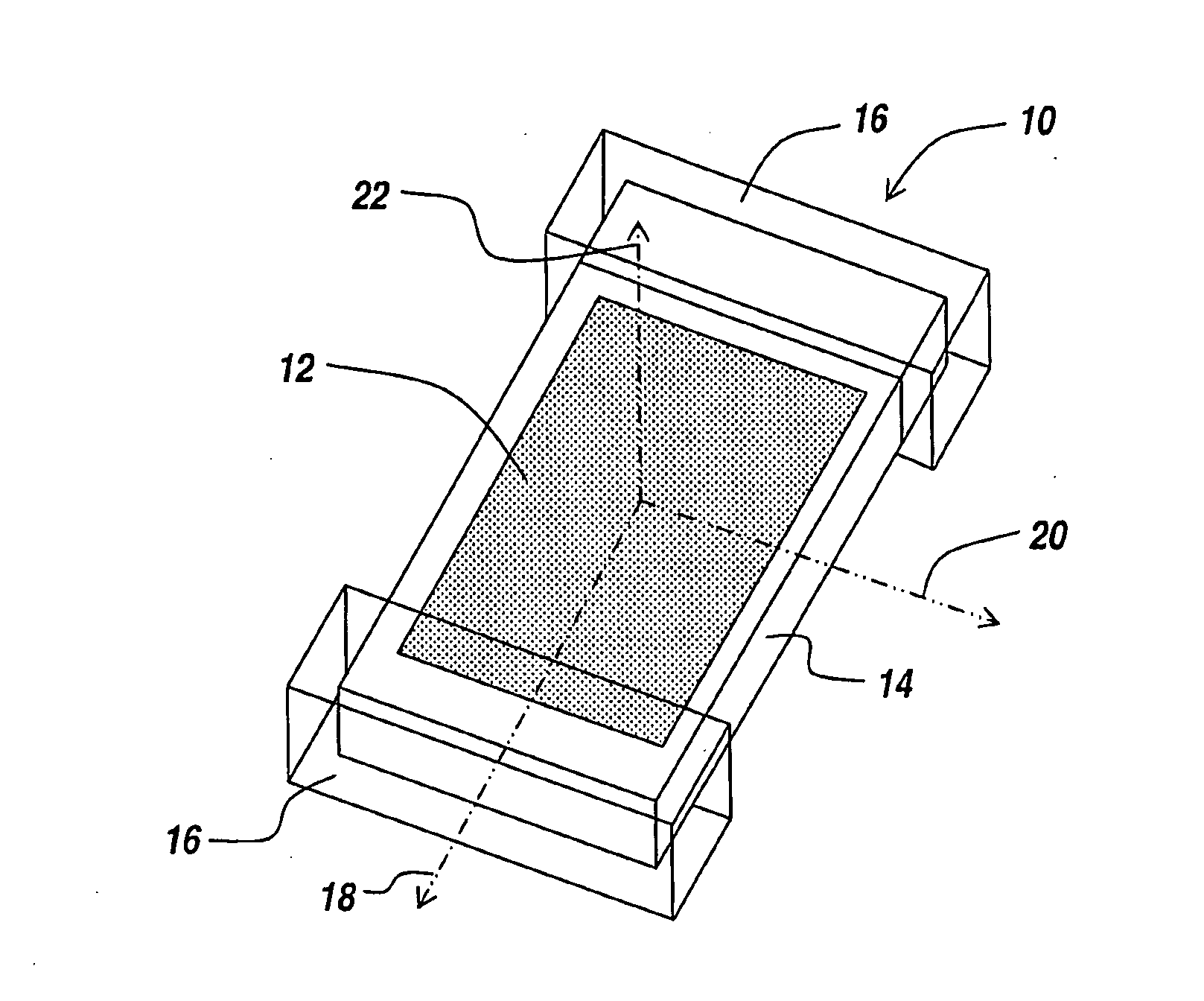

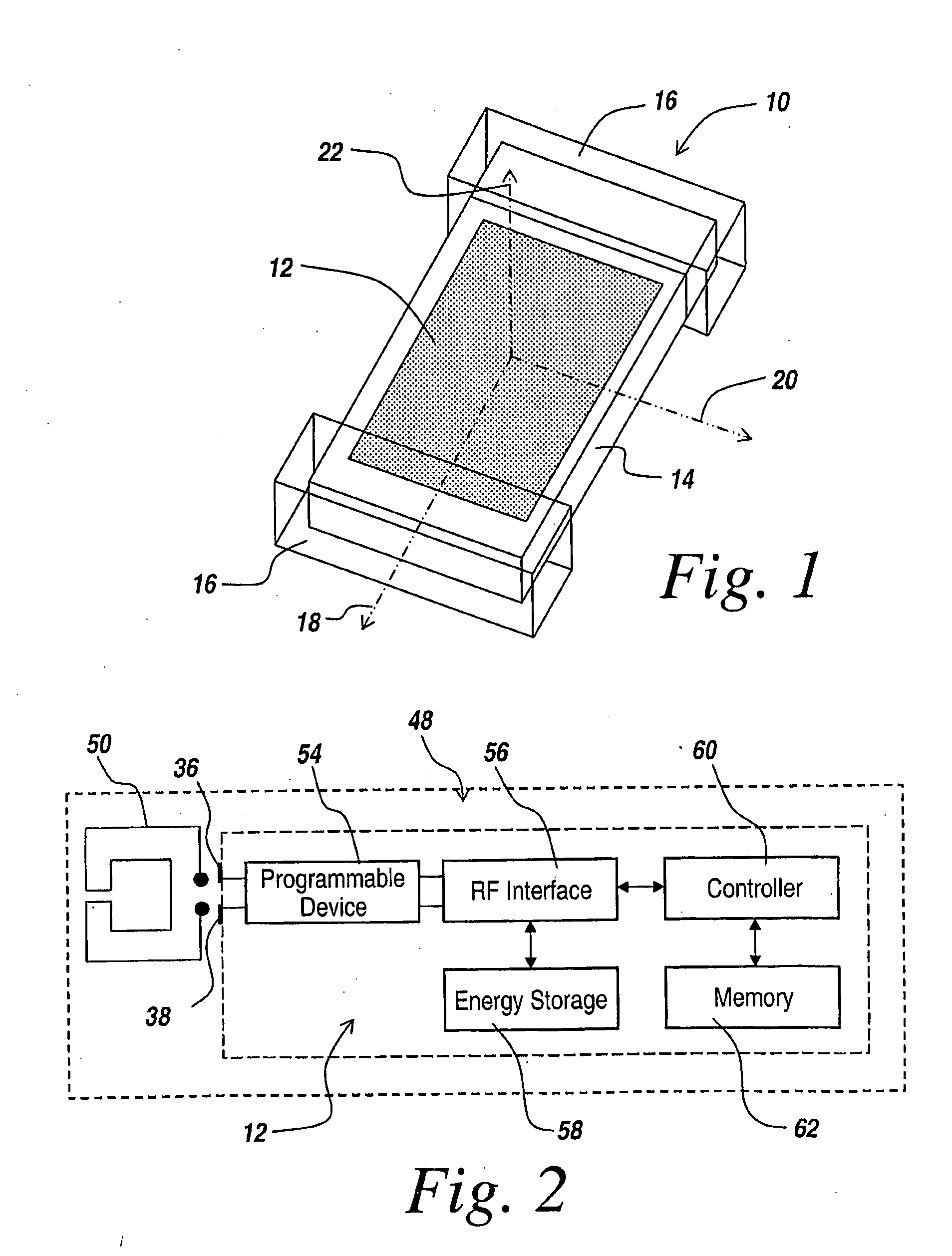

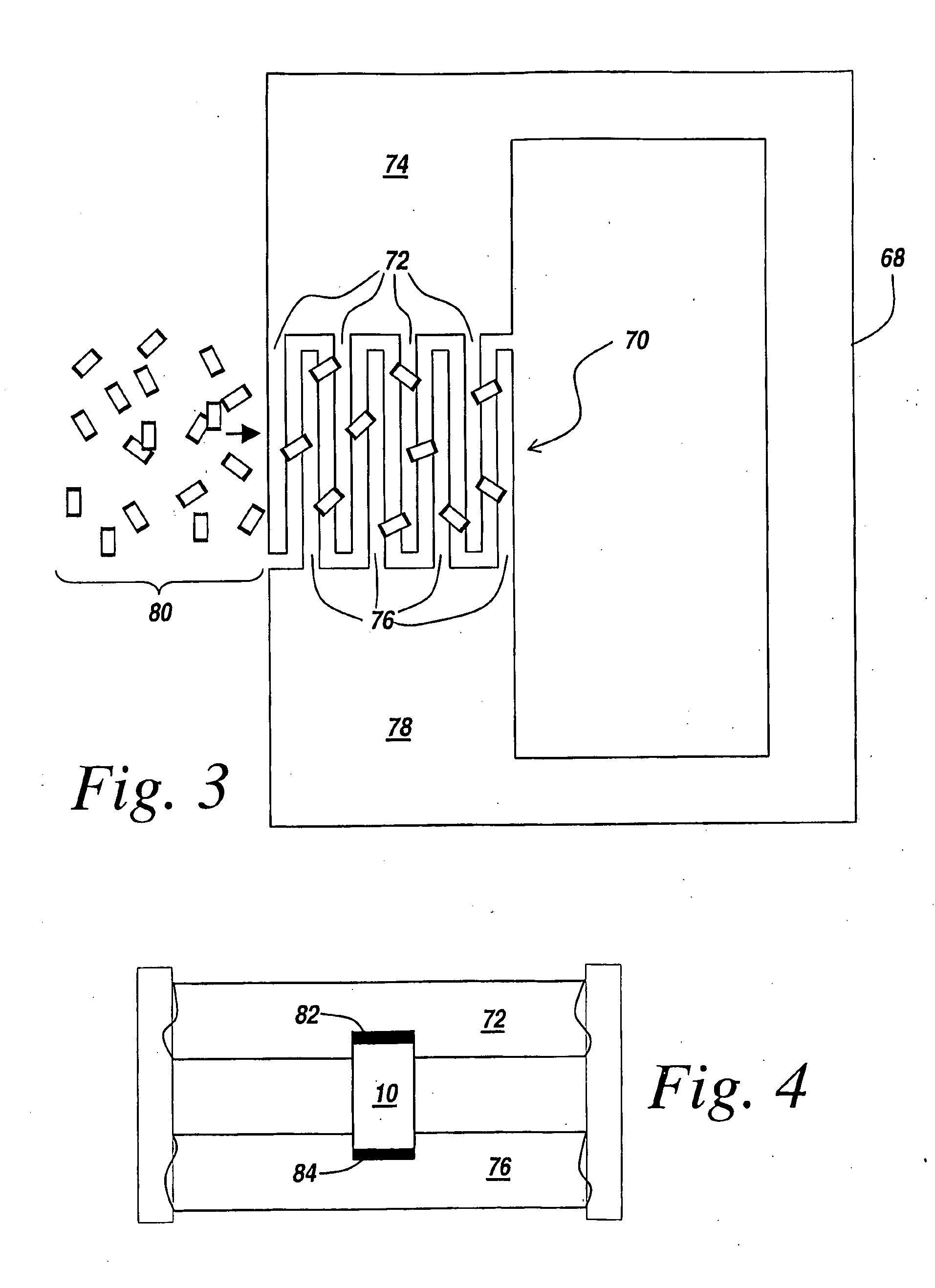

Methods for coupling an RFID chip to an antenna

ActiveUS20090128289A1Raise the possibilityQuick and inexpensive placement of chipRadiating elements structural formsComponent plug-in assemblagesFeed point

A method for mounting multiple small RFID chips onto larger antenna. The chips are mechanically aligned with an interdigitated gap at the feed point of the antenna by electrostatic or magnetic techniques. In an alternate embodiment RF field coupling between the chips and the antenna is employed.

Owner:RADIOFIDO

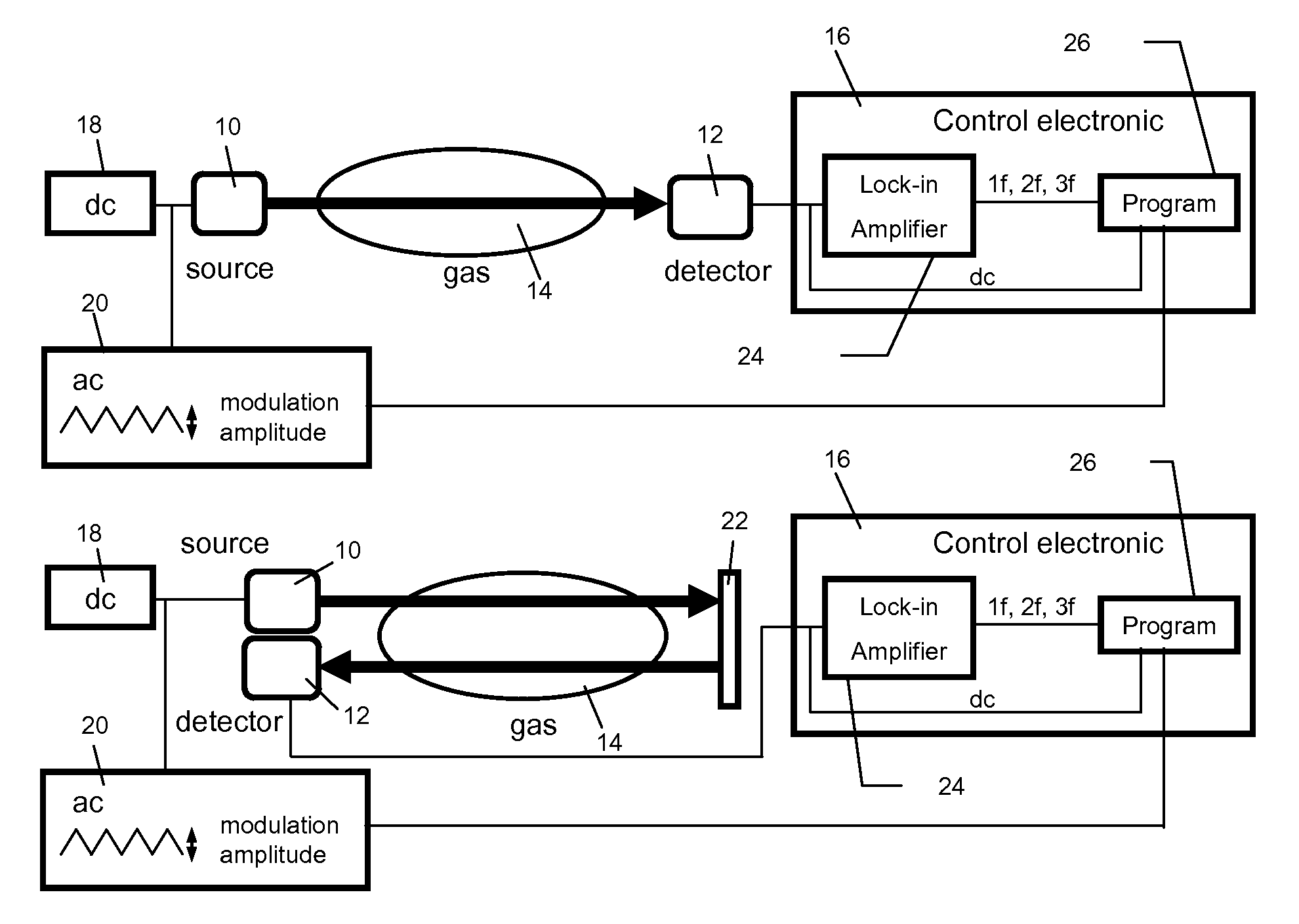

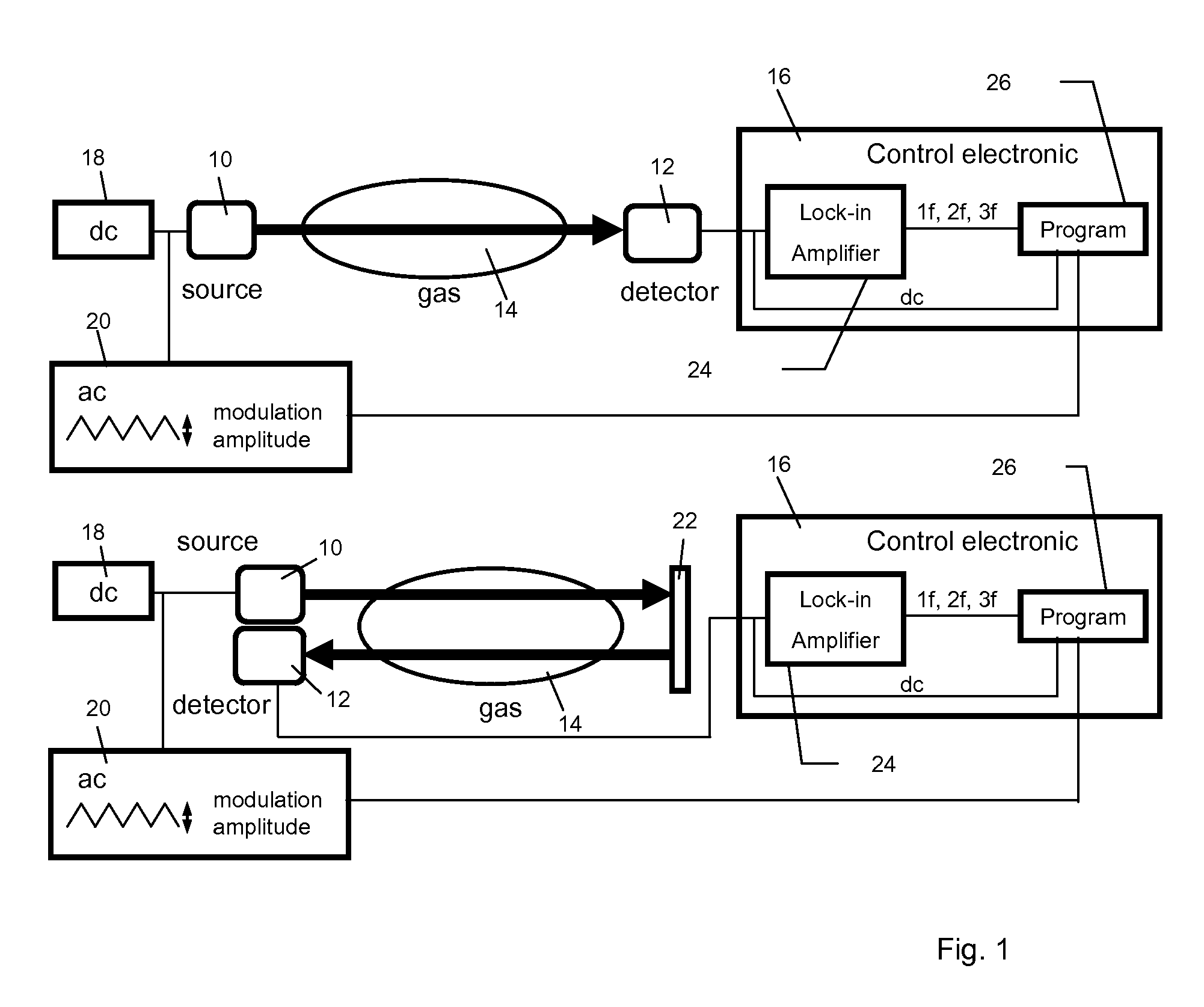

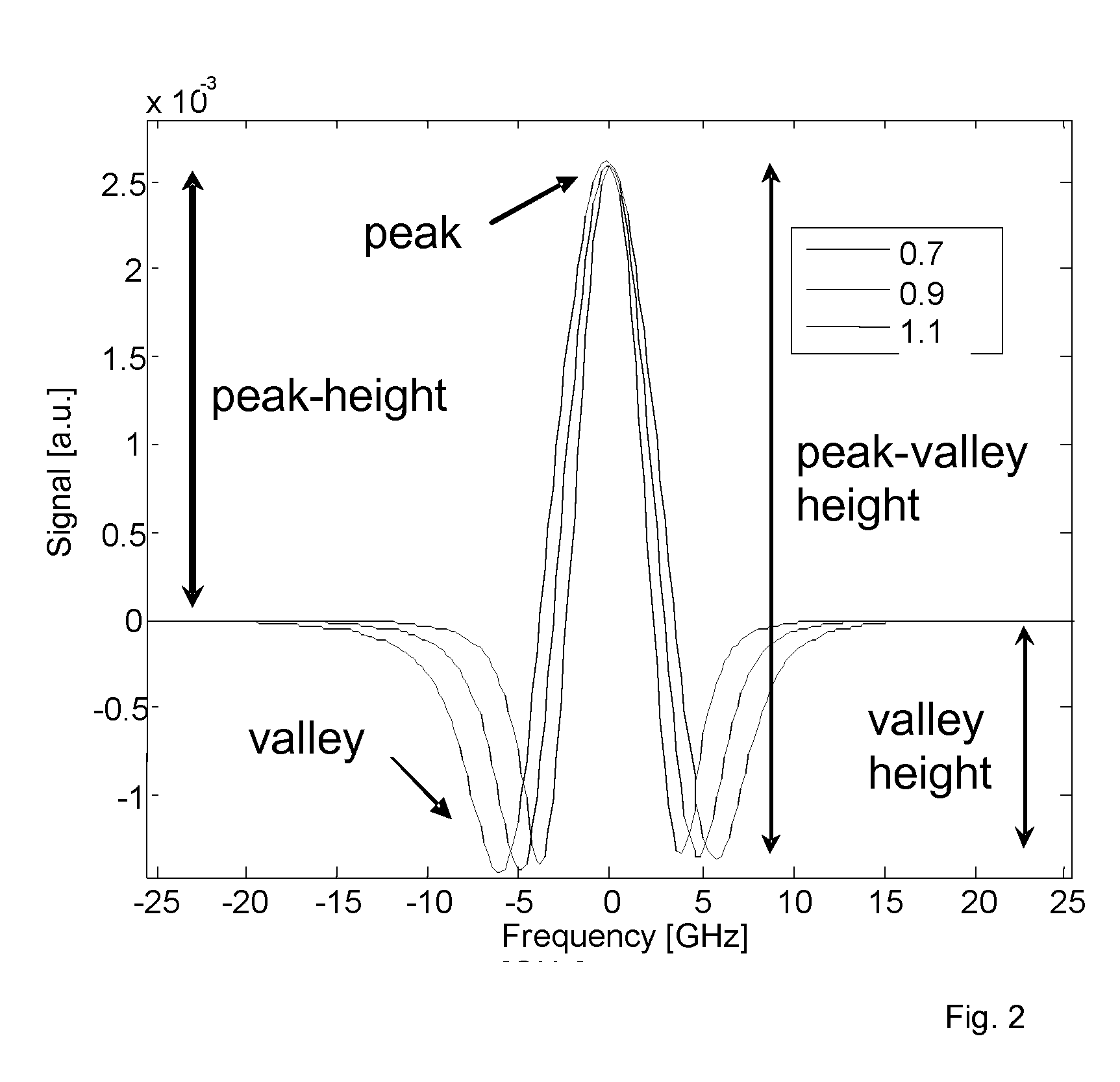

Method and apparatus for detecting a gas concentration with reduced pressure dependency

ActiveUS20120283961A1Reduce dependence of pressureEasy CalibrationTransmissivity measurementsColor/spectral properties measurementsPressure dependencyProduct gas

This invention relates to a method that makes the measurement of a trace gas concentration invariant or at least less affected to pressure variations in the gas and atmospheric pressure changes. This method neither requires a pressure sensor nor a pressure calibration routine. Furthermore, the method can be applied to other gas species present in the background gas or to the background gas itself that cross-interfere with the target gas of interest. This allows removing any pressure dependency of cross-interference parameters of other gas species and / or the background gas. The new method for accurately measuring a gas concentration is based on optimizing the wavelength modulation amplitude of the laser to minimum pressure dependency.

Owner:AXETRIS AG

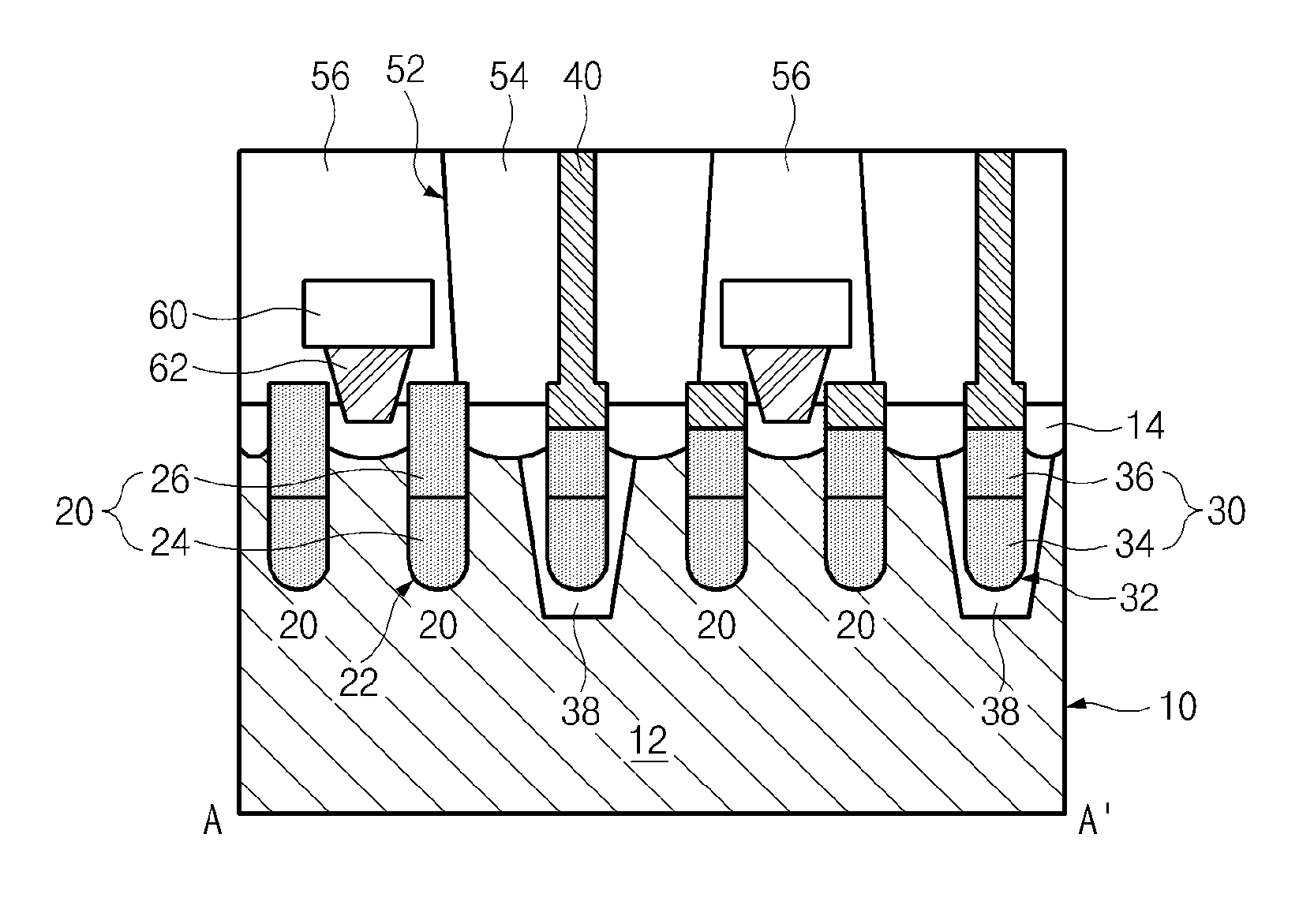

Semiconductor device and method of manufacturing the same

ActiveUS20120211830A1Reduce contact resistanceIncrease widthTransistorSolid-state devicesDevice materialEngineering

A semiconductor device and a method of fabricating the same are provided, in which a full overlap between a storage node contact and an active region to solve an overlay in an etching process and an etching width of a storage node is increased to improve a processing margin. The semiconductor device includes a main gate and a device isolation structure disposed in a semiconductor device, an isolation pattern disposed over the device isolation structure, and contact plugs disposed at each side of the isolation pattern.

Owner:SK HYNIX INC

LCD and manufacturing method thereof

InactiveCN101430464AIncrease line widthReduce drippingPhotomechanical apparatusNon-linear opticsCapacitanceCapacitive effect

The invention relates to a liquid crystal display device and a manufacture method thereof. The liquid crystal display device comprises a first basic board, a second basic board as well as a data signal line and a grid scanning line which are arranged on the second basic board; wherein, the first basic board is provided with a plurality of strip optical spacers. The liquid crystal display device can reduce the capacitance effect generated by the liquid crystal on the data signal line, improves the writing capacity of the signal data line, and can reduce the line width of the data signal line and improves the aperture opening ratio.

Owner:SHANGHAI SVA LIQUID CRYSTAL DISPLAY

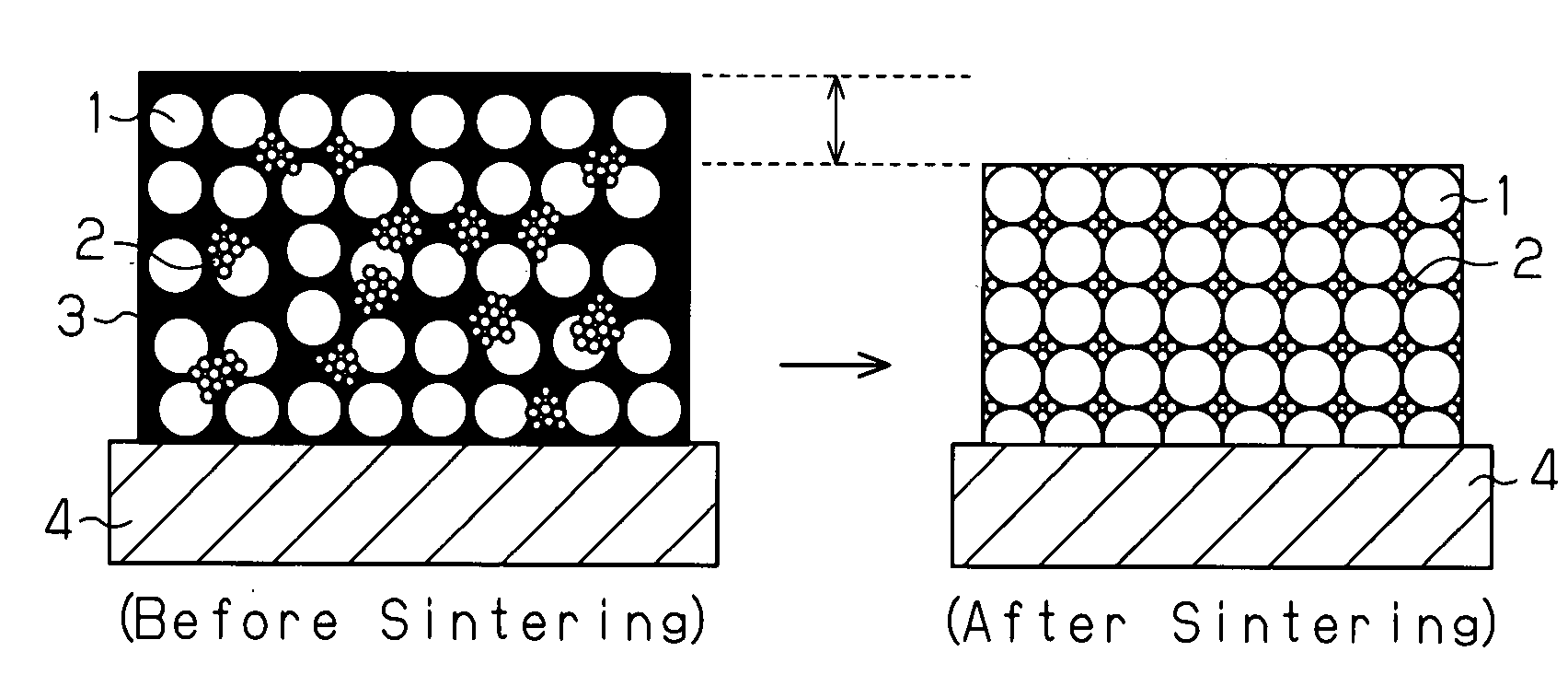

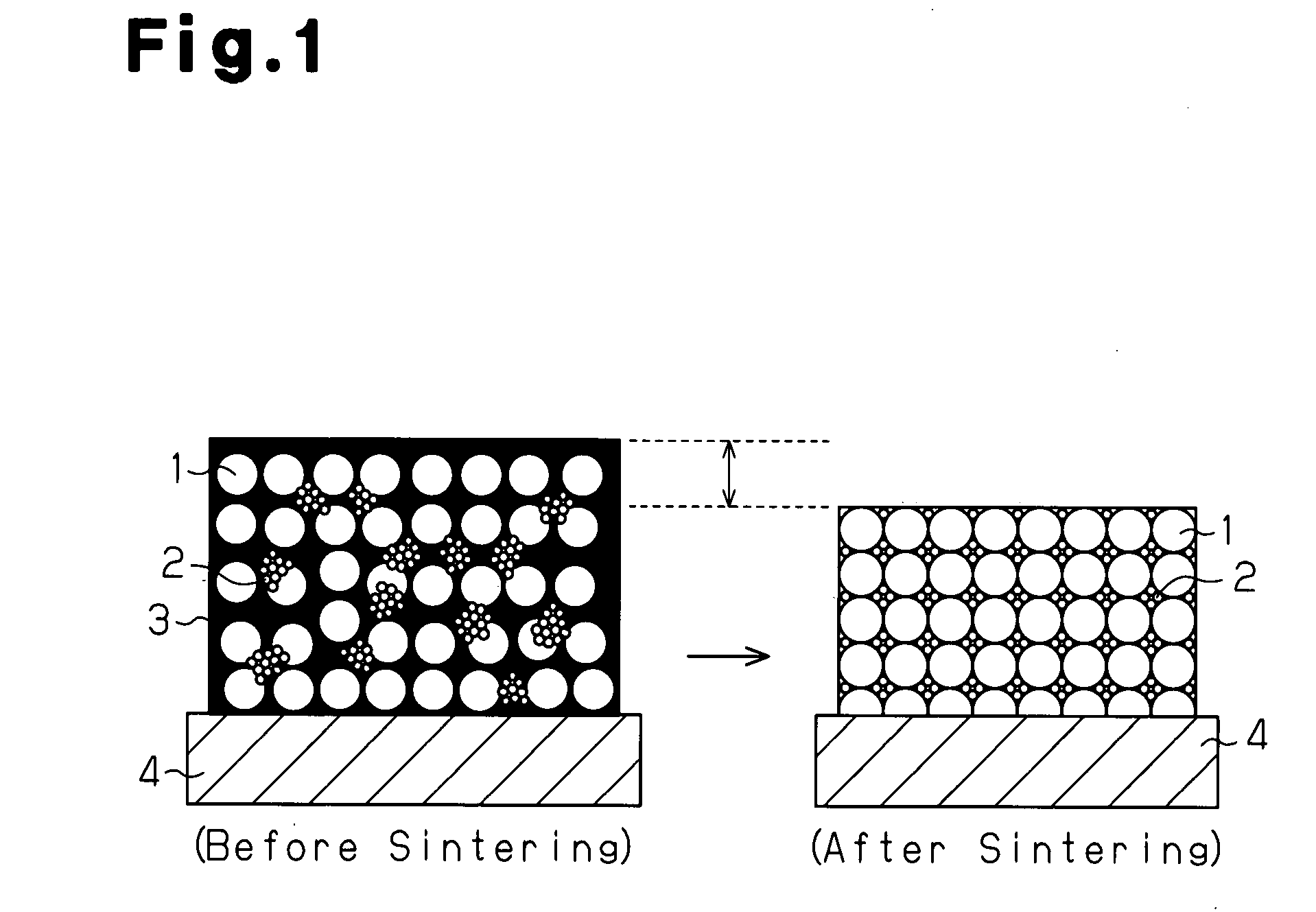

Conductive Paste and Wiring Board Using It

InactiveUS20090107707A1Inhibition resistanceLower volume resistivityConductive layers on insulating-supportsConductive materialConductive pasteFrit

A conductive paste is mainly composed of a metal powder, a glass frit, and an organic vehicle. The total content amount of the metal powder and glass frit with respect to the entire conductive paste is 85 wt % or more. The viscosity at a rotational speed of 1 rpm measured at 25° C. with an E type rotating viscometer is 100 Pa·s or more and 400 Pa·s or less.

Owner:SUMITOMO ELECTRIC IND LTD

Production method of grids curb wall

ActiveCN101197275AImprove consistencyOvercome the problem of poor thickness consistencySemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingDielectric layerSemiconductor

The invention relates to a manufacturing method for grid side wall, which comprises the following step of: providing a semi-conductor substrate with a grid and forming a dielectric layer on the semi-conductor substrate along the surface of the grid; measuring the thickness of the dielectric layer of the grid side wall and computing the difference between the thickness and the objective thickness of side wall; computing the etching time T according to the difference and the etching rate for the dielectric layer; etching the dielectric layer for the time of T. The method can compensate the variation of thickness of the deposited dielectric layer, thus overcoming the problem of bad uniformity of the carved side wall thickness caused by different thicknesses of the dielectric layer.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Rapid subtractive manufacturing process of circuit boards

InactiveCN101600299AHigh precisionEmission reductionPrinted circuit manufactureManufacturing cost reductionCopper plating

The invention relates to a rapid subtractive manufacturing process of circuit boards. In the process, ink-jet printing technology is adopted and graphs are transferred to the circuit boards by a spray head by means of ink; the working procedure is as follows: punching-deburring, cleaning and passivating-copper plating-cleaning-front and back coating-front and back graphic printing-graphic curing-etching-cleaning and passivating-quality inspecting-solder mask ink front and back printing and UV curing-UV curing-text ink front and back printing and UV curing-UV curing-tin spraying and surface processing-molding-electrical testing-quality inspecting-packaging-factory leaving; the manufacturing process takes about 5h. The process has the advantages of simpleness, convenience, one-step forming, sharp graphic margin, high circuit graph precision, simple materials, manufacturing cost reduction, manufacturing cycle shrinkage and economic benefit increase; wherein, the line width of the circuit graph is increased to be less than 1 / 1000 from 3 / 1000 and the graphs are mainly transferred by means of ink. The electroplating link is omitted, thereby dramatically the energy consumption and industrial wastewater discharge, and ensuring good energy saving and environmental protection effects and low cost.

Owner:陈立峰

Method of forming photoresist pattern

InactiveCN1421745AReduce line widthIncrease line widthSemiconductor/solid-state device manufacturingPhotomechanical coating apparatusOptoelectronicsPhotoresist

The method of forming photoresist pattern includes forming photoresist layer on the substrate, the first time exposure of the photoresist layer with mask; the first development to form the first photoresist pattern; the second time exposure of the first photoresist pattern layer to expose the decompose part of the first photoresist pattern layer and to form exposed decomposed layer; the second development to eliminate the exposed decomposed layer and to form the second positive photoresist pattern layer with pattern size smaller than that of the first photoresist pattern layer.

Owner:MACRONIX INT CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com