Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

336 results about "Pattern size" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

UV Curable Silsesquioxane Resins For Nanoprint Lithography

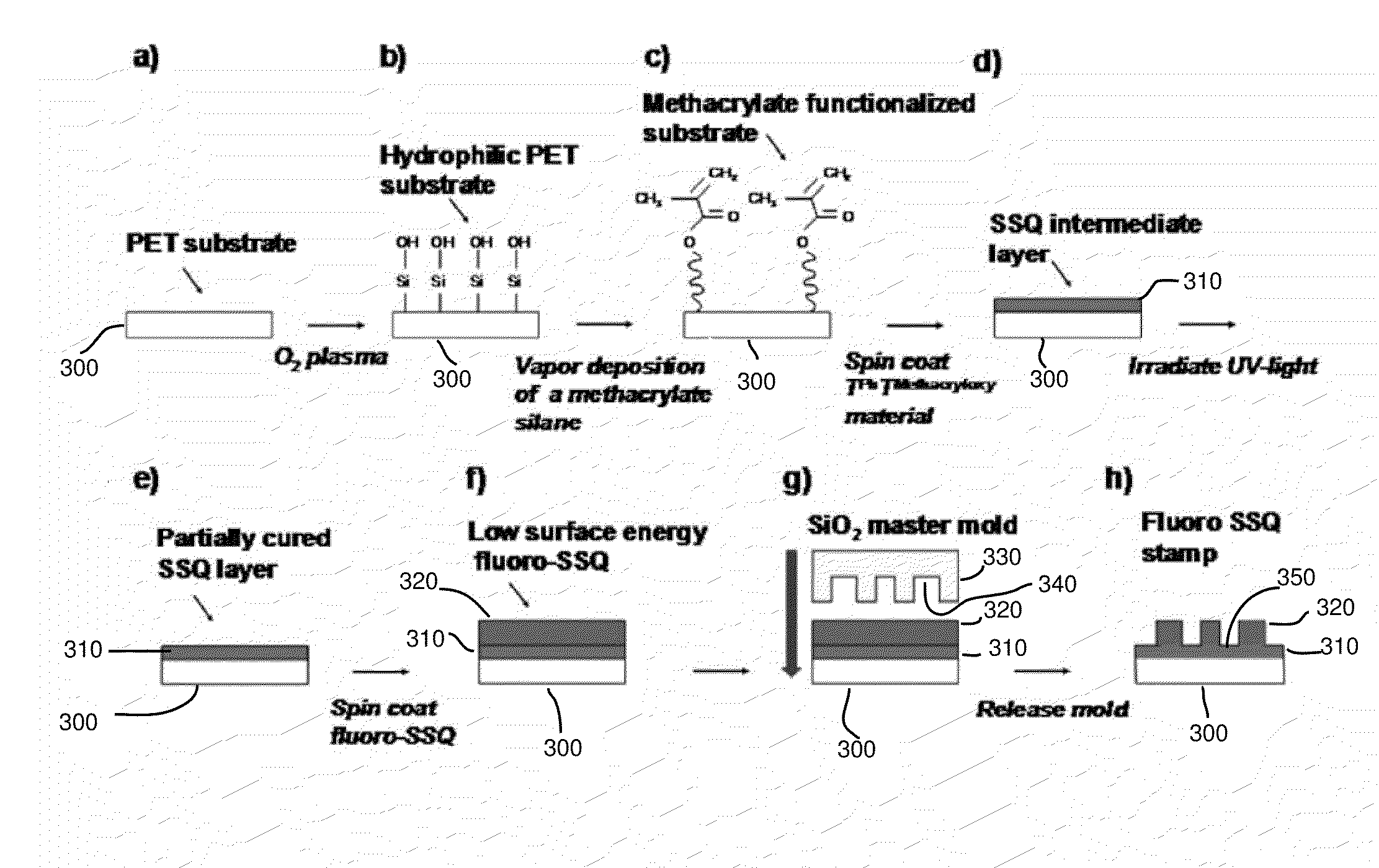

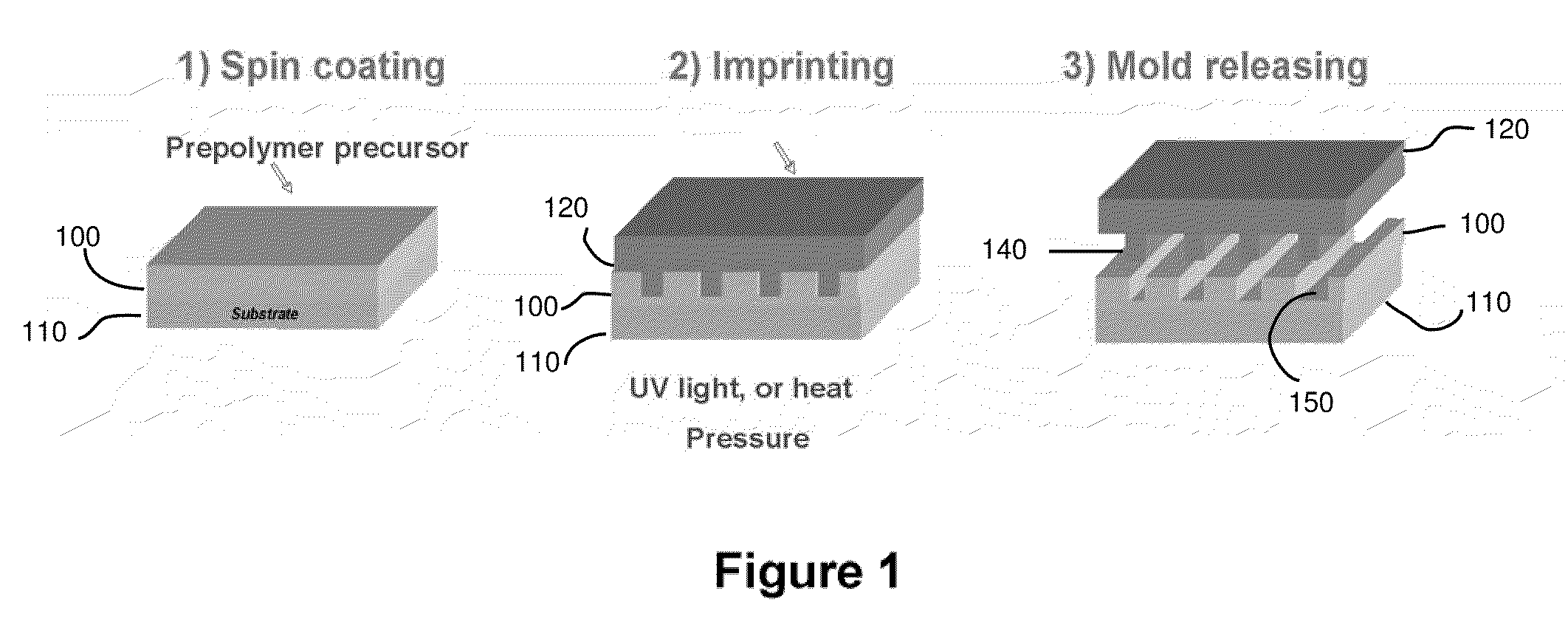

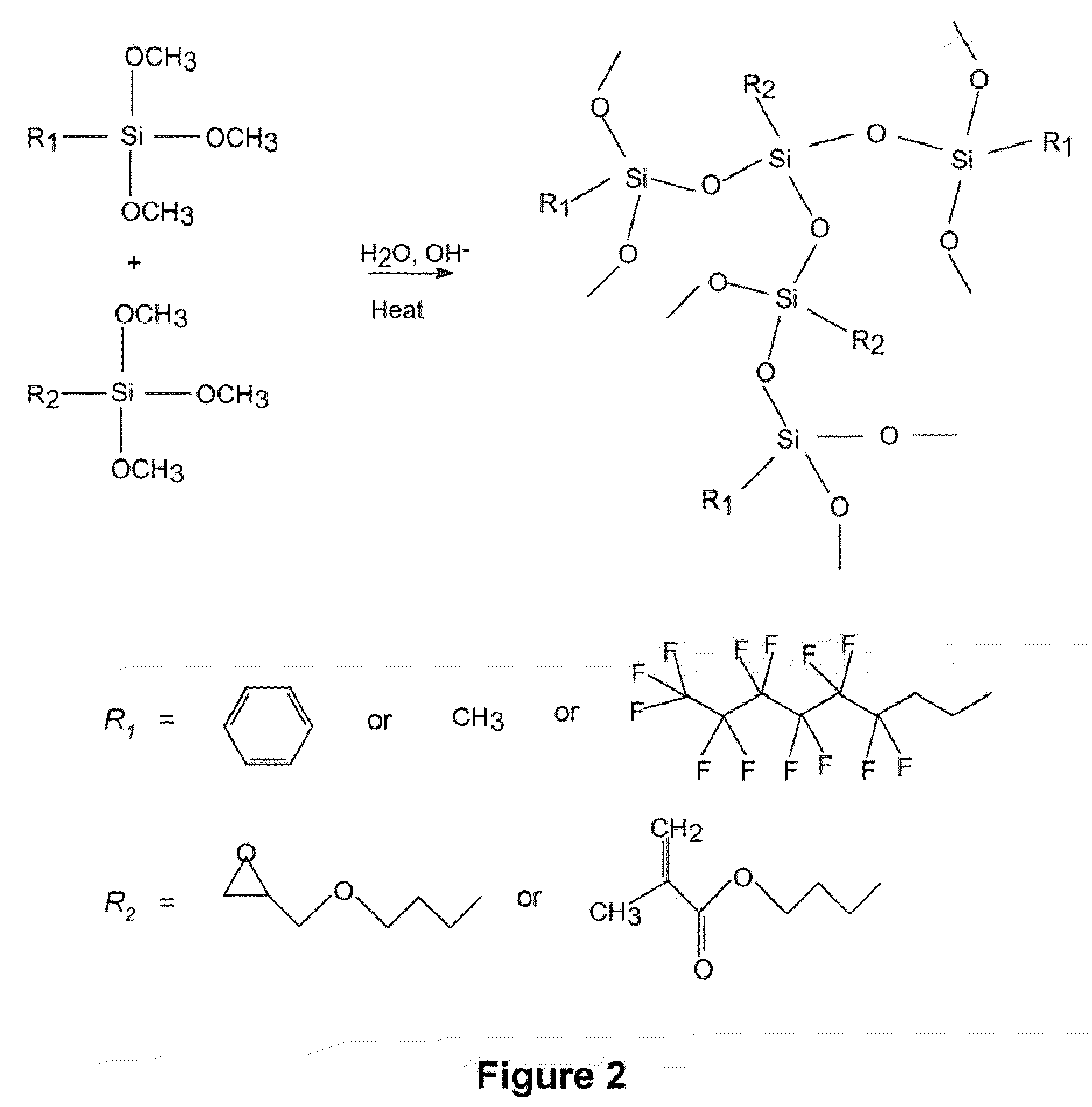

ActiveUS20090256287A1Simple compositionImprove methodPhotosensitive materialsNanoinformaticsNanolithographyResist

Radiation-curable silsesquioxane resin materials are employed for micro- and nanolithography. The resin materials can include a radiation-curable silsesquioxane resin and a photo-initiator having low viscosity. The low viscosity of the liquid system allows imprinting with low pressure and low temperature; e.g. room temperature. The resist's dry etching resistance is increased and the cured film is more easily separated from the mask. Due to its high modulus after cure, the material allows the fabrication of micro- and nano-features having high aspect ratios while providing a high throughput. Various pattern sizes, for example, ranging from tens of microns to as small as a few nanometers, may be achieved with the UV-curable material system.

Owner:RGT UNIV OF MICHIGAN

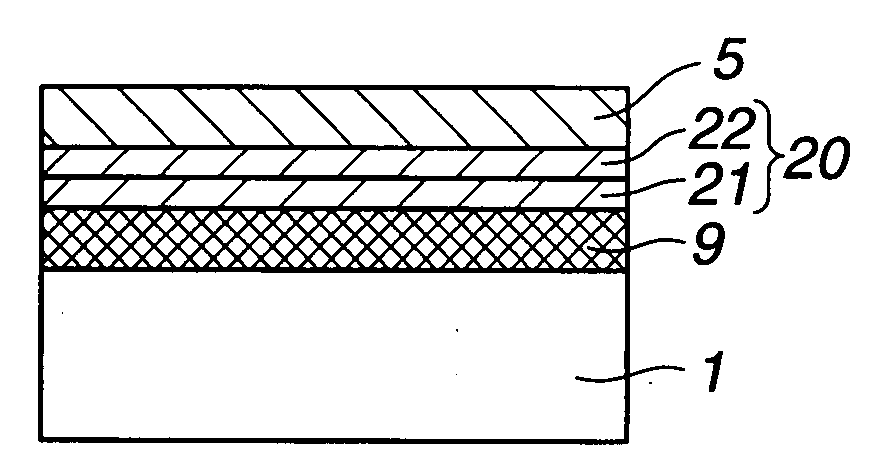

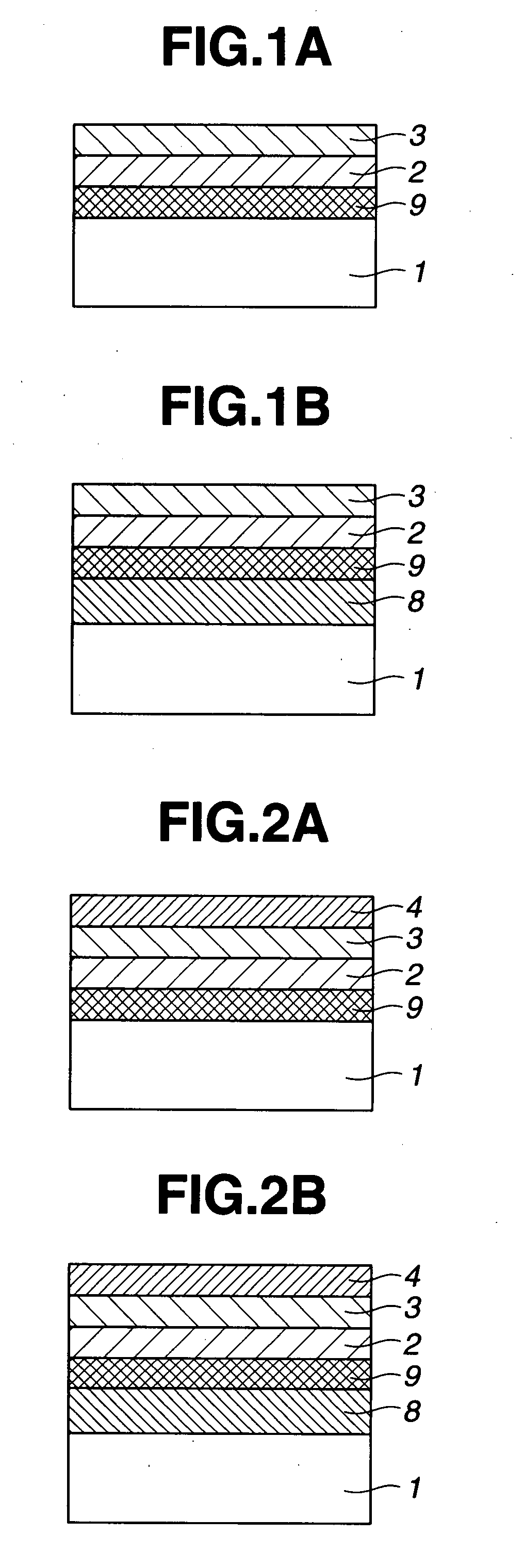

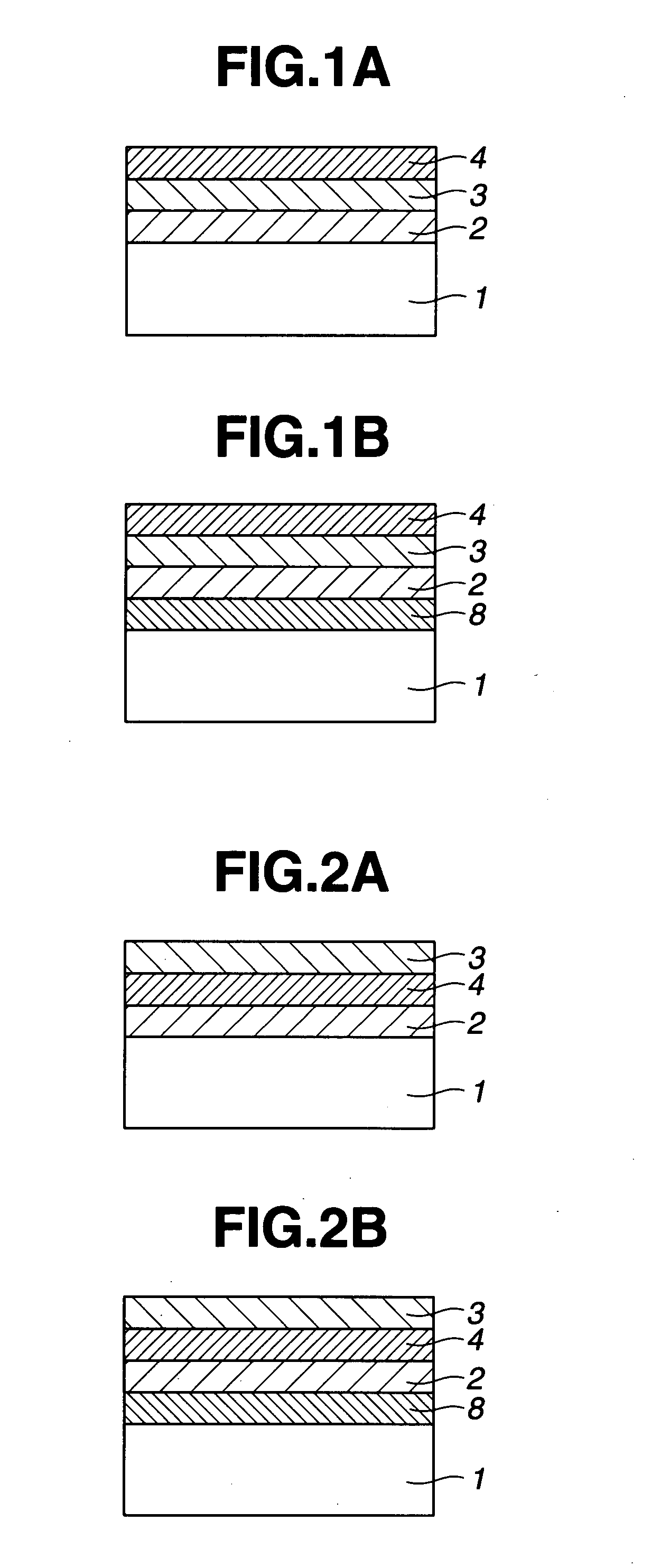

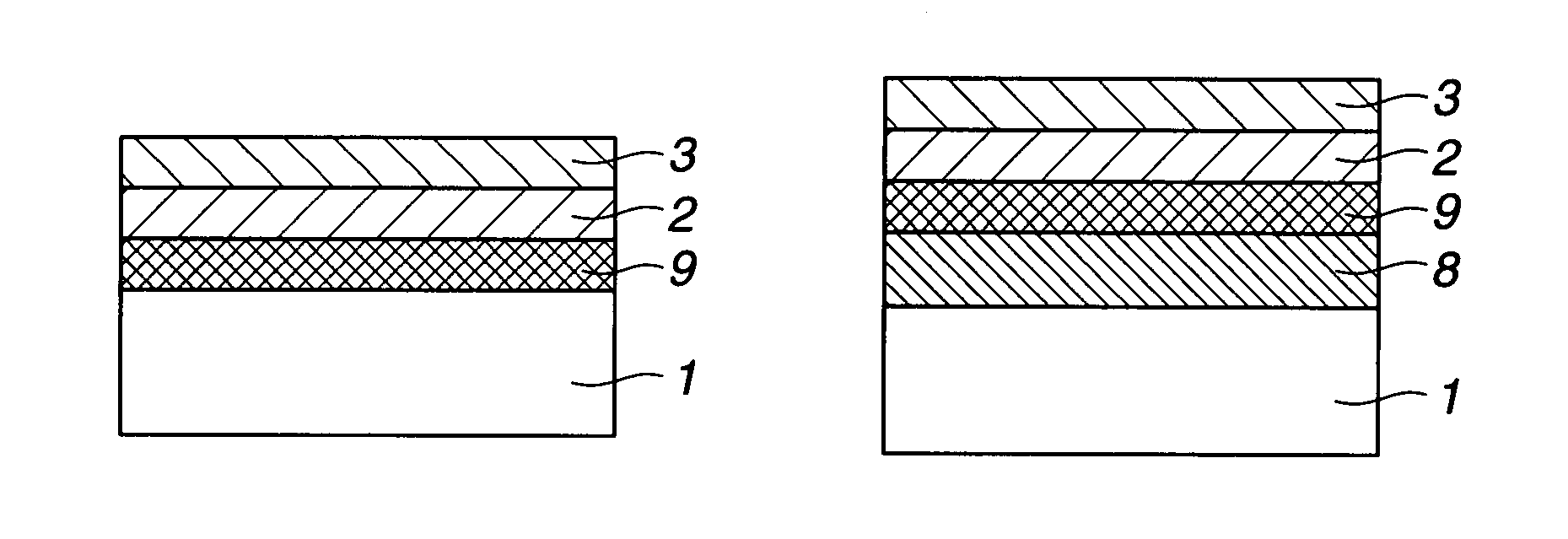

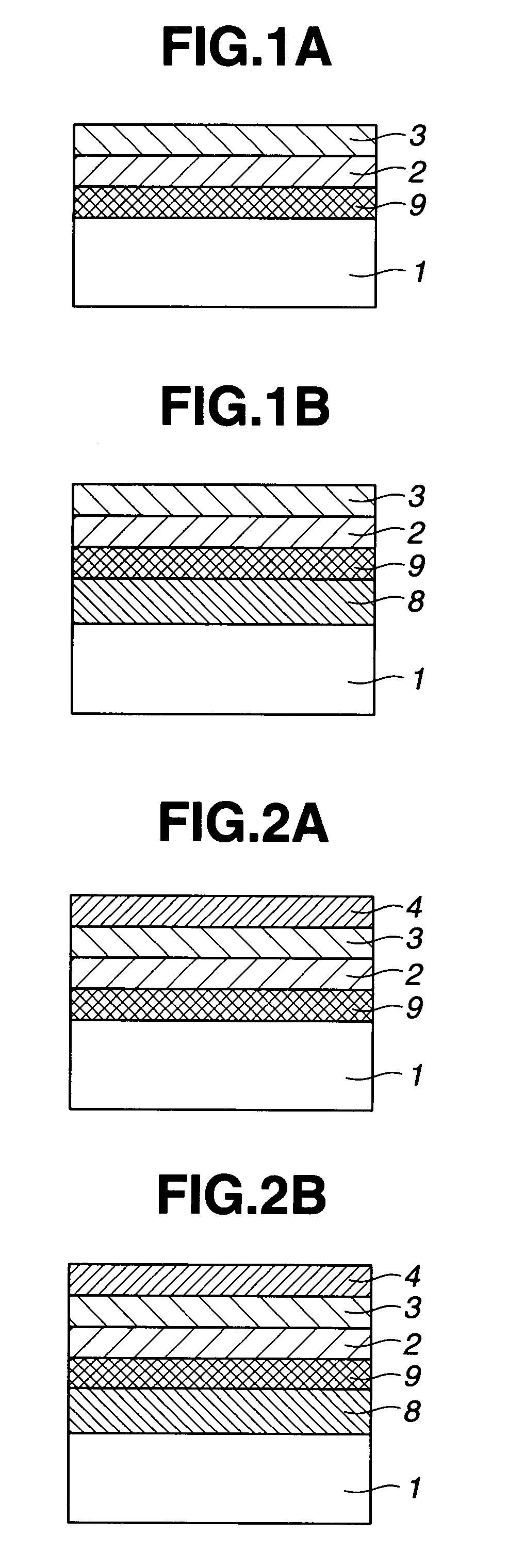

Photomask blank and photomask

ActiveUS20070212618A1High resolutionMinimized pattern densityPhotomechanical apparatusSemiconductor/solid-state device manufacturingSiliconDry etching

A photomask blank is provided comprising an etch stop film which is disposed on a transparent substrate and is resistant to fluorine dry etching and removable by chlorine dry etching, a light-shielding film disposed on the etch stop film and including at least one layer composed of a transition metal / silicon material, and an antireflective film disposed on the light-shielding film. When the light-shielding film is dry etched to form a pattern, pattern size variation arising from pattern density dependency is reduced, so that a photomask is produced at a high accuracy.

Owner:SHIN ETSU CHEM IND CO LTD +1

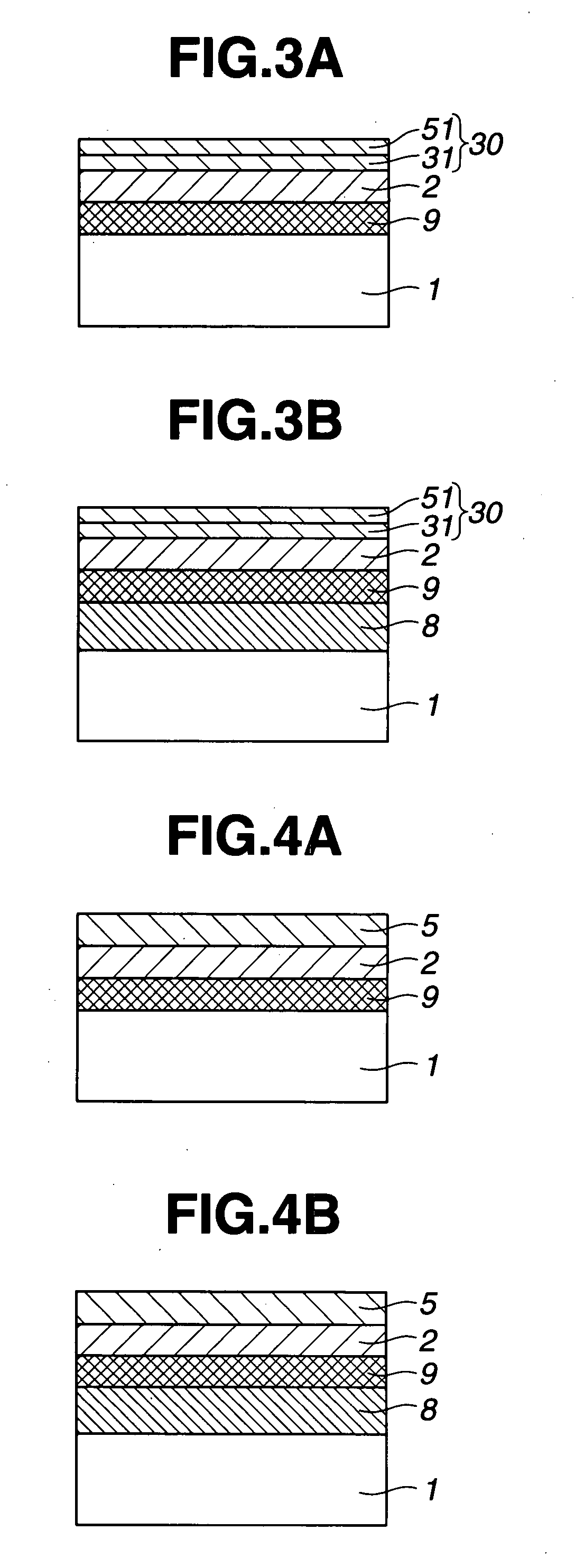

Photomask blank and photomask making method

ActiveUS20070212619A1High resolutionImprove accuracyPhotomechanical apparatusSemiconductor/solid-state device manufacturingOptoelectronicsDry etching

A photomask blank comprises a transparent substrate, a light-shielding film deposited on the substrate and comprising a metal or metal compound susceptible to fluorine dry etching, and an etching mask film deposited on the light-shielding film and comprising another metal or metal compound resistant to fluorine dry etching. When the light-shielding film is dry etched to form a pattern, pattern size variation arising from pattern density dependency is reduced, so that a photomask is produced at a high accuracy.

Owner:SHIN ETSU CHEM IND CO LTD +1

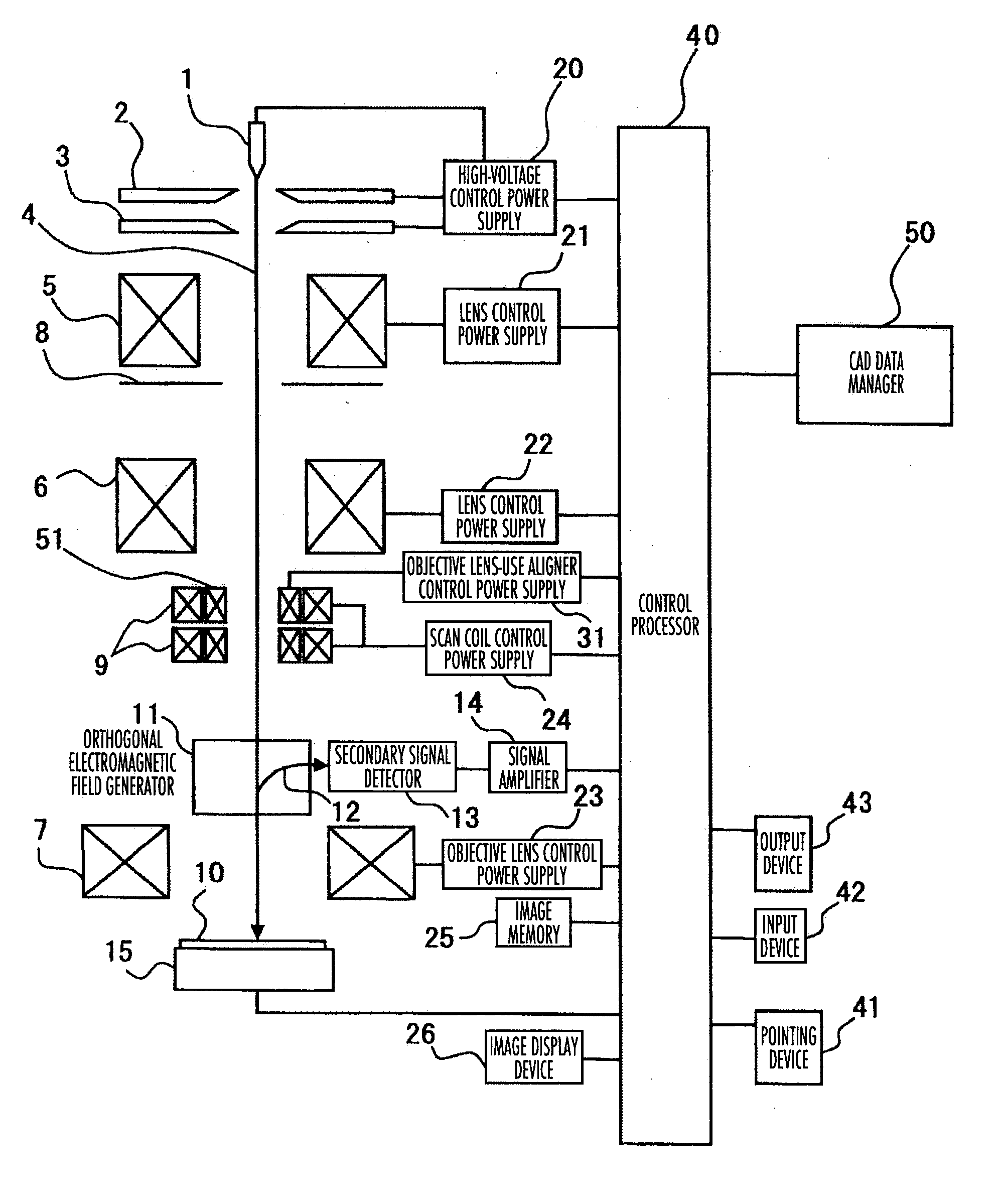

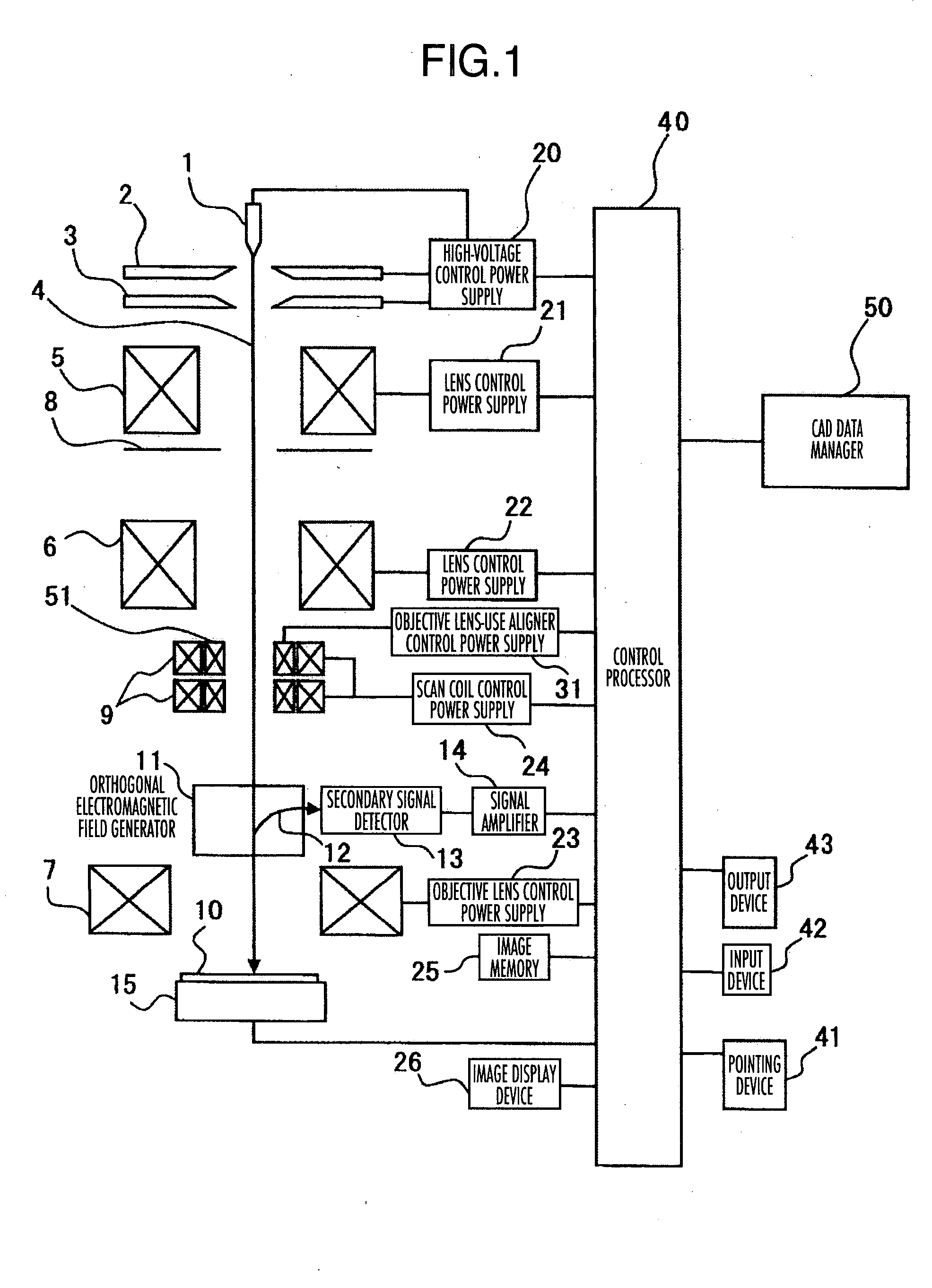

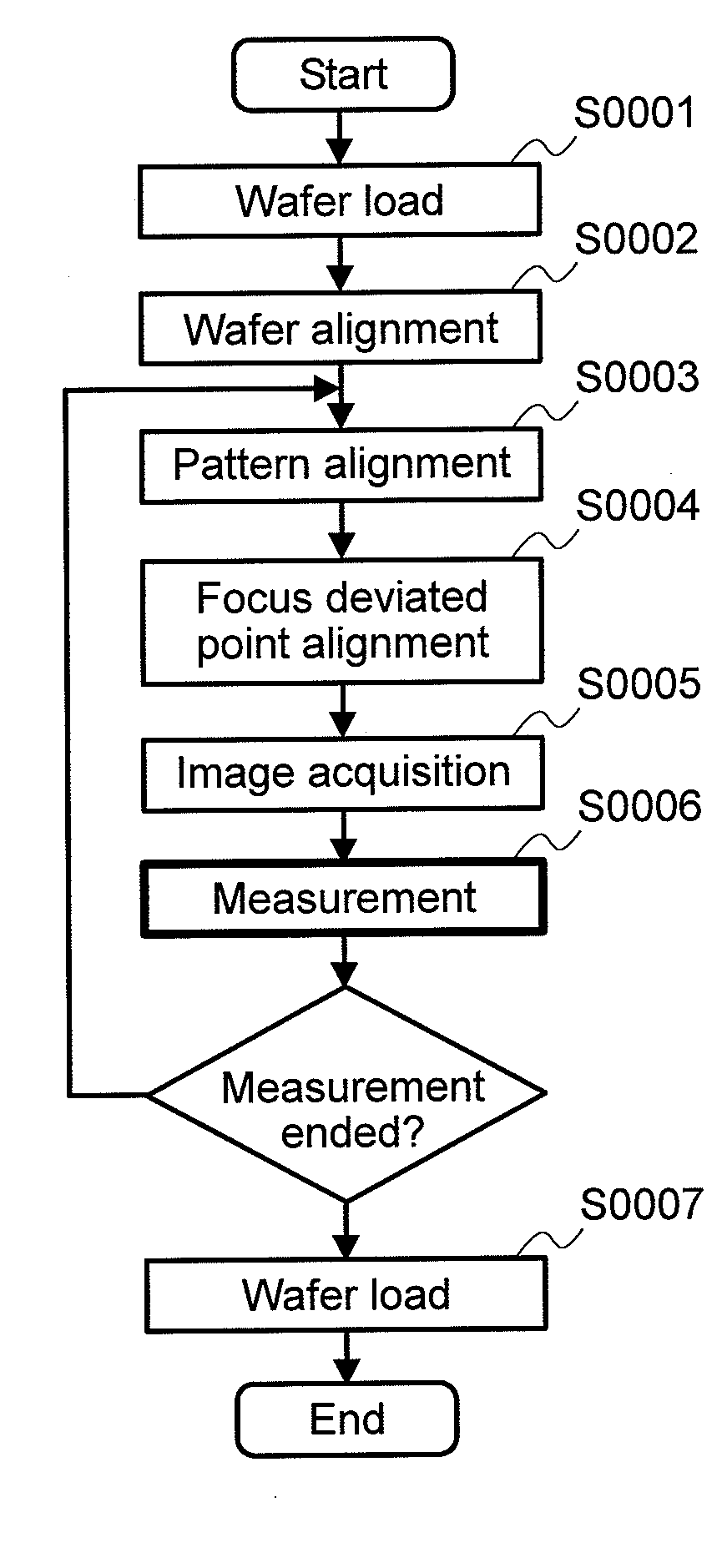

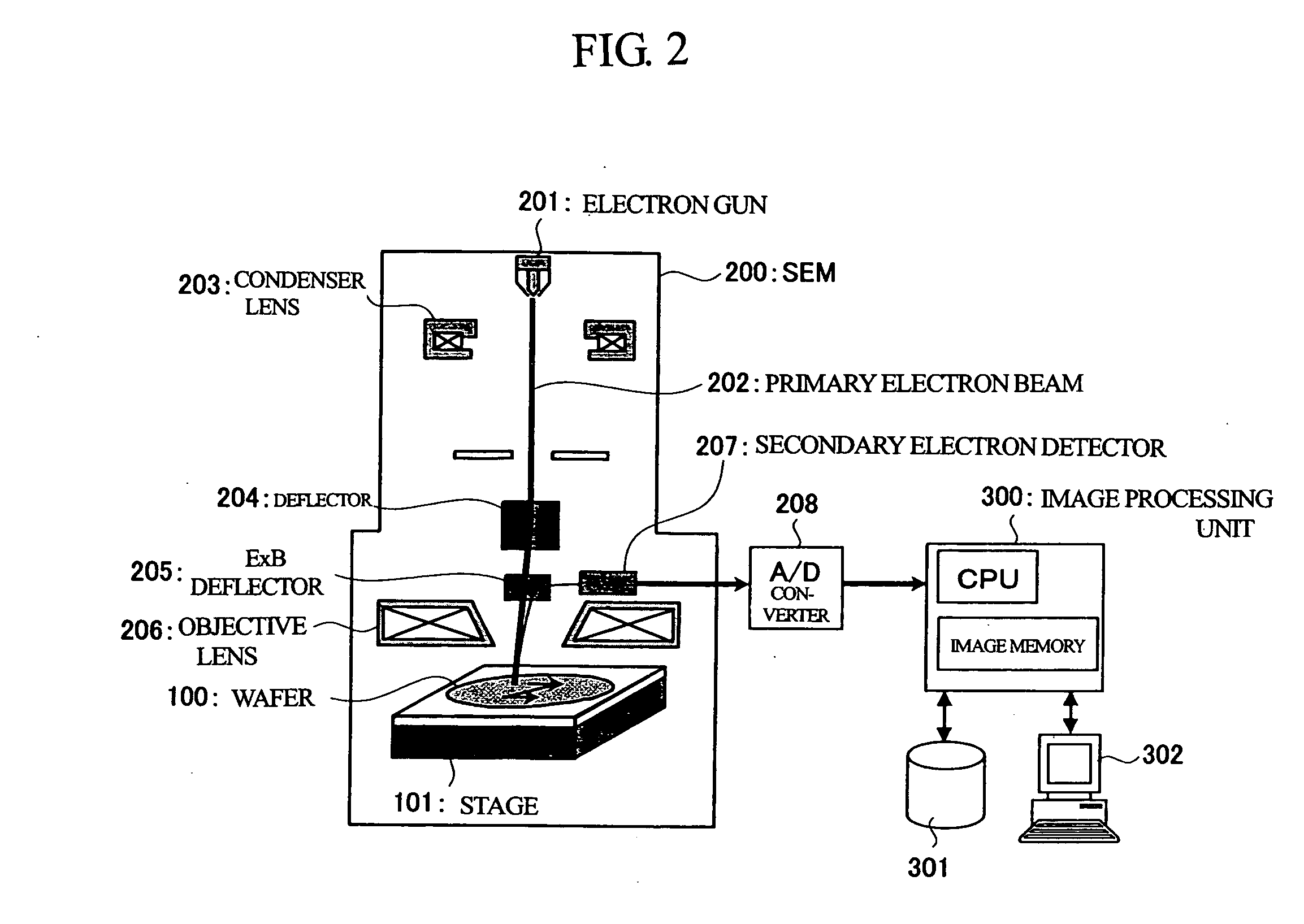

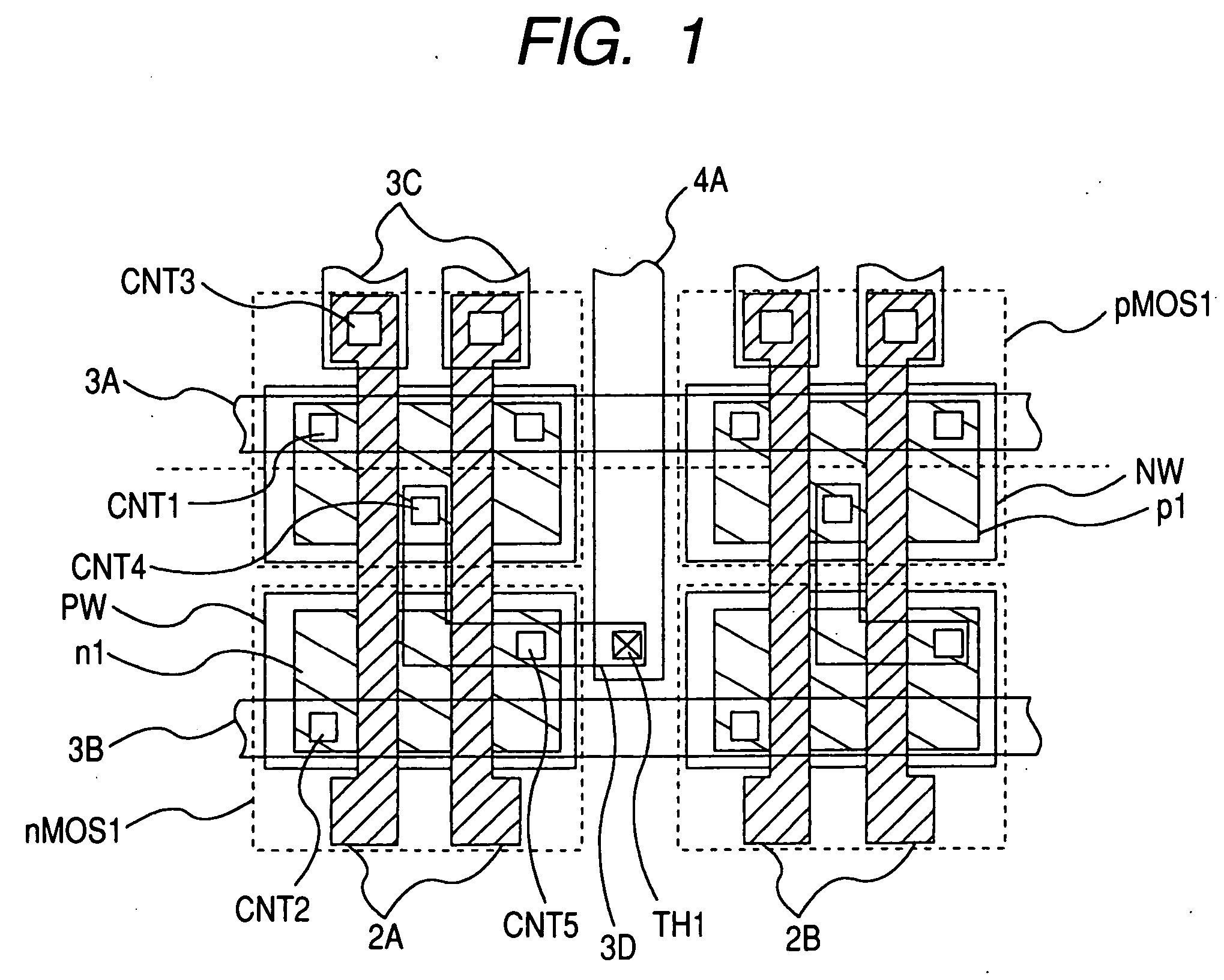

Workpiece size measurement method and apparatus

ActiveUS20070221842A1Increased complexityImprove measurement efficiencyMaterial analysis using wave/particle radiationCharacter and pattern recognitionSize measurementEngineering

A workpiece size measurement method suitable for length measurement of multilayered circuit elements with increased complexities is disclosed. This method employs a technique for changing measurement conditions in a way pursuant to either an image of workpiece or the situation of a target semiconductor circuit element to be measured when measuring pattern sizes on the workpiece image using design data of the semiconductor circuit element. With such an arrangement, adequate measurement conditions are selectable in accordance with the state of workpiece image and / or the state of a circuit element formed on the workpiece, thereby making it possible to improve the measurement efficiency. A workpiece size measurement apparatus using the technique is also disclosed.

Owner:HITACHI HIGH-TECH CORP

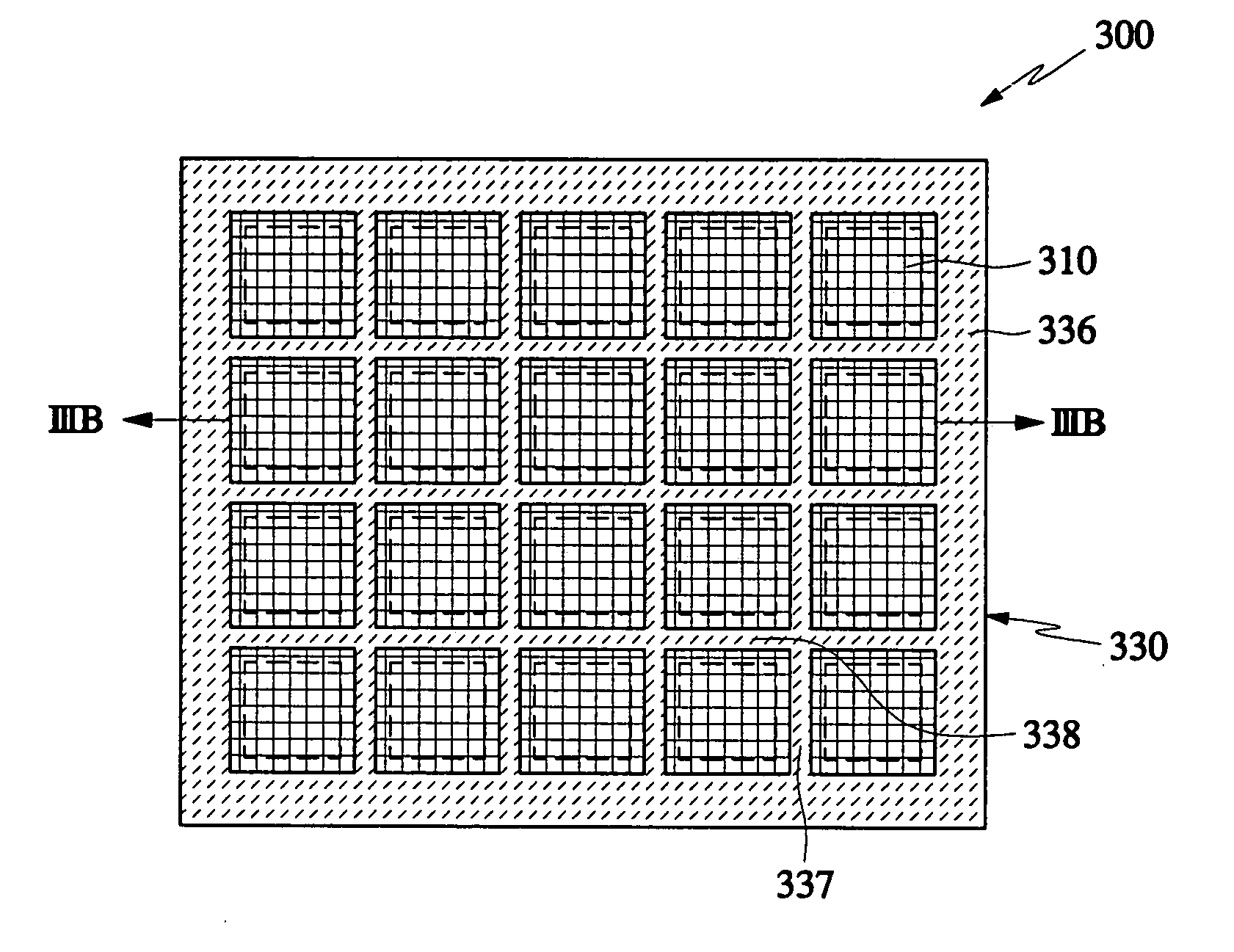

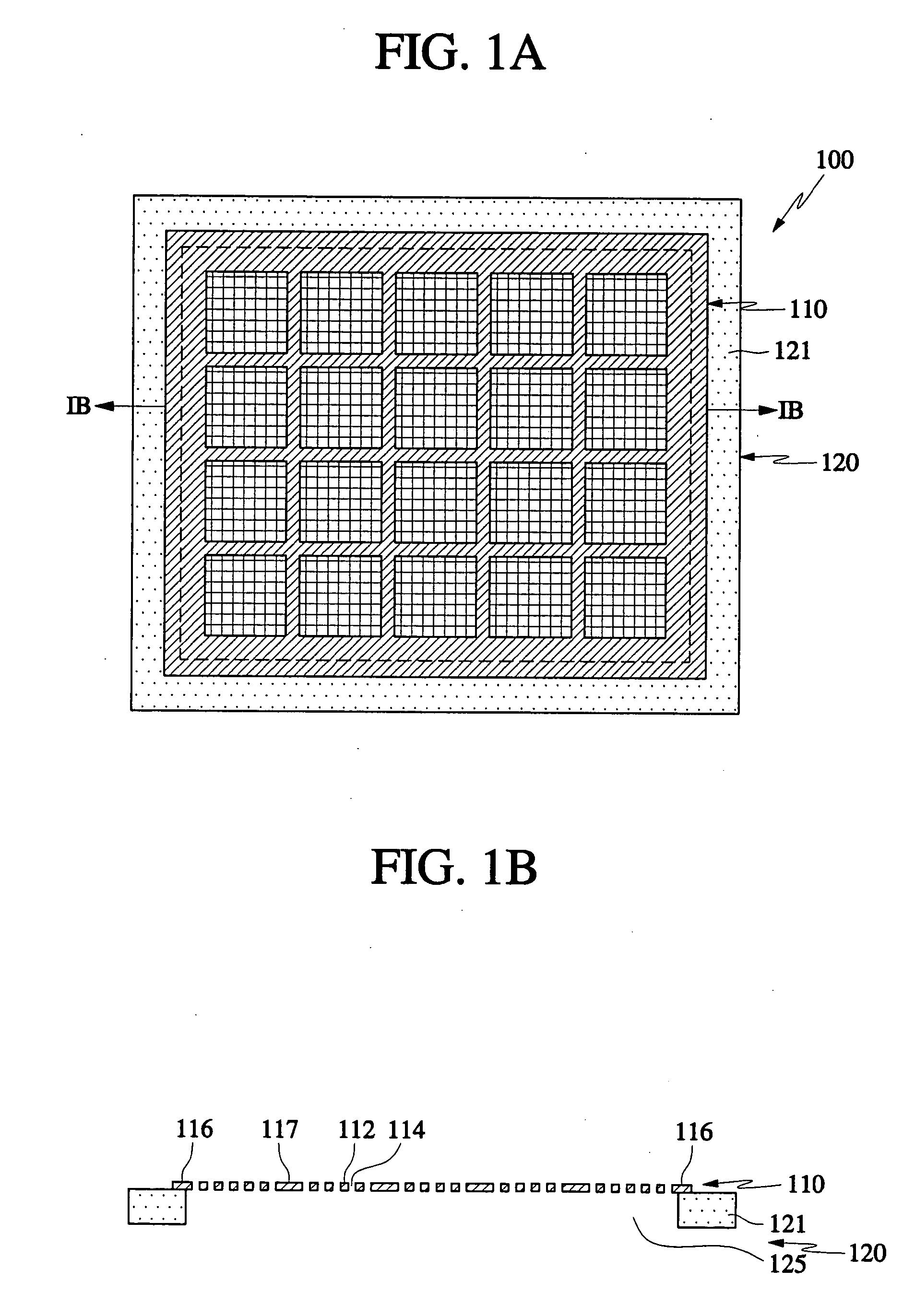

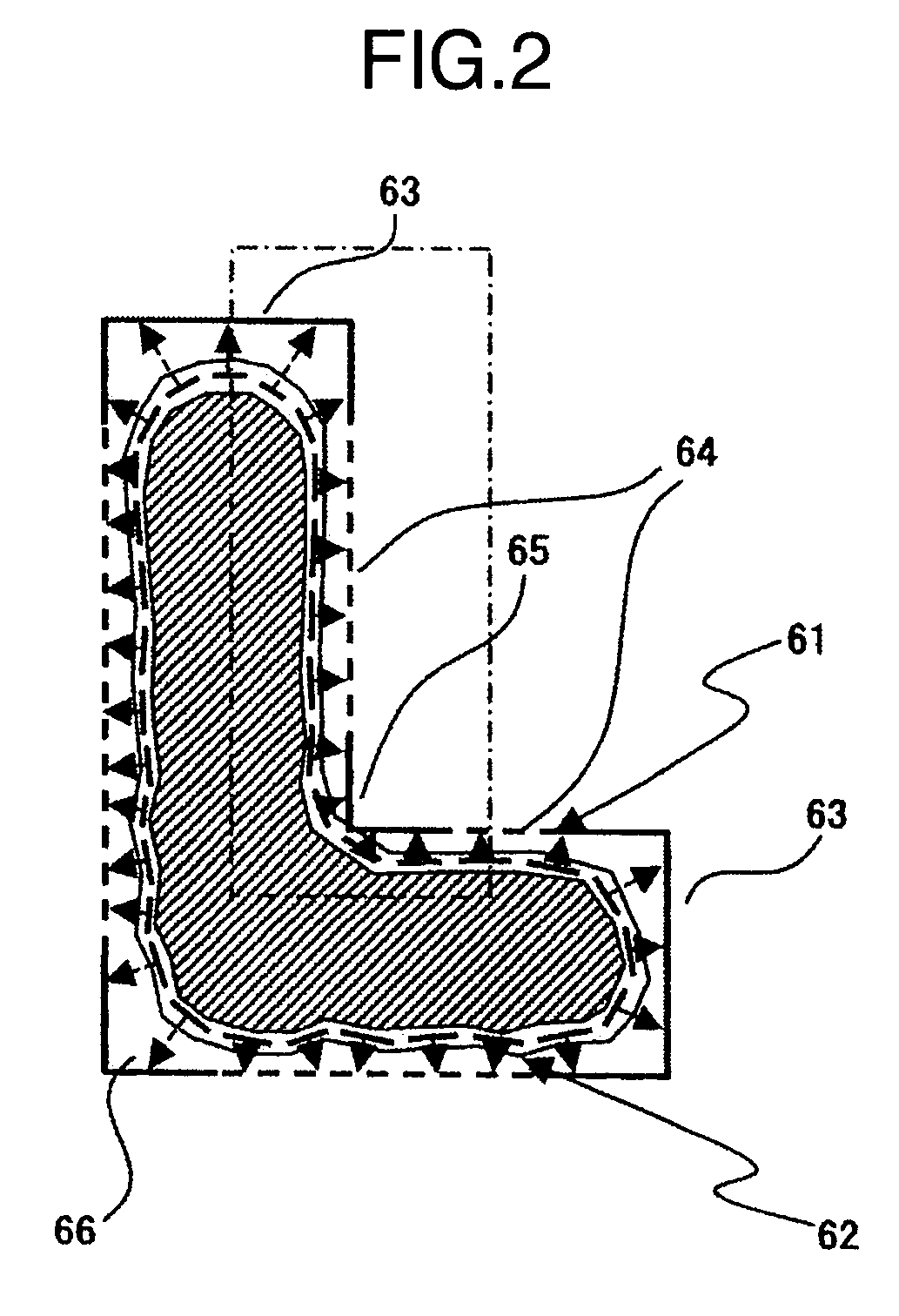

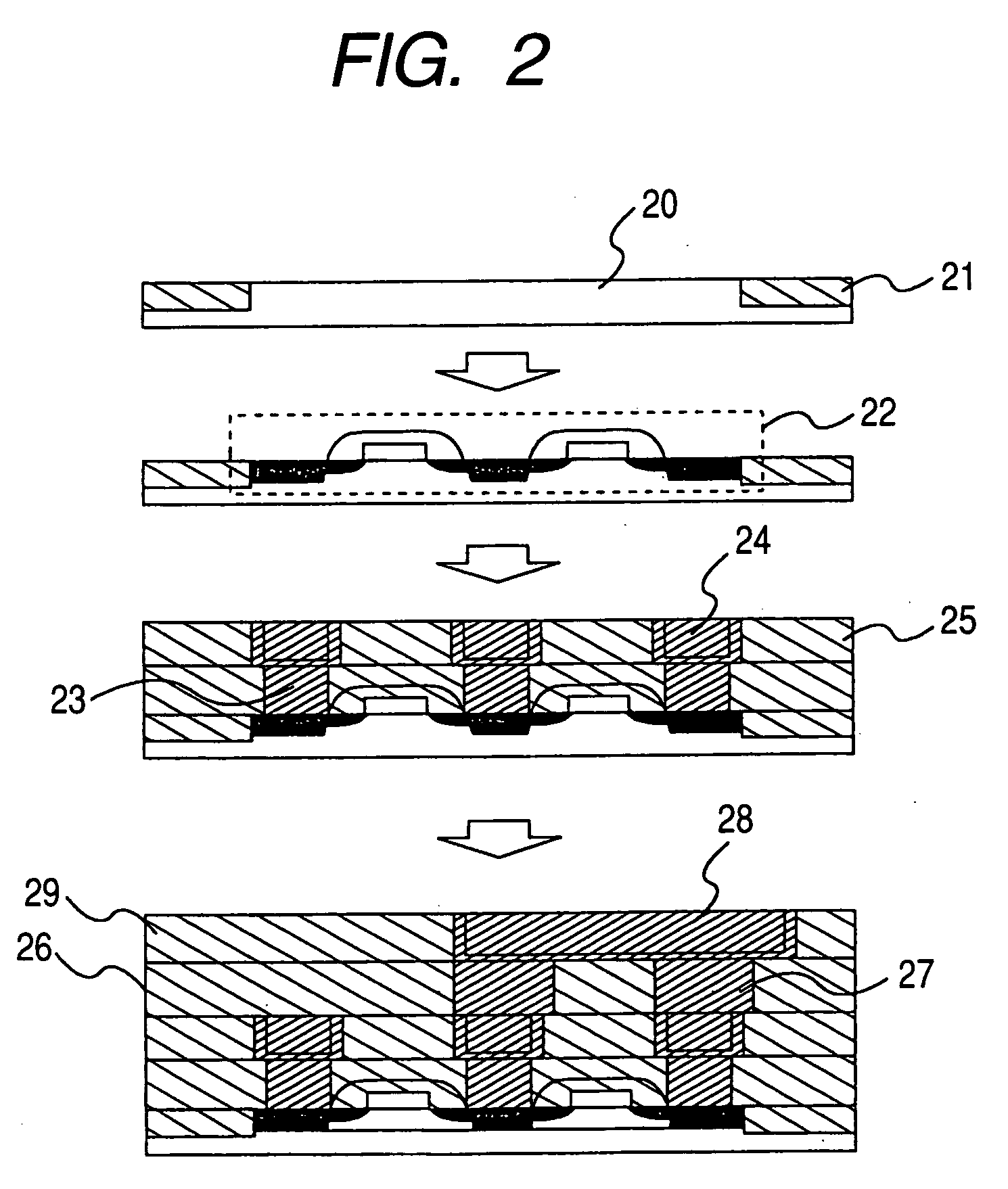

Deposition mask for display device and method for fabricating the same

A mask for depositing a thin film and a method for fabricating the same, which is easy to ensure a positioning accuracy and a pattern size accuracy and is suitable for a high definition display device. The deposition mask of the invention has at least one pattern mask having the same patterns as the patterns that are to be formed on a substrate and a frame mask which has at least one opening. The pattern mask is individually fixed to the frame mask at a region of the frame mask corresponding to the opening. The deposition mask is fabricated by preparing at least one pattern mask having the same patterns as the patterns that are to be formed on a substrate and a frame mask having at least one opening. The method also involves aligning the pattern mask to the opening of the frame mask and fixing the pattern mask, which is aligned with the opening, to the frame mask.

Owner:SAMSUNG DISPLAY CO LTD

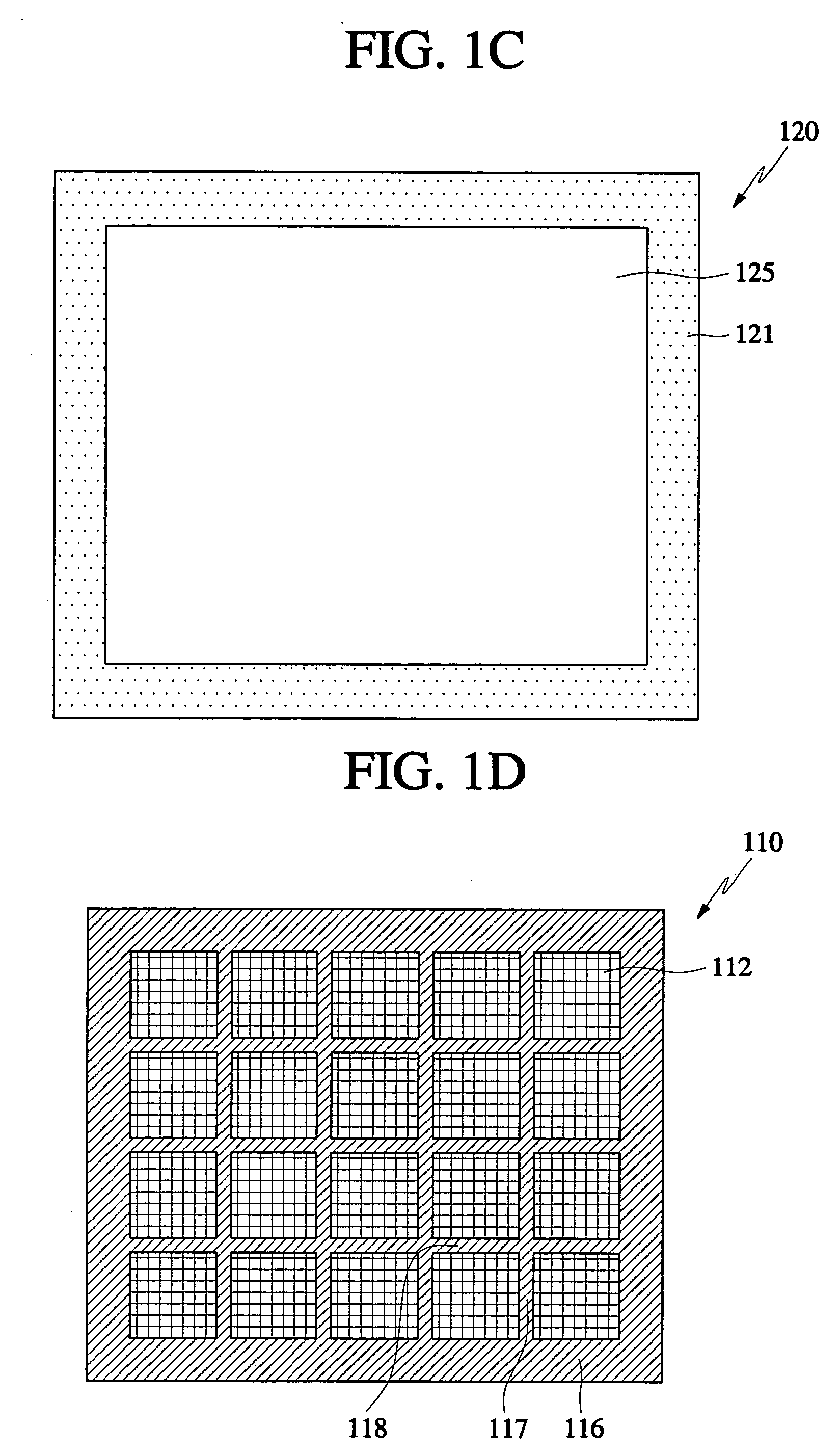

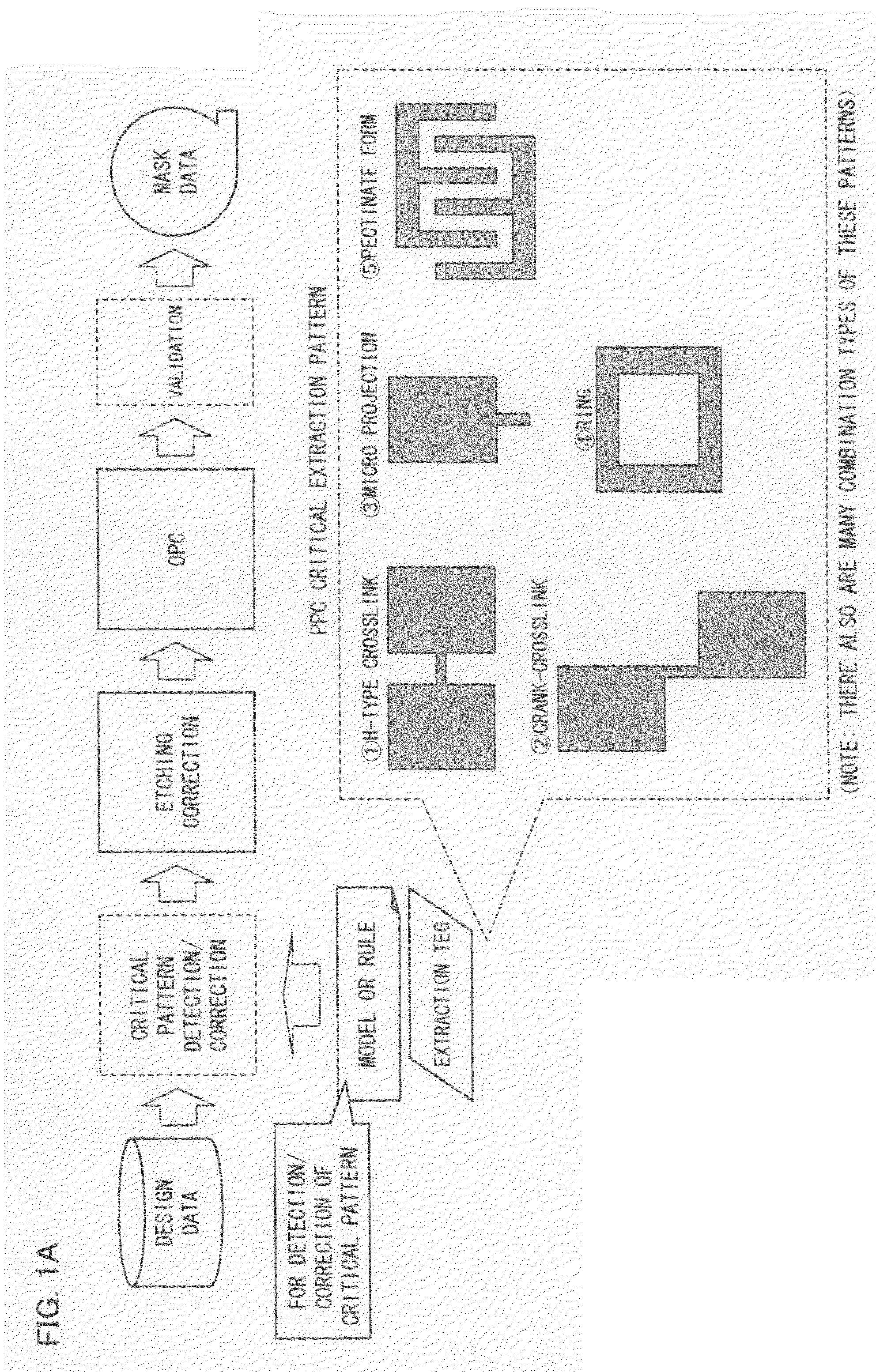

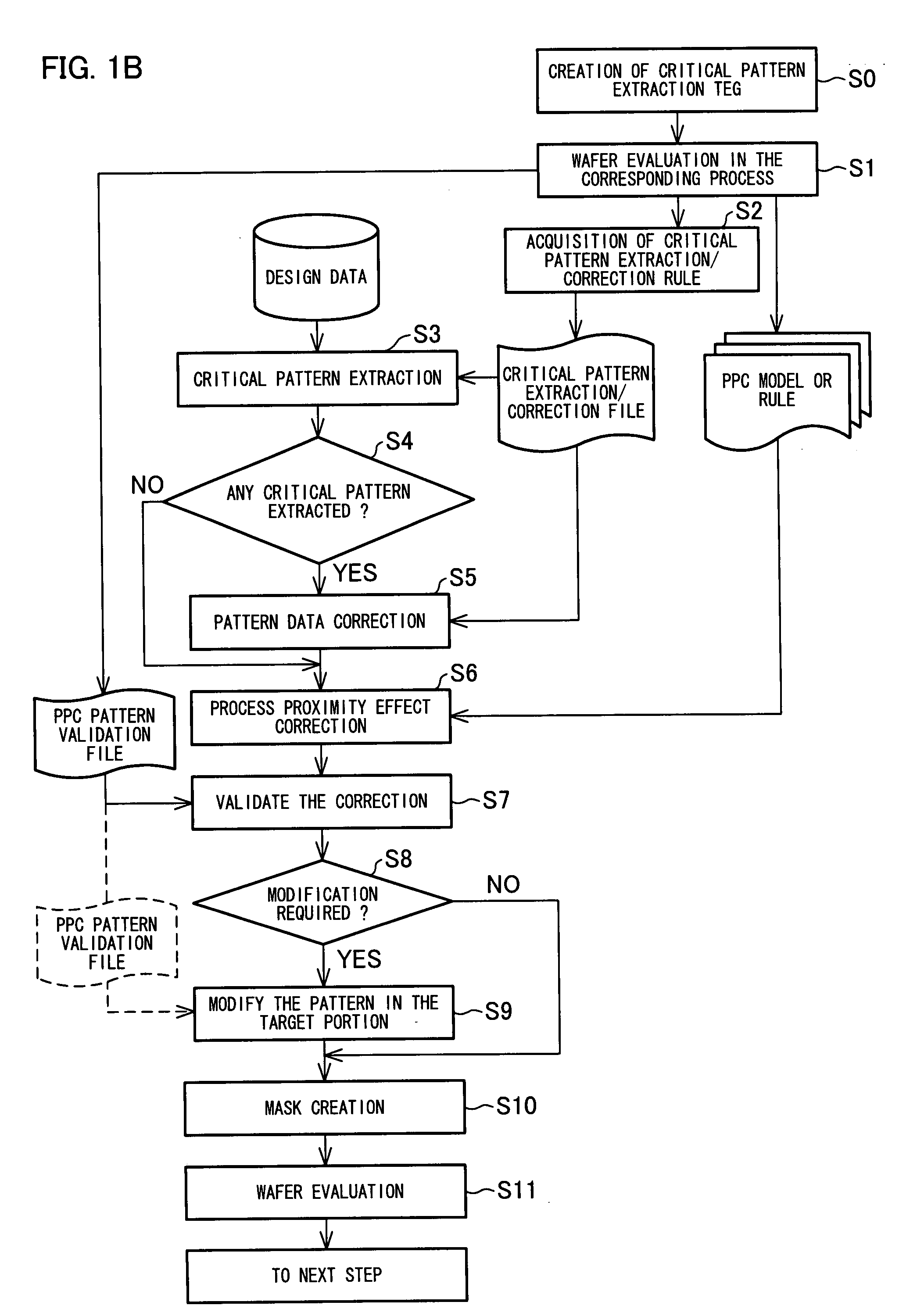

Correction method and correction system for design data or mask data, validation method and validation system for design data or mask data, yield estimation method for semiconductor integrated circuit, method for imporving design rule, mask production method, and semiconductor integrated circuit production method

InactiveUS20080003510A1Wastes in costWastes in development periodPhotomechanical apparatusSemiconductor/solid-state device manufacturingResistValidation methods

The subject invention provides a correction method for design data or mask data comprising the steps of:(i) carrying out PPC of design data or mask data;(ii) exposing and developing a resist with an evaluation mask including a critical pattern which becomes critical in a process, etching a circuit material using the resist having been developed, and measuring pattern sizes of the developed resist and the etched circuit material; (iii) extracting parameter numerical condition for preventing the design data or the mask data from being critical after OPC or PPC, as a rule or as a model based on the pattern sizes of the resist and the circuit material; (iv) extracting a critical pattern with a parameter not satisfying the foregoing rule or the model from the design data or the mask data; and (v) correcting the critical pattern.With this method, the present invention provides such as a validation / correction method for design data or mask data by which a pattern which becomes critical in a process is extracted in advance so that the pattern can be corrected. Consequently, the process spec is achieved in a short period of time after OPC or process proximity effect correction (PPC).

Owner:SHARP KK

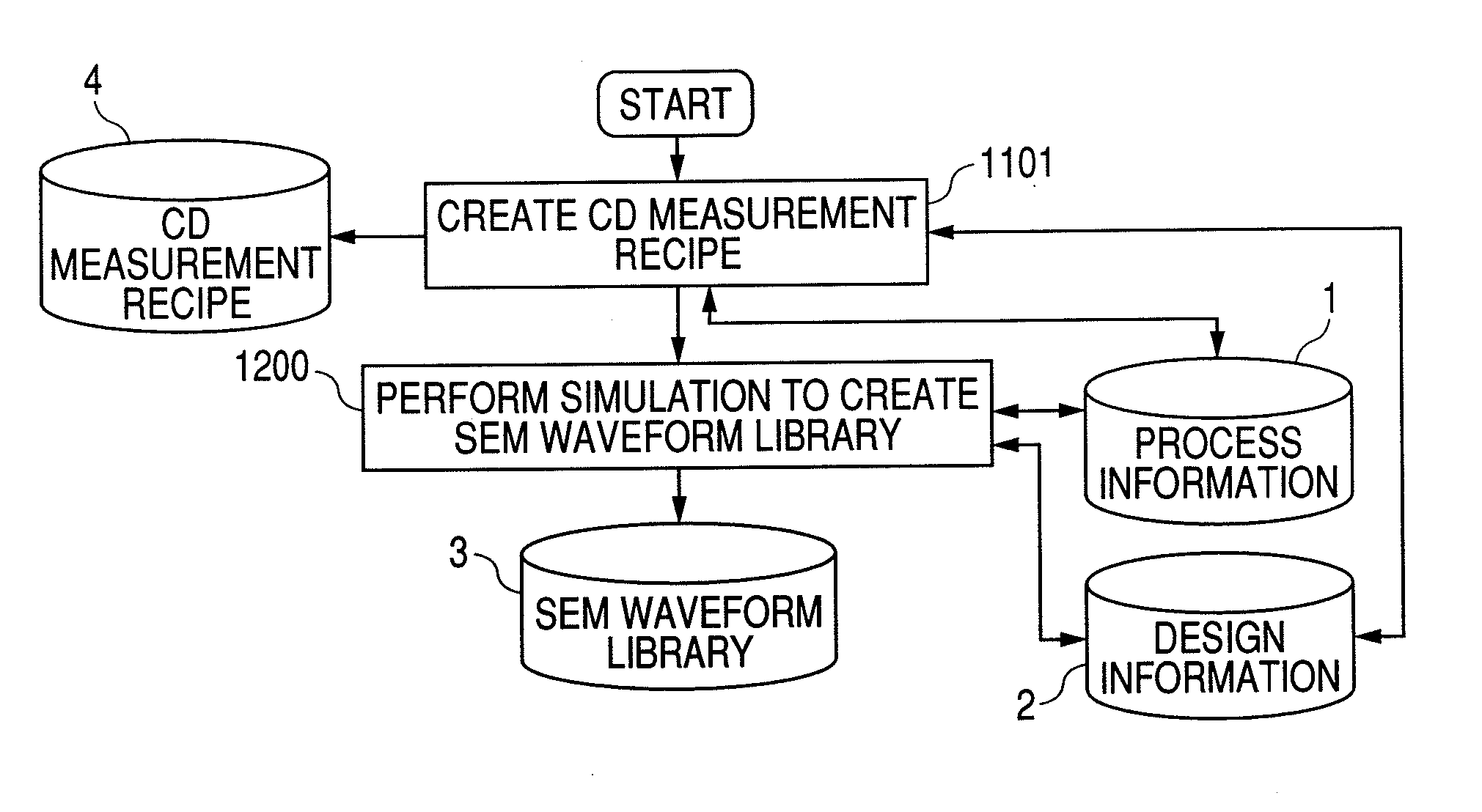

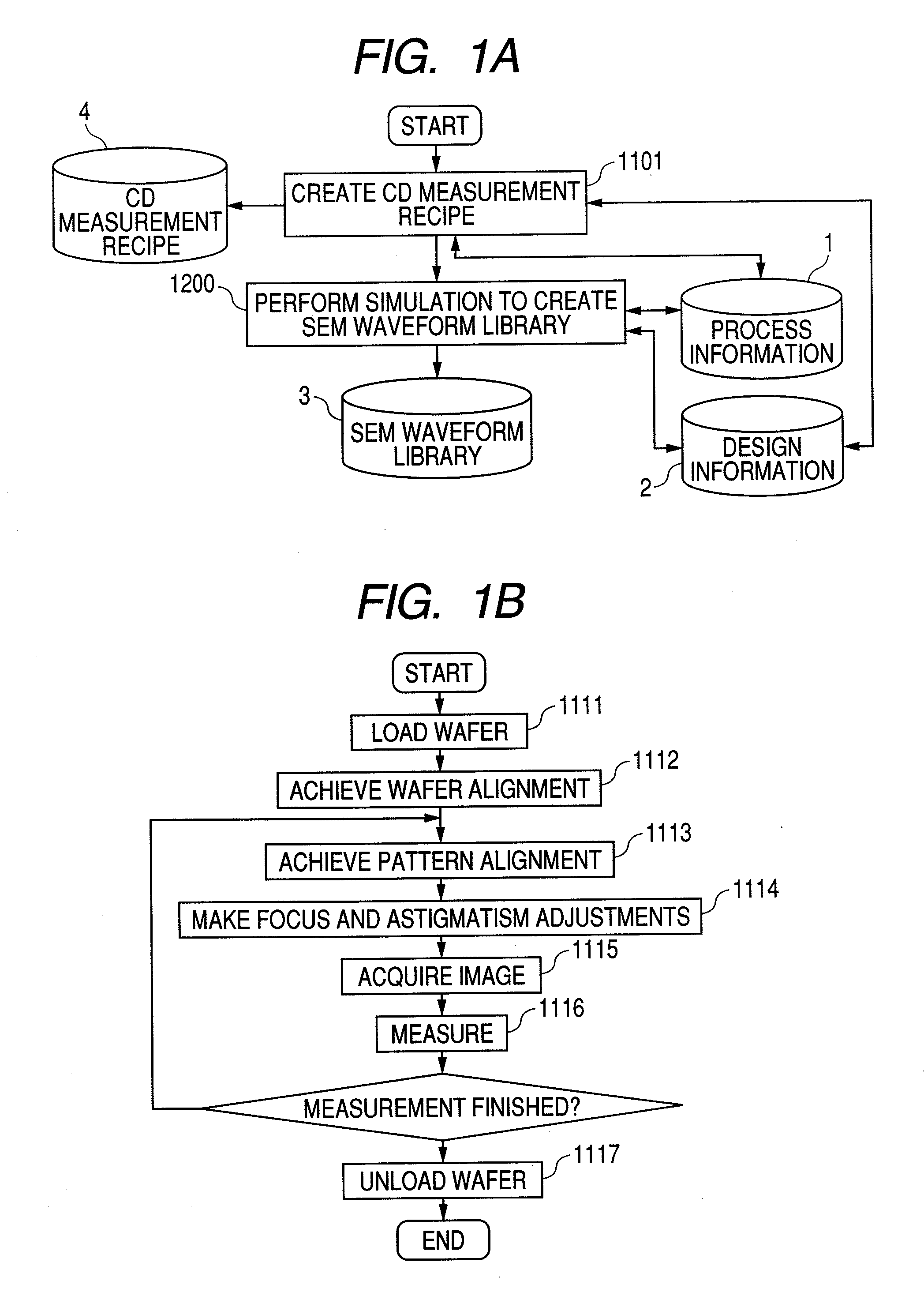

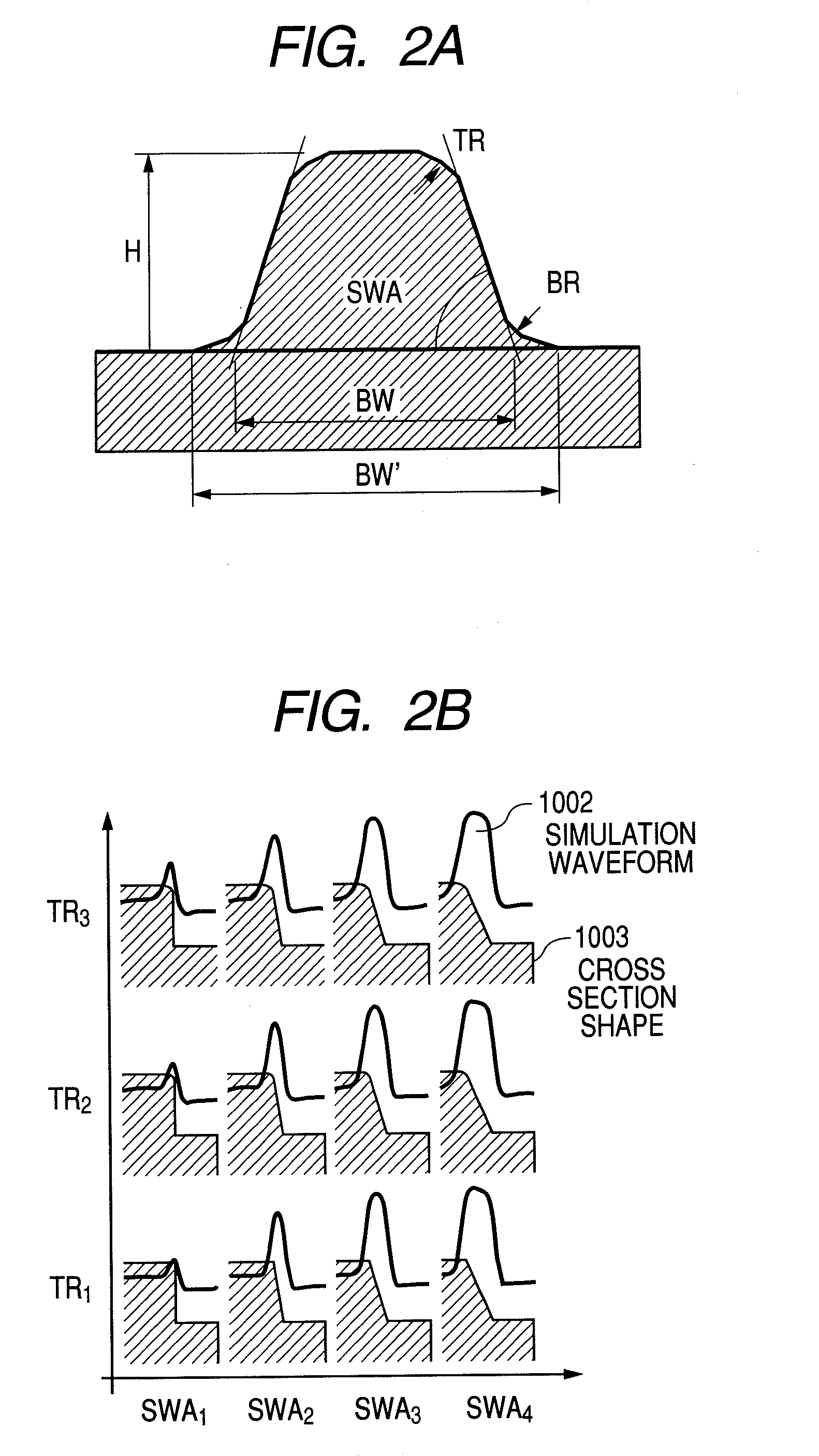

Method for measuring a pattern dimension using a scanning electron microscope

ActiveUS20070187595A1Reduce in quantityDegrading measuring repeatabilityMaterial analysis using wave/particle radiationElectric discharge tubesWave shapeElectron microscope

To provide a consistent, high-speed, high-precision measurement method based on an electron beam simulation by reflecting the apparatus characteristics of a CD-SEM in an electron beam simulation, the present invention discloses a method for measuring a measurement target pattern with a CD-SEM, the method comprising the steps of performing an electron beam simulation on various target pattern shapes, which is reflected apparatus characteristic and image acquisition conditions; creating SEM simulated waveforms; storing a combination of the created SEM simulated waveforms and pattern shape information corresponding to the created SEM simulated waveforms as a library; comparing an acquired actual electron microscope image with the SEM simulated waveforms; selecting the SEM simulated waveform that is most similar to the actual electron microscope image; and estimating the shape of the measurement target pattern from the pattern shape information corresponding to the selected SEM simulated waveform.

Owner:HITACHI HIGH-TECH CORP

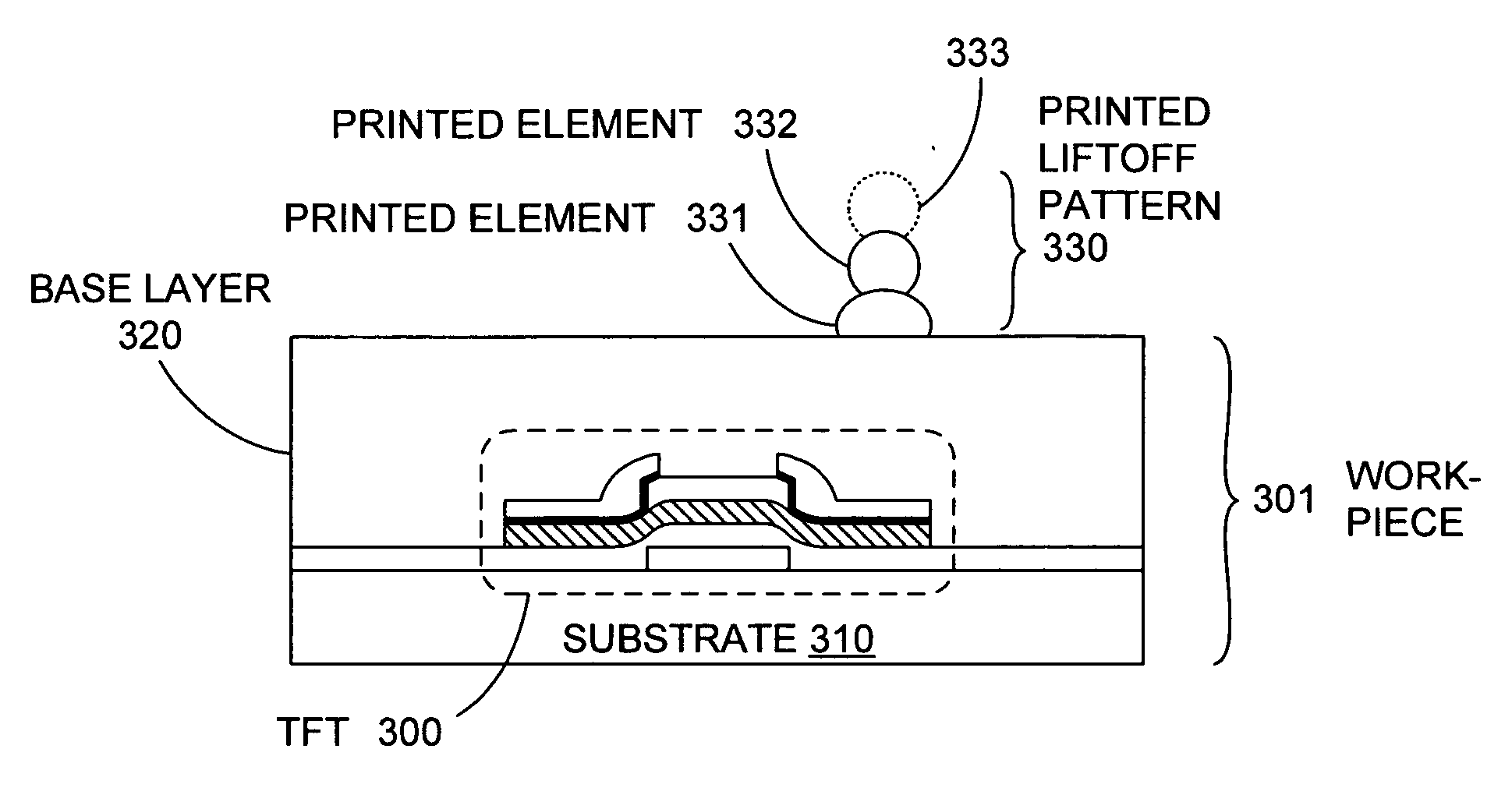

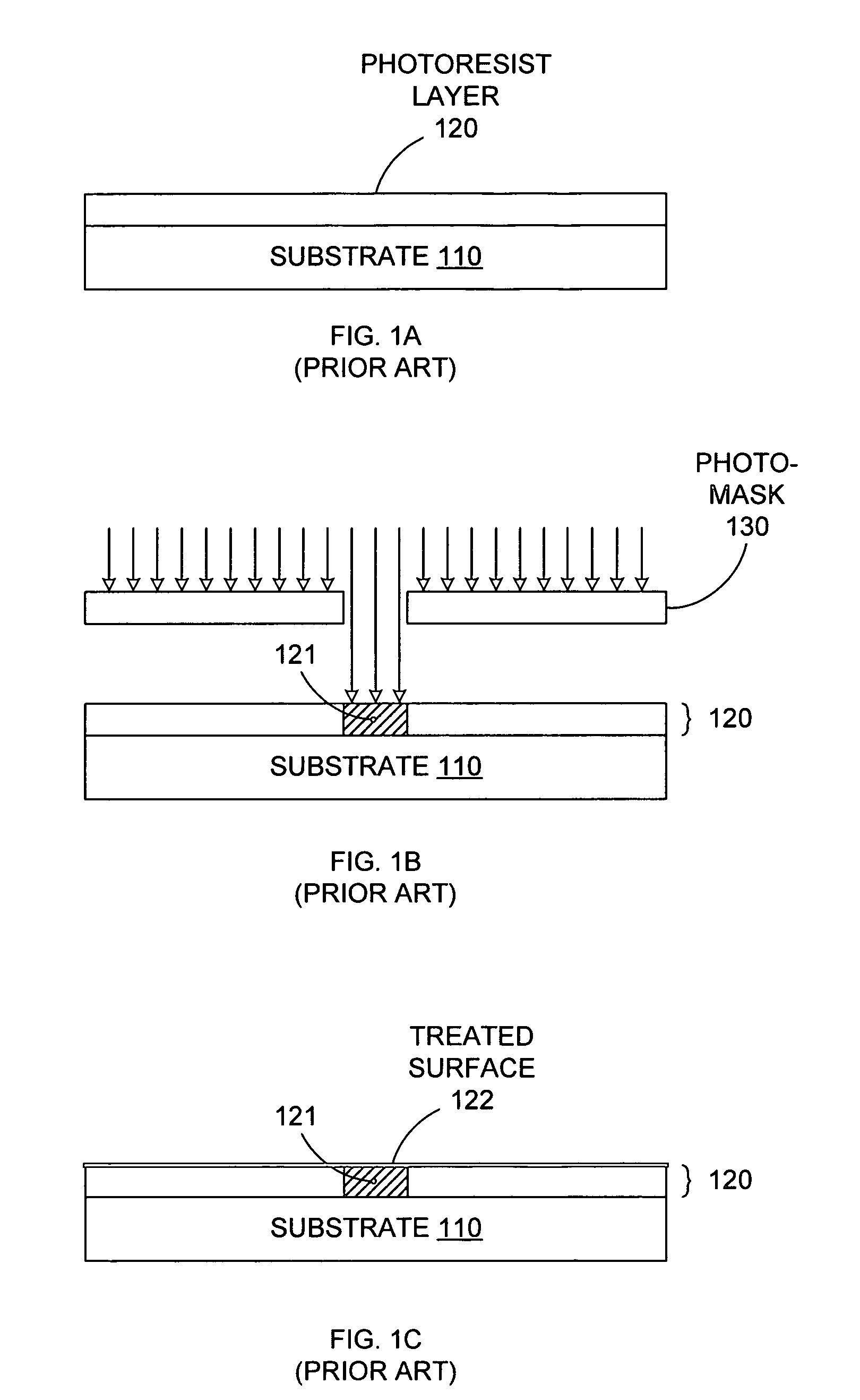

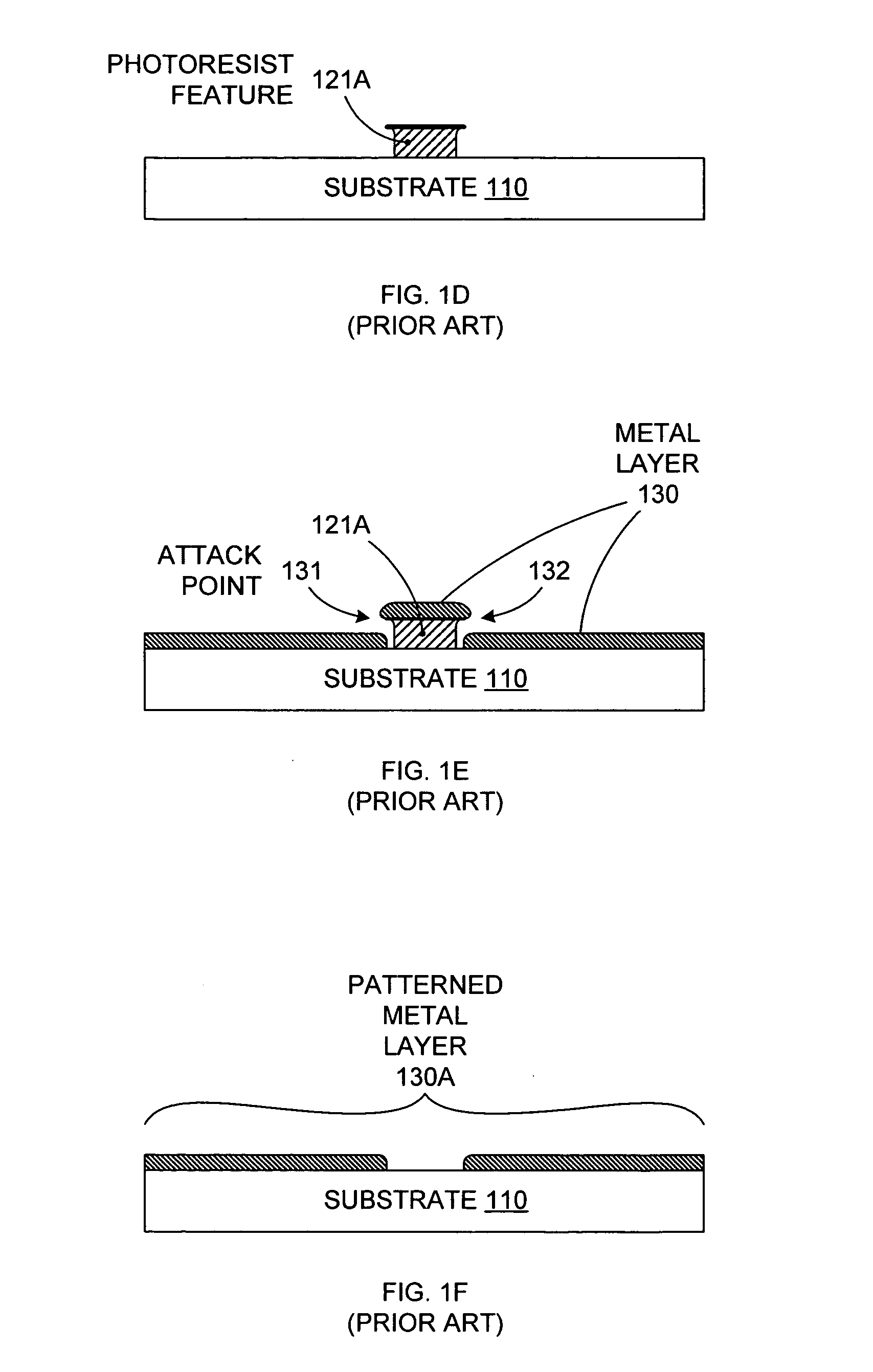

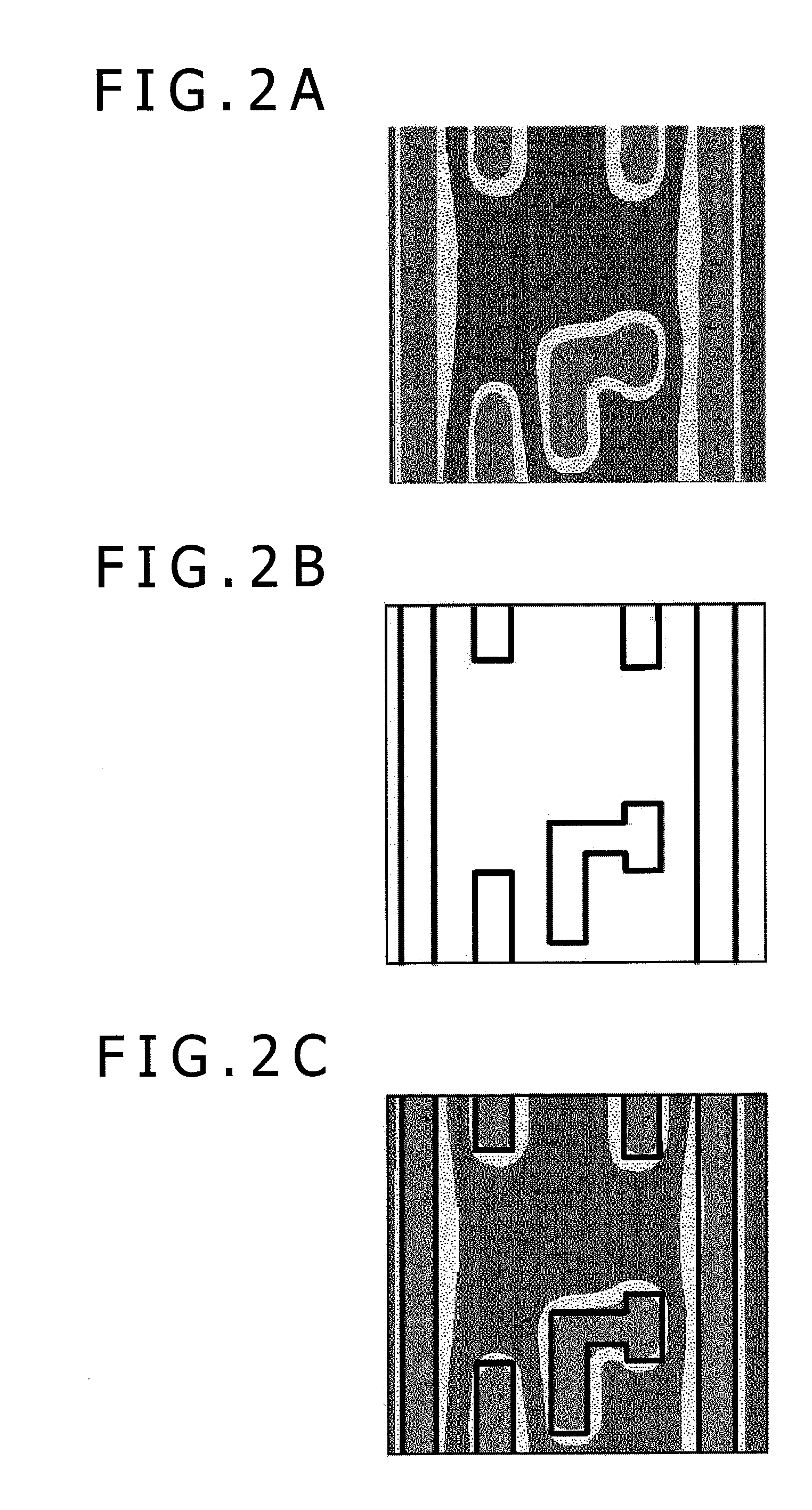

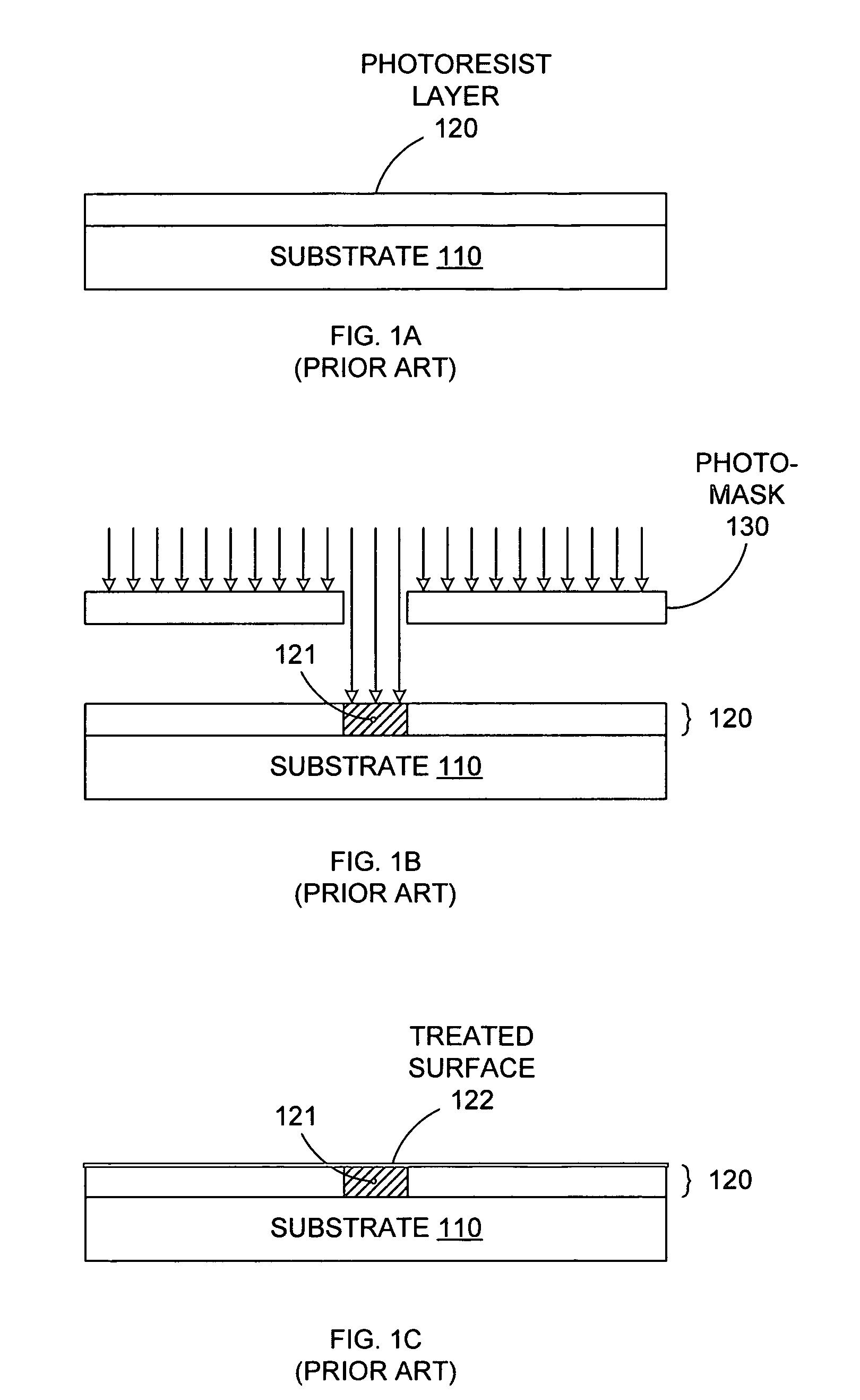

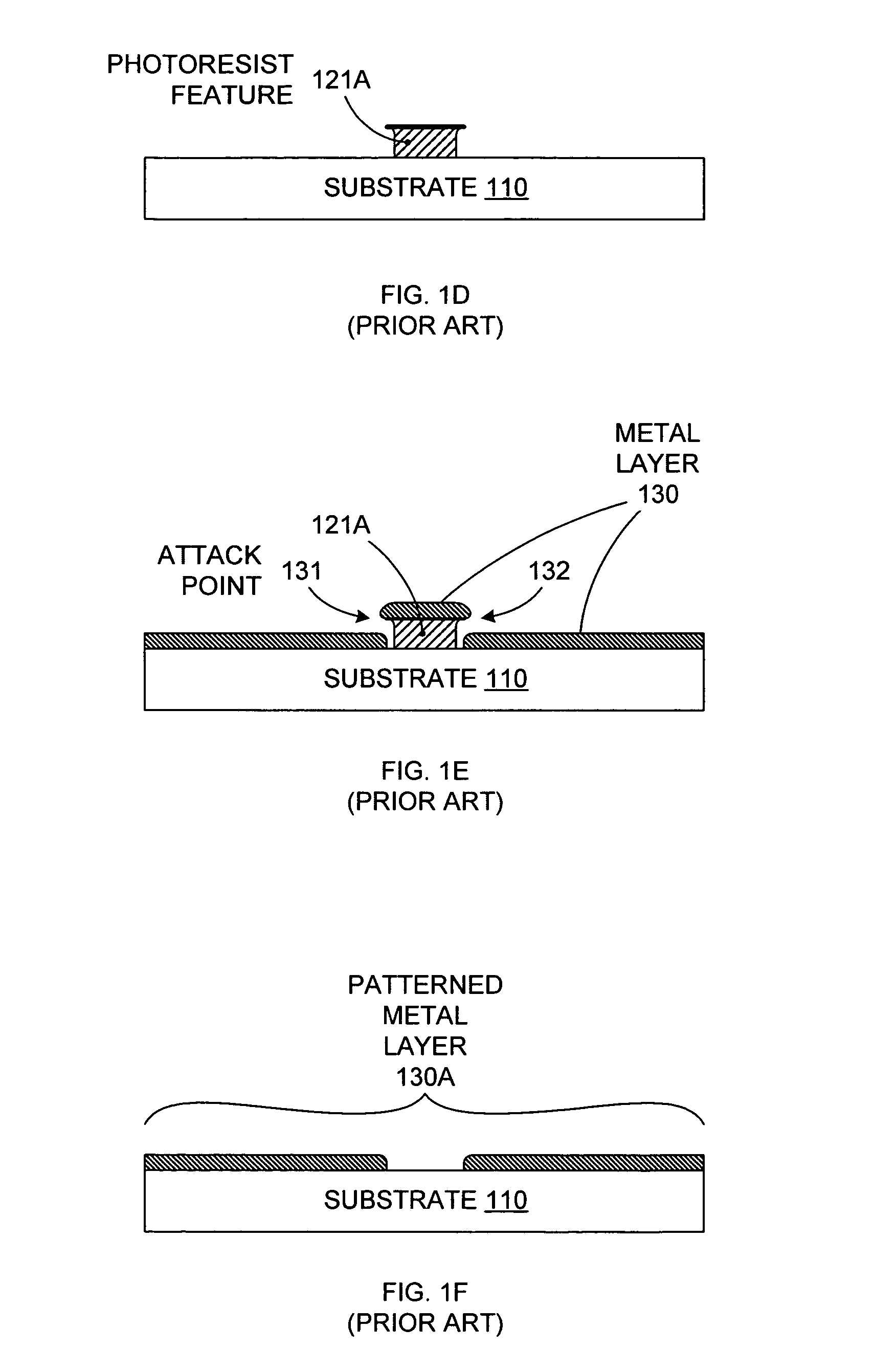

Patterning using wax printing and lift off

InactiveUS20050136358A1Low production costEasy alignmentTransistorPhotomechanical apparatusWaxImage resolution

A method for performing a liftoff operation involves printing a liftoff pattern using low-resolution patterning techniques to form fine feature patterns. The resulting feature size is defined by the spacing between printed patterns rather than the printed pattern size. By controlling the cross-sectional profile of the printed liftoff pattern, mask structures may be formed from the liftoff operation having beneficial etch-mask aperture profiles. For example, a multi-layer printed liftoff pattern can be used to create converging aperture profiles in a patterned layer. The patterned layer can then be used as an etch mask, where the converging aperture profiles result in desirable diverging etched features.

Owner:PALO ALTO RES CENT INC

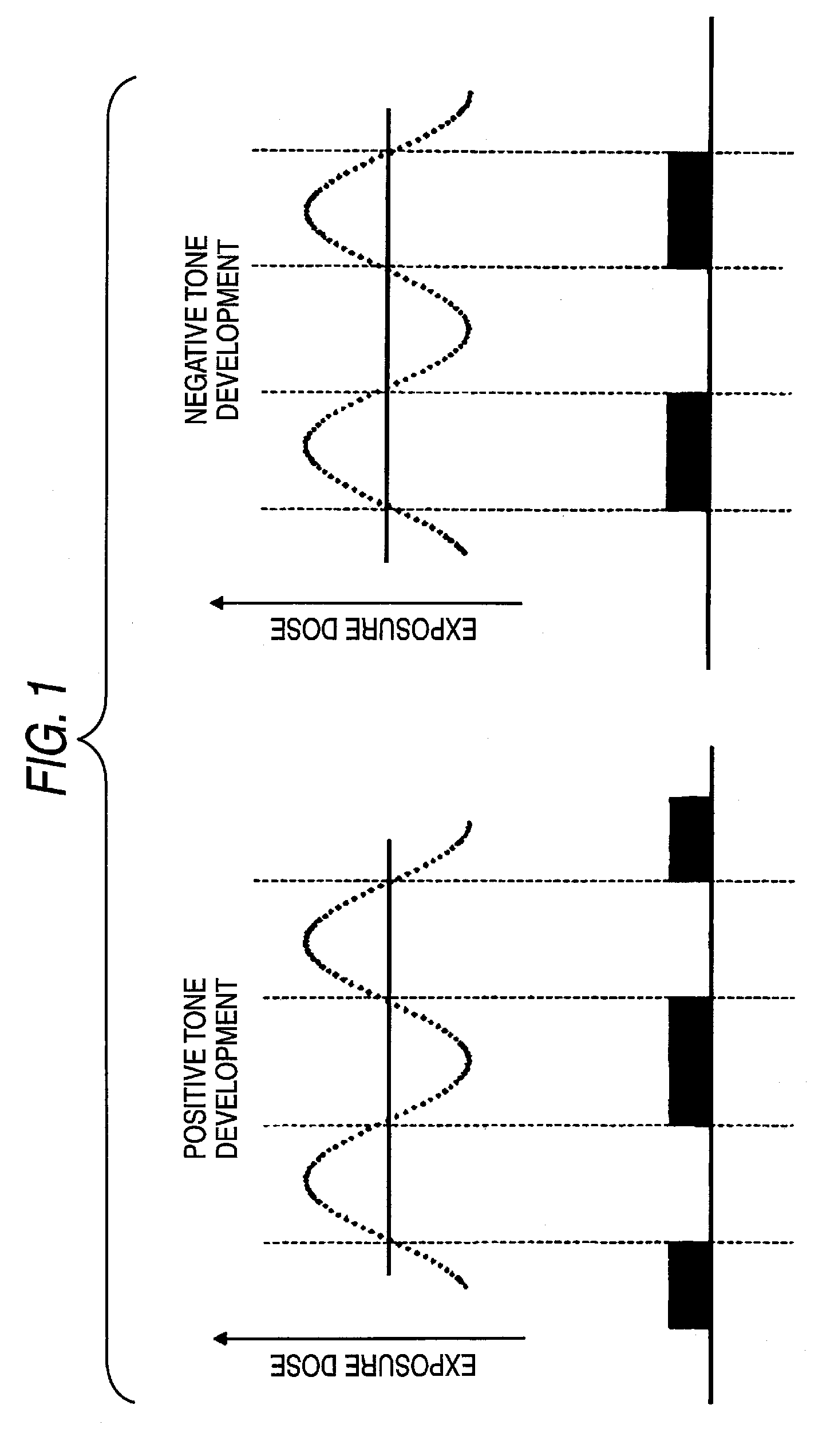

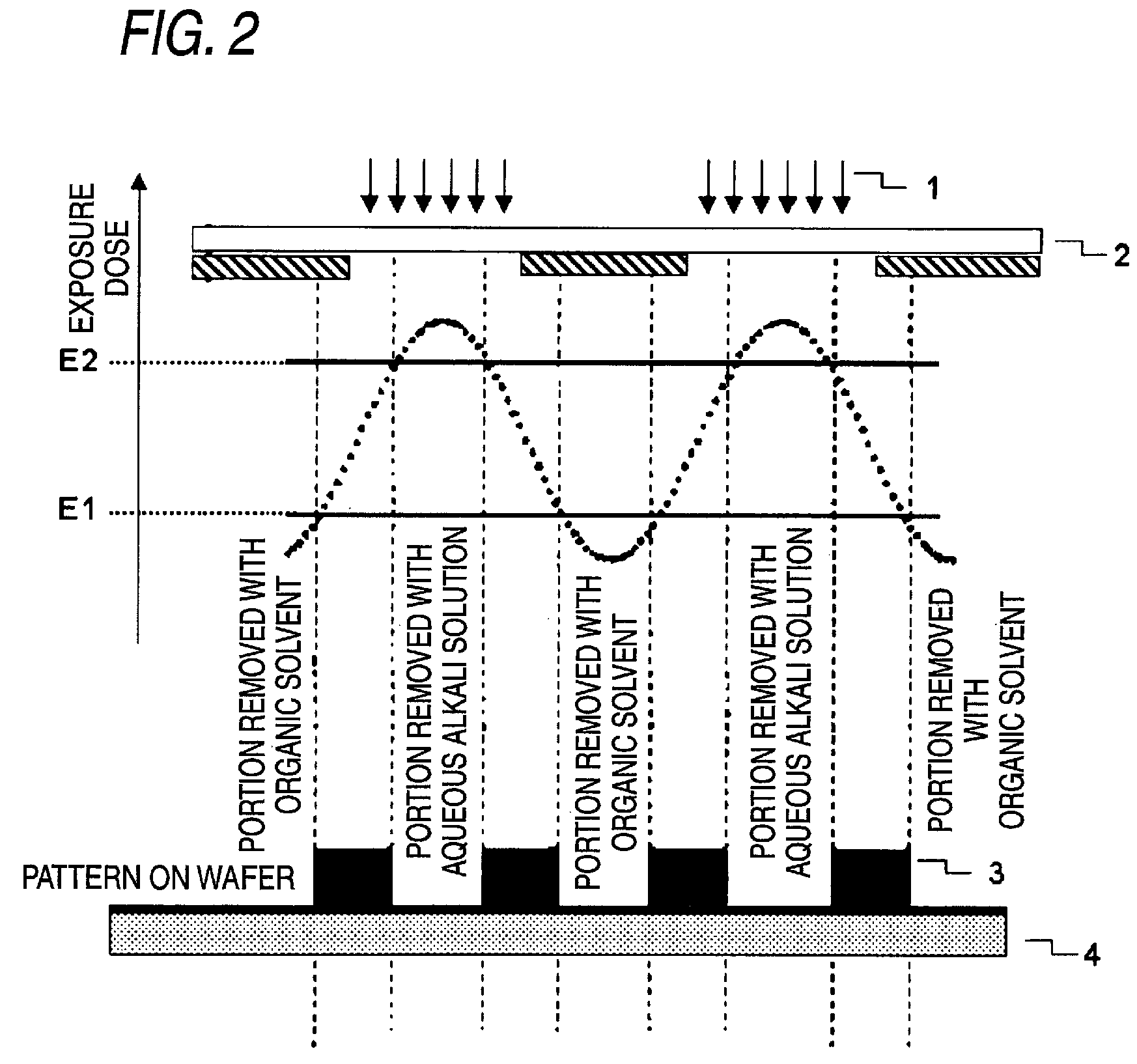

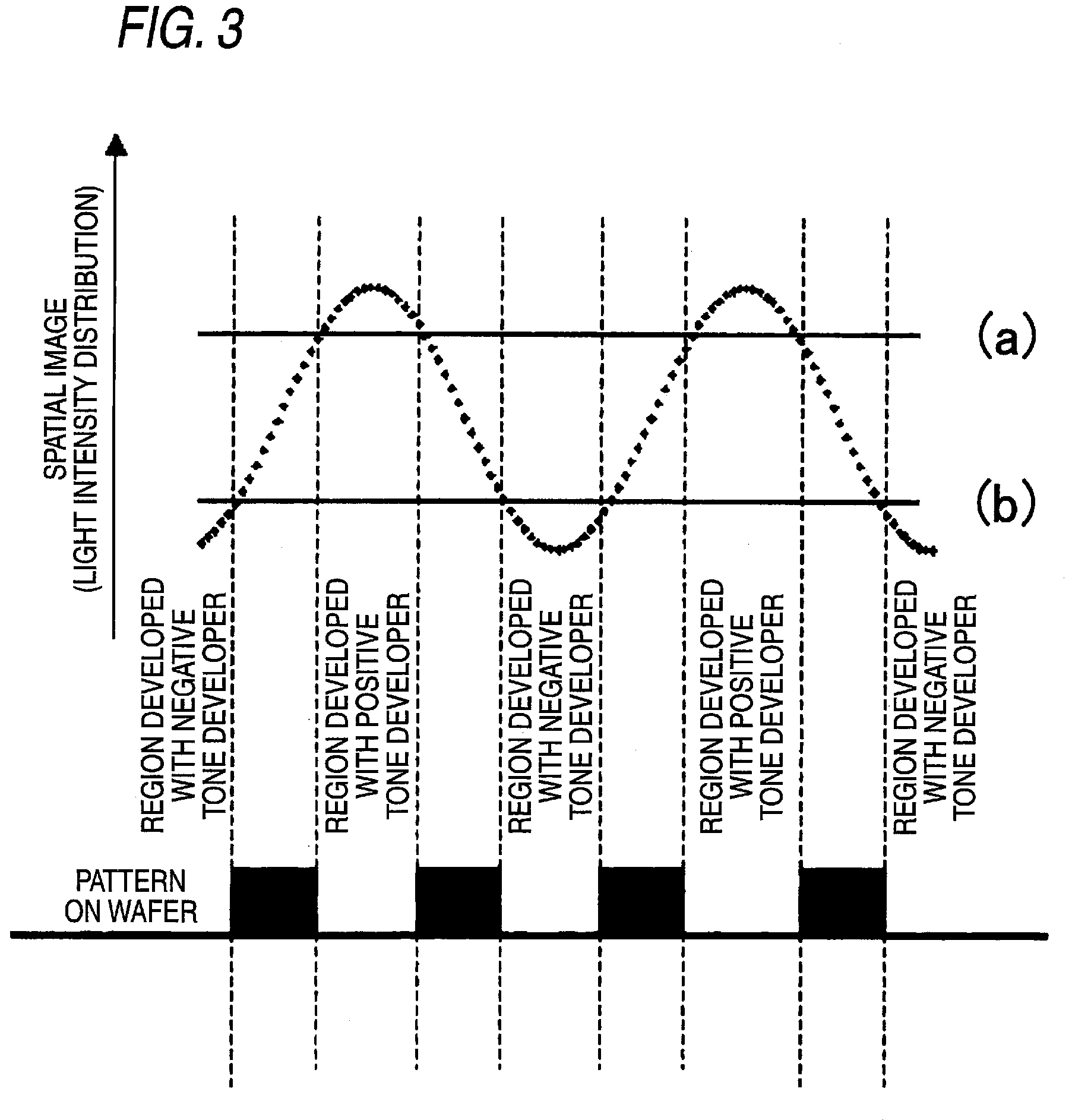

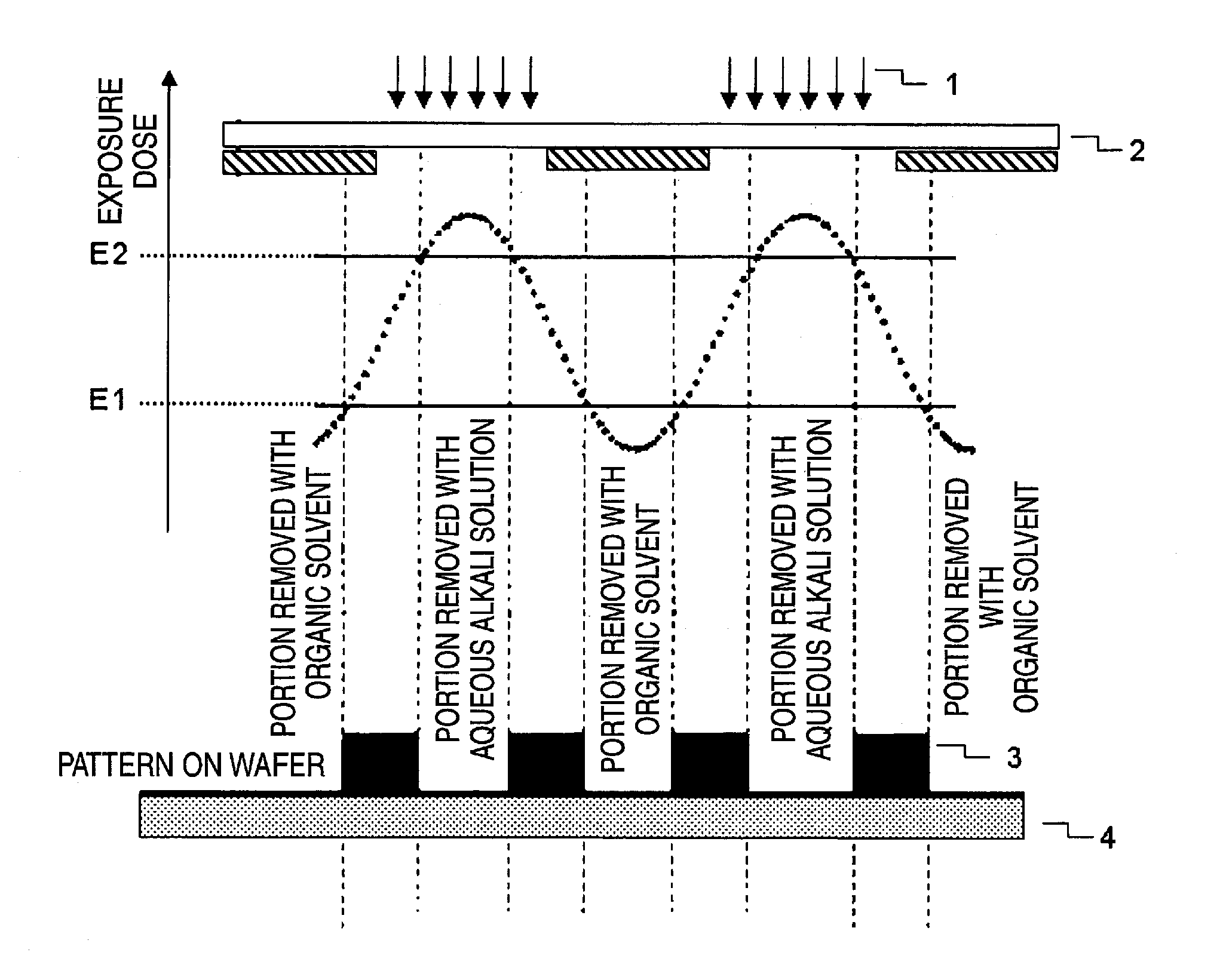

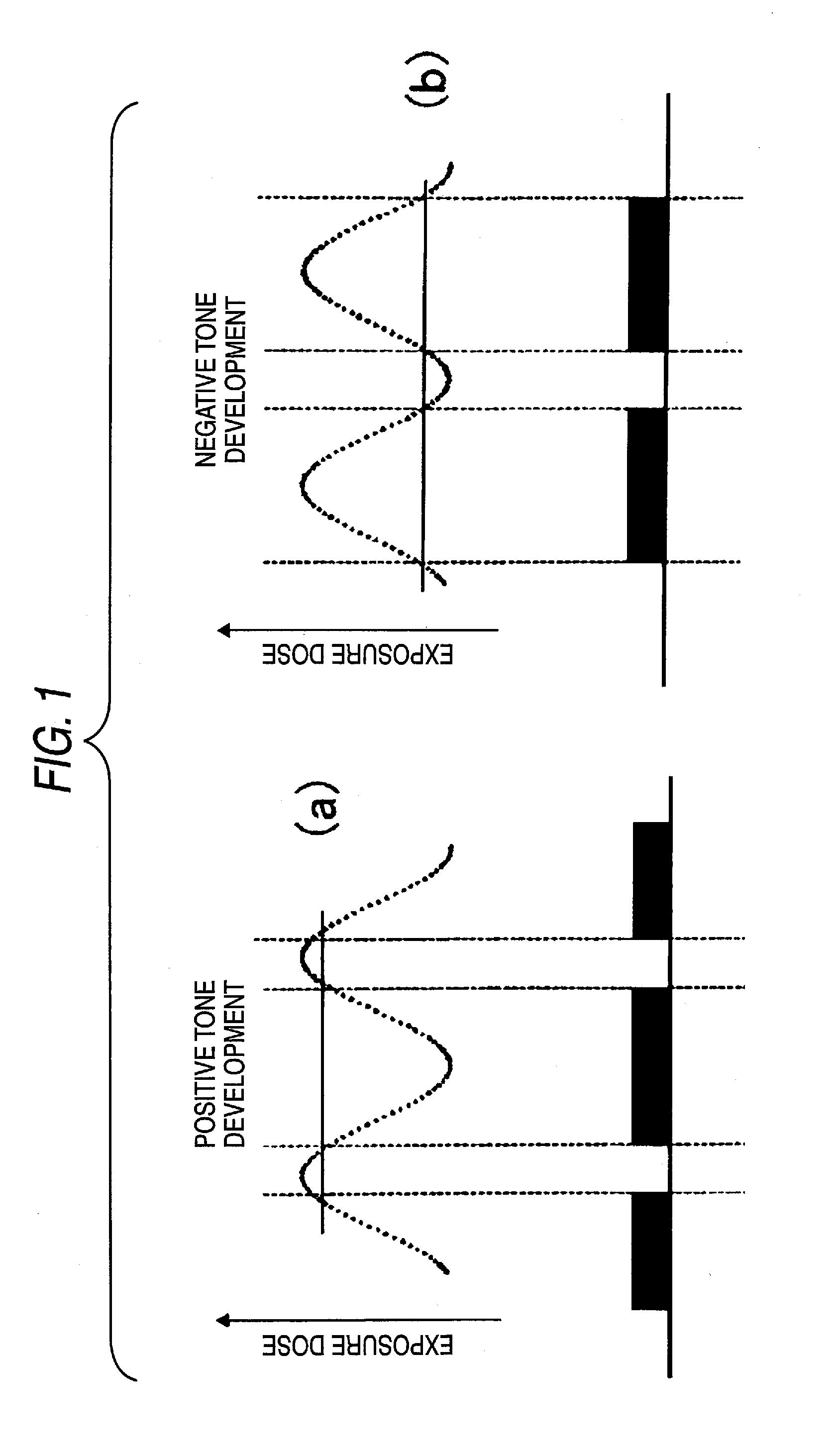

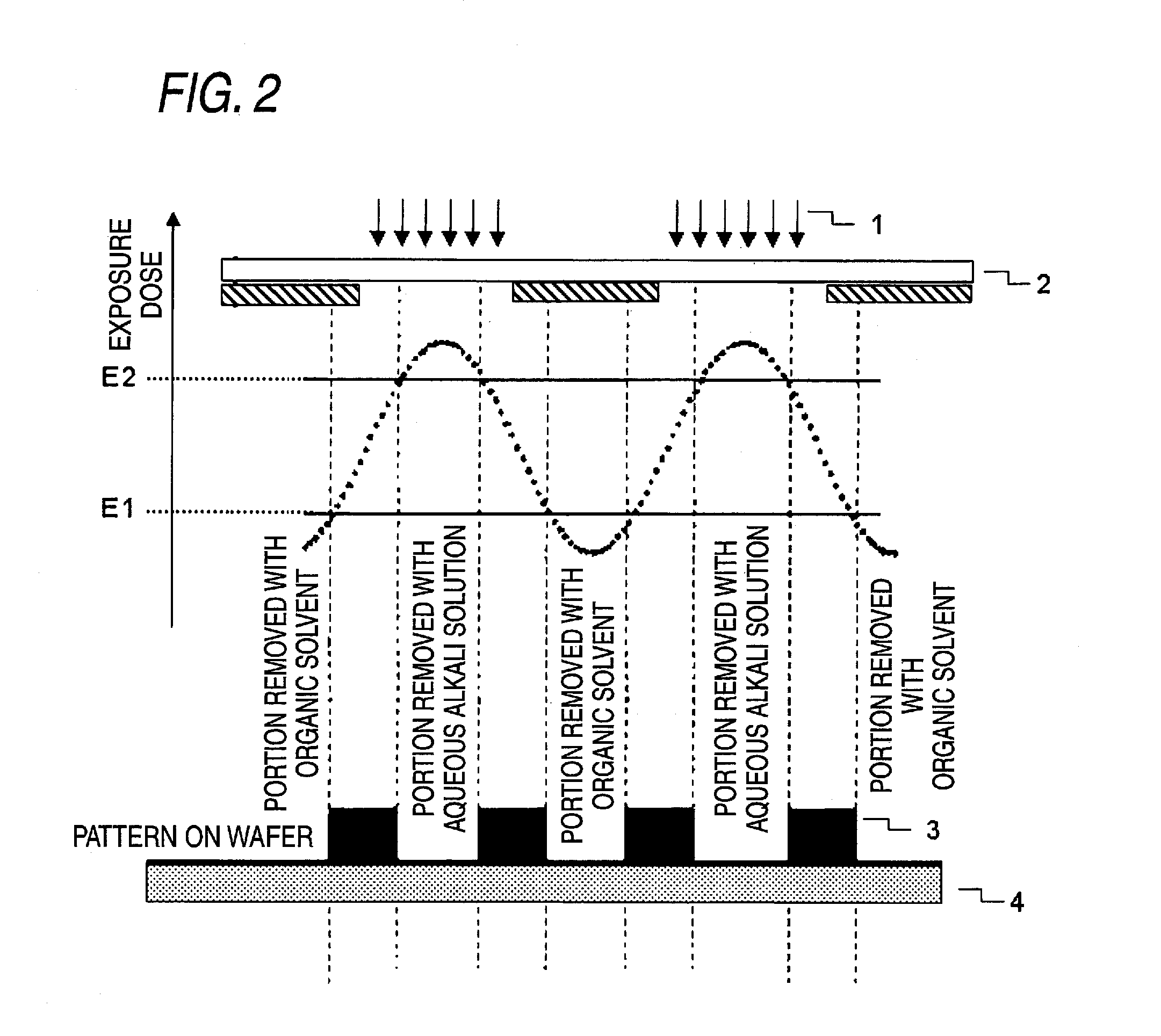

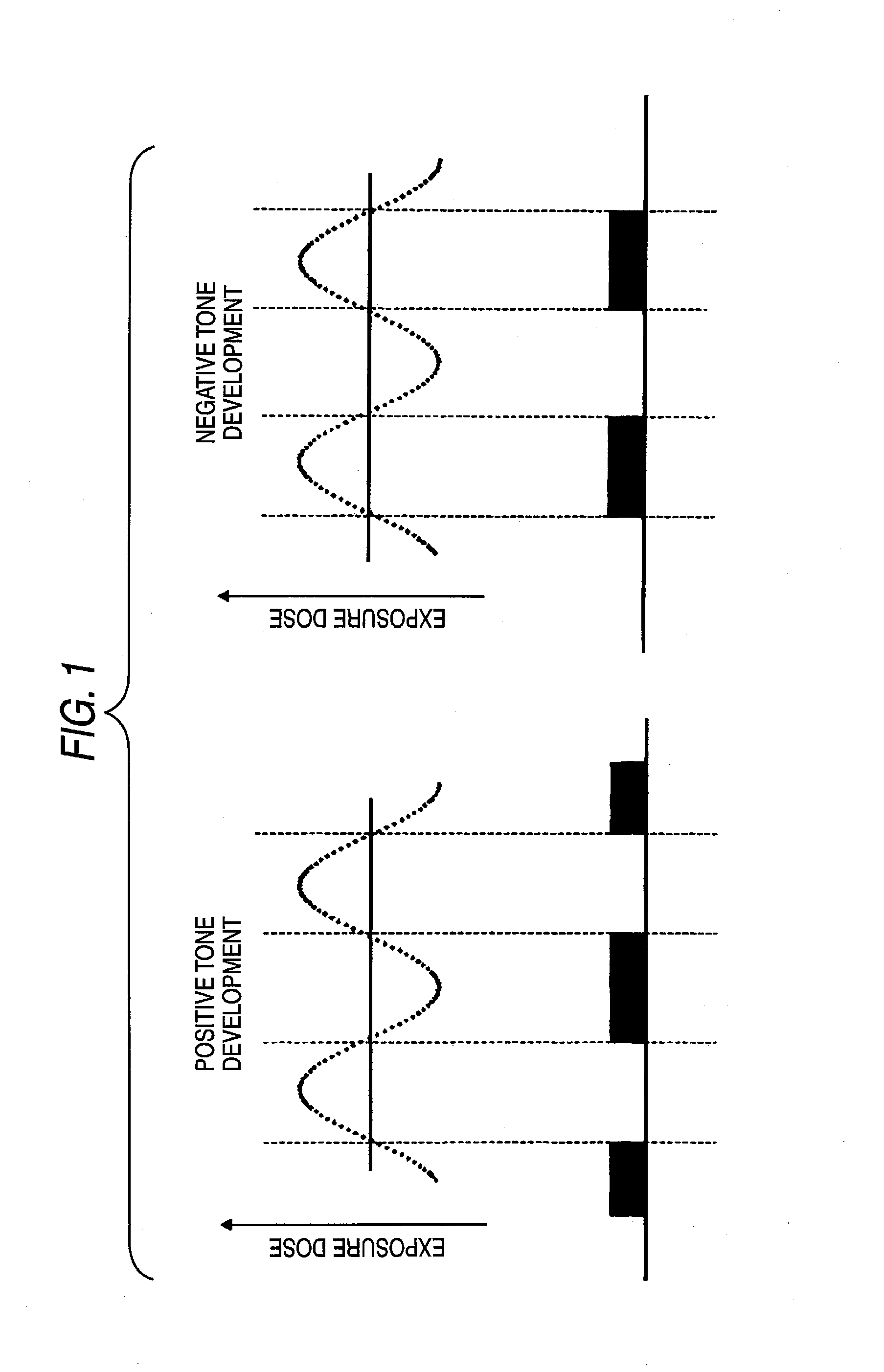

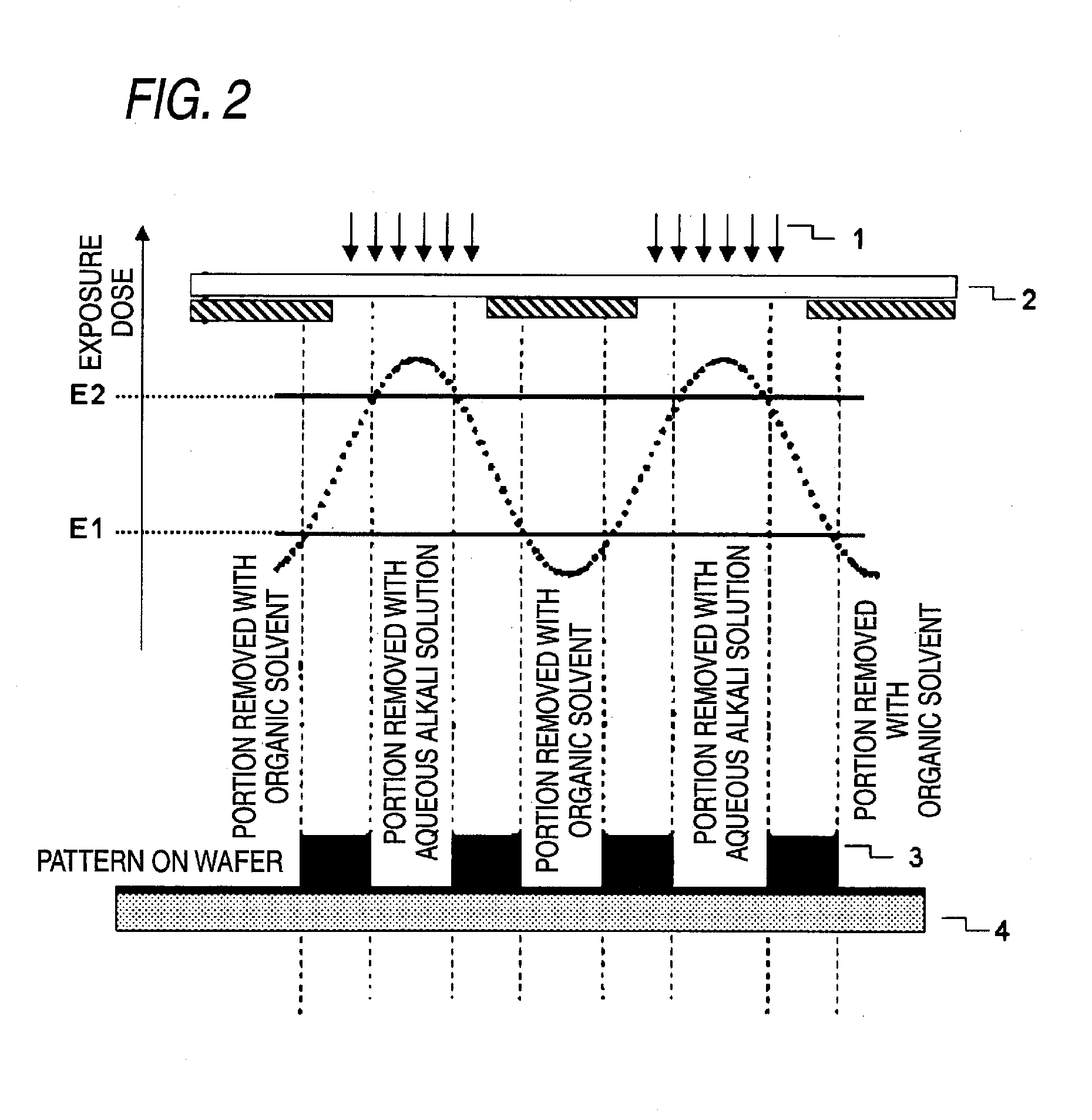

Resist composition for negative tone development and pattern forming method using the same

InactiveUS7851140B2Enhance the imageImprove in-plane uniformityPhotosensitive materialsRadiation applicationsIn planeActinic Rays

Owner:FUJIFILM CORP

Resist composition for negative tone development and pattern forming method using the same

ActiveUS20100190106A1Improve accuracySmall line edge roughnessPhotosensitive materialsPhotomechanical exposure apparatusIn planeActinic Rays

For stably forming a high-precision fine pattern and thereby producing a highly integrated electronic device with high precision, a resist composition for negative tone development, which can reduce the line edge roughness and enhance the in-plane uniformity of the pattern dimension and furthermore, can ensure excellent bridge margin, and a pattern forming method using the same are provided.A resist composition for negative tone development, comprising (A) a resin capable of increasing the polarity by the action of an acid to increase the solubility in a positive tone developer and decrease the solubility in a negative tone developer, (B) a compound capable of generating an acid upon irradiation with an actinic ray or radiation, and (C) a solvent, wherein the logP value of the acid generated from the (B) compound capable of generating an acid upon irradiation with an actinic ray or radiation is from 1.5 to 12.0; and a pattern forming method using the same.

Owner:FUJIFILM CORP

Resist composition for negative tone development and pattern forming method using the same

InactiveUS20100167201A1Reduced line edge roughnessImprove in-plane uniformityPhotosensitive materialsRadiation applicationsIn planeActinic Rays

To provide a resist composition for negative tone development, which can form a pattern having a good profile improved in the pattern undercut and moreover, can reduce the line edge roughness and enhance the in-plane uniformity of the pattern dimension, and a pattern forming method using the same.A resist composition for negative tone development, comprising (A) a resin capable of increasing the polarity by the action of an acid to increase the solubility in a positive tone developer and decrease the solubility in a negative tone developer, (B) a compound capable of generating an acid having an acid dissociation index pKa of −4.0 or less upon irradiation with an actinic ray or radiation, and (C) a solvent; and a pattern forming method using the same.

Owner:FUJIFILM CORP

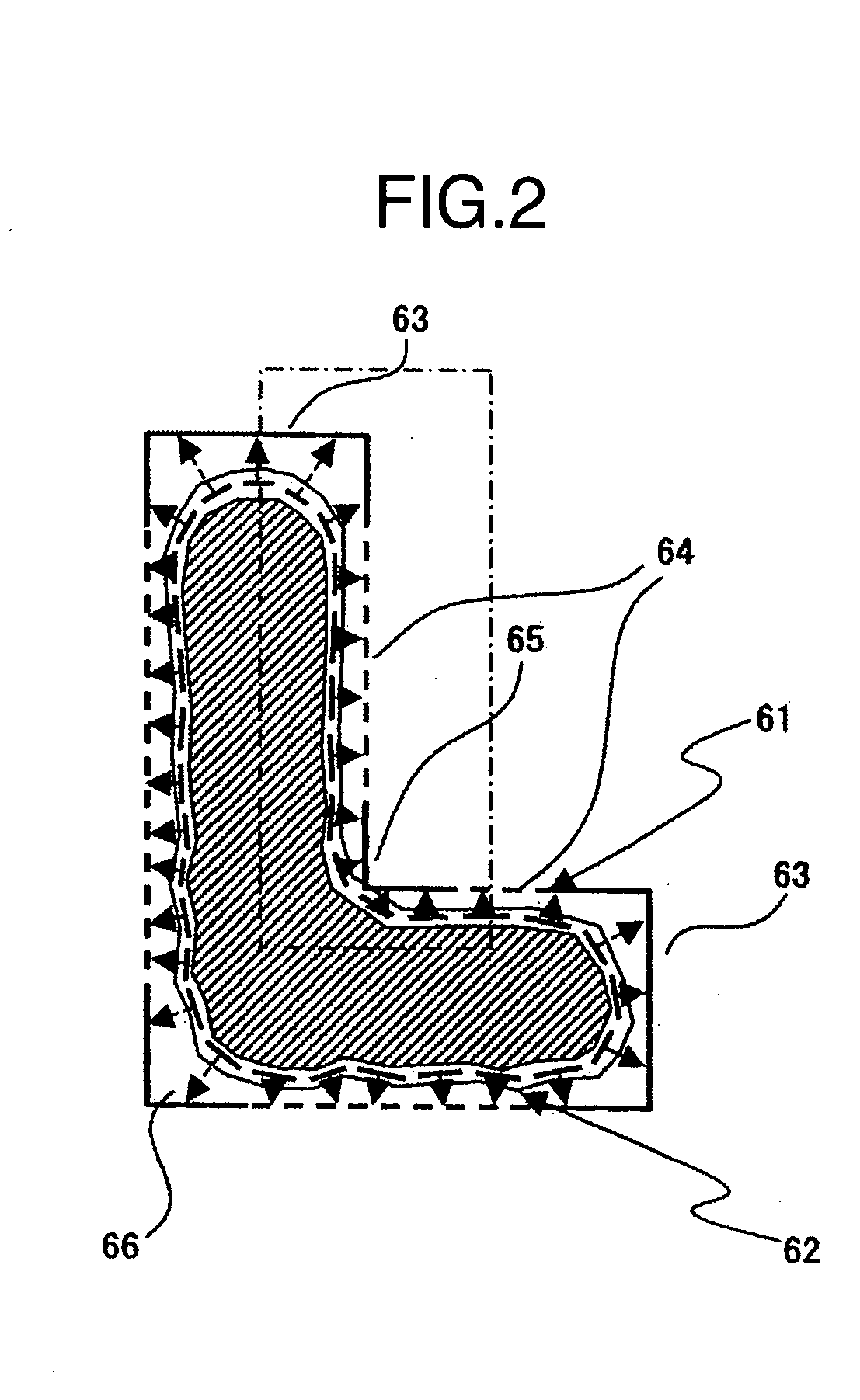

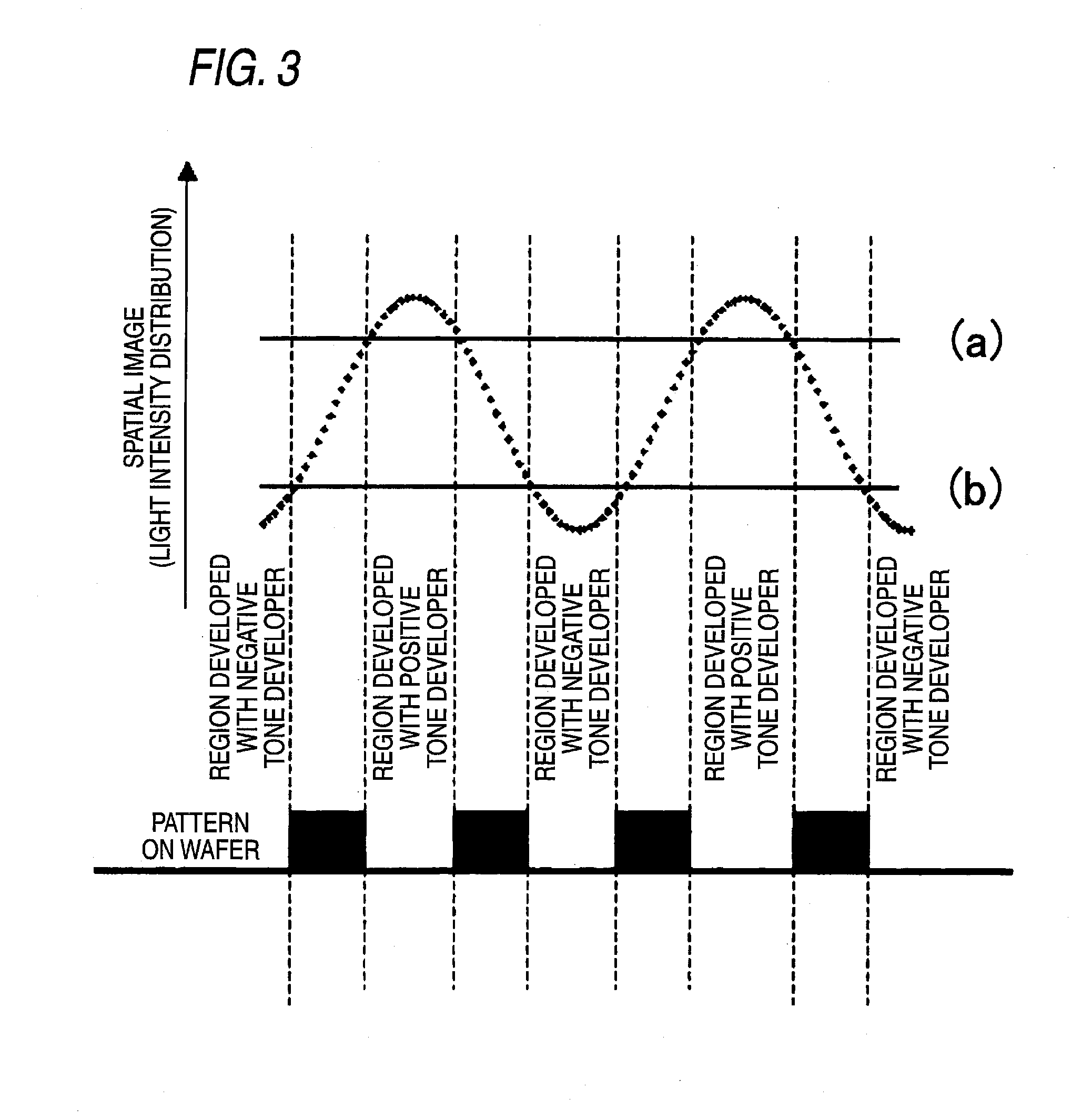

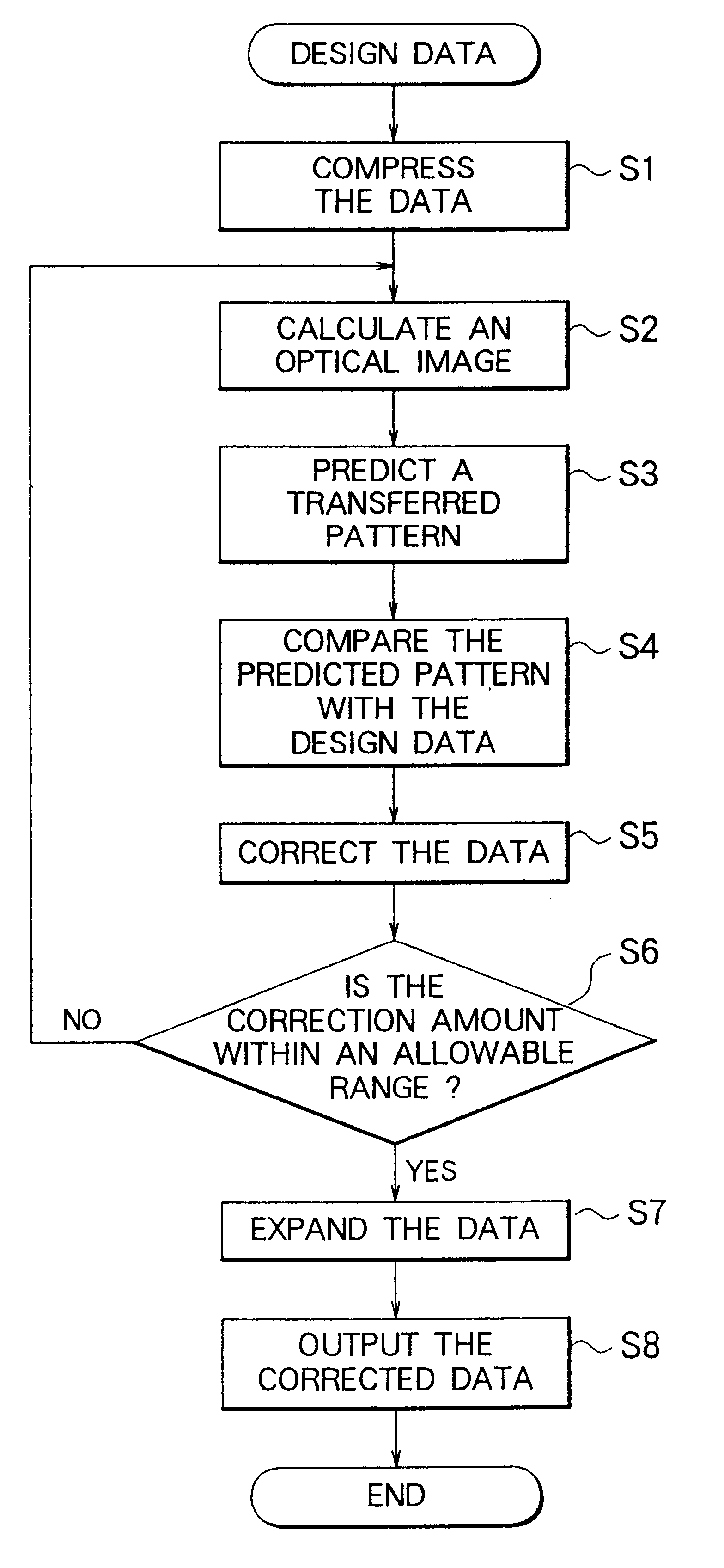

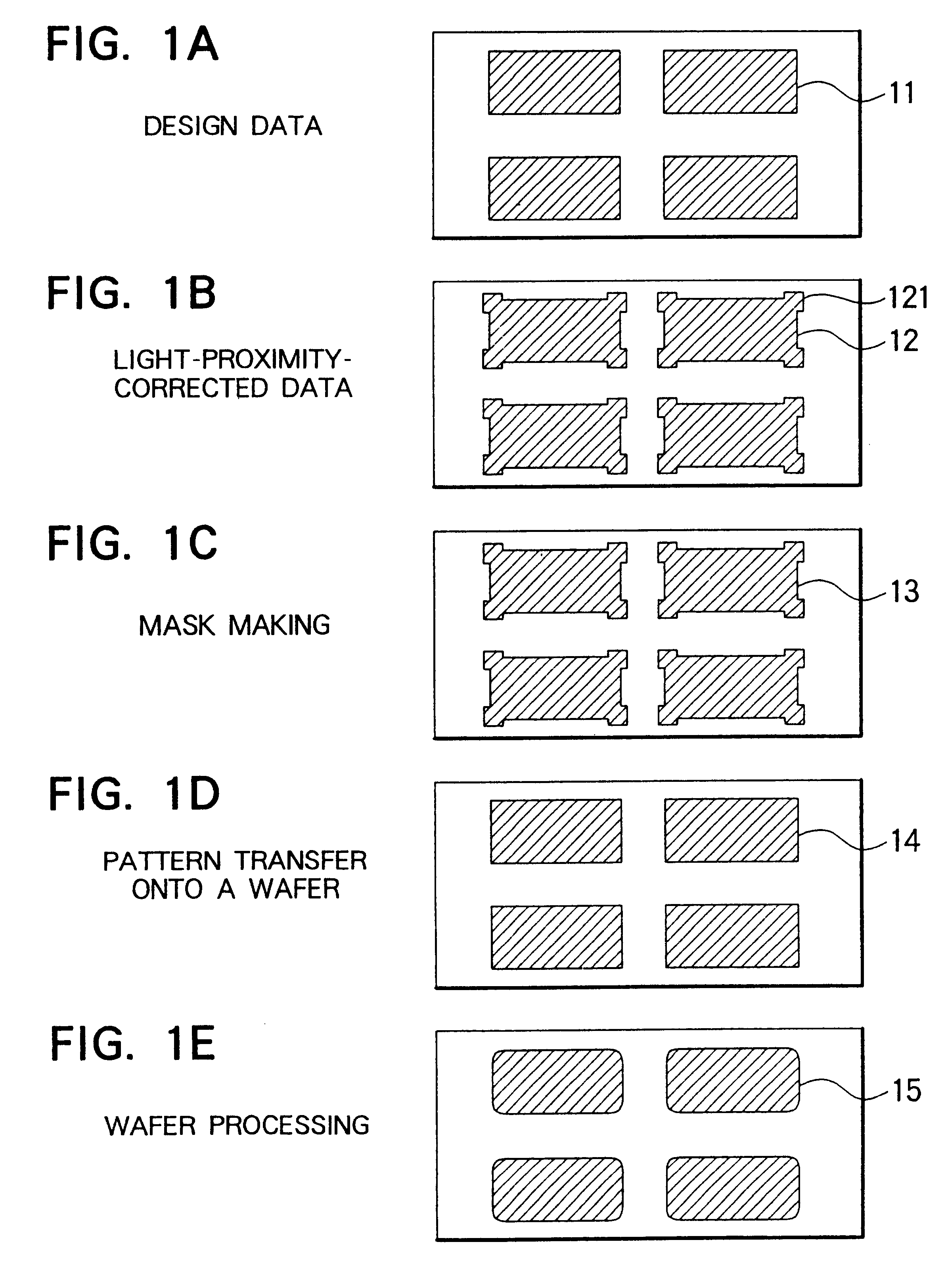

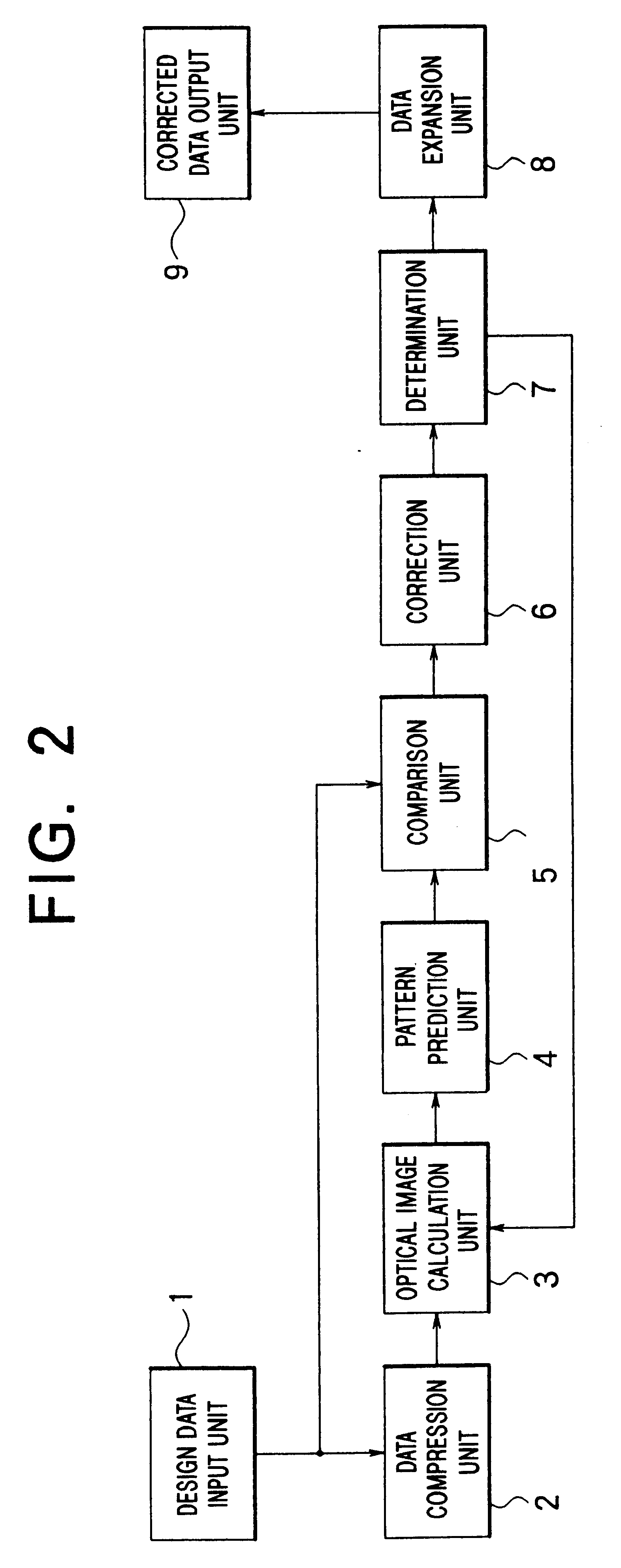

Method of forming a pattern using proximity-effect-correction

InactiveUS6453274B2Semiconductor/solid-state device manufacturingImage codingProjection imageDesign data

A method of correcting light proximity effects includes the steps of: compressing design data of a circuit pattern (step S1); generating a projection image which is formed during a process of transferring a pattern onto a wafer, the projection image being generated according to the design data (step S2); predicting the size of the transferred pattern, said prediction being performed from the projection image (step S3); calculating the difference between the predicted size of the transferred pattern and the pattern size designated by the design data (step S4); correcting the compressed design data by an amount equal to the above-described difference (step S5); judging whether the correction amount is within an allowable range (step S6); expanding the corrected data after the correction amount has fallen within the allowable range (step S7); and outputting the resultant data (step S8).

Owner:RENESAS ELECTRONICS CORP

Photomask blank and photomask

ActiveUS7767366B2High resolutionMinimized pattern densityPhotomechanical apparatusSemiconductor/solid-state device manufacturingDry etchingSilicon

A photomask blank is provided comprising an etch stop film which is disposed on a transparent substrate and is resistant to fluorine dry etching and removable by chlorine dry etching, a light-shielding film disposed on the etch stop film and including at least one layer composed of a transition metal / silicon material, and an antireflective film disposed on the light-shielding film. When the light-shielding film is dry etched to form a pattern, pattern size variation arising from pattern density dependency is reduced, so that a photomask is produced at a high accuracy.

Owner:SHIN ETSU CHEM IND CO LTD +1

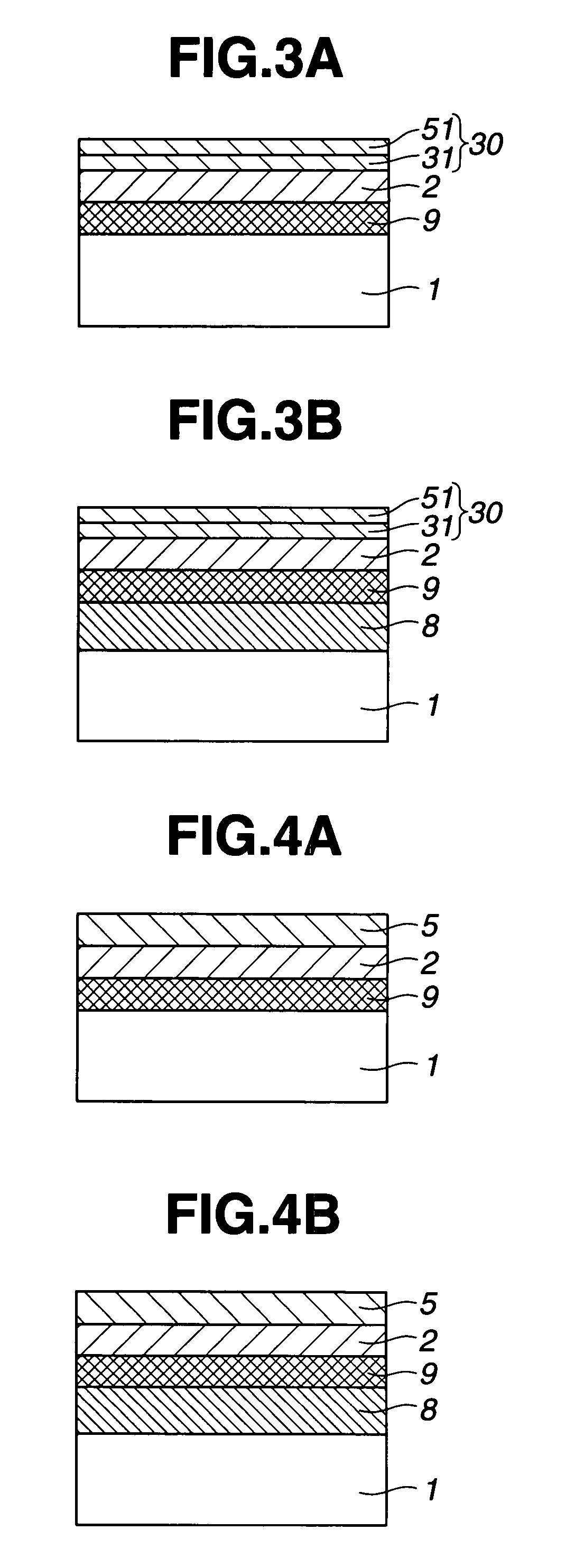

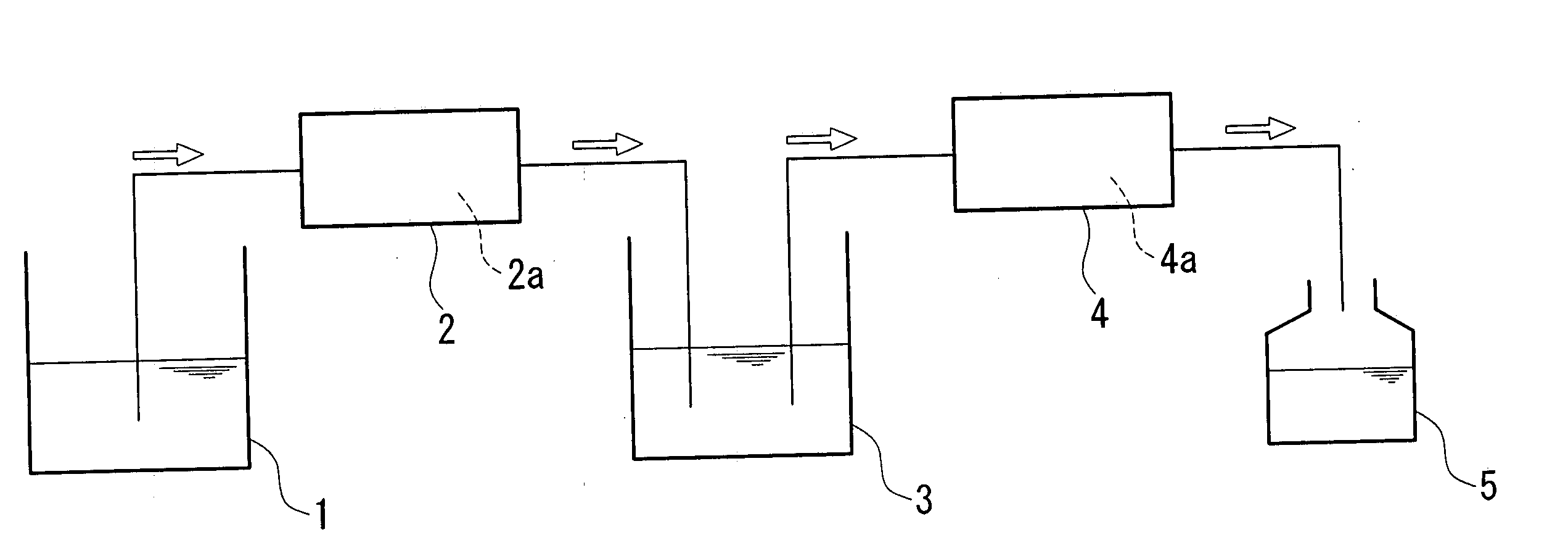

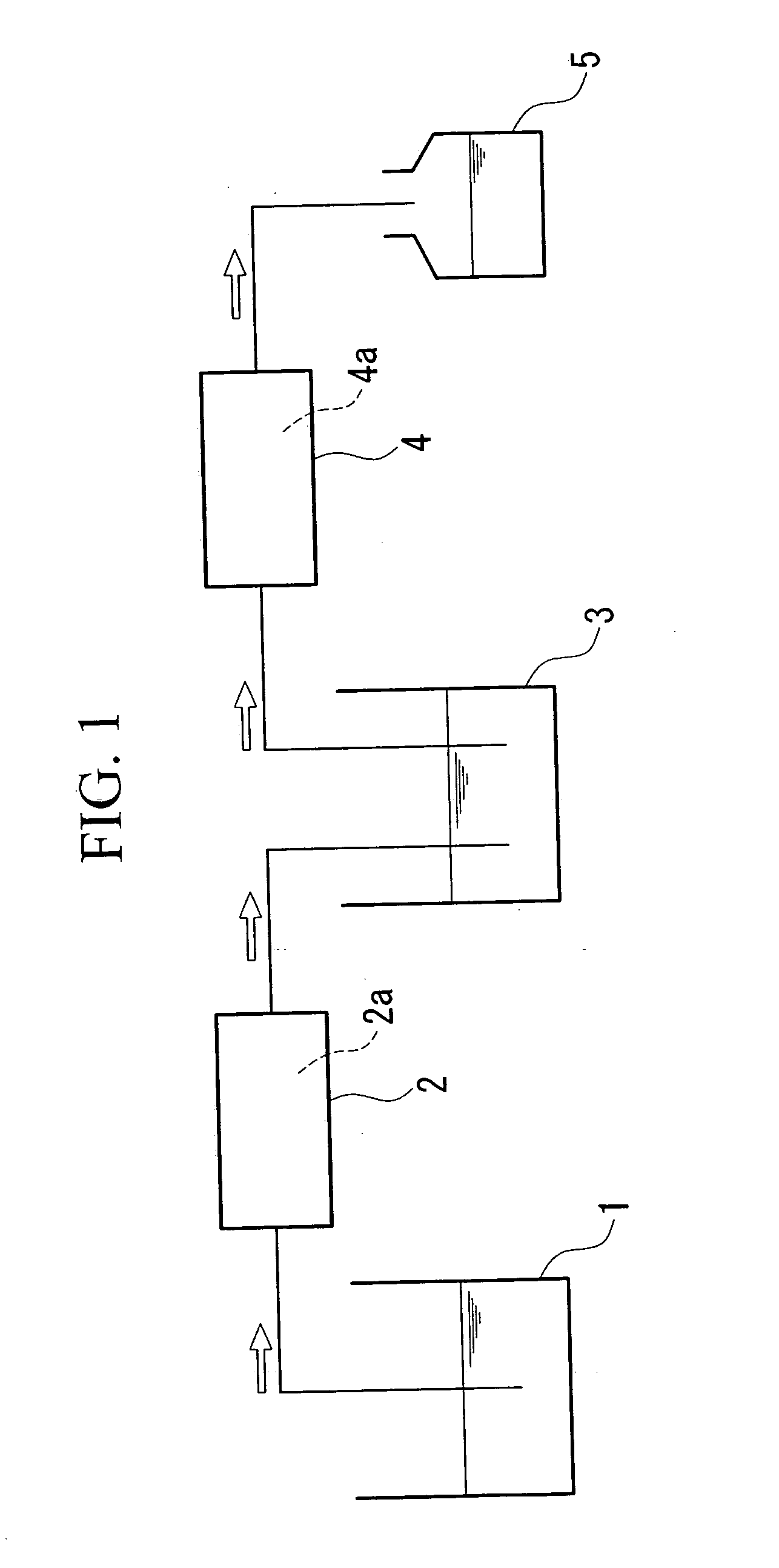

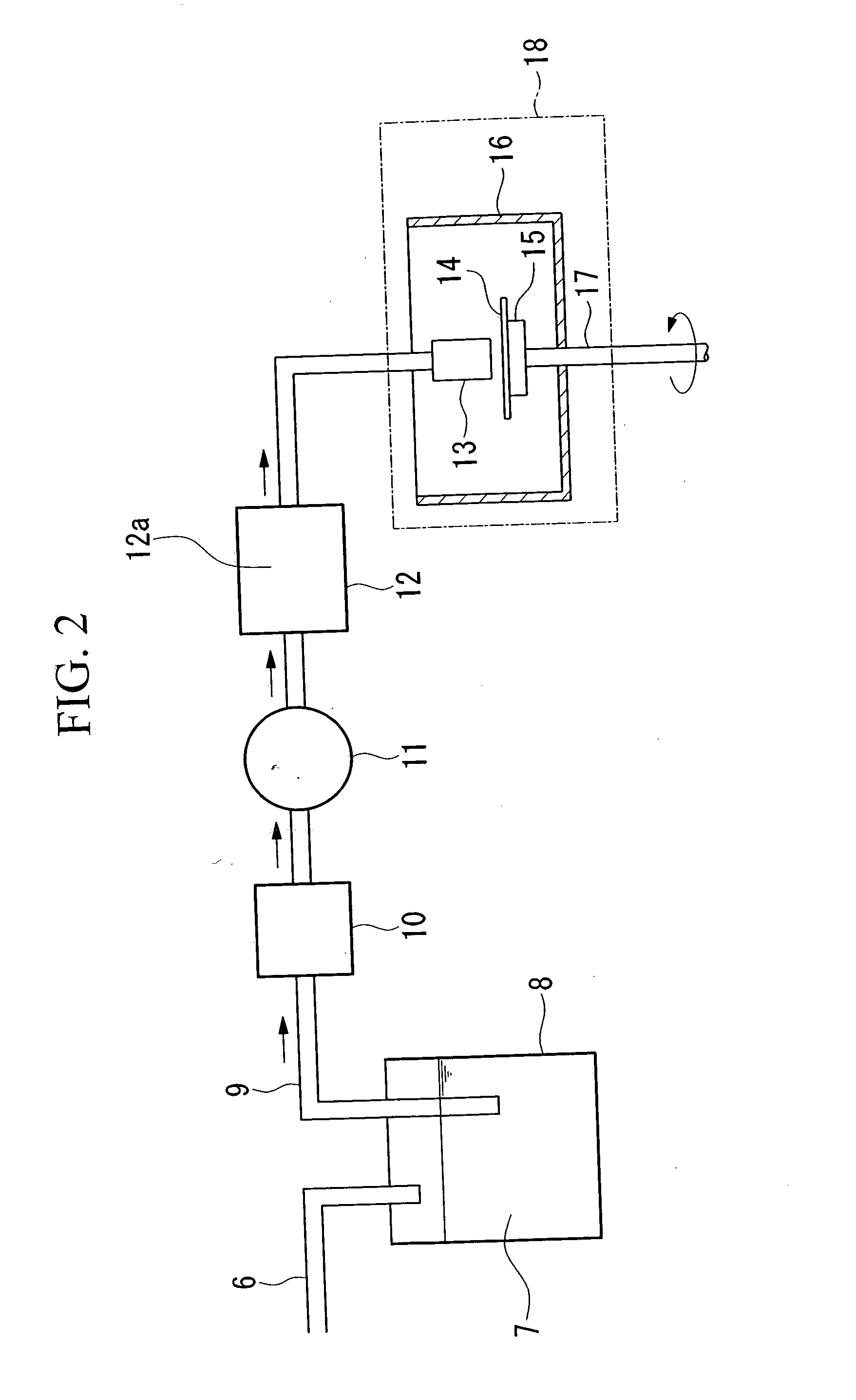

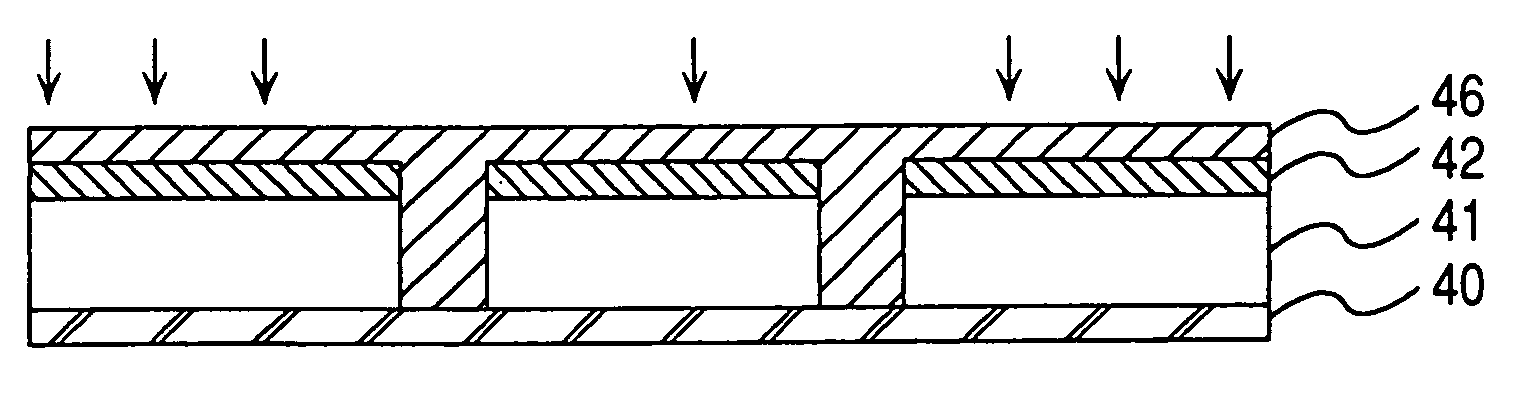

Process for producing photoresist composition, filter, coater and photoresist composition

ActiveUS20060014098A1Reduce defectsGood storage stabilityUltrafiltrationSemiconductor/solid-state device manufacturingZeta potentialResist

A technique to acquire a photoresist composition which can reduce occurrence of defects of a resist pattern after development is provided. Further, a technique to obtain a photoresist composition having excellent storage stability characteristics as a resist solution (storage stability); and a technique to obtain a photoresist composition which reduces the change of sensitivity and resist pattern size after treatment almost completely are provided. A photoresist composition containing a resin component (A), an acid-generating component (B) for generating an acid under exposure, and an organic solvent (C) is passed through a first filter 2a equipped with a first membrane having zeta potential of more than −20 mV but no more than 15 mV in distilled water of pH 7.0.

Owner:TOKYO OHKA KOGYO CO LTD

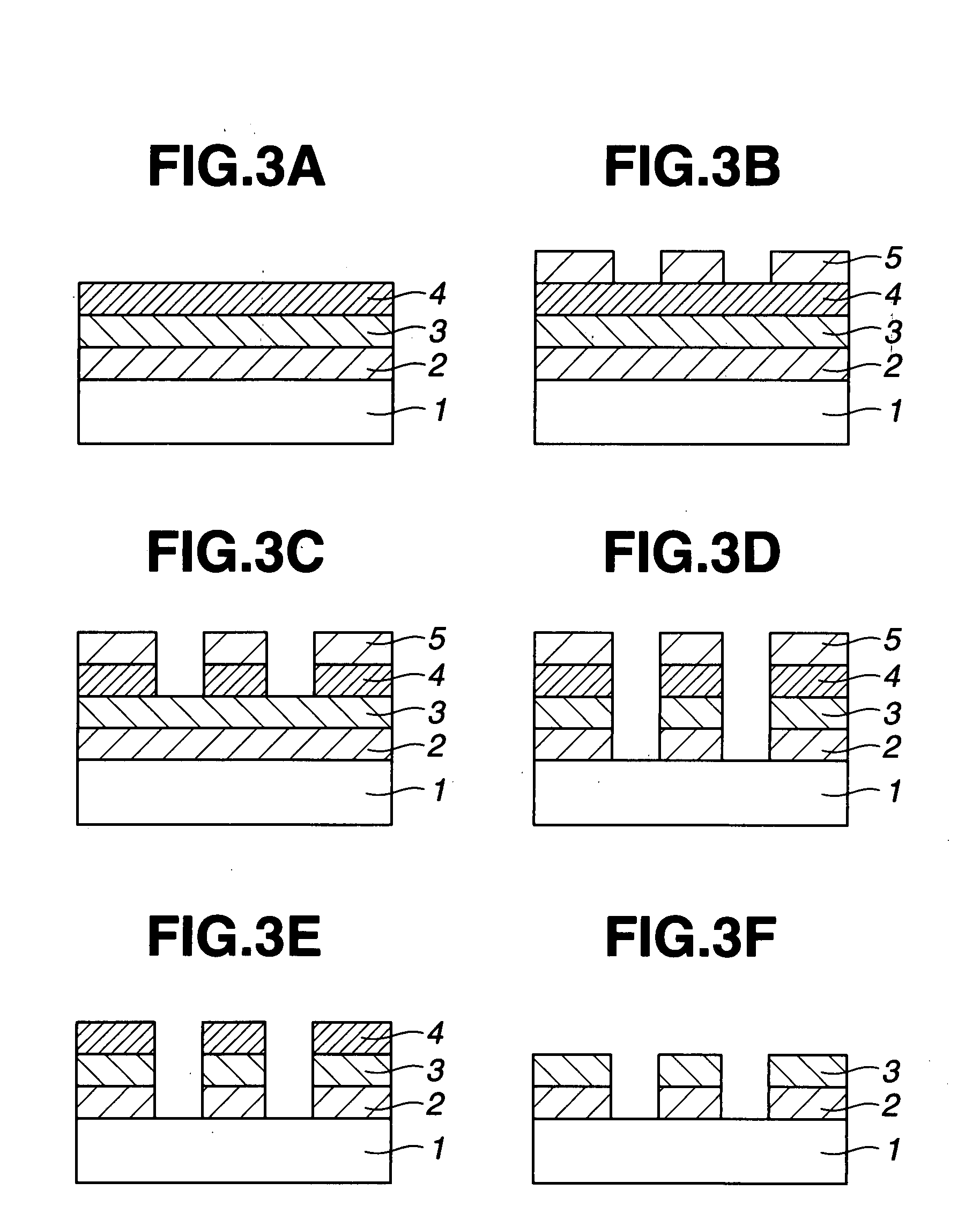

Method for reducing pattern dimension in photoresist layer

The invention discloses improvements in the so-called coated thermal flow process for reducing the pattern dimension of a patterned resist layer on a substrate to accomplish increased fineness of resist patterning, in which a coating layer of a water-soluble resin formed on the patterned resist layer is heat-treated to effect thermal shrinkage of the coating layer with simultaneous reduction of the pattern dimension followed by removal of the coating layer by washing with water. The improvement of the process is obtained by using an aqueous coating solution admixed with a water-soluble amine compound such as triethanolamine in addition to a water-soluble resin such as a polyacrylic acid-based polymer. Further improvements can be obtained by selecting the water-soluble resin from specific copolymers including copolymers of (meth)acrylic acid and a nitrogen-containing monomer such as N-vinylpyrrolidone, N-vinylimidazolidinone and N-acryl-oylmorpholine as well as copolymers of N-vinylpyrrolidone and N-vinylimidazolidinone in a specified copolymerization ratio.

Owner:SUGETA YOSHIKI +2

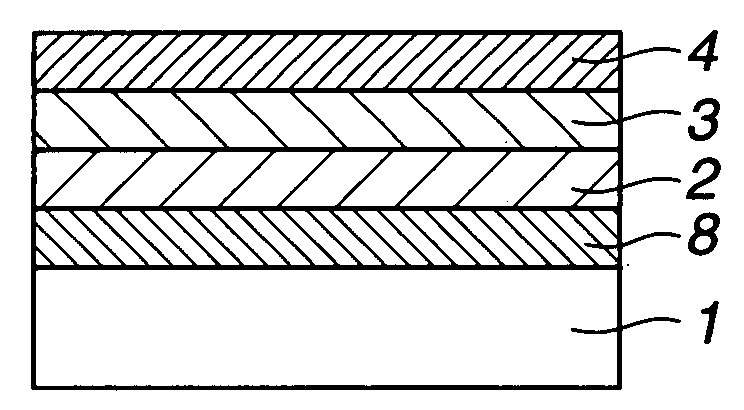

Reflective mask blank for EUV lithography and reflective mask for EUV lithography

ActiveUS20130196255A1Reduce decreaseReduce unnecessary contactOriginals for photomechanical treatmentResistLithographic artist

A reflective mask for an extreme ultra violet (EUV) lithography obtained by forming a mask pattern in an absorber layer of an reflective mask blank is useful in semiconductor production. The EUV reflective mask has two regions of a mask pattern region and a region outside the mask pattern region. The mask pattern region has the absorber layer and a non-absorber layer on the reflective layer of an substrate, wherein the region outside the mask pattern region has an EUV reflective layer, an EUV absorber layer, and a light shielding layer for suppressing reflection of EUV light and DUV-Vis light having a wavelength of from 190 to 500 nm. The EUV reflective mask reduces unnecessary exposure of resist formed on a substrate to reflected light from the region outside the mask pattern region and reduces a pattern size to produce an accurate transfer pattern.

Owner:ASAHI GLASS CO LTD

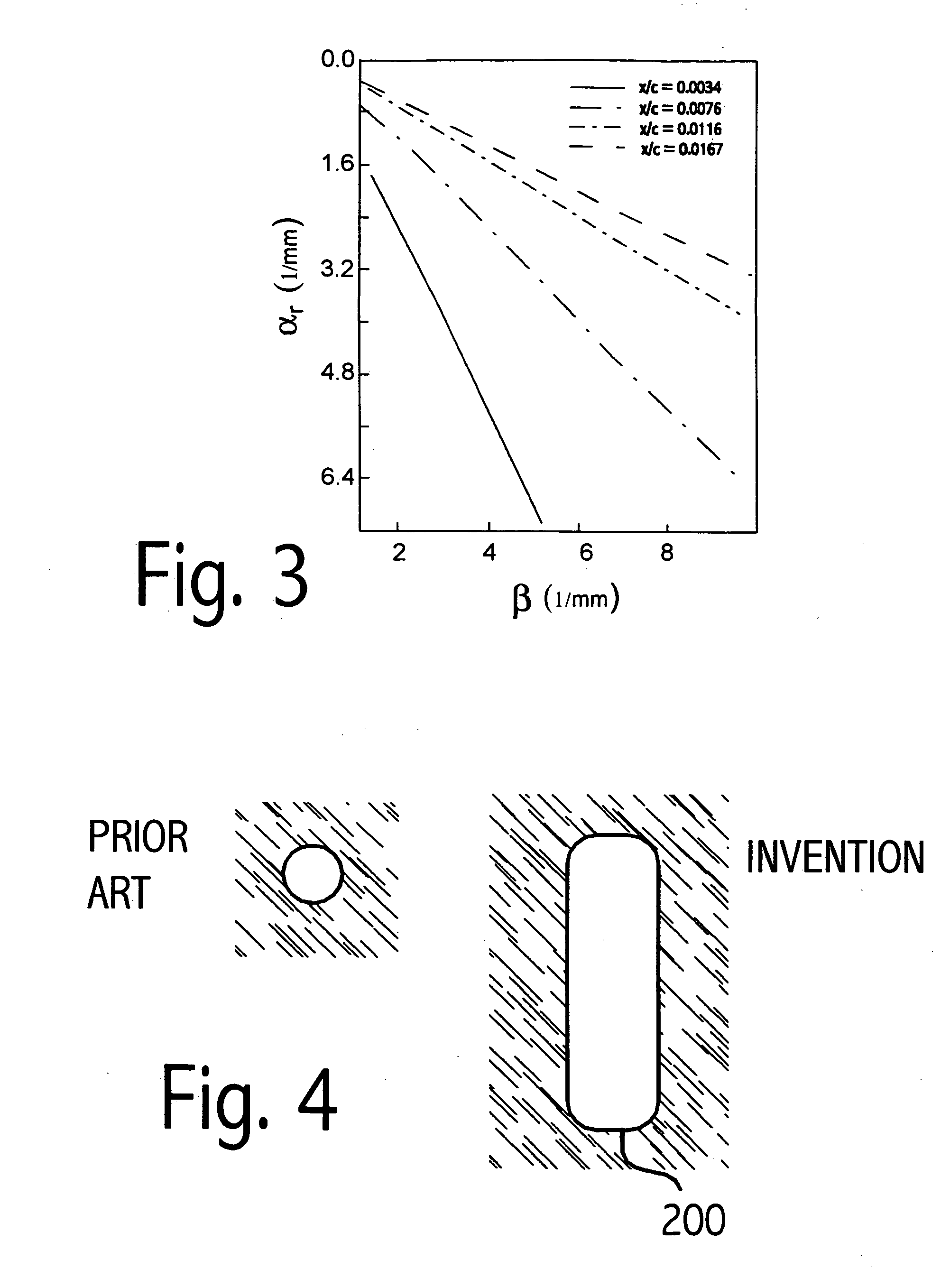

Perforated skin structure for laminar-flow systems

InactiveUS20050178924A1Improve thermal conductivityEnhanced advantageBoundary layer controlsWingsThrottle controlEngineering

The outer skin (100) of an aerodynamic body (40) has perforations (200) arranged in particular patterns in respective spanwise extending groups or bundles (250). Each perforation is preferably a micro-slot with a length of 100 to 3000 μm and a width of 50 to 250 μm. Air is sucked through the micro-slots from the boundary layer flowing over the outer skin, to achieve boundary layer control. In each bundle, the pattern, size, orientation, and other parameters of the micro-slots are designed to achieve mutual destructive interference of flow disturbances arising due to the suction, to minimize the excitation of flow instabilities in the boundary layer. Particularly, the spatial spectrum of the perforation pattern of a given bundle is essentially absent of significant energy at predetermined wavelengths of predetermined flow instabilities that otherwise appear in the boundary layer air flow. The aerodynamic body further includes supporting ribs (300) extending parallel to the perforation bundles (250) and a perforated inner plate (400) providing a throttling control of the suction flow through groups of the bundles.

Owner:AIRBUS OPERATIONS GMBH

Integrated optical metrology and lithographic process track for dynamic critical dimension control

InactiveUS20060222975A1High yieldImprove throughputCooking-vessel lids/coversPhotomechanical apparatusResistProcess engineering

A method and apparatus for improving a yield and throughput of a lithographic process track, the method including providing a first resist layer on a first process wafer; forming a first resist pattern in the first resist layer including a heating process according to a first temperature profile wherein the heating process comprises a plurality of temperature controllable heating zones; producing and collecting scattered light spectra from the first resist pattern processing the scattered light spectrum to obtain 3-dimensional information including first resist pattern critical dimensions; determining a second temperature profile for performing the heating process to achieve targeted resist pattern critical dimensions including a second resist pattern on a second process wafer; and, forming the second resist pattern dimensions including the heating process according to the second temperature profile.

Owner:TAIWAN SEMICON MFG CO LTD

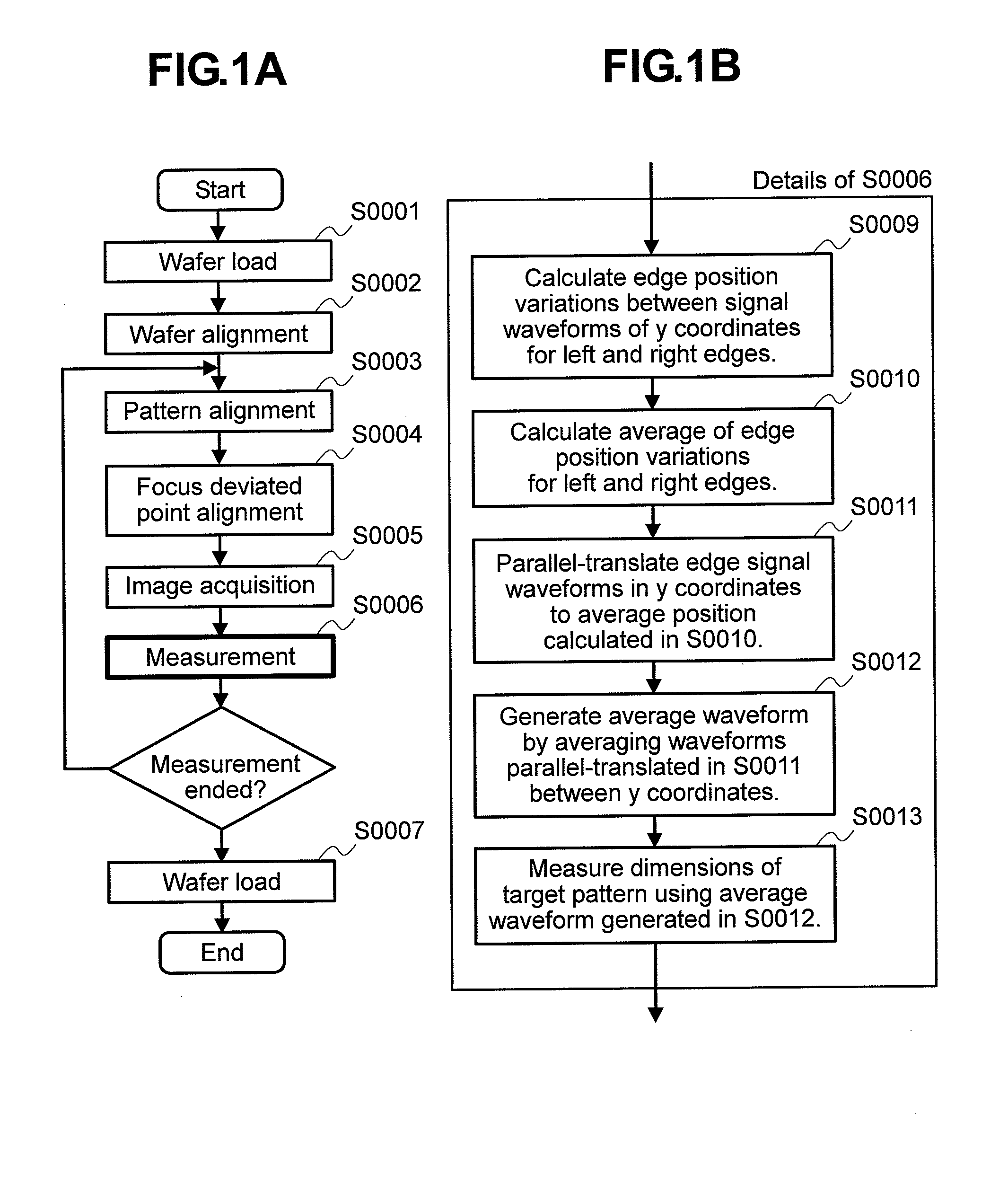

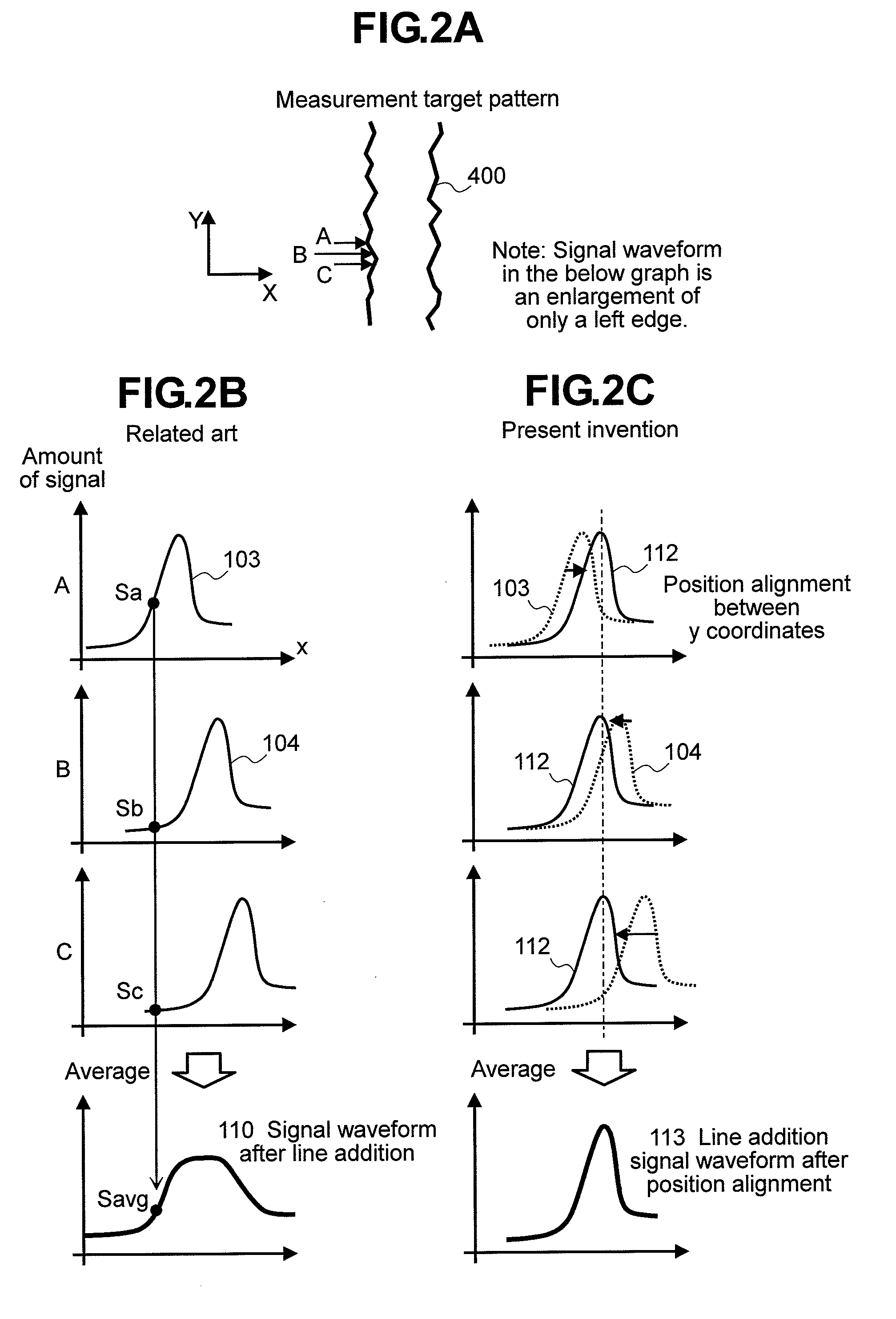

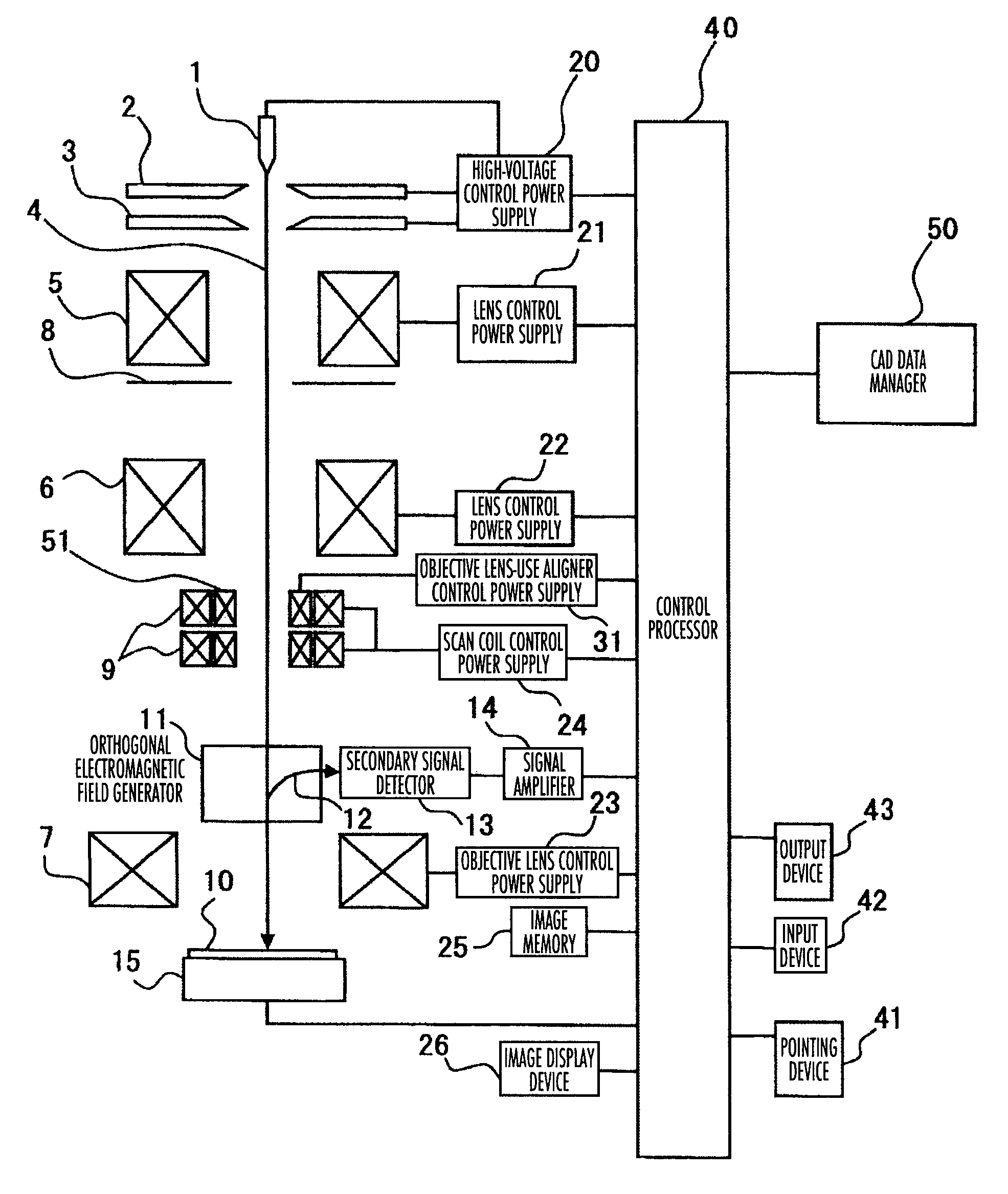

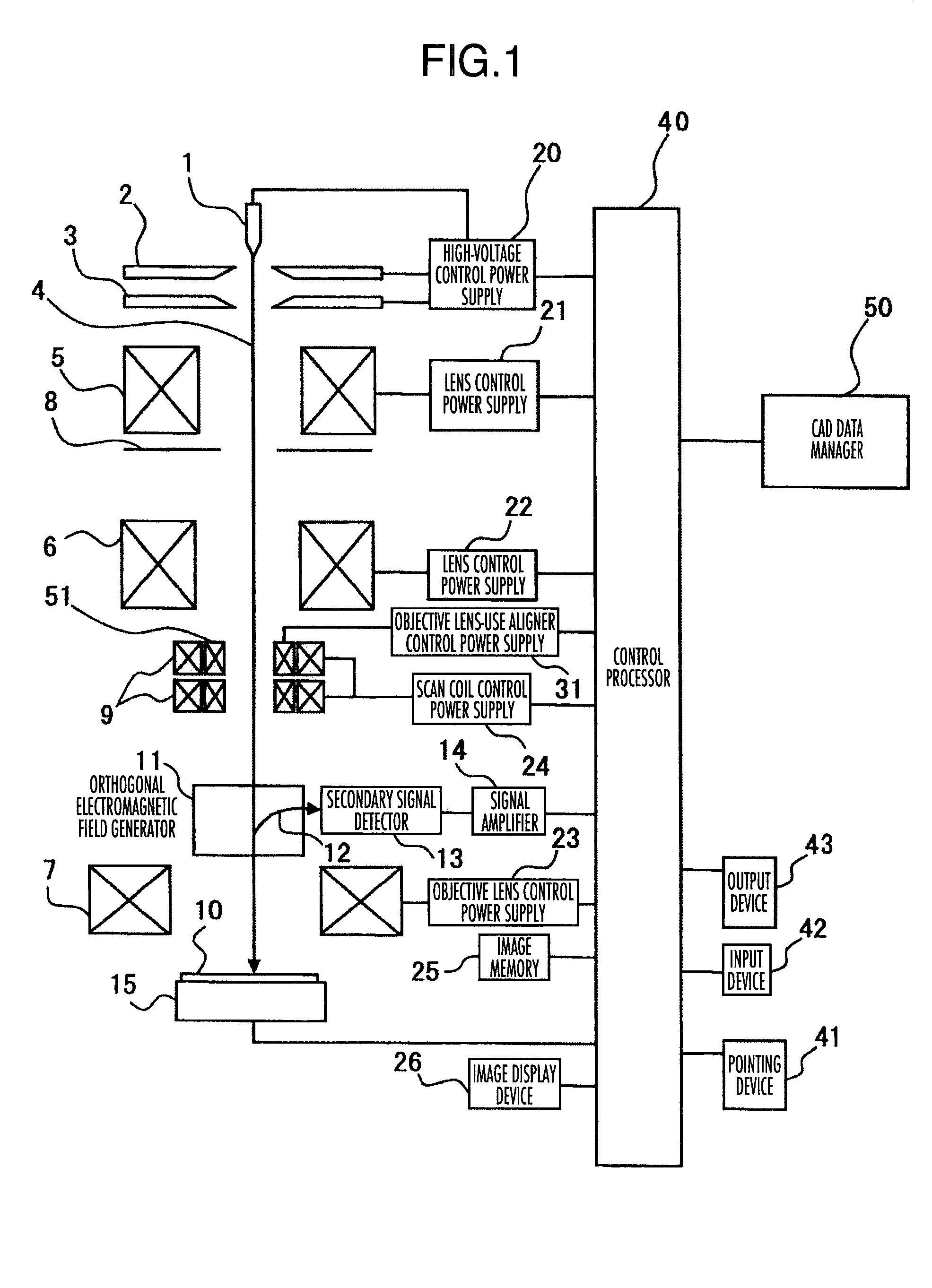

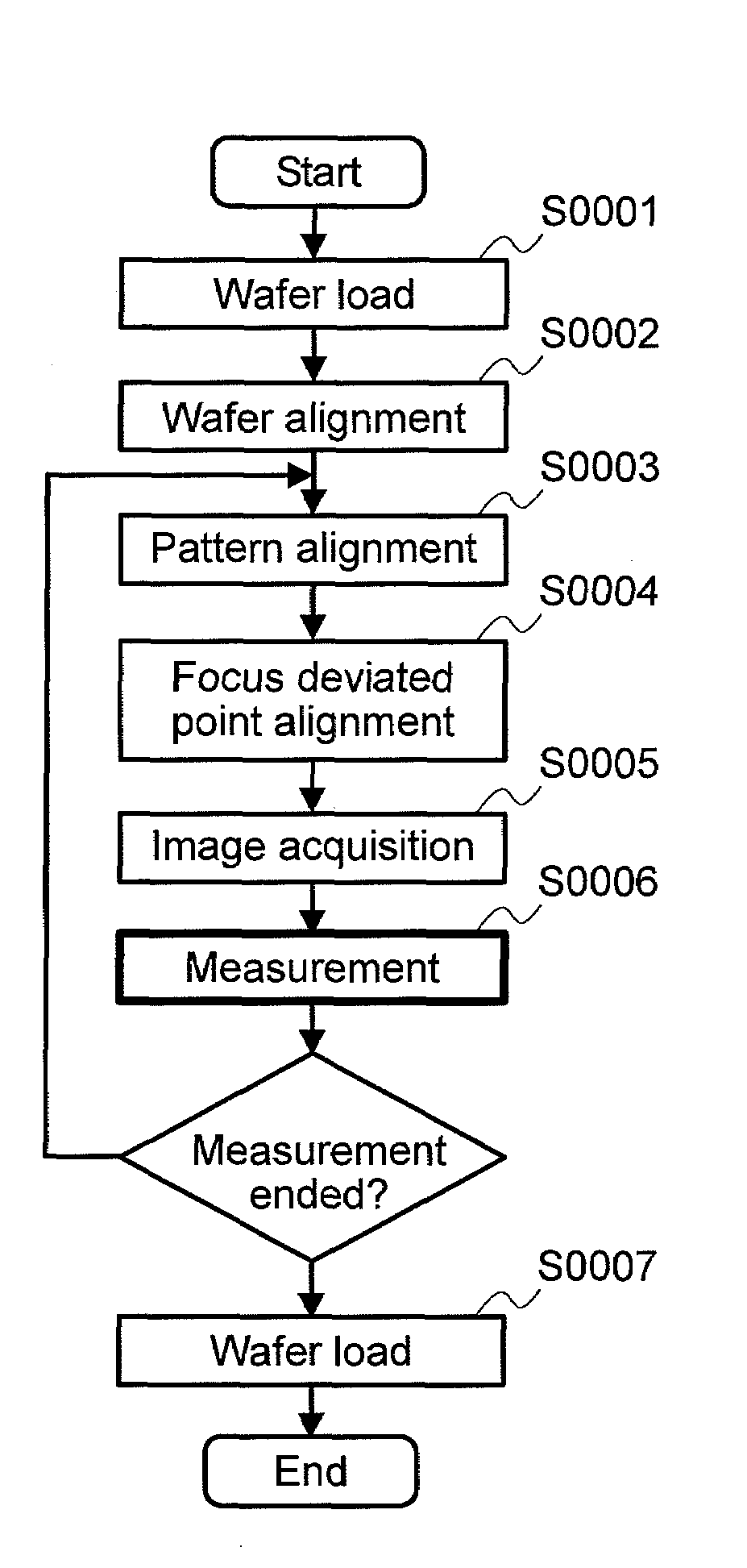

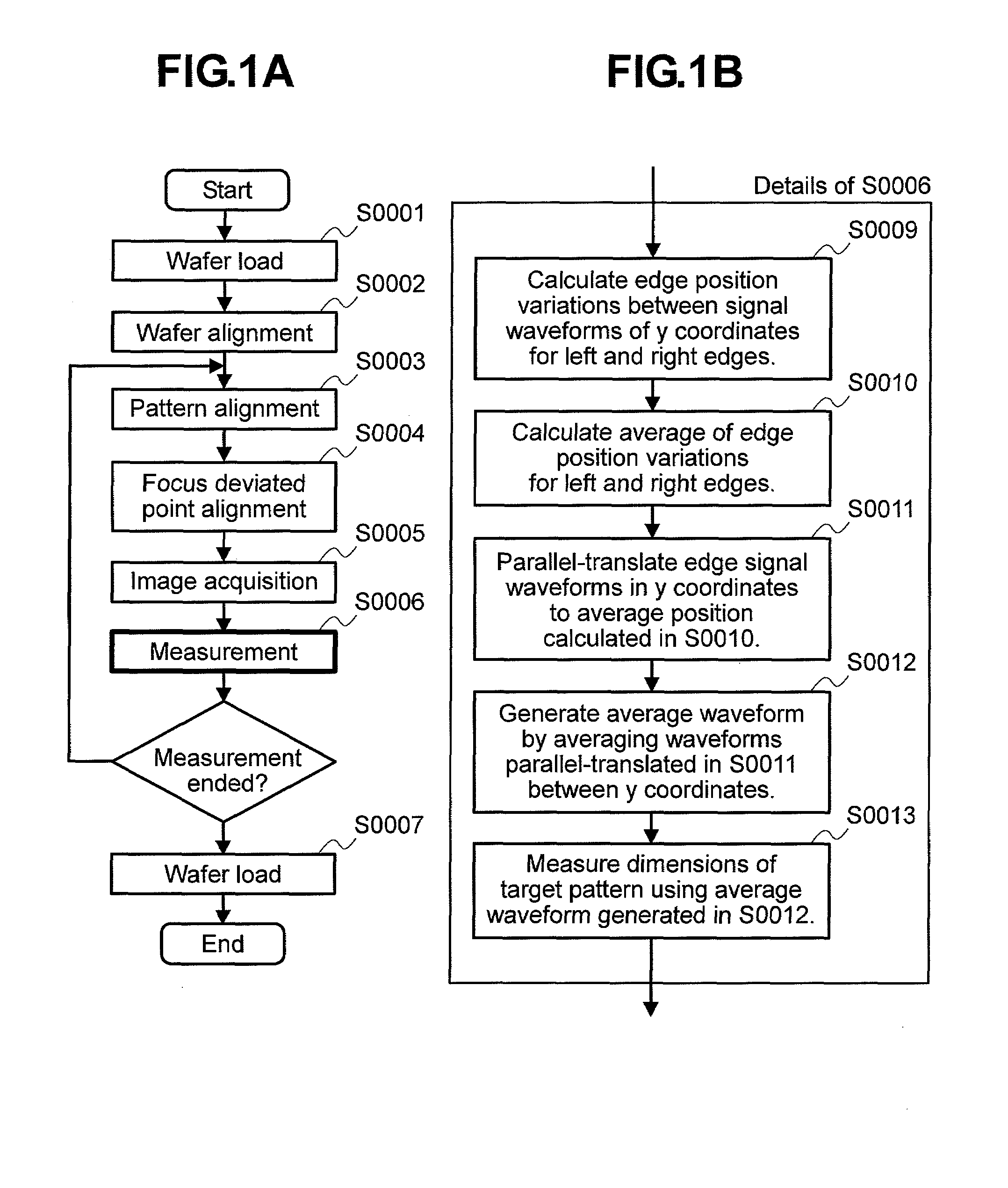

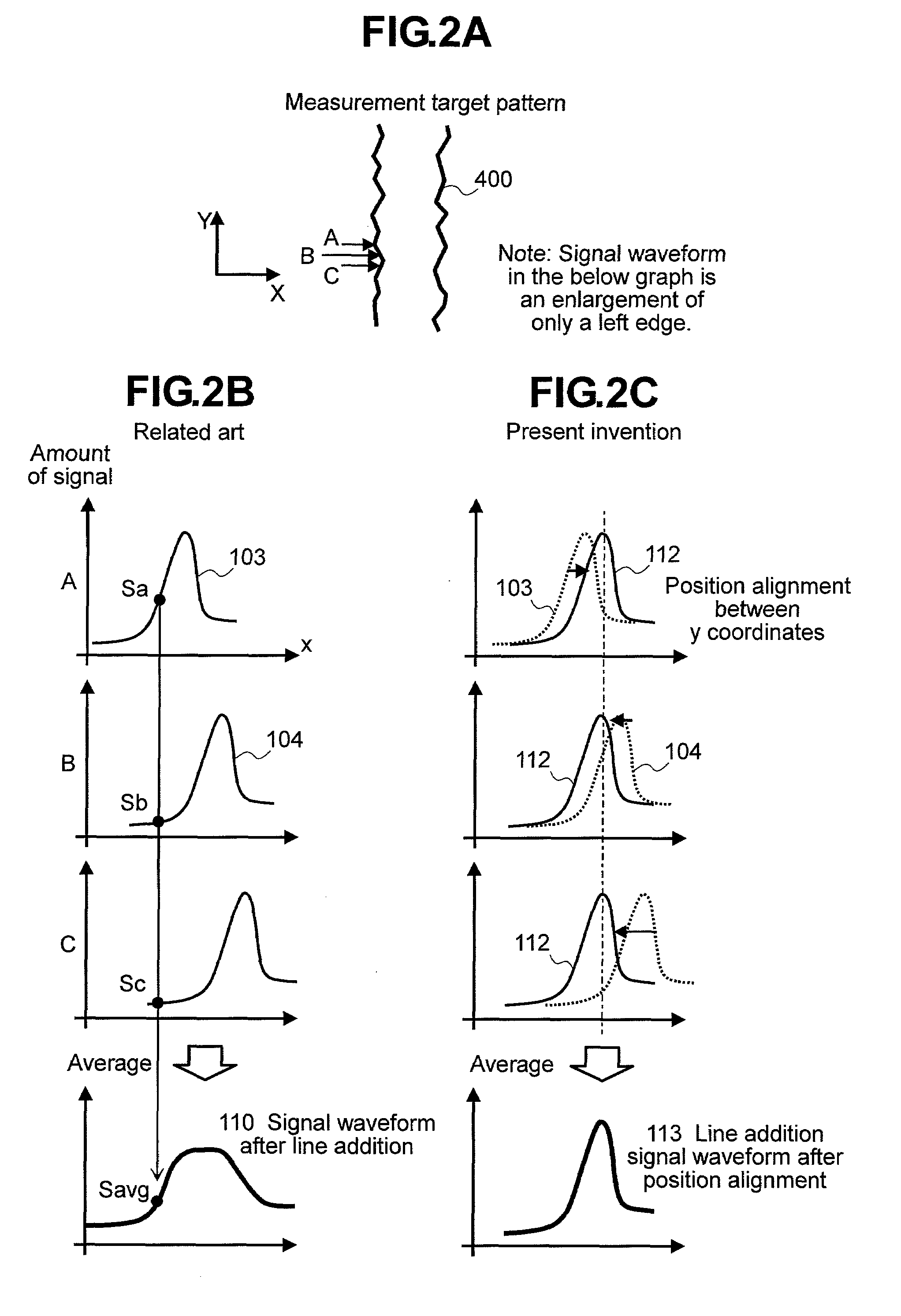

Method and apparatus for measuring pattern dimensions

InactiveUS20080197280A1Reduce impactRepeatability of measurementSemiconductor/solid-state device testing/measurementRadiation applicationsObservational errorImage averaging

It is difficult for a material having low resistance to electron beam irradiation to obtain an electron microscopic image having a high S / N ratio. A conventional image smoothing process can improve stability of measurement, but this process has a problem of measurement errors for absolute values, reduction of sensitivity, deterioration of quality of cubic shape information and the like. In the present invention, by performing an image averaging process without deteriorating cubic shape information of a signal waveform in consideration of dimension deviation of a measurement target pattern, measurement stability is compatible with improvement of precision and sensitivity. Accordingly, it is possible to realize measurement of pattern dimensions and shapes with high precision and control of a highly sensitive semiconductor manufacturing process using the measurement.

Owner:HITACHI HIGH-TECH CORP

Method, device and computer program of length measurement

ActiveUS8019161B2Increased complexityImprove measurement efficiencyMaterial analysis using wave/particle radiationCharacter and pattern recognitionSize measurementLength measurement

A workpiece size measurement method suitable for length measurement of multilayered circuit elements with increased complexities is disclosed. This method employs a technique for changing measurement conditions in a way pursuant to either an image of workpiece or the situation of a target semiconductor circuit element to be measured when measuring pattern sizes on the workpiece image using design data of the semiconductor circuit element. With such an arrangement, adequate measurement conditions are selectable in accordance with the state of workpiece image and / or the state of a circuit element formed on the workpiece, thereby making it possible to improve the measurement efficiency. A workpiece size measurement apparatus using the technique is also disclosed.

Owner:HITACHI HIGH-TECH CORP

Method of measuring pattern dimension and method of controlling semiconductor device process

ActiveUS20050116182A1Precise DimensionsReduce the amount of calculationMaterial analysis using wave/particle radiationSemiconductor/solid-state device testing/measurementDevice materialDimension measurement

This invention provides a method of measuring semiconductor pattern dimensions capable of realizing a stable and highly precise pattern dimension measurement technique even when the pattern cross-sectional shapes are changed and making the calculation amount relatively small to reduce the calculation time. More specifically, the relationship between cross-sectional shapes of a pattern and measurement errors in a specified image processing technique is evaluated in advance by the electron beam simulation in a pattern measurement system in a length measuring SEM, and in the actual dimension measurement, dimensions of an evaluation objective pattern are measured from image signals of a scanning electron microscope, and errors of the dimensional measurement of the evaluation objective pattern are estimated and revised based on the relationship between cross-sectional shapes of a pattern and measurement errors evaluated in advance, thereby realizing highly precise measurement where dimensional errors depending on pattern solid shapes are eliminated.

Owner:HITACHI HIGH-TECH CORP

Method for reducing pattern dimension in photoresist layer

InactiveUS20050058950A1Dimension of pattern decreasePhotosensitive materialsSemiconductor/solid-state device manufacturingResistMeth-

The invention discloses improvements in the so-called coated thermal flow process for reducing the pattern dimension of a patterned resist layer on a substrate to accomplish increased fineness of resist patterning, in which a coating layer of a water-soluble resin formed on the patterned resist layer is heat-treated to effect thermal shrinkage of the coating layer with simultaneous reduction of the pattern dimension followed by removal of the coating layer by washing with water. The improvement of the process is obtained by using an aqueous coating solution admixed with a water-soluble amine compound such as triethanolamine in addition to a water-soluble resin such as a polyacrylic acid-based polymer. Further improvements can be obtained by selecting the water-soluble resin from specific copolymers including copolymers of (meth)acrylic acid and a nitrogen-containing monomer such as N-vinylpyrrolidone, N-vinylimidazolidinone and N-acryl-oylmorpholine as well as copolymers of N-vinylpyrrolidone and N-vinylimidazolidinone in a specified copolymerization ratio.

Owner:SUGETA YOSHIKI +2

Method for producing electronic device

ActiveUS20060105273A1Low costImprove performanceSolid-state devicesSemiconductor/solid-state device manufacturingResistSolubility

There is a problem in that when the demand accuracy with respect to a semiconductor pattern dimension comes close to a resist molecule size with miniaturization, the device performance is deteriorated due to edge roughness of a resist pattern to exert a bad influence on the system performance. The present invention overcomes the problem by the procedure in which super-molecules which are small in dimension as compared with the conventional polymers are used as main components, the reaction number required for the change of molecule solubility is made constant and as large as possible, and an acid generator is made clathrate or combinatory n super molecules to make an acid catalyst concentration large. As a result, it is possible to form a pattern of molecular accuracy with high productivity even with respect to the pattern dimension less than 50 nm, thereby realizing the high performance system.

Owner:RENESAS ELECTRONICS CORP

Method and apparatus for measuring pattern dimensions

InactiveUS7633061B2Reduce impactRepeatability of measurementSemiconductor/solid-state device testing/measurementRadiation applicationsObservational errorWave shape

Owner:HITACHI HIGH-TECH CORP

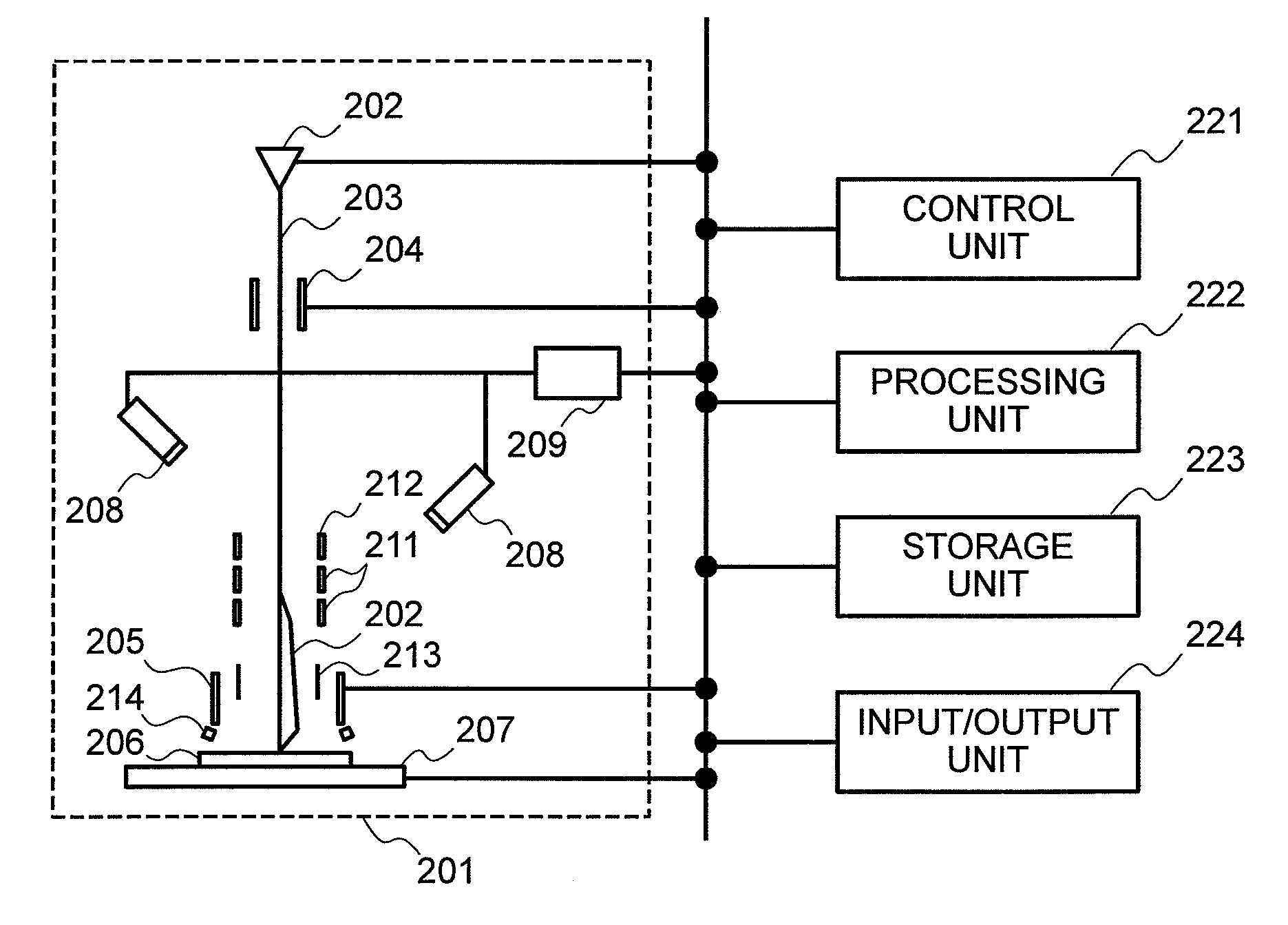

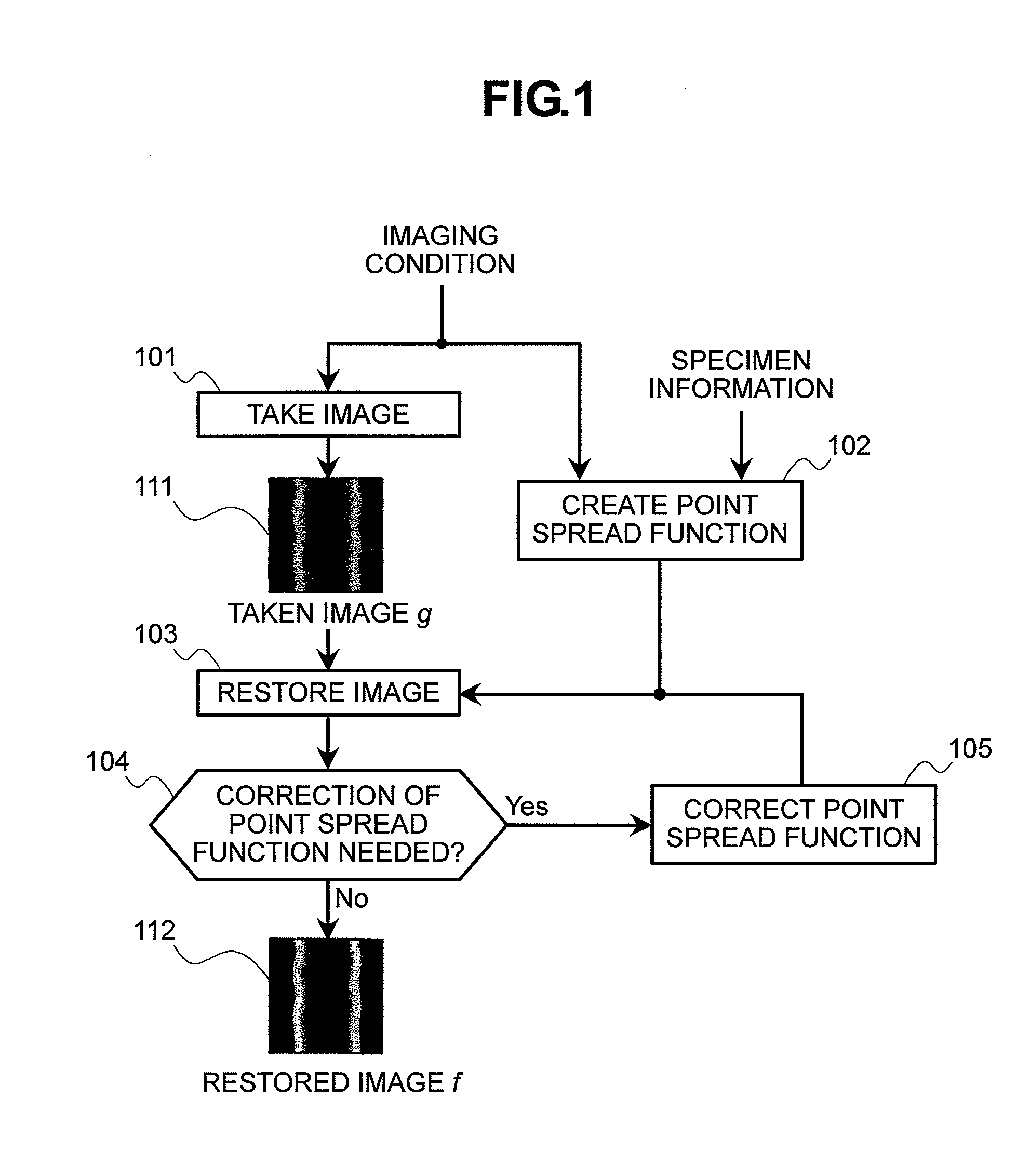

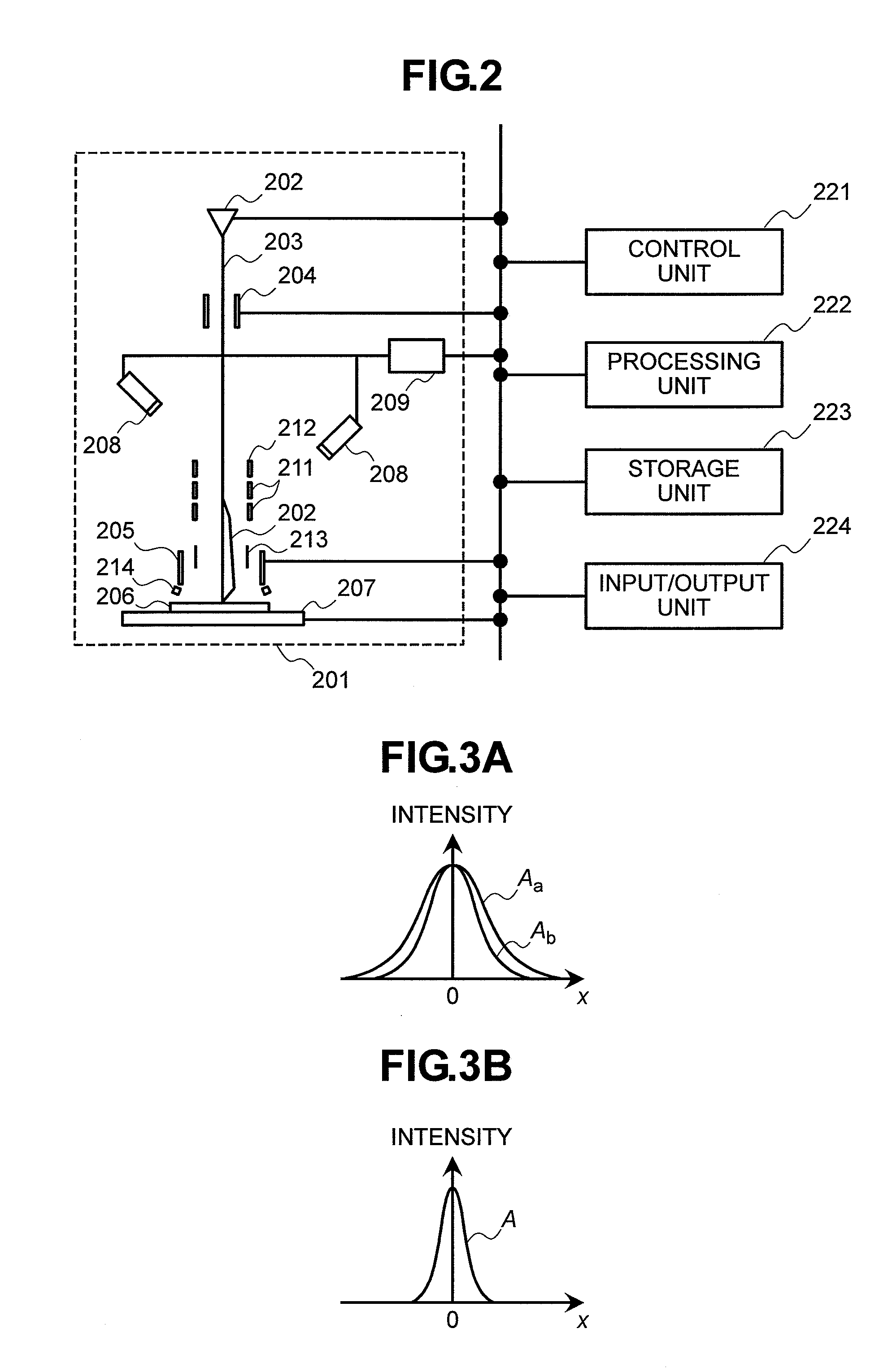

Scanning electron microscope and method for processing an image obtained by the scanning electron microscope

ActiveUS20080251719A1Accurate calculationThermometer detailsMaterial analysis using wave/particle radiationImaging conditionScanning tunneling microscope

In the case where a specimen is imaged by a scanning electron microscope, it is intended to acquire an image of a high quality having a noise component reduced, thereby to improve the precision of an image processing. The intensity distribution of a beam is calculated on the basis of an imaging condition or specimen information, and an image restoration is performed by using a resolving power deterioration factor other than the beam intensity distribution as a target of a deterioration mode, so that a high resolving power image can be acquired under various conditions. In the scanning electron microscope for semiconductor inspections and semiconductor measurements, the restored image is used for pattern size measurement, defect detections, defect classifications and so on, so that the measurements can be improved in precision and so that the defect detections and classifications can be made high precise.

Owner:HITACHI HIGH-TECH CORP

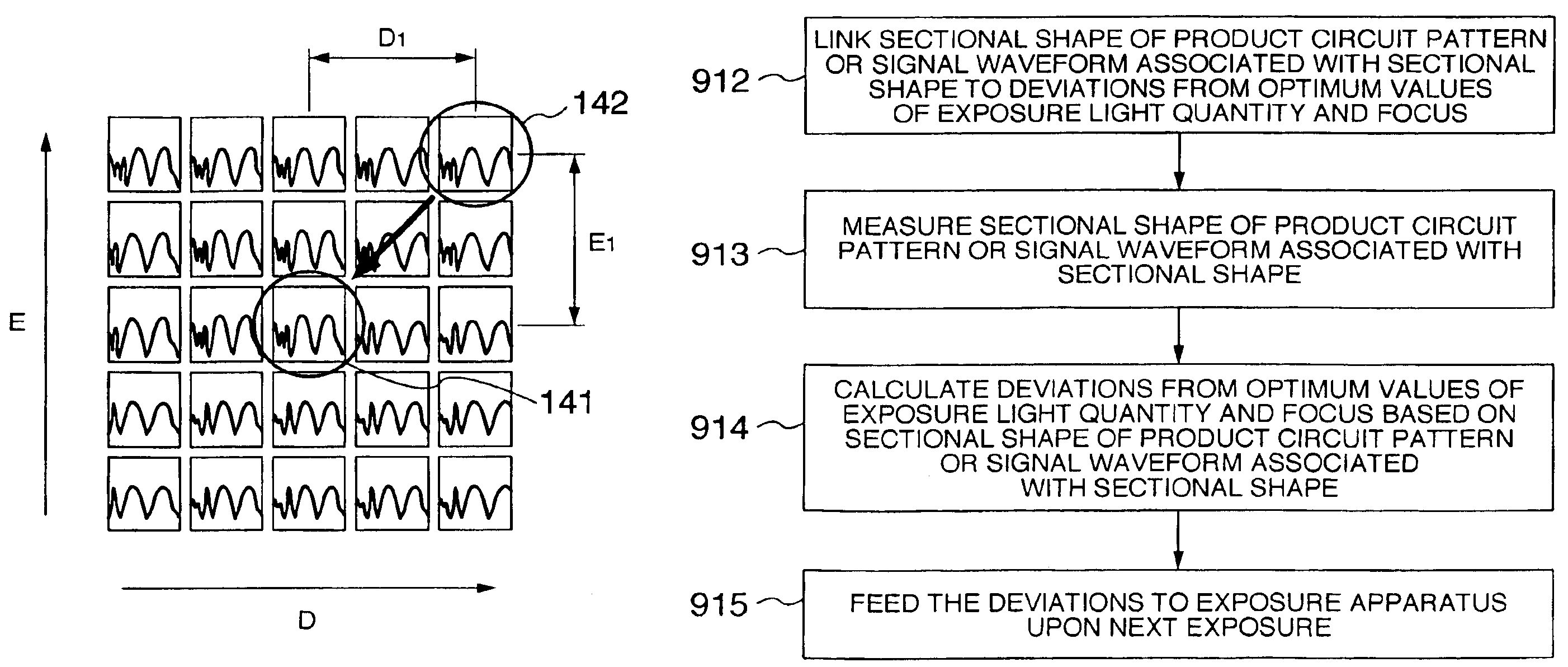

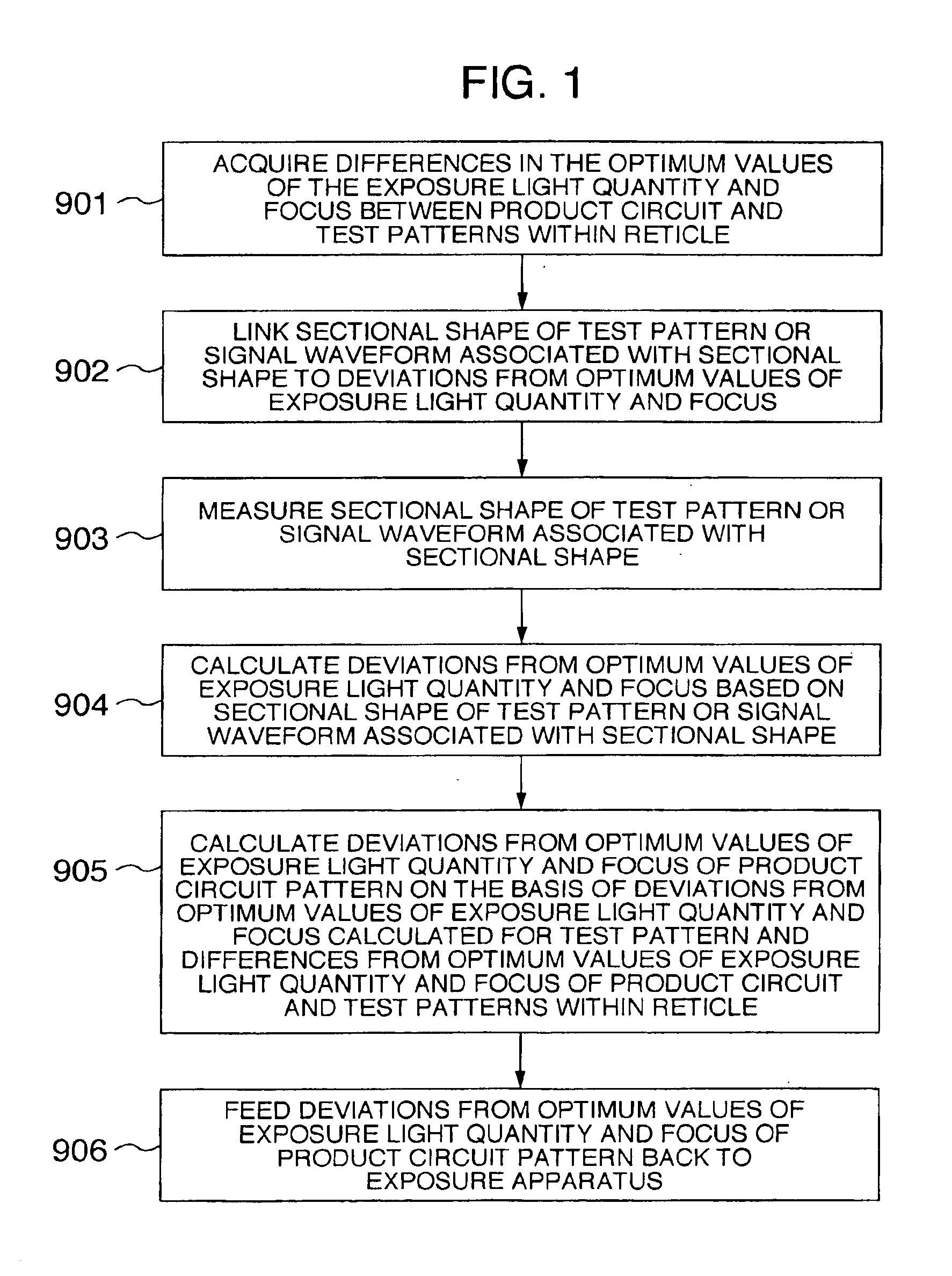

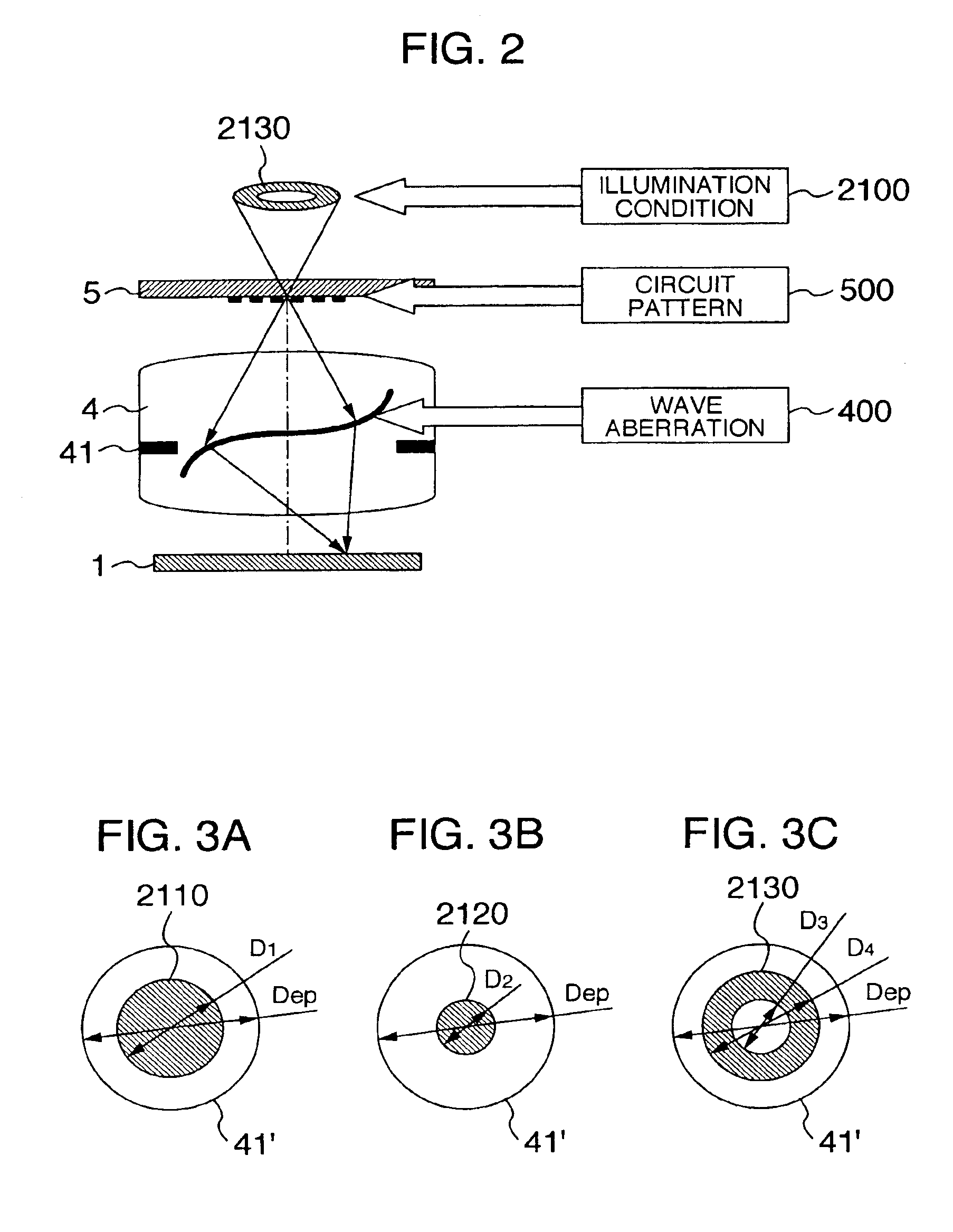

Method and its apparatus for manufacturing semiconductor device

InactiveUS6869807B2Increase productionEliminate needSemiconductor/solid-state device testing/measurementProjector focusing arrangementWave aberrationSemiconductor

Deviations from optimum values of the exposure light quantity and focus of test and product circuit patterns are predicted from the dimensions of the patterns, illumination conditions and the wave aberration of an exposure lens. A signal waveform of scatterometry of the test pattern is linked to the deviations from the optimum values of the exposure light quantity and focus to form a library. The test pattern after exposed and developed in actual steps is collated with the signal waveform in the library measured by the scatterometry to find deviations from the optimum values of the exposure light quantity and focus of the test pattern. Deviations of the optimum values of a product circuit pattern from the deviations of the test pattern are acquired on the basis of the deviations, and the acquired deviations are fed back to subsequent exposure steps.

Owner:HITACHI LTD

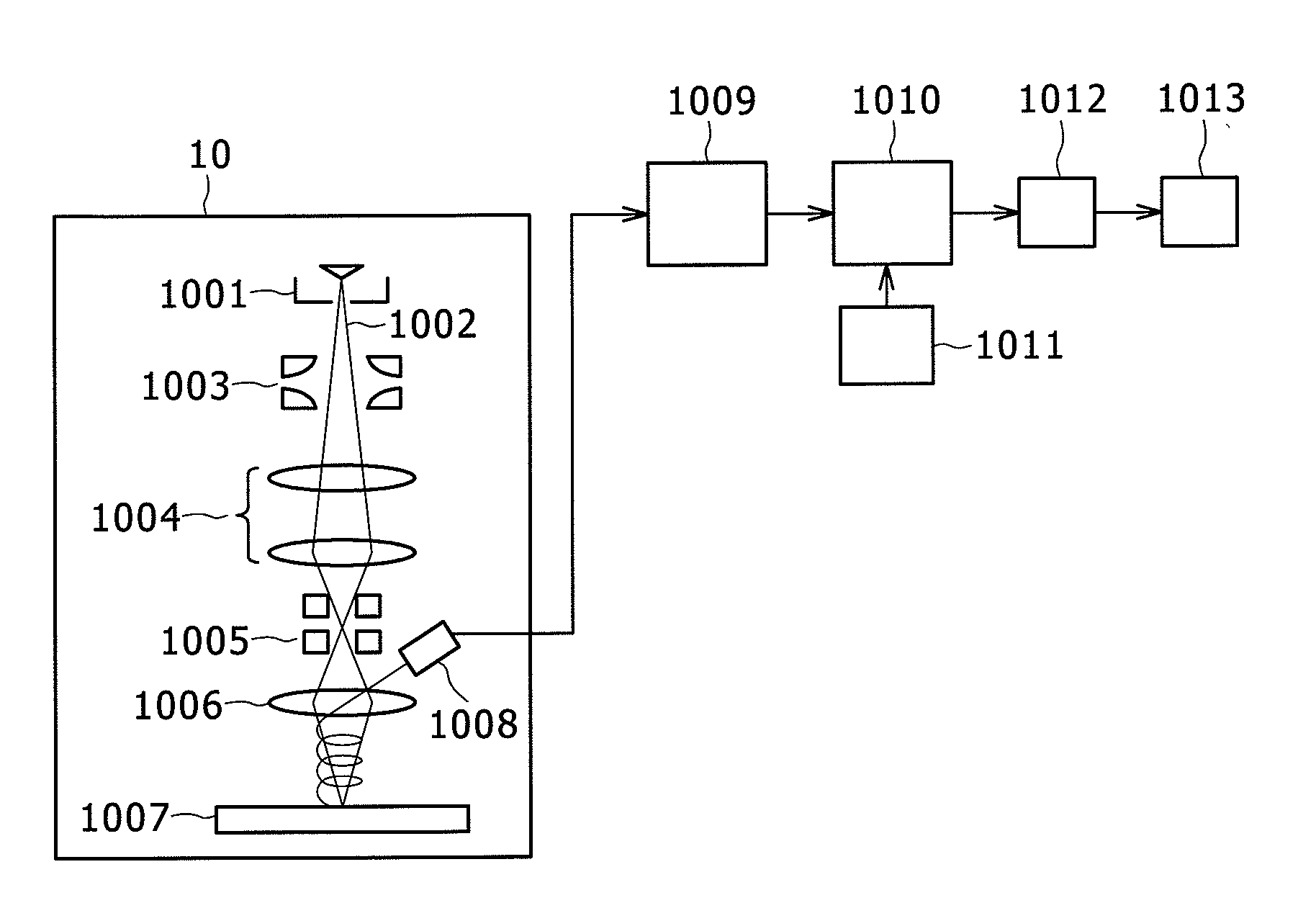

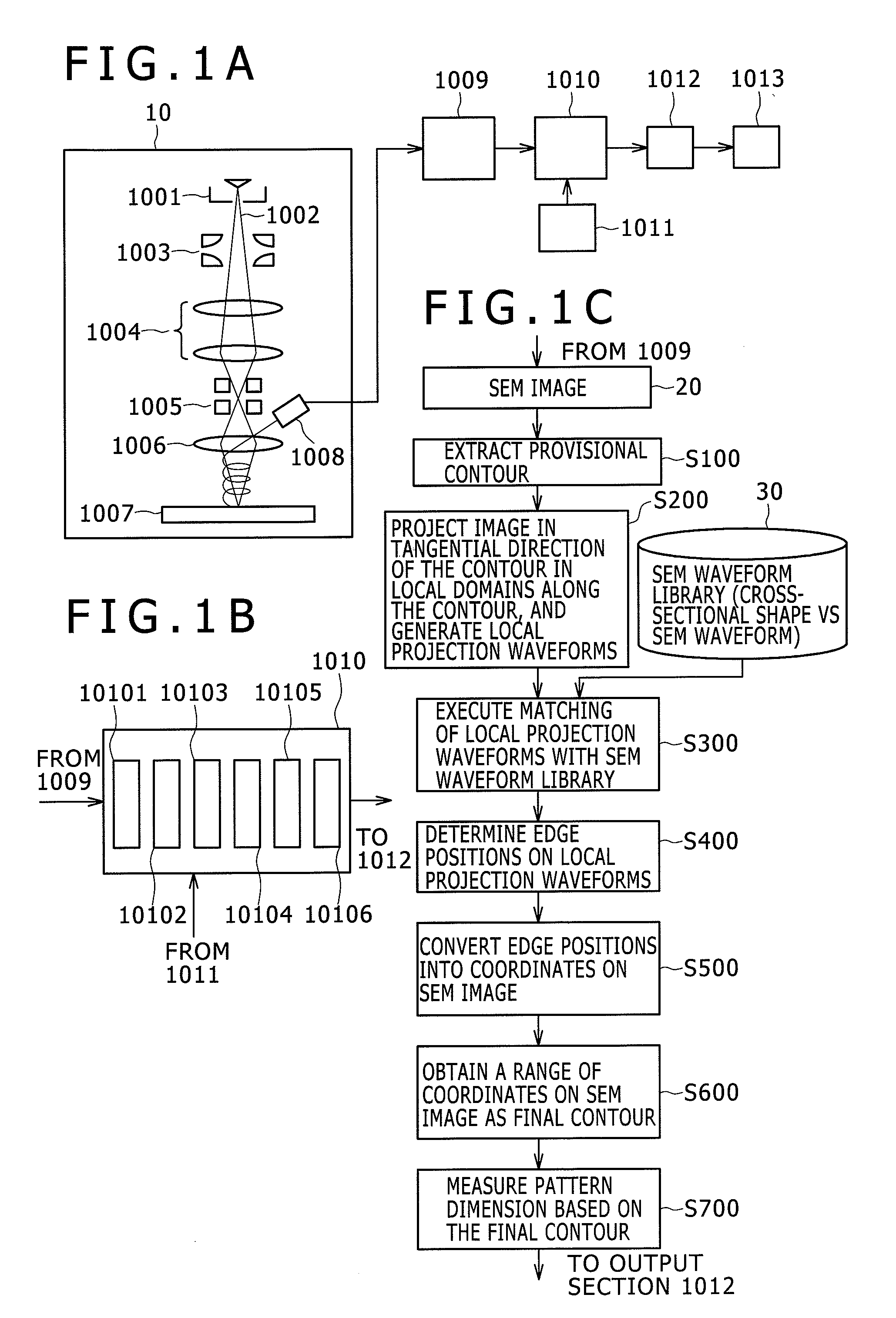

Scanning Electron Microscope system and Method for Measuring Dimensions of Patterns Formed on Semiconductor Device By Using the System

ActiveUS20090212212A1Reliable dimension measurementReliable measurementMaterial analysis using wave/particle radiationPhotomechanical apparatusWave shapeScanning electron microscope

The present invention is for providing a scanning electron microscope system adapted to output contour information fitting in with the real pattern edge end of a sample, and is arranged to generate a local projection waveform by projecting the scanning electron microscope image in the tangential direction with respect to the pattern edge at each point of the pattern edge of the scanning electron microscope image, estimate the cross-sectional shape of the pattern transferred on the sample by applying the local projection waveform generated at each point to a library, which has previously been created, correlating the cross-sectional shape with the electron beam signal waveform, obtain position coordinate of the edge end fitting in with the cross-sectional shape, and output the contour of the pattern as a range of position coordinates.

Owner:HITACHI HIGH-TECH CORP

Patterning using wax printing and lift off

InactiveUS7309563B2Low production costSimplify the patterning processTransistorPhotomechanical apparatusWaxImage resolution

A method for performing a liftoff operation involves printing a liftoff pattern using low-resolution patterning techniques to form fine feature patterns. The resulting feature size is defined by the spacing between printed patterns rather than the printed pattern size. By controlling the cross-sectional profile of the printed liftoff pattern, mask structures may be formed from the liftoff operation having beneficial etch-mask aperture profiles. For example, a multi-layer printed liftoff pattern can be used to create converging aperture profiles in a patterned layer. The patterned layer can then be used as an etch mask, where the converging aperture profiles result in desirable diverging etched features.

Owner:PALO ALTO RES CENT INC

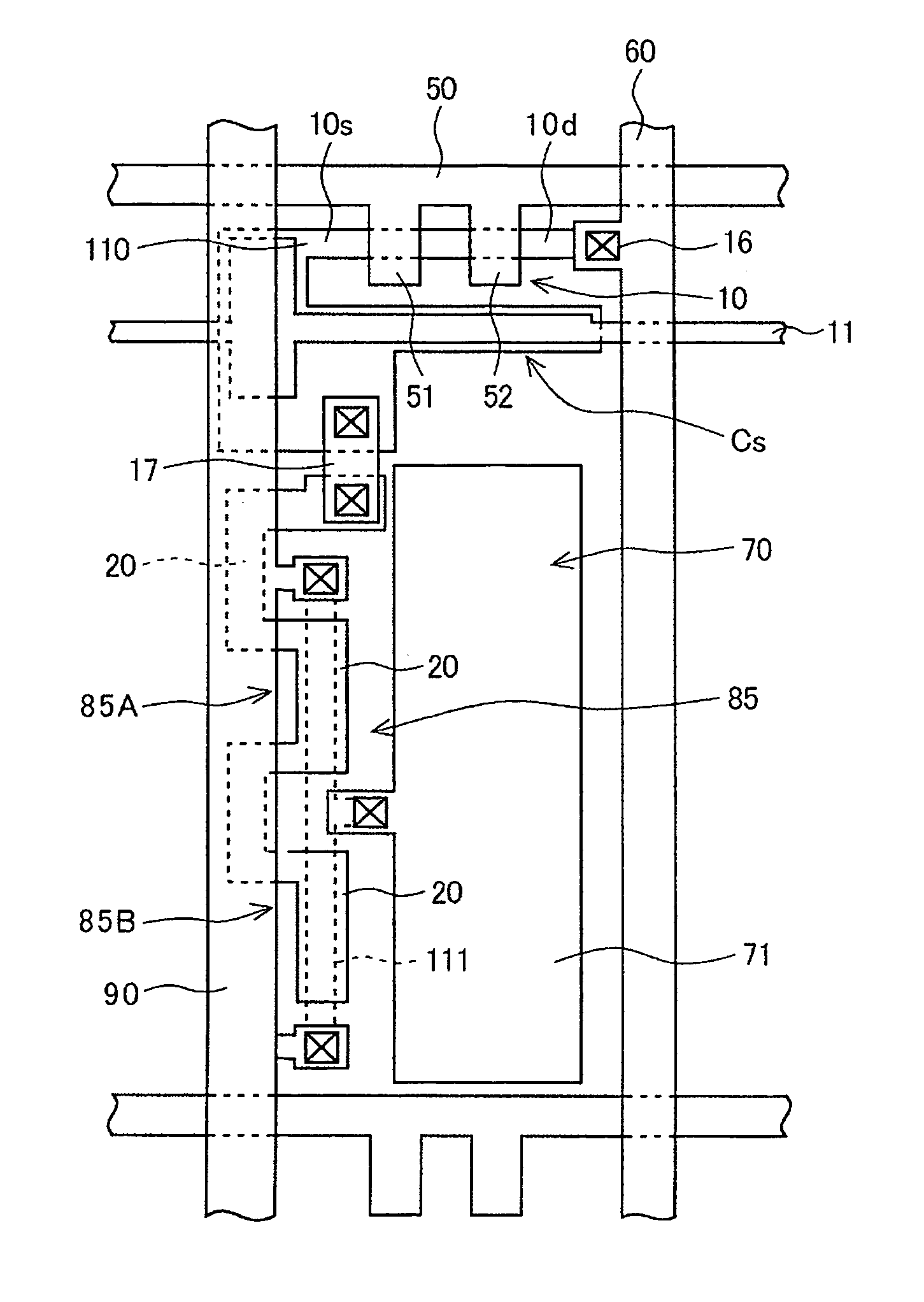

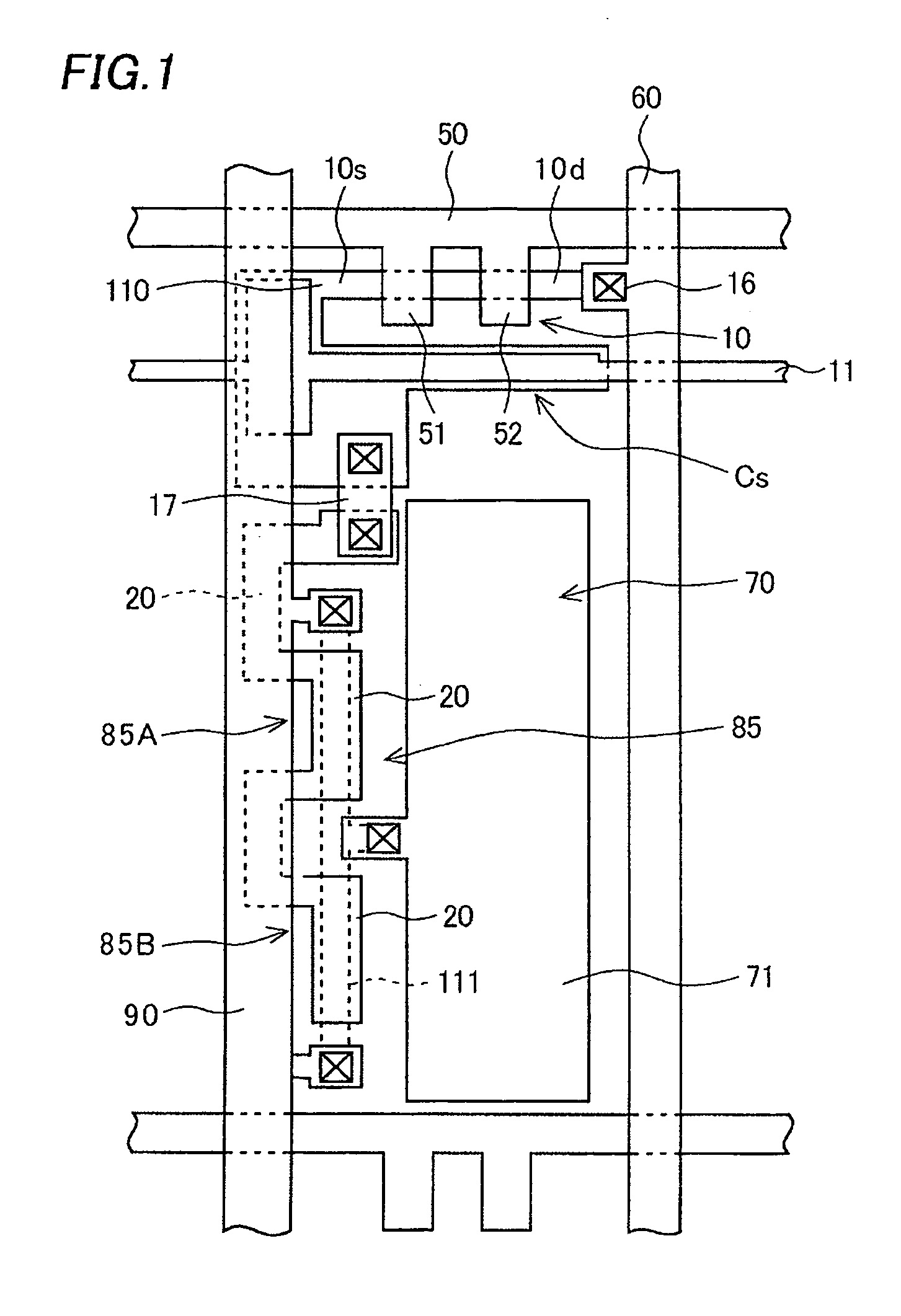

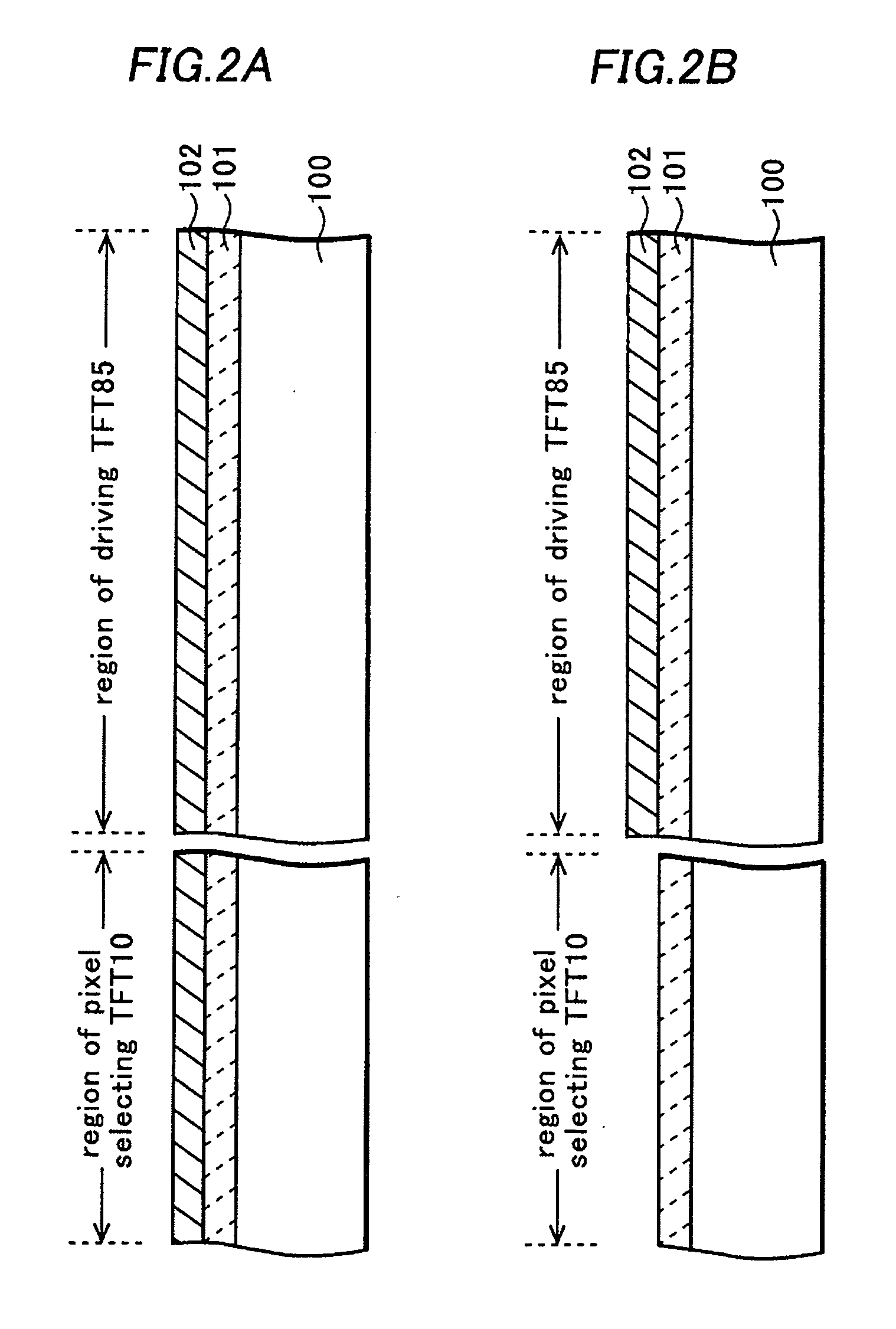

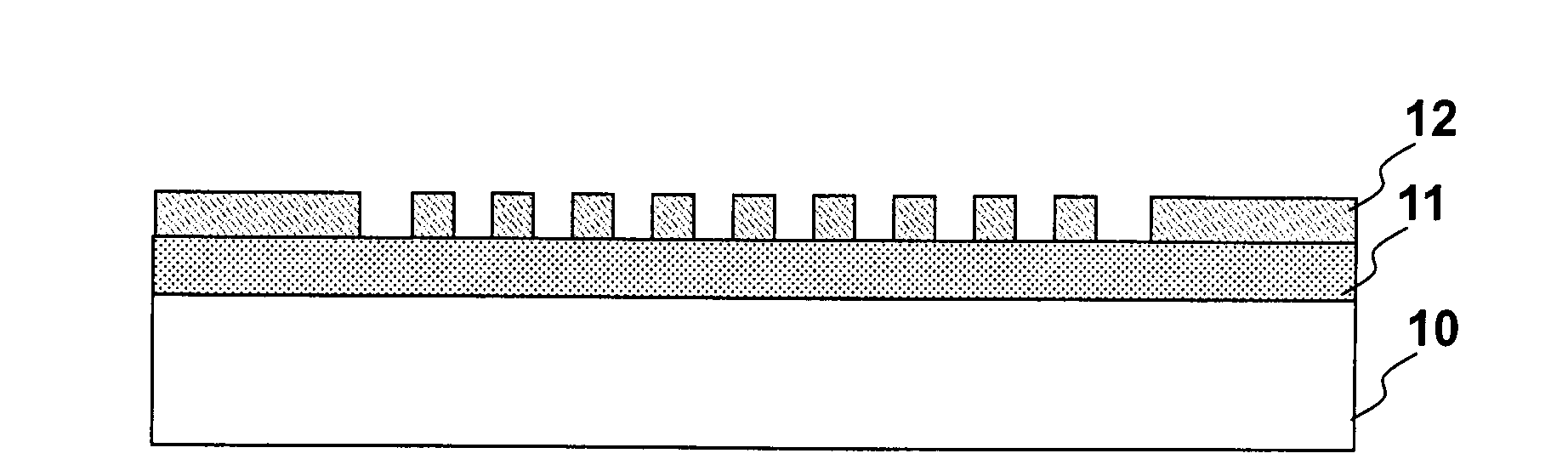

Display device and manufacturing method of the same

InactiveUS20050225253A1Large grainTransistorStatic indicating devicesDisplay deviceCharge carrier mobility

The invention is directed to reduction of a pattern size of a driving transistor of an emissive element and an improvement of an aperture ratio of a pixel. A second active layer of a driving TFT is formed of a two laminated polysilicon layers. The upper polysilicon layer is formed at the same time when a polysilicon layer forming a first active layer of a pixel selecting TFT is formed, and has a same thickness as that of the first active layer. Therefore, the second active layer is formed thicker by a film thickness of the lower polysilicon layer. An average crystal grain size of the second active layer is smaller than an average crystal grain size of the first active layer. Therefore, a carrier mobility of the driving TFT is lower than a carrier mobility of the pixel selecting TFT. This can shorten a channel length of the driving TFT.

Owner:SANYO ELECTRIC CO LTD

Photomask manufacturing method and semiconductor device manufacturing method

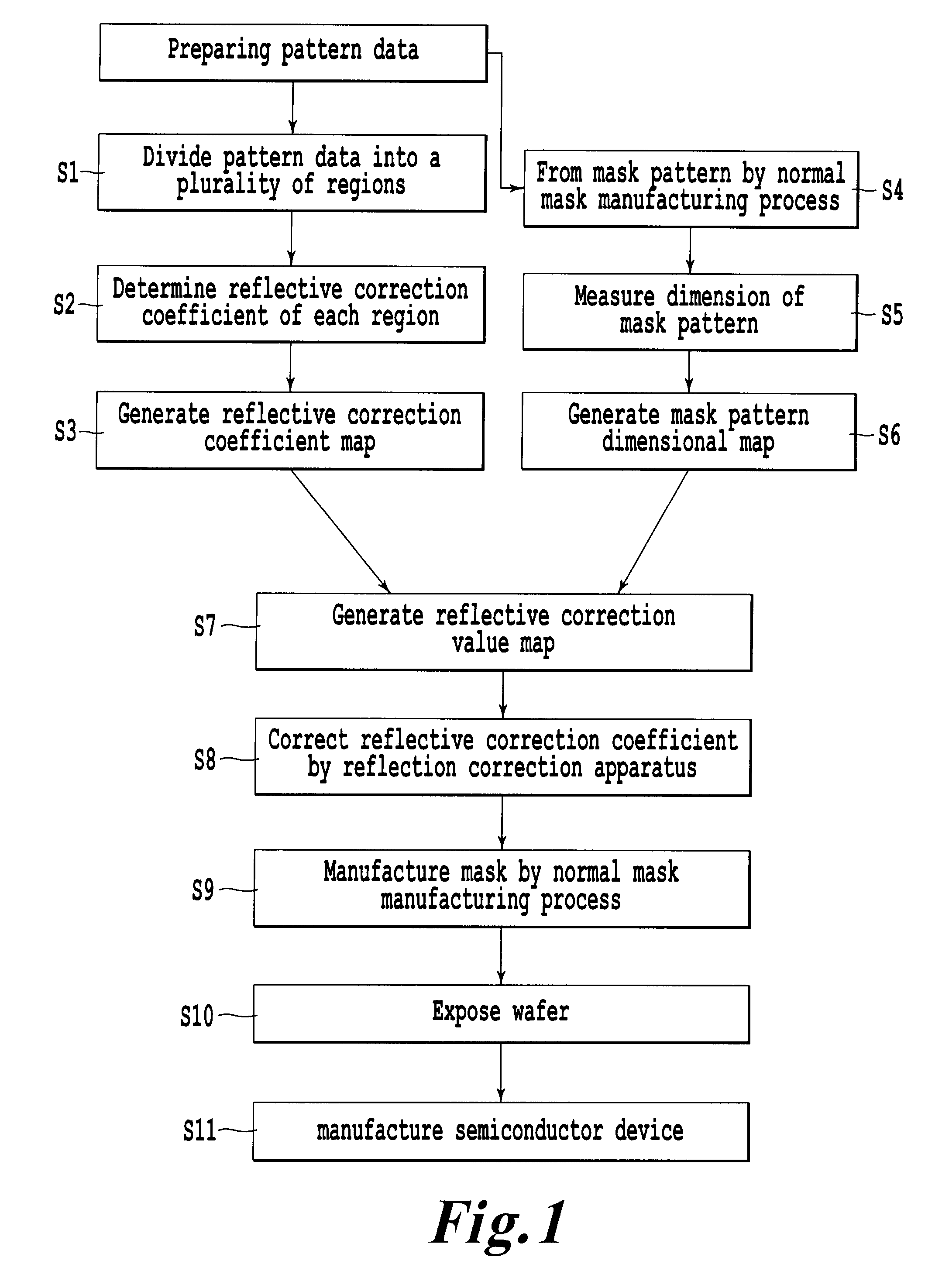

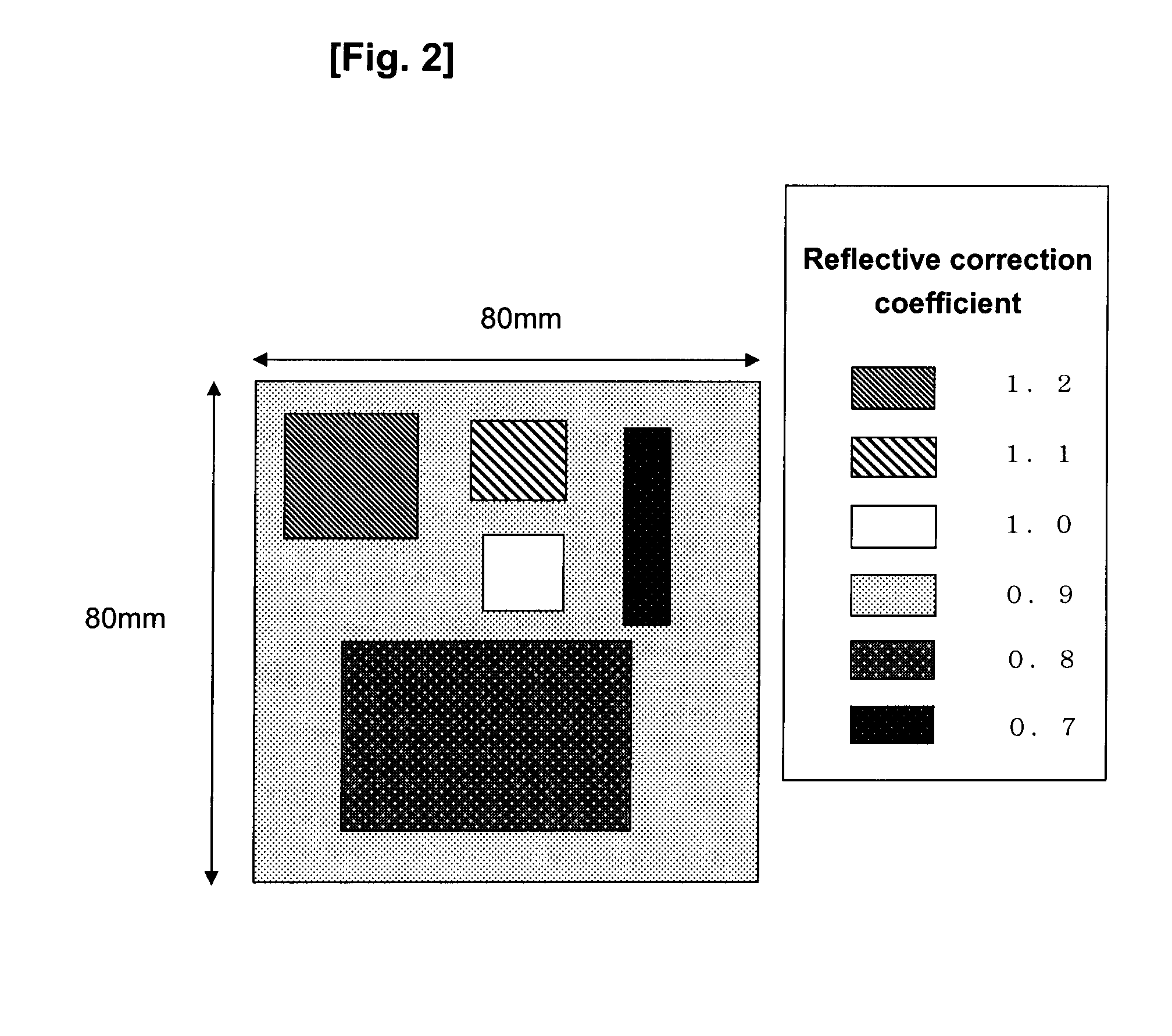

ActiveUS20080311486A1NanoinformaticsSemiconductor/solid-state device manufacturingReflective layerSemiconductor

A photomask manufacturing method. A pattern dimensional map is generated by preparing a photomask in which a reflective layer formed on a substrate and an absorber pattern is formed on the layer. A reflection correction coefficient map is generated by dividing a mask region, where the absorber pattern is formed, into a plurality of subregions, and determining a reflection correction coefficient for each subregion. The reflection correction value of each subregion is calculated based on the dimensional difference indicated in the pattern dimensional map and the reflection correction coefficient of each subregion. A reflection coefficient of each reflective layer region corresponding to each subregion is changed based on the reflection correction value.

Owner:KIOXIA CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com