Production method of grids curb wall

A manufacturing method and gate sidewall technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem of inability to respond to changes in the thickness of sidewall material layers, poor line width and contour consistency of sidewalls, etc. problems, to reduce costs, improve process windows and maintainability, and improve stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

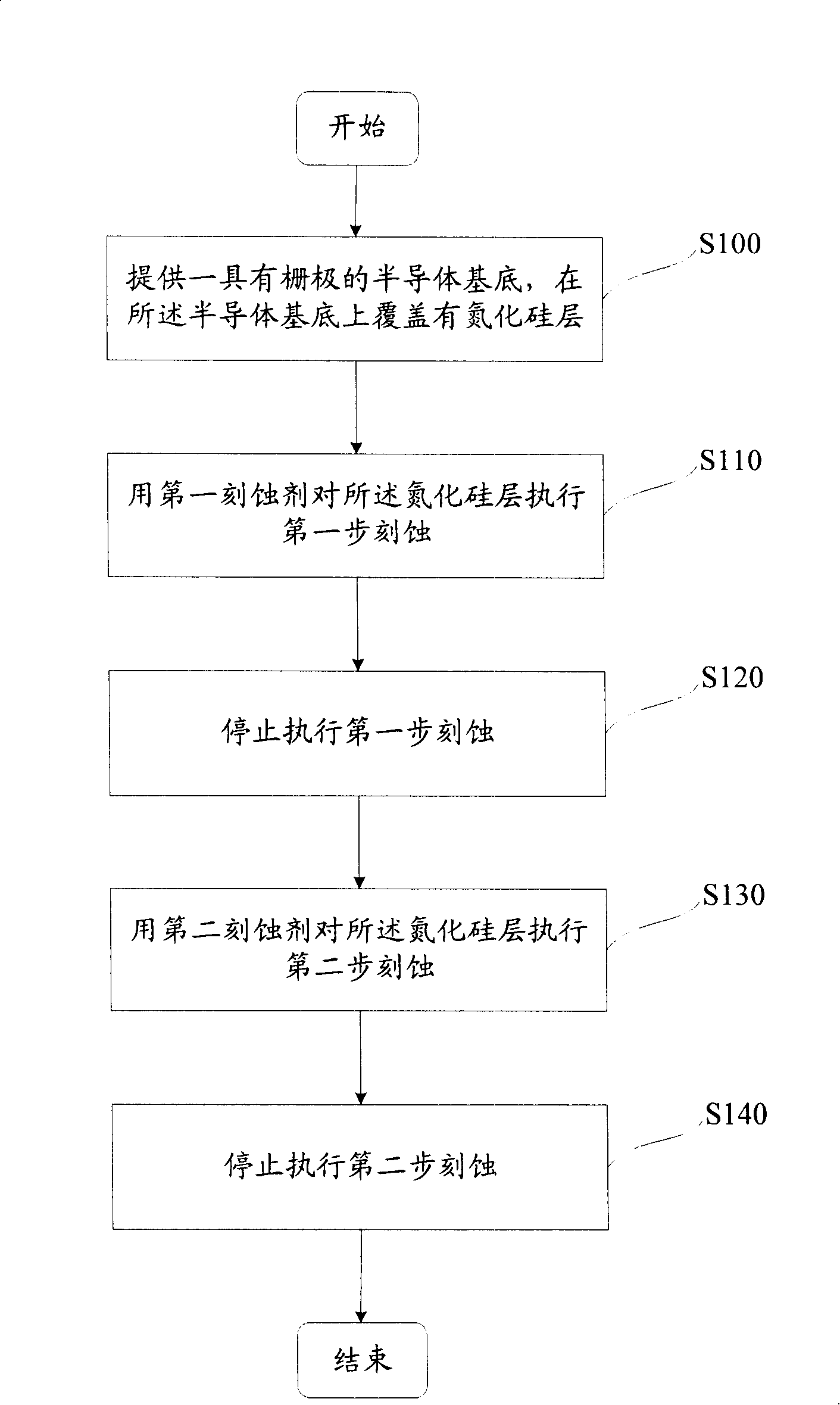

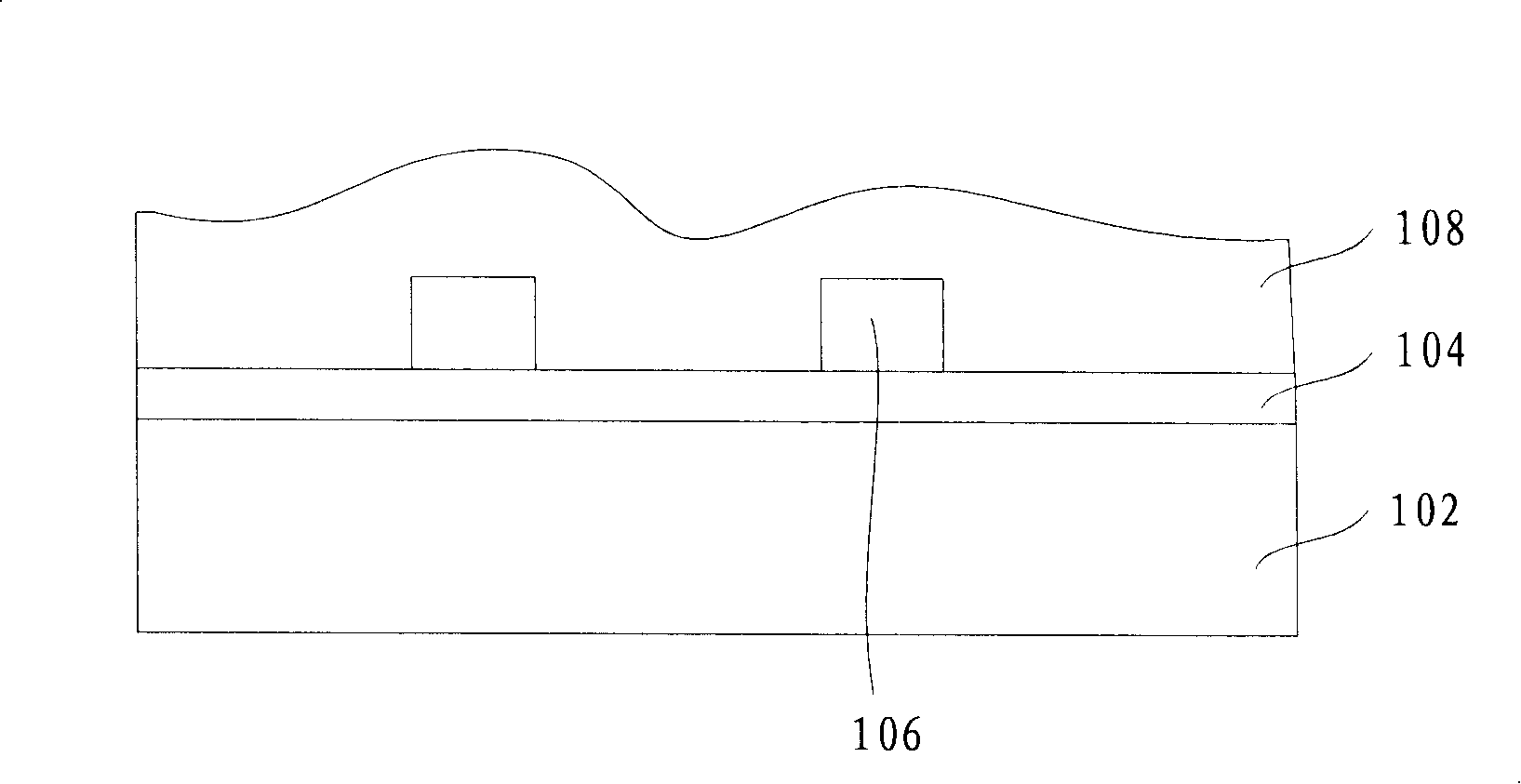

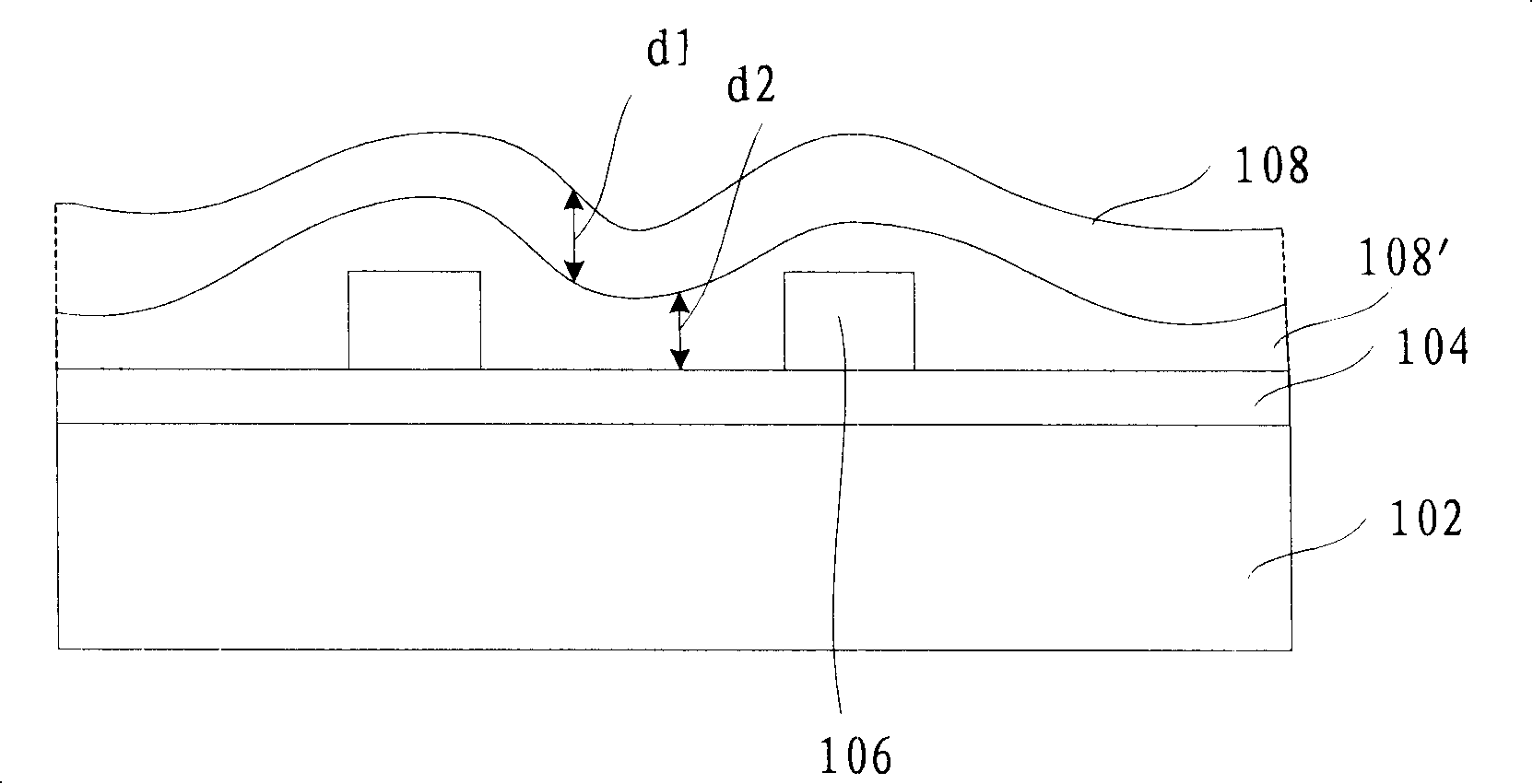

[0032] The manufacturing method of the gate spacer of the present invention first measures the thickness of the dielectric layer deposited on the surface of the gate by an optical critical dimension measurement (OCD, Optical Critical Dimension) method, and then according to the difference between the thickness and the target thickness of the spacer and the calculated The etching rate of the dielectric layer determines the etching time, and the dielectric layer is etched according to the determined time to form sidewalls. The method of the invention can avoid the change of the line width and profile of the side wall after etching caused by the difference in the thickness of the dielectric layer on the wafer, and can improve the consisten...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com