Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

199results about How to "Dispersion suppression" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

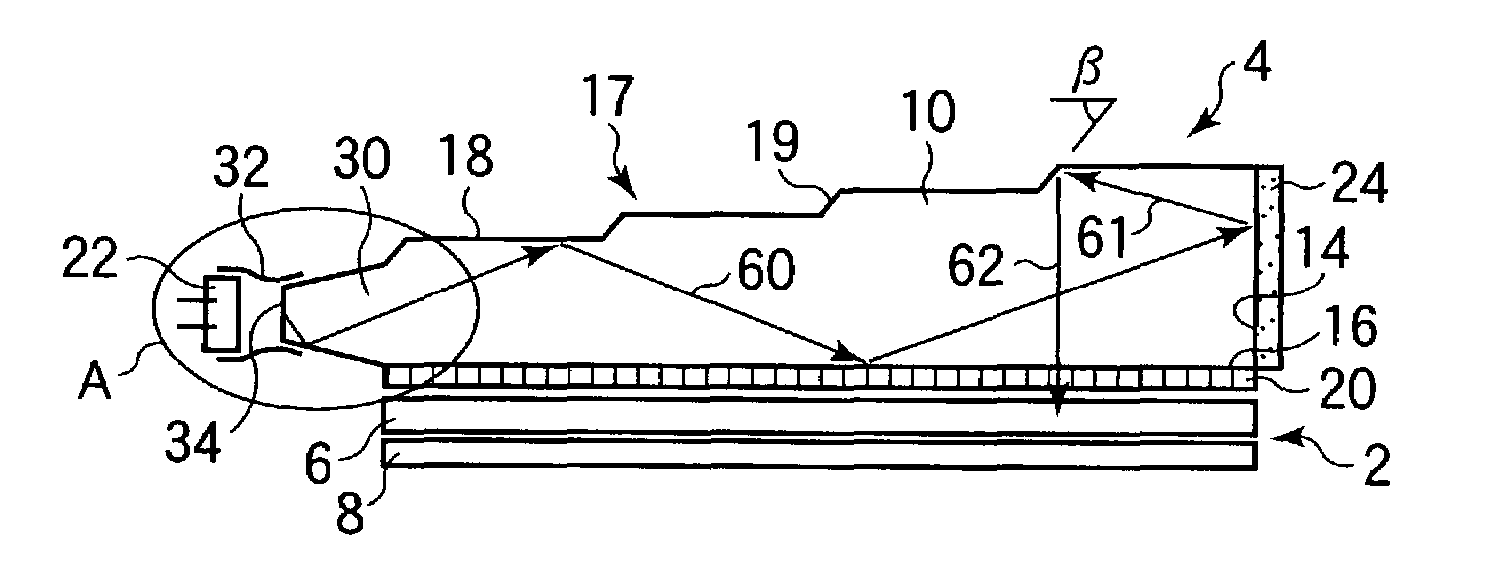

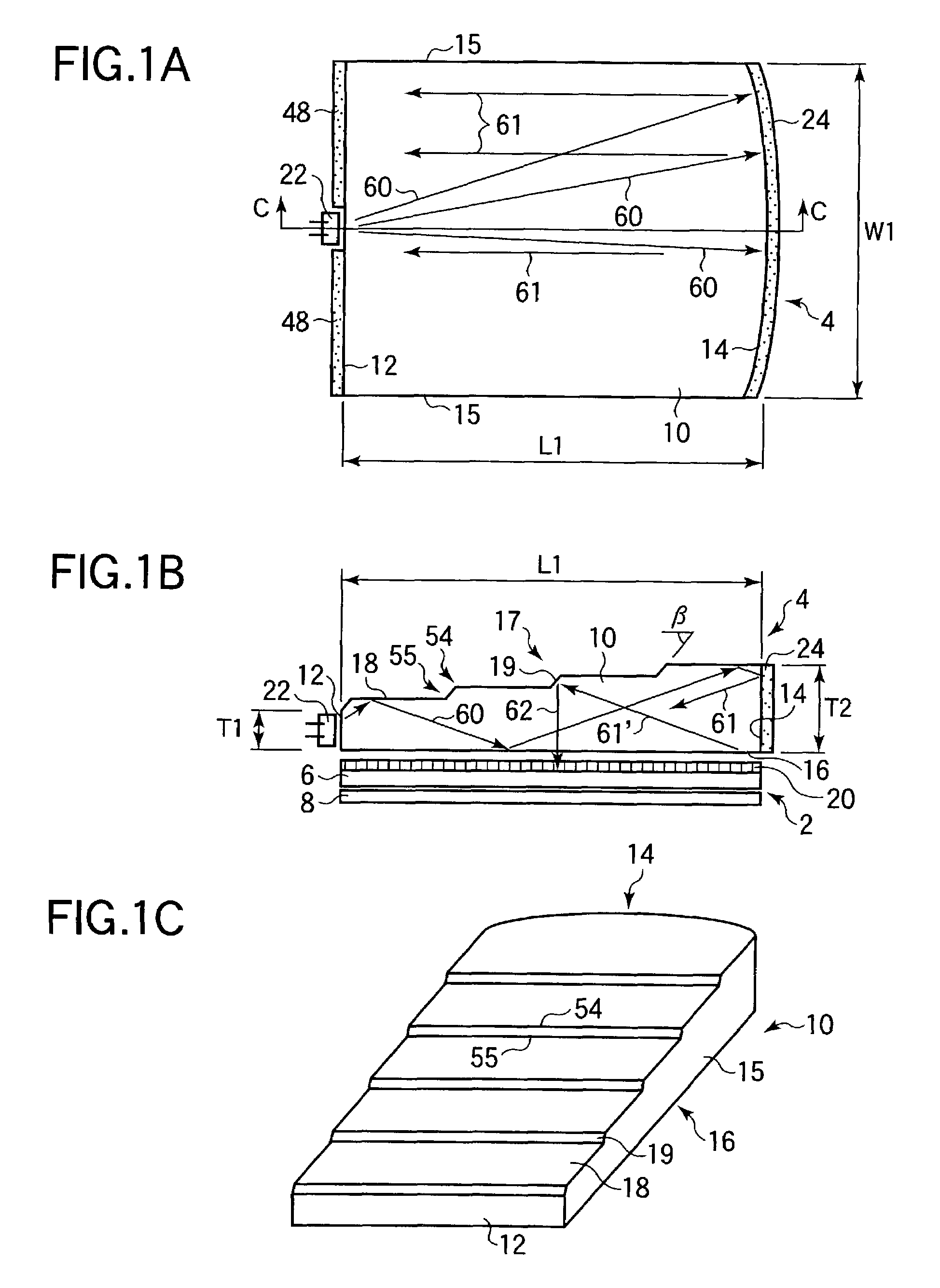

Light guide plate, light source device equipped therewith and display device

InactiveUS7073933B2Dispersion suppressionIncrease contrastPoint-like light sourceMeasurement apparatus componentsForming faceLight guide

A display device used for a display unit of portable electronic equipment, a light source device therefor and a light guide plate, suppressing dispersion in the brightness and featuring a high contrast and a good display quality. The constitution includes a light incidence surface on where light emitted from an LED falls, a light reflection surface formed facing the light incidence surface and reflects light from the light incidence surface, a light outgoing surface arranged between the light incidence surface and the light reflection surface, and has a circularly polarizing plate intimately adhered onto the surface thereof, and an opposing surface formed facing the light outgoing surface and in which there are alternately arranged first opposing surfaces for guiding the incident light to the light outgoing surface as well as to the light reflection surface, and second opposing surfaces for emitting the light reflected by the light reflection surface through the light outgoing surface.

Owner:SHARP KK

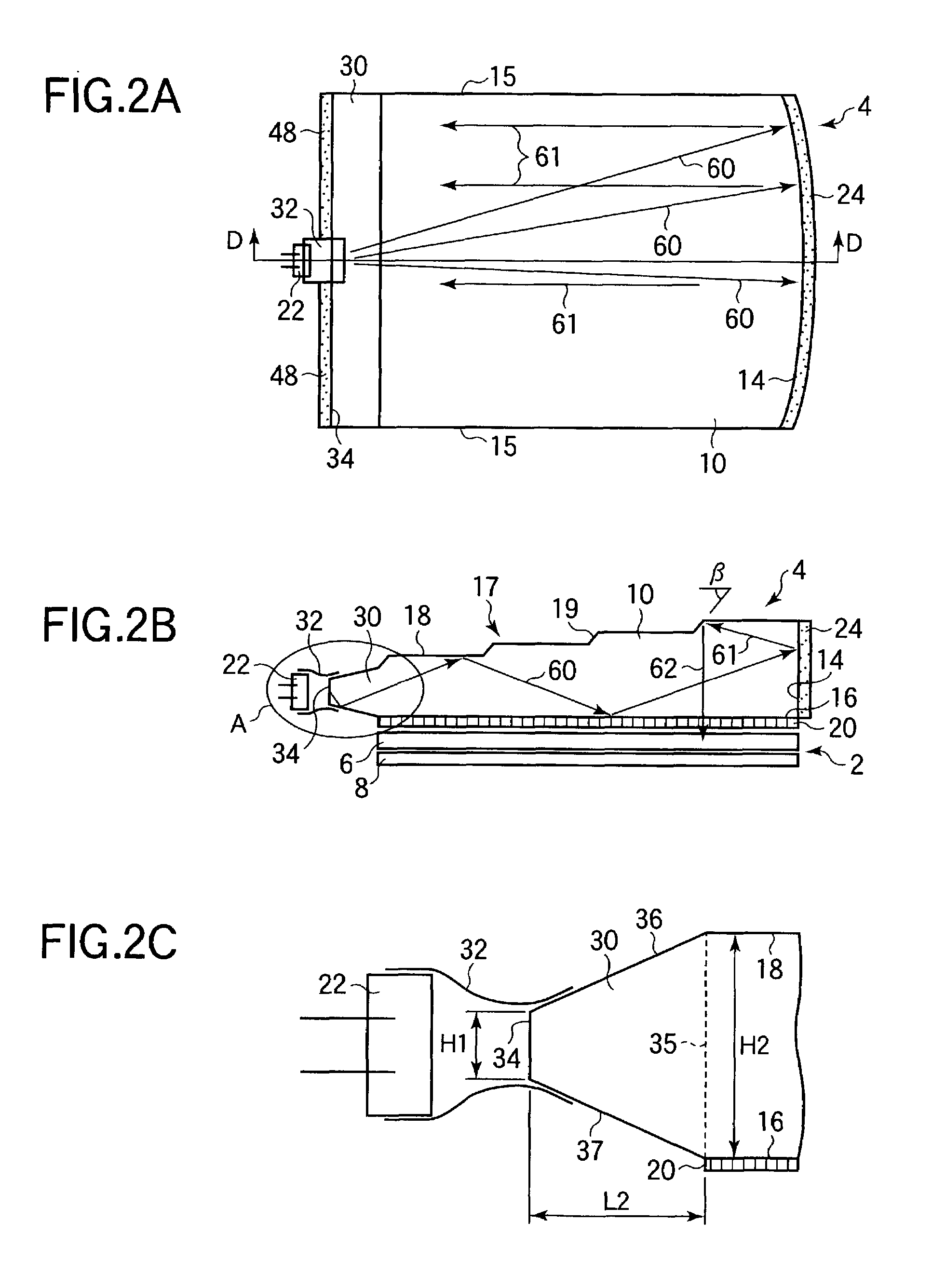

Optical fiber

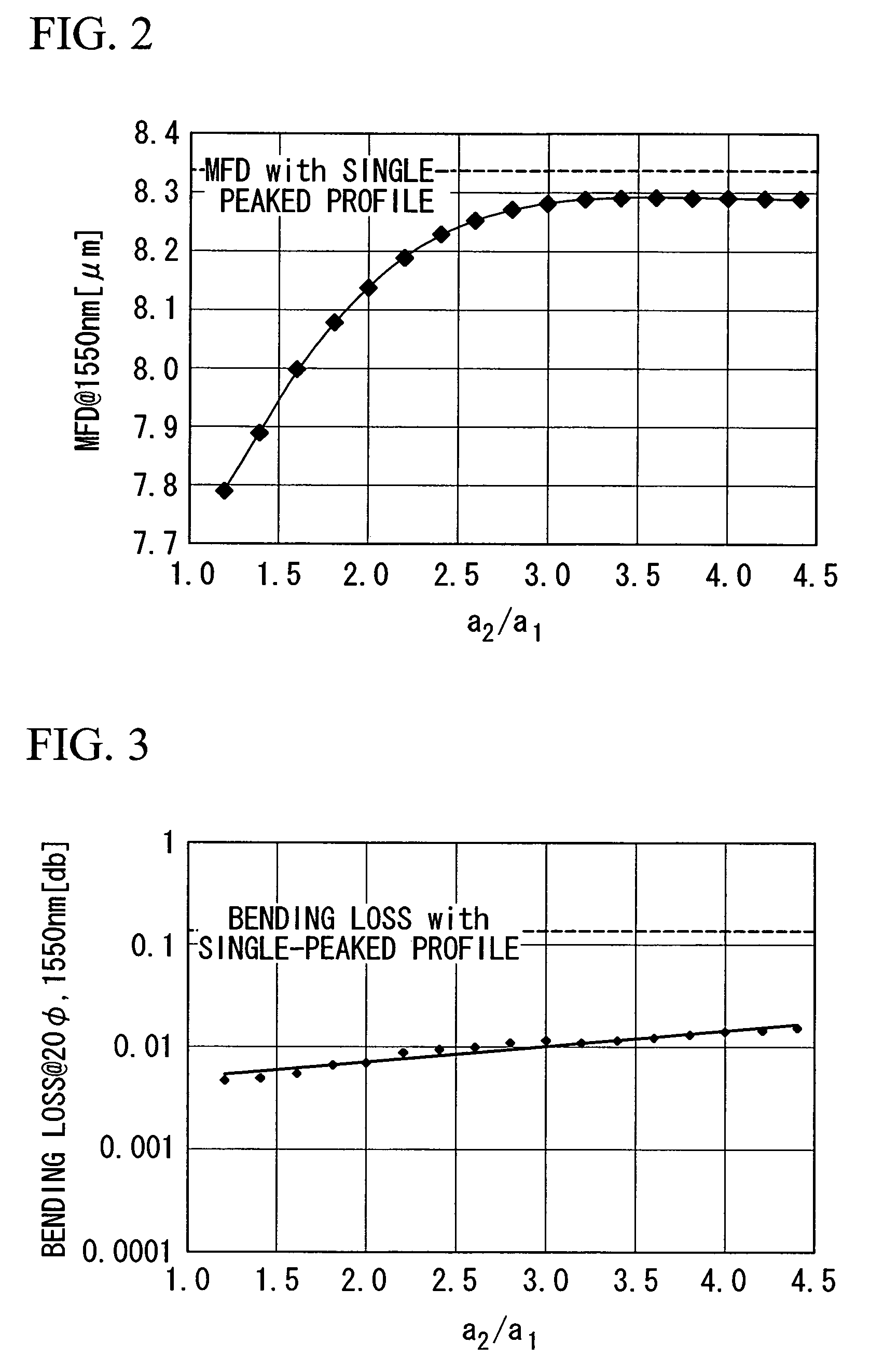

ActiveUS7164835B2Lower refractive indexReduce dispersionOptical fibre with multilayer core/claddingOptical waveguide light guideRelative refractive indexMaterials science

An optical fiber includes: a core at a center; a first cladding layer; a second cladding layer; and a third cladding layer. A maximum refractive index of the core is greater than any of maximum refractive indices of the first cladding layer, the second cladding layer, and the third cladding layer, and the maximum refractive index of the second cladding layer is smaller than any of the maximum refractive indices of the first and the third cladding layer. Additionally, a ratio of a2 / a1 is not less than about 2.5 and not more than about 4.5, where a1 represents the radius of the core, and a2 represents the radius of an outer periphery of the first cladding layer, and a relative refractive index difference of the core with respect to a maximum refractive index of the third cladding layer is not less than 0.20% and not more than 0.70%.

Owner:FUJIKURA LTD

Manufacturing method of display apparatus and manufacturing apparatus

InactiveUS20090170230A1Improve display characteristicsChromaticity can be suppressedLiquid surface applicatorsStatic indicating devicesOptoelectronics

Owner:CASIO COMPUTER CO LTD

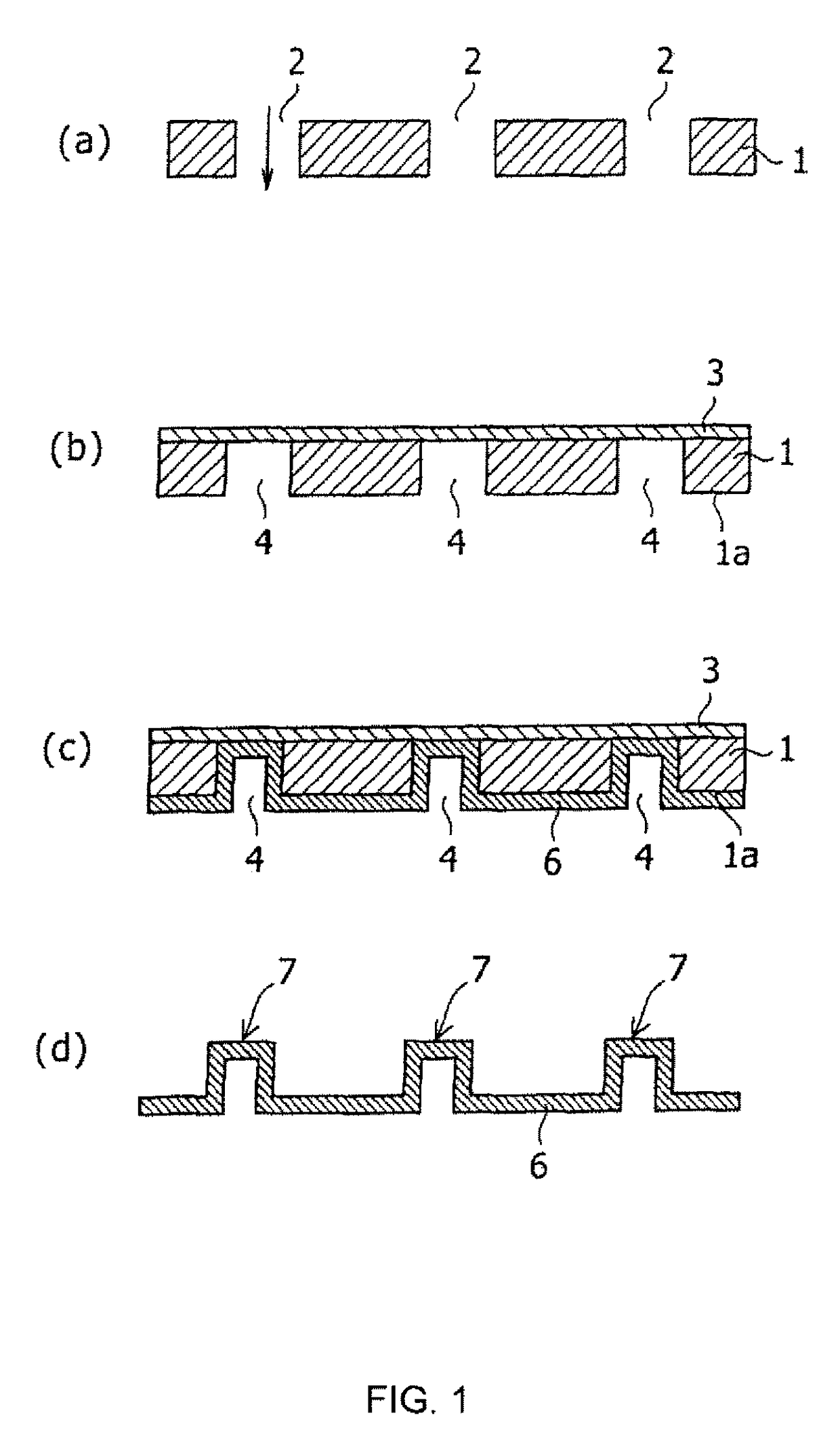

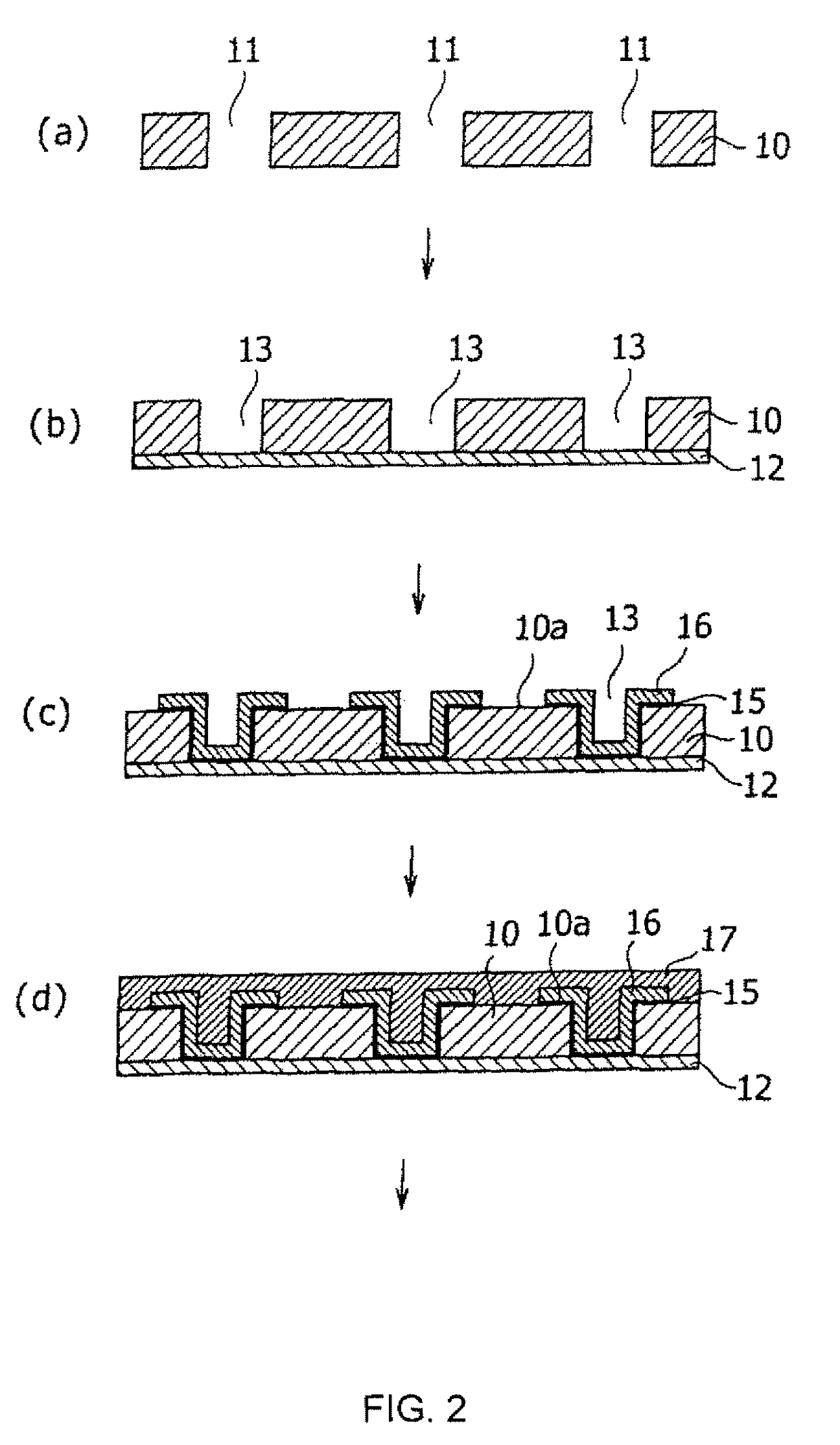

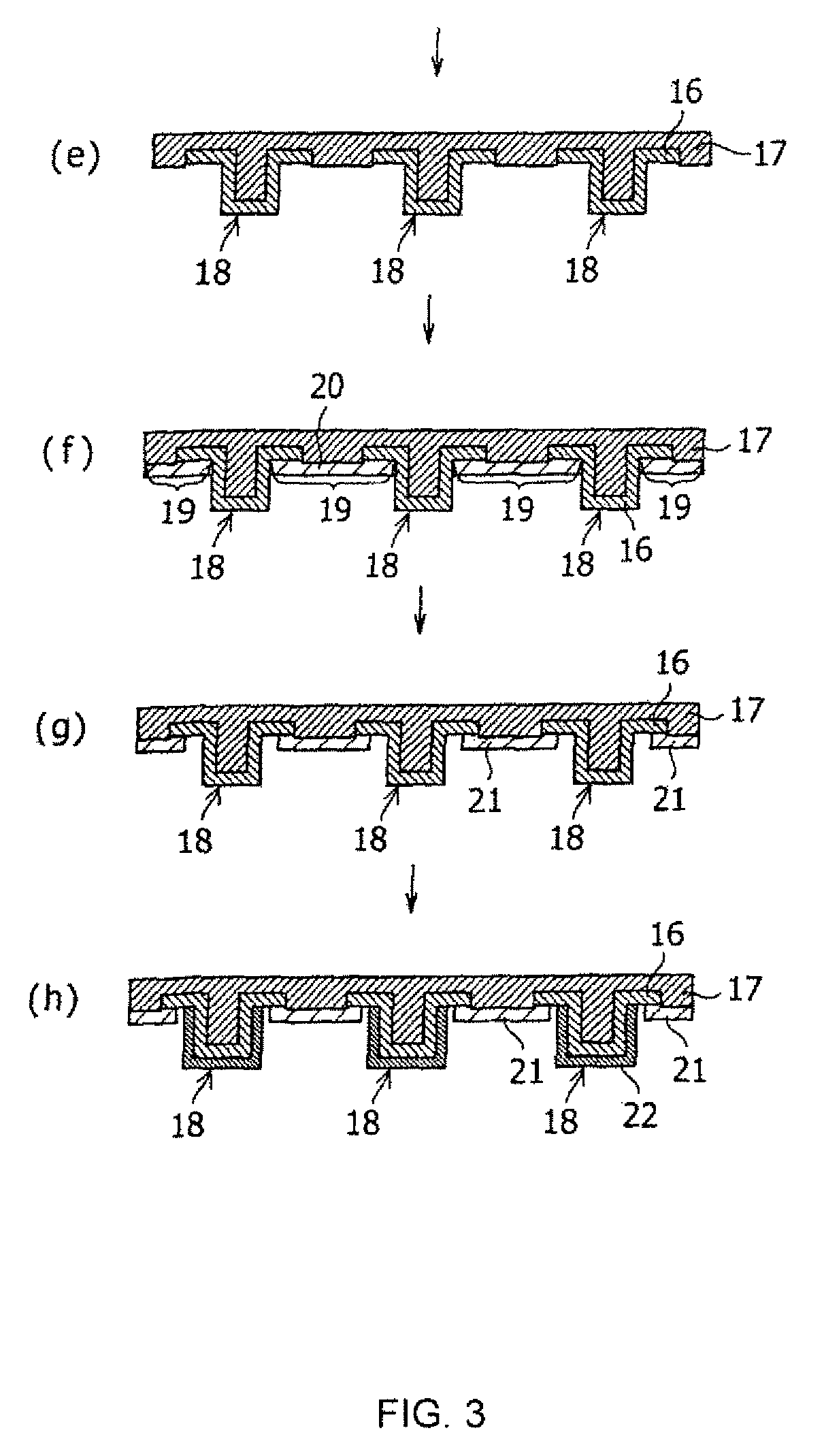

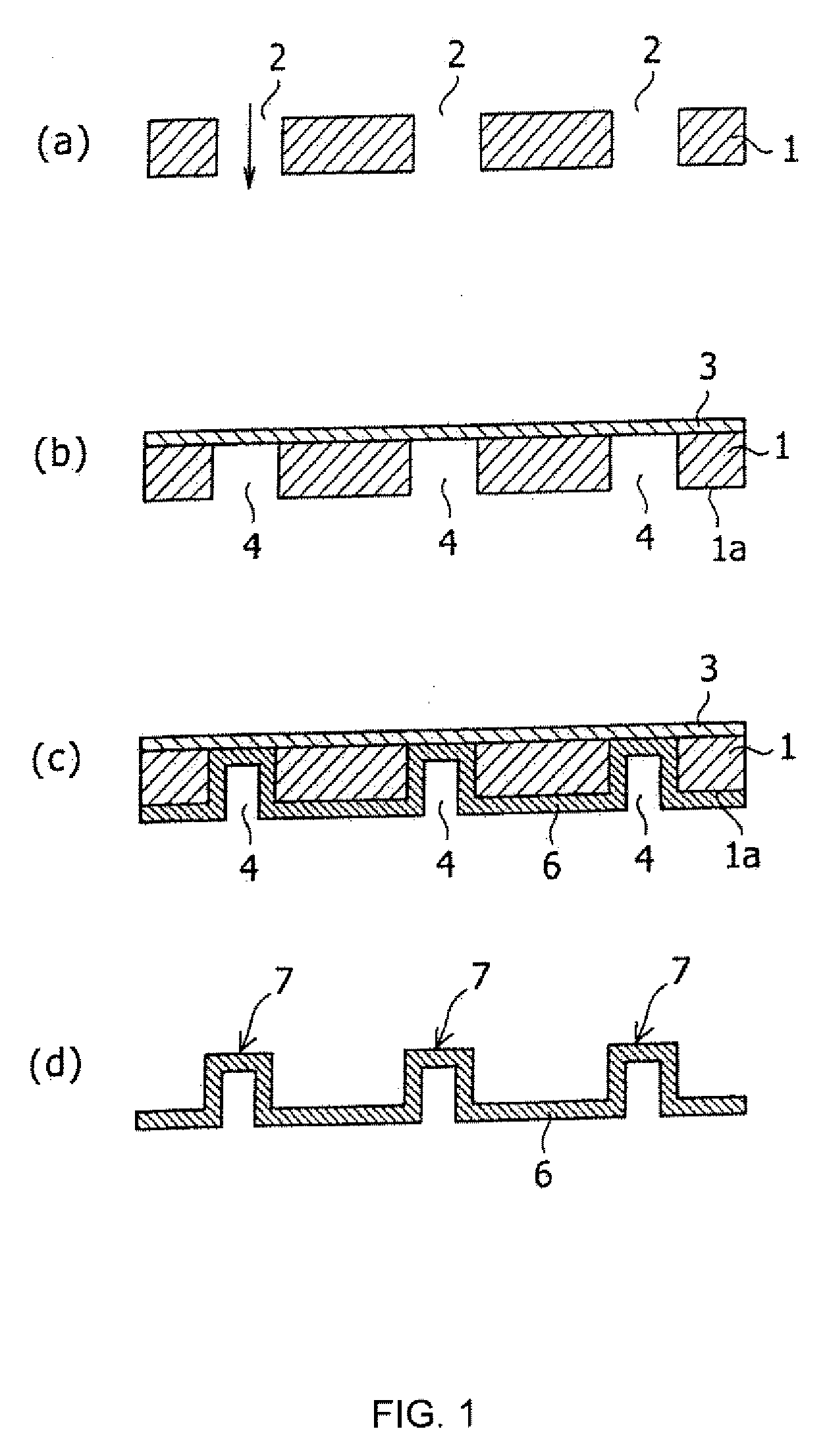

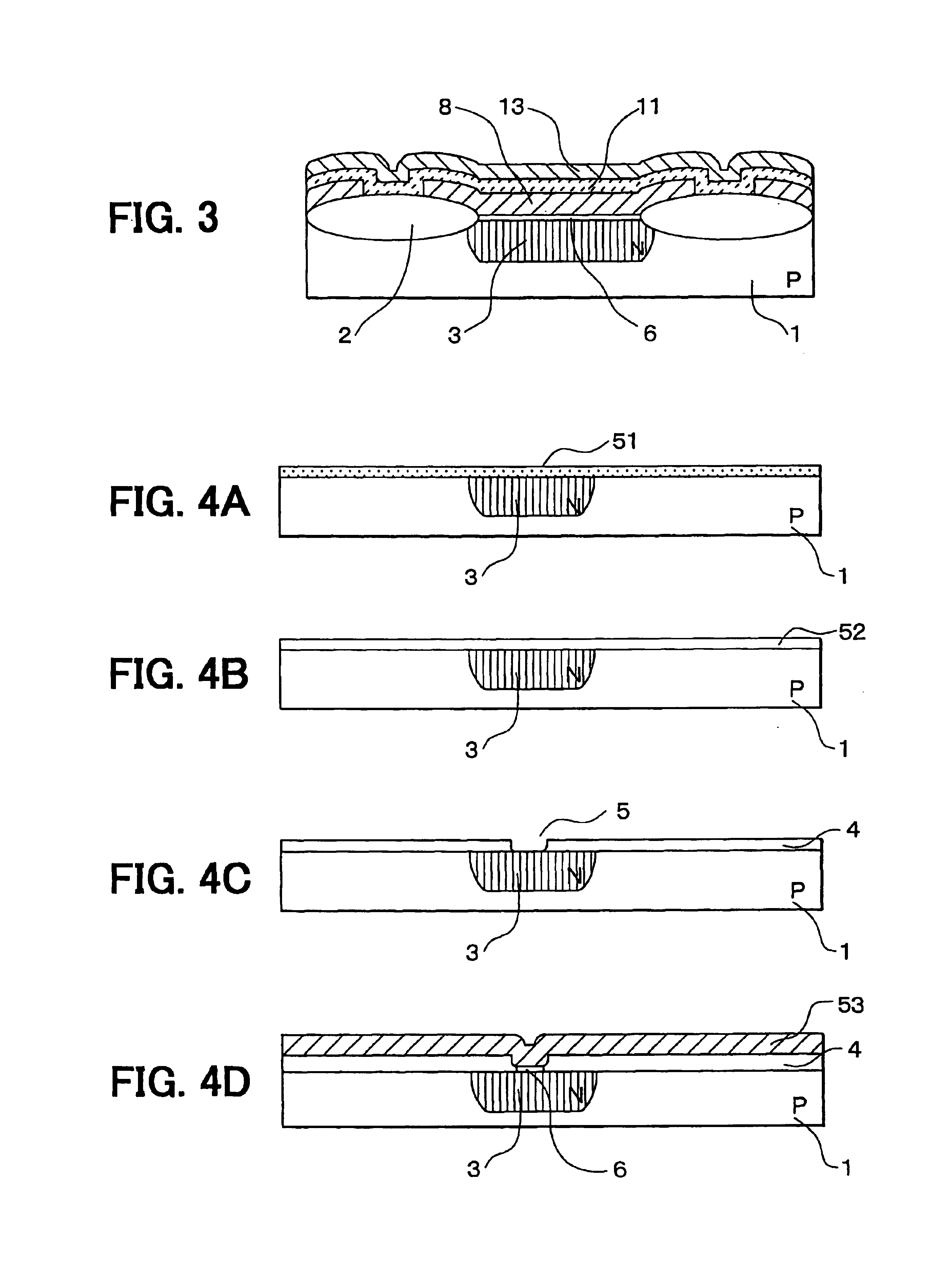

Bump structure formed from using removable mandrel

InactiveUS8119516B2High aspect ratioFine pitchSemiconductor/solid-state device detailsPrinted circuit aspectsEngineeringInterconnection

A method for forming a bump structure and a bump structure for conductive interconnection with another element having at least one of microelectronic devices or wiring thereon, used as an electric connection in an electronic circuit, includes the steps of forming a mandrel by steps including forming at least one opening extending through a bump-forming die body in the thickness direction thereof and positioning a bump-forming die lid on a surface of the bump-forming die body so as to cover one end of the opening and to thereby define a bump-forming recess. The bump-forming die body may be comprised of a metal sheet. A metal layer is formed at least on an inner surface of the bump-forming die lid exposed within the bump-forming recess. The mandrel is removed so as to expose the metal layer and form a bump structure.

Owner:INVENSAS CORP

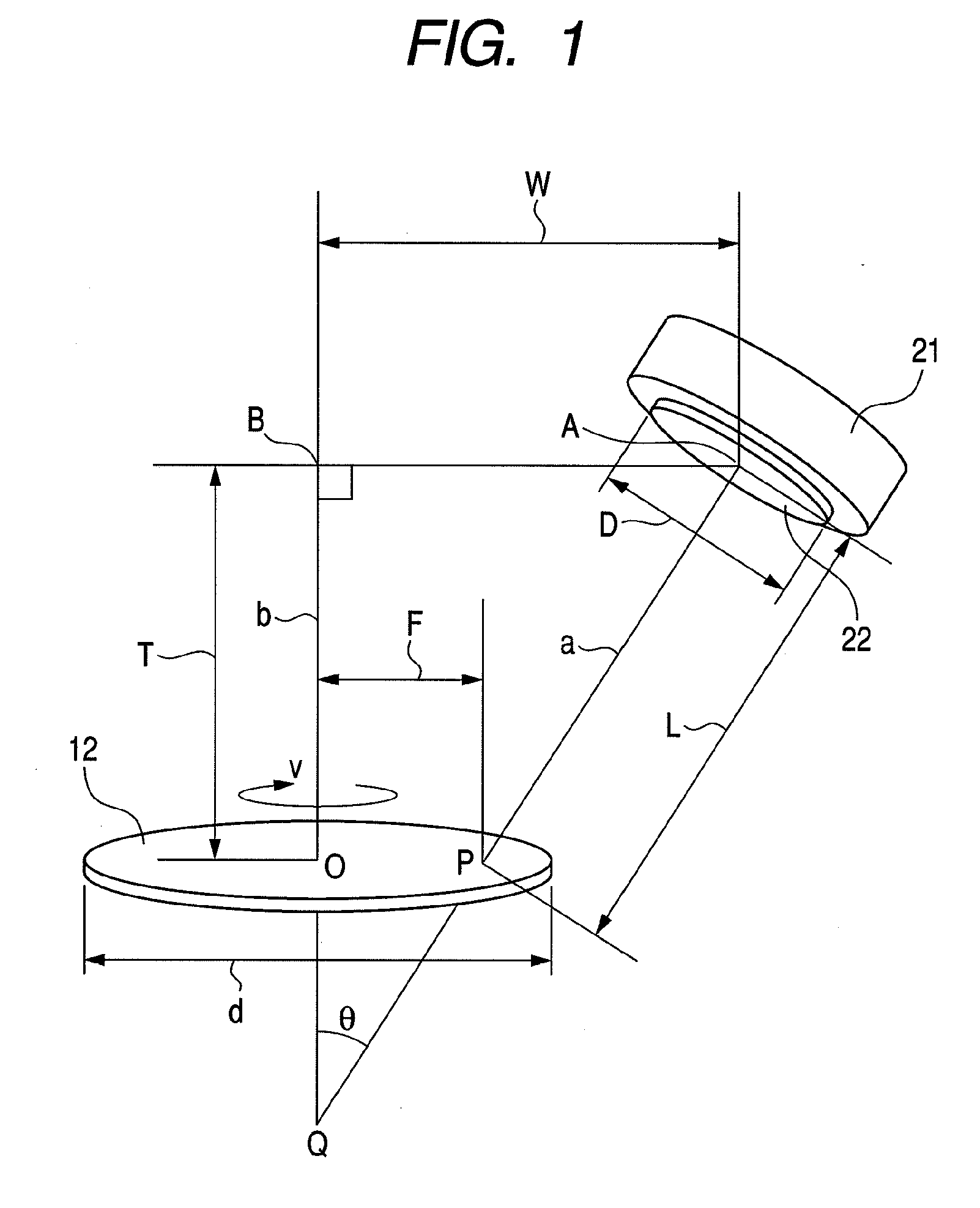

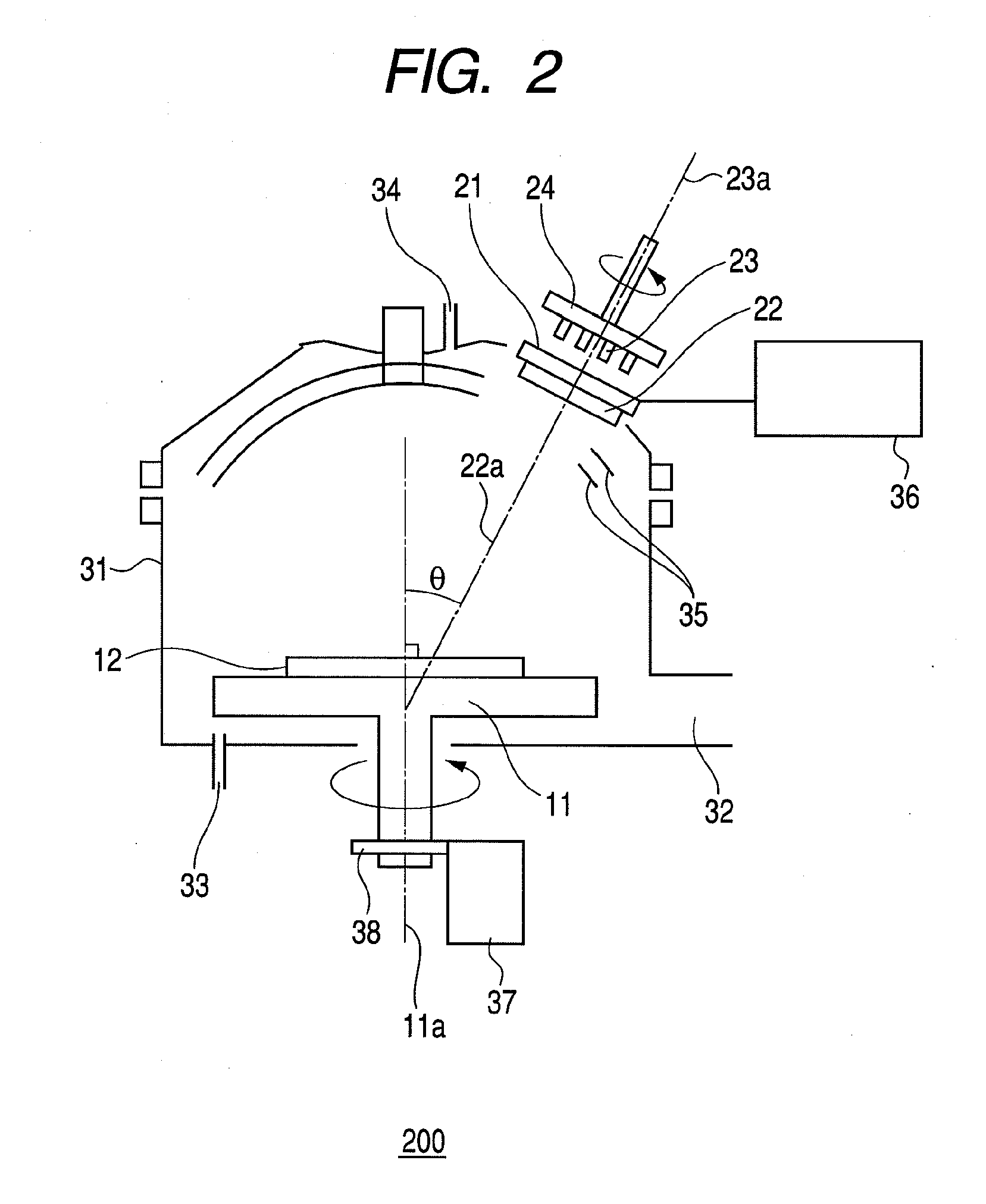

Sputtering method and sputtering apparatus

InactiveUS20100133092A1Highly integratedImprove uniformityVacuum evaporation coatingSputtering coatingMaterials science

A sputtering method and a sputtering apparatus are provided in which a target is disposed being inclined relative to a substrate placed on a substrate-placing table so that the condition of d≧D is satisfied, (d is the diameter of the substrate, and D is the diameter of the target), and the total number of rotations R of the substrate-placing table from the beginning of film-deposition on the substrate to the completion thereof becomes ten or more. Also the sputtering method and the sputtering apparatus are provided in which the rotational speed V of the substrate-placing table is controlled so that the total number of rotations R thereof satisfies the formula of0.95×S−0.025≦R≦1.05×S+0.025at R≦10, (R is the total number of rotations of the substrate-placing table from the beginning of film-deposition on the substrate to the completion thereof, and S is the value of the number of total rotations R rounded off to integer).

Owner:CANON ANELVA CORP

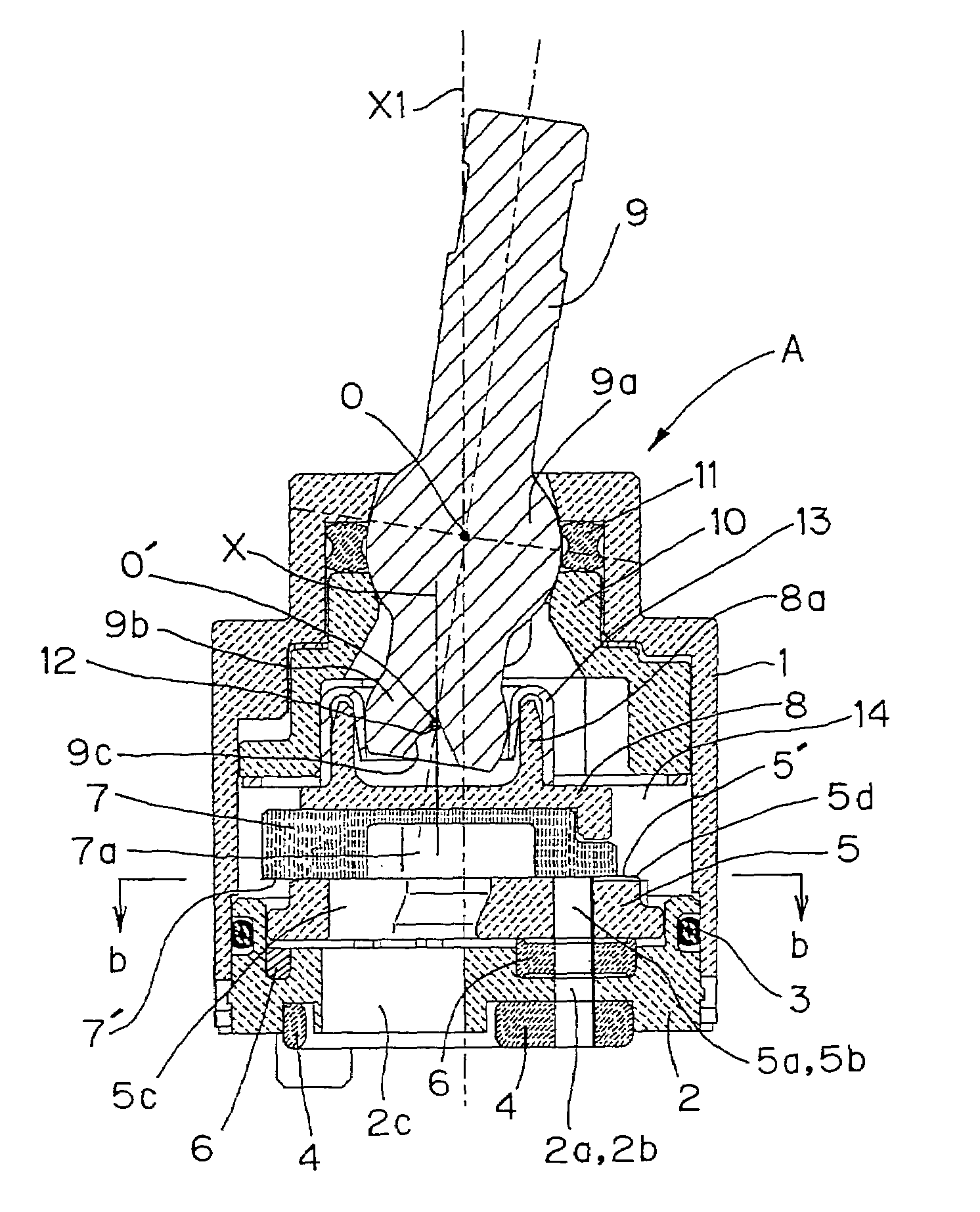

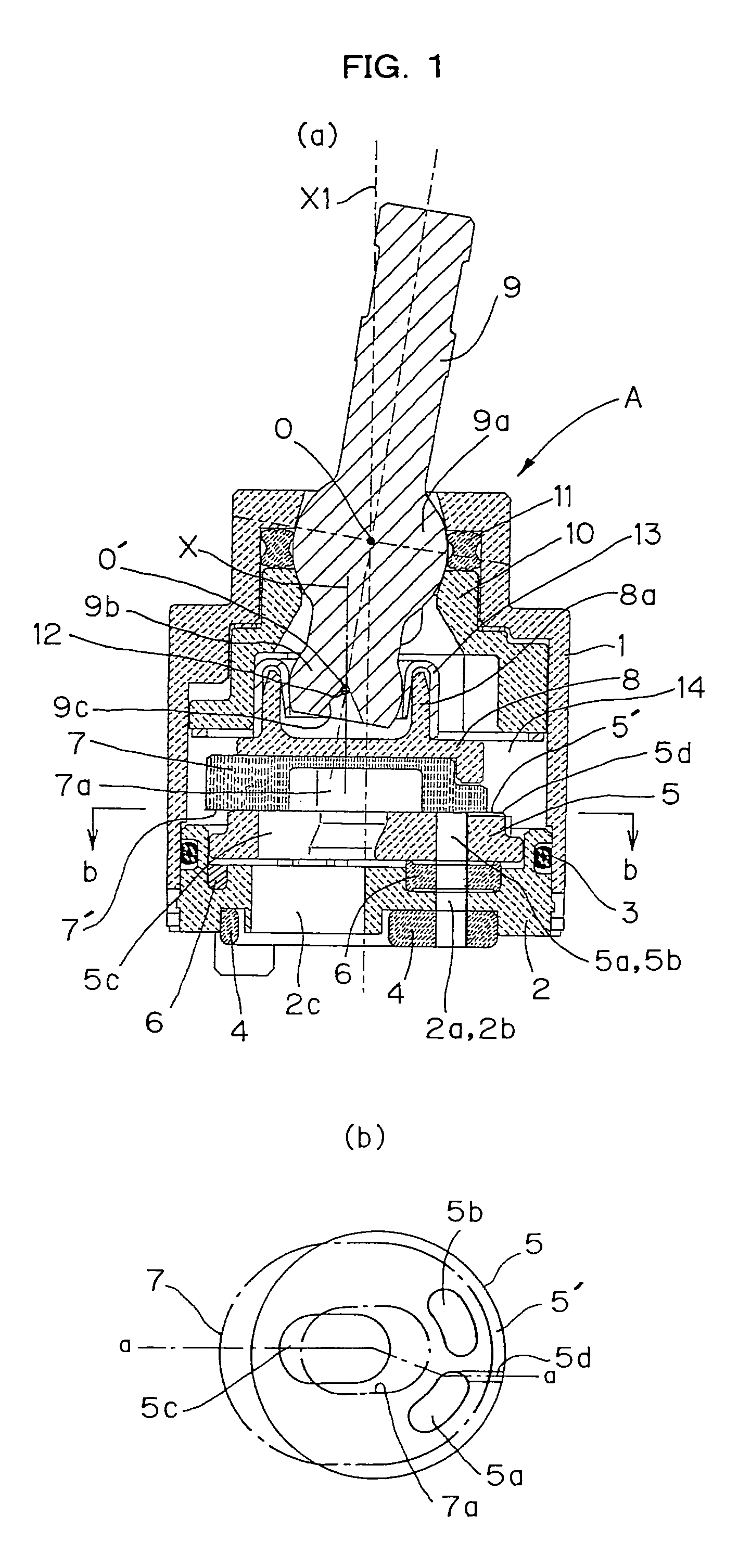

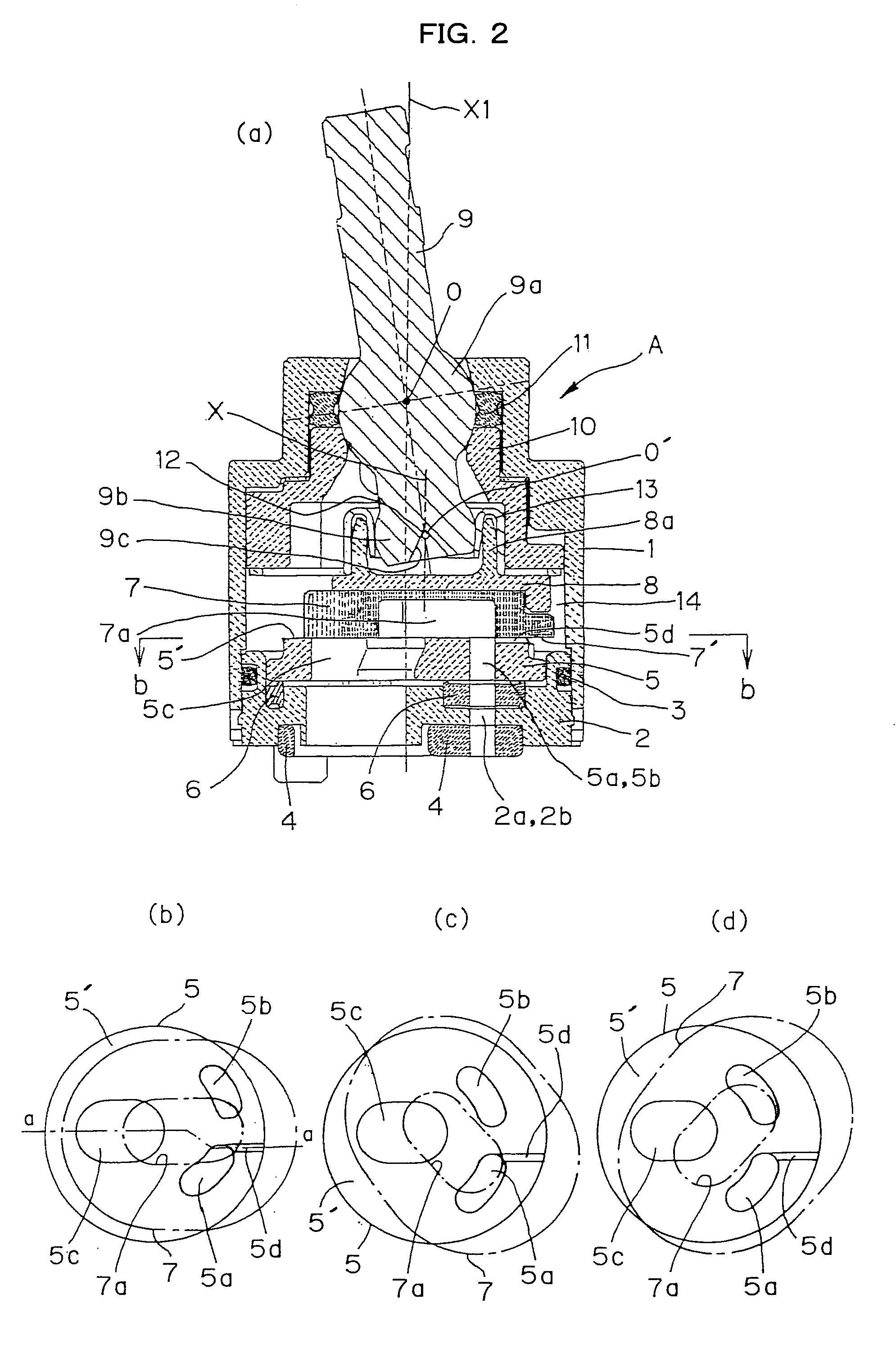

Disc valve

InactiveUS7134452B2Dispersion suppressionMultiple way valvesThin material handlingEngineeringClosed space

A disk valve comprises an inlet port, an outlet port, a first disk provided with a first through hole communicating with the inlet port and extending axially and a second through hole communicating with the outlet port and extending axially, and a second disk provided with a concave capable of communicating with the first through hole and the second through hole of the first disk on one end face and slidably and movably contacting one end face of the first disk at the one end face. A closed space is formed radially outside the second disk, and the second disk slides relative to the first disk to adjust the degree of overlap between the concave of the second disk and the first through hole of the first disk. The slidably and movably contacting part between the first disk and the second disk is self-lubricated. The disk valve further comprises a communication passage for always placing the first through hole into communication with the closed space radially outside the second disk. A portion of the one end face of the first disk adjacent to the part slidably and movably contacting the second disk opposes the closed space

Owner:TOTO LTD

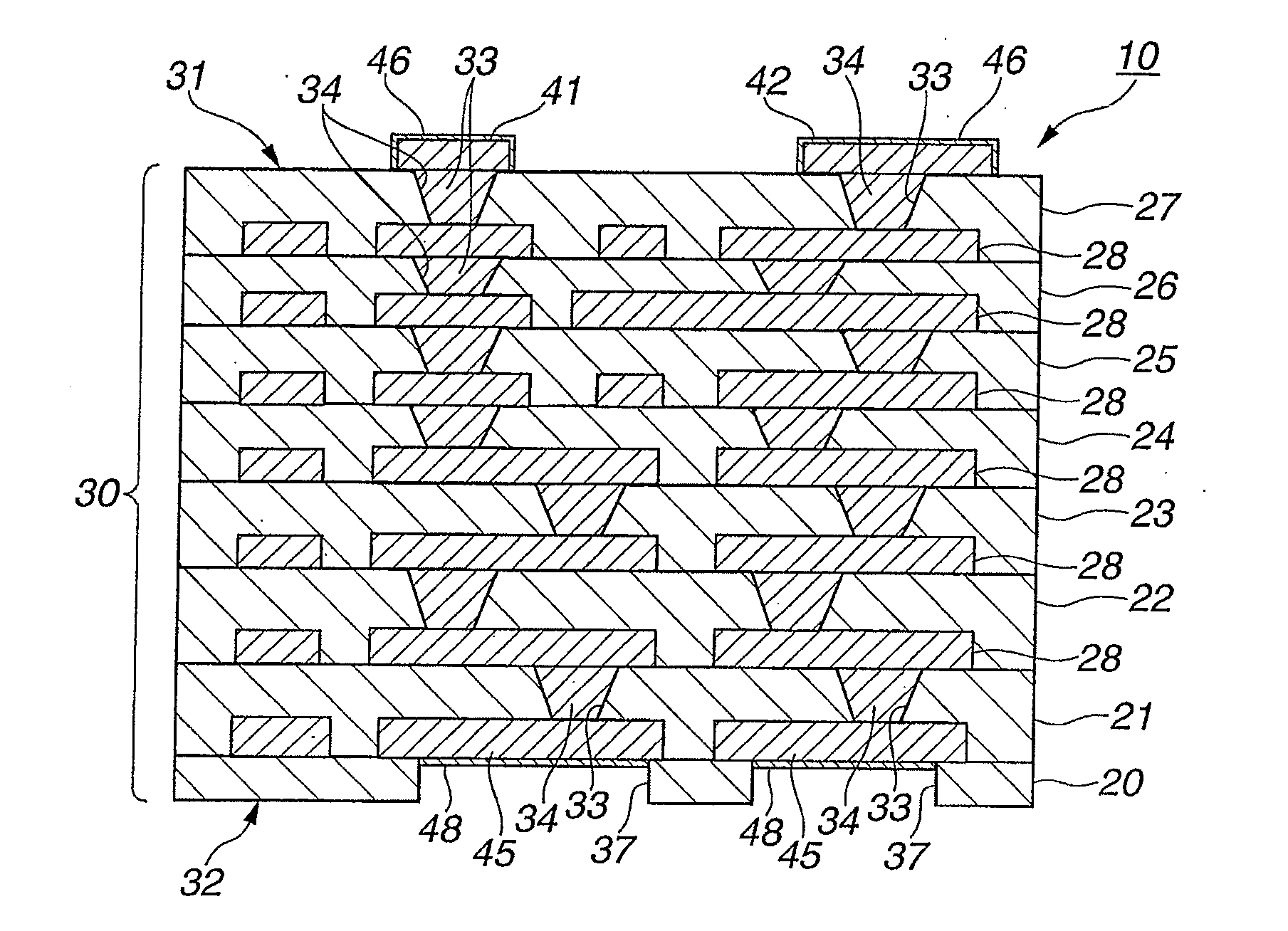

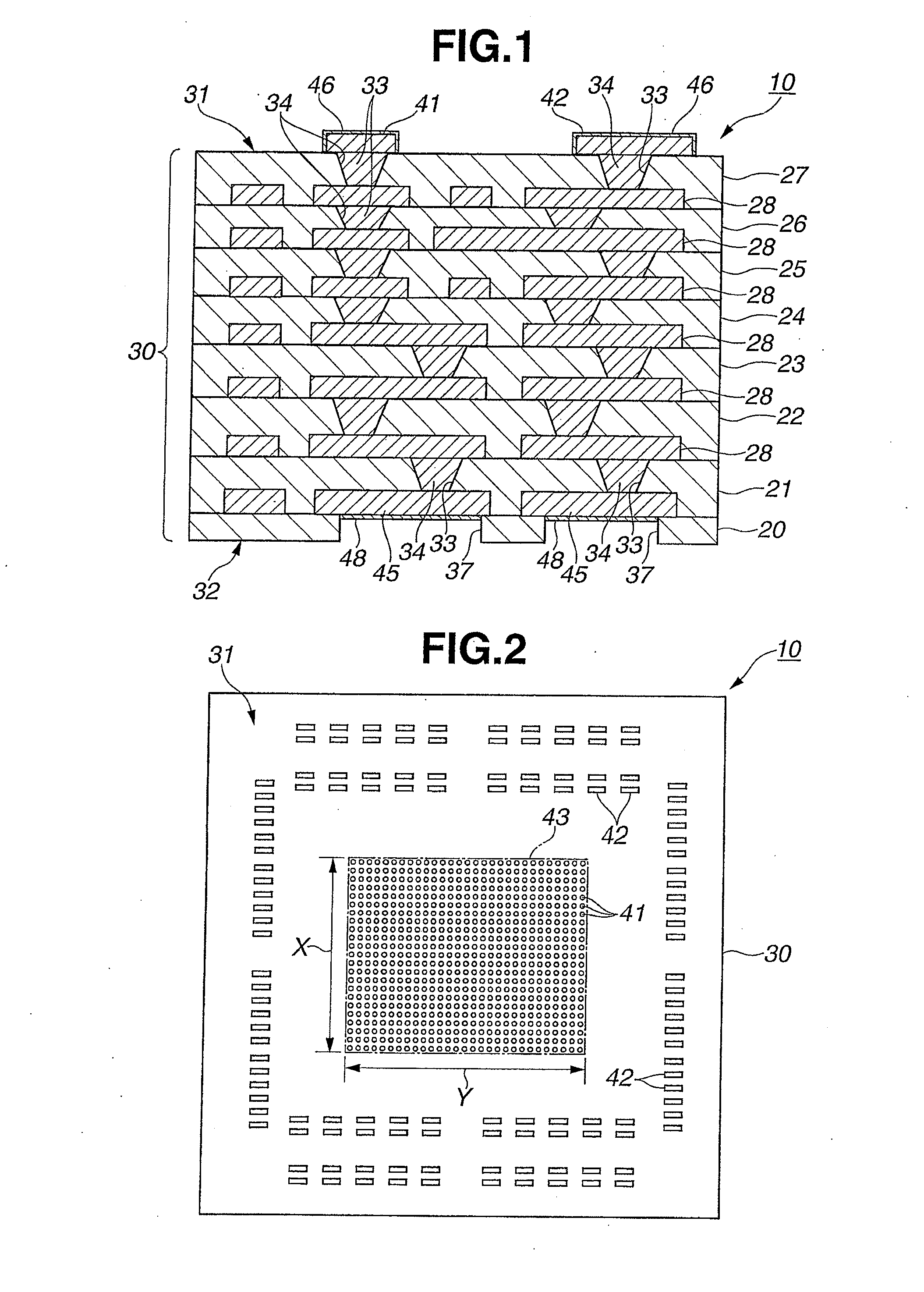

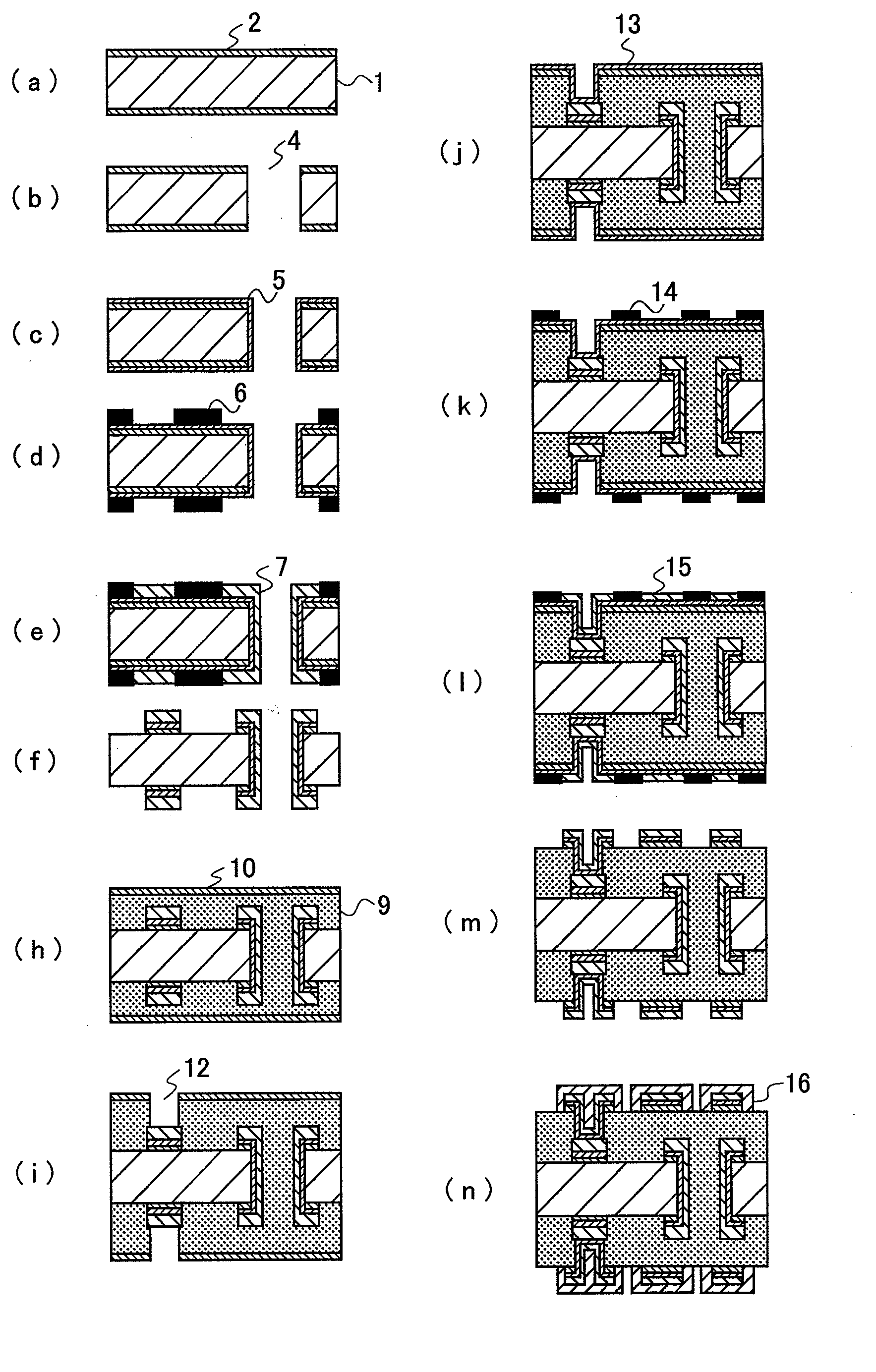

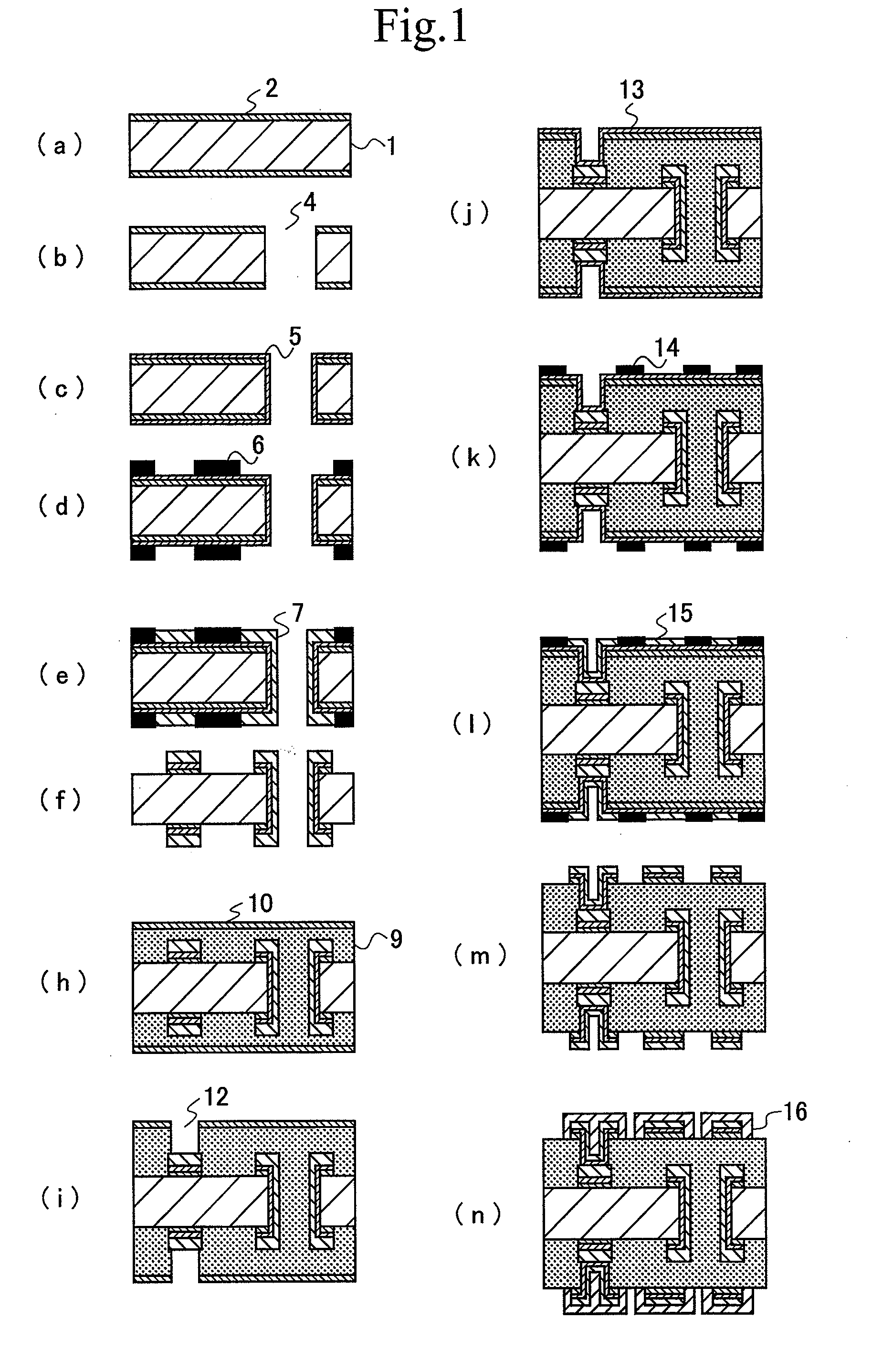

Method of manufacturing multilayer wiring substrate, and multilayer wiring substrate

InactiveUS20120312590A1Suppress manufacturing costIncrease manufacturing costSemiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorEngineering

Disclosed is a method of manufacturing a multilayer wiring substrate having a principal plane of the substrate and a rear plane thereof, having a structure such that a plurality of resin insulating layers and a plurality of conductor layers are laminated, and a plurality of chip component connecting terminals to which chip components are connectable are disposed on the principal plane of the substrate. This method has a feature including a plating layer forming process in which product plating layers which provide the plurality of chip component connecting terminals and a dummy plating layer on the surrounding of the product plating layers are formed on the surface of an exposed outermost resin insulating layer at the principal plane of the substrate. This method permits a thickness dispersion of the chip component connecting terminals to be suppressed and permits a connection reliability thereof to the chip components to be increased.

Owner:NGK SPARK PLUG CO LTD

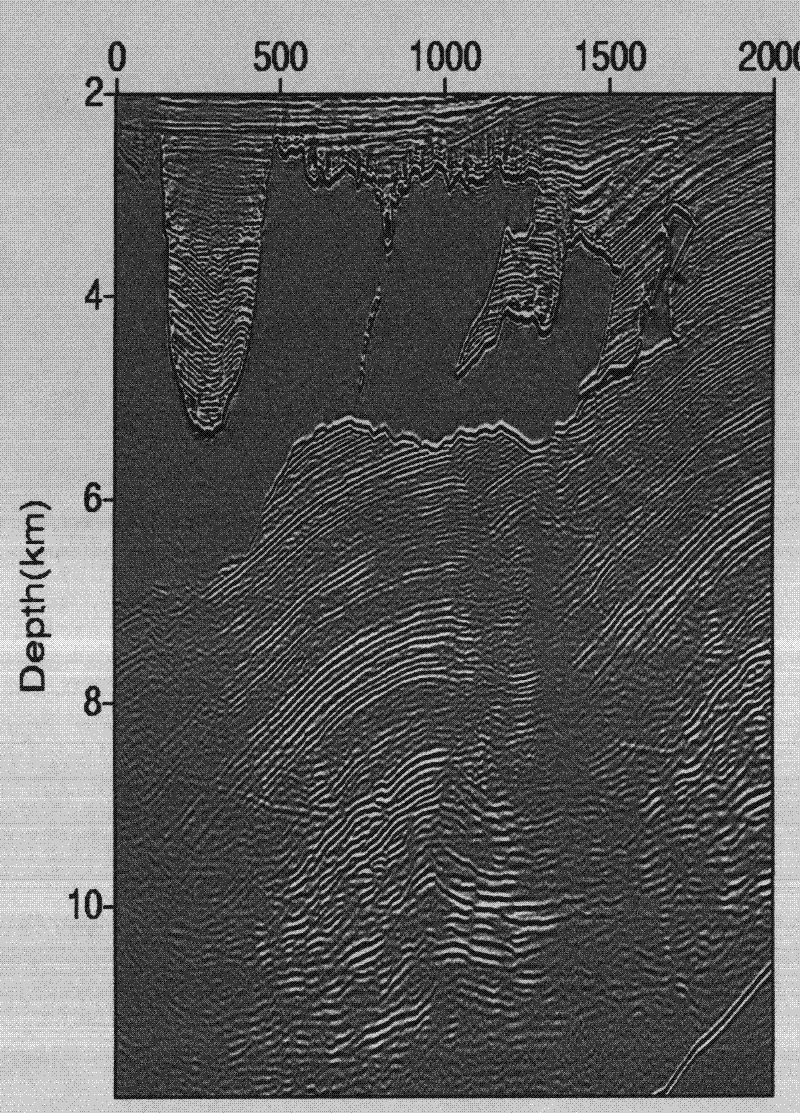

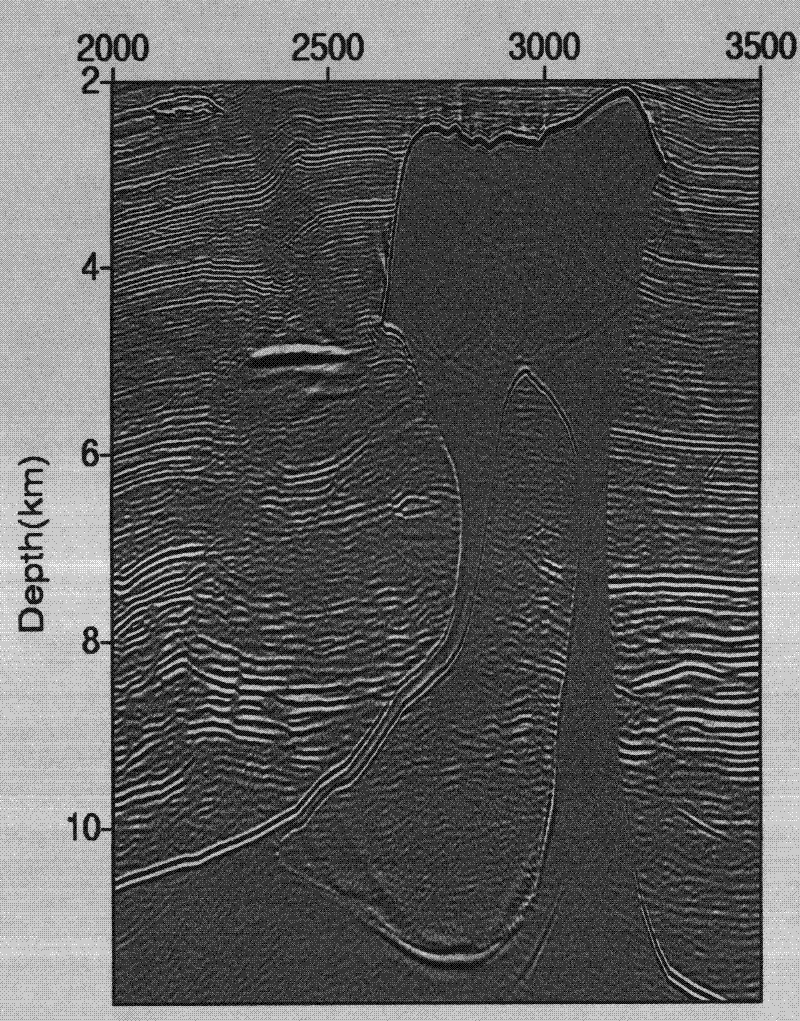

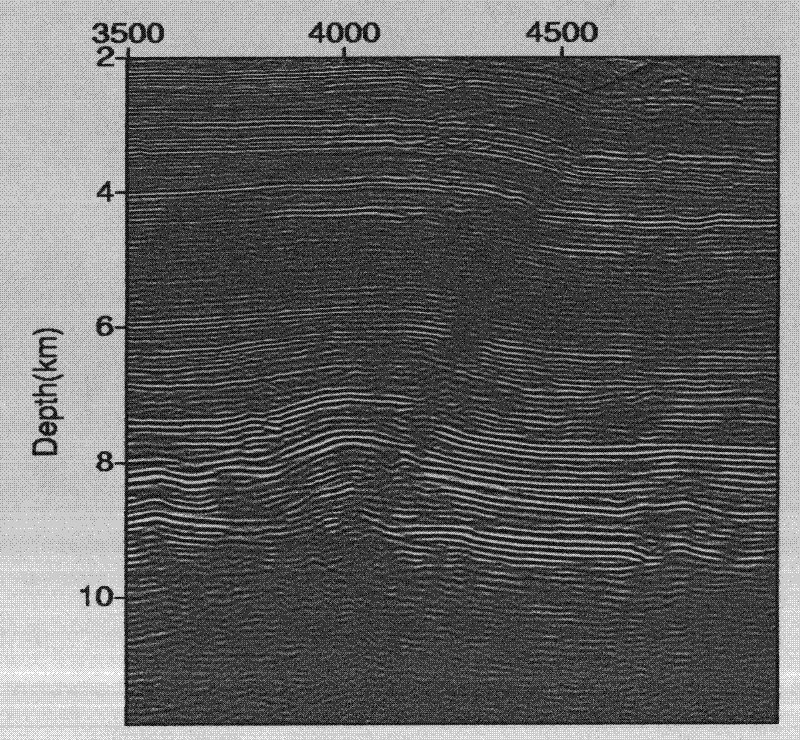

A Staggered Grid 3D Seismic Prestack Reverse Time Migration Imaging Method Based on Small GPU Storage

ActiveCN102269820ASuppress low frequency noiseDispersion suppressionSeismic signal processingWave equationReflected waves

A staggered grid 3D seismic prestack reverse time migration imaging method based on GPU small storage capacity is a very important technology for 3D prestack depth migration imaging of complex structures. The reverse time migration method based on the two-way wave equation has been realized, which can accurately image the rotary wave and the large-angle reflected wave, and at the same time solve the problem of the large amount of calculation of this method. Utilizing parallel computing technology based on GPU hardware, staggered grid difference format, checkpoint storage and other technologies, and relying on Laplace imaging conditions, the pre-stack reverse time migration imaging of 3D seismic data is realized, which greatly shortens the computing time. The efficiency has been increased hundreds of times, and the imaging accuracy has been significantly improved.

Owner:SINO GEOPHYSICAL CO LTD

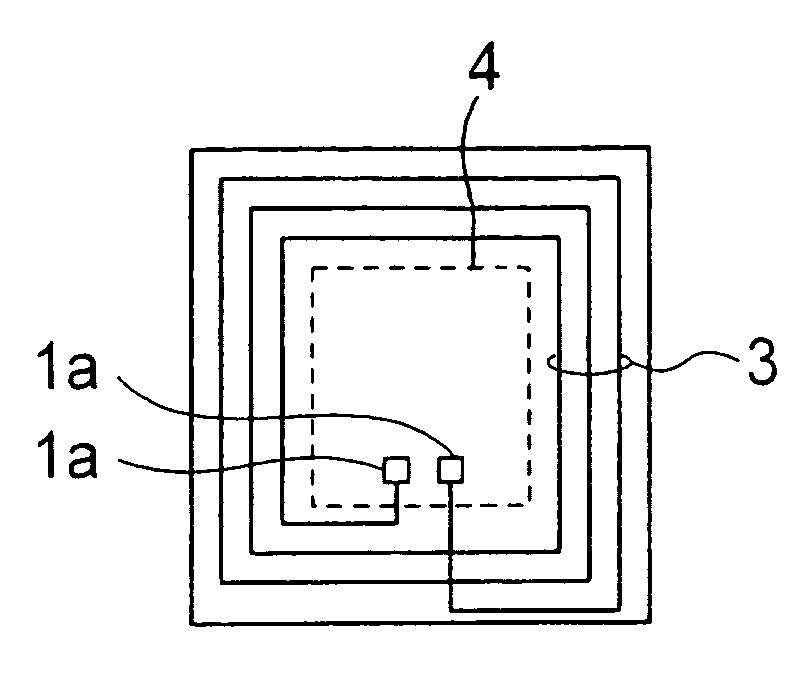

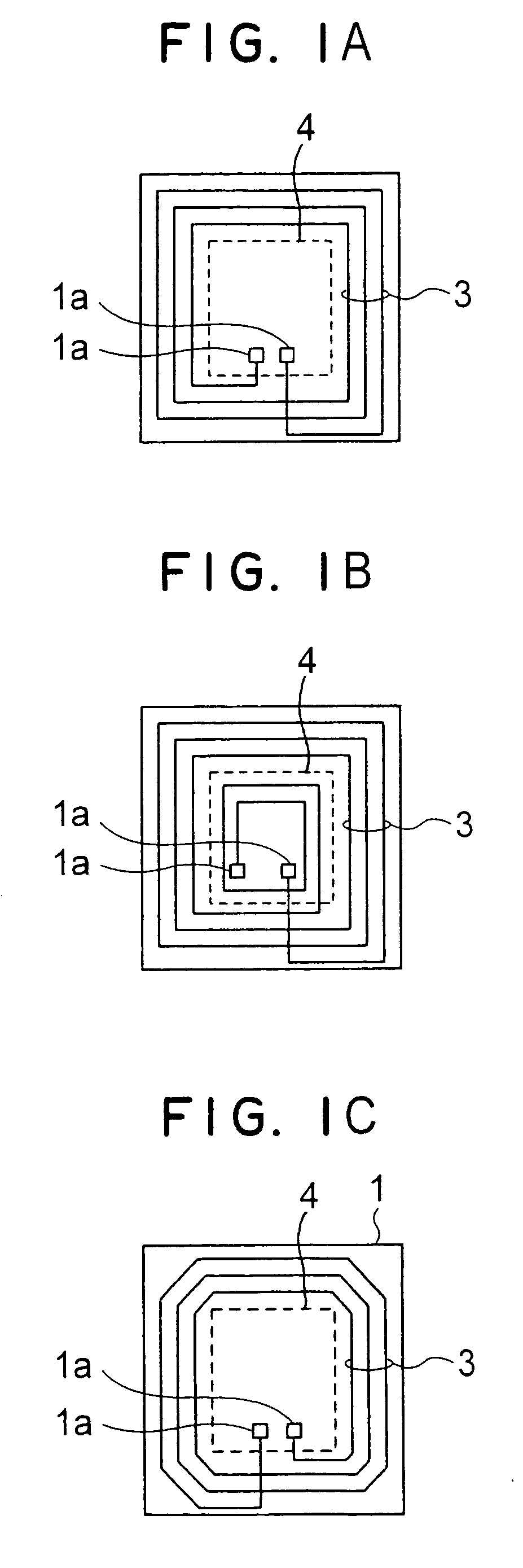

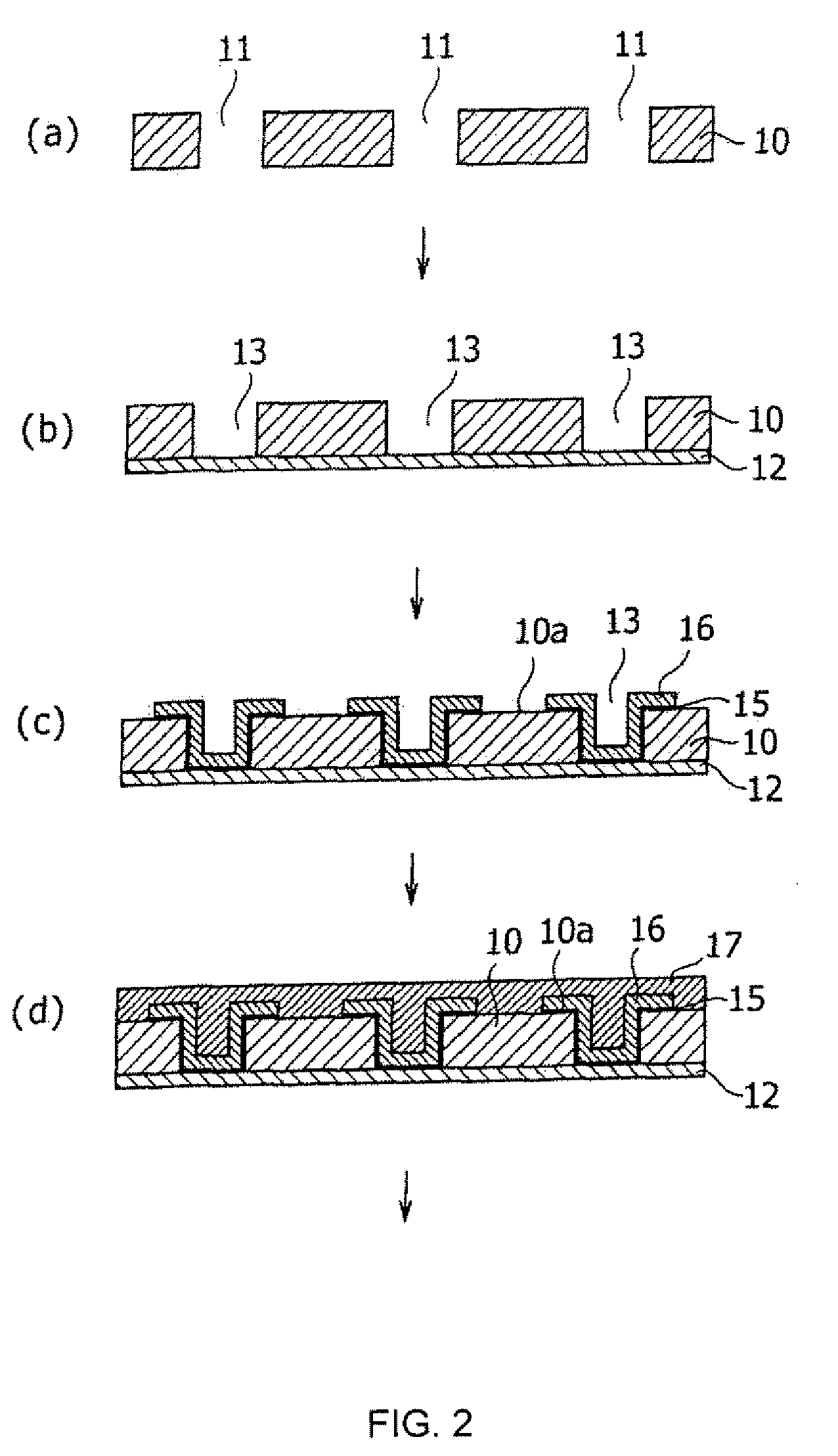

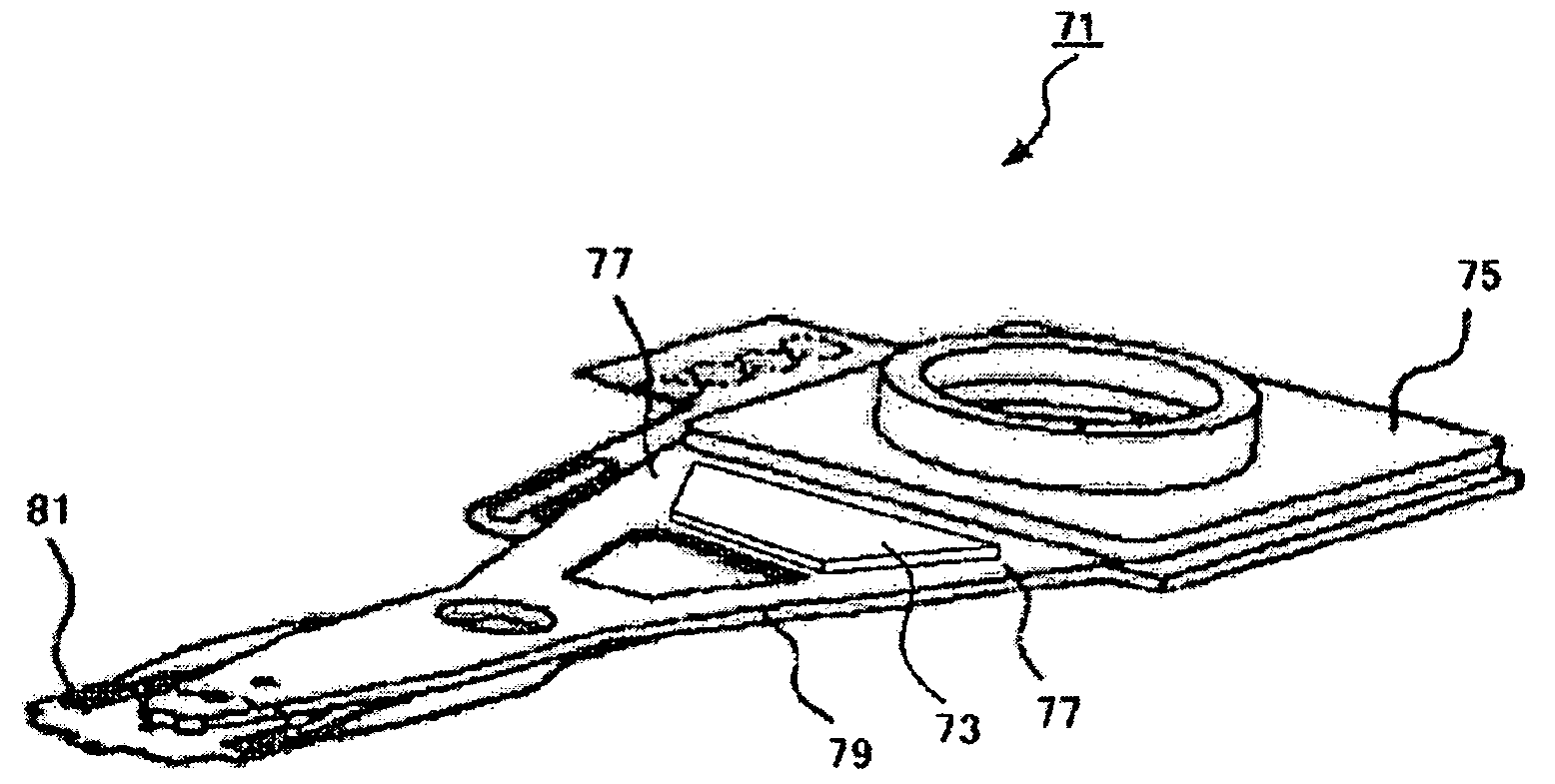

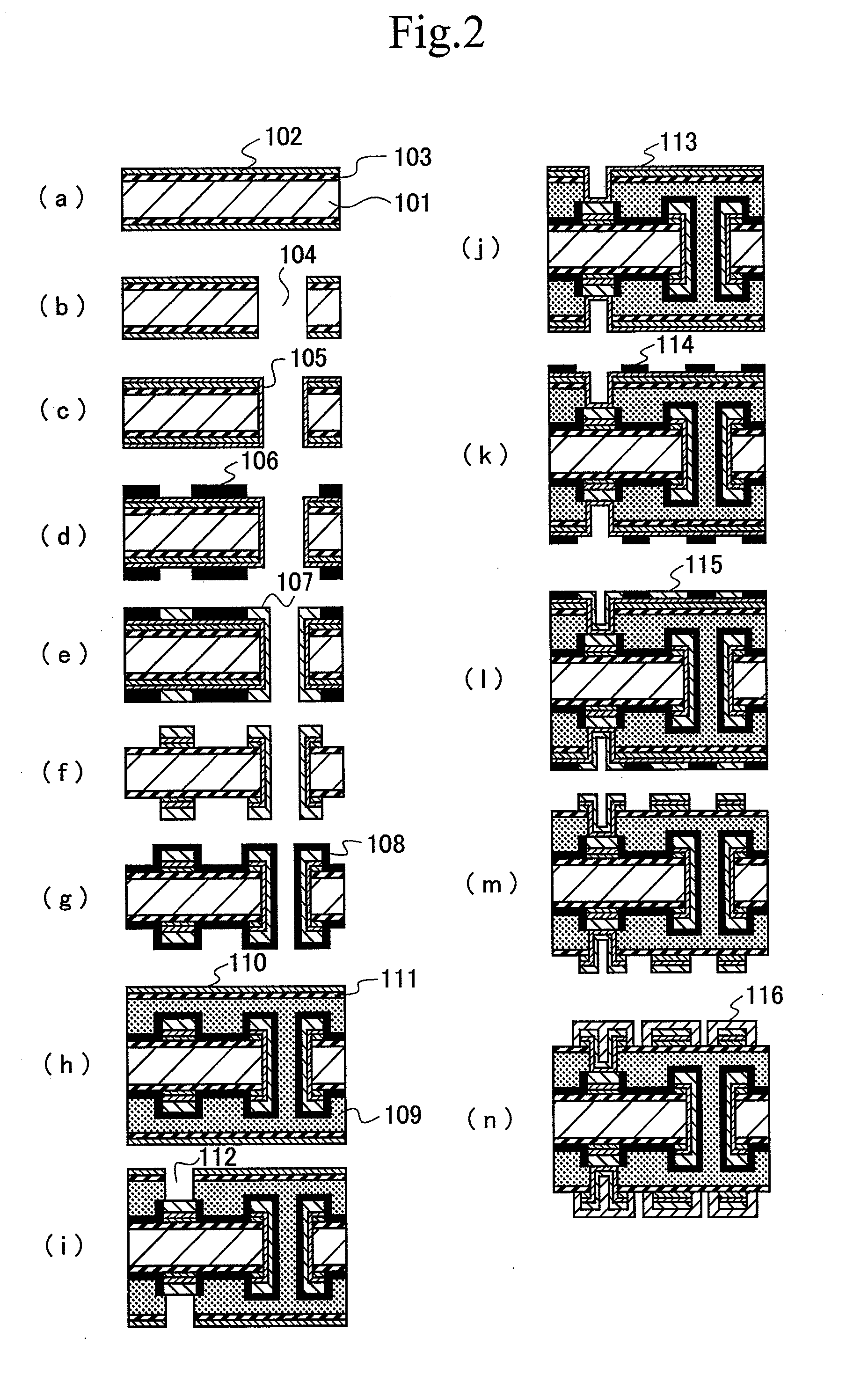

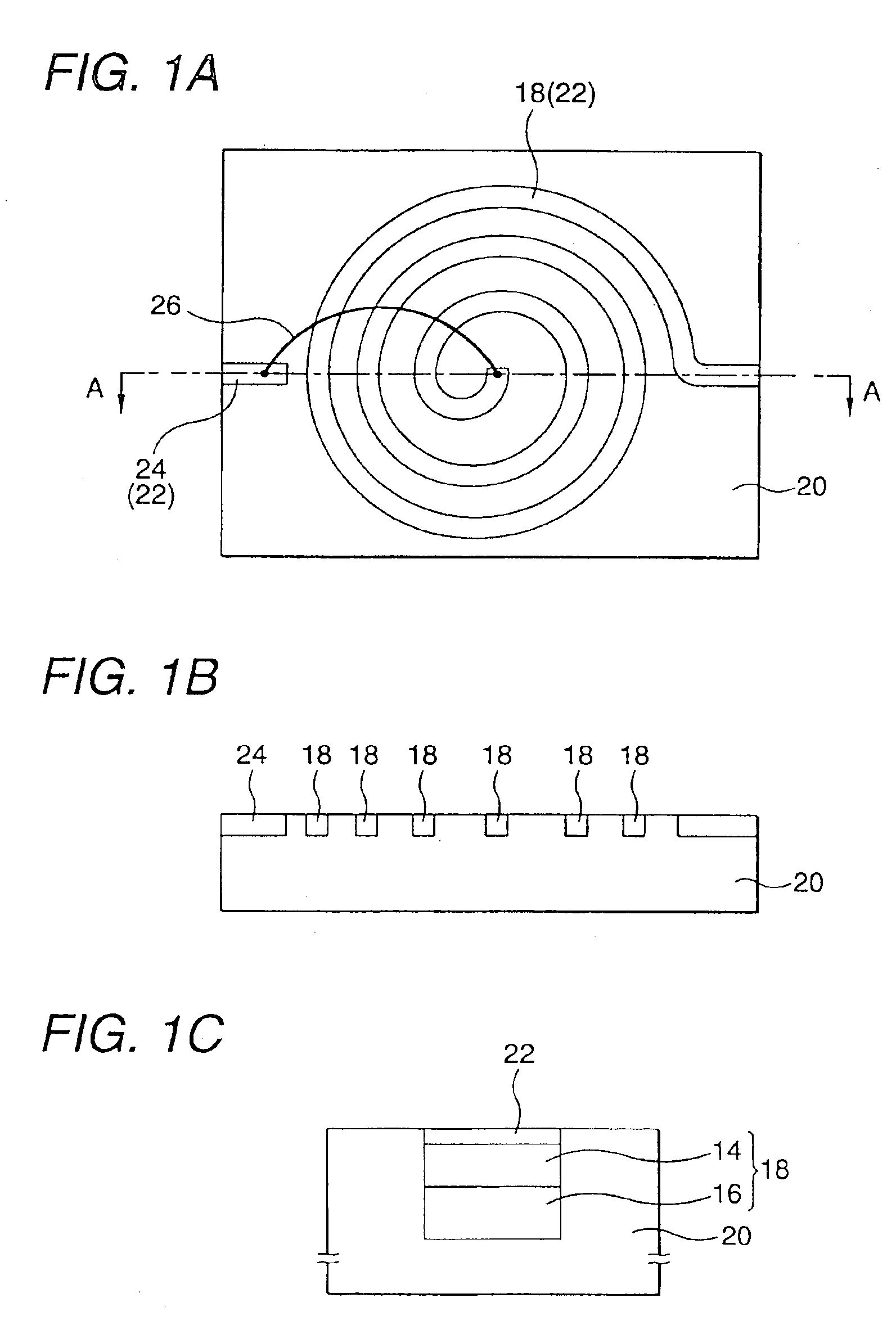

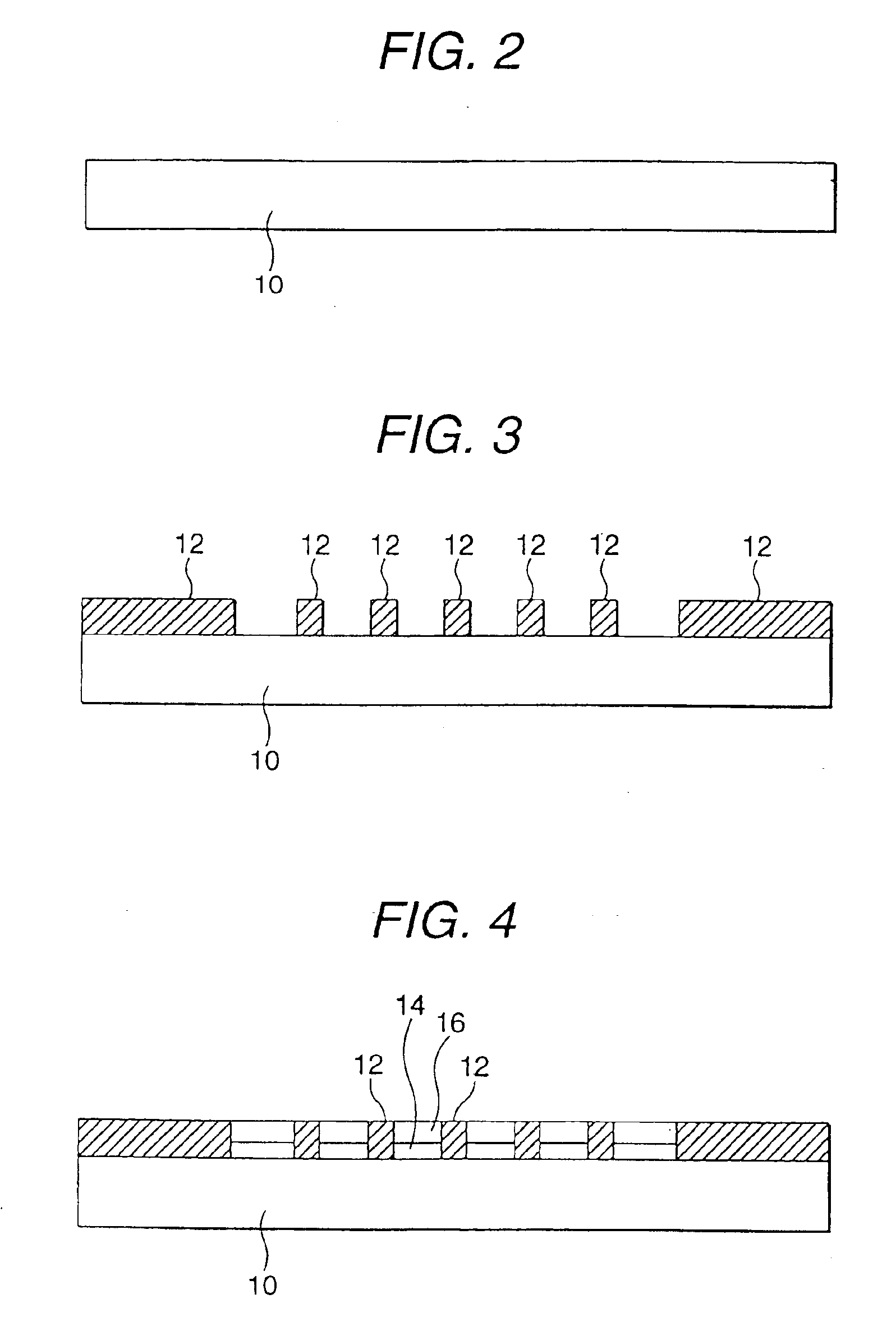

Method of manufacturing an IC coil mounted in an information carrier

InactiveUS7129145B2Energy lossReduce lossesSemiconductor/solid-state device detailsSolid-state devicesMulti materialElectrical conductor

An information carrier in which an IC element formed integrally with a coil is mounted and which has an extended communication range and a method of manufacturing the same and a structure of the IC element appropriately suited for this sort of information carrier and a method of manufacturing the same. In the IC element, a conductor constituting the coil 3 is implemented in a multilayer structure including a metal-sputtered layer or alternatively a metal-evaporated layer 6 and a metal-plated layer 7. In the method of manufacturing the IC element, a precision electroforming method is employed as a means for forming the metal-plated layer 7. The information carrier is implemented in such a structure in which the IC element 1 is disposed at a center portion in a planar direction of a substrate 21. In a method of manufacturing the information carrier, strip material or materials 41 to 45 a given one of which has mounted thereon desired parts inclusive of the IC elements are manufactured, whereon desired information carriers 20a, . . . , 20h are formed by punching the strip material(s).

Owner:HITACHT MAXELL LTD

Process for forming a bump structure and bump structure

InactiveUS20090121351A1High aspect ratioFine pitchSemiconductor/solid-state device detailsPrinted circuit aspectsEngineeringInterconnection

A method for forming a bump structure and a bump structure for conductive interconnection with another element having at least one of microelectronic devices or wiring thereon, used as an electric connection in an electronic circuit, includes the steps of forming a mandrel by steps including forming at least one opening extending through a bump-forming die body in the thickness direction thereof and positioning a bump-forming die lid on a surface of the bump-forming die body so as to cover one end of the opening and to thereby define a bump-forming recess. The bump-forming die body may be comprised of a metal sheet. A metal layer is formed at least on an inner surface of the bump-forming die lid exposed within the bump-forming recess. The mandrel is removed so as to expose the metal layer and form a bump structure.

Owner:INVENSAS CORP

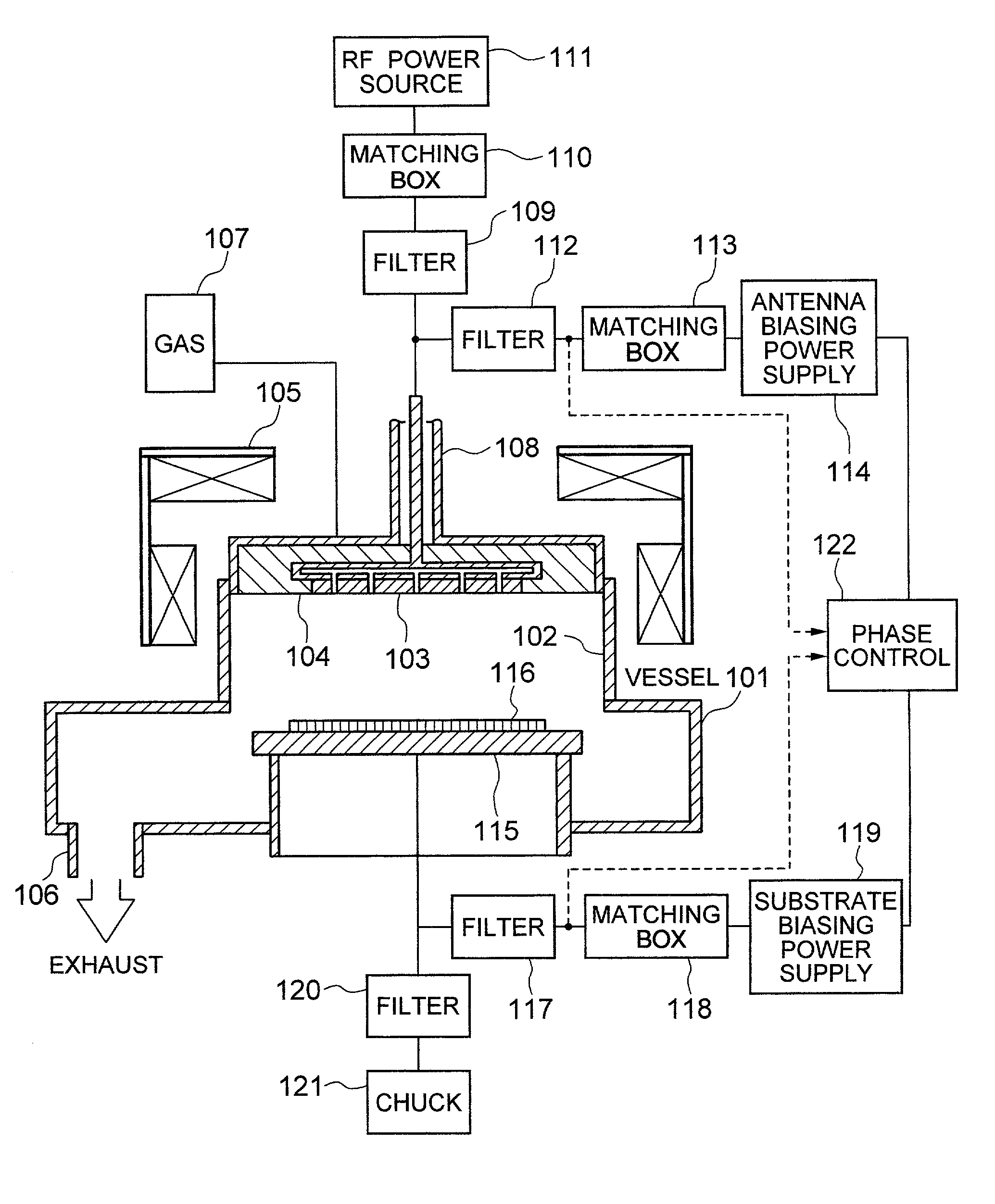

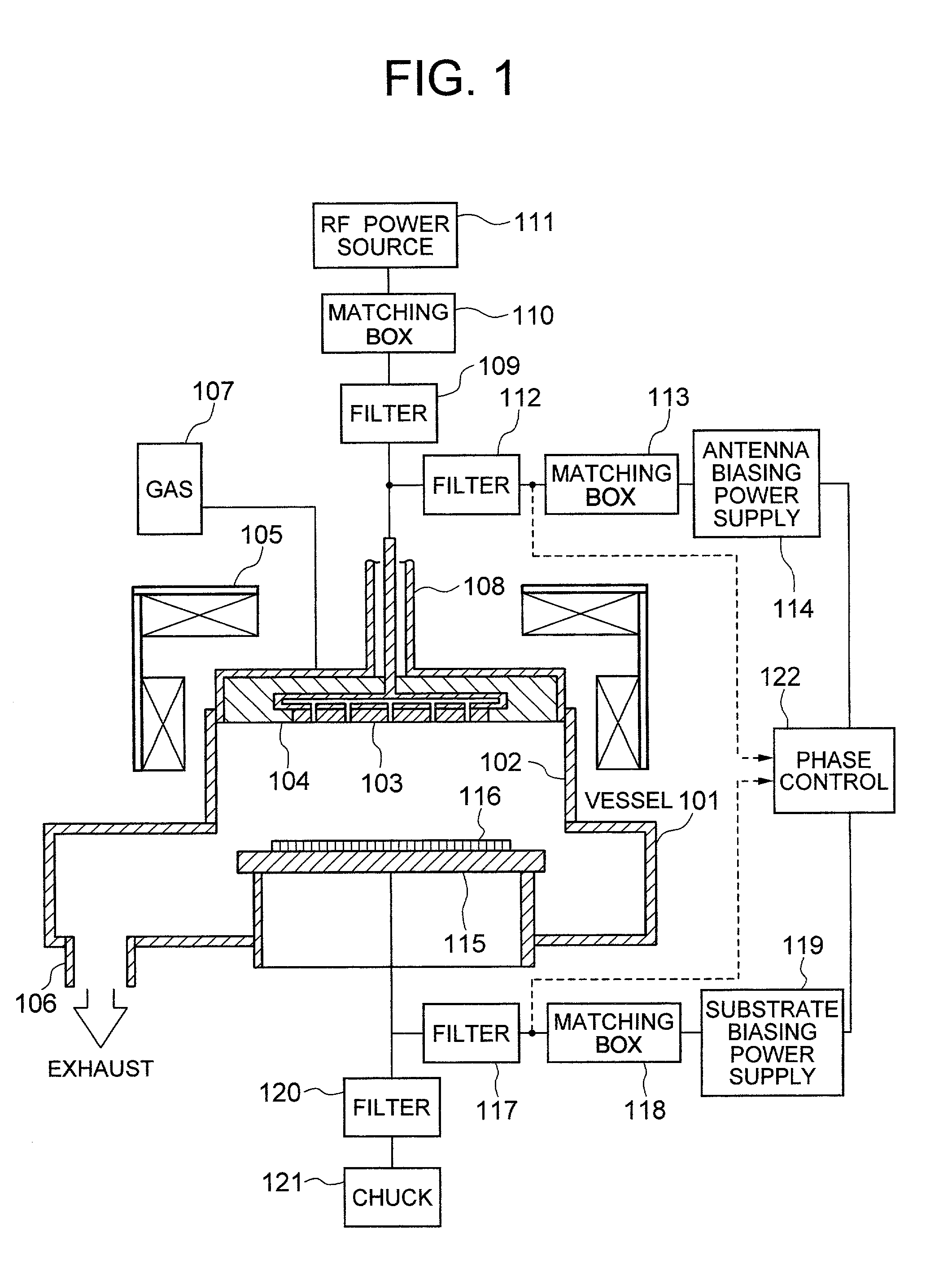

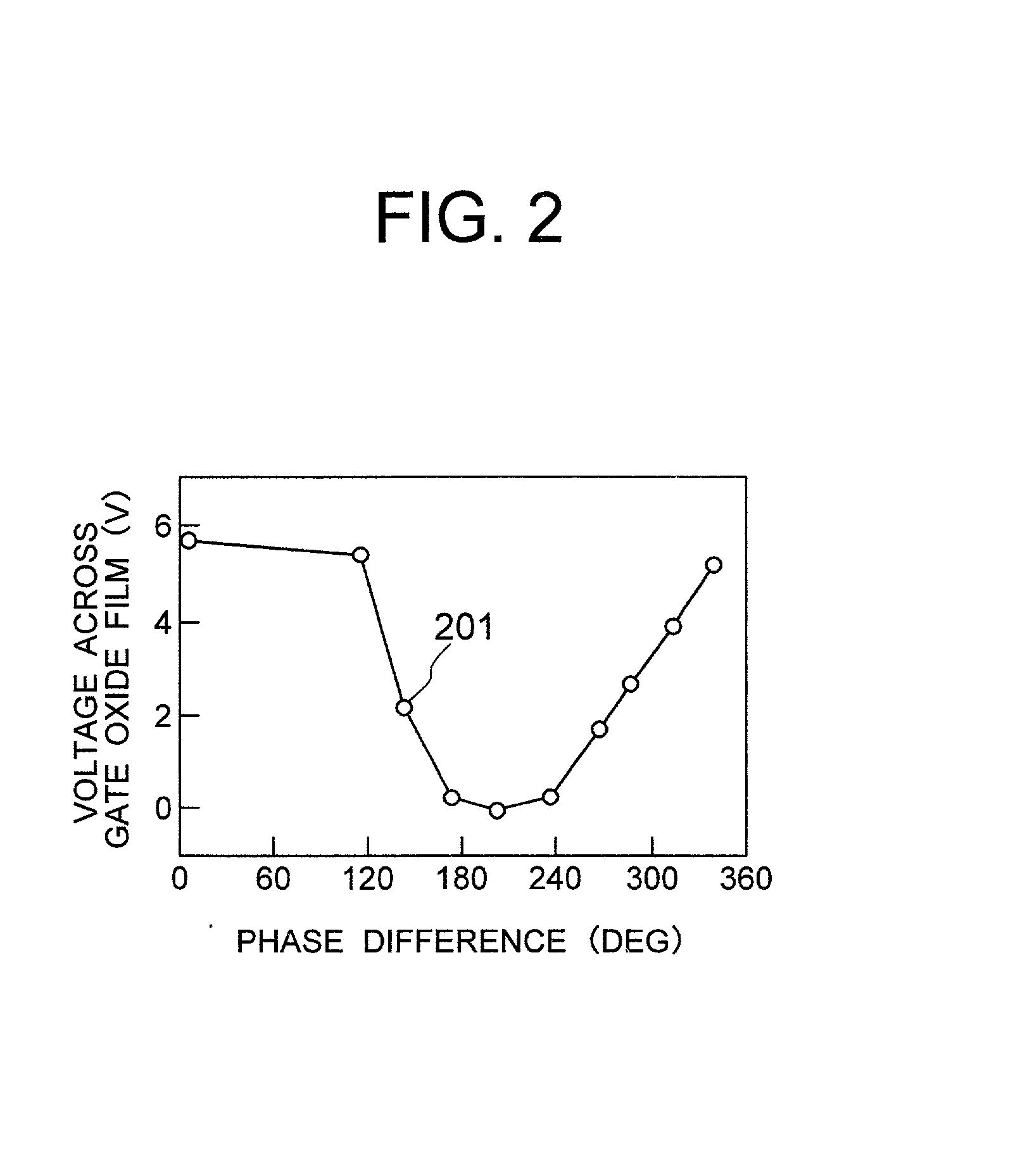

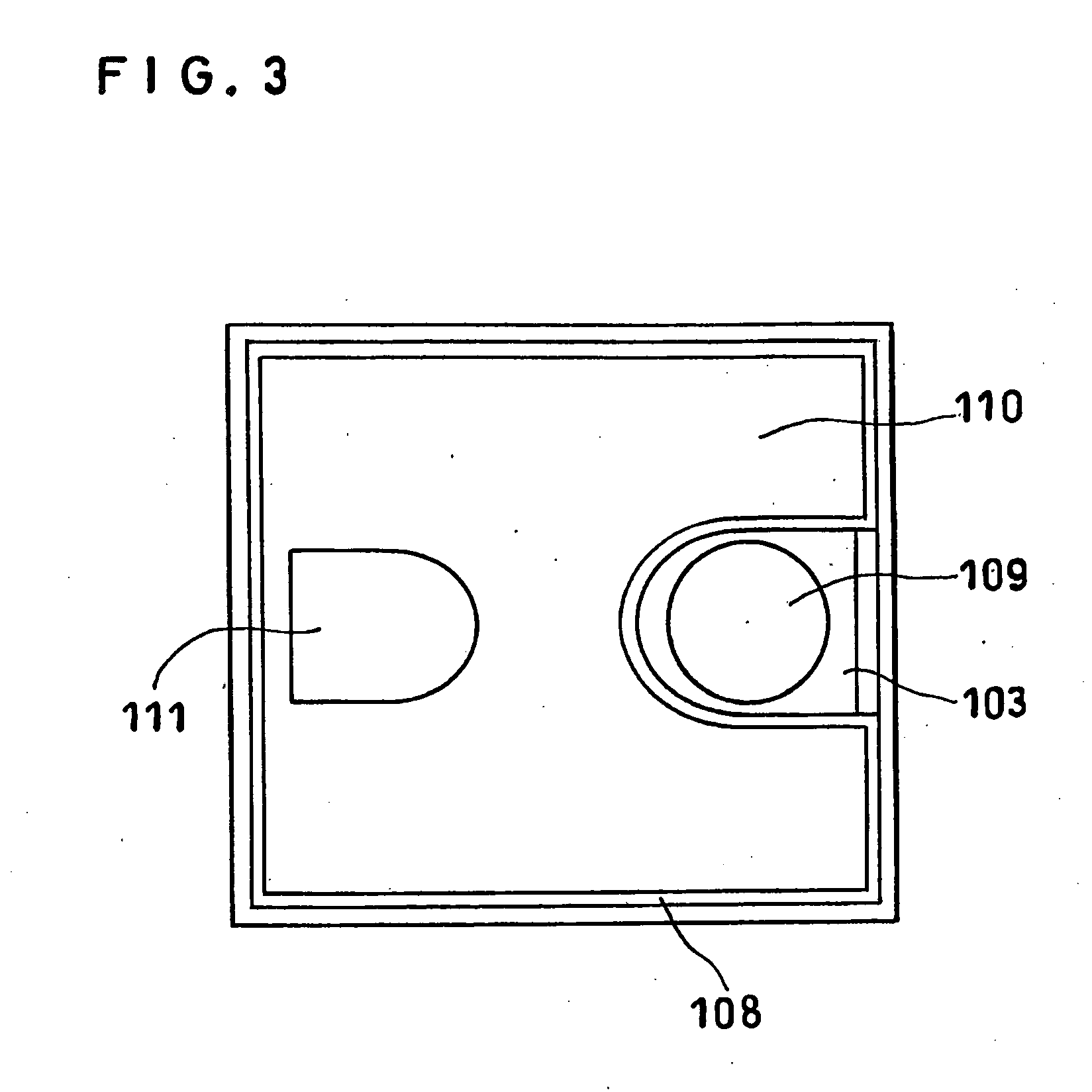

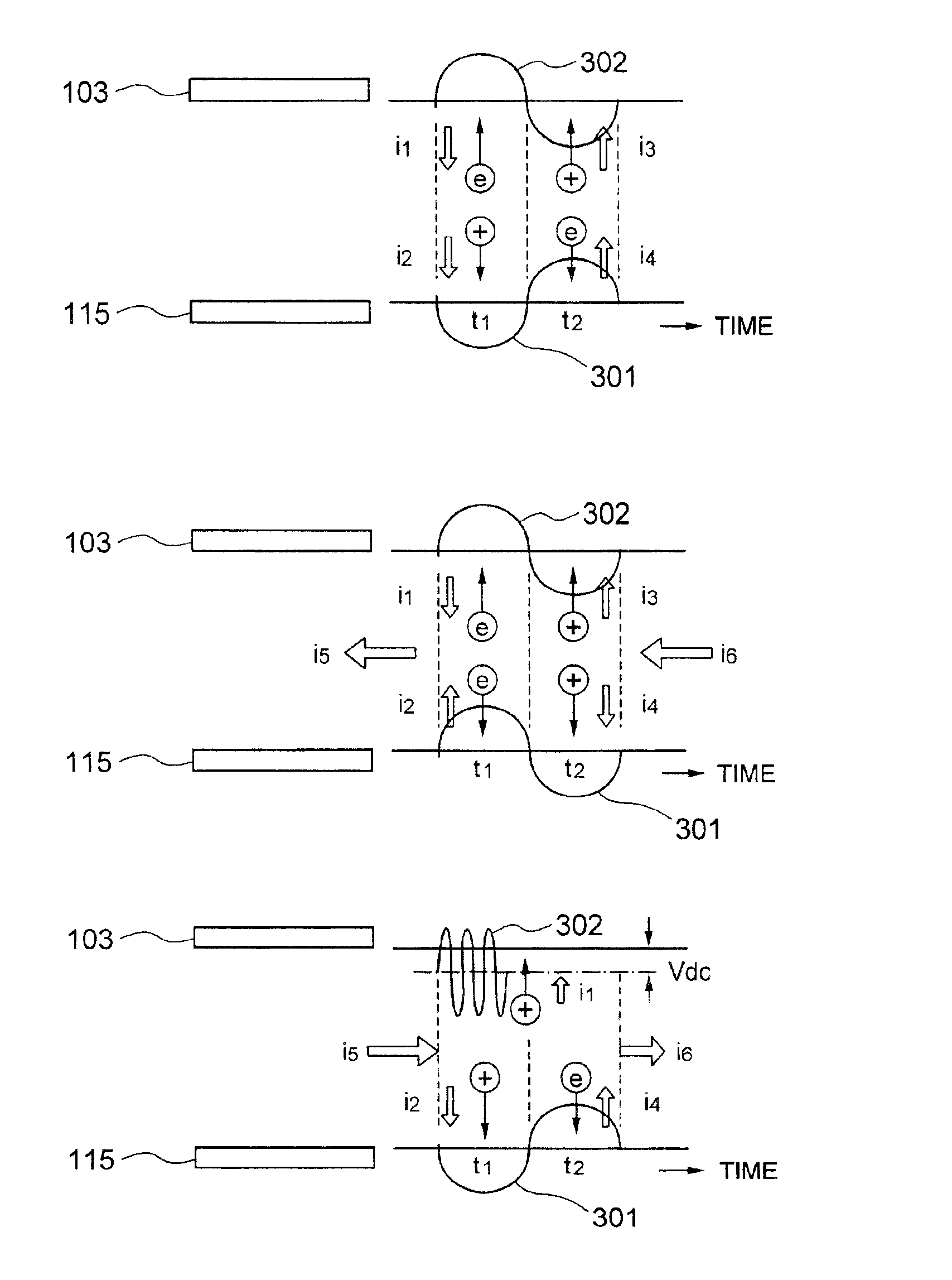

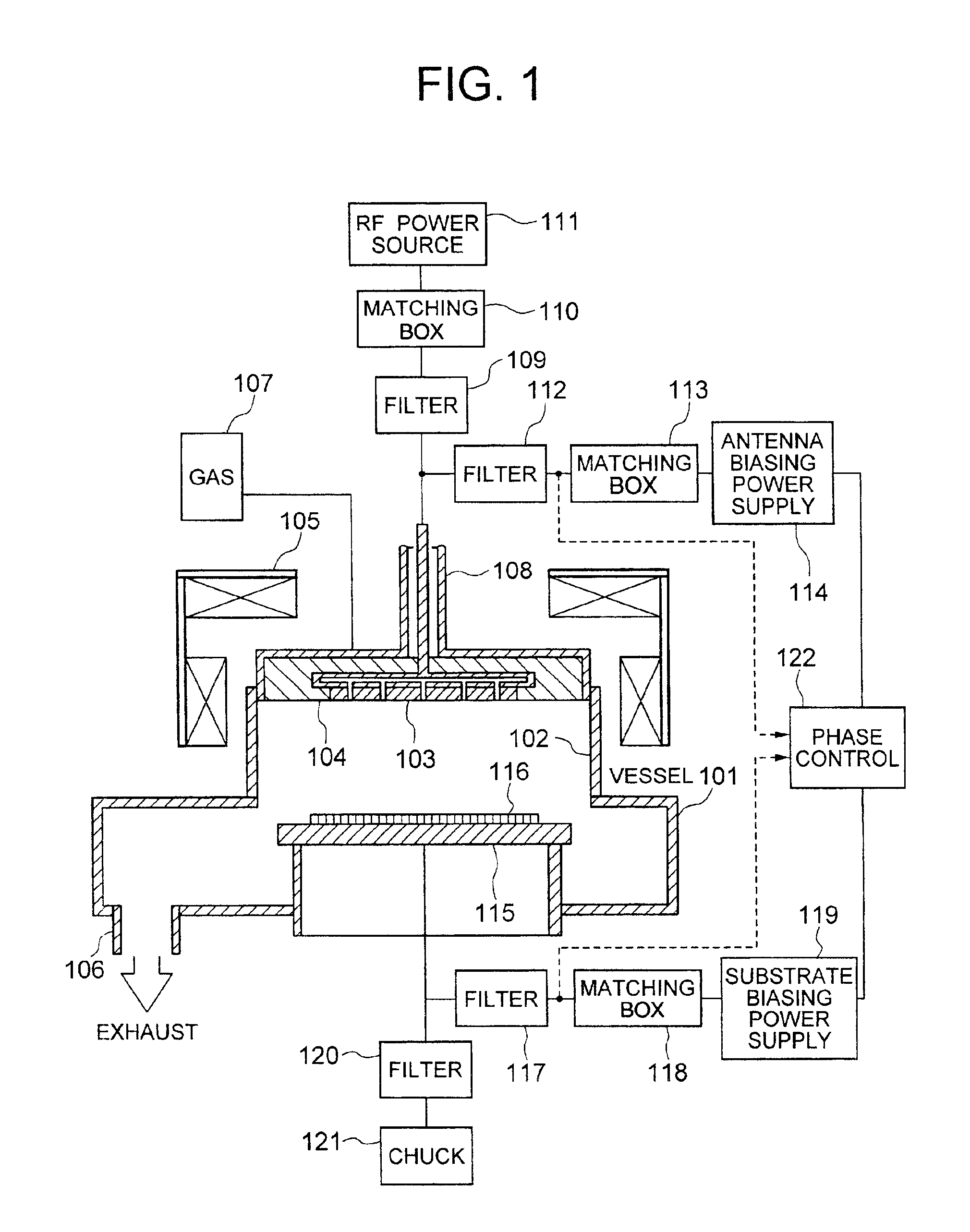

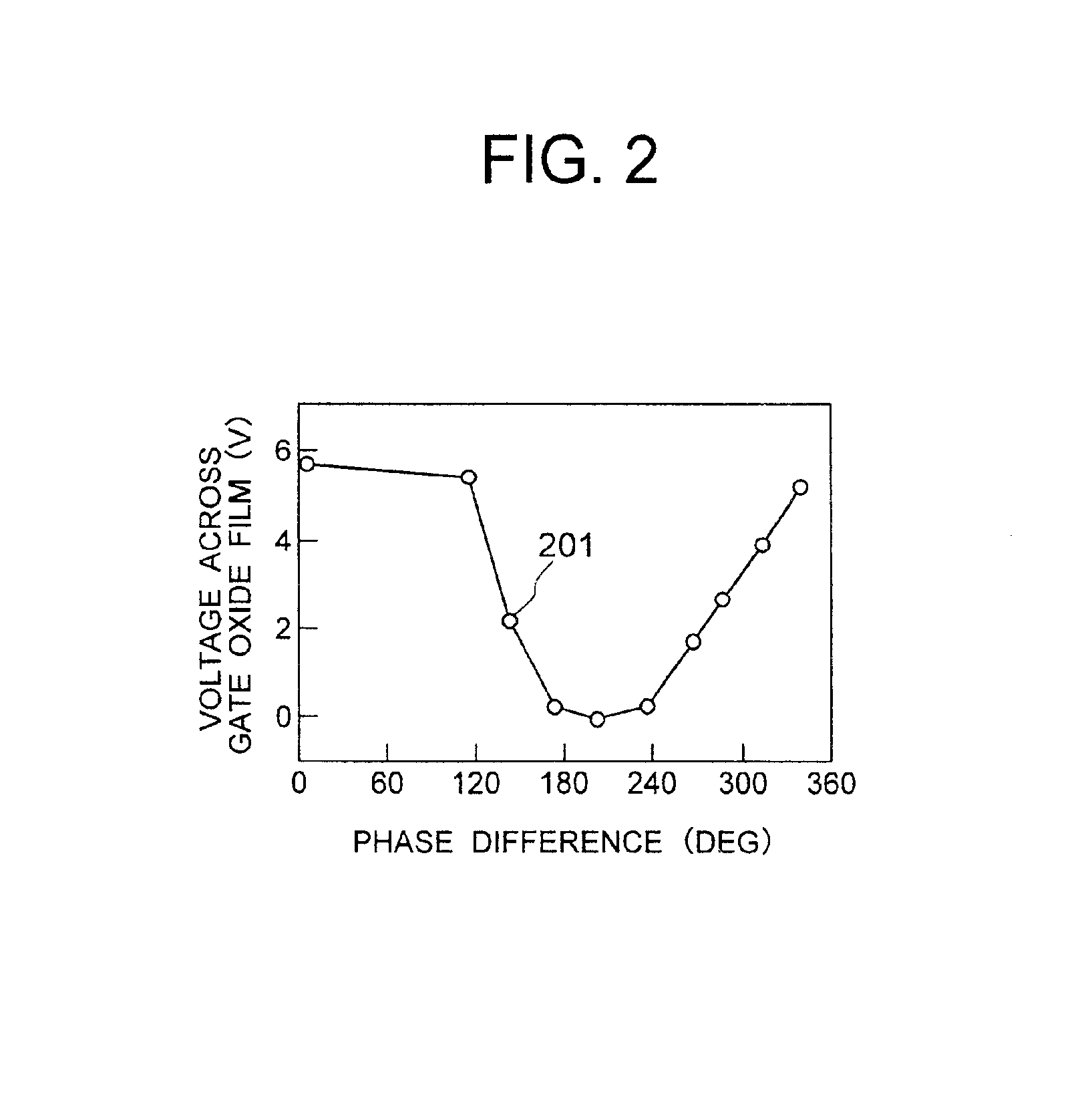

Plasma processing apparatus and method with controlled biasing functions

InactiveUS20020031617A1Improve accuracyHigh-precision surface treatmentElectric discharge tubesDecorative surface effectsIonEtching

Processing technique using plasma to process the surface of a sample such as semiconductor device. The phases of RF bias voltages applied to a substrate electrode and an antenna electrode opposed thereto are controlled to be opposite to each other so that either one of the electrodes is forced to always function as ground. Therefore, the current flowing to cross the magnetic field for controlling the plasma is decreased, and the potential distribution difference in the surface of the sample to be processed is reduced, so that the charging damage can be suppressed. Energy of ions incident to the sample to be processed can be controlled to perform high-precision etching. The plasma potential can also be controlled so that the strength of the ion impact to the inner wall of the chamber can be reduced, thereby reducing particles detached from the inner wall of the processing apparatus to improve the throughput.

Owner:HITACHI LTD

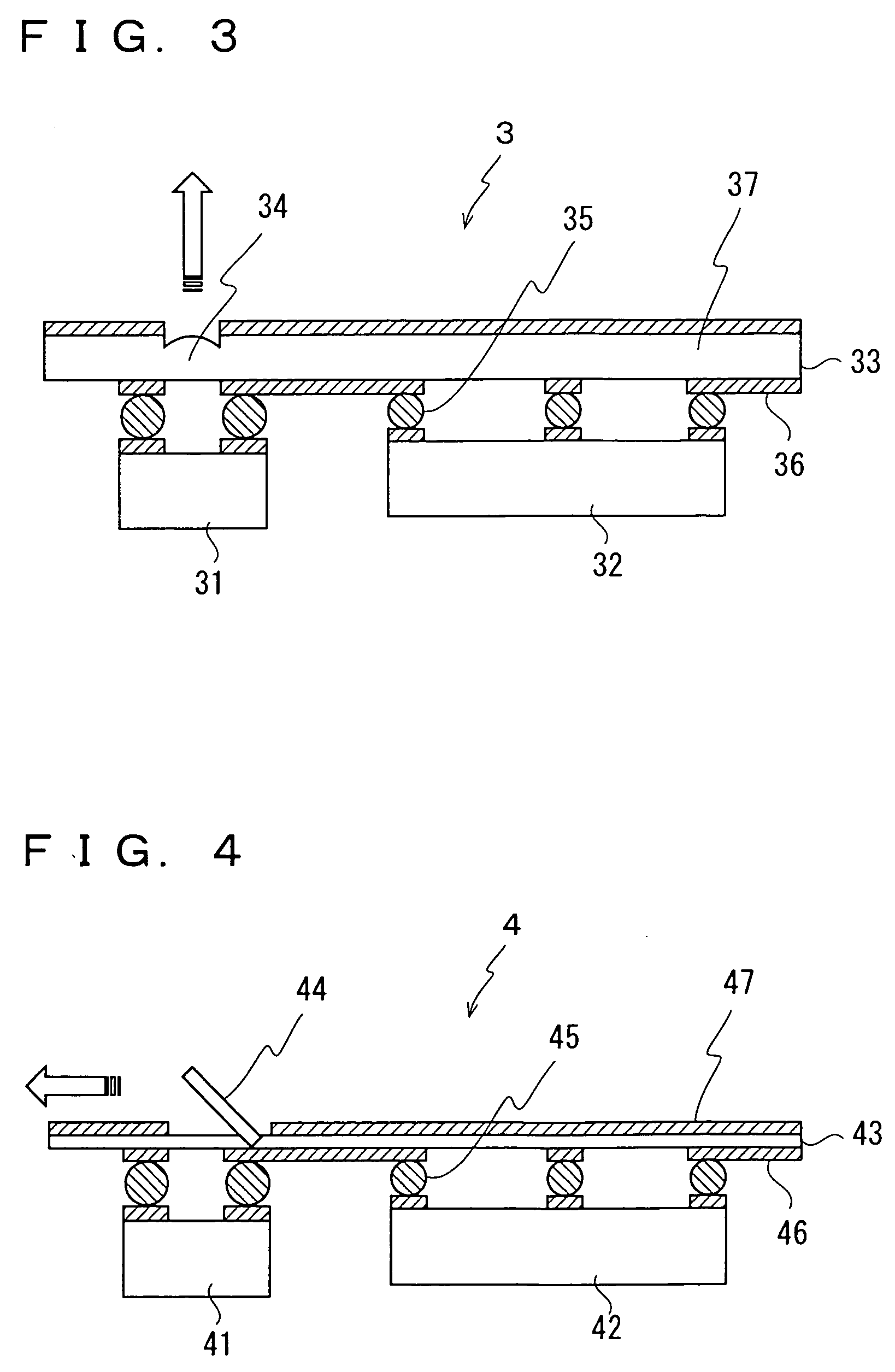

Method for manufacturing a head suspension

ActiveUS8151440B2Dispersion suppressionImprove productivityElectrical transducersRecord information storageProduction rateVibration control

A method for manufacturing a head suspension is capable of suppressing the dispersion in the vibration control effect of a head suspension and improve productivity, the manufacturing method includes a step of punching, by use of a hollow punch having a tooth portion at a distal end thereof, a vibration damper piece out from a base material having a vibration damper provided detachably on a liner through an attaching surface, to hold the vibration damper piece on a hollow internal surface of the punch, a step of positioning the punch holding the vibration damper piece on an objective portion of a semi-finished head suspension, and a step of attaching, by use of an extruding implement, the vibration damper piece on the objective portion with the attaching surface through extruding the vibration damper piece from the punch.

Owner:NHK SPRING CO LTD

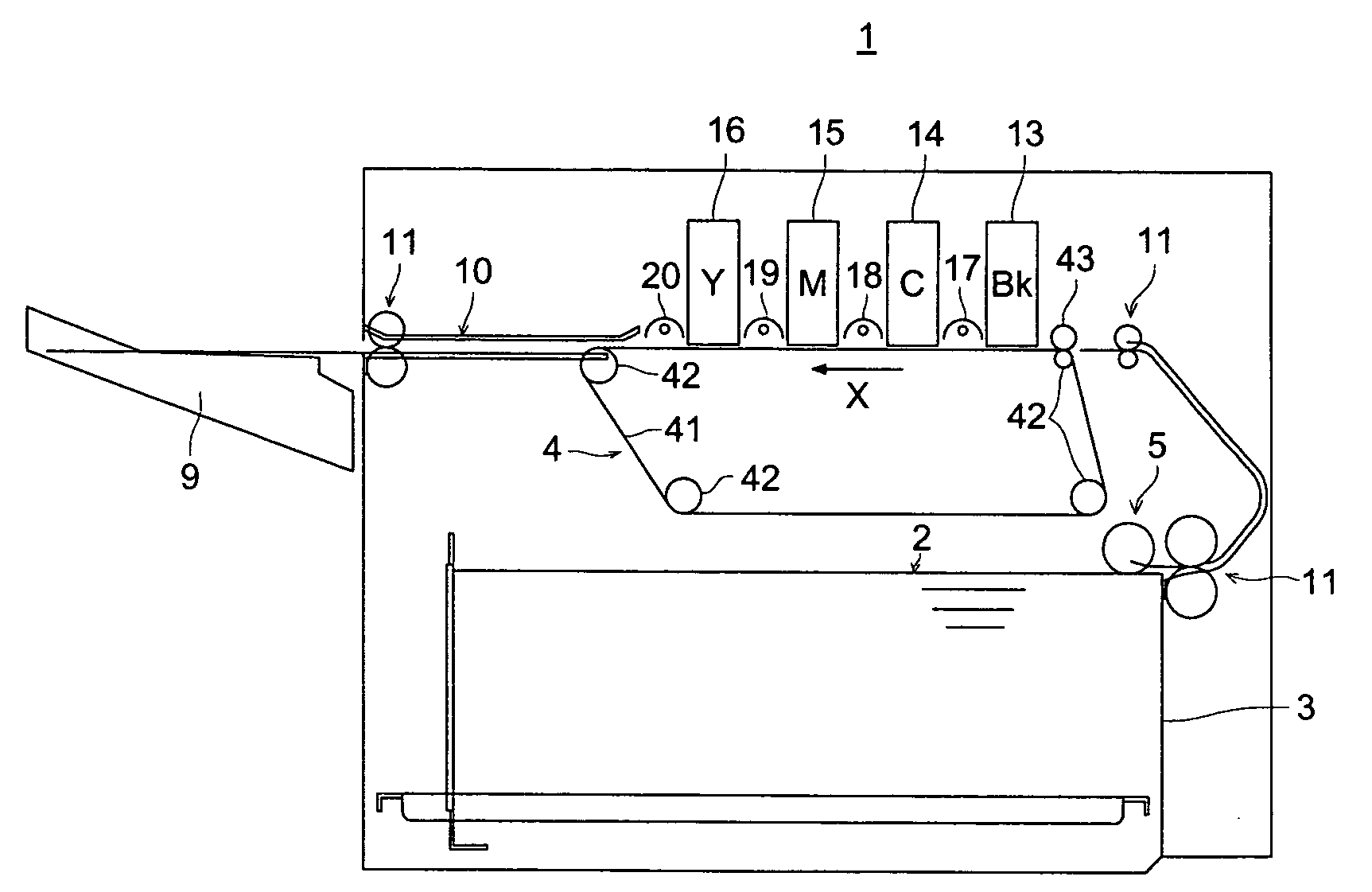

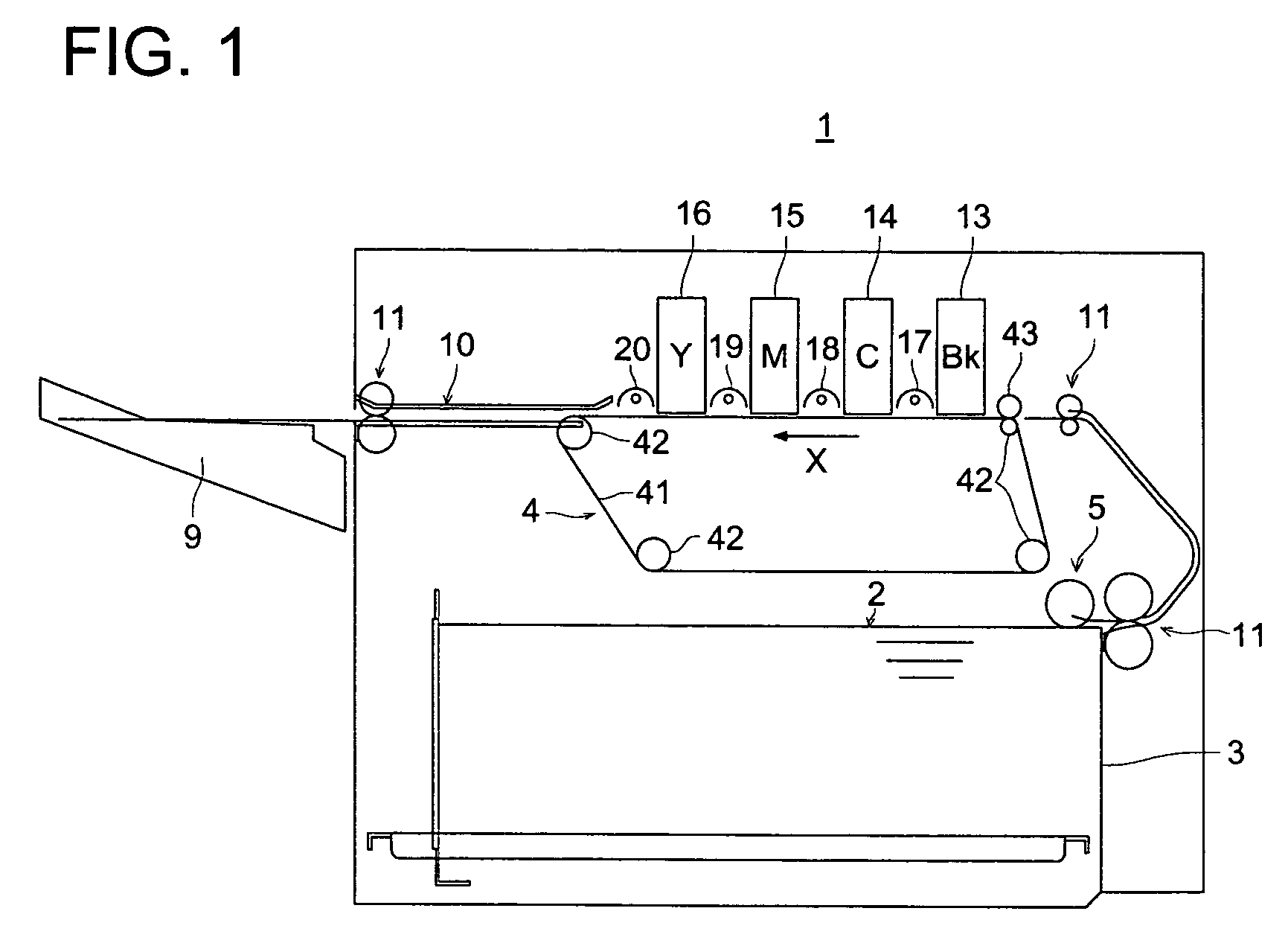

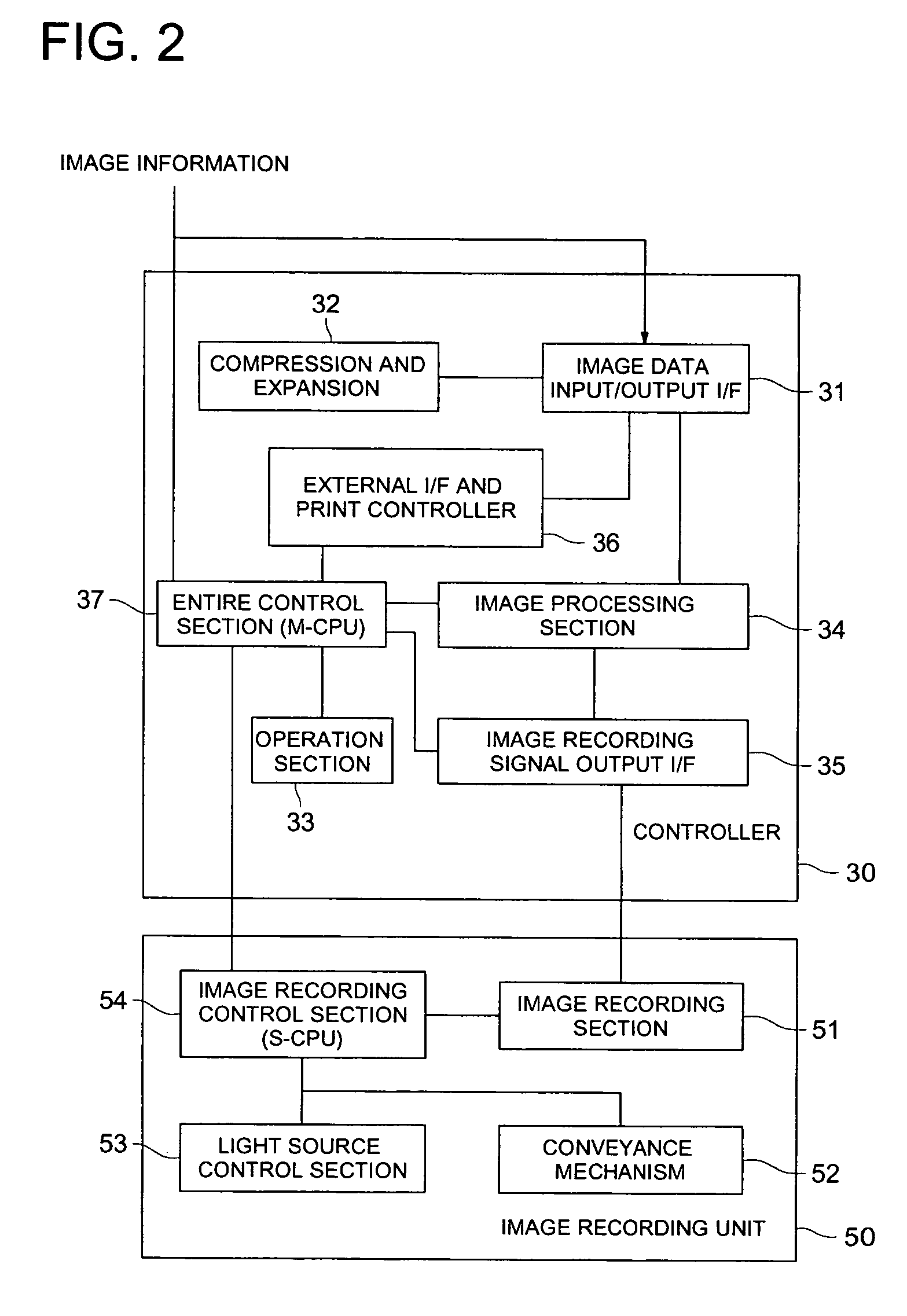

Image forming apparatus having a plurality of printing heads

ActiveUS7152970B2High quality imagingDispersion suppressionInking apparatusOther printing apparatusLight energyImage recording

In an image recording apparatus equipped with plural printing heads each for jetting ink drops having a photo-setting property towards a recording medium, a conveyance unit for conveying the recording medium to the printing heads, and each of plural light radiation devices for radiating light to the ink drops landed on the recording medium to harden, is arranged at the downstream side of each of the plural printing heads, one having largest light energy, which is located at the most downstream position among the plural light radiation devices is determined at least to satisfy the light energy necessary for hardening of the ink drops jetted by any one of the printing heads positioned upstream thereof, and the light energy becomes smaller gradually for every light radiation device in the order from the light radiation device at the most downstream position to those at more upstream positions.

Owner:KONICA MINOLTA INC

Method, apparatus and jig for manufacturing head suspension, and head suspension

ActiveUS20090183359A1Dispersion suppressionImprove productivityElectrical transducersRecord information storageProduction rateVibration control

A method for manufacturing a head suspension is capable of suppressing the dispersion in the vibration control effect of a head suspension and improve productivity, the manufacturing method includes a step of punching, by use of a hollow punch having a tooth portion at a distal end thereof, a vibration damper piece out from a base material having a vibration damper provided detachably on a liner through an attaching surface, to hold the vibration damper piece on a hollow internal surface of the punch, a step of positioning the punch holding the vibration damper piece on an objective portion of a semi-finished head suspension, and a step of attaching, by use of an extruding implement, the vibration damper piece on the objective portion with the attaching surface through extruding the vibration damper piece from the punch.

Owner:NHK SPRING CO LTD

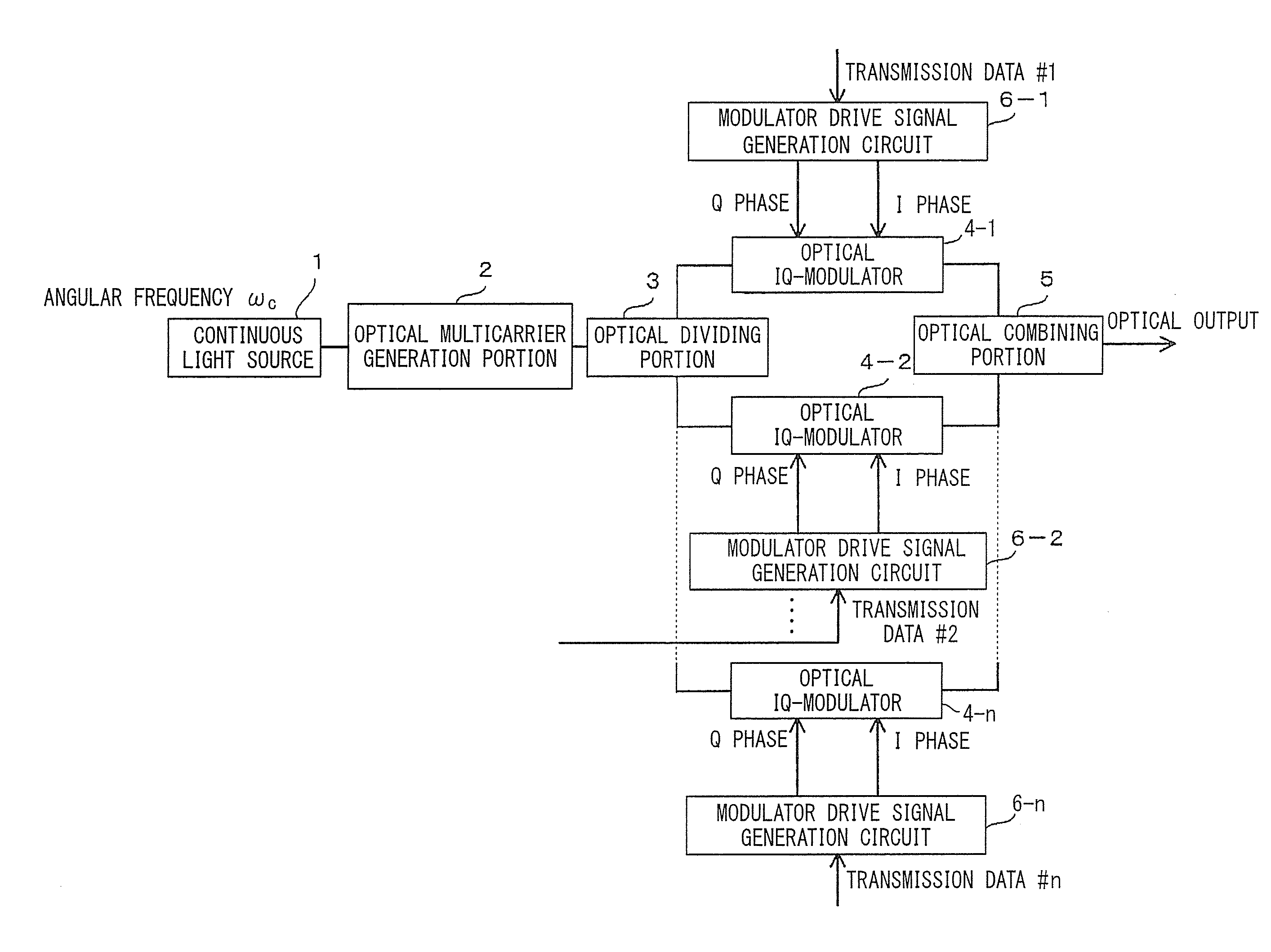

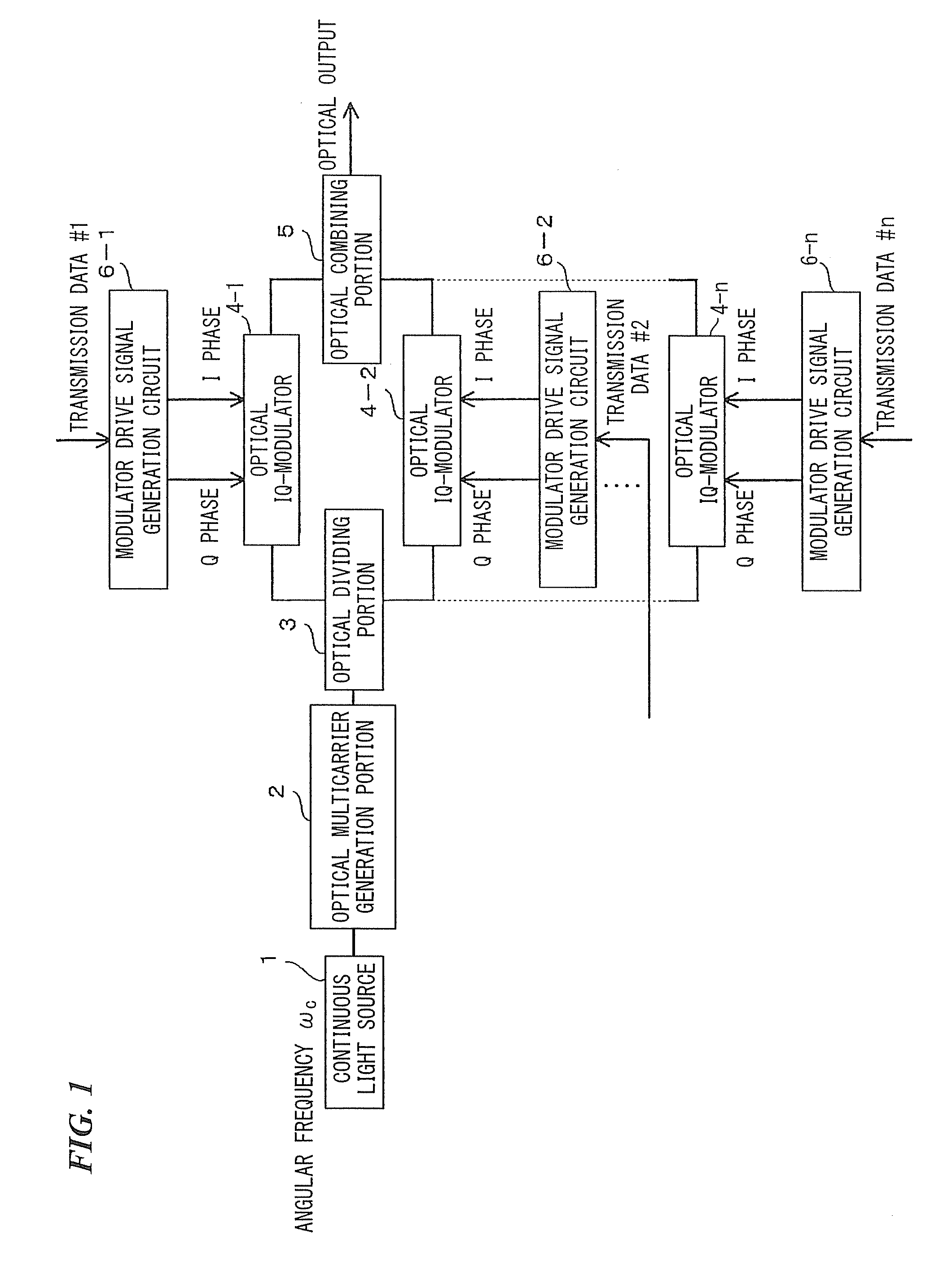

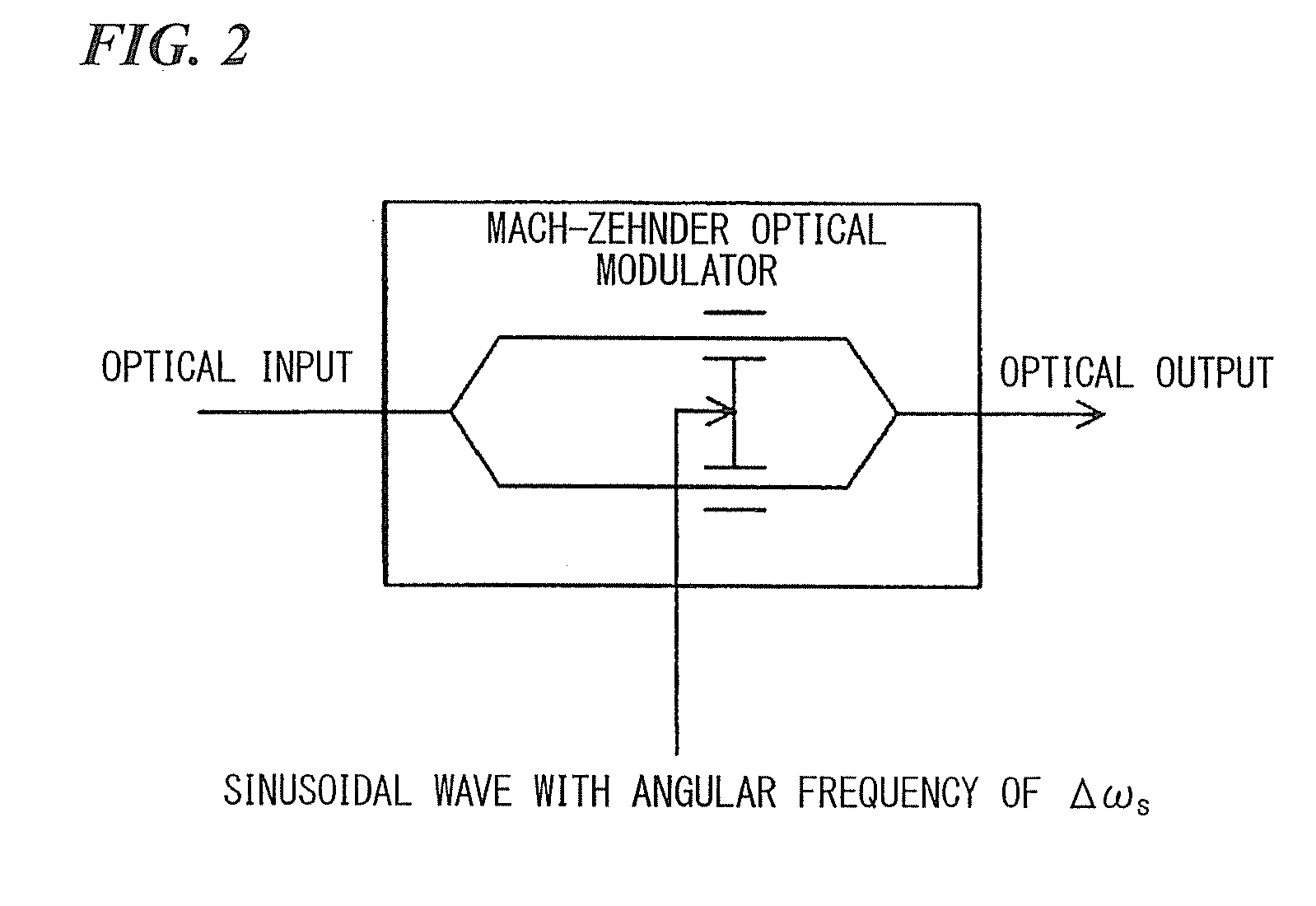

Optical modulation circuit and optical transmission system

ActiveUS20100220376A1Reduce numberDispersion suppressionWavelength-division multiplex systemsDistortion/dispersion eliminationPhysicsPhase shifted

An optical modulator and an optical transmission system convert continuous light of a multiple wavelength light source, which generates the continuous light with a fixed and complete phase but different frequencies, to a modulator driving signal so as to generate a light subcarrier with each frequency at the center and modulate the continuous light to the light subcarrier by using the modulator driving signal. In the case where an optical modulation is carried out by an optical IQ-modulator, transmitting data, for example, is converted to two parallel data A(t) and B(t), an I phase signal, in which the data A(t)+B(t) are modulated with a clock signal with a frequency ω, and a Q phase signal, in which the data A(t)−B(t) are modulated with a clock signal with a π / 2 phase shifted, are generated, and the I phase signal and the Q phase signal are applied to electrodes of the optical IQ-modulator, respectively.

Owner:NIPPON TELEGRAPH & TELEPHONE CORP

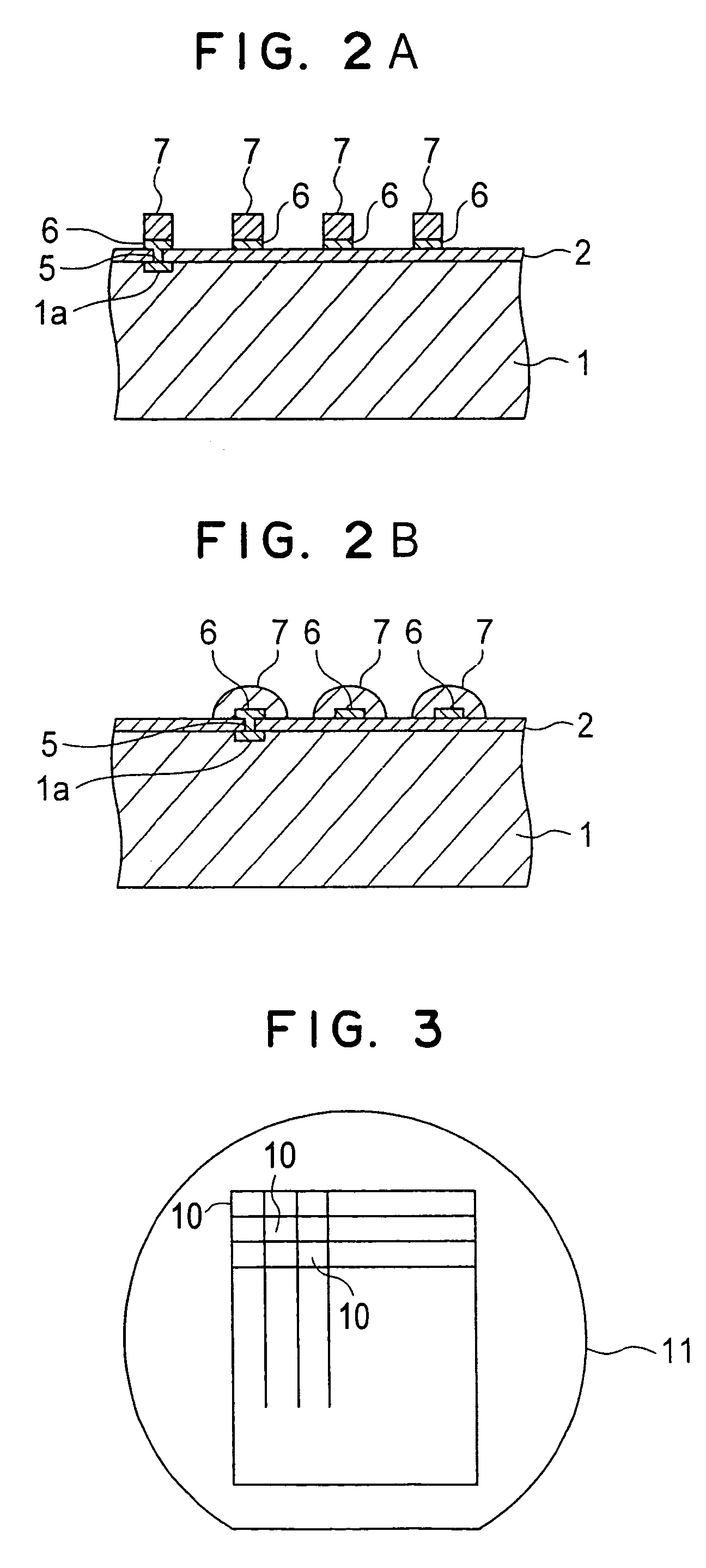

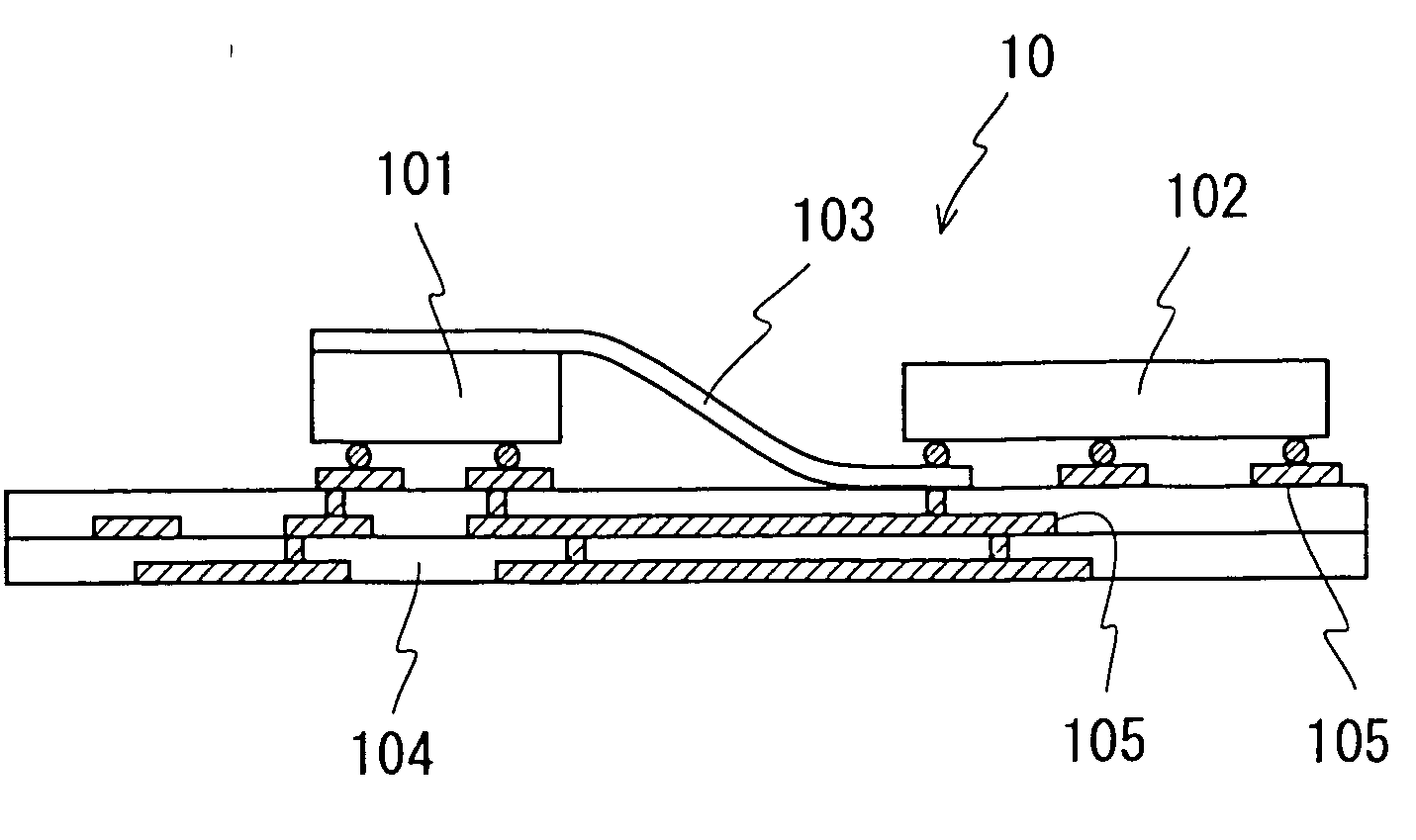

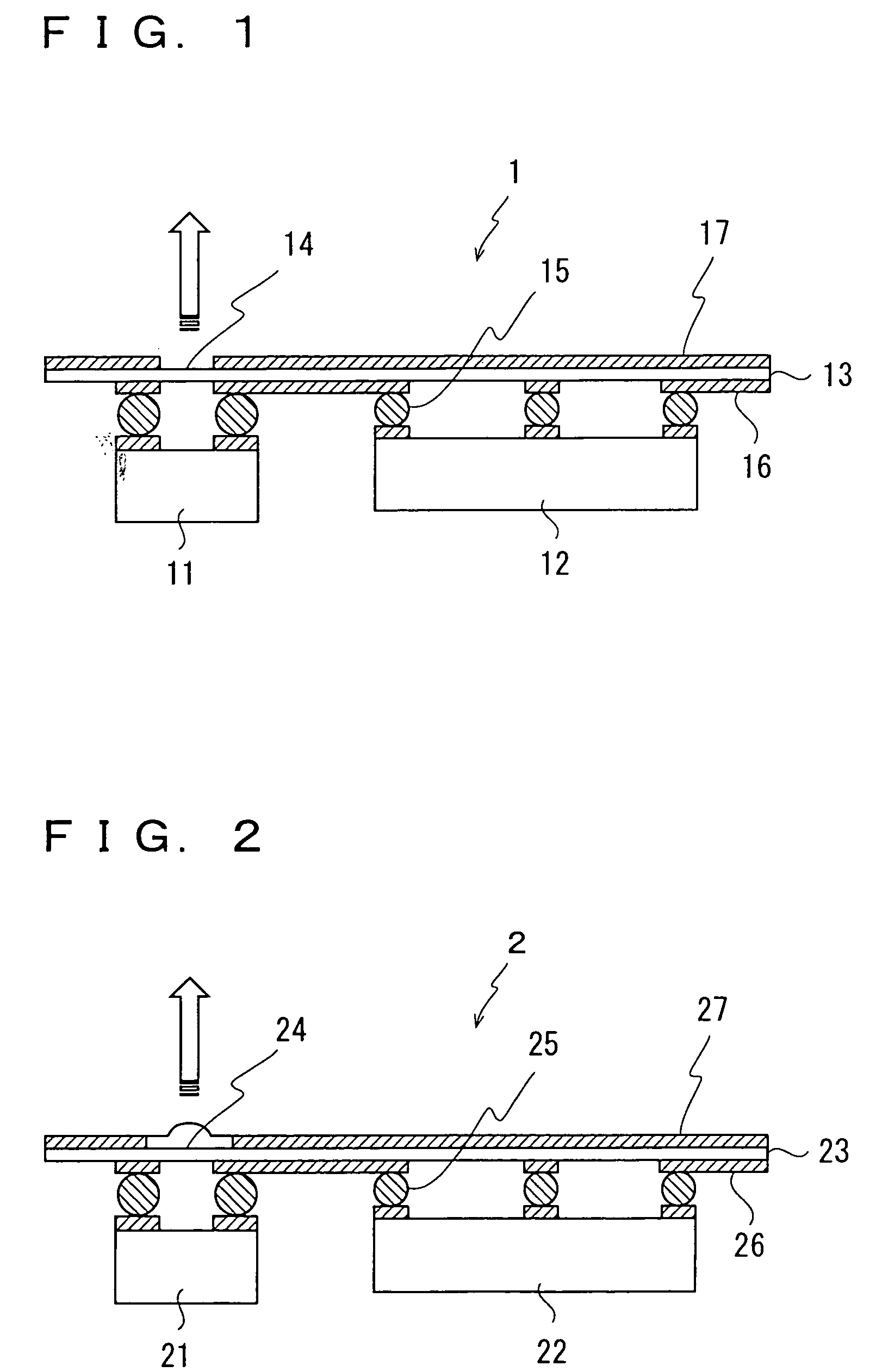

Optoelectronic hybrid integrated module and light input/output apparatus having the same as component

InactiveUS20050180679A1Low number of componentsReduce the number of processesSemiconductor laser structural detailsSolid-state devicesCouplingOptical axis

On the back surface of a transparent plate having a light extracting part 14 for outputting lights to the outside, an electrode 16 for wiring, and an electrode 17 for an electromagnetic shield, an optical device 11 is flip-chip mounted right under the light extracting part 14, an a driver IC 12 is flip-chip mounted at a desired position with metal bumps 15. When currents driving the optical device 11 flow from the driver IC 12 according to an electric logical signal from the outside, an optical signal is emitted from the optical device 11, and is output to the outside through the light extracting part 14. The light extracting part 14 may be provided with a light coupling material or an optical axis converter.

Owner:NEC CORP

Formation method of metal layer on resin layer, printed wiring board, and producution method thereof

ActiveUS20070277373A1Improve accuracyImprove electrical performancePrinted circuit assemblingLine/current collector detailsElectrical conductorSurface roughness

A printed wiring board having a conductor circuit comprising a copper layer adjacent to an insulating layer and an electroless gold plating, wherein the insulating layer has ten-point mean surface roughness (Rz) of 2.0 μm or less is provided. According to the present invention, there is no such a defect that gold plating is deposited on a resin, and fine wiring formation with accuracy is realized.

Owner:RESONAC CORPORATION

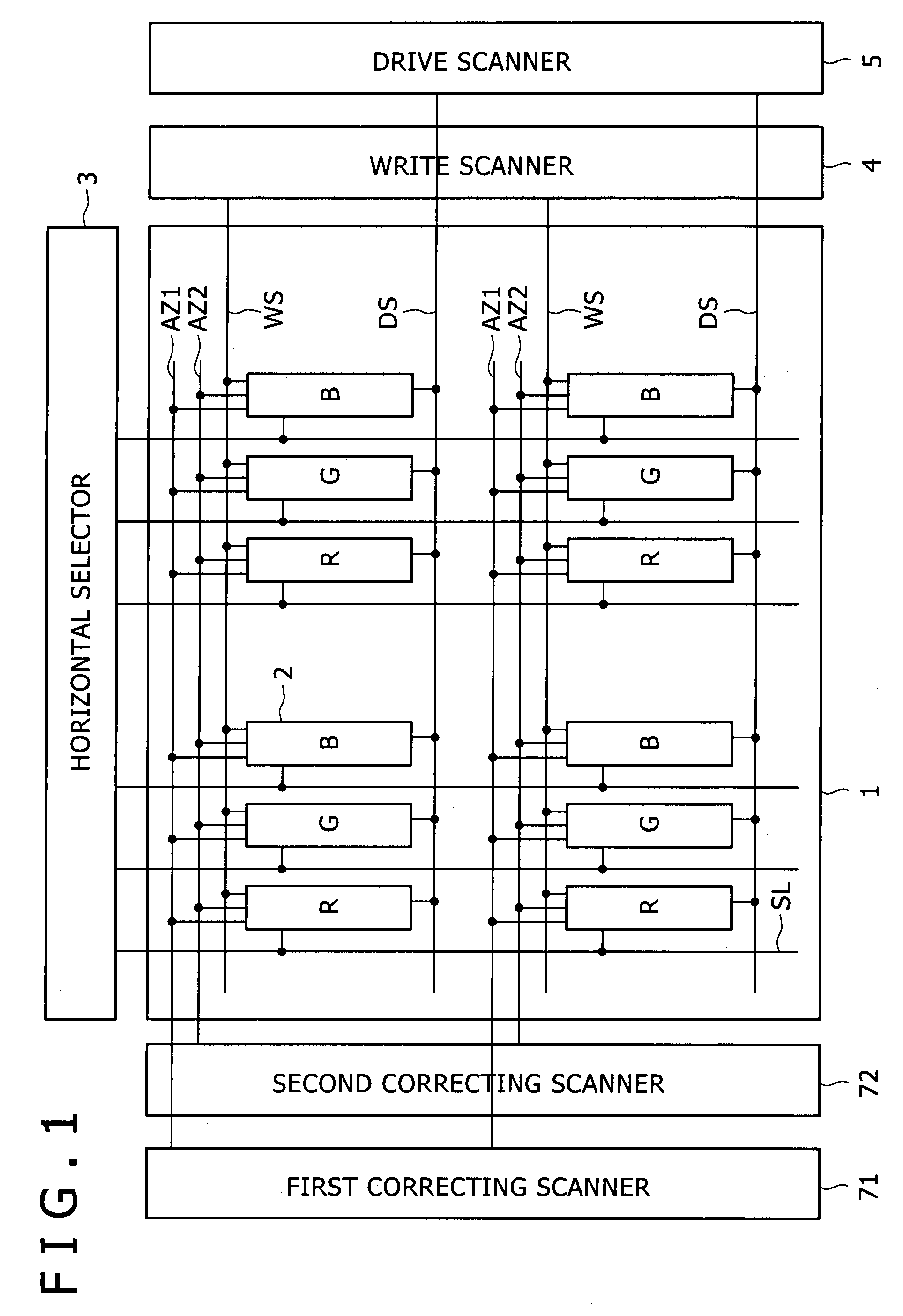

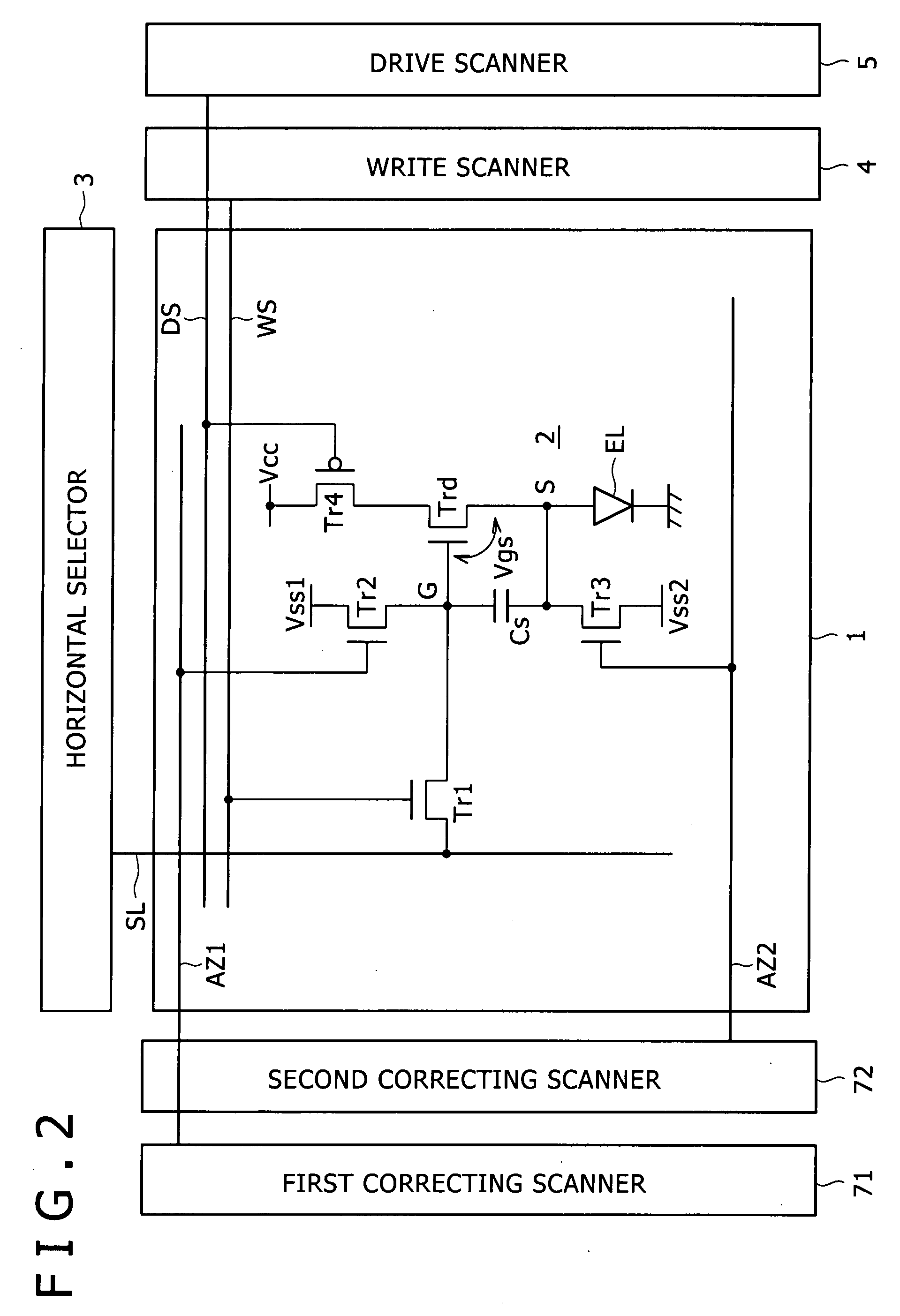

Electro-optical device and electronic apparatus

InactiveCN101399283AImprove display qualityDispersion suppressionLayered productsElectroluminescent light sourcesElectricityLight-emitting diode

This invention provides an electro-optical device having organic light emitting diode, comprising: a plurality of first electrodes mounted on a substrate; a partition having a first partition and a second partition; the first partition mounted at the circumference section of a plurality of first electrodes, consisting a side part and an upper part and having lyophily; the second partition formed on the upper part of the first partition and having lyophobicity; a functional layer mounted on the first electrode of the region surrounded by the first partition and the second partition, at least comprising an organic light emitting layer; a second electrode mounted on the function layer; a first opening section of the first partition is wider than a second opening section of the lower end of the second partition, thereby making a film thickness formed by drying liquid droplets filled in a liquid droplet ejection region surrounded by a partition be uniform.

Owner:SEIKO EPSON CORP

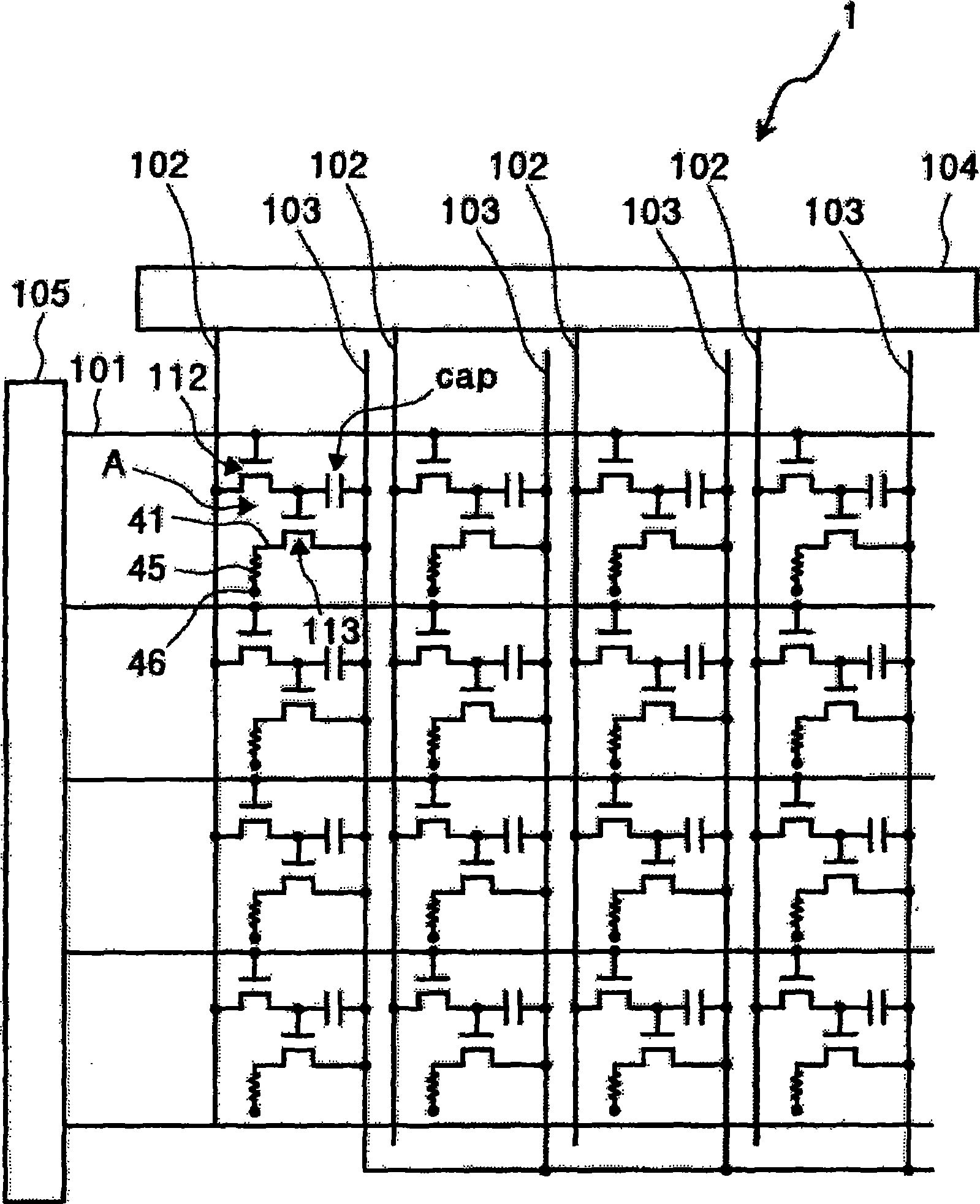

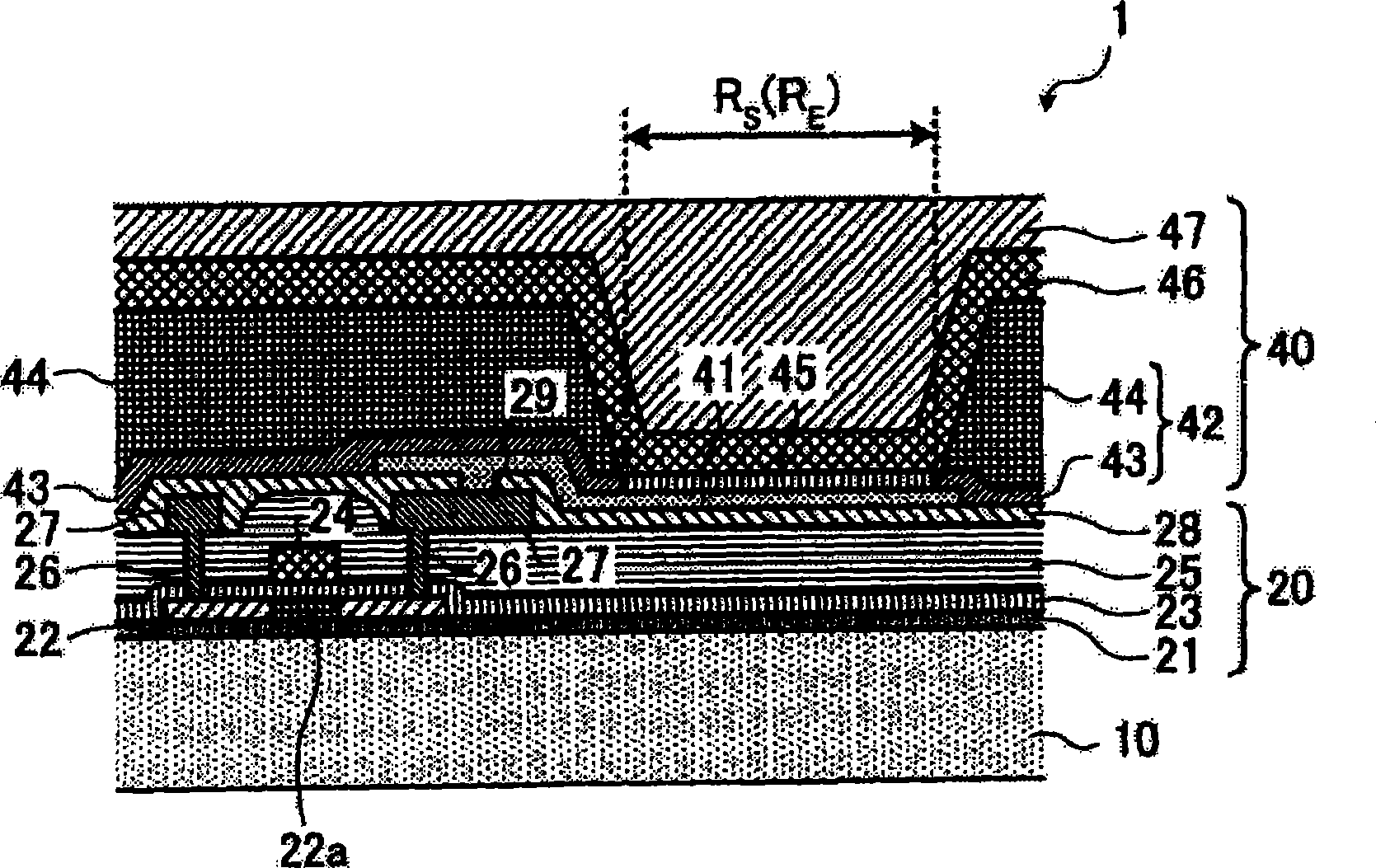

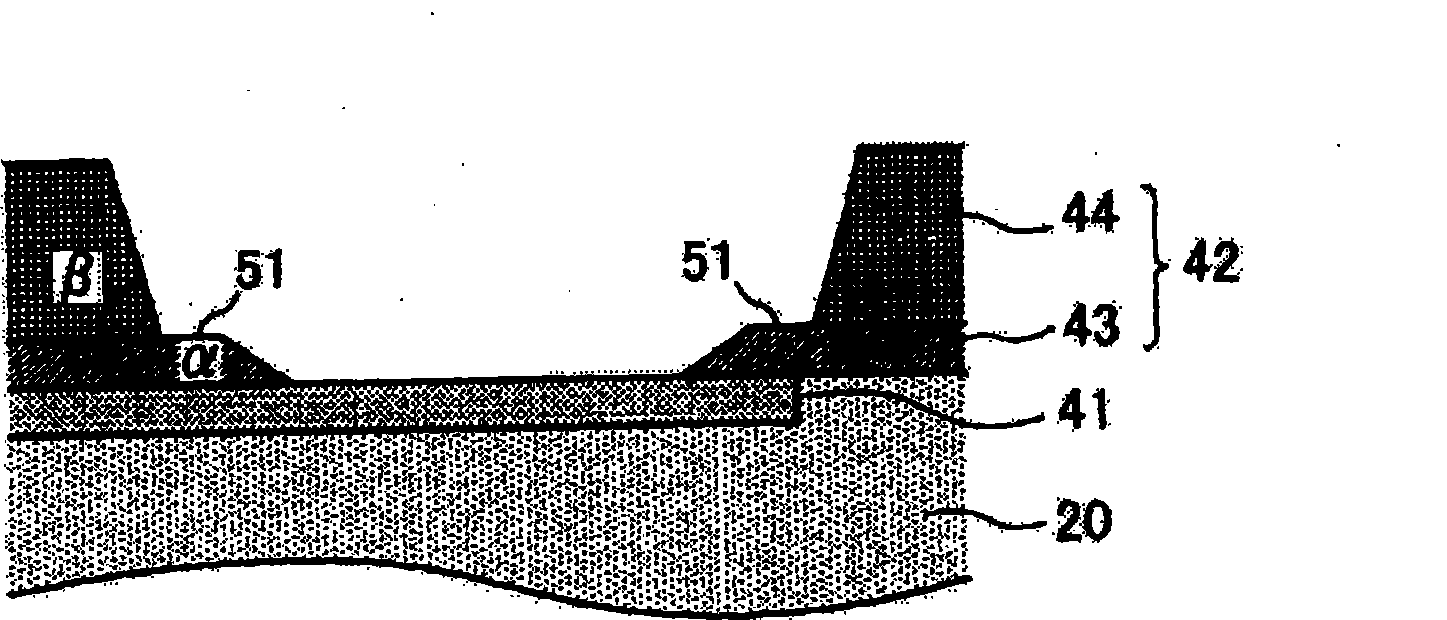

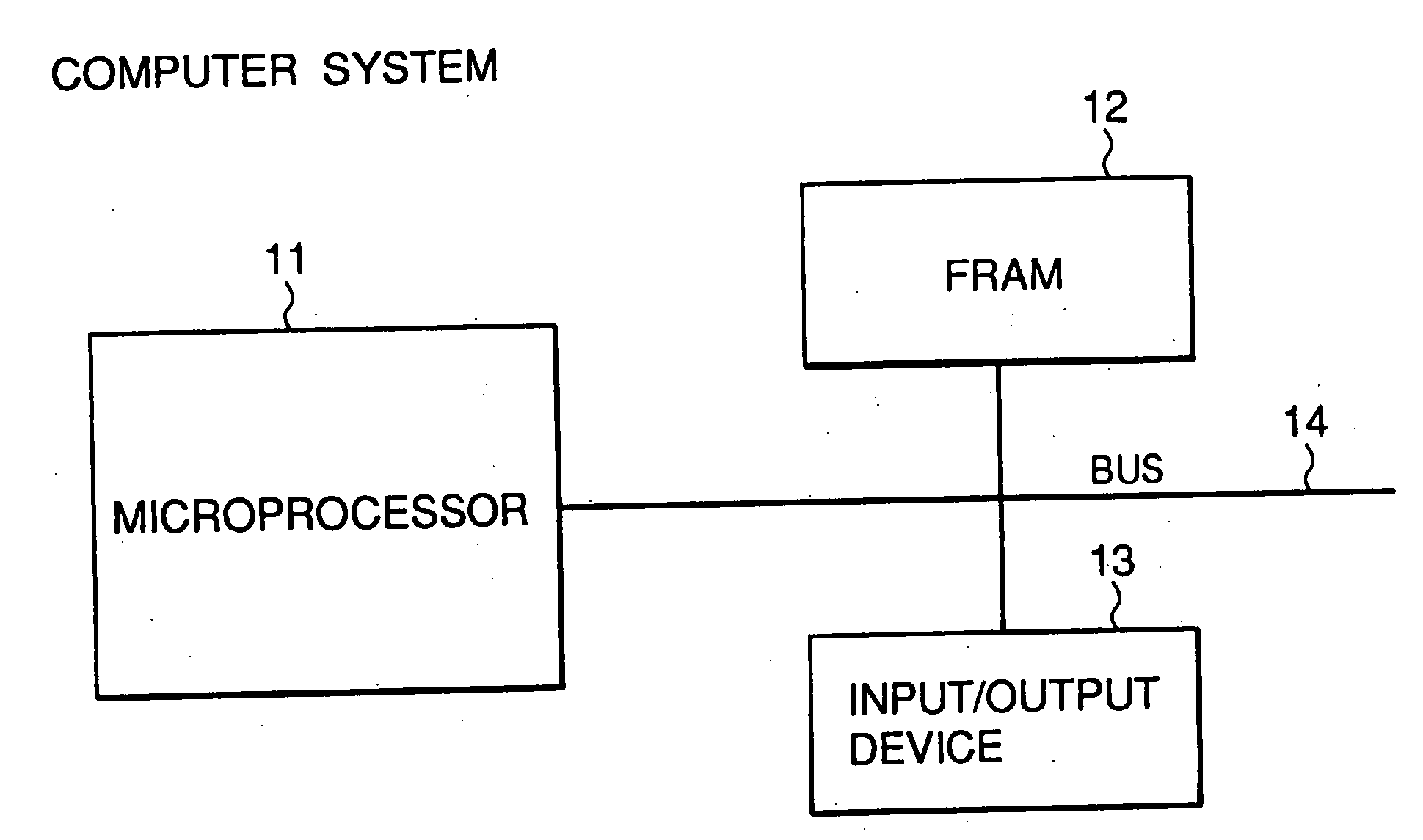

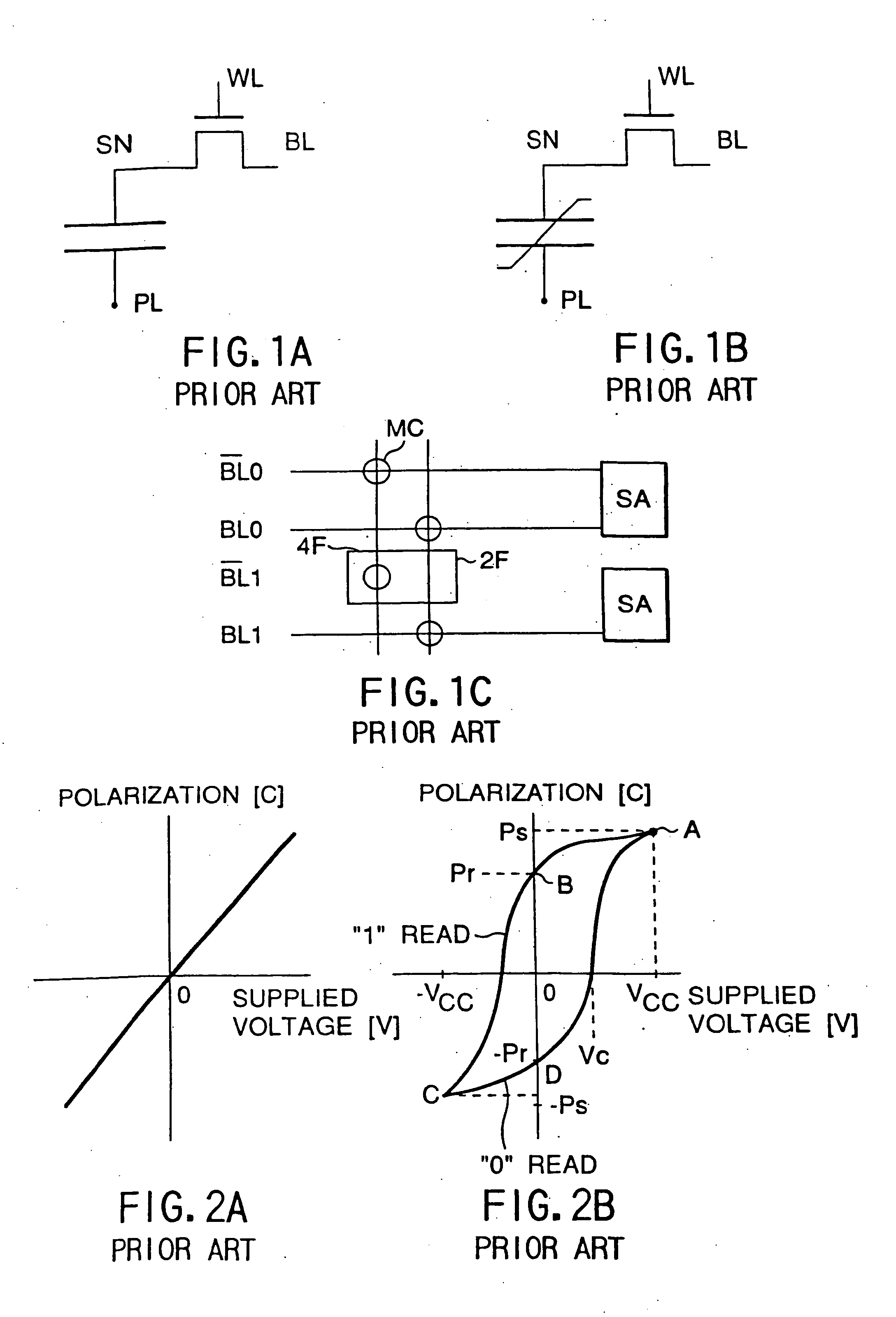

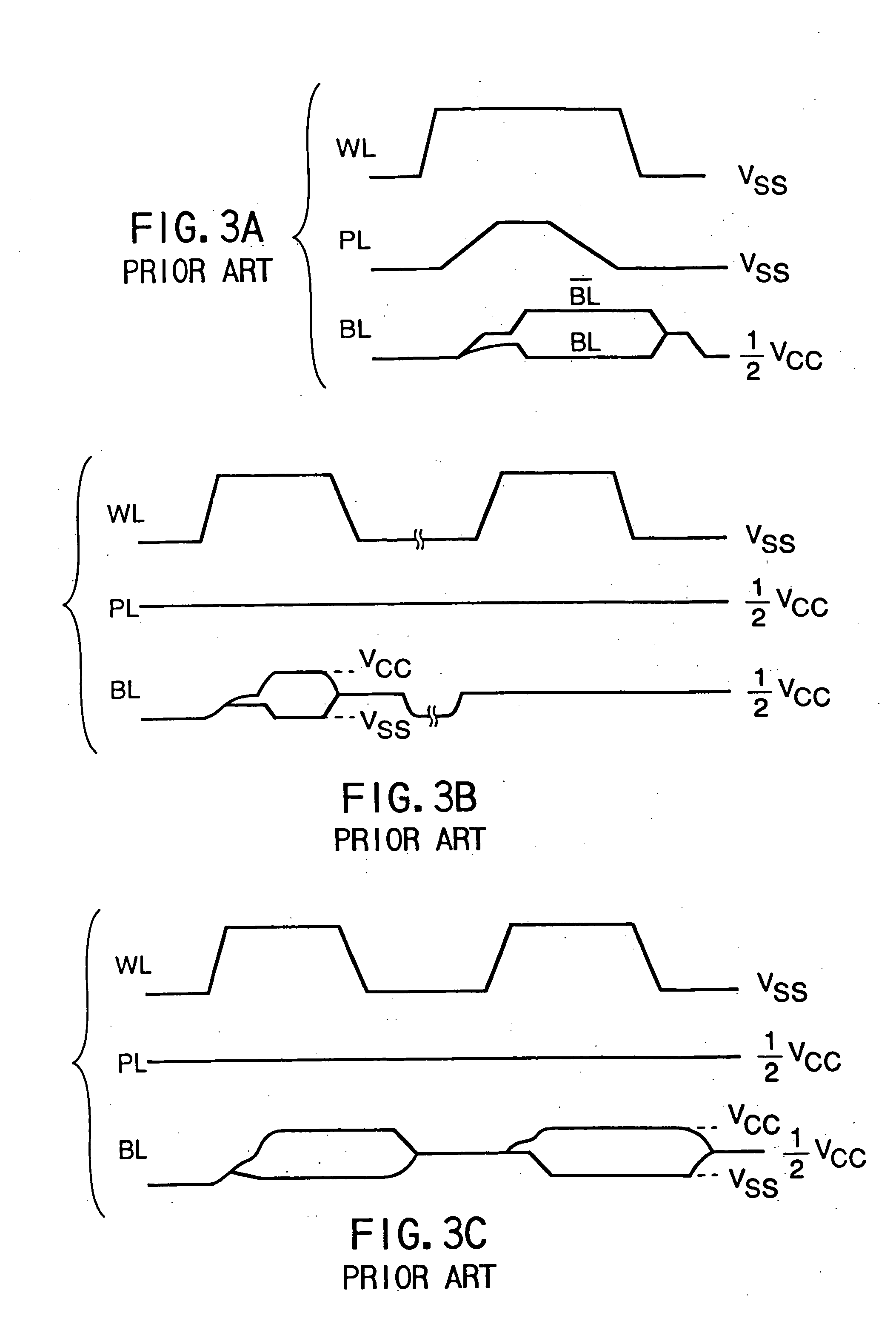

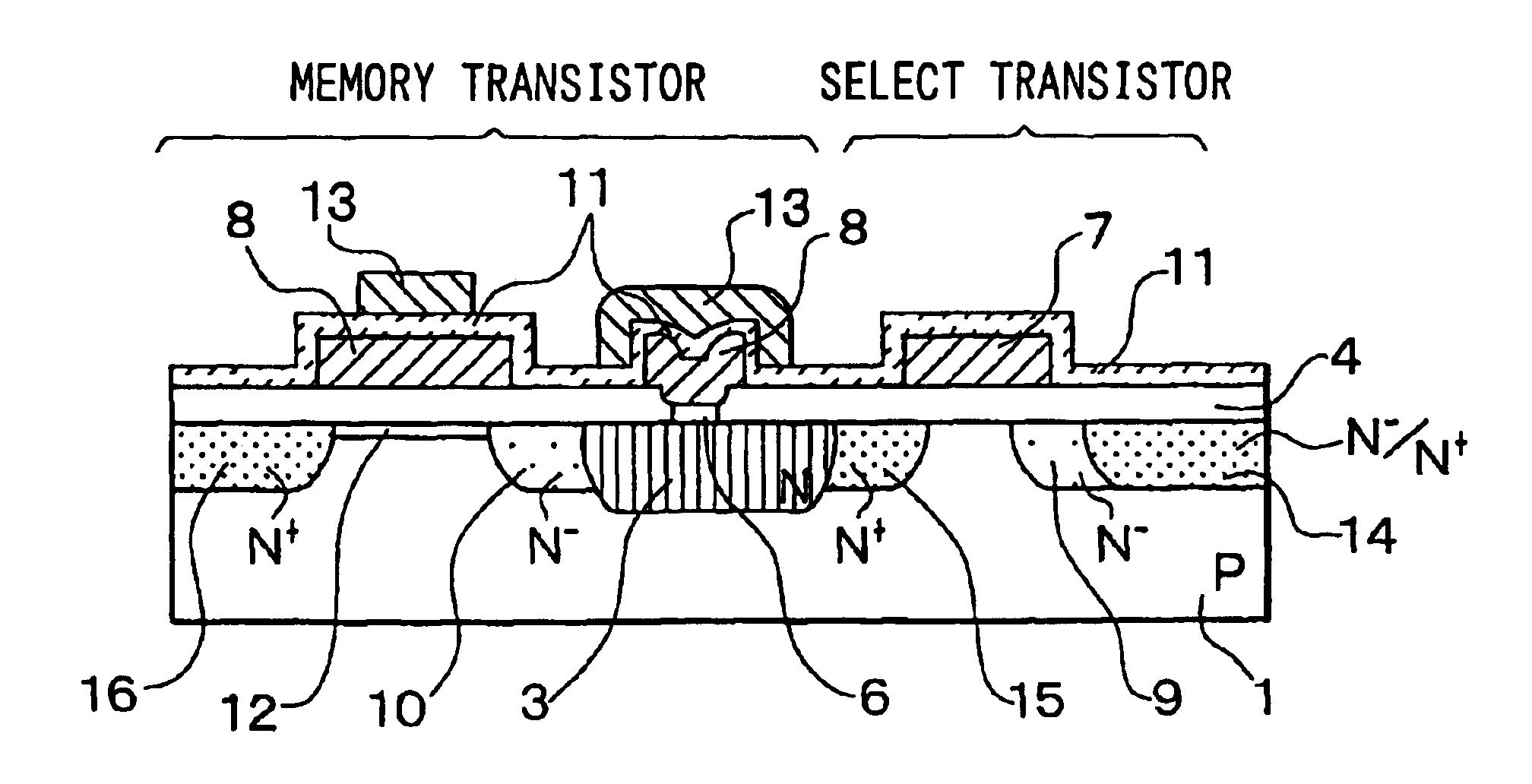

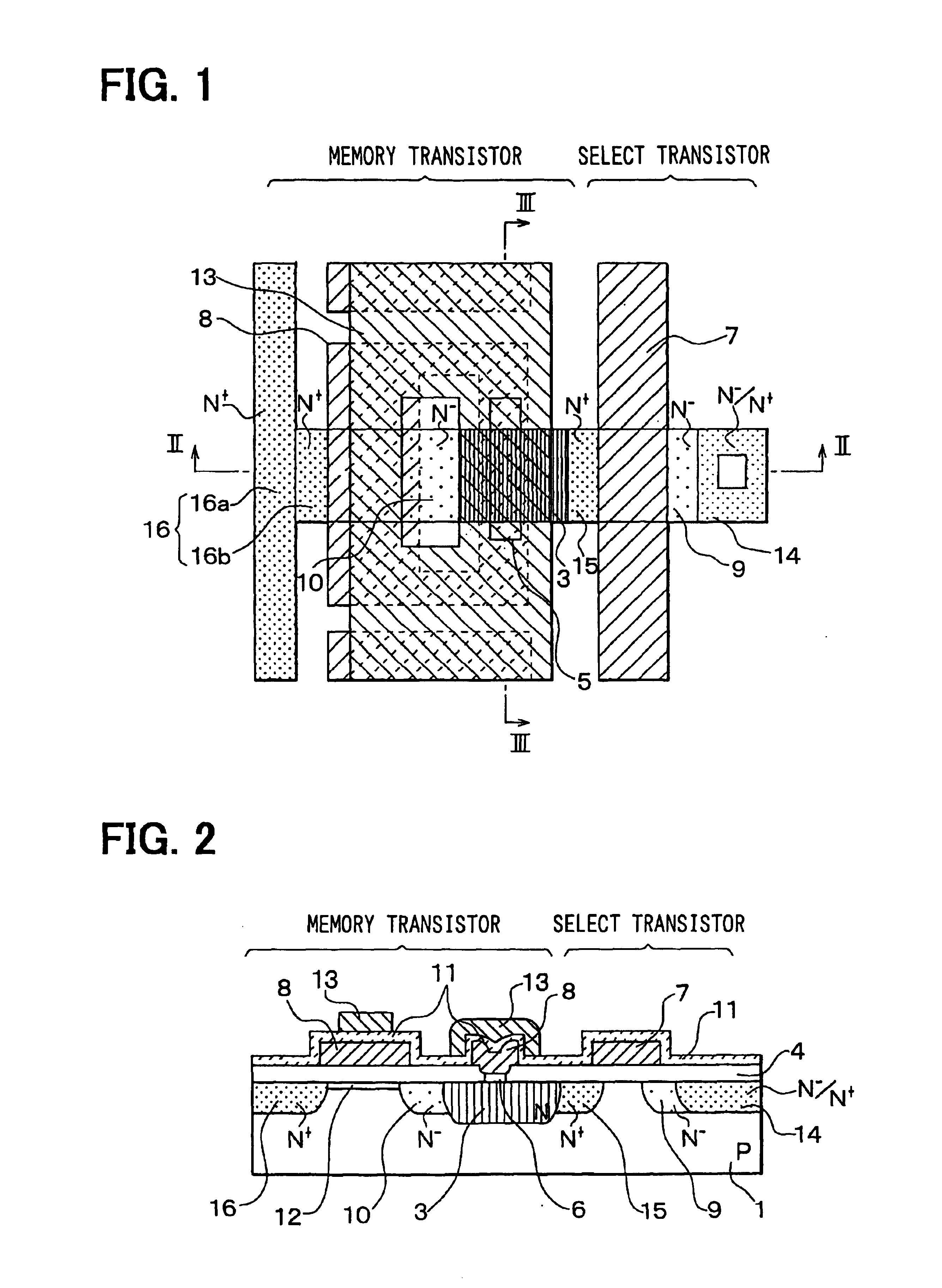

Semiconductor memory device and various systems mounting them

InactiveUS20050063225A1Dispersion suppressionEasy to produceSolid-state devicesDigital storageBit lineEngineering

A semiconductor memory device comprises a plurality of memory cells each having a source terminal and a drain terminal and a ferroelectric capacitor having a first terminal connected to the source terminal, wherein the plurality of memory cells are connected in series, and one or more selected transistors connected to at least one terminal of the series connected memory cells to constitute a memory cell block, the memory cell block having one terminal connected to a bitline and another terminal connected to a plate electrode, and wherein two memory cell blocks, which are respectively connected to two bit lines forming a bit line pair and also connected to the same word line, are respectively connected to a first plate electrode and a second plate electrode.

Owner:TOSHIBA MEMORY CORP

EEPROM and EEPROM manufacturing method

InactiveUS6914288B2Suppress reduction of overwriting life and deterioration of charge holding characteristicSimple methodTransistorSolid-state devicesEngineeringTransistor

A memory transistor of an EEPROM has a floating gate electrode of a shape such that it covers the entirety of a tunnel film and a channel region and does not cover a region between the channel region and an embedded layer. And, a control gate electrode is formed on an interlayer insulating film on the floating gate electrode into a shape such that it is wider than the floating gate electrode above the tunnel film, and is narrower than the floating gate electrode above the channel region.

Owner:DENSO CORP

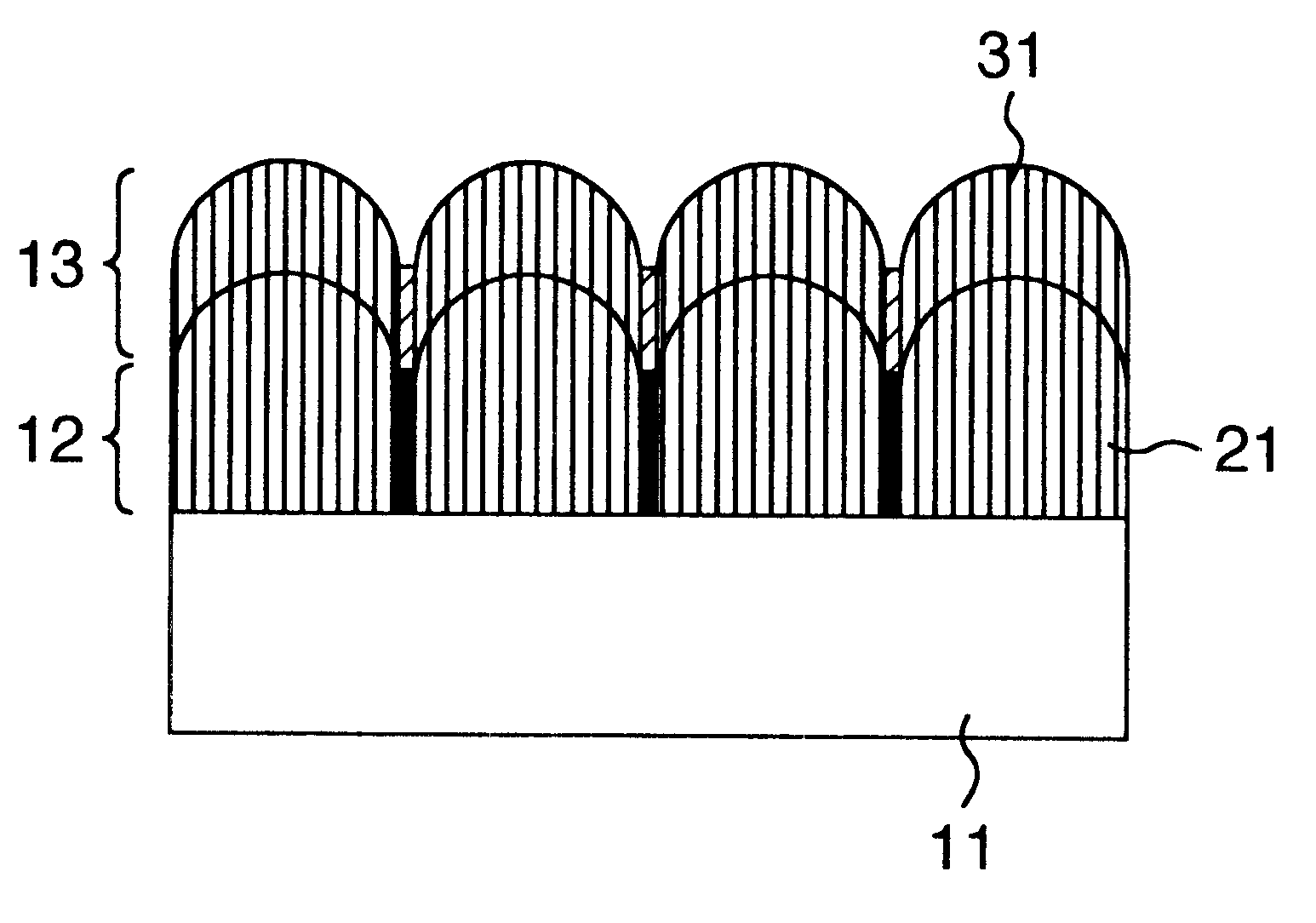

Magnetic recording disk

InactiveUS6472047B1Reduced magnetic interactionReduce demagnetizationBase layers for recording layersVacuum evaporation coatingSilicon oxideTitanium oxide

The magnetic recording medium includes an underlayer 12 formed of an inorganic compound layer, and a magnetic layer 13 formed over the underlayer 12. The inorganic compound layer as the underlayer 12 has crystal grains and at least one kind of oxide, the crystal grains having as main elements at least one of cobalt oxide, chromium oxide, iron oxide and nickel oxide, the at least one kind of oxide lying as a non-crystalline phase in grain boundaries between the crystal grains and selected from among silicon oxide, aluminum oxide, titanium oxide, tantalum oxide and zinc oxide.

Owner:HITACHT MAXELL LTD +1

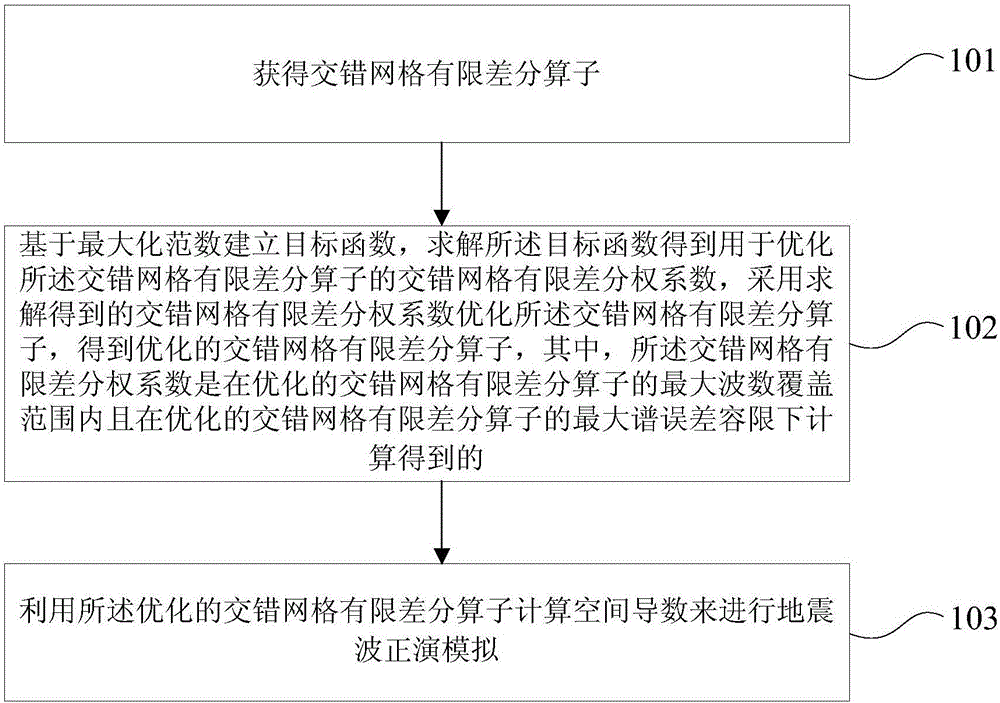

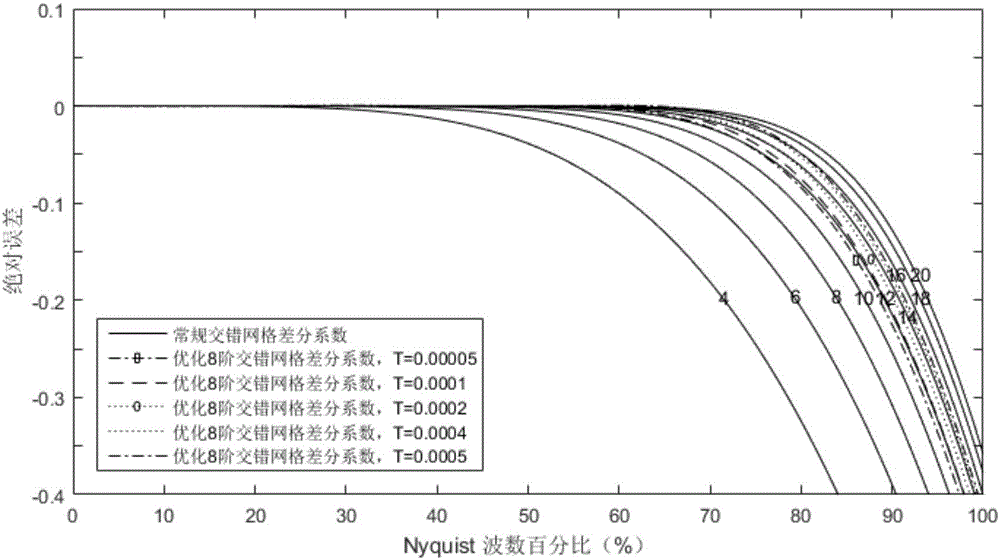

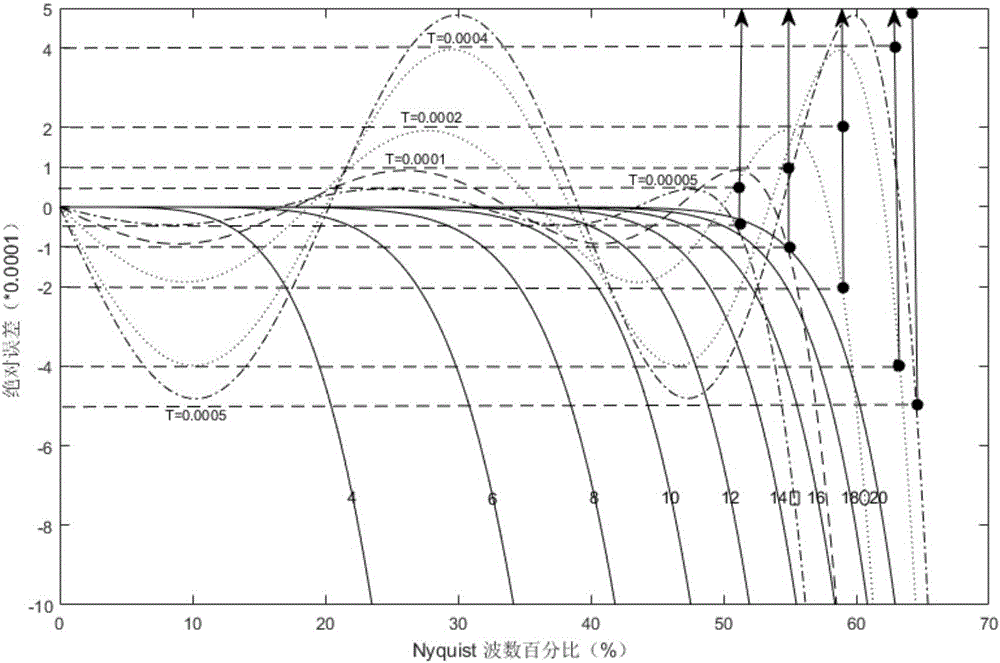

Globally optimized staggered mesh finite-difference forward simulation method and device

InactiveCN106842306AFlexible processControlling Absolute Spectral ErrorSeismic signal processingGlobal optimizationFrequency dispersion

The embodiment of the invention provides a globally optimized staggered mesh finite-difference forward simulation method and device. The method comprises the steps that a staggered mesh finite-difference operator is obtained; a target function is established based on a maximized norm and is calculated to obtain a staggered mesh finite-difference decentralization coefficient for optimizing the staggered mesh finite-difference operator, wherein the staggered mesh finite-difference decentralization coefficient is calculated in the maximum wave number coverage range of the optimized staggered mesh finite-difference operator and under the maximum spectrum error margin of the optimized staggered mesh finite-difference operator; the calculated staggered mesh finite-difference decentralization coefficient is adopted to optimize the spatial staggered mesh finite-difference operator, and forward simulation of seismic waves is performed. By adopting the scheme, absolute spectrum errors of the optimized staggered mesh finite-difference operator are more flexibly controlled, numerical value frequency dispersion is more effectively constrained, and the seismic simulation precision is improved.

Owner:INST OF GEOLOGY & GEOPHYSICS CHINESE ACAD OF SCI

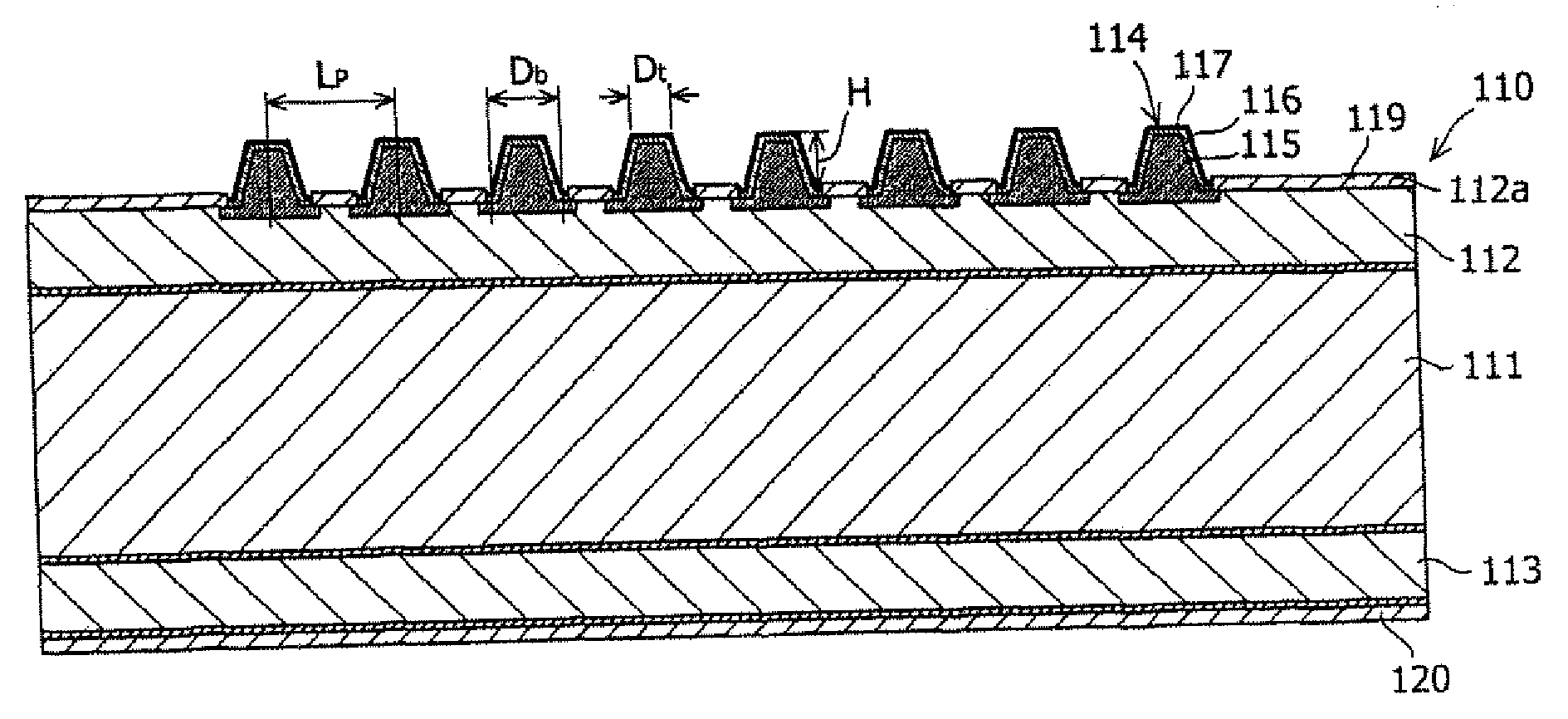

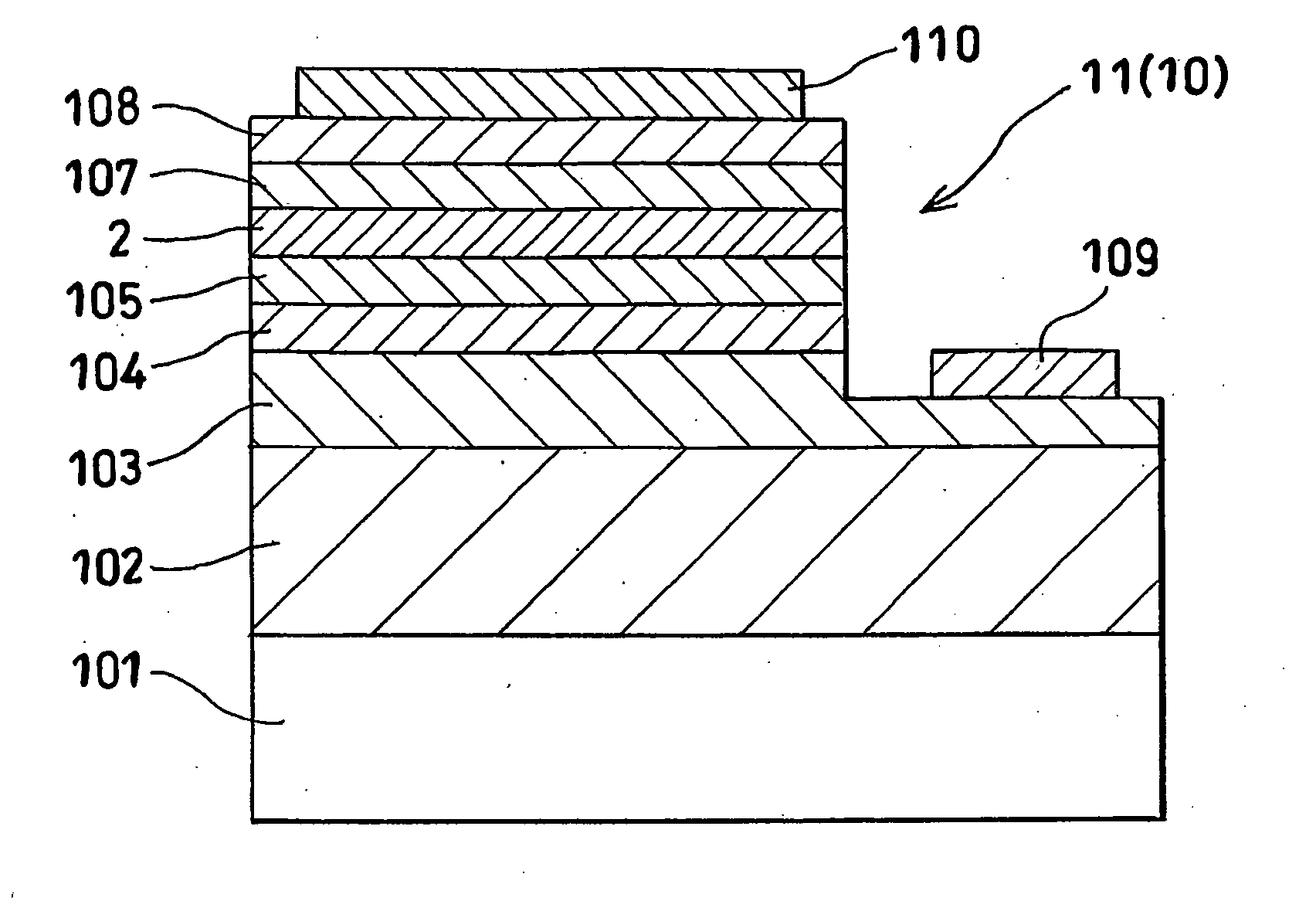

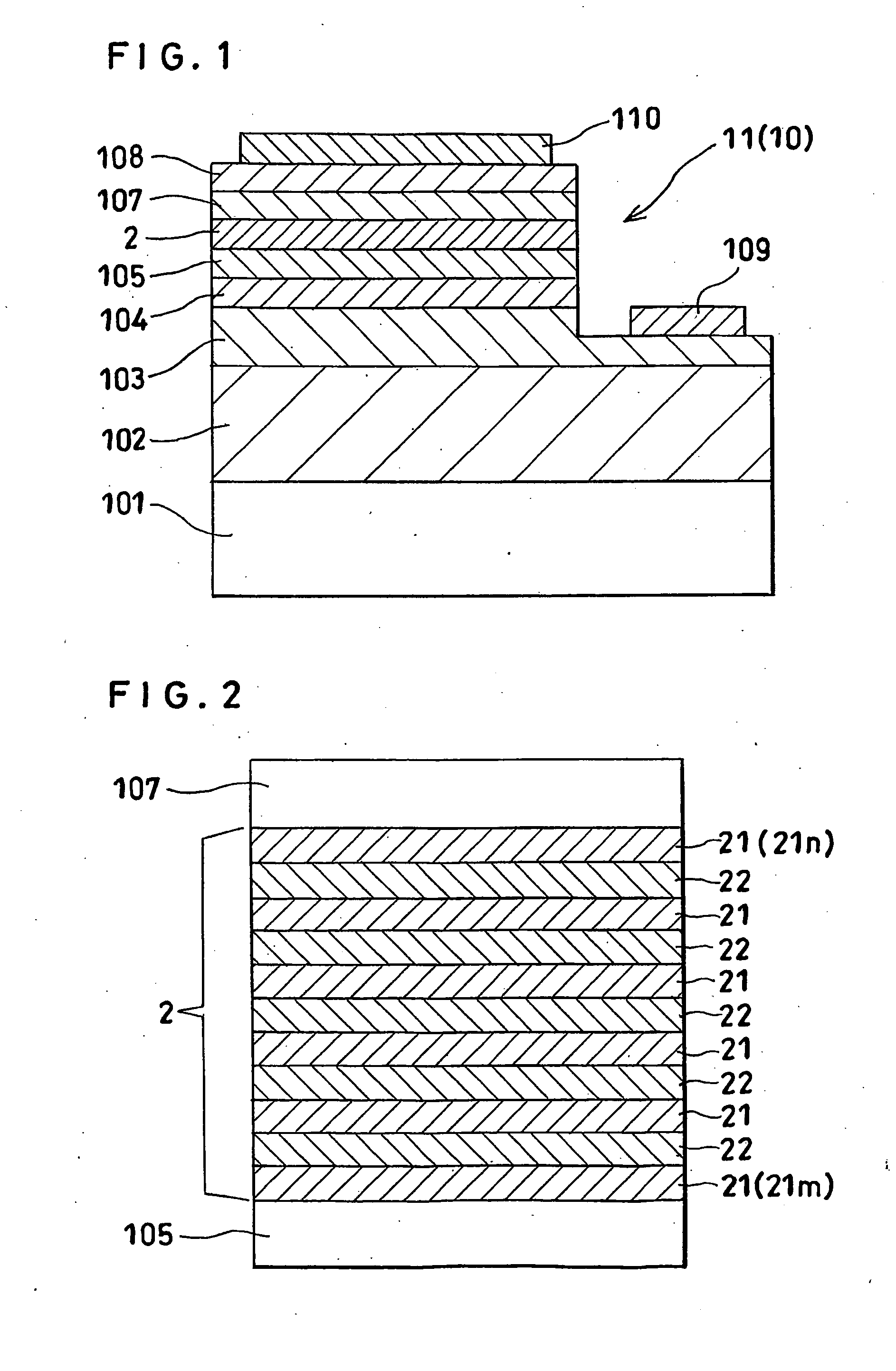

Pn Junction Type Group III Nitride Semiconductor Light-Emitting Device

ActiveUS20080230794A1Dispersion suppressionHigh luminous outputOptical wave guidanceLaser detailsLight emitting deviceNitride semiconductors

A pn junction type Group III nitride semiconductor light-emitting device 10 (11) of the present invention has a light-emitting layer 2 of multiple quantum well structure in which well layers 22 and barrier layers 21 including Group III nitride semiconductors are alternately stacked periodically between an n-type clad layer 105 and a p-type clad layer 107 which are formed on a crystal substrate and which include Group III nitride semiconductors, in which one end layer 21m of the light-emitting layer 2 is closest to and opposed to the n-type clad layer, and the other end layer 21n of the light-emitting layer 2 is closest to and opposed to the p-type clad layer, both the one and the other end layers are barrier layers, and the other end layer 21n is thicker than the barrier layer of the one end layer.

Owner:TOYODA GOSEI CO LTD

Plasma processing apparatus and method with controlled biasing functions

InactiveUS6875366B2Increase volumePotential distribution is reducedElectric discharge tubesDecorative surface effectsEtchingPower flow

Processing technique using plasma to process the surface of a sample such as semiconductor device. The phases of RF bias voltages applied to a substrate electrode and an antenna electrode opposed thereto are controlled to be opposite to each other so that either one of the electrodes is forced to always function as ground. Therefore, the current flowing to cross the magnetic field for controlling the plasma is decreased, and the potential distribution difference in the surface of the sample to be processed is reduced, so that the charging damage can be suppressed. Energy of ions incident to the sample to be processed can be controlled to perform high-precision etching. The plasma potential can also be controlled so that the strength of the ion impact to the inner wall of the chamber can be reduced, thereby reducing particles detached from the inner wall of the processing apparatus to improve the throughput.

Owner:HITACHI LTD

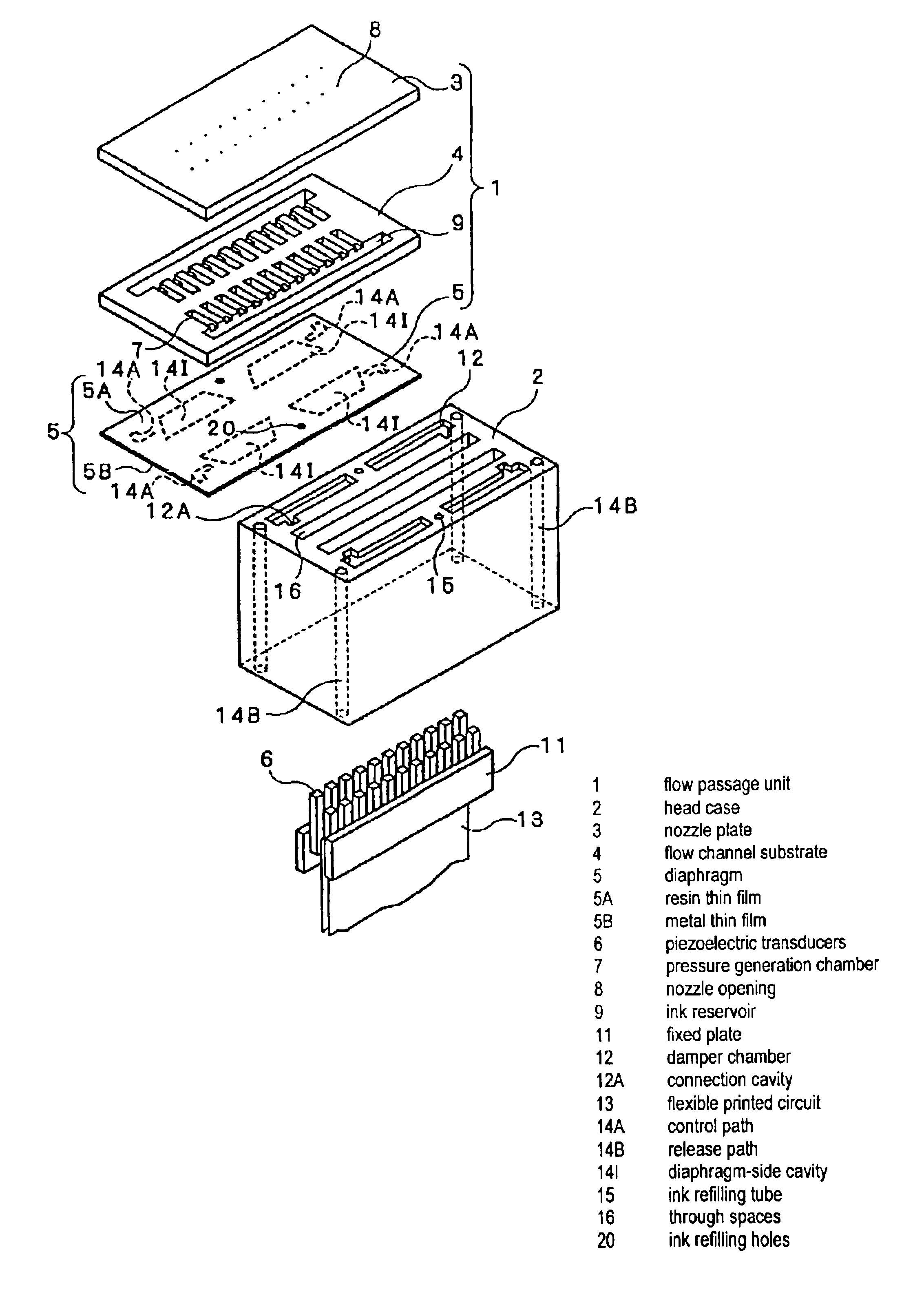

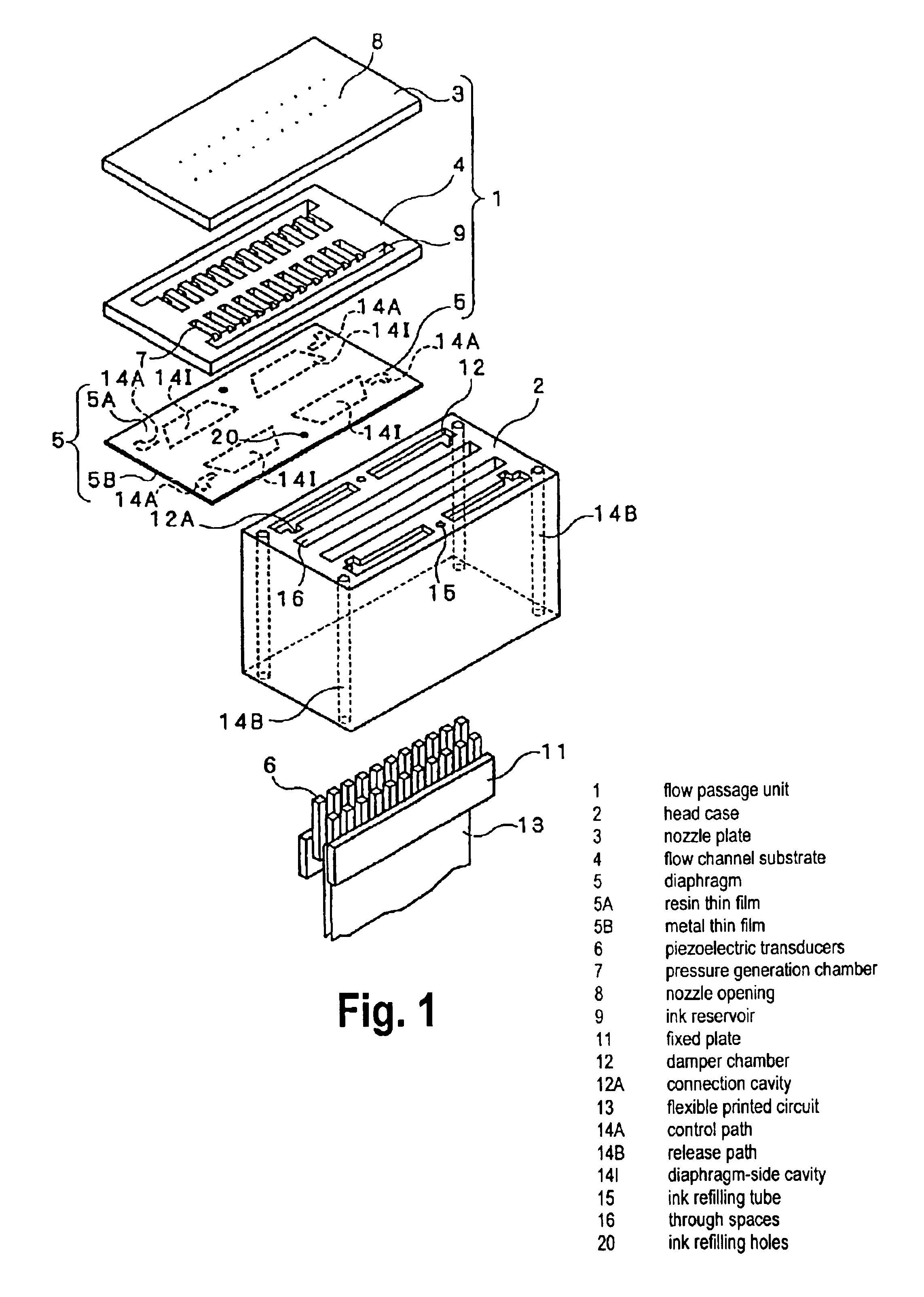

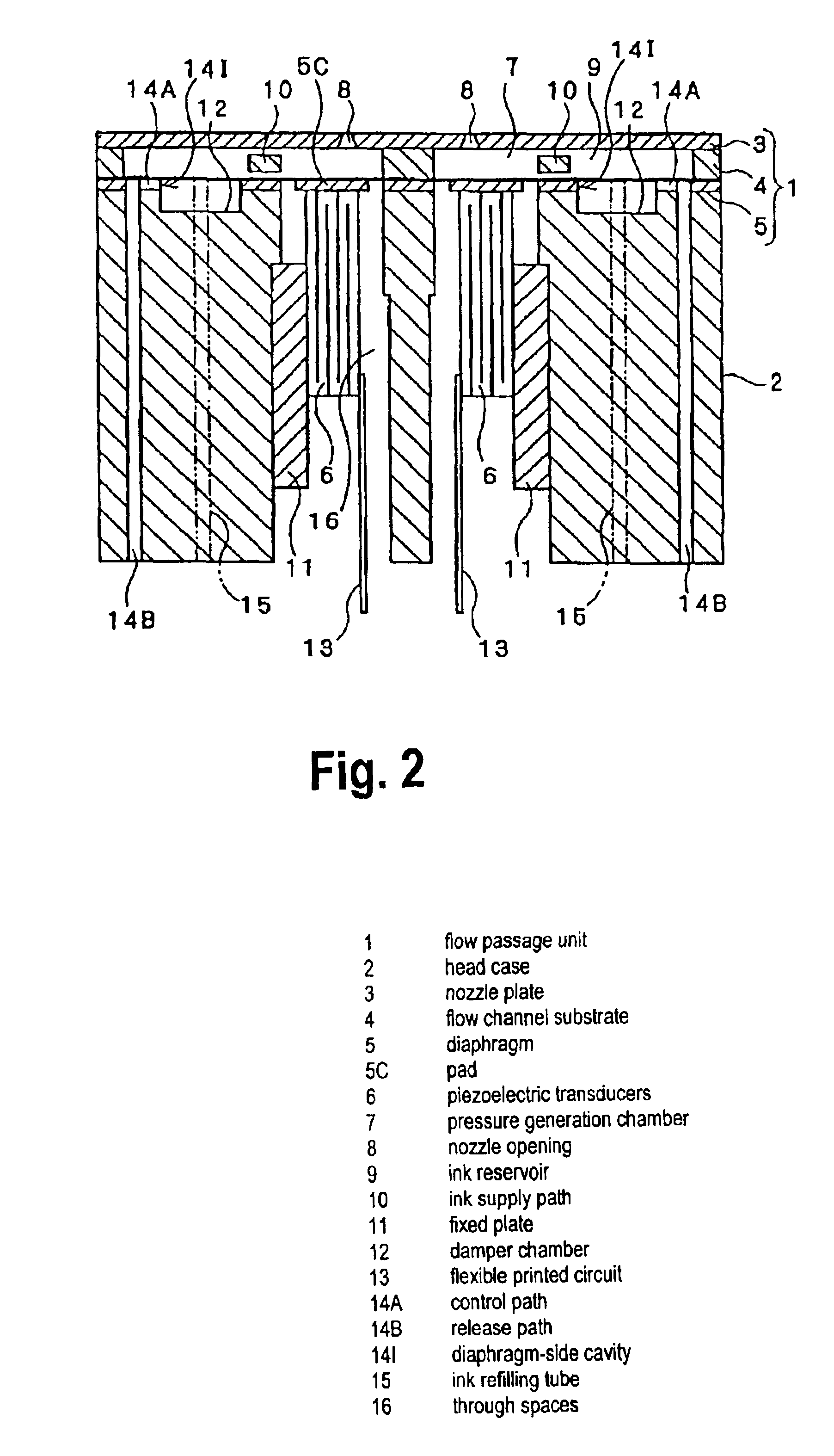

Liquid jet head

InactiveUS7070263B2Dispersion suppressionControl flowInking apparatusLiquid spraying apparatusLiquid jetPressure generation

A liquid jet head and apparatus prevent an increase in the viscosity of liquid in the liquid path during long term storage. The recording head has a liquid path unit 1 with nozzle openings 8, pressure generation chambers 7, liquid reservoirs 9, and a diaphragm 5, and a head case 2 bonded to the liquid path unit 1. A damper chamber 12 for releasing pressure change inside the liquid reservoir is formed at a part of the head case or seal plate 5 corresponding to the liquid reservoir 9. A release path 14B for releasing pressure in the damper chamber to the air is formed in the head case. A control path 14A communicating with the damper chamber and release path and having a specific flow resistance restricting dispersion of moisture vapor from the liquid is formed in the head case and / or seal plate.

Owner:SEIKO EPSON CORP

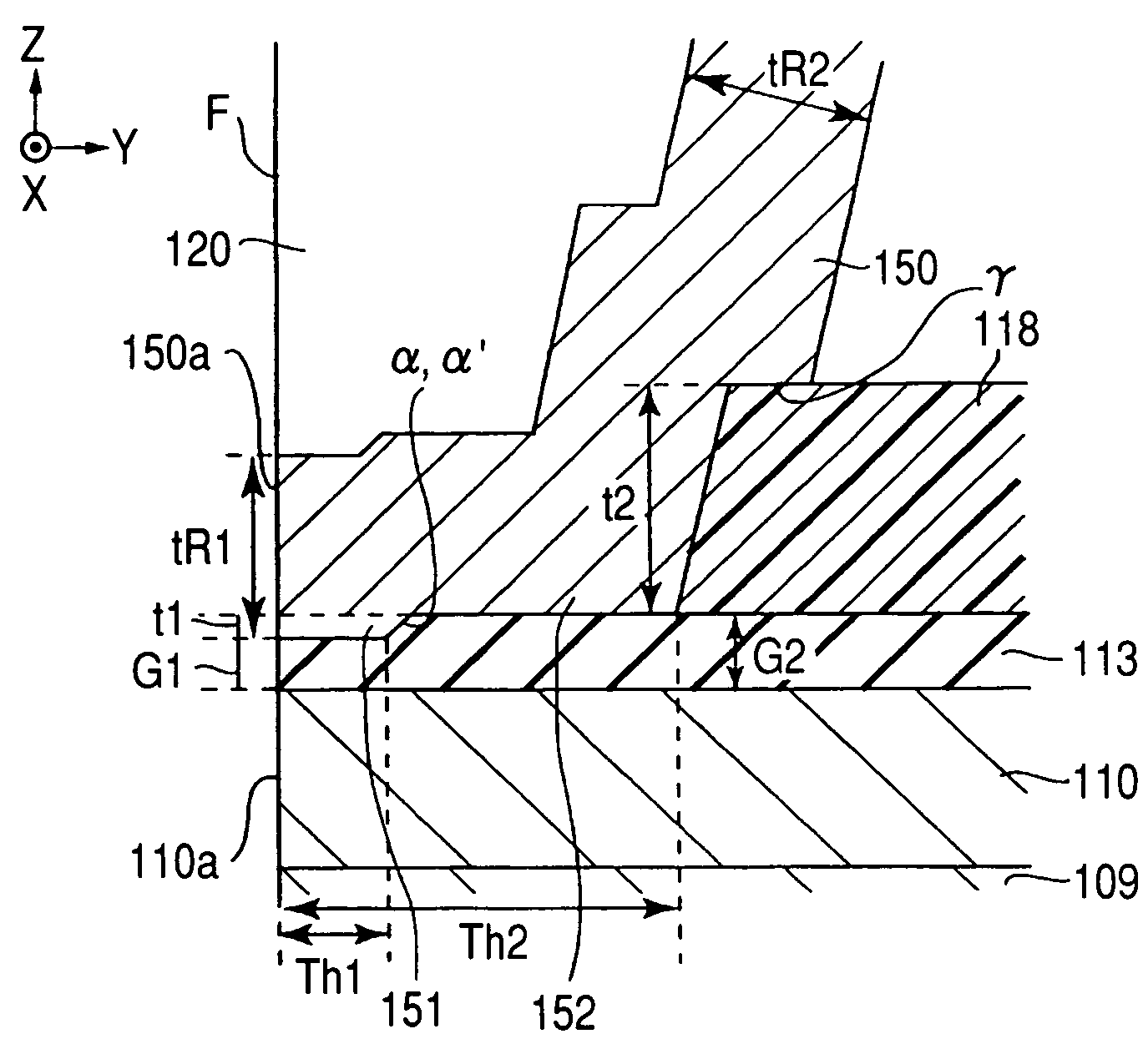

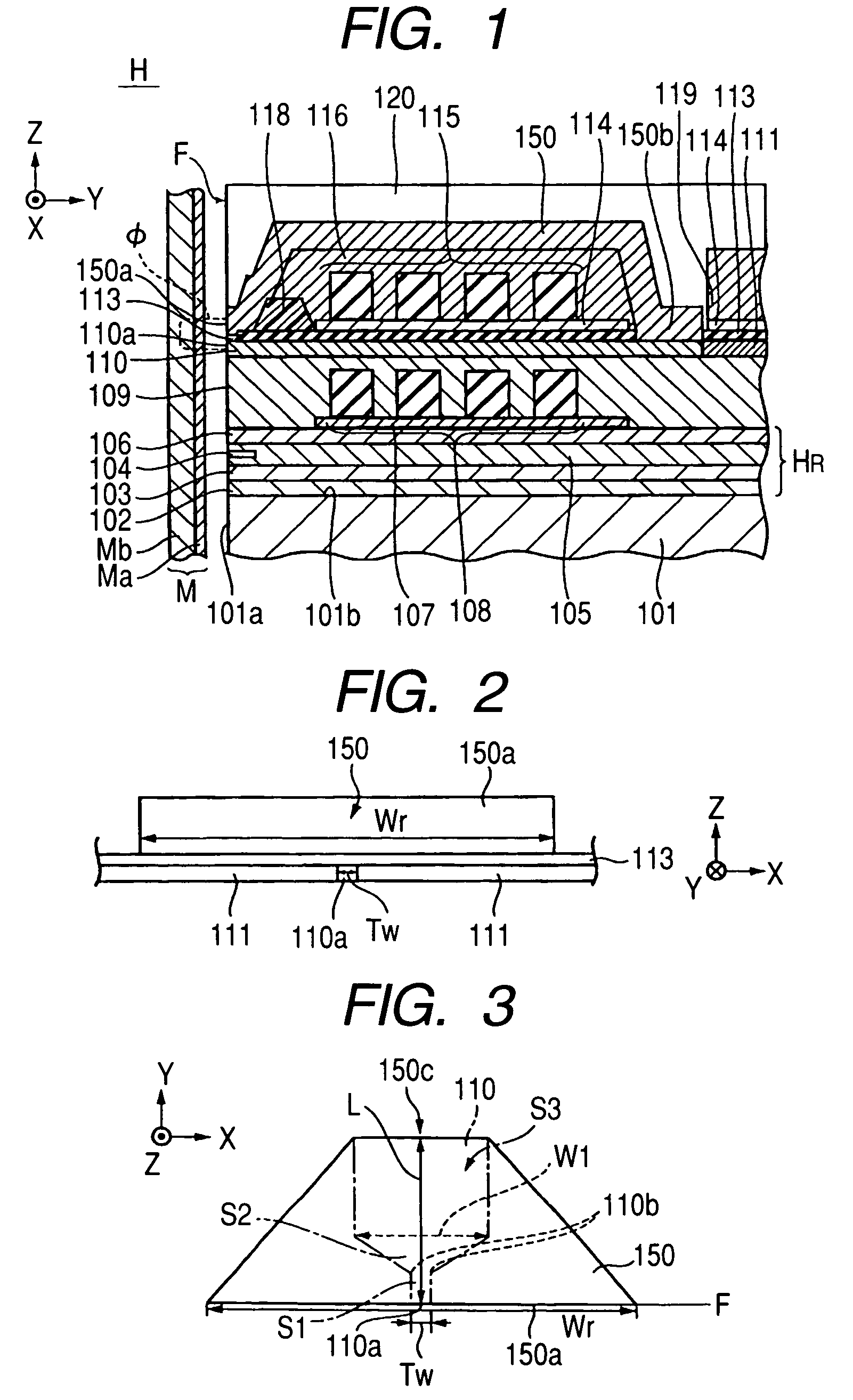

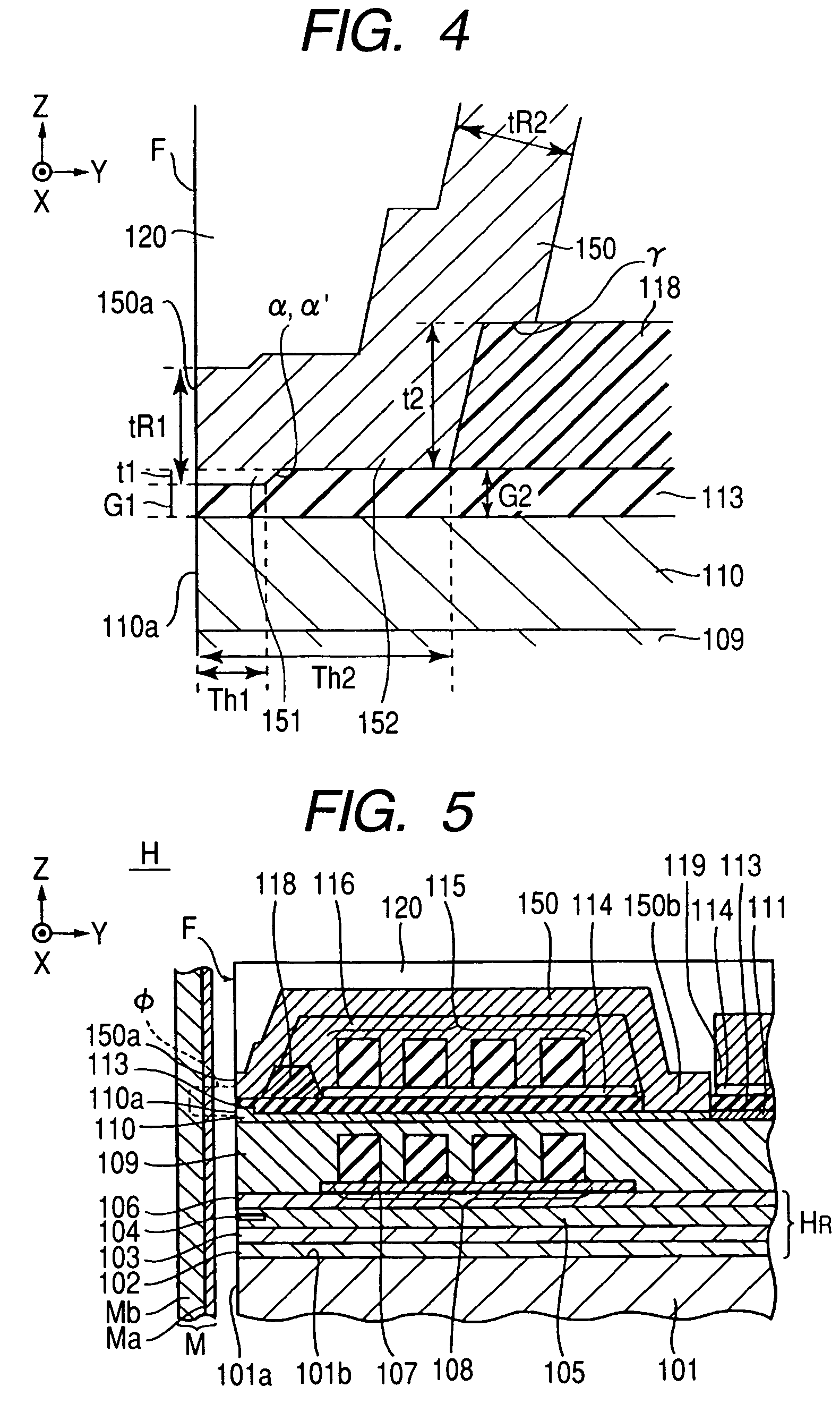

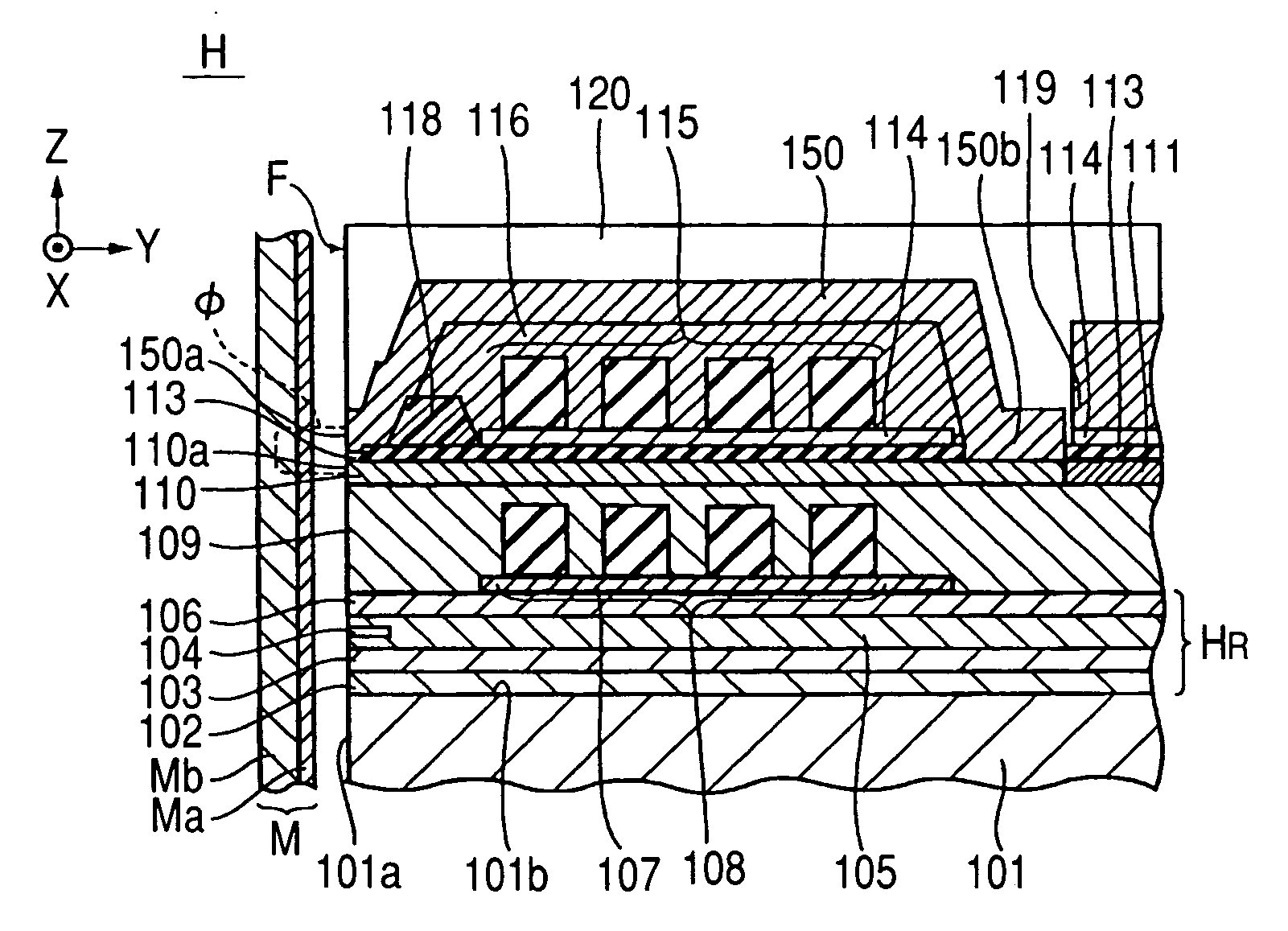

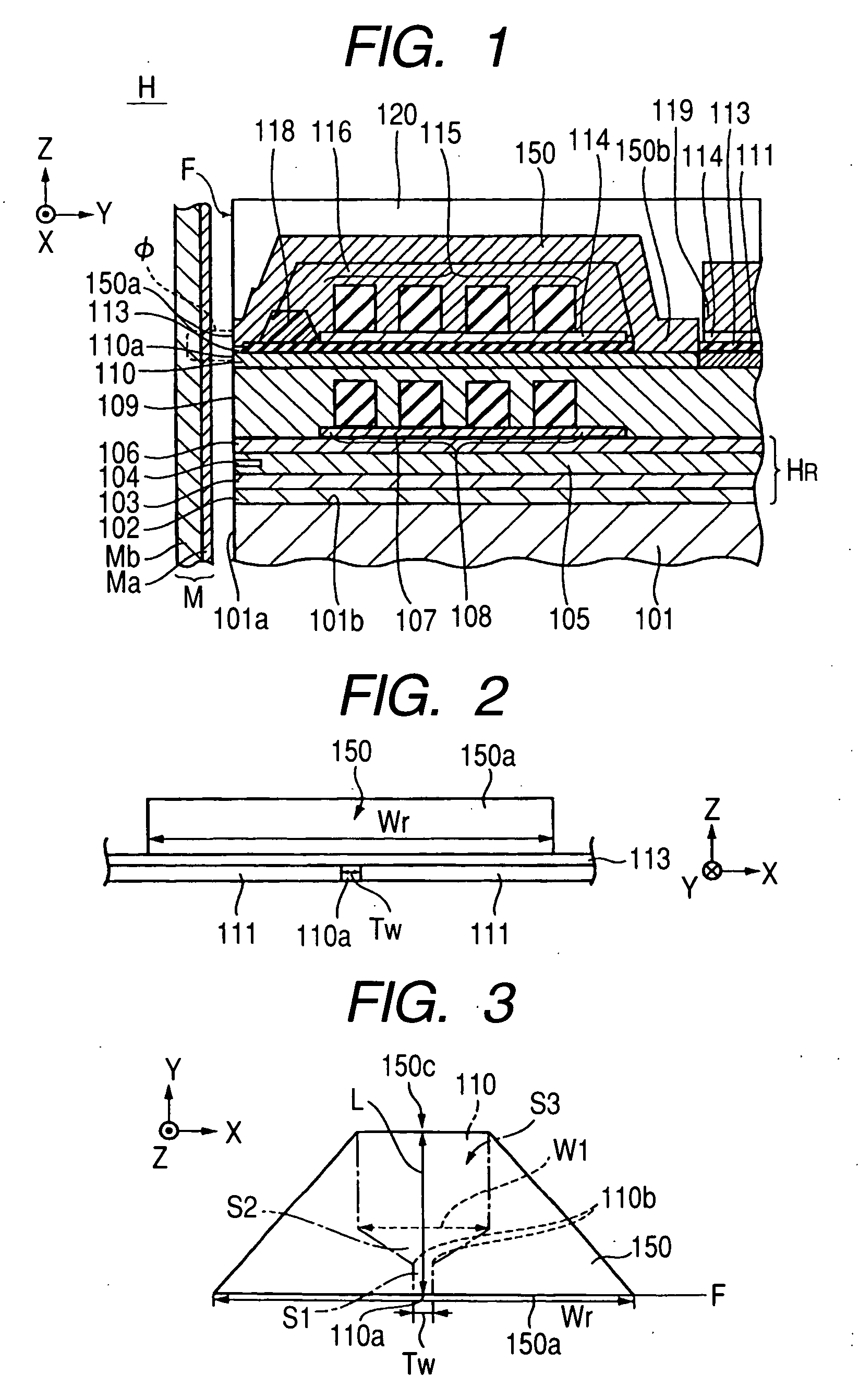

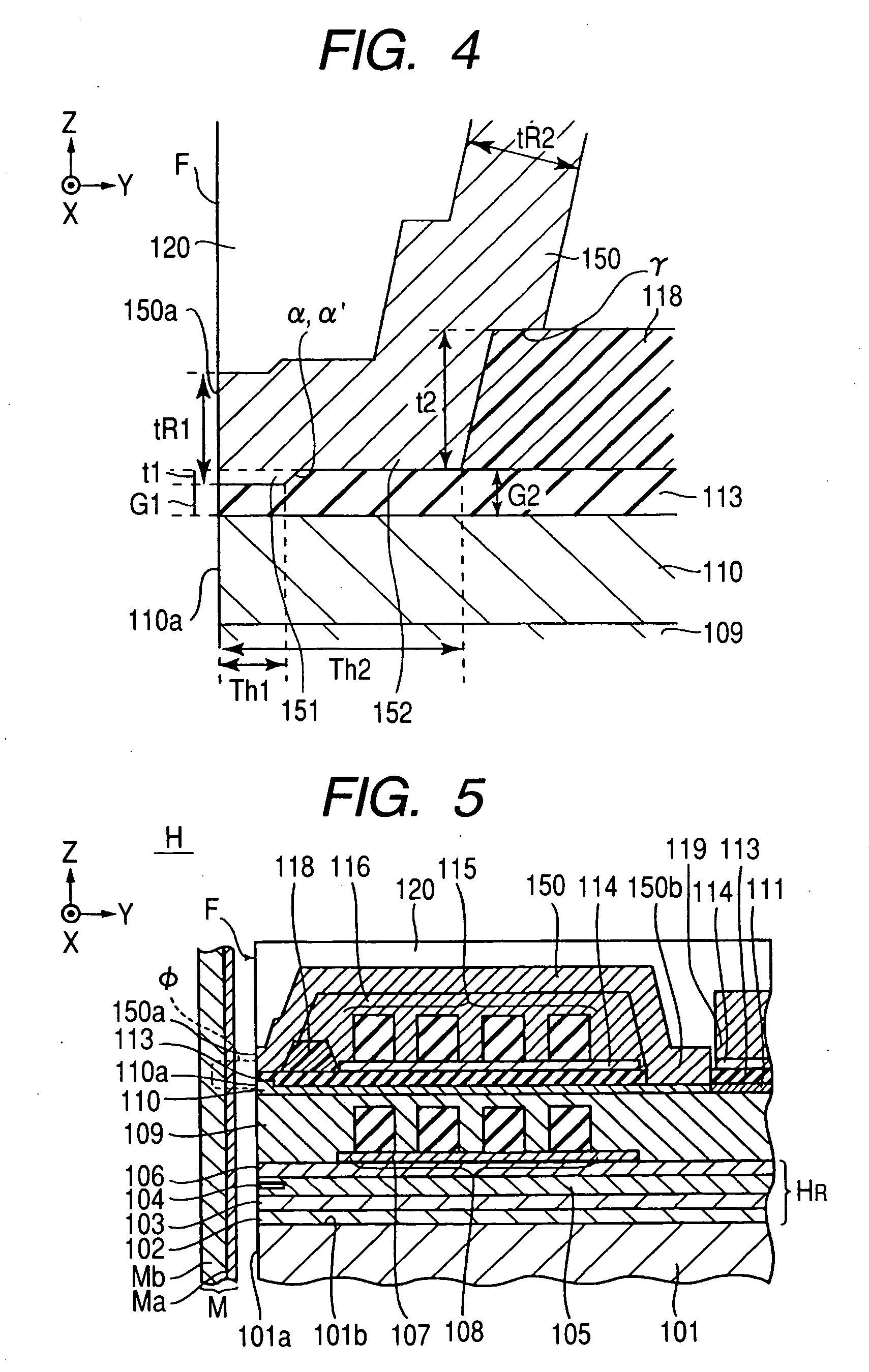

Perpendicular magnetic recording head having a stepped portion and method of manufacturing the same

ActiveUS7643246B2Improving gradientIncrease intensityManufacture head surfaceRecord information storageMagnetic polesNon magnetic

Owner:TDK CORPARATION

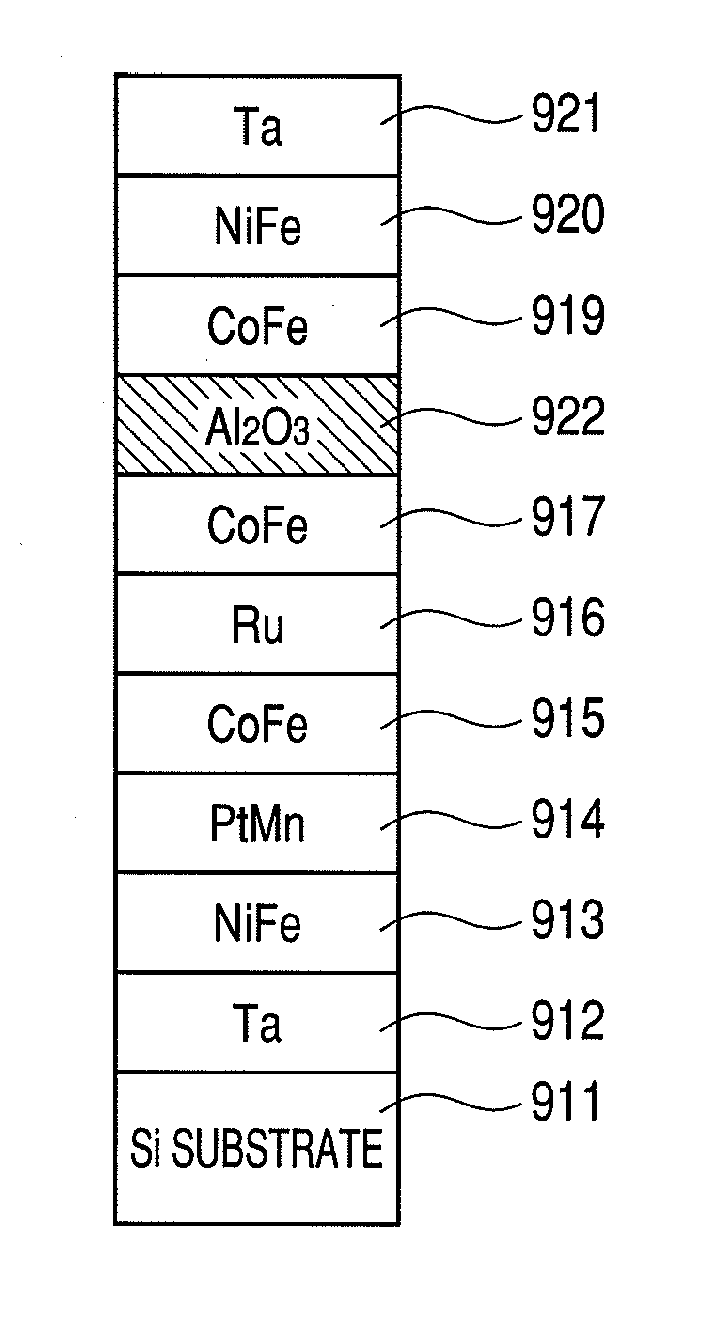

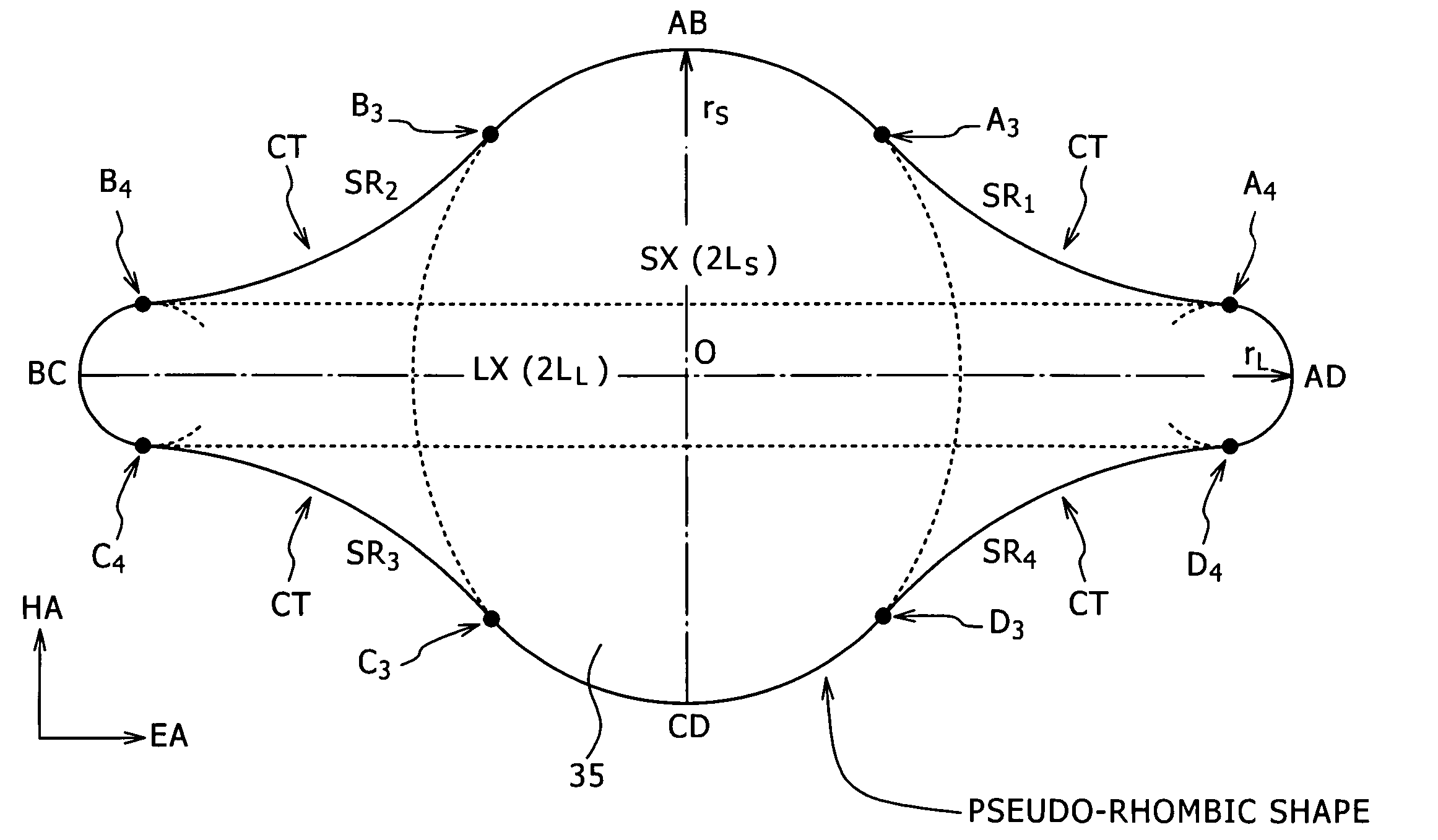

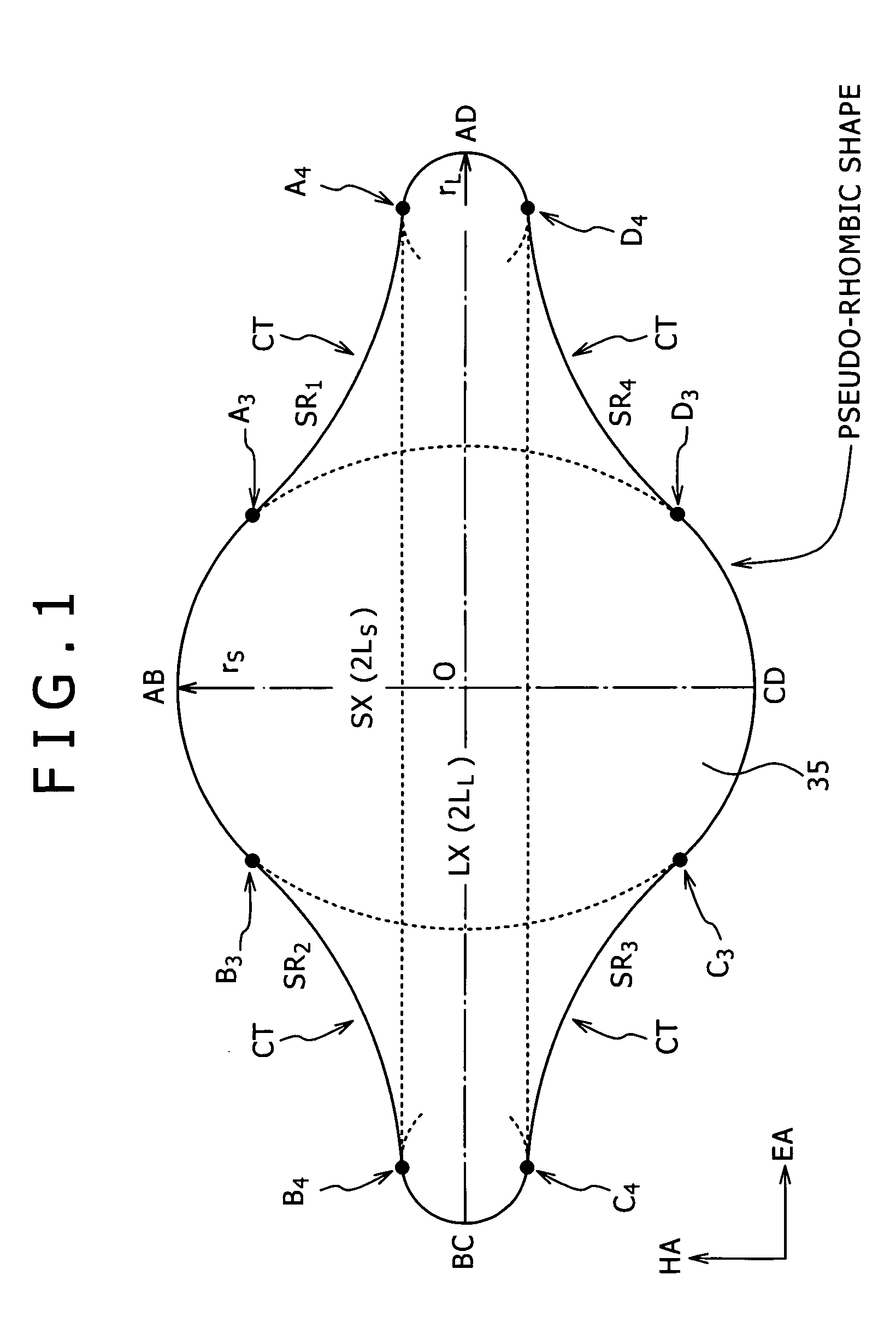

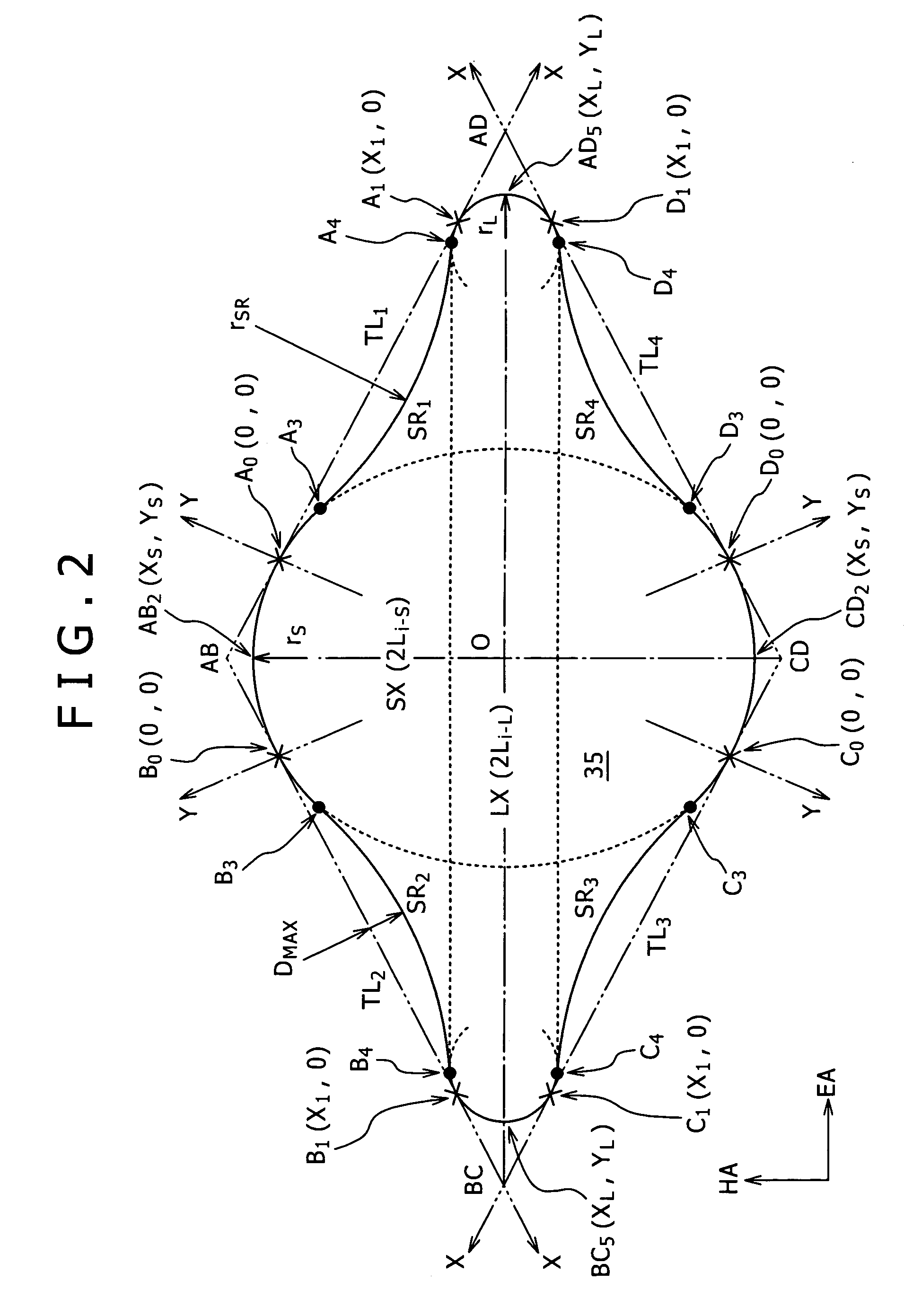

Nonvolatile magnetic memory device and photomask

InactiveUS20050276090A1Dispersion suppressionHigh degree of integrationNanoinformaticsMagnetic-field-controlled resistorsMagnetic reluctanceMagnetic memory

Disclosed is a nonvolatile magnetic memory device including a magntoresistance device having a recording layer formed of a ferromagnetic material for storing information by use of variation in resistance depending on the magnetization inversion state. The plan-view shape of the recording layer includes a pseudo-rhombic shape having four sides, at least two of the four sides each include a smooth curve having a central portion curved toward the center of the pseudo-rhombic shape. The easy axis of magnetization of the recording layer is substantially parallel to the longer axis of the pseudo-rhombic shape. The hard axis of magnetization of the recording layer is substantially parallel to the shorter axis of the pseudo-rhombic shape. The sides constituting the plan-view shape of the recording layer are smoothly connected to each other.

Owner:SONY CORP

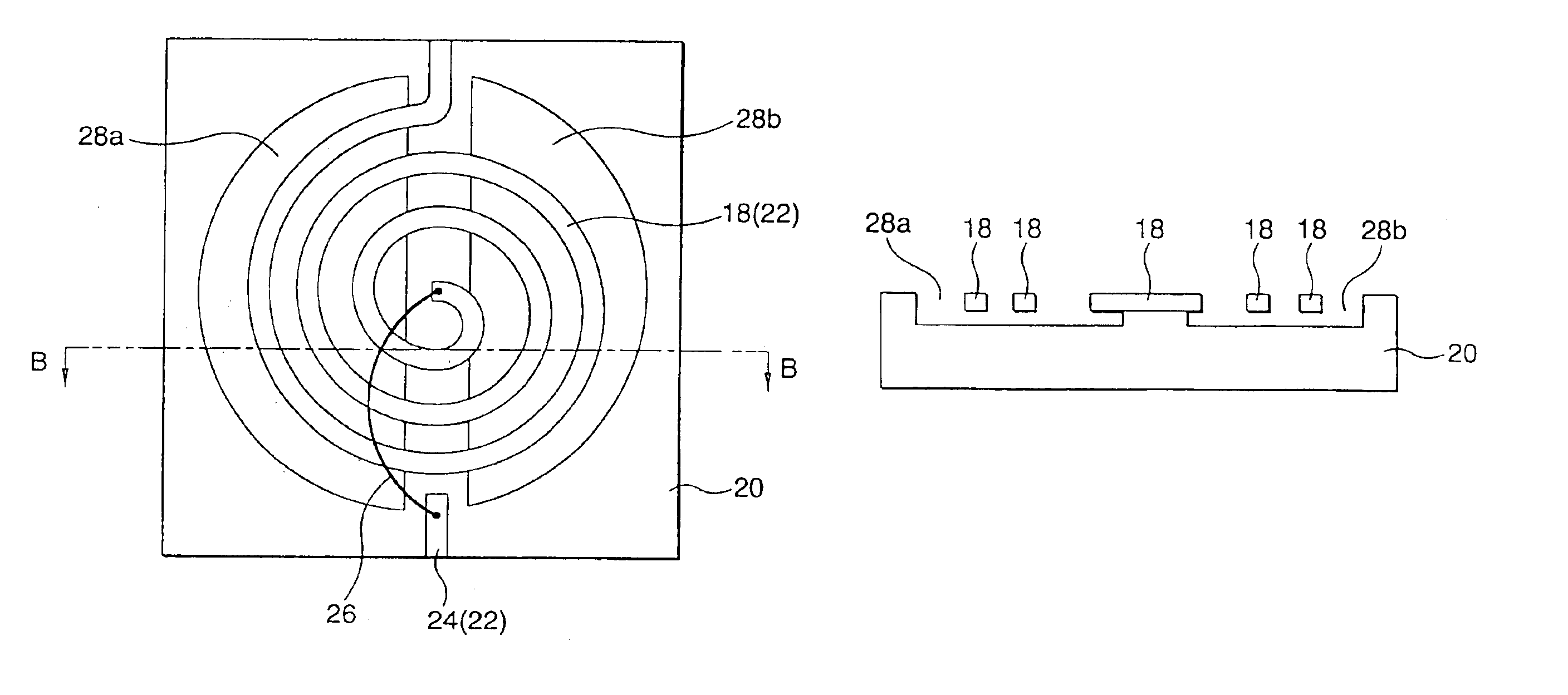

High-frequency coil device and method of manufacturing the same

InactiveUS6940385B2Easy to joinIncrease valueTransformers/inductances coils/windings/connectionsPrinted inductancesCoil inductanceDielectric substrate

In a high-frequency coil device having small dispersion in coil inductance and suitable for use in GHz band and a method of manufacturing the high-frequency coil device, a spirally-shaped fine-pitch coil is embedded in the surface of a polyimide layer as a dielectric substrate so that the bottom surface and side surface of the coil is covered by the polyimide layer. The spirally-shaped coil has an Ni—Cu laminate structure in which an Ni plating layer and a Cu plating layer are laminated, and also the side surface thereof is made substantially vertical while the width thereof is uniform with high precision. The surface of the spirally-shaped coil, that is, the surface of the Ni plating layer serving as the upper layer is coated with an Au plating layer.

Owner:SONY CORP

Perpendicular magnetic recording head and method of manufacturing the same

ActiveUS20070064343A1Improving gradientIncrease intensityRecord information storageHeads for perpendicular magnetisationsMagnetic polesEngineering

A magnetic recording head and a method of manufacturing the magnetic recording head are provided. The perpendicular magnetic recording head includes a main magnetic pole layer and a return path layer that face each other with a gap therebetween in a lamination direction. A non-magnetic insulating layer is interposed between the main magnetic pole layer and the return path layer. At least one stepped portion is formed on a facing surface of at least one of the main magnetic pole layer and the return path layer.

Owner:TDK CORPARATION

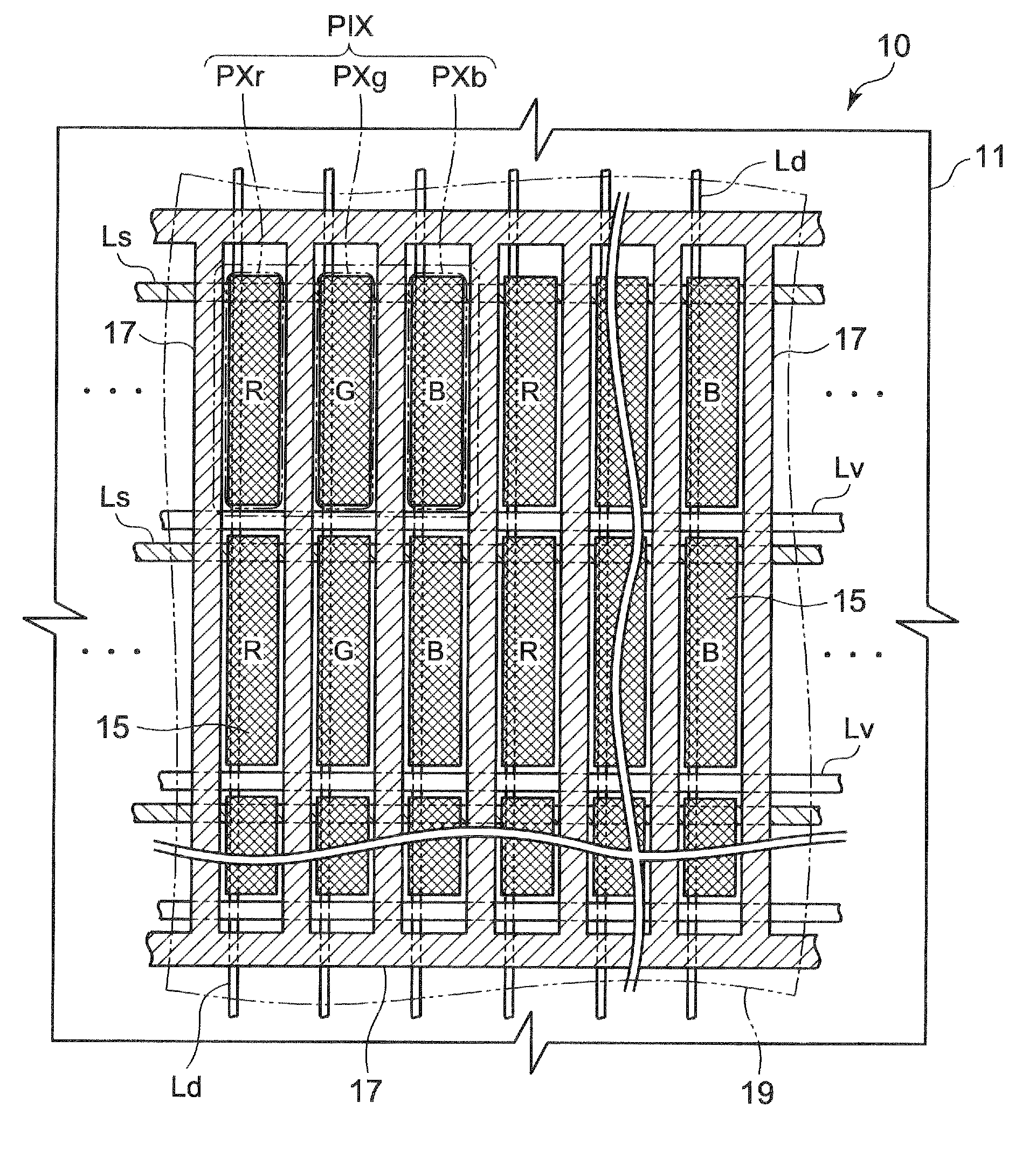

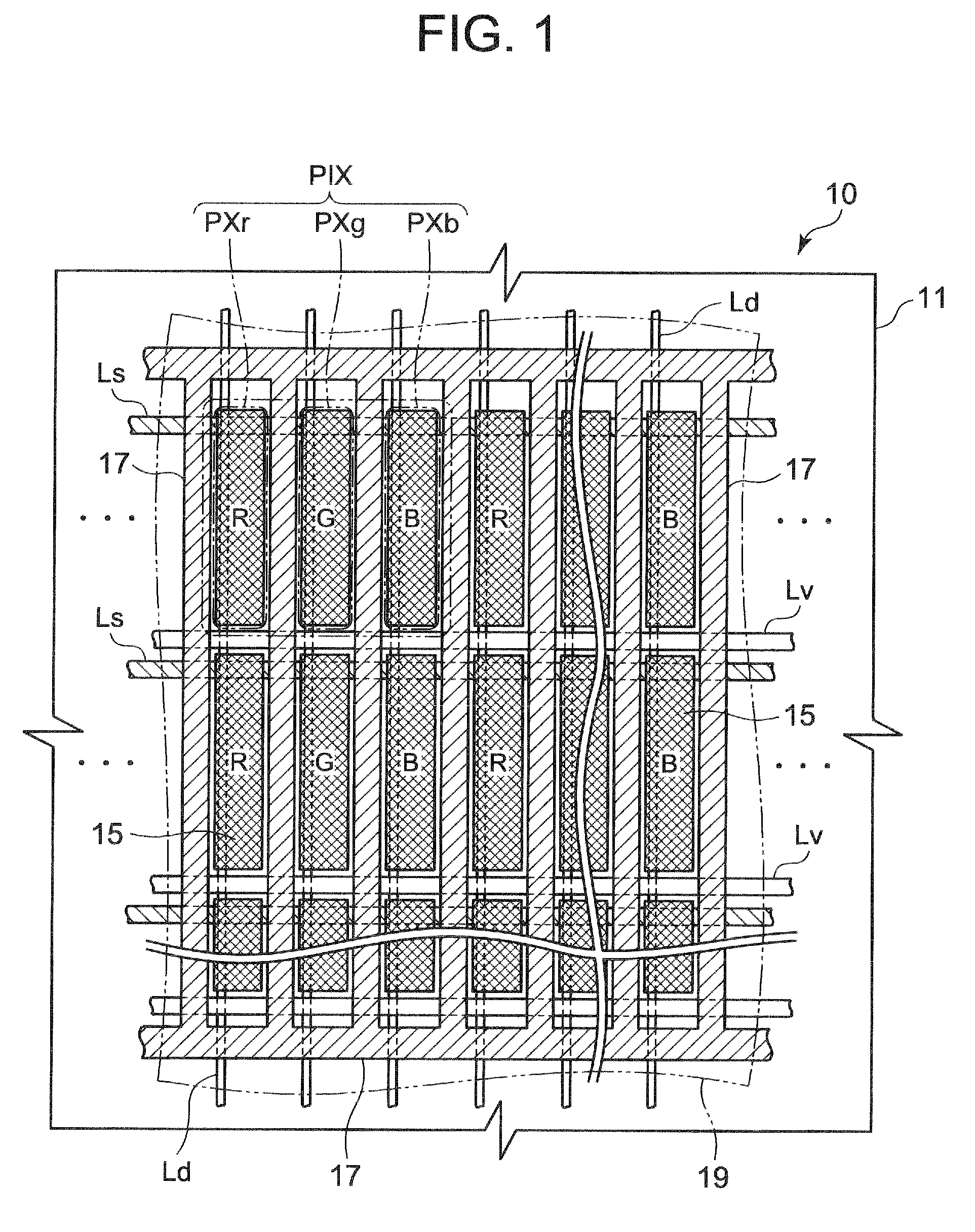

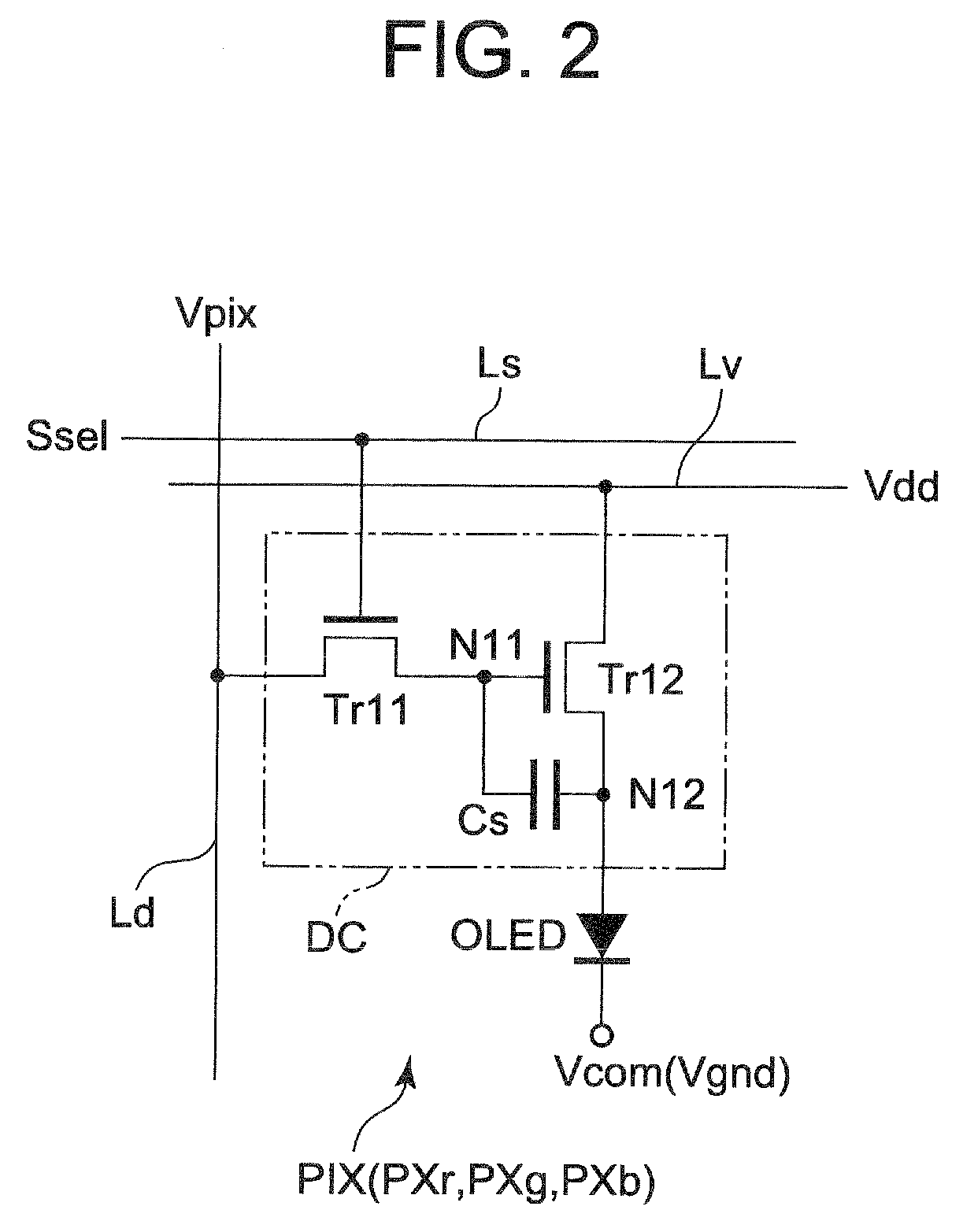

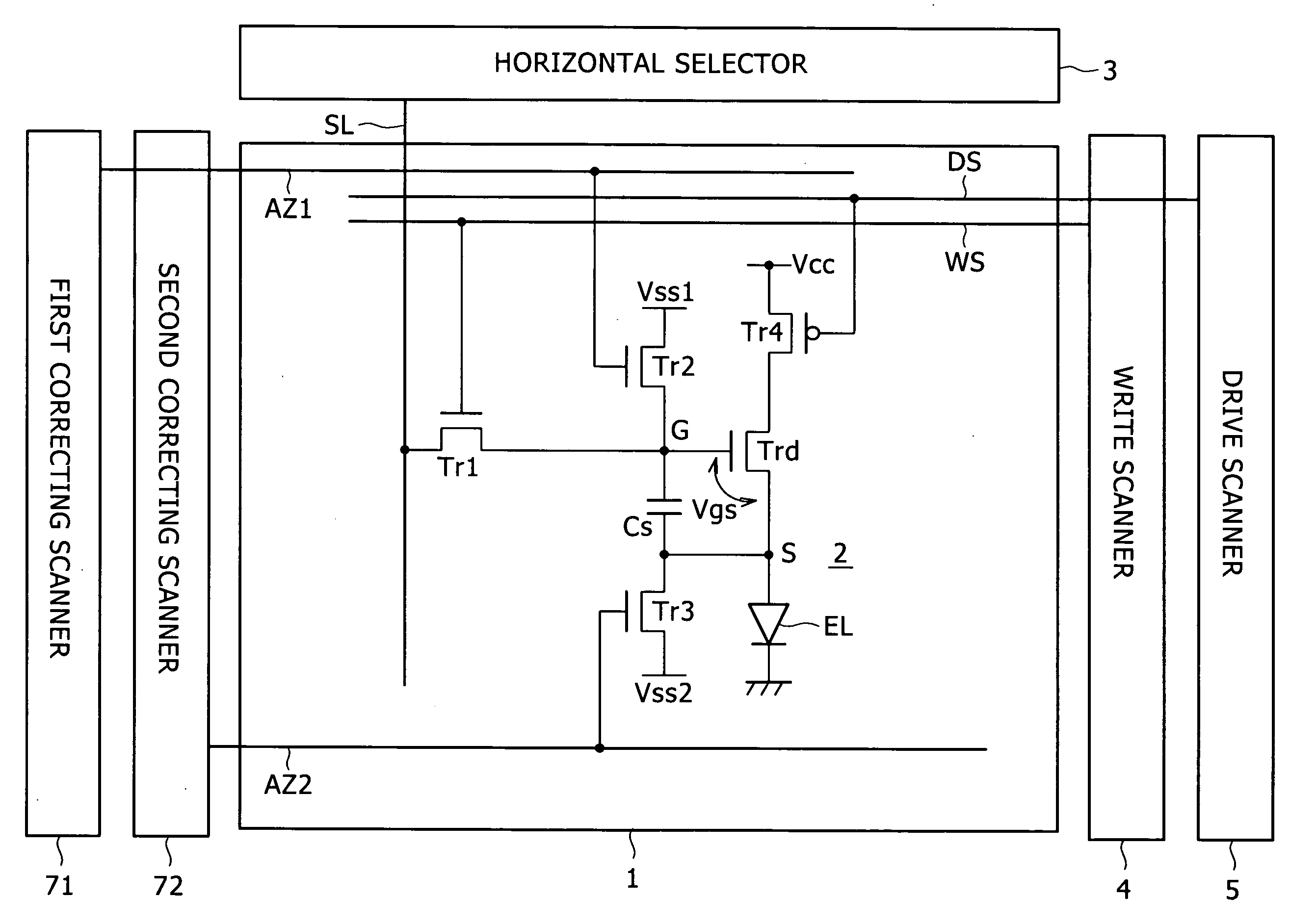

Pixel circuit and display apparatus

InactiveUS20080074363A1Increase productionReduce manufacturing costElectrical apparatusStatic indicating devicesDriving currentSample image

Disclosed herein is a pixel circuit, including: three pixels to which three primary colors are allocated; a power supply line. In the pixel circuit, each of the three pixels includes a sampling transistor configured to sample an image signal, a retaining capacitor configured to retain the sampled image signal, a drive transistor configured to output drive current corresponding to the retained image signal within a predetermined light emission period, and a light emitting element configured to emit light in the color allocated to the three pixels in response to the drive current. The pixel circuit includes a single switching transistor disposed commonly to the three pixels for connecting the drive transistors of the pixels to the power supply line within the light emission period.

Owner:SONY CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com