Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

163results about How to "Fine pitch" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

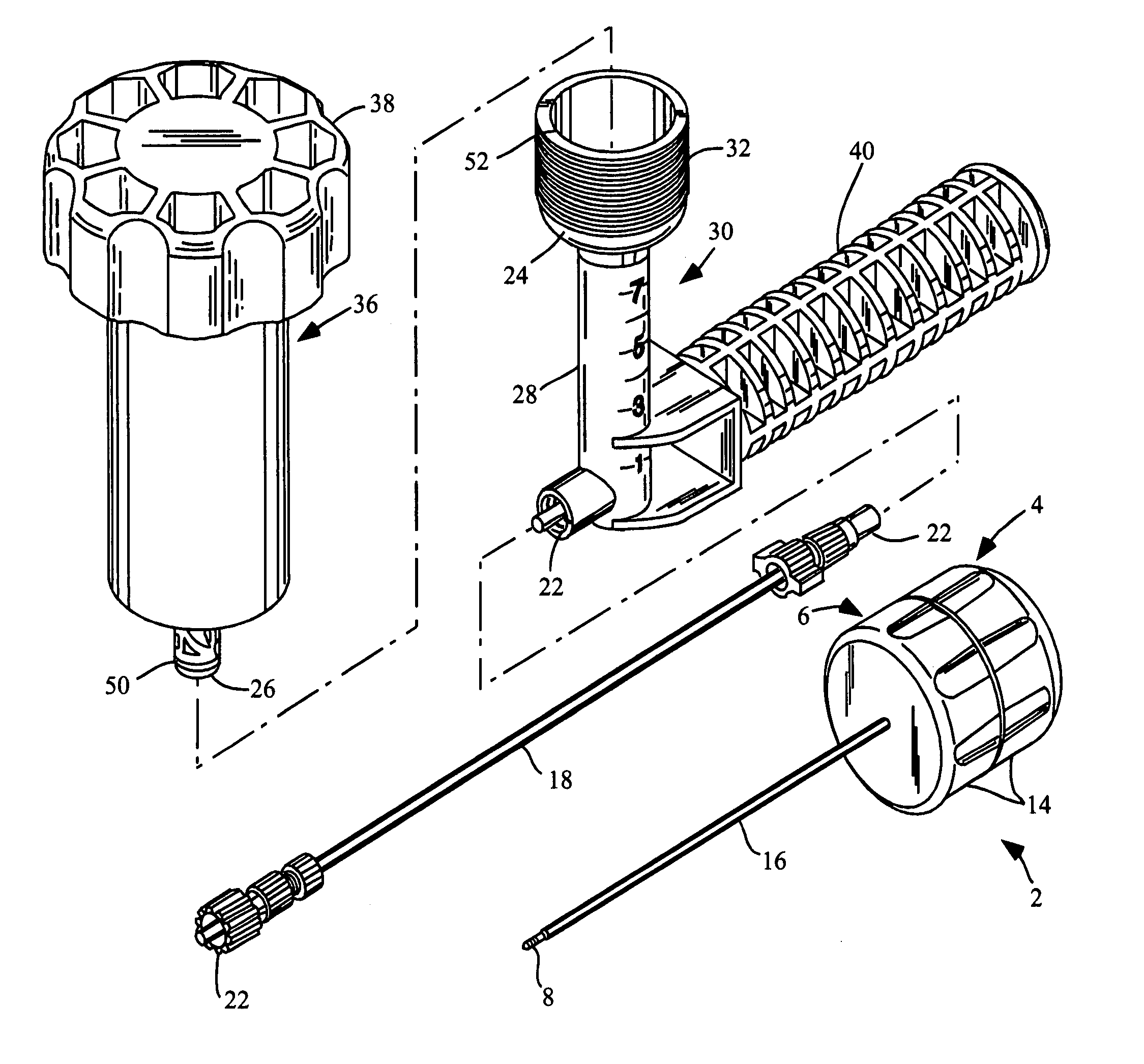

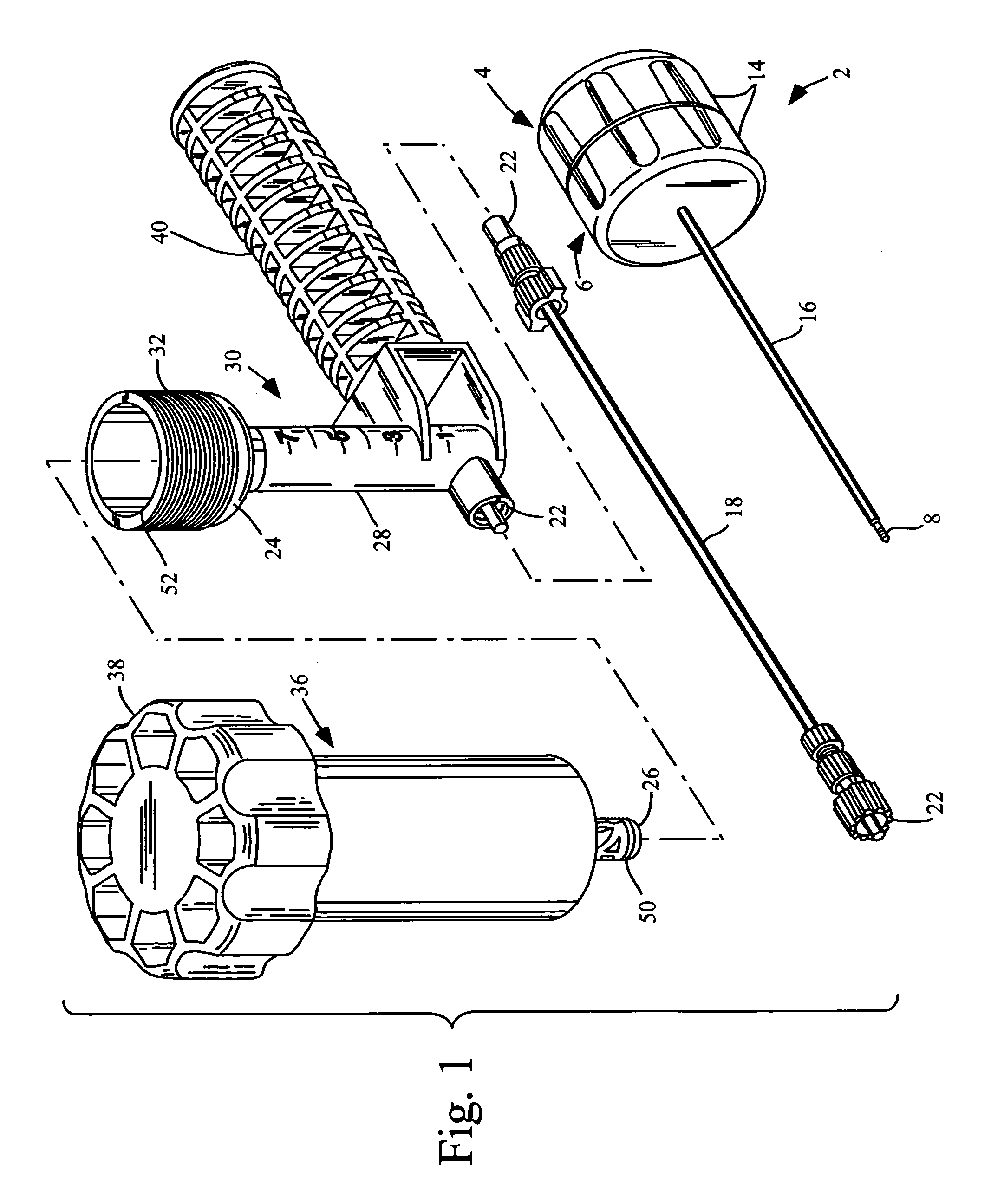

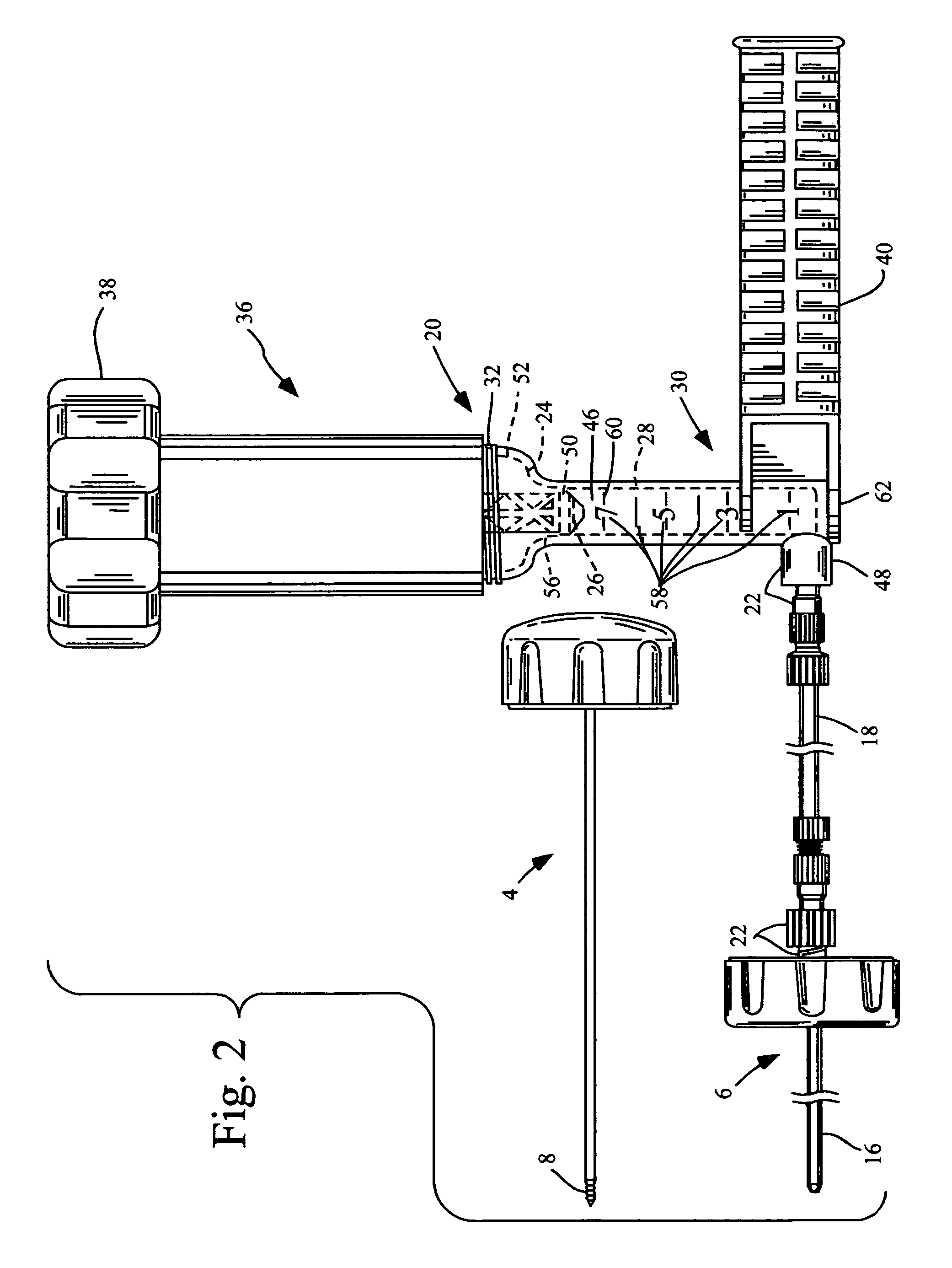

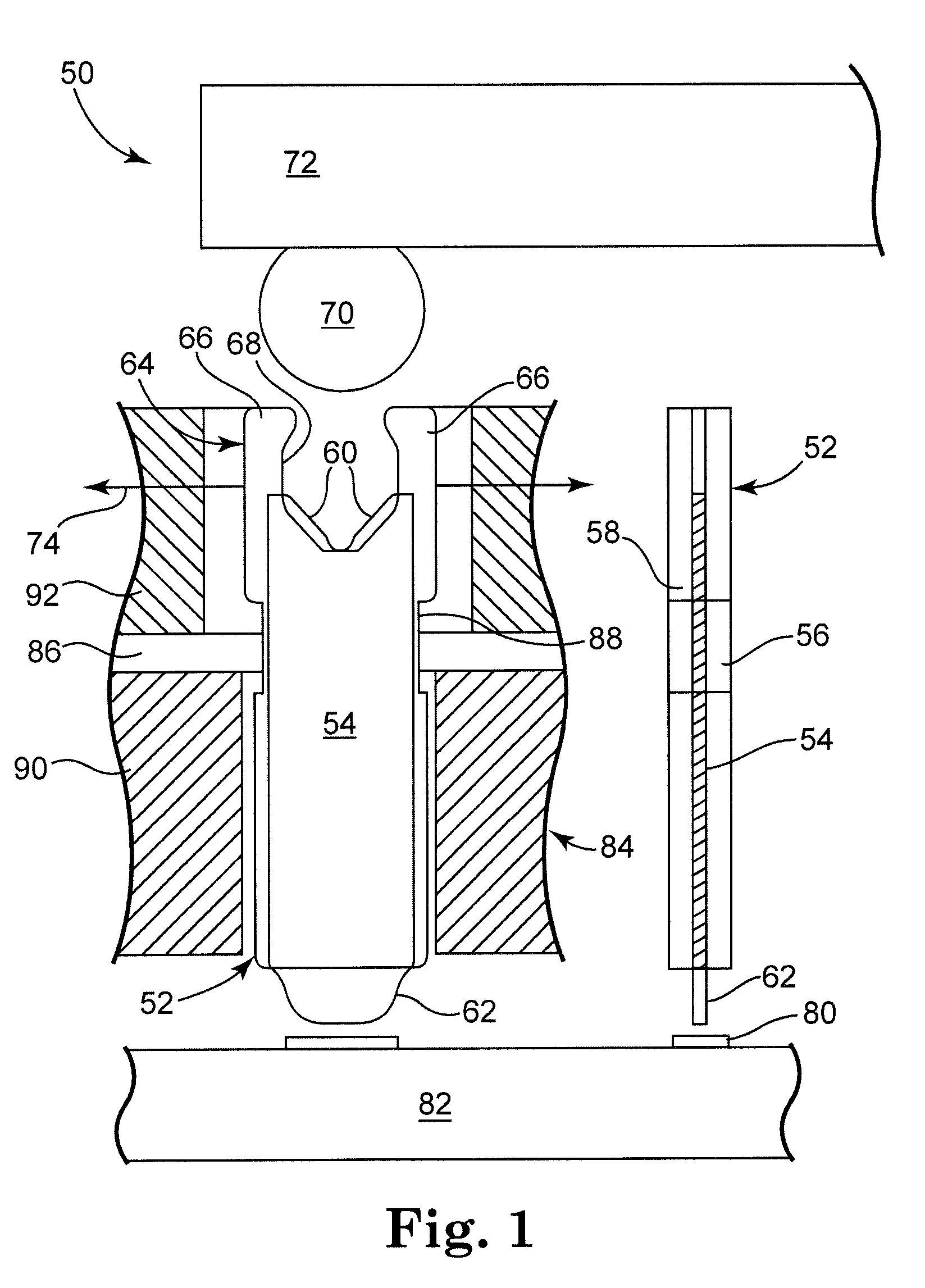

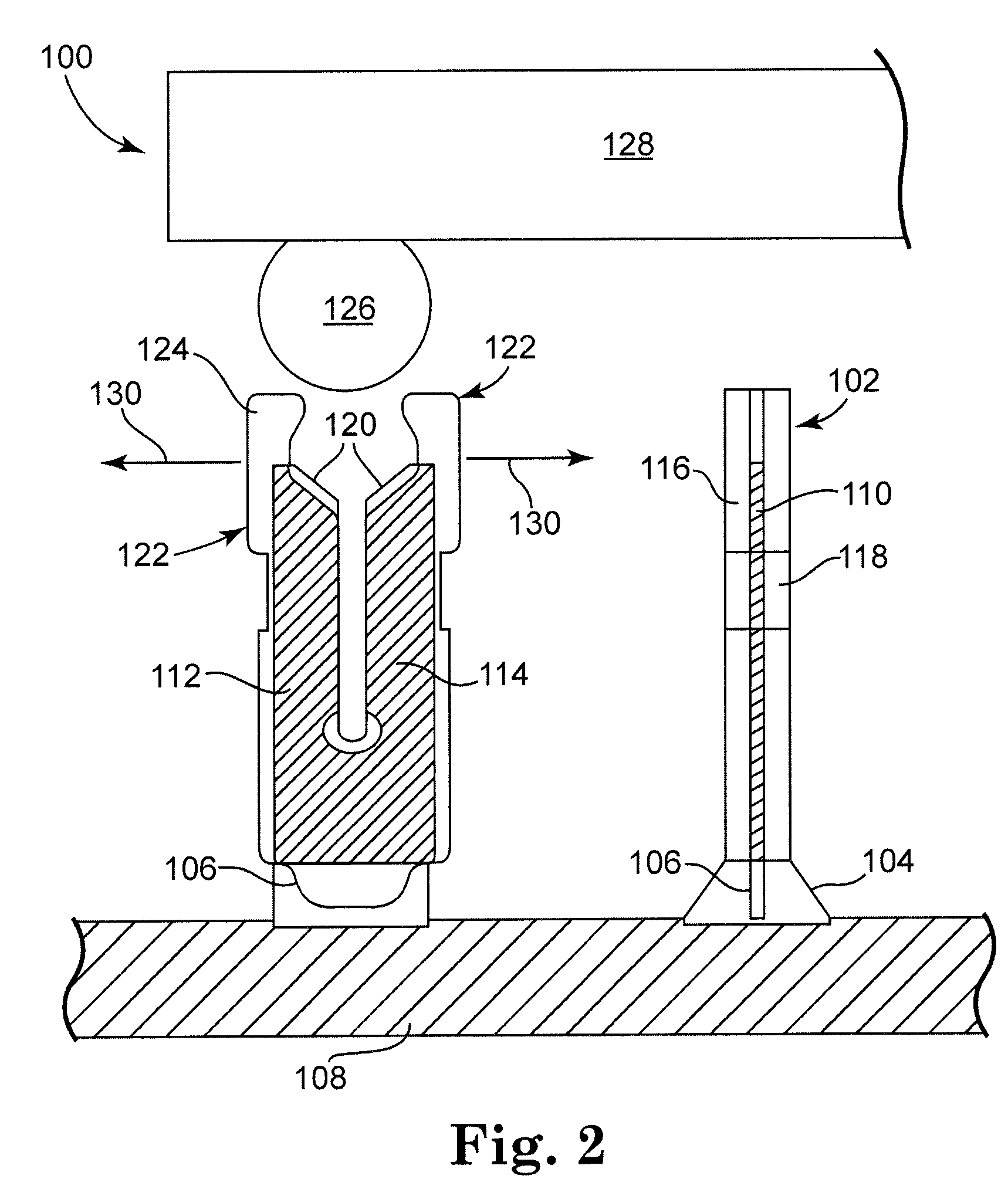

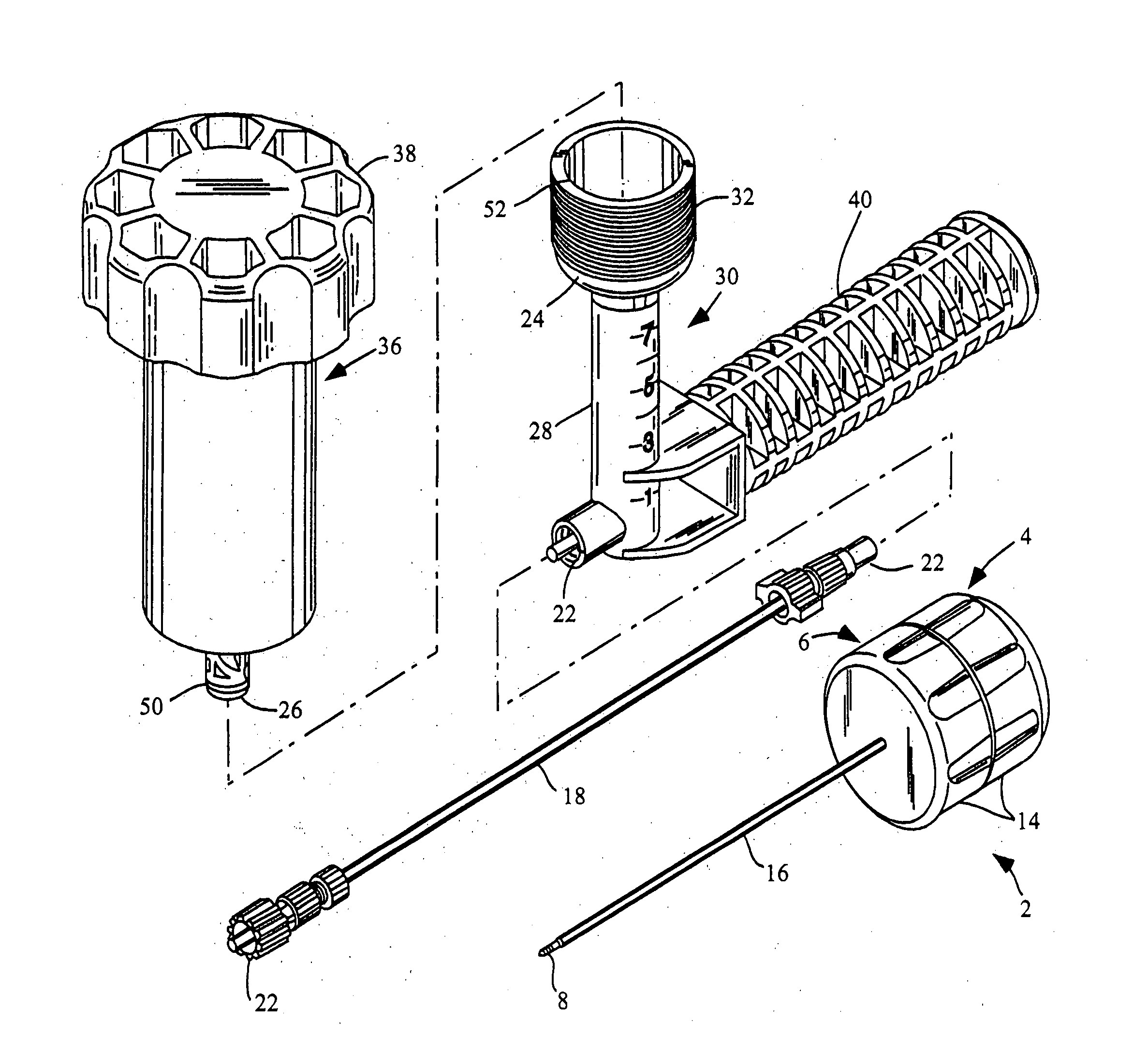

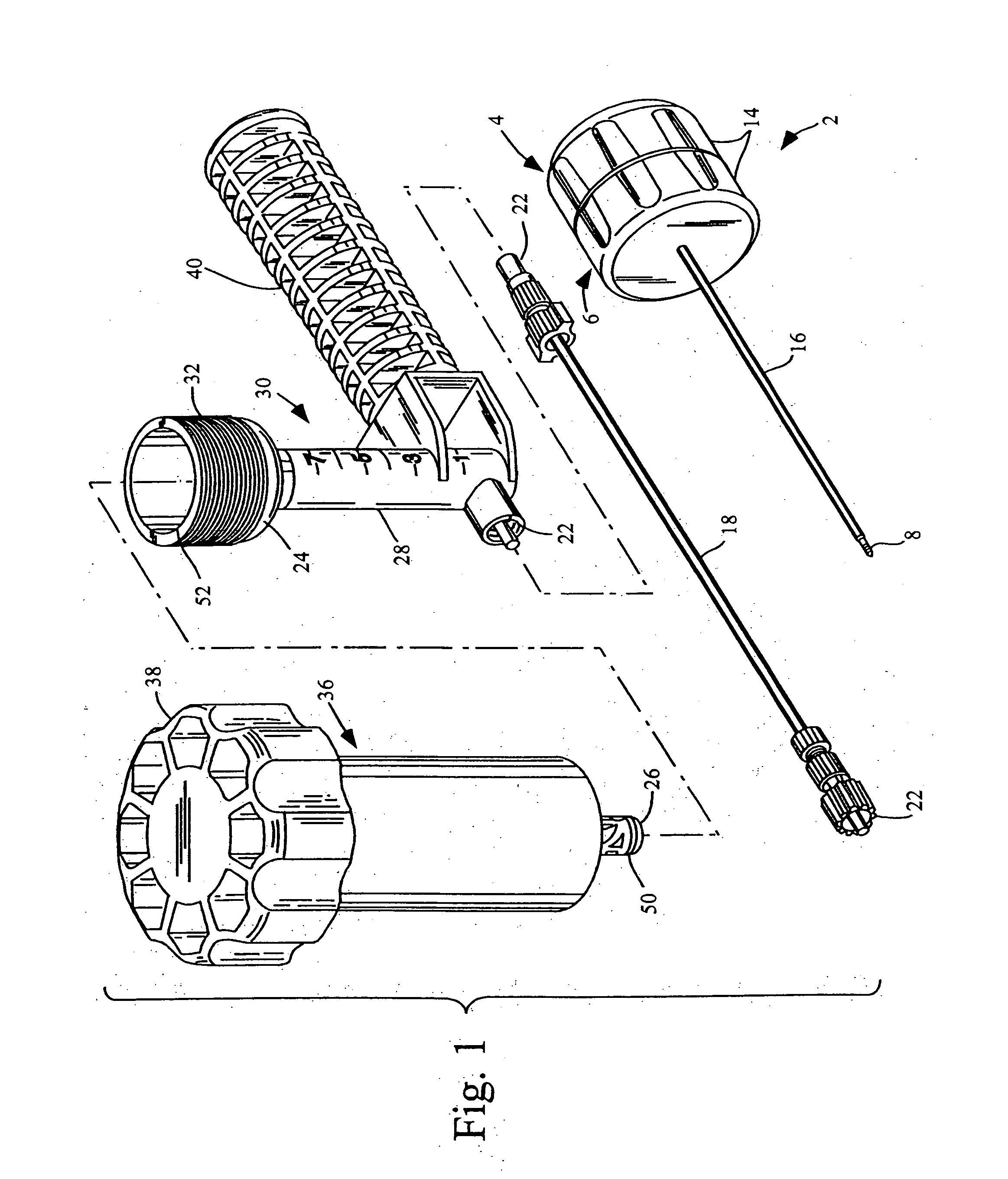

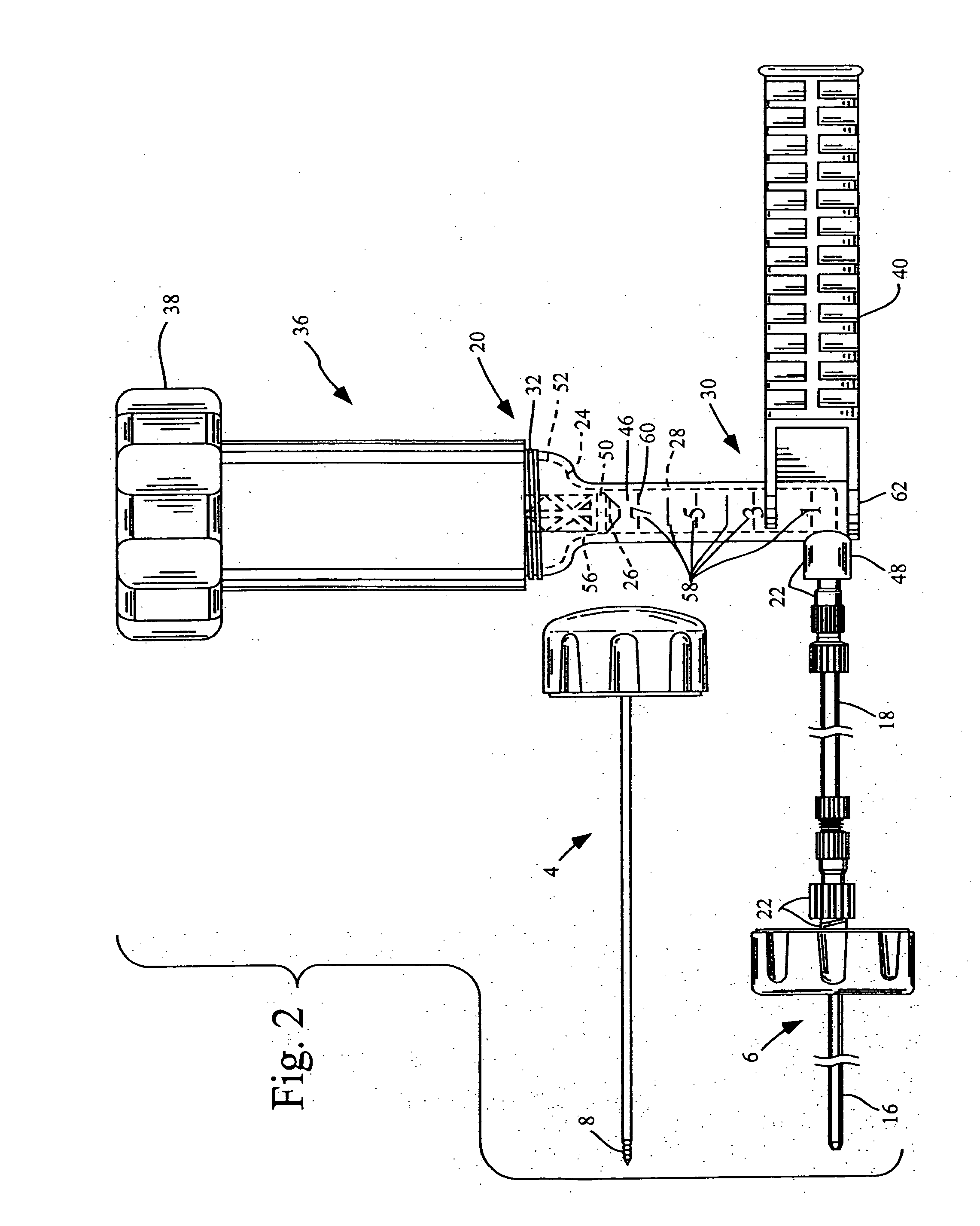

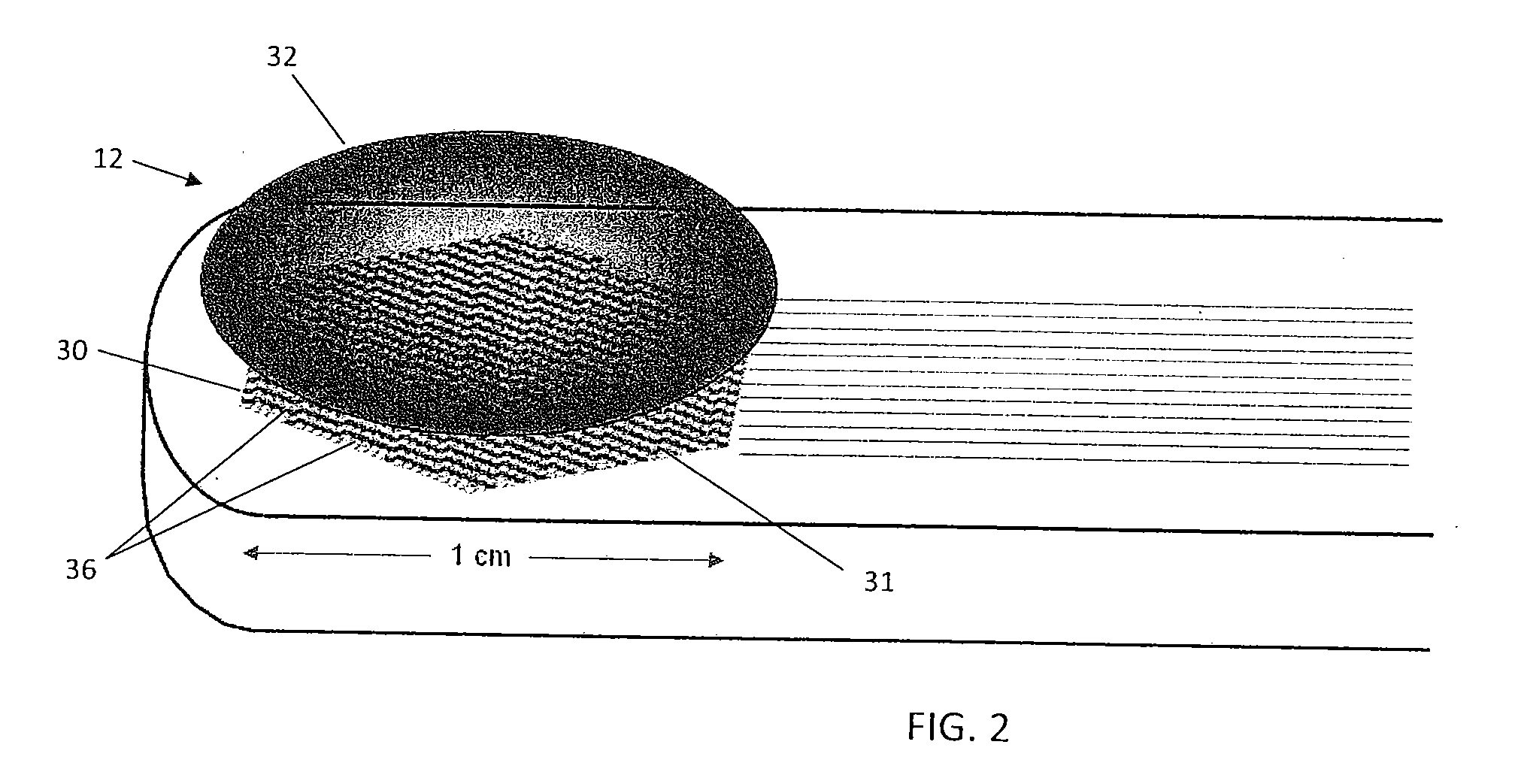

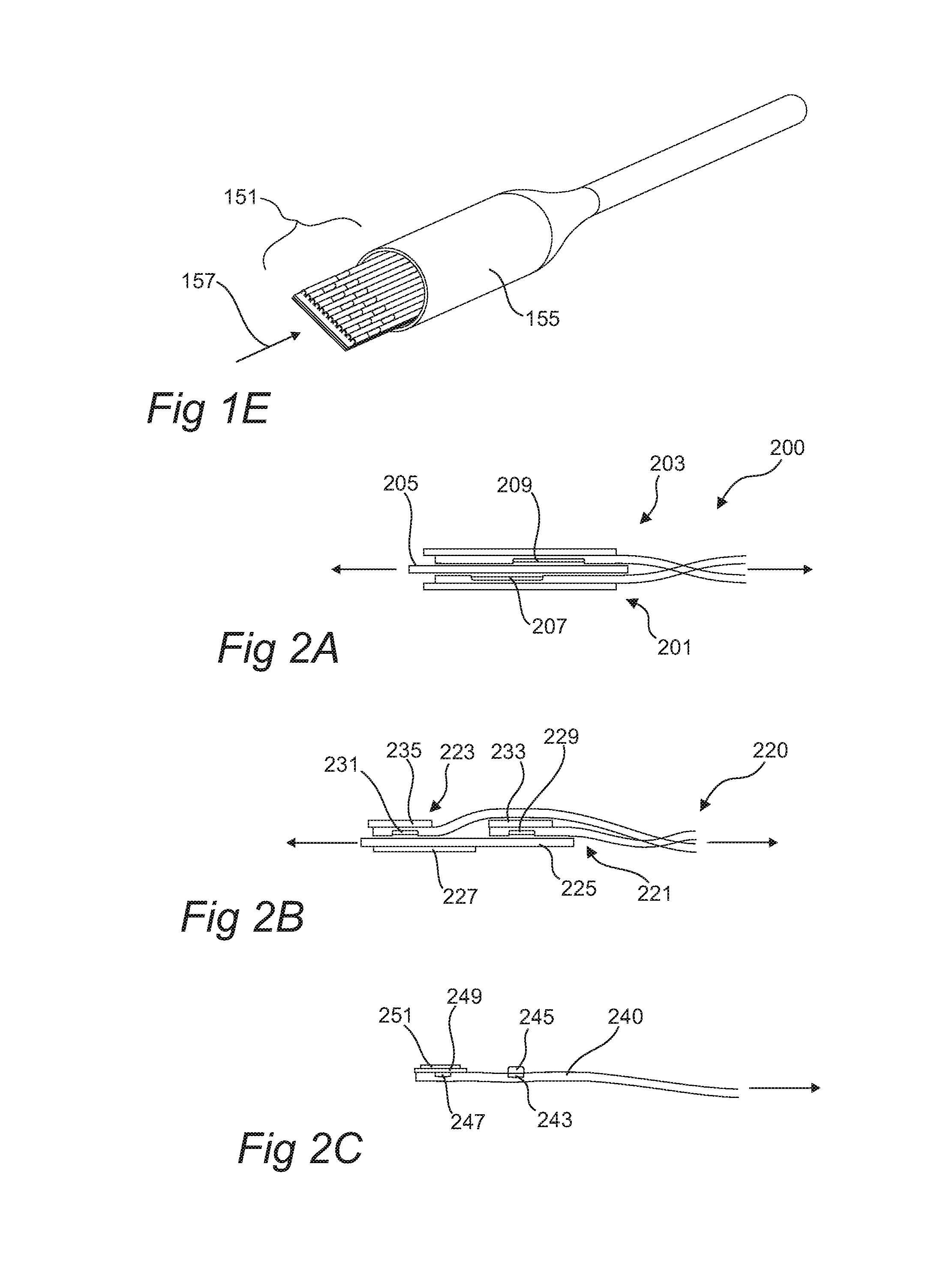

Methods for delivering tissue implant material with a high pressure applicator

InactiveUS7048743B2Increased margin of errorAvoid pollutionJoint implantsIntravenous devicesReady to useHigh pressure

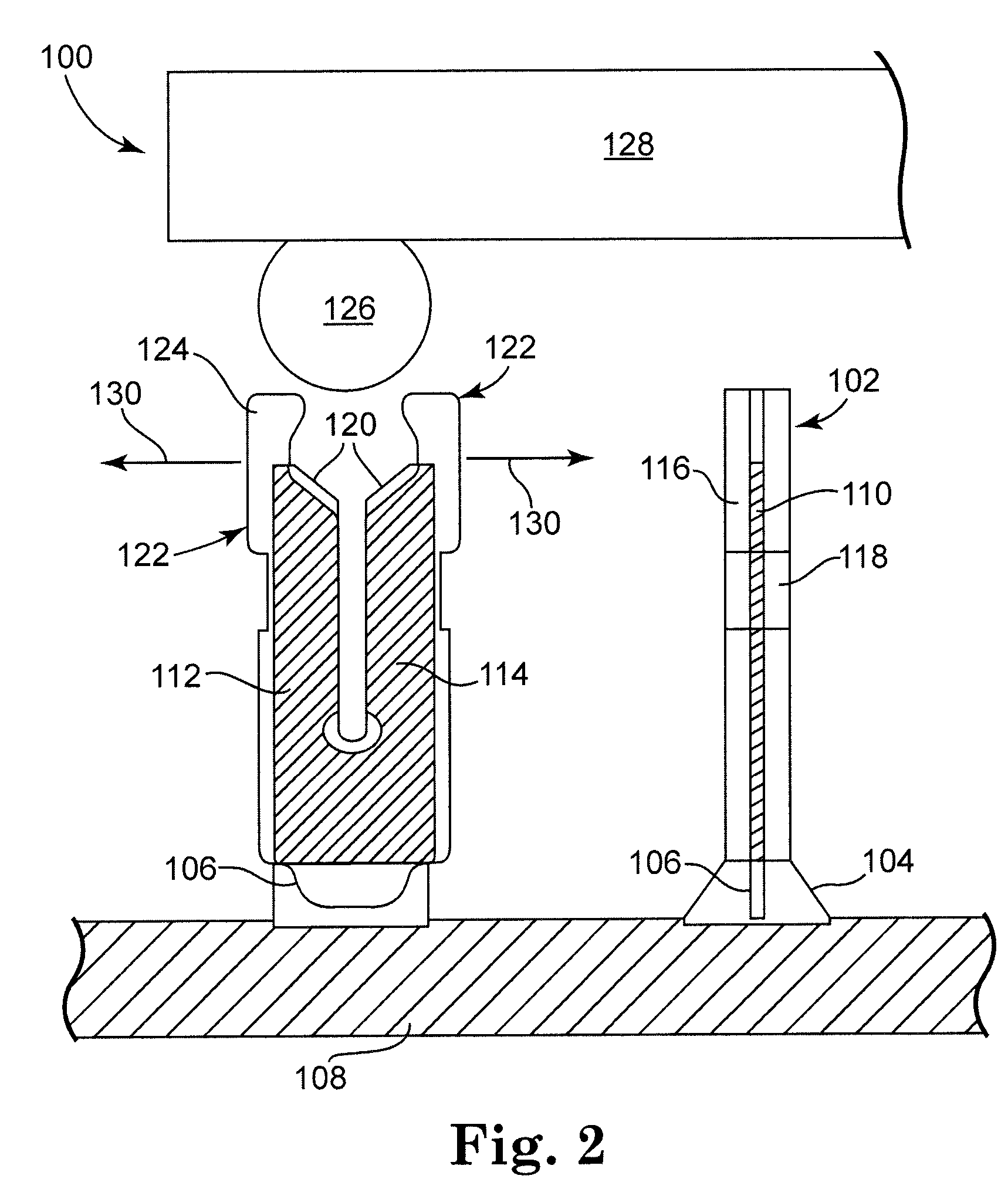

This relates to an improved delivery system for accurately loading and controlling the delivery of flowable material to a patient. Particularly, the system may be used in the injection of hard tissue implant materials such as PMMA under pressures up to about 4000 psi. The system includes an applicator with a first column having an implant material introduction section adapted to provide for effective loading of the implant material and a second column housing a piston. The introduction section has a larger size than that of a vessel section or bore in which the requisite pressure seal between the piston and bore wall is formed. The first column may include an introduction section flared open to an included larger funnel-like opening or a separate funnel may be used that interfaces with the introduction section to facilitate the introduction of implant material. Handles on the first and second columns to be turned relative to each other to advance the columns toward each other may be provided for manual actuation of the applicator to drive implant material through a cannula and deliver implant material to a desired site.

Owner:NEUROTHERM

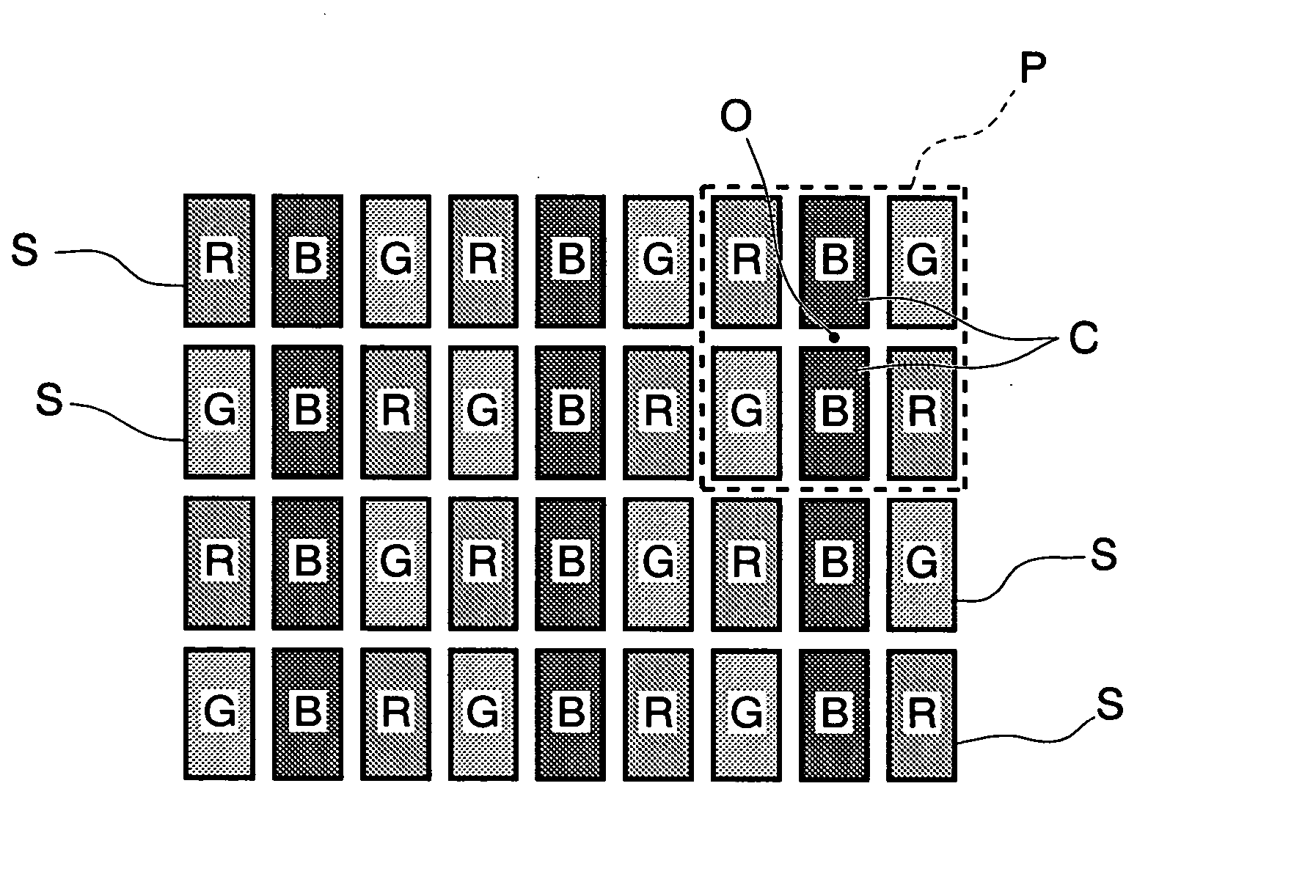

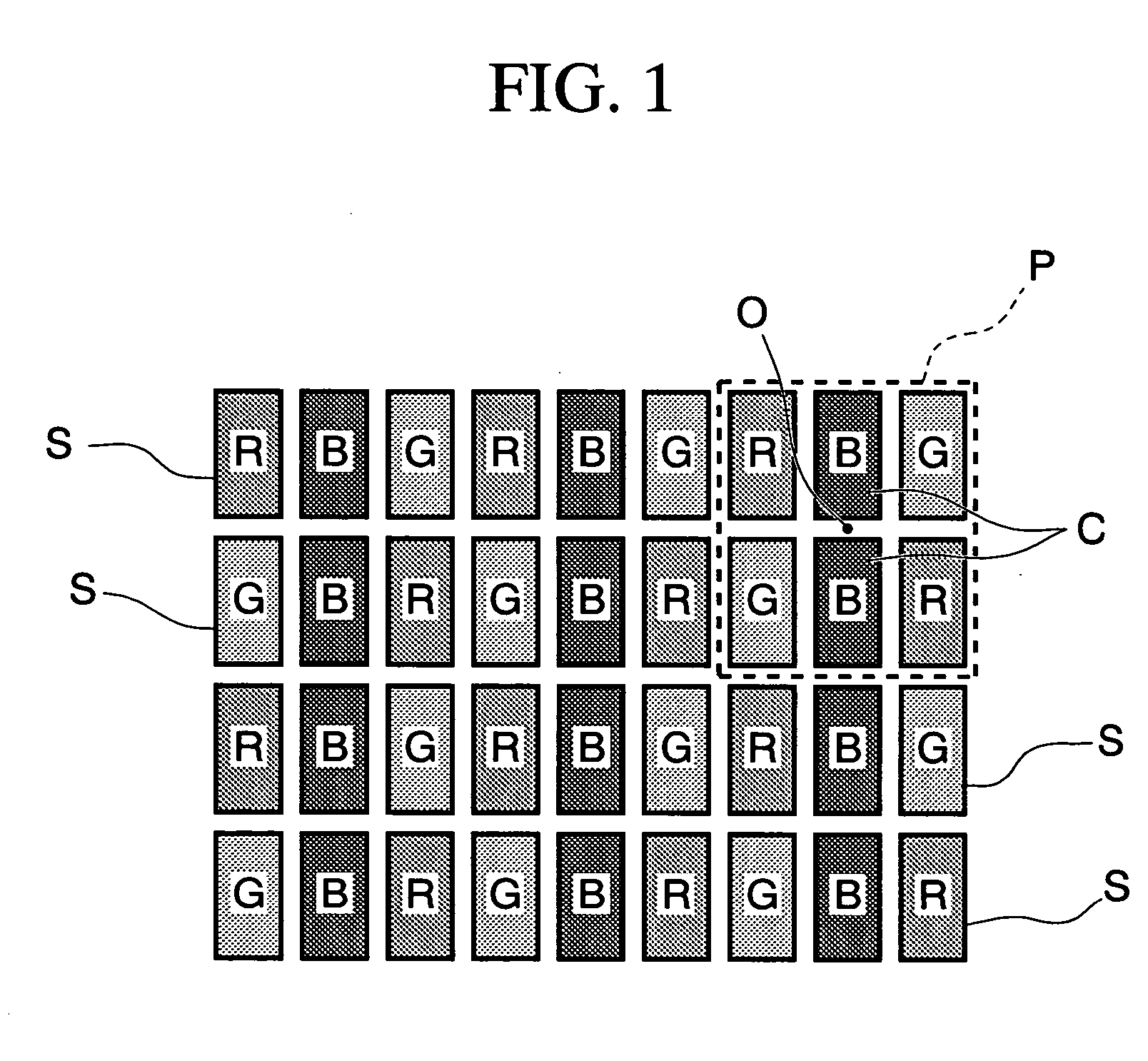

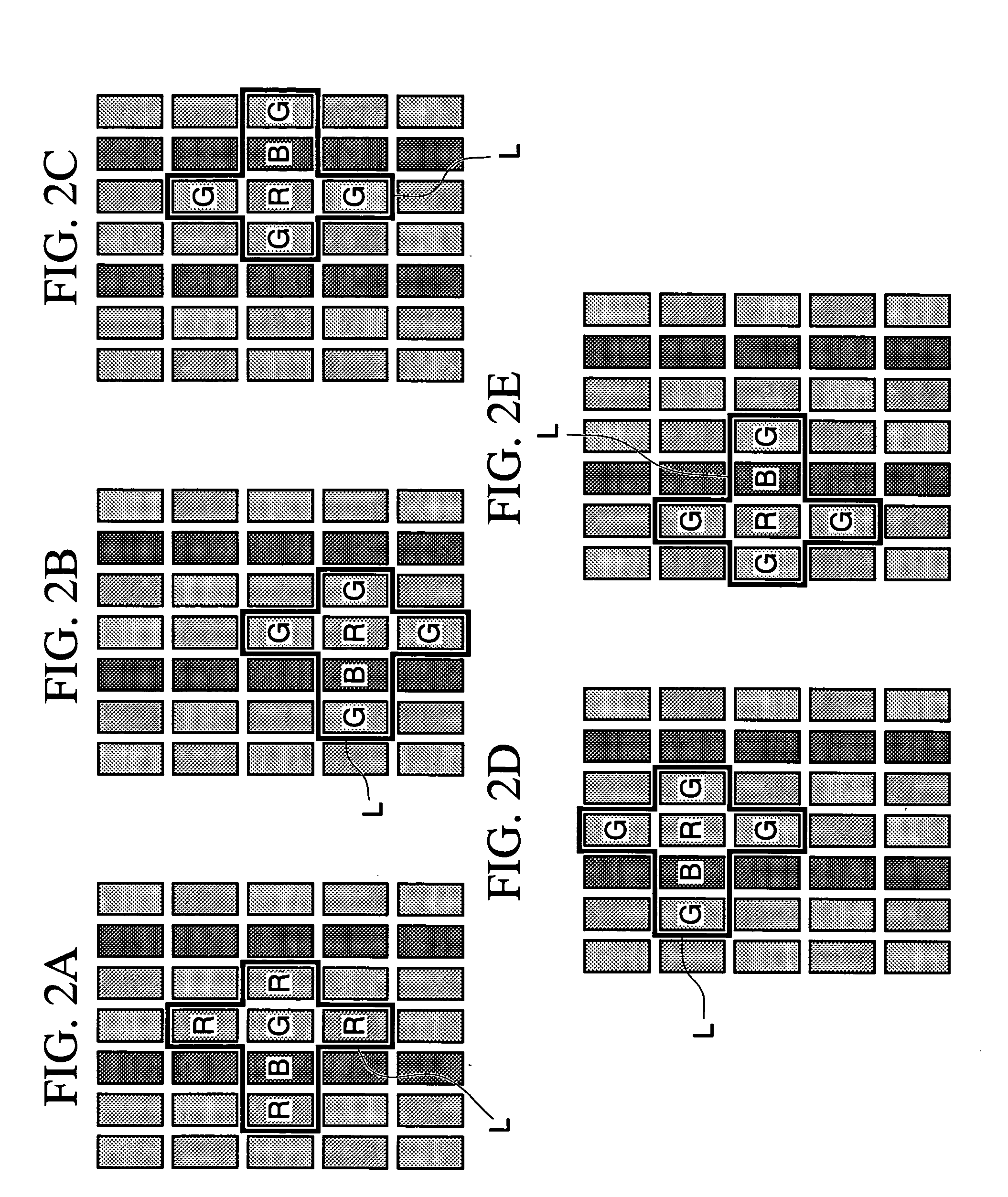

Organic electroluminescent device and electronic apparatus

ActiveUS20050001542A1Easy to displayImproving apparent resolutionDischarge tube luminescnet screensElectroluminescent light sourcesOptoelectronicsOrganic electroluminescence

Owner:ELEMENT CAPITAL COMMERCIAL CO PTE LTD

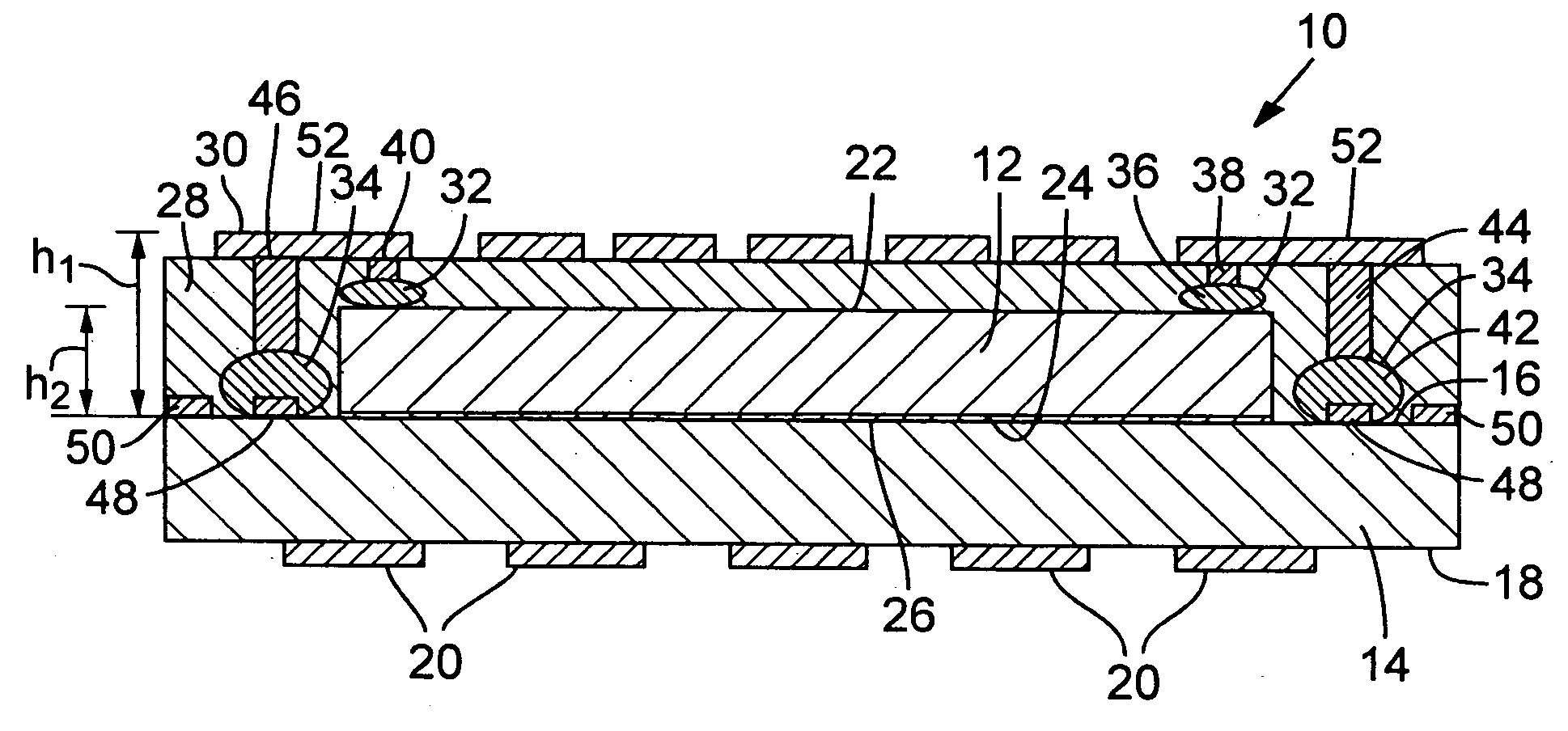

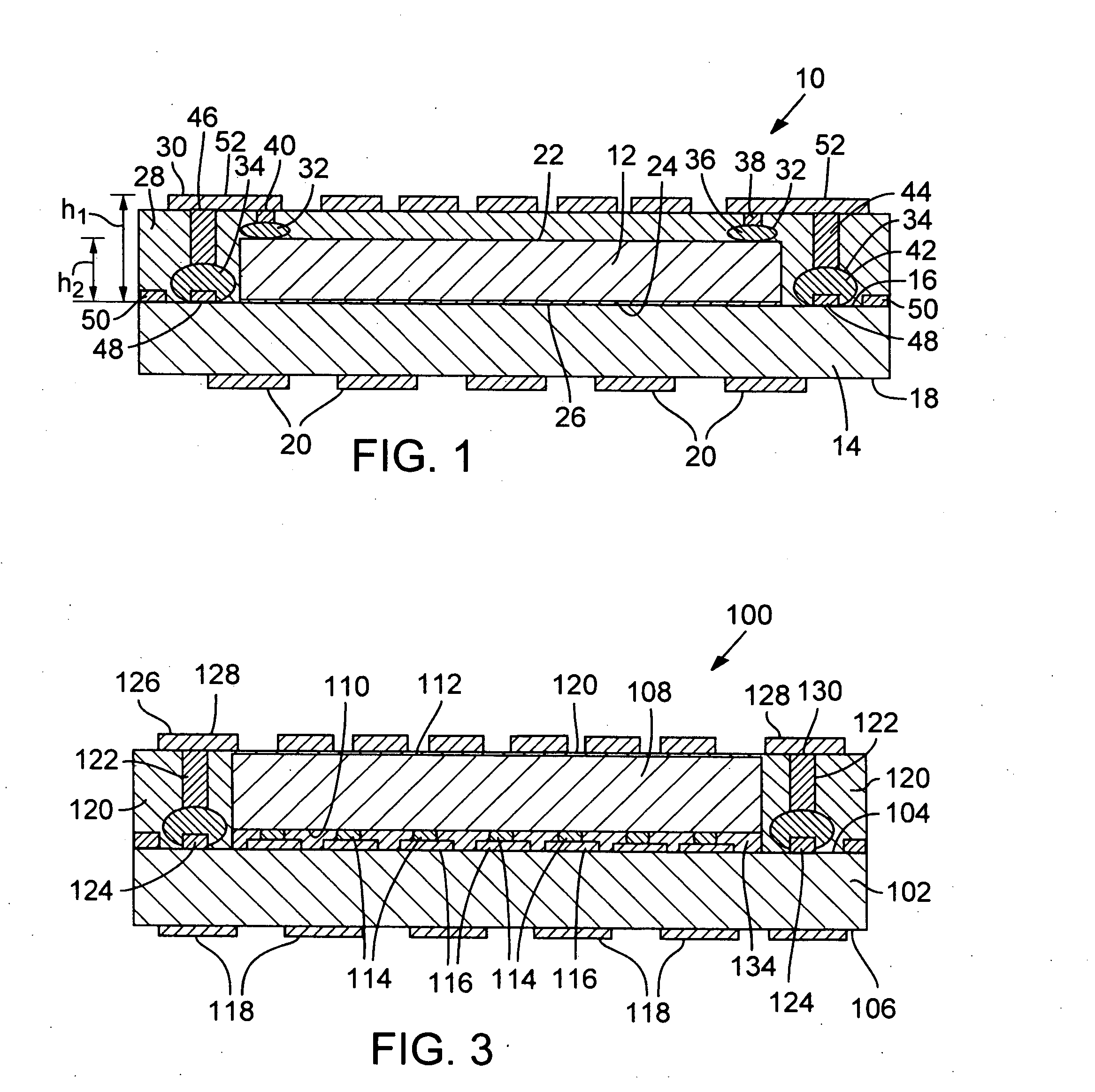

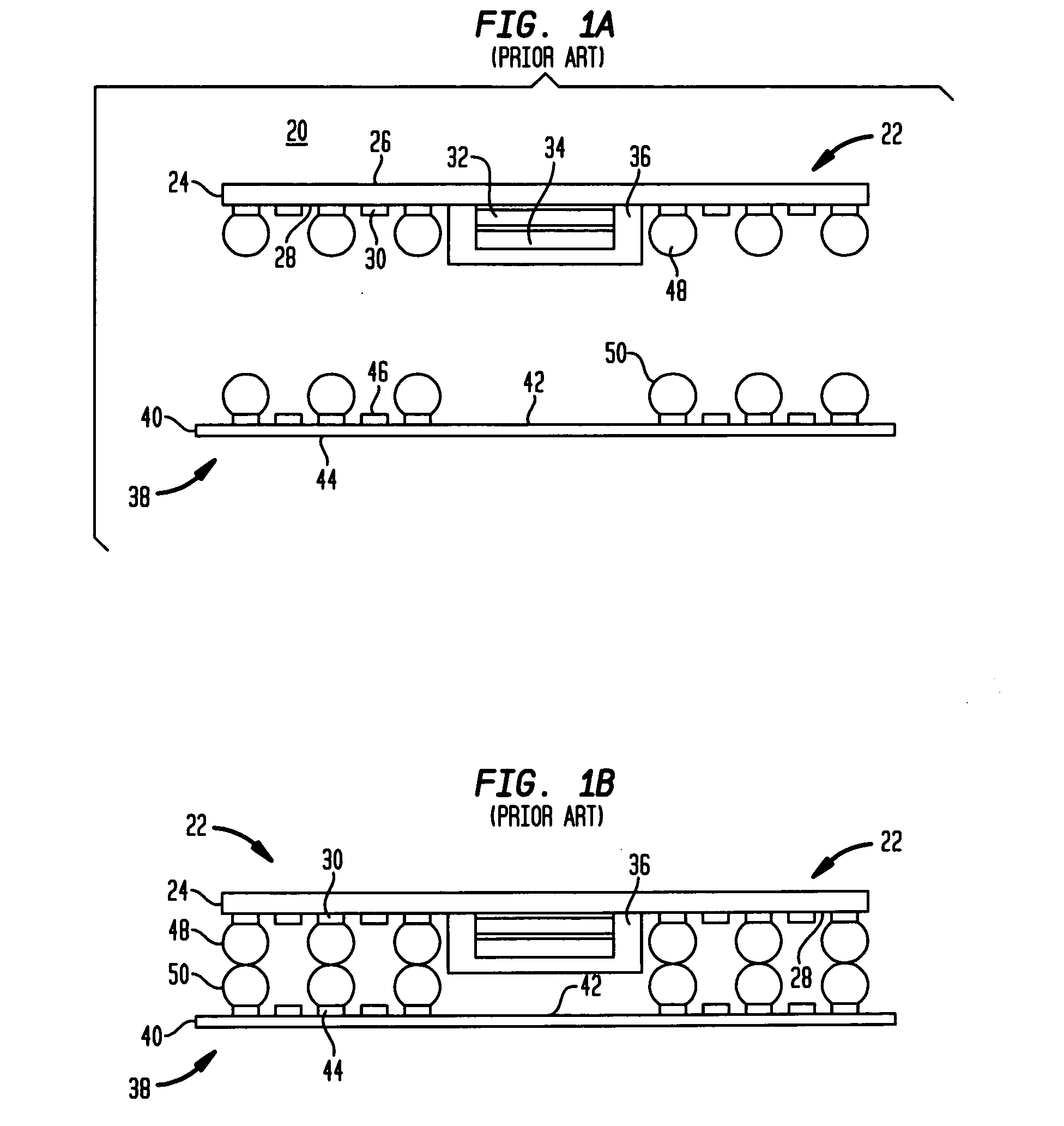

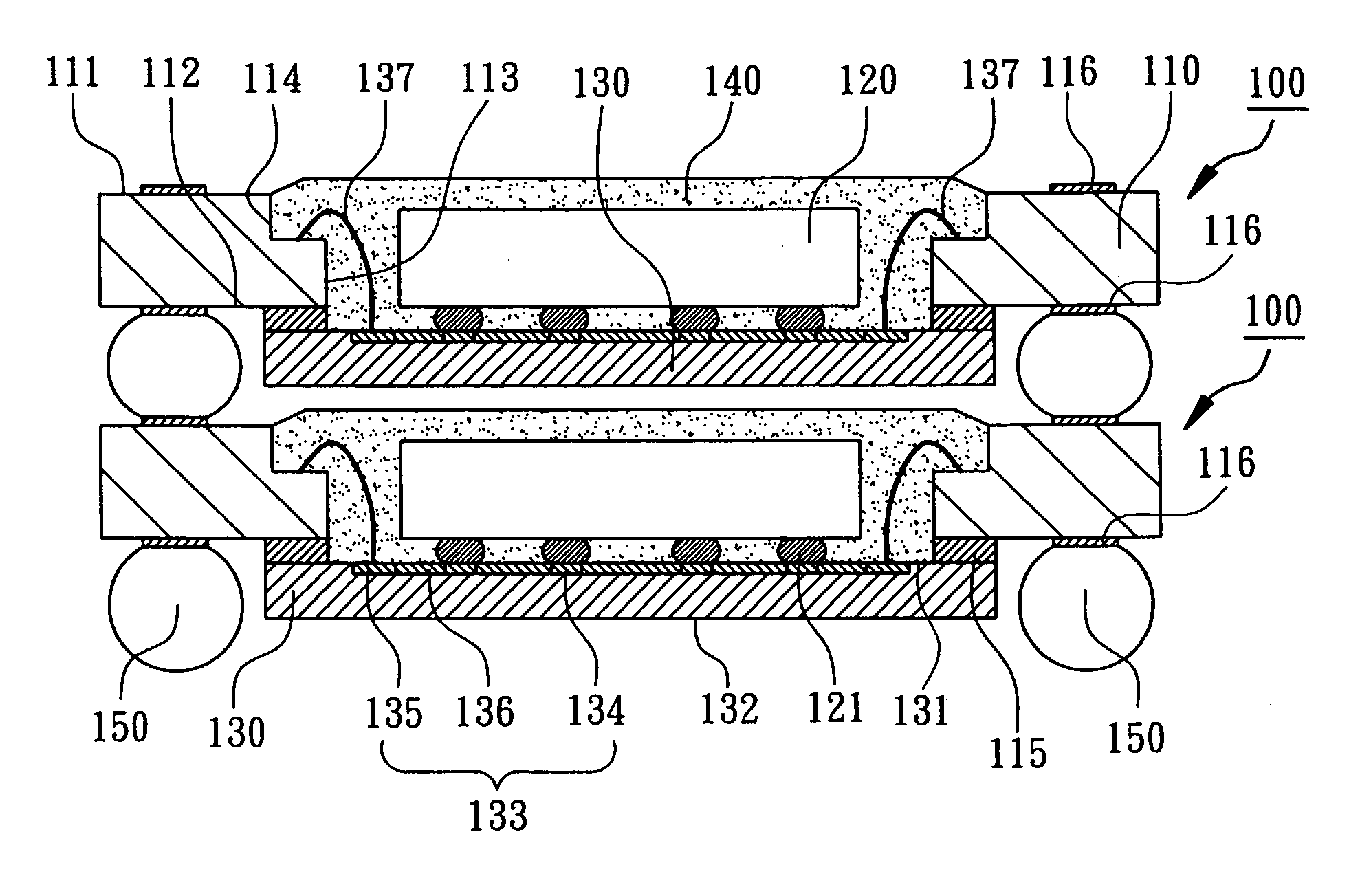

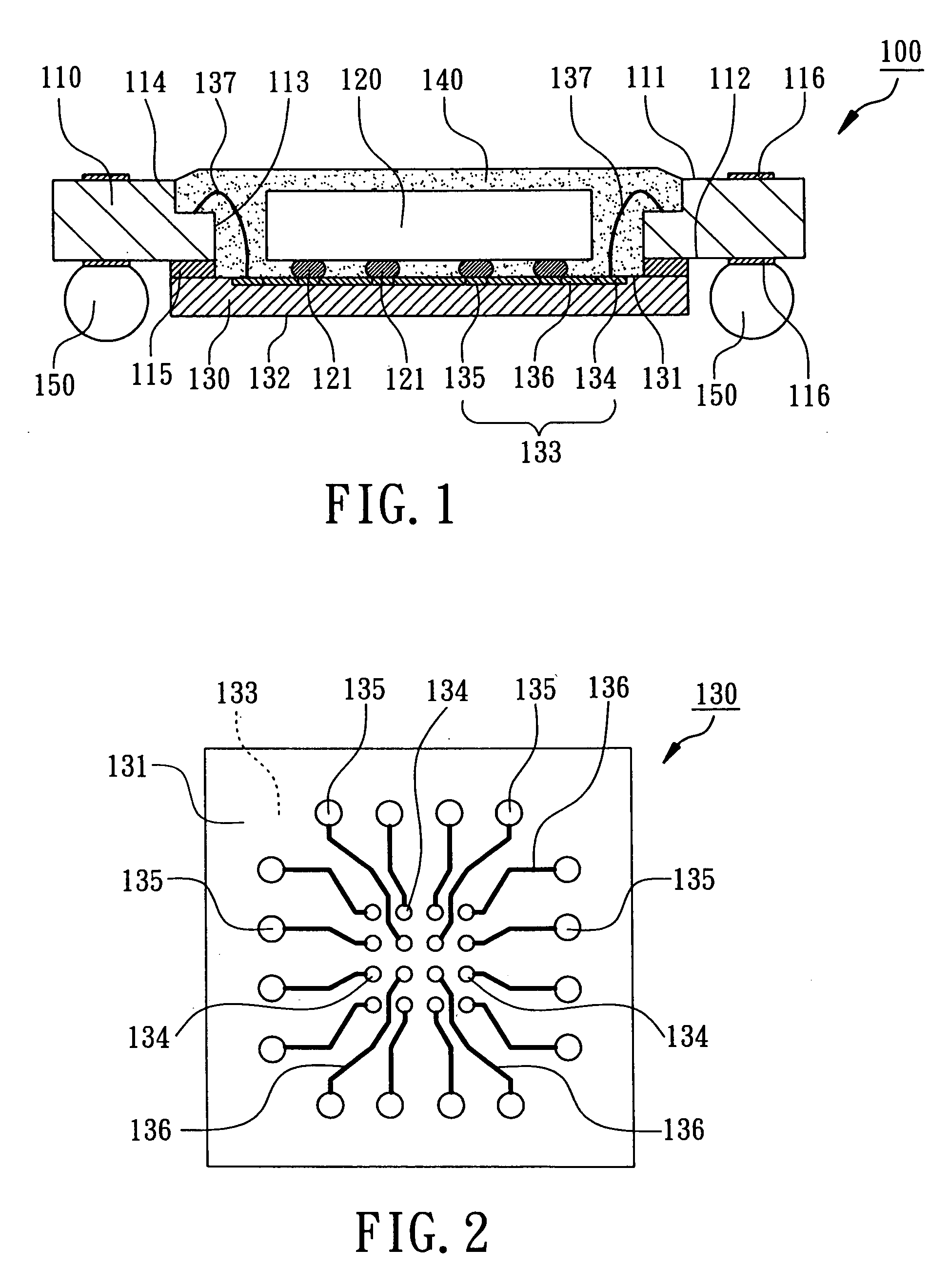

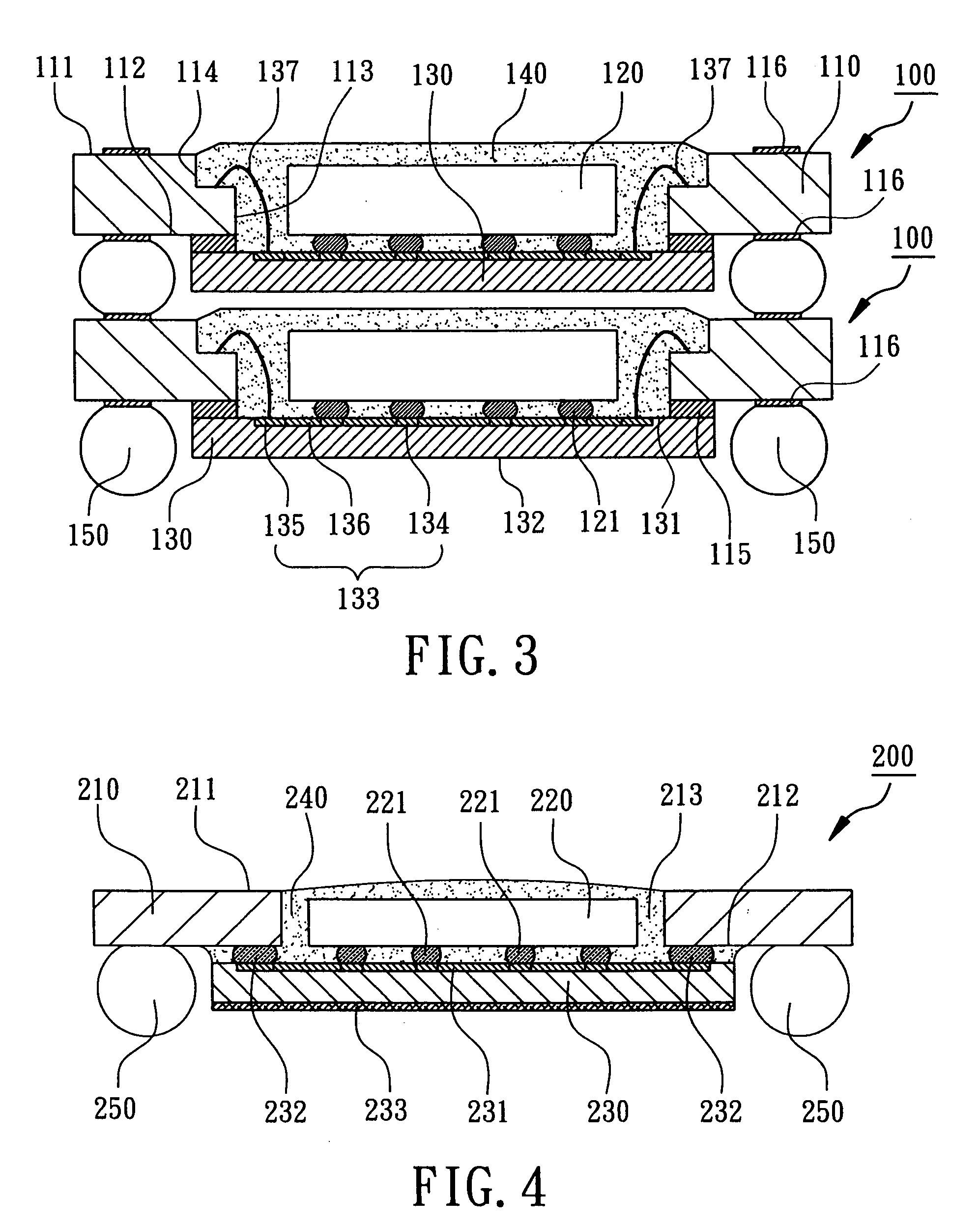

Semiconductor package with embedded die

ActiveUS20080111233A1Fine pitchFirmly connectedSemiconductor/solid-state device detailsSolid-state devicesEngineeringFlip chip

A semiconductor package having an embedded die and solid vertical interconnections, such as stud bump interconnections, for increased integration in the direction of the z-axis (i.e., in a direction normal to the circuit side of the die). The semiconductor package can include a die mounted in a face-up configuration (similar to a wire bond package) or in a face-down or flip chip configuration.

Owner:STATS CHIPPAC INC

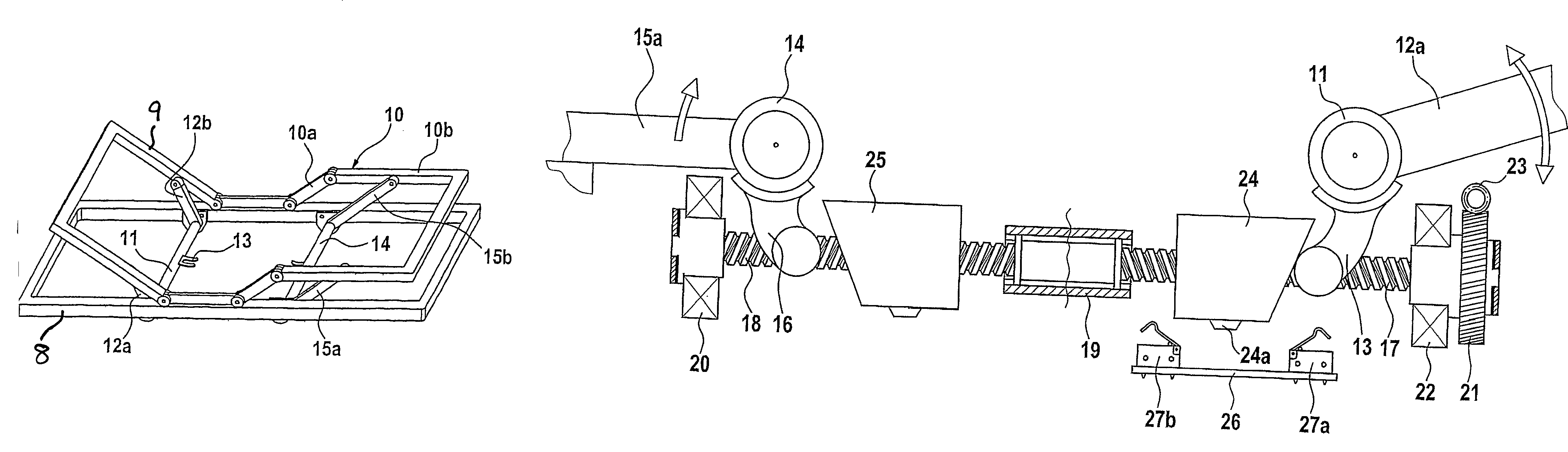

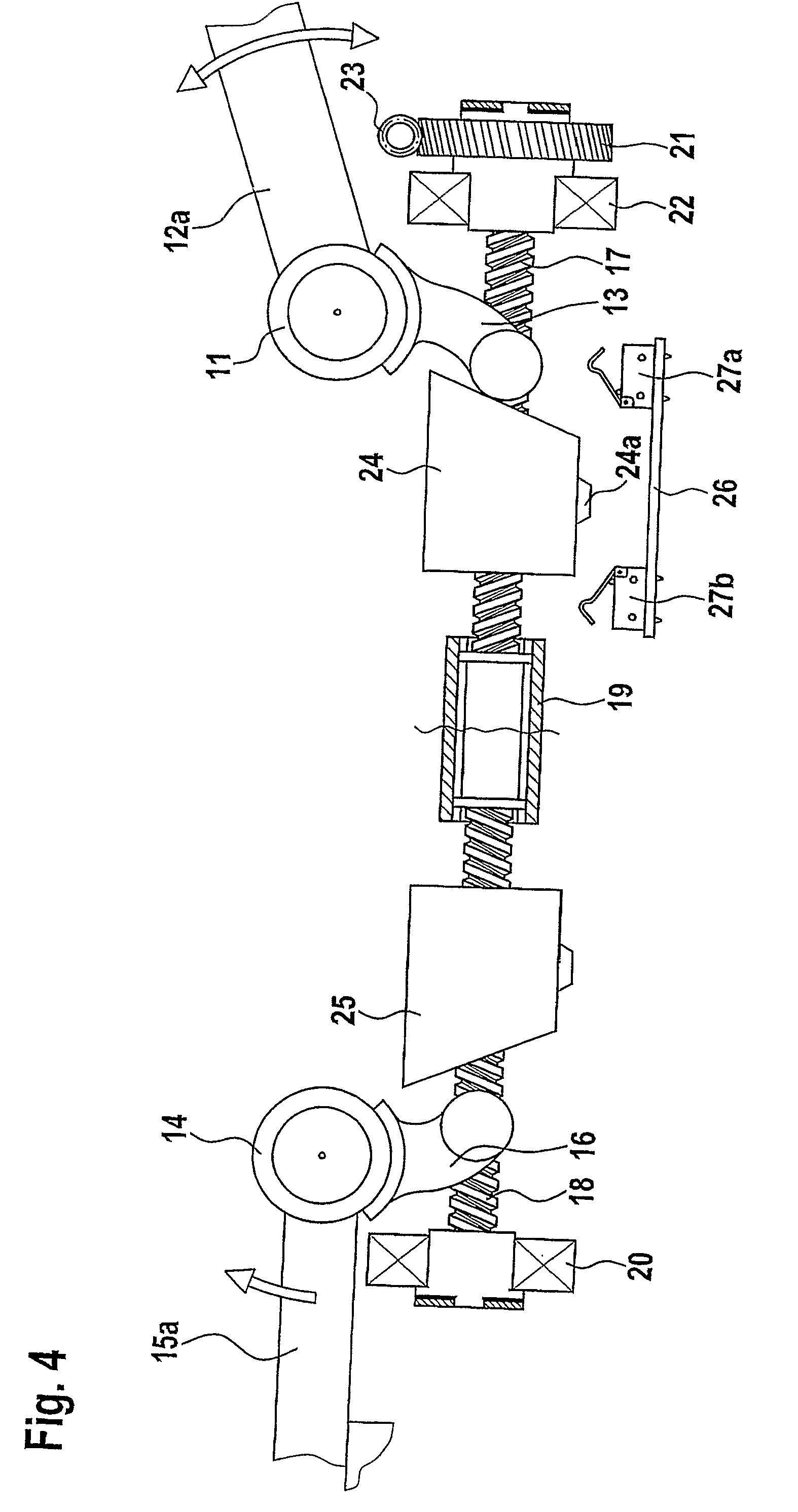

Linear actuator for beds, slatted beds or chairs

InactiveUS7596820B2Manual control is simpleSimplifying motorDC motor speed/torque controlOperating chairsLinear actuatorControl theory

An actuator for beds, slatted beds or chairs of the type accommodating, in a cabinet, two drive units based on a spindle and a spindle nut configured as an adjustment element, cooperating with an arm of a rotary shaft for a backrest section and a legrest section, respectively, in the bed, the mattress support or the chair. The two spindles are rotational interconnected and are driven by a common reversible electric motor. By having just one motor and one transmissions, as well as no switching mechanism between the two spindles, a simple and inexpensive structure is provided.

Owner:LINAK AS

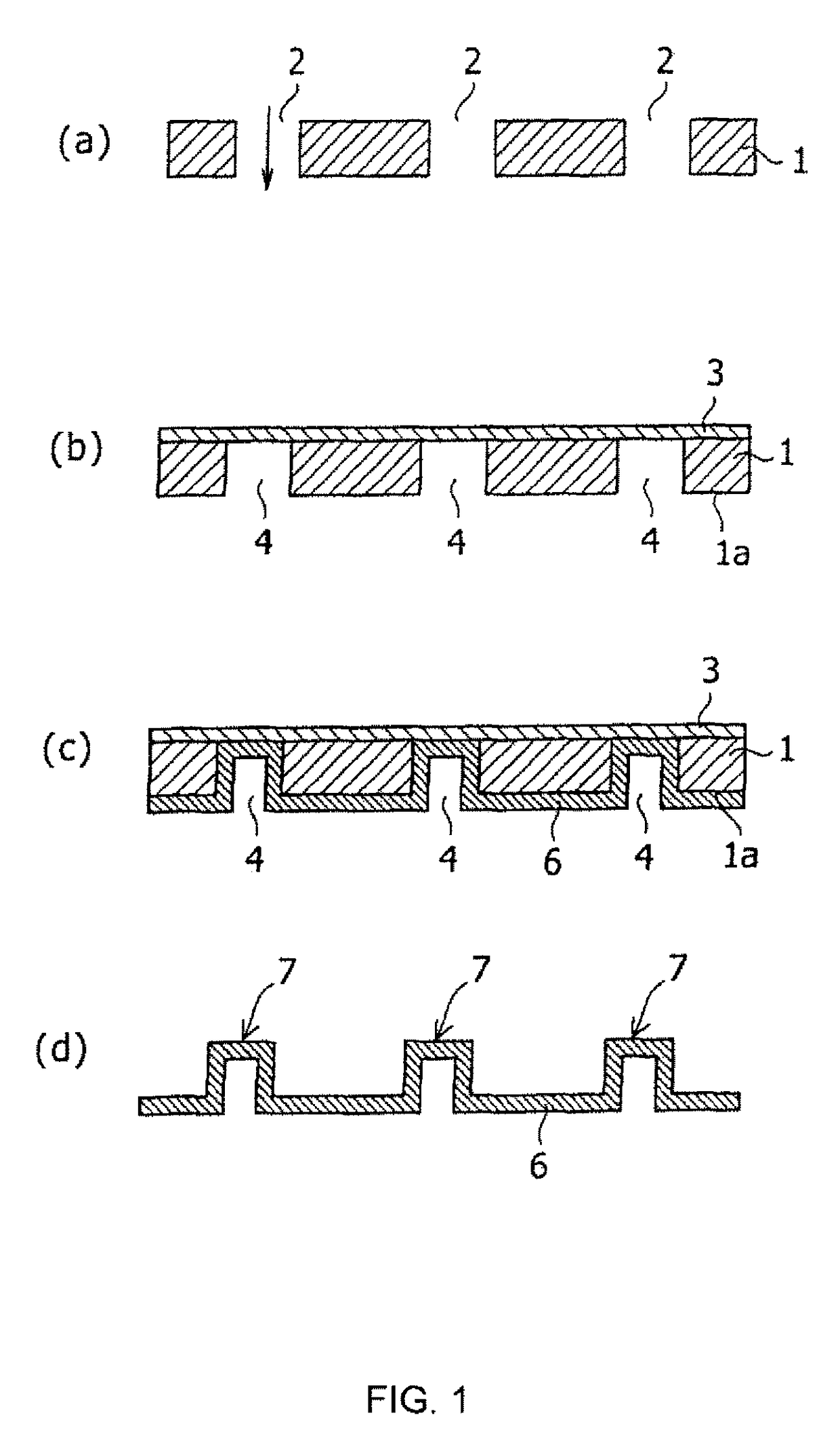

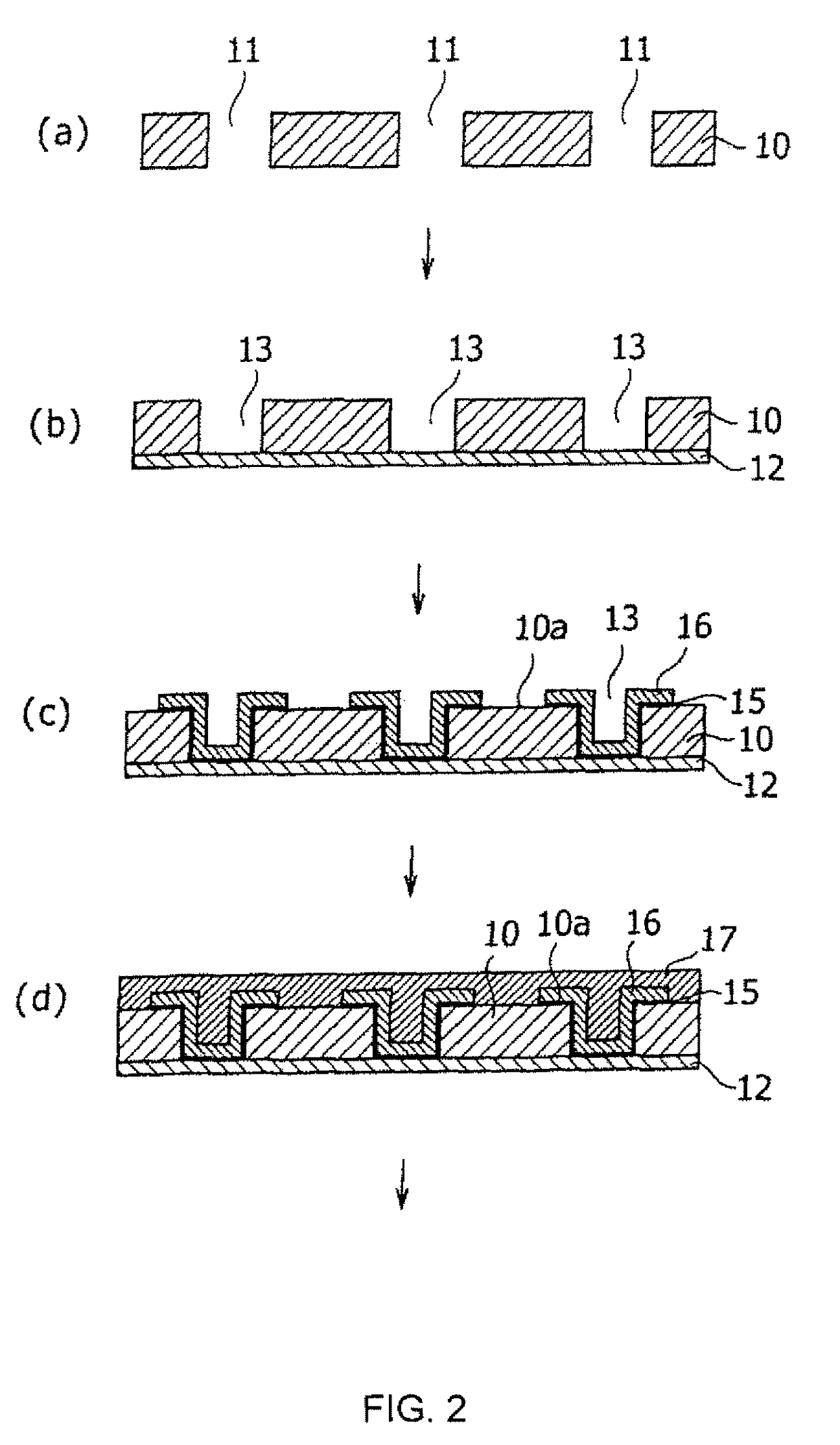

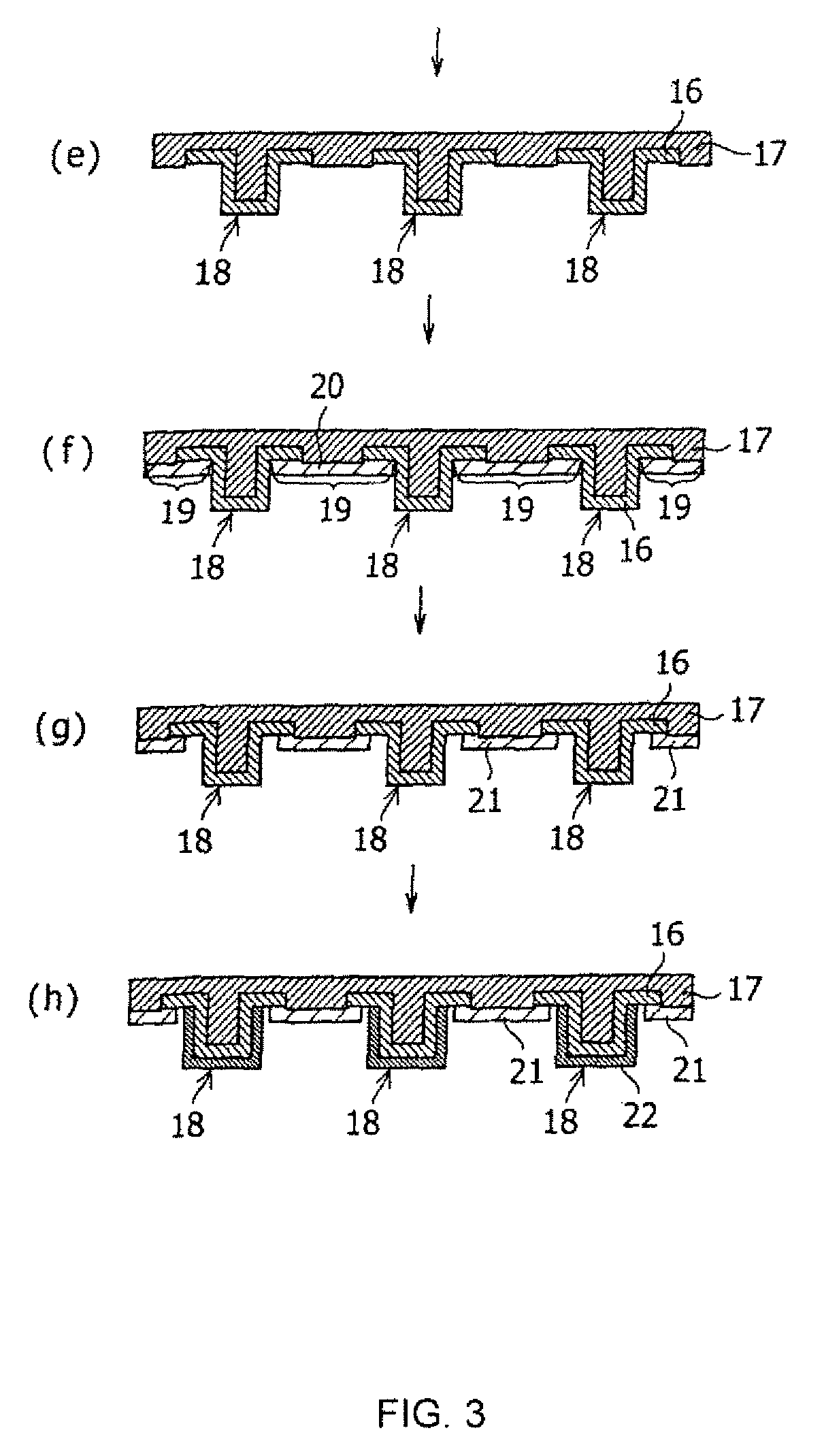

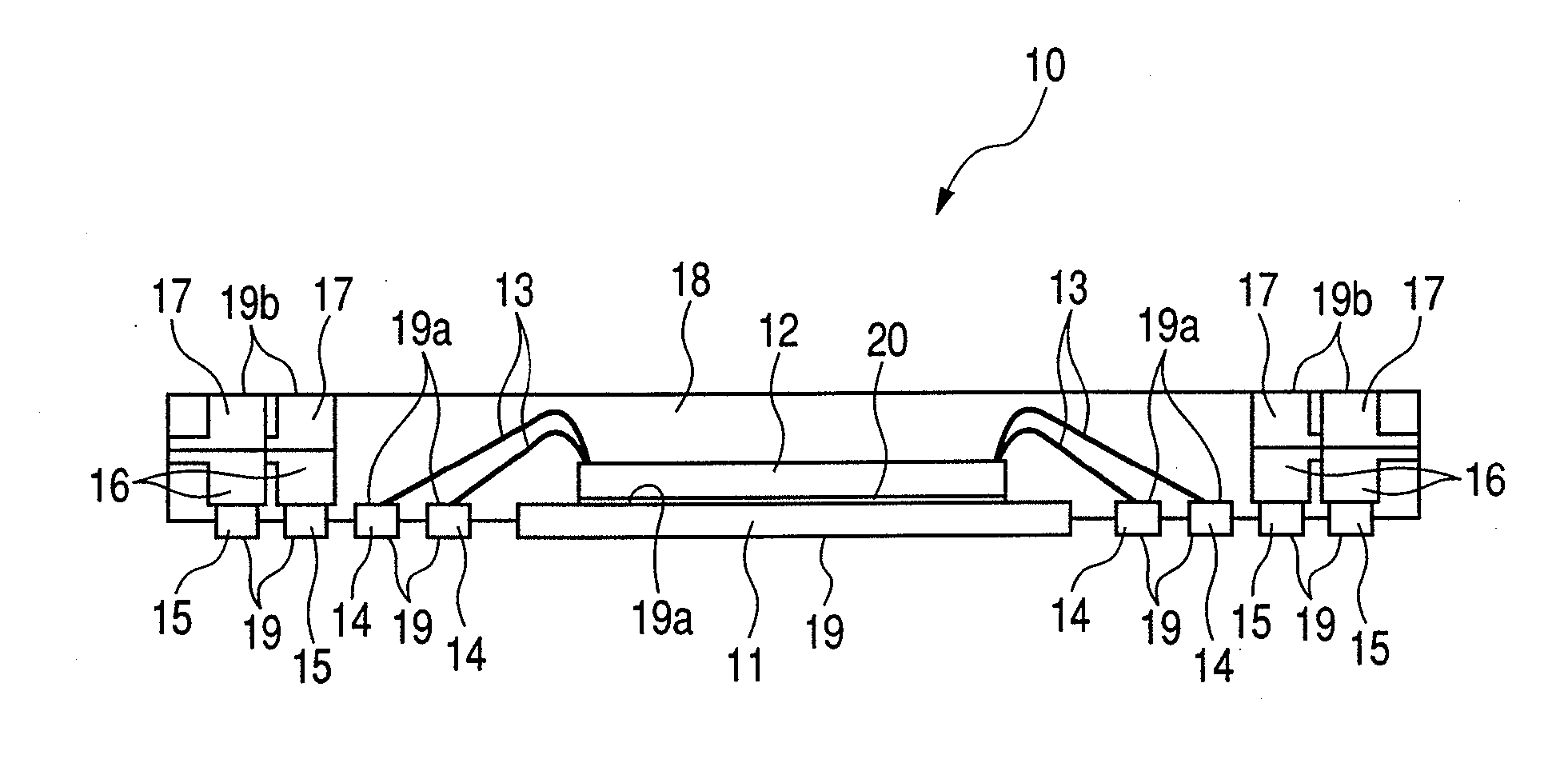

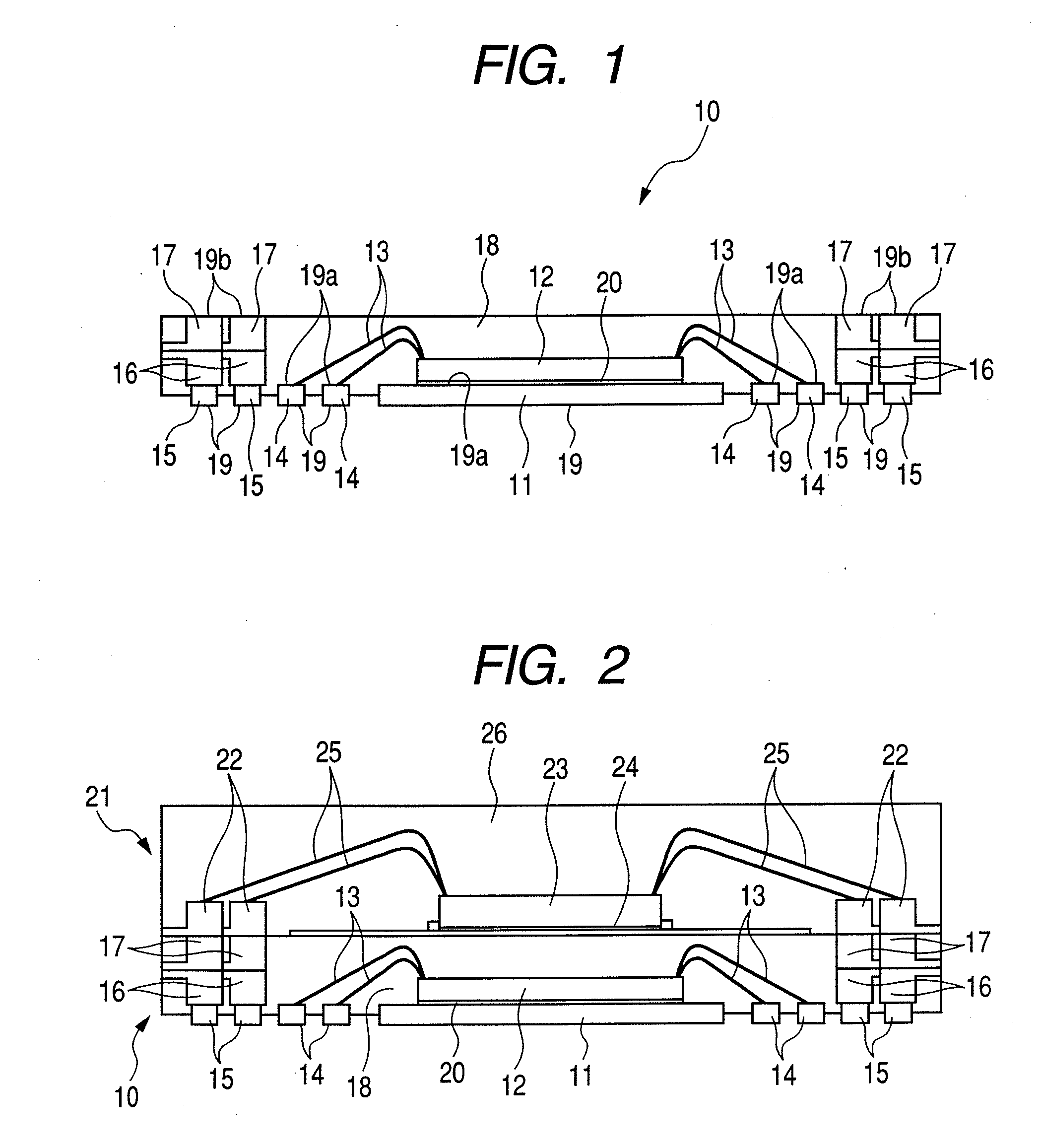

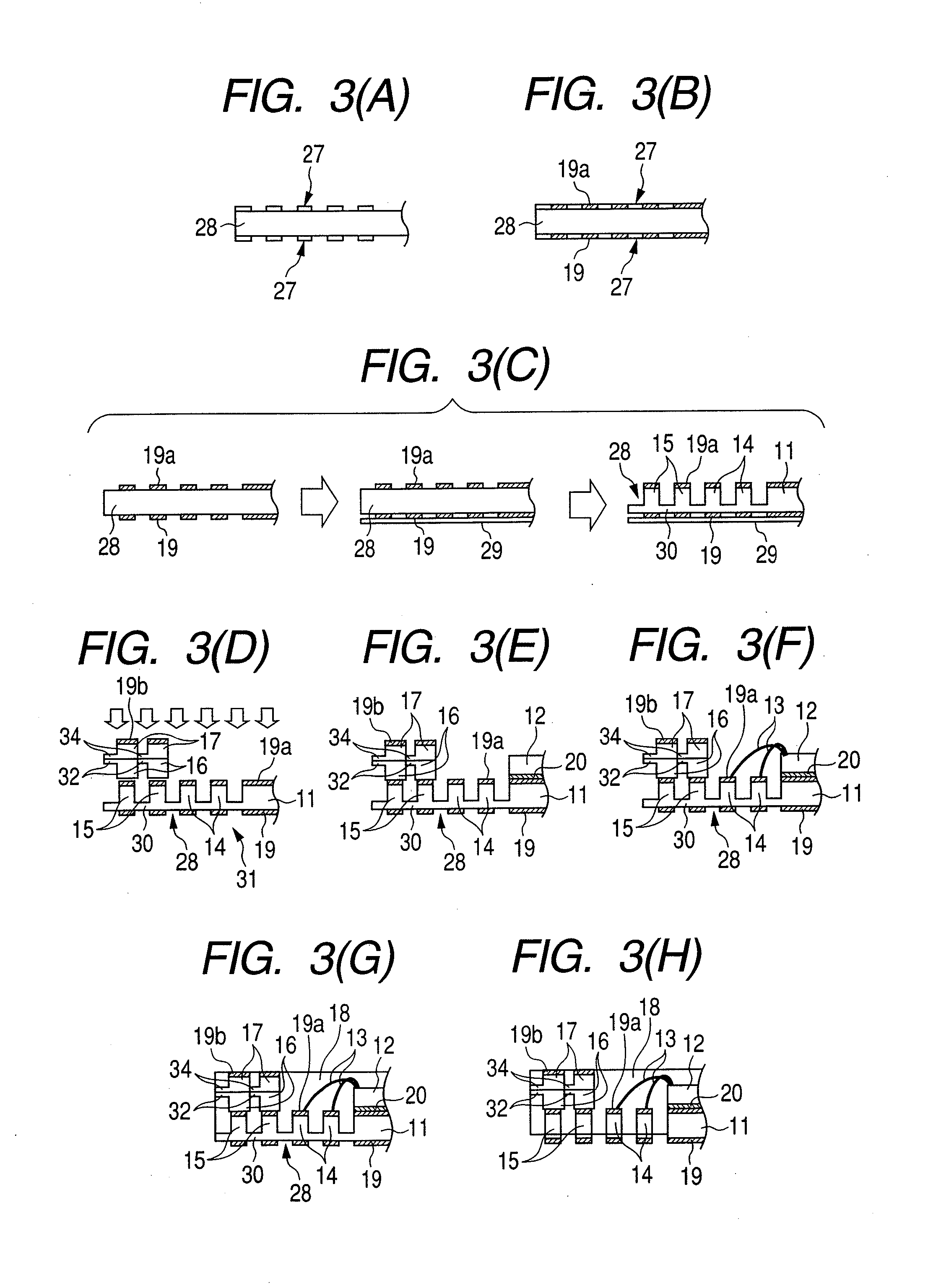

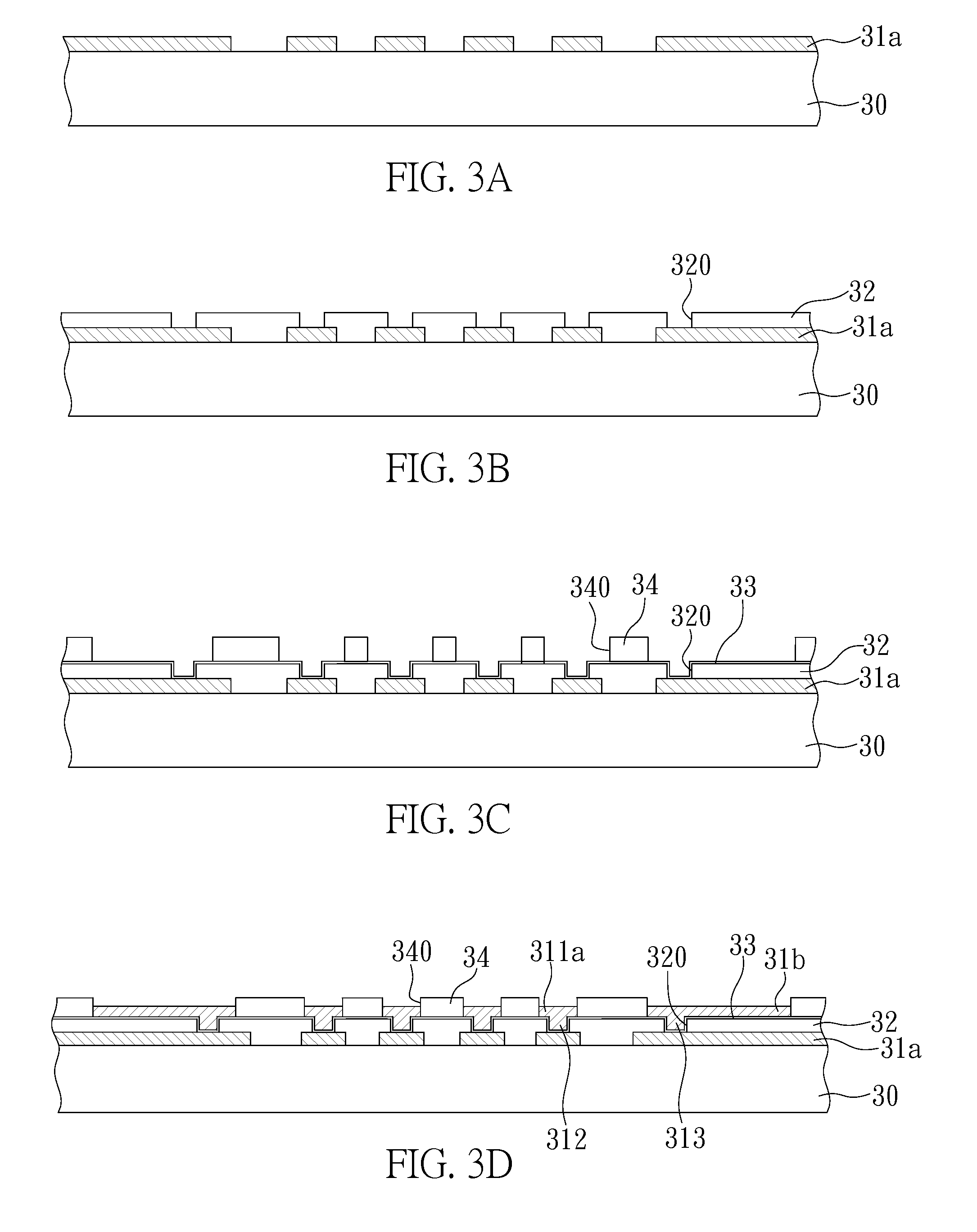

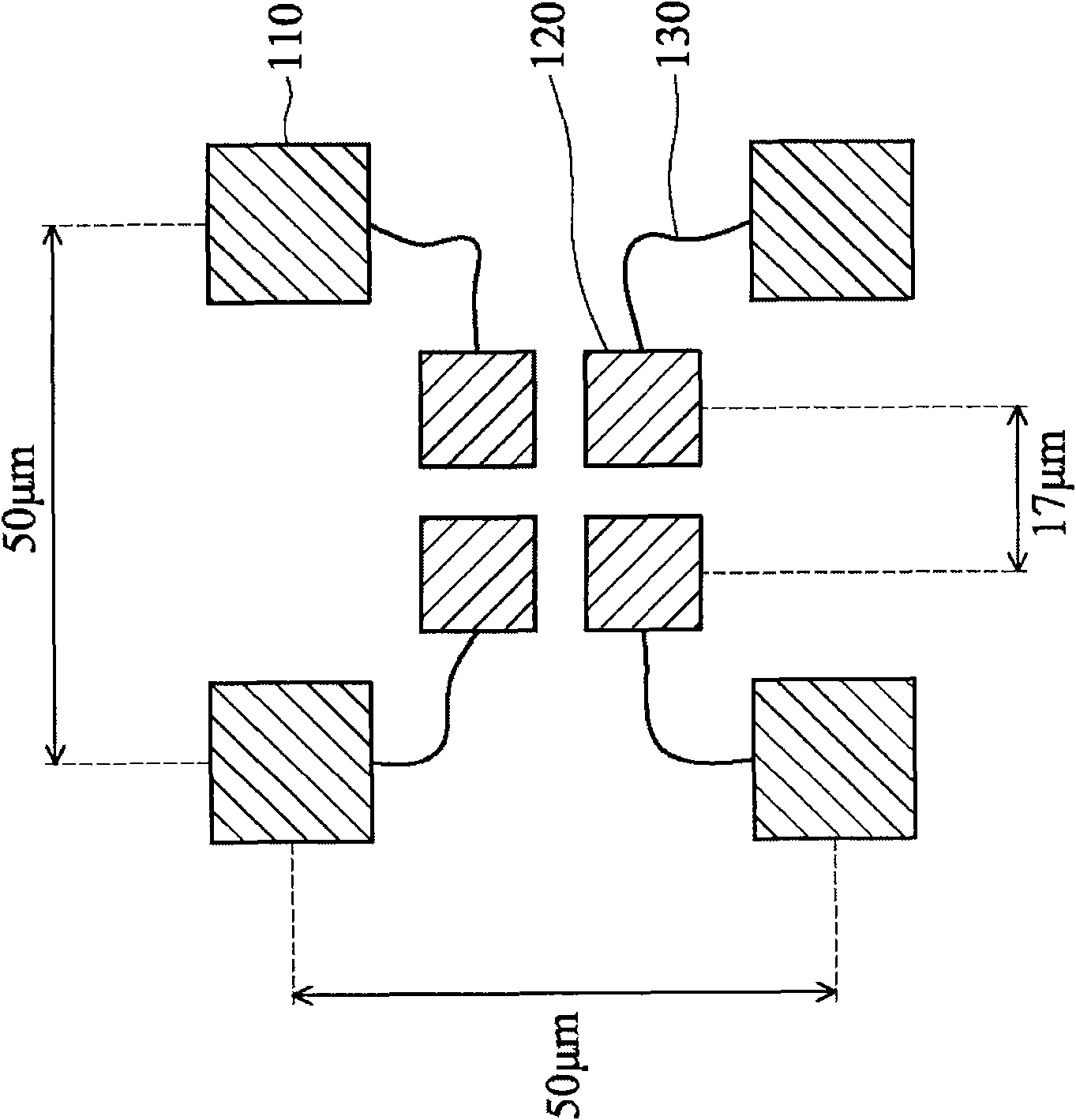

Bump structure formed from using removable mandrel

InactiveUS8119516B2High aspect ratioFine pitchSemiconductor/solid-state device detailsPrinted circuit aspectsEngineeringInterconnection

A method for forming a bump structure and a bump structure for conductive interconnection with another element having at least one of microelectronic devices or wiring thereon, used as an electric connection in an electronic circuit, includes the steps of forming a mandrel by steps including forming at least one opening extending through a bump-forming die body in the thickness direction thereof and positioning a bump-forming die lid on a surface of the bump-forming die body so as to cover one end of the opening and to thereby define a bump-forming recess. The bump-forming die body may be comprised of a metal sheet. A metal layer is formed at least on an inner surface of the bump-forming die lid exposed within the bump-forming recess. The mandrel is removed so as to expose the metal layer and form a bump structure.

Owner:INVENSAS CORP

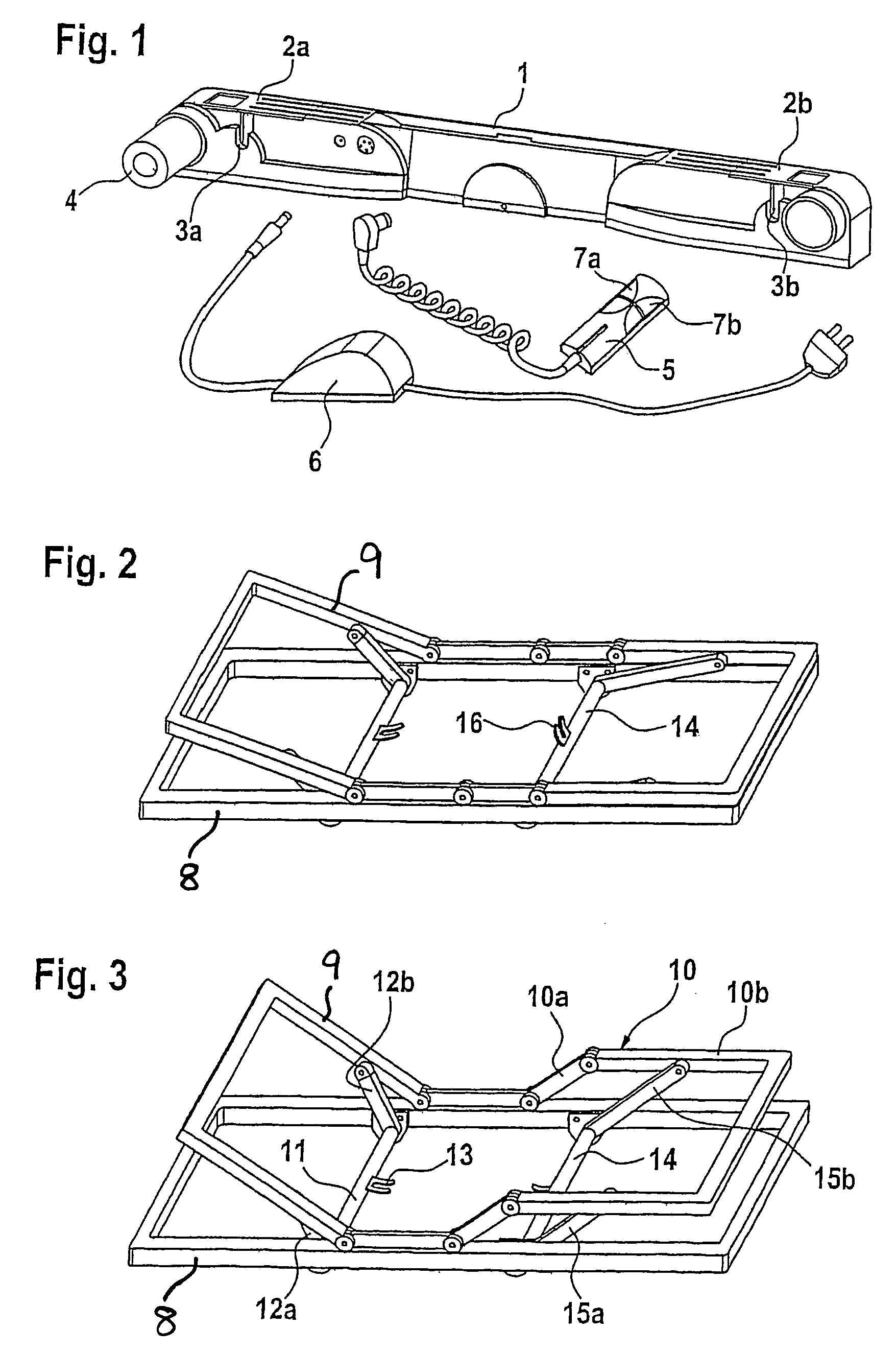

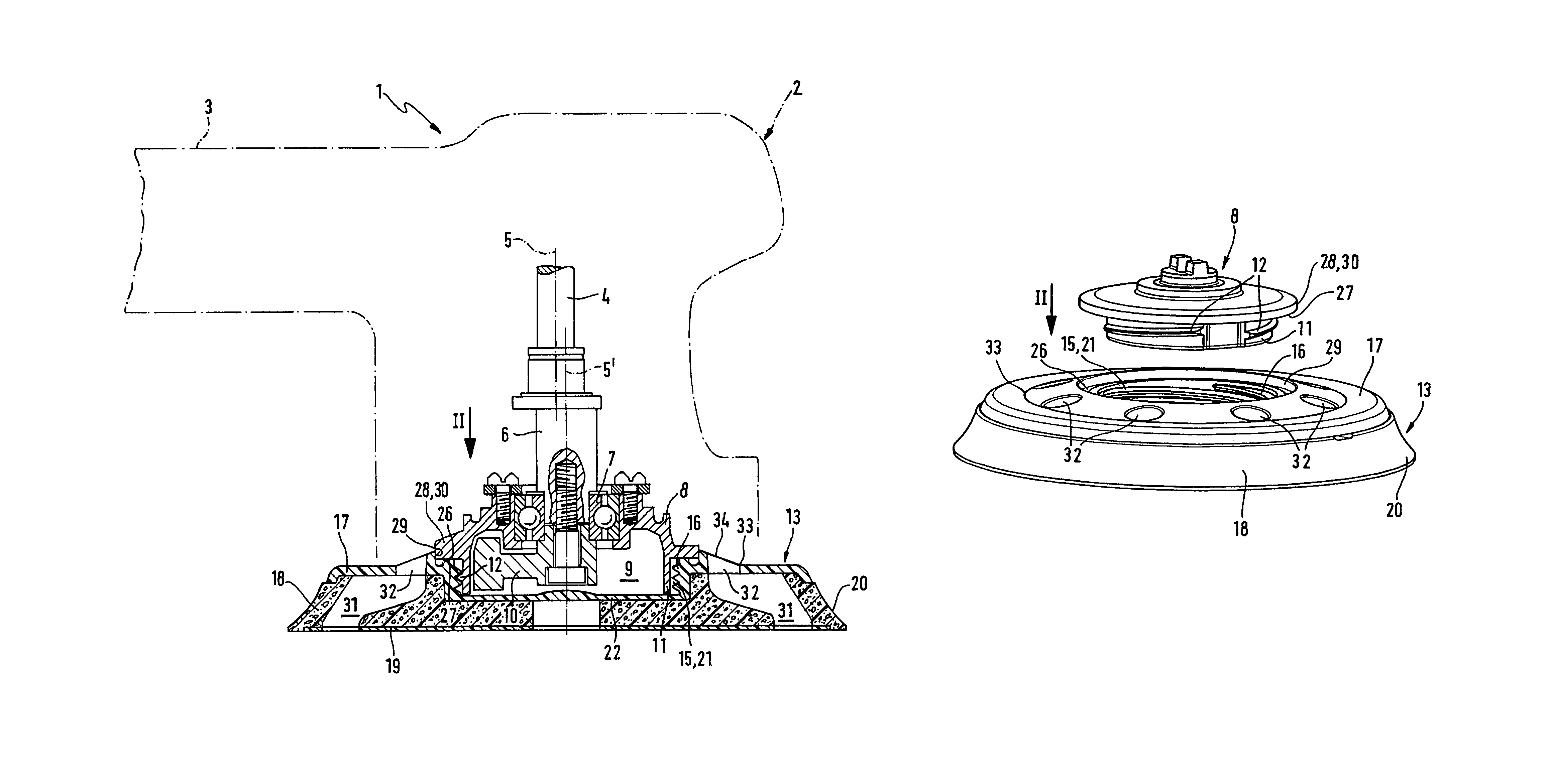

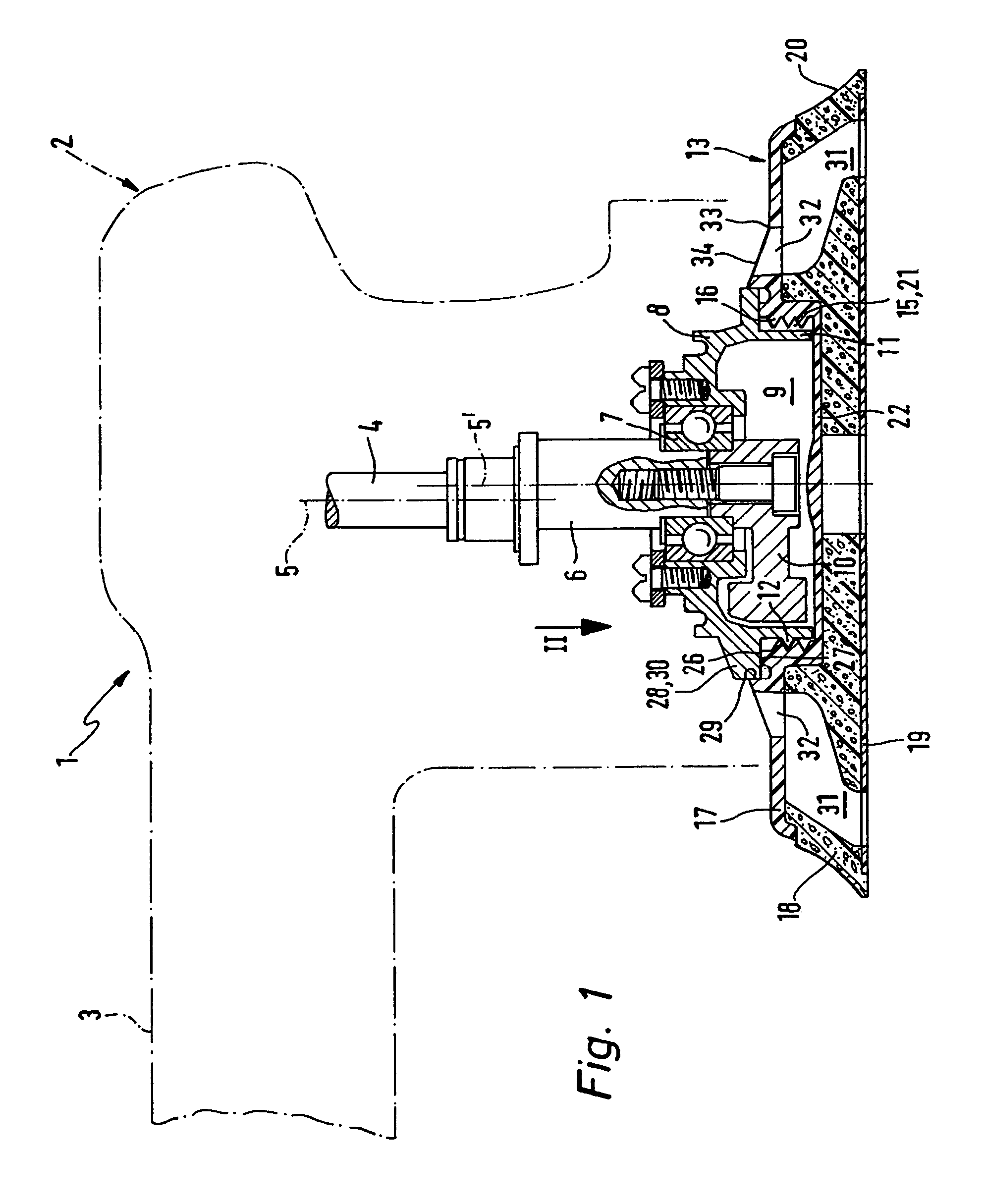

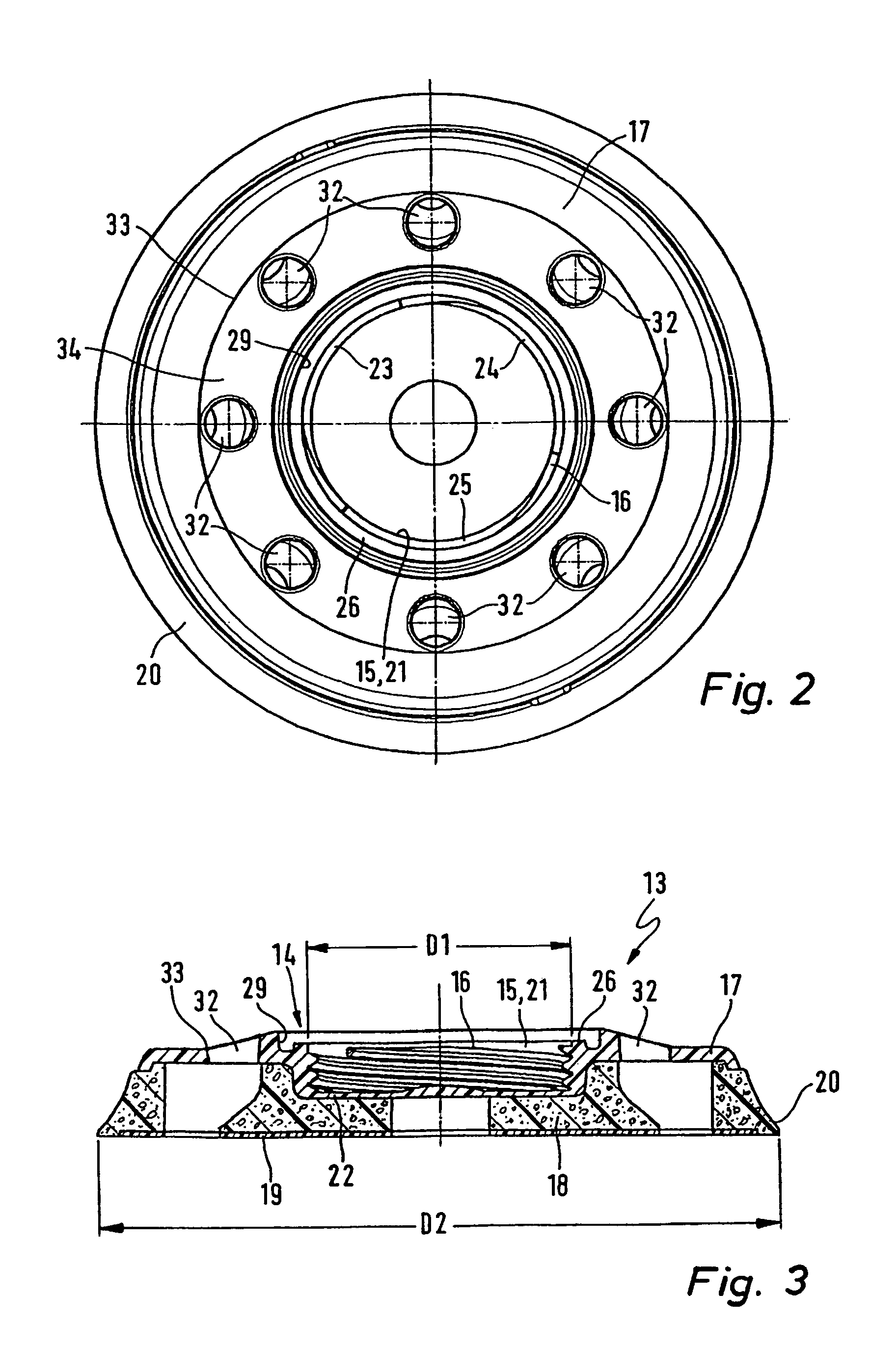

Grinding disk

ActiveUS7029384B2High torqueFine pitchGrinding wheel securing apparatusRevolution surface grinding machinesDiameter ratioEngineering

A grinding disk (13) for manually held, motor-driven grinders (1) has a centrally arranged fastening recess (15) open at the grinding disk upper side with an internal thread arrangement (16), with which the grinding disk (13) can be screwed onto a connecting part (8), which is arranged on the side of the grinder and is driven for the grinding motion during operation, and which connecting part has a thread section (11) with an external thread arrangement (12), which is associated with the internal thread arrangement (16) of the grinding disk (13). The internal thread arrangement (16) is formed by a multiple thread with at least two thread courses, which are arranged angularly offset to one another. The diameter ratio between the diameter of the internal thread arrangement (16) and the outside diameter of the grinding disk (13) is at least approximately 0.25.

Owner:FESTOOL GMBH

Composite contact for fine pitch electrical interconnect assembly

InactiveUS20090127698A1High dielectric constantImprove electrical performanceSemiconductor/solid-state device detailsCoupling device detailsCouplingEngineering

An electrical interconnect assembly for electrically interconnecting terminals on a first circuit member with terminals on a second circuit member. The electrical interconnect includes a housing having a plurality of through openings extending between a first surface and a second surface. A plurality of composite contacts are positioned in a plurality of the through openings. The composite contacts include a conductive member having a central portion and at least first and second interface portions. One or more polymeric layers extend along at least the central portion conductive member. One or more coupling features on the composite contacts engage with the housing. At least one engagement feature formed in the polymeric layers proximate the first interface portion mechanically couples with the terminals on the first circuit member.

Owner:R&D SOCKETS INC

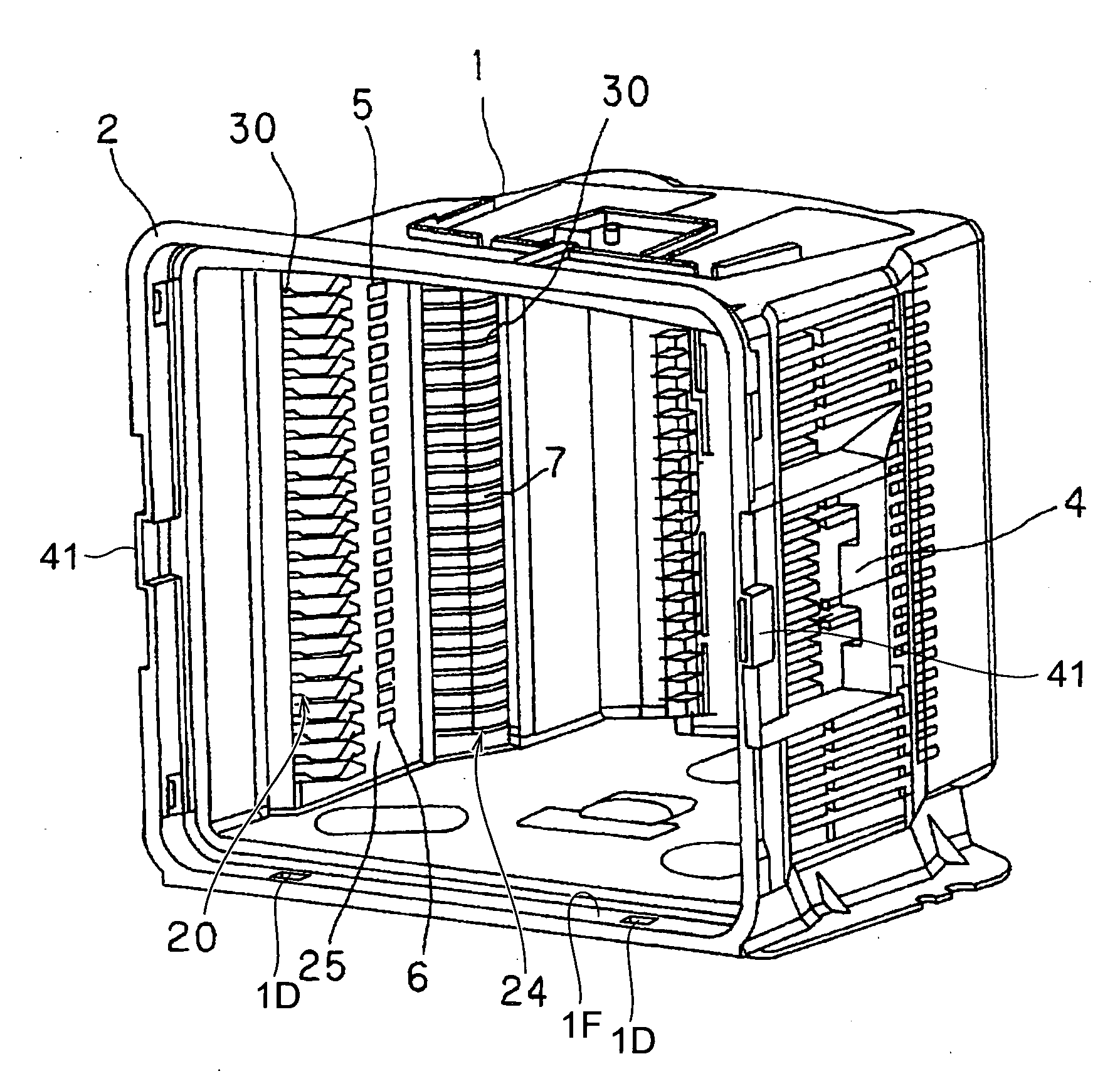

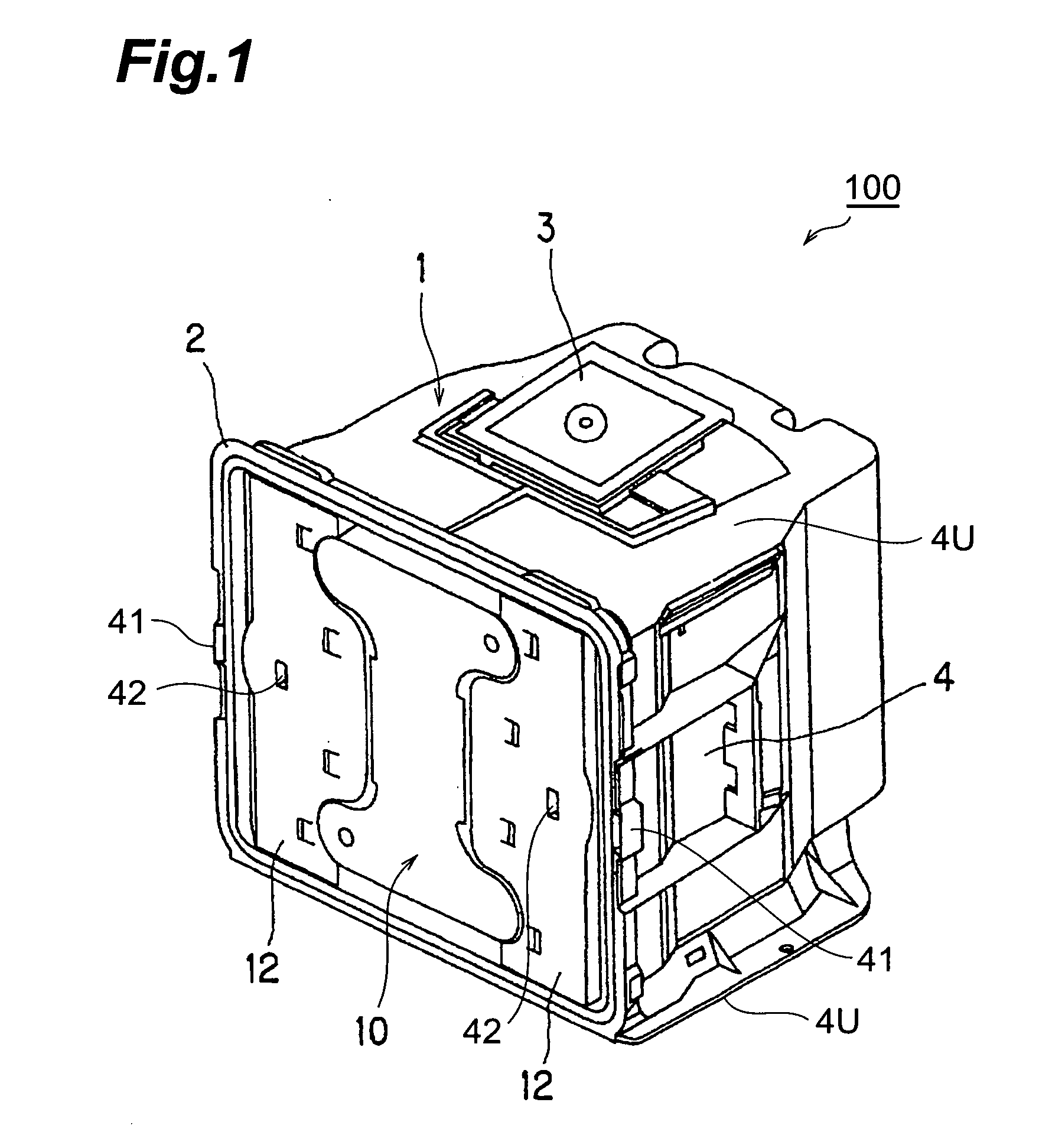

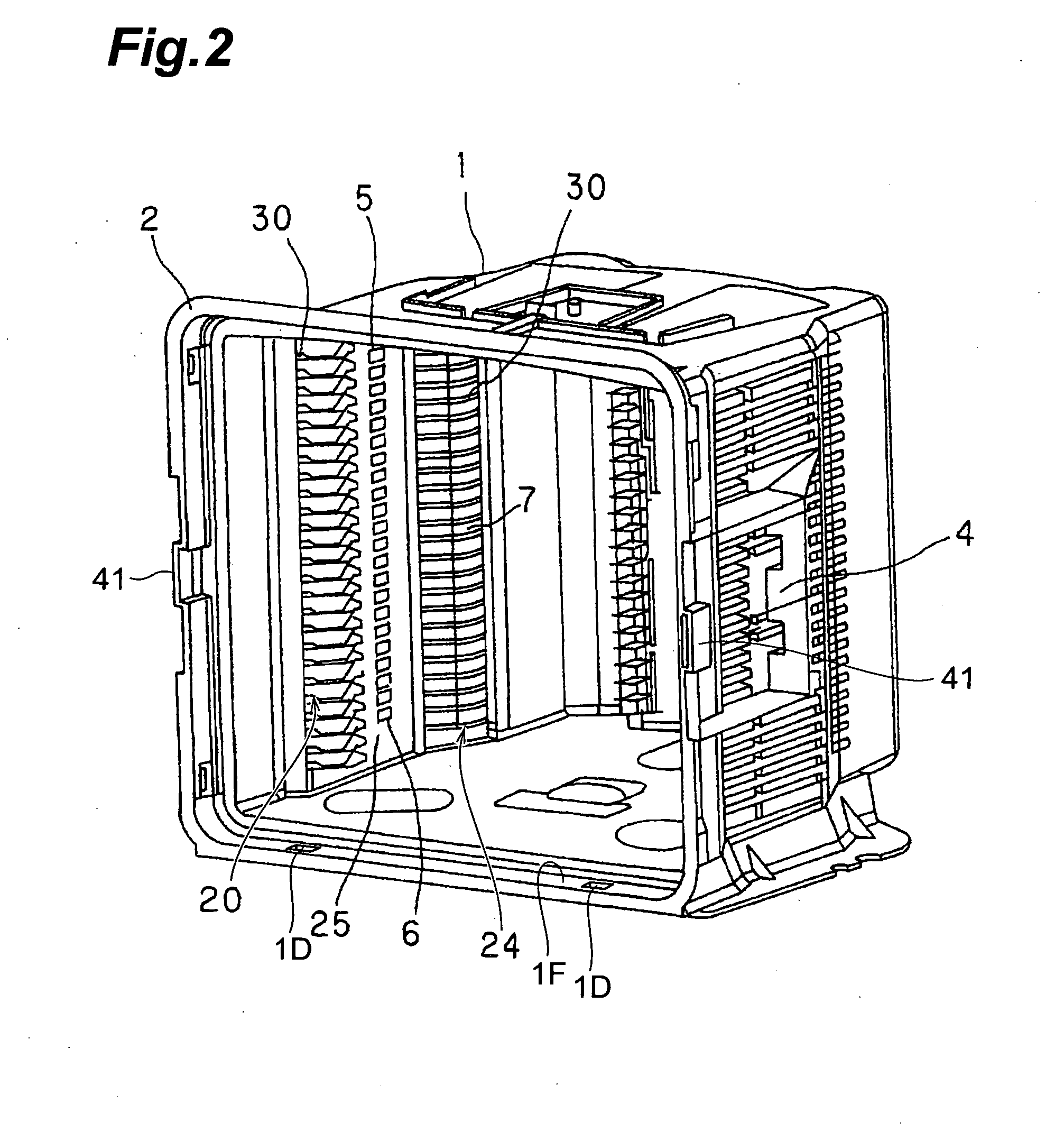

Substrate storage container and method for manufacturing the same

InactiveUS20060283774A1Prevent contamination and scratchingFine pitchSemiconductor/solid-state device manufacturingOther accessoriesEngineeringMechanical engineering

A substrate storage container includes a container main body, first supporting parts and second supporting parts. The container main body includes a back wall and a pair of side walls in order to store a substrate between the side walls. The first supporting parts are opposingly disposed on each side wall in order to support a peripheral edge part of the substrate. The second supporting parts are opposingly disposed on each side wall in order to support the peripheral edge part of the substrate and positioned between the back wall and the first supporting parts. The first supporting parts and the second supporting parts are covered with a resin layer having a lower frictional property than that of the container main body.

Owner:SHIN-ETSU POLYMER CO LTD

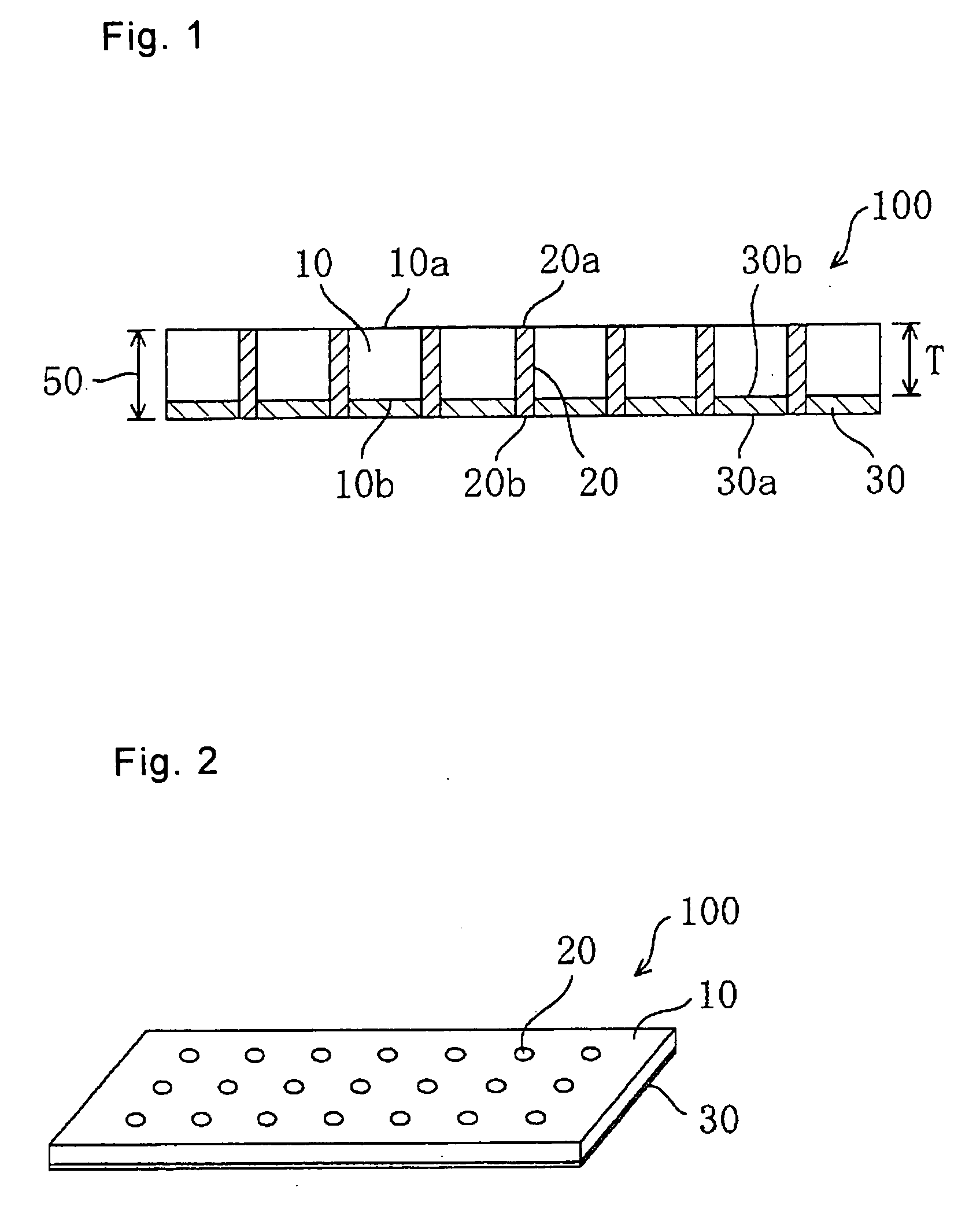

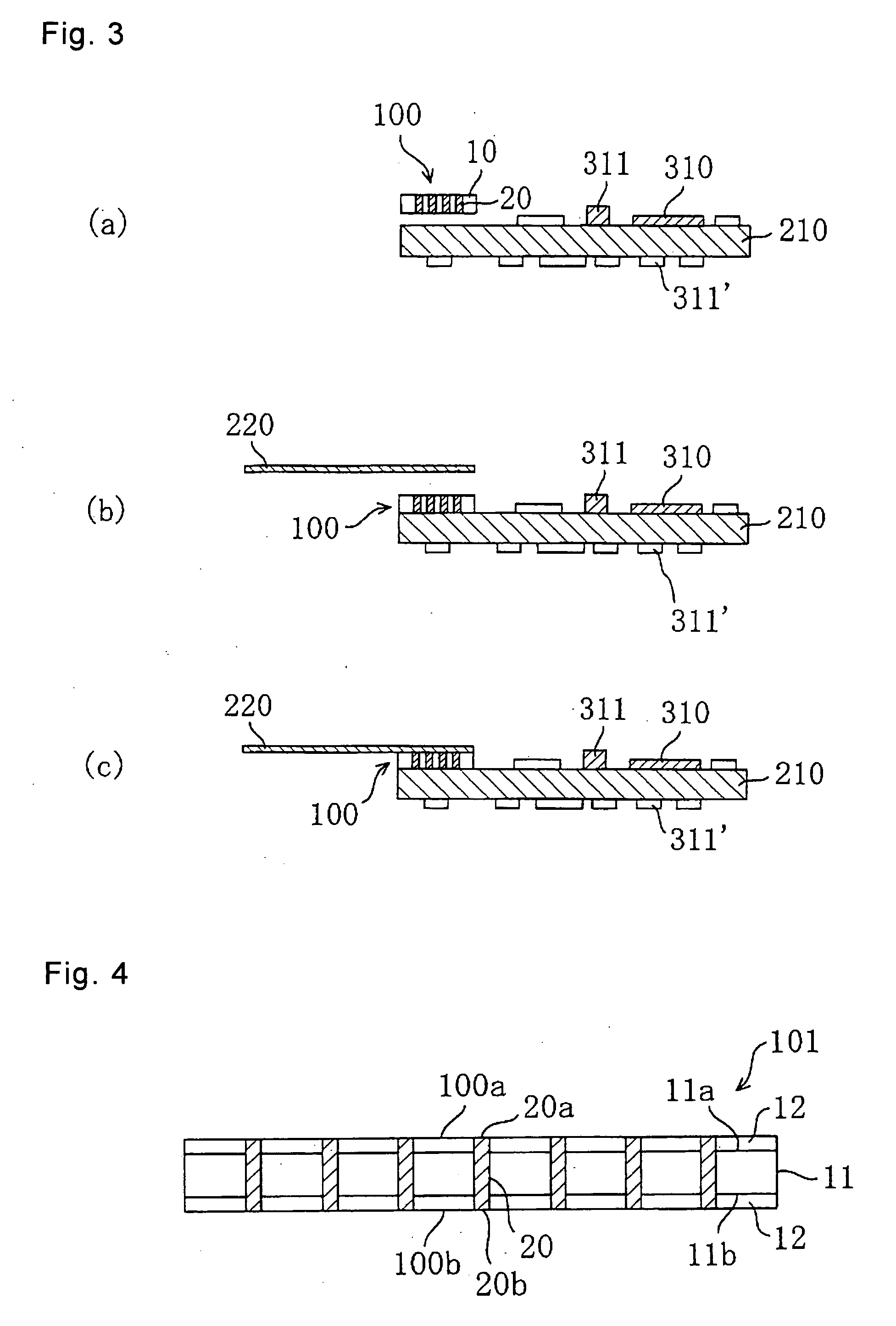

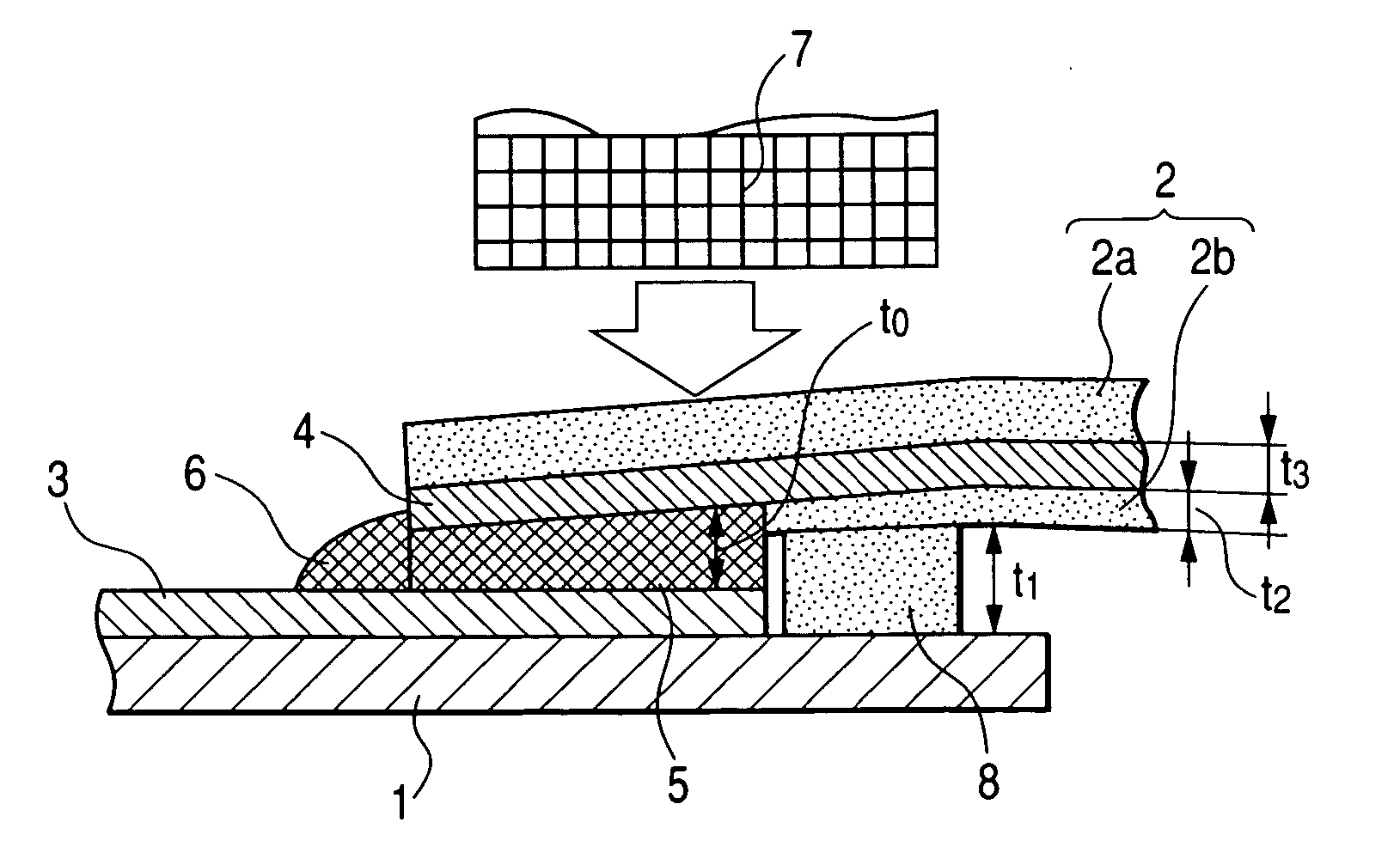

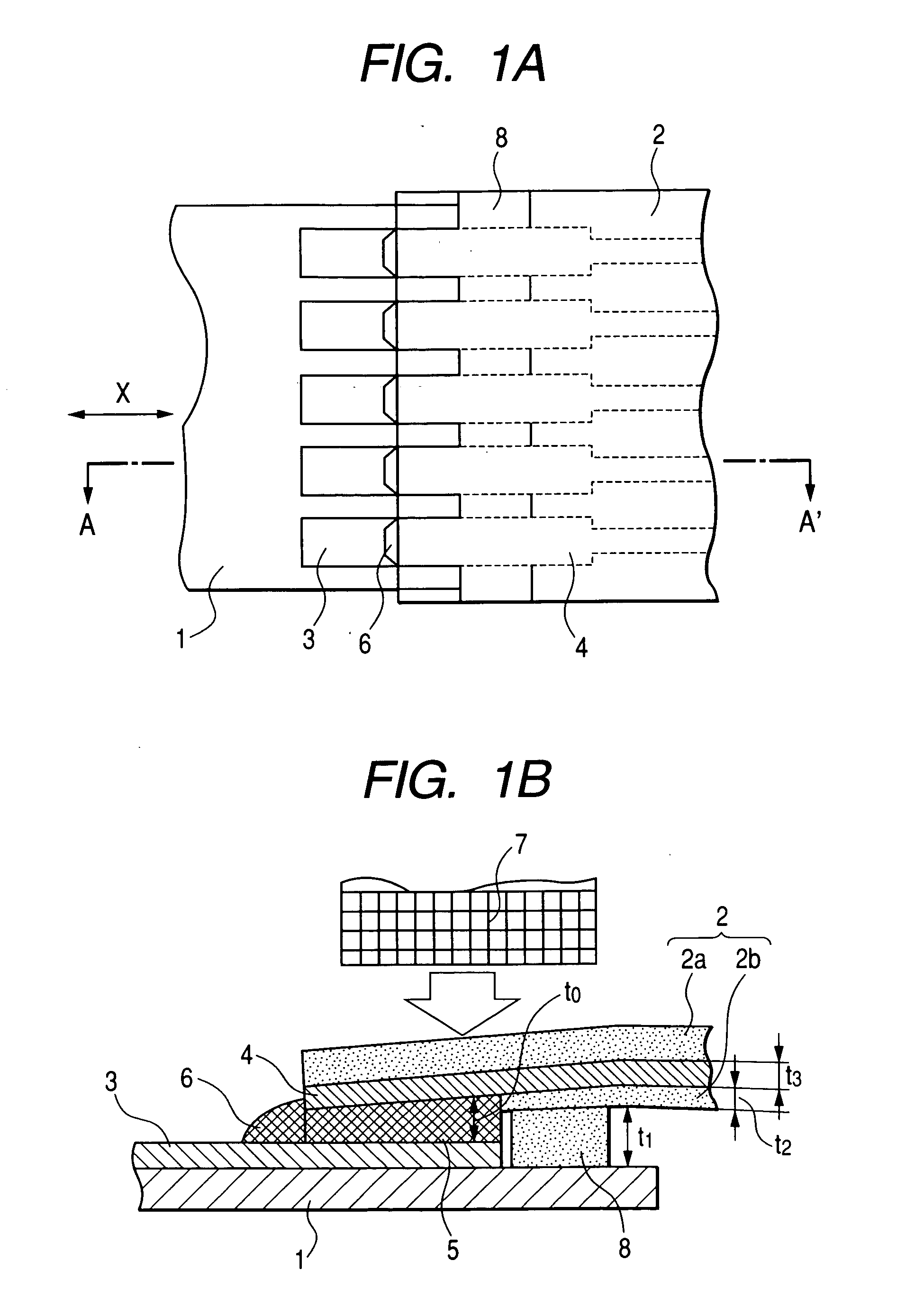

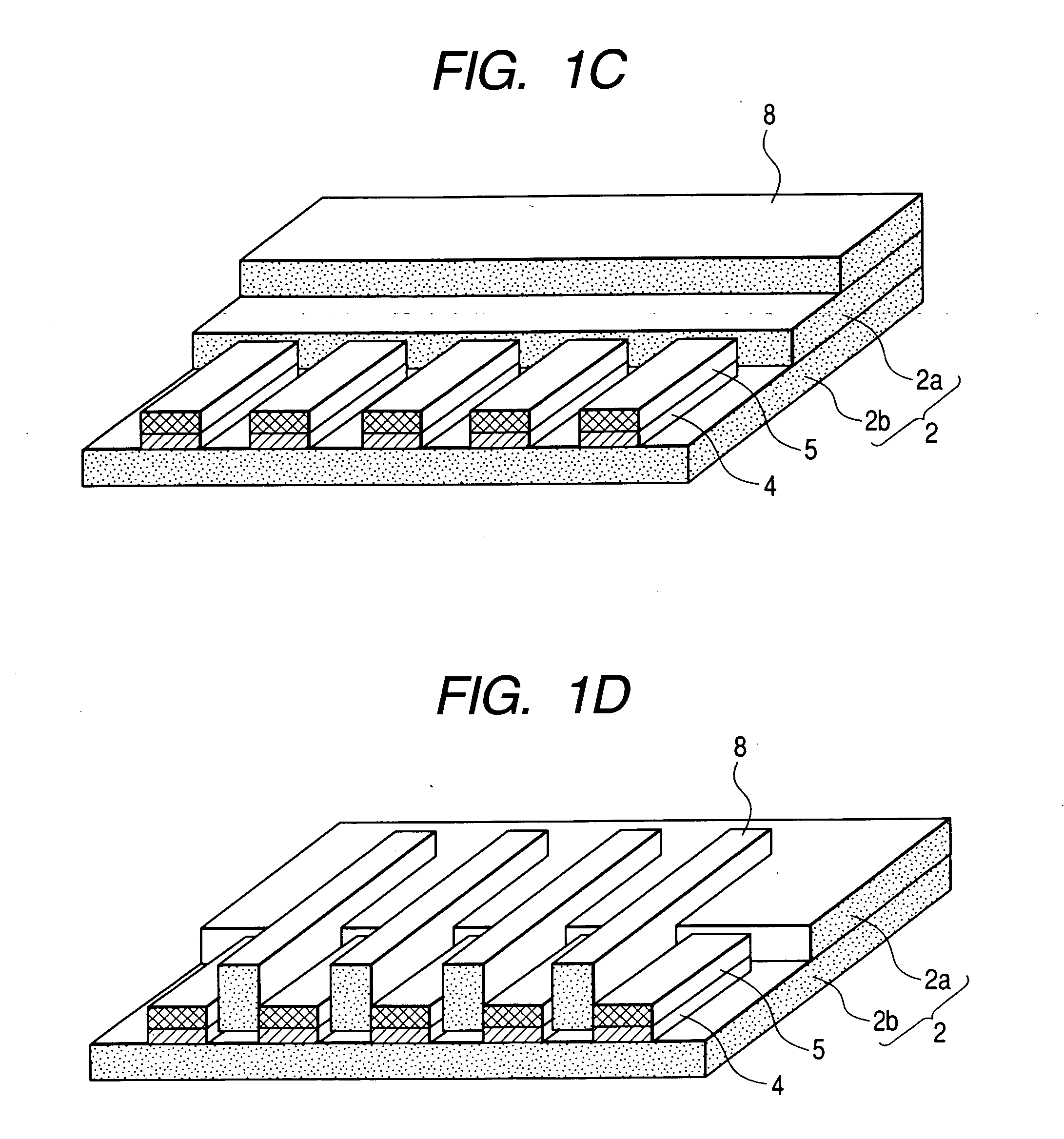

Connector sheet and wiring board, and production processes of the same

InactiveUS20050057906A1Low costHigh wiring densityPrinted circuit assemblingPrinted electric component incorporationEngineeringElectrically conductive

There is provided a connector sheet which includes an insulation sheet substrate having a front surface and a rear surface opposing to the front surface, and electrically conductive members each passing through the sheet substrate along a thickness direction of the sheet substrate, and the front surface and the rear surface contain a thermoset resin, and have tackiness under a first condition and develop adhesiveness under a second condition which is different from the first condition.

Owner:PANASONIC CORP

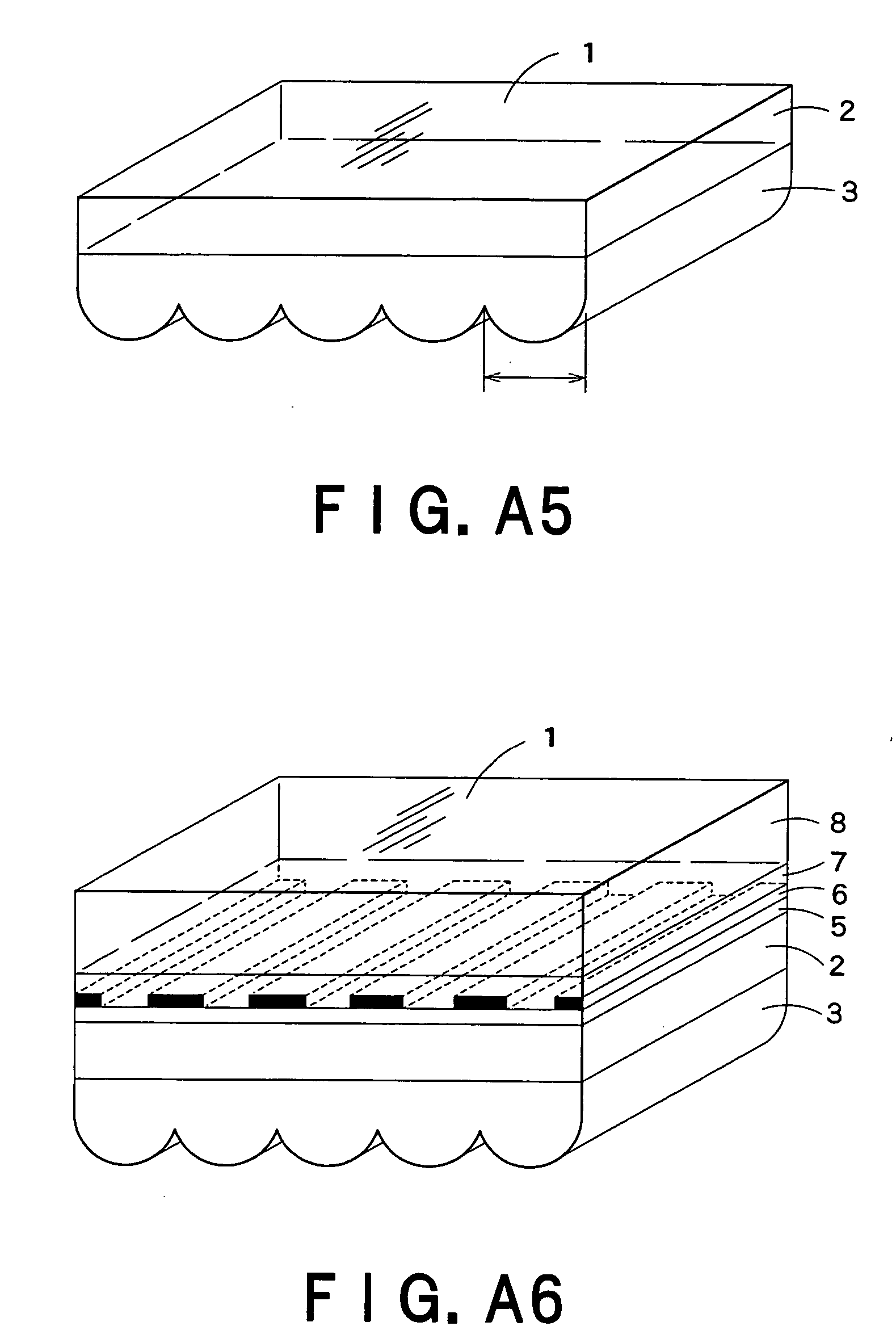

High pressure delivery system

This relates to an improved delivery system for accurately loading and controlling the delivery of flowable material to a patient. Particularly, the system may be used in the injection of hard tissue implant materials such as PMMA under pressures up to about 4000 psi. The system includes an applicator with a first column having an implant material introduction section adapted to provide for effective loading of the implant material and a second column housing a piston. The introduction section has a larger size than that of a vessel section or bore in which the requisite pressure seal between the piston and bore wall is formed. The first column may include an introduction section flared open to an included larger funnel-like opening or a separate funnel may be used that interfaces with the introduction section to facilitate the introduction of implant material. Handles on the first and second columns to be turned relative to each other to advance the columns toward each other may be provided for manual actuation of the applicator to drive implant material through a cannula and deliver implant material to a desired site.

Owner:NEUROTHERM

Semiconductor device, lead-frame product used for the same and method for manufacturing the same

InactiveUS20080067649A1Easy to manufactureLow costSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorLead frame

A semiconductor device includes a semiconductor element; a group of back-inner terminals coupled with the semiconductor element through bonding wires and arranged in an area array shape so as to be exposed inside of the bottom; a group of back-outer terminals arranged outside the group of back-inner terminals; a group of front-outer terminals located immediately above the back-outer terminals to be exposed from the front surface, which are electrically coupled with the back-outer terminals located immediately therebelow through coupling conductors, respectively; and a sealing resin which seals the semiconductor element and bonding wires and non-exposed portions of said back-inner terminals, back-outer terminals and front-outer terminals. On at least the respective terminal faces of said back-inner terminals, back-outer terminals and front-outer terminals, noble-metal plated layers are formed.

Owner:MITSUI HIGH TEC INC

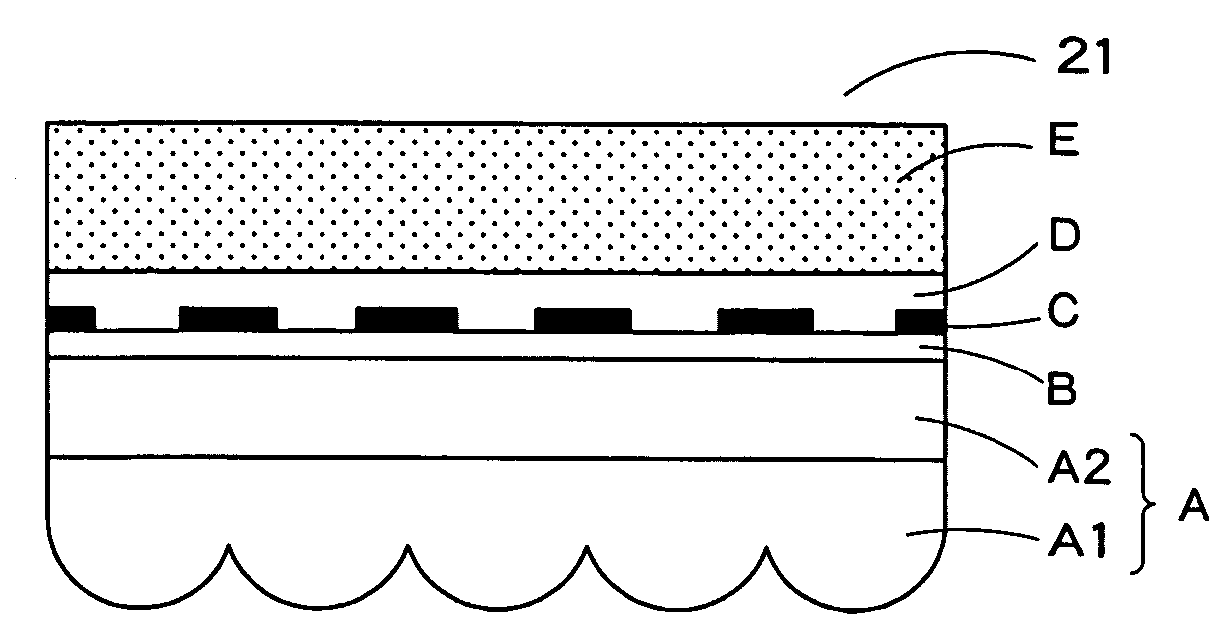

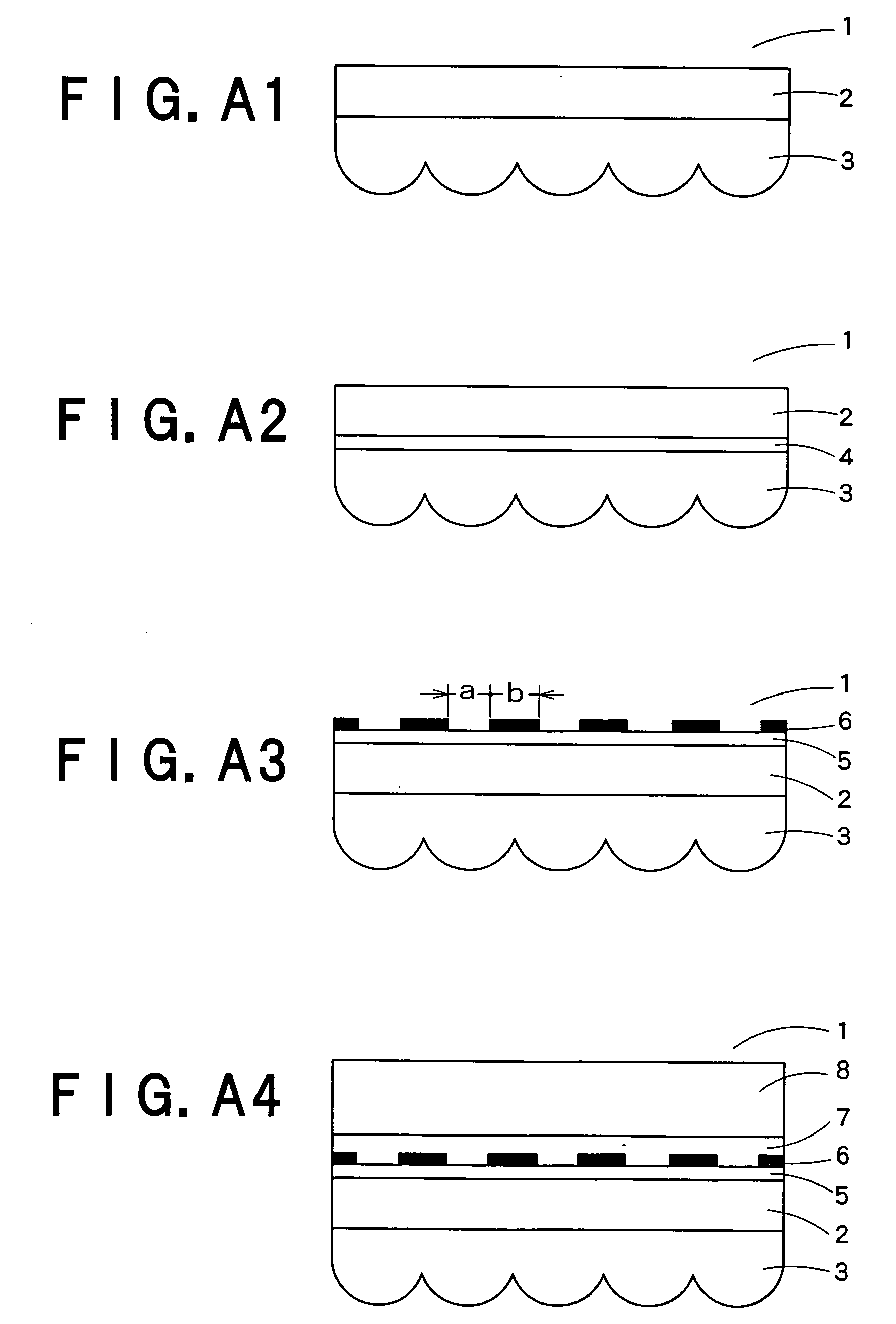

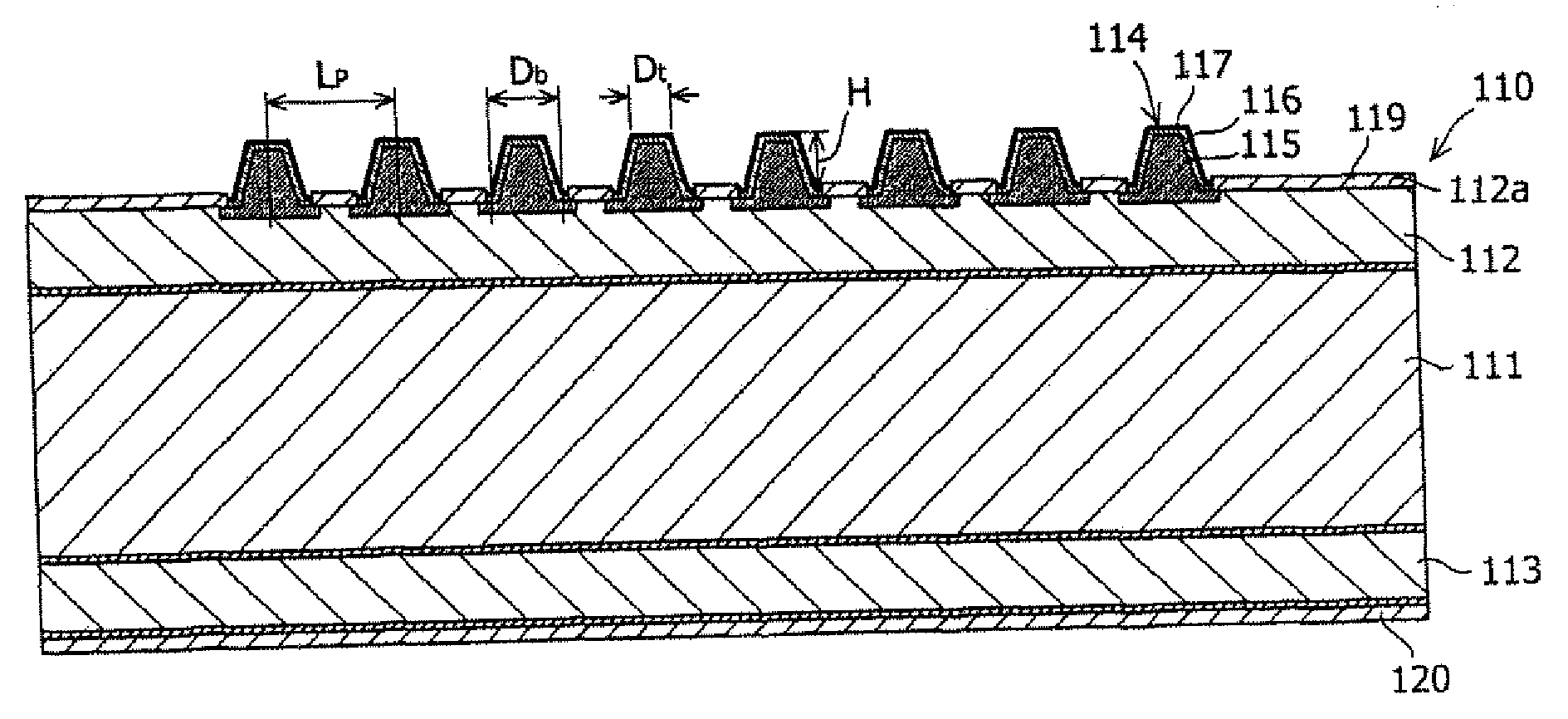

Optical sheet and process for producing the same

InactiveUS20050052737A1Low costFine pitchDiffusing elementsDuplicating/marking methodsCylindrical lensOptics

Disclosed are a fine-pitch and lightweight optical sheet and a production process which can produce the optical sheet very easily at low cost. The optical sheet comprises an optical function layer formed of a thermoplastic resin. The optical function layer has been formed by shaping the surface of the thermoplastic resin into cylindrical lenses, and the pitch of the shaped cylindrical lenses is not more than 150 μm.

Owner:DAI NIPPON PRINTING CO LTD

Composite contact for fine pitch electrical interconnect assembly

InactiveUS8044502B2High dielectric constantImprove electrical performanceSemiconductor/solid-state device detailsCoupling device detailsCouplingFine pitch

An electrical interconnect assembly for electrically interconnecting terminals on a first circuit member with terminals on a second circuit member. The electrical interconnect includes a housing having a plurality of through openings extending between a first surface and a second surface. A plurality of composite contacts are positioned in a plurality of the through openings. The composite contacts include a conductive member having a central portion and at least first and second interface portions. One or more polymeric layers extend along at least the central portion conductive member. One or more coupling features on the composite contacts engage with the housing. At least one engagement feature formed in the polymeric layers proximate the first interface portion mechanically couples with the terminals on the first circuit member.

Owner:R&D SOCKETS INC

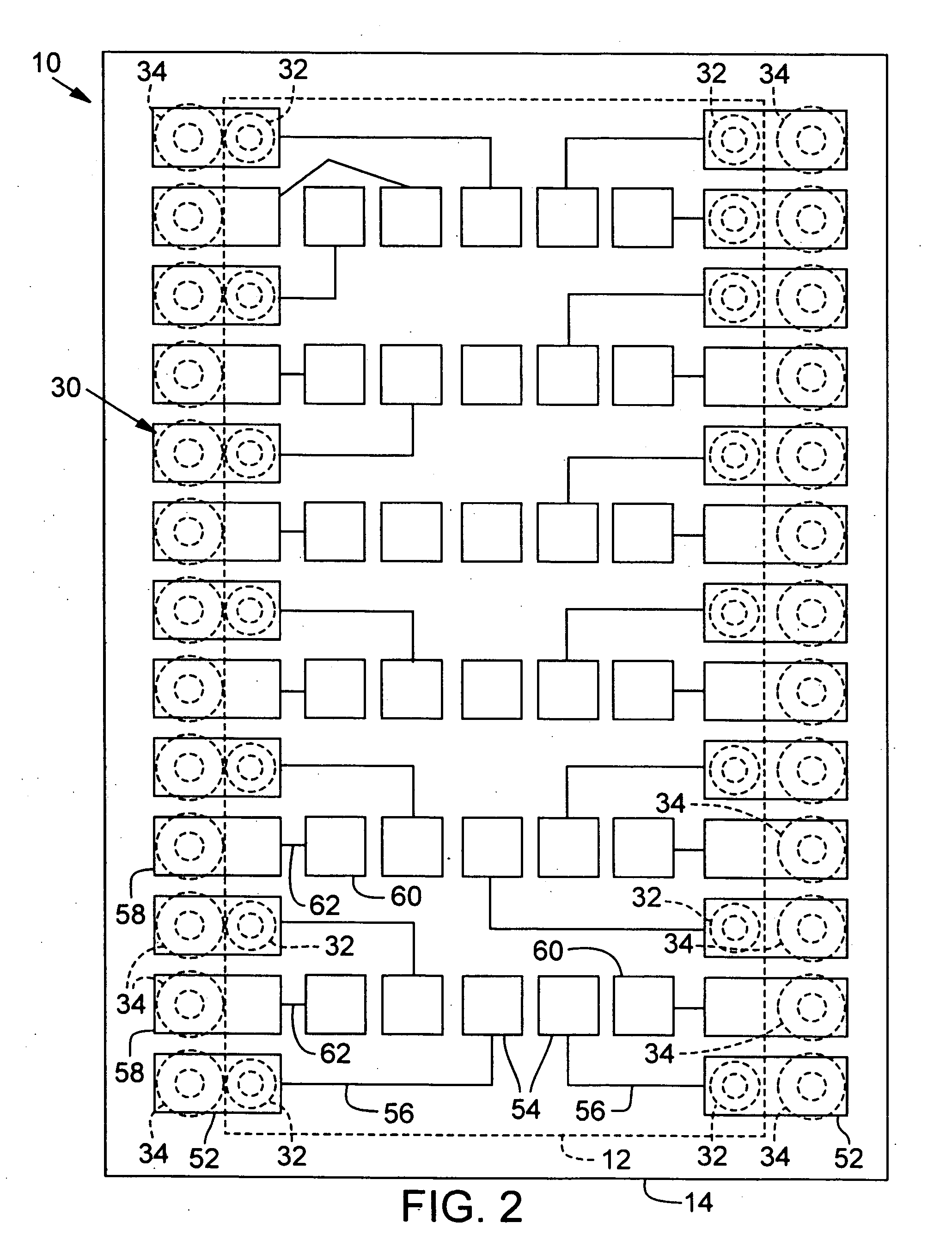

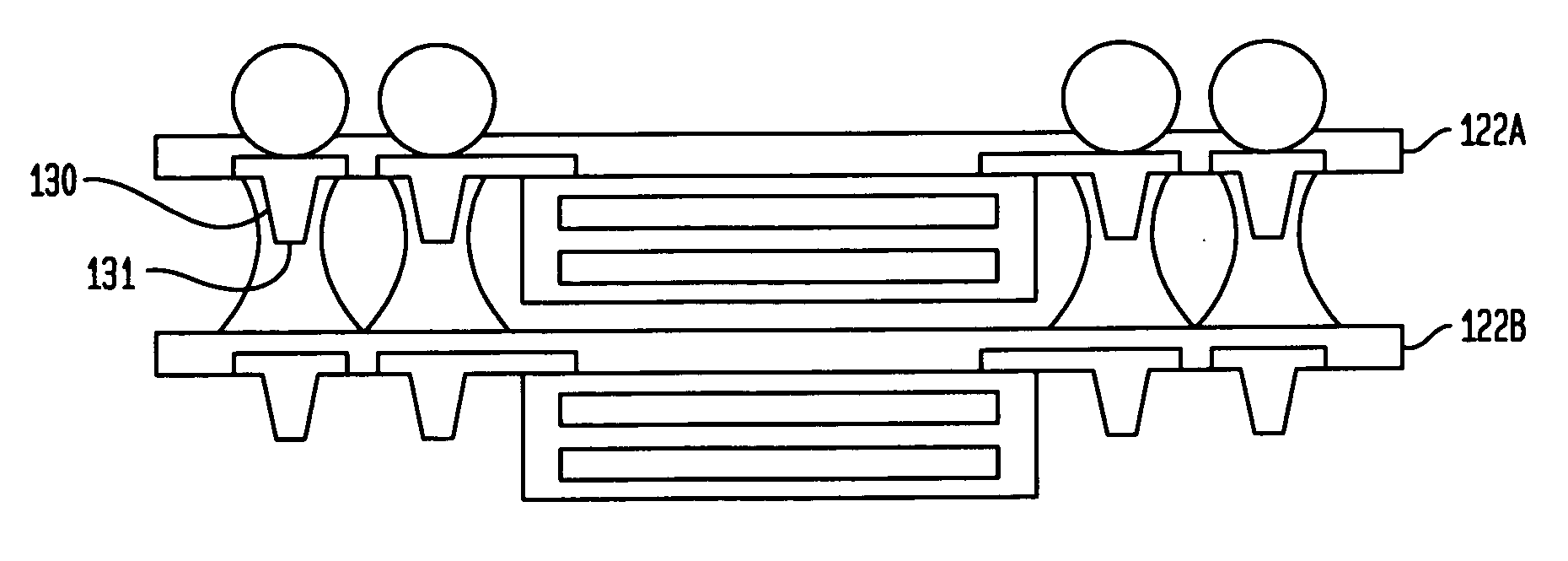

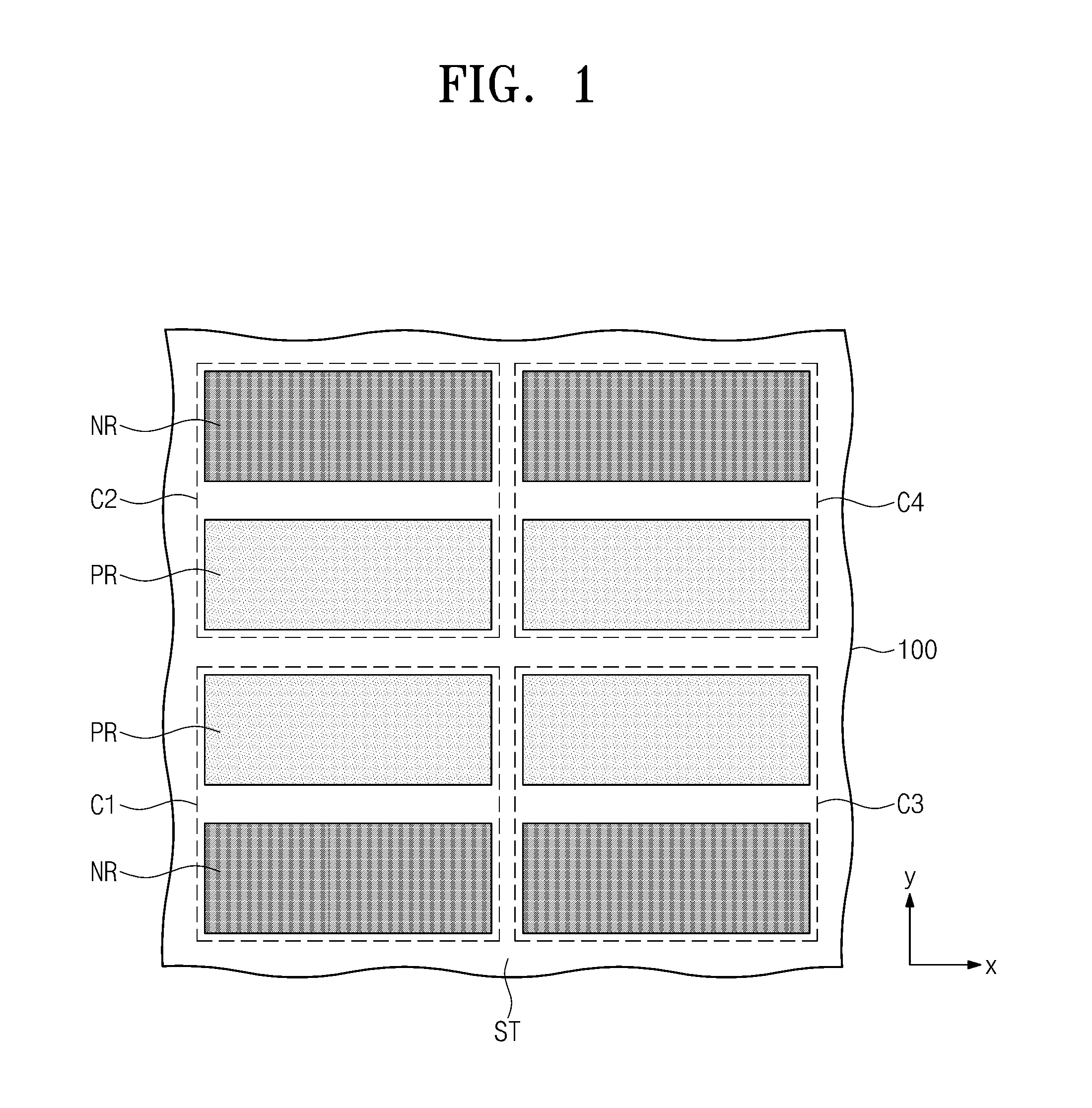

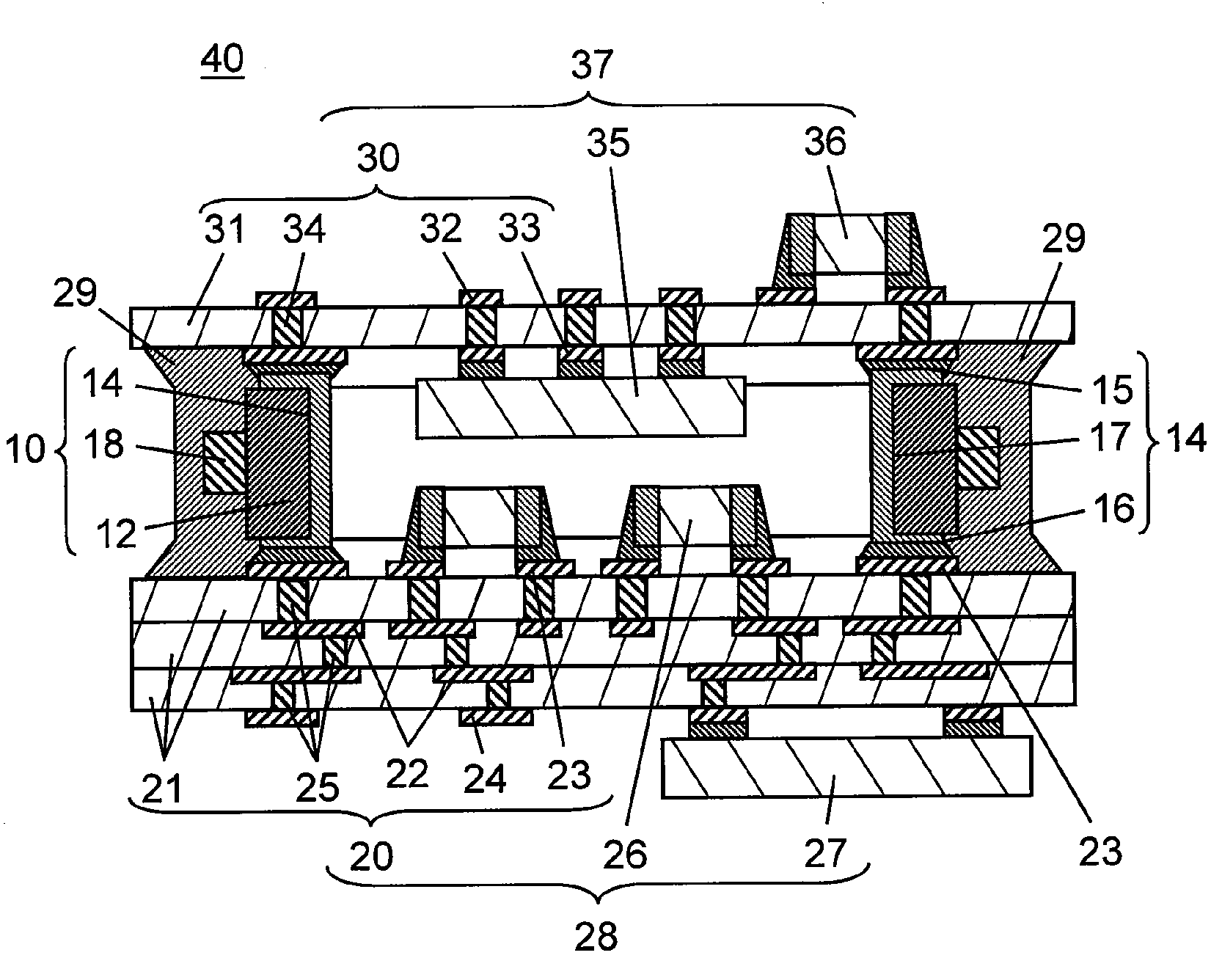

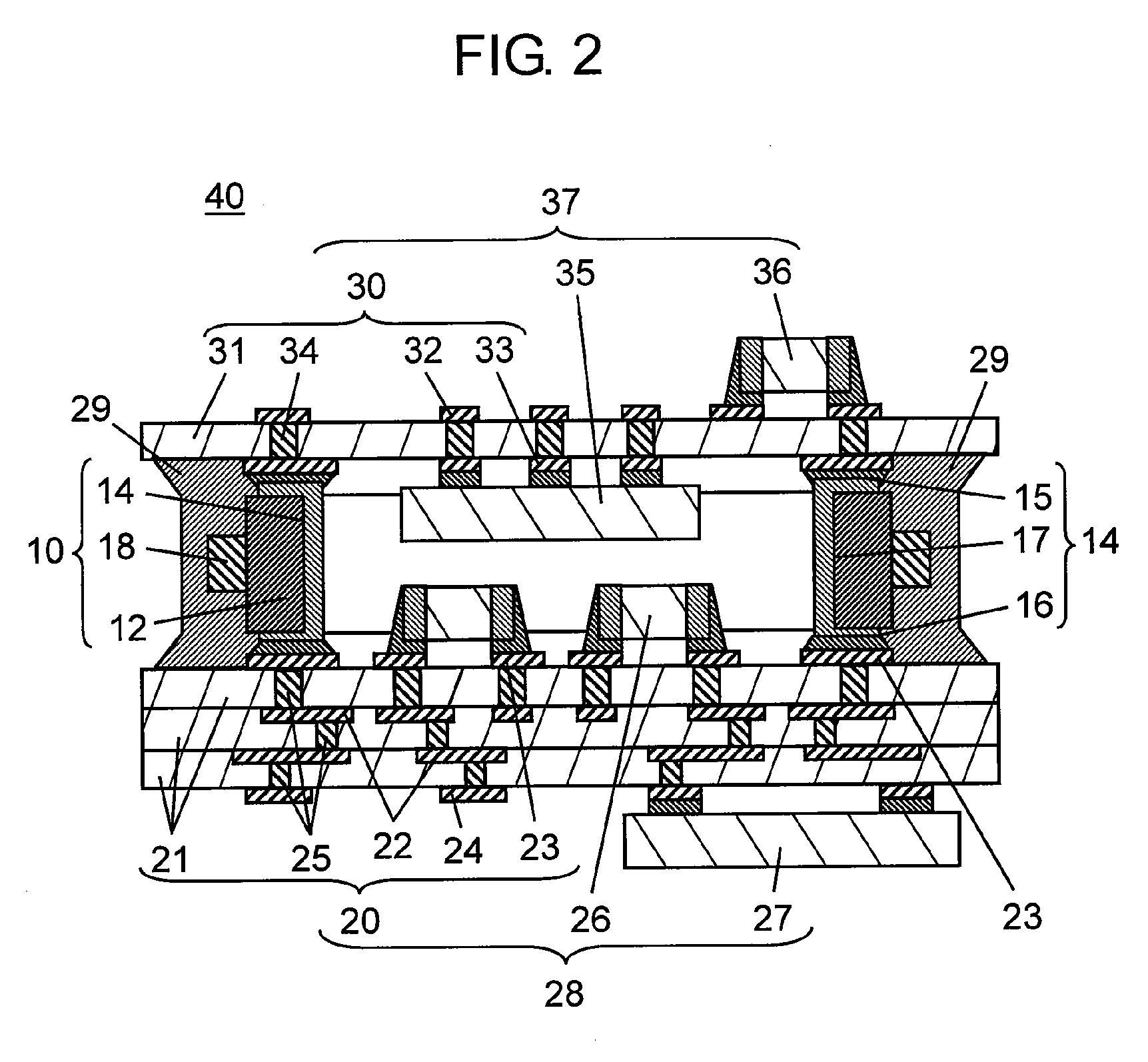

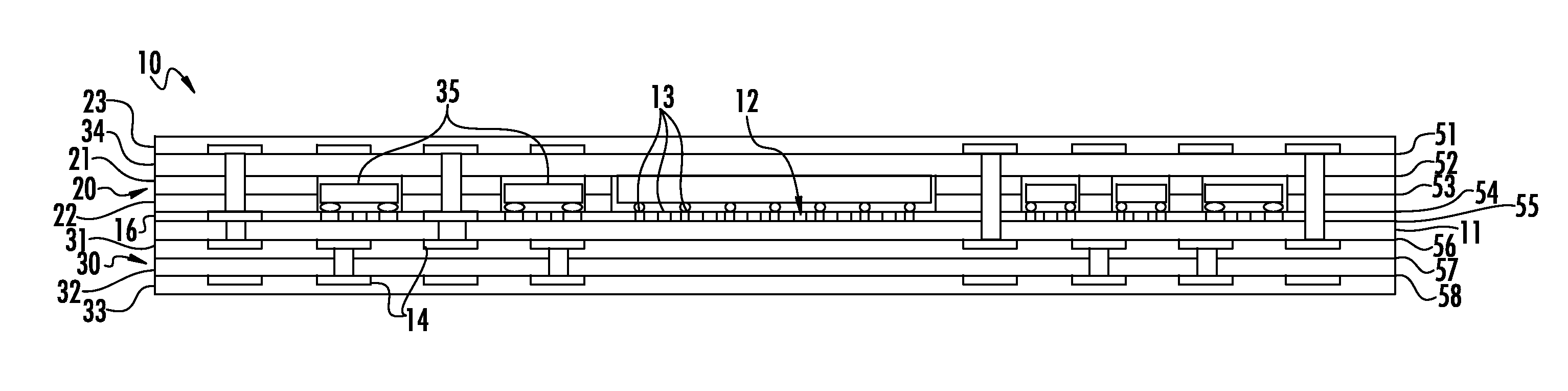

Microelectronic assemblies having very fine pitch stacking

ActiveUS20070148819A1Easy to testAvoid the needSemiconductor/solid-state device detailsSolid-state devicesSolder ballEngineering

A microelectronic assembly includes two or more microelectronic packages stacked at a fine pitch, which is finer than the pitch that is possible when using solder balls for making the joint. Each stackable package desirably includes a substrate having pins projecting from one surface of the substrate and solder balls projecting from the other surface of the substrate. Each stackable package may have one or more die attached to one or more of the surfaces of the substrate. In certain embodiments, die may be attached to both surfaces of the substrate. The dies may be electrically interconnected with the substrate using wire bonds, flip chip bonding, leads and / or stud bumping. The die may be encapsulated in an encapsulated material, under-filled or glob topped. In certain preferred embodiments, the combination of the conductive post height and ball height is equal to or greater than the height of the encapsulated or molded chip structure. The combination of the conductive post height and the ball height must be at least equal to the height of the encapsulated chip structure so that the conductive elements are able to span the gap between layers of the assembly. After the tips of the conductive pads are in contact with the solder masses, the solder masses are reflowed to form a permanent electrical interconnection between the stacked microelectronic packages. During reflow, the reflowed solder will wick up around the conductive posts to form elongated solder columns. In addition, when the solder is reflowed, surface tension pulls the opposing layers of the assembly toward one another and provides a self-centering action for the conductive posts.

Owner:TESSERA INC

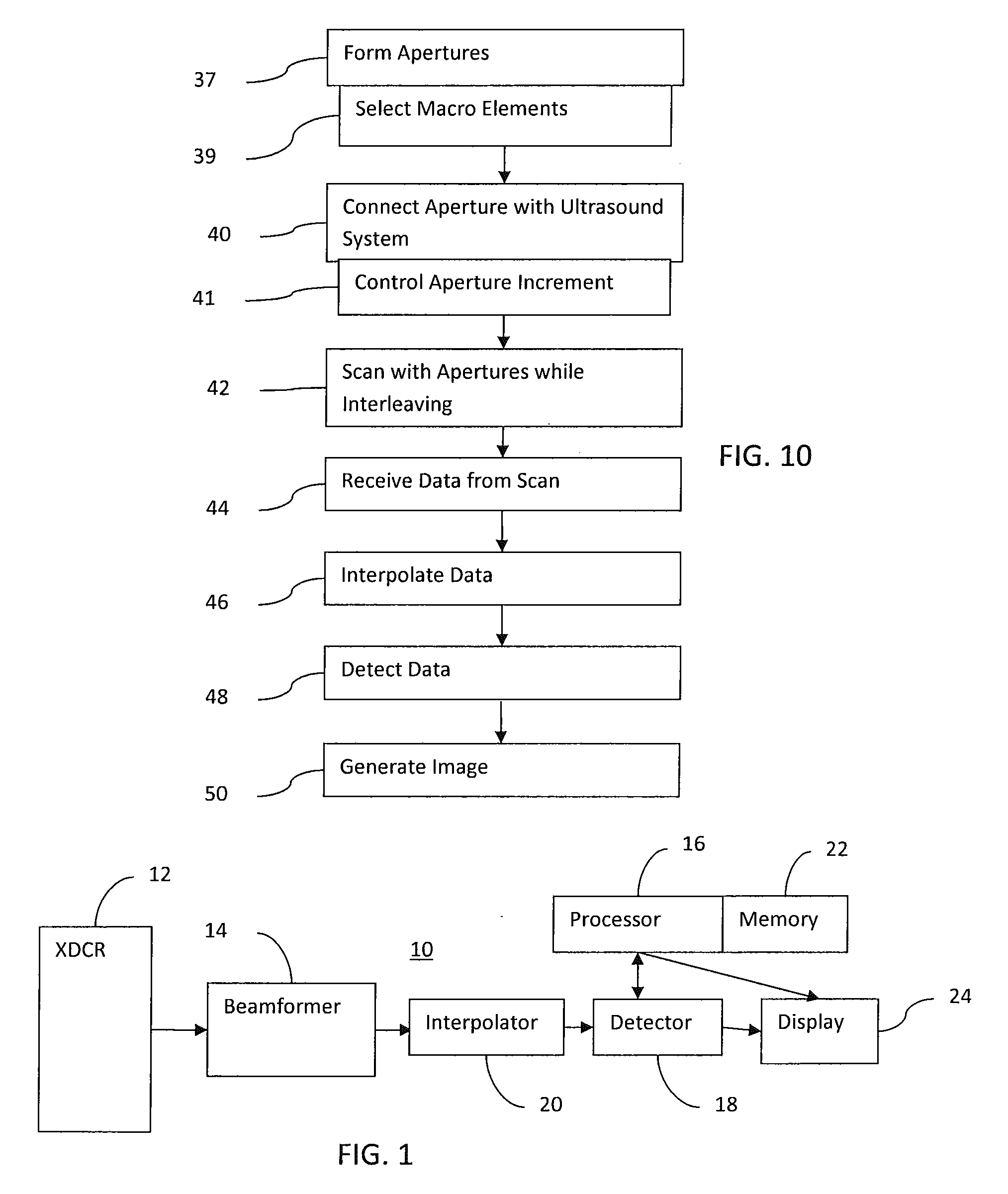

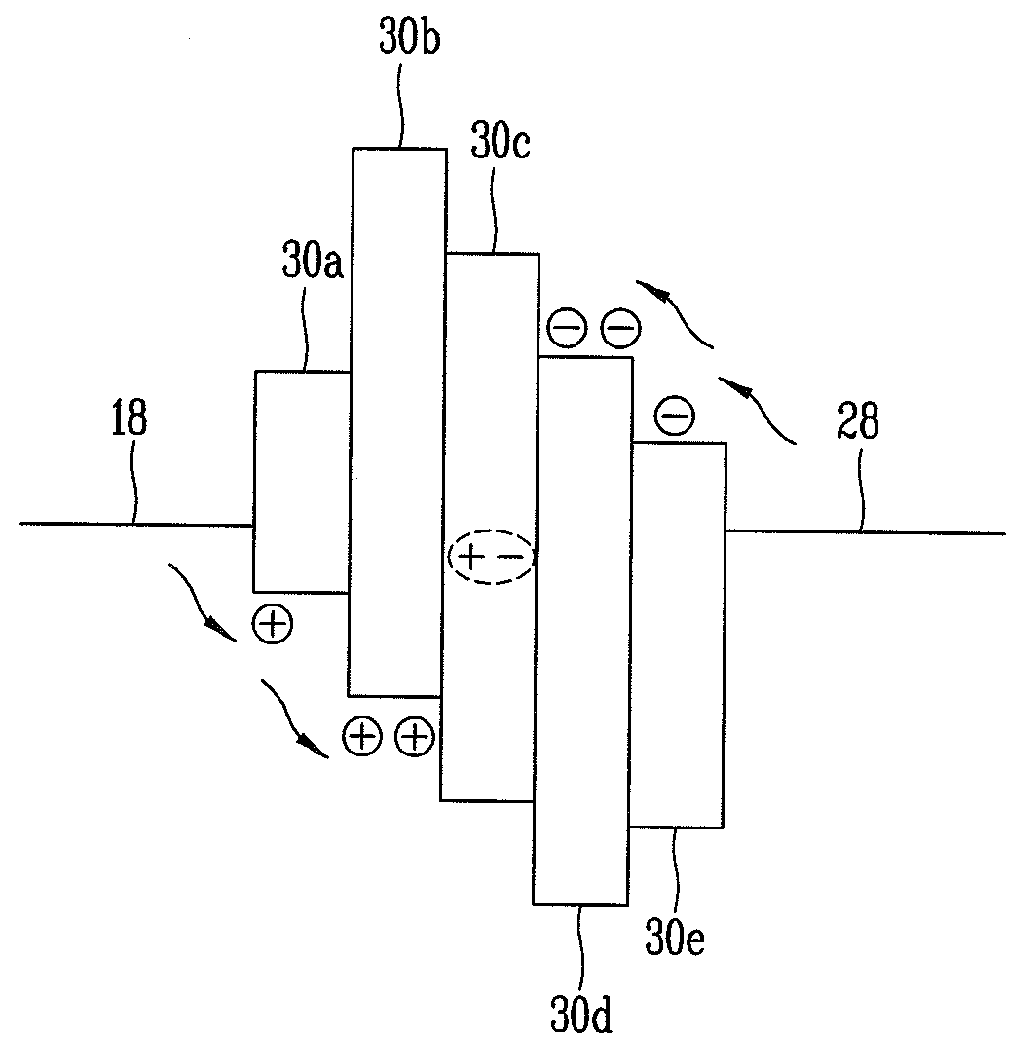

Redistribution Layer in an Ultrasound Diagnostic Imaging Transducer

ActiveUS20110021923A1Good energyReduce peakMaterial analysis using sonic/ultrasonic/infrasonic wavesInfrasonic diagnosticsUltrasound imagingRedistribution layer

Medical diagnostic ultrasound imaging is performed with a multi-dimensional transducer array and an imaging system for planar scanning. The elements of the array may be distributed on a periodic grid with aperiodic shifts in position. When a one-dimensional array is formed on the array, the aperiodic shifts better distribute acoustic energies, reducing peaks in side lobes. Using a layered structure of switches underneath the acoustic elements, side lobes may be further reduced. The switches are used for interconnecting elements to form macro elements of the one-dimensional aperture on the multi-dimensional array. The switches are distributed on a grid corresponding to the desired imaging frequency. The acoustic elements are distributed with a finer pitch. The finer pitch allows formation of the macro elements for the one-dimensional aperture where the edges of the macro elements have fewer or no periodic patterns.

Owner:SIEMENS MEDICAL SOLUTIONS USA INC

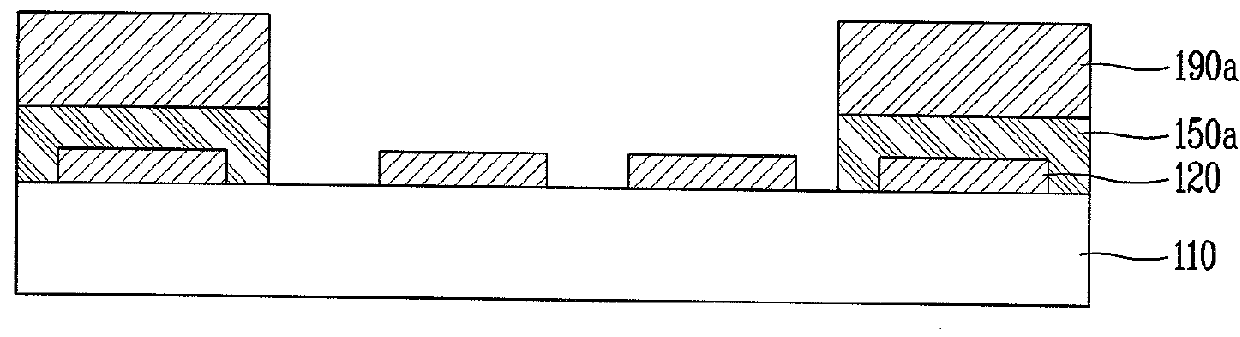

Semiconductor package substrate

ActiveUS7705456B2High bonding strengthImprove the layout densitySemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipSemiconductor package

Owner:PHOENIX PRECISION TECH CORP

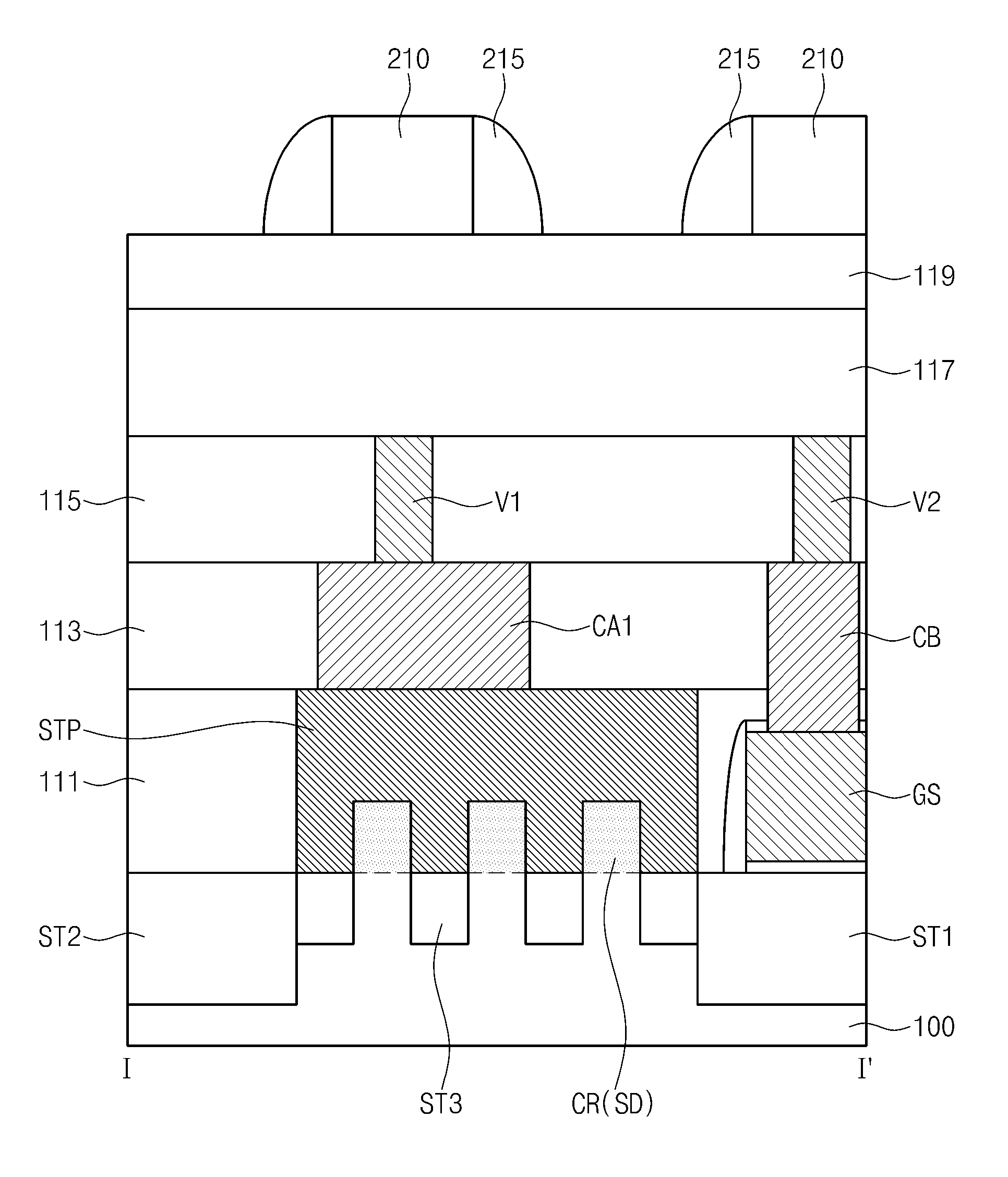

Semiconductor device

ActiveUS20150102413A1Improve integration densityEasy to changeSemiconductor/solid-state device detailsSolid-state devicesDevice materialLogic cell

Provided is a semiconductor device including a substrate with a plurality of logic cells, transistors provided in the plurality of logic cells, contact plugs connected to electrodes of the transistors, first via plugs in contact with top surfaces of the contact plugs, and first wires in contact with top surfaces of the first via plugs. The first wires may include a common conductive line connected to the plurality of logic cells through the contact plugs, and all of the first wires may be shaped like a straight line extending parallel to a specific direction.

Owner:SAMSUNG ELECTRONICS CO LTD

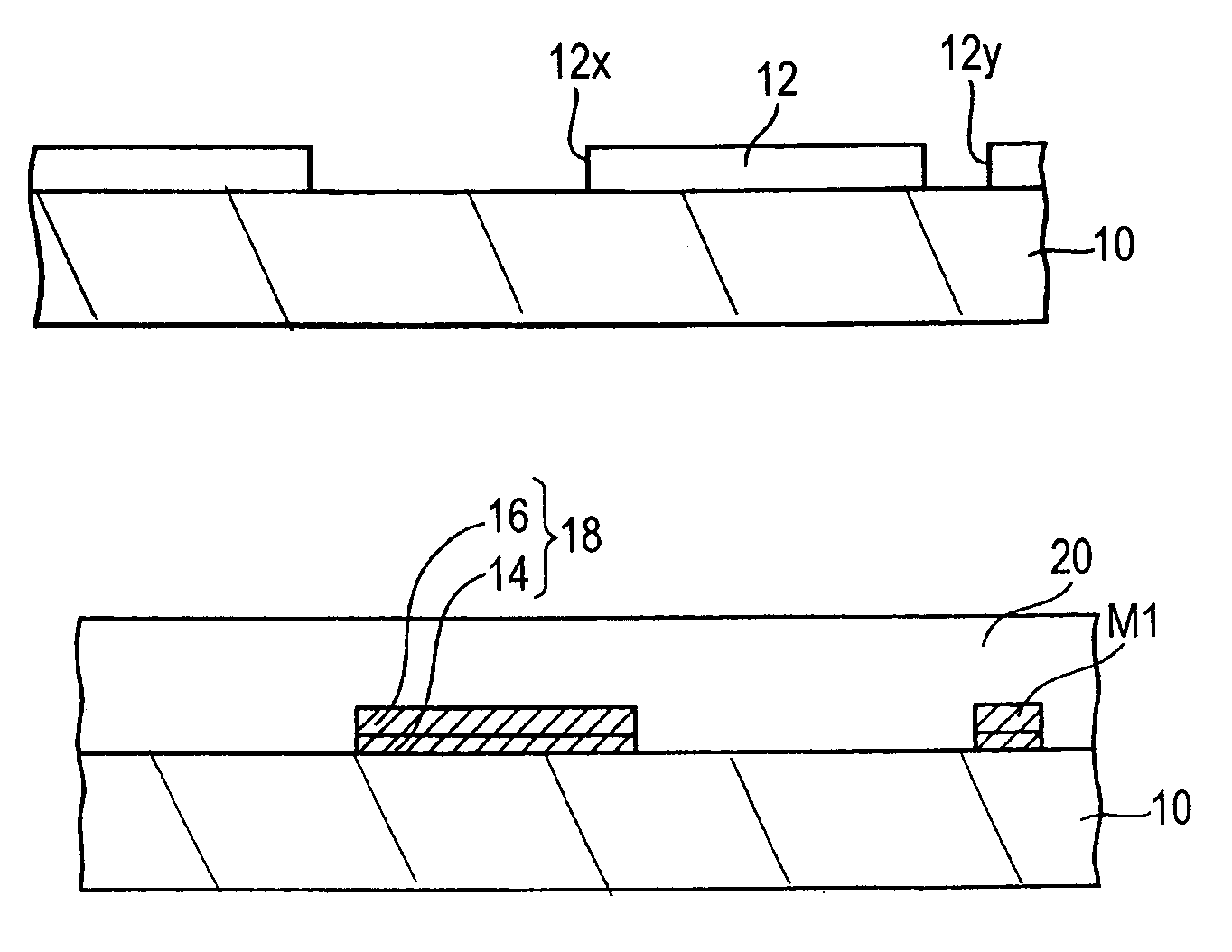

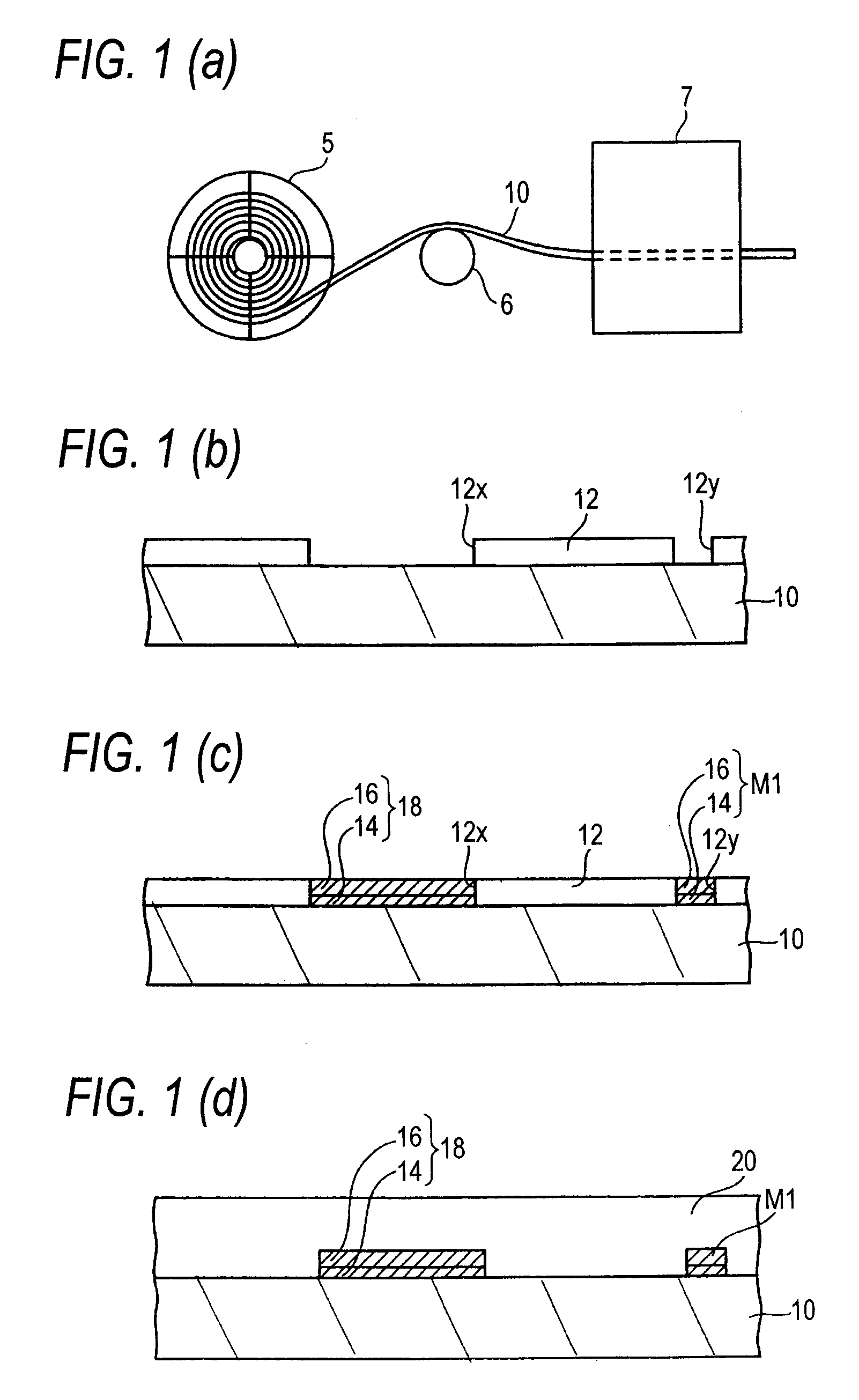

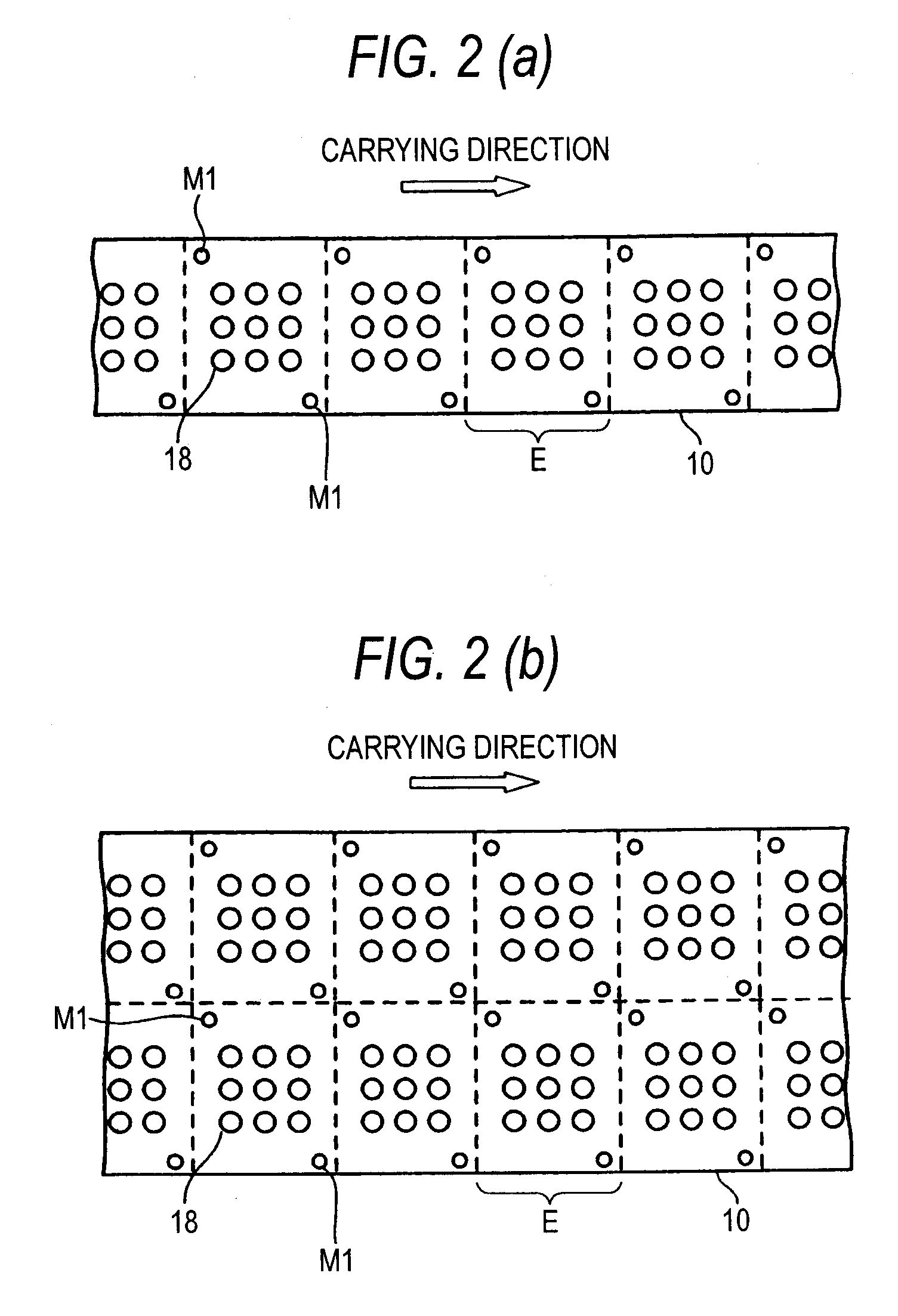

Method of manufacturing flexible circuit substrate

InactiveUS20060223236A1Improve responseIncrease the number ofPaper-money handling devicesSemiconductor/solid-state device detailsFlexible circuitsMetal sheet

Connection pads and alignment marks are formed on a long metal thin plate that is carried in a longitudinal direction, and then an insulating layer for covering the connection pads is formed. Then, via holes, which are aligned and arranged on the connection pads by utilizing the alignment marks, are formed in portions of the insulating layer. Then, n-layered (n is an integer of 1 or more) wiring layers connected to the connection pads via the via holes are formed, and the connection pads and the insulating layer are exposed by removing the metal thin plate.

Owner:SHINKO ELECTRIC IND CO LTD

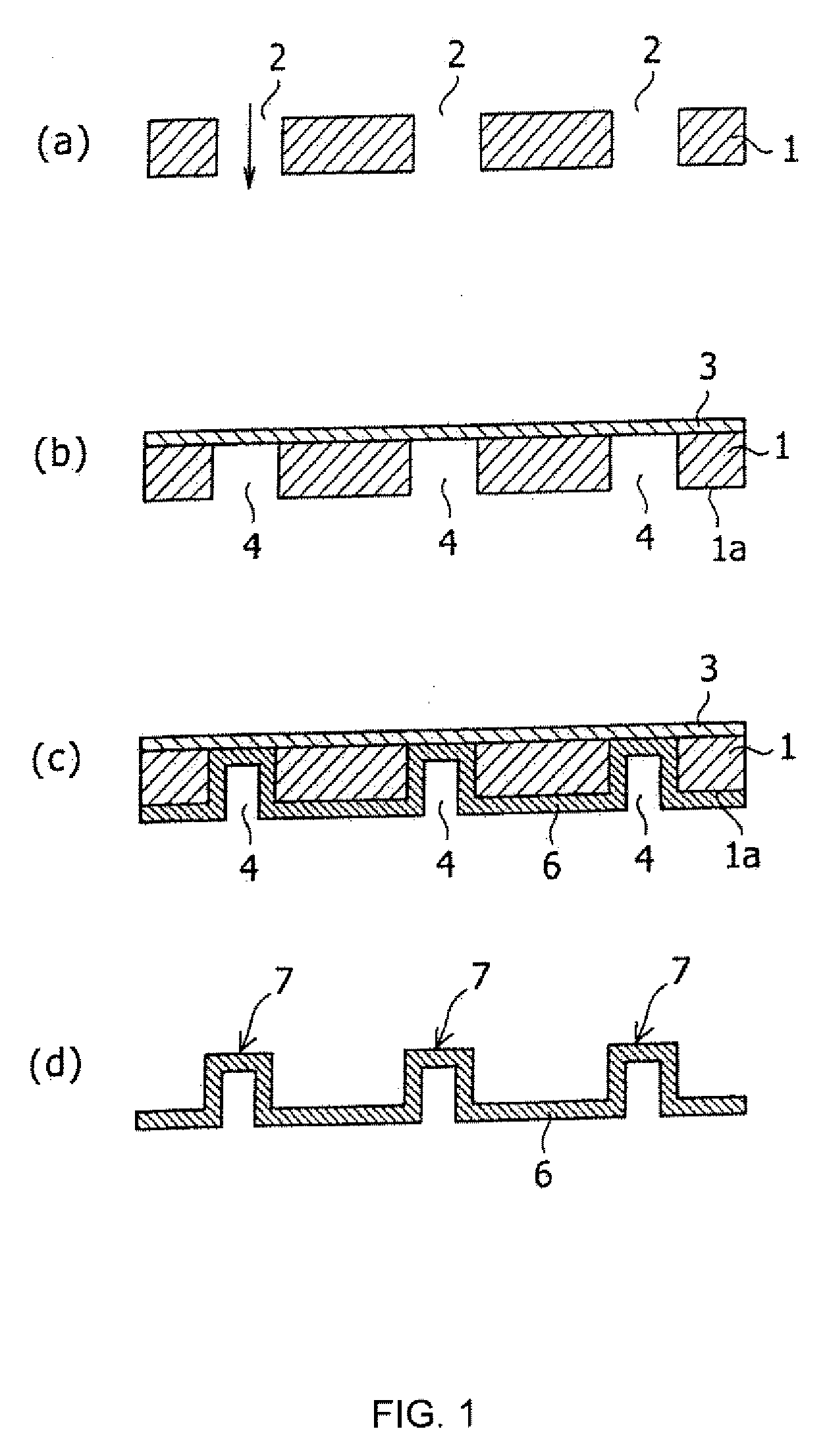

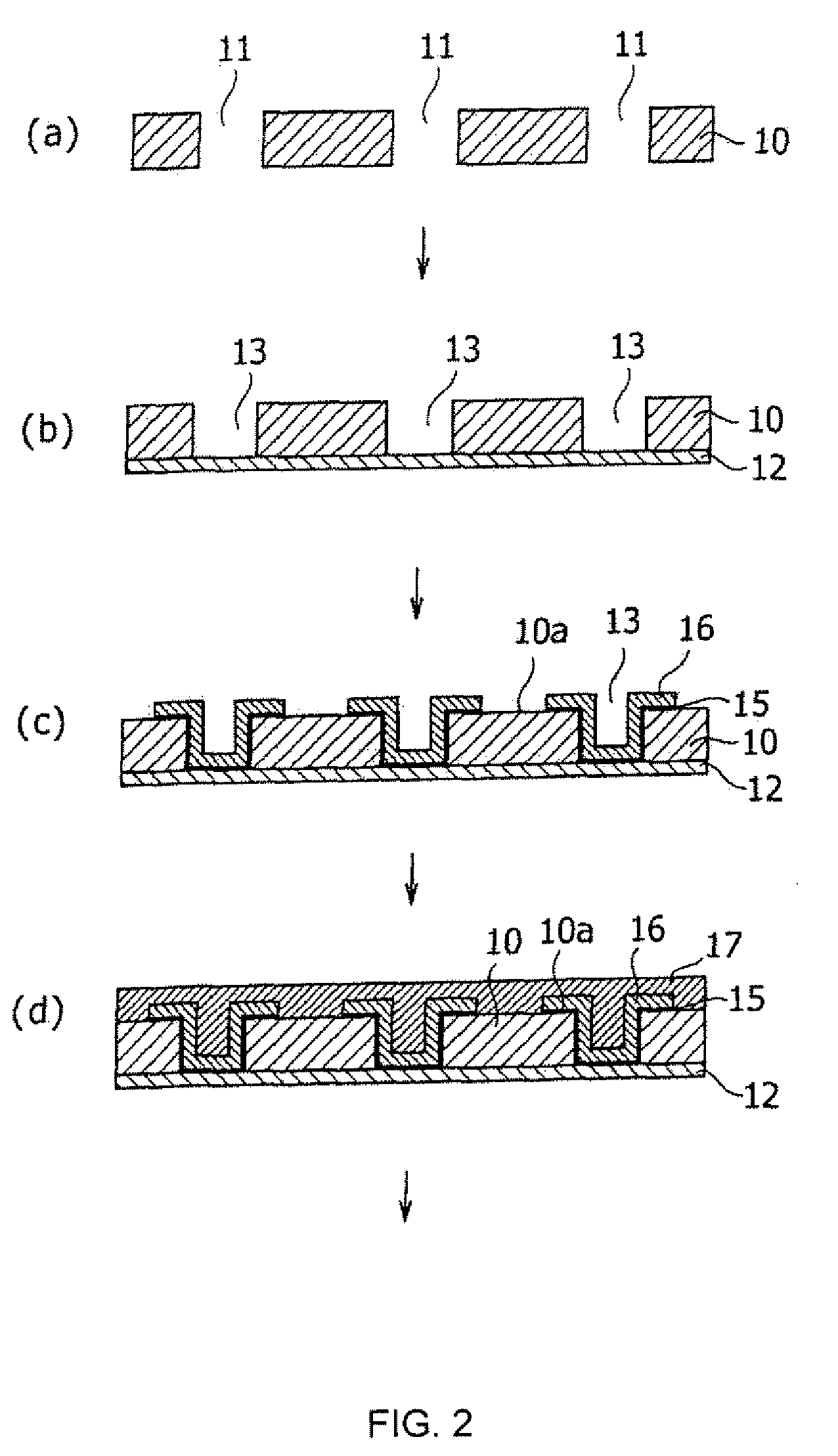

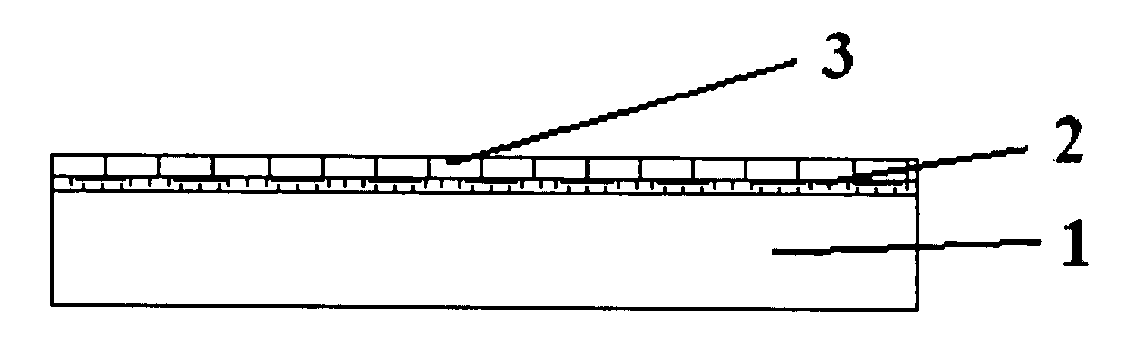

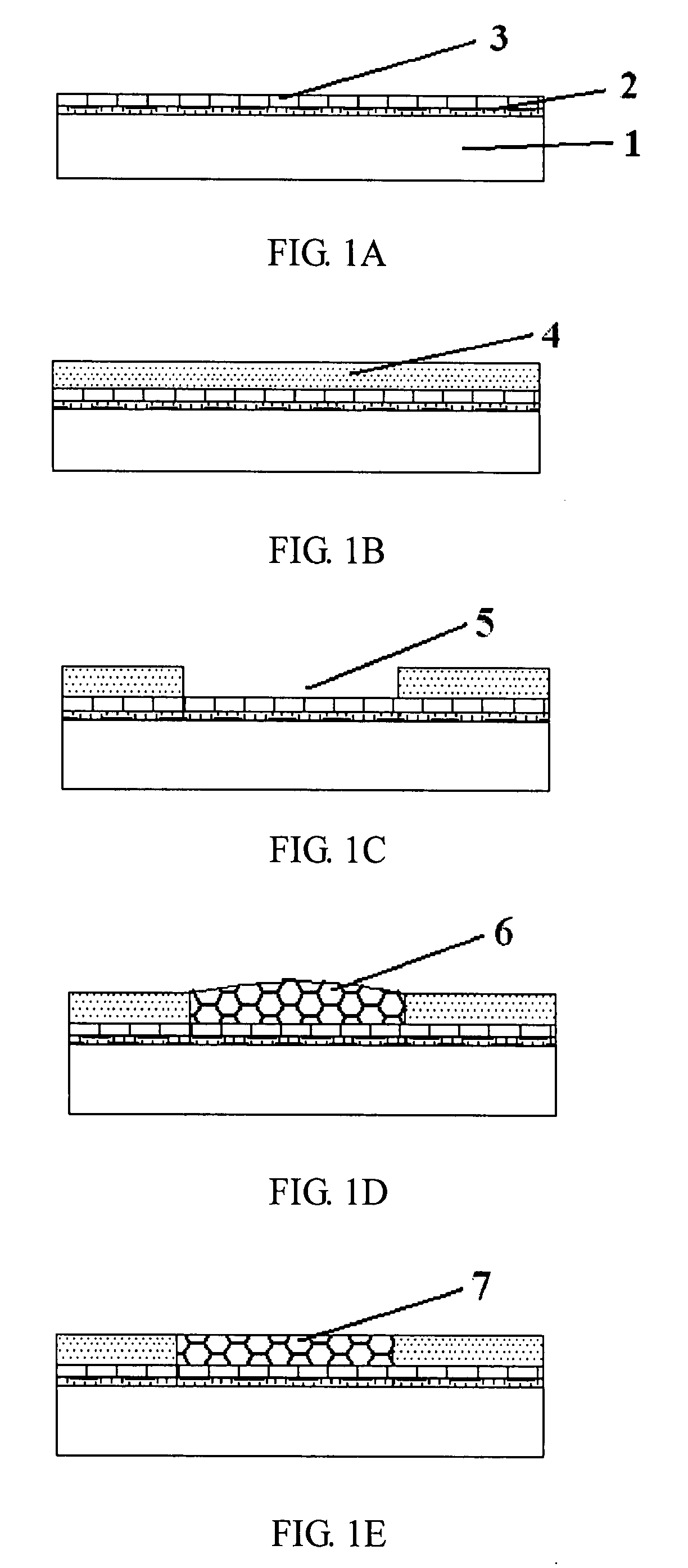

Process for forming a bump structure and bump structure

InactiveUS20090121351A1High aspect ratioFine pitchSemiconductor/solid-state device detailsPrinted circuit aspectsEngineeringInterconnection

A method for forming a bump structure and a bump structure for conductive interconnection with another element having at least one of microelectronic devices or wiring thereon, used as an electric connection in an electronic circuit, includes the steps of forming a mandrel by steps including forming at least one opening extending through a bump-forming die body in the thickness direction thereof and positioning a bump-forming die lid on a surface of the bump-forming die body so as to cover one end of the opening and to thereby define a bump-forming recess. The bump-forming die body may be comprised of a metal sheet. A metal layer is formed at least on an inner surface of the bump-forming die lid exposed within the bump-forming recess. The mandrel is removed so as to expose the metal layer and form a bump structure.

Owner:INVENSAS CORP

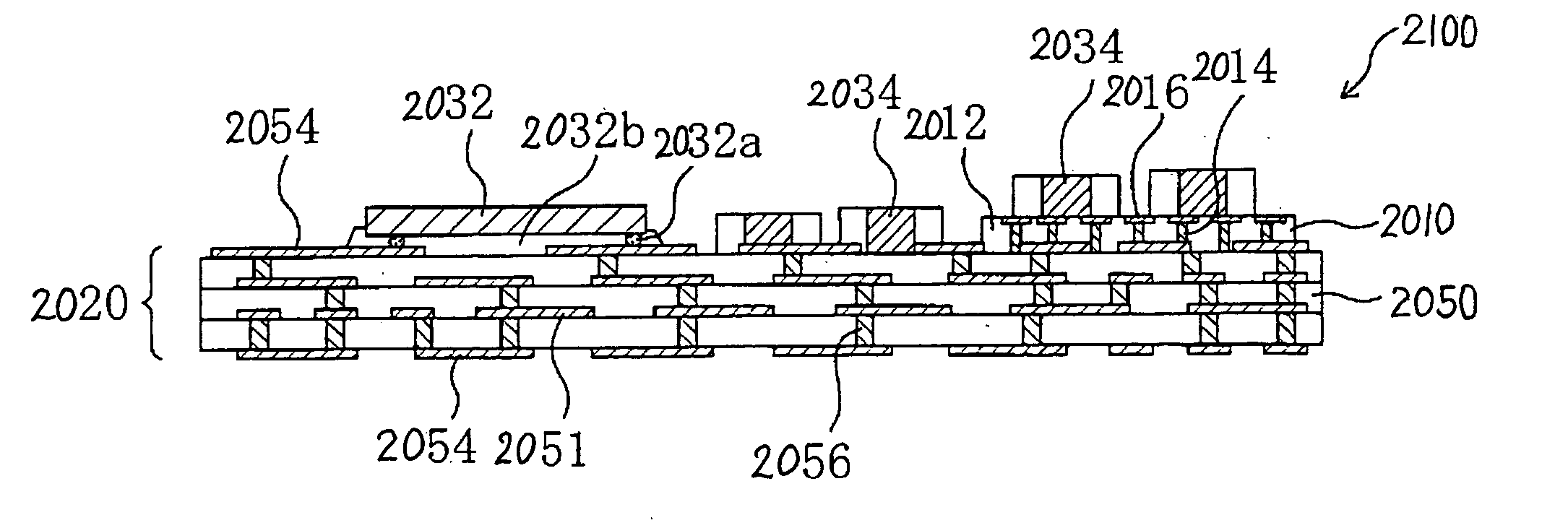

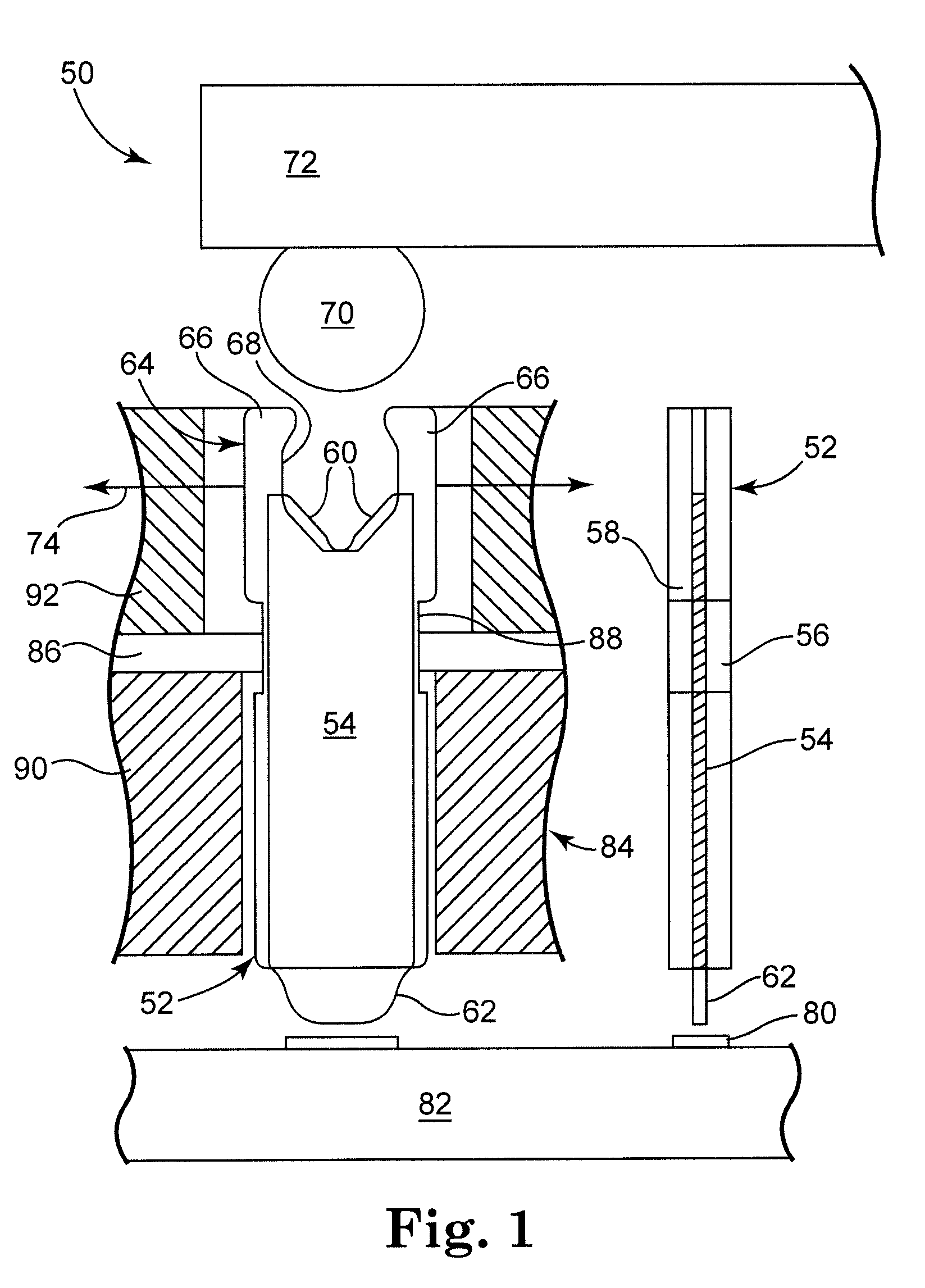

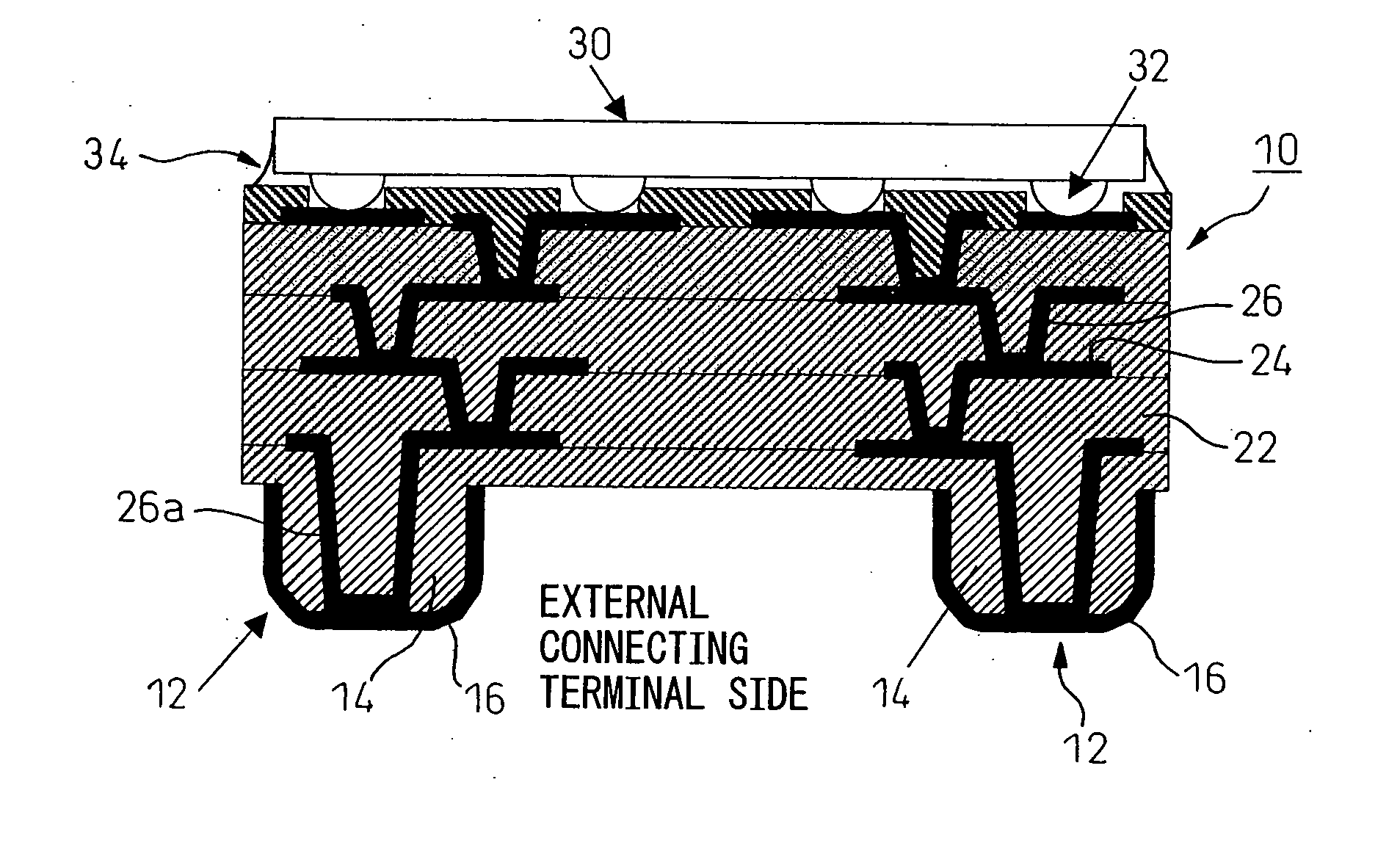

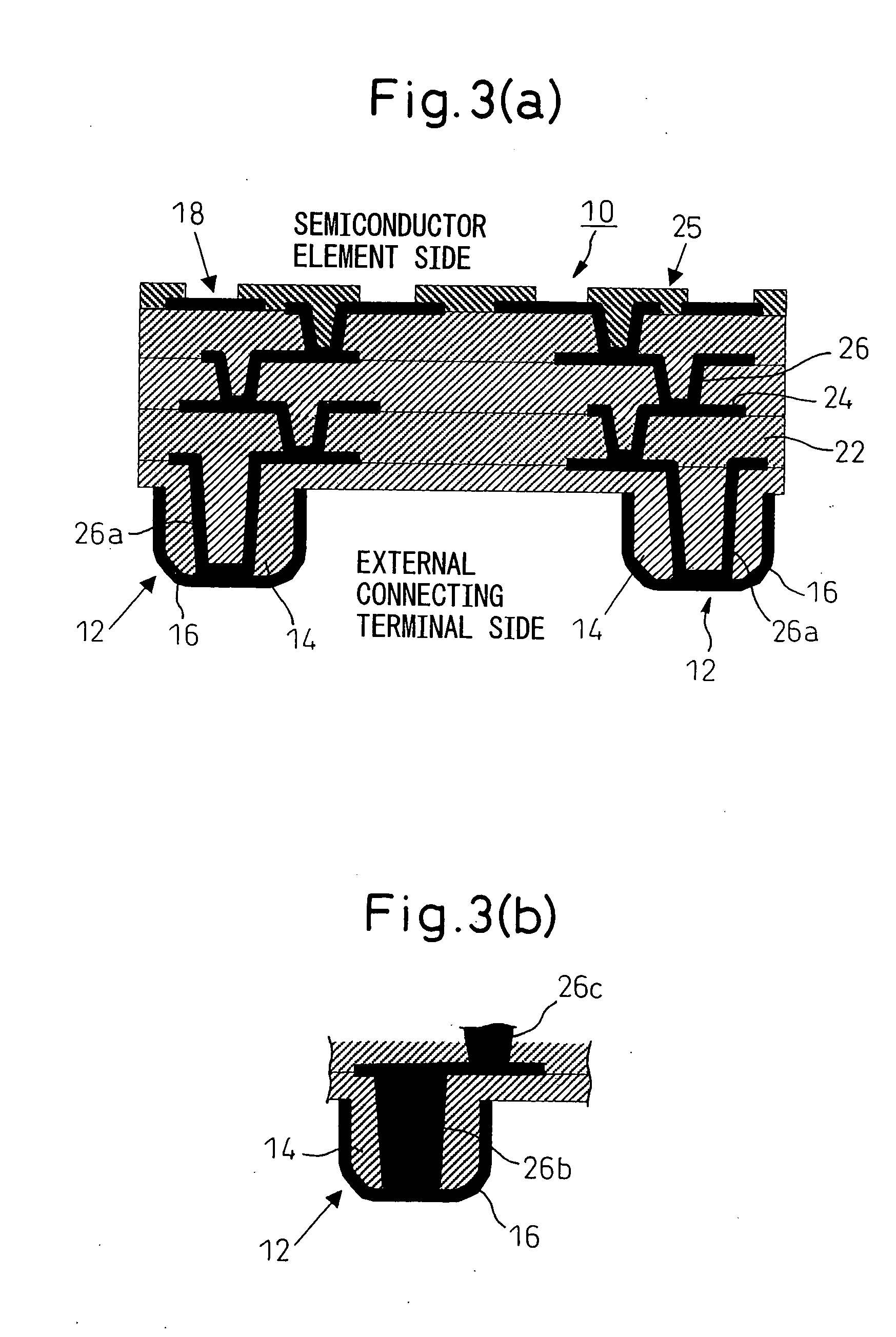

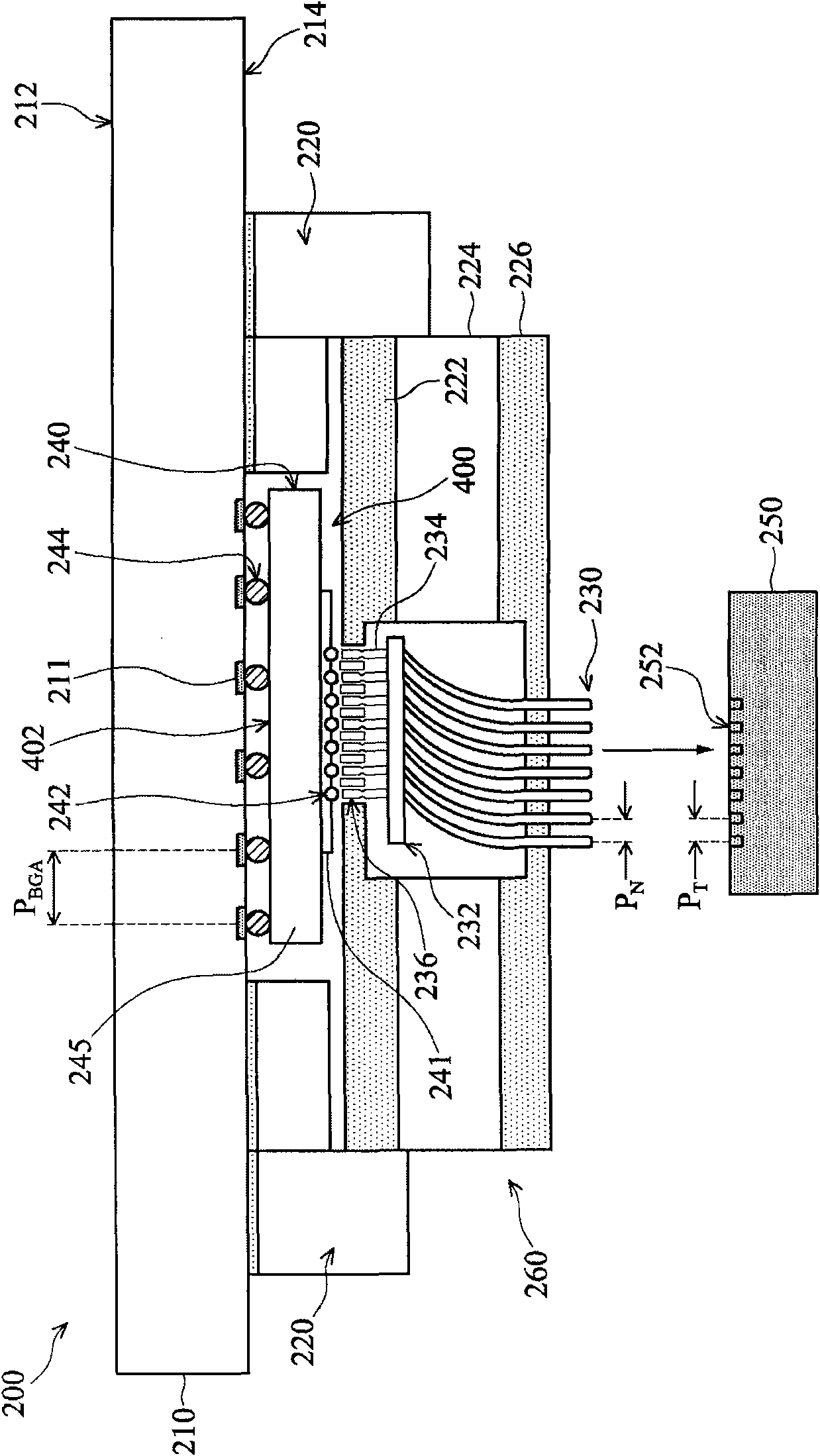

Semiconductor package and fabrication method

ActiveUS20060131730A1Solve the real problemFirmly connectedSemiconductor/solid-state device detailsPrinted circuit aspectsElectrical conductorSemiconductor package

A semiconductor package and a fabrication method thereof are disclosed, whereby an environmental problem is solved by using external connection terminals or semiconductor element-mounting terminals containing a smaller amount of lead, while at the same time achieving a fine pitch of the terminals. The semiconductor package includes a board (20) including a plurality of insulating resin layers, semiconductor element-mounting terminals (18) formed on the uppermost surface of the board, and external connection terminals (12) formed on the bottom surface thereof. Each external connection terminal (12) is formed as a bump projected downward from the bottom surface of the package, and each bump is filled with the insulating resin (14) while the surface thereof is covered by a metal (16). Wiring (24), (26) including a conductor via (26a) electrically connect the metal of the metal layer 16 and the semiconductor element-mounting terminals (18).

Owner:SHINKO ELECTRIC IND CO LTD

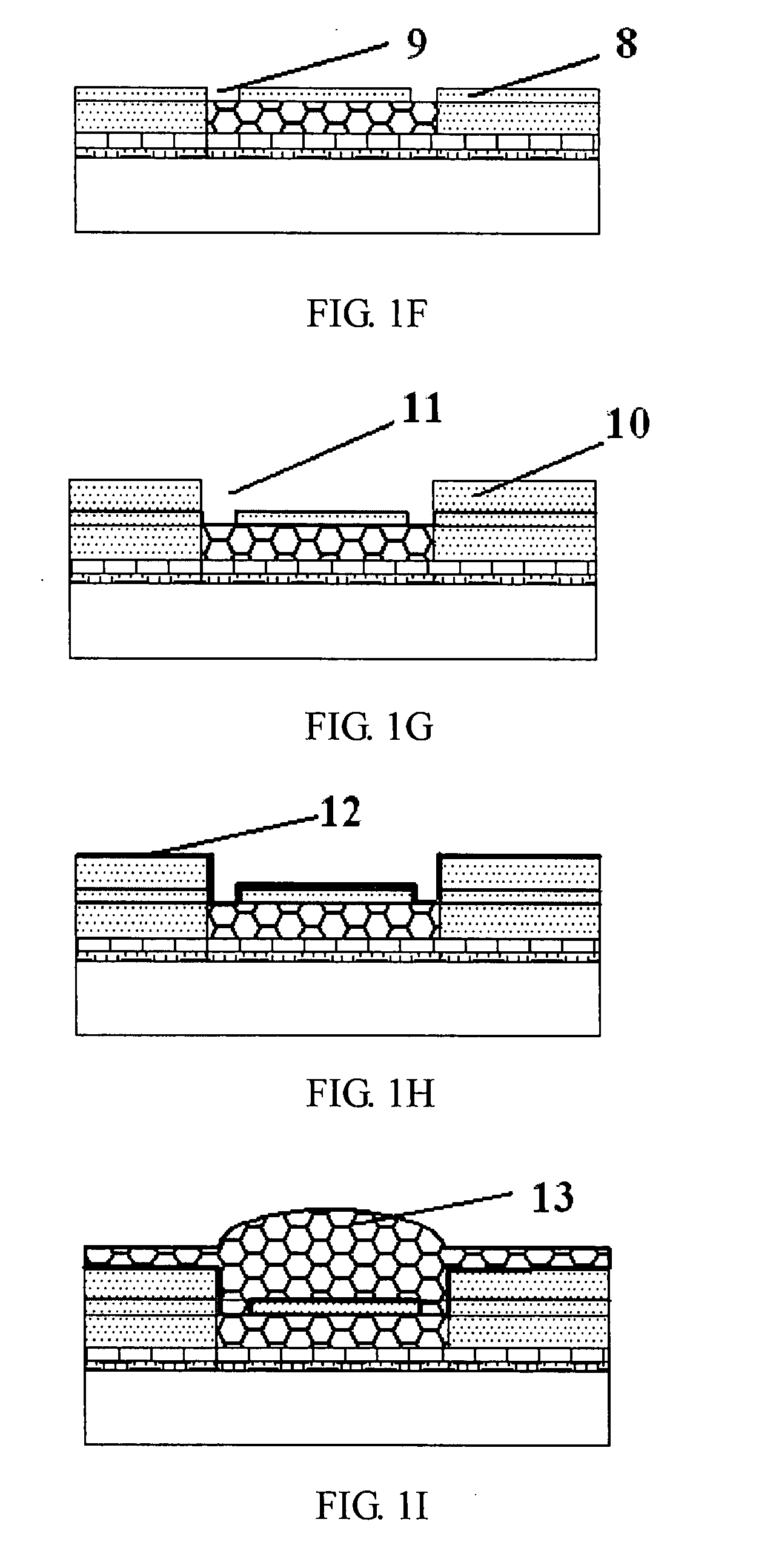

Fabrication method for drug-eluting stent with medicine-compatible loading mechanisms

A MEMS-based fabrication process is disclosed to fabricate a hollow seamless drug-eluting stent. This stent fabrication process is characterized by using a photolithography process, a composite electroplating process, and a polishing process to mass-produce drug-eluting seamless stents. Combining a multi-layers photolithography process with a multi-layers composite electroforming process could make the formation of micro-holes, micro-caves, or micro-trenches integrated with this hollow seamless eluting-stent for any anti-thrombosis drug loading or filling.

Owner:HUANG JUNG TANG

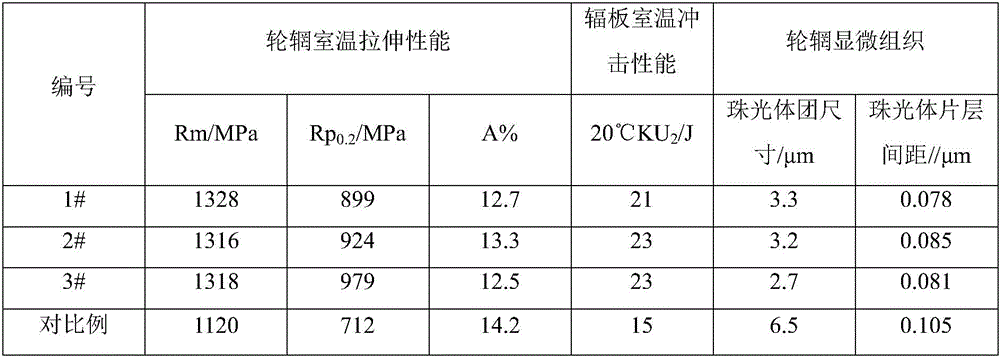

High strength and high toughness heavy haul train wheel steel and heat treatment method thereof

ActiveCN106521315AReduce the amount of processingExcellent match between toughness and plasticityFurnace typesHeat treatment furnacesRoom temperatureQuenching

Belonging to the technical field of steel for railway wheels, the invention relates to a high strength and high toughness heavy haul train wheel steel and a heat treatment method thereof. The steel comprises the following chemical components by weight percentage (wt.%): 0.75-0.85wt.% of C, 0.80-1.00wt.% of Si, 0.40-0.80wt.% of Cr, 0.30-0.50wt.% of Mn, 0.01-0.03wt.% of Nb, 0.02-0.06wt.% of V, 0.010-0.025wt.% of Al, less than 0.015wt.% of P, less than 0.015wt.% of S, and the balance Fe and unavoidable impurities. After conventional smelting, casting and forging, a wheel is subjected to a novel heat treatment process adopting tread quenching and sub-sectional cooling. After heat treatment, the structure at a standard tensile test position of a rim is a fully lamellar perlite structure, the size of a pearlite colony is 2-6microm, and the pearlite interlamellar spacing is 0.05-0.09microm. The room temperature tensile strength of the rim is 1200MPa grade, the percentage elongation after fracture is greater than 12%, and the web 20DEG C impact energy KU2 is greater than 20J. Therefore, the high strength and high toughness heavy haul train wheel steel has excellent strength and toughness matching, and can be used for heavy haul trains.

Owner:CENT IRON & STEEL RES INST +1

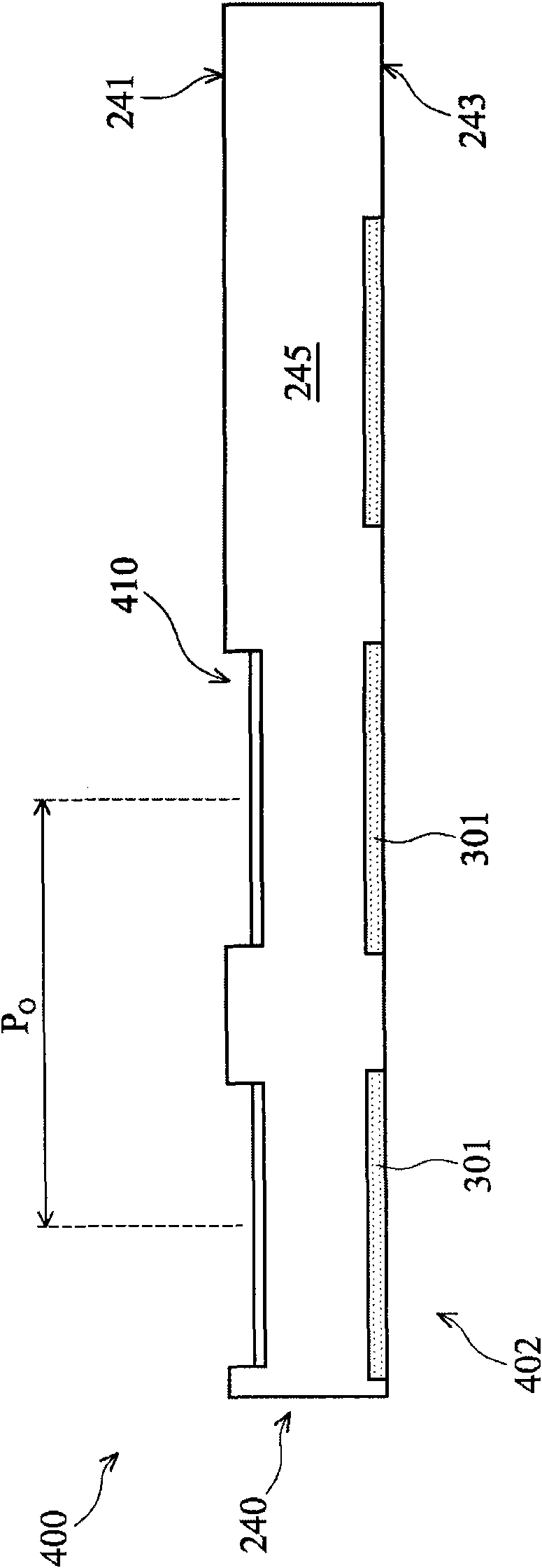

Substrate Joining Member and Three-Dimensional Structure Using the Same

InactiveUS20090009979A1Reliable maintenanceFine pitchPrinted circuit aspectsSoldering apparatusEngineeringConductive materials

Owner:PANASONIC CORP

Flip-chip package

ActiveUS20050046039A1Improve cooling effectEliminating flip-chip stress of chipSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerEngineering

A flip-chip package comprises a substrate with an opening. A dummy die is disposed onto the substrate corresponding to the opening so as to form a composite chip carrier with a chip cavity. The dummy die has a redistribution layer which includes a plurality of flip-chip pads for flip-chip connection of a chip and a plurality of connecting pads around the dummy die for connecting the substrate. The dummy die mounts at least a chip by flip chip connection for being an electrical interface medium between the chip and the substrate in order to achieve thinner package thickness, high heat dissipation, fine pitch flip-chip mounting and eliminating flip-chip stress on the chip.

Owner:ADVANCED SEMICON ENG INC

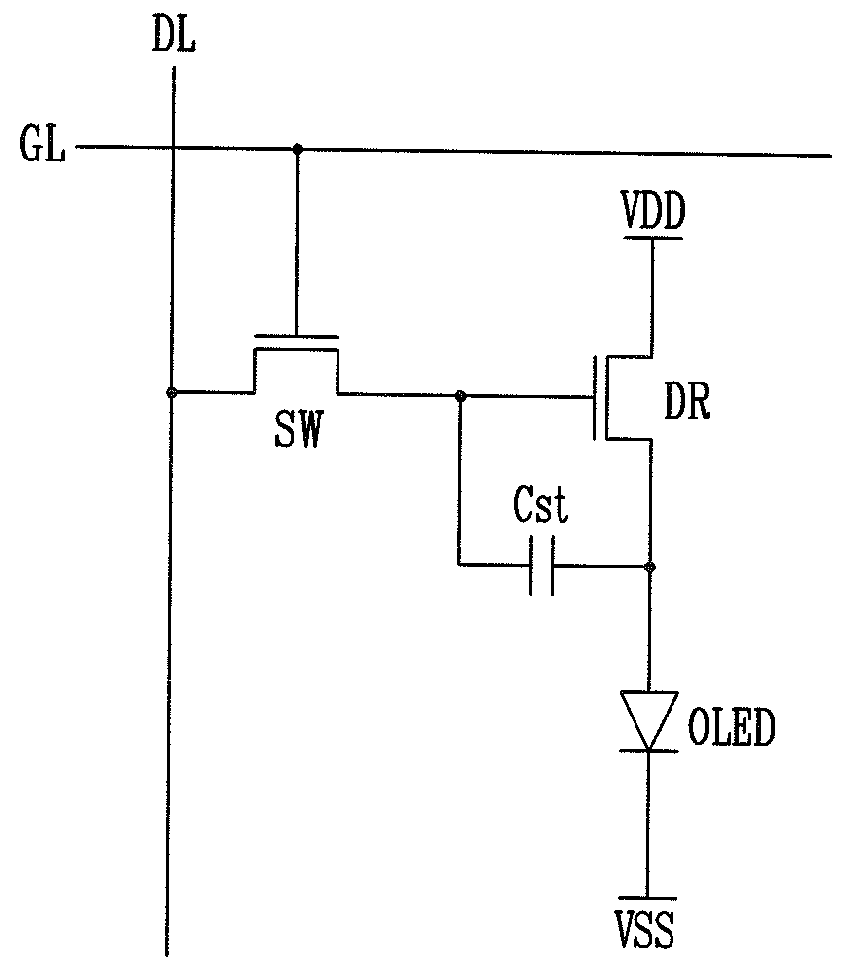

Organic Light Emitting Diode Display Device and Method of Fabricating the Same

ActiveUS20130075768A1Simple processImprove efficiencySolid-state devicesSemiconductor/solid-state device manufacturingDisplay deviceOrganic compound

In an organic light emitting diode (OLED) display device and a method for fabricating the same, OLED pixels are patterned through a photolithography process, so a large area patterning can be performed and a fine pitch can be obtained, and an organic compound layer can be protected by forming a buffer layer of a metal oxide on an upper portion of the organic compound layer or patterning the organic compound layer by using a cathode as a mask, improving device efficiency. In addition, among red, green, and blue pixels, two pixels are patterned through a lift-off process and the other remaining one is deposited to be formed without patterning, the process can be simplified and efficiency can be increased.

Owner:LG DISPLAY CO LTD

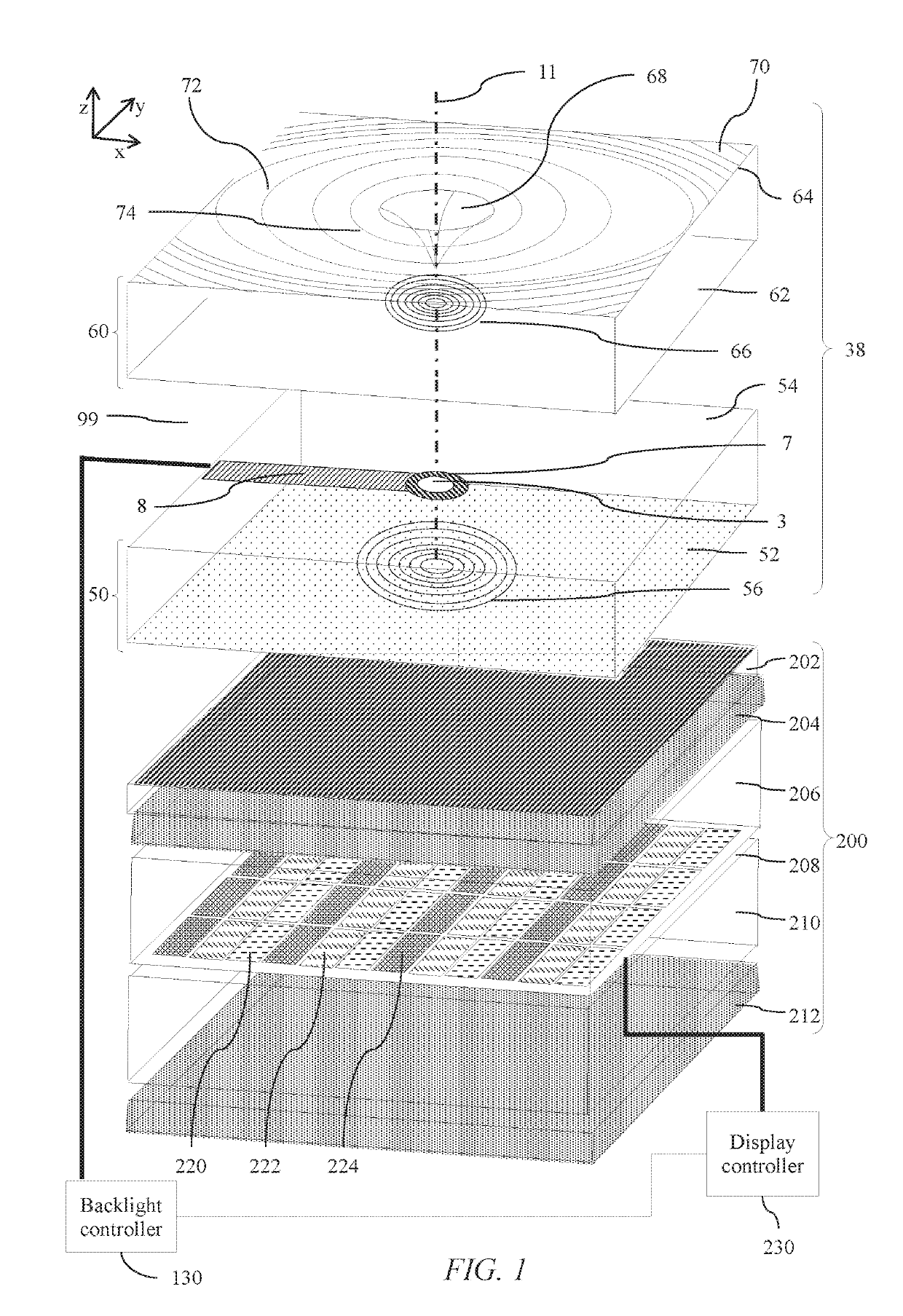

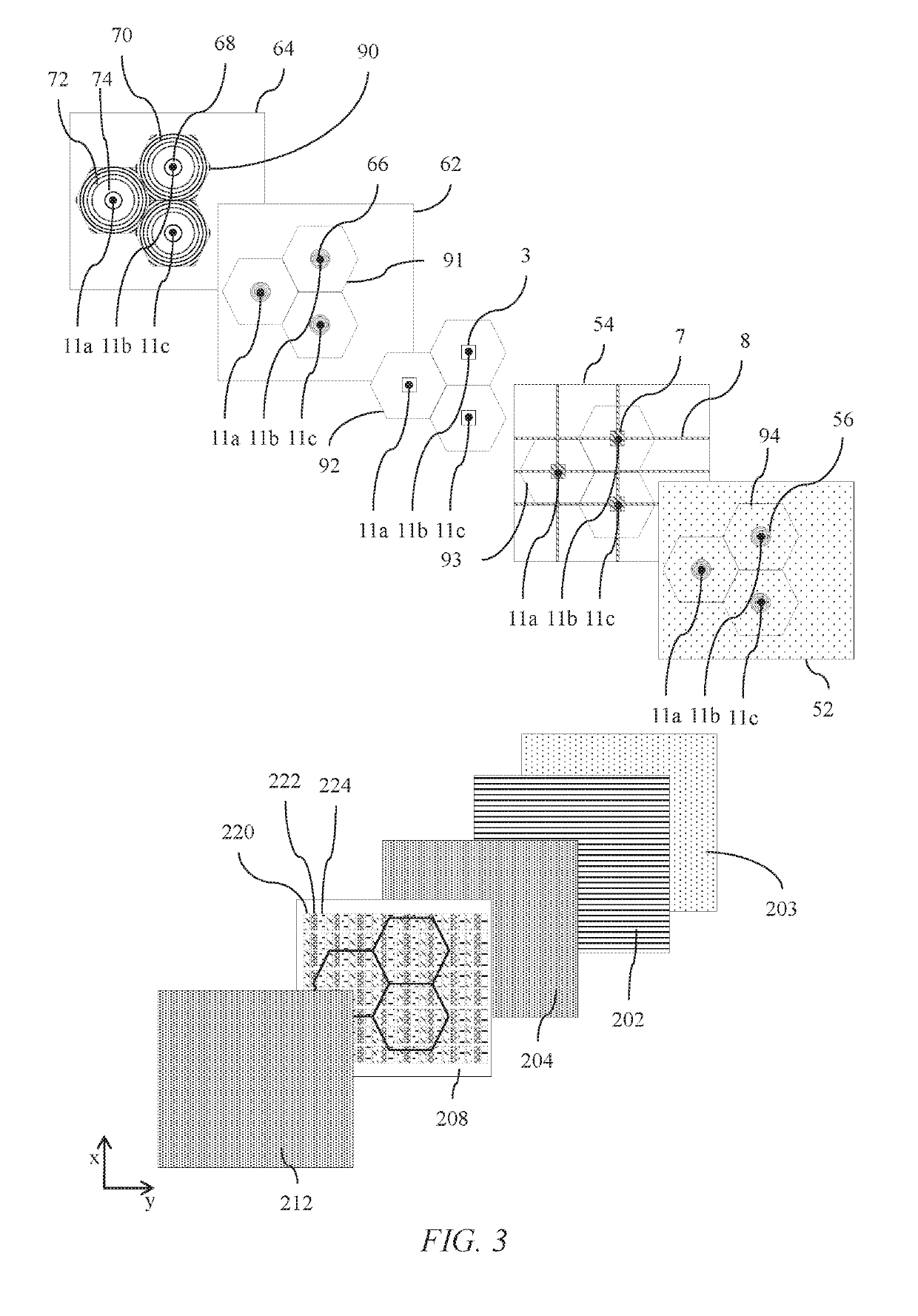

Illumination apparatus

ActiveUS20190278135A1Reduce edge widthSmall bezel widthCondensersNon-linear opticsLight equipmentLed array

Owner:REALD SPARK LLC

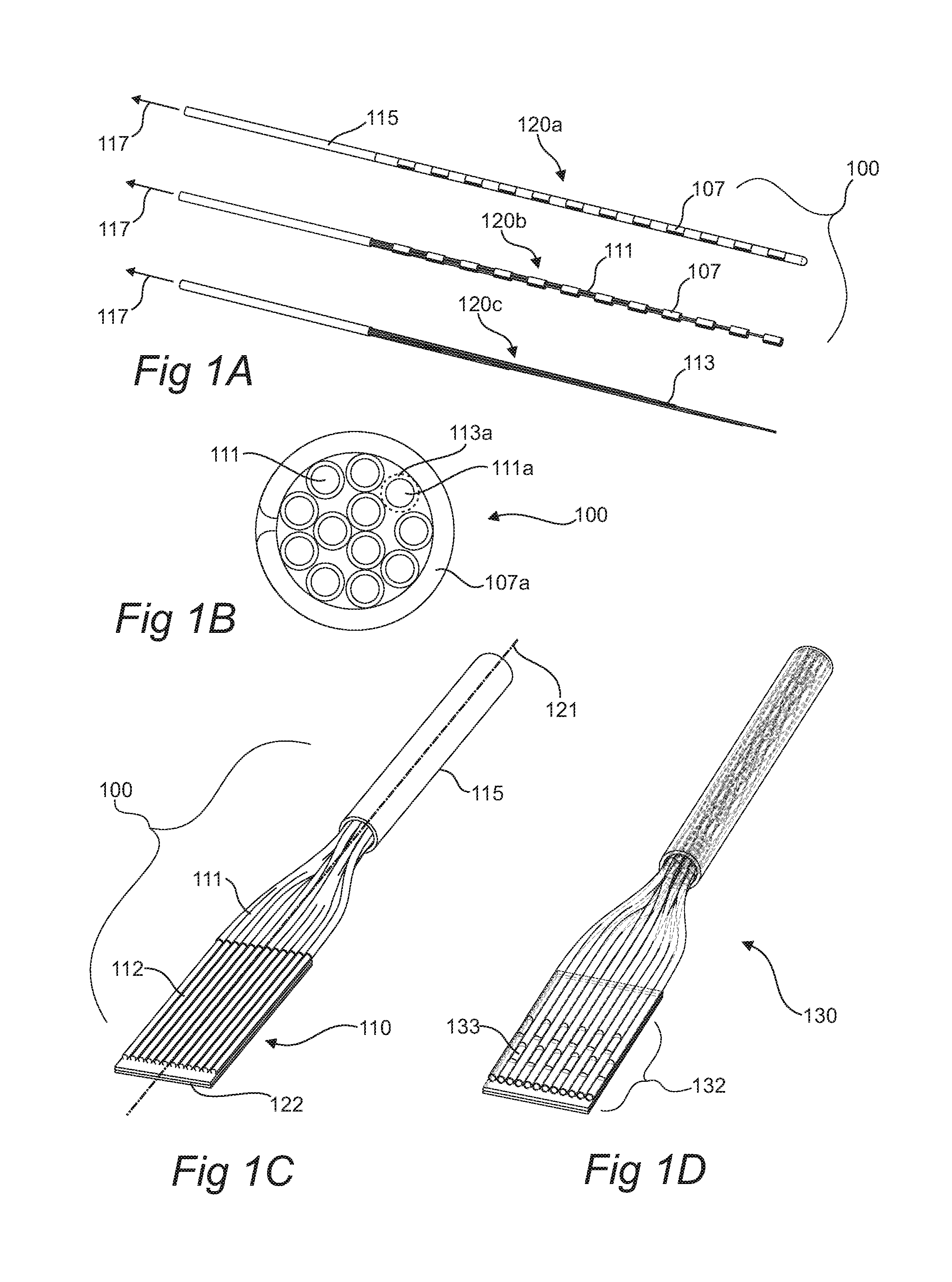

Elongated Conductors and Methods of Making and Using the Same

ActiveUS20160351292A1Small diameterHigh bulk densityMagnetic/electric field screeningInternal electrodesBiomedical engineeringElectrical conductor

Owner:AUTONOMIX MEDICAL

Electronic device having liquid crystal polymer solder mask and outer sealing layers, and associated methods

ActiveUS20120181073A1Efficiently attachedFine pitchPrinted circuit assemblingPrinted circuit aspectsSolder maskSolder paste

An electronic device includes a substrate with a circuit layer thereon that has a solder pad. There is a liquid crystal polymer (LCP) solder mask on the substrate that has an aperture aligned with the solder pad. There is a fused seam between the substrate and the LCP solder mask. Solder is in the aperture, and a circuit component is electrically coupled to the solder pad via the solder. A first dielectric layer stack having a first plurality of dielectric layers is on the LCP solder mask and has an aperture aligned with the solder pad. There is a first LCP outer sealing layer on the first dielectric layer stack, and a second dielectric layer stack having a second plurality of dielectric layers on the substrate on a side thereof opposite the LCP solder mask. Further, there is a second LCP outer sealing layer on the second dielectric layer stack.

Owner:HARRIS CORP

Fabrication method of space transformer for semiconductor test probe card

ActiveCN101673694AReduced pitch distributionFine pitchSemiconductor/solid-state device testing/measurementElectronic circuit testingGround planeEngineering

The invention discloses a space transformer for a semiconductor test probe card and a method of fabrication. The method may include depositing a first metal layer as a ground plane on a space transformer substrate having a plurality of first contact test pads defining a first pitch spacing, depositing a first dielectric layer on the ground plane, forming a plurality of second test contacts defining a second pitch spacing different than, the first pitch spacing, and forming a plurality of redistribution leads on the first dielectric layer to electrically couple the first contact test pads to the second contact test pads. In some embodiments, the redistribution leads may be built directly on the space transformer substrate. The method may be used in one embodiment to remanufacture an existing space transformer to produce fine pitch test pads having a pitch spacing smaller than the original test pads. In some embodiments, the test pads may be C4 test pads. The invention shortens the spacedistribution of the contact test pads.

Owner:TAIWAN SEMICON MFG CO LTD

Connection structure of rigid printed circuit board and flexible circuit, the connection process and the circuit module using it

InactiveUS20050176310A1Improve reliabilityLow costPrinted circuit assemblingLine/current collector detailsResistFlexible circuits

In a connection structure of a rigid printed circuit board and a flexible circuit each having a plurality of connection terminals, there are provided a connection structure that can obtain a necessary connection strength and prevent short-circuiting between adjacent connection terminals, and a connection process thereof. A rigid printed circuit board having a plurality of connection terminals is superimposed on a flexible circuit that puts a conductive pattern having connection terminals having the same configuration as that of the connection terminals of the rigid printed circuit board at an end thereof by flexible insulating resin, and connected to the flexible circuit with a solder due to thermo compression. A solder resist is disposed on the flexible insulating resin on the flexible circuit, and the solder connection can be realized by using a solder plating formed on one or both electrodes of the rigid printed circuit board and the flexible circuit while an amount of occlusion gas is controlled.

Owner:OPNEXT JAPAN INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com