Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

68results about How to "High wiring density" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

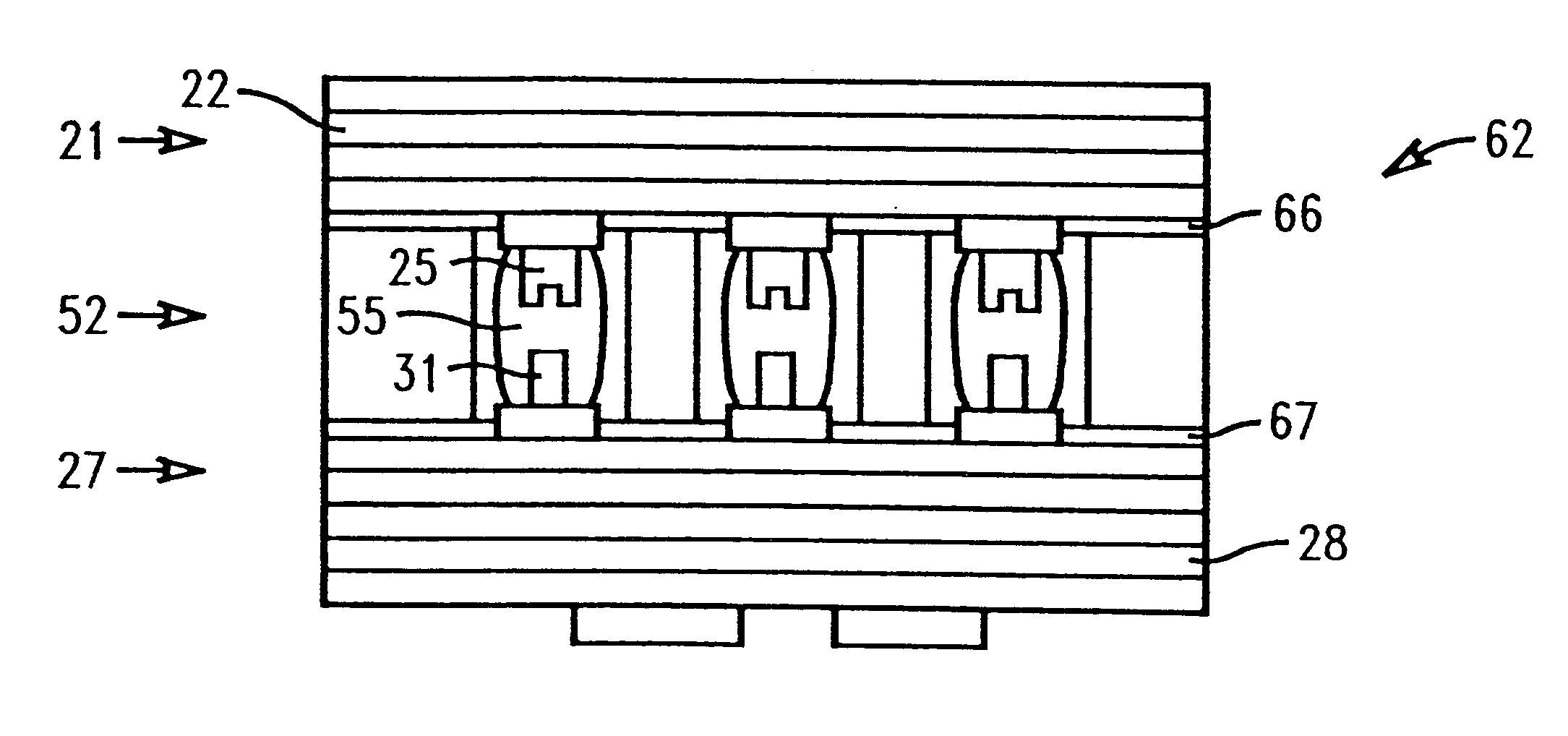

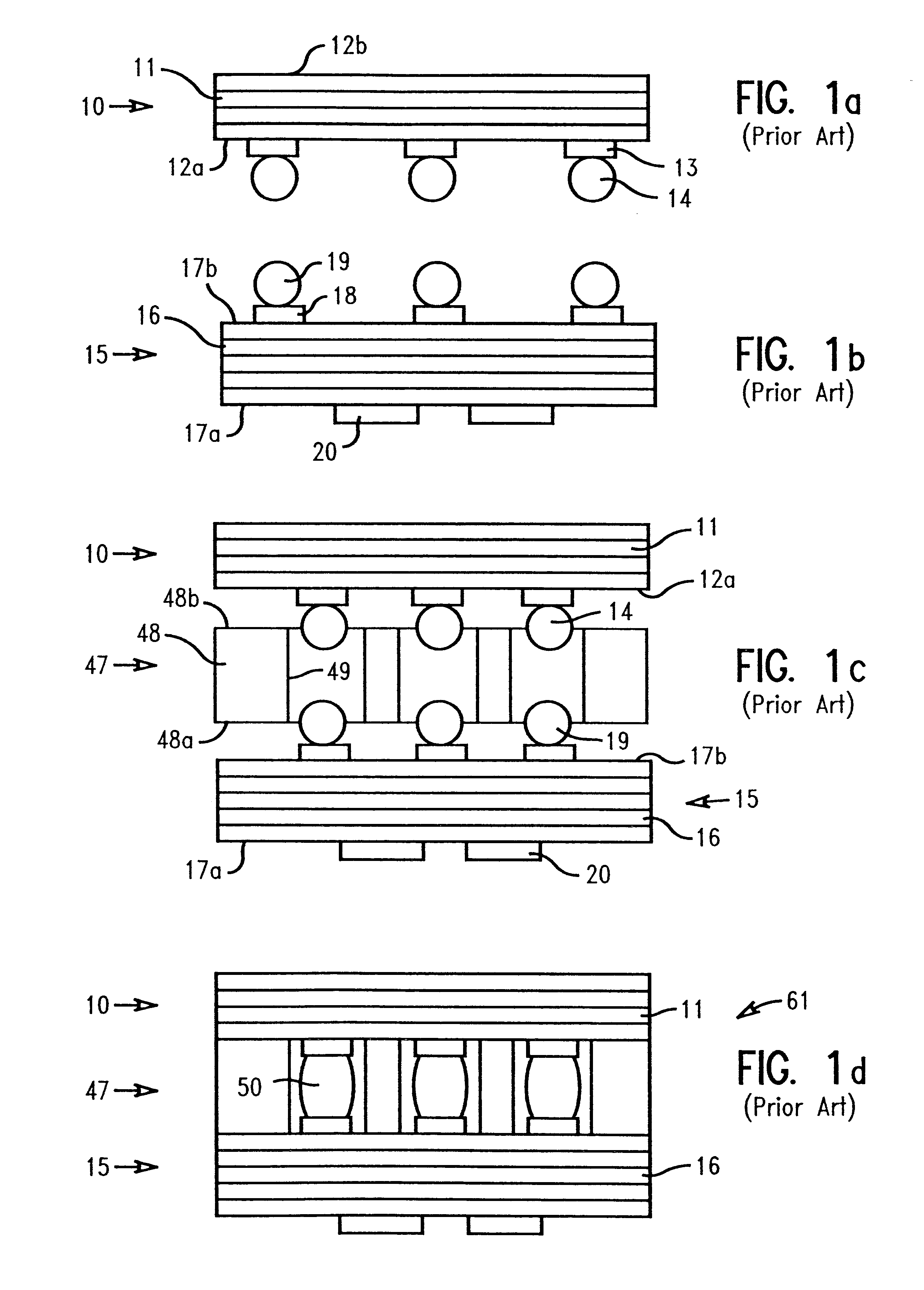

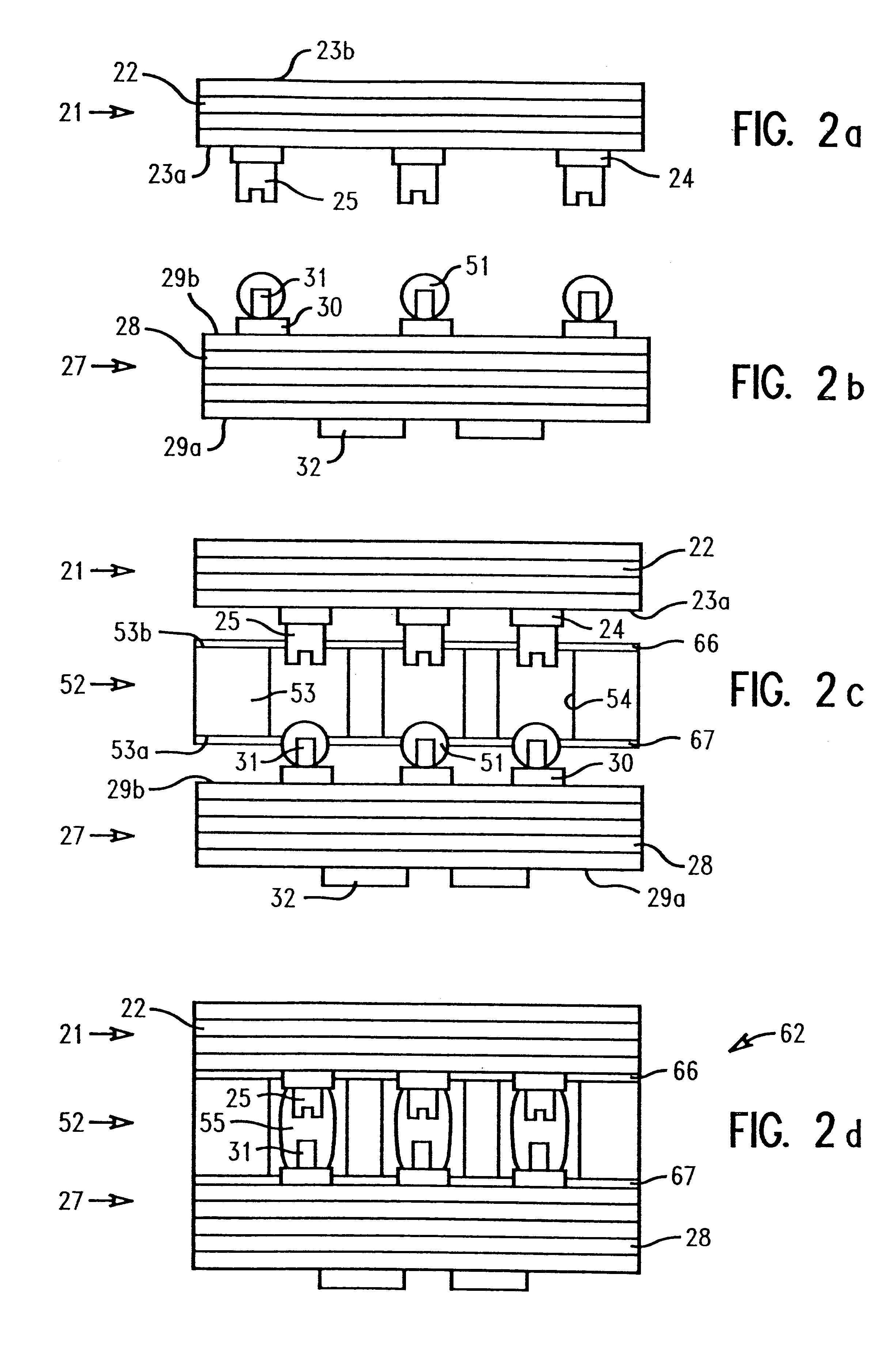

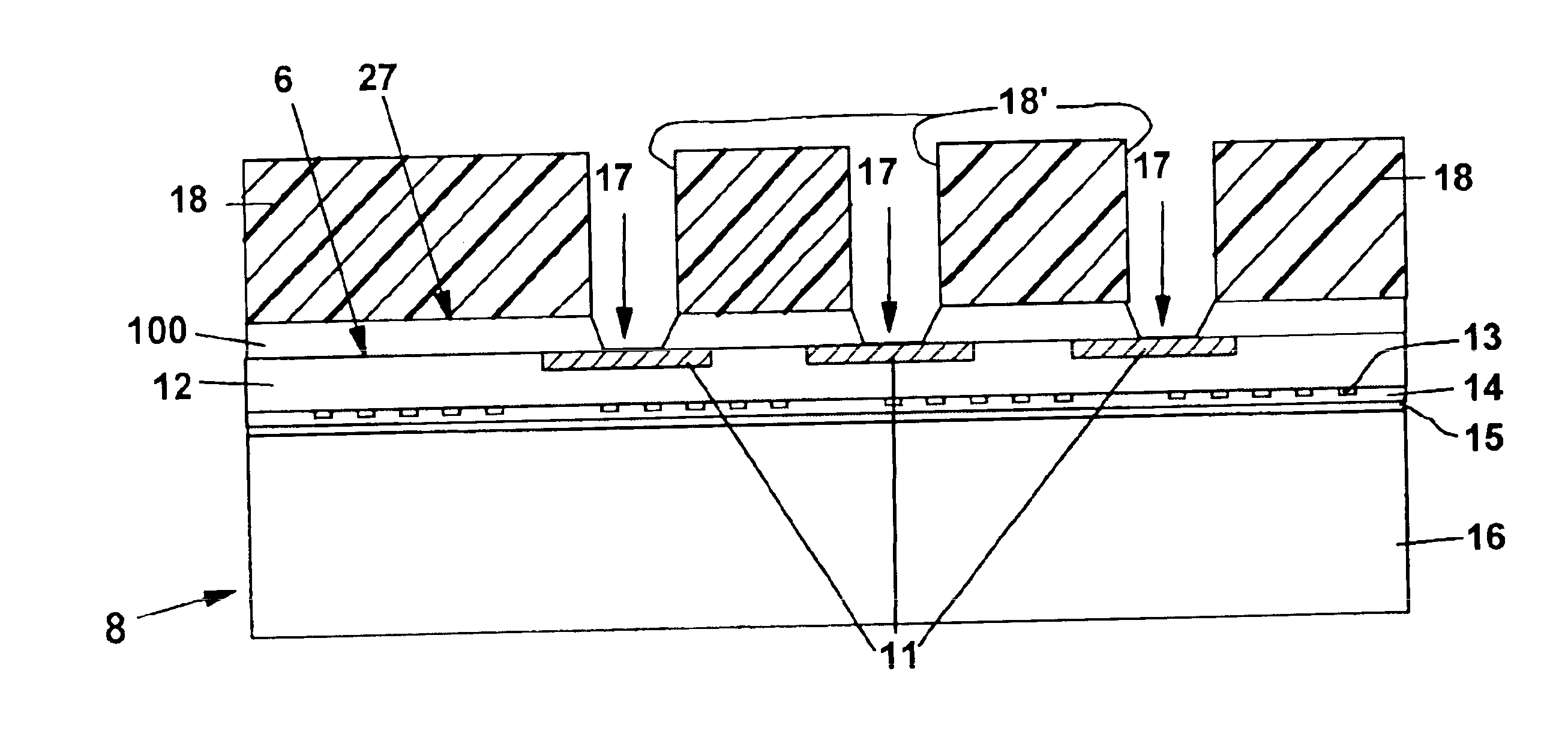

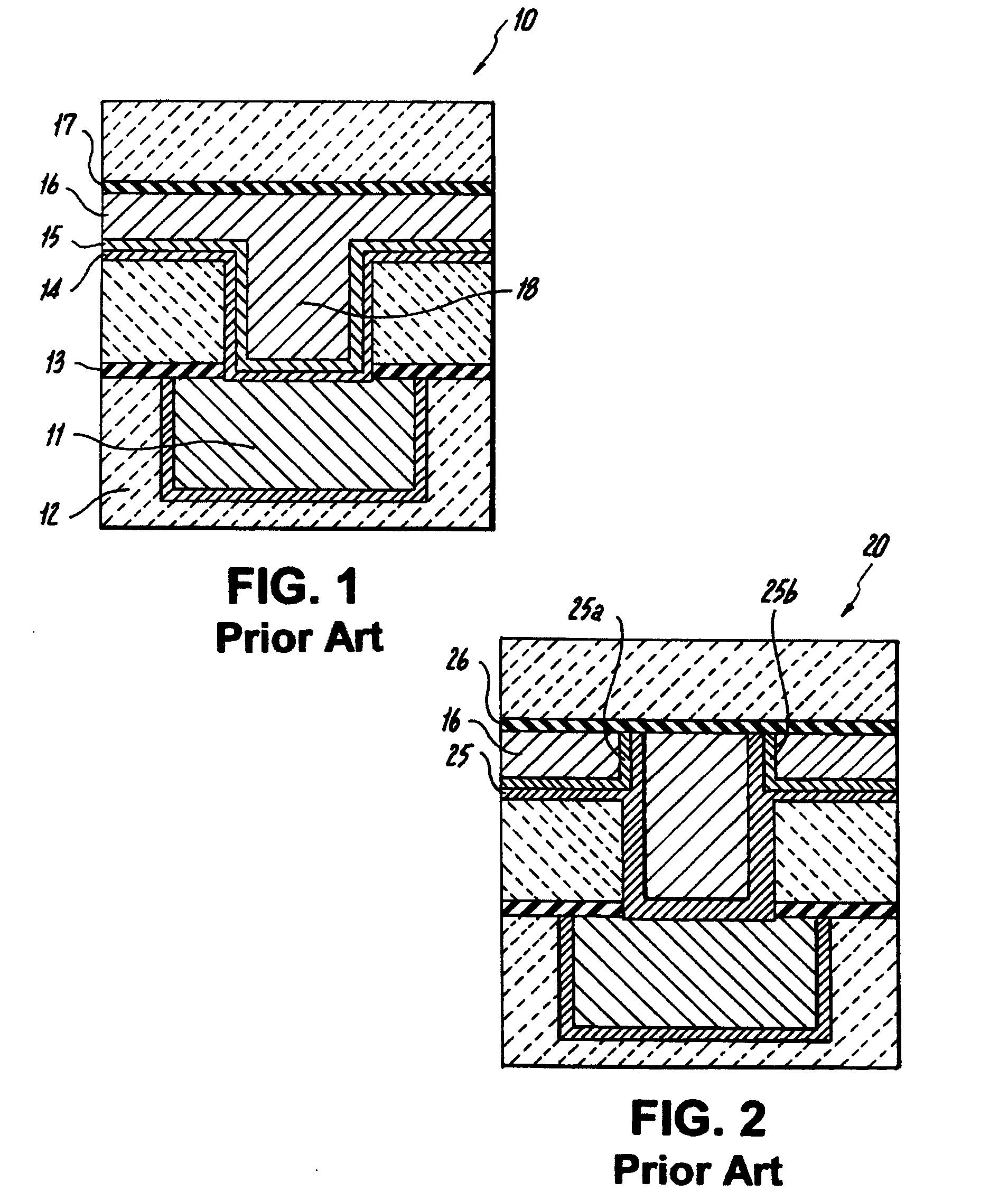

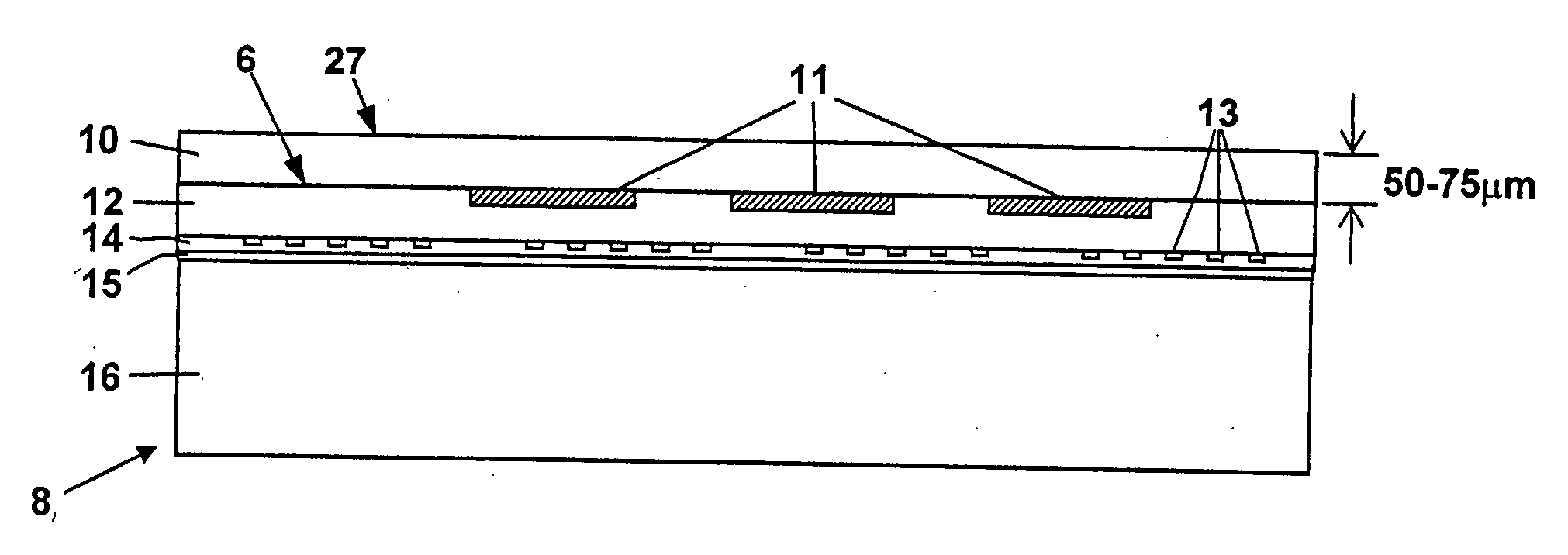

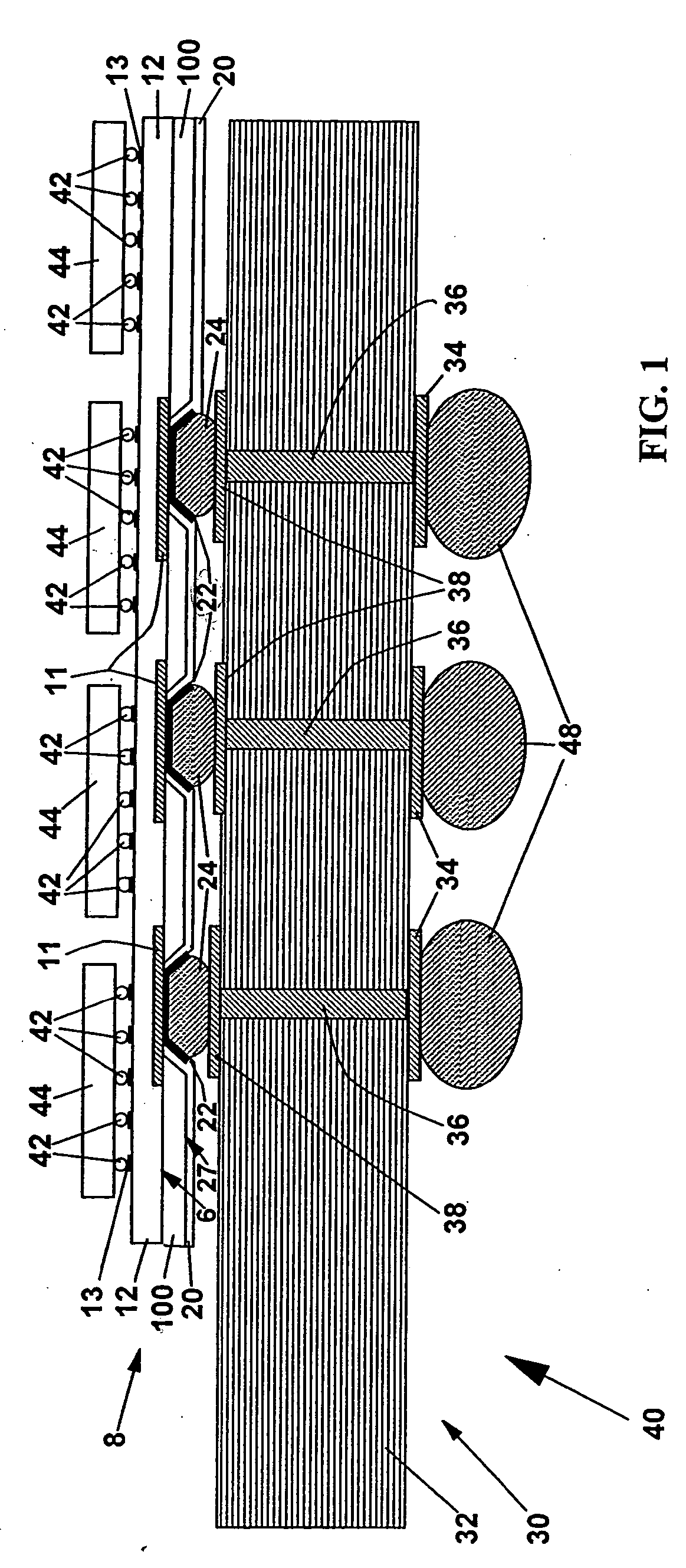

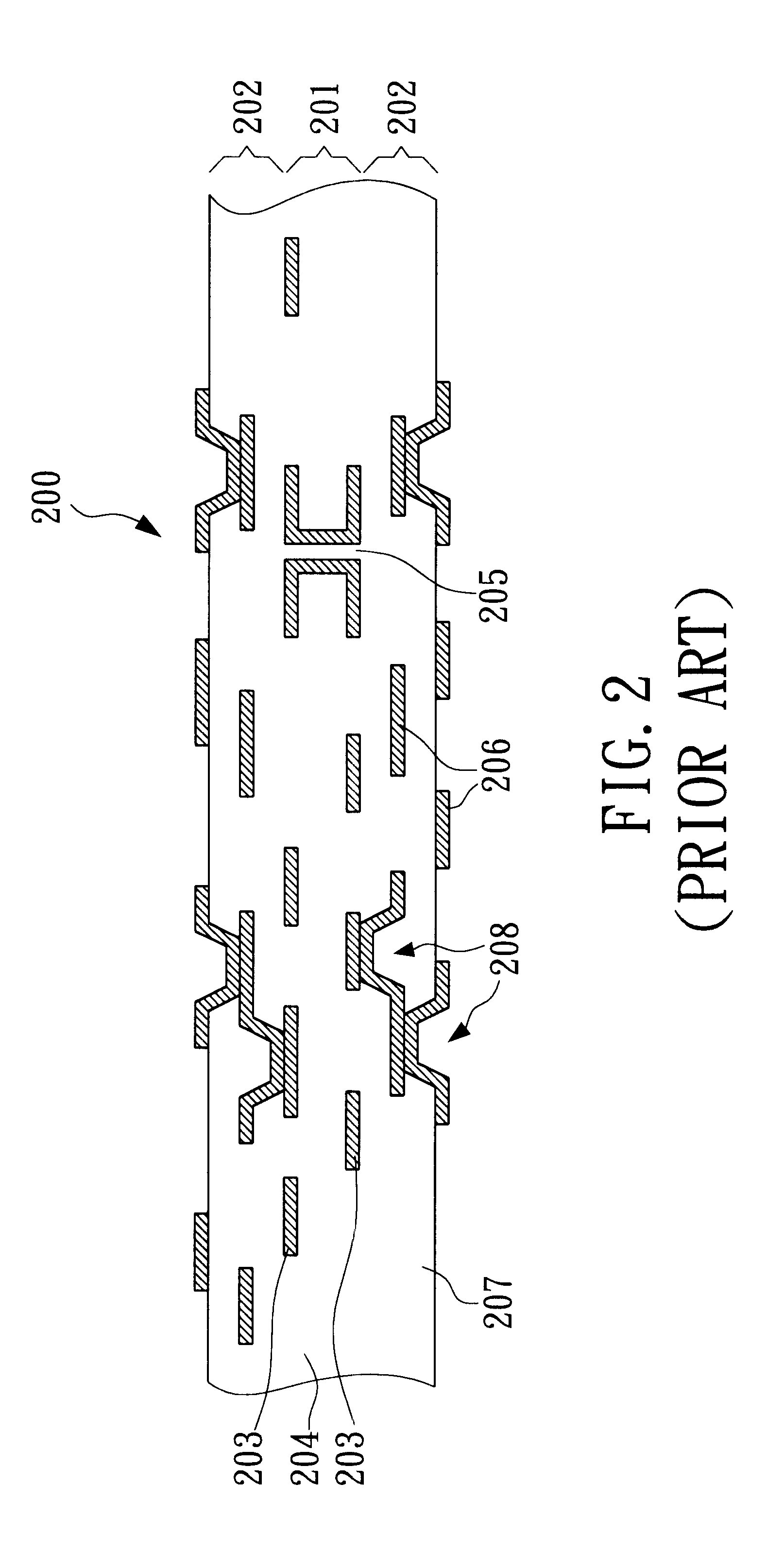

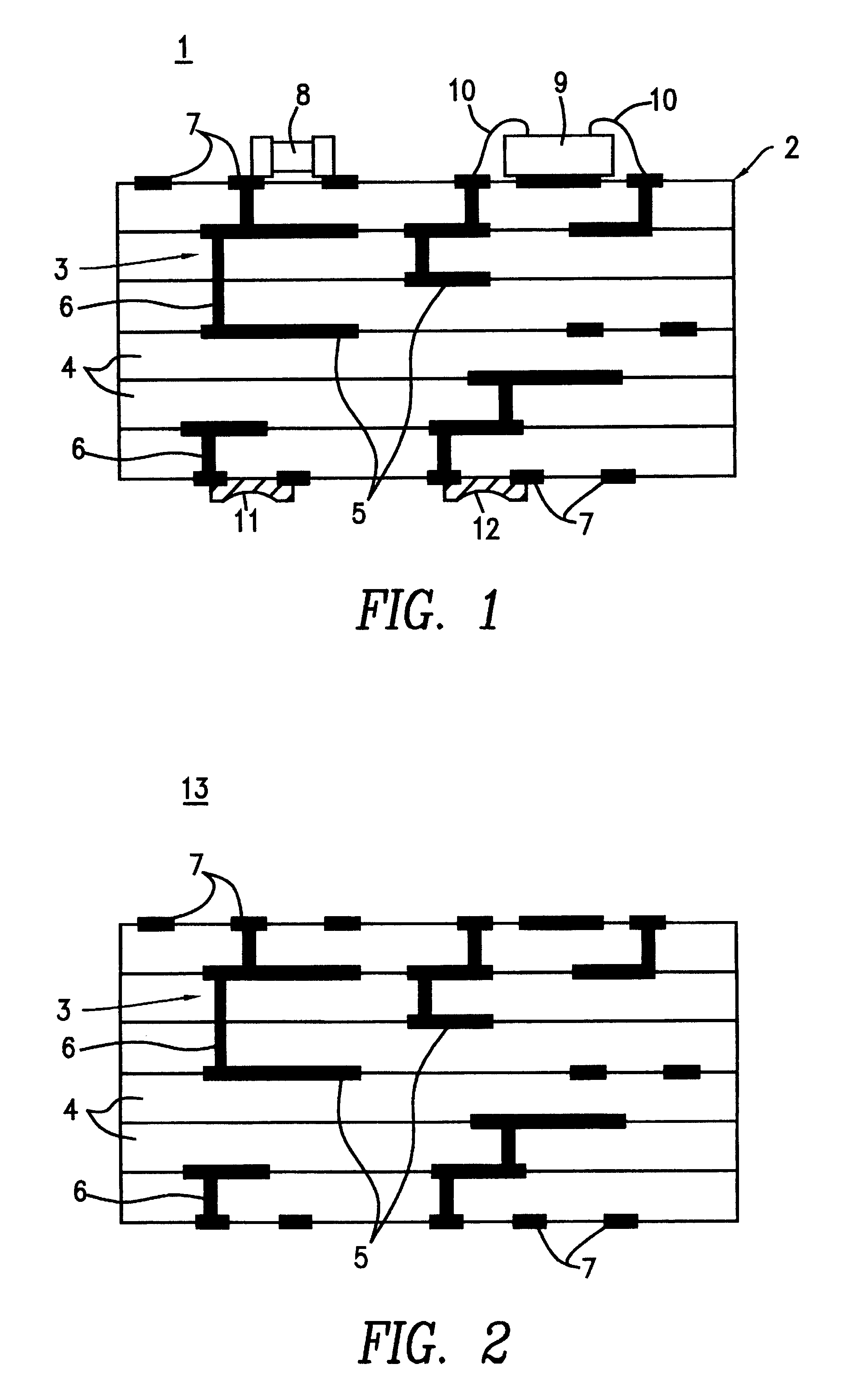

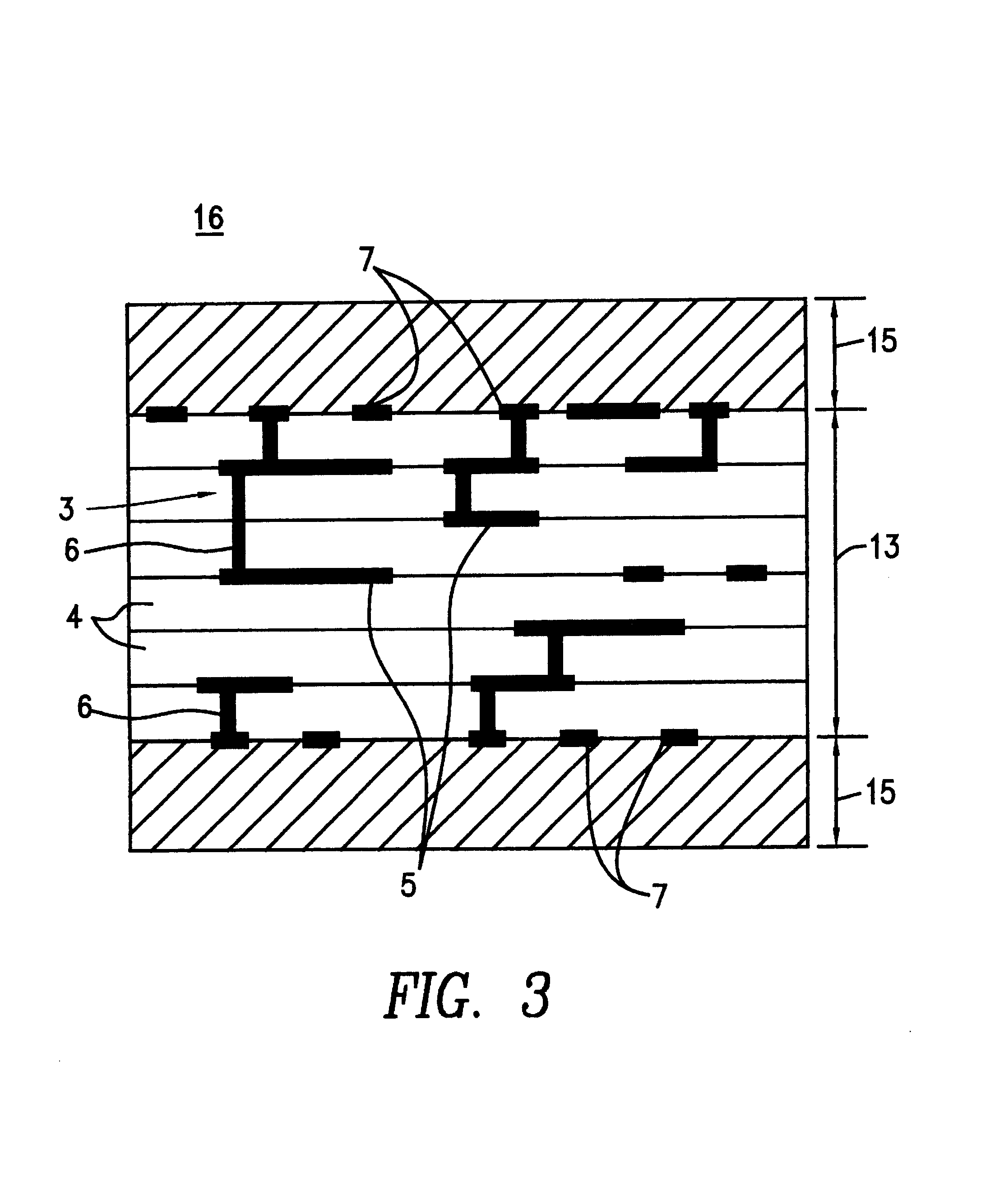

Method and structure to prevent distortion and expansion of organic spacer layer for thin film transfer-join technology

InactiveUS6329609B1Cost-effective and reliableReduces distortion of and damage to and surface topographyPrinted circuit assemblingElectrically conductive connectionsContact padAdhesive

An electronic component structure assembly comprising a thin film structure bonded to a multilayer ceramic substrate (MLC) using solder connections and wherein a non-conductive, compliant spacer preferably with a layer of thermoplastic adhesive on each surface thereof is interposed between the underlying MLC carrier and overlying thin film structure. The spacer includes a pattern of through-holes which corresponds to opposing contact pads of the thin film structure and MLC. The contact pads of at least one of the thin film structure or MLC have posts (e.g., metallic) thereon and the posts extend partly into the spacer through-holes whereby the height of the posts are greater than the thickness of the adhesive. The posts of the MLC have solder bumps thereon. After reflow under pressure the thin film structure is electrically and mechanically connected to the MLC and the join method has been found to provide a reliable and cost-effective process. The joined components also have enhanced operating life.

Owner:IBM CORP

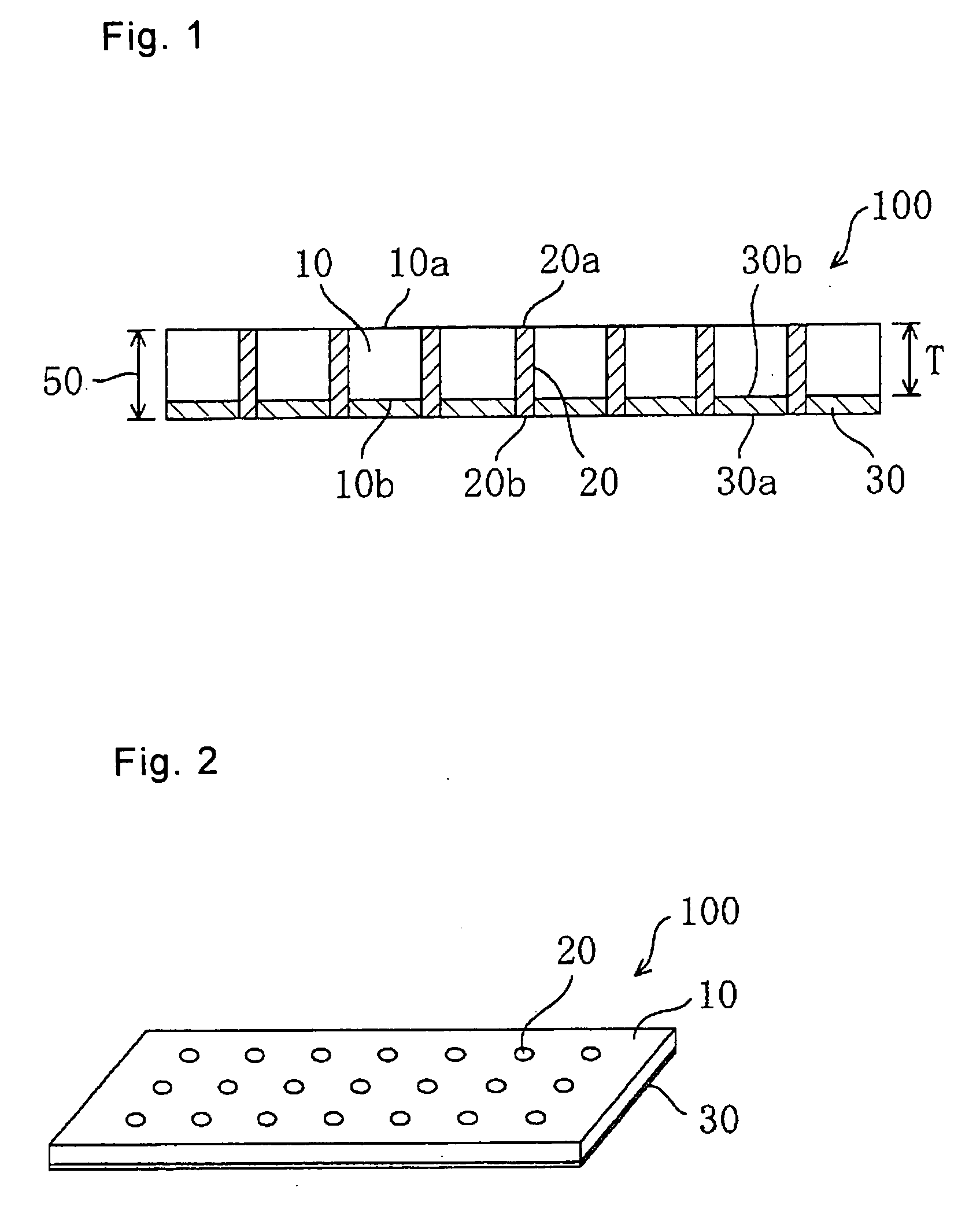

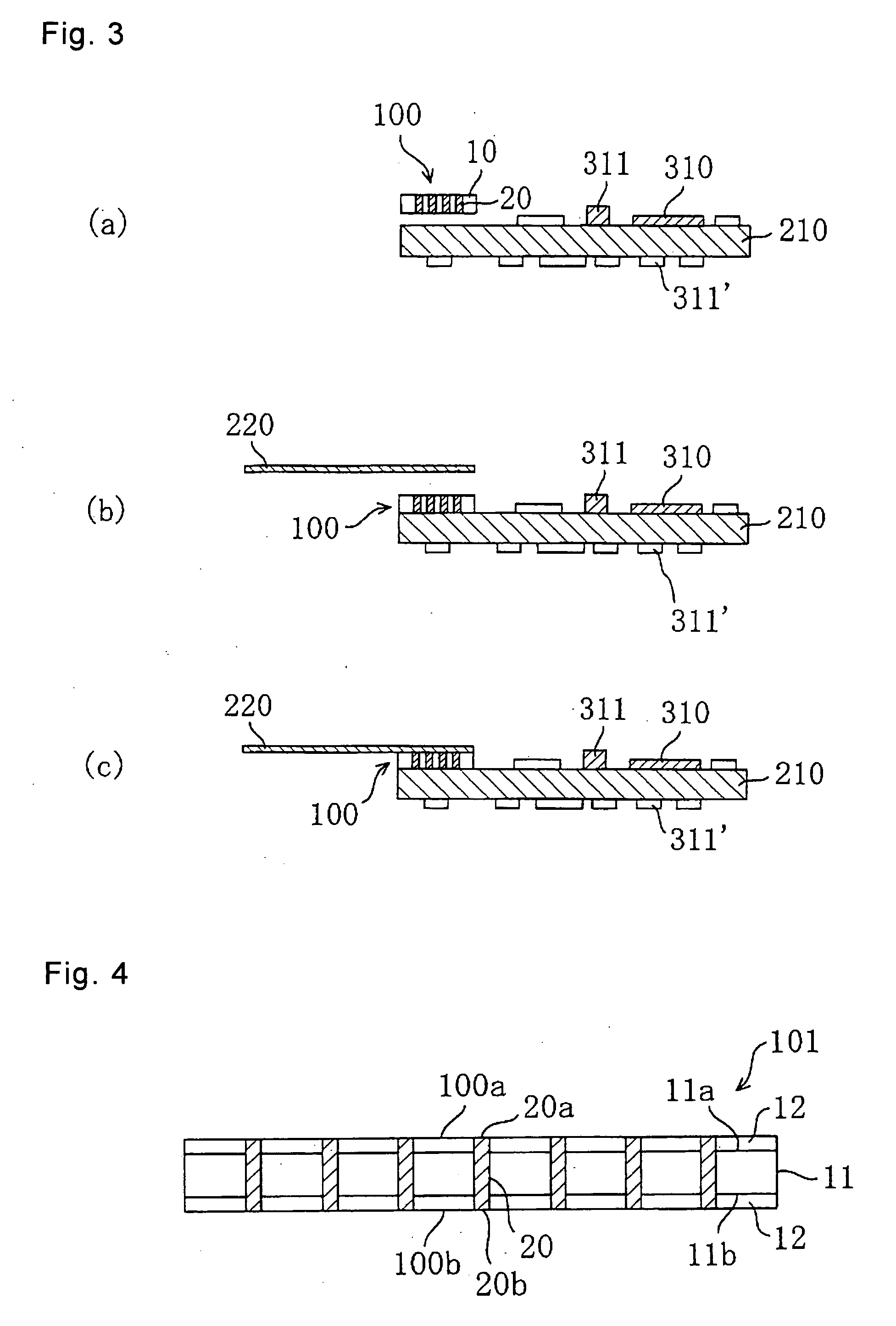

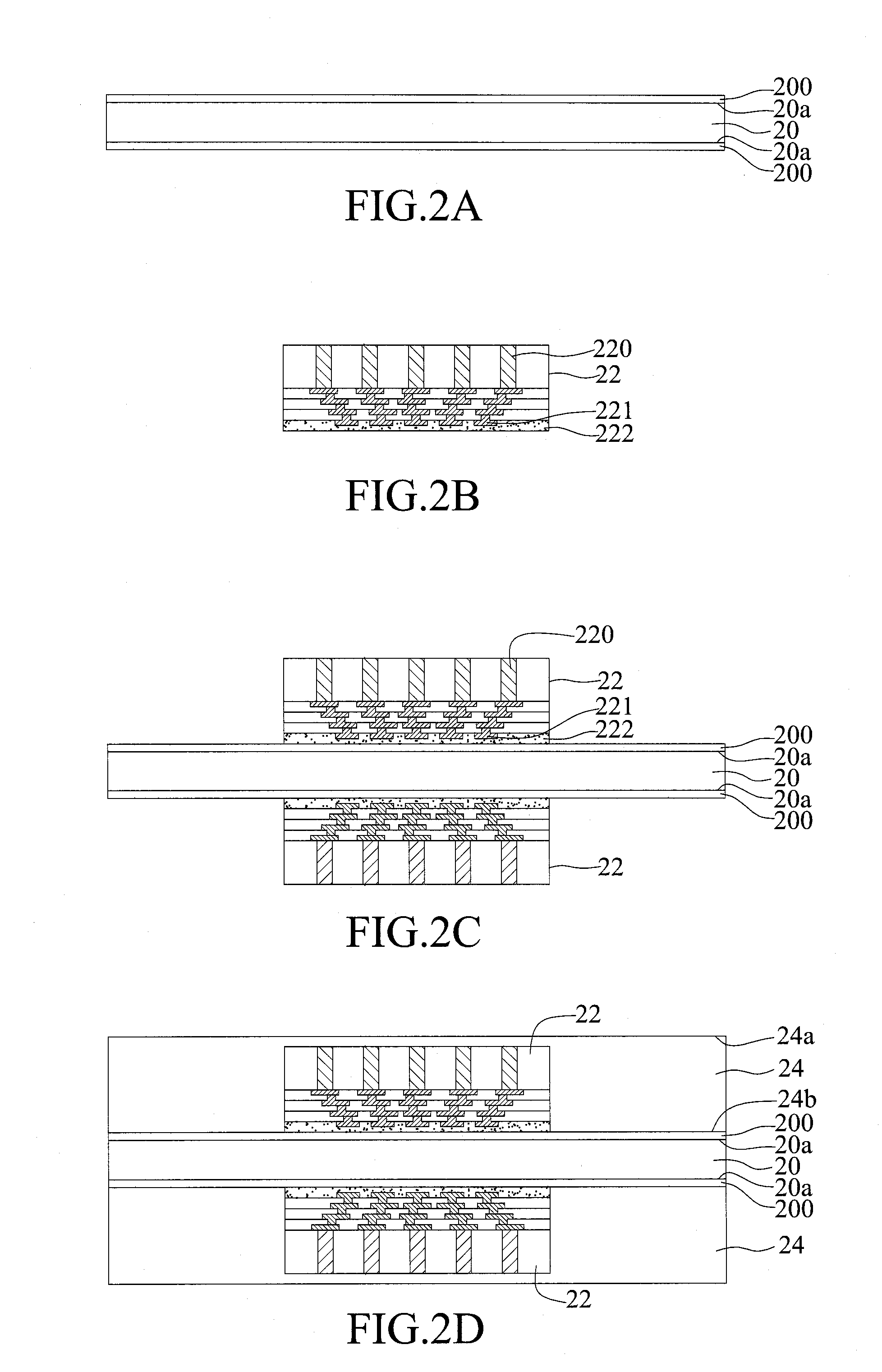

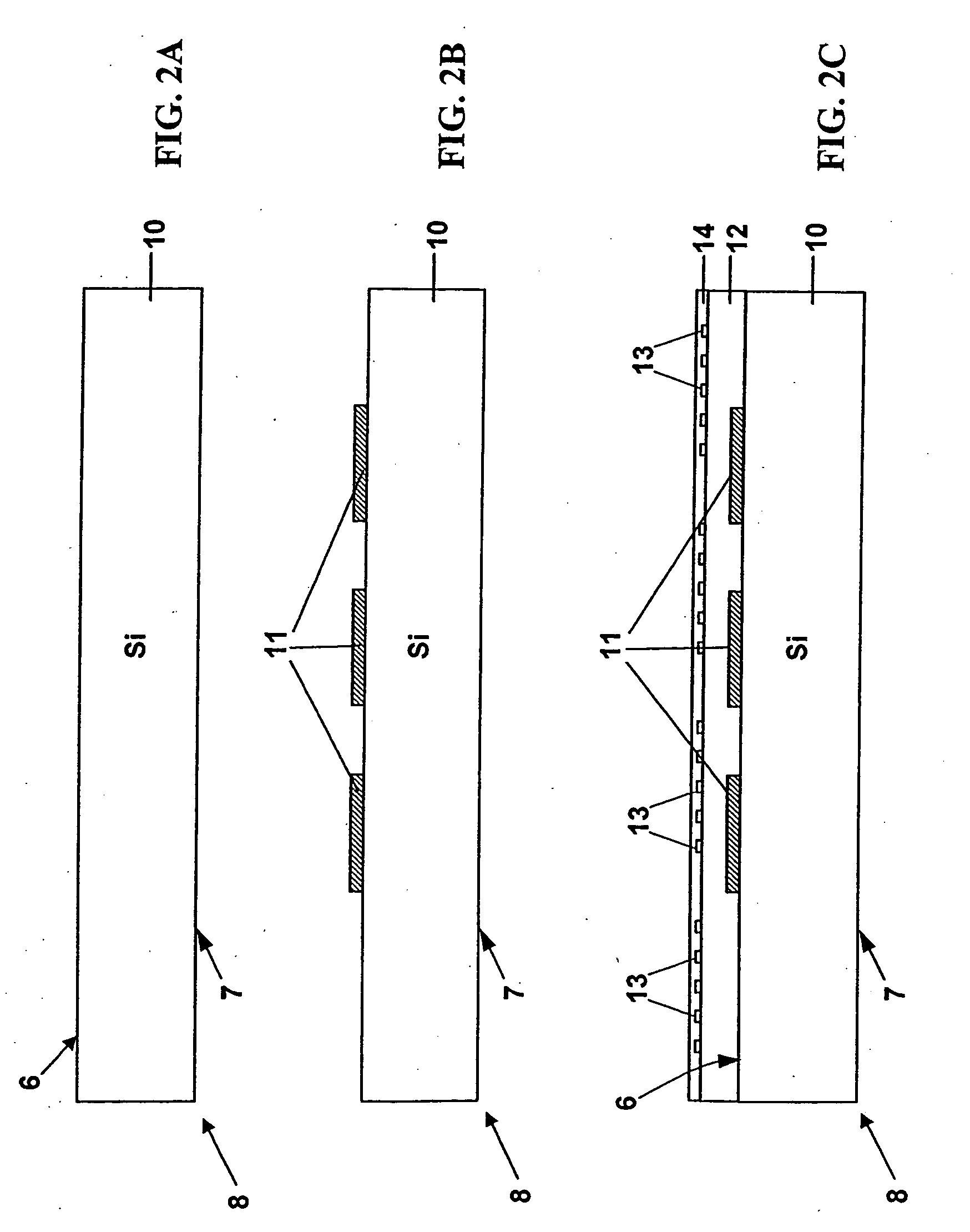

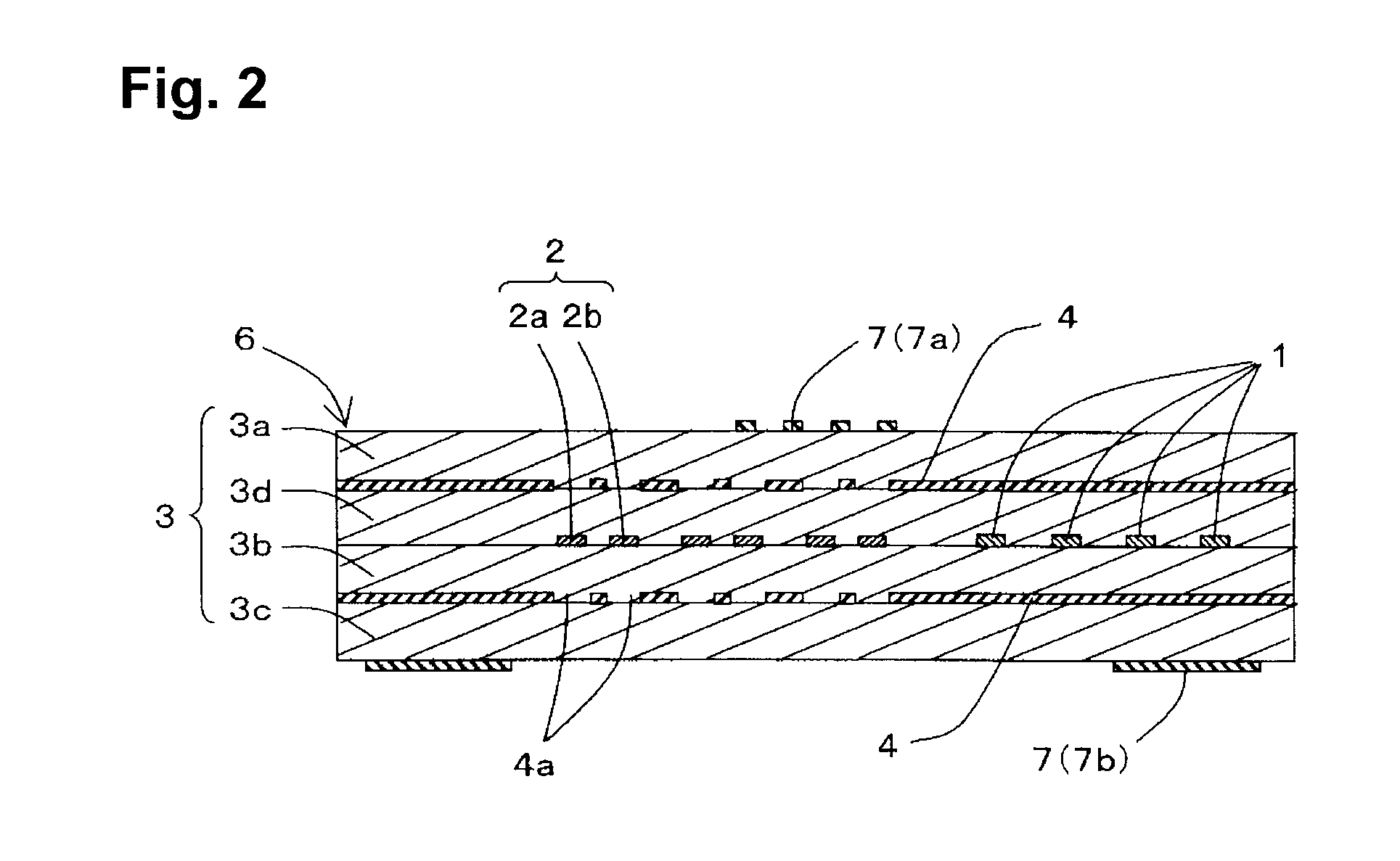

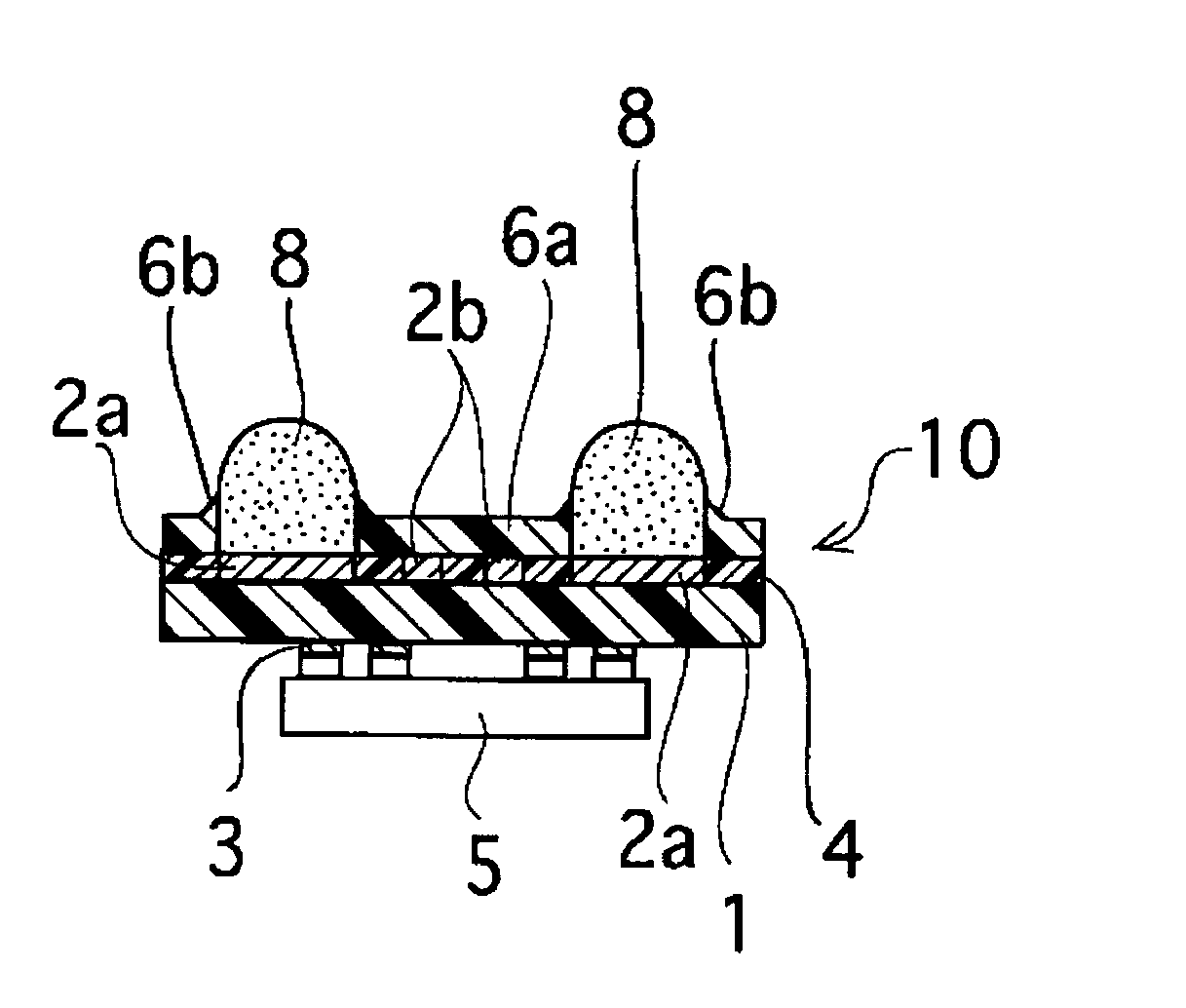

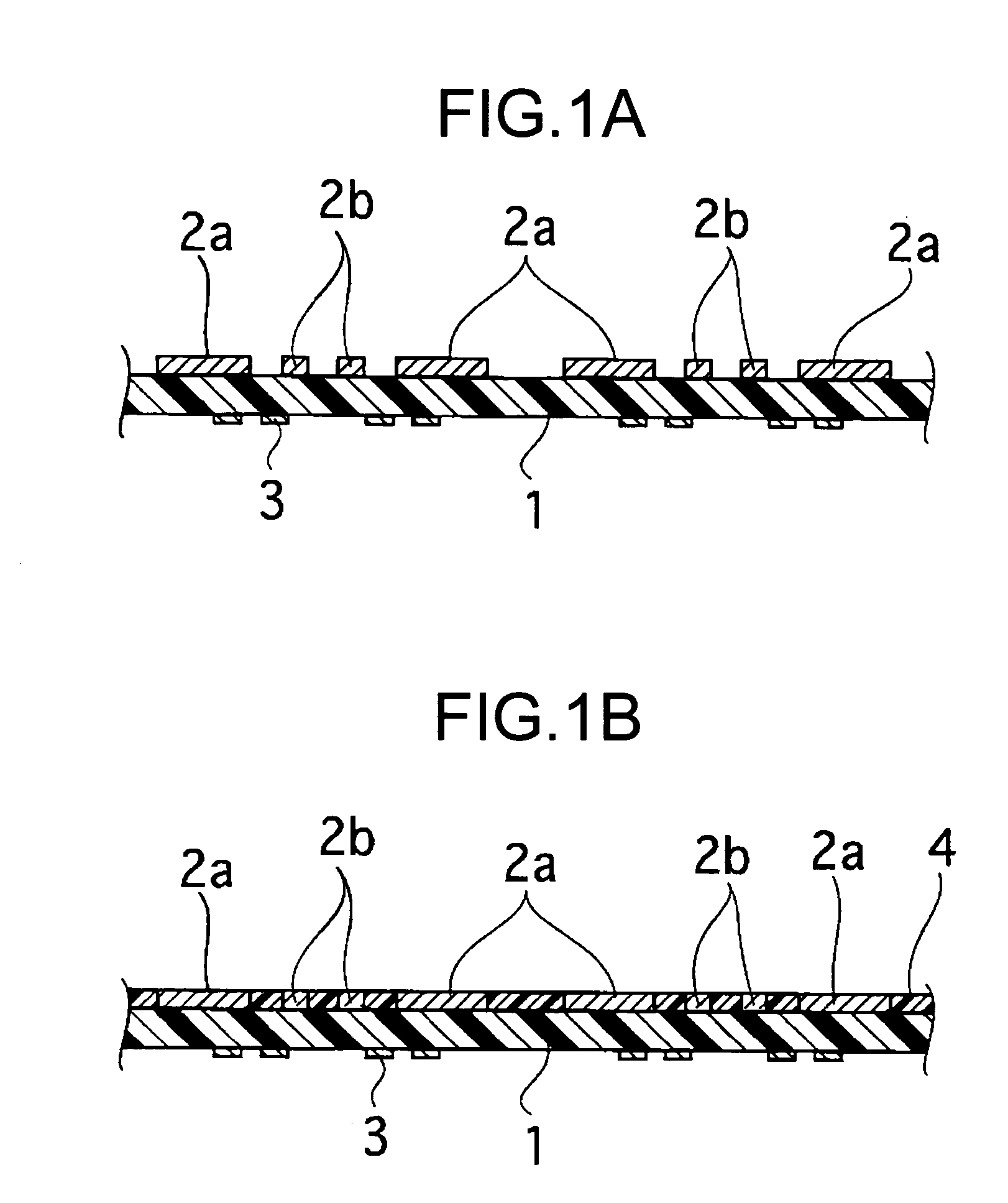

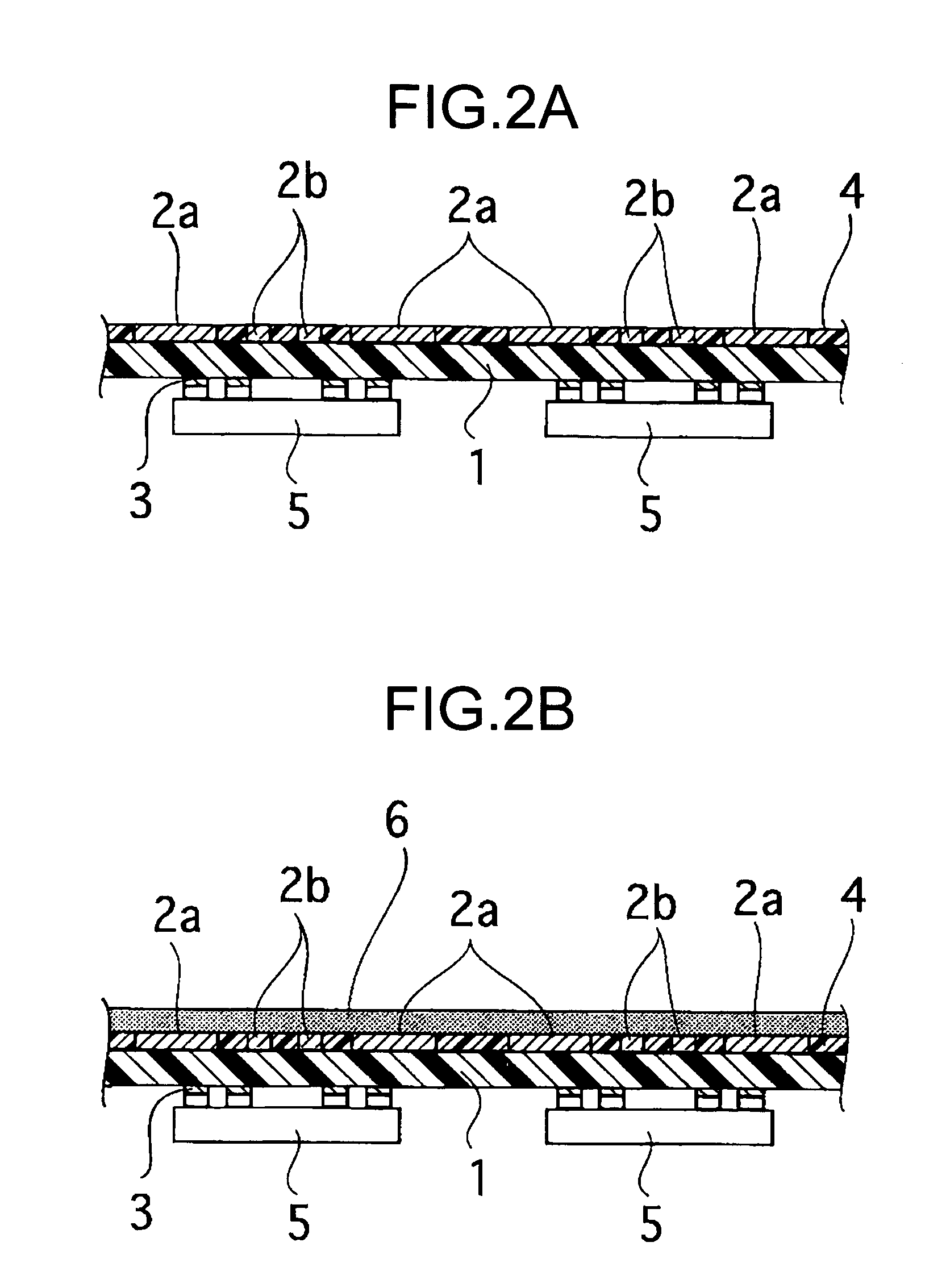

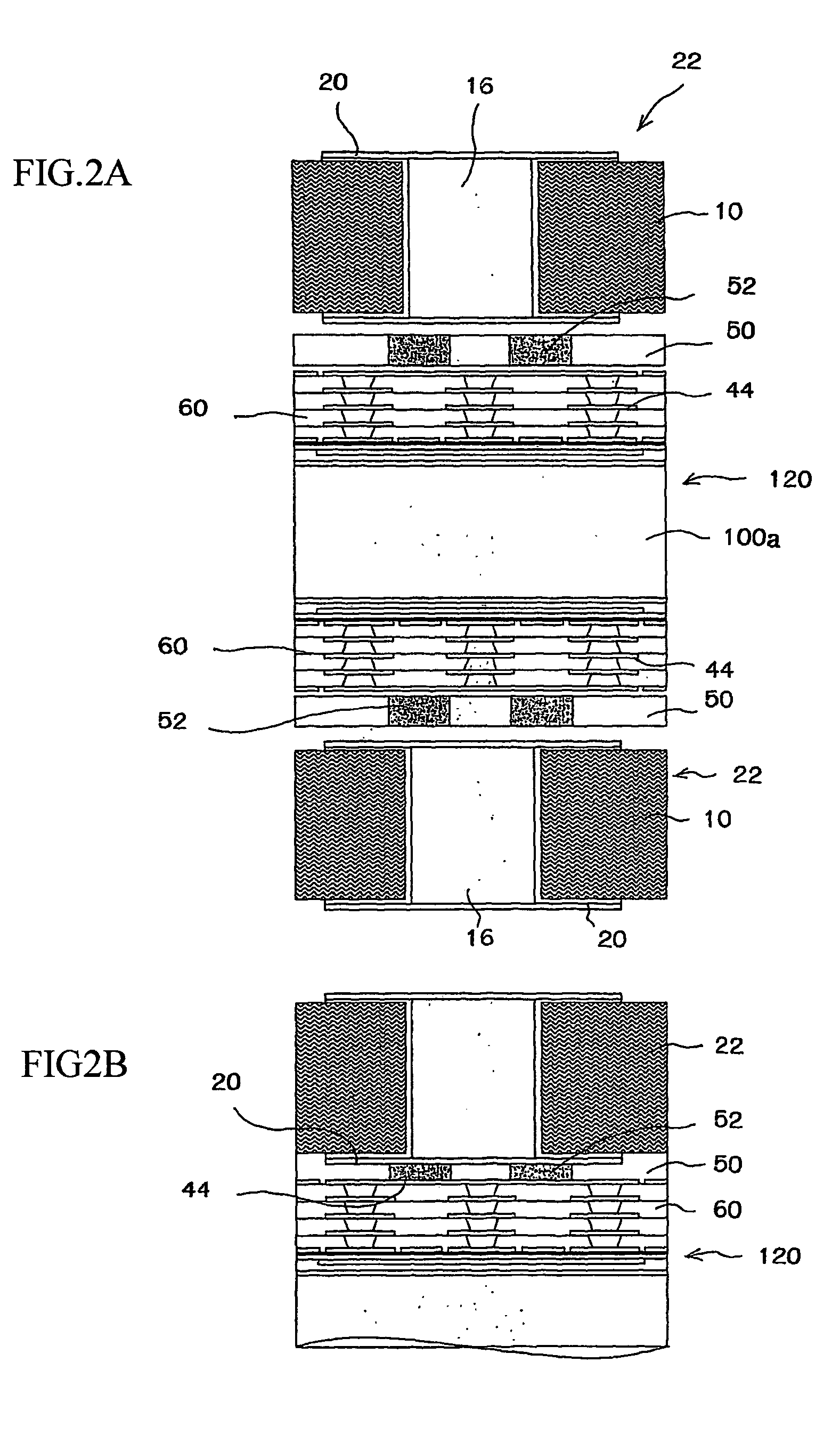

Connector sheet and wiring board, and production processes of the same

InactiveUS20050057906A1Low costHigh wiring densityPrinted circuit assemblingPrinted electric component incorporationEngineeringElectrically conductive

There is provided a connector sheet which includes an insulation sheet substrate having a front surface and a rear surface opposing to the front surface, and electrically conductive members each passing through the sheet substrate along a thickness direction of the sheet substrate, and the front surface and the rear surface contain a thermoset resin, and have tackiness under a first condition and develop adhesiveness under a second condition which is different from the first condition.

Owner:PANASONIC CORP

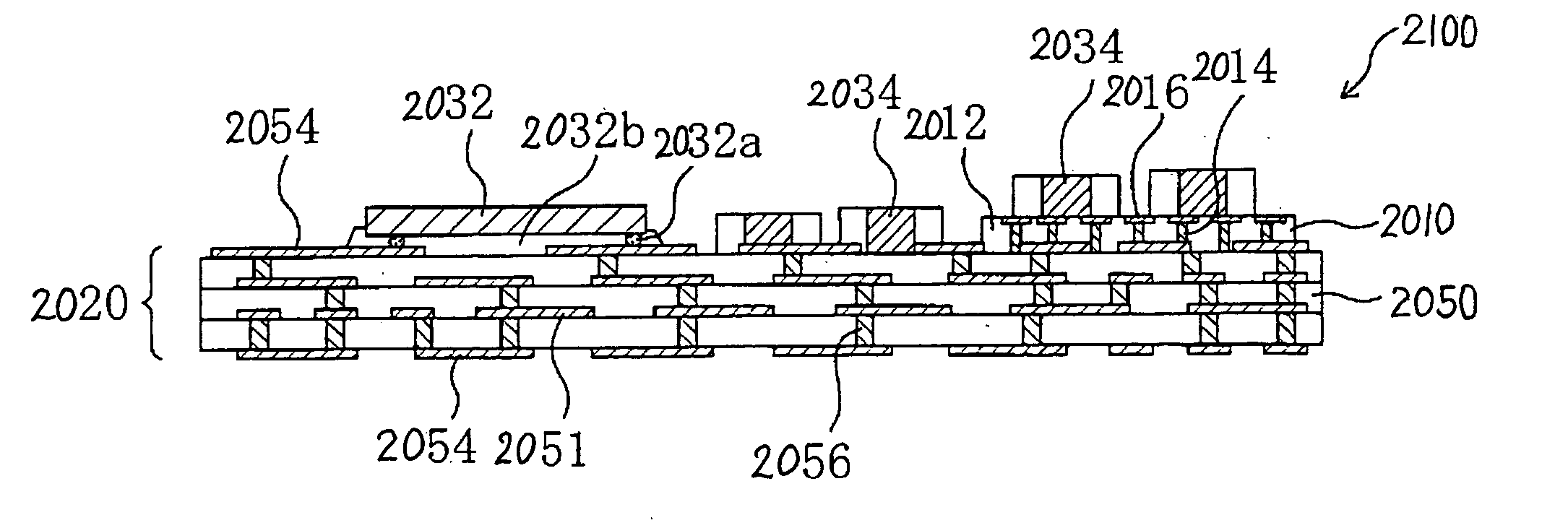

Method of manufacture of silicon based package

InactiveUS6878608B2Minimize the numberLarge reliable viasSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorInterconnection

A silicon based package (SBP) is formed starting with a thick wafer, which serves as the base for the SBP, composed of silicon which has a first surface and a reverse surface which are planar. Then form an interconnection structure including multilayer conductor patterns over the first surface. Form a temporary bond between the SBP and a wafer holder, with the wafer holder being a rigid structure. Thin the wafer to a desired thickness to form an Ultra Thin Silicon Wafer (UTSW) for the SBP. Forming via holes which extend through the UTSW, forming metallization in the via holes which extends through the UTSW, making electrical contact to the interconnection structure on the first surface. Then bond the metallization in the via holes to pads of a carrier.

Owner:GLOBALFOUNDRIES INC

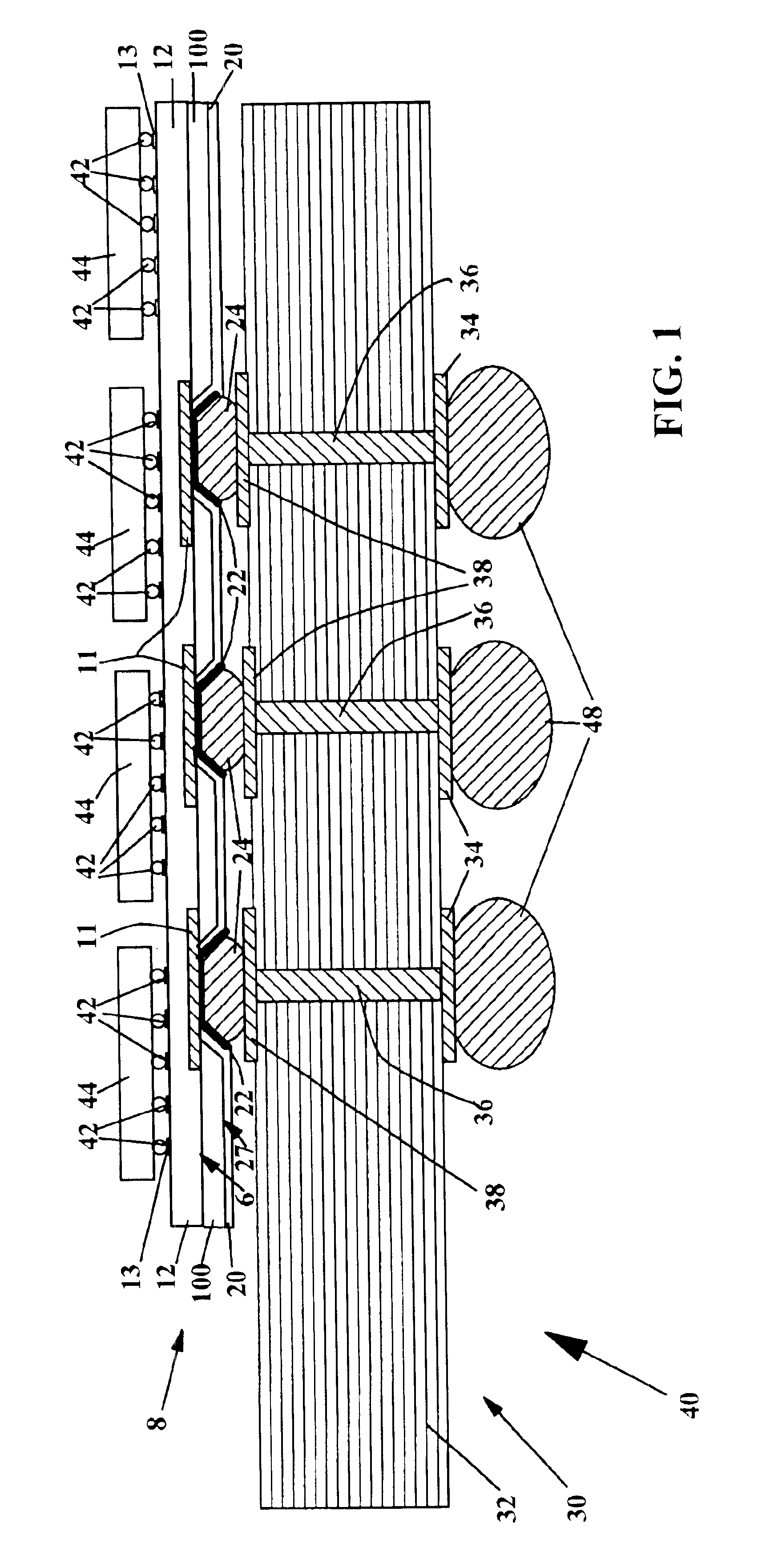

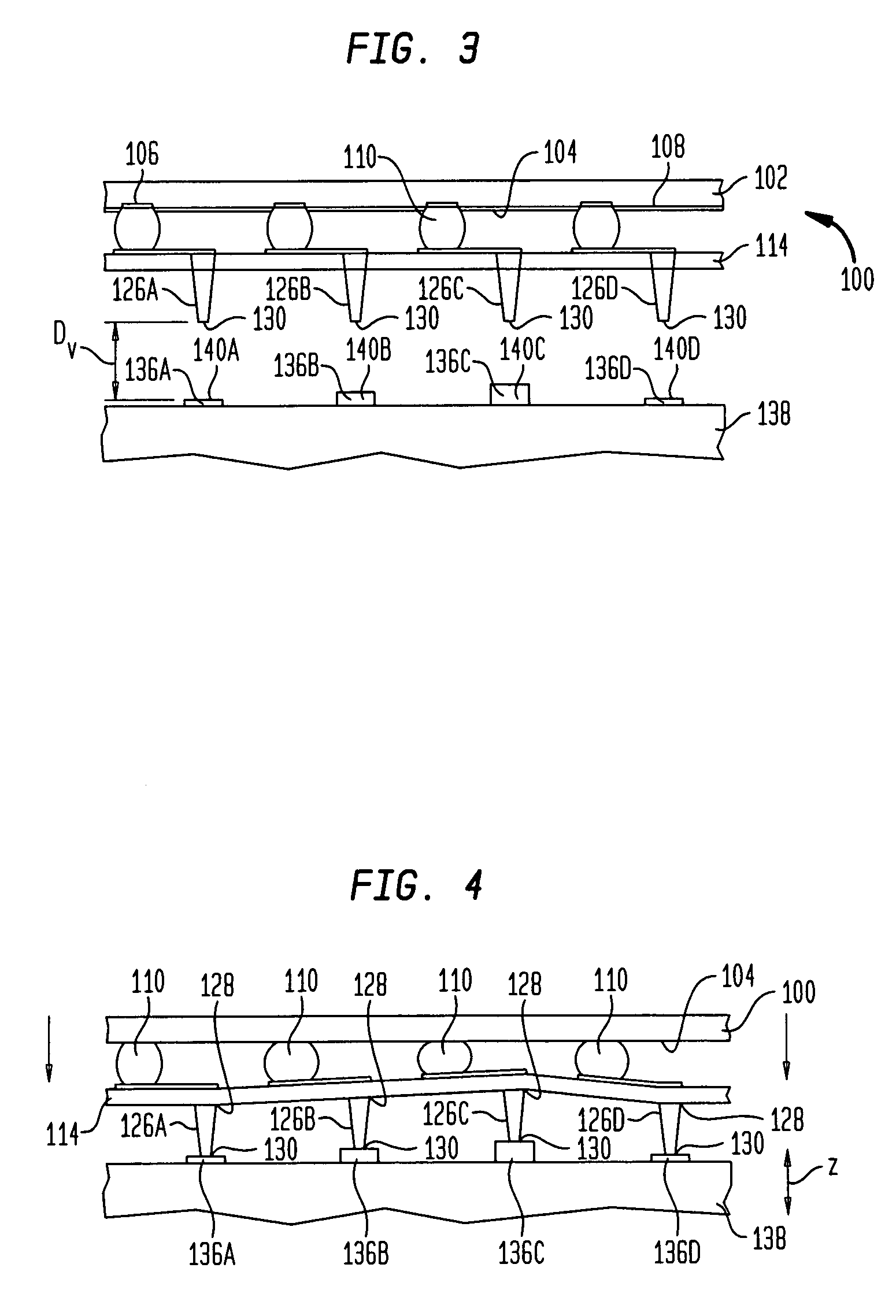

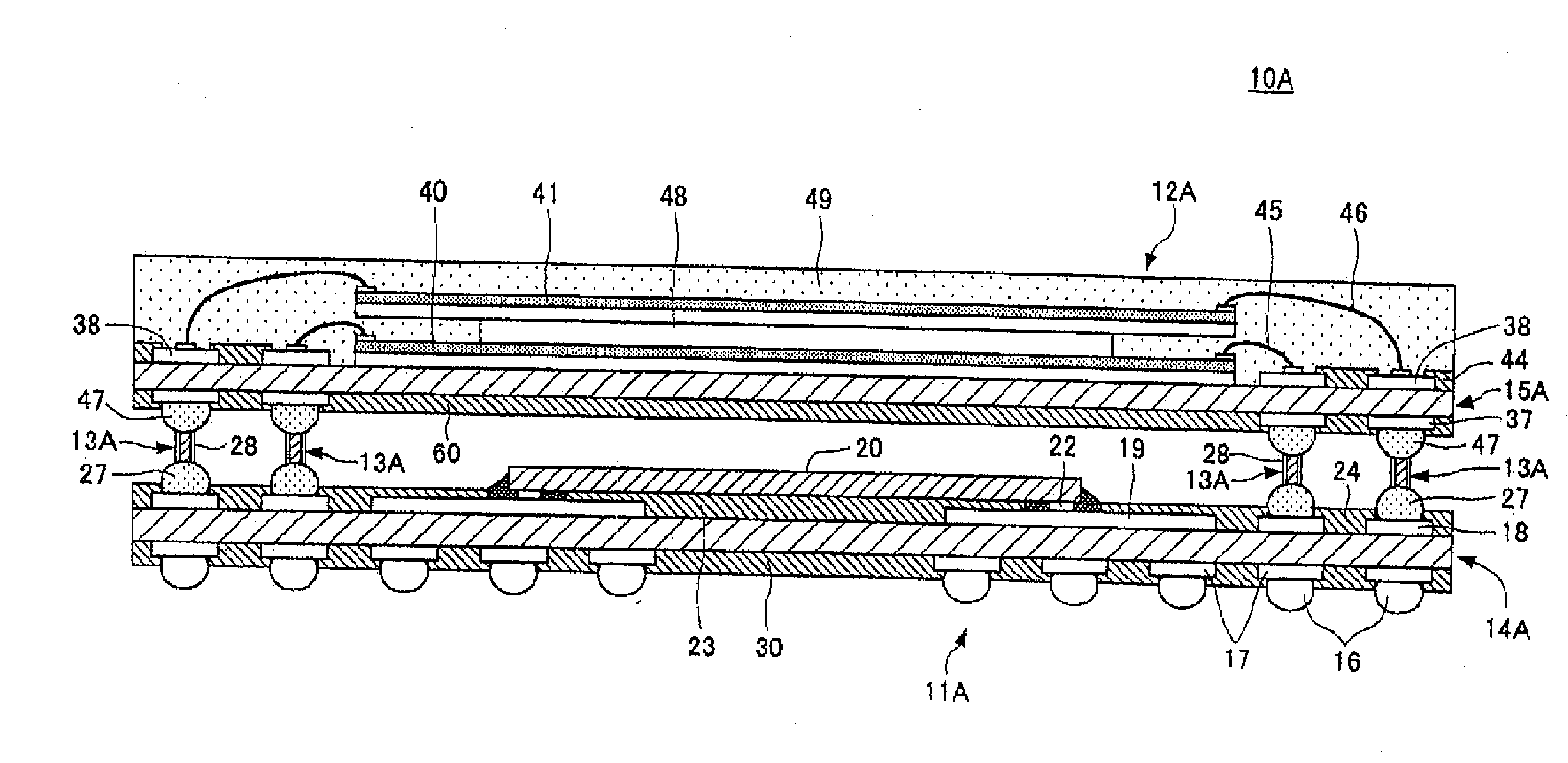

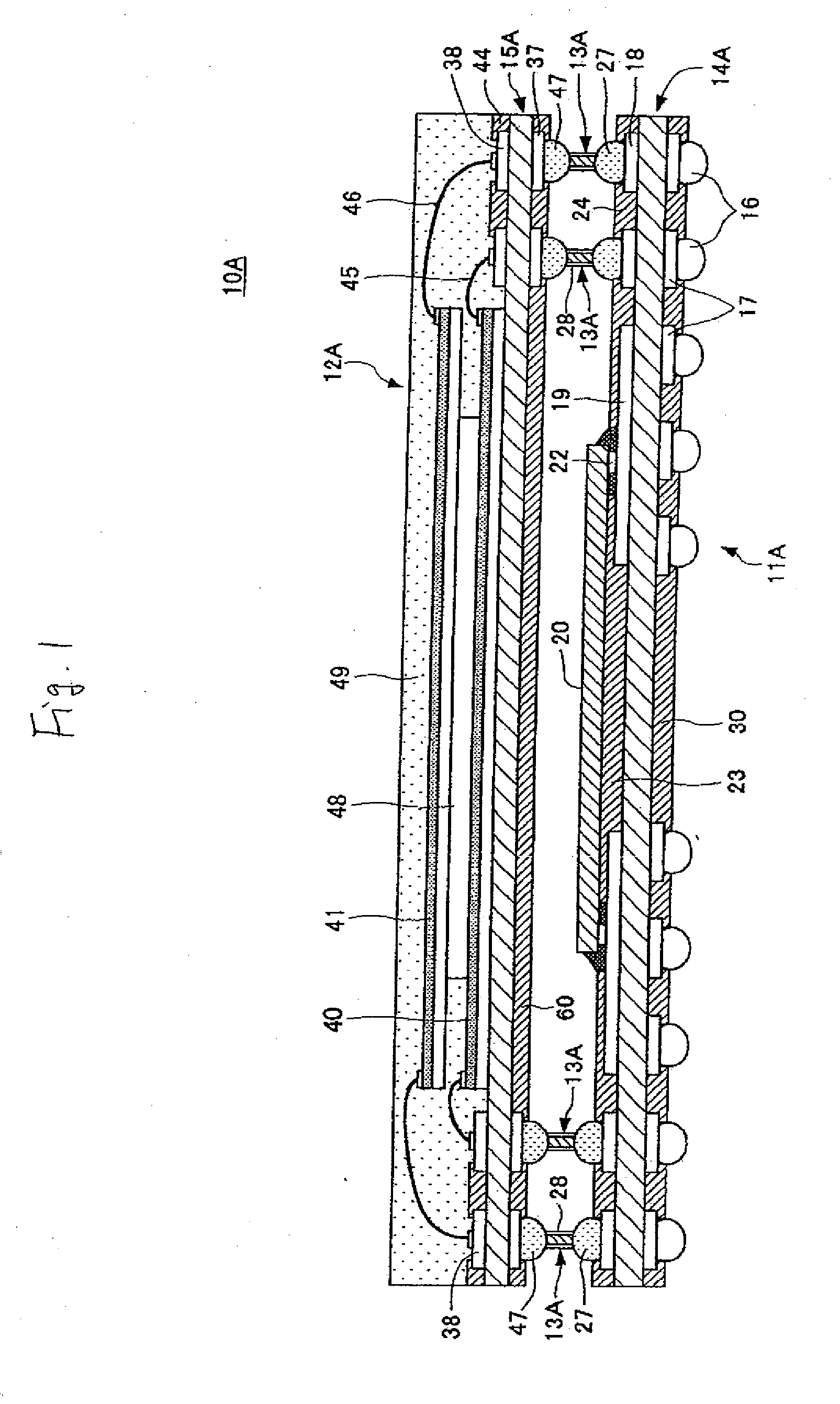

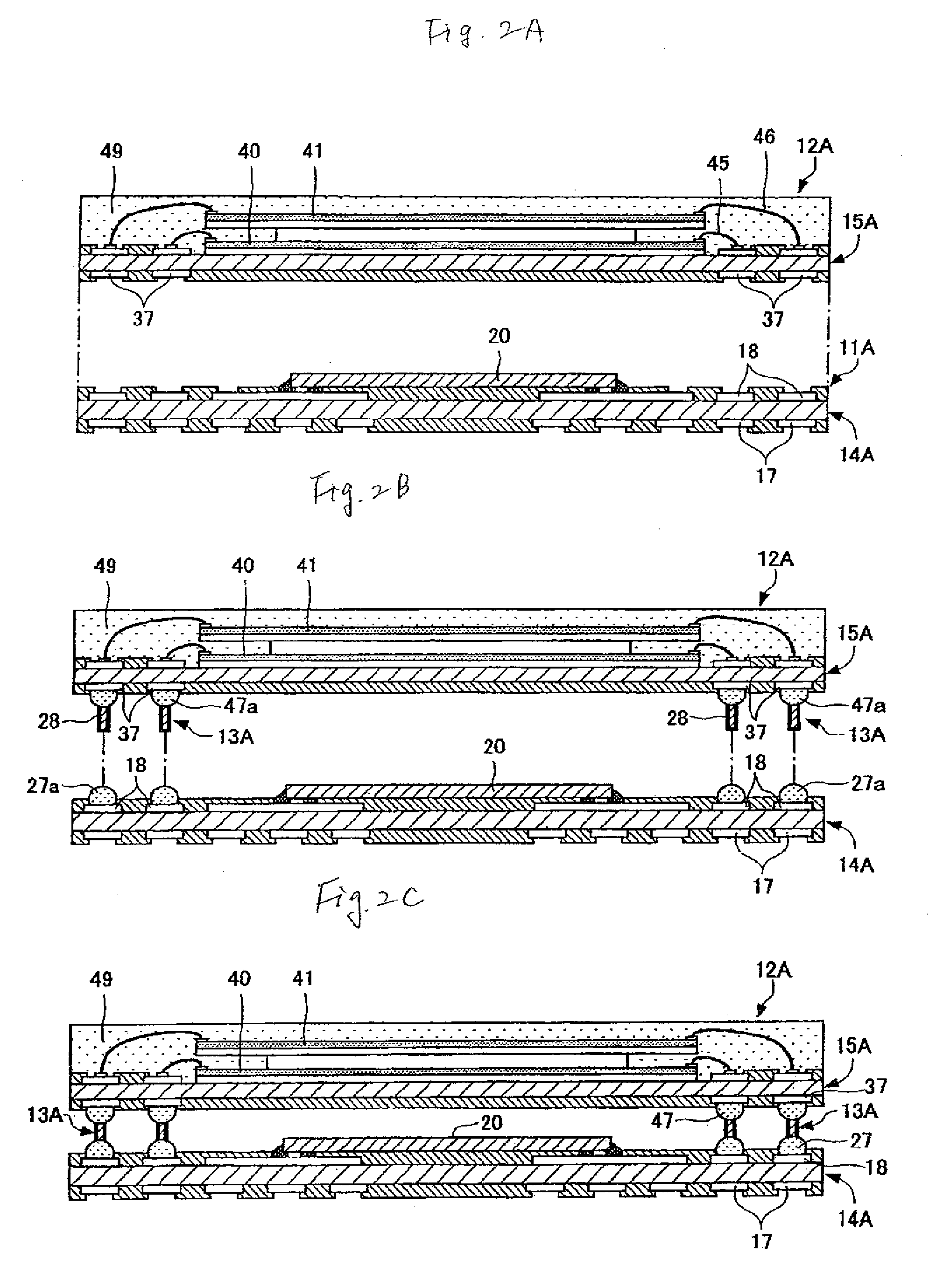

Microelectronic packages and methods therefor

ActiveUS7719121B2Convenient heightHigh wiring densitySemiconductor/solid-state device detailsSolid-state devicesEngineeringElectronic component

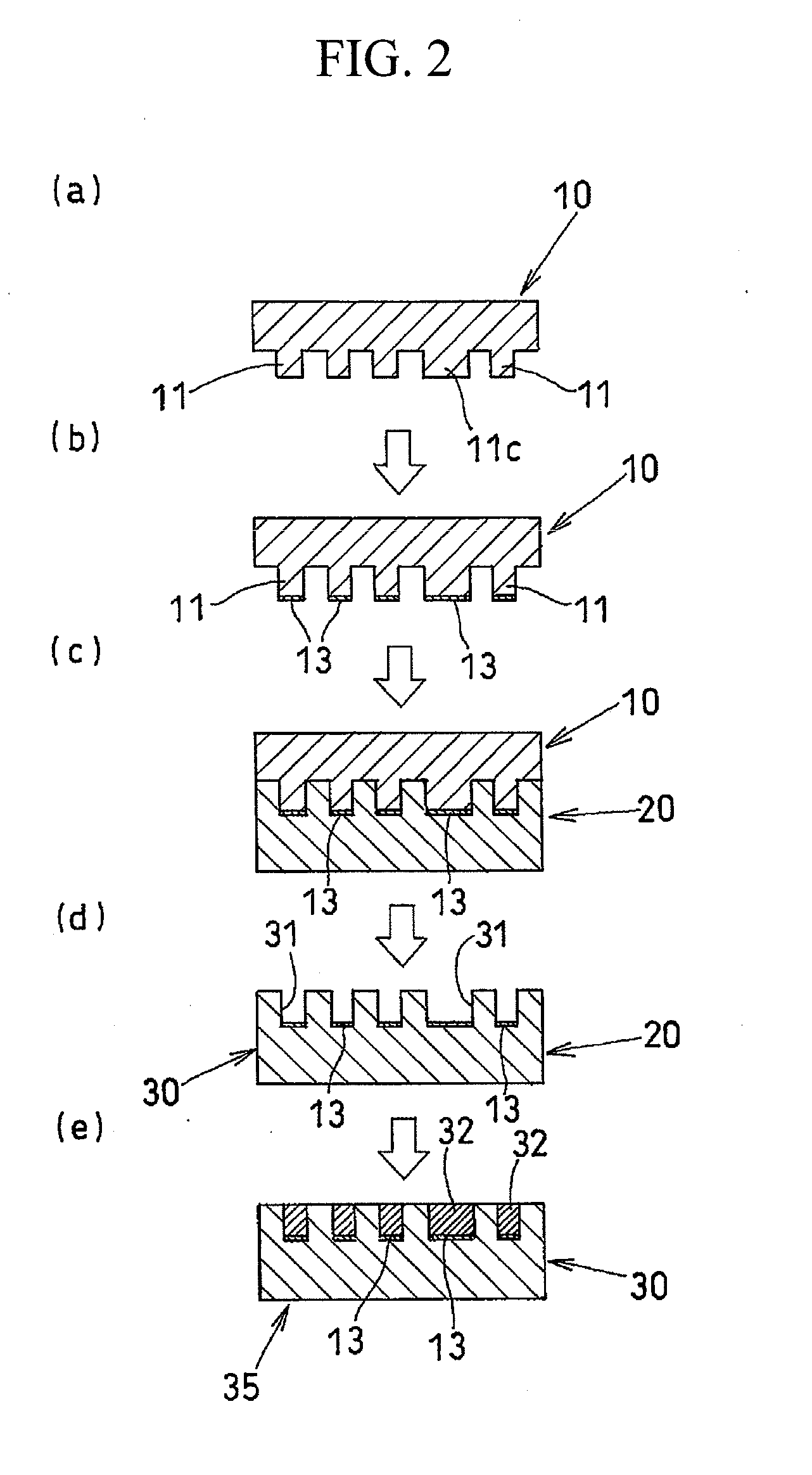

A microelectronic package includes a microelectronic element having contacts, a flexible substrate spaced from and overlying the microelectronic element and a plurality of conductive posts extending from the flexible substrate and projecting away from the microelectronic element. The conductive posts are electrically interconnected with the microelectronic element. Each conductive post has a conductive base that is in contact with the flexible substrate and a conductive tip that extends from the base, with the base of the conductive post having a larger diameter than the tip of the conductive post. In certain embodiments, the conductive base and the conductive tip have a cylindrical shape.

Owner:TESSERA INC

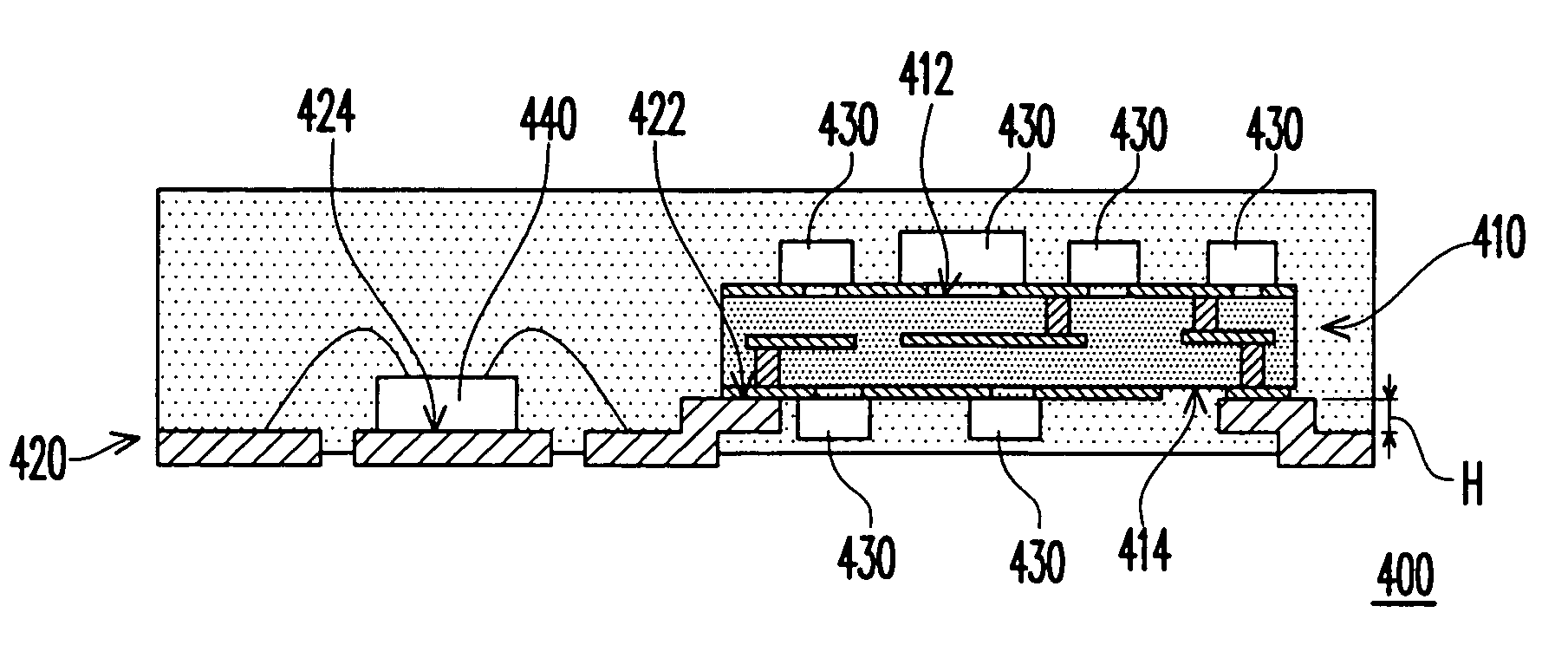

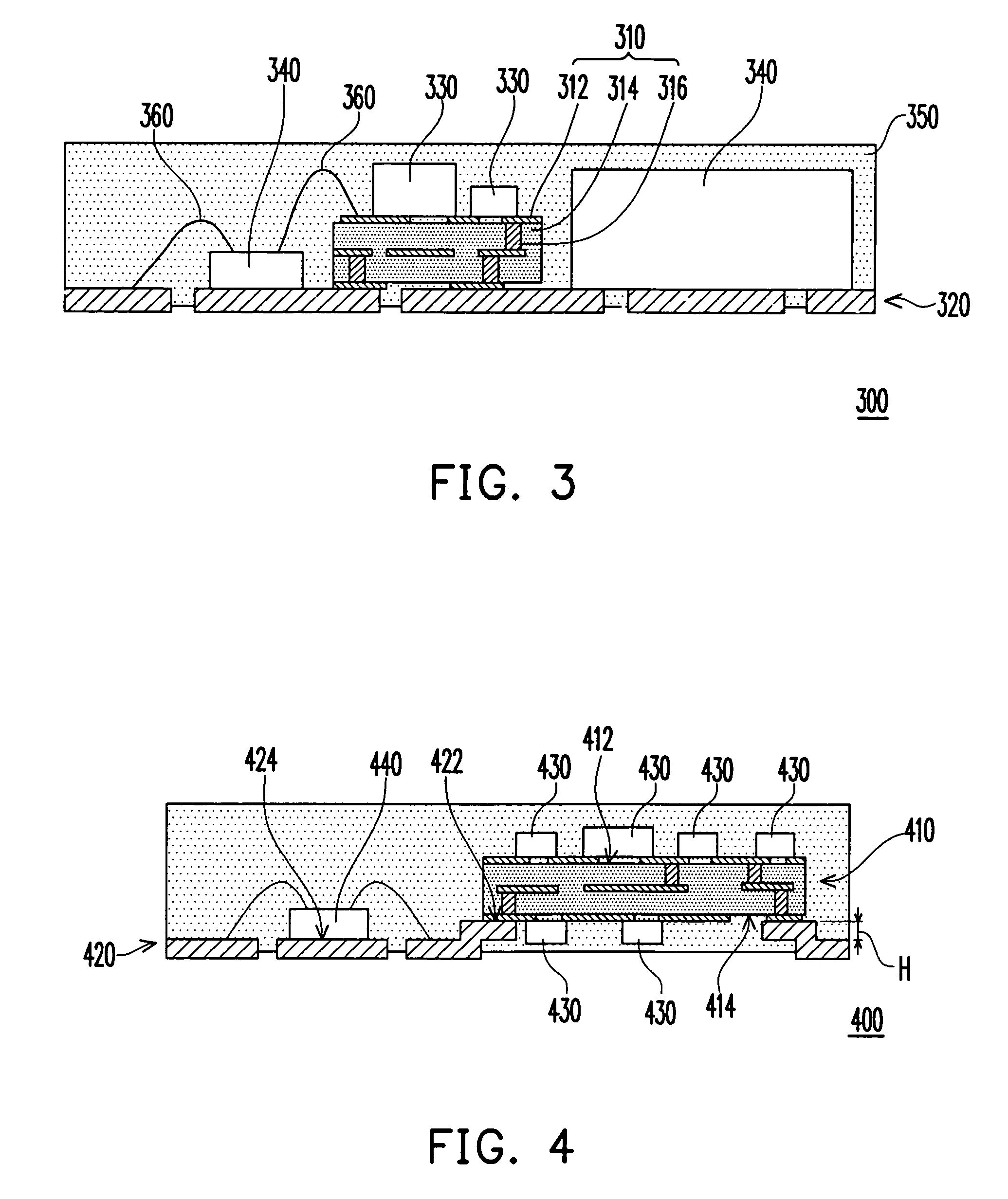

Package structure having through-silicon-via (TSV) chip embedded therein and fabrication method thereof

InactiveUS20120049366A1High wiring densitySemiconductor/solid-state device detailsSolid-state devicesElectricitySemiconductor chip

A package structure includes a dielectric layer having a first surface and a second surface; a through-silicon-via (TSV) chip embedded in the dielectric layer, wherein the TSV chip has a plurality of conductive TSVs, and electrode pads formed on a surface of the TSV chip that are electrically connected to the conductive TSVs and exposed from the second surface of the dielectric layer; and a first circuit layer formed on the first surface of the dielectric layer, wherein the first circuit layer is connected to the conductive TSVs of the TSV chip by the conductive blind vias, so that the high wiring density semiconductor chip can be disposed on the electrode pads of the TSV chip in order to integrate high wiring density semiconductor chips. The invention also provides a fabrication method for fabricating the package structure having an embedded TSV chip.

Owner:UNIMICRON TECH CORP

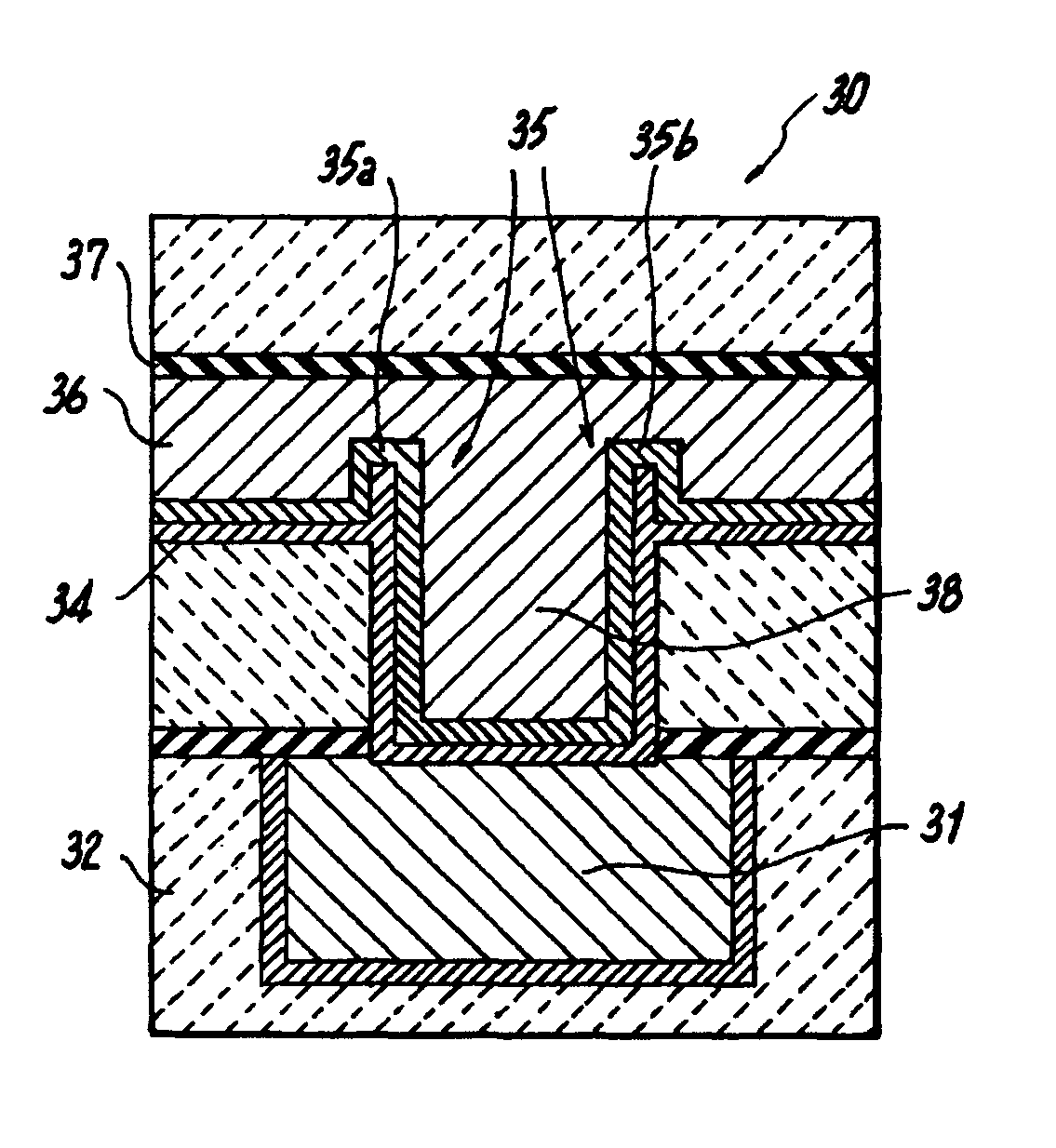

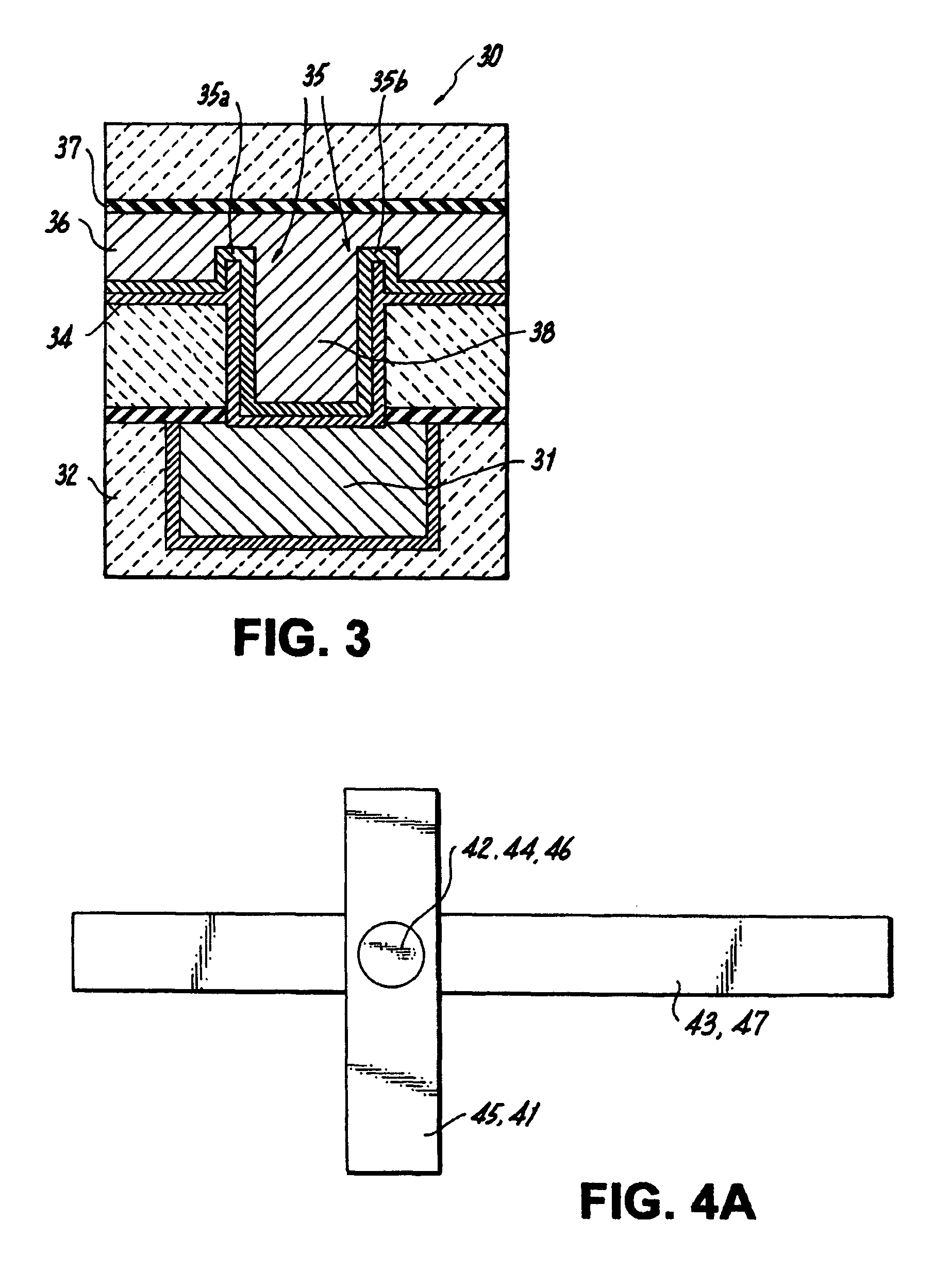

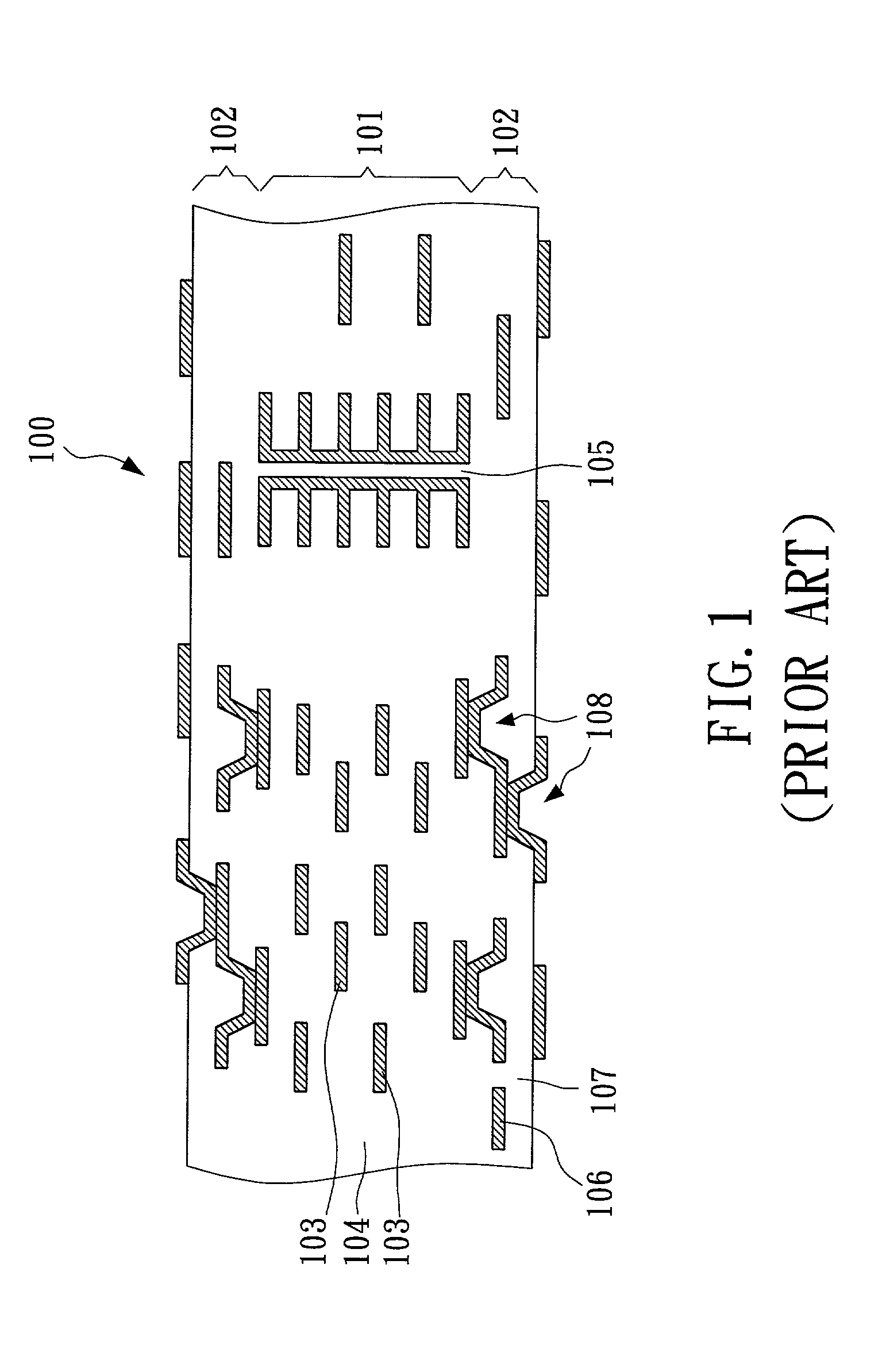

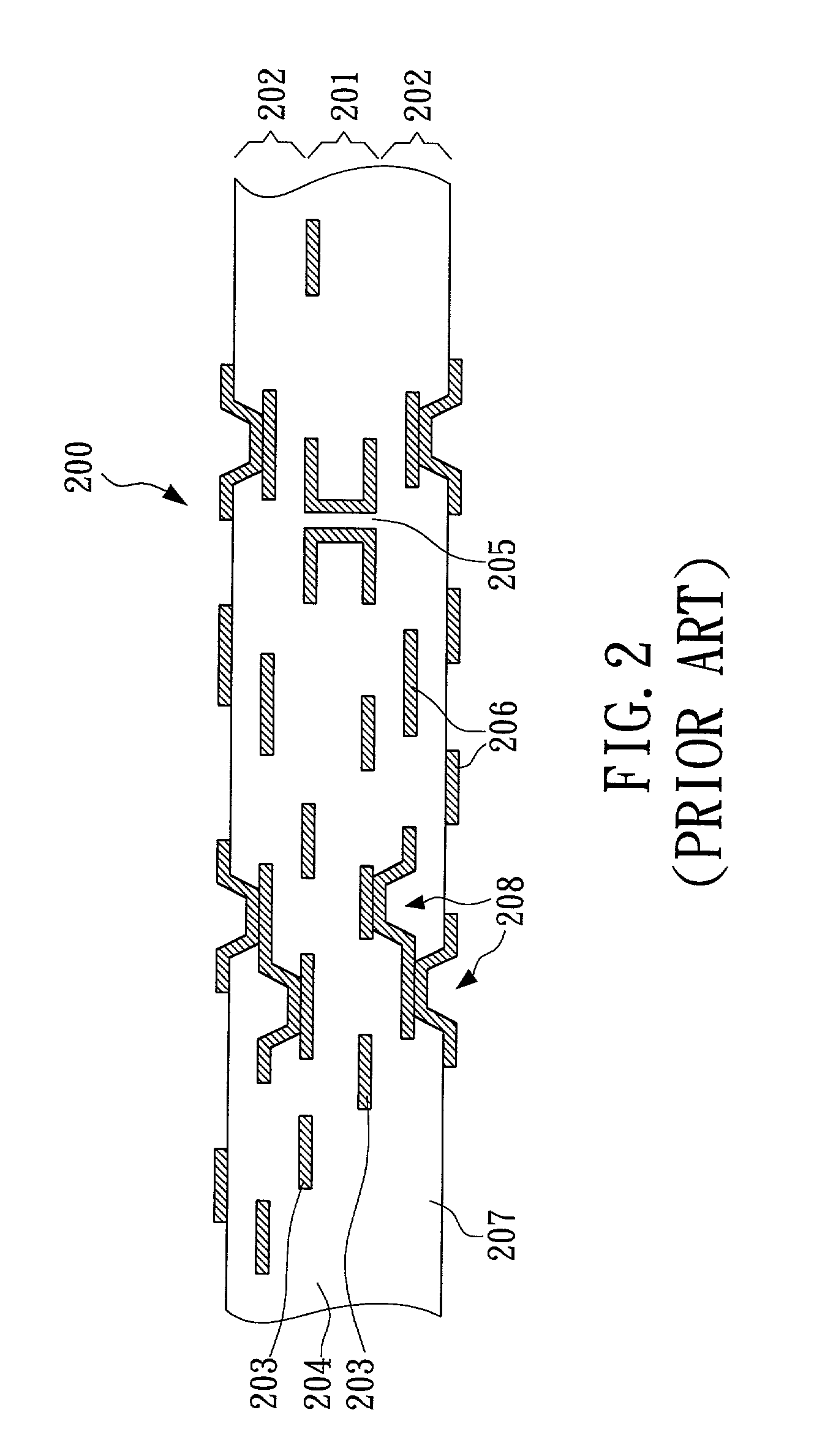

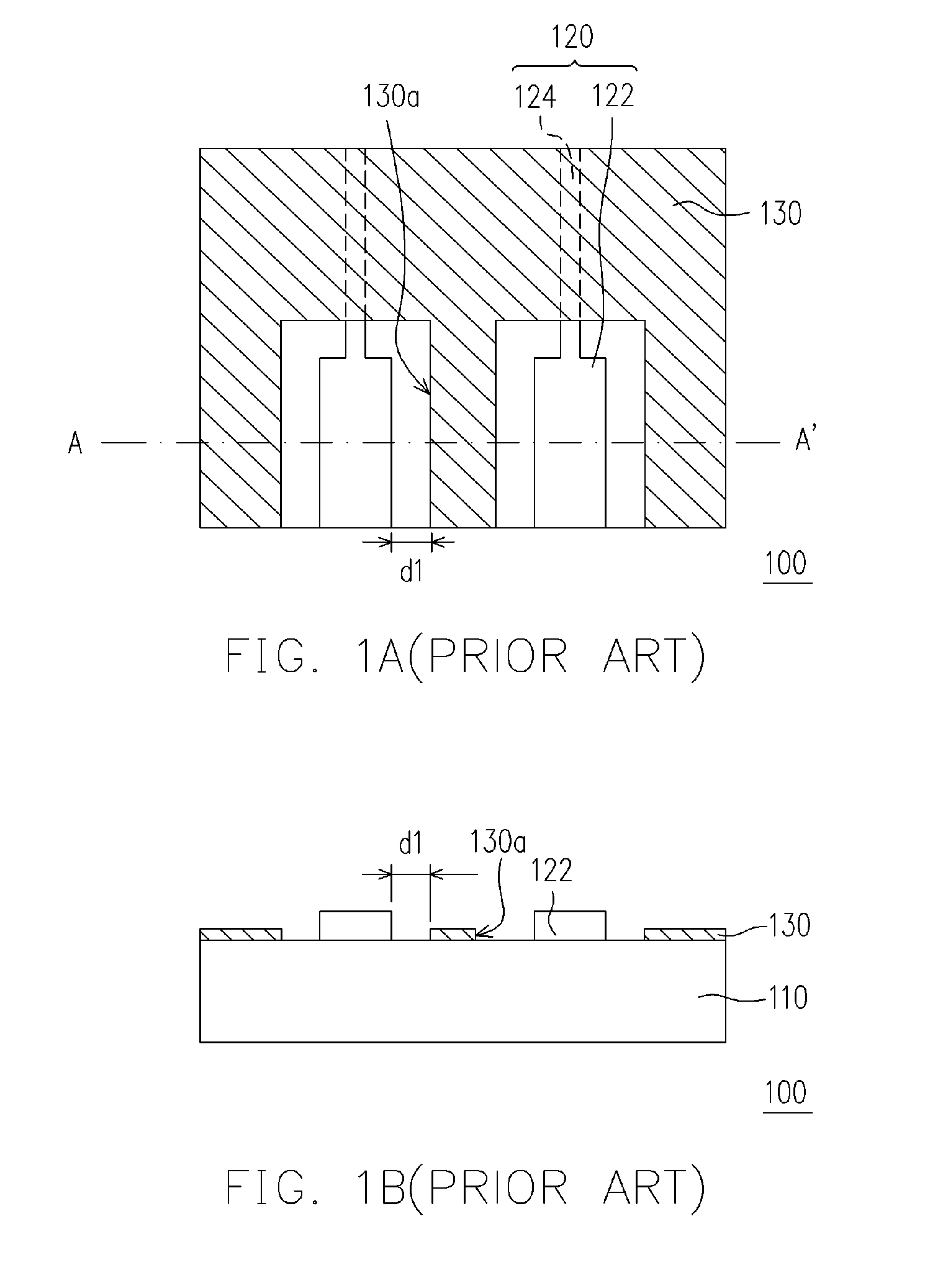

Partial inter-locking metal contact structure for semiconductor devices and method of manufacture

InactiveUS20050112957A1Improves Structural IntegrityHigh wiring densitySemiconductor/solid-state device detailsSolid-state devicesDevice materialEngineering

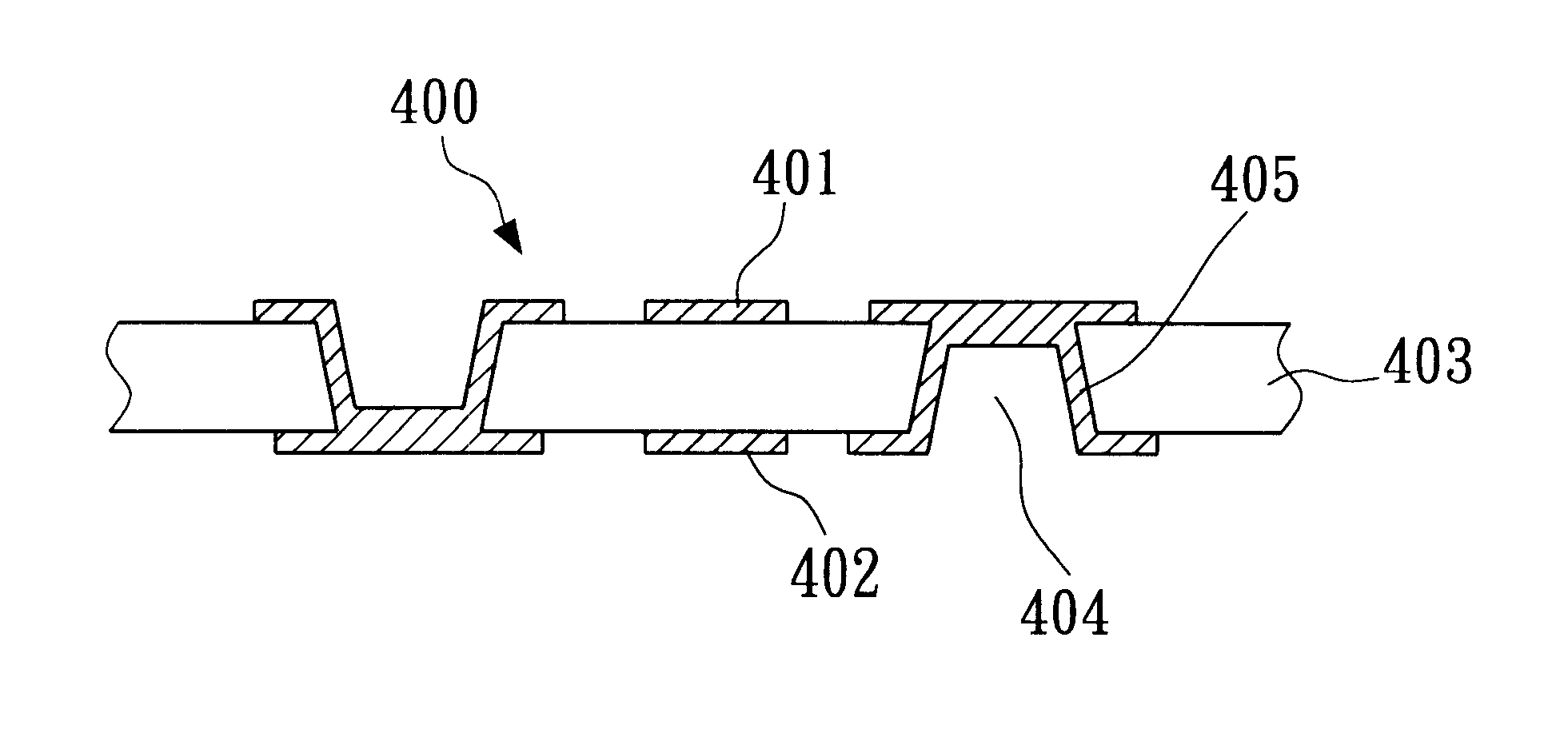

A structure and method of fabricating a “Lego”-like interlocking contact for high wiring density semiconductors is characterized in that the barrier liner formed in the contact via extends only partially upwards into the adjacent wire level. As a consequence, current crowding and related reliability problems associated with conventional prior art interconnect structures is avoided and structural integrity of the contact via (metal stud) structure is enhanced. The novel “crown” shape of the Lego-like interlocking contact structure that is fabricated to extend in an upward direction may be employed for other integrated circuit applications including forming capacitor (e.g., MIMCAP) and heat sink structures due to its increased surface area.

Owner:IBM CORP

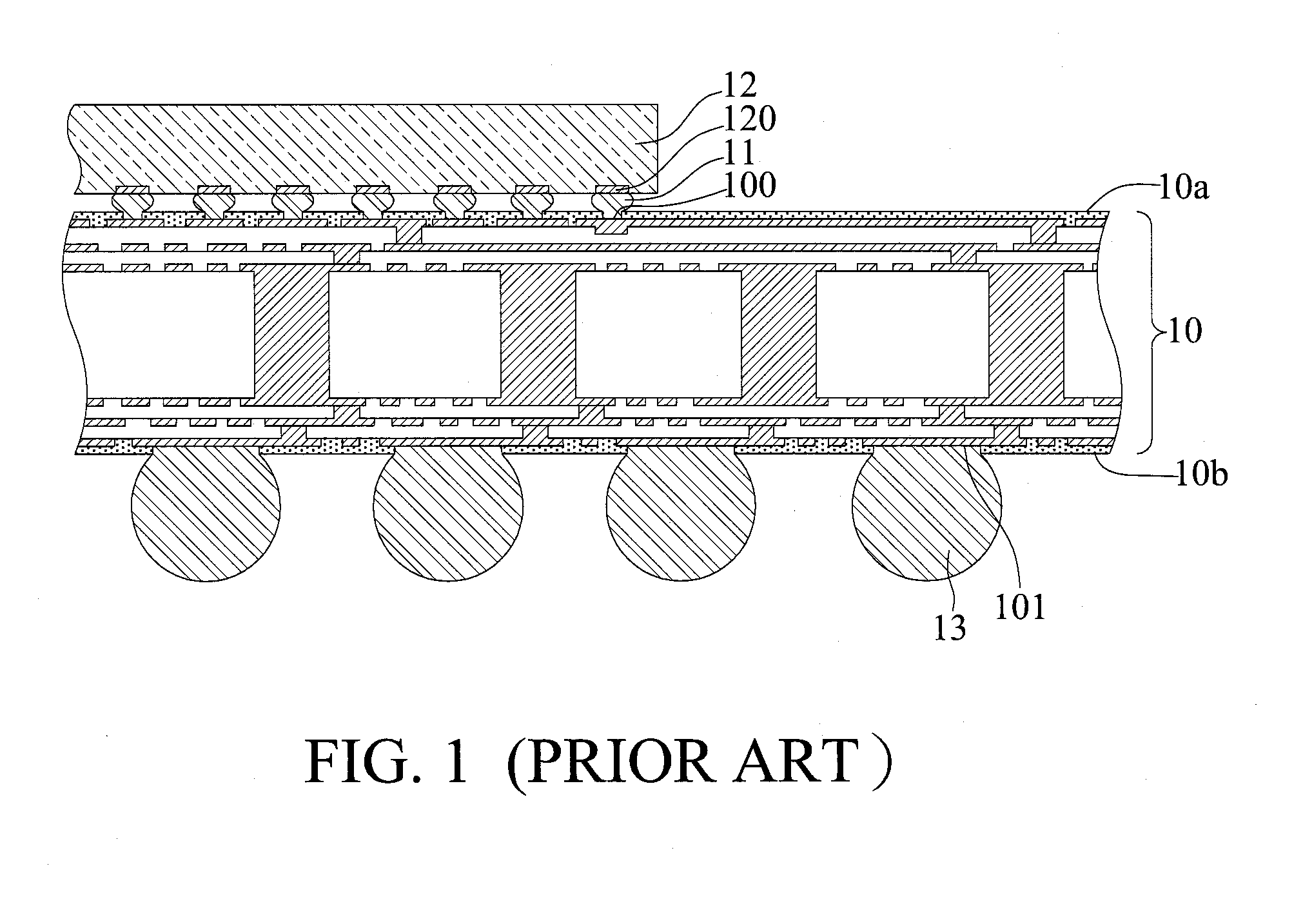

Stacked package and method for manufacturing the package

ActiveUS20080142944A1Reduce number of component and costHigh wiring densityFinal product manufactureSemiconductor/solid-state device detailsSemiconductor componentsR package

In a stacked package in which a plurality of packages having semiconductor elements mounted on substrates are stacked, while being electrically connected together, by use of connection sections, wherein the connection sections are formed from pillar-like members and solder joint sections and the upper package is supported on the lower package by pillar-like members.

Owner:SHINKO ELECTRIC IND CO LTD

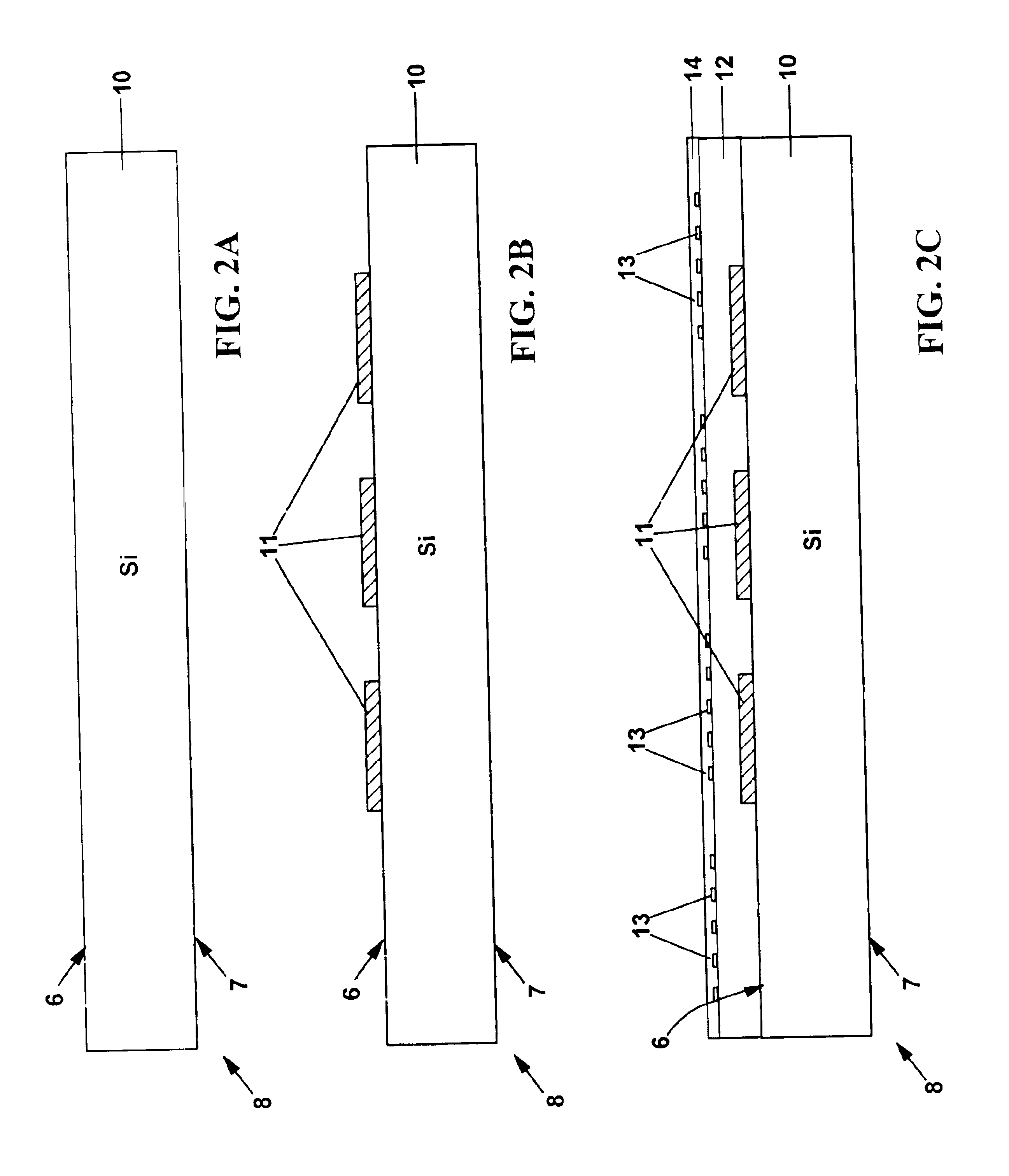

Method of manufacture of silicon based package and devices manufactured thereby

InactiveUS20070111385A1Large reliable viasMinimize the numberSemiconductor/solid-state device detailsSolid-state devicesElectrical conductorEngineering

A Silicon Based Package (SBP) is formed starting with a thick wafer, which serves as the base for the SBP, composed of silicon which has a first surface and a reverse surface which are planar. Then form an interconnection structure including metal capture structures in contact with the first surface and multilayer conductor patterns over the first surface. Form a temporary bond between the SBP and a wafer holder, with the wafer holder being a rigid structure. Thin the reverse side of the wafer to a desired thickness to form an Ultra Thin Silicon Wafer (UTSW) for the SBP. Form via holes with tapered or vertical sidewalls, which extend through the UTSW to reach the metal capture structures. Then form metal pads in the via holes which extend through the UTSW, making electrical contact to the metal capture structures. Then bond the metal pads in the via holes to pads of a carrier.

Owner:GLOBALFOUNDRIES U S INC

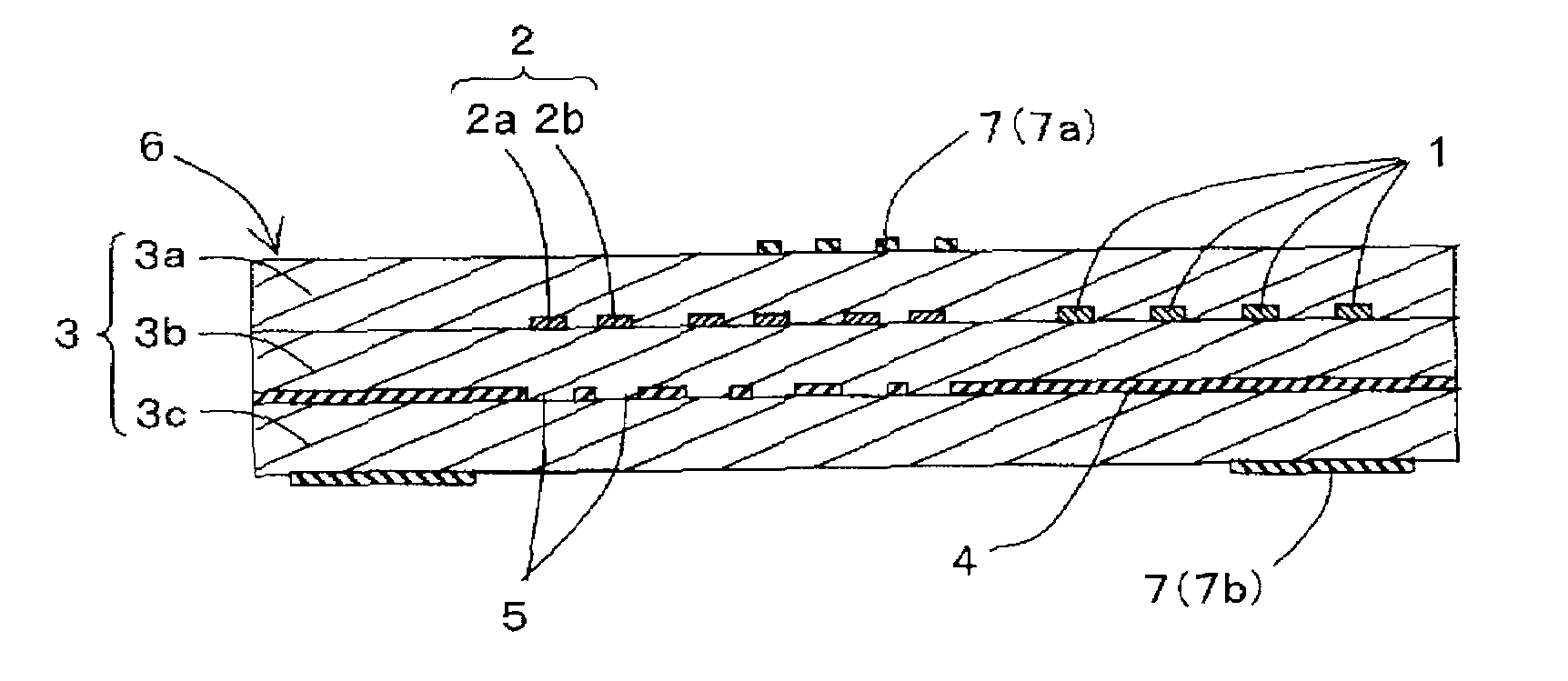

Wiring structure, multilayer wiring board, and electronic device

InactiveUS20070222052A1Facilitates impedance matchingHigh wiring densitySemiconductor/solid-state device detailsHigh frequency circuit adaptationsWave shapeSignal lines

A wiring structure includes a general signal line, a differential signal line having a pair of signal wiring lines and a reference potential layer. The signal wiring lines respectively transmit differential signals of which waveforms are inverted from each other. The reference potential layer is arranged to have a distance from the general signal line and the differential signal line, and has a non-formed portion in a region to be electromagnetically coupled to the differential signal line.

Owner:KYOCERA CORP

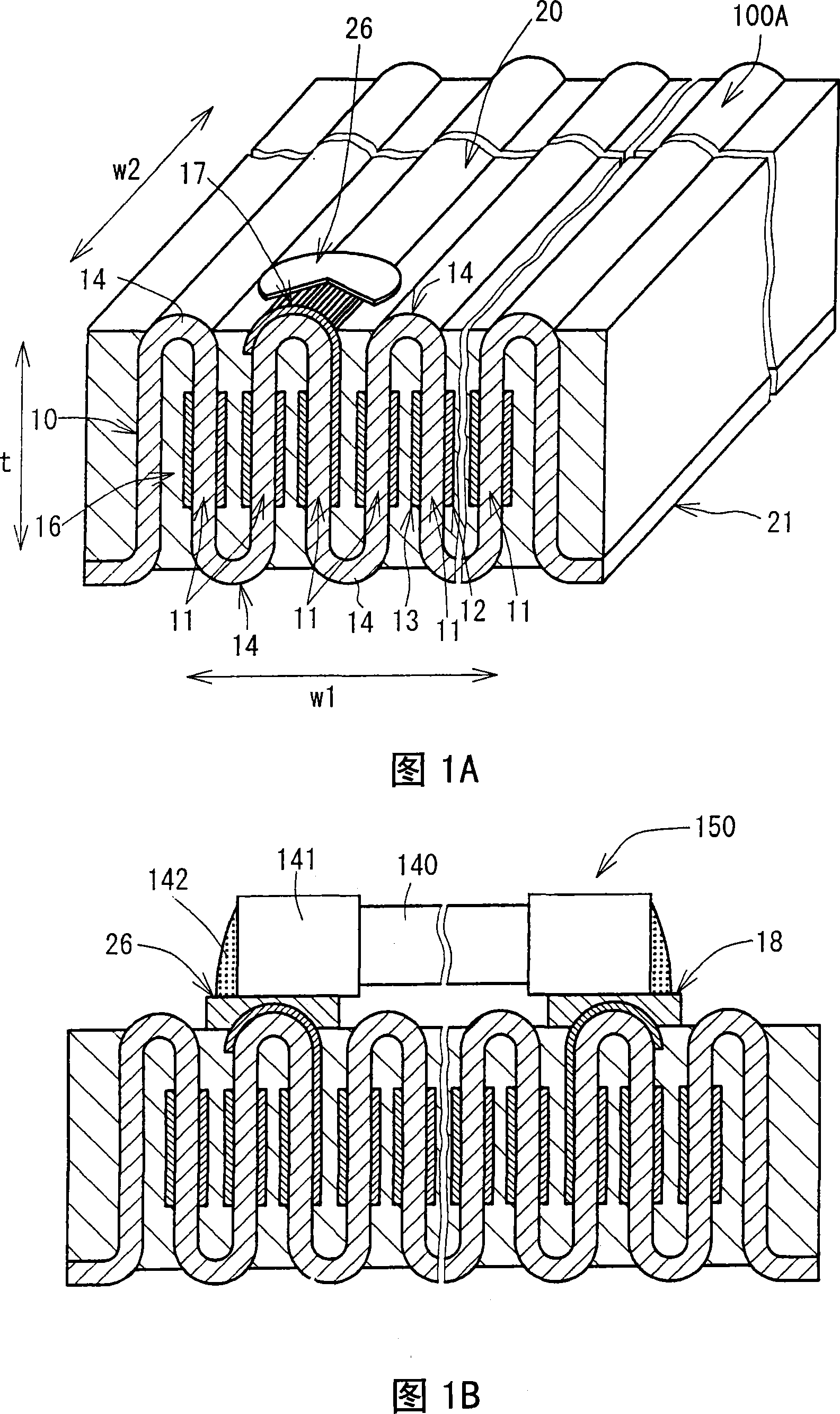

Thin film magnetic head and manufacturing method thereof

ActiveUS20050128639A1Maximize sectional areaLower coil resistanceConstruction of head windingsRecord information storageEngineeringHelix

The invention is directed to improvement of a write element of a thin film magnetic head. In said write element, a first coil and a second coil are provided on a first insulating film formed on one surface of a first magnetic film and surround in a spiral form a back gap portion. A second yoke portion in the upper position comprises a wide portion, a narrow portion and a sloping flare portion. The wide portion has a flat surface and is connected to the first magnetic film by a back gap portion at the rear of the medium-facing surface. The narrow portion forms the second pole portion and the surface of the narrow portion being at a lower position than the surface of the wide portion. The sloping flare portion extends from the narrow portion to the wide portion, gradually increasing in width and its surface sloping upward away from the surface of the narrow portion to the surface of the wide portion.

Owner:HEADWAY TECH INC +1

Thin core substrate for fabricating a build-up circuit board

InactiveUS20020152611A1High wiring densityPrinted circuit assemblingLine/current collector detailsElectrically conductive

Disclosed is a method of preparing a thin core substrate for fabricating a build-up multilayer circuit board. The method involves the use of an insulating layer which is covered with the electrically conductive sheets. The openings are made in the electrically conductive layers at the predetermined positions, where the vias are also formed in the insulating layer. An electrically conductive layer is deposited to cover the vias. After the electrically conductive sheets and layer are patterned, a thin core substrate is constructed. The build-up layers are then made at least one side of the thin core substrate to form a build-up multilayer circuit board.

Owner:PHOENIX PRECISION TECH CORP

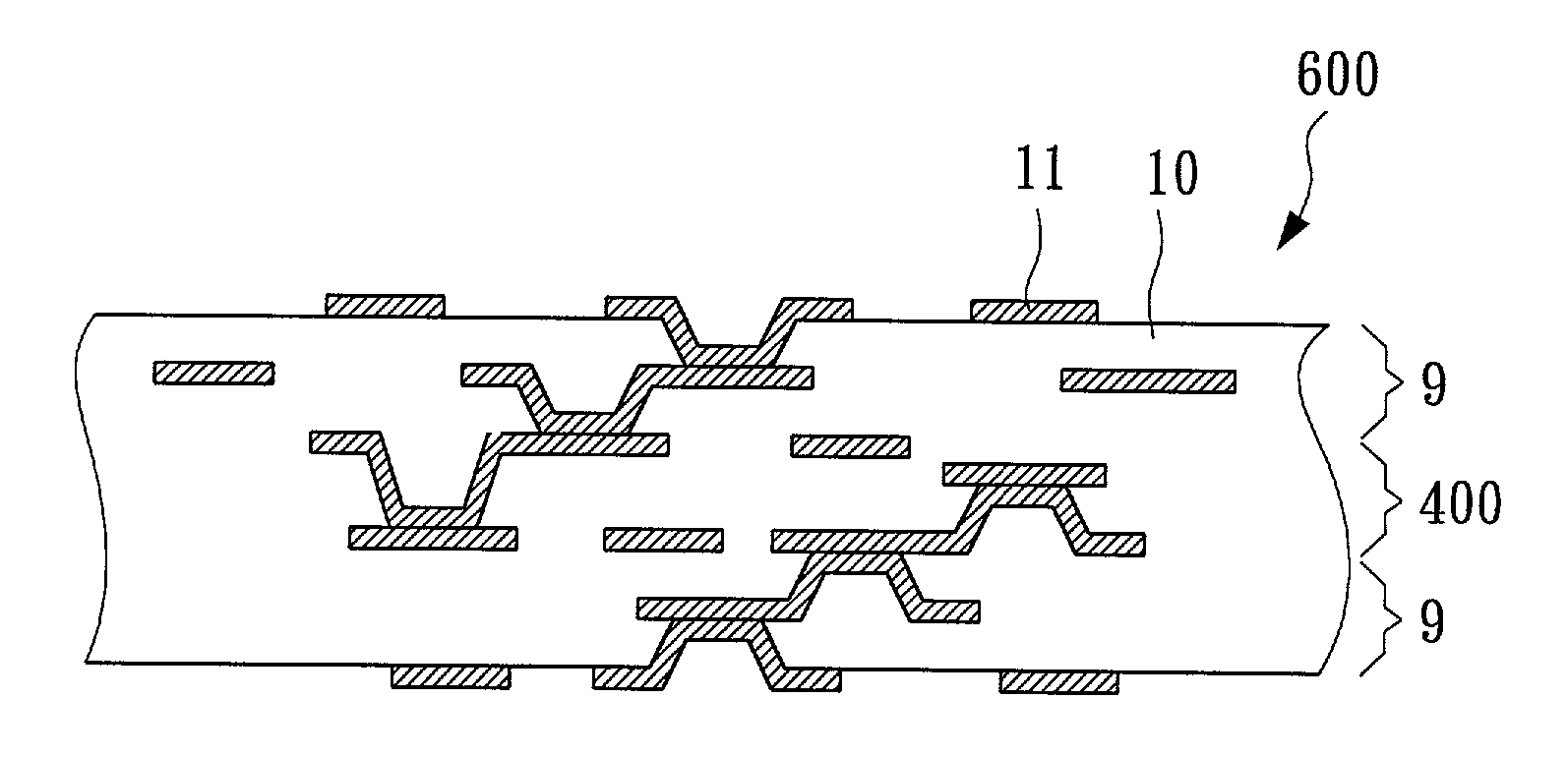

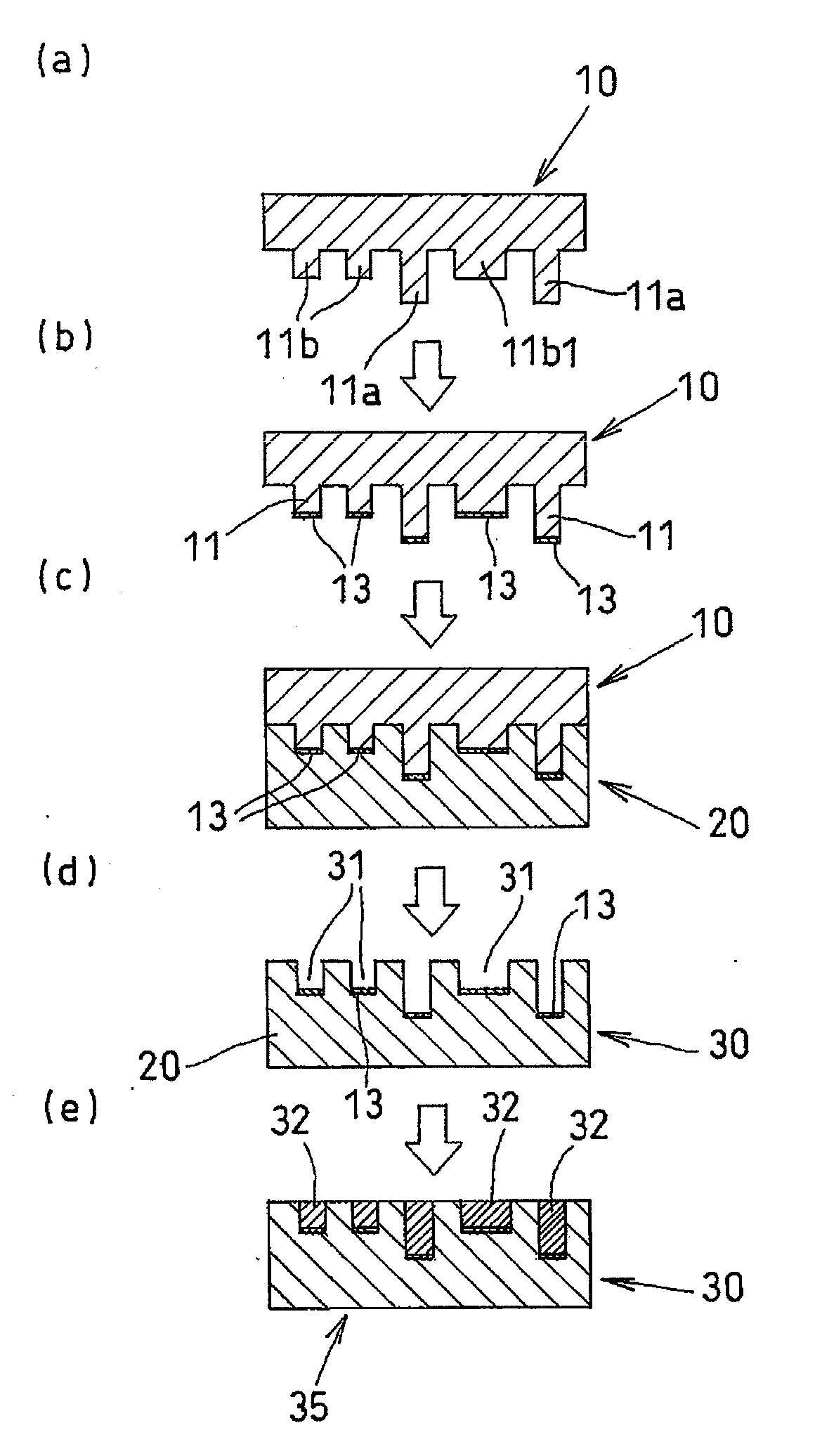

Circuit board and method for manufacturing the same

InactiveUS20100270057A1Simple manufacturing processHigh densityLine/current collector detailsPrinted circuit aspectsHigh densityConductive materials

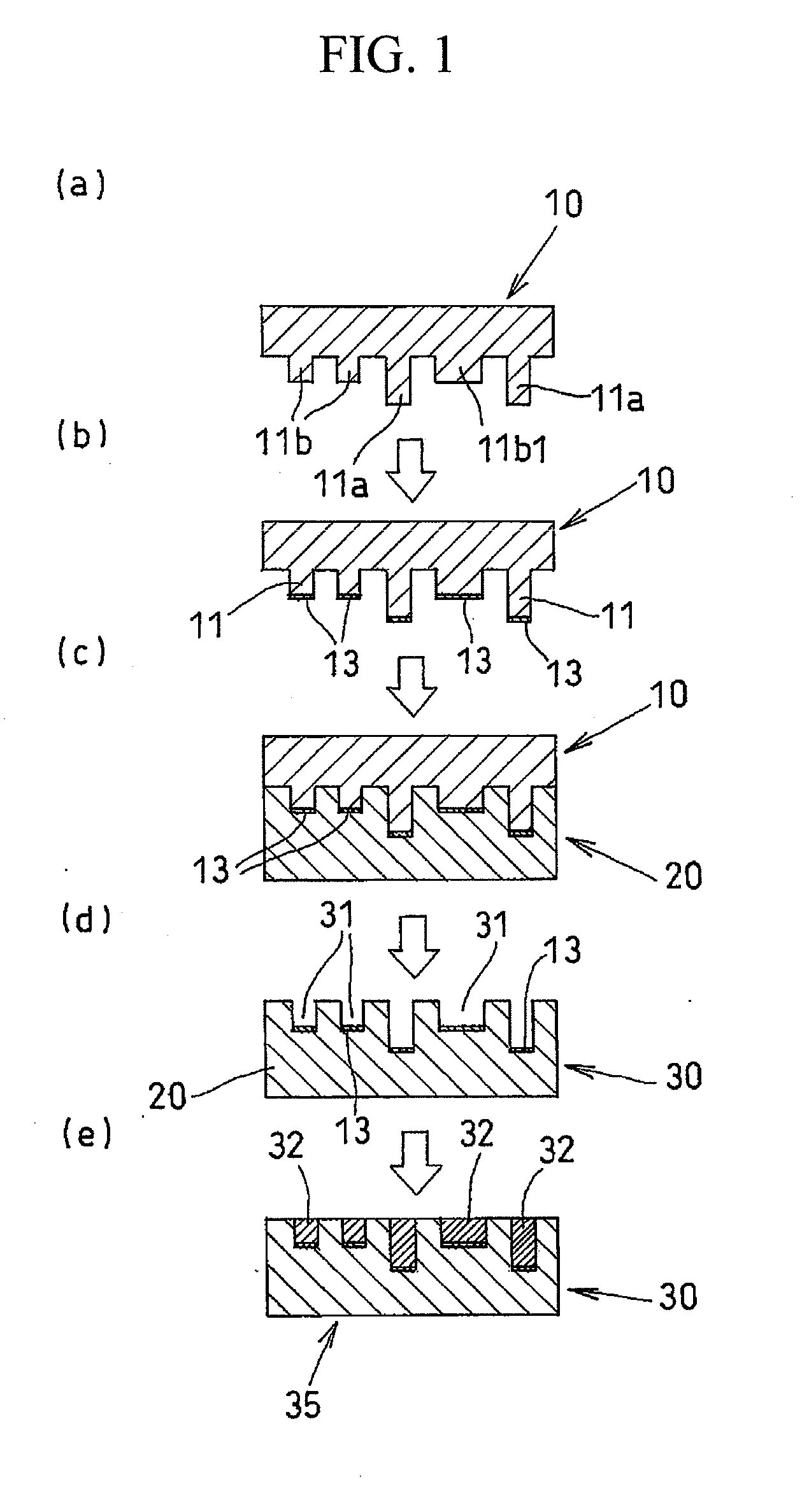

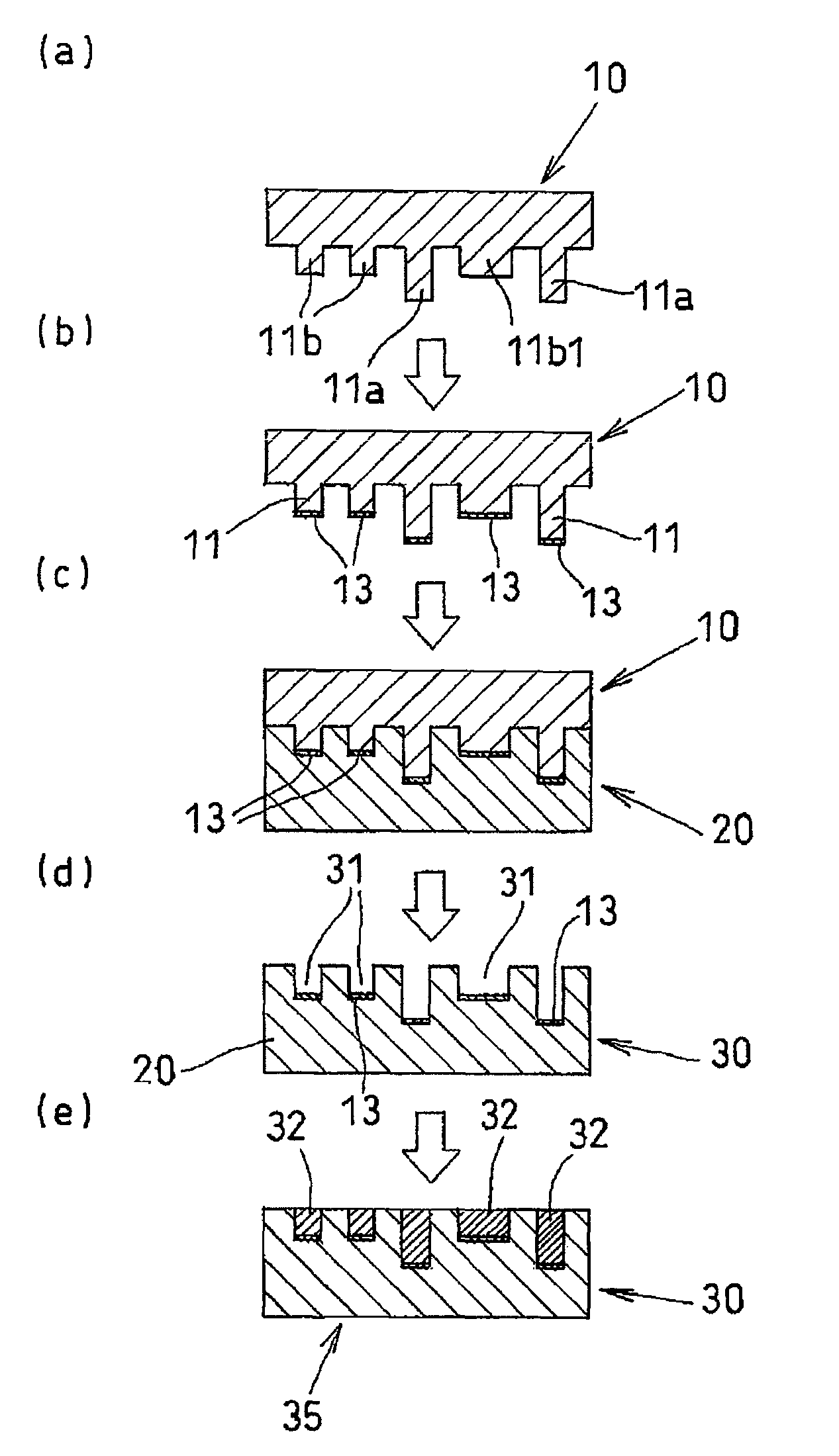

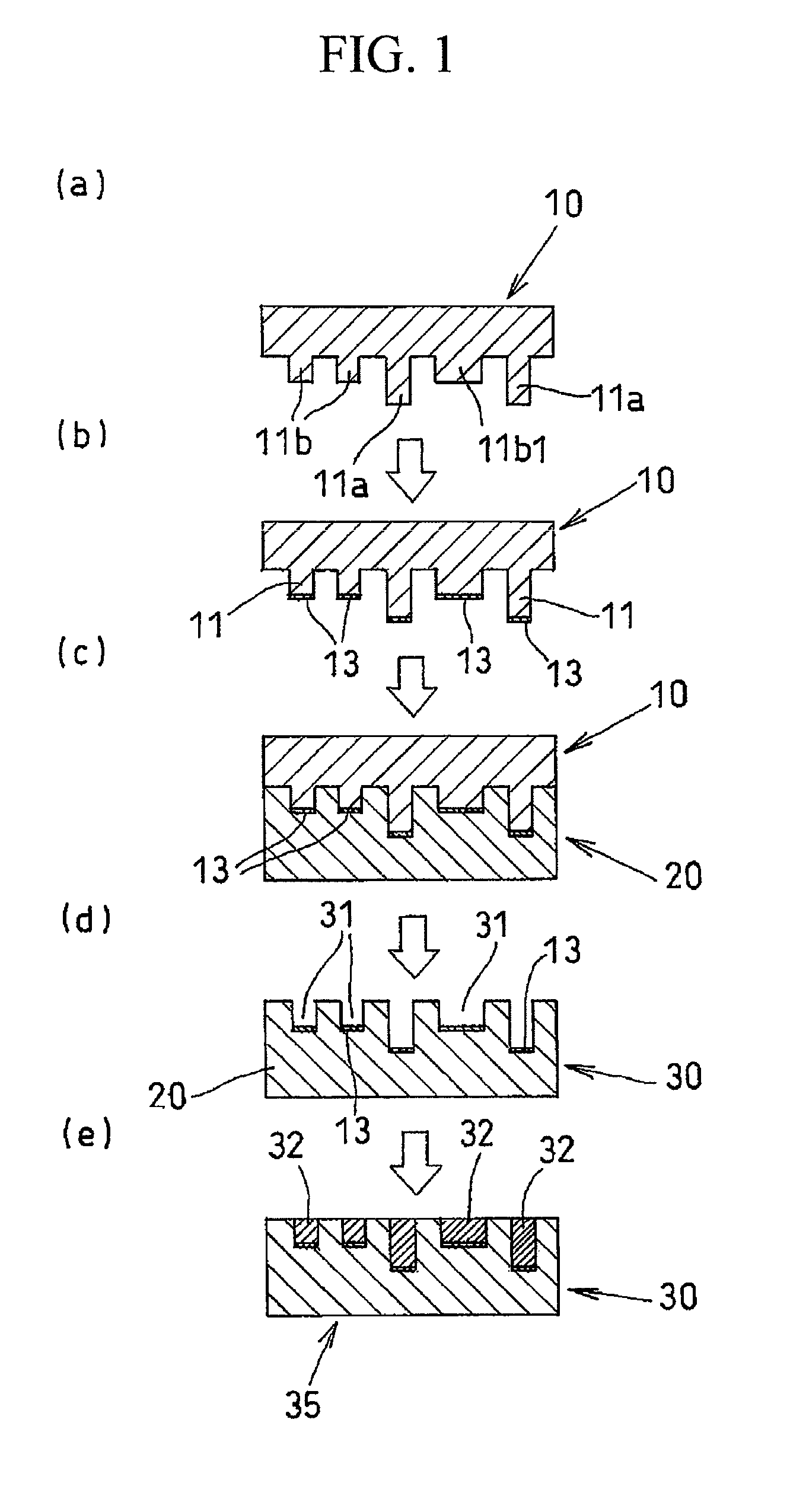

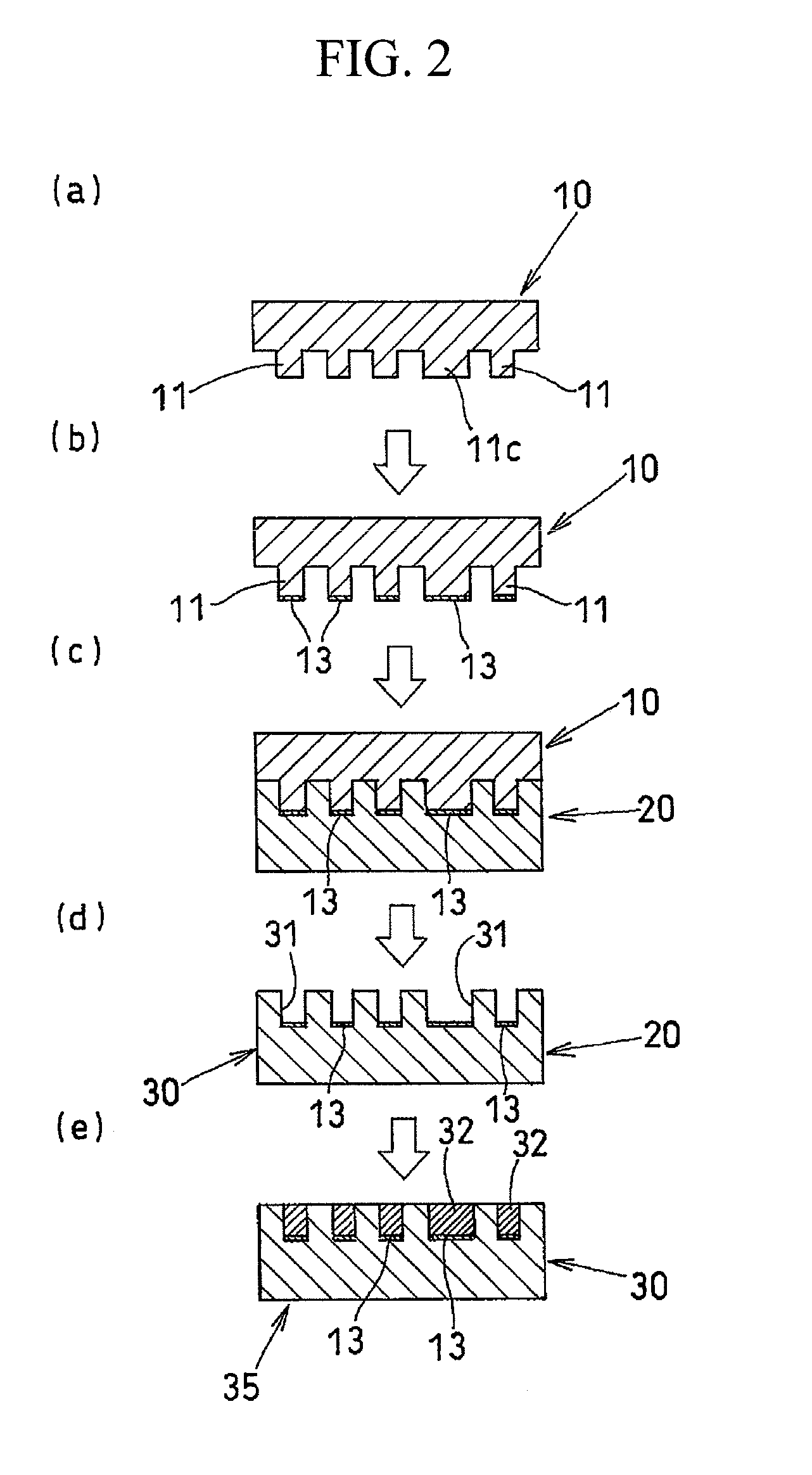

According to the present invention, a circuit board having a further-microfabricated circuit pattern that can be manufactured in further simplified steps is obtained. For such purpose, a mold 10, which has protrusions 11 formed in a pattern corresponding to a circuit pattern, is used to apply a conductive material layer (metal paste) 13 to head portions of the protrusions 11 of the mold 10. The mold is heat- and pressure-welded to the surface of a substrate 20 that is made of a resin film or the like. Accordingly, a pattern comprising the protrusions 11 and the conductive material layer (metal paste) 13 are transferred to the substrate 20. After transfer, the resin substrate (resin molding 30) is immersed in a copper sulfate plating bath for electrolytic plating treatment. Copper ions in the plating bath were deposited inside each recess 31 while the conductive material layer 13 is used as a base material for the formation of a metal wiring 32. A pattern of the recesses 31 transferred to the substrate-20 side is determined depending on a pattern comprising the protrusions 11 on the mold 10. Thus, a microfabricated high-density circuit pattern formed with metal wirings 32 having arbitrary aspect ratios can be obtained.

Owner:TOYOTA JIDOSHA KK

Thin core substrate for fabricating a build-up circuit board

InactiveUS6574863B2High wiring densityPrinted circuit assemblingLine/current collector detailsMaterials scienceElectrically conductive

Disclosed is a method of preparing a thin core substrate for fabricating a build-up multilayer circuit board. The method involves the use of an insulating layer which is covered with the electrically conductive sheets. The openings are made in the electrically conductive layers at the predetermined positions, where the vias are also formed in the insulating layer. An electrically conductive layer is deposited to cover the vias. After the electrically conductive sheets and layer are patterned, a thin core substrate is constructed. The build-up layers are then made at least one side of the thin core substrate to form a build-up multilayer circuit board.

Owner:PHOENIX PRECISION TECH CORP

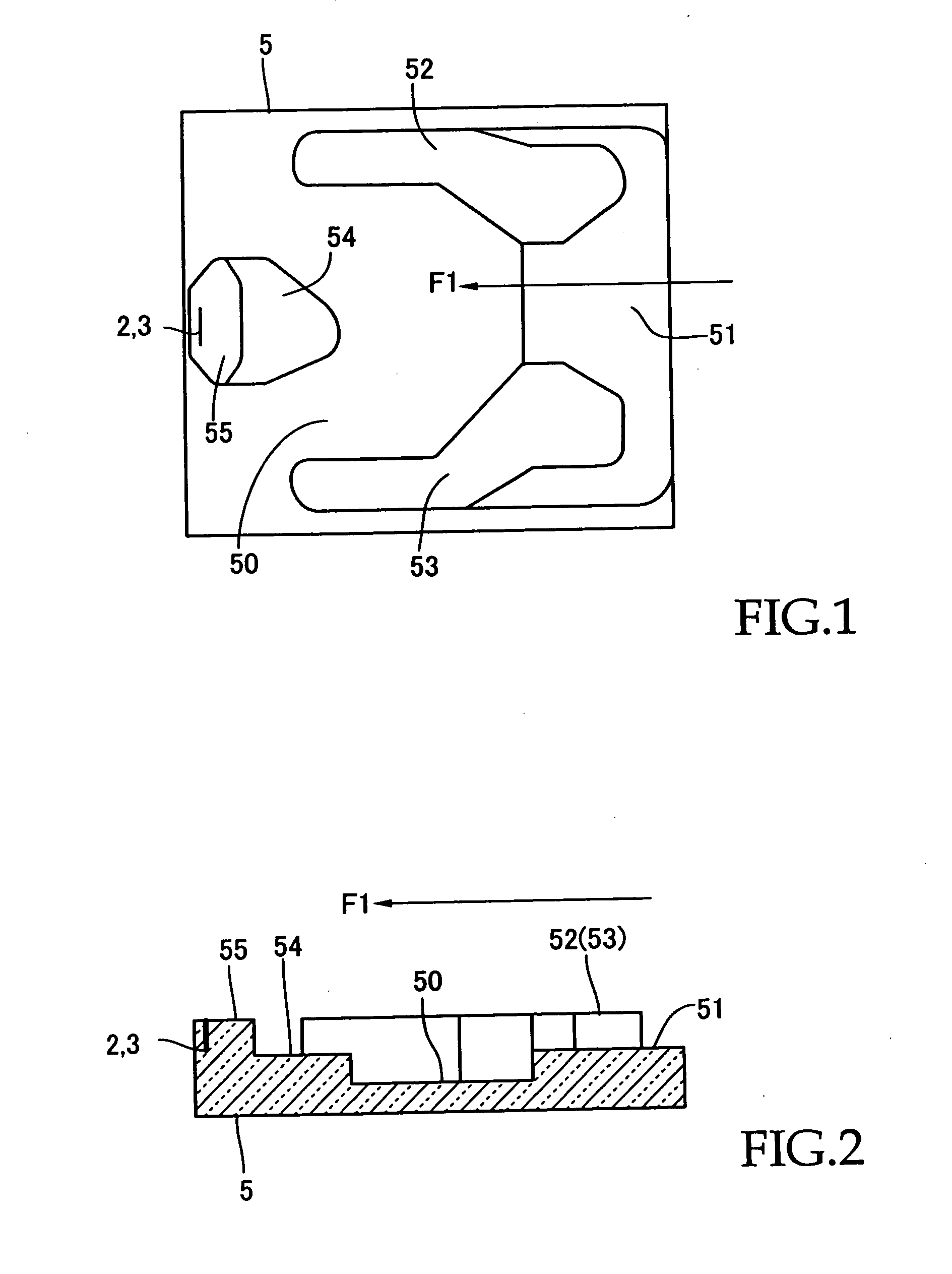

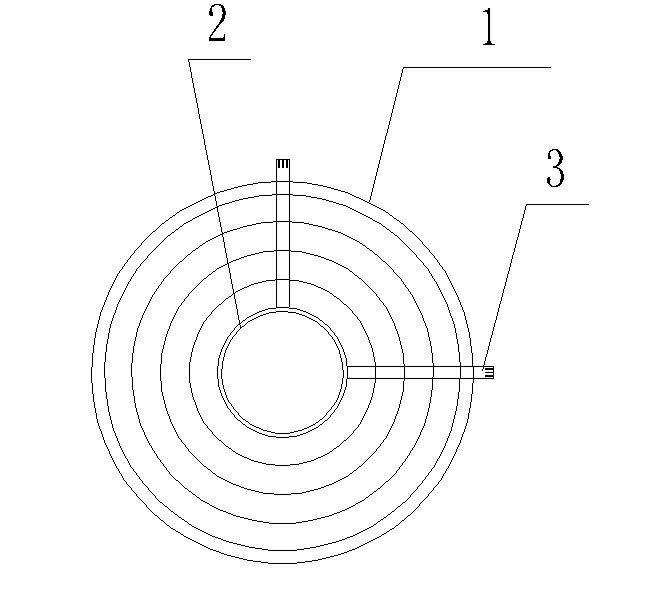

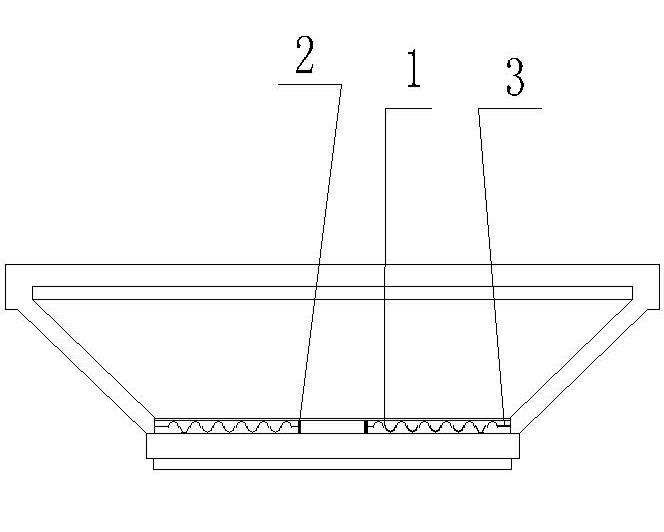

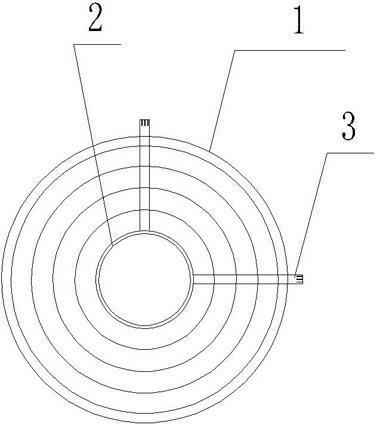

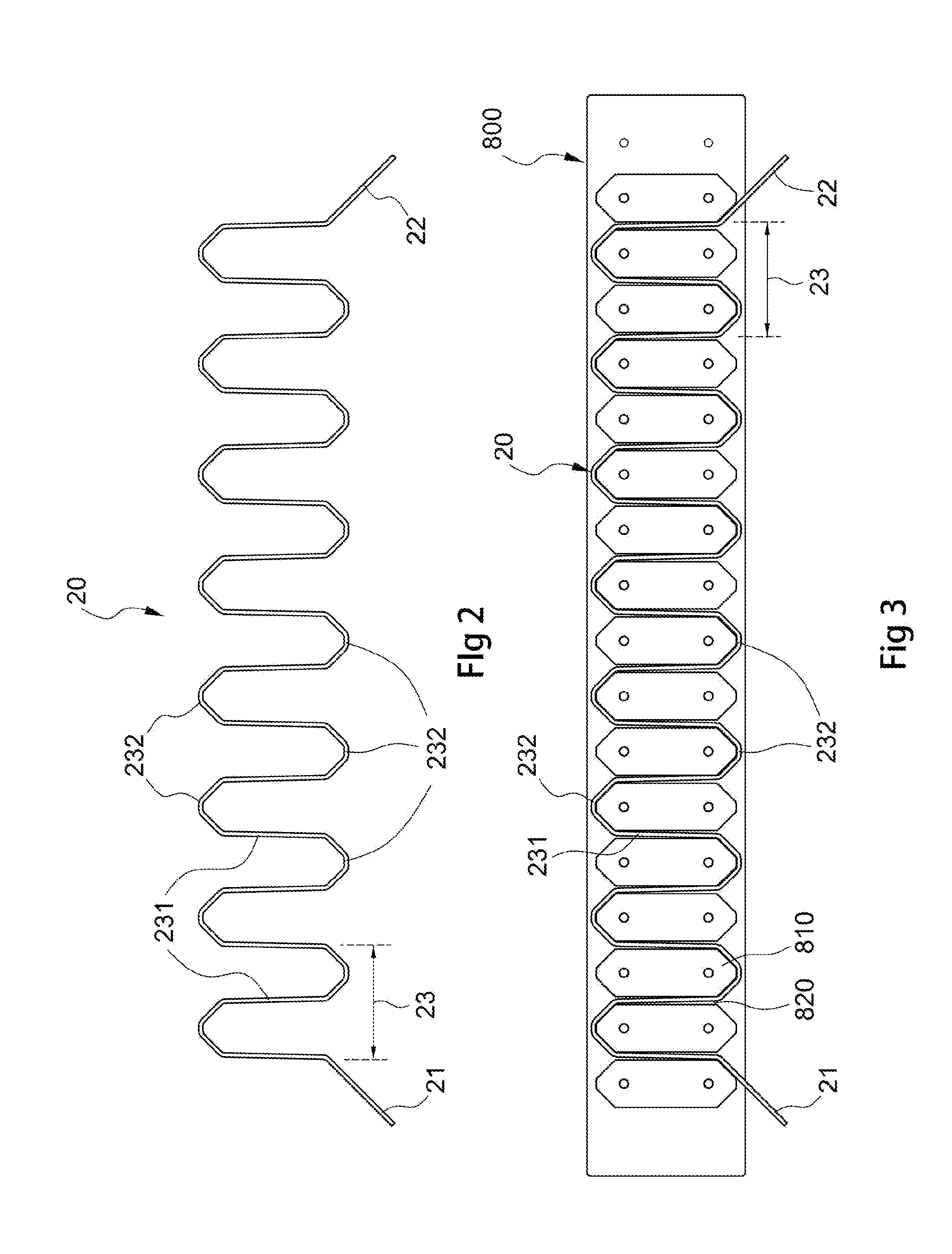

Conductive elastic wave for loudspeaker

ActiveCN102611968AHigh wiring densityReduce weightDiaphragm mounting/tensioningLoudspeakerVoice coil

The invention discloses a conductive elastic wave for a loudspeaker, which comprises an elastic wave main body, wherein a wave peak, a wave trough and a voice coil are arranged on the elastic wave main body; and the cross section is of a wave structure. The conductive elastic wave for the loudspeaker is characterized in that two or a plurality of FPCs (Flexible Printed Circuit) are arranged on the wave peak and the wave trough of the elastic wave; one end of each of the FPCs are connected with the voice coil; a connecting end is arranged at the other end of each of the FPCs; a connecting power supply stretches out from the outer side of the elastic wave main body; the FPCs are connected with the elastic wave main body integrally in the way of hot-pressing, or penetration or sewing; and two of the FPCs are arranged vertically on the surface of the elastic wave. The thickness of each FPC is 0.01mm-2mm, and the conductive elastic wave for the loudspeaker has the advantages of simple structure, low production cost, good effect and the like.

Owner:陈志豪 +1

Junction structure and junction method for conductive projection

InactiveUS7053315B2Avoid warpingLarge heightPrinted circuit assemblingElectrically conductive connectionsUV curingElectrical conductor

To provide a junction structure and a junction method for conductive projection advantageous in that a required reinforcement strength can be obtained while suppressing the amount of a reinforcing resin material supplied to prevent warpage due to curing shrinkage. A conductive projection is joined to the surface of a conductor portion formed at the same level as that of the surface of the insulating layer so that a root portion of the projection is surrounded by a fillet-form resin material. The resin material contains an activator which assists in the junction between the conductive projection and the conductor portion when the resin material is in an uncured state, and is fused by heating to wet and rise the root portion of the conductive projection so as to be in a fillet form. The resin material is cured by an ultraviolet light while excluding the resin material on the conductor portion.

Owner:SONY CORP

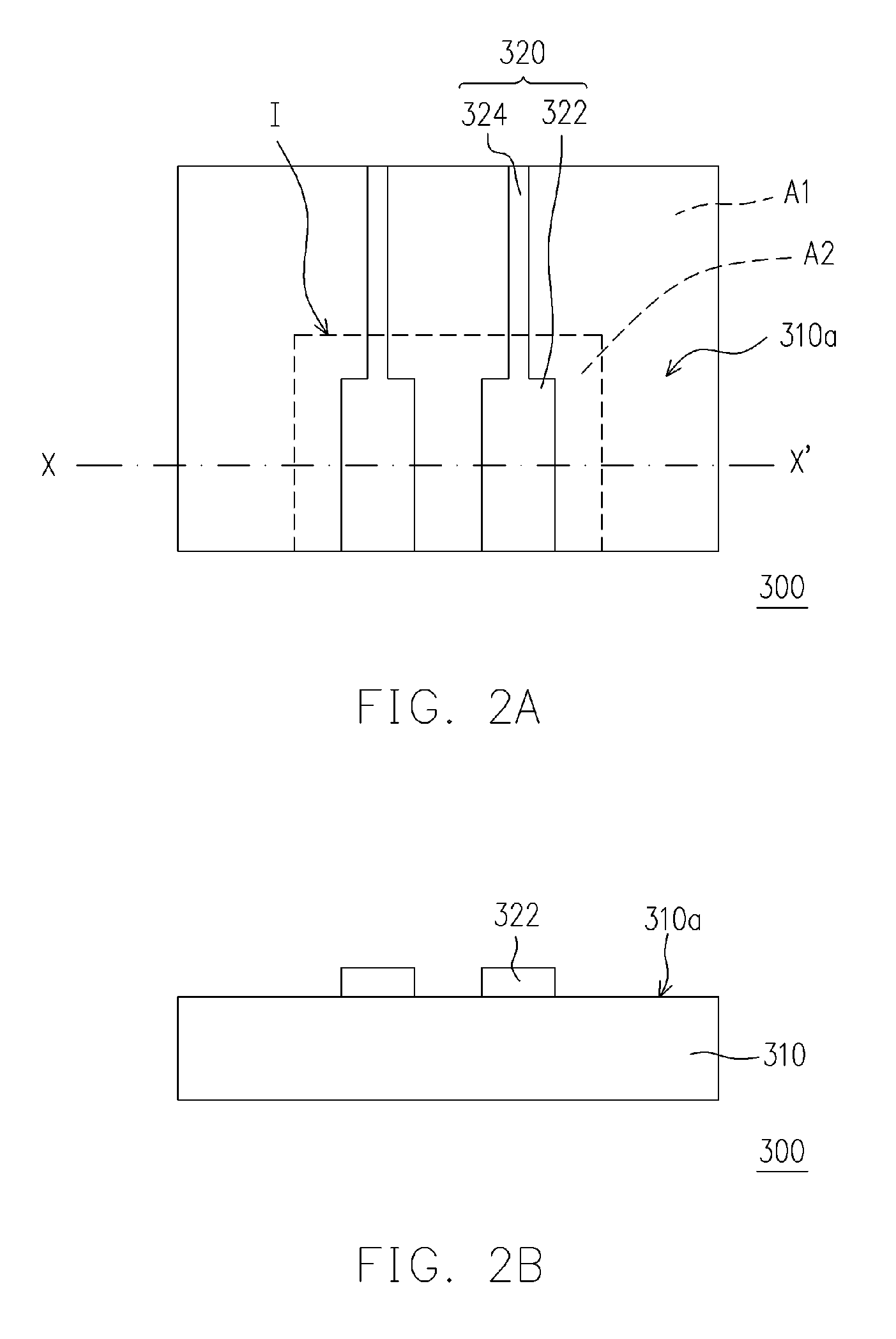

Method of forming solder mask and wiring board with solder mask

ActiveUS20070099123A1Shorten the timeHigh wiring densityPhotomechanical apparatusSemiconductor/solid-state device manufacturingProduction rateScreen printing

A method of forming solder mask, suitable for forming a solder mask on the surface of a wiring board, is provided. The surface of the wiring board includes a first region and a second region, and the surface of the wiring board has a wiring pattern thereon. The method includes forming a first sub solder mask in the first region on the surface of the wiring board by performing a screen-printing or a photolithographic process, and forming a second sub solder mask in the second region on the surface of the wiring board by performing an ink-jet printing process. The method not only improves the precision of the solder mask alignment on the wiring board and its reliability, but also increases the production rate and lowers the manufacturing cost.

Owner:UNIMICRON TECH CORP

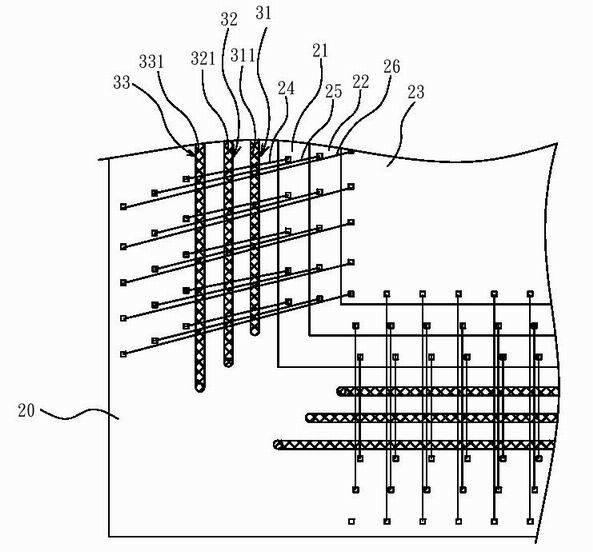

Wiring board

InactiveCN101015236AHigh densityImprove reliabilityPrinted circuit detailsMultilayer circuit manufactureElectrical conductorHigh density

To provide a mutilayer wiring board wherein high density wiring exceeding the application limit of the conventional build up wiring boards is made possible. A wiring board is provided with a board, which is formed by stacking along a board flat plane direction a plurality of dielectric layers arranged along a facing direction of the both main planes of the board, and an inner conductor pattern arranged on the surface of the dielectric layer. The adjacent dielectric layers are integrally formed to be communicated with each other by being connected at the layer edges on one of the board main planes. The connecting portions of the adjacent dielectric layers are alternately provided on one of the board main planes, and the dielectric layers are formed in a shape of one dielectric sheet which is arranged by being bent.

Owner:PANASONIC CORP

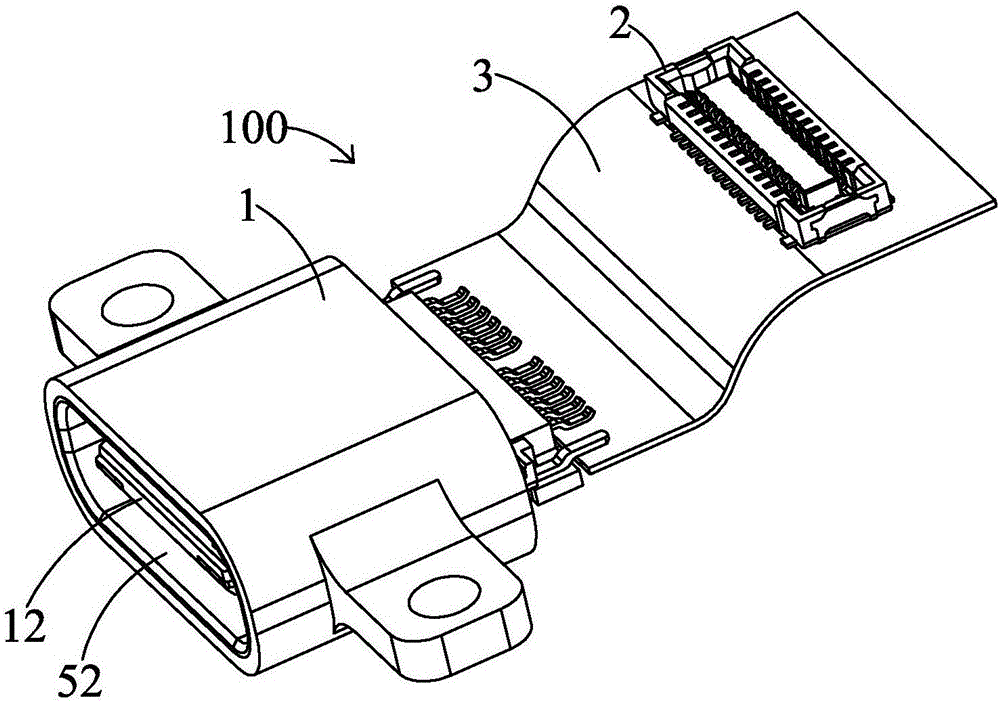

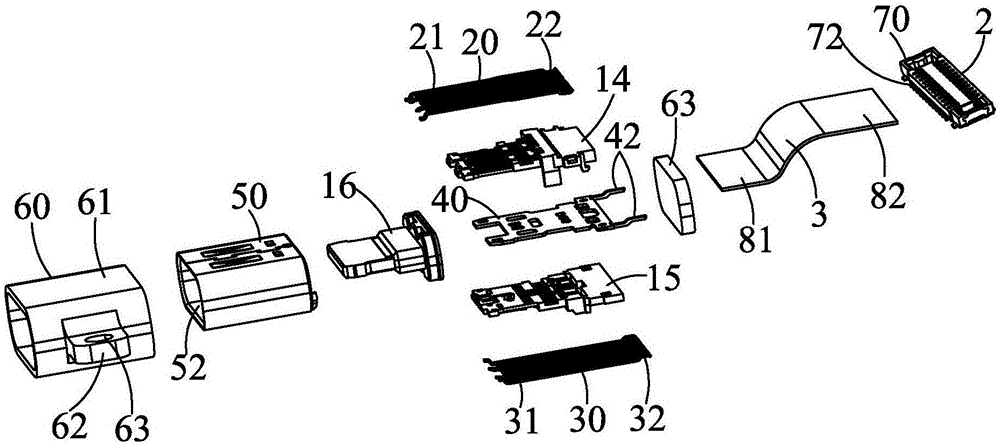

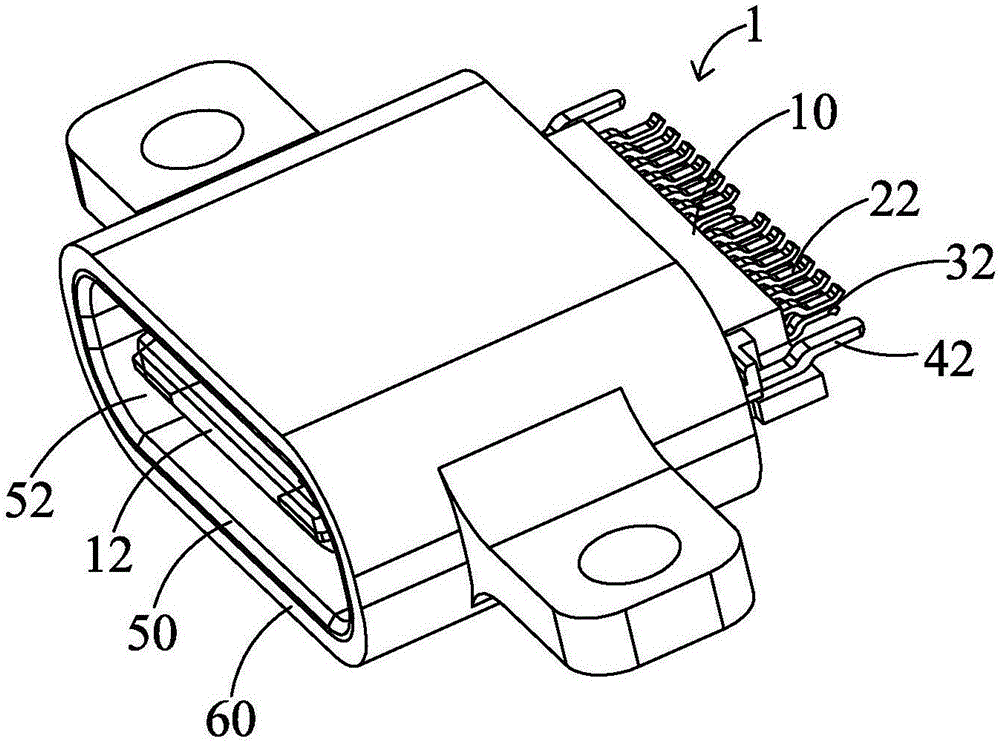

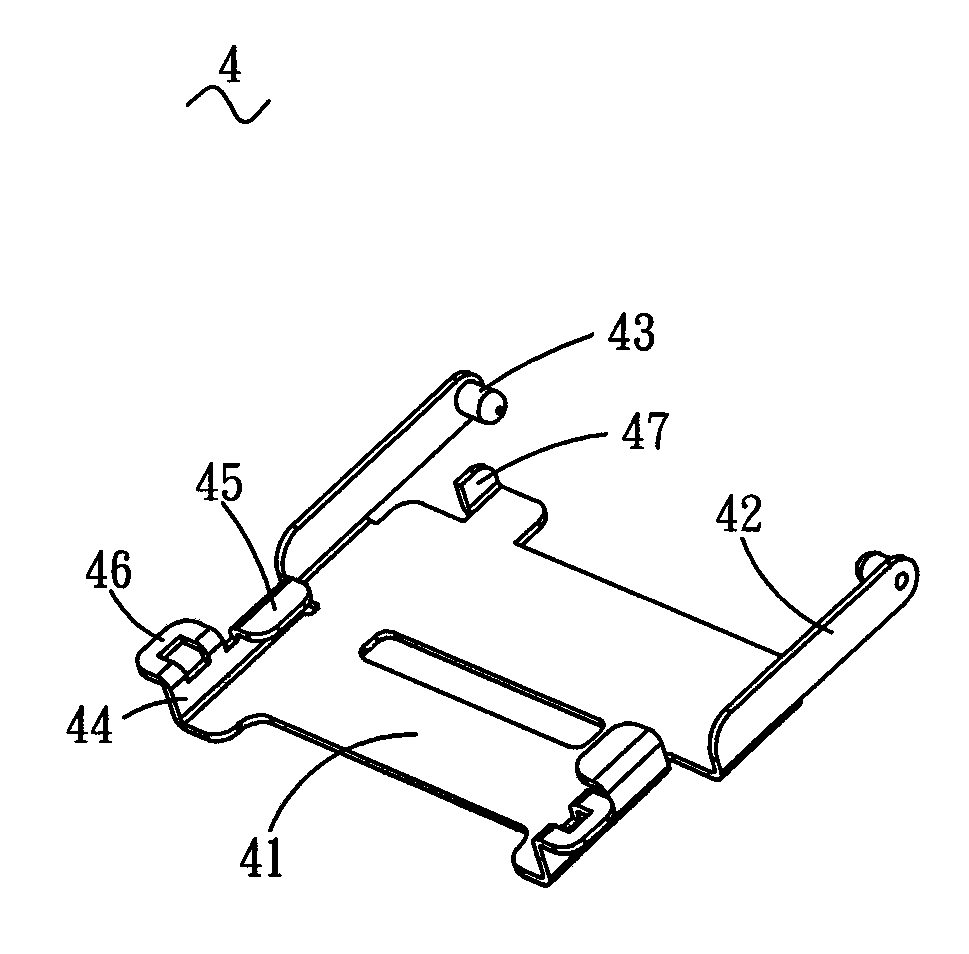

Electrical connector assembly

ActiveCN106711723AHigh wiring densityReduce weightCoupling contact membersFlexible circuitsButt joint

The present invention relates to an electrical connector assembly. The electrical connector assembly comprises a first connector and a second connector for connecting a female circuit board; the first connector comprises an insulating body as well as a first terminal group, a second terminal group and a metal spacer which are all accommodated in the insulating body; the insulating body includes a main body portion and a tongue plate projecting forwardly from the main body portion; the electrical connector assembly further comprises a flexible circuit board connected with the first connector and the second connector; the second connector is a board-to-board connector; the second connector is convenient to be in butt joint with the board-to-board connector on the female circuit board; and the flexible circuit board can easily and conveniently change the position of the first connector in an electronic device, so that different installation height (offset) requirements can be satisfied, new molds are not required to be manufactured, the categories of products can be decreased, and costs can be decreased.

Owner:LINKCONN ELECTRONICS

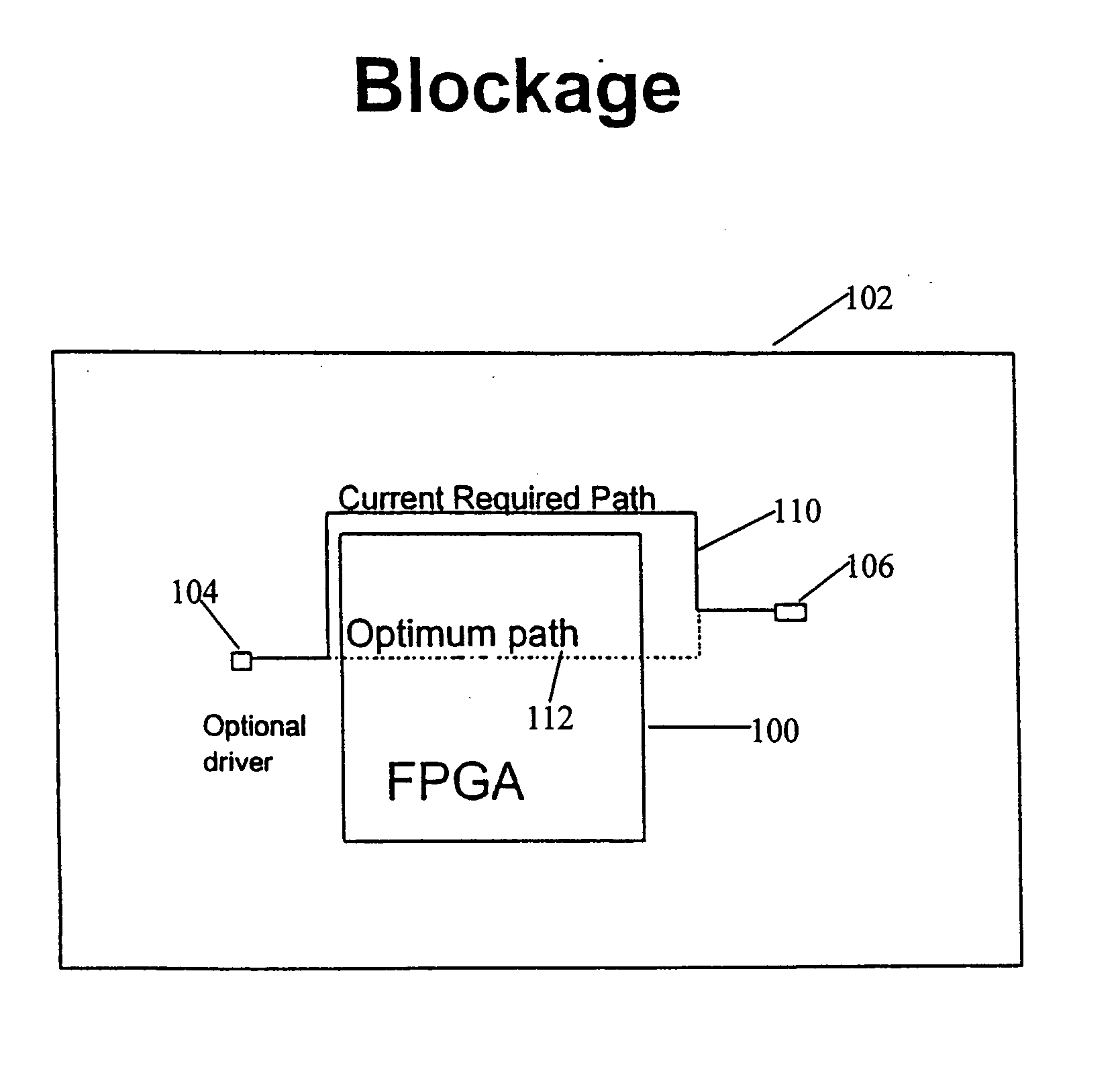

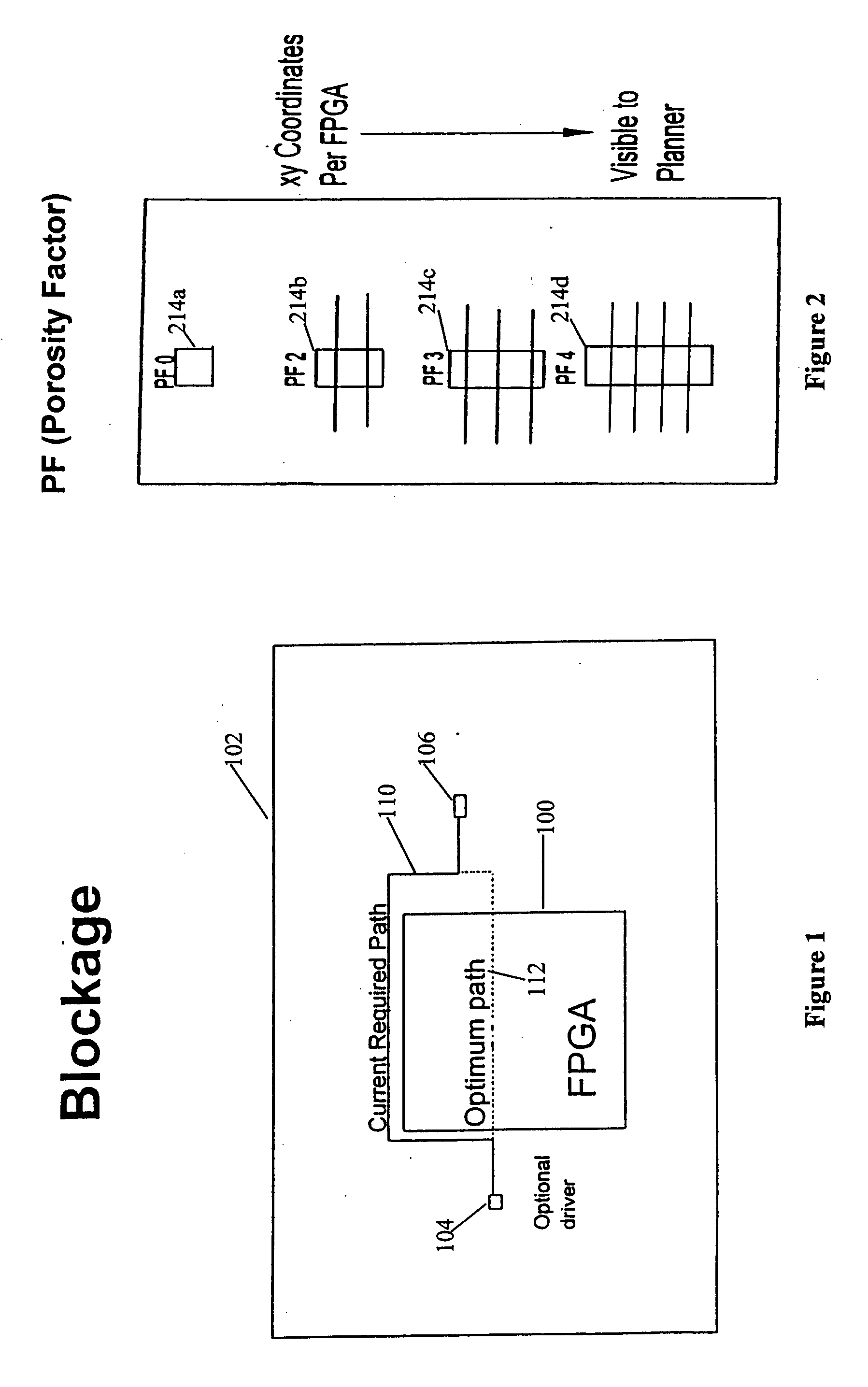

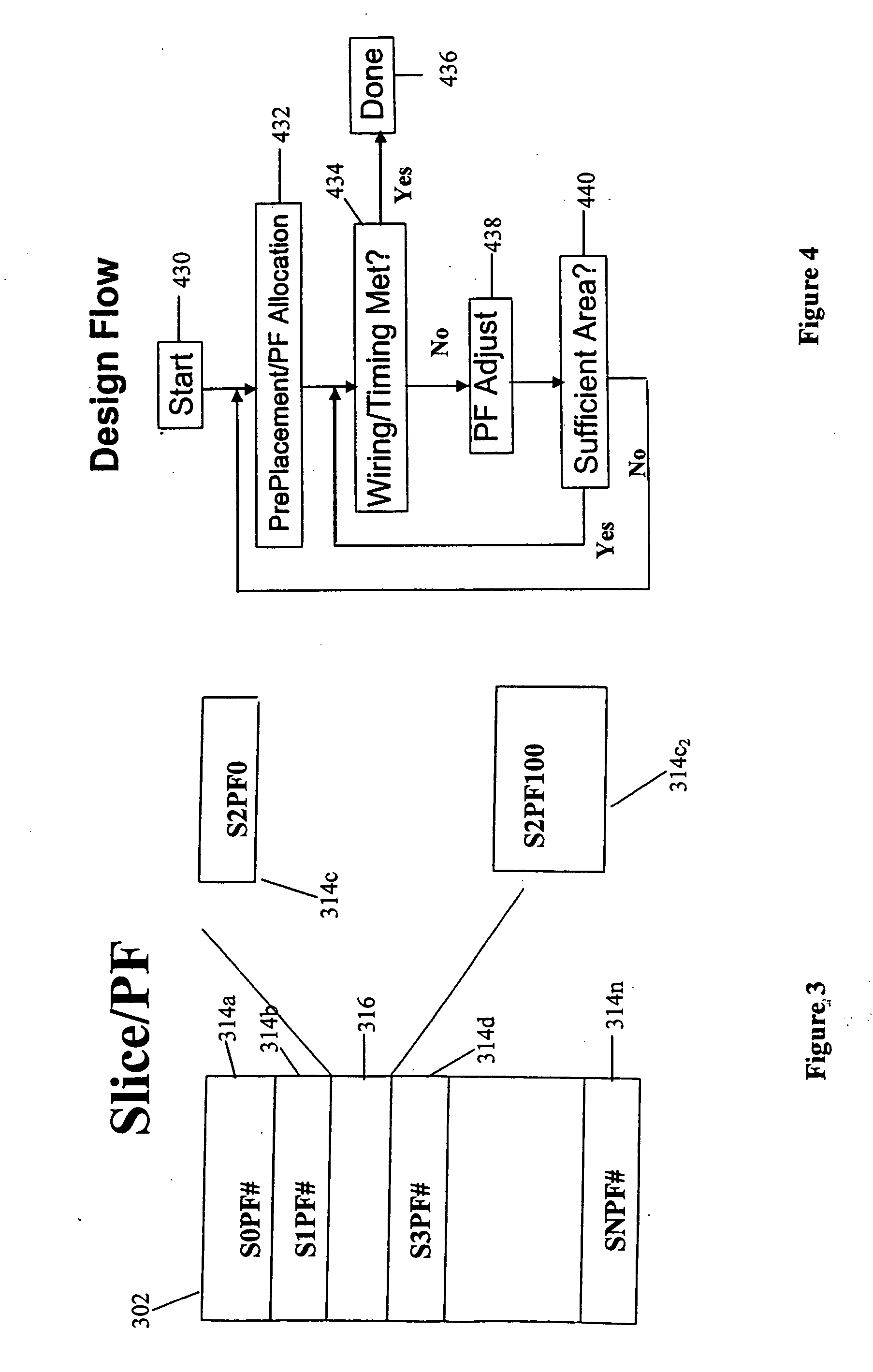

FPGA blocks with adjustable porosity pass thru

InactiveUS20050121698A1Minimizing chip floor planMinimizing timing impactSemiconductor/solid-state device detailsSolid-state devicesPorositySemiconductor chip

A field programmable gate array is described for use in a semiconductor chip such as a VLSI chip. The array is provided with variable wire-through porosity to allow for optimum chip-level routing through the array. This is achieved by dividing the array into blocks which can be individually assessed for required porosity. Then blocks that have been prefabricated with differing porosities are placed in the macro to optimize local chip level routing. The routing of wires is determined by developing a chip floor plan to include early timing allocation and a proposed placement of the array. The floor plan is then overlaid with critical logical wiring nets. From this, an initial selection of blocks is made based on proposed wiring density, and the macro is assembled with the blocks strategically placed therein. The procedure is likewise applicable to other types of densely obstructed cores embedded with a chip.

Owner:IBM CORP

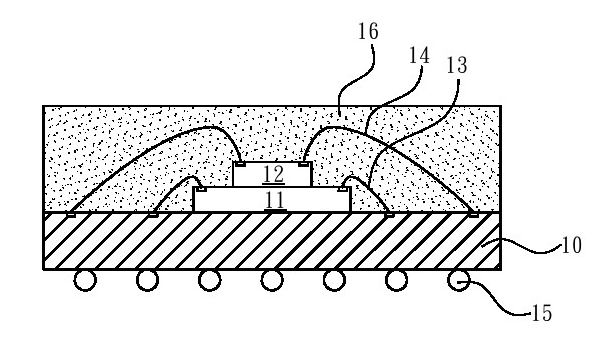

Ball grid array (BGA) package structure

InactiveCN102074517APrevent wire collapse defectsAvoid offsetSemiconductor/solid-state device detailsSolid-state devicesEngineeringBall grid array

The invention discloses a ball grid array (BGA) package structure, which is characterized in that wire carriages are utilized to support corresponding wires so as to prevent the wires from collapsing in a vertical direction, and effectively separate the wires in an upper layer from the wires in a lower layer. Meanwhile, the wire carriages are provided with rough insulating surfaces, and can further prevent the wires from deviating and being rushed in a horizontal direction. Therefore, the structure can effectively avoid the wires in any two adjacent layers or the left and right wires from generating contact short circuit.

Owner:ASE ASSEMBLY & TEST SHANGHAI

Wiring board manufacturing method

InactiveUS7377030B2High wiring densityLow thermal expansion coefficientSemiconductor/solid-state device detailsSolid-state devicesEngineeringPower strip

Owner:FUJITSU LTD

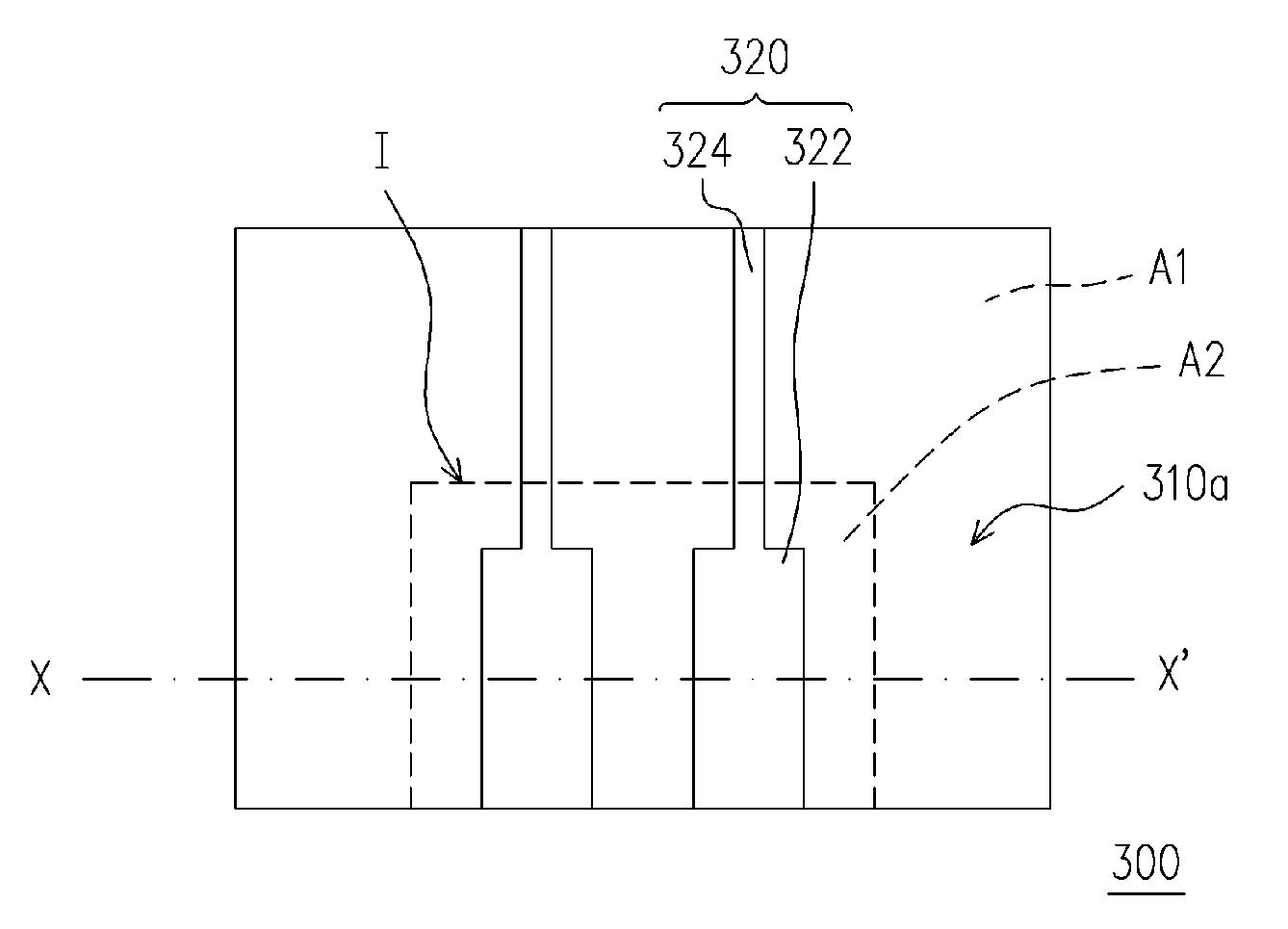

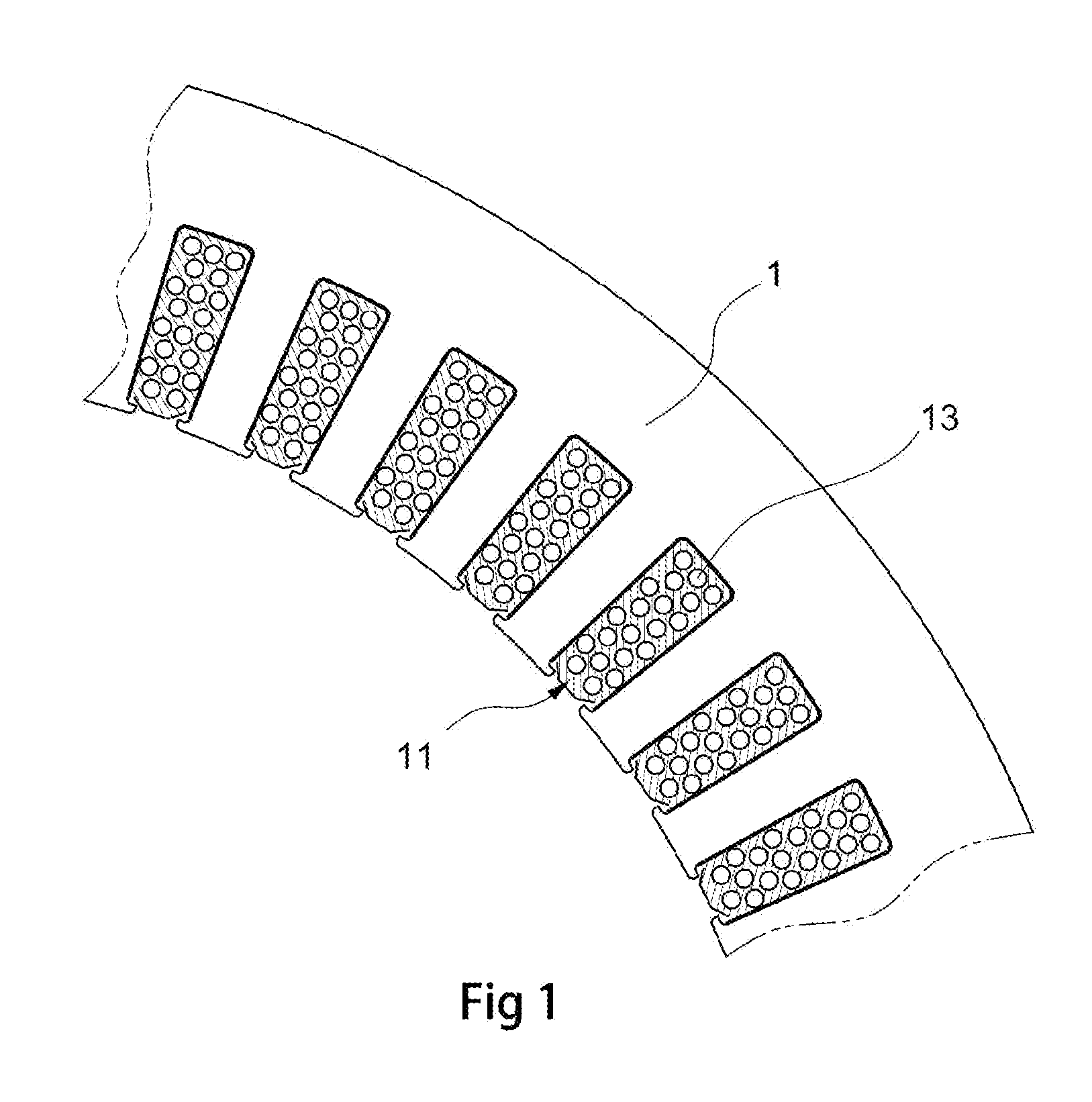

Method for manufacturing a circuit board

InactiveUS8261437B2Simple manufacturing processHigh densityLine/current collector detailsPrinted circuit aspectsHigh densityEngineering

According to the present invention, a circuit board having a further-microfabricated circuit pattern that can be manufactured in further simplified steps is obtained. For such purpose, a mold 10, which has protrusions 11 formed in a pattern corresponding to a circuit pattern, is used to apply a conductive material layer (metal paste) 13 to head portions of the protrusions 11 of the mold 10. The mold is heat- and pressure-welded to the surface of a substrate 20 that is made of a resin film or the like. Accordingly, a pattern comprising the protrusions 11 and the conductive material layer (metal paste) 13 are transferred to the substrate 20. After transfer, the resin substrate (resin molding 30) is immersed in a copper sulfate plating bath for electrolytic plating treatment. Copper ions in the plating bath were deposited inside each recess 31 while the conductive material layer 13 is used as a base material for the formation of a metal wiring 32. A pattern of the recesses 31 transferred to the substrate-20 side is determined depending on a pattern comprising the protrusions 11 on the mold 10. Thus, a microfabricated high-density circuit pattern formed with metal wirings 32 having arbitrary aspect ratios can be obtained.

Owner:TOYOTA JIDOSHA KK

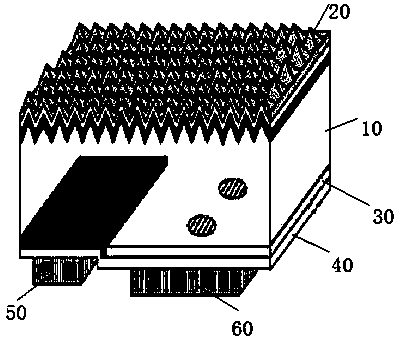

Inorganic flexible LED color display screen and preparation method

InactiveCN108630115AEasy to stack alternatelySolve bottlenecksIdentification meansPolyesterFlexible circuits

The invention discloses an inorganic flexible LED color display screen and a preparation method. The preparation method comprises the following steps: forming a flexible circuit board by using a layerof a basic layer, multiple layers of insulating layers and multiple layers of electrode layers, wherein the basic layer is a bottom layer, and successively and alternately installing the insulating layers and the electrode layers on the basic layer; selecting PET polyester plate or PI polyimide plate, plating a layer of a conducting film on the plate, etching a common circuit to prepare the basiclayer through a laser; using PI polyimide solution, and preparing the insulating layers by using silk-screen printing; using conducting ink containing nano-silver carbon, and preparing the electrodelayers by using 3D ink-jet printing; and finally, pasting an LED light-emitting device on the flexible circuit board by using a chip mounter, and covering by a protecting layer prepared by transparentflexible protecting glue. The display has the characteristics of good flexibility, light weight of a finished product, convenient installation, and small influence to luminescence uniformity and visual effect after curled. The preparation method is capable of overcoming a bottleneck of large-scale display screen preparation, and guaranteeing the preparation of the inorganic flexible LED color display screen.

Owner:EAST CHINA NORMAL UNIV

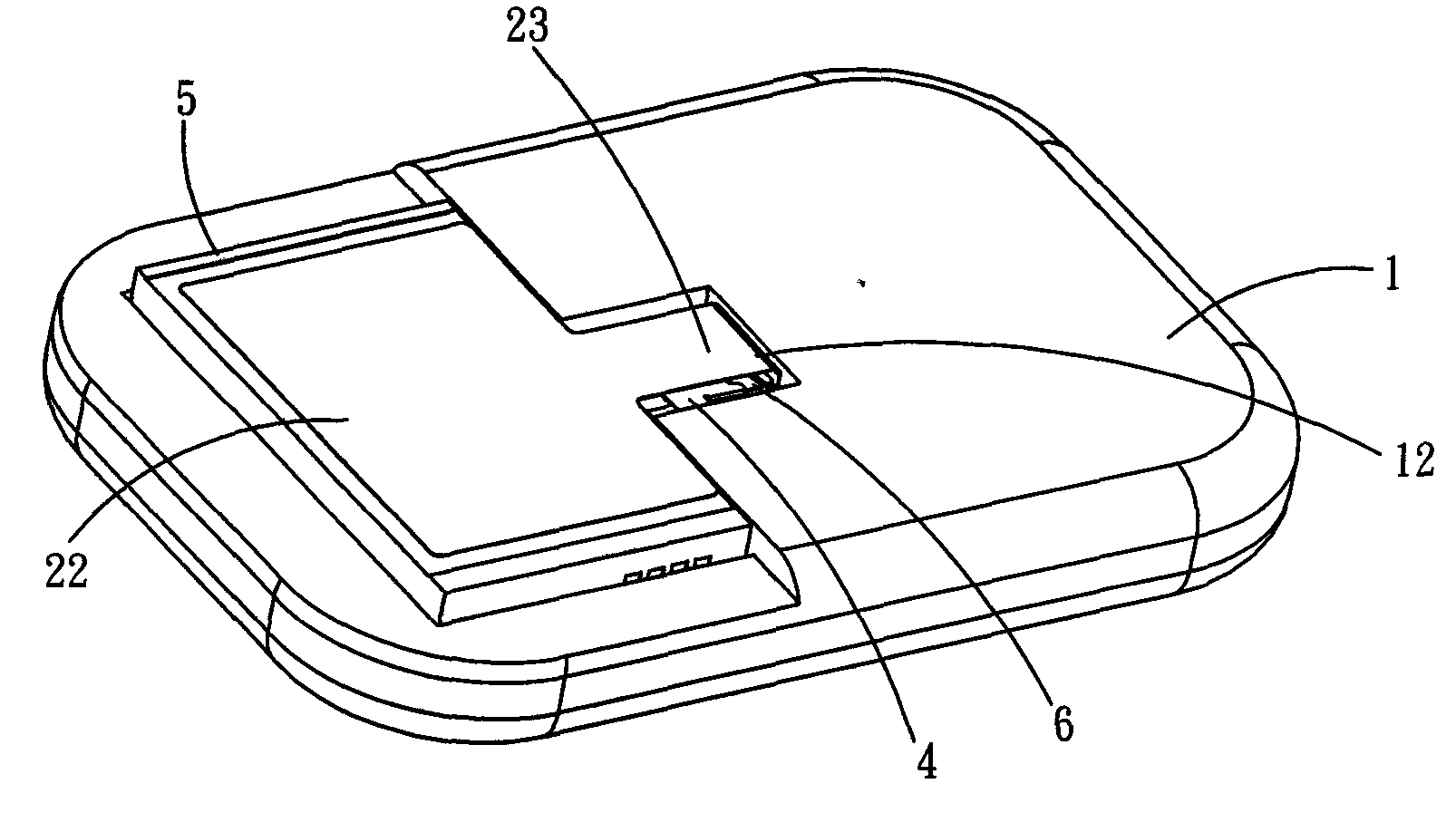

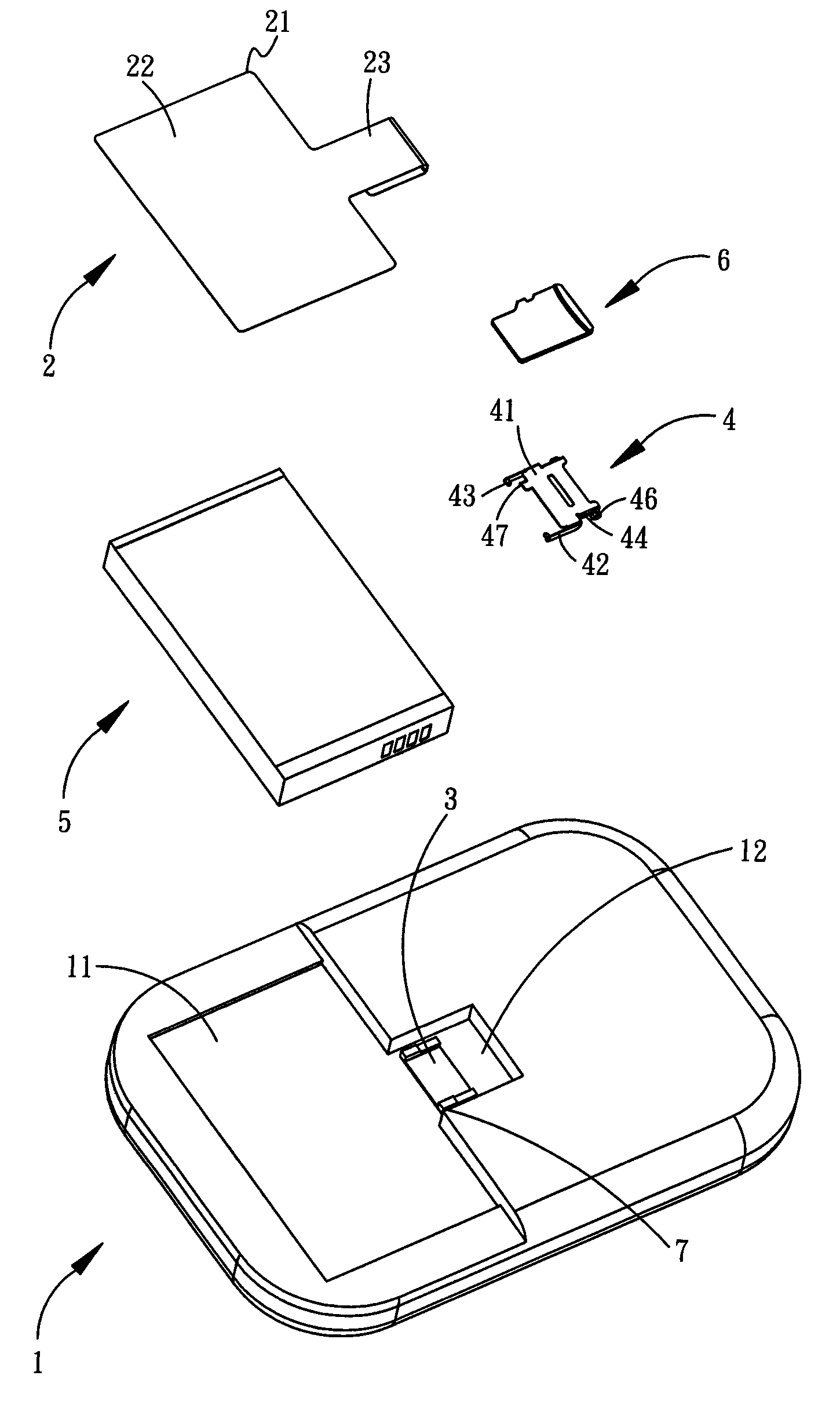

Hand-held device with short-range wireless communication antenna and assembly method thereof

ActiveCN102055063AHigh wiring densityReduce weightAntenna supports/mountingsTransmissionFlexible circuitsEngineering

The invention discloses a hand-held device with a short-range wireless communication antenna and an assembly method thereof. The hand-held device comprises a body, a short-range wireless communication antenna, a battery and a hold-down piece pivoted on the body, wherein a battery groove is formed on the body; an accommodating groove is formed on one side of the battery groove; a circuit board is also arranged in the body; the battery is arranged in the battery groove; the hold-down piece is pivoted on the body and is arranged in the accommodating groove; the short-range wireless communicationantenna is prepared from a flexible circuit board and comprises an antenna area and a connection area connected to one side of the antenna area; the connection area of the short-range wireless communication antenna is detachably clamped in the hold-down piece and is connected with the circuit board; and the antenna area leans against the surface of the battery flexibly. The short-range wireless communication antenna is assembled in the hand-held device detachably, and an assembly process is simple; and when the hand-held device is replaced, the short-range wireless communication antenna can be utilized repeatedly.

Owner:FUGANG ELECTRONICS KUNSHAN +1

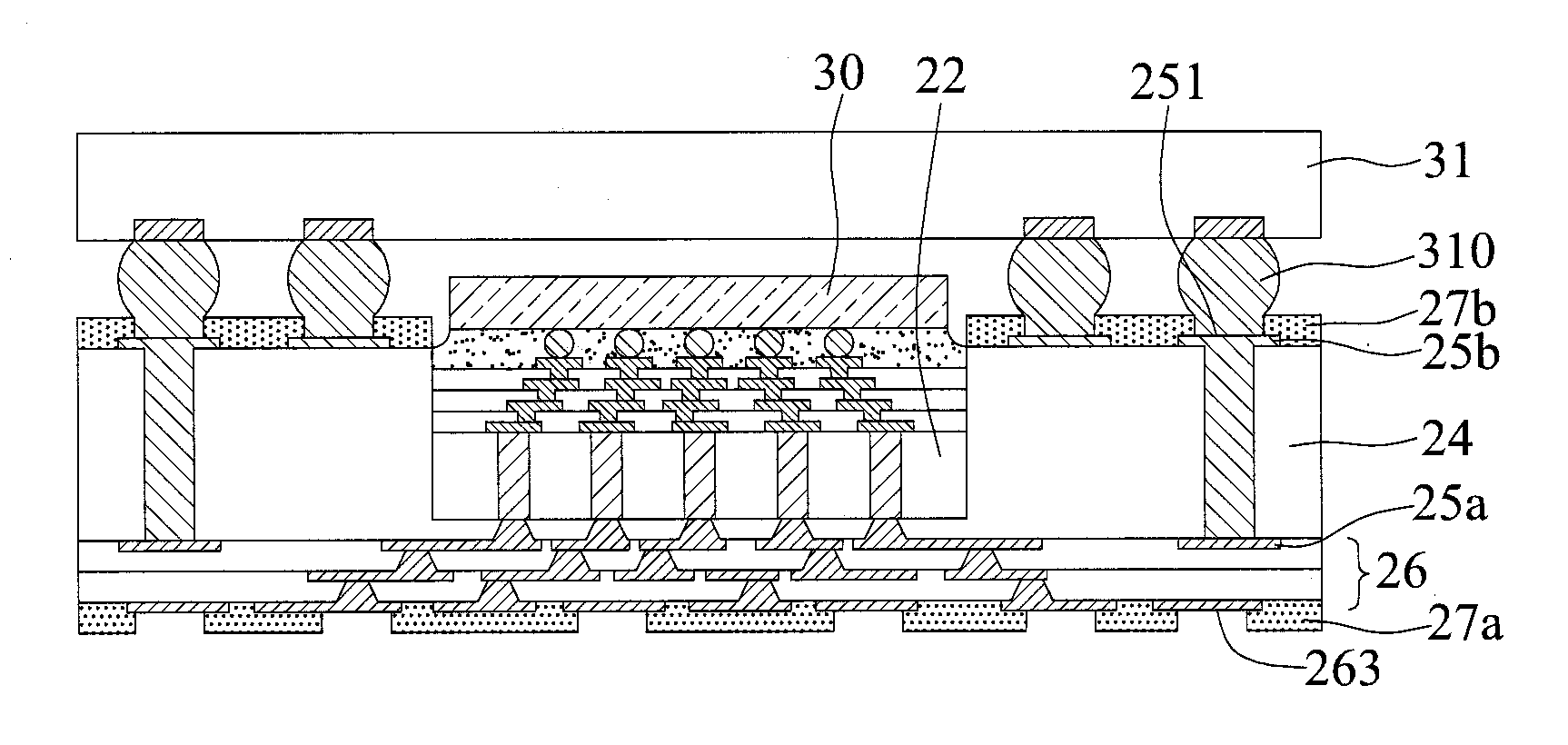

Package structure

ActiveUS7551455B2High wiring densityIncrease ratingsSemiconductor/solid-state device detailsSolid-state devicesElectronic component

A package structure including a first carrier, a second carrier, at least a first electronic component and at least a second electronic component is provided. The second carrier is electrically connected to the first carrier. The first electronic component is disposed on the first carrier and electrically connected to the first carrier. The second electronic component is disposed on the second carrier and electrically connected to the second carrier.

Owner:CYNTEC

Glass-ceramic composition for ceramic electronic part, ceramic electronic part, and method for manufacturing multilayer ceramic electronic part

InactiveUS6667256B2Preventing the density of the obtained substrate bodyImprove transverse breaking strengthSemiconductor/solid-state device detailsSolid-state devicesAntimony oxideCerium oxide

When ceramic electronic parts such as multilayer ceramic substrates that have a substrate body and metal wiring conductors comprising silver are manufactured, a composition comprising not only a borosilicate glass powder and a ceramic powder, but also an additive powder comprising at least one of cerium oxide, bismuth, bismuth oxide, antimony and antimony oxide is used as a composition for preparing the substrate body. Gray discoloration of the substrate body and yellow discoloration in the vicinities of the metal wiring conductors can be prevented.

Owner:MURATA MFG CO LTD

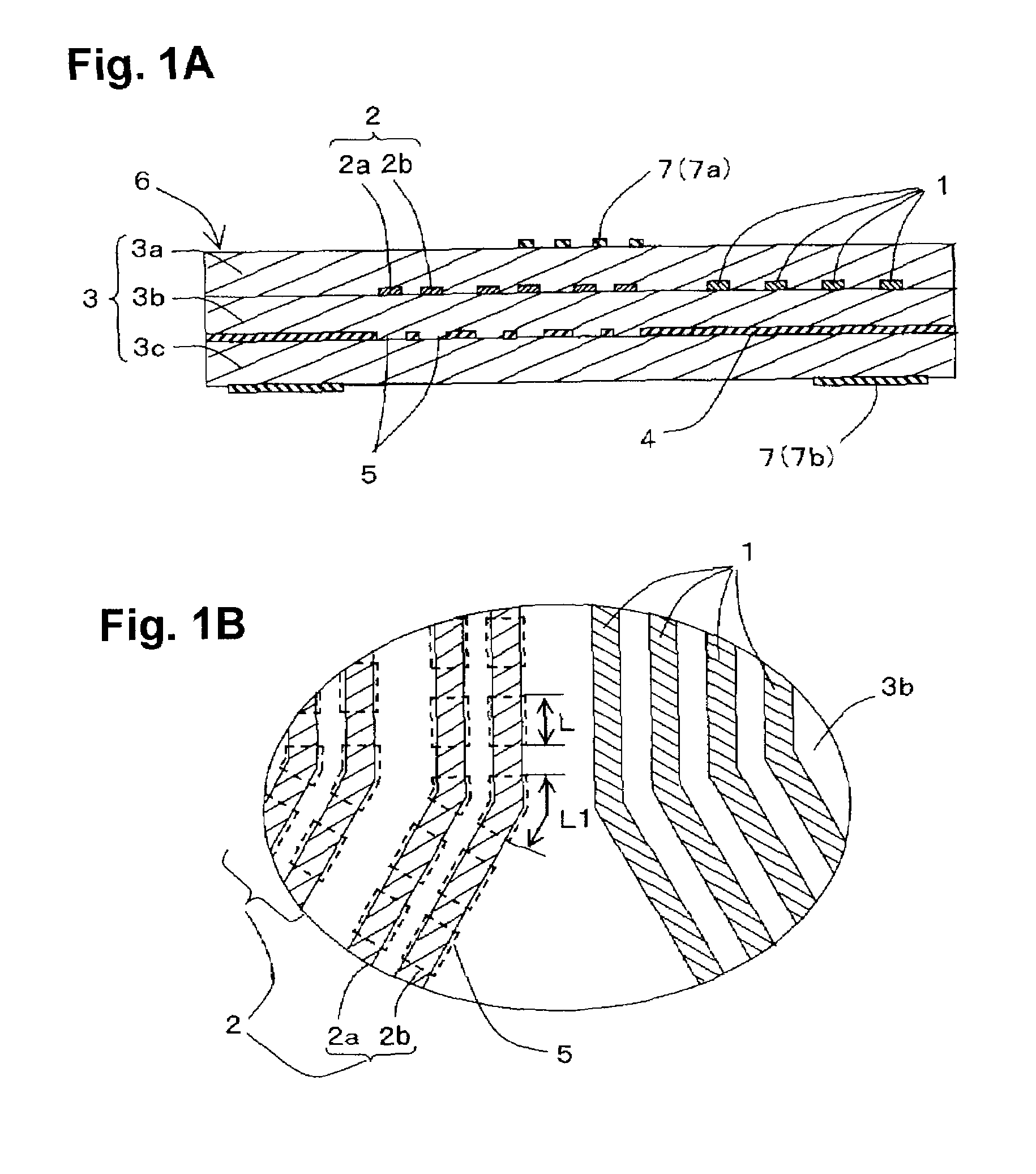

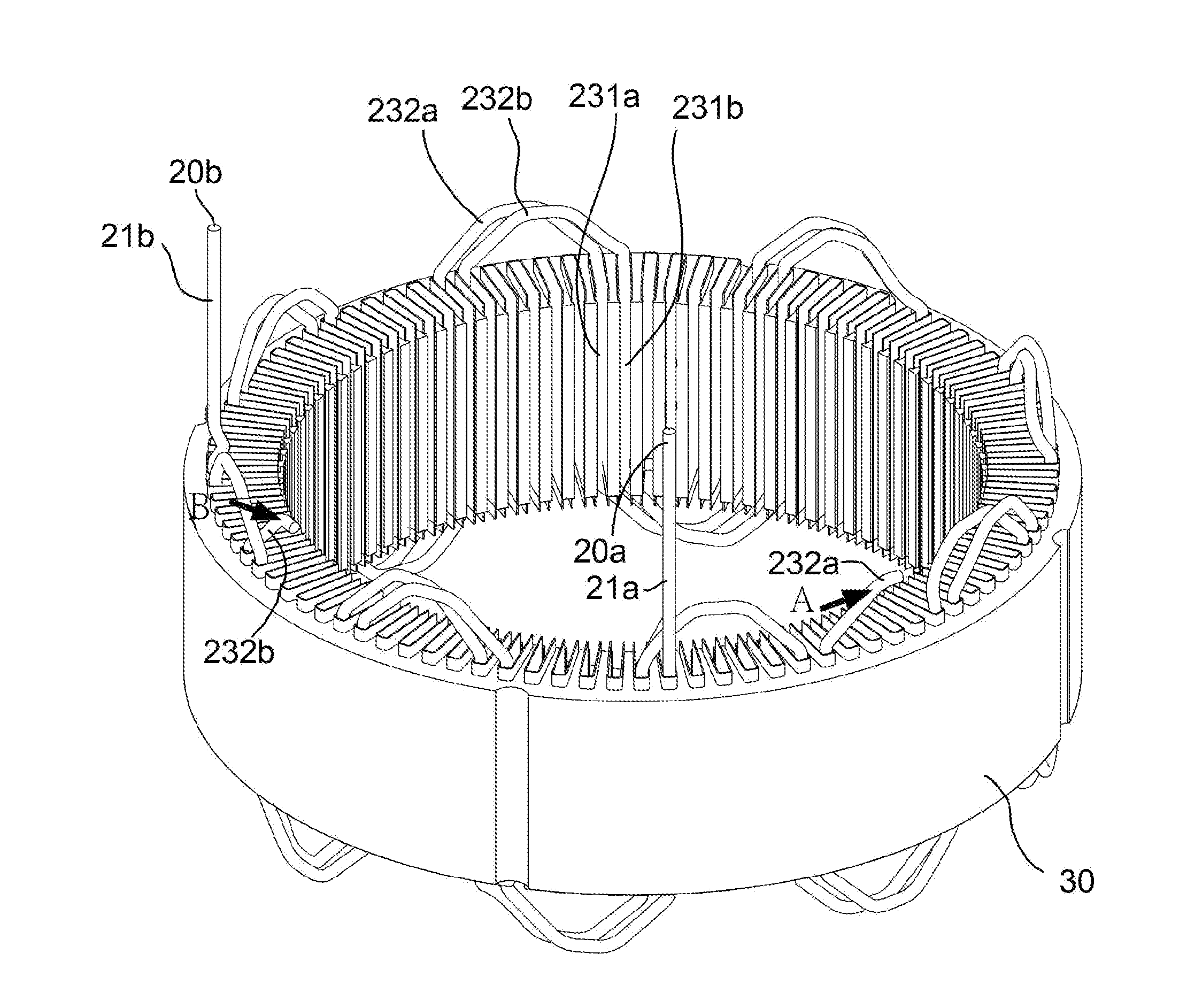

Method of Manufacturing Wound Stator for Alternating-Current Generator

InactiveUS20160006328A1High wiring densityIncrease power generationManufacturing dynamo-electric machinesWindings conductor shape/form/constructionWave shapeAlternating current

The present invention relates to a method of manufacturing a wound stator. The method promises the following steps: (1) providing a stator, which has a plurality of radial grooves arranged at an inner circumference of the stator, (2) providing a plurality of wires for the stator, and (3) sequentially embedding the straight portions of each wire in corresponding grooves of the stator so that each of the grooves is embedded with the wires. Each of the plurality of wire comprises: a first end, a second end, and a plurality of wave-shaped coils located between the first end and second end. Each wave-shaped coil is formed of straight portions and curved portions that alternate with each other.

Owner:VICTORY INDAL

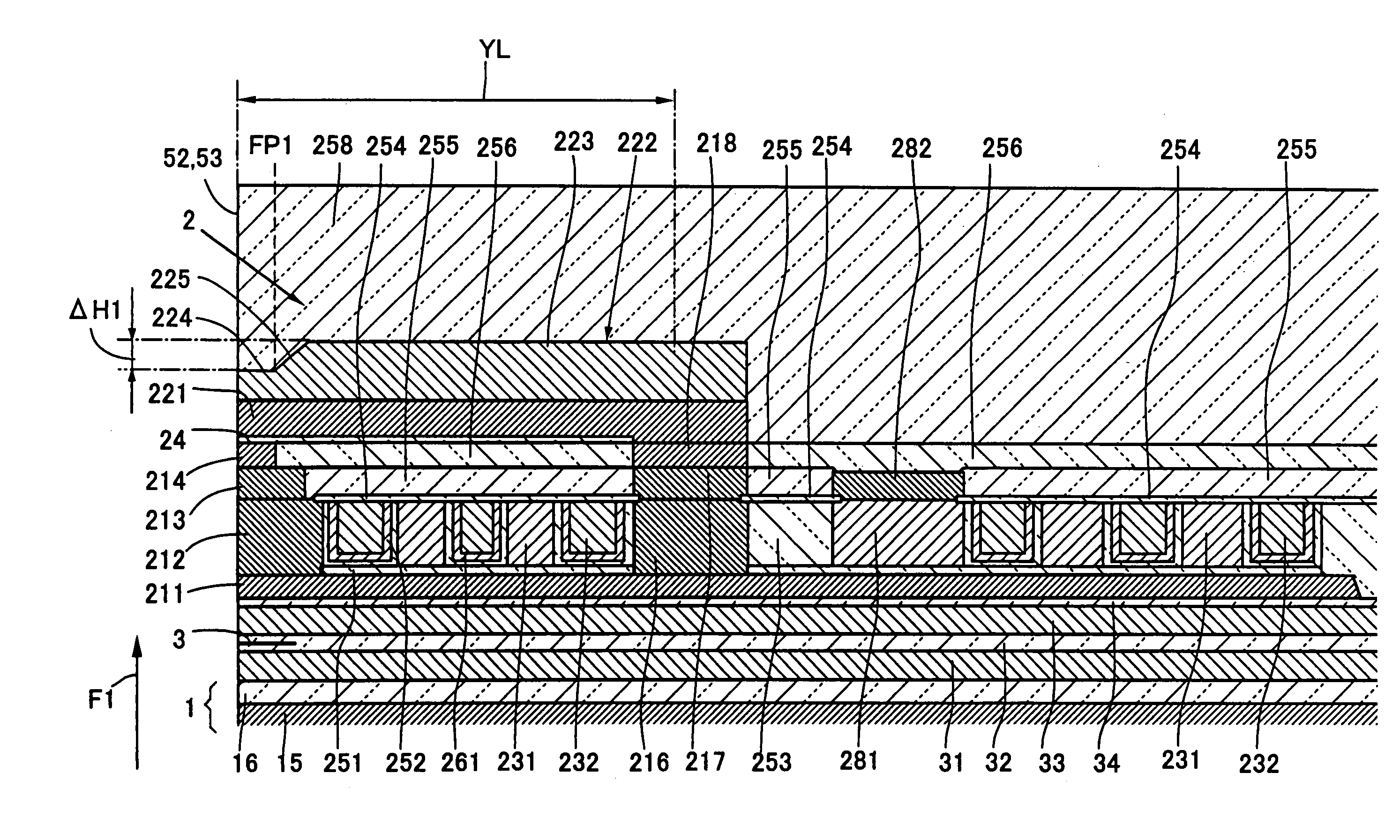

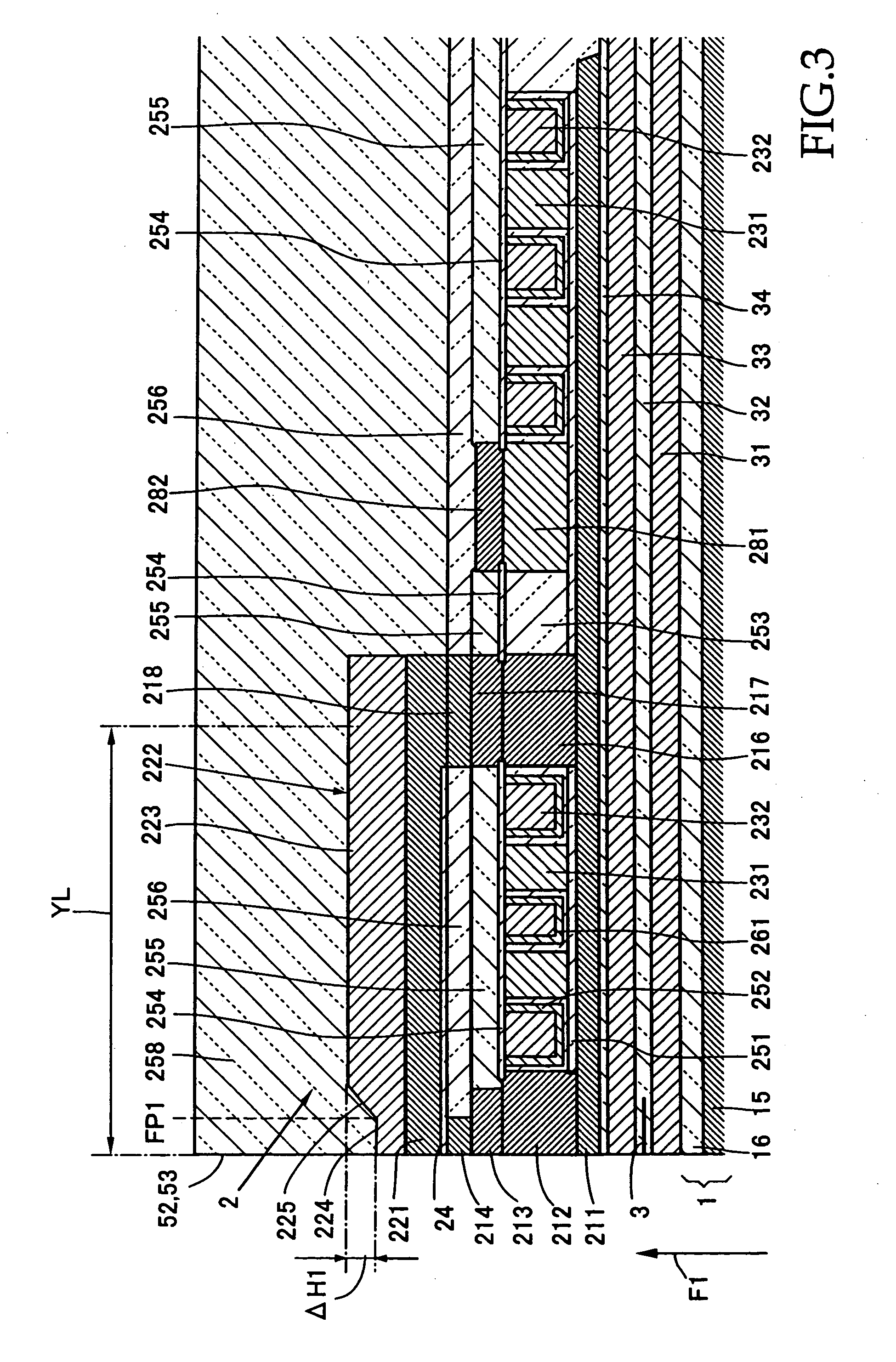

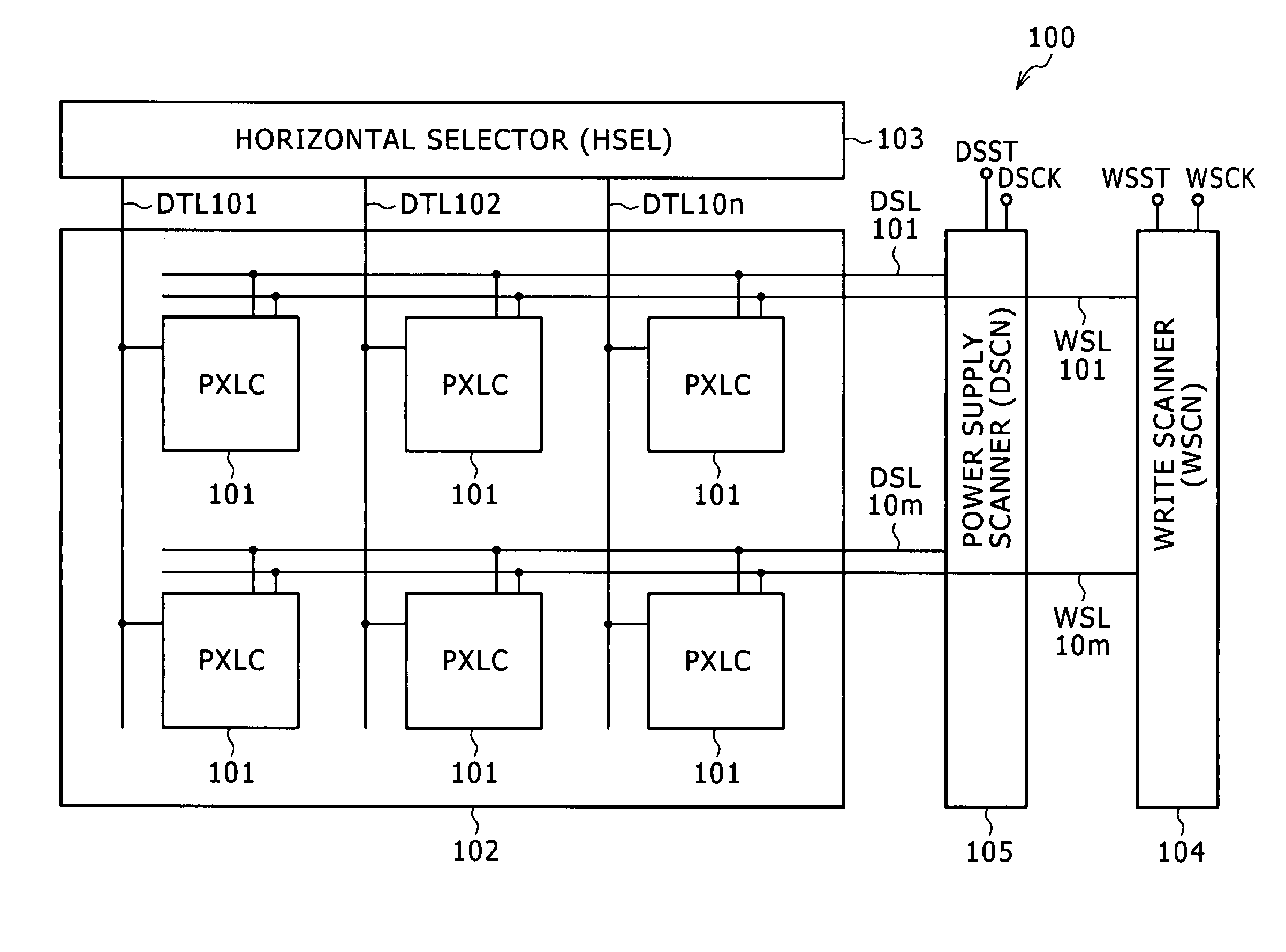

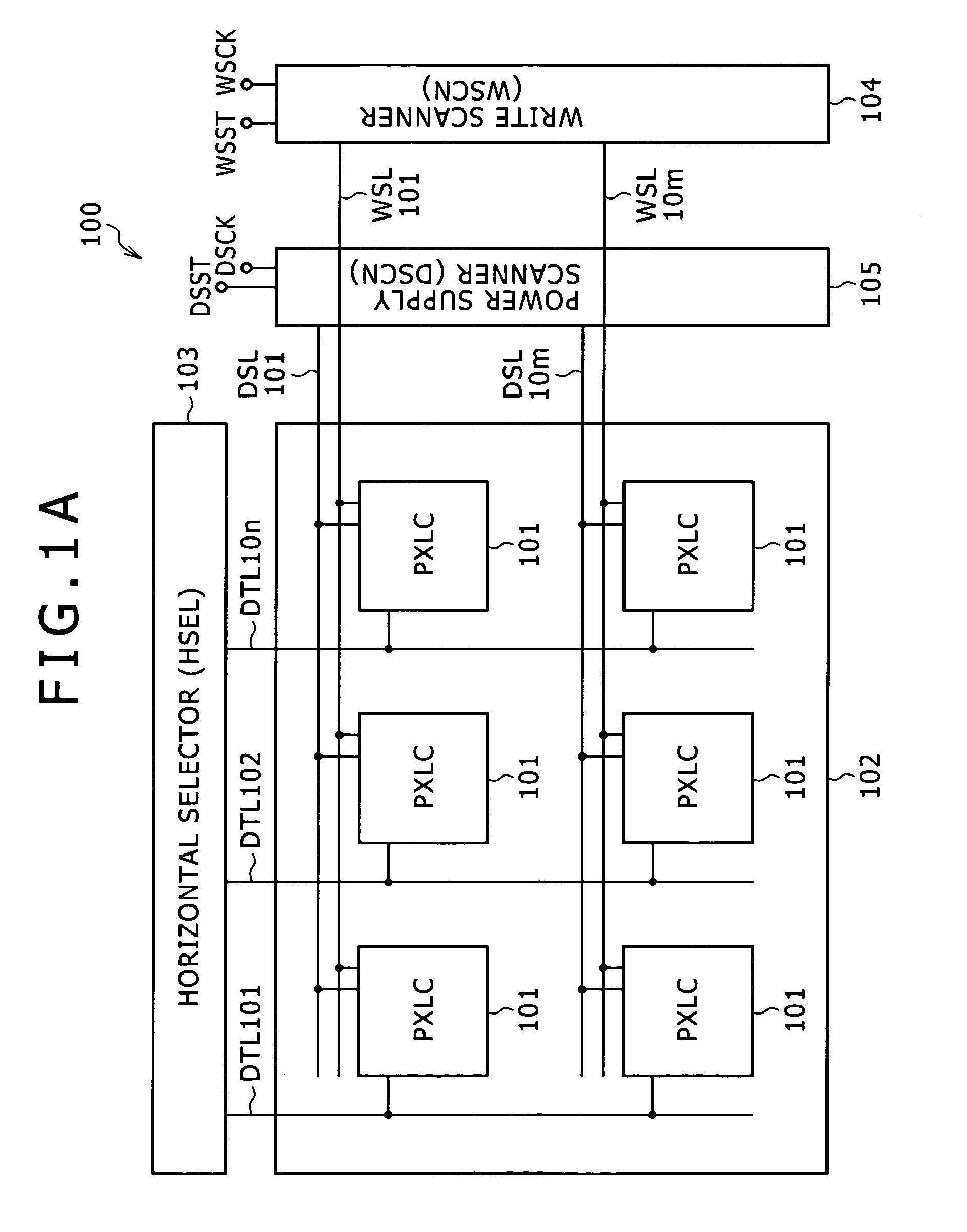

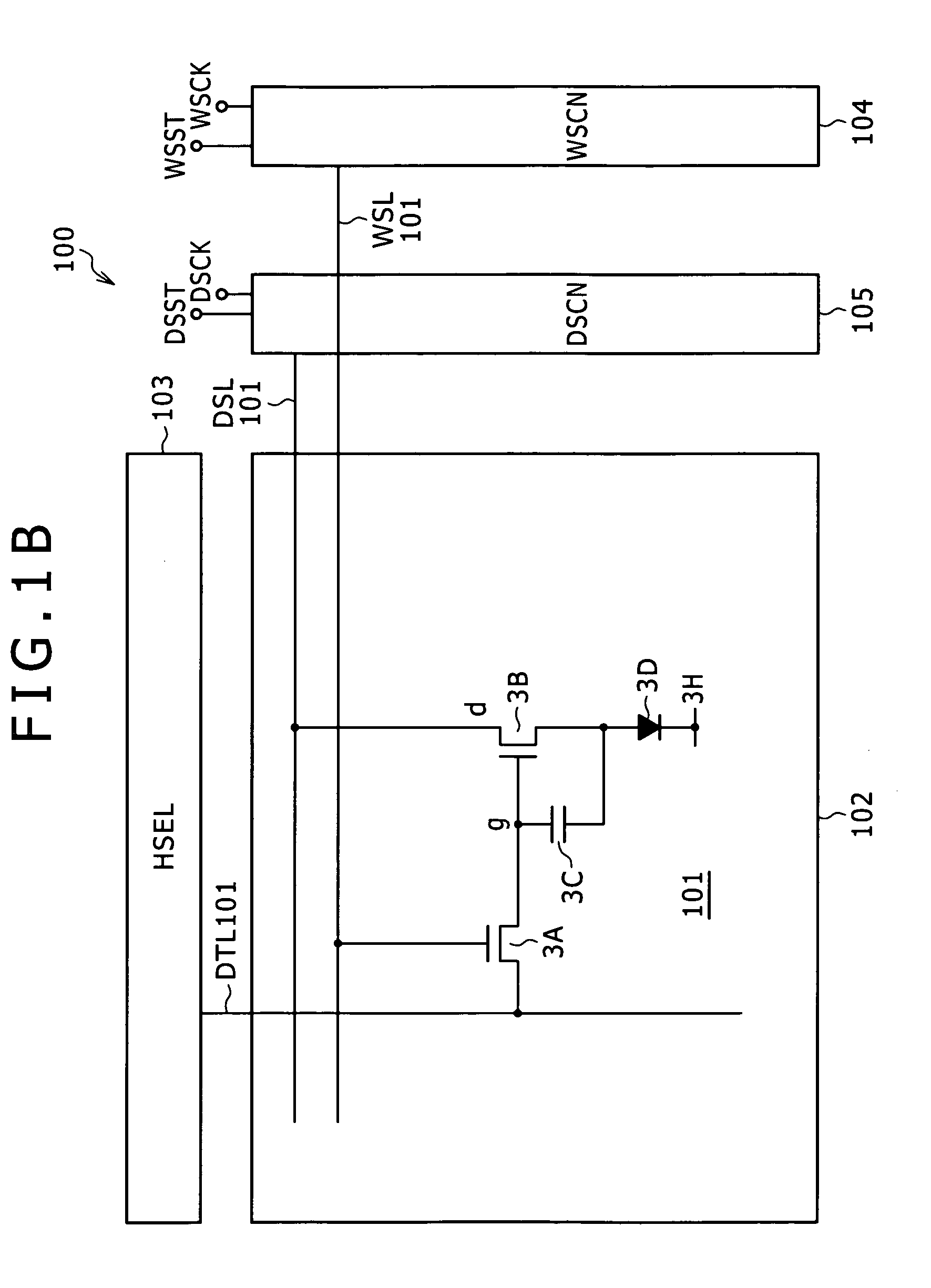

Display device and electronic device

ActiveUS20090167646A1Reduce percentageReduce manufacturing costStatic indicating devicesSolid-state devicesDisplay devicePixel array

The present invention provides a display device includes: a pixel array section including a set of pixels arranged in a form of a matrix; and a driving section for driving the pixel array section.

Owner:JOLED INC

Solar battery piece assembly and assembling method thereof

InactiveCN108172654ALow costAffect lifeSoldering apparatusPhotovoltaic energy generationElectrical batteryFlexible circuits

The invention relates to a solar battery piece assembly and an assembling method thereof. The solar battery piece assembly comprises a solar battery piece, low-temperature lead-free tin paste and a flexible circuit board; and the solar battery piece is welded on the flexible circuit board by using the low-temperature lead-free tin paste through a backflow welding manner. By adoption of a solder-strip-free battery pack series technology, the problem of influence to the collection efficiency of a photovoltaic module current from the quality of a solder strip in the conventional process is eliminated; the low-temperature lead-free tin paste is adopted between the battery piece and the flexible circuit board, and the backflow peak temperature is controlled to be 190 DEG C or below, so that thephenomena of solar battery piece cracking or hidden cracking caused by an overhigh welding temperature can be avoided; meanwhile, silver paste is not used, so that production cost is greatly lowered;by taking the flexible board as the welding circuit board, the thickness of the solar battery assembly can be greatly lowered; and therefore, the solar battery piece assembly has the characteristicsof low limitation on the overall wiring space of the assembly, high wiring density, high flexibility and less process steps.

Owner:BEIJING COMPO ADVANCED TECH

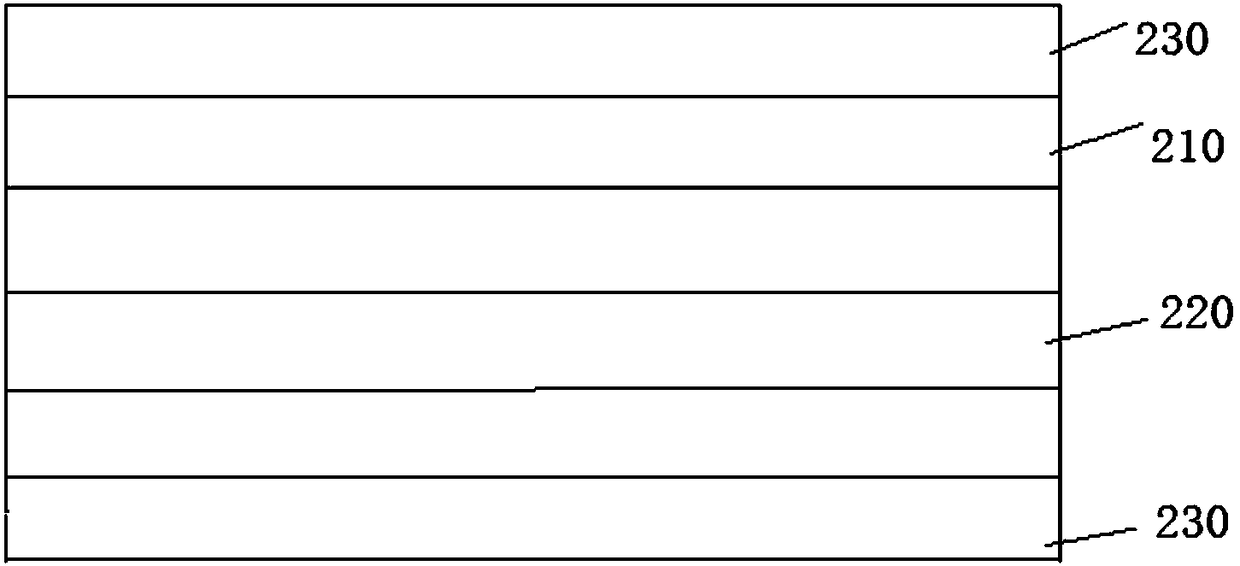

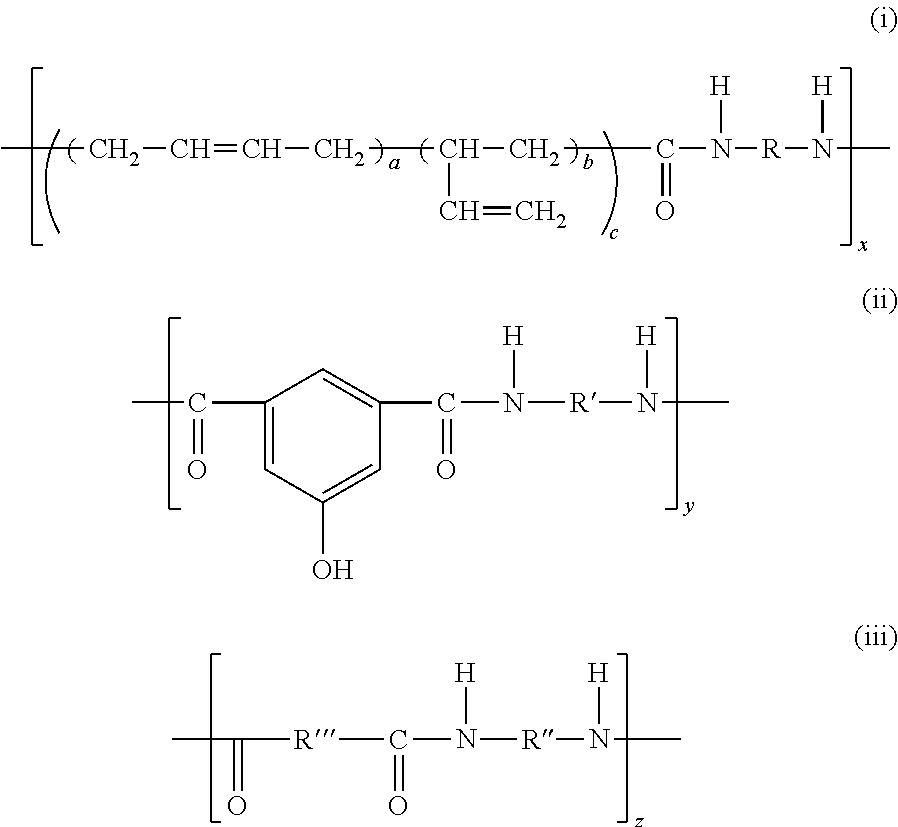

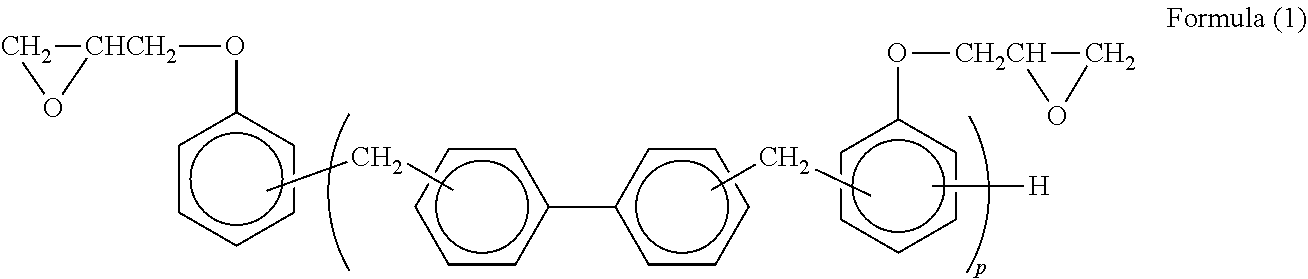

Primer layer for plating process, laminate for circuit board and production method for same, and multilayer circuit board and production method for same

InactiveUS20140151091A1Increase stickinessHigh wiring densityAnimal housingAdhesivesEpoxyHigh density

Disclosed are a primer layer for plating process exhibiting high adhesiveness to an electroless copper plating and capable of coping with high density of wirings of semiconductor packages; a laminate for wiring board having the primer layer and a method for manufacture thereof; and a multilayer wiring board having the primer layer and a method for manufacture thereof. Specifically disclosed are a primer layer for plating process formed of a resin composition for primer layer including (A) a polyfunctional epoxy resin, (B) an epoxy resin curing agent, and (C) a phenolic hydroxyl group-containing polybutadiene-modified polyamide resin having specified structural units, wherein a blending proportion of the component (C) is 5 parts by mass or more and less than 25 parts by mass based on 100 parts by mass of a total sum of the component (A) and the component (B); a laminate for wiring board having the primer layer and a method for manufacture thereof; and a multilayer wiring board having the primer layer and a method for manufacture thereof.

Owner:HITACHI CHEM CO LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com