Fabrication method of space transformer for semiconductor test probe card

A technology of space transformation and testing probes, which is applied in the field of probe cards, can solve problems such as incompatibilities, and achieve the effect of reducing pitch distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0058] In order to make the above-mentioned and other objects, features, and advantages of the present invention more clearly understood, the preferred embodiments are specifically listed below, together with the accompanying drawings, and are described in detail as follows:

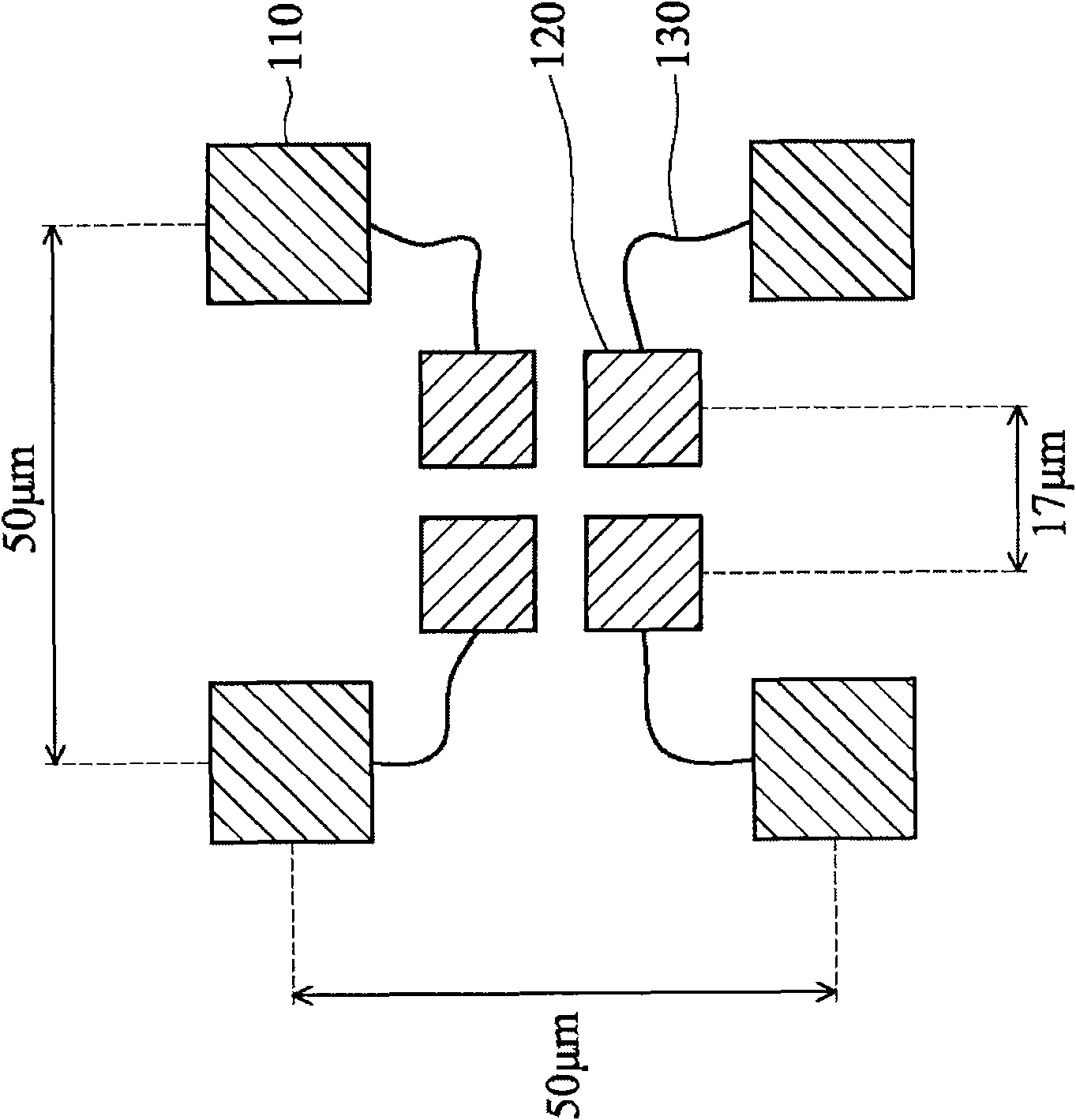

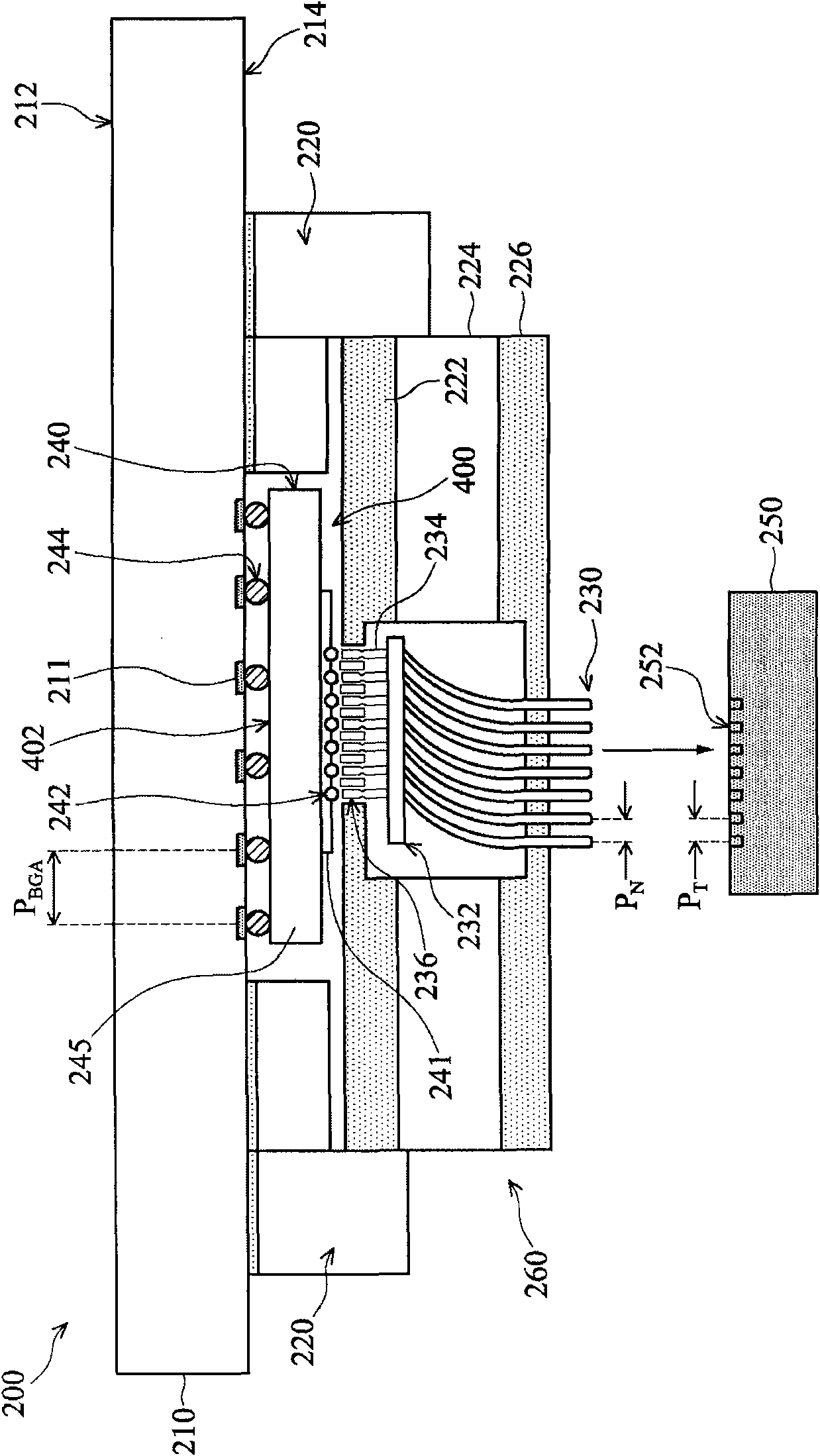

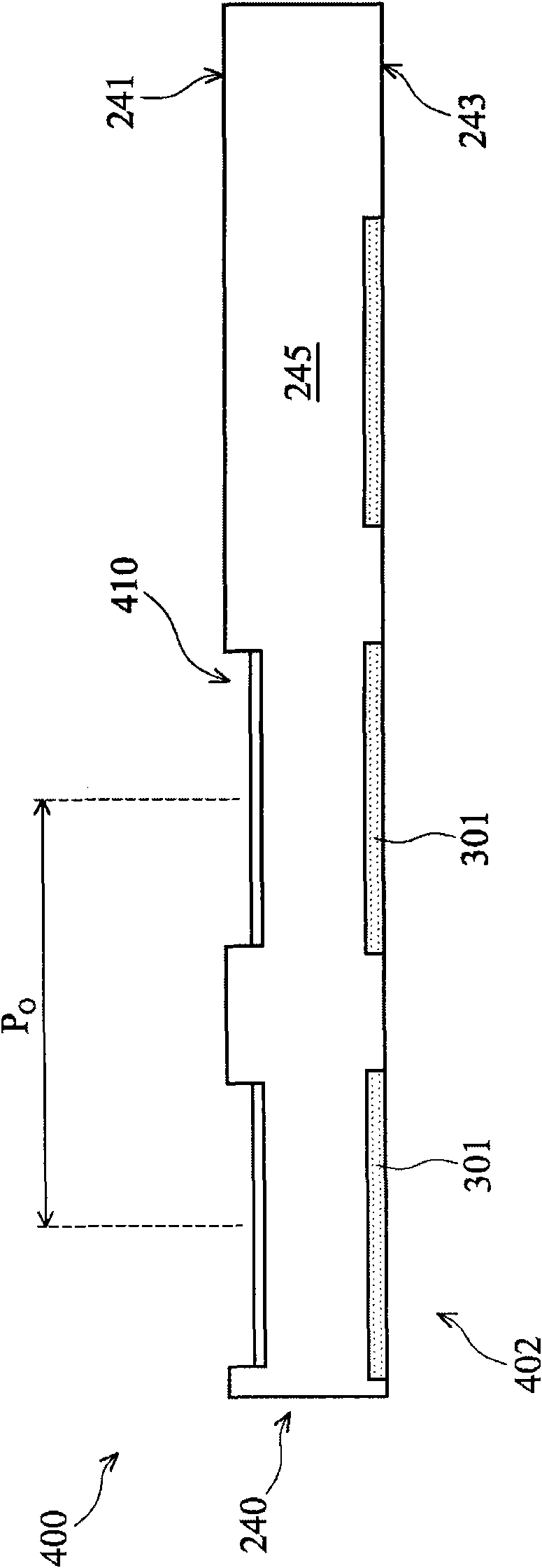

[0059] figure 2 An exemplary embodiment is shown of a commercially available test probe card 200 having a space transformer 240 with fine pitch C4 contact pads that has been modified by the method proposed by the present invention array. The test probe card 200 may be any suitable commercially available test probe card, such as, but not limited to, the Probe with Needle Probes from Wentworth Laboratories, Inc. of Brookfield, CT. card, or from ofLivermore, CA obtained with Probe card for needle probes. The above-mentioned probe card is preferably selected to have a spacing or pitch of 50 microns or less for the test needle-like probes, so as to have the same spacing or spacing as the test pad 110 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com