Barrier material and process for Cu interconnect

a barrier material and interconnection technology, applied in the direction of semiconductor devices, semiconductor/solid-state device details, electrical apparatus, etc., can solve the problems of limiting device performance, signal propagation delay caused, copper may not be deposited in higher amounts in an efficient manner, etc., to achieve the effect of improving electromigration performan

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] The operation and fabrication of the presently preferred embodiments are discussed in detail below. However, the embodiments and examples described herein are not the only applications or uses contemplated for the invention. The specific embodiments discussed are merely illustrative of specific ways to make and use the invention, and do not limit the scope of the invention or the appended claims.

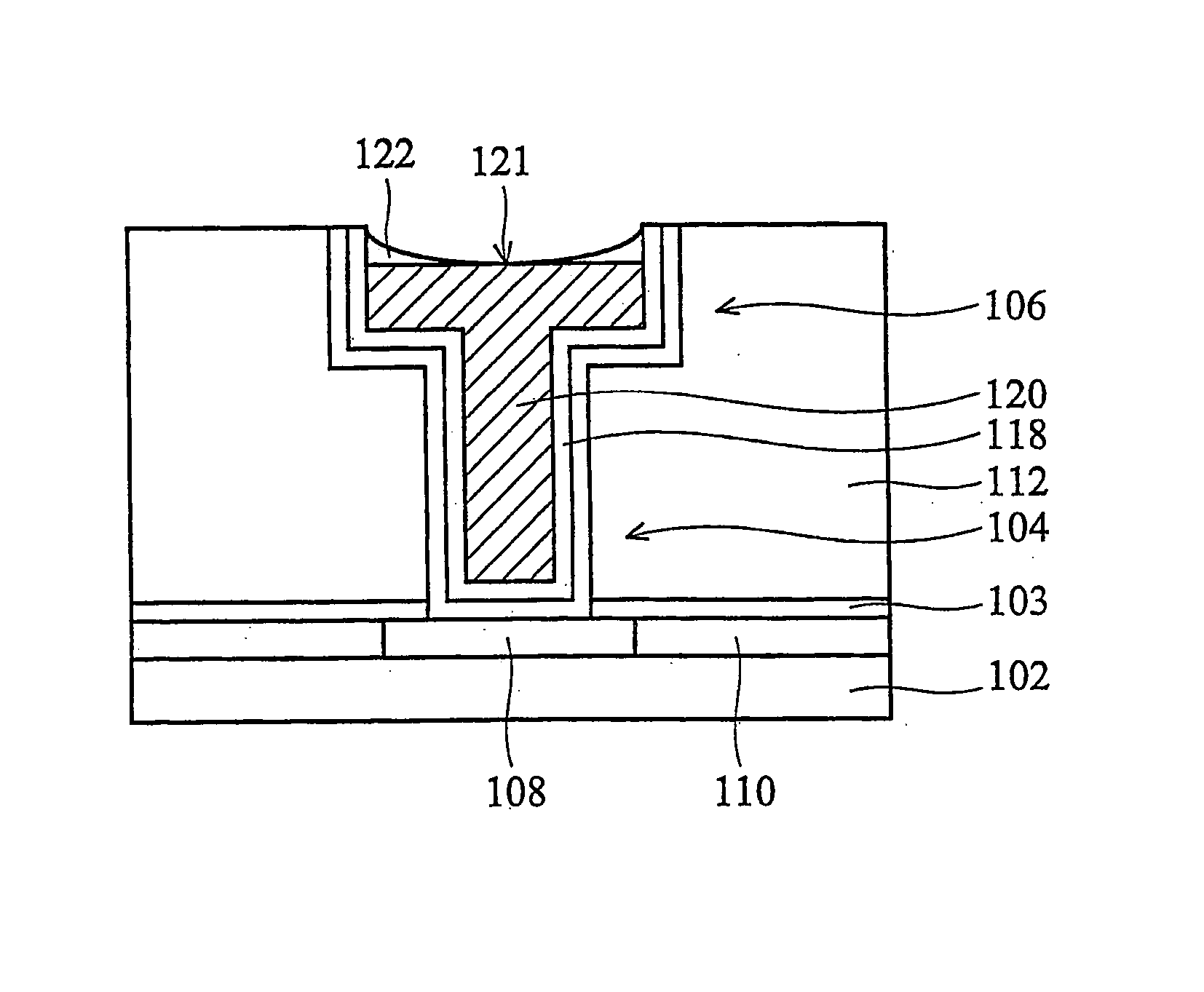

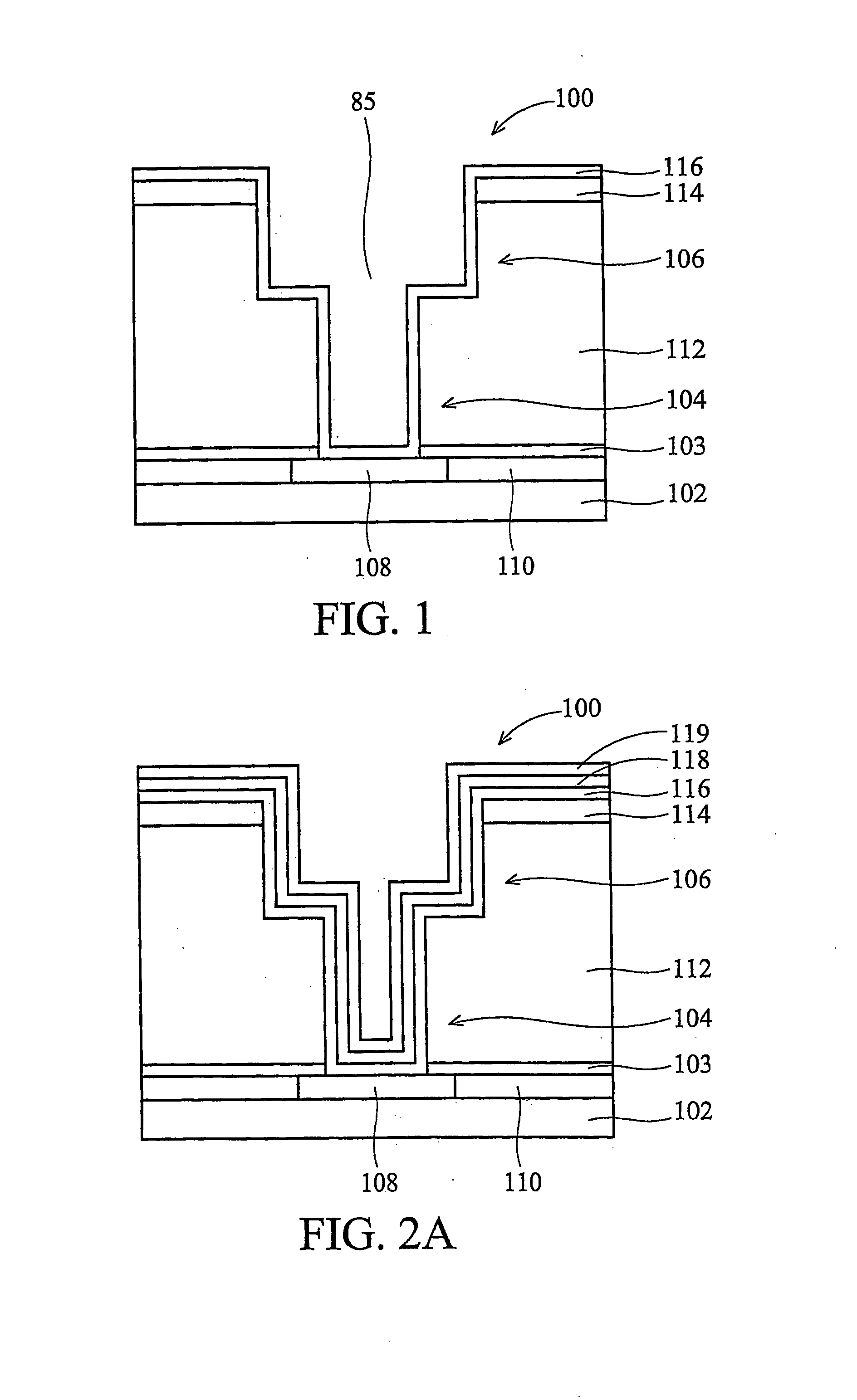

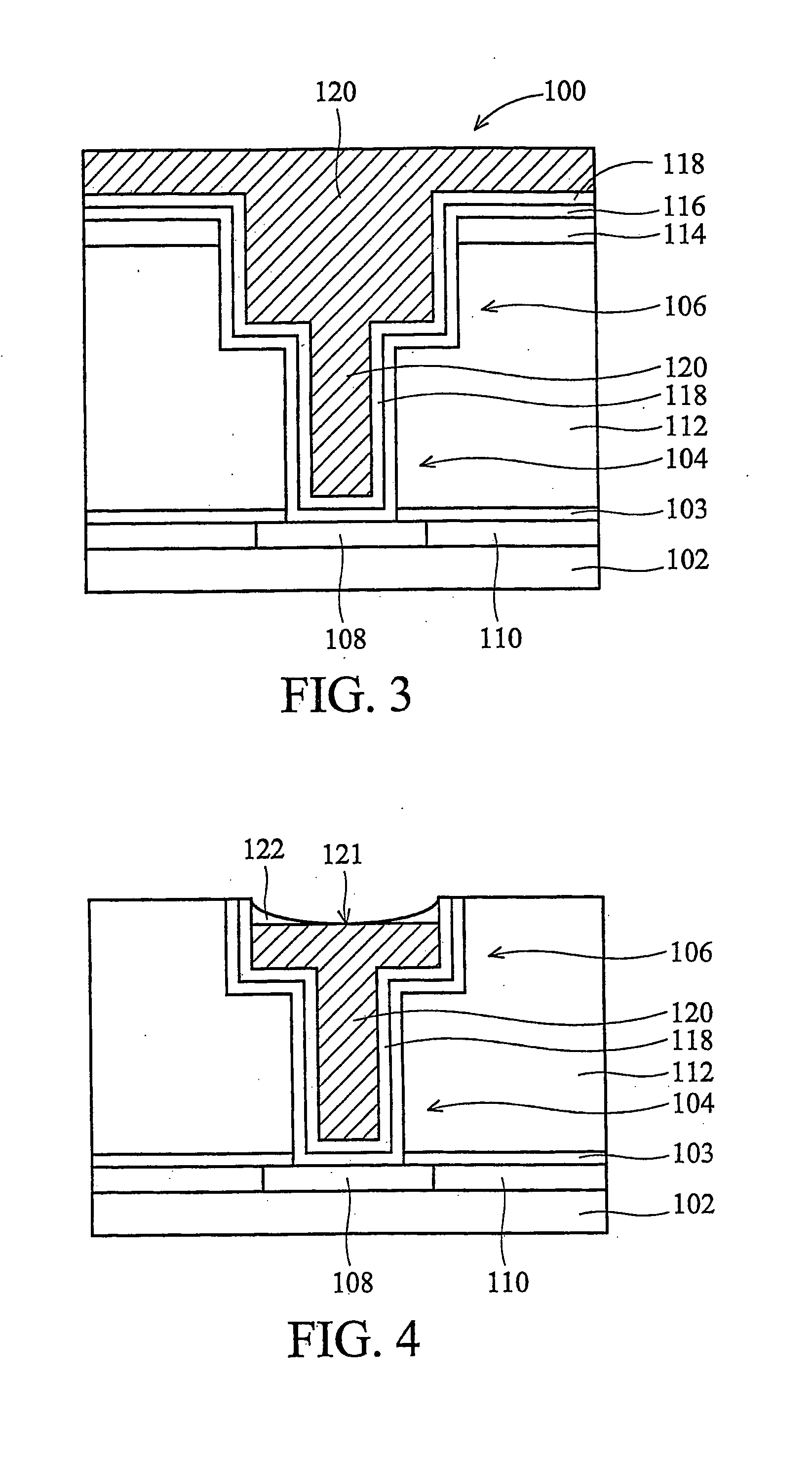

[0027] This invention relates generally to semiconductor device fabrication and more particularly to a structure and method for improved resistance to electromigration problems with conductive lines and vias, such as copper, between interconnected layers. The present invention will now be described with respect to preferred embodiments in a specific context, namely the creation of copper conductive lines and vias in the damascene process. It is believed that embodiments of this invention are particularly advantageous when used in this process. It is further believed that embodiments ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| channel length | aaaaa | aaaaa |

| dielectric constant | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com