Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

478results about How to "High error rate" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Interference-based routing in a wireless mesh network

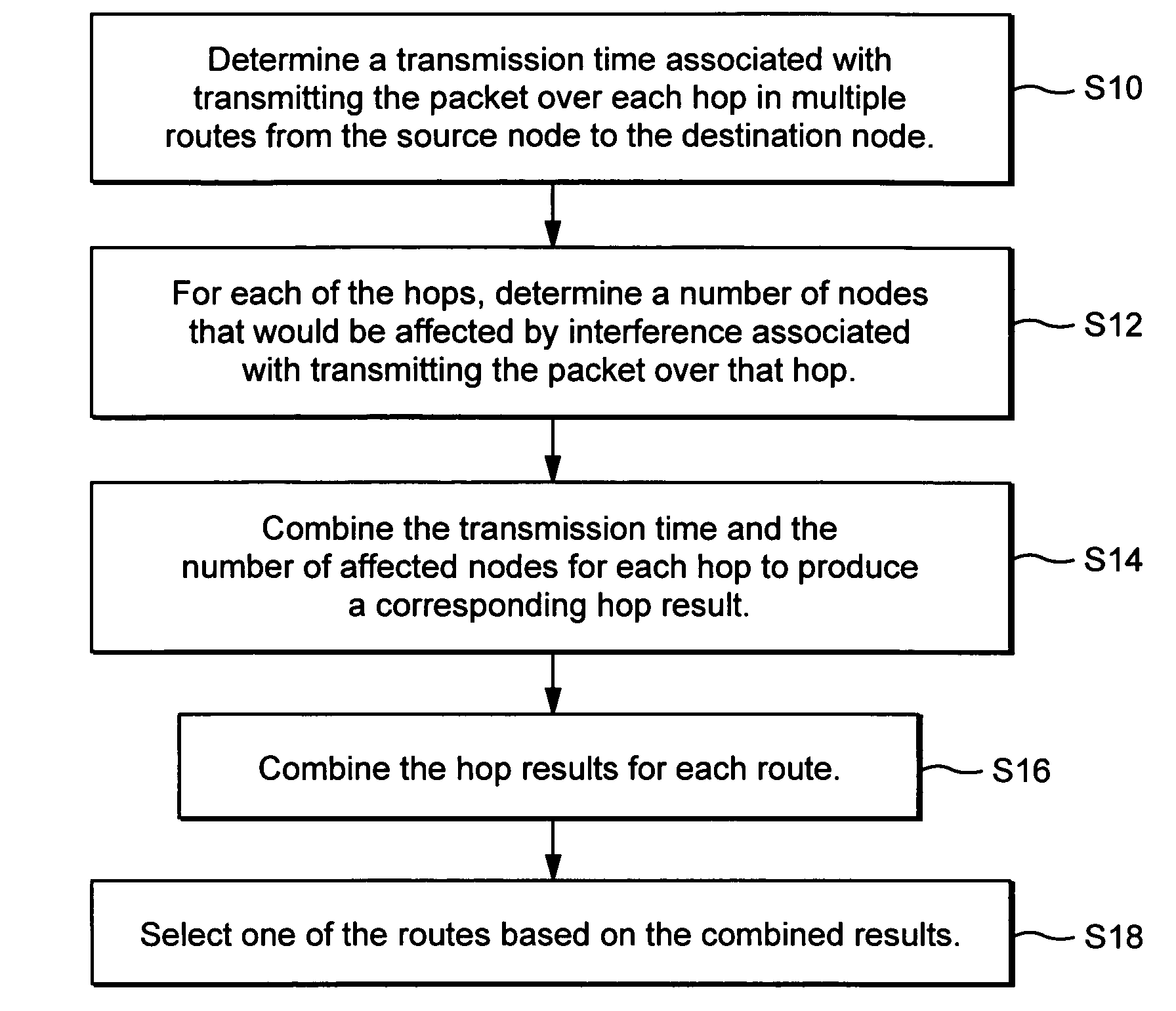

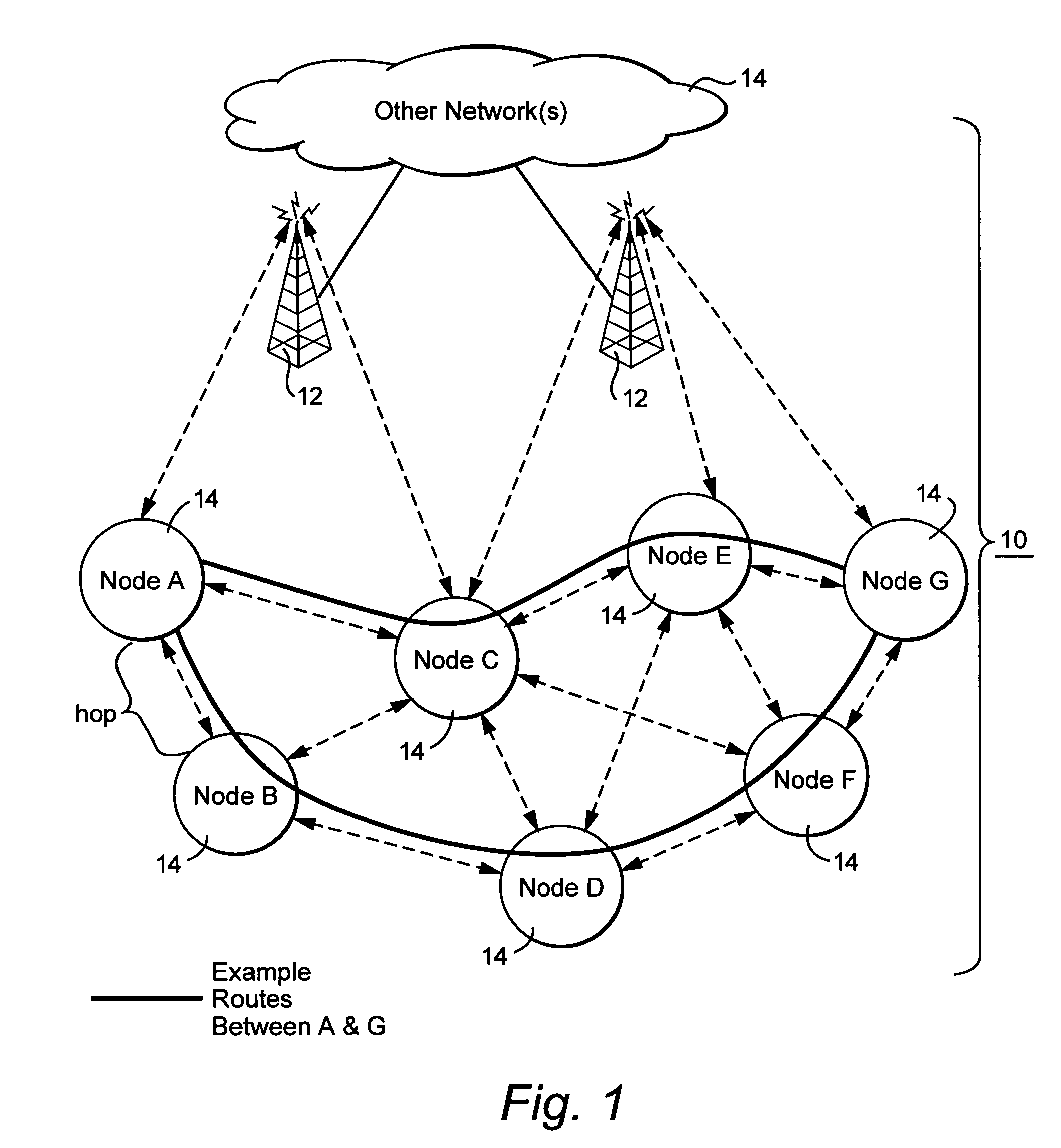

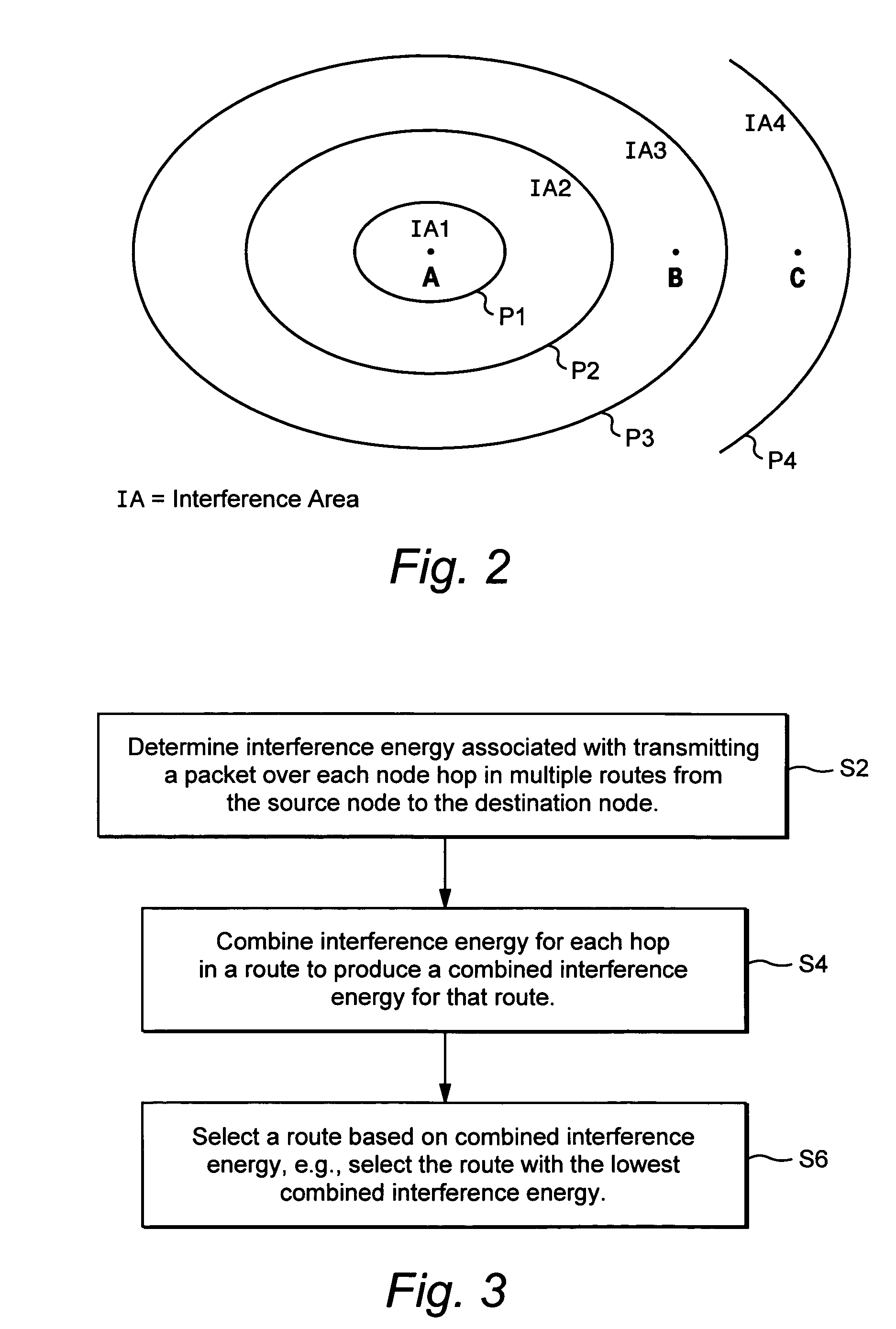

ActiveUS7554998B2Low costReduce data rateEnergy efficient ICTError preventionComputer networkWireless mesh network

Route selection through a wireless mesh network between a source node and a destination node is based on minimizing generated interference in order to increase the capacity of the network. An interference energy associated with transmitting a packet over each hop in multiple routes from the source node to the destination node is determined. The interference energy for each hop is combined to generate a combined interference energy for each route. One of the routes is selected based on the combined interference energy determined for each route.

Owner:TELEFON AB LM ERICSSON (PUBL)

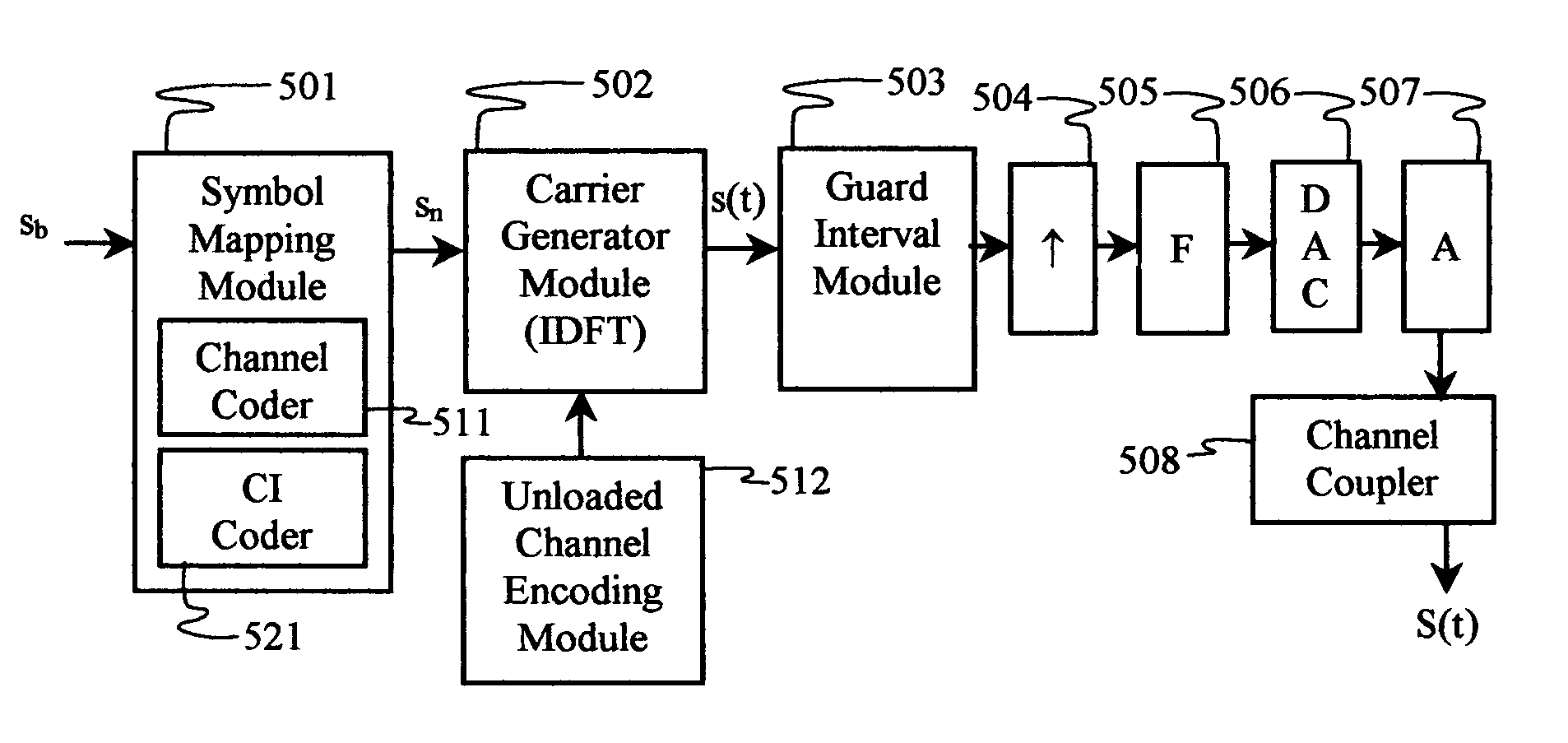

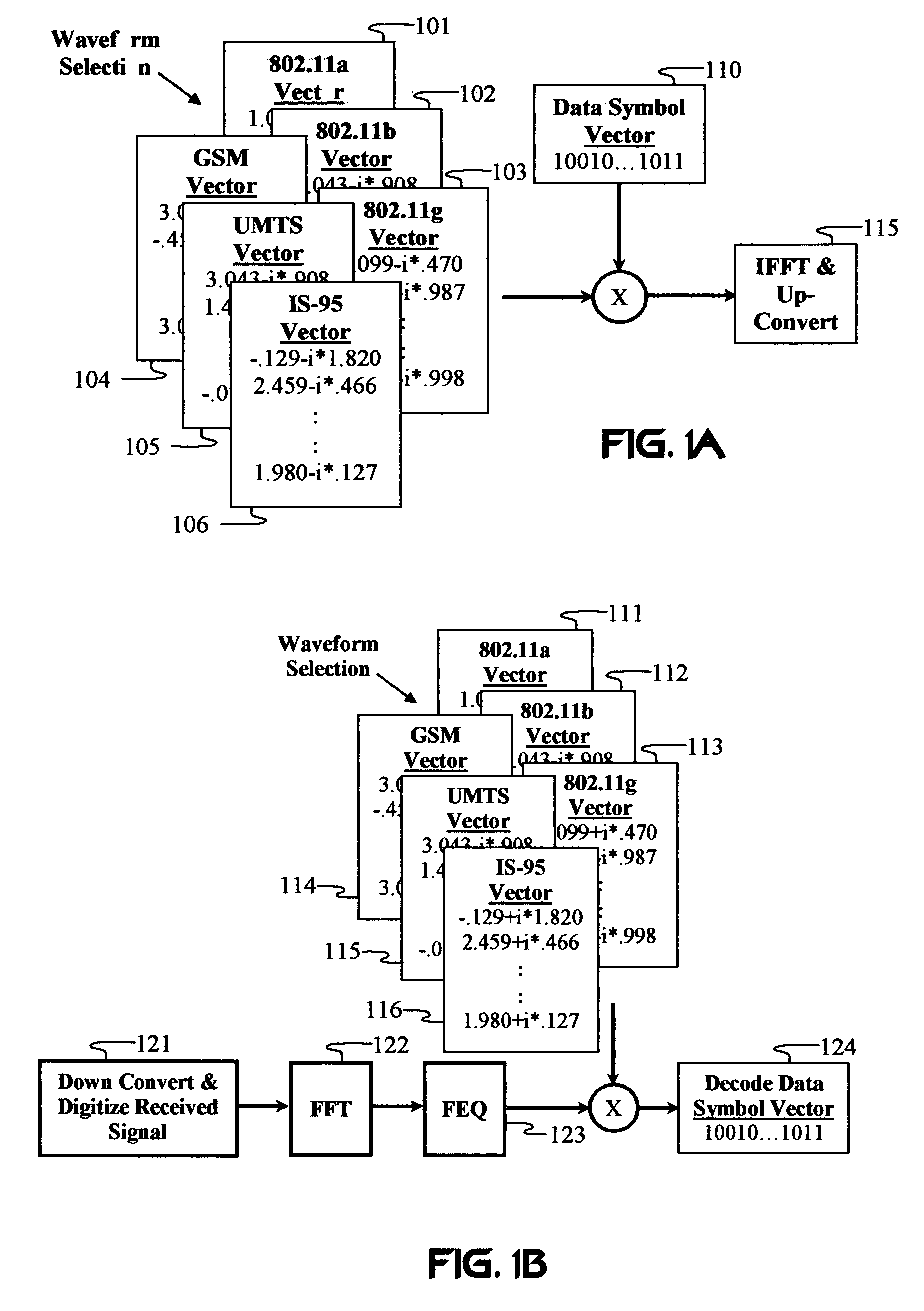

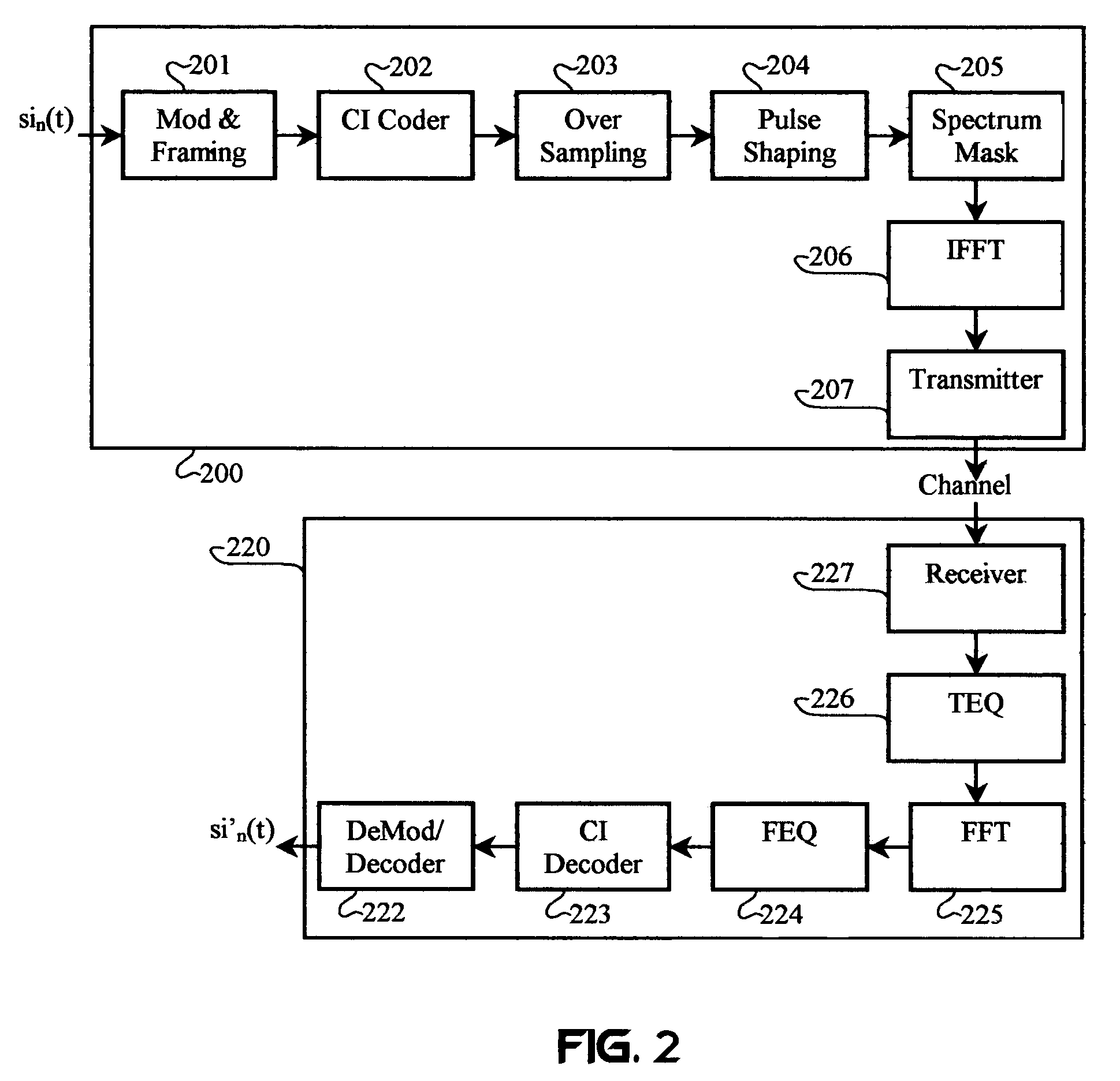

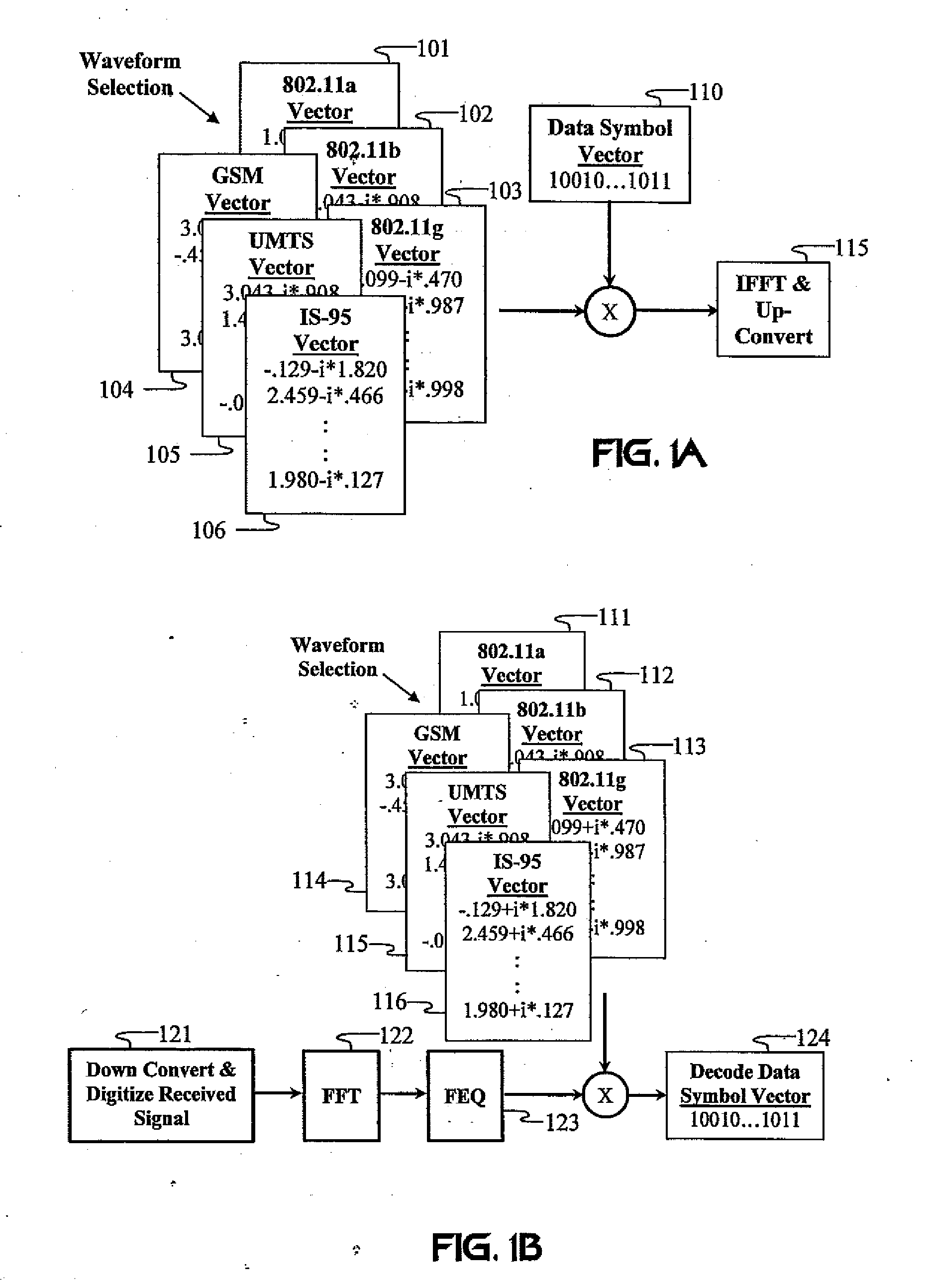

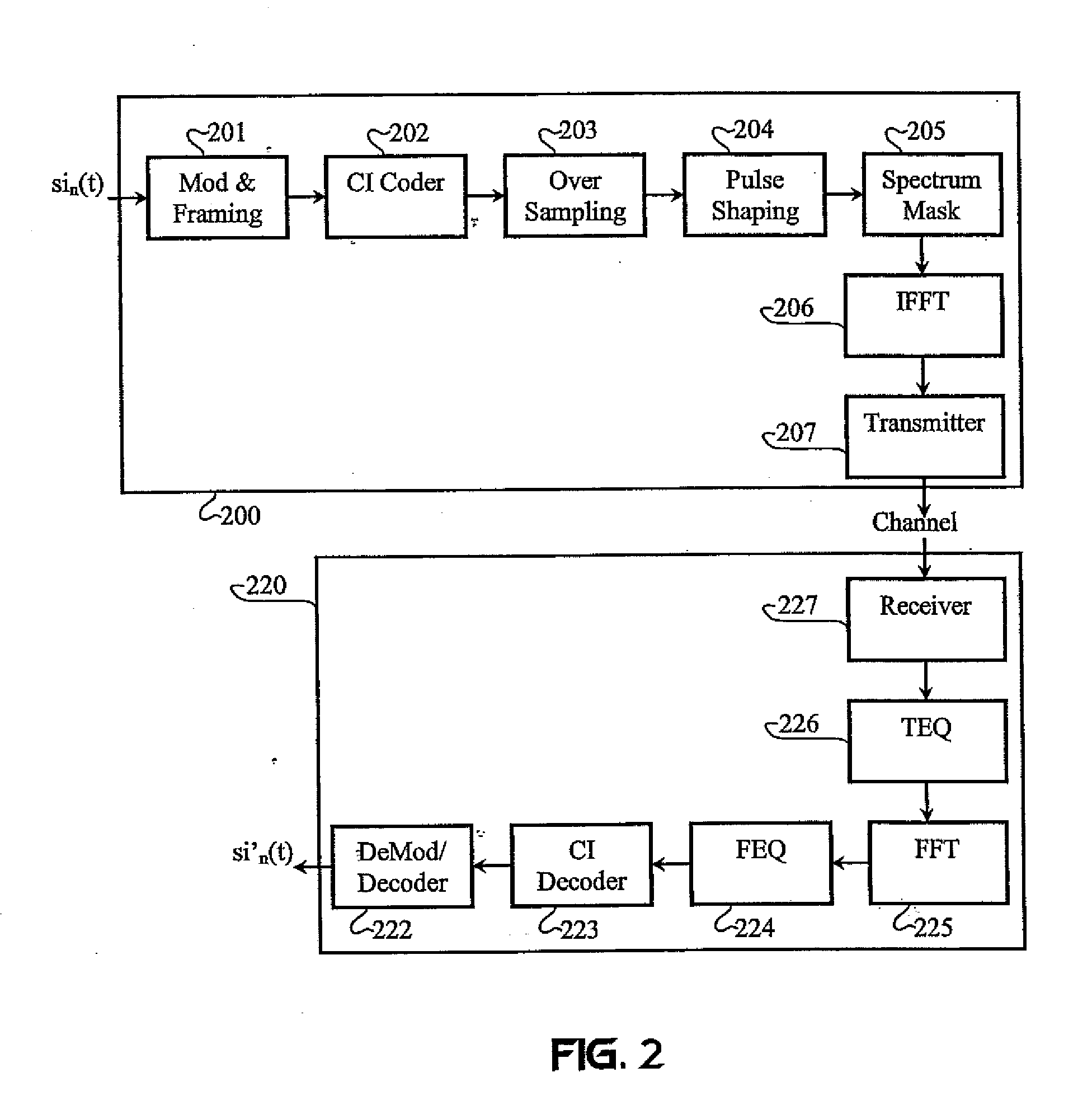

Software adaptable high performance multicarrier transmission protocol

InactiveUS7418043B2Reduce PAPREnhance other technique used for PAPR mitigationModulated carrier system with waveletsSecret communicationTransmission protocolTime domain

Techniques for reducing peak-to-average power in multicarrier transmitters employ peak cancellation with subcarriers that are impaired by existing channel conditions. The use of Carrier Interferometry (CI) coding further improves the effectiveness of peak reduction. CI coding can also be impressed onto pulse sequences in the time domain, which enhances spectral selection and facilitates peak-power control.

Owner:DEPARTMENT 13 INC

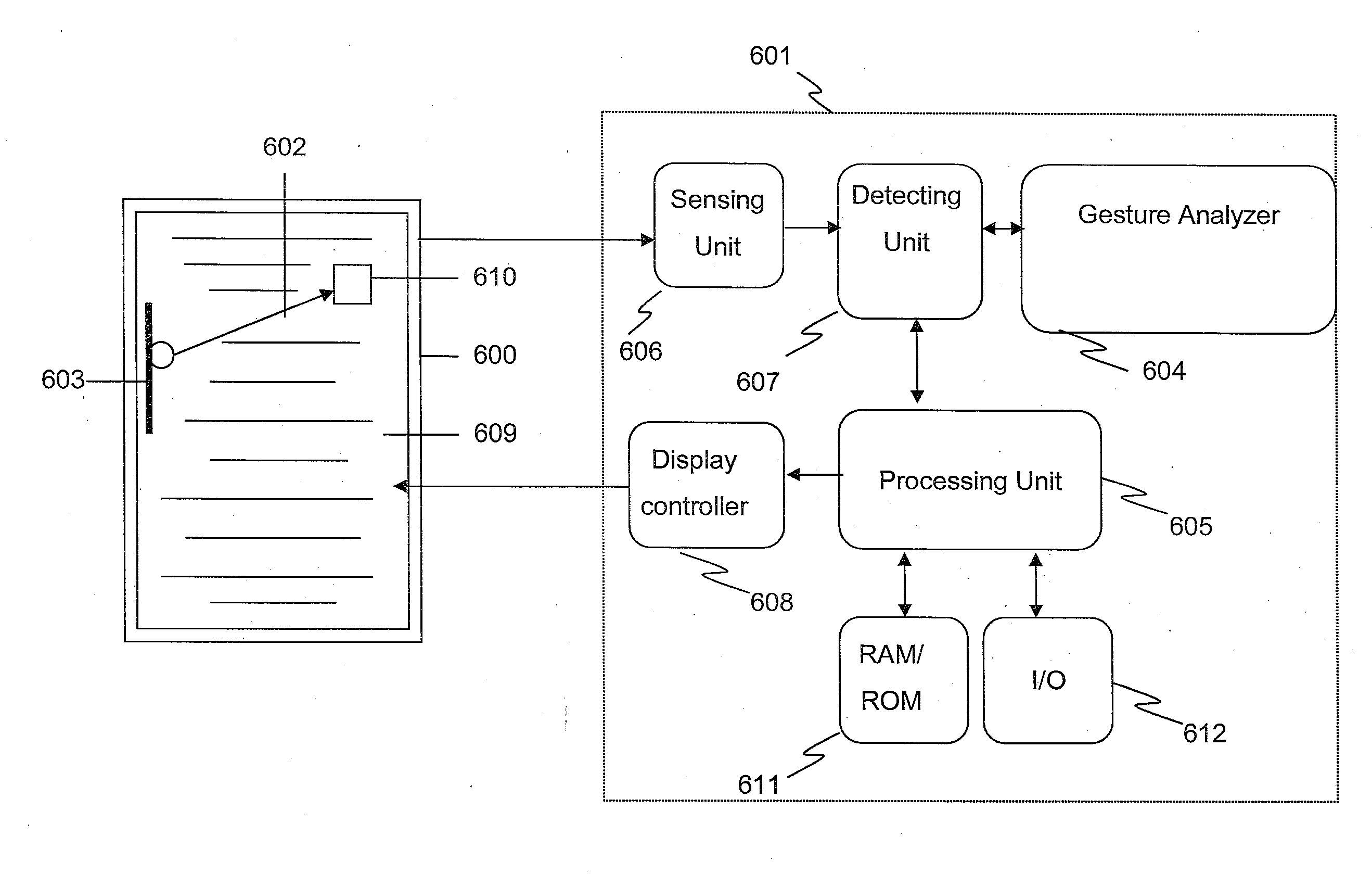

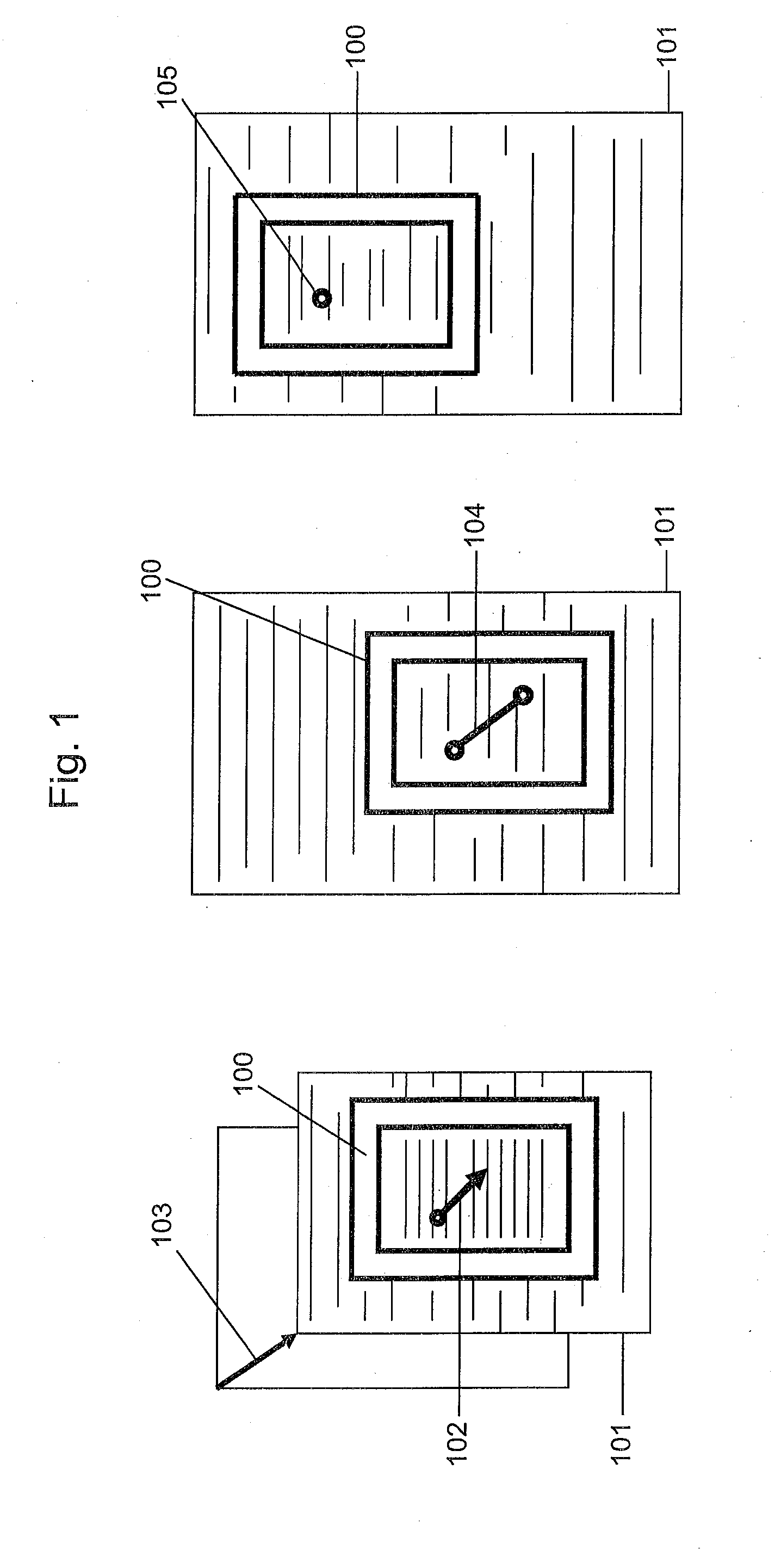

Multiple selection on devices with many gestures

ActiveUS20100050076A1Minimal display spaceIncrease probabilityInput/output for user-computer interactionGraph readingDisplay deviceMulti-touch

Owner:FUJIFILM BUSINESS INNOVATION CORP

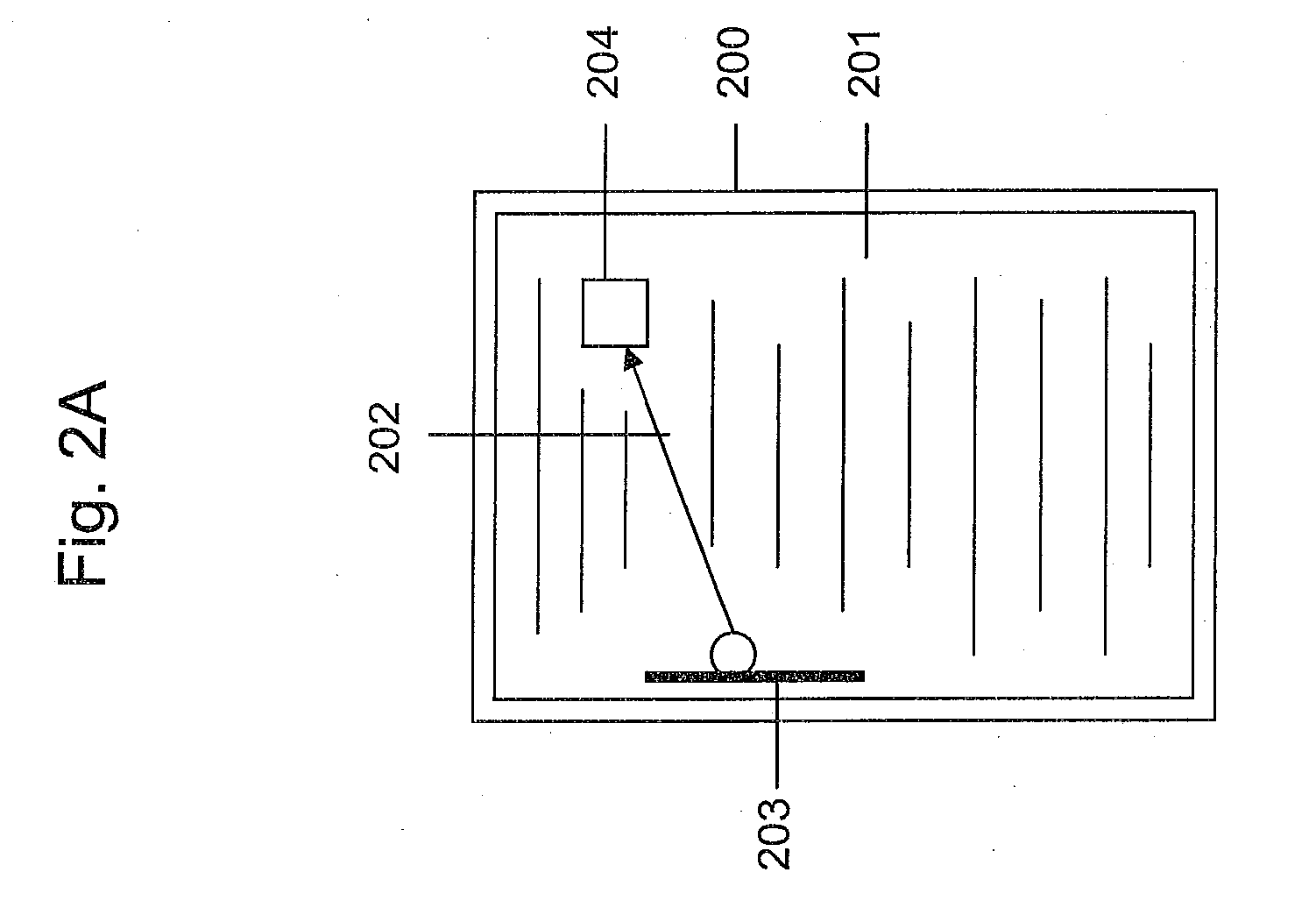

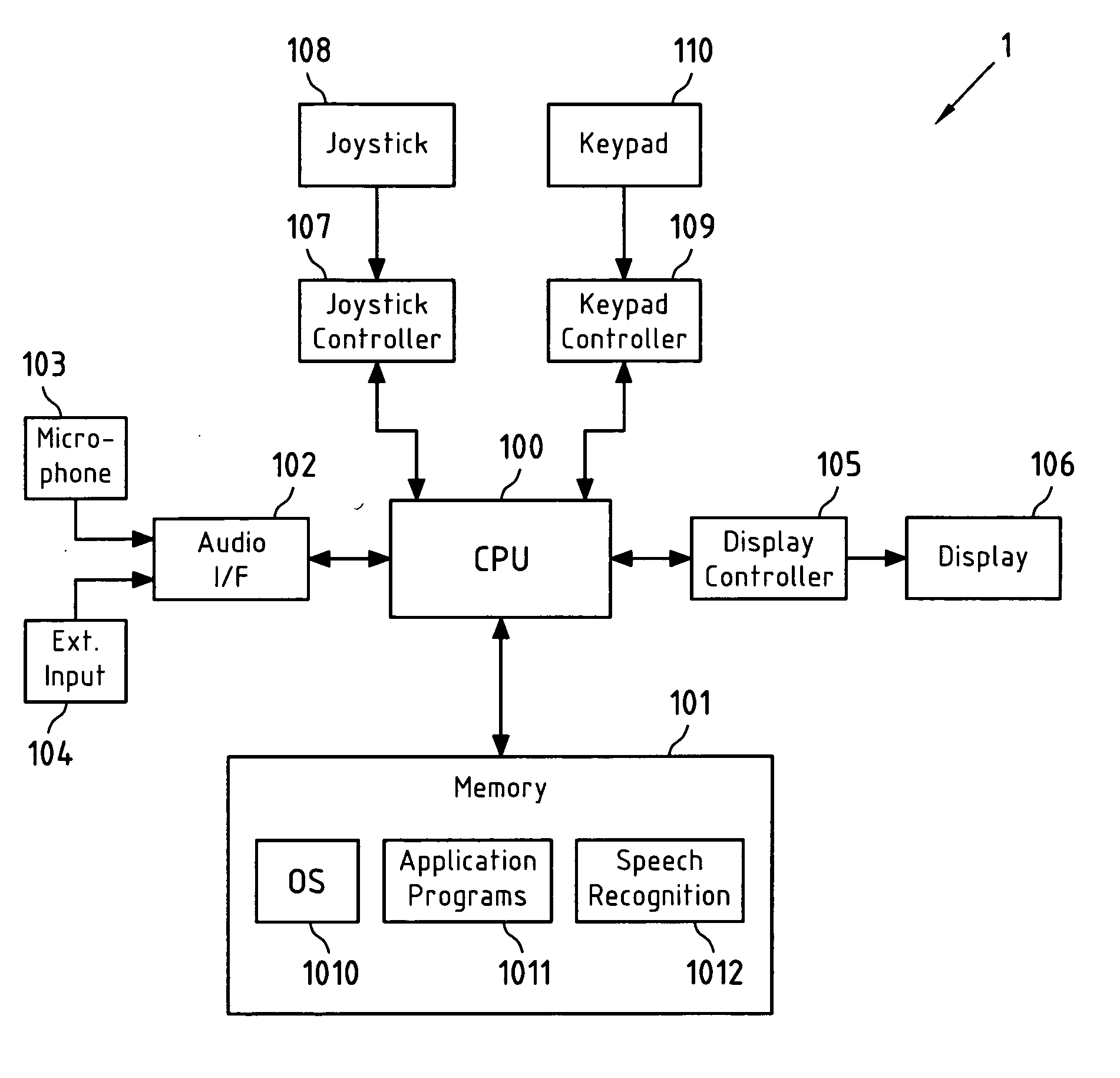

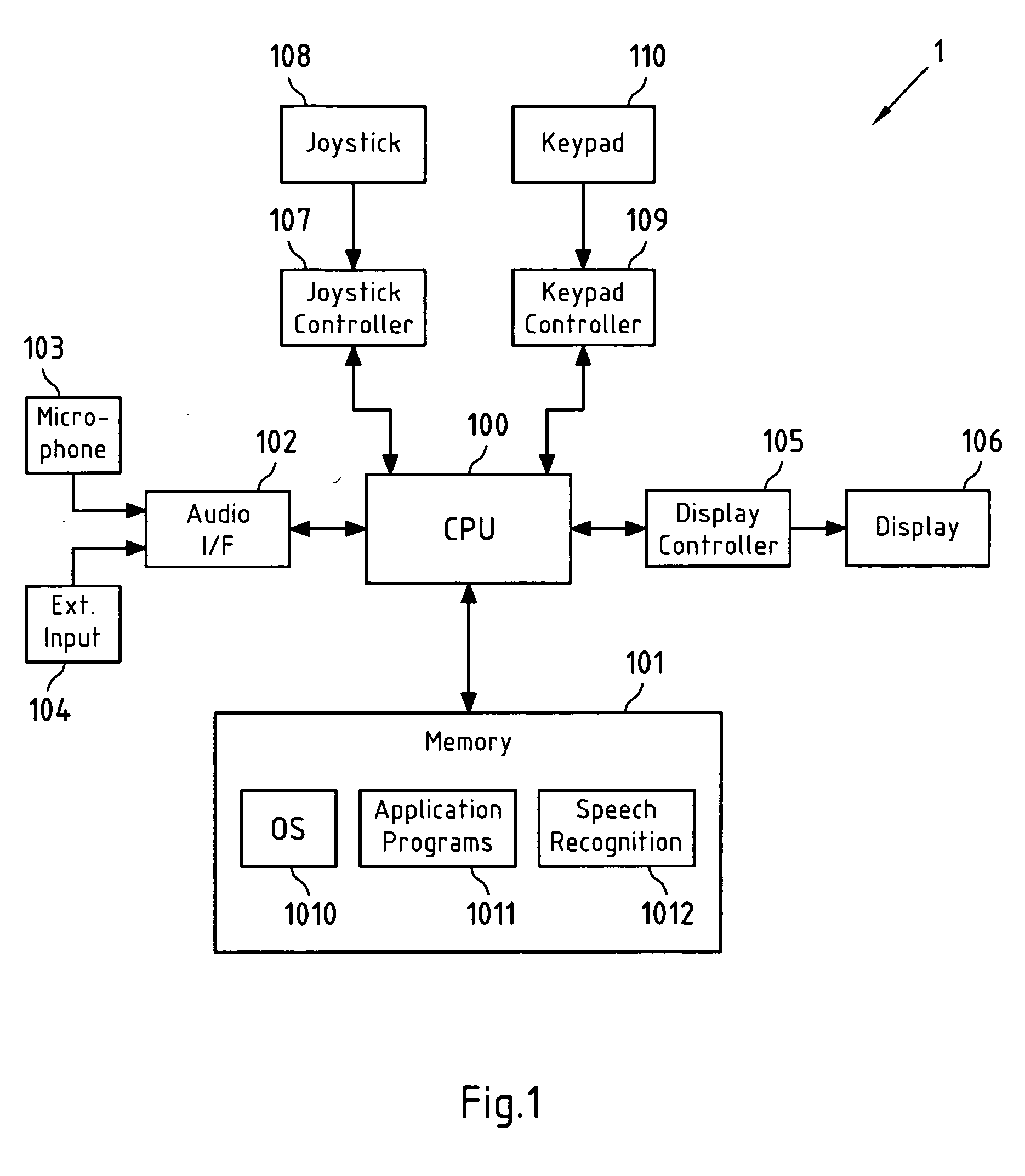

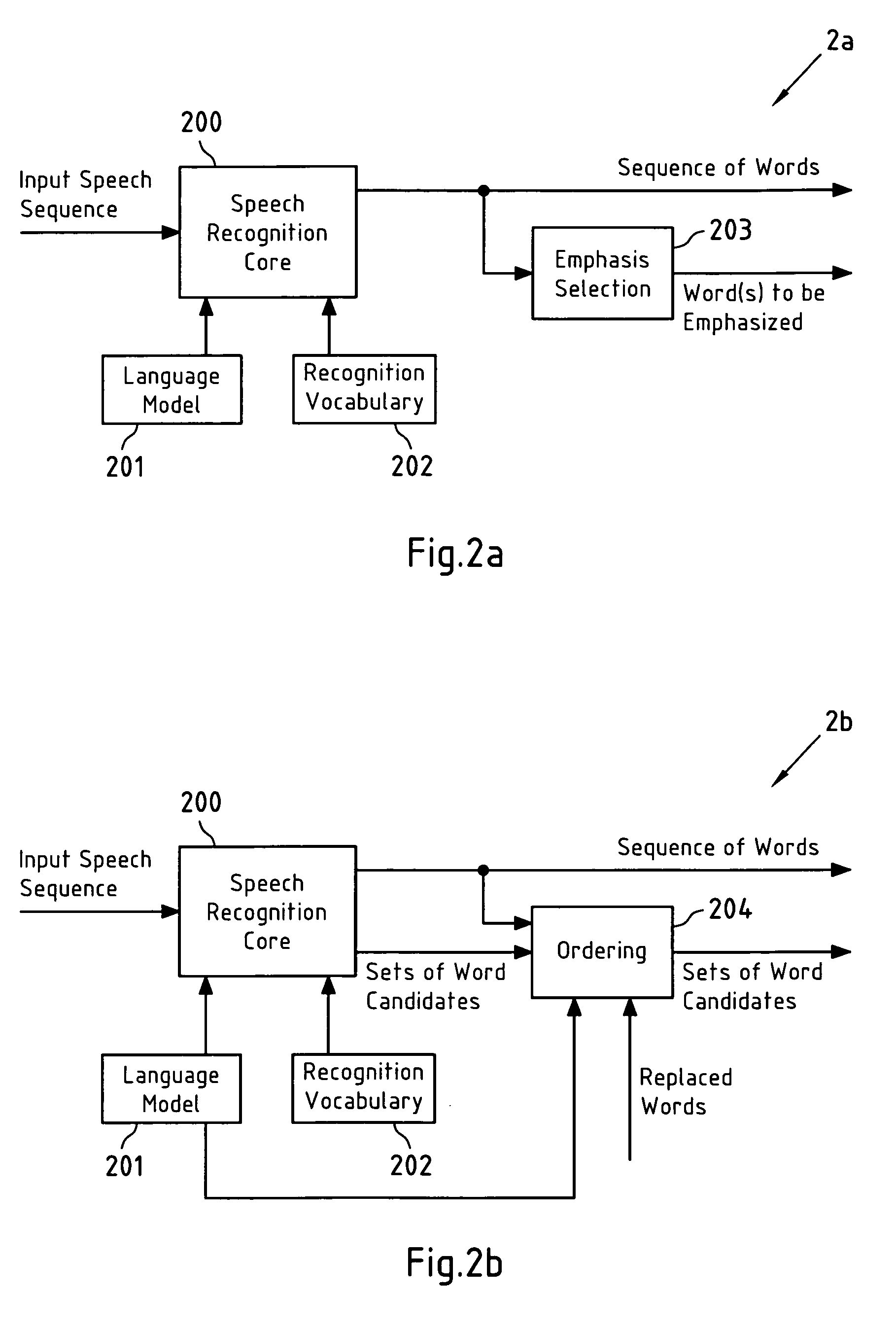

Error correction for speech recognition systems

Words in a sequence of words that is obtained from speech recognition of an input speech sequence are presented to a user, and at least one of the words in the sequence of words is replaced, in case it has been selected by a user for correction. Words with a low recognition confidence value are emphasized; alternative word candidates for the at least one selected word are ordered according to an ordering criterion; after replacing a word, an order of alternative word candidates for neighboring words in the sequence is updated; the replacement word is derived from a spoken representation of the at least one selected word by speech recognition with a limited vocabulary; and the word that replaces the at least one selected word is derived from a spoken and spelled representation of the at least one selected word.

Owner:NOKIA CORP

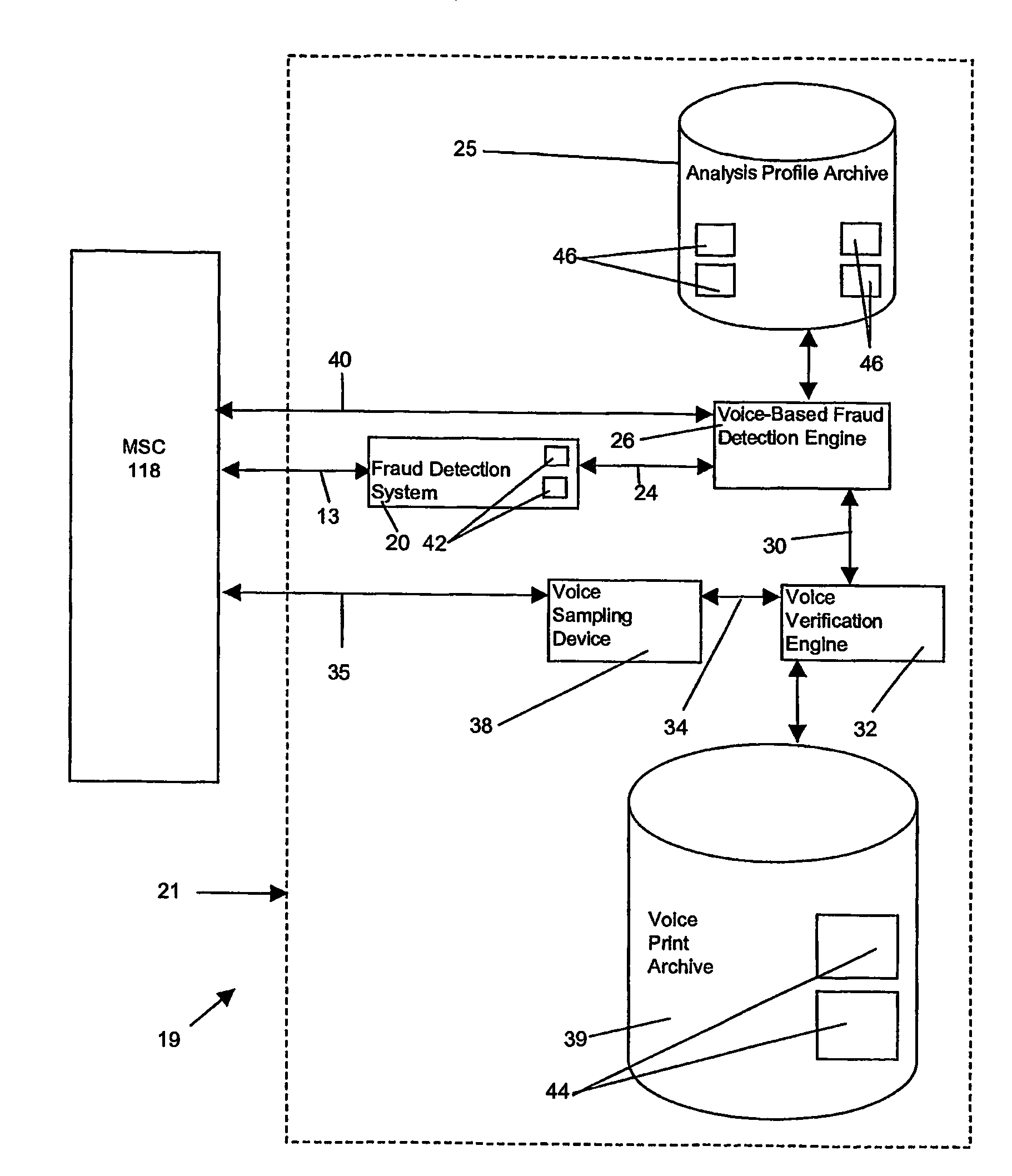

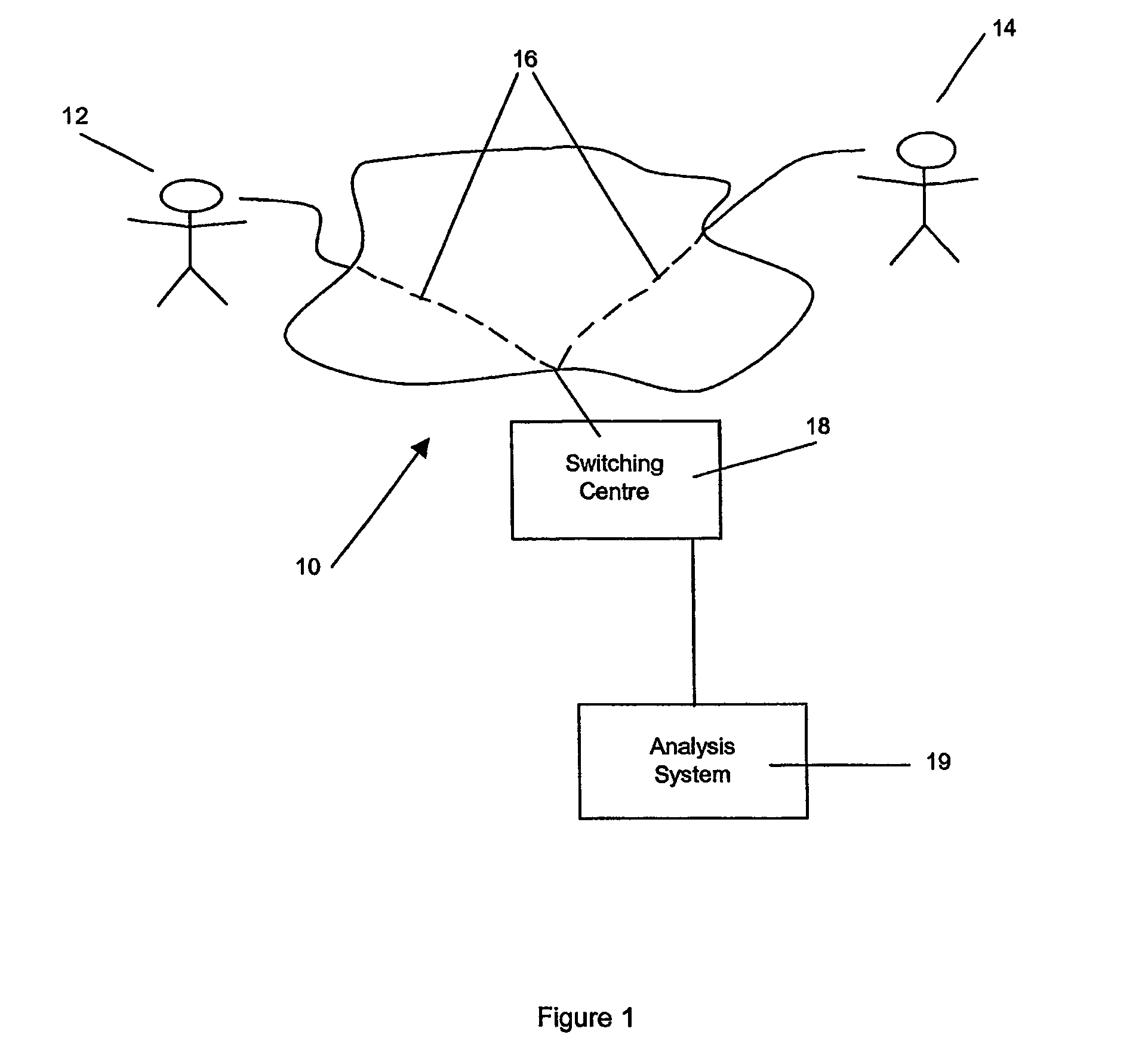

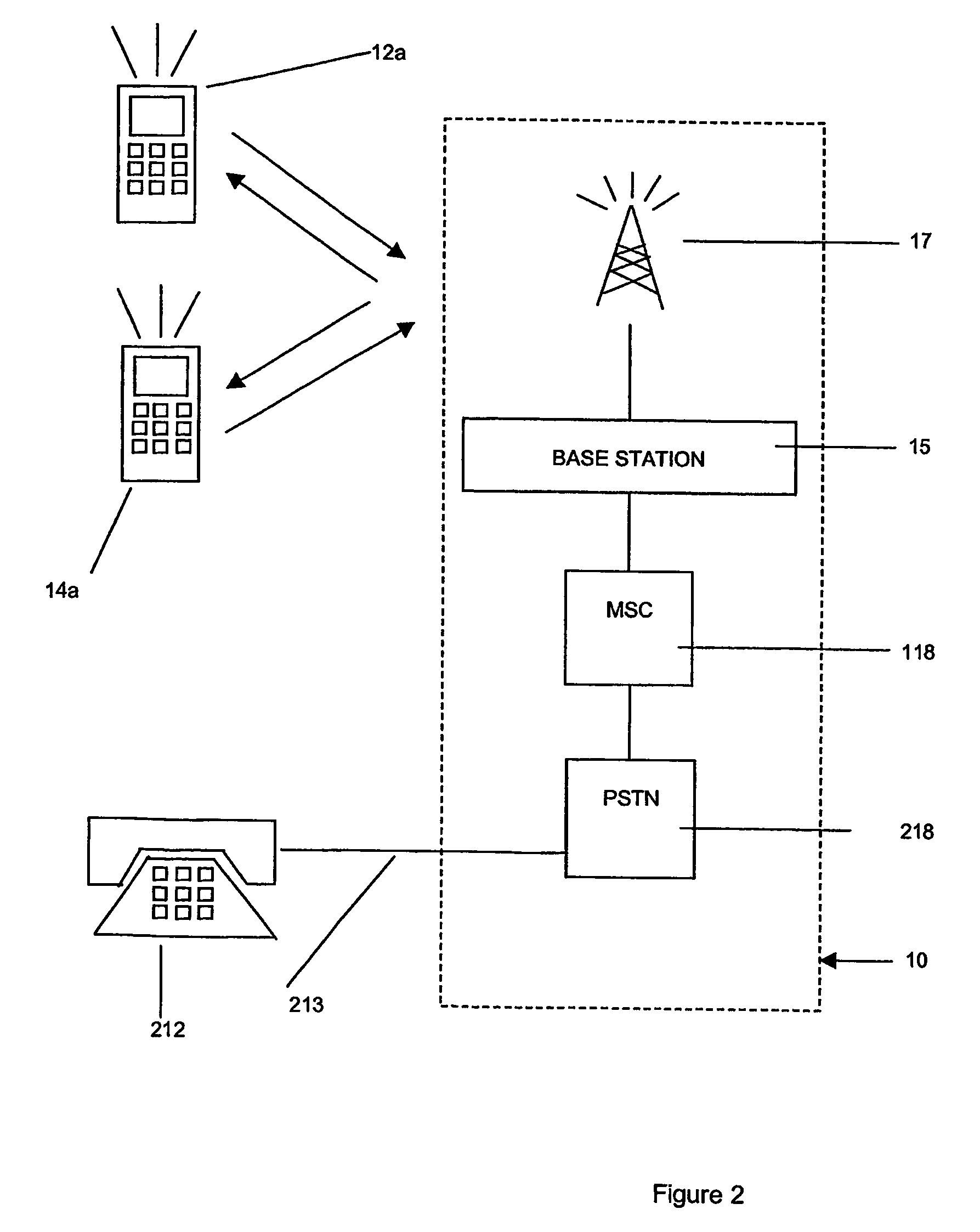

System and method for the detection and termination of fraudulent services

InactiveUS7512221B2High error rateMaximize throughputUnauthorised/fraudulent call preventionEavesdropping prevention circuitsComputer networkFinancial transaction

A system is disclosed for the automatic detection of fraudulent activity on a transaction network, for which each transaction over the network has an associated identifier. In one embodiment, the system includes voice comparison means for comparing a first sampled voice of a user of a first transaction with a subsequently sampled voice of a user of a subsequent transaction having an identical identifier to that of the first transaction. Control means in the form of a voice-based fraud detection engine is provided for determining, from said comparison, a profile of user usage that is representative of a total number of different users of the associated identifier. In a preferred embodiment, the system also includes voice sampling means for sampling a voice of the user of the first transaction to generate a first voice sample.

Owner:CEREBRUS SOLUTIONS LTD

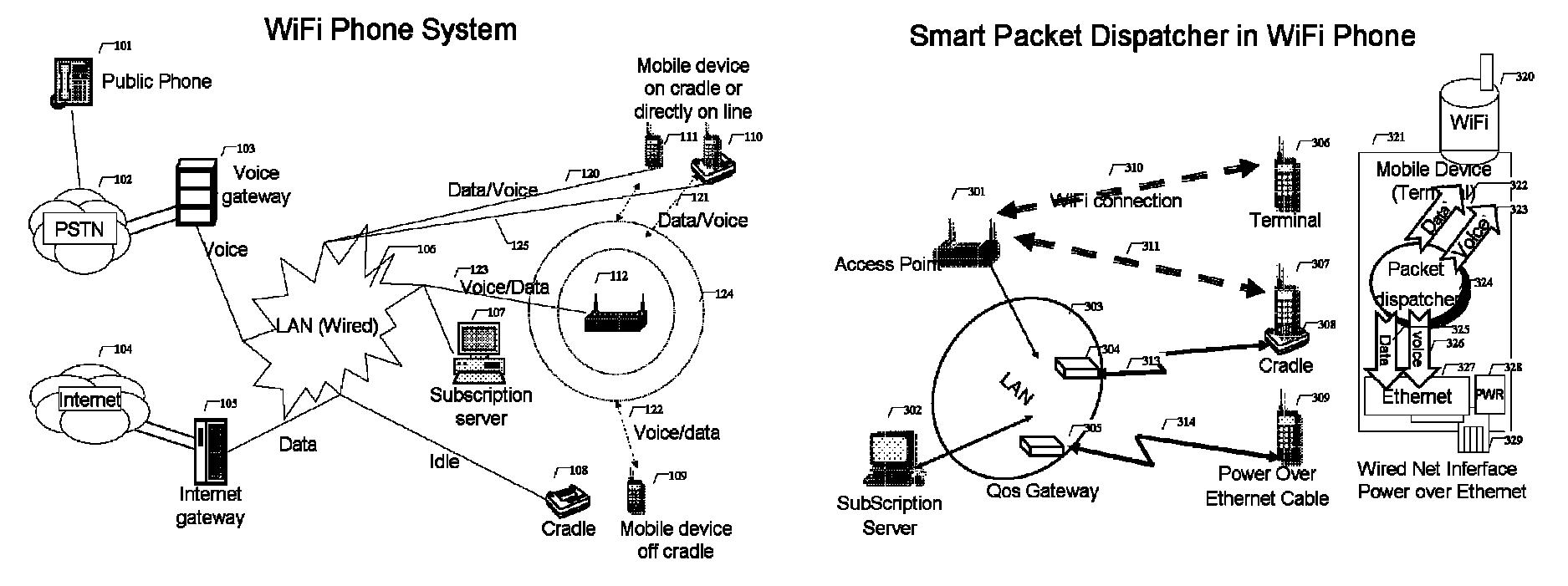

WiFi phone system

ActiveUS8503340B1Small rangeFast transferNetwork topologiesSubstation equipmentQuality of serviceData stream

A voice communication system over WiFi 802.11 network includes: WiFi phone devices, subscription servers and wireless access points. Through voice and data gateways the system can transfer both voice and data streams through WiFi; Phone devices with both wired and WiFi wireless interfaces can automatically switches between wired network and wireless network through WiFi access points. Subscription server maintains the current status of each device every time it changes location. Voice packets are prioritized over regular data packets and dispatched to different network interface by smart packet dispatcher. Quality of service for voice conversation over WiFi is achieved by various methods: piggy-tail method and ACK enhancements and other improvements to reduce delay and latency of real time voice packets.

Owner:XU YONGYONG

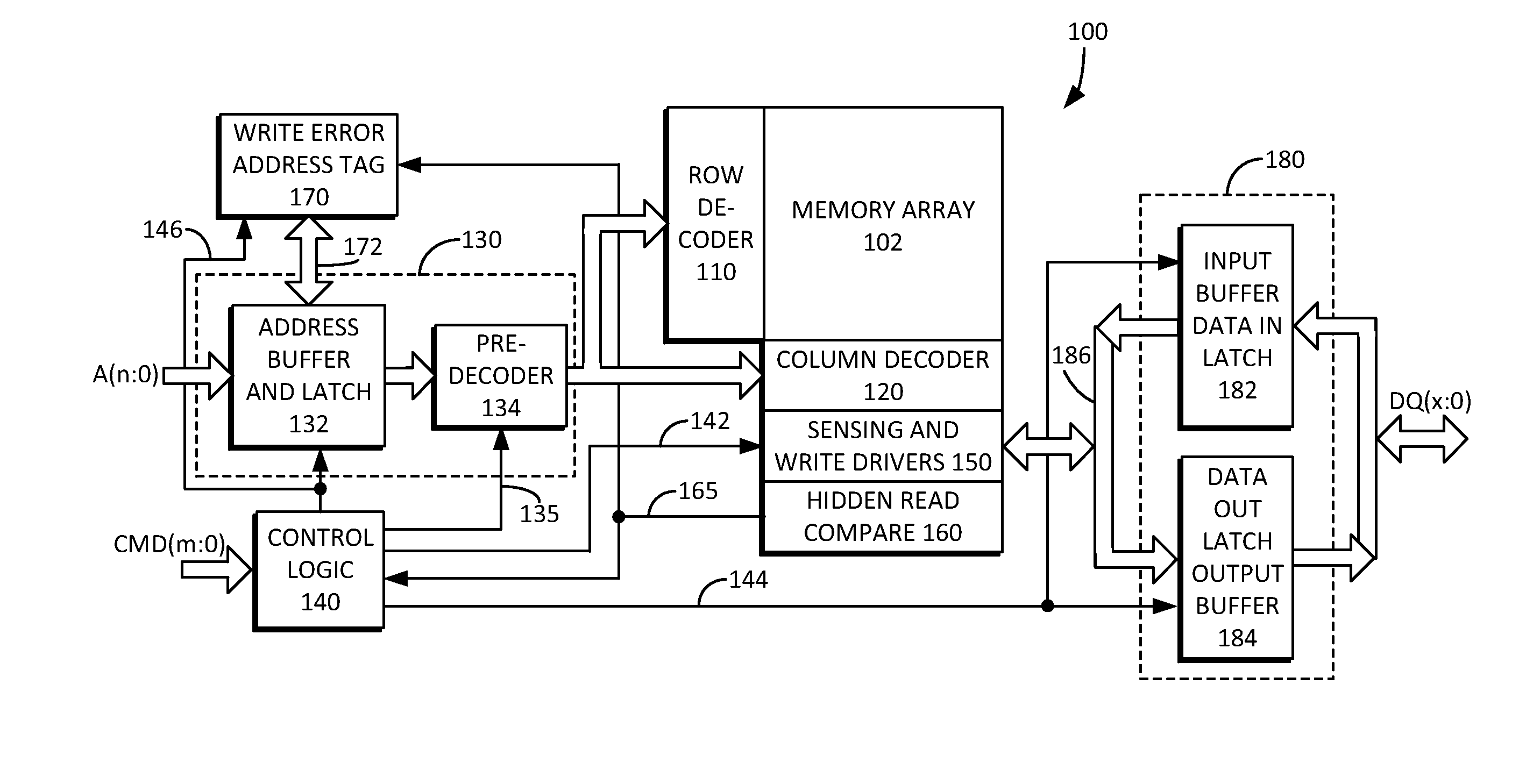

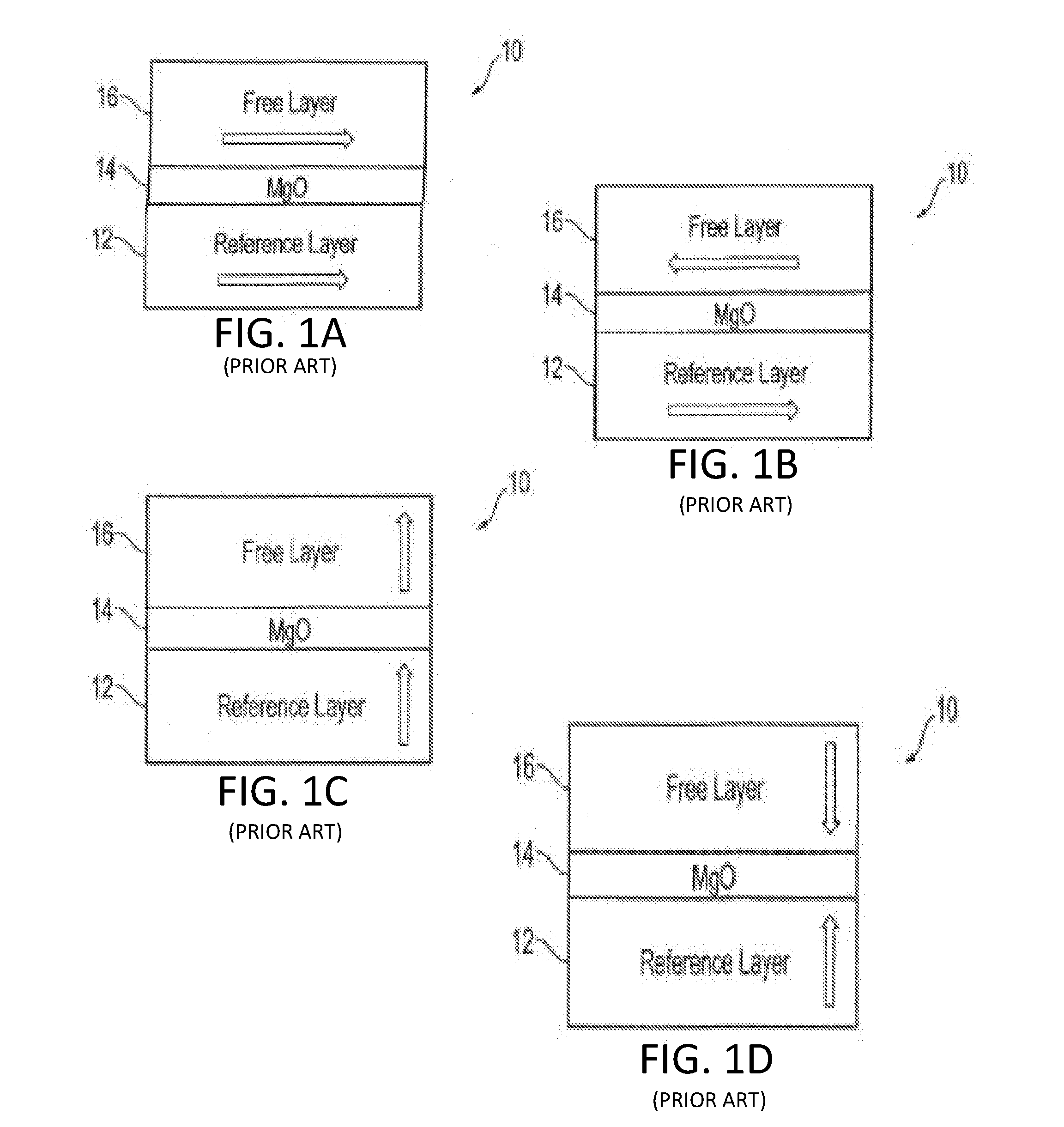

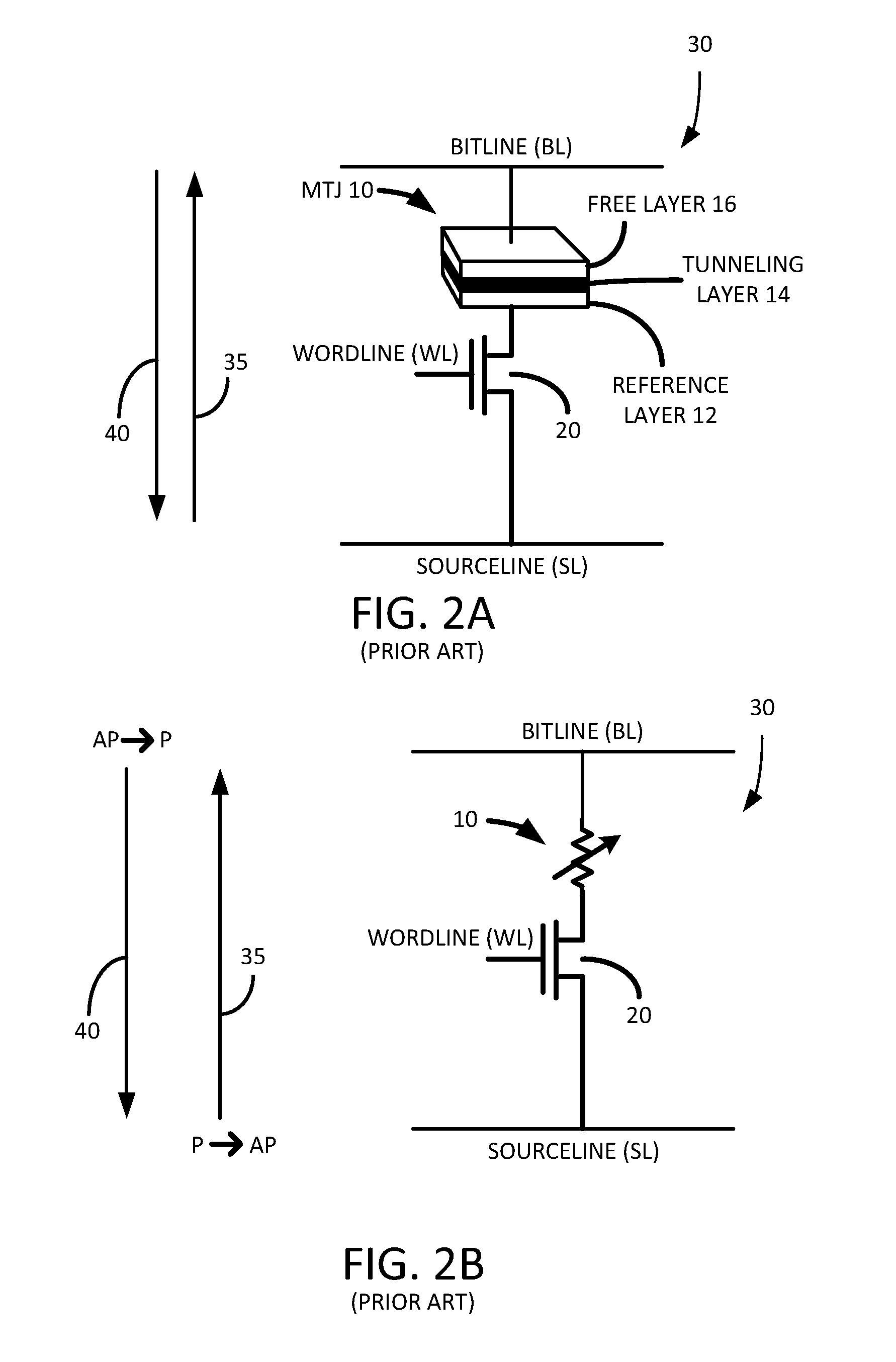

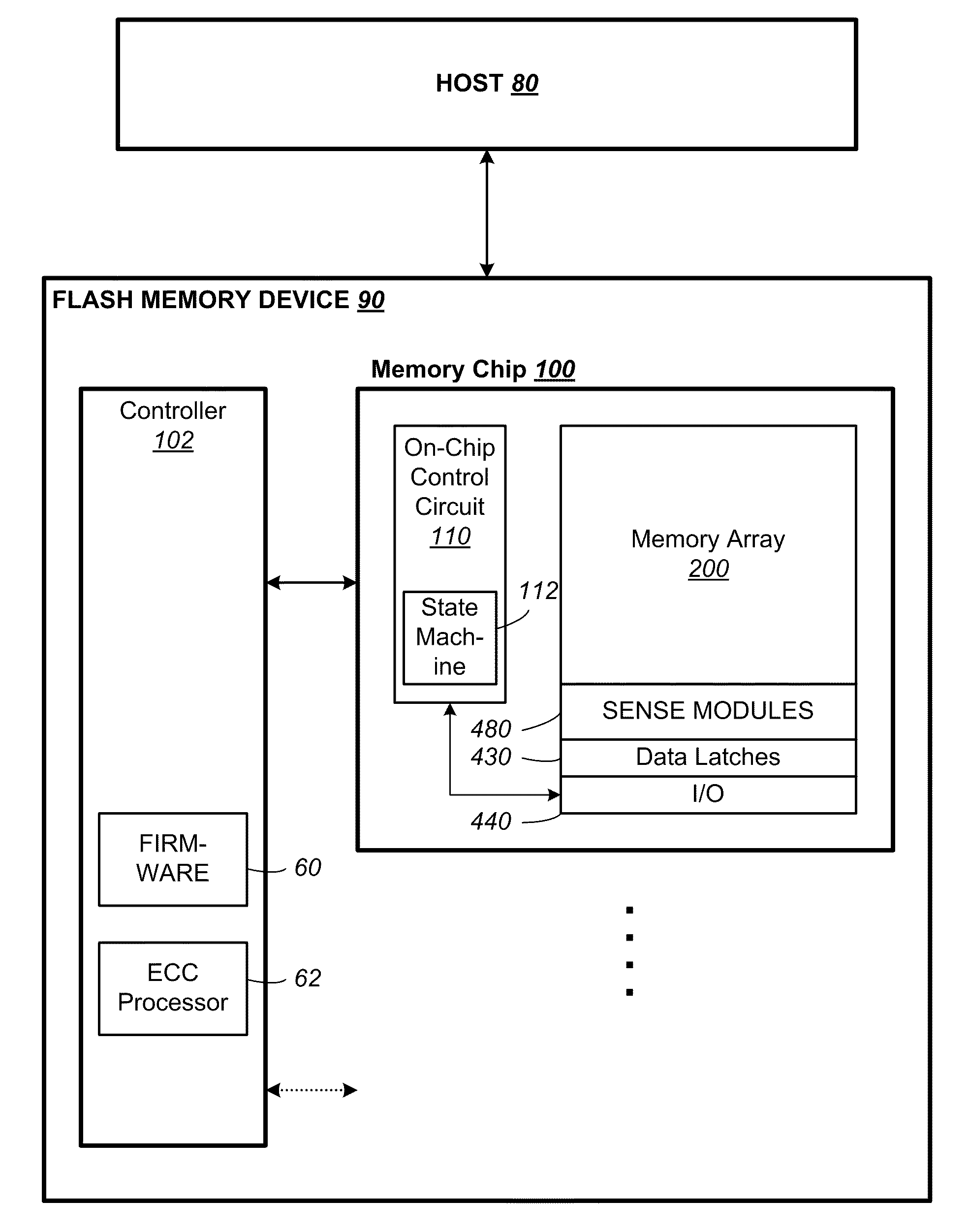

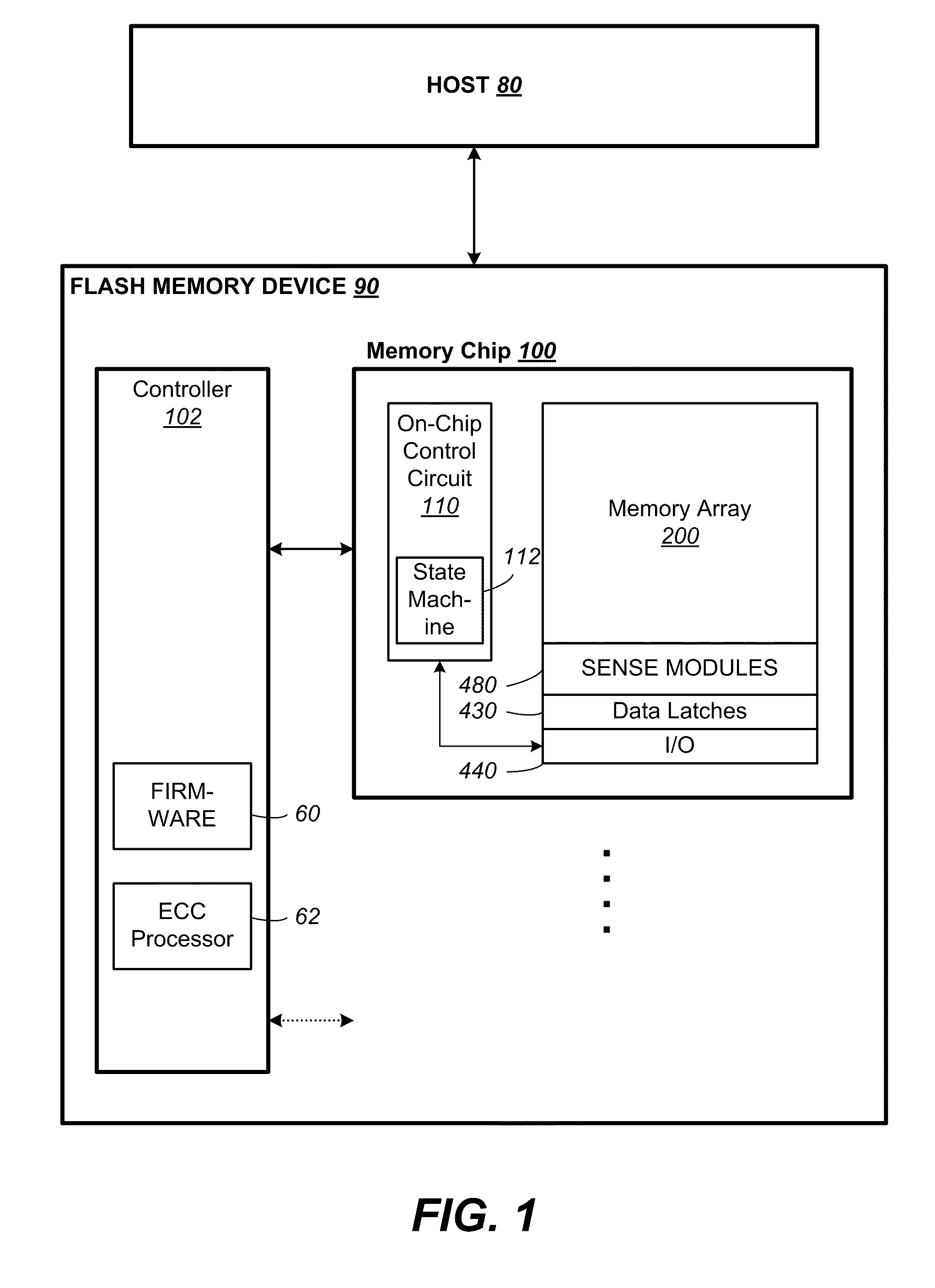

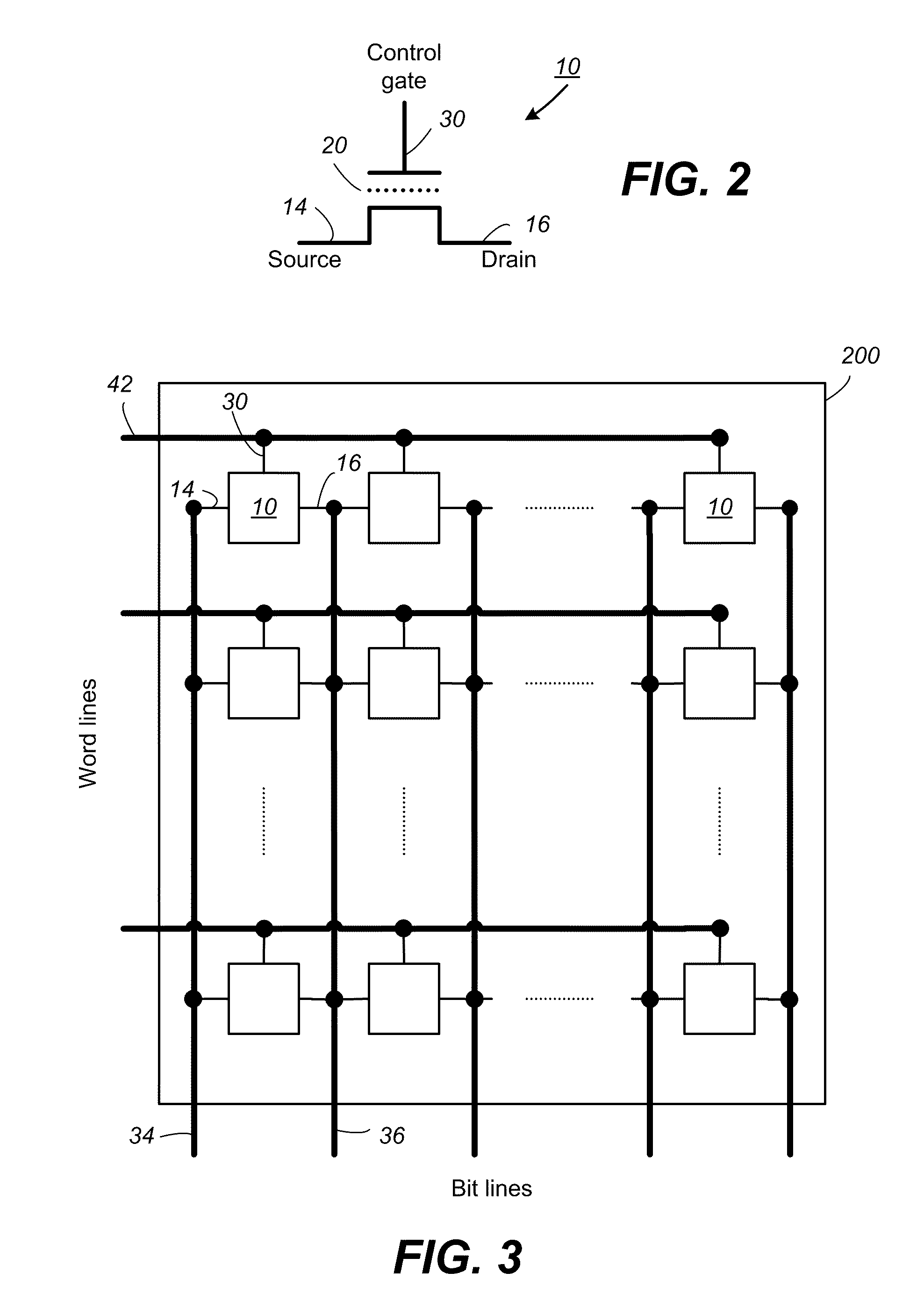

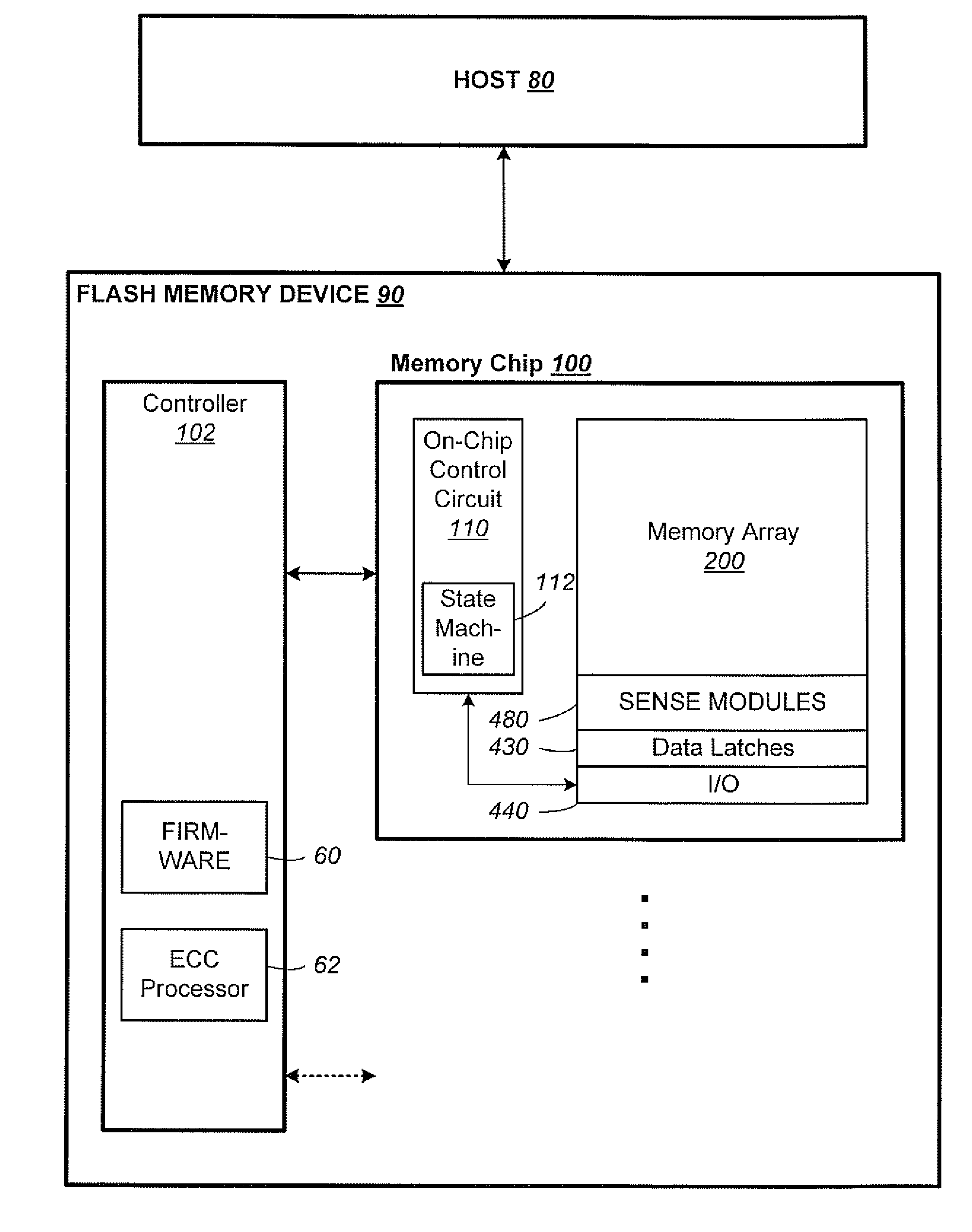

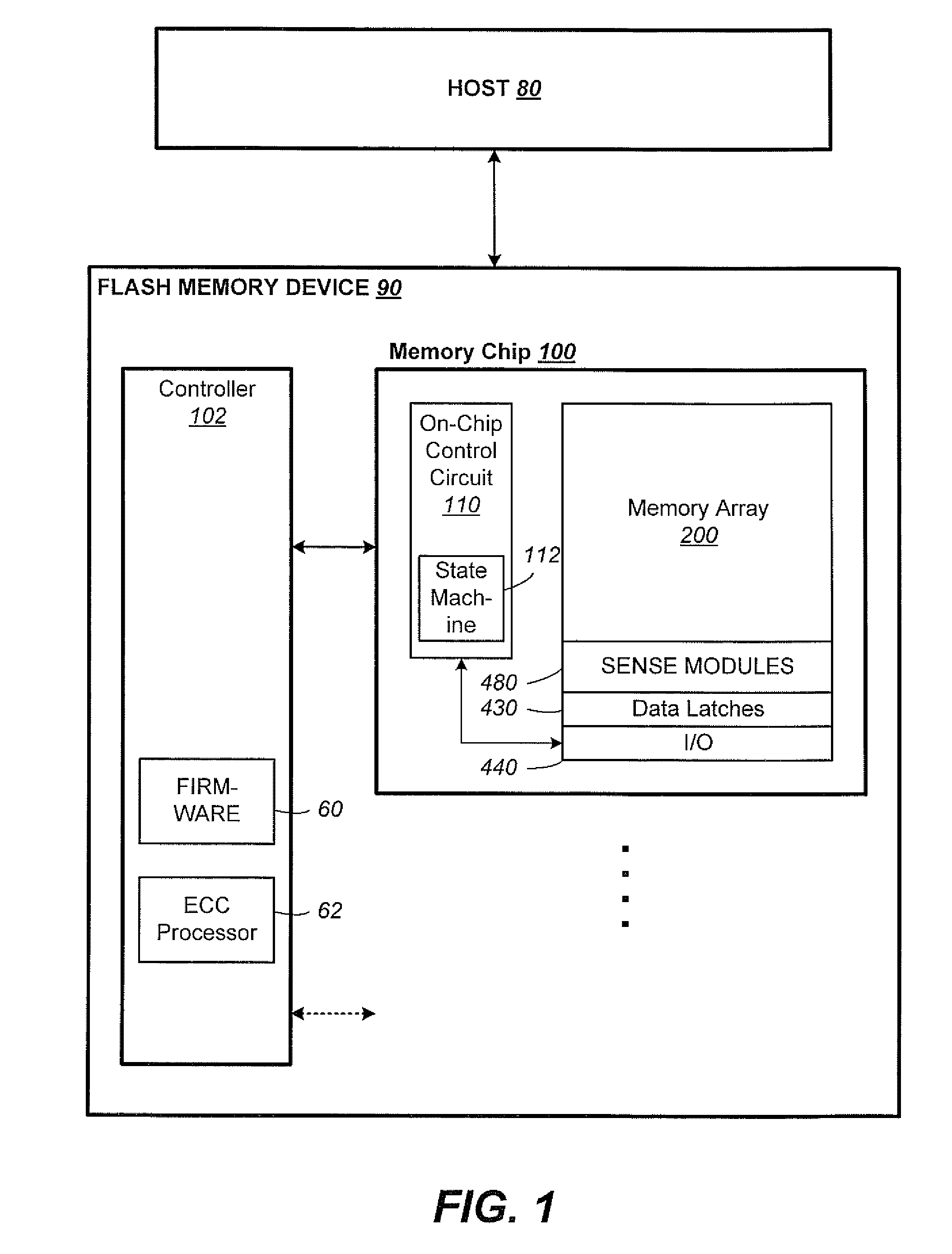

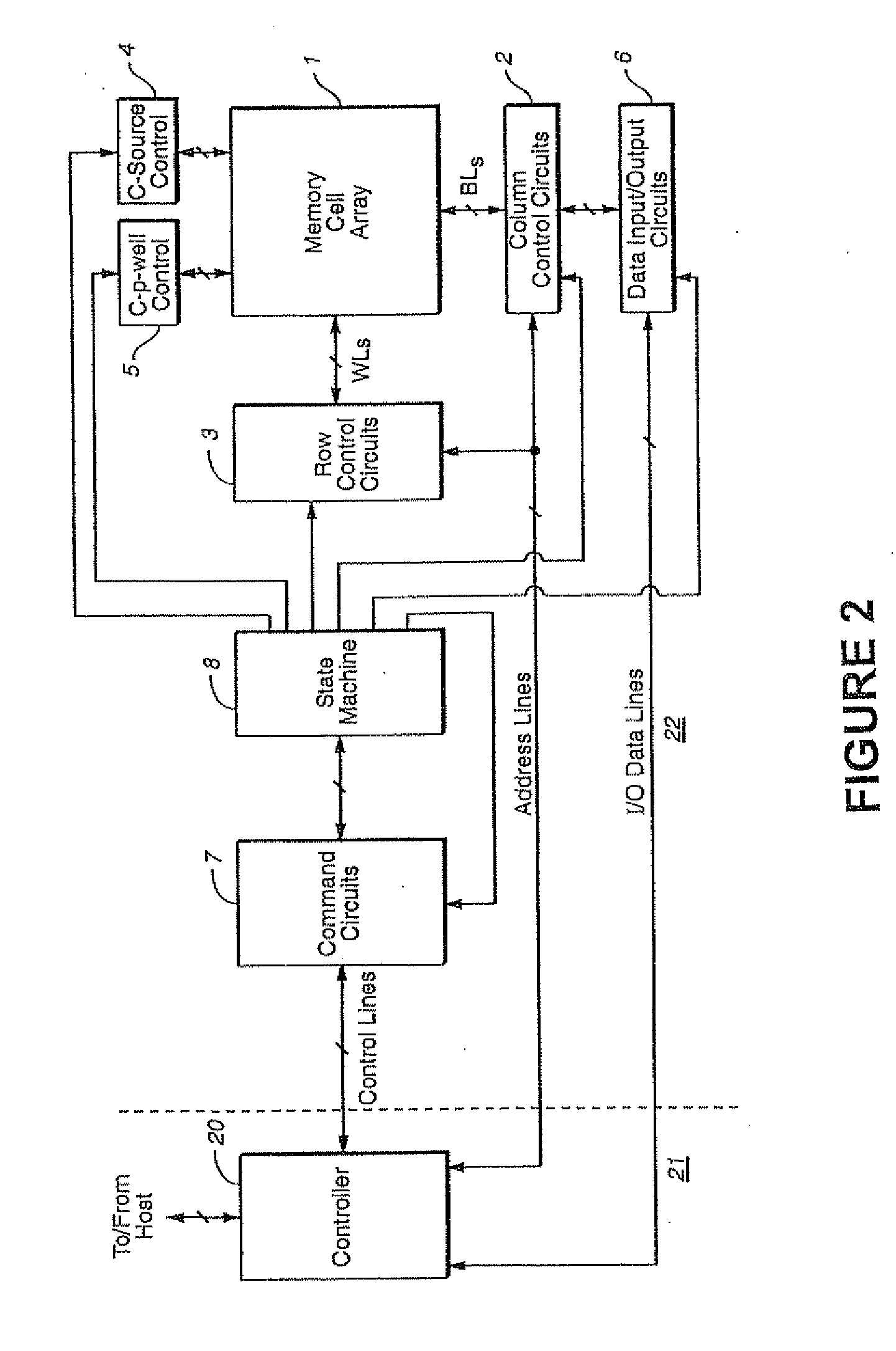

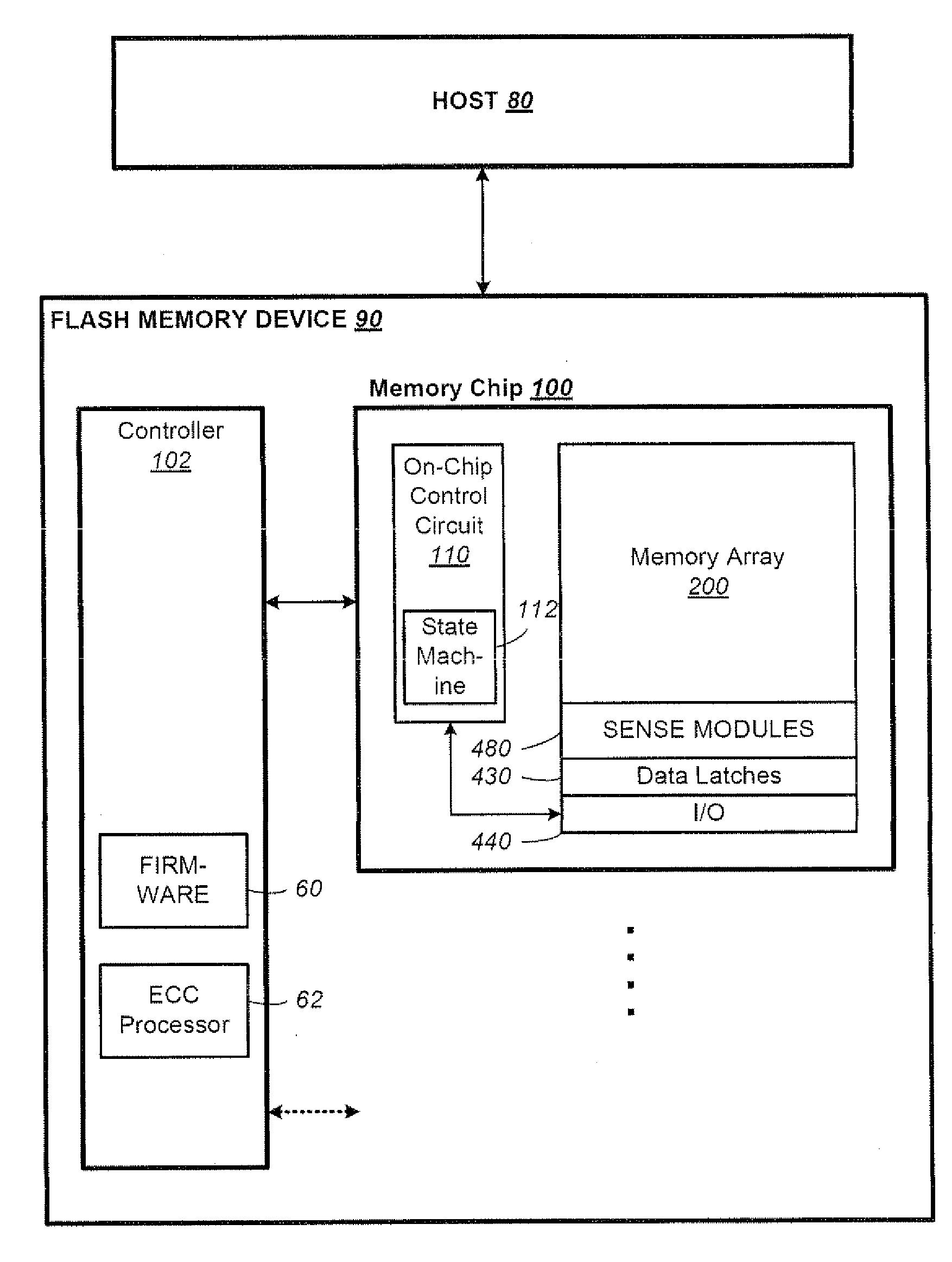

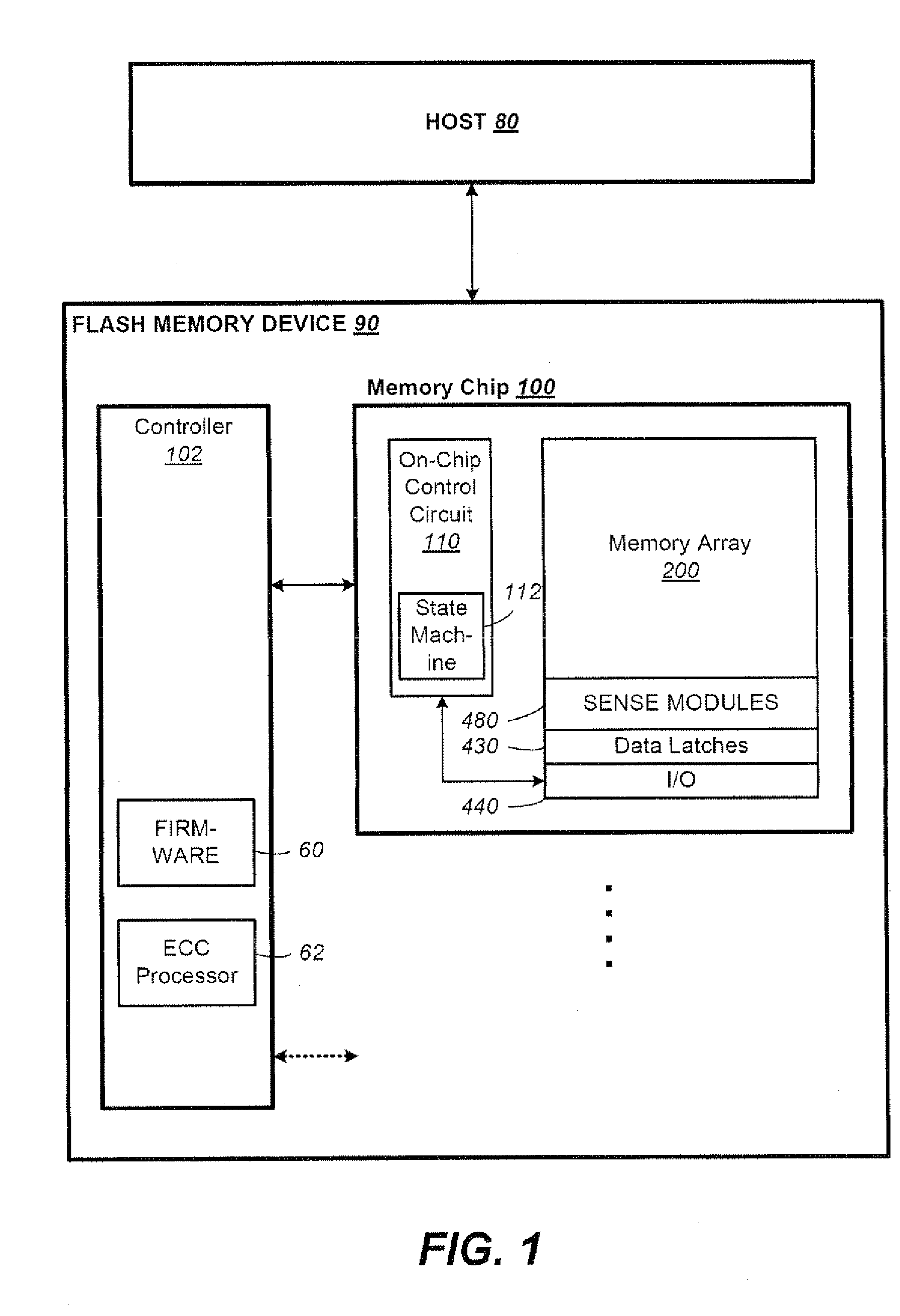

Method and system for providing a smart memory architecture

ActiveUS20140157065A1High rateHigh error rateError detection/correctionDigital computer detailsMemory chipSmart memory

A smart memory system preferably includes a memory including one or more memory chips, and a processor including one or more memory processor chips. The system may include a smart memory controller capable of performing a bit error rate built-in self test. The smart memory control may include bit error rate controller logic configured to control the bit error rate built-in self test. A write error rate test pattern generator may generate a write error test pattern for the bit error rate built-in self test. A read error rate test pattern generator may generate a read error test pattern for the built-in self test. The smart memory controller may internally generate an error rate timing pattern, perform built-in self test, measure the resulting error rate, automatically adjust one or more test parameters based on the measured error rate, and repeat the built-in self test using the adjusted parameters.

Owner:SAMSUNG ELECTRONICS CO LTD

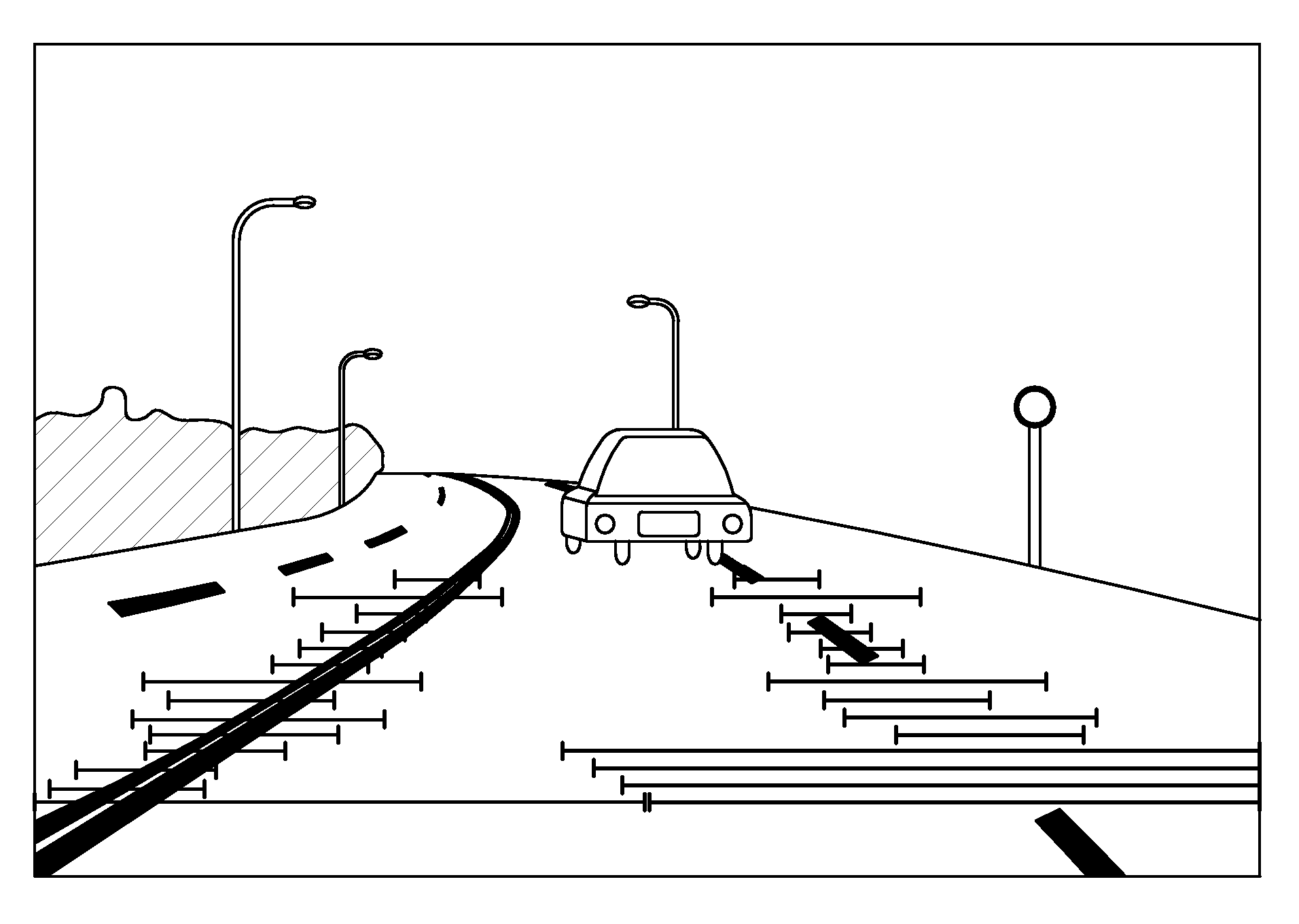

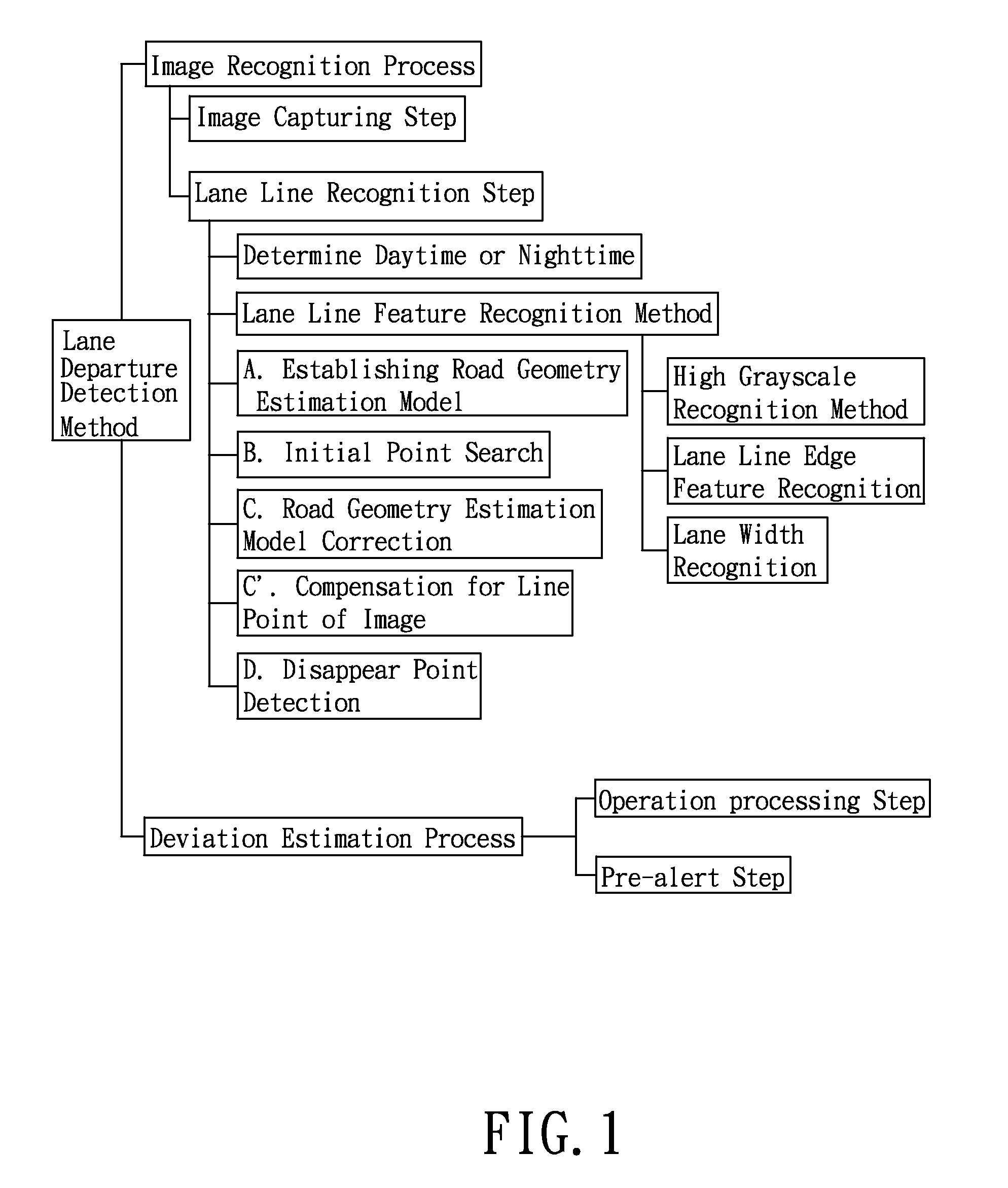

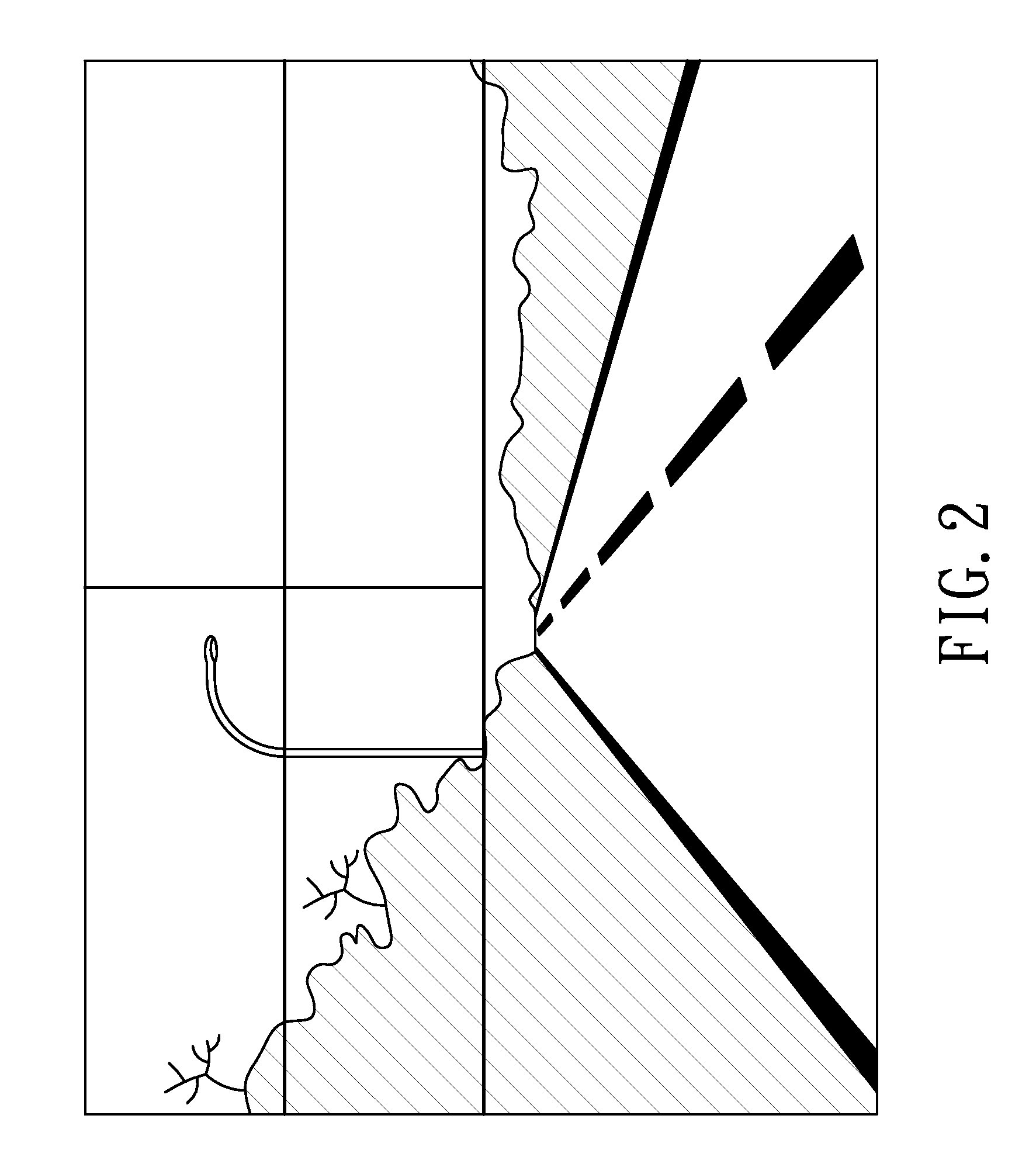

Method for detecting lane departure and apparatus thereof

ActiveUS20100002911A1Improve shortcomingsResponse time is insufficientCharacter and pattern recognitionColor television detailsDriver/operatorComputer graphics (images)

A method for detecting the lane departure of a vehicle includes an image recognition process and a deviation estimation process. The image recognition process includes the following steps: an image capturing step for capturing image frame data by using an image capturing unit; and a lane line recognition for analyzing the image frame data for determining the lane lines. By using a quadratic curve fitting equation, a plurality of lane line being detected so as to establish a road geometry estimation model. The road geometry estimation model is inputted into the deviation estimation process to detect the lane departure of the vehicle so as to alert the driver. Furthermore, an apparatus for detecting the deviation of the vehicle, comprising: an image capturing unit, a processing unit and a signal output unit.

Owner:AUTOMOTIVE RES & TESTING CENT

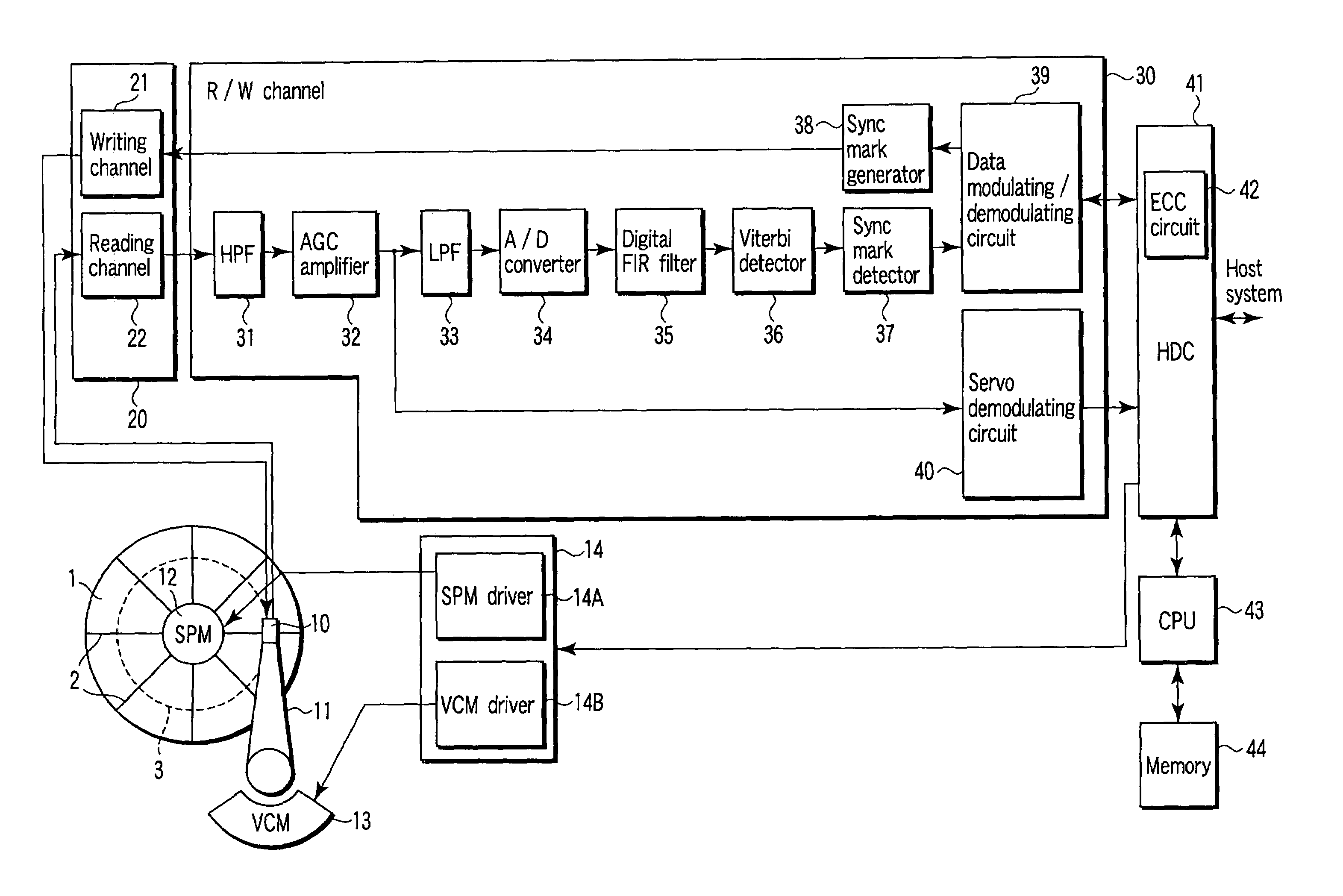

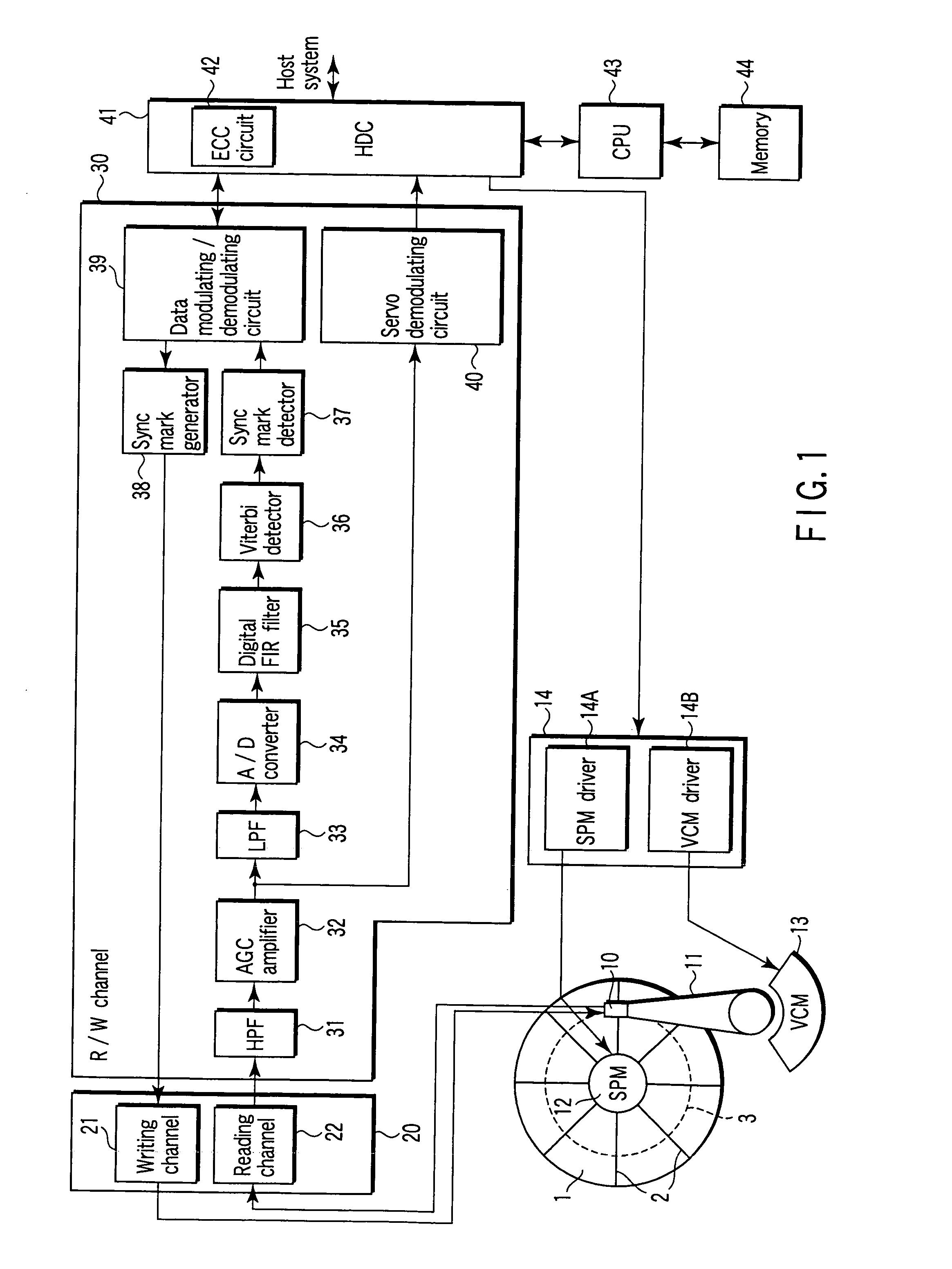

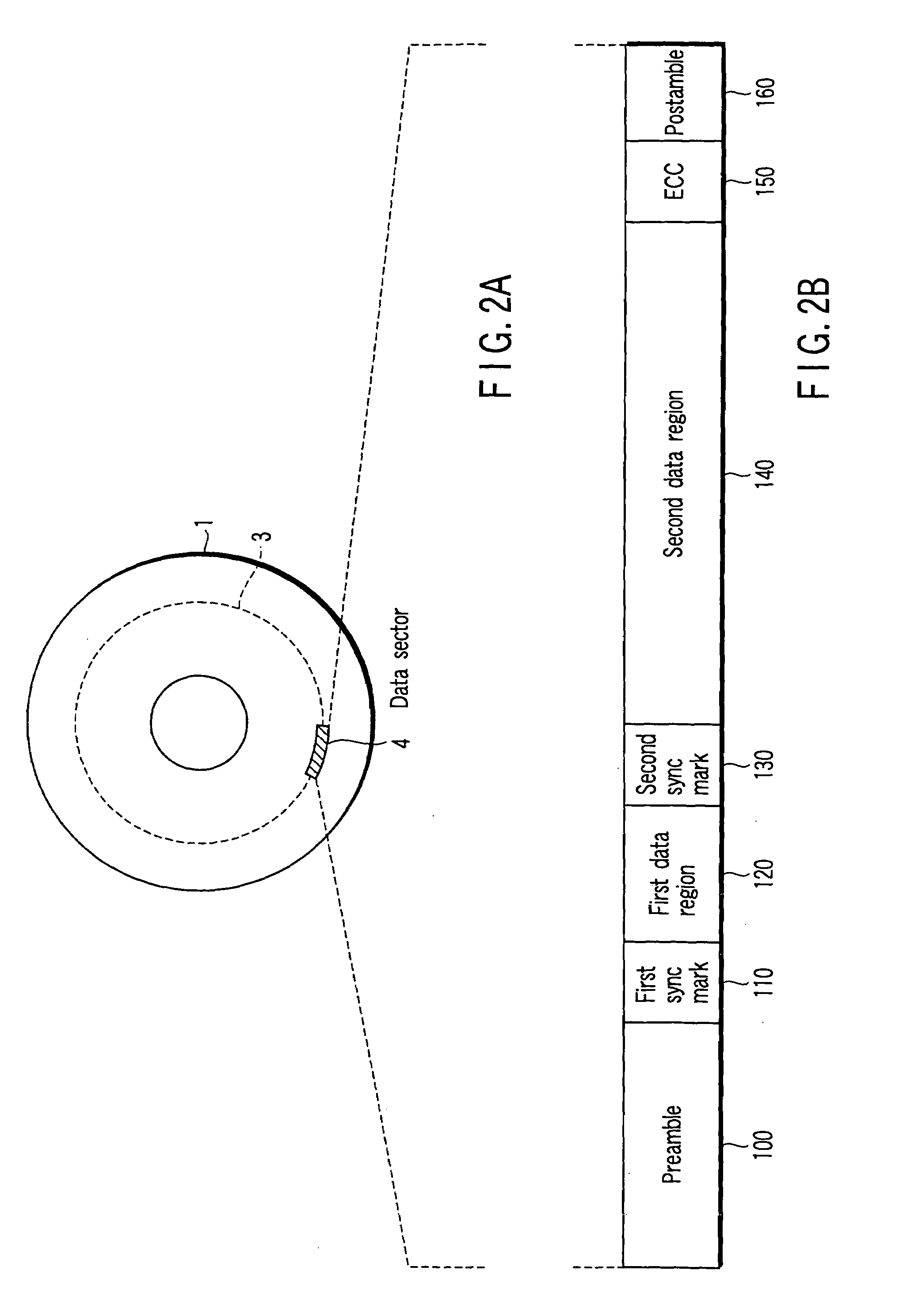

Method and apparatus for decoding sync marks in a disk

InactiveUS7203015B2High error rateIncrease probabilityModification of read/write signalsDisc-shaped record carriersComputer scienceBit-length

In a disk drive that performs perpendicular magnetic recording, the read / write channel has a sync mark generator. The sync mark generator generates a second sync mark before the read / write channel operates to write data on a disk. The second sync mark has a bit pattern including a series of bits representing positive polarity and a series of bits representing negative polarity. The series of bits, which is longer than the other, has a bit length that is at least 50% but less than 85% of the total bit length of the second sync mark.

Owner:KK TOSHIBA

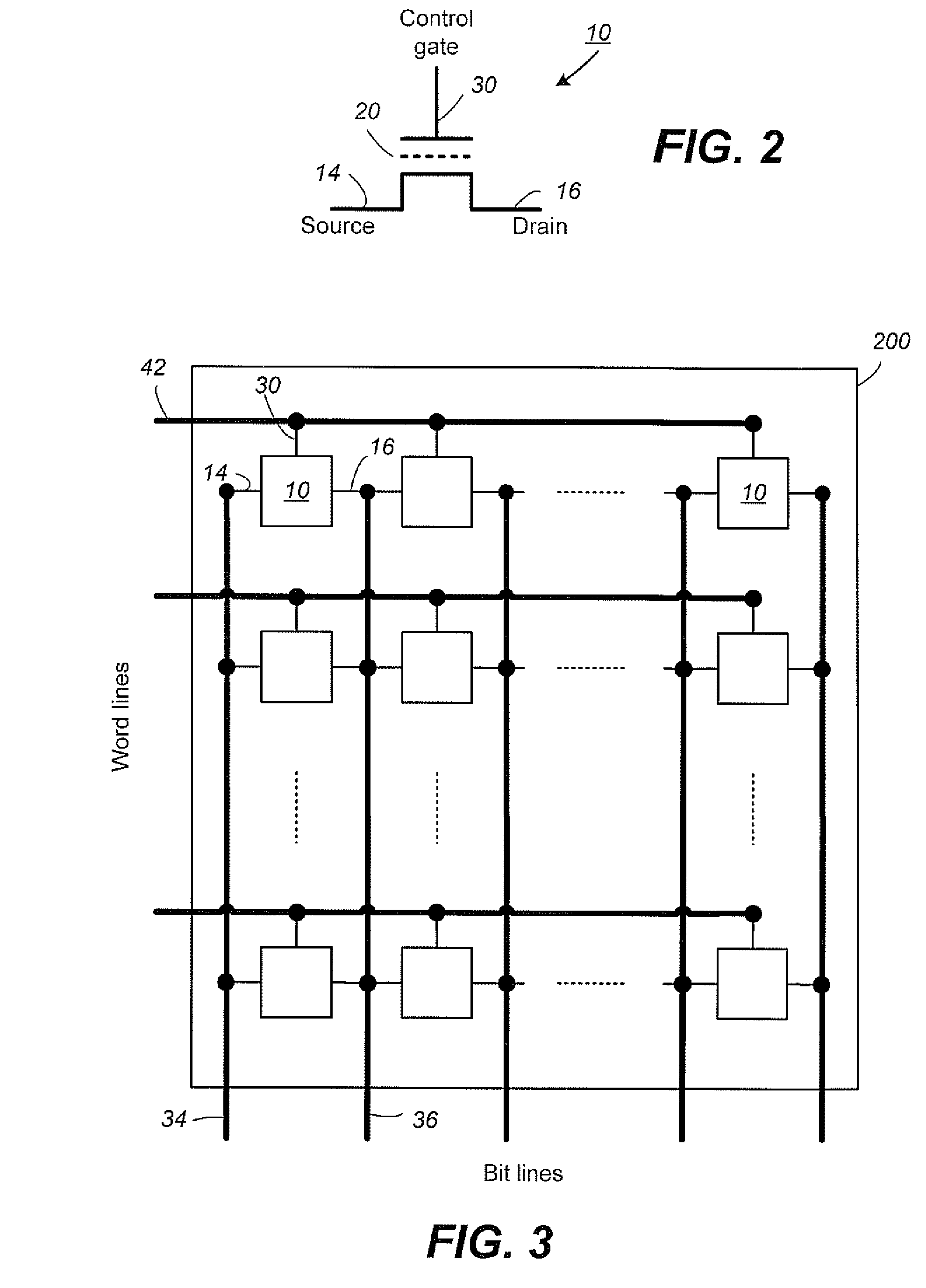

Non-Volatile Memory And Method With Accelerated Post-Write Read To Manage Errors

ActiveUS20110096601A1Small errorHigh error rateRead-only memoriesDigital storageData errorPosted write

Data errors in non-volatile memory inevitably increase with usage and with higher density of bits stored per cell. The memory is configured to have a first portion operating with less error but of lower density storage, and a second portion operating with a higher density but less robust storage. An error management provides reading and checking the copy after copying to the second portion. If the copy has excessive error bits, it is repeated in a different location either in the second or first portion. The reading and checking of the copy is accelerated by reading only a sample of it. The sample is selected from a subset of the copy having its own ECC and estimated to represent a worst error rate among the copy it is sampling. One embodiment has the sample taken from one bit of each multi-bit memory cell of a group.

Owner:SANDISK TECH LLC

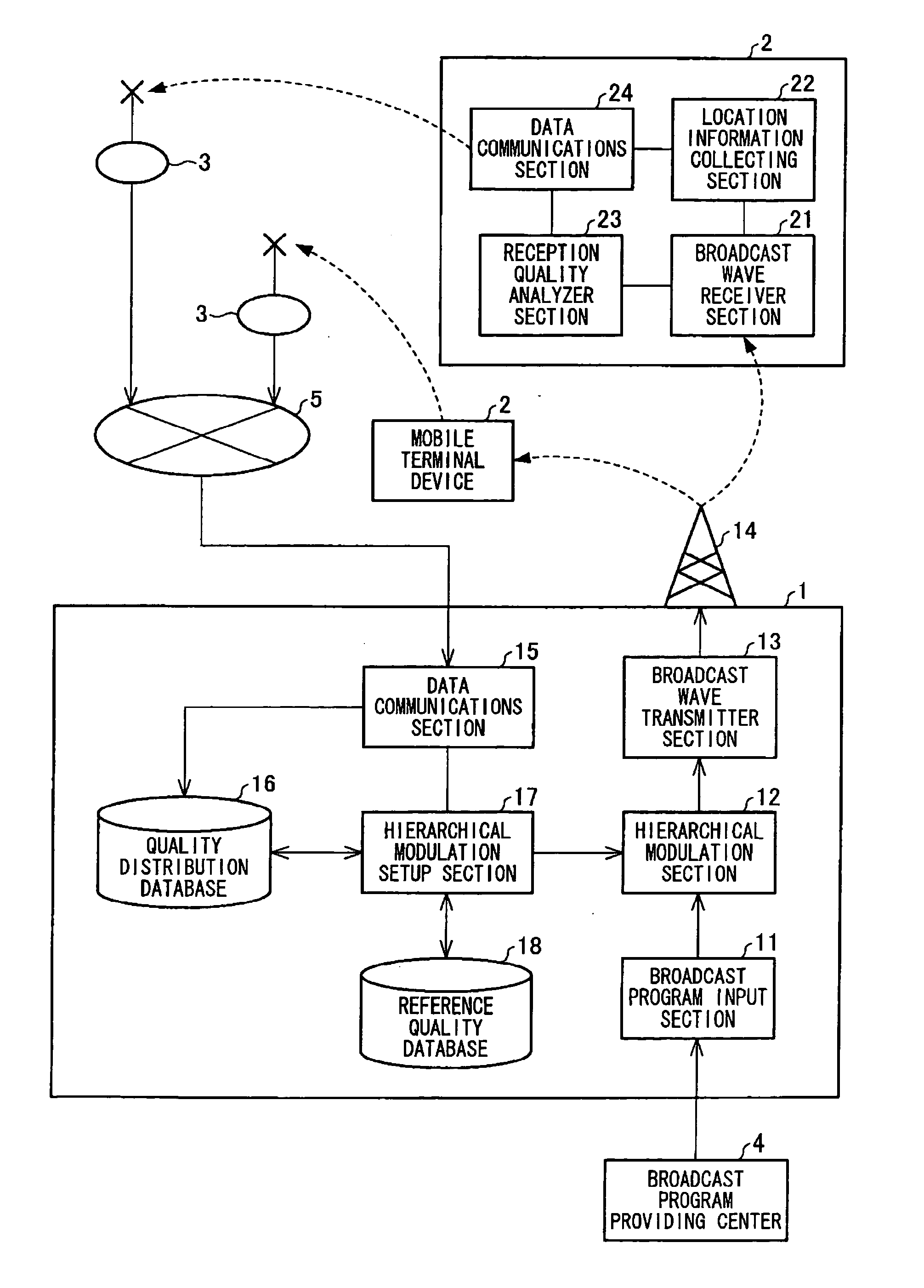

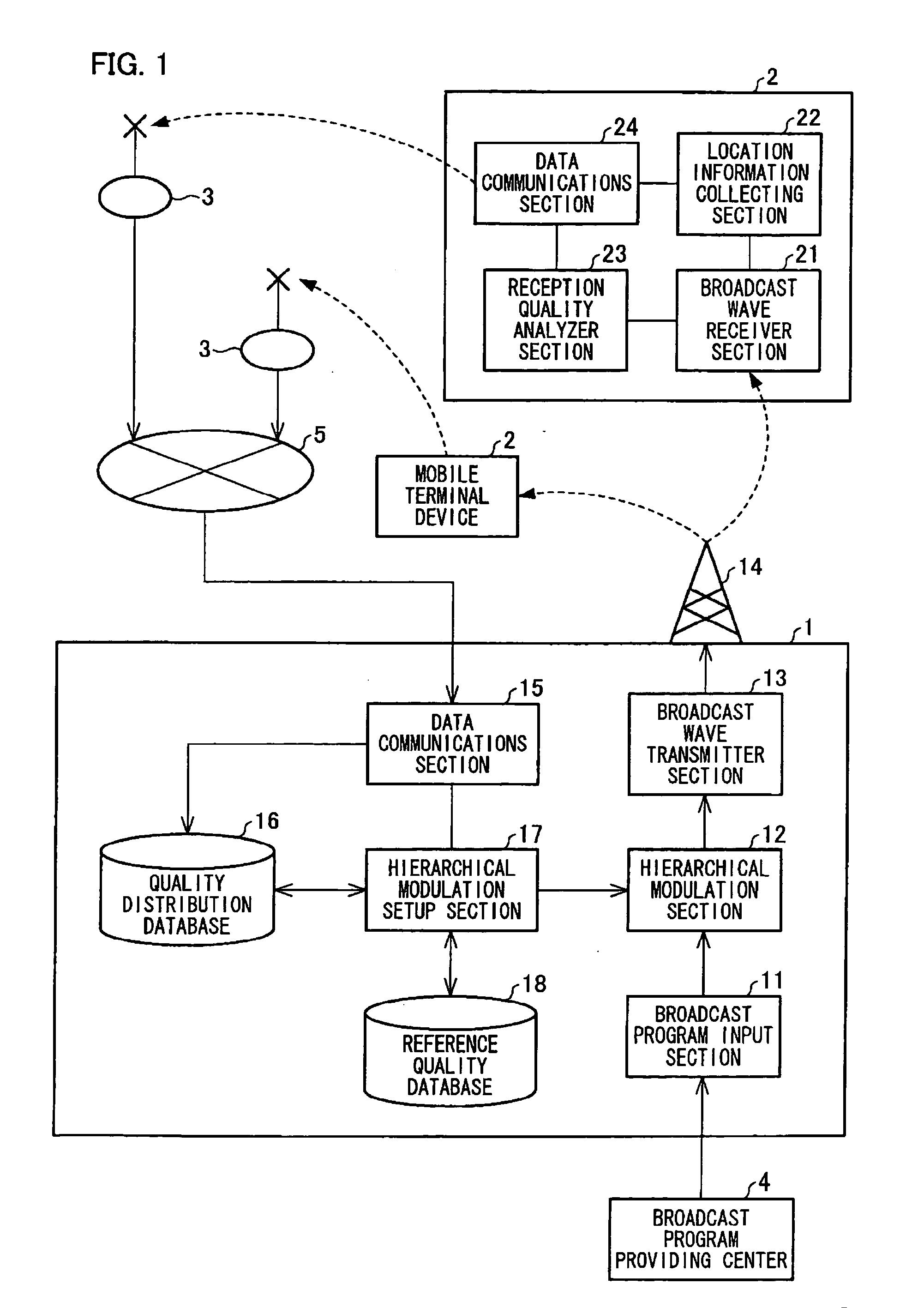

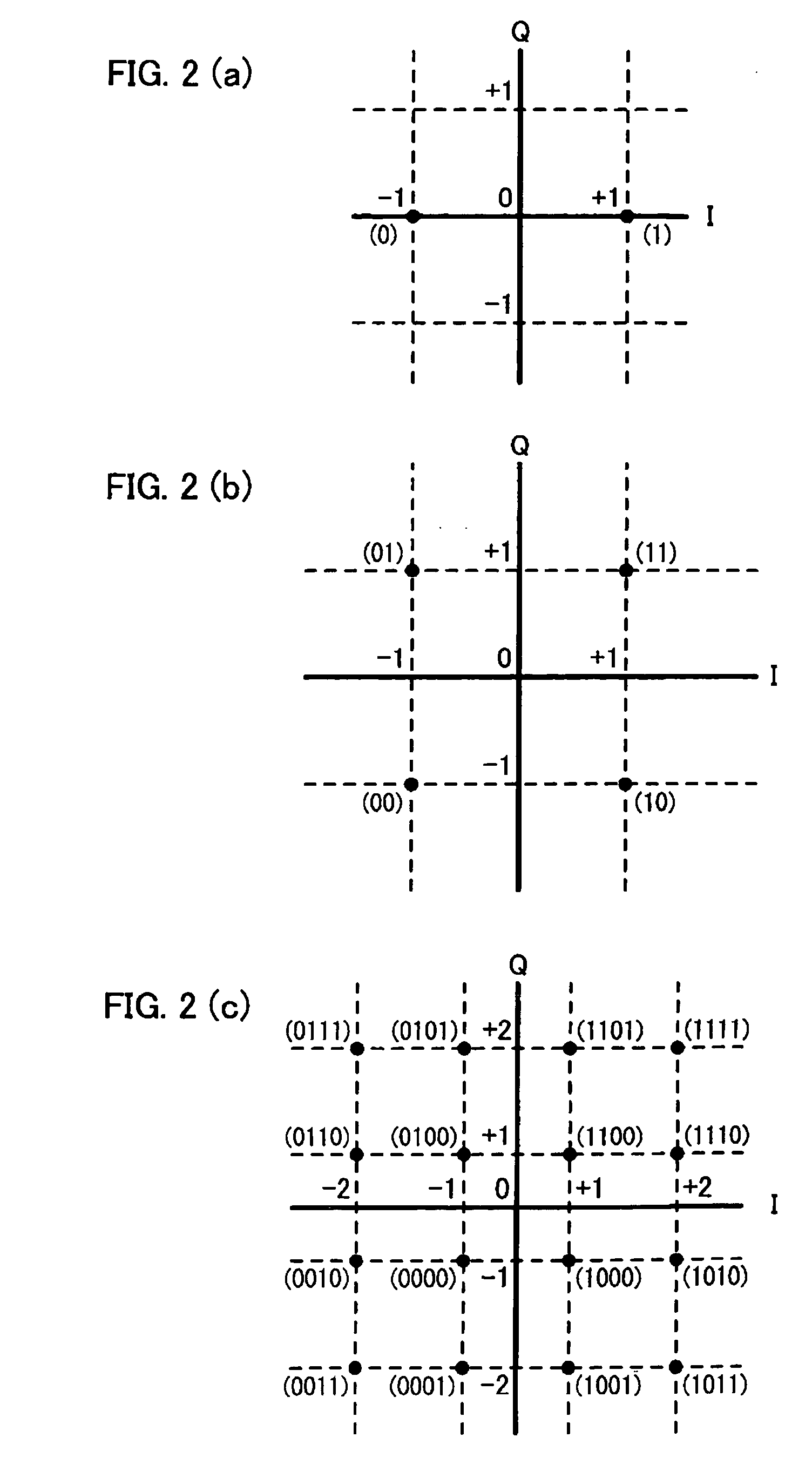

Broadcasting base station device, mobile terminal device, hierarchical modulation setup method, broadcast system, and hierarchical modulation setup computer program

InactiveUS20070054624A1High error rateReduce error rateBroadcast with distributionModulated-carrier systemsTerminal equipmentConstellation

A broadcasting base station device transmits broadcast signals modulated by a hierarchical modulation scheme to a mobile terminal device. A hierarchical modulation setup section compares the reception quality of the broadcast signals at the location of the mobile terminal device to predetermined reference quality. Based on the result of the comparison, the hierarchical modulation setup section specifies a hierarchical modulation scheme. For example, the constellation in each quadrant is reduced or enlarged. Accordingly, the broadcasting base station device can transmit optimal broadcast signals that match with actual reception quality to each mobile terminal device.

Owner:SHARP KK

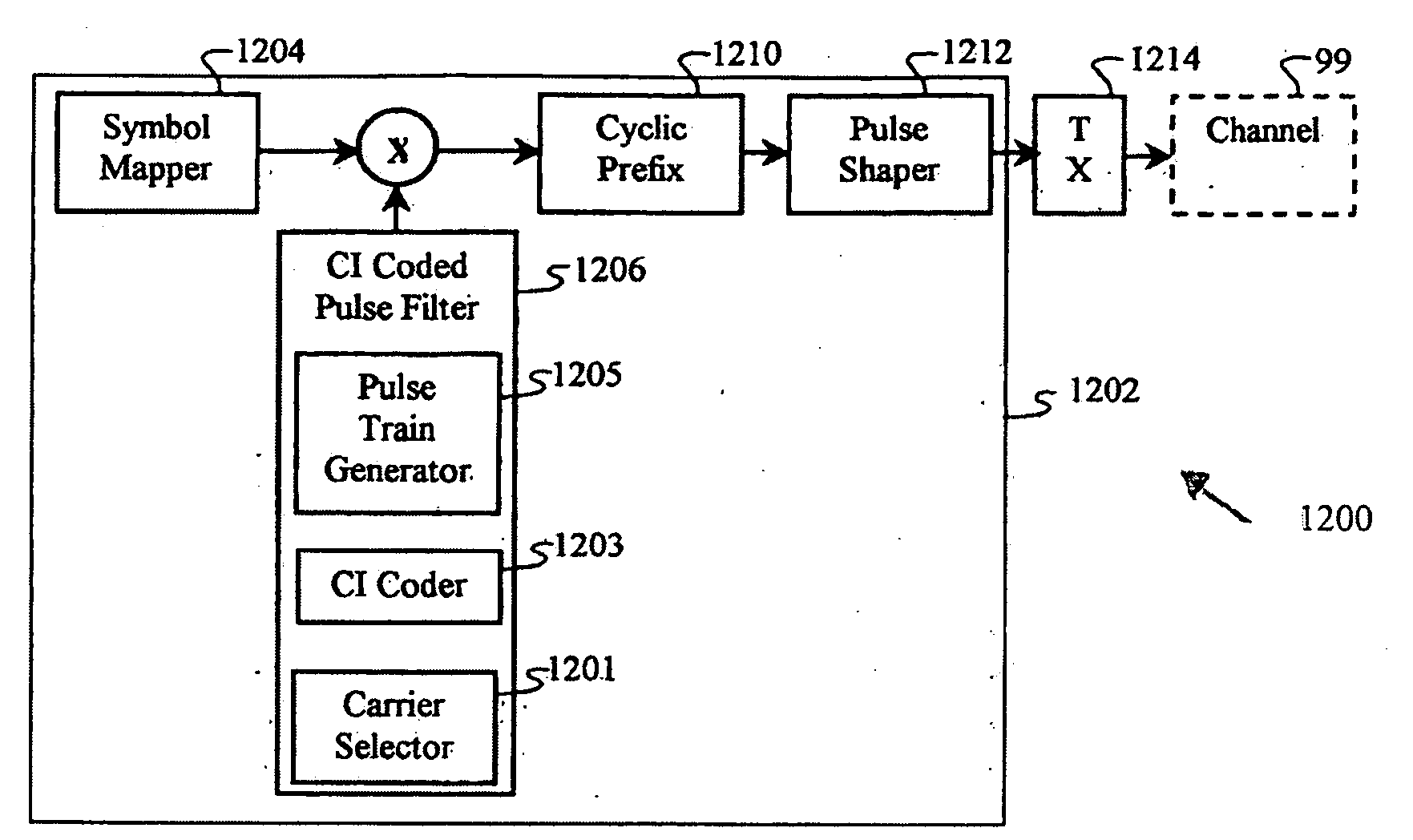

Software Adaptable High Performance Multicarrier Transmission Protocol

InactiveUS20080310484A1Reduce PAPRReduce complexityModulated carrier system with waveletsSecret communicationTransmission protocolFrequency spectrum

Techniques for reducing peak-to-average power in multicarrier transmitters employ peak cancellation with subcarriers that are impaired by existing channel conditions. The use of Carrier Interferometry (CI) coding further improves the effectiveness of peak reduction. CI coding can also be impressed onto pulse sequences in the time domain, which enhances spectral selection and facilitates peak-power control.

Owner:DEPARTMENT 13 INC

Non-Volatile Memory And Method With Post-Write Read And Adaptive Re-Write To Manage Errors

ActiveUS20110099418A1Small marginReduce memory costMemory adressing/allocation/relocationRead-only memoriesHigh densityQuality assurance

Data errors in non-volatile memory inevitably increase with usage and with higher density of bits stored per cell. For acceptable quality assurance, conventional error correction codes (“ECC”) have to correct a maximum number of error bits up to the far tail end of a statistical population. The present memory is configured to have a first portion operating with less error but of lower density storage, and a second portion operating with a higher density but less robust storage. If excessive error bits (at the far tail-end) occur after writing a group of data to the second portion, the data is adaptively rewritten to the first portion which will produce less error bits. Preferably, the data is initially written to a cache also in the first portion to provide source data for any rewrites. Thus, a more efficient ECC not requiring to correcting for the far tail end can be used.

Owner:SANDISK TECH LLC

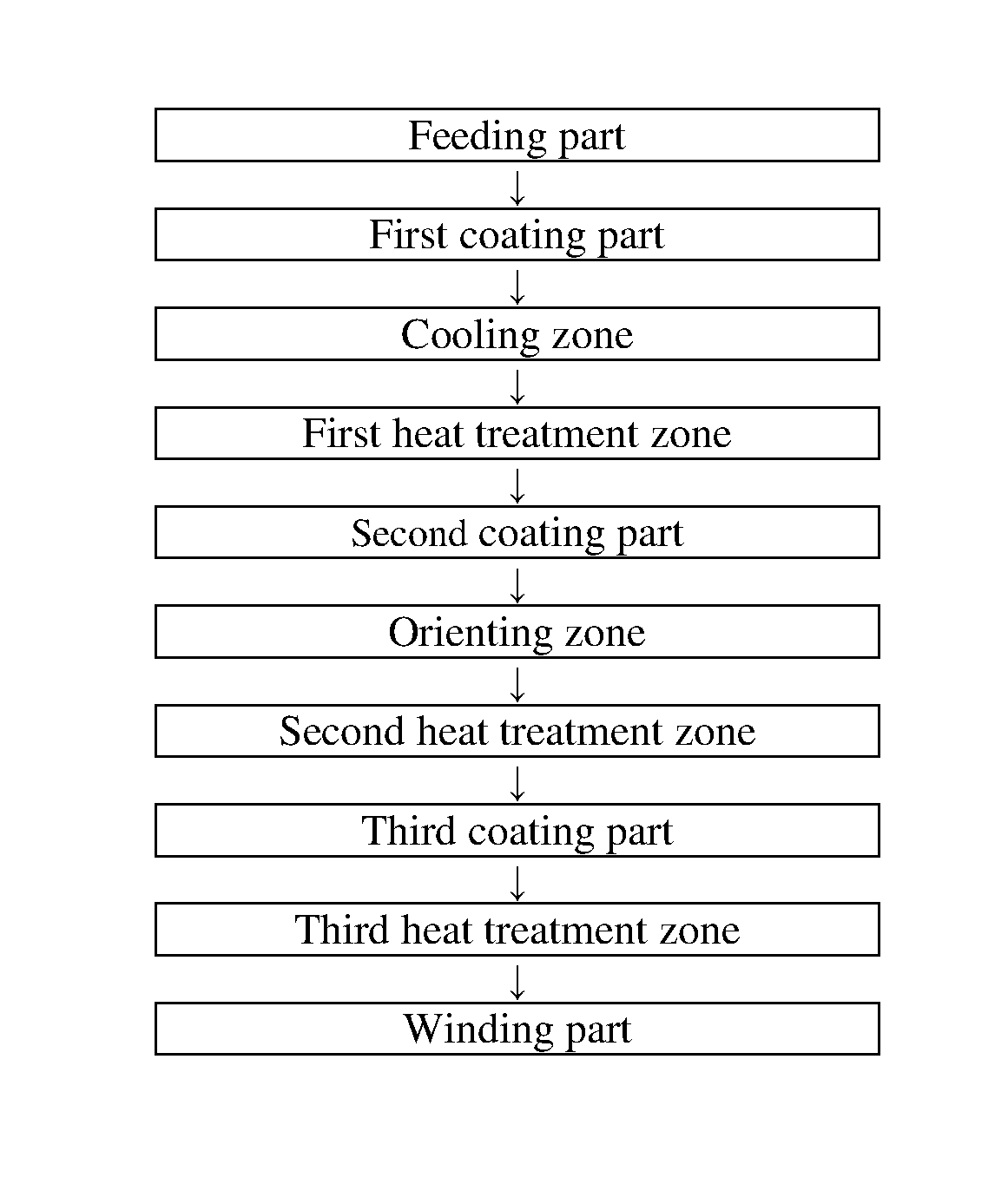

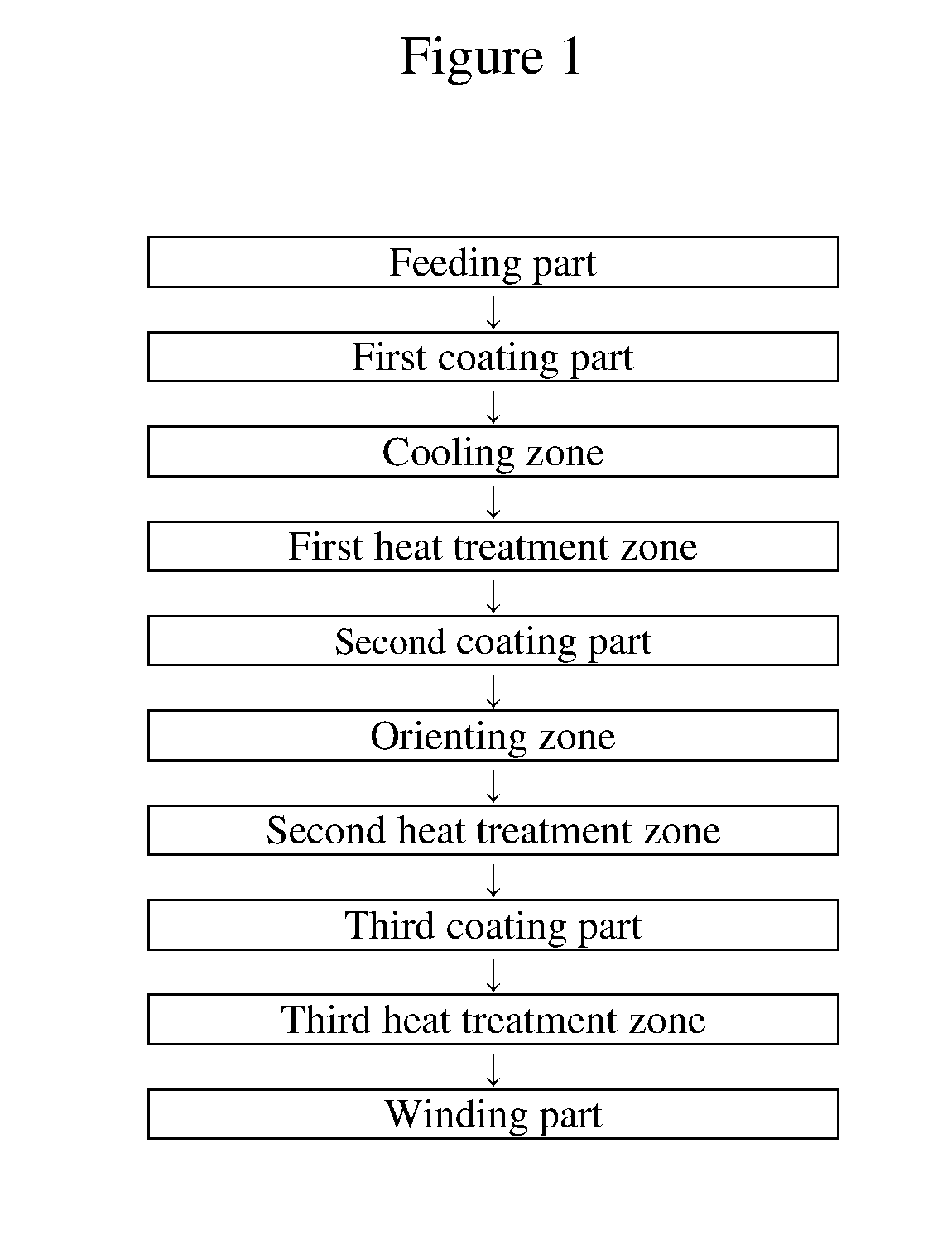

Magnetic tape and method of manufacturing the same

ActiveUS9721605B2Avoid it happening againImprove the immunityBase layers for recording layersRecord information storageMedicineMagnetic tape

Provided is a magnetic tape, which comprises, on a nonmagnetic support, a nonmagnetic layer comprising nonmagnetic powder and binder, and on the nonmagnetic layer, a magnetic layer comprising ferromagnetic powder and binder; wherein at least the magnetic layer comprises one or more components selected from the group consisting of a fatty acid and a fatty acid amide; a quantity of components selected from the group consisting of a fatty acid and a fatty acid amide per unit area of the magnetic tape among components that are extracted from a surface on the magnetic layer side of the magnetic tape is less than or equal to 15.0 mg / m2, and a concentration of carbon, C, that is obtained by X-ray photoelectron spectroscopy conducted at a photoelectron take-off angle of 10 degrees on the surface on the magnetic layer side of the magnetic tape is greater than or equal to 50 atom %.

Owner:FUJIFILM CORP

Magnetic tape and method of manufacturing the same

ActiveUS20160189740A1Avoid it happening againImprove the immunityBase layers for recording layersTape carriersMagnetic tapeNon magnetic

Provided is a magnetic tape, which comprises, on a nonmagnetic support, a nonmagnetic layer comprising nonmagnetic powder and binder, and on the nonmagnetic layer, a magnetic layer comprising ferromagnetic powder and binder; wherein at least the magnetic layer comprises one or more components selected from the group consisting of a fatty acid and a fatty acid amide; a quantity of components selected from the group consisting of a fatty acid and a fatty acid amide per unit area of the magnetic tape among components that are extracted from a surface on the magnetic layer side of the magnetic tape is less than or equal to 15.0 mg / m2, and a concentration of carbon, C, that is obtained by X-ray photoelectron spectroscopy conducted at a photoelectron take-off angle of 10 degrees on the surface on the magnetic layer side of the magnetic tape is greater than or equal to 50 atom %.

Owner:FUJIFILM CORP

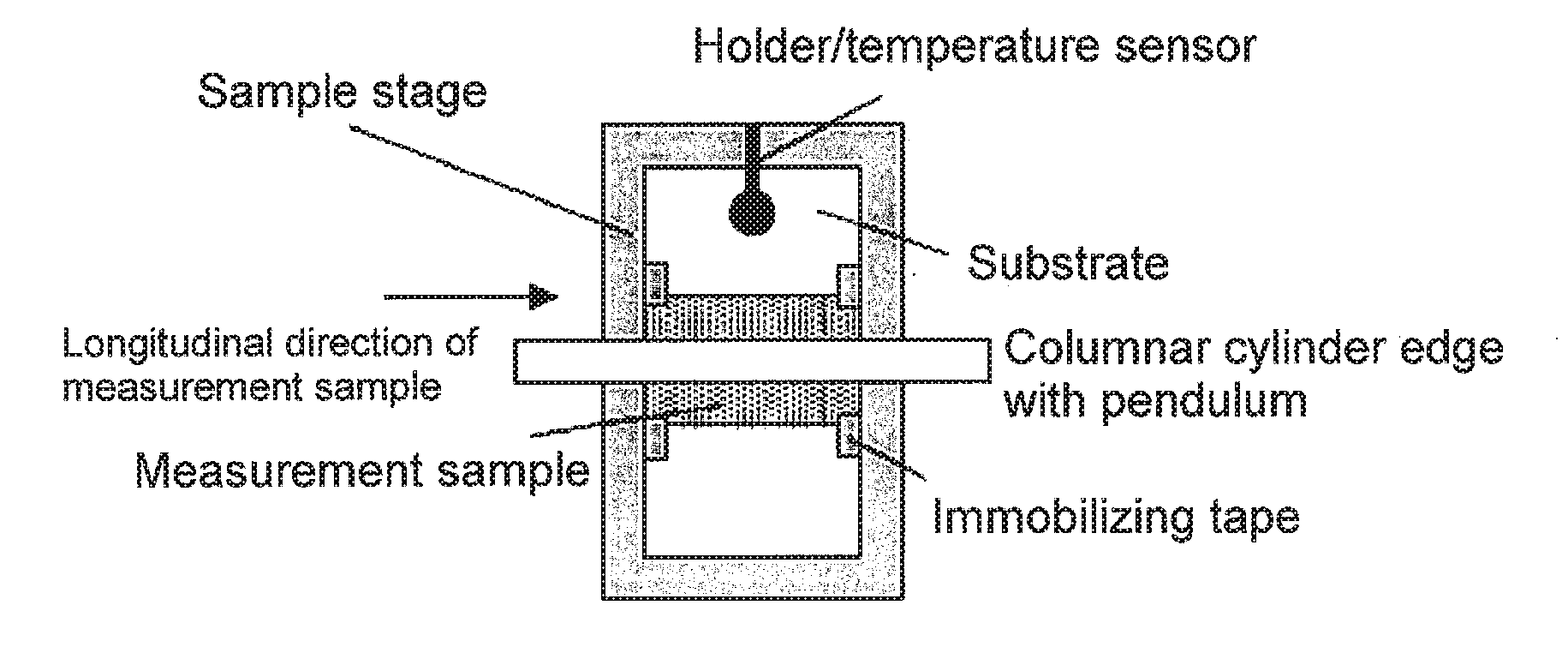

Magnetic tape and method of manufacturing the same

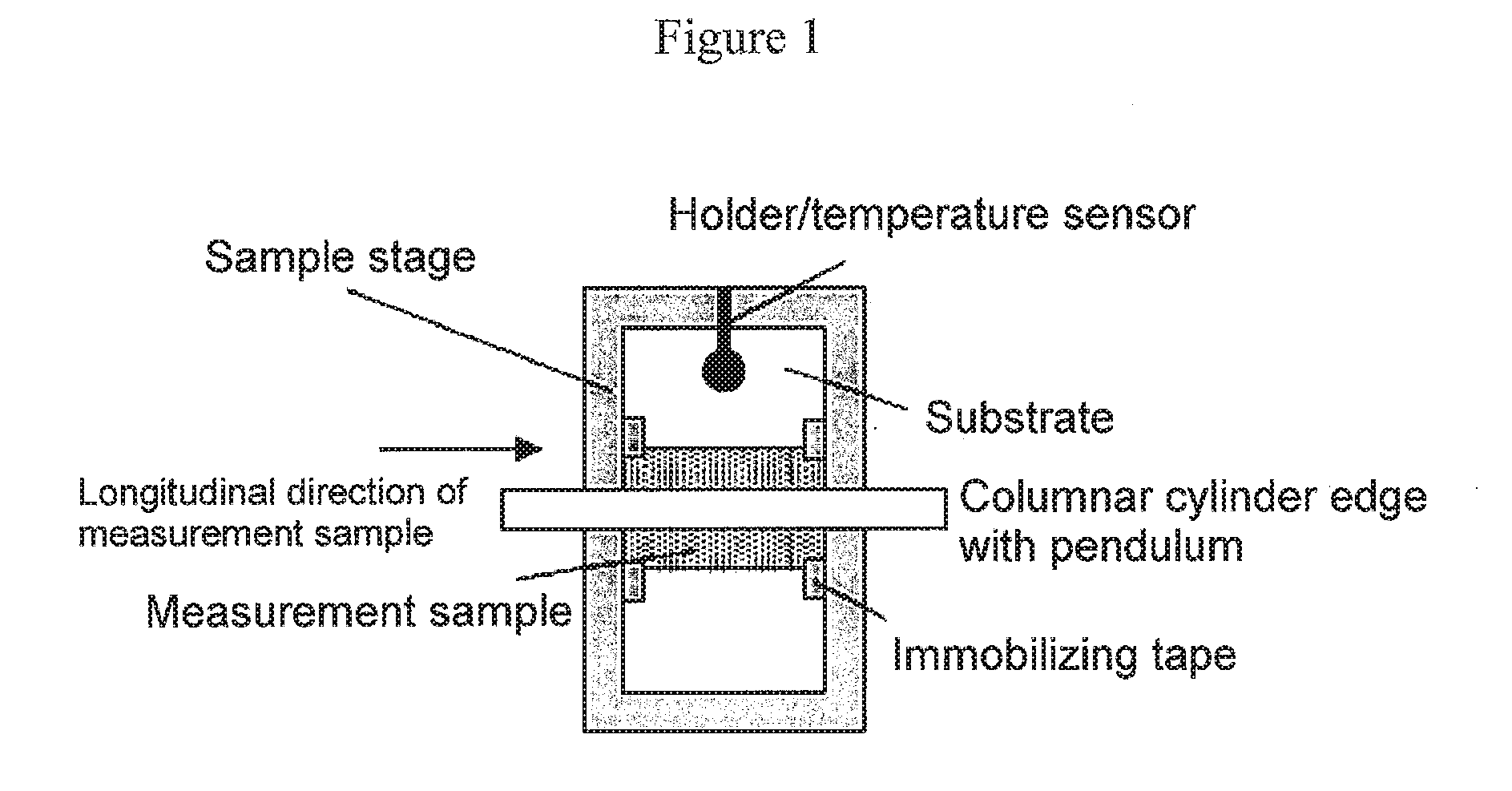

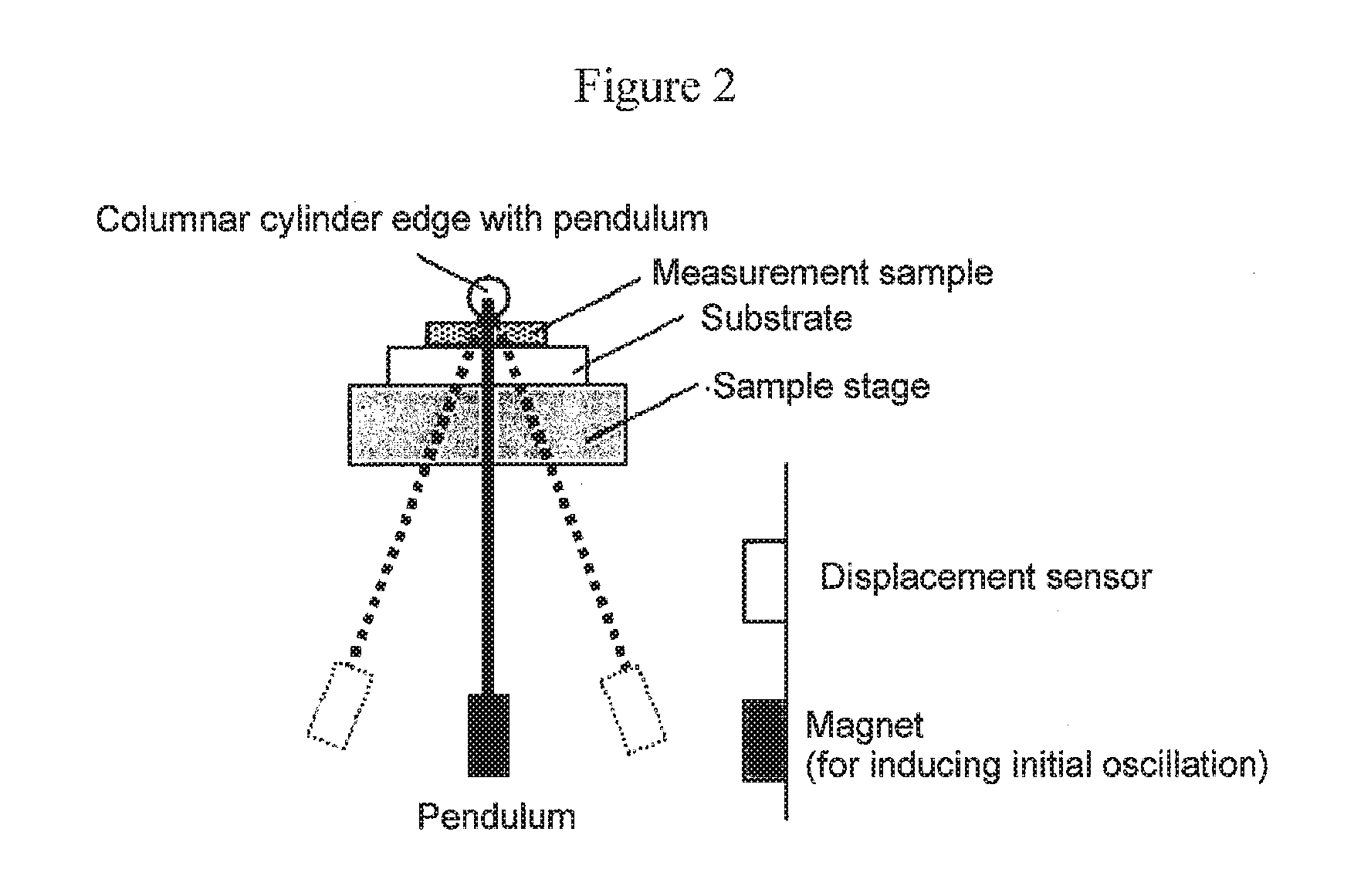

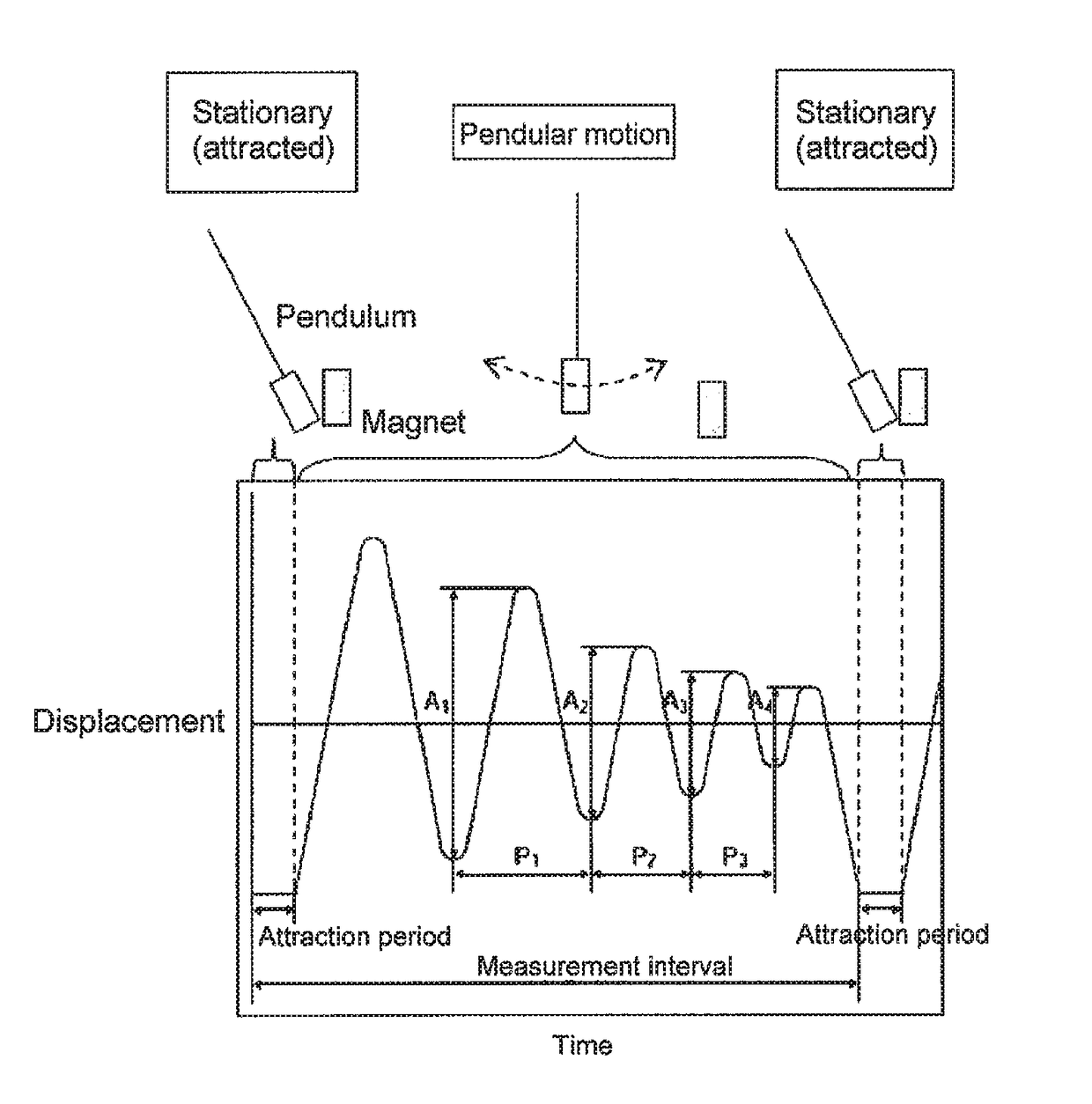

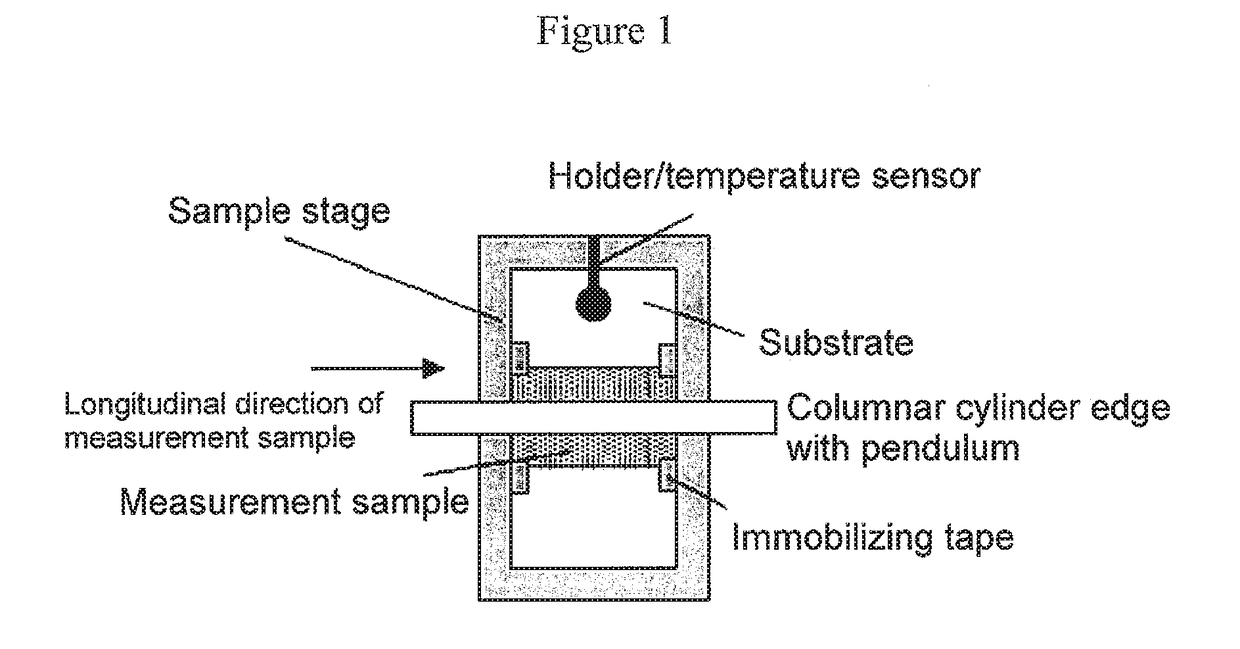

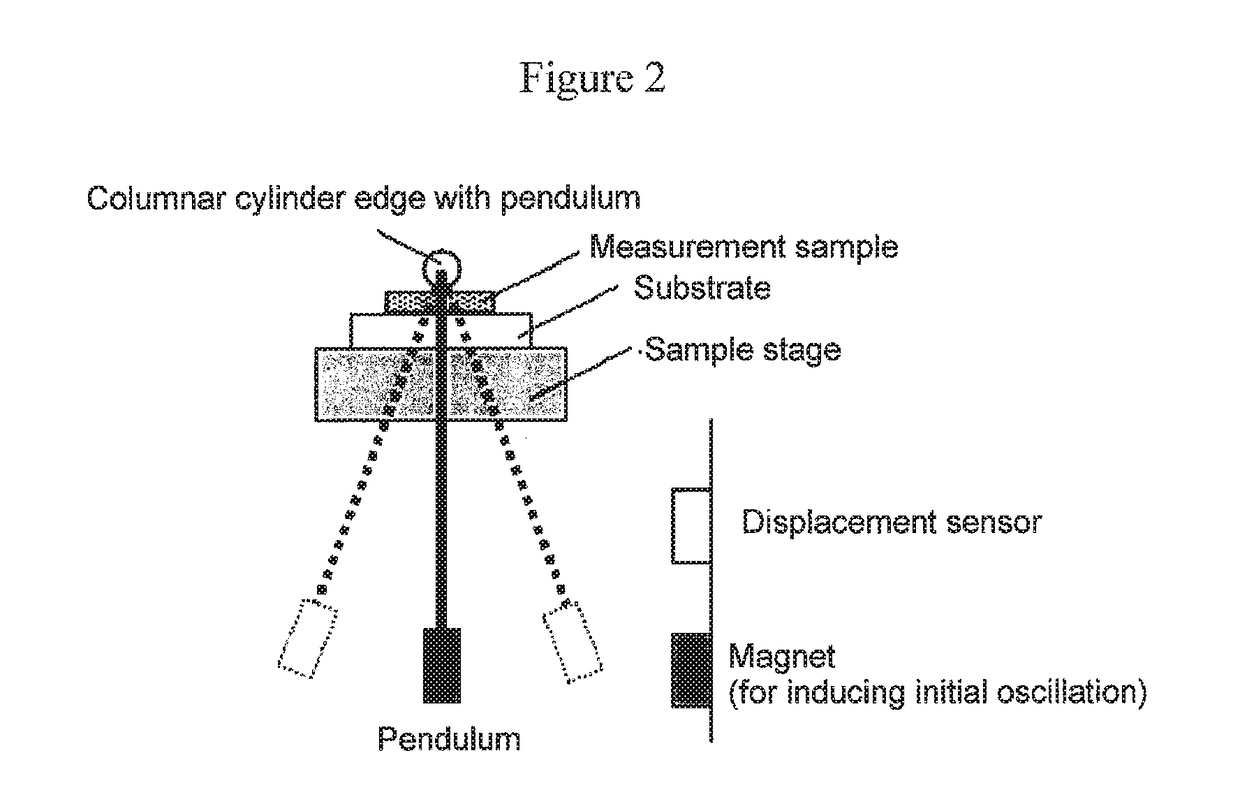

ActiveUS20170053671A1Increase recording capacityReduce thicknessTape carriersRecord information storageMagnetic tapeNon magnetic

The magnetic tape has a magnetic layer containing ferromagnetic powder and binder on the surface on one side of a nonmagnetic support and has a backcoat layer containing nonmagnetic powder and binder on the surface on the other side of the nonmagnetic support, wherein the backcoat layer is less than or equal to 0.30 μm in thickness; and the logarithmic decrement as determined by a pendulum viscoelasticity test on the surface on the backcoat layer side of the magnetic tape is less than or equal to 0.060.

Owner:FUJIFILM CORP

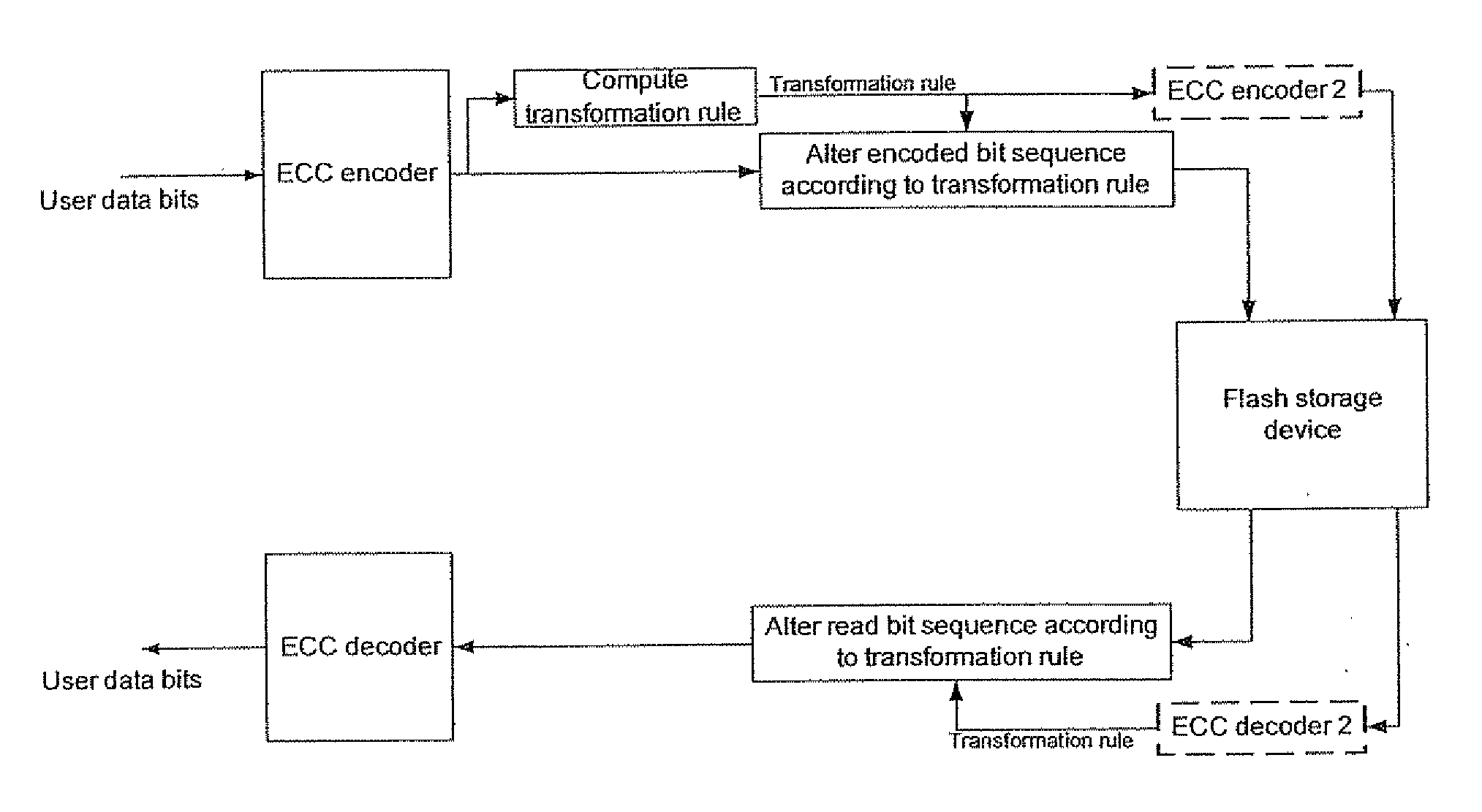

Avoiding errors in a flash memory by using substitution transformations

InactiveUS20080158948A1Reduce impactImprove reliabilityMemory loss protectionRead-only memoriesMemory cellAlgorithm

Owner:RAMOT AT TEL AVIV UNIV LTD

Magnetic tape having controlled surface properties of the backcoat layer and method of manufacturing the same

ActiveUS10026435B2Increase recording capacityReduce thicknessTape carriersRecord information storageMagnetic tapeNon magnetic

The magnetic tape has a magnetic layer containing ferromagnetic powder and binder on the surface on one side of a nonmagnetic support and has a backcoat layer containing nonmagnetic powder and binder on the surface on the other side of the nonmagnetic support, wherein the backcoat layer is less than or equal to 0.30 μm in thickness; and the logarithmic decrement as determined by a pendulum viscoelasticity test on the surface on the backcoat layer side of the magnetic tape is less than or equal to 0.060.

Owner:FUJIFILM CORP

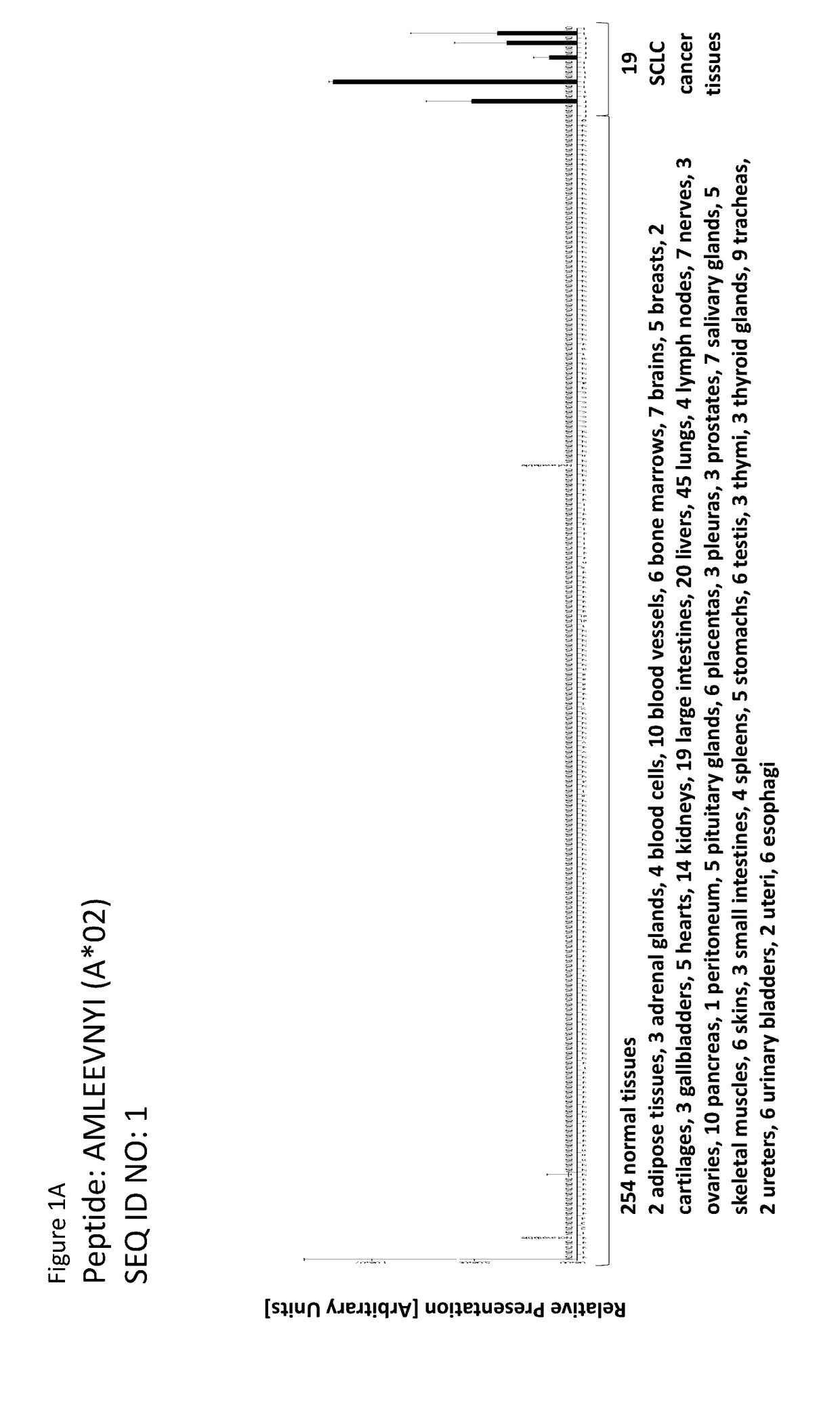

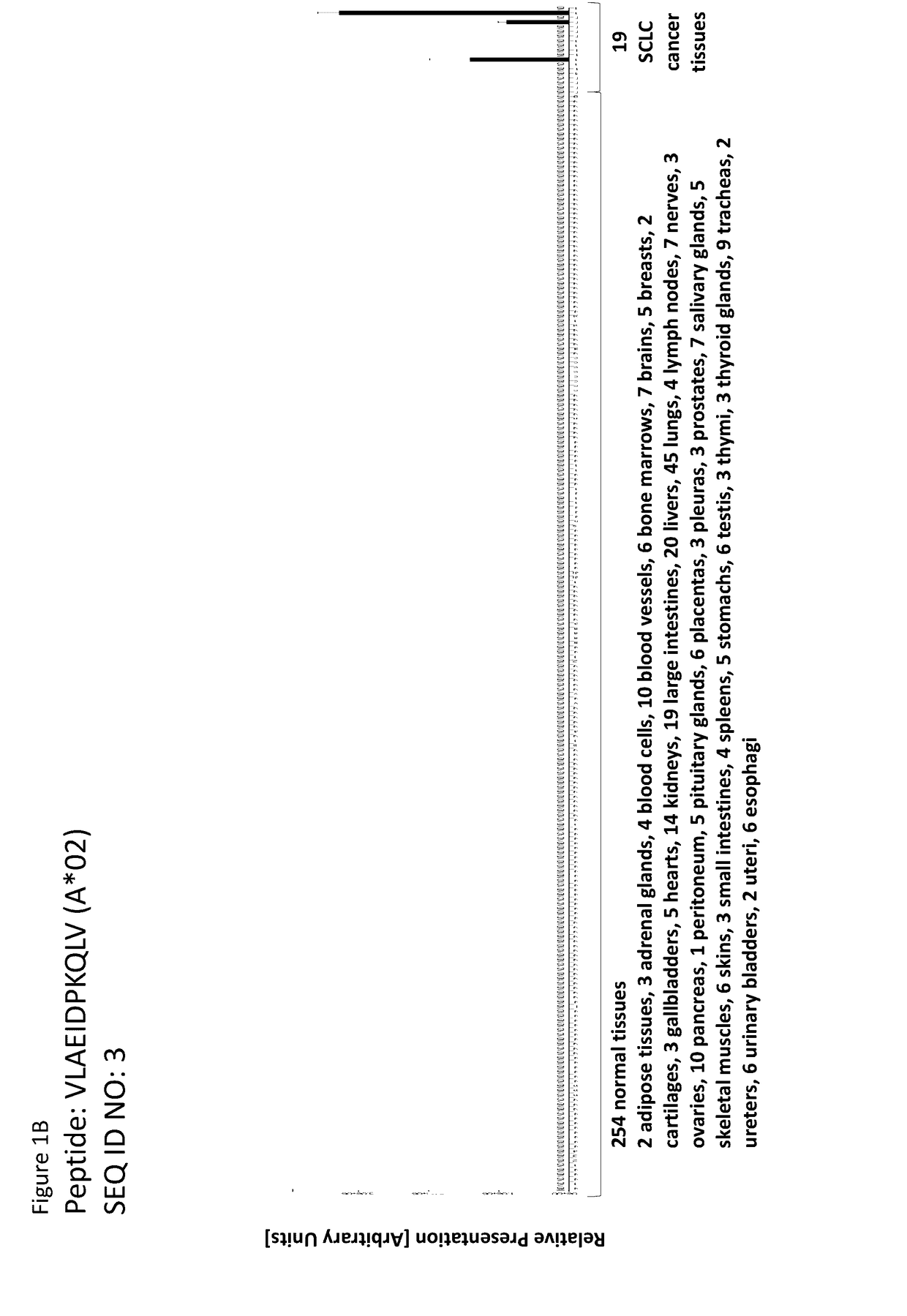

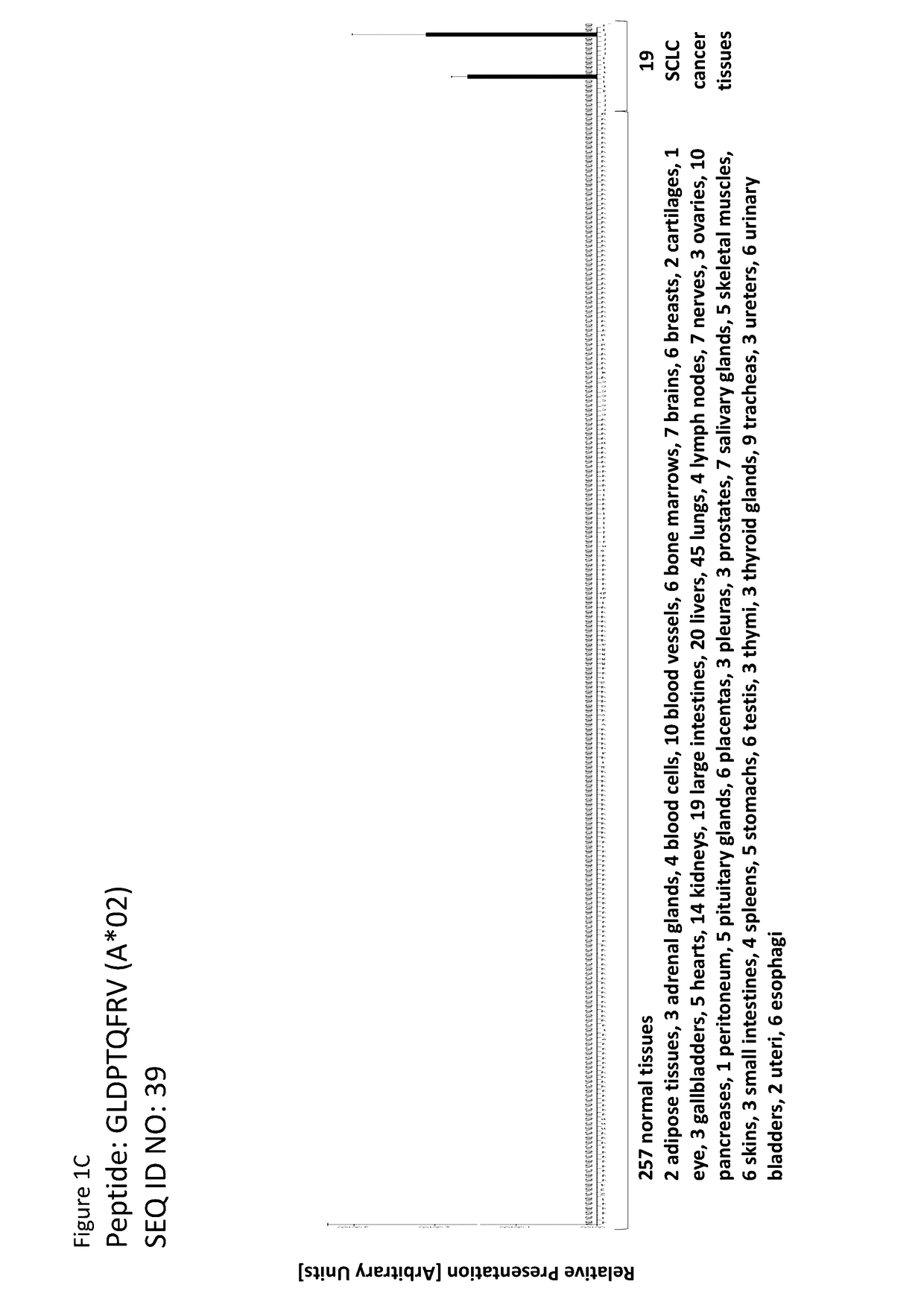

Novel peptides and combination of peptides for use in immunotherapy against small cell lung cancer and other cancers

ActiveUS20170096461A1High error rateIncrease in motilityNervous disorderAntibody mimetics/scaffoldsPeptideDrug

The present invention relates to peptides, proteins, nucleic acids and cells for use in immunotherapeutic methods. In particular, the present invention relates to the immunotherapy of cancer. The present invention furthermore relates to tumor-associated T-cell peptide epitopes, alone or in combination with other tumor-associated peptides that can for example serve as active pharmaceutical ingredients of vaccine compositions that stimulate anti-tumor immune responses, or to stimulate T cells ex vivo and transfer into patients. Peptides bound to molecules of the major histocompatibility complex (MHC), or peptides as such, can also be targets of antibodies, soluble T-cell receptors, and other binding molecules.

Owner:IMMATICS BIOTECHNOLOGIES GMBH

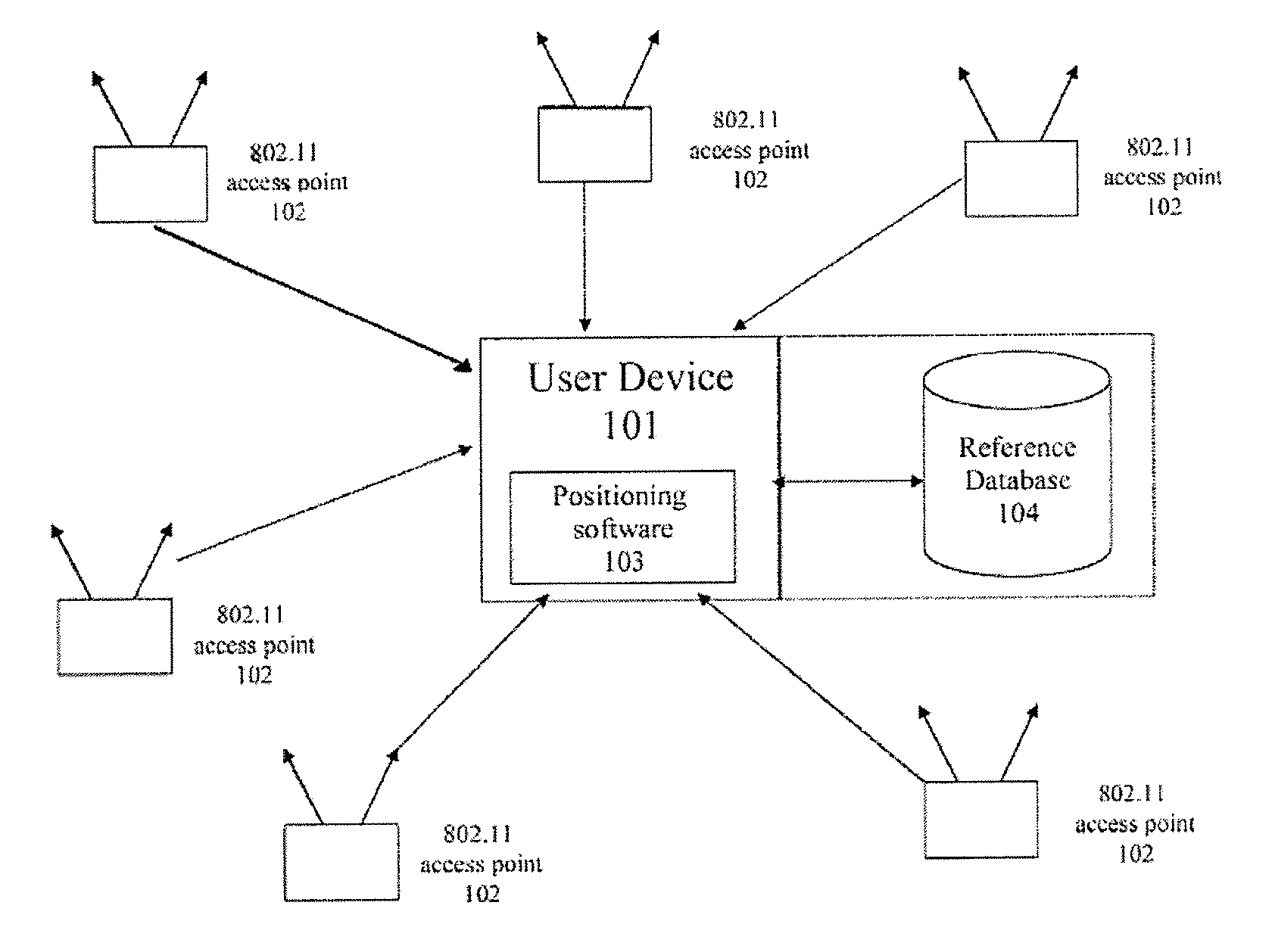

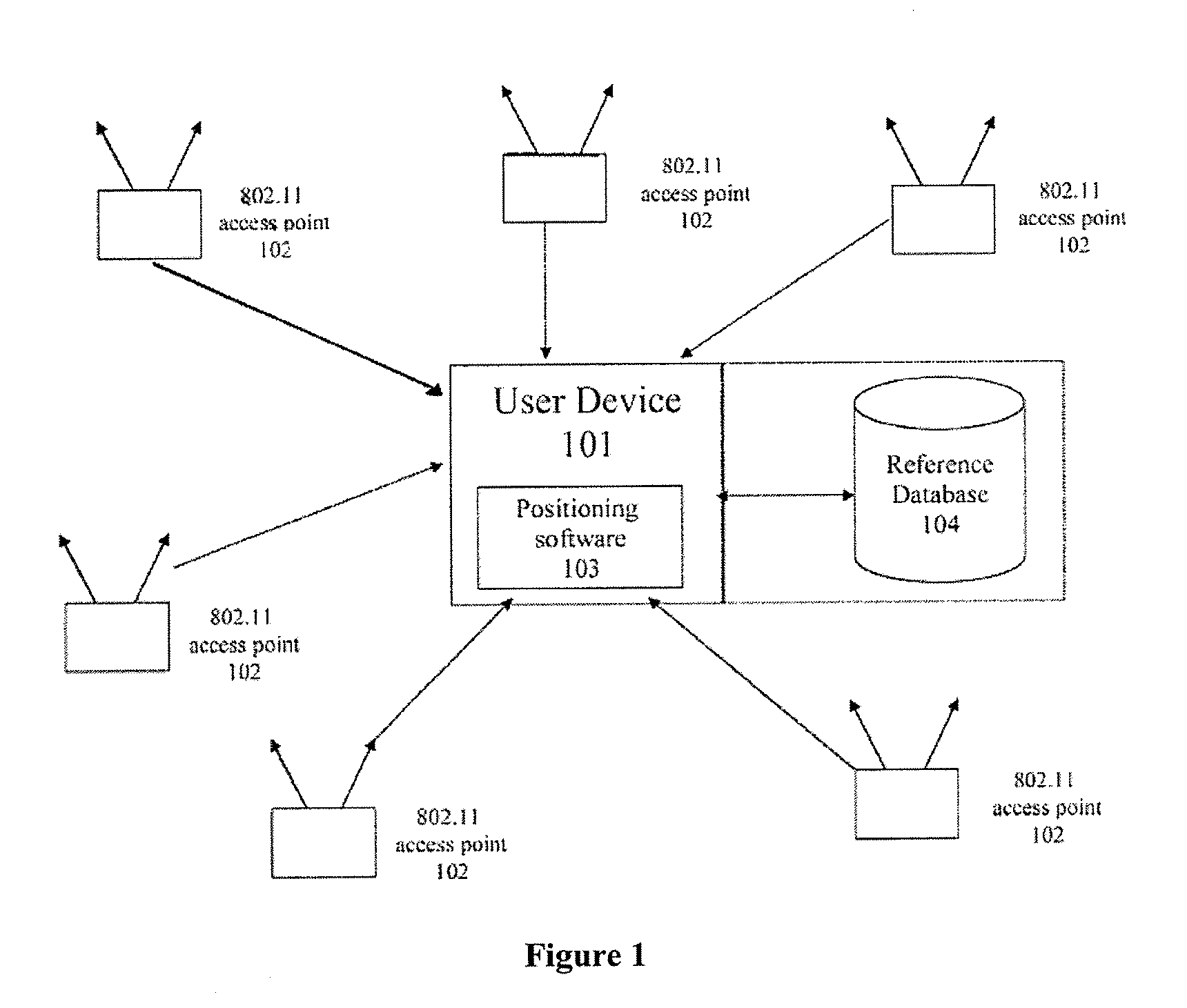

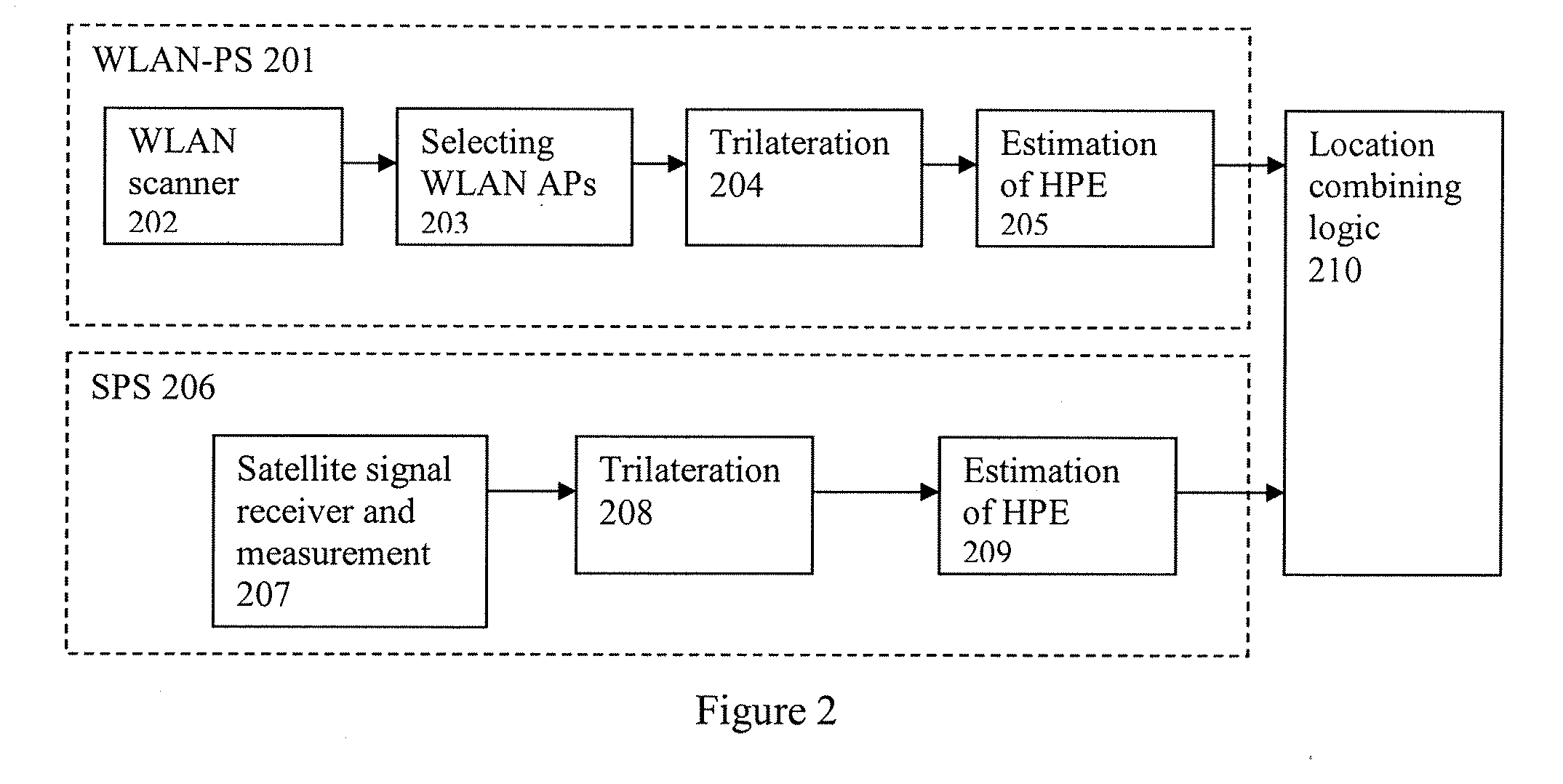

Methods and systems for improving the accuracy of expected error estimation in a hybrid positioning system

InactiveUS20090303113A1Expected errorHigh expected errorPosition fixationBeacon systemsHybrid positioning systemLocation determination

This disclosure describes methods and systems for improving the accuracy of expected error estimation in a hybrid positioning system. In some embodiments, the method of determining an expected error in a location determination of a WLAN and satellite enabled device can include determining a WLAN location estimate and an expected error estimate for the WLAN location estimate, obtaining measurements from at least two satellites, and determining the expected error of the location determination by evaluating the consistency of the satellite positioning system measurements to the WLAN positioning system location estimation.

Owner:SKYHOOK WIRELESS

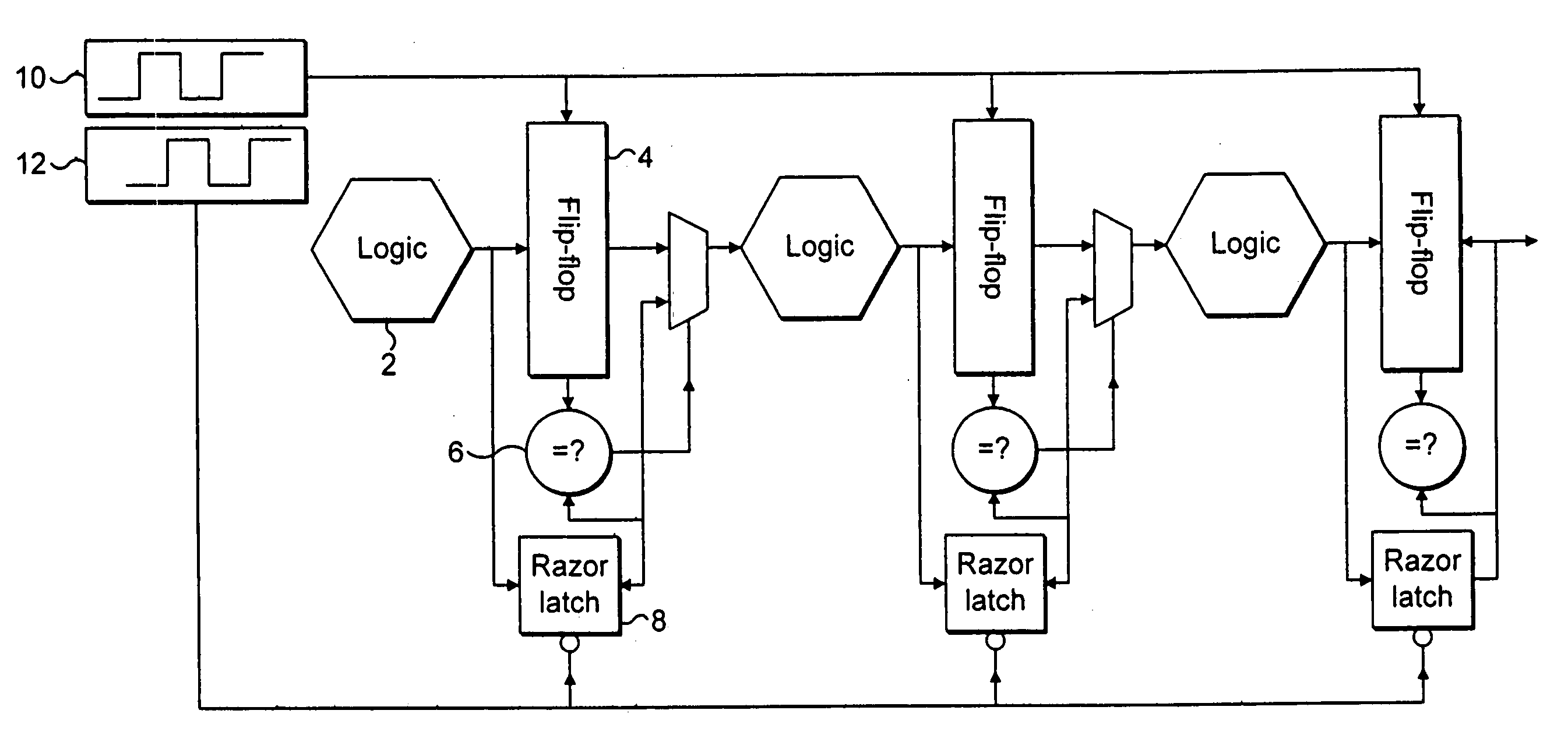

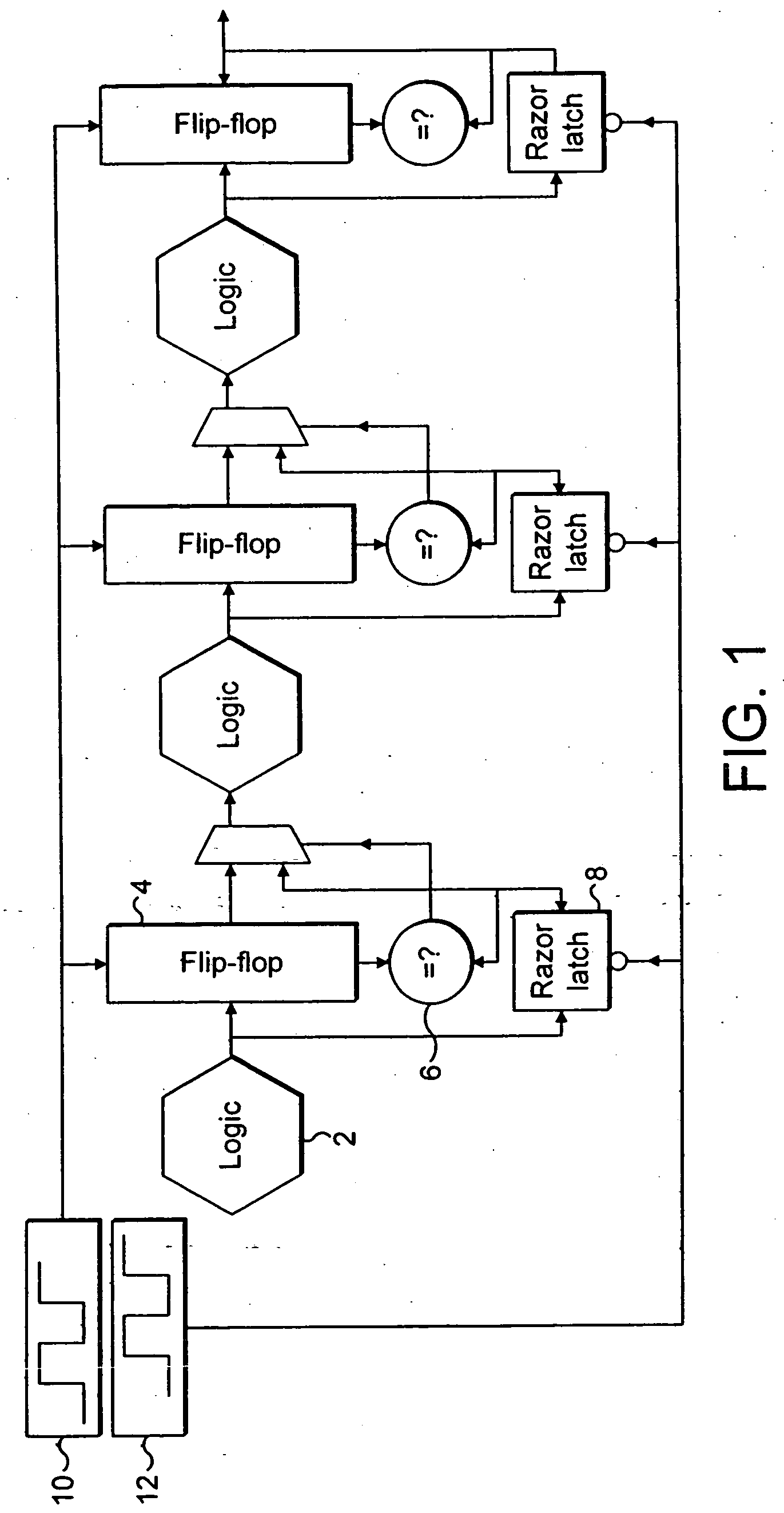

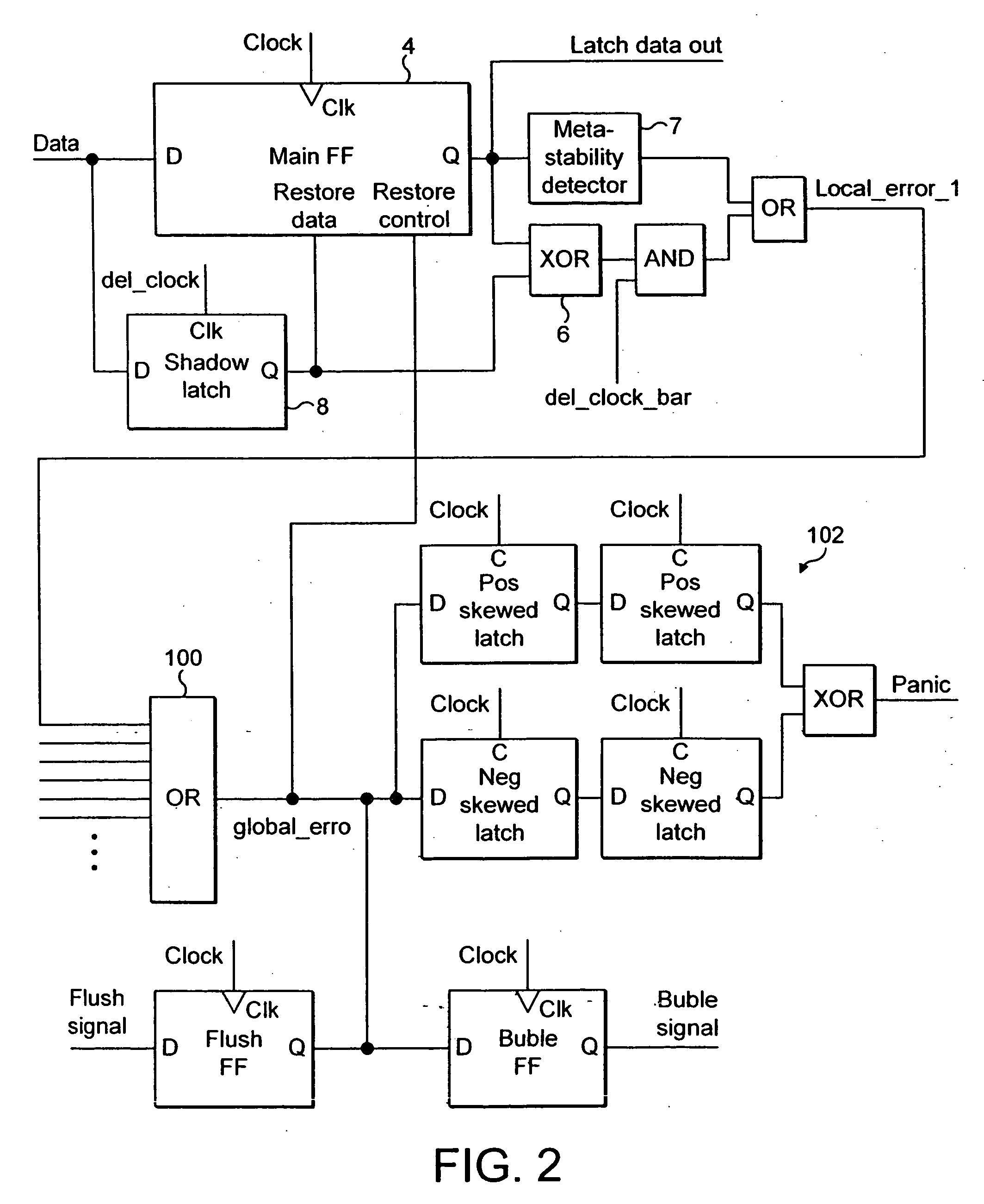

Error recovery within processing stages of an integrated circuit

ActiveUS20050246613A1Easy to modifyReduce the possibilityCode conversionFrequency/rate-modulated pulse demodulationError checkClock rate

An integrated circuit includes a plurality of processing stages each including processing logic 1014, a non-delayed signal-capture element 1016, a delayed signal-capture element 1018 and a comparator 1024. The non-delayed signal-capture element 1016 captures an output from the processing logic 1014 at a non-delayed capture time. At a later delayed capture time, the delayed signal-capture element 1018 also captures a value from the processing logic 1014. An error detection circuit 1026 and error correction circuit 1028 detect and correct random errors in the delayed value and supplies an error-checked delayed value to the comparator 1024. The comparator 1024 compares the error-checked delayed value and the non-delayed value and if they are not equal this indicates that the non-delayed value was captured too soon and should be replaced by the error-checked delayed value. The non-delayed value is passed to the subsequent processing stage immediately following its capture and accordingly error recovery mechanisms are used to suppress the erroneous processing which has occurred by the subsequent processing stages, such as gating the clock and allowing the correct signal values to propagate through the subsequent processing logic before restarting the clock. The operating parameters of the integrated circuit, such as the clock frequency, the operating voltage, the body biased voltage, temperature and the like are adjusted so as to maintain a finite non-zero error rate in a manner that increases overall performance.

Owner:ARM LTD +1

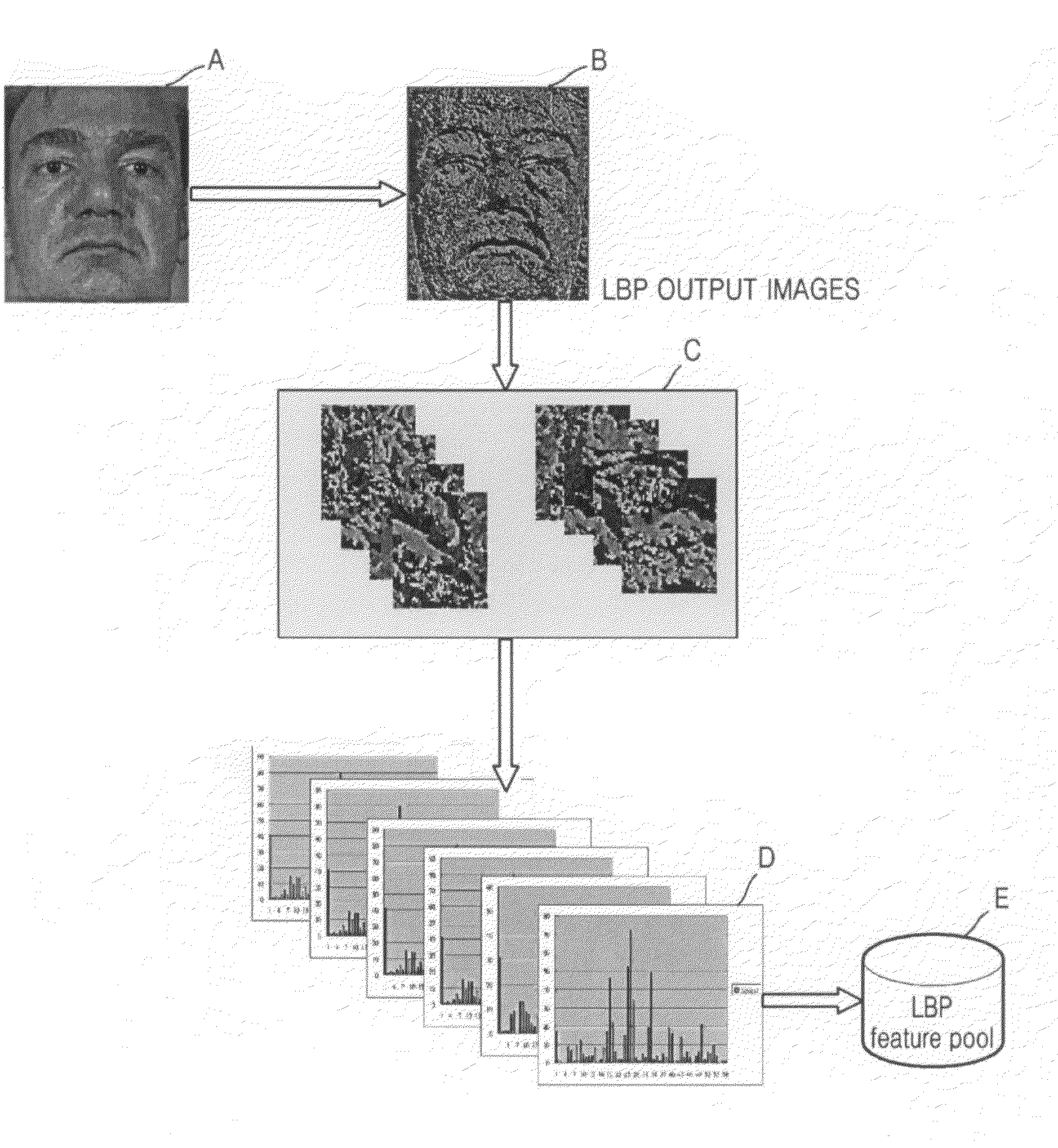

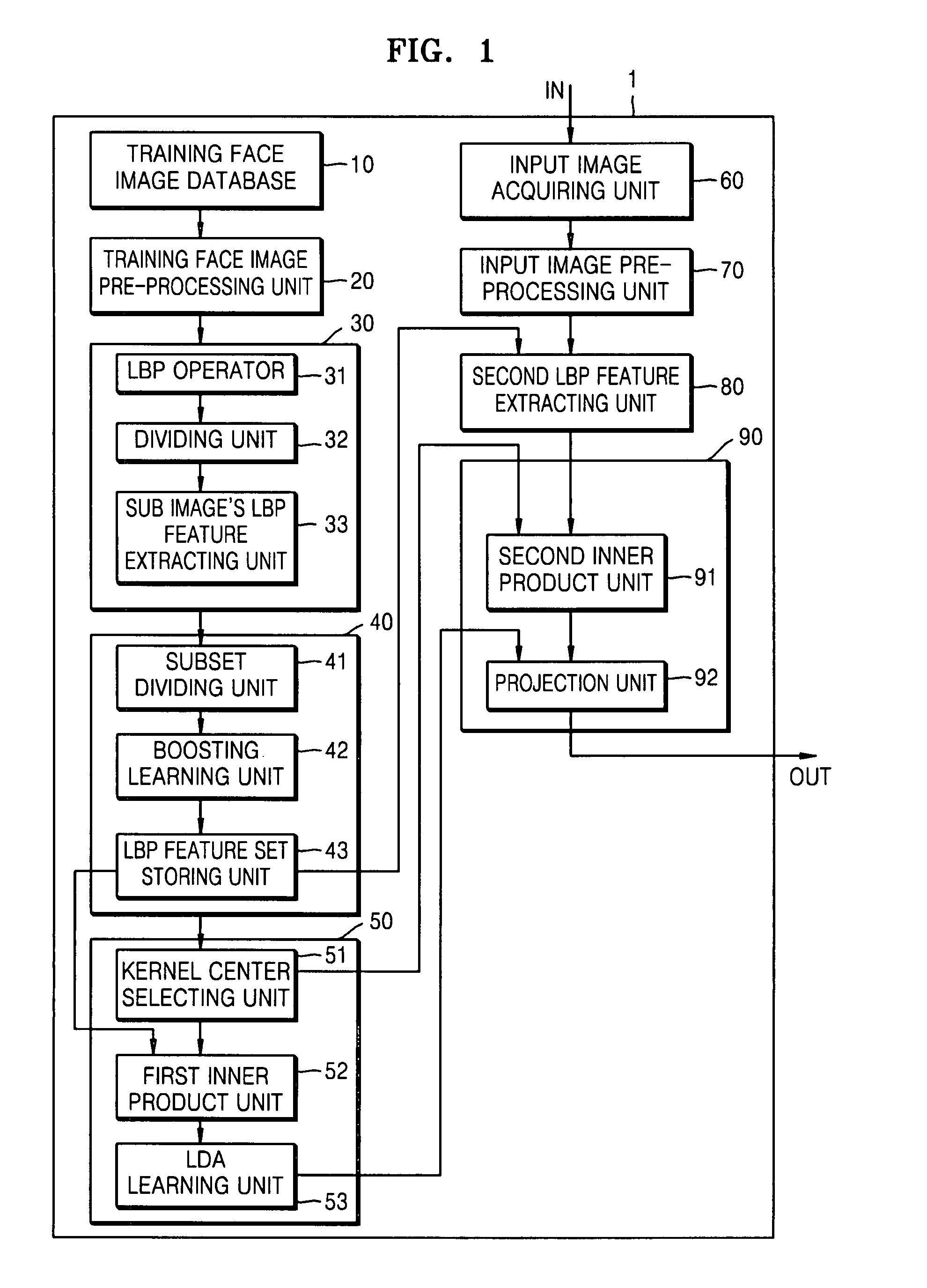

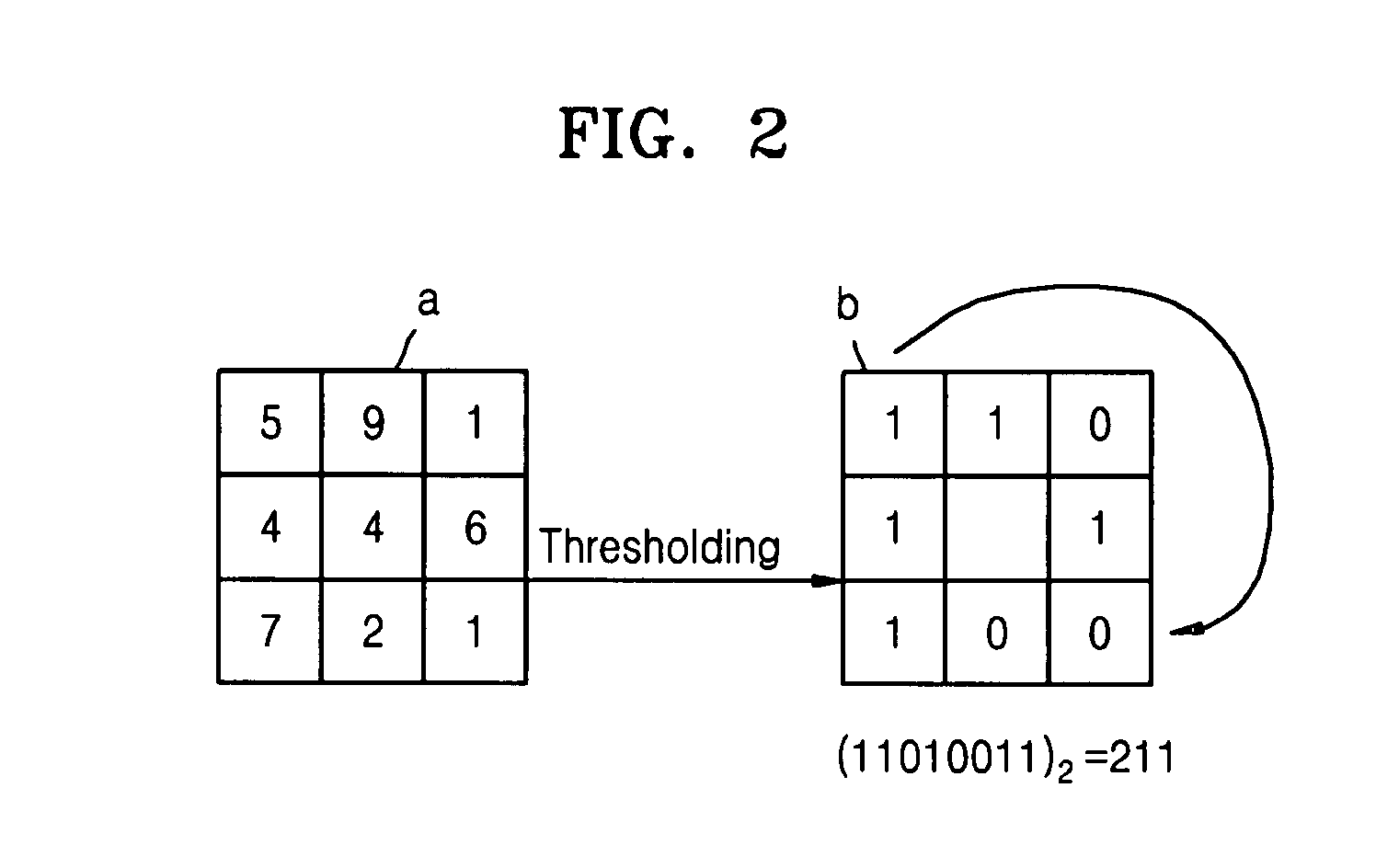

Method and apparatus for generating face descriptor using extended local binary patterns, and method and apparatus for face recognition using extended local binary patterns

InactiveUS20080166026A1Reduce processing timeHigh error rateCharacter and pattern recognitionSupervised learningAuthentication

A face descriptor generating method and apparatus and face recognition method and apparatus using extended local binary pattern (LBP) are provided.Since LBP features are selected by performing a supervised learning process on the extended LBP features and the selected extended LBP features are used in face recognition, it is possible to reduce errors in face recognition or identity verification and to increase face recognition efficiency. In addition, the extended LBP features are used so that it is possible to overcome the problem of time-consumption of the process.

Owner:SAMSUNG ELECTRONICS CO LTD

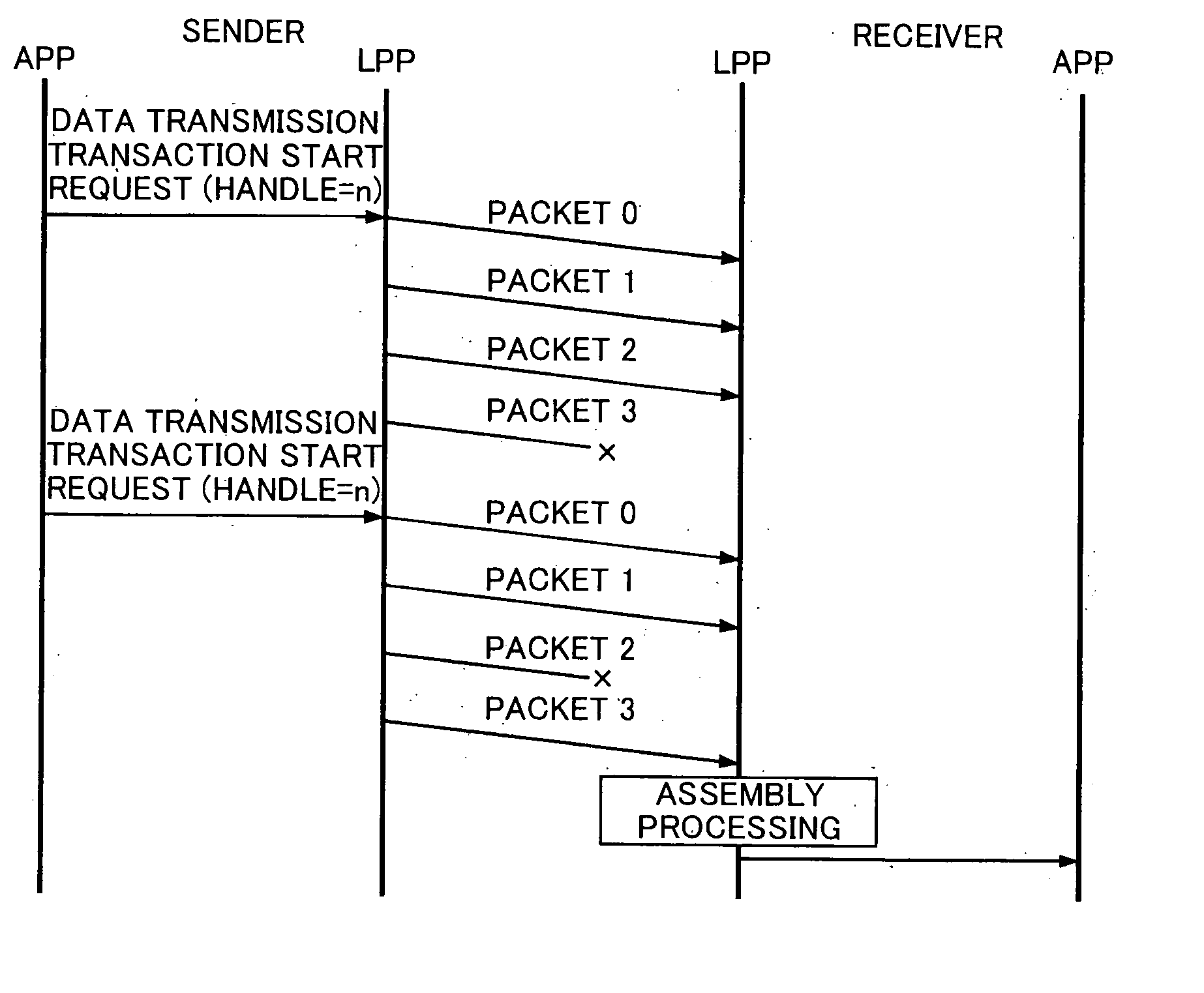

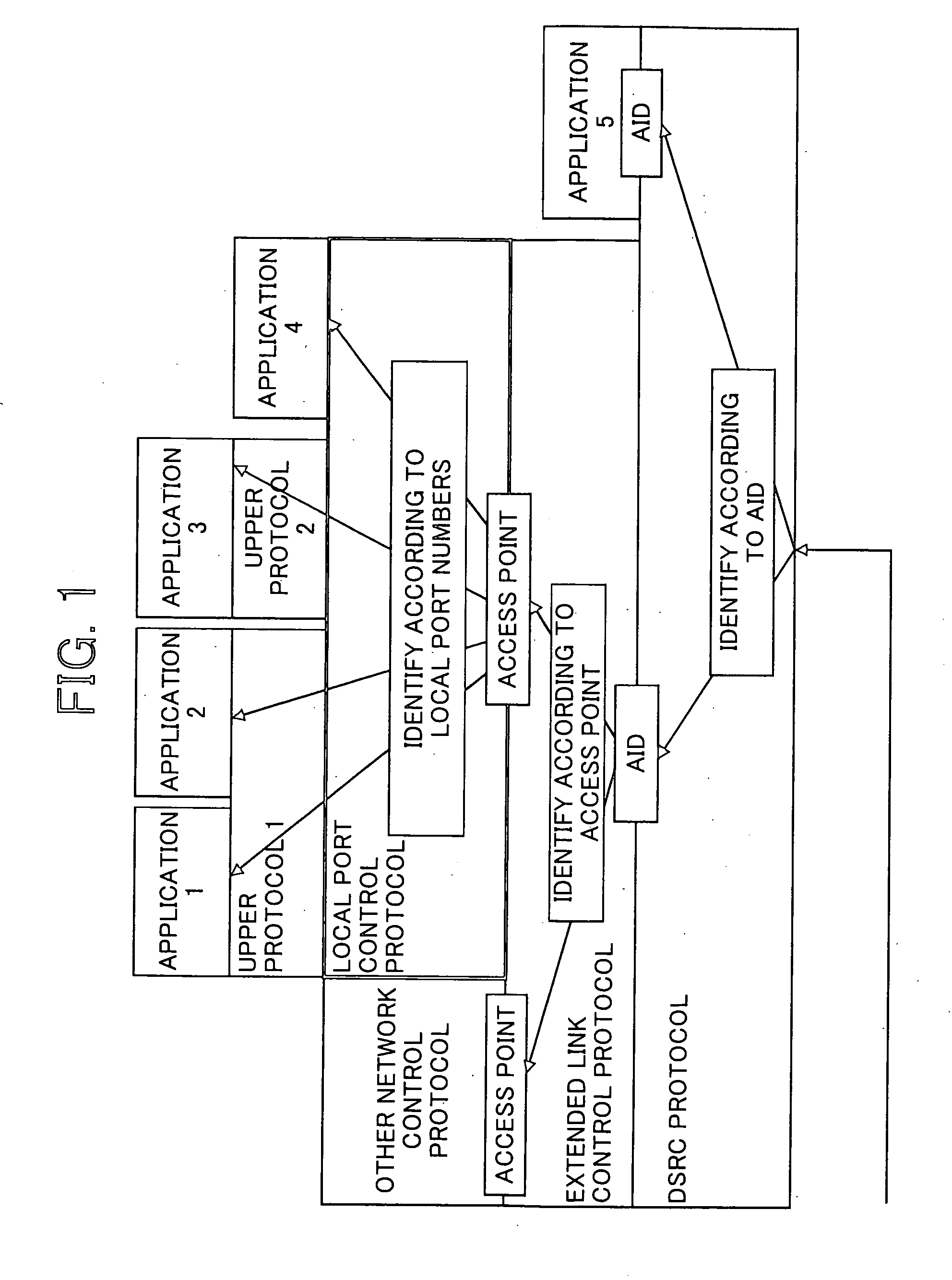

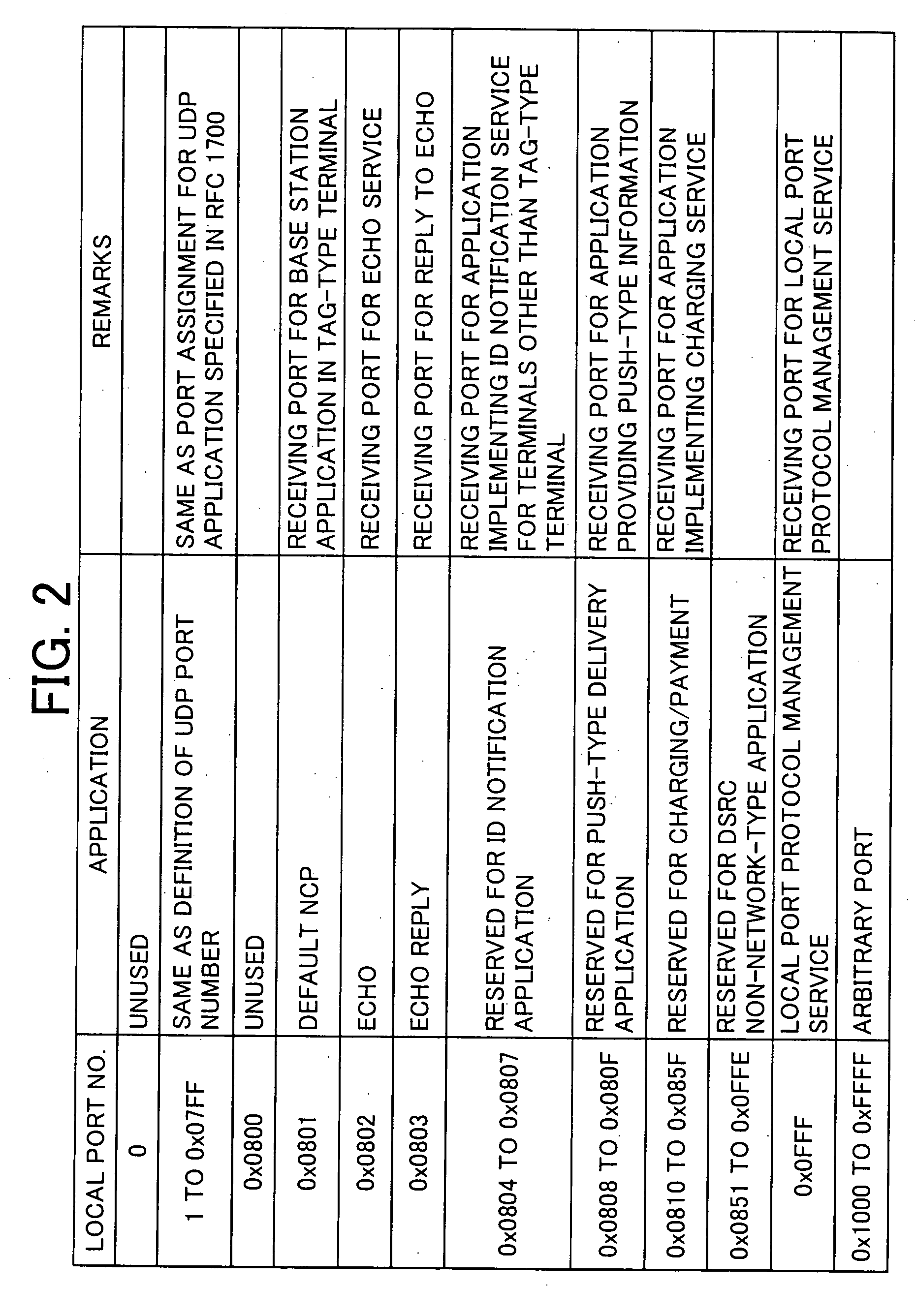

Between-load-and-vehicle communication system

InactiveUS20060193282A1High error rateReduce overheadError prevention/detection by using return channelNetwork traffic/resource managementTransaction managementTransaction service

A roadside-to-vehicle communication system for providing a mobile station with application service by utilizing roadside-to-vehicle communication implemented between the mobile station that travels on a road and a base station system installed along the road provides non-network-type communication protocols that can implement diverse application services, even when the mobile station is moving. The roadside-to-vehicle communication system includes transfer service processing entities for implementing data transfer among applications and transaction management entities have undelivered data resenders, data send / receive for each message, and a message segmenter / assembler that provides unidirectional data transmission and request-response transaction services.

Owner:MITSUBISHI ELECTRIC CORP

Non-Volatile Memory and Method with Accelerated Post-Write Read Using Combined Verification of Multiple Pages

ActiveUS20130031430A1High error rateDigital storageRedundant hardware error correctionCombinational verificationOperating system

A post-write read operation, using a combined verification of multiple pages of data, is presented. In a simultaneous verification of multiple pages in a block, the controller evaluates a combined function of the multiple pages, instead of evaluating each page separately. In one exemplary embodiment, the combined function is formed by XORing the pages together. Such a combined verification of multiple pages based on the read data can significantly reduce the controller involvement, lowering the required bus and ECC bandwidth for a post-write read and hence allow efficient post-write reads when the number of dies is large.

Owner:SANDISK TECH LLC

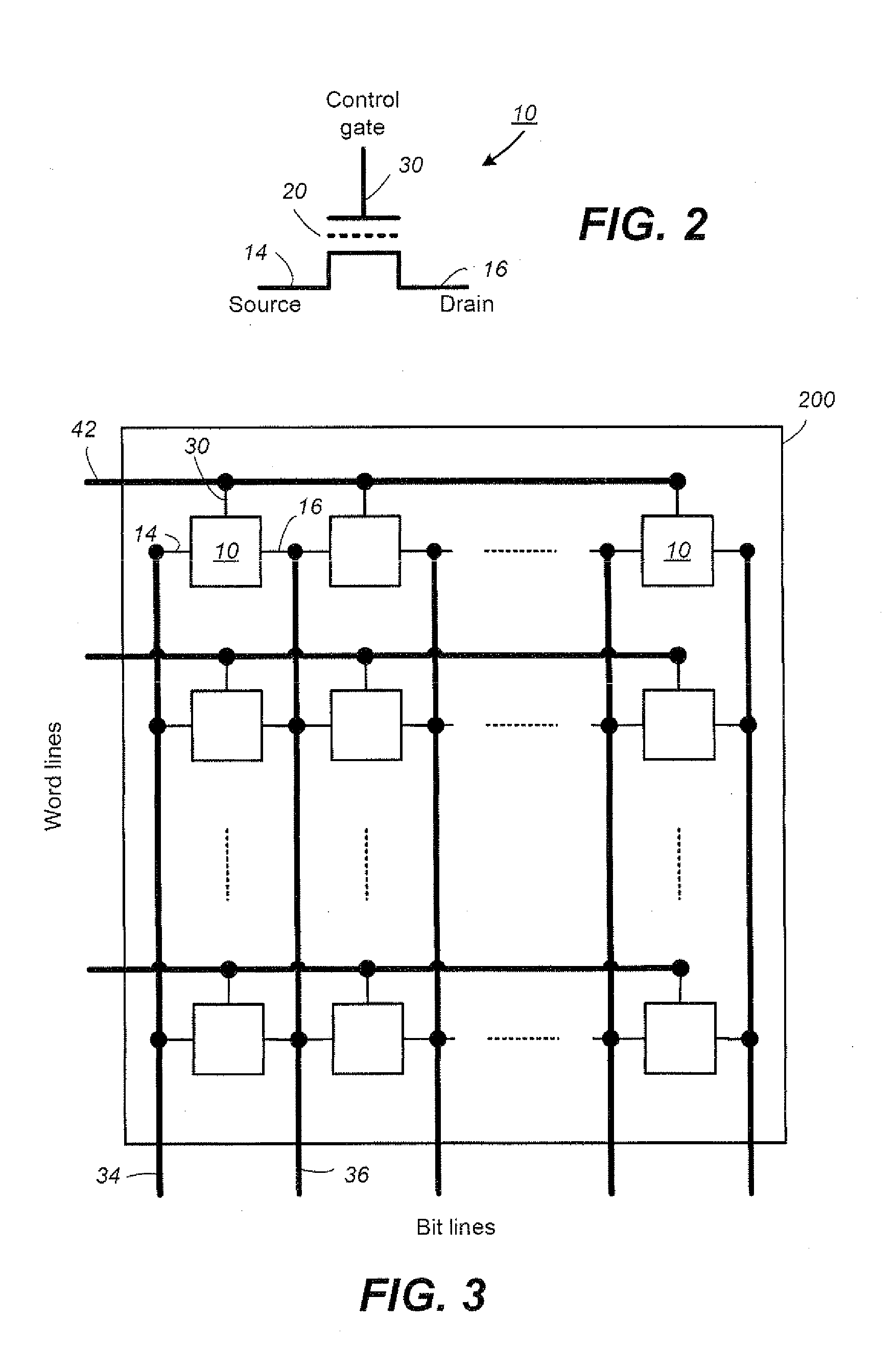

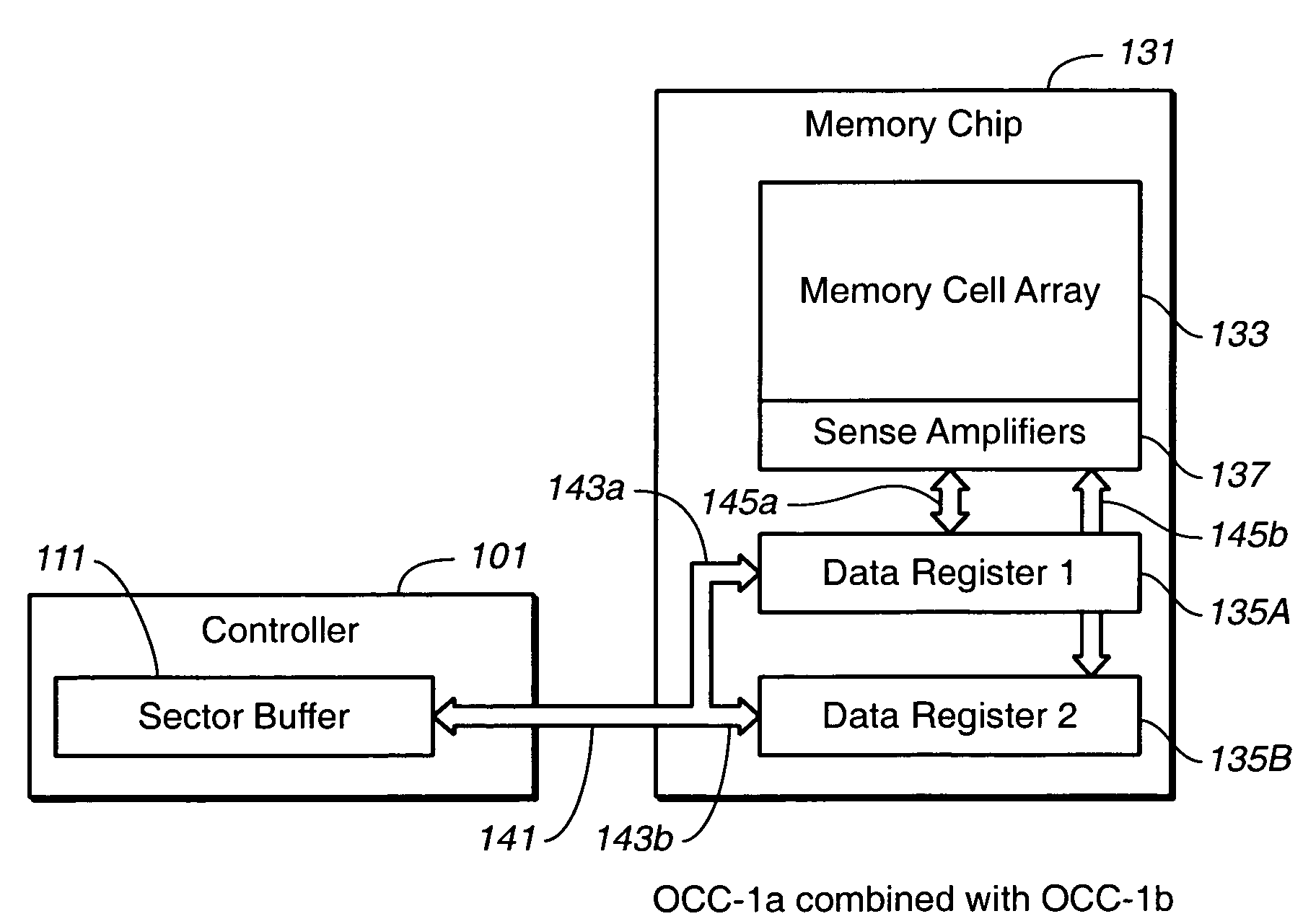

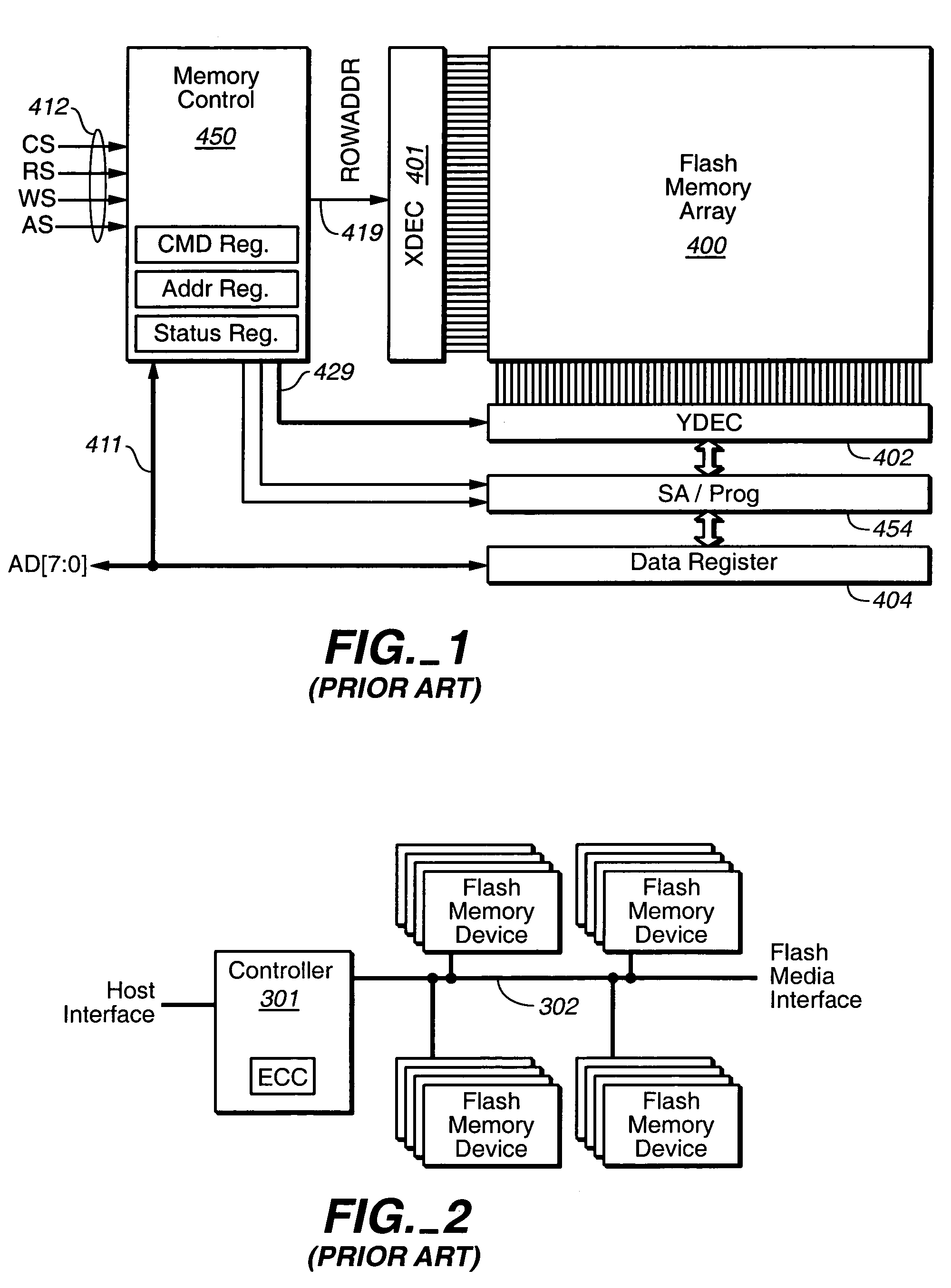

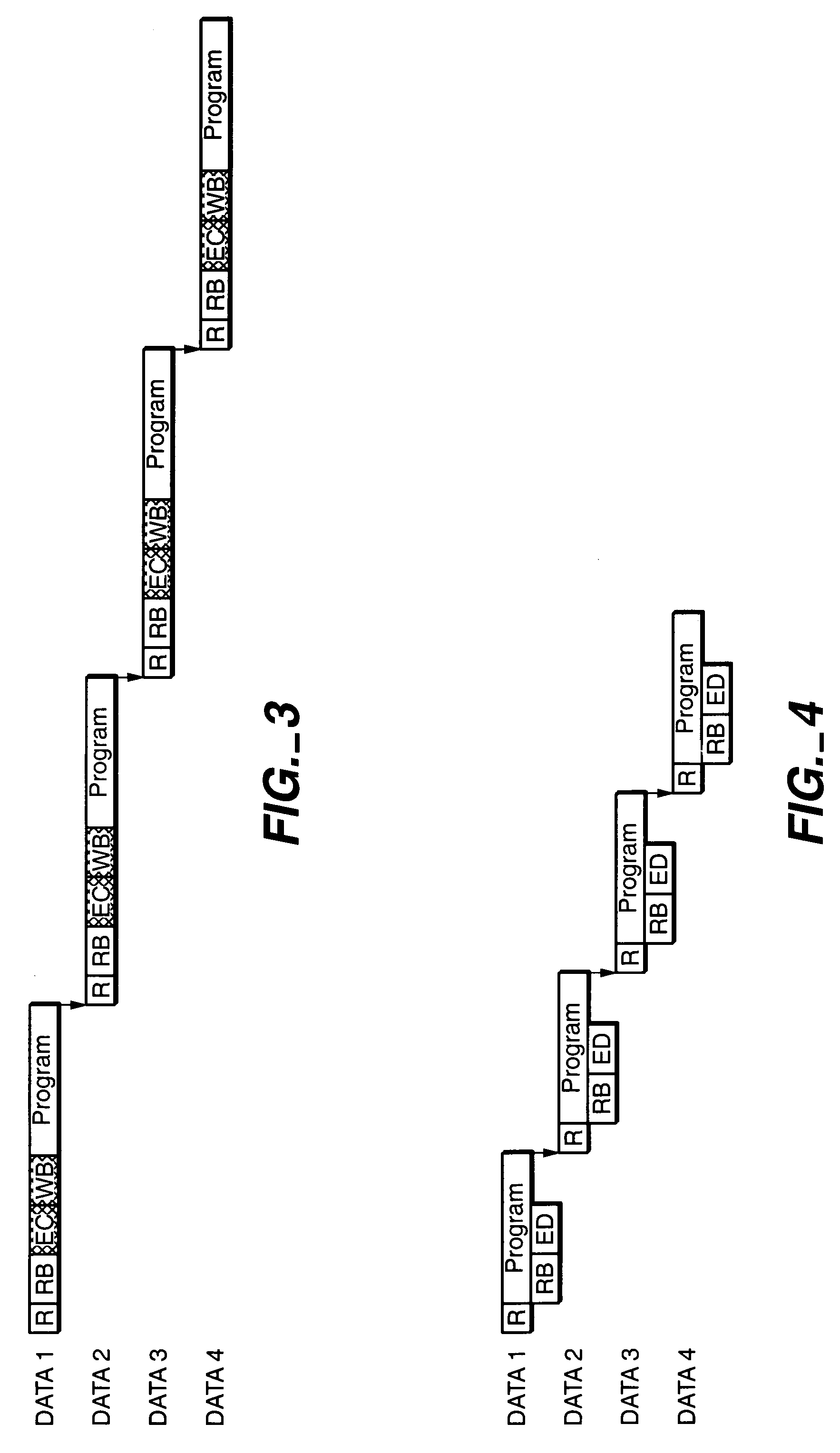

Pipelined data relocation and improved chip architectures

ActiveUS7490283B2High error rateComplex data operationError detection/correctionRead-only memoriesPresent methodProcessor register

The present invention present methods and architectures for the pipelining of read operation with write operations. In particular, methods are presented for pipelining data relocation operations that allow for the checking and correction of data in the controller prior to its being re-written, but diminish or eliminate the additional time penalty this would normally incur. A number of architectural improvements are described to facilitate these methods, including: introducing two registers on the memory where each is independently accessible by the controller; allowing a first memory register to be written from while a second register is written to; introducing two registers on the memory where the contents of the registers can be swapped.

Owner:SANDISK TECH LLC

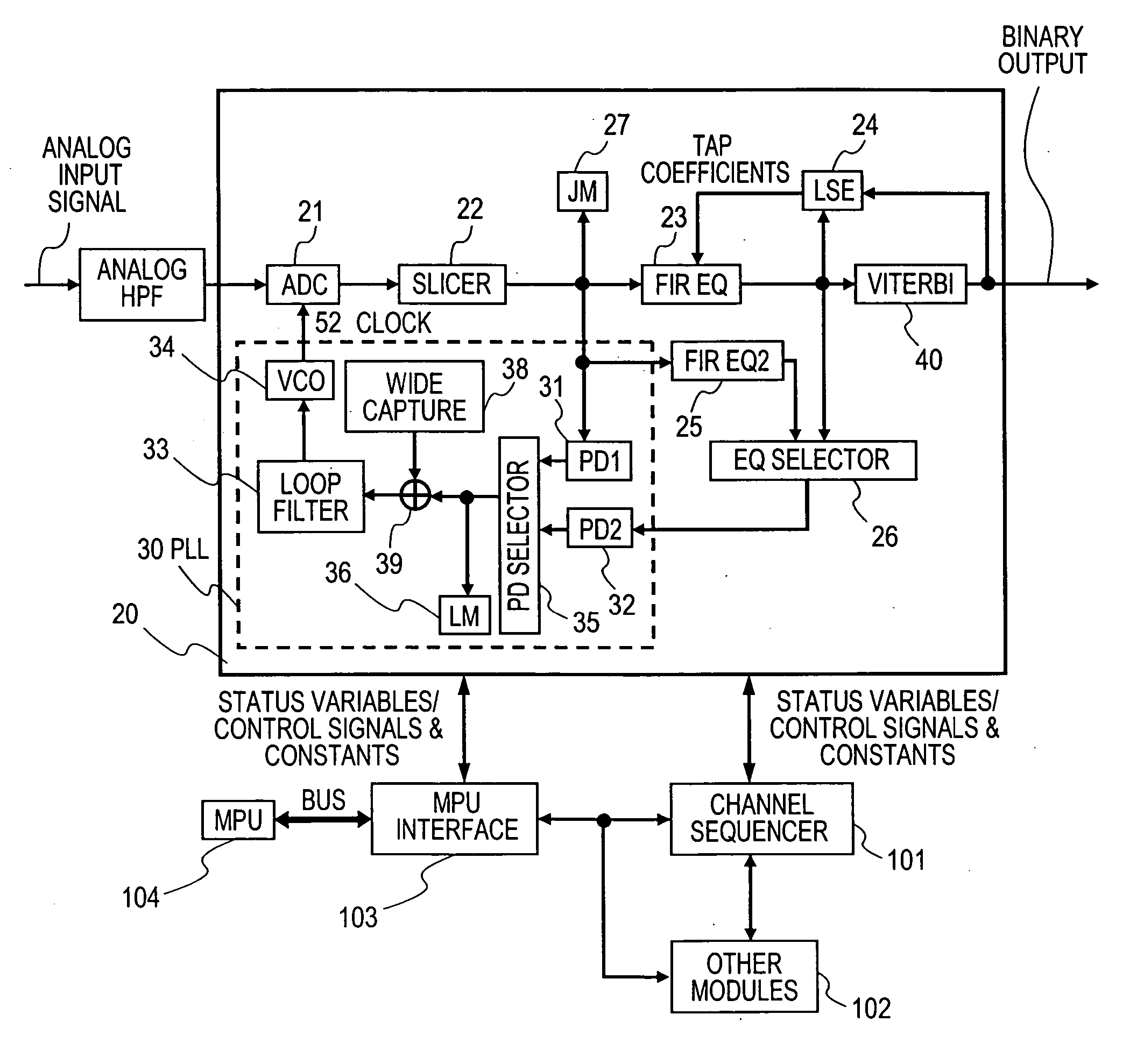

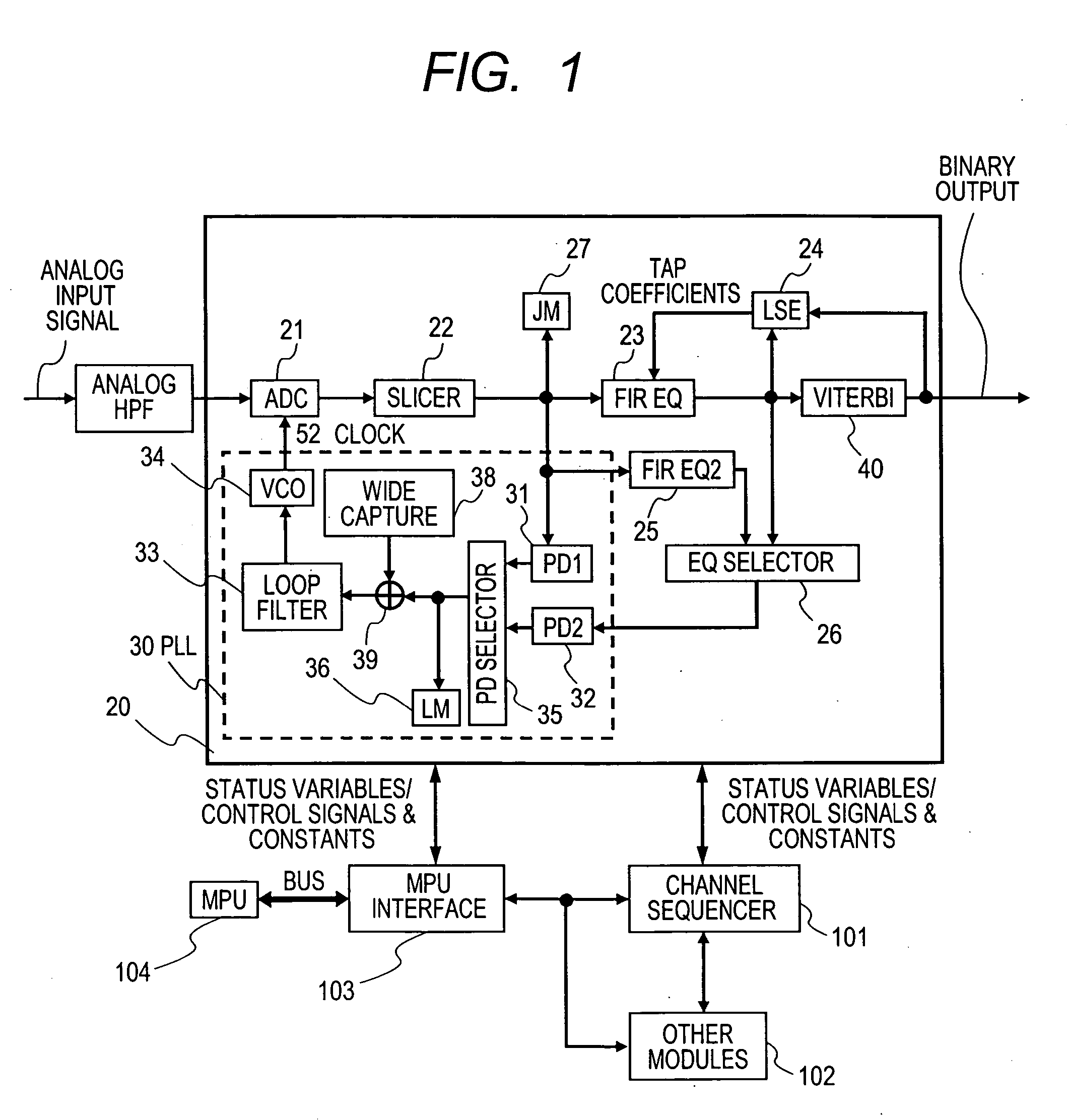

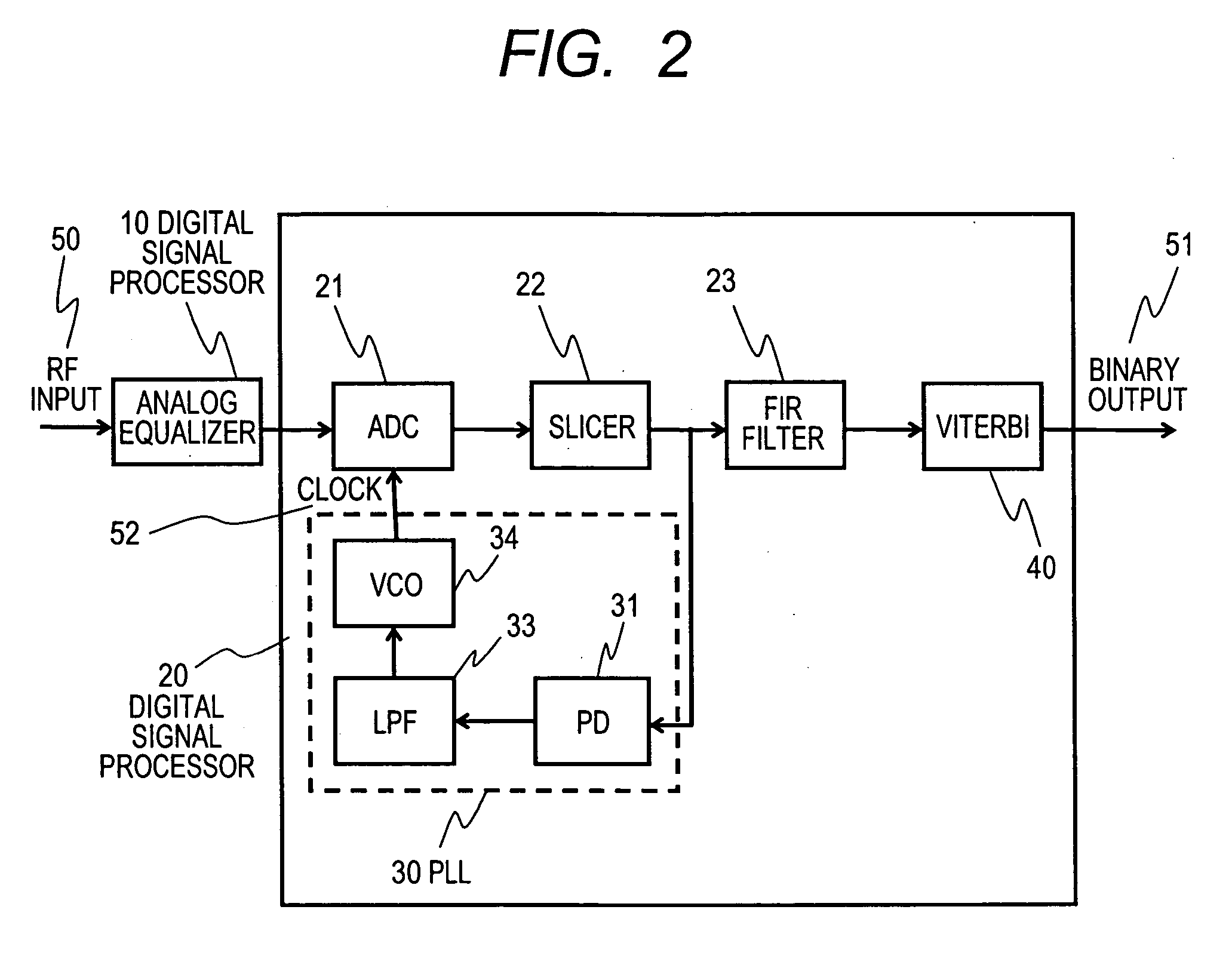

Information read device and read signal processing circuit

ActiveUS20060280240A1High error rateSatisfied with the effectMultiple-port networksFilamentary/web record carriersSignal processing circuitsSignal-to-noise ratio (imaging)

An optical disk read signal processing system for Blu-ray disc systems to ensure stable phase-locked locked operation even with a low signal-to-noise ratio. This system changes a loop configuration of a phase lock loop circuit according to the operating state, and utilizes a FIR equalizer for phase detection. This system attains a low error rate even when the signal-to-noise ratio of an input signal is low, and avoids pulse edges with low phase detection accuracy or signal pulse streams with a high possibility of being mistakenly detected as an edge in conventional methods, and also supports diverse types of input signals.

Owner:HITACHI CONSUMER ELECTRONICS CORP

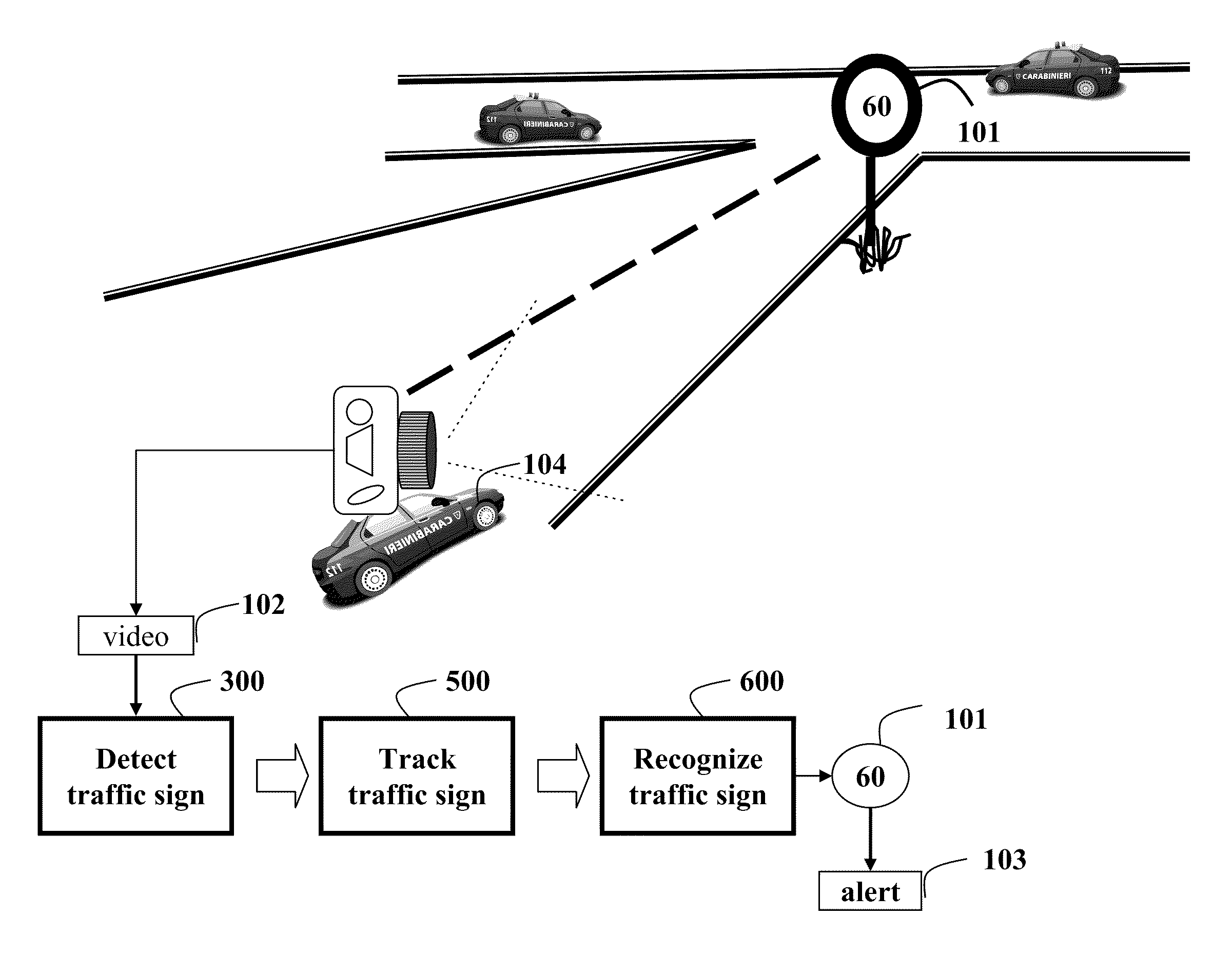

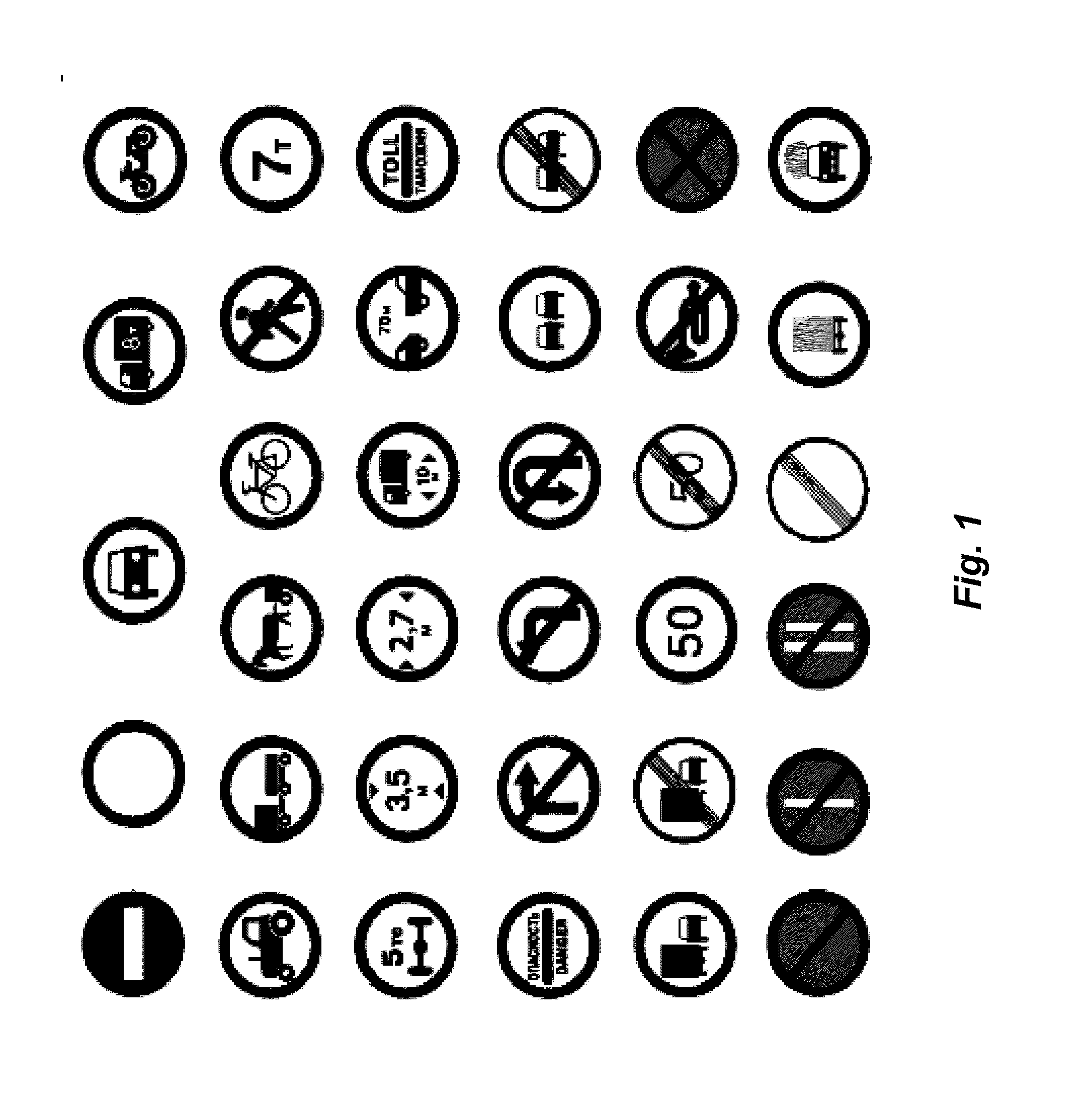

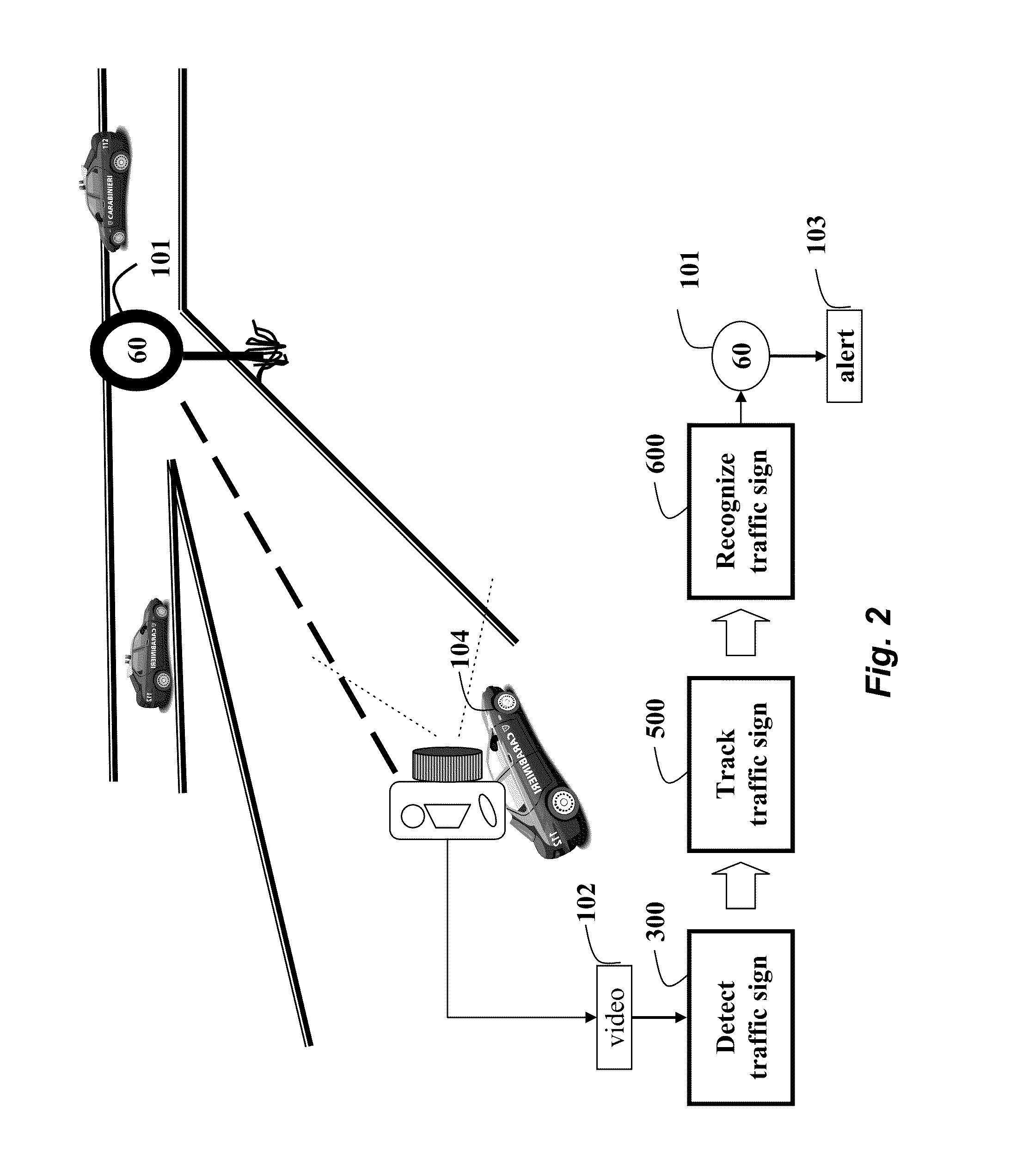

Method for Recognizing Traffic Signs

ActiveUS20110109476A1High error rateReduce error rateArrangements for variable traffic instructionsCharacter and pattern recognitionMobile vehicleTraffic sign

A method recognizes a set of traffic signs in a sequence of images acquired of a vehicle environment by a camera mounted in a moving vehicle by detecting in each image, a region of interest (ROI) using a parameter space transform. The ROI is tracked and classified as a particular one of the signs. The classifier only uses a same class and a different class, and a regression function to update the classifier.

Owner:MITSUBISHI ELECTRIC RES LAB INC

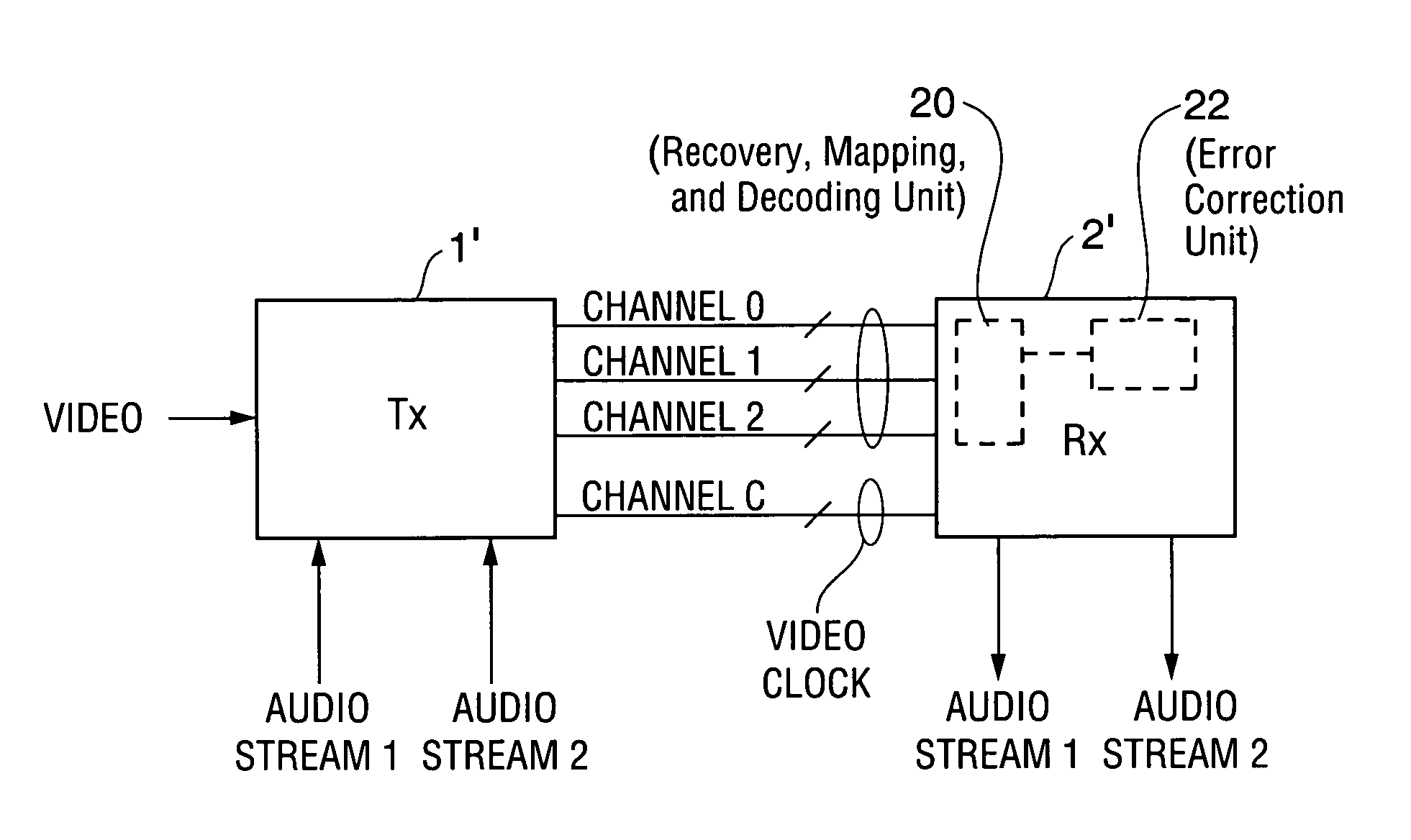

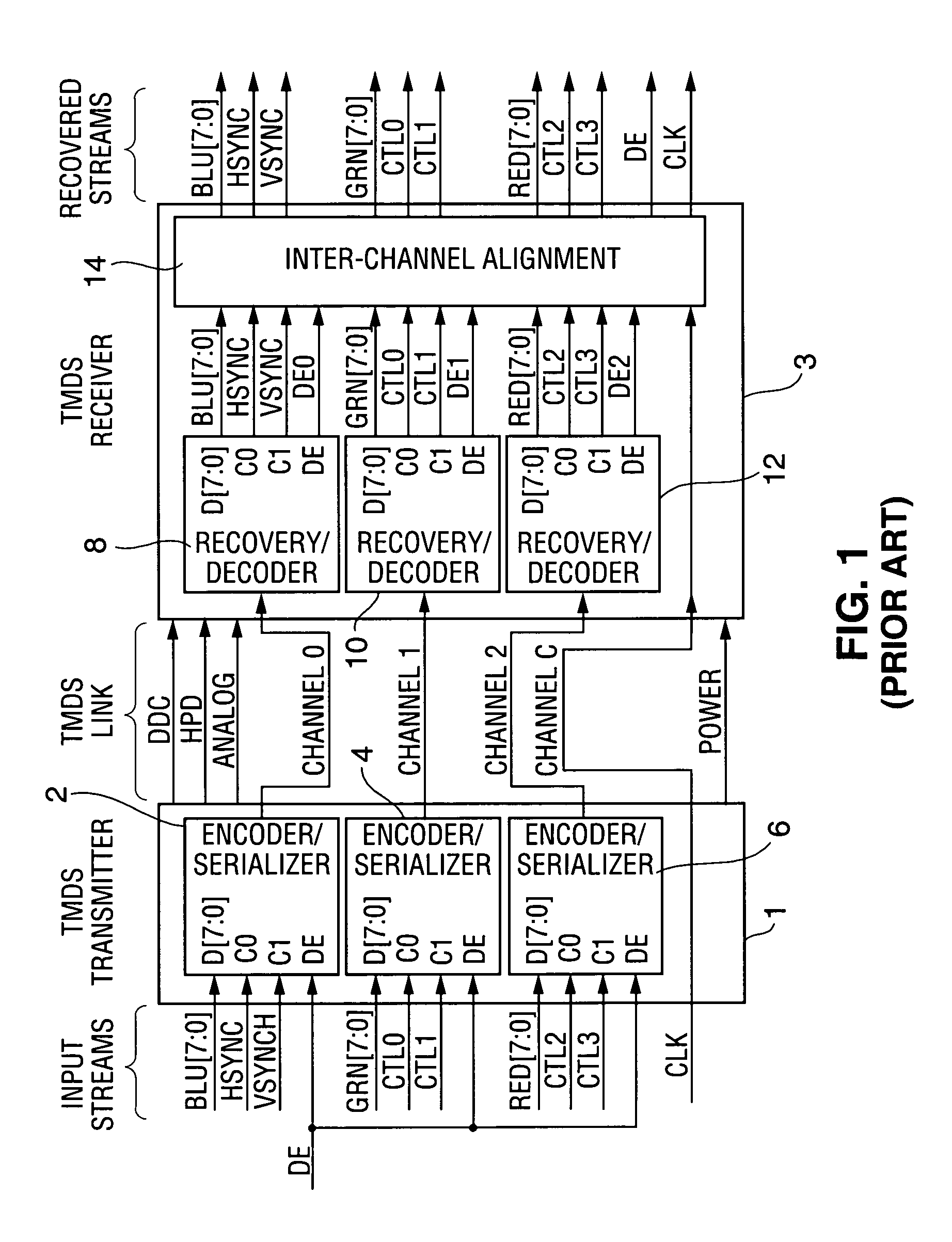

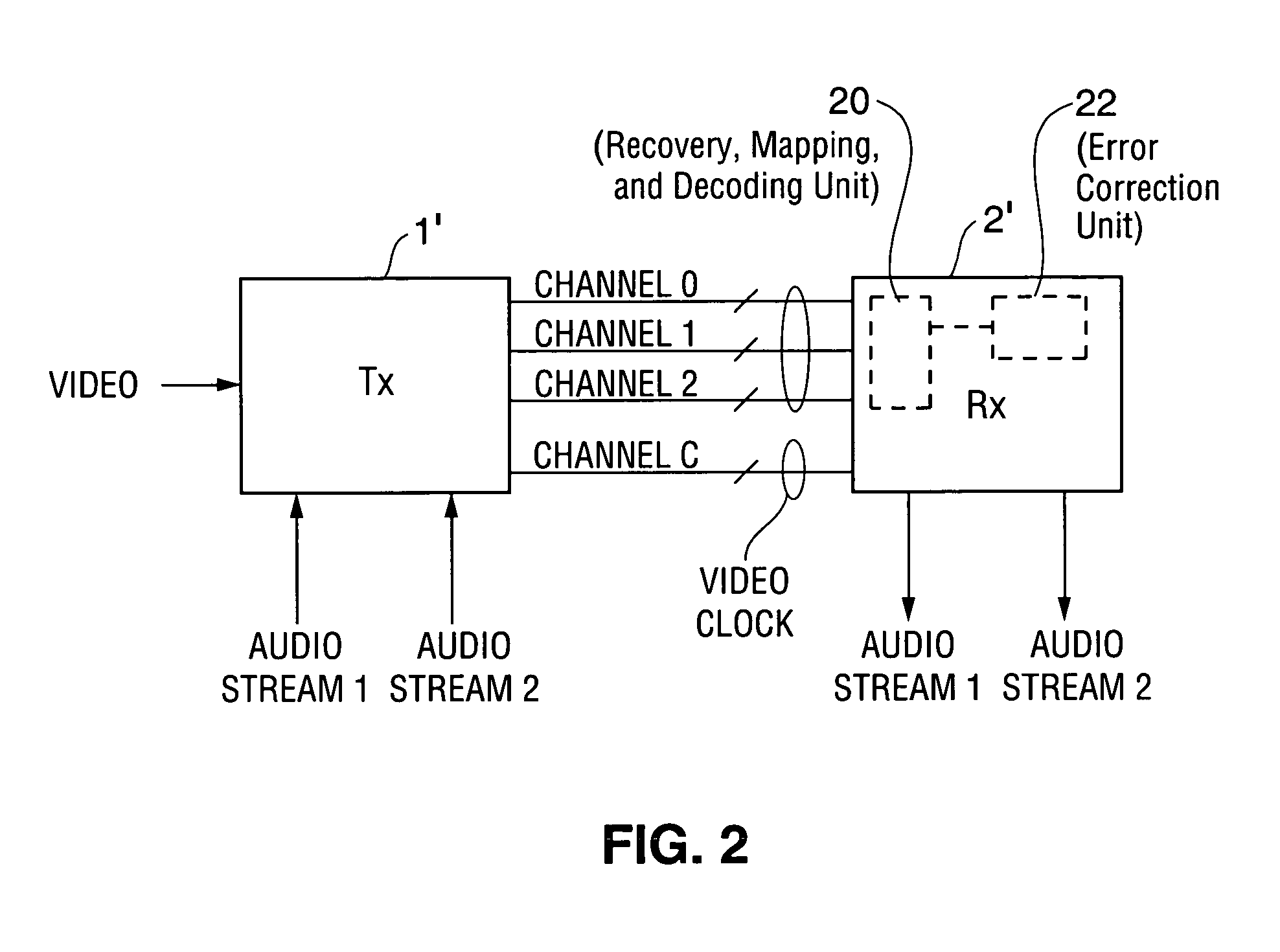

Method and system for reducing inter-symbol interference effects in transmission over a serial link with mapping of each word in a cluster of received words to a single transmitted word

InactiveUS7257163B2Reduce bit error rateIncreased source data transmission rateError detection/prevention using signal quality detectorPicture reproducers using cathode ray tubesSymbol of a differential operatorComputer science

A system in which encoded data (e.g., encoded video and auxiliary data) are transmitted over a serial link. Other aspects of the invention are transmitters for use in encoding data for transmission over a serial link, receivers for receiving such data, and methods for sending encoded data over a serial link. Source data to be transmitted are encoded using a subset of a full set of code words. The subset consists of preferred code words. Disjoint clusters of code words in the full set are predetermined. Each cluster includes one or more of the preferred words, and optionally also at least one additional code word that is similar to a preferred word of the cluster in the sense that it is likely to be generated as a result of probable bit errors in transmission, or transmission and decoding, of such preferred word. Each preferred word of a cluster is indicative of a single source data value. Each received code word in a cluster is mapped to the source data value determined by each preferred word of the cluster.

Owner:KONINKLJIJKE PHILIPS NV

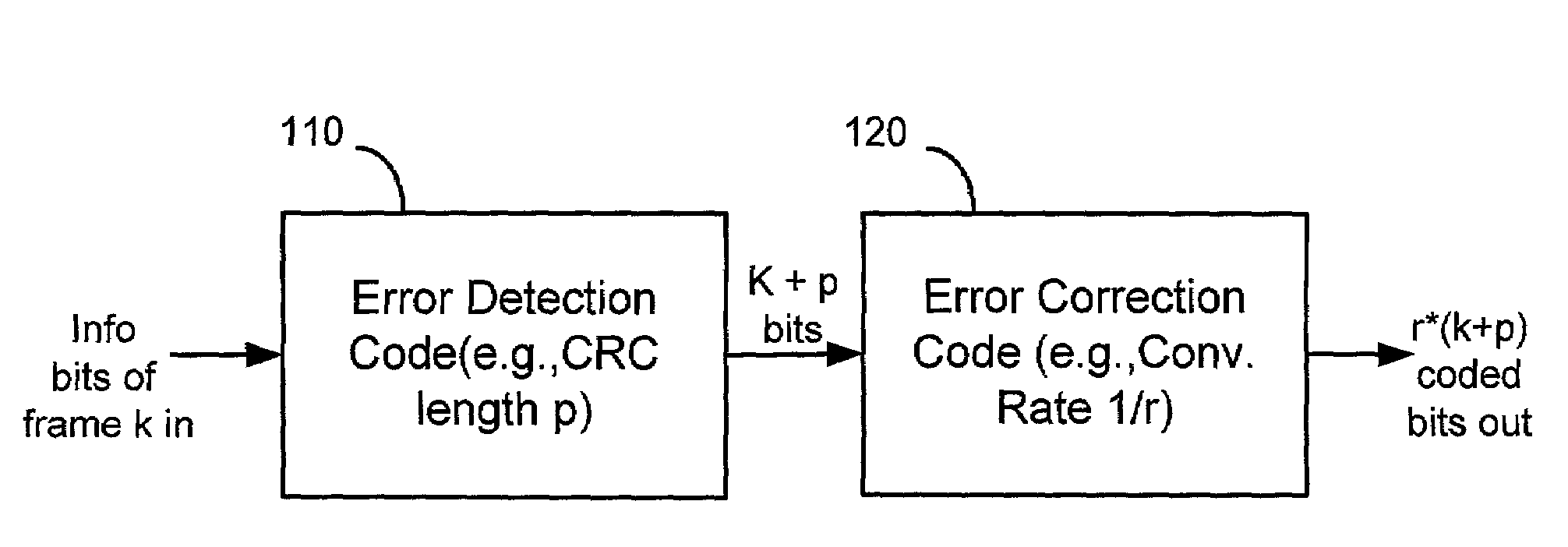

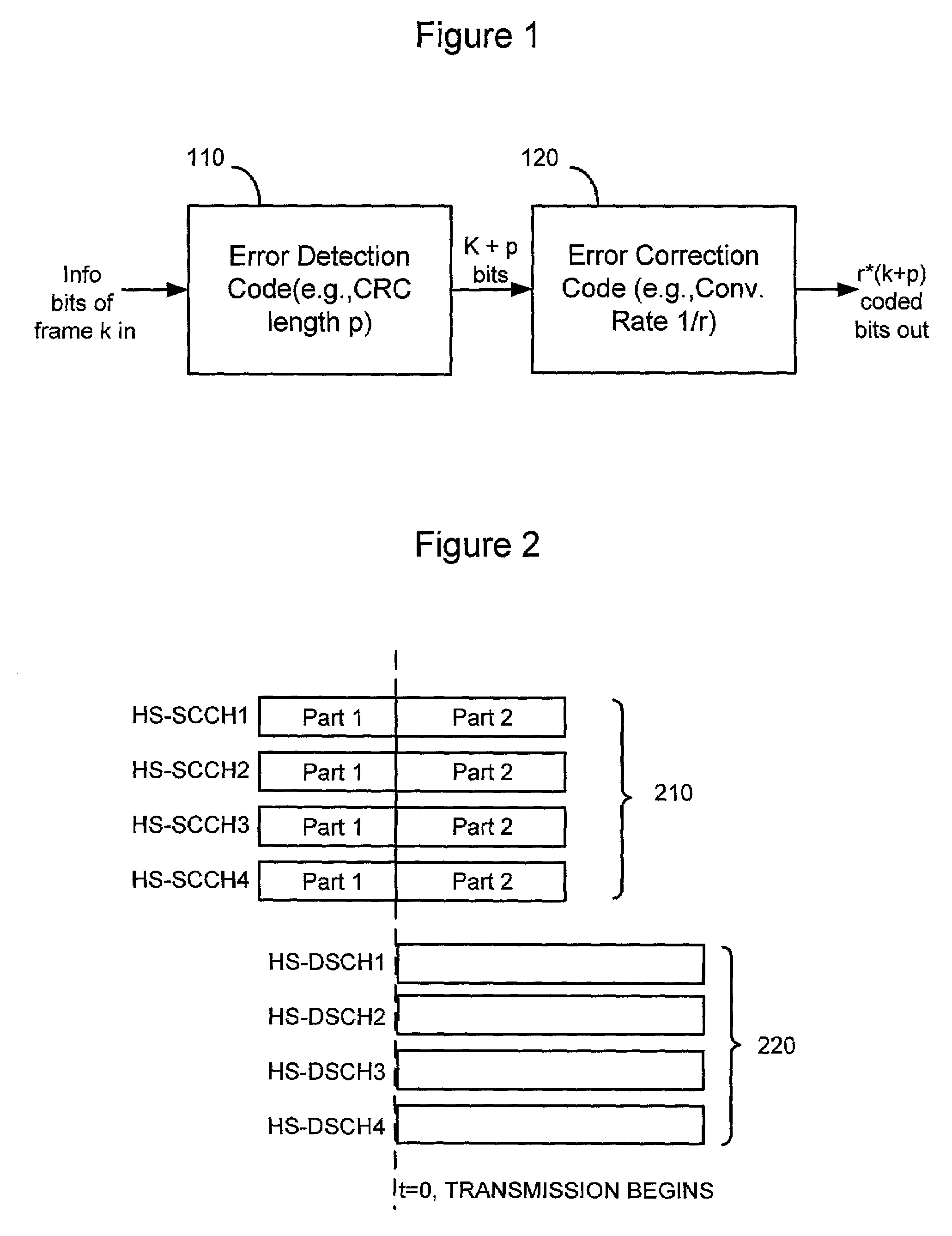

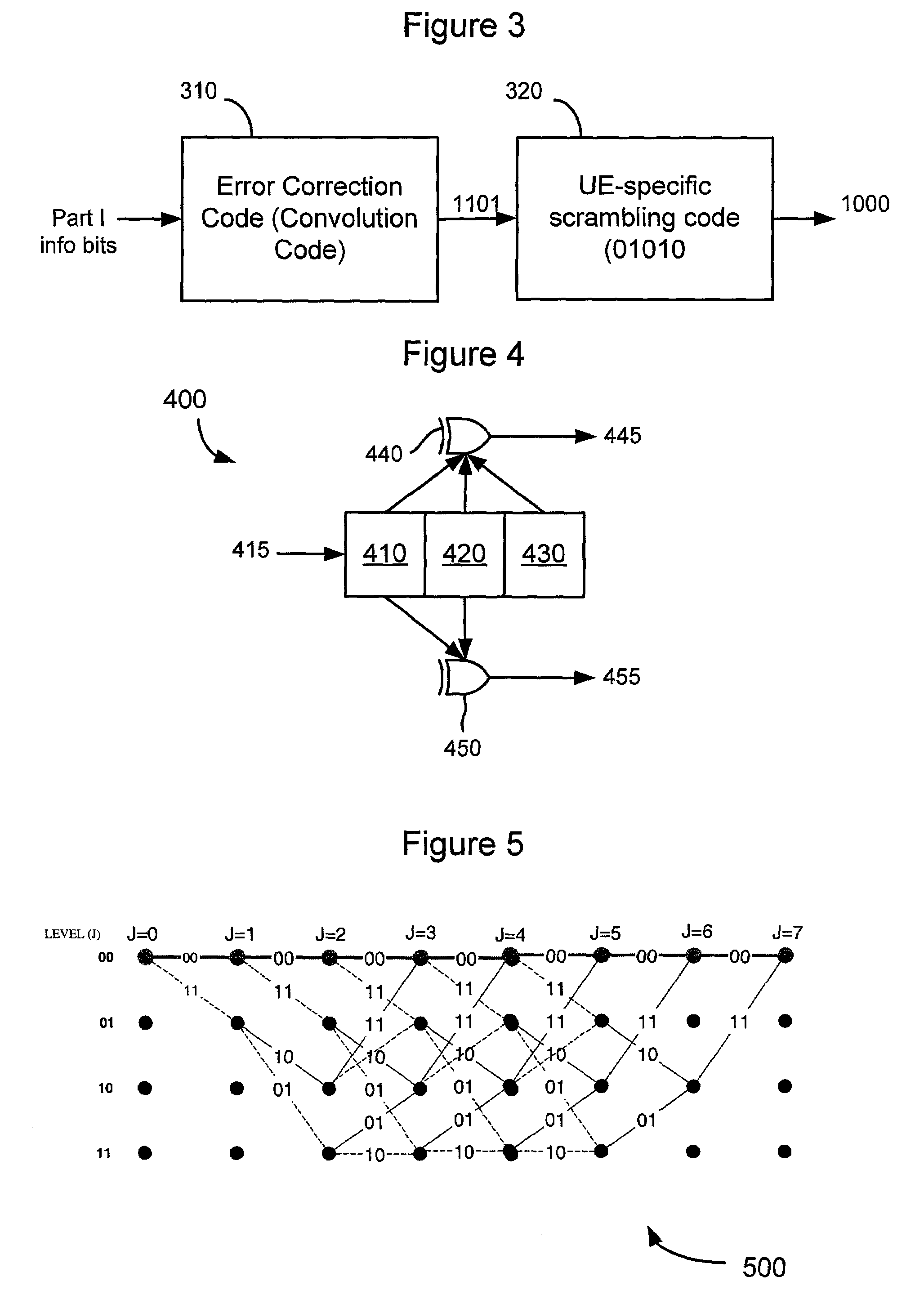

Error detection methods in wireless communication systems

InactiveUS7162675B2Efficient and reliableHigh error rateError prevention/detection by using return channelOther decoding techniquesCommunications systemControl channel

The error detection method includes decoding a portion of each control channel that is simultaneously received by a user equipment (UE) in a wireless communication system. The UE is provided with techniques to determine if one or more of the control channels were successfully received during the decoding step. If more than one control channel was successfully received, the method selects only one of the successfully received control channels based on calculated path metric differences (PMD) that serve as a “tie-breaking” mechanism to select the correct control channel for a particular UE.

Owner:LUCENT TECH INC +1

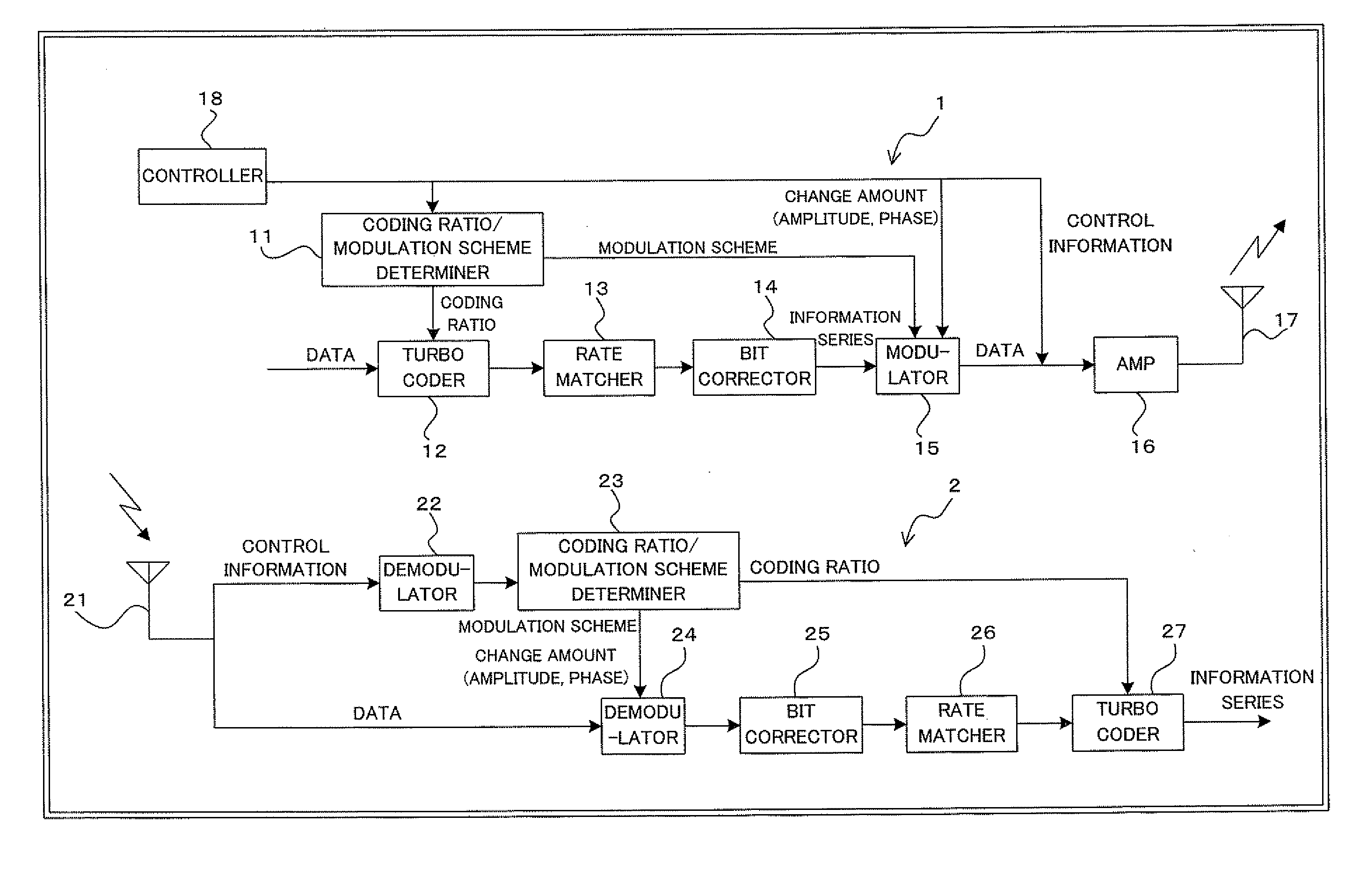

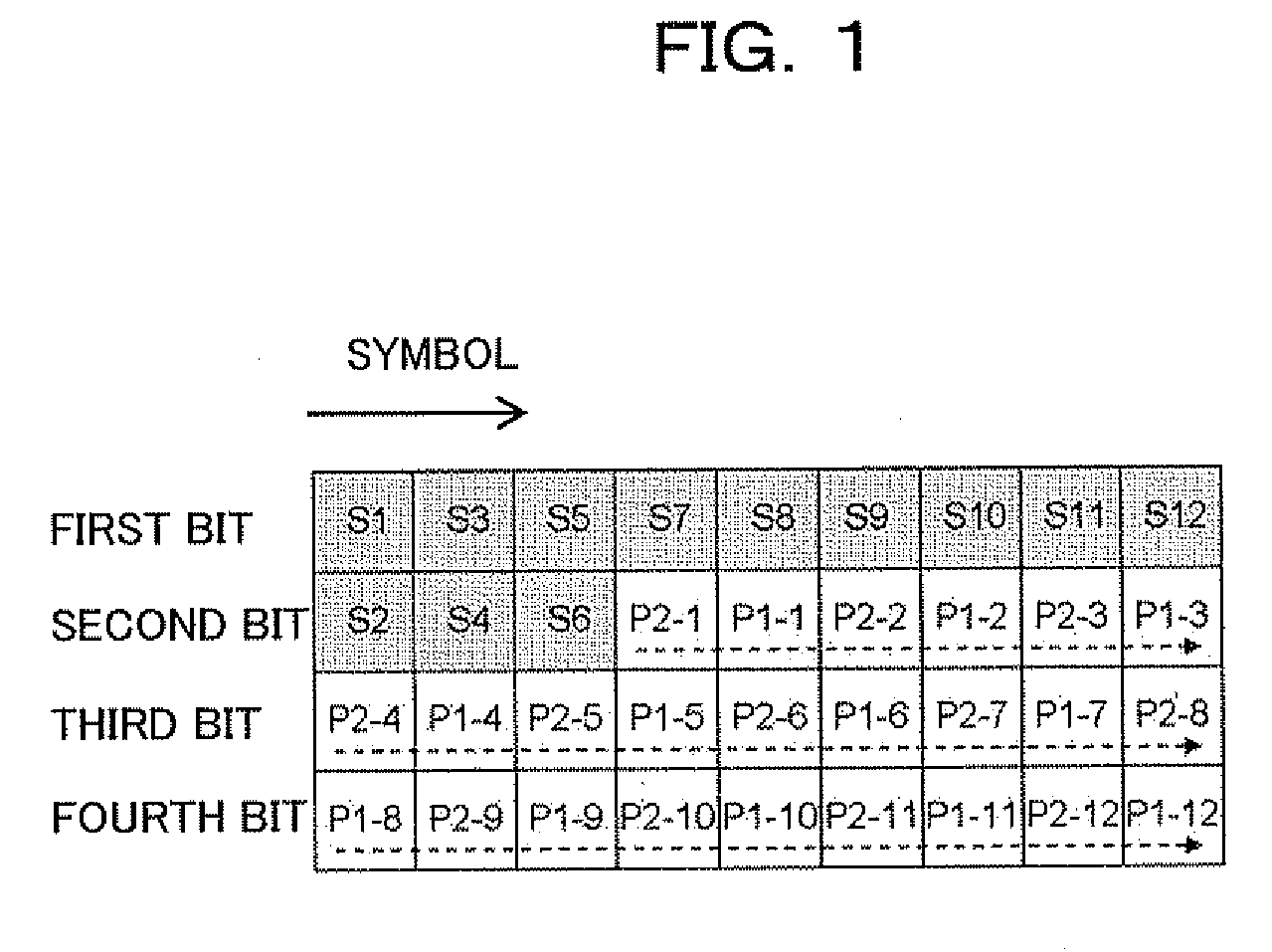

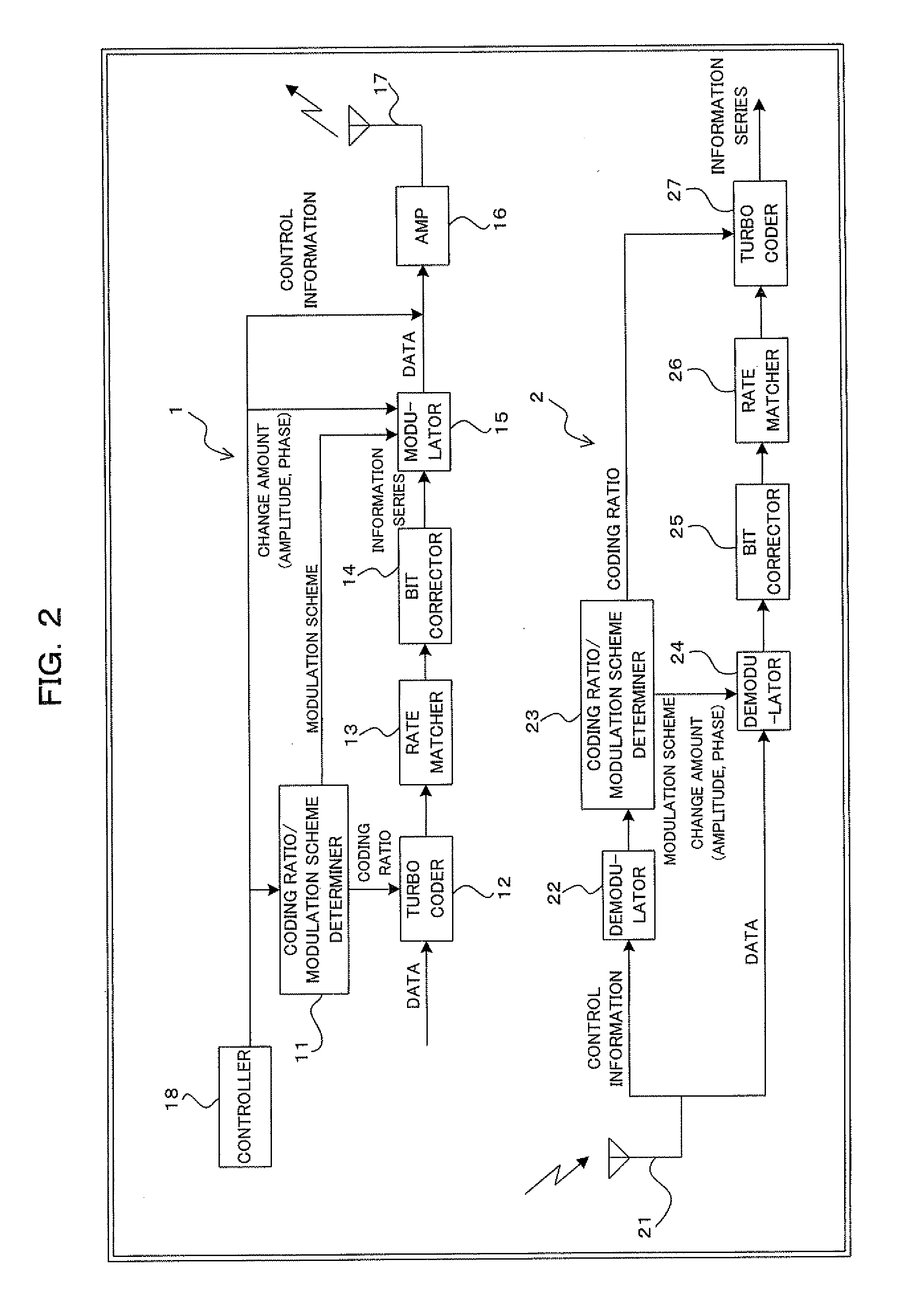

Digital radio communications method using multi-level modulation scheme and transmitter and receiver

InactiveUS20090161786A1Sufficient effectHigh error rateError correction/detection using trellis codingCode conversionComputer hardwareCommunications system

A transmitter for use in digital radio communications systems includes: a bit corrector controls bit arrangement in such a manner that a code having high significance, out of multiple codes obtained by coding, is allocated with high priority to a bit having a tendency that the likelihood enlarges at the time of symbol decision on a receiver; a multi-level modulator allocates the code to the multiple bits in accordance with a predetermined symbol arrangement; and a symbol arrangement controller controls the symbol arrangement from equal distance arrangement to another arrangement in accordance with a ratio of the codes different in significance. To control symbol arrangement increases the effect of bit correction and improves an error rate on the receiver.

Owner:FUJITSU LTD

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com