Memory system and memory card

a memory system and memory card technology, applied in the field of memory system and memory card, can solve the problems of increasing the size and the relative long processing time required, etc., and achieve the reduction of the number of nonvolatile memory chips required to construct the memory card, the reduction of the effect of reducing the cost of the memory card

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

Memory System

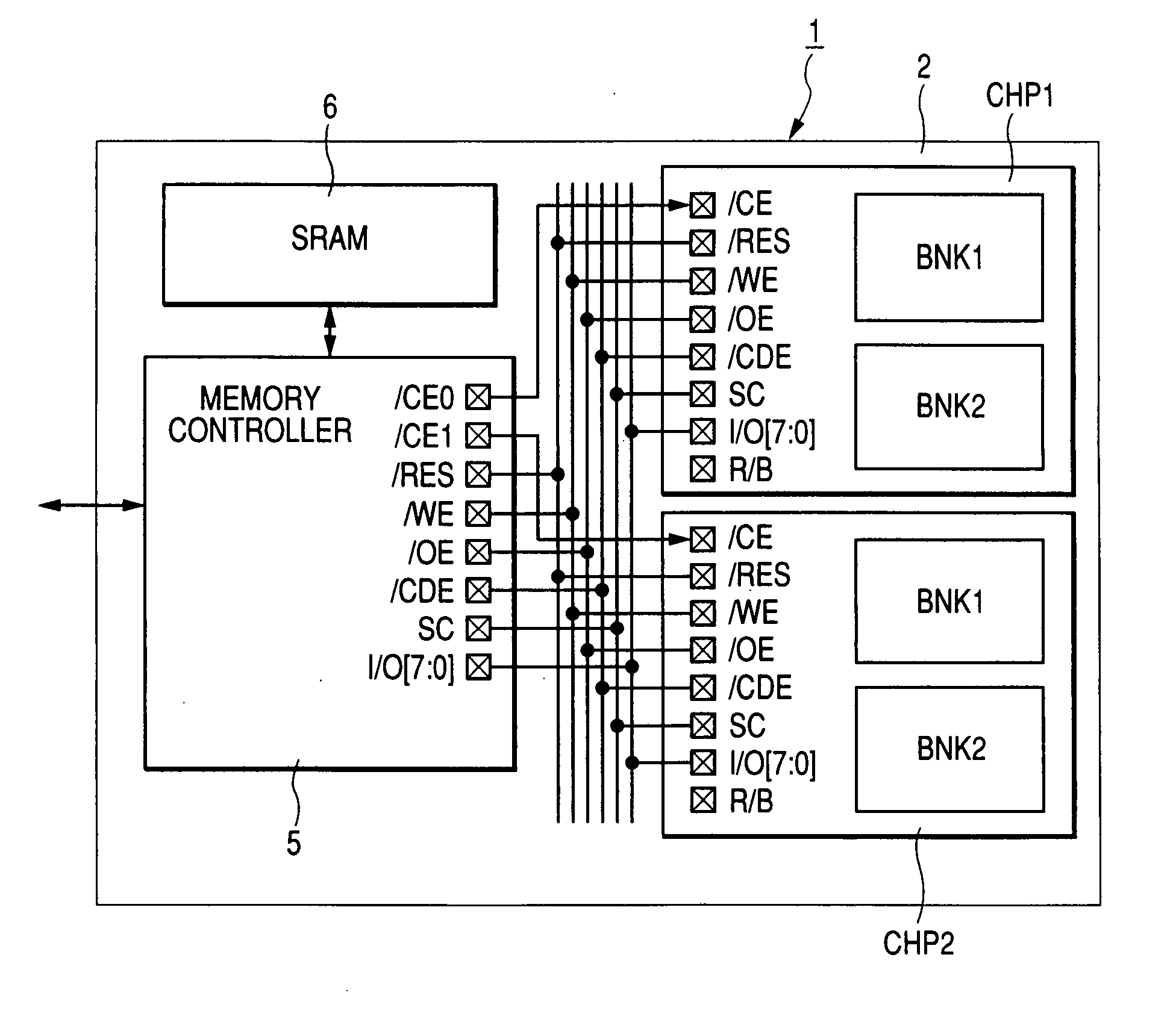

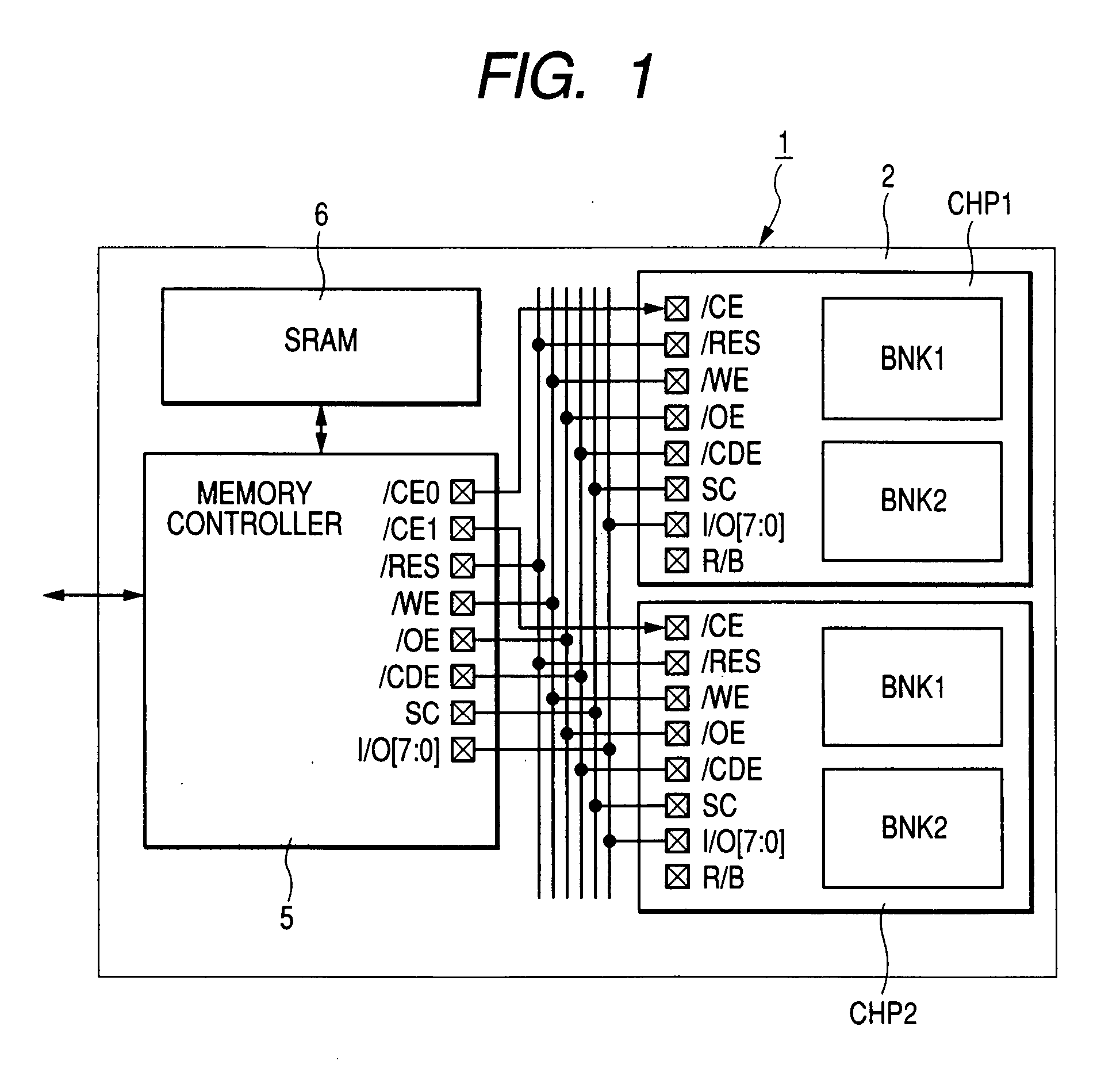

[0061]FIG. 1 shows a memory card as an example of a memory system according to the invention. A memory card 1 shown in the diagram has, on a card board 2, plural nonvolatile memory chips, for example, two flash memory chips CHP1 and CHP2 each having plural, for example, two memory banks BNK1 and BNK2 which can operate independently of each other, a memory controller 5 which can control an access to each of the flash memory chips CHP1 and CHP2, and an SRAM 6 connected to the memory controller 5. The SRAM 6 can be used as a data buffer for temporarily storing write data onto the flash memory chips CHP1 and CHP2. The memory controller 5 can selectively instruct the simultaneous writing operation or interleave writing operation on the memory banks BNK1 and BNK2 of the flash memory chips CHP1 and CHP2.

[0062] The details of the flash memory chips CHP1 and CHP2 will be described later. The functions for responding to the instruction of the simultaneous writing operation or ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com