Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

84results about How to "Suppression of floating body effect" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

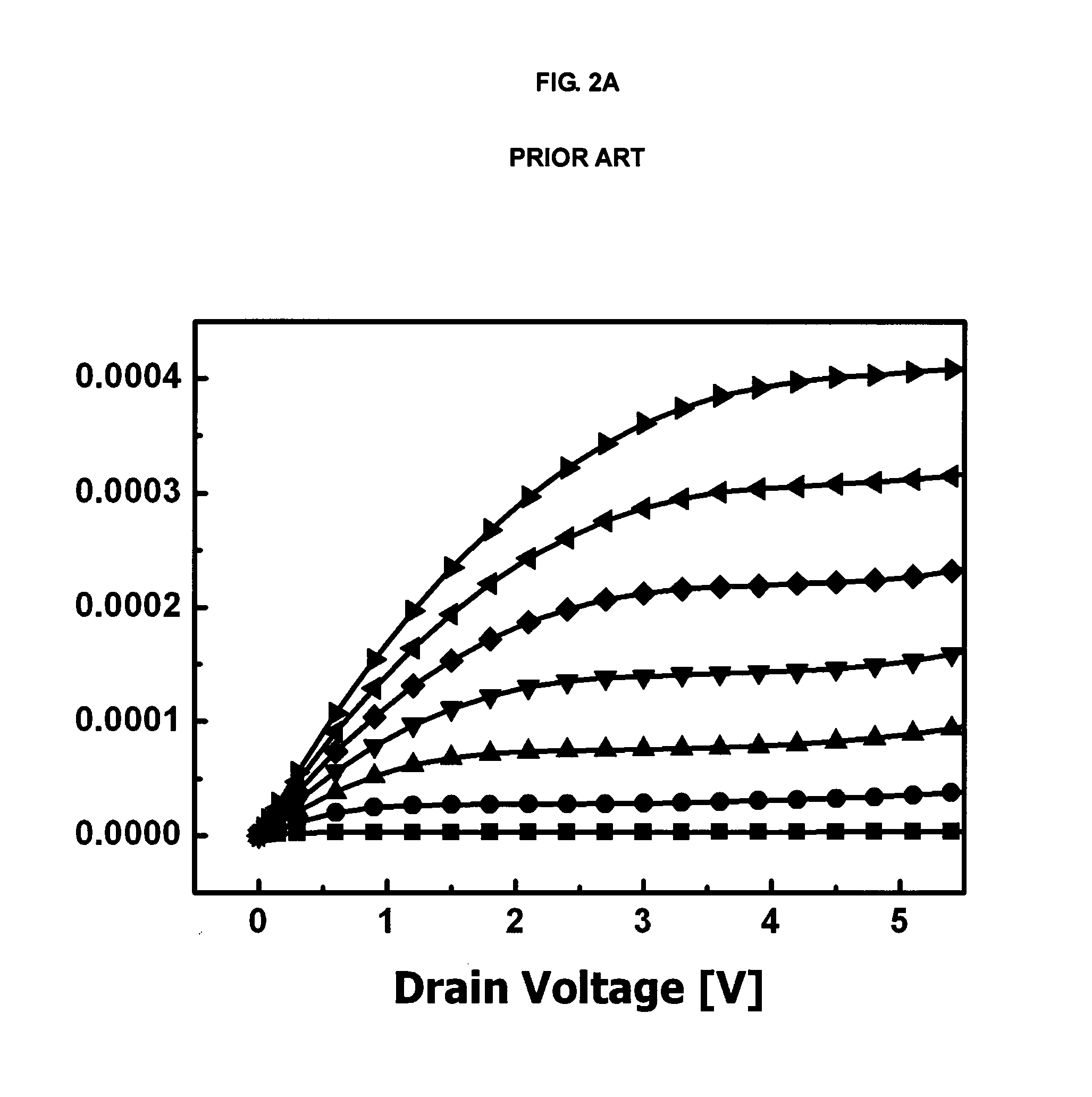

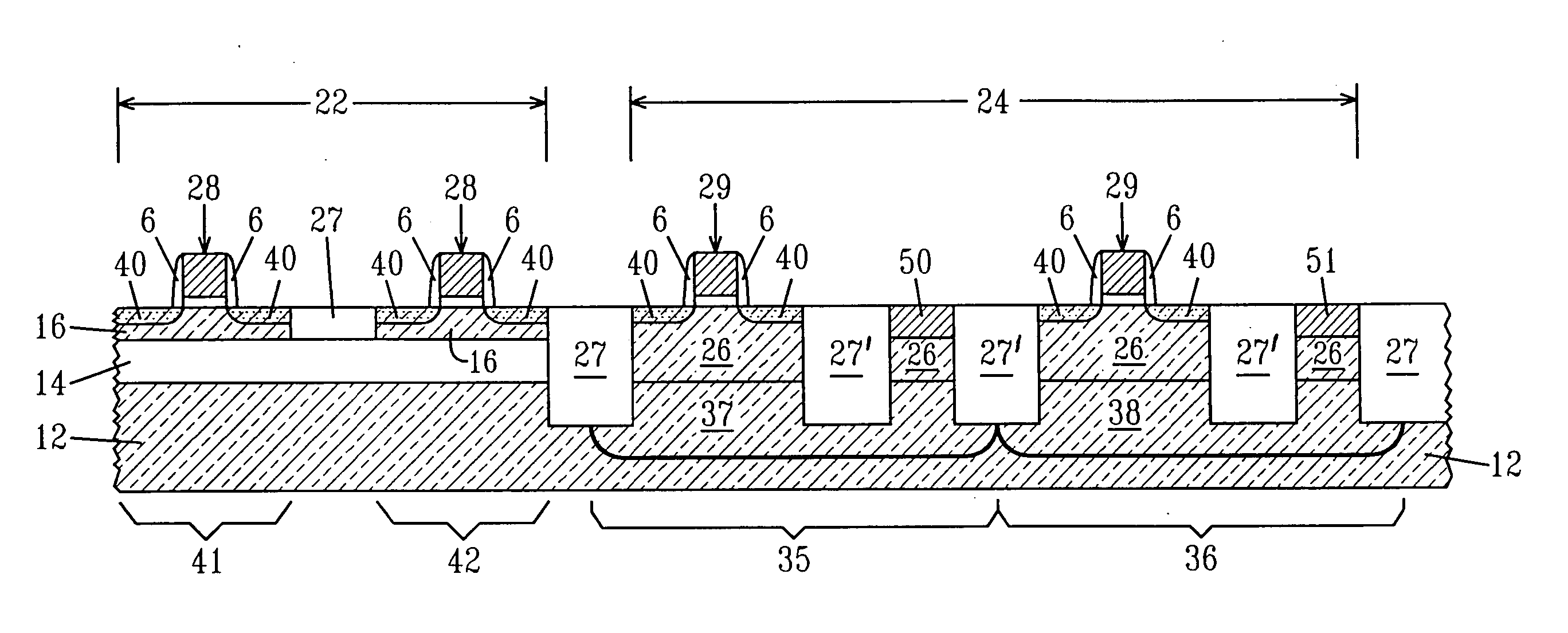

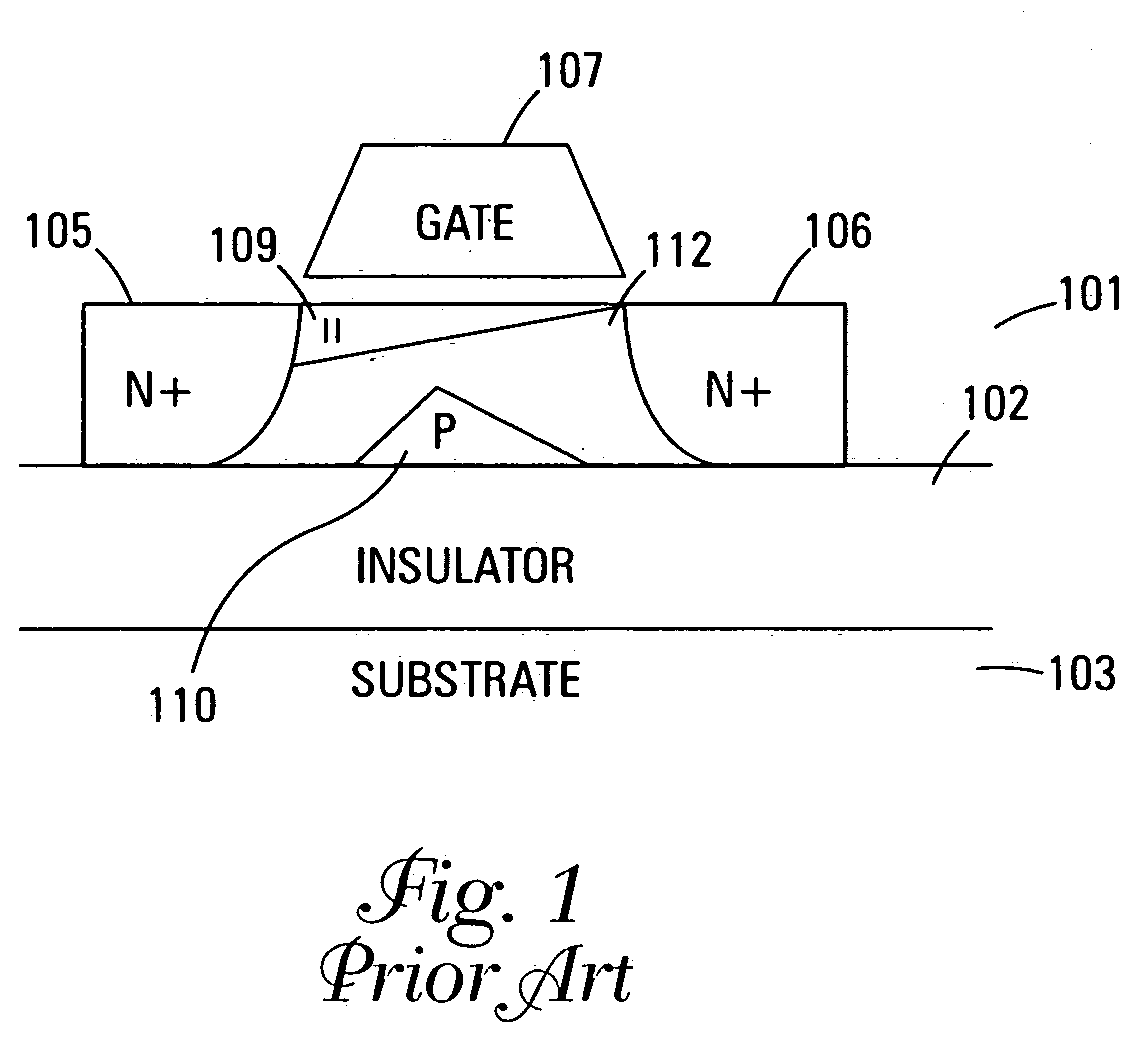

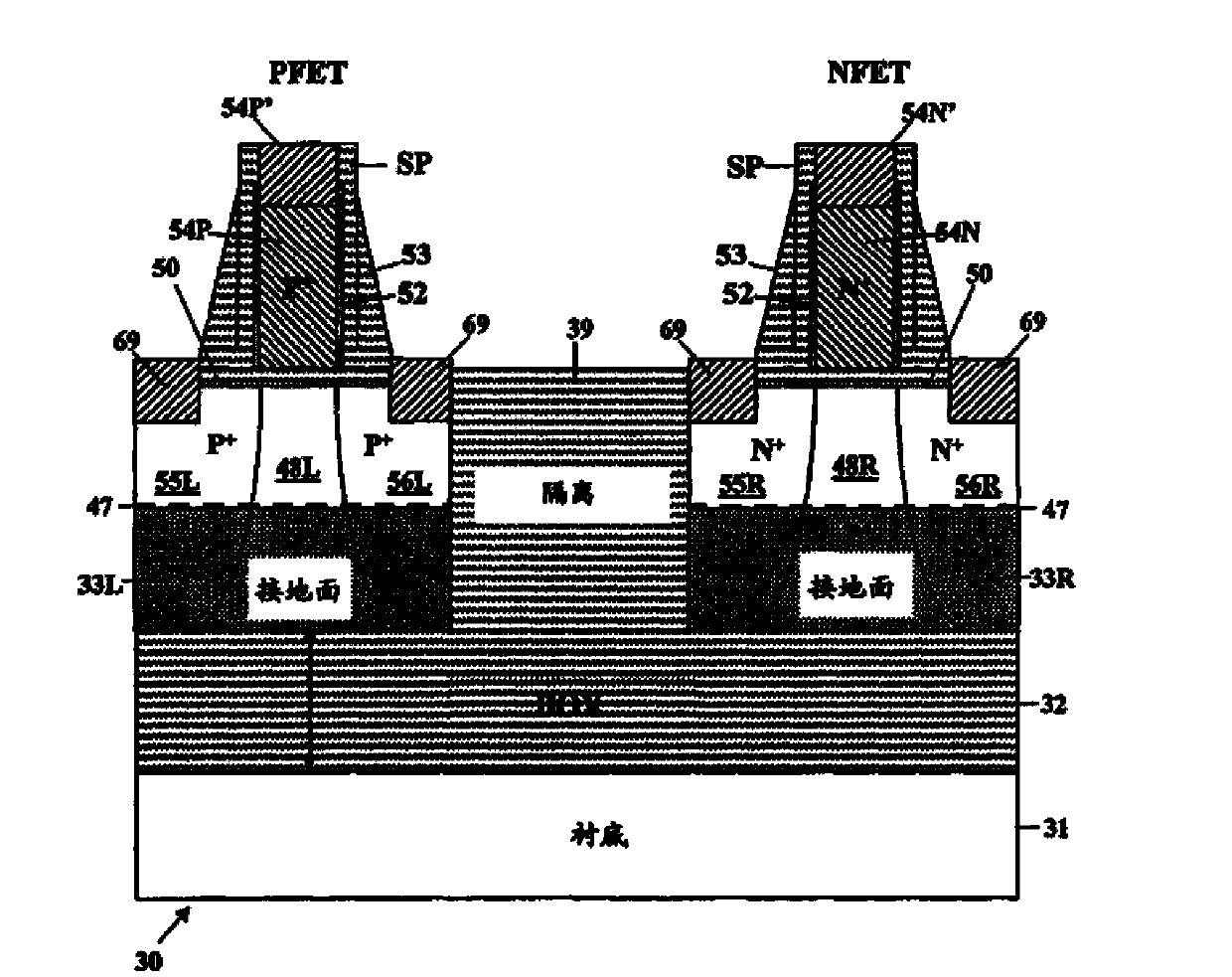

Semiconductor-on-insulator chip incorporating strained-channel partially-depleted, fully-depleted, and multiple-gate transistors

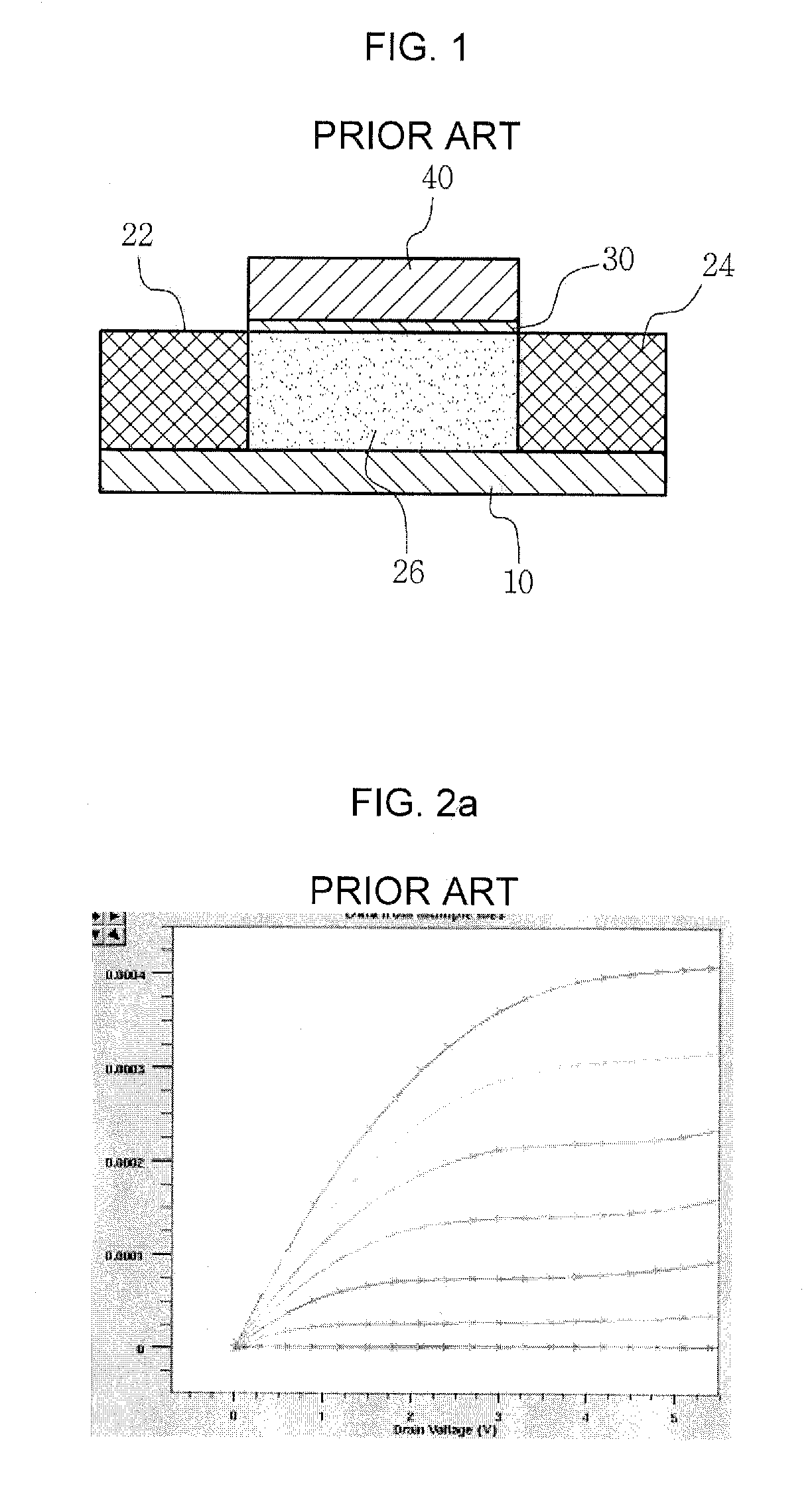

InactiveUS6867433B2Good effectSuppression of floating body effectTransistorSolid-state devicesMOSFETSemiconductor chip

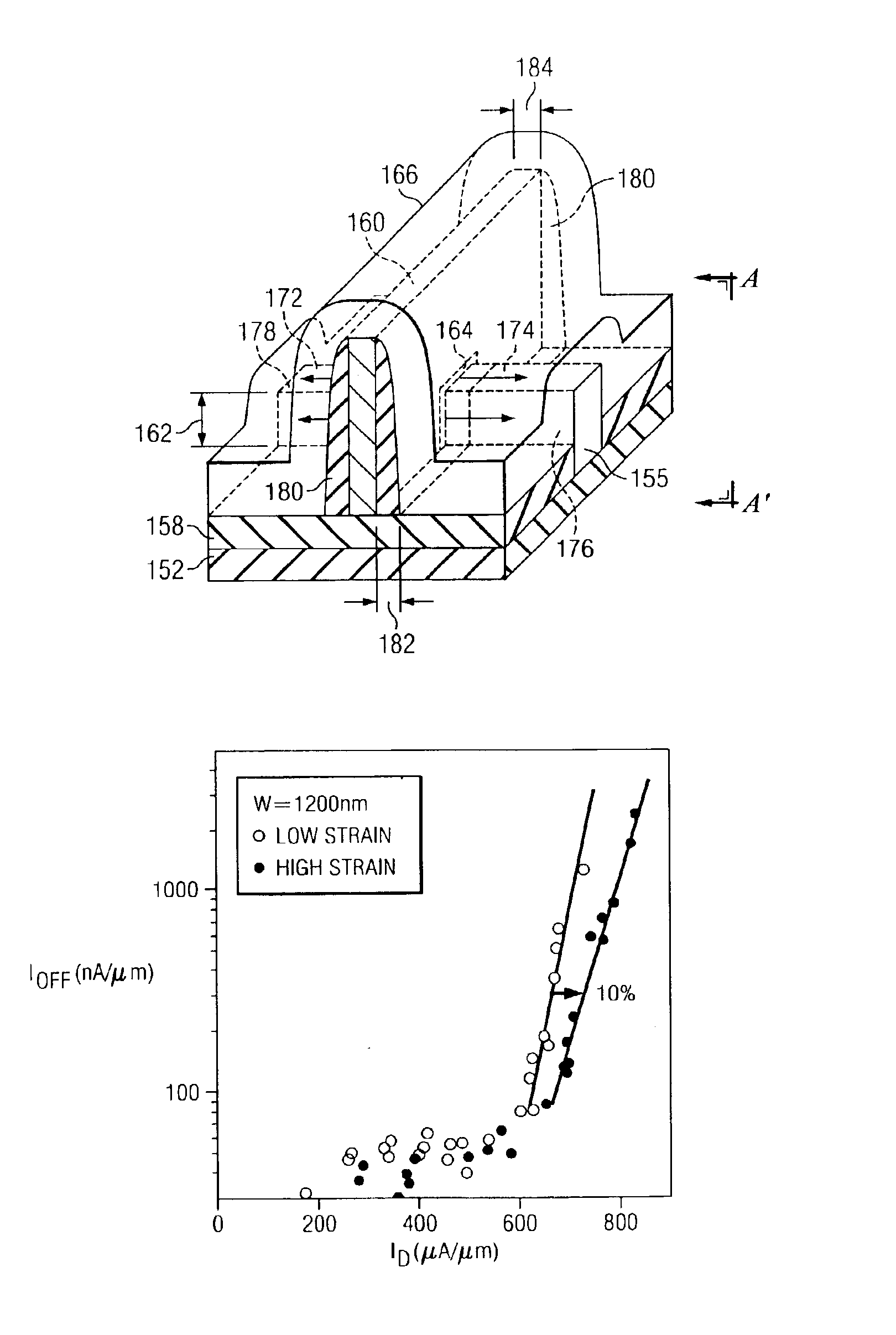

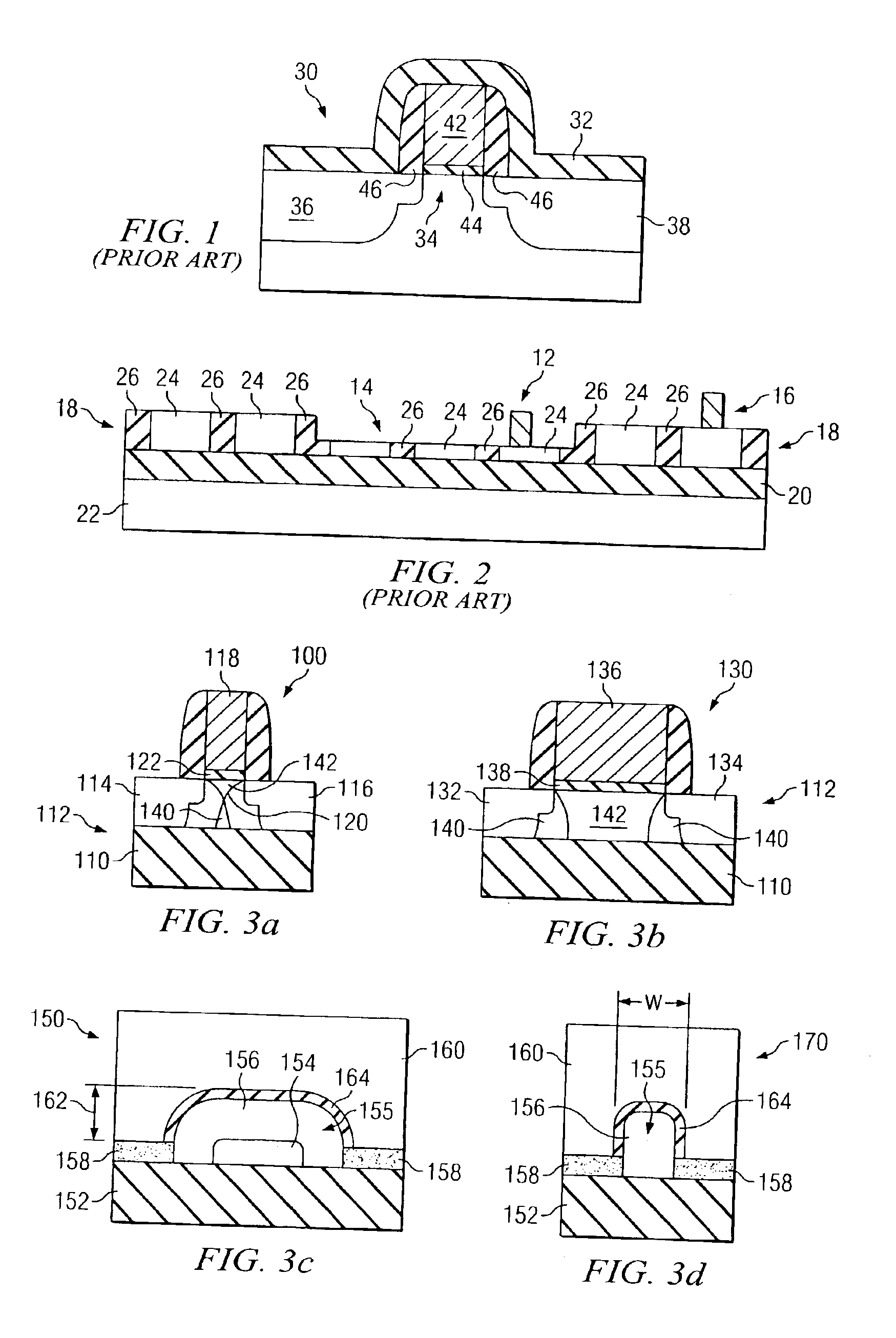

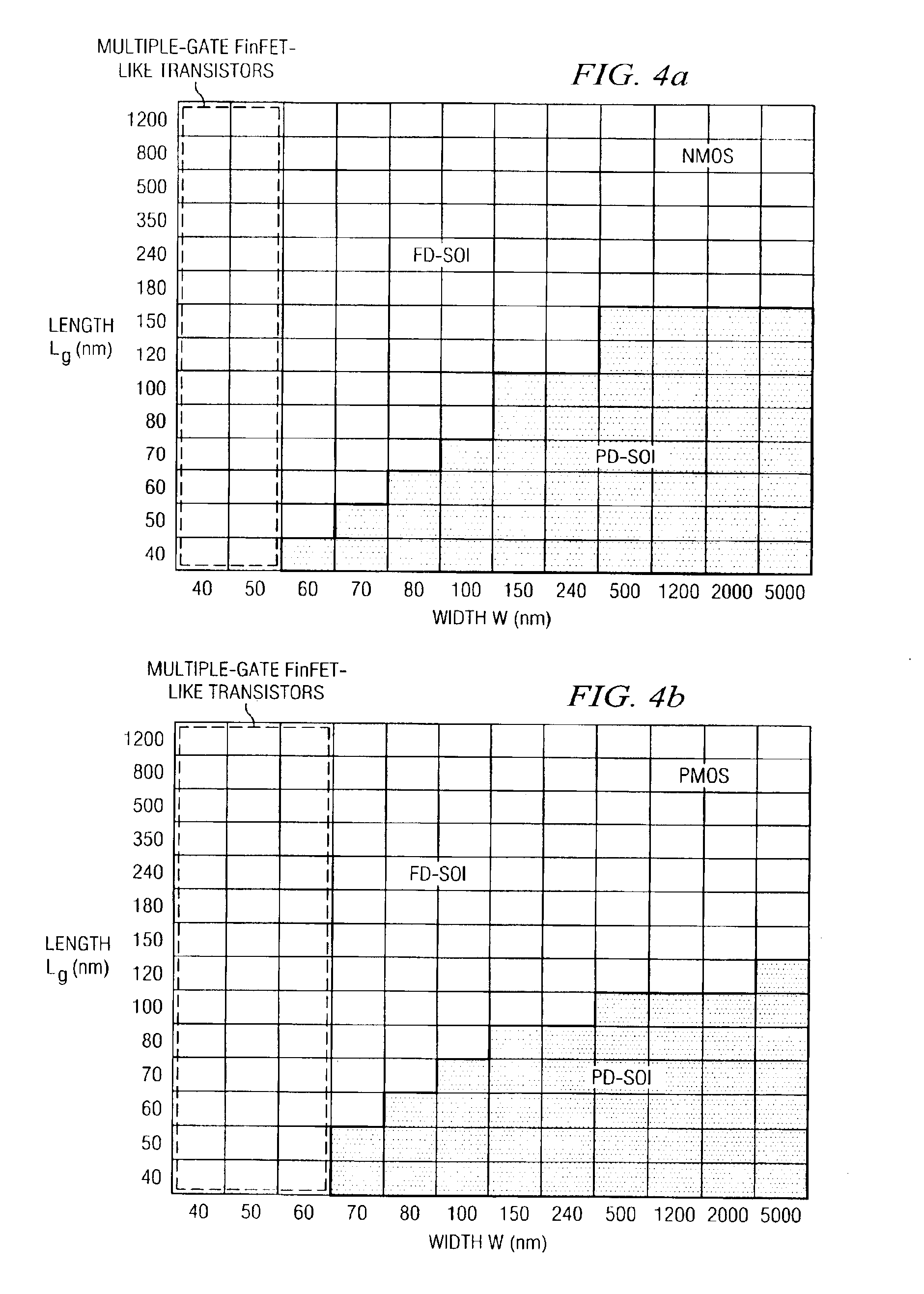

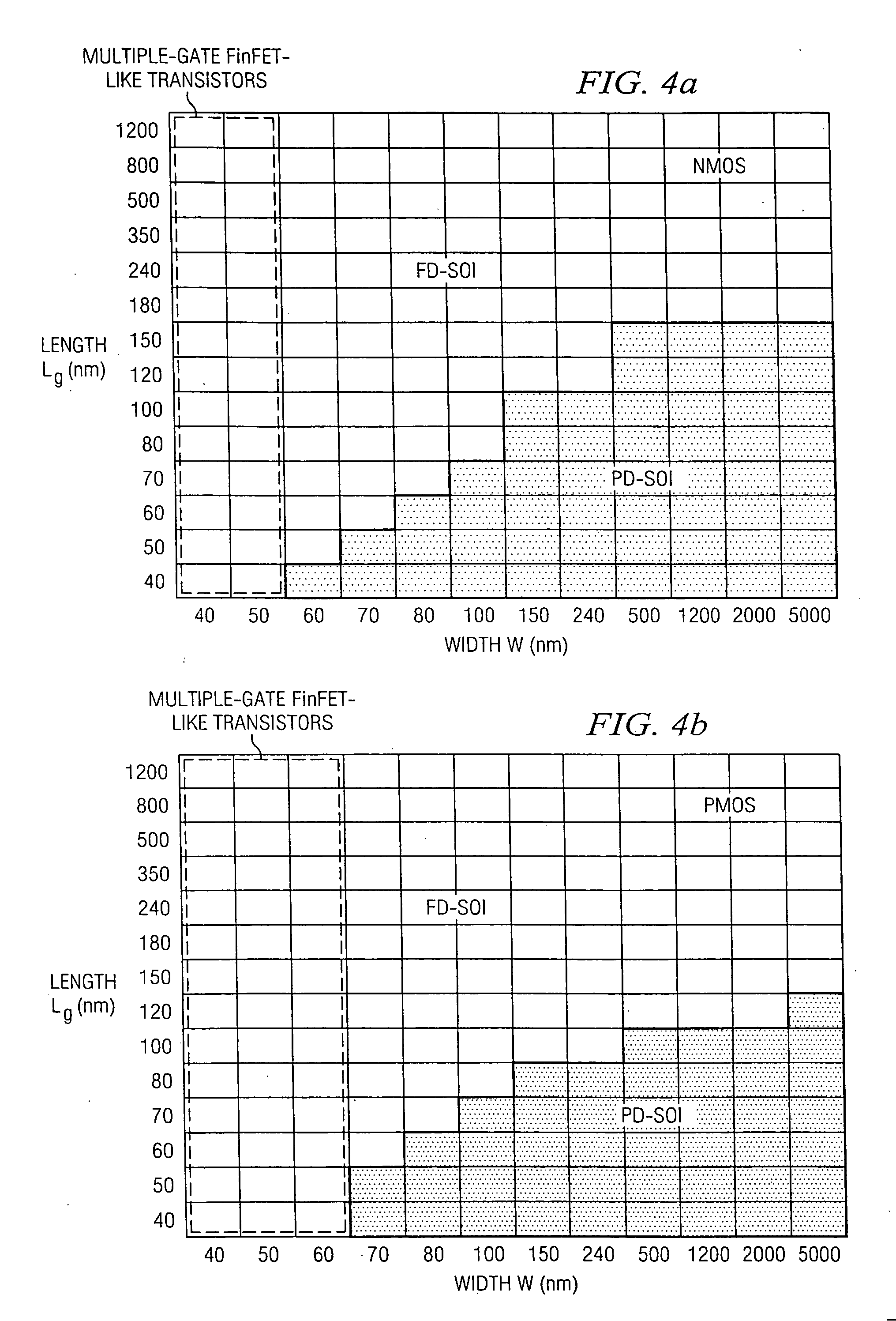

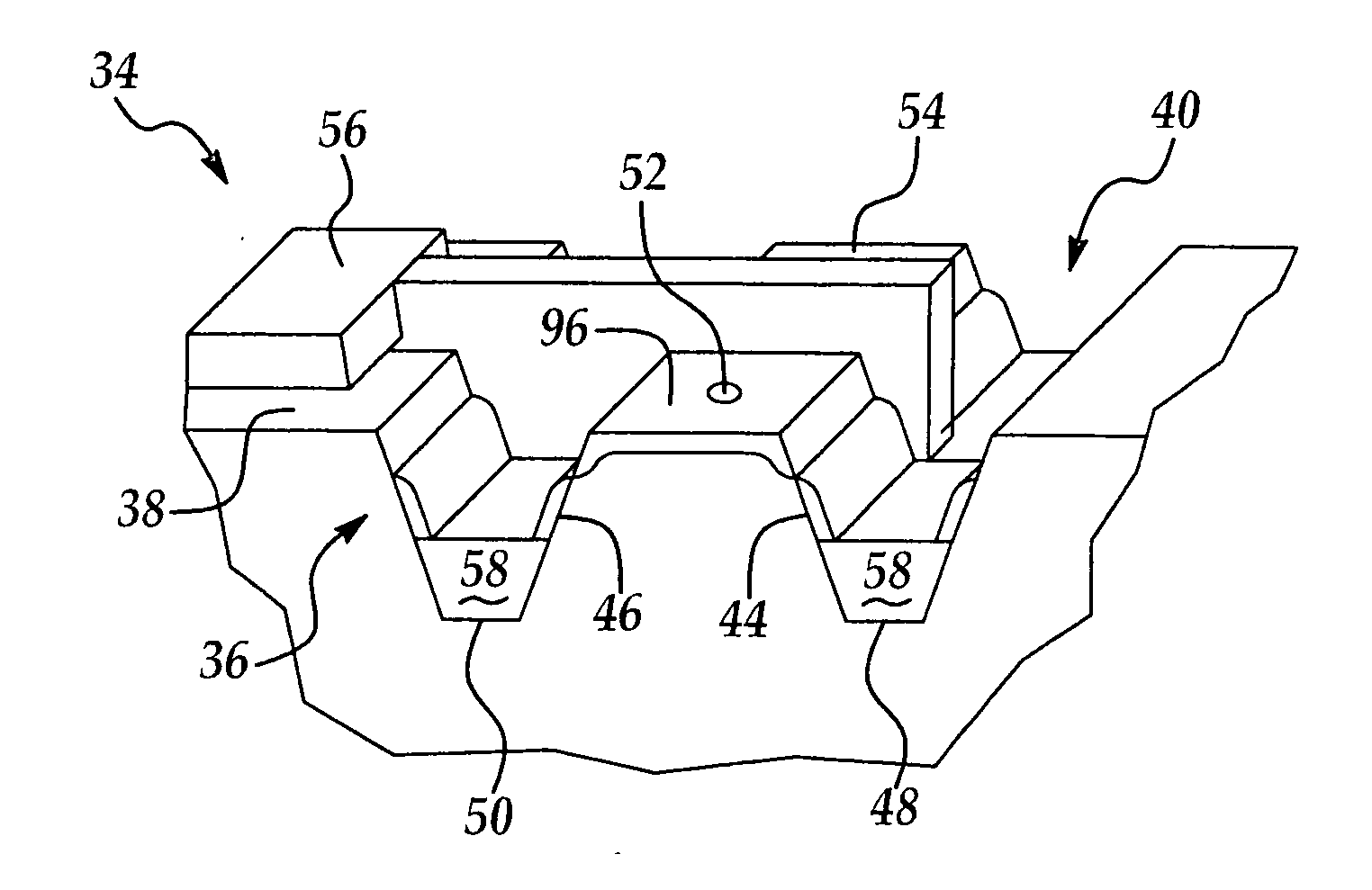

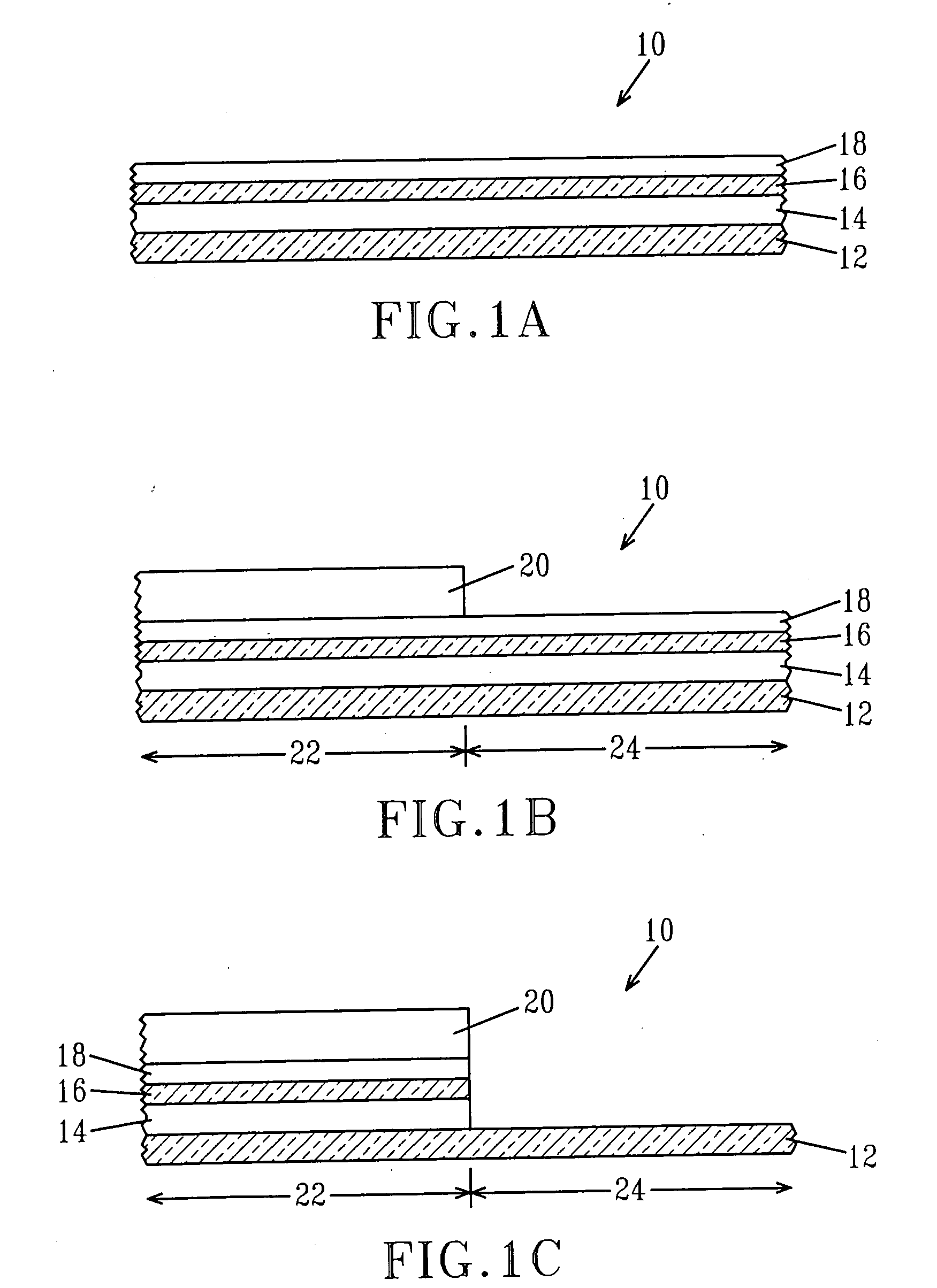

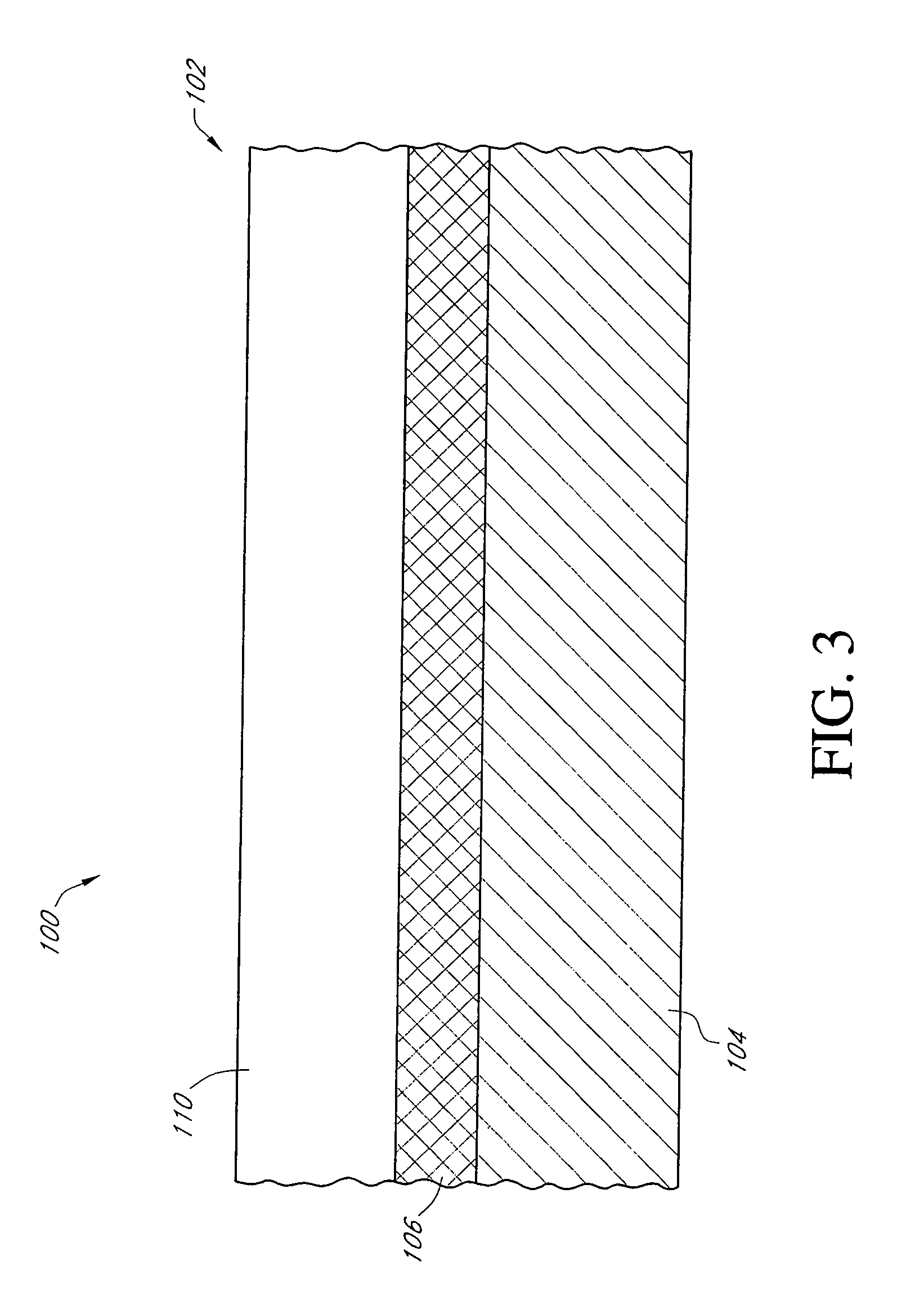

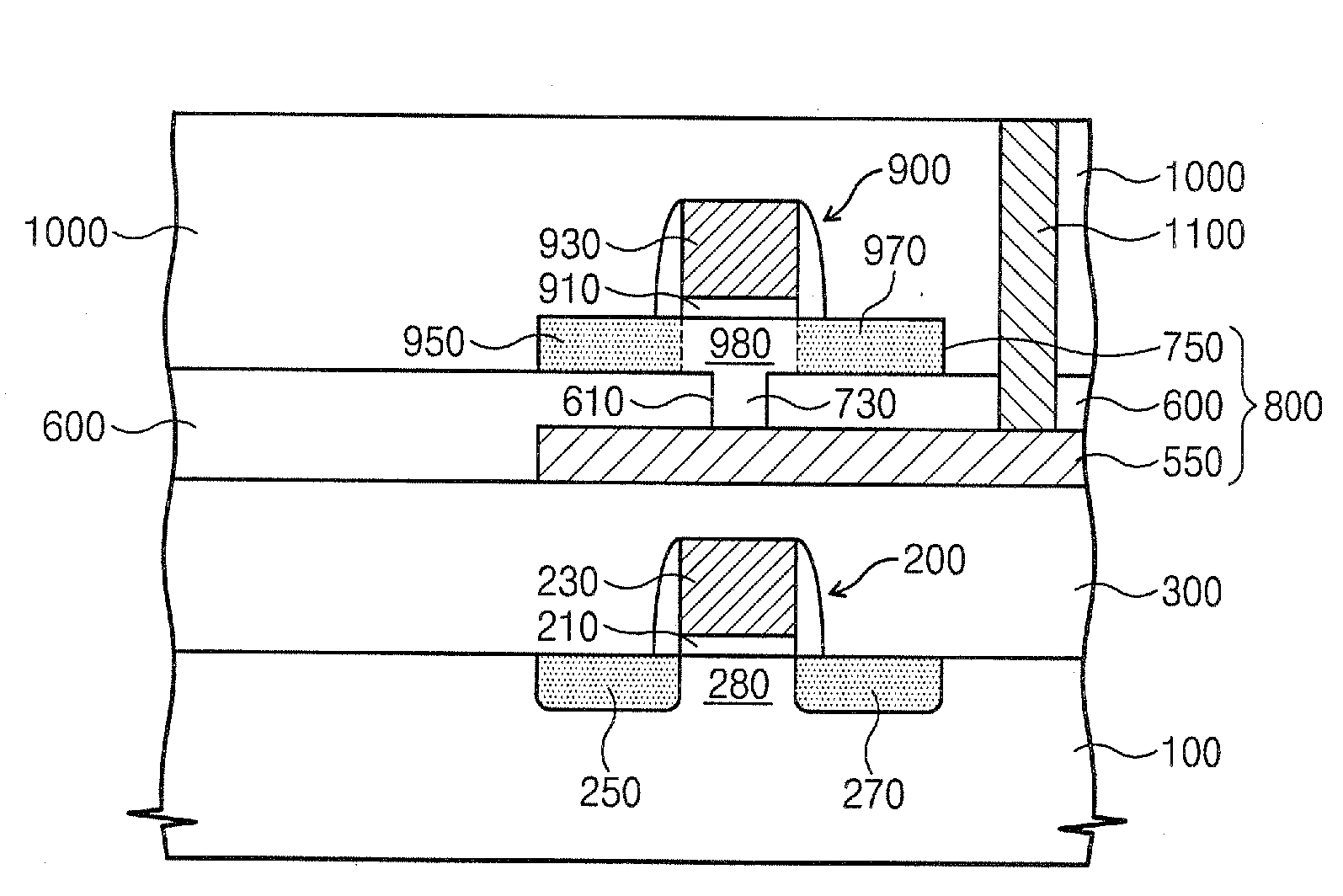

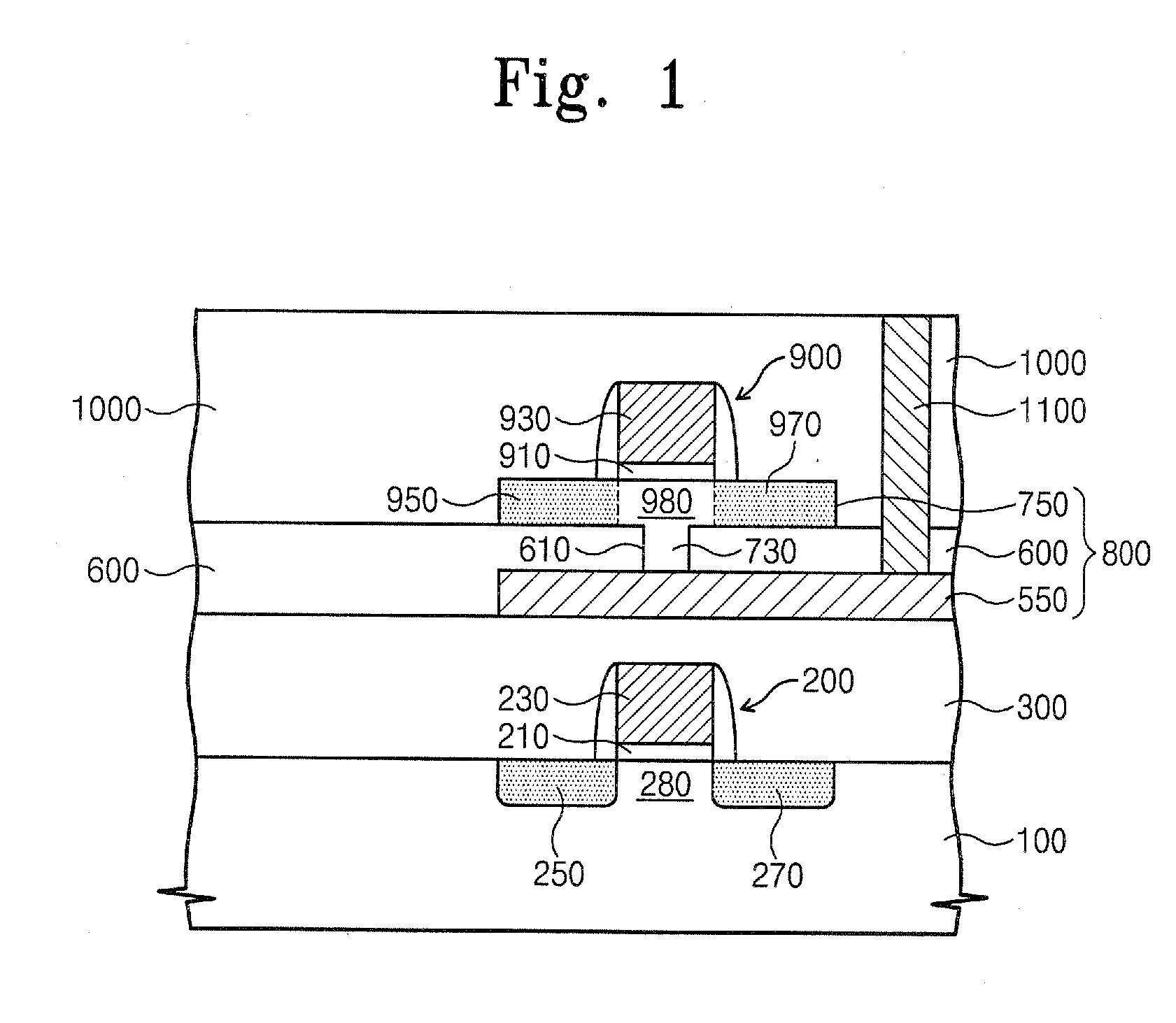

In accordance with a preferred embodiment of the present invention, a silicon-on-insulator (SOI) chip includes a silicon layer of a predetermined thickness overlying an insulator layer. A multiple-gate fully-depleted SOI MOSFET including a strained channel region is formed on a first portion of the silicon layer. A planar SOI MOSFET including a strained channel region formed on another portion of the silicon layer. For example, the planar SOI MOSFET can be a planar fully-depleted SOI (FD-SOI) MOSFET or the planar SOI MOSFET can be a planar partially-depleted SOI (PD-SOI) MOSFET.

Owner:TAIWAN SEMICON MFG CO LTD

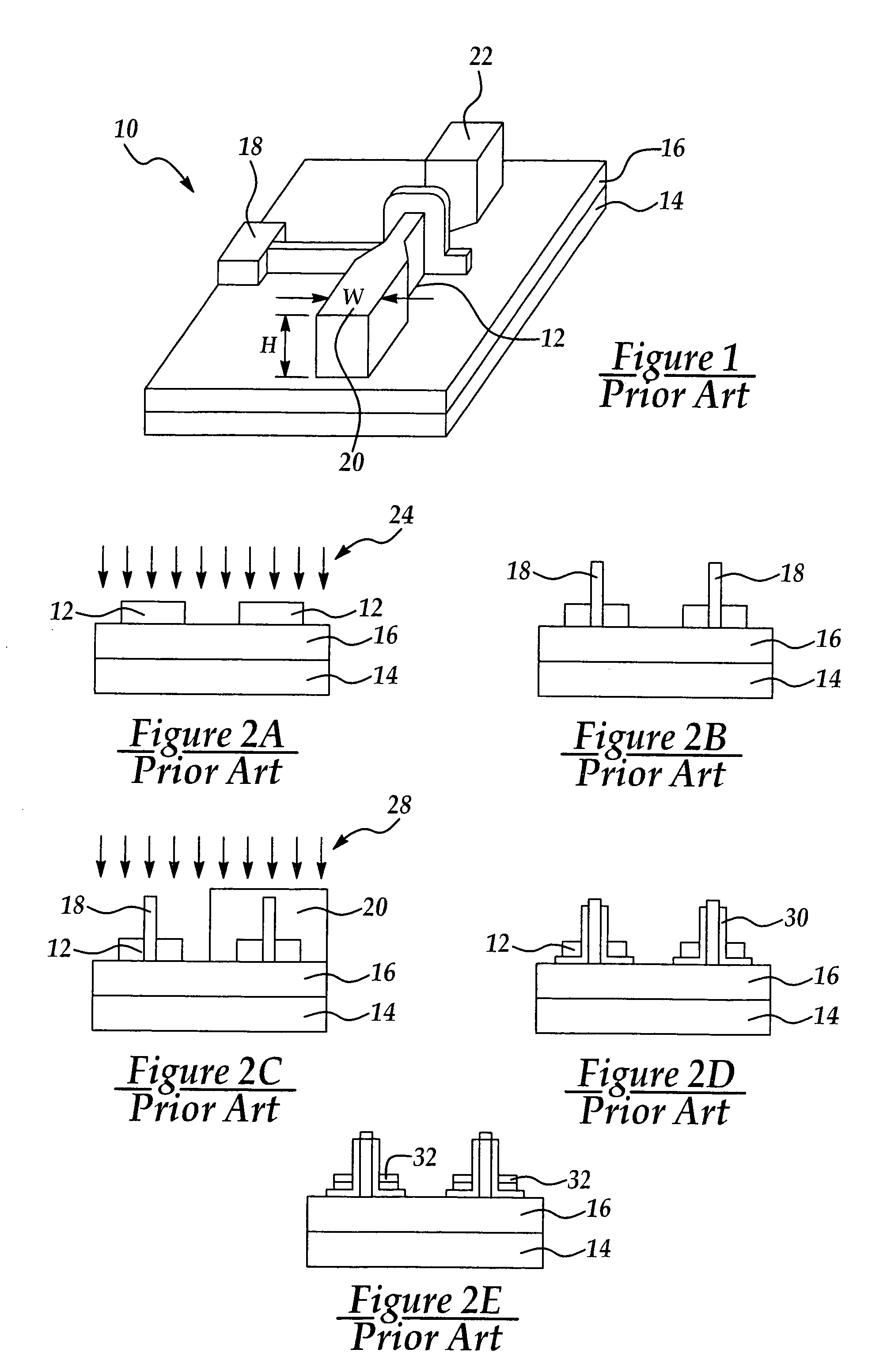

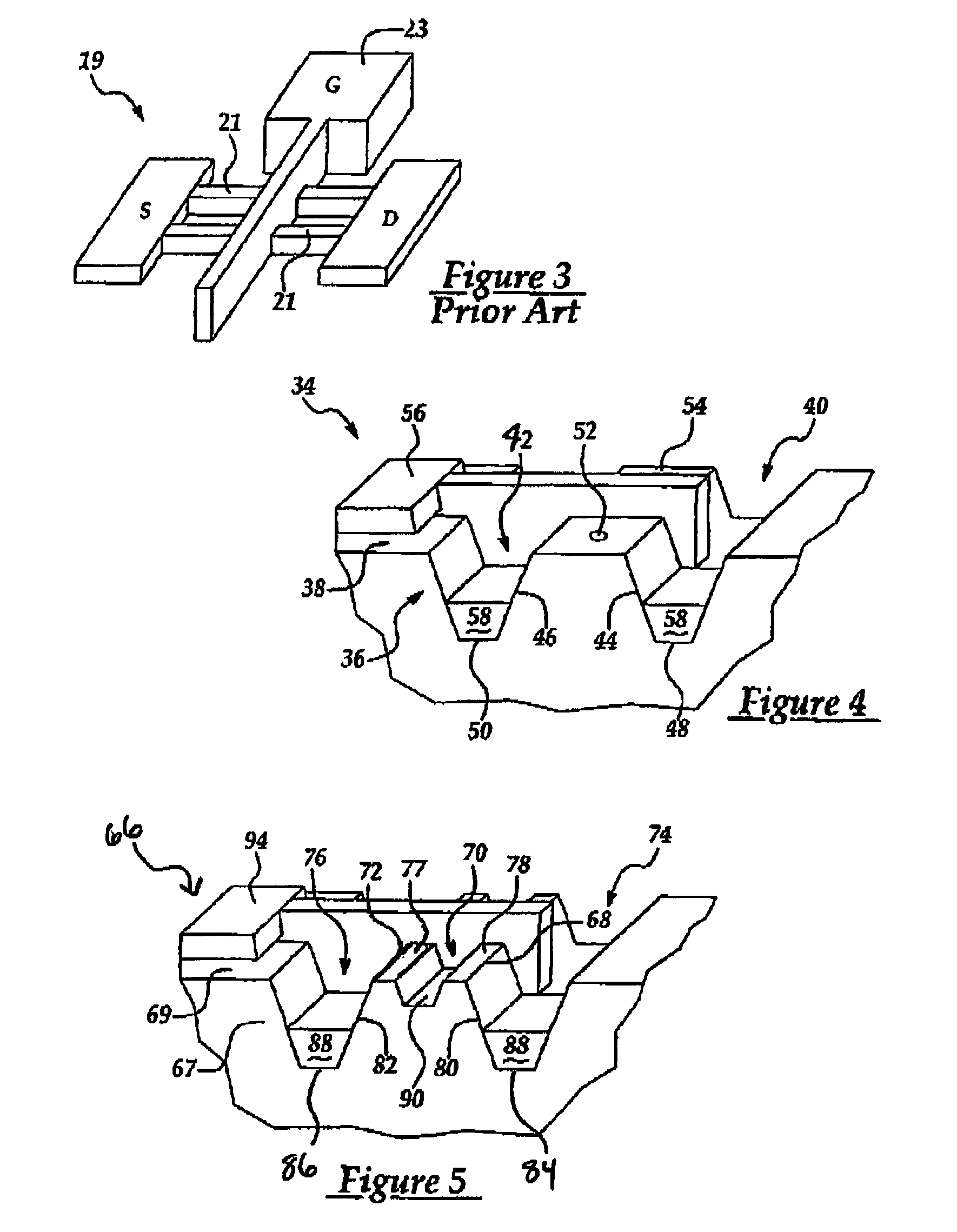

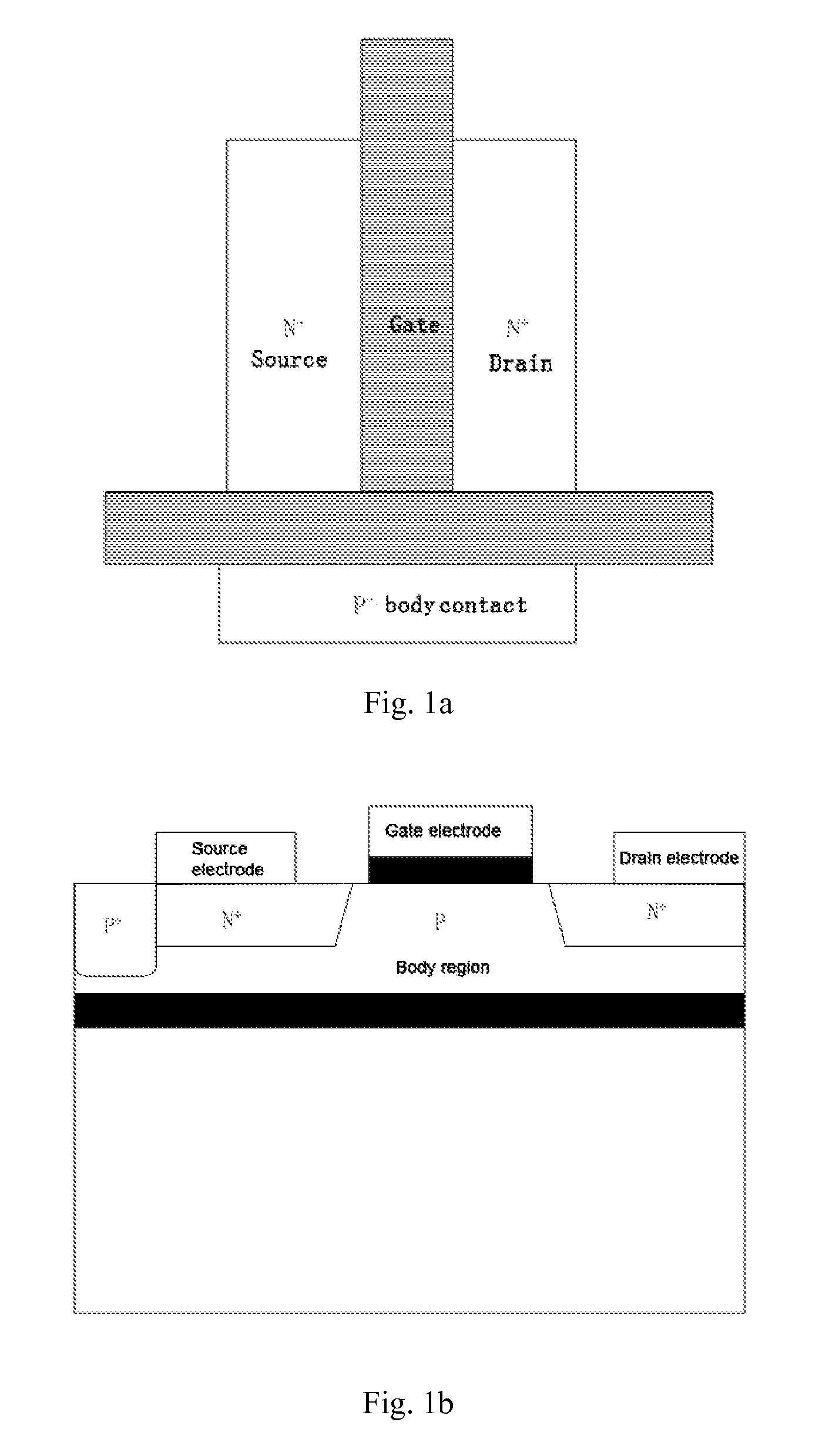

Quasi-plannar and FinFET-like transistors on bulk silicon

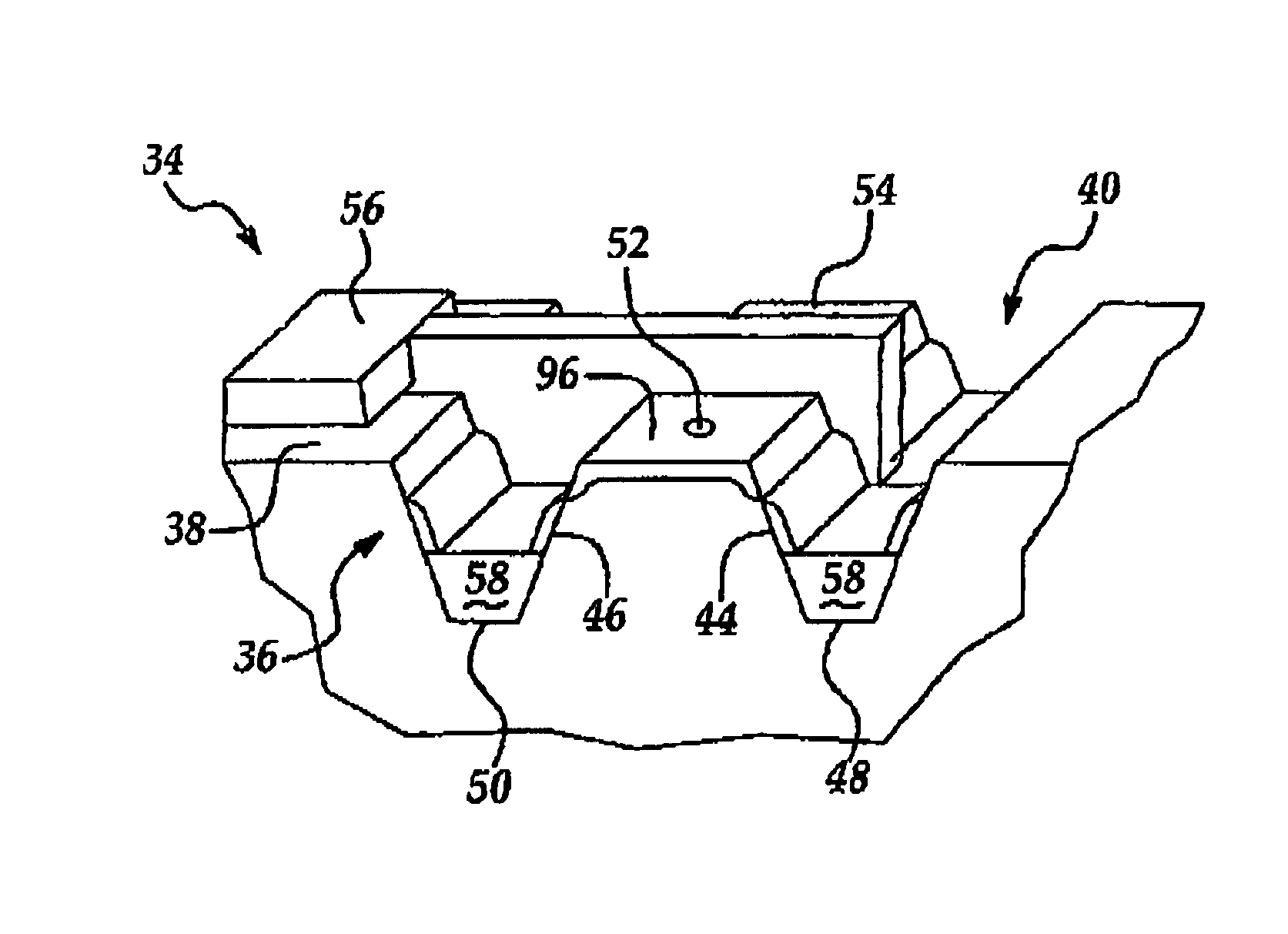

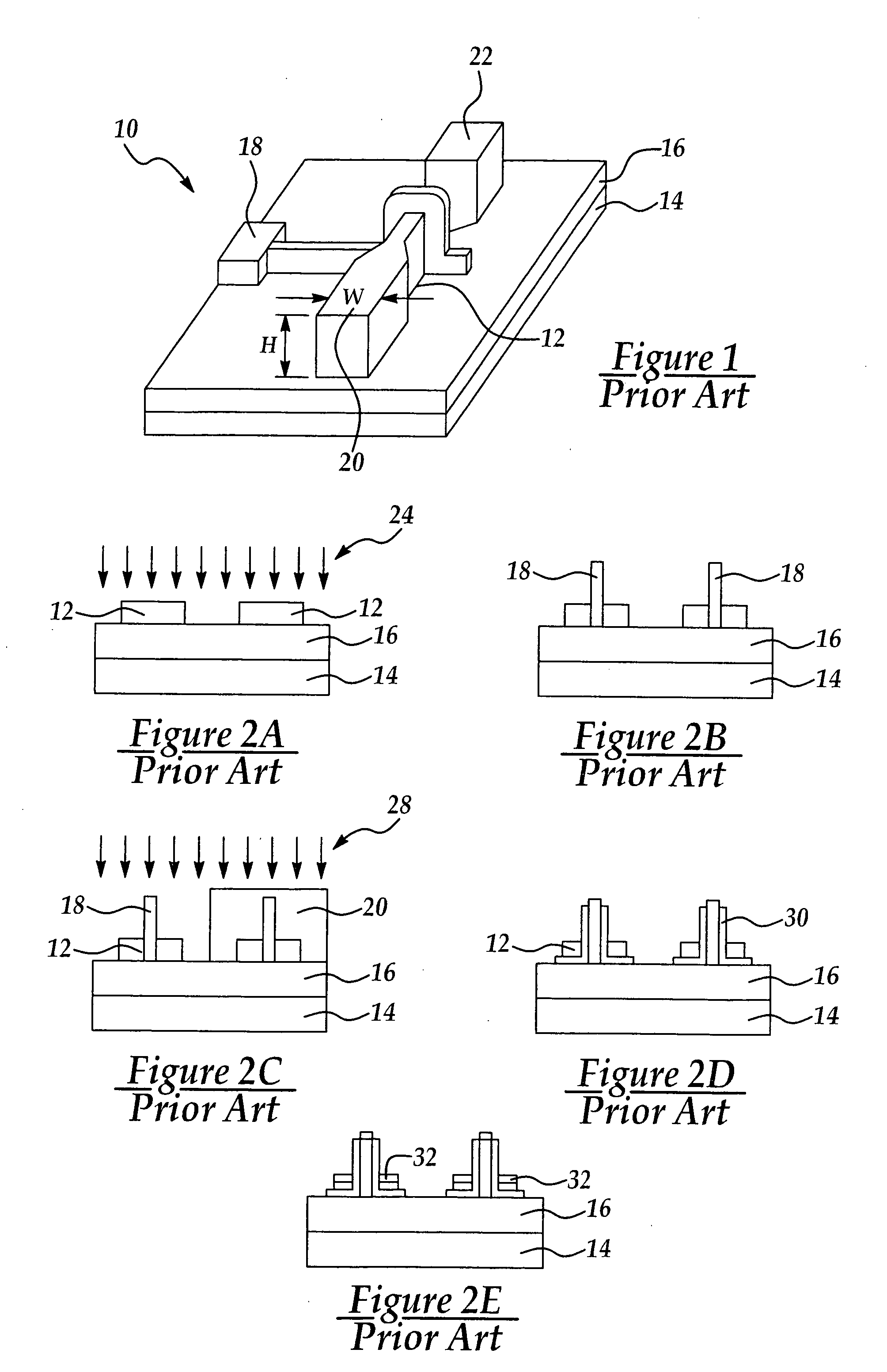

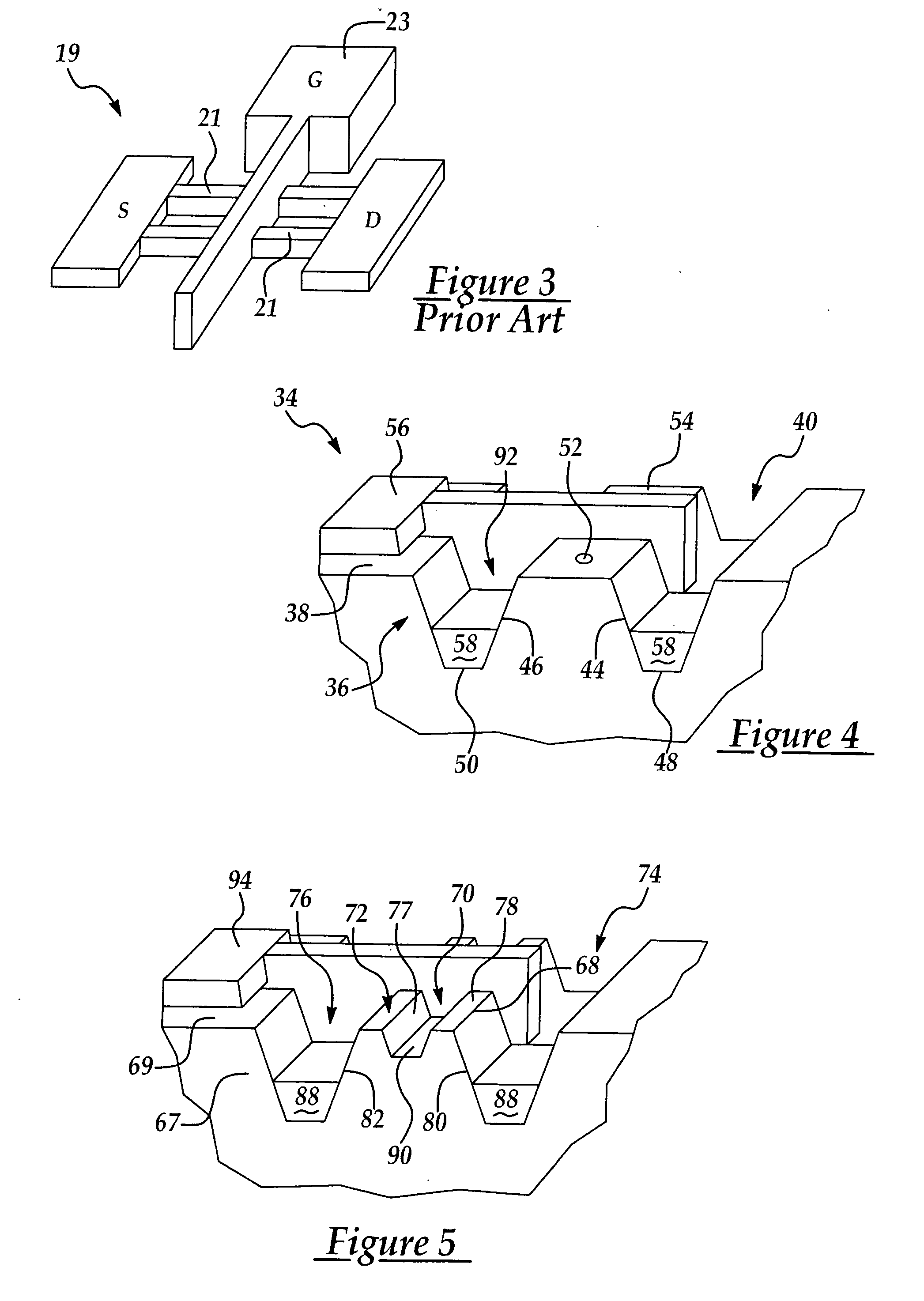

The types of quasi-planar CMOS and FinFET-like transistor devices on a bulk silicon substrate are disclosed. A first device has a doped and recessed channel formed in a shallow trench sidewall. A second device has a doped, recessed channel and has a plurality of edge-fins juxtaposed on an edge of an active region of the device. A third device has an undoped recessed channel formed in a sidewall of a shallow trench, wherein the undoped recessed channel further has a plurality of edge-fins disposed thereon. Additionally, an extra mask may be added to each device to allow for fabrication of both conventional transistors and FinFET-like transistors on bulk silicon. The extra mask may protect the source and drain areas from recess etching of the silicon substrate. Several methods of fabricating each device are also disclosed.

Owner:TAIWAN SEMICON MFG CO LTD

Semiconductor-on-insulator chip incorporating strained-channel partially-depleted, fully-depleted, and multiple-gate transistors

InactiveUS20050093067A1Good effectSuppression of floating body effectTransistorSolid-state devicesMOSFETSemiconductor chip

In accordance with a preferred embodiment of the present invention, a silicon-on-insulator (SOI) chip includes a silicon layer of a predetermined thickness overlying an insulator layer. A multiple-gate fully-depleted SOI MOSFET including a strained channel region is formed on a first portion of the silicon layer. A planar SOI MOSFET including a strained channel region formed on another portion of the silicon layer. For example, the planar SOI MOSFET can be a planar fully-depleted SOI (FD-SOI) MOSFET or the planar SOI MOSFET can be a planar partially-depleted SOI (PD-SOI) MOSFET.

Owner:TAIWAN SEMICON MFG CO LTD

Quasi-plannar and FinFET-like transistors on bulk silicon

The types of quasi-planar CMOS and FinFET-like transistor devices on a bulk silicon substrate are disclosed. A first device has a doped and recessed channel formed in a shallow trench sidewall. A second device has a doped, recessed channel and has a plurality of edge-fins juxtaposed on an edge of an active region of the device. A third device has an undoped recessed channel formed in a sidewall of a shallow trench, wherein the undoped recessed channel further has a plurality of edge-fins disposed thereon. Additionally, an extra mask may be added to each device to allow for fabrication of both conventional transistors and FinFET-like transistors on bulk silicon. The extra mask may protect the source and drain areas from recess etching of the silicon substrate. Several methods of fabricating each device are also disclosed.

Owner:TAIWAN SEMICON MFG CO LTD

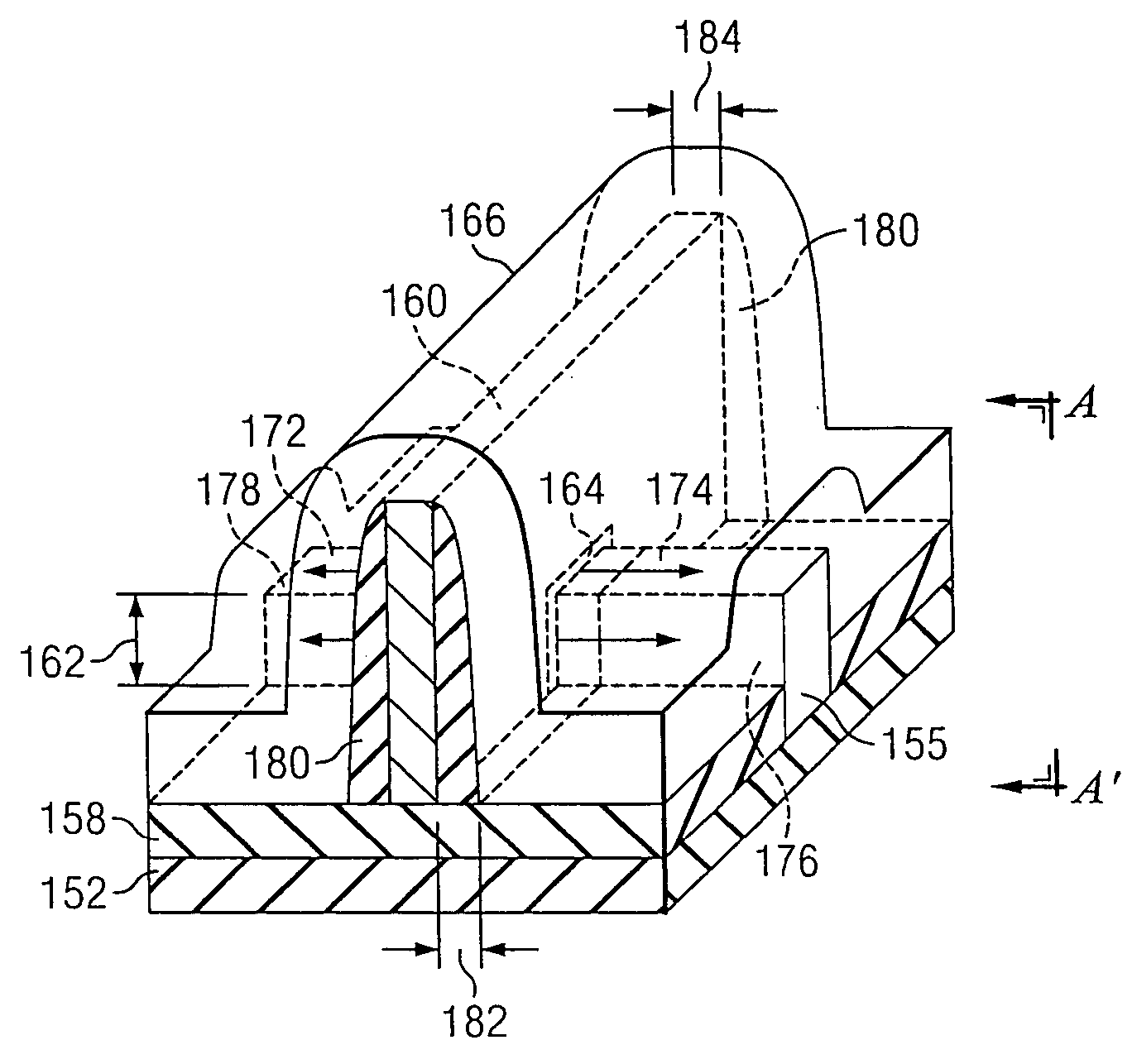

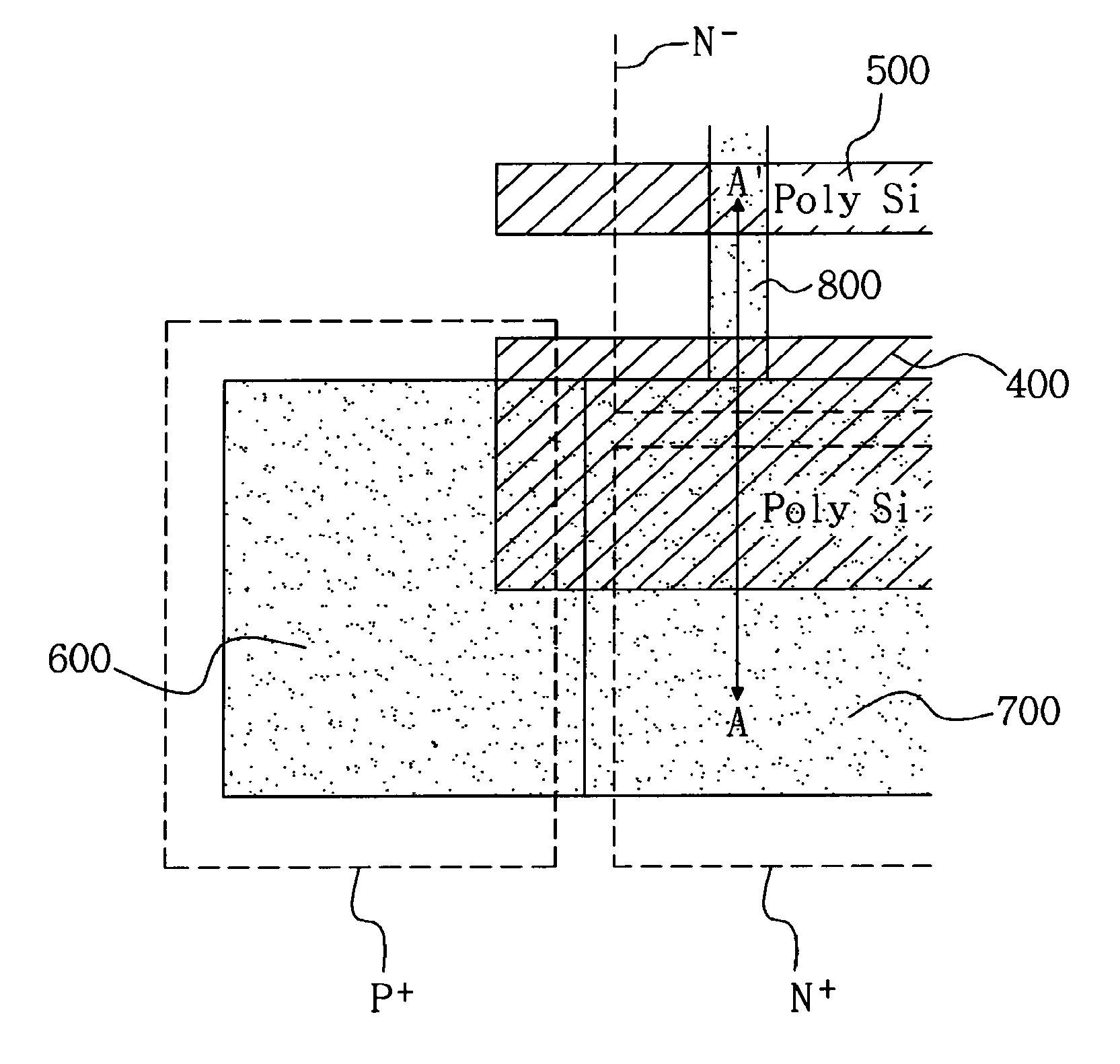

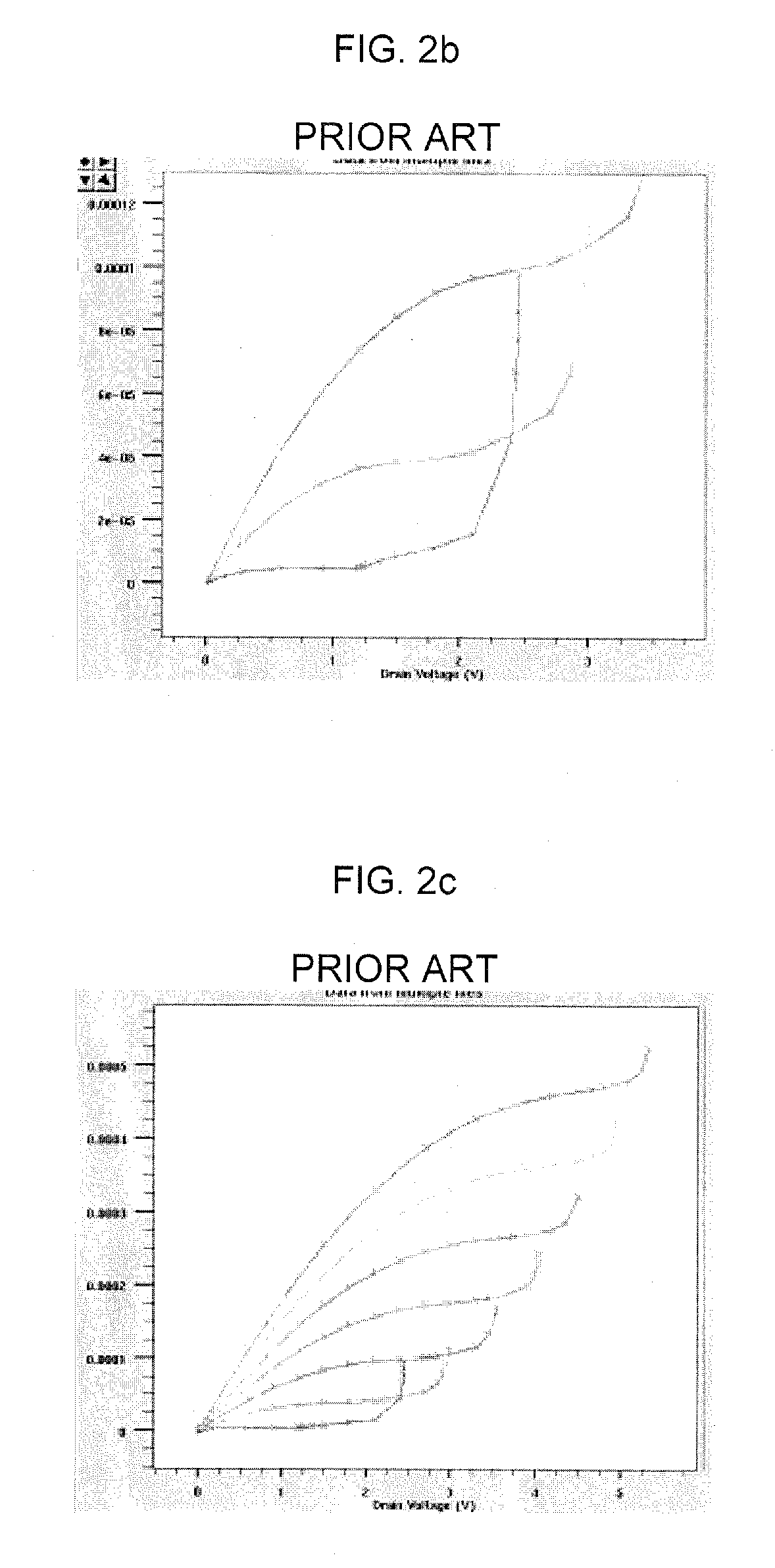

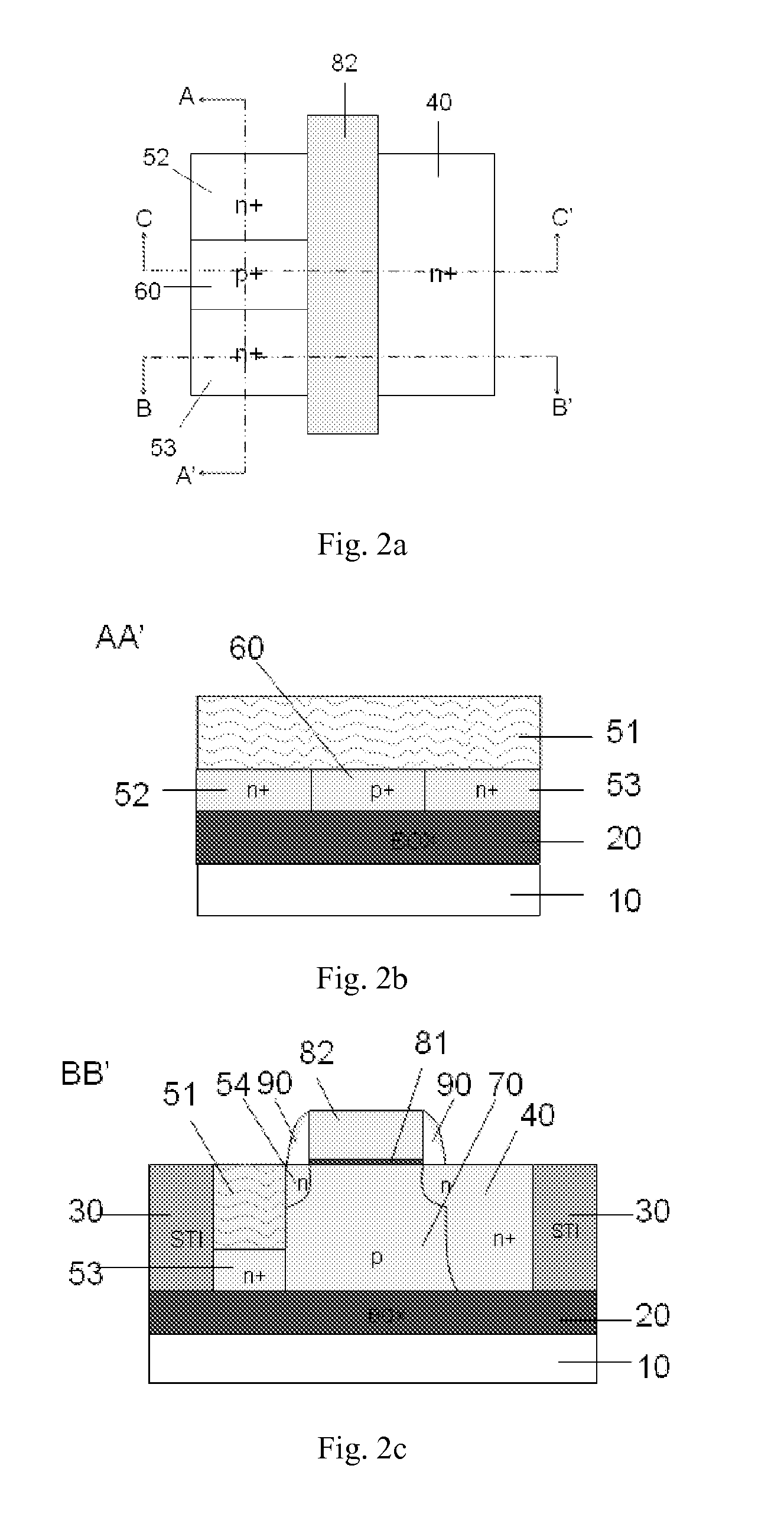

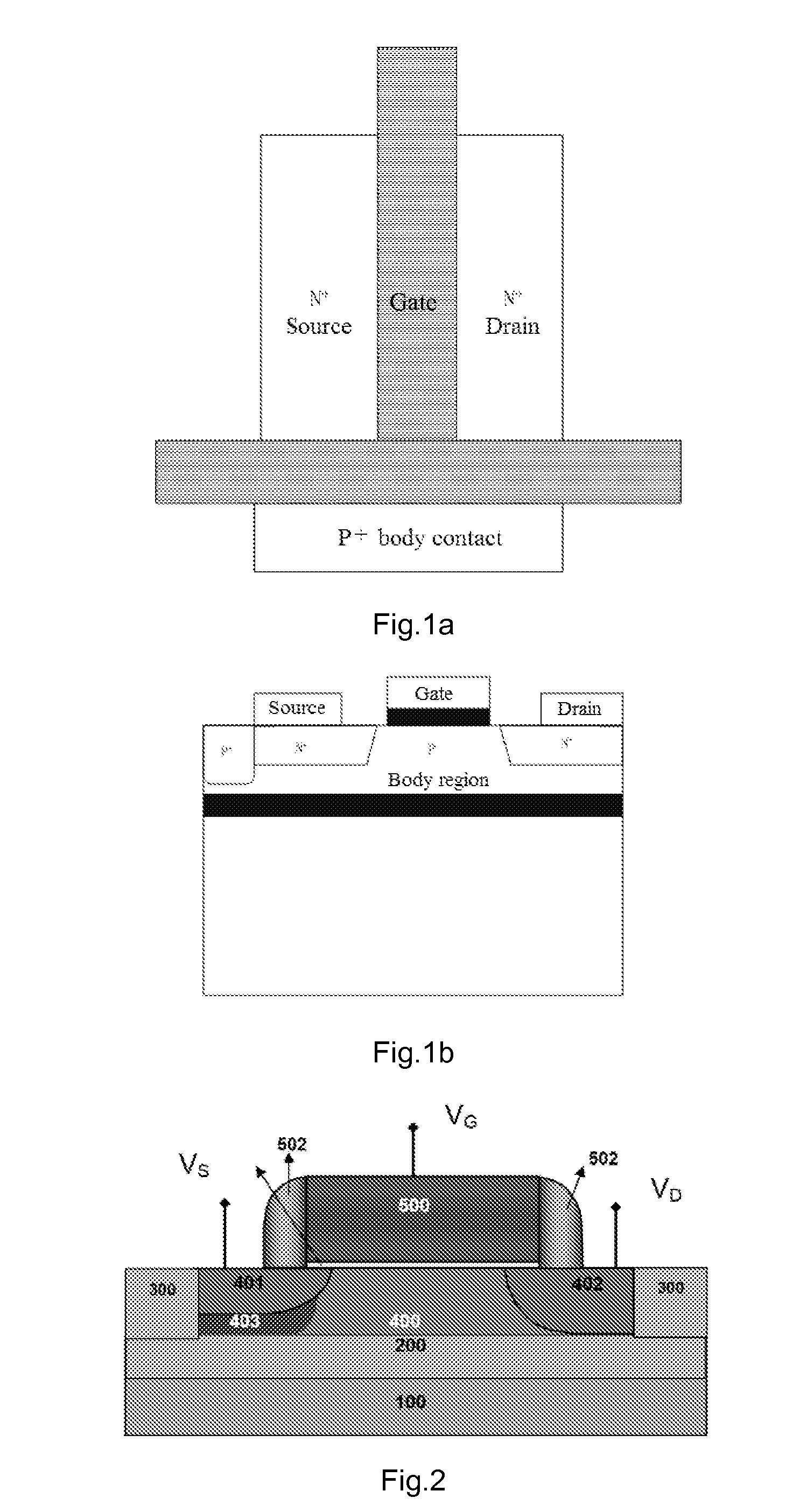

Body biasing structure of SOI

ActiveUS7432552B2Suppression of floating body effectTransistorSolid-state devicesMOSFETFloating body effect

Owner:SEOUL NAT UNIV R&DB FOUND +1

Hybrid crystal orientation CMOS structure for adaptive well biasing and for power and performance enhancement

ActiveUS20060231893A1Suppression of floating body effectAdjustable voltageTransistorSolid-state devicesPerformance enhancementFloating body effect

The present invention provides a semiconducting structure including a substrate having an SOI region and a bulk-Si region, wherein the SOI region and the bulk-Si region have a same or differing crystallographic orientation; an isolation region separating the SOI region from the bulk-Si region; and at least one first device located in the SOI region and at least one second device located in the bulk-Si region. The SOI region has an silicon layer atop an insulating layer. The bulk-Si region further comprises a well region underlying the second device and a contact to the well region, wherein the contact stabilizes floating body effects. The well contact is also used to control the threshold voltages of the FETs in the bulk-Si region to optimized the power and performance of circuits built from the combination of the SOI and bulk-Si region FETs.

Owner:GLOBALFOUNDRIES US INC

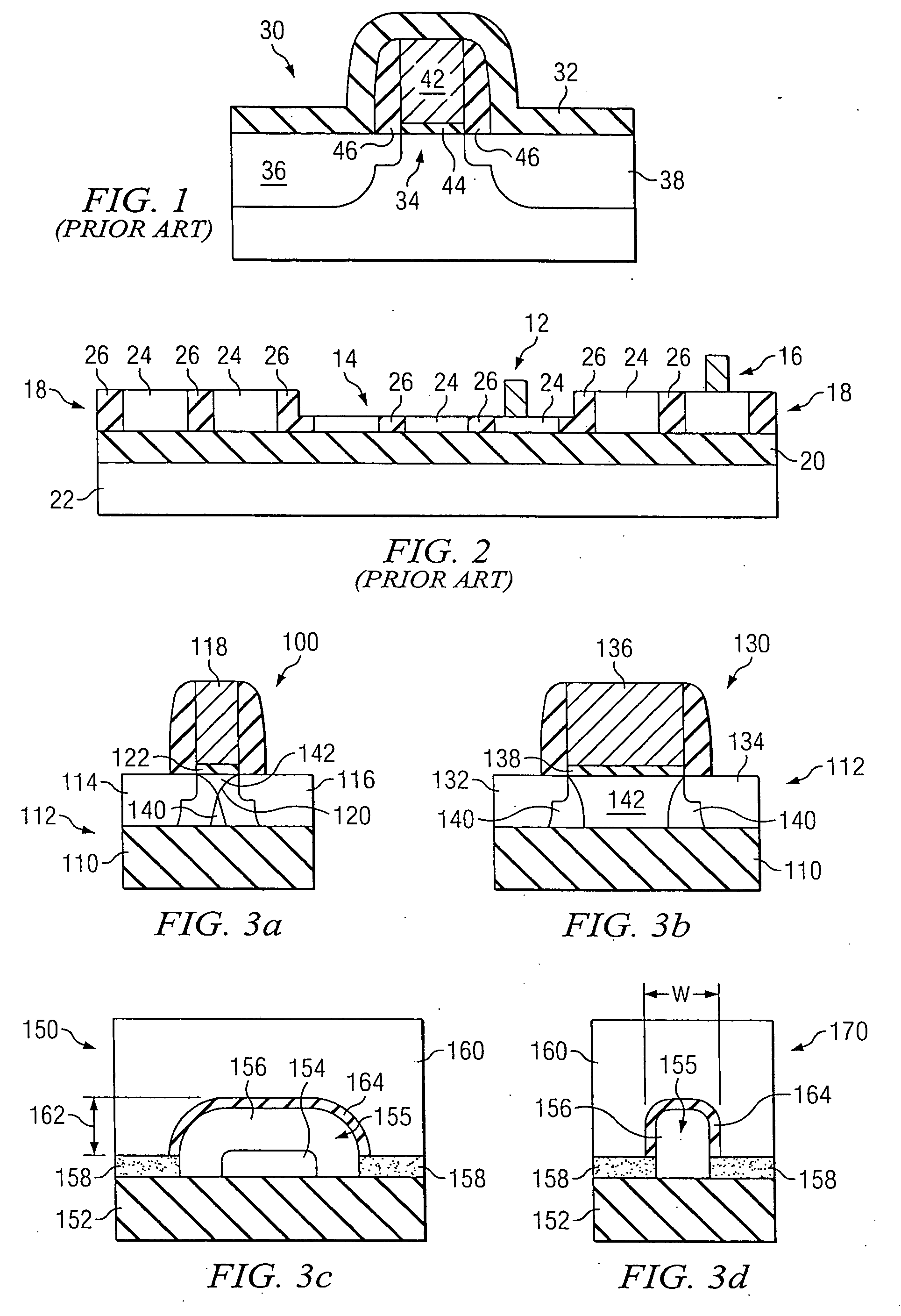

FinFET device with reduced DIBL

ActiveUS7009250B1Reduce resistanceSuppression of floating body effectSolid-state devicesSemiconductor/solid-state device manufacturingBorophosphosilicate glassEngineering

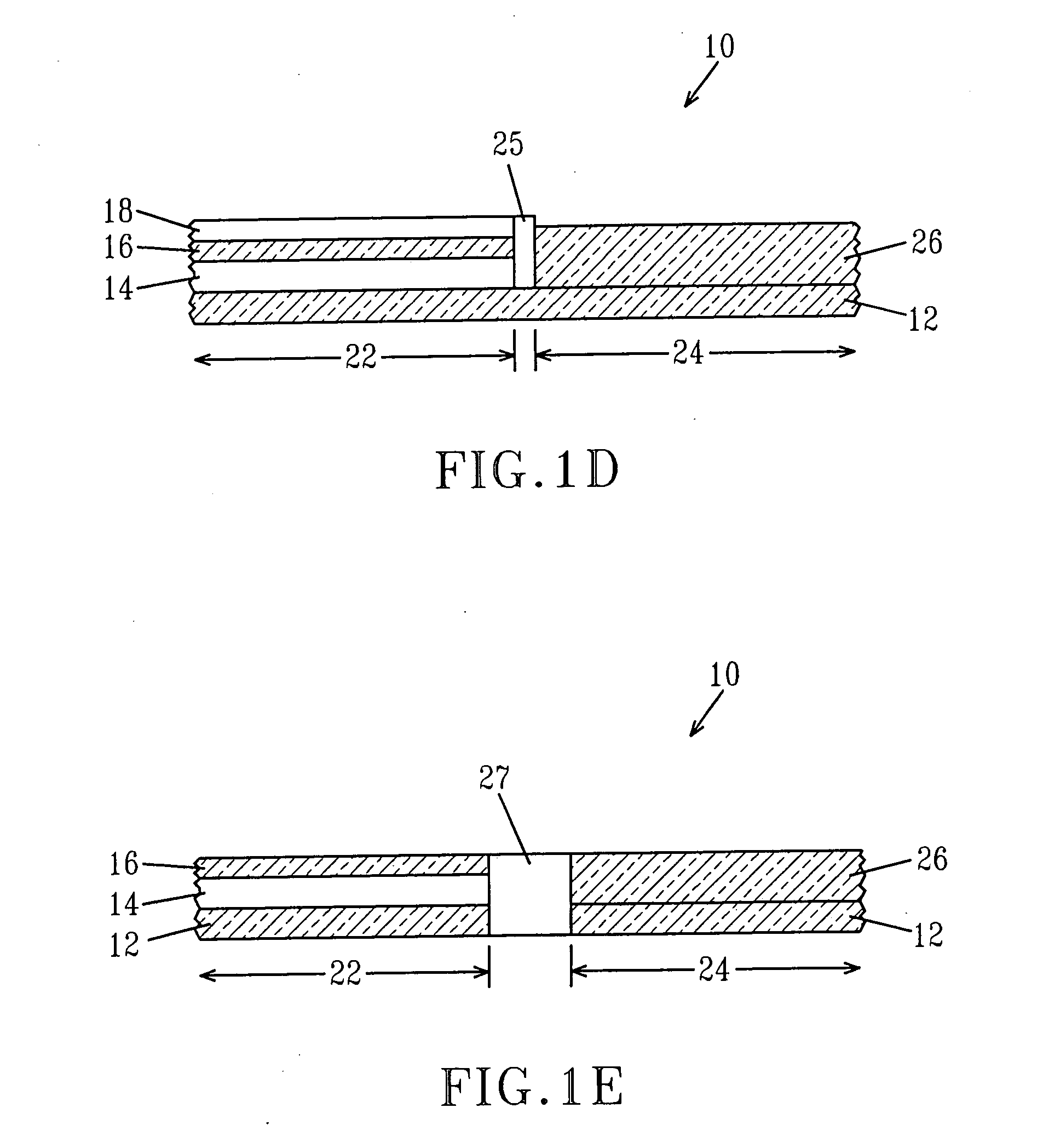

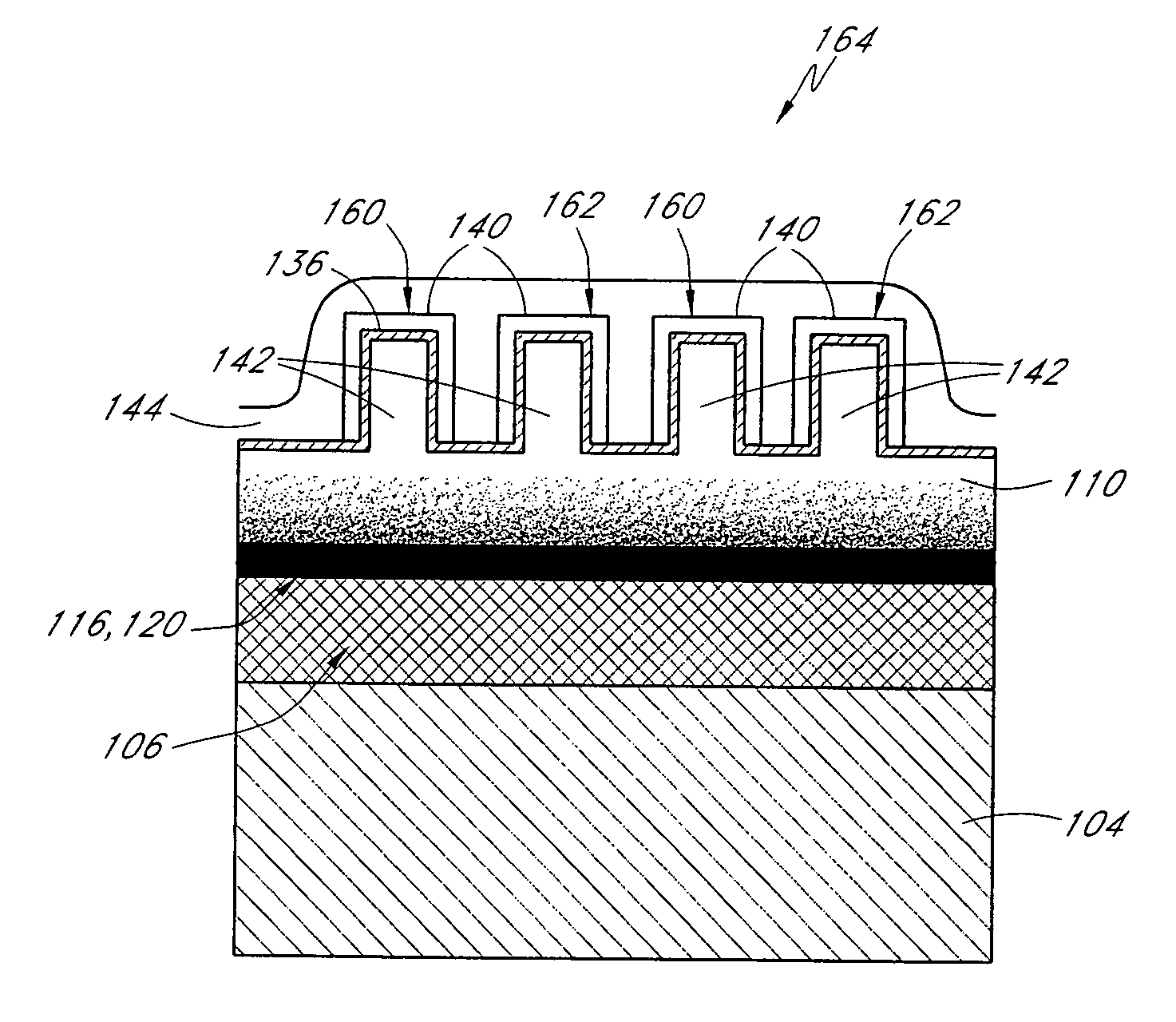

FinFET devices formed with a Silicon On Insulator (SOI) technology with reduced Drain Induced Barrier Lowering (DIBL) characteristics and methods for producing the same. The methods involve dopant implants into the insulator layer, thereby creating borophosphosilicate glass (BPSG) diffusion sources within the insulation layer underlying the active regions of the SOI wafer. Backend high temperature processing steps induce diffusion of the dopants contained in the diffusion source into the active regions, thereby forming a retrograde dopant profile extending towards the channel region. The method can be selectively applied to selected portions of a wafer to tailor device characteristics, such as for memory cells.

Owner:MICRON TECH INC

Semiconductor device and method for forming the same

InactiveUS20070181880A1Suppression of floating body effectEliminate the effects ofTransistorAuxillariesInsulation layerDevice material

A semiconductor device includes a conductive layer formed on a semiconductor substrate. An insulation layer is formed on the conductive layer and includes an opening defined therein that exposes the conductive layer. A semiconductor pattern is formed on the insulation layer and is electrically connected to the conductive layer through the opening. A transistor is formed on the semiconductor pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

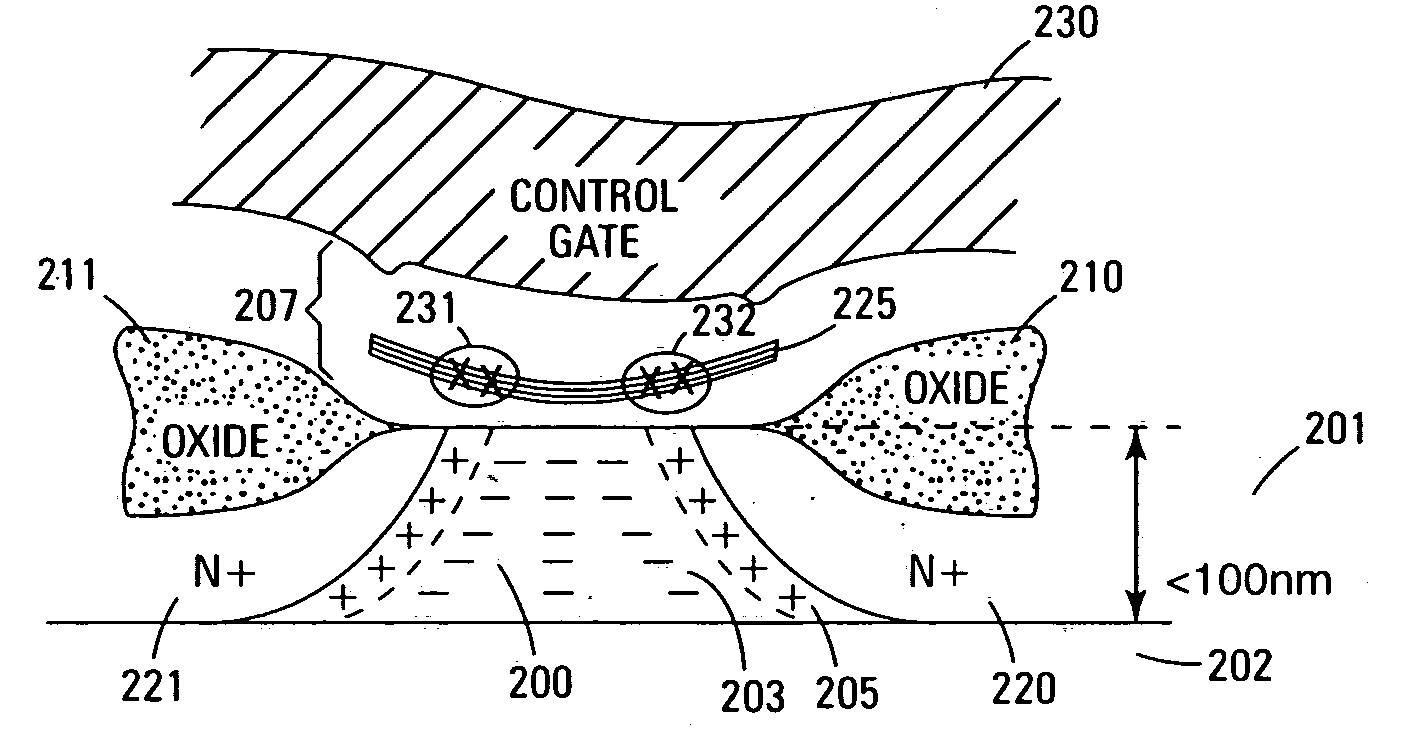

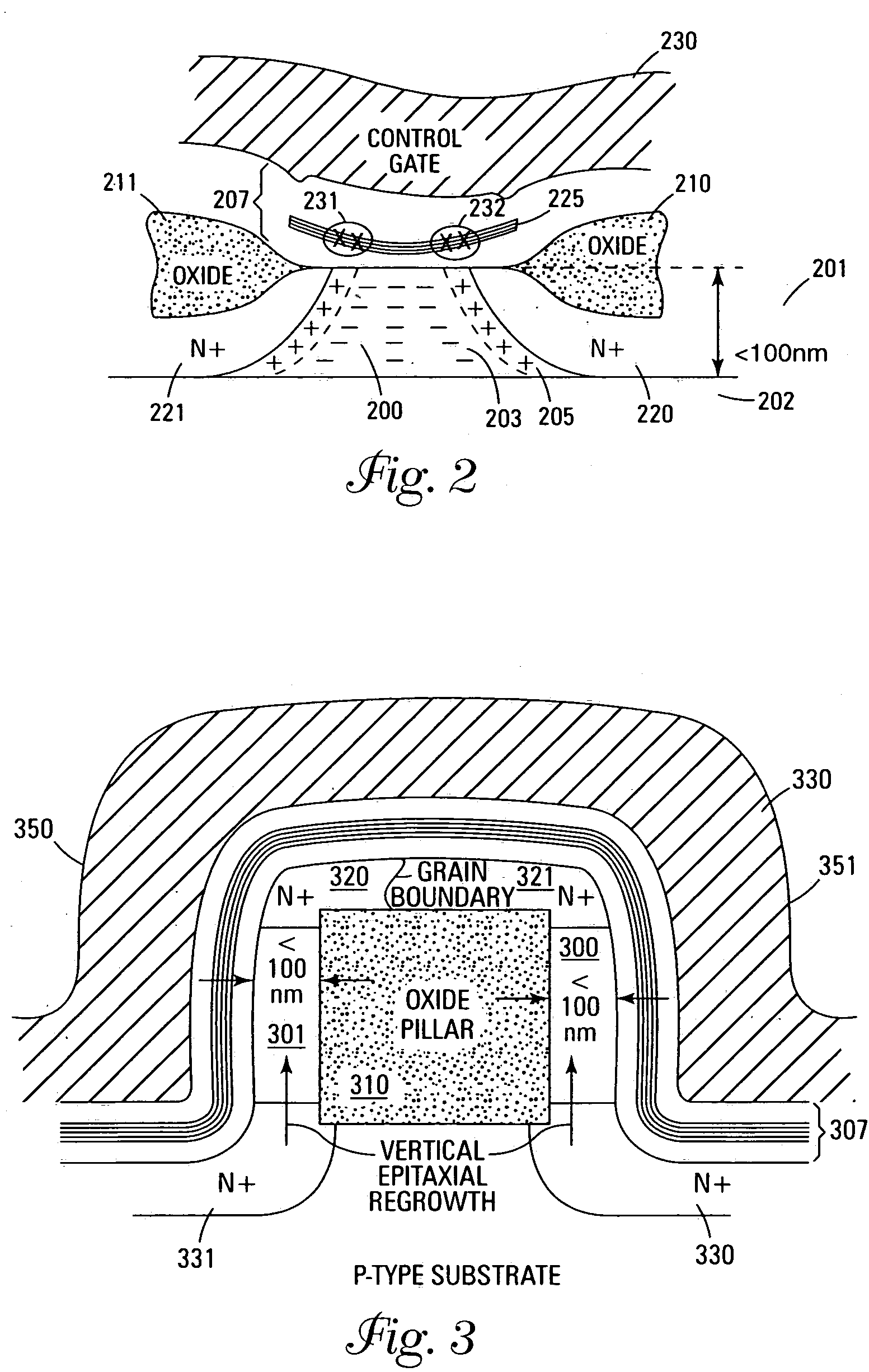

NROM flash memory devices on ultrathin silicon

ActiveUS20050106811A1Suppression of floating body effectSolid-state devicesSemiconductor/solid-state device manufacturingInsulation layerGate insulator

An NROM flash memory cell is implemented in an ultra-thin silicon-on-insulator structure. In a planar device, the channel between the source / drain areas is normally fully depleted. An oxide layer provides an insulation layer between the source / drain areas and the gate insulator layer on top. A control gate is formed on top of the gate insulator layer. In a vertical device, an oxide pillar extends from the substrate with a source / drain area on either side of the pillar side. Epitaxial regrowth is used to form ultra-thin silicon body regions along the sidewalls of the oxide pillar. Second source / drain areas are formed on top of this structure. The gate insulator and control gate are formed on top.

Owner:MICRON TECH INC

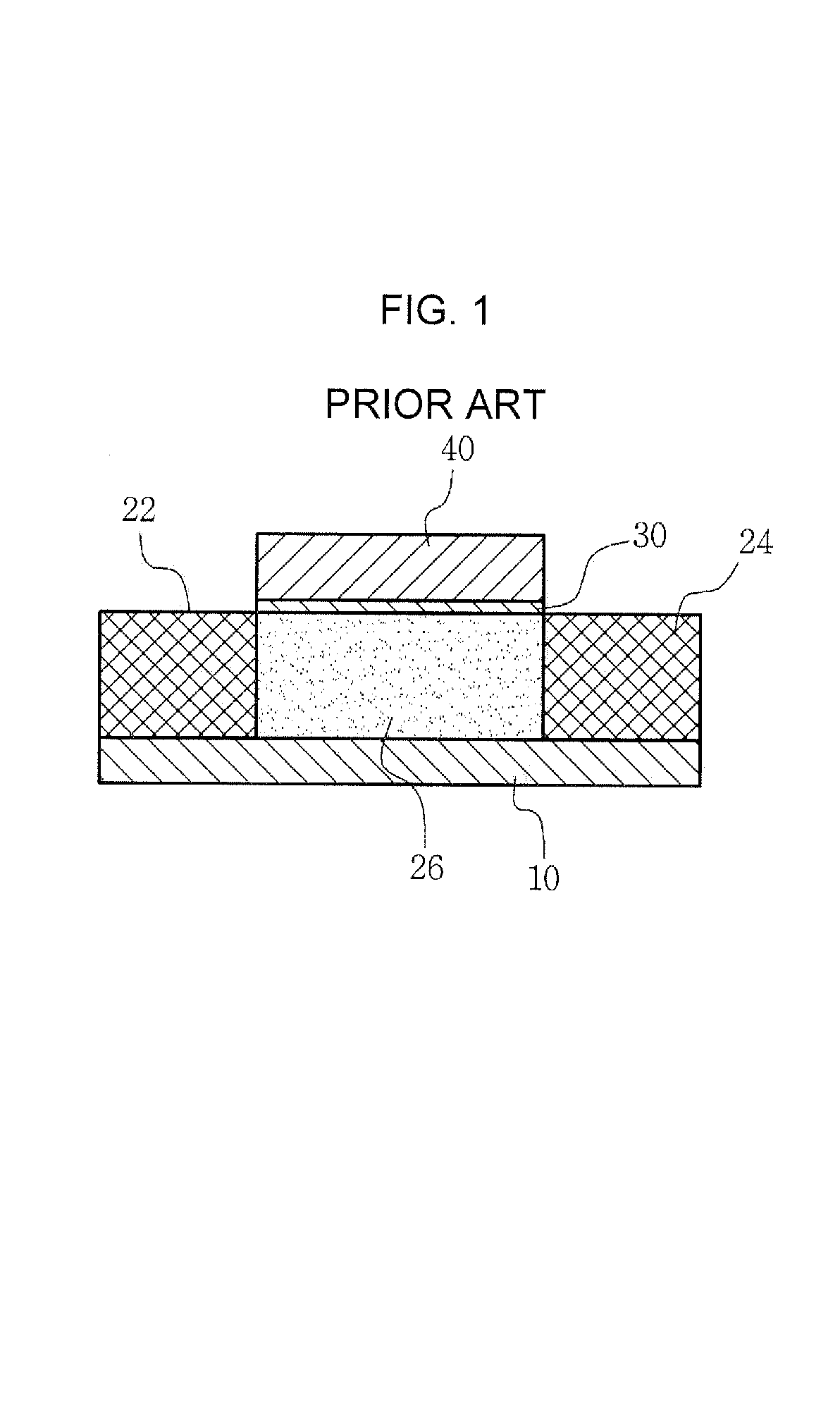

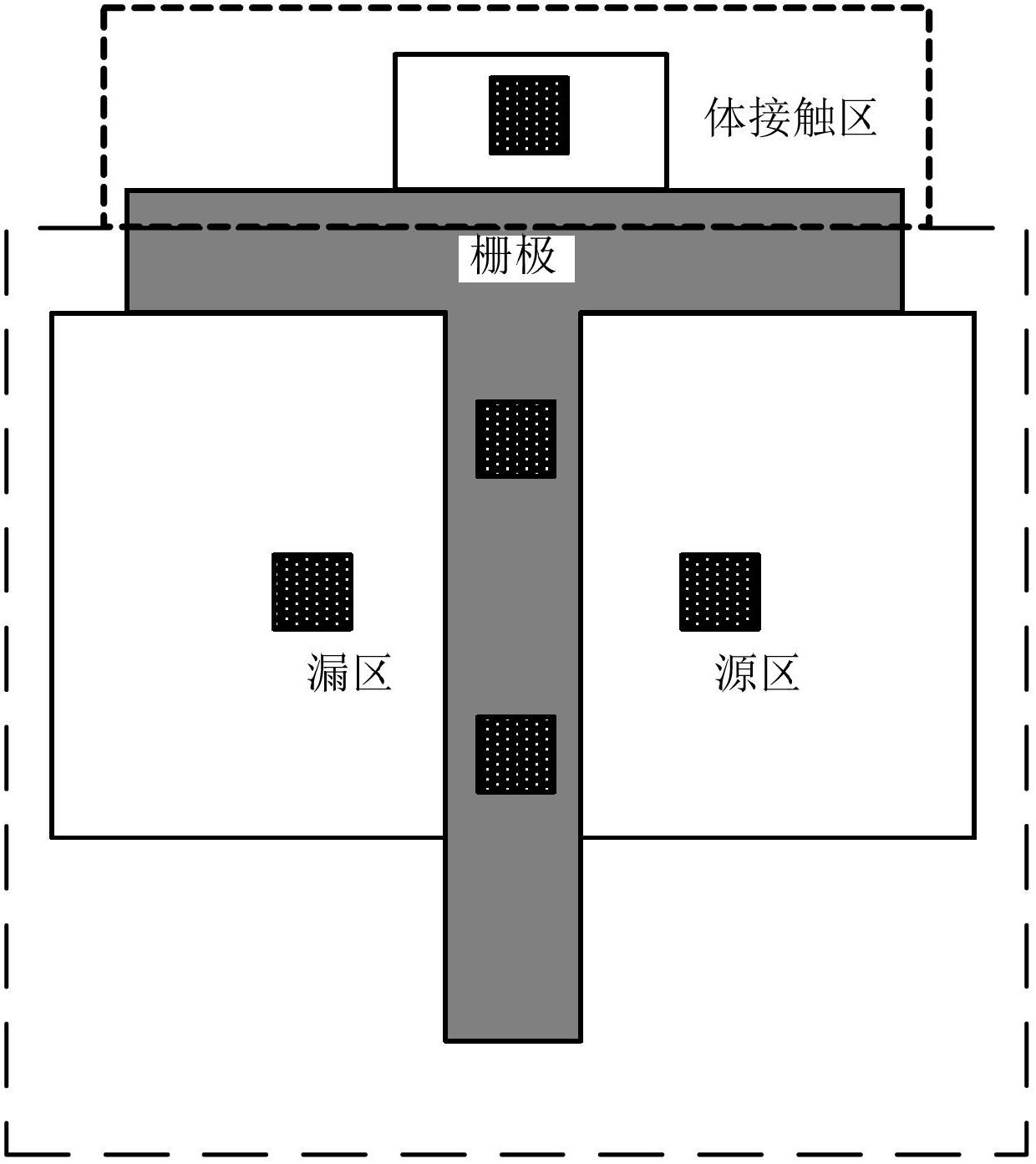

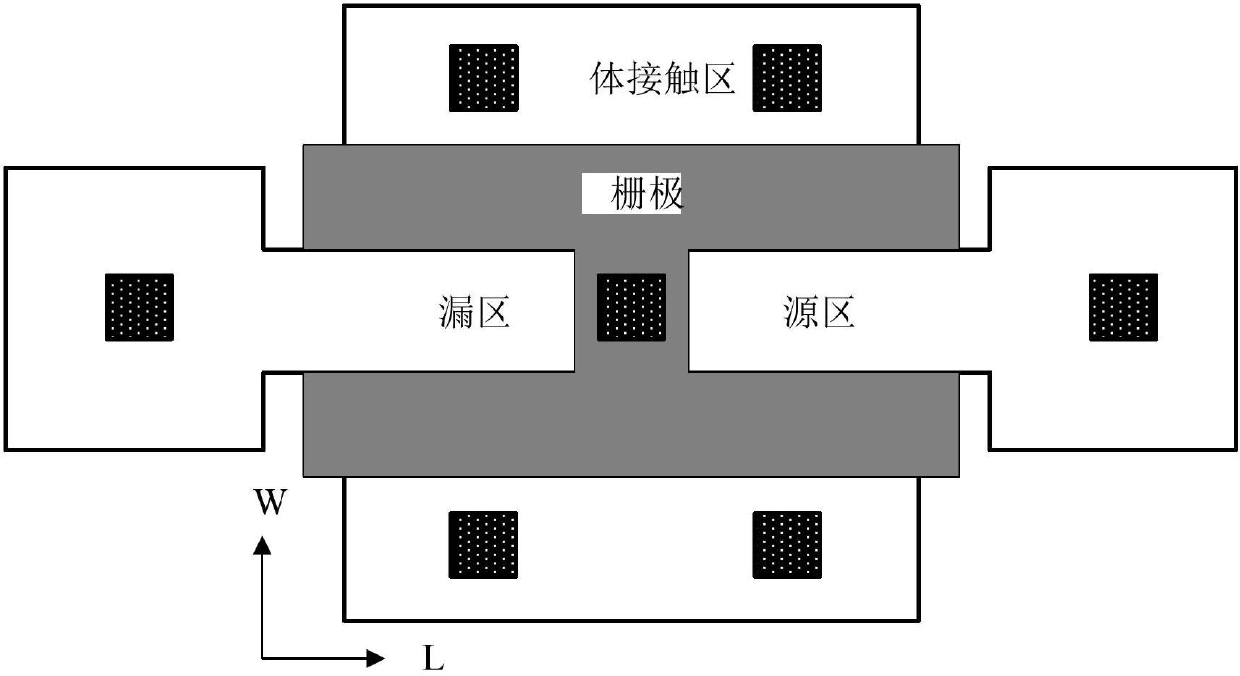

Silicon-on-insulator (SOI) metal-oxide-semiconductor (MOS) transistor

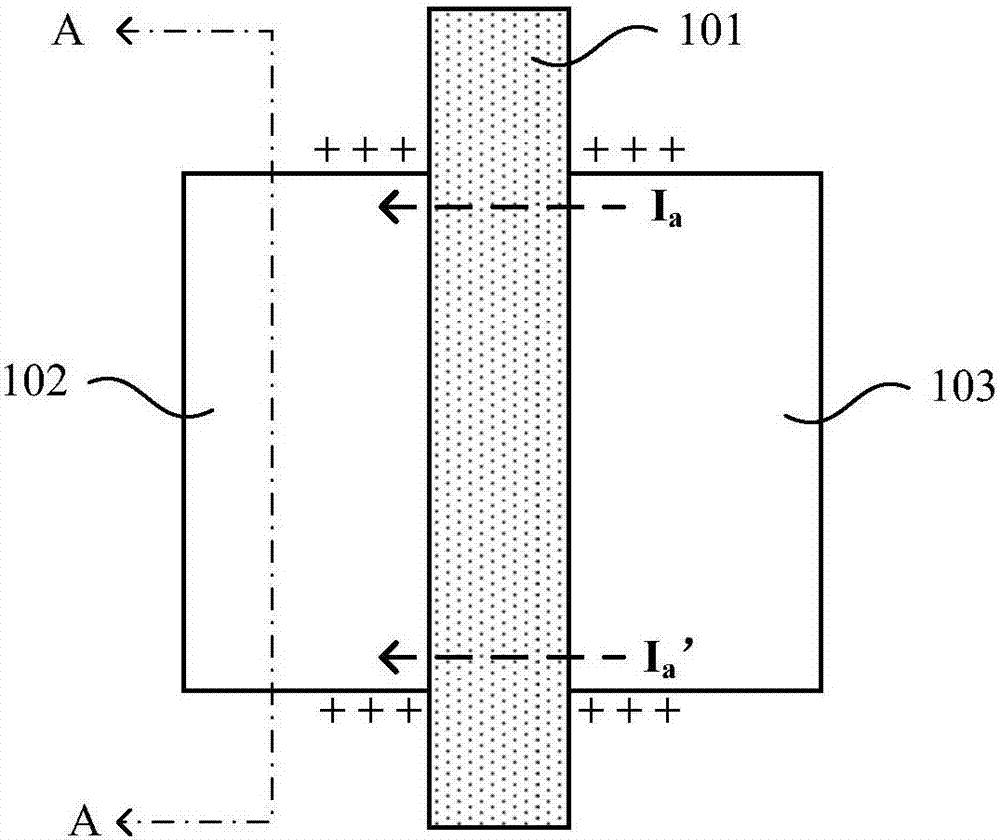

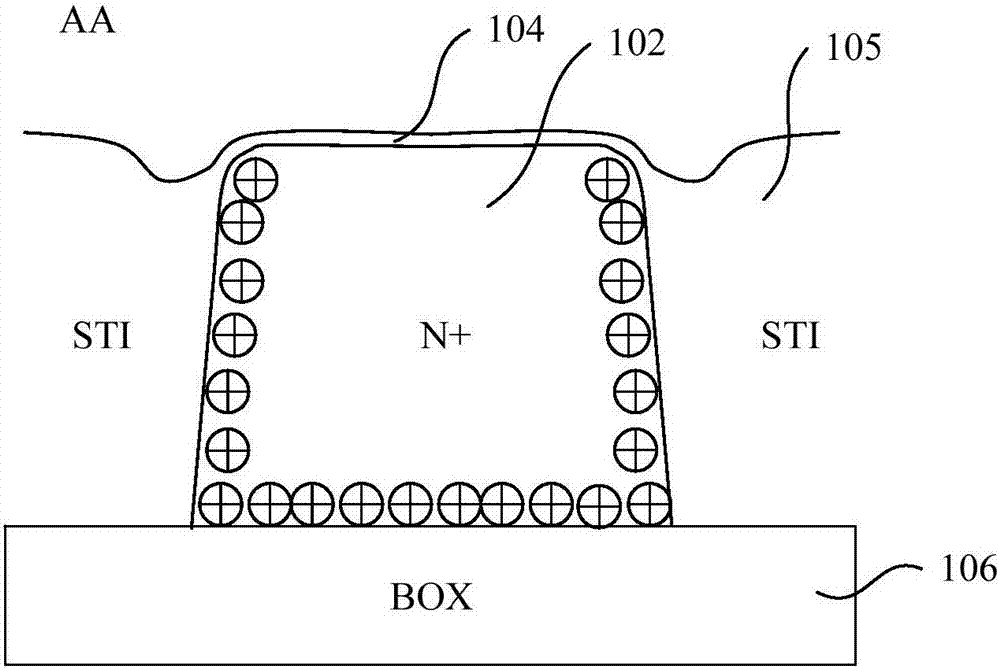

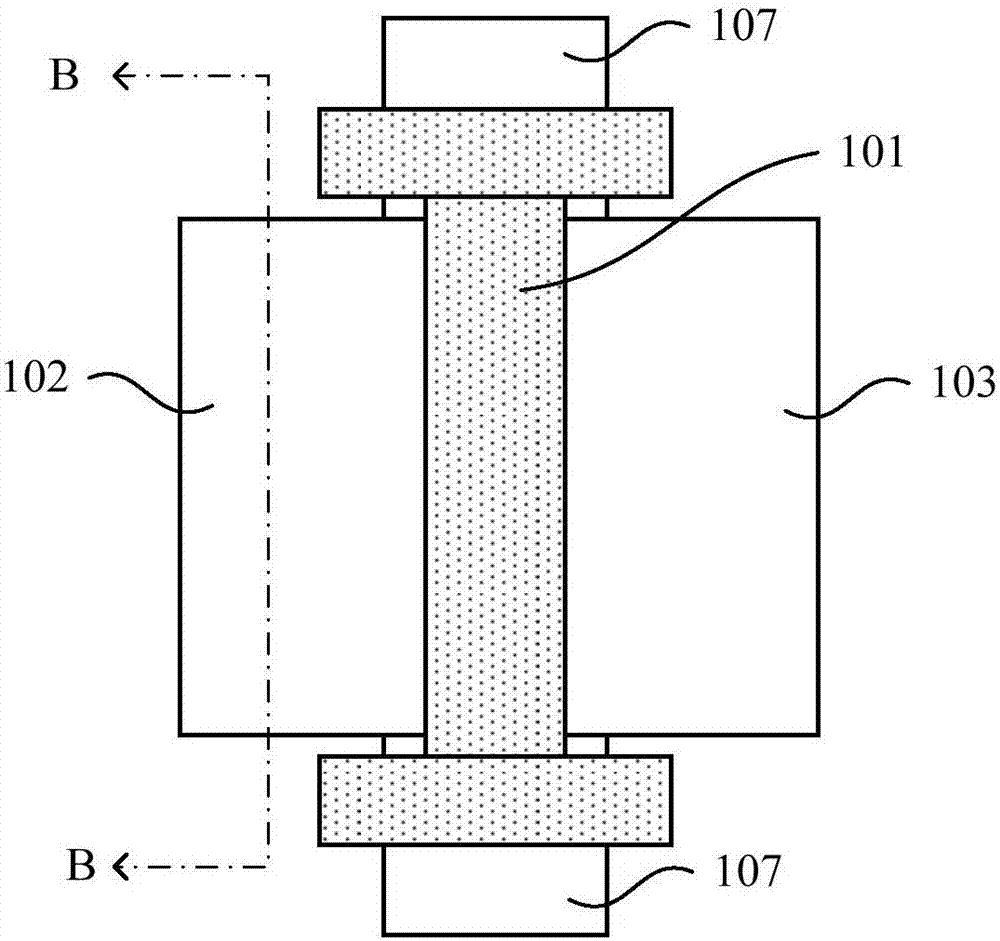

InactiveCN102683417ASuppression of floating body effectSolve the problem of source-drain asymmetrySemiconductor devicesFloating body effectBody contact

The invention provides a silicon-on-insulator (SOI) metal-oxide-semiconductor (MOS) transistor which comprises a device active region which has a continuous shape, a grid, a source region, a drain region and a body contacting active region, wherein the device active region is formed in an SOI layer of an SOI substrate; the grid extends by crossing the device active region; the source region and the drain region are respectively positioned in the device active region at the two sides of the grid; and the body contacting active region is independent with the device active region, and electrically connected with a channel region below the grid without being isolated to the bottom. The SOI MOS transistor provided in the invention is beneficial to inhibiting the floating body effect, the influences of the parasitic capacitance and the parasitic resistance of a channel transistor are decreased, and the side leakage current is reduced.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

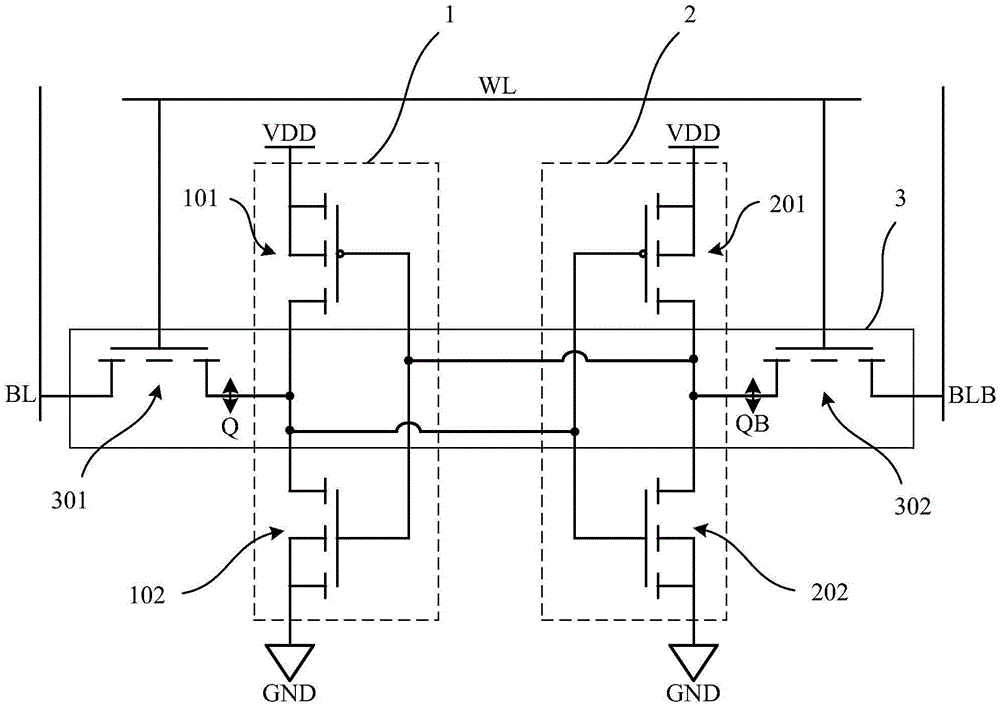

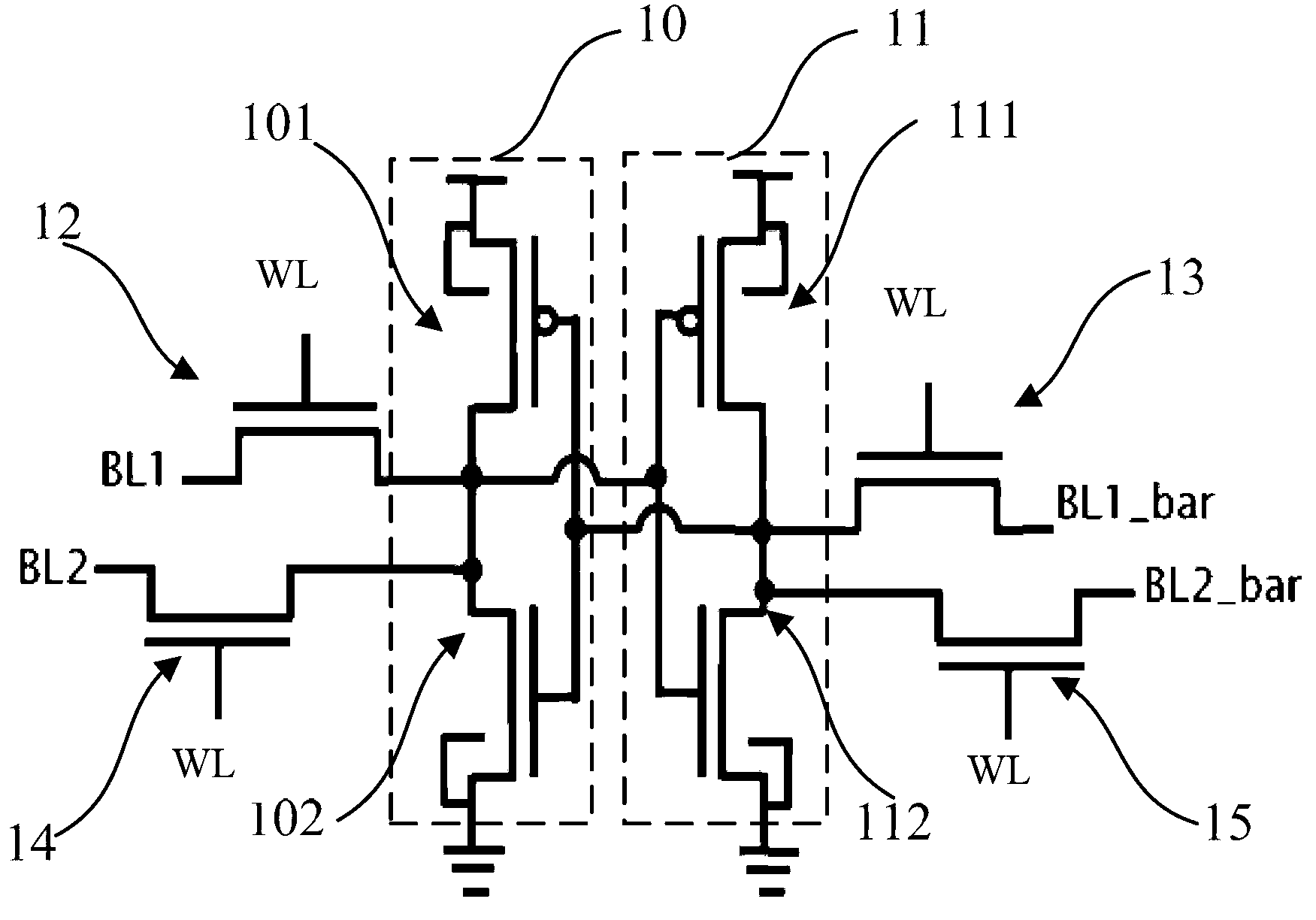

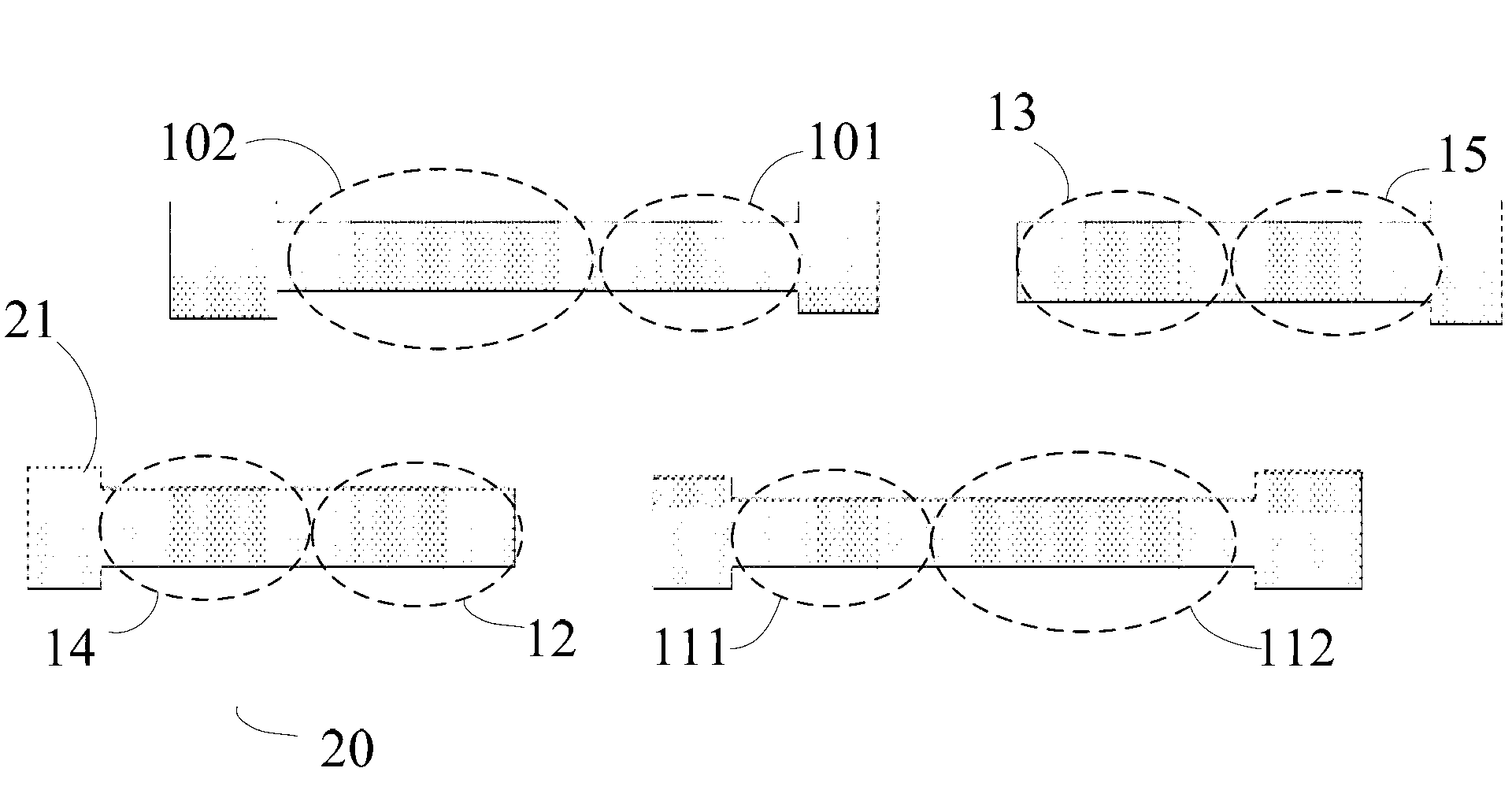

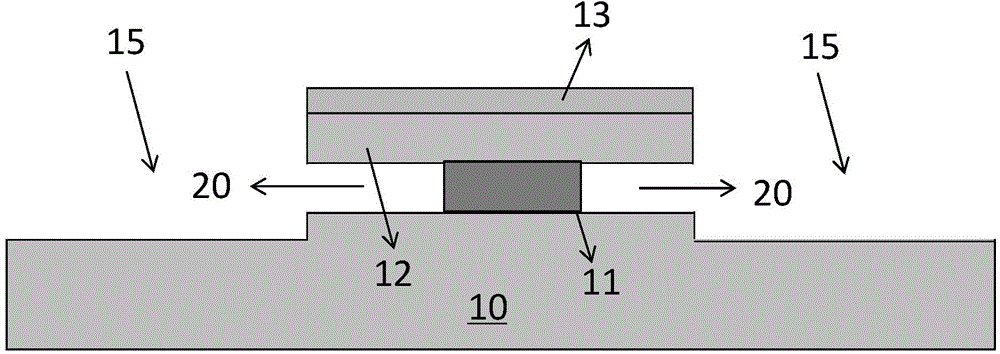

SOI single-port SRAM (Static Random Access Memory) unit and a preparation method thereof

ActiveCN105551518AImprove noise immunitySize matchSolid-state devicesSemiconductor/solid-state device manufacturingFloating body effectStatic random-access memory

The invention provides an SOI single-port SRAM unit and a preparation method thereof. The unit comprises a first phase inverter composed of a first PMOS transistor and a first NMOS transistor; a second phase inverter composed of a second PMOS transistor and a second NMOS transistor; an obtaining transistor composed of a third NMOS transistor and a fourth NMOS transistor. In the SRAM unit, the four transistors forming the first phase inverter and the second phase inverter are L-type gates; heavy dopant contact regions are arranged in the regions at the outer sides of the bending angles of the L-type gates. According to the unit and the method of the invention, leakage power consumption and transistor threshold voltage drift resulted from the floating body effect and parasitic triode effect in the PD SOI instrument can be effectively inhibited under the condition of sacrificing a relatively small unit area; the anti-noise capability of the unit is improved; the preparation technique of the invention introduces no extra mask plate and is fully compatible with the exiting logic technique; the inner part of the unit is a center symmetrical structure which is beneficial for matching the size and the threshold voltage of the MOS tube and for matching an array and is convenient for a full-custom SRAM chip.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

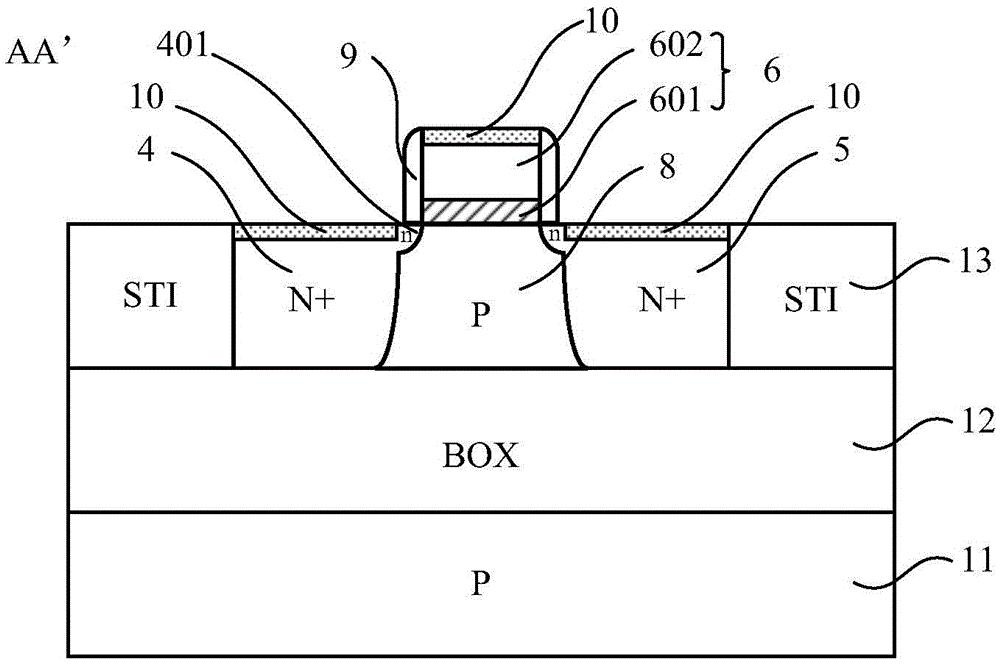

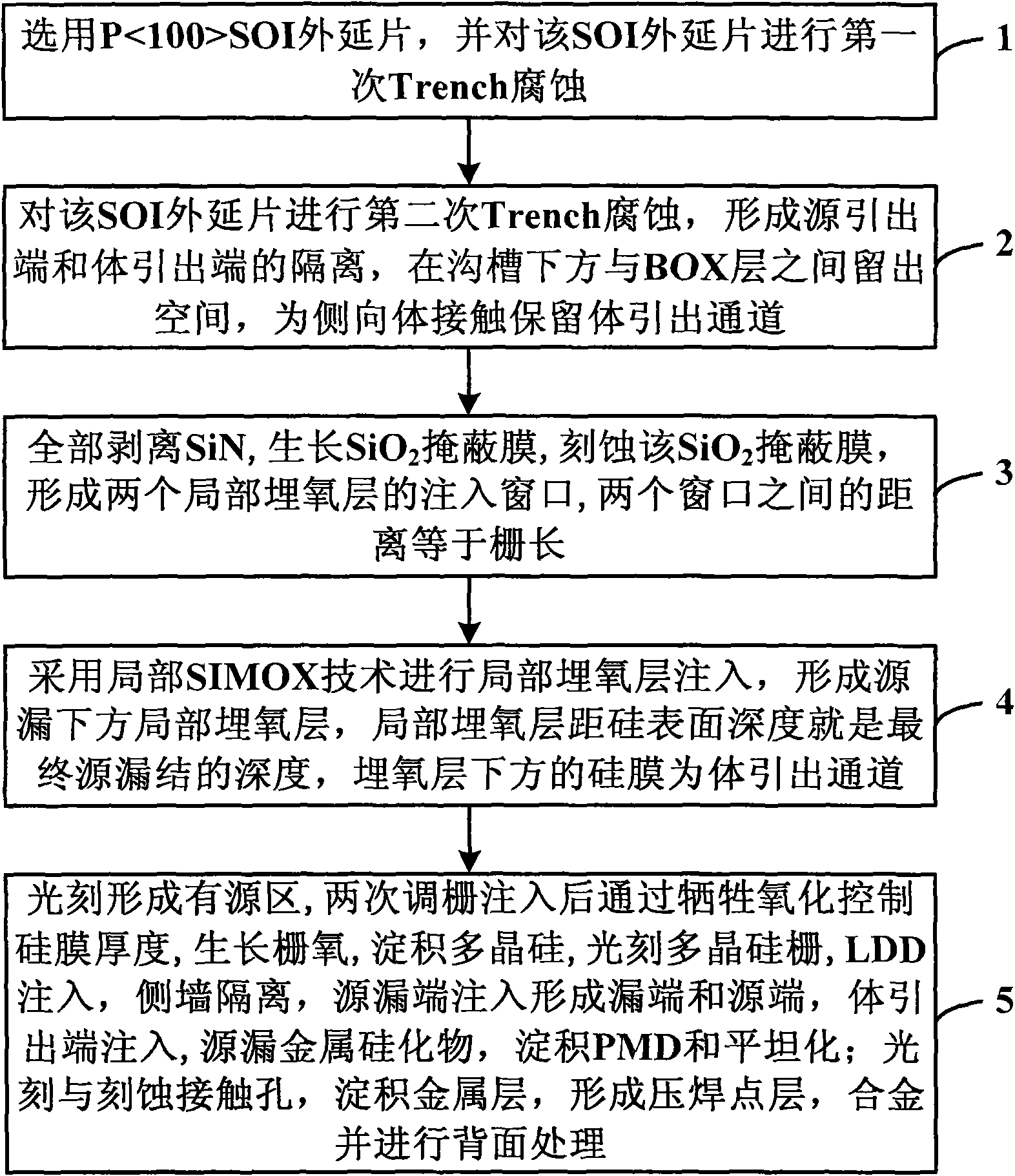

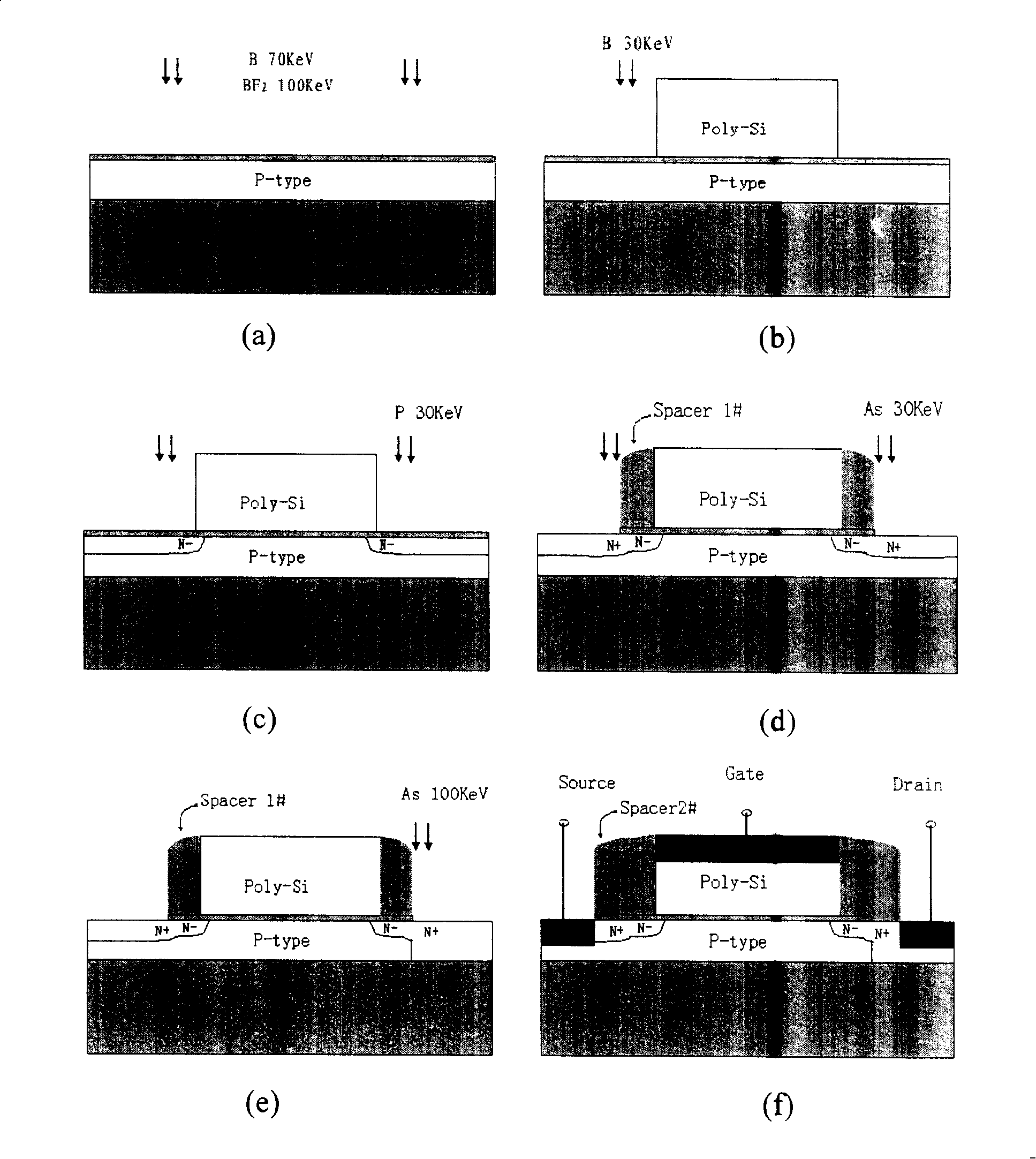

Method for manufacturing body-contact structure of partially depleted SOI MOSFET

ActiveCN101621009AReduce possession effectInhibition of possession effectSemiconductor/solid-state device manufacturingMOSFETBody contact

The invention discloses a method for manufacturing a body-contact structure of a partially depleted SOI MOSFET, which comprises the following steps: selecting a P<100>SOI epitaxial wafer and subjecting the SOI epitaxial wafer to primary Trench corrosion; performing secondary Trench corrosion to form an isolation layer between a source leading-out end and a body leading-out end and preserving a space between the bottom of a trench and a BOX layer to preserve a body leading-out channel for lateral body contact; stripping SiN completely, growing a SiO2 mask film and etching the SiO2 mask film to form injection windows of two local buried oxide layers; injecting the local buried oxide layers to form local buried oxide layers under source and drain regions; forming an active region by photoetching, performing tuned grid injection twice, controlling the thickness of a silicon film by sacrificial oxidation, growing gate oxide, depositing polysilicon, etching a polysilicon gate, performing LDD injection and side wall isolation, performing source and drain end injection to form a drain end and a source end, performing body leading-out end injection, growing source and drain silicide and performing PMD and planarization; and photoetching and etching contact holes, depositing a metal layer to form a pad layer and alloy, and performing back treatment.

Owner:BEIJING ZHONGKE XINWEITE SCI & TECH DEV

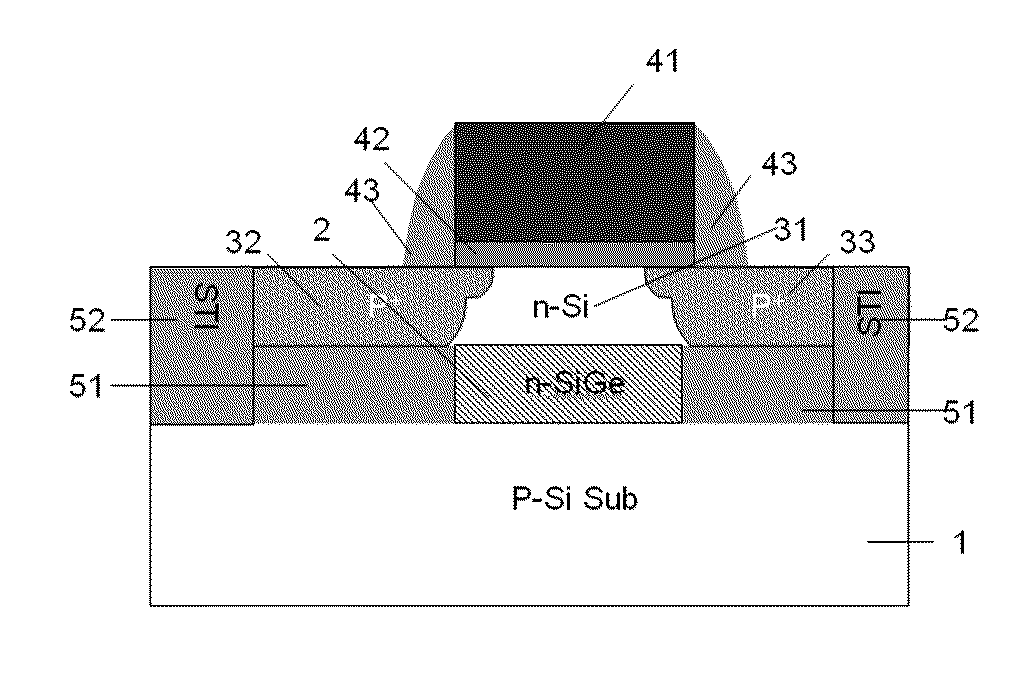

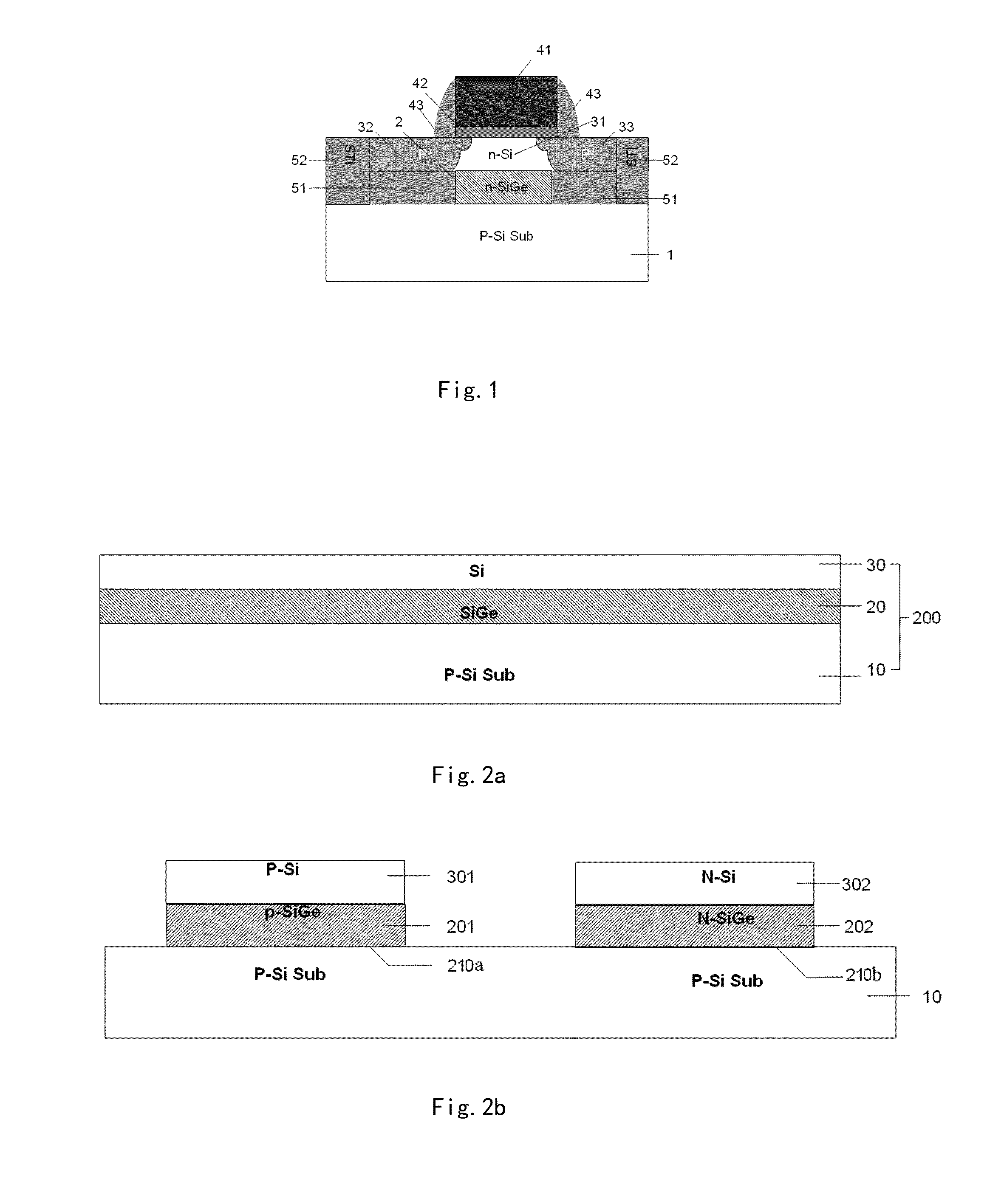

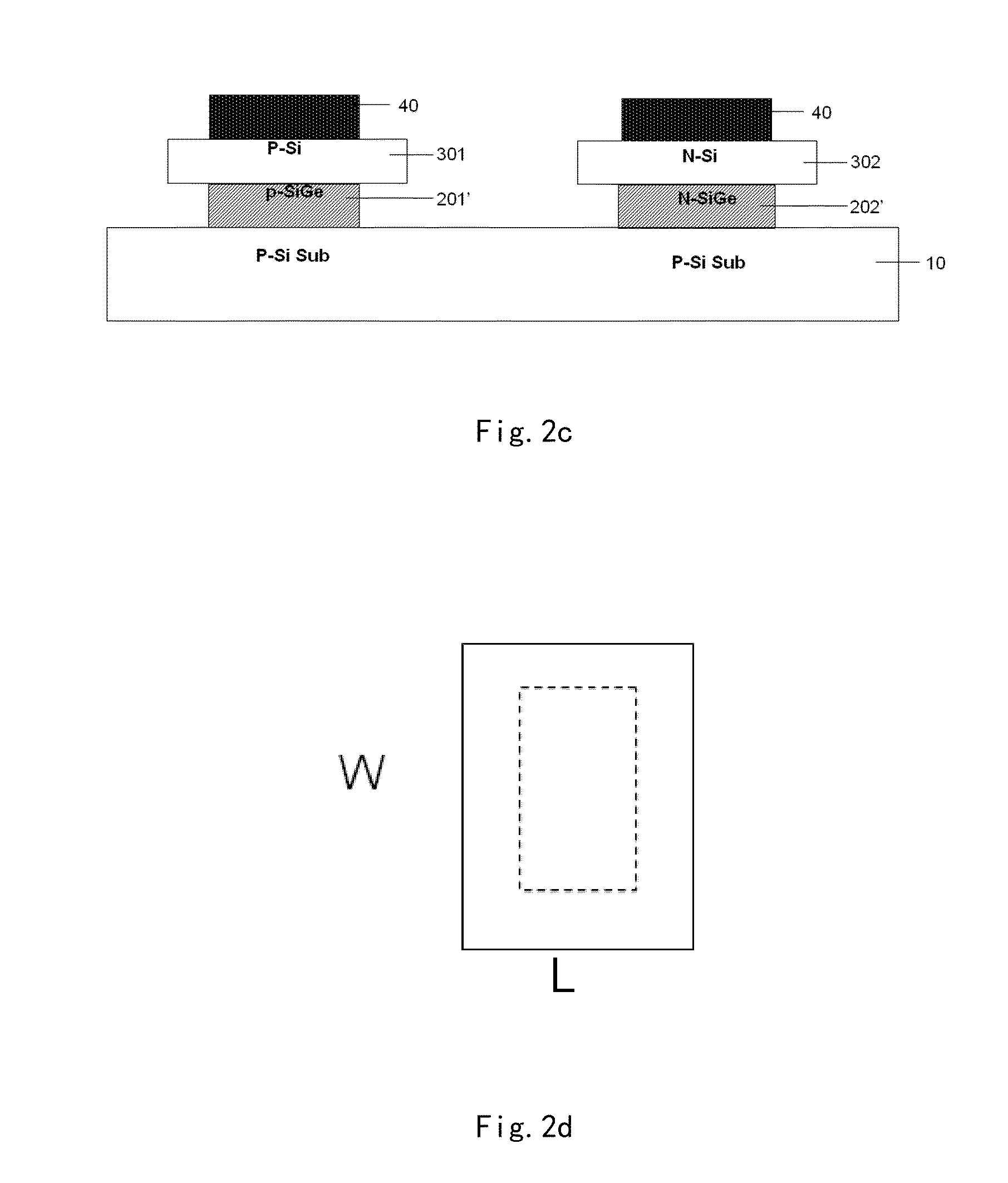

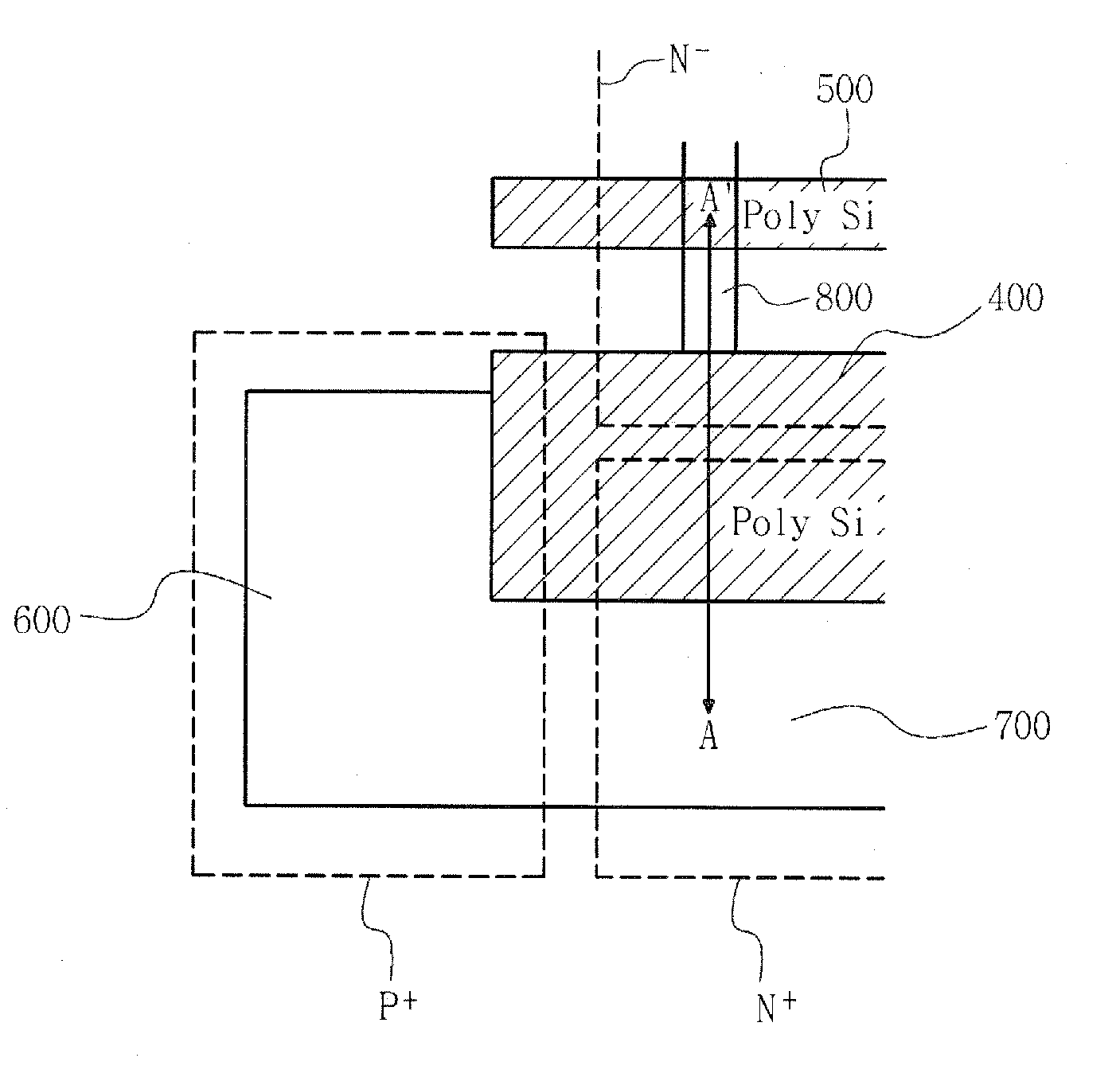

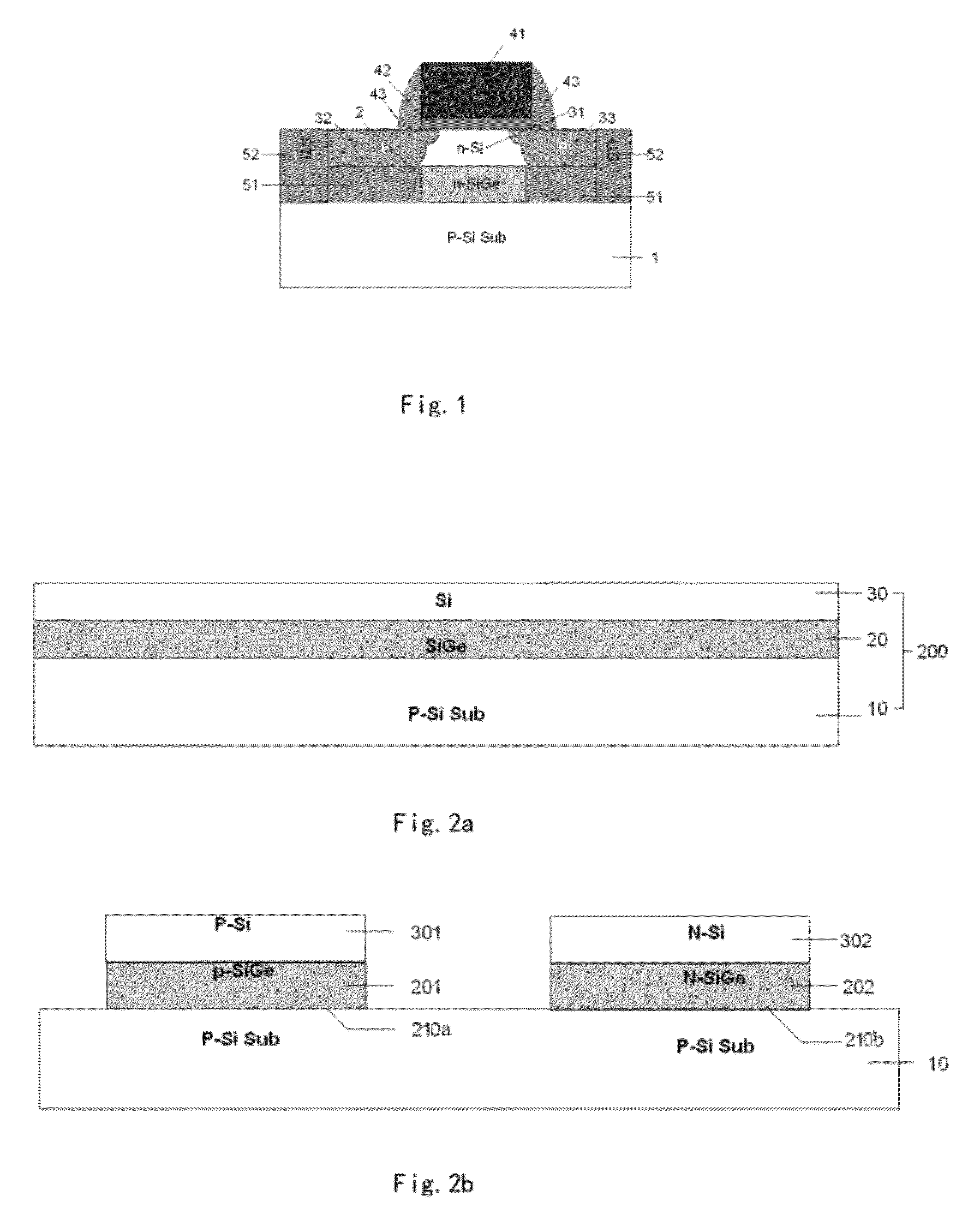

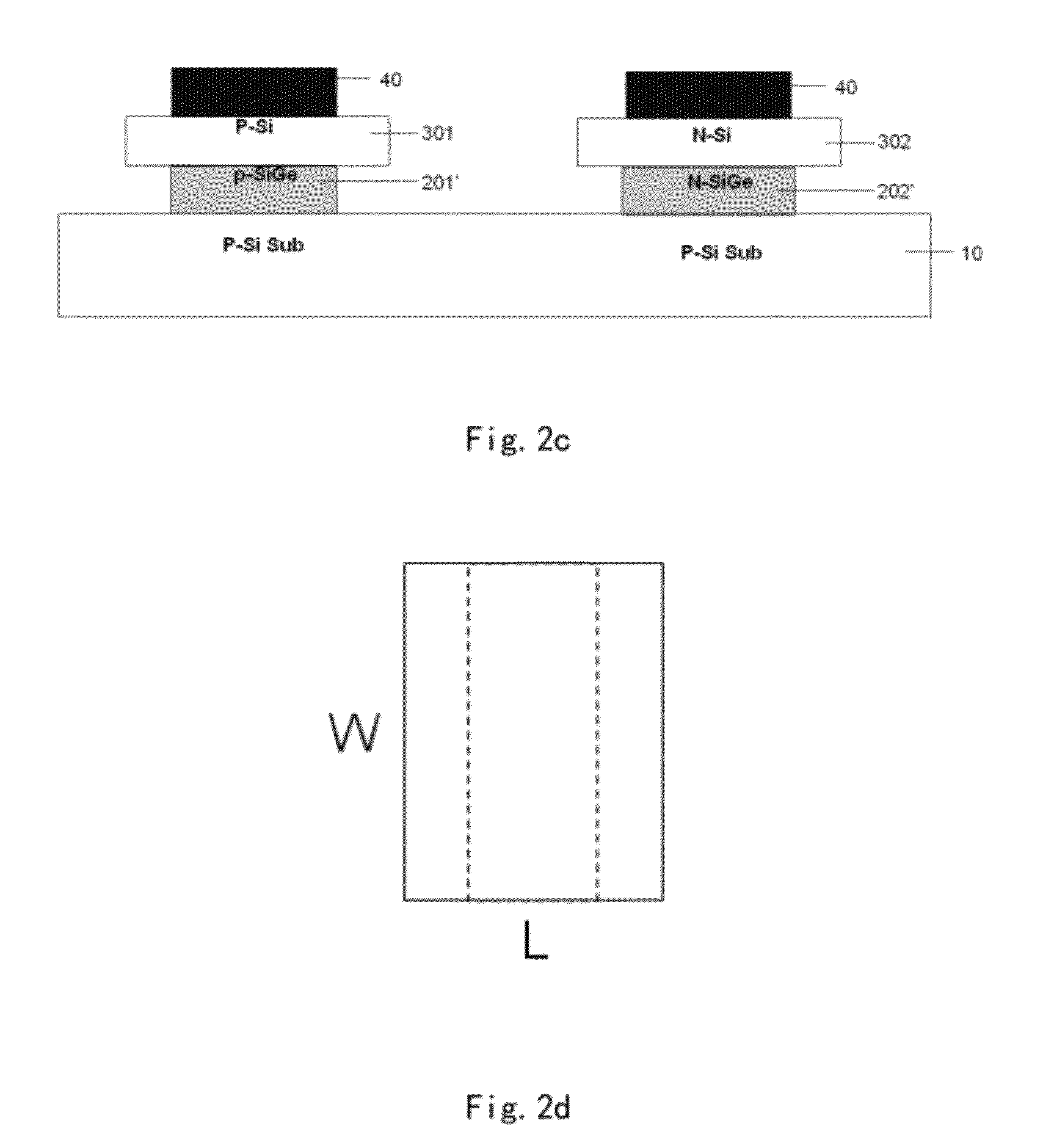

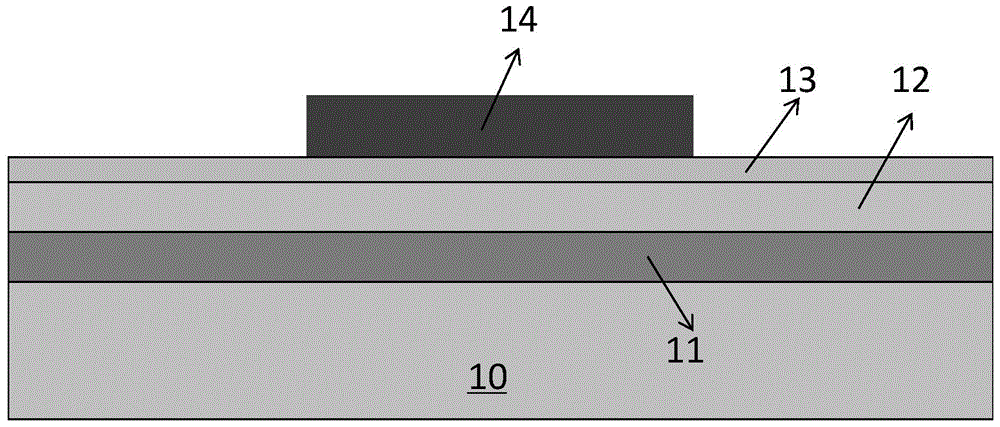

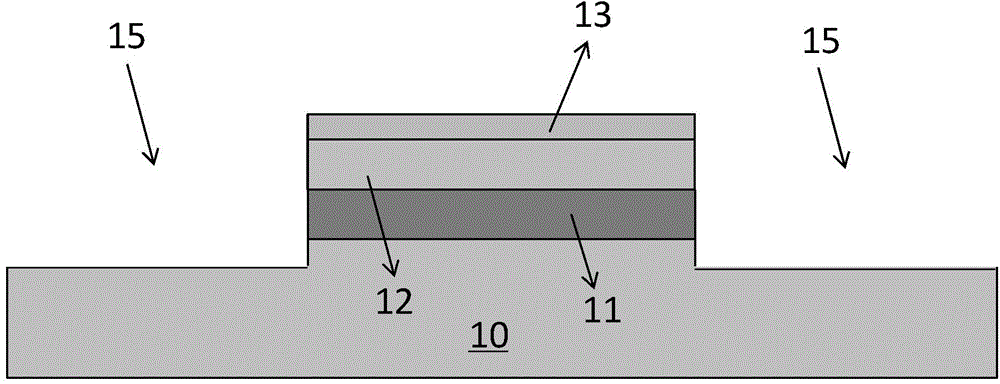

Mos device for eliminating floating body effects and self-heating effects

InactiveUS20120018809A1Suppression of floating body effectReduce self-heating effectSolid-state devicesSemiconductor/solid-state device manufacturingFloating chargeFloating body effect

A MOS device having low floating charge and low self-heating effects are disclosed. The device includes a connective layer coupling the active gate channel to the Si substrate. The connective layer provides electrical and thermal passages during device operation, which could eliminate floating effects and self-heating effects. An example of a MOS device having a SiGe connector between a Si active channel and a Si substrate is disclosed in detail and a manufacturing process is provided.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

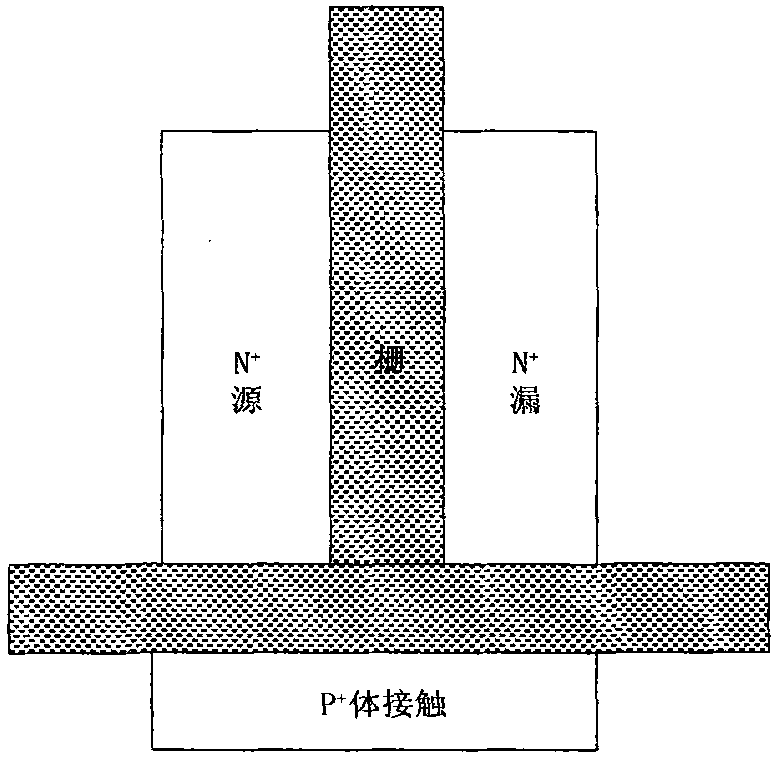

Body biasing structure of soi

ActiveUS20060278927A1Suppression of floating body effectTransistorSolid-state devicesMOSFETFloating body effect

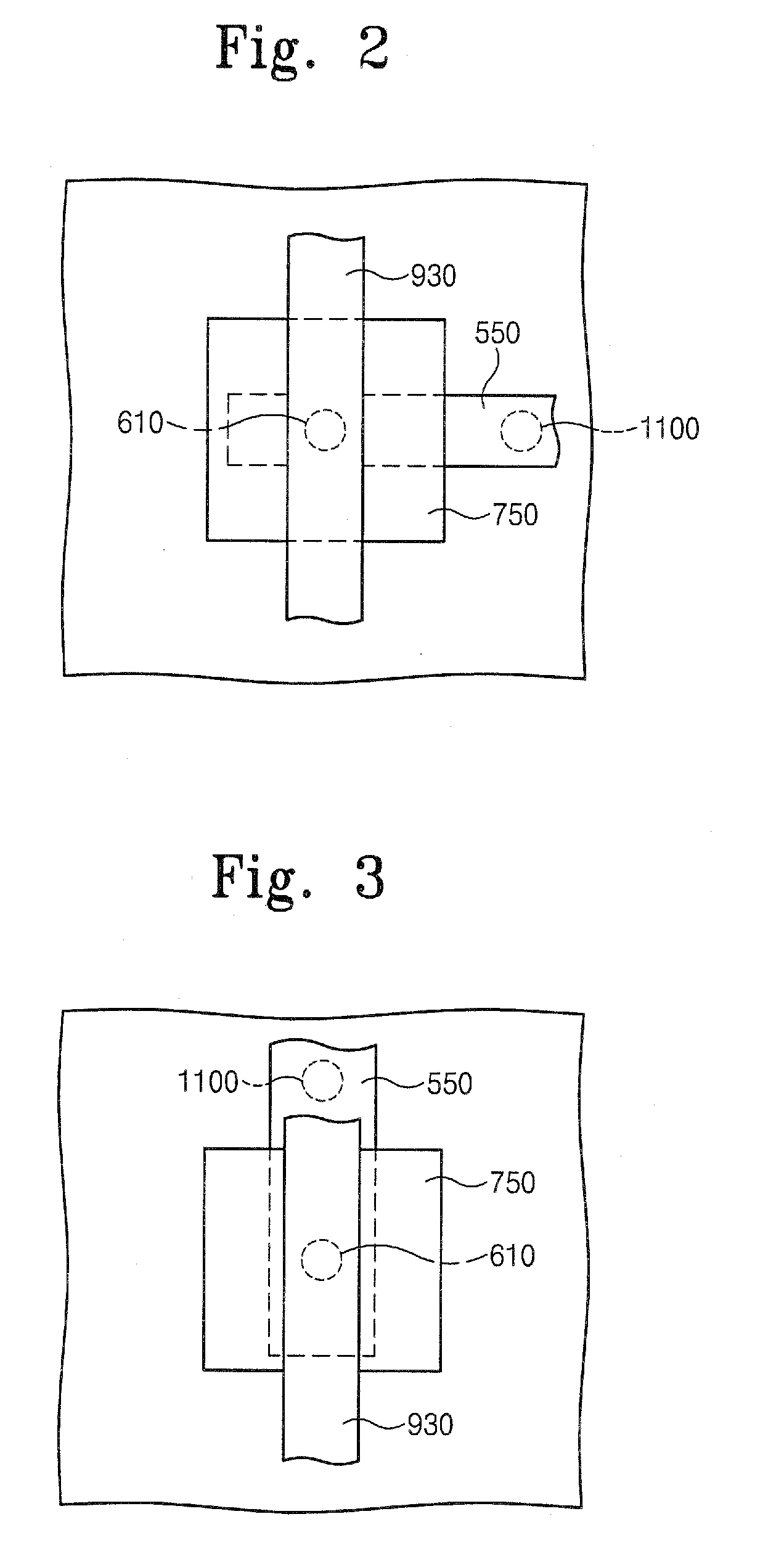

A body biasing structure of devices connected in series on an SOI substrate is provided. According to some embodiments, the shallow junction of common source / drain regions enables all devices to bias by only one body contact on an SOI substrate like a conventional bulk MOSFET, and the floating body effect on an SOI substrate can be prevented.

Owner:SEOUL NAT UNIV R&DB FOUND +1

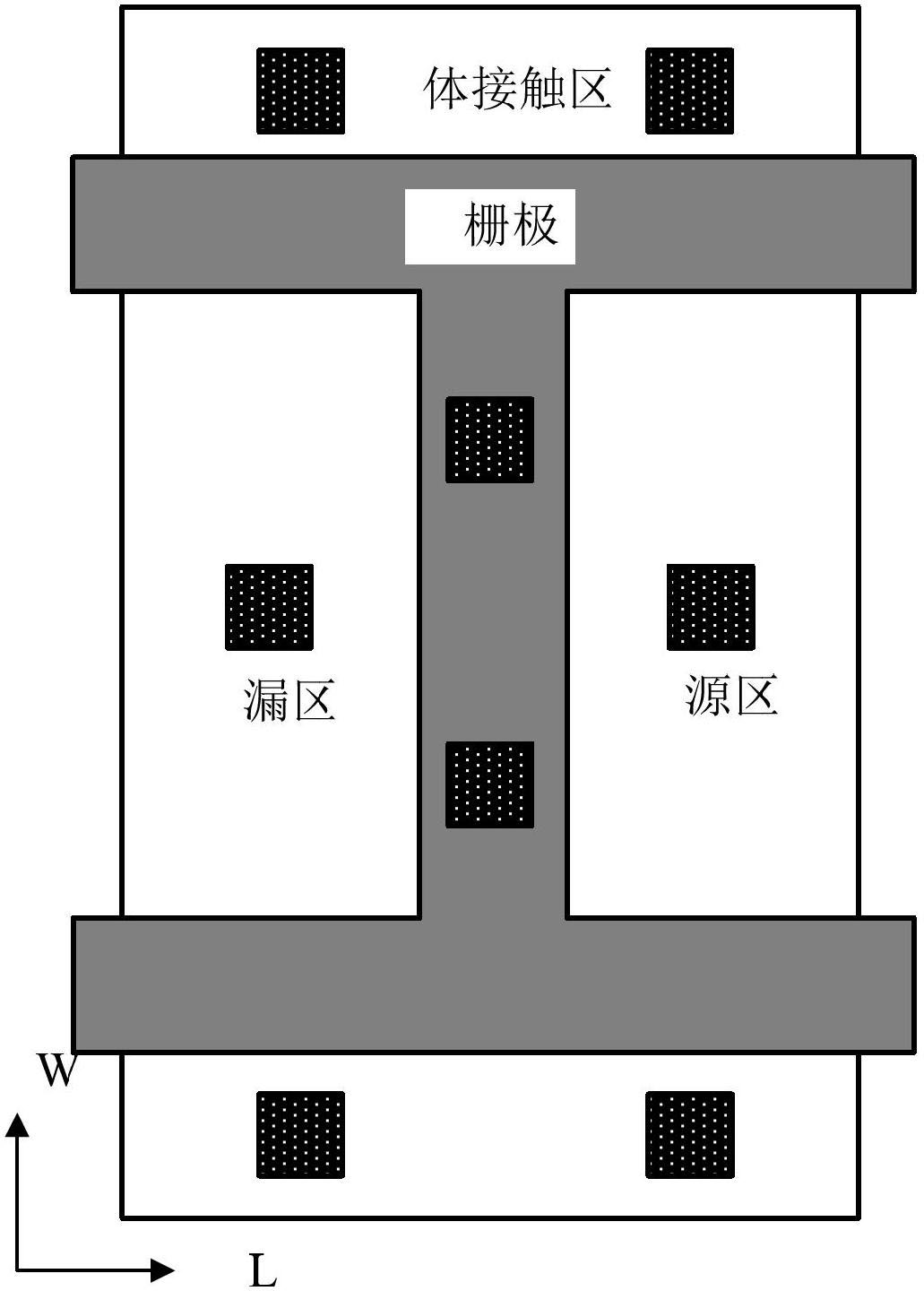

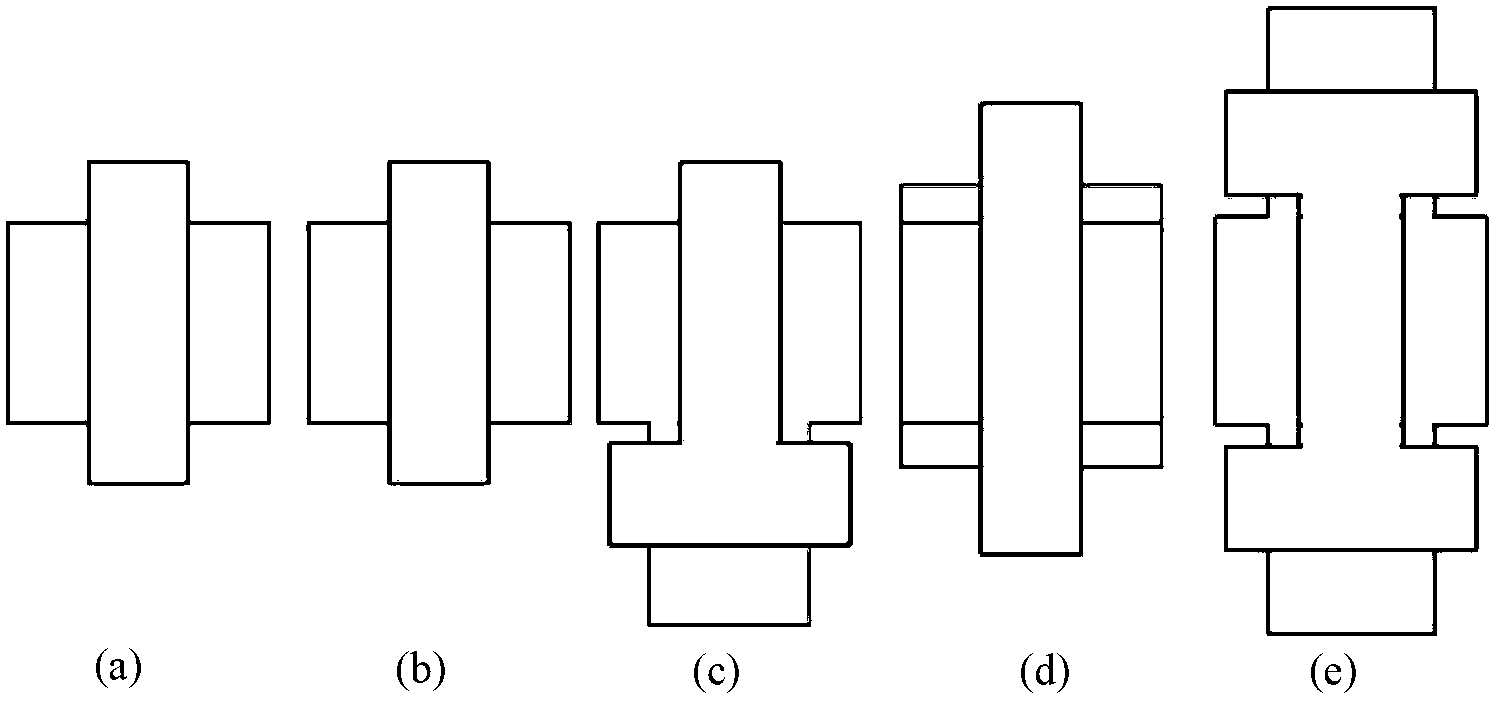

SOI MOS transistor

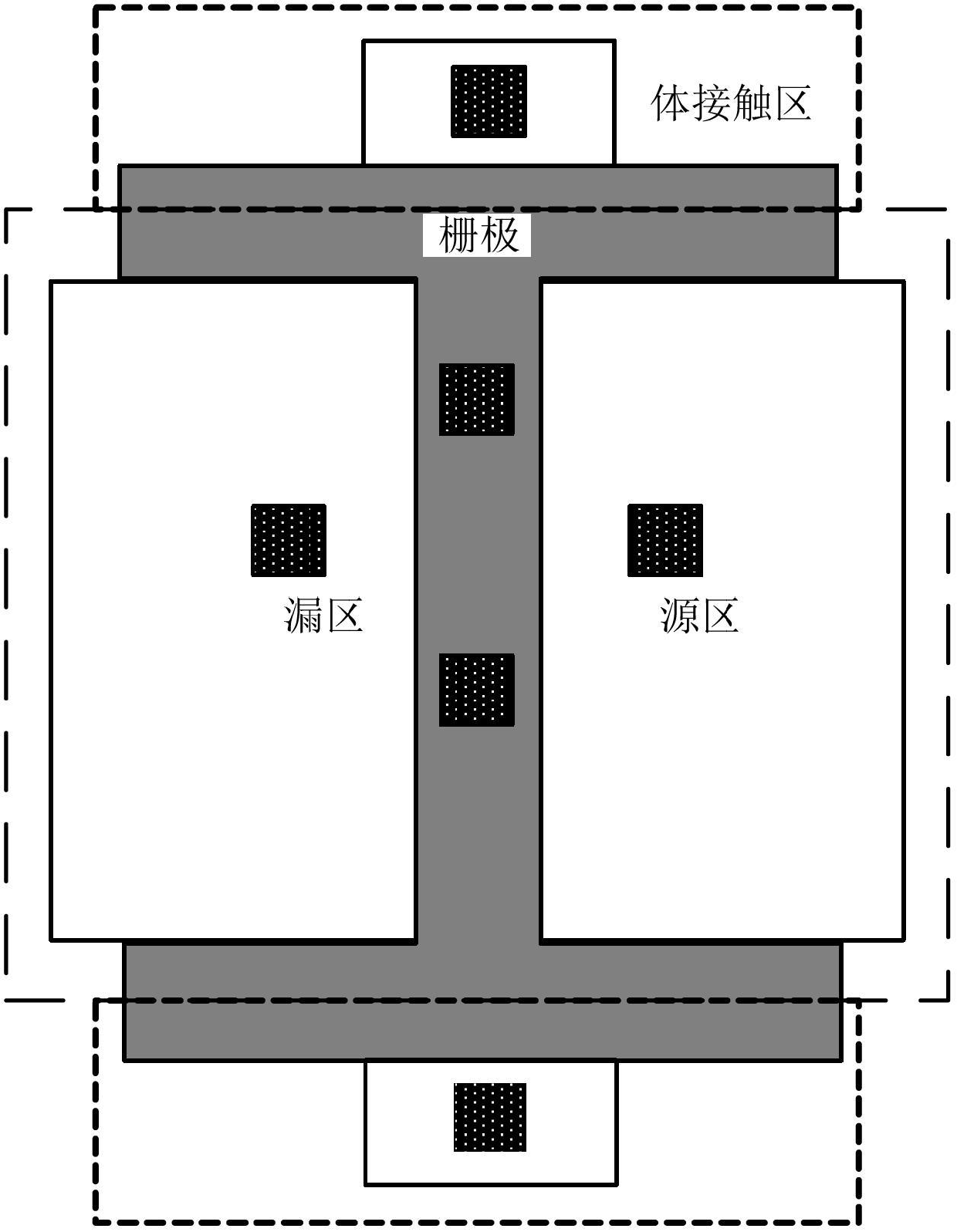

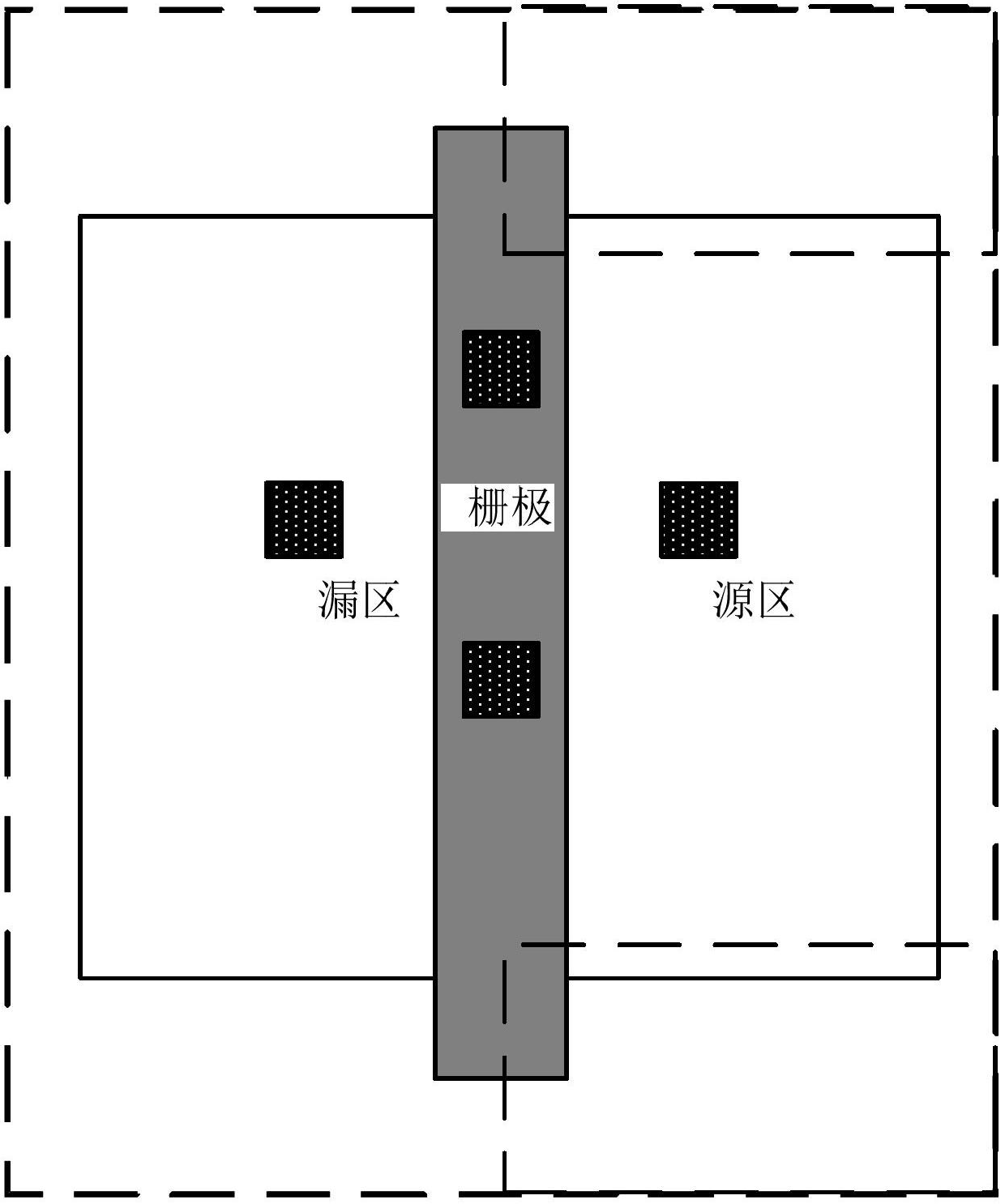

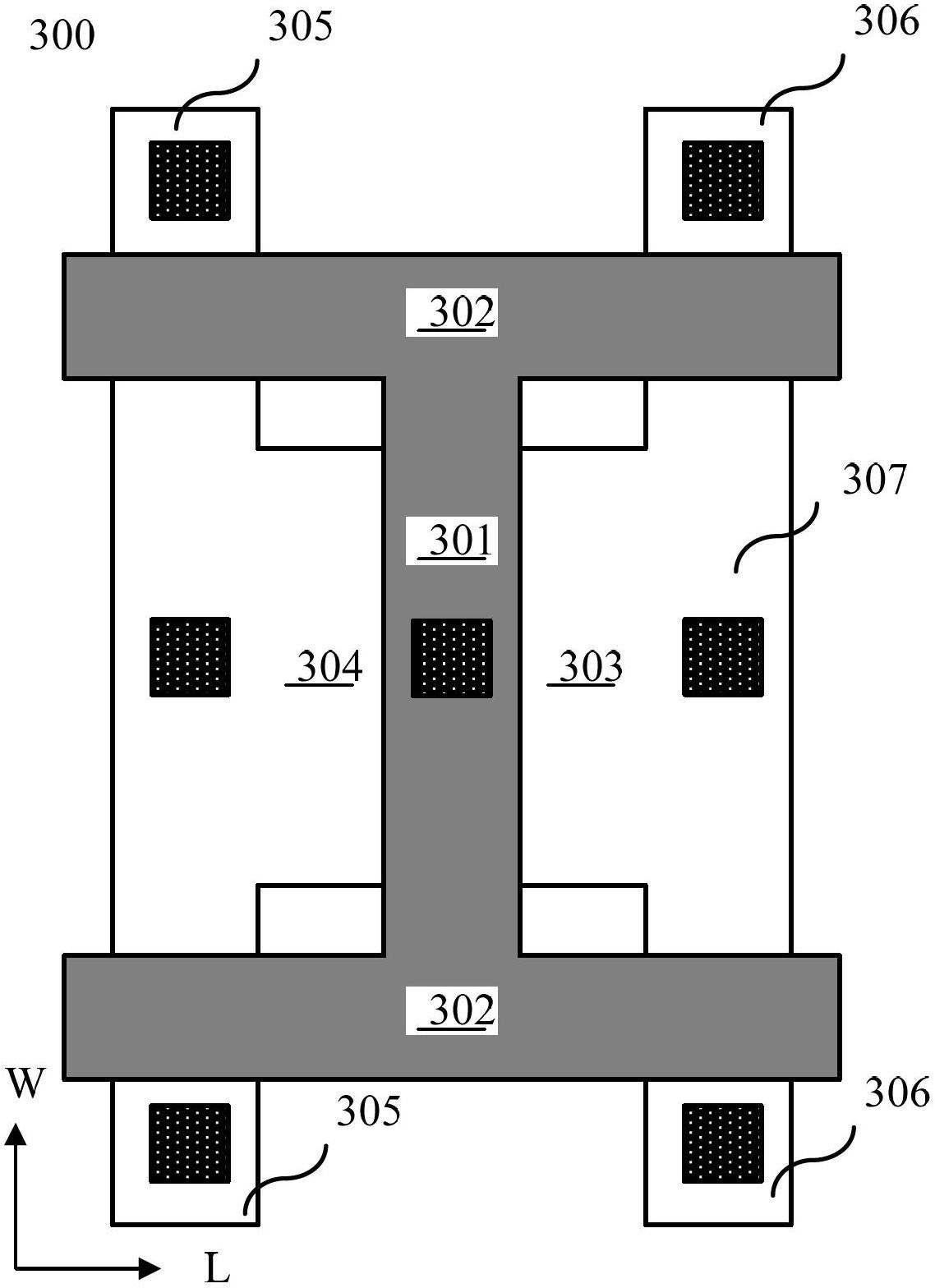

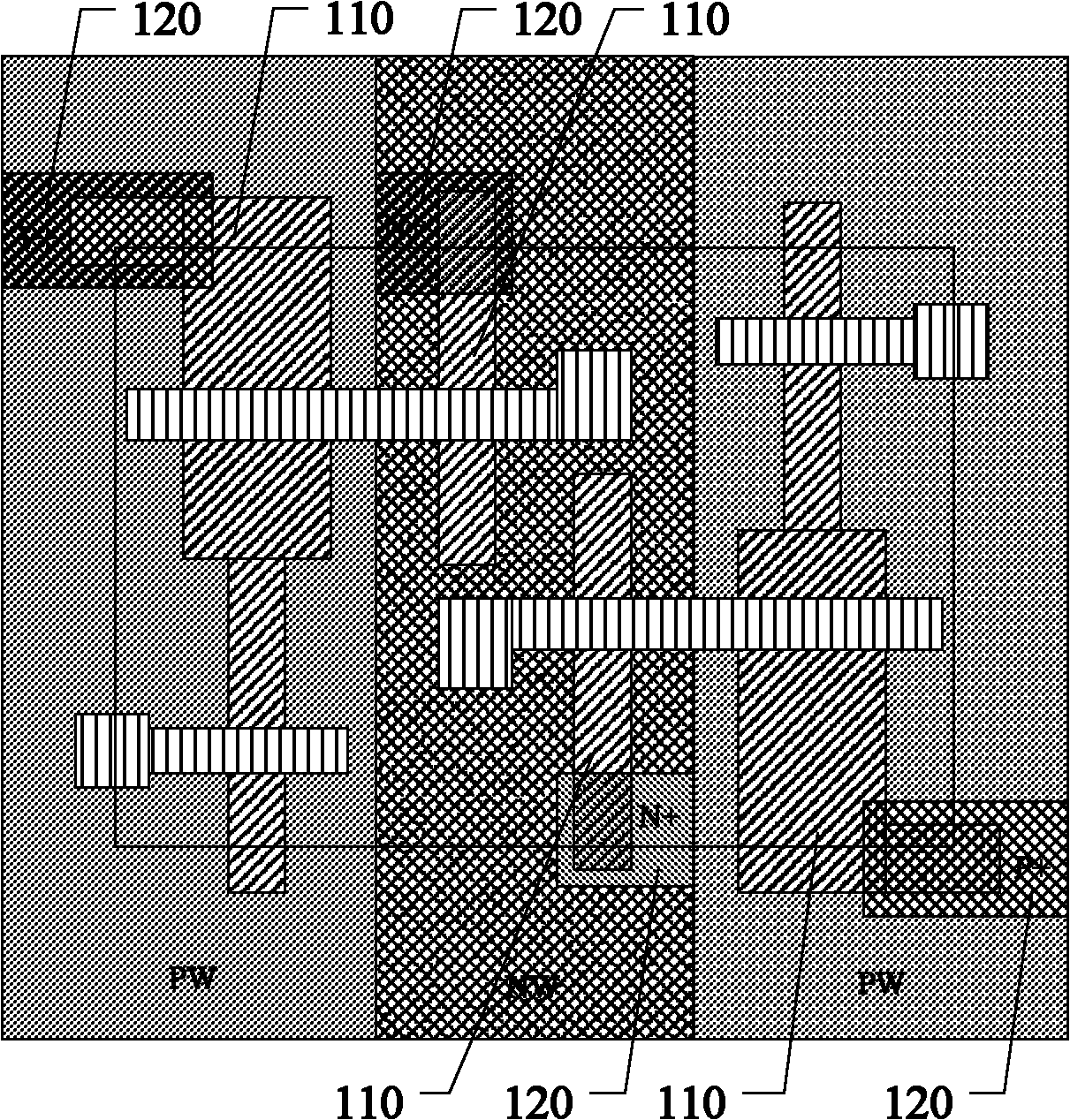

ActiveCN102683416ASuppression of floating body effectReduce parasitic capacitanceSemiconductor devicesElectrical resistance and conductanceFloating body effect

The invention provides an SOI (silicon on insulator) MOS (metal oxide semiconductor) transistor which comprises active areas, an H-shaped or T-shaped grid, a source area, a drain area, a source end body contact area and a drain end body contact area, wherein the active areas have a continuous shape and are formed in an SOI layer of an SOI substrate; the H-shaped or T-shaped grid comprises a main grid part and at least one expansion grid part; each expansion grid part is located at a tail end of the main grid part in the width direction and extends in the length direction of the main grid part; the source area and drain area are located in the active areas on the two sides of the main grid part respectively; the source end body contact area is located in the active area on one side of the source area and isolated from the source area by the expansion grid part; the drain end body contact area is located in the active area on one side of the drain area and isolated from the drain area by the expansion grid part; and if a source end body contact area and / or a drain end body contact area are arranged on the outer side of an expansion grid part, the main grid part extends a boundary exceeding the active area in the width direction at one end of the expansion grid part. The SOI MOS transistor provided by the invention can more effectively suppress the floating body effect and reduce the lateral leakage, body resistance and parasitic capacitance.

Owner:BEIJING ZHONGKE XINWEITE SCI & TECH DEV

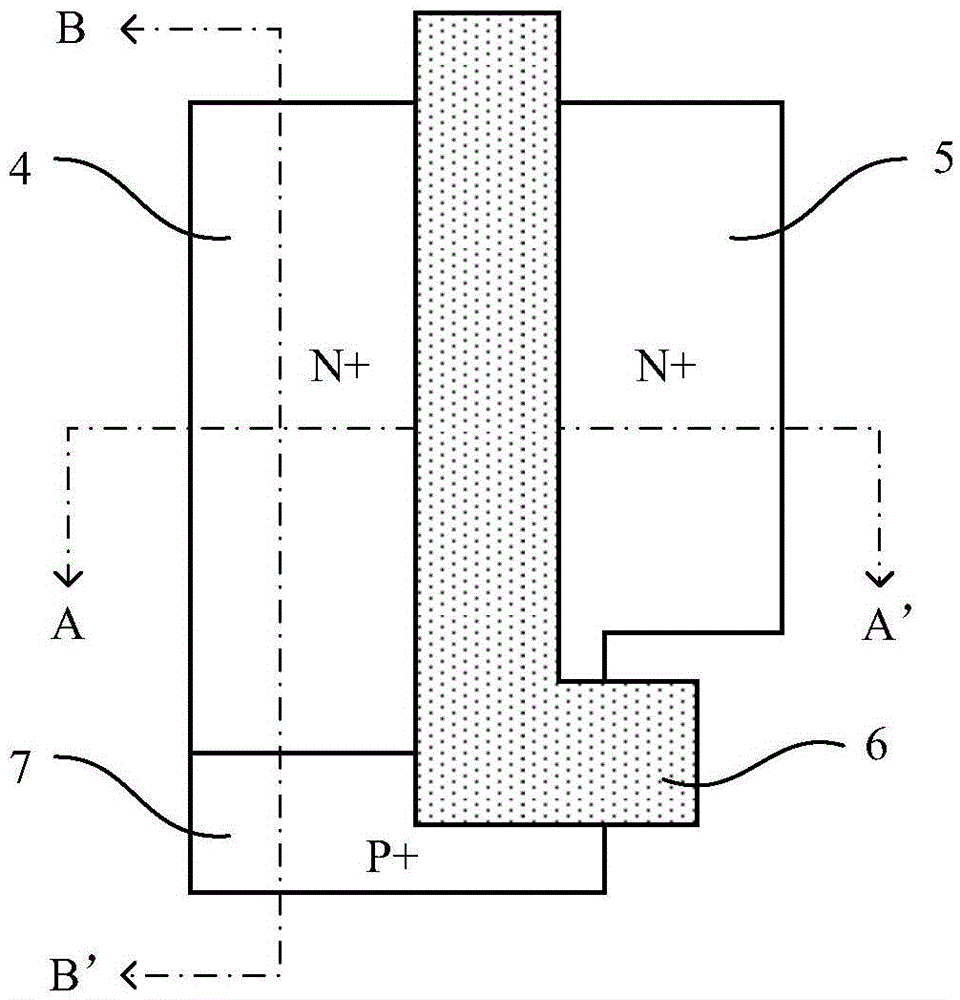

SOI-based MOS device structure and manufacturing method thereof

ActiveCN107516676AReduce areaGuaranteed Effective WidthTransistorSemiconductor/solid-state device manufacturingBody contactEngineering

The invention provides an SOI-based MOS device structure and a manufacturing method thereof. The structure comprises a backing bottom, an insulation buried layer, an active region and a shallow trench isolation structure, wherein an MOS device is formed in the active region, the MOS device comprises a grid region, a body region under the grid region, a first conductive type source region on the first lateral side in the body region and a second conductive type drain region on the second lateral side of the body region. The two ends of the grid region extend in the second lateral side direction to form an L-shaped bending corner. The active region further comprises a second conductive type body contact region, which is in contact with the body region and encloses the two vertical ends and bottom portion of the active region. The doping density of the contact region is greater than that of the body region. Box power leakage, upper and lower corner power leakage and sidewall power leakage due to the total dose effect of SOI device, the effective width of the source region can be ensured, and the driving capacity of the device may not be damaged.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Semiconductor device with height-controllable fin and preparation method

ActiveCN103681275AGood static performanceEliminate parasitic capacitanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceIsotropic etching

The invention relates to a semiconductor device with a height-controllable fin and a preparation method. The preparation method comprises the following steps: providing a semiconductor substrate; forming a first semiconductor material layer, a second semiconductor material layer and a hard mask layer on the substrate; etching the hard mask layer, a second semiconductor material layer and a first semiconductor material layer to form a trench and a fin pattern; performing isotropic etching to remove a part of the first semiconductor material layer in the fin pattern to form a virtual fin with reduced critical size; depositing dielectric layers to fill the trench and cover the fin pattern; etching the dielectric layers till the second semiconductor material layer below, in order to expose the second semiconductor material layer to form the fin. The preparation process of the fin is easy to control, and the obtained device is more stable.

Owner:SEMICON MFG INT (SHANGHAI) CORP

Mos device for eliminating floating body effects and self-heating effects

InactiveUS20120025267A1Suppression of floating body effectReduce self-heating effectTransistorSolid-state devicesFloating body effectEngineering

A SOI MOS device for eliminating floating body effects and self-heating effects are disclosed. The device includes a connective layer coupling the active gate channel to the Si substrate. The connective layer provides electrical and thermal passages during device operation, which could eliminate floating body effects and self-heating effects. An example of a MOS device having a SiGe connector between a Si active channel and a Si substrate is disclosed in detail and a manufacturing process is provided.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

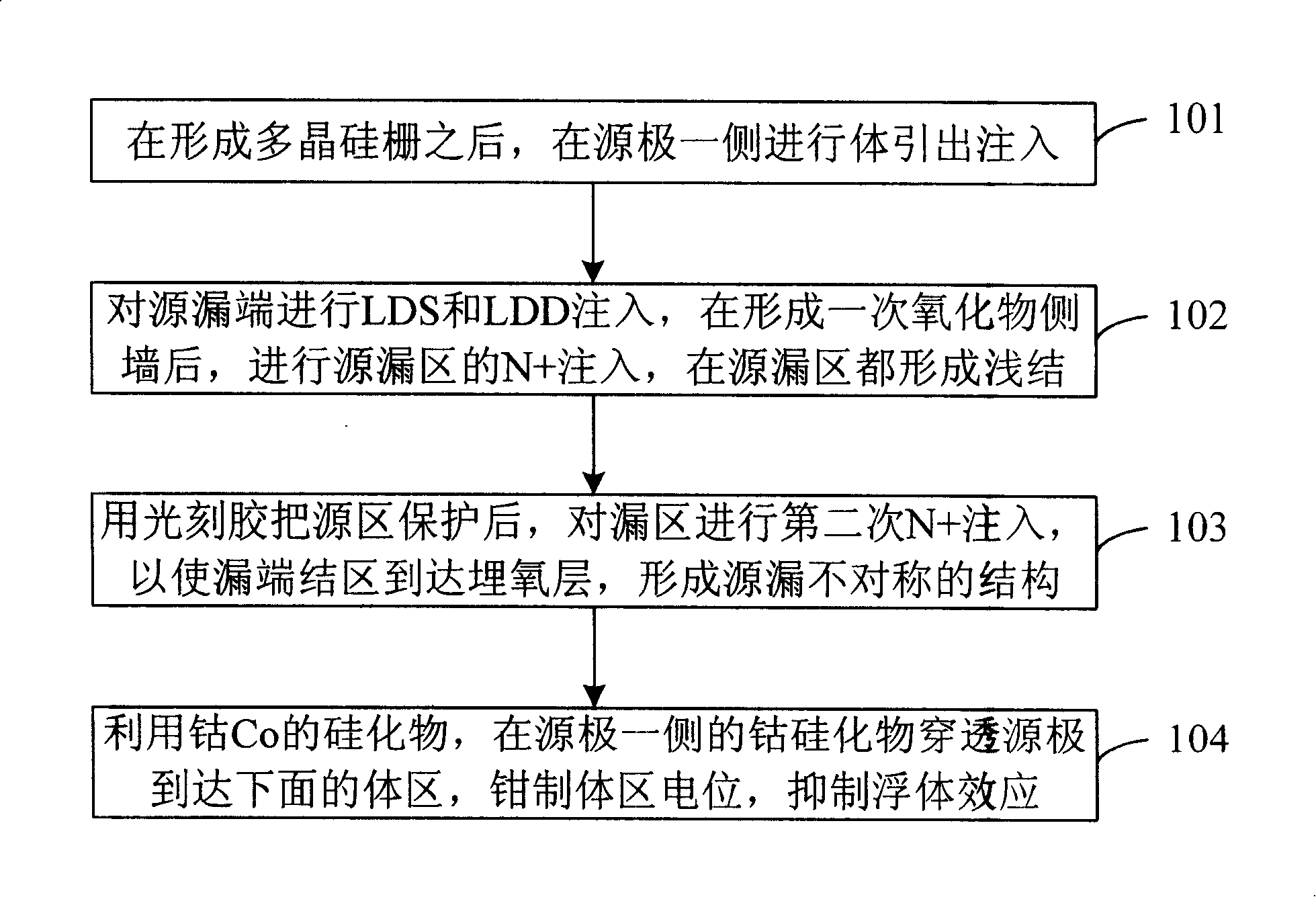

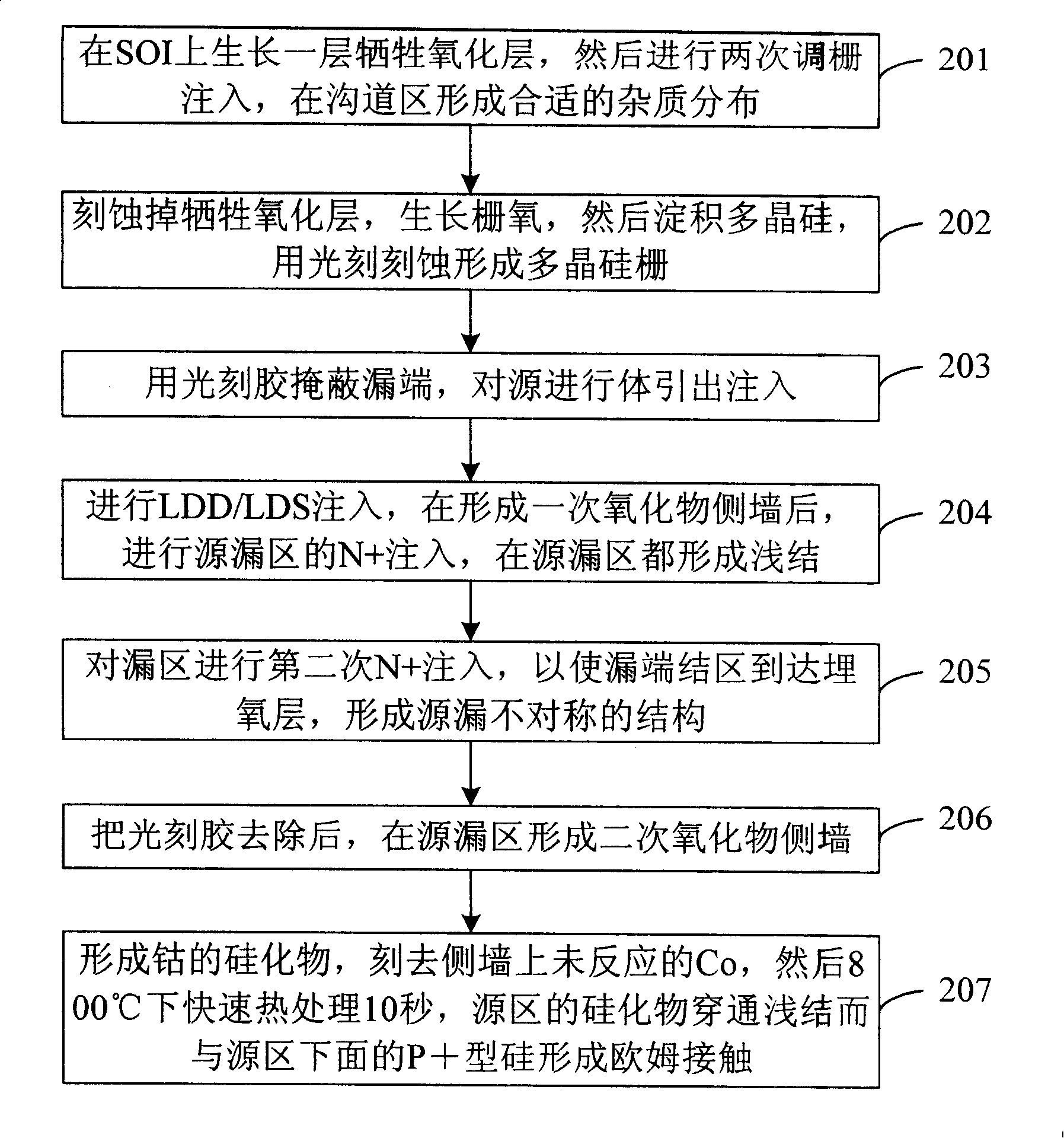

Method for realizing portion exhaust insulators upper silicon device physical contact

InactiveCN101231956ASuppression of floating body effectImprove performanceSemiconductor/solid-state device manufacturingResistFloating body effect

The invention relates to the technical field of body contact of SOI devices in the semiconductor technology, and discloses a method for achieving body contact of some depleted SOI devices. The invention comprises the following steps: A. after a polysilicon gate is formed, a body is led out and injected on one side of a source electrode; B. LDS and LDD are injected into source / drain ends; after a primary oxide side wall is formed, N+ is injected into source / drain areas to form shallow junctions in the source / drain areas; C. after the source area is protected with photosensitive resist, the drain area is injected with N+ for the second time so that a junction area on the drain end reaches a buried oxide layer, thus forming a source / drain unsymmetrical structure; D. cobaltic silicide is used; the cobaltic silicide on one side of a source electrode penetrates the source electrode and reaches a body area below, which limits the potential of the body area and inhibits floating effect. By adopting the invention, not only the floating effect is effectively inhibited, but also the performance of some depleted SOI devices is improved. In addition, the invention is compatible with standard complementary metal-oxide-semiconductor transistors, and has the advantages of simple process, low cost and so on.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

Eight-transistor static random access memory unit

ActiveCN103325788AEliminate the floating body effectHighly integratedSolid-state devicesSemiconductor devicesFloating body effectBody region

The invention provides an eight-transistor static random access memory unit which at least comprises a first phase inverter, a second phase inverter and a transmission gate. The first phase inverter is composed of a first PMOS transistor and a first NMOS transistor. The second phase inverter is composed of a second PMOS transistor and a second NMOS transistor. The transmission gate is composed of a third NMOS transistor, a fourth NMOS transistor, a fifth NMOS transistor and a sixth NMOS transistor. The first PMOS transistor, the first NMOS transistor, the second PMOS transistor and the second NMOS transistor are all of source body ohmic contact body leading-out structures. According to the eight-transistor static random access memory unit, heavy doping with the same polarity as the polarity of a body area is carried out on a source region of each transistor, the ohmic contact between the source regions and the body regions is achieved, the floating body effects of partial used-up SOI transistors are eliminated, the processes and the domain are not required to be additionally increased, and the high integration density of the unit is ensured. The eight-transistor static random access memory unit is compatible with a conventional CMOS process and suitable for industrial production.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

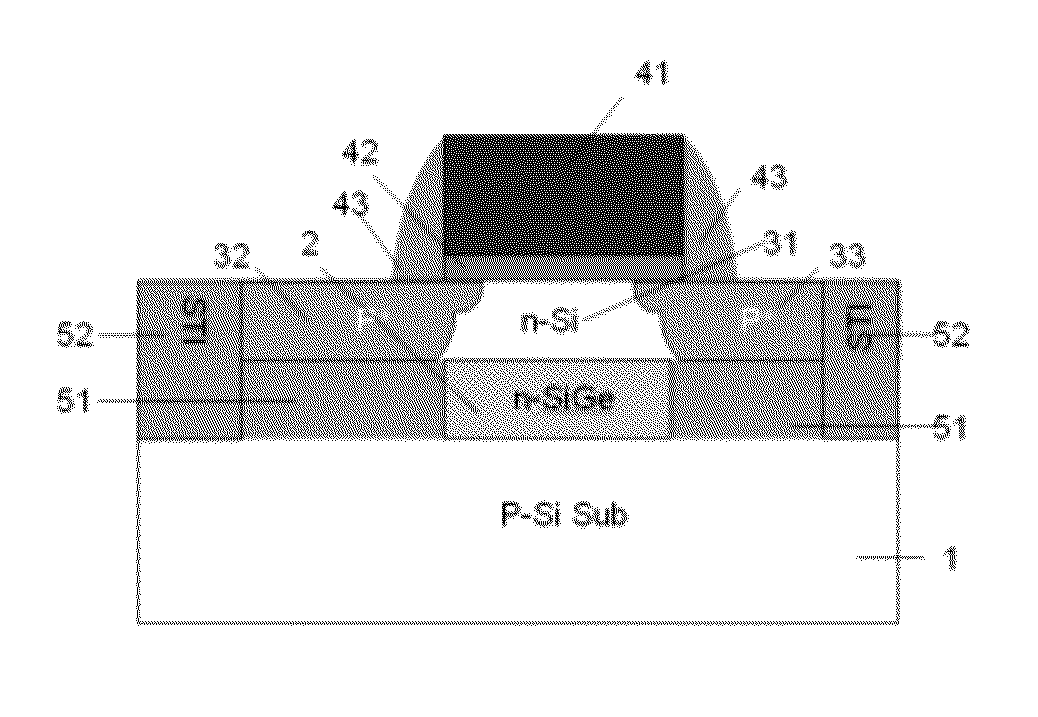

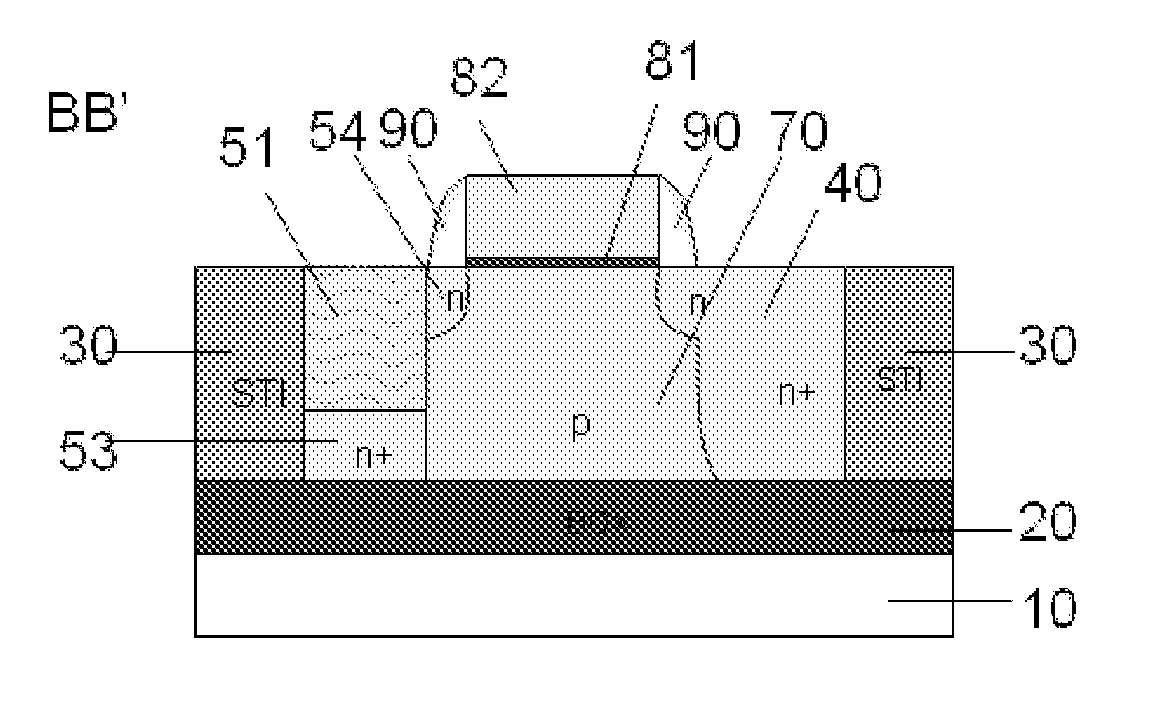

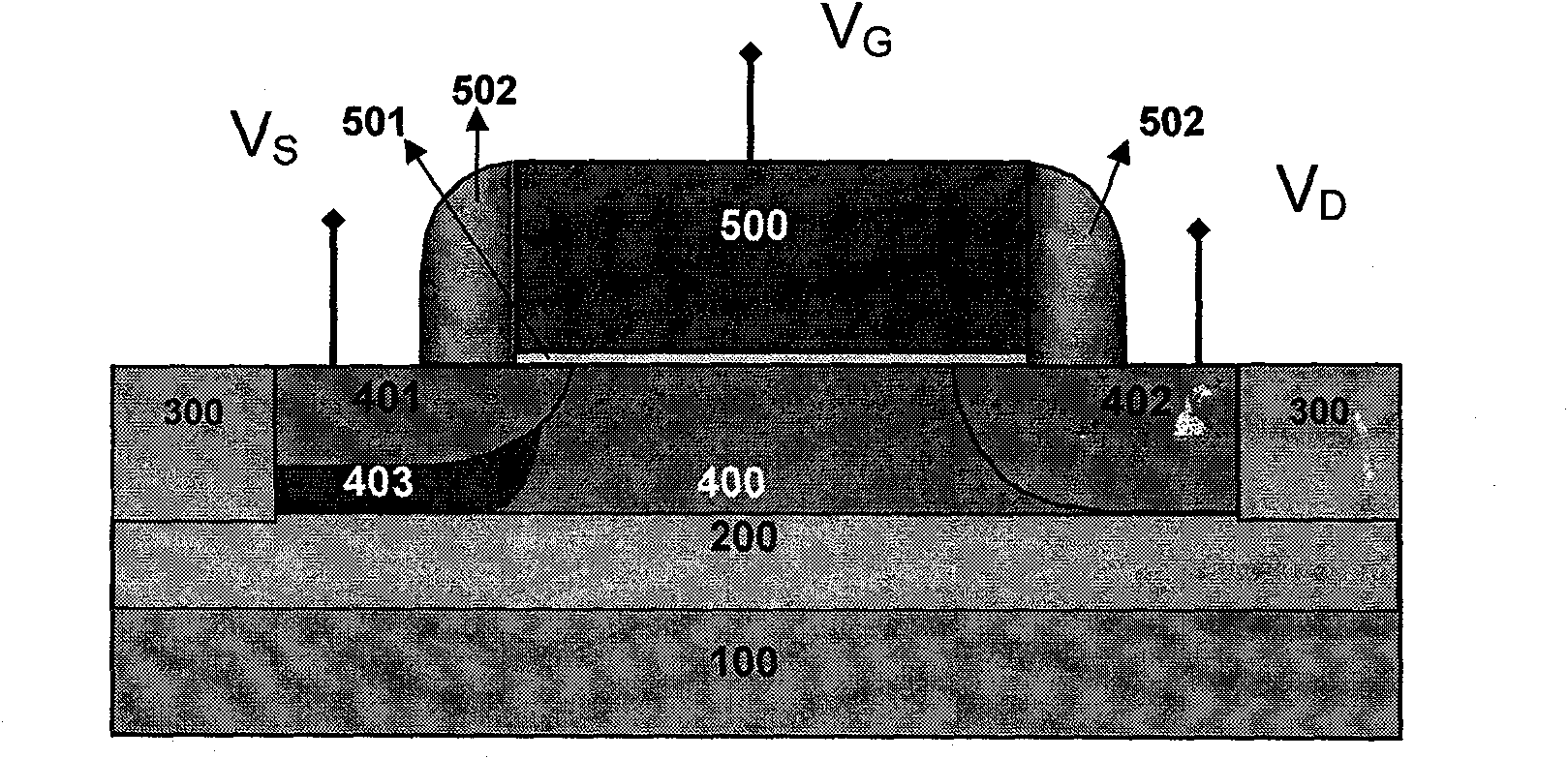

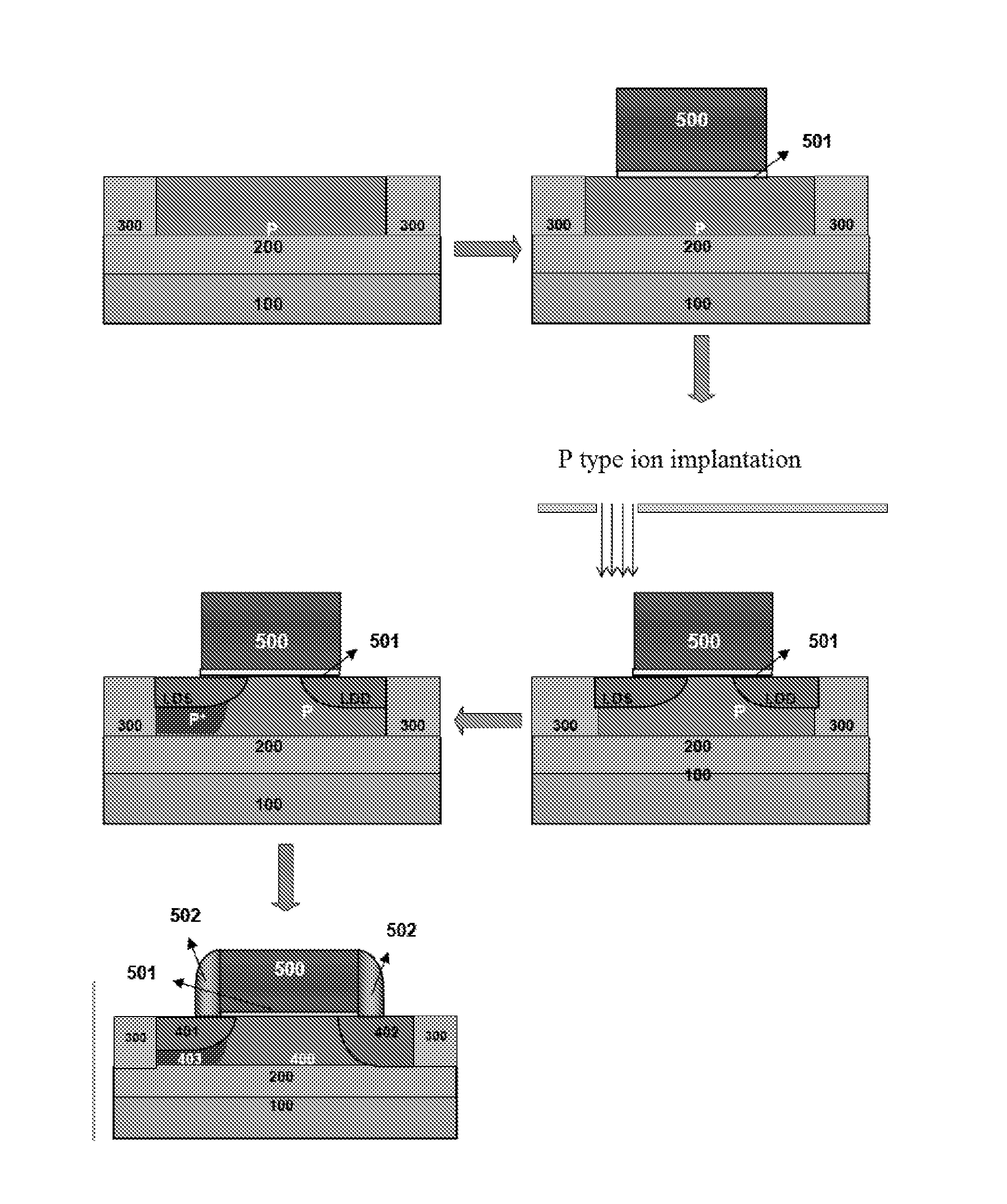

Soi mos device having bts structure and manufacturing method thereof

InactiveUS20120012931A1Improved BTS structureSuppression of floating body effectSolid-state devicesSemiconductor/solid-state device manufacturingCMOSFloating body effect

The present invention discloses a SOI MOS device having BTS structure and manufacturing method thereof. The source region of the SOI MOS device comprises: two heavily doped N-type regions, a heavily doped P-type region formed between the two heavily doped N-type regions, a silicide formed above the heavily doped N-type regions and the heavily doped P-type region, and a shallow N-type region which is contact to the silicide; an ohmic contact is formed between the heavily doped P-type region and the silicide thereon to release the holes accumulated in body region of the SOI MOS device and eliminate floating body effects thereof without increasing the chip area and also overcome the disadvantages such as decreased effective channel width of the devices in the BTS structure of the prior art. The manufacturing method comprises steps of: forming a heavily doped P-type region via ion implantation, forming a metal layer above the source region and forming a silicide via the heat treatment between the metal layer and the Si underneath. The device in the present invention could be fabricated via simplified fabricating process with great compatibility with traditional CMOS technology.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Semiconductor device and manufacturing method thereof

InactiveCN105261587ALow costReduce power consumptionSemiconductor/solid-state device manufacturingSemiconductor devicesElectricityElectrical conductor

The invention provides a semiconductor device, which comprises a substrate, a second conductor layer, a third conductor layer, isolating structures, hollow cavities, oxide layers, oxidation barrier layers on the oxide layers, and a device structure, wherein the substrate comprises a first semiconductor material; the second conductor layer is located on the substrate; the third conductor layer is located on the second conductor layer; the isolating structure is located at two sides of the third semiconductor layer above the substrate; and the hollow cavities are located at the end parts of the second semiconductor layer and between the third semiconductor layer and the substrate; the oxide layers and the oxidation barrier layers thereon are located on the inner surfaces of the hollow cavities and on the side walls of the isolating structures; the device structure is located on the third semiconductor layer; and source-drain regions of the device structure are located above the hollow cavities. The device structure provided by the invention simultaneously has the advantages of a bulk-silicon device and an SOI device, and has the characteristics of low cost, small electricity leakage, low power consumption, high speed, relatively simple process and high integration level.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

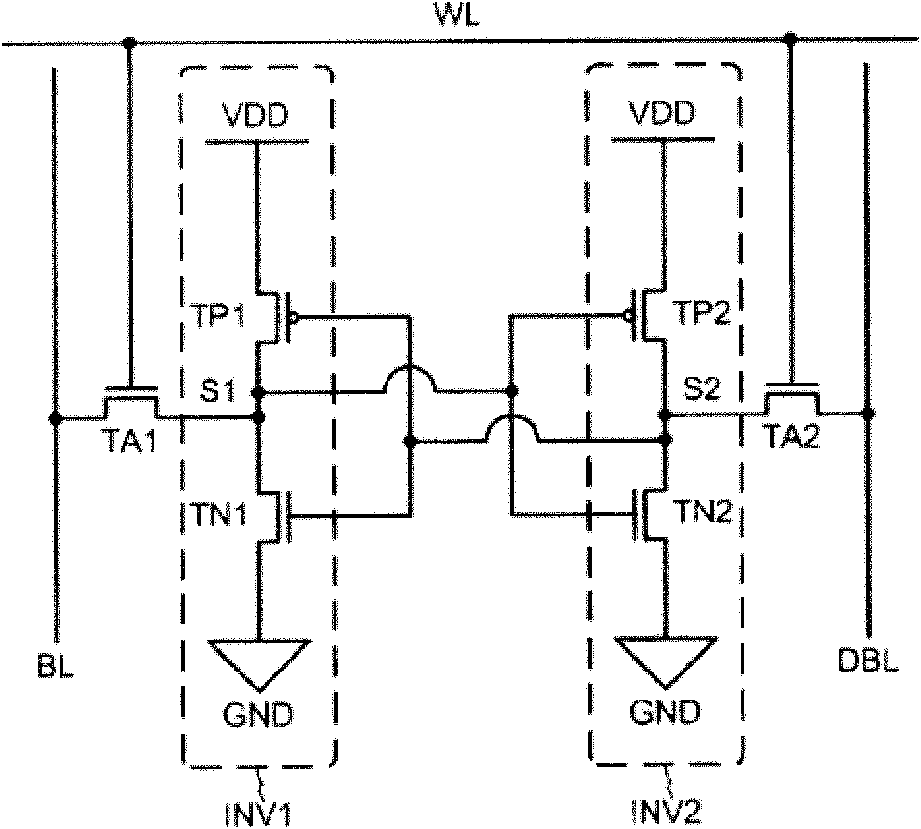

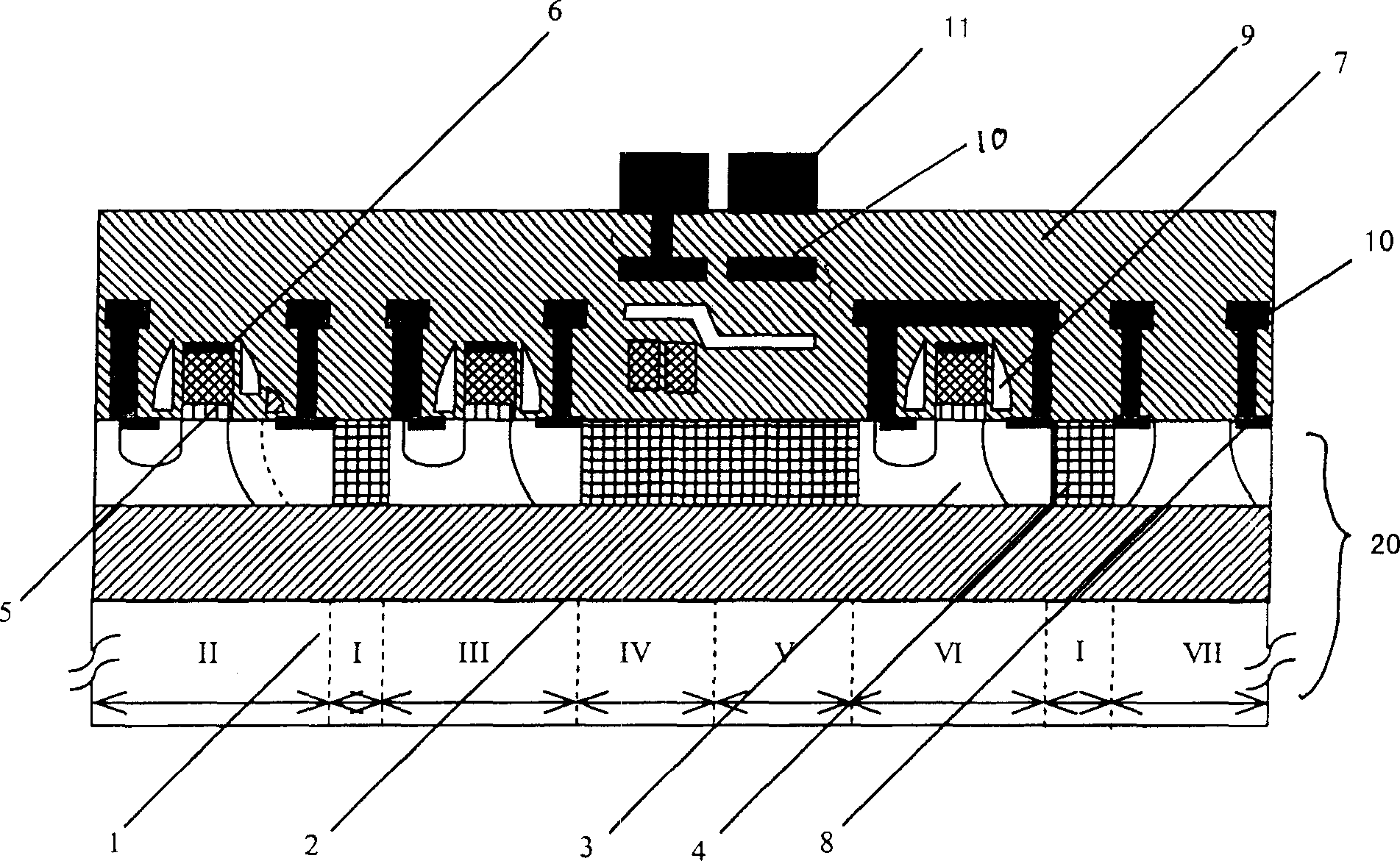

Static random access memory on silicon substrate of insulator and manufacturing method thereof

ActiveCN102176455ASuppression of floating body effectReduce the numberSolid-state devicesSemiconductor/solid-state device manufacturingFloating body effectStatic random-access memory

The invention provides a static random access memory on silicon substrate of an insulator and a manufacturing method thereof. The adjacent and different types of transistors are isolated from each other by a shallow trench so that the source areas of the adjacent and different types of transistors are completely isolated; the latch-up effect in the silicon substrate does not generate; meanwhile, the adjacent and the same kind of transistors are isolated by an ultra-shallow trench so that body areas among the adjacent and the same kind of transistors are communicated with each other; ions are injected in the source areas on the communicated area in a plurality of memory units to form derivation areas of the body areas, which have the same doping type as the body areas and are in contact with the body areas; and a floating body effect of the communicated area in the memory units can be removed by each derivation area of each body area. The static random access memory formed on the silicon substrate of the insulator reduces the number of the derivation areas of the body areas and the area of a device effectively and eliminates the floating body effect of the body areas.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

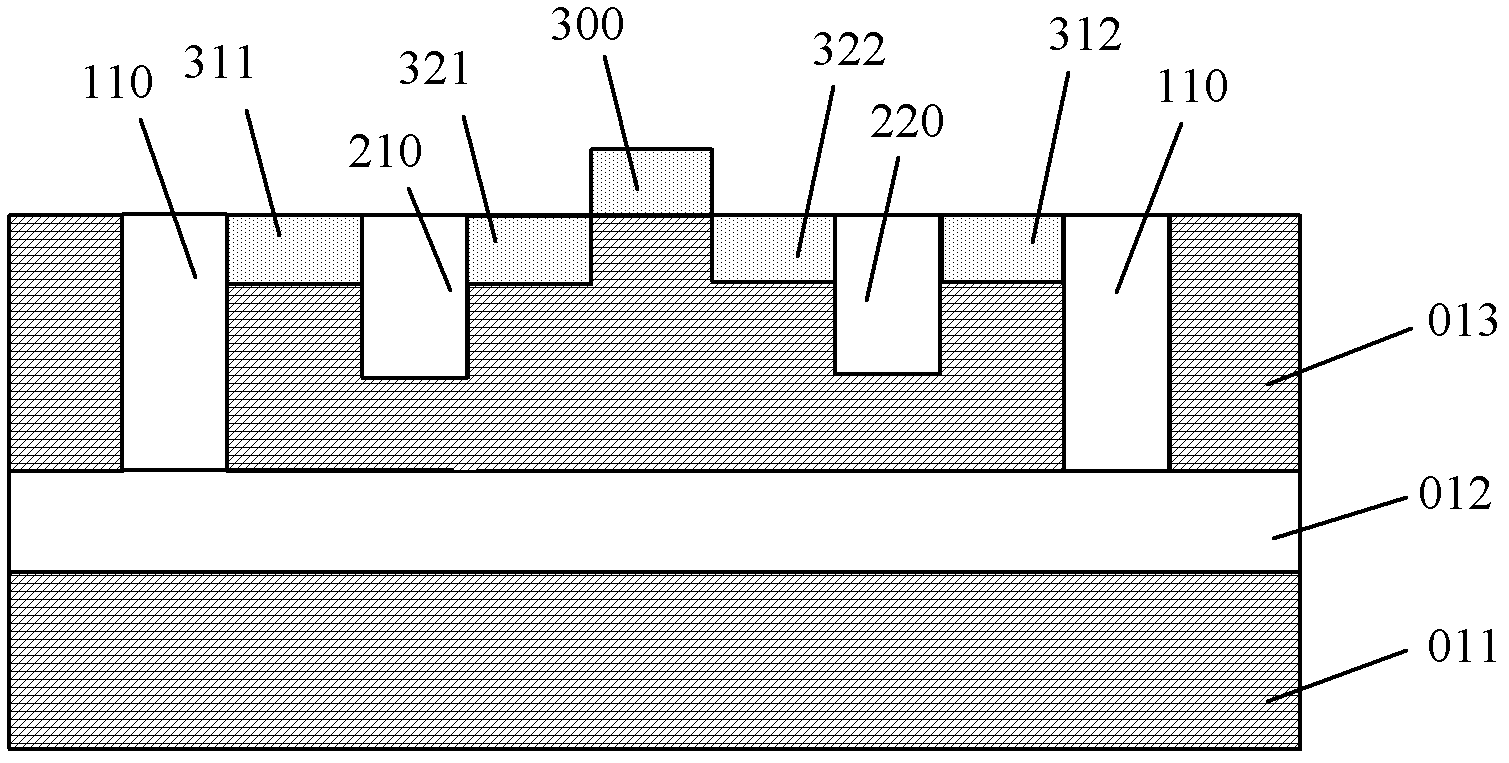

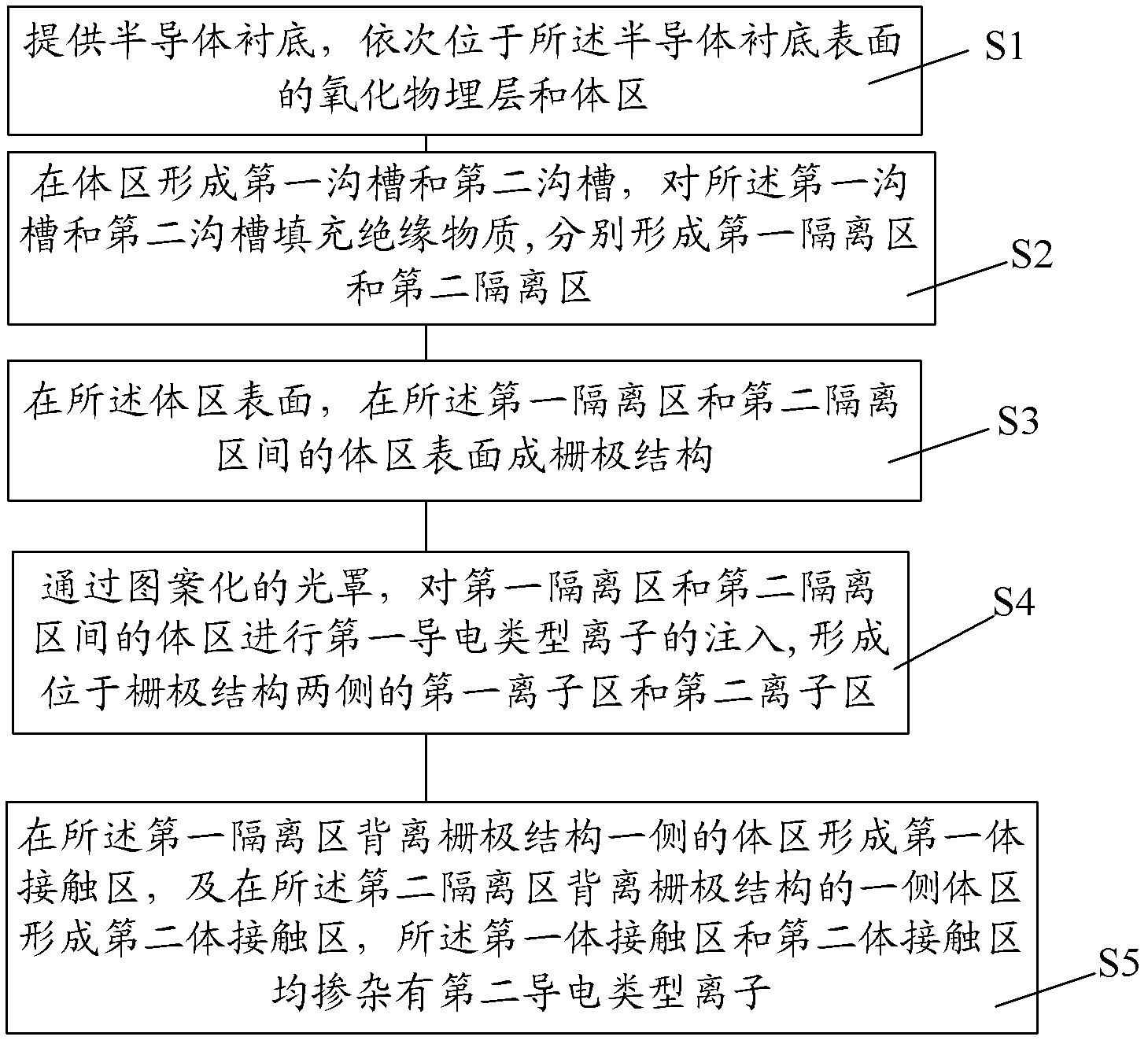

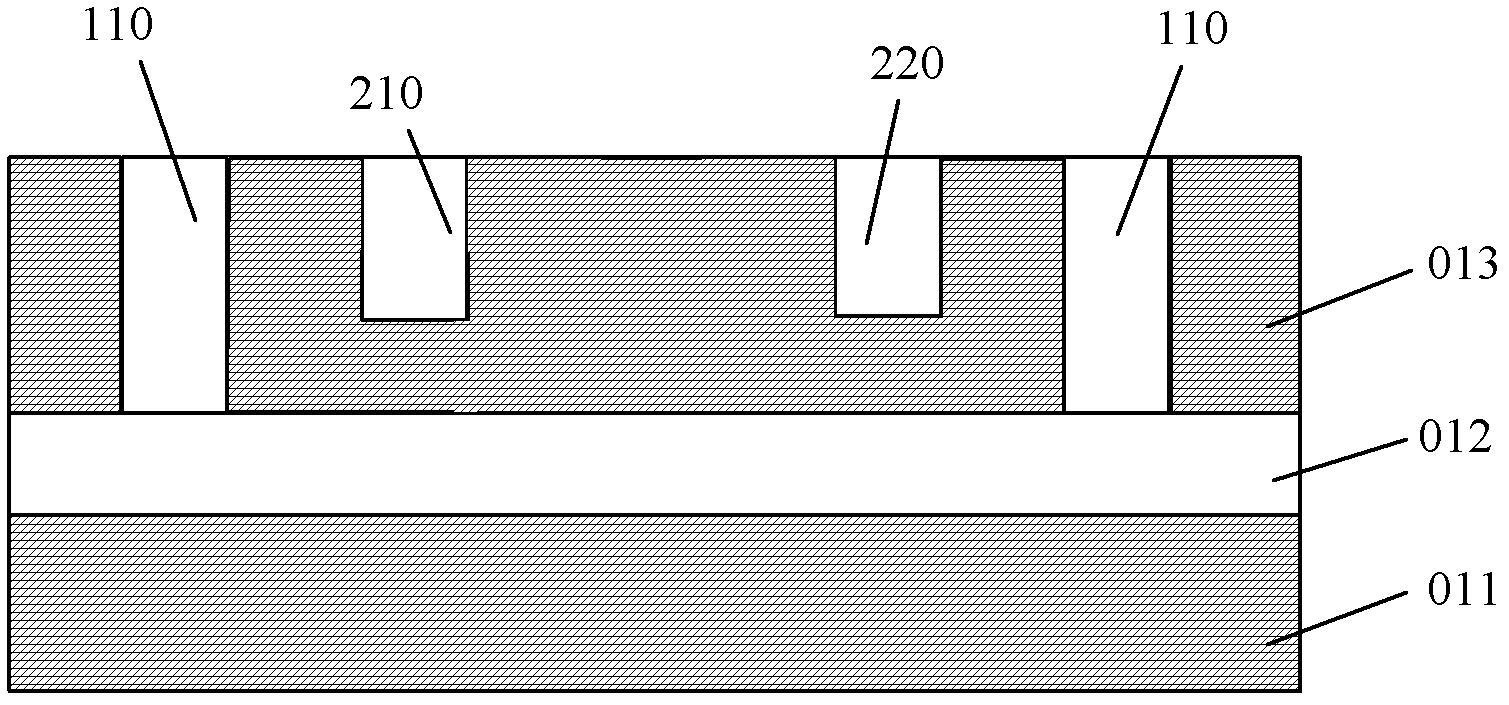

Silicon-on-insulator (SOI) body contact metal oxide semiconductor (MOS) transistor and forming method thereof

ActiveCN102208449ASuppression of floating body effectImprove device performanceSemiconductor/solid-state device manufacturingSemiconductor devicesOxide semiconductorFloating body effect

The invention provides a silicon-on-insulator (SOI) body contact metal oxide semiconductor (MOS) transistor, which comprises a semiconductor substrate, an oxide buried layer, a body region, a grid structure, a first ion region, a second ion region, a first body contact region and a second body contact region, wherein the oxide buried layer and the body region are positioned on the surface of the semiconductor substrate in turn; the grid structure is positioned on the surface of the body region; the first ion region and the second ion region are positioned in the body region on two sides of the grid structure; first conductive ions are doped in the first ion region and the second ion region; the first body contact region is positioned in the body region of the first ion region on one side deviated from the grid structure; the second body contact region is positioned in the body region of the second ion region on one side deviated from the grid structure; and second conductive ions are doped in the first body contact region and the second body contact region. The invention also provides a method for forming the SOI body contact MOS transistor. By the SOI body contact MOS transistor and the forming method thereof, a floating body effect can be suppressed, and the device performance is improved.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

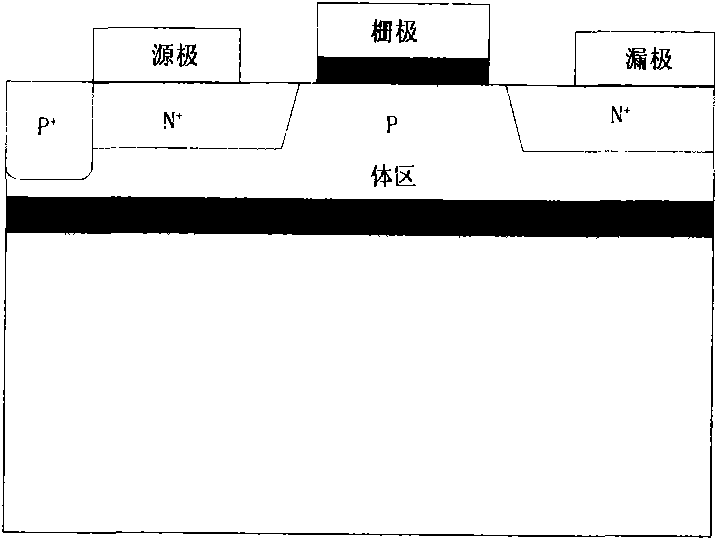

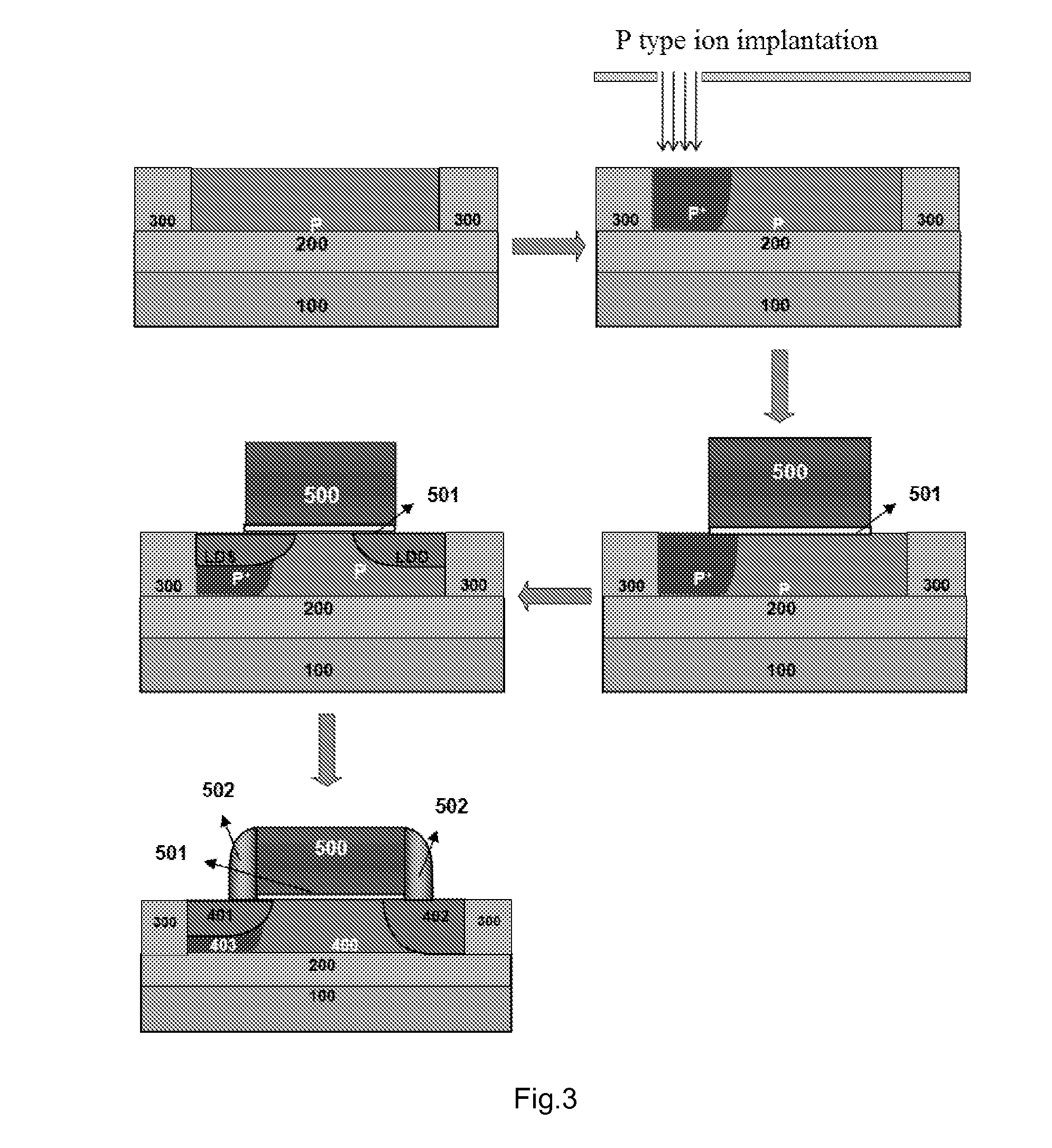

MOS structure for inhibiting SOI floating-body effect and manufacturing method thereof

InactiveCN101872737AWork will not affectDoes not increase the areaSemiconductor/solid-state device manufacturingSemiconductor devicesFloating body effectEngineering

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

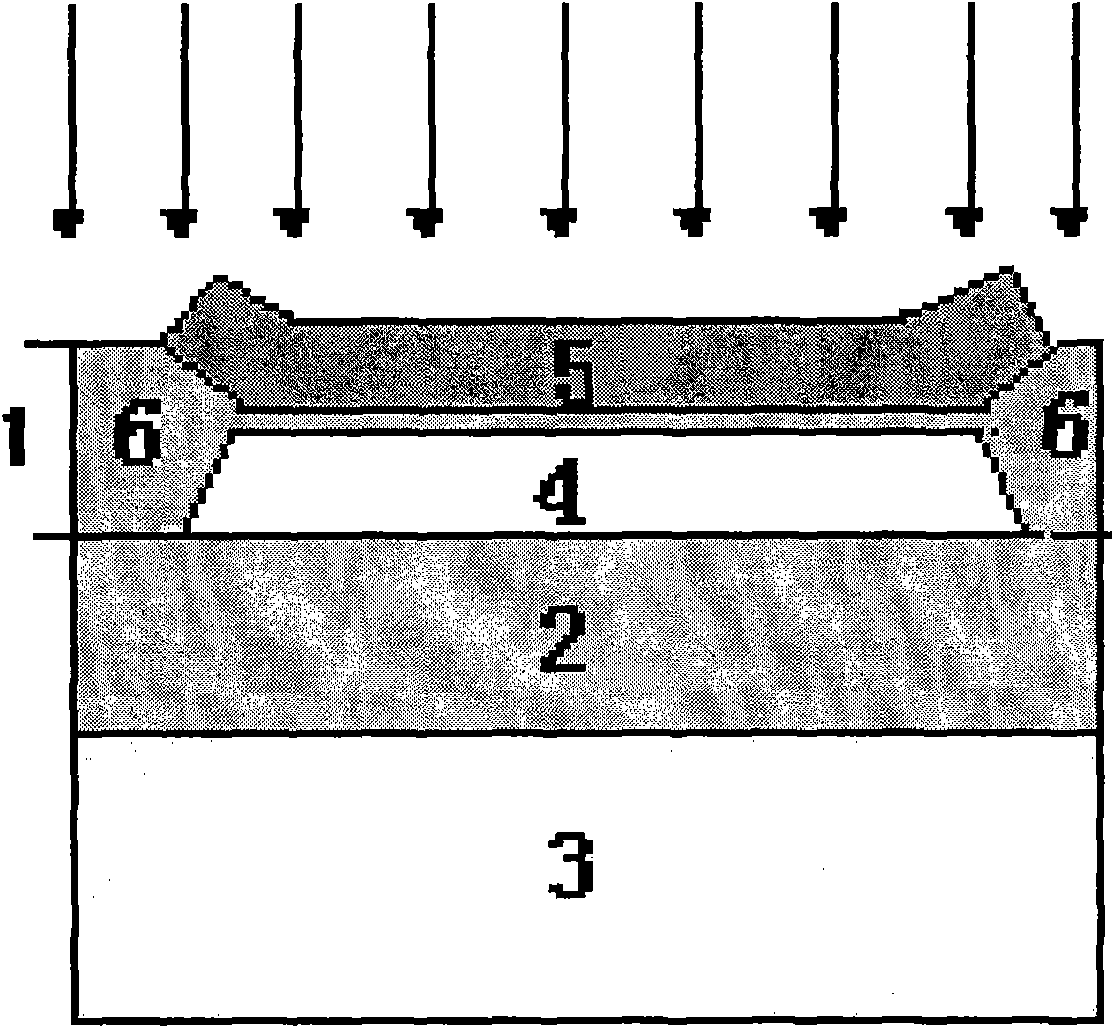

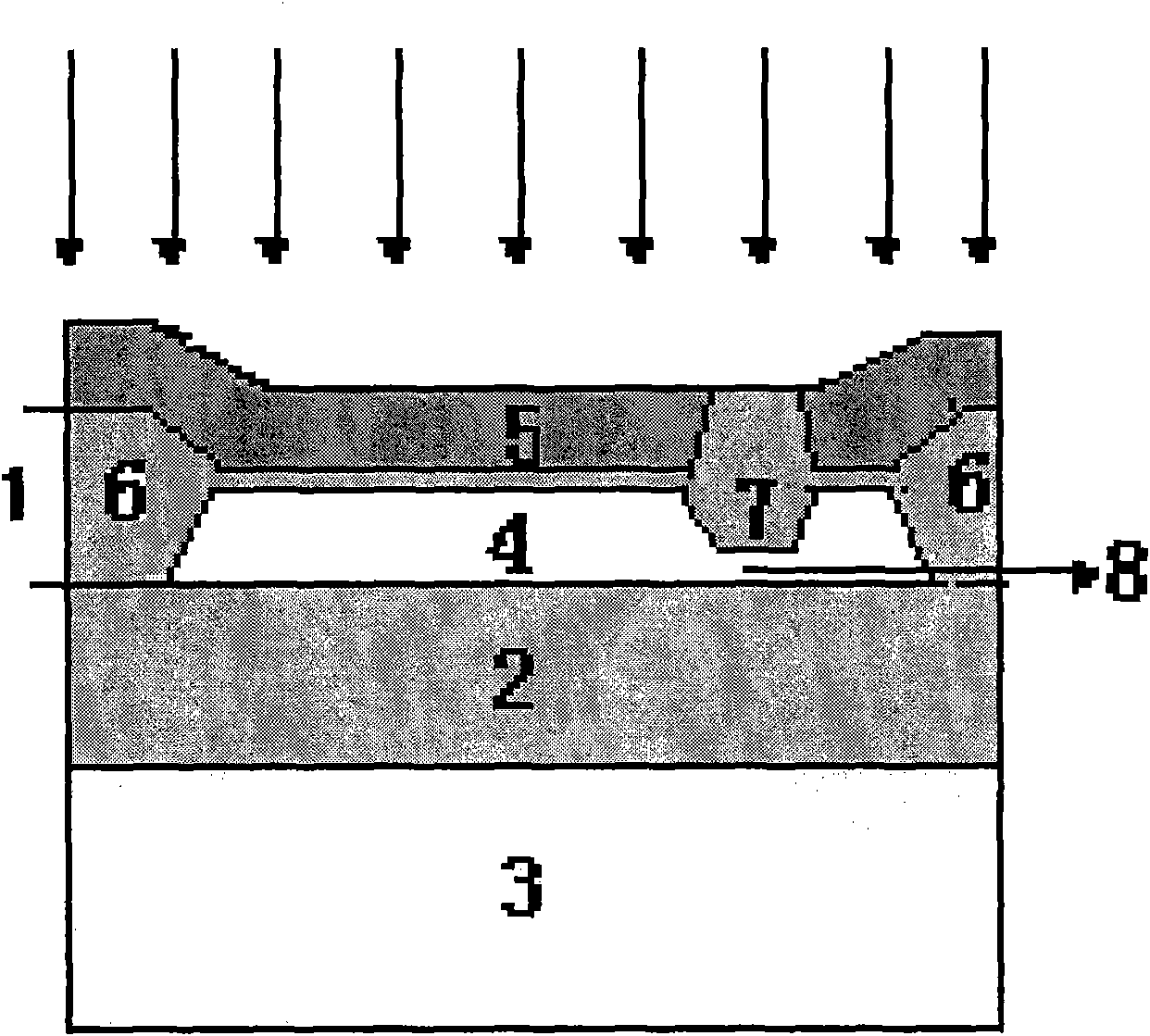

MOS Structure with Suppressed SOI Floating Body Effect and Manufacturing Method thereof

InactiveUS20110291191A1Reduce chip areaProcess compatibleSolid-state devicesSemiconductor/solid-state device manufacturingFloating body effectInsulation layer

The present invention discloses a MOS structure with suppressed floating body effect including a substrate, a buried insulation layer provided on the substrate, and an active area provided on the buried insulation layer comprising a body region, a first conductive type source region and a first conductive type drain region provided on both sides of the body region respectively and a gate region provide on top of the body region, wherein the active area further comprises a highly doped second conductive type region between the first conductive type source region and the buried insulation layer. For manufacturing this structure, implant ions into a first conductive type source region via a mask having an opening thereon forming a highly doped second conductive type region under the first conductive type source region and above the buried insulation layer. The present invention will not increase chip area and is compatible with conventional CMOS process.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

Integration structure and making method of insulator silicon radio frequency integrated circuit

InactiveCN1705132AHigh quality factorImprove RF performanceSolid-state devicesSemiconductor/solid-state device manufacturingTitanium disilicideSurface oxidation

An integrated structure for insulator silicon RF IC, which contains an insulated silicon substrate containing monocrystal layer, isolation oxidation layer and silicon thin layer, field oxidation layer formed in silicon thin and connected with isolation oxidation layer by adopting local field oxidation isolation technology for preventing device leakage, grid oxidation layer formed on silicon thin surface, polycrystalline silicon layer deposited on grid oxidation layer, silicon nitride layer formed around the polycrystalline, titanium disilicide thin layer dot distributed on silicon thin layer, first aluminium film formed on titanium disilicide thin layer, a silicon dioxide layer formed on field oxidation layer, polycrystalline layer, silicon nitride layer, titanium disilicide thin layer and first aluminium film, part of first layer of aluminium film inlaid in silicon dioxide layer, second aluminium film partially connected with first aluminium film and formed on silicon dioxide layer.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

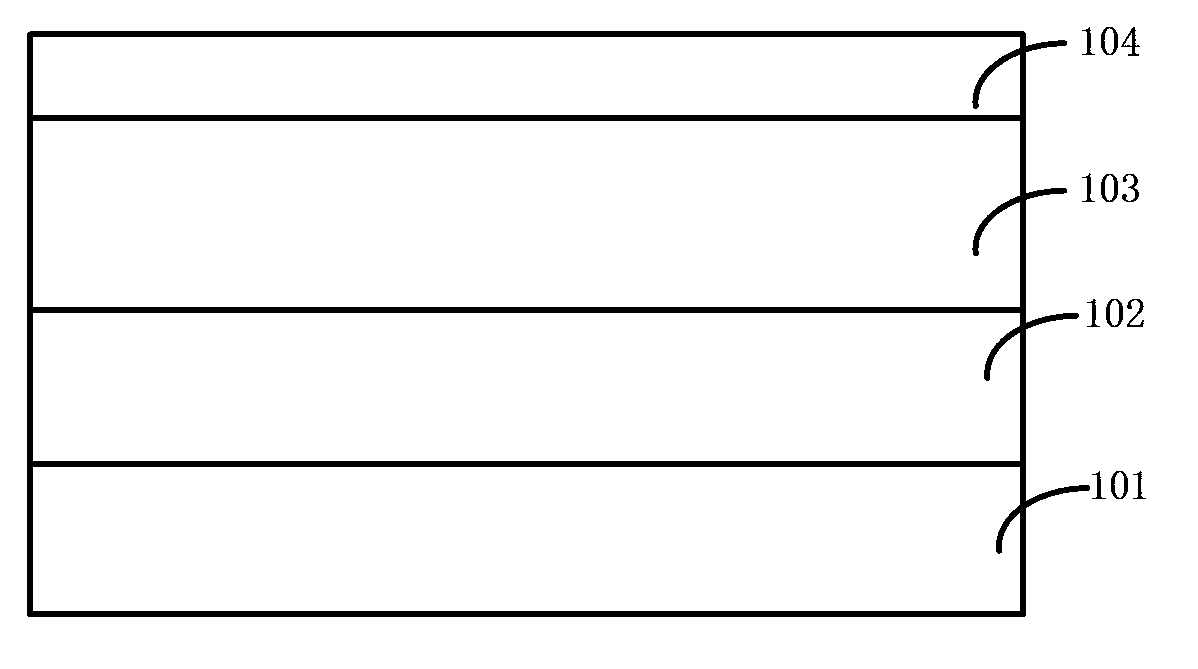

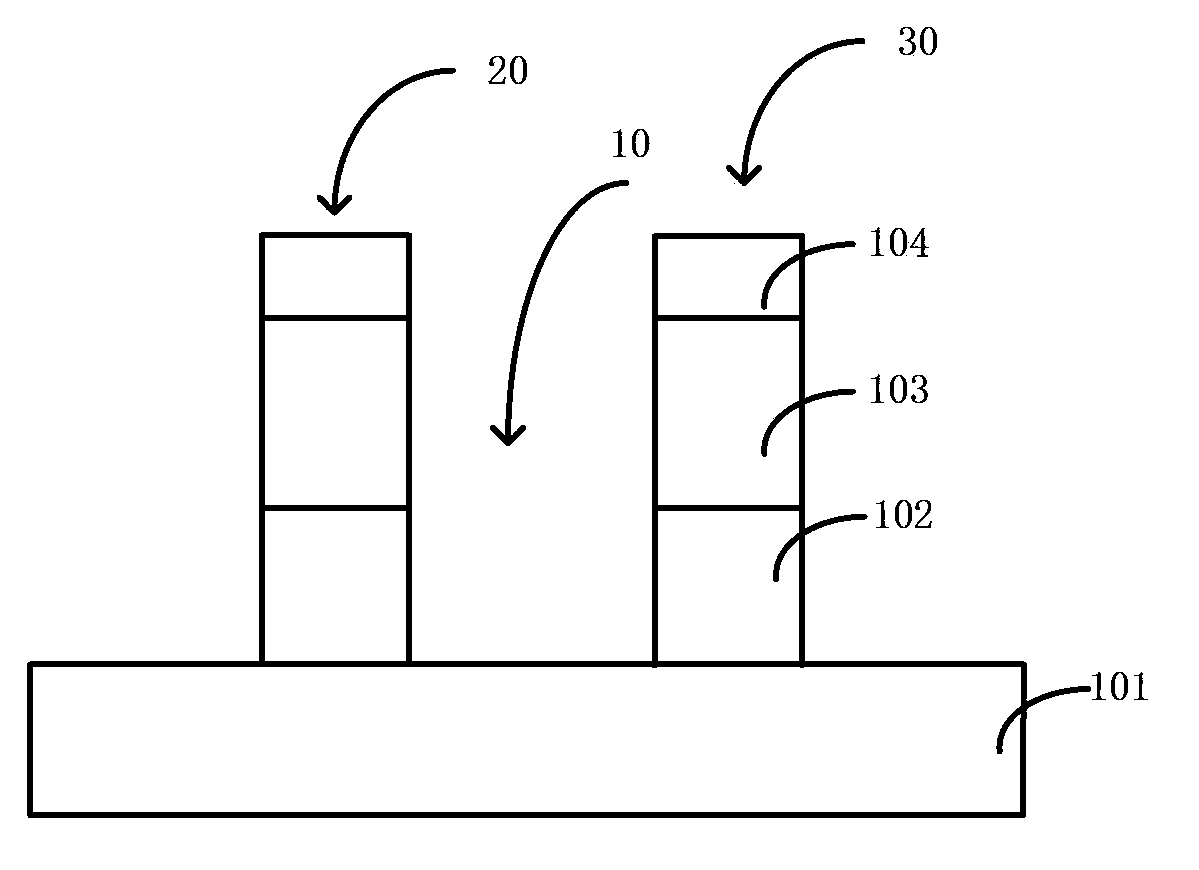

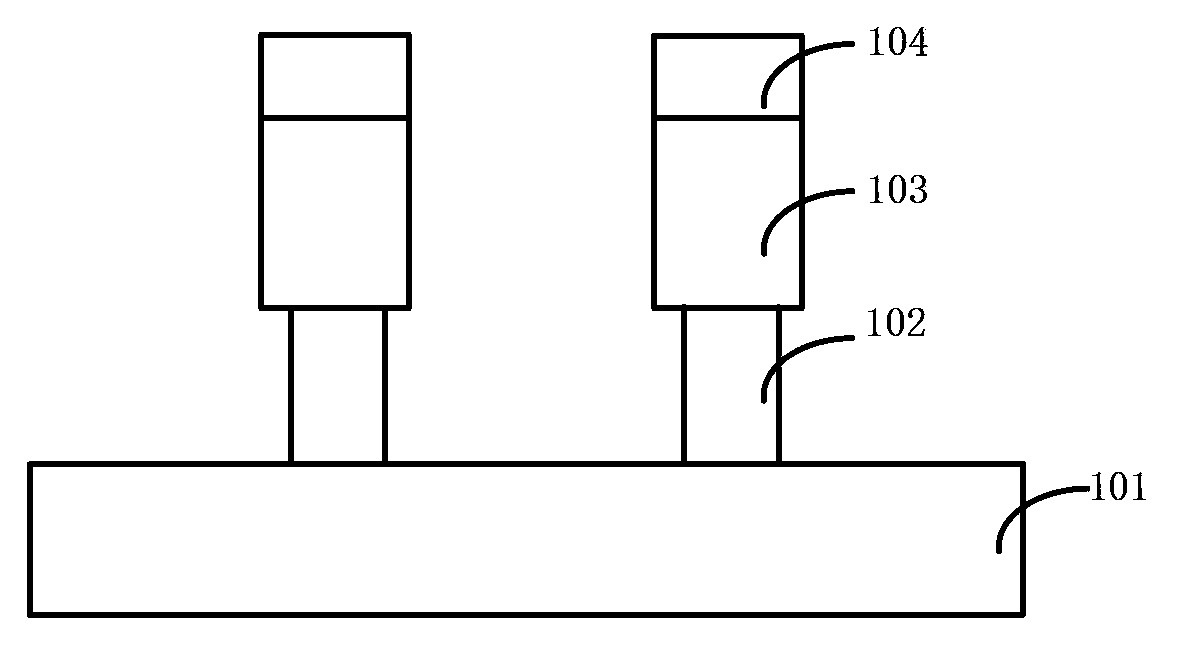

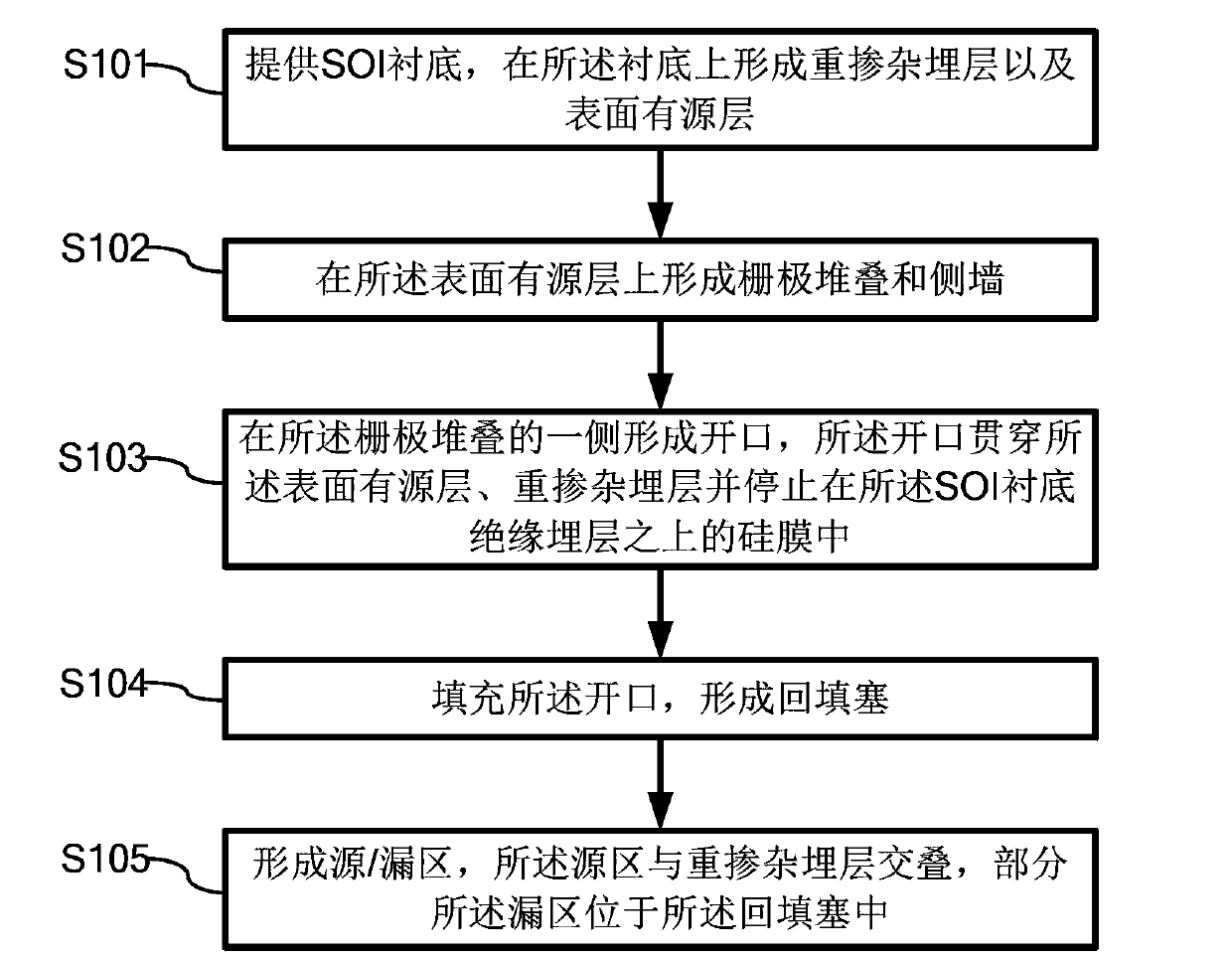

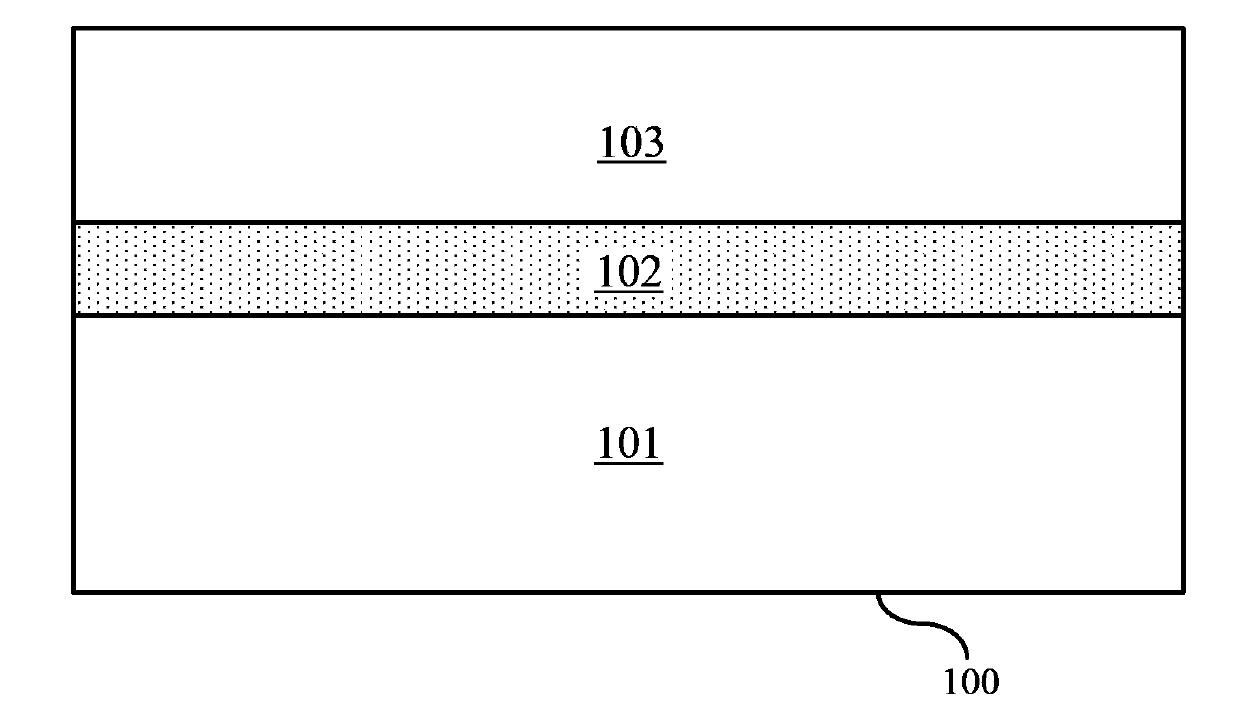

Semiconductor structure and manufacturing method thereof

ActiveCN103377947AReduce widthSuppression of floating body effectTransistorSolid-state devicesFloating body effectSemiconductor structure

The invention provides a manufacturing method of a semiconductor structure. The method includes the steps of step 1, providing an SOI substrate and forming a heavy doping buried layer and a surface active layer on the substrate, step 2, forming a grid pile and a side wall on the substrate, step 3, forming an opening in one side of the grid pile, wherein the opening penetrates through the surface active layer and the heavy doping buried layer and stops in a silicon film above an insulation buried layer of the SOI substrate, step4, filling the opening to form a backfill plug, and step 5, forming a source region / drain region, wherein the source region and the heavy doping buried layer are overlapped, and partial drain region is placed in the backfill plug. Correspondingly, the invention further provides the semiconductor structure. According to the semiconductor structure and the manufacturing method thereof, the heavy doping buried layer is beneficial to reducing the width of a source region depletion layer / a drain region depletion layer and restricting the short-channel effect; the heavy doping buried layer and the source region are overlapped to form heavy doping pn junctions, therefore, the floating body effect of SOI MOS devices is effectively restricted, semiconductor device performance is effectively improved, leading out on regions is not needed, and the area and cost of devices are saved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

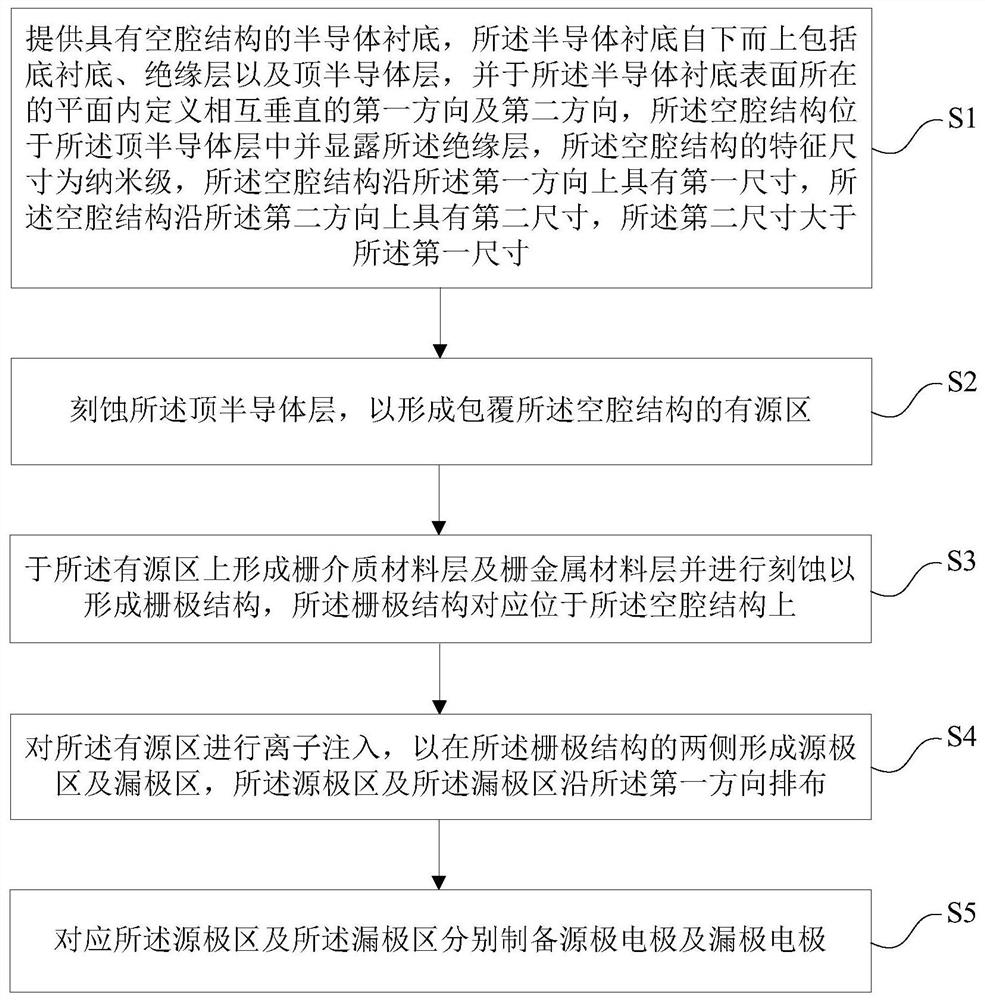

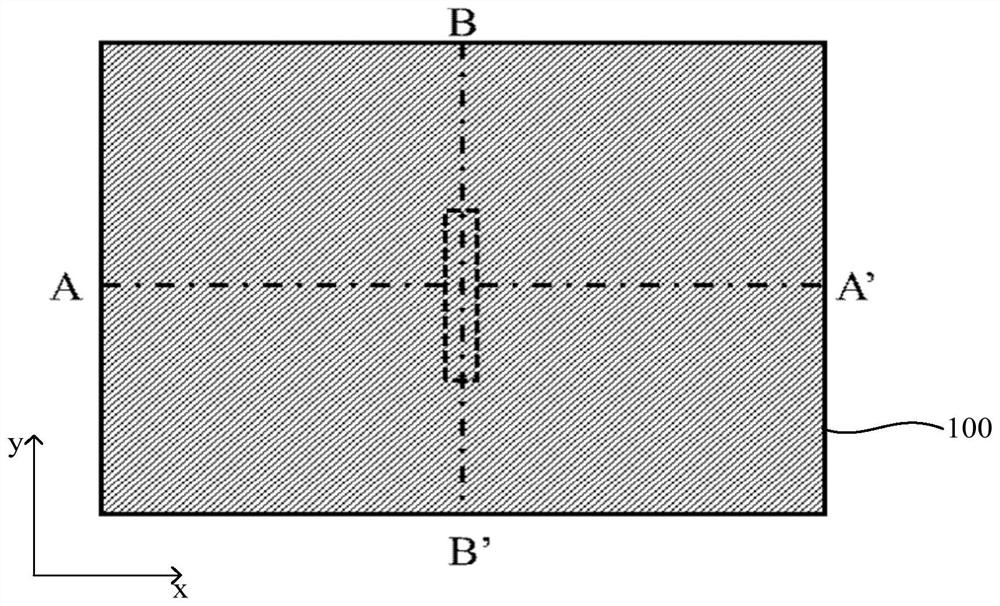

SOI device capable of improving self-heating effect and preparation method thereof

ActiveCN111986996AGuaranteed breakageReduce self-heating effectTransistorSemiconductor/solid-state device manufacturingFloating body effectEngineering

The invention provides an SOI device capable of improving a self-heating effect and a preparation method thereof. The preparation comprises the steps: providing a semiconductor substrate with a cavitystructure, enabling the cavity structure to be located in a top semiconductor layer and exposing an insulating layer, preparing an active region coating the cavity structure, and preparing a gate electrode structure, a source-drain region and a source-drain electrode. The SOI substrate with the nanoscale cavity is adopted, the cavity structure is located in the top semiconductor layer, the size of the cavity is effectively reduced, the cavity is in the nanoscale size in the channel length direction, the heat dissipation path of the device cannot be obviously blocked, and compared with a device with a large-size cavity, the self-heating effect is relieved. Theoretically, the thickness of the top semiconductor layer above the cavity can reach 2 nm, it is guaranteed that top silicon is not damaged, a channel can be completely exhausted by a gate electrode, and the floating body effect is effectively restrained. The cavity is located in the top semiconductor layer and makes contact with the insulating layer, parasitic charges in the insulating layer cannot be introduced into a parasitic channel at the bottom of the top semiconductor layer, and the total dose radiation effect is effectively restrained.

Owner:SHANGHAI INST OF MICROSYSTEM & INFORMATION TECH CHINESE ACAD OF SCI

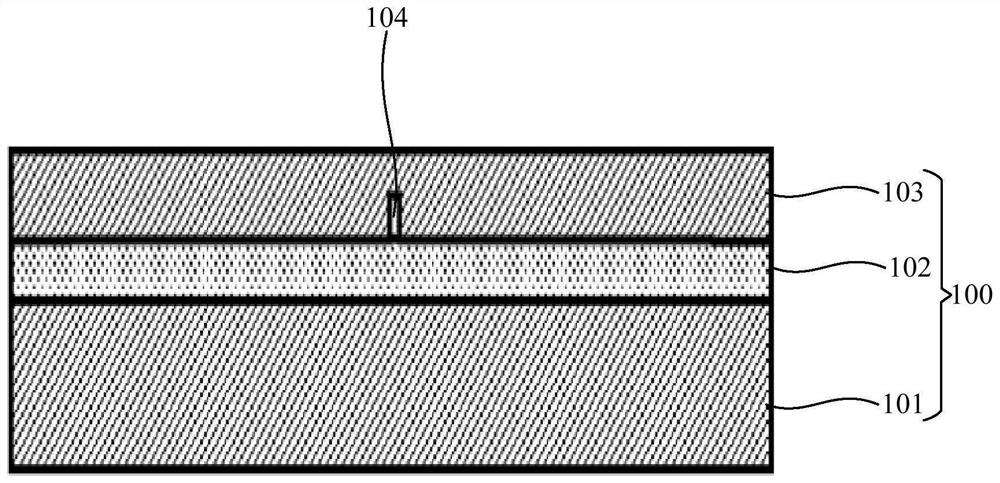

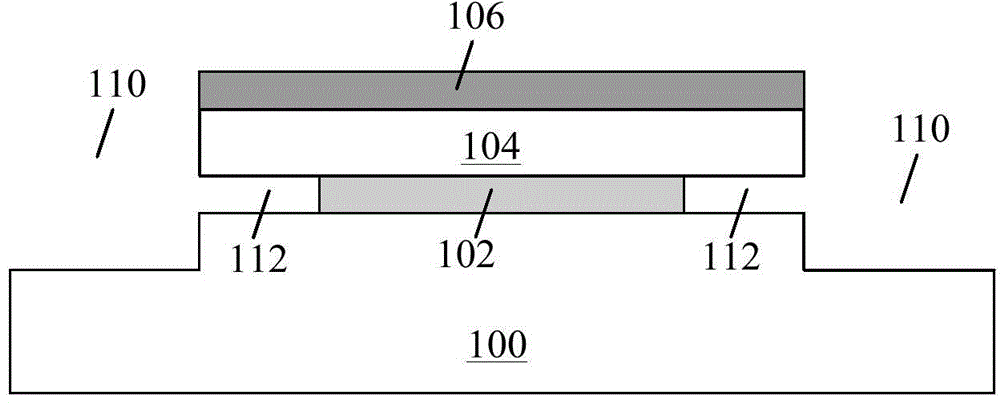

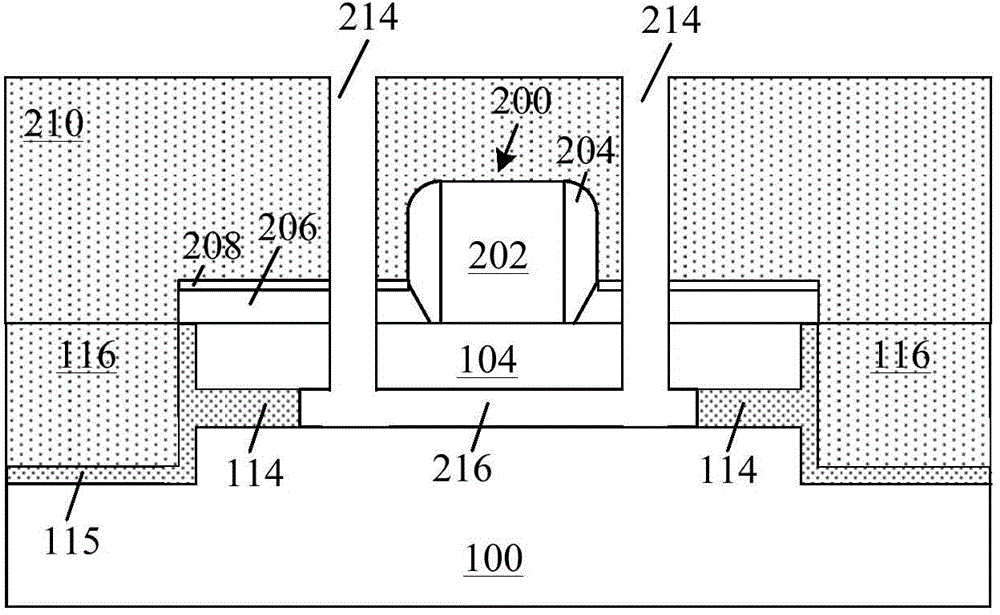

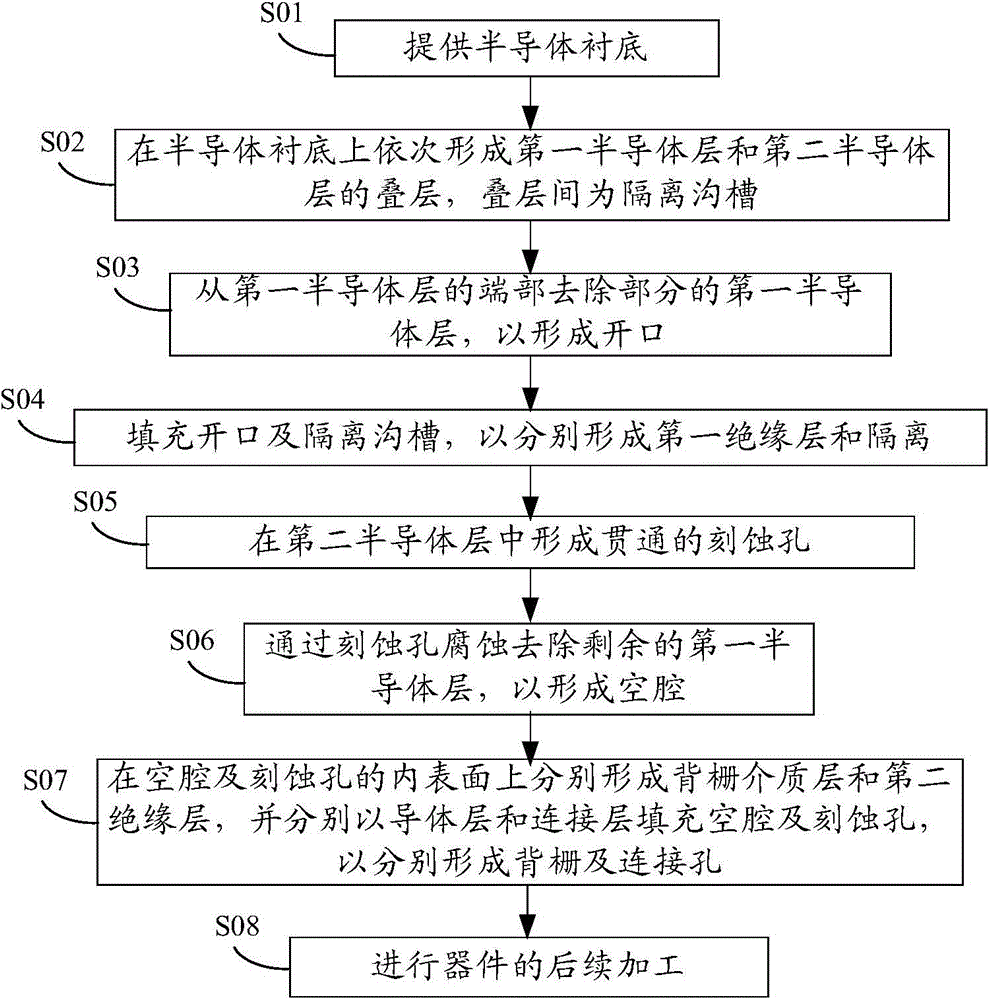

Semiconductor device and manufacturing method thereof

ActiveCN105702618ALow costReduce leakageSemiconductor/solid-state device manufacturingSemiconductor devicesElectrical conductorInsulation layer

The invention discloses a manufacturing method of a semiconductor device. The method comprises steps that a semiconductor substrate is provided; a first semiconductor layer and a second semiconductor layer are sequentially laminated on the semiconductor substrate, and an isolation groove is formed between the first semiconductor layer and the second semiconductor layer; a part of the first semiconductor layer is removed from the end portion of the first semiconductor layer to form an opening; the opening and the isolation groove are filled to form a first insulation layer and isolation respectively; a through etching hole is formed on the second semiconductor layer; the residual part of the first semiconductor layer is corroded through the through etching hole to form a chamber; a back gate dielectric layer and a second insulation layer are respectively formed on inner surfaces of the chamber and the etching hole, and the chamber and the etching hole are respectively filled through a conductor layer and a connection layer to form a back gate and a connection hole; subsequent device processing is carried out. Through the method, a similar SOI device with a back gate structure is realized.

Owner:北京中科微投资管理有限责任公司

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com