MOS structure for inhibiting SOI floating-body effect and manufacturing method thereof

A technology of MOS structure and floating body effect, applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of reducing body potential, increasing device area, and increasing parasitic effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

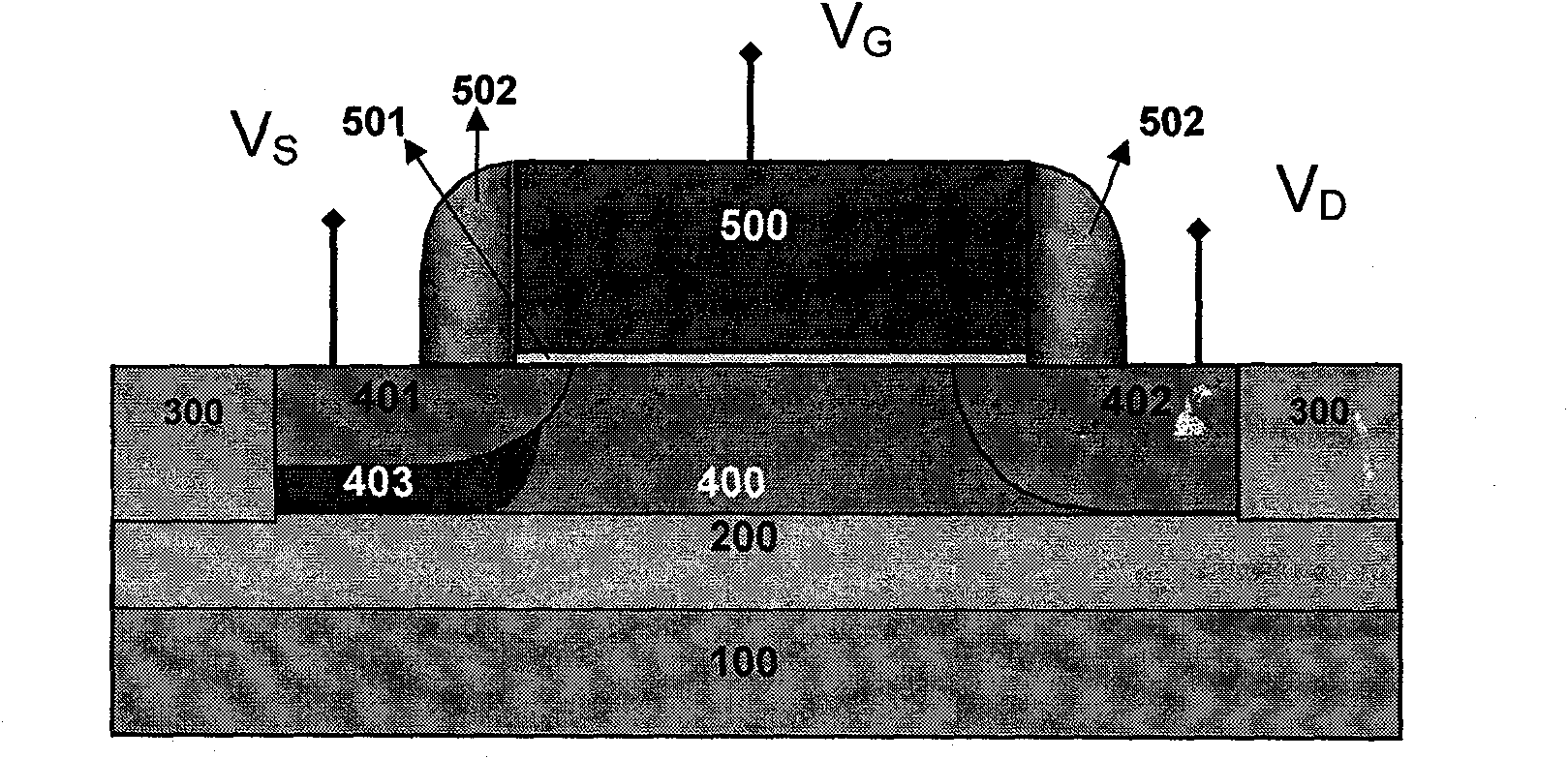

[0025] This embodiment provides a method for fabricating a MOS structure that suppresses the floating body effect, such as image 3 shown, including the following steps:

[0026] First, a shallow trench isolation structure 300 is formed on the semiconductor material (SOI or GOI, etc.) with a buried insulating layer 200, the active area is isolated, and P ion implantation is performed in the active area; then, a mask is added , the mask is opened at the position of the first conductivity type source region 401, and heavily doped P ions are implanted vertically through the mask to form a heavily doped P-type region; then the gate dielectric layer 501 and the gate electrode 500 are fabricated, Lightly doped source region (LDS) and lightly doped drain region (LDD) are performed, and finally N ion implantation is performed in the source region and the drain region to form the first conductivity type source region 401 and the first conductivity type drain region 402, between them A...

Embodiment 2

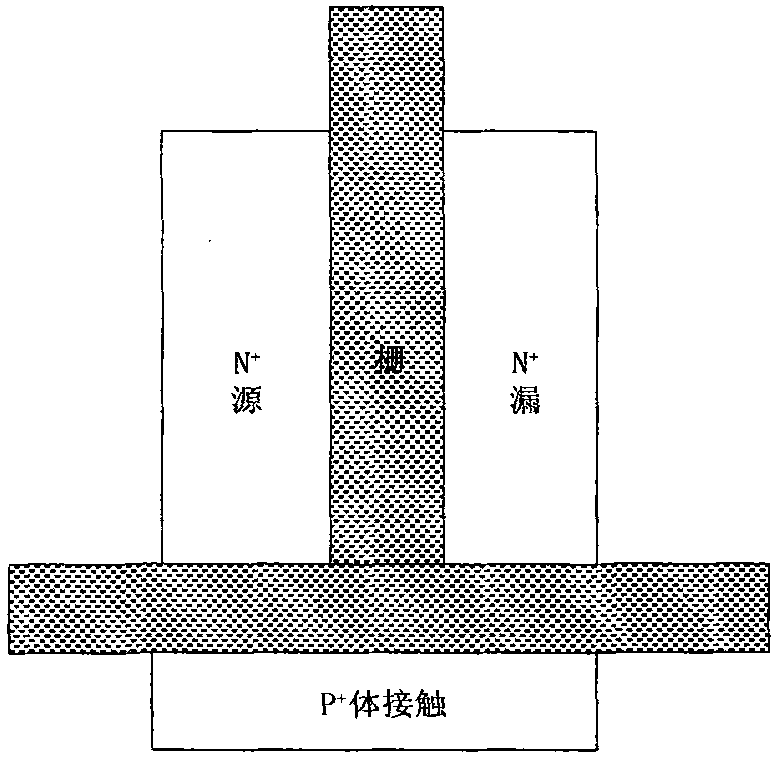

[0028] This embodiment provides another method for fabricating a MOS structure that suppresses the floating body effect, such as Figure 4 shown, including the following steps:

[0029]First, a shallow trench isolation structure 300 is fabricated on the semiconductor material (SOI or GOI, etc.) with a buried insulating layer 200, the active area is isolated, and P ion implantation is performed in the active area; then the gate dielectric layer 501, The gate electrode 500 is lightly doped in the source region (LDS) and lightly doped in the drain region (LDD); then, a mask is added, and the mask is opened at the position of the source region 401 of the first conductivity type, through the mask Perform heavily doped P ion implantation vertically to form a heavily doped P-type region under the lightly doped source region (LDS); finally perform N ion implantation in the source region and drain region to form the first conductivity type source region 401 and The drain region 402 of...

Embodiment 3

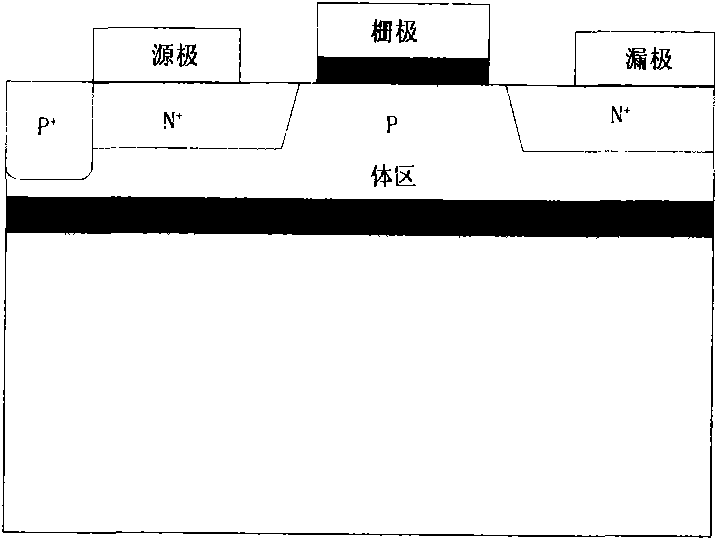

[0031] This embodiment provides a third method of fabricating a MOS structure that suppresses the floating body effect, such as Figure 5 As shown, the method forms a body region 400, a first conductivity type source region 401 and a first conductivity type drain respectively located at both ends of the body region 400 on a semiconductor material (SOI or GOI, etc.) having a buried insulating layer 200. region 402, and the gate region (gate dielectric layer 501, gate electrode 500, insulator dielectric spacer isolation structure 502) located on the body region 400, add a mask plate, through the mask plate to the first The conductivity type source region 401 is vertically implanted with ions, so that the region below the source region 401 and above the buried insulating layer 200 forms a heavily doped second conductivity type region 403 .

[0032] In order to analyze the performance of the MOS structure of the present invention, the structure is simulated, and the simulation res...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com