Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

212results about How to "Improve reliability and performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

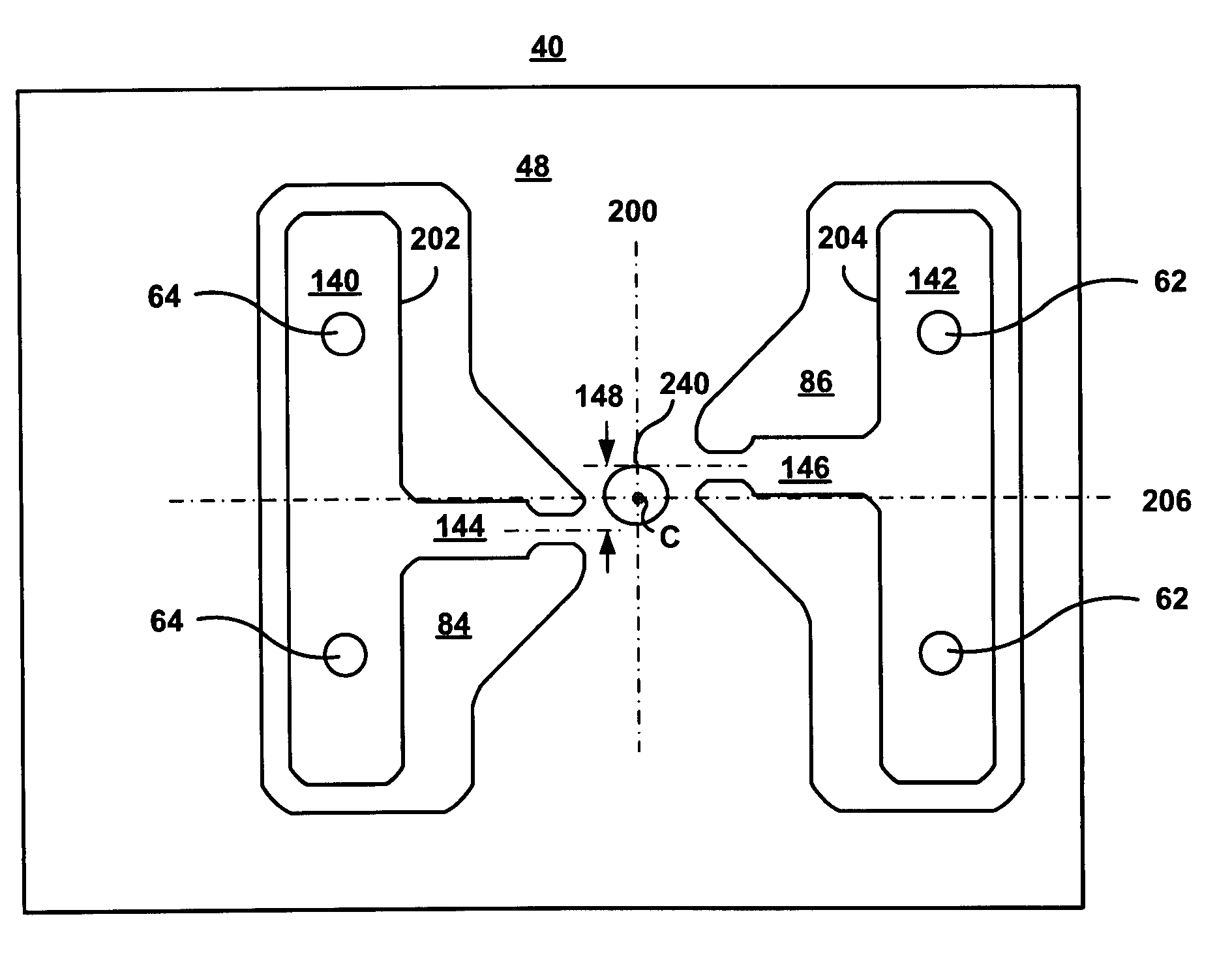

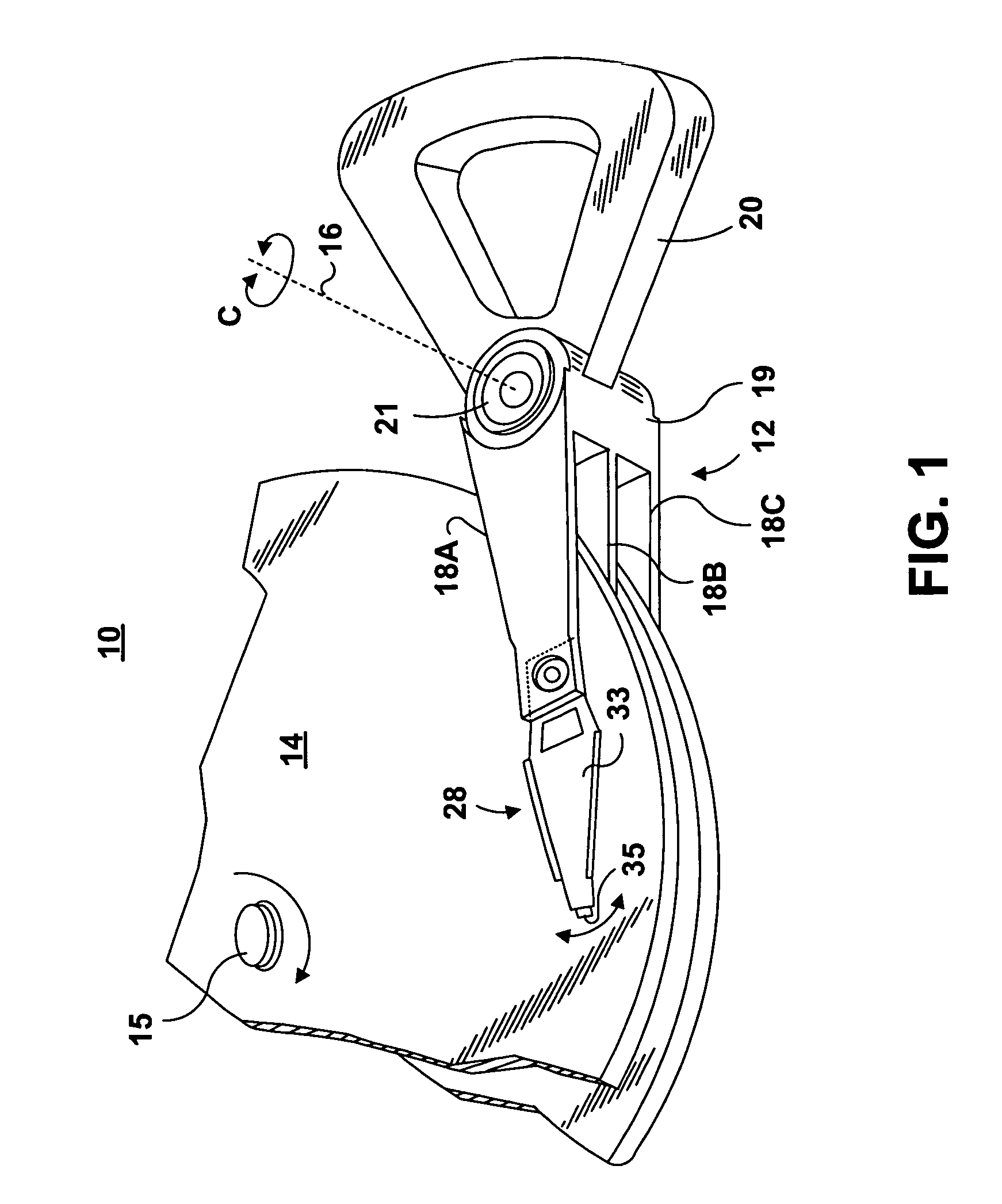

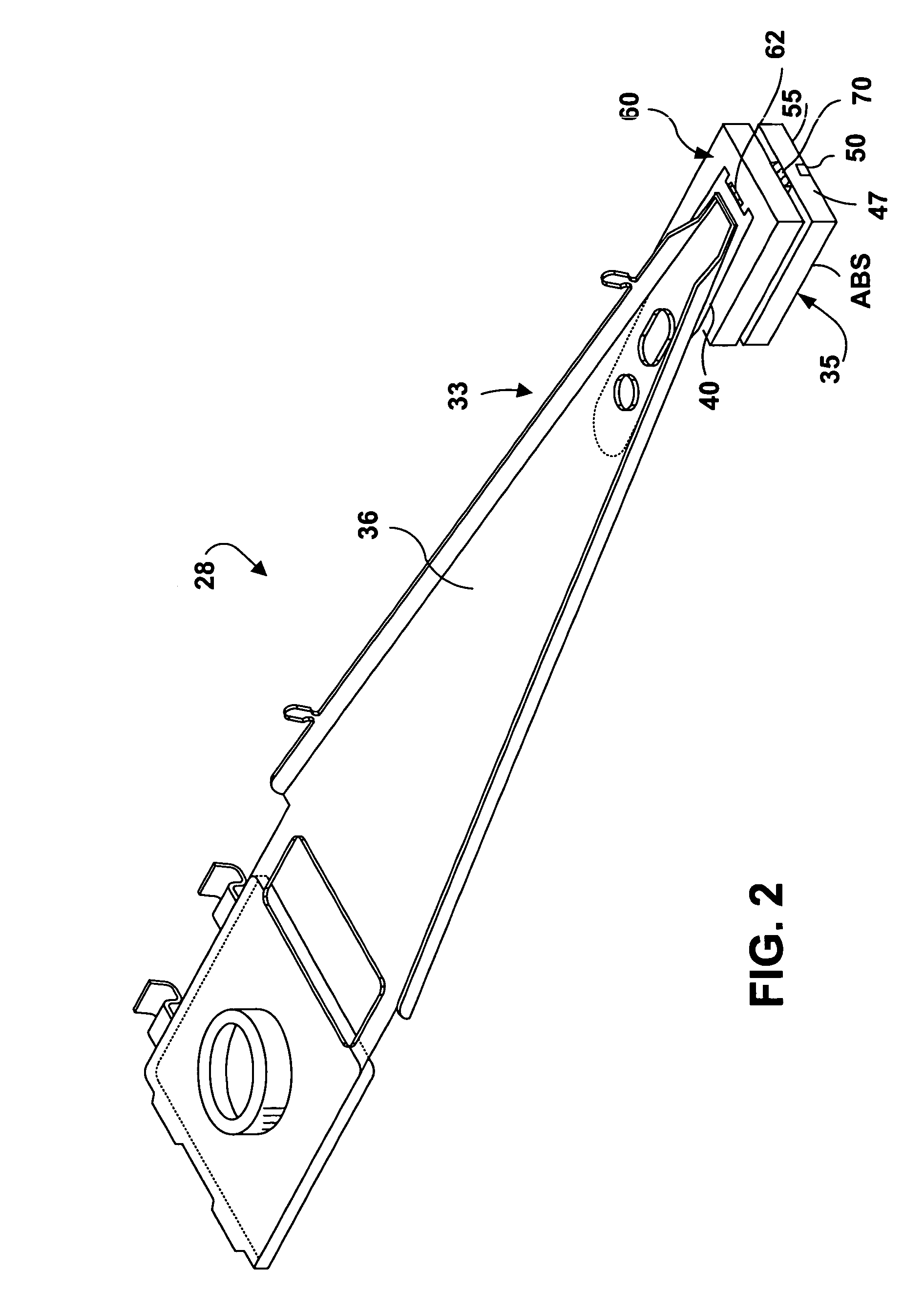

Dimple pivot post for a rotary co-located microactuator

InactiveUS7057857B1Eliminate deformationImprove performanceRecord information storageMounting/attachment of transducer headAdhesiveEngineering

A rotary microactuator-based head-gimbal assembly design controls the unwanted deflection of a flexure in a data storage device and eliminates hinge deformation. The head-gimbal assembly maintains the co-planarity of the hinged islands in the microactuator under the applied load acting on the flexure and two associated hinged islands. The dimple post is placed at the dimple loading region of the flexure tongue and has the same height as adhesive dams on paddles secured to the hinged islands. The dimple post is formed by branching one of the existing conductive traces covered by a photoresist layer to the dimple loading region on flexure tongue. In an alternative embodiment, the dimple post is secured to the dimple loading region of the flexure tongue by means of adhesives with a variety of viscosity and elastic moduli.

Owner:WESTERN DIGITAL TECH INC

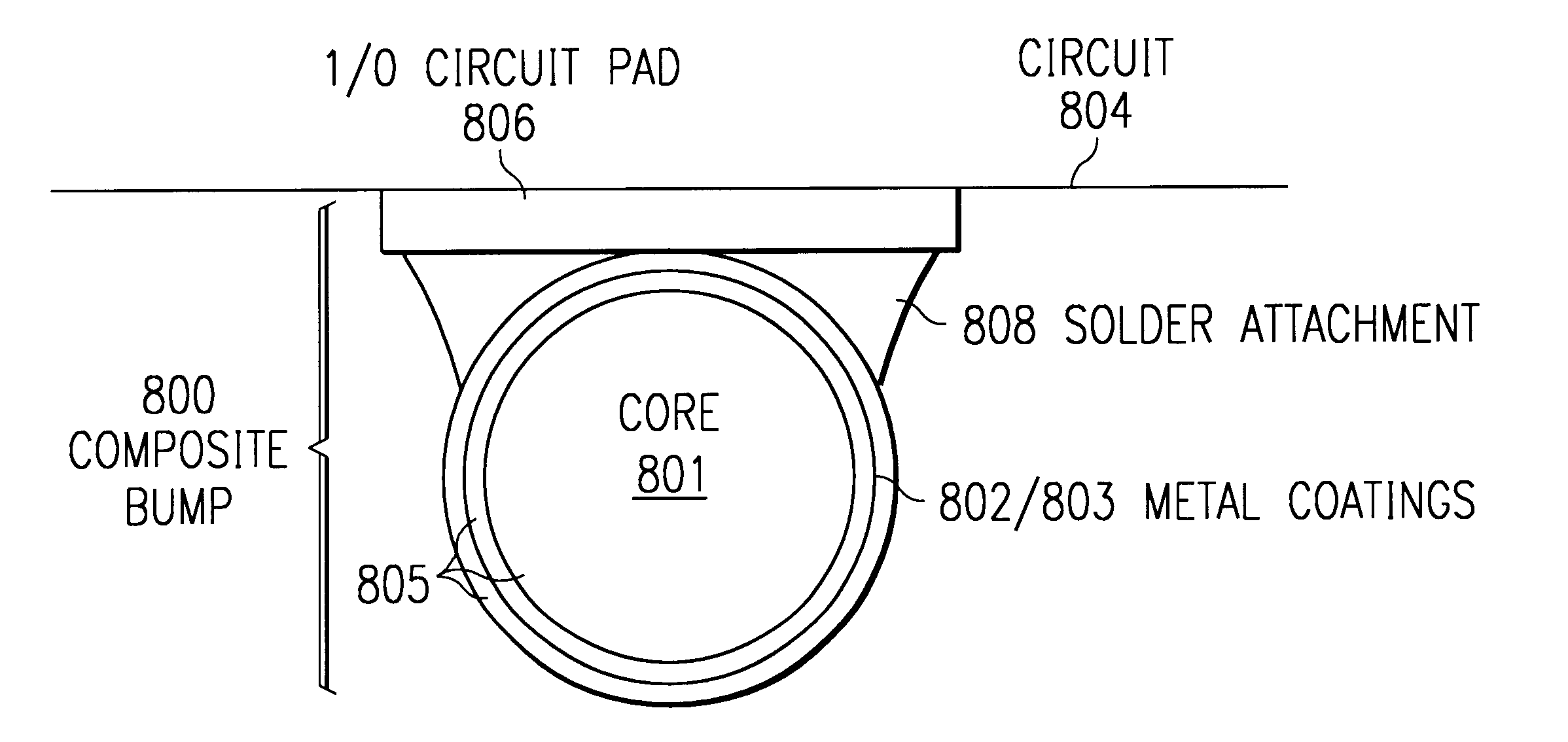

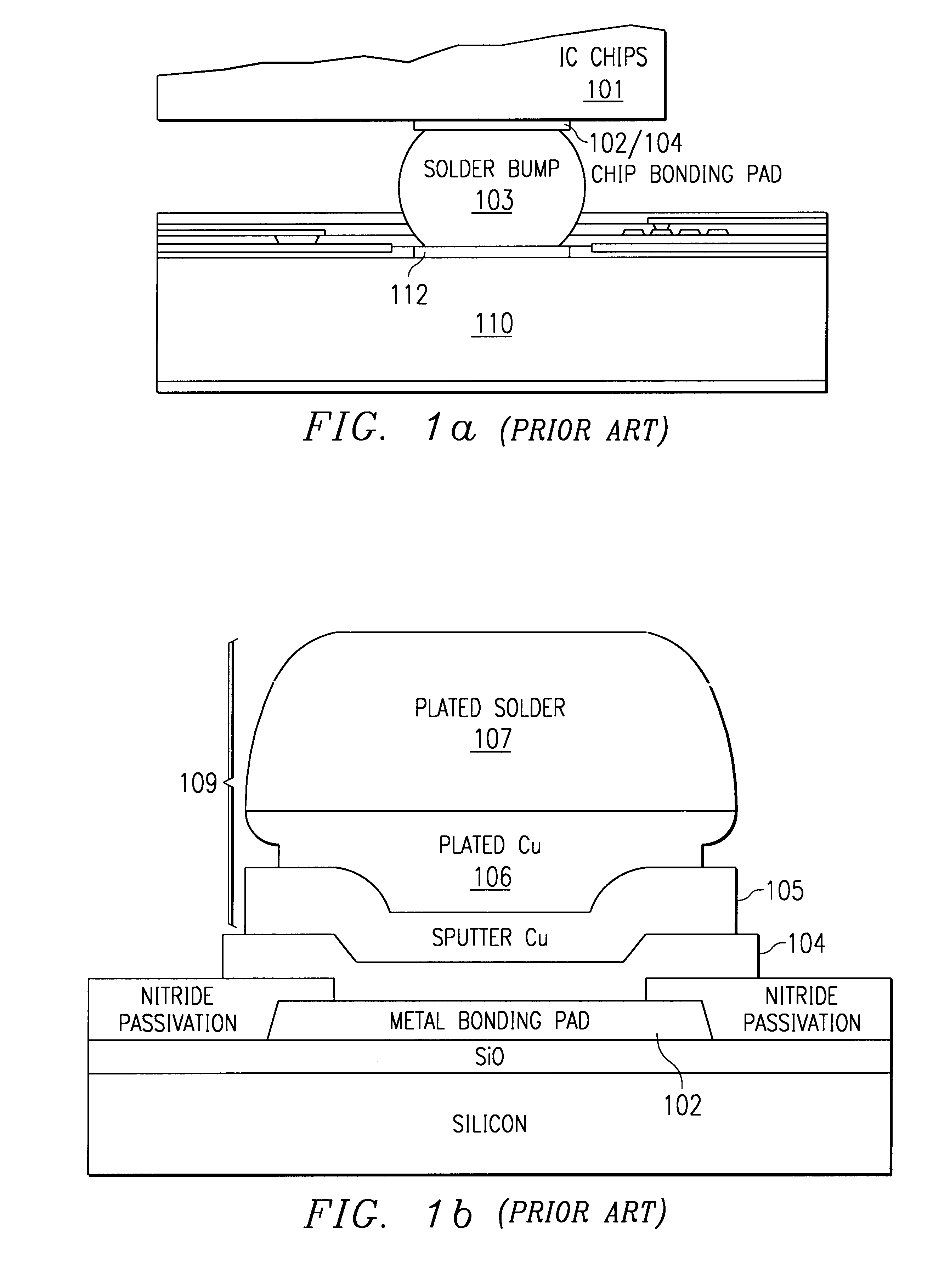

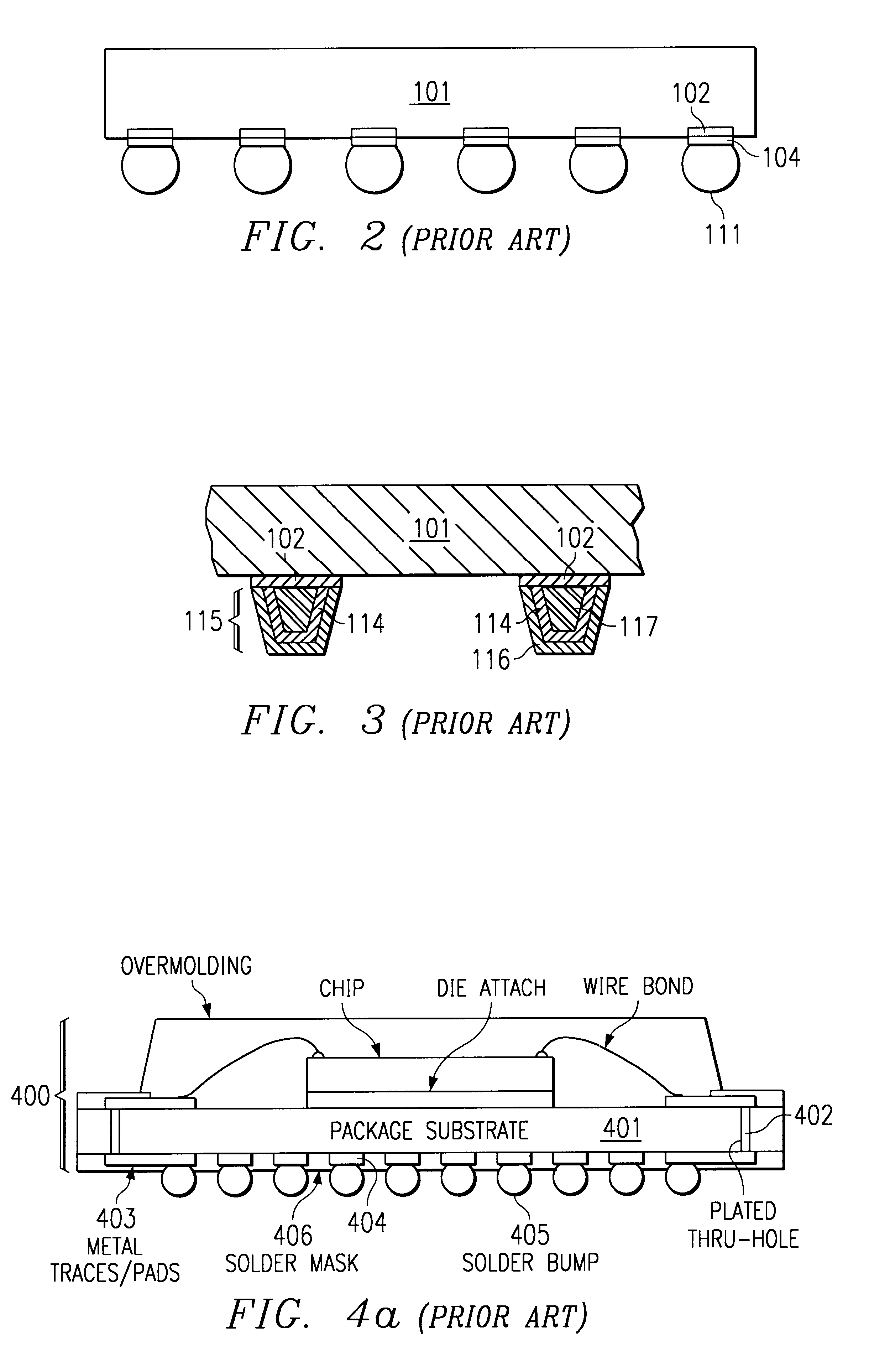

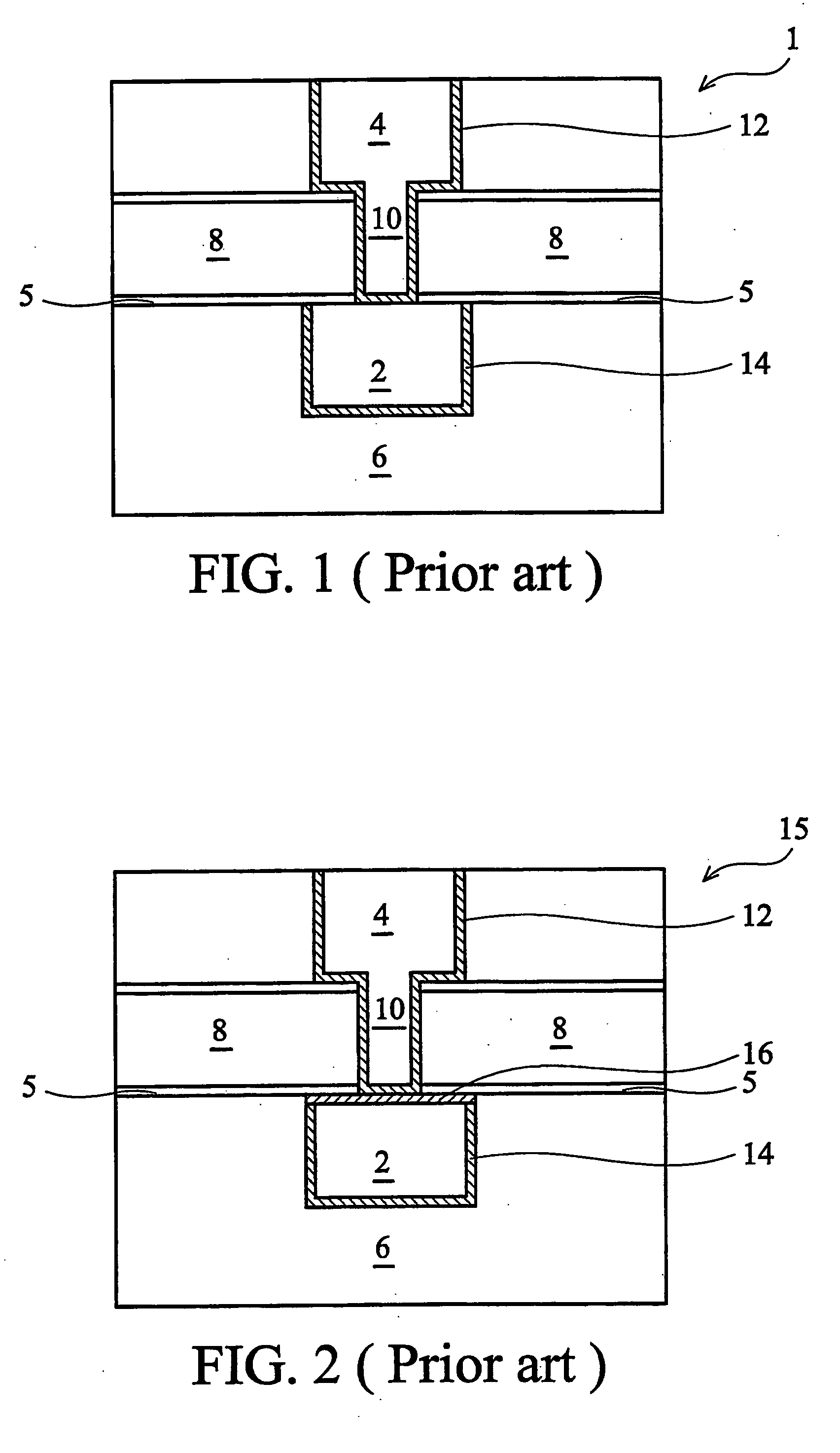

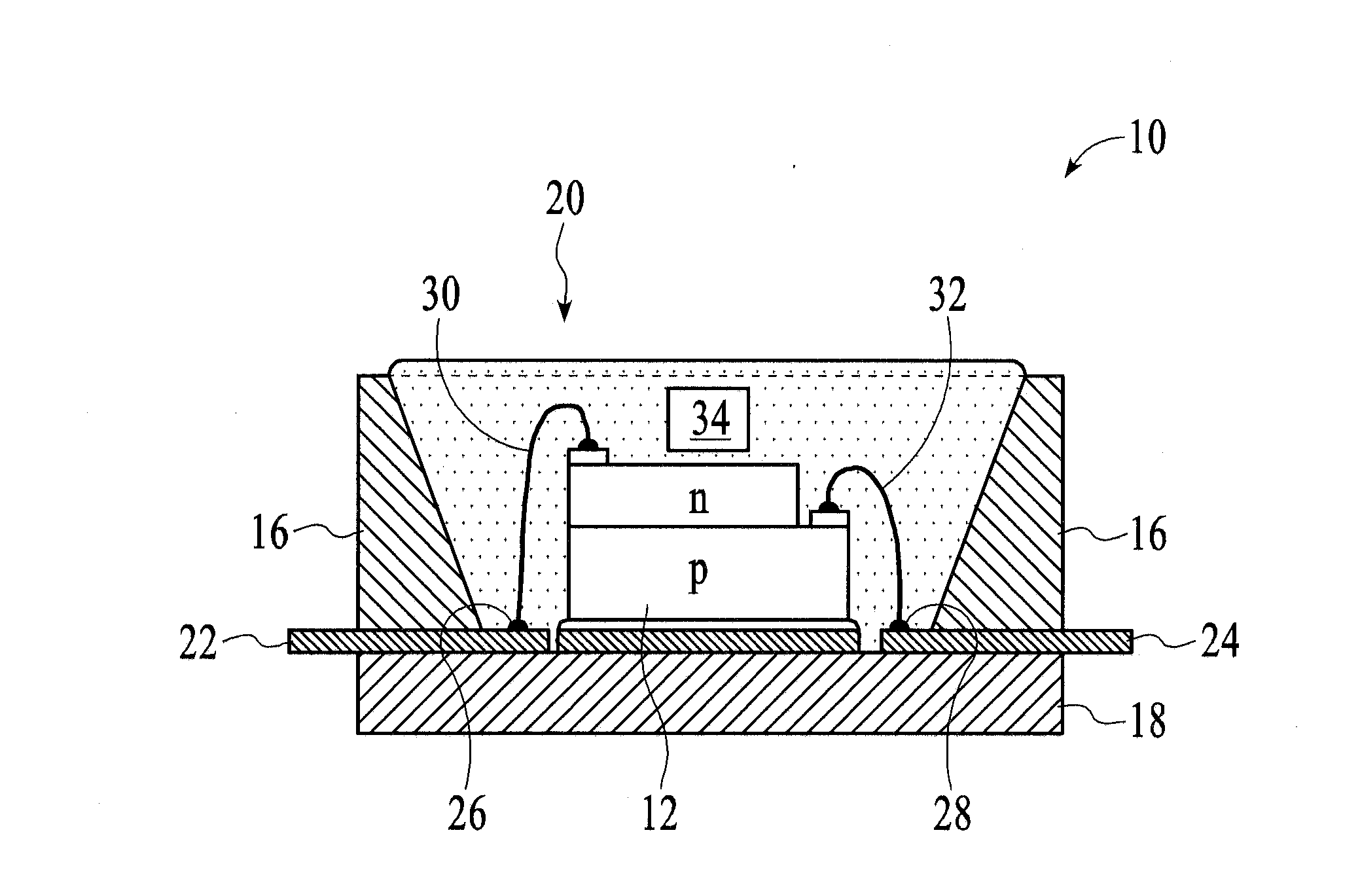

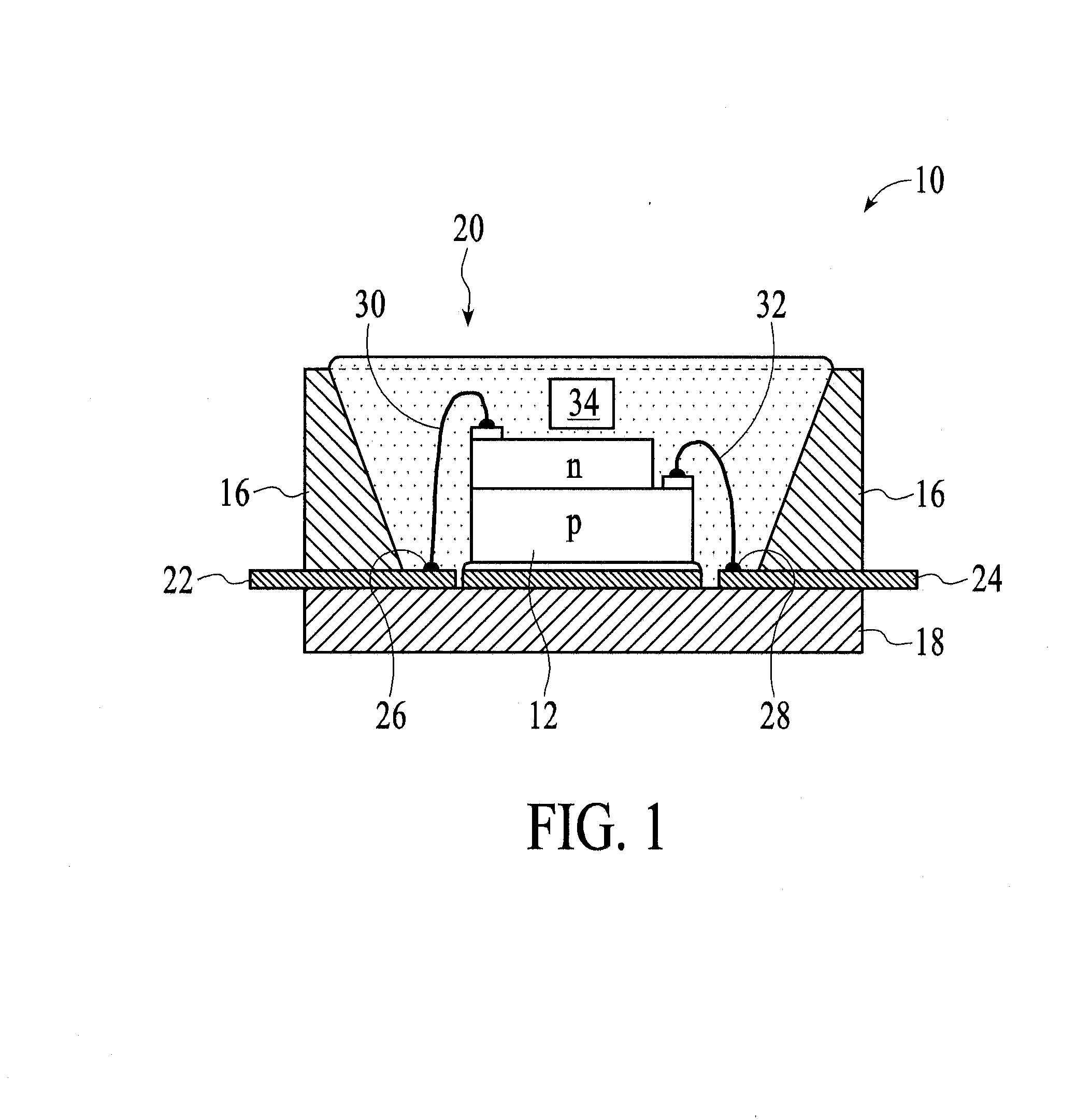

Composite connection structure and method of manufacturing

InactiveUS6337445B1Improve reliability and performanceImprove thermal conductivityPrinted circuit assemblingFinal product manufactureContact padSolder paste

A bump connection structure and a method of attachment to integrated circuits or packages is provided which comprises a prefabricated core structure coated with solderable metal layers to form a composite bump. Said composite bump is aligned to contact pads of the chip or package which have been coated with solder paste, and the assembly heated to form a metallurgical bond. The prefabricated core structures are comprised of metal, plastic or ceramic of the size and dictated by package standards. The connection structure is preferably lead free.

Owner:TEXAS INSTR INC

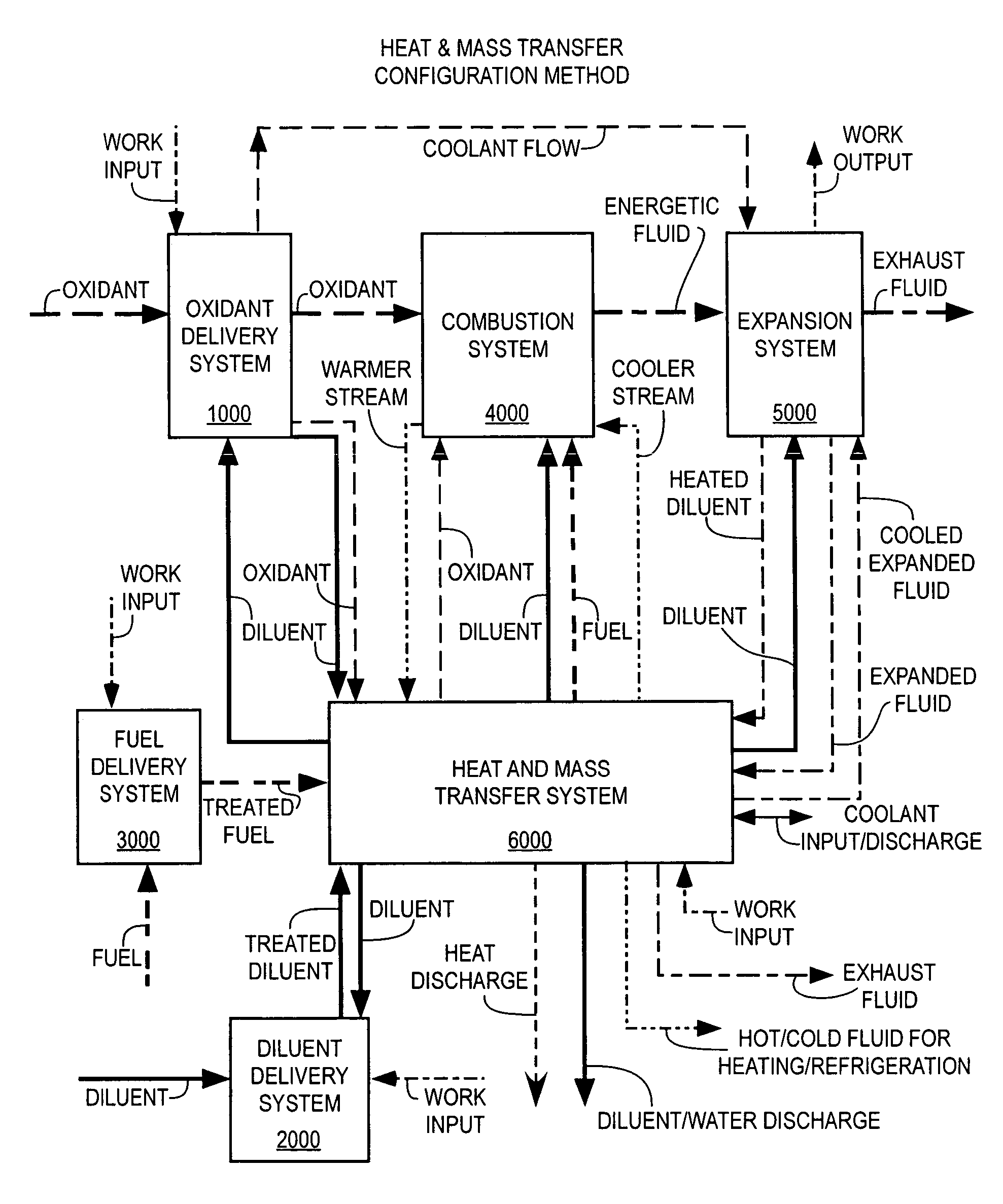

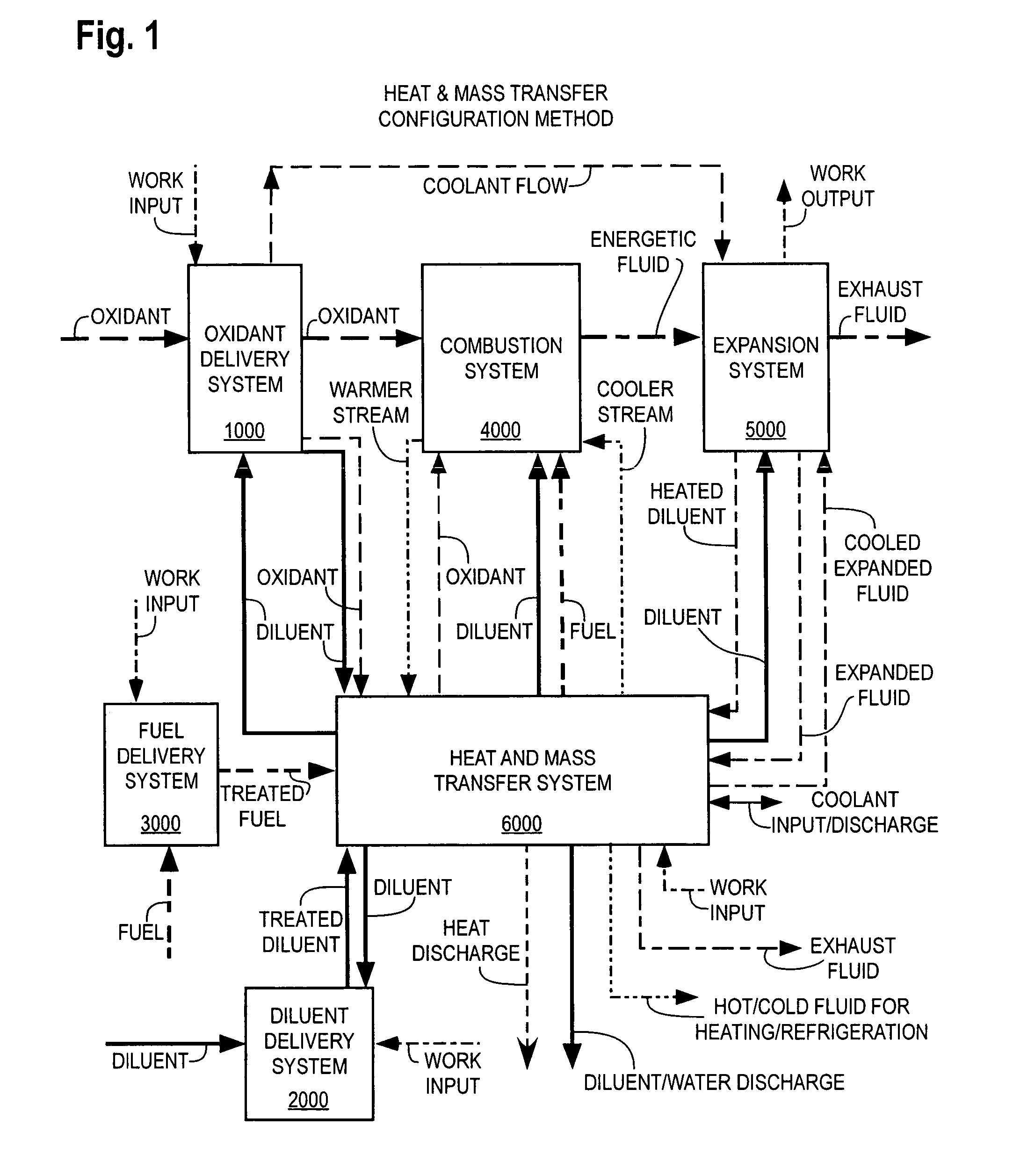

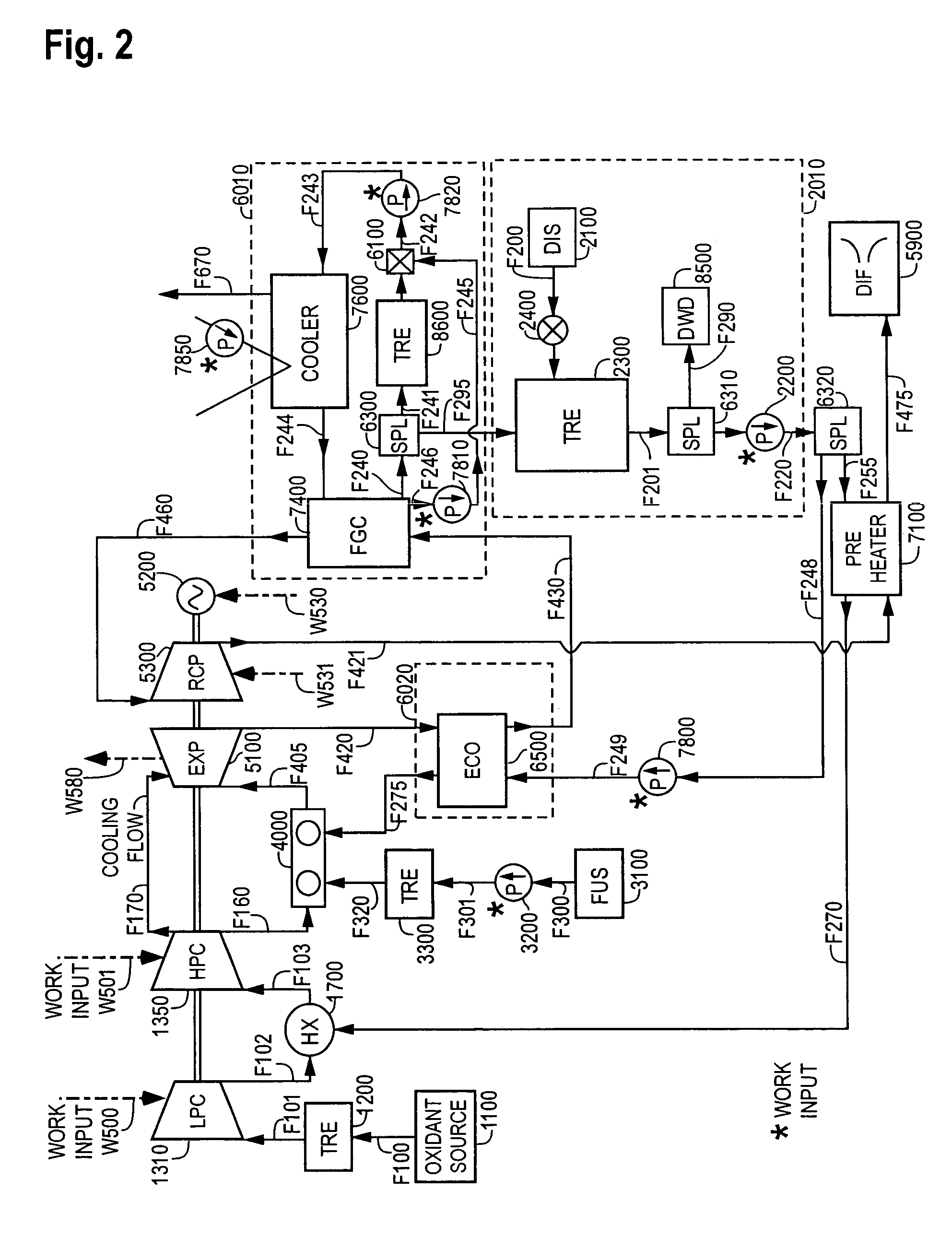

Thermodynamic cycles using thermal diluent

ActiveUS7416137B2Improve reliability and performanceReduce expenseLiquid fuel feeder/distributionGas turbine plantsInlet temperatureFluid composition

A thermodynamic system that produces mechanical, electrical power, and / or fluid streams for heating or cooling. The cycle contains a combustion system that produces an energetic fluid by combustion of a fuel with an oxidant. A thermal diluent may be used in the cycle to improve performance, including but not limited to power, efficiency, economics, emissions, dynamic and off-peak load performance, and / or turbine inlet temperature (TIT) regulation and cooling heated components. The cycle preferably includes a heat recovery system and a condenser or other means to recover and recycle heat and the thermal diluent from the energetic fluid to improve the cycle thermodynamic efficiency and reduce energy conversion costs. The cycle may also include controls for temperatures, pressures, and flow rates throughout the cycle, and controls power output, efficiency, and energetic fluid composition.

Owner:VAST HLDG LLC

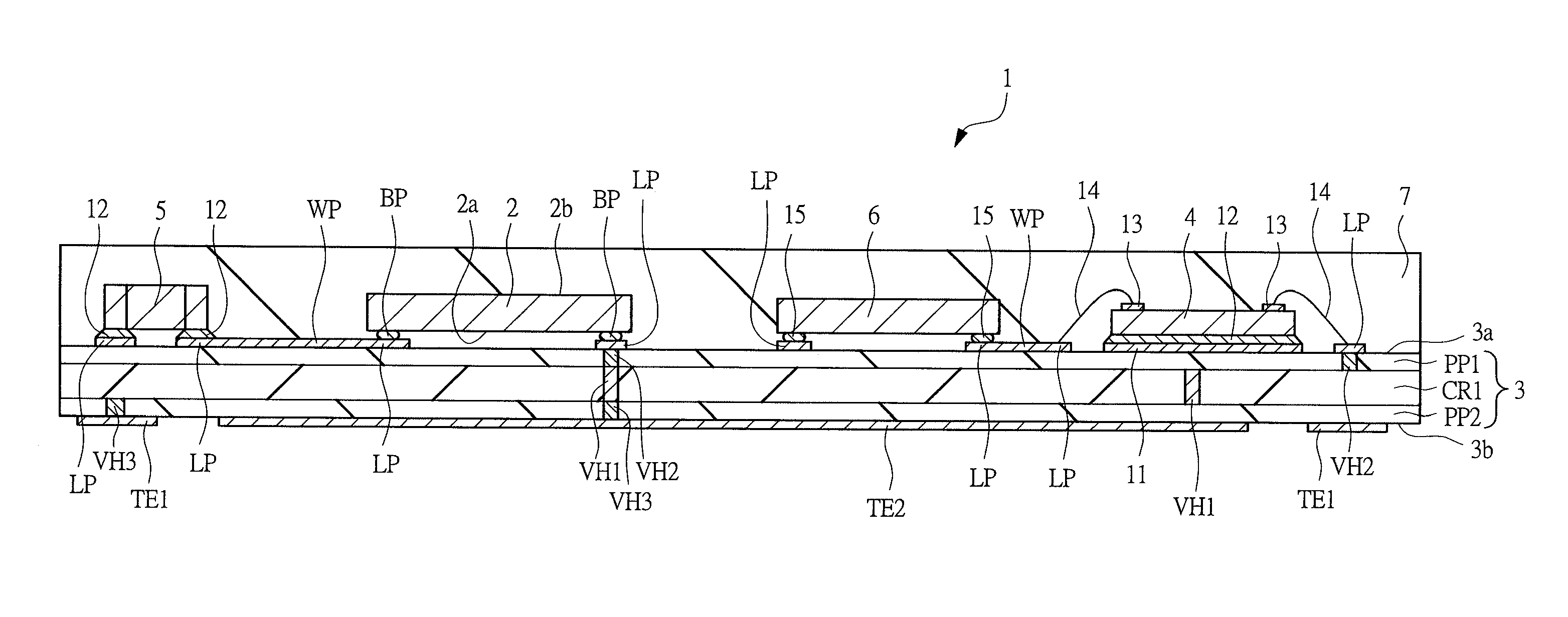

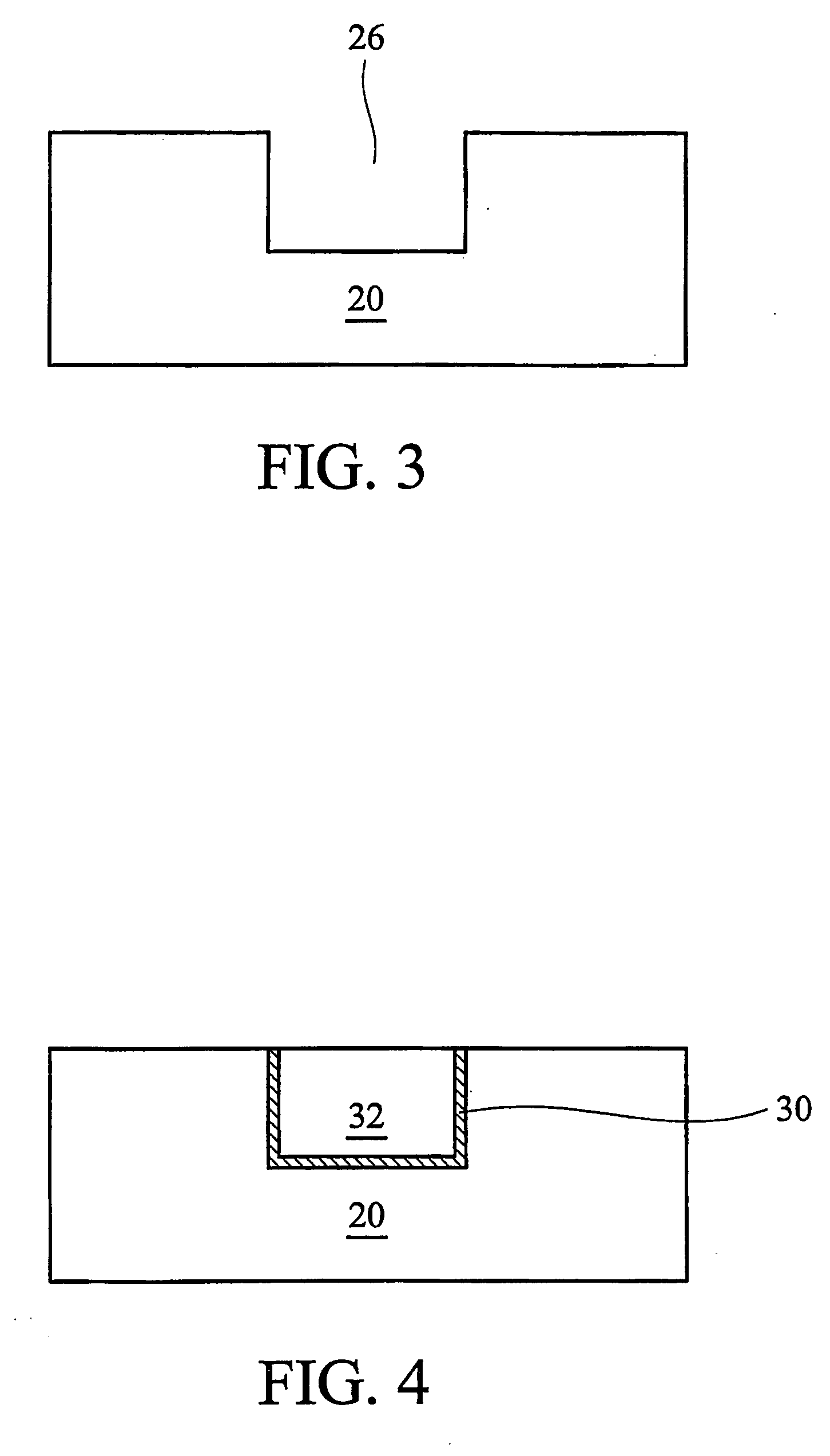

Semiconductor device and manufacturing method thereof

ActiveUS20100109052A1Small sizeReduce semiconductor areaTransistorSemiconductor/solid-state device detailsAudio power amplifierElectrical conductor

In a semiconductor chip in which LDMOSFET elements for power amplifier circuits used for a power amplifier module are formed, a source bump electrode is disposed on an LDMOSFET formation region in which a plurality of source regions, a plurality of drain regions and a plurality of gate electrodes for the LDMOSFET elements are formed. The source bump electrode is formed on a source pad mainly made of aluminum via a source conductor layer which is thicker than the source pad and mainly made of copper. No resin film is interposed between the source bump electrode and the source conductor layer.

Owner:MURATA MFG CO LTD

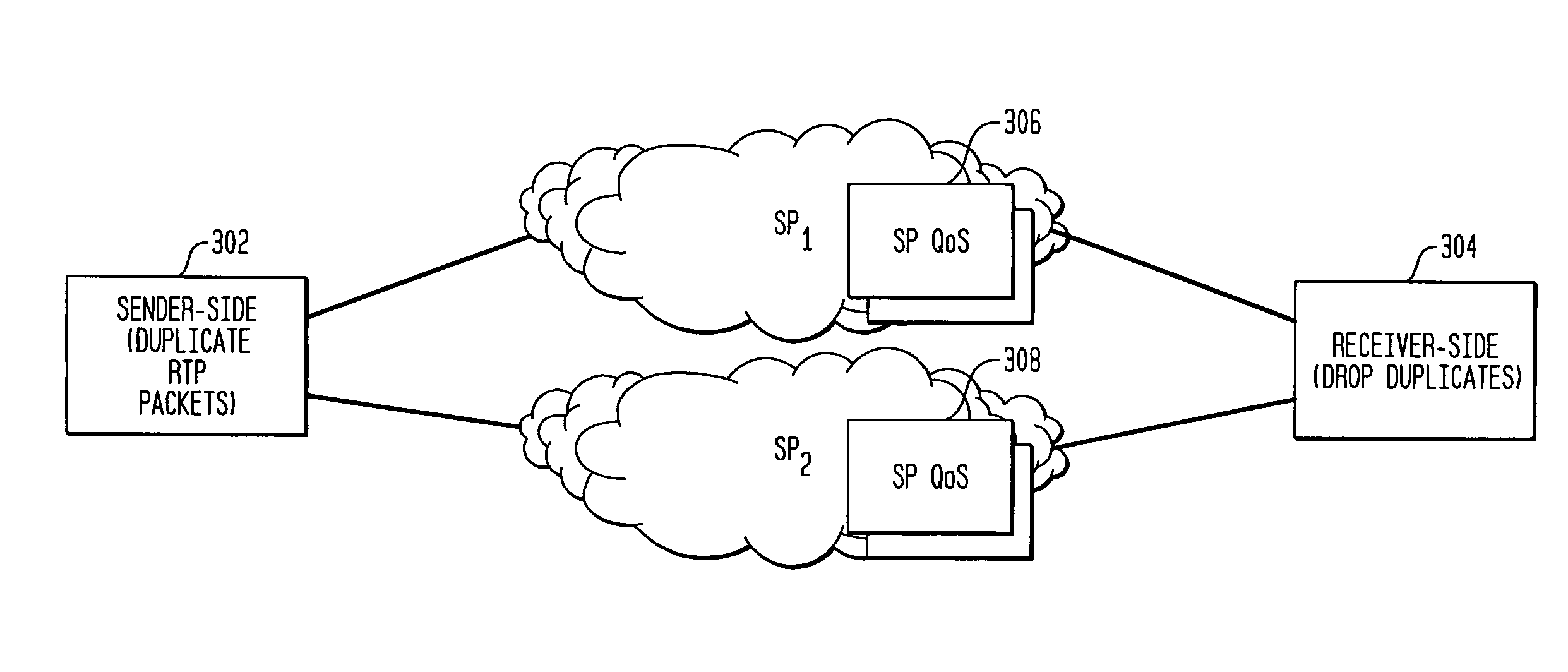

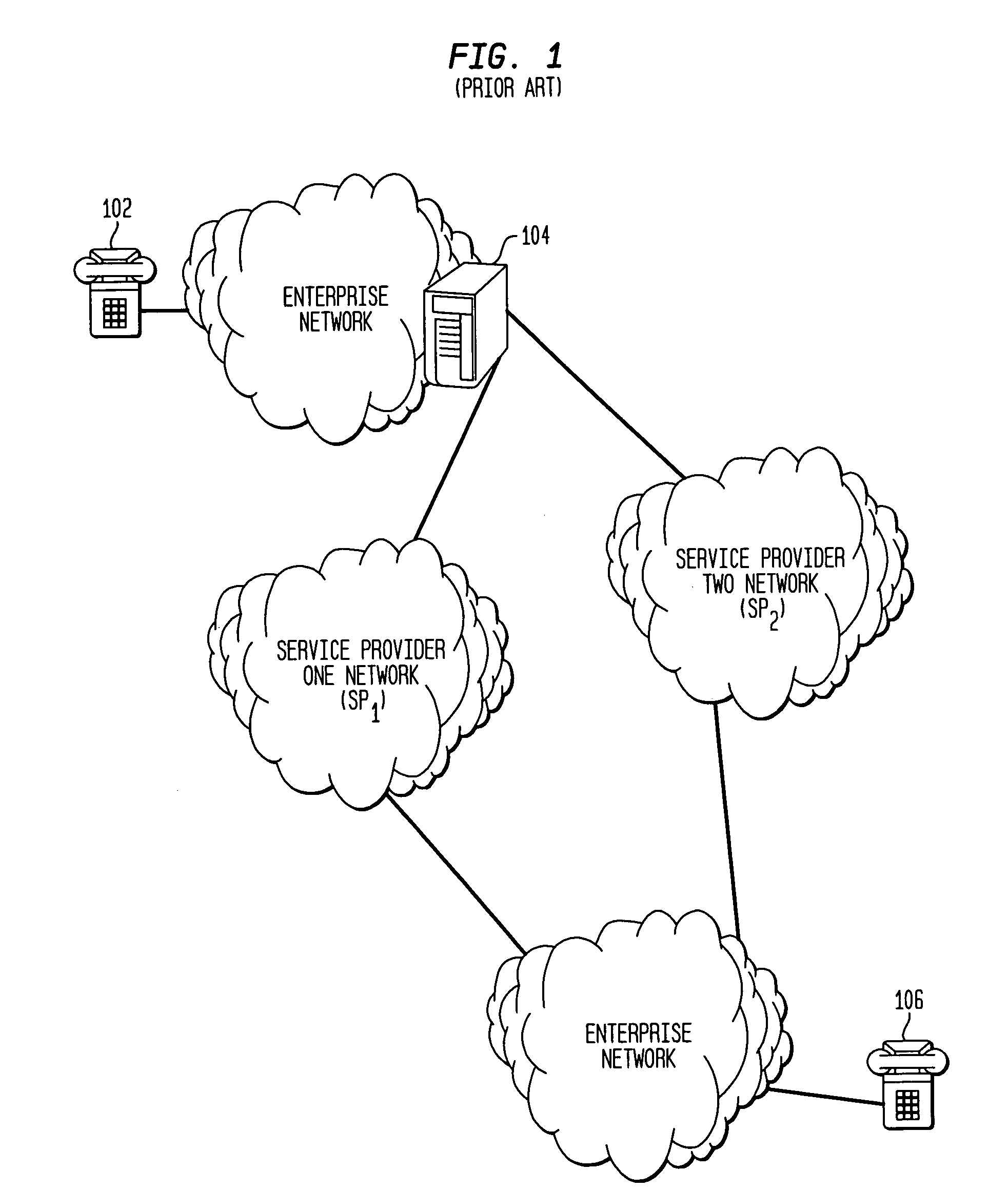

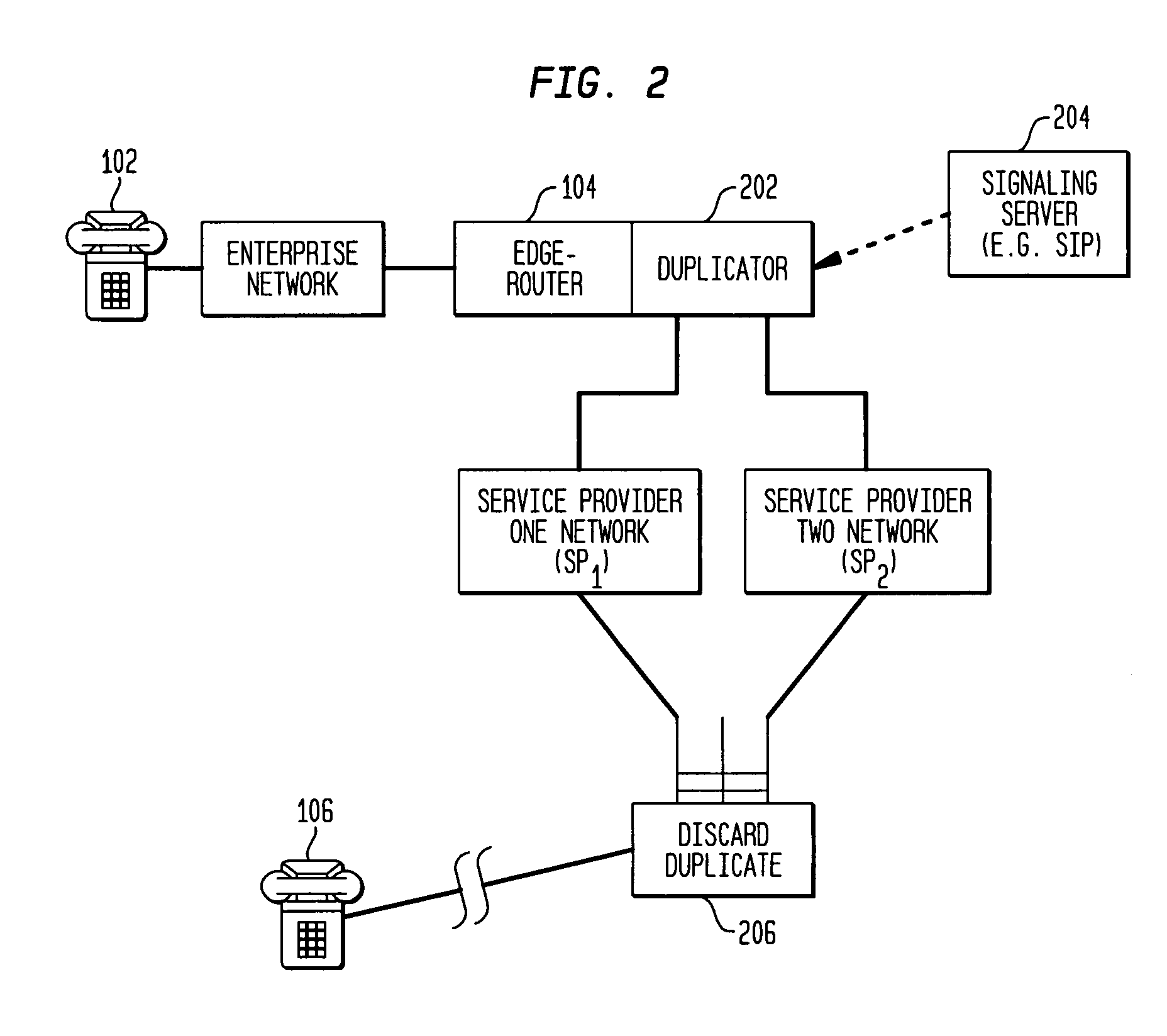

System and method to improve the resiliency and performance of enterprise networks by utilizing in-built network redundancy

ActiveUS7188189B2Improve reliabilityImprove performanceData switching by path configurationMultiple digital computer combinationsService provisionNetwork packet

The present invention is a system and method to improve the reliability and performance of existing enterprise IP networks which have dual-homed (or multi-homed) network architectures. In one aspect of the invention packets related to a selected category of transmission (e.g., VoIP) are duplicated at an edge router and sent over both (multiple) service providers. After traversing the service provider networks, only the first-to-arrive packets are kept and the later-arriving copies are discarded. In so doing, the result is better protection against node failures, link failures, and packet errors, and also better QoS performance under normal (fault-free) operation.

Owner:AVAYA INC

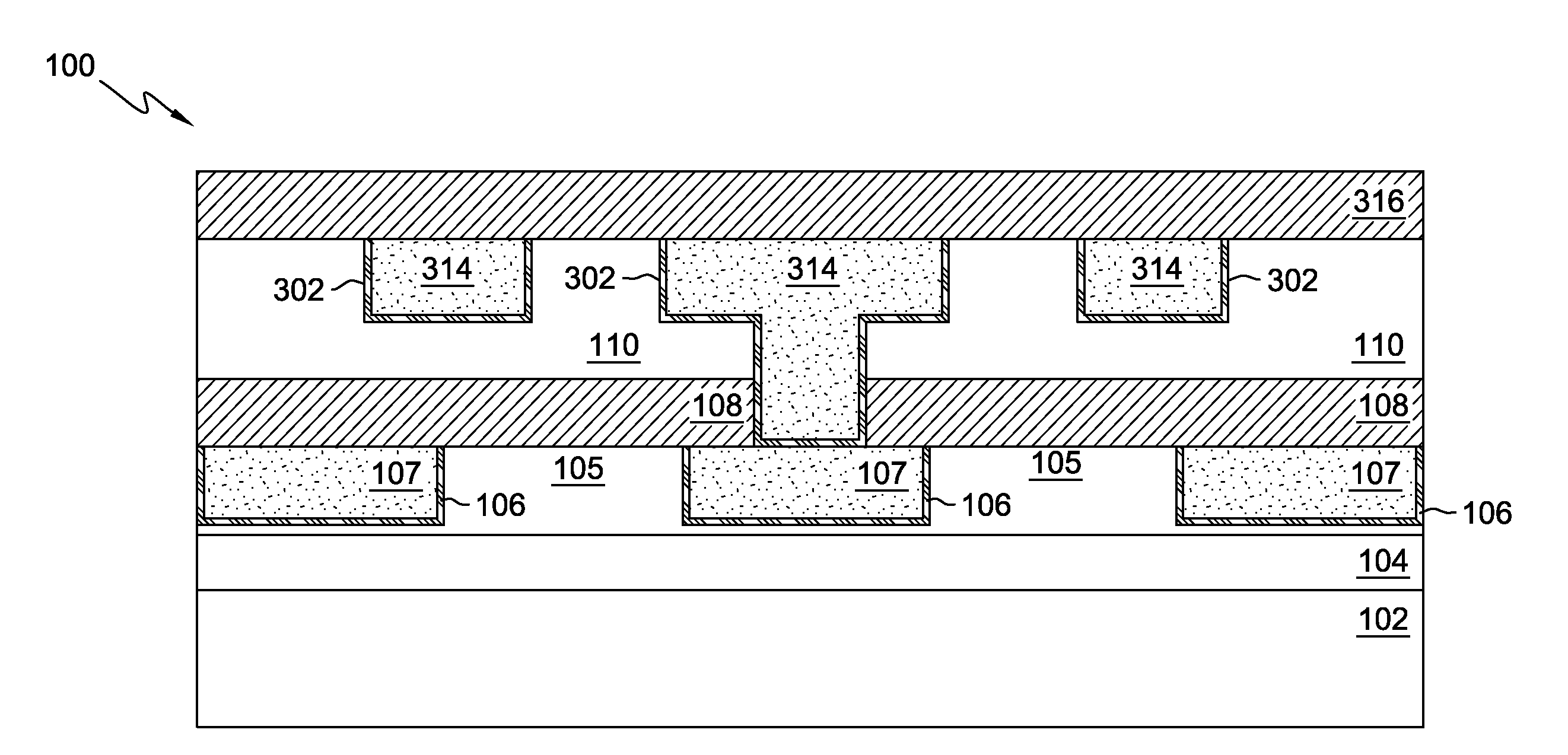

Semiconductor interconnect structure having a graphene-based barrier metal layer

ActiveUS20130113102A1Improve performanceImprove reliabilityMaterial nanotechnologySemiconductor/solid-state device detailsDiffusionGraphene

An interconnect structure and method for fabricating the interconnect structure having enhanced performance and reliability, by utilizing a graphene-based barrier metal layer to block oxygen intrusion from a dielectric layer into the interconnect structure and block copper diffusion from the interconnect structure into the dielectric layer, are disclosed. At least one opening is formed in a dielectric layer. A graphene-based barrier metal layer disposed on the dielectric layer is formed. A seed layer disposed on the graphene-based barrier metal layer is formed. An electroplated copper layer disposed on the seed layer is formed. A planarized surface is formed, wherein a portion of the graphene-based barrier metal layer, the seed layer, and the electroplated copper layer are removed. In addition, a capping layer disposed on the planarized surface is formed.

Owner:SAMSUNG ELECTRONICS CO LTD

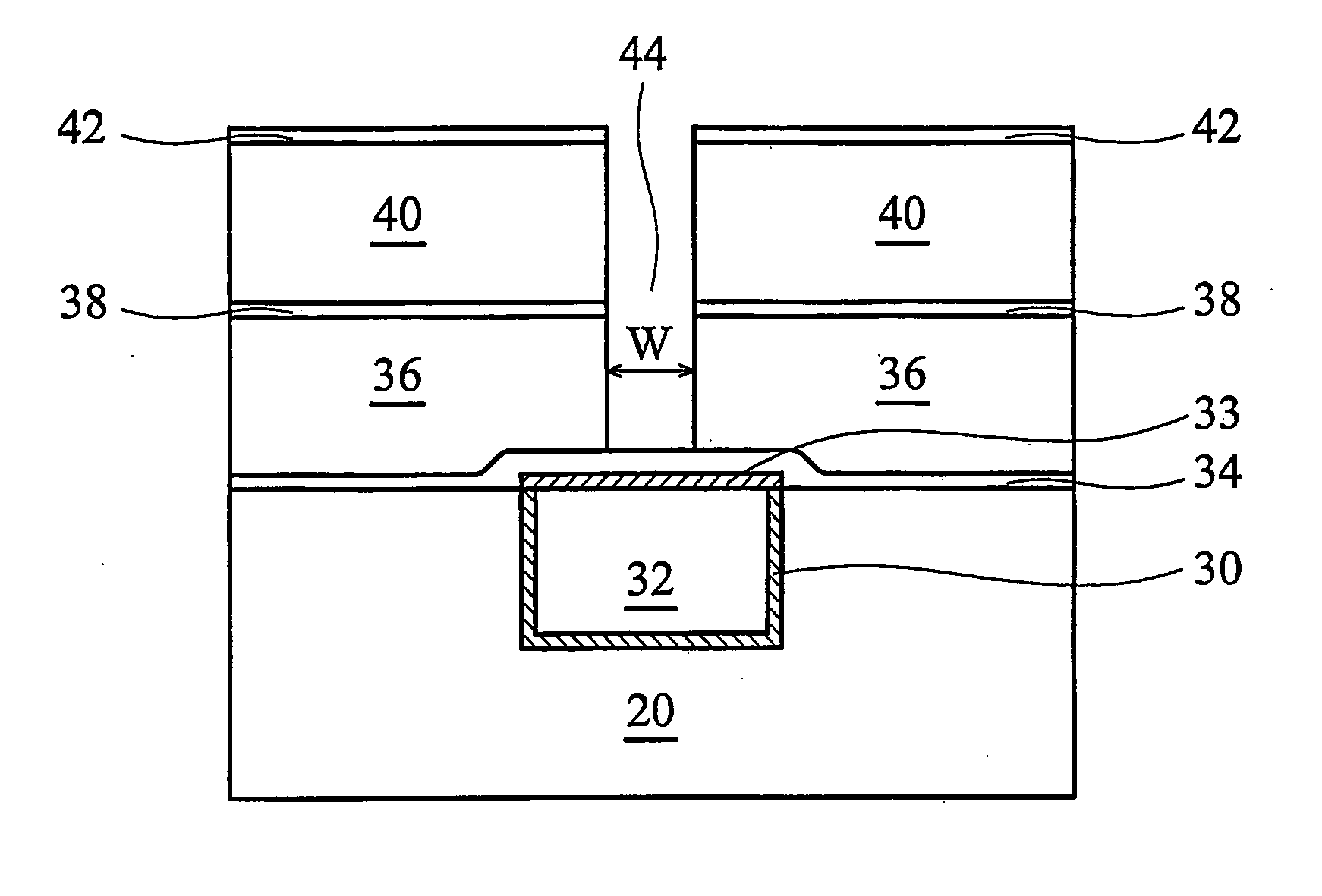

Damascene interconnect structure with cap layer

ActiveUS20060118962A1Improve reliability and performanceHigh contact resistanceSemiconductor/solid-state device detailsSolid-state devicesIntegrated circuit interconnectDielectric

A method of forming an integrated circuit interconnect structure is presented. A first conductive line is formed over a semiconductor substrate. A conductive cap layer is formed on the first conductive line to improve device reliability. An etch stop layer (ESL) is formed on the conductive cap layer. An inter-level dielectric (IMD) is formed on the ESL. A via opening and a trench are formed in the ESL, IMD, and conductive cap layer. A recess is formed in the first conductive line. The recess can be formed by over etching when the first dielectric is etched, or by a separate process such as argon sputtering. A second conductive line is formed filling the trench, opening and recess.

Owner:TAIWAN SEMICON MFG CO LTD

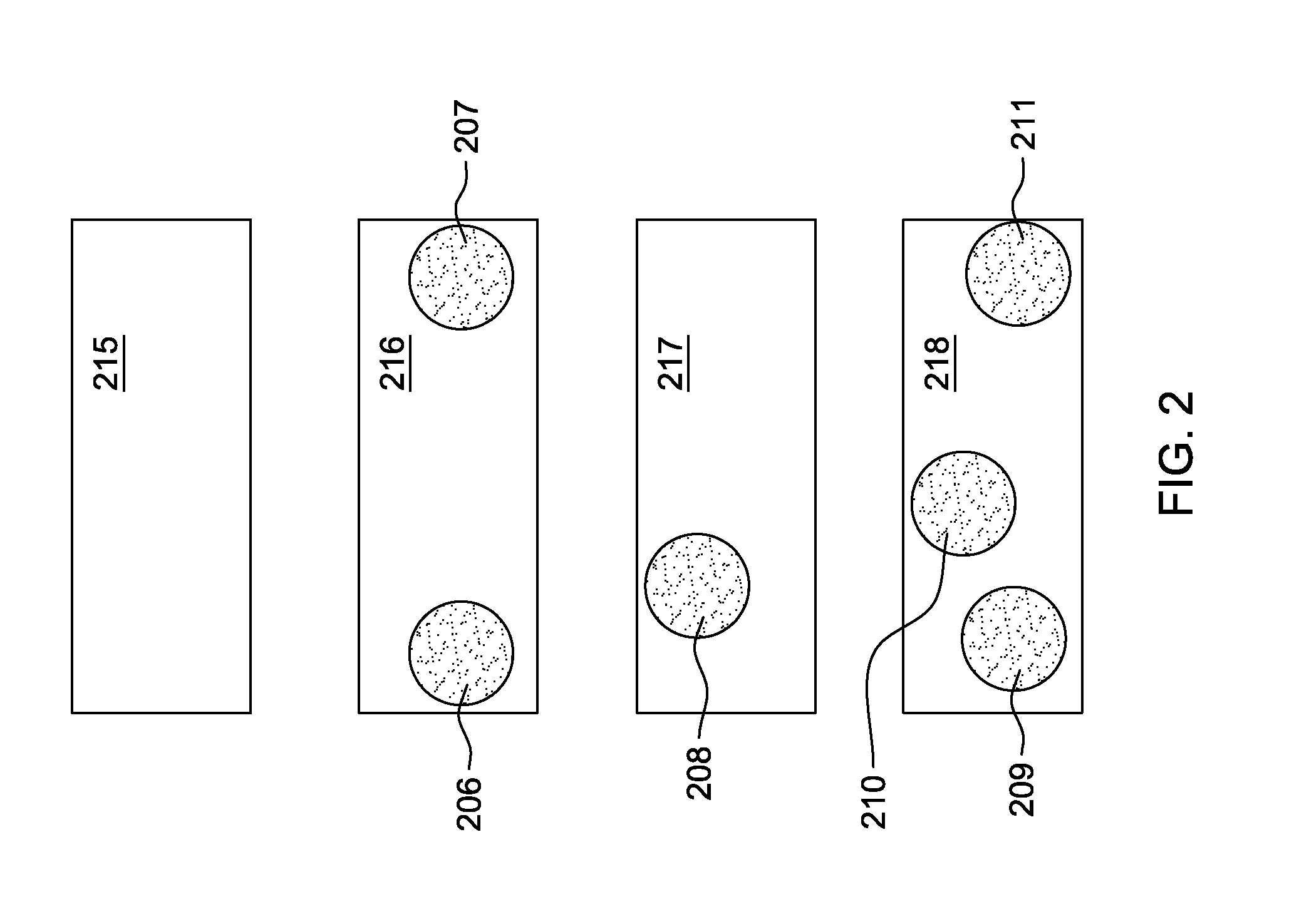

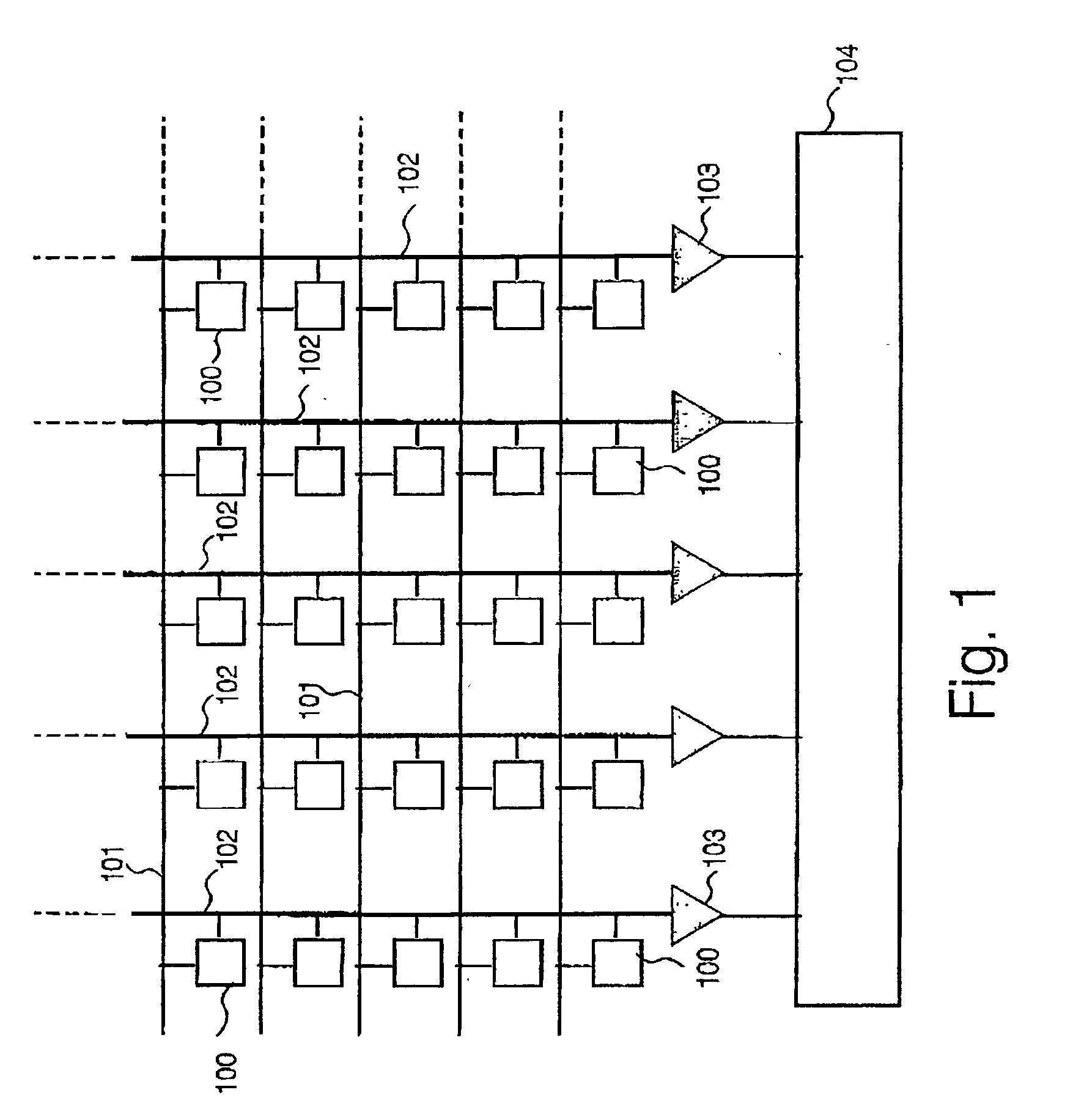

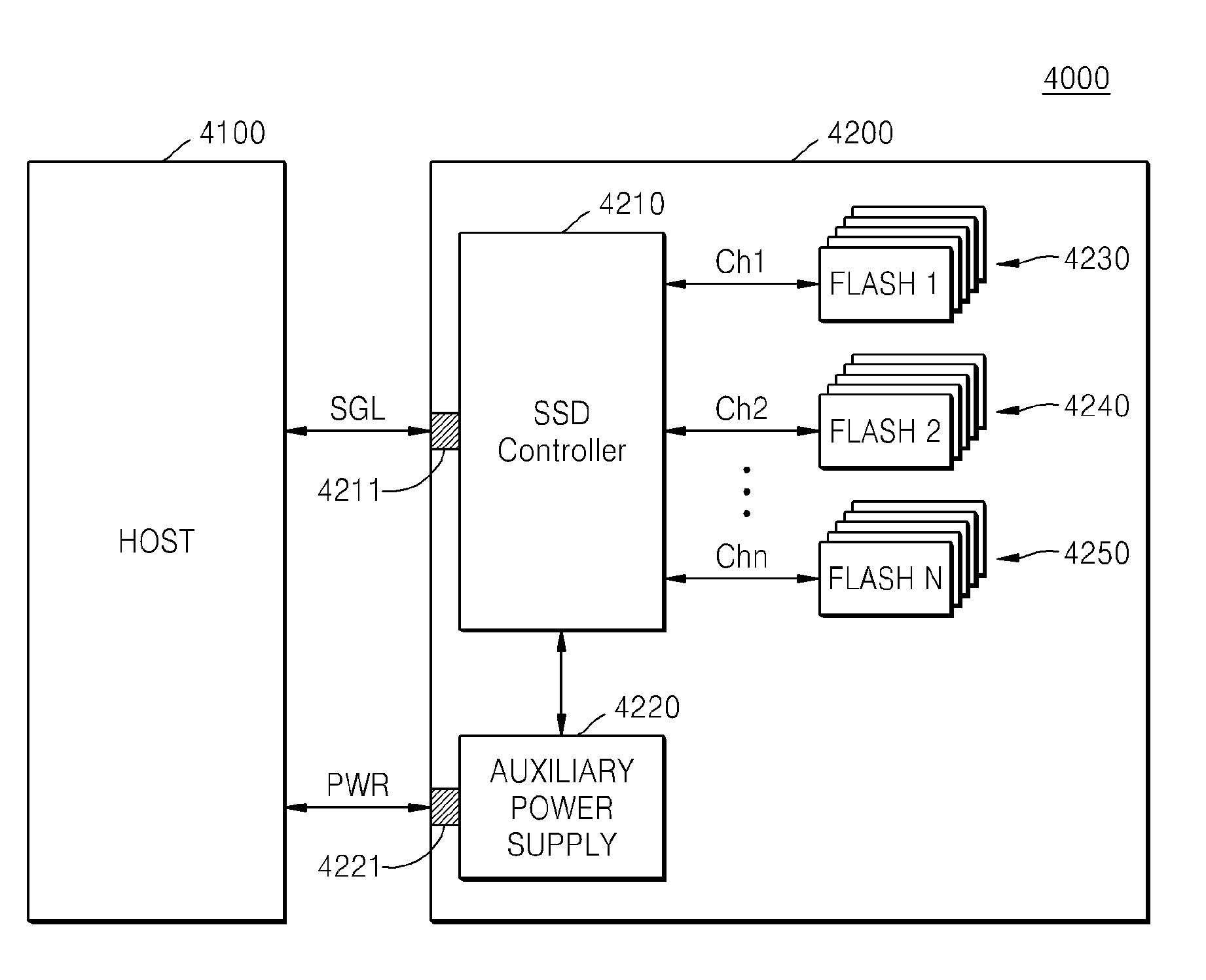

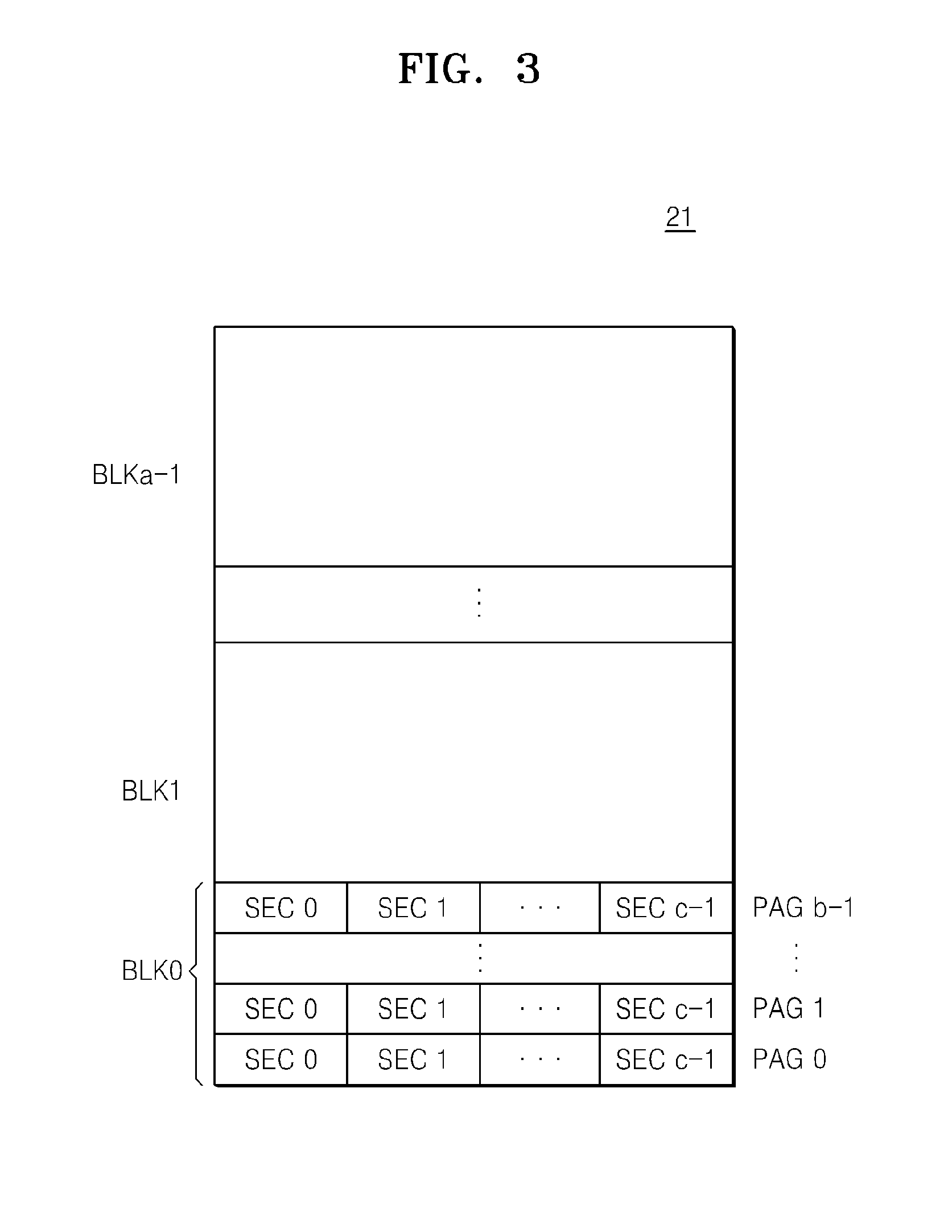

Data balancing scheme in solid state storage devices

InactiveUS20020159285A1Improve reliability and performanceLarge in characteristicsRead-only memoriesDigital storageSolid-state storageOriginal data

A data storage device comprises at least one array of memory elements arranged in a plurality of rows and columns; coding means for coding an input data into a form having a balanced proportion of "1's and "0's, said coding means comprising means for applying an output of a pseudo random bit sequence generator to said incoming data, wherein the coded data is stored in the array of memory elements such that the "1's and "0's are spatially distributed relatively evenly across the plurality of memory elements; and decoding means for decoding the coded data read from the plurality of memory elements, into the original data.

Owner:SAMSUNG ELECTRONICS CO LTD

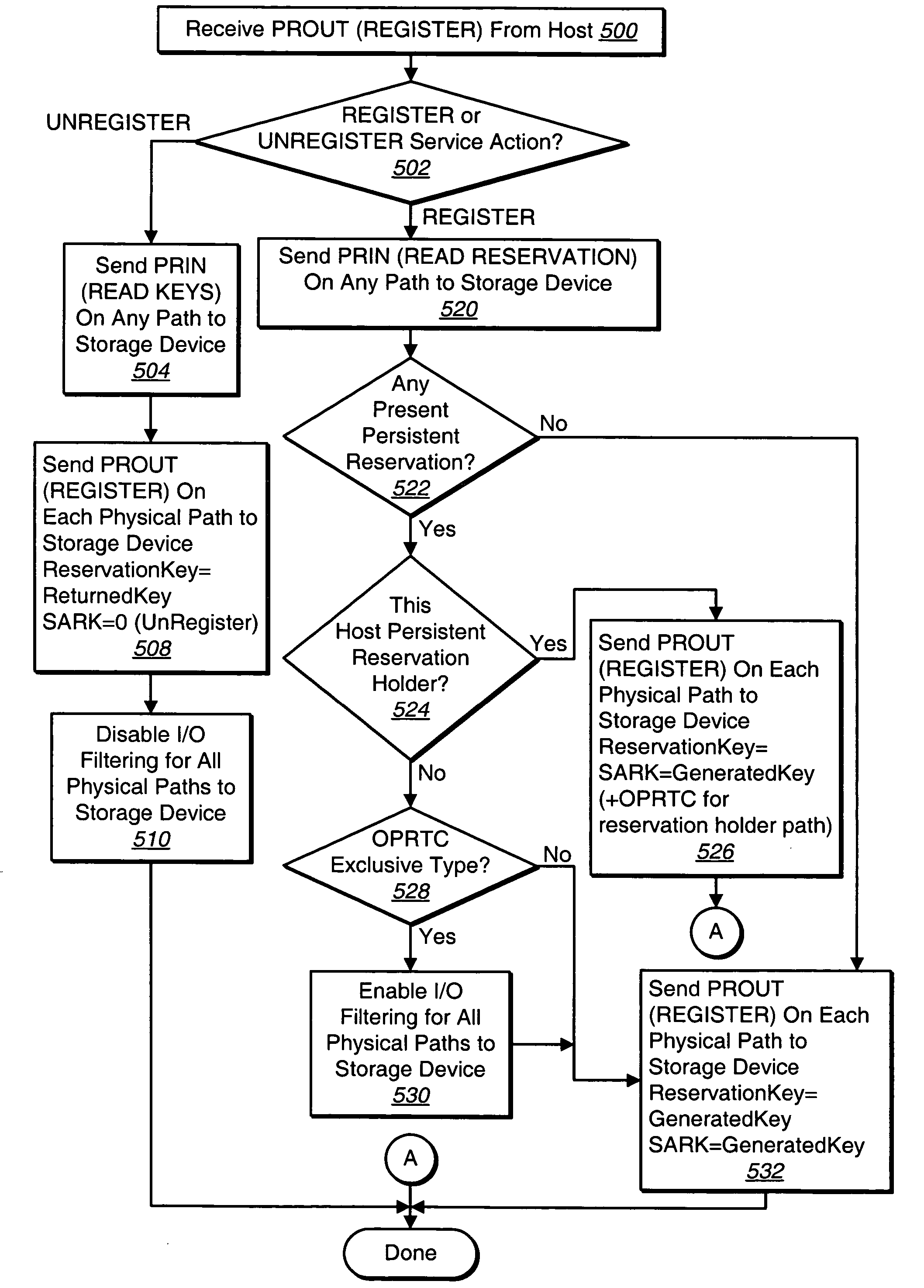

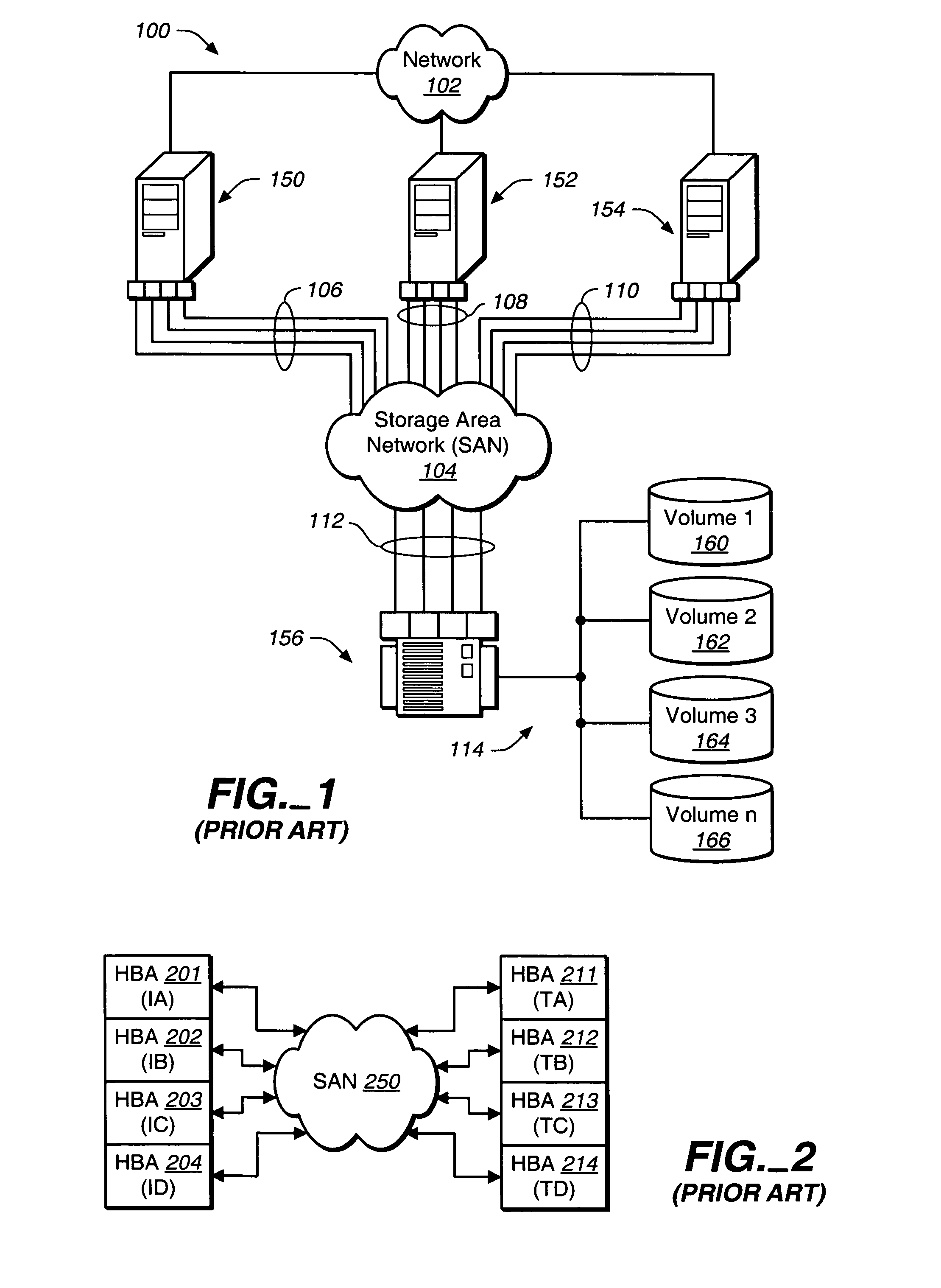

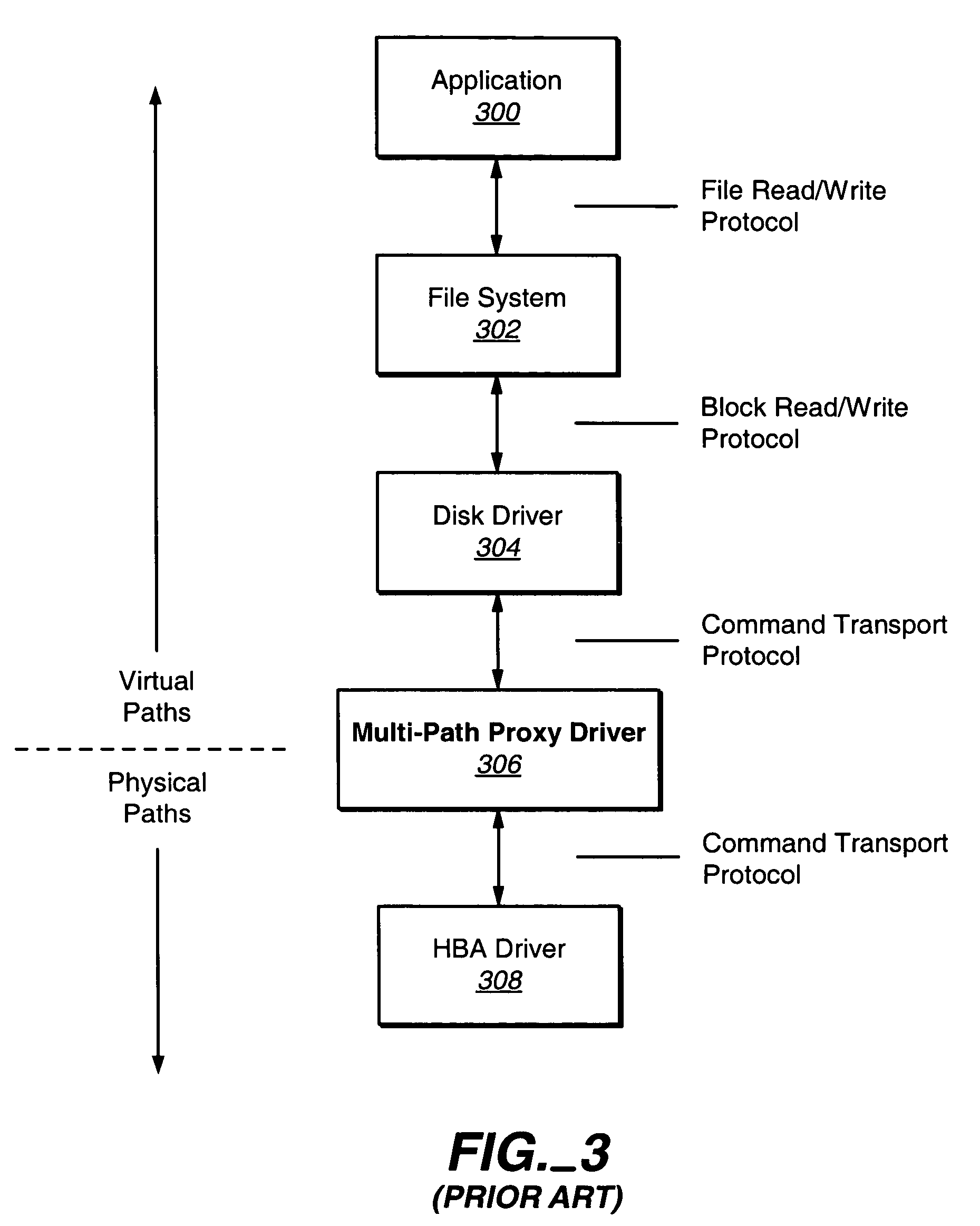

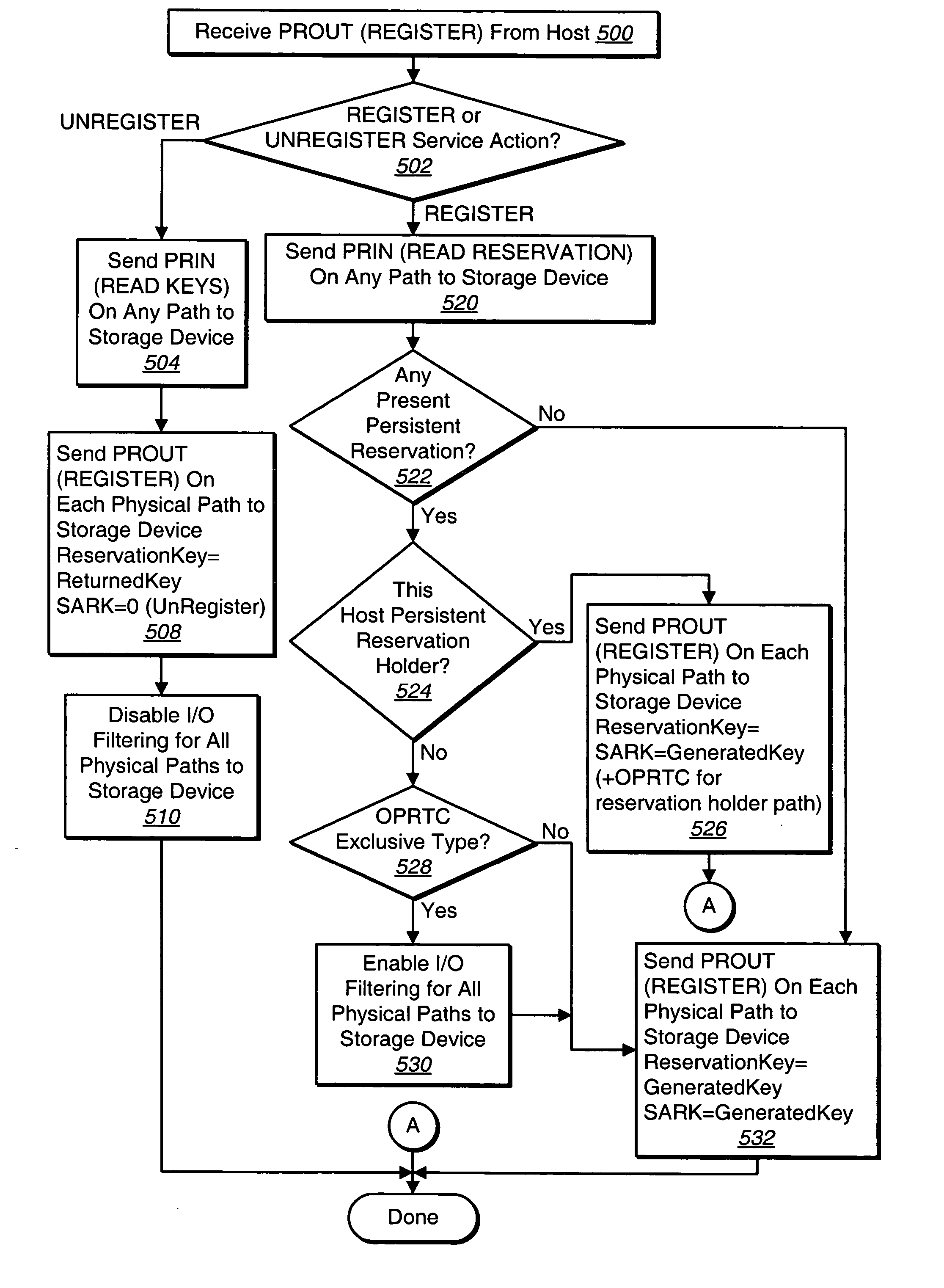

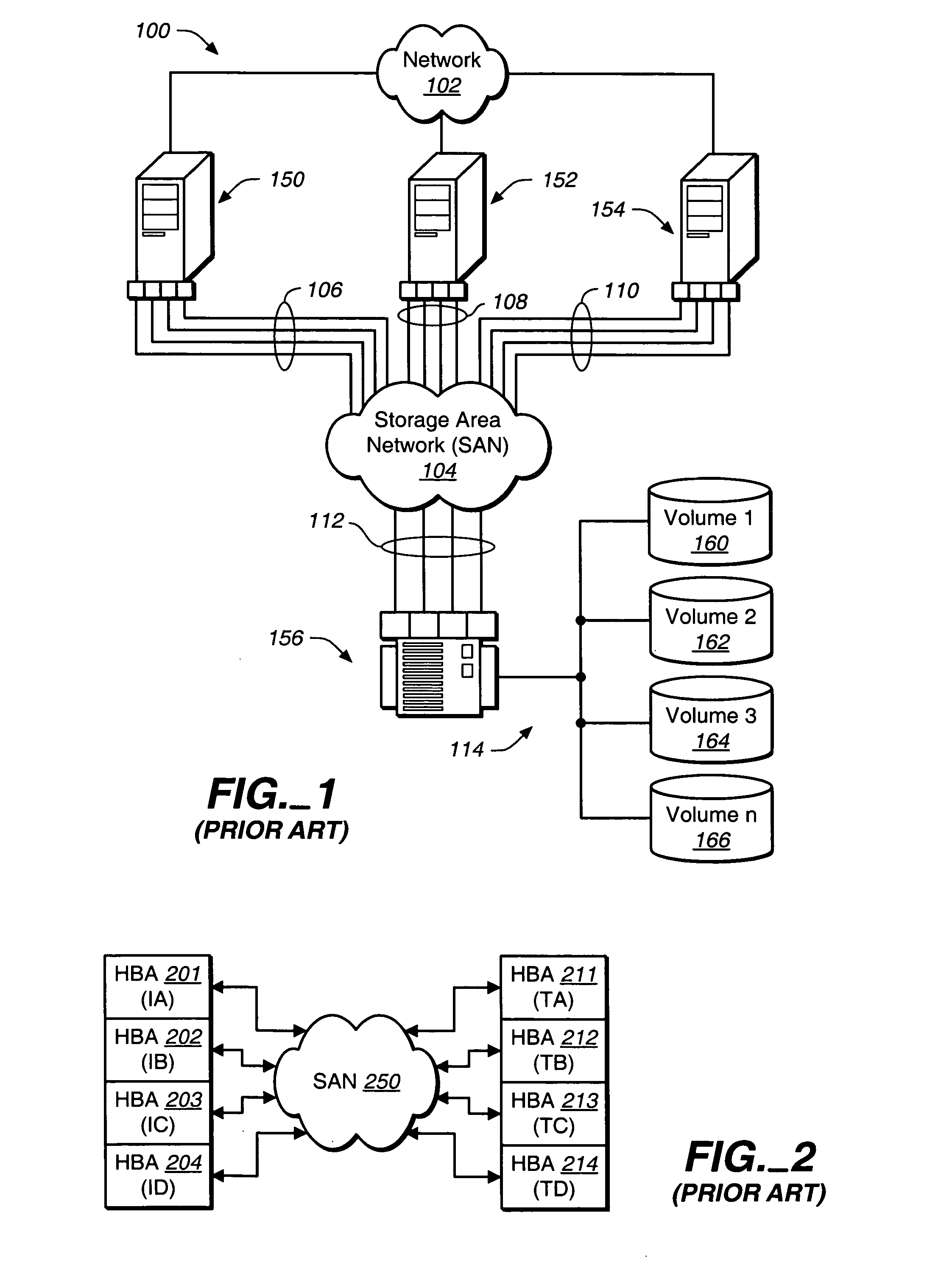

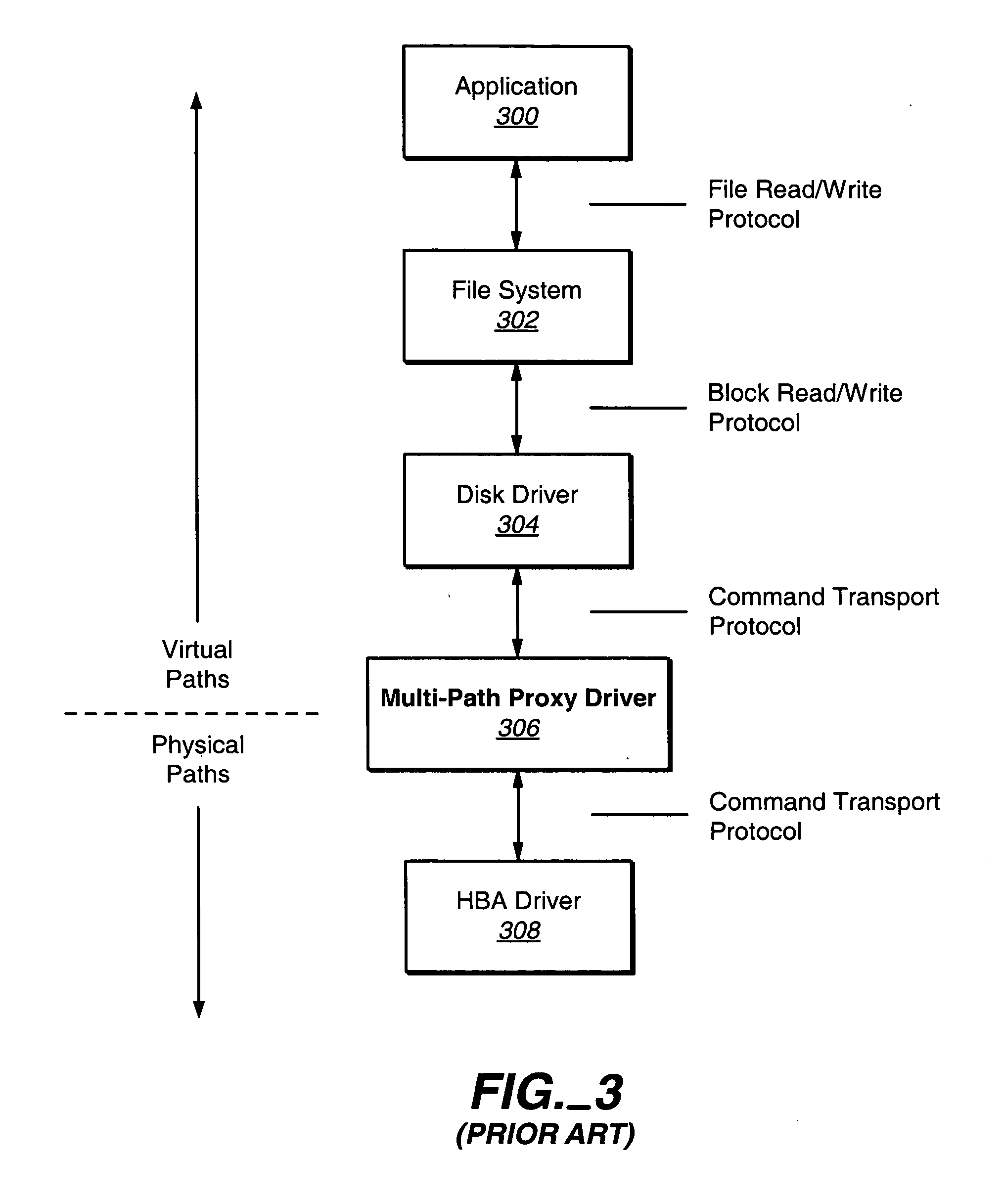

Methods and structure for supporting persistent reservations in a multiple-path storage environment

ActiveUS7313636B2Improve reliability and performanceGood conditionInput/output processes for data processingData conversionSCSIProcessing element

Owner:NETWORK APPLIANCE INC

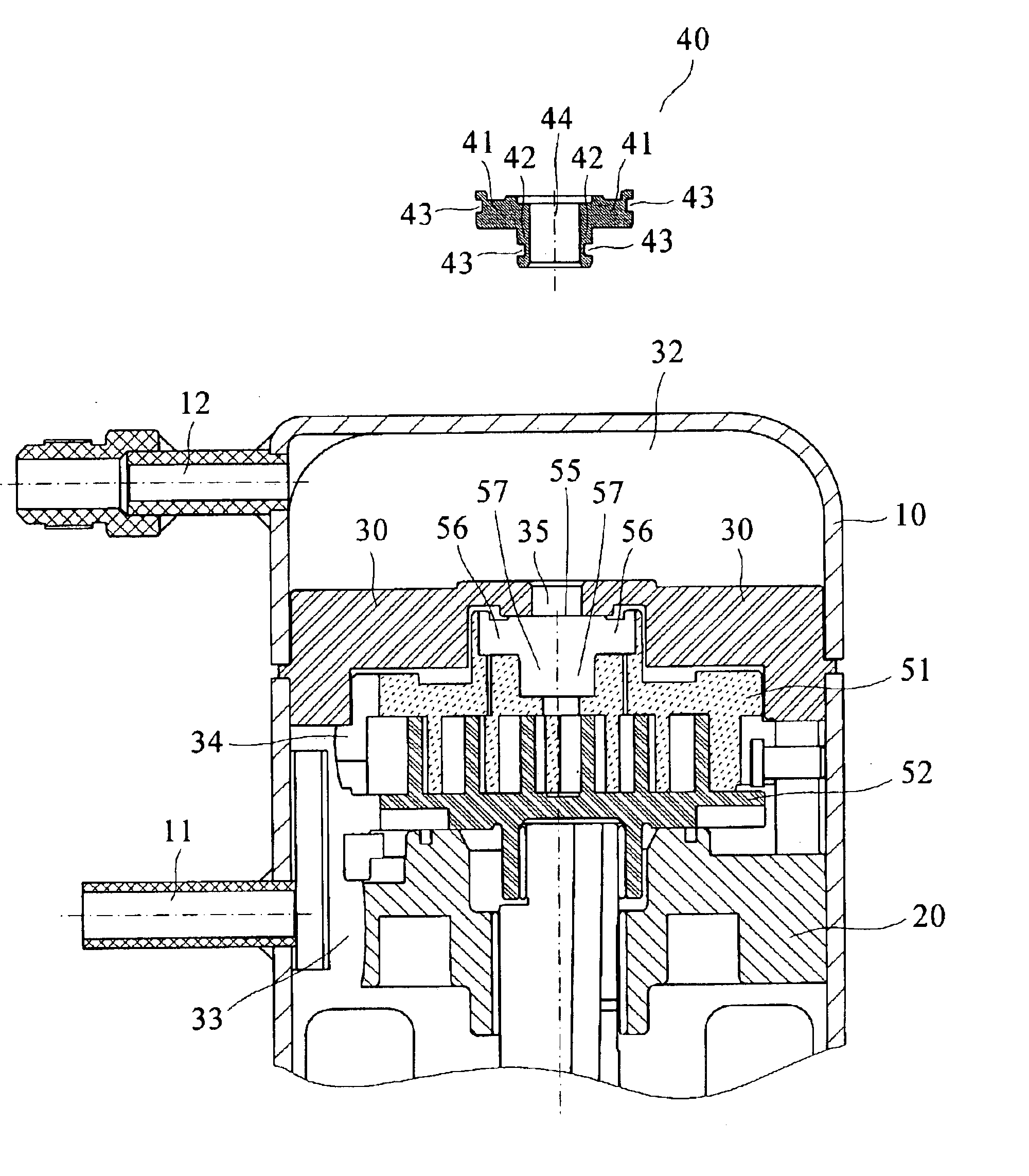

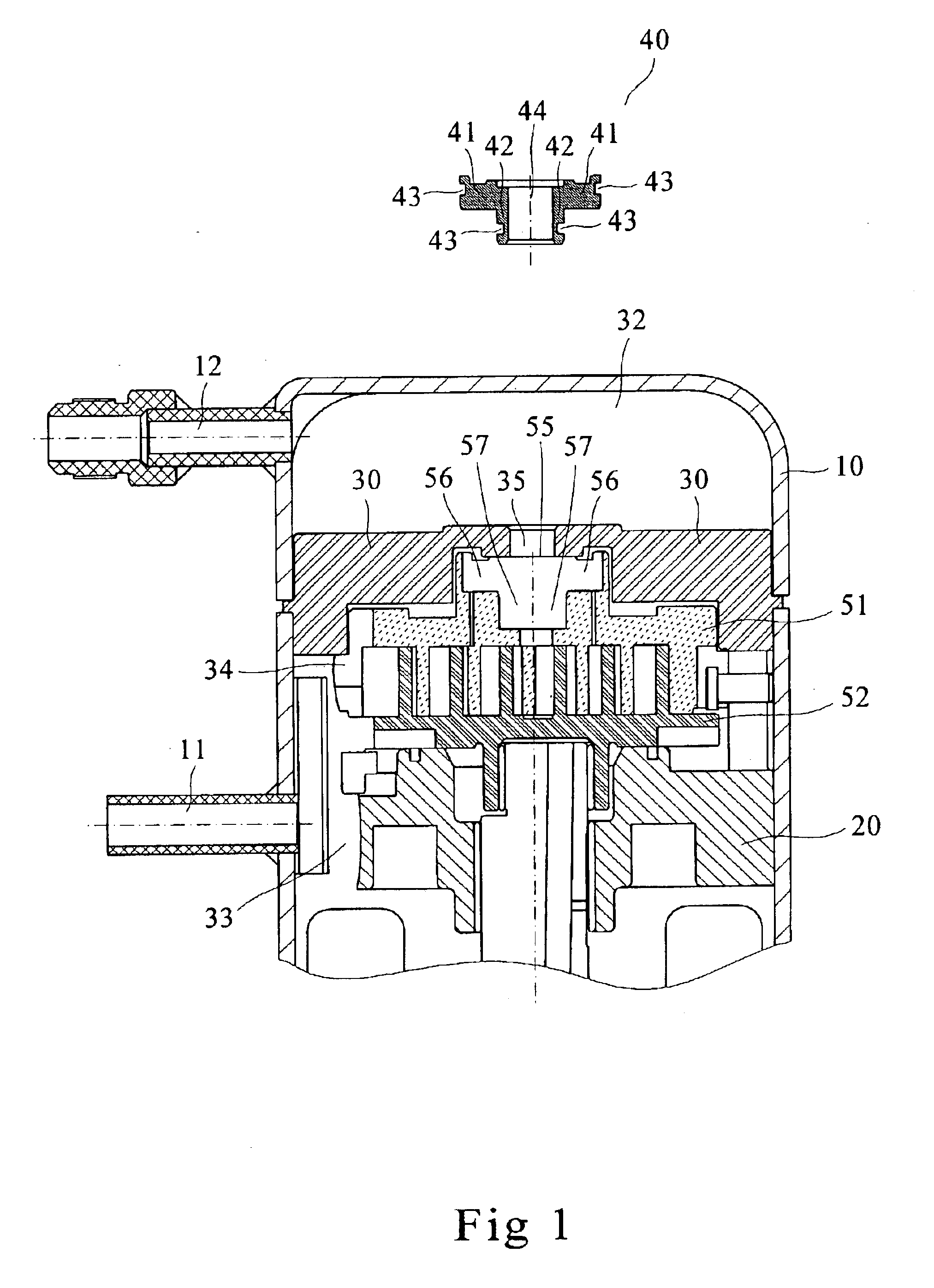

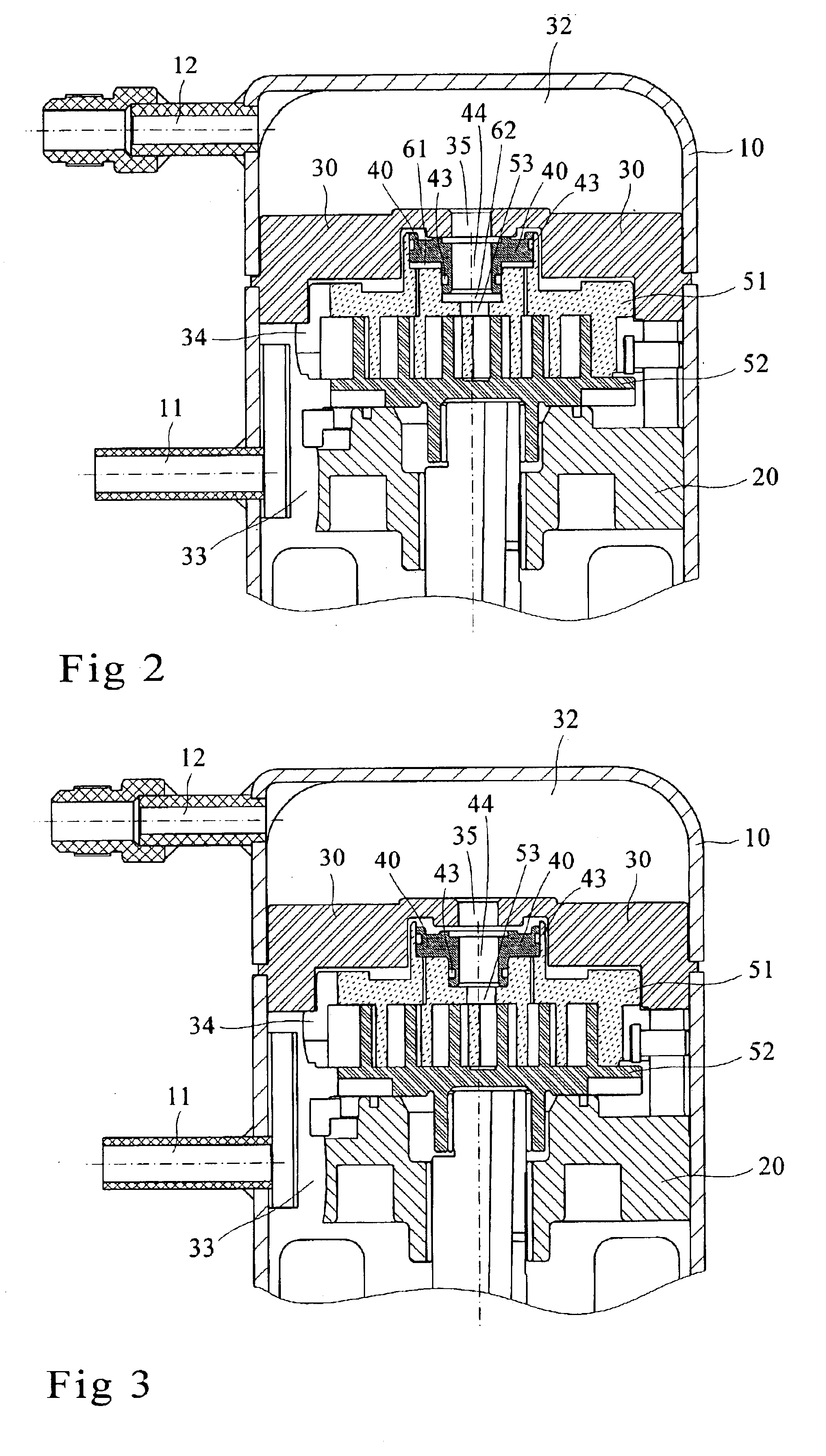

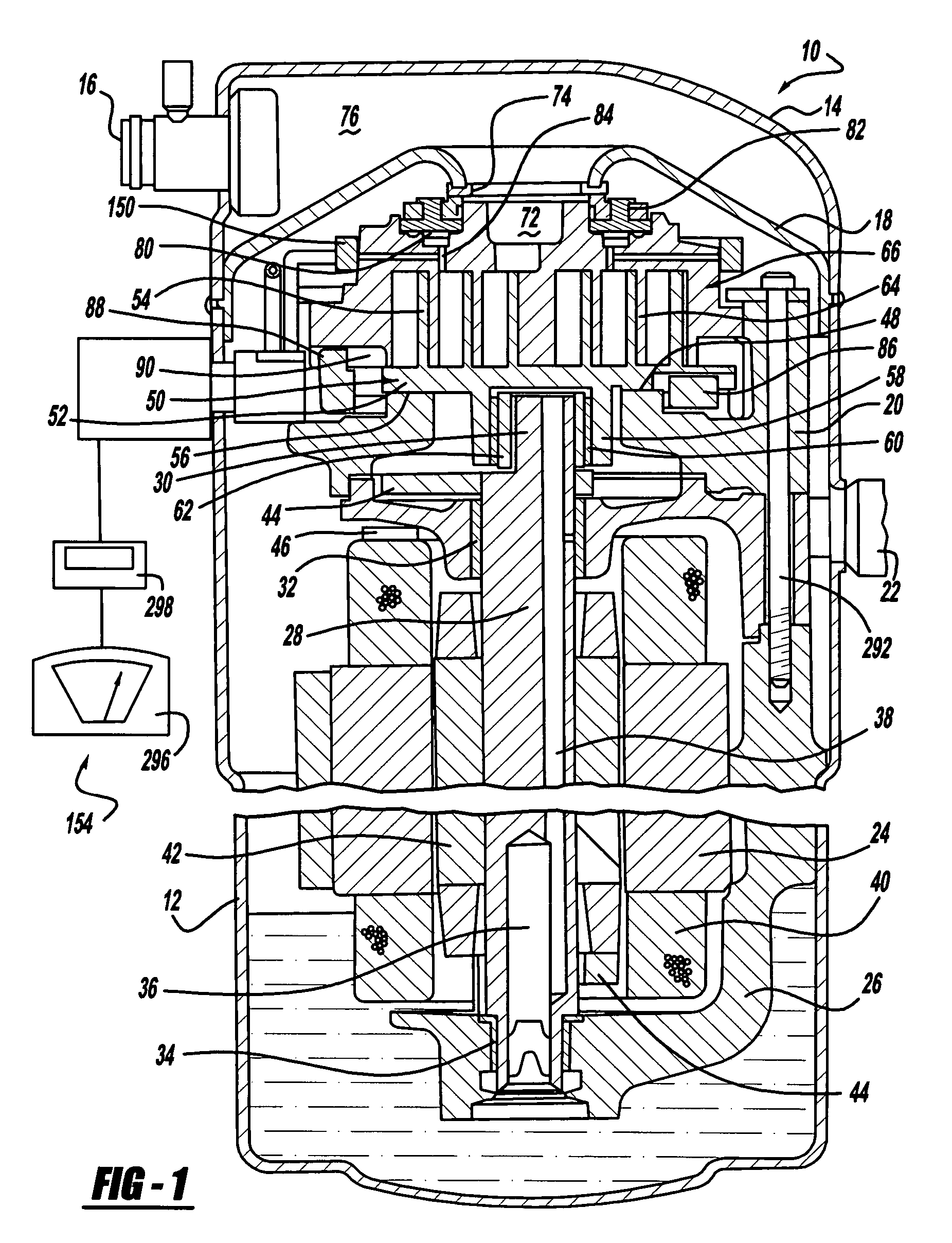

Load-regulating device for scroll type compressors

InactiveUS6913448B2Quickly build up pressurePrevent leakageEngine of arcuate-engagement typeOscillating piston enginesEngineeringLoad regulation

A load-regulating device for scroll type compressors comprising a compressor housing, a bracket body, a partition block, a gliding block, a pair of scrolls and a plurality of air chambers, wherein the gliding block being coupled with the pair of scrolls for defining a plurality of air chambers on the scrolls, the pressure variation in the air chambers is then utilized for causing the motion of the gliding block, enabling the compressor to cause the gliding block by means of the pressure variation to motion upwardly as the compressor is actuated, and preventing the fluid in the high-pressure chamber from leaking towards the low-pressure chamber, thus allowing the compressors to quickly build up the pressure; the gliding block is caused by the pressure variation to motion downwardly at times when the compression ratio is excessively high, so as to relieve part of the load, thus improving the performance and reliability of the compressors.

Owner:IND TECH RES INST

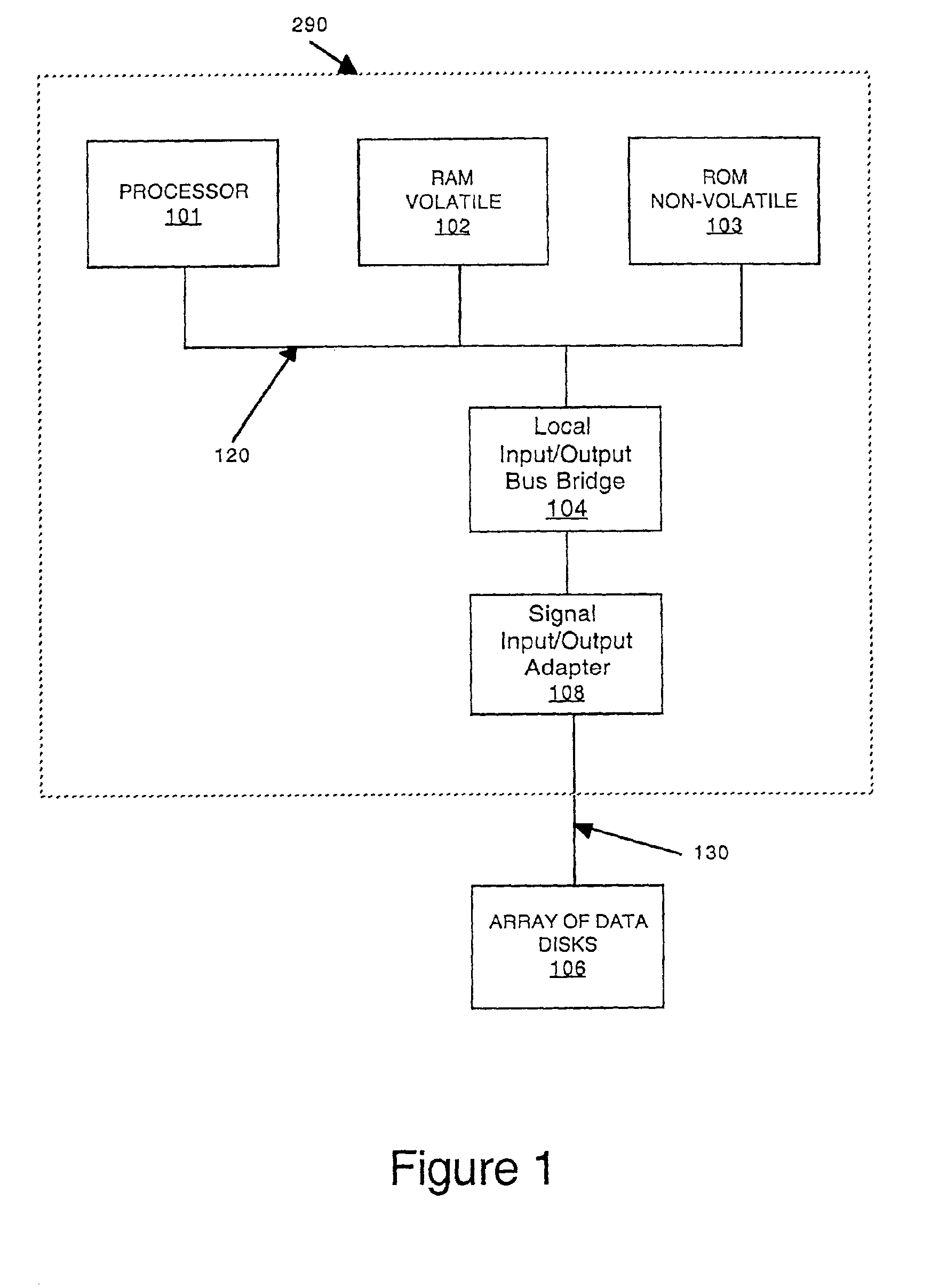

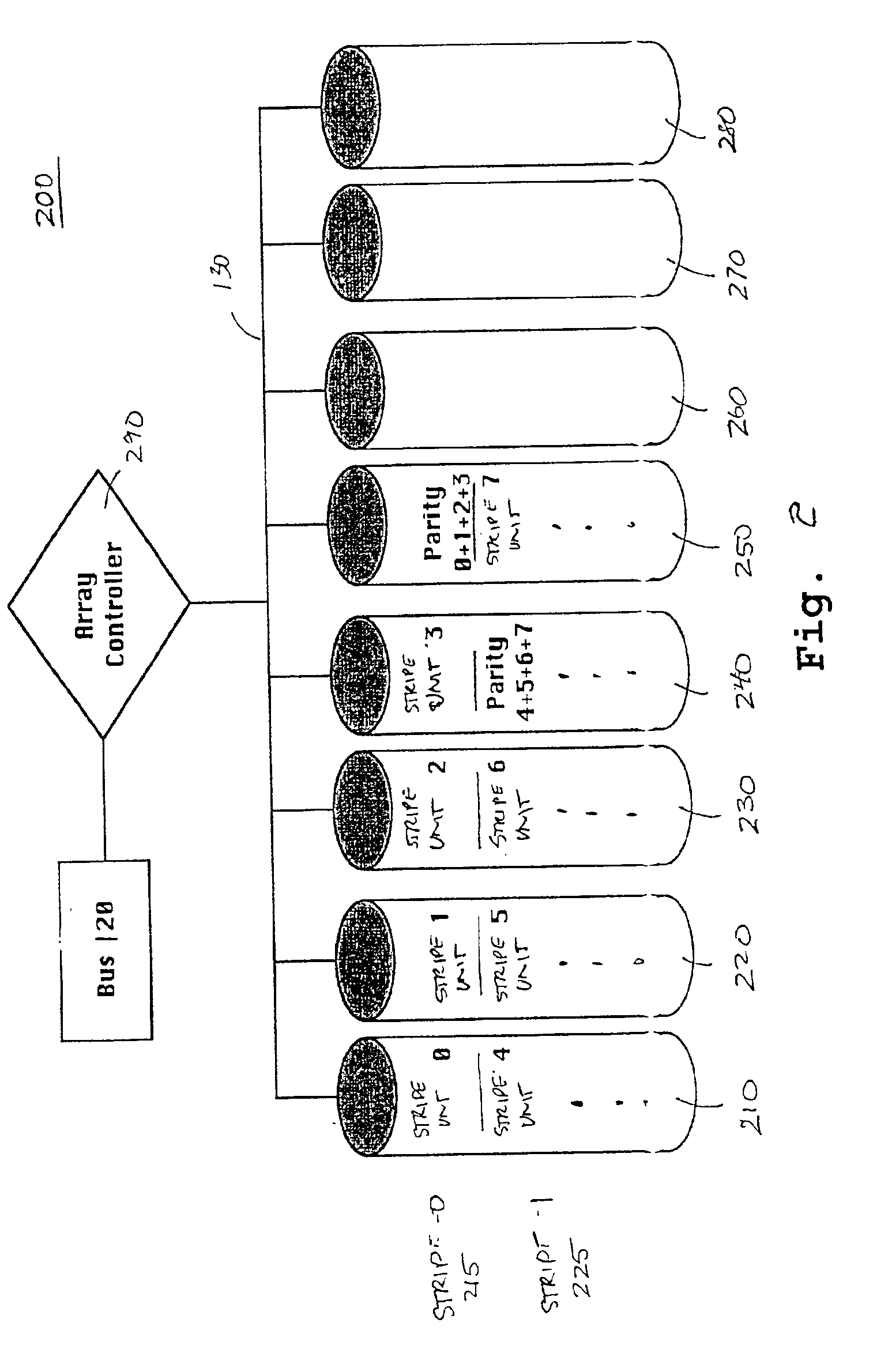

Method and system for striping spares in a data storage system including an array of disk drives

InactiveUS6934804B2Improve reliabilityImprove performanceMemory loss protectionRedundant data error correctionGranularityData store

Method and apparatus for striping spare storage in a data storage system. Specifically the present invention describes a method and apparatus for storing data and spare storage in a data storage system having a plurality of physical storage devices. The plurality of physical storage devices is partitioned into a plurality of slices. Logical units of storage (LUNs) are created, wherein each LUN contains data, spare, and data redundancy. Each of the plurality of slices is assigned to one of the plurality of LUNs so as to distribute storage of data, data redundancy, and spare across all of the plurality of physical storage devices. Distribution of spare storage is concentrated at the inner zone of each of the plurality of physical storage devices. The data and spare storage can be distributed uniformly or with varying granularities across all of the plurality of physical storage devices.

Owner:ORACLE INT CORP

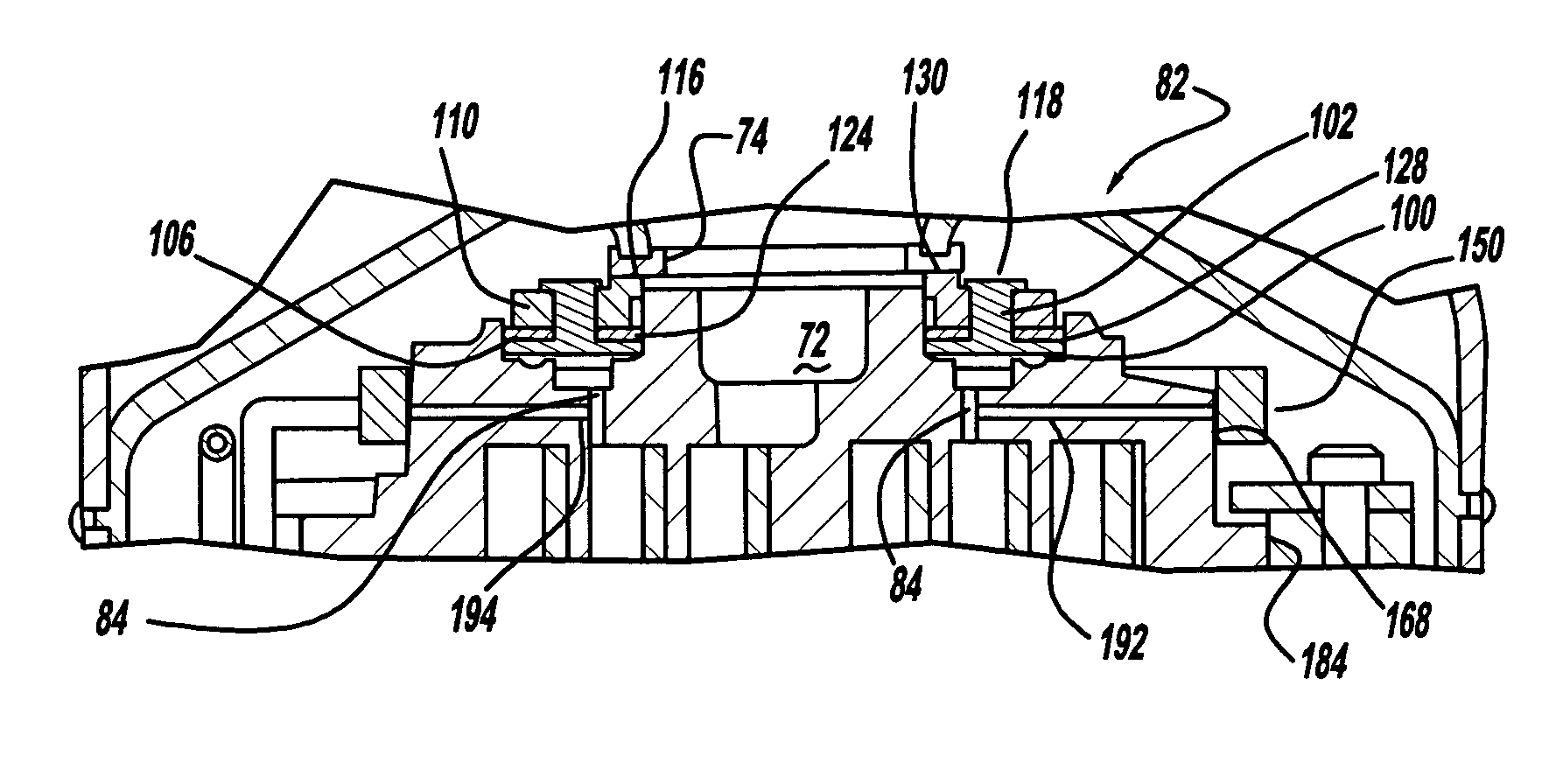

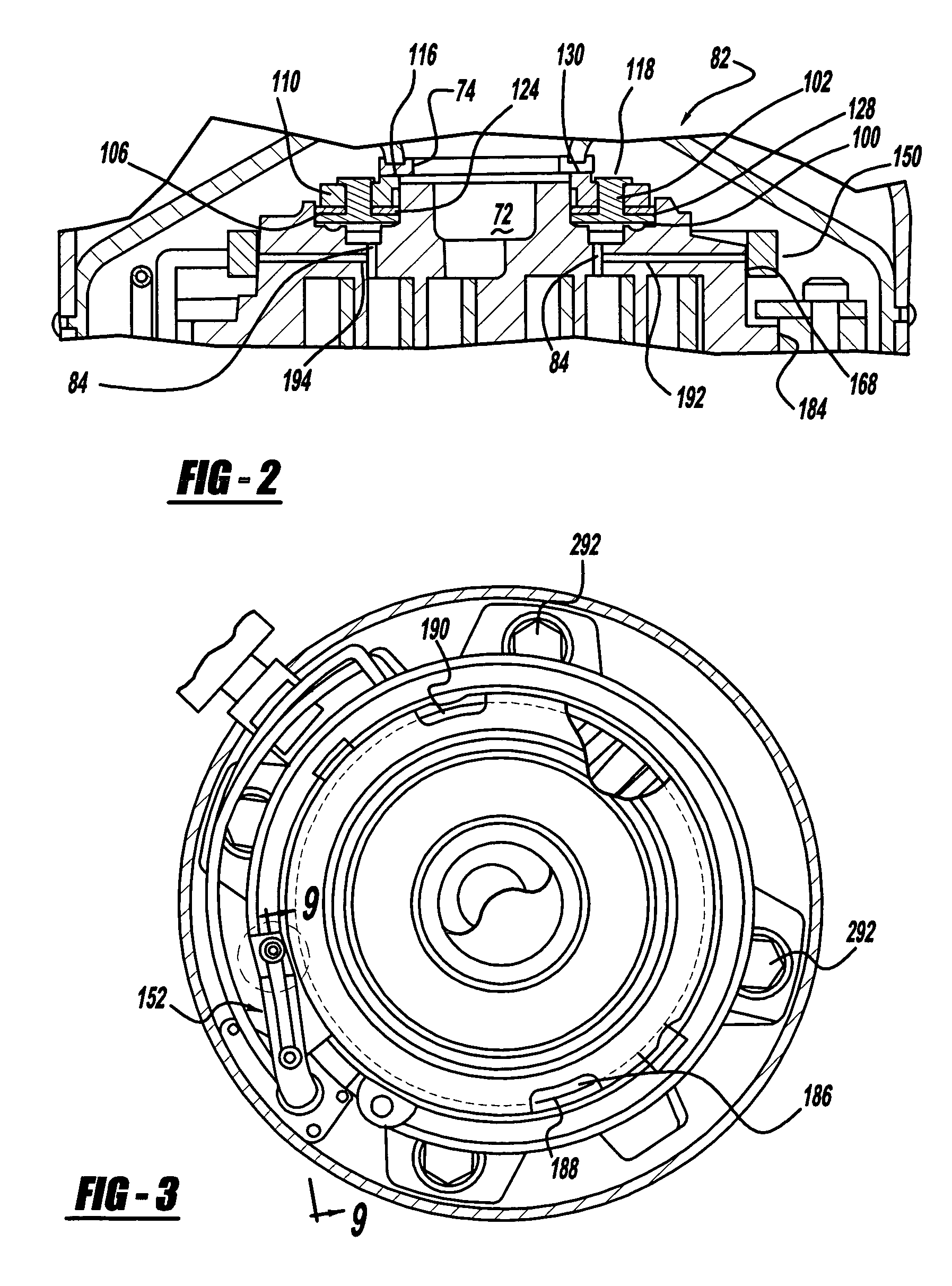

Capacity modulated scroll compressor

InactiveUS20070036661A1Reduce compressionCapacity modulationRotary/oscillating piston combinations for elastic fluidsSealing arrangement for pumpsElectrical and Electronics engineeringScroll compressor

A scroll compressor has a biasing chamber which contains a pressurized fluid. The pressurized fluid within the chamber biases the two scroll members together. A rotatable ring is attached to one of the scroll members to open and close a passage leading to this biasing chamber. When the ring opens the passage in one embodiment, this releases the pressurized fluid to remove the load, biasing the two scroll members together. When the biasing load is removed, the two scroll members separate, creating a leakage path between discharge and suction to reduce the capacity of the scroll compressor. When the ring opens the passage in another embodiment, a delayed suction passage is opened to reduce the capacity of the compressor.

Owner:EMERSON CLIMATE TECH INC

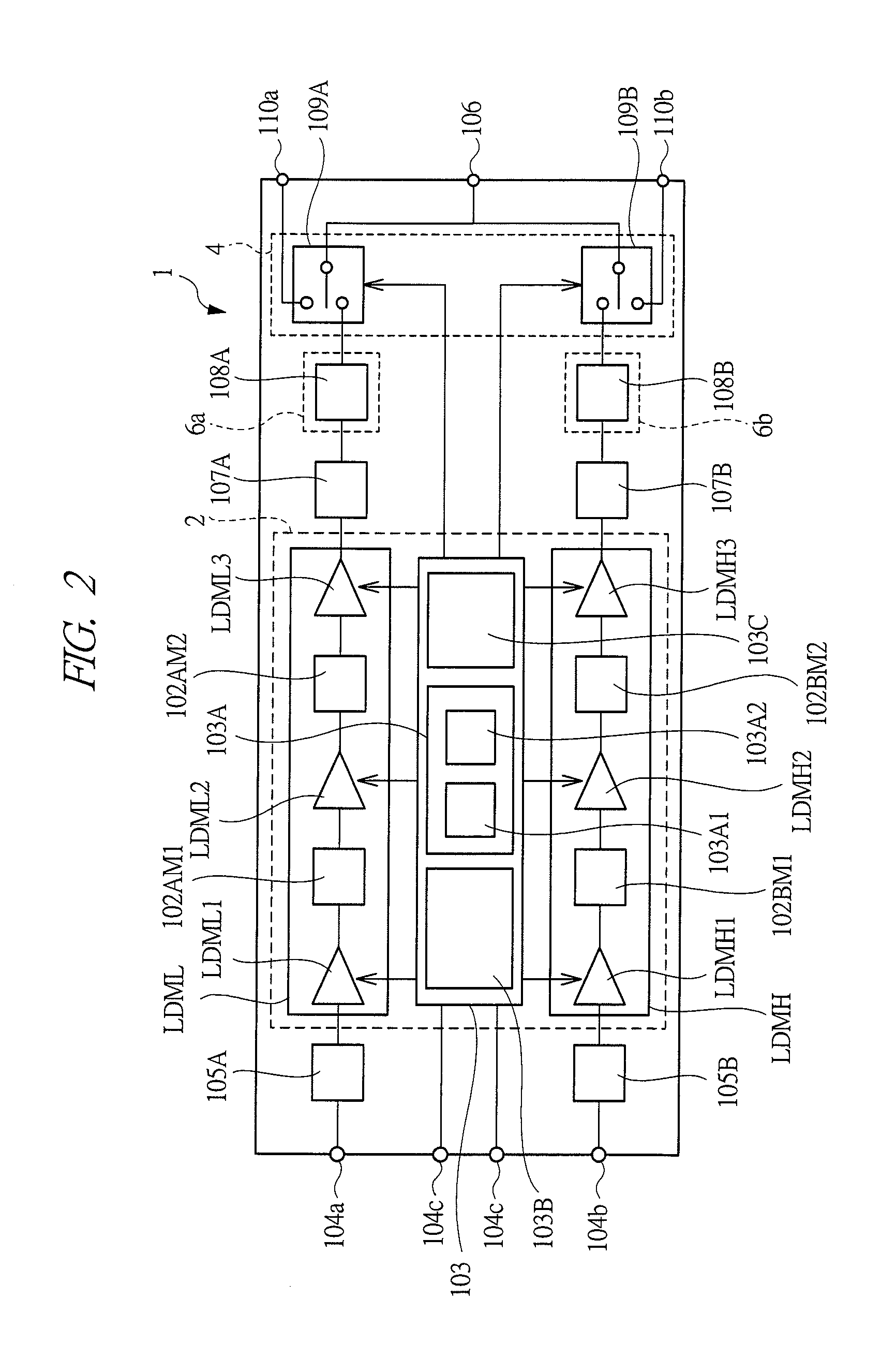

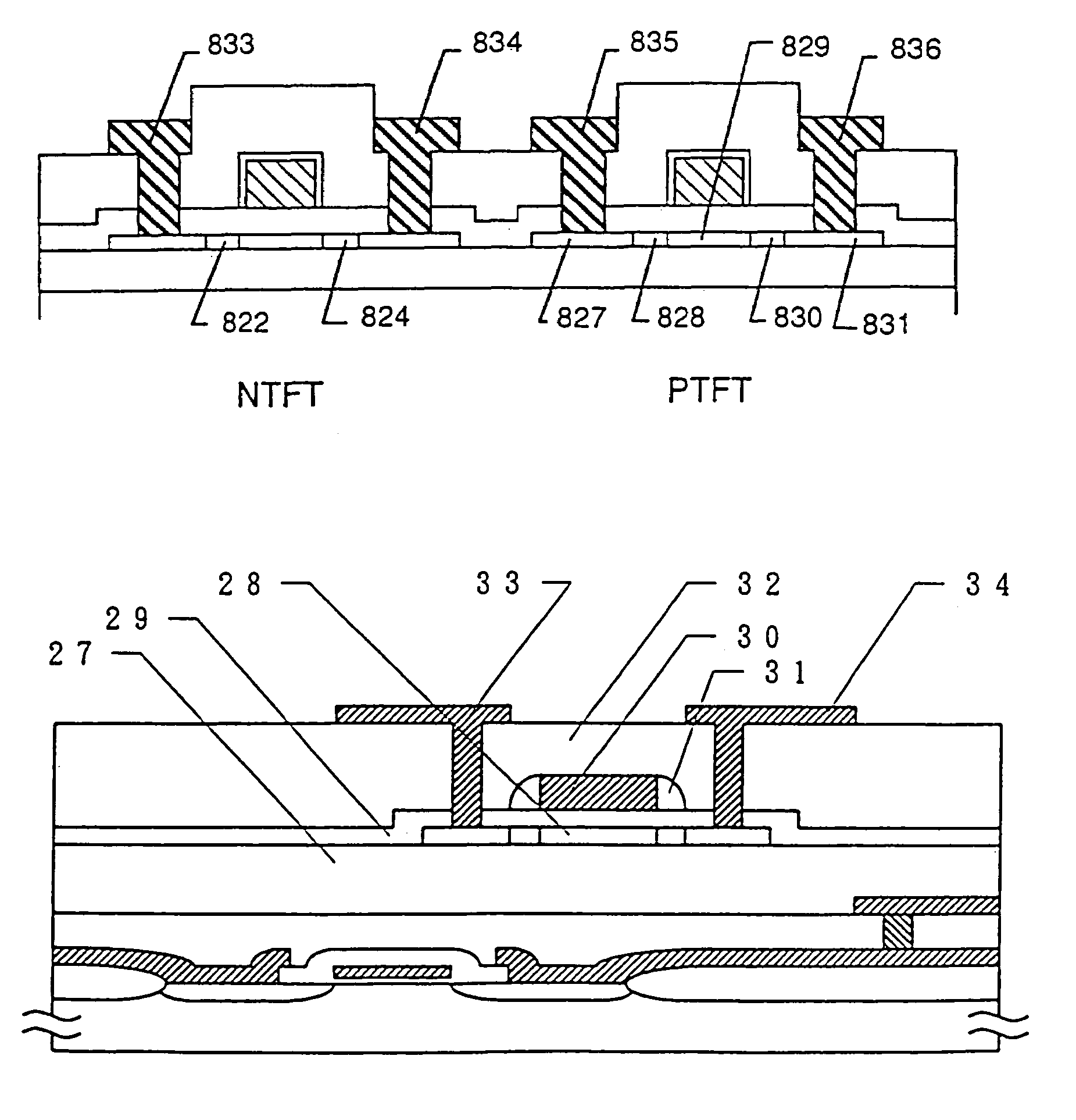

Semiconductor device and manufacturing method thereof

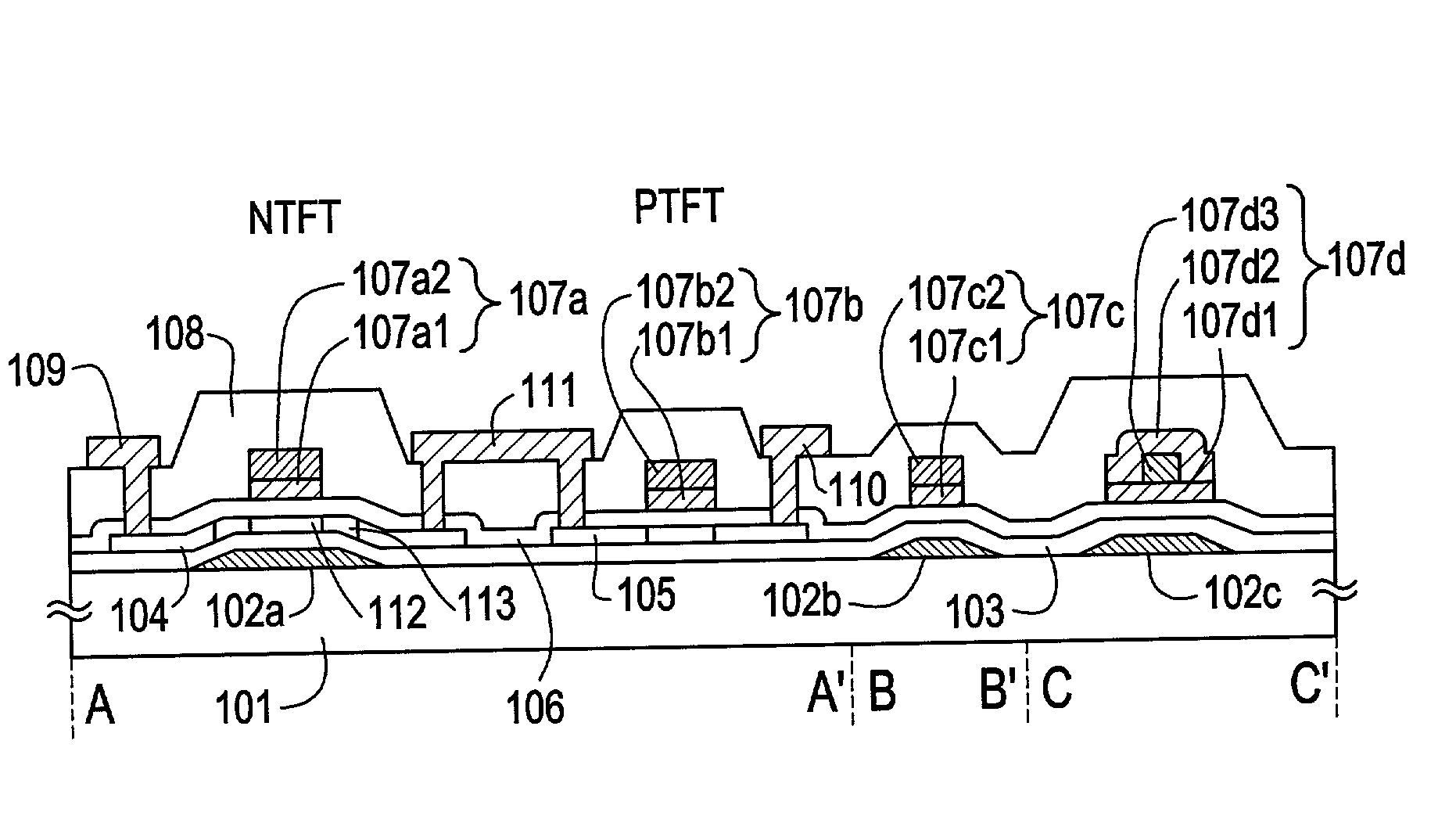

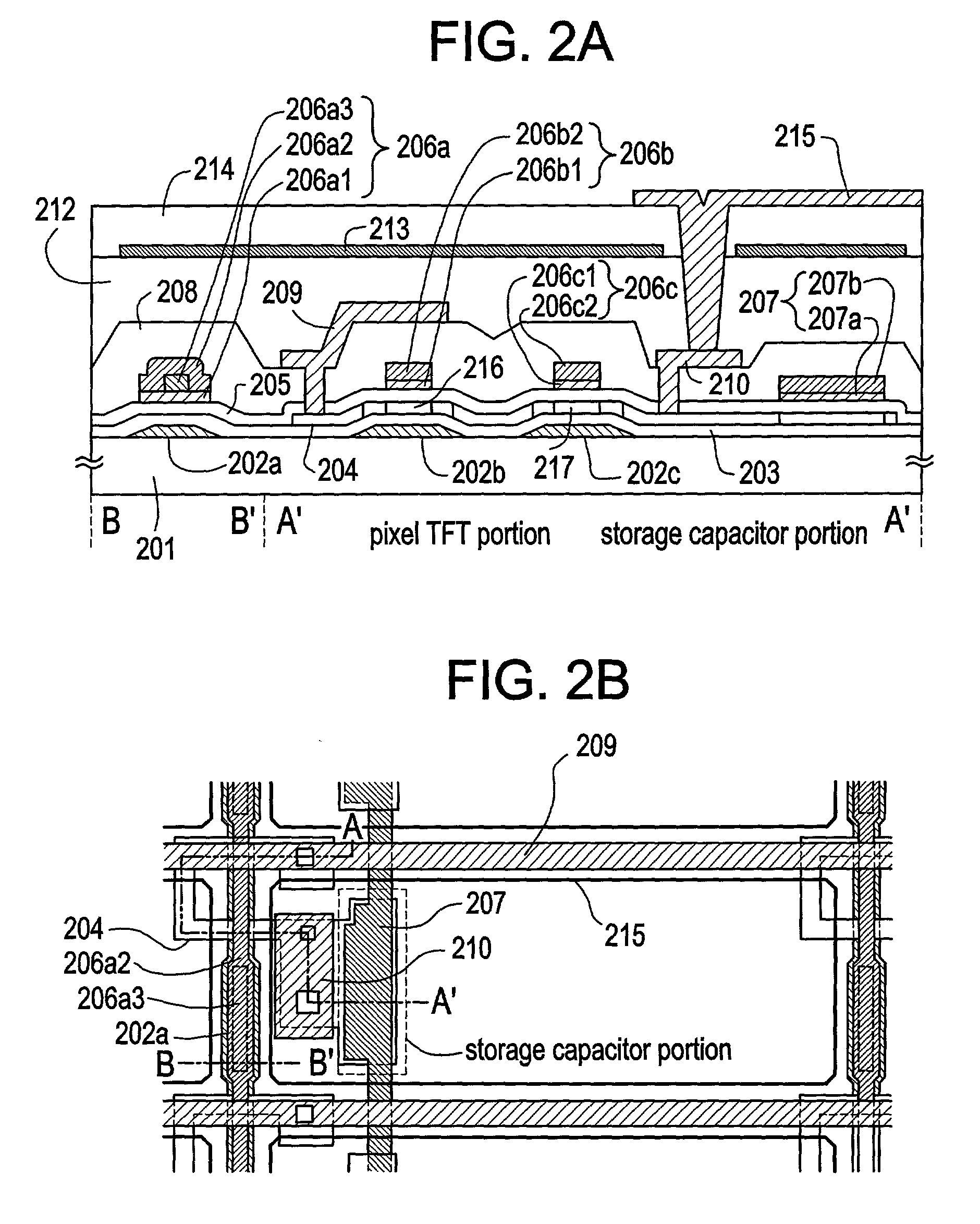

InactiveUS20020175376A1Improve reliability and performanceFunction increaseTransistorSolid-state devicesCMOSEngineering

In a CMOS circuit formed on a substrate 101, a subordinate gate wiring line (a first wiring line) 102a and main gate wiring line (a second wiring line) 107a are provided in an n-channel TFT. The LDD regions 113 overlaps the first wiring line 102a and does not overlap the second wiring line 107a. Thus, when a gate voltage is applied to the first wiring line, the GOLD structure is formed, while no applying forms the LLD structure. In this way, the GOLD structure and the LLD structure can be used appropriately in accordance with the respective specifications required for the circuits.

Owner:SEMICON ENERGY LAB CO LTD

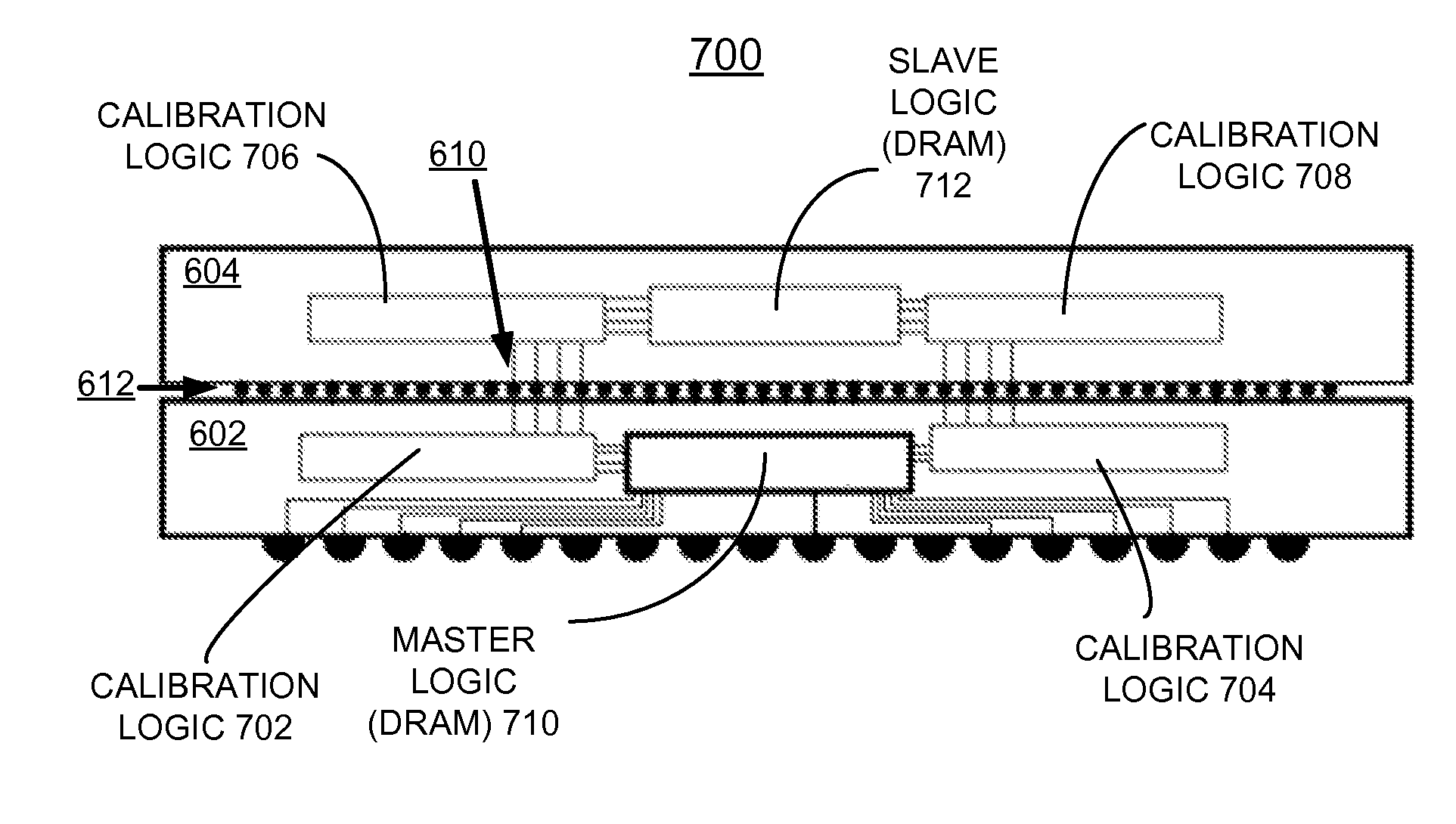

Iimplementing chip to chip calibration within a TSV stack

ActiveUS20130038380A1Overcome disadvantageOvercome disadvantagesImpedence convertorsSemiconductor/solid-state device detailsEngineeringControl circuit

A method and circuit for implementing a chip to chip calibration in a chip stack, for example, with through silicon vias (TSV) stack, and a design structure on which the subject circuit resides are provided. A first chip and a second chip are included within a semiconductor chip stack. The semiconductor chip stack includes a vertical stack optionally provided with Though Silicon Via (TSV) stacking of the chips. At least one of the first chip and the second chip includes a calibration control circuit and a performance indicator circuit coupled to the calibration control circuit to train and calibrate at least one of the first chip and the second chip to provide enhanced performance and reliability for the semiconductor chip stack.

Owner:IBM CORP

Methods and structure for supporting persistent reservations in a multiple-path storage environment

ActiveUS20050278465A1Improve reliabilityImprove performanceMemory systemsInput/output processes for data processingSCSIProcessing element

A persistent reservation emulation structure to emulate exclusive reservation SCSI-3 protocol features in a host system having multiple paths to a storage device. An enhanced multiple-path driver layer (or other processing elements) provide emulation of persistent reservation commands directed from a host system to a storage device. The driver does not forward exclusive type reservations to the storage device but rather emulates the desired exclusive operations on the systems behalf using only non-exclusive reservation types. The emulated reservation handling enables parallel use of multiple paths between a host system and a storage device to improve reliability and / or performance of the storage device.

Owner:NETWORK APPLIANCE INC

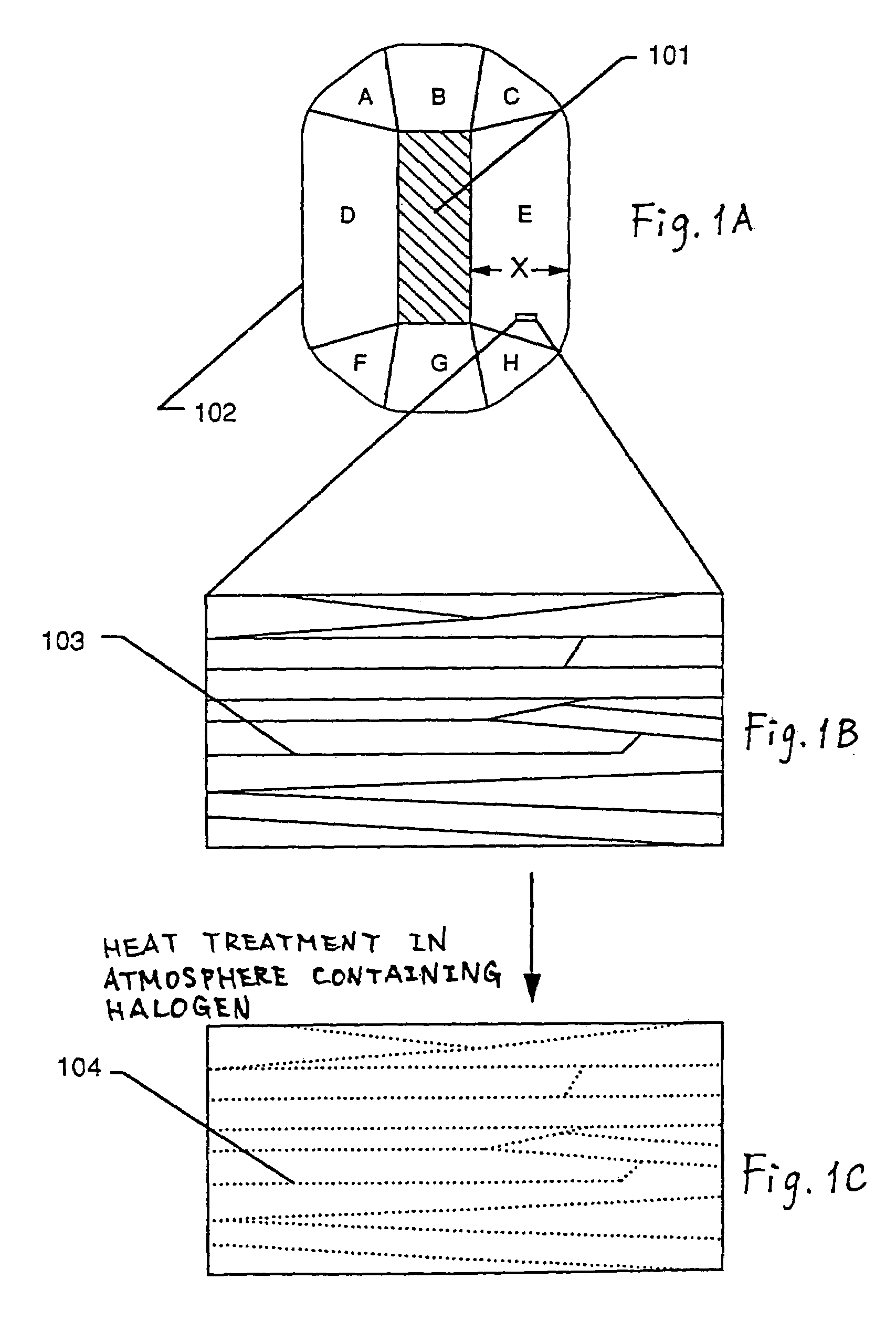

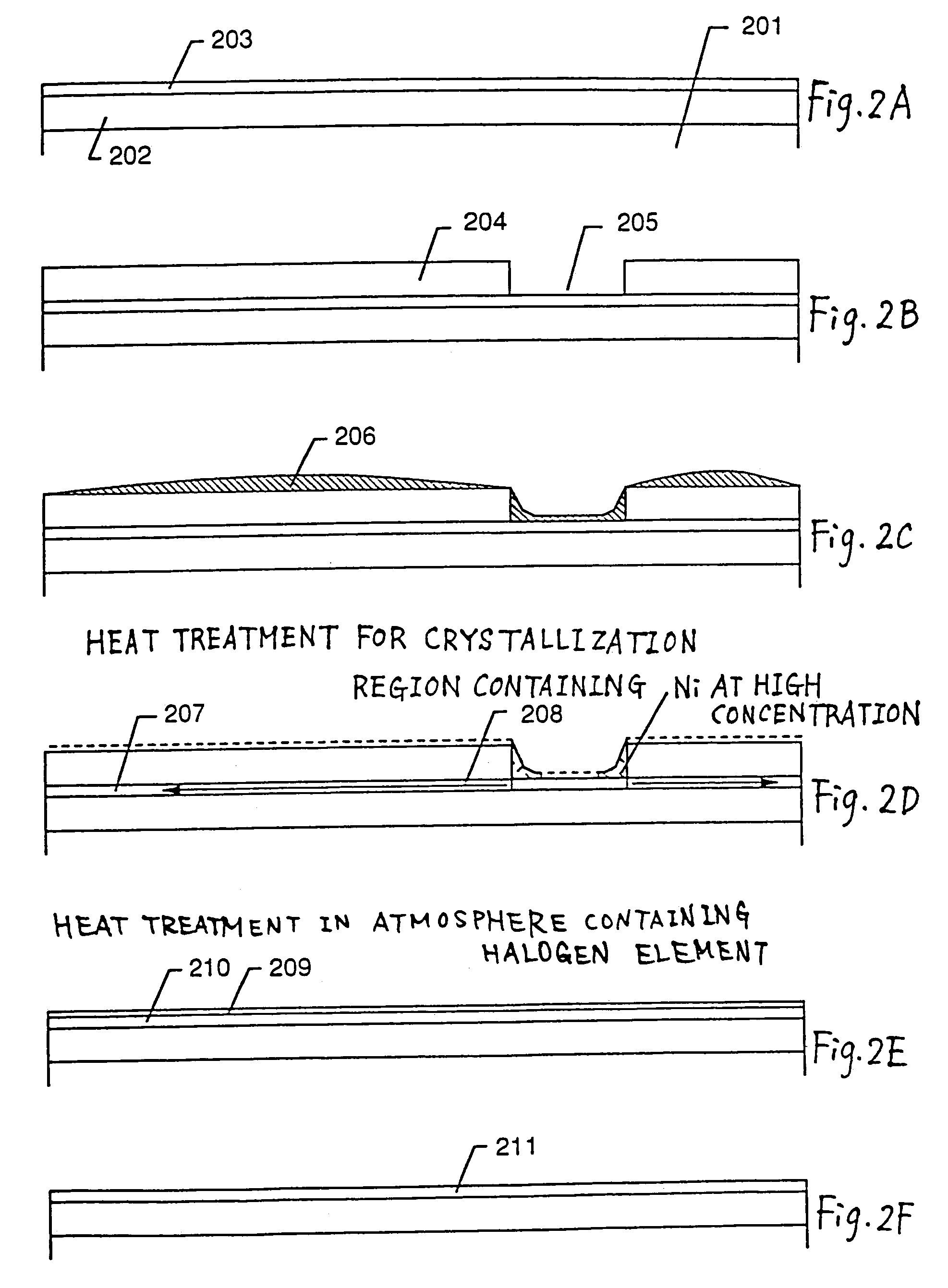

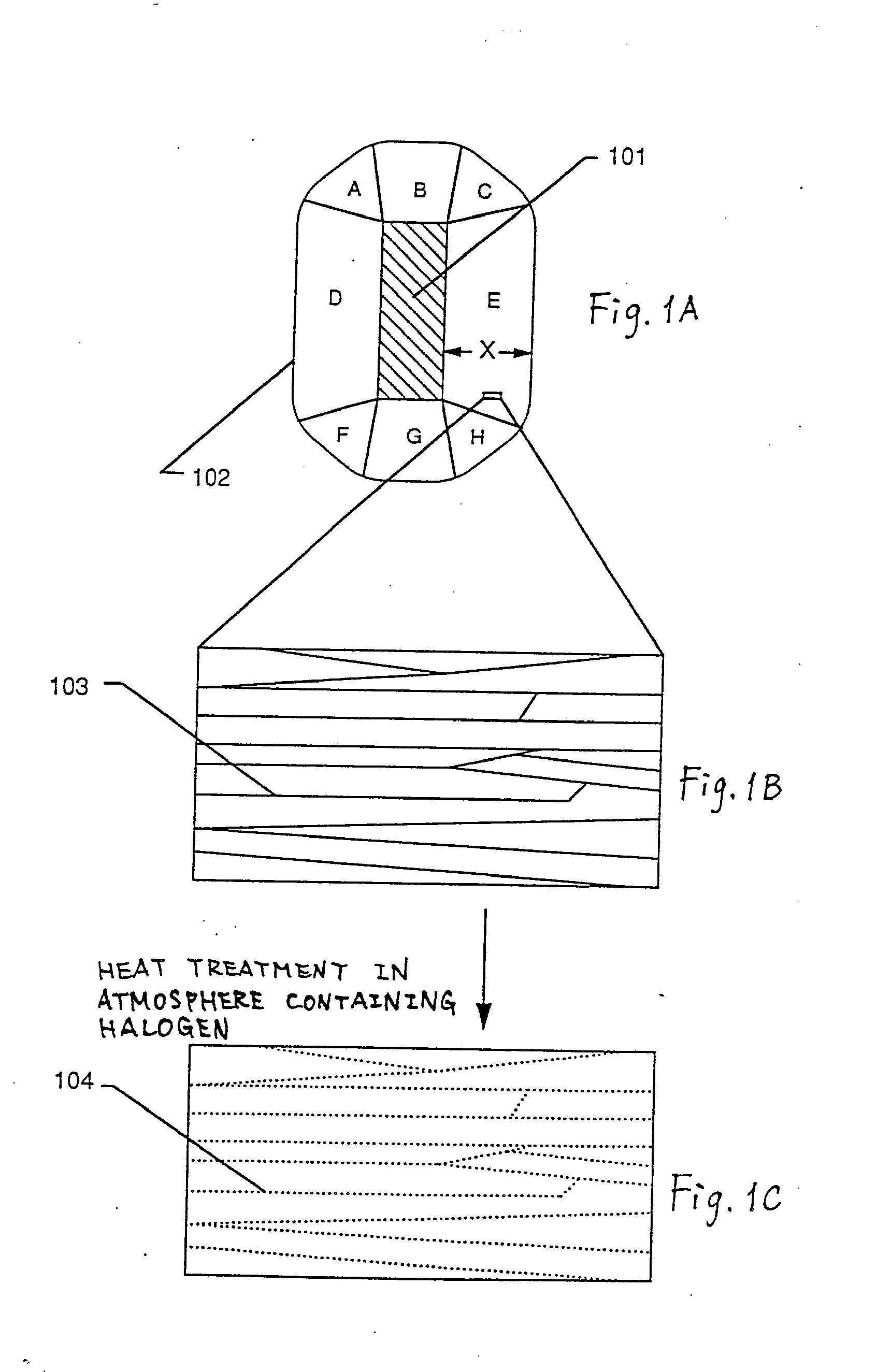

Semiconductor thin film and method of manufacturing the same and semiconductor device and method of manufacturing the same

InactiveUS7172929B2Avoid problemsImprove performanceTransistorSolid-state devicesSingle crystalCrystallinity

A thin film semiconductor transistor structure has a substrate with a dielectric surface, and an active layer made of a semiconductor thin film exhibiting a crystallinity as equivalent to the single-crystalline. To fabricate the transistor, the semiconductor thin film is formed on the substrate, which film includes a mixture of a plurality of crystals which may be columnar crystals and / or capillary crystal substantially parallel to the substrate. The resultant structure is then subject to thermal oxidation in a chosen atmosphere containing halogen, thereby removing away any metallic element as contained in the film. This may enable formation of a mono-domain region in which the individual columnar or capillary crystal is in contact with any adjacent crystals and which is capable of being substantially deemed to be a single-crystalline region without presence or inclusion of any crystal grain boundaries therein. This region is for use in forming the active layer of the transistor.

Owner:SEMICON ENERGY LAB CO LTD

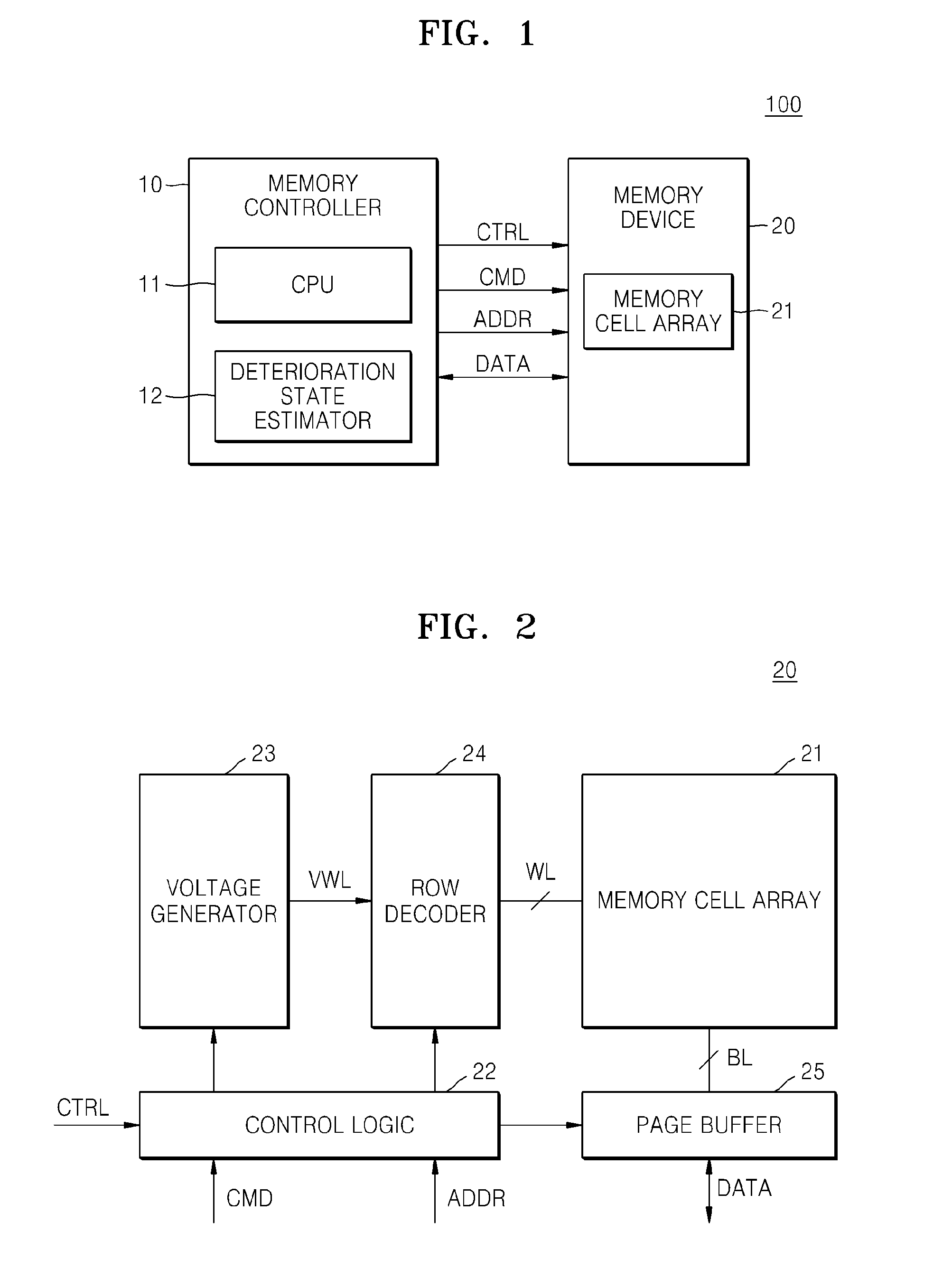

Method of estimating deterioration state of memory device and related method of wear leveling

ActiveUS20150043282A1Improve reliabilityImprove performanceRead-only memoriesDigital storageStorage cellWear leveling

A method of estimating a deterioration state of a memory device comprises reading data from selected memory cells connected to a selected wordline of a memory cell array by applying to the selected wordline a plurality of distinct read voltages having values corresponding to at least one valley of threshold voltage distributions of the selected memory cells, generating quality estimation information indicating states of the threshold voltage distributions using the data read from the selected memory cells, and determining a deterioration state of a storage area including the selected memory cells based on the generated quality estimation information.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor thin film and method of manufacturing the same and semiconductor device and method of manufacturing the same

InactiveUS20070252206A1Improve reliability and performanceHigh crystallinityTransistorSolid-state devicesOptoelectronicsSingle crystal

A thin film semiconductor transistor structure has a substrate with a dielectric surface, and an active layer made of a semiconductor thin film exhibiting a crystallinity as equivalent to the single-crystalline. To fabricate the transistor, the semiconductor thin film is formed on the substrate, which film includes a mixture of a plurality of crystals which may be columnar crystals and / or capillary crystal substantially parallel to the substrate. The resultant structure is then subject to thermal oxidation in a chosen atmosphere containing halogen, thereby removing away any metallic element as contained in the film. This may enable formation of a mono-domain region in which the individual columnar or capillary crystal is in contact with any adjacent crystals and which is capable of being substantially deemed to be a single-crystalline region without presence or inclusion of any crystal grain boundaries therein. This region is for use in forming the active layer of the transistor.

Owner:SEMICON ENERGY LAB CO LTD

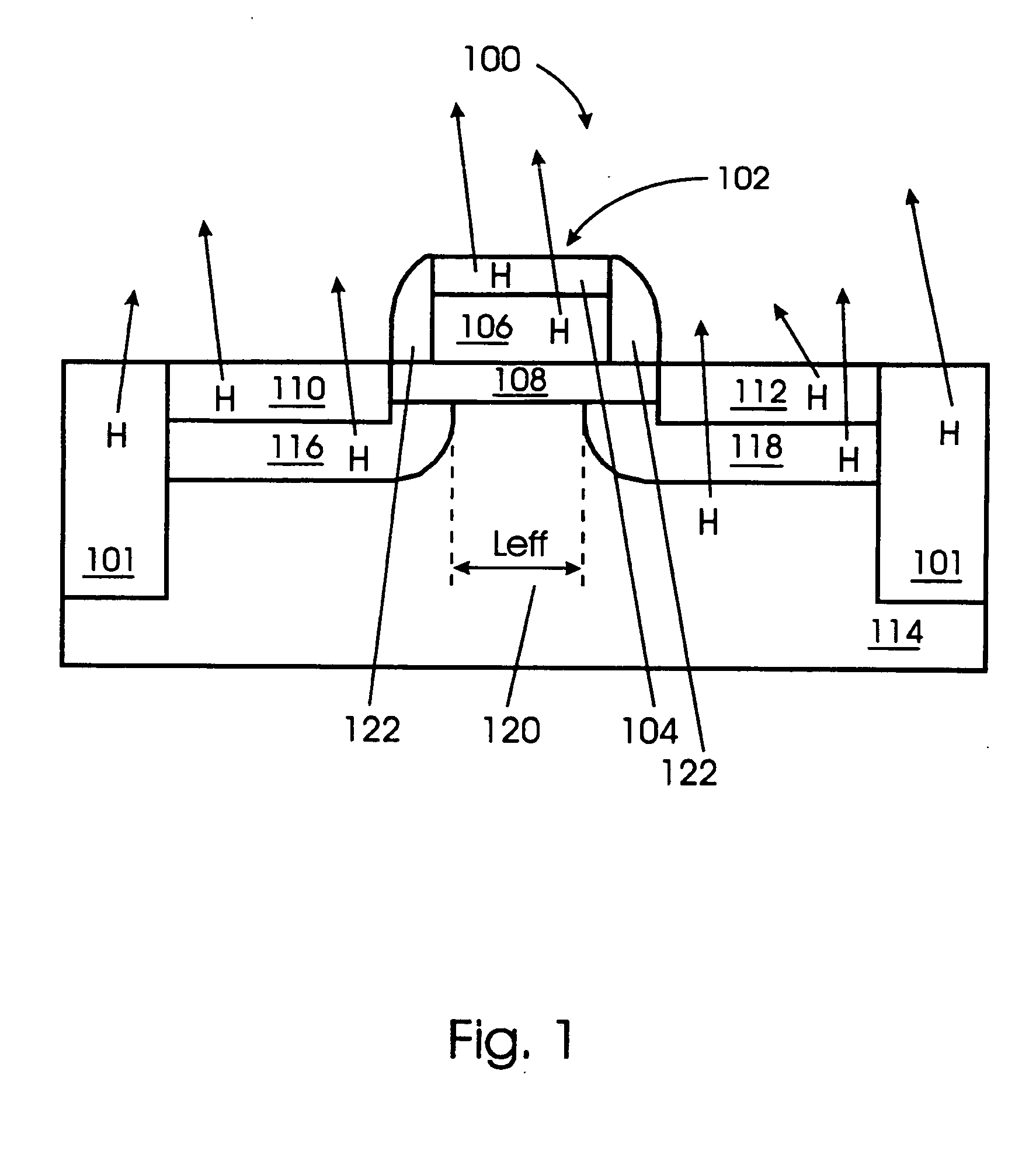

Implantation of deuterium in MOS and DRAM devices

InactiveUS20050255684A1Improve performanceImprove reliabilitySolid-state devicesSemiconductor/solid-state device manufacturingMOSFETHydrogen

A structure and method passivates dangling silicon bonds by the introduction of deuterium into a Metal Oxide Semiconductor Field Effect Transistor (MOSFET) by ion implantation. The process of implantation provides precise placement of deuterium at optimum locations within the gate stack to create stable silicon-deuterium bond terminations at the Si—SiO2 interface within the gate-channel region. The deuterium is encapsulated in the MOSFET by the use of a Silicon Nitride (SiN) barrier mask. The ability of deuterium to passivate dangling silicon bonds is maximized by removing hydrogen present in the MOSFET and by use of an absorption layer to create a deuterium rich region.

Owner:PDF SOLUTIONS INC

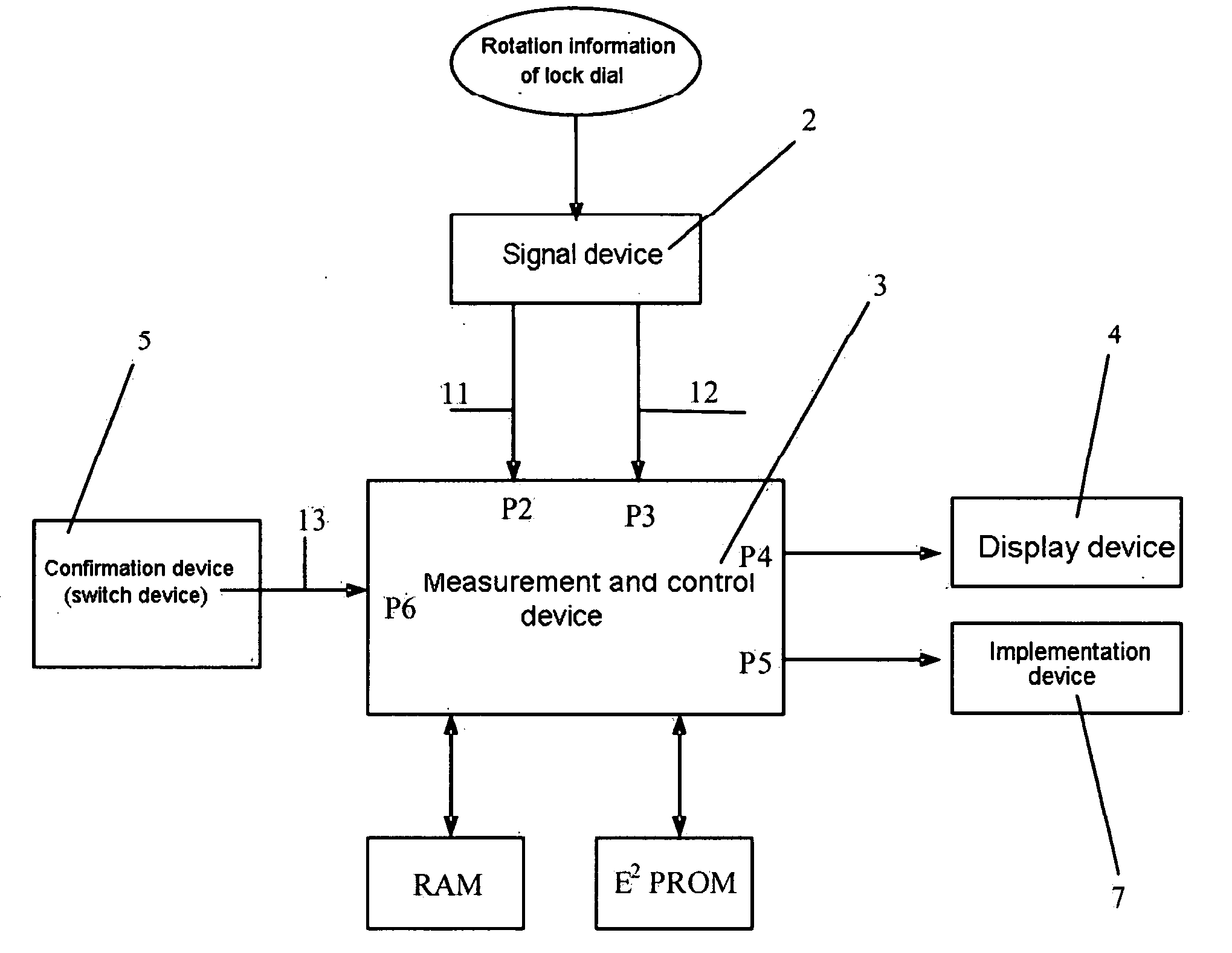

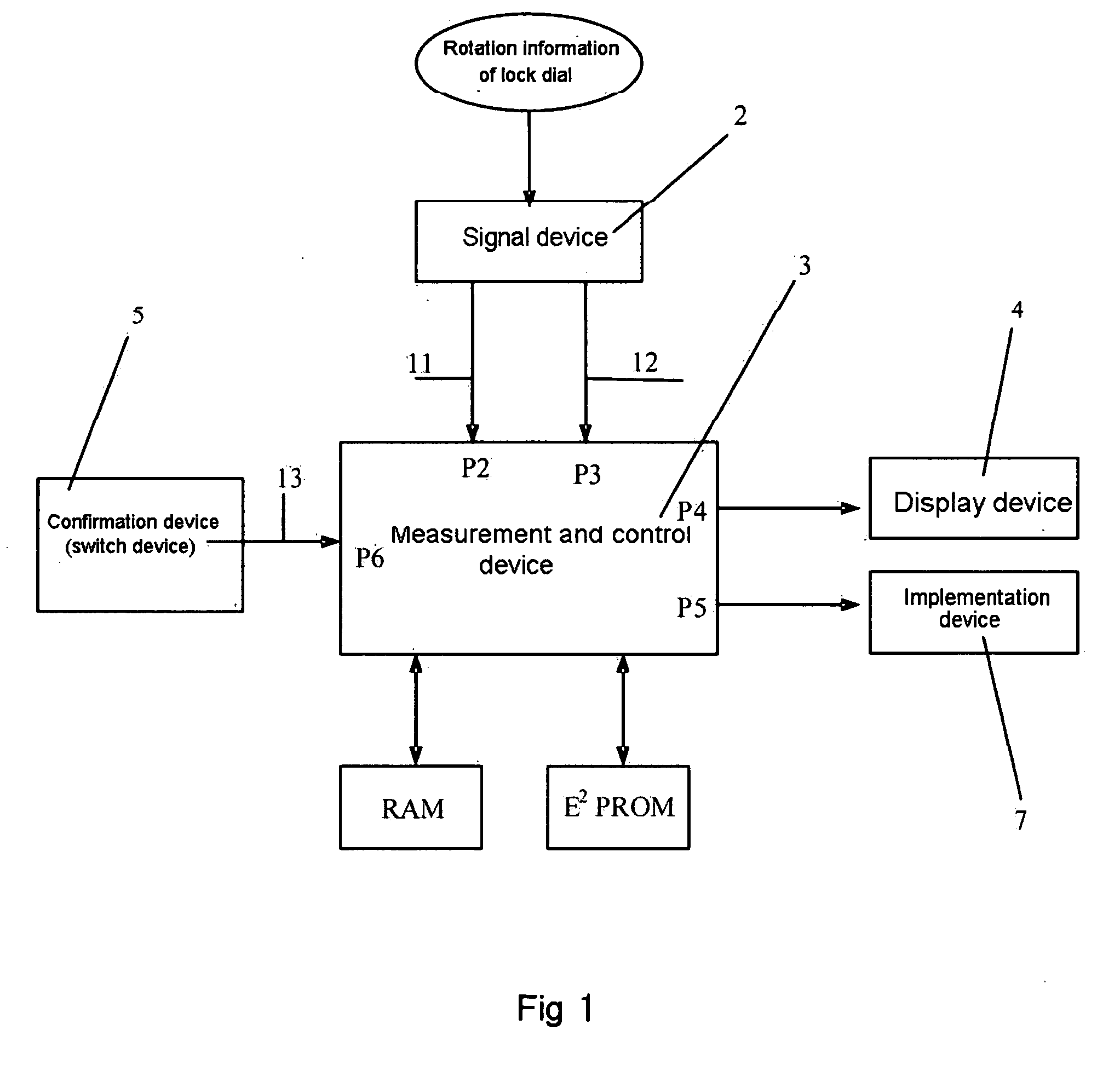

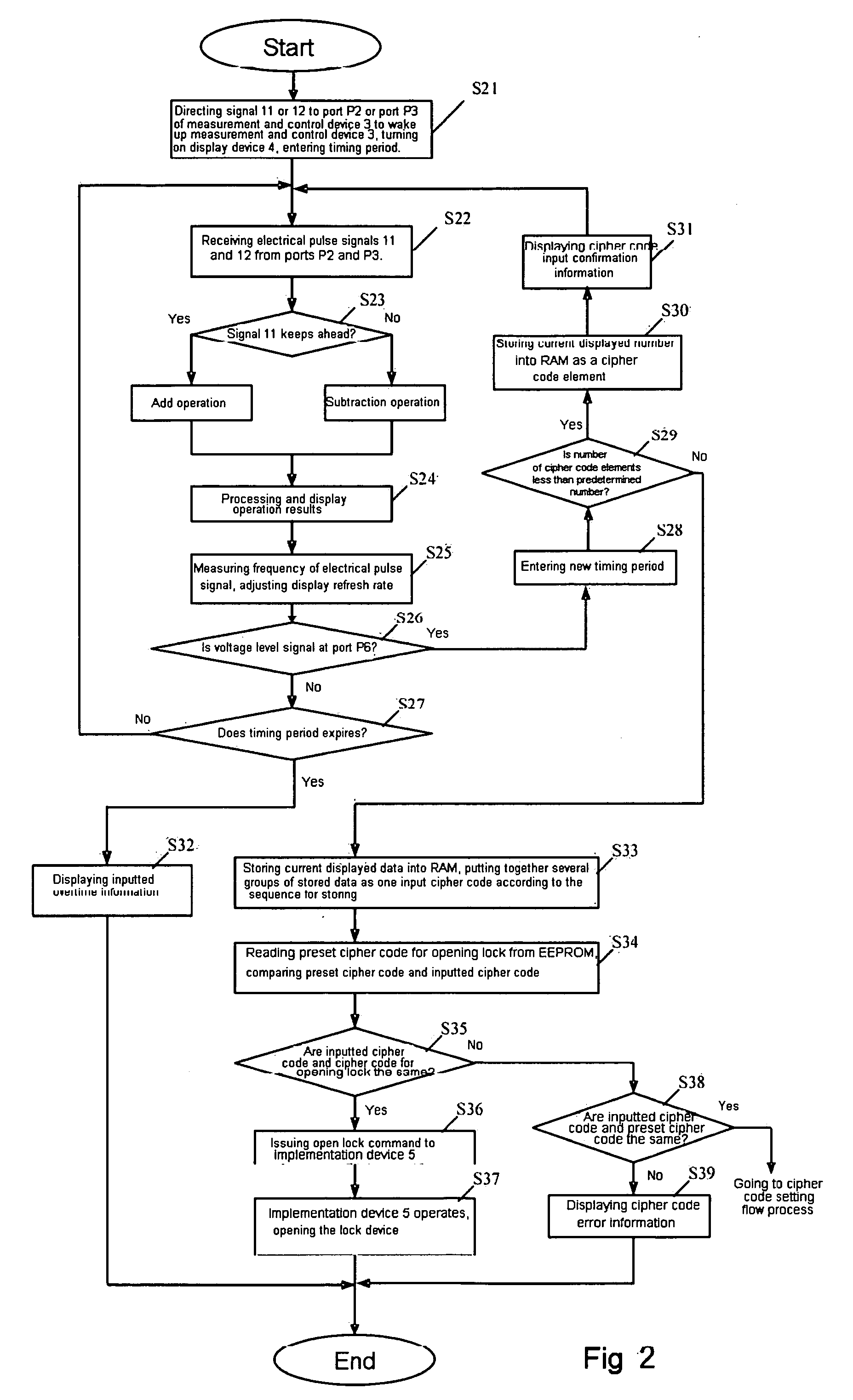

Input device, input method and application of electronic cipher code lock

InactiveUS20070133802A1Simple structureImprove reliability and performanceElectric permutation locksIndividual entry/exit registersCoded elementInput device

The invention provides an input device of the electronic cipher code lock and a corresponding input method thereof, wherein a signal device produces cipher code input information and converts said information into two groups of electrical pulse signals; a measurement and control device measures the electrical pulse signals, decides the order of the electrical pulse signals and calculates correspondingly such that said signals are converted into character sequences including the cipher code elements, and decides whether the current cipher code elements are confirmed to be inputted or not and decides whether the input of all the cipher code elements is completed or not; a confirmation device produces a conformation signal for inputting the cipher code elements; and a display device displays said character sequences and preset prompt information in a rolling and refreshing manner. The invention also provides a door lock handle and a panel of the cipher code lock for the chests and bags applying the above said input device of the electronic cipher code lock. In said input device of the electronic cipher code lock and the application thereof, the operation parts do not contact with the circuit, the reliability and the security protection performance have been improved significantly. Furthermore, the operation for inputting the cipher code and the operation for changing the cipher code are very convenient and intuitional.

Owner:SHANGHAI BUDDY TECHONOLOGICAL

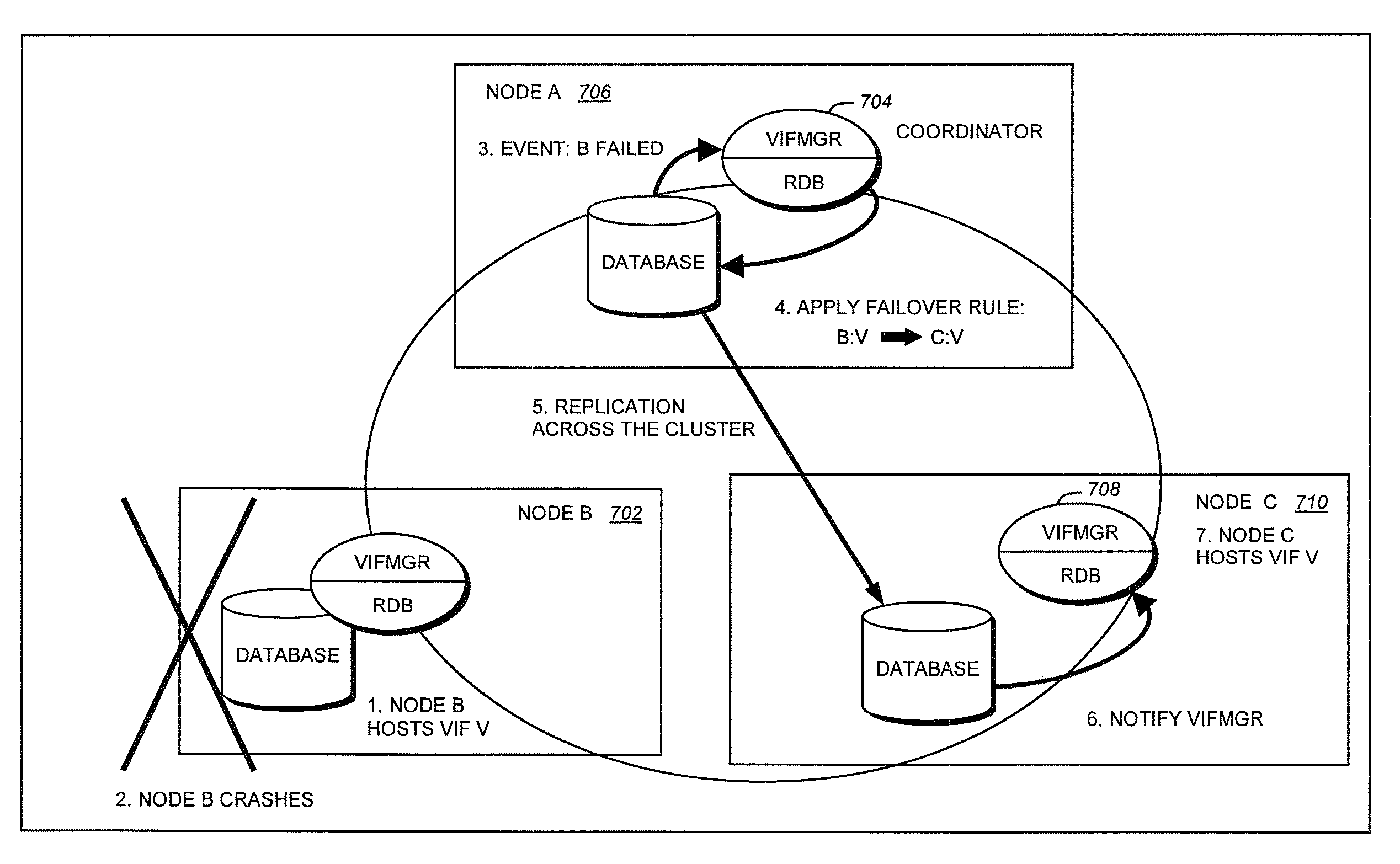

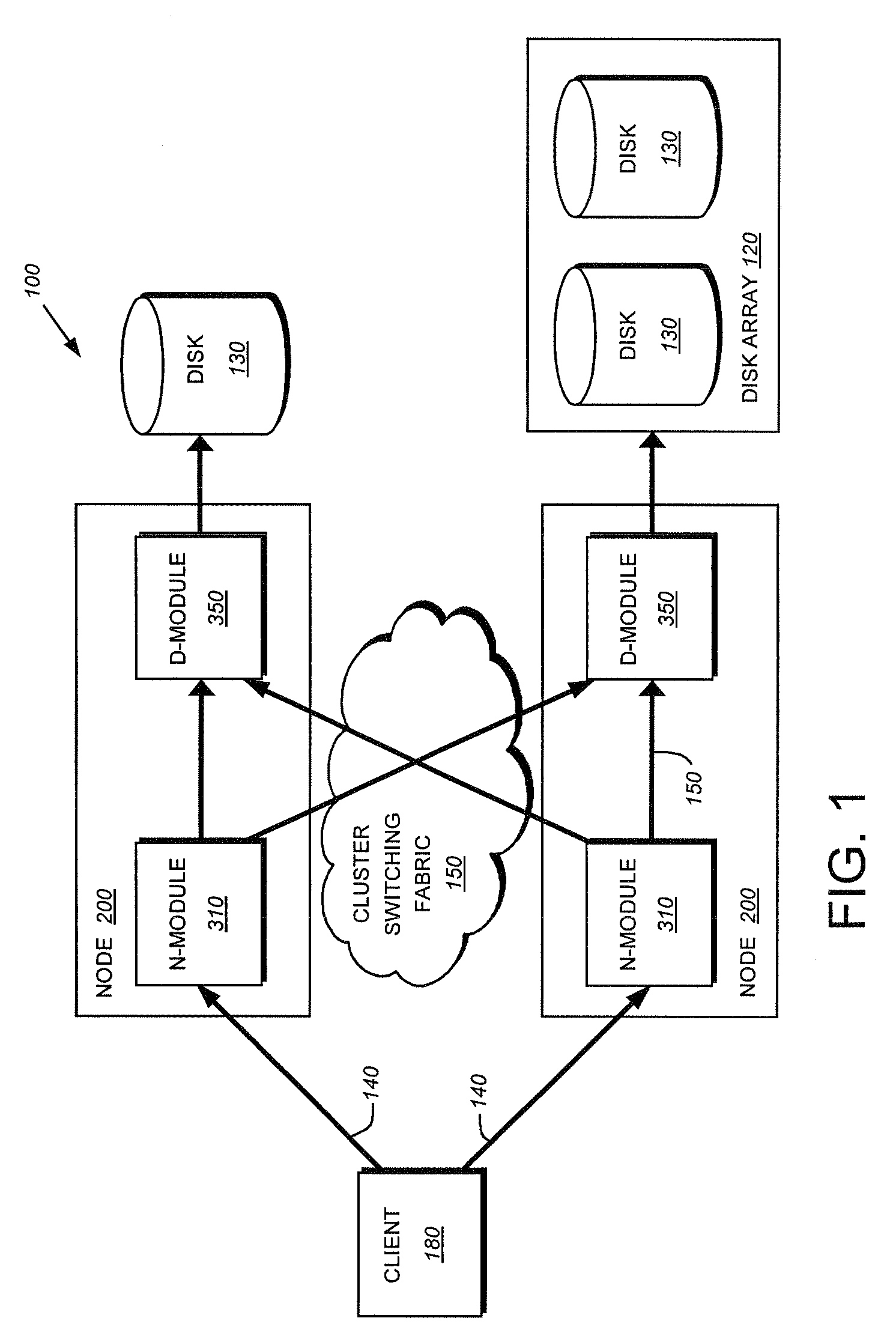

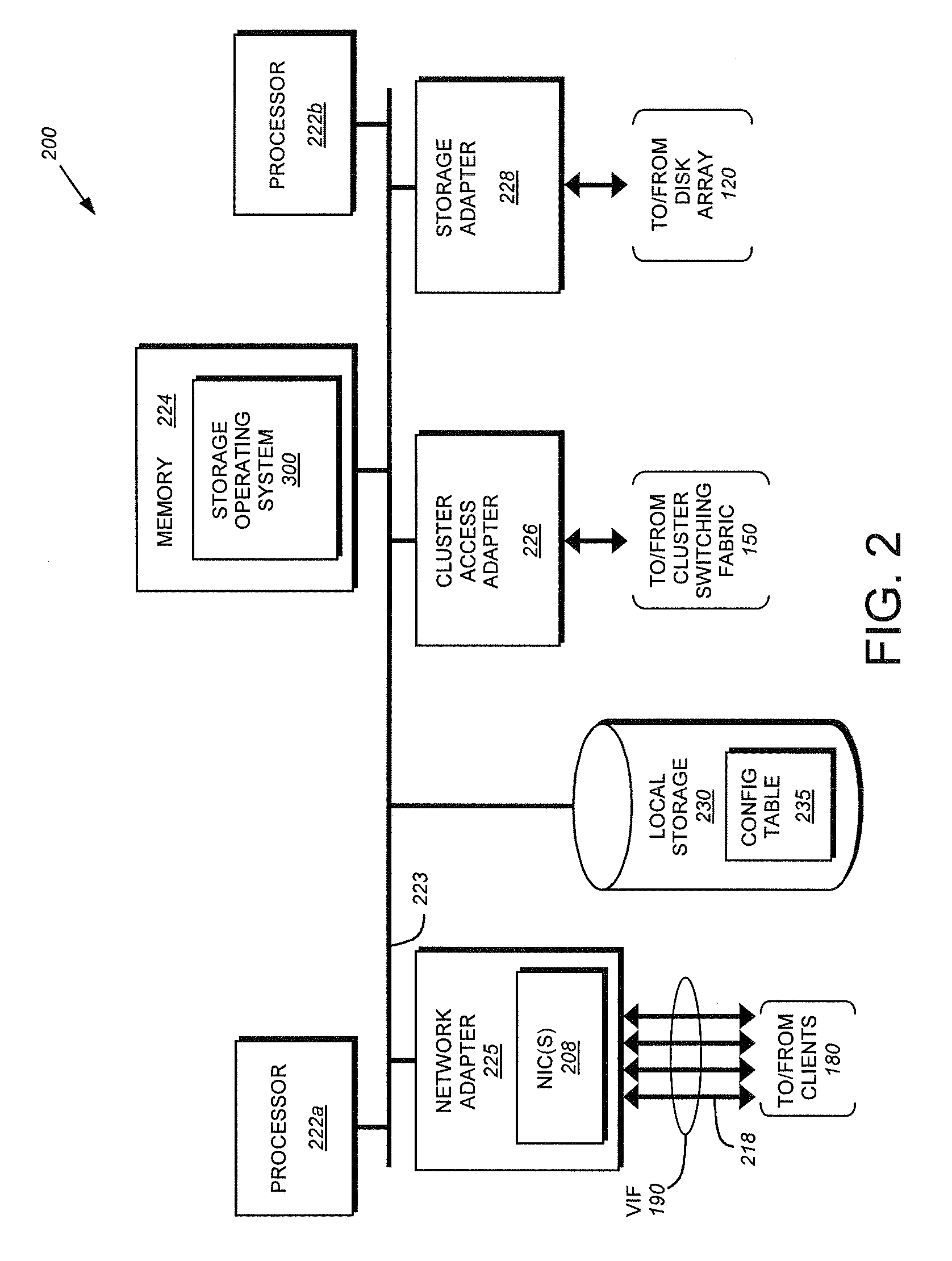

System and method for virtual interface failover within a cluster

ActiveUS7734947B1Improve performanceImprove reliabilityError detection/correctionFailoverDatabase services

A cluster-wide published configuration system and method is provided for assigning host nodes to virtual interfaces (VIFs) in a cluster of data storage systems. A coordinating VIF manager publishes a set of failover rules using a replication database. The coordinating VIF manager monitors VIF hosting status within a cluster. In the event of a VIF failure, the coordinating VIF manager publishes a reassignment of host nodes using a single read-write transaction of a replication database service. Secondary VIF managers in the cluster must perform VIF hosting in accordance to the reassignment. If a secondary VIF manager can not activate an assigned VIF it must publishing new reassignment of VIF hosts via the replication database service.

Owner:NETWORK APPLIANCE INC

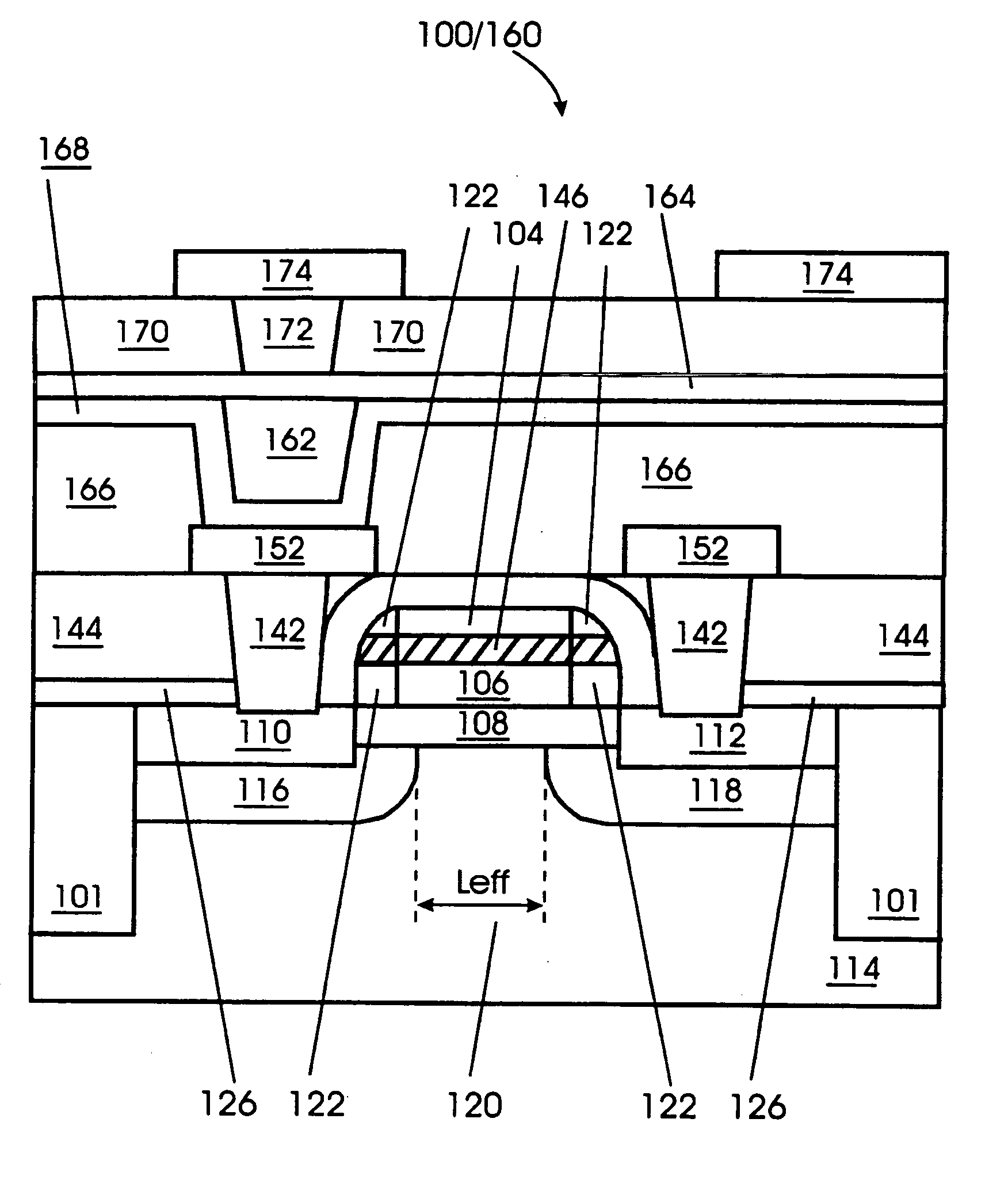

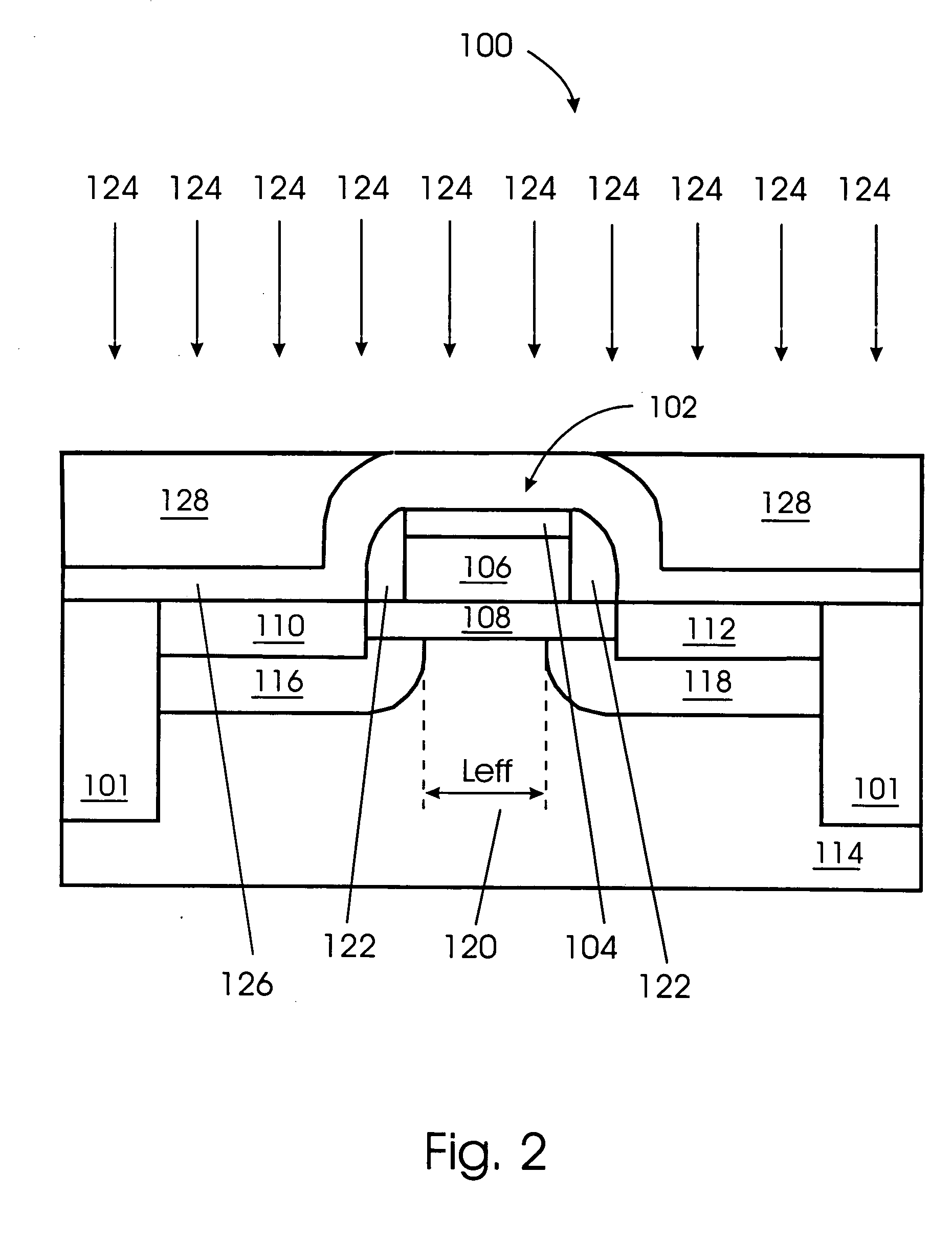

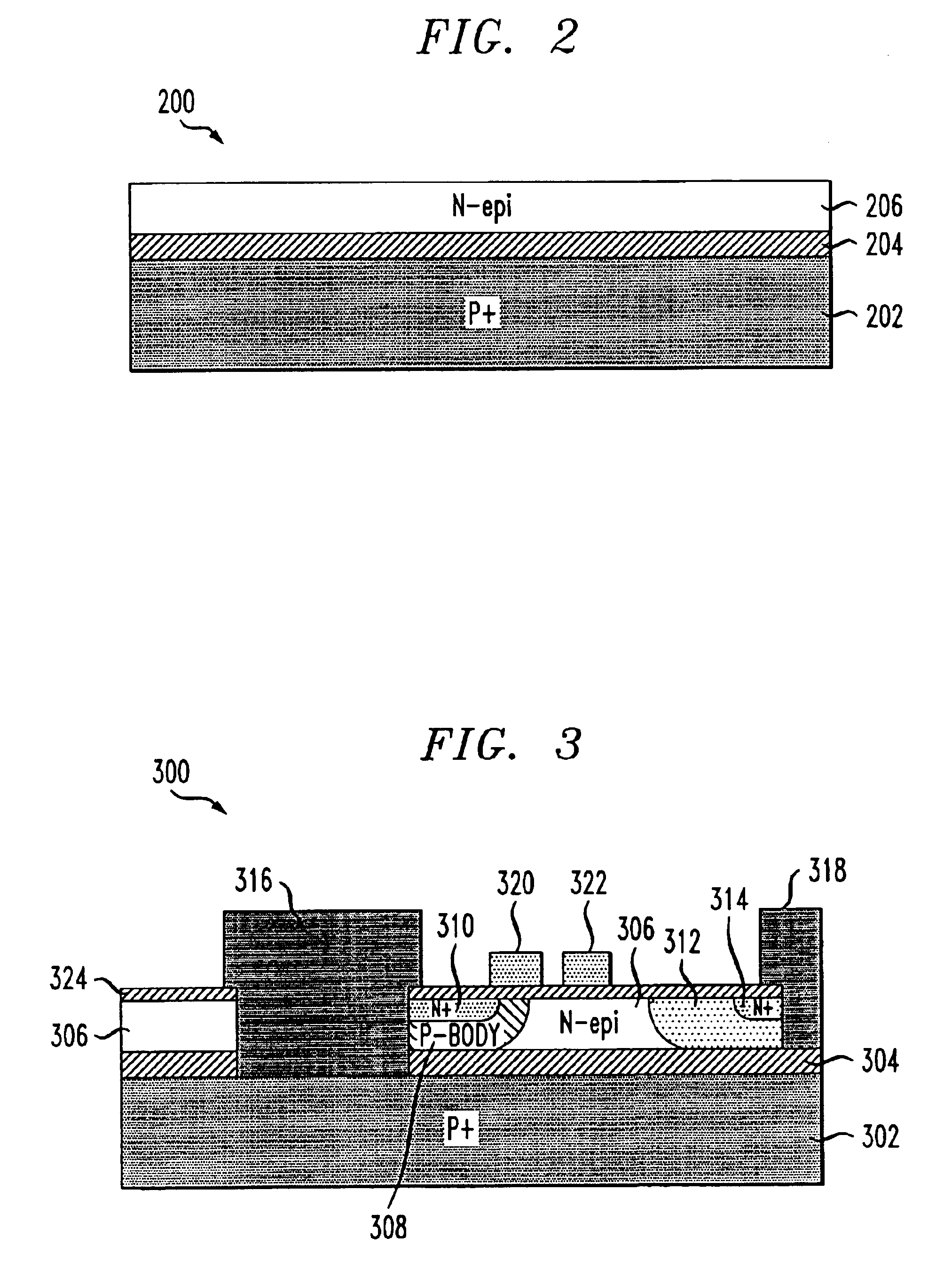

Metal-oxide-semiconductor device formed in silicon-on-insulator

ActiveUS6890804B1Improve performanceImprove reliabilityTransistorAntibacterial agentsDevice formElectrical connection

A semiconductor device includes a substrate of a first conductivity type, an insulating layer formed on at least a portion of the substrate, and an epitaxial layer of a second conductivity type formed on at least a portion of the insulating layer. First and second source / drain regions of the second conductivity type are formed in the epitaxial layer proximate an upper surface of the epitaxial layer, the first and second source / drain regions being spaced laterally from one another. A gate is formed above the epitaxial layer proximate the upper surface of the epitaxial layer and at least partially between the first and second source / drain regions. The device further includes a first source / drain contact formed through the epitaxial layer and insulating layer, the first source / drain contact configured so as to be in direct electrical connection with the substrate, the first source / drain region and the epitaxial layer, and a second source / drain contact formed through the epitaxial layer, the second source / drain contact configured so as to be in direct electrical connection with the second source / drain region.

Owner:BELL SEMICON LLC

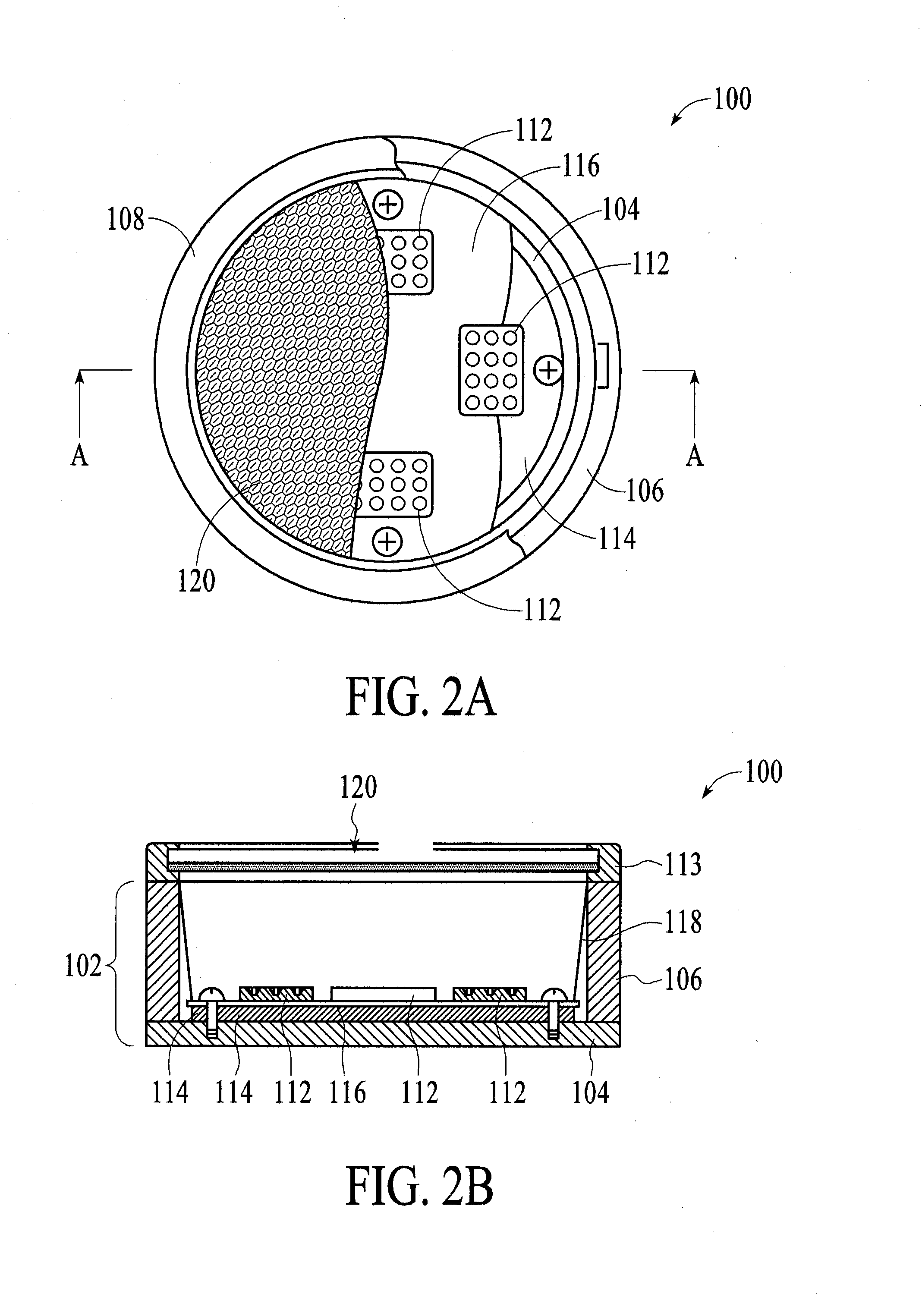

Coatings for Photoluminescent Materials

ActiveUS20130127332A1Improve performanceImprove reliabilityDischarge tube luminescnet screensElectroluminescent light sourcesPhosphorPhotoluminescence

The teachings are generally directed to phosphors having combination coatings with multifunctional characteristics that increase the performance and / or reliability of the phosphor. The teachings include highly reliable phosphors having coatings that contain more than one inorganic component, more than one layer, more than one thicknesses, more than one combination of layers or thicknesses, a gradient-interface between components, a primer thickness or layer to inhibit or prevent leaching of phosphor components into the coatings, a sealant layer to inhibit or prevent entry of moisture or oxygen from the environment, a mixed composition layer as a sealant and multifunctional combination coatings.

Owner:INTEMATIX

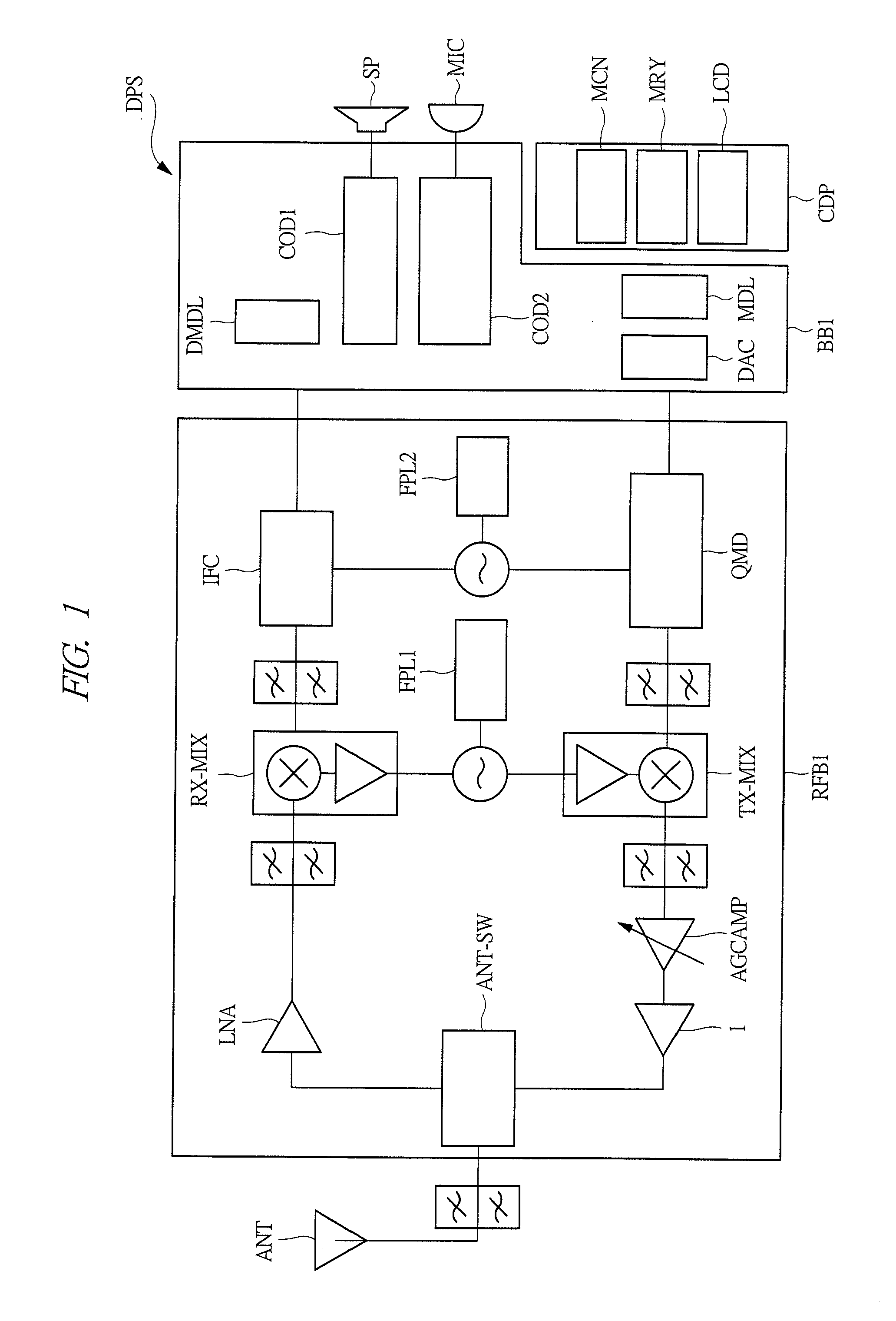

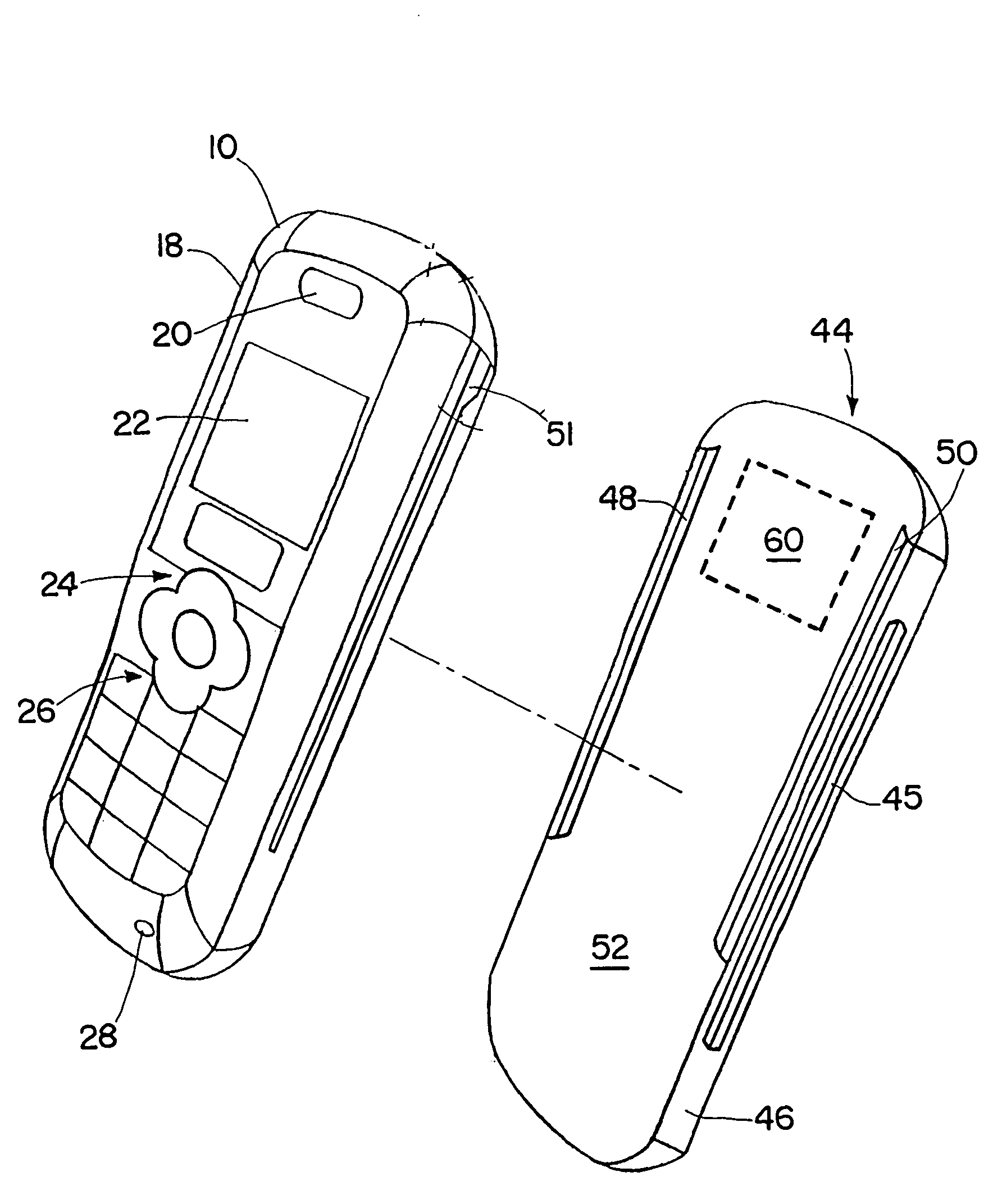

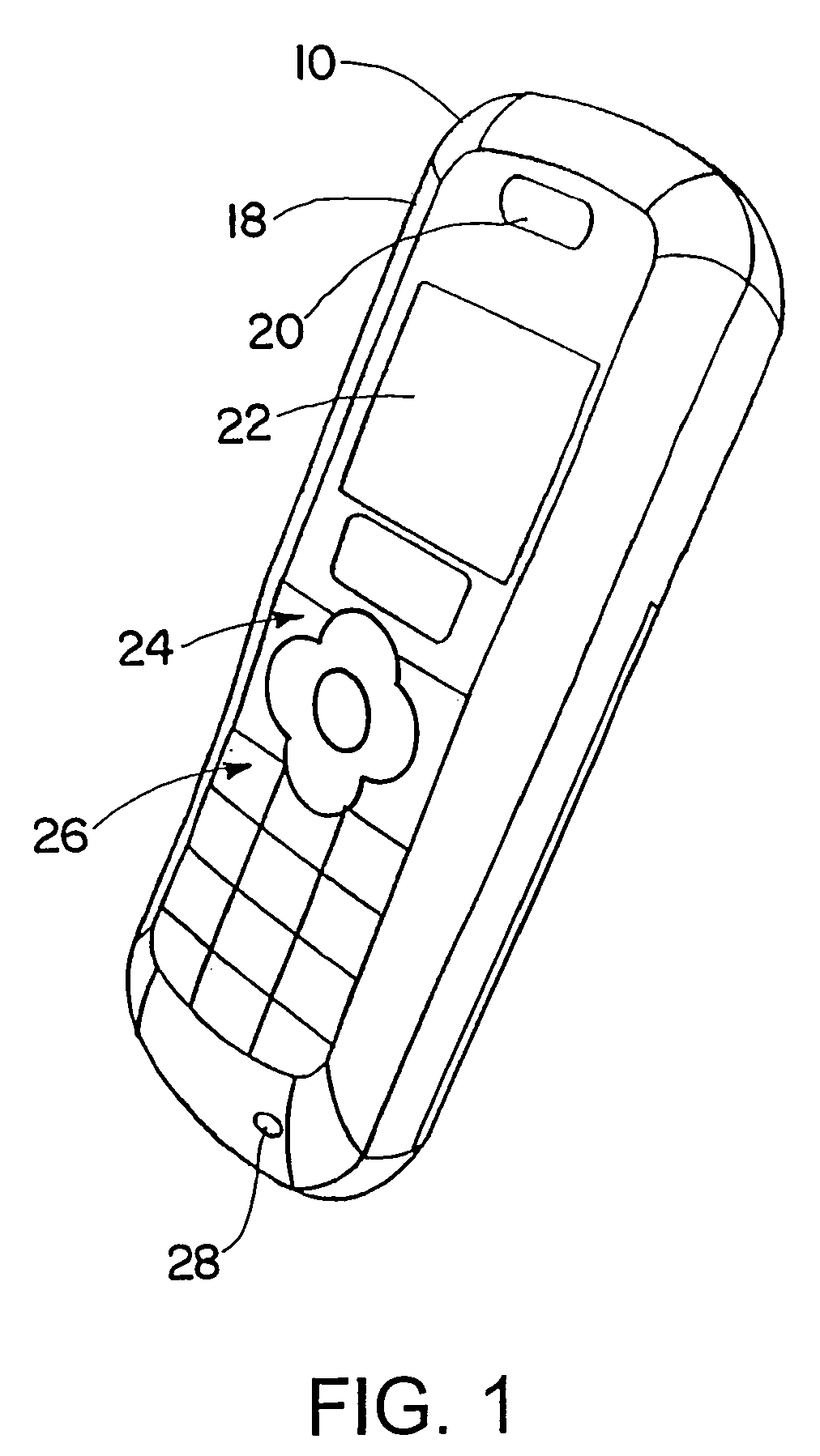

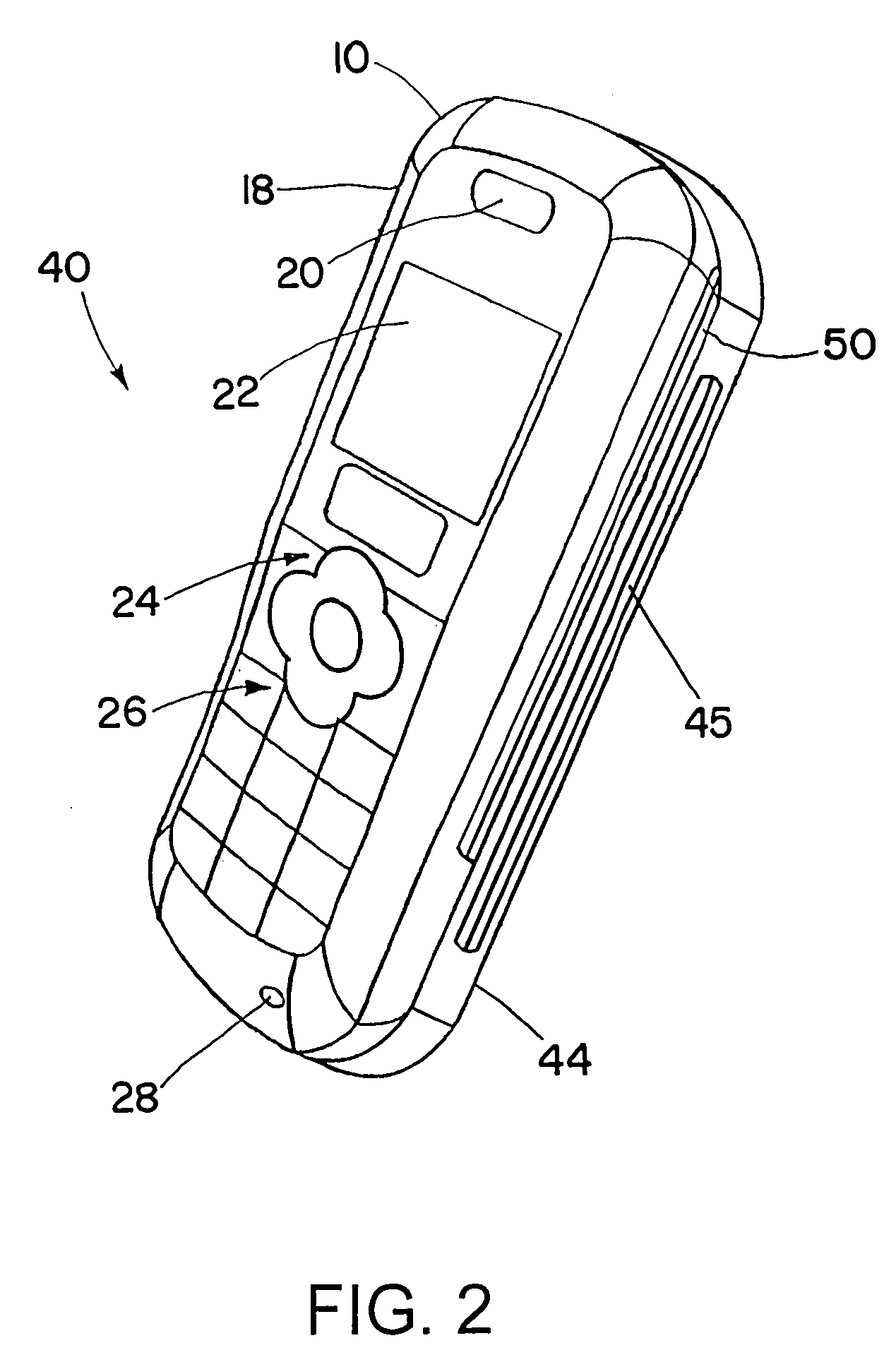

External heat sink for electronic device

InactiveUS20080310108A1Improve performanceImprove reliabilitySubstation equipmentCooling/ventilation/heating modificationsEngineeringLoudspeaker

An external heat sink device that can be attached to an electronic device during periods of excess heat generation, such as during a gaming session, for example. The external heat sink device can be removed from the electronic device during times of relatively lower heat generation. Other external accessories can be associated with the external heat sink device, such as an external antenna, speakers, game input device, power supply, etc.

Owner:SONY ERICSSON MOBILE COMM AB

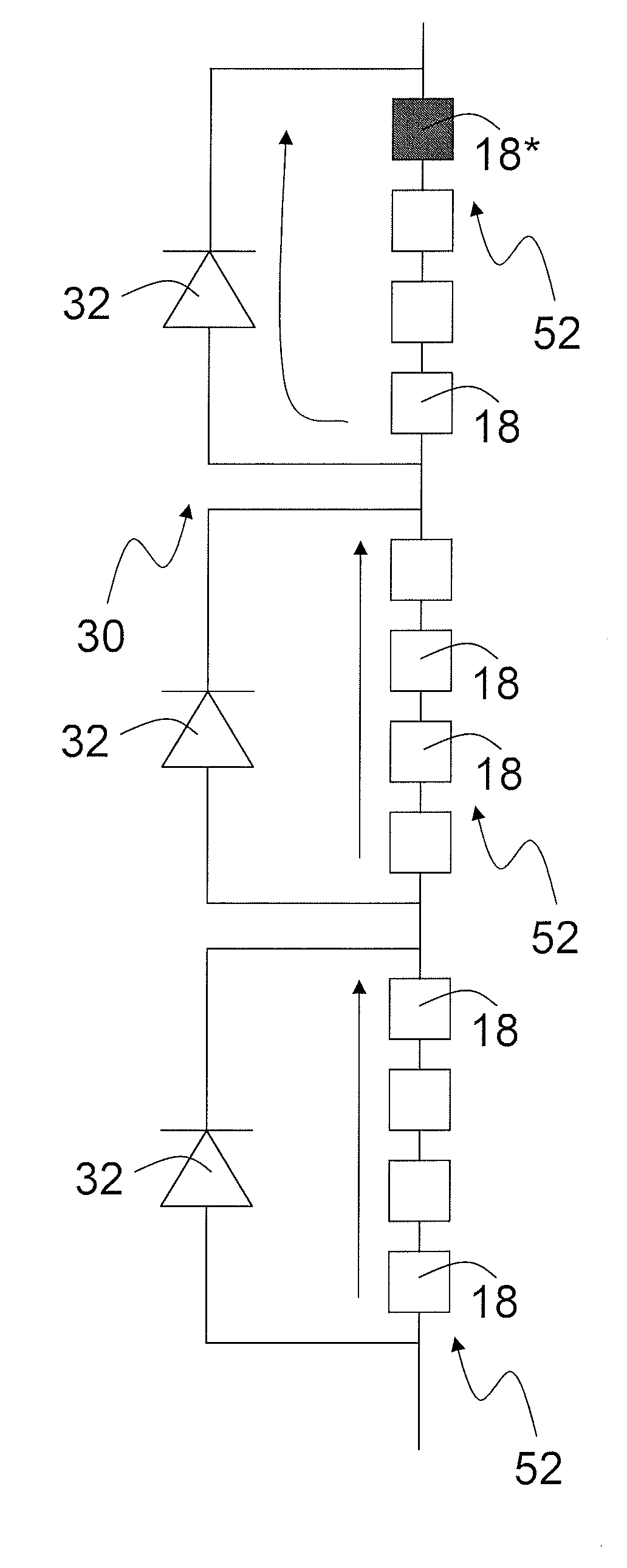

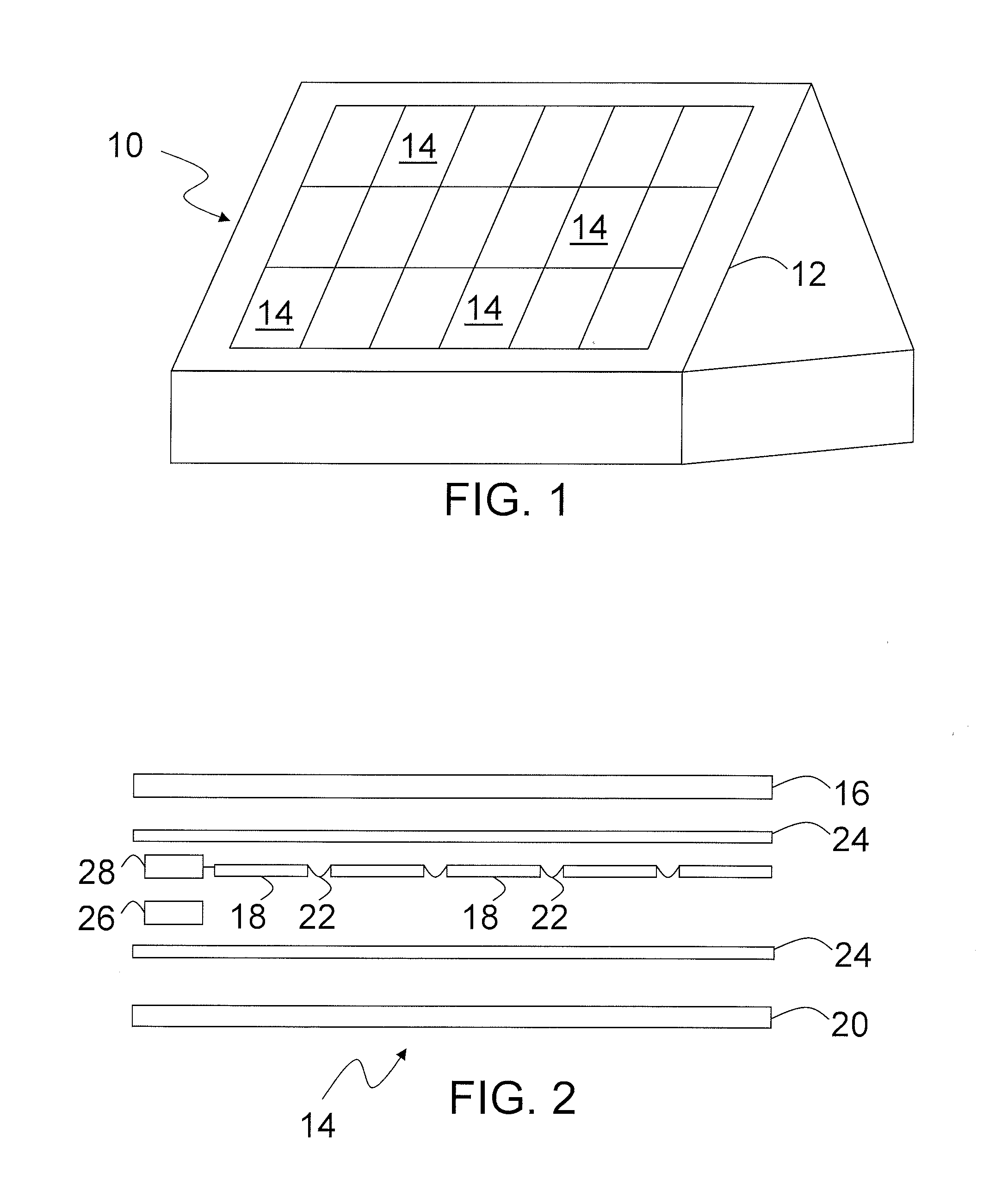

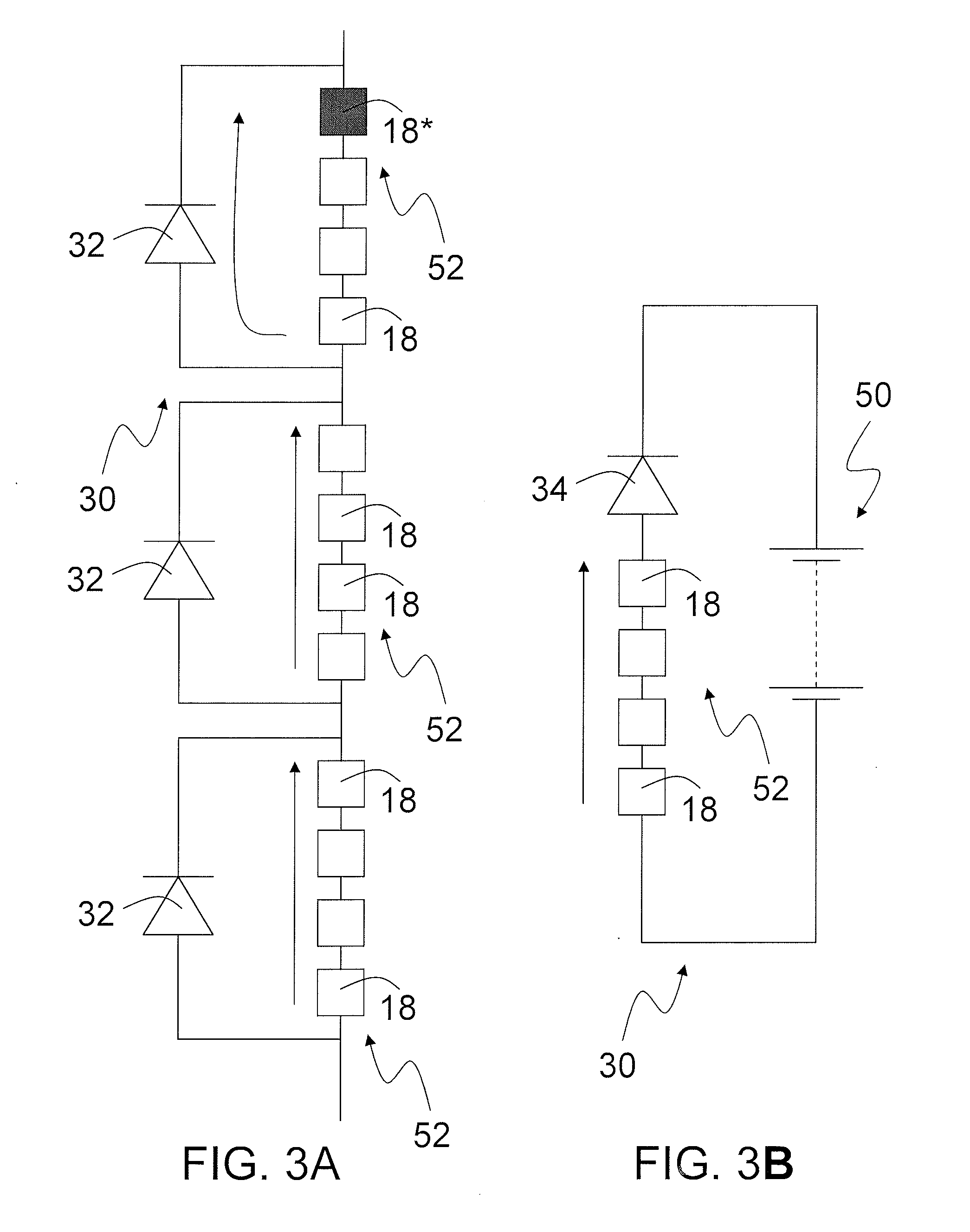

Photovoltaic Module Failure Detection Devices and Methods

InactiveUS20110088744A1Improve reliability and performanceLow costPhotovoltaic monitoringPV power plantsElectricityEffective solution

Photovoltaic module failure detection devices and methods provide reliable, low cost, and effective solutions with visual indication of a temperature of diodes during installation, commissioning, operation, and / or maintenance. Indication of diode temperatures and / or detection of diode failures assures proper installation, improves output, expedites maintenance, increases safety, and / or raises reliability. A photovoltaic module for converting light into electricity includes one or more solar cells, and a transparent front sheet disposed over the one or more solar cells. The photovoltaic module includes a back sheet opposite the transparent front sheet, and one or more electrical circuits with one or more diodes connected to at least a portion of the one or more solar cells. The module includes one or more temperature indication devices in communication with at least a portion of the one or more diodes and disposed between the transparent front sheet and the back sheet.

Owner:BP CORP NORTH AMERICA INC

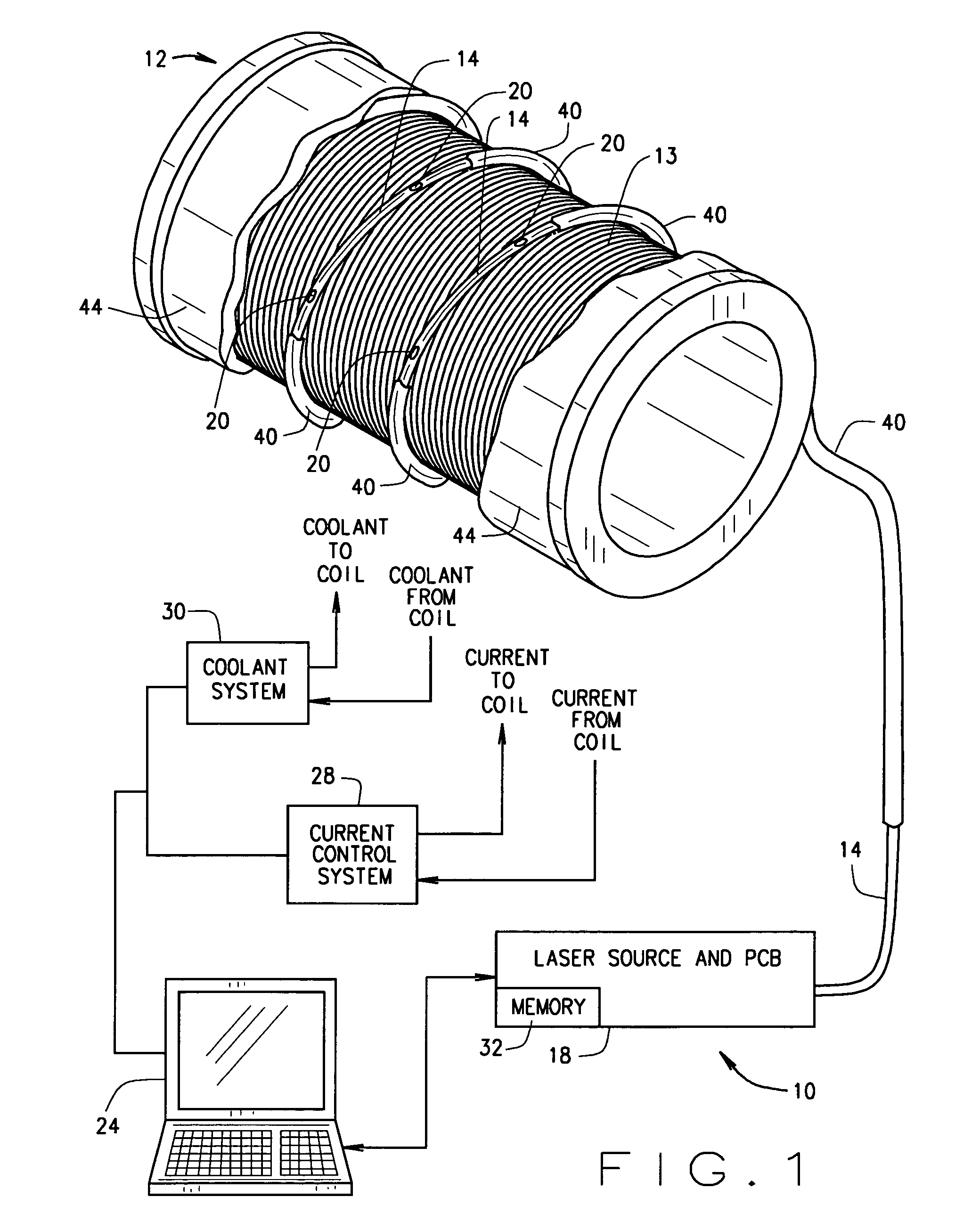

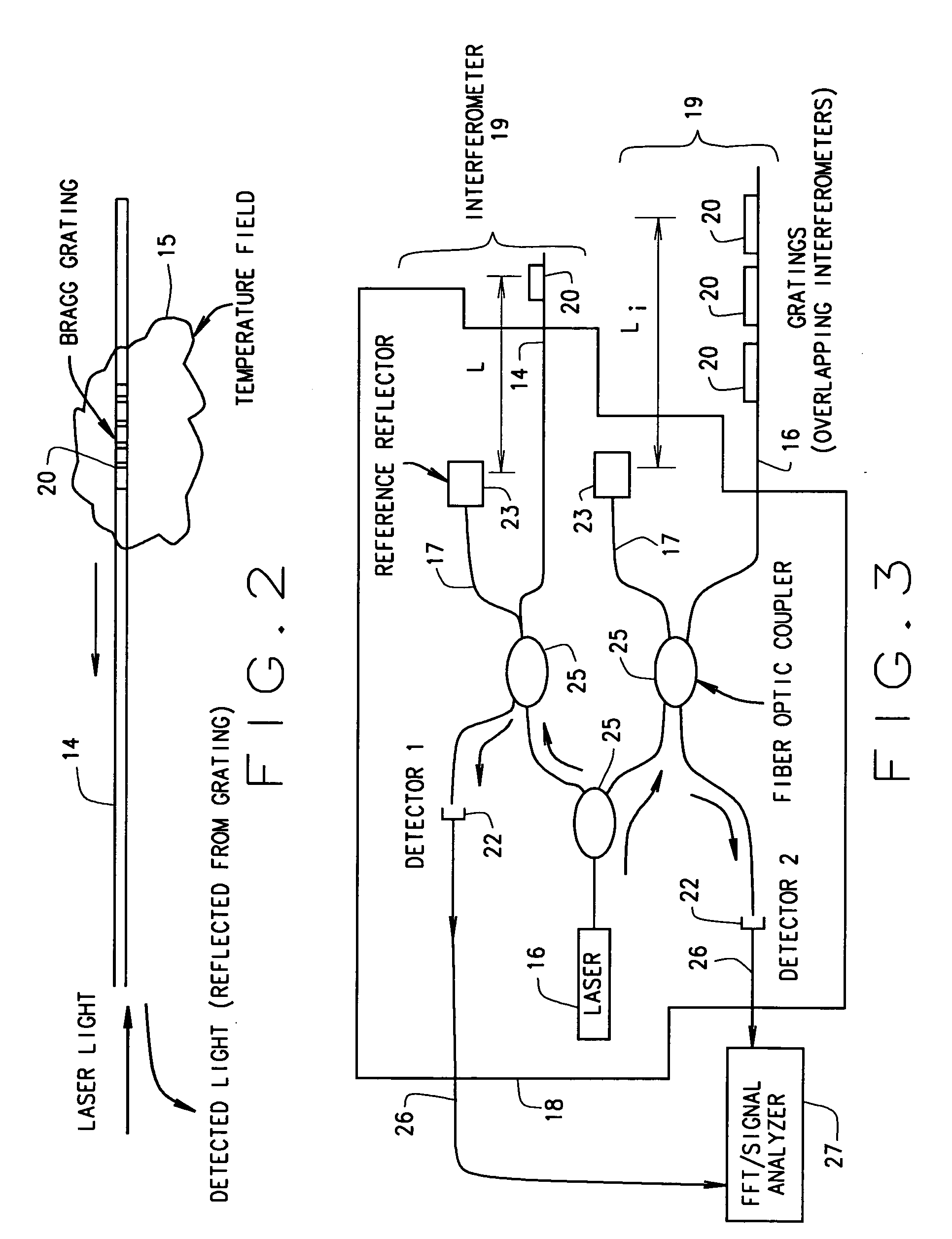

Methods and apparatus for temperature measurement and control in electromagnetic coils

InactiveUS20050129088A1Improve reliability and performanceAvoid transmitting strainRadiation pyrometryThermometers using physical/chemical changesElectricityGrating

A method for monitoring temperature in at least one location of an electromagnetic coil assembly having at least one electrical winding. The method includes passing a light through a non-magnetic optical fiber inserted into a sheath that is wound with the electrical winding. The sheath is wound and cast with the electromagnetic coil assembly, and the optical fiber is slidably inserted therein. The optical fiber has a core containing at least a first Bragg grating etched therein. The method further includes detecting a wavelength of light reflected from the first Bragg grating and determining a temperature of the electromagnetic coil assembly at a location of the first Bragg grating utilizing the detected wavelength of the light reflected from the first Bragg grating.

Owner:GE MEDICAL SYST GLOBAL TECH CO LLC

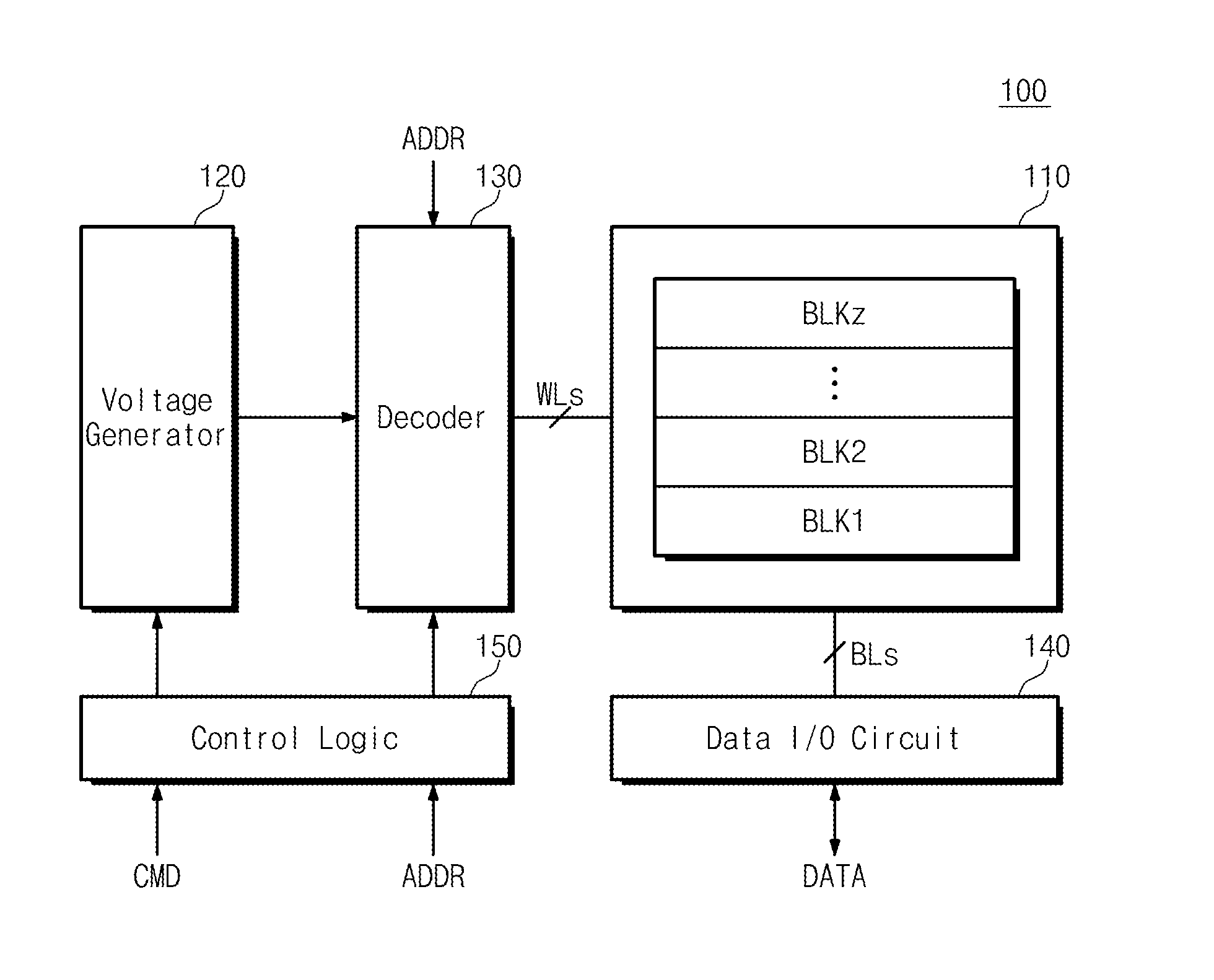

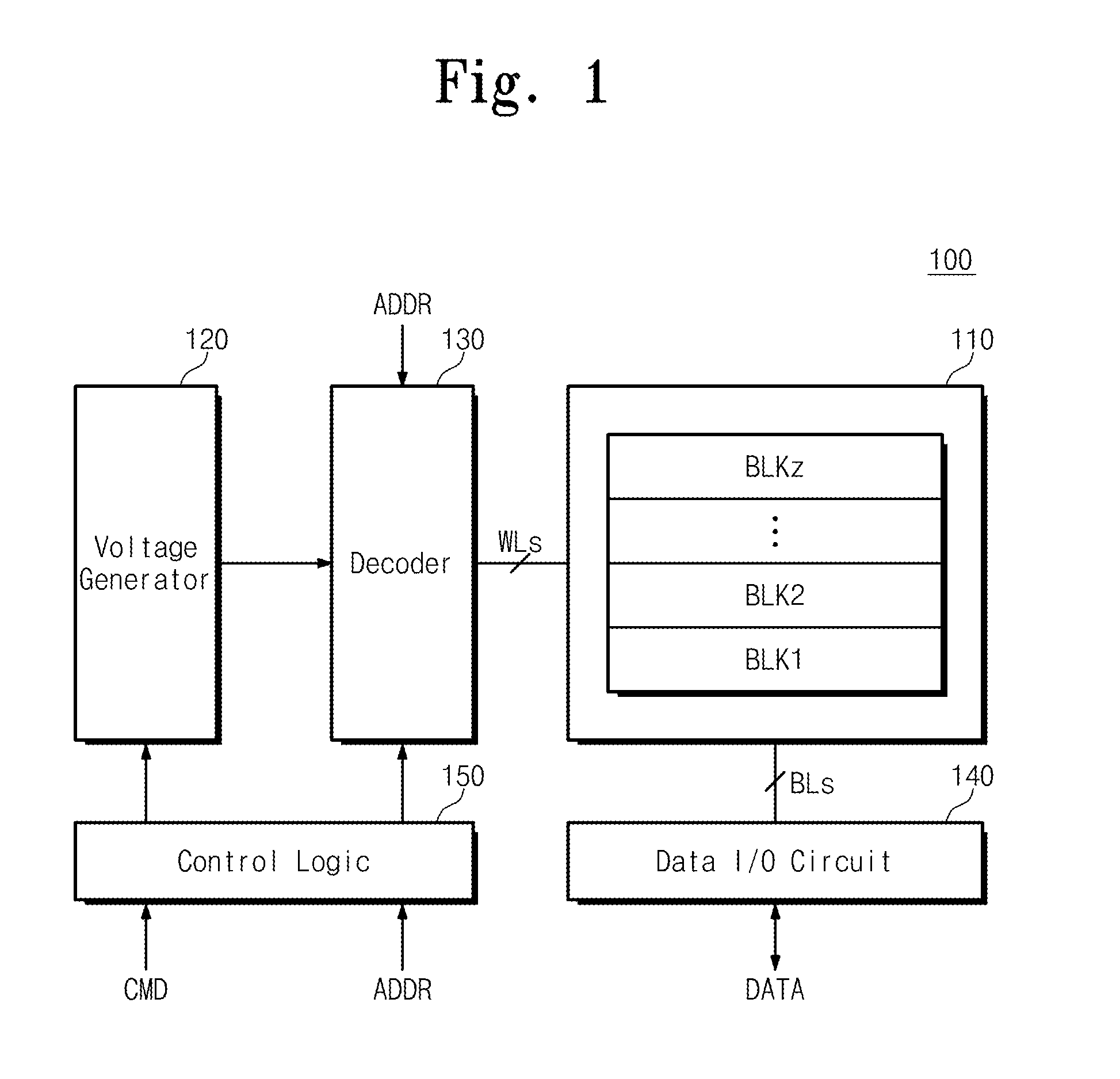

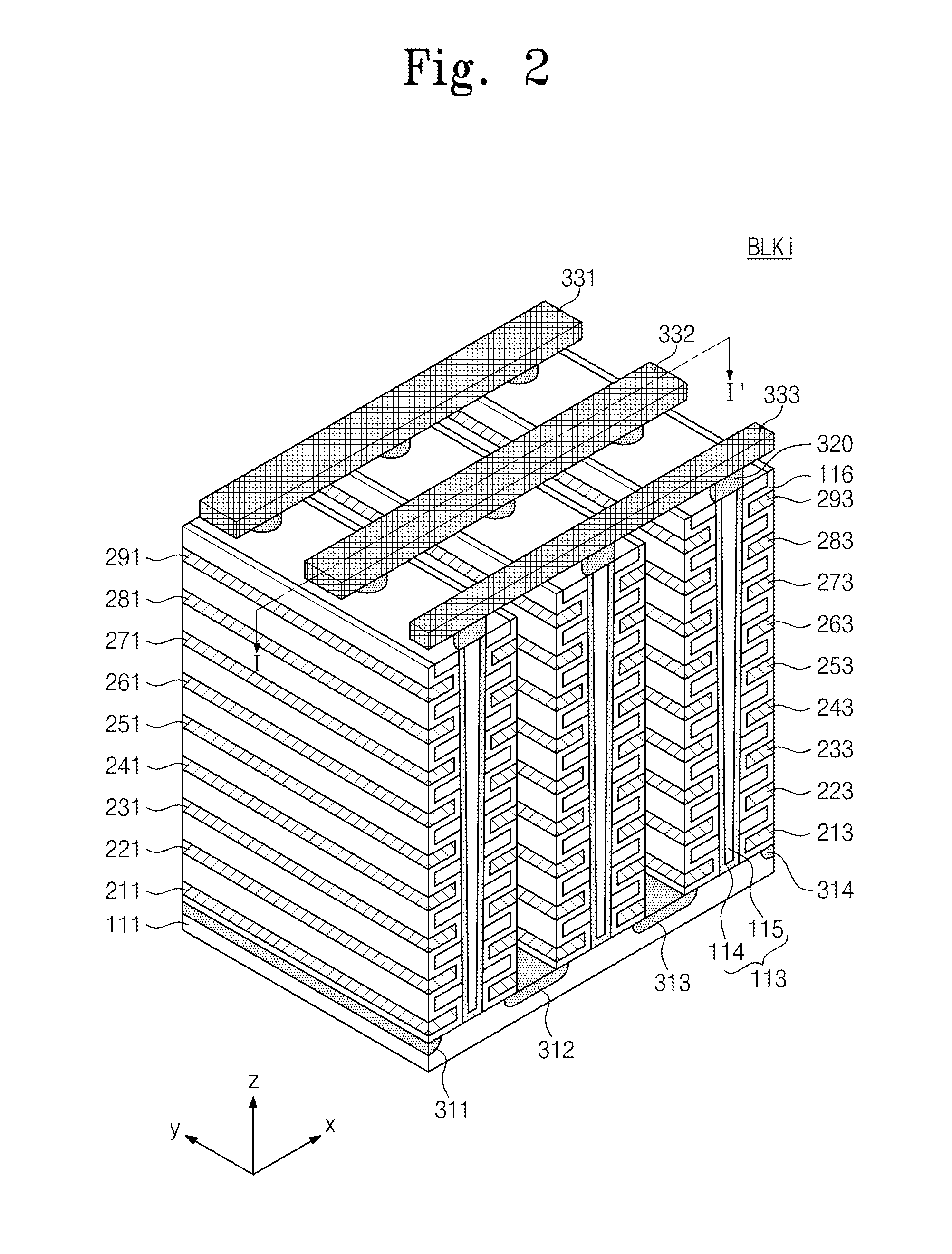

Nonvolatile memory device and related method of operation

ActiveUS20130286747A1Improve performanceImprove reliabilityRead-only memoriesDigital storageCommon wordOperating system

A nonvolatile memory device comprises cell strings formed in a direction substantially perpendicular to a substrate and is configured to select memory cells in units corresponding to a string selection line. The device selects a page to be programmed among pages sharing a common word line, determines a level of a program voltage to be provided to the selected page according to a location of a string selection line corresponding to the selected page, and writes data in the selected page using the determined level of the program voltage.

Owner:SAMSUNG ELECTRONICS CO LTD

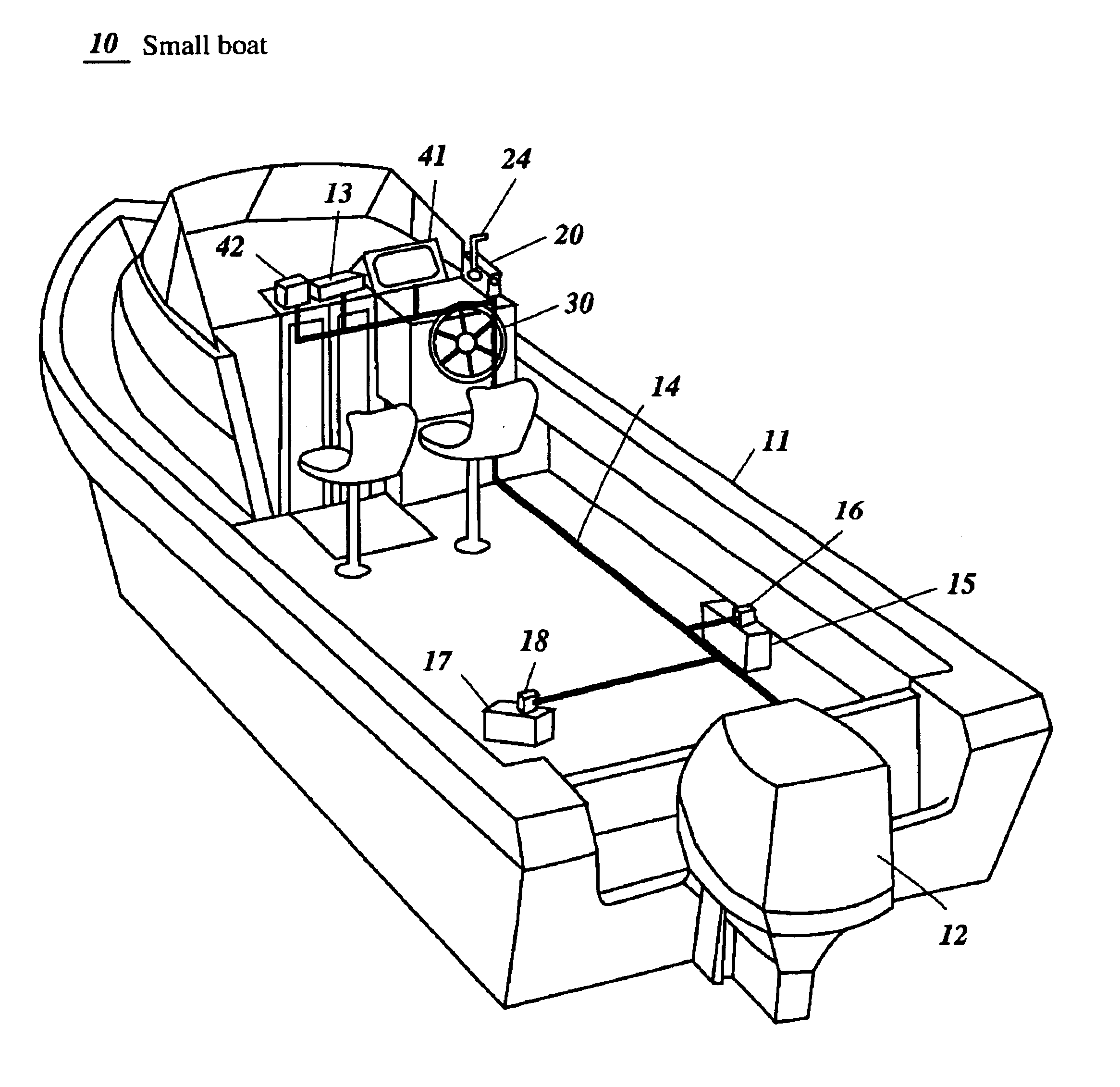

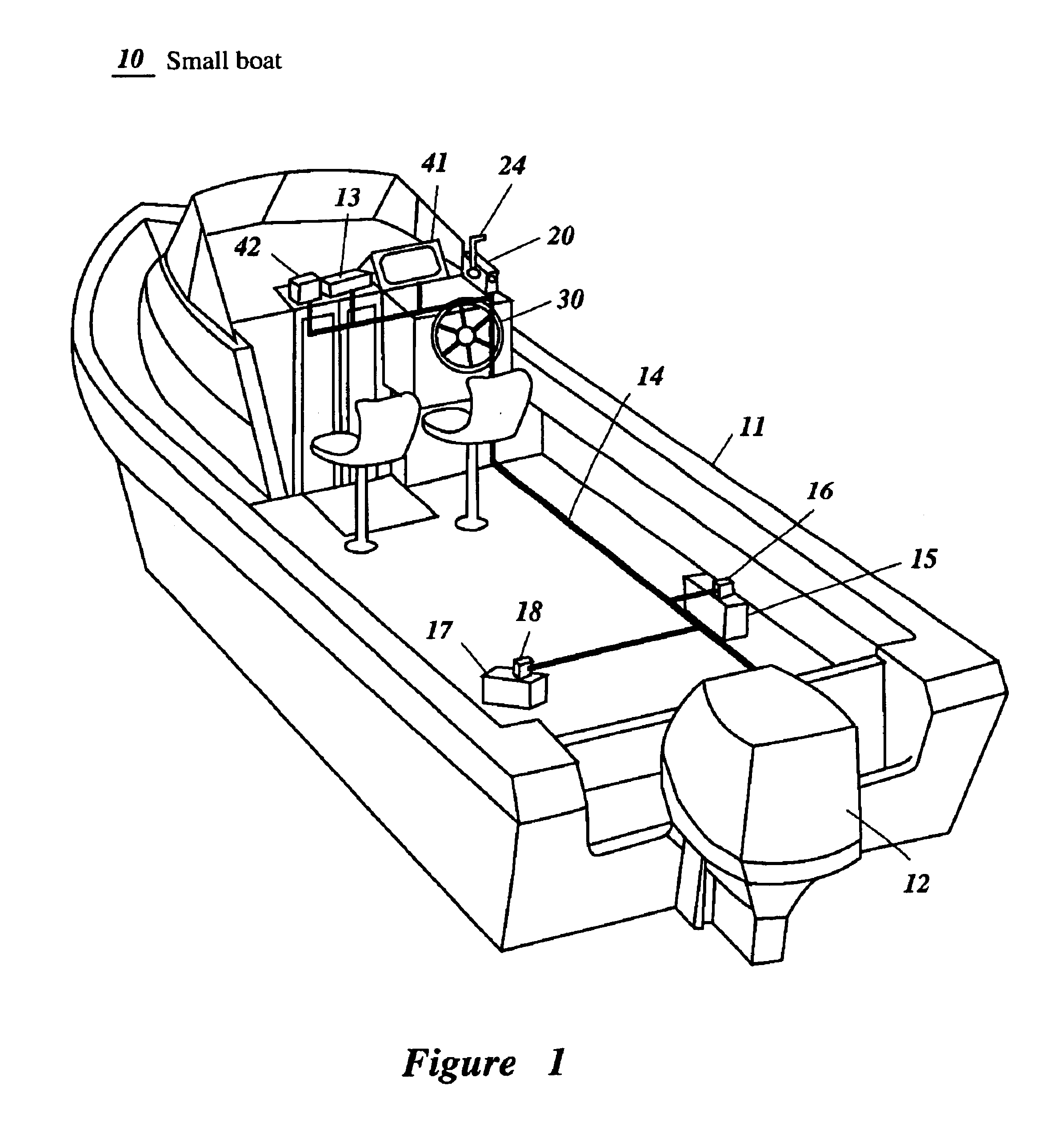

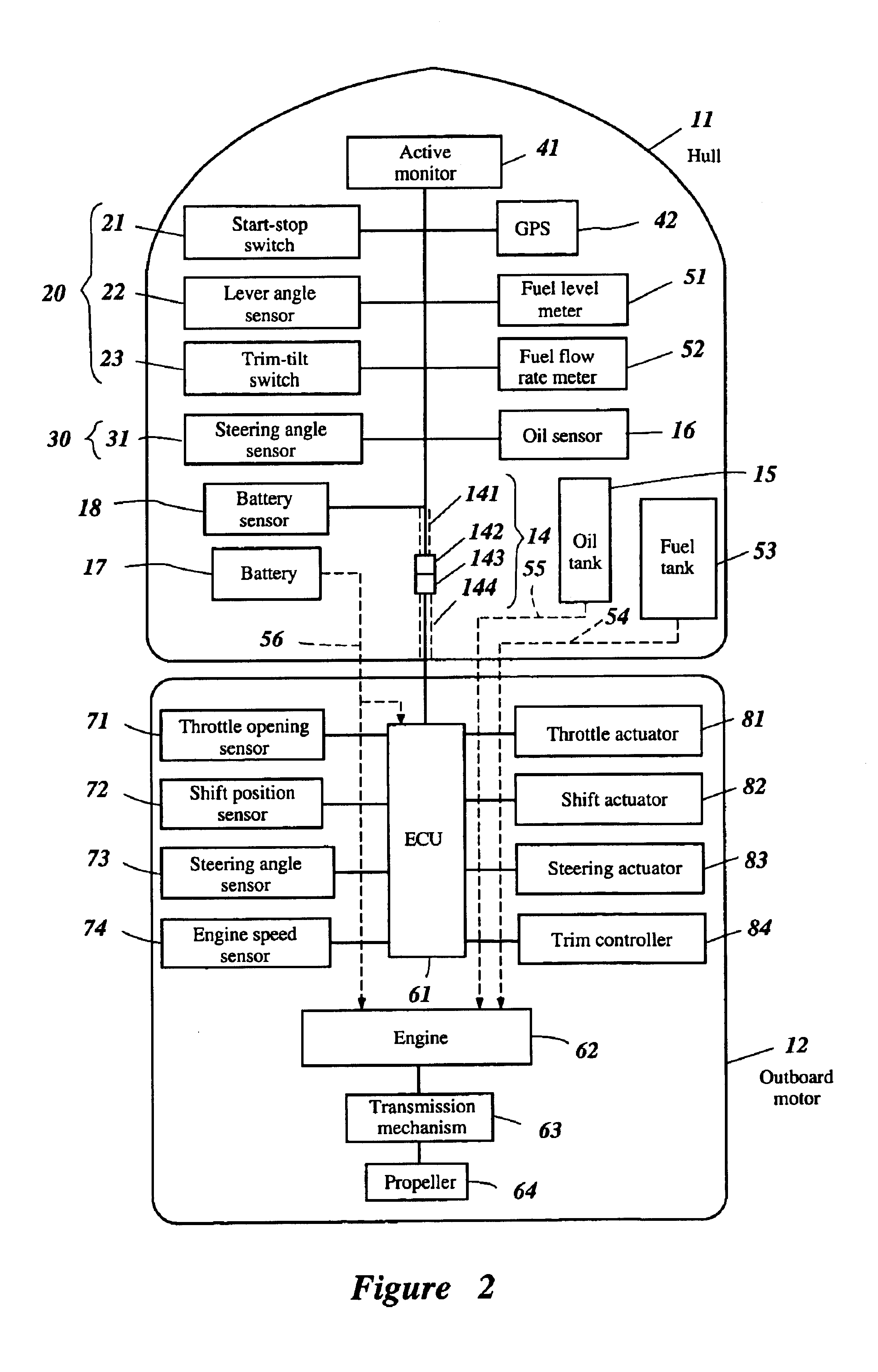

Small watercraft and outboard motor

InactiveUS6910927B2Improve reliabilitySimplified installation timePropulsion power plantsOutboard propulsion unitsWatercraftActuator

A small watercraft and outboard motor are configured so that operator-activated command signals are communicated from a control unit in the hull of the watercraft via a local area network to engine component actuators in the outboard motor. The local area network enables a simplified connection to be used between the watercraft hull and the outboard motor to provide communication of the command signals as well as to provide communication of navigational and engine parameter information. The local area network enables the user to operate the watercraft with increased reliability. Because of the small number (e.g., one) of control connections required between the hull and the outboard motor, the process for installing the outboard motor onto the watercraft hull is greatly simplified, which reduces the time and the cost initial installation and the cost of repair.

Owner:YAMAHA MARINE KK

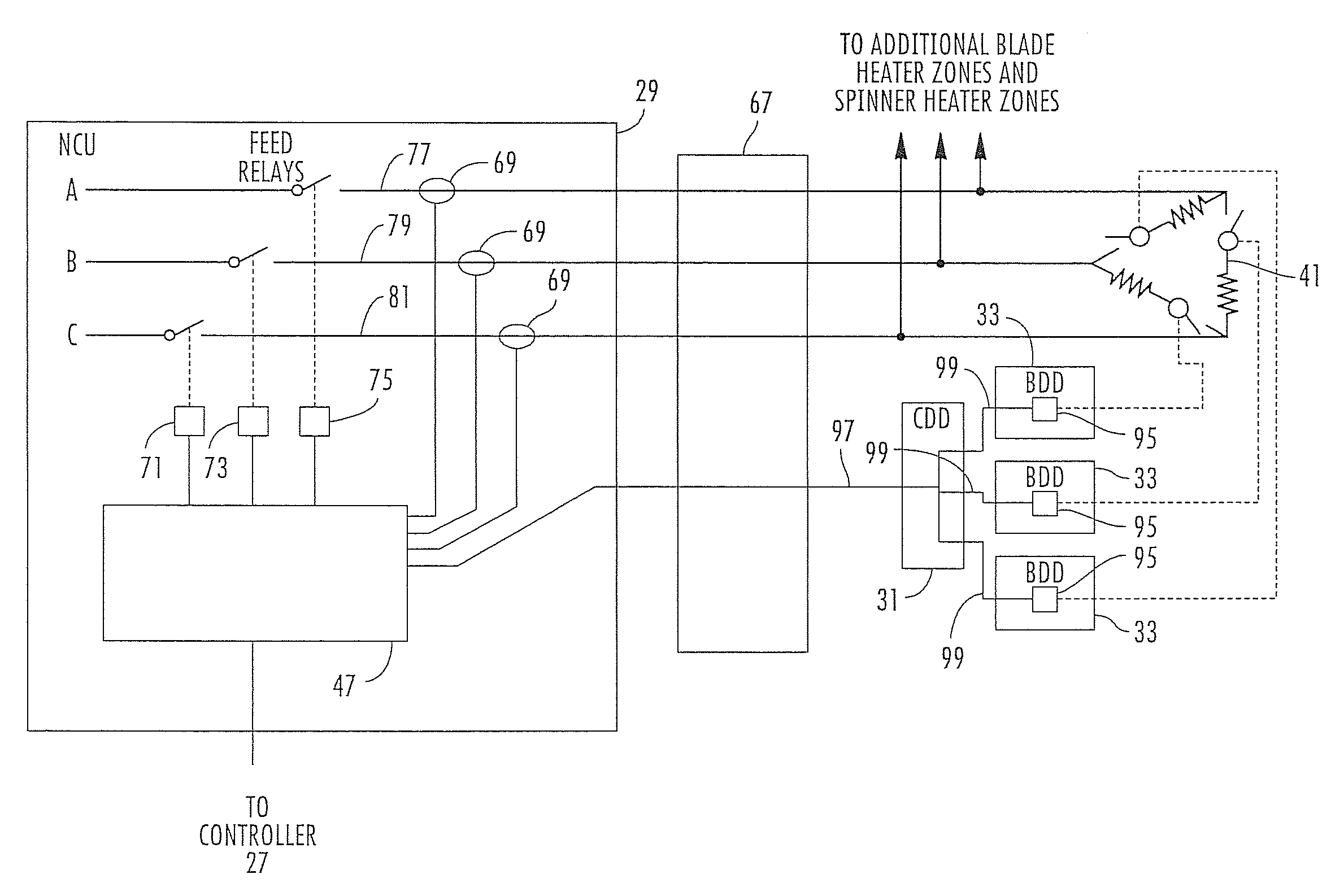

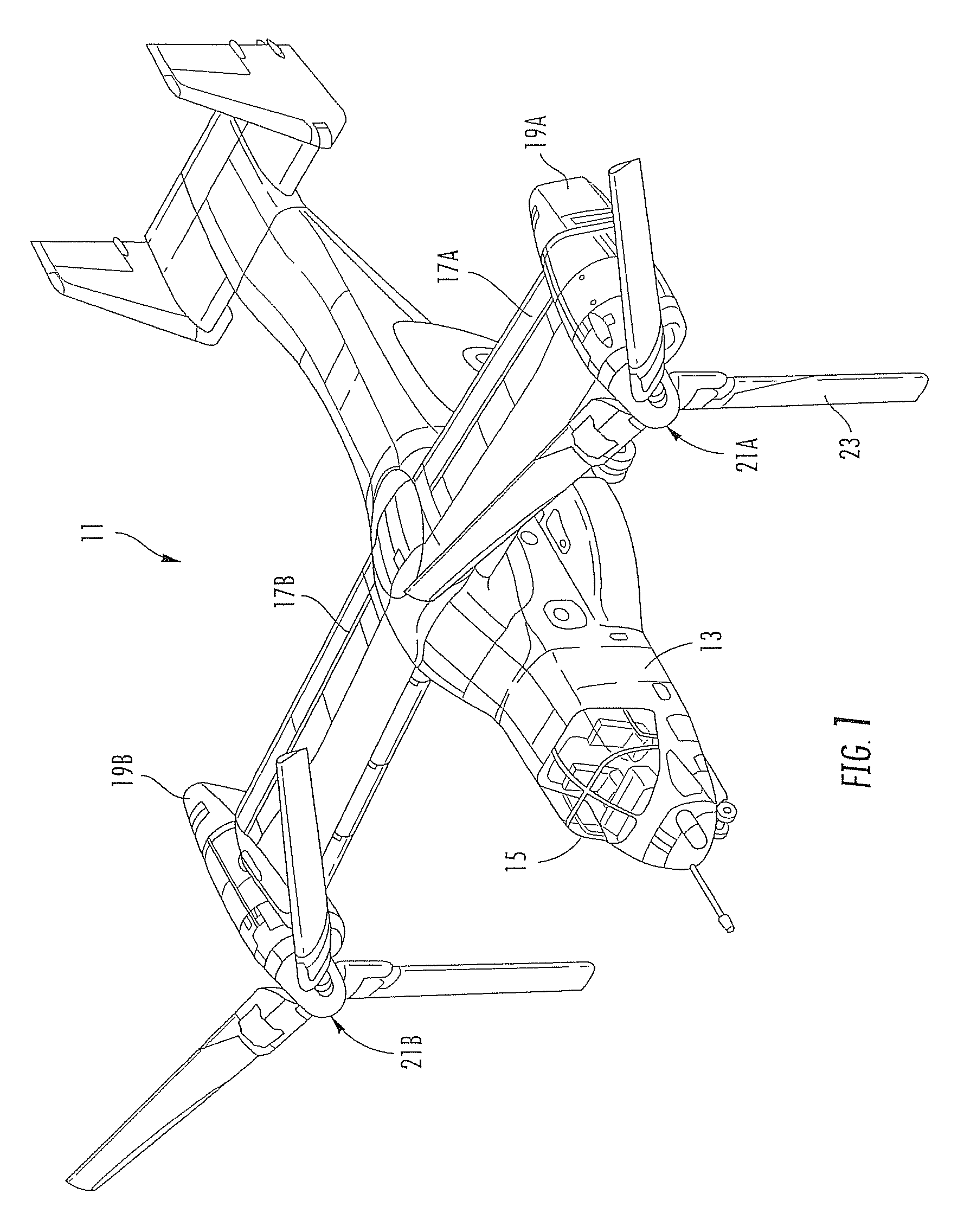

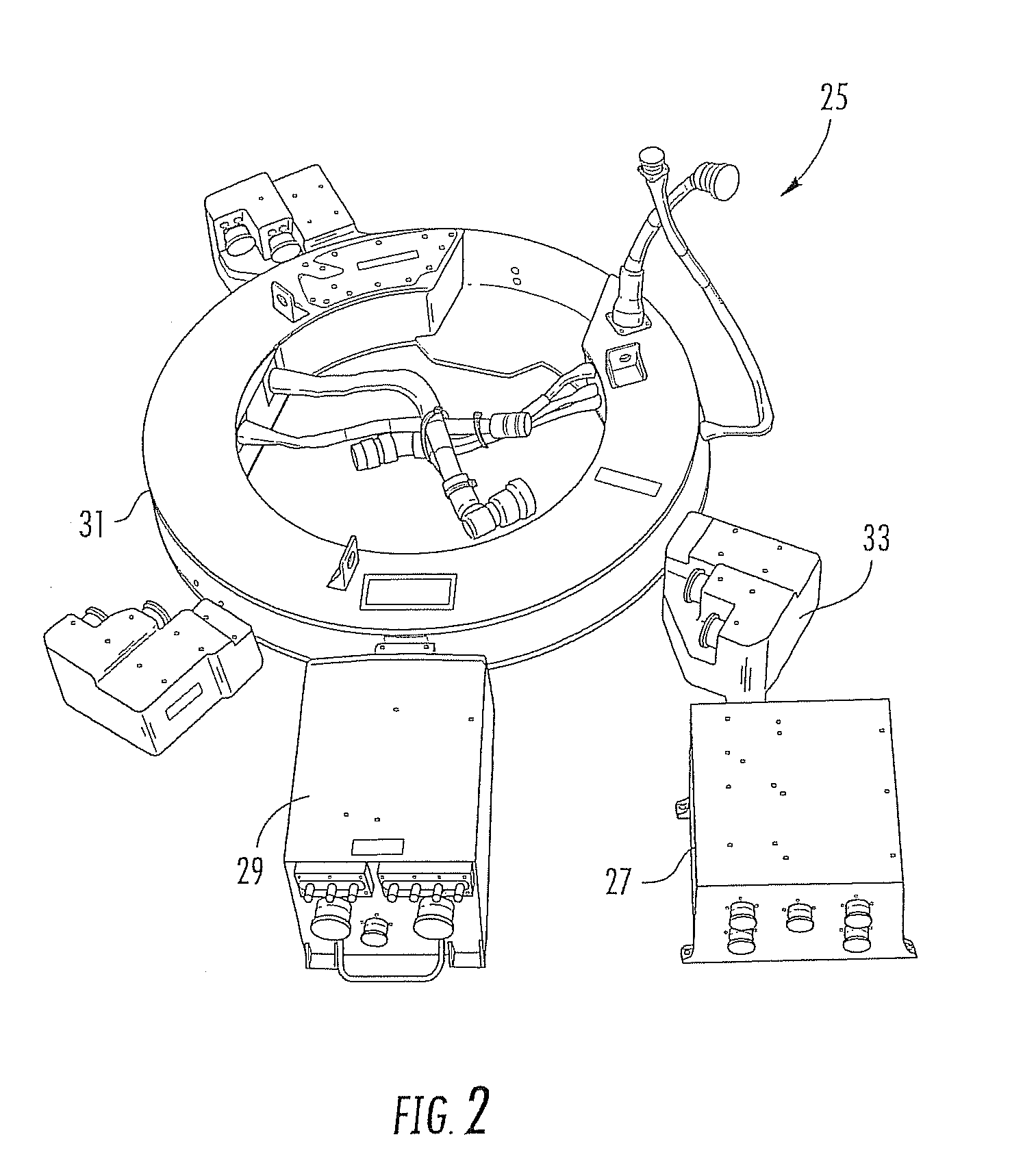

Ice management system for tiltrotor aircraft

ActiveUS7604202B2Improve reliability and performanceLow costDe-icing equipmentsVertical landing/take-off aircraftsFlight vehicleManagement system

Owner:TEXTRON INNOVATIONS

Method of heat treatment for desensitizing a nikel-based alloy relative to environmentally-assisted craking, in particular for a nuclear for a nuclear reactor fuel assembly and for a nuclear reactor, and a part made of the alloy and subjected to the treatment

ActiveUS20100116383A1Low stress levelImprove reliability and performanceNuclear reactor coreNuclear reactor

A heat treatment method for desensitizing a nickel-based alloy with respect to environmentally-assisted cracking, the alloy having the following composition in percentages by weight: C≦0.10%; Mn≦0.5%; Si≦0.5%; P≦0.015%; S≦0.015%; Ni≧40%; Cr=12%-40%; Co≦10%; Al≦5%; Mo=0.1%-15%; Ti≦5%; B≦0.01%; Cu≦5%; W=0.1%-15%; Nb=0-10%; Ta≦10%; the balance being Fe, and inevitable impurities that result from processing, characterized in that the alloy is held at 950° C.-1160° C. in an atmosphere of pure hydrogen or containing at least 100 ppm of hydrogen mixed with an inert gas. A part made of a nickel-based alloy having the composition and that has been subjected to the heat treatment.

Owner:AREVA NP SAS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com