Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

93results about How to "Improve breakdown performance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

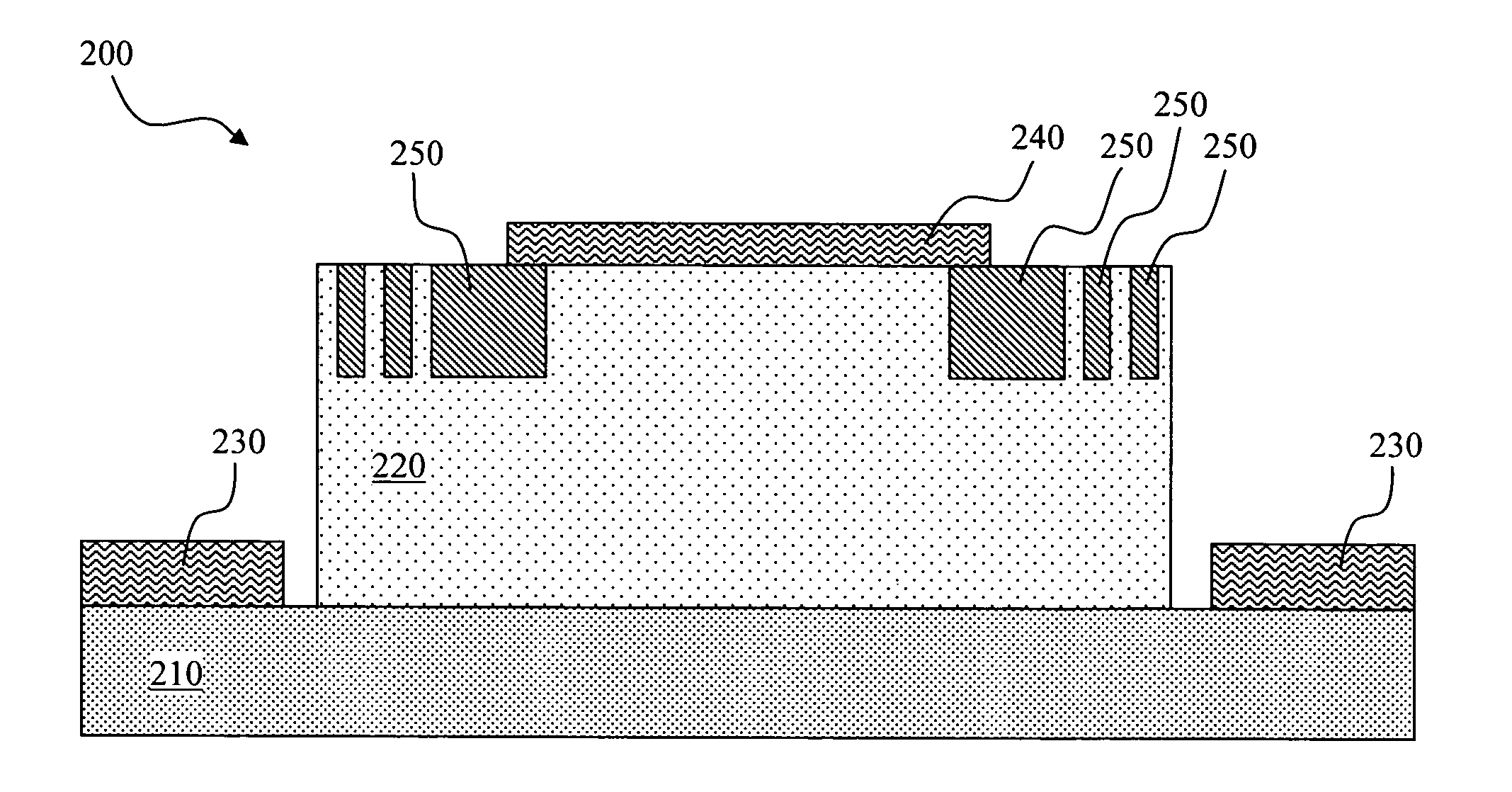

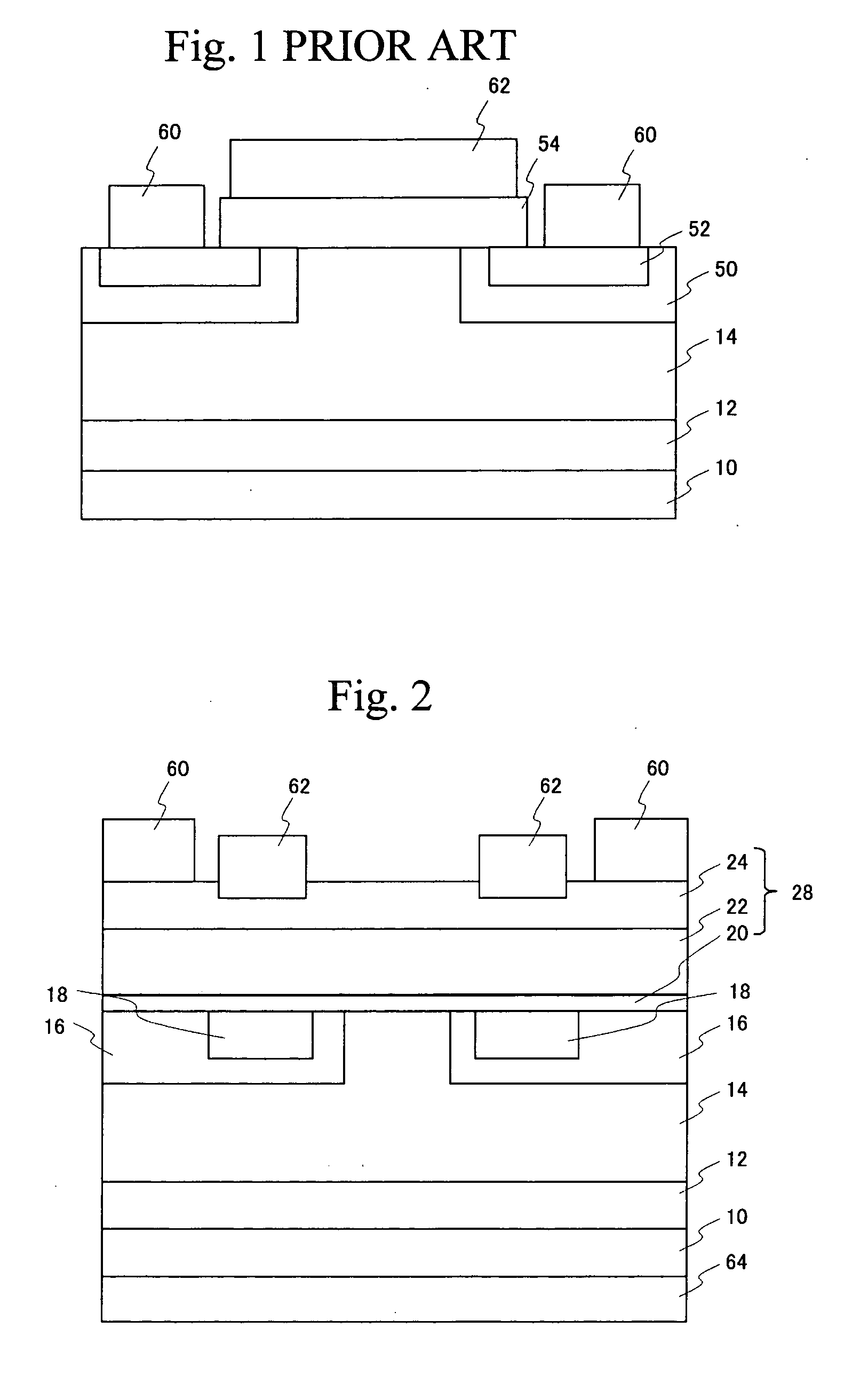

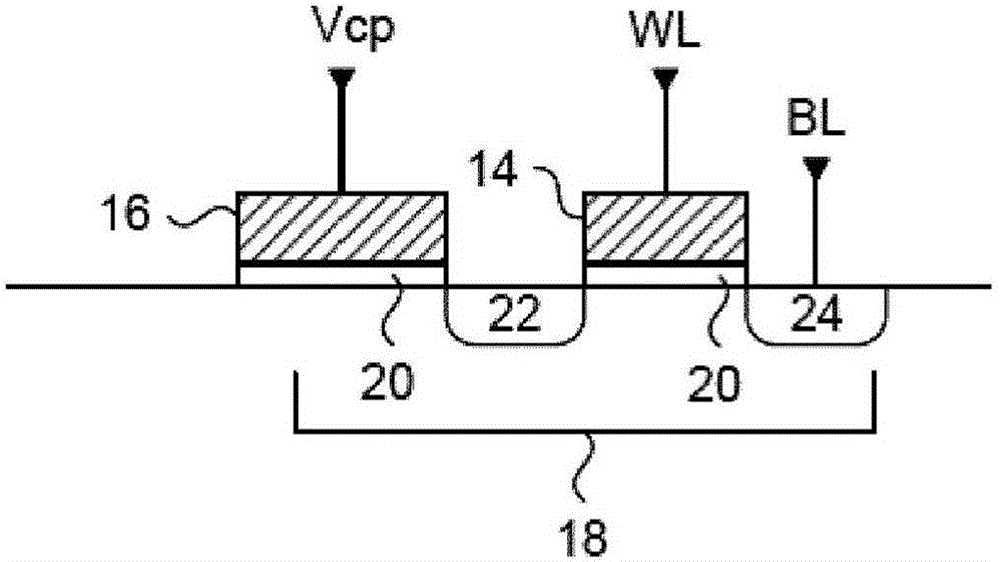

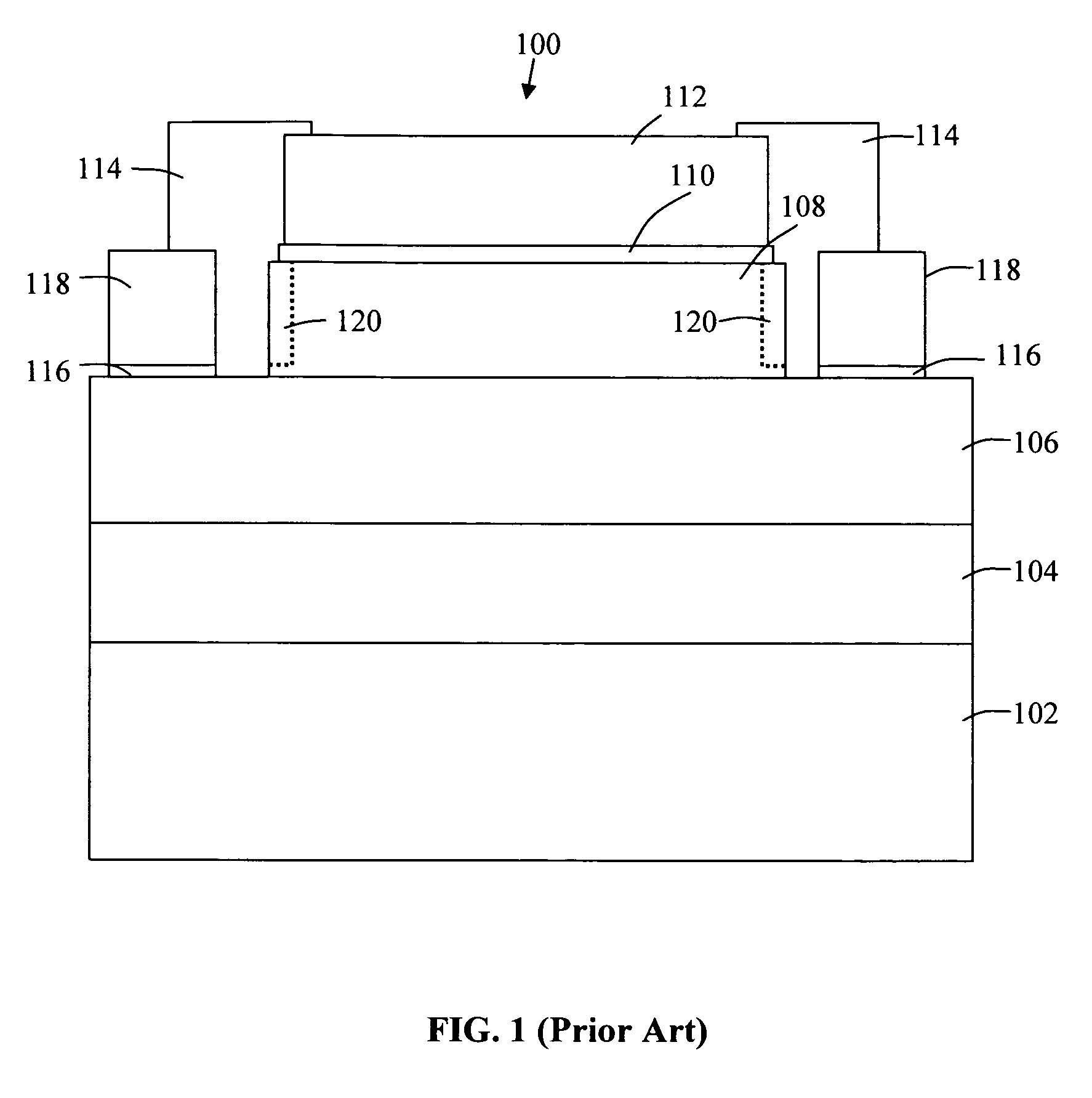

Gallium nitride semiconductor device with improved termination scheme

ActiveUS20110101369A1Uniform densityImproved termination structureSemiconductor/solid-state device manufacturingDiodeGallium nitrideSemiconductor

This invention discloses a gallium nitride based semiconductor power device disposed in a semiconductor substrate. The power device comprises a termination area disposed at a peripheral area of the semiconductor power device comprises a termination structure having at least a guard ring disposed in a trench filled with doped gallium-based epitaxial layer therein.

Owner:ALPHA & OMEGA SEMICON INC

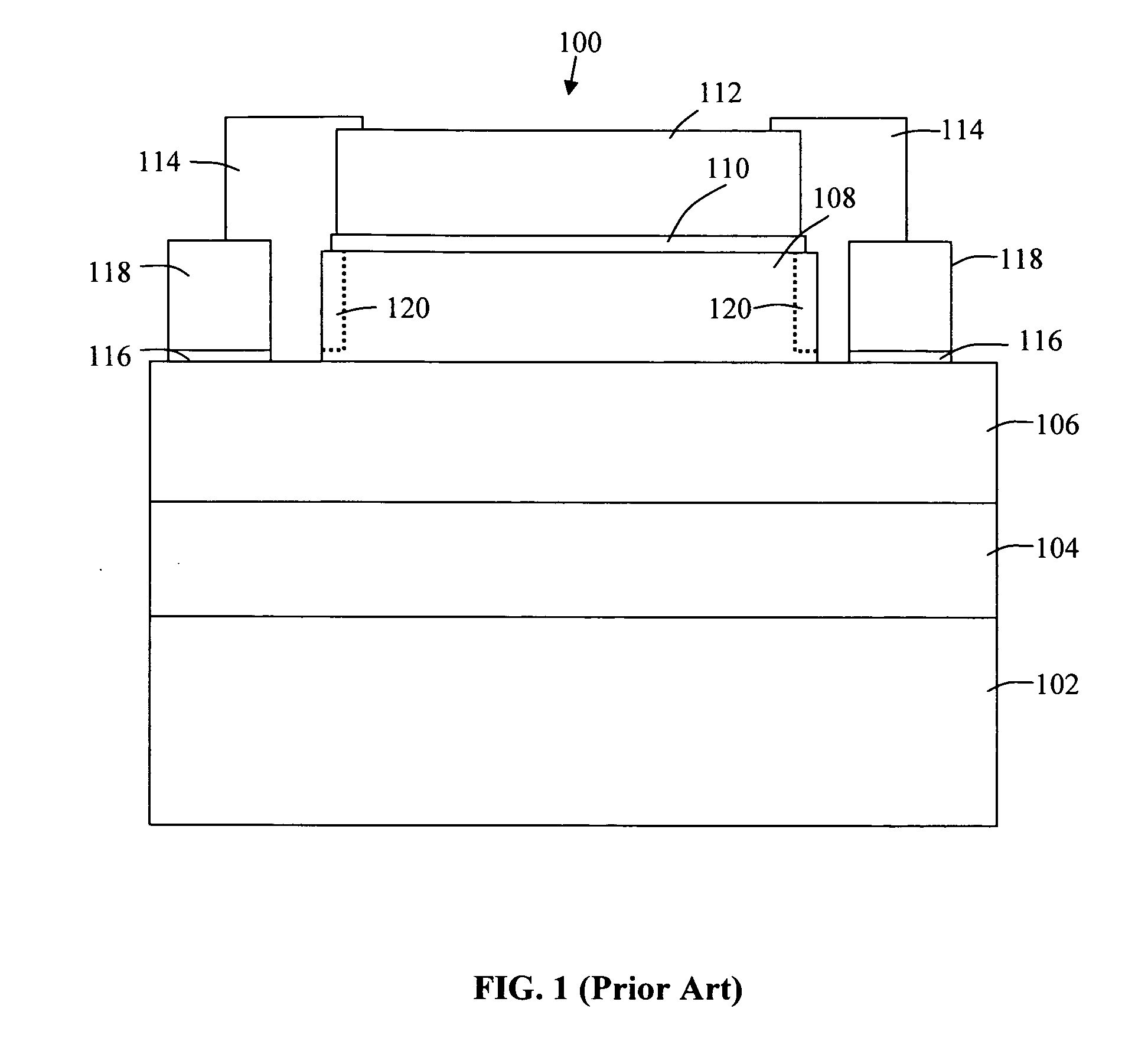

Semiconductor device and fabrication method of the same

InactiveUS20060219997A1Improve breakdown performanceLower on-resistanceTransistorSemiconductor/solid-state device manufacturingDevice materialSemiconductor

A semiconductor device includes a substrate, a SiC drift layer formed above the substrate, a GaN-based semiconductor layer that is formed on the SiC drift layer and includes a channel layer, a source electrode and a gate electrode formed on the GaN-based semiconductor layer, current blocking regions formed in portions of the SiC drift layer and located below the source and gate electrodes, and a drain electrode formed on a surface that opposes the GaN-based semiconductor layer across the SiC layer.

Owner:SUMITOMO ELECTRIC DEVICE INNOVATIONS

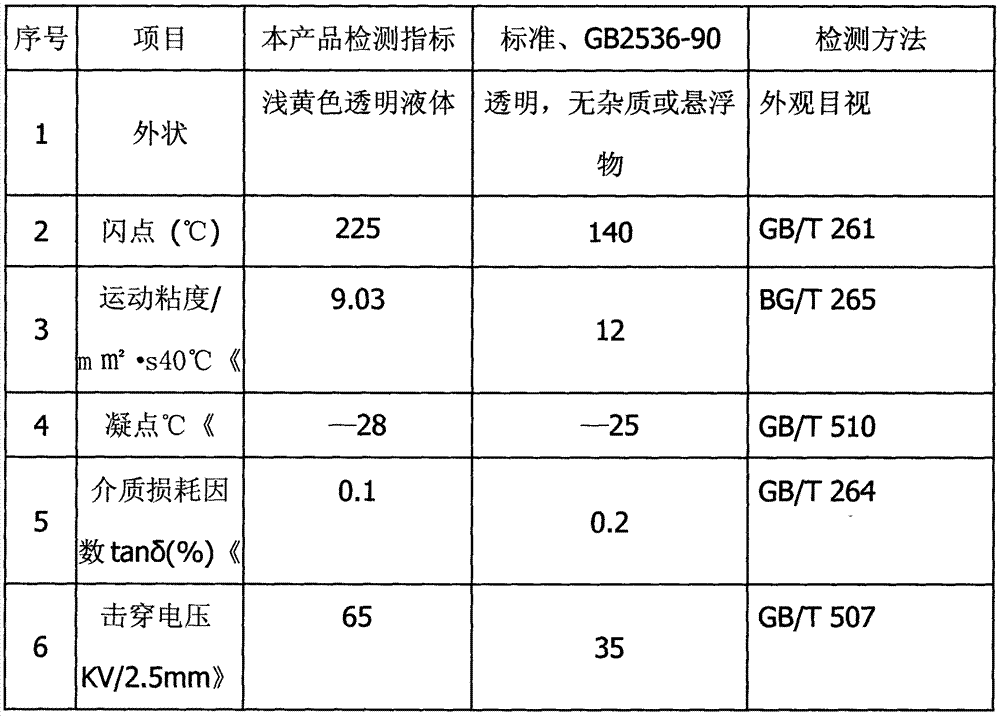

Transformer oil and preparation method thereof

InactiveCN103695098AImprove thermal conductivityImprove breakdown performanceLubricant compositionNanoparticleAntioxidant

The invention discloses a transformer oil and a preparation method thereof. The transformer oil comprises the following components by weight: 0.05% of an antioxidant, 0.03% of a surfactant, 0.03% of BN nanoparticles and the balance of transformer base oil. The invention has the beneficial effects of substantially improving thermal conductivity and breakdown performance of the transformer oil, and at the same time increasing the dielectric strength of the transformer oil.

Owner:JIYUAN POWER SUPPLY COMPANY OF STATE GRID HENAN ELECTRIC POWER

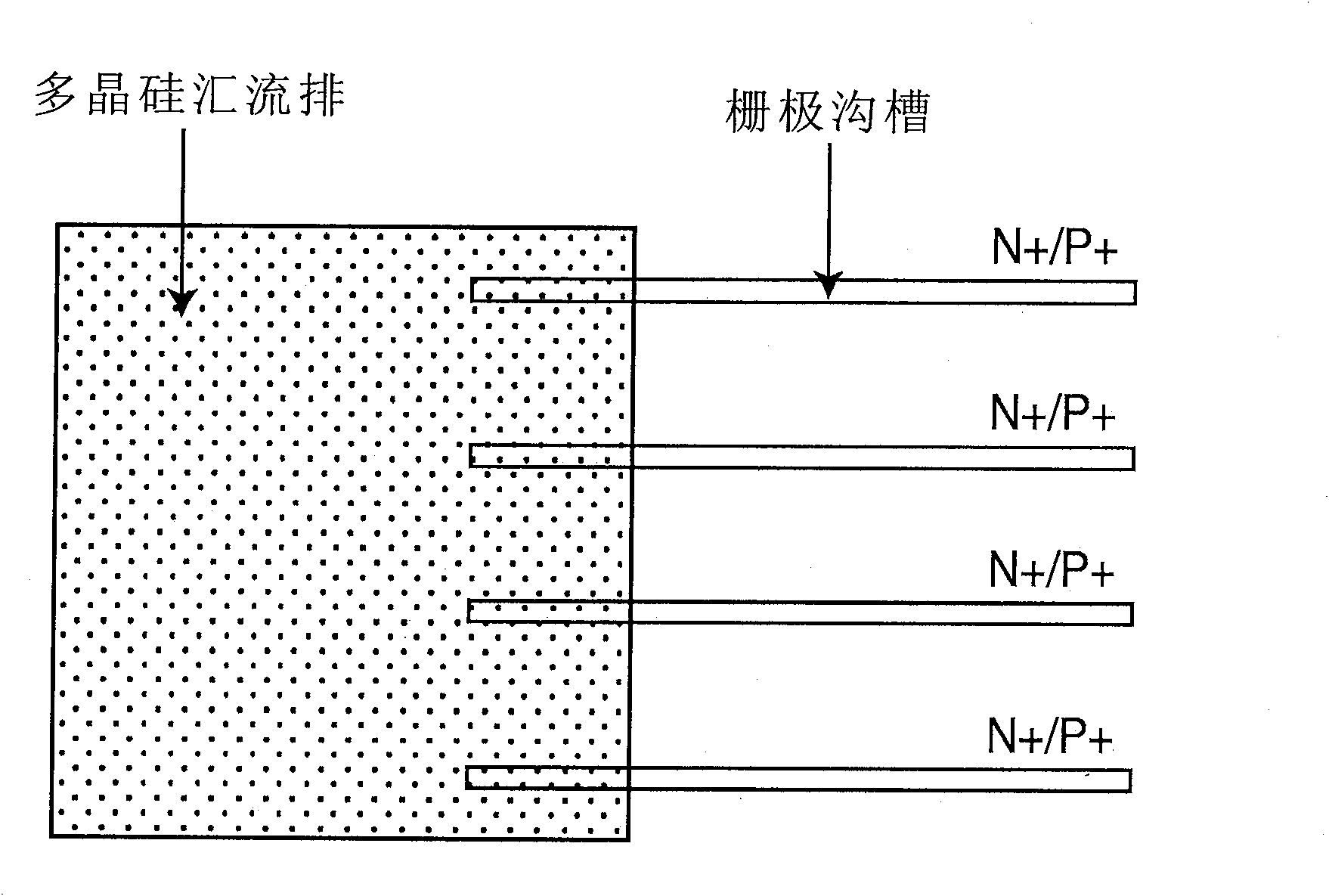

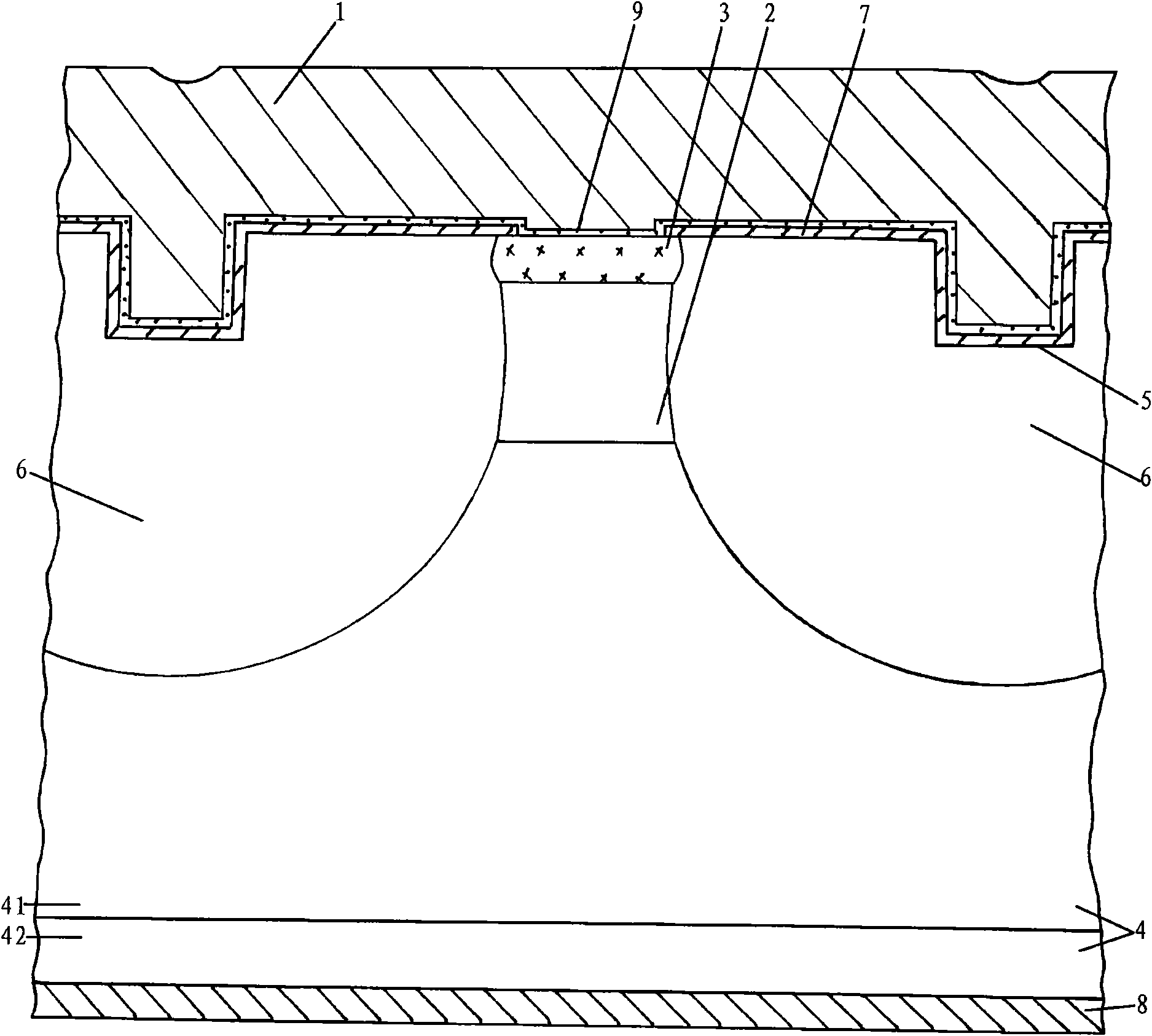

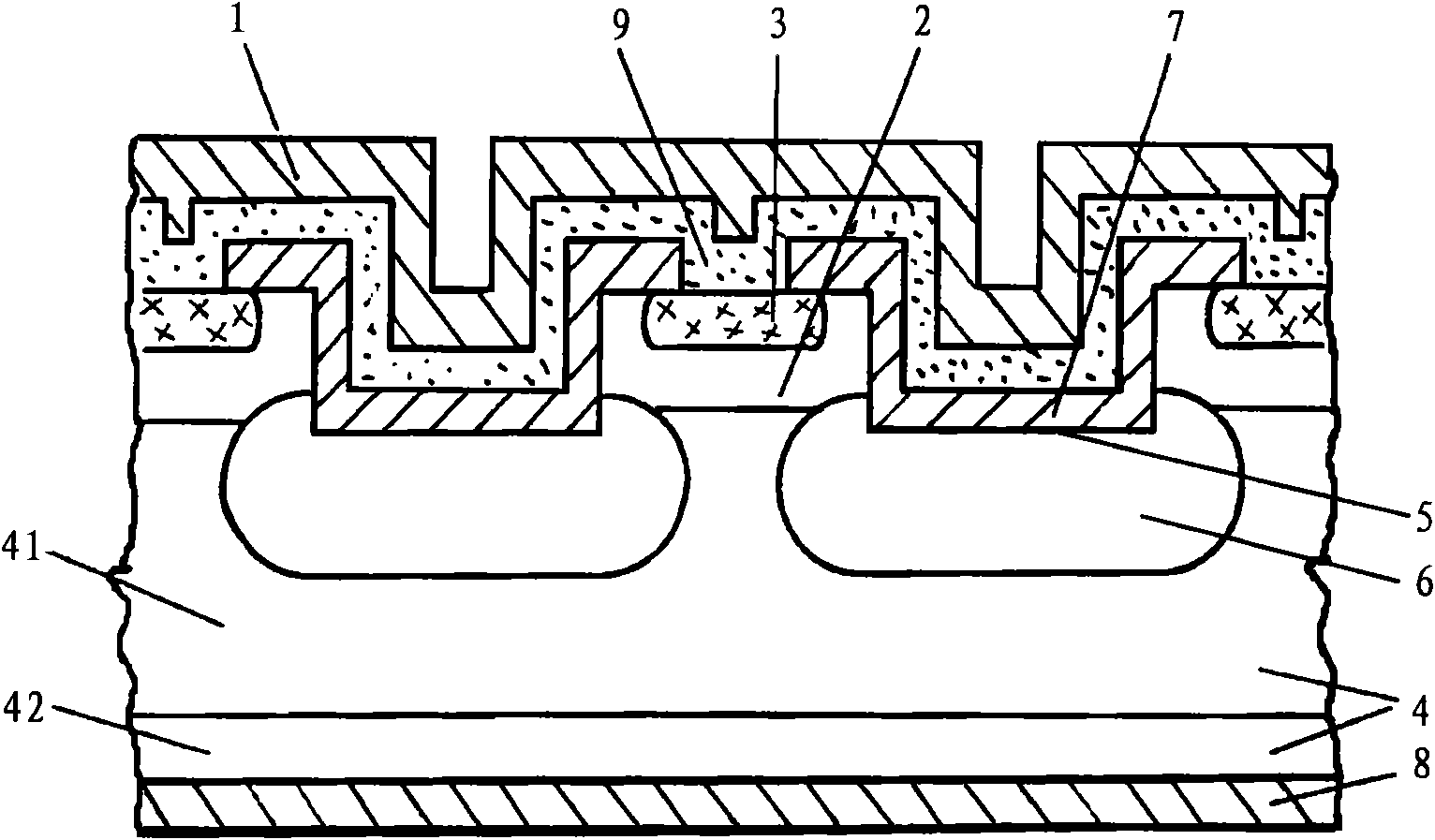

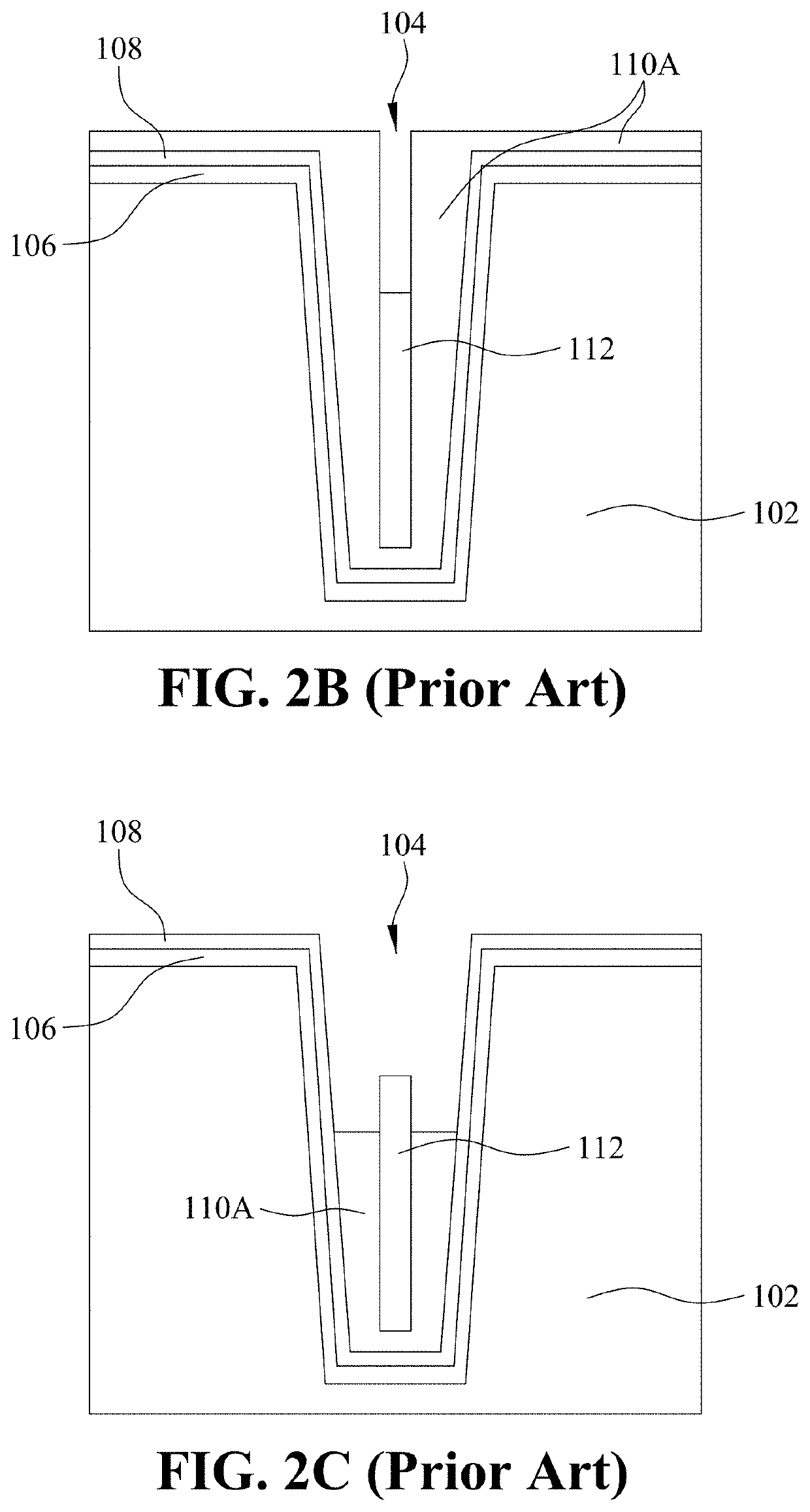

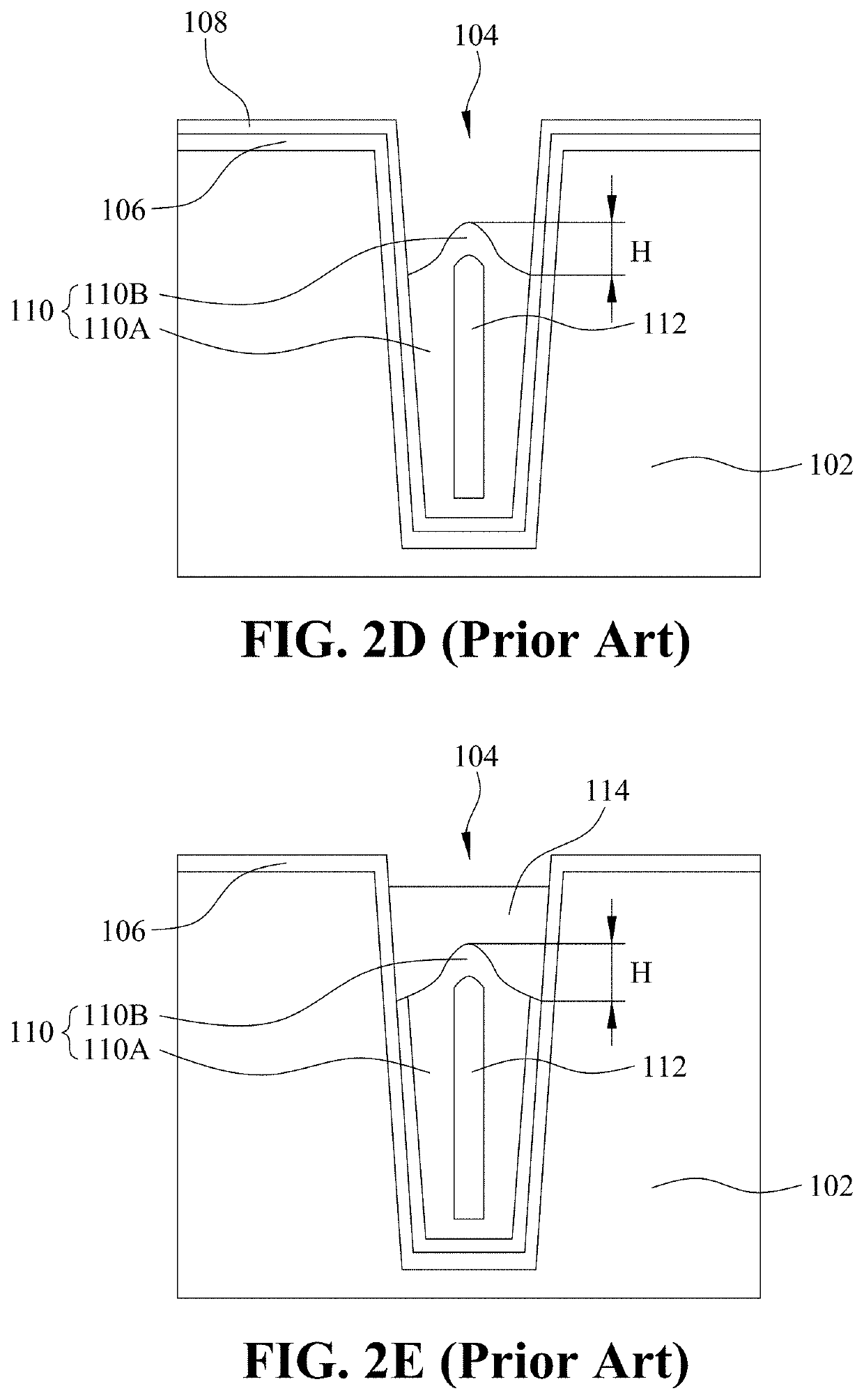

Trench type semiconductor device and fabrication method for the same

ActiveUS8193579B2Reduce resistanceImprove breakdown performanceSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

The trench type semiconductor device includes a gate insulating film placed on the bottom surface and the sidewall surface of the trench formed from the surface of a first base layer; a gate electrode placed on the gate insulating film and fills up into a trench; an interlayer insulating film covering the gate electrode; a second base layer placed on the surface of the first base layer, and is formed more shallowly than the bottom surface of the trench; a source layer placed on the surface of the second base layer; a source electrode connected to the second base layer in the bottom surface of a self-aligned contact trench formed in the second base layer by applying the interlayer insulating film as a mask, and is connected to the source layer in the sidewall surface; a drain layer placed at the back side of the first base layer; and a drain electrode placed at the drain layer, for achieving the minute structure by the self-alignment, reducing the on resistance, and improving the breakdown capability, and providing a fabrication method for the same.

Owner:ROHM CO LTD

Edge termination with improved breakdown voltage

ActiveCN102318045AImprove breakdown performanceImprove breakdown voltageSolid-state devicesSemiconductor/solid-state device manufacturingMOSFETEngineering

A MOSFET switch which has a low surface electric field at an edge termination area, and also has increased breakdown voltage. The MOSFET switch has a new edge termination structure employing an N-P-N sandwich structure. The MOSFET switch also has a polysilicon field plate configuration operative to enhance any spreading of any depletion layer located at an edge of a main PN junction of the N-P-N sandwich structure.

Owner:MAXPOWER SEMICON INC

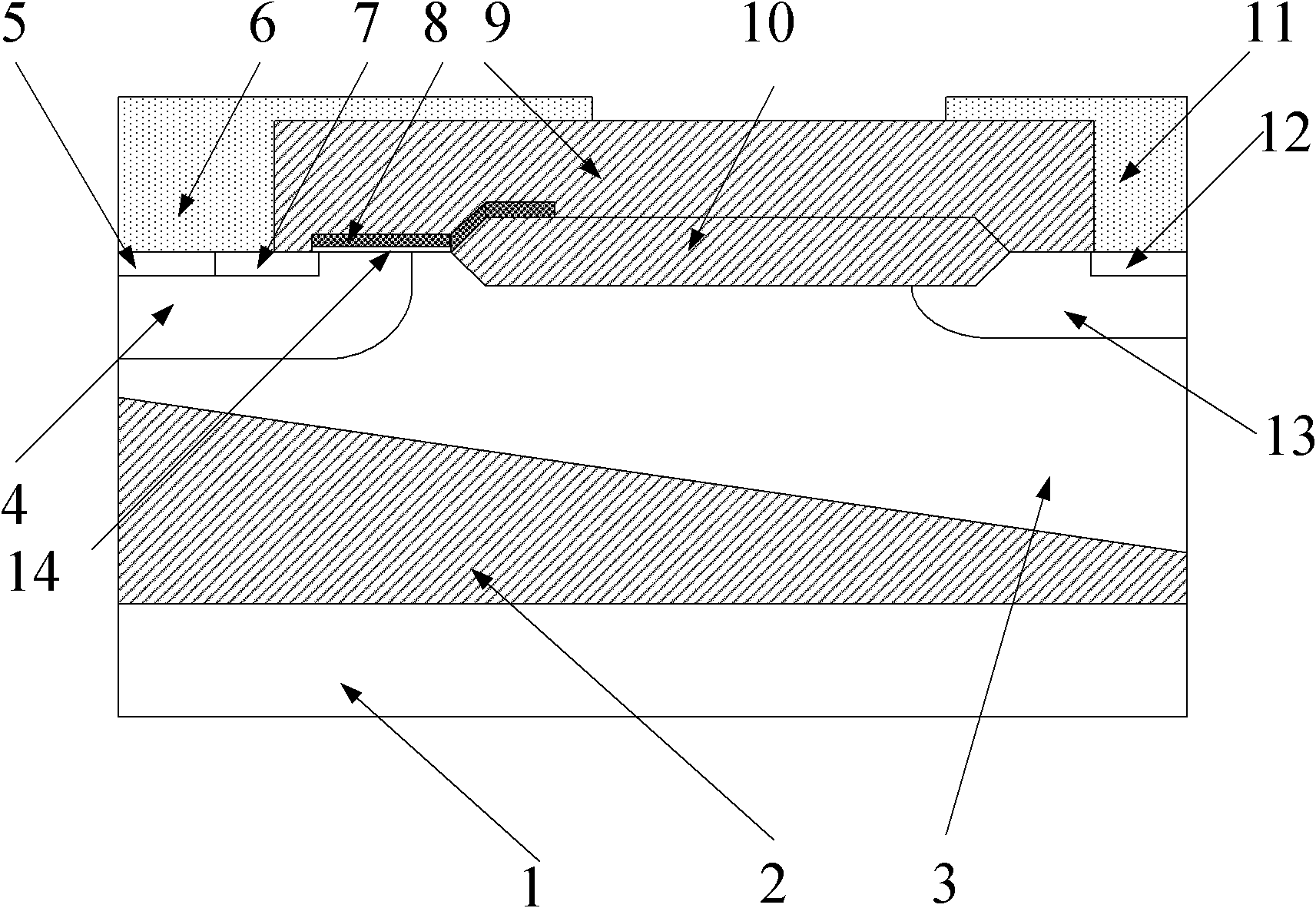

SOI (Silicon on Insulator) variable buried oxide layer thickness device and preparation method thereof

ActiveCN101916784AAchieve linear variable dopingUniform surface electric fieldSolid-state devicesSemiconductor/solid-state device manufacturingOptoelectronicsLayer thickness

The invention relates to an SOI (Silicon on Insulator) technology, which solves the problems of uneven distribution of electric field with both high ends and low middle during breakdown and insufficient utilization of a drift area of a traditional SOILDMOS (Silicon on Insulator Lateral Double Diffused Metal Oxide Semiconductor) device. The invention provides an SOI variable buried oxide layer thickness device and a preparation method thereof. in the technical scheme, the SOI variable buried oxide layer thickness device comprises a source electrode, a drain electrode, a buried oxide layer and n-shaped top SOI impurity material layer, and is characterized in that the thickness of the buried oxide layer is gradually reduced from the source electrode to the drain electrode; and the thickness of the n-shaped top SOI impurity material layer is gradually increased from the source electrode to the drain electrode. The invention has the advantage of largely enhanced breakdown performance, and is suitable for the SOILDMOS device.

Owner:SICHUAN CHANGHONG ELECTRIC CO LTD

Anti-fuse memory cell

ActiveCN105849861AImprove breakdown performanceUniform thicknessSemiconductor/solid-state device detailsSolid-state devicesThin oxideGate oxide

An anti-fuse memory cell having a variable thickness gate oxide. The variable thickness gate oxide is formed by depositing a first oxide over a channel region of the anti-fuse memory cell, removing the first oxide in a thin oxide area of the channel region, and then thermally growing a second oxide in the thin oxide area. The remaining first oxide defines a thick oxide area of the channel region. The second oxide growth occurs under the remaining first oxide, but at a rate less than thermal oxide growth in the thin oxide area. This results in a combined thickness of the first oxide and the second oxide in the thick oxide area being greater than second oxide in the thin oxide area.

Owner:SYNOPSYS INC

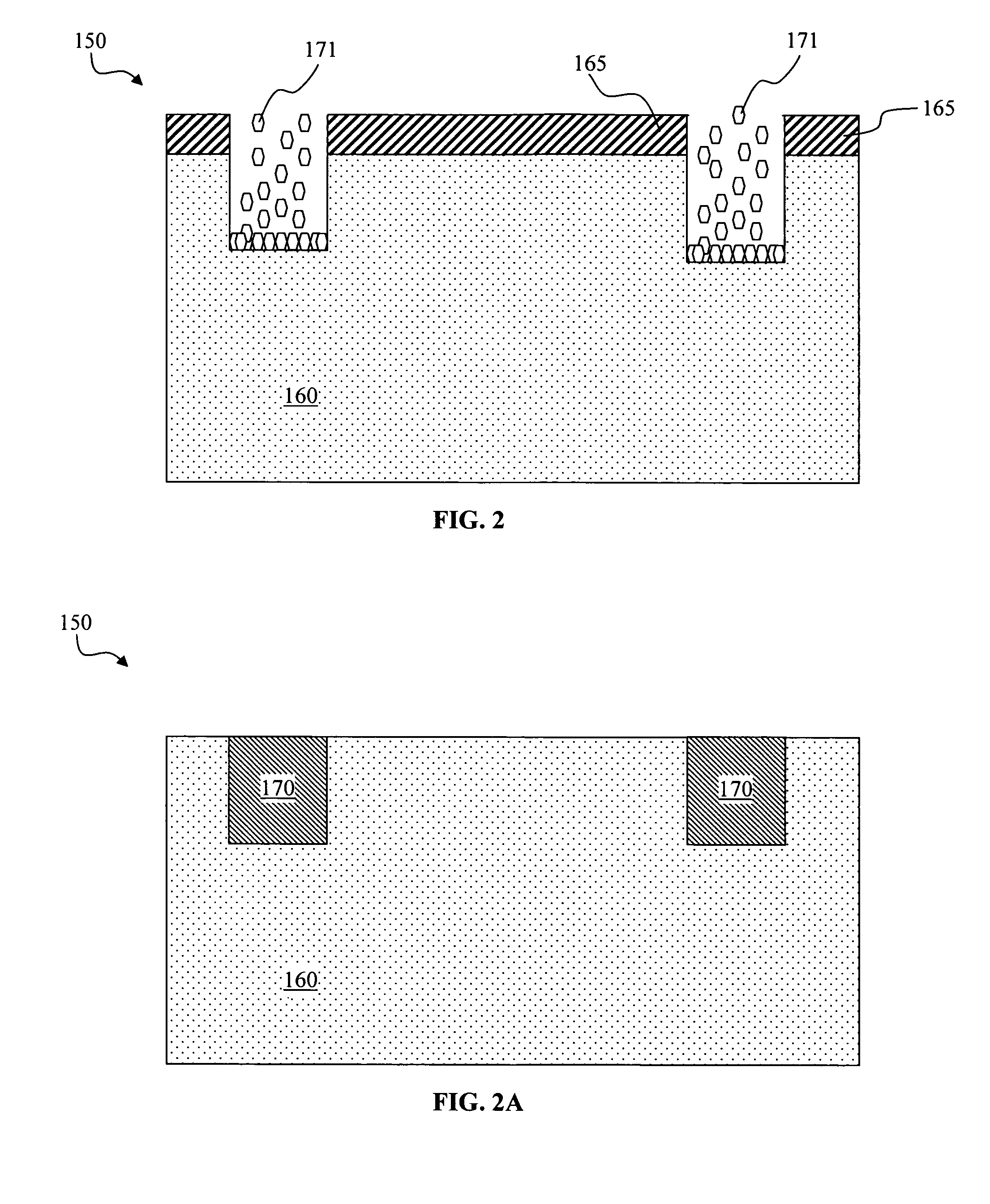

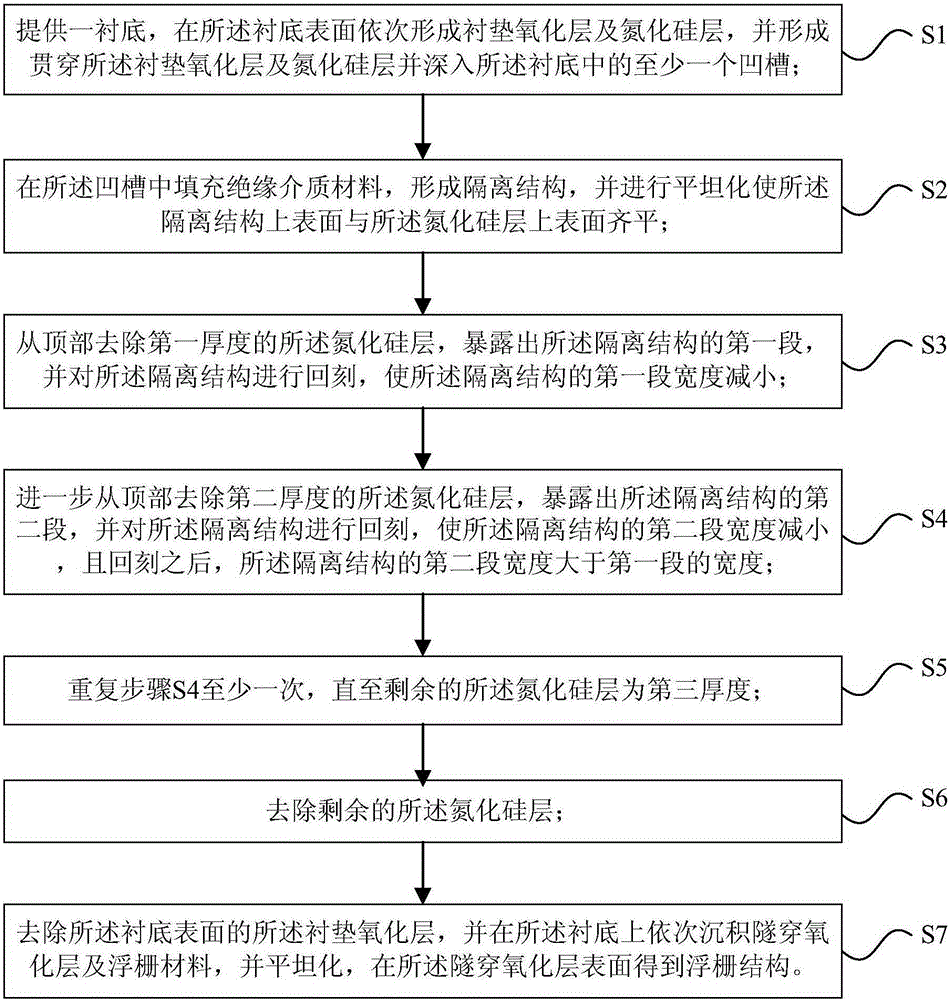

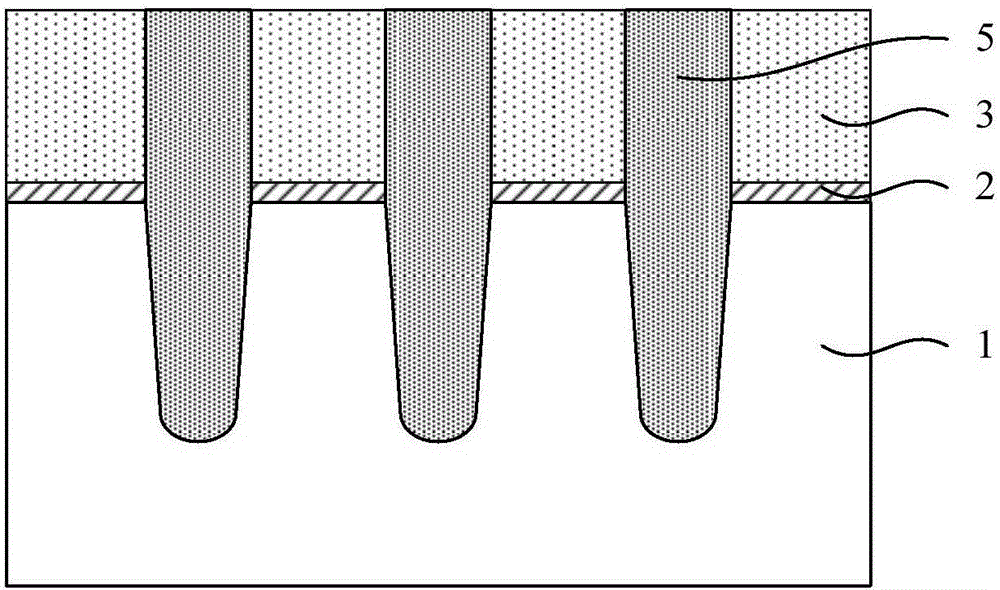

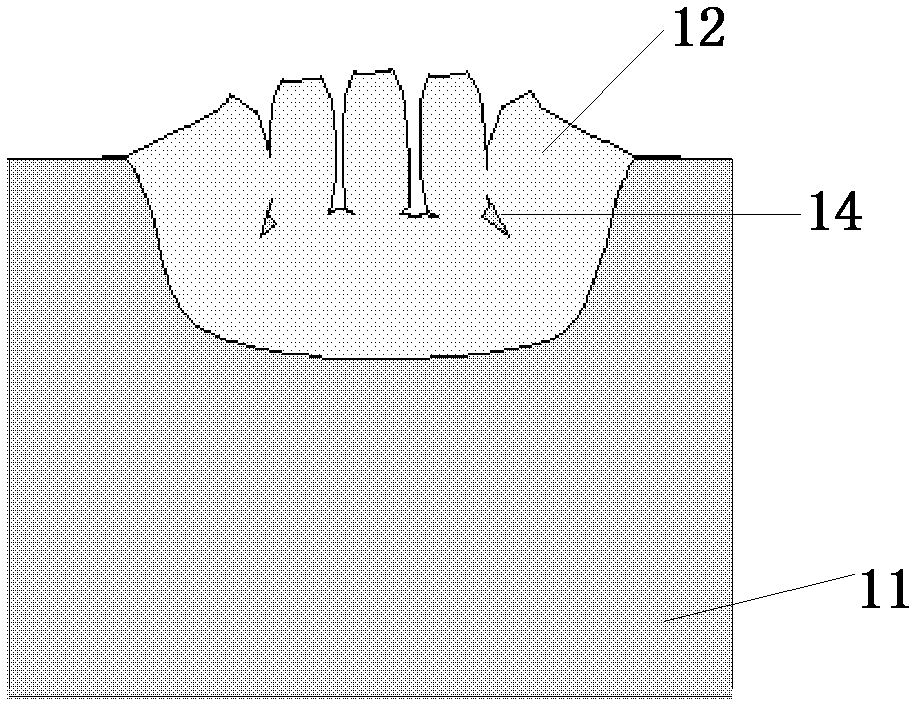

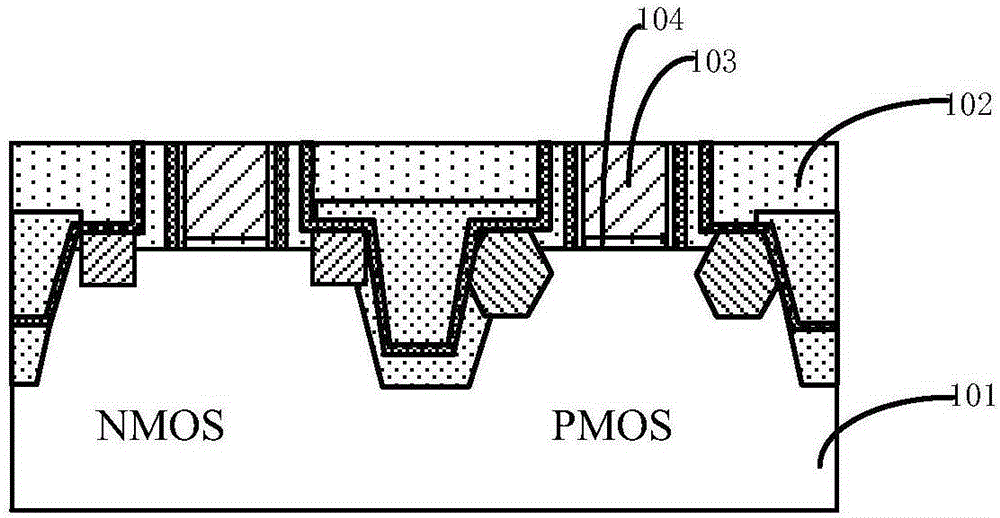

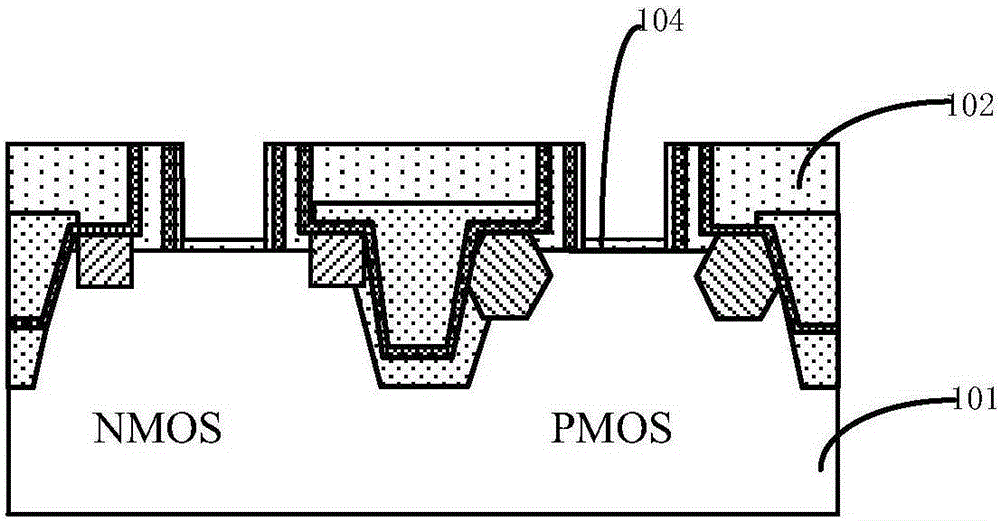

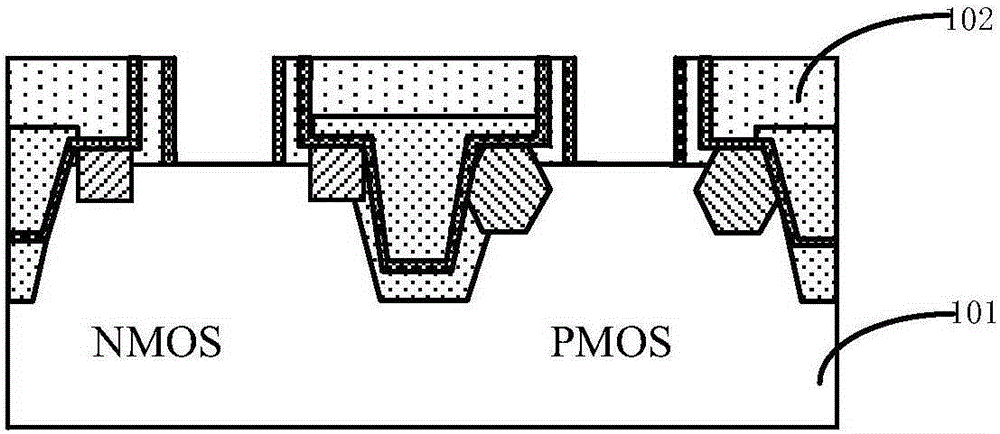

Semiconductor structure manufacturing method

ActiveCN106469730ARegulatory TopographyEasy to fillSolid-state devicesSemiconductor devicesSemiconductor structureEngineering

The invention discloses a semiconductor structure manufacturing method, which comprises the following steps: 1) forming at least one concave groove that penetrates a silicon nitride layer and goes deep into a substrate; 2) forming an isolation structure; 3) removing from the top a first thickness silicon nitride layer so as to expose the first section of the isolation structure; and conducting an etchback to the isolation structure to reduce the width of the first section; 4) further removing a second thickness silicon nitride layer so as to expose the second section of the isolation structure; and conducting an etchback to the isolation structure to reduce the width of the second section; 5) repeating the step 4 at least one time until the remaining silicon nitride layer is provided with a third thickness; 6) removing the remaining silicon nitride layer; and 7) depositing and obtaining a floating gate structure. According to the invention, in the manufacturing process of the floating gate, the floating gate is gradually enlarged to fill the upper opening while the active region CD at the bottom does not have to be enlarged. In this way, it is possible to enlarge the processing window and effectively avoid the appearance of holes in the floating gate. And it is also possible to better regulate the shape and appearance of the floating gate, increase the coupling rate of components and improve the breakdown performance between the active region and the control gate.

Owner:SEMICON MFG INT (SHANGHAI) CORP

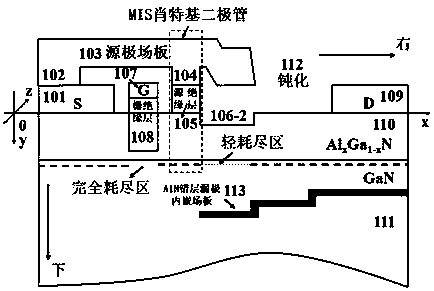

Lateral diffusion eGaN HEMT device integrating reverse diode and embedded drain electrode field plate

ActiveCN110212028AImprove breakdown characteristicsImprove breakdown resistanceSemiconductor devicesLateral diffusionBackward diode

The invention discloses a lateral diffusion eGaN HEMT device integrating a reverse diode and an embedded drain electrode field plate. The device comprises a GaN buffer layer, an AlGaN barrier layer, agate electrode, an under-gate insulating layer, a source electrode, a source electrode extension section, a source electrode field plate, an MIS schottky diode extension section, an MIS schottky diode insulating layer, a p-type GaN or groove, a drain electrode, a passivation layer and an AlN staggered-layer drain electrode embedded field plate, wherein the MIS schottky diode insulating layer is prepared in the middle region, towards the MIS schottky diode extension section and the AlGAN barrier layer surface, of the source electrode field plate; the side, close to the drain electrode, of thediode adopts the p-type GaN or groove, so that the breakdown characteristic of the device is improved; the embedded staggered-layer field plate is adopted below the drain electrode, so that anti-breakdown capability of the drain electrode to the substrate is improved; the design of the staggered layer is suitable for the gradual change distribution of the drain electrode electric field from rightto left, so that the breakdown characteristic of the device is improved; and the source electrode field plate is extended, the gate electrode is wrapped, the MIS schottky diode is formed on the gate drain side, and the diode is made into a block isolation mode, so that the drain electrode current is greatly improved.

Owner:SHANDONG JIANZHU UNIV

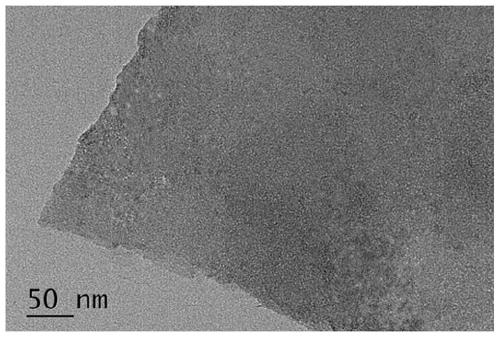

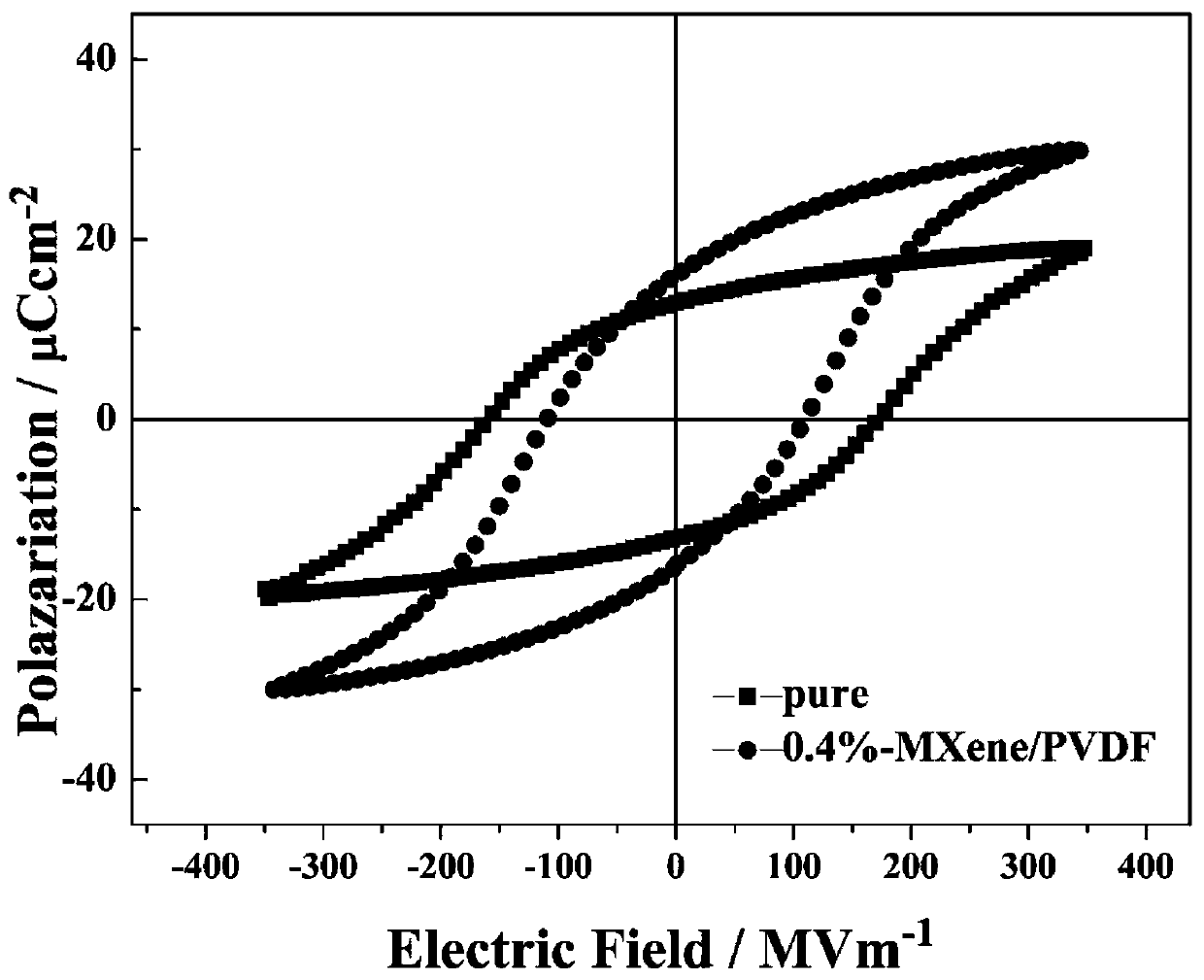

Polymer-based piezoelectric film, and preparation method and application thereof

ActiveCN111363277AExcellent piezoelectric propertiesImprove breakdown performancePiezoelectric/electrostrictive device manufacture/assemblySynthetic resin layered productsPolymer sciencePolyvinylidenefluoride-trifluoroethylene

The invention belongs to the technical field of piezoelectric materials, and particularly relates to a polymer-based piezoelectric film and a preparation method and application thereof. The polymer-based piezoelectric film provided by the invention comprises a polymer and a doped two-dimensional layered structure compound, wherein a mass ratio of the polymer to the two-dimensional layered structure compound is 100: (0.1-2); the polymer is one or more selected from a group consisting of polyvinylidene fluoride, polyvinylidene fluoride-hexafluoropropylene and polyvinylidene fluoride-trifluoroethylene; the chemical composition of the two-dimensional layered structure compound is M<n+1>X<n>T<y>, n is equal to 1, 2 or 3, M is a transition metal element, T is a -O, -OH or -F functional group, and X is a carbon element or a nitrogen element. According to the polymer-based piezoelectric film provided by the invention, the problem that the piezoelectric property of a traditional PVDF material is insufficient is solved; and experimental effect shows that the polymer-based piezoelectric film provided by the invention has good flexibility and excellent ferroelectric property and piezoelectricproperty.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

Gate associated transistor of trough arsenic-doped polysilicon structure

InactiveCN101552285AImprove breakdown performanceReduce failure rateSemiconductor devicesHigh resistivityPrice ratio

The invention relates to a gate associated transistor of a trough arsenic-doped polysilicon structure, a plurality of N-type high doping concentration emitting regions are arranged on the upper surface of a silicon substrate wafer, the lower layer of the silicon substrate wafer is an N-type low resistivity layer, the upper layer thereof is an N-type high resistivity layer, and a doped polysilicon layer is connected on tops of the emitting regions. The gate associated transistor is characterized in that an impurity source for doping the polysilicon is arsenic, and the thickness of the doped polysilicon is 0.01-0.30 mu m. The gate associated transistor has the advantages that the anti-avalanche breakdown ability is enhanced, the failure rate in applications is reduced by two orders of magnitude and the gate associated transistor has significant effects of low cost and high performance-price ratio.

Owner:HANGZHOU UG MIN SEMICON TECH CO LTD

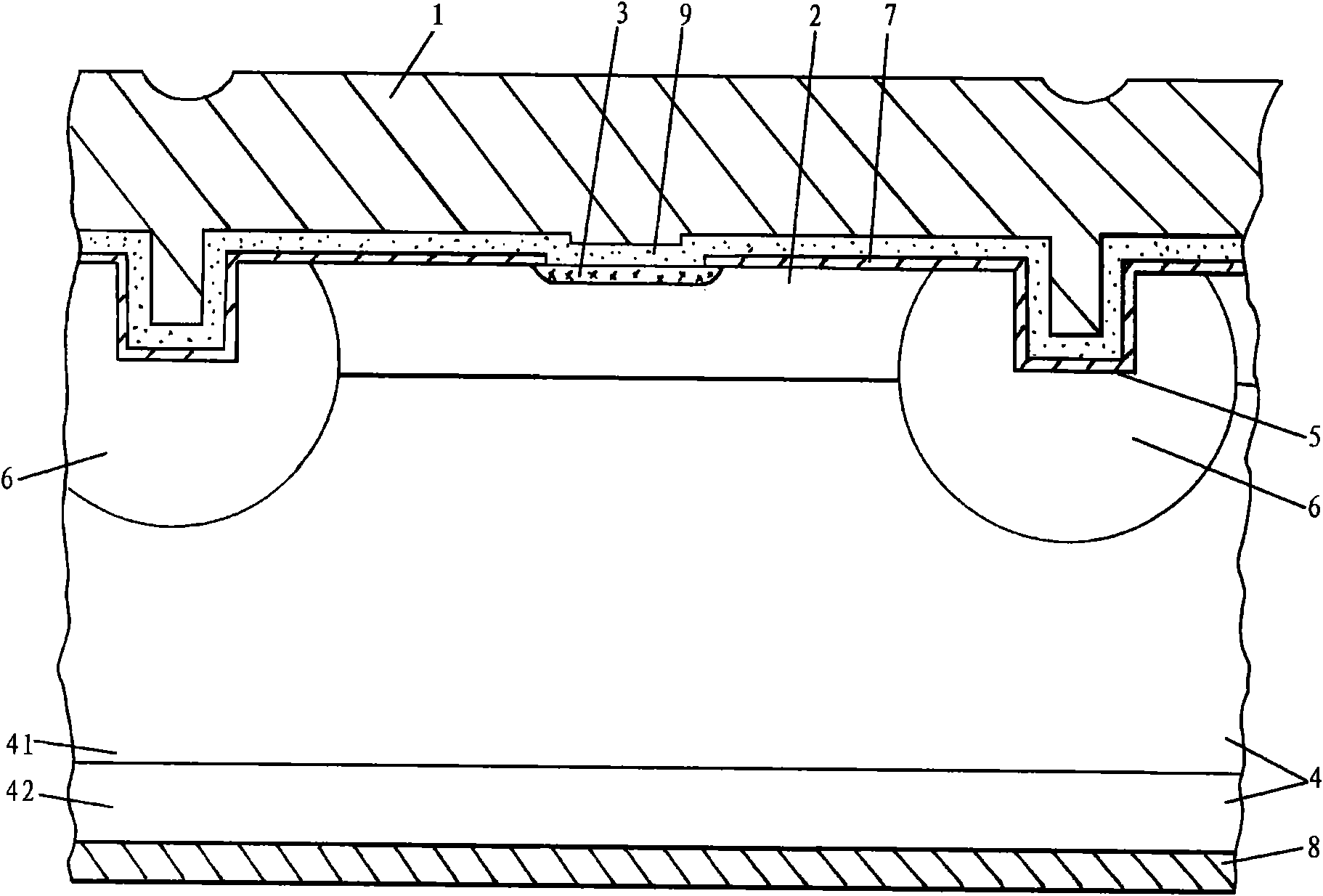

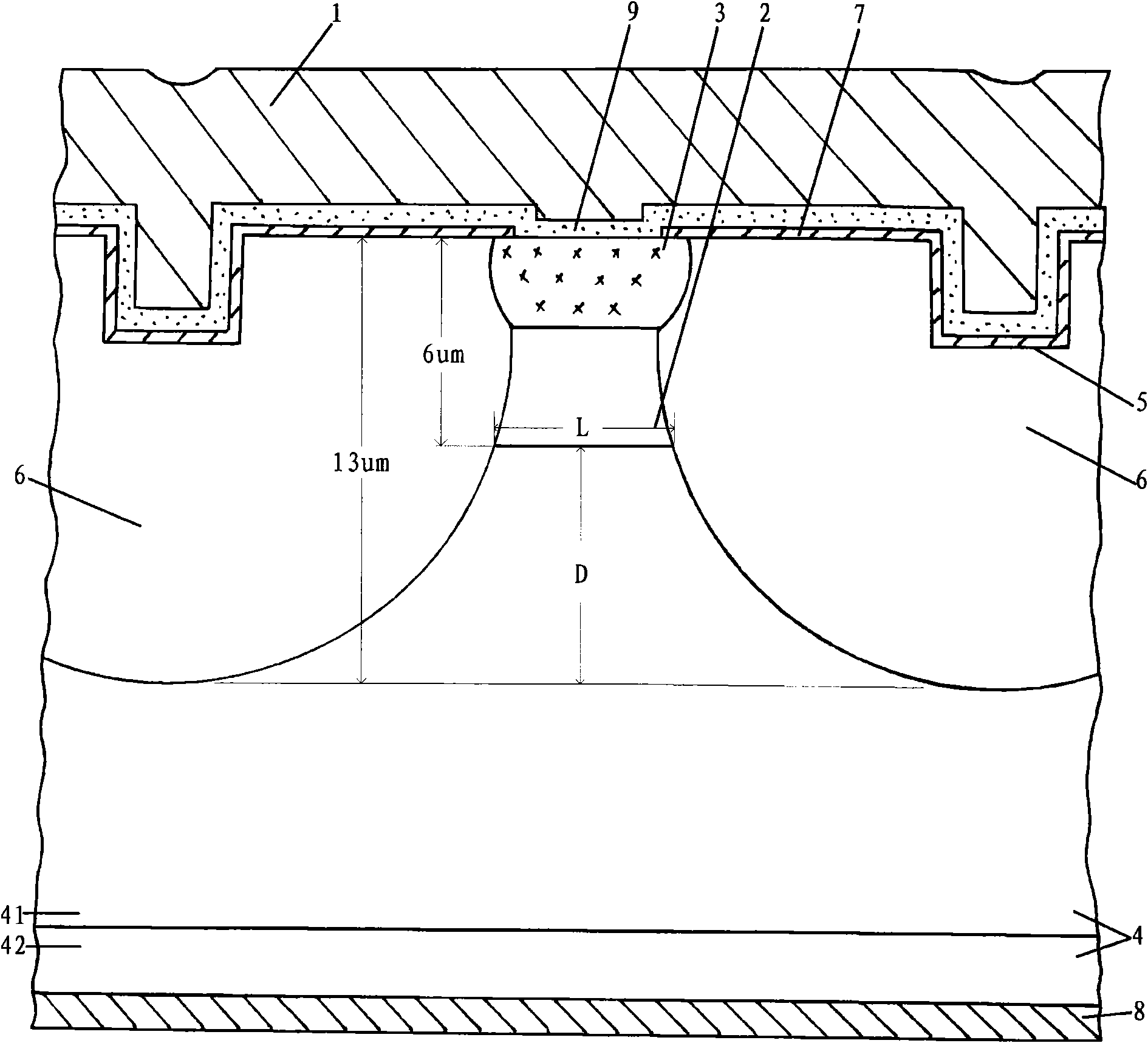

Gate associated transistor with grooved gate polysilicon structure

InactiveCN101527317AImprove breakdown performanceReduce failure rateTransistorFailure rateHigh resistivity

The invention relates to a gate associated transistor with a grooved gate polysilicon structure, wherein the upper surface of a silicon substrate slice taking a first conductivity type low-resistivity layer as a lower layer and a first conductivity type high-resistivity layer as an upper layer is provided with a plurality of first conductivity type emitter regions with high doping concentration, and the emitter regions are connected with doped polysilicon layers. The gate associated transistor is characterized in that the junction depths of the emitter regions are more than 1mu m, and the junction depths of base regions are between 4.5 and 8mu m; the junction depths of grooved gate regions are between 6.5 and 12mu m; and the ratio of a distance L between junctures of the two adjacent grooved gate regions with high doping concentration and the base regions to the difference D of the distance from the bottoms of the grooved gate regions to the upper surface of the silicon substrate slice and the junction depths of the base regions is that L / D is less than 1.8. The gate associated transistor has the advantages that the ability for resisting avalanche breakdown is strengthened, the failure rate in application is reduced by 1 to 2 orders of magnitude; and the gate associated transistor has remarkable functions of low cost and high performance-price ratio.

Owner:李思敏

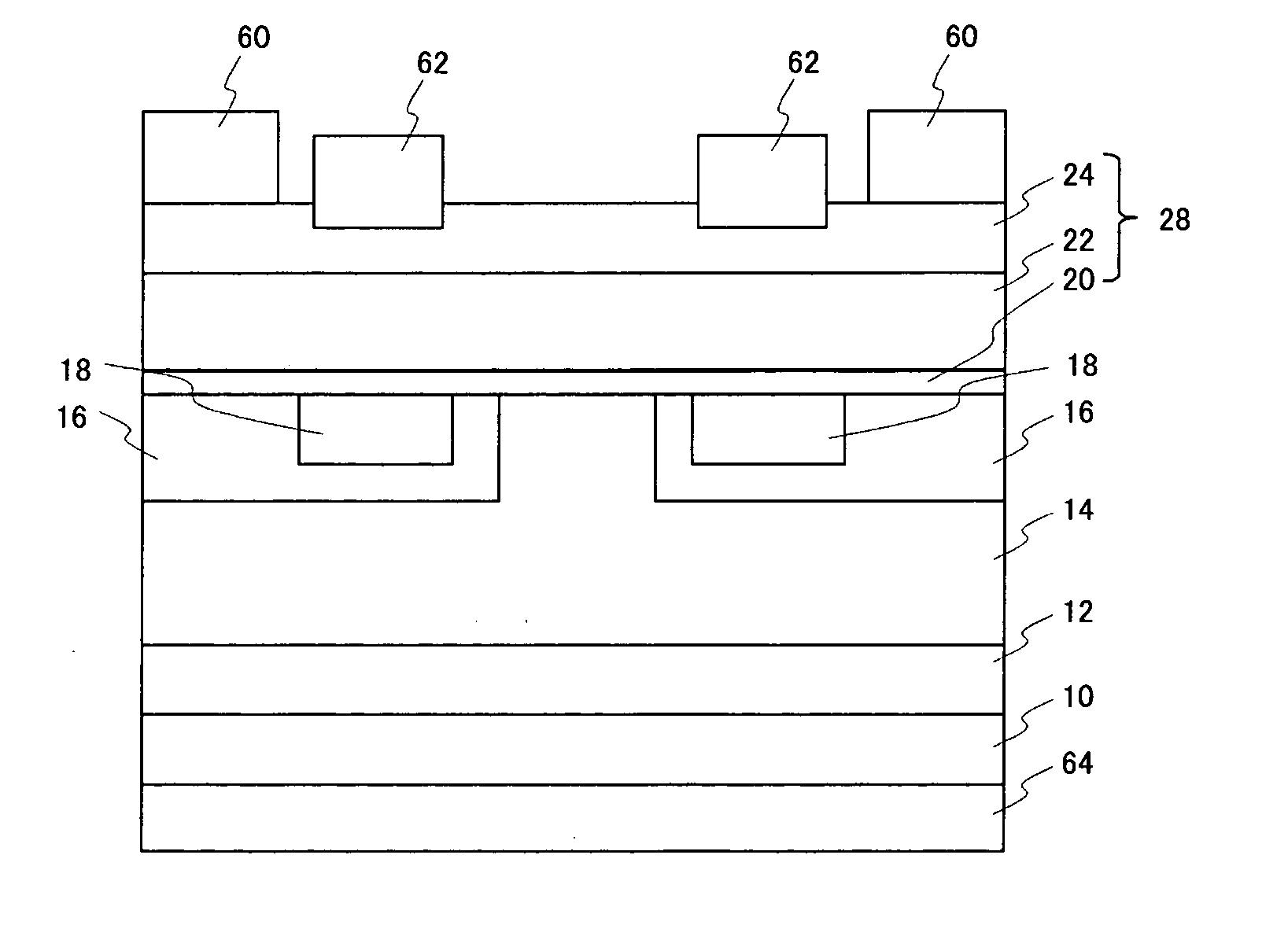

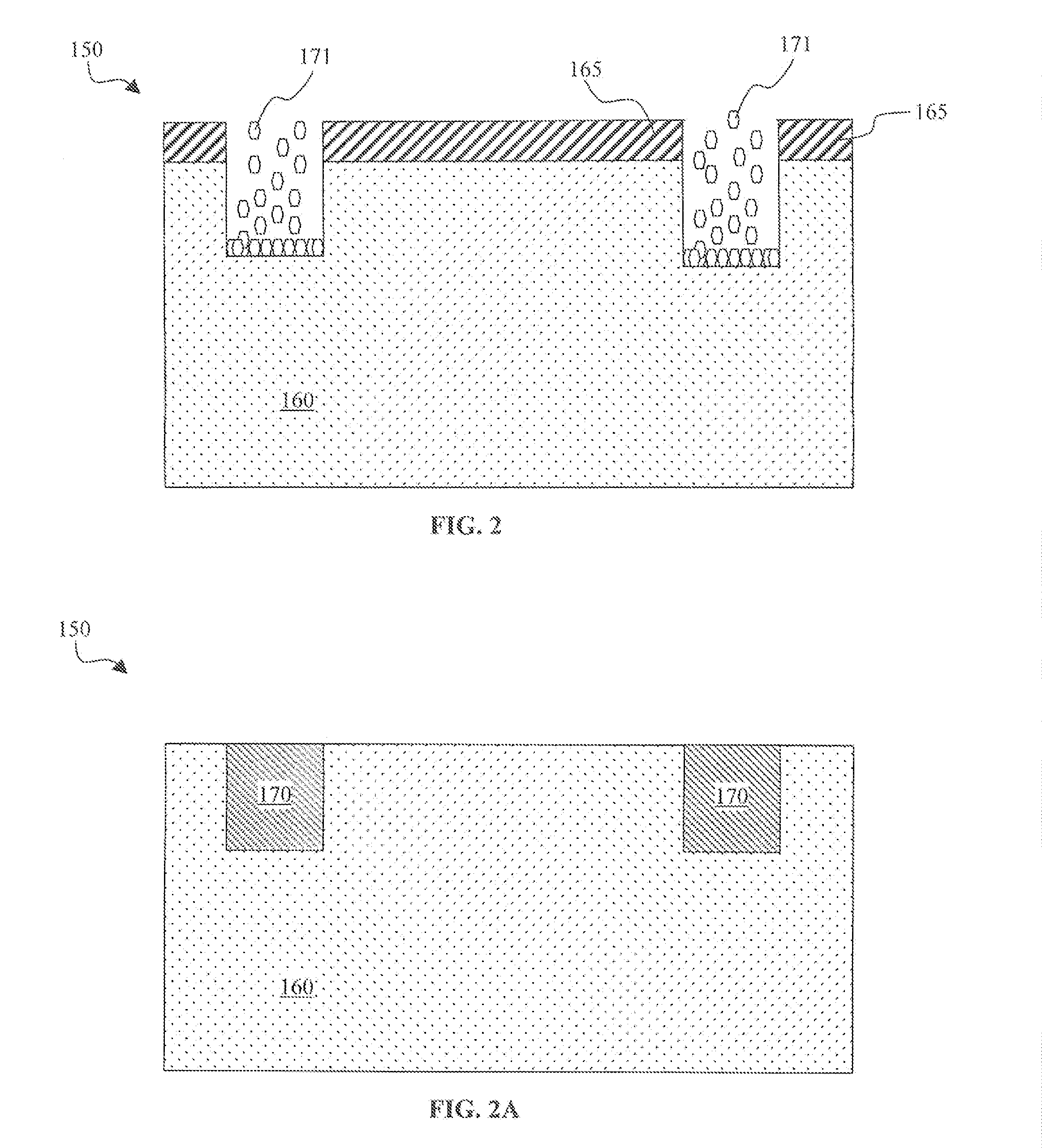

High Electron Mobility Transistor with Periodically Carbon Doped Gallium Nitride

ActiveUS20160099345A1Improve breakdown performanceImprove structural qualityTransistorSemiconductor/solid-state device manufacturingCarbon dopedGallium nitride

A method for forming a high electron mobility transistor (HEMT) device with a plurality of alternating layers of one or more undoped gallium nitride (GaN) layers and one or more carbon doped gallium nitride layers (c-GaN), and an HEMT device formed by the method is disclosed. In one embodiment, the method includes forming a channel layer stack on a substrate, the channel layer stack having a plurality of alternating layers of one or more undoped gallium nitride (GaN) layers and one or more carbon doped gallium nitride layers (c-GaN). The method further includes forming a barrier layer on the channel layer stack. In one embodiment, the channel layer stack is formed by growing each of the one or more undoped gallium nitride (GaN) layers in growth conditions that suppress the incorporation of carbon in gallium nitride, and growing each of the one or more carbon doped gallium nitride (c-GaN) layers in growth conditions that promote the incorporation of carbon in gallium nitride.

Owner:KK TOSHIBA

Super-low dielectric constant (k) material thin film and preparation method thereof

InactiveCN102683275AImprove leakage performanceImprove breakdown performanceSemiconductor/solid-state device detailsSolid-state devicesYoung's modulusSolvent

The invention belongs to the technical field of super-large-scale integrated circuits and particularly relates to a super-low k material thin film and a preparation method thereof. The preparation method comprises the following steps of: preparing a sol solution by taking 1,2-bi(triethoxy silicon substrate) ethane (BTEE) as a precursor and adding surfactant P123, HCl, ethanol and deionized water; and then obtaining the super-low k material thin film by adopting a spin coating technology and carrying out post annealing treatment. By virtue of the control on the proportions of the precursor, the surfactant, catalyst and solvent, as well as the control on spin coating film-forming conditions and post treatment conditions, the super-low k material SiCOH thin film, which has the characteristics that the k value is 2.1-2.5, the leakage current density under electric field intensity of 1MV / cm is 1.5*10<-6> to 3.4*10<-9> A / cm<2>, and the Young modulus is 21.05-24.15 Gpa, is obtained.

Owner:FUDAN UNIV

Semiconductor device and fabrication method of the same

InactiveUS7723751B2Improve breakdown performanceLower on-resistanceTransistorSemiconductor/solid-state device manufacturingSemiconductorSemiconductor device

A semiconductor device includes a substrate, a SiC drift layer formed above the substrate, a GaN-based semiconductor layer that is formed on the SiC drift layer and includes a channel layer, a source electrode and a gate electrode formed on the GaN-based semiconductor layer, current blocking regions formed in portions of the SiC drift layer and located below the source and gate electrodes, and a drain electrode formed on a surface that opposes the GaN-based semiconductor layer across the SiC layer.

Owner:SUMITOMO ELECTRIC DEVICE INNOVATIONS

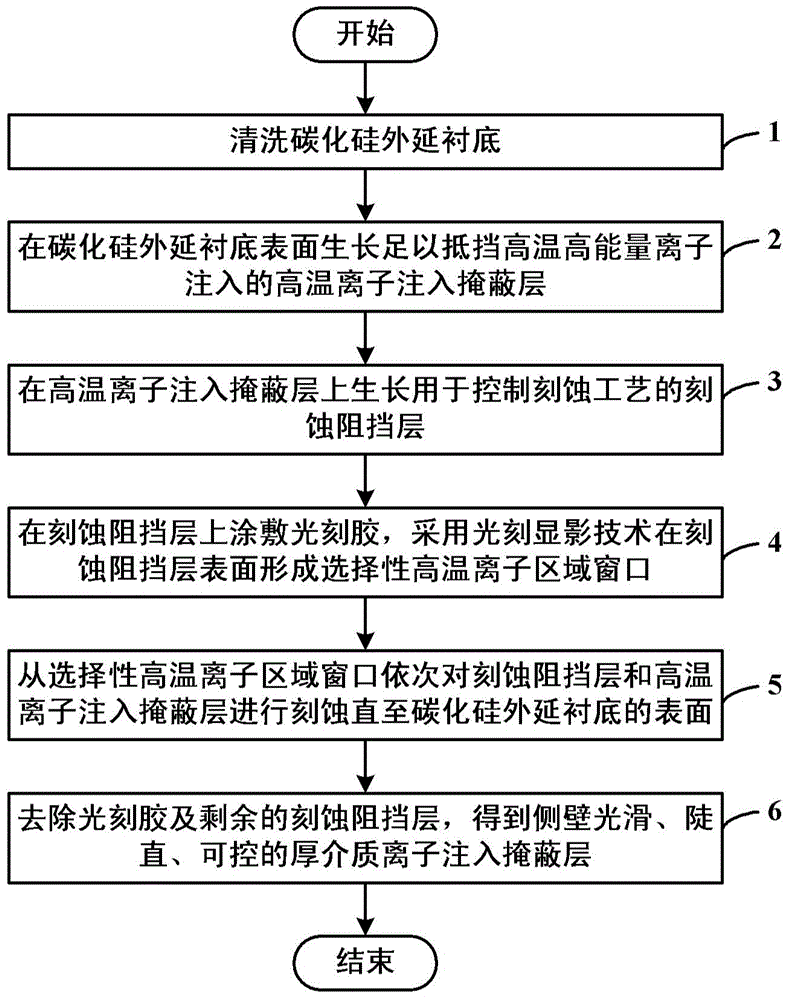

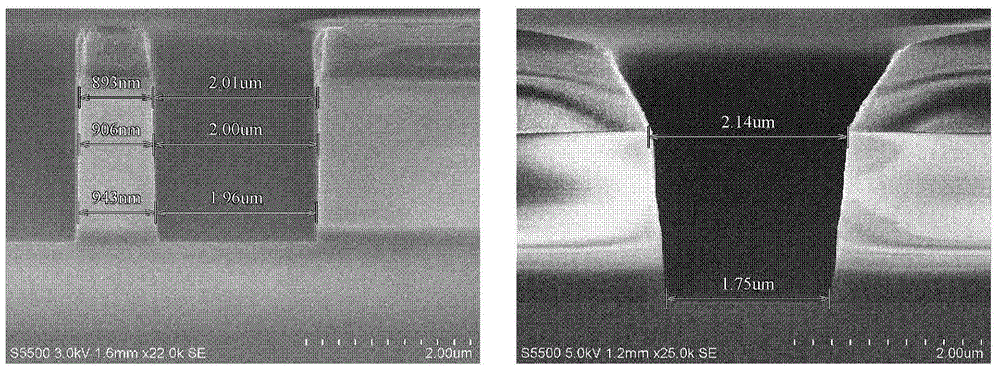

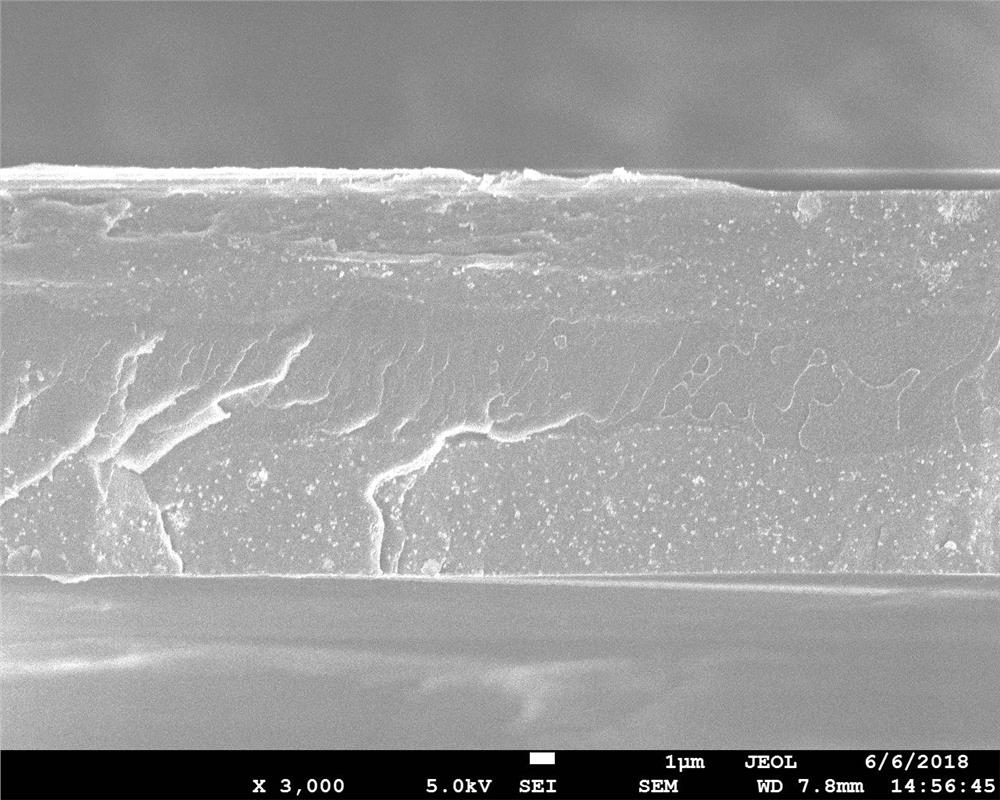

Method for accurately controlling steepness when silicon carbide high-temperature ions are injected into mask

ActiveCN103560078ASatisfy injection requirementsPerformance is not affectedSemiconductor/solid-state device manufacturingHigh energyOptoelectronics

The invention discloses a method for accurately controlling steepness when silicon carbide high-temperature ions are injected into a mask. The method comprises the steps that a silicon carbide epitaxial substrate is cleaned; a high-temperature ion injection masking layer capable of sufficiently resisting against the injected high-temperature and high-energy ions grows on the surface of the silicon carbide epitaxial substrate; an etching resisting layer used for controlling an etching process grows on the high-temperature ion injection masking layer; photoresist coats the etching resisting layer, and a selective high-temperature ion area window is formed in the surface of the etching resisting layer by adopting a photoetching developing technology, etching is sequentially carried out on the etching resisting layer and the high-temperature ion injection masking layer from the selective high-temperature ion area window to the surface of the silicon carbide epitaxial substrate; the photoresist and the unnecessary etching resisting layer are removed to obtain the steep and controllable thick-medium ion injection masking layer with the smooth lateral wall. By means of the method, angle control over an etching surface is carried out accurately, the steep thick-medium ion injection masking layer with the smooth lateral wall is obtained, and good uniformity and strong controllability of the selective ion injection area are guaranteed.

Owner:江苏中科汉韵半导体有限公司

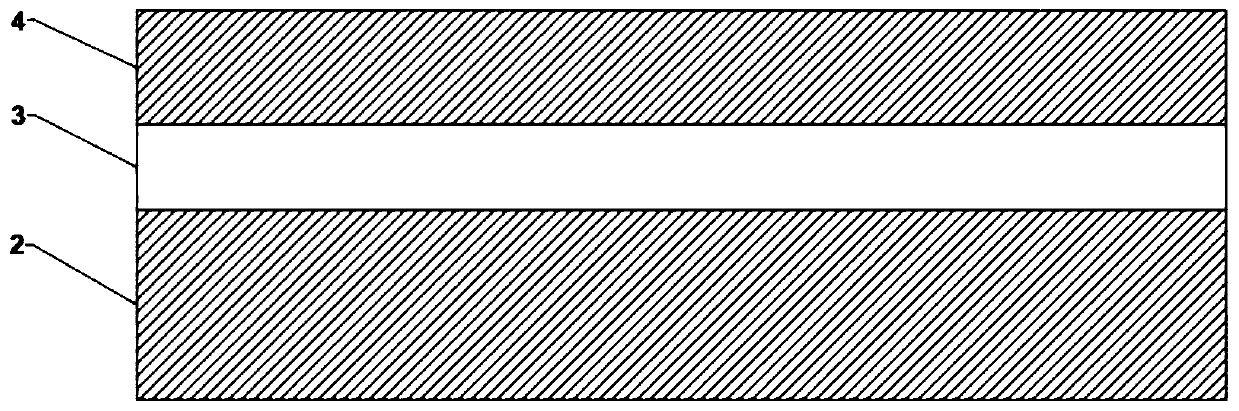

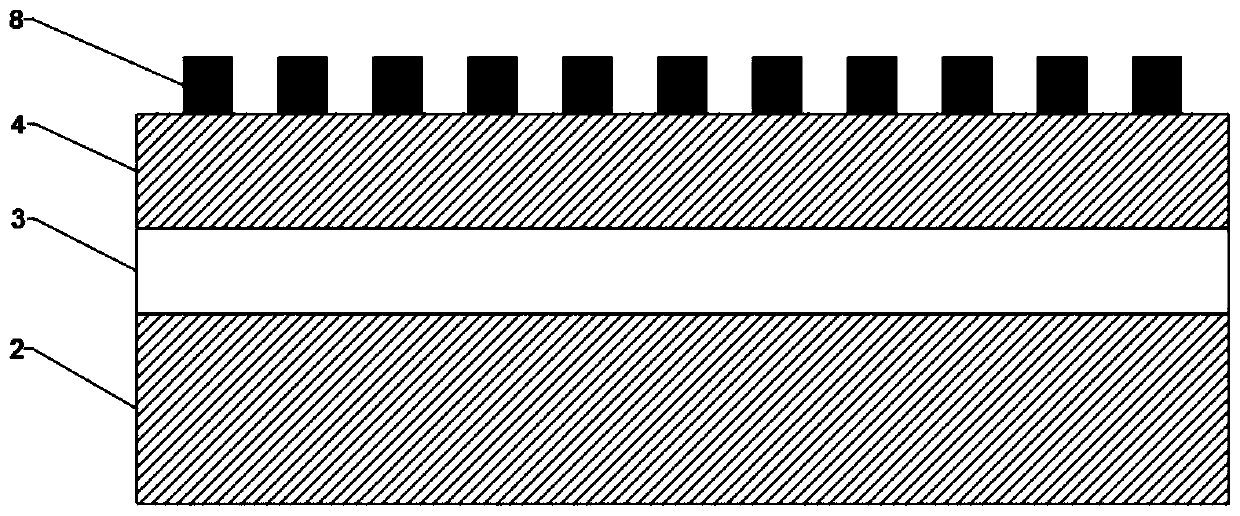

Method for preparing local oxidization termination ring of semiconductor device

ActiveCN102208334AImprove breakdown performanceSemiconductor/solid-state device manufacturingSemiconductorBreakdown voltage

The invention relates to a method for preparing a local oxidization termination ring of a semiconductor device, which comprises the following steps of: forming a pad oxide layer and a silicon nitride layer in an edge zone of the semiconductor device on a silicon substrate; etching the pad oxide layer, the silicon nitride layer and the silicon substrate to form a plurality of grooves; carrying out local oxidation on silicon in the grooves to form a field oxide layer; and removing the pad oxide layer and the silicon nitride layer. The local oxide termination ring of the semiconductor device, which is prepared by adopting the method, has high breakdown voltage and can well improve the breakdown property of the semiconductor device.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Gallium nitride semiconductor device with improved termination scheme

This invention discloses a gallium nitride based semiconductor power device disposed in a semiconductor substrate. The power device comprises a termination area disposed at a peripheral area of the semiconductor power device comprises a termination structure having at least a guard ring disposed in a trench filled with doped gallium-based epitaxial layer therein.

Owner:ALPHA & OMEGA SEMICON INC

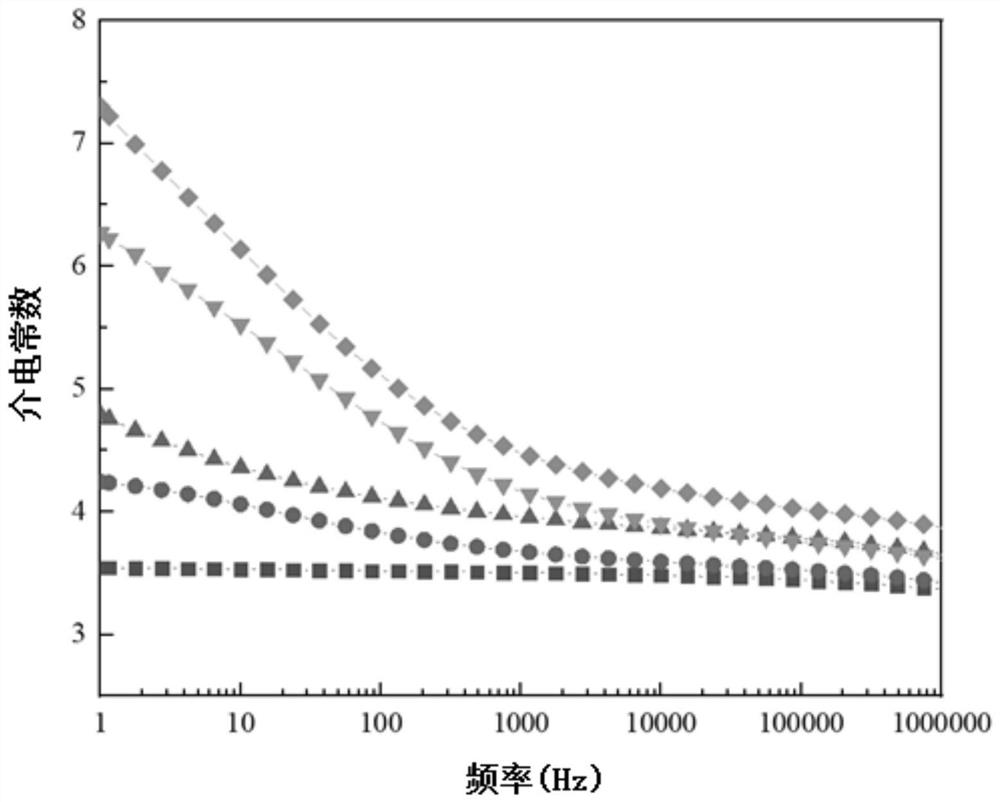

Dielectric composite material and preparation method thereof

InactiveCN108570201AHigh dielectric constantBreakdown field strengthElectro-spinningMonocomponent halogenated hydrocarbon artificial filamentDispersityHexafluoropropylene

The invention relates to a dielectric composite material and a preparation method thereof. The preparation method is characterized by comprising the following steps: carrying out hydroxylating treatment on the surfaces of barium titanate particles, then adding fluorine-containing monomers to initiate polymerization, and obtaining modified barium titanate with a core-shell structure; then using themodified barium titanate and a vinylidene fluoride-hexafluoropropylene copolymer to prepare and obtain an electrostatic spinning solvent, and then utilizing an electrostatic spinning process to obtain the dielectric composite material. The dielectric composite material and the preparation method have the beneficial effects that the barium titanate particles have a high dielectric constant, the vinylidene fluoride-hexafluoropropylene copolymer has a good breakdown property; by introduction of the fluorine-containing monomers, the monomer molecular chains have a certain quantity of fluorine atoms and are similar to a matrix polymer PVDF-HFP (Polyvinylidene Fluoride-Hexafluoropropylene) respectively, and the surfaces of the particles are coated with the monomers, so that the effect of mild transition is achieved, the compatibility between the particles and the matrix can be improved, further the particles have good dispersity, and the dielectric composite material has a high dielectric constant, high breakdown field strength and low dielectric loss.

Owner:RESEARCH INSTITUTE OF TSINGHUA UNIVERSITY IN SHENZHEN

Junction barrier Schottky diode with a floating field ring terminal structure and a preparation method thereof

InactiveCN110364575AImprove featuresImprove leakage performanceSemiconductor/solid-state device manufacturingDiodeOhmic contactSchottky diode

The invention provides a junction barrier Schottky diode with a floating field ring terminal structure and a preparation method thereof, and belongs to the technical field of semiconductors. The diodecomprises a ohmic contact metal cathode, a substrate, a first epitaxial layer, a second epitaxial layer, a comb-shaped p region, a Schottky contact metal anode and an insulating layer from the bottomup, wherein the comb-shaped p region includes a plurality of PN junction p regions arranged at intervals and a plurality of floating field rings arranged at intervals on two sides of the outer side PN junction p regions. The invention further provides a preparation method of the junction barrier Schottky diode with the floating field ring terminal structure. The diode adjusts the electric field distribution through the comb-shaped PN junction structure, avoids the concentration of the electric field, disperses the electric field concentrated at the edge of the P-type region among a pluralityof field rings and reduces the maximum value of the electric field. In addition, the appropriate field ring width and gap are selected, and the electric field concentrated at the outmost field ring can be dispersed among the field rings, thereby avoiding the device breakdown caused by the excessively high local electric field.

Owner:CHANGCHUN INST OF OPTICS FINE MECHANICS & PHYSICS CHINESE ACAD OF SCI

Semiconductor device, preparation method thereof and electronic device

ActiveCN106601619AImprove performanceImprove yieldSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceOxygen vacancy

The invention relates to a semiconductor device, a preparation method thereof and an electronic device. The method comprises the steps that S1) a semiconductor substrate is provided, fins and virtual grid oxide layers and virtual grids surrounding the fins are formed on the semiconductor substrate, and interlayer dielectric layers which fill gaps between the adjacent virtual grids are also formed on the semiconductor substrate; S2) the virtual grids and the virtual grid oxide layers are removed to form virtual openings and expose the semiconductor substrate; S3) the exposed semiconductor substrate is oxidized chemically to form an interface layer; S4) a high k dielectric layer and a coverage layer are formed on the interlayer dielectric layers, the surface of the virtual openings and the interface layer; S5) low-temperature annealing is carried out in the oxygen-containing atmosphere to carry out passivation on oxygen vacancies in the interface layer; S6) a barrier layer is formed on the coverage layer; and S7) a high-temperature annealing technology is executed to make the interface layer compact.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

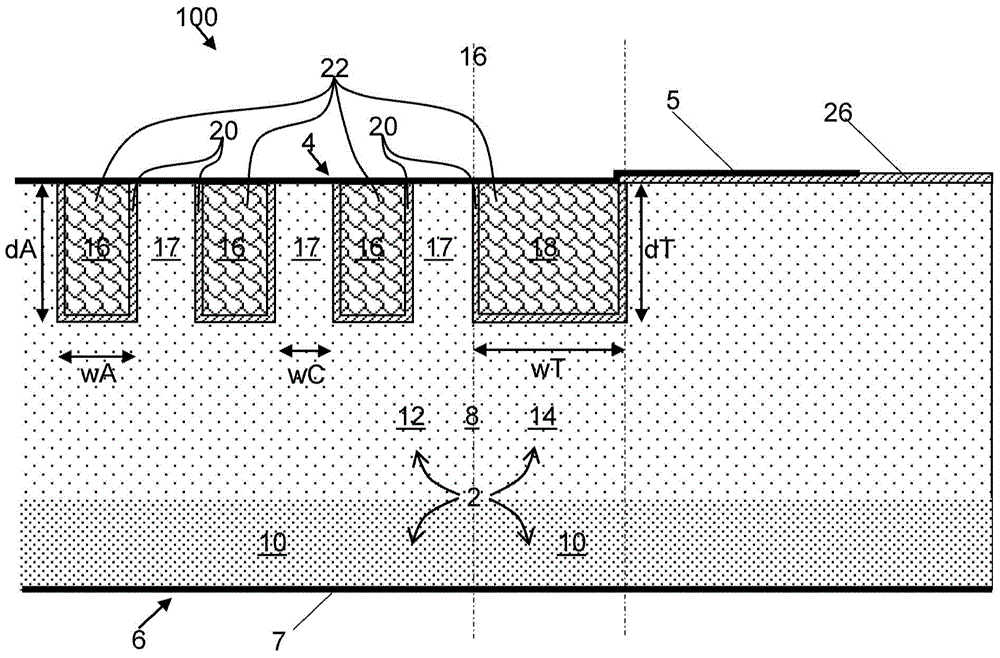

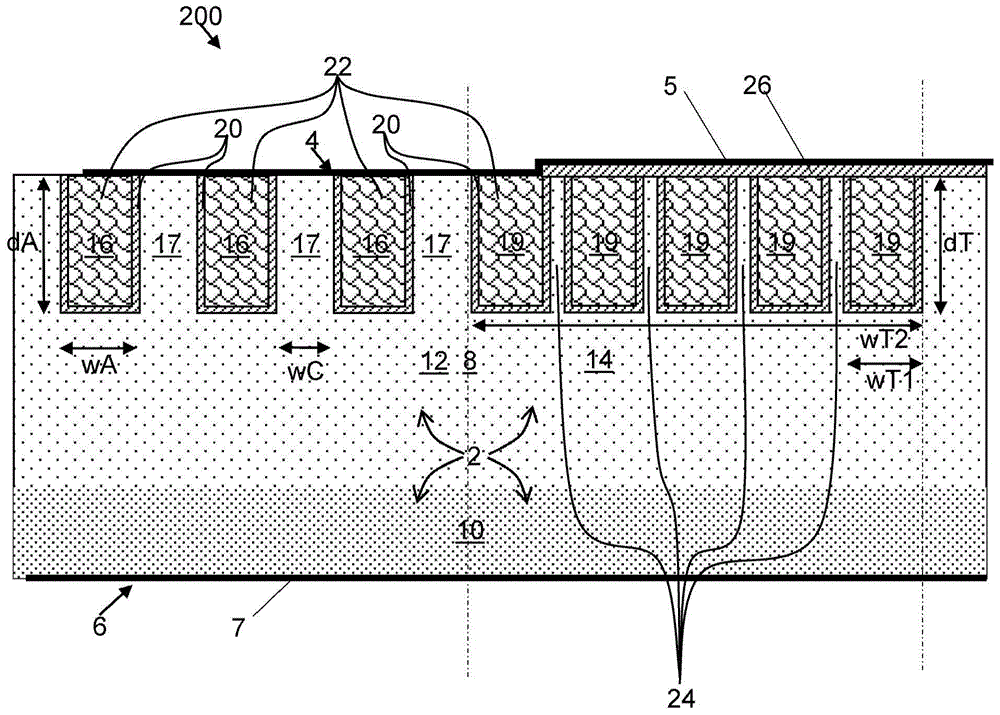

Semiconductor device and associated method of manufacture

ActiveCN105895709AFlat surfaceSimple processSemiconductor/solid-state device manufacturingSemiconductor devicesPower semiconductor deviceConductive materials

The disclosure relates to a semiconductor device comprising a body having: a first surface and an opposing second surface; a first semiconductor layer adjacent to the first surface; an active region comprising: a plurality of active trenches in the first surface, the plurality of active trenches extending from the first surface into the first semiconductor layer and having an active trench width, and a plurality of active cells, each active cell provided in the first semiconductor layer adjacent to an active trench, the active cells having an active cell width; and a termination region at a periphery of the first surface comprising: at least one termination trench, the at least one termination trench extending from the first surface into the first semiconductor layer, wherein the termination region has a width that is greater than the active trench width; and a number of termination trench separators having a width that is less than the active cell width, wherein the active trenches and the at least one termination trench each comprise a first insulator layer adjacent to the first semiconductor layer of the body, and wherein conductive material is disposed on the first insulating layer within each of the active trenches.

Owner:NEXPERIA BV

Process for producing dielectric ceramic composition

InactiveCN1337928AImprove reliabilityAvoid depositionFixed capacitor dielectricBarium titanateDielectric ceramics

Owner:TDK CORPARATION

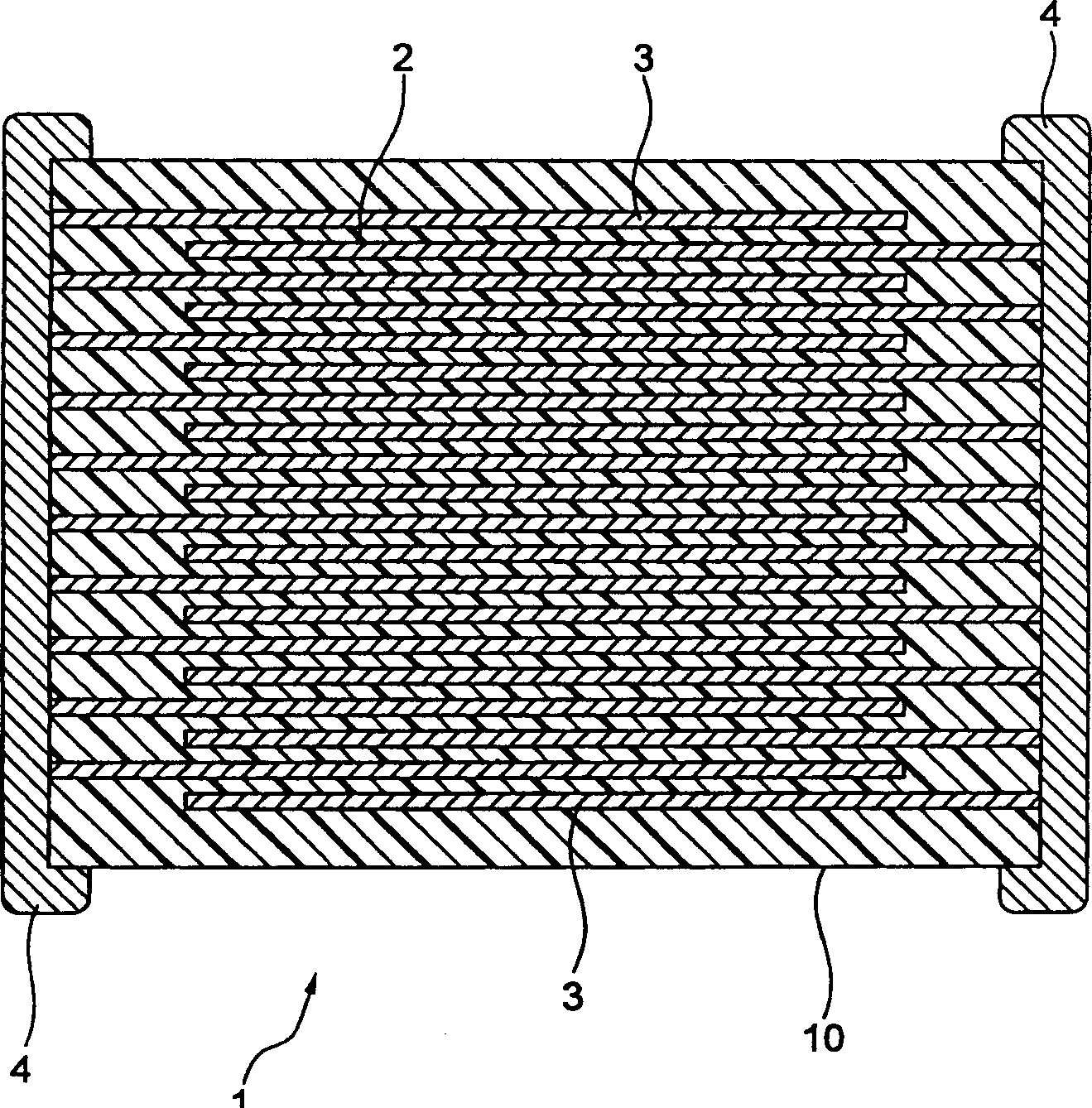

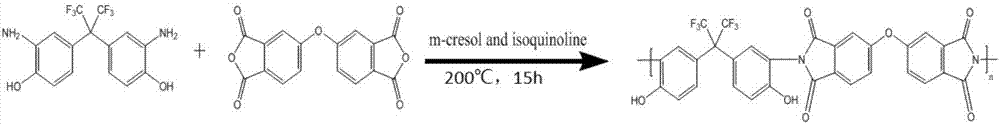

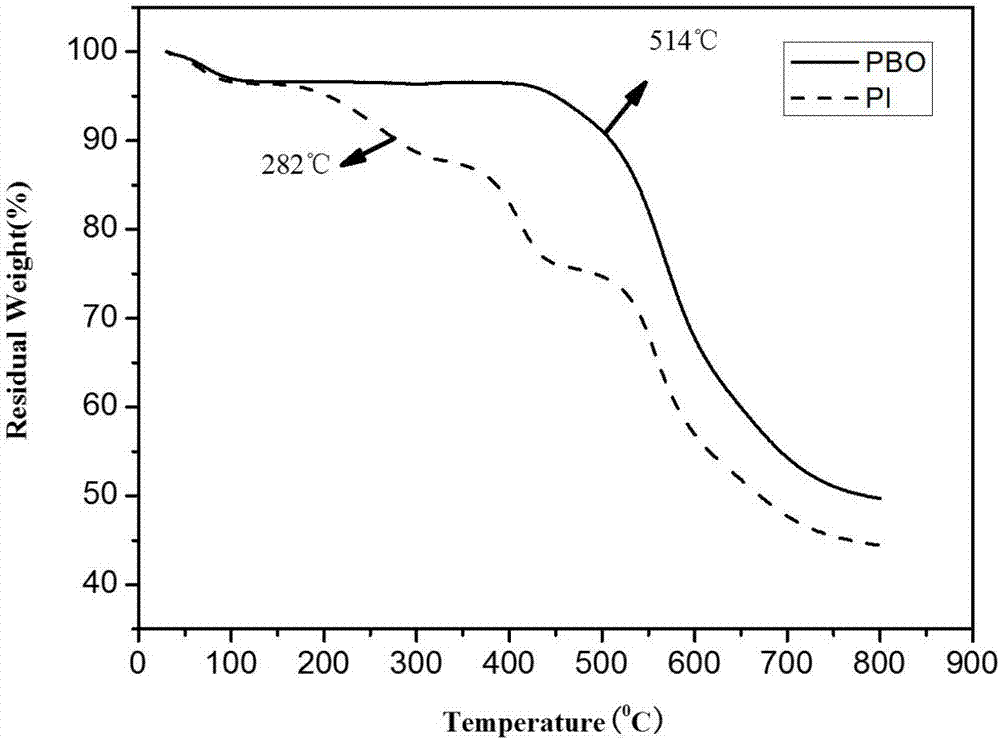

Preparation method of film capacitor composite dielectric film

InactiveCN107474251AEasy to makeEasy to operateThin/thick film capacitorStacked capacitorsComposite filmHigh energy

The invention discloses a preparation method of a film capacitor composite dielectric film. The preparation method comprises the following steps: (1) adopting a one-step method to synthesize a fluorine-containing phenolic hydroxyl group polyimide precursor; (2) adopting an intercalation stripping method to prepare a high dielectric oxide nanosheet; (3) preparing a two-phase polyimide / oxide nanosheet dielectric enhancer uniformly-mixed solution, or a multi-phase (three-phase) polyimide / oxide nanosheet dielectric enhancer / boron nitride nanosheet heat conduction enhancer uniformly-mixed solution; (4) drying to obtain a two-phase or multi-phase (three-phase) fluorine-containing phenolic hydroxyl group polyimide / nanosheet composite film; and (5) carrying out high temperature treatment in nitrogen condition to obtain a two-phase or multi-phase (three-phase) fluorine-containing polybenzoxazole high temperature resistant aromatic heterocycte / nanosheet composite dielectric film. The film capacitor composite dielectric film prepared in the invention has excellent performance such as high temperature resistance, high disruptive strength, dielectric constant adjustability and high energy storage density, and the process is simple, green and environmentally-friendly and can be used for large-scale manufacturing.

Owner:NANJING UNIV OF TECH

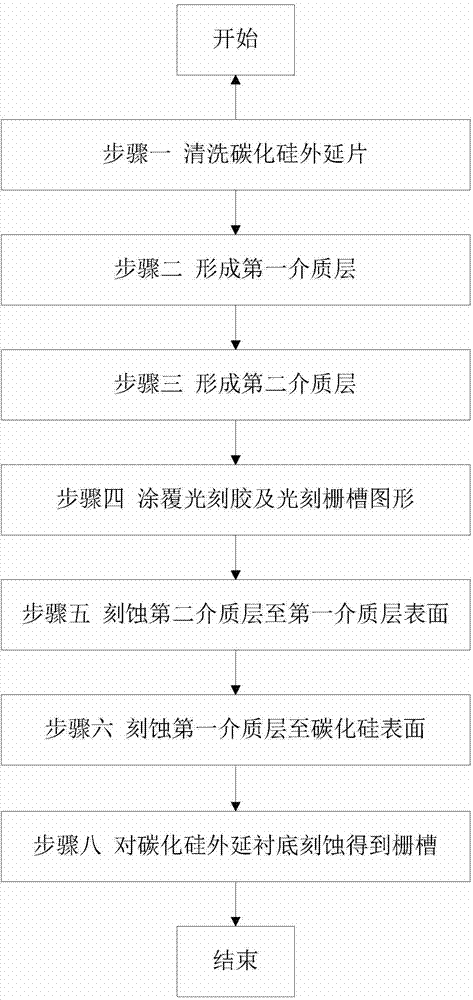

Grating groove manufacturing method for silicon carbide device

InactiveCN104733324AEasy to controlReduce the effect of electric field concentrationSemiconductor/solid-state device manufacturingSemiconductor devicesManufacturing technologyGrating

The invention relates to a semiconductor manufacturing technology, in particular to a grating groove manufacturing method for silicon carbide UMOS device. According to the grating groove manufacturing method for the silicon carbide device, mainly, a dielectric layer on a silicon carbide epitaxial wafer is etched according to a grating groove area window, part of the dielectric layer on the upper surface of silicon carbide is reserved during etching, and then the part of the dielectric layer is corroded through a corrosion technology, so that the area where the dielectric layer makes contact with the silicon carbide epitaxial wafer forms a smooth arc, and a silicon carbide grating groove structure with a steep side wall, without a micro groove and with smooth bottom feet is formed on the silicon carbide epitaxial wafer after etching. The method has the advantages that the silicon carbide grating groove structure with the steep side wall, without the micro groove and with the smooth bottom feet is obtained, the electric field concentration effect at the bottom of a groove grate is reduced, and breakdown property and reliability of the device are improved. The method is particularly applicable to silicon carbide grating groove structure manufacturing.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Preparation method of high-breakdown and high-dielectric FPE-based composite material film

ActiveCN113480760ASolve dielectric lossResolving the presence of a marked increase in conductivityPolyesterComposite film

The invention discloses a preparation method of a high-breakdown and high-dielectric FPE-based composite material film, and relates to the technical field of FPE-based composite material films. The invention aims to solve the problems that the dielectric constant of a traditional composite material film taking FPE as a matrix is low, the dielectric loss and the conductivity of the composite film doped with filler are obviously increased, and the breakdown field strength is reduced. The method comprises the following steps: adding hexagonal boron nitride nanosheets into a methyl pyrrolidone solution, and carrying out ultrasonic dispersion to obtain a mixed solution a; adding SiO2 particles into the mixed solution a, and performing ultrasonic dispersion to obtain a mixed solution b; adding fluorene polyester particles into the mixed solution b, and conducting stirring for 1-2 hours to obtain a stirred mixed solution b; and uniformly coating one surface of a pretreated substrate with the stirred mixed solution b, heating the substrate, carrying out heat preservation, finally cooling the substrate to room temperature, and stripping the film on the substrate to obtain the high-breakdown and high-dielectric FPE-based composite material film.

Owner:HARBIN UNIV OF SCI & TECH

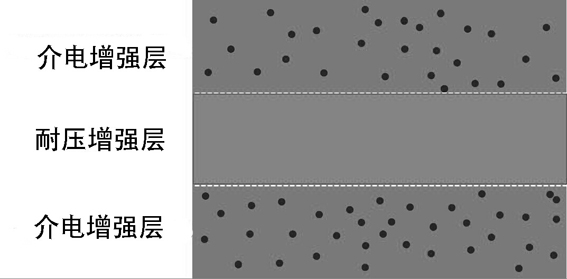

Composite dielectric material with three-layer structure and preparation method thereof

PendingCN112373162AExcellent dielectric propertiesEffective control of electric field distributionSynthetic resin layered productsLaminationEnergy storage efficiencyUltrasonic dispersion

The invention discloses a composite dielectric material with a three-layer structure. The material comprises dielectric enhancement layers and a voltage-withstanding enhancement layer clamped betweenthe dielectric enhancement layers, the dielectric enhancement layers are made of a ferroelectric polymer / dielectric ceramic filler compound, and the voltage-withstanding enhancement layer is a lineardielectric high-molecular polymer. The invention further provides a preparation method of the composite dielectric material. The preparation method comprises the following steps: S1, dissolving a ferroelectric polymer in N,N-dimethylformamide, adding a dielectric ceramic filler, carrying out ultrasonic dispersion to obtain a mixed solution, coating a quartz glass plate with the mixed solution, andconducting drying and scraping to obtain a dielectric reinforced film; S2, coating the quartz glass plate with the N,N-dimethylformamide solution of the linear dielectric high-molecular polymer, andconducting drying and scraping to obtain a pressure-resistant reinforced film; and S3, clamping the pressure-resistant reinforced film between the dielectric reinforced films, carrying out hot press molding, and conducting cooling to obtain the composite dielectric material with a three-layer structure. The composite dielectric material has high energy storage efficiency and energy storage density.

Owner:HUBEI UNIV OF SCI & TECH

Method for manufacturing a gallium nitride based semiconductor device with improved termination scheme

ActiveUS8372738B2Uniform densityImproves Structural IntegritySemiconductor/solid-state device manufacturingDiodeGallium nitrideSemiconductor

This invention discloses a gallium nitride based semiconductor power device disposed in a semiconductor substrate. The power device comprises a termination area disposed at a peripheral area of the semiconductor power device comprises a termination structure having at least a guard ring disposed in a trench filled with doped gallium-based epitaxial layer therein.

Owner:ALPHA & OMEGA SEMICON INC

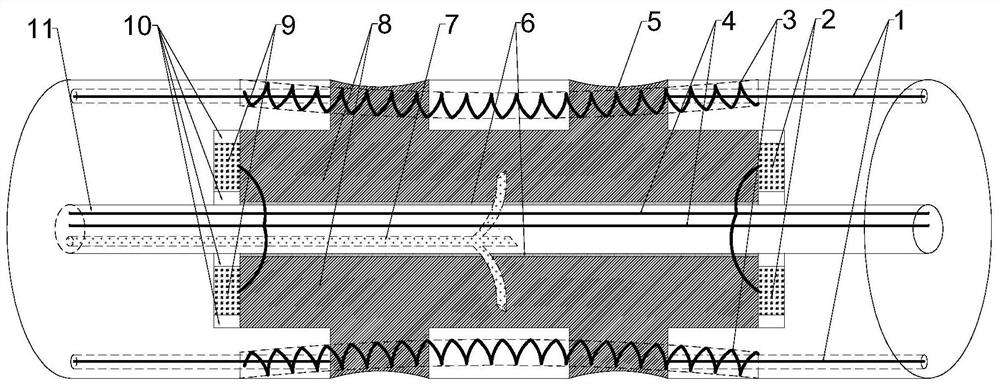

Split gate structure, power mos device, and manufacturing method

ActiveUS20210296453A1Improve performanceFlatnessSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringCondensed matter physics

A split gate structure is disclosed. The split gate structure includes a first polysilicon, a characteristic oxide, and a second polysilicon sequentially disposed in a trench in a vertical direction upward from a bottom of the trench. An upper surface of the characteristic oxide has a height difference less than 1500 Å between a higher center portion and a lower periphery portion. The split gate structure effectively improves the breakdown performance and the IGSS performance. A power MOS device having the split gate structure and a manufacturing method of the split gate structure are also provided.

Owner:HEJIAN TECH SUZHOU

Punching device and method based on cooperation of nanofluid electro-hydraulic breakdown and infrared thermal radiation

ActiveCN112459722AImprove thermal conductivityIncrease transfer speedThermal drillingFluid removalEngineeringCoal

The invention relates to a nanofluid-based electro-hydraulic breakdown and infrared thermal radiation coordinated punching device and method, the device comprises a drill rod, a movable hole packer, an electro-hydraulic breakdown assembly and an infrared radiation heating assembly, the punching device is installed at a planned punching position, the hole packer is used for sealing a hole, and theelectro-hydraulic breakdown assembly and the infrared radiation heating assembly are installed at the same time. Then a liquid injection pump station is used for injecting nanofluid into the liquid injection cavity, then a high-voltage electric pulse generator supplies power to the positive and negative electrode plates to trigger the electro-hydraulic effect to conduct punching, and finally an infrared heater is started to crack the coal body through thermal stress. The high-pressure electro-hydraulic punching technology and the infrared thermal radiation heating technology are combined by adopting the nanofluid which is an energy transport working medium with high heat transfer performance, the advantages that electro-hydraulic breakdown is convenient and easy to precisely control can beexerted, the coal body can be rapidly heated and cracked by utilizing infrared radiation heating, and the purposes of coal seam permeability improvement and crack development are efficiently achieved. The method is simple, reliable in performance and convenient to maintain, and has a wide engineering application prospect.

Owner:CHINA UNIV OF MINING & TECH

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com