Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

109results about How to "Improve breakdown characteristics" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

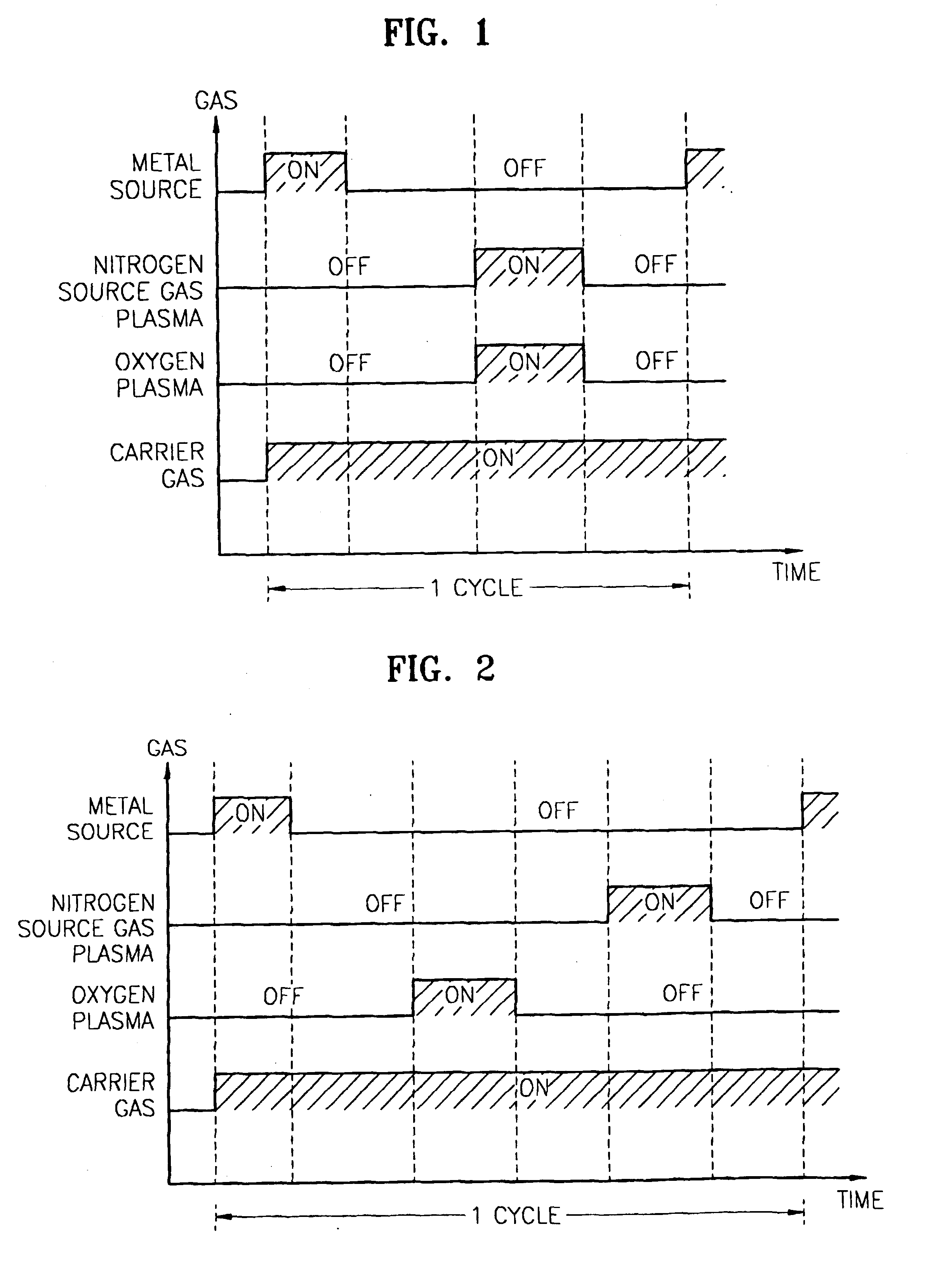

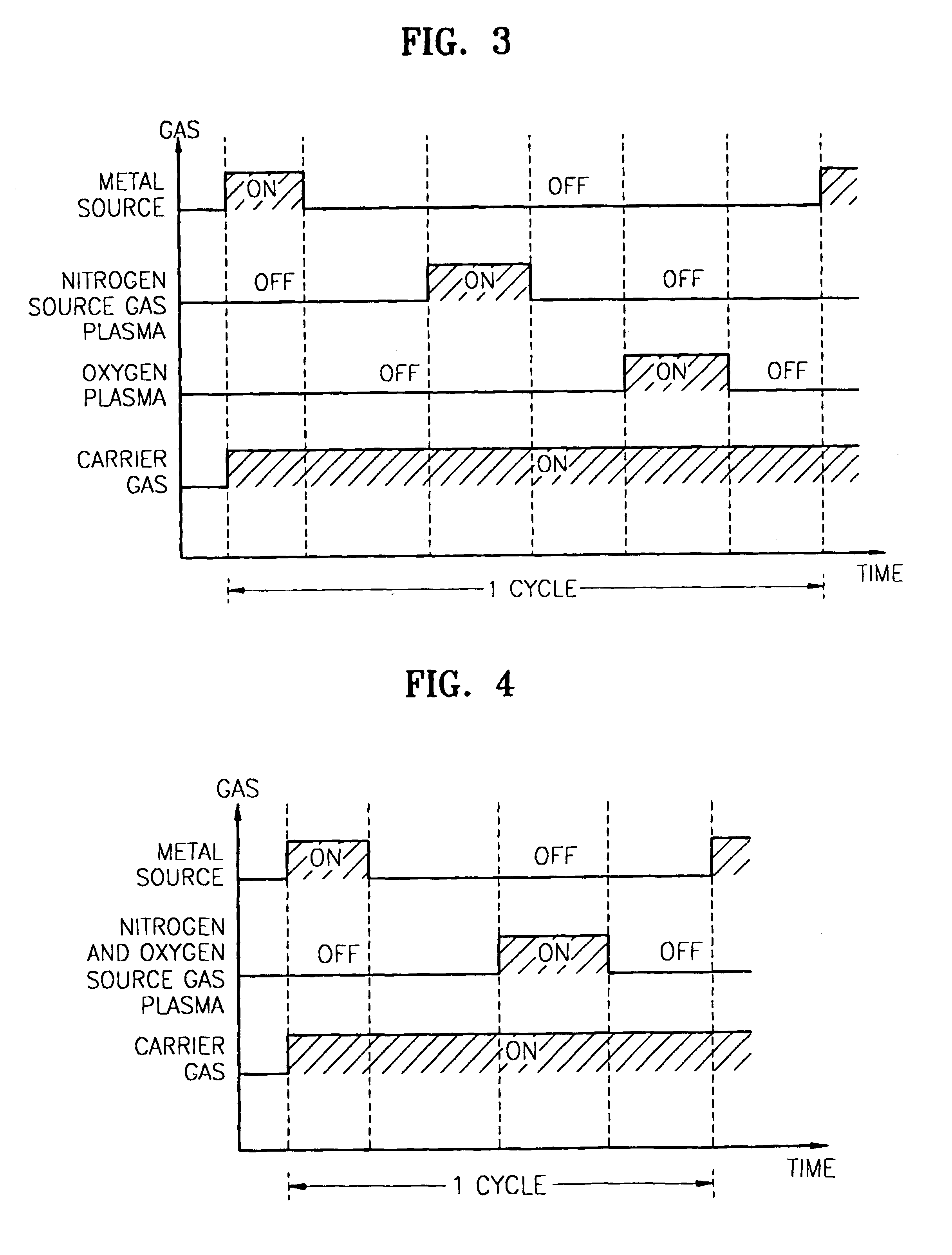

Method for forming introgen-containing oxide thin film using plasma enhanced atomic layer deposition

InactiveUS20040077182A1Density of thinThin rateSemiconductor/solid-state device manufacturingChemical vapor deposition coatingHigh rateNitrogen source

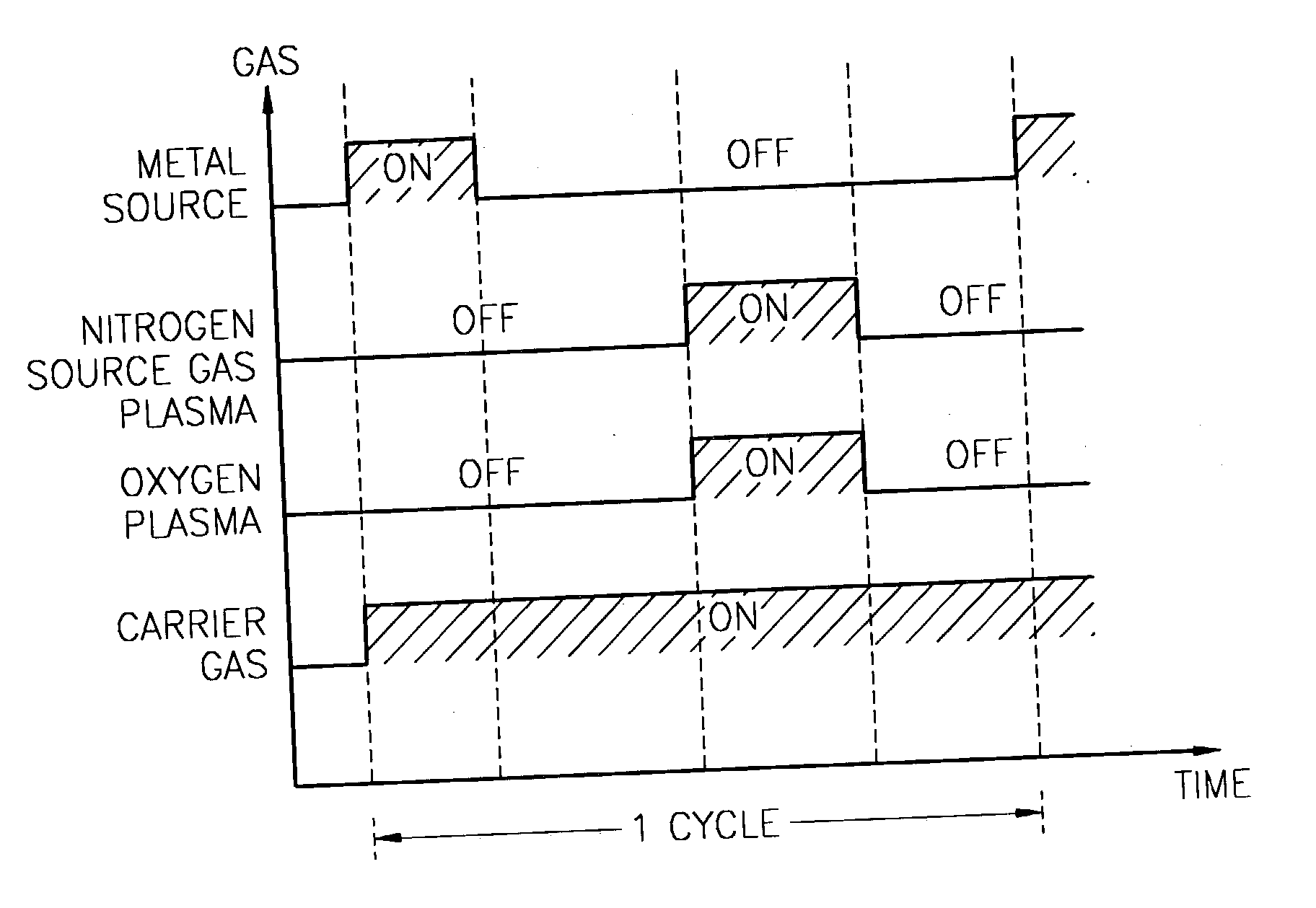

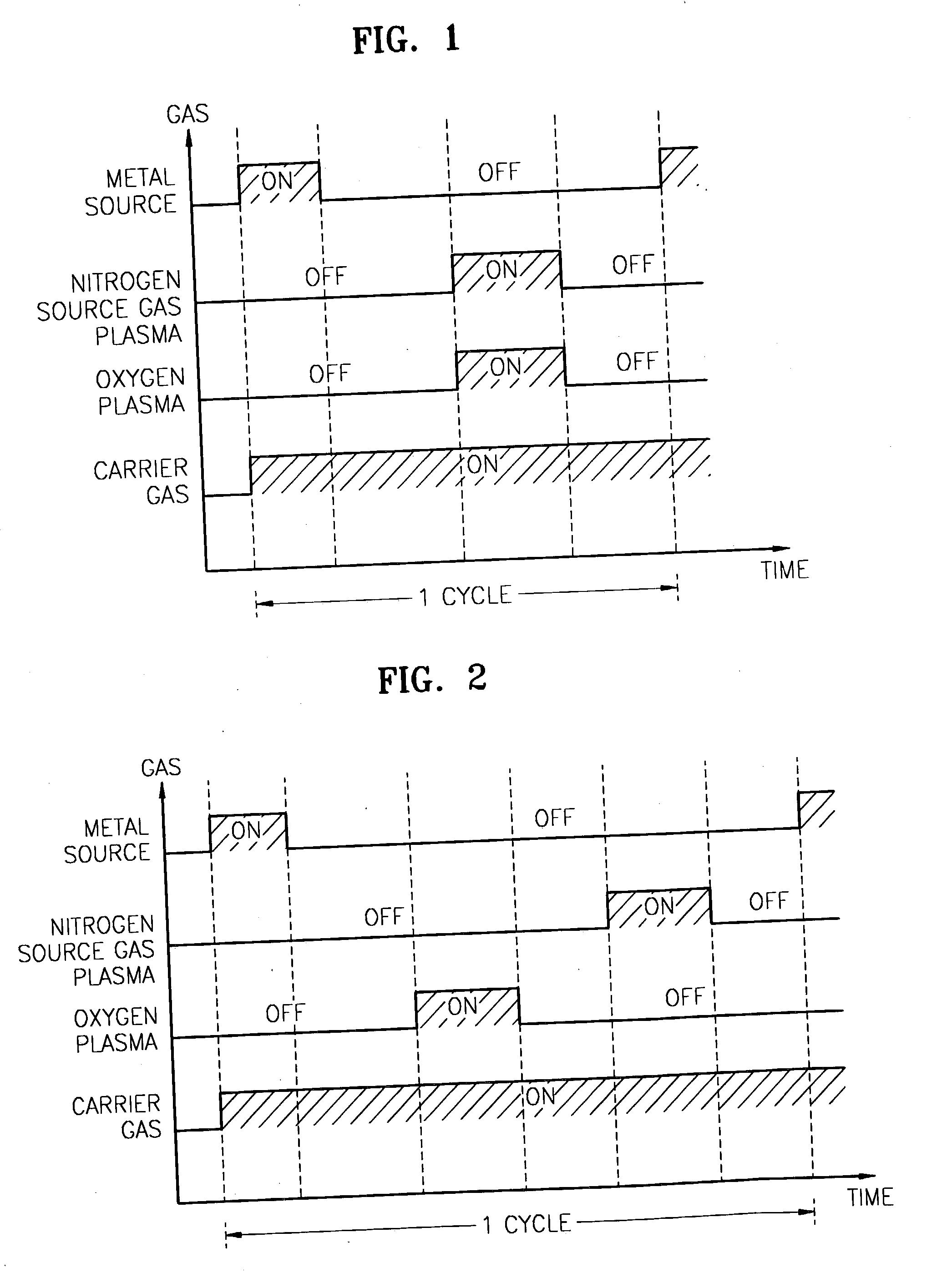

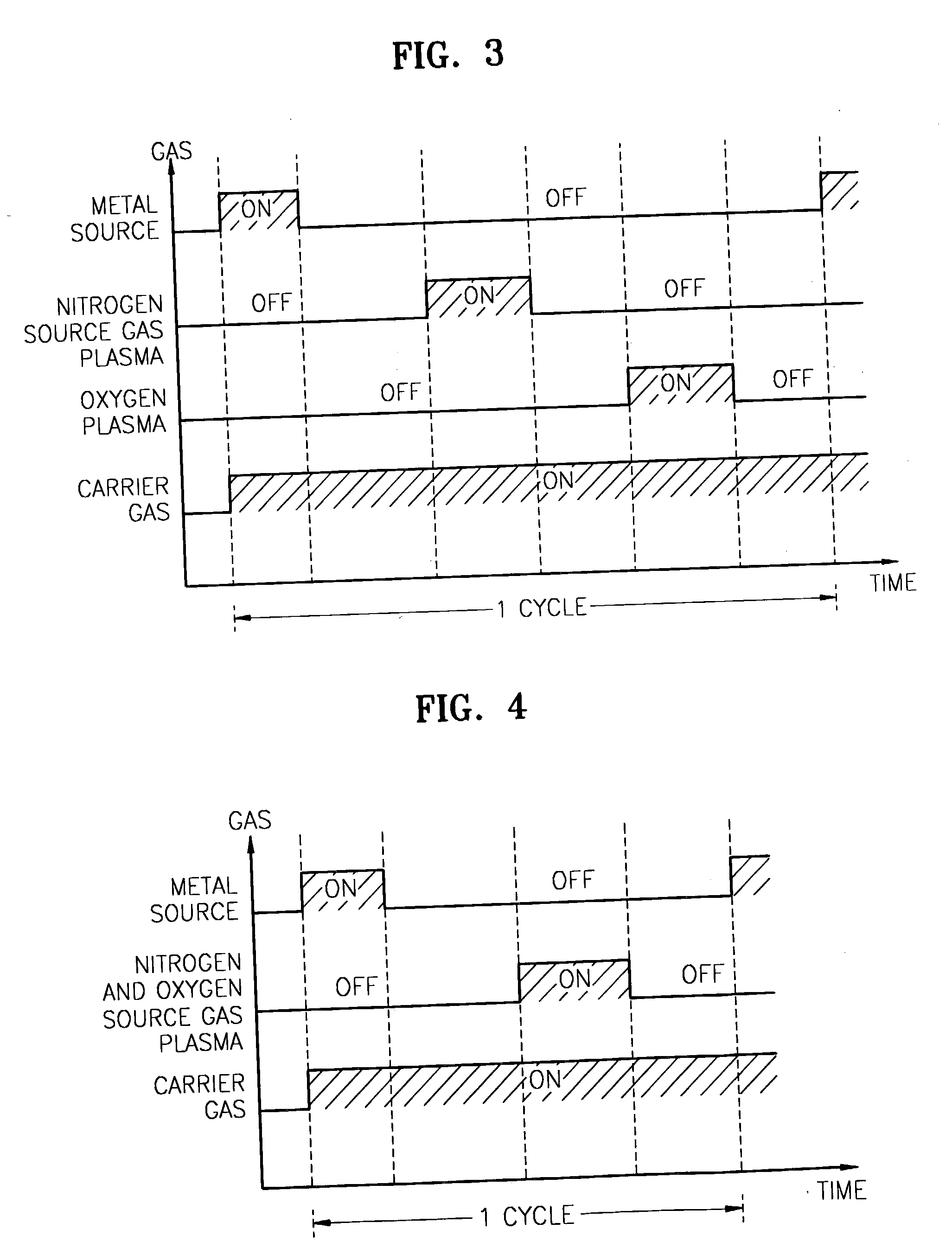

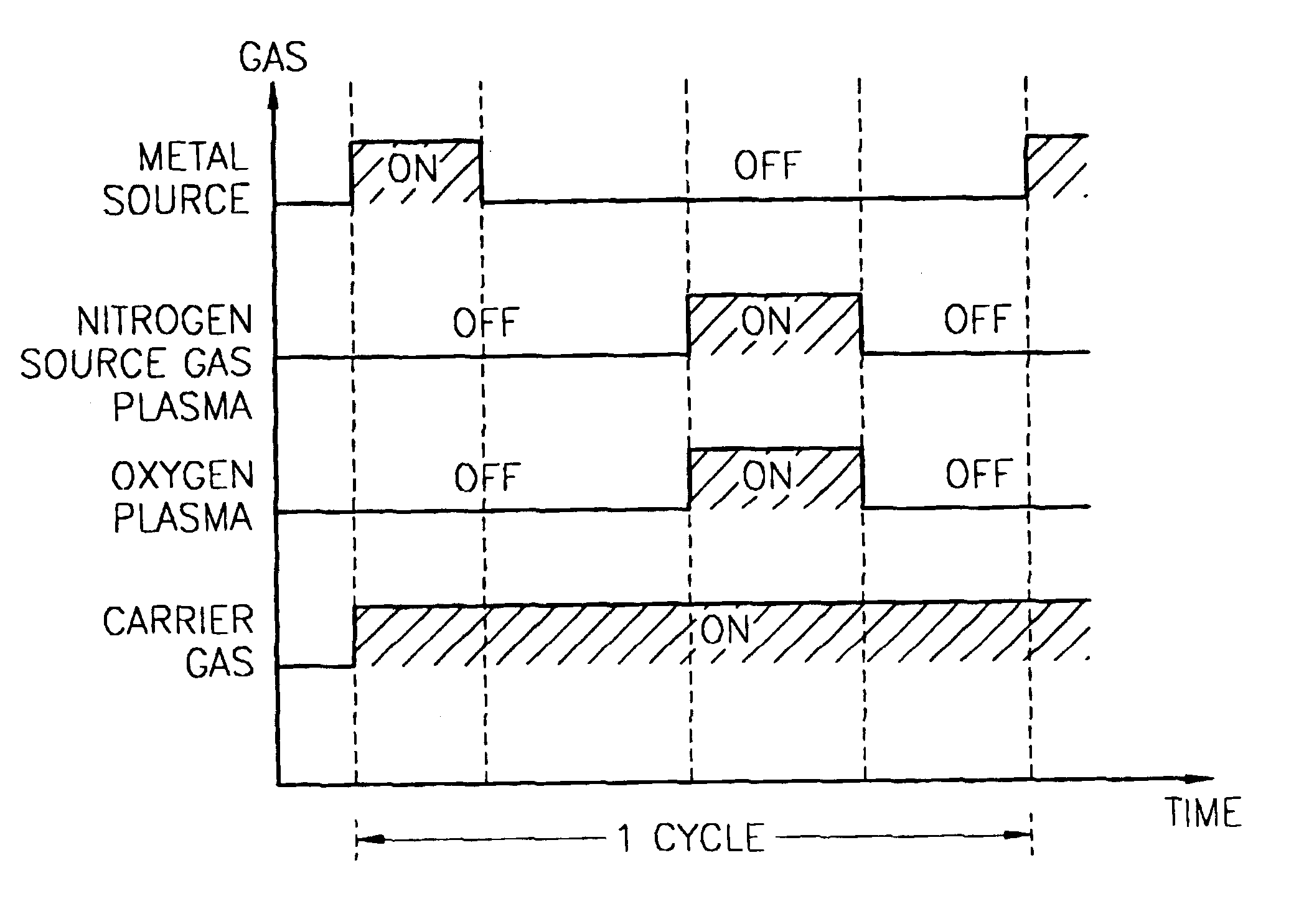

A method for forming a nitrogen-containing oxide thin film by using plasma enhanced atomic layer deposition is provided. In the method, the nitrogen-containing oxide thin film is deposited by supplying a metal source compound and oxygen gas into a reactor in a cyclic fashion with sequential alternating pulses of the metal source compound and the oxygen gas, wherein the oxygen gas is activated into plasma in synchronization of the pulsing thereof, and a nitrogen source gas is further sequentially pulsed into the reactor and activated into plasma over the substrate in synchronization with the pulsing thereof. According to the method, a dense nitrogen-containing oxide thin film can be deposited at a high rate, and a trace of nitrogen atoms can be incorporated in situ into the nitrogen-containing oxide thin film, thereby increasing the breakdown voltage of the film.

Owner:ELECTRONICS & TELECOMM RES INST

Method for forming nitrogen-containing oxide thin film using plasma enhanced atomic layer deposition

InactiveUS6723642B1Density of thinThin rateSemiconductor/solid-state device manufacturingChemical vapor deposition coatingNitrogen sourceNitrogen oxide

A method for forming a nitrogen-containing oxide thin film by using plasma enhanced atomic layer deposition is provided. In the method, the nitrogen-containing oxide thin film is deposited by supplying a metal source compound and oxygen gas into a reactor in a cyclic fashion with sequential alternating pulses of the metal source compound and the oxygen gas, wherein the oxygen gas is activated into plasma in synchronization of the pulsing thereof, and a nitrogen source gas is further sequentially pulsed into the reactor and activated into plasma over the substrate in synchronization with the pulsing thereof. According to the method, a dense nitrogen-containing oxide thin film can be deposited at a high rate, and a trace of nitrogen atoms can be incorporated in situ into the nitrogen-containing oxide thin film, thereby increasing the breakdown voltage of the film.

Owner:ELECTRONICS & TELECOMM RES INST

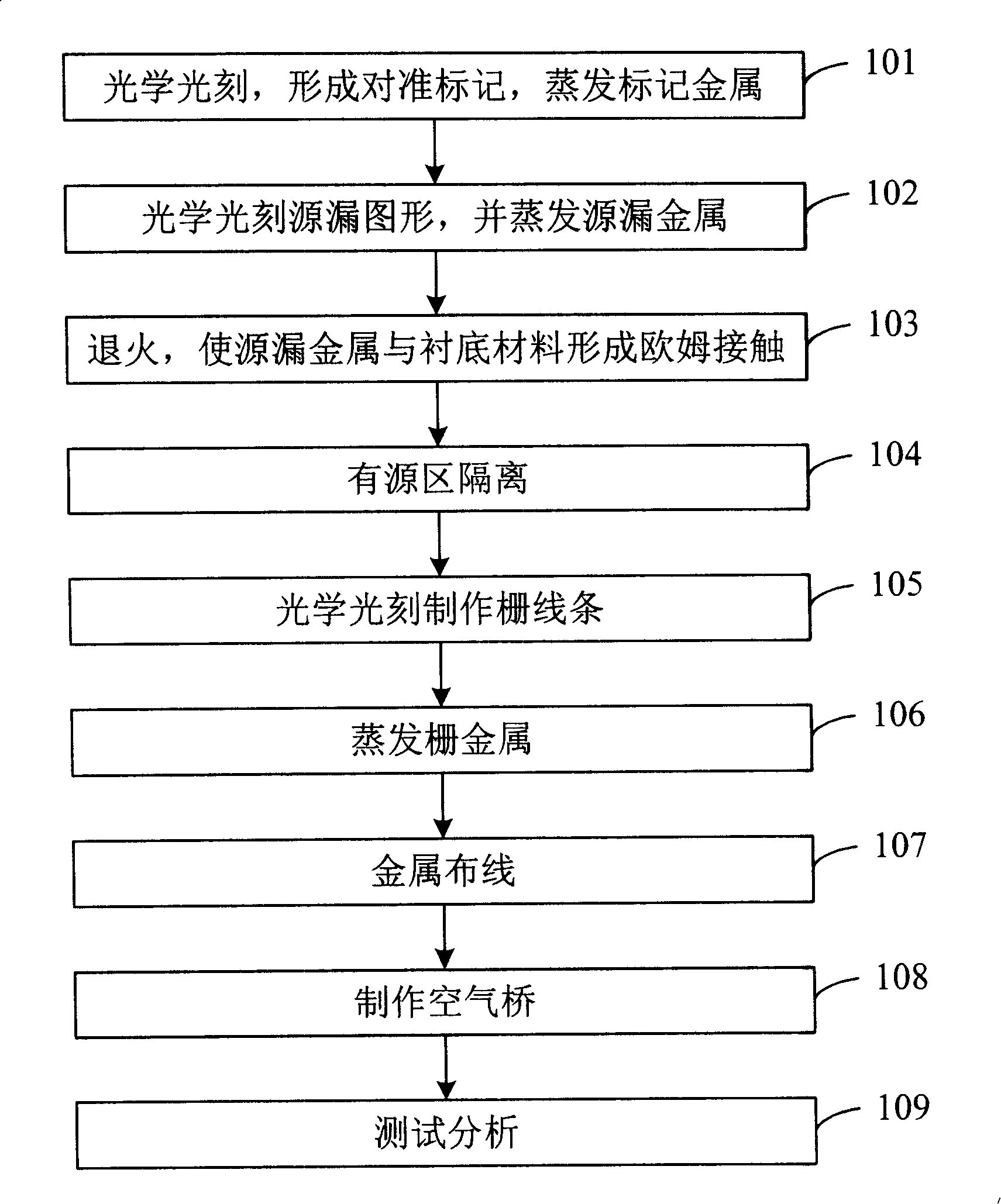

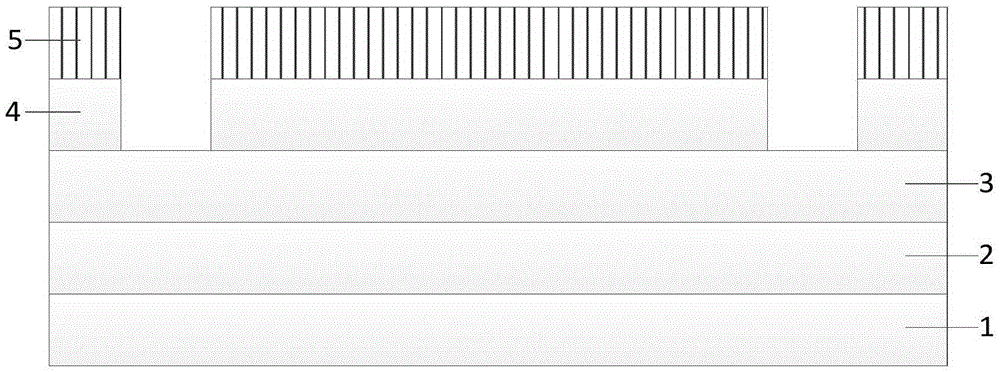

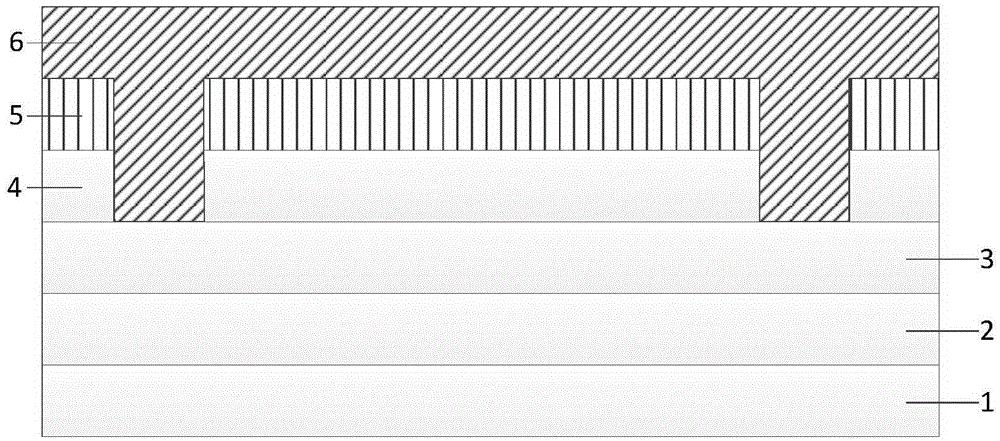

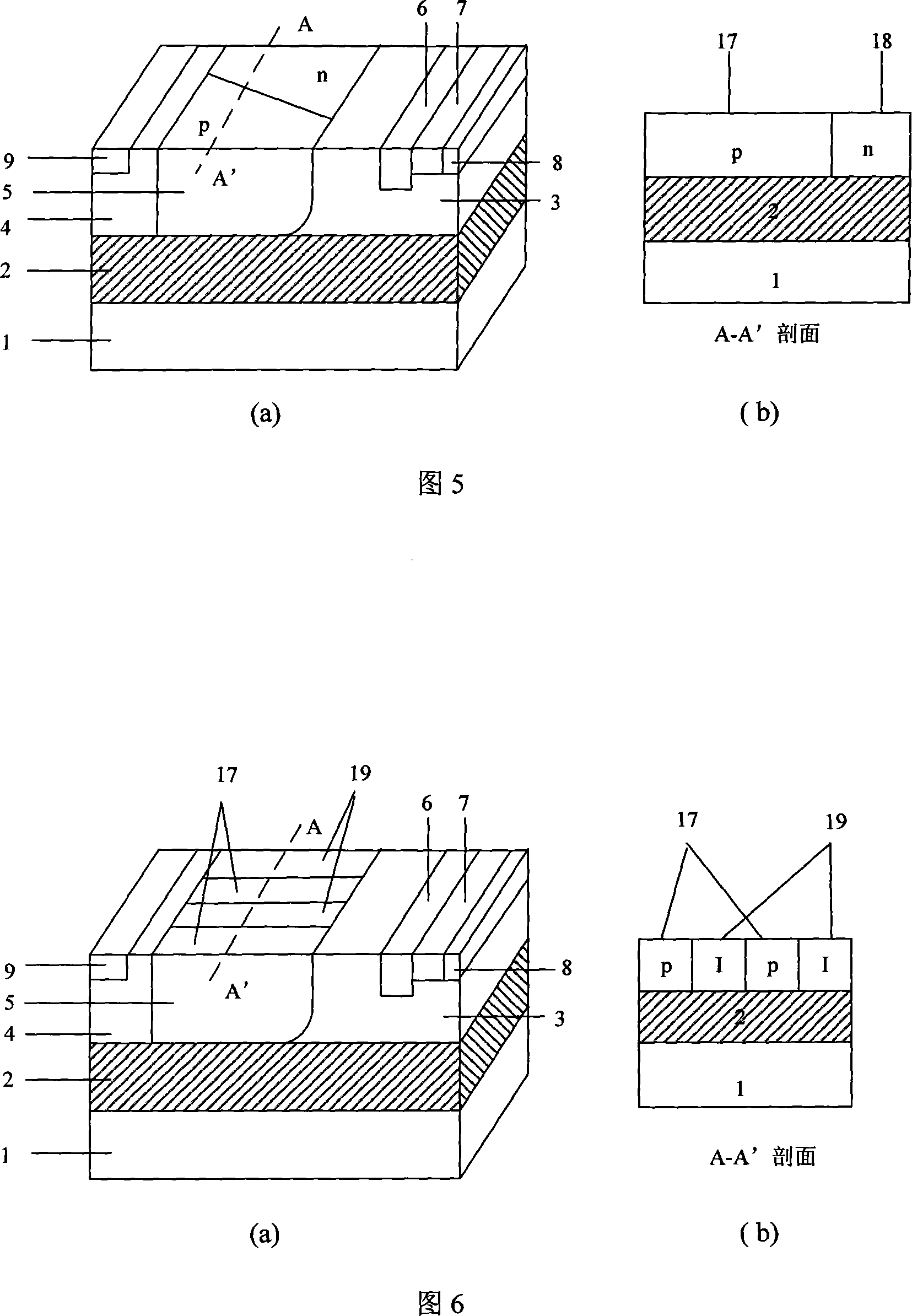

Field effect transistor multi-layer field plate device and method for making the same

InactiveCN101232045AImprove breakdown characteristicsInhibit current collapse phenomenonSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsMicrowave power

The invention relates to the field of microwave power device technology in semiconductor material and discloses a method for fabricating an AlGaN / GaN high-electron mobility transistor (AlGaN / GaN HEMT) multilayer field plate device. The method comprises, based on common AlGaN / GaN HEMT device fabrication process, firstly fabricating a gate connection field plate after forming a gate metal contact, secondly fabricating a source connection field plate, and forming the AlGaN / GaN HEMT multilayer field plate device. The invention simultaneously discloses an AlGaN / GaN HEMT multilayer field plate device. The invention can greatly improve the breakdown characteristics of the AlGaN / GaN HEMT device and effectively suppress the current collapse of the AlGaN / GaN HEMT device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

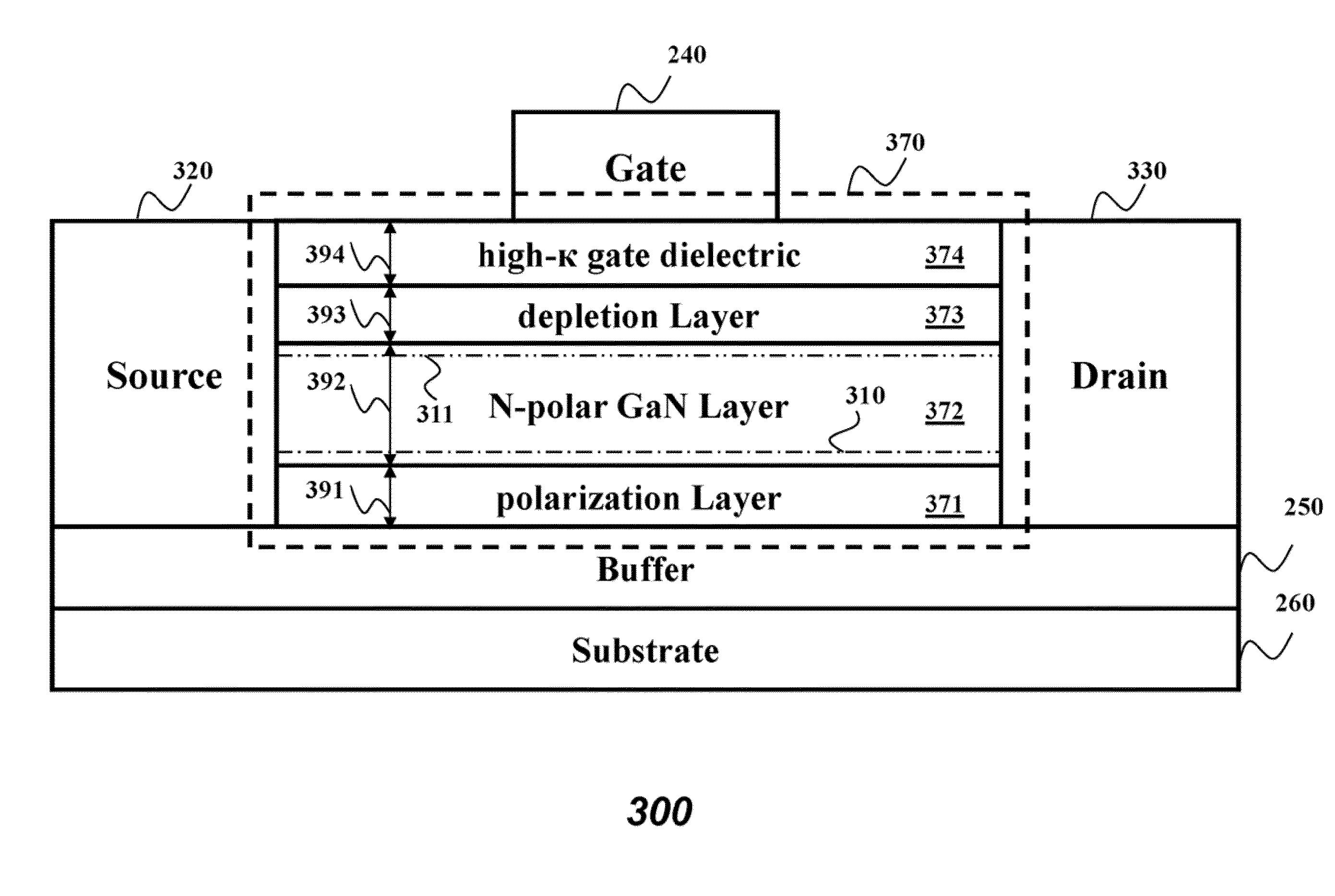

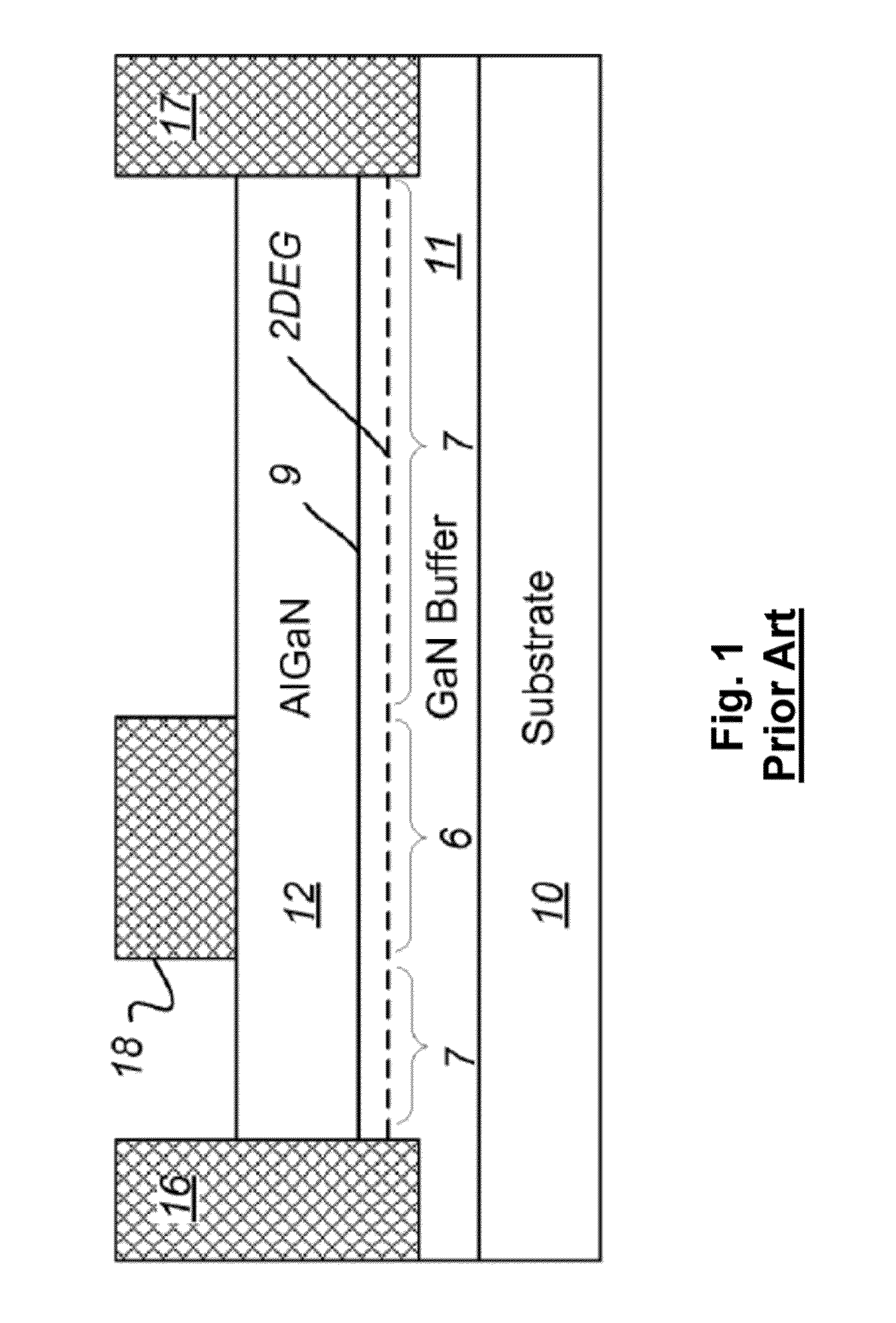

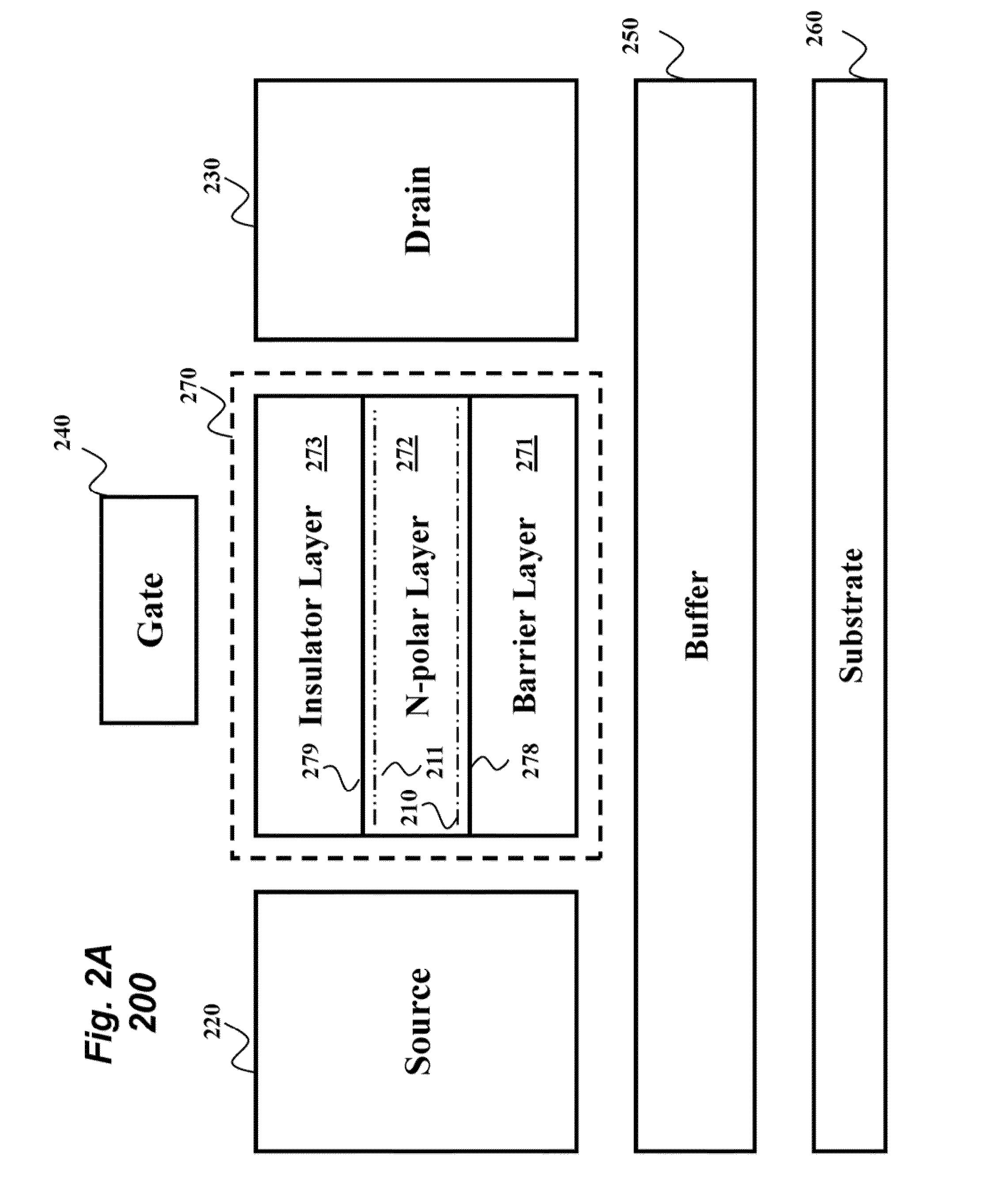

High Electron Mobility Transistors with Multiple Channels

ActiveUS20130141156A1Current-carrying capability can be increasedHigh electron mobilitySolid-state devicesStatic storageCarrier signalHigh electron

A device includes a source for transmitting an electronic charge through a conduction path; a drain for receiving the electronic charge; a stack for providing at least part of the conduction path; and a gate operatively connected to the stack for controlling a conduction of the electronic charge. The stack includes an insulator layer, an N-polar layer and a barrier layer selected such that, during an operation of the device, the conduction path formed in the N-polar layer includes a two-dimensional electron gas (2DEG) channel and an inversion carrier channel.

Owner:MITSUBISHI ELECTRIC CORP +1

Gallium-nitride field effect transistor and manufacturing method therefor

InactiveCN106601809AImprove breakdown characteristicsImprove pressure resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesPower flowGallium nitride

The invention provides a gallium-nitride field effect transistor, and the field effect transistor comprises a substrate, an epitaxial layer, a passivation layer, a first oxidation layer, a source electrode, a drain electrode, a grid electrode, a second oxidation layer and a field plate layer, wherein the epitaxial layer, the passivation layer, the first oxidation layer, the source electrode, the drain electrode, the grid electrode, the second oxidation layer and the field plate layer are sequentially formed on the substrate. The field plate layer is electrically connected with the source electrode through a metal lead, and is partly opposite to the grid electrode. The invention also provides a manufacturing method for the gallium-nitride field effect transistor. According to the invention, the grid electrode and the field plate layer are arranged to be partly opposite, so the current collapse can be inhibited so as to improve the breakdown characteristics of a device. Moreover, the electric field density between the first field plate layer and the drain electrode can be reduced, thereby improving the withstand voltage of the device.

Owner:PEKING UNIV +2

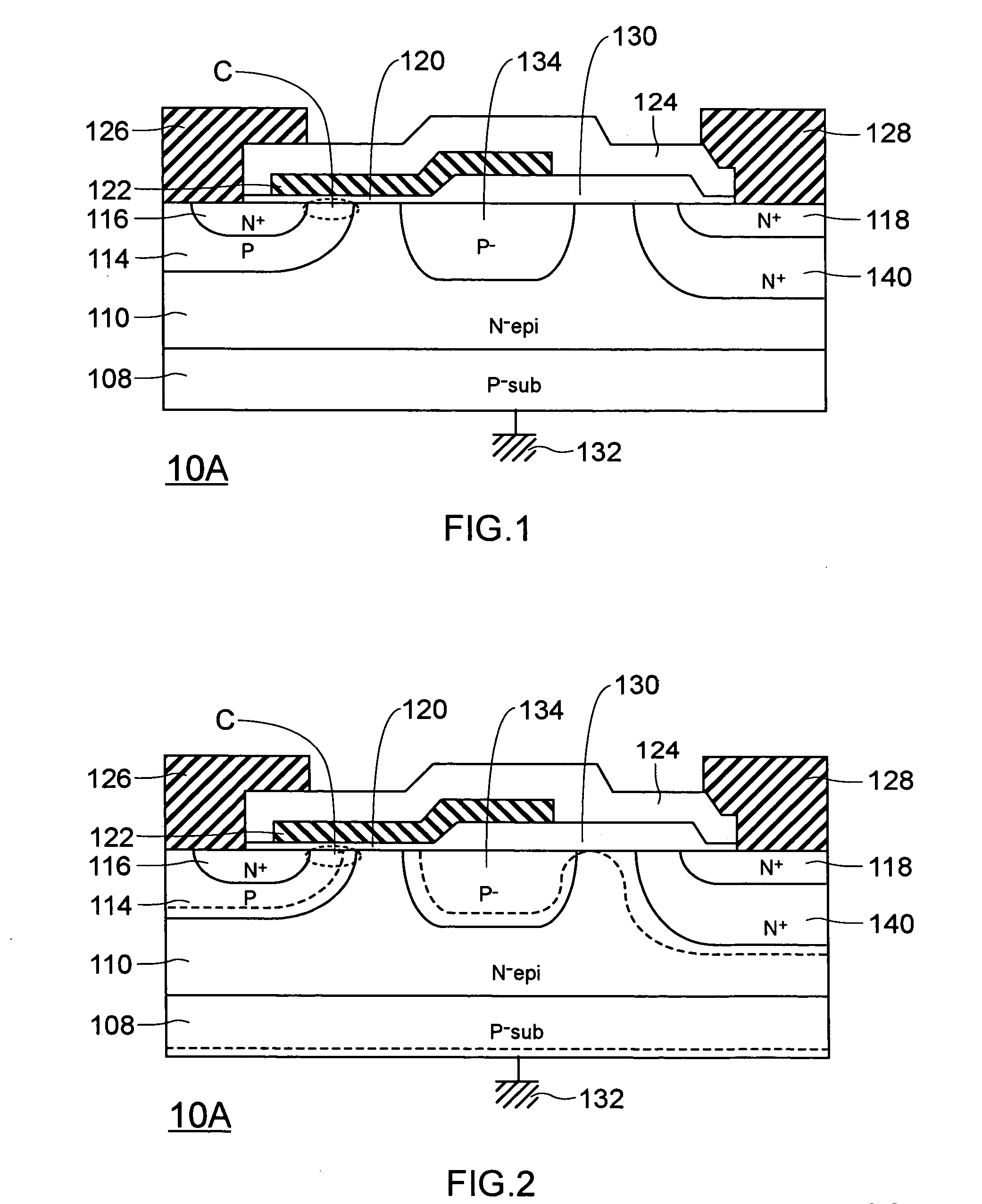

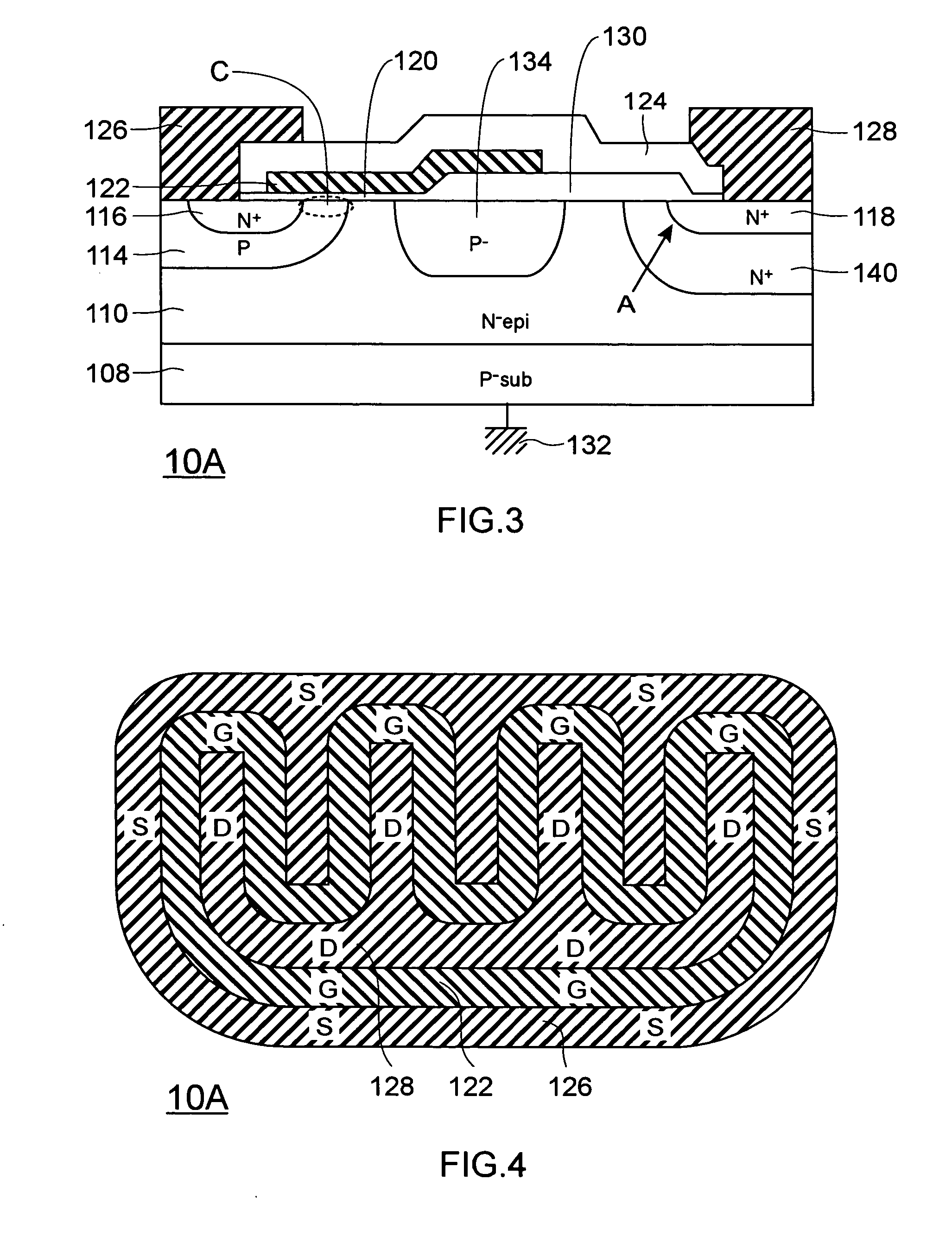

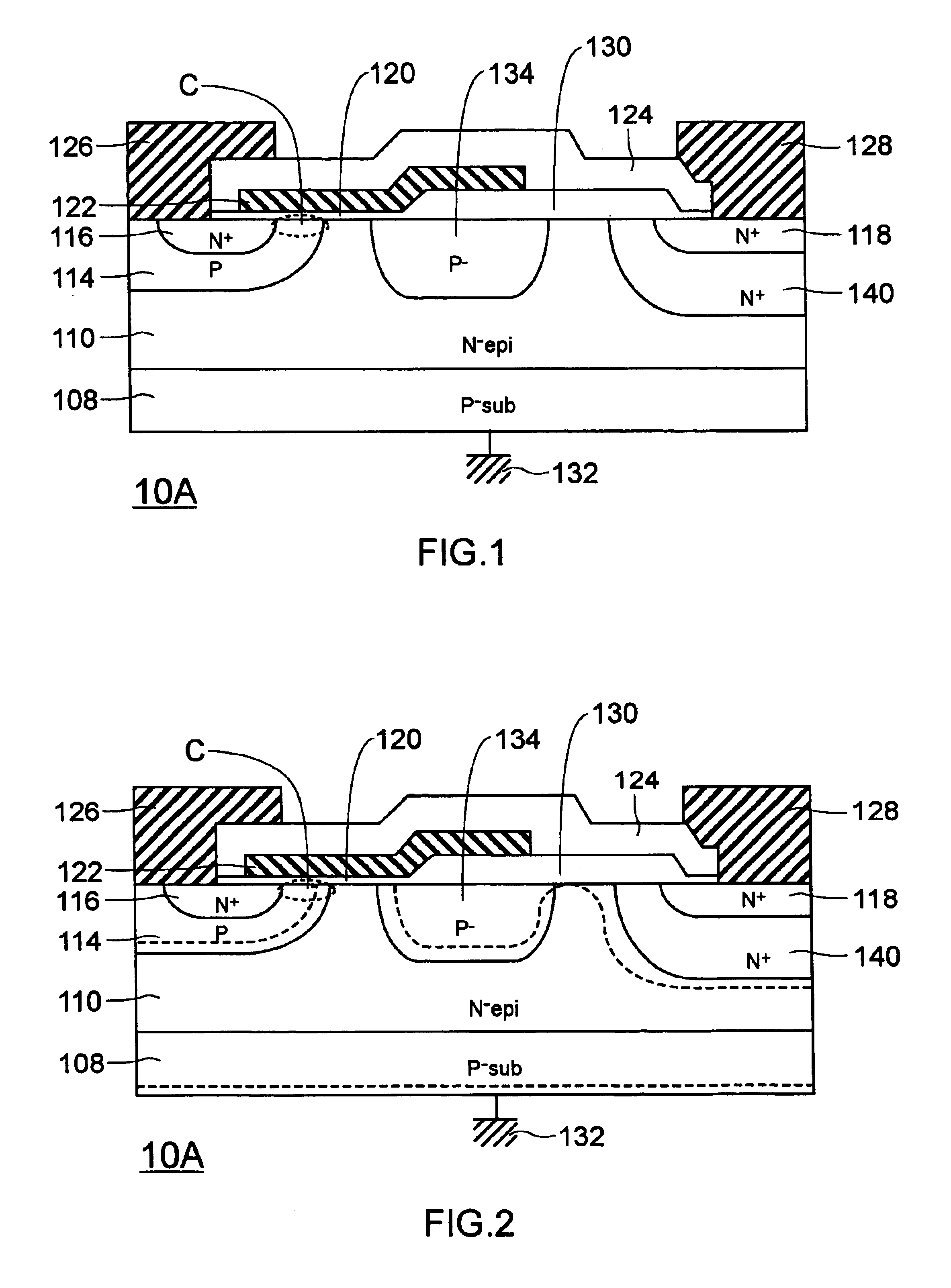

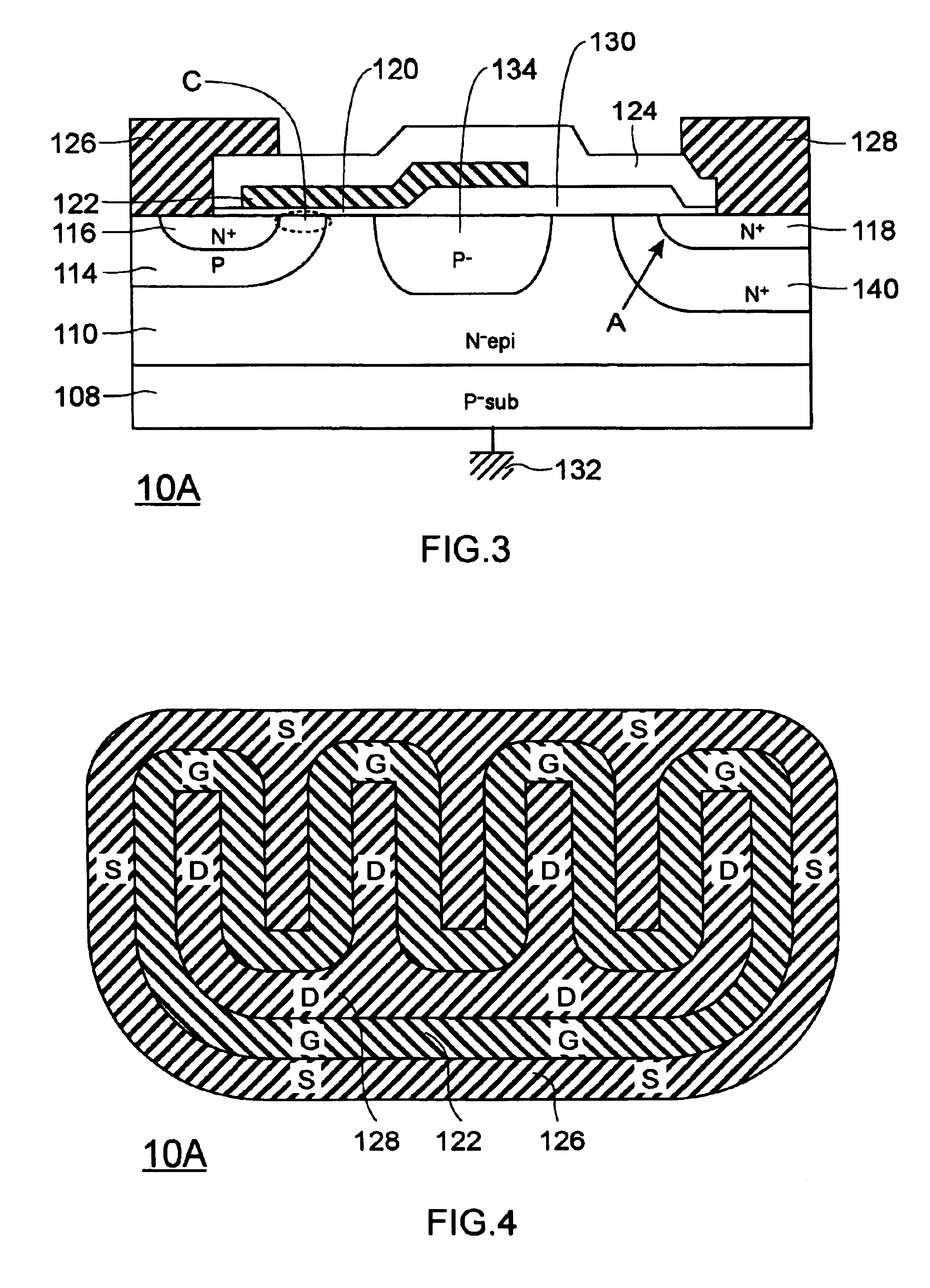

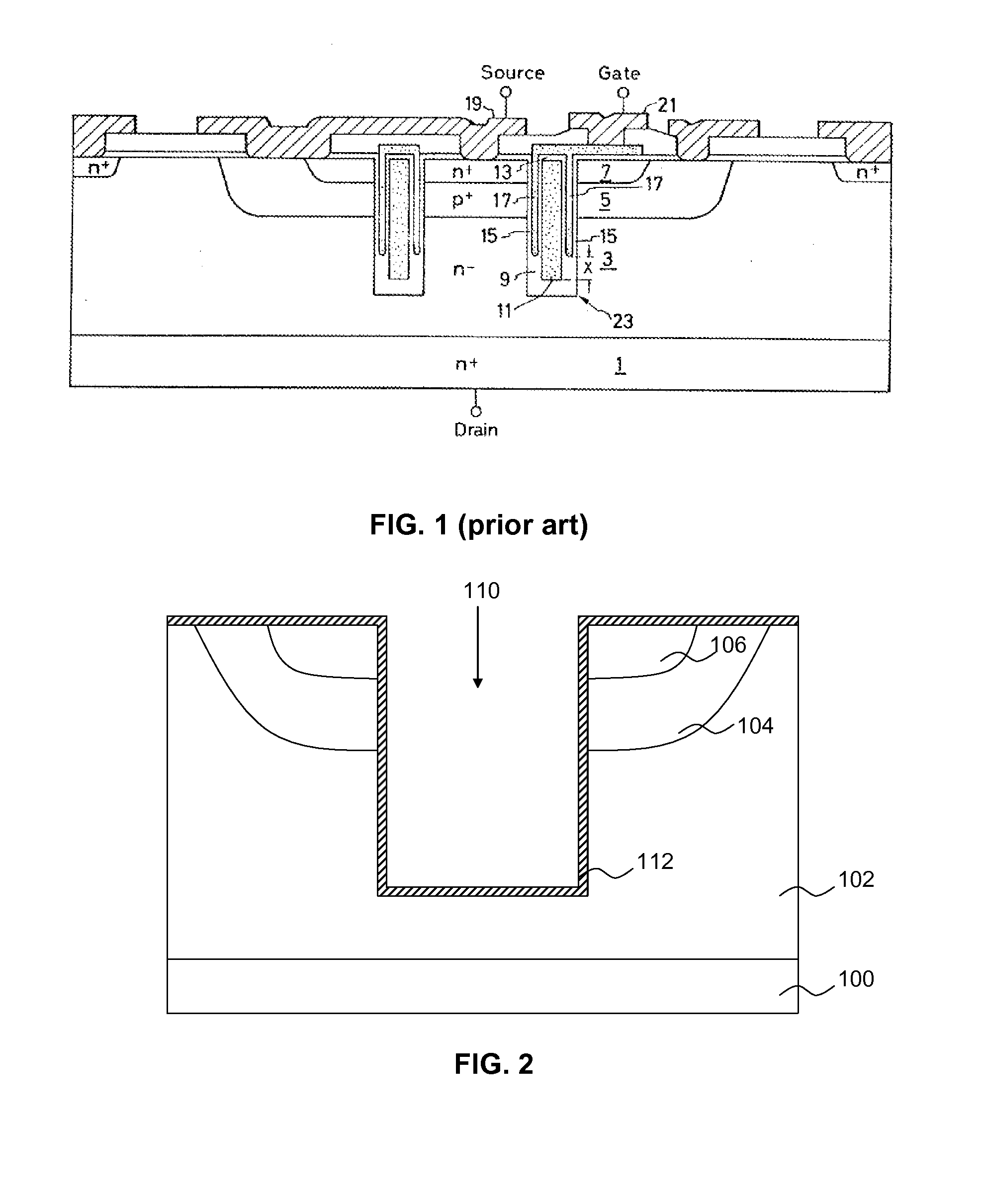

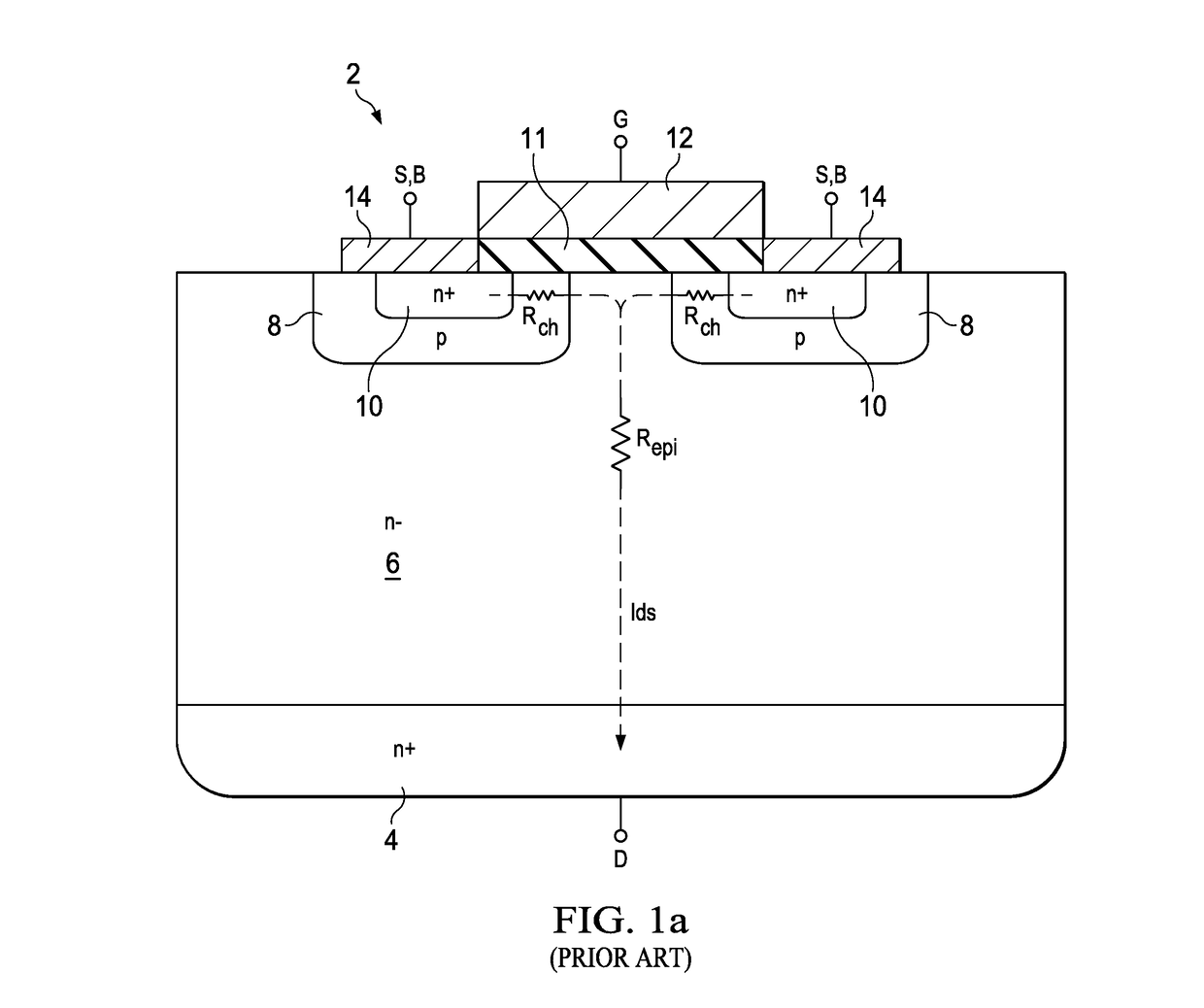

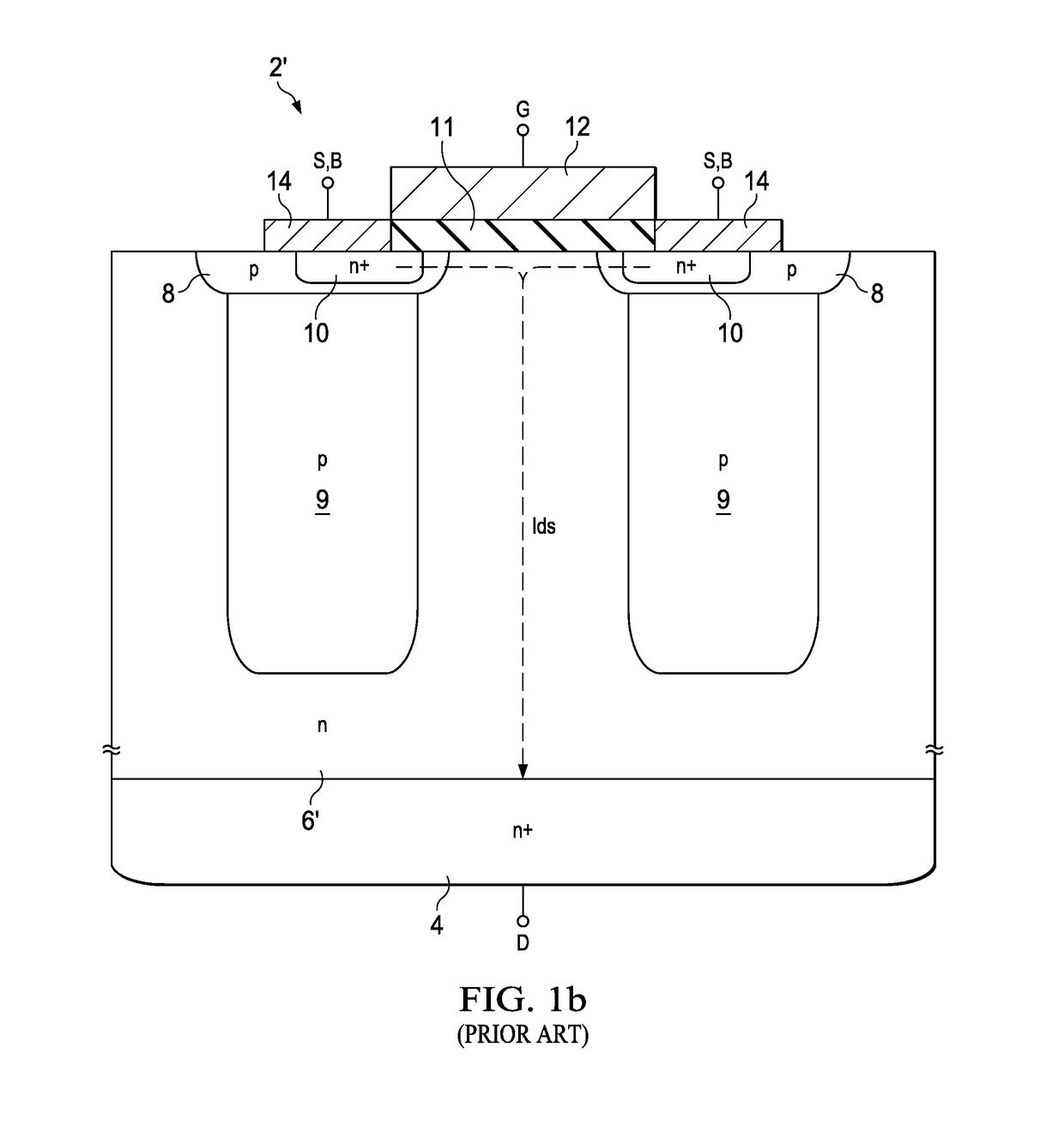

Lateral short-channel dmos, method of manufacturing the same, and semiconductor device

InactiveUS20050062125A1Lower resistanceReduce resistanceSemiconductor/solid-state device manufacturingSemiconductor devicesHigh concentrationDevice material

A lateral short-channel DMOS according to the present invention is a lateral short-channel DMOS in which an N−-type semiconductor region is formed, with the surface of the N−-type semiconductor region becoming almost completely depleted during reverse bias. The lateral short-channel DMOS 10A according to the present invention includes an N−-type epitaxial layer 110 that is formed in one surface of a P−-type semiconductor substrate 108, a P-type well 114 that is formed in the surface of the N−-type epitaxial layer 110 and includes a channel forming region C, an N+-type source region 116 that is formed in a surface of the P-type well 114, an N+-type drain region 118 formed in a surface of the N−-type epitaxial layer 110, and a gate electrode 122 formed via a gate insulating film 120 in at least an upper part of the channel forming region C out of a region from the N+-type source region 116 to the N+-type drain region 118. The lateral short-channel DMOS 10A according to the present invention also includes an N+-type well 140 that is formed in a surface of the N-type epitaxial layer 110 and includes a higher concentration of N-type dopant than the N−-type epitaxial layer 110 and a lower concentration of N-type dopant than the N+-type drain region 118, with the N+-type drain region 118 being formed in a surface of this N+-type well 140. As described above, according to the present invention, ON resistance is reduced while maintaining high breakdown characteristics, so that it is possible to provide a lateral short-channel DMOS with high breakdown characteristics and superior current driving characteristics.

Owner:SHINDENGEN ELECTRIC MFG CO LTD

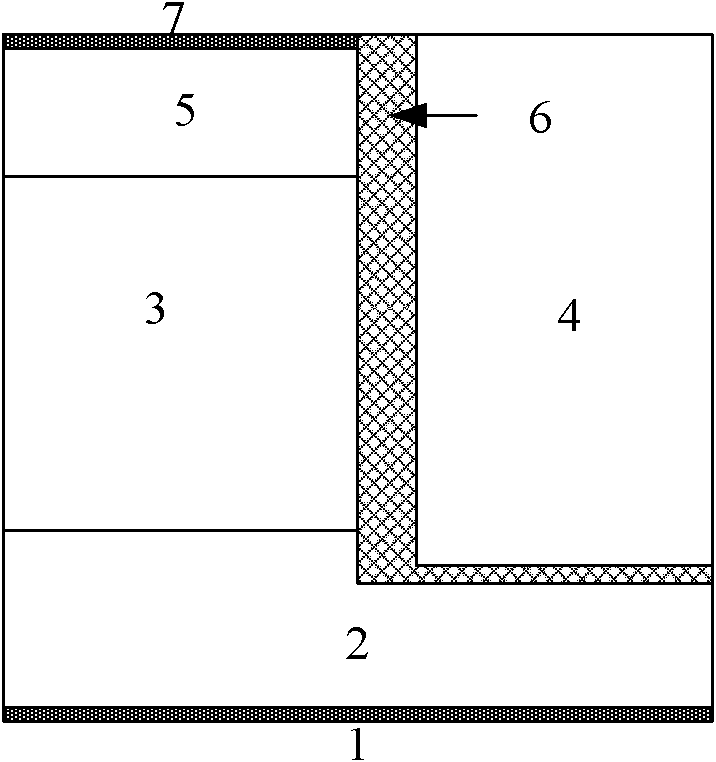

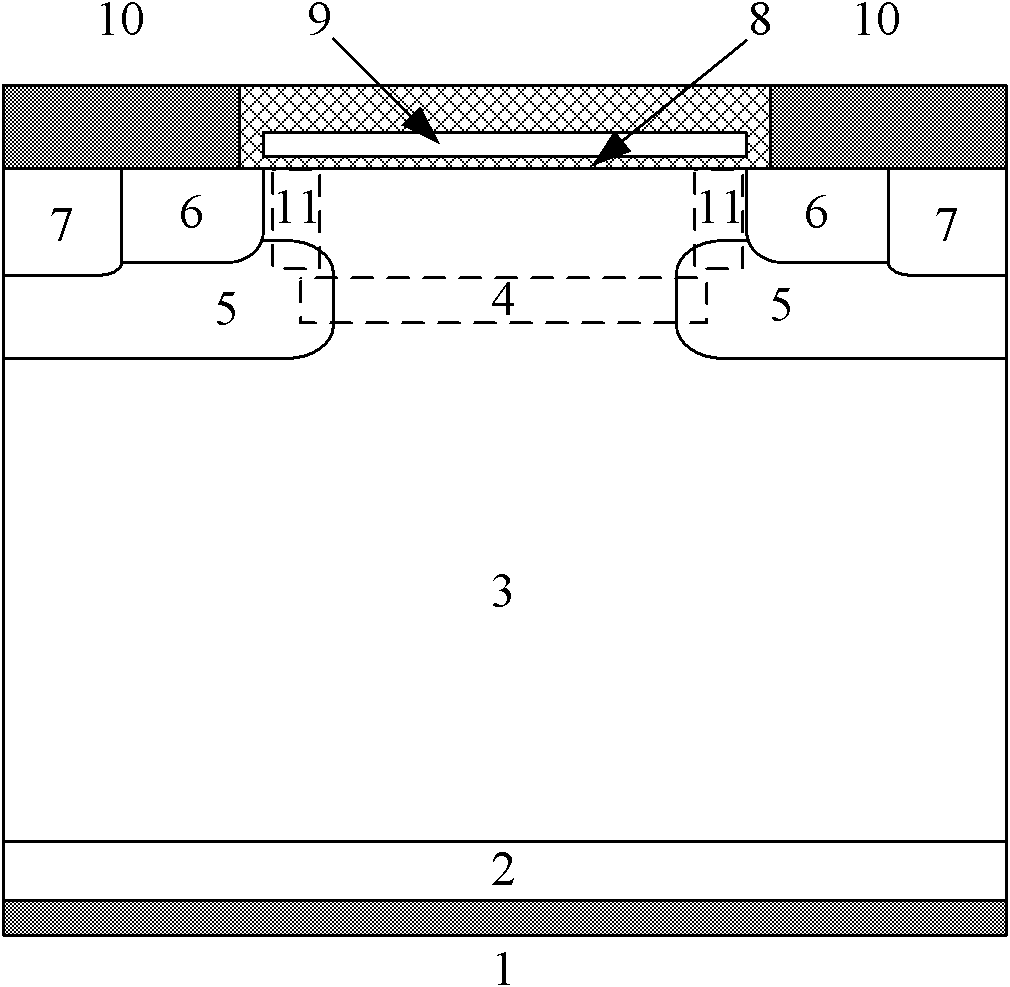

Thin film SOI thick grid oxygen power device with grid field plate

InactiveCN101221986AFast switching speedImprove breakdown characteristicsSemiconductor devicesPeak valueOxygen

The invention belongs to the semi-conductor power device technical field. A SOI layer of the device is thinner (1to 2um); a grid oxide layer is thick (100 to 800nm); a grid field plate gets across a grid and extends above a drift region. An active expansion region positioned below the thick grid oxide layer and connected with a source region can be also arranged in the body of the device to assure the more effective formation of the whole device. The grid oxide layer of the invention is thicker, can bear high grid-source voltage and meet the need of a level displacement circuit; the SIO layer is thinner, can decrease the parasitic effect of the device and reduce consumption; through adding the grid field plate striding over the grid on the surface of the power device, the depletion of the drift region can be increased, the electric field peak value on the silicon surface at the tail end of the grid is decreased, the breakdown characteristic of the device is improved, further more the concentration of the drift region is helped to improve, and the on-state resistance of the device is decreased. The invention has the advantages of low parasitic effect, fast speed, low power consumption, strong radiation-resistant ability and so on, and is compatible with the standard process. By adopting the invention, various high-voltage, high-speed and low conducting loss devices of excellent performance can be produced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

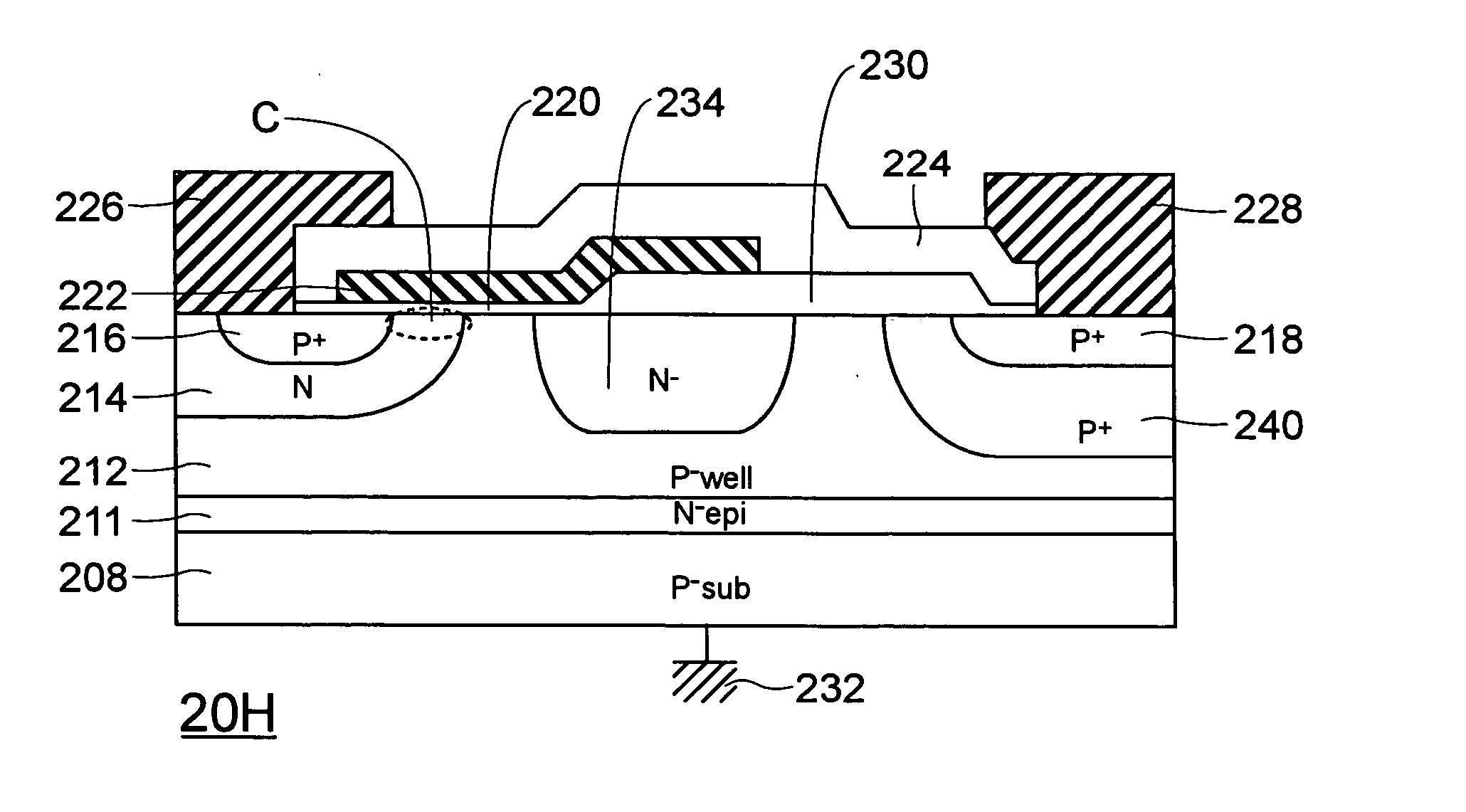

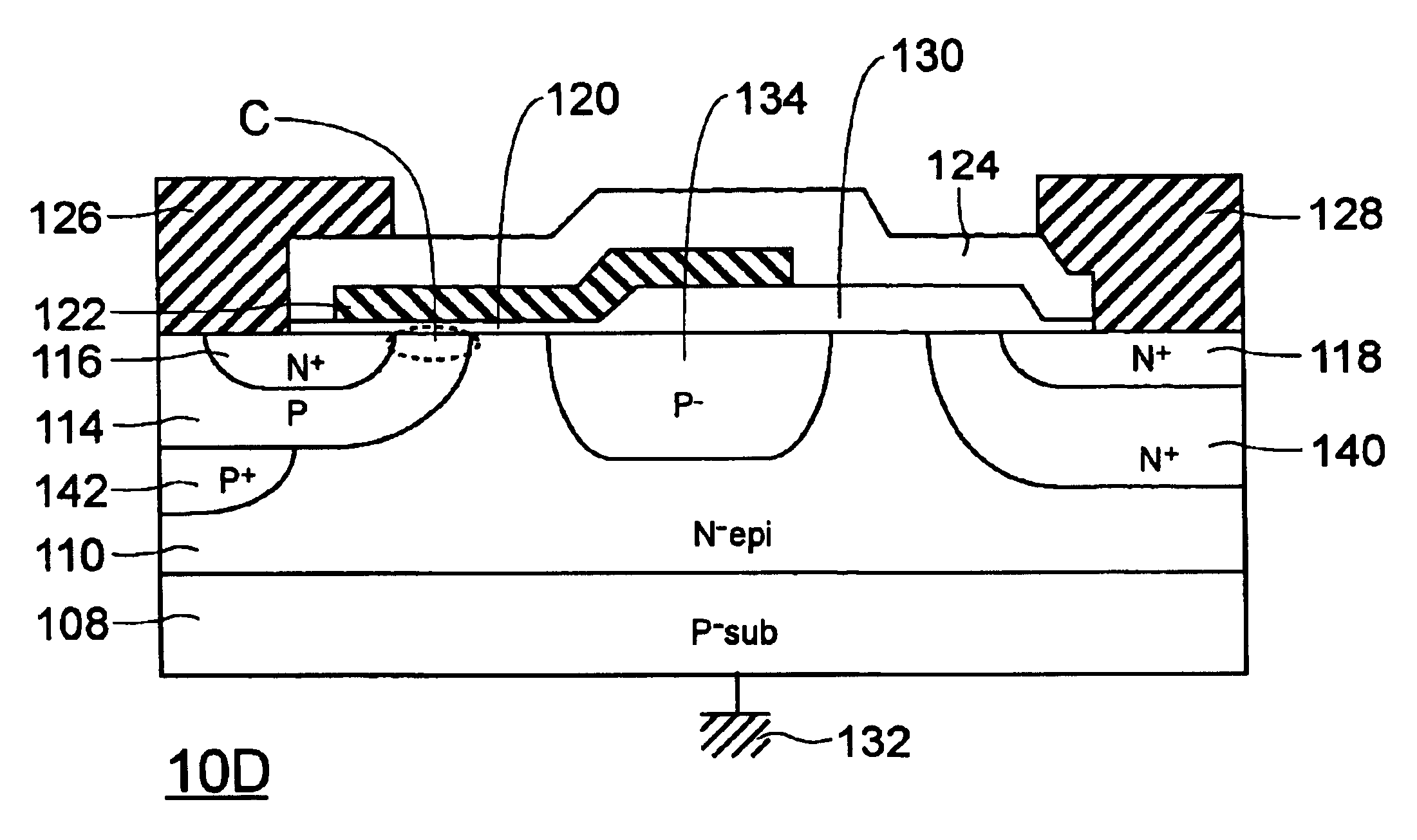

Lateral short-channel DMOS, method of manufacturing the same, and semiconductor device

InactiveUS6946705B2Improve breakdown characteristicsSuperior current driving characteristicSemiconductor/solid-state device manufacturingSemiconductor devicesDopantSemiconductor

A lateral short-channel DMOS includes an N−-type epitaxial layer 110 in a P−-type semiconductor substrate 108, a P-type well 114 in the N−-type epitaxial layer 110 with a channel forming region C, an N+-type source region 116 in the P-type well 114, an N+-type drain region 118 in N−-type epitaxial layer 110, and a gate electrode 122 formed via a gate insulating film 120 in at least an upper part of the channel forming region C out of a region from the N+-type source region 116 to the N+-type drain region 118. The lateral short-channel DMOS also includes an N+-type well 140 that is formed in the N−-type epitaxial layer 110 and includes a concentration of N-type dopant higher than the N−-type epitaxial layer 110 and lower than the N+-type drain region 118, with the N+-type drain region 118 being formed in this N+-type well 140.

Owner:SHINDENGEN ELECTRIC MFG CO LTD

Semiconductor device with improved breakdown properties and manufacturing method thereof

ActiveUS7709889B2Improve breakdown characteristicsImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringSemiconductor

Owner:AMI SEMICON BELGIUM

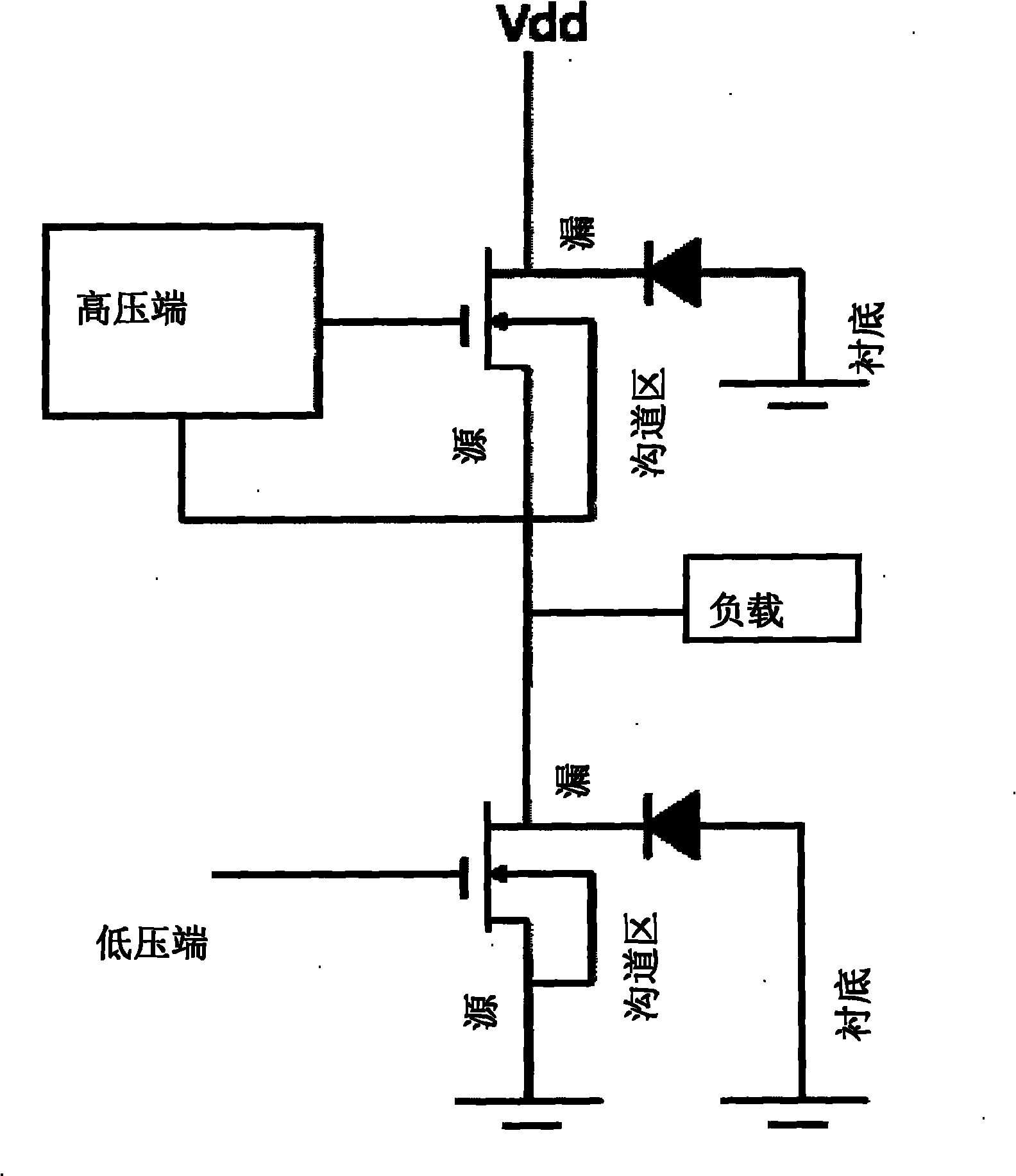

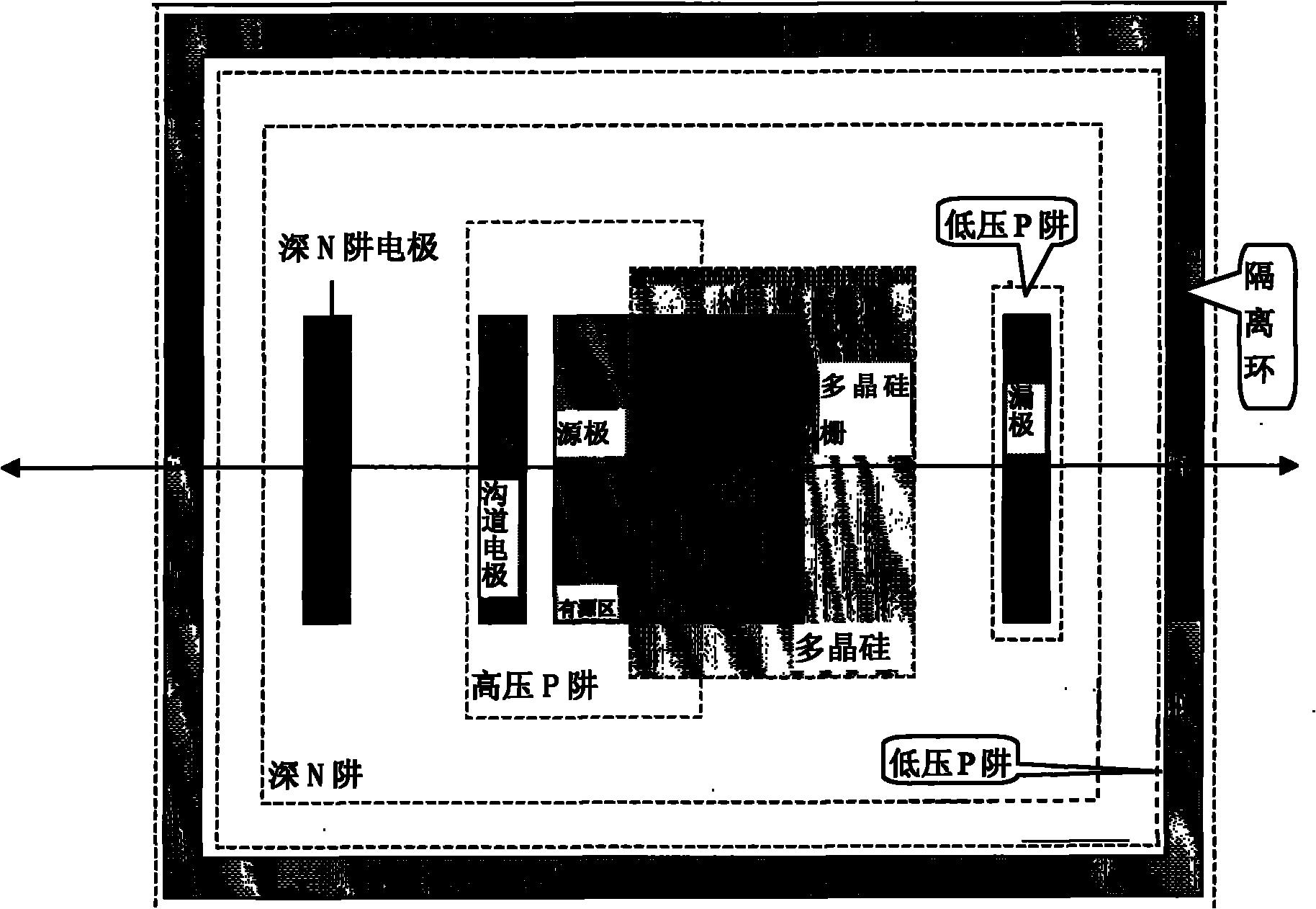

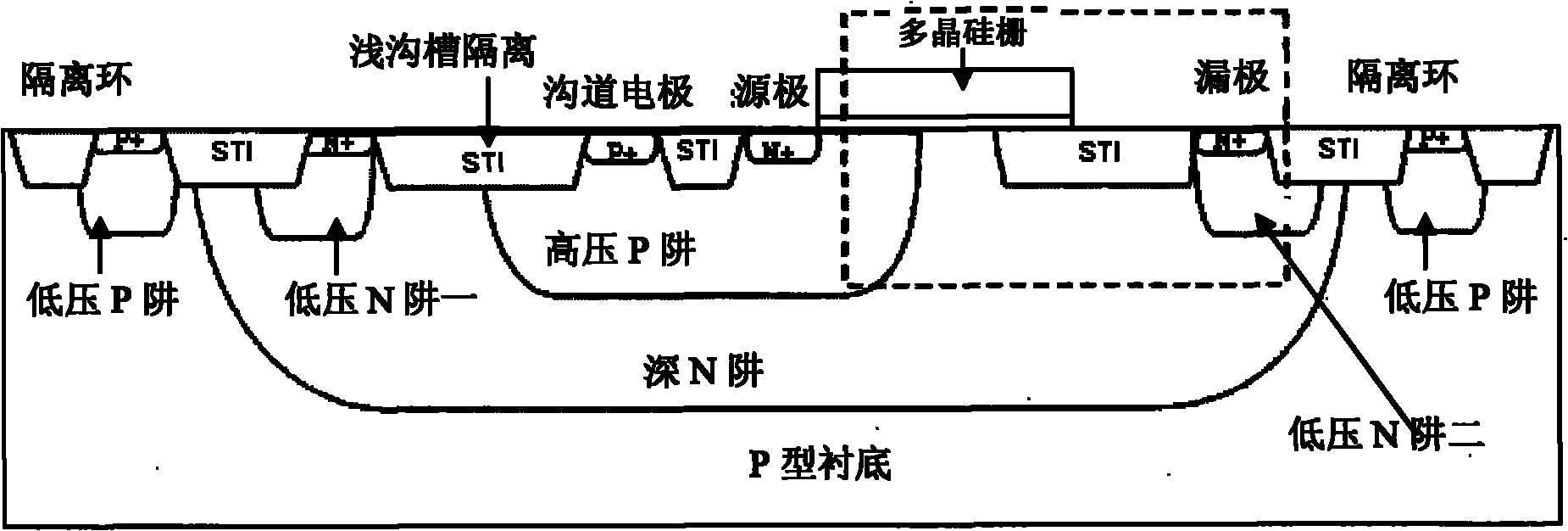

High-voltage insulation type LDNMOS (laterally diffused metal oxide semiconductor) device and manufacture method thereof

ActiveCN102136493AImprove breakdown characteristicsImprove Rdson featuresSolid-state devicesSemiconductor/solid-state device manufacturingLow voltageSilicon oxide

The invention discloses a high-voltage insulation type LDNMOS (laterally diffused metal oxide semiconductor) device, which comprises a deep N well, a channel region, a source region, a drain region, and a polysilicon fence. Shallow channel insulation is formed in the deep N well between the drain region and the channel region; a high voltage P well and a low voltage N well are formed in the deep N well at the bottom part of the shallow channel insulation; and a drift region of the device consists of the deep N well between the drain region and the channel region, the low voltage N well and the high voltage P well. The invention also discloses a manufacture method for the high-voltage insulation type LDNMOS (laterally diffused metal oxide semiconductor) device. The invention can be realized by only alternating the domains of a high voltage P well of a current high-voltage insulation type LDNMOS and a low voltage N well of a current SONOS (silicon oxide nitride oxide semiconductor) without needing to add a photomask; therefore, the puncturing characteristic of the high voltage device and the on resistance characteristic of the source and the drain can be optimized simultaneously, and the cost can be greatly reduced.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

AlGaN/GaN HEMT multilayer field plate device of concave grid groove and manufacturing method thereof

InactiveCN101276837AImprove breakdown voltageEliminate collapseSemiconductor/solid-state device manufacturingSemiconductor devicesSemiconductor materialsGrid connection

The invention relates to the technical field of microwave power device in semiconductor materials, discloses a AlGaN / GaN HEMT multilayer field board device of recessed grid, and meanwhile discloses a method for manufacturing AlGaN / GaN HEMT multilayer field board device of the recessed grid; on the basis of common AlGaN / GaN HEMT device manufacturing process, the method comprises the steps of photo-etching grid images after forming Ohm contact of a source electrode and a drain electrode, etching AlGaN extension layer of a part of the grid image, after evaporating grid metal, firstly manufacturing a grid connection field board and then a source connection field board to form the AlGaN / GaN HEMT multilayer field board device of the recessed grid. Utilization of the invention can efficiently improve puncturing characteristic, transconductance and threshold value voltage of the AlGaN / GaN HEMT device, and at the same time of improving the device plus, availably suppress phenomenon of current collapse of the AlGaN / GaN HEMT device.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

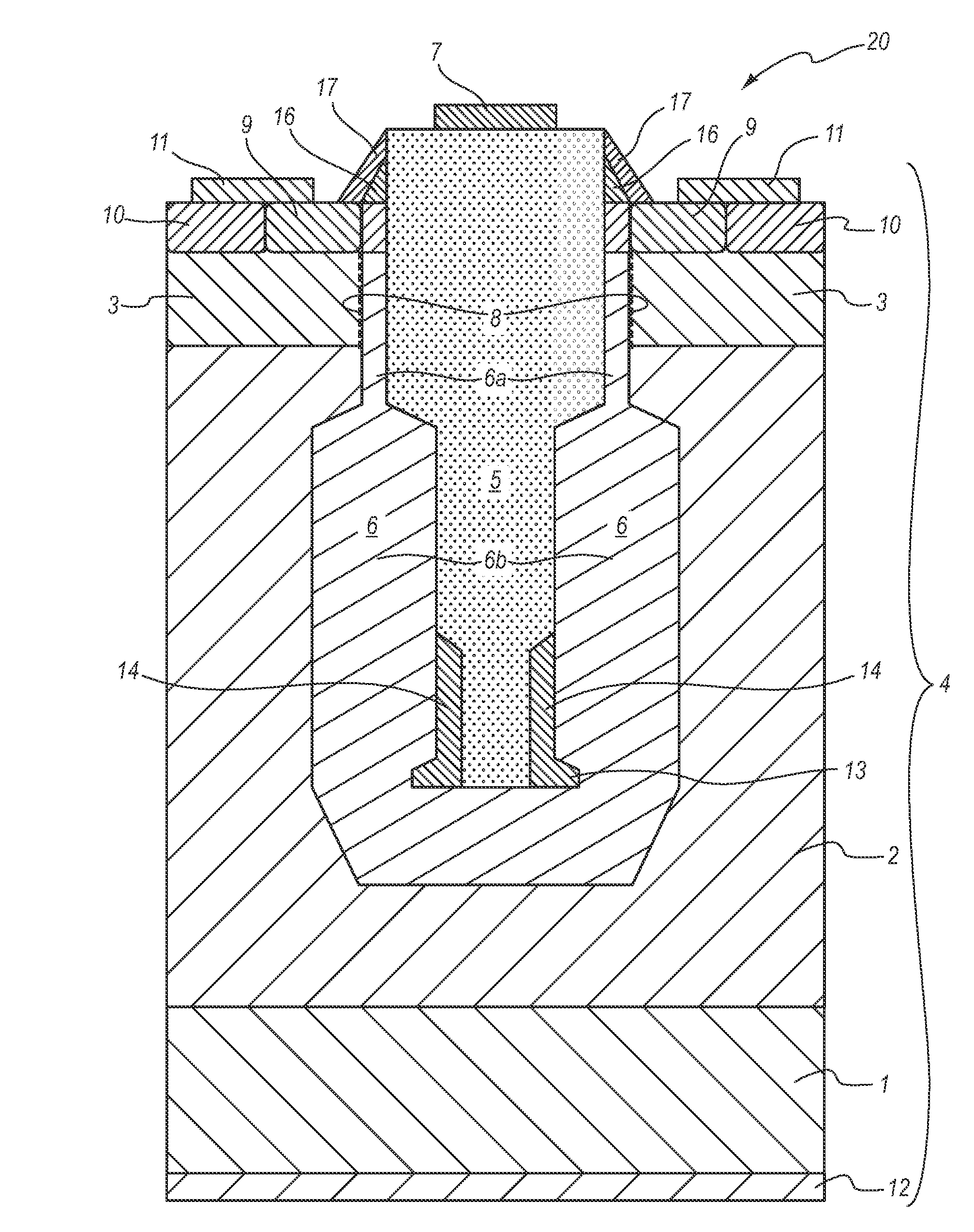

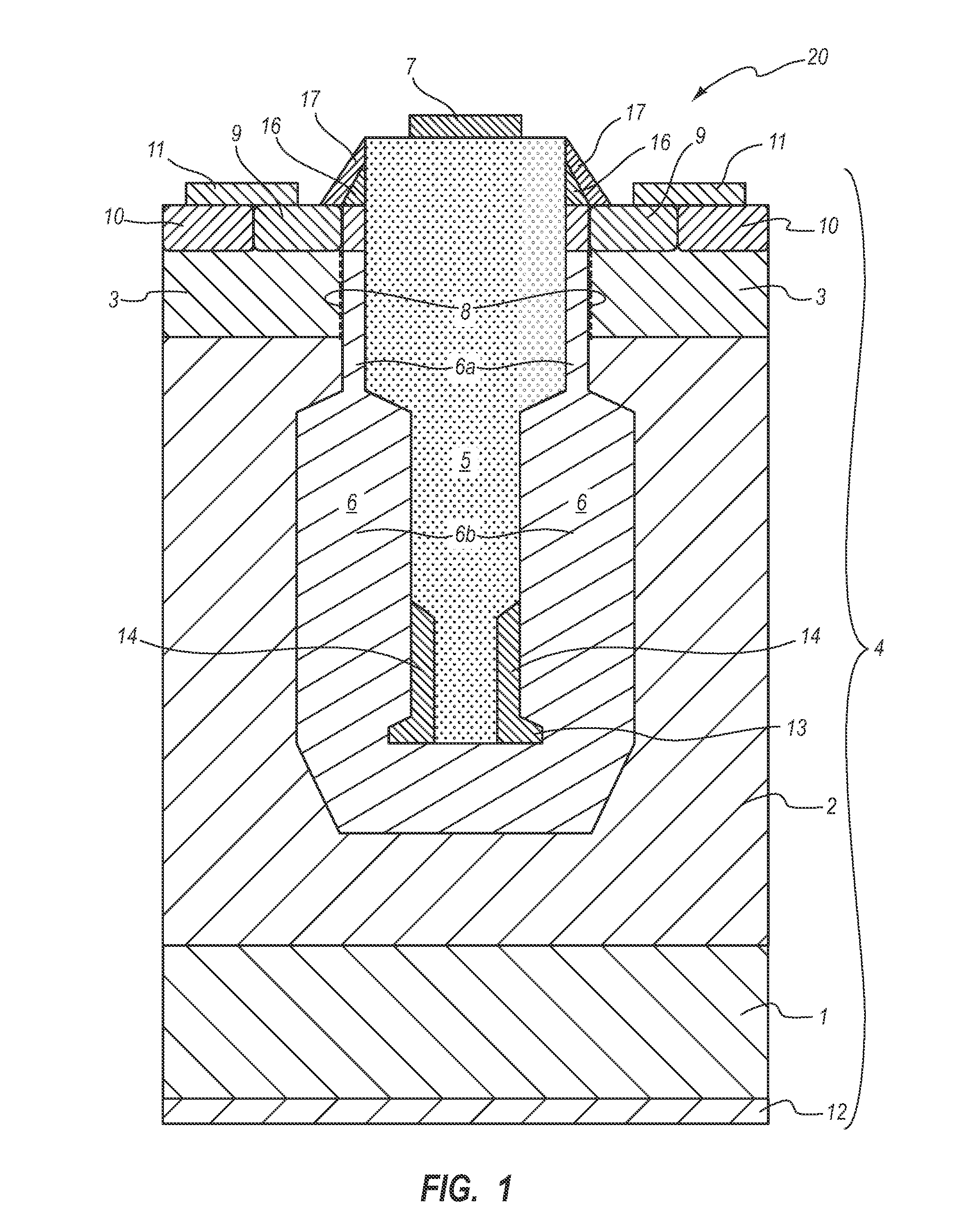

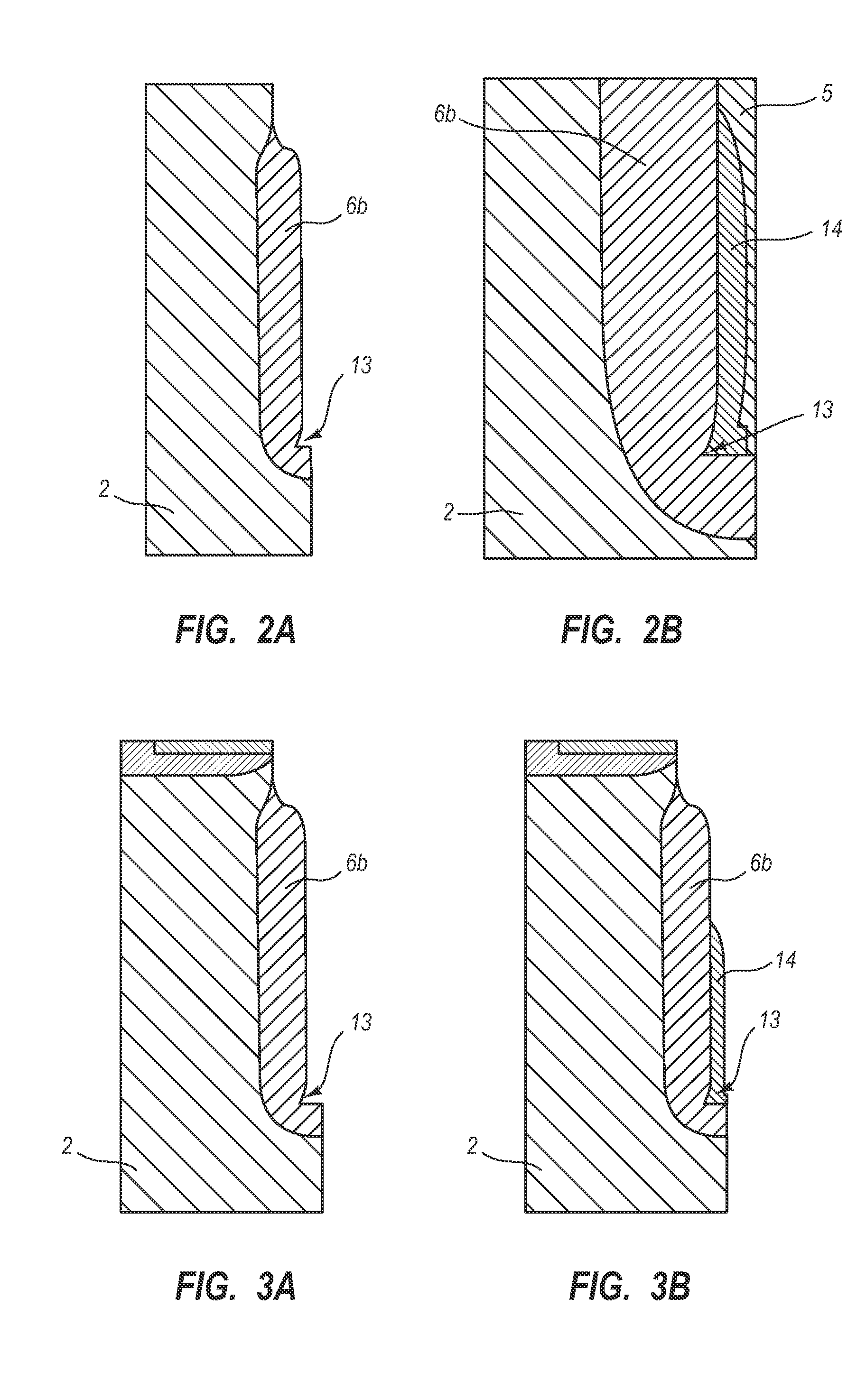

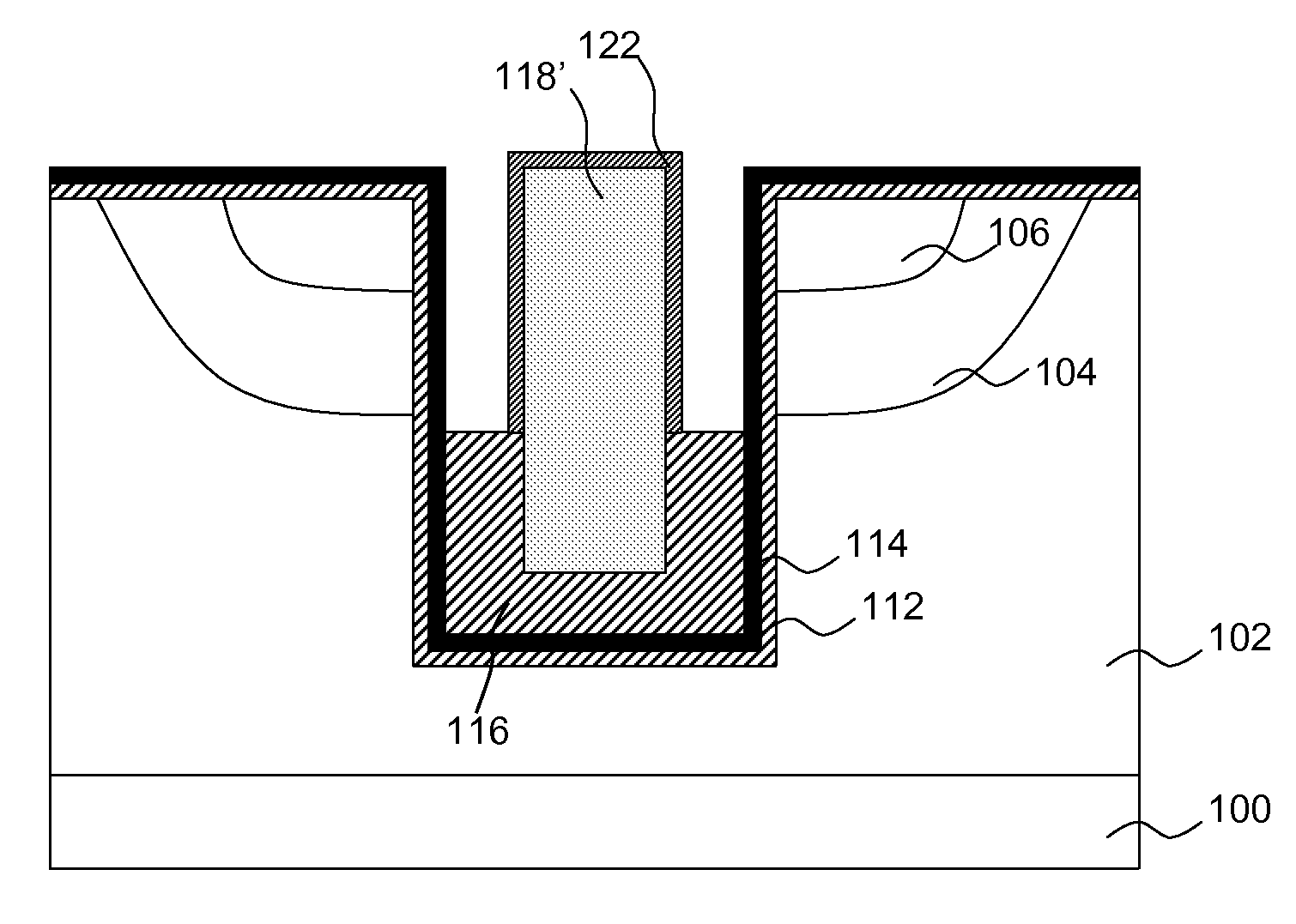

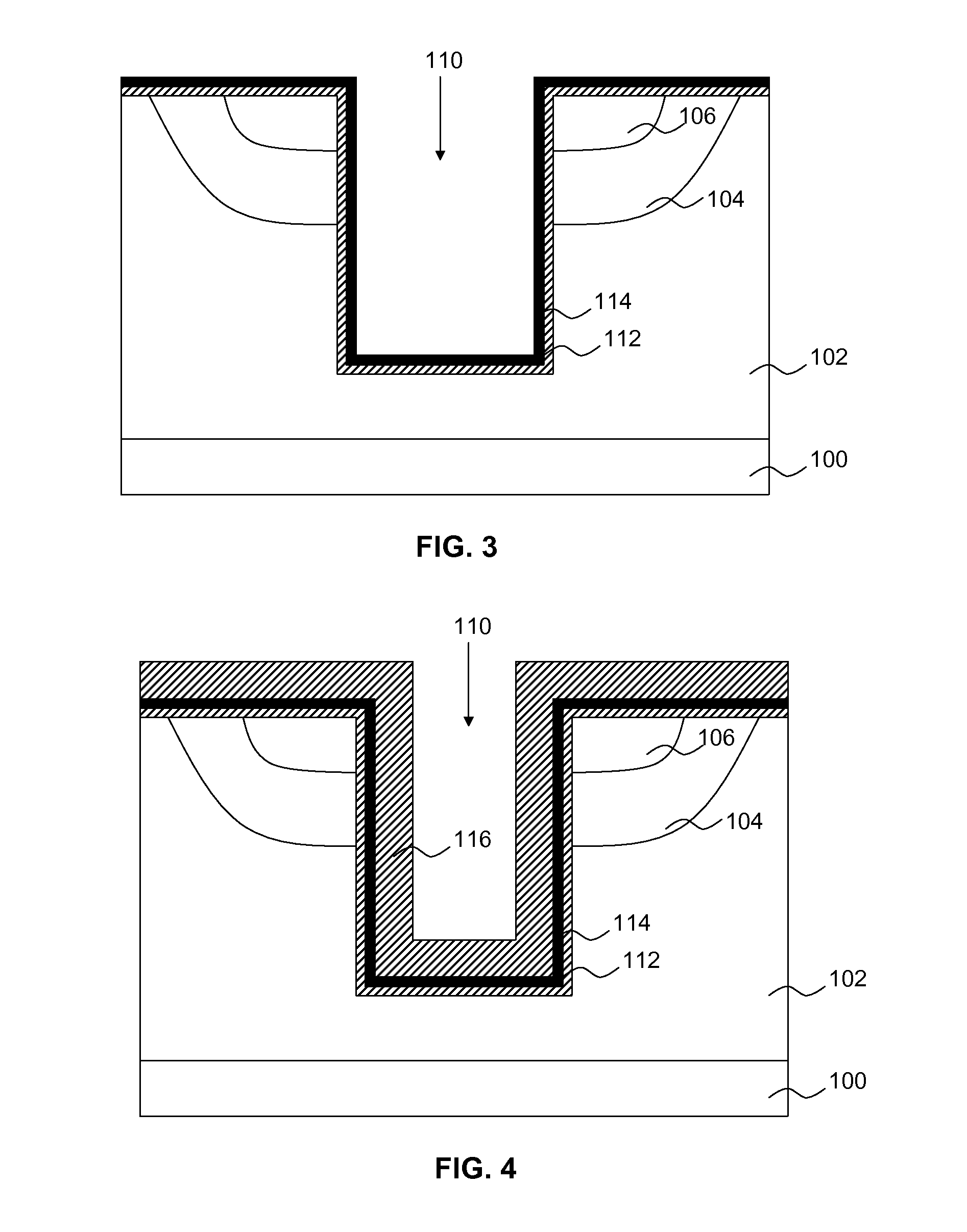

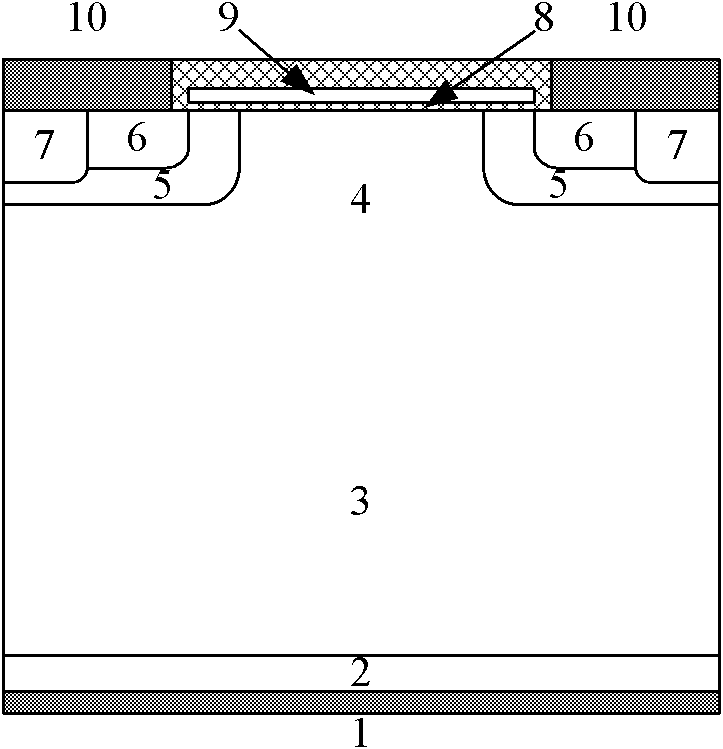

Vertical transistor manufacturing method and vertical transistor

InactiveUS20120168859A1Improve breakdown characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricGate dielectric

A method is disclosed of manufacturing a vertical transistor which comprises providing a substrate including a vertical stack of regions including a source region separated from a drain region by a channel region; forming a trench in said substrate, said trench at least partially extending into said vertical stack of regions; lining said trench with a stack comprising a gate dielectric liner, an etch protection layer and a further insulating layer; filling the remainder of the trench with a shield electrode material; exposing a top portion of the shield electrode material by removing the further insulating layer to a first depth in said trench; forming a inter electrode dielectric on the exposed shield electrode material; removing the etch protection layer to the first depth from said trench; and forming a gate electrode in said trench between the inter electrode dielectric liner and the exposed portion of the gate dielectric liner.

Owner:NXP BV

Low-voltage buried channel VDMOS (vertical double-diffused metal oxide semiconductor) device

InactiveCN102097479AImprove breakdown voltageLower breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesLow voltageSemiconductor structure

The invention provides a low-voltage buried channel VDMOS (vertical double-diffused metal oxide semiconductor) device, belonging to the technical field of semiconductor devices. The device has the following beneficial effects: the channel resistance is greatly reduced by adopting the buried layer channel structure; the MOS gate oxide layer is very thin; the MOS surface field effect is utilized; an accumulation layer is formed when forward voltage is applied between the gate and the source while a depletion layer is formed when backward voltage is applied between the gate and the source; and electron or hole accumulation occurs on the lower semiconductor surface of the gate oxide layer under low forward gate voltage, thus acquiring extremely low resistance and good switch characteristics. The device can be widely applied to portable power supplies and CPU power supply systems.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Thin layer SOILIGBT device

InactiveCN101431097AReduce power consumptionStrong radiation resistanceSemiconductor devicesThin layerConduction loss

The invention relates to a folium SOILIGBT device which belongs to the technical field of semiconductor power device. The thickness of SOI layer of the device is 1 mu m to 2 mu m; a cavity barrier layer is arranged between a body zone and a drift zone; the cavity is blocked in the drift zone to the utmost extent; and then the cavity consistence near the side of a cathode in the drift zone is increased; and conduction losses of the device are reduced. A P type depletion zone can also be added near the cavity barrier layer to assist to deplete the N type cavity barrier layer, and so drift zone depletion is strengthened when the device bears a high pressure, and breakdown characteristics of the device are improved. The folium SOILIGBT device has the advantages of small parasitics, fast speed, low power consumption, strong anti-radiation performance, and is compatible with the standard process. An LIGBT device having good performance, high pressure, high speed and low conduction losses can be made when the folium SOILIGBT device is adopted.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

Horizontal dispersion oxide semiconductor of heterogeneous bar multi-step field electrode board

InactiveCN101079446AIncrease the number ofIncrease the average electric fieldSemiconductor devicesDouble diffusionTransconductance

The invention discloses a lateral double diffusion metal oxide semiconductor of a heterogeneous grip multi step field polar plate, which is characterized by the following: equipping with the heterogeneous double-grip structure of the source grip and the leakage grip; composing the multi step field polar plate of the first step field polar plate and the second step field polar plate, connecting with the source grip, the leakage grip, the first step field polar plate and the second step field polar plate orderly; equipping with the source and the leakage in the channel trap section and the trap drift section; equipping with grip oxide layer among the source grip, the leakage grip and the channel trap section, equipping with the trap contact hole in the channel trap section; equipping the field oxide layer among the first step field polar plate, the second step field polar plate and the trap draft section; covering the oxide layer on the multi step field polar plate; making the channel trap section and the trap draft section on the underlay. The invention improves the driving current and the transconductance, which reduces the conducting resistance and the power consumption.

Owner:ANHUI UNIVERSITY

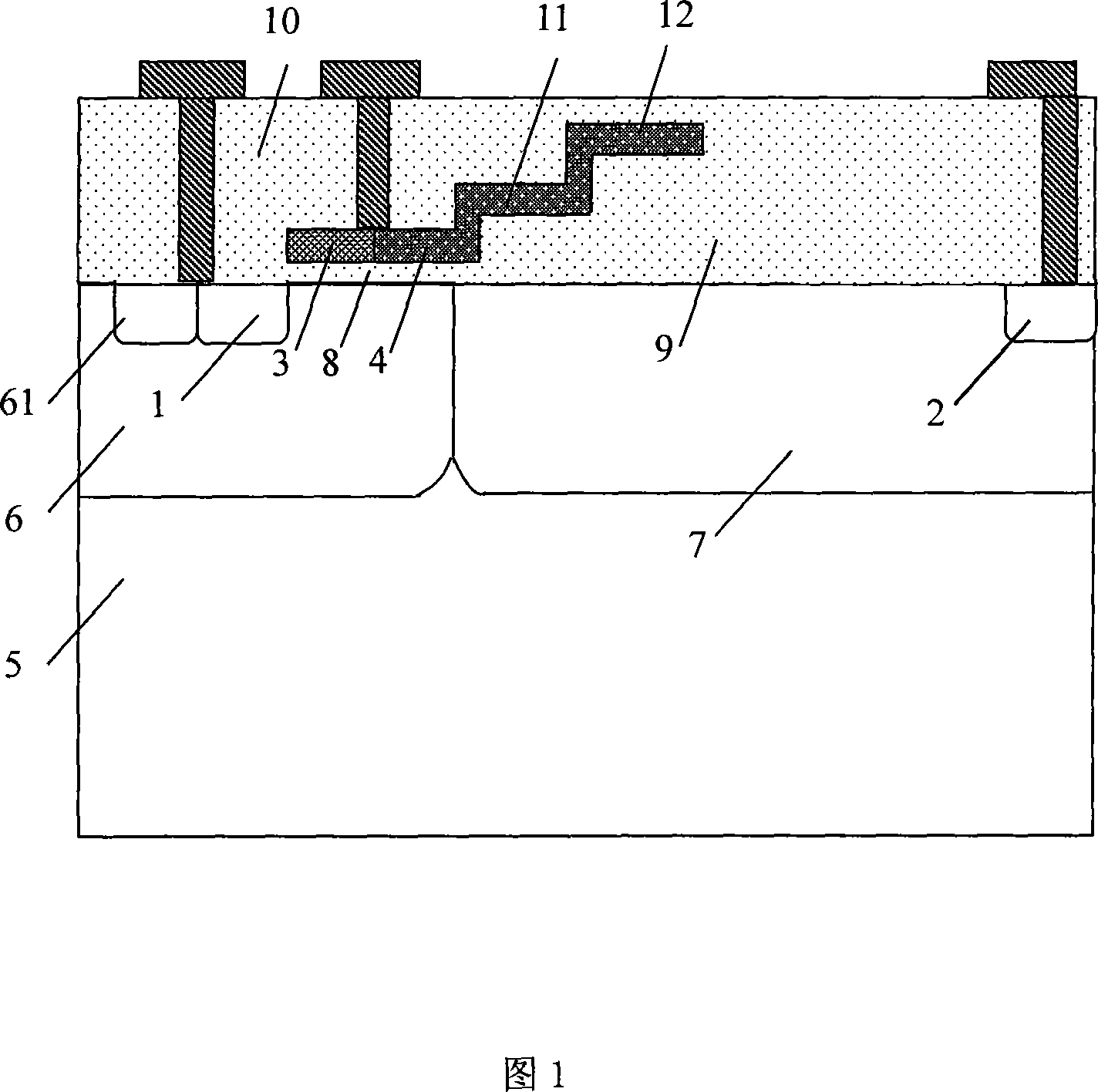

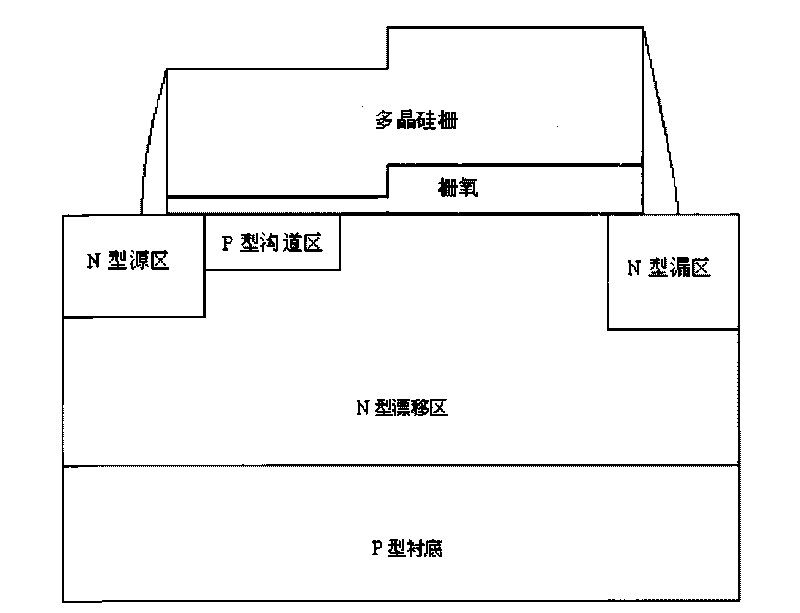

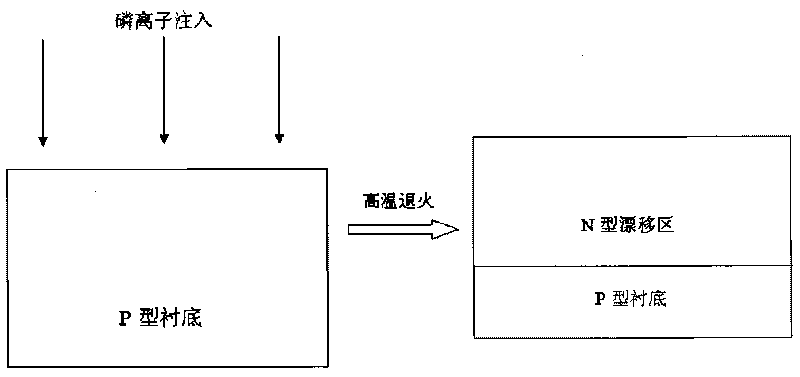

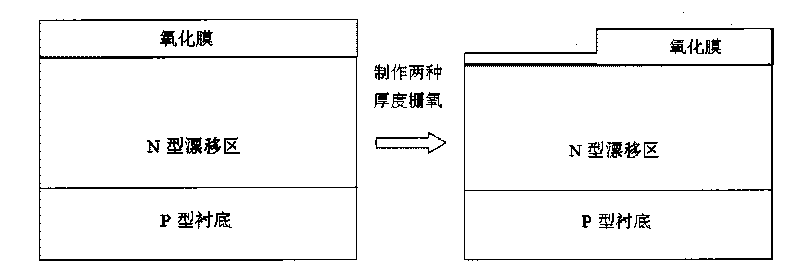

Fully-automatic aligning high-pressure N-shaped DMOS device and manufacturing method thereof

ActiveCN101752251ASmall sizeImprove performanceSemiconductor/solid-state device manufacturingSemiconductor devicesPolycrystalline siliconSilicon oxide

The invention discloses a method for manufacturing a fully-automatic aligning high-pressure N-shaped DMOS device (Diffused metal silicon oxide semiconductor field effect transistor), which comprises the following steps: injecting phosphorus with large energy in a whole N-shaped DMOS area and pushing at a high temperature to form an N-shaped drift region; injecting large-angle boron from a source port of a P-shaped channel after a polysilicon gate is etched and compensating the formed N-shaped drift region; causing the polysilicon gate to cover the whole N-shaped drift region; adopting a heterogeneous gate oxidation layer, adopting the conventional thin gate oxidation layer in a P-shaped channel region and manufacturing a thick gate oxidation layer on the N-shaped drift region nearby a drain electrode. The invention discloses a dully-automatic aligning high-pressure N-shaped DMOS device. The invention can achieve the minimum dimension of the N-shaped DMOS device and obtain a minimum on-state resistance.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

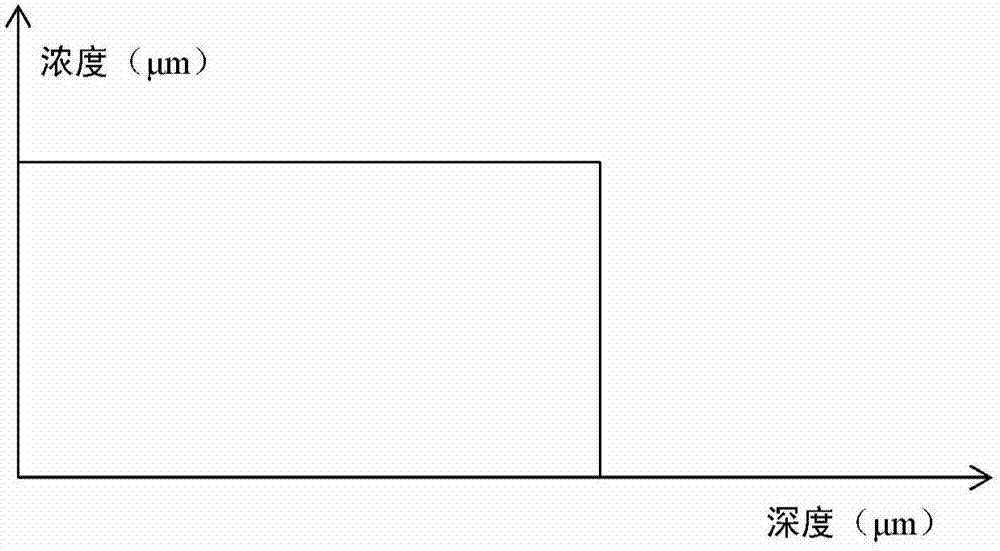

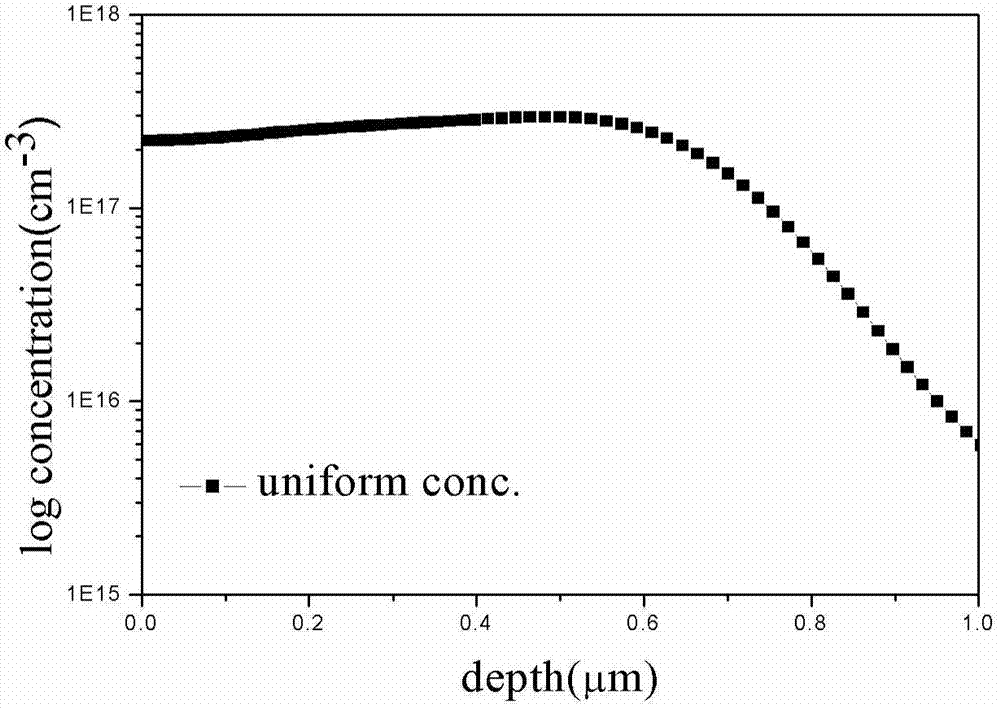

SiC metal oxide semiconductor field effect transistor and production method thereof

ActiveCN104241338AReduce Design ComplexityReduce the possibility of introducing adverse influence factorsSemiconductor/solid-state device manufacturingSemiconductor devicesDielectricEnergy integration

The invention discloses an SiC metal oxide semiconductor field effect transistor and a production method thereof. The SiC metal oxide semiconductor transistor comprises a source electrode, a gate electrode, an SiO2 oxide media dielectric, an N+ source region, a P+ contact region, an optimized doped P well, an optimized doped main junction, an N- epitaxial layer, a buffer layer, an N+ substrate, a drain electrode, optimized doped field limiting rings, a cut-off region and an isolation dielectric. According to the production method of the SiC metal oxide semiconductor field effect transistor, the SiC metal oxide semiconductor field effect transistor of a P- well and terminal structure in optimized concentration distribution is formed by means of Al injection with less energy integration, the production process is relatively simple, and conduction and breakdown characteristics of the transistor are taken into consideration. The SiC metal oxide semiconductor field effect transistor produced by the method can be used for power-switch power supply circuits, DC / DC, AC / DC and DC / AC converters and the like.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

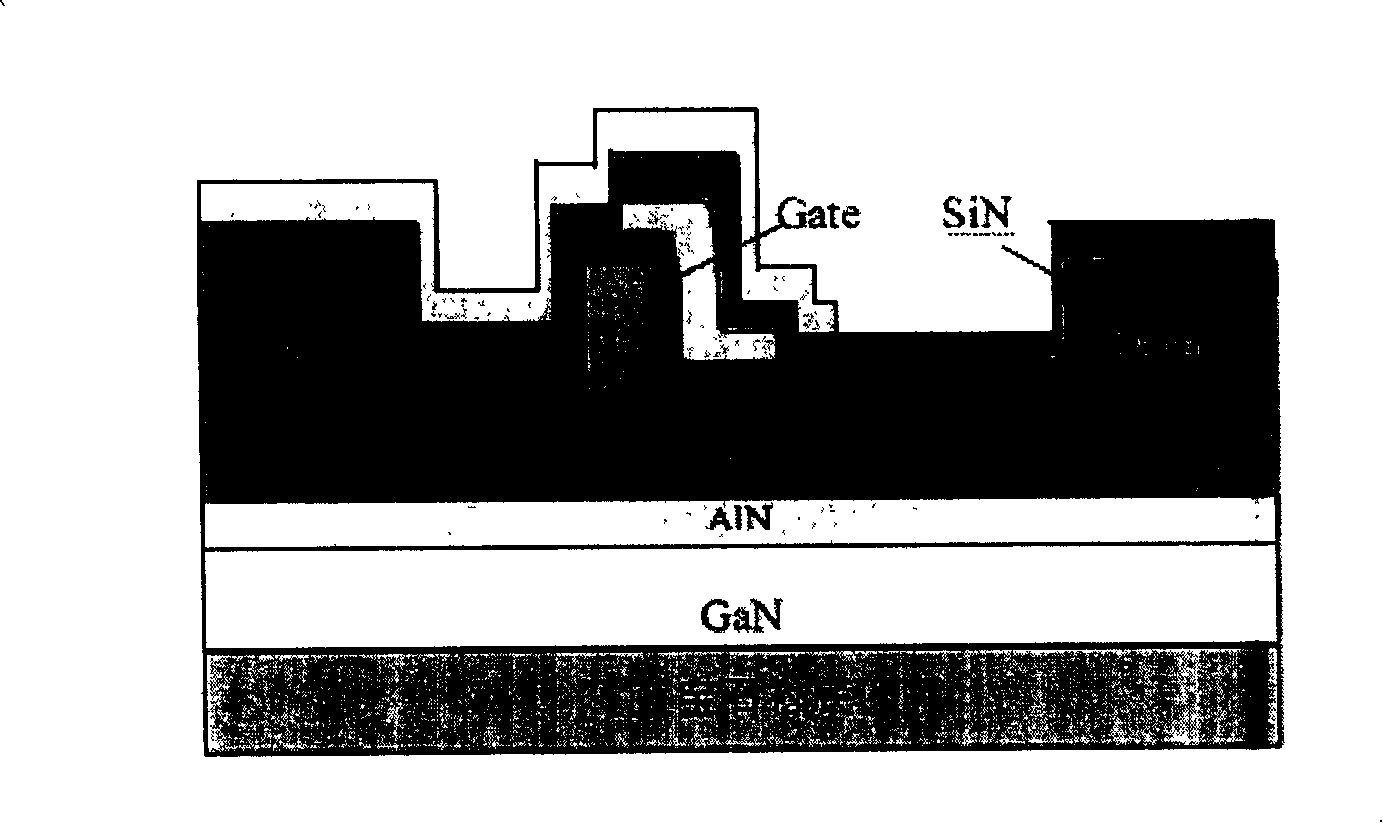

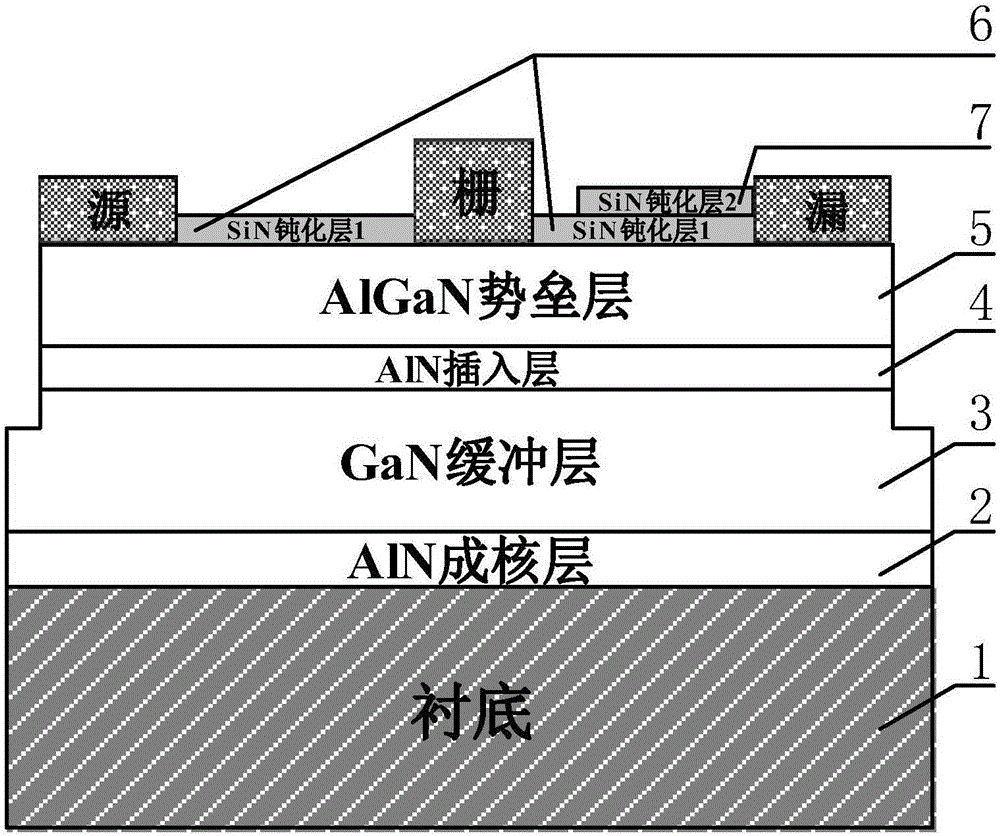

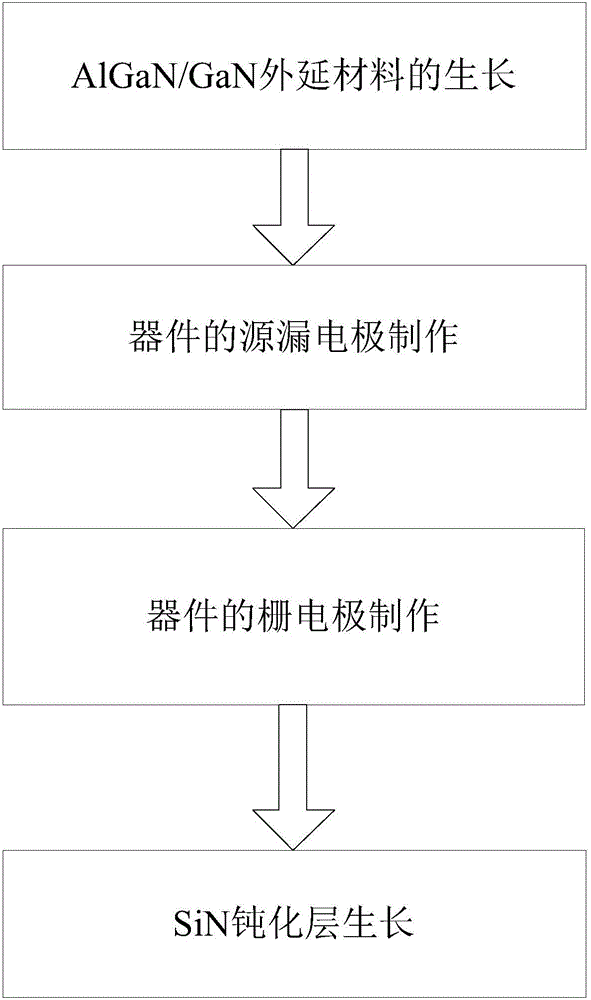

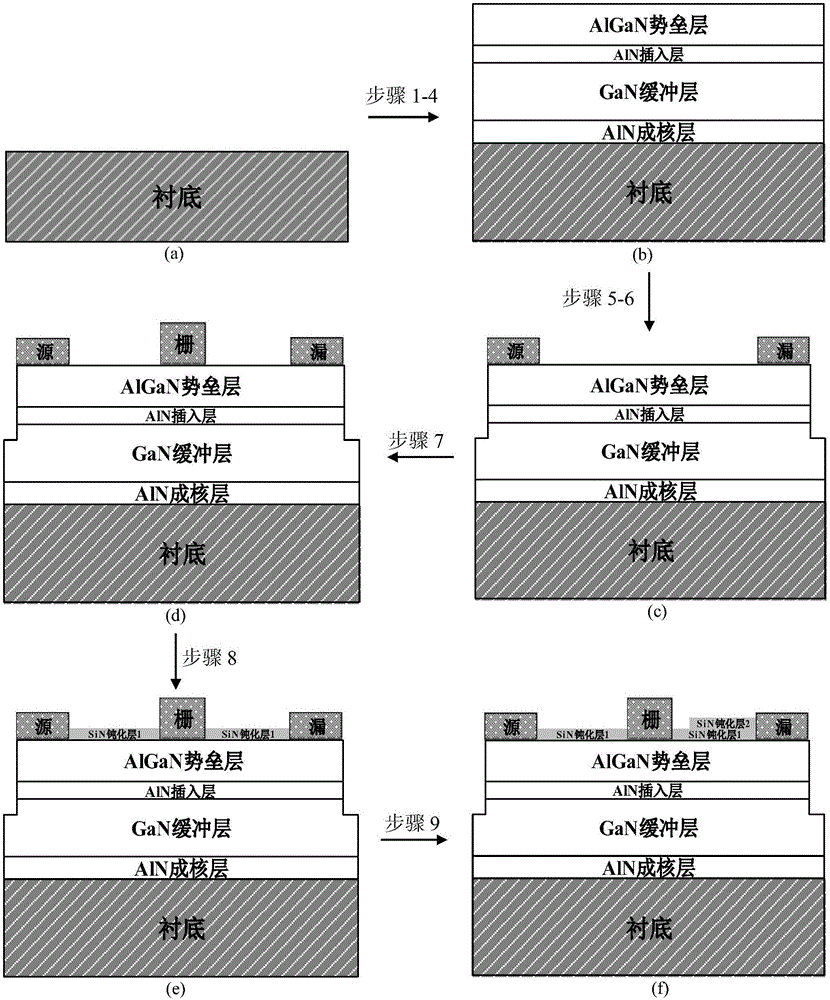

Thin barrier enhanced AlGaN/GaN high-electron-mobility transistor and manufacturing method thereof

ActiveCN105931999AImprove manufacturing precisionAvoid etch damageSemiconductor/solid-state device detailsSolid-state devicesElectron mobilityModulation effect

The invention discloses a thin barrier enhanced AlGaN / GaN high-electron-mobility transistor device and a manufacturing method thereof, and mainly solves the problems of poor breakdown performance and low output current of the existing similar devices. The technical scheme is that a self-aligned technology is introduced in the SiN passivation layer growth process of the device, and an aligned LDD-HEMT is formed by utilizing the modulation effect of thin and thick SiN passivation layers on channels. The device comprises a substrate, an AlN nucleating layer, a GaN buffer layer, an AlN inserting layer, an AlGaN barrier layer, SiN passivation layers and gate, source and drain electrodes which are arranged from the bottom to the top. There are two SiN passivation layers. After completion of manufacturing of the gate electrode, the first SiN passivation layer is deposited by utilizing the self-aligned effect of the gate electrode, and then the second SiN passivation layer is deposited close to the drain electrode region between the gate electrode and the drain electrode so that the aligned LDD structure is formed. Breakdown voltage and saturation output current of the device are high, and damage introduced in the manufacturing process is low.

Owner:西安电子科技大学重庆集成电路创新研究院

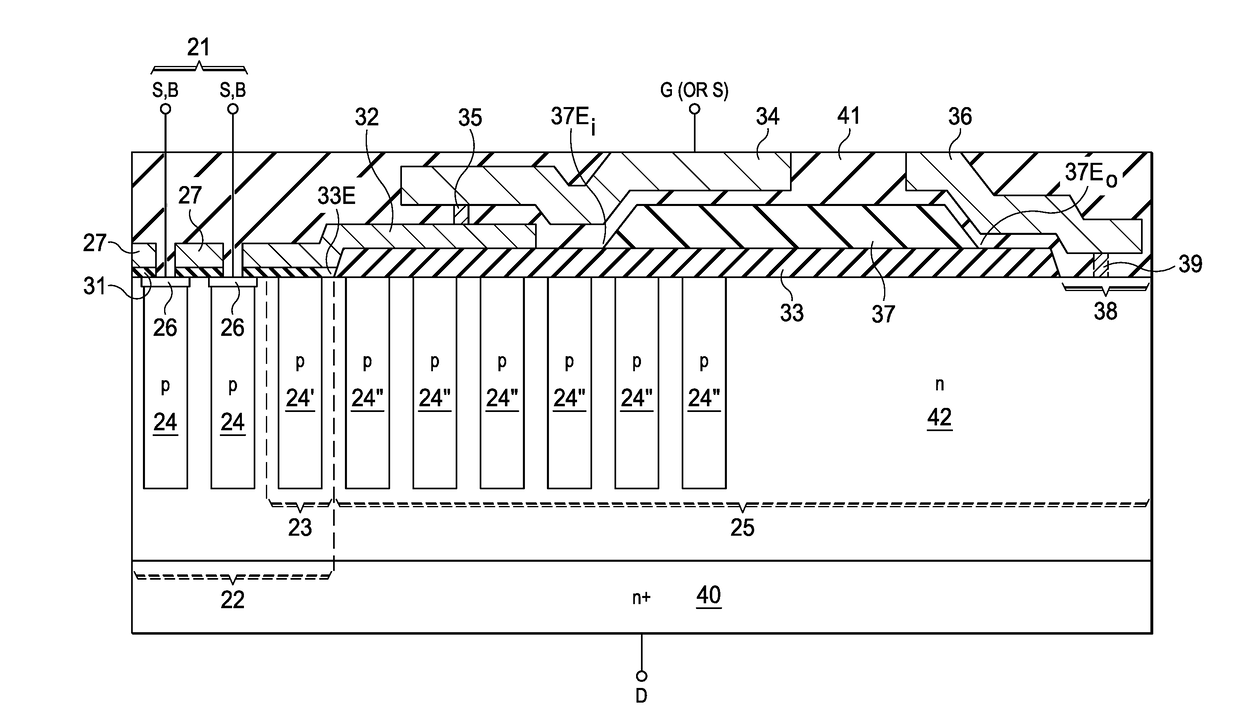

Termination Region Architecture for Vertical Power Transistors

InactiveUS20170098705A1Improve breakdown characteristicsReduced termination region chip areaSemiconductor devicesMOSFETPower switching

A vertical power switching device, such as a vertical superjunction metal-oxide-semiconductor field-effect-transistor (MOSFET), in which termination structures in the corners of the integrated circuit are stretched to efficiently shape the lateral electric field. Termination structures in the device include such features as doped regions, field plates, insulator films, and high-voltage conductive regions and elements at the applied substrate voltage. Edges of these termination structures are shaped and placed according to a 2nd-order smooth, non-circular analytic function so as to extend deeper into the die corner from the core region of the device than a constant-distance path. Also disclosed are electrically floating guard rings in the termination region, to inhibit triggering of parasitic p-n-p-n structures.

Owner:D3 SEMICON

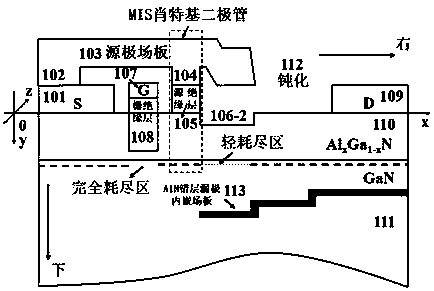

Lateral diffusion eGaN HEMT device integrating reverse diode and embedded drain electrode field plate

ActiveCN110212028AImprove breakdown characteristicsImprove breakdown resistanceSemiconductor devicesLateral diffusionBackward diode

The invention discloses a lateral diffusion eGaN HEMT device integrating a reverse diode and an embedded drain electrode field plate. The device comprises a GaN buffer layer, an AlGaN barrier layer, agate electrode, an under-gate insulating layer, a source electrode, a source electrode extension section, a source electrode field plate, an MIS schottky diode extension section, an MIS schottky diode insulating layer, a p-type GaN or groove, a drain electrode, a passivation layer and an AlN staggered-layer drain electrode embedded field plate, wherein the MIS schottky diode insulating layer is prepared in the middle region, towards the MIS schottky diode extension section and the AlGAN barrier layer surface, of the source electrode field plate; the side, close to the drain electrode, of thediode adopts the p-type GaN or groove, so that the breakdown characteristic of the device is improved; the embedded staggered-layer field plate is adopted below the drain electrode, so that anti-breakdown capability of the drain electrode to the substrate is improved; the design of the staggered layer is suitable for the gradual change distribution of the drain electrode electric field from rightto left, so that the breakdown characteristic of the device is improved; and the source electrode field plate is extended, the gate electrode is wrapped, the MIS schottky diode is formed on the gate drain side, and the diode is made into a block isolation mode, so that the drain electrode current is greatly improved.

Owner:SHANDONG JIANZHU UNIV

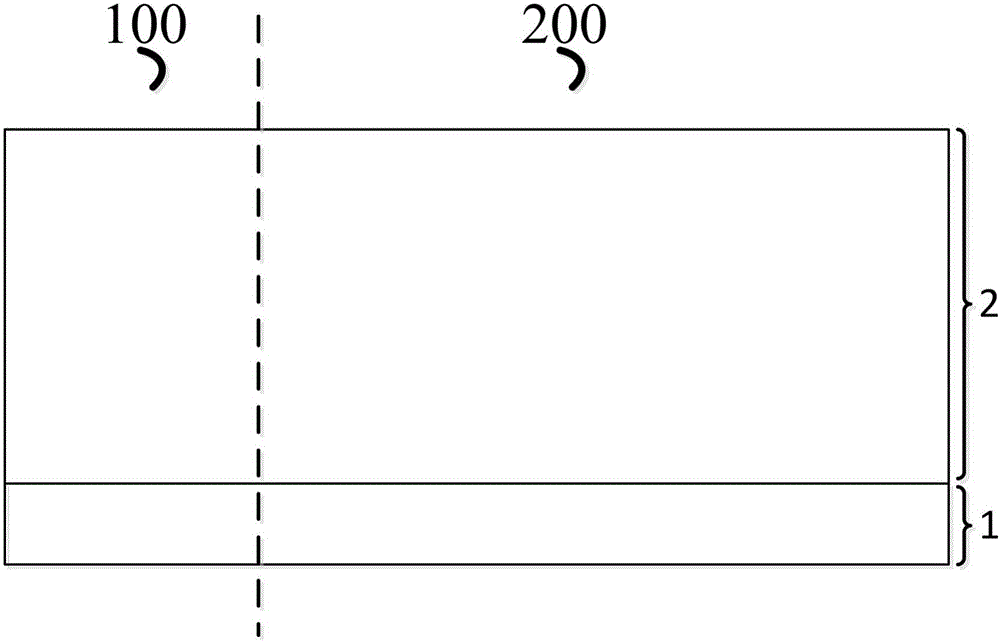

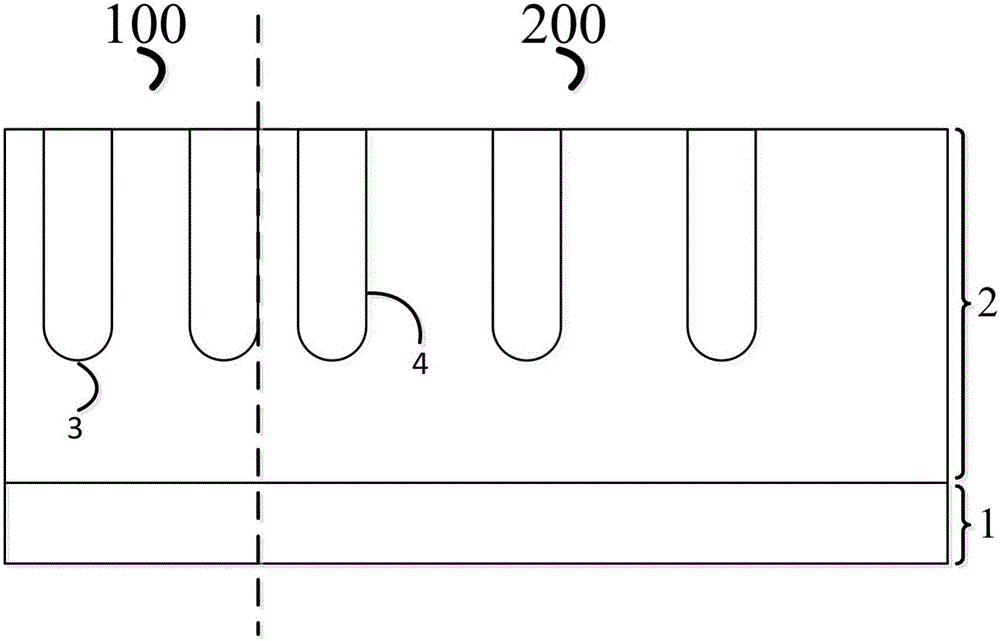

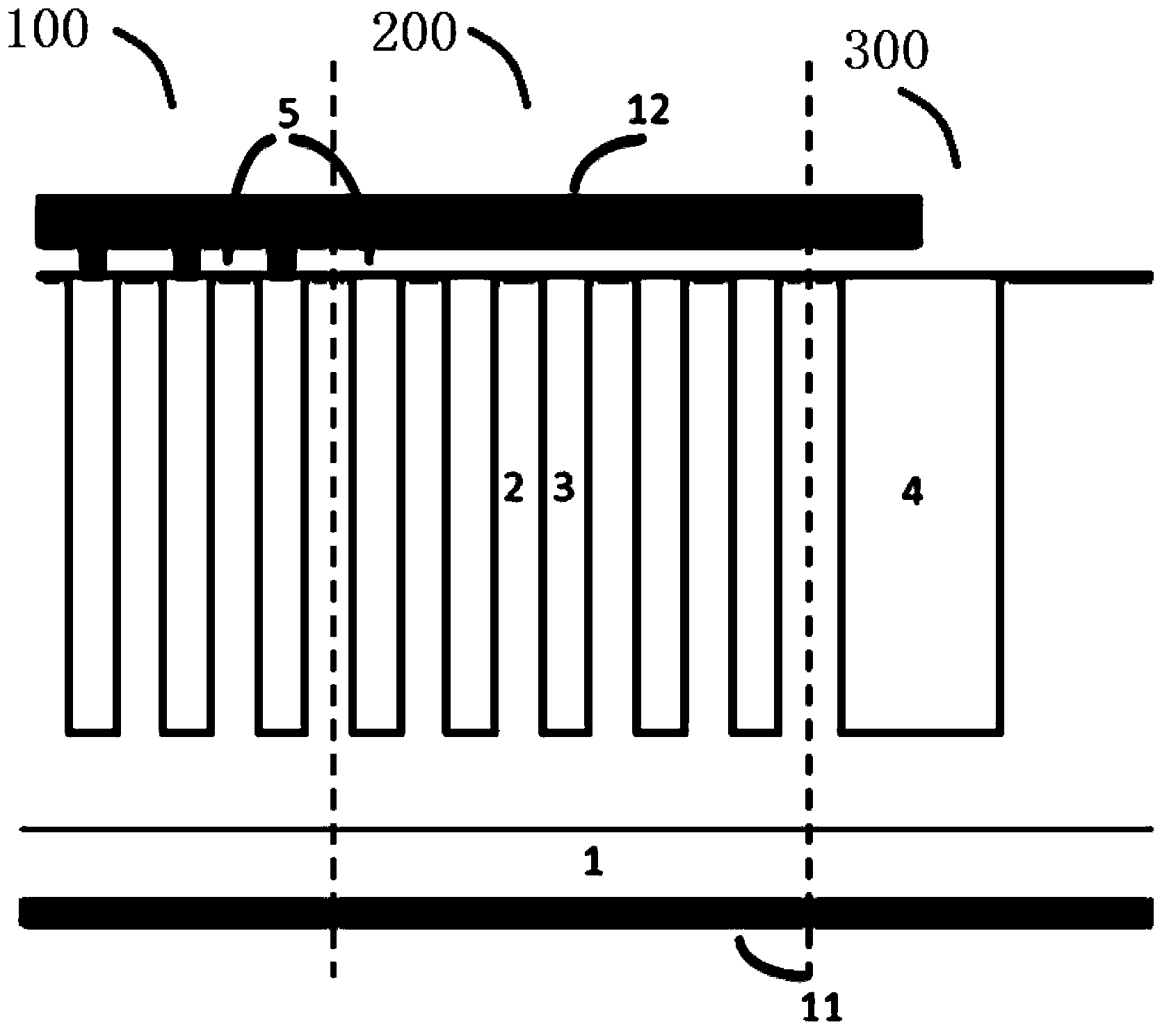

Semiconductor structure suitable for charge coupled device and manufacturing method of semiconductor structure

InactiveCN105679810AIncrease exhaustEnhanced depletionSemiconductor/solid-state device manufacturingSemiconductor devicesElectricitySemiconductor structure

The present invention relates to a semiconductor structure suitable for a charge-coupled device and a manufacturing method thereof. On the cross section of the semiconductor device, a second well region of a second conductivity type is provided in a first conductivity type drift region of a terminal protection region, The second well region of the second conductivity type is located in the upper part of the drift region of the first conductivity type, and a plurality of terminal trenches are arranged in the terminal protection zone, and the terminal trenches are located in the second well region of the second conductivity type, and the depth extends to into the drift region of the first conductivity type under the second well region of the second conductivity type; the termination dielectric body and the terminal conductor are filled in the termination trench, and the termination conductor is the same as the adjacent active region outside the termination trench The second conductivity type second well region on the side is electrically connected. The invention has a compact structure, can effectively improve the high-voltage resistance characteristic of the device, is compatible with the existing technology, reduces the cost, has wide application range, and is safe and reliable.

Owner:WUXI NCE POWER

Junction terminal applied to deep-groove super-junction device and manufacturing method thereof

ActiveCN103887338AEasy to makeImprove breakdown characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesHigh dielectric permittivityEngineering

The invention discloses a junction terminal applied to a deep-groove super-junction device and a manufacturing method thereof. The junction terminal comprises a semiconductor substrate, a first electrode, a semiconductor region, and a second electrode, wherein the first electrode is formed on the lower end surface of the semiconductor substrate; the semiconductor region is formed on the upper end surface of the semiconductor substrate and is provided with a first conductive type; the semiconductor region comprises an active region, a first terminal region, and a second terminal region. The active region is provided with a plurality of first grooves, and the first grooves are internally filled with semiconductor material with a second conductive type; the first terminal region is provided with a plurality of third grooves, and the third grooves are internally filled with semiconductor material with a second conductive type; the second terminal region is provided with a plurality of second grooves, and the second grooves are internally provided with insulated material with high dielectric constants. The second electrode is connected with the first grooves of the active region and covers the active region, the first terminal region and the second terminal region. The junction terminal of the invention can improve high voltage-resisting characteristics of the junction terminal device.

Owner:QST CORP

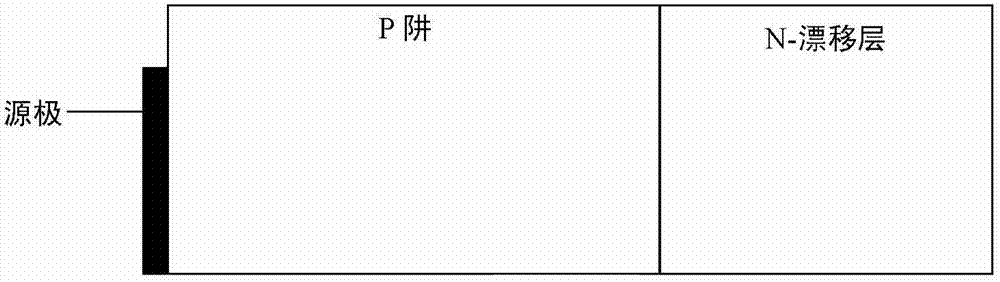

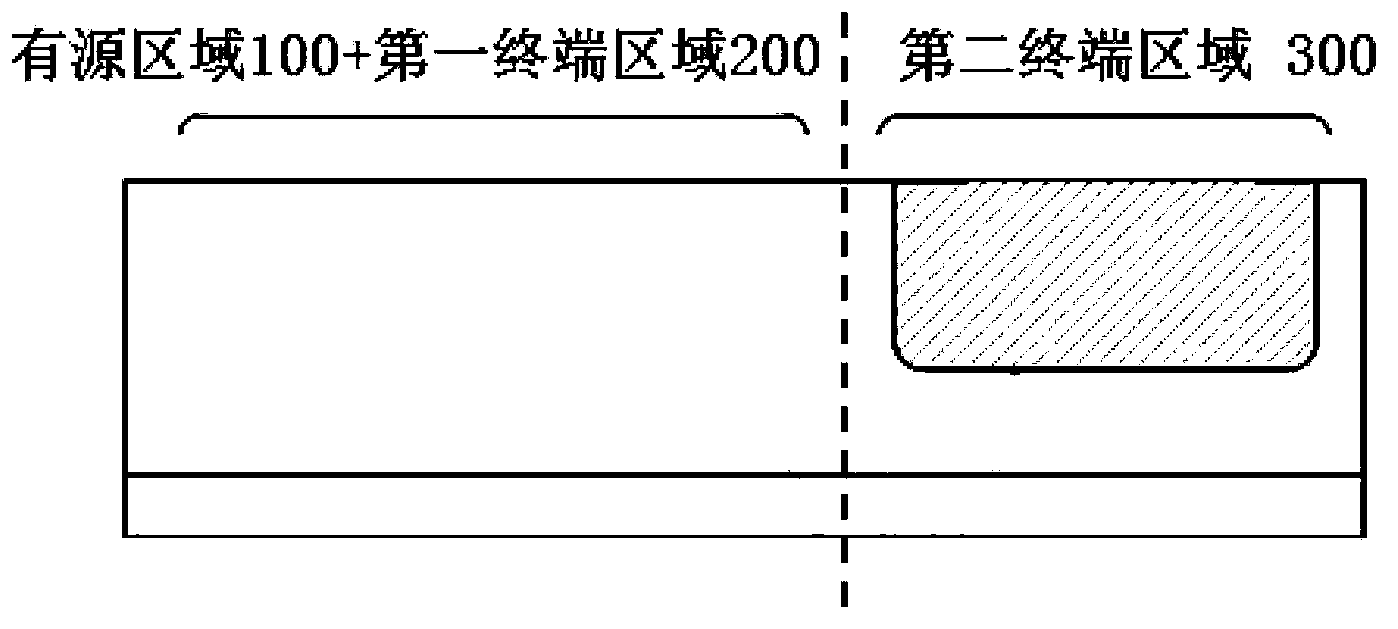

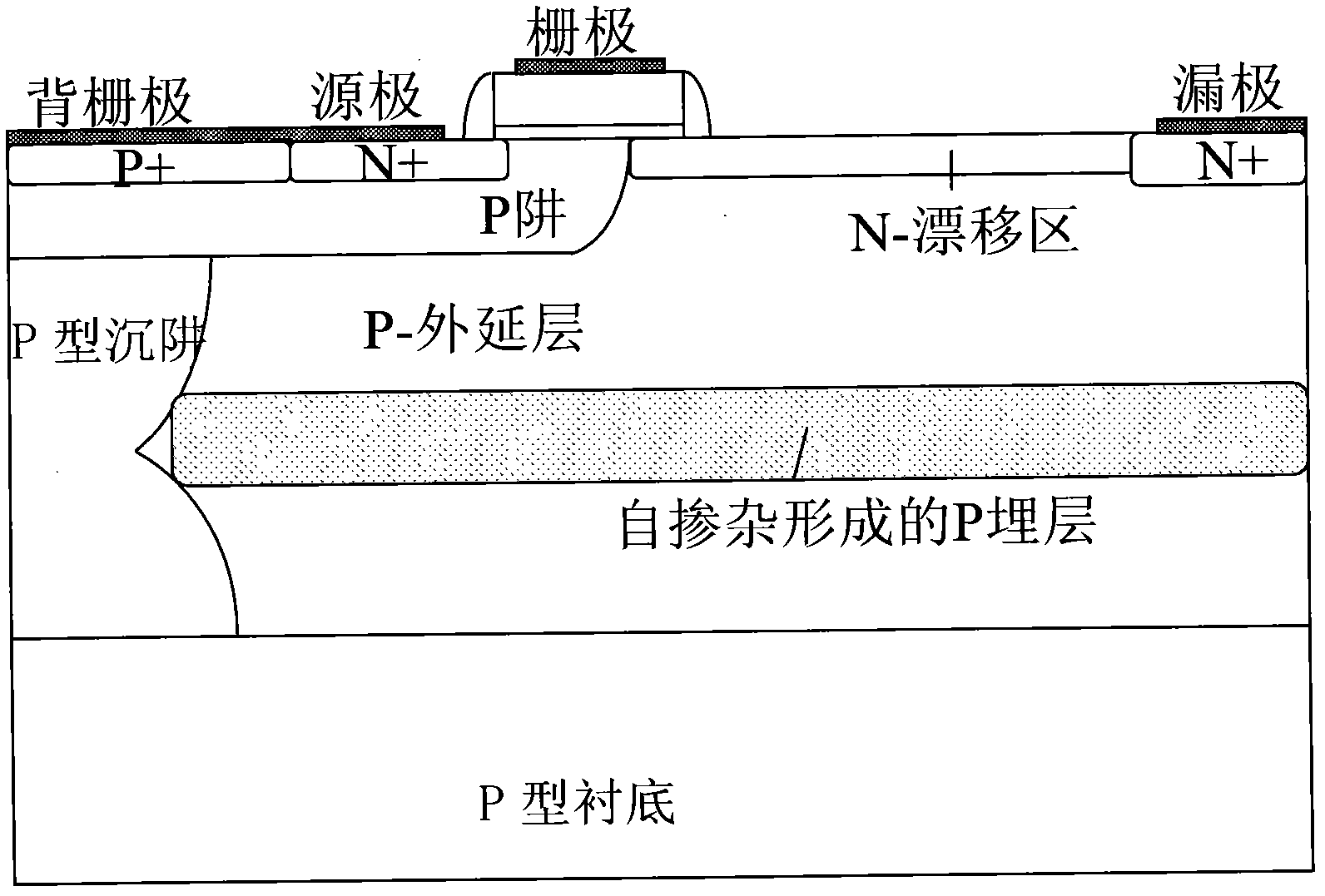

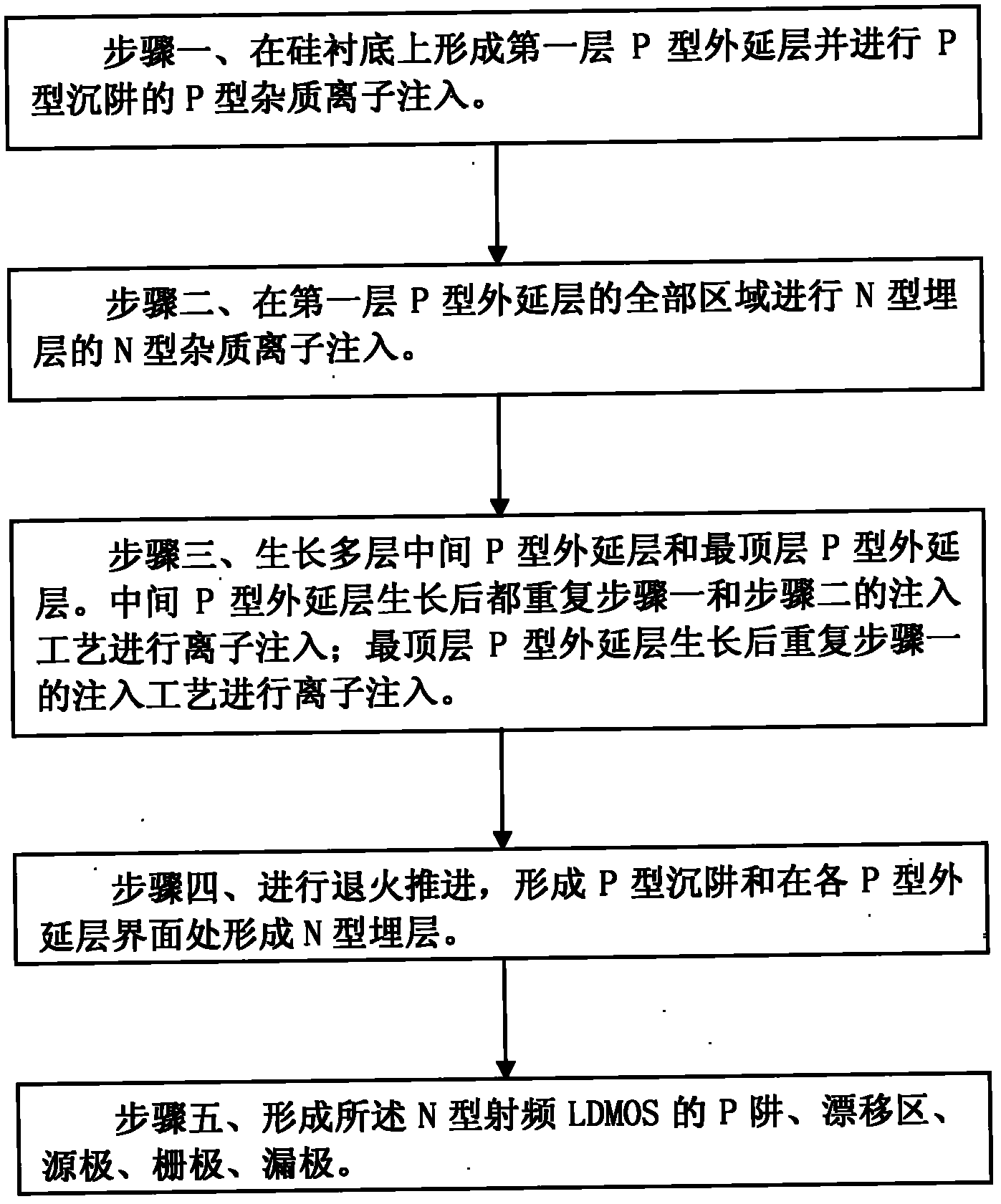

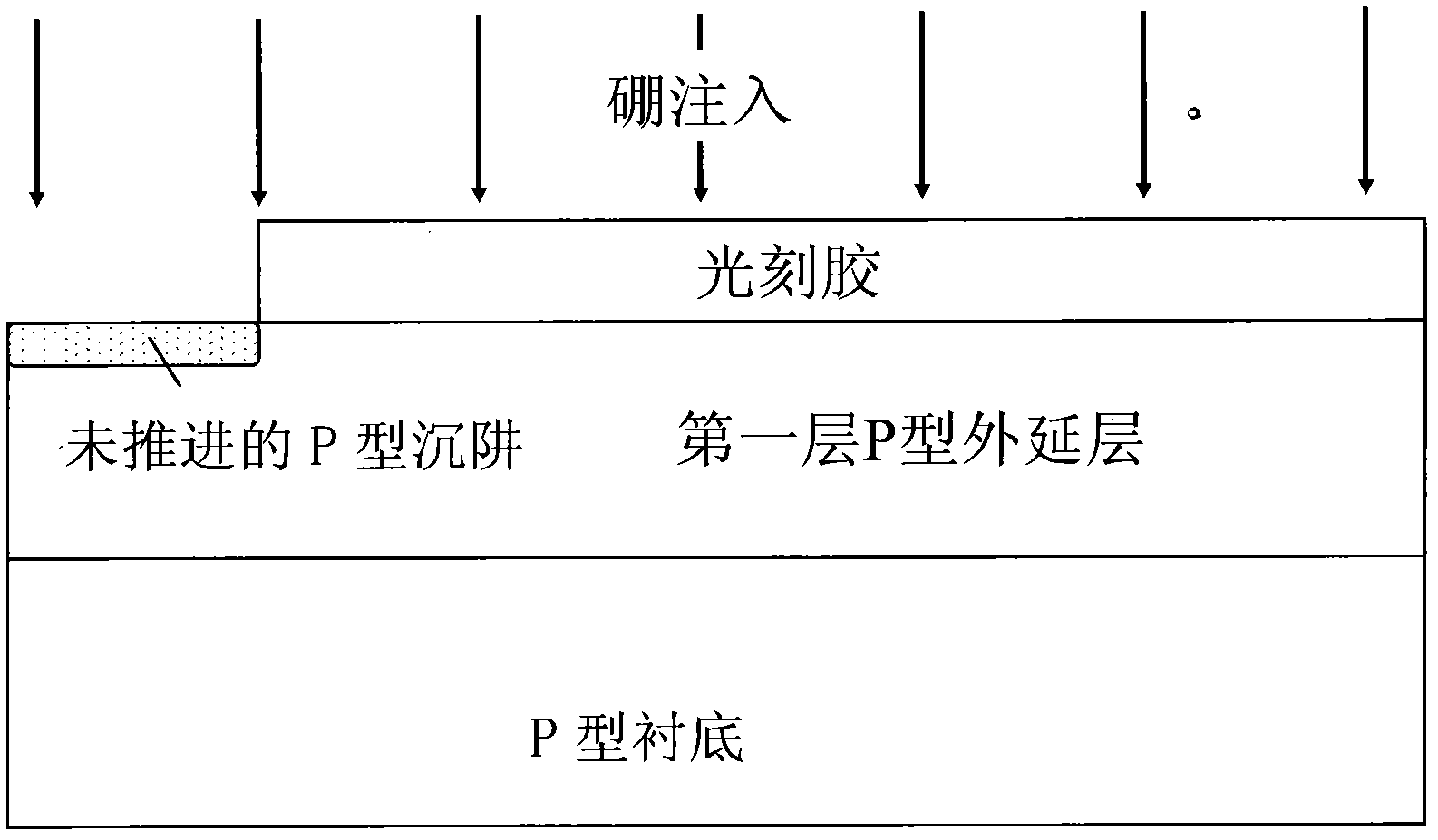

Manufacturing method of N-type radio frequency lateral double-diffused metal-oxide semiconductor (LDMOS)

ActiveCN102376570AImprove the problem of breakdown voltage dropImprove breakdown characteristicsSemiconductor/solid-state device manufacturingLDMOSImpurity ions

The invention discloses a manufacturing method of an N-type radio frequency lateral double-diffused metal-oxide semiconductor (LDMOS), which comprises the steps that: a first P-type epitaxial layer is formed on a silicon substrate and the P-type impurity ion implantation of a P-type sink trap is carried out; the N-type impurity ion implantation of an N-type embedded layer is carried out in all areas of the first P-type epitaxial layer; a plurality of middle P-type epitaxial layers and a top P-type epitaxial layer are grown; the implantation processes in Steps 1 and 2 are repeated after the middle P-type epitaxial layers are grown for ion implantation; the implantation process in Step 1 is repeated after the top P-type epitaxial layer is grown for ion implantation; and annealing advance iscarried out to form the P-type sink trap and the N-type embedded layer is formed at the interfaces of the P-type epitaxial layers. The P trap of the N-type radio frequency LDMOS, a drift area, a source, a grid and a drain are formed. The method can significantly improve the breakdown characteristic of a device, is not restricted by the increased thicknesses of the epitaxial layers, and has the characteristics of low process cost, adjustability and strong applicability.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

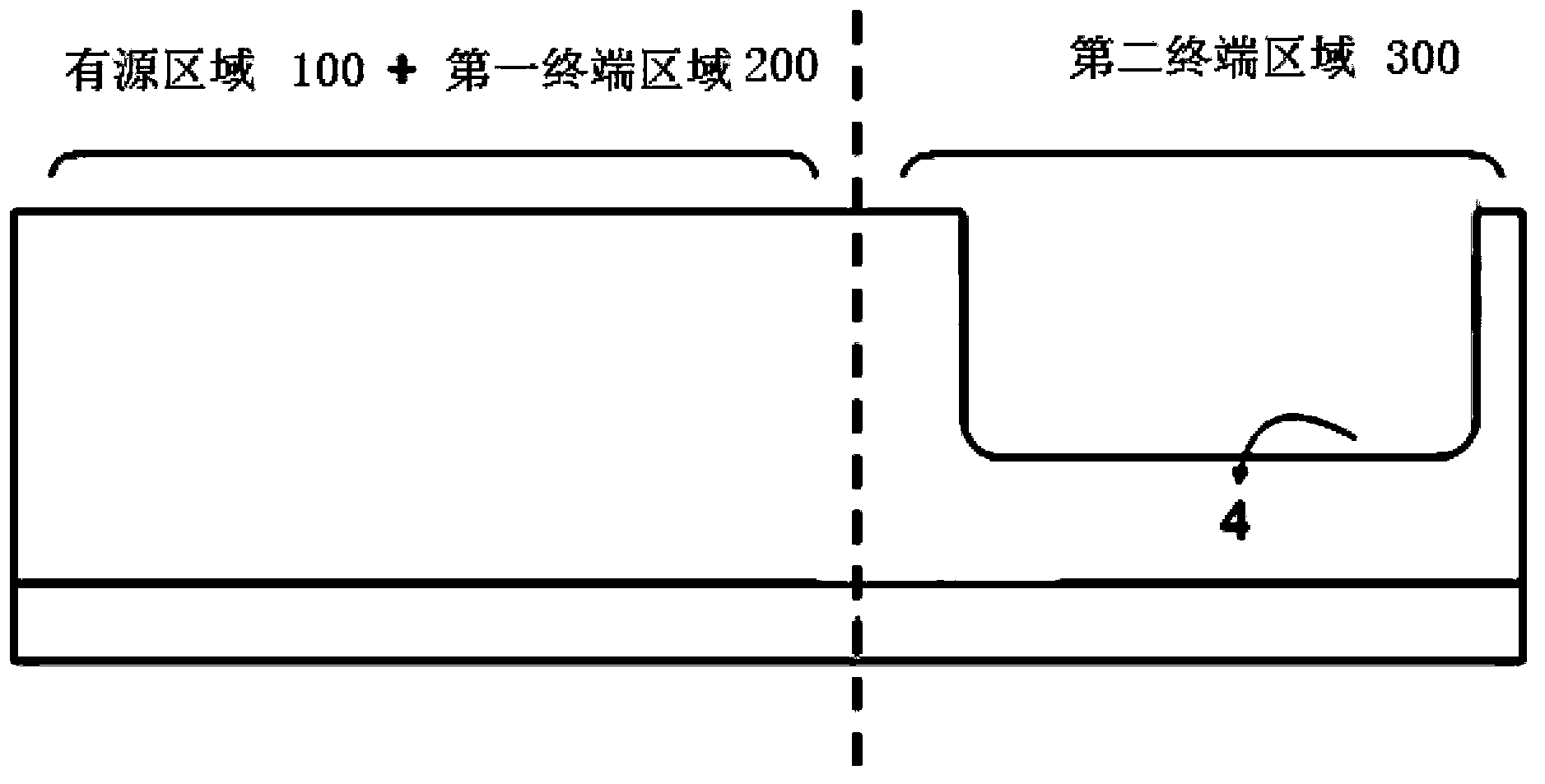

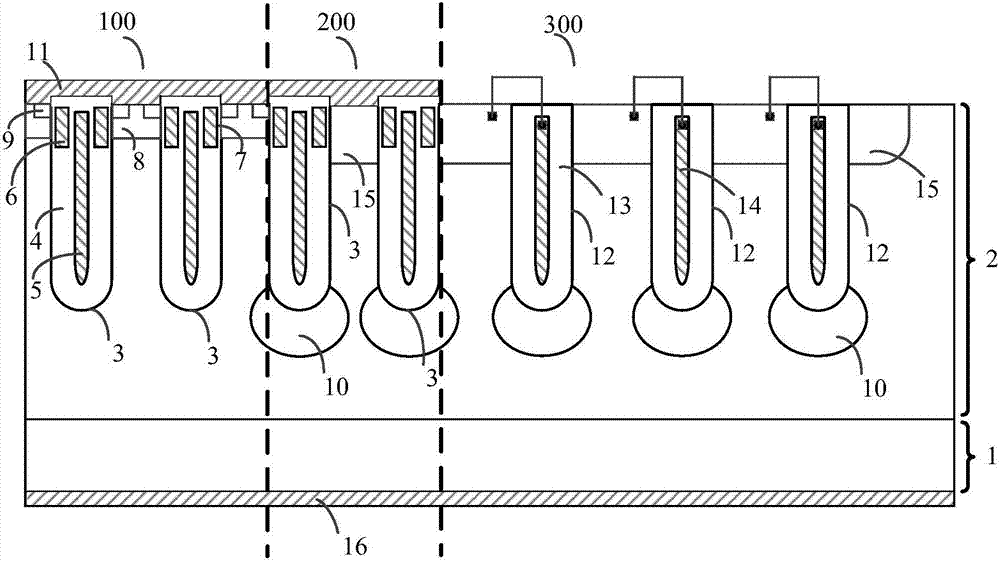

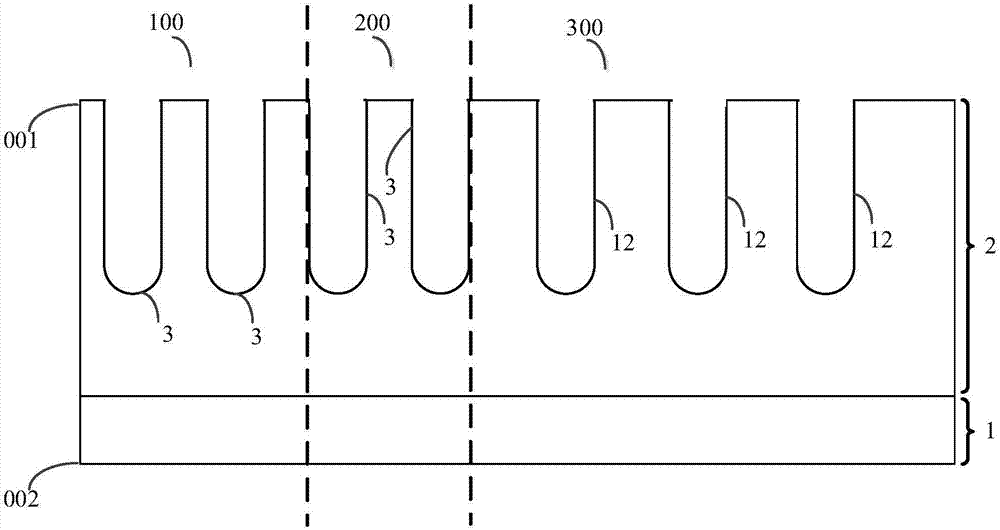

Power semiconductor device structure suitable for deep groove and manufacturing method

ActiveCN107403839AImprove pressure resistanceBoost level depletionEfficient power electronics conversionSemiconductor/solid-state device manufacturingPower semiconductor deviceDevice material

The invention relates to a power semiconductor device structure suitable for a deep groove and a manufacturing method. The power semiconductor device structure is characterized in that on the cross section of a semiconductor device, a second conductive type of a second well region is arranged on the surface of a first conductive type of a drift region of a terminal protection region; a plurality of a second type of grooves are formed in the second conductive type of the second well region; central regions in the second type of the grooves are filled with a second type of conductors and a second type of dielectric bodies located on the outer circles of the second type of the conductors; the second type of the conductors are electrically connected with the second conductive type of the second well region close to one side of a terminal transitional region outside the second type of the grooves in which the second type of the conductors are located; and a second conductive type of third well regions are arranged below a first type of grooves in the terminal transitional region and the second type of the grooves in the terminal protection region. According to the structure, the high voltage resistance of the device can be effectively improved; a manufacturing process is compatible with an existing semiconductor process; the application range is wide; and the production cost is reduced.

Owner:WUXI NCE POWER

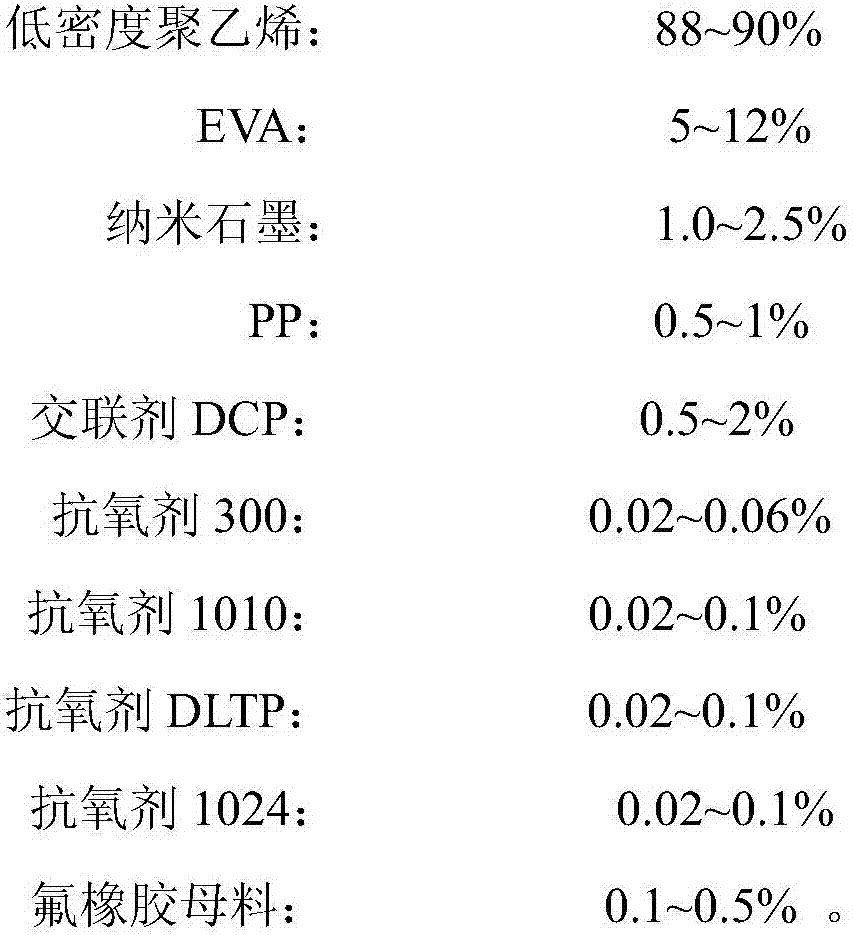

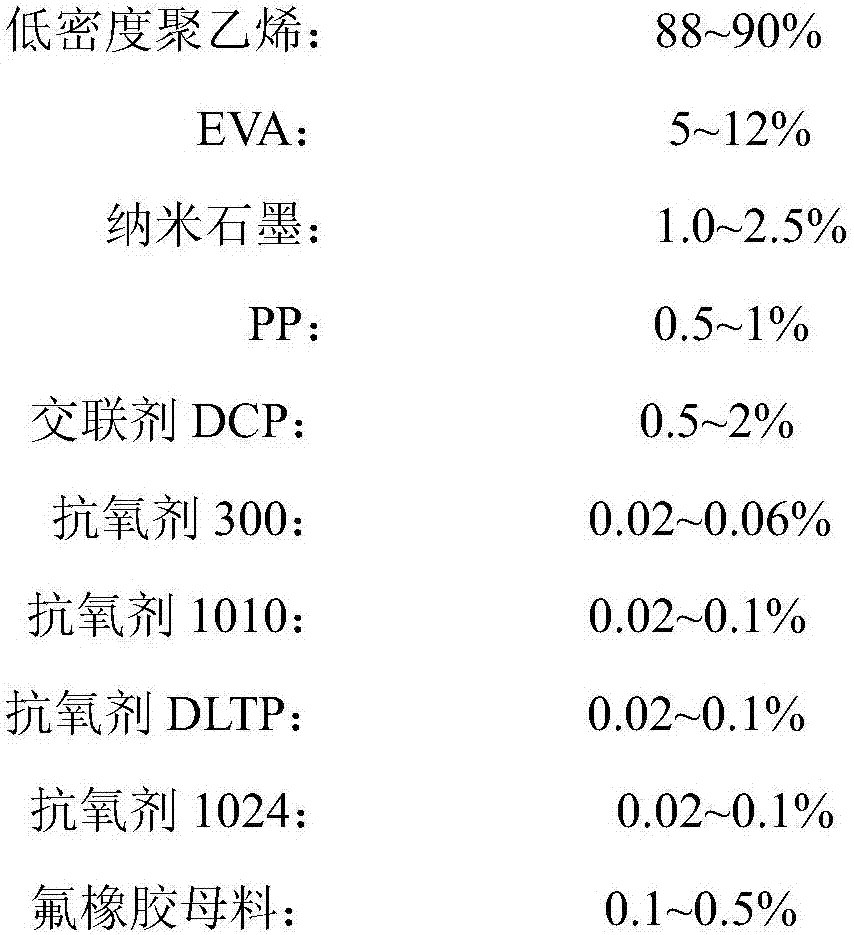

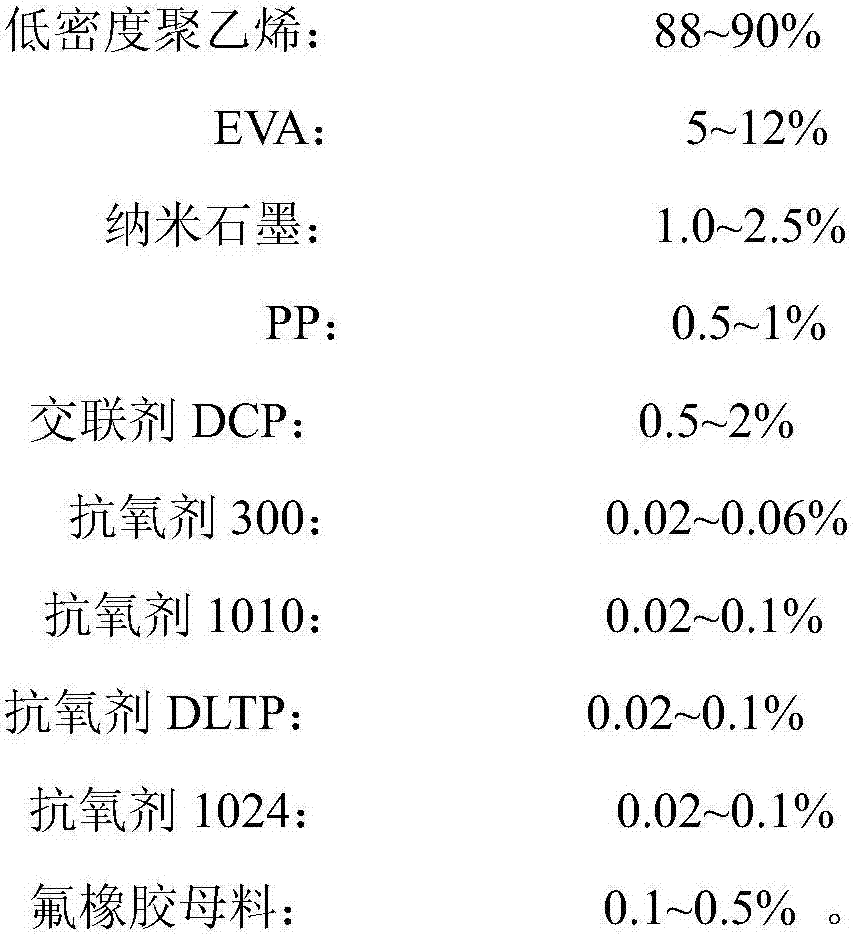

Crosslinked polyethylene electric-insulation material and preparation method thereof

InactiveCN106867077AImprove thermal conductivityEvenly distributedPlastic/resin/waxes insulatorsLow-density polyethylenePolymer science

The invention relates to the field of electric-insulation materials, particularly a crosslinked polyethylene electric-insulation material and a preparation method thereof. The invention aims to solve the problems of low breakdown voltage and high aging tendency in the existing crosslinked polyethylene electric-insulation material, and provides a crosslinked polyethylene electric-insulation material with favorable breakdown characteristics and aging resistance. The preparation method comprises the following steps: proportionally taking 100 parts of low-density polyethylene, EVA (ethylene-vinyl acetate), nano graphite, PP (polypropylene), a crosslinking agent DCP (dicumyl peroxide), an antioxidant 300, an antioxidant 1010, an antioxidant DLTP (dilauryl thiodipropionate), an antioxidant 1024 and a fluororubber master batch, mixing, melting, carrying out crosslinking reaction, and drying to obtain the crosslinked polyethylene electric-insulation material. The crosslinked polyethylene material has excellent breakdown characteristics and favorable thermal conductivity, and is beneficial to lowering the working temperature of the electric-insulation material and prolonging the service life of the material. The crosslinked polyethylene electric-insulation material is suitable for manufacturing high-voltage direct-current transmission line cables.

Owner:HARBIN UNIV OF SCI & TECH

Hyperbranched polymer-SiO2 modified epoxy resin insulating material and preparation method thereof

InactiveCN110776806APolymer branching degreeReduced effectivenessNon-macromolecular adhesive additivesEpoxy resin adhesivesPolymer sciencePolymer modified

The invention relates to the technical field of epoxy resin adhesives, and discloses a hyperbranched polymer-SiO2 modified epoxy resin insulating material and a preparation method thereof. The hyperbranched polymer-SiO2 modified epoxy resin insulating material is prepared from the following formula materials: hyperbranched polymer, nanosilicon dioxide, a silane coupling agent, a catalyst, dodecylsuccinic anhydride and epoxy resin. A three-dimensional net-like spherical structure of the hyperbranched polymer has a high degree of molecular branching, so that nano-SiO2 is uniformly dispersed on the huge specific surface of the hyperbranched polymer, nano-SiO2 agglomeration is reduced, nano-SiO2 reduces the effective charge and charge accumulation in a coating interface area, the diffusion rate of a carrier is reduced, the formation of conductive paths is suppressed, the breakdown characteristics of epoxy resin coatings are improved, the hyperbranched polymer has excellent elastic expansion structure and good structural stability, the crosslinking density of the epoxy resin is increased, the mobility of a molecular segment of the epoxy resin is suppressed, and the impact cross sectioncaused by the stress expansion of the resin is reduced.

Owner:王利玲

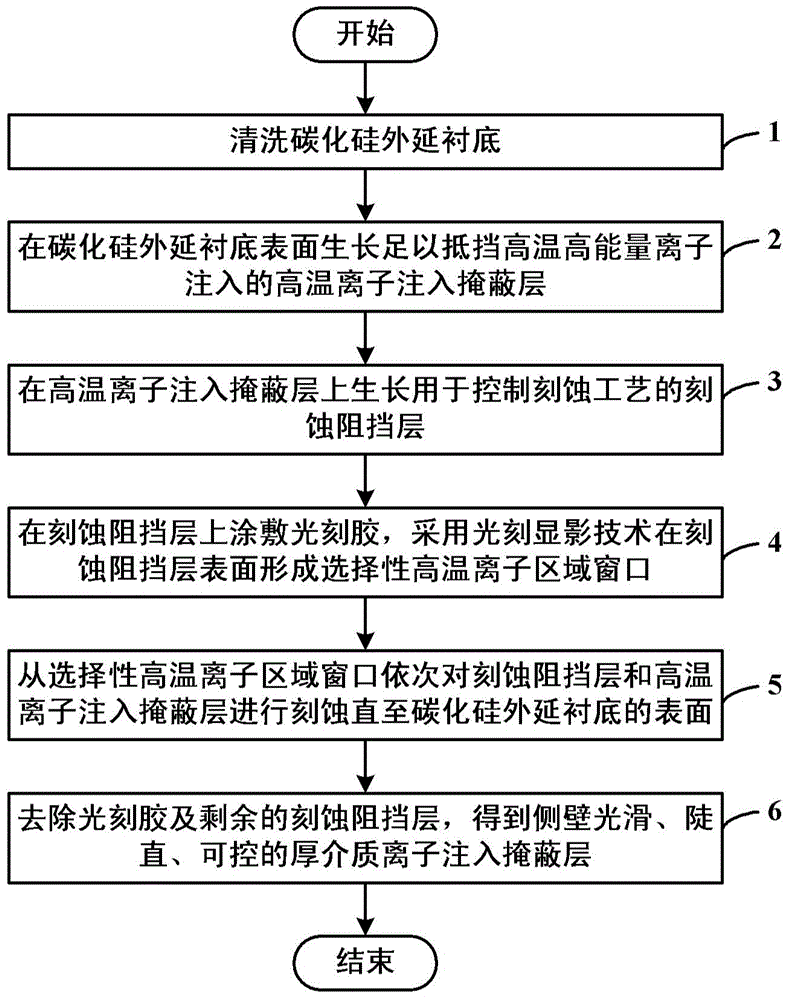

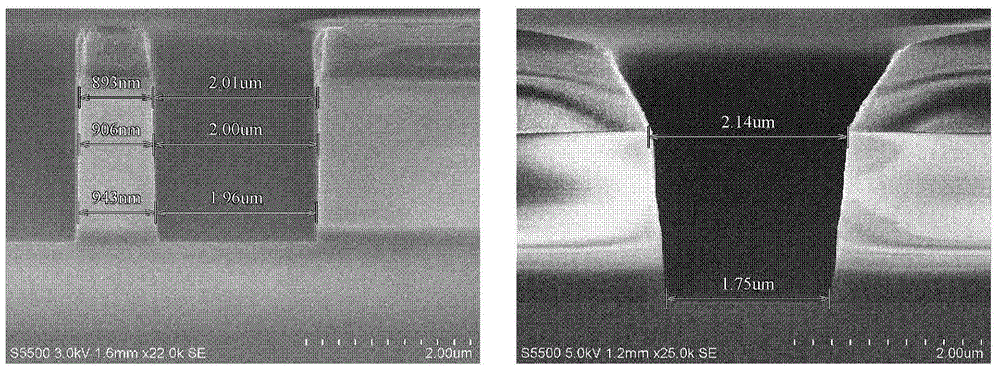

Method for accurately controlling steepness when silicon carbide high-temperature ions are injected into mask

ActiveCN103560078ASatisfy injection requirementsPerformance is not affectedSemiconductor/solid-state device manufacturingHigh energyOptoelectronics

The invention discloses a method for accurately controlling steepness when silicon carbide high-temperature ions are injected into a mask. The method comprises the steps that a silicon carbide epitaxial substrate is cleaned; a high-temperature ion injection masking layer capable of sufficiently resisting against the injected high-temperature and high-energy ions grows on the surface of the silicon carbide epitaxial substrate; an etching resisting layer used for controlling an etching process grows on the high-temperature ion injection masking layer; photoresist coats the etching resisting layer, and a selective high-temperature ion area window is formed in the surface of the etching resisting layer by adopting a photoetching developing technology, etching is sequentially carried out on the etching resisting layer and the high-temperature ion injection masking layer from the selective high-temperature ion area window to the surface of the silicon carbide epitaxial substrate; the photoresist and the unnecessary etching resisting layer are removed to obtain the steep and controllable thick-medium ion injection masking layer with the smooth lateral wall. By means of the method, angle control over an etching surface is carried out accurately, the steep thick-medium ion injection masking layer with the smooth lateral wall is obtained, and good uniformity and strong controllability of the selective ion injection area are guaranteed.

Owner:江苏中科汉韵半导体有限公司

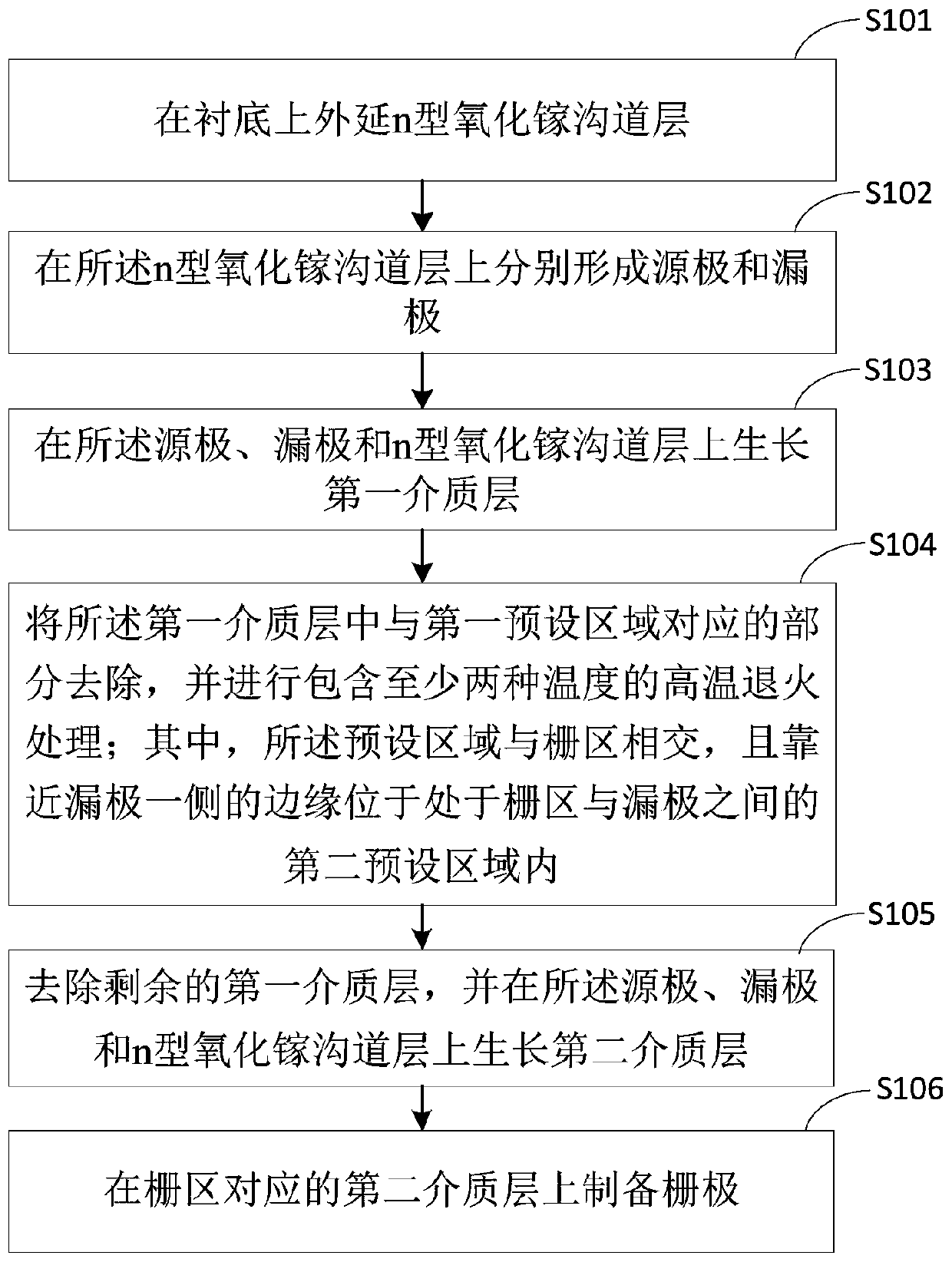

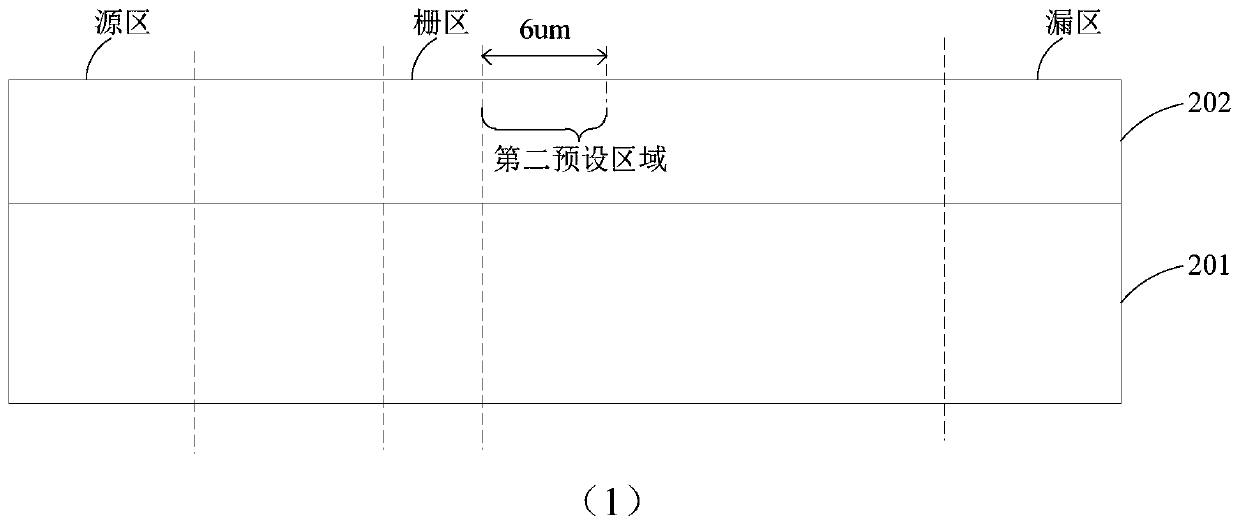

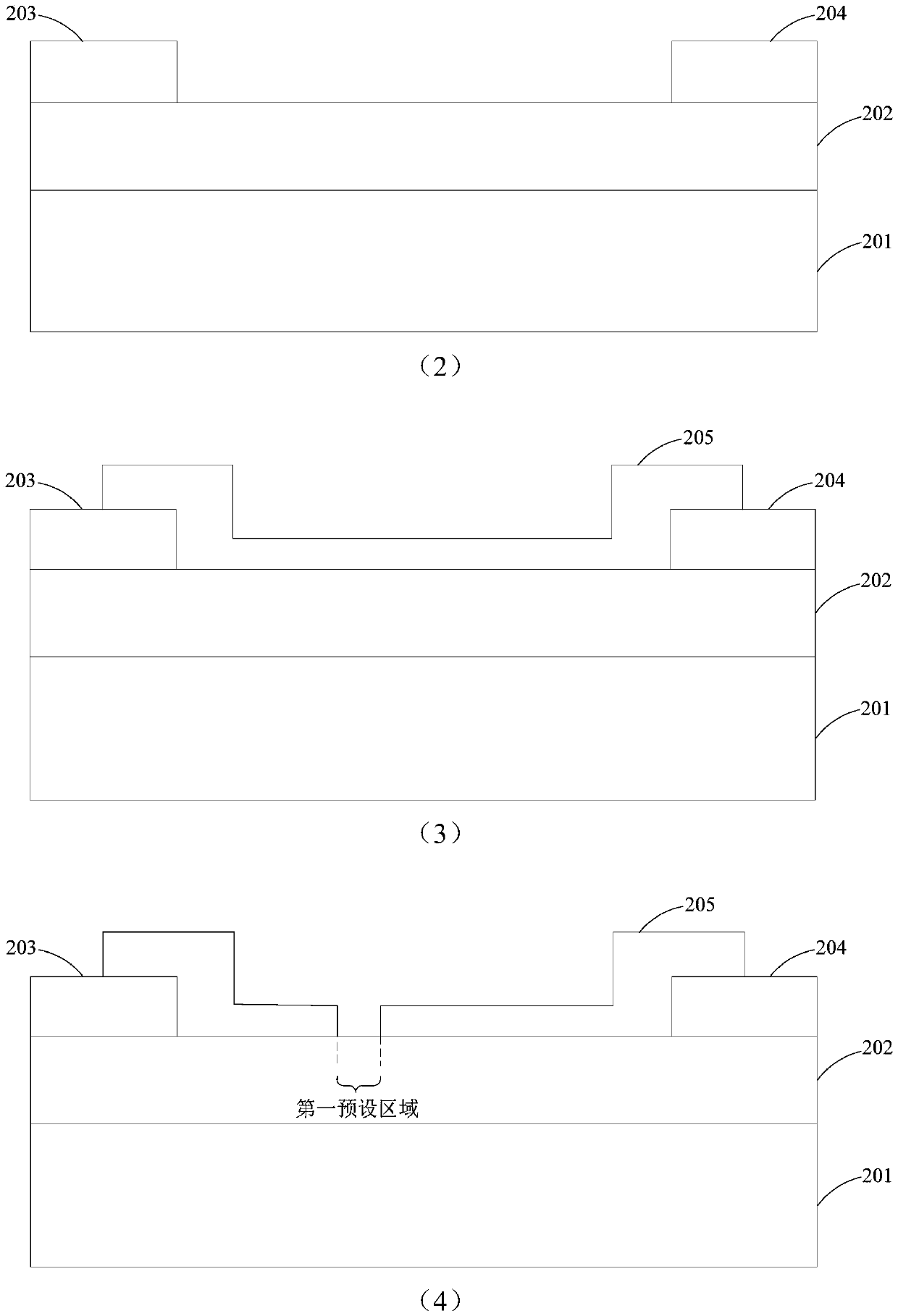

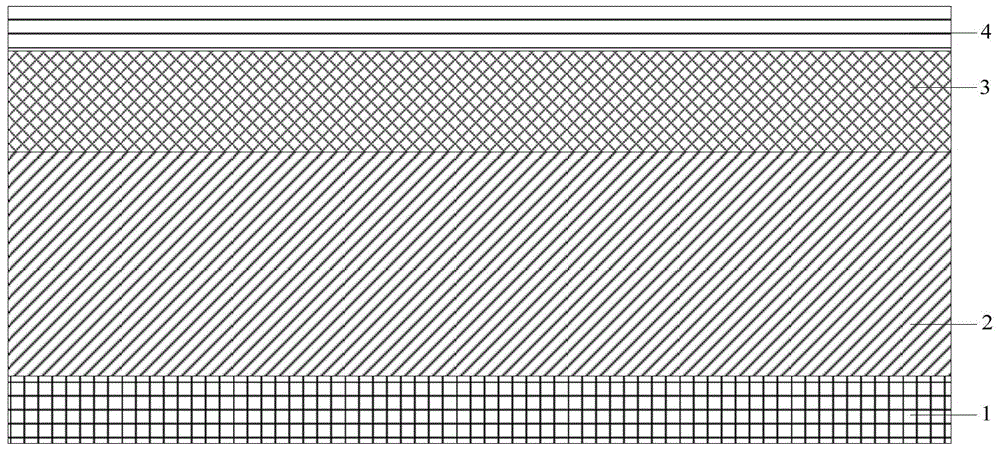

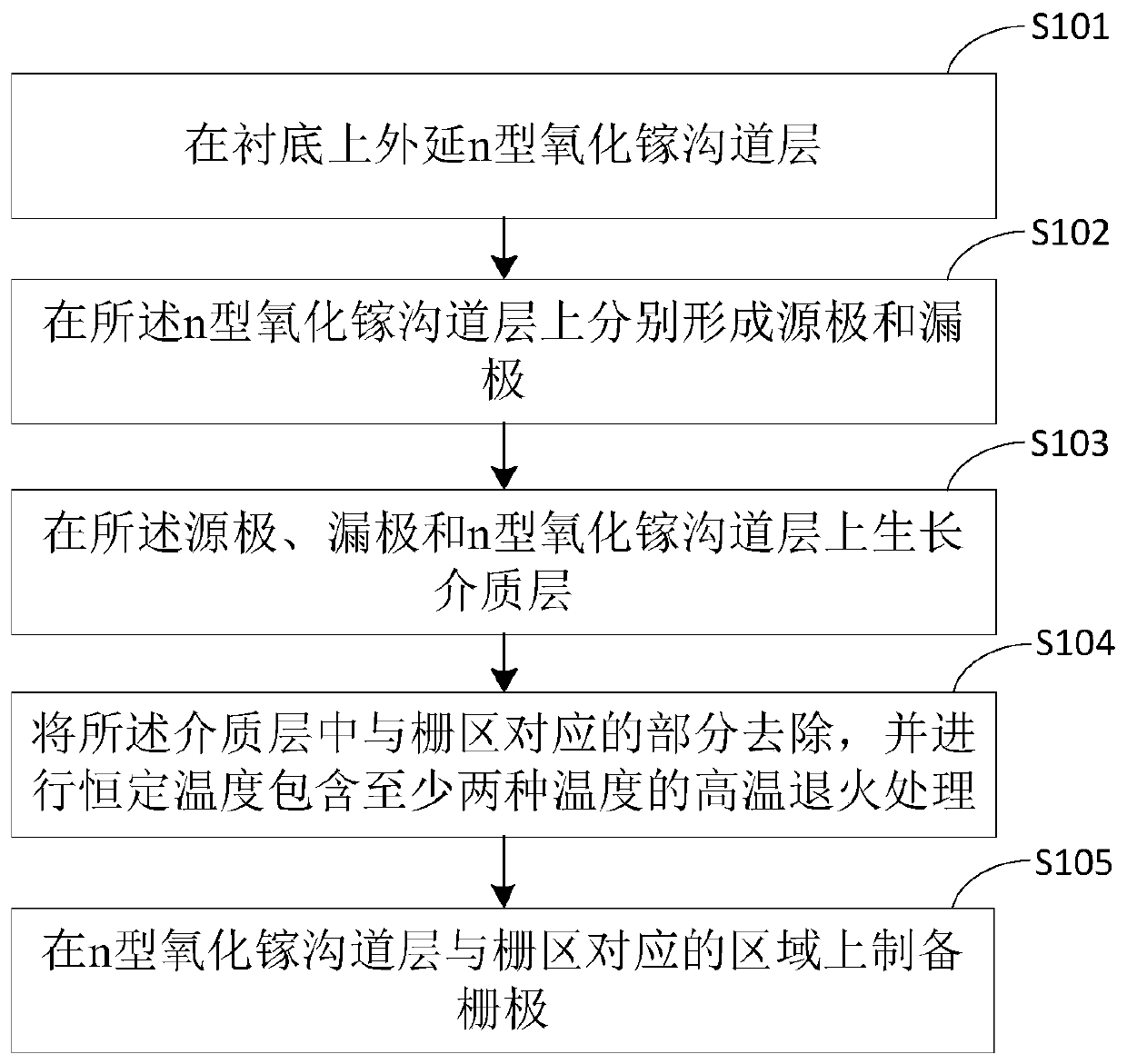

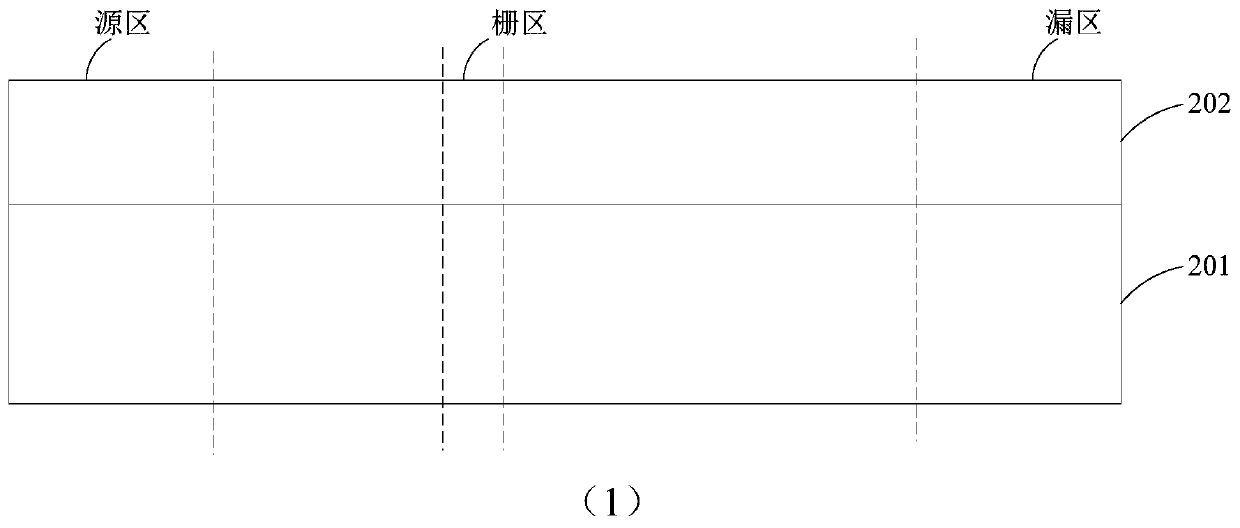

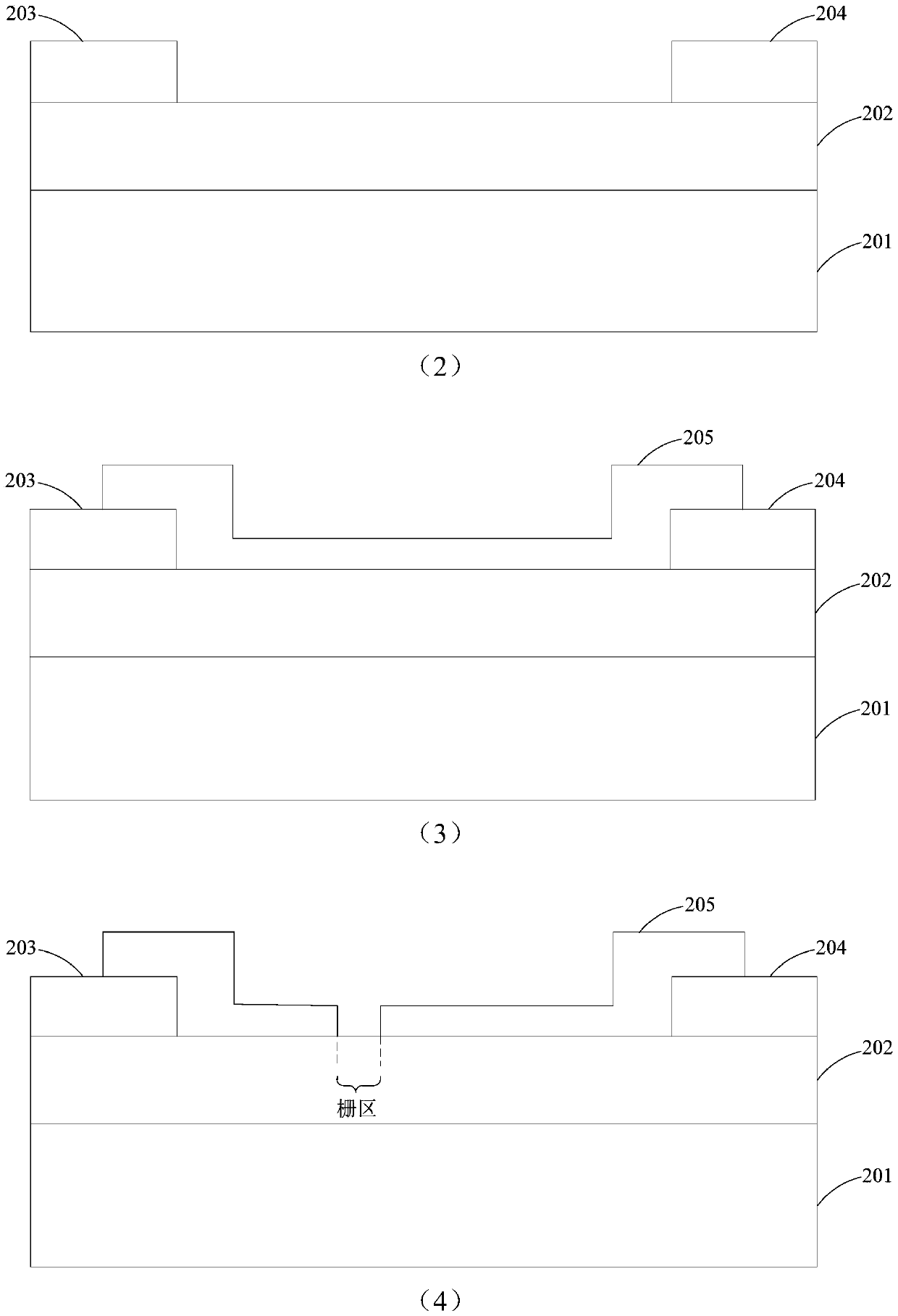

Gallium oxide field-effect transistor and fabrication method thereof

ActiveCN110223920AImprove breakdown characteristicsConduction characteristics unchangedSemiconductor/solid-state device manufacturingSemiconductor devicesTwo temperatureField-effect transistor

The invention relates to the field of semiconductors, in particular to a gallium oxide field-effect transistor and a fabrication method thereof. The method comprises the steps of epitaxially growing an n-type gallium oxide channel layer on a substrate; forming a source and a drain on the n-type gallium oxide channel layer; growing a first dielectric layer on the source, the drain and the n-type gallium oxide channel layer; removing a part, corresponding to a first preset region, in the first dielectric layer, and performing high-temperature annealing processing comprising at least two temperatures, wherein the preset region intersects with a gate region, and an edge near to one side of the drain is arranged in a second preset region arranged between the gate region and the drain; removingthe remaining first dielectric layer, and growing a second dielectric layer on the source, the drain and the n-type gallium oxide channel layer; and fabricating a gate on the second dielectric layer corresponding to the gate region. By the method, the breakdown characteristic of the device can be improved, and the unchanged conduction characteristic of the device is maintained.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

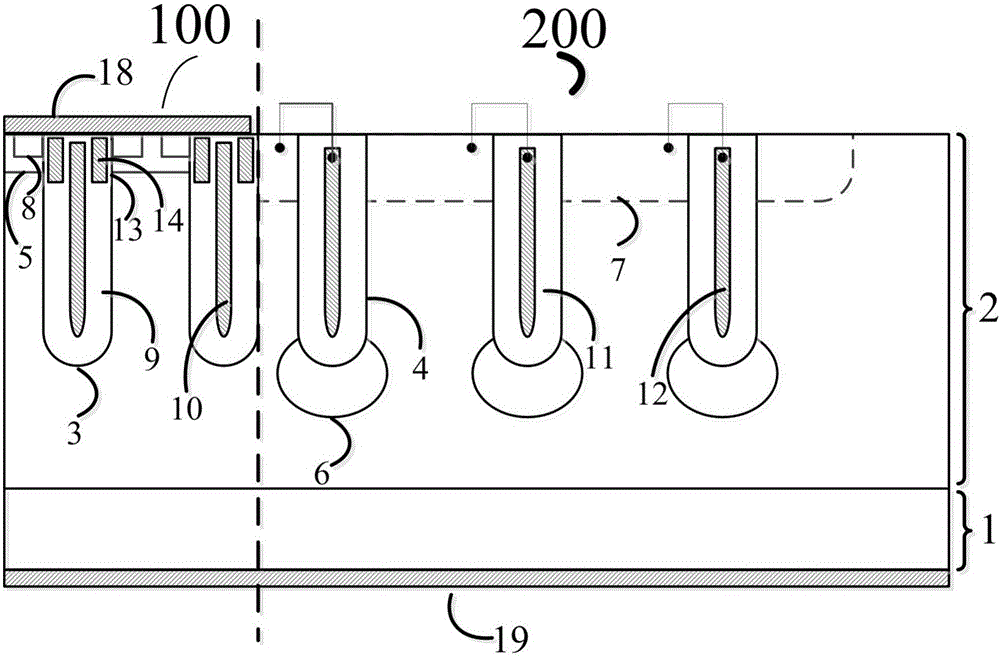

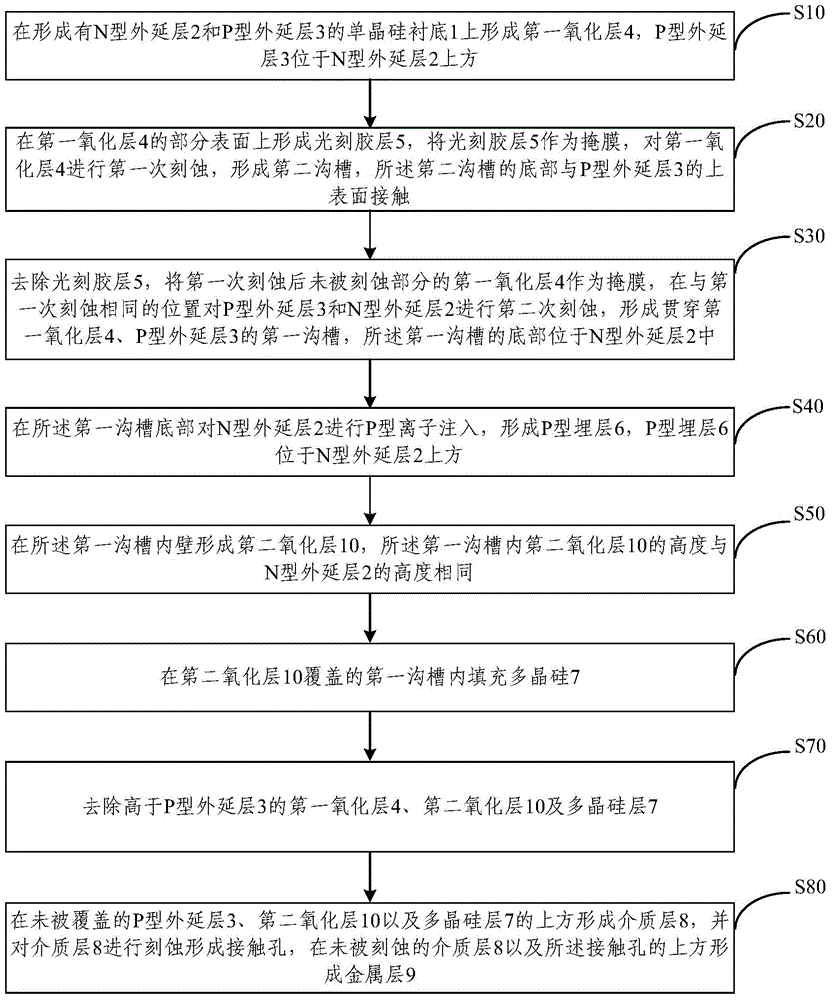

Groove power device with buried layer and manufacturing method thereof

InactiveCN106158631ALower on-resistanceImprove breakdown characteristicsSemiconductor/solid-state device manufacturingSemiconductor devicesOptoelectronicsIon implantation

The invention discloses a groove power device with a buried layer and a manufacturing method thereof. The manufacturing method comprises the steps that a first oxide layer is formed on a substrate on which a first epitaxial layer and a second epitaxial layer are formed, and the second epitaxial is arranged on the first epitaxial layer; the first oxide layer, the second epitaxial layer and the first epitaxial layer are etched so that a first groove which penetrates through the first oxide layer and the bottom part of the second epitaxial layer to be arranged in the first epitaxial layer is formed; P-type ion injection is performed on the first epitaxial layer at the bottom part of the first groove so that a P-type buried layer arranged on the first epitaxial layer is formed; a second oxide layer having the same height with the first epitaxial layer is formed on the internal wall of the first groove; and polycrystalline silicon is filled in the first groove covered by the second oxide layer, and the first and second oxide layers higher than the second epitaxial layer and the polycrystalline silicon layer are removed. According to the method, withstand voltage of the depletion layer of the groove power device can be enhanced, conduction resistance of the device can be reduced under the same withstand voltage, and the withstand voltage capacity of the bottom corner of the groove can be enhanced so that the breakdown properties of the device can be greatly improved.

Owner:PEKING UNIV FOUNDER GRP CO LTD +1

Gallium oxide field effect transistor and preparation method thereof

ActiveCN110164769AImprove breakdown characteristicsConduction characteristics unchangedSemiconductor/solid-state device manufacturingSemiconductor devicesTwo temperatureField-effect transistor

The invention relates to the field of semiconductors, and especially relates to a gallium oxide field effect transistor and a preparation method thereof. The method comprises the steps of epitaxiallygrowing an n-type gallium oxide channel layer on a substrate; respectively forming a source electrode and a drain electrode on the n-type gallium oxide channel layer; growing a dielectric layer on thesource electrode, the drain electrode and the n-type gallium oxide channel layer; removing the part corresponding to a grid region in the dielectric layer, and carrying out high-temperature annealingtreatment containing at least two temperatures; and preparing a grid electrode on the n-type gallium oxide channel layer in an area corresponding to the grid region. The method of the invention can improve the breakdown characteristics of the device and keep the conduction characteristics of the device unchanged.

Owner:THE 13TH RES INST OF CHINA ELECTRONICS TECH GRP CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com