Junction terminal applied to deep-groove super-junction device and manufacturing method thereof

A technology of superjunction devices and junction terminals, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve problems such as extremely high requirements for trench filling quality, increased etching and filling time, and increased process technical difficulty. , to achieve the effect of reducing etching and filling time, increasing capacity and good compatibility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

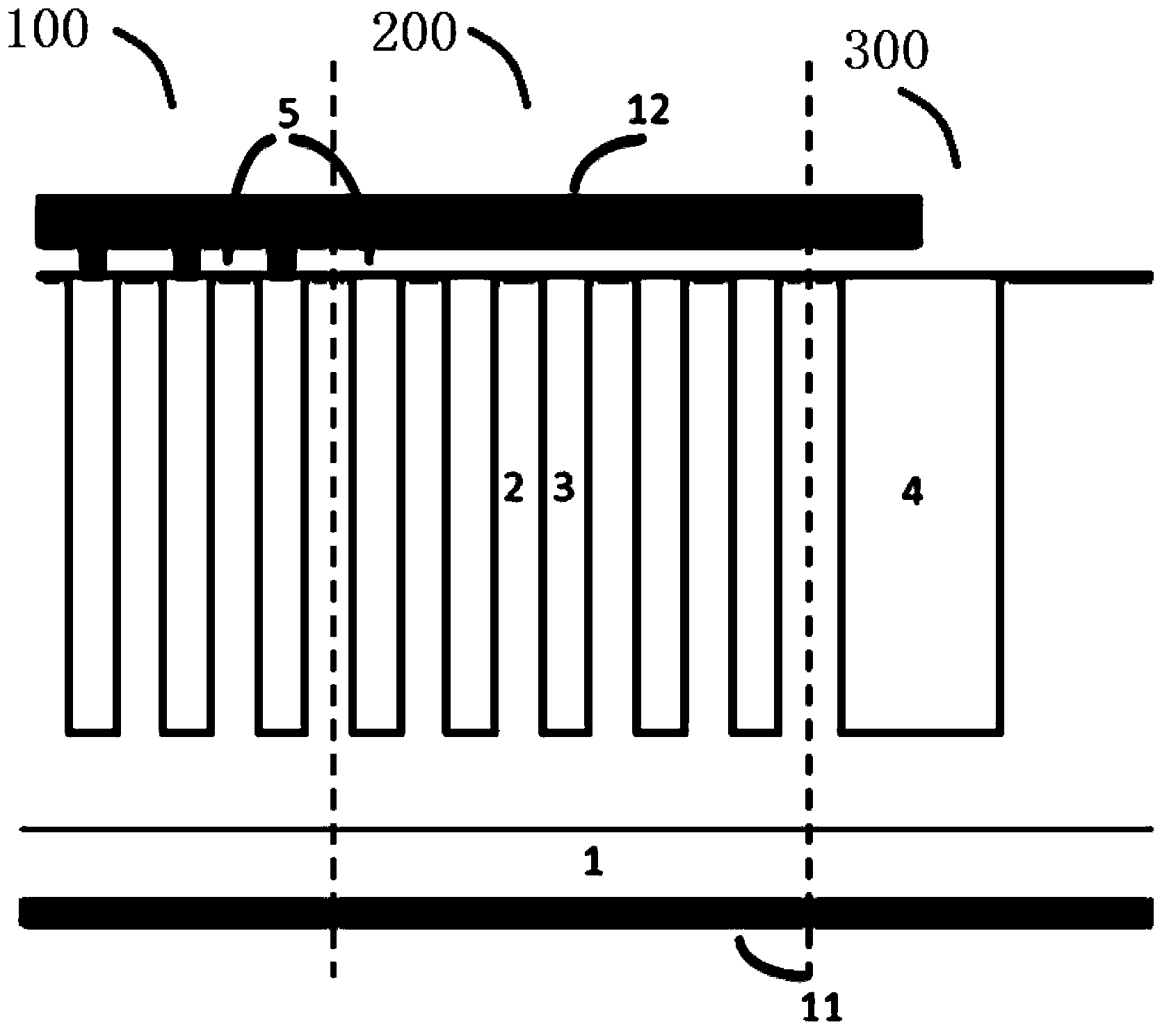

[0040] see figure 1 , the present invention discloses a junction terminal suitable for deep trench super junction devices, the junction terminal comprising: a semiconductor substrate 1, a first electrode 11, a semiconductor region 2, and a second electrode.

[0041] The semiconductor substrate 1 is a semiconductor material with a first doping type, with a doping resistivity of about 0.002-0.008 ohm.cm, typically an As or Sb doped N-type silicon substrate.

[0042] The first electrode 11 is formed on the lower end surface (back surface) of the semiconductor substrate 1; the semiconductor region 2 is formed on the upper end surface of the semiconductor substrate 1, which has the first conductivity type (ie, the first doping type), and the semiconductor region 2 A typical material is a Ph-doped N-type silicon epitaxial material with a resistivity of 1-10ohm.cm.

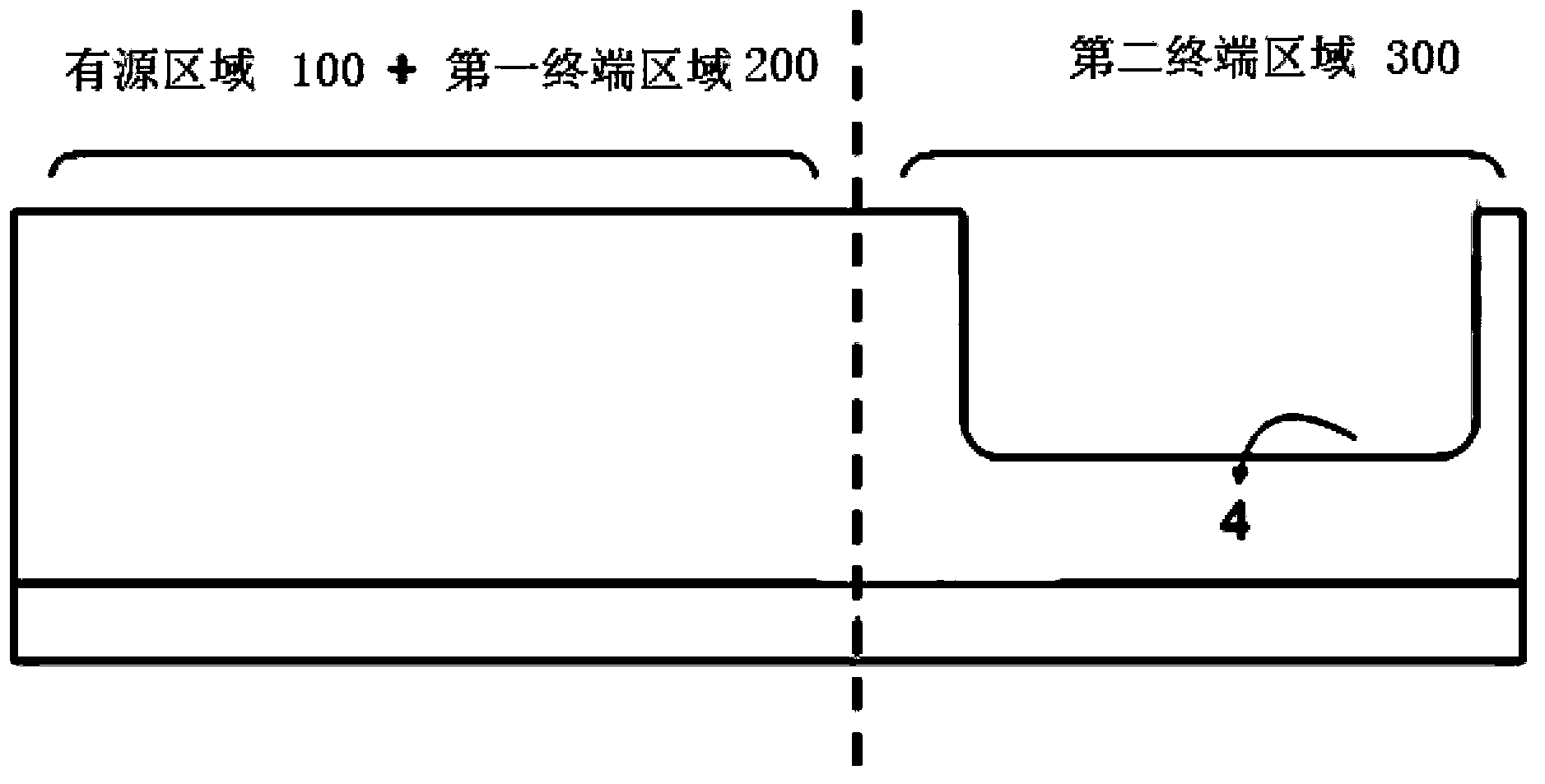

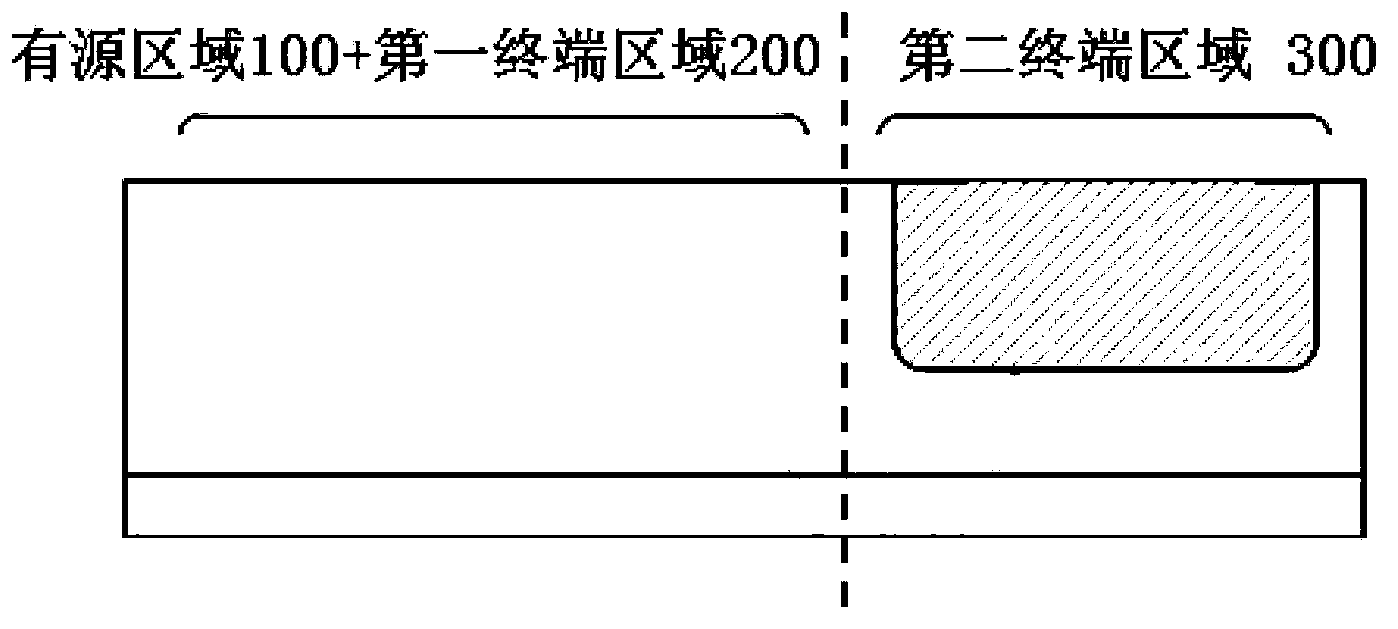

[0043] The semiconductor region includes: an active region, a first termination region, and a second termination regi...

Embodiment 2

[0053] The difference between this embodiment and Embodiment 1 is that in this embodiment, the preparation method of the junction terminal of the present invention includes the following steps:

[0054] [Step S1] Combine figure 1 As shown, an N-type epitaxial layer (semiconductor region 2 ), such as a Ph-doped low-doped epitaxial layer with a thickness of 48 um, is grown on a heavily doped silicon substrate (semiconductor substrate 1 ). Then etch the fourth trench 6 of the terminal region 2 on the N-type epitaxial layer (such as Figure 4 ), the depth and width of the trench are determined by the withstand voltage of the device and the doping concentration of the substrate, and the trench opening size and its spacing are selected according to the reasonable design value of the oxidation process, and then completely oxidized by the method of growing silicon dioxide at high temperature silicon between the fourth trenches 6 in the terminal region two, and the oxide layer grown a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com