Low-voltage buried channel VDMOS (vertical double-diffused metal oxide semiconductor) device

A low-voltage, device technology, applied in the field of low-voltage buried trench VDMOS devices, can solve the problem of large reverse leakage current

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

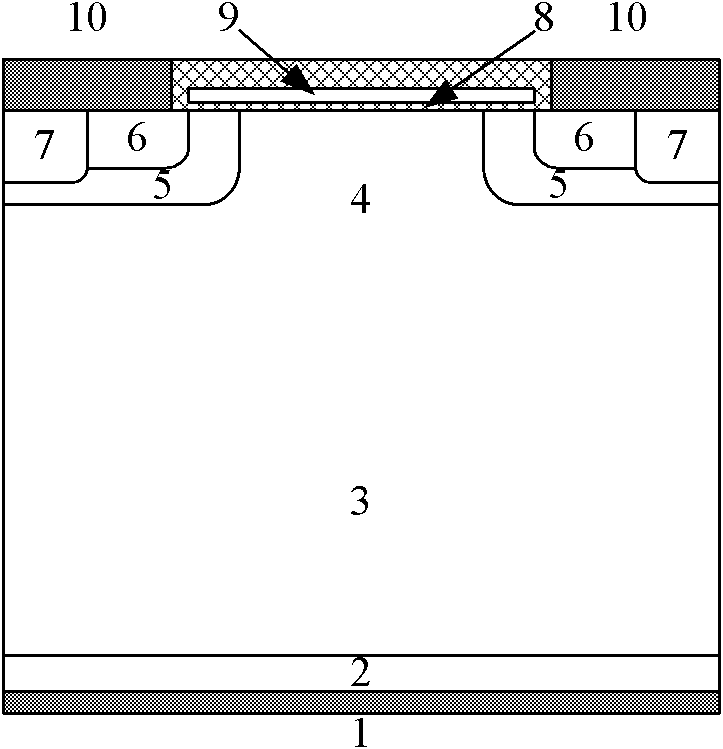

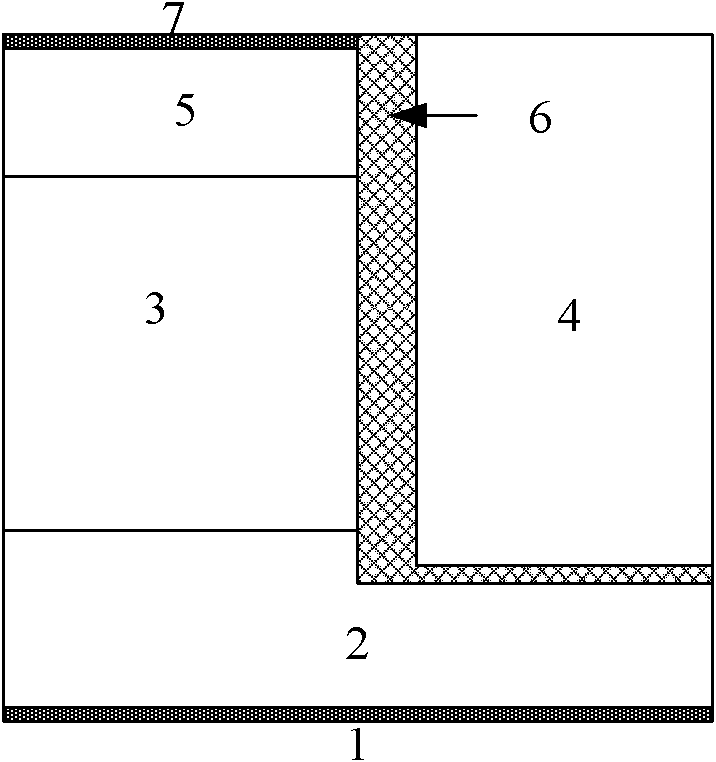

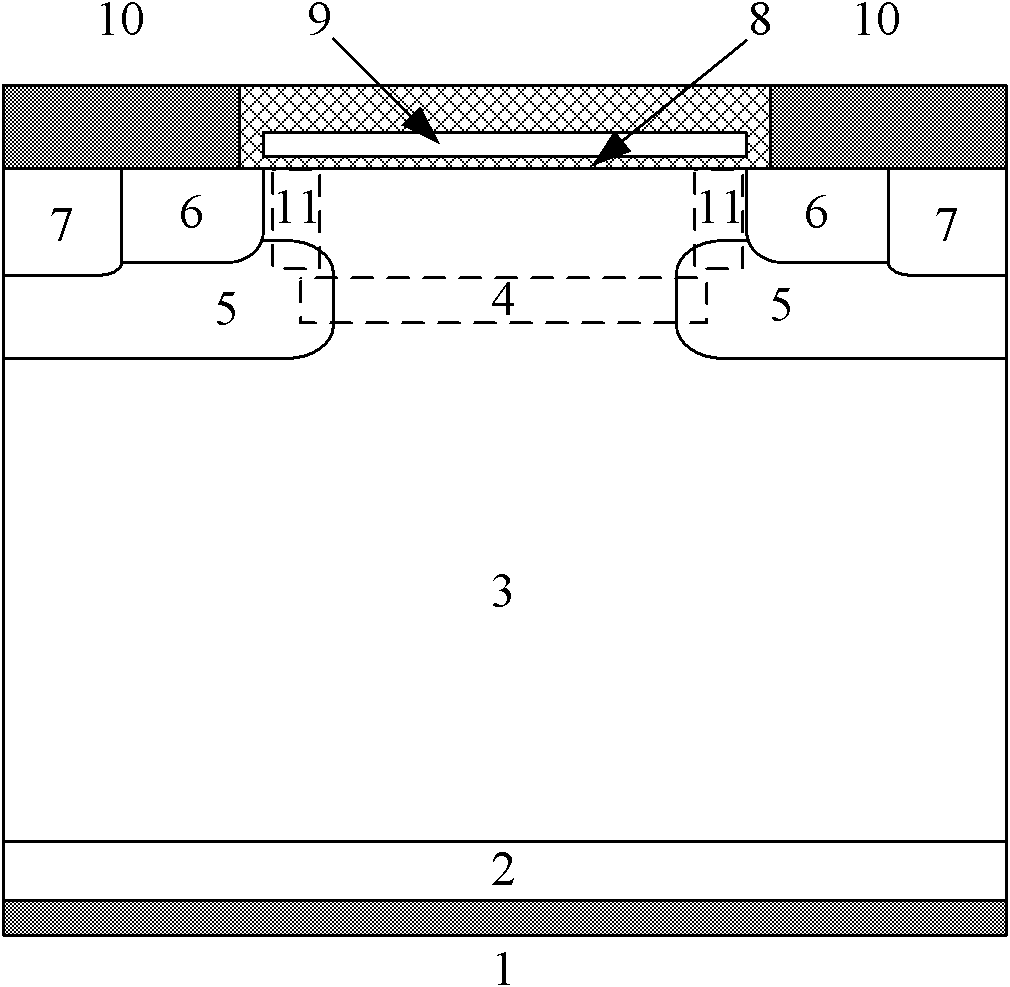

[0025] A low voltage buried trench VDMOS, such as image 3 shown, including metallized cathode 1, N + Substrate Region 2, N - Epitaxial layer 3, JFET region 4, deep P body region 5, P-type heavily doped region 6, N-type heavily doped region 7, gate oxide layer 8, polysilicon gate electrode 9, metalized anode 10, buried Trench structure11.

[0026] A low-voltage buried trench VDMOS device, its embodiment can be prepared by the following method, and the process steps are:

[0027] 1. Preparation of monocrystalline silicon, using N-type heavily doped zone-melted monocrystalline silicon (N-type impurity) substrate 2 with a doping concentration of 1.8×10 19 cm -3 , with a crystal orientation of and a thickness of 5 μm.

[0028] 2. Growth of the epitaxial layer, using the vapor phase epitaxy VPE method to grow 3 μm N on the substrate 2 at a temperature of 1000 ° C and under vacuum conditions. - Epitaxial layer 3, phosphorus doping concentration is 2×10 16 cm -3 .

[0029] ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com