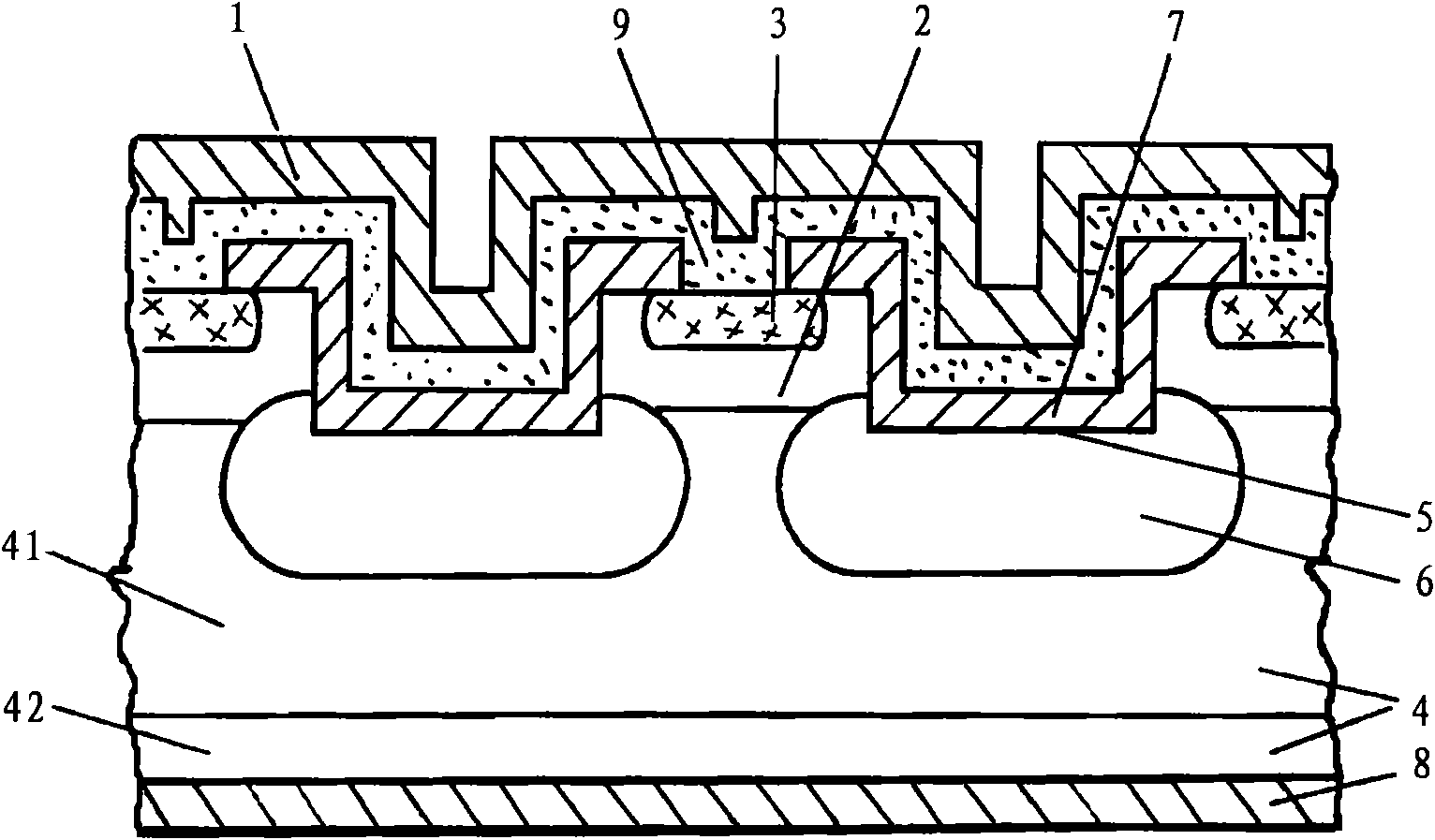

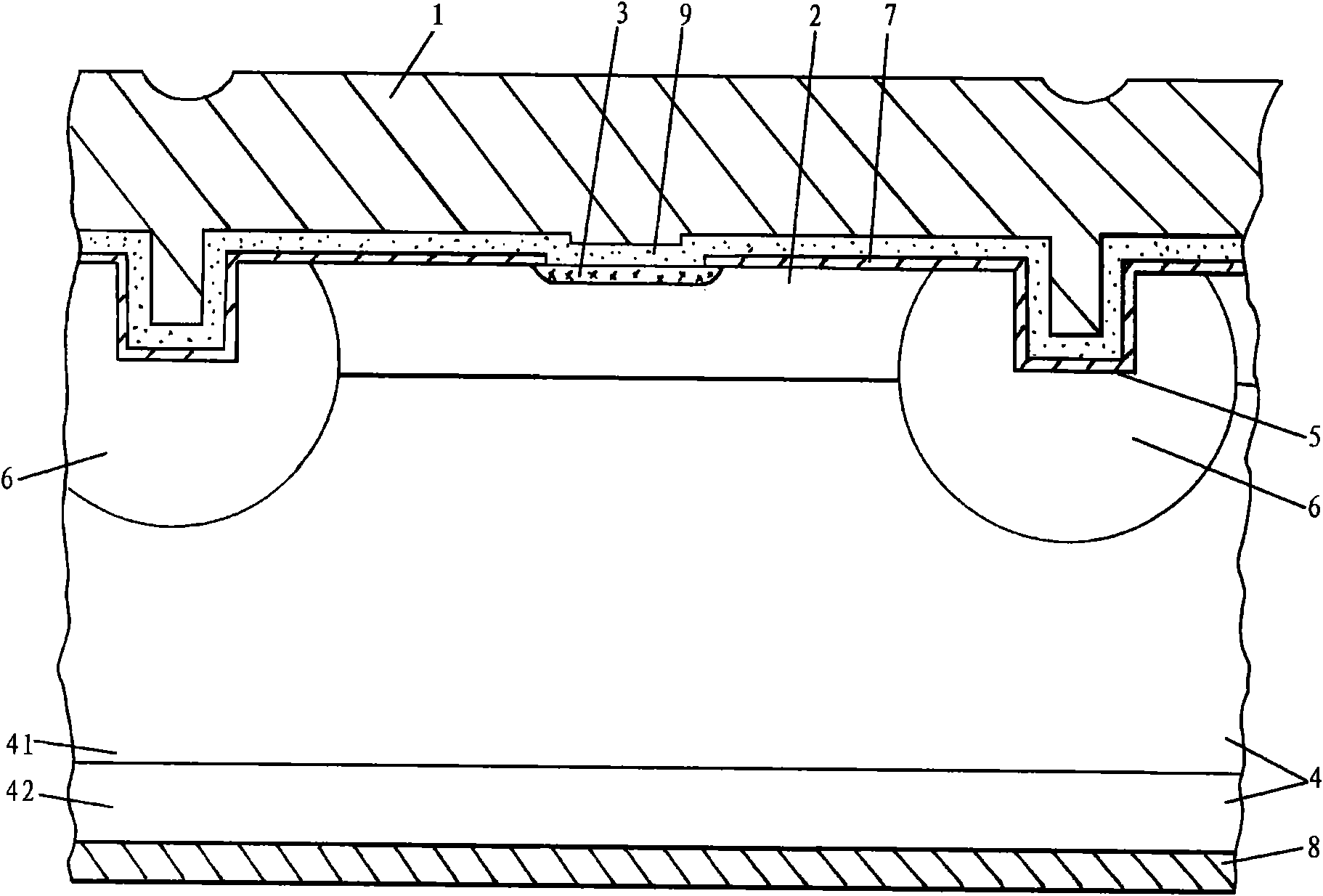

Gate associated transistor with grooved gate polysilicon structure

A technology of combined gate transistors and gate polysilicon, which is applied in the field of silicon semiconductor devices, can solve problems such as poor resistance to avalanche breakdown, and achieve the effects of enhanced ability to resist avalanche breakdown, low cost, and high cost performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

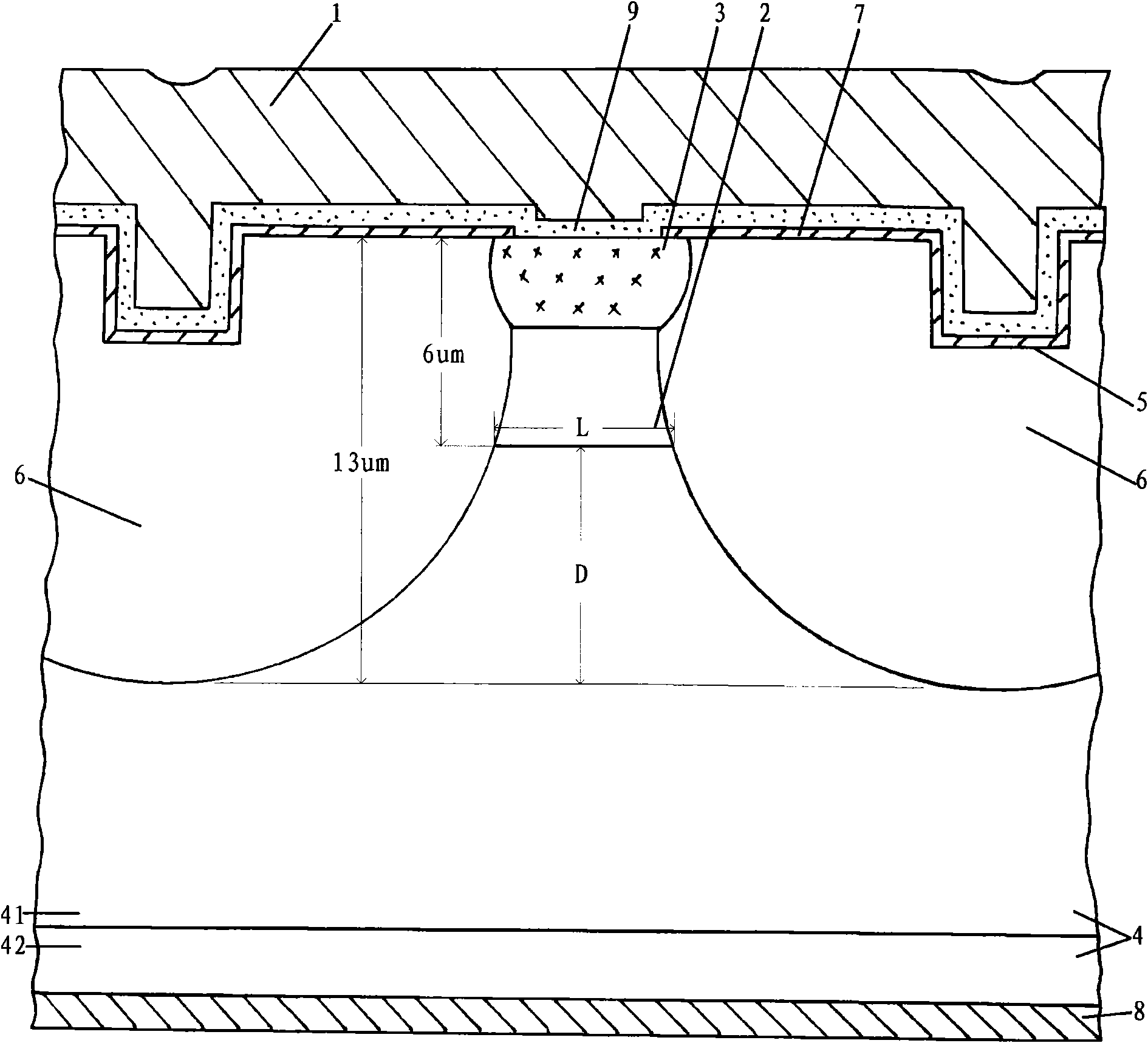

[0026] exist image 3 In the embodiment of the combined gate transistor with the groove gate polysilicon structure shown, the lower layer 42 of the silicon substrate 4 is the collector electrode, which is N with a thickness of 420 μm and a resistivity of 0.01Ω·cm. + type silicon, the upper layer 41 is N with a thickness of 60 μm and a resistivity of 35Ω·cm - type silicon. A plurality of parallel elongated grooves 5 are formed on the upper surface of the silicon substrate 4, the distance between two adjacent grooves 5 is 20 μm, and the depth of the grooves 5 is 3 μm. The bottom of the groove is formed by implanting boron ions and advancing + Type high-concentration trench gate region 6, the surface concentration of boron is IE19-2E20 / cm 3 , a junction depth of 10 μm. The upper surface of the upper layer 41 of the silicon substrate is implanted and diffused with boron ions to form a P-type base region 2, and the surface concentration of boron in the P-type base region 2 is 1...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com