Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

45 results about "Solar transition region" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

The solar transition region is a region of the Sun's atmosphere, between the chromosphere and corona. It is visible from space using telescopes that can sense ultraviolet. Helium ionization is important because it is a critical part of the formation of the corona: when solar material is cool enough that the helium within it is only partially ionized (i.e. retains one of its two electrons), the material cools by radiation very effectively via both black-body radiation and direct coupling to the helium Lyman continuum. This condition holds at the top of the chromosphere, where the equilibrium temperature is a few tens of thousands of kelvins.

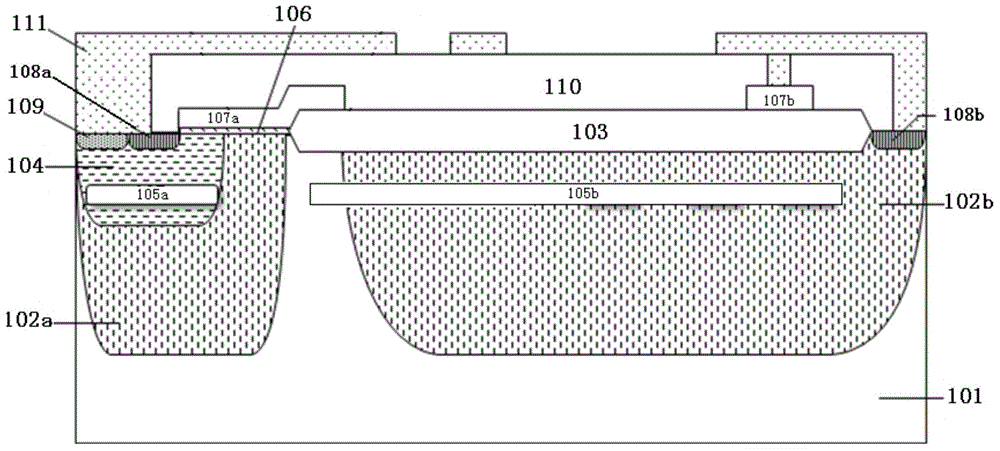

Non-volatile memory device

ActiveUS20090242964A1Reduce variationLess thickness variationSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringSemiconductor

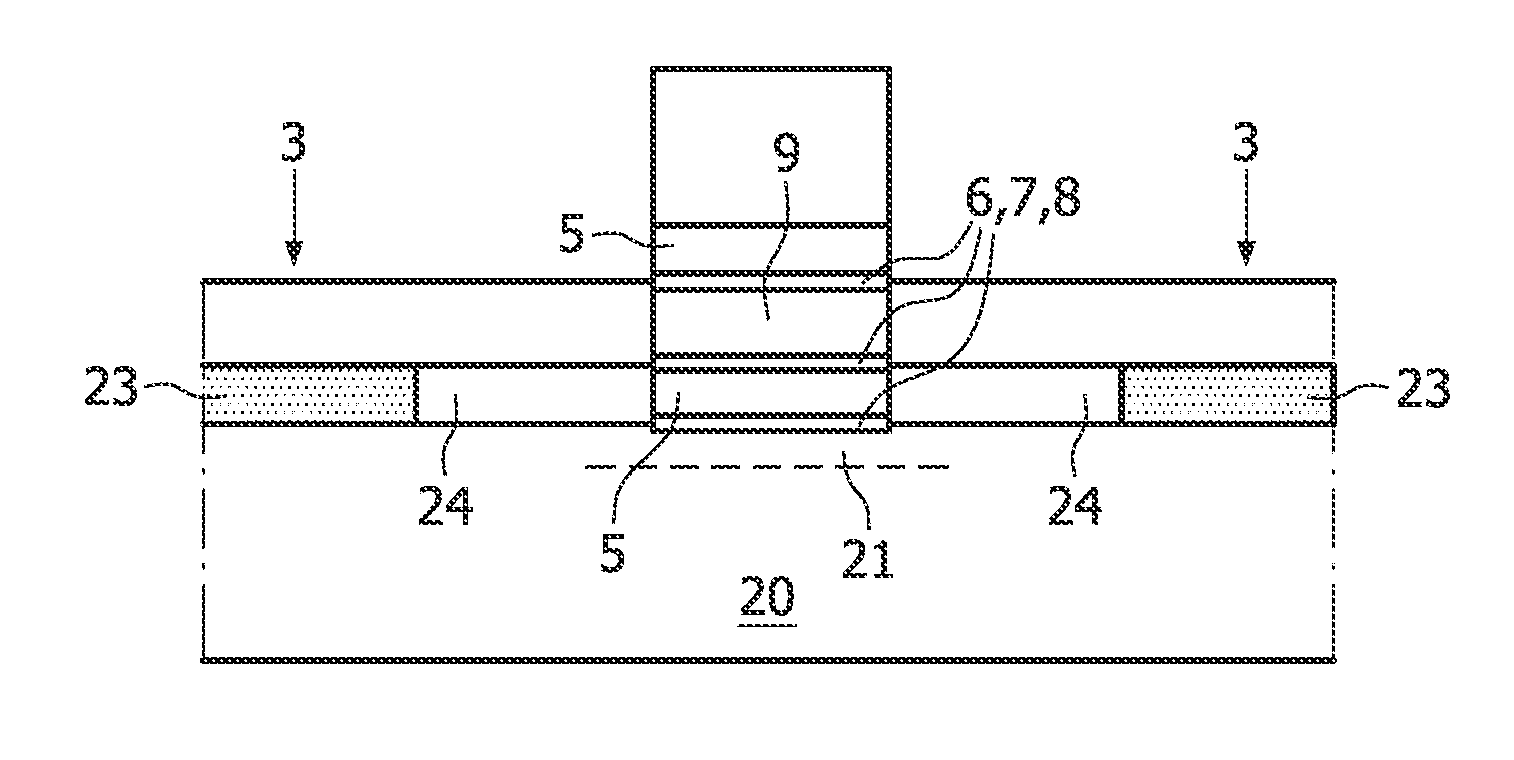

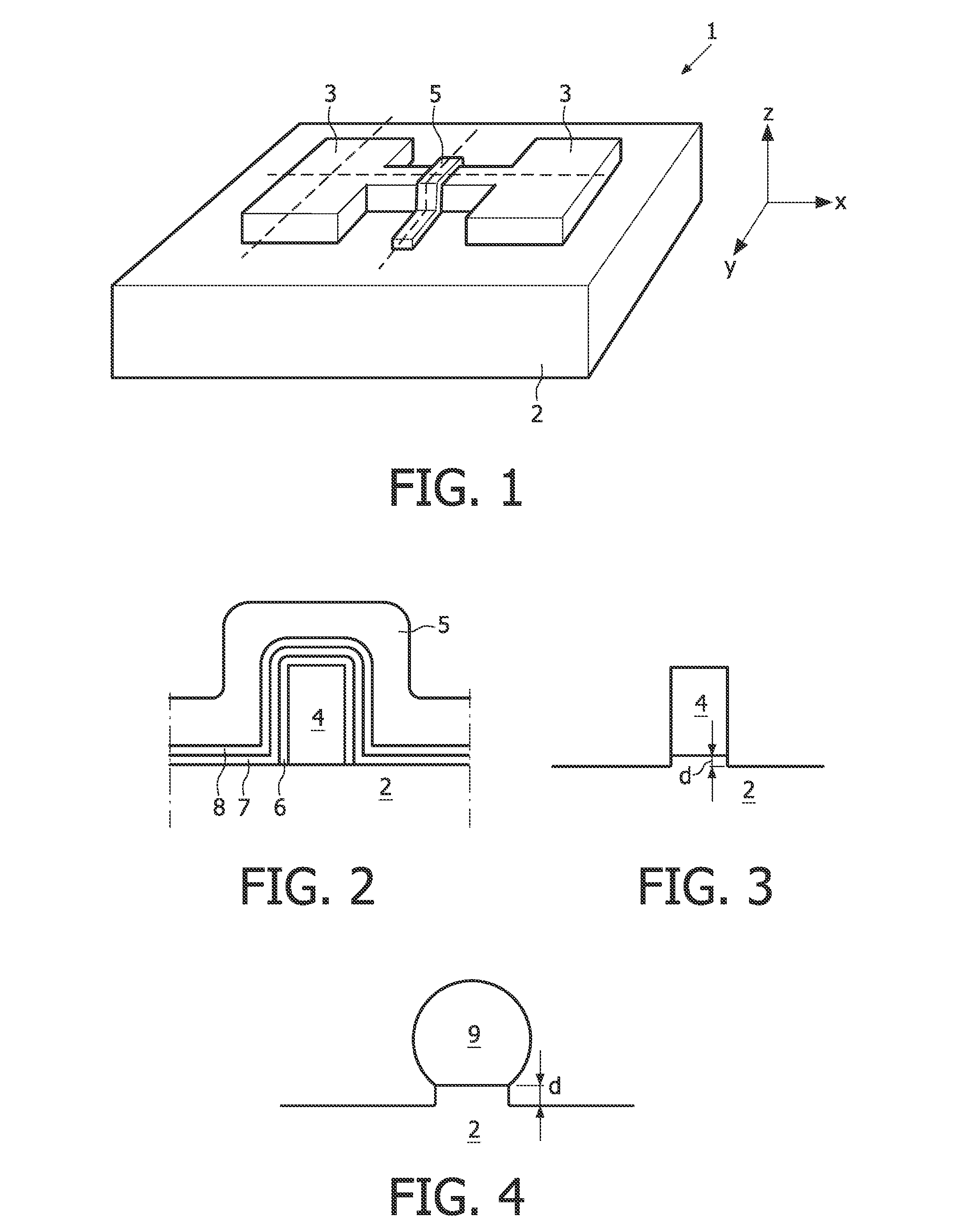

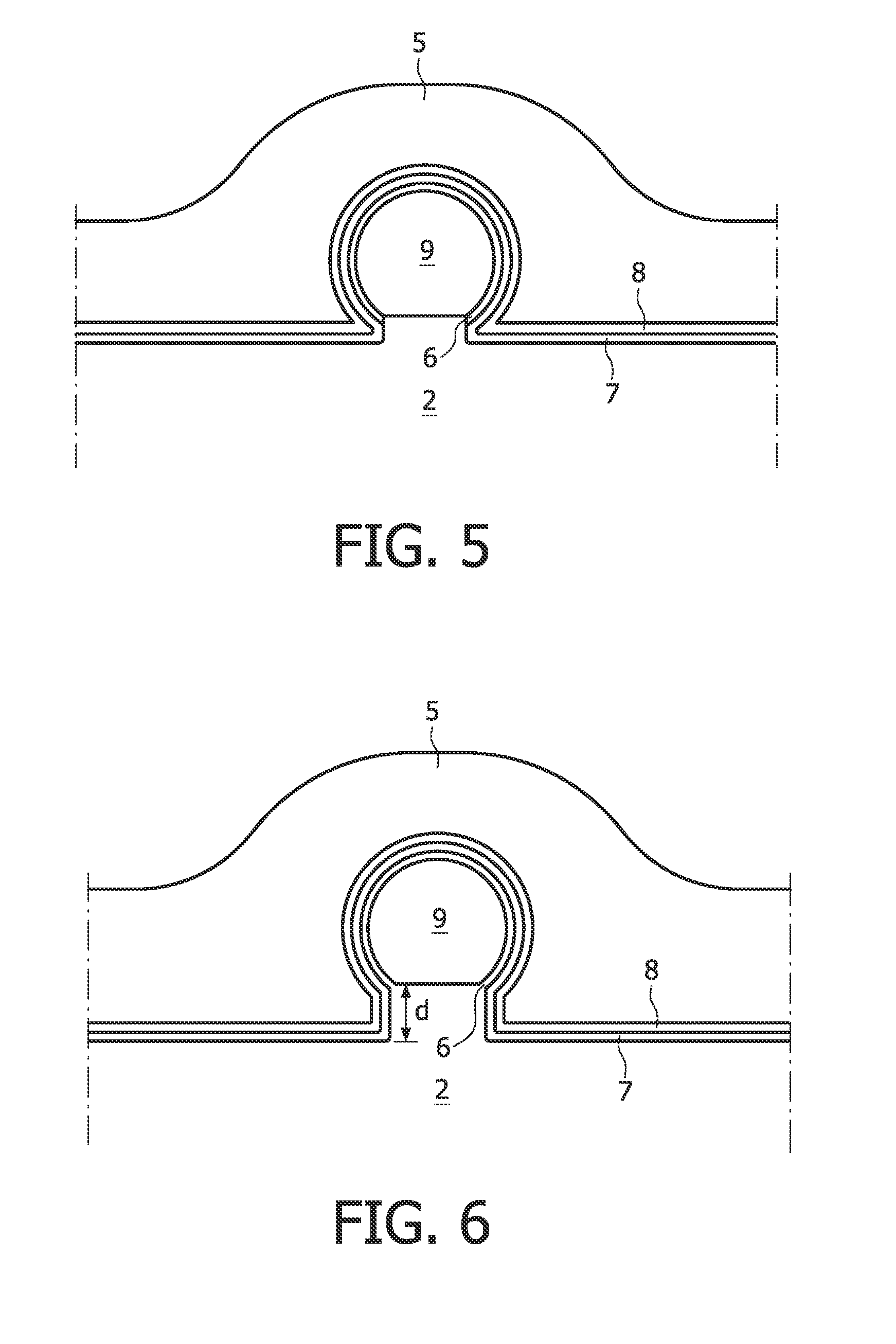

A finFET-based non-volatile memory device on a semiconductor substrate includes source and drain regions, a fin body, a charge trapping stack and a gate. The fin body extends between the source and the drain region as a connection. The charge trapping stack covers a portion of the fin body and the gate covers the charge trapping stack at the location of the fin body. The fin body has a corner-free shape for at least ¾ of the circumference of the fin body which lacks distinct crystal faces and transition zones in between the crystal faces.

Owner:III HLDG 6

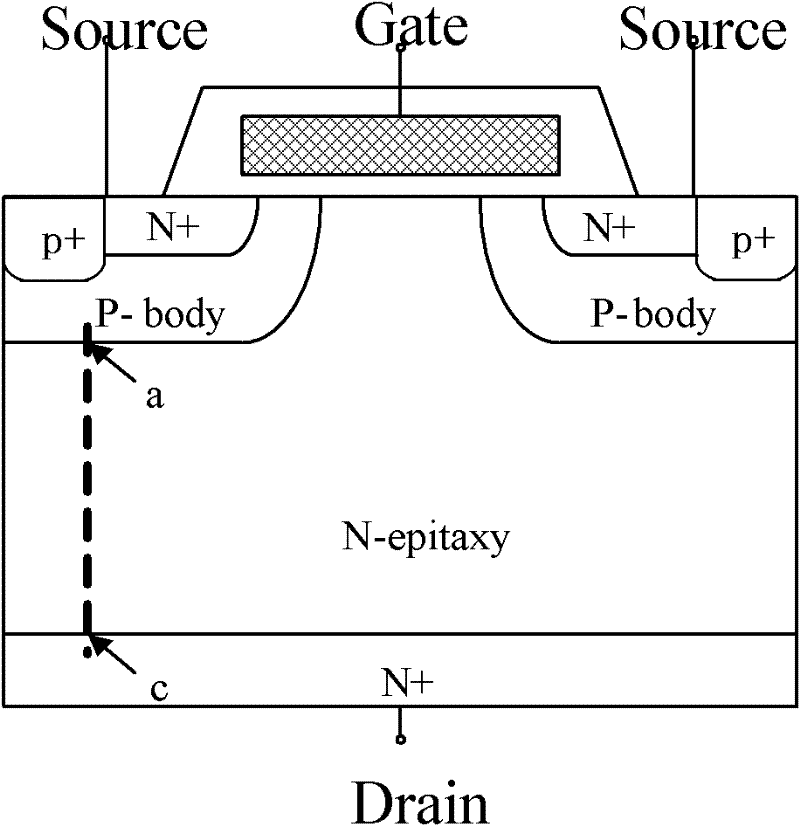

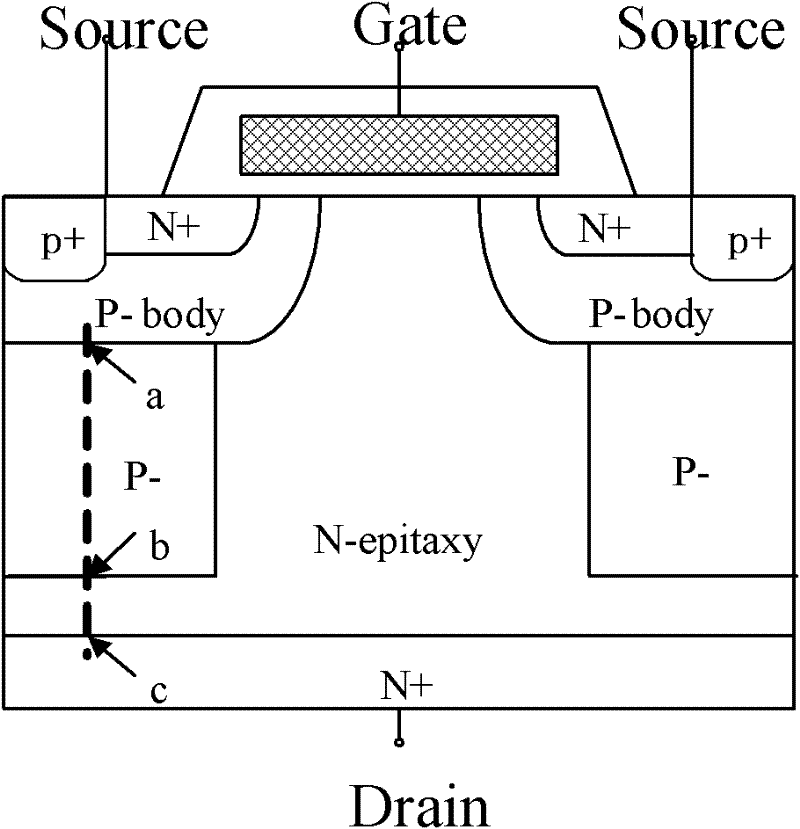

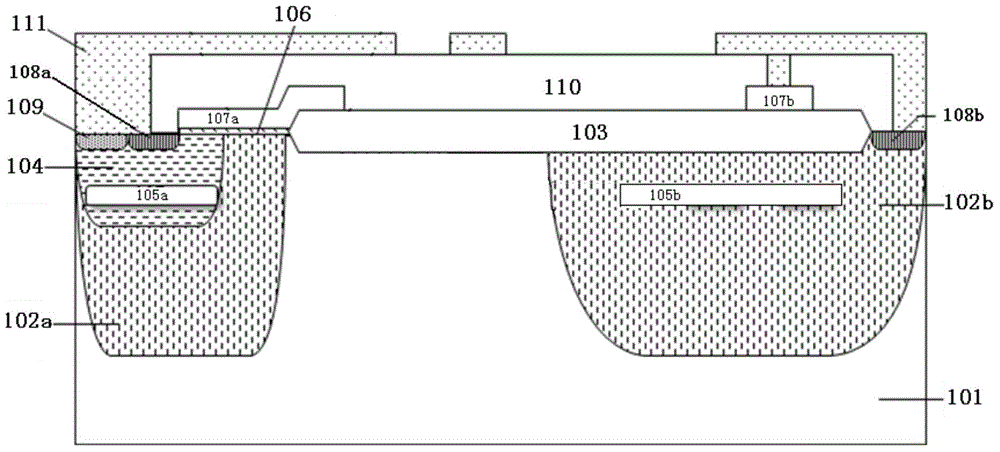

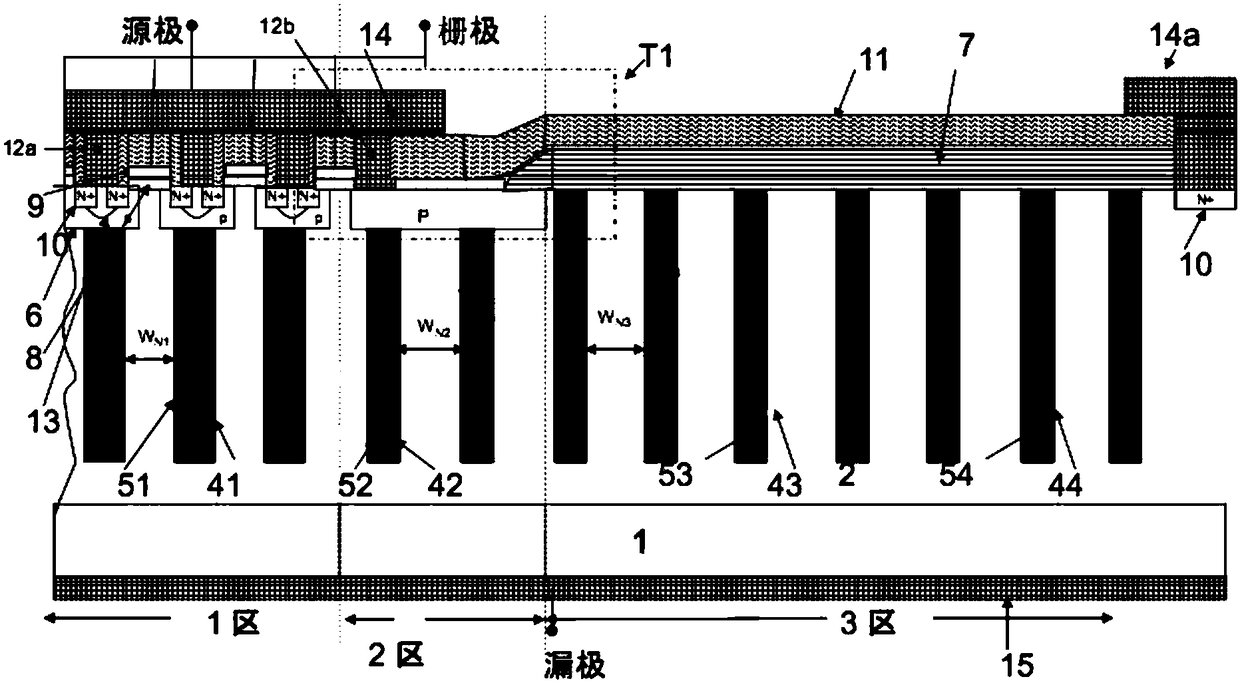

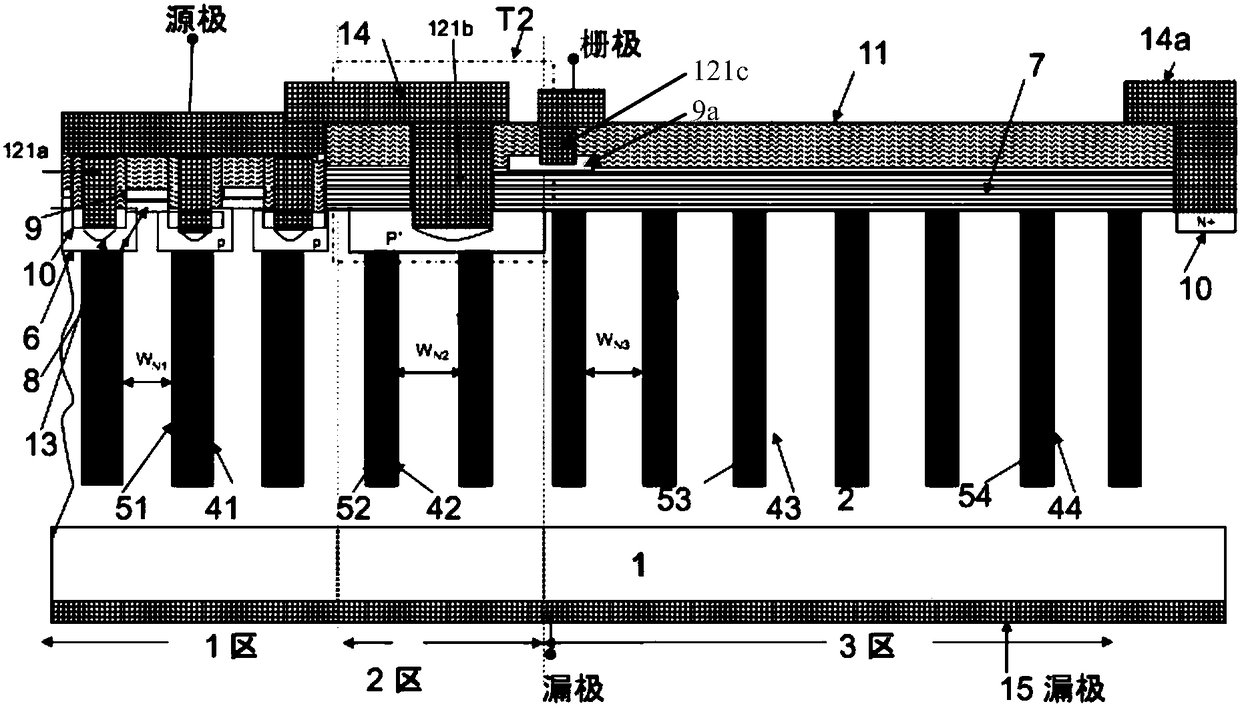

Rapid superjunction longitudinal double-diffusion metal oxide semiconductor transistor

InactiveCN101969073AExpand quicklyImprove pressure resistanceSemiconductor devicesDouble diffusionEngineering

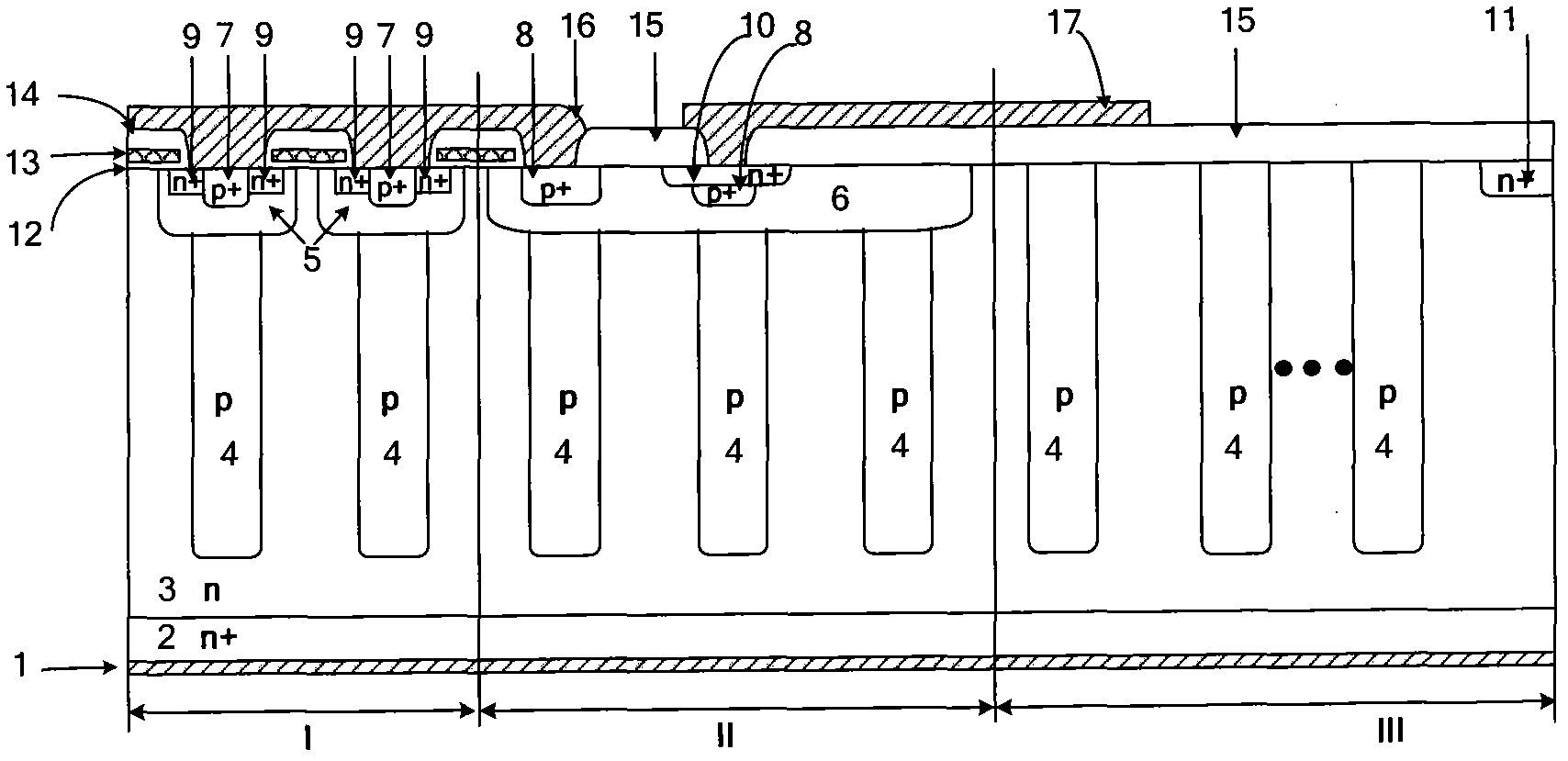

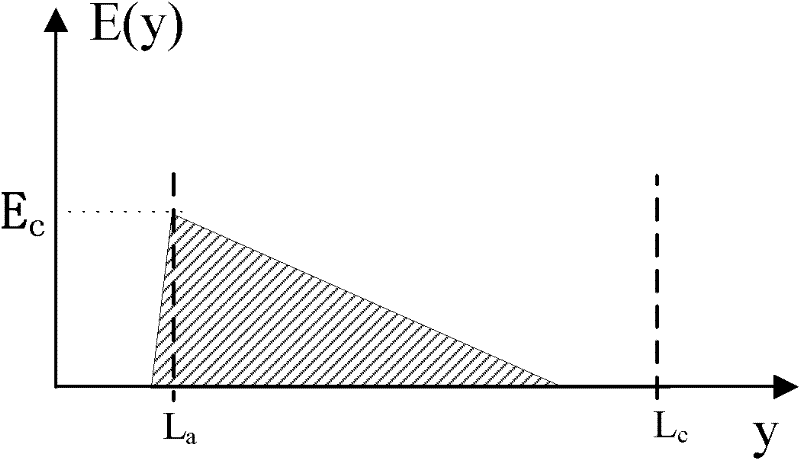

The invention relates to a rapid superjunction longitudinal double-diffusion metal oxide semiconductor transistor which comprises a cell area, a terminal area and a transition area, wherein the terminal area is arranged at the outermost periphery of a chip; the transition area is positioned between the cell area and the terminal area; the bottoms of the cell area, the transition area and the terminal area (III) are provided with drain electrode metal; a heavy doping n-type silicon substrate is arranged on the drain electrode metal and used as a drain area of the chip; an n-type doping epitaxial layer is arranged on the heavy doping n-type silicon substrate; and a discontinuous p-type doping columnar semiconductor area is arranged in the n-type doping epitaxial layer. The rapid superjunction longitudinal double-diffusion metal oxide semiconductor transistor is characterized in that an n-type heavy doping semiconductor area is arranged in a second p-type doping semiconductor area in the transition area, and the surface of the n-type heavy doping semiconductor area is provided with a contact hole which is connected with a metal layer to form a ground contact electrode of the chip. The invention can effectively reduce the reverse recovery charge of a device and improve the reverse recovery characteristics under the conditions of not increasing the process cost or changing the main parameter of the device.

Owner:SOUTHEAST UNIV

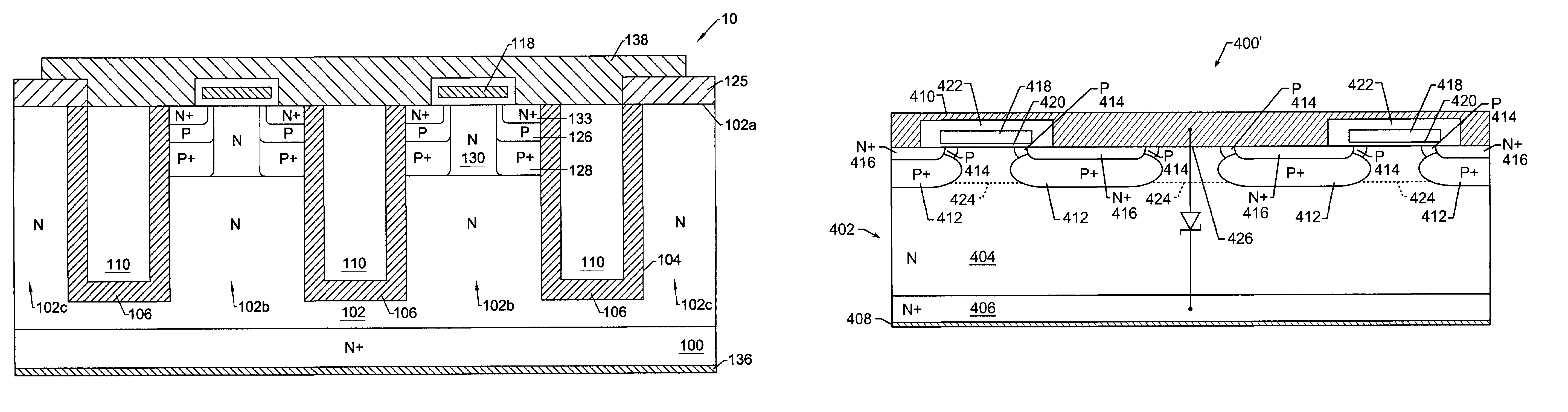

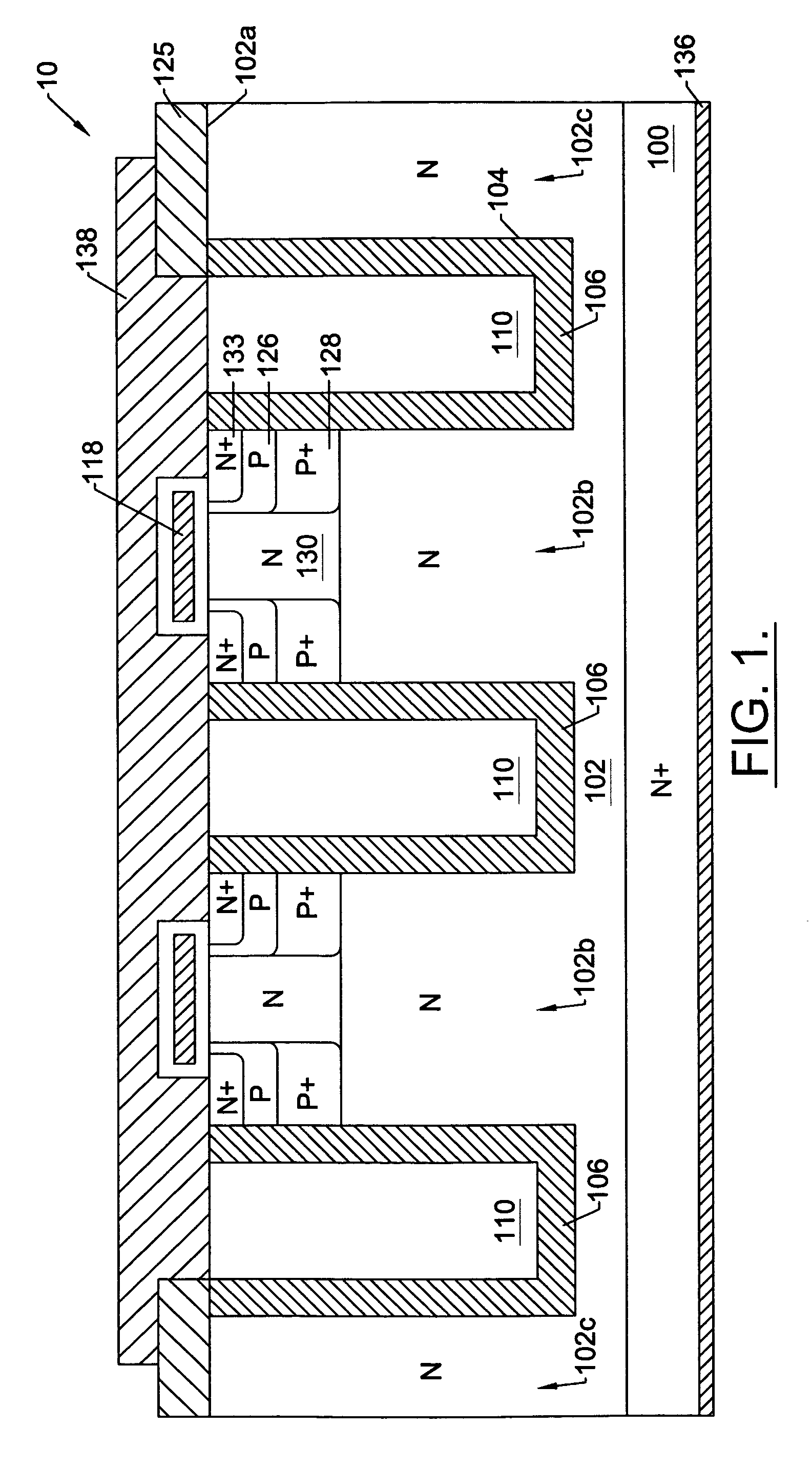

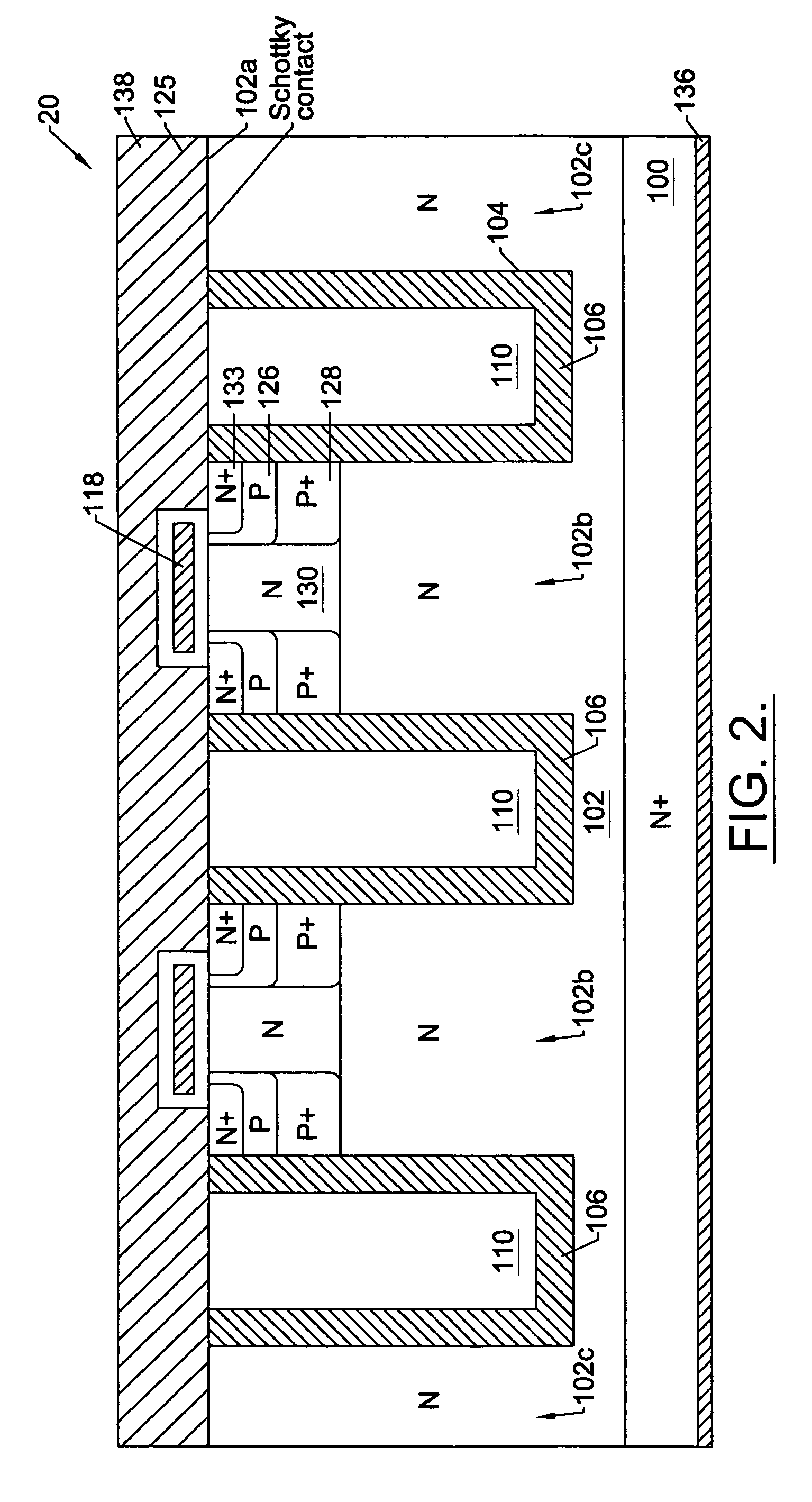

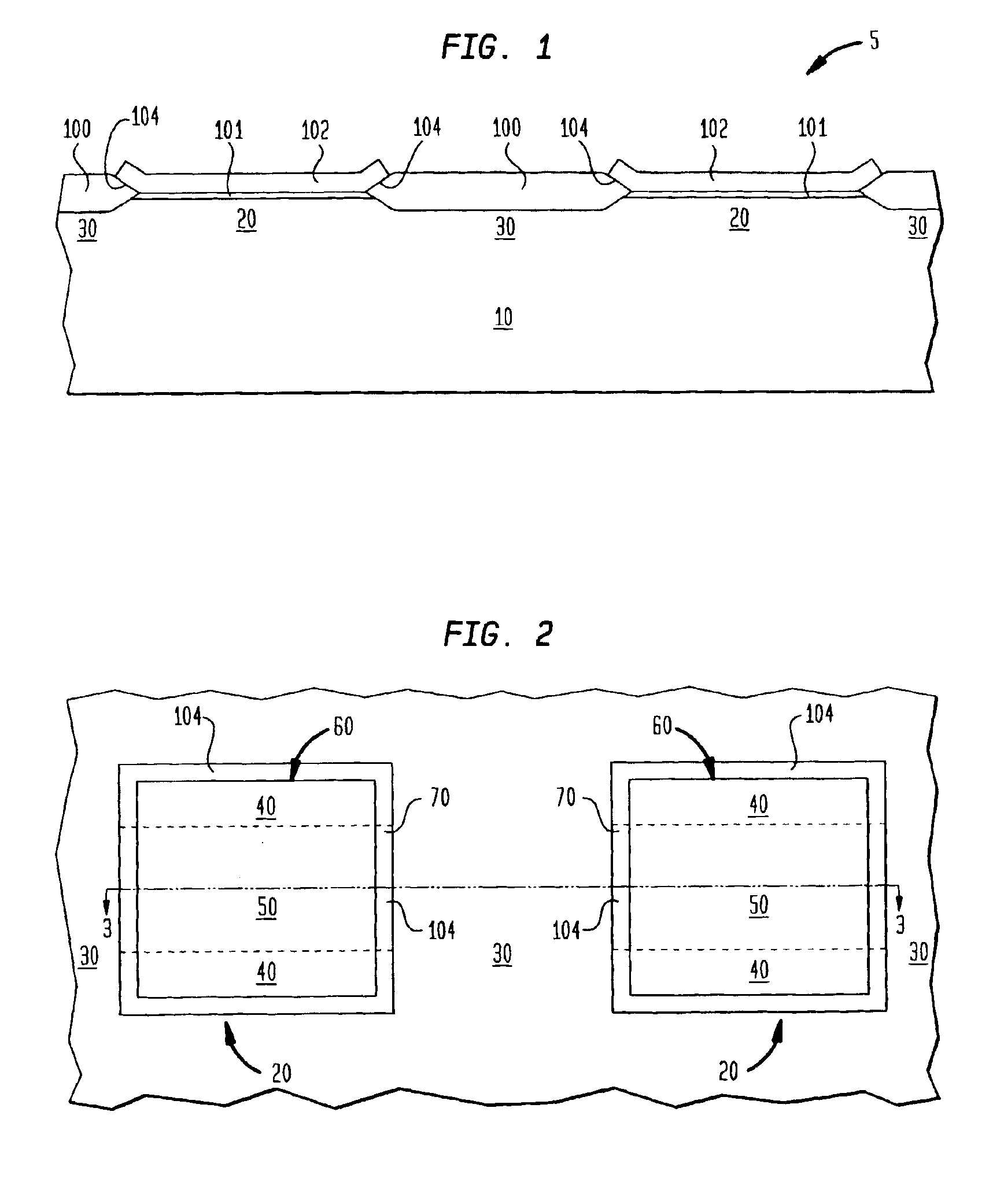

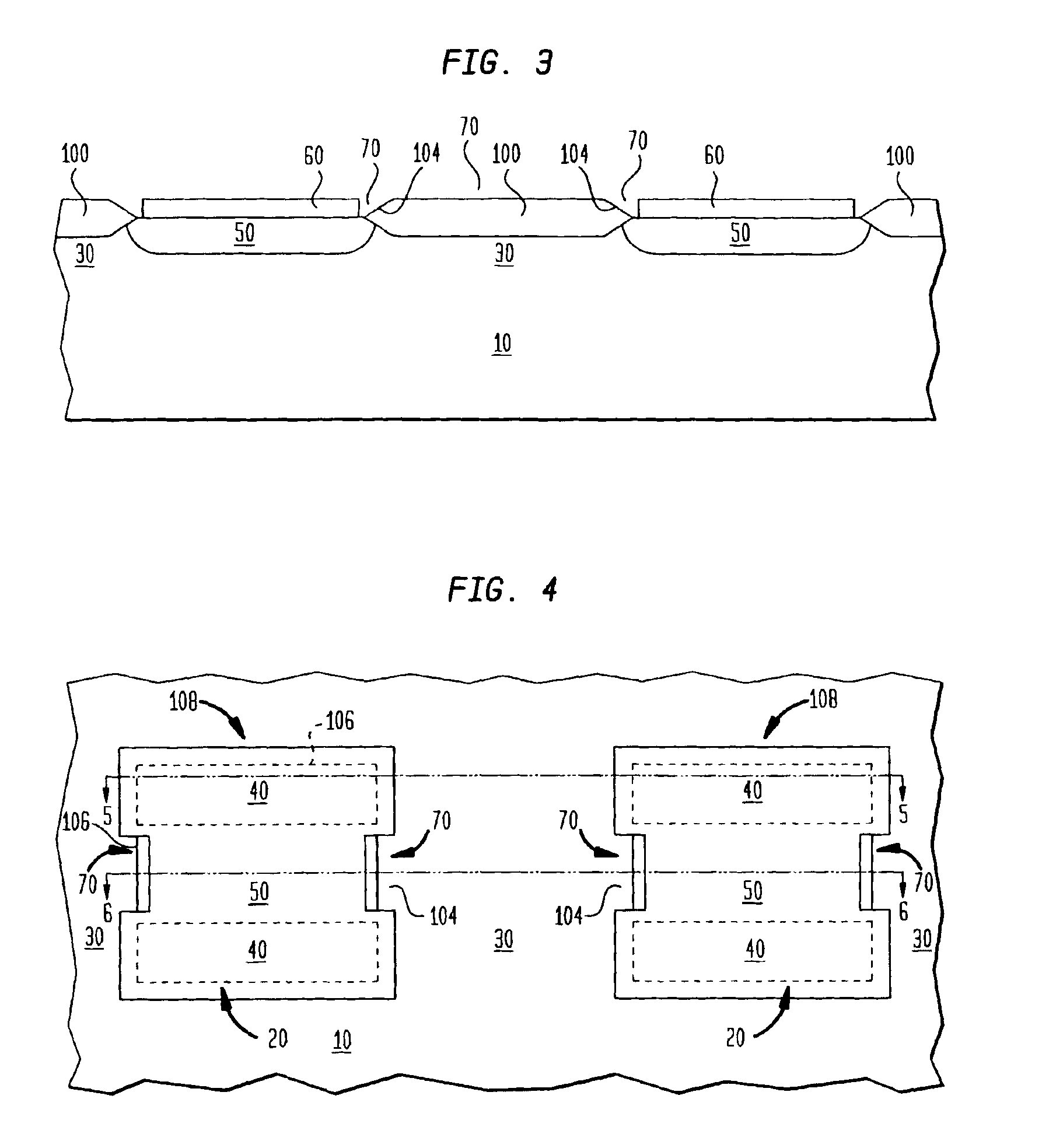

Methods of forming power semiconductor devices having laterally extending base shielding regions

InactiveUS7041559B2Avoiding characteristicHigh dopingSemiconductor/solid-state device manufacturingDiodePower semiconductor deviceDopant

Methods of forming power semiconductor devices include forming a semiconductor substrate having a drift region of first conductivity type therein and a transition region of first conductivity type that extends between the drift region and a first surface of the semiconductor substrate. A gate electrode is formed on the first surface. Base and base shielding region dopants are implanted into the transition region using the gate electrode as an implant mask. A plurality of annealing steps are performed so that the base shielding region dopants are driven in laterally and vertically to substantially their full and final depth within the substrate and thereby define first and second base shielding regions that constrict a neck of the transition region to a minimum width.

Owner:SEMICON COMPONENTS IND LLC

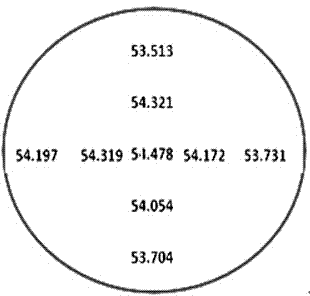

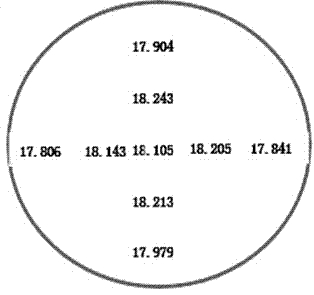

Method for growing high-resistance thick layer silicon epitaxy on 6-inch heavily As-doped silicon substrate

ActiveCN104851784AInactive doping effect suppressionImprove uniformitySemiconductor/solid-state device manufacturingSemiconductor devicesSlip lineHigh resistance

The invention relates to a method for growing a high-resistance thick layer silicon epitaxy on a 6-inch heavily As-doped silicon substrate. In the method, a normal-pressure flat plate type epitaxial furnace is adopted. The method comprises the following steps: (1) corroding an epitaxial furnace base by using hydrogen chloride with the purity of not less than 99.99 percent at a high temperature; (2) loading a silicon substrate sheet in the epitaxial furnace, purging a cavity of the epitaxial furnace for 8-10min by sequentially using nitrogen and hydrogen with purities of not less than 99.99 percent; (3) performing in-situ corrosion on the surface of the silicon substrate sheet by using hydrogen chloride gas; (4) purging the surface of the silicon substrate sheet by large-flow hydrogen; (5) growing an intrinsic epitaxial layer on the substrate by using non-doped trichlorosilane; (6) growing a doped epitaxial layer; and (7) cooling after the epitaxial layer reaches a preset temperature during growing. The method has the beneficial effects of being used for successfully preparing a high-resistance thick layer silicon epitaxy structure with thickness non-uniformity of less than 1 percent and specific resistance non-uniformity of less than 1 percent, without defects of a stacking fault, dislocation, a slip line and fog, with an optimal transition region width of less than 4 micrometers, good uniformity and a narrow transition region, and capable of completely meeting a requirement of a power MOS device on a silicon epitaxial material in an aspect of a parameter.

Owner:CHINA ELECTRONICS TECH GRP NO 46 RES INST +1

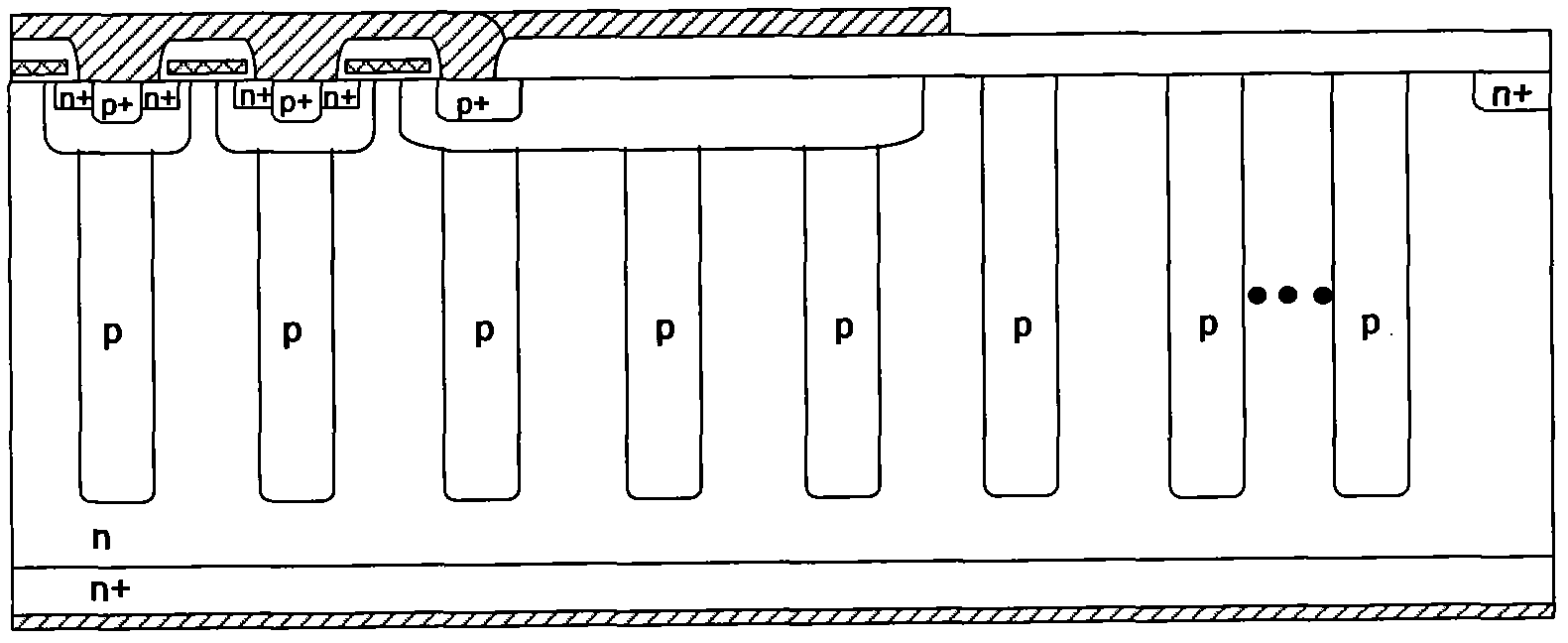

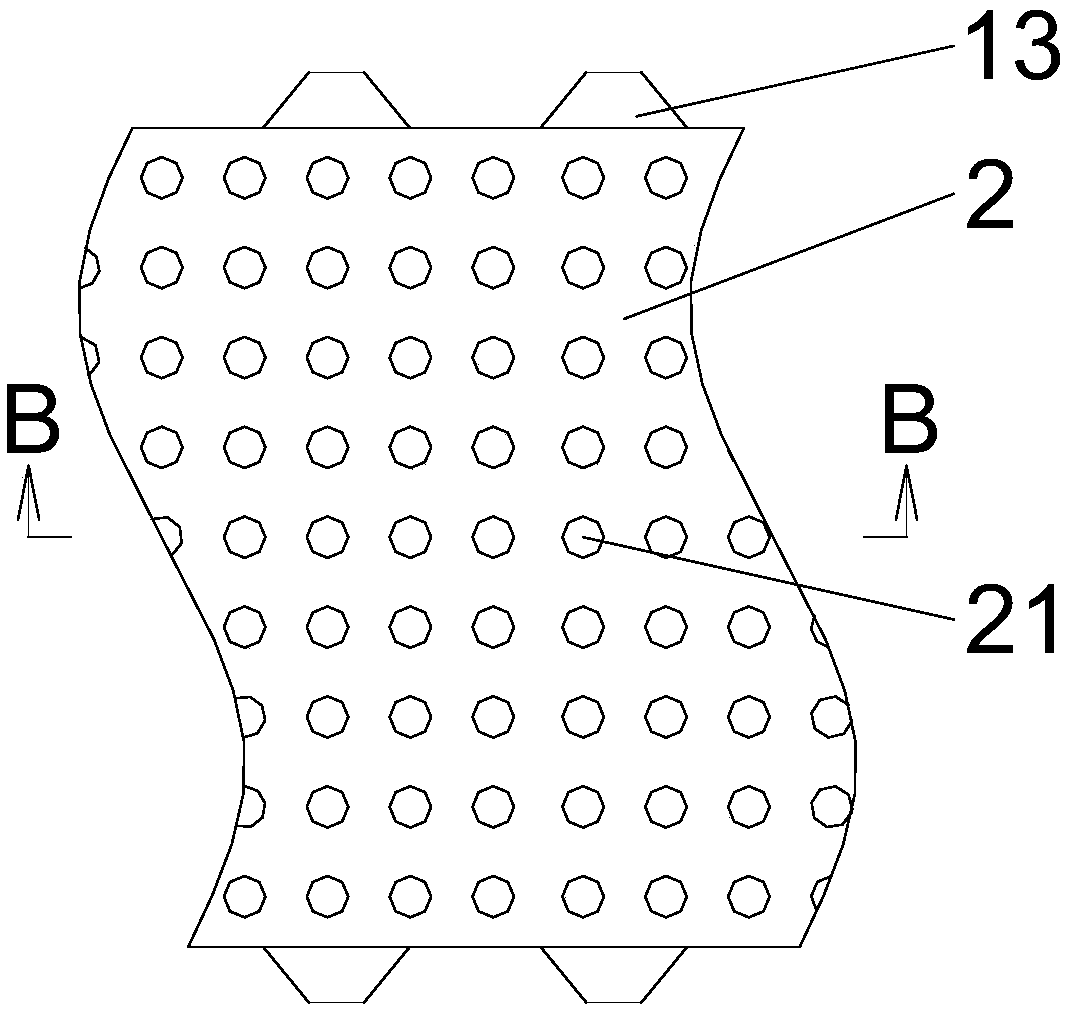

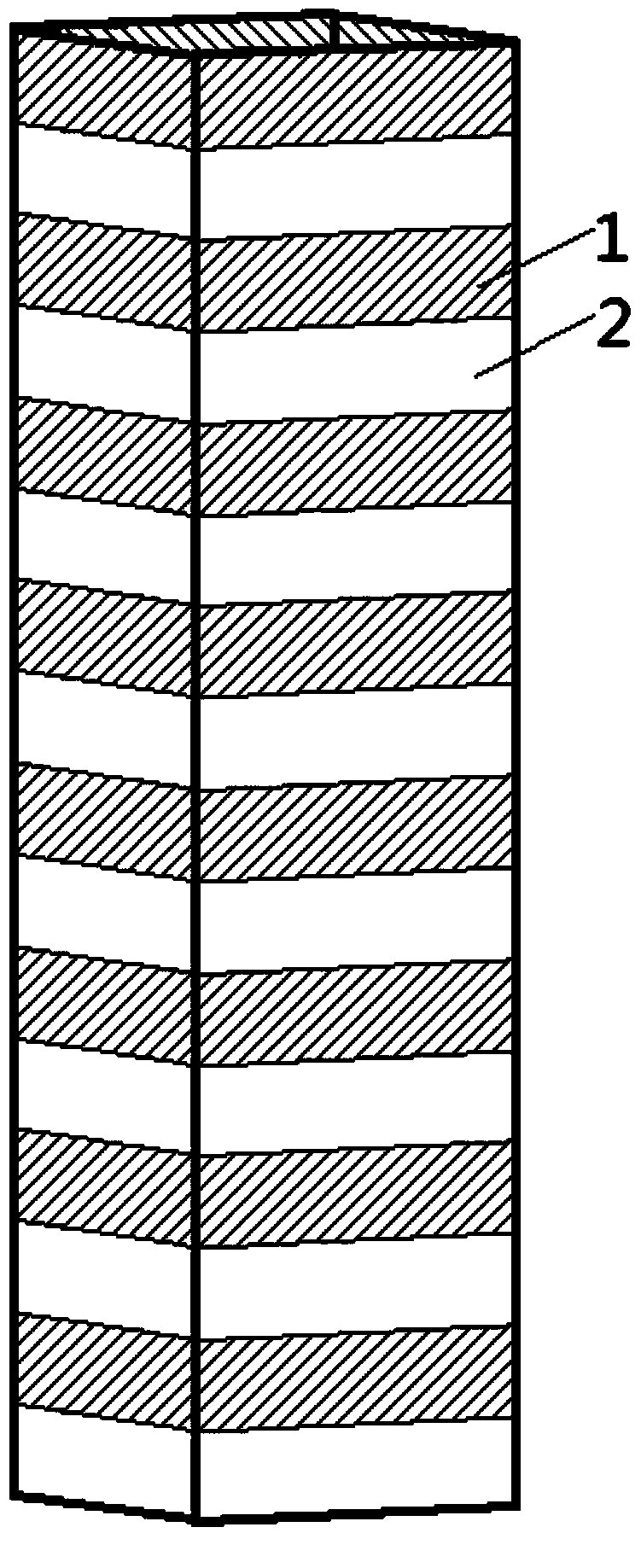

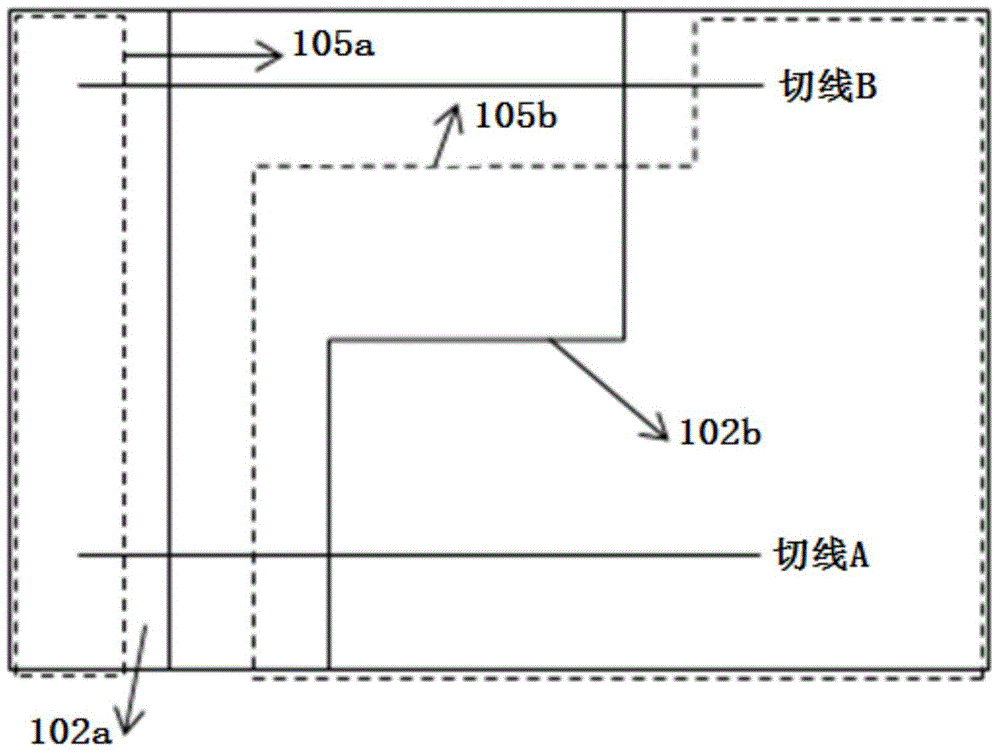

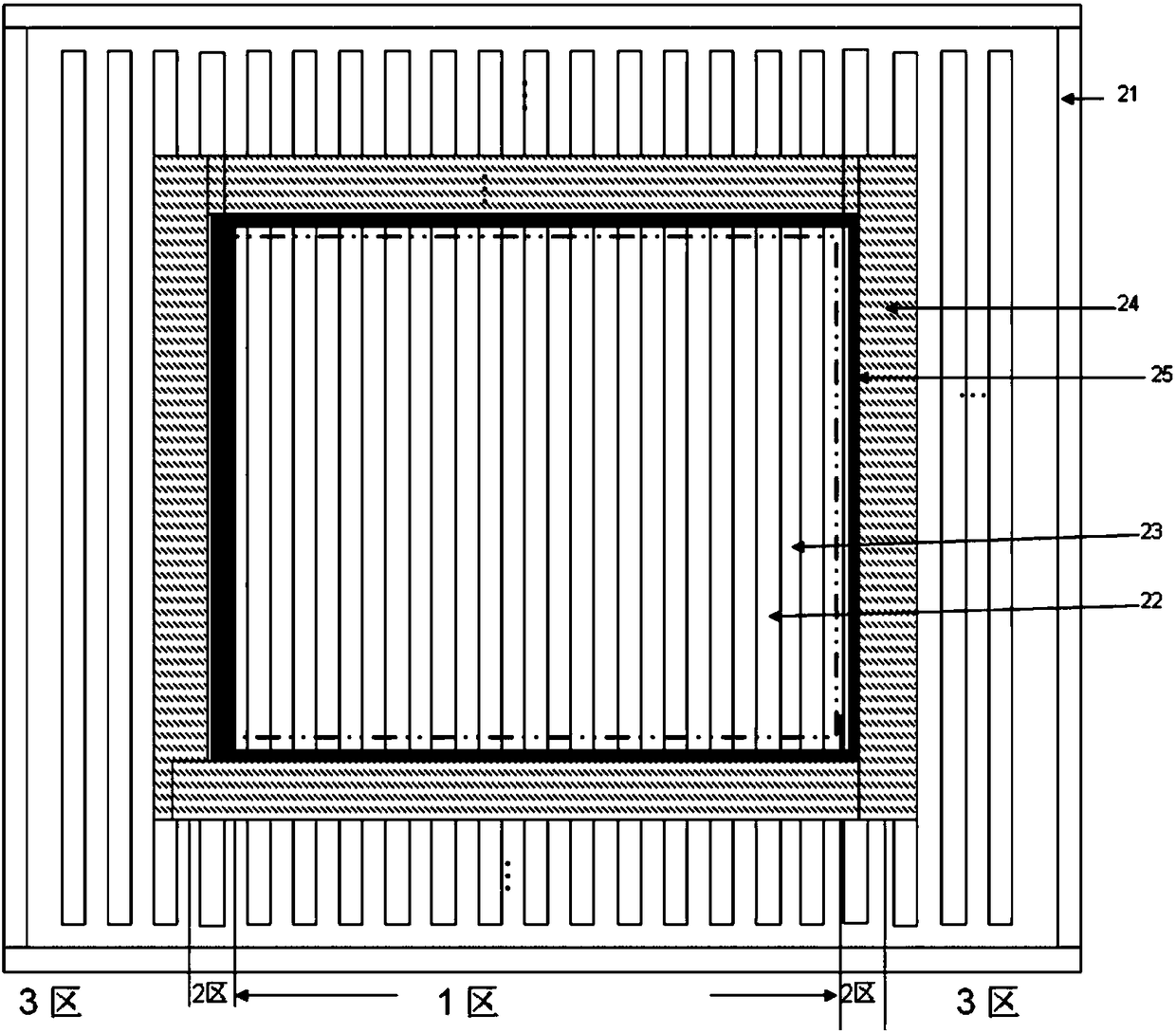

Vertical double-diffused metal oxide semiconductor power device with super junction structure

InactiveCN102231390AImprove performanceImprove breakdown voltageSemiconductor devicesCell regionBreakdown voltage

The invention relates to the technical field of semiconductor devices, in particular to a vertical double-diffused metal oxide semiconductor power device with a super junction structure. The vertical double-diffused metal oxide semiconductor power device comprises a cell region I, a transition region II and a terminal region III, wherein the transition region II surrounds the cell region, and the terminal region III surrounds the transition region. The vertical double-diffused metal oxide semiconductor power device is characterized in that an insulating medium material is arranged at the bottom of a second conduction type cylindrical semiconductor region in the cell region I. The invention has the beneficial effects that the distribution of an electric field is close to ideal uniform distribution, a breakdown voltage of a practical super junction structure device is increased and performances of the device are further improved according to the vertical double-diffused metal oxide semiconductor power device with the improved super junction structure.

Owner:ZHEJIANG UNIV

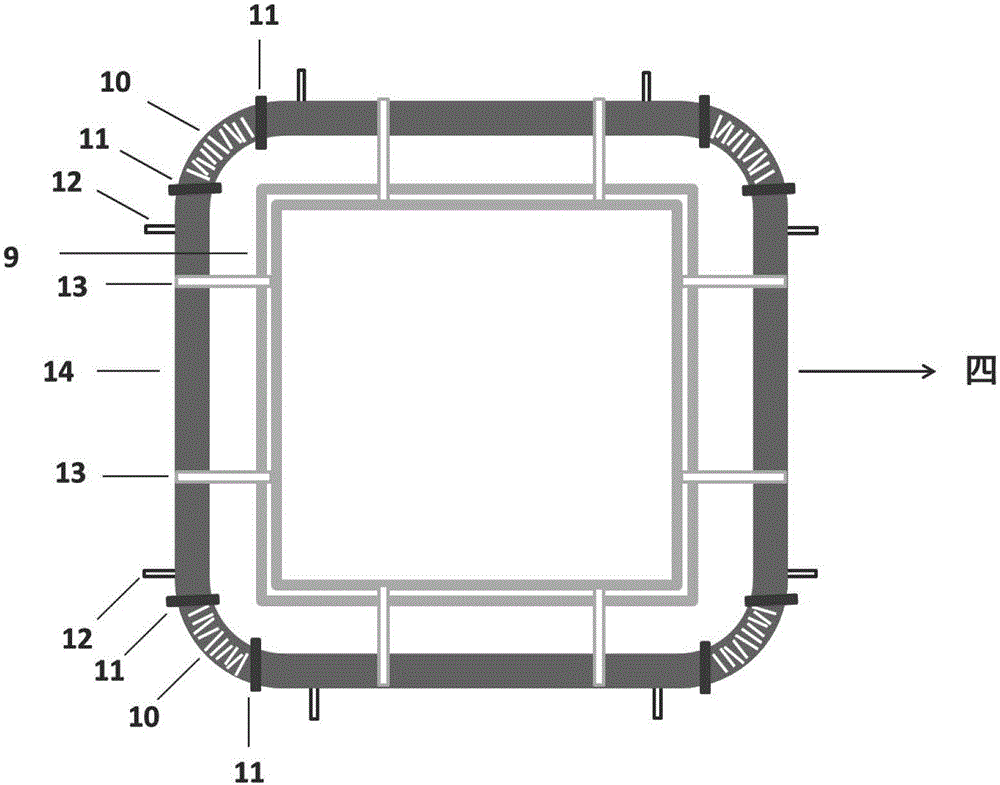

Current collector, positive electrode plate fabricated by employing same and battery cell

PendingCN108736016AImprove securityImprove conductivityFinal product manufactureElectrode carriers/collectorsConductive coatingEngineering

The invention discloses a current collector. The current collector comprises a conductive network and polymer porous films, wherein transition regions of the conductive network are respectively arranged at a group of opposite sides of a grid region and are continued along the side edges, tab regions are arranged at an outer sides of the transition regions and are connected, the polymer porous films are respectively attached onto an upper surface and a lower surface of the conductive network, the polymer porous films cover the grid regions and transition strip regions, and holes of the polymerporous films are corresponding to connection lines on the grid regions. The invention simultaneously discloses a positive electrode plate fabricated by employing the same. A conductive coating layer and a positive electrode material layer are sequentially coated on a surface of an outer side of the current collector and at least correspondingly cover the polymer porous films, the holes of the polymer porous films are filled with the conductive coating layer, and the conductive coating layer reaches the connection lines of the grid regions. The current collector has the advantages that the structural strength, the overcurrent capability and the conductivity of the current collector and the adhesivity of the positive electrode material are improved, and the burr short-circuit probability easy to generate on the current collector on the positive electrode plate during abusing is reduced.

Owner:ETRUST POWER ETP GRP LTD

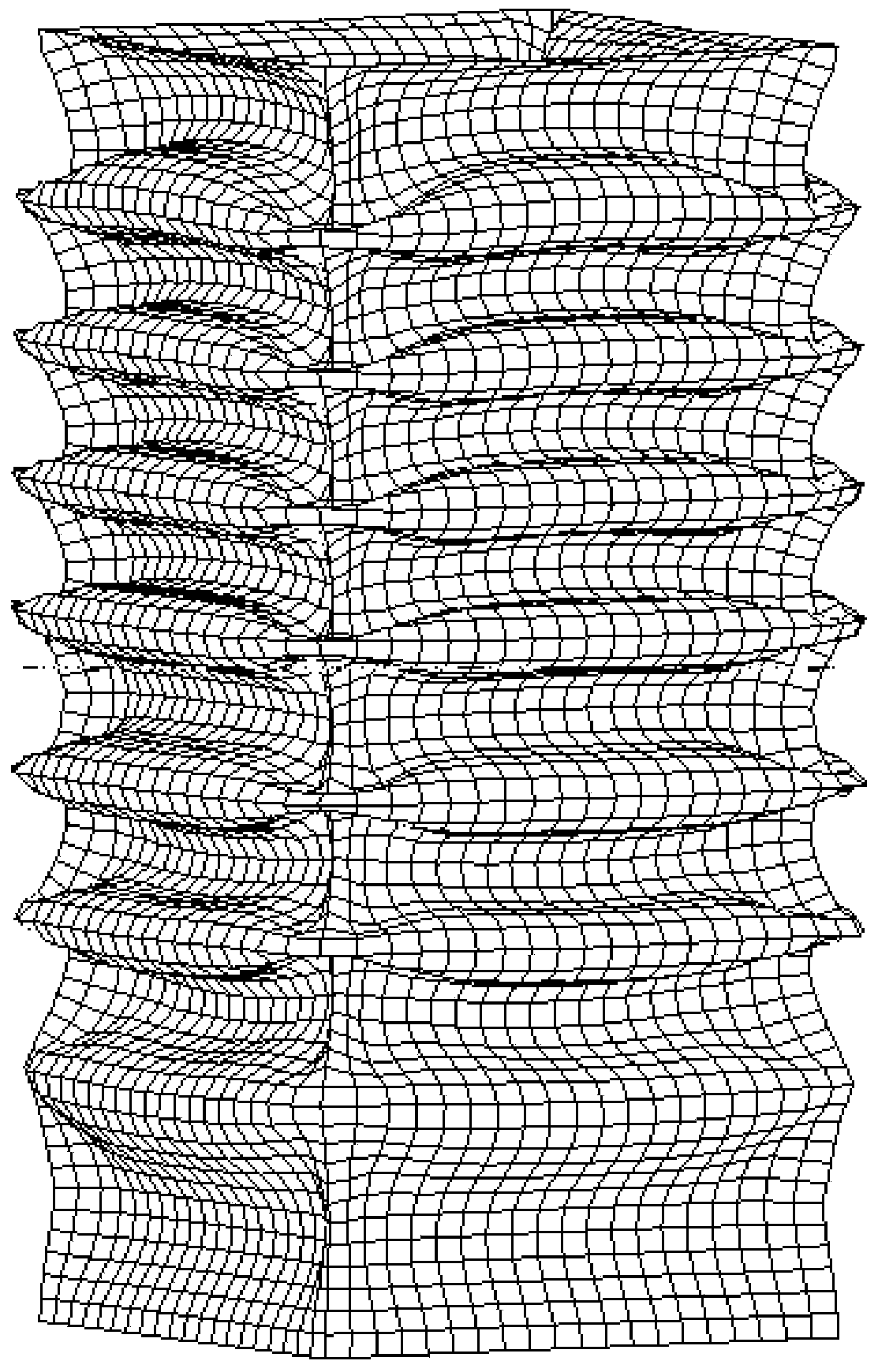

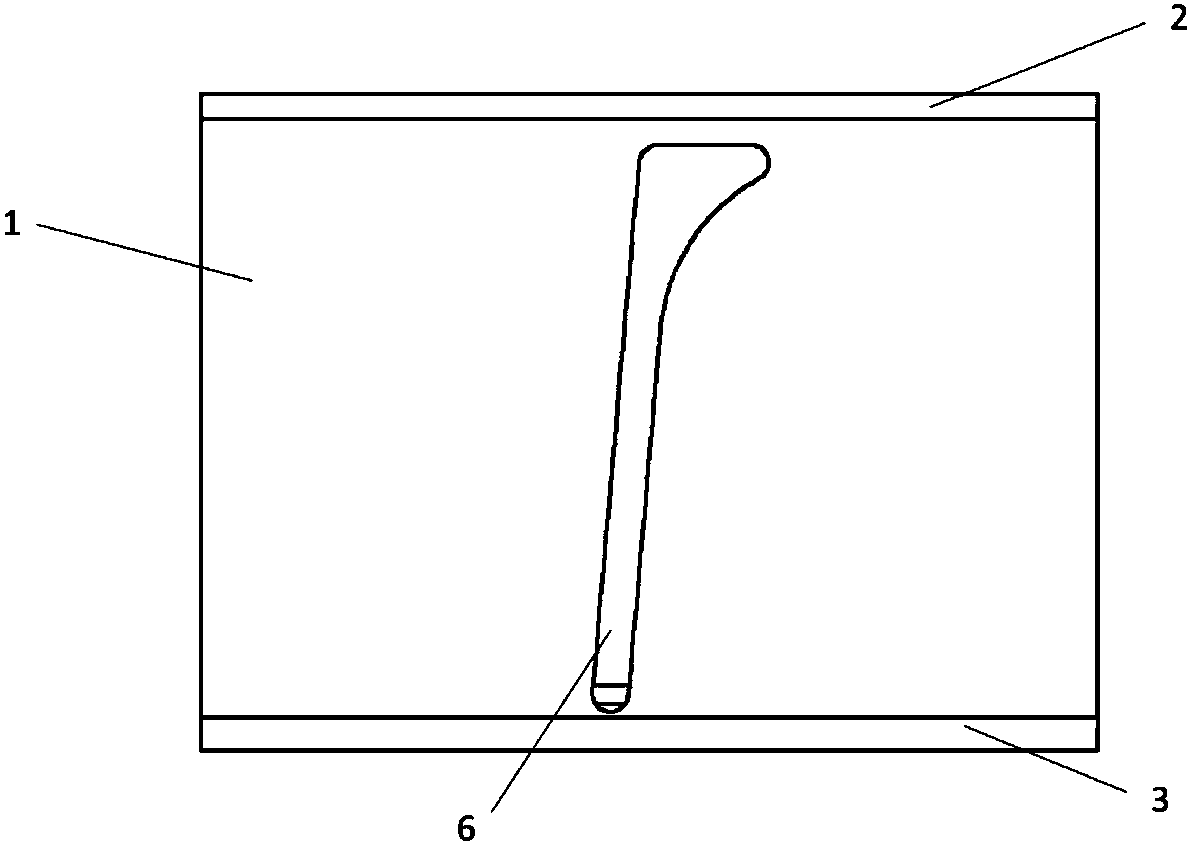

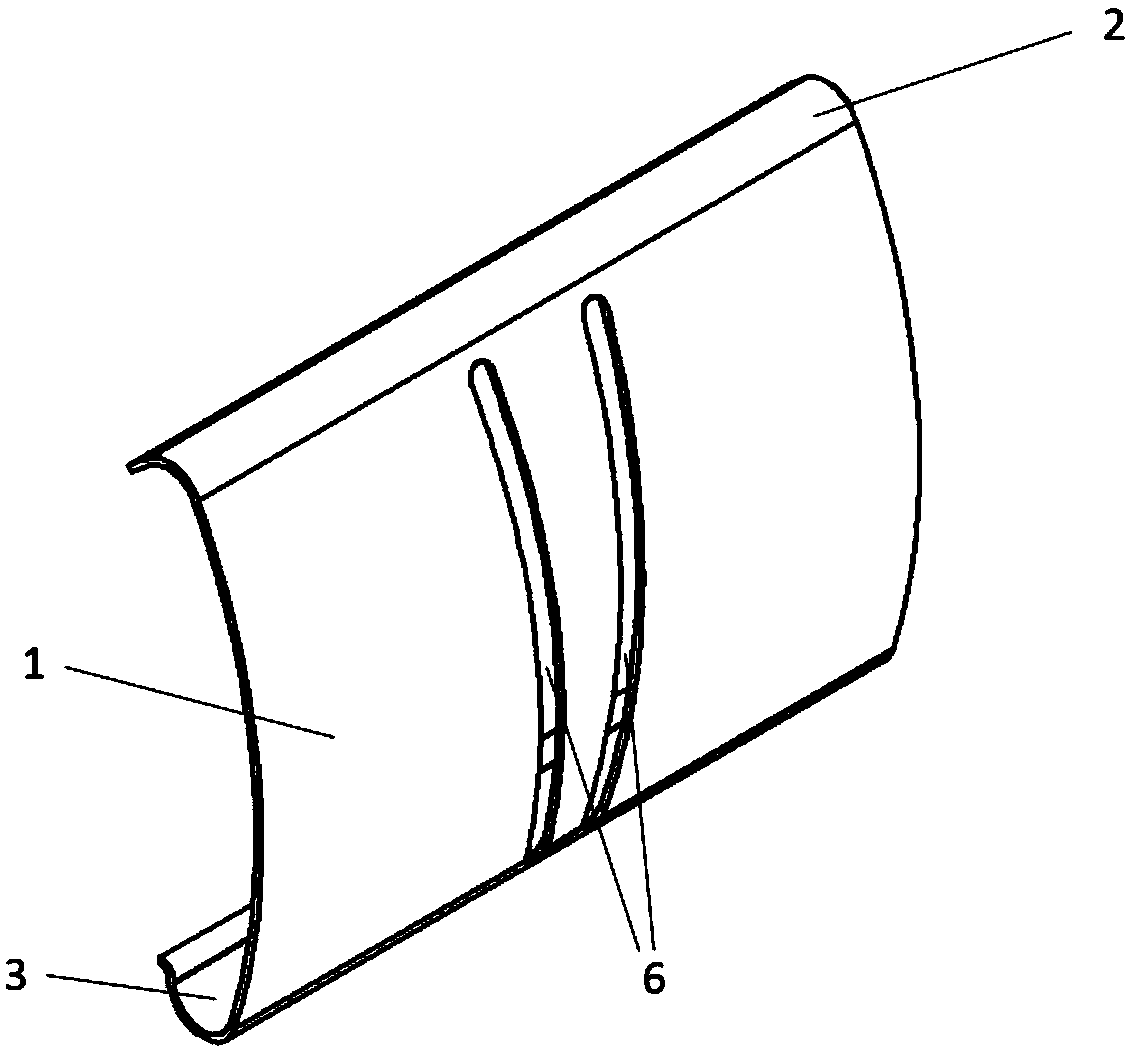

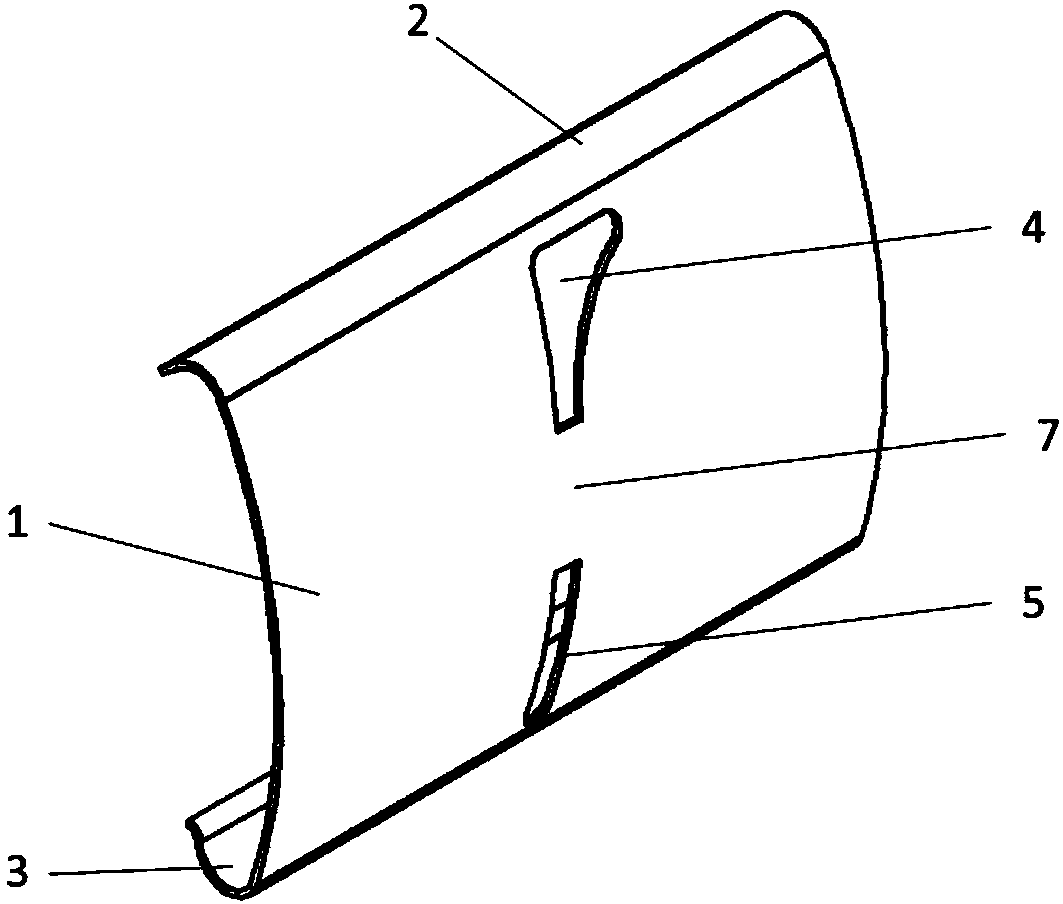

Surface nanotechnology locally-processed thin-wall energy absorption tube

The invention provides a surface nanotechnology locally-processed thin-wall energy absorption tube, and belongs to the technical field of automobile collision. The surface nanotechnology locally-processed thin-wall energy absorption tube is characterized in that surface local nanotechnology processing is performed on the structure of the thin-wall energy absorption tube, the design of interval strip-shaped or interval sheet-shaped nanocrystallization areas locally distributed in the axial direction and the annular direction and a layout design are adopted in the surface local nanotechnology processing, and a single local nanocrystallization surface shape design and a nanocrystallization degree design are further adopted in the surface local nanotechnology processing. The thin-wall energy absorption tube is divided into one to three sections and a transition section, and different surface nanocrystallization layout designs are adopted in the sections. The surface nanotechnology locally-processed thin-wall energy absorption tube has the advantages that through surface nanometer local process of the thin-wall energy absorption tube, a specific buckling mode and a specific development path of the thin-wall tube are induced, the effect that energy absorption is conducted at different sections when impact occurs is achieved, and the energy absorption effect of the thin-wall tube is improved. According to the design method of the thin-wall energy absorption tube, the structure of the energy absorption tube and the process of the energy absorption tube are made to be simple, the appearance of an original thin-wall tube is kept, and the thin-wall energy absorption tube further has the advantages of stability and controllability, and can be applied to automobile energy absorption structures, anti-collision safety equipment and other carrying vehicle energy absorption devices.

Owner:DALIAN UNIV OF TECH

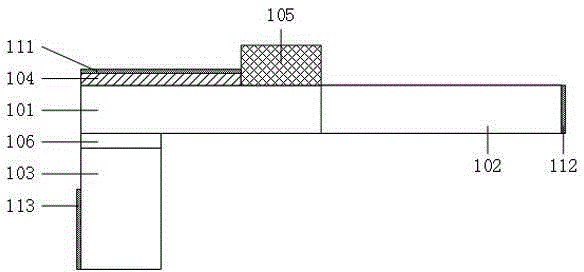

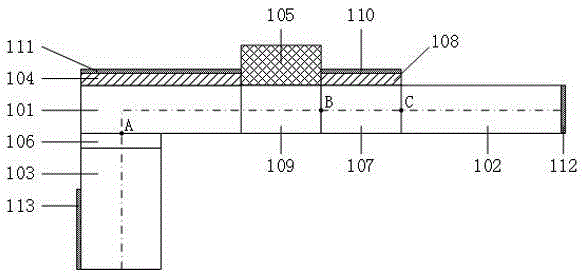

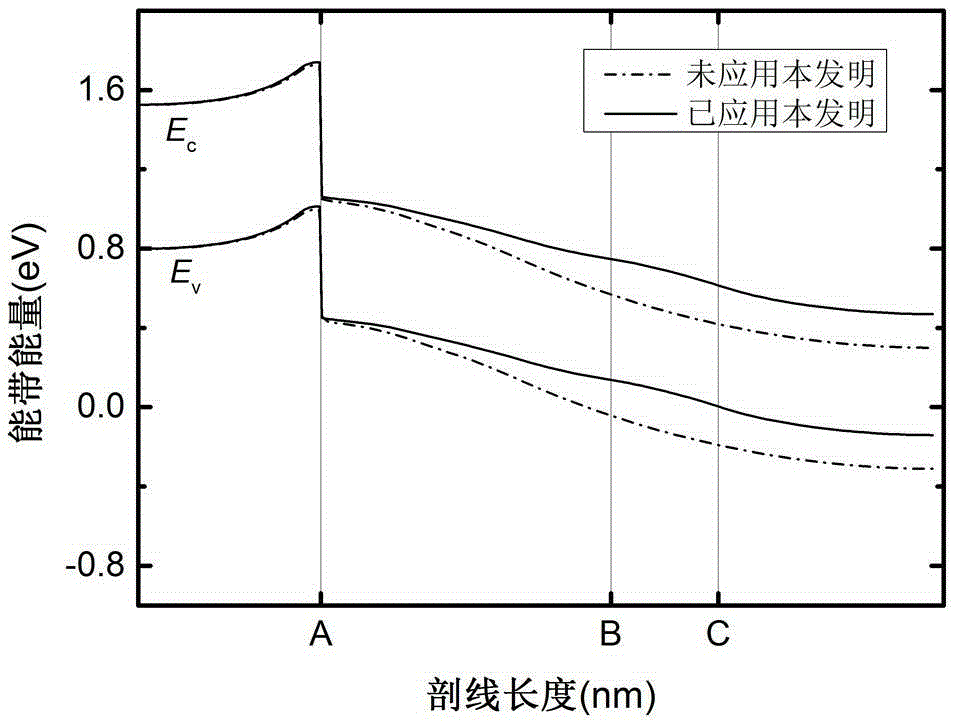

Low off-state current tunneling field effect transistor

InactiveCN105405875AReduce performanceImprove performanceSemiconductor devicesGate dielectricSubthreshold swing

The invention discloses a low off-state current tunneling field effect transistor, comprises a source region, a channel region, a drain region and a first gate dielectric layer, wherein the channel region is provided with the first gate dielectric layer, the first gate dielectric layer is provided with a first grid, the source region is arranged under the channel region and close to the lower part of the channel region, the source region is provided with a source electrode, the drain region is arranged at one side of the channel region, a drain electrode is arranged at the right end of the drain region, an adjusting region is arranged between the channel region and the drain region, a transition region is arranged between the channel region and the adjusting region, a second gate dielectric layer is arranged on the adjusting region and is provided with a second grid, the first grid and the second grid are connected together through a lead to function as the grid of the whole field effect transistor, and an isolation region is arranged on the transition region. Since the adjusting region is introduced between the channel region and the drain region, the equivalent resistance of the adjusting region functions so that the low off-state current tunneling field effect transistor can obtain lower subthreshold swing and quiescent dissipation, thus improving the performance of the low off-state current tunneling field effect transistor.

Owner:XIANGTAN UNIV

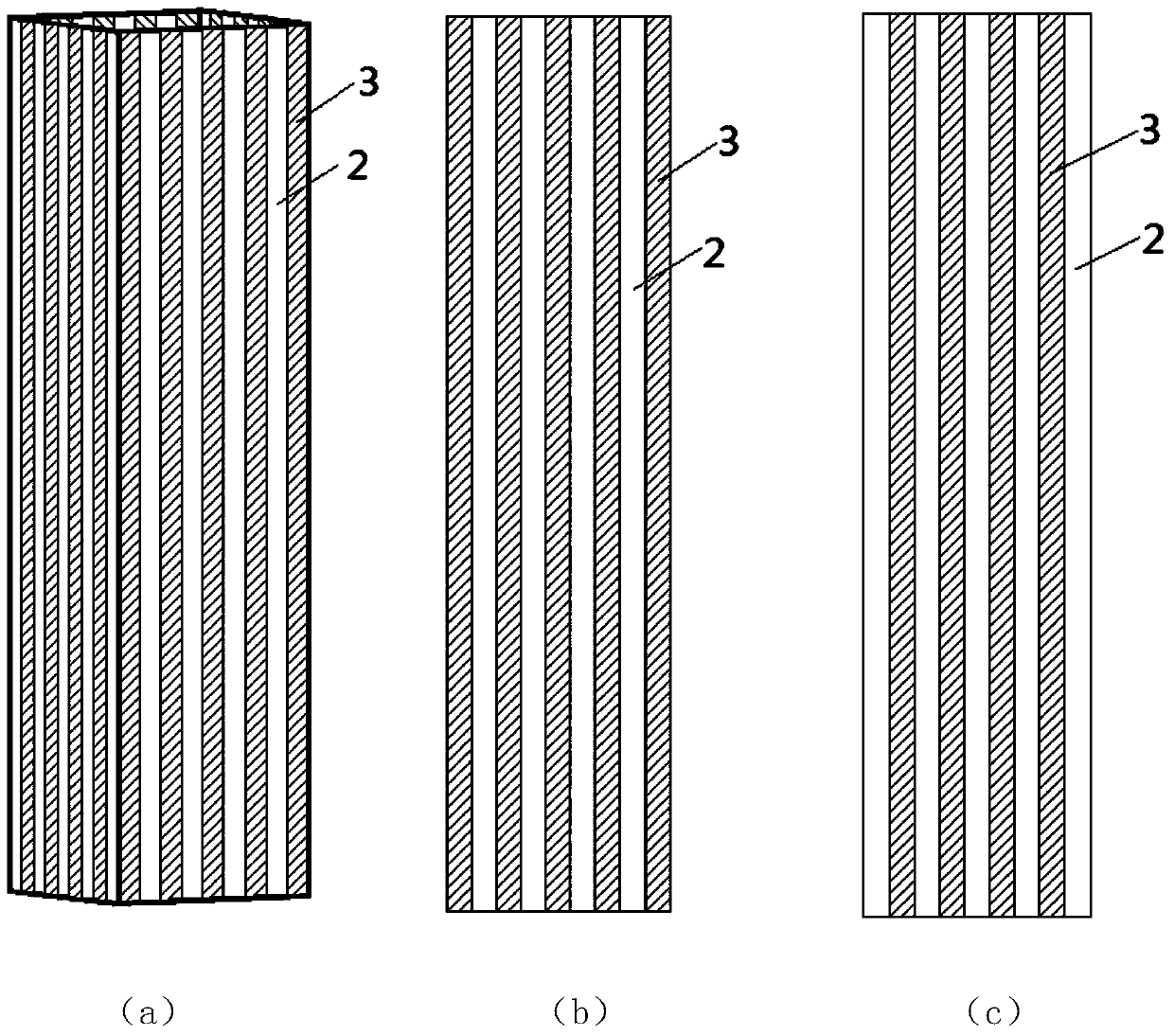

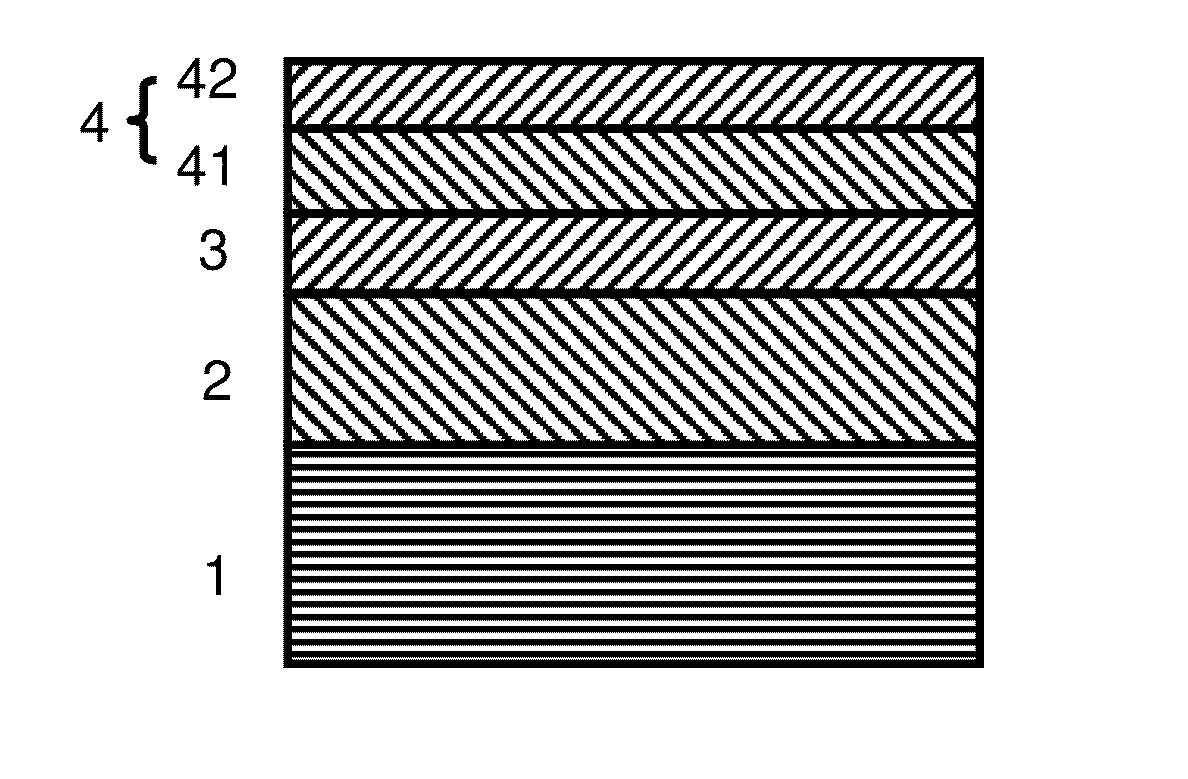

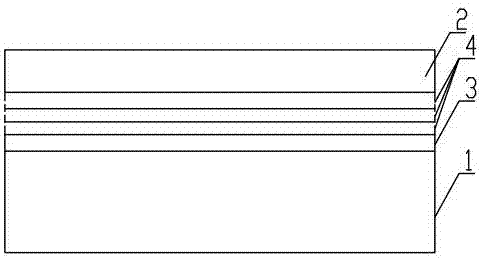

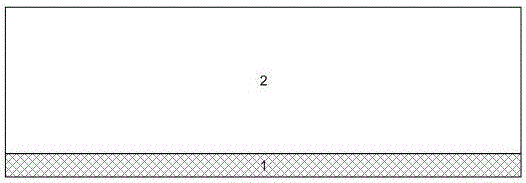

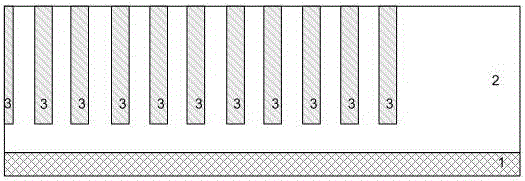

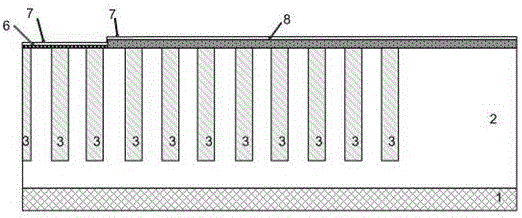

Solar spectrum selective absorption coating and its manufacturing method

InactiveUS20150316289A1Good spectral selectivityReduce concentrationSolar heat devicesVacuum evaporation coatingAbsorptanceManufacturing technology

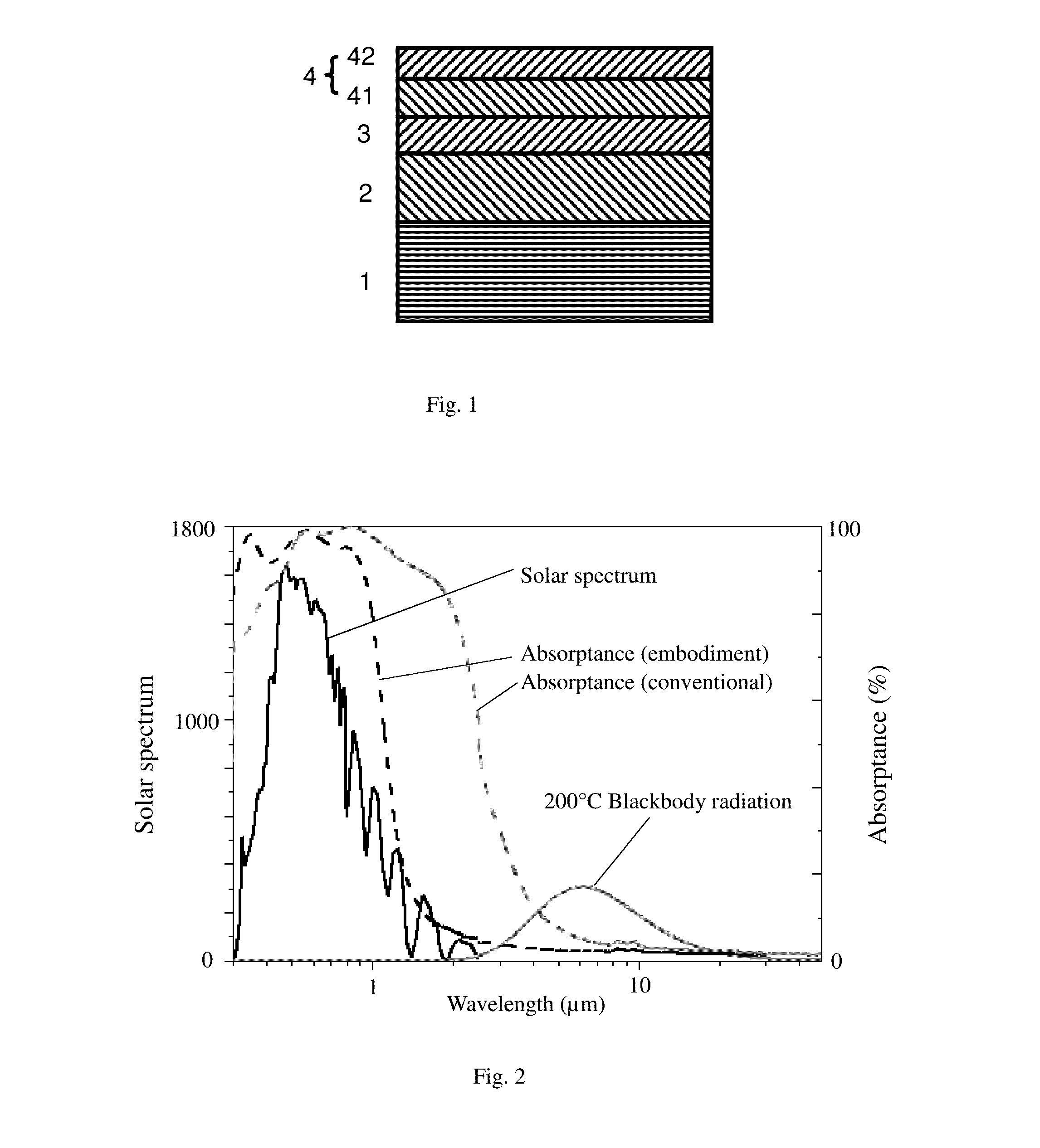

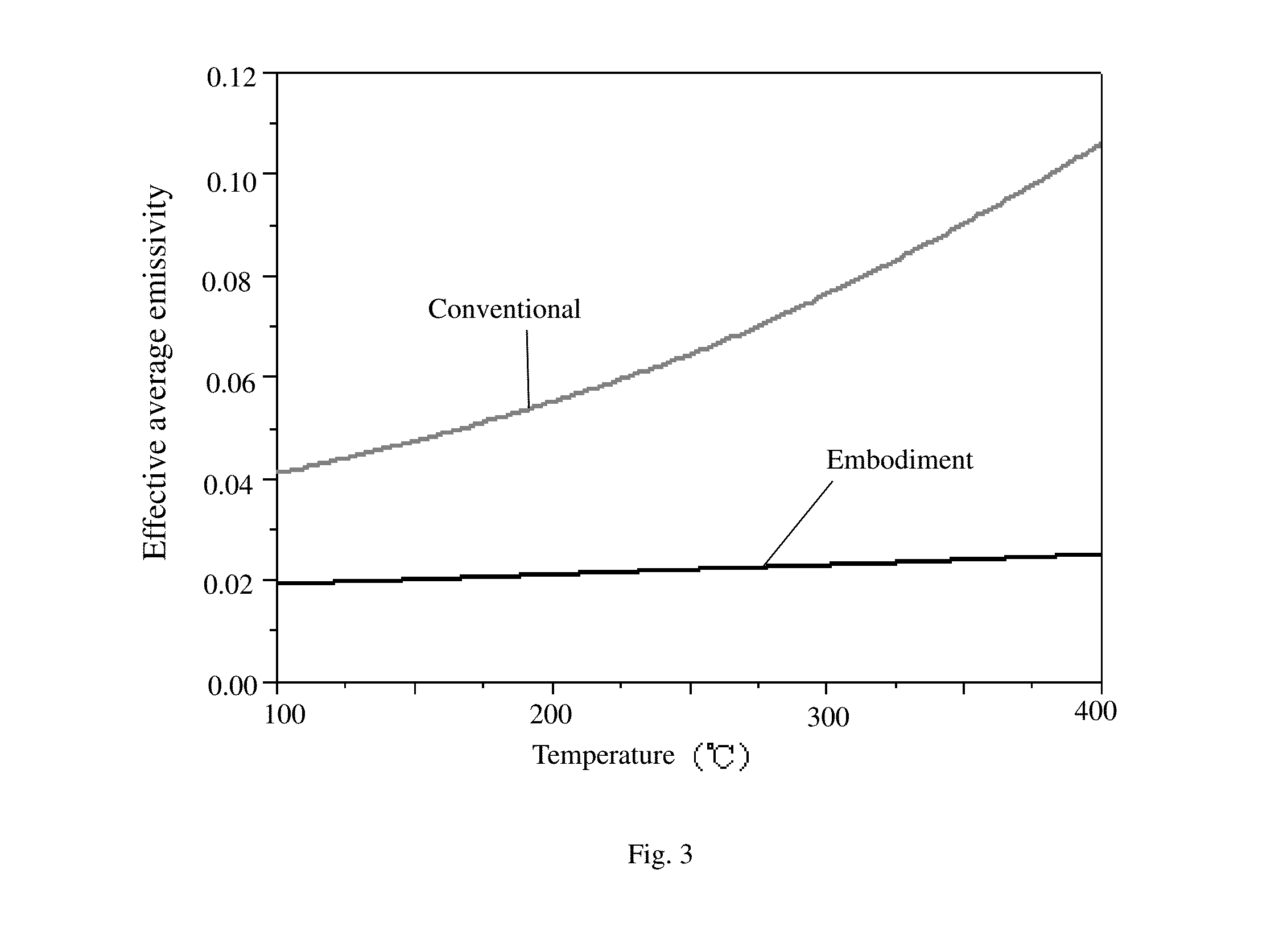

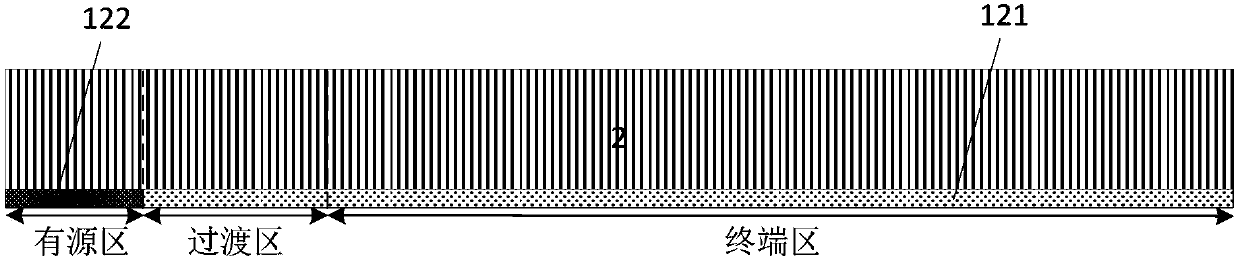

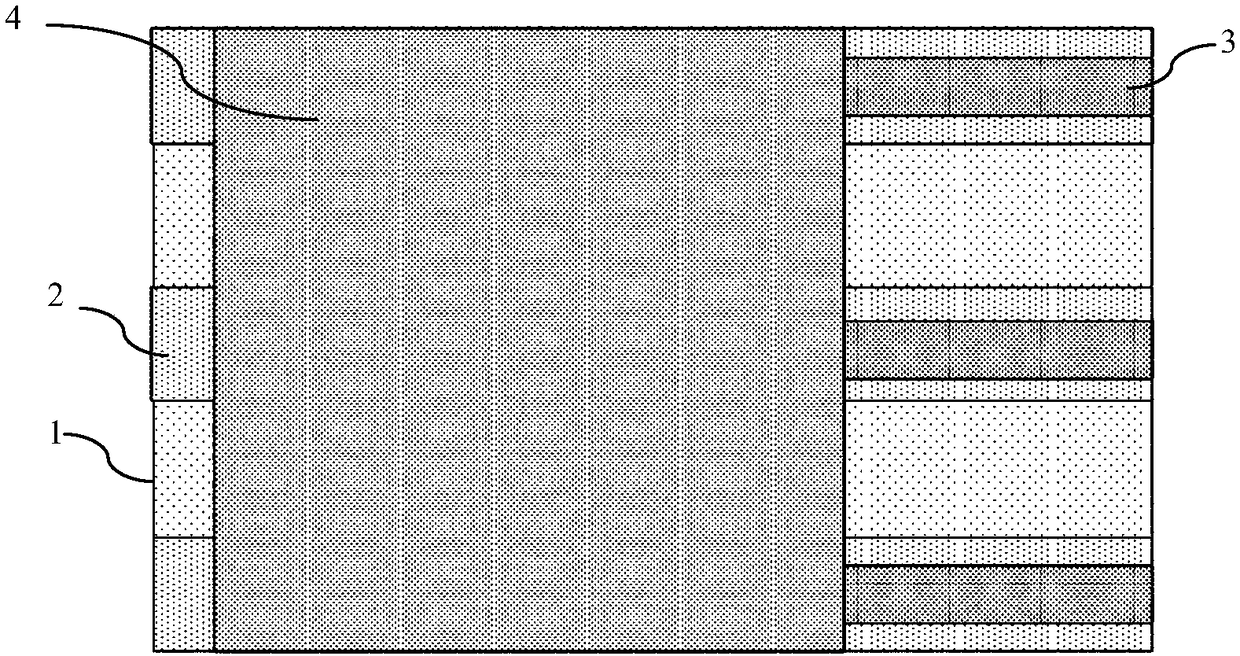

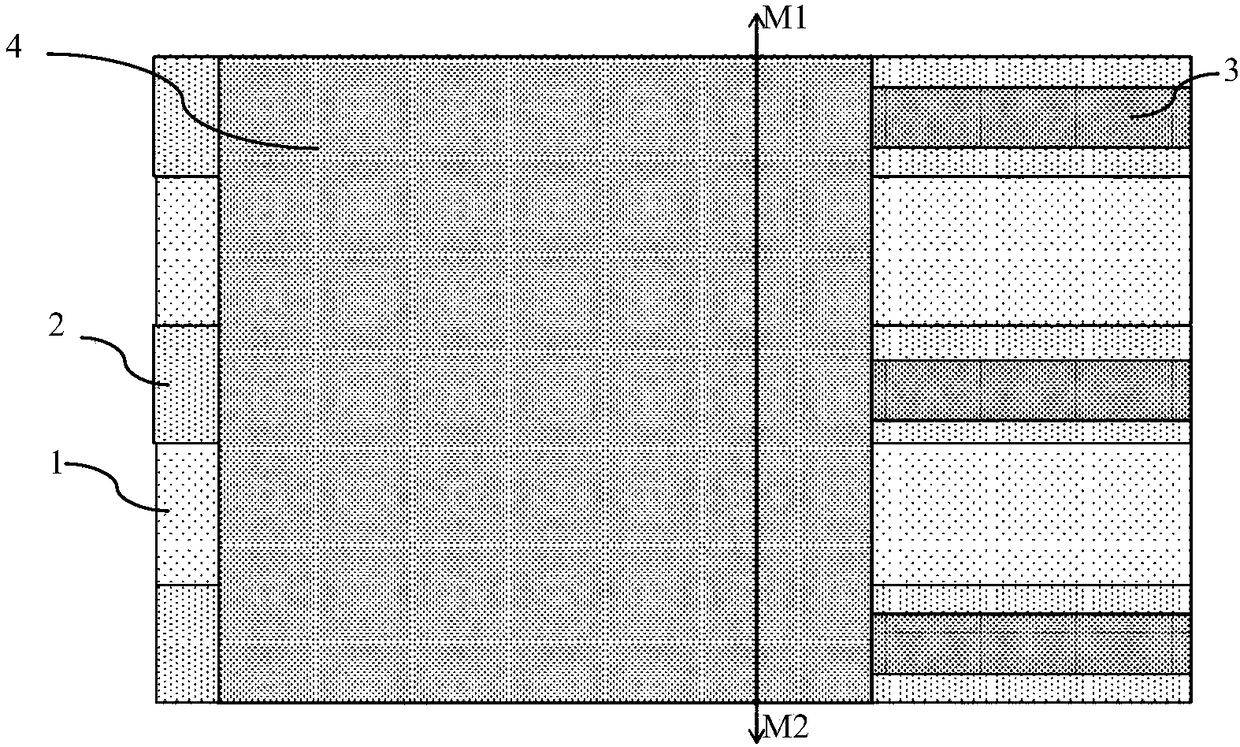

A solar spectrum selective absorption coating is disclosed. The coating includes, from the substrate to the air interface: substrate 1, infrared reflective layer 2, semiconductor absorption layer 3 (Ge), and antireflection layer 4 formed by a higher refractive-index dielectric layer 41 and a lower refractive-index dielectric layer 42. The solar spectrum selective absorption coating has superior spectrum selectivity, with a steep transition zone between solar absorption and infrared reflection zones. It has a relatively high absorptance α in the solar spectrum range (0.3-2 μm), and a very low absorptance / emissivity ε in the infrared thermal radiation spectrum range (2-50 μm); its a / c ratio is significantly higher than current commercially available products, making it suitable for medium-temperature solar heat collectors using low-power optical concentration. The manufacturing process is simple and does not require complex deposition equipment, so it is suitable for low-cost large-scale production.

Owner:TAHOE TECH

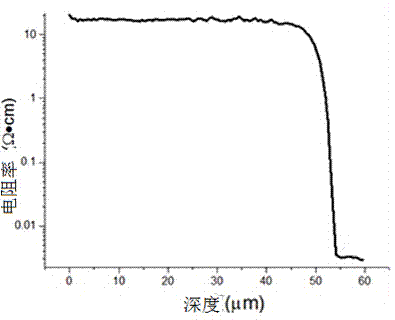

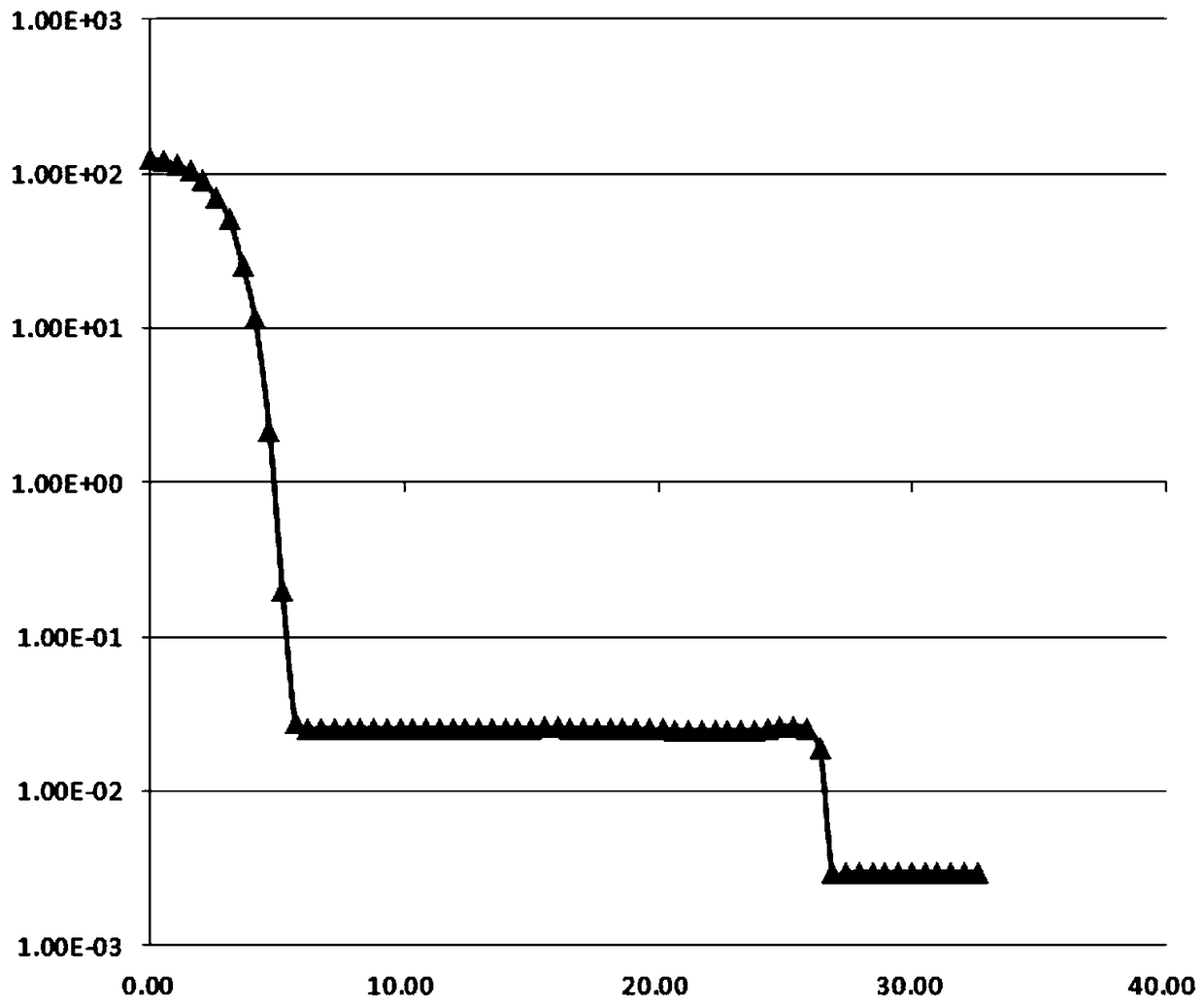

Control method for epitaxial layer transition zone on re-mixed arsenic underlay

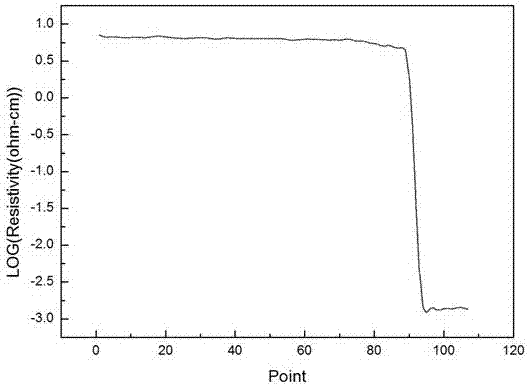

ActiveCN101110356AResistivity gradient increasesHigh resistivitySemiconductor/solid-state device manufacturingMemory effectGrow light

The invention discloses a control method for an external extension transition section on a heavy doping arsenic underlay, which adopts chemical vapor deposition technology to grow light doping thin silicon extension layer at two times on a n-type heavy doping arsenic silicon underlay. After the growing of a first own extension layer, reduce the temperature to 870 to 930 DEG C. and take it out. During the process, remove the memory effect by putting in a HCI erosion base. After the completion of erosion, place the piece in furnace under the temperature of 870 to 930 DEG C. and then grow the residual extension layer. By checking and comparing the extension layer made with ordinary method and the method in the invention via an extension resistance analyzer, it is proved that the extension layer made of the method in the invention has steepy transition section and resistance of the extension layer has excellent evenness.

Owner:HEBEI POSHING ELECTRONICS TECH

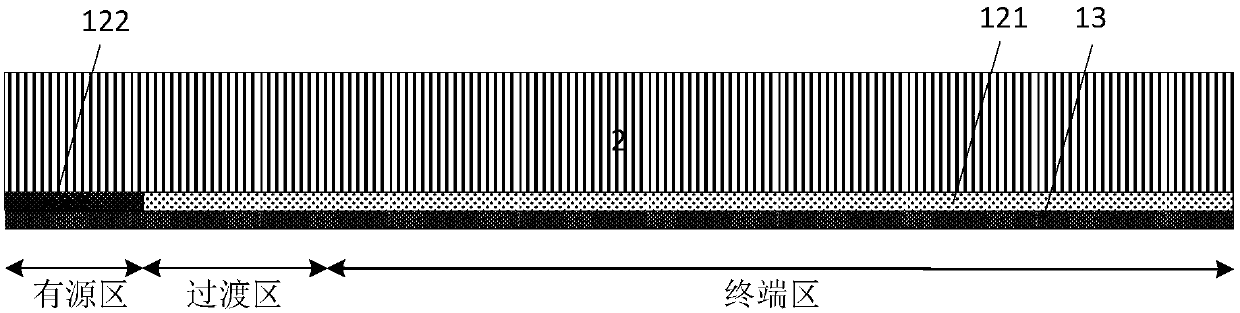

Back surface structure of IGBT chip, IGBT chip structure and preparation method thereof

ActiveCN109671771AImprove reliabilityAvoid overheatingTransistorSemiconductor/solid-state device manufacturingState of artOhmic contact

The invention discloses a back surface structure of an IGBT chip, an IGBT chip structure and a preparation method thereof. The back surface structure comprises: a buffer layer and a doped layer, the doped layer is formed by ion implantation in the buffer layer; the doped layer of a terminal region and a transition region is subjected to high-temperature annealing treatment; a doped layer of the active region is subjected to twice high-temperature annealing treatment to achieve different hole injection efficiencies of the active region and the terminal region so as to improve the current concentration problem in the IGBT transition region and improve the reliability. Compared to the prior art of a treatment mode that a photolithography process is used to implant different doses of doping ions on the back side of the active region and the terminal region to achieve different injection efficiencies of the back surface collectors of the active region and the terminal region, the back surface structure of the IGBT chip, the IGBT chip structure and the preparation method thereof only employ the annealing process to omit the photolithography process so as to save the manufacturing cost. An inert ion defect layer is implanted in the buffer layer to form a defect layer, so that the IGBT back surface collector can adopt a higher doping concentration, and the IGBT back surface and the back surface metal easily form good ohmic contact, thereby reducing the IGBT on-state voltage drop.

Owner:GLOBAL ENERGY INTERCONNECTION RES INST CO LTD +2

Silicon epitaxial wafer and preparation method thereof

ActiveCN106952965AImprove softness factorMaintain electrical propertiesSemiconductor/solid-state device manufacturingSemiconductor devicesHigh resistanceDopant

The invention discloses a silicon epitaxial wafer and a preparation method thereof, and relates to the technical field of manufacturing or processing methods of semiconductor devices. The preparation method comprises the following steps: directly growing a low-resistance epitaxial layer on the upper surface of a silicon substrate; growing a linear gradient epitaxial layer every 5-10 microns on the upper surface of the low-resistance epitaxial layer, calculating a doping flow rate corresponding to a linear resistance value of the gradient epitaxial layer for doping during growing; and growing a high-resistance epitaxial layer on the upper surface of an outermost linear gradient epitaxial layer. An inner layer epitaxial layer of the epitaxial wafer provided by the invention comprises two or more linear gradient epitaxial layers; the linear gradient epitaxial layer adopts multi-layer growth; and a small amount of dopant among layers preferentially enters a reaction chamber to change an epitaxial growth environment. Meanwhile, by using a simultaneously gradient flow rate method (namely, a ramp method), not only is a softness factor of the device improved, but also original electric characteristics of the device are kept, so that a controllable linear distribution parameter of a transition zone is totally realized, and the repeatability and the consistency are high.

Owner:HEBEI POSHING ELECTRONICS TECH

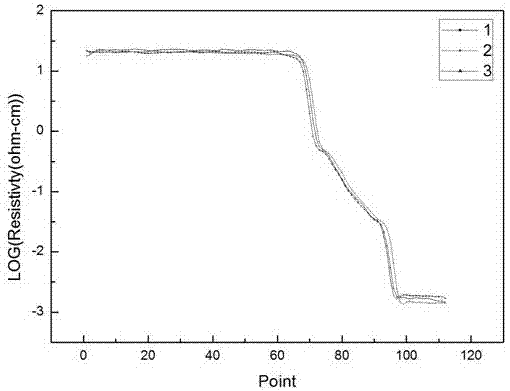

Control method for extension slice equability for 6 inch As back lining MOS part

ActiveCN101123179AImproved resistivity edge uniformityBest time to catch upSemiconductor/solid-state device manufacturingElectrical resistance and conductanceDorsal closure

The present invention discloses a 6 inch As dorsal closure substrate MOS device epitaxial slice uniformity controlling method. The processing steps of the method are: HCL in-situ polishing--first high-flow H2 drive gas--temperature reduction--growth of intrinsic layer--the second high-flow H2 drive gas--the process of growth of epitaxial layer of remaining thick. The time for the first high-flow H2 drive gas is 20 to 30 minutes, the time for the second high-flow H2 drive gas is 5 to 10 minutes. After repeat tests, the optimal drive gas time of the present invention is capable of controlling self-doping, increasing epitaxial slice electrical resistivity edge uniformity. The spreading resistance flatness and the transition zone abruptness of the epitaxial slice produced by the present invention are better than those of epitaxial slice produced by traditional method.

Owner:HEBEI POSHING ELECTRONICS TECH

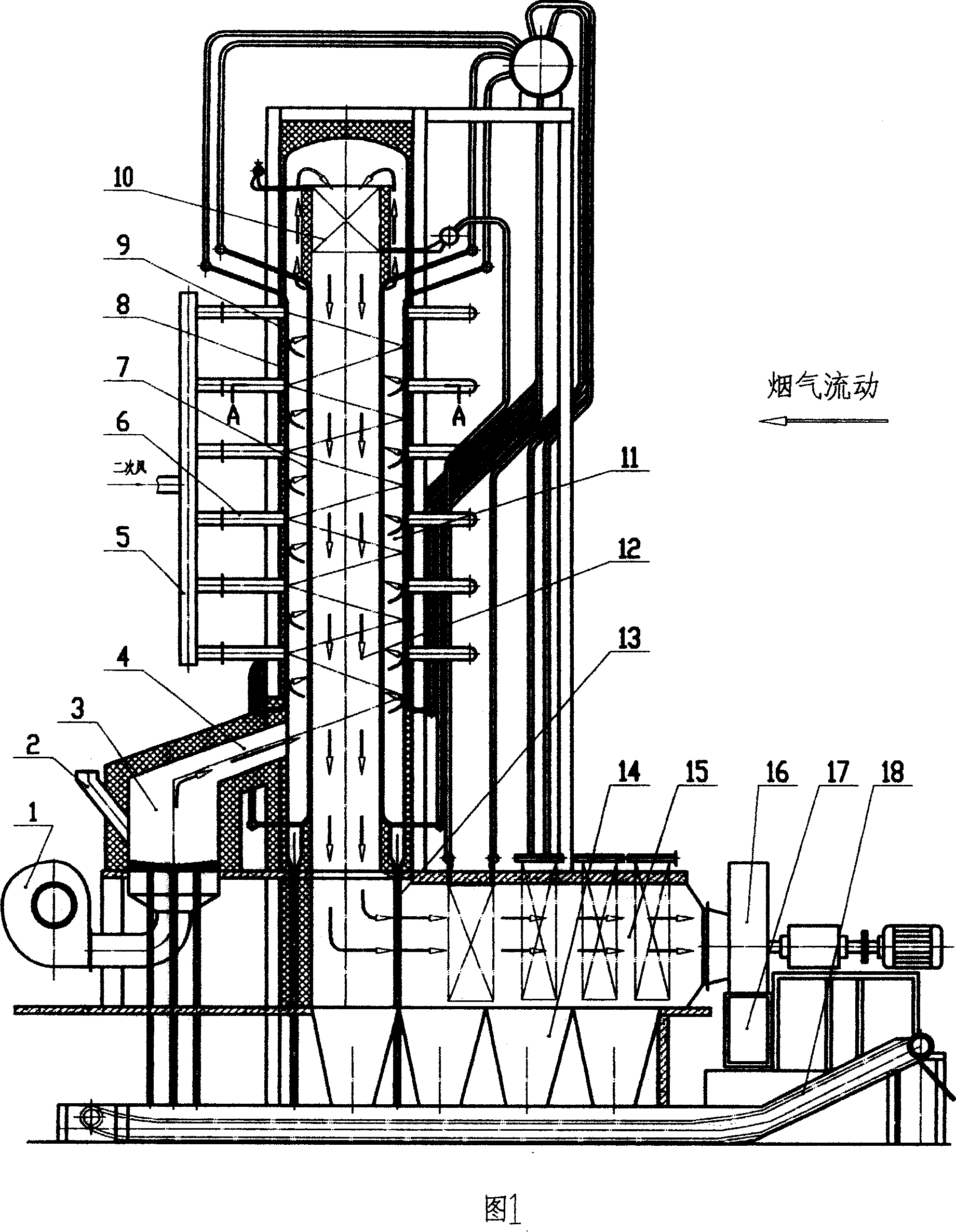

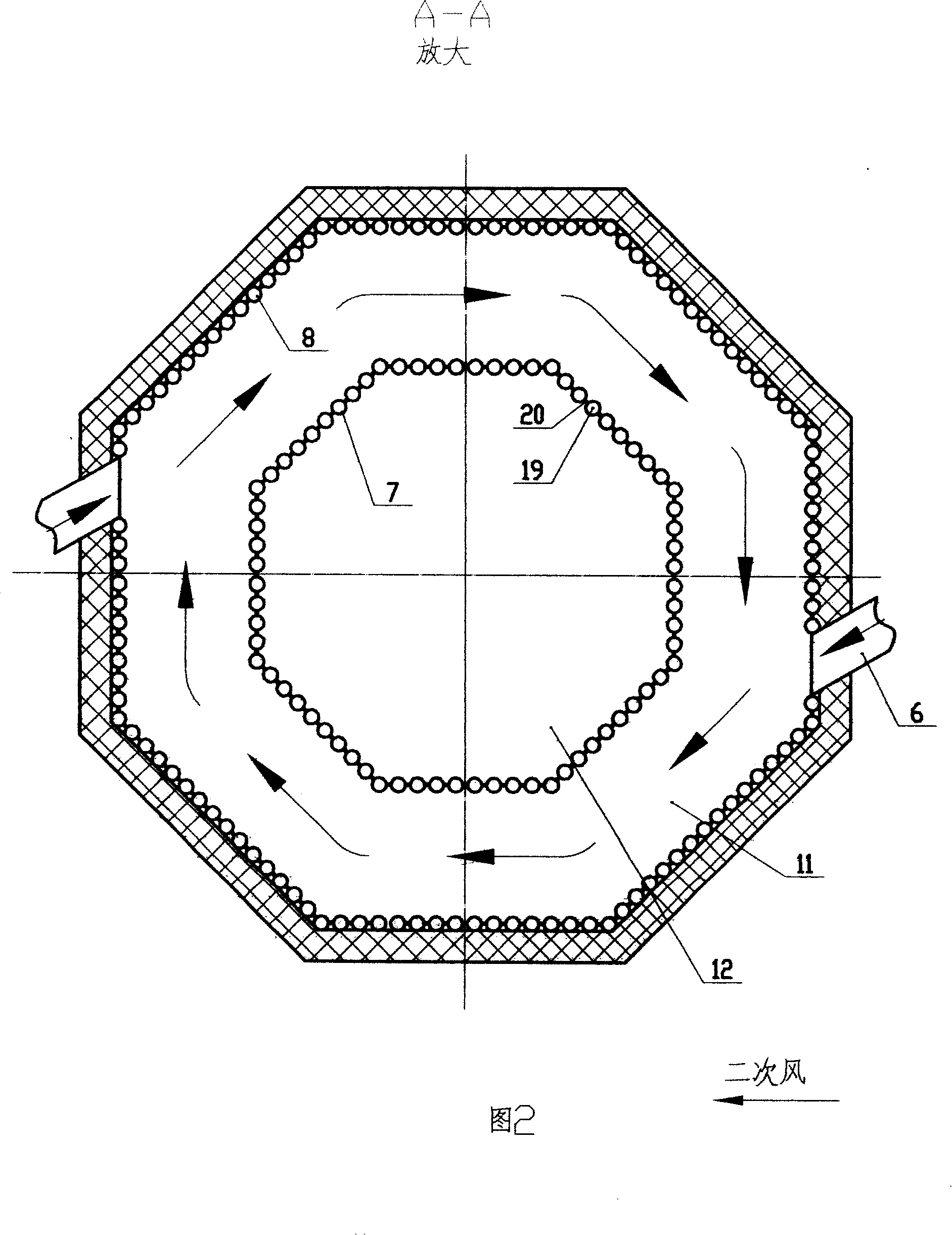

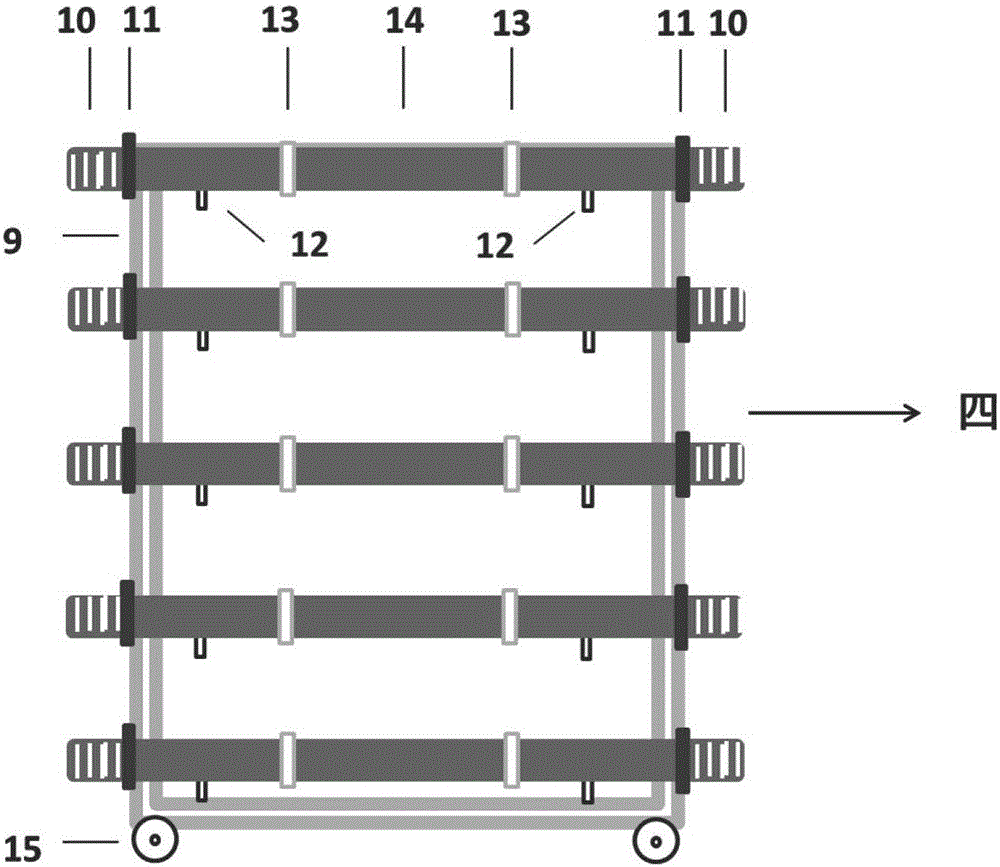

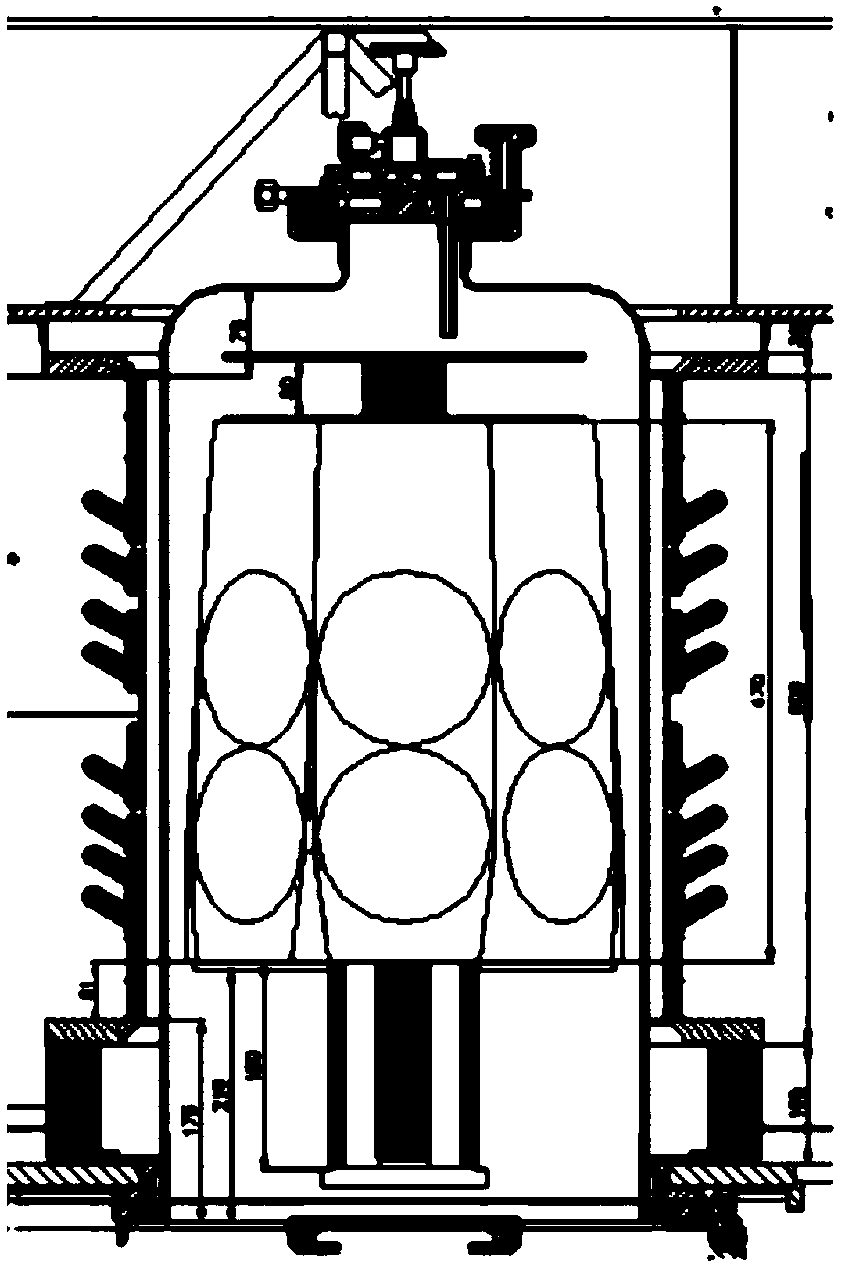

Fluid bed boiler for combusting biomass

InactiveCN101122387AGood for spin upHigh thermal efficiencyFluidized bed combustionApparatus for fluidised bed combustionFailure rateFlue gas

A biomass combustion fluidized bed boiler mainly comprises a fluidized bed boiler body. The boiler is characterized in that an independent hearth (3) at the high-temperature area is arranged, and communicates with an annular passage (11) between a round or nearly round polygonal internal cylinder (7) and a round or nearly round polygonal external cylinder (8), which are formed by a hearth transition area (4) and a membrane water cooling wall. A central flue (12) is arranged inside the internal cylinder (7), and a multi-stage secondary air nozzle (6) is arranged in the annular passage (11). As the independent hearth (3) at the high-temperature area is arranged, the invention settles the problem that a traditional boiler cannot hold a fuel layer and can combust the biomass granule fuel independently. The nearly-round polygonal structure of the annular passage (11) between the internal cylinder (7) and the external cylinder (8) is favorable for rotatory ascending of the flue gas. Moreover, the internal and external double heat exchange promotes the thermal efficiency of the boiler. The flue gas is segregated at a plurality of places, which promotes the environmental protection. The annular passage together with the secondary air replaces a high-temperature segregator and a medium-temperature segregator of a traditional boiler. The manufacture process is simple and the failure rate is greatly reduced.

Owner:朴显泽 +2

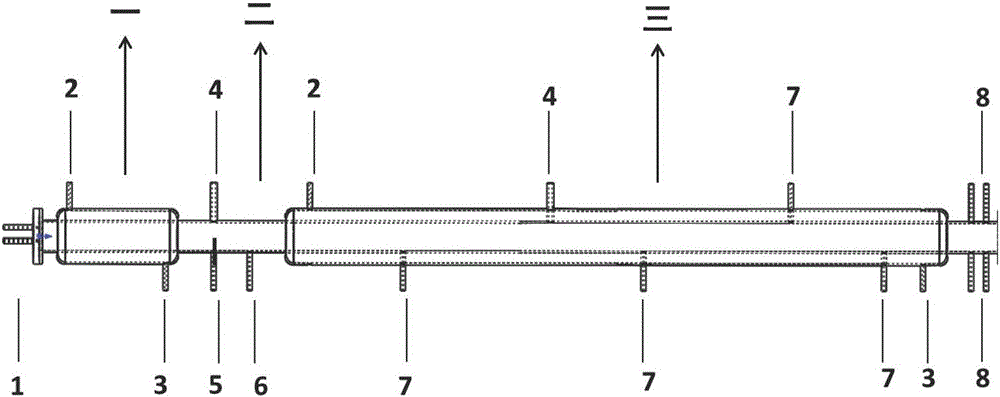

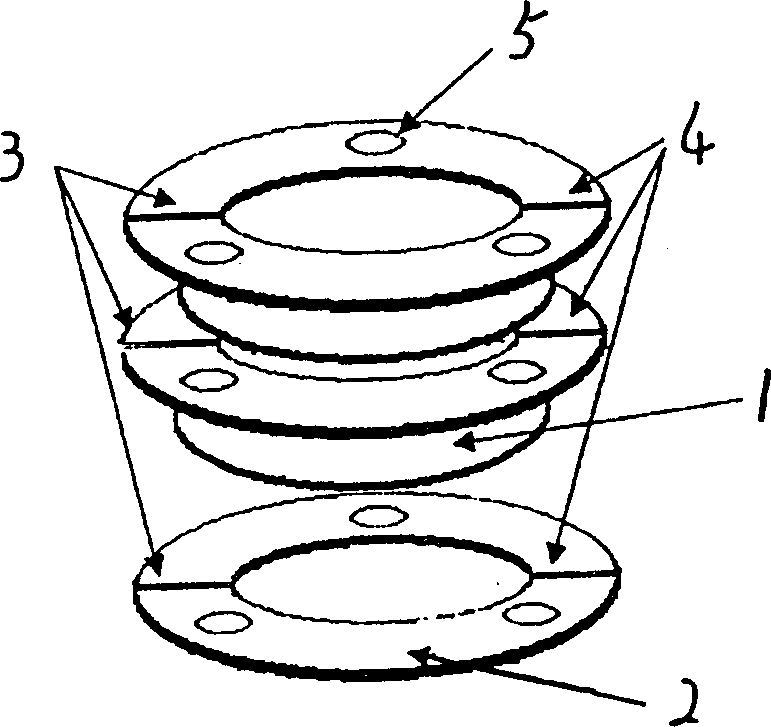

Flowing reaction device allowing forming and growing of new particles of atmospheric aerosol

ActiveCN106644850AIncrease the lengthExtended reaction timeParticle size analysisWater bathsElectrical mobility

The invention discloses a flowing reaction device allowing forming and growing of new particles of atmospheric aerosol. The length of the flowing reaction device is about 22 meters. The flowing reaction device comprises four parts of a sample injection region (I), a transition region (II), a nucleation region (III) and a growing region (IV), wherein the sample injection region comprises three sample inlets and a set of water bath heating water inlets and outlets; the transition region comprises a temperature humidity detecting opening, a low-volatility substance sample inlet and a primary sampling opening; the nucleation region comprises a set of water inlets and outlets for controlling temperature of water bath, a plurality of intermediate sampling openings and a temperature humidity detecting opening formed in the upper part of the nucleation region; the growing region comprises a plurality of growing region sampling openings; the change of the particle number concentration and the change of the particle diameter of each sampling opening are detected through scanning an electrical mobility particle diameter spectrometer. The flowing reaction device disclosed by the invention can be used for researching the generative mechanism and the rising characteristic of the new particles in the atmosphere, so that the dynamics of the nucleation of the aerosol is further researched, and the flowing reaction device has the characteristics of being high in precision, good in stability, simple and convenient to operate, and the like.

Owner:UNIV OF SCI & TECH OF CHINA

Terminal structure of super-junction MOS and manufacturing method thereof

The invention relates to a terminal structure of a super-junction MOS and a manufacturing method thereof. The terminal structure of the super-junction MOS comprises P-type columns and N-type columns; as a polycrystalline field plate is adopted by a transition region from an active region to a terminal region, electric field distribution is transited smoothly and steadily from the active region to the terminal region, and then electric field charges are balanced by utilizing a P-type column and N-type column alternating structure of the terminal region; an N-type epitaxial layer is grown on a heavily doped N+ substrate, an oxide layer is grown on the surface of the epitaxial layer, grooves of the active region and groove rings of the terminal region are etched through a photo-mask by utilizing trench etching; and if the width of the groove is a, the interval of the grooves of the active region is b and the interval of the grooves of the terminal region is c, c is greater than a but less than or equal to b. By simplifying the structure of the terminal region, the disadvantage of impurity introduction when other structures such as the polycrystalline field plate are introduced at a device terminal can be prevented. Meanwhile, damage to the device per se is reduced, and the stability of device performance is improved under the condition of not affecting the technology.

Owner:SHANGHAI CHANGYUAN WAYON MICROELECTRONICS

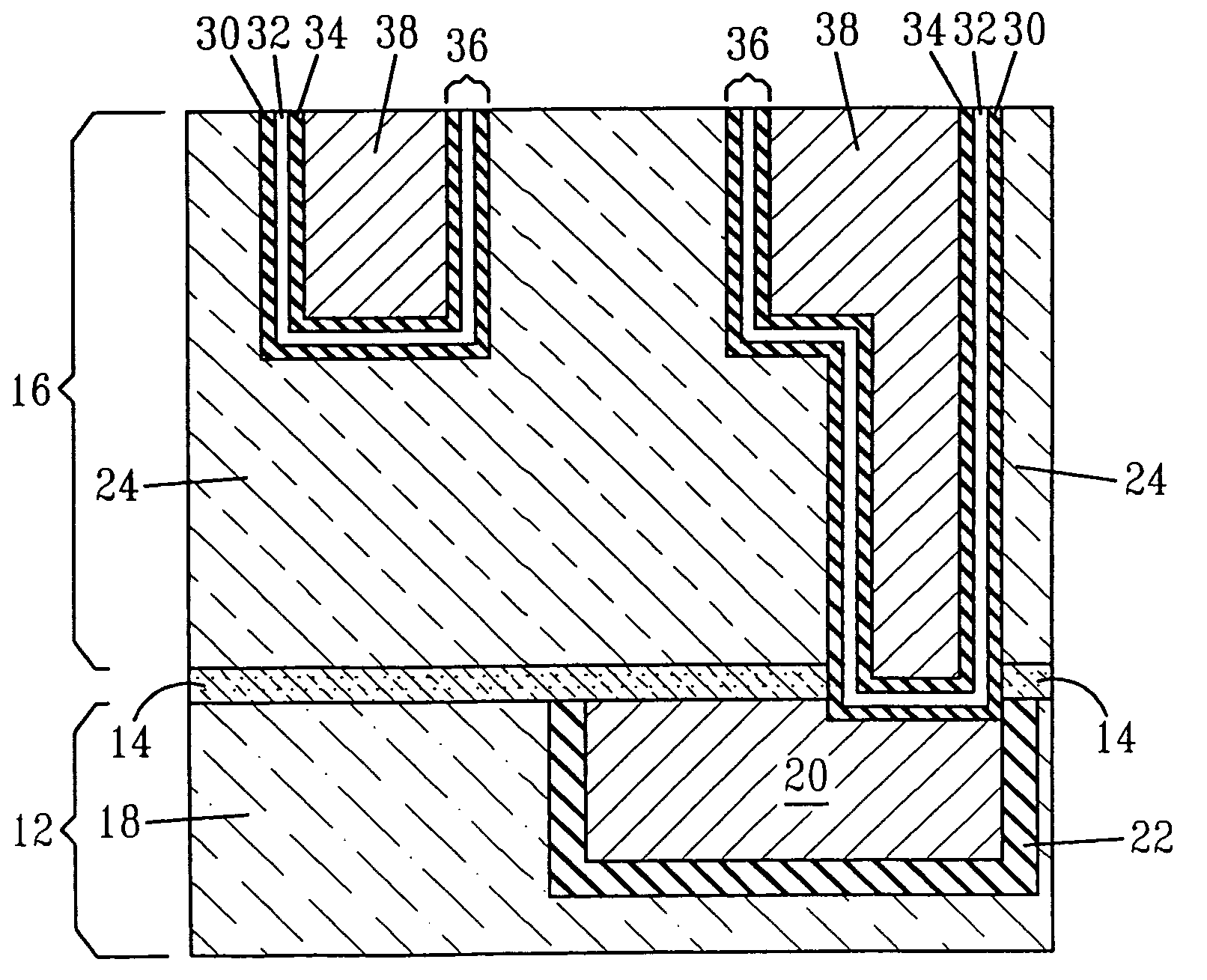

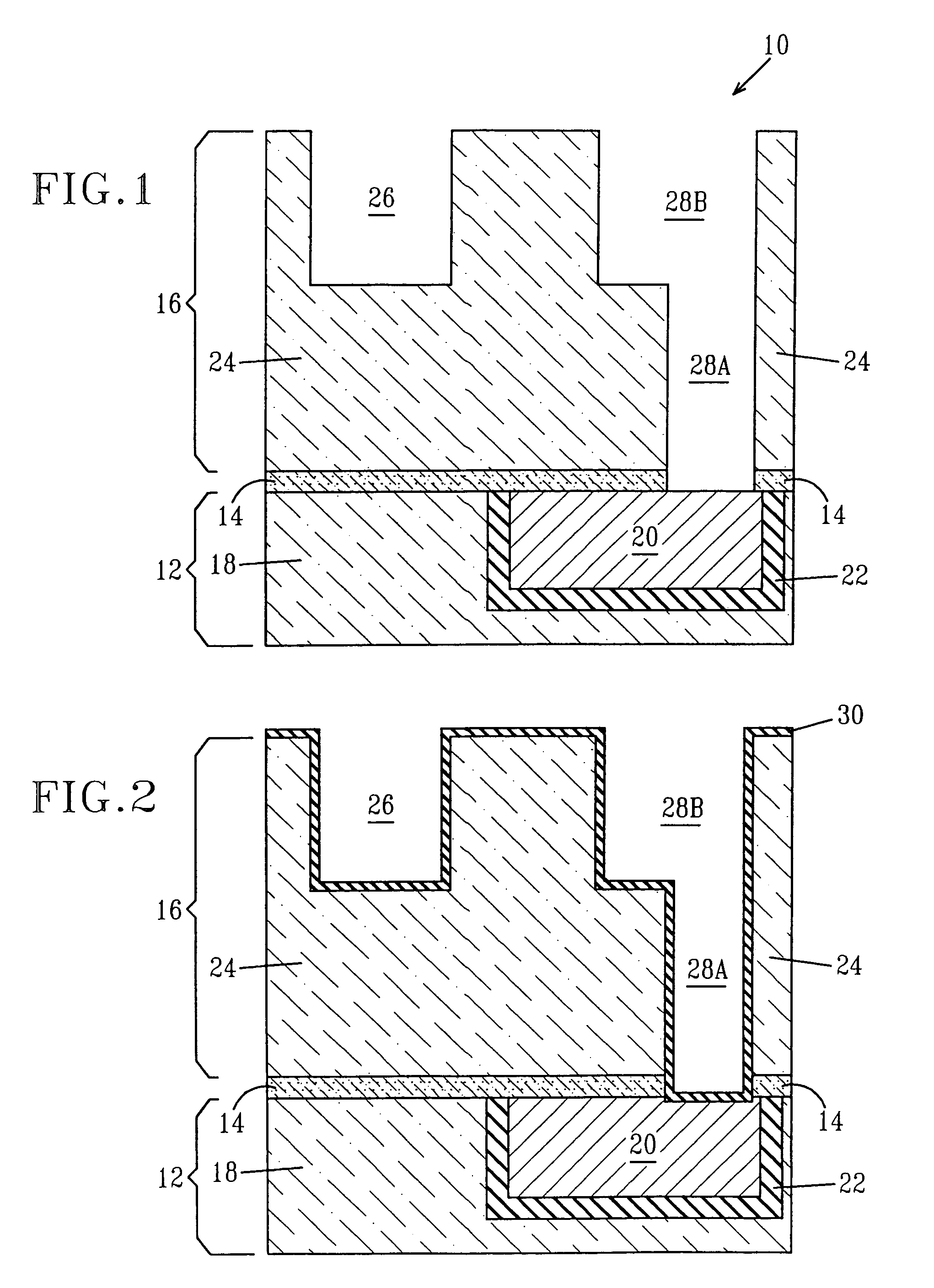

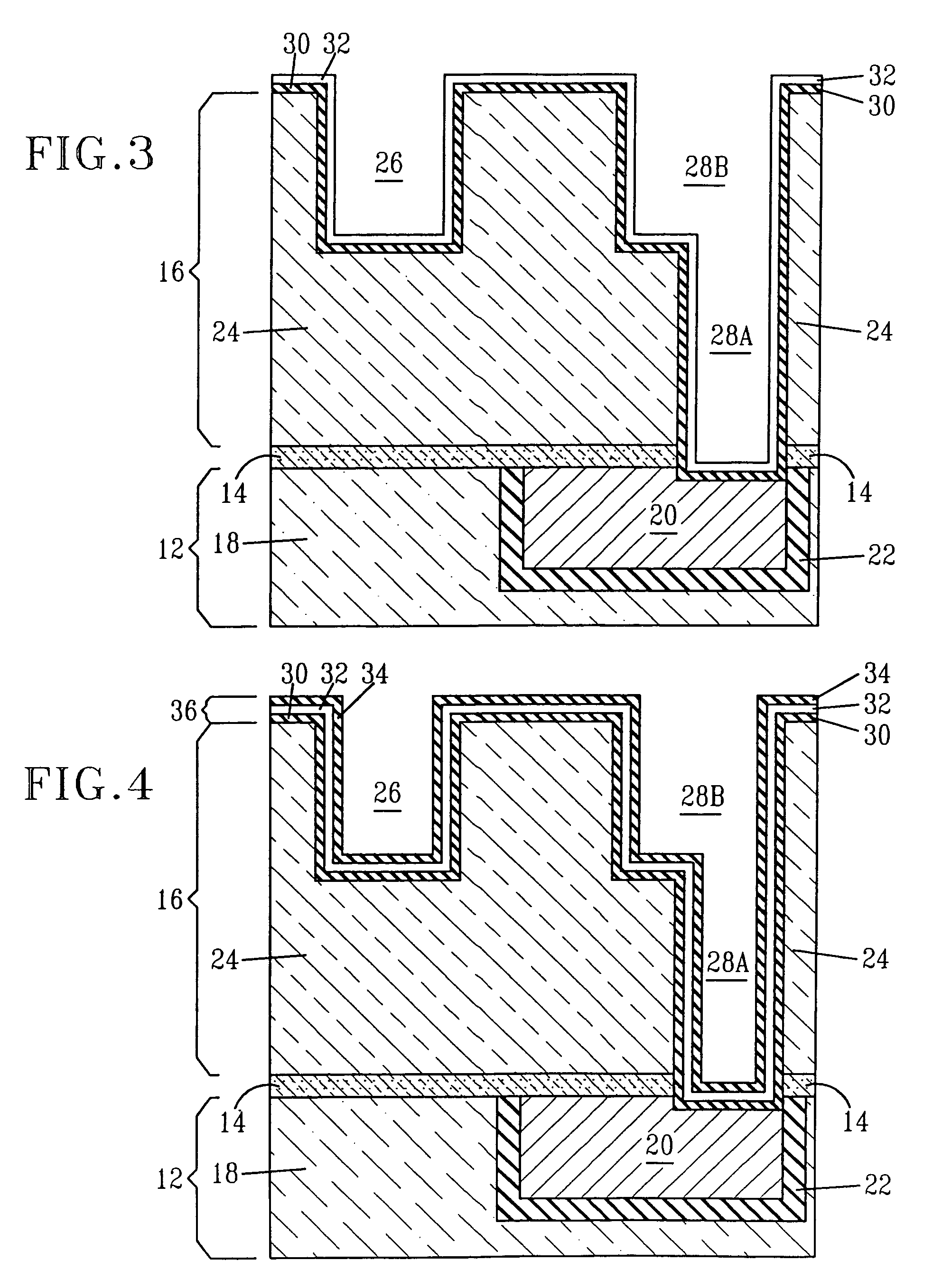

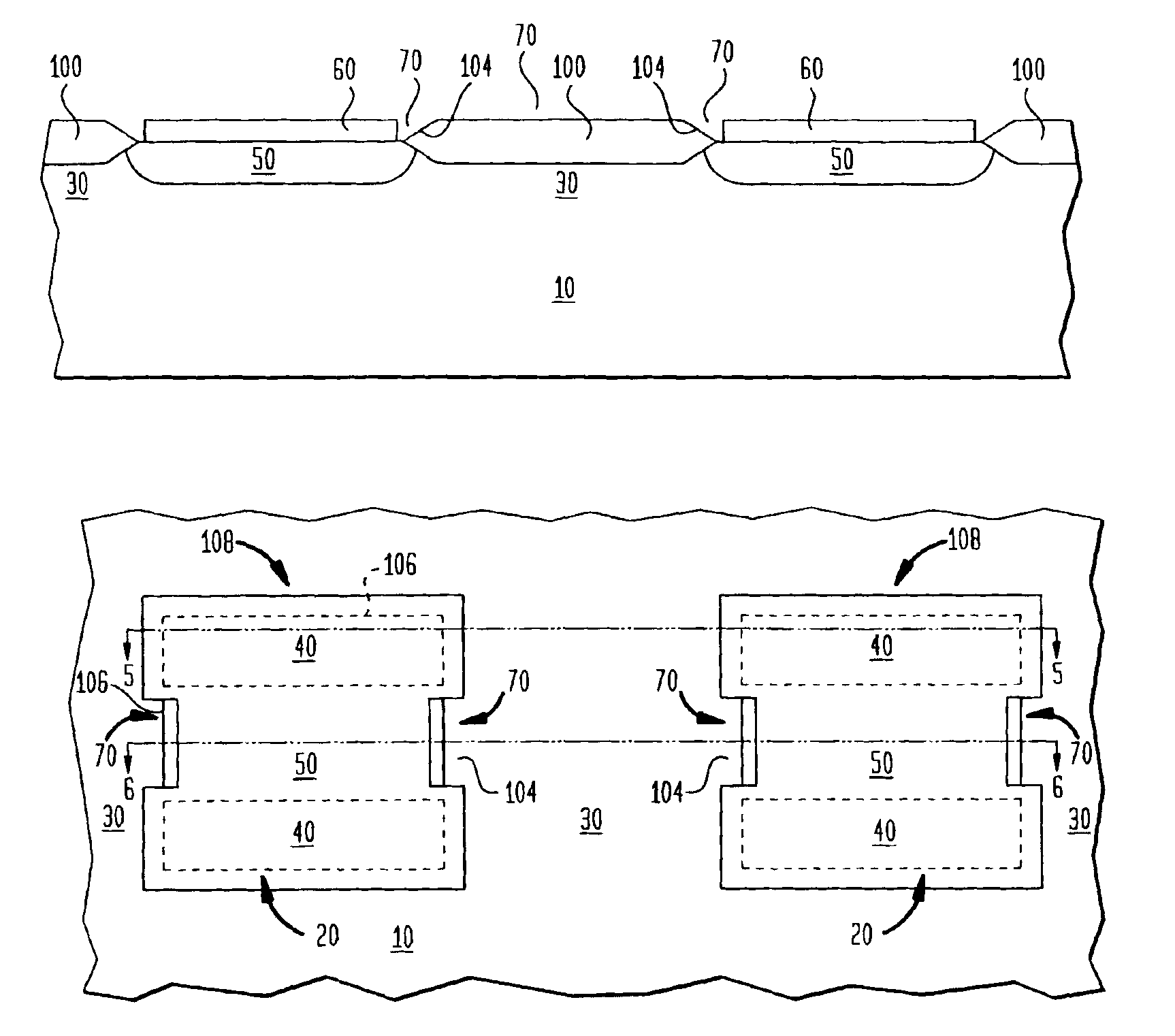

Plating seed layer including an oxygen/nitrogen transition region for barrier enhancement

InactiveUS7215006B2Simple materialEnhances diffusion barrier resistanceSemiconductor/solid-state device detailsSolid-state devicesNitrogenConductive materials

Owner:GLOBALFOUNDRIES INC

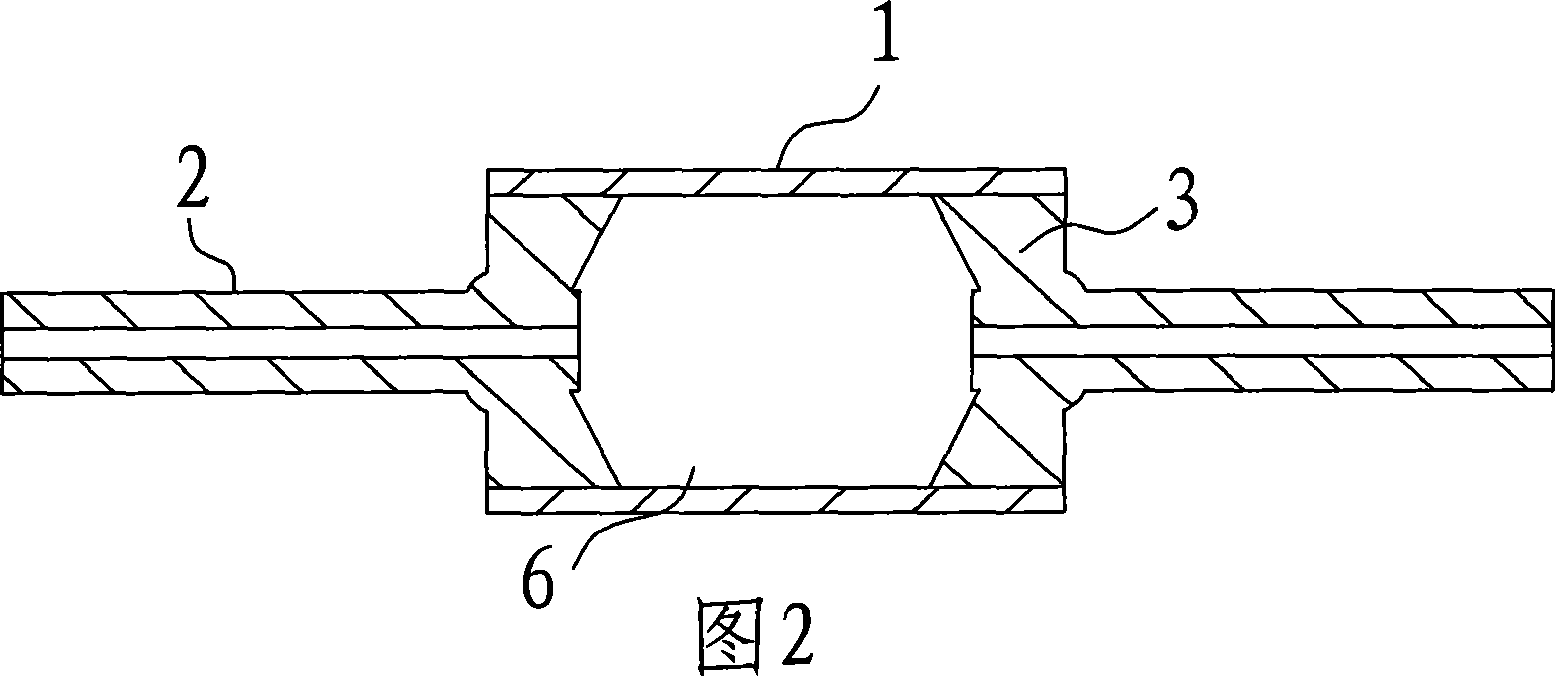

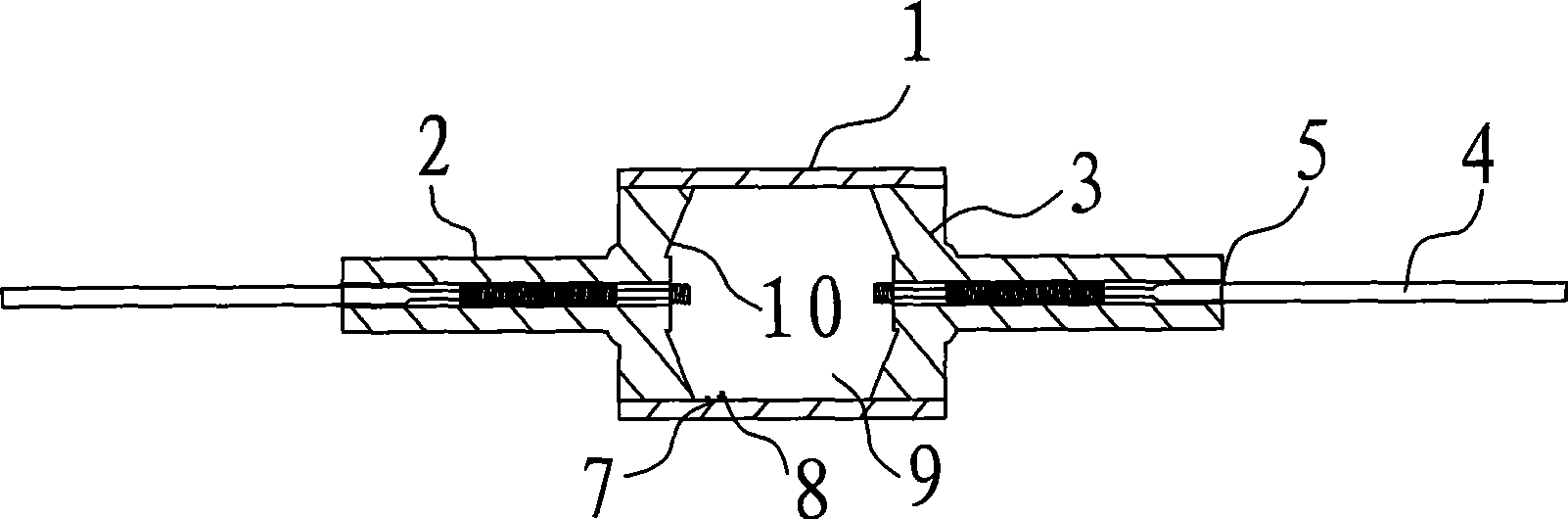

Electric arc tube for ceramic metal halide lamp

InactiveCN101419894AReasonable designSimple structureGas discharge lamp detailsElectric arc furnaceFiller metal

The invention relates to an electric arc tube of a ceramics metal halide lamp in the technical field of electric light source. The invention is designed to aim at the technical problem that the structure design on the existing products needs to be improved. The electric arc tube is baked and manufactured by taking a high-purity a-Al203 polycrystal semi-transparent alumina (PCA) ceramics; an electrode component is inserted into a ceramics discharging cavity by a tail tube; the clearance between the electrode component and the tail tube is sealed by a glass solder. The invention is mainly designed in that the outer diameter surface of a transition area is vertical to a main tube and the tail tube; the ceramics discharging cavity of the inner diameter surface of the transition area is conical; metal halides, Hg and cushion gases are filled in the ceramics discharging cavity; a convex-concave area is arranged at the connection location of the inner diameter surface and the tail tube. The electric arc tube of a ceramics metal halide lamp is more reasonable in design, is simple in structure and has the characteristics of higher stability, color rendering, light efficiency, longer service life and miniaturization, is suitable for being assembled in the body of a jacklight as well as the illumination on the occasions like show windows, marketplaces, car exhibition halls, commercial streets, and the like.

Owner:NINGBO YAMAO OPTOELECTRONICS CO LTD

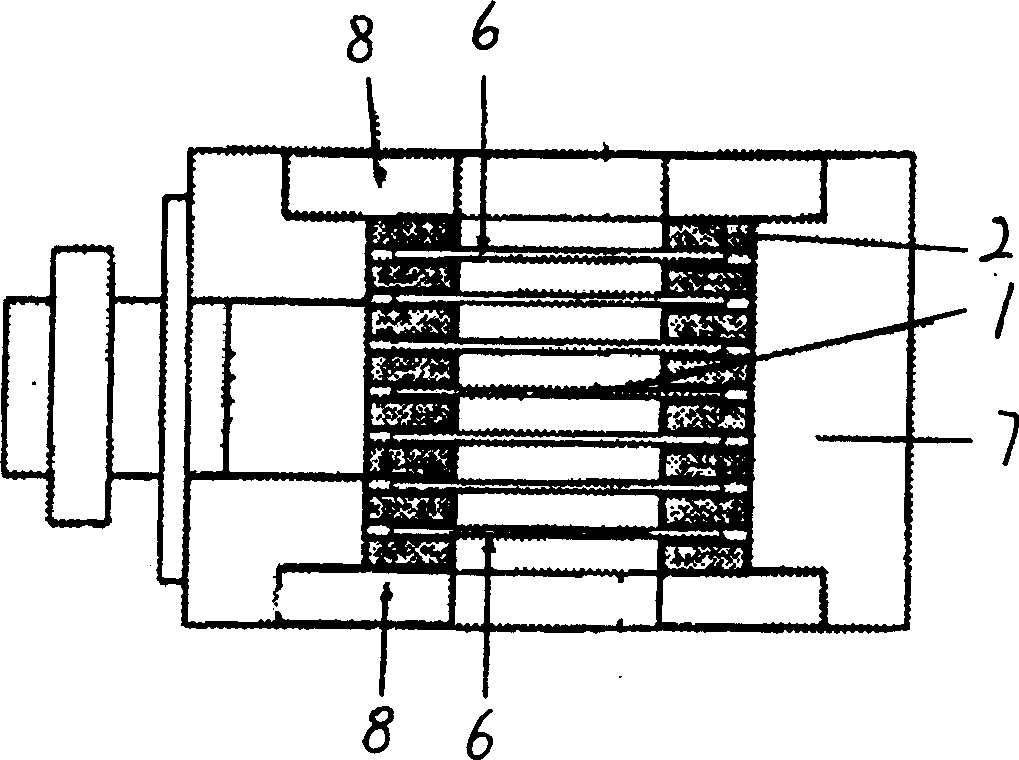

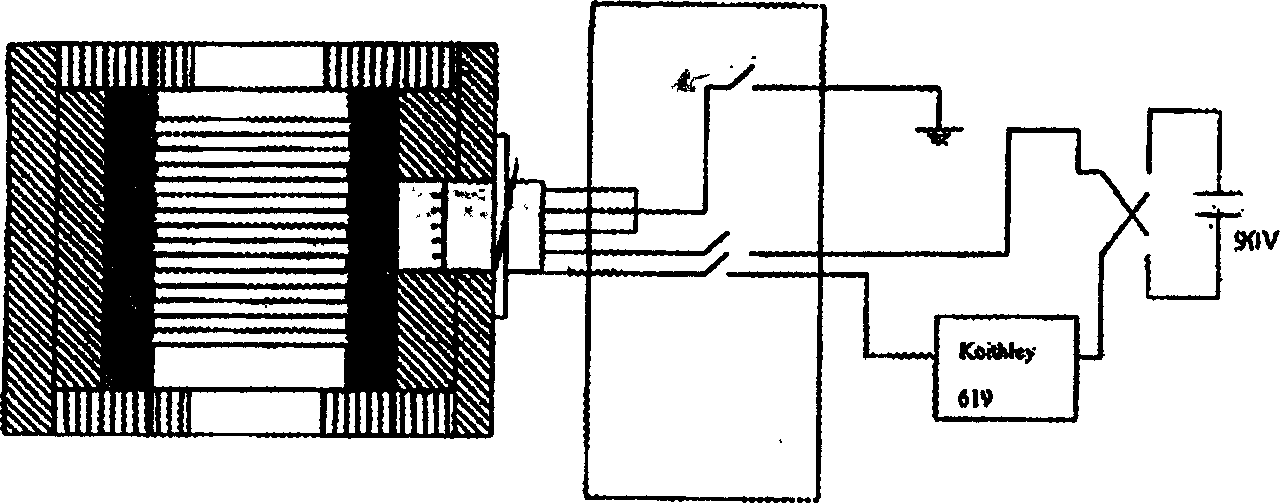

Multi-layer plane ionization chamber for measuring boundary dosage distribution of different material

The invention refers to a multilayer plate ionization chamber measuring the interface dosage distribution of different material. In order to measure the dosage strengthening effect, it design a ionization chamber with high-purity aluminum foil as electrode board, the aluminum foil used as the electrode board and organic glass spaced with each other and set in the aluminum-made shell, and two-layer and polar plates being active structure and located on two sides of the ionization chamber, respectively; it can measure X-ray (30-100keV) interface dosage distribution for different material and thus know the X-ray damage strengthening gene for some devices.

Owner:NORTHWEST INST OF NUCLEAR TECH

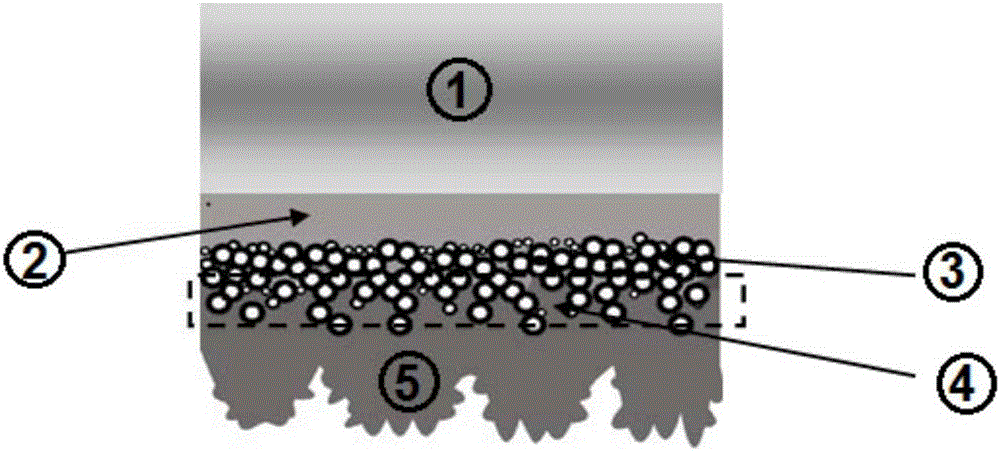

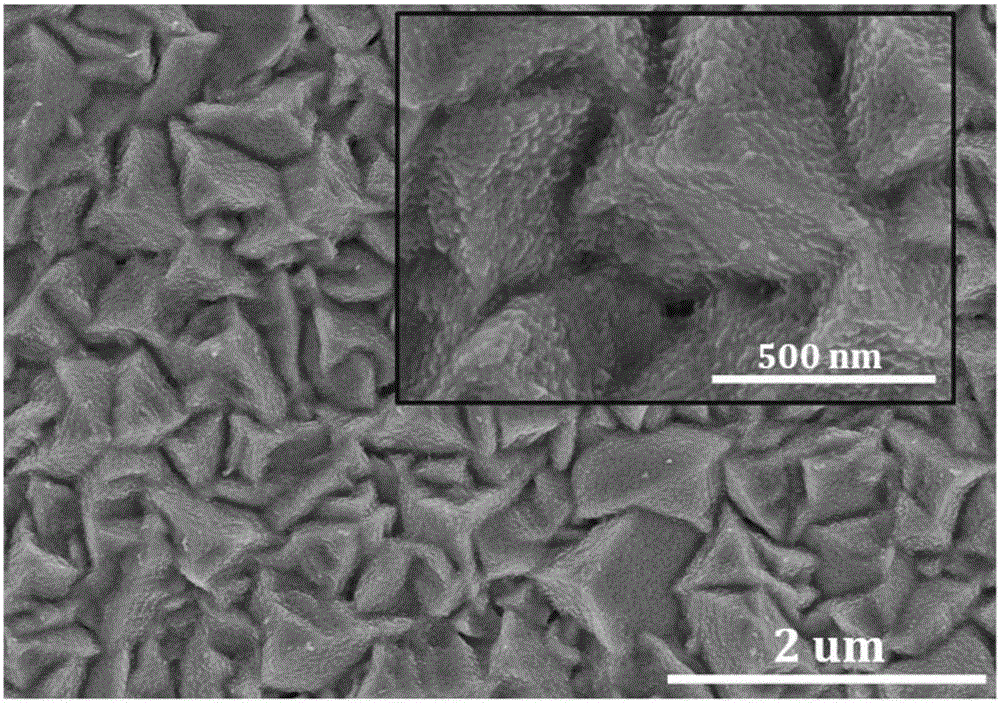

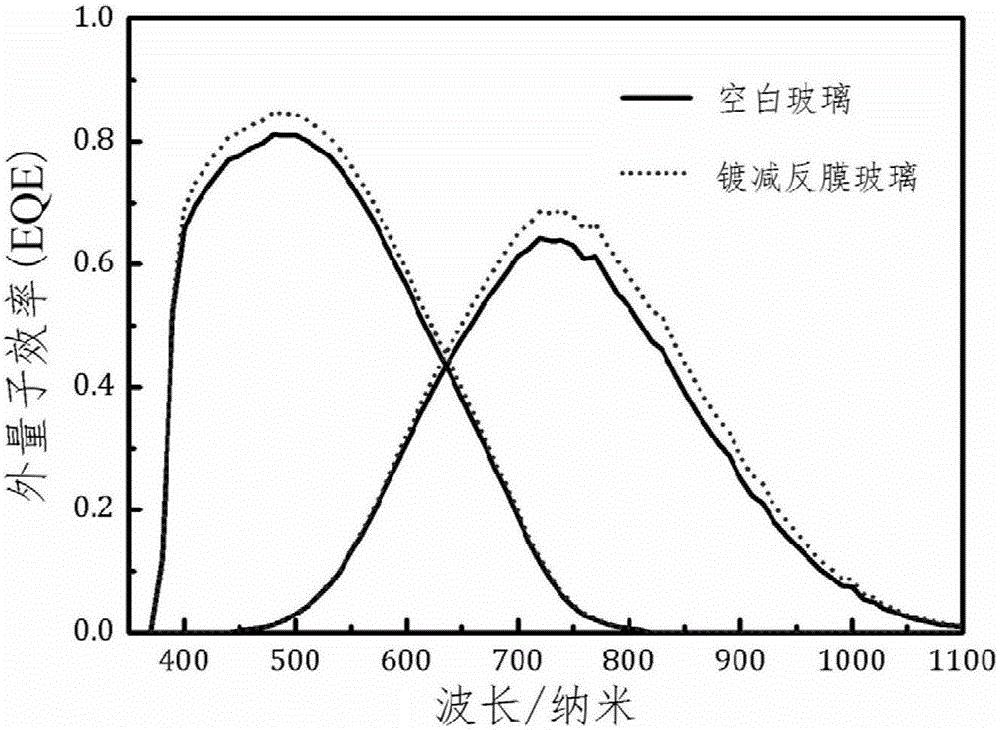

Thin film capable of simultaneously achieving anti-reflection and multi-structure light trapping, and preparation method thereof

InactiveCN105161548AReduce reflectionReduced index mismatchPhotovoltaic energy generationSemiconductor devicesTrappingRefractive index

The present invention discloses a thin film capable of simultaneously achieving anti-reflection and multi-structure light trapping, comprising a dielectric thin film layer, a main body thin film layer and a transparent conducting oxide layer in order from the bottom up; wherein the refractive index of the dielectric thin film layer is 1.3-2; the main body thin film layer is formed by film formation of sol B, the sol B is prepared by hybridization processing of hollow SiO2 nano particle sol and nano binder sol; the mass ratio of the hollow SiO2 nano particle sol to the nano binder sol in the sol B is 1:0-1; the transparent conducting oxide layer is contacted with the main body thin film layer, and transparent conducting oxides in the transparent conducting oxide layer are fused with hollow SiO2 nano particles in the main body thin film layer to form a transition region. The thin film of the present invention can simultaneously achieve anti-reflection and multi-structure light trapping, and has good effects on both long wavelength light and short wavelength light.

Owner:NINGBO INST OF MATERIALS TECH & ENG CHINESE ACADEMY OF SCI

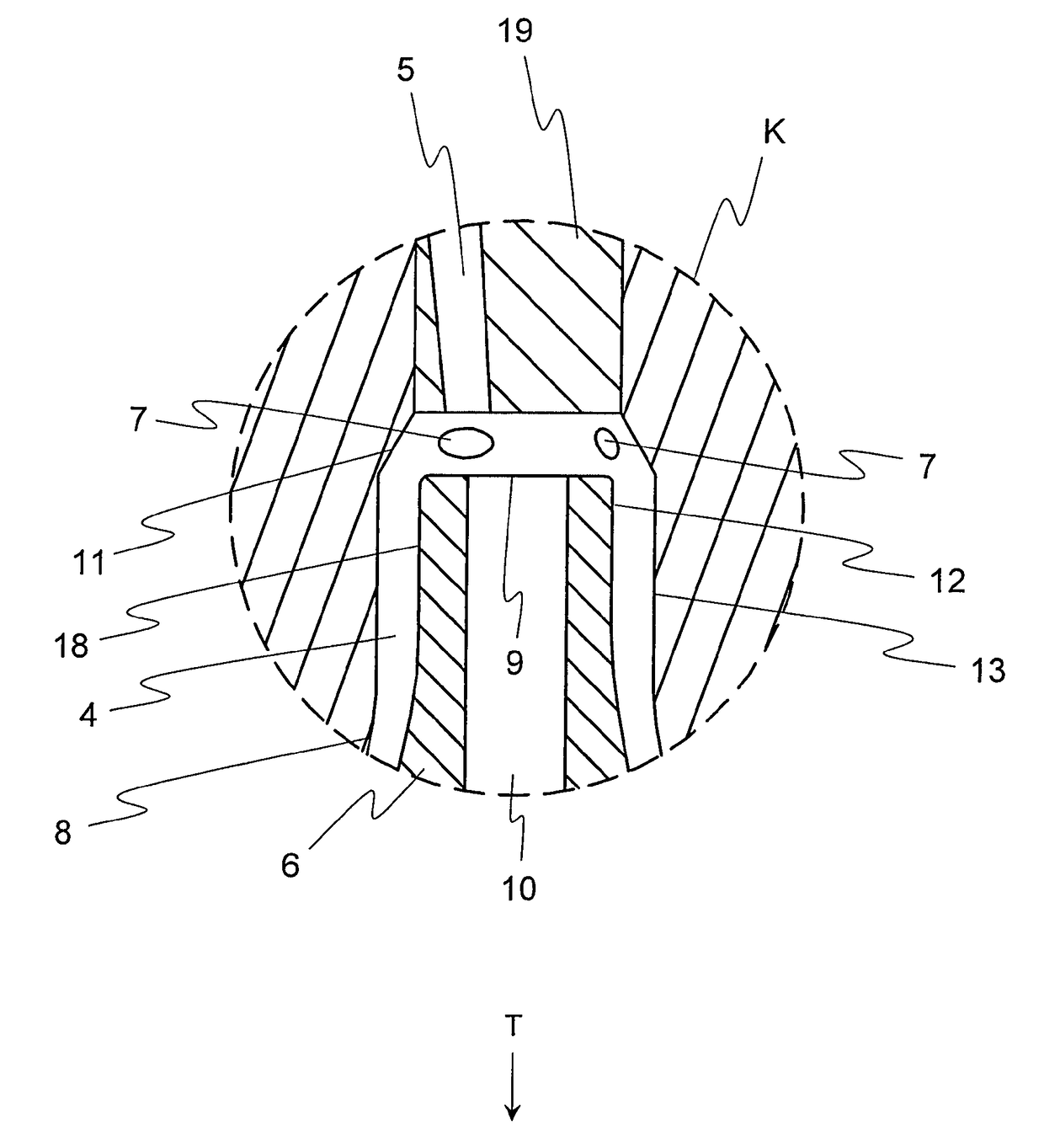

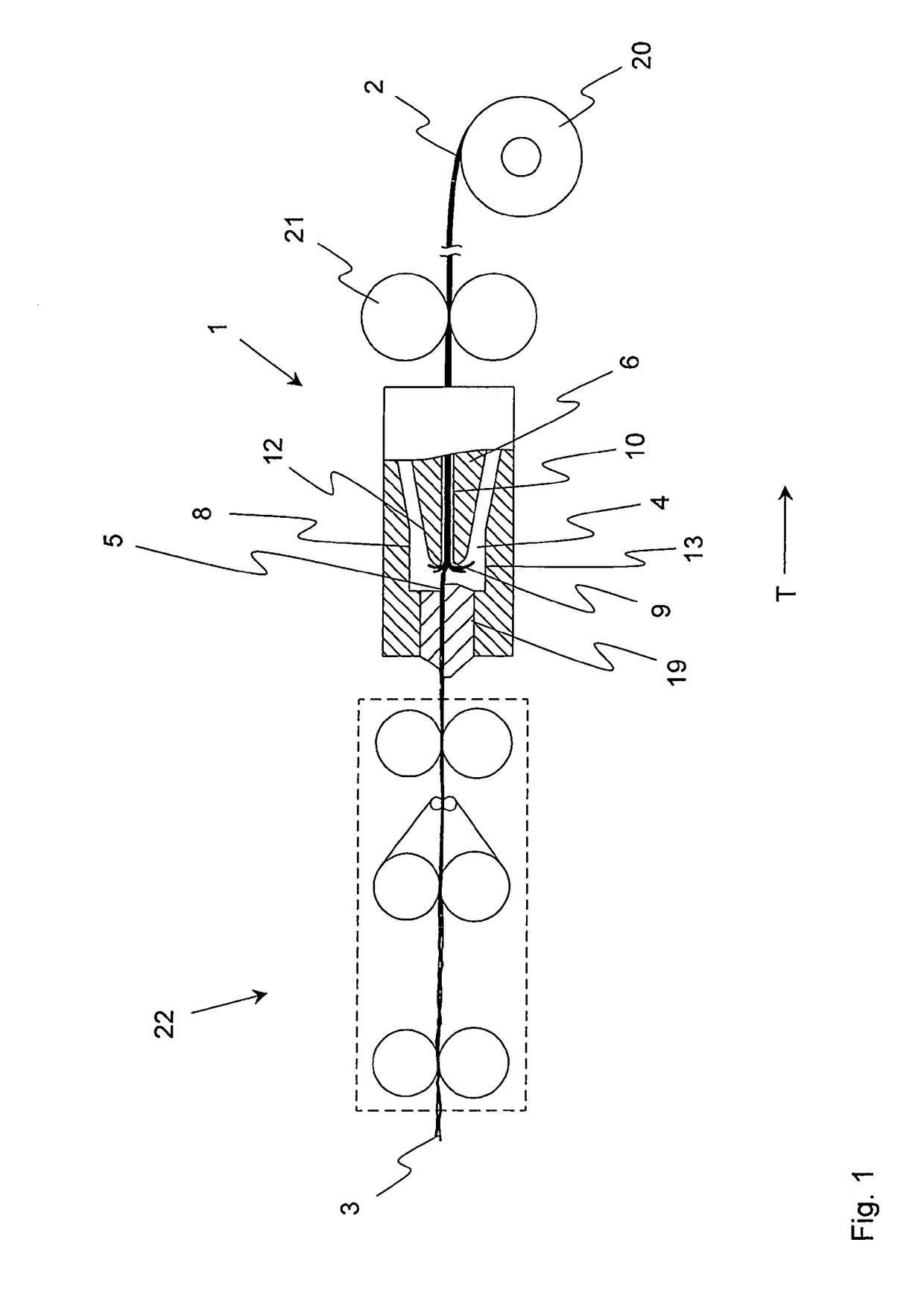

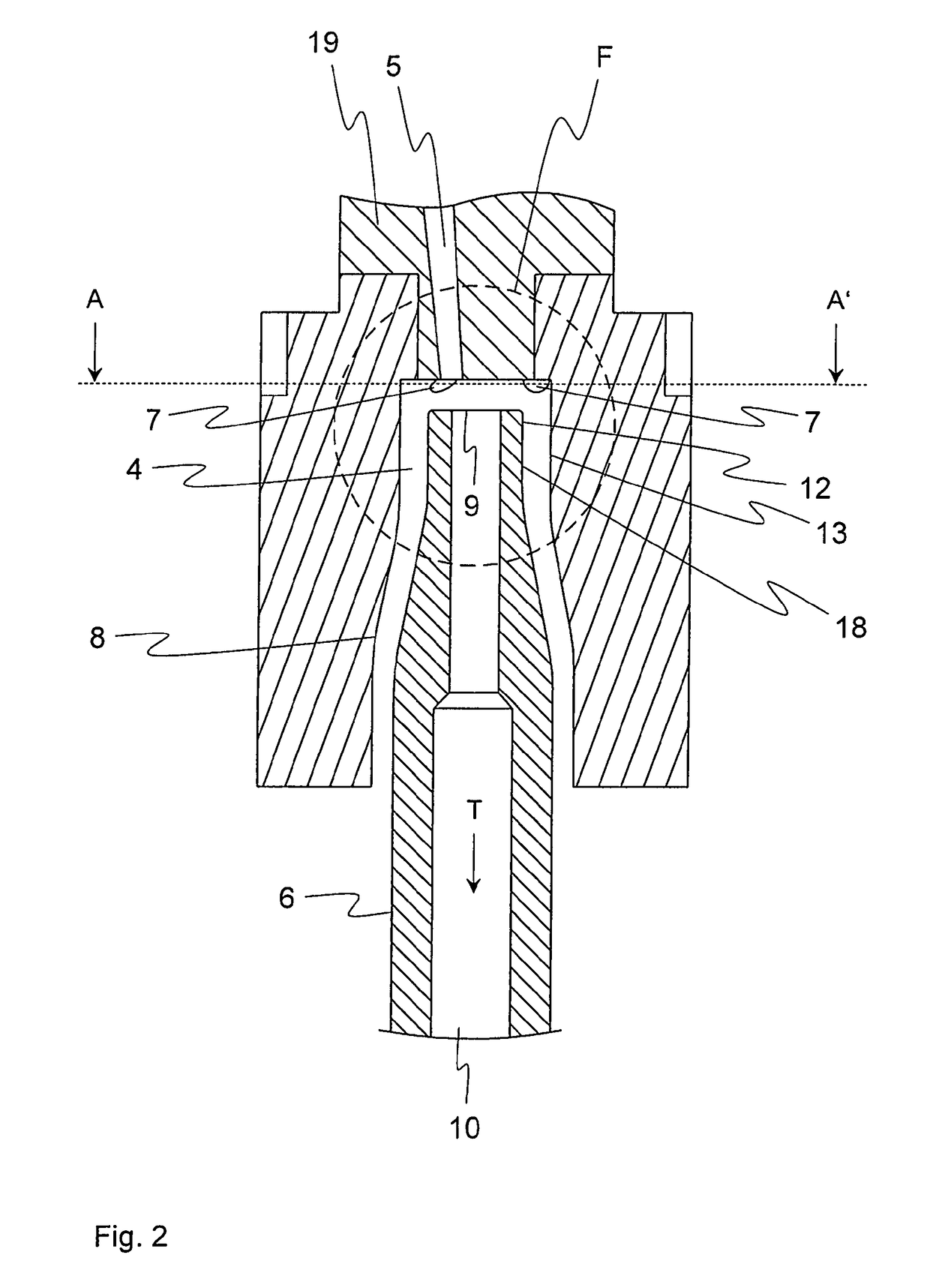

Spinning station of a spinning preparation machine

ActiveUS9677197B2Reliable and consistent mannerDrafting machinesContinuous wound-up machinesYarnFiber bundle

A spinning preparation machine for producing a roving from a fiber bundle includes a vortex chamber having an infeed opening for the fiber bundle and a yarn forming element extending at least partially into the vortex chamber. The spinning station includes spin nozzles, which lead into the vortex chamber in the region of a wall enclosing the vortex chamber and via which air is introduced into the vortex chamber in a specified direction of rotation in order to set the fiber bundle, which is fed in a transport direction, into rotation in the region of an inlet mouth of the yarn forming element. The yarn forming element includes a draw-off channel, which adjoins the inlet mouth and via which the yarn can be drawn out of the vortex chamber. The wall of the vortex chamber has a transition section, which adjoins the infeed opening, and has the shape of the circumferential surface of a truncated cone, and the diameter of which increases in the transport direction. The spin nozzles lead into the vortex chamber in the region of the transition section and each has a direction of flow that is oriented in the direction of an outer surface of the wall enclosing the vortex chamber.

Owner:MASCHINENFABRIK RIETER AG

Control method for epitaxial layer transition zone on re-mixed arsenic underlay

ActiveCN100485873CLow impurity contentSteep transition zoneSemiconductor/solid-state device manufacturingMemory effectGrow light

Owner:HEBEI POSHING ELECTRONICS TECH

Isolated NLDMOS (N type Laterally Diffused Metal Oxide Semiconductor) device

ActiveCN104638013AImprove driving abilityImprove breakdown voltageSemiconductor/solid-state device manufacturingSemiconductor devicesP type siliconBreakdown voltage

The invention discloses an isolated NLDMOS (N type Laterally Diffused Metal Oxide Semiconductor) device. Terminals are positioned at the upper end and lower end of a cellular area; two independent N type deep traps are formed on a type P silicon substrate; field oxide is formed above the P type silicon substrate between a left N type deep trap and a right N type deep trap, and above the left part of the right N type trap; a drift P type injection area is formed in the P type silicon substrate and the right N type deep trap below the field oxide; the left N type deep trap, the right N type deep trap, the field oxide and the drift P type injection area extend toward an upper end and a lower end to the terminals; in the terminals, the left side of the right N type deep trap moves rightwards, the left side of the drift P type injection area moves rightwards, and the drift P type injection area is integrally arranged inside the right N type deep trap; in transition areas between the cellular area and the terminals, the left side of the right N type deep trap is in slowly changing transition; the left side of the drift P type injection area is slowly changing transition. By adopting the isolated NLDMOS device, the current driving capability can be enhanced, and the breakdown voltage is increased.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

Radiation hardened semiconductor device

InactiveUS6855618B2Improve the environmentReduce stepsSemiconductor/solid-state device manufacturingBoronSemiconductor

A method for manufacturing a radiation hardened semiconductor device, having defined active region and isolation region. The isolation region containing an isolation material and active region containing a transition region between active and isolation region, sometimes denoted a bird's beak region. Wherein the transition region is implanted with germanium and boron, to prevent formation of leakage paths between active devices, or within an active device. The implanted area can be further limited to that area of the transition region that is adapted to be covered by a gate material, such as polysilicon.

Owner:AEROFLEX COLORADO SPRINGS INC

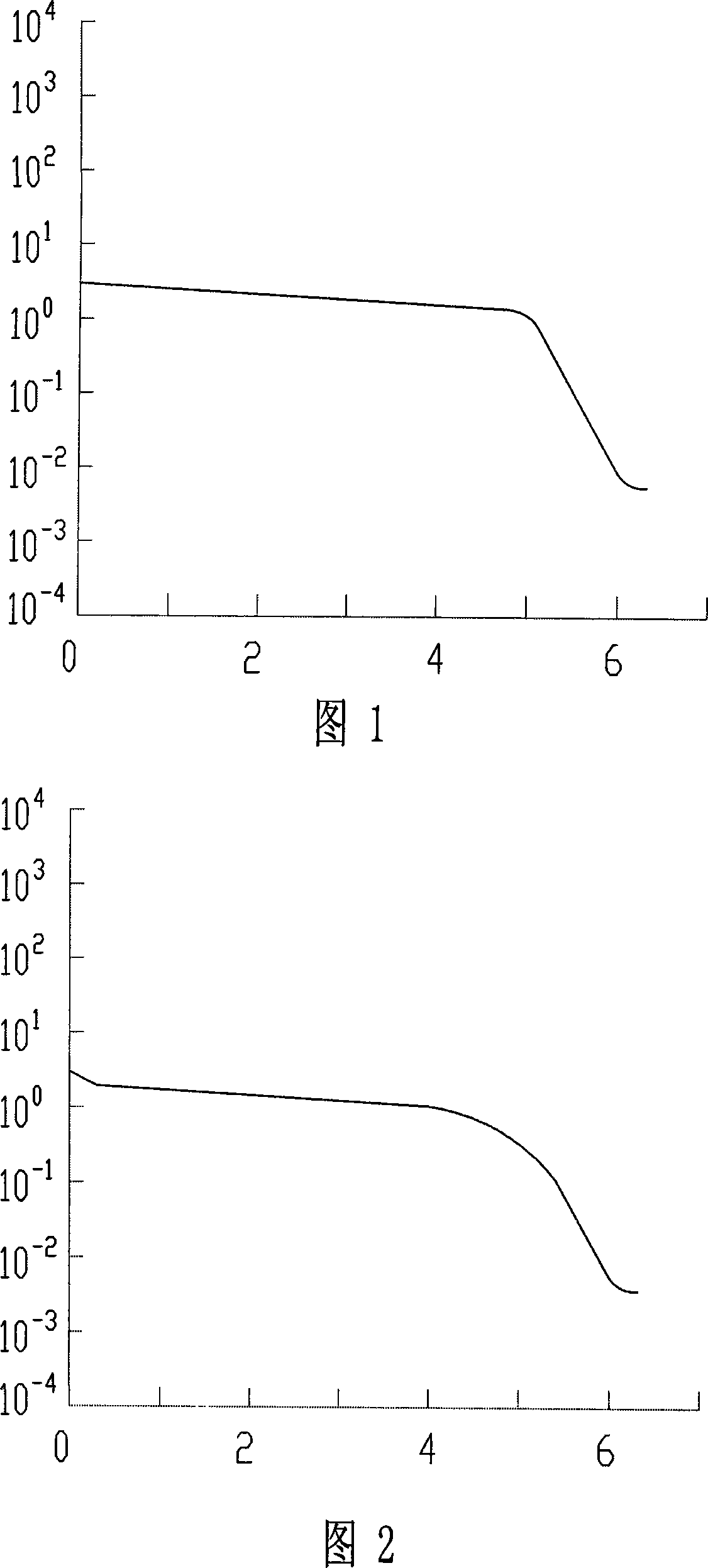

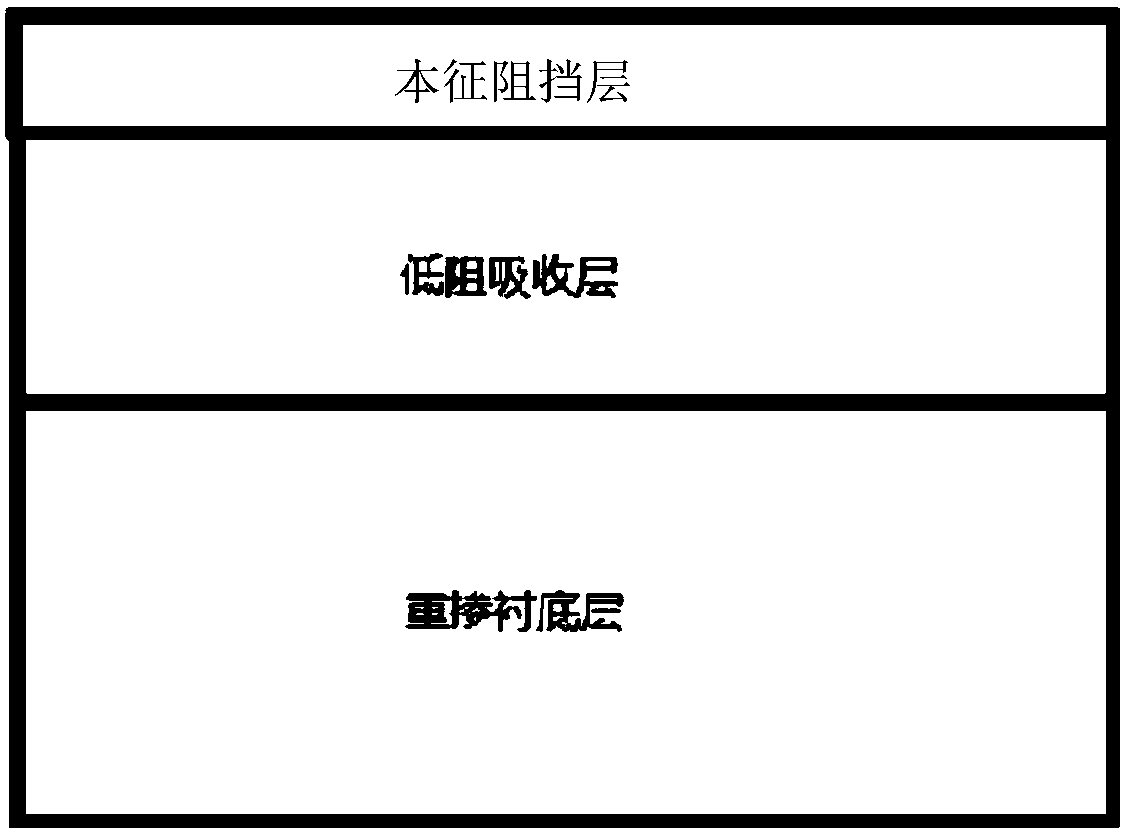

Novel infrared detector BIB silicon epitaxial wafer manufacturing method

ActiveCN108767053AReduce self-doping effectsHigh resistivityFinal product manufactureSemiconductor/solid-state device manufacturingLow speedTwo step

The present invention relates to a novel infrared detector BIB silicon epitaxial wafer manufacturing method. An N-type (100) polished wafer with heavily doped As, the electrical resistivity is <=0.004[Omega].cm, and there is not a back-seal substrate. In order to reduce the back-face self doping influence, a silicon package process is adapted. Surface impurities and defects are removed through HCI in-situ high-temperature polishing so as to improve the substrate surface quality. Substrate self-doping is reduced through a high-flow high-temperature blowdown process. a two-step extrapolation isemploys to allow a low-resistance absorption layer and an intrinsic layer to be separately grown, and high-flow H2 cooling blowdown between the two steps; and a cavity is subjected to high-flow gas corrosion prior to wafer installation of the epitaxy of the intrinsic layer, the low-speed and low-temperature growth is performed when epitaxy is performed. The novel infrared detector BIB silicon epitaxial wafer manufacturing method controls self-doping, a transition area of the absorption layer and the substrate is steep, the intrinsic barrier layer has a wide flat area so as to meet the demandof the BIB device design.

Owner:NANJING GUOSHENG ELECTRONICS

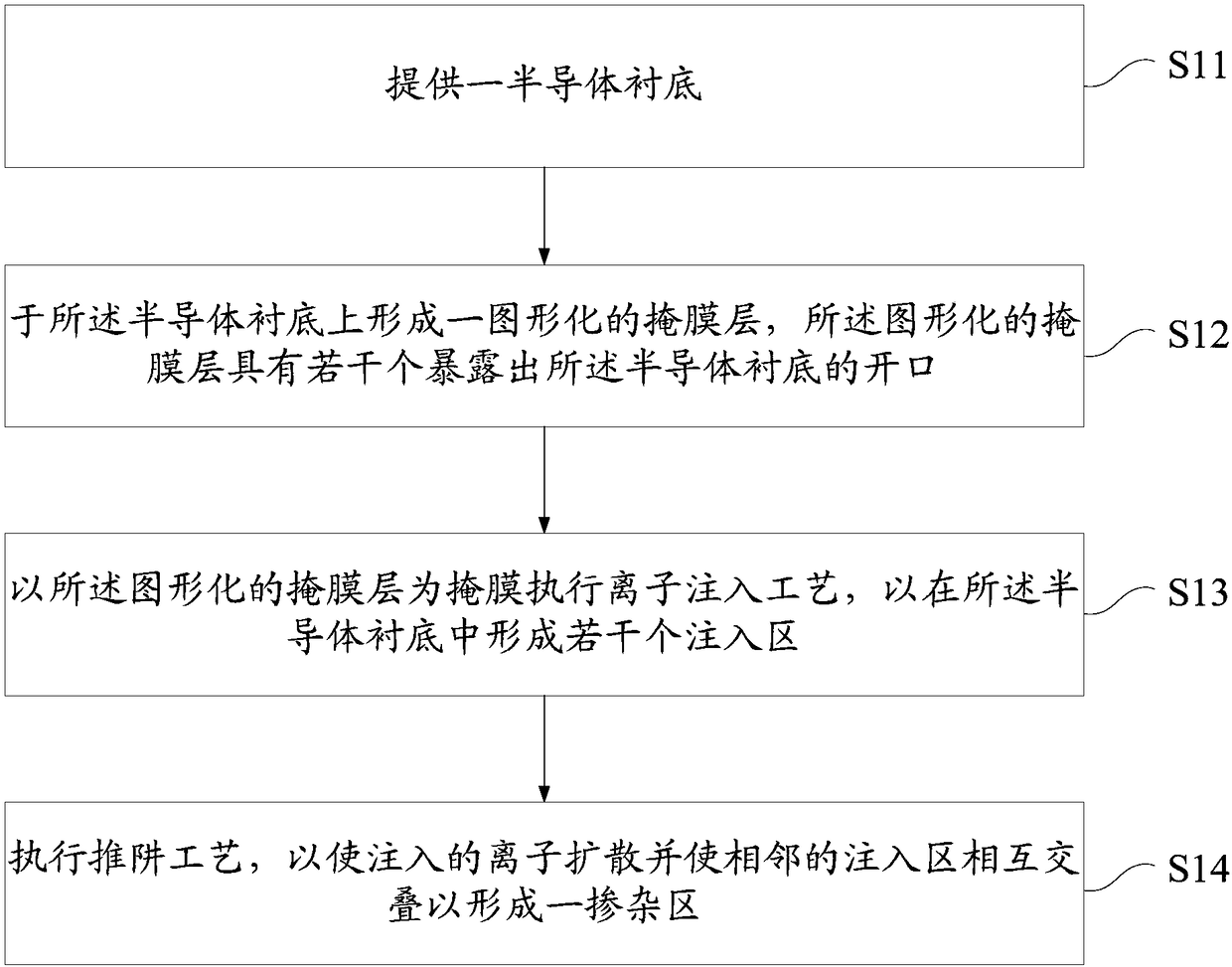

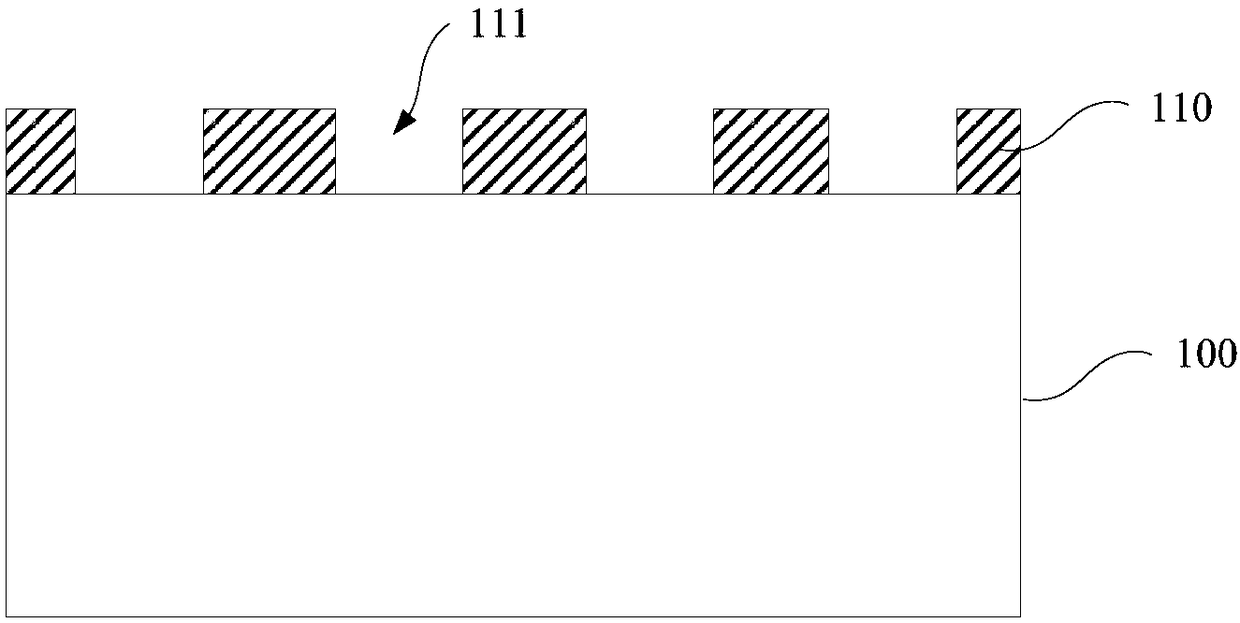

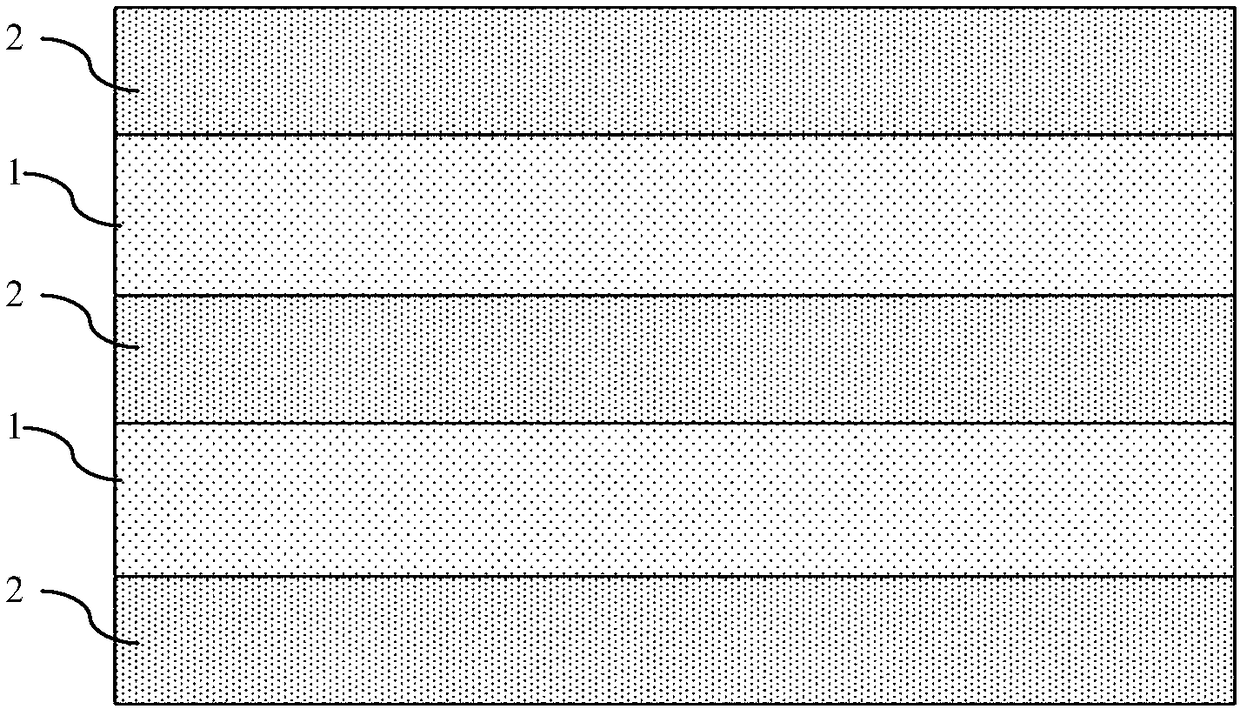

Doped region and IGBT device forming methods, and doped region and IGBT device structures

ActiveCN108933078AReduce doping concentrationIncrease the resistance valueSemiconductor/solid-state device manufacturingSemiconductor devicesMultiple injectionBallast resistor

The invention provides doped region and IGBT device forming methods, and doped region and IGBT device structures. The doped region forming method comprises the following steps: a plurality of injection regions are formed on a semiconductor substrate, and then ions in the plurality of injection regions are diffused by push-trap process so that adjacent injection regions are mutual overlapped to form a doped region. The multiple injection regions form the doped region through ion diffusion, and then the formed doped region has a low doping concentration in a condition that the area of the dopedregion is not changed. So, when the doped region is formed in an interface of an IGBT device, a resistance value of a ballast resistor in the interface can be effectively increased, and suppression intensity of a convergence effect of hole carriers of the interface can be improved without increasing the area of the interface.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

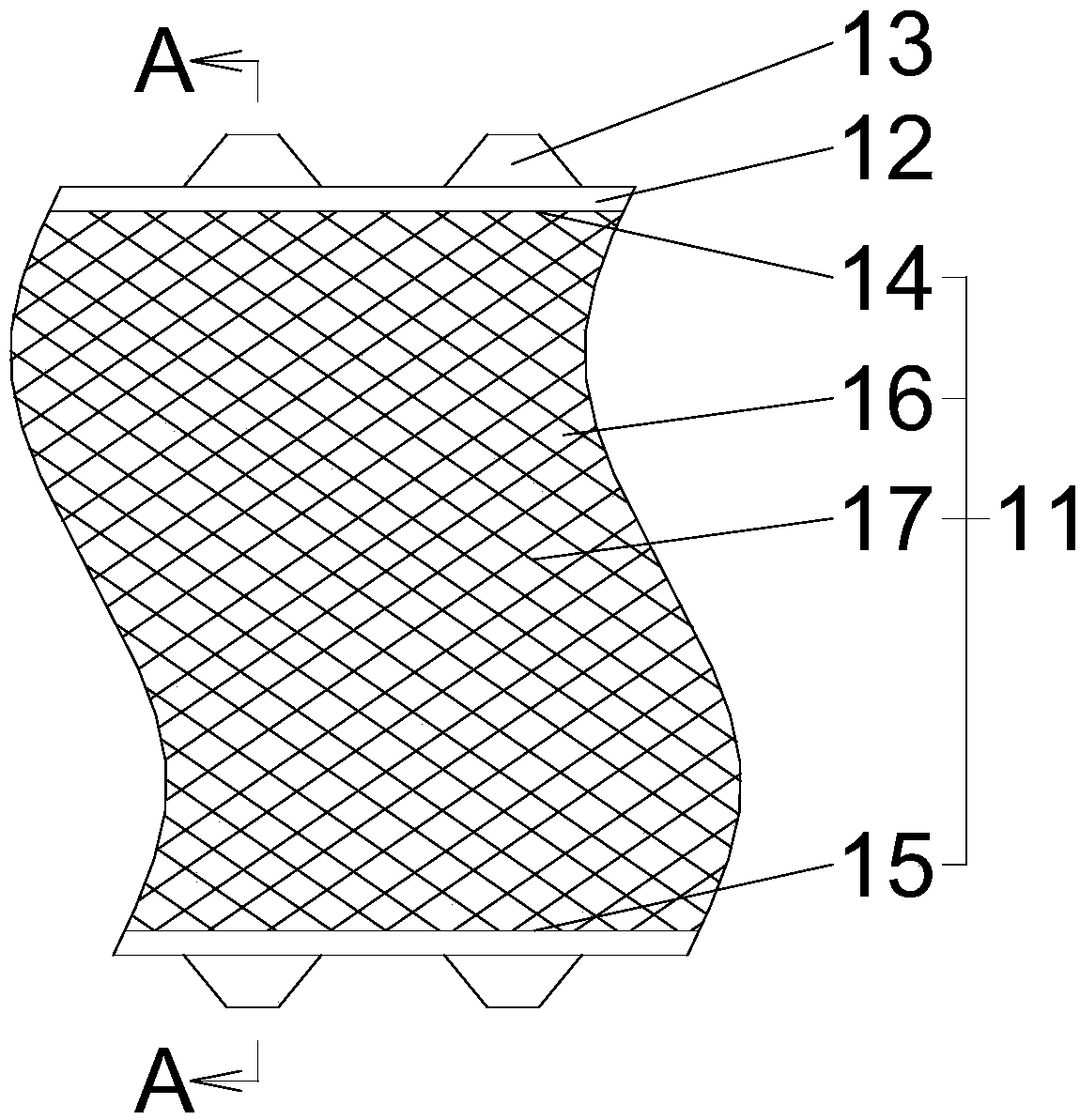

A superjunction device and a method for manufacturing the same

ActiveCN109148557AAspect ratioImplement self-aligned injectionSemiconductor/solid-state device manufacturingSemiconductor devicesCapacitanceElectrical resistance and conductance

A superjunction device is disclosed. A protective epoxidation film surrounding the periphery of the charge flow region is provided, the aspect ratio of the contact hole in the transition region is greater than or equal to the aspect ratio of the contact hole in the charge flow region, and the tungsten plug process is used to fill the contact holes with different aspect ratios reliably at the sametime. The width of the P-type well is smaller than the width of the P-type column, and a slowly varying junction diode is formed between the P-type well and the N-type region. The invention also discloses a manufacturing method of a superjunction device. The invention can reliably fill the contact hole in the transition region when the height-to-width ratio is high, at that same time, the anti-avalanche breakdown ability of the device is not affect by the contact hole process of the transition region, and the influence of the P-type well on the width of the N-type region at the position of thechannel region is reduce, so that the on resistance of the device is reduced; and the nonlinearity of the output capacitance of the device is improved and the EMI problem in device application is improved.

Owner:SHENZHEN SANRISE TECH CO LTD

Super-junction device and manufacturing method thereof

ActiveCN108428733AReduce photolithography processReduce injectionSemiconductor/solid-state device manufacturingSemiconductor devicesEngineeringJFET

The invention discloses a super-junction device, which is characterized in that a protective epoxy film exposes a charge flow region, completely covers a transition region and completely or mostly covers a terminal region, the setting of the protective epoxy film enables a JFET region and a source region to realize comprehensive injection, and the JFET region is enabled to be overlapped with eachP-type well and reduces the doping concentration on the surface of each corresponding P-type well, thereby enabling the overall doping concentration of the P-type wells to be increased under the condition of maintaining the threshold voltage of the device to be unchanged, and being capable of improving the avalanche current tolerance of the device. The invention further discloses a manufacturing method of the super-junction device. The super-junction device can keep the threshold voltage of the device to be unchanged while improving the injection dose of the P-type wells, so that the charge flow region and the transition region are enabled to be improved in avalanche current tolerance, and thus the performance of the device is improved; and the number of times of the photoetching process can also be reduced, the performance and reliability of the device can be maintained, the manufacturing cost can be reduced, and the production cycle can be shortened.

Owner:SHENZHEN SANRISE TECH CO LTD

Energy-saving condensing piece of compact spinning device

InactiveCN108330573AEasy to fixReduce the cross-sectional areaDrafting machinesEngineeringEnergy consumption

The invention discloses an energy-saving condensing piece of a compact spinning device. The energy-saving condensing piece comprises a condensing piece body, an upper condensing groove, a transition area, a lower condensing groove, an upper arc and a lower arc. The condensing piece is fixedly installed on a special pipe through the upper arc and the lower arc; because the upper and lower condensing grooves are arranged and the transition area is arranged in the middle, the total opening area of the condensing grooves is reduced, the air flow rate is reduced, the workload of a negative pressureblower is reduced, accordingly, energy consumption is reduced, the effects of energy conservation and emission reduction are achieved, and meanwhile, the condensing effect is ensured.

Owner:JINJIANG HAOMING MACHINERY

Super-junction metal oxide field effect transistor with surface buffering ring terminal structure

ActiveCN101840933BDoes not affect internal concentration distributionIncrease the surface radius of curvatureSemiconductor devicesHigh concentrationTransverse pressure

The invention discloses a super-junction metal-oxide field effect transistor with a surface buffering ring terminal structure, comprising an N-type doped semiconductor substrate, wherein an N-type doped epitaxial layer is arranged on the N-type doped semiconductor substrate, a P-type doped deep well region is arranged inside the N-type doped epitaxial layer, a P-type doped region and a P-type doped buffer region are arranged at the upper side of the P-type doped deep well region, and a high-concentration N-type doped region is arranged in the P-type doped region; polysilicon is arranged abovepartial gate oxide layer, and the polysilicon forms a polysilicon field plate structure at a terminal structure region and also forms a double-layer field plate together with a metal field plate which extends to a traditional region from a source end in the super-junction metal oxide field effect transistor with the surface buffering ring terminal structure; therefore, the surface field peak value can be reduced, the surface potential distribution is optimized, and the transverse pressure resistance level of components is effectively improved.

Owner:SUZHOU POWERON IC DESIGN

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com