Isolated NLDMOS (N type Laterally Diffused Metal Oxide Semiconductor) device

An isolation type and device technology, which is applied in semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve problems such as low breakdown voltage and unbalanced size change, and achieve the goal of improving breakdown voltage and current drive capability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

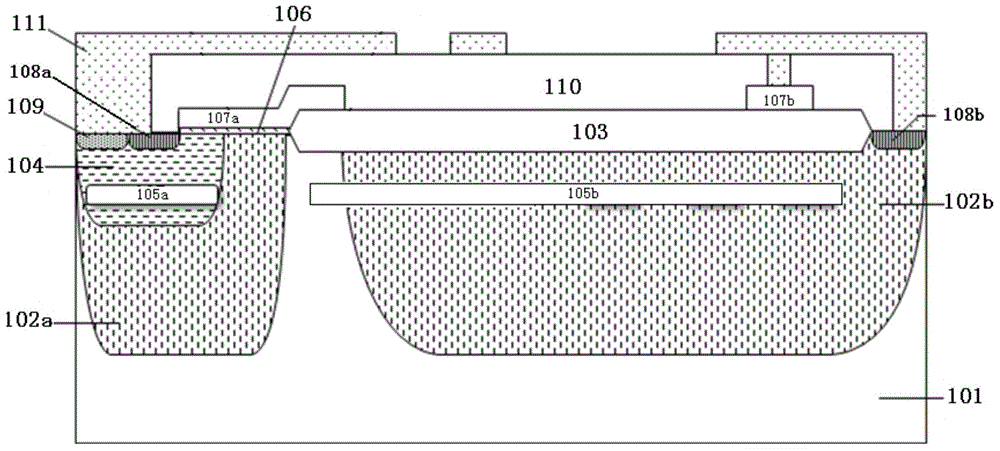

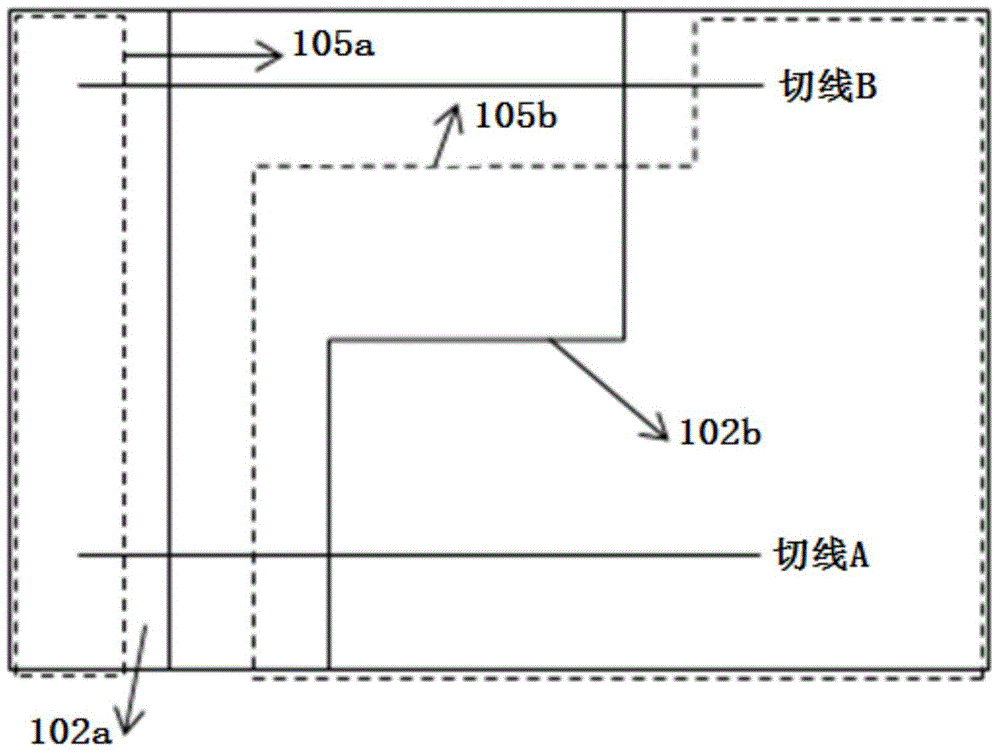

[0037] For isolated NLDMOS devices, the terminals are located at the upper and lower ends of the cell region, and the longitudinal cross-sectional structure of the cell region is as follows: figure 1 As shown, two independent N-type deep wells, a left N-type deep well 102a and a right N-type deep well 102b, are formed on the P-type silicon substrate 101;

[0038] The left N-type deep well 102a has a P well 104 formed on the left;

[0039] In the P well 104, a P-type heavily doped region 109 and a source N-type heavily doped region 108a are formed on the left;

[0040] A gate oxide layer 106 is formed above the right part of the P well 104 and above the right part of the left N-type deep well 102a;

[0041] Field oxygen 103 is formed above the P-type silicon substrate 101 between the left N-type deep well 102a and the right N-type deep well 102b, and above the left part of the right N-type deep well 102b;

[0042] The right N-type deep well 102b has a drain N-type heavily dop...

Embodiment 2

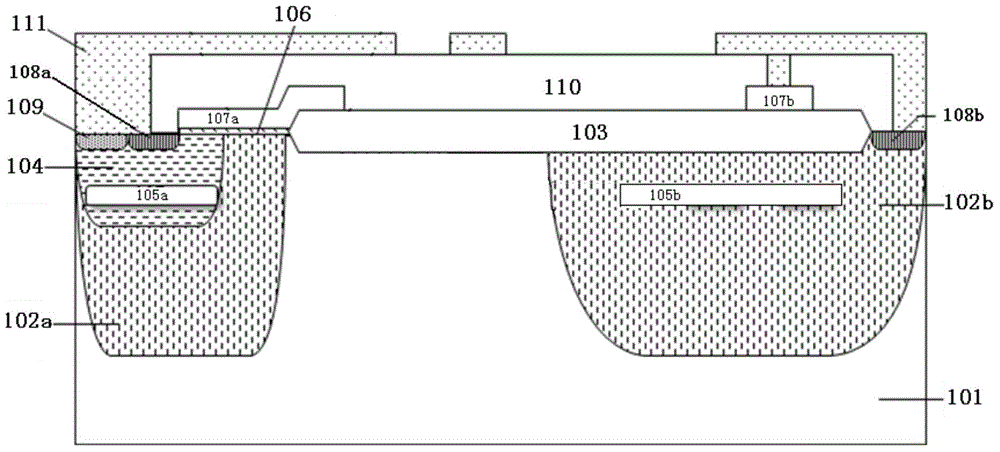

[0053] Based on the isolated NLDMOS device of Embodiment 1, a drain terminal polysilicon field plate 107b is formed above the right part of the field oxide 103;

[0054] The interlayer dielectric 110 covers the surface of the device;

[0055] The P-type heavily doped region 109 and the source N-type heavily doped region 108a are short-circuited together by a metal 111 passing through the interlayer dielectric 110;

[0056] The drain terminal N-type heavily doped region 108b is short-circuited with the drain terminal polysilicon field plate 107b through another metal 111 passing through the interlayer dielectric 110;

[0057] Preferably, a source end P-type implantation region 105a is formed in the P well 104 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com