Silicon epitaxial wafer and preparation method thereof

A technology of silicon epitaxial wafers and epitaxial layers, which is applied in the manufacture of semiconductor/solid-state devices, electrical components, circuits, etc., can solve the problems of large influence of self-doping effect, difficult overlap of center and edge transition regions, etc., and improve the softness factor , maintain electrical characteristics, controllable effect of linear distribution parameters

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

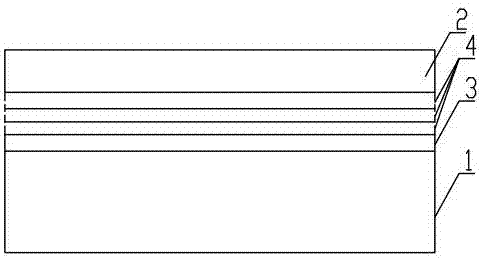

[0035] The embodiment of the present invention discloses a silicon epitaxial wafer, such as image 3 As shown, the epitaxial wafer includes a silicon substrate 1, the inner epitaxial layer is located on the upper surface of the substrate, and the high resistance epitaxial layer 2 is located on the upper surface of the inner epitaxial layer; the inner epitaxial layer includes The low-resistance epitaxial layer 3 on the lower side and more than two linear graded epitaxial layers 4 on the upper surface of the low-resistance epitaxial layer 3 .

[0036] Preferably, the silicon epitaxial wafer meets the following parameters: the silicon substrate 1 uses an N-type polished wafer heavily doped with arsenic. The thickness of the low-resistance epitaxial layer 3 is 0.5 μm-2 μm, and the resistivity is 0.5Ω.cm-10Ω.cm. The thickness of the single-layer linear graded epitaxial layer 4 is 5 μm-10 μm, and the first to nth linear graded epitaxial layers are arranged from bottom to top, and ...

Embodiment 2

[0039] The main equipment used in the method of the present invention is an Italian PE-3061D epitaxial furnace, and the base is a high-purity graphite base.

[0040] Such as Figure 4 As shown, the present invention also discloses a method for preparing a silicon epitaxial wafer, the method comprising the steps of:

[0041] S101: directly growing a low-resistance epitaxial layer 3 on the upper surface of the silicon substrate 1;

[0042] S102: growing a layer of linear graded epitaxial layer 4 every 5 μm-10 μm on the upper surface of the low-resistance epitaxial layer 3, and calculating the doping flux corresponding to the linear resistance value of the graded epitaxial layer during growth for doping;

[0043] S103: growing a high-resistance epitaxial layer 2 on the upper surface of the outermost linear graded epitaxial layer 4 .

Embodiment 3

[0045] The main equipment used in the method of the present invention is an Italian PE-3061D epitaxial furnace, and the base is a high-purity graphite base.

[0046] like Figure 5 As shown, the present invention also discloses a method for preparing a silicon epitaxial wafer, the method comprising the steps of:

[0047] S201: Treatment of the epitaxial furnace: before loading the silicon substrate, the reaction chamber of the epitaxial furnace is thoroughly treated with HCl at high temperature to ensure the purity of the chamber, and then the graphite base is coated with silicon.

[0048] S202: Wafer pretreatment: using H 2 The natural oxide layer of the silicon substrate is baked to reduce the self-doping effect and ensure the consistency of resistivity in the chip.

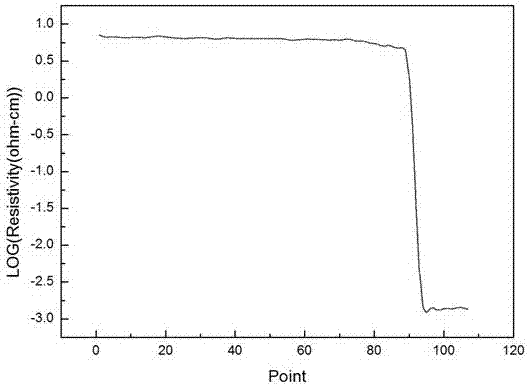

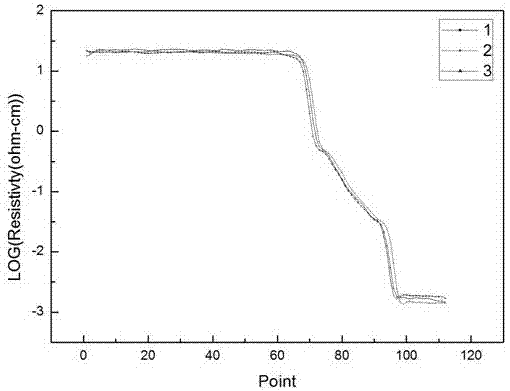

[0049] S203: Epitaxial layer growth: the first layer grows a low-resistance epitaxial layer with a thickness of 0.5 microns-2 microns and a resistivity of 0.5 ohm.cm-1ohm.cm, and then grows more than two line...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Resistivity | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com