Patents

Literature

Hiro is an intelligent assistant for R&D personnel, combined with Patent DNA, to facilitate innovative research.

358results about How to "Relieve heat stress" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

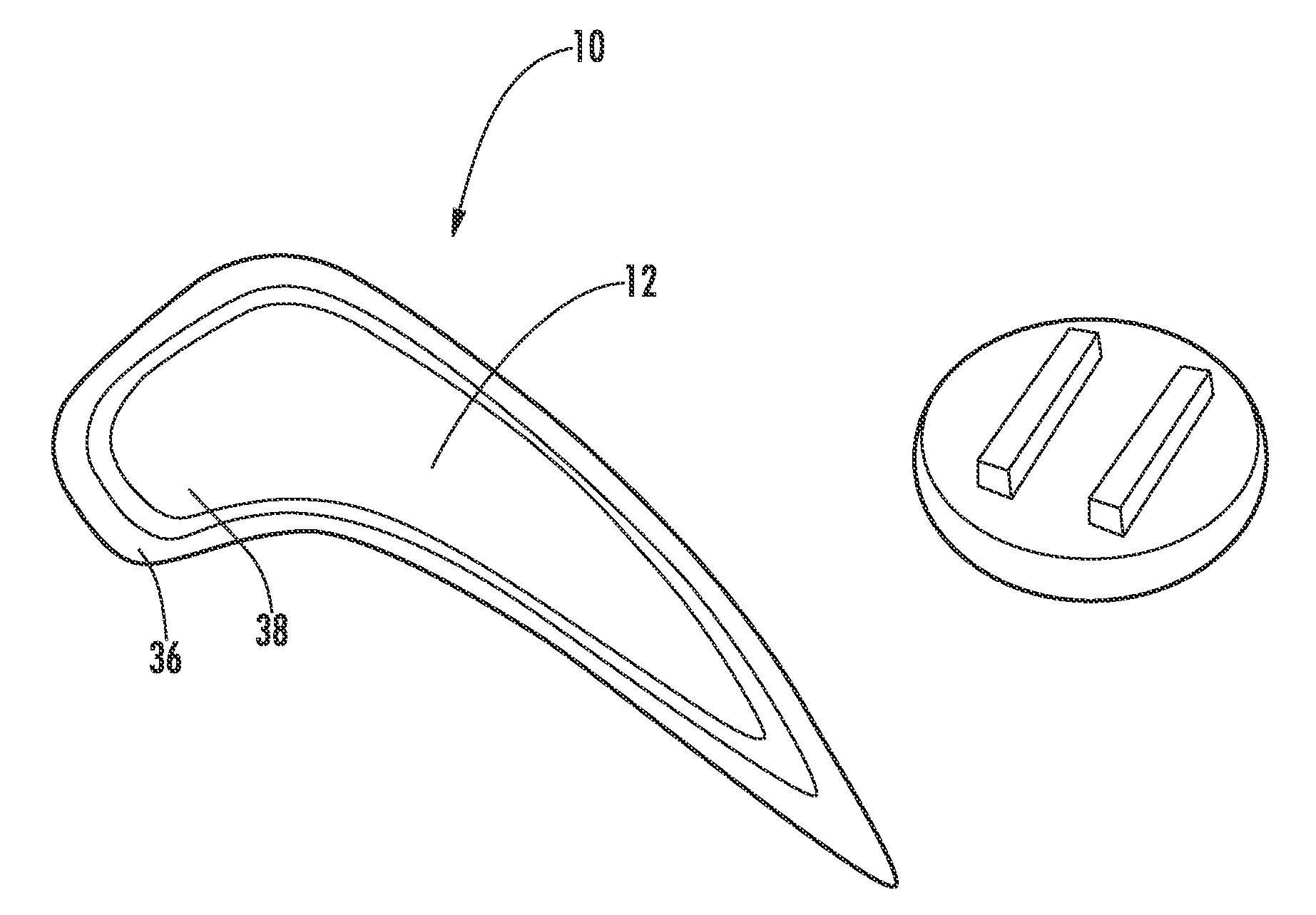

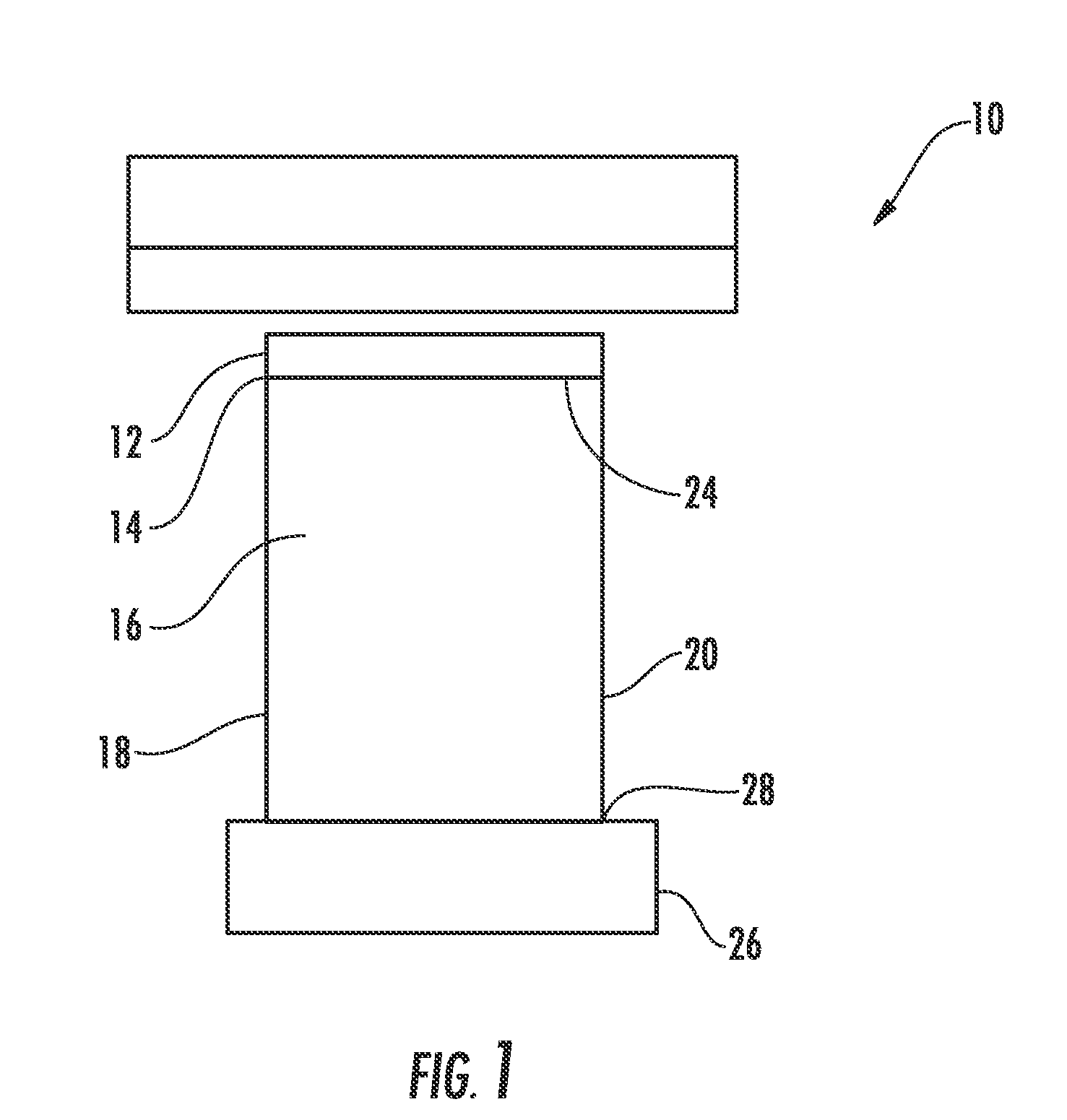

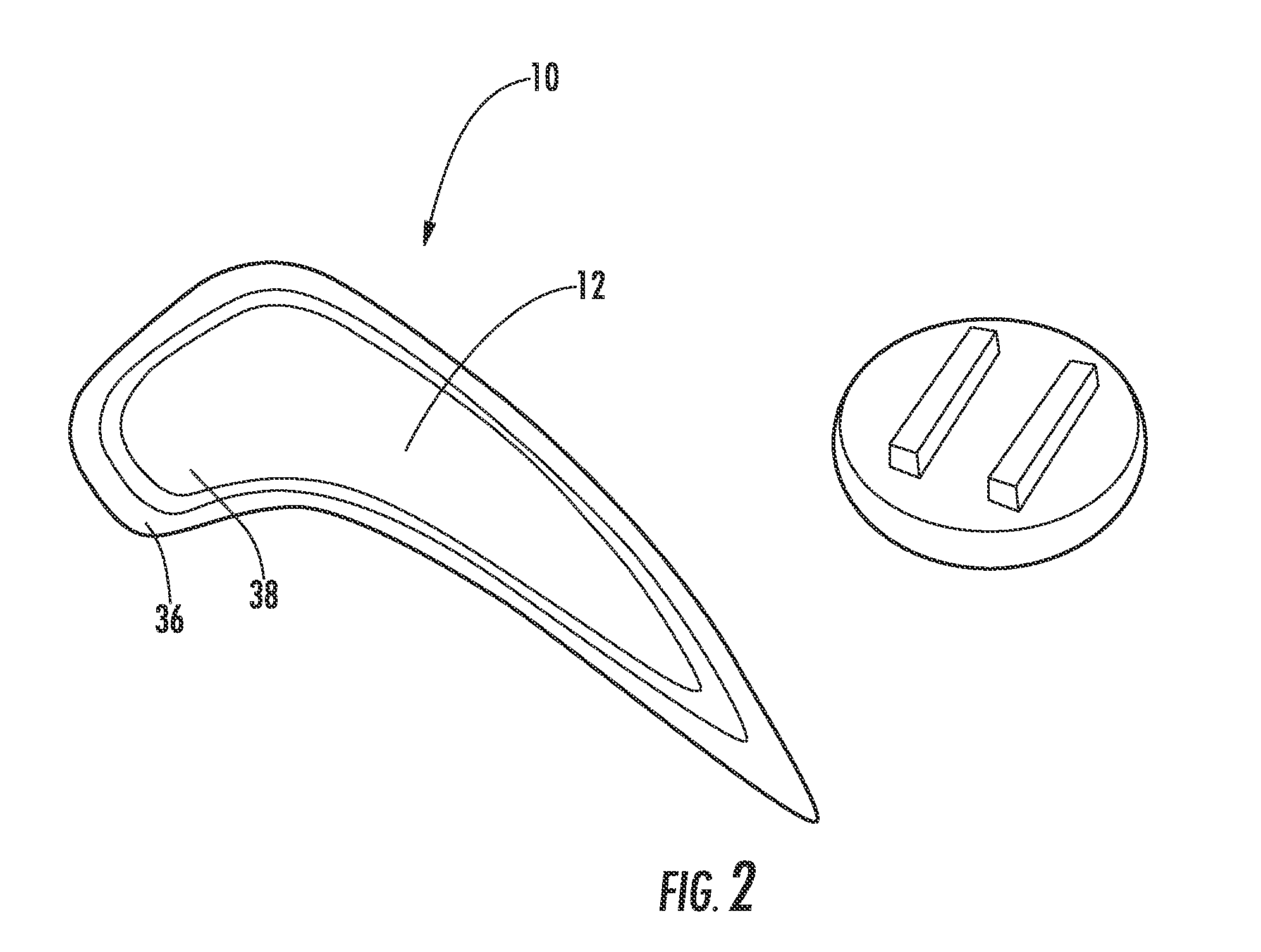

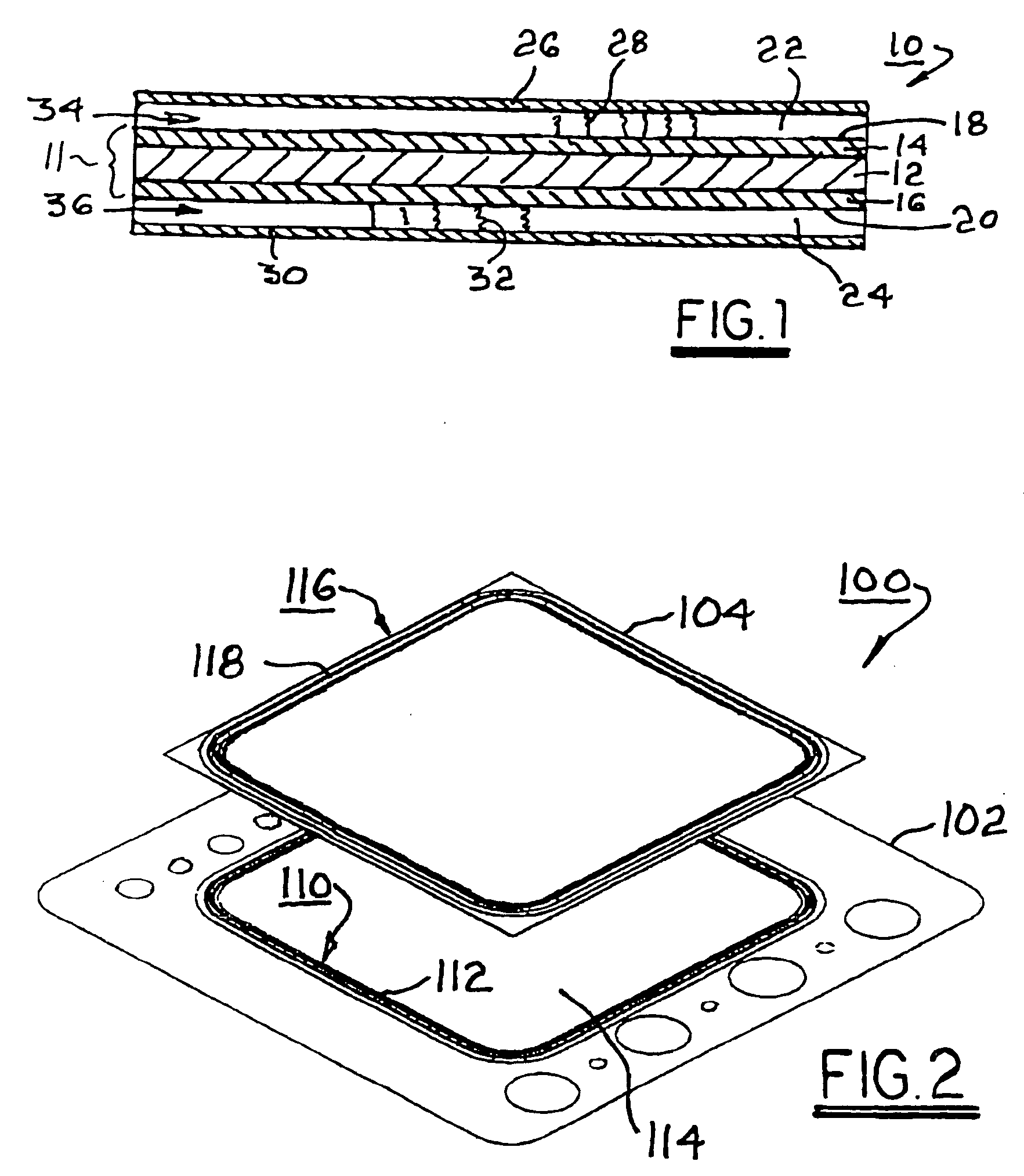

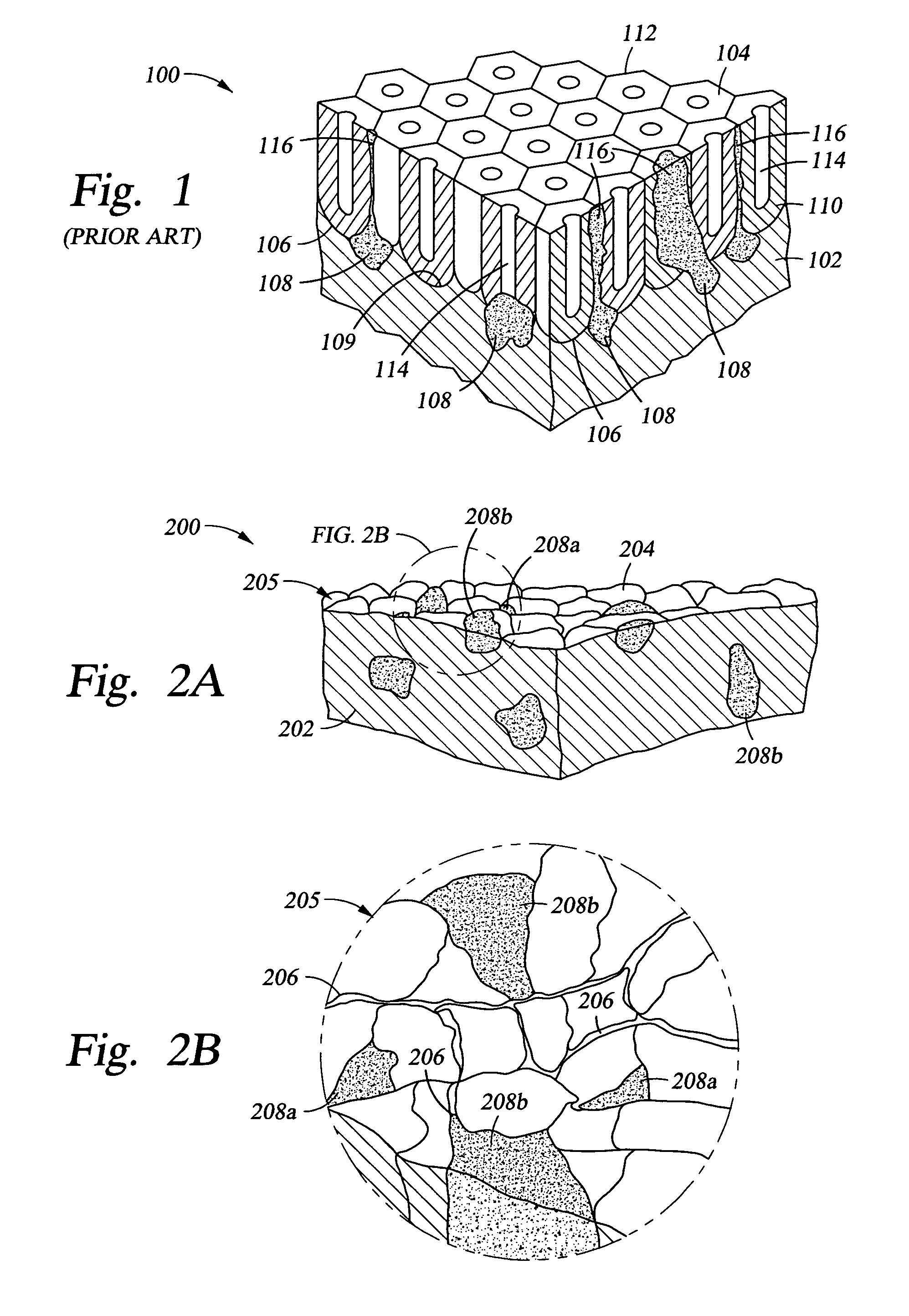

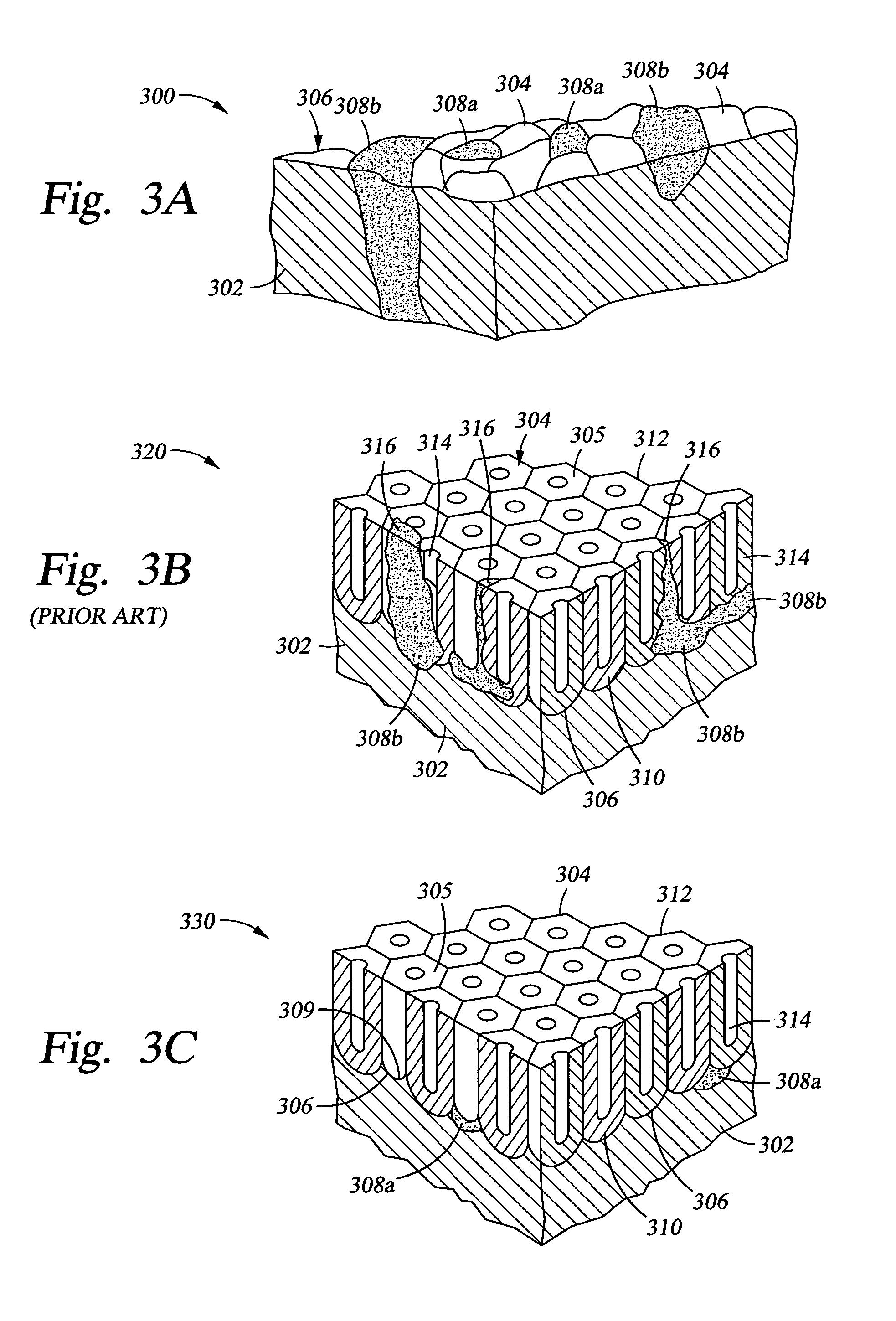

Turbine blade squealer tip

InactiveUS20120034101A1Improve efficiencyLess cooling fluidsPropellersRotary propellersSelective laser meltingMulti material

A turbine blade having a squealer tip coupled to a radially outer end of the turbine blade that is usable in a gas turbine engine is disclosed. The squealer tip may require less cooling air and may therefore be more efficient than conventional configurations. The squealer tip may be formed from one or more materials such as oxide dispersion strengthened alloys and FeCrAl alloys. The squealer tip may be formed from a plurality of segmented tips extending radially outward and spaced apart from each other. For example, the squealer tip may be formed from two rails extending radially outward and spaced apart from each other. The two rails may be formed from outer and inner rails that each form a continuous ring. The squealer tip may be attached to the tip with a transient liquid phase bond or an additive manufacturing process, such as, a selective laser melting process.

Owner:SIEMENS ENERGY INC

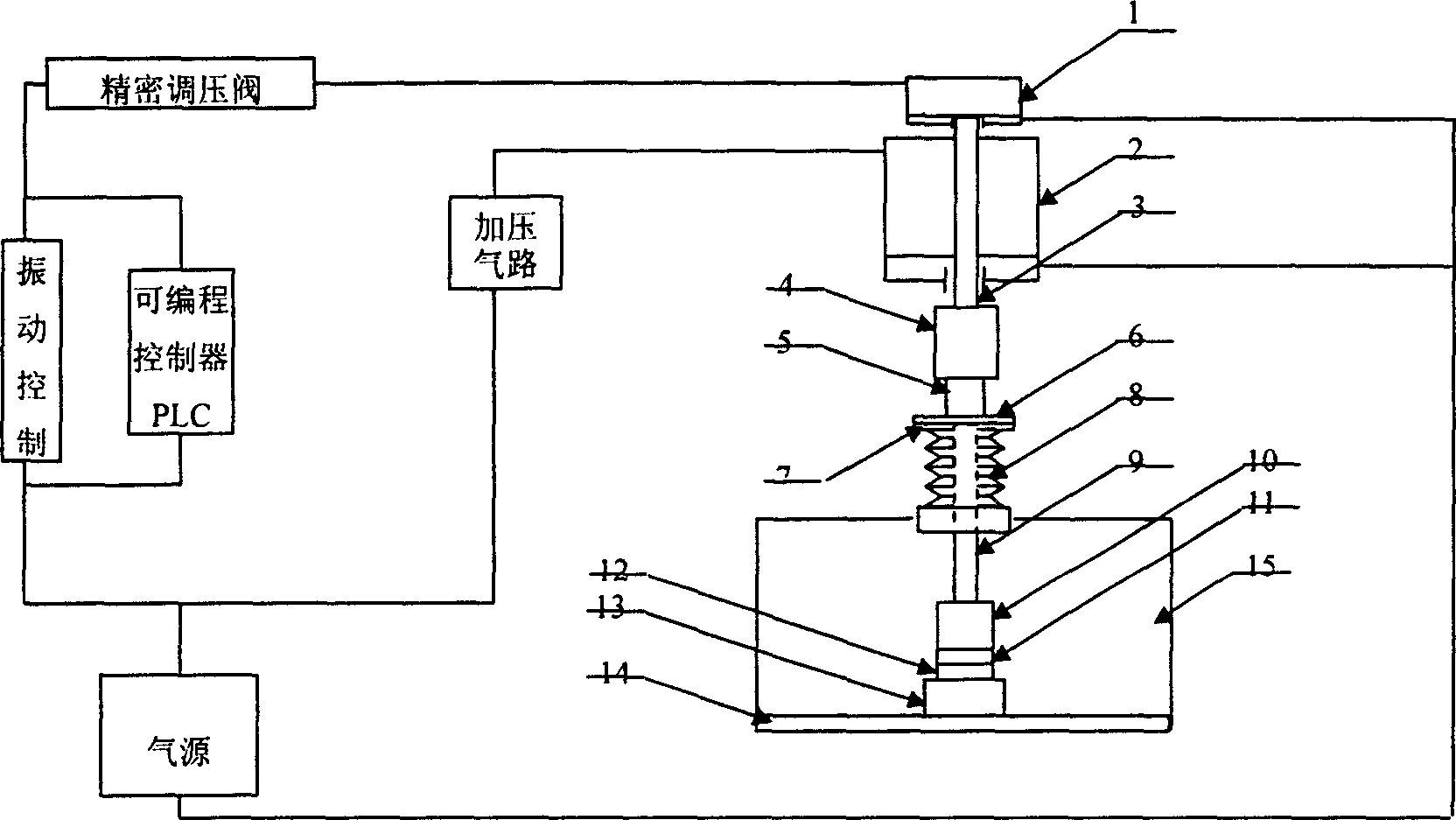

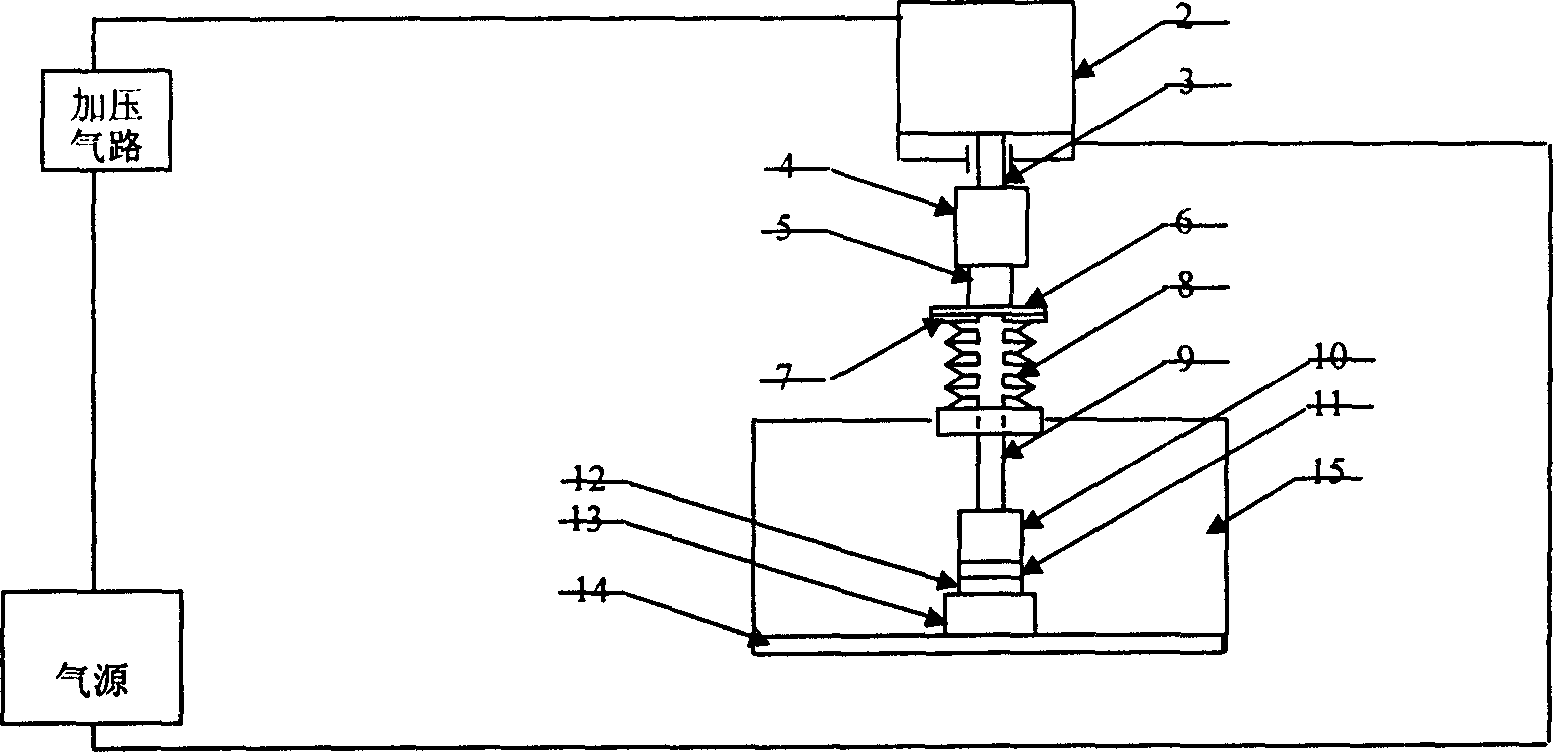

Pressurizing device and method for vacuum diffusion welding machine

InactiveCN1669718ALow soldering temperatureReduce welding soak timeNon-electric welding apparatusVibration controlEngineering

This invention disclose a pressure device for vacuum diffusion welding, with the purposes of solving problem of long time weld, too high temperature, which is characterized in adding a vibrating cylinder (1) to present device, precise pressure regulating valve, vibration controlling valve controlled by PLC and PLC matching with (1), wherein, vibrating cylinder (1) and pressure valve (2) share a pressure axis (3), other parts are all rigidly attached, vibrating cylinder (1) is attached to gas source circuit via precise regulating valve and vibration controlling valve and parallel to pressure circuit. The invention can lower welding temperature by 30-300Deg.C, reduce welding time by 20-50%, and improve efficiency of device by 1-3 times.

Owner:NORTHWESTERN POLYTECHNICAL UNIV

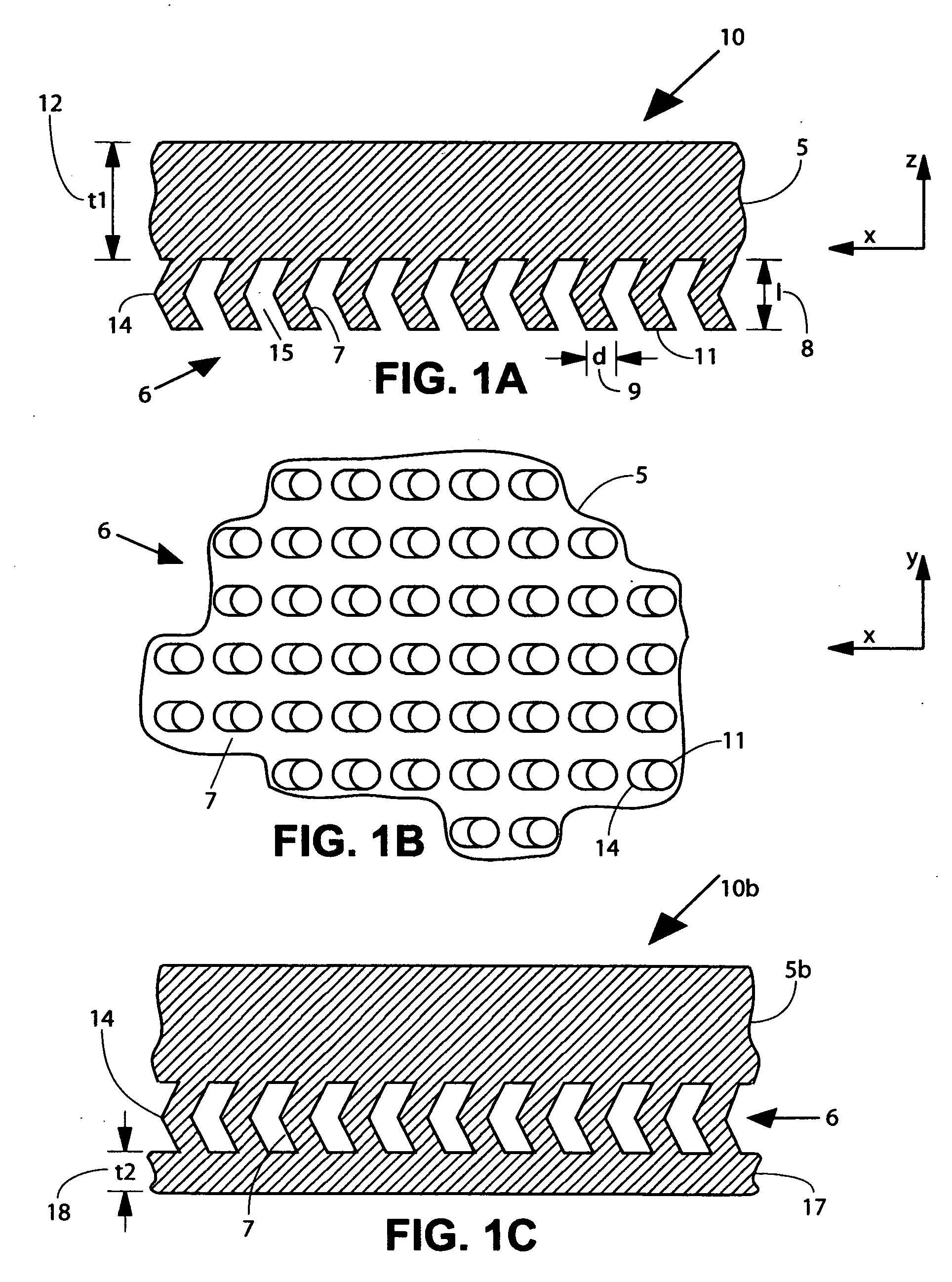

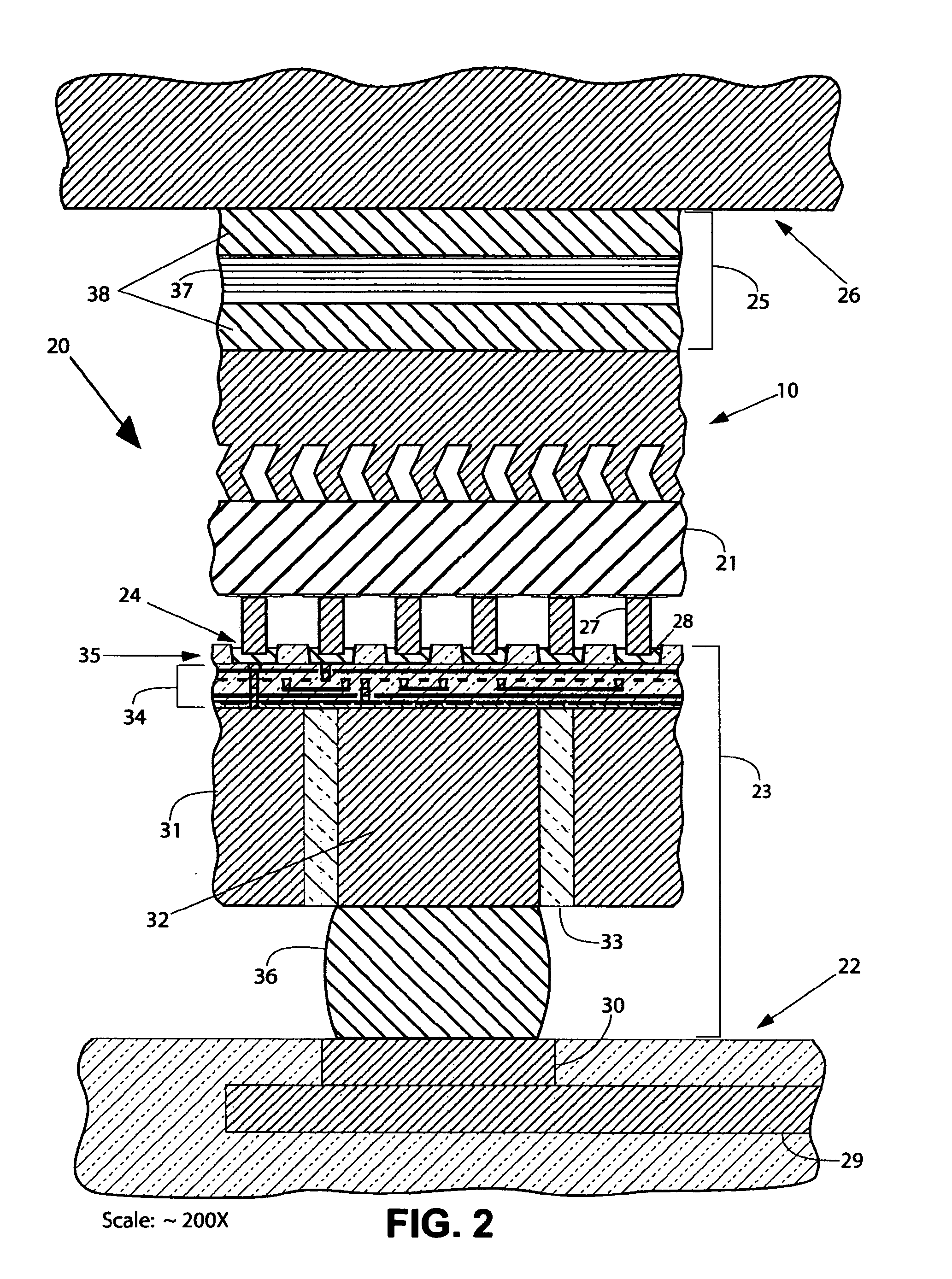

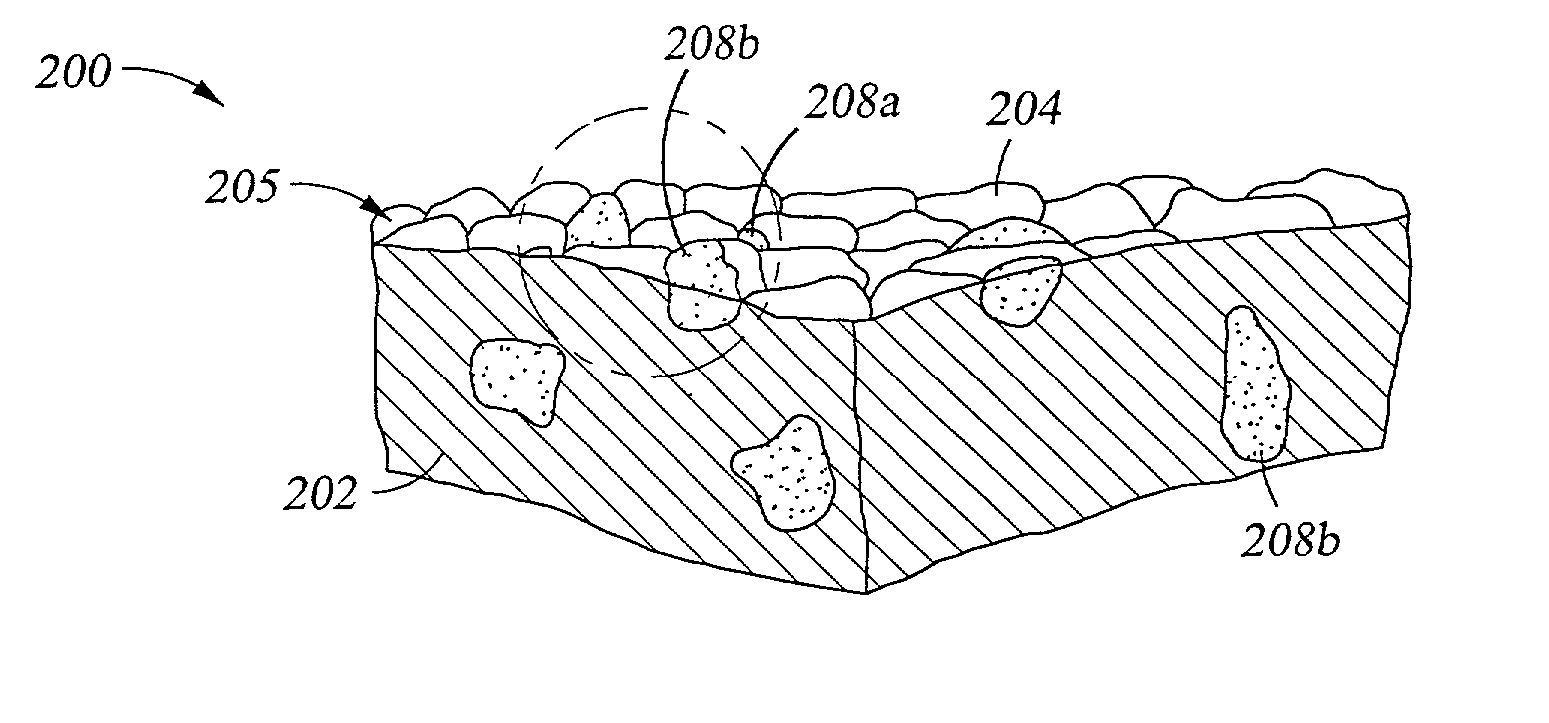

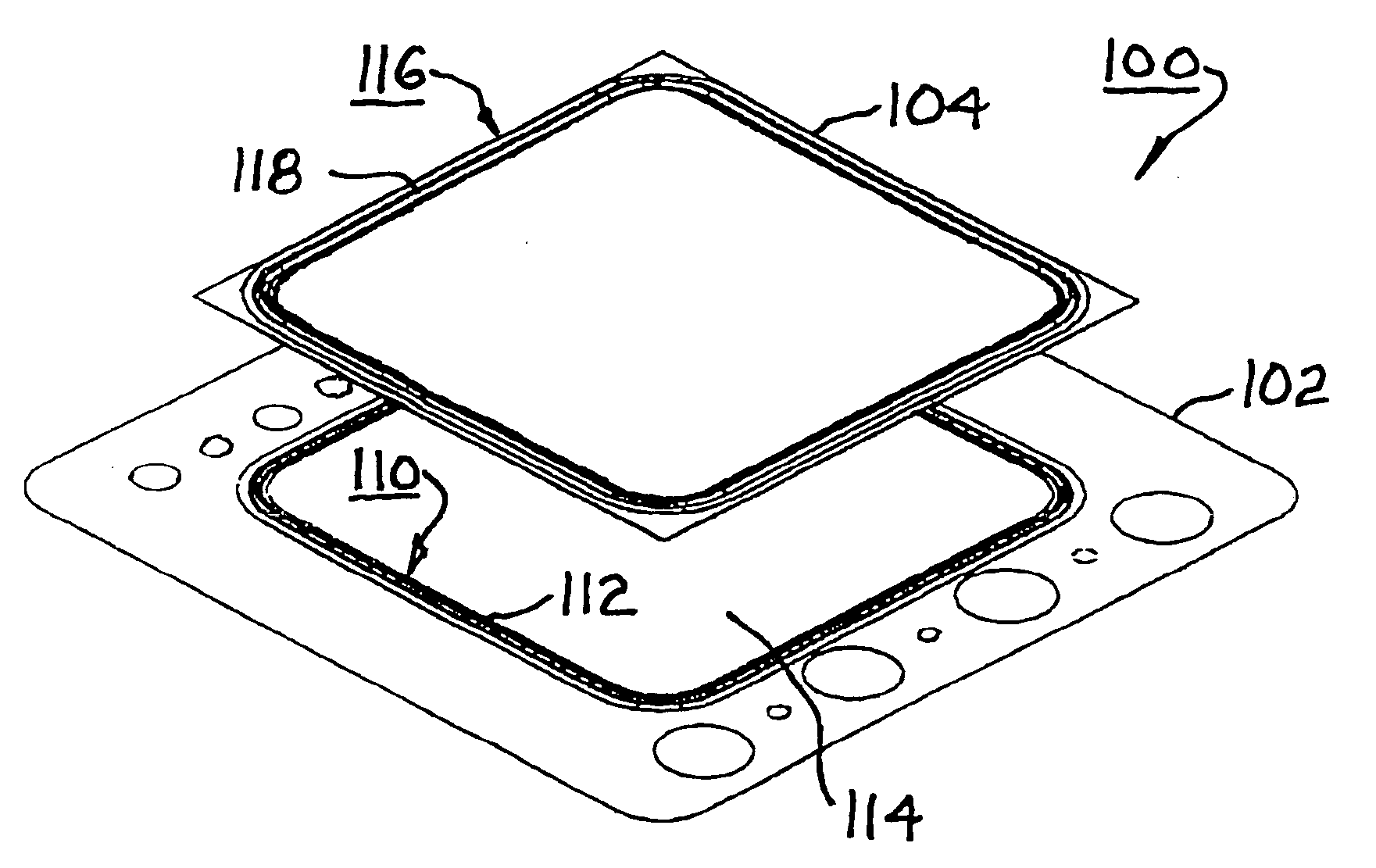

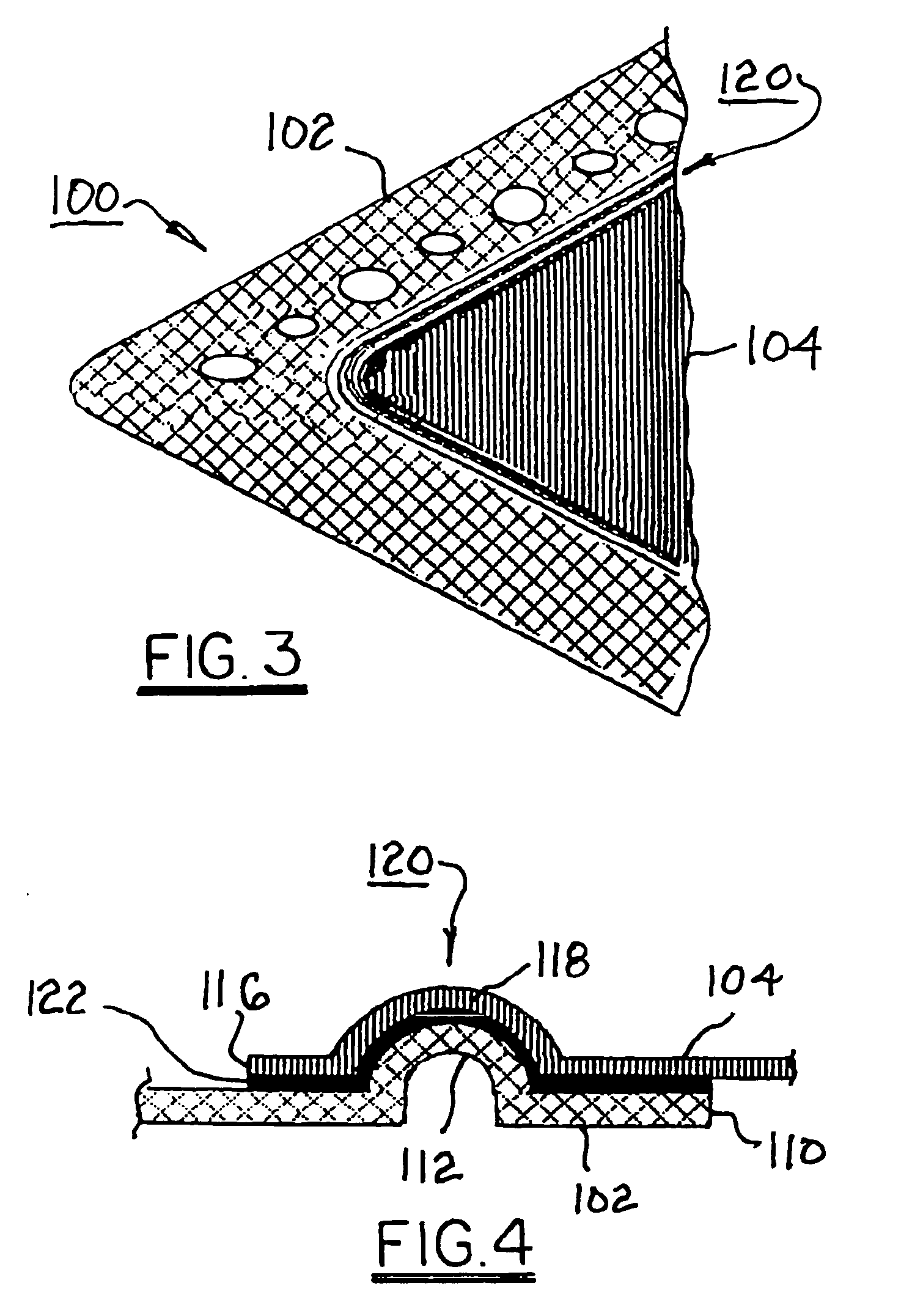

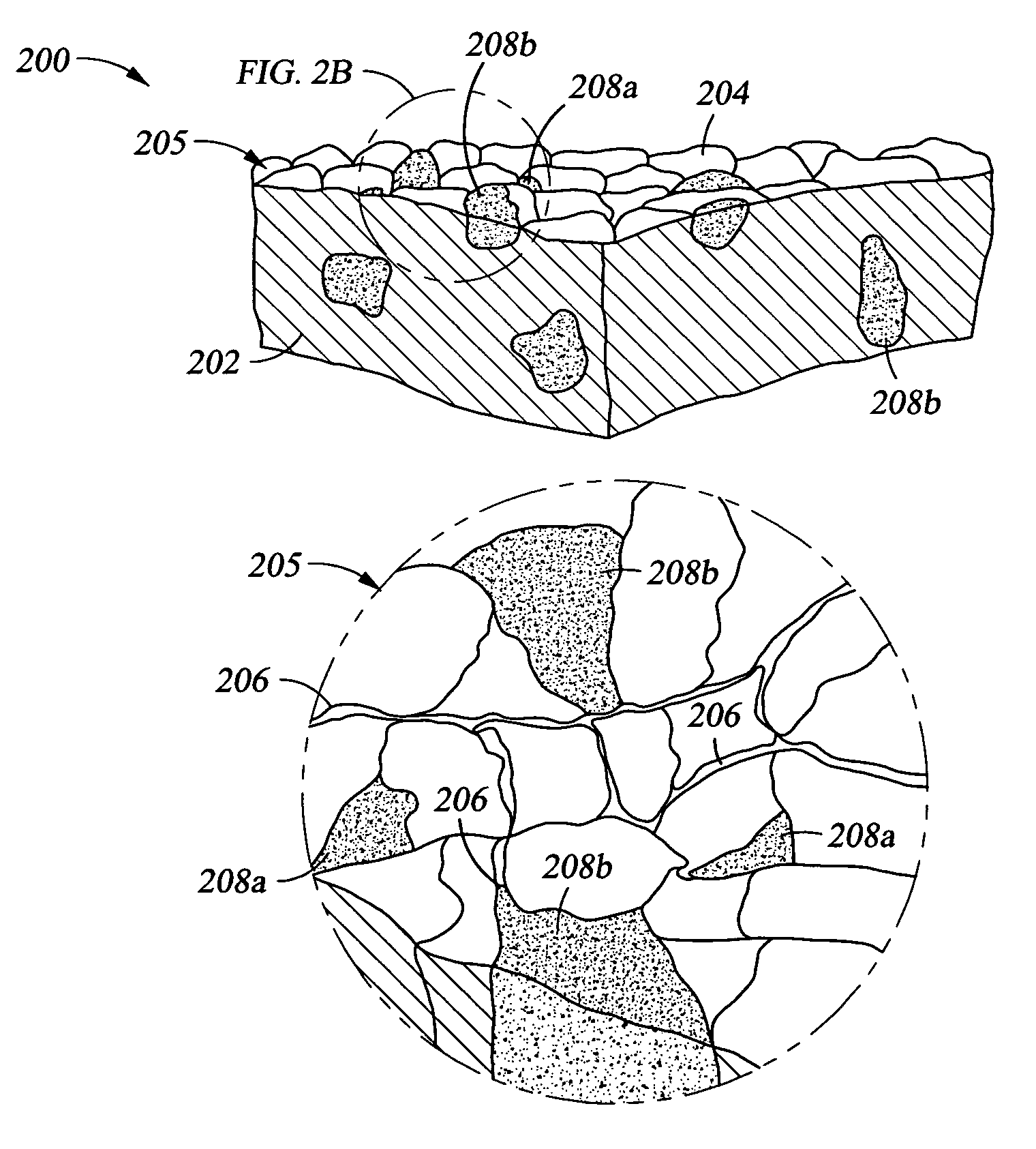

Adaptive interface using flexible fingers

InactiveUS20060077638A1Ease mechanical stressEase thermal stressSemiconductor/solid-state device detailsSolid-state devicesThermal greaseSemiconductor chip

A multi-function interface adaptor comprises a base layer and flexible fingers extending from it. The interface adaptor is interposed between two objects to provide a mechanical and / or thermal interface with stress relief or shock absorption. Using bent fingers operating like springs, shocks and distributed stresses can be relieved in the plane of the adaptor, as well as normal to the plane. A preferred embodiment is an Interface Adaptor that replaces thermal grease between a semiconductor chip and its associated heat sink.

Owner:PETER C SALMON LLC A CALIFORNIA LIMITED LIABILITY

Ladle bottom castable and preparation method thereof

The invention relates to a ladle bottom castable and a preparation method thereof. The technical scheme is as follows: 60-70wt% of titanium-iron slag particles are taken as aggregate, and 25-35wt% of titanium-iron slag fine powder, 1-4wt% of zirconia micro powder and 2-5wt% of titanium oxide micro powder are taken as substrate materials; according to the content of the aggregate and the substrate materials, the substrate materials are uniformly mixed firstly, and then the uniformly mixed substrate materials are added to the aggregate to be uniformly mixed; silica sol accounting for 3-7wt% of the sum of the substrate materials and the aggregate is added, and the mixture is uniformly stirred, subjected to vibratory compaction, cured for 6-12 h under the condition of room temperature and finally subjected to heat preservation for 12-24 h under the condition of 90-110 DEG C to prepare the ladle bottom castable. The ladle bottom castable and the preparation method have the characteristics of low cost and simple process, and the prepared ladle bottom castable has good high-temperature volume stability and good corrosion resistance to slag.

Owner:WUHAN UNIV OF SCI & TECH +1

Heat-stress-resistant fermented feed for laying hen and preparation method thereof

InactiveCN104304819ARelieve heat stressImprove micro-ecological environmentAnimal feeding stuffAdditive ingredientCorn steep liquor

The invention discloses heat-stress-resistant fermented feed for a laying hen. The heat-stress-resistant fermented feed is prepared from the following raw materials: corn, soybean meal, cottonseed meal, apple pomace, chili meal, corn steep liquor sprayed corn husk, wheat bran, bacteria liquid, compound premixed feed and water, wherein the bacteria liquid is prepared from enterococcus aureus, bacillus subtilis, saccharomyces cerevisiae, brown sugar and water. The preparation method of the heat-stress-resistant fermented feed comprises the following steps: crushing the raw material, mixing the dried material, preparing the bacteria liquid, secondarily mixing the wet feed, and conducting anaerobic fermentation. The heat-stress-resistant fermented feed disclosed by the invention has the following benefits: the main essential nutrients in the fermented feed are approximate to that of complete feed for the laying hen and comprise active beneficial bacteria, gamma-aminobutyric acid, organic acid and other active factors; the feed can be added to the daily ration of the laying hen based on the rate of 5-15% to obviously improve the laying rate of the laying hen, the feed-gain ratio, the broken egg rate and the oxidation resistance, synergistically give play to multiple action of the beneficial bacteria on microecologic control to bacterial flora in the gastrointestinal tract, nerve regulation to the central nervous system by the neurotransmitter, and buffering of the organic acid to respiratory alkalosis due to high temperature, and obviously resist against the heat stress due to high temperature in summer for the laying hen.

Owner:ANHUI SCI & TECH UNIV

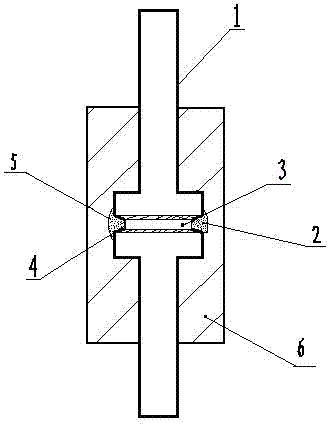

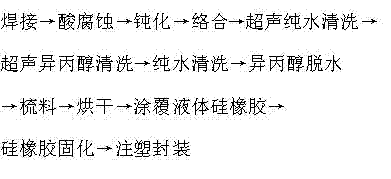

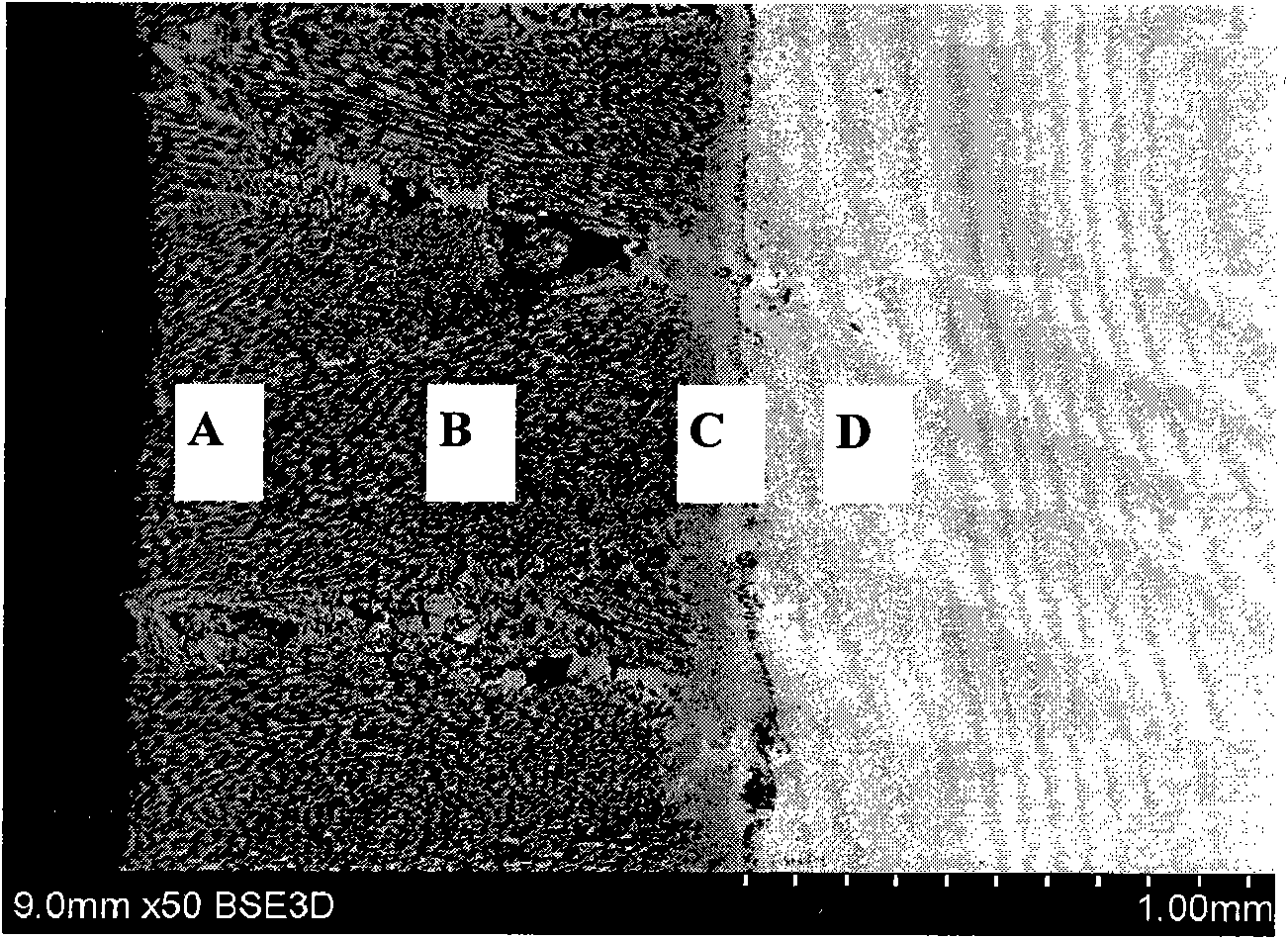

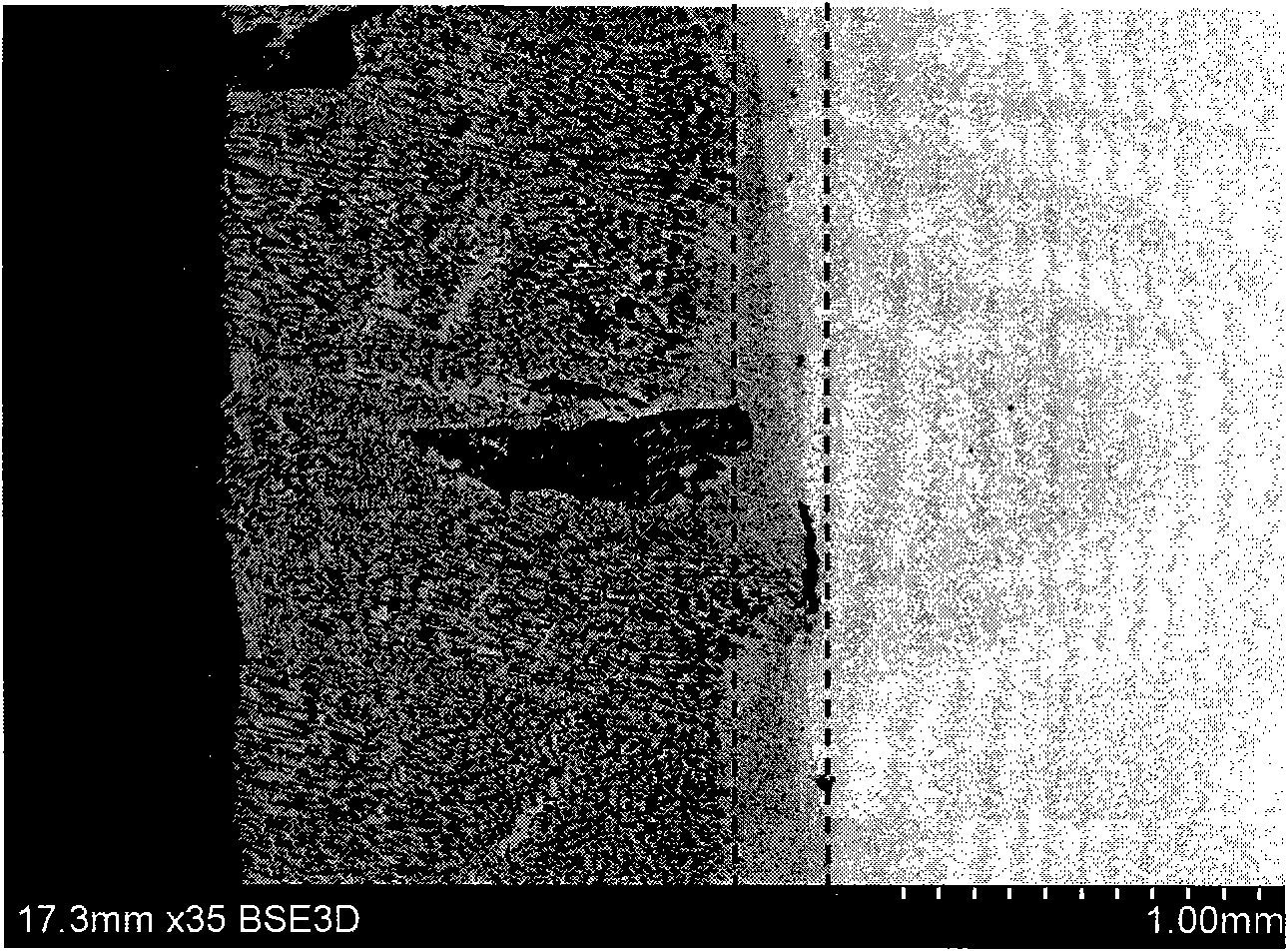

A plastic-encapsulated power diode and its manufacturing process

InactiveCN102263140AAvoid shockRelieve heat stressSemiconductor/solid-state device manufacturingSemiconductor devicesEpoxyManufacturing technology

The invention discloses a plastic-encapsulated power diode and a manufacturing process thereof, and relates to the technical field of semiconductor discrete devices. Its manufacturing process does not adopt the cleaning and dehydration process of organic solvents such as isopropanol and absolute ethanol in the prior art, and the water washing and dehydration process after cleaning with organic solvents is omitted; the chip connected with the wire is put into a heated oven Baking in medium temperature for 4-10 hours, the oven temperature is 200-250°C, and the hydrogen-nitrogen mixed gas or clean air is passed through the oven; put the chip coated with liquid epoxy resin or liquid silicone rubber into the oven at 150±10°C to cure the glue for 10 -60 minutes. Compared with the prior art, the product of the invention has excellent high-temperature characteristics, consistency and reliability.

Owner:SHANDONG YIGUANG ELECTRONICS

Nickel-based high temperature solder and preparation method thereof

ActiveCN101890591AImprove wettabilityRelieve heat stressWelding/cutting media/materialsWelding/soldering/cutting articlesSolderingMechanical properties of carbon nanotubes

The invention discloses a nickel-based high temperature solder and a preparation method thereof, relates to a nickel-based solder and a preparation method thereof and solves the problem of poor mechanical property of a soldered joint of a C / SiC composite material and a nickel-based ultrahigh-temperature alloy caused by violent reaction between the ceramic matrixes of the conventional nickel-based solder and the C / SiC composite material. The solder is prepared from Si powder, TiH2 powder and Ni powder. The preparation method comprises the following steps of: adding acetone into mixed powder of the Si powder, the TiH2 powder and the Ni powder to obtain suspension; and carrying out ultrasonic processing on the suspension, drying the processed suspension and grinding the dried suspension to obtain the solder. Based on binary eutectic compositions of the Ni powder and the Si powder, the solder has higher Si content and has good wettability and low cost for soldering of the C / SiC composite material and the nickel-based ultrahigh-temperature alloy. The soldered joint has good room temperature strength of 80 to 102MPa and good high temperature mechanical property of 800 to 1,000 DEG C. The nickel-based high temperature solder is applicable for brazing connection of graphite or a C / C composite material and the nickel-based ultrahigh-temperature alloy.

Owner:HARBIN INST OF TECH

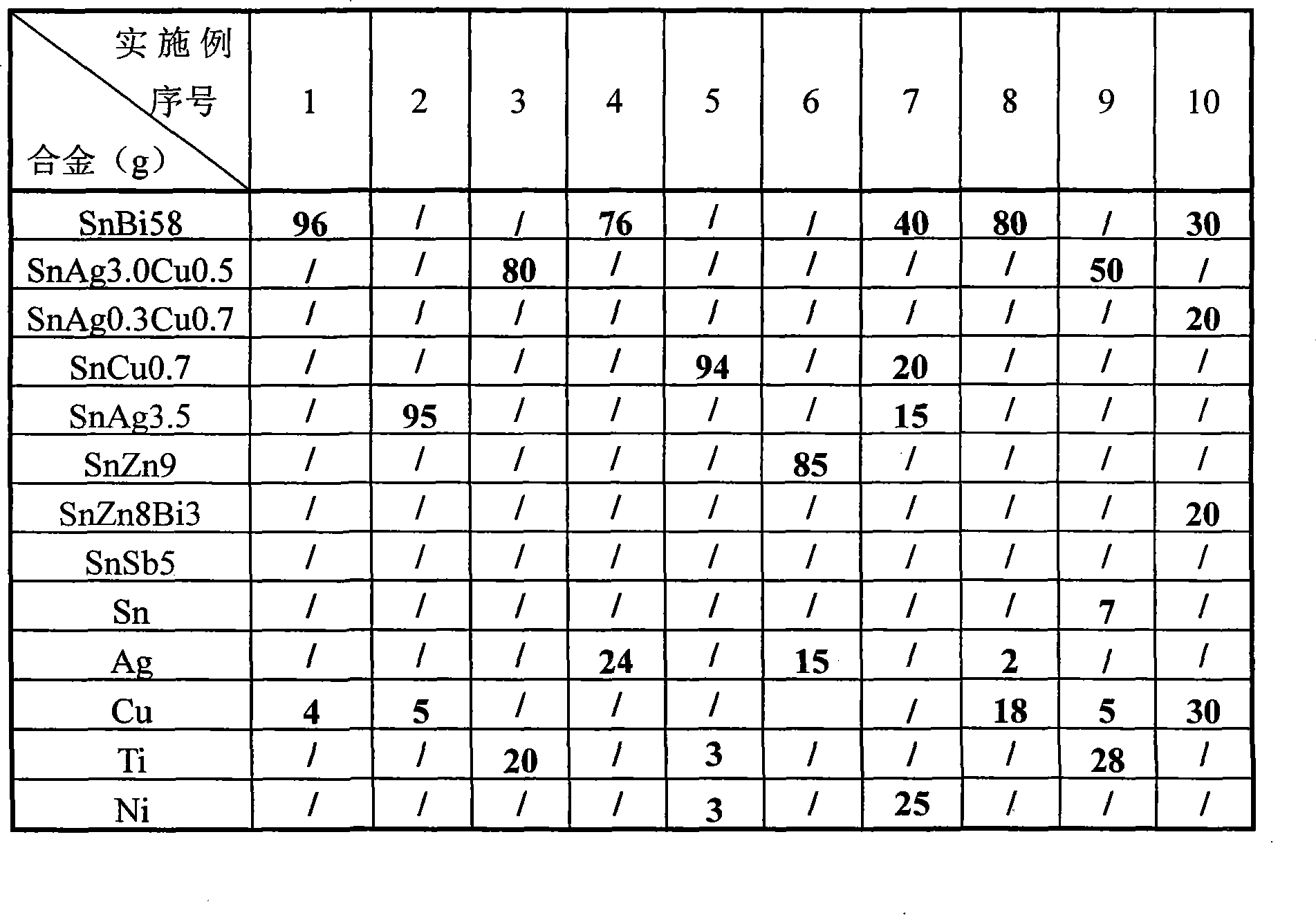

Low temperature leadless welding material for electronic component

InactiveCN101362261AAvoid damageImprove reliabilityWelding/cutting media/materialsSoldering mediaMetallic materialsTemperature resistance

The invention relates to an electronic packaging braze welding material and a technology thereof, in particular to a low temperature lead-free welding material used for electronic elements, which belongs to the technical field of metallic material engineering. The invention can replace high temperature welding, and ensure the welding spot to have good electrical conductivity, high temperature resistance and impact resistance. For the welding material, kaiserzinn welding powder or pure tin powder and high melting point metal powder Ag, Cu, Ti and Ni are mixed according to certain proportion, and solder paste is prepared by adding appropriate flux; or kaiserzinn welding powder and metal powder Ag, Cu, Ti and Ni are mixed according to certain proportion to prepare solder paste, so as to weld high melting point weld layer through lead-free solder paste at low temperature.

Owner:BEIJING COMPO ADVANCED TECH +1

Reserve sow mixed feed capable of increasing production performance of sow and preparation method

ActiveCN103583927AImprove responsivenessIncrease hypothalamus-pituitary-ovary luteinizing functionFood processingAnimal feeding stuffHypothalamusPasqueflowers

The invention discloses a reserve sow mixed feed capable of increasing production performance of sow and a preparation method. The feed is prepared according to physiological characteristics of reserve sow, a plurality of raw materials are employed for combining, the nutrition enables complementation, and the feed is a daily food designed according to balance of amino acid, balance of calcium phosphate and balance of electrolyte. According to the invention, natural traditional Chinese medicines such as root of large-flowered skullcap and semen cuscutae are added for increasing the reactivity of pituitary gland to LRH and reactivity of ovary to LH, and increasing hypothalamus-pituitary-ovary luteinizing function to promote growth and maturity of the reserve sow reproduction system, so that body maturity and sexual maturity of sow enable synchronization, and sow can have a plurality of piglets with strong body. No antibiotic is added in the feed, natural Chinese herbal medicine additives such as pasque flower, coptis, phellodendron and ash bark enable health care to alimentary canal, reserve sow intestinal tract health is improved, immunity is increased, sow physique is enhanced, production performance of sow in a production period is increased, hereditary capacity of reserve sow can be performed with maximum limit, thereby, sow can have more and stronger piglets.

Owner:HUAIAN ZHENGCHANG FEED

Ceramic matrix composite material applied to high-speed motor car brake disc and preparation method thereof

The invention discloses a ceramic matrix composite material applied to a high-speed motor car brake disc and a preparation method of the ceramic matrix composite material. The ceramic matrix composite material consists of a gradient SiC matrix and a C / C framework, and is characterized in that the gradient SiC matrix consists of silicon carbide and carbon; the percentage of silicon carbide to carbon in the matrix is increased to be 100% from 0%; the C / C framework is prepared by depositing a layer of carbon matrix on a carbon fiber woven body, and using chloromethyl silane, dichloromethyl silane and trichloromethyl silane as precursors so as to obtain the SiC and C matrixes of different ratios by using a chemical vapor deposition method. The ceramic matrix composite material well combines the advantages of the C / C composite material and the C / SiC composite material, thermal stress caused by thermal shock can be effectively alleviated, the thermal shock resistance is obviously enhanced, and the ceramic matrix composite material has great application prospect in the high-speed motor car brake disc.

Owner:TAICANG PAIOU TECH CONSULTING SERVICE

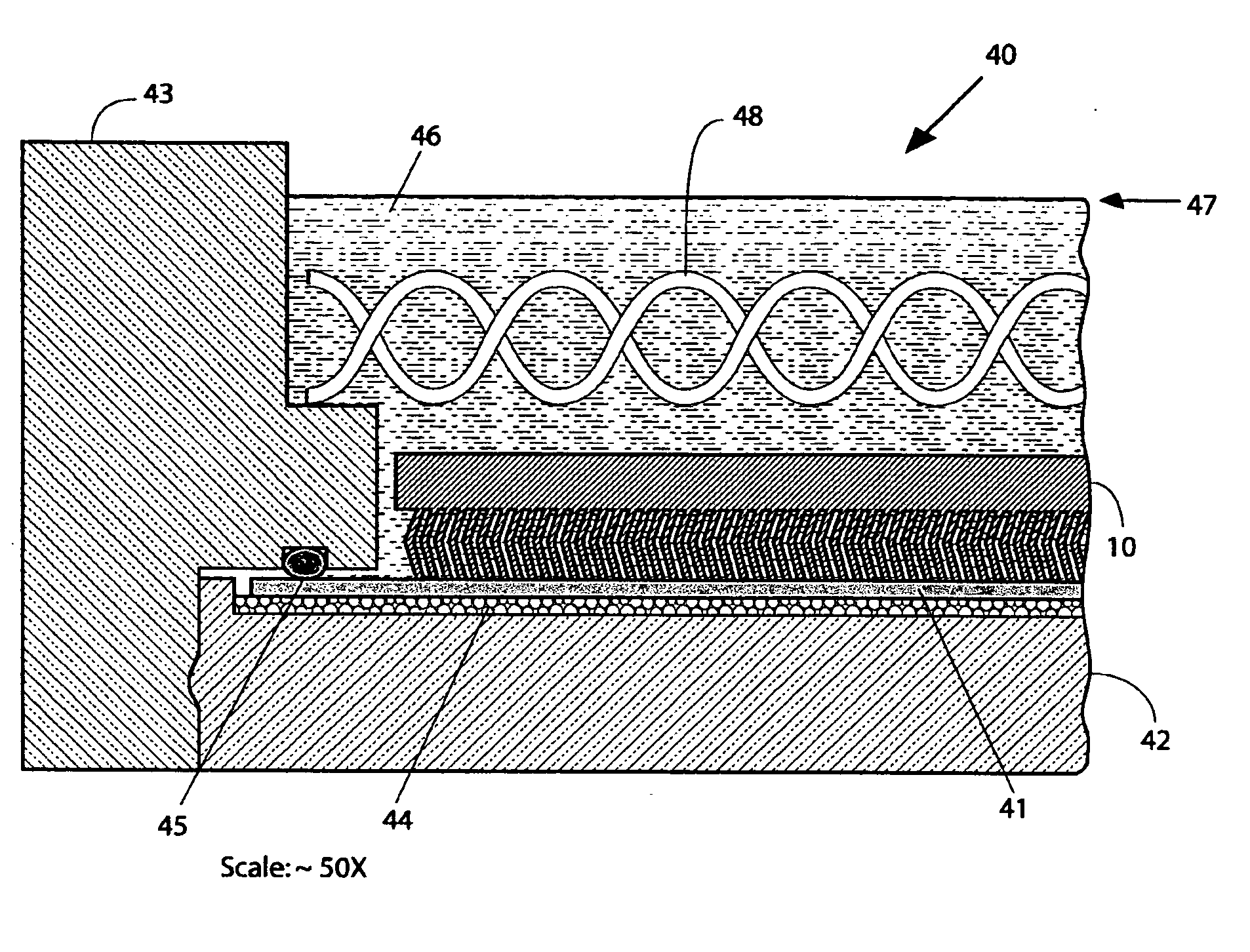

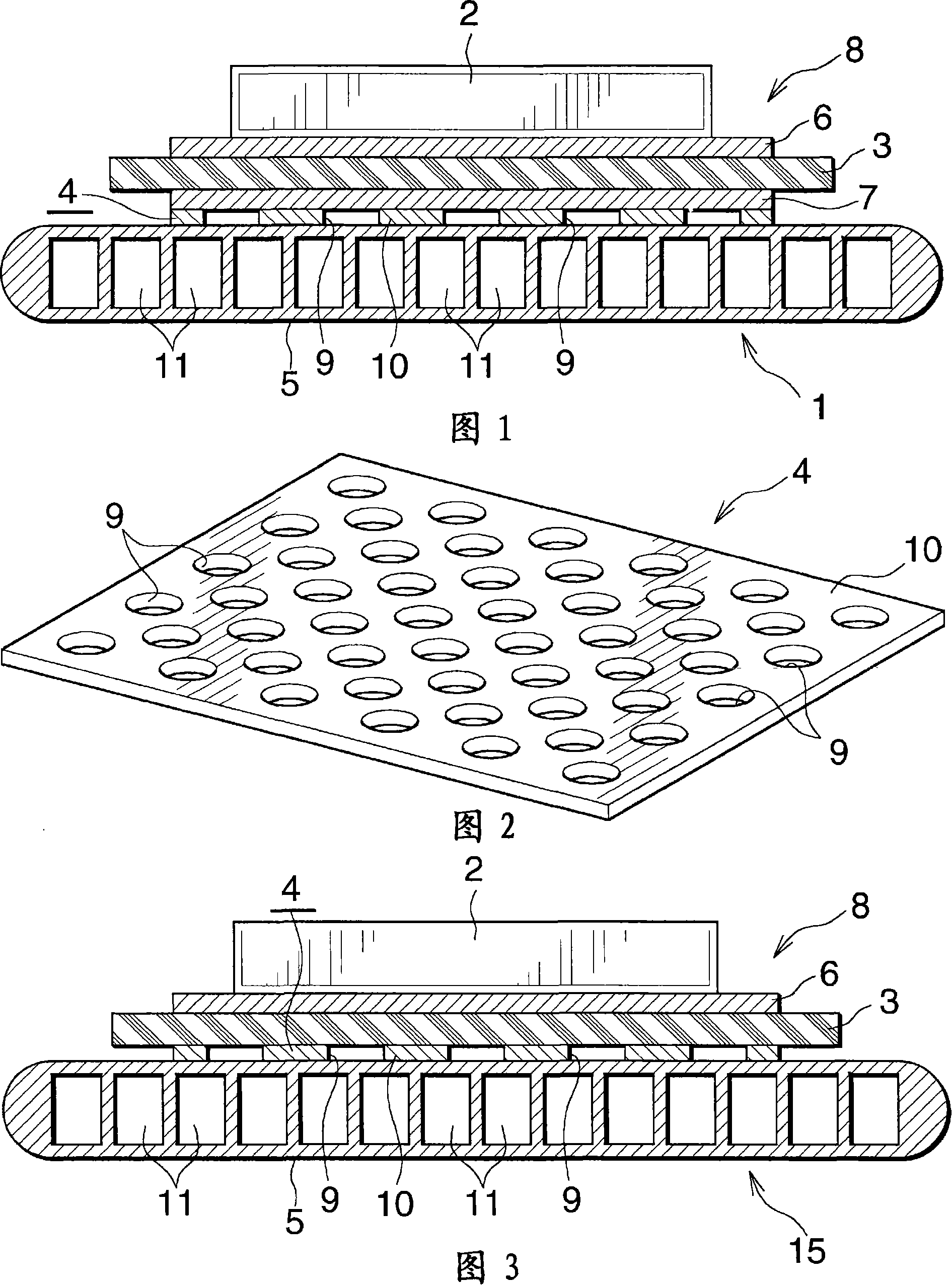

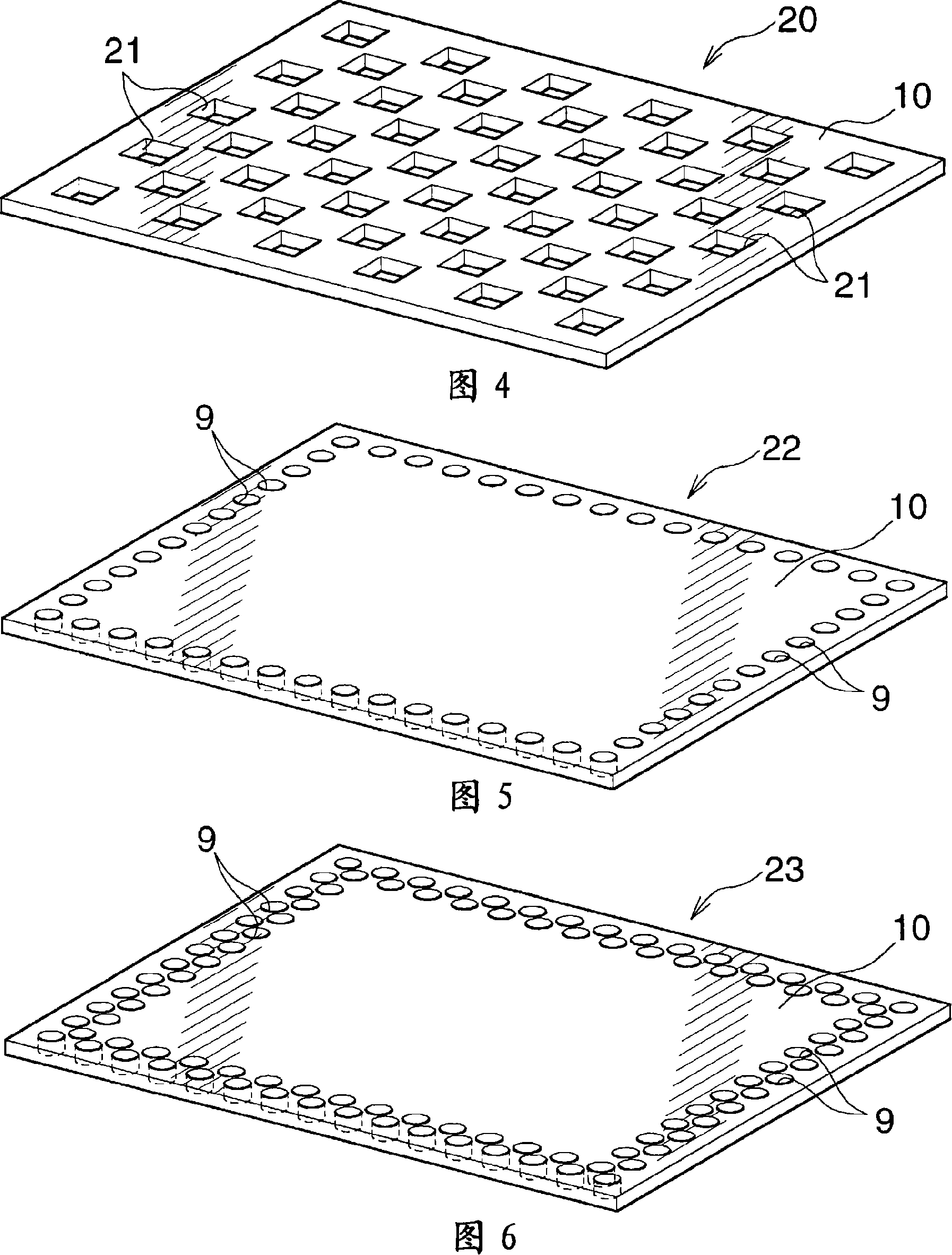

Heat sink device

InactiveCN101156241AImprove thermal conductivityLow costFinal product manufactureSemiconductor/solid-state device detailsOptoelectronicsMetal

A heat sink device (1) is provided with an insulating substrate (3) whose one plane is permitted to be a heat generating body mounting plane, and a heat sink (5) fixed on the other plane of the insulating substrate (3). A metal layer (7) is formed on the plane of the insulating substrate (3), opposite to the heat generating body mounting plane. A stress relaxing member (4), which is composed of an aluminum plate (10) provided with a plurality of through holes (9) and has the through holes (9) as stress absorbing spaces, is arranged between the metal layer (7) of the insulating substrate (3) and the heat sink (5). The stress relaxing member (4) is soldered to the metal layer (7) of the insulating substrate (3) and the heat sink (5). The heat sink device (1) reduces material cost and improves heat sink performance.

Owner:RESONAC HOLDINGS CORPORATION

Antiwear nickel phosphor functionalized gradient plate preparation method

The invention discloses a preparation method for wearable nickel phosphate function gradient plating coat, which comprises: with design idea for gradient material, using single-bath electroplating method, preparing the coat with phosphate content gradient varying by boosting current density gradually and controlling deposition time. This product has proper phosphate content gradient and thermal expansion coefficient to release the thermal stress problem and high bond strength and abrasion resistance. This method can replace current used technique.

Owner:LANZHOU INST OF CHEM PHYSICS CHINESE ACAD OF SCI

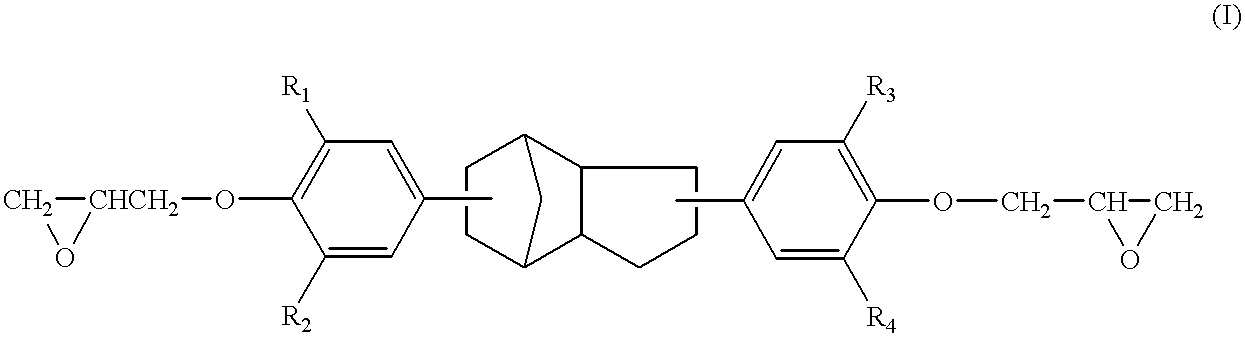

Adhesive sheet for semiconductor connecting substrate, adhesive-backed tape for TAB, adhesive-backed tape for wire bonding connection, semiconductor connecting substrate, and semiconductor device

InactiveUS20020025431A1Moderate modulusModerate coefficientSemiconductor/solid-state device detailsSolid-state devicesEpoxyTectorial membrane

An adhesive sheet for a semiconductor connecting substrate consisting of a laminate having an adhesive layer on a substrate, wherein said adhesive layer contains a thermoplastic resin (A) and an epoxy resin (B) and said epoxy resin (B) contains at least one epoxy resin (B) selected from (I) dicyclopentadiene skeleton-containing epoxy resins, (II) terpene skeleton-containing epoxy resins, and (III) biphenyl skeleton-containing epoxy resins, as an essential component; an adhesive-backed tape for TAB consisting of a laminate having an adhesive layer and a protective film layer on a flexible organic insulating film. The adhesive sheet for a semiconductor connecting substrate, the adhesive-backed tape for TAB and the adhesive-backed tape for wire bonding connection of the present invention are excellent in adhesive strength, insulatability, dimensional accuracy, etc., and can improve the reliability of a semiconductor integrated circuit connecting substrate and a semiconductor device respectively for high density packaging.

Owner:TORAY IND INC

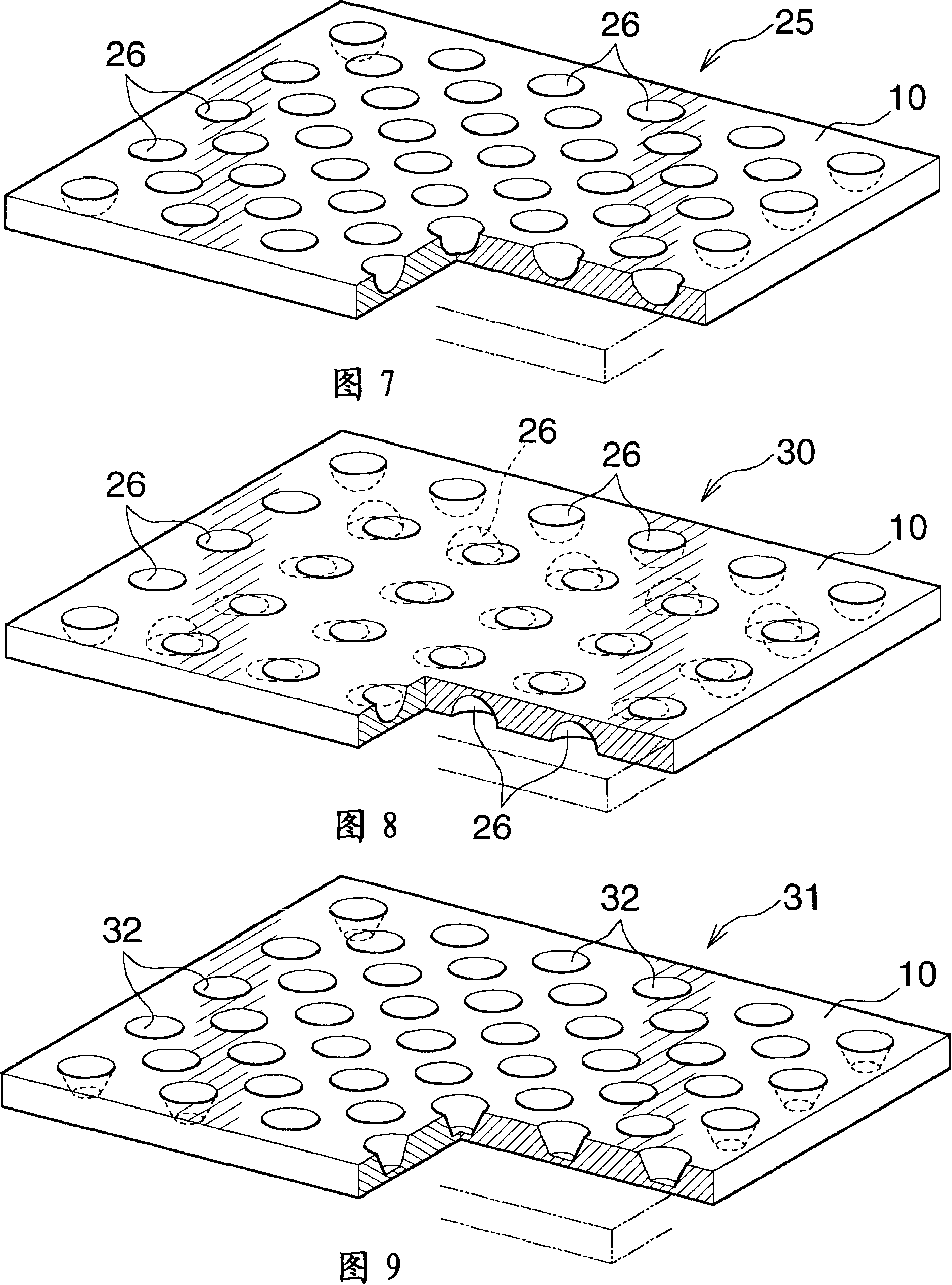

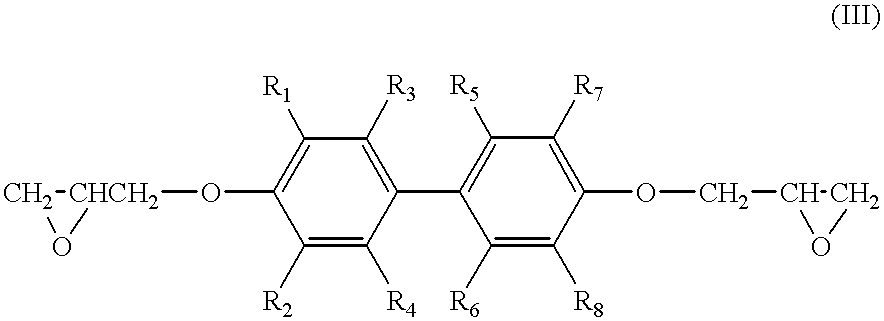

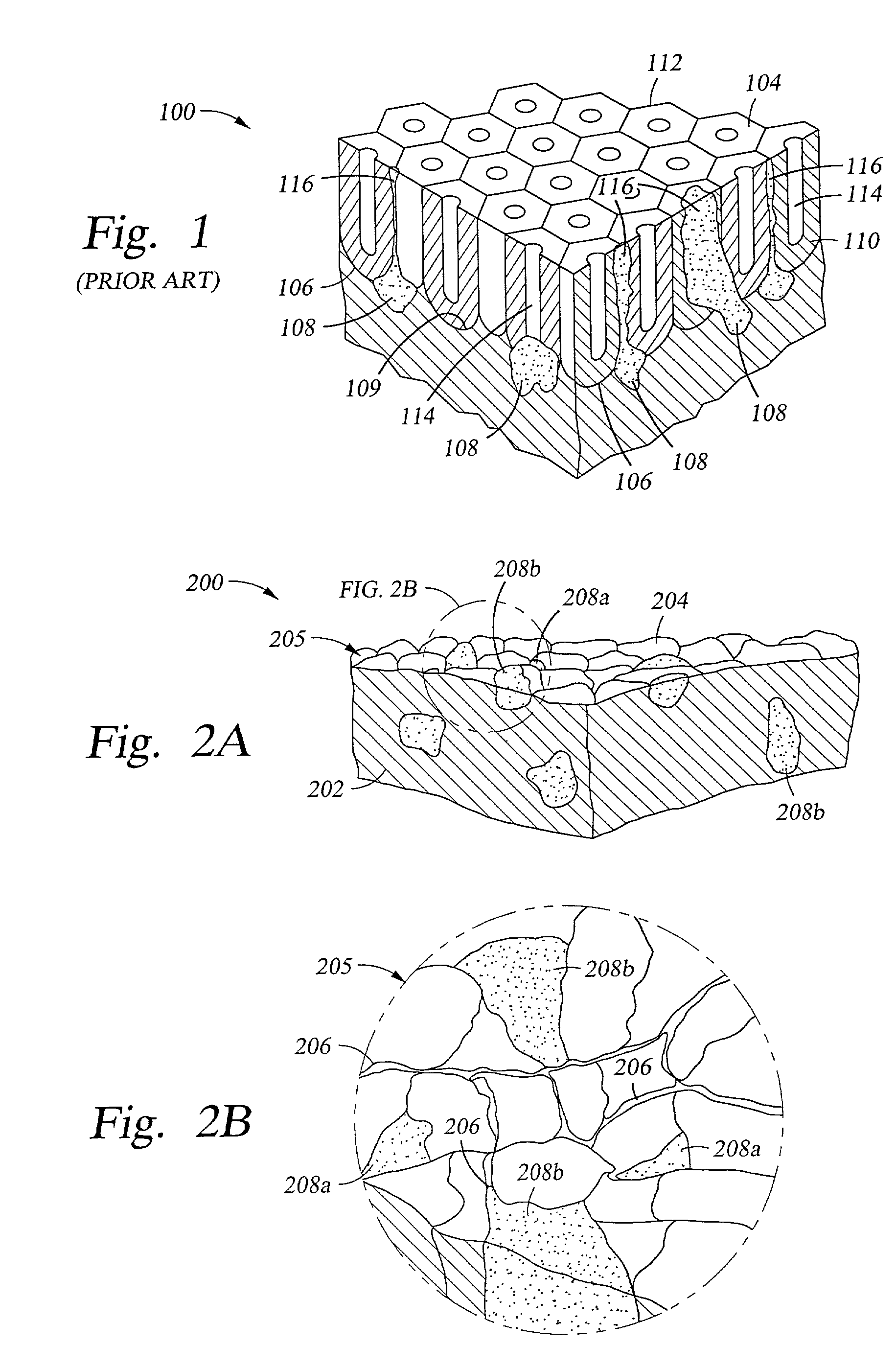

Honeycomb structure

InactiveCN1883908AGood dispersionRelieve heat stressGas treatmentPhysical/chemical process catalystsFiberInorganic particle

A honeycomb structure body where thermal stress caused by a local temperature change in the body can be relaxed, where a crack does not occur, that has high strength and durability, that is resistant to thermal shock and vibration, and where catalyst components can be highly dispersed. The honeycomb structure body is constructed such that column-like honeycomb units are bound together, with seal material layers in between, and the honeycomb units each have a large number of cells arranged side by side, with cell walls in between, so as to be oriented in the longitudinal direction of the units. The honeycomb units contain inorganic particles, and inorganic fibers and / or whiskers, the area of a cross-section of each honeycomb unit orthogonal to the longitudinal direction of each unit is in the range of 5 - 50 cm2, and the thermal expansion coefficient alphaL of the seal material layers and the thermal expansion coefficient alphaF of the honeycomb units satisfy the relationship of 0.01 <= |alphaL-alphaF| / alphaF<= 1.0.

Owner:IBIDEN CO LTD

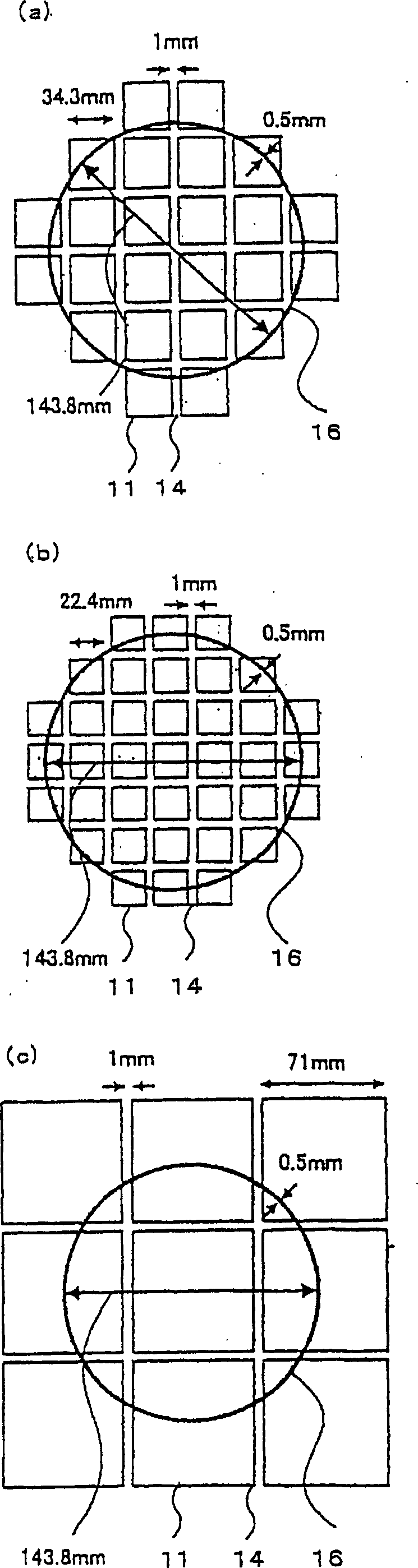

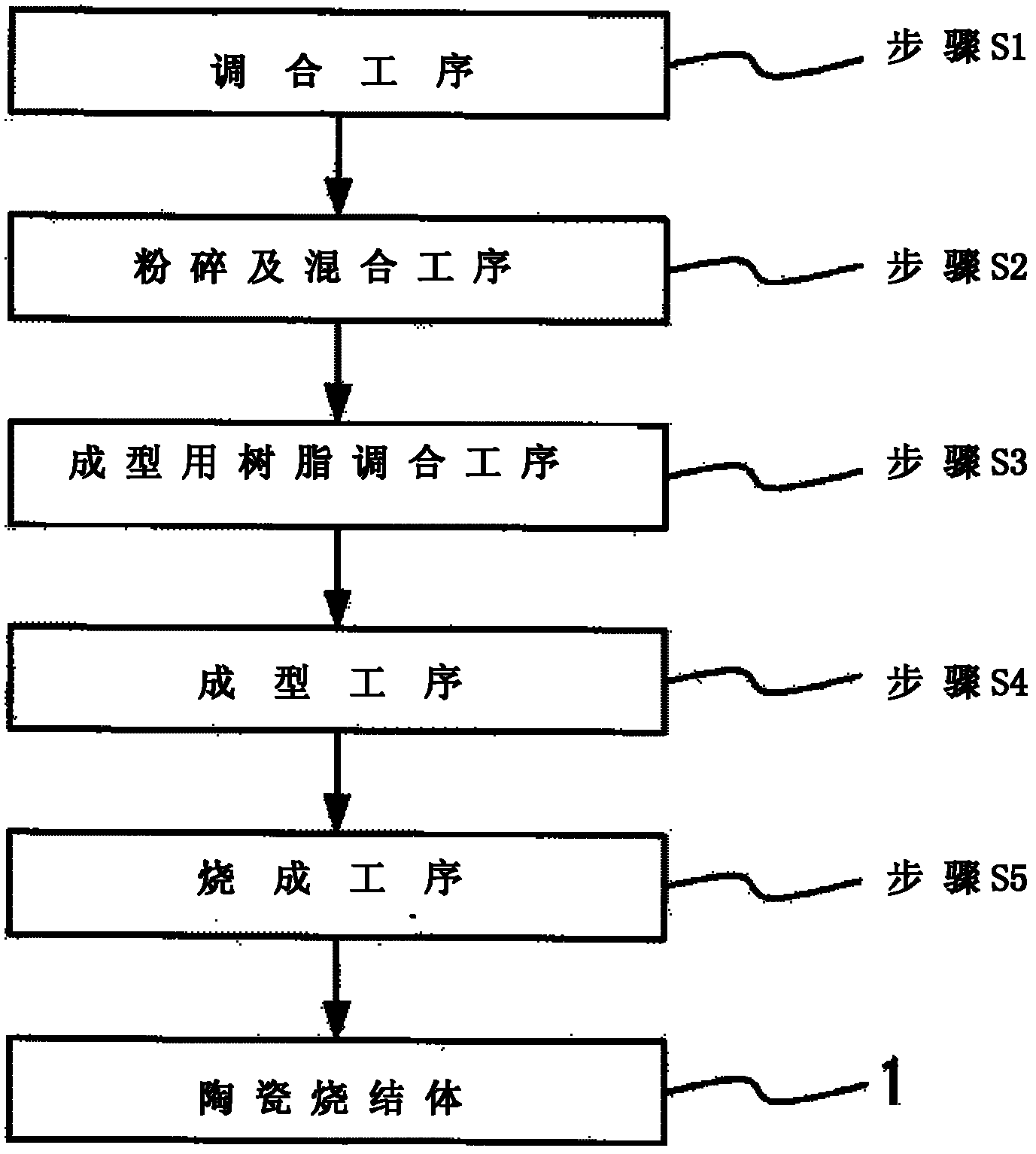

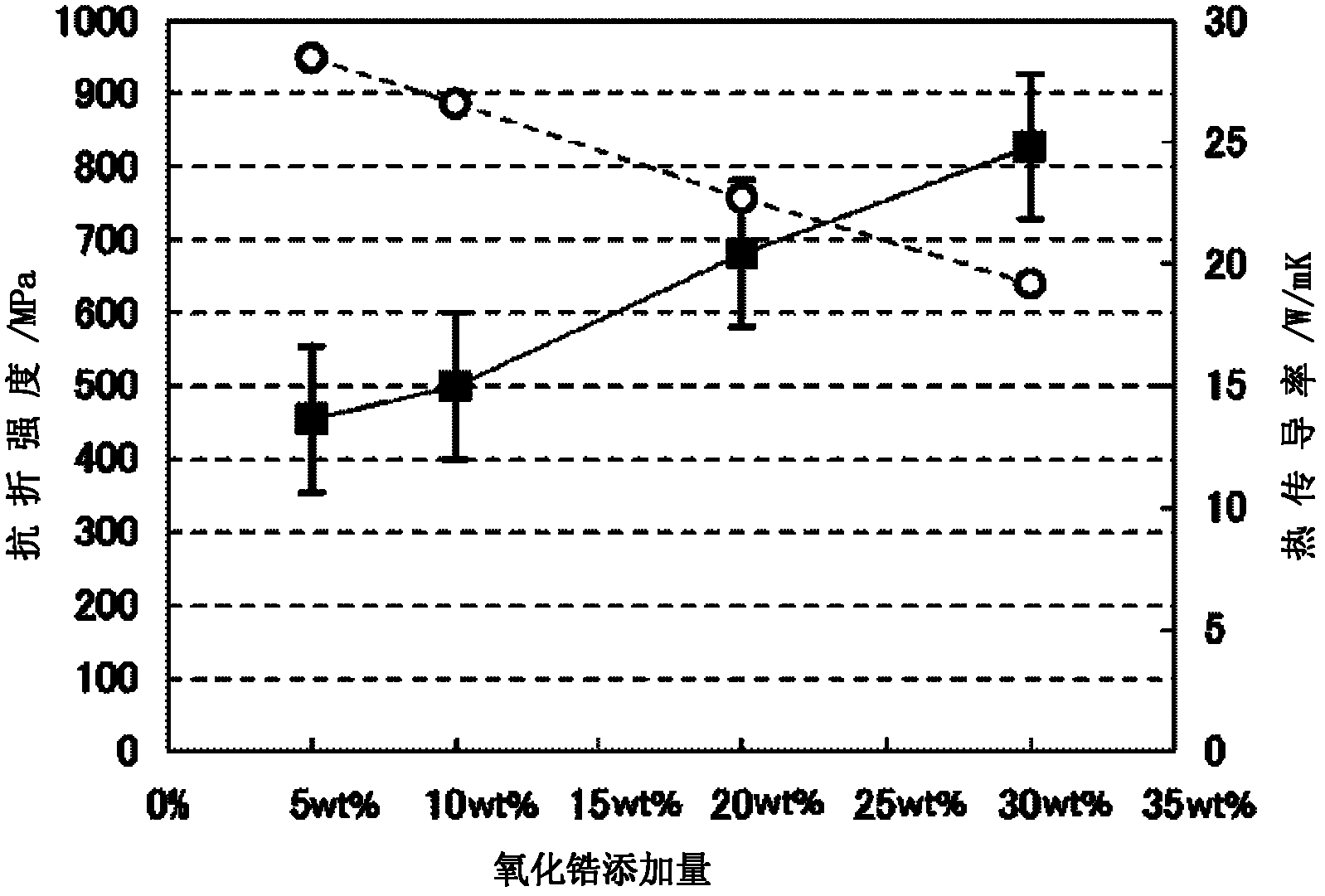

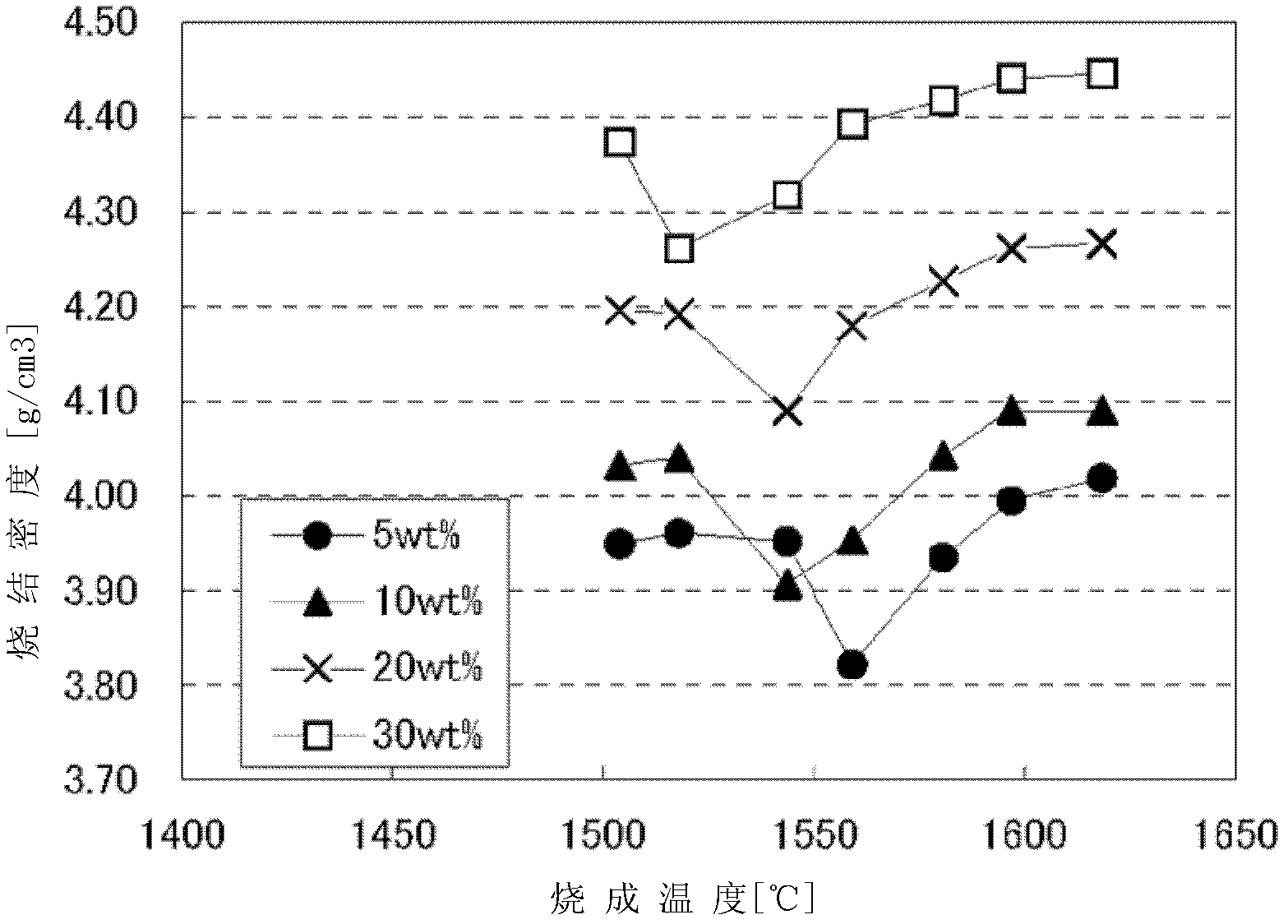

Sintered ceramic and substrate comprising same for semiconductor device

InactiveCN102395540ARelieve heat stressSemiconductor/solid-state device detailsSolid-state devicesCopperElectronic component

Owner:SUMITOMO METAL SMI ELECTRONICS DEVICES

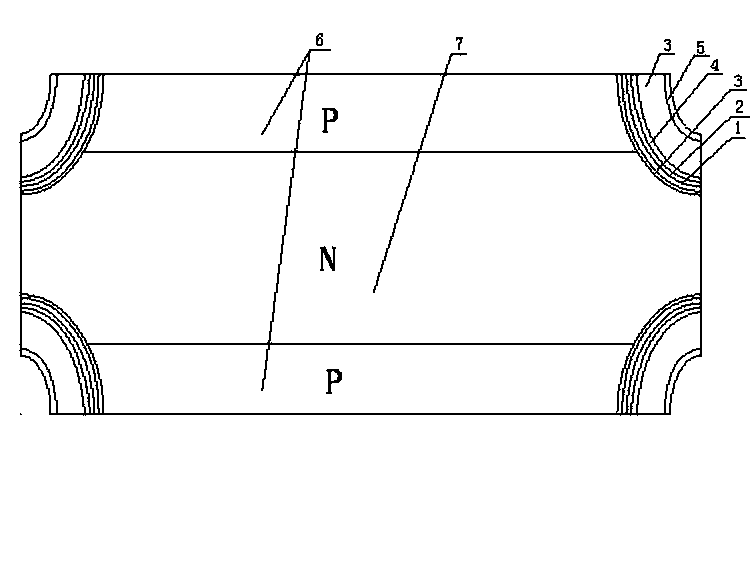

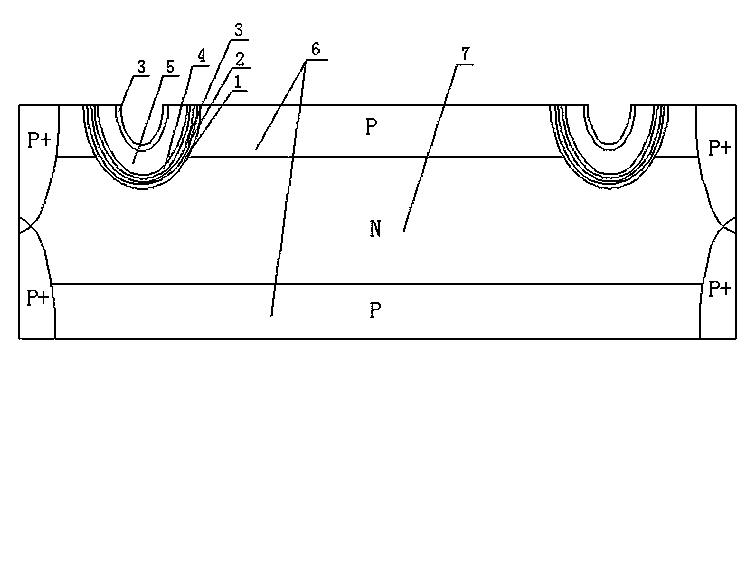

Multilayer composite membrane passivation structure of table top high-power semiconductor device and manufacturing technology of multilayer composite membrane passivation structure of table top high-power semiconductor device

ActiveCN103730430ARepair damageImprove breakdown voltagePolycrystalline material growthSemiconductor/solid-state device detailsManufacturing technologyPolycrystalline silicon

The invention discloses a multilayer composite membrane passivation structure of a table top high-power semiconductor device. The multilayer composite membrane passivation structure comprises P-type boron junction areas and an N-type phosphorus junction area, the upper end and the lower end of the N-type phosphorus junction area are provided with the P-type phosphorus areas respectively, and an alpha-polycrystalline silicon layer, a semi-insulating polycrystalline silicon thin membrane, a low-temperature heat oxidation layer, a high-temperature Si3N4 thin membrane, a negative charge glass passivation layer and a low-temperature heat oxidation layer are sequentially arranged on the surface of a PN junction of a table top of the table top high-power semiconductor device from inside to outside. A manufacturing technology of the multilayer composite membrane passivation structure of the table top high-power semiconductor device includes the following steps: a, depositing the alpha-polycrystalline silicon, b, depositing semi-insulating polycrystalline silicon, c, depositing the low-temperature heat oxidation layer, d, depositing Si3N4, e, conducting passivation on glass, and f, depositing the low-temperature heat oxidation layer in the outmost layer. The multilayer composite membrane passivation structure and the manufacturing technology have the advantages that the alpha-polycrystalline silicon layer is deposited, so that crystal lattice adaptation can be achieved, damage to crystal lattices of a silicon wafer in a groove can be repaired, leaked currents in the surfaces of junctions are reduced, and the stability and the reliability of the device at the high temperature are improved.

Owner:江苏吉莱微电子股份有限公司

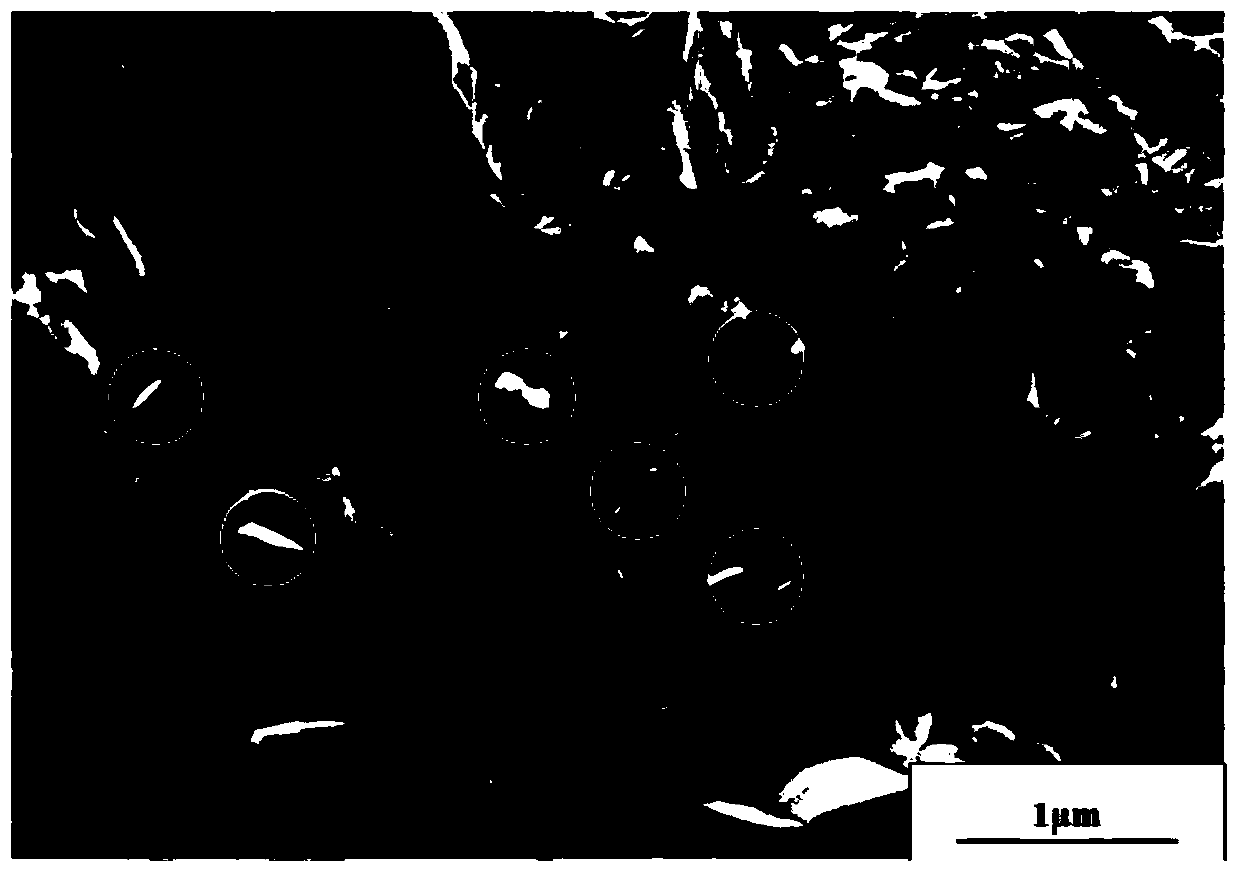

Halogen-resistant, anodized aluminum for use in semiconductor processing apparatus

InactiveUS7033447B2Excellent abrasion resistanceHigh densityAnodisationSemiconductor/solid-state device manufacturingParticulatesHalogen

We have discovered that the formation of particulate inclusions at the surface of an aluminum alloy article, which inclusions interfere with a smooth transition from the alloy surface to an overlying aluminum oxide protective film, can be controlled by maintaining the content of mobile and nonmobile impurities within a specific range and controlling the particulate size and distribution of the mobile and nonmobile impurities and compounds thereof; by heat-treating the aluminum alloy at a temperature less than about 330° C.; and by creating the aluminum oxide protective film by employing a particular electrolytic process. When these factors are taken into consideration, an improved aluminum oxide protective film is obtained.

Owner:APPLIED MATERIALS INC

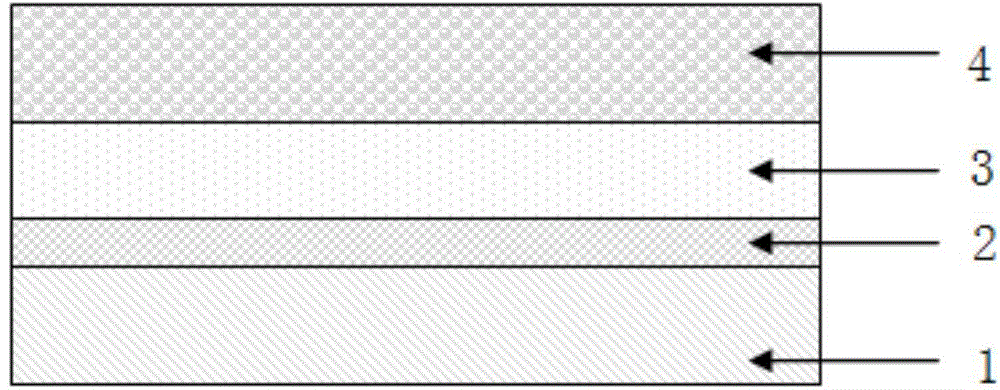

Method for restoring cold roll through preparing gradient coating via laser cladding

ActiveCN104404510ADense tissueNo crack defectMetallic material coating processesSand blastingOptoelectronics

The invention relates to a method for restoring a cold roll through preparing a gradient coating via laser cladding. The method comprises the following steps: 1) carrying out polishing, cleaning and sand blasting on the to-be-restored area of the cold roll; 2) paving a brazing flux on the surface of the to-be-restored area of the cold roll, paving brazing filler metal powder on the brazing flux and preparing a first transition layer through a high-temperature heating manner; 3) pacing transition material powder on the surface of the first transition layer and preparing a second transition layer through laser cladding; 4) paving alloy powder on the surface of the second transition layer and preparing a third gradient layer through laser cladding. The method starts with the structural design of a cladding layer, and the cladding layer is designed into an alloy gradient layer with a multilayer structure, so that the problem that the cold roll is easy to crack, relatively low in bonding strength and easy to fall off after the restoration is solved.

Owner:九江中科神光科技有限公司

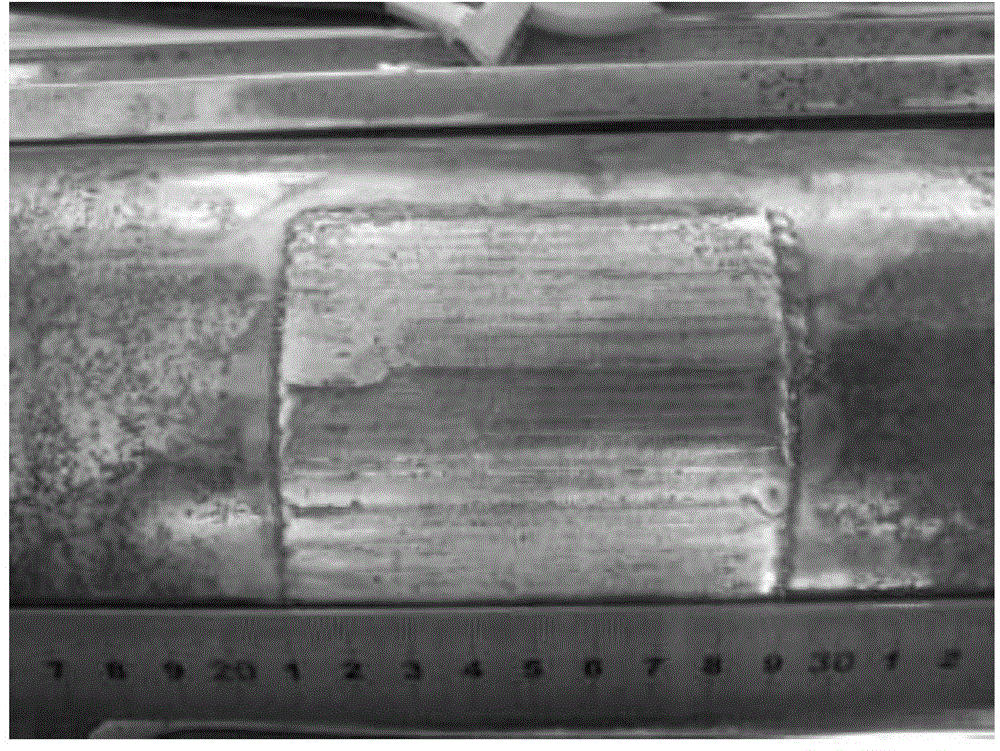

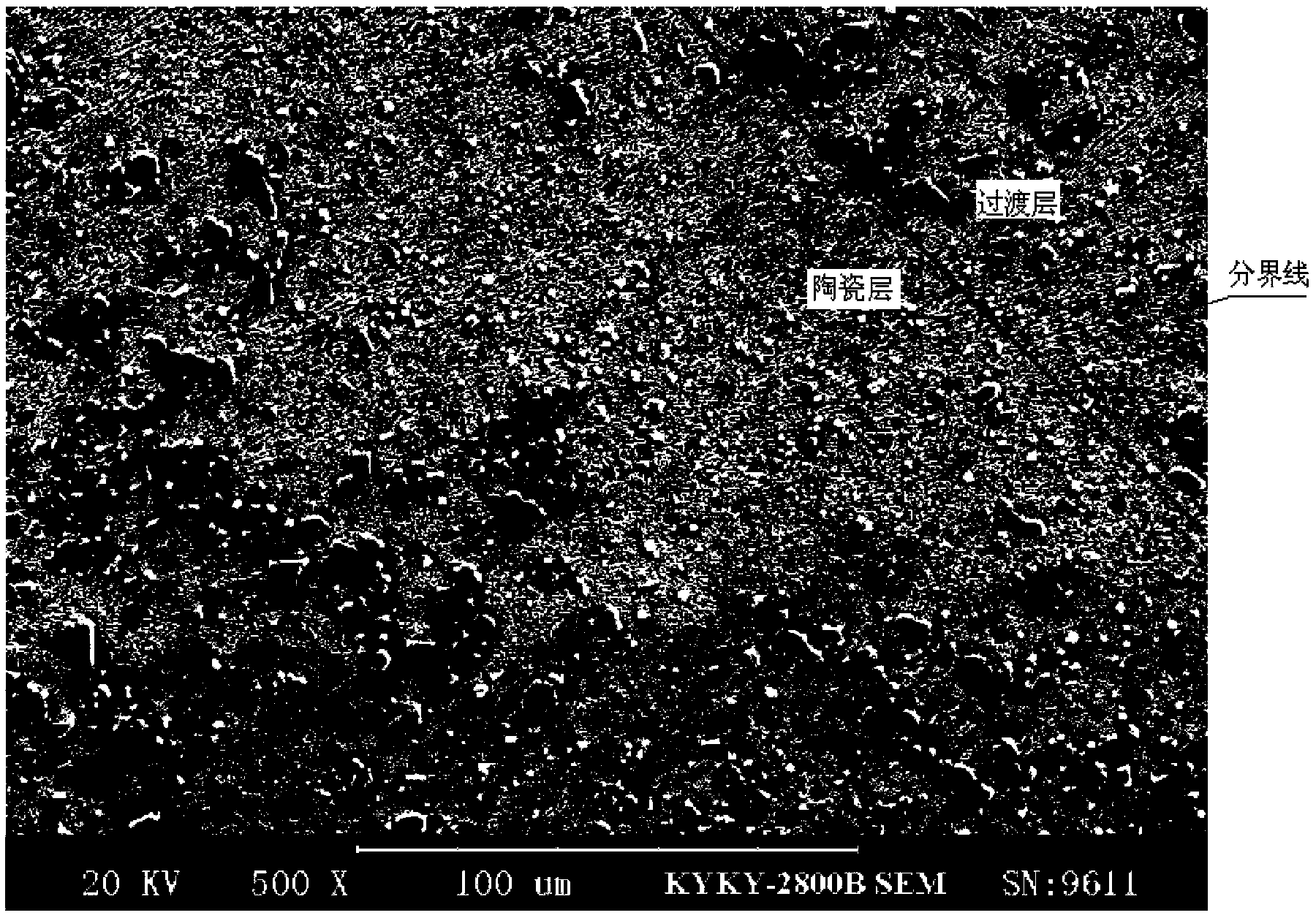

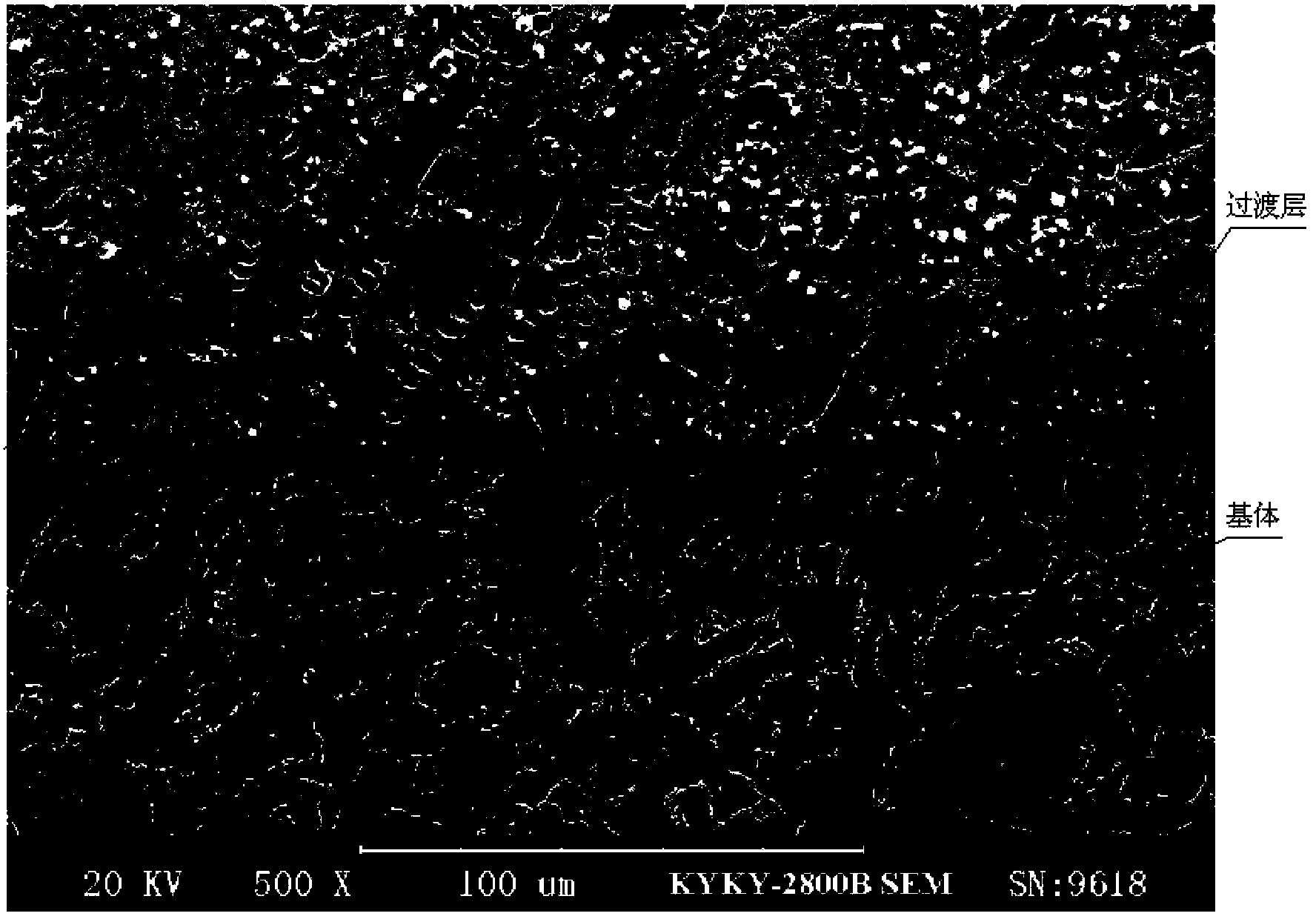

Preparation method of zirconia thermal barrier coating based on roller

ActiveCN103911581ARelieve heat stressAchieve continuous transitionMolten spray coatingEfficient propulsion technologiesYttriumThermal barrier coating

A preparation method of a zirconia thermal barrier coating based on a roller mainly performs preheating, cleaning, sand blasting roughening treatment of a processed roller; the method comprises the following steps: spraying NiCoCrAlY alloy powder on a roller surface by plasma spraying equipment to form a transition layer with a thickness of 0.1-0.2 mm, performing air plasma spraying by zirconia powder stabilized with yttrium oxide with a mass fraction of 8% to form a ceramic layer with a thickness of 0.3-0.4 mm, and performing remelting processing of the plasma sprayed surface by a 2000-w direct current rapid excitation crossflow-type CO2 laser with a pressure of 0.25 MPa, an adjusted laser power range of 350-600 w, a defocusing amount of 40-60 mm, a scanning speed of 3-8 mm / s, a spot diameter of 4.5 mm, a specific laser energy of 37.2 J / mm2, and an overlapping rate of 30%. The method of the invention effectively reduces the temperature of the roller surface, prolongs the service life of the roller, and improves the production benefit.

Owner:YANSHAN UNIV

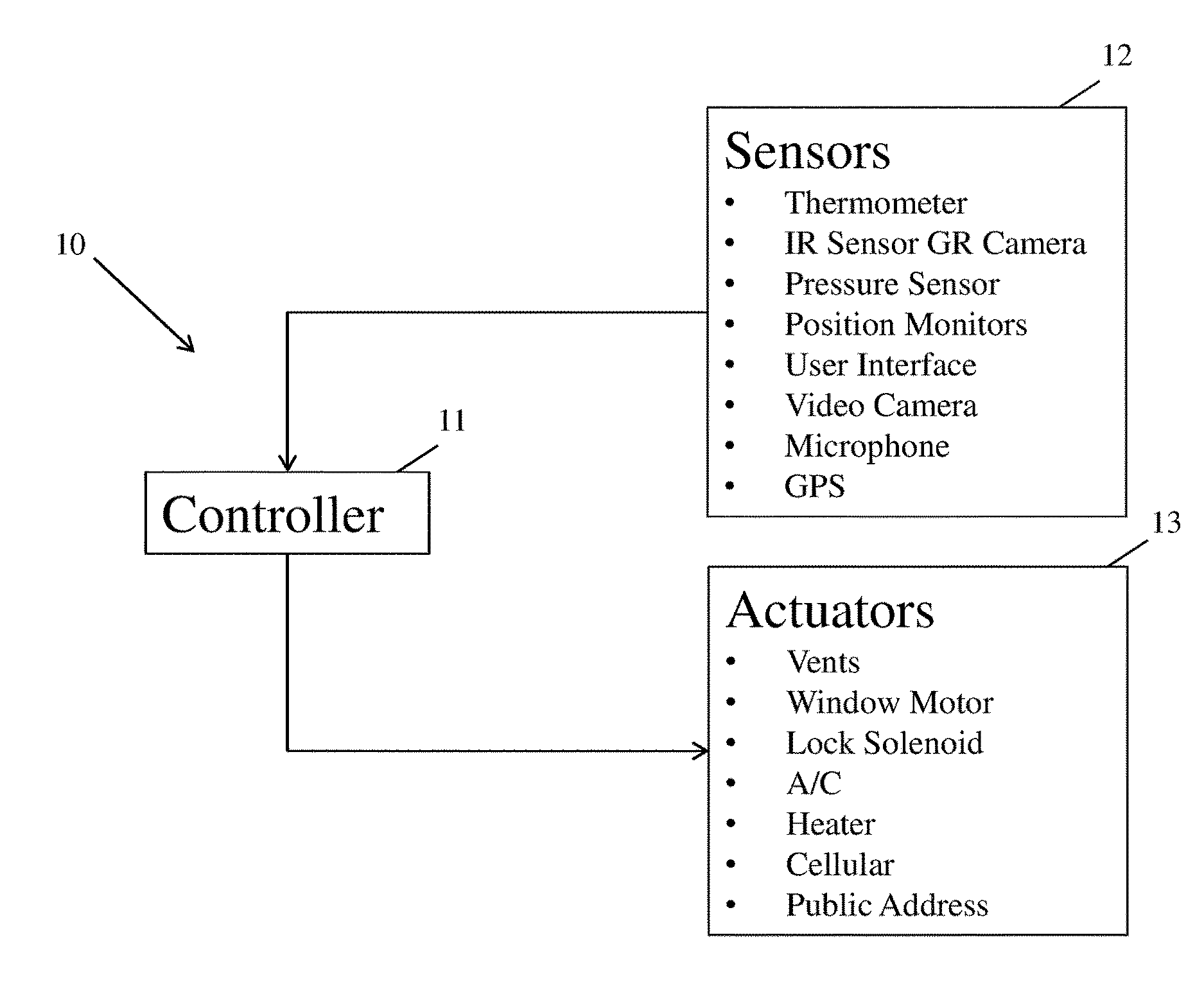

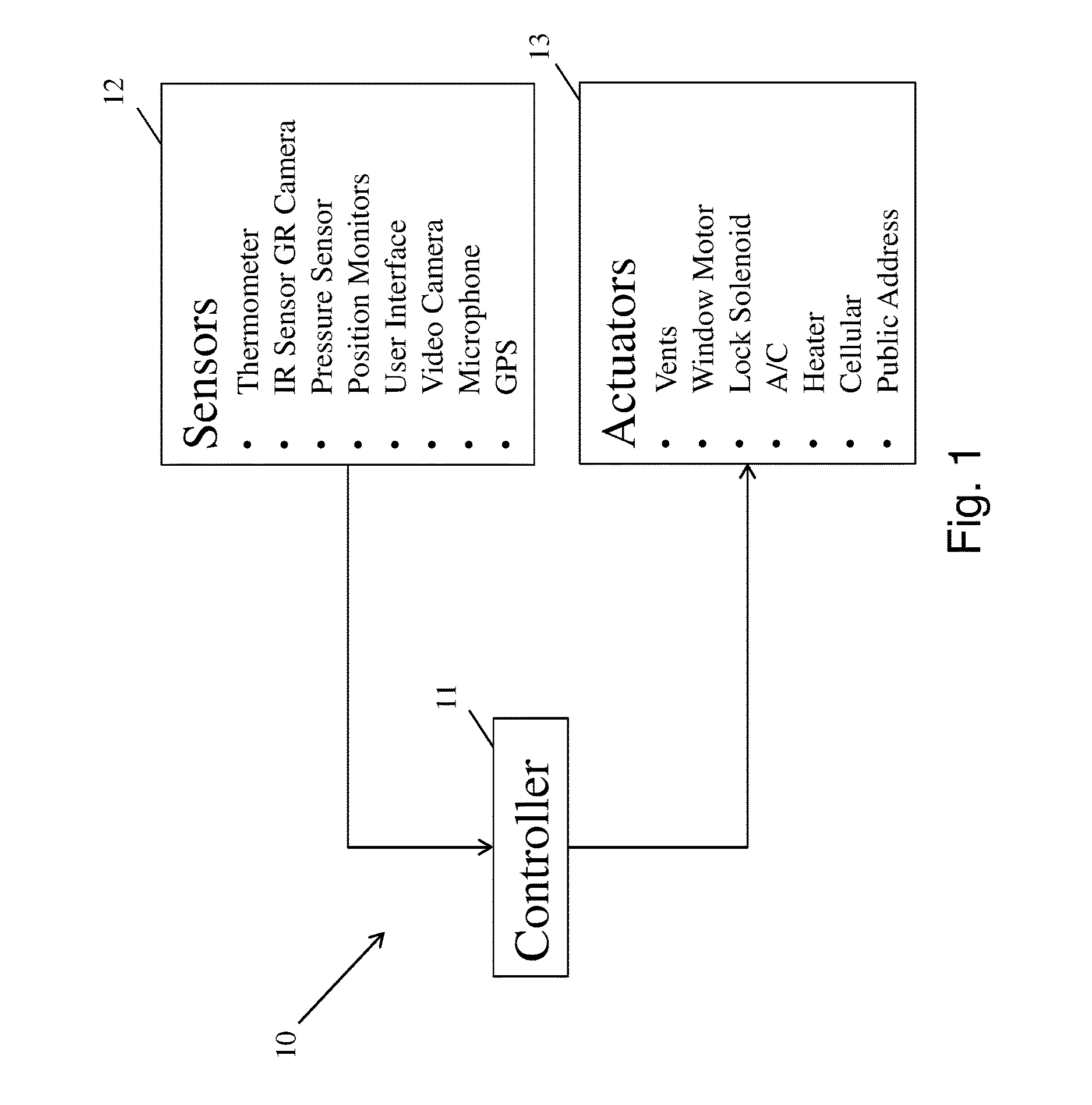

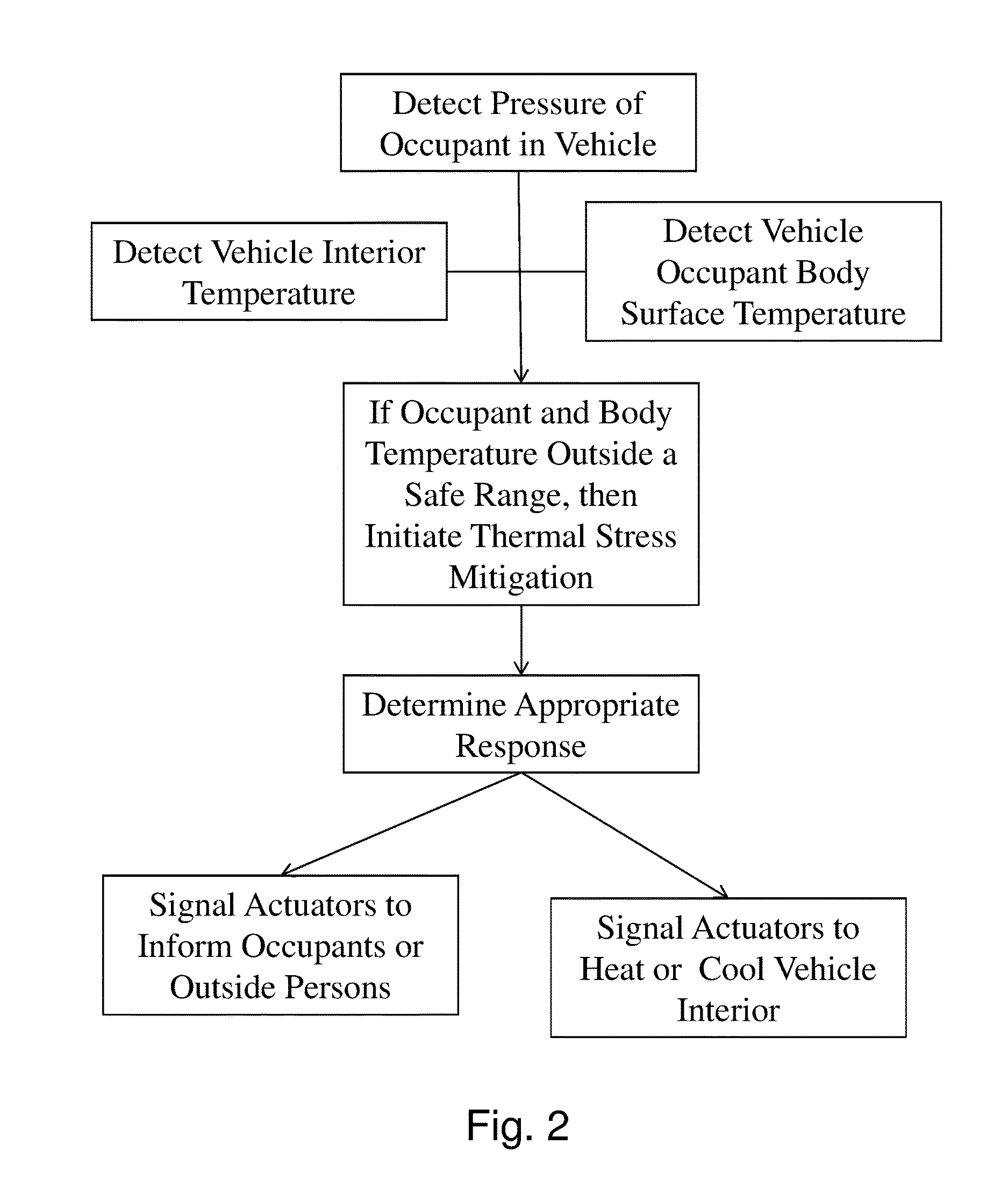

Vehicle Extreme Temperature Safety Systems

ActiveUS20170028811A1Reduce thermal stressPrevent exposureAir-treating devicesDiagnostics using spectroscopyStress conditionsExtreme temperature

Safety systems to prevent or mitigate thermal stress conditions in a vehicle. Systems include sensors to detect conditions in and around a vehicle, particularly the temperature inside the vehicle and the condition of occupants. System controllers receive the sensor information, determine the thermal stress status of occupants, and activate appropriate actuators configured to reduce thermal stress in the vehicle.

Owner:BRAEBURN INC

Hybrid interconnect for a solid-oxide fuel cell stack

InactiveUS20060216567A1Relieving thermal expansion differenceRelieve heat stressFuel cells groupingLayered productsLap jointEngineering

An electrical interconnect for a fuel cell assembly comprising a peripheral frame formed of one or more materials having a coefficient of thermal expansion similar to that of adjacent elements to which the interconnect must be bonded and a central portion formed of a corrosion-resistant material for conducting electric current between adjacent fuel cells. Preferably, the central portion is attached to the peripheral frame via a brazed corrugated lap joint for relieving thermal expansion differences between the frame and the central portion. Preferably, the joint includes an interlayer of a ductile material, for example, a nickel, copper, silver or gold layer, which helps to relieve thermal stress between the frame and the central portion.

Owner:DELPHI TECH INC

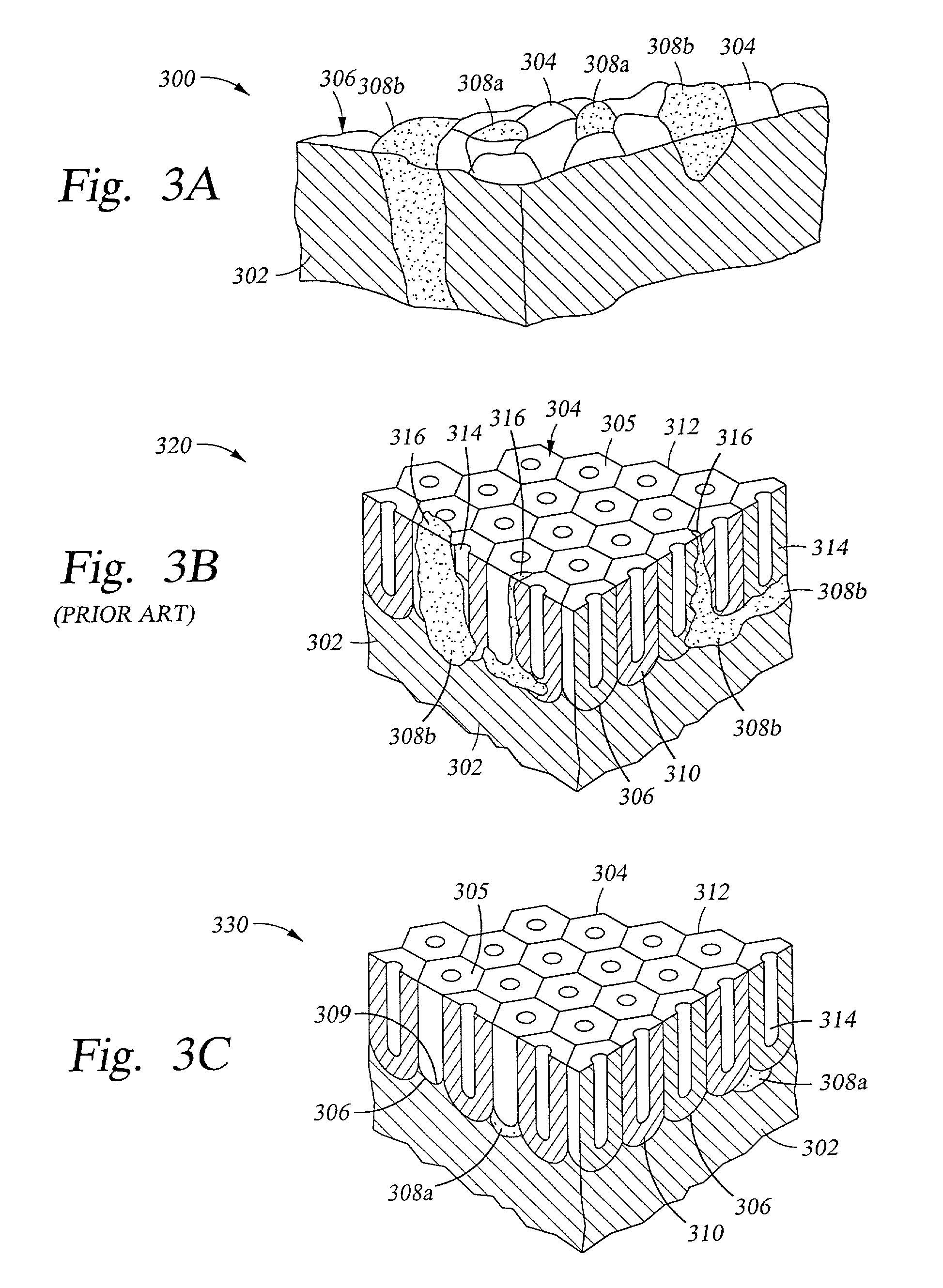

Gradient heat prevention/insulation ceramic base composite material and preparation method thereof

The invention discloses a gradient heat shielding / heat insulating ceramic matrix composite material and a preparation method thereof, and relates to a ceramic matrix composite material and a preparation method thereof. The invention solves the problem of single heat conductivity of the existing boride ceramic matrix homogeneous composite material, and provides a gradient heat shielding / heat insulating ceramic matrix composite material and a preparation method thereof. The material of the invention consists of a heat shielding layer, a first intermediate layer, a second intermediate layer, a third intermediate layer and a heat insulating layer. The preparation method of the material of the invention comprises the following steps: raw material powder treated with ultrasonic cleaning, ball-milling and drying and used for preparing all the layers are laid in a graphite mould in a flat way according to the sequence, then, under the condition of inert atmosphere, the temperature of the mixture is raised and maintained for 5min to obtain the material. The preparation technology of the invention is simple, the cost is low, the room temperature heat conductivity of the heat shielding end of the invention is 89.77W / m per DEG C, the heat conductivity at 1800 DEG C is 61.86W / m per DEG C; while the room temperature heat conductivity of the heat insulating end can reach 8.58W / m per DEG C minimally; and the heat conductivity at 1800 DEG C can reach 18.27W / m per DEG C minimally.

Owner:HARBIN INST OF TECH

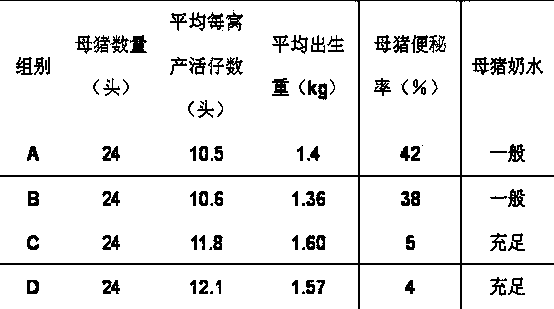

Pregnant sow feed for comprehensively preventing constipation of sow

InactiveCN103829034AReduce usageReduce heat stressFood processingAnimal feeding stuffSugar beetCalcium

The invention discloses a pregnant sow feed for comprehensively preventing constipation of a sow. The pregnant sow feed is prepared from the components: maize, bran, ginkgo biloba leaf slags, garlic residues, sugar beet pulp, soybean hull, DDGS (Distillers Dried Grains With Soluble), bean pulp, soybean oil, mountain flour, calcium hydrophosphate, salt, potassium chloride, gypsum powder, mirabilite, rheum officinale, sodium bicarbonate, choline chloride, 30 percent glycine betaine, microecologics, xylooligosaccharide and 1 percent premix. With the adoption of the pregnant sow feed with the formula, the heat stress of the sow is weakened, the constipation occurrence rate of the pregnant sow is lowered by 20-40 percent, the previous embryo survival rate of the pregnant sow can be increased so as to enable the number born alive of the sow to be increased by 10-18 percent, the sow birth process is shortened, the piglet birth weight is increased by 10-20 percent, and the economic benefit of pig production is increased.

Owner:XUZHOU ZHENGCHANG FEED

Gradient wear-resistant coating for carrier roller of conveyor belt and preparation method of gradient wear-resistant coating

ActiveCN103361591AHigh hardnessHigh bonding strengthMolten spray coatingPlasma welding apparatusWear resistantCeramic coating

The invention discloses a gradient wear-resistant coating for a carrier roller of a conveyor belt and a preparation method of the gradient wear-resistant coating. The gradient wear-resistant coating is characterized in that a layer of NiCrBSi self-fluxing alloy powder is spray-welded on the surface of a preprocessed carbon steel carrier roller as a transition layer, and the NiCrBSi self-fluxing alloy powder and the mixed powder of Fe, Ti, WC and B4C are simultaneously spray-welded on the transition layer so as to form a ceramic coating on the transition layer, wherein a nickel-base self-fluxing alloy is taken as an adhesive base phase of the ceramic coating, and TiB2, TiC, Fe2B, Fe3C and WC high-hardness ceramic particles are taken as wear-resistant strengthening phases of the ceramic coating. According to the gradient wear-resistant coating, the nickel-base self-fluxing alloy is taken as the transition layer between the ceramic coating and the carbon steel carrier roller, the wettability is good, and the transition layer presents good metallurgical bonding with a matrix; and meanwhile, the thermal stresses of the coating and matrix materials are relieved, and the residual stress in the coating is reduced, so that the coating simultaneously has excellent wear resistance and corrosion resistance.

Owner:SHANDONG UNIV OF SCI & TECH

Bainite auctile iron isothermal quenching technology

InactiveCN1718768AAvoid the disadvantages of easy deformation and crackingImprove cooling effectAlloyDuctile iron

An isothermal quenching technology for the nodular graphite cast iron of bainite includes such steps as heating to bainite temp region, holding the temp for a certain time, cooling in water, cooling in isothermal furnace, and cooling in air. Its advantages are high quality of product, no pollution, and low cost.

Owner:MATERIAL SCI RES INST SHANDONG INST OFCIVIL ENG

Halogen-resistant, anodized aluminum for use in semiconductor processing apparatus

InactiveUS7048814B2Excellent abrasion resistanceHigh densityAnodisationVacuum evaporation coatingParticulatesHalogen

We have discovered that the formation of particulate inclusions at the surface of an aluminum alloy article, which inclusions interfere with a smooth transition from the alloy surface to an overlying aluminum oxide protective film can be controlled by maintaining the content of mobile impurities within a specific range and controlling the particulate size and distribution of the mobile impurities and compounds thereof; by heat-treating the aluminum alloy at a temperature less than about 330° C.; and by creating the aluminum oxide protective film by employing a particular electrolytic process. When these factors are taken into consideration, an improved aluminum oxide protective film is obtained.

Owner:APPLIED MATERIALS INC

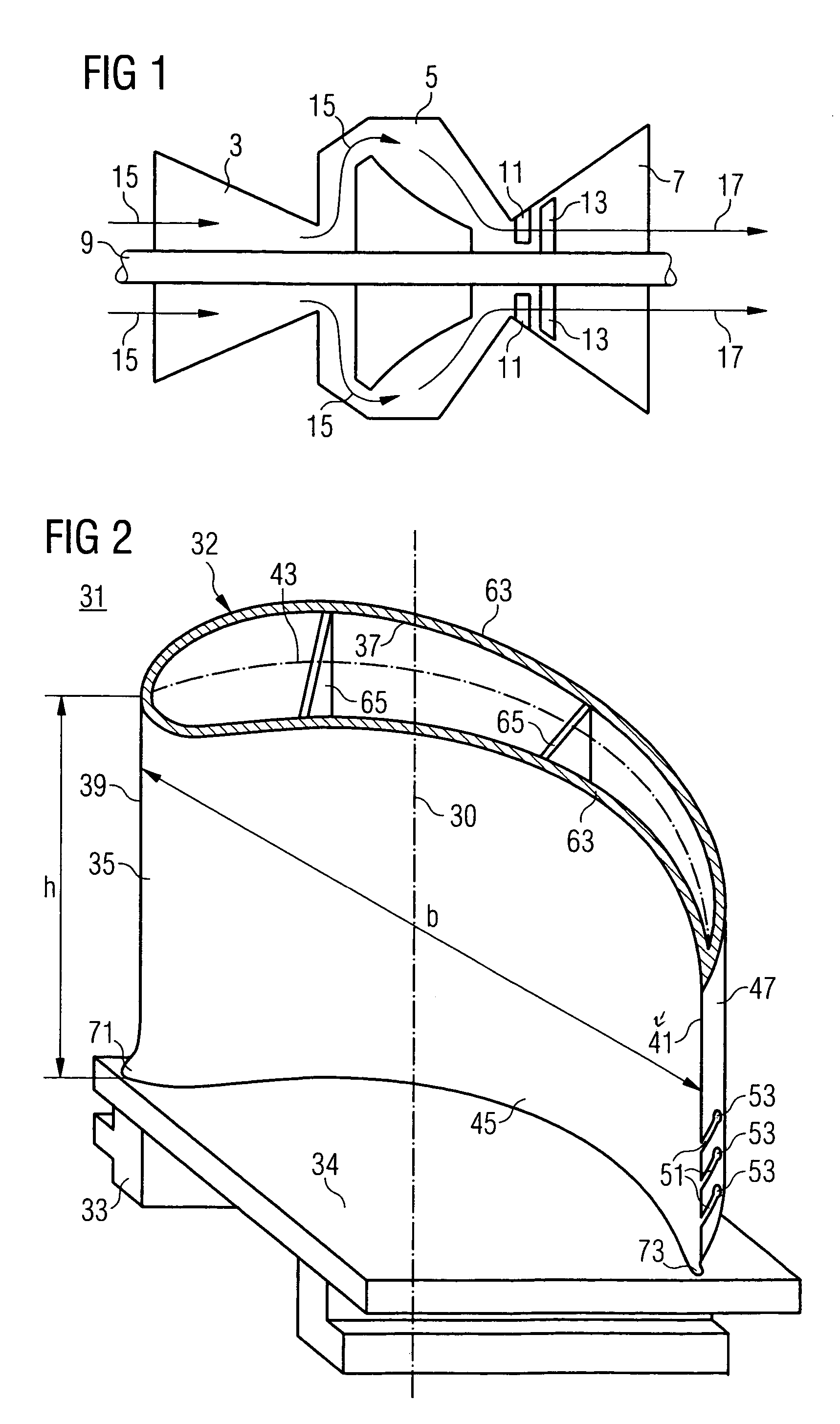

Blade of a turbine

InactiveUS7160084B2Reducing surface curvatureRelieve pressurePropellersRotary propellersTurbine bladeThermal expansion

The invention relates to a turbine blade (31) having a root region (33), a tip region (37) and a blade airfoil (35), a rounded portion (73) being formed between the root region (33) and the blade airfoil (35), and relief slots (51) passing through the blade trailing edge (41) in the region of this rounded portion (73), thermal expansions being compensated for and thus thermal stresses being minimized by these relief slots (51).

Owner:SIEMENS AG

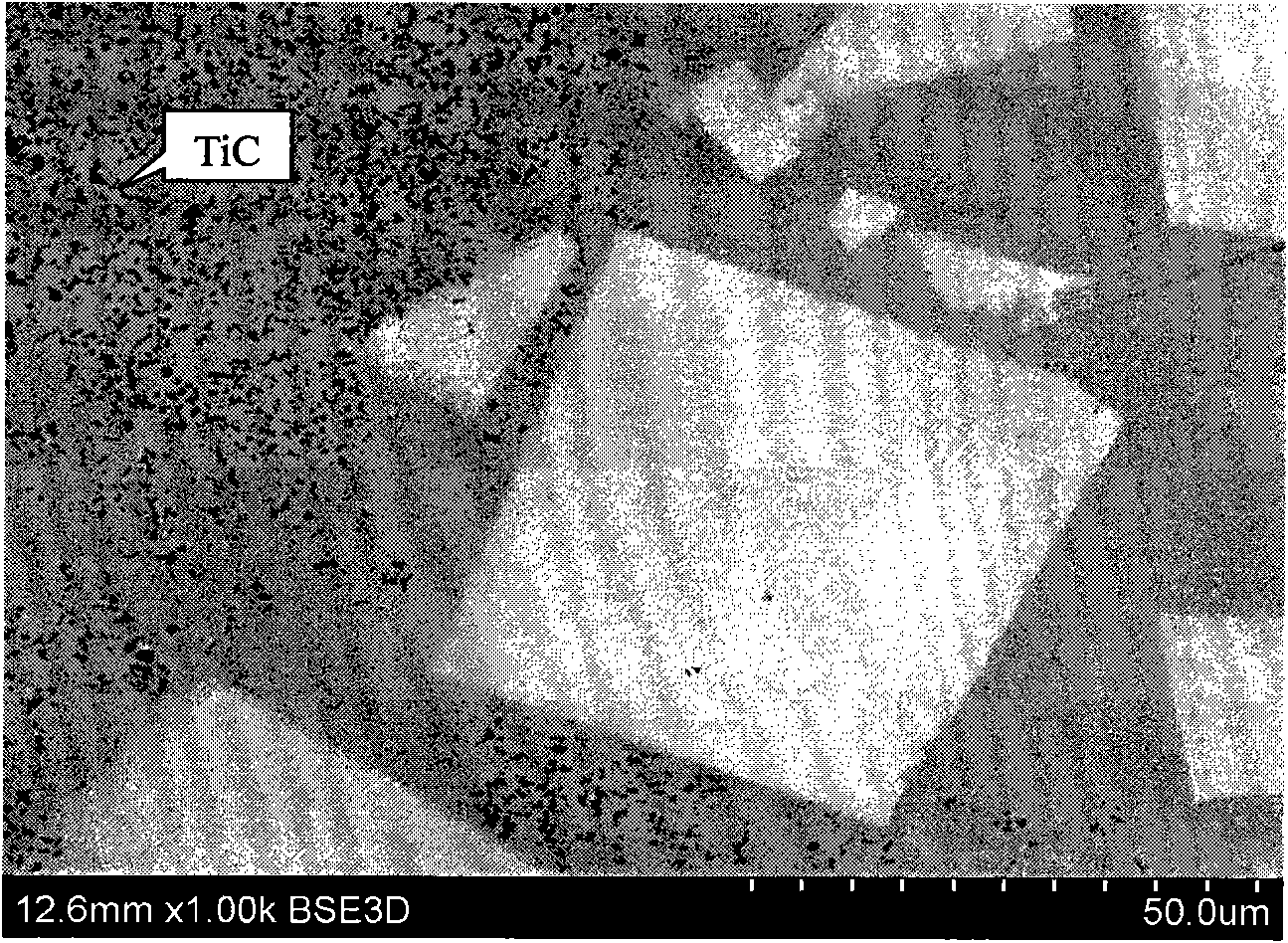

Ceramic phase reinforced copper-based composite solder and preparation method thereof

InactiveCN102211260ALow costLow melting pointWelding/cutting media/materialsSoldering mediaWhiskersComposite solder

The invention discloses a ceramic phase reinforced copper-based composite solder and a preparation method thereof, relates to a copper-based composite solder and a preparation method thereof, and aims to solve the problems that an Ag-Cu-Ti solder has high cost, and low joint strength caused by residual stress in the conventional ceramic connection method. The ceramic phase reinforced copper-based composite solder comprises Cu powder, Sn powder, Ti powder and B powder. The method comprises the following steps of: mixing the Cu powder, the Sn powder, the Ti powder and the B powder to obtain mixed powder; and adding the mixed powder and ceramic balls into a ball-milling tank of a planetary ball mill, and performing ball milling for 1 to 5 hours at a rate of 300r / min under the protection of argon gas to obtain a uniformly mixed Cu-Sn-Ti-B composite solder. Soldering cost is reduced, and thermal mismatching between metal and ceramic is adjusted by growing TiB crystal whiskers in a joint in situ, so that the usability of the soldered joint is improved. The solder is applied to the soldering connection of the ceramic.

Owner:HARBIN INST OF TECH

Method for preparing monocrystalline silicon carbide nanofiber/silicon carbide ceramic matrix composite material by reaction sintering

ActiveCN110256082ARelieve heat stressImprove mechanical properties and service lifeCarbon blackMonocrystalline silicon

The invention discloses a method for preparing a monocrystalline silicon carbide nanofiber / silicon carbide ceramic matrix composite material by reaction sintering. The method comprises the following steps: preparing a SiC nanofiber coated with a carbon / BN coating from a monocrystalline silicon carbide nanofiber; impregnating or stirring and dispersing the SiC nanofiber in an ethanol / water suspension containing nanometer carbon black / silicon carbide particles; and preparing a SiCNf preform by vacuum suction filtration or rolling: placing the above interfacial layer deposited nanofiber preform in a molding die, further carrying out press molding, carrying out high-temperature dumping to obtain a high-density SiCNf preform, and then performing reaction infiltration. Compared with in-situ grown SiC nanowire / fiber (SiCnf) reinforced SiC ceramic matrix composite materials, the composite material of the invention has the advantages of easiness in preparation of the interfacial coating of the SiCNf and the matrix, high volume content of the SiCNf, and high density.

Owner:ZHEJIANG SCI-TECH UNIV

Test blanket module for international thermonuclear experimental reactor with low toroidal field waviness

InactiveCN103187106AStop the spreadRelieve heat stressNuclear energy generationThermonuclear fusion reactorTritiumFerromagnetism

The invention belongs to the technical field of test blanket modules (TBMs), and particularly relates to a test blanket module for an international thermonuclear experimental reactor (ITER) with low toroidal field waviness, which can reduce the toroidal magnetic field waviness caused by a ferromagnetic material in the test blanket module. A front end structure of the test blanket module comprises a first wall, a tritium breeding region, an upper and lower cover plate and a separation rack that adopt RAFM (Reduced Activation Ferritic / Martensitic) steel as a structural material; a rear plate of the test blanket module adopts a non-ferromagnetic material 316LN as a major structural material; interfaces of the front end structure and the rear plate are connected by a middle transition layer structure; and the middle transition layer is a nickel alloy at the working condition temperature of 300-400 DEG C, and is a composite layer of the nickel alloy and the 316LN material at the working condition temperature of 400-500 DEG C. The influence of the TBM on the toroidal field waviness of the ITER is reduced greatly, the nickel alloy is adopted as the middle transition layer in a member design, so that the anisotropic material connection between the RAFM steel and the 316LN steel is realized, and the effect is obvious.

Owner:SOUTHWESTERN INST OF PHYSICS

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com